JAJSC33I - FEBRUARY 2015 - REVISED JANUARY 2025

# DP83867IR/CR 堅牢で耐性の高い 10/100/1000 イーサネット物理層トランシ-バ

# 1 特長

- 超低 RGMII レイテンシの TX < 90ns、RX < 290ns

- TSN (Time Sensitive Network) 準拠

- 低消費電力 457mW

- IEC 61000-4-2 で 8000V を超える ESD 保護

- EN55011 Class B 放射規格を満たす

- RX/TX で 16 の RGMII 遅延モードをプログラム可能

- MDI 終端抵抗を内蔵

- MII/GMII/RGMII 終端インピーダンスをプログラム可能

- WoL (Wake-on-LAN) パケット検出

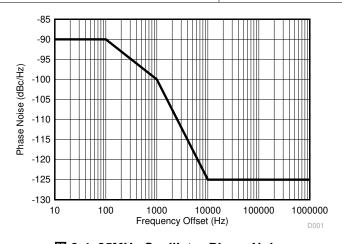

- 25MHz または 125MHz の同期クロック出力

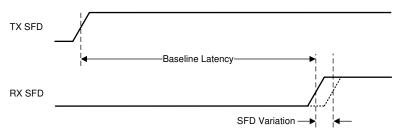

- IEEE 1588 タイム スタンプの SOF(Start of Frame) 検出

- RJ45 ミラー モード

- IEEE 802.3 10BASE-Te, 100BASE-TX, 1000BASE-T 仕様と完全互換

- ケーブル診断

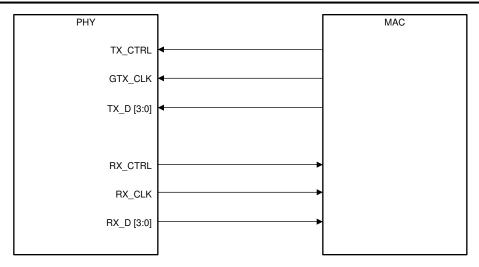

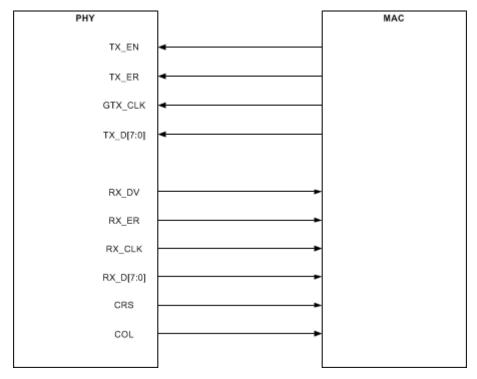

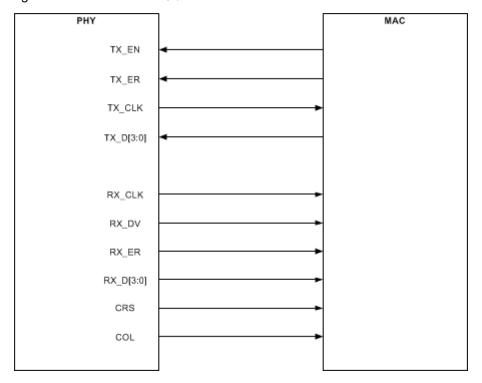

- MII、GMII、および RGMII MAC インターフェイス オプ

- I/O 電圧を構成可能 (3.3V、2.5V、1.8V)

- 高速なリンクドロップ モード

- JTAG のサポート

# 2 アプリケーション

- モーター・ドライブ

- 産業用ファクトリ・オートメーション

- フィールド・バス・サポート

- 産業用組み込みコンピュータ

- 有線および無線通信インフラストラクチャ

- 試験/測定機器

- コンシューマ・エレクトロニクス

#### 3 概要

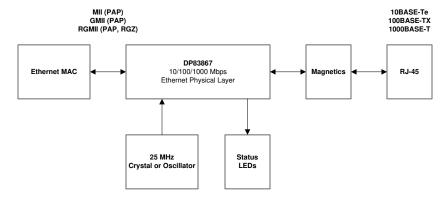

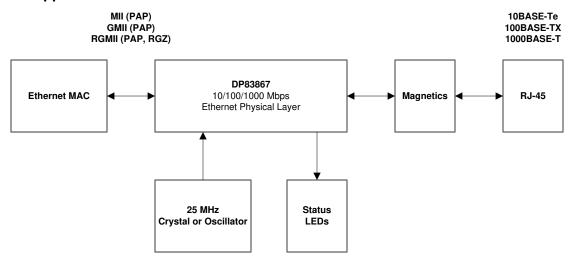

DP83867 デバイスは堅牢で低消費電力の、必要な機能 がすべて揃った物理層トランシーバで、PMD サブレイヤ を内蔵しており、10BASE-Te、100BASE-TX、 1000BASE-T の各イーサネット プロトコルをサポートして います。**DP83867** は **ESD** 保護用に最適化されており、 IEC 61000-4-2 で 8kV を超える保護を実現しています (直接接触)。

DP83867 は、10/100/1000Mbps のイーサネット LAN を 簡単に実装できるよう設計されています。外部の変圧器を 通して、DP83867 をツイスト ペアのメディアへ直接に接続 することが可能です。このデバイスは、IEEE 802.3 標準 Media Independent Interface (MII), IEEE 802.3 Gigabit Media Independent Interface (GMII) または Reduced GMII (RGMII) により、MAC 層へ直接接続され ます。QFP パッケージ は MII/GMII/RGMII をサポートし、 QFN パッケージは RGMII をサポートします。

DP83867 は、同期イーサネットクロック出力など、高精度 のクロック同期を提供します。 DP83867 には、低レイテン シを備え、IEEE 1588 のフレーム開始検出も提供されま

DP83867 は、フル動作時の消費電力がわずか 490mW (PAP) と 457mW (RGZ) です。Wake on LAN を使用し て、システムの消費電力を低減できます。

#### パッケージ情報

|              | THE PARTY OF THE P |                    |                          |  |  |  |  |  |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------------|--|--|--|--|--|--|

| 部品番号         | 温度                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | パッケージ(1)           | パッケージ サイズ <sup>(2)</sup> |  |  |  |  |  |  |

| DP83867IRPAP | -40°C ∼ +85°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PAP (HTQFP、<br>64) | 12mm × 12mm              |  |  |  |  |  |  |

| DP83867IRRGZ | -40°C ∼ +85°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | RGZ (VQFN、<br>48)  | 7mm × 7mm                |  |  |  |  |  |  |

| DP83867CRRGZ | 0°C ∼ +70°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | RGZ (VQFN、<br>48)  | 7mm × 7mm                |  |  |  |  |  |  |

- (1) 供給されているすべてのパッケージについては、セクション 11 を 参照してください。

- パッケージ サイズ (長さ×幅) は公称値で、該当する場合はピンも

# **Table of Contents**

| 1 特長                                              | . 1 |

|---------------------------------------------------|-----|

| 2 アプリケーション                                        | 1   |

| 3 概要                                              | . 1 |

| 4 Device Comparison                               | .4  |

| 5 Pin Configuration and Functions                 |     |

| 5.1 Unused Pins                                   |     |

| 6 Specifications                                  | 11  |

| 6.1 Absolute Maximum Ratings                      | 11  |

| 6.2 ESD Ratings                                   | 11  |

| 6.3 Recommended Operating Conditions              | 12  |

| 6.4 Thermal Information                           |     |

| 6.5 Electrical Characteristics                    |     |

| 6.6 Power-Up Timing                               |     |

| 6.7 Reset Timing                                  | 15  |

| 6.8 MII Serial Management Timing                  | 15  |

| 6.9 RGMII Timing                                  |     |

| 6.10 GMII Transmit Timing                         | 16  |

| 6.11 GMII Receive Timing                          |     |

| 6.12 100Mbps MII Transmit Timing                  |     |

| 6.13 100Mbps MII Receive Timing (2)               |     |

| 6.14 10Mbps MII Transmit Timing                   |     |

| 6.15 10Mbps MII Receive Timing                    |     |

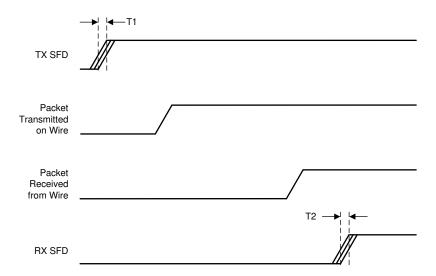

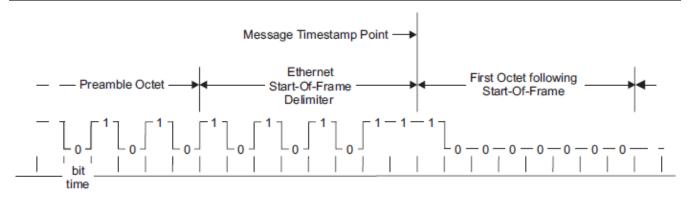

| 6.16 DP83867IR/CR Start of Frame Detection Timing |     |

| 6.17 Timing Diagrams                              | 18  |

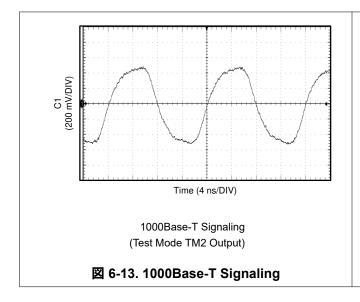

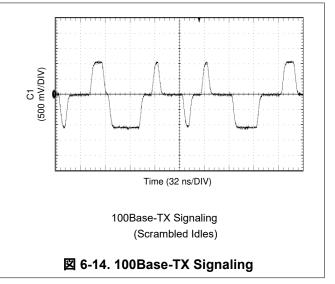

| 6.18 Typical Characteristics            | 22              |

|-----------------------------------------|-----------------|

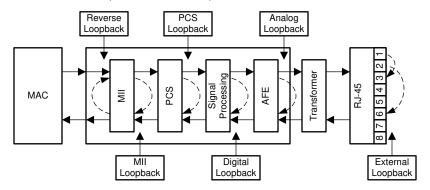

| 7 Detailed Description                  | <mark>23</mark> |

| 7.1 Overview                            |                 |

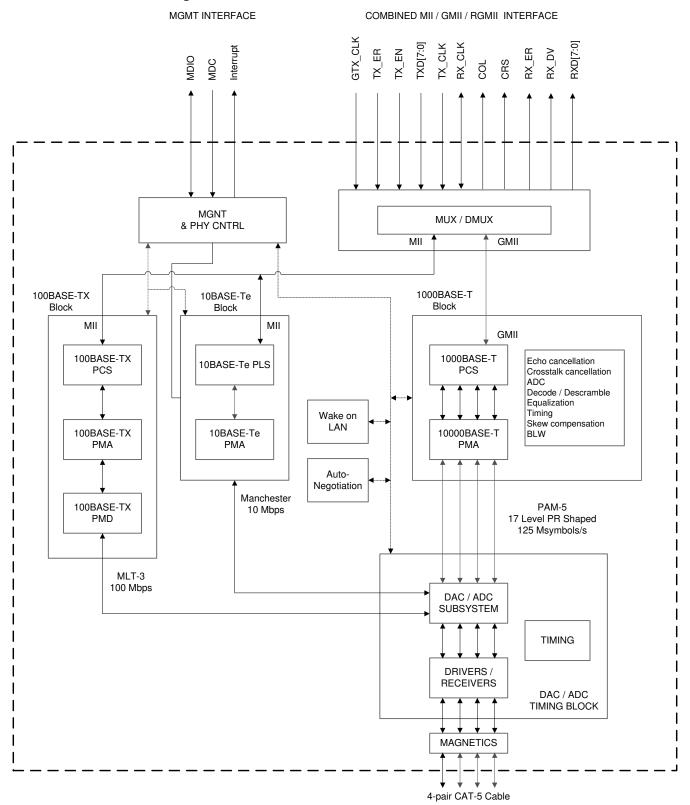

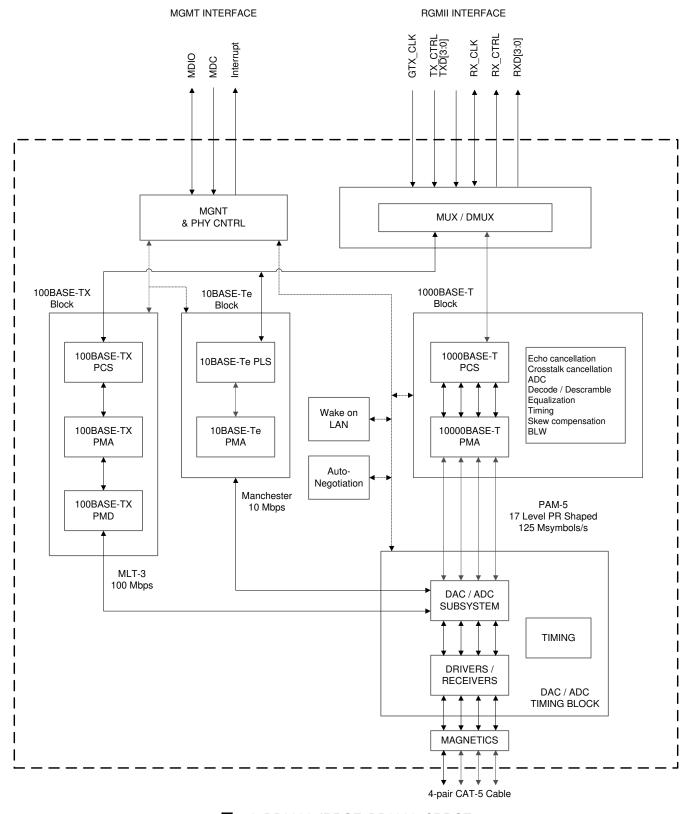

| 7.2 Functional Block Diagram            |                 |

| 7.3 Feature Description                 |                 |

| 7.4 Device Functional Modes             |                 |

| 7.5 Programming                         | 45              |

| 7.6 Register Maps                       | 53              |

| 8 Application and Implementation        |                 |

| 8.1 Application Information             |                 |

| 8.2 Typical Application                 | 114             |

| 8.3 Power Supply Recommendations        | 120             |

| 8.4 Layout                              | 123             |

| 9 Device and Documentation Support      | 127             |

| 9.1 Documentation Support               | 127             |

| 9.2ドキュメントの更新通知を受け取る方法                   | 127             |

| 9.3 サポート・リソース                           |                 |

| 9.4 Trademarks                          |                 |

| 9.5 静電気放電に関する注意事項                       |                 |

| 9.6 用語集                                 |                 |

| 10 Revision History                     |                 |

| 11 Mechanical, Packaging, and Orderable | 121             |

| Information                             | 128             |

| v                                       | 120             |

# 4 Device Comparison

表 4-1. Device Features Comparison

| DEVICE       | MAC            | TEMPERATURE RANGE |      | TEMPERATURE GRADE |  |

|--------------|----------------|-------------------|------|-------------------|--|

| DP83867CRRGZ | RGMII          | 0°C               | 70°C | Commercial        |  |

| DP83867IRRGZ | RGMII          | -40°C             | 85°C | Industrial        |  |

| DP83867IRPAP | MII/GMII/RGMII | -40°C             | 85°C | Industrial        |  |

# **5 Pin Configuration and Functions**

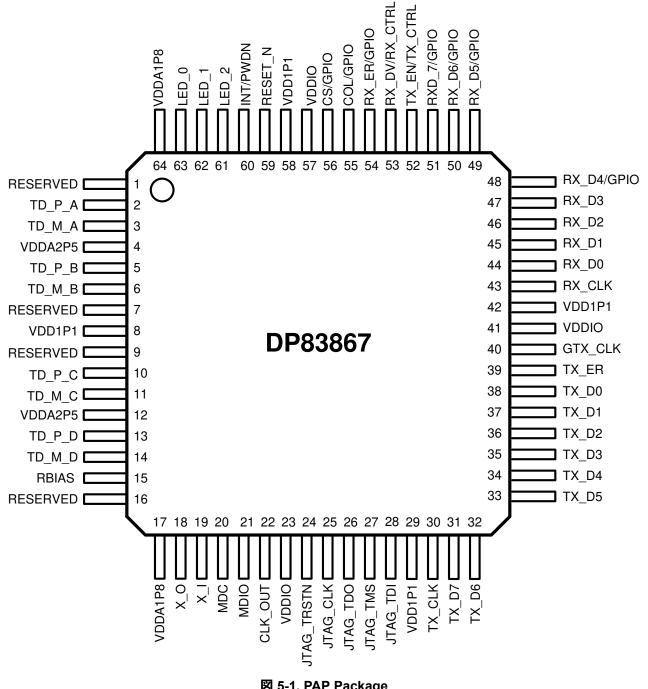

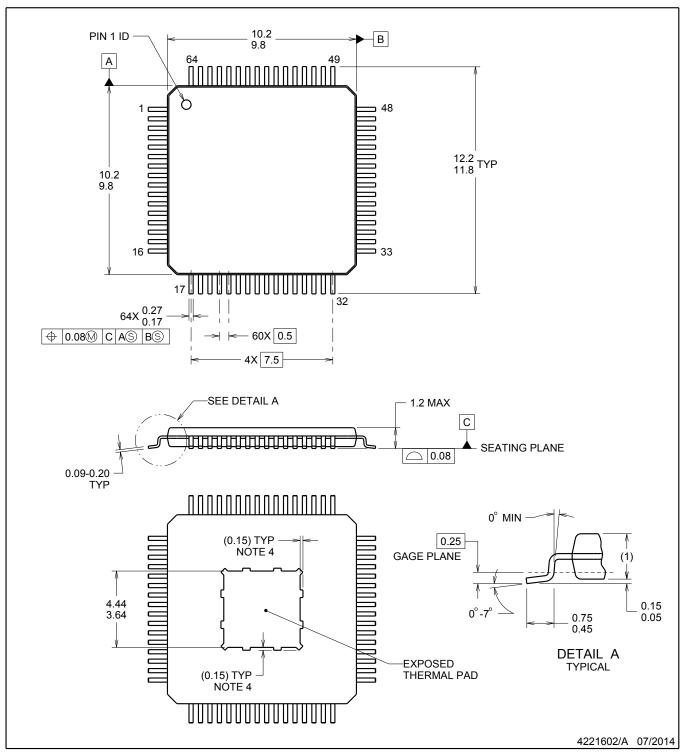

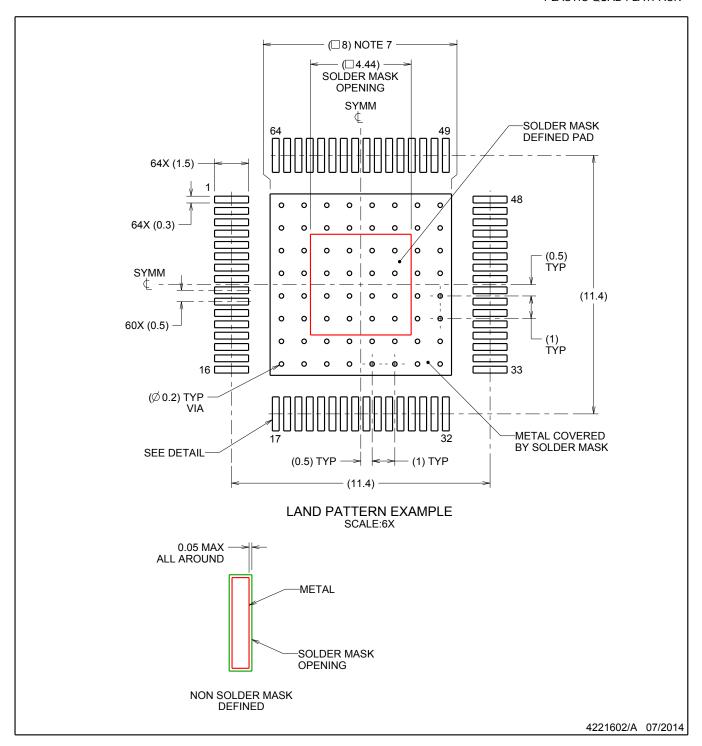

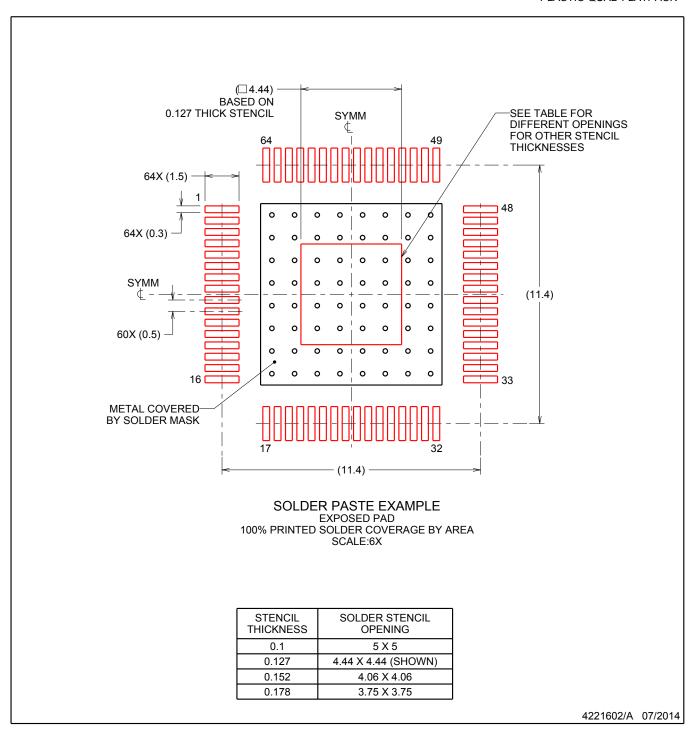

図 5-1. PAP Package

Product Folder Links: DP83867IR DP83867CR

# 64-Pin HTQFP Top View

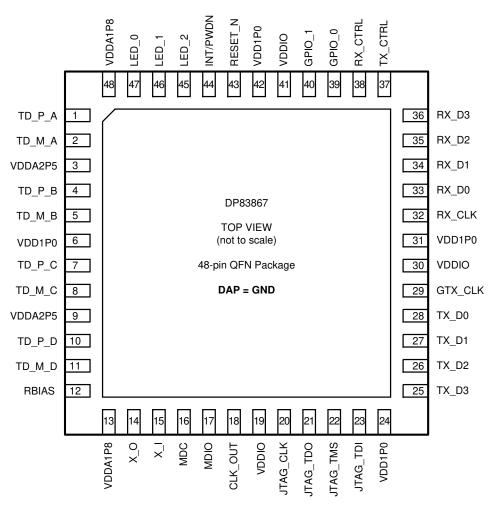

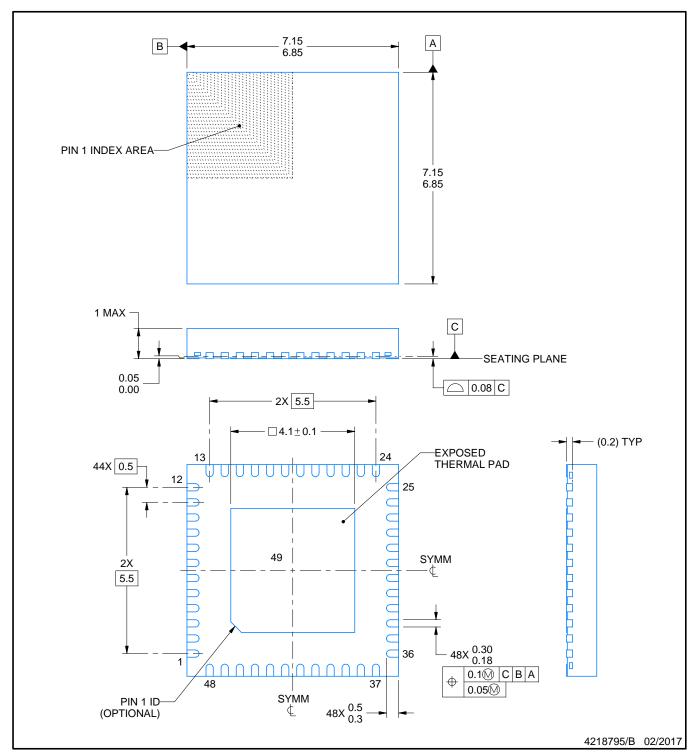

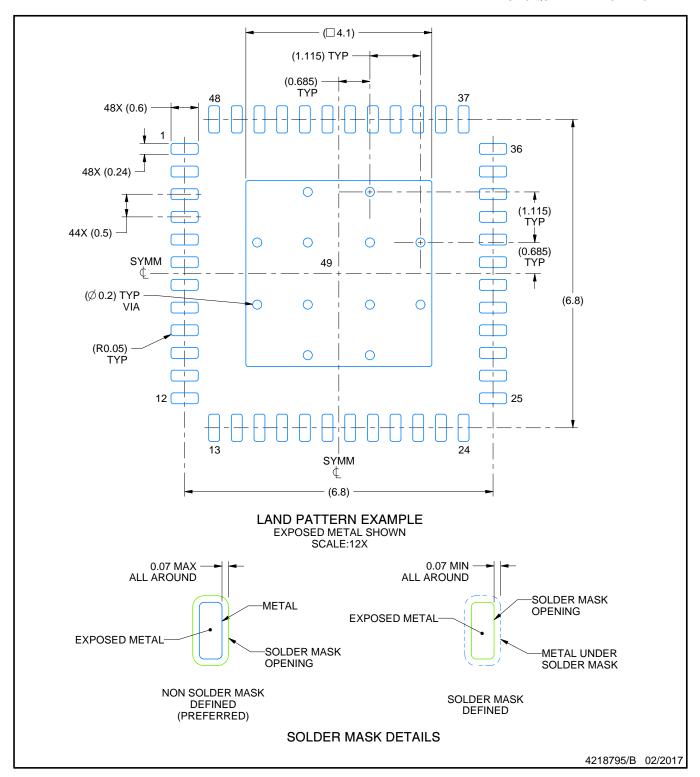

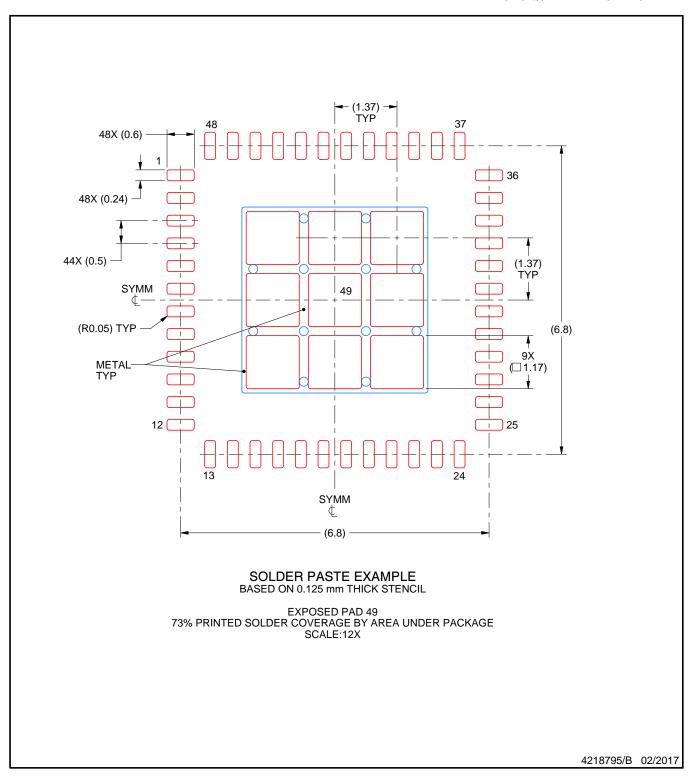

図 5-2. RGZ Package 48-Pin QFN Top View

## 表 5-1. Pin Functions

|                | PIN   |       | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                             |  |  |

|----------------|-------|-------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME           | HTQFP | VQFN  | ITPE(''             | DESCRIPTION                                                                                                                                                                                                                                             |  |  |

| MAC INTERFACES |       | RGMII |                     |                                                                                                                                                                                                                                                         |  |  |

| TX_CLK         | 30    |       | 0                   | MII TRANSMIT CLOCK: TX_CLK is a continuous clock signal driven by the PHY during 10Mbps or 100Mbps MII mode. TX_CLK clocks the data or error out of the MAC layer and into the PHY.                                                                     |  |  |

|                |       |       |                     | The TX_CLK clock frequency is 2.5MHz in 10BASE-Te and 25MHz in 100BASE-TX mode.                                                                                                                                                                         |  |  |

| TX_D7          | 31    |       | I, PD               | GMII TRANSMIT DATA Bit 7: This signal carries data from the MAC to the PHY in GMII mode. This pin is synchronous to the transmit clock GTX_CLK.                                                                                                         |  |  |

| TX_D6          | 30    |       | I, PD               | GMII TRANSMIT DATA Bit 6: This signal carries data from the MAC to the PHY in GMII mode. This pin is synchronous to the transmit clock GTX_CLK.                                                                                                         |  |  |

| TX_D5          | 33    |       | I, PD               | GMII TRANSMIT DATA Bit 5: This signal carries data from the MAC to the PHY in GMII mode. This pin is synchronous to the transmit clock GTX_CLK.                                                                                                         |  |  |

| TX_D4          | 34    |       | I, PD               | GMII TRANSMIT DATA Bit 4: This signal carries data from the MAC to the PHY in GMII mode. This pin is synchronous to the transmit clock GTX_CLK.                                                                                                         |  |  |

| TX_D3          | 35    | 25    | I, PD               | TRANSMIT DATA Bit 3: This signal carries data from the MAC to the PHY in GMII, RGMII, and MII modes. In GMII and RGMII modes, this pin is synchronous to the transmit clock GTX_CLK. In MII mode, this pin is synchronous to the transmit clock TX_CLK. |  |  |

| TX_D2          | 36    | 26    | I, PD               | TRANSMIT DATA Bit 2: This signal carries data from the MAC to the PHY in GMII, RGMII, and MII modes. In GMII and RGMII modes, his pin is synchronous to the transmit clock GTX_CLK. In MII mode, this pin is synchronous to the transmit clock TX_CLK.  |  |  |

| TX_D1          | 37    | 27    | I, PD               | TRANSMIT DATA Bit 1: This signal carries data from the MAC to the PHY in GMII, RGMII, and MII modes. In GMII and RGMII modes, this pin is synchronous to the transmit clock GTX_CLK. In MII mode, this pin is synchronous to the transmit clock TX_CLK. |  |  |

| TX_D0          | 38    | 28    | I, PD               | TRANSMIT DATA Bit 0: This signal carries data from the MAC to the PHY in GMII, RGMII, and MII modes. In GMII and RGMII modes, this pin is synchronous to the transmit clock GTX_CLK. In MII mode, this pin is synchronous to the transmit clock TX_CLK. |  |  |

|                |       |       |                     | GMII TRANSMIT ERROR: This signal is used in GMII mode to force the PHY to transmit invalid symbols. The TX_ER signal is synchronous to the GMII transmit clock GTX_CLK.                                                                                 |  |  |

| TX_ER          | 39    |       | I, PD               | In MII 4B nibble mode, assertion of Transmit Error by the controller causes the PHY to issue invalid symbols followed by Halt (H) symbols until deassertion occurs.                                                                                     |  |  |

|                |       |       |                     | In GMII mode, assertion causes the PHY to emit one or more code-groups that are invalid data or delimiter in the transmitted frame.                                                                                                                     |  |  |

| GTX_CLK        | 40    | 29    | I, PD               | GMII and RGMII TRANSMIT CLOCK: This continuous clock signal is sourced from the MAC layer to the PHY. Nominal frequency is 125MHz.                                                                                                                      |  |  |

|                |       |       |                     | RECEIVE CLOCK: Provides the recovered receive clocks for different modes of operation:                                                                                                                                                                  |  |  |

| RX_CLK         | 43    | 32    | 0                   | 2.5MHz in 10Mbps mode.                                                                                                                                                                                                                                  |  |  |

|                |       |       |                     | 25MHz in 100Mbps mode.                                                                                                                                                                                                                                  |  |  |

|                |       |       |                     | 125MHz in 1000Mbps GMII and RGMII mode.                                                                                                                                                                                                                 |  |  |

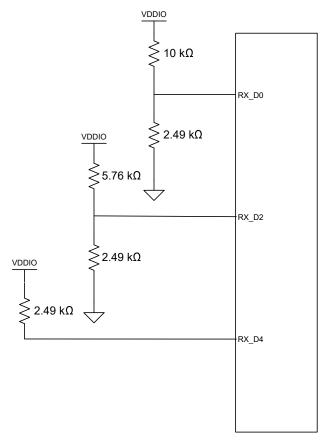

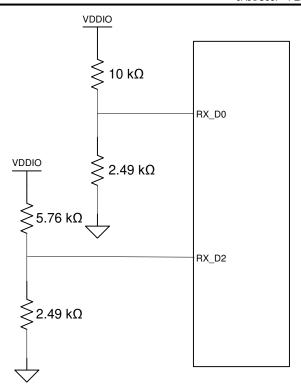

| RX_D0          | 44    | 33    | S, O, PD            | RECIEVE DATA Bit 0: This signal carries data from the PHY to the MAC in GMII, RGMII, and MII modes. This pin is synchronous to the receive clock RX_CLK.                                                                                                |  |  |

| RX_D1          | 45    | 34    | O, PD               | RECIEVE DATA Bit 1: This signal carries data from the PHY to the MAC in GMII, RGMII, and MII modes. This pin is synchronous to the receive clock RX_CLK.                                                                                                |  |  |

| RX_D2          | 46    | 35    | S, O, PD            | RECIEVE DATA Bit 2: This signal carries data from the PHY to the MAC in GMII, RGMII, and MII modes. This pin is synchronous to the receive clock RX_CLK.                                                                                                |  |  |

# 表 5-1. Pin Functions (続き)

| PIN               |       | TYPE <sup>(1)</sup> | DESCRIPTION                                                     |                                                                                                                                                                                                                                                           |

|-------------------|-------|---------------------|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME              | HTQFP | VQFN                | 11PE(')                                                         | DESCRIPTION                                                                                                                                                                                                                                               |

| RX_D3             | 47    | 36                  | O, PD                                                           | RECIEVE DATA Bit 3: This signal carries data from the PHY to the MAC in GMII, RGMII, and MII modes. This pin is synchronous to the receive clock RX_CLK.                                                                                                  |

| RX_D4             | 48    |                     | S, O, PD                                                        | RECIEVE DATA Bit 4: This signal carries data from the PHY to the MAC in GMII mode. This pin is synchronous to the receive clock RX_CLK.                                                                                                                   |

| RX_D5             | 49    |                     | S, O, PD                                                        | RECIEVE DATA Bit 5: This signal carries data from the PHY to the MAC in GMII mode. This pin is synchronous to the receive clock RX_CLK.                                                                                                                   |

| RX_D6             | 50    |                     | S, O, PD                                                        | RECIEVE DATA Bit 6: This signal carries data from the PHY to the MAC in GMII mode. This pin is synchronous to the receive clock RX_CLK.                                                                                                                   |

| RX_D7             | 51    |                     | S, O, PD                                                        | RECIEVE DATA Bit 7: This signal carries data from the PHY to the MAC in GMII mode. This pin is synchronous to the receive clock RX_CLK.                                                                                                                   |

| TX_EN / TX_CTRL   | 52    | 37                  | I, PD                                                           | TRANSMIT ENABLE or TRANSMIT CONTROL: In MII or GMII mode, it is an active high input sourced from MAC layer to indicate transmission data is available on the TXD.                                                                                        |

|                   |       |                     |                                                                 | In RGMII mode, the pin combines the transmit enable and the transmit error signals of GMII mode using both clock edges.                                                                                                                                   |

| RX_DV / RX_CTRL   | 50    | 00                  |                                                                 | RECEIVE DATA VALID or RECEIVE CONTROL: In MII and GMII modes, the pin is asserted high to indicate that valid data is present on the corresponding RXD[3:0] in MII mode and RXD[7:0] in GMII mode.                                                        |

| (Straps Required) | 53    | 38                  | S, O, PD                                                        | In RGMII mode, the receive data available and receive error are combined (RXDV_ER) using both rising and falling edges of the receive clock (RX_CLK).                                                                                                     |

| RX_ER / GPIO      |       |                     | O, PD                                                           | RECEIVE ERROR: In 10Mbps, 100Mbps and 1000Mbps mode this active high output indicates that the PHY has detected a Receive Error. The RX_ER signal is synchronous with the receive clock (RX_CLK).                                                         |

|                   |       |                     |                                                                 | In RGMII, the RX_ER pin is not used.                                                                                                                                                                                                                      |

| COL / GPIO        |       |                     | O, PD                                                           | COLLISION DETECT: Asserted high to indicate detection of a collision condition (assertion of CRS due to simultaneous transmit and receive activity) in Half-Duplex modes. This signal is not synchronous to either MII clock (GTX_CLK, TX_CLK or RX_CLK). |

|                   |       |                     | This signal is not defined and stays low for Full-Duplex modes. |                                                                                                                                                                                                                                                           |

|                   |       |                     |                                                                 | In RGMII mode, COL is not used.                                                                                                                                                                                                                           |

|                   |       |                     |                                                                 | CARRIER SENSE: CRS is asserted high to indicate the presence of a carrier due to receive or transmit activity in Half-Duplex mode.                                                                                                                        |

| CRS               | 56    |                     | S, O, PD                                                        | For 10BASE-Te and 100BASE-TX Full-Duplex operation CRS is asserted when a received packet is detected. This signal is not defined for 1000BASE-T Full-Duplex mode.                                                                                        |

|                   |       |                     |                                                                 | In RGMII mode, CRS is not used.                                                                                                                                                                                                                           |

|                   |       |                     | 1                                                               | I .                                                                                                                                                                                                                                                       |

# 表 5-1. Pin Functions (続き)

|                | PIN      |      | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------|----------|------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME           | HTQFP    | VQFN | 11PE\''             | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                        |

| GENERAL PURPO  | OSE I/O  |      |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| GPIO_0         |          | 39   | S, O, PD            | General Purpose I/O: This signal provides a multi-function configurable I/O. Please refer to the GPIO_MUX_CTRL register for details.                                                                                                                                                                                                                                                                                               |

| GPIO_1         |          | 40   | S, O, PD            | General Purpose I/O: This signal provides a multi-function configurable I/O. Please refer to the GPIO_MUX_CTRL register for details.                                                                                                                                                                                                                                                                                               |

| MANAGEMENT IN  | ITERFACE |      |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| MDC            | 20       | 16   | I, PD               | MANAGEMENT DATA CLOCK: Synchronous clock to the MDIO serial management input/output data. This clock can be asynchronous to the MAC transmit and receive clocks. The maximum clock rate is 25MHz and no minimum.                                                                                                                                                                                                                   |

| MDIO           | 21       | 17   | I/O                 | MANAGEMENT DATA I/O: Bi-directional management instruction/data signal that is sourced by the management station or the PHY during portions of communication. This pin requires pullup resistor. The IEEE specified resistor value is $1.5 \mathrm{k}\Omega$ , but a $2.2 \mathrm{k}\Omega$ is acceptable.                                                                                                                         |

|                |          |      |                     | INTERRUPT / POWER DOWN:                                                                                                                                                                                                                                                                                                                                                                                                            |

|                |          |      |                     | The default function of this pin is POWER DOWN.                                                                                                                                                                                                                                                                                                                                                                                    |

| INT / PWDN     | 60       | 44   | I/O, PU             | POWER DOWN: Asserting this signal low enables the Power Down mode of operation. In this mode, the device is in a power down state and consume minimum power. Register access is available through the Management Interface to configure and power up the device.                                                                                                                                                                   |

|                |          |      |                     | INTERRUPT: This pin can be programmed as an interrupt output instead of a Power down input. In this mode, Interrupts is asserted low using this pin. When operating this pin as an interrupt, the pin is an open-drain architecture. Register access is required for the pin to be used as an interrupt mechanism. When operating this pin as an interrupt, an external $2.2k\Omega$ connected to the VDDIO supply is recommended. |

| RESET          |          |      |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| RESET_N        | 59       | 43   | I, PU               | RESET: The active low RESET initializes or re-initializes the DP83867. All internal registers re-initialize to the default state upon assertion of RESET. The RESET input must be held low for a minimum of 1µs.                                                                                                                                                                                                                   |

| CLOCK INTERFA  | CE       |      |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                    |

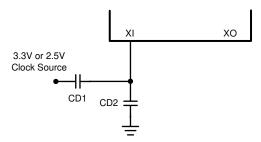

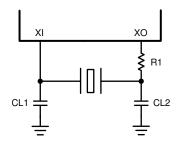

| XI             | 19       | 15   | I                   | CRYSTAL/OSCILLATOR INPUT: 25MHz oscillator or crystal input (50ppm)                                                                                                                                                                                                                                                                                                                                                                |

| хо             | 18       | 14   | 0                   | CRYSTAL OUTPUT: Second terminal for 25MHz crystal. Must be left floating if a clock oscillator is used.                                                                                                                                                                                                                                                                                                                            |

| CLK_OUT        | 22       | 18   | 0                   | CLOCK OUTPUT: Output clock                                                                                                                                                                                                                                                                                                                                                                                                         |

| JTAG INTERFACE | <b>.</b> |      | •                   |                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| JTAG_CLK       | 25       | 20   | I, PU               | JTAG TEST CLOCK: IEEE 1149.1 Test Clock input, primary clock source for all test logic input and output controlled by the testing entity. Supports a maximum clock frequency of 2.5MHz.                                                                                                                                                                                                                                            |

| JTAG_TDO       | 26       | 21   | 0                   | JTAG TEST DATA OUTPUT: IEEE 1149.1 Test Data Output pin, the most recent test results are scanned out of the device via TDO.                                                                                                                                                                                                                                                                                                       |

| JTAG_TMS       | 27       | 22   | I, PU               | JTAG TEST MODE SELECT: IEEE 1149.1 Test Mode Select pin, the TMS pin sequences the Tap Controller (16-state FSM) to select the desired test instruction.                                                                                                                                                                                                                                                                           |

| JTAG_TDI       | 28       | 23   | I, PU               | JTAG TEST DATA INPUT: IEEE 1149.1 Test Data Input pin, test data is scanned into the device via TDI.                                                                                                                                                                                                                                                                                                                               |

| JTAG_TRSTN     | 24       |      | I, PU               | JTAG TEST RESET: IEEE 1149.1 Test Reset pin, active low reset provides fo asynchronous reset of the Tap Controller. This reset has no effect on the device registers.                                                                                                                                                                                                                                                              |

# 表 5-1. Pin Functions (続き)

|               | PIN               |                   | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                     |  |  |

|---------------|-------------------|-------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME          | HTQFP             | VQFN              | IYPE(')             | DESCRIPTION                                                                                                                                                                     |  |  |

| LED INTERFACE |                   |                   |                     |                                                                                                                                                                                 |  |  |

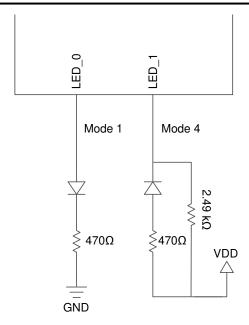

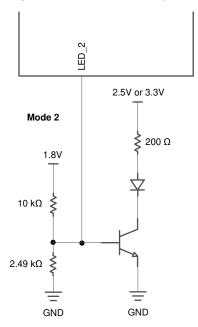

| LED 2         | 61                | 45                | S, I/O, PD          | LED_2: By default, this pin indicates receive or transmit activity. Additional functionality is configurable via LEDCR1[11:8] register bits.                                    |  |  |

| _             |                   |                   |                     | NOTE: This pin is a Strap Configuration pin for RGZ devices only.                                                                                                               |  |  |

| LED_1         | 62                | 46                | S, I/O, PD          | LED_1: By default, this pin indicates that 1000BASE-T link is established. Additional functionality is configurable via LEDCR1[7:4] register bits.                              |  |  |

| LED_0         | 63                | 47                | S, I/O, PD          | LED_0: By default, this pin indicates that link is established. Additional functionality is configurable via LEDCR1[3:0] register bits.                                         |  |  |

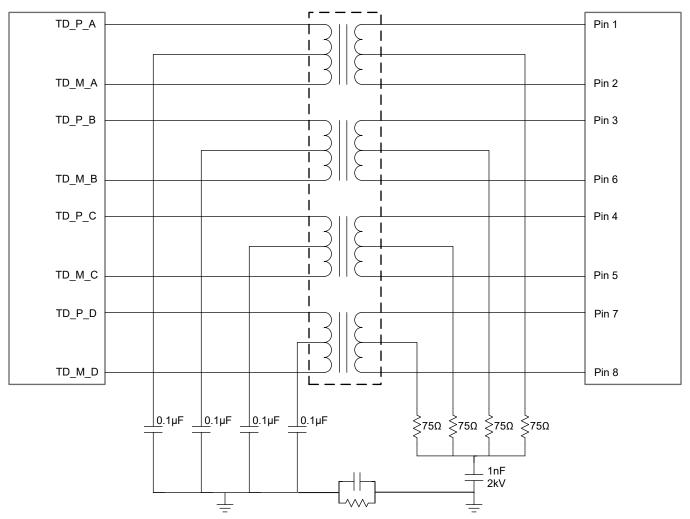

| MEDIA DEPENDE | NT INTERFACE      |                   |                     |                                                                                                                                                                                 |  |  |

| TD_P_A        | 2                 | 1                 | Α                   | Differential Transmit and Receive Signals                                                                                                                                       |  |  |

| TD_M_A        | 3                 | 2                 | Α                   | Differential Transmit and Receive Signals                                                                                                                                       |  |  |

| TD_P_B        | 5                 | 4                 | Α                   | Differential Transmit and Receive Signals                                                                                                                                       |  |  |

| TD_M_B        | 6                 | 5                 | Α                   | Differential Transmit and Receive Signals                                                                                                                                       |  |  |

| TD_P_C        | 10                | 7                 | Α                   | Differential Transmit and Receive Signals                                                                                                                                       |  |  |

| TD_M_C        | 11                | 8                 | Α                   | Differential Transmit and Receive Signals                                                                                                                                       |  |  |

| TD_P_D        | 13                | 10                | Α                   | Differential Transmit and Receive Signals                                                                                                                                       |  |  |

| TD_M_D        | 14                | 11                | Α                   | Differential Transmit and Receive Signals                                                                                                                                       |  |  |

| OTHER PINS    |                   |                   |                     |                                                                                                                                                                                 |  |  |

| Reserved      | 1, 7, 9, 16       |                   | Α                   | Reserved                                                                                                                                                                        |  |  |

| RBIAS         | 15                | 12                | Α                   | Bias Resistor Connection. A $11k\Omega$ +/-1% resistor can be connected from RBIAS to GND.                                                                                      |  |  |

| POWER AND GR  | OUND PINS         |                   |                     |                                                                                                                                                                                 |  |  |

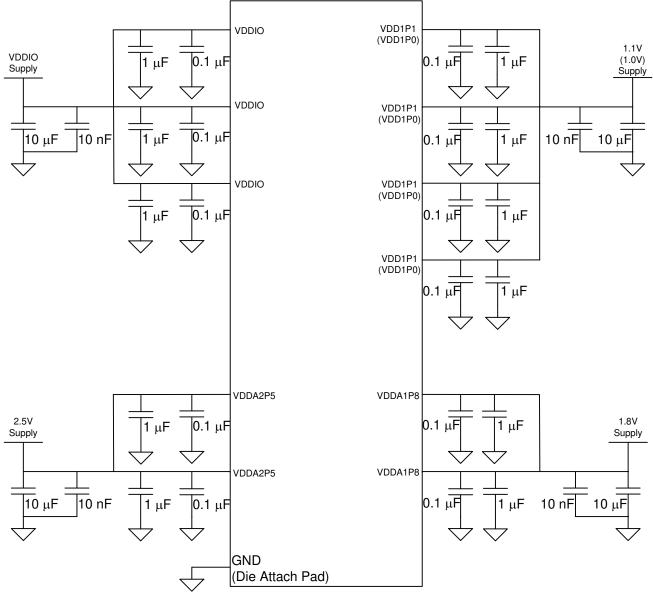

| VDDIO         | 23, 41, 57        | 19, 30, 41        | Р                   | I/O Power: 1.8V (±5%), 2.5V (±5%) or 3.3V (±5%). Each pin requires a 1µF & 0.1µF capacitor to GND                                                                               |  |  |

|               |                   |                   |                     | 1.8V Analog Supply (+/-5%).                                                                                                                                                     |  |  |

| VDDA1P8       | 17. 64            | 13. 48            | P                   | No external supply is required for this pin. When unused, no connections can be made to this pin.                                                                               |  |  |

| voorm o       | ,,,,,,,           | 10, 10            | ·                   | For additional power savings, an external 1.8V supply can be connected to these pins. When using an external supply, each pin requires a $1\mu F~\&~0.1\mu F$ capacitor to GND. |  |  |

| VDDA2P5       | 4, 12             | 3, 9              | Р                   | 2.5V Analog Supply (+/-5%). Each pin requires a $1\mu F~\&~0.1\mu F$ capacitor to GND                                                                                           |  |  |

| VDD1P1        | 8, 29, 42, 58     |                   | Р                   | 1.1V Analog Supply (+/-5%). Each pin requires a $1\mu F$ & $0.1\mu F$ capacitor to GND                                                                                          |  |  |

| VDD1P0        |                   | 6, 24, 31,<br>42  | Р                   | 1.0V Analog Supply (+15.5%,-5%). Each pin requires a 1 $\mu$ F & 0.1 $\mu$ F capacito to GND                                                                                    |  |  |

| GND           | Die Attach<br>Pad | Die Attach<br>Pad | Р                   | Ground                                                                                                                                                                          |  |  |

## (1) The functionality of the pins are defined below.

Type I: Input

Type O: Output

• Type I/O: Input /Output

• Type PD or PU: Internal Pull-down or Pull-up

Type S: Strap Configuration Pin

Type: A Analog pins

#### 5.1 Unused Pins

DP83867 has internal pullups or pulldowns on most pins. The data sheet details which pins have internal pullups or pulldowns and which pins require external pull resistors.

Even though a device can have internal pullup or pulldown resistors, a good practice is to terminate unused inputs rather than allowing them to float. Floating inputs can result in unstable conditions. This recommendation does not apply to VDD1P8 pins. When unused, these pins can be left floating. A safer practice to pull an unused input pin high or low with a pullup or pulldown resistor. Another possibility to group together adjacent unused input pins, and as a group pull them up or down using a single resistor.

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                     |                          |                                | MIN  | MAX | UNIT |

|---------------------|--------------------------|--------------------------------|------|-----|------|

|                     | VDDA2P5                  |                                | -0.3 | 3   | V    |

|                     | VDDA1P8                  |                                | -0.3 | 2.1 |      |

| Supply voltage      | (VDD1P1/VDD1P0)          |                                | -0.3 | 1.3 |      |

| Supply voltage      |                          | 3.3V option                    | -0.3 | 3.8 | V    |

|                     | VDDIO                    | 2.5V option                    | -0.3 | 3   |      |

|                     |                          | 1.8V option                    | -0.3 | 2.1 |      |

|                     | MDI                      | MDI                            |      | 6.5 |      |

|                     | MAC interface, MDIO, I   | MAC interface, MDIO, MDC, GPIO |      |     | V    |

| Pins                | INT/PWDN, RESET          | INT/PWDN, RESET                |      |     |      |

|                     | JTAG                     | JTAG                           |      |     |      |

|                     | XI (Oscillator Clock Inp | XI (Oscillator Clock Input)    |      | 2.1 | V    |

| Storage temperature | e, T <sub>stg</sub>      |                                | -60  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings can cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods can affect device reliability.

# 6.2 ESD Ratings

|             |                                       |                                                                       |                                                  | VALUE | UNIT |

|-------------|---------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------|-------|------|

|             |                                       | All pins except Media Dependent Interface pins                        | ±2500                                            |       |      |

| \<br>\<br>\ |                                       | Human-body model (HBM), per ANSI/<br>ESDA/JEDEC JS-001 <sup>(1)</sup> | Media Dependent Interface pins (IRPAP/IRRGZ) (2) | ±8000 | V    |

| V(ESD)      |                                       |                                                                       | Media Dependent Interface pins (CRRGZ)           | ±6000 | V    |

|             | Charged-device model (CDM), per JEDEC | specification JESD22-C101 <sup>(3)</sup>                              | ±1500 (RGZ)<br>±750 (PAP)                        |       |      |

<sup>(1)</sup> JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 500V HBM is possible with the necessary precautions. Pins listed as ±8V and/or ± 2V can actually have higher performance.

<sup>(2)</sup> MDI Pins tested as per IEC 61000-4-2 standards.

<sup>(3)</sup> JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 250V CDM is possible with the necessary precautions. Pins listed as ±500V can actually have higher performance.

# **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                                |                           |                           | MIN             | TYP | MAX   | UNIT |

|--------------------------------|---------------------------|---------------------------|-----------------|-----|-------|------|

|                                | VDDA2P5                   | VDDA2P5                   |                 | 2.5 | 2.625 |      |

|                                | VDDA1P8                   |                           | 1.71            | 1.8 | 1.89  |      |

|                                | VDD1P1 (PAP)              |                           | 1.045           | 1.1 | 1.155 |      |

| Supply voltage                 | VDD1P0 (RGZ)              | VDD1P0 (RGZ)              |                 | 1   | 1.155 | V    |

|                                | VDDIO                     | 3.3V option               | 3.15            | 3.3 | 3.45  |      |

|                                |                           | 2.5V option               | 2.375           | 2.5 | 2.625 |      |

|                                |                           | 1.8V option               | 1.71            | 1.8 | 1.89  |      |

| Operating free air temperature | Commercial (DP83867CRRGZ) |                           | 0               | 25  | 70    | °C   |

| Operating free all temperature |                           |                           | -40             | 25  | 85    | °C   |

| Operating junction temperature | Commercial (DP83867CRRGZ) |                           | 0               |     | 90    | °C   |

|                                | Industrial (DP8386        | Industrial (DP83867IRRGZ) |                 |     | 105   | °C   |

|                                | Industrial (DP83867IRPAP) |                           | <del>-4</del> 0 |     | 105   | C    |

### **6.4 Thermal Information**

|                       | THERMAL METRIC <sup>(1)</sup>                | DP83867IR   | DP83867IR,<br>DP83867CR |      |

|-----------------------|----------------------------------------------|-------------|-------------------------|------|

|                       |                                              | PAP (HTQFP) | RGZ (QFN)               | UNIT |

|                       |                                              | 64 PINS     | 48 PINS                 |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 30.9        | 30.8                    | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 13.6        | 18.7                    | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 0.9         | 1.4                     | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 15.6        | 7.5                     | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter   | 0.4         | 0.3                     | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 15.5        | 7.5                     | °C/W |

For more information about traditional and new thermal metrics, see the <u>Semiconductor and IC Package Thermal Metrics</u> application report.

#### 6.5 Electrical Characteristics

The electrical ratings specified in this section apply to all specifications in this document, unless otherwise noted. These specifications are interpreted as conditions that do not degrade the device parametric or functional specifications for the life of the product containing the device.

|                         | PARAMETER                 | TEST CONDITIONS        | MIN                     | TYP | MAX | UNIT |

|-------------------------|---------------------------|------------------------|-------------------------|-----|-----|------|

| 3.3V V <sub>DDIO</sub>  |                           |                        |                         |     | '   |      |

| V <sub>OH</sub>         | High level output voltage | I <sub>OH</sub> = -4mA | 2                       |     |     | V    |

| V <sub>OL</sub>         | Low level output voltage  | I <sub>OL</sub> = 4mA  |                         |     | 0.6 | V    |

| V <sub>IH</sub>         | High level input voltage  |                        | 1.7                     |     |     | V    |

| V <sub>IL</sub>         | Low level input voltage   |                        |                         |     | 0.7 | V    |

| 2.5V V <sub>VDDIO</sub> |                           | 1                      |                         |     |     |      |

| V <sub>OH</sub>         | High level output voltage | $I_{OH} = -4mA$        | V <sub>DDIO</sub> × 0.8 |     |     | V    |

| V <sub>OL</sub>         | Low level output voltage  | I <sub>OL</sub> = 4mA  |                         |     | 0.6 | V    |

| V <sub>IH</sub>         | High level input voltage  |                        | 1.7                     |     |     | V    |

| V <sub>IL</sub>         | Low level input voltage   |                        |                         |     | 0.7 | V    |

| 1.8V V <sub>DDIO</sub>  |                           | ,                      |                         |     |     |      |

# 6.5 Electrical Characteristics (続き)

The electrical ratings specified in this section apply to all specifications in this document, unless otherwise noted. These specifications are interpreted as conditions that do not degrade the device parametric or functional specifications for the life of the product containing the device.

|                      | PARAMETER                             | TEST CONDITIONS                                            | MIN                     | TYP M     | AΧ          | UNIT         |

|----------------------|---------------------------------------|------------------------------------------------------------|-------------------------|-----------|-------------|--------------|

| V <sub>OH</sub>      | High level output voltage             | I <sub>OH</sub> = -1mA                                     | V <sub>DDIO</sub> – 0.2 |           |             | V            |

| V <sub>OL</sub>      | Low level output voltage              | I <sub>OL</sub> = 1mA                                      |                         | (         | 0.2         | V            |

| V <sub>IH</sub>      | High level input voltage              |                                                            | 0.7 × V <sub>DDIO</sub> |           |             | V            |

| V <sub>IL</sub>      | Low level input voltage               |                                                            |                         | 0.2 × VDD | 10          | V            |

| XI INPUT V           | OLTAGE                                |                                                            |                         |           |             |              |

| V <sub>OSC</sub>     | Input voltage for 25MHz<br>Oscillator |                                                            | 1.5                     |           | 1.9         | Vpp          |

| V <sub>IH</sub>      | High level input voltage              |                                                            | 1.4                     |           |             | V            |

| V <sub>IL</sub>      | Low level input voltage               |                                                            |                         | 0.        | 45          | V            |

| DC CHARA             | CTERISTICS                            |                                                            |                         |           |             |              |

| I <sub>IH</sub>      | Input high current                    | VIN = VDD, T <sub>A</sub> = -40°C to<br>+85°C              | -10                     |           | 10          | μΑ           |

| I <sub>IL</sub>      | Input low current                     | VIN = GND, T <sub>A</sub> = -40°C to<br>+85°C              | -10                     |           | 10          | μΑ           |

| I <sub>OZ</sub>      | TRI-STATE output current              | VOUT = VDD, VOUT = GND,<br>T <sub>A</sub> = -40°C to +85°C | -10                     |           | 10          | μA           |

| C <sub>IN</sub>      | Input capacitance                     | See (3)                                                    |                         |           | 5           | pF           |

| VOD                  | SGMII                                 |                                                            |                         |           |             |              |

| PMD OUTP             | PUTS                                  |                                                            |                         |           |             |              |

|                      | MDI                                   | IRPAP/IRRGZ                                                | 1.54                    | 1.75 1.   | 96          | V Peak       |

| $V_{OD-10}$          | MDI                                   | CRRGZ                                                      |                         | 1.75      |             | Differential |

| \/                   | MDI                                   | IRPAP/IRRGZ                                                | 0.95                    | 1 1.      | 05          | V Peak       |

| V <sub>OD-100</sub>  | MDI                                   | CRRGZ                                                      |                         | 1         |             | Differential |

| \ /                  | MDI                                   | IRPAP/IRRGZ                                                | 0.67                    | 0.745 0.  | 0.82 V Peak |              |

| V <sub>OD-1000</sub> | MDI                                   | CRRGZ                                                      |                         | 0.745     | Differenti  |              |

# 6.5 Electrical Characteristics (続き)

The electrical ratings specified in this section apply to all specifications in this document, unless otherwise noted. These specifications are interpreted as conditions that do not degrade the device parametric or functional specifications for the life of the product containing the device.

|              | PARAMETER                                                 | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|--------------|-----------------------------------------------------------|-----------------|-----|-----|-----|------|

| POWER CON    | SUMPTION                                                  |                 |     |     |     |      |

| PAP          |                                                           |                 |     |     |     |      |

| P1000        | Power consumption, 2 supplies (1) (2)                     |                 |     | 530 |     | mW   |

| P1000        | Power consumption, optional 3rd supply <sup>(1)</sup> (2) |                 |     | 490 |     | mW   |

| IDD25        | Supply Current, 2 supplies                                |                 |     | 141 |     | mA   |

| IDD11        |                                                           |                 |     | 125 |     | mA   |

| IDDIO (1.8V) |                                                           |                 |     | 22  |     | mA   |

| IDD25        | Supply Current, optional 3rd supply                       |                 |     | 90  |     | mA   |

| IDD11        |                                                           |                 |     | 125 |     | mA   |

| IDD18        |                                                           |                 |     | 51  |     | mA   |

| IDDIO (1.8V) |                                                           |                 |     | 19  |     | mA   |

| RGZ          |                                                           |                 |     |     |     |      |

| P1000        | Power consumption, 2 supplies (1) (2)                     |                 |     | 495 |     | mW   |

| P1000        | Power consumption, optional 3rd supply <sup>(1)</sup> (2) |                 |     | 457 |     | mW   |

| IDD25        | Supply Current, 2 supplies                                |                 |     | 137 |     | mA   |

| IDD10        |                                                           |                 |     | 108 |     | mA   |

| IDDIO (1.8V) |                                                           |                 |     | 24  |     | mA   |

| IDD25        | Supply Current, optional 3rd supply                       |                 |     | 86  |     | mA   |

| IDD10        |                                                           |                 |     | 108 |     | mA   |

| IDD18        |                                                           |                 |     | 50  |     | mA   |

| IDDIO (1.8V) |                                                           |                 |     | 24  |     | mA   |

- (1) Power consumption represents total operational power for 1000BASE-T.

- (2) See セクション 8.3 for details on 2-supply and 3-supply configuration.

- (3) Specified by production test, characterization, or design.

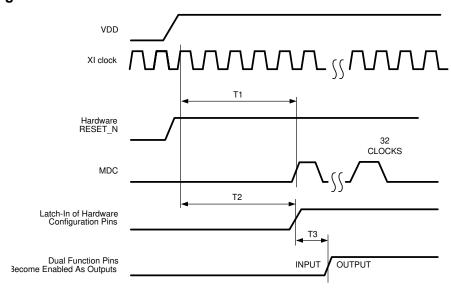

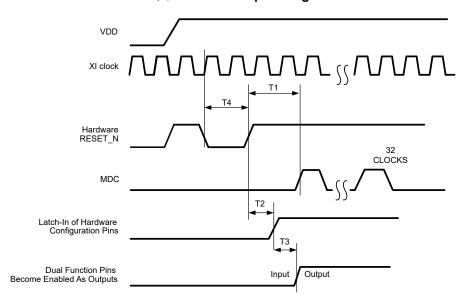

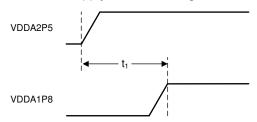

## 6.6 Power-Up Timing

### See **図 6-1**.

|    | PARAMETER                                                                    | TEST CONDITIONS (1)                                              | MIN | NOM | MAX | UNIT |

|----|------------------------------------------------------------------------------|------------------------------------------------------------------|-----|-----|-----|------|

| T1 | Post power-up stabilization time prior to MDC preamble for register accesses | MDIO is pulled high for 32-bit serial management initialization. |     | 200 |     | ms   |

| T2 | Hardware configuration latch-in time from power up                           | Hardware Configuration Pins are described in セクション 7.5.1.        |     | 200 |     | ms   |

| Т3 | Hardware configuration pins transition to output drivers                     |                                                                  |     | 64  |     | ns   |

(1) Specified by production test, characterization, or design.

# 6.7 Reset Timing

See **図 6-2**.

|    | PARAMETER                                                                                | TEST CONDITIONS (1)                                                                                                         | MIN | NOM | MAX | UNIT |

|----|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| T1 | Post RESET stabilization time prior to MDC preamble for register accesses                | MDIO is pulled high for 32-bit serial management initialization.  MDC can toggle during this period when MDIO remains high. |     | 195 |     | μs   |

| T2 | Hardware configuration latch-in time from the deassertion of RESET (either soft or hard) | Hardware Configuration Pins are described in セクション 7.5.1.                                                                   |     | 120 |     | ns   |

| Т3 | Hardware configuration pins transition to output drivers                                 |                                                                                                                             |     | 64  |     | ns   |

| T4 | RESET pulse width                                                                        | X1 Clock must be stable for a minimum of 1µs during RESET pulse low time                                                    | 1   |     |     | μs   |

<sup>(1)</sup> Specified by production test, characterization, or design.

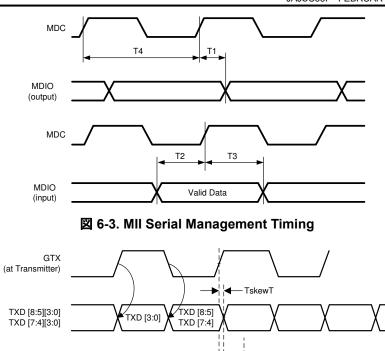

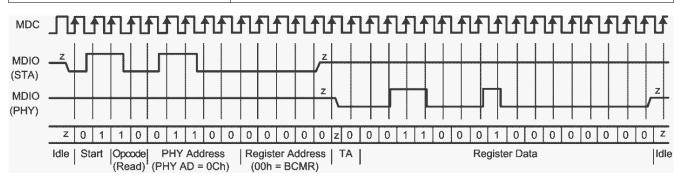

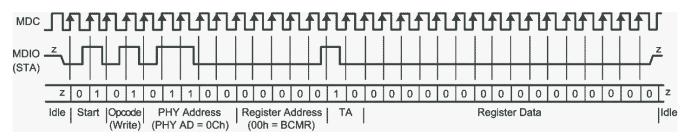

# 6.8 MII Serial Management Timing

See **図 6-3**.

|    | PARAMETER                       | TEST CONDITIONS (1) | MIN | NOM | MAX | UNIT |

|----|---------------------------------|---------------------|-----|-----|-----|------|

| T1 | MDC to MDIO (output) delay time |                     | 0   |     | 10  | ns   |

| T2 | MDIO (input) to MDC setup time  |                     | 10  |     |     | ns   |

| T3 | MDIO (input) to MDC hold time   |                     | 10  |     |     | ns   |

| T4 | MDC frequency                   |                     |     | 2.5 | 25  | MHz  |

<sup>(1)</sup> Specified by production test, characterization, or design.

## 6.9 RGMII Timing

See 図 6-4 and .図 6-5

|                     | PARAMETER                                                       | TEST CONDITIONS (5) | MIN  | NOM | MAX  | UNIT |

|---------------------|-----------------------------------------------------------------|---------------------|------|-----|------|------|

| T <sub>skewT</sub>  | Data to Clock output Skew (at Transmitter)                      | See <sup>(1)</sup>  | -500 | 0   | 500  | ps   |

| T <sub>skewR</sub>  | Data to Clock input Skew (at Receiver)                          | See <sup>(1)</sup>  | 1    | 1.8 | 2.6  | ns   |

| T <sub>setupT</sub> | Data to Clock output Setup<br>(at Transmitter – internal delay) | See <sup>(4)</sup>  | 1.2  | 2   |      | ns   |

| T <sub>holdT</sub>  | Clock to Data output Hold<br>(at Transmitter – internal delay)  | See <sup>(4)</sup>  | 1.2  | 2   |      | ns   |

| T <sub>setupR</sub> | Data to Clock input Setup<br>(at Reciever – internal delay)     | See <sup>(4)</sup>  | 1    | 2   |      | ns   |

| T <sub>holdR</sub>  | Clock to Data input Hold<br>(at Receiver – internal delay)      | See <sup>(4)</sup>  | 1    | 2   |      | ns   |

| T <sub>cyc</sub>    | Clock Cycle Duration                                            | See <sup>(2)</sup>  | 7.2  | 8   | 8.8  | ns   |

| Duty_G              | Duty Cycle for Gigabit                                          | See (3) (7)         | 45   | 50  | 55%  |      |

| Duty_T              | Duty Cycle for 10/100T                                          | See (3) (7)         | 40   | 50  | 60%  |      |

| T <sub>R</sub>      | Rise Time (20% to 80%)                                          |                     |      |     | 0.75 | ns   |

| T <sub>F</sub>      | Fall Time (20% to 80%)                                          |                     |      |     | 0.75 | ns   |

| T <sub>TXLAT</sub>  | RGMII to MDI Latency                                            | See <sup>(6)</sup>  |      | 88  |      | ns   |

| T <sub>RXLAT</sub>  | MDI to RGMII Latency                                            | See <sup>(6)</sup>  |      | 288 |      | ns   |

<sup>(1)</sup> When operating without RGMII internal delay, the PCB design requires clocks to be routed such that an additional trace delay of greater than 1.5ns is added to the associated clock signal.

<sup>(2)</sup> For 10Mbps and 100Mbps, Tcyc scales to 400ns ± 40ns and 40ns ± 4ns.

- (3) Duty cycle can be stretched or shrunk during speed changes or while transitioning to a received packet's clock domain as long as minimum duty cycle is not violated and stretching occurs for no more that three Tcyc of the lowest speed transitioned between.

- (4) Device can operate with or without internal delay.

- (5) Specified by production test, characterization, or design.

- (6) Operating in 1000Base-T.

- (7) Duty cycle values are defined in percentages of the nominal clock speed. For example, the minimum Gigabit RGMII clock pulse duration is 45 % of 8ns.

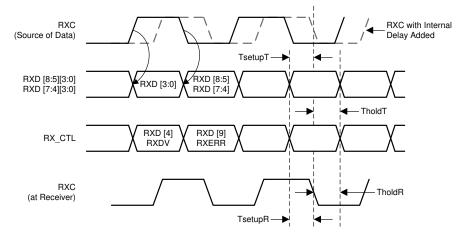

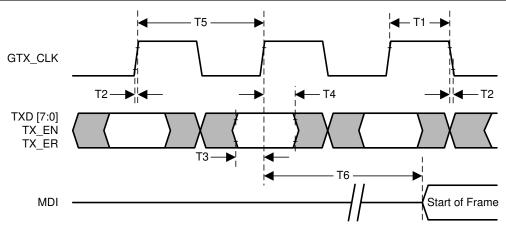

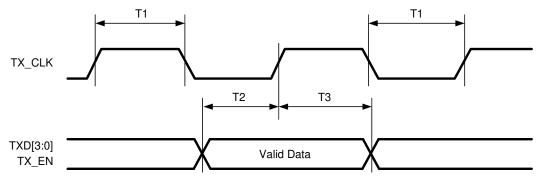

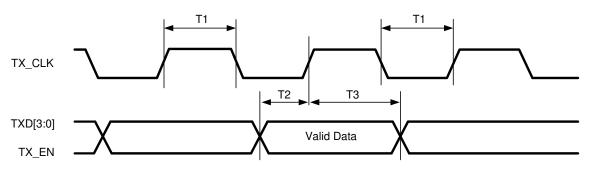

## 6.10 GMII Transmit Timing

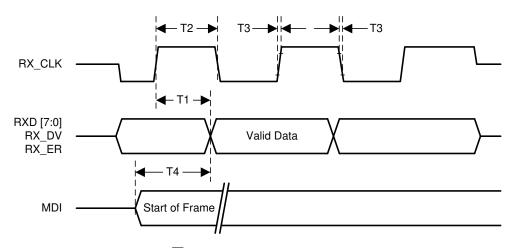

See Timing Diagrams.

|    | PARAMETER                                                         | TEST CONDITIONS (2) | MIN  | NOM | MAX | UNIT |

|----|-------------------------------------------------------------------|---------------------|------|-----|-----|------|

| T1 | GTX_CLK Duty Cycle                                                |                     | 40%  |     | 60% |      |

| T2 | GTX_CLK Rise / Fall Time                                          |                     |      |     | 1   | ns   |

| Т3 | Setup from valid TXD, TX_EN and TX_ER to rising edge of GTX_CLK   |                     | 2    |     |     | ns   |

| T4 | Hold from rising edge of GTX_CLK to invalid TXD, TX_EN, and TX_ER |                     | 0.5  |     |     | ns   |

| T5 | GTX_CLK Stability                                                 |                     | -100 |     | 100 | ppm  |

| T6 | GMII to MDI Latency                                               | See (1)             |      | 72  |     | ns   |

- (1) Operating in 1000Base-T.

- (2) Specified by production test, characterization, or design.

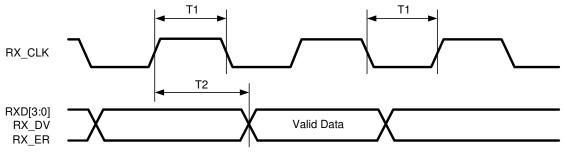

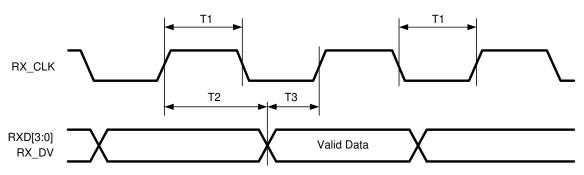

### 6.11 GMII Receive Timing

See Timing Diagrams.

|    | PARAMETER                                            | TEST CONDITIONS (2) | MIN | NOM | MAX | UNIT |

|----|------------------------------------------------------|---------------------|-----|-----|-----|------|

| T1 | Rising edge of RX_CLK to RXD, RX_DV, and RX_ER delay |                     | 0.5 |     | 5.5 | ns   |

| T2 | RX_CLK Duty Cycle                                    |                     | 40% |     | 60% |      |

| Т3 | RX_CLK Rise / Fall Time                              |                     |     |     | 1   | ns   |

| T4 | MDI to GMII Latency                                  | See <sup>(1)</sup>  |     | 264 |     | ns   |

- (1) Operating in 1000Base-T.

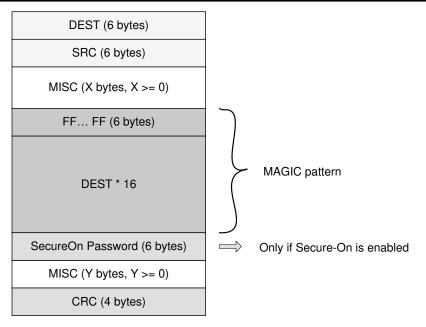

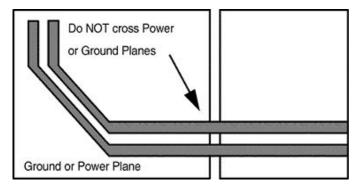

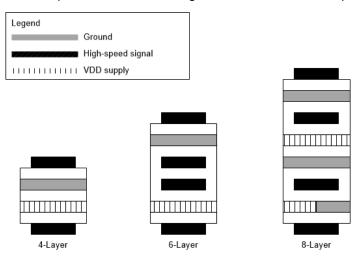

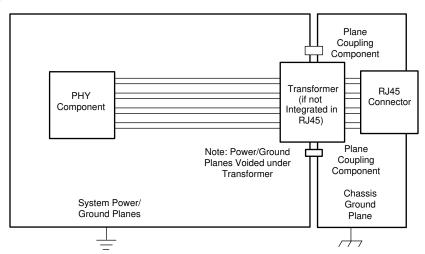

- (2) Specified by production test, characterization, or design.