# DRV7308 3 相 650V、5A、GaN インテリジェントパワー モジュール

## 1 特長

- 650V エンハンスメントモード GaN FET 内蔵、3相 PWM モーター ドライバ

- 最大 450V の動作電圧

- 650V 絶対最大定格電圧

- 高い出力電流能力: 5A ピーク電流

- 小さな導通損失: GaN FET により低いオン抵抗:  $T_A = 25^\circ\text{C}$  で  $205\text{m}\Omega R_{DS(ON)}$

- 低いスイッチング損失: ゼロ逆回復、低出力容量、スルーレート制御

- 低歪: 非常に小さい伝搬遅延 < 135ns、非常に小さいアダプティブ デッドタイム < 200ns

- 相ノード電圧のスルーレート制御を備えたゲートドライブを内蔵

- スルーレートを  $5\text{V}/\mu\text{s} \sim 40\text{V}/\mu\text{s}$  で選択可能

- 高速ブートストラップ GaN 整流器内蔵

- 1 または 2 または 3 本のシャント電流センシングをサポートするローサイド GaN FET オープンソースピン

- 最大 100kHz のハード スイッチングをサポート

- 電流検出用のアンプ内蔵

- 3.3V および 5V ロジック入力をサポート、最大 20V

- すべてのローサイド GaN FET を同時にオンにする BRAKE ピン

- 温度センサ内蔵

- モーター位相 (OUTx) と隣接するピン間の距離: >1.6mm

- VM と GND の間の空間距離: 2mm

- 保護機能内蔵

- GVDD およびブートストラップ低電圧誤動作防止

- ローサイド GaN FET の過電流保護

- 過熱保護

- PWM アダプティブ デッドタイム挿入

- 3 相すべての電流制限保護

- フォルト状況表示ピン (nFAULT)

## 2 アプリケーション

- 冷蔵庫 / 冷凍庫

- 家電製品および HVAC ポンプおよびファン

- 食器洗い機

- 小型家電製品

- 住宅用エアコン

- 換気扇フード

- ブラシレス DC モーター モジュール

## 3 説明

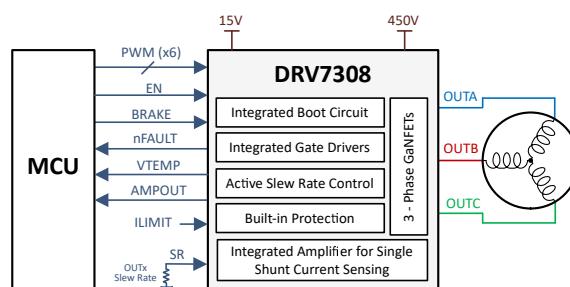

DRV7308 は 3 相インテリジェントパワー モジュール (IPM) であり、205mΩ、650V の e モード窒化ガリウム (GaN) で構成されており、最大 450V DC レールの 3 相 BLDC/PMSM モーターを駆動できます。BLDC モータの磁界方向制御 (FOC)、正弦波電流制御、および台形 (6 ステップ) 電流制御に適しています。このデバイスは、20kHz のスイッチング周波数で、QFN 12mm × 12mm パッケージの 3 相変調 FOC 駆動 250W モーター ドライブ アプリケーションで 99% を超える効率を実現し、ヒートシンクは不要です。このデバイスは、非常に短いデッドタイムで非常に静かな動作を実現するのに役立ちます。ブートストラップ整流器とブートストラップ電流制限を内蔵しているため、外部ブートストラップダイオードは不要です。

### 注

安全のため、過電圧および過電流保護機能付きの絶縁された試験装置の使用を推奨します。デバイスを動作させるときは、安全な筐体を使用することを推奨します。

### パッケージ情報

| 部品番号    | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|---------|----------------------|--------------------------|

| DRV7308 | REN (VQFN, 65)       | 12.00 mm × 12.00 mm      |

(1) 詳細については、「メカニカル、パッケージ、および注文情報」を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合にビンも含まれます。

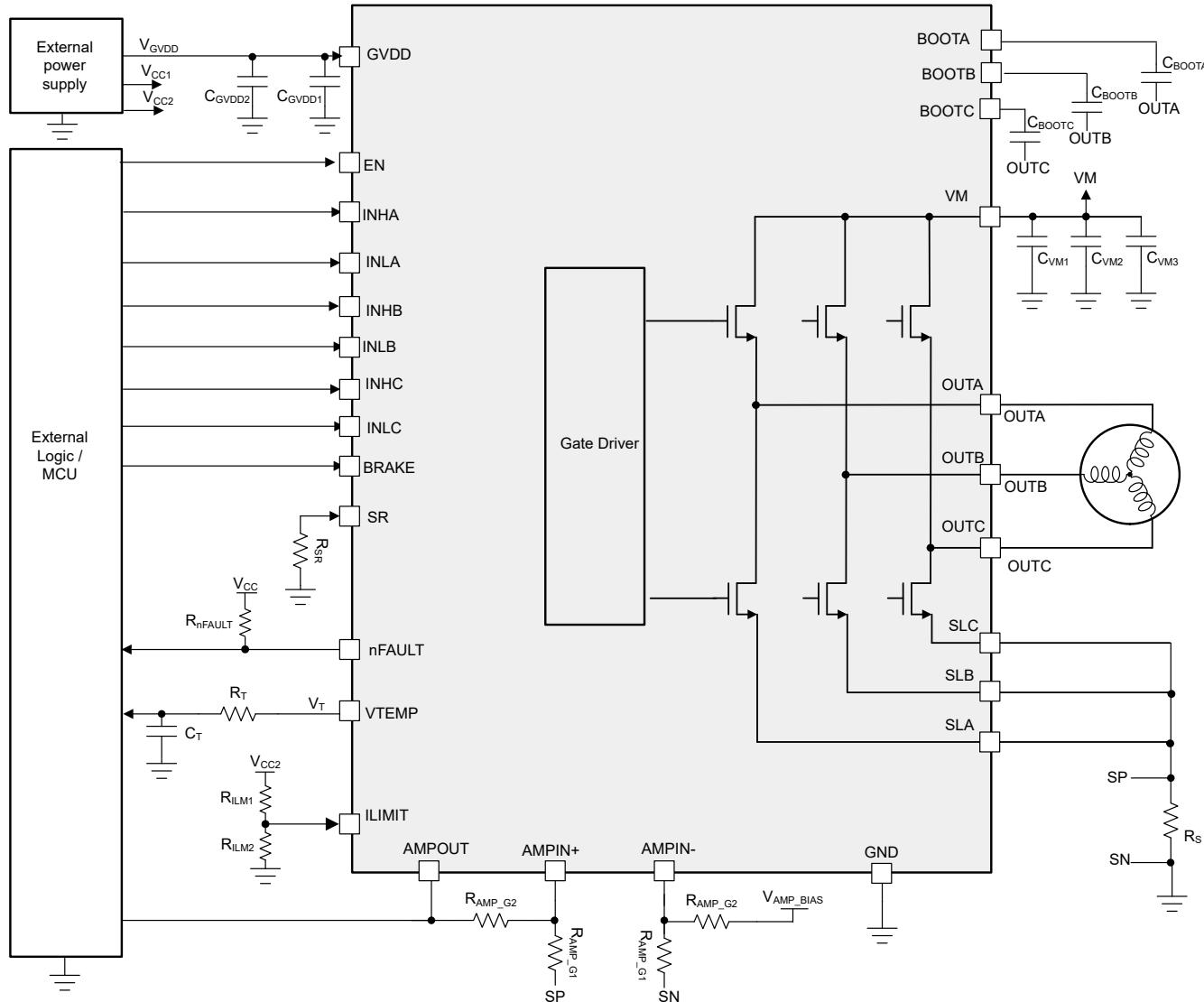

概略回路図

**⚠️** このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあります。TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

English Data Sheet: [SLVSGJ9](#)

## 目次

|                   |    |                              |    |

|-------------------|----|------------------------------|----|

| 1 特長.....         | 1  | 13 アプリケーションと実装.....          | 19 |

| 2 アプリケーション.....   | 1  | 13.1 アプリケーション情報.....         | 19 |

| 3 説明.....         | 1  | 13.2 代表的なアプリケーション.....       | 19 |

| 4 ピン構成および機能.....  | 3  | 14 レイアウト.....                | 26 |

| 5 絶対最大定格.....     | 5  | 14.1 レイアウトのガイドライン.....       | 26 |

| 6 ESD 定格.....     | 5  | 14.2 レイアウト例.....             | 26 |

| 7 推奨動作条件.....     | 5  | 15 改訂履歴.....                 | 26 |

| 8 熱に関する情報.....    | 6  | 16 デバイスおよびドキュメントのサポート.....   | 28 |

| 9 電気的特性.....      | 6  | 16.1 ドキュメントのサポート.....        | 28 |

| 10 タイミング図.....    | 10 | 16.2 ドキュメントの更新通知を受け取る方法..... | 28 |

| 11 代表的特性.....     | 10 | 16.3 サポート・リソース.....          | 28 |

| 12 詳細説明.....      | 11 | 16.4 商標.....                 | 28 |

| 12.1 概要.....      | 11 | 16.5 静電気放電に関する注意事項.....      | 28 |

| 12.2 機能ブロック図..... | 12 | 16.6 用語集.....                | 28 |

| 12.3 機能説明.....    | 12 | 17 メカニカル、パッケージ、および注文情報.....  | 28 |

| 12.4 保護.....      | 15 | 17.1 テープおよびリール情報.....        | 29 |

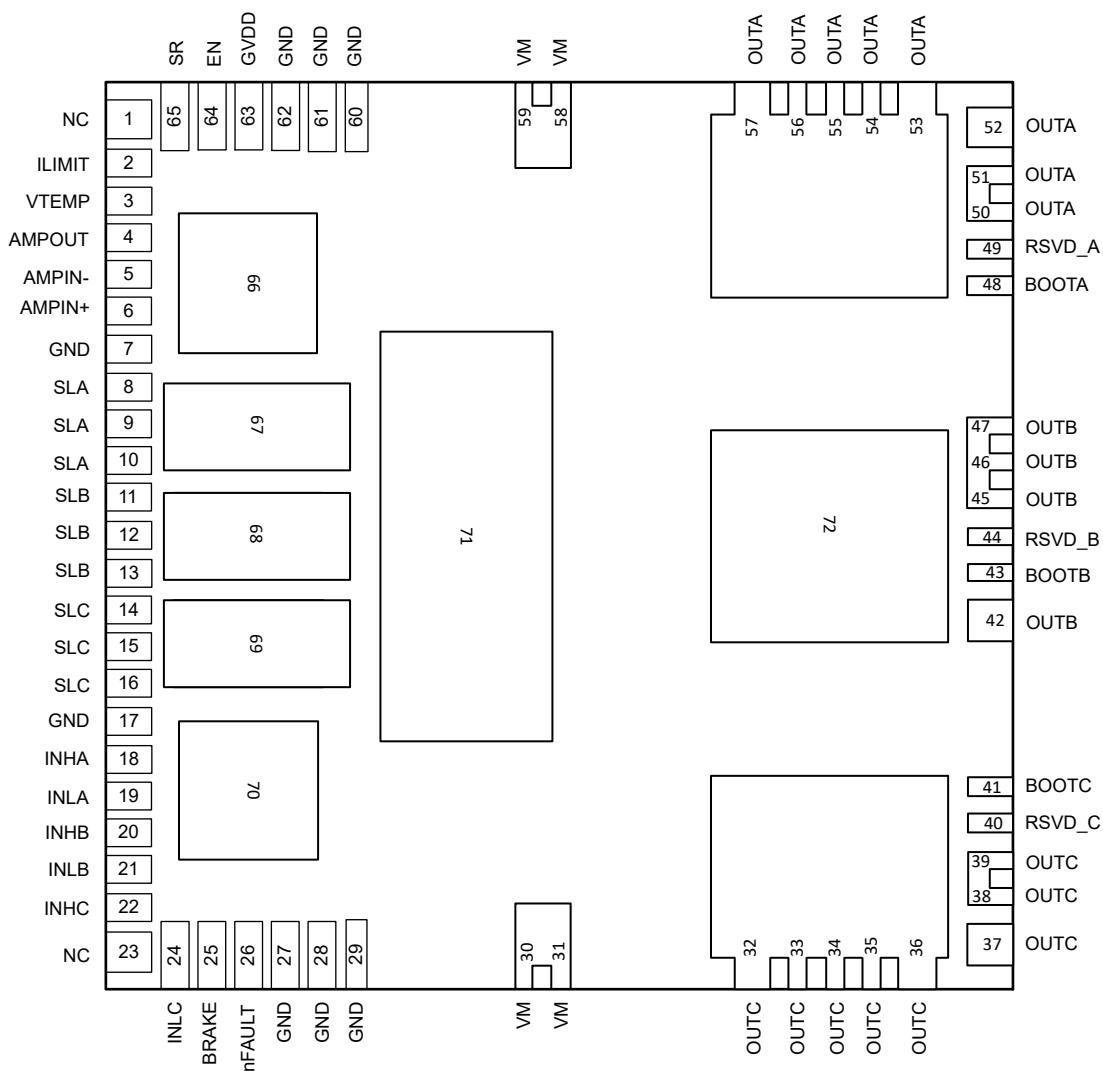

## 4 ピン構成および機能

図 4-1. DRV7308 VQFN (露出サーマルパッド付き) 上面図

**表 4-1. ピンの機能**

| ピン     |                                           | タイプ <sup>(1)</sup> | 説明                                                                                                                  |

|--------|-------------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------|

| 名称     | 番号                                        |                    |                                                                                                                     |

| AMPIN- | 5                                         | I                  | オペアンプの反転入力                                                                                                          |

| AMPIN+ | 6                                         | I                  | オペアンプの非反転入力                                                                                                         |

| AMPOUT | 4                                         | O                  | オペアンプの出力端子                                                                                                          |

| BOOTA  | 48                                        | P                  | 位相 A のブートストラップ電源。BOOTA と OUTA の間に GVDD 定格コンデンサを配置する必要があります。                                                         |

| BOOTB  | 43                                        | P                  | 位相 B のブートストラップ電源。BOOTB と OUTB の間に GVDD 定格コンデンサを配置する必要があります。                                                         |

| BOOTC  | 41                                        | P                  | 位相 C のブートストラップ電源。BOOTC と OUTC の間に GVDD 定格コンデンサを配置する必要があります。                                                         |

| BRAKE  | 25                                        | I                  | モーター ブレーキ信号このピンがロジック High になると、すべてのローサイド GaN FET がオンになり、すべてのハイサイド GaN FET がオフになります                                  |

| EN     | 64                                        | I                  | ドライバインペブル ピンこのピンがロジック Low になると、デバイスはシャットダウン モードに移行し、すべての GaN FET がオフになります。20μs ~ 40μs の Low パルスを使うとフォルト条件をリセットできます。 |

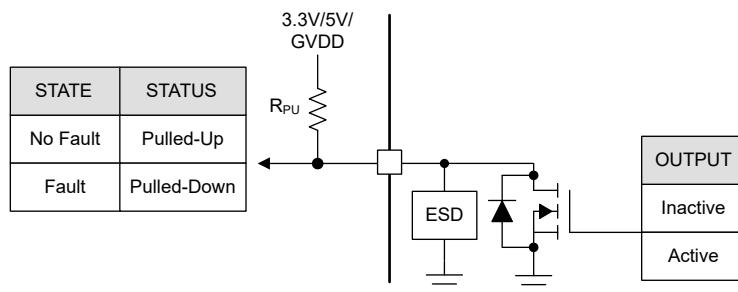

| nFAULT | 26                                        | O                  | フォルト通知ピン。フォルト条件によりロジック Low に駆動。オープンドレイン出力には外部ブルアップが必要です。                                                            |

| ILIMIT | 2                                         | I                  | 内部過電流制限コンパレータのリファレンス電圧                                                                                              |

| INHA   | 18                                        | I                  | OUTA のハイサイドドライバ制御入力。このピンは、ハイサイド GaN FET の出力を制御します。                                                                  |

| INHB   | 20                                        | I                  | OUTB のハイサイドドライバ制御入力。このピンは、ハイサイド GaN FET の出力を制御します。                                                                  |

| INHC   | 22                                        | I                  | OUTC のハイサイドドライバ制御入力。このピンは、ハイサイド GaN FET の出力を制御します。                                                                  |

| INLA   | 19                                        | I                  | OUTA のローサイドドライバ制御入力。このピンは、ローサイド GaN FET の出力を制御します。                                                                  |

| INLB   | 21                                        | I                  | OUTB のローサイドドライバ制御入力。このピンは、ローサイド GaN FET の出力を制御します。                                                                  |

| INLC   | 24                                        | I                  | OUTC のローサイドドライバ制御入力。このピンは、ローサイド GaN FET の出力を制御します。                                                                  |

| NC     | 1, 23                                     |                    | 接続なし、GND に接続可能                                                                                                      |

| RSVD_A | 49                                        | I                  | 予約済みピン。ピンを OUTA に接続                                                                                                 |

| RSVD_B | 44                                        | I                  | 予約済みピン。ピンを OUTB に接続                                                                                                 |

| RSVD_C | 40                                        | I                  | 予約済みピン。ピンを OUTC に接続                                                                                                 |

| OUTA   | 50-57                                     | P                  | ハーフブリッジ出力 A                                                                                                         |

| OUTB   | 42, 45-47, 72                             | P                  | ハーフブリッジ出力 B                                                                                                         |

| OUTC   | 32-39                                     | P                  | ハーフブリッジ出力 C                                                                                                         |

| GND    | 7, 17, 27, 28, 29, 60, 61, 62, 66, 70, 71 | G                  | デバイス電源および信号グランド。システム グランドに接続                                                                                        |

| SLA    | 8, 9, 10, 67                              | P                  | 位相 A ハーフブリッジ ローサイド ソース                                                                                              |

| SLB    | 11, 12, 13, 68                            | P                  | 位相 B ハーフブリッジ ローサイド ソース                                                                                              |

| SLC    | 14, 15, 16, 69                            | P                  | 位相 C ハーフブリッジ ローサイド ソース                                                                                              |

| SR     | 65                                        | I                  | OUTx 電圧スルーレート制御。スルーレートを設定するため、SR ピンと GND、または SR ピンと GVDD の間に抵抗を接続します                                                |

| GVDD   | 63                                        | P                  | 低電圧電源。1μF の GVDD 定格セラミックコンデンサ 1 個と GVDD 定格のバルクコンデンサ 1 個で GND にバイパスします                                               |

| VM     | 30, 31, 58, 59                            | P                  | 電源。モーター電源電圧に接続し、0.1μF コンデンサと VM 定格のバルクコンデンサ 1 つを使用して GND にバイパスします。ピン 30 と 31 は、ピン 58 と 59 に内部で接続されています。             |

| VTEMP  | 3                                         | O                  | 温度センサ出力                                                                                                             |

(1) I = 入力、O = 出力、I/O = 入力または出力、G = グランド、P = 電源。

## 5 絶対最大定格

動作温度範囲内 (特に記述のない限り) [\(2\)](#)

|                                                          | 最小値       | 最大値                | 単位 |

|----------------------------------------------------------|-----------|--------------------|----|

| ドレイン - ソース間ブロッキング電圧 (FET オフ)<br>( $V_{DS}$ )             |           | 650 <sup>(1)</sup> | V  |

| VM と GND 間に印加される DC 電圧                                   |           | 450                | V  |

| ドレイン DC 電流 ( $I_{DC}$ ) ( $T_J = 150^\circ\text{C}$ 時)   |           | 4                  | A  |

| 位相ノード ピンの電圧は GND が基準 (FETs オフ) (OUTA、OUTB、OUTC)、SL = GND | $-V_{SD}$ | 650                | V  |

| BOOTx ピン電圧は OUTx が基準 (BOOTA、<br>BOOTB、BOOTC)             | -0.5      | 20                 | V  |

| ピン電圧 - GVDD から GND へ                                     | -0.5      | 20                 | V  |

| ピン電圧 - INx、EN、BRAKE、nFAULT から<br>GND へ                   | -0.5      | 20                 | V  |

| ピン電圧 - SLx から GND (DC) へ                                 | -2.5      | +2.5               | V  |

| ピン電圧 - AMPIN+、AMPIN-、AMPOUT、<br>ILIMIT、SR から GND へ       | -0.5      | $V_{GVDD} + 0.3$   | V  |

| オペアンプの出力電流 (AMPOUT)                                      |           | 20                 | mA |

| 動作時周囲温度                                                  | -40       | 125                | °C |

| 動作時接合部温度 ( $T_J$ )                                       | -40       | 150                | °C |

| 保存温度 ( $T_{stg}$ )                                       | -55       | 150                | °C |

(1) 製品寿命は  $V_{DS}$  電圧に依存します。

(2) 「絶対最大定格」外での操作は、デバイスに恒久的な損傷を引き起こす可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用した場合、本デバイスは完全に機能するとは限らず、このことが本デバイスの信頼性、機能、性能に影響を及ぼし、本デバイスの寿命を縮める可能性があります。

## 6 ESD 定格

|             |      | 値                                                         | 単位         |

|-------------|------|-----------------------------------------------------------|------------|

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM) ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>      | $\pm 2000$ |

|             |      | デバイス帯電モデル (CDM)、ANSI/ESDA/JEDEC JS-002 に準拠 <sup>(2)</sup> | $\pm 500$  |

(1) JEDEC ドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

(2) JEDEC ドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

## 7 推奨動作条件

動作温度範囲内 (特に記述のない限り)

|              |                  |                    | 最小値  | 公称値    | 最大値    | 単位  |

|--------------|------------------|--------------------|------|--------|--------|-----|

| $V_{VM}$     | DC 電源電圧          | VM                 | 0    | 450    | 450    | V   |

| $V_{GVDD}$   | ゲートドライバ電源電圧      | GVDD               | 10.8 | 18     | 18     | V   |

| $f_{PWM}$    | PWM 周波数          | OUTA、OUTB、OUTC     |      | 20     | 100    | KHz |

| $V_{IN}$     | ロジック入力電圧         | INHx、INLx、EN、BRAKE | -0.1 | 20     | 20     | V   |

| $V_{OD}$     | オープンドレイン プルアップ電圧 | nFAULT             | -0.1 | 20     | 20     | V   |

| $I_{OD}$     | オープンドレイン出力シンク電流  | nFAULT             | 0    | 5      | 5      | mA  |

| $V_{SR}$     | スルーレートピン電圧       | SR                 |      | $GVDD$ | $GVDD$ | V   |

| $V_{SLx}$    | SLx ピン電圧         | SLA、SLB、SLC        | -1   | 1      | 1      | V   |

| $V_{AMPINx}$ | アンプ入力ピン電圧        | AMPIN+、AMPIN-      | -0.1 | 5      | 5      | V   |

動作温度範囲内 (特に記述のない限り)

|                |             |                         | 最小値 | 公称値 | 最大値 | 単位          |

|----------------|-------------|-------------------------|-----|-----|-----|-------------|

| $V_{ILIMIT}$   | 過電流保護リファレンス | $I_{LIMIT}$             | 0.2 | 2   |     | V           |

| $T_{PWIN\_ON}$ | 最小入力パルス幅    | INH, INL <sup>(1)</sup> | 0.5 |     |     | $\mu s$     |

| $T_A$          |             |                         | -40 | 100 |     | $^{\circ}C$ |

| $T_J$          |             |                         | -40 | 125 |     | $^{\circ}C$ |

(1) 入力パルス幅が推奨値よりも小さい場合、デバイスは入力への応答を行わないことがあります

## 8 熱に関する情報

| 熱評価基準 <sup>(1)</sup>        | デバイス                          |      | 単位            |  |

|-----------------------------|-------------------------------|------|---------------|--|

|                             | REN (VQFN)                    |      |               |  |

|                             | 40 ピン                         |      |               |  |

| $R_{\theta JA}$             | 接合部から周囲への熱抵抗                  | 21.2 | $^{\circ}C/W$ |  |

| $R_{\theta JC(\text{top})}$ | 接合部からケース(上面)への熱抵抗             | 5.5  | $^{\circ}C/W$ |  |

| $R_{\theta JB}$             | 接合部から基板への熱抵抗                  | 6.0  | $^{\circ}C/W$ |  |

| $\Psi_{JT}$                 | 接合部から上面への特性パラメータ              | 4.0  | $^{\circ}C/W$ |  |

| $\Psi_{JB}$                 | 接合部から基板への特性パラメータ              | 5.8  | $^{\circ}C/W$ |  |

| $R_{\theta JC(\text{bot})}$ | 接合部からケース(底面)への熱抵抗 (GaNFETあたり) | 1    | $^{\circ}C/W$ |  |

(1) 従来および最新の熱評価基準の詳細については、『半導体およびICパッケージの熱評価基準』アプリケーションレポートを参照してください。

## 9 電気的特性

$T_J = -40^{\circ}C \sim 150^{\circ}C$ 、 $V_{GVDD} = 15V$ 、EN = High (特に記述のない限り)。標準値には  $T_A = 25^{\circ}C$ 、 $V_{GVDD} = 15V$  が適用されます。

| パラメータ                | テスト条件                                                                              | 最小値 | 標準値 | 最大値 | 単位        |

|----------------------|------------------------------------------------------------------------------------|-----|-----|-----|-----------|

| <b>GaN パワー ランジスタ</b> |                                                                                    |     |     |     |           |

| $R_{DS(ON)}$         | GaN ランジスタ オン抵抗 $V_{GVDD} = 15V$ 、 $I_{OUTx} = 1A$ 、 $T_J = 25^{\circ}C$ 、          | 205 | 320 |     | $m\Omega$ |

| $R_{DS(ON)}$         | GaN ランジスタ オン抵抗 $V_{GVDD} = 15V$ 、 $I_{OUTx} = 1A$ 、 $T_J = 150^{\circ}C$ 、         | 370 |     |     | $m\Omega$ |

| $V_{SD}$             | 第3象限モードのソース-ドレイン電圧 $INx = 0V$ 、 $ISD = 0.1A$ 、 $T_J = 25^{\circ}C$                 | 1.5 | 2.5 |     | V         |

| $V_{SD}$             | 第3象限モードのソース-ドレイン電圧 $INx = 0V$ 、 $ISD = 4A$ 、 $T_J = 25^{\circ}C$                   | 2.8 |     |     | V         |

| $Q_{RR}$             | 逆方向回復電荷 $V_R = 300V$ 、 $I_{SD} = 4A$ 、 $dI_{SD}/dt = 0.2A/ns$                      |     | 0   |     | nC        |

| <b>スイッチング特性</b>      |                                                                                    |     |     |     |           |

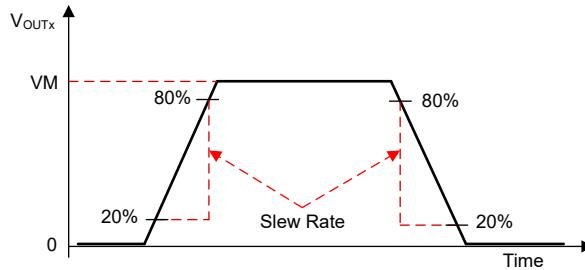

| SR                   | Low から High へのスイッチング (20% から 80% への立ち上がり) 時の位相ピンのスルーレート $V_{VM} = 300V$ 、SR 設定 = 0 | 4   |     |     | $V/ns$    |

| SR                   | High から Low へスイッチングする位相ピンのスルーレート (80% から 20% への立ち下がり) $V_{VM} = 300V$ 、SR 設定 = 0   | 4   |     |     | $V/ns$    |

| SR                   | Low から High へのスイッチング (20% から 80% への立ち上がり) 時の位相ピンのスルーレート $V_{VM} = 300V$ 、SR 設定 = 1 | 10  |     |     | $V/ns$    |

| SR                   | High から Low へスイッチングする位相ピンのスルーレート (80% から 20% への立ち下がり) $V_{VM} = 300V$ 、SR 設定 = 1   | 10  |     |     | $V/ns$    |

| SR                   | Low から High へのスイッチング (20% から 80% への立ち上がり) 時の位相ピンのスルーレート $V_{VM} = 300V$ 、SR 設定 = 2 | 20  |     |     | $V/ns$    |

$T_J = -40^\circ\text{C} \sim 150^\circ\text{C}$ 、 $V_{\text{GVDD}} = 15\text{V}$ 、EN = High (特に記述のない限り)。標準値には  $T_A = 25^\circ\text{C}$ 、 $V_{\text{GVDD}} = 15\text{V}$  が適用されます。

| パラメータ                         |                                                         | テスト条件                                                                                                                    | 最小値 | 標準値 | 最大値 | 単位            |

|-------------------------------|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|---------------|

| SR                            | High から Low へスイッチングする位相ピンのスルーレート (80% から 20% への立ち下がり)   | $V_{\text{VM}} = 300\text{V}$ 、SR 設定 = 2                                                                                 |     | 20  |     | $\text{V/ns}$ |

| SR                            | Low から High へのスイッチング (20% から 80% への立ち上がり) 時の位相ピンのスルーレート | $V_{\text{VM}} = 300\text{V}$ 、SR 設定 = 3                                                                                 |     | 40  |     | $\text{V/ns}$ |

| SR                            | High から Low へスイッチングする位相ピンのスルーレート (80% から 20% への立ち下がり)   | $V_{\text{VM}} = 300\text{V}$ 、SR 設定 = 3                                                                                 |     | 40  |     | $\text{V/ns}$ |

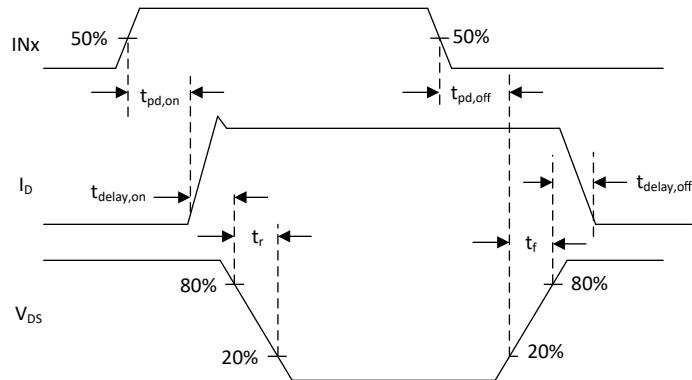

| $t_{\text{pd},\text{on}}$     | 伝搬遅延、ターンオン                                              | $V_{\text{INHx}}, V_{\text{INLx}} = \text{ロジック Low から High}$ 、 $V_{\text{VM}} = 300\text{V}$ 、 $I_D = 4\text{A}$ 、SR = 0 |     | 125 |     | $\text{ns}$   |

| $t_{\text{delay},\text{on}}$  | ターンオン遅延時間                                               | $V_{\text{INHx}}, V_{\text{INLx}} = \text{ロジック Low から High}$ 、 $V_{\text{VM}} = 300\text{V}$ 、 $I_D = 4\text{A}$ 、SR = 0 |     | 75  |     | $\text{ns}$   |

| $t_{\text{pd},\text{off}}$    | 伝搬遅延、ターンオフ                                              | $V_{\text{INHx}}, V_{\text{INLx}} = \text{ロジック High から Low}$ 、 $V_{\text{VM}} = 300\text{V}$ 、 $I_D = 4\text{A}$ 、SR = 0 |     | 135 |     | $\text{ns}$   |

| $t_{\text{delay},\text{off}}$ | ターンオフ遅延時間                                               | $V_{\text{INHx}}, V_{\text{INLx}} = \text{ロジック High から Low}$ 、 $V_{\text{VM}} = 300\text{V}$ 、 $I_D = 4\text{A}$ 、SR = 0 |     | 75  |     | $\text{ns}$   |

| $t_{\text{DEAD}}$             | 出力デッドタイム (High から Low)                                  | $V_{\text{VM}} = 300\text{V}$ 、 $I_{\text{OUTx}} = 4\text{A}$ 、位相ノード (OUTx) から流れ出る電流 SR = 0, 1                           |     | 40  |     | $\text{ns}$   |

| $t_{\text{DEAD}}$             | 出力デッドタイム (High から Low)                                  | $V_{\text{VM}} = 300\text{V}$ 、 $I_{\text{OUTx}} = 4\text{A}$ 、位相ノード (OUTx) に流れ込む電流 (OUTx)、SR = 0                        |     | 100 |     | $\text{ns}$   |

| $t_{\text{DEAD}}$             | 出力デッドタイム (High から Low)                                  | $V_{\text{VM}} = 300\text{V}$ 、 $I_{\text{OUTx}} = 4\text{A}$ 、位相ノード (OUTx) に流れ込む電流、SR = 1 または 2 または 3                   |     | 100 |     | $\text{ns}$   |

| $t_{\text{DEAD}}$             | 出力デッドタイム (Low から High)                                  | $V_{\text{VM}} = 300\text{V}$ 、 $I_{\text{OUTx}} = 4\text{A}$ 、位相ノード (OUTx) に流れ込む電流                                      |     | 40  |     | $\text{ns}$   |

| $t_{\text{start}}$            | 起動時間                                                    | $V_{\text{GVDD}} > V_{\text{GVDD\_UV\_ON}}$ EN = Low から High、INLx = 1、ローサイド GaNFET ターンオン                                 |     |     | 2   | $\text{ms}$   |

| $t_{\text{off}}$              | デバイスのターンオフ時間 - スリープへ                                    | $V_{\text{GVDD}} > V_{\text{GVDD\_UV\_ON}}$ EN = High から Low へ                                                           | 40  | 80  |     | $\text{us}$   |

| $t_{\text{clr\_flt}}$         | EN を使用してラッチされたフォルトをクリアする時間                              | EN = Low パルス幅                                                                                                            | 15  | 40  |     | $\text{us}$   |

| $t_{\text{off}}$              | デバイスのターンオフ時間 — ゲートドライバオフ                                | $V_{\text{GVDD}} > V_{\text{GVDD\_UV\_ON}}$ EN = High から Low、INLx = 1、ローサイド GaNFET ターンオフ                                 |     | 80  |     | $\mu\text{s}$ |

#### GVDD 電源

|                            |                                               |                                                                                                                                                   |     |     |               |

|----------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|---------------|

| $I_{\text{GVDD,Q}}$        | GVDD 動作電流、ドライバインエーブル、スイッチングなし                 | EN = High、 $V_{\text{VM}} = 300\text{V}$ 、INx = 0                                                                                                 | 2.3 |     | $\text{mA}$   |

| $I_{\text{GVDD,3SW}}$      | GVDD 平均動作電流、ドライバインエーブル、GaN スイッチング、OUTx ピンは無負荷 | EN = High、 $F_{\text{sw}} = 20\text{kHz}$ 、50% 相補 PWM での 3 ハーフブリッジ スイッチング、 $V_{\text{VM}} = 300\text{V}$ 、 $V_{\text{GVDD}} = 15\text{V}$ 、SR = 0 |     | 3.7 | $\text{mA}$   |

| $V_{\text{GVDD\_UV\_R}}$   | GVDD 低電圧スレッショルド - 立ち上がり                       | GVDD 立ち上がり                                                                                                                                        |     | 10  | $\text{V}$    |

| $V_{\text{GVDD\_UV\_F}}$   | GVDD 低電圧スレッショルド - 立ち下がり                       | GVDD 立ち下がり                                                                                                                                        | 9   |     | $\text{V}$    |

| $V_{\text{GVDD\_UV\_HYS}}$ | GVDD 低電圧検出ヒステリシス                              | GVDD 立ち上がりから立ち下がりまでのスレッショルド                                                                                                                       | 500 |     | $\text{mV}$   |

| $t_{\text{UVLO\_GVDD}}$    | GVDD 低電圧グリッヂ除去時間                              |                                                                                                                                                   |     | 20  | $\mu\text{s}$ |

#### ブートストラップ電源

|                      |                  |                                                                |    |          |

|----------------------|------------------|----------------------------------------------------------------|----|----------|

| $R_{\text{DS\_BST}}$ | ブートストラップ整流器のオン抵抗 | $V_{\text{GVDD}} = 15\text{V}$ 、 $V_{\text{VM}} = 300\text{V}$ | 30 | $\Omega$ |

|----------------------|------------------|----------------------------------------------------------------|----|----------|

$T_J = -40^\circ\text{C} \sim 150^\circ\text{C}$ 、 $V_{\text{GVDD}} = 15\text{V}$ 、EN = High (特に記述のない限り)。標準値には  $T_A = 25^\circ\text{C}$ 、 $V_{\text{GVDD}} = 15\text{V}$  が適用されます。

| パラメータ                     |                       | テスト条件                                                                                                                                                                                    | 最小値 | 標準値 | 最大値           | 単位 |

|---------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|---------------|----|

| $I_{\text{LMT\_BST}}$     | ブートストラップ整流器の電流制限      | EN = High、 $V_{\text{GVDD}} = 15\text{V}$ 、 $V_{\text{VM}} = 300\text{V}$ 、 $\text{INLx} = \text{High}$ 、 $\text{INHx} = \text{Low}$ 、 $V_{\text{BOOTx}} - V_{\text{OUTx}} = 12\text{V}$ | 150 | 250 | mA            |    |

| $I_{\text{BST\_PK}}$      | ブートストラップ整流器のピーク過渡電流   | EN = High、 $V_{\text{GVDD}} = 15\text{V}$ 、 $V_{\text{VM}} = 300\text{V}$ 、 $\text{INLx} = \text{High}$ 、 $\text{INHx} = \text{Low}$ 、 $V_{\text{BOOTx}} - V_{\text{OUTx}} = 0\text{V}$  | 350 |     | mA            |    |

| $I_{\text{BST\_Q}}$       | ブートストラップ静止電流          | EN = High、 $\text{INHx} = \text{Low}$ 、 $\text{INLx} = \text{Low}$ 、 $V_{\text{GVDD}} = 15\text{V}$ 、 $V_{\text{BOOTx}} - V_{\text{OUTx}} = 12\text{V}$                                  | 100 | 145 | $\mu\text{A}$ |    |

| $I_{\text{BST\_Q}}$       | ブートストラップ静止電流          | EN = High、 $\text{INHx} = \text{High}$ 、 $\text{INLx} = \text{Low}$ 、 $V_{\text{GVDD}} = 15\text{V}$ 、 $V_{\text{BOOTx}} - V_{\text{OUTx}} = 12\text{V}$                                 | 350 |     | $\mu\text{A}$ |    |

| $V_{\text{BST\_UV}}$      | ブートストラップ電源低電圧         | BOOTx 立ち上がり                                                                                                                                                                              |     | 9   | V             |    |

| $V_{\text{BST\_UV}}$      | ブートストラップ電源低電圧         | BOOTx 立ち下がり                                                                                                                                                                              | 8   |     | V             |    |

| $V_{\text{BST\_UV\_HYS}}$ | ブートストラップ電源低電圧ヒステリシス   |                                                                                                                                                                                          | 500 |     | mV            |    |

| $t_{\text{BST\_UV}}$      | ブートストラップ電源低電圧グリッヂ除去時間 |                                                                                                                                                                                          | 20  |     | $\mu\text{s}$ |    |

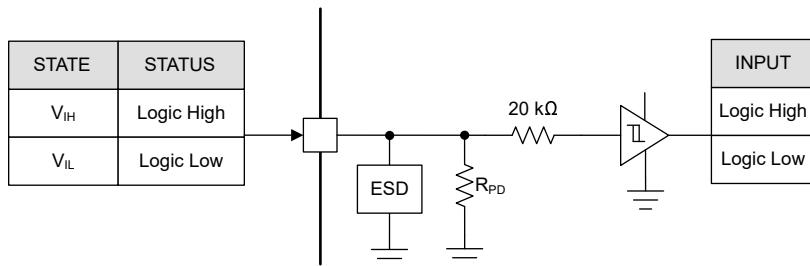

#### ロジック レベル入力 (EN, INHx, INLx, BRAKE)

|                  |                                       |                       |      |      |               |    |

|------------------|---------------------------------------|-----------------------|------|------|---------------|----|

| $V_{\text{IL}}$  | 入力ロジック Low 電圧                         | INHx, INLx, BRAKE, EN | 0.8  |      | V             |    |

| $V_{\text{IH}}$  | 入力ロジック High 電圧                        | INHx, INLx, BRAKE, EN | 2.2  |      | V             |    |

| $V_{\text{HYS}}$ | 入力ロジック ヒステリシス                         | INHx, INLx, BRAKE, EN | 300  | 450  | 650           | mV |

| $I_{\text{IL}}$  | 入力ロジック Low 電流 (INHx, INLx, BRAKE, EN) | $V_I = 0\text{V}$     | -1   | 1    | $\mu\text{A}$ |    |

| $I_{\text{IL}}$  | 入力ロジック Low 電流 (BRAKE, EN)             | $V_I = 0\text{V}$     | -1   | 1    | $\mu\text{A}$ |    |

| $R_{\text{PD}}$  | 入力プルダウン抵抗                             | INHx, INLx, EN        | 70   | 100  | 130           | kΩ |

| $R_{\text{PD}}$  | 入力プルダウン抵抗                             | BRAKE                 | 15   | 20   | 25            | kΩ |

| $t_{\text{deg}}$ | 入力ロジックのグリッヂ除去時間                       | INHx, INLx            | 25   | 50   | ns            |    |

| $t_{\text{deg}}$ | 入力ロジックのグリッヂ除去時間                       | EN                    | 80   |      | $\mu\text{s}$ |    |

| $t_{\text{deg}}$ | 入力ロジックのグリッヂ除去時間                       | BRAKE                 | 1200 | 2000 | ns            |    |

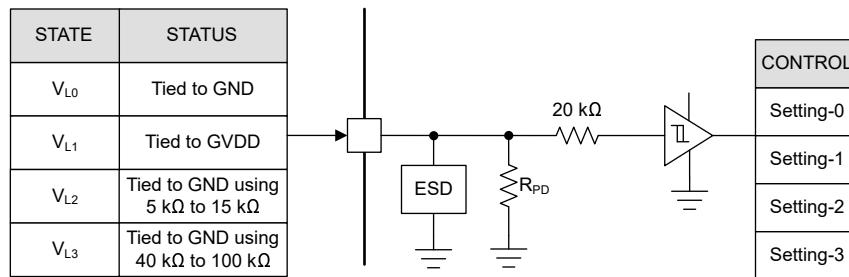

#### マルチレベル入力 (SR)

|                 |           |                                                               |    |     |    |

|-----------------|-----------|---------------------------------------------------------------|----|-----|----|

| $R_{\text{L1}}$ | SR 設定 = 0 | GND に接続                                                       | 0  | 1   | kΩ |

| $R_{\text{L2}}$ | SR 設定 = 1 | GVDD に接続                                                      | 0  | 1   | kΩ |

| $R_{\text{L3}}$ | SR 設定 = 2 | R を GND に接続 ( $R = 5\text{k}\Omega \sim 15\text{k}\Omega$ )   | 5  | 15  | kΩ |

| $R_{\text{L4}}$ | SR 設定 = 3 | R を GND に接続 ( $R = 40\text{k}\Omega \sim 100\text{k}\Omega$ ) | 40 | 100 | kΩ |

#### オープンドレイン出力 (nFAULT)

|                 |                |                              |     |    |               |

|-----------------|----------------|------------------------------|-----|----|---------------|

| $V_{\text{OL}}$ | 出力ロジック Low 電圧  | $I_{\text{OD}} = 5\text{mA}$ | 0.4 |    | V             |

| $I_{\text{OH}}$ | 出力ロジック High 電流 | $V_{\text{OD}} = 5\text{V}$  | -1  | 1  | $\mu\text{A}$ |

| $C_{\text{OD}}$ | 出力容量           |                              |     | 30 | pF            |

#### GaN プリドライバ保護

|                           |                            |                                                                                            |     |     |                     |

|---------------------------|----------------------------|--------------------------------------------------------------------------------------------|-----|-----|---------------------|

| $I_{\text{OCP\_GaN}}$     | ローサイド GaN FET 過電流検出スレッショルド | $V_{\text{GVDD}} = 15\text{V}$ 、 $V_{\text{VM}} = 300\text{V}$ 、 $T_J = 25^\circ\text{C}$  | 7.5 | 24  | A                   |

| $I_{\text{OCP\_GaN}}$     | ローサイド GaN FET 過電流検出スレッショルド | $V_{\text{GVDD}} = 15\text{V}$ 、 $V_{\text{VM}} = 300\text{V}$ 、 $T_J = 125^\circ\text{C}$ | 5   |     | A                   |

| $t_{\text{OCP\_GaN\_BT}}$ | ランキング時間 (グリッヂ除去を含む)        | $V_{\text{GVDD}} = 15\text{V}$ 、 $V_{\text{VM}} = 300\text{V}$                             | 150 |     | ns                  |

| $t_{\text{OCP\_GaN\_PD}}$ | 伝搬遅延 (FET がオフになるまで)        | $V_{\text{GVDD}} = 15\text{V}$ 、 $V_{\text{VM}} = 300\text{V}$                             | 50  |     | ns                  |

| $T_{\text{SD\_RISE}}$     | サーマル シャットダウン立ち上がり          | ダイ温度 ( $T_J$ )                                                                             | 145 | 165 | $185^\circ\text{C}$ |

| $T_{\text{SD\_FALL}}$     | サーマル シャットダウン立ち下がり          | ダイ温度 ( $T_J$ )                                                                             | 125 | 145 | $165^\circ\text{C}$ |

$T_J = -40^\circ\text{C} \sim 150^\circ\text{C}$ 、 $V_{\text{GVDD}} = 15\text{V}$ 、EN = High (特に記述のない限り)。標準値には  $T_A = 25^\circ\text{C}$ 、 $V_{\text{GVDD}} = 15\text{V}$  が適用されます。

| パラメータ                      |                                              | テスト条件                                                                                                   | 最小値  | 標準値  | 最大値 | 単位    |

|----------------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------|------|------|-----|-------|

| $T_{\text{SD\_HYST}}$      | サーマル シャットダウン ヒステリシス                          | ダイ温度 ( $T_J$ )                                                                                          | 13   | 20   |     | °C    |

| <b>電流制限コンパレータ (ILIMIT)</b> |                                              |                                                                                                         |      |      |     |       |

| $I_b$                      | 入力バイアス電流 (ILIMIT)                            | $V_{\text{ILIMIT}} = 0.5\text{V}$                                                                       |      | 1    |     | μA    |

| $V_{\text{off}}$           | ILIMIT コンパレータ入力電圧オフセット                       | $V_{\text{ILIMIT}} = 1.0\text{V}$                                                                       |      | ±2.5 |     | mV    |

| $V_{\text{ILIMIT\_DIS}}$   | ILIMIT OCP を無効化するための最小 ILIMIT 電圧             |                                                                                                         | 2.2  | 2.6  |     | V     |

| $V_{\text{ILIMIT}}$        | ILIMIT での動作電圧範囲                              |                                                                                                         |      | 2    |     | V     |

| $t_{\text{blank}}$         | INHx/INLx のオン / オフからすべての SLx 入力の過電流検出ブランкиング |                                                                                                         | 400  | 620  |     | ns    |

| $t_{\text{deglitch}}$      | 過電流検出グリッチ除去時間                                |                                                                                                         | 190  | 330  |     | ns    |

| $t_{\text{filter}}$        | ILIMIT コンパレータ入力 RC フィルタ時間 (SLx)              | $V_{\text{SLx}} = 0 \sim 1\text{V}$ ステップ、 $V_{\text{ILIMIT}} = 0.63\text{V}$                            | 250  | 450  |     | ns    |

| $t_{\text{filter}}$        | ILIMIT リファレンス電圧入力 RC フィルタ時間 (ILIMIT)         | $V_{\text{ILIMIT}} = 1 \sim 0\text{V}$ ステップ、 $V_{\text{SLx}} = 0.37\text{V}$                            | 600  | 1000 |     | ns    |

| $t_{\text{pd\_OFF}}$       | ILIMIT 過電流検出からすべての GaN FET がターンオフするまでの伝搬遅延時間 | $V_{\text{ILIMIT}} = 0.63\text{V}$ 、 $V_{\text{SLx}} = 0 \sim 1\text{V}$ ステップ、 $\text{INx} = \text{一定}$ |      | 1.2  |     | μs    |

| $t_{\text{pd\_FAULT}}$     | ILIMIT 過電流検出から nFAULT ピン通知までの伝搬遅延時間          | $V_{\text{ILIMIT}} = 0.63\text{V}$ 、 $V_{\text{SLx}} = 0 \sim 1\text{V}$ ステップ、 $\text{INx} = \text{一定}$ |      | 1    |     | μs    |

| <b>オペアンプ</b>               |                                              |                                                                                                         |      |      |     |       |

| $V_{\text{LINEAR}}$        | 出力電圧スイング                                     | $R_L = 10\text{k}$ から GND                                                                               | 0.02 | 4.9  |     | V     |

| $\text{GBW}$               | ゲイン帯域幅積                                      | $\text{RL} = 10\text{k}$ 、 $G = +1$                                                                     |      | 11   |     | MHz   |

| $V_{\text{SR\_opamp}}$     | 出力電圧スルーレート                                   | $\text{RL} = 10\text{k}$ 、 $G = +1$                                                                     |      | 26   |     | V/μs  |

| $t_{\text{set}}$           | ±1% までのセトリング タイム                             | 2V ステップ、 $G = +1$ 、 $\text{CL} = 130\text{pF}$ 、 $\text{RL} = 10\text{k}$                               |      | 0.4  |     | μs    |

| $A_{\text{OL}}$            | 開ループ電圧ゲイン                                    | 0.04 V < VAMPOUT < 4.8 V、 $\text{RL} = 10\text{kΩ}$ から GND                                              |      | 106  |     | dB    |

| $\Phi_m$                   | 位相マージン                                       | $G = +1$ 、 $\text{RL} = 10\text{k}$                                                                     |      | 60   |     | °     |

| $V_{\text{COM}}$           | コモン モード入力範囲                                  |                                                                                                         | 0    | 5    |     | V     |

| $V_{\text{OFF}}$           | 入力オフセット電圧誤差                                  | $\text{TA} = -40^\circ\text{C} \sim 125^\circ\text{C}$                                                  |      | ±1   |     | mV    |

| $V_{\text{DRIFT}}$         | オフセットドリフト                                    | $\text{TA} = -40^\circ\text{C} \sim 125^\circ\text{C}$                                                  |      | ±2   |     | μV/°C |

| $I_{\text{bias}}$          | 入力バイアス電流                                     | $V_{\text{AMPIN-}} = V_{\text{AMPIN+}} = 2.5\text{V}$                                                   |      | ±100 |     | nA    |

| $I_{\text{bias\_off}}$     | 入力バイアス オフセット電流                               | $V_{\text{AMPIN-}} = V_{\text{AMPIN+}} = 2.5\text{V}$                                                   |      | ±10  |     | nA    |

| $\text{CMRR}$              | 同相除去比                                        | -0.1V < VCM < 5V、 $\text{TA} = -40^\circ\text{C} \sim 125^\circ\text{C}$                                |      | 96   |     | dB    |

| $I_{\text{SC\_opamp}}$     | 短絡電流                                         |                                                                                                         |      | ±20  |     | mA    |

| $Z_o$                      | オープン ループ出力インピーダンス                            | $f = 5\text{MHz}$                                                                                       |      | 250  |     | Ω     |

| $C_L$                      | 容量性負荷駆動能力                                    |                                                                                                         |      | 130  |     | pF    |

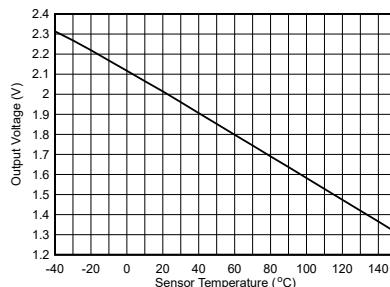

| <b>温度センサ</b>               |                                              |                                                                                                         |      |      |     |       |

| $V_T$                      | 温度検出素子出力 (VTEMP) 電圧                          | $\text{TA} = 25^\circ\text{C}$                                                                          |      | 1.98 |     | V     |

| $R_T$                      | VTEMP ピンの最小負荷抵抗                              | $V_T$ のテスト条件                                                                                            | 90   |      |     | kΩ    |

| $C_T$                      | VTEMP ピンの最大負荷抵抗                              | $V_T$ のテスト条件                                                                                            |      | 130  |     | pF    |

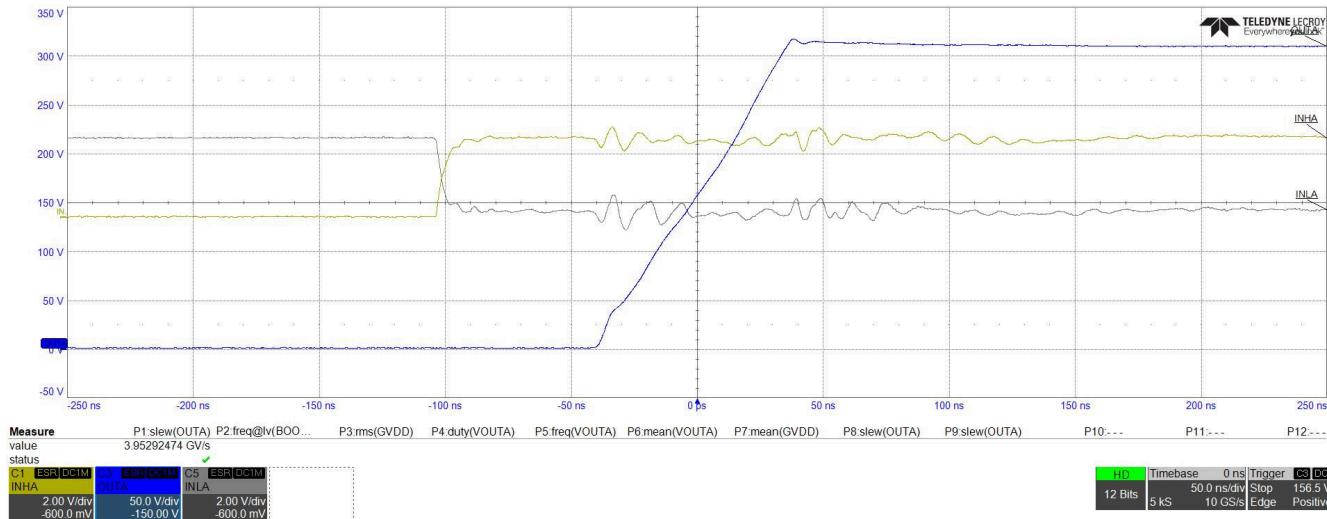

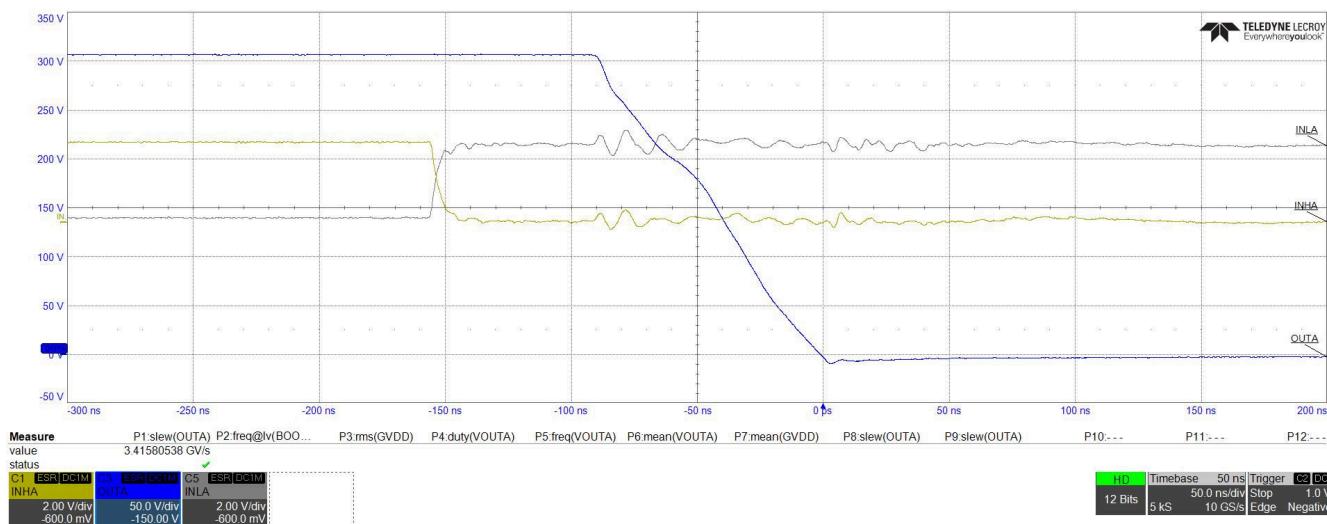

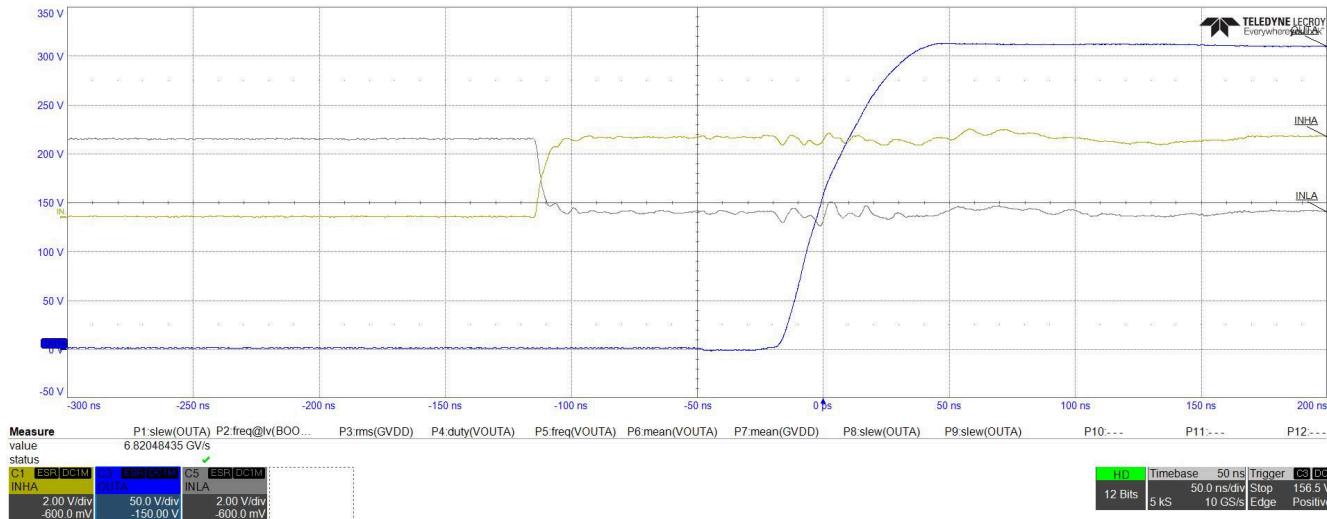

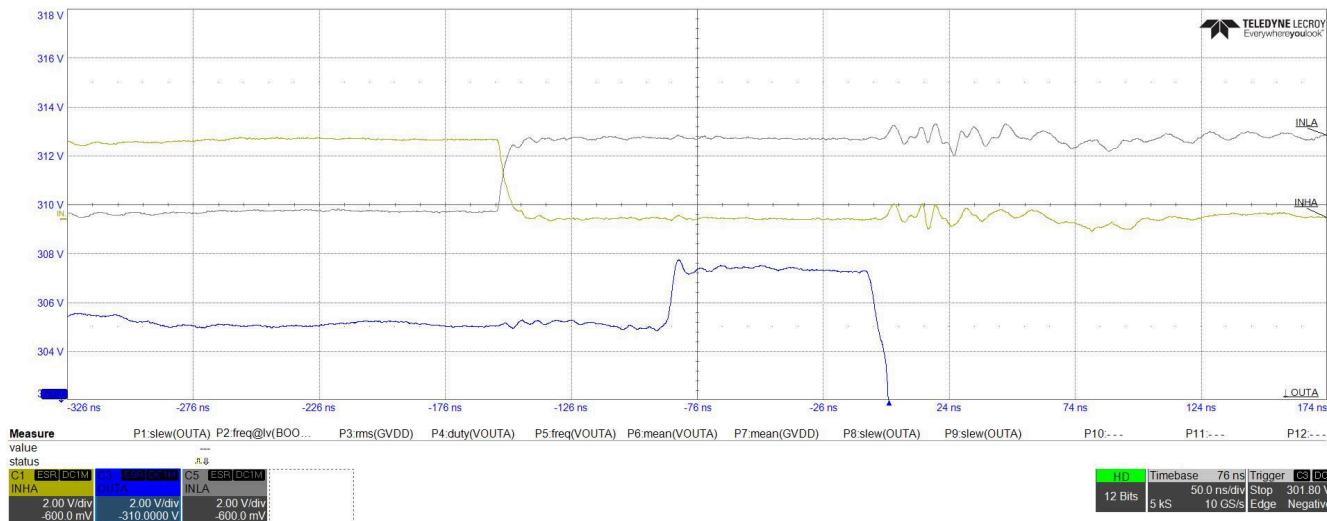

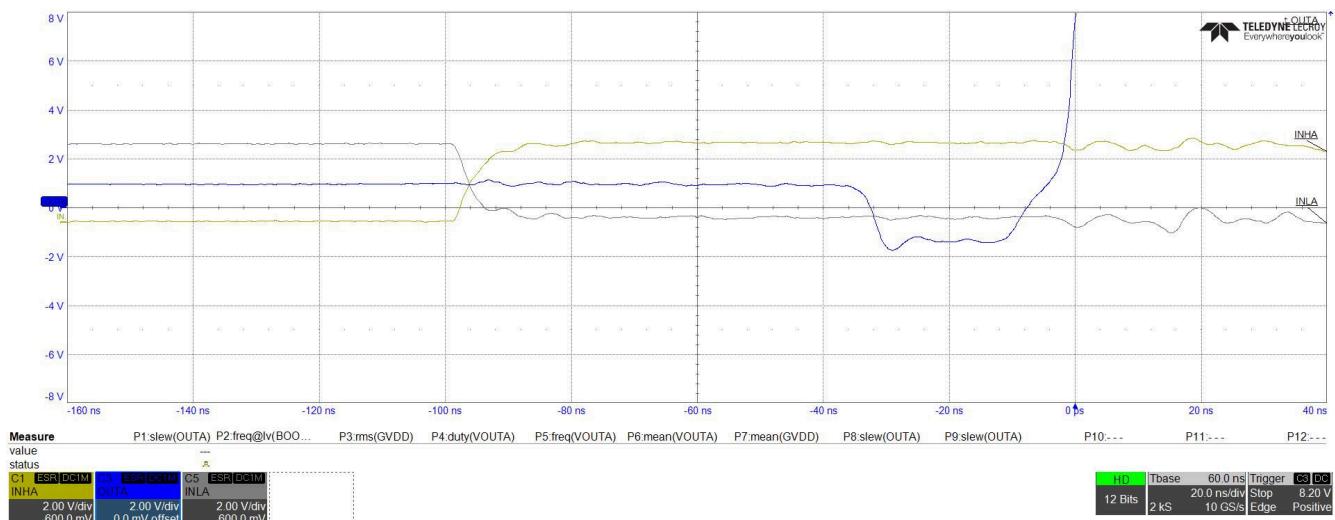

図 10-1. DRV7308 ターンオンおよびターンオフのスイッチング特性

## 11 代表的特性

図 11-1. センサ温度全体の温度センサ出力

## 12 詳細説明

### 12.1 概要

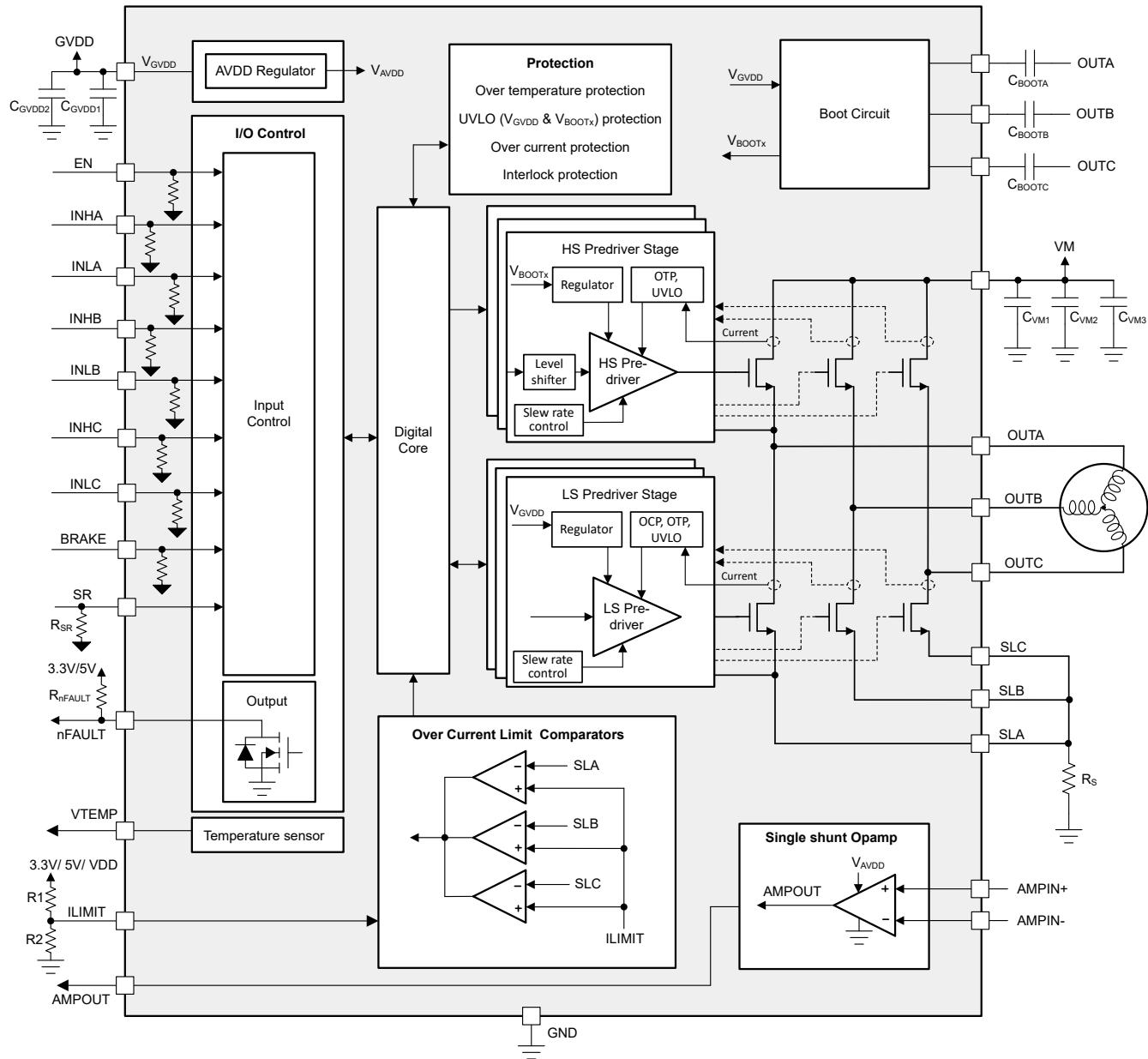

DRV7308 は、3 つの内蔵ハーフ H ブリッジ  $205\text{m}\Omega$ 、 $650\text{V}$  の e モード窒化ガリウム (GaN) を備えた 3 相 IPM で、最大  $450\text{V DC}$  レールの 3 相 BLDC/PMSM モーターを駆動します。デバイスは、BLDC モータの磁界方向制御 (FOC)、正弦波電流制御、および台形電流制御に適しています。すべての GaN FET 用にプリドライバが内蔵されており、位相ノード電圧のスルーレート制御が可能です。低い  $R_{DS\_ON}$ 、スルーレート制御、ゼロ逆方向回復、および低出力容量により、3 相変調、FOC 駆動、 $250\text{W}$  モーター ドライブ アプリケーションで 99% を超える効率を実現し、ヒートシンクが不要になります。

このデバイスには、過電流制限、過熱保護、ローサイド GaN FET の過電流保護、GVDD およびブートストラップ電源の低電圧保護、貫通電流状態を回避するためのアダプティブ デッドタイム挿入などの一連の保護機能が統合されています。

このデバイスは、GaN FET を内蔵したブートストラップ整流器と過渡電流制限機能を内蔵しており、外部ブートダイオードが不要になります。DRV7308 は、3、2、1 シャント電流検出をサポートするため、GaN FET の 3 つのローサイドソースピンすべてを備えています。このデバイスは、FOC での 1 つのシャント電流センシングと BLDC モーターの台形波制御のために、 $11\text{MHz } 15\text{V}/\mu\text{s}$  オペアンプを内蔵しています。

デッドタイムが短いため、BLDC/PMSM モーターの非常に静かな動作を実現できます。伝搬遅延が短いため、歪みの低減と高精度の平均電流検出を実現できます。

DRV7308 は、VQFN 12mm x 12mm パッケージで供給されます。

## 12.2 機能ブロック図

図 12-1. DRV7308 のブロック図

## 12.3 機能説明

### 12.3.1 出力ステージ

DRV7308 デバイスは、3 相ブリッジ構成で接続された内蔵の 205mΩ (1 つの GaN FET オン状態抵抗) エンハンスマントモード GaN (EGaN) FET で構成されています。このデバイスは、GVDD の低電圧外部電源を使用する内蔵ブートストラップコントローラと整流器を使用するローサイドおよびハイサイド GaN FET のプリドライバを内蔵しています。適切に使用される外部ブートストラップコンデンサにより、定義された時間にわたって 100% のデューティサイクルをサポートできます。

### 12.3.2 入力制御ロジック

DRV7308 は、INH<sub>x</sub> ピンと INL<sub>x</sub> ピンの PWM 入力信号に基づいて GaN FET の状態を制御します。デバイスは BRAKE 信号を使用して、モーター駆動にブレーキをかけます。BRAKE 信号がロジック High になると、INH<sub>x</sub> ピンと INL<sub>x</sub> ピンが無効になり、すべてのローサイド GaN トランジスタがオンになります。EN ピンにロジック Low が発生すると、デバイスはシャットオフ モード (すべてのゲートドライバと GaN FET がオフ状態) に入り、INH<sub>x</sub>、INL<sub>x</sub>、および BRAKE ピンのステータスを無視します。EN ピンの 20 ~ 40μs のロジック Low パルスにより、デバイスは OCP および OTP フォルトからリセットされます。[表 12-1](#) に、入力制御ロジックの真理値表を示します。

**表 12-1. 入力制御ロジック**

| EN | BRAKE | INH <sub>x</sub> | INL <sub>x</sub> | ハイサイド GaN FET | ローサイド GaN FET | 説明                                                 |

|----|-------|------------------|------------------|---------------|---------------|----------------------------------------------------|

| 0  | X     | X                | X                | OFF           | OFF           | デバイスはシャットダウン状態で、すべての出力はハイインピーダンス状態                 |

| 1  | 1     | X                | X                | OFF           | オン            | BRAKE。すべてのローサイド GaN FET がオンで、すべてのハイサイド GaN FET がオフ |

| 1  | 0     | 1                | 1                | OFF           | OFF           | OUT <sub>x</sub> はハイインピーダンス                        |

| 1  | 0     | 0                | 0                | OFF           | OFF           | OUT <sub>x</sub> はハイインピーダンス                        |

| 1  | 0     | 1                | 0                | オン            | OFF           | OUT <sub>x</sub> は VM に接続                          |

| 1  | 0     | 0                | 1                | OFF           | オン            | OUT <sub>x</sub> は SL <sub>x</sub> ノードに接続          |

### 12.3.3 イネーブル(EN) ピン機能

EN ピンが Low になると、デバイスは低消費電力のスリープ モードに移行します。スリープモードでは、すべての GaNFET はオフ—Gan プリドライバ、内蔵オペアンプ、温度センサ、GaN OCP、デジタルコア LDO、発振器はすべてオフ。EN ピンでの立ち下がりエッジの後、 $t_{off}$  時間が経過するとデバイスがスリープ モードに移行します。EN ピンが High になると、デバイスのスリープ モードは自動的に終了します。 $t_{start}$  時間が経過すると、デバイスは入力可能な状態になります。

#### 注

EN ピンを通してデバイスがパワーアップおよびパワーダウンしている間は、内部レギュレータが有効化または無効化されるため、nFAULT ピンは Low に保持されます。レギュレータが有効化または無効化された後、nFAULT ピンは自動的に解放されます。

### 12.3.4 温度センサ出力(VTEMP)

DRV7308 には、デバイス温度を検出する温度センサが組み込まれています。温度センサの出力は、温度によって変化するアナログ電圧です。

### 12.3.5 ブレーキ機能

BRAKE ピンにより、INH<sub>x</sub> および INL<sub>x</sub> ピンのステータスとは無関係に、すべてのローサイド GaNFET をオンにできます。ブレーキには、内部プルダウン抵抗があります。未使用時は、BRAKE ピンを外部で GND に接続します。BRAKE ピンがロジック High になると、すべてのローサイド GaNFET をオンにすることで、デバイスはブレーキに入ります。

#### 注

BRAKE High コマンドを適用する際は、モーターの逆起電力によって非常に高い電流が流れる可能性があるため、注意してください。BRAKE 動作中、GaNFET を流れる最大電流は、GaNFET 電流と接合部温度の動作制限値内でなければなりません。

### 12.3.6 スルーレート制御(SR)

DRV7308 は、SR ピンの設定により、OUTx ピンでの電圧の上昇および下降のスルーレートをオプションで制御できます。ユーザーは SR ピンを構成することで、5V/ns、10V/ns、20V/ns、40V/ns のスルーレートを設定できます。スルーレートは、GaNFET のゲート電流を調整することで制御します。

図 12-2. DRV7308 スルーレート制御

注

20V/ns と 40V/ns のスルーレートが高い場合は、TI は RC 時定数 50ns のコンデンサをシャント抵抗の両端に追加することを推奨します。

### 12.3.7 デッドタイム

このデバイスは、GaNFET のクロス導通に対して包括的な保護が施されています。ハーフブリッジ構成では、デッドタイム ( $t_{DEAD}$ ) を挿入することで貫通電流を回避するため、ハイサイドおよびローサイド GaNFET の動作が制御されます。このプロセスは、ローサイド GaNFET のゲートソース電圧 (VGS) および同じハーフブリッジの位相ノード (OUTx) 電圧を検出するアダプティブ デッドタイム回路を使用して実装されます。

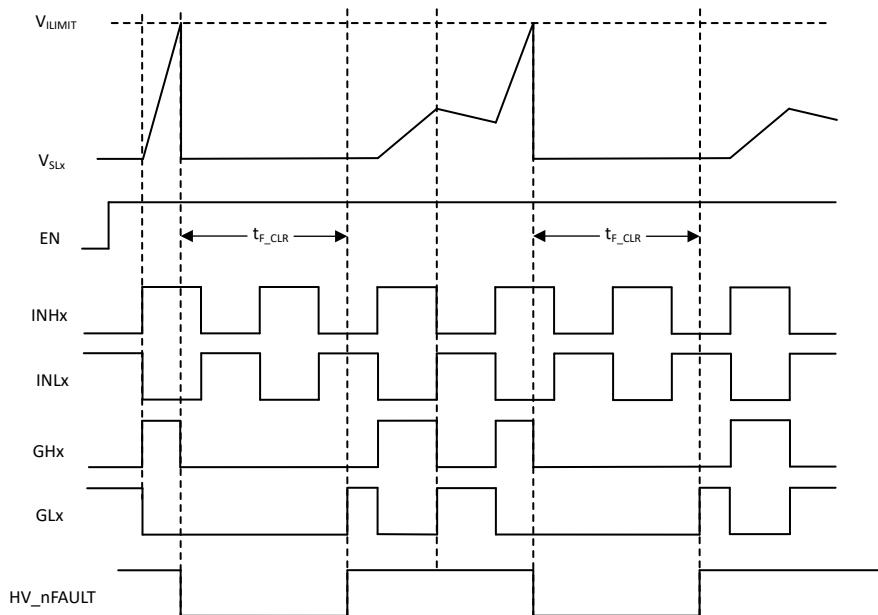

### 12.3.8 電流制限機能(ILIMIT)

DRV7308 には、SLx 電圧を監視する電流制限機能が組み込まれています。DRV7308 には 3 つのコンパレータが内蔵されており、それぞれ SLA、SLB、SLC ピンの電圧を個別に監視します。3 つのコンパレータすべてのリファレンス電圧は、ILIMIT ピンを使って外部から供給されます。ILIMIT ピンの電圧が 2V を下回ると、電流制限回路が有効になり、SLx 電圧が ILIMIT ピンの電圧を上回ると、デバイスはすべての GaNFET を  $t_{FCLR}$  の間オフにします。入力制御信号のステータスに応じて、 $t_{F CLR}$  が経過すると GaNFET は再度オンになります。ILIMIT 機能は、ILIMIT ピンの電圧を  $V_{ILIMIT\_DIS}$  を上回る値にプルアップすることで無効化できます。

過電流コンパレータでは、INHx と INLx のエッジごとに  $t_{blank}$  のブランкиング時間があります。コンパレータ出力が Low から High にトグルすると、コンパレータには  $t_{degitch}$  のグリッチ除去時間も発生します。

注

TI は、ノイズによる誤トリップを防止するため、0.2V を超える ILIMIT 電圧を推奨します。システム レベルの設計を考慮して、ILIMIT で適切な電圧を選択し、ノイズの影響を排除し、それに応じて SLx ピンのシャント抵抗値を選択します。

### 12.3.9 ピン配置図

このセクションには、すべてのデジタル入出力ピンの I/O 構造が示されています。

#### 12.3.9.1.4 レベル入力ピン

図 12-3 に、4 レベル SR ピンの構造を示します。

図 12-3.4 レベル入力ピン

### 12.3.9.2 オープンドレインピン

図 12-4 に、オープンドレイン出力ピン、オープンドレインモードの nFAULT の構造を示します。オープンドレイン出力を適切に機能させるためには、外部プルアップ抵抗が必要です。

図 12-4. オープンドレイン出力ピン構造

### 12.3.9.3 ロジックレベル入力ピン(内部プルダウン)

図 12-5 に、ロジックレベルピン EN、INHx、INLx、ILIMIT、BRAKE の入力構造を示します。入力は電圧または外部抵抗で行うことができます。

図 12-5. ロジックレベル入力ピンの構造

## 12.4 保護

DRV7308 は GaN FET の過電流保護 (GaN\_OCP)、過熱シャットダウン (OTSD)、GVDD およびブートストラップ電源低電圧保護 (GVDD\_UVLO および VBOOT\_UVLO)、電流制限 (ILIMIT) を内蔵しています。表 12-2 に、各種フォルトの詳細を示します。

表 12-2. フォルト動作および応答

| FAULT                              | 条件                                      | 通知     | GaN プリッジ                                           | 復帰                                                 |

|------------------------------------|-----------------------------------------|--------|----------------------------------------------------|----------------------------------------------------|

| GaN 過電流保護 (GaN_OCP) <sup>(1)</sup> | ローサイド GaN FET 電流 > I <sub>OCP_GaN</sub> | nFAULT | すべての GaN プリドライバがオフになり、その結果、ハイインピーダンスになります (3 相すべて) | ラッチ。EN ピン上の 20μs から 40μs へのトグル パルスまたは GVDD 電源リサイクル |

表 12-2. フォルト動作および応答 (続き)

| FAULT                          | 条件                           | 通知     | GAN ブリッジ                                                 | 復帰                                                 |

|--------------------------------|------------------------------|--------|----------------------------------------------------------|----------------------------------------------------|

| SLx 過電流制限 (ILIMIT)             | $V_{SLx} > V_{ILIMIT}$       | nFAULT | すべての GaN プリドライバがオフになります、その結果、ハイインピーダンスになります (3 相すべて)     | 再試行 <sup>(2)</sup> 。フォルトクリア時間 $> t_{F\_CLR}$       |

| GVDD 低電圧                       | $V_{GVDD} < V_{GVDD\_UV}$    | nFAULT | すべての GaN プリドライバがオフになります、その結果、ハイインピーダンスになります (3 相すべて)     | 自動: $V_{GVDD} > V_{GVDD\_UVLO}$                    |

| ブート電源低電圧 (BOOTx と OUTx ピン間の電圧) | $V_{BOOTx} < V_{BST\_UV}$    | -      | 影響を受けるハイサイド GaN プリドライバがオフになります。他のすべての GaNFET は引き続き動作します。 | 自動: $V_{BOOTx} > V_{BST\_UV}$                      |

| サーマル シャットダウン (OTSD)            | $T_J > T_{SD}$ 、ローサイド GaNFET | nFAULT | すべての GaN プリドライバがオフになります、その結果、ハイインピーダンスになります (3 相すべて)     | 自動 $T_J < T_{SD}$                                  |

|                                | $T_J > T_{SD}$ 、ハイサイド GaNFET |        |                                                          | ラッチ。EN ピン上の 20μs から 40μs へのトグル パルスまたは GVDD 電源リサイクル |

(1) ローサイド GaN FET のみの過電流検出。

(2) nFAULT の立ち下がりエッジより前に、PWM 入力 (INHx, INLx) が Low になっている必要があります。

**注**

ローサイド GaN FET には GaN 過電流保護 (GaN OCP) があります。

**警告**

SL 過電流制限 (ILIMIT) の復帰条件は、nFAULT の立ち下がりエッジより前に PWM 入力 (INHx, INLx) が Low である場合に有効です。

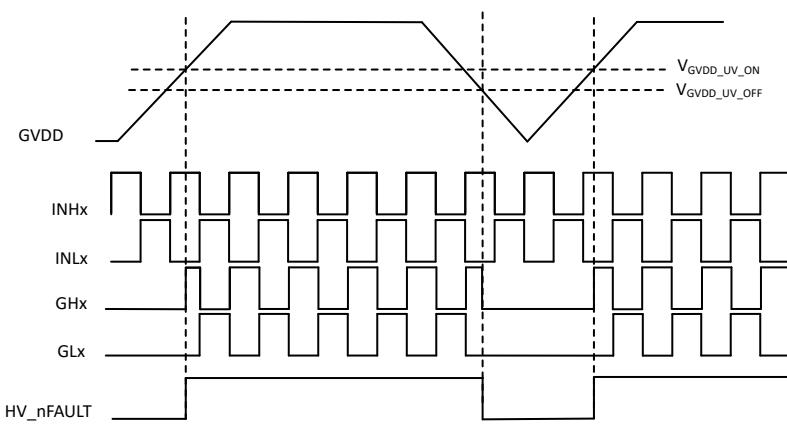

**12.4.1 GVDD 低電圧ロックアウト**

GVDD ピンの電圧が  $V_{GVDD\_UV}$  スレッショルドを下回ると、常に GaN FET プリドライバをオフにすることで、すべての内蔵 GaNFET をオフにします。GVDD\_UV 条件が解消されると、通常動作が再開されます。GVDD\_UV は、nFAULT ピンを Low に駆動することにより通知されます。

図 12-6. GVDD 低電圧ロックアウト

**12.4.2 ブートストラップ低電圧ロックアウト**

ブートストラップ コンデンサ (BOOTx から OUTx への電圧) ピンの両端の電圧が  $V_{BST\_UV}$  スレッショルドを下回ると、常にハイサイド プリドライバをオフにすることで、対応するハイサイド GaN FET がオフになります。他すべての GaN FET

は、INx ピンによって指示されたとおりに動作し続けます。BST\_UV 状態が解消された後、次の INHx パルスの立ち上がりエッジで、通常動作が再開されます。BOOTx 低電圧は nFAULT ピンでは通知されません。

図 12-7. ブートストラップ低電圧ロックアウト

#### 12.4.3 電流制限保護

DRV7308 には、過負荷の発生からデバイスと外部モーター負荷を保護するための 3 つのコンパレータが統合されています。DRV7308 には 3 つのコンパレータが内蔵されており、それぞれ SLA、SLB、SLC ピンの電圧を個別に監視します。ILIMIT ピンの電圧が 2V を下回ると、電流制限回路が有効になり、SLx 電圧が ILIMIT ピンの電圧を上回ると、デバイスはすべての GaN FET を  $t_{F\_CLR}$  の間オフにします。入力制御信号のステータスに応じて、 $t_{F\_CLR}$  が経過すると GaNFET は再度オンになります。nFAULT ピンを Low に駆動することにより、この電流制限が通知されます。

図 12-8. 電流制限動作

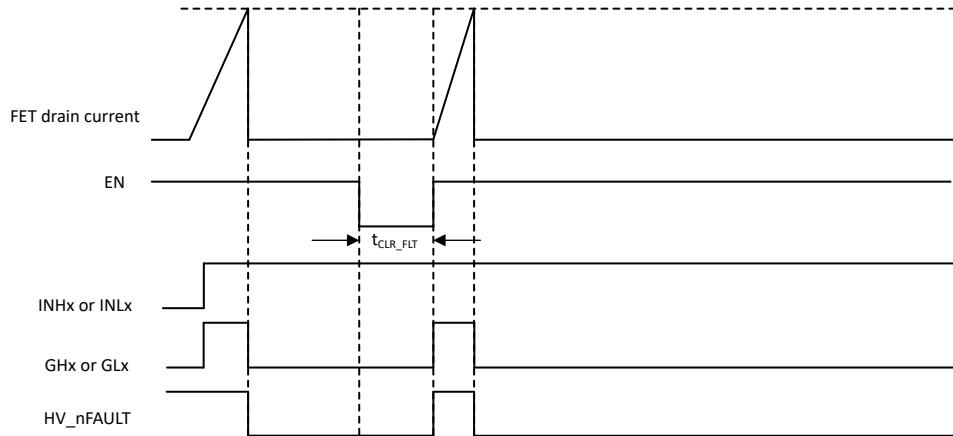

#### 12.4.4 GaNFET 過電流保護

DRV7308 は、ハイサイドおよびローサイド GaN FET ごとに過電流保護を内蔵しており、GaN FET の VDS を監視します。任意の時点で、GaN FET 電流が  $I_{OCP\_GaN}$  を超えると、すべての内蔵 GaNFET は GaN FET プリドライバをオフにすることでオフになり、EN ピンの 20 $\mu$ s から 40 $\mu$ s へのトグル パルスまたは GVDD 電源リサイクルによってクリアされるまでラッチされます。nFAULT ピンを Low に駆動することにより、過電流イベントが通知されます。

図 12-9. GaNFET 過電流保護

#### 12.4.5 サーマルシャットダウン(OTS)

GaN FET 付近のダイ温度がサーマルシャットダウン制限 ( $T_{OTSD}$ ) のトリップポイントを上回ると、すべての GaNFET が無効になります。nFAULT ピンが Low に駆動されます。ハイサイド GaN FET の温度上昇により OTSD イベントが検出された場合に、過熱状態が解消され、EN ピンの  $20\mu s$  から  $40\mu s$  へのトグルパルスによって、または GVDD 電源リサイクルによってフォルトがクリアされると、通常動作が再開されます (ドライバの動作が再開され、nFAULT ピンが解放されます)。ローサイド GaN FET の温度上昇により OTSD イベントが検出された場合に、過熱状態が解消されると、通常動作が再開されます。

## 13 アプリケーションと実装

### 注

以下のアプリケーション情報は、テキサス・インスツルメンツの製品仕様に含まれるものではなく、テキサス・インスツルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。また、お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 13.1 アプリケーション情報

DRV7308 は、主に 3 相ブラシレス DC モーター制御のアプリケーションで使用されます。「」の設計手順では、DRV7308 デバイスの使用方法と設定方法を中心に説明します。

### 13.2 代表的なアプリケーション

#### 13.2.1 アプリケーション

図 13-1 に、DRV7308 の代表的な 3 相モーター ドライブ アプリケーションの図を示します。

図 13-1. DRV7308 の代表的なアプリケーション回路

### 13.2.1.1 アプリケーション情報

表 13-1 に、ドライバの外付け部品の推奨値を示します。

表 13-1. DRV7308 の外付け部品

| 部品                 | PIN1  | PIN2 | 推奨                                   |

|--------------------|-------|------|--------------------------------------|

| C <sub>VM1</sub>   | VM    | GND  | X5R または X7R、0.1μF、VM 定格コンデンサ         |

| C <sub>VM2</sub>   | VM    | GND  | X5R または X7R、0.1μF、VM 定格コンデンサ（オプション）  |

| C <sub>VM3</sub>   | VM    | GND  | ≥ 10μF、VM 定格コンデンサ                    |

| C <sub>GVDD1</sub> | GVDD  | GND  | X5R または X7R、0.1μF、GVDD 定格コンデンサ       |

| C <sub>GVDD2</sub> | GVDD  | GND  | ≥ 10μF、GVDD 定格コンデンサ                  |

| C <sub>BOOTA</sub> | BOOTA | OUTA | X5R または X7R、1μF ~ 220μF、GVDD 定格コンデンサ |

| C <sub>BOOTB</sub> | BOOTB | OUTB | X5R または X7R、1μF ~ 220μF、GVDD 定格コンデンサ |

| C <sub>BOOTC</sub> | BOOTC | OUTC | X5R または X7R、1μF ~ 220μF、GVDD 定格コンデンサ |

| R <sub>SR</sub>    | SR    | GND  | スルーレート設定を決定するための抵抗                   |

表 13-1. DRV7308 の外付け部品 (続き)

| 部品                    | PIN1                | PIN2                 | 推奨                                                                                                                                                                              |

|-----------------------|---------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R <sub>nFAULT</sub>   | nFAULT              | 3.3V/ 5.5V / GVDD    | 5.1kΩ、プルアップ抵抗                                                                                                                                                                   |

| R <sub>ILM1</sub>     | ILIMIT              | 3.3V/ 5.5V / GVDD    | 必要な ILIMIT スレッショルドに基づいています                                                                                                                                                      |

| R <sub>ILM2</sub>     | ILIMIT              | GND                  | 必要な ILIMIT スレッショルドに基づいています                                                                                                                                                      |

| R <sub>VTEMP</sub>    | VTEMP               | システム                 | オプション。VTEMP 出力フィルタ抵抗。100Ω、およびアプリケーションによって異なります。                                                                                                                                 |

| C <sub>VTEMP</sub>    | VTEMP               | GND                  | オプション。VTEMP 出力フィルタコンデンサ < 130pF。                                                                                                                                                |

| R <sub>AMP_G2</sub>   | AMPOUT              | AMPIN+               | アンプ ゲイン抵抗 2。アプリケーションによって異なります。                                                                                                                                                  |

| R <sub>AMP_G1</sub>   | AMPIN+              | V <sub>AMP_REF</sub> | アンプ ゲイン抵抗 1。アプリケーションによって異なります。                                                                                                                                                  |

| R <sub>S</sub>        | SLx (SP)            | GND(SN)              | モーター位相電流を測定するローサイド Rshunt 抵抗 (I <sub>LS_PHASE</sub> )。予測される電流センス出力電圧 = R <sub>S</sub> × I <sub>LS_PHASE</sub> × R <sub>AMP_G2</sub> /R <sub>AMP_G1</sub> + V <sub>AMP_REF</sub> |

| V <sub>CC1</sub>      | システム                | GND                  | システム I/O リファレンス電圧。3.3V、5V、または GVDD                                                                                                                                              |

| V <sub>CC2</sub>      | システム                | GND                  | システム I/O リファレンス電圧。3.3V、5V。VCC1 が 5V を上回る場合にのみ、VCC2 を VCC1 から分離する必要があります。                                                                                                        |

| V <sub>AMP_bias</sub> | R <sub>AMP_G2</sub> | システム                 | オプション。システム電流センス測定バイアス電圧                                                                                                                                                         |

### 注

TI は、未使用の場合でも、nFAULT ピンにプルアップを接続することを推奨します。

#### 13.2.2 アプリケーション曲線

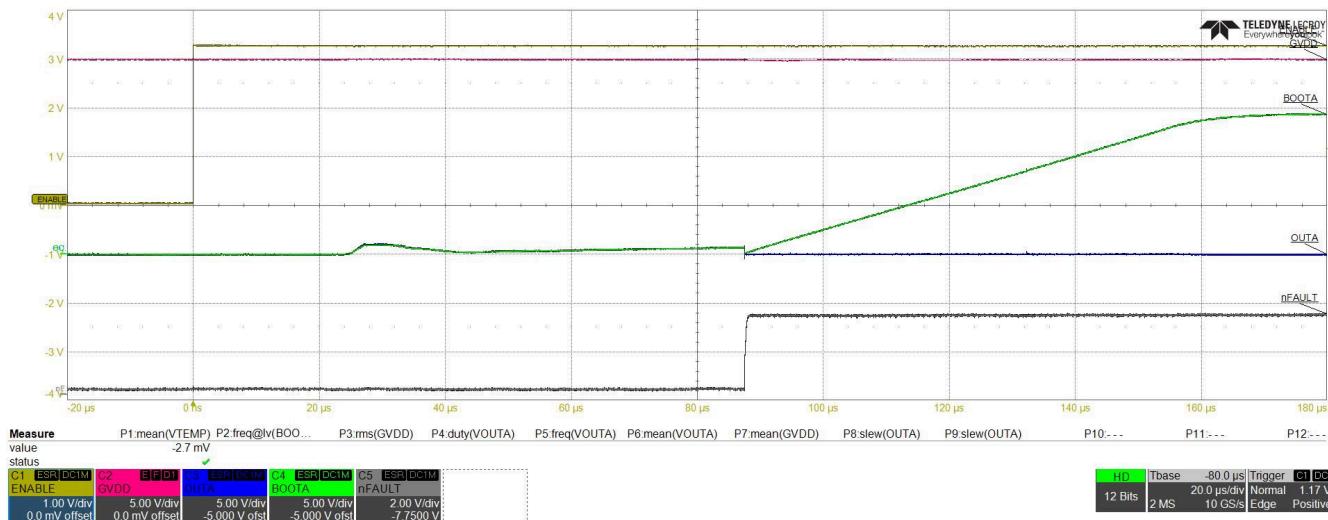

図 13-2. デバイスパワーアップ (EN ピン Low から High)

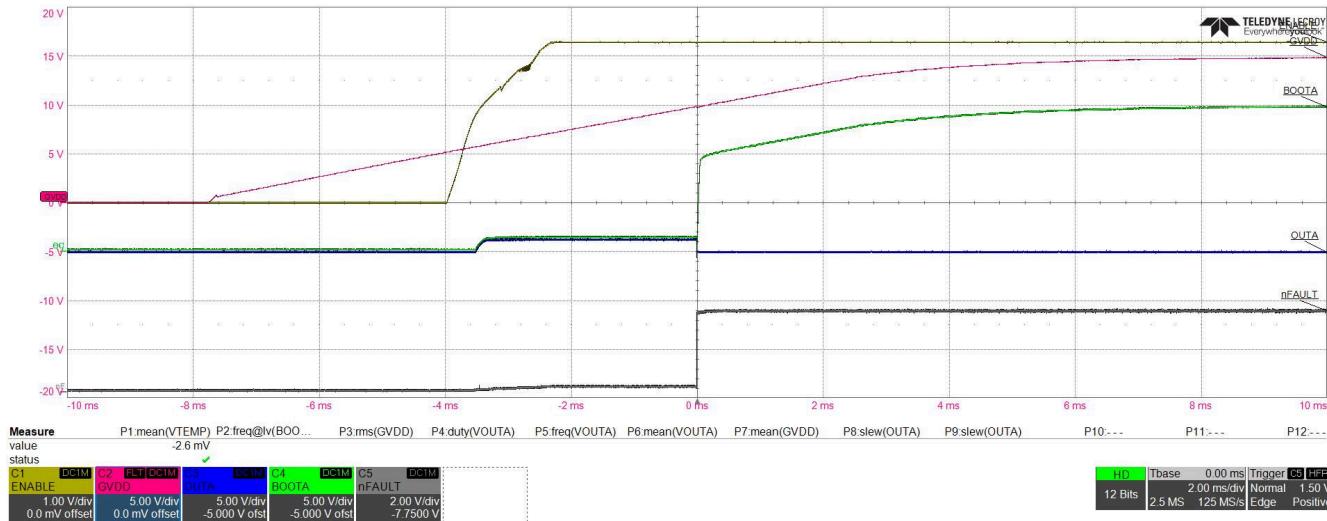

図 13-3. デバイス パワー アップ (GVDD 起動)

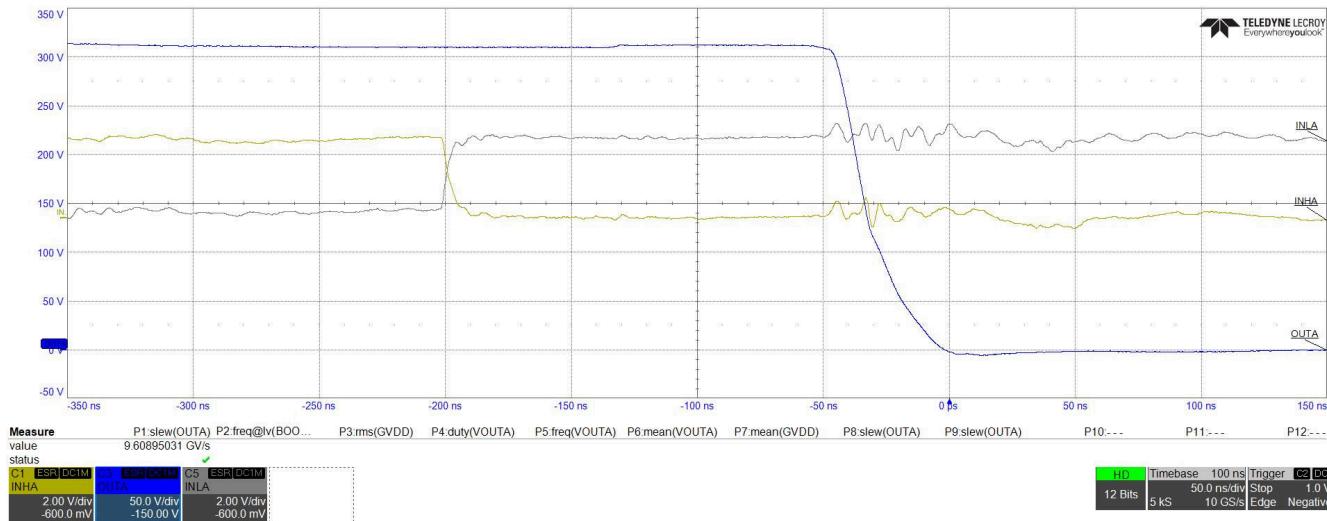

図 13-4. モーター位相ノード OUTA スイッチング - 立ち下がりエッジ (モーター負荷からデバイスへの位相電流)

図 13-5. モーター位相ノード OUTA スイッチング - 立ち上がりリエッジ (モーター負荷からデバイスへの位相電流)

図 13-6. モーター位相ノード OUTA スイッチング - 立ち下がりリエッジ (デバイスからモーター負荷への位相電流)

図 13-7. モーター位相ノード OUTA スイッチング - 立ち上がりエッジ (モーター負荷からデバイスへの位相電流)

図 13-8. モーターの位相ノード出力スイッチング - ハイサイド GaN FET 第 3 象限動作 (モーター負荷からデバイスへの位相電流)

図 13-9. モーターの位相ノード出力スイッチング - ローサイド GaN FET 第 3 象限動作 (デバイスからモーター負荷への位相電流)

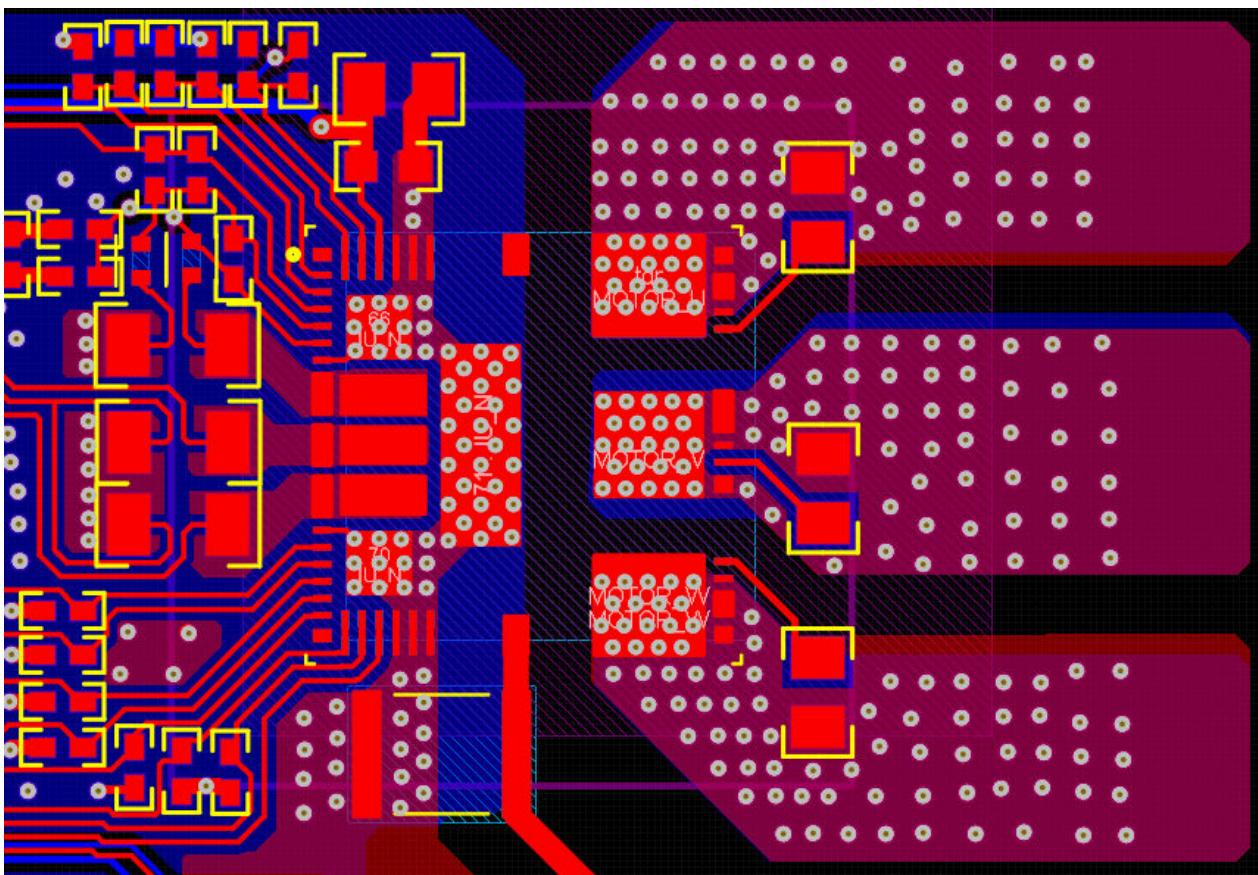

## 14 レイアウト

### 14.1 レイアウトのガイドライン

バルクコンデンサは、モータードライバデバイスを通る大電流パスの距離ができるだけ短くなるように配置する必要があります。接続用の金属パターンはできる限り幅を広くし、PCB層を接続する際には多数のビアを使用する必要があります。これらの手法により、インダクタンスが最小限に抑えられ、バルクコンデンサが大電流を供給できるようになります。

GVDDデカッピングコンデンサ、VMピンからGNDへの高周波コンデンサなどの小さい値のコンデンサ、ブートストラップコンデンサは、デバイスピンの近くに配置する必要があります。

電源ループ面積を最小化するには、シャント抵抗をデバイスのSLxピンの近くに配置し、シャント抵抗の端に銅ポリゴンを使用して、電流パックをVMピンのデカッピングコンデンサに上層のより広いパターンで戻すか、下層の十分な数のステイチングビアを使って銅ポリゴンを通します。

熱性能を高めるため、OUTxとGNDの回路の銅プレーンを最大化します。[図14-1](#)に示されているように、熱性能を最大化するには、OUTxパッドとGNDパッドに複数のステイチングビアを使用し、上層と下層により大きな銅プレーンを使用します。

VMピンのデカッピングコンデンサは、任意の側のVMピンに、または両方のピンに接続できます。VMピンはデバイス内で内部的に短絡しているため、PCB上で外部から短絡する必要はありません。

### 14.2 レイアウト例

図 14-1. VQFN パッケージの推奨レイアウト

## 15 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision * (May 2024) to Revision A (October 2025) | Page |

|-----------------------------------------------------------------|------|

| • デバイスのステータスを「量産データ」に更新。.....                                   | 1    |

## 16 デバイスおよびドキュメントのサポート

テキサス・インスツルメンツでは、幅広い開発ツールを提供しています。デバイスの性能の評価、コードの生成、ソリューションの開発を行うためのツールとソフトウェアを以下で紹介します。

### 16.1 ドキュメントのサポート

#### 16.1.1 関連資料

- テキサス・インスツルメンツ、『放熱性能向上のための DRV7308 を使用したレイアウト設計ガイド』アプリケーションノート

- テキサス・インスツルメンツ、『3 相統合型 GaN テクノロジーによりモータードライブ性能を最大化する方法』、ホワイトペーパー

- テキサス・インスツルメンツ、『DRV7308 評価基板 ユーザー ガイド』

- テキサス・インスツルメンツ、『GaN ベースのモーター システム設計で家電製品のエネルギー効率を改善し、コストを削減』、技術資料

- テキサス・インスツルメンツ、『電力損失とデバイス温度を推定するための DRV7308 の温度計算ツール、設計ツール、シミュレーション』

### 16.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 16.3 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの使用条件を参照してください。

### 16.4 商標

テキサス・インスツルメンツ E2E™ is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

### 16.5 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことをお勧めします。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 16.6 用語集

#### テキサス・インスツルメンツ用語集

この用語集には、用語や略語の一覧および定義が記載されています。

## 17 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのプラウザ版を使用している場合は、画面左側の説明をご覧ください。

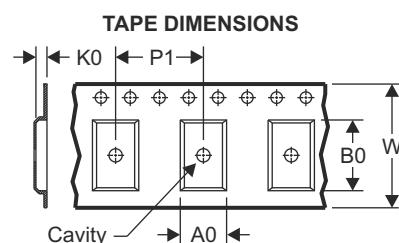

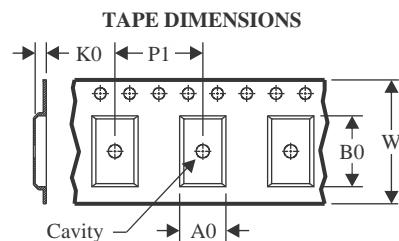

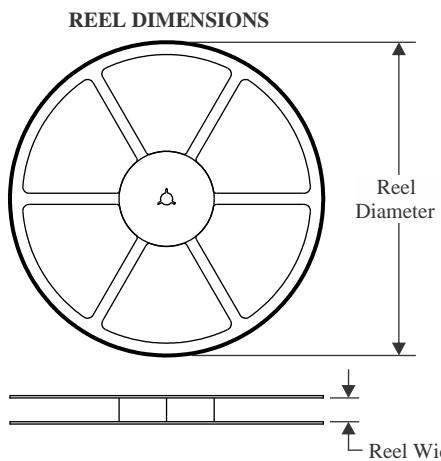

## 17.1 テープおよびリール情報

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

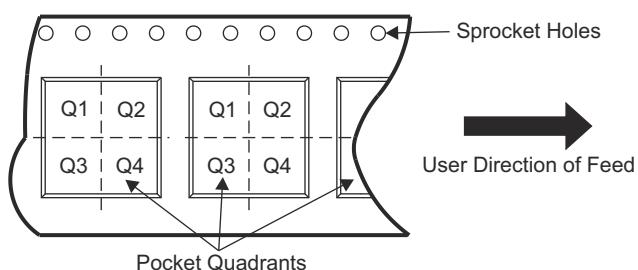

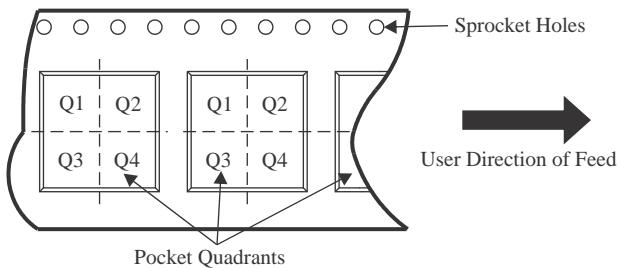

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| デバイス         | パッケージタイプ | パッケージ図 | ピン | SPQ  | リール直径 (mm) | リール幅 W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | ピン1の象限 |

|--------------|----------|--------|----|------|------------|--------------|---------|---------|---------|---------|--------|--------|

| DRV7308HRENR | VQFN     | REN    | 65 | 2000 | 330.0      | 24.4         | 12.4    | 12.4    | 1.5     | 1.5     | 24.4   | Q1     |

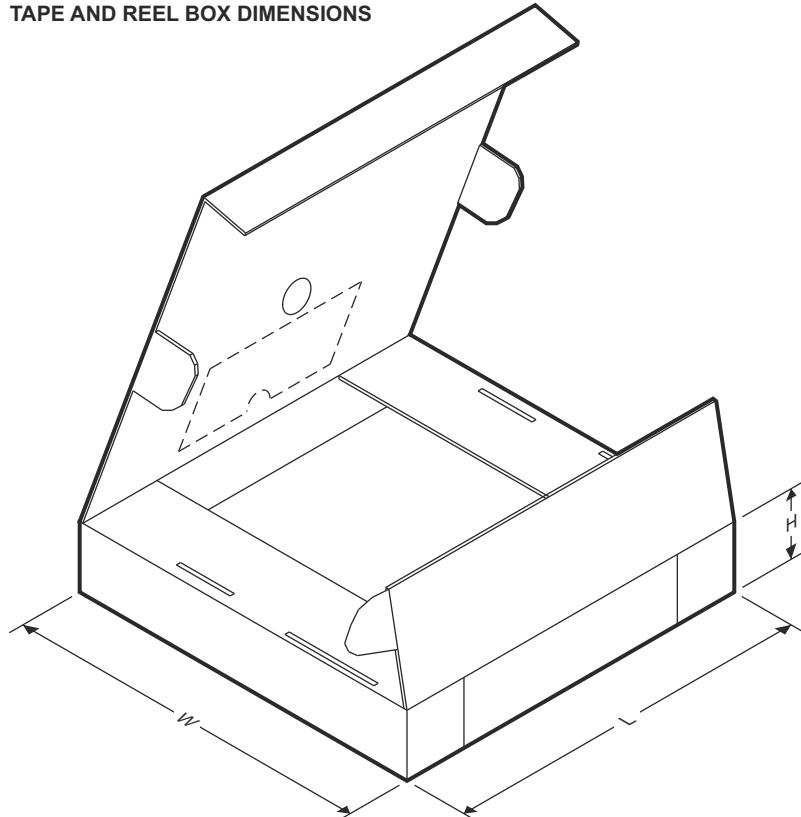

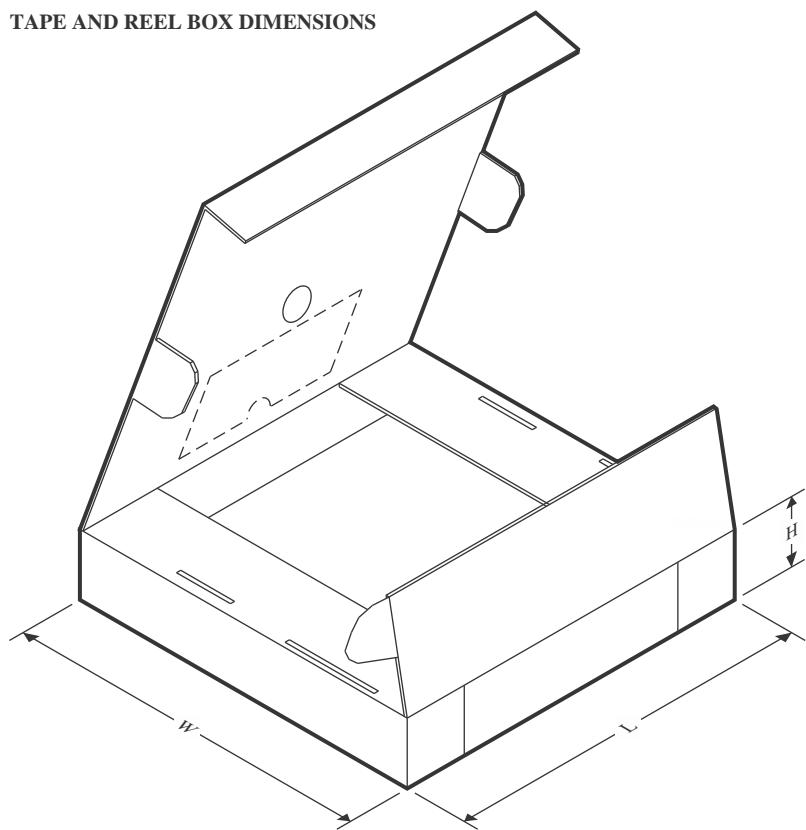

## TAPE AND REEL BOX DIMENSIONS

| デバイス         | パッケージタイプ | パッケージ図 | ピン | SPQ  | 長さ (mm) | 幅 (mm) | 高さ (mm) |

|--------------|----------|--------|----|------|---------|--------|---------|

| DRV7308HRENR | VQFN     | REN    | 65 | 2000 | 12.4    | 12.4   | 1.5     |

**REN0065A**

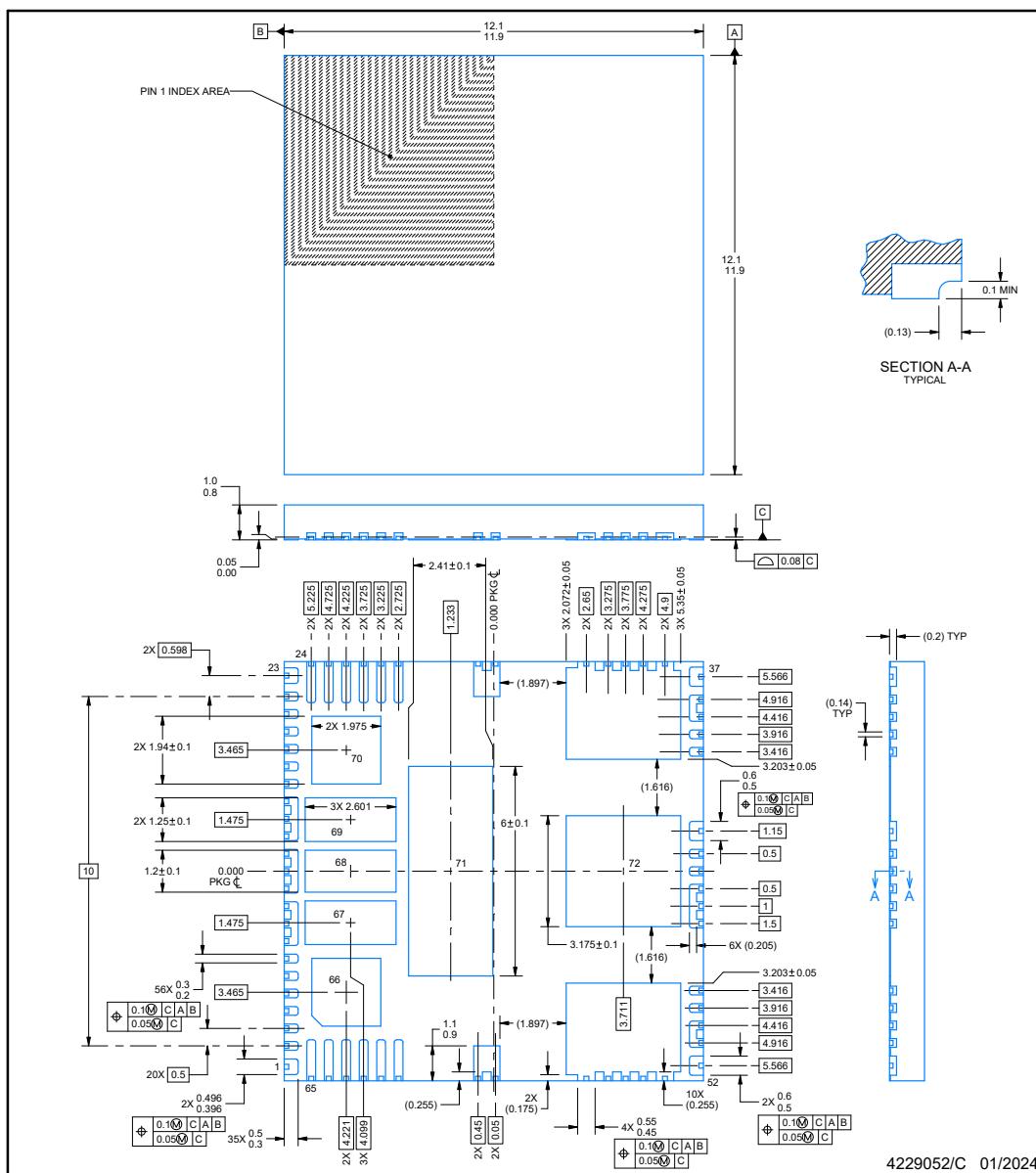

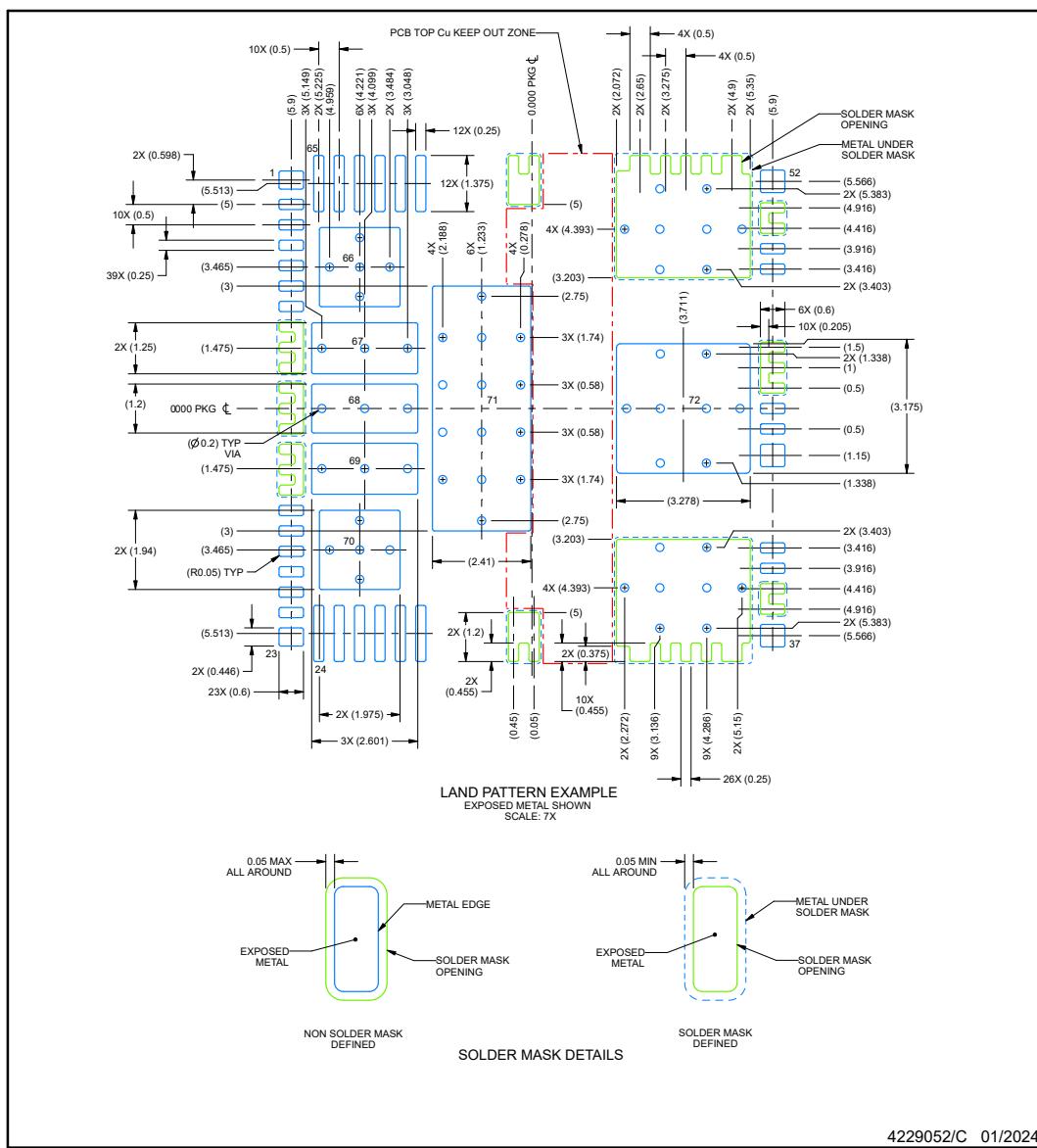

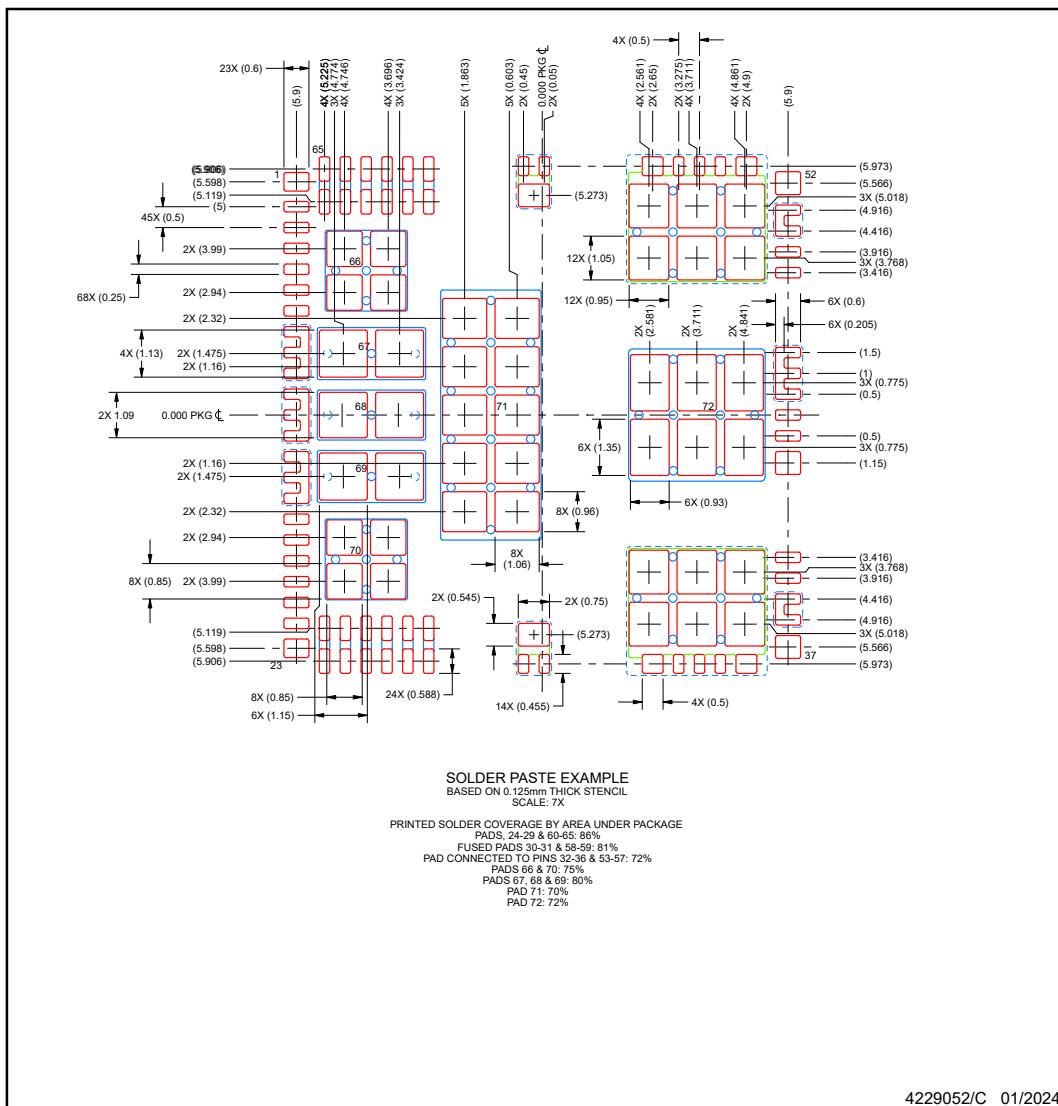

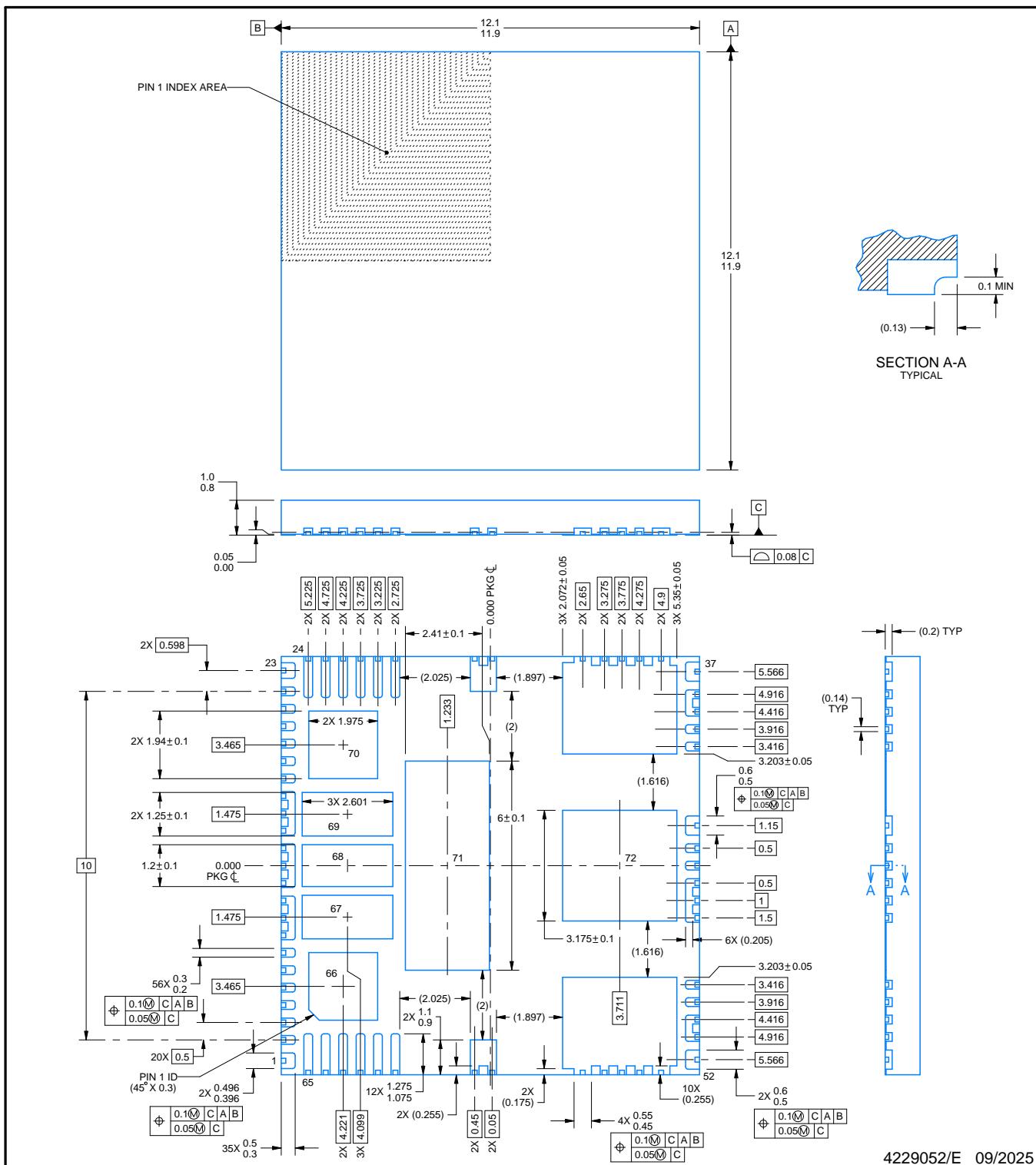

## **PACKAGE OUTLINE**

## **VQFN - 1 mm max height**

PLASTIC QUAD FLATPACK - NO LEAD

**NOTES:**

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. The package thermal pad(s) must be soldered to the printed circuit board for thermal and mechanical performance.

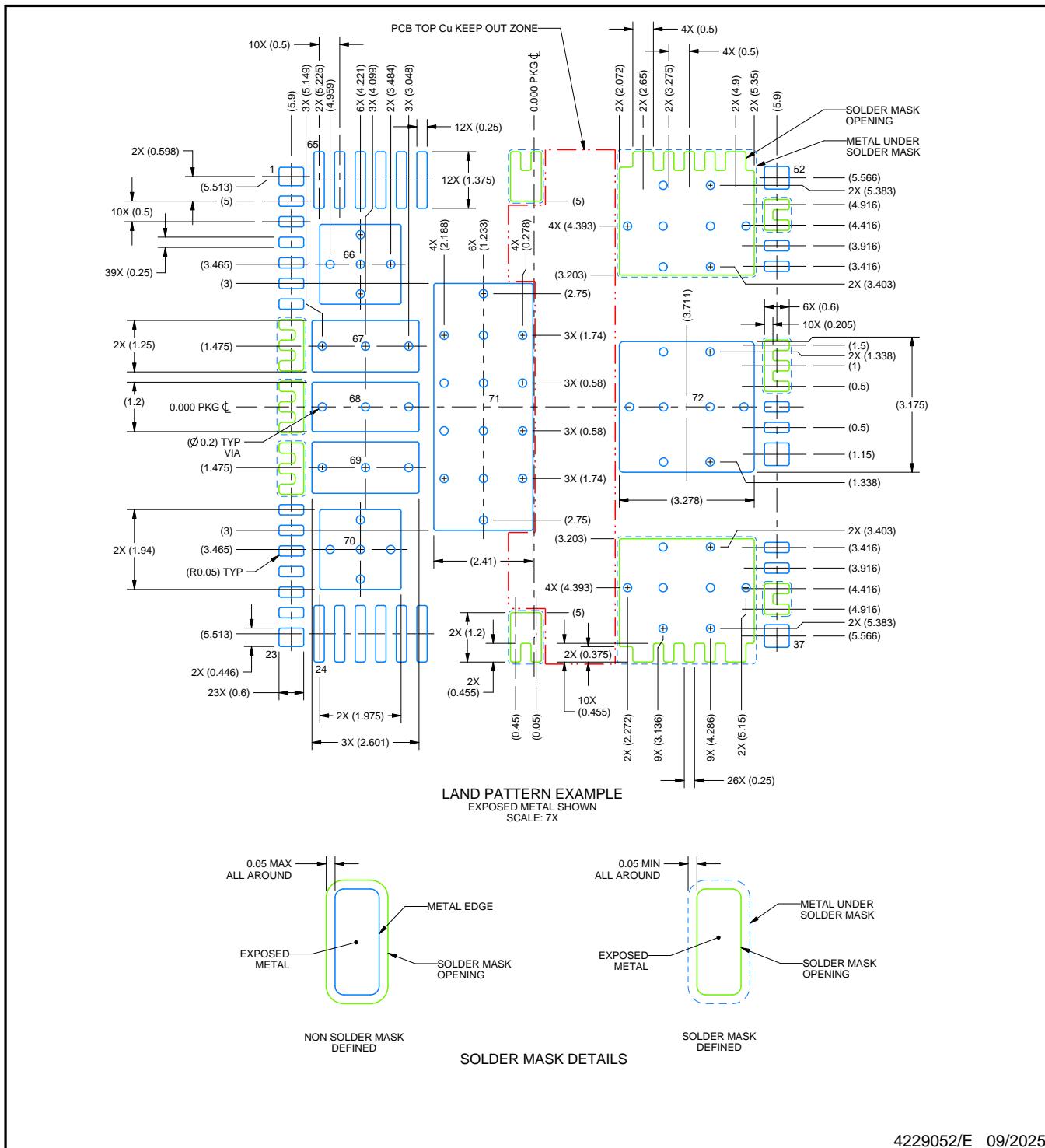

**REN0065A****EXAMPLE BOARD LAYOUT****VQFN - 1 mm max height**

PLASTIC QUAD FLATPACK - NO LEAD

## REN0065A

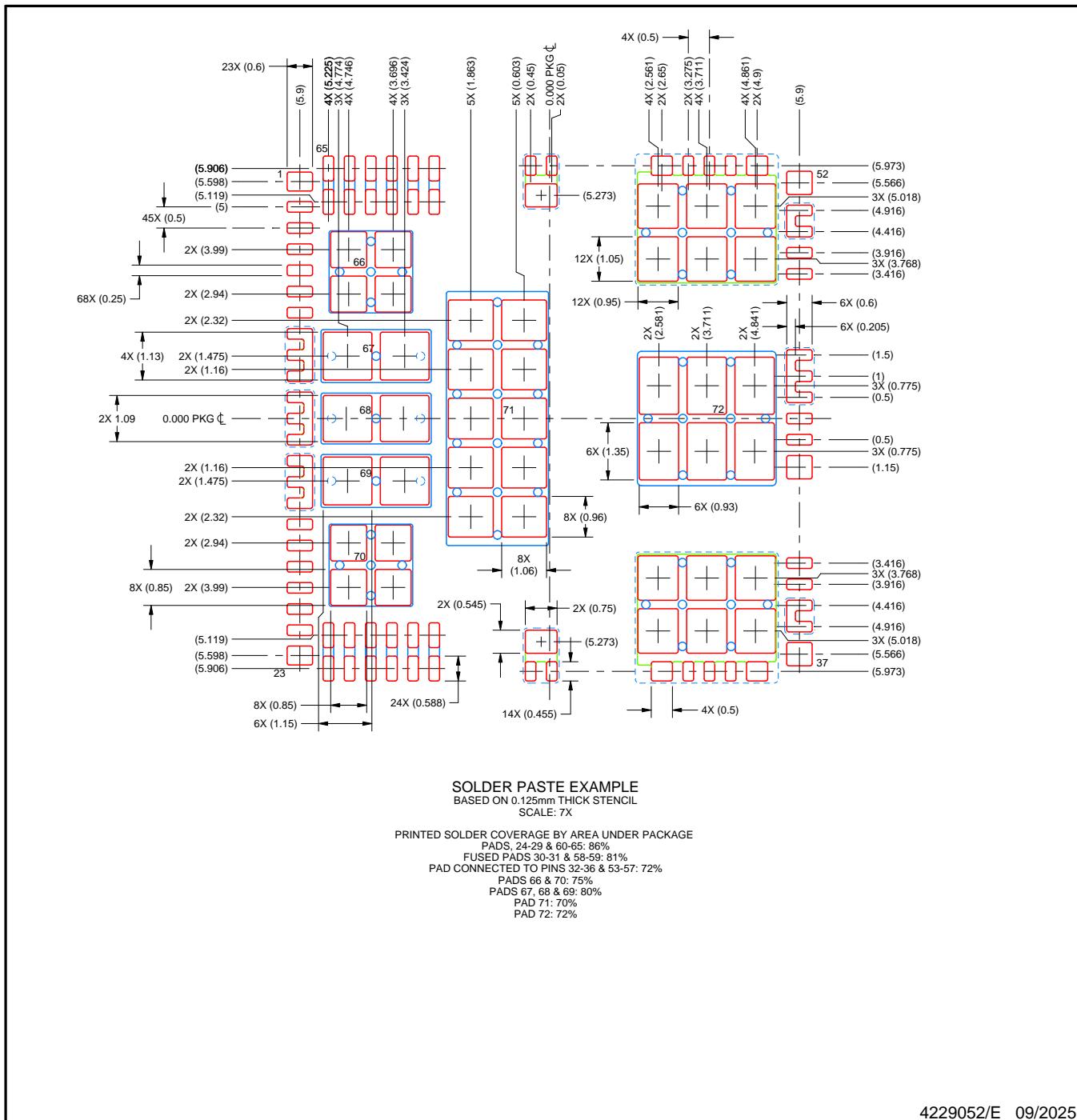

## EXAMPLE STENCIL DESIGN

VQFN - 1 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins  | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|-----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| DRV7308RENR           | Active        | Production           | VQFN (REN)   65 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-3-260C-168HRS               | -40 to 125   | 7308 NNNNC          |

| PDRV7308HRENR.A       | Active        | Preproduction        | VQFN (REN)   68 | 3000   LARGE T&R      | -           | Call TI                              | Call TI                           | -40 to 125   |                     |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

## TAPE AND REEL INFORMATION

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|-------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| DRV7308RENR | VQFN         | REN             | 65   | 3000 | 330.0              | 24.4               | 12.3    | 12.3    | 1.1     | 16.0    | 24.0   | Q2            |

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|------|-------------|------------|-------------|

| DRV7308RENR | VQFN         | REN             | 65   | 3000 | 367.0       | 367.0      | 45.0        |

# REN0065A

## PACKAGE OUTLINE

### VQFN - 1 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

## **EXAMPLE BOARD LAYOUT**

**REN0065A**

## VQFN - 1 mm max height

#### **PLASTIC QUAD FLATPACK - NO LEAD**

4229052/E 09/2025

---

**NOTES: (continued)**

- This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 ([www.ti.com/lit/slua271](http://www.ti.com/lit/slua271)).

- Vias are optional depending on application, refer to device data sheet. If some or all are implemented, recommended via locations are shown.

## EXAMPLE STENCIL DESIGN

**REN0065A**

## VQFN - 1 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

## NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2026, Texas Instruments Incorporated

最終更新日：2025 年 10 月