# DS90UH941AS-Q1 2K DSI から FPD-Link III へのブリッジ・シリアライザ、ビデオ分割機能 / HDCP 機能搭載

## 1 特長

- 次の結果で車載アプリケーション用に AEC-Q100 認定済み

- デバイス温度グレード 2:-40°C~+105°C の動作時周囲温度範囲

- 最高 210MHz のピクセル・クロック周波数に対応し、24 ビット色深度で 3K (2880×1620) 30Hz、QXGA (2048×1536)、2K (2880×1080)、WUXGA (1920×1200)、1080p60 (1920×1080) 解像度を実現

- MIPI D-PHY/ディスプレイ・シリアル・インターフェイス (DSI) レシーバにより、ビデオ・プロセッサまたは FPGA と高帯域幅で接続

- それぞれ最大 4 つのデータ・レーンを備えたデュアル DSI 入力ポート

- レーンごとに最大 1.5Gbps

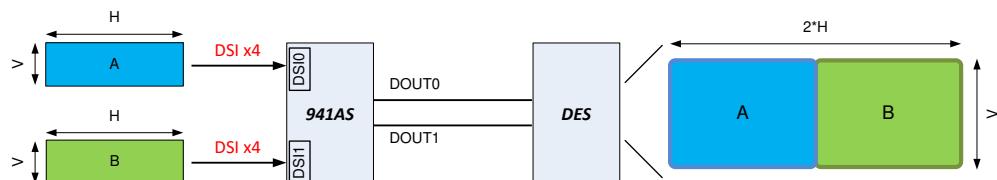

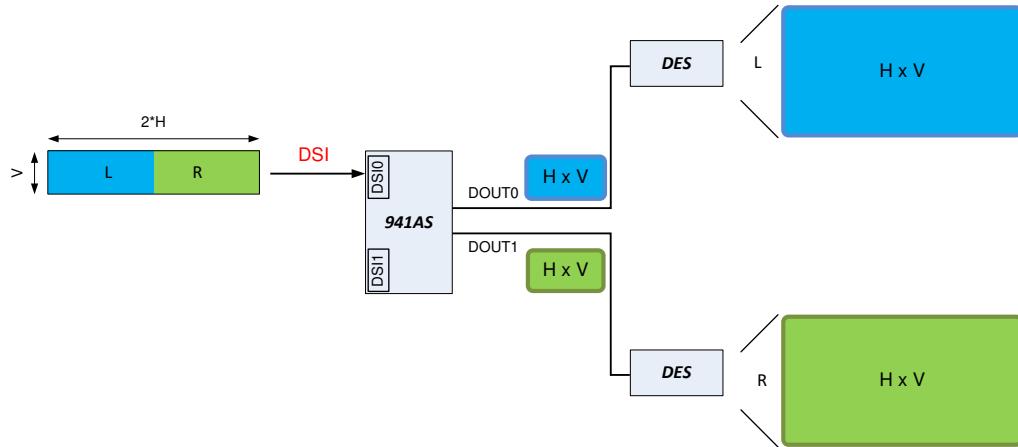

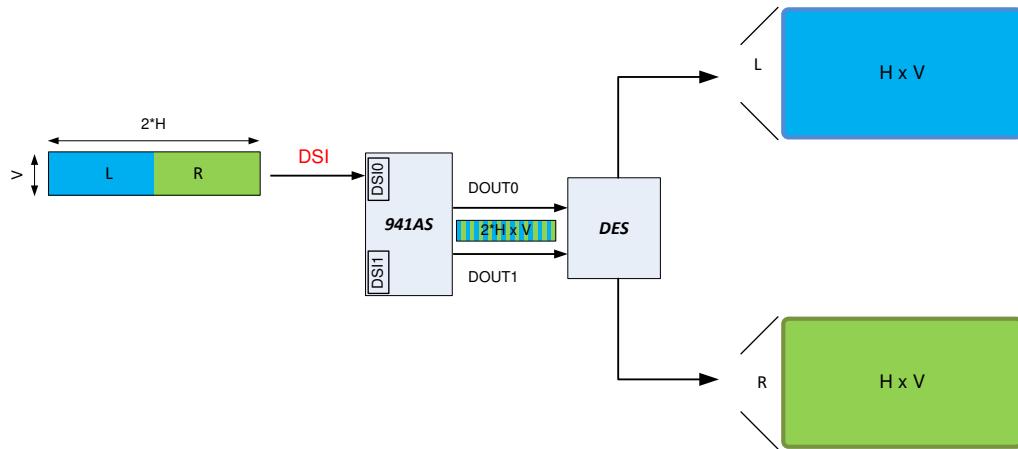

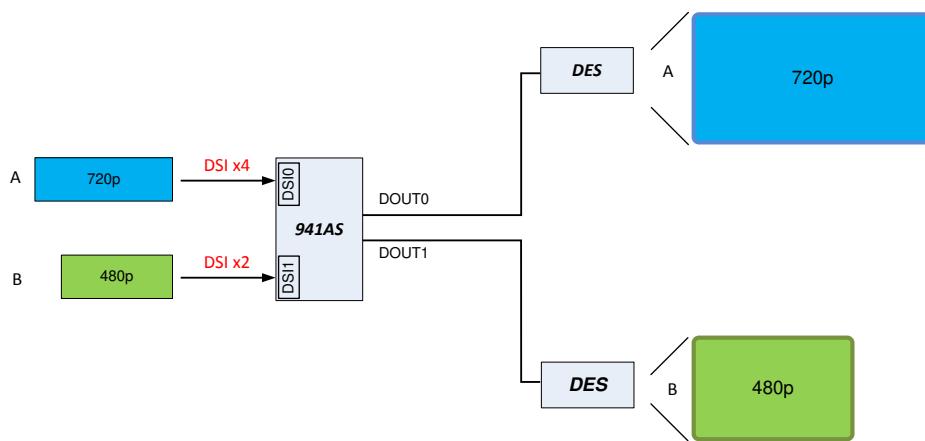

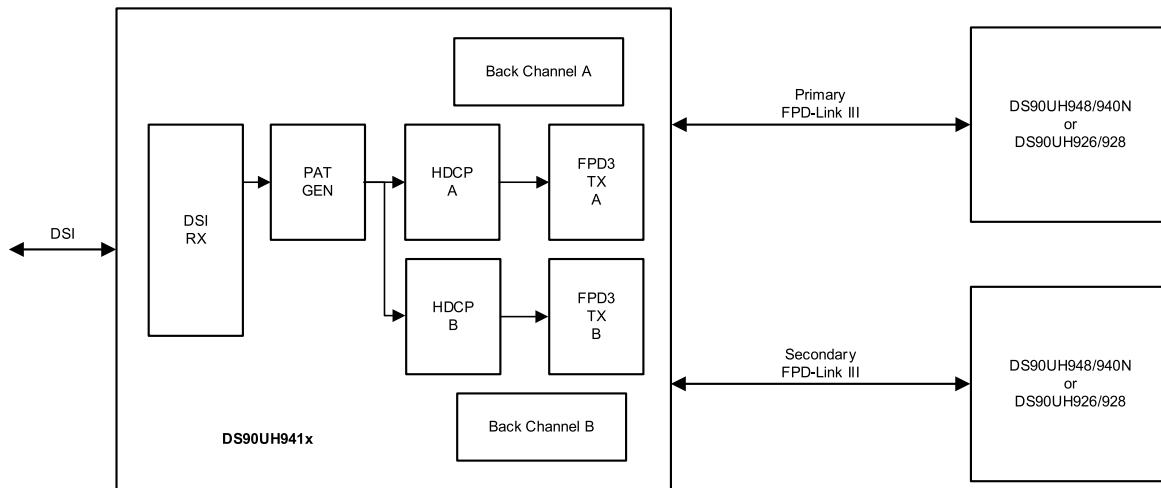

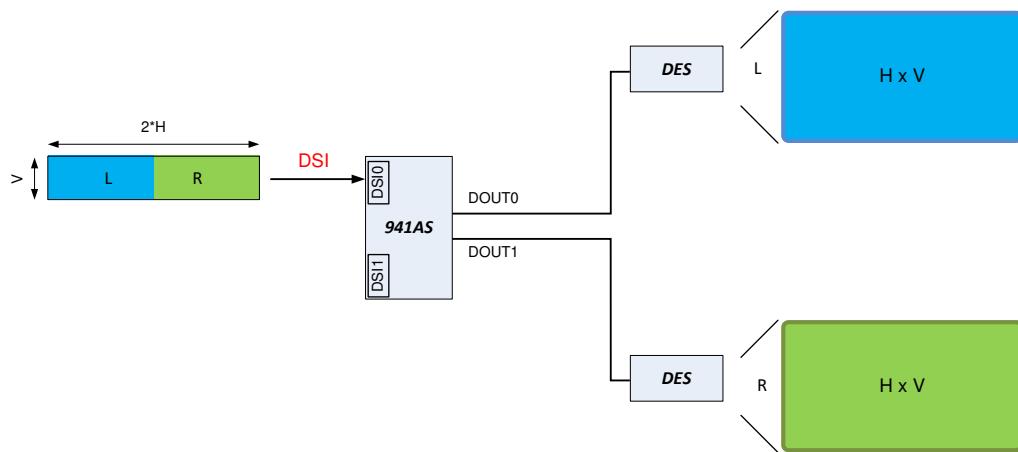

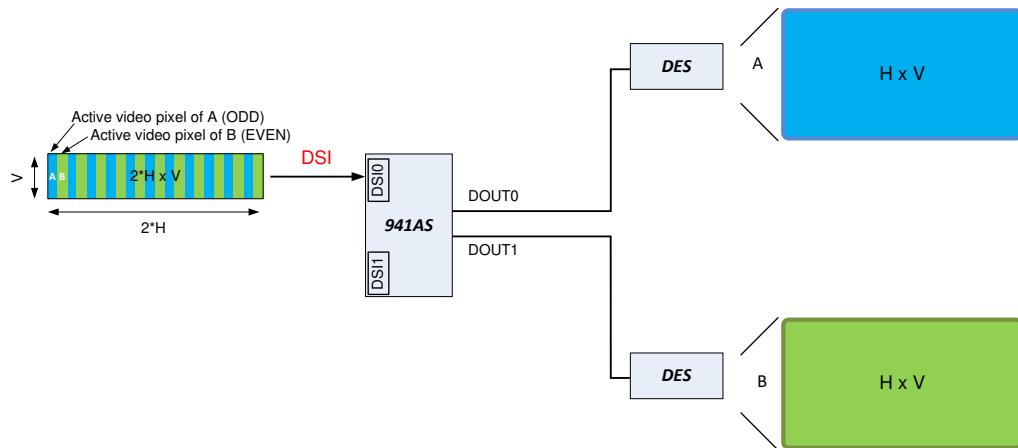

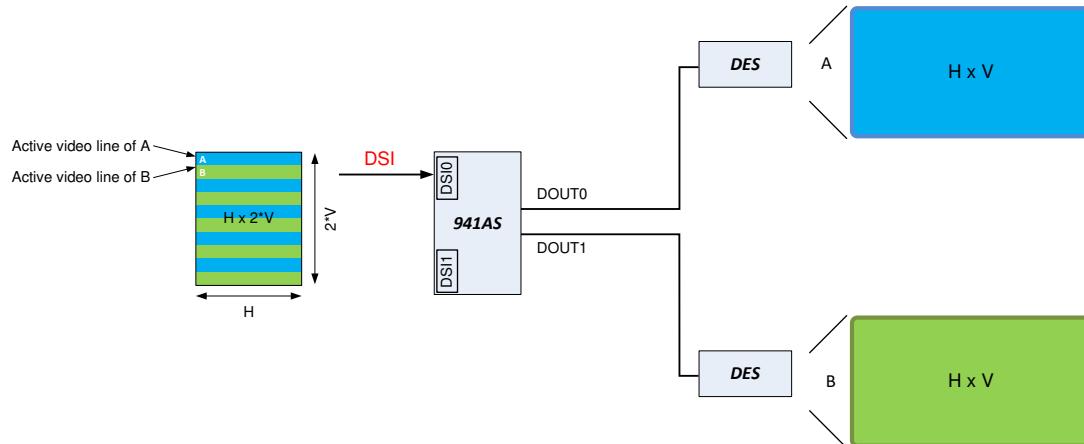

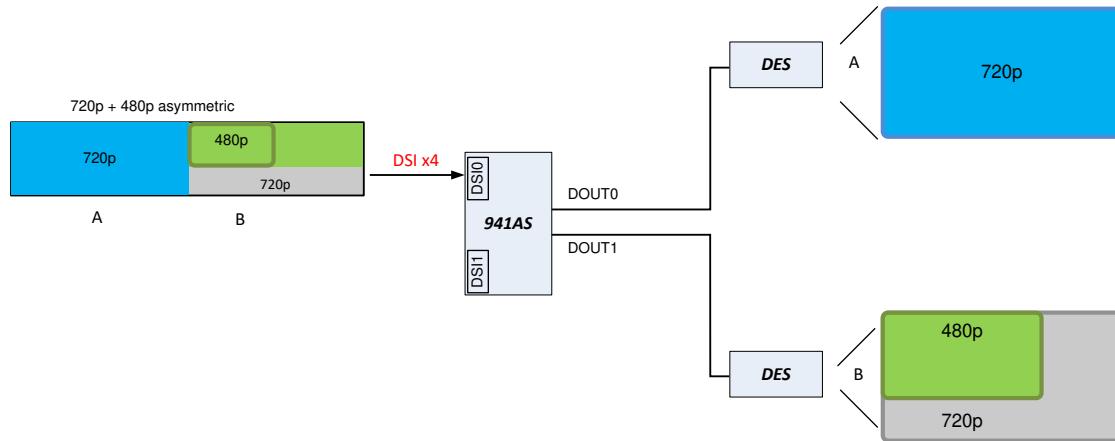

- 対称型および非対称型のパック解除機能を備えたスーパーフレーム

- ECC および CRC 生成

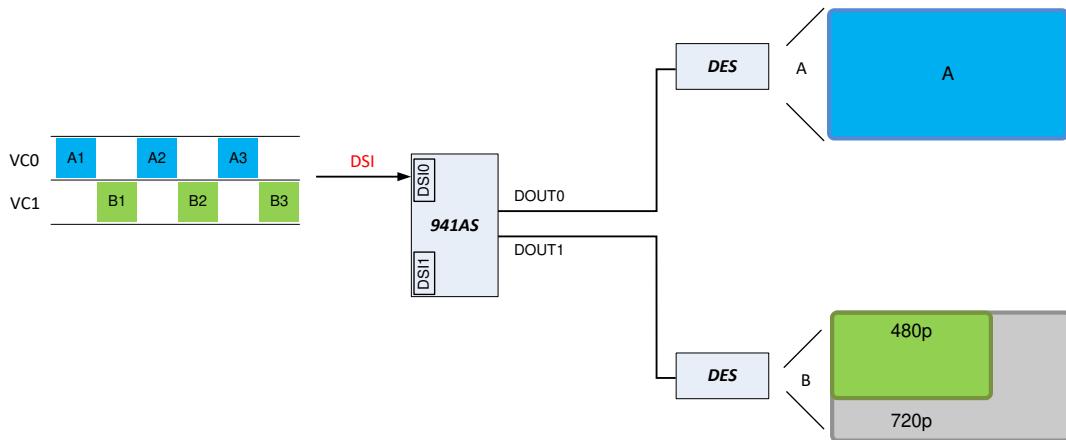

- 仮想チャネル機能

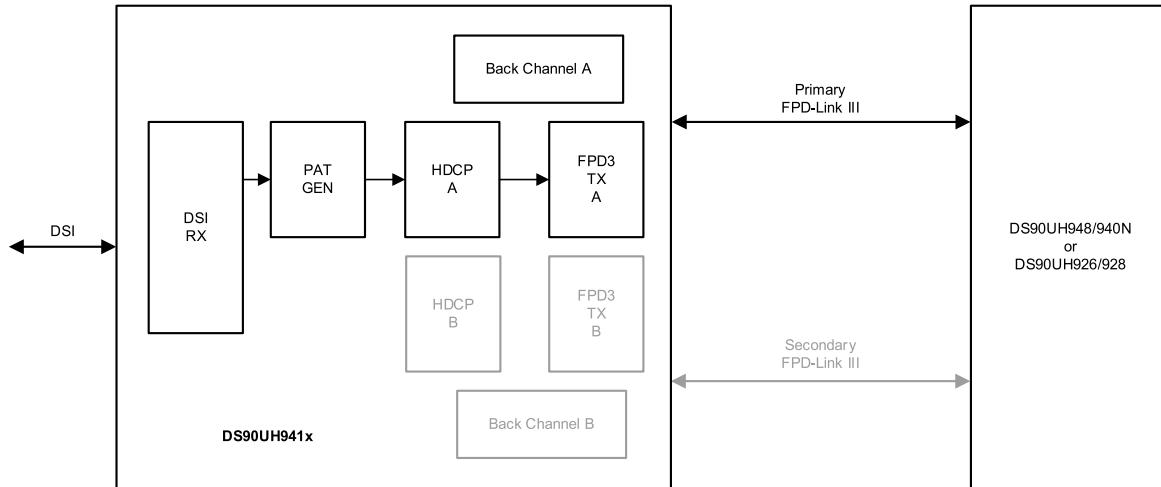

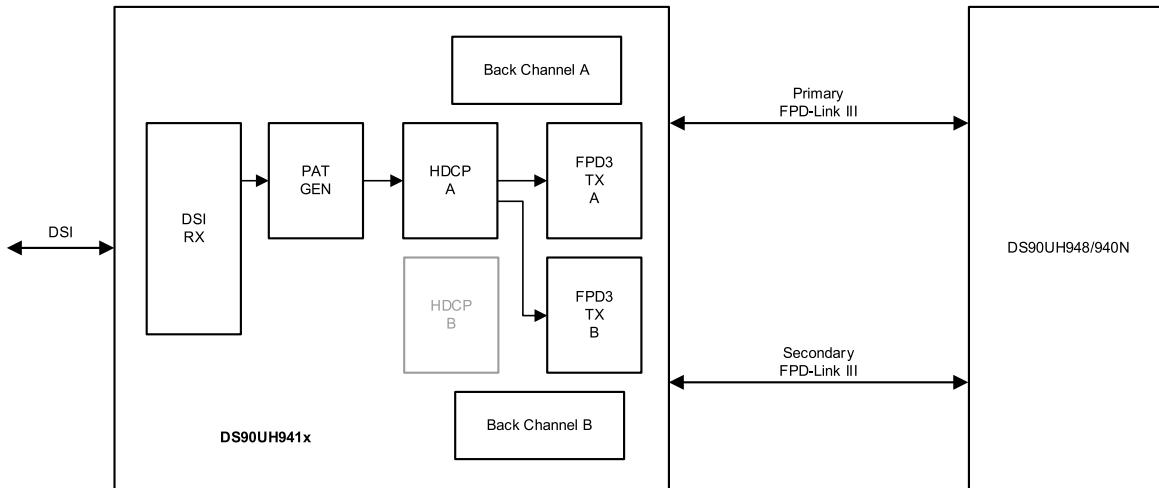

- シングルおよびデュアル FPD-Link III 出力

- シングル・リンク: 最高 105MHz のピクセル・クロック

- デュアル・リンク: 最高 210MHz のピクセル・クロック

- **機能安全対応**

- ISO 26262 システムの設計に役立つ資料を利用可能

- 対称型および非対称型のビデオ分割

- HDCP v1.4 暗号エンジンを内蔵し、キーをオンチップに保存

## 2 アプリケーション

- 車載インフォテインメント

- IVI ヘッド・ユニットおよび HMI モジュール

- 集中情報ディスプレイ

- デジタル計器クラスタ

- リアシート・エンターテインメント・システム

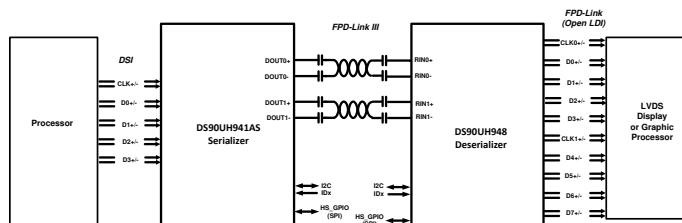

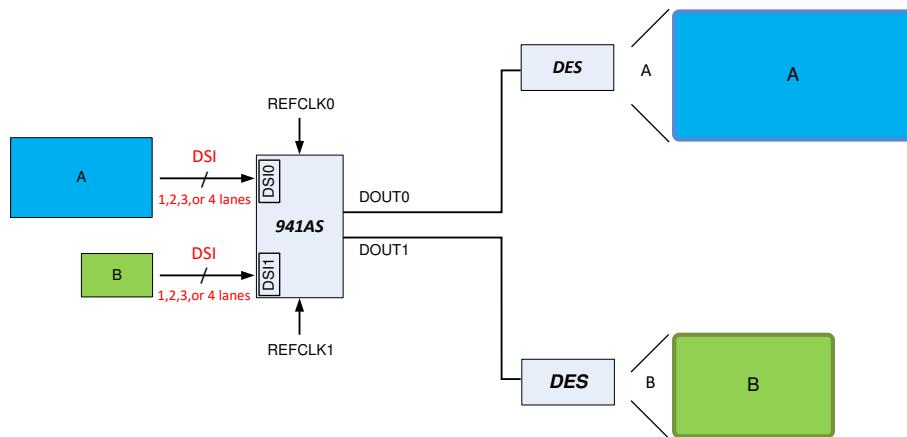

アプリケーション図

## 3 概要

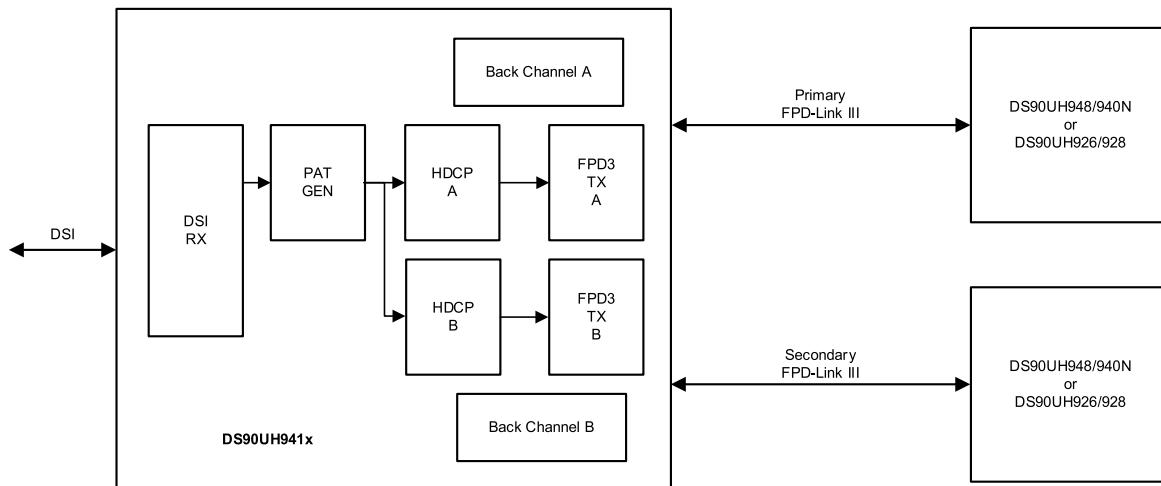

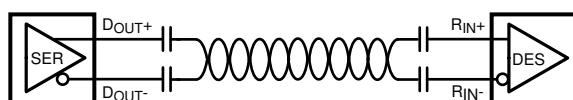

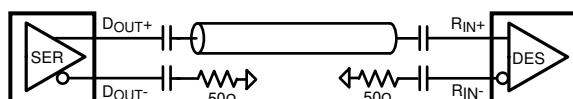

DS90UH941AS-Q1 は、DSI から FPD-Link III へのデュアル・ブリッジ・シリアライザであり、車載用インフォテインメント・アプリケーション用に設計されています。FPD-Link III の DS90UH940N-Q1、DS90UH948-Q1、DS90UH924-Q1、DS90UH926-Q1、DS90UH928-Q1 デシリアライザと組み合わせることで、DS90UH941AS-Q1 は、コスト効率の優れた 50Ω のシングル・エンド同軸ケーブルまたは 100Ω の差動シールド付きツイストペア (STP) およびシールド付きツイスト・カワッド (STQ) ケーブルで 1 または 2 レーンの高速シリアル・ストリームを供給できます。インフォテインメント・システムのディスプレイの数と多様性が増え続けるのに応じて、DS90UH941AS-Q1 は対称型と非対称型の両方の分割に対応できます。

DS90UH941AS-Q1 はビデオ・データを 2 つの差動ペア上に統合できるため、システム設計が簡素化し、アプリケーションの相互接続のサイズと重量が減少します。

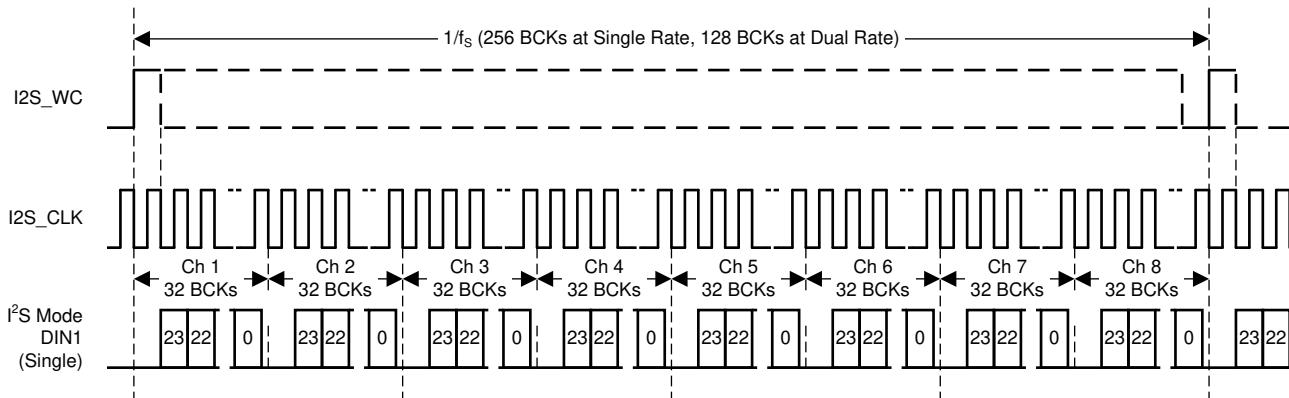

FPD-Link III インターフェイスはビデオおよびオーディオ・データの伝送と、I2C 通信を含む全二重制御をサポートし、同じ高速シリアル・リンク上で最大 8 つの I2S オーディオ・チャネルを使用できます。低電圧の差動信号、データのスクランブル処理、およびランダム化を使用することで、EMI が最小限に抑えられます。

### 製品情報

| 部品番号(1)        | パッケージ     | 本体サイズ (公称)      |

|----------------|-----------|-----------------|

| DS90UH941AS-Q1 | VQFN (64) | 9.00mm × 9.00mm |

(1) 利用可能なパッケージについては、このデータシートの末尾にある注文情報を参照してください。

英語版の TI 製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、必ず最新版の英語版をご参照ください。

## 目次

|                      |    |                        |     |

|----------------------|----|------------------------|-----|

| 1 特長                 | 1  | 8.3 機能説明               | 22  |

| 2 アプリケーション           | 1  | 8.4 デバイスの機能モード         | 40  |

| 3 概要                 | 1  | 8.5 プログラミング            | 58  |

| 4 改訂履歴               | 2  | 8.6 レジスタ・マップ           | 61  |

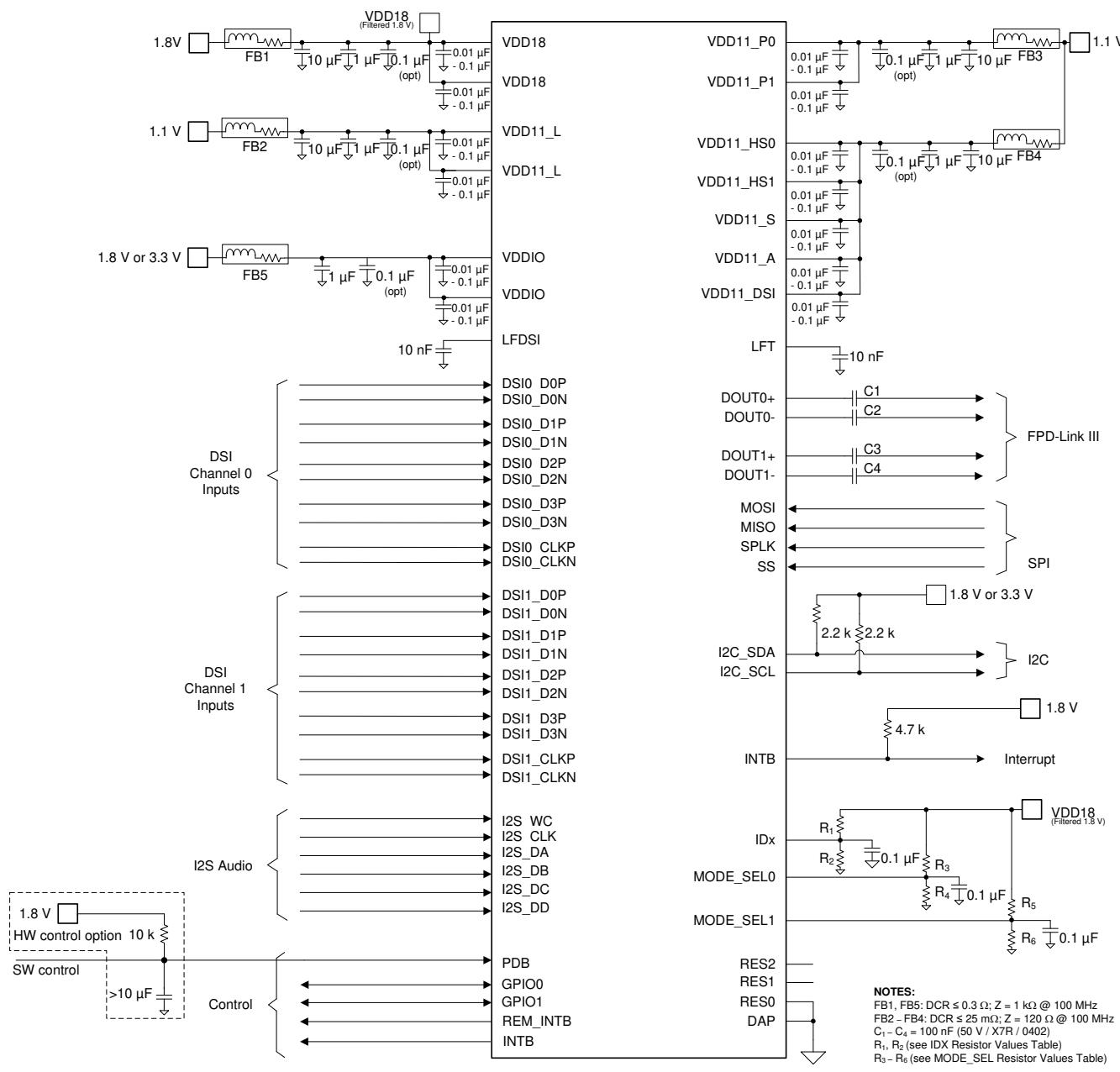

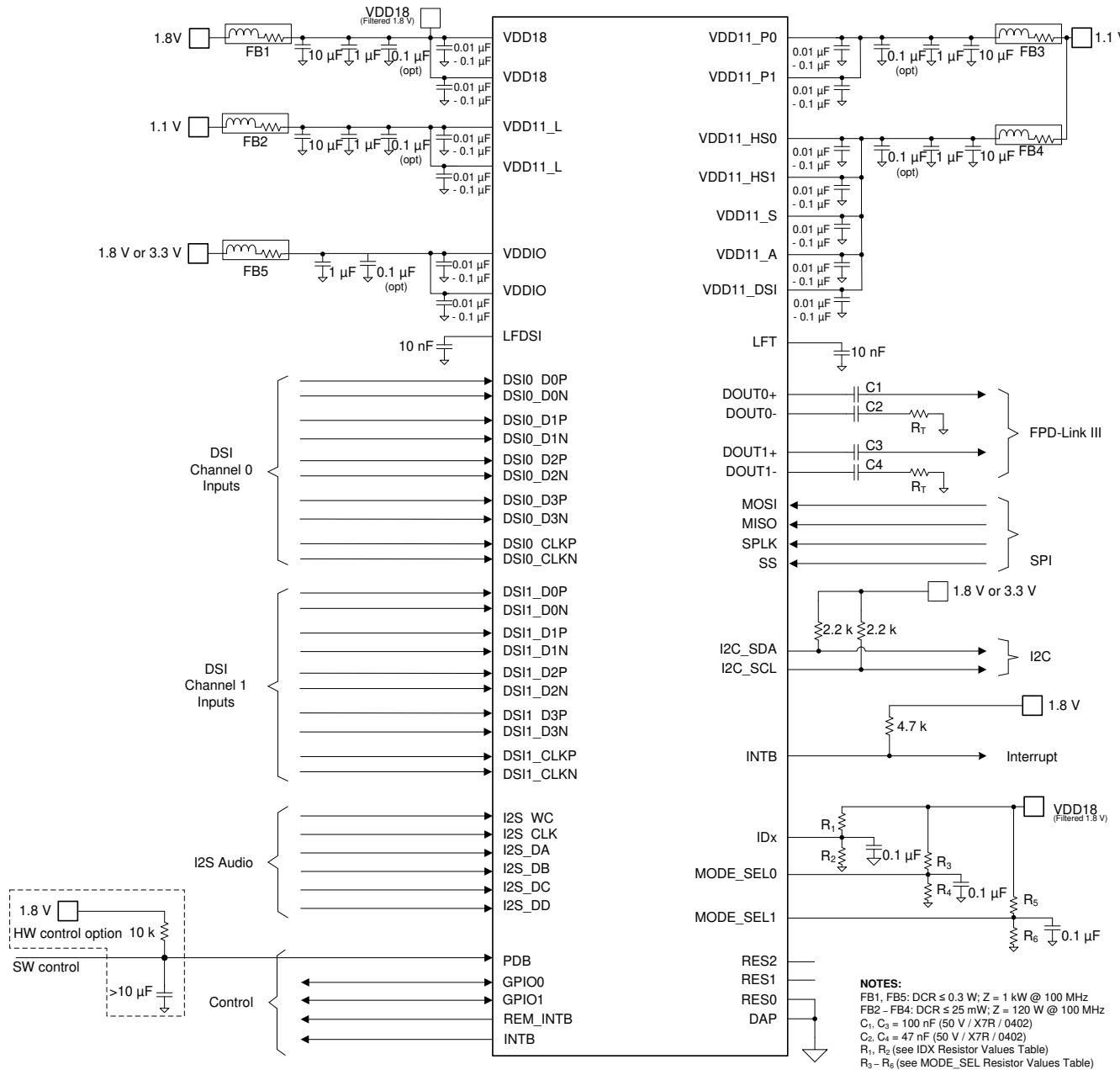

| 5 概要 (続き)            | 4  | 9 アプリケーションと実装          | 148 |

| 6 ピン構成と機能            | 4  | 9.1 アプリケーション情報         | 148 |

| ピン機能                 | 4  | 9.2 代表的なアプリケーション       | 149 |

| 7 仕様                 | 9  | 10 電源に関する推奨事項          | 153 |

| 7.1 絶対最大定格           | 9  | 10.1 VDD 電源            | 153 |

| 7.2 ESD 定格           | 9  | 10.2 パワーアップと初期化        | 153 |

| 7.3 推奨動作条件           | 9  | 11 レイアウト               | 157 |

| 7.4 熱に関する情報          | 10 | 11.1 レイアウトのガイドライン      | 157 |

| 7.5 DC 電気的特性         | 11 | 11.2 レイアウト例            | 159 |

| 7.6 AC 電気的特性         | 16 | 12 デバイスおよびドキュメントのサポート  | 160 |

| 7.7 外部クロック基準の推奨タイミング | 18 | 12.1 ドキュメントのサポート       | 160 |

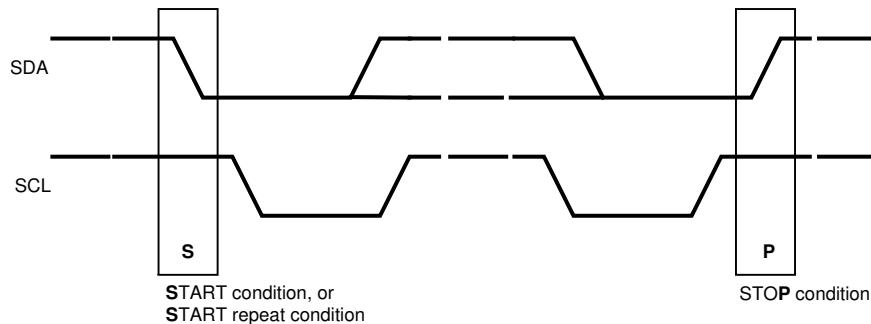

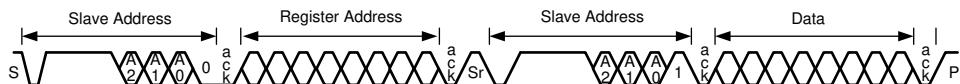

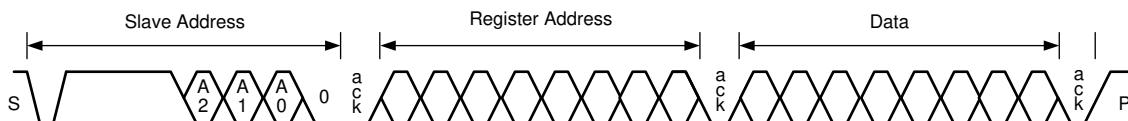

| 7.8 シリアル制御バスの推奨タイミング | 19 | 12.2 サポート・リソース         | 160 |

| 7.9 タイミング図           | 20 | 12.3 商標                | 160 |

| 8 詳細説明               | 22 | 12.4 静電気放電に関する注意事項     | 160 |

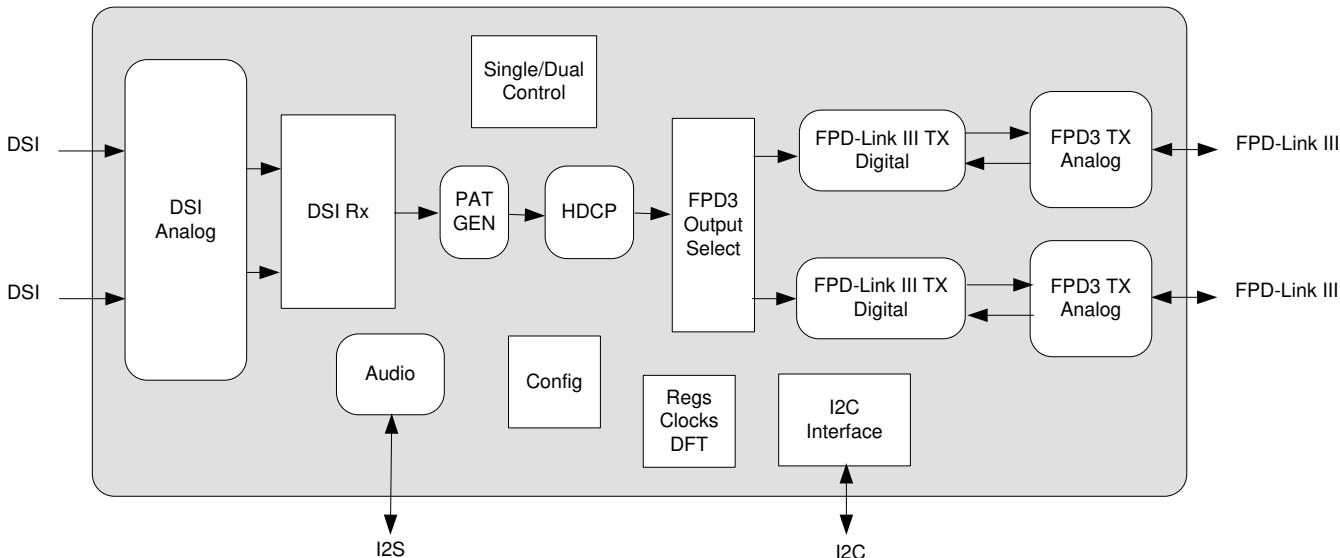

| 8.1 概要               | 22 | 12.5 用語集               | 160 |

| 8.2 機能ブロック図          | 22 | 13 メカニカル、パッケージ、および注文情報 | 161 |

## 4 改訂履歴

| Changes from Revision A (October 2020) to Revision B (January 2021) | Page |

|---------------------------------------------------------------------|------|

| • RES1 ピンの説明を更新。                                                    | 4    |

| • 絶対最大定格の FPD-Link III の出力電圧を 1.32V に更新。                            | 9    |

| • アナログ電圧を 1.32V に更新。                                                | 9    |

| • ESD HBM のその他のピンの定格を $\pm 2500\text{V}$ に変更。                       | 9    |

| • DSI UI の瞬時値の最大値を 6.67ns に変更。                                      | 16   |

| • サポートされる DSI ビデオ形式に注を追加。各ビデオ・ラインは、1 つの DSI パケットとして送信されます。          | 26   |

| • スプリッタ・モードのアプリケーション・レポートへの参照を追加。                                   | 29   |

| • 内部パターン生成のアプリケーション・ノート名を更新。                                        | 39   |

| • レジスタの説明に合わせてクロック・モードの説明を変更。                                       | 40   |

| • 2:2 モードのサンプル・コードを修正。                                              | 49   |

| • -Q1 を含むようにデバイス名を更新。                                               | 49   |

| • レプリケート・モードを有効化する方法を明確化。                                           | 50   |

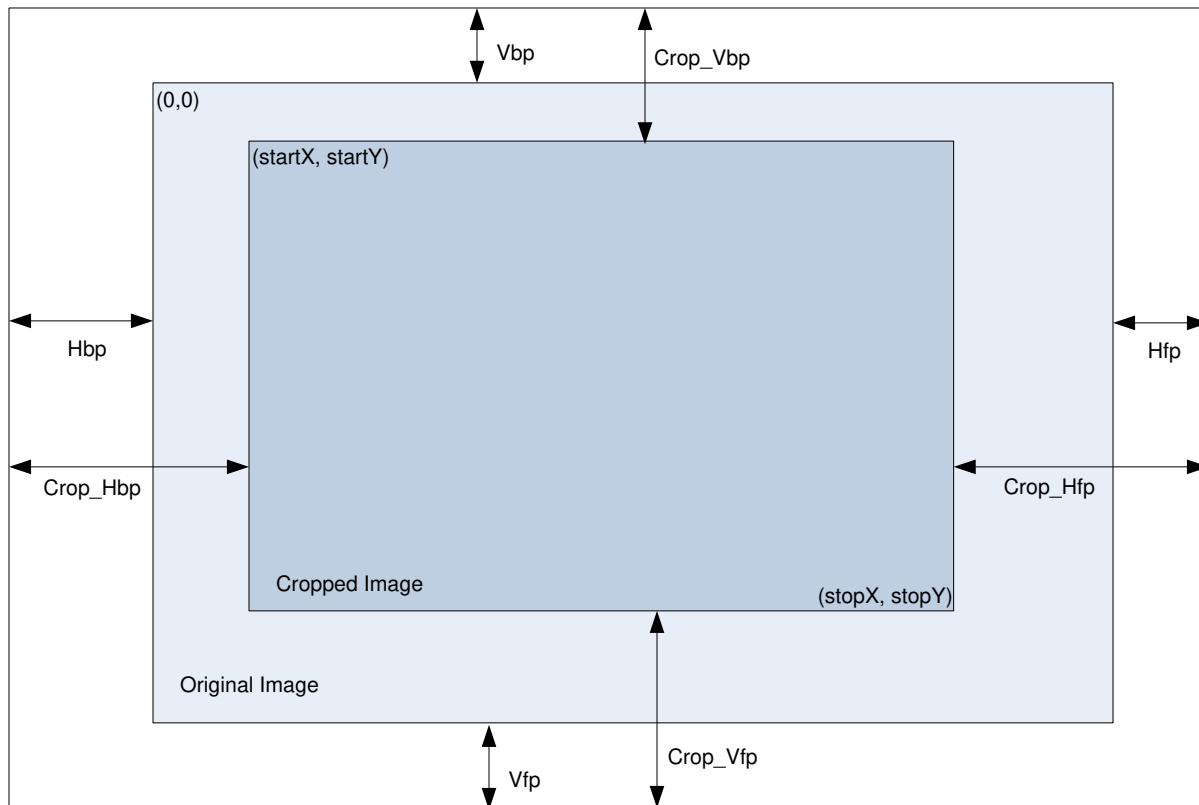

| • クロッピングによる非対称型分割の図を更新。                                             | 53   |

| • VC-ID による非対称型分割の図を更新。                                             | 55   |

| • レジスタ・アドレス形式を修正。                                                   | 62   |

| • レジスタ 0x3[1] の説明を更新。                                               | 62   |

| • スプリッタ・モードのレジスタ 0x3E[6:5] がレジスタ 0x56 よりも優先度が高いことを明確化。              | 62   |

| • レジスタ 0x56[1:0] のリセット値を 0 に更新。                                     | 62   |

| • レジスタ 0x56[1:0] はスプリッタ・モードでは使用できないことを明確化。                          | 62   |

| • レジスタ 0x5A[2] を予約済みに変更。                                            | 62   |

| • SLAVE_ID および SLAVE_ALIAS_ID レジスタがポート専用であることを明確化。                  | 62   |

| • レジスタ 0x56[1:0] の説明を更新。                                            | 62   |

| • DSI_ERR_COUNT レジスタ・アドレスを訂正。                                       | 122  |

| • アナログ間接レジスタのページを追加。                                                | 137  |

| • 内部 DSI クロック設定の初期化を含むように電源オン・シーケンスを更新。                             | 153  |

- 941AS デバイス開発ガイドへのリンクを追加..... [153](#)

---

| <b>Changes from Revision * (May 2019) to Revision A (October 2020)</b> | <b>Page</b>       |

|------------------------------------------------------------------------|-------------------|

| • 「特長」の箇条書き項目に「機能安全対応」を追加.....                                         | <a href="#">1</a> |

---

## 5 概要 (続き)

DS90UH941AS-Q1 は MIPI DSI 入力をシリアル化することで、2K、WUXGA および 1080p60 までのビデオ解像度、24 ビット・カラー深度に対応しています。下位互換モードでは、DS90UH941AS-Q1 は、WXGA および 720p までの解像度、24 ビット・カラー深度に 1 つの差動リンクで対応しています。

DS90UH941AS-Q1 は、シリアライザおよびデシリアライザに HDCP 暗号エンジンを持つ HDCP アプリケーションをサポートします。DSI ビデオ・データは、FPD-Link III インターフェイスへの送信前に暗号化され、デシリアライザで復号されます。

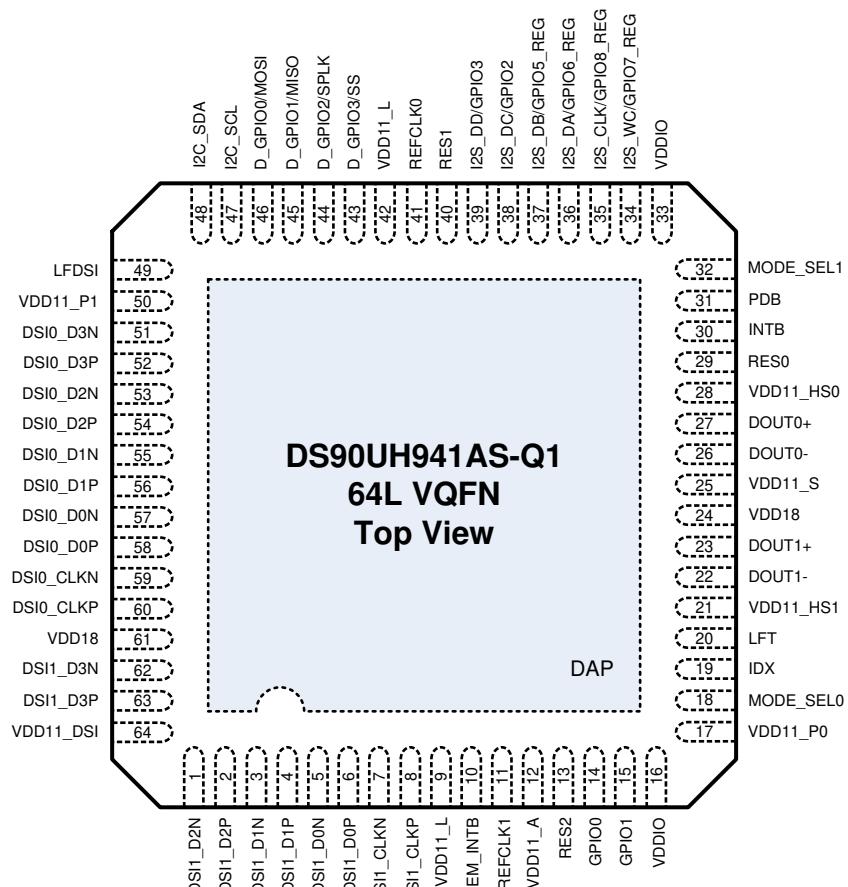

## 6 ピン構成と機能

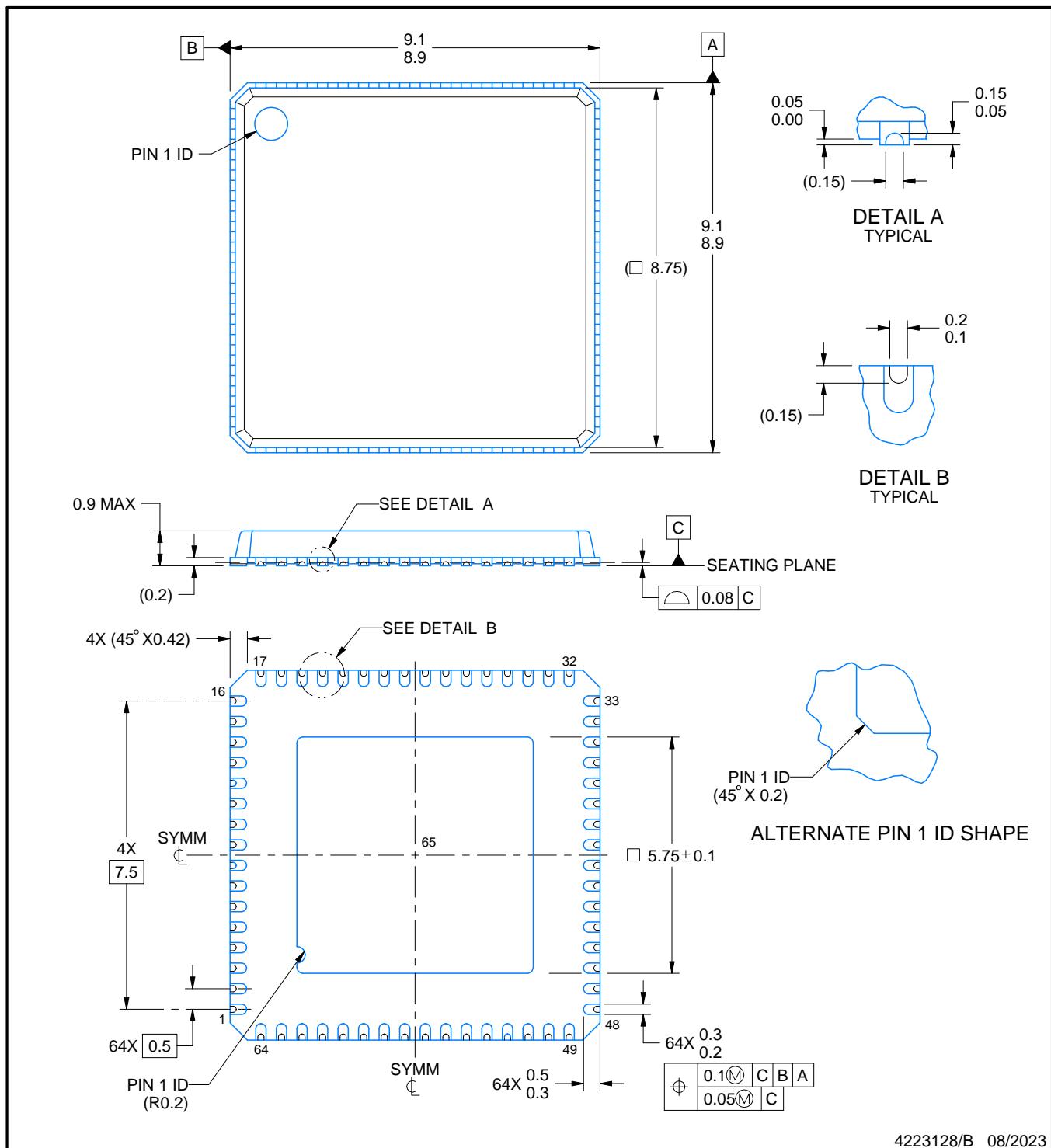

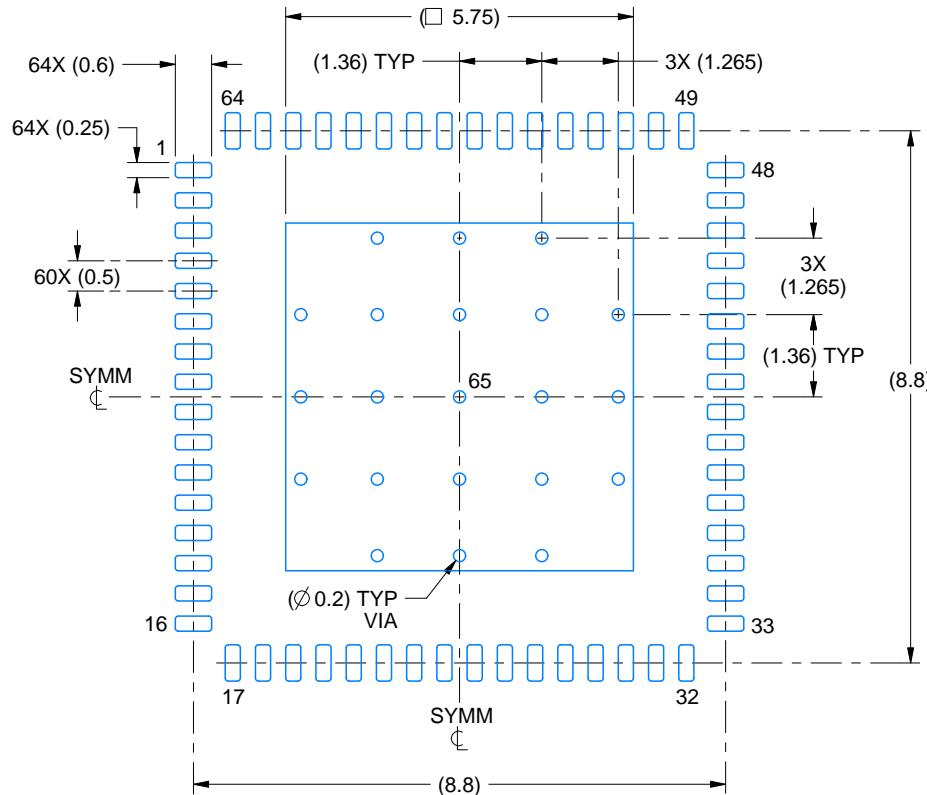

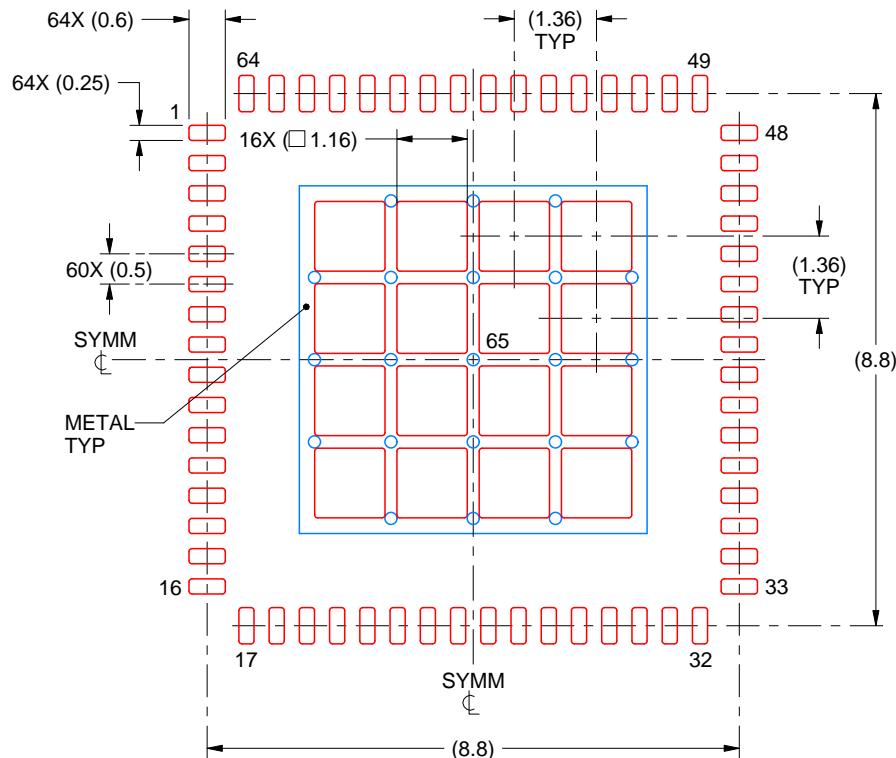

図 6-1. RTD パッケージ 64 ピン VQFN 上面図

### ピン機能

| ピン            |    | I/O、タイプ | 説明 |

|---------------|----|---------|----|

| 名前            | 番号 |         |    |

| MIPI DSI 入力ピン |    |         |    |

| ピン        |    | I/O、タイプ | 説明                                                                                                                                |

|-----------|----|---------|-----------------------------------------------------------------------------------------------------------------------------------|

| 名前        | 番号 |         |                                                                                                                                   |

| DSI0_D0P  | 58 | I       | DSI RX ポート 0 差動データ入力ピン<br>DEVICE_CFG (0x02h) および BRIDGE_CTL (0x4Fh) レジスタを使って DSI RX を制御します。これらのピンを使用しない場合、グランドに接続するか、未接続ピンにできます。  |

| DSI0_D0N  | 57 | I       |                                                                                                                                   |

| DSI0_D1P  | 56 | I       |                                                                                                                                   |

| DSI0_D1N  | 55 | I       |                                                                                                                                   |

| DSI0_D2P  | 54 | I       |                                                                                                                                   |

| DSI0_D2N  | 53 | I       |                                                                                                                                   |

| DSI0_D3P  | 52 | I       |                                                                                                                                   |

| DSI0_D3N  | 51 | I       |                                                                                                                                   |

| DSI0_CLKP | 60 | I       | DSI RX ポート 0 差動クロック入力ピン<br>DEVICE_CFG (0x02h) および BRIDGE_CTL (0x4Fh) レジスタを使って DSI RX を制御します。これらのピンを使用しない場合、グランドに接続するか、未接続ピンにできます。 |

| DSI0_CLKN | 59 | I       |                                                                                                                                   |

| DSI1_D0P  | 6  | I       | DSI RX ポート 1 差動データ入力ピン<br>DEVICE_CFG (0x02h) および BRIDGE_CTL (0x4Fh) レジスタを使って DSI RX を制御します。これらのピンを使用しない場合、グランドに接続するか、未接続ピンにできます。  |

| DSI1_D0N  | 5  | I       |                                                                                                                                   |

| DSI1_D1P  | 4  | I       |                                                                                                                                   |

| DSI1_D1N  | 3  | I       |                                                                                                                                   |

| DSI1_D2P  | 2  | I       |                                                                                                                                   |

| DSI1_D2N  | 1  | I       |                                                                                                                                   |

| DSI1_D3P  | 63 | I       |                                                                                                                                   |

| DSI1_D3N  | 62 | I       |                                                                                                                                   |

| DSI1_CLKP | 8  | I       | DSI RX ポート 1 差動クロック入力ピン<br>DEVICE_CFG (0x02h) および BRIDGE_CTL (0x4Fh) レジスタを使って DSI RX を制御します。これらのピンを使用しない場合、グランドに接続するか、未接続ピンにできます。 |

| DSI1_CLKN | 7  | I       |                                                                                                                                   |

| LFDSI     | 49 | D       | DSI ループ・フィルタ・ピン<br>このピンとグランドとの間に $10nF$ のコンデンサを接続します。                                                                             |

#### FPD-LINK III インターフェイス・ピン

|         |    |       |                                                                                                                                                                                                                     |

|---------|----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DOUT0-  | 26 | I/O   | FPD-Link III TX ポート 0 ピン<br>このポートは、FPD-Link III 高速フォワード・チャネル・ビデオおよび制御データを送信し、バック・チャネル制御データを受信します。STP または同軸ケーブルを使用して、互換性のある FPD-Link III デシリアライザ RX と接続できます。I/O は、表 9-1 に従って AC 結合する必要があります。ポートを使わない場合、そのピンを未接続にします。 |

| DOUT0+  | 27 | I/O   |                                                                                                                                                                                                                     |

| DOUT1-  | 22 | I/O   | FPD-Link III TX ポート 1 ピン<br>このポートは、FPD-Link III 高速フォワード・チャネル・ビデオおよび制御データを送信し、バック・チャネル制御データを受信します。STP または同軸ケーブルを使用して、互換性のある FPD-Link III デシリアライザ RX と接続できます。I/O は、表 9-1 に従って AC 結合する必要があります。ポートを使わない場合、そのピンを未接続にします。 |

| DOUT1+  | 23 | I/O   |                                                                                                                                                                                                                     |

| LFT     | 20 | D     | FPD-Link III ループ・フィルタ・ピン<br>このピンとグランドとの間に $10nF$ のコンデンサを接続します。                                                                                                                                                      |

| REFCLK0 | 41 | I, PD | 外部基準クロック入力ピン<br>独立 2:2 または非対称スプリッタ・モード時の FPD-Link III ポート 0 の外部基準クロック入力ピンです。このピンは通常、低ジッタのクロック源に接続します。 $25k\Omega$ の内部プルダウンを備えています。このピンを使わない場合、未接続にするか、GND に接続します。                                                   |

| REFCLK1 | 11 | I, PD | 独立 2:2 または非対称スプリッタ・モード時の FPD-Link III ポート 1 の外部基準クロック入力ピン<br>このピンは通常、低ジッタのクロック源に接続します。 $25k\Omega$ の内部プルダウンを備えています。このピンを使わない場合、未接続にするか、GND に接続します。                                                                  |

#### 制御ピン

|           |    |         |                                                                                                                         |

|-----------|----|---------|-------------------------------------------------------------------------------------------------------------------------|

| I2C_SDA   | 48 | I/O, OD | I2C データ入出力インターフェイス・ピン<br>オープン・ドレイン。 $2.2k\Omega \sim 4.7k\Omega$ で $1.8V$ または $3.3V$ にブリッピングすることを推奨します。 <sup>(1)</sup>  |

| I2C_SCL   | 47 | I/O, OD | I2C クロック入出力インターフェイス・ピン<br>オープン・ドレイン。 $2.2k\Omega \sim 4.7k\Omega$ で $1.8V$ または $3.3V$ にブリッピングすることを推奨します。 <sup>(1)</sup> |

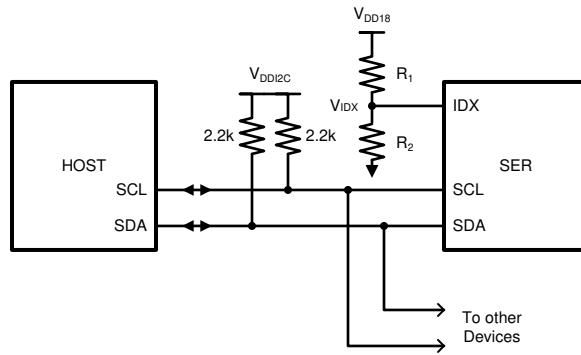

| IDX       | 19 | I, S    | I2C シリアル制御バスのデバイス ID アドレス選択設定ピン<br>表 8-12 に従って分圧器を構成するため、VDD18 への外部ブリッピングと GND への外部プルダウンを接続します。オープン(未接続)にしないでください。      |

| MODE_SEL0 | 18 | I, S    | モード選択 0 設定ピン<br>表 8-8 に従って分圧器を構成するため、VDD18 への外部ブリッピングと GND への外部プルダウンを接続します。                                             |

| ピン                                    |    | I/O、タイプ | 説明                                                                                                                                                                                                                                                                                                                                 |

|---------------------------------------|----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名前                                    | 番号 |         |                                                                                                                                                                                                                                                                                                                                    |

| MODE_SEL1                             | 32 | I, S    | モード選択 1 設定ピン<br><a href="#">表 8-8</a> とに従って分圧器を構成するため、VDD18 への外部プルアップと GND への外部プルダウンを接続します。                                                                                                                                                                                                                                        |

| PDB                                   | 31 | I, PD   | パワーダウン(反転)入力ピン。<br>通常、プルダウン付きのプロセッサ GPIO に接続します。PDB 入力を High にすると、本デバイスは有効化され、内部レジスタとステート・マシンがデフォルト値にリセットされます。PDB 信号を Low にアサートすると、本デバイスの電源がオフになり、消費電力が最小化されます。このピンのデフォルトの機能は PDB = Low です。<br>50kΩ の内部プルダウンが有効化されることでパワーダウンします。電源が印加され、必要な最小限のレベルに達するまで、PDB は Low を維持する必要があります。<br>PDB = 1、デバイスを有効化(通常動作)<br>PDB = 0、デバイスをパワーダウン。 |

| INTB                                  | 30 | O, OD   | 割り込み出力ピン<br>INTB はアクティブ Low のオープン・ドレインであり、ステータス・レジスタによって制御されます。「 <a href="#">セクション 8.3.8</a> 」を参照してください。<br>INTB = H、通常動作<br>INTB = L、割り込み要求<br>プルアップの推奨値: VDDIO に対して 4.7kΩ。オープン(未接続)のままにしないでください。                                                                                                                                 |

| REM_INTB                              | 10 | O       | リモート割り込み出力ピン<br>REM_INTB は、リモート・デバイスからの INTB_IN 信号のステータスを直接反映します。このピンのステータスをリセットおよび変更するに個別のシリアルライザ・レジスタを読み出す必要はありません。このピンを使わない場合、未接続にします。                                                                                                                                                                                          |

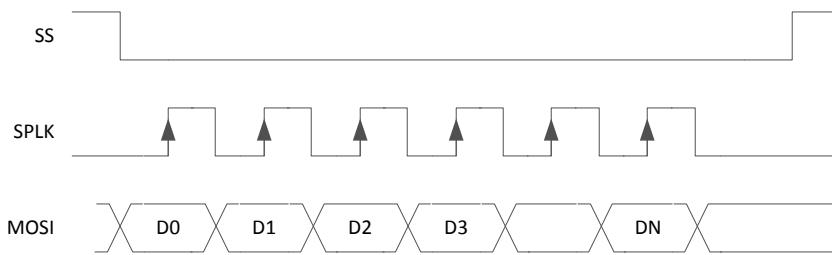

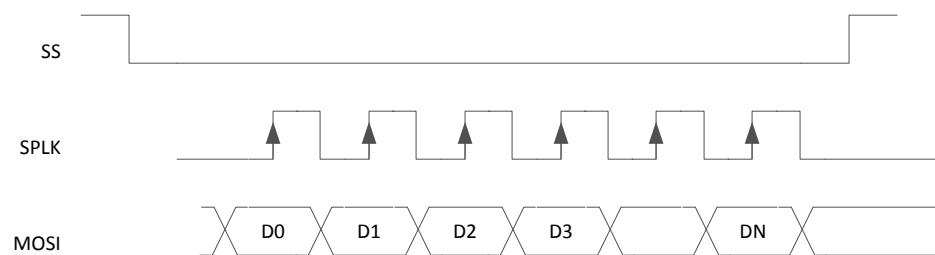

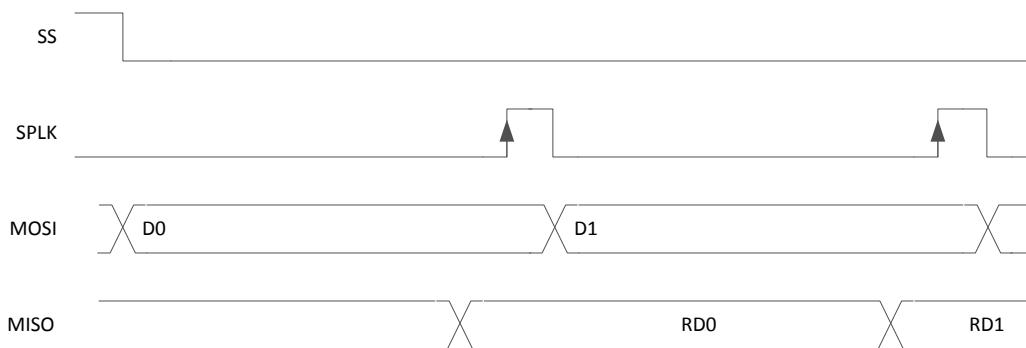

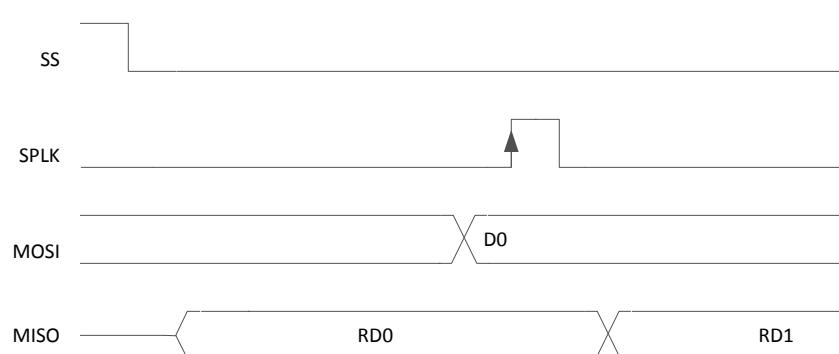

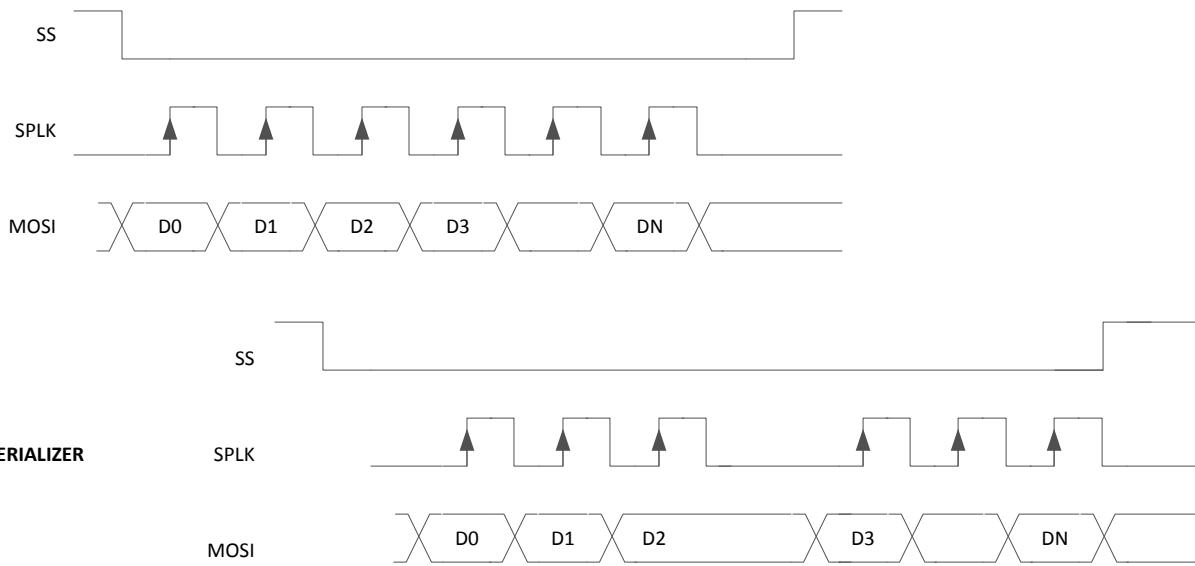

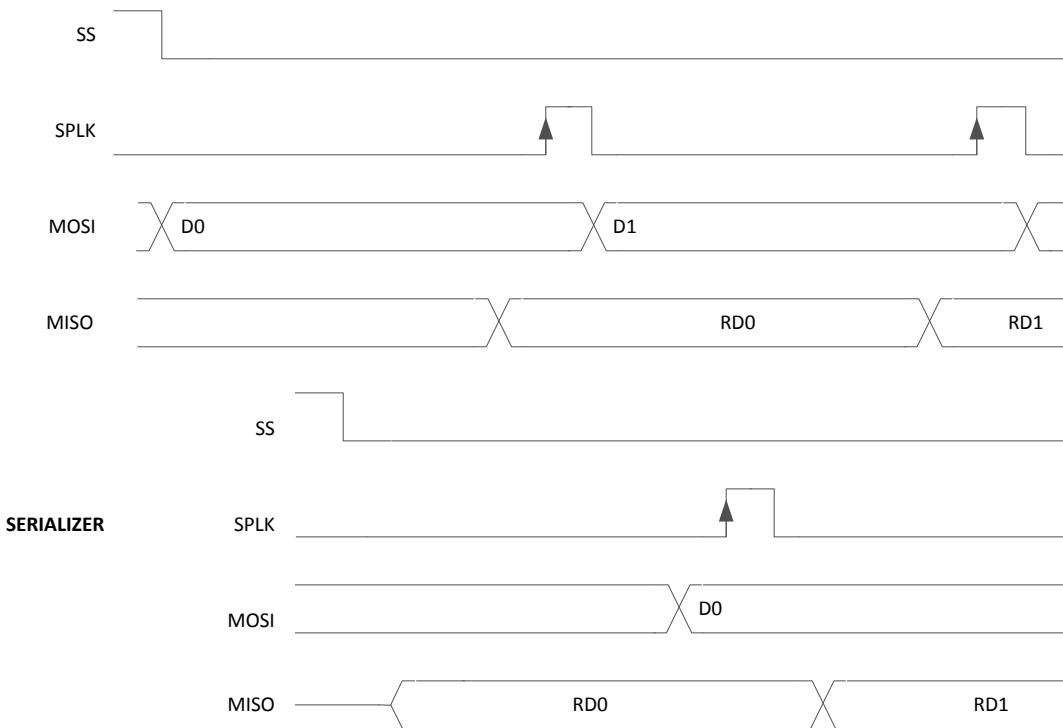

| <b>SPI ピン (デュアル FPD-LINK III モード)</b> |    |         |                                                                                                                                                                                                                                                                                                                                    |

| MOSI                                  | 46 | I/O, PD | SPI マスター出力スレーブ入力ピン<br>デュアル・リンク・モードでのみ使用できます。D_GPIO0 と共有されます。このピンを使わない場合、かつデフォルト状態(25kΩ のプルダウン抵抗が有効)の場合、このピンを未接続ピンにできます。                                                                                                                                                                                                            |

| MISO                                  | 45 | I/O, PD | SPI マスター入力スレーブ出力ピン<br>デュアル・リンク・モードでのみ使用できます。D_GPIO1 と共有されます。このピンを使わない場合、かつデフォルト状態(25kΩ のプルダウン抵抗が有効)の場合、このピンを未接続ピンにできます。                                                                                                                                                                                                            |

| SPLK                                  | 44 | I/O, PD | SPI クロック・ピン<br>デュアル・リンク・モードでのみ使用できます。D_GPIO2 と共有されます。このピンを使わない場合、かつデフォルト状態(25kΩ のプルダウン抵抗が有効)の場合、このピンを未接続ピンにできます。                                                                                                                                                                                                                   |

| SS                                    | 43 | I/O, PD | SPI スレーブ選択ピン<br>デュアル・リンク・モードでのみ使用できます。D_GPIO3 と共有されます。このピンを使わない場合、かつデフォルト状態(25kΩ のプルダウン抵抗が有効)の場合、このピンを未接続ピンにできます。                                                                                                                                                                                                                  |

| <b>高速 GPIO ピン</b>                     |    |         |                                                                                                                                                                                                                                                                                                                                    |

| D_GPIO0                               | 46 | I/O, PD | 高速 GPIO0 ピン<br>デュアル・リンク・モードでのみ使用できます。MOSI と共有されます。このピンを使わない場合、かつデフォルト状態(25kΩ のプルダウン抵抗が有効)の場合、このピンを未接続ピンにできます。                                                                                                                                                                                                                      |

| D_GPIO1                               | 45 | I/O, PD | 高速 GPIO1 ピン<br>デュアル・リンク・モードでのみ使用できます。MISO と共有されます。このピンを使わない場合、かつデフォルト状態(25kΩ のプルダウン抵抗が有効)の場合、このピンを未接続ピンにできます。                                                                                                                                                                                                                      |

| D_GPIO2                               | 44 | I/O, PD | 高速 GPIO2 ピン<br>デュアル・リンク・モードでのみ使用できます。SPLK と共有されます。このピンを使わない場合、かつデフォルト状態(25kΩ のプルダウン抵抗が有効)の場合、このピンを未接続ピンにできます。                                                                                                                                                                                                                      |

| D_GPIO3                               | 43 | I/O, PD | 高速 GPIO3 ピン<br>デュアル・リンク・モードでのみ使用できます。SS と共有されます。このピンを使わない場合、かつデフォルト状態(25kΩ のプルダウン抵抗が有効)の場合、このピンを未接続ピンにできます。                                                                                                                                                                                                                        |

| <b>GPIO ピン</b>                        |    |         |                                                                                                                                                                                                                                                                                                                                    |

| GPIO0                                 | 14 | I/O, PD | 汎用入出力 0 ピン<br>このピンを使わない場合、かつデフォルト状態(25kΩ のプルダウン抵抗が有効)の場合、このピンを未接続ピンにできます。                                                                                                                                                                                                                                                          |

| GPIO1                                 | 15 | I/O, PD | 汎用入出力 1 ピン<br>このピンを使わない場合、かつデフォルト状態(25kΩ のプルダウン抵抗が有効)の場合、このピンを未接続ピンにできます。                                                                                                                                                                                                                                                          |

| GPIO2                                 | 38 | I/O, PD | 汎用入出力 2 ピン<br>I2S_DC と共有されます。このピンを使わない場合、かつデフォルト状態(25kΩ のプルダウン抵抗が有効)の場合、このピンを未接続ピンにできます。                                                                                                                                                                                                                                           |

| GPIO3                                 | 39 | I/O, PD | 汎用入出力 3 ピン<br>I2S_DD と共有されます。このピンを使わない場合、かつデフォルト状態(25kΩ のプルダウン抵抗が有効)の場合、このピンを未接続ピンにできます。                                                                                                                                                                                                                                           |

| <b>レジスタ専用 GPIO ピン</b>                 |    |         |                                                                                                                                                                                                                                                                                                                                    |

| ピン                               |          | I/O、タイプ | 説明                                                                                                                                                                                                  |

|----------------------------------|----------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名前                               | 番号       |         |                                                                                                                                                                                                     |

| GPIO5_REG                        | 37       | I/O、PD  | 汎用入出力 5 ピン<br>ローカル・レジスタ制御専用。 <b>I2S_DB</b> と共有されます。このピンを使わない場合、かつデフォルト状態 (25kΩ のプルダウン抵抗が有効) の場合、このピンを未接続ピンにできます。                                                                                    |

| GPIO6_REG                        | 36       | I/O、PD  | 汎用入出力 6 ピン<br>ローカル・レジスタ制御専用。 <b>I2S_DA</b> と共有されます。このピンを使わない場合、かつデフォルト状態 (25kΩ のプルダウン抵抗が有効) の場合、このピンを未接続ピンにできます。                                                                                    |

| GPIO7_REG                        | 34       | I/O、PD  | 汎用入出力 7 ピン<br>ローカル・レジスタ制御専用。 <b>I2S_WC</b> と共有されます。このピンを使わない場合、かつデフォルト状態 (25kΩ のプルダウン抵抗が有効) の場合、このピンを未接続ピンにできます。                                                                                    |

| GPIO8_REG                        | 35       | I/O、PD  | 汎用入出力 8 ピン<br>ローカル・レジスタ制御専用。 <b>I2S_CLK</b> と共有されます。このピンを使わない場合、かつデフォルト状態 (25kΩ のプルダウン抵抗が有効) の場合、このピンを未接続ピンにできます。                                                                                   |

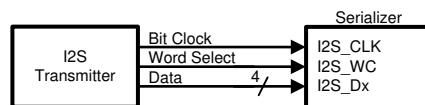

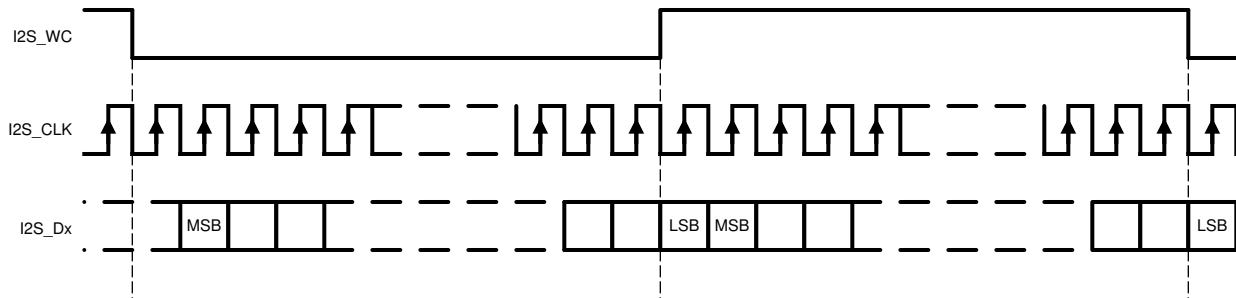

| <b>スレーブ・モード・ローカル I2S チャネル・ピン</b> |          |         |                                                                                                                                                                                                     |

| I2S_WC                           | 34       | I/O、PD  | スレーブ・モード I2S ワード・クロック入力ピン<br><b>GPIO7_REG</b> と共有されます。このピンを使わない場合、かつデフォルト状態 (25kΩ のプルダウン抵抗が有効) の場合、このピンを未接続ピンにできます。                                                                                 |

| I2S_CLK                          | 35       | I/O、PD  | スレーブ・モード I2S クロック入力ピン<br><b>GPIO8_REG</b> と共有されます。このピンを使わない場合、かつデフォルト状態 (25kΩ のプルダウン抵抗が有効) の場合、このピンを未接続ピンにできます。                                                                                     |

| I2S_DA                           | 36       | I/O、PD  | スレーブ・モード I2S データ入力ピン<br><b>GPIO6_REG</b> と共有されます。このピンを使わない場合、かつデフォルト状態 (25kΩ のプルダウン抵抗が有効) の場合、このピンを未接続ピンにできます。                                                                                      |

| I2S_DB                           | 37       | I/O、PD  | スレーブ・モード I2S データ入力ピン<br><b>GPIO2_REG</b> と共有されます。このピンを使わない場合、かつデフォルト状態 (25kΩ のプルダウン抵抗が有効) の場合、このピンを未接続ピンにできます。                                                                                      |

| I2S_DC                           | 38       | I/O、PD  | スレーブ・モード I2S データ入力ピン<br><b>GPIO2</b> と共有されます。このピンを使わない場合、かつデフォルト状態 (25kΩ のプルダウン抵抗が有効) の場合、このピンを未接続ピンにできます。                                                                                          |

| I2S_DD                           | 39       | I/O、PD  | スレーブ・モード I2S データ入力ピン<br><b>GPIO3</b> と共有されます。このピンを使わない場合、かつデフォルト状態 (25kΩ のプルダウン抵抗が有効) の場合、このピンを未接続ピンにできます。                                                                                          |

| <b>電源ピンとグランド・ピン</b>              |          |         |                                                                                                                                                                                                     |

| GND                              | DAP      | G       | DAP は、VQFN パッケージの裏側の中央にある大きな金属接触部です。グランド・プレーンに接続します。                                                                                                                                                |

| VDD18                            | 24<br>61 | P       | 1.8V (±5%) 電源ピン<br>各 VDD ピンと GND との間に 0.1μF または 0.01μF のコンデンサを接続する必要があります。ピン・グループに対して 1μF と 10μF のデカッピングを追加することを推奨します。                                                                              |

| VDD11_P0                         | 17       | P       | 1.1V (±5%) 電源ピン<br>各 VDD ピンと GND との間に 0.1μF または 0.01μF のコンデンサを接続する必要があります。ピン・グループに対して 1μF と 10μF のデカッピングを追加することを推奨します。                                                                              |

| VDD11_P1                         | 50       | P       |                                                                                                                                                                                                     |

| VDD11_DSI                        | 64       | P       | 1.1V (±5%) 電源ピン<br>各 VDD ピンと GND との間に 0.1μF または 0.01μF のコンデンサを接続する必要があります。ピン・グループに対して 1μF と 10μF のデカッピングを追加することを推奨します。                                                                              |

| VDD11_A                          | 12       | P       |                                                                                                                                                                                                     |

| VDD11_HS0                        | 28       | P       |                                                                                                                                                                                                     |

| VDD11_HS1                        | 21       | P       |                                                                                                                                                                                                     |

| VDD11_S                          | 25       | P       |                                                                                                                                                                                                     |

| VDD11_L                          | 9<br>42  | P       | 1.1V (±5%) 電源ピン<br>各 VDD ピンと GND との間に 0.1μF または 0.01μF のコンデンサを接続する必要があります。ピン・グループに対して 1μF と 10μF のデカッピングを追加することを推奨します。                                                                              |

| VDDIO                            | 16、33    | P       | 1.8V (±5%) または 3.3V (±10%) LVCMOS I/O 電源ピン<br>各 VDD ピンと GND との間に 0.1μF または 0.01μF のコンデンサを接続する必要があります。ピン・グループに対して 1μF のデカッピングを追加することを推奨します。1.8V VDDIO オプションを選択する場合、VDDIO と VDD18 は同じ電源から供給する必要があります。 |

| <b>その他のピン</b>                    |          |         |                                                                                                                                                                                                     |

| RES0                             | 29       | —       | 予約済み。GND に接続。                                                                                                                                                                                       |

| RES1                             | 40       | —       | 予約済み。未接続にする必要があります。                                                                                                                                                                                 |

| RES2                             | 13       | —       | 予約済み。未接続にする必要があります。                                                                                                                                                                                 |

(1) 最適なプルアップ抵抗値は、I2C 動作モードによって異なります。『[I2C バスのプルアップ抵抗値の計算](#)』(SLVA689) を参照してください。

以下に、各ピンの I/O セルの機能の定義を示します。タイプ:

- **I** = 入力

- **O** = 出力

- **I/O** = 入出力

- **OD** = オープン・ドレイン

- **PD** = 内部プルダウン

- **P, G** = 電源、グランド

- **D** = 内部 LDO 出力のデカップリング・ピン

- **S** = ストラップ入力

## 7 仕様

### 7.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り) [\(1\)](#) [\(2\)](#)

|                   |                                                                                                                                                                                           | 最小値  | 最大値                 | 単位 |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------|----|

| 電源電圧              | VDD11 (VDD11_P0、VDD11_P1、VDD11_DSI、VDD11_A、VDD11_HS0、VDD11_HS1、VDD11_S、VDD11_L)                                                                                                           | -0.3 | 1.32                | V  |

|                   | VDD18                                                                                                                                                                                     | -0.3 | 2.16                |    |

|                   | VDDIO                                                                                                                                                                                     | -0.3 | 3.96                |    |

| DSI 入力電圧          | DSI0_D0P、DSI0_D0N、DSI0_D1P、DSI0_D1N、DSI0_D2P、DSI0_D2N、DSI0_D3P、DSI0_D3N、DSI0_CLKP、DSI0_CLKN、DSI1_D0P、DSI1_D0N、DSI1_D1P、DSI1_D1N、DSI1_D2P、DSI1_D2N、DSI1_D3P、DSI1_D3N、DSI1_CLKP、DSI1_CLKN   | -0.3 | 2.16                | V  |

| LVC MOS I/O 電圧    | PDB、GPIO0、GPIO1、GPIO2、GPIO3、D_GPIO0、D_GPIO1、D_GPIO2、D_GPIO3、GPIO5_REG、GPIO6_REG、GPIO7_REG、GPIO8_REG、MOSI、MISO、SPLK、SS、I2C_WC、I2S_CLK、I2S_DA、I2S_DB、I2S_DC、I2S_DD、REM_INTB、REFCLK0、REFCLK1 | -0.3 | $V_{(VDDIO)} + 0.3$ | V  |

| 構成入力電圧            | IDX、MODE_SEL0、MODE_SEL1                                                                                                                                                                   | -0.3 | 2.16                | V  |

| オープン・ドレン電圧        | I2C_SDA、I2C_SCL、INTB                                                                                                                                                                      | -0.3 | 3.96                | V  |

| FPD-Link III 出力電圧 | DOUT0+、DOUT0-、DOUT1+、DOUT1-                                                                                                                                                               | -0.3 | 1.32                | V  |

| アナログ電圧            | LFDSI、LFT                                                                                                                                                                                 | -0.3 | 1.32                | V  |

| 接合部温度、 $T_J$      |                                                                                                                                                                                           |      | 150                 | °C |

| 保存温度、 $T_{stg}$   |                                                                                                                                                                                           | -65  | 150                 | °C |

(1) 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみについて示しており、このデータシートの「推奨動作条件」に示された値を超える状態で本製品が正常に動作することを暗黙的に示すものではありません。絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

(2) 半田付け仕様については、[www.ti.com](http://www.ti.com) の製品フォルダと『半田付けの絶対最大定格』(SNOA549) を参照してください。

### 7.2 ESD 定格

|             |       |                                                                                                 | 値                                  | 単位          |

|-------------|-------|-------------------------------------------------------------------------------------------------|------------------------------------|-------------|

| $V_{(ESD)}$ | 静電気放電 | 人体モデル (HBM)、AEC Q100-002 準拠 <a href="#">(1)</a>                                                 | (DOUT0+、DOUT0-、DOUT1+、DOUT1-)      | $\pm 8000$  |

|             |       |                                                                                                 | その他のピン                             | $\pm 2500$  |

|             |       | デバイス帯電モデル (CDM)、AEC Q100-011 準拠                                                                 |                                    | $\pm 1000$  |

|             |       | (IEC 61000-4-2)<br>$R_D = 330\Omega$ , $C_S = 150pF$                                            | 空中放電 (DOUT0+、DOUT0-、DOUT1+、DOUT1-) | $\pm 15000$ |

|             |       |                                                                                                 | 接触放電 (DOUT0+、DOUT0-、DOUT1+、DOUT1-) | $\pm 10000$ |

|             |       | (ISO10605)<br>$R_D = 330\Omega$ , $C_S = 150pF$<br>$R_D = 2k\Omega$ , $C_S = 150pF$ または $330pF$ | 空中放電 (DOUT0+、DOUT0-、DOUT1+、DOUT1-) | $\pm 21000$ |

|             |       |                                                                                                 | 接触放電 (DOUT0+、DOUT0-、DOUT1+、DOUT1-) | $\pm 10000$ |

(1) AEC Q100-002 は、HBM ストレス試験を ANSI/ESDA/JEDEC JS-001 仕様に従って実施しなければならないと規定しています。

### 7.3 推奨動作条件

|                          |                                              | 最小値   | 公称値 | 最大値   | 単位   |

|--------------------------|----------------------------------------------|-------|-----|-------|------|

| 電源電圧                     | $V_{(VDD11)}$                                | 1.045 | 1.1 | 1.155 | V    |

|                          | $V_{(VDD18)}$                                | 1.71  | 1.8 | 1.89  |      |

| LVC MOS I/O の電源電圧        | $V_{(VDDIO)} = 1.8V$                         | 1.71  | 1.8 | 1.89  | V    |

|                          | または $V_{(VDDIO)} = 3.3V$                     | 3     | 3.3 | 3.6   |      |

| オープン・ドレン電圧               | INTB = $V_{(INTB)}$ 、I2C ピン = $V_{(VDDI2C)}$ | 1.71  |     | 3.6   | V    |

| 自由気流での動作温度、 $T_A$        |                                              | -40   | 25  | 105   | °C   |

| MIPI データ・レート (DSI レーンごと) |                                              | 150   |     | 1500  | Mbps |

| MIPI DSI HS クロック周波数      |                                              | 75    |     | 750   | MHz  |

|                                                    |                              | 最小値   | 公称値  | 最大値 | 単位    |

|----------------------------------------------------|------------------------------|-------|------|-----|-------|

| ローカル I <sub>C</sub> 周波数、f <sub>I<sub>C</sub></sub> |                              |       |      | 1   | MHz   |

| 基準クロック周波数、f <sub>REFCLK</sub>                      |                              | 25    | 210  |     | MHz   |

| エーボンを含む基準クロック周波数の安定性                               |                              | -100  | 100  |     | ppm   |

| スペクトラム拡散基準クロック変調のパーセンテージ                           | REFCLK、センター・スプレッド            | -0.25 | 0.25 |     | %     |

|                                                    | REFCLK、アップ・スプレッド             | 0     | 0.5  |     | %     |

|                                                    | REFCLK、ダウン・スプレッド             | -0.5  | 0    |     | %     |

| 電源ノイズ (DC~50MHz)                                   | V <sub>(VDD11)</sub>         |       |      | 25  | mVp-p |

|                                                    | V <sub>(VDD18)</sub>         |       |      | 50  |       |

|                                                    | V <sub>(VDDIO) = 1.8V</sub>  |       |      | 50  |       |

|                                                    | V <sub>(VDDIO) = 3.3V</sub>  |       |      | 50  |       |

|                                                    | V <sub>(VDDI2C) = 1.8V</sub> |       |      | 50  |       |

|                                                    | V <sub>(VDDI2C) = 3.3V</sub> |       |      | 100 |       |

## 7.4 熱に関する情報

| 熱評価基準 (1)             |                   | DS90UH941AS-Q1 | 単位   |

|-----------------------|-------------------|----------------|------|

|                       |                   | RTD (VQFN)     |      |

|                       |                   | 64 ピン          |      |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗      | 24.2           | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース(上面)への熱抵抗 | 11.2           | °C/W |

| R <sub>θJC(bot)</sub> | 接合部からケース(底面)への熱抵抗 | 0.5            | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗      | 7.9            | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への熱特性パラメータ | 0.1            | °C/W |

| Ψ <sub>JB</sub>       | 接合部から基板への熱特性パラメータ | 7.9            | °C/W |

- (1) 従来および新しい熱特性の詳細については、アプリケーション・レポート『半導体および IC パッケージの熱測定値』、[SPRA953](#) を参照してください。

## 7.5 DC 電気的特性

推奨動作電源電圧および温度範囲内 (特に記述のない限り)

| パラメータ                  | テスト条件           | ピン / 周波数                                                                                                                                                                  | 最小値                                                                                                                                                                                                                                                   | 標準値                  | 最大値                  | 単位 |

|------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|----|

| <b>消費電力</b>            |                 |                                                                                                                                                                           |                                                                                                                                                                                                                                                       |                      |                      |    |

| P <sub>T</sub>         | 総消費電力、通常動作      | シングル、4 レーン、DSI 入力、<br>$f_{DSI\_CLK} = 630\text{MHz}$ ( $f_{PCLK} = 210\text{MHz}$ )、<br>デュアル・リンク FPD-Link III 出力、<br>ライン・レート = 3.675Gbps、<br>格子パターン、<br>$R_L = 100\Omega$ | VDD11, VDD18、<br>VDDIO                                                                                                                                                                                                                                |                      | 800                  | mW |

| <b>消費電流</b>            |                 |                                                                                                                                                                           |                                                                                                                                                                                                                                                       |                      |                      |    |

| I <sub>DD</sub>        | 消費電流、通常モード      | シングル、4 レーン、DSI 入力、<br>$f_{DSI\_CLK} = 630\text{MHz}$ ( $f_{PCLK} = 210\text{MHz}$ )、<br>デュアル・リンク FPD-Link III 出力、<br>ライン・レート = 3.675Gbps、<br>格子パターン、<br>$R_L = 100\Omega$ | VDD11                                                                                                                                                                                                                                                 | 165                  | 500                  | mA |

|                        |                 |                                                                                                                                                                           | VDD18                                                                                                                                                                                                                                                 | 25                   | 45                   | mA |

|                        |                 |                                                                                                                                                                           | VDDIO                                                                                                                                                                                                                                                 | 2                    | 10                   | mA |

| I <sub>DDZ</sub>       | 消費電流、パワーダウン・モード | PDB = L                                                                                                                                                                   | VDD11                                                                                                                                                                                                                                                 |                      | 140                  | mA |

|                        |                 |                                                                                                                                                                           | VDD18                                                                                                                                                                                                                                                 |                      | 15                   | mA |

|                        |                 |                                                                                                                                                                           | VDDIO                                                                                                                                                                                                                                                 |                      | 4                    | mA |

| <b>1.8V LVCMOS I/O</b> |                 |                                                                                                                                                                           |                                                                                                                                                                                                                                                       |                      |                      |    |

| V <sub>IH</sub>        | High レベル入力電圧    | $V_{(VDDIO)} = 1.71\text{V} \sim 1.89\text{V}$                                                                                                                            | PDB, GPIO0,<br>GPIO1, GPIO2,<br>GPIO3, D_GPIO0,<br>D_GPIO1,<br>D_GPIO2,<br>D_GPIO3,<br>GPIO5_REG,<br>GPIO6_REG,<br>GPIO7_REG,<br>GPIO8_REG,<br>MOSI, MISO,<br>SPLK, SS,<br>I2C_WC, I2S_CLK,<br>I2S_DA, I2S_DB,<br>I2S_DC, I2S_DD,<br>REFCLK0, REFCLK1 | 0.65 × $V_{(VDDIO)}$ | V                    |    |

| V <sub>IL</sub>        | Low レベル入力電圧     | $V_{(VDDIO)} = 1.71\text{V} \sim 1.89\text{V}$                                                                                                                            |                                                                                                                                                                                                                                                       | 0                    | 0.35 × $V_{(VDDIO)}$ | V  |

| I <sub>IH</sub>        | 入力 High 電流      | V <sub>IN</sub> = $V_{(VDDIO)} = 1.71\text{V} \sim 1.89\text{V}$ 、内部プルダウンは有効                                                                                              | GPIO0, GPIO1,<br>GPIO2, GPIO3,<br>D_GPIO0,<br>D_GPIO1,<br>D_GPIO2,<br>D_GPIO3,<br>GPIO5_REG,<br>GPIO6_REG,<br>GPIO7_REG,<br>GPIO8_REG,<br>MOSI, MISO,<br>SPLK, SS,<br>I2C_WC, I2S_CLK,<br>I2S_DA, I2S_DB,<br>I2S_DC, I2S_DD,<br>REFCLK0, REFCLK1      | 0                    | 100                  | μA |

|                        |                 | V <sub>IN</sub> = $V_{(VDDIO)} = 1.71\text{V} \sim 1.89\text{V}$ 、内部プルダウンは無効                                                                                              |                                                                                                                                                                                                                                                       | 0                    | 10                   | μA |

推奨動作電源電圧および温度範囲内 (特に記述のない限り)

| パラメータ          |              | テスト条件                                              | ピン / 周波数                                                                                                                                                                                                                                              | 最小値 | 標準値 | 最大値 | 単位      |

|----------------|--------------|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|---------|

| $I_{IL}$       | 入力 Low 電流    | $V_{IN} = 0V$                                      | PDB, GPIO0、<br>GPIO1, GPIO2、<br>GPIO3, D_GPIO0、<br>D_GPIO1、<br>D_GPIO2、<br>D_GPIO3、<br>GPIO5_REG、<br>GPIO6_REG、<br>GPIO7_REG、<br>GPIO8_REG、<br>MOSI, MISO、<br>SPLK, SS、<br>I2C_WC, I2S_CLK、<br>I2S_DA, I2S_DB、<br>I2S_DC, I2S_DD、<br>REFCLK0, REFCLK1 | -20 |     | 20  | $\mu A$ |

| $I_{IN-STRAP}$ | ストラップ・ピン入力電流 | $V_{IN} = 0V$ または $V_{(VDDIO)} = 1.71V \sim 1.89V$ | IDX, MODE_SEL0、<br>MODE_SEL1                                                                                                                                                                                                                          | -1  |     | 1   | $\mu A$ |

推奨動作電源電圧および温度範囲内 (特に記述のない限り)

| パラメータ           |                 | テスト条件                                                     | ピン / 周波数                                                                                                                                                                                    | 最小値                         | 標準値 | 最大値  | 単位 |

|-----------------|-----------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----|------|----|

| V <sub>OH</sub> | High レベル出力電圧    | I <sub>OH</sub> = -2mA、V <sub>(VDDIO)</sub> = 1.71V~1.89V | GPIO0, GPIO1, GPIO2, GPIO3, D_GPIO0, D_GPIO1, D_GPIO2, D_GPIO3, GPIO5_REG, GPIO6_REG, GPIO7_REG, GPIO8_REG, MOSI, MISO, SPLK, SS, I2C_WC, I2S_CLK, I2S_DA, I2S_DB, I2S_DC, I2S_DD, REM_INTB | V <sub>(VDDIO)</sub> - 0.45 |     |      | V  |

| V <sub>OL</sub> | Low レベル出力電圧     | I <sub>OL</sub> = 2mA、V <sub>(VDDIO)</sub> = 1.71V~1.89V  |                                                                                                                                                                                             | 0                           |     | 0.45 | V  |

| I <sub>OS</sub> | 出力短絡電流          | V <sub>OUT</sub> = 0V                                     |                                                                                                                                                                                             | -35                         |     |      | mA |

| I <sub>OZ</sub> | TRI-STATE™ 出力電流 | V <sub>OUT</sub> = 0V または V <sub>DDIO</sub> 、PDB = L      |                                                                                                                                                                                             | -20                         |     | 20   | μA |

### 3.3V LVCMOS I/O

|                 |              |                                                                   |                                                                                                                                                                                                          |     |                      |    |

|-----------------|--------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------|----|

| V <sub>IH</sub> | High レベル入力電圧 | V <sub>(VDDIO)</sub> = 3.0V~3.6V                                  | PDB, GPIO0, GPIO1, GPIO2, GPIO3, D_GPIO0, D_GPIO1, D_GPIO2, D_GPIO3, GPIO5_REG, GPIO6_REG, GPIO7_REG, GPIO8_REG, MOSI, MISO, SPLK, SS, I2C_WC, I2S_CLK, I2S_DA, I2S_DB, I2S_DC, I2S_DD, REFCLK0, REFCLK1 | 2.0 | V <sub>(VDDIO)</sub> | V  |

| V <sub>IL</sub> | Low レベル入力電圧  | V <sub>(VDDIO)</sub> = 3.0V~3.6V                                  |                                                                                                                                                                                                          | 0   | 0.8                  | V  |

| I <sub>IH</sub> | 入力 High 電流   | V <sub>IN</sub> = V <sub>(VDDIO)</sub> = 3.0V~3.6V、内部ブレダ<br>ウンは有効 | GPIO0, GPIO1, GPIO2, GPIO3, D_GPIO0, D_GPIO1, D_GPIO2, D_GPIO3, GPIO5_REG, GPIO6_REG, GPIO7_REG, GPIO8_REG, MOSI, MISO, SPLK, SS, I2C_WC, I2S_CLK, I2S_DA, I2S_DB, I2S_DC, I2S_DD, REFCLK0, REFCLK1      | 0   | 180                  | μA |

|                 |              | V <sub>IN</sub> = V <sub>(VDDIO)</sub> = 3.0V~3.6V、内部ブレダ<br>ウンは無効 |                                                                                                                                                                                                          |     | 25                   | μA |

| I <sub>IL</sub> | 入力 Low 電流    | V <sub>IN</sub> = 0V                                              | PDB, GPIO0, GPIO1, GPIO2, GPIO3, D_GPIO0, D_GPIO1, D_GPIO2, D_GPIO3, GPIO5_REG, GPIO6_REG, GPIO7_REG, GPIO8_REG, MOSI, MISO, SPLK, SS, I2C_WC, I2S_CLK, I2S_DA, I2S_DB, I2S_DC, I2S_DD, REFCLK0, REFCLK1 | -20 | 20                   | μA |

|                 |              |                                                                   |                                                                                                                                                                                                          |     |                      |    |

**DS90UH941AS-Q1**

JAJSHA5B – MAY 2019 – REVISED JANUARY 2021

推奨動作電源電圧および温度範囲内 (特に記述のない限り)

| パラメータ           |                 | テスト条件                                                   | ピン / 周波数                                                                                                                                                                                                                          | 最小値 | 標準値                  | 最大値 | 単位 |

|-----------------|-----------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------|-----|----|

| V <sub>OH</sub> | High レベル出力電圧    | I <sub>OH</sub> = -4mA、V <sub>(VDDIO)</sub> = 3.0V~3.6V | GPIO0、GPIO1、<br>GPIO2、GPIO3、<br>D_GPIO0、<br>D_GPIO1、<br>D_GPIO2、<br>D_GPIO3、<br>GPIO5_REG、<br>GPIO6_REG、<br>GPIO7_REG、<br>GPIO8_REG、<br>MOSI、MISO、<br>SPLK_SS、<br>I2C_WC、I2S_CLK、<br>I2S_DA、I2S_DB、<br>I2S_DC、I2S_DD、<br>REM_INTB | 2.4 | V <sub>(VDDIO)</sub> | V   |    |

| V <sub>OL</sub> | Low レベル出力電圧     | I <sub>OL</sub> = 4mA、V <sub>(VDDIO)</sub> = 3.0V~3.6V  |                                                                                                                                                                                                                                   | 0   | 0.4                  | V   |    |

| I <sub>os</sub> | 出力短絡電流          | V <sub>OUT</sub> = 0V                                   |                                                                                                                                                                                                                                   | -60 |                      | mA  |    |

| I <sub>oz</sub> | TRI-STATE™ 出力電流 | V <sub>OUT</sub> = 0V または V <sub>(VDDIO)</sub> 、PDB = L |                                                                                                                                                                                                                                   | -20 | 20                   | μA  |    |

## オープン・ドレイン出力

|                 |            |                                                          |      |     |      |    |

|-----------------|------------|----------------------------------------------------------|------|-----|------|----|

| V <sub>OL</sub> | 出力 Low レベル | V <sub>(VDDIO)</sub> = 3.0V~3.6V、I <sub>OL</sub> = 4mA   | INTB | 0   | 0.4  | V  |

|                 |            | V <sub>(VDDIO)</sub> = 1.71V~1.89V、I <sub>OL</sub> = 2mA |      | 0   | 0.45 |    |

| I <sub>OH</sub> | 出力リーケ電流    | V <sub>(VDDIO)</sub>                                     |      | -20 | 20   | μA |

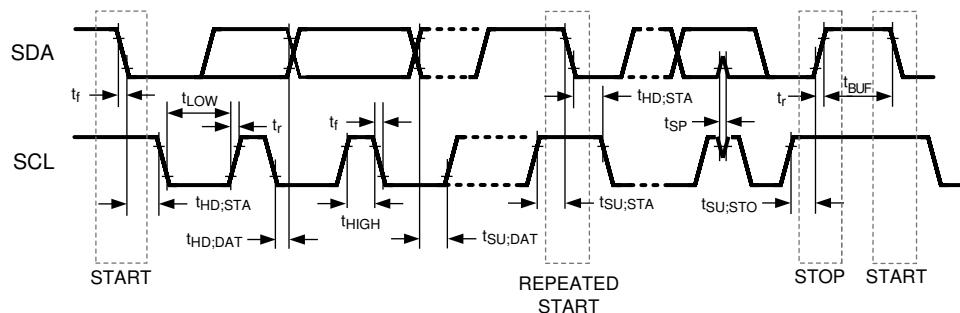

## シリアル制御バス I/O

|                  |             |                                                              |                 |                            |                            |    |

|------------------|-------------|--------------------------------------------------------------|-----------------|----------------------------|----------------------------|----|

| V <sub>IH</sub>  | 入力 High レベル |                                                              | I2C_SCL、I2C_SDA | 0.7 × V <sub>(VDDIO)</sub> | V <sub>(VDDIO)</sub>       | V  |

| V <sub>IL</sub>  | 入力 Low レベル  |                                                              |                 | 0                          | 0.3 × V <sub>(VDDIO)</sub> | V  |

| V <sub>HYS</sub> | 入力ヒステリシス    |                                                              |                 | 50                         |                            | mV |

| V <sub>OL1</sub> | 出力 Low レベル  | V <sub>(VDDIO)</sub> = 3.0V~3.6V、<br>I <sub>OL</sub> = 3mA   |                 | 0                          | 0.4                        | V  |

|                  |             | V <sub>(VDDIO)</sub> = 3.0V~3.6V、<br>I <sub>OL</sub> = 20mA  |                 | 0                          | 0.4                        | V  |

| V <sub>OL2</sub> | 出力 Low レベル  | V <sub>(VDDIO)</sub> = 1.71V~<br>1.89V、I <sub>OL</sub> = 2mA |                 | 0                          | 0.2 × V <sub>(VDDIO)</sub> | V  |

| I <sub>IH</sub>  | 入力 High 電流  | V <sub>IN</sub> = V <sub>(VDDIO)</sub>                       |                 | -10                        | 10                         | μA |

| I <sub>IL</sub>  | 入力 Low 電流   | V <sub>IN</sub> = 0V                                         |                 | -10                        | 10                         | μA |

| C <sub>IN</sub>  | 入力容量        |                                                              |                 | 5                          |                            | pF |

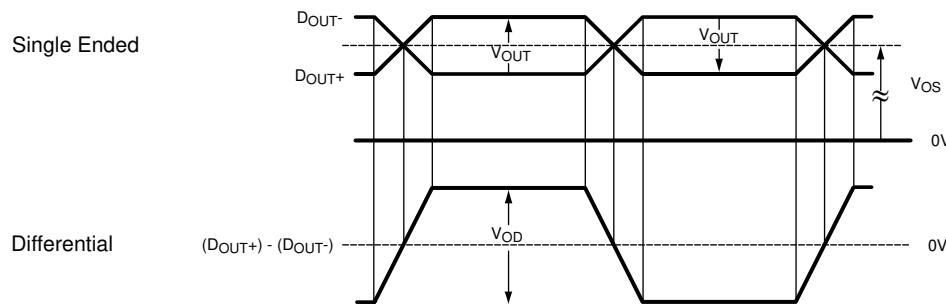

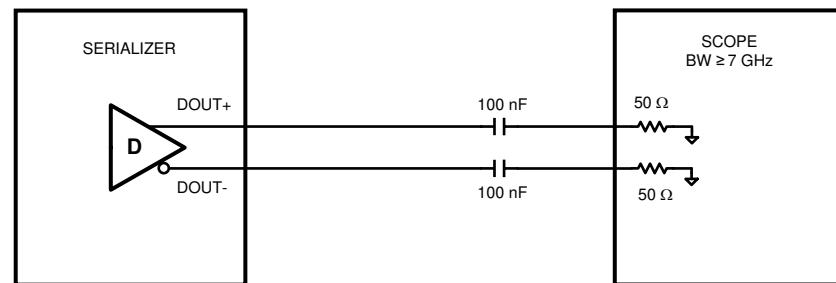

## FPD-LINK III トランシーバ

|                    |                      |                                      |                                |     |      |                   |

|--------------------|----------------------|--------------------------------------|--------------------------------|-----|------|-------------------|

| V <sub>ODp-p</sub> | 差動出力電圧               | R <sub>L</sub> = 100Ω<br>パック・チャネルは無効 | DOUT0+、DOU0-、<br>DOUT1+、DOUT1- | 900 | 1200 | mV <sub>p-p</sub> |

| V <sub>OUT</sub>   | シングルエンド出力電圧          | R <sub>L</sub> = 50Ω<br>パック・チャネルは無効  |                                | 450 | 600  | mV                |

| ΔV <sub>OD</sub>   | 出力電圧アンバランス           | R <sub>L</sub> = 100Ω                |                                | 1   | 50   | mV                |

| V <sub>os</sub>    | 出力オフセット電圧            | R <sub>L</sub> = 100Ω                |                                | 550 |      | mV                |

| ΔV <sub>os</sub>   | オフセット電圧アンバランス        | R <sub>L</sub> = 100Ω                |                                | 1   | 50   | mV                |

| I <sub>os</sub>    | 出力短絡電流               | FPD-link III 出力 = 0V                 |                                | -20 |      | mA                |

| R <sub>T</sub>     | 終端抵抗                 | 差動                                   |                                | 80  | 100  | 120               |

|                    |                      | シングルエンド                              |                                | 40  | 50   | 60                |

| V <sub>ID-BC</sub> | 差動パック・チャネル入力振幅       | パック・チャネル・データ・レート = 5、10、<br>20Mbps   |                                | 170 |      | mV                |

| V <sub>IN-BC</sub> | シングルエンド・パック・チャネル入力振幅 |                                      |                                | 170 |      | mV                |

推奨動作電源電圧および温度範囲内 (特に記述のない限り)

| パラメータ                 | テスト条件                    | ピン / 周波数                      | 最小値                                                                                                                                                                                                                                                                 | 標準値                                                                                                                                                                                                                                                                 | 最大値 | 単位     |

|-----------------------|--------------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------|

| <b>DSI HS RX レシーバ</b> |                          |                               |                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                     |     |        |

| V <sub>CMRX(DC)</sub> | 同相電圧、HS 受信モード            | 定常状態                          | 定常状態                                                                                                                                                                                                                                                                | DSI0_D0P、<br>DSI0_D0N、<br>DSI0_D1P、<br>DSI0_D1N、<br>DSI0_D2P、<br>DSI0_D2N、<br>DSI0_D3P、<br>DSI0_D3N、<br>DSI0_CLKP、<br>DSI0_CLKN、<br>DSI1_D0P、<br>DSI1_D0N、<br>DSI1_D1P、<br>DSI1_D1N、<br>DSI1_D2P、<br>DSI1_D2N、<br>DSI1_D3P、<br>DSI1_D3N、<br>DSI1_CLKP、<br>DSI1_CLKN | 70  | 330 mV |

| V <sub>CMRX(DC)</sub> | 同相電圧、HS 受信モード            | 定常状態                          | データ・レート ≤ 1.5Gbps                                                                                                                                                                                                                                                   | DSI0_D0P、<br>DSI0_D0N、<br>DSI0_D1P、<br>DSI0_D1N、<br>DSI0_D2P、<br>DSI0_D2N、<br>DSI0_D3P、<br>DSI0_D3N、<br>DSI0_CLKP、<br>DSI0_CLKN、<br>DSI1_D0P、<br>DSI1_D0N、<br>DSI1_D1P、<br>DSI1_D1N、<br>DSI1_D2P、<br>DSI1_D2N、<br>DSI1_D3P、<br>DSI1_D3N、<br>DSI1_CLKP、<br>DSI1_CLKN | 70  | 330 mV |

| V <sub>IDTH</sub>     | 差動入力 High スレッショルド        | 70                            |                                                                                                                                                                                                                                                                     | mV                                                                                                                                                                                                                                                                  |     |        |

| V <sub>IDTL</sub>     | 差動入力 Low スレッショルド         | -70                           |                                                                                                                                                                                                                                                                     | mV                                                                                                                                                                                                                                                                  |     |        |

| V <sub>IH-HS</sub>    | シングルエンド入力 High 電圧        | 460                           |                                                                                                                                                                                                                                                                     | mV                                                                                                                                                                                                                                                                  |     |        |

| V <sub>IL-HS</sub>    | シングルエンド入力 Low 電圧         | -40                           |                                                                                                                                                                                                                                                                     | mV                                                                                                                                                                                                                                                                  |     |        |

| V <sub>TERM-EN</sub>  | HS 終端有効時のシングルエンド・スレッショルド | 450                           |                                                                                                                                                                                                                                                                     | mV                                                                                                                                                                                                                                                                  |     |        |

| Z <sub>ID</sub>       | 差動入力インピーダンス              | 80 100 125                    |                                                                                                                                                                                                                                                                     | Ω                                                                                                                                                                                                                                                                   |     |        |

| <b>DSI LPRX レシーバ</b>  |                          |                               |                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                     |     |        |

| V <sub>IH-LP</sub>    | LP ロジック 1 入力電圧           | 対応データ・レートが 1.5Gbps 以下の場合に適用可能 | DSI0_D0P、<br>DSI0_D0N、<br>DSI0_D1P、<br>DSI0_D1N、<br>DSI0_D2P、<br>DSI0_D2N、<br>DSI0_D3P、<br>DSI0_D3N、<br>DSI0_CLKP、<br>DSI0_CLKN、<br>DSI1_D0P、<br>DSI1_D0N、<br>DSI1_D1P、<br>DSI1_D1N、<br>DSI1_D2P、<br>DSI1_D2N、<br>DSI1_D3P、<br>DSI1_D3N、<br>DSI1_CLKP、<br>DSI1_CLKN | 880                                                                                                                                                                                                                                                                 | mV  |        |

| V <sub>IL-LP</sub>    | LP ロジック 0 入力電圧           | ULP 状態を除く                     |                                                                                                                                                                                                                                                                     | 550                                                                                                                                                                                                                                                                 | mV  |        |

| V <sub>HYST</sub>     | 入力ヒステリシス                 |                               |                                                                                                                                                                                                                                                                     | 25                                                                                                                                                                                                                                                                  | mV  |        |

## 7.6 AC 電気的特性

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ                      | テスト条件                     | ピン / 周波数                                                       | 最小値 | 標準値                     | 最大値 | 単位     |

|----------------------------|---------------------------|----------------------------------------------------------------|-----|-------------------------|-----|--------|

| <b>GPIO のタイミング</b>         |                           |                                                                |     |                         |     |        |

| $f_{GPIO\_FC}$             | フォワード・チャネル GPIO の最大周波数    | シングル FPD-Link III                                              |     | $(1/4) \times f_{PCLK}$ |     | MHz    |

|                            |                           | デュアル FPD-Link III                                              |     |                         |     |        |

| $t_{GPIO\_FC\_JL}$         | フォワード・チャネル GPIO のジッタ      | シングル FPD-Link III                                              |     | $(1/8) \times f_{PCLK}$ |     | MHz    |

|                            |                           | デュアル FPD-Link III                                              |     |                         |     |        |

| $f_{GPIO\_BC}$             | バック・チャネル GPIO の最大周波数      | BC レート = 20Mbps、通常 GPIO モード (DES)、4 つの GPIO                    |     | 1/f <sub>PCLK</sub>     | ns  | kHz    |

| $f_{GPIO\_BC}$             |                           | BC レート = 20Mbps、高速 GPIO モード、4 つの GPIO                          |     |                         |     |        |

| $f_{GPIO\_BC}$             |                           | BC レート = 20Mbps、高速 GPIO モード、2 つの GPIO                          |     |                         |     |        |

| $f_{GPIO\_BC}$             |                           | BC レート = 20Mbps、高速 GPIO モード、1 つの GPIO                          |     |                         |     |        |

| $t_{GPIO\_BC}$             |                           | BC レート = 20Mbps、通常 GPIO モード (DES)、4 つの GPIO                    |     |                         |     |        |

| $t_{GPIO\_BC}$             | バック・チャネル GPIO のジッタ        | BC レート = 20Mbps、高速 GPIO モード、4 つの GPIO                          |     | 2/f <sub>PCLK</sub>     | ns  | kHz    |

| $t_{GPIO\_BC}$             |                           | BC レート = 20Mbps、高速 GPIO モード、2 つの GPIO                          |     |                         |     |        |

| $t_{GPIO\_BC}$             |                           | BC レート = 20Mbps、高速 GPIO モード、1 つの GPIO                          |     |                         |     |        |

| $t_{GPO\_LHT}$             | GPO の Low から High への遷移時間  | $C_L = 8pF$ (集中負荷)、デフォルト・レジスタ                                  |     | 133                     | kHz | kHz    |

| $t_{GPO\_HLT}$             | GPO の High から Low への遷移時間  |                                                                |     |                         |     |        |

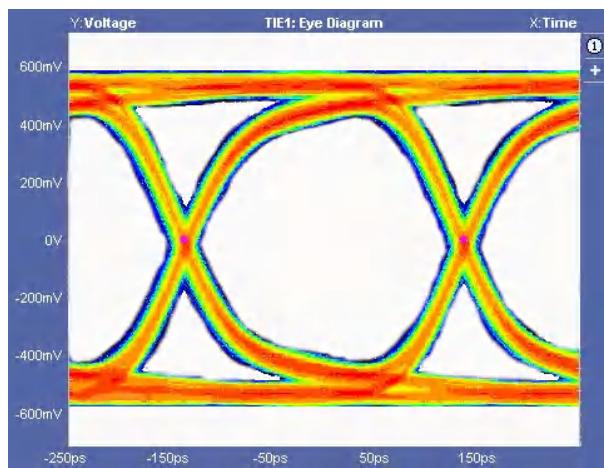

| <b>FPD-Link III のタイミング</b> |                           |                                                                |     |                         |     |        |

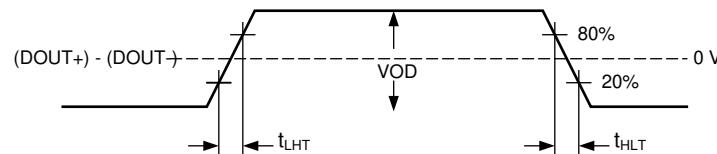

| $t_{LHT}$                  | 低電圧差動の Low から High への遷移時間 | GPIO0, GPIO1, GPIO2, GPIO3, D_GPIO0, D_GPIO1, D_GPIO2, D_GPIO3 |     | 80                      | 120 | ps     |

| $t_{HLT}$                  | 低電圧差動の High から Low への遷移時間 |                                                                |     |                         |     |        |

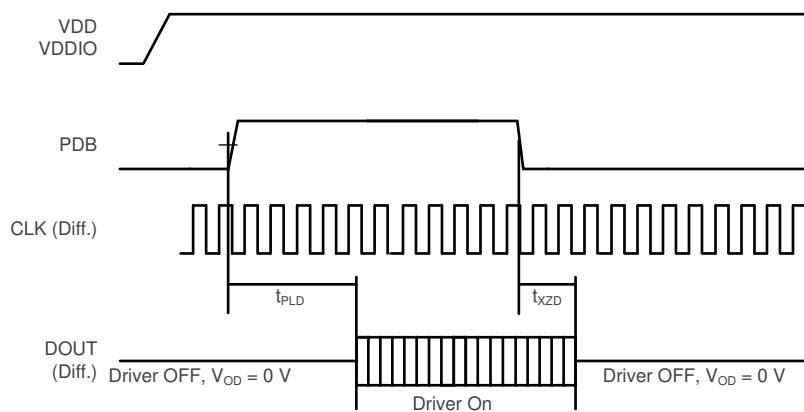

| $t_{XZD}$                  | 出力のアクティブからオフへの遅延          |                                                                |     |                         |     |        |

| $t_{PLD}$                  | ロック時間                     |                                                                |     |                         |     |        |

| $t_{SD}$                   | 遅延 - レイテンシ                |                                                                |     |                         |     |        |

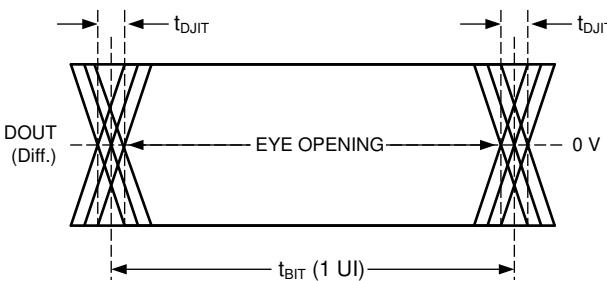

| $t_{JITR}$                 | 出力のランダム・ジッタ               |                                                                |     |                         |     |        |

| $t_{JITD}$                 | 出力の確定的ジッタ                 |                                                                |     |                         |     |        |

| $t_{JIT}$                  | 出力の総合ジッタ                  |                                                                |     |                         |     |        |

| $E_H$                      | アイの高さ                     |                                                                |     |                         |     |        |

| $t_{JITR}$                 | 出力のランダム・ジッタ               |                                                                |     |                         |     |        |

| $t_{JITD}$                 | 出力の確定的ジッタ                 |                                                                |     |                         |     |        |

| $t_{JIT}$                  | 出力の総合ジッタ                  |                                                                |     |                         |     |        |

| $E_H$                      | アイの高さ                     |                                                                |     |                         |     |        |

| $\lambda_{STXBW}$          | ジッタ伝達関数 (-3dB 帯域幅)        |                                                                |     |                         |     |        |

| $\delta_{STX}$             | ジッタ伝達関数のピーキング             |                                                                |     |                         |     |        |

| $V_{BCDR}$                 | バック・チャネルのデータ・レート          | デフォルト (デシリアルライザ)                                               |     | 5                       | dB  | $Mbps$ |

|                            |                           | HSCC_MODE (デシリアルライザ)                                           |     |                         |     |        |

|                            |                           | HSCC_MODE (デシリアルライザ)                                           |     |                         |     |        |

自由気流での動作温度範囲内 (特に記述のない限り)

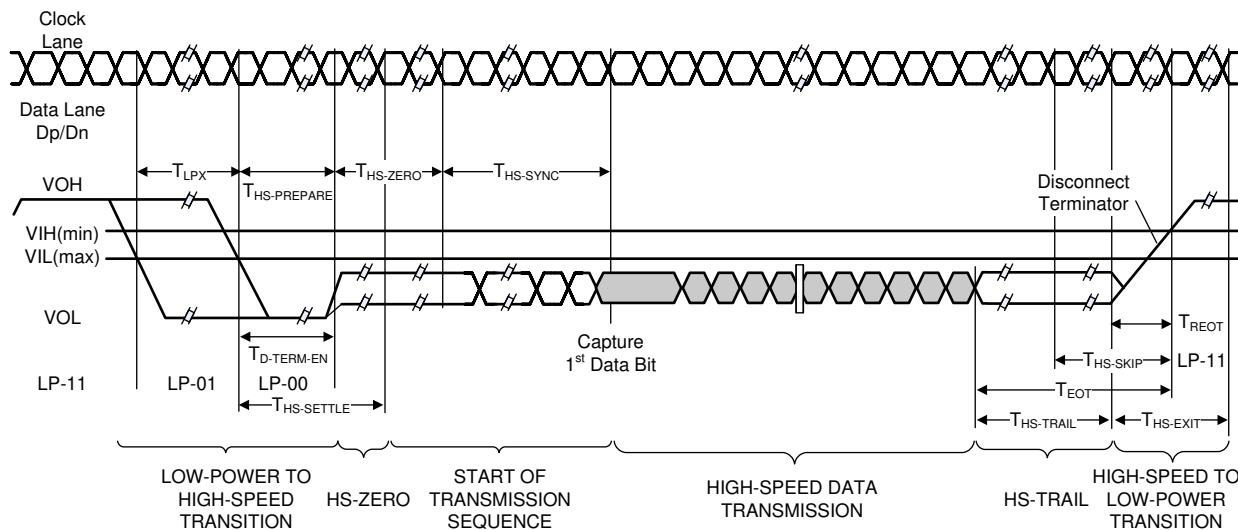

| パラメータ                  | テスト条件        | ピン / 周波数                                                                                                                                                                                                                                                            | 最小値                                                                                                                                                                                                                                                                 | 標準値   | 最大値  | 単位                                |

|------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-----------------------------------|

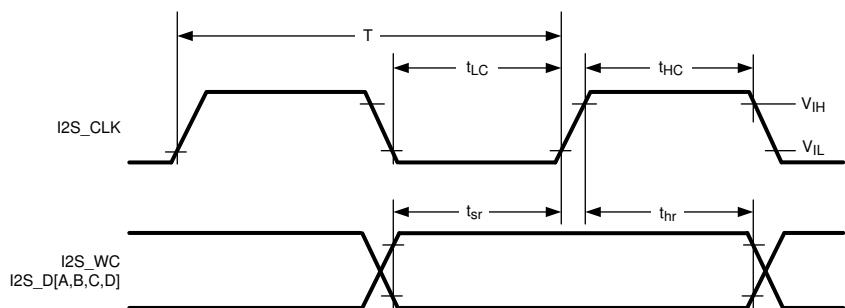

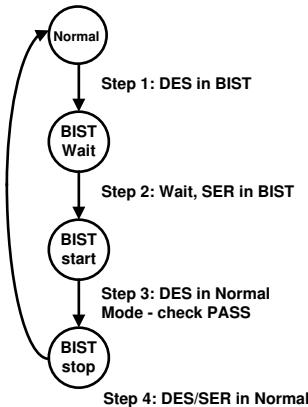

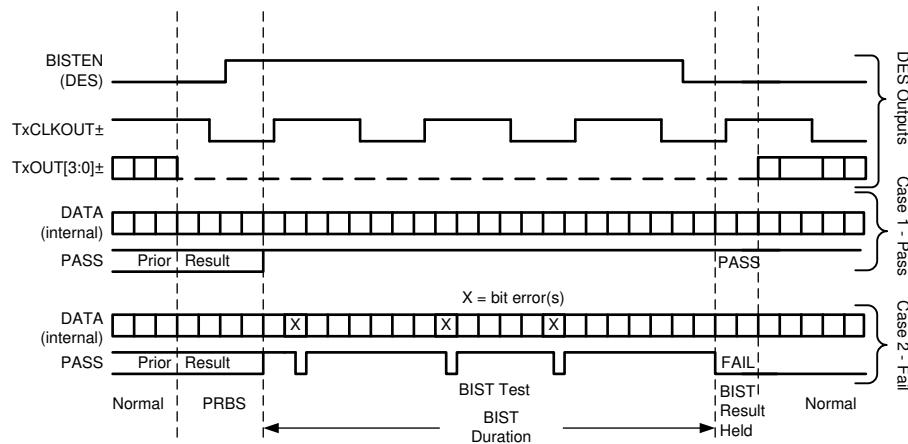

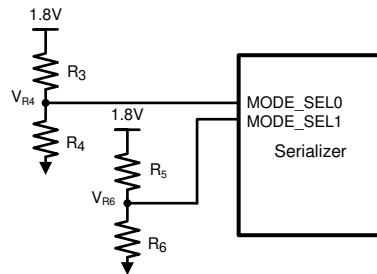

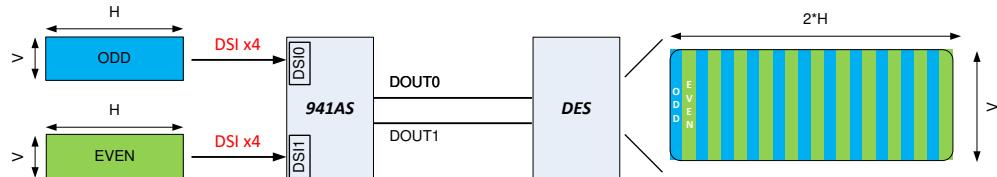

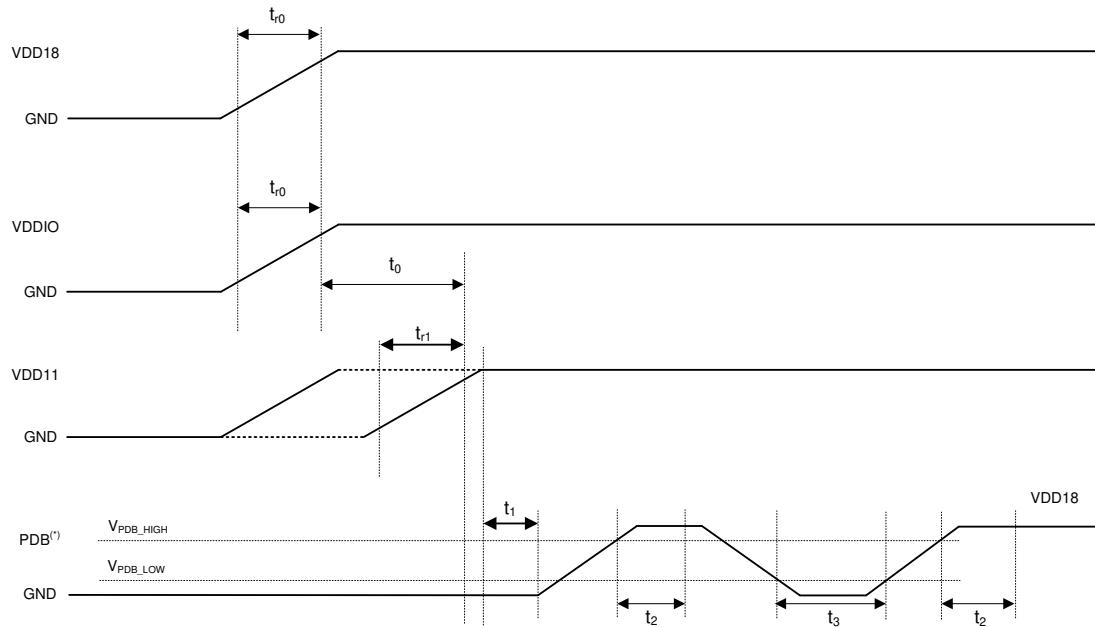

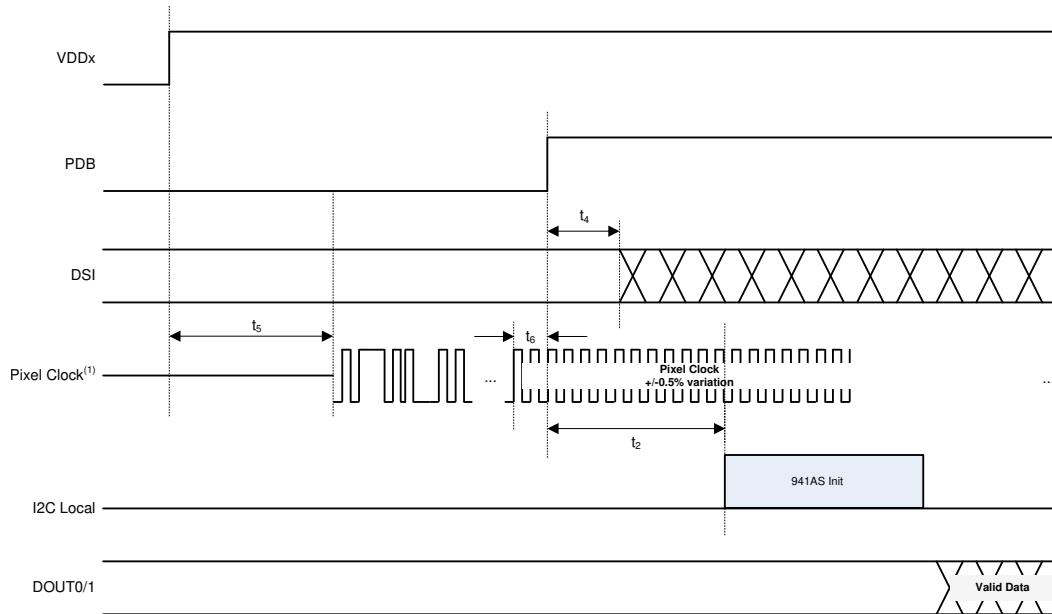

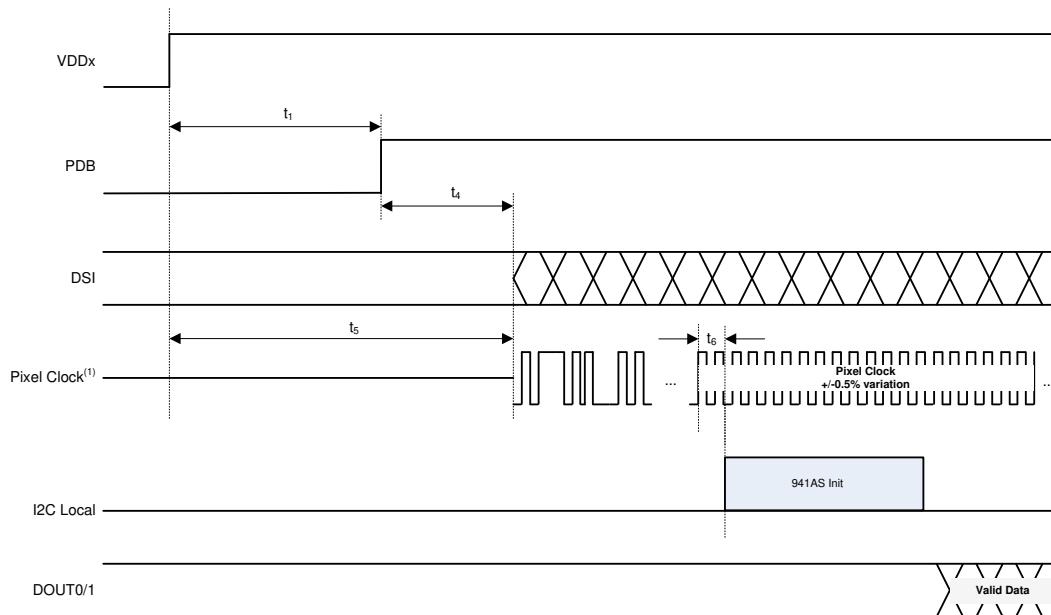

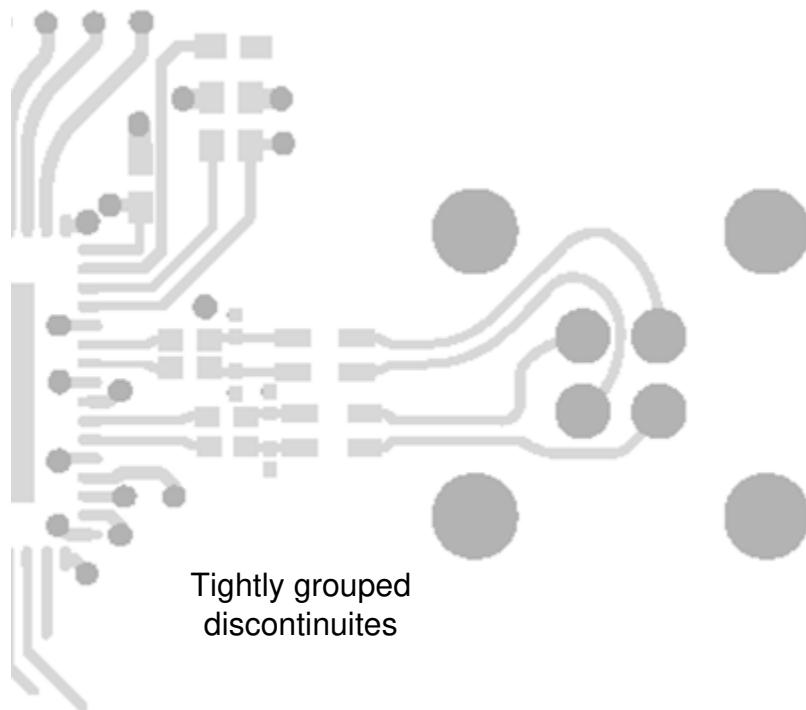

| <b>DSI LPRX レシーバ</b>   |              |                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                     |       |      |                                   |