# **DS90UR907Q**

DS90UR907Q 5 - 65 MHz 24-bit Color FPD-Link to FPD-Link II Converter

Literature Number: JAJSB12

# **DS90UR907Q**

2010年7月

# 5 ~ 65MHz、24 ビット・カラー FPD-Link/FPD-Link II コンバータ

#### 概要

DS90UR907Q は、FPD-Link を FPD-Link II に変換します。具体的には、4つの小振幅差動信号 (LVDS) データ/制御ストリームと1対の LVDS クロック・ペア (FPD-Link) を単一ペア上の高速シリアル化インタフェース(FPD-Link II) に変換します。このシリアル・バス方式では、クロックとデータの間で問題となるスキューが発生しないため、システム設計が大幅に容易になるほか、コネクタ・ピン数やインターコネクトのサイズ、重量、コストを削減して、PCB レイアウト全般を簡素化できます。また、DC バランス・エンコード機能を搭載しており、AC 結合によるインターコネクトをサポートします。

DS90UR907Q は、4 つの LVDS データ/制御ストリームを変換、バランス化、レベル・シフトを行い、1 対の LVDS クロック・ペア (FPD-Link) を単一のシリアル・データ・ストリーム (FPD-Link II) に埋め込みます。FPD-Link 上の最大で24 ビットのRGBが3つのビデオ制御信号とともにシリアル化されます。

シリアル伝送は、ユーザーが選択可能なデエンファシスと、差動出力レベル選択機能によって最適化されています。また、LVDSの使用と、スペクトラム拡散クロックの互換性によってEMIが最小限に抑えられています。

LVDS 技術を利用した FPD-Link 入力は、ホストの物理インタフェースへの配線を削減し、高速、低消費電力、低 EMI のデータ転送に最適です。

このデバイスは、 36 ピンの LLP パッケージで供給され、 -40  $\mathbb{C}\sim+105$   $\mathbb{C}$ のオートモーティブ AEC-Q100 グレード 2 の温度範囲が指定されています。

#### 特長

- 5 ~ 65MHz をサポート (140Mbps ~ 1.82Gbps のシリアル・ リンク)

- 5 チャネル (4 データ+ 1 クロック) FPD-Link レシーバ入力

- 最大 10m の AC 結合した STP インターコネクト

- 出力終端を内蔵

- @ Speed リンク BIST モード

- オプションの I<sup>2</sup>C 互換シリアル制御バス

- RGB888 + VS、HS、DEをサポート

- パワーダウン・モードで消費電力を削減

- ランダマイザ / スクランブラ DC バランス化したデータ・スト リーム

- 低 EMI FPD-Link 入力

- 選択可能な出力 VOD と可変のデエンファシス

- 1.8V または 3.3V に対応した制御バス・インタフェース

- オートモーティブ・グレード製品: AEC-Q100グレード2認定

- 8kV を超える HBM と ISO 10605 ESD 定格

- 下位互換モードにより旧世代のデバイスとともに使用可能

#### アプリケーション

- 自動車のナビゲーション用ディスプレイ

- 自動車のエンターテインメント用ディスプレイ

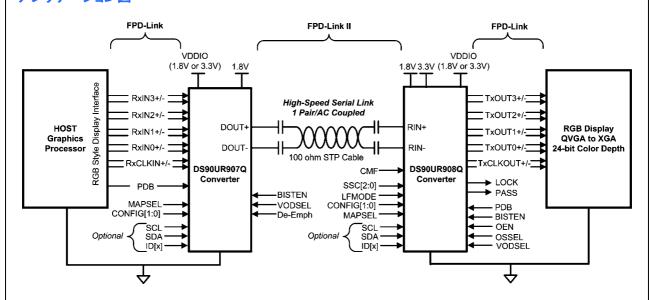

## アプリケーション図

TRI-STATE® はナショナル セミコンダクターの登録商標です。

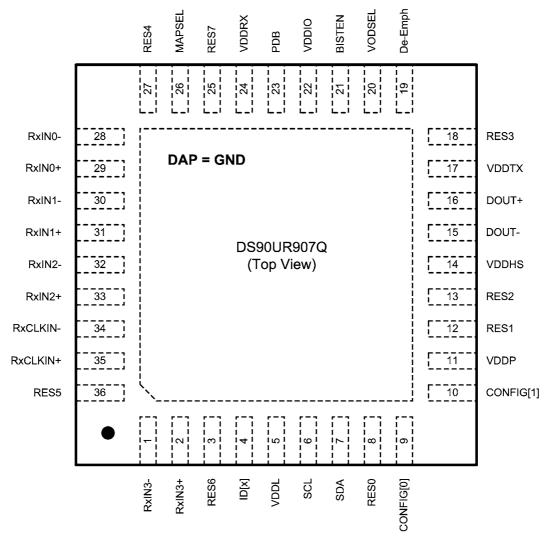

# DS90UR907Q ピン配置図

### DS90UR907Q — Top View

# ピン説明

| ピン名         | ピン番号                 | 入出力、タイプ | 説明                                                                  |

|-------------|----------------------|---------|---------------------------------------------------------------------|

| FPD-Link 入  | カインタフェース             | ξ       |                                                                     |

| RxIN[3:0] + | 2, 33, 31, 29        | I、LVDS  | 非反転 LVDS データ入力<br>このペアで標準の LVDS レベルを得るには、外付けの $100\Omega$ 終端が必要です。  |

| RxIN[3:0] — | 1, 34, 32, 30,<br>28 | I、LVDS  | 反転 LVDS データ入力<br>このペアで標準の LVDS レベルを得るには、外付けの $100\Omega$ 終端が必要です。   |

| RxCLKIN +   | 35                   | I, LVDS | 非反転 LVDS クロック入力<br>このペアで標準の LVDS レベルを得るには、外付けの $100\Omega$ 終端が必要です。 |

| RxCLKIN -   | 34                   | I、LVDS  | 反転 LVDS クロック入力<br>このペアで標準の LVDS レベルを得るには、外付けの $100\Omega$ 終端が必要です。  |

# **ピン説明**(つづき)

| ピン名         | ピン番号           | 入出力、タイプ                      | 説明                                                              |

|-------------|----------------|------------------------------|-----------------------------------------------------------------|

| 制御と構成       |                |                              |                                                                 |

| PDB         | 23             | I, LVCMOS                    | パワーダウン・モード入力                                                    |

|             |                | プルダウンあり                      | PDB = 1: デバイスがイネーブルになります (通常動作)。                                |

|             |                |                              | 「アプリケーション情報」の「パワーオン要件とPDB ピン」を参照してください。                         |

|             |                |                              | PDB = 0: デバイスがパワーダウン状態になります。                                    |

|             |                |                              | デバイスがパワーダウン状態になると、ドライバ出力 (DOUT + / - ) はいずれ                     |

|             |                |                              | もロジック High になり、PLL がシャットダウンされ、IDD が最小限になります。                    |

|             |                |                              | 制御レジスタはリセットされます。                                                |

| VODSEL      | 20             | I, LVCMOS                    | 差動ドライバ出力電圧の選択 — ピンまたはレジスタの制御                                    |

|             |                | プルダウンあり                      | VODSEL = 1: LVDS VOD は± 450mV、900mVp-p (typ)です。一長いケー            |

|             |                |                              | ブル / De-E アプリケーション                                              |

| D. FI.      | 10             | . 71.2                       | VODSEL = 0: LVDS VOD は± 300mV、600mVp-p (typ) です。                |

| De-Emph     | 19             | I、アナログ                       | デエンファシス制御 ― ピンまたはレジスタの制御                                        |

|             |                | プルアップあり                      | De-Emph = 開放 (フロート): ディスエーブル                                    |

|             |                |                              | デエンファシスをイネーブルにするには、このピンと GND の間に抵抗を接続するか、レジスタを使って制御します。         |

|             |                |                              | Table 3 を参照してください。                                              |

| MAPSEL      | 26             | I, LVCMOS                    | FPD-Link マップの選択 — ピンまたはレジスタの制御                                  |

| OLL         | 20             | プルダウンあり                      | MAPSEL = 1: RxIN3 + / - に MSB。 Figure 17                        |

|             |                | 27 <b>4</b> 7 7 <b>4</b> 633 | MAPSEL = 0: RxIN3 + $/$ - $\sqrt{c}$ LSB <sub>o</sub> Figure 16 |

| CONFIG[1:0] | 10, 9          | I, LVCMOS                    | 動作モード                                                           |

| COM IG[1.0] | 10, )          | プルダウンあり                      | デバイスの動作モードと、インタフェースするデバイスを決定します。Table 1                         |

|             |                | <i>&gt; /• / / • 0//</i>     | CONFIG[1:0] = 00: DS90UR906 または DS90UR908 とインタフェース。 制御          |

|             |                |                              | 信号フィルタはディスエーブル                                                  |

|             |                |                              | CONFIG[1:0] = 01: DS90UR906 または DS90UR908 とインタフェース。 制御          |

|             |                |                              | 信号フィルタはイネーブル                                                    |

|             |                |                              | CONFIG [1:0] = 10: DS90UR124、DS99R124 とインタフェース                  |

|             |                |                              | CONFIG [1:0] = 11: DS90C124 とインタフェース                            |

| ID[x]       | 4              | I、アナログ                       | シリアル制御バスのデバイス ID アドレスの選択 — オプション                                |

|             |                |                              | グラウンドに接続された抵抗と $1.8V$ レールに接続された $10k\Omega$ プルアップ。              |

|             |                |                              | Table 4 を参照してください。                                              |

| SCL         | 6              | I、LVCMOS                     | シリアル制御バスのクロック入力 ― オプション                                         |

|             |                |                              | $SCL$ は、 $V_{DDIO}$ に接続された外付けプルアップ抵抗を必要とします。                    |

| SDA         | 7              | I/O、LVCMOS                   | シリアル制御バスのデータ入出力 ― オプション                                         |

|             |                | オープン・ドレイン                    | SDA は、 $V_{\rm DDIO}$ に接続された外付けプルアップ抵抗を必要とします。                  |

| BISTEN      | 21             | I, LVCMOS                    | BIST モードーオプション                                                  |

|             |                | プルダウンあり                      | BISTEN = 1: BIST がイネーブルになります。                                   |

| DEGLE OF    | 25.2.26.25     |                              | BISTEN = 0: BIST がディスエーブルになります。                                 |

| RES[7:0]    | 25, 3, 36, 27, | I、LVCMOS                     | 予約済み - Low に固定します。                                              |

|             | 18, 13, 12, 8  | プルダウンあり                      |                                                                 |

|             | ノリアル・インタ       |                              | T                                                               |

| DOUT +      | 16             | O、LVDS                       | 非反転出力                                                           |

|             |                |                              | 出力は 100nF コンデンサにより AC 結合される必要があります。                             |

| DOUT -      | 15             | O、LVDS                       | 反転出力                                                            |

|             |                |                              | 出力は 100nF コンデンサにより AC 結合される必要があります。                             |

| 電源とグラウン     |                |                              |                                                                 |

| VDDL        | 5              | 電源                           | ロジック電源、1.8V ± 5%                                                |

| VDDP        | 11             | 電源                           | PLL 電源、 1.8V ± 5%                                               |

| VDDHS       | 14             | 電源                           | TX 高速ロジック電源、 1.8V ± 5%                                          |

| VDDTX       | 17             | 電源                           | 出力ドライバ電源、1.8V ± 5%                                              |

| VDDRX       | 24             | 電源                           | RX 電源、1.8V ± 5%                                                 |

| VDDIO       | 22             | 電源                           | LVCMOS I/O 電源と FPD-Link I/O 電源、 <b>1.8V ± 5%または 3.3V ± 10%</b>  |

|             |                |                              |                                                                 |

| GND         | DAP            | グラウンド                        | DAP は、LLP パッケージの中央底面にある、金属の大きな接触面です。 少                          |

$NOTE: 1 = High, \ 0 = Low$

VDD ( $V_{DDn}$  および  $V_{DDIO}$ ) の電源ランプは、 1.5 ms 未満の単調上昇である必要があります。

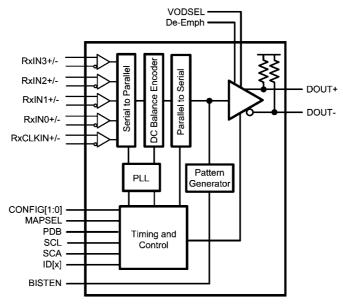

# ブロック図

FDP-Link to FPD-Link II Convertor

# 製品情報

| NSID          | Package Description                          | Quantity | SPEC | Package ID |

|---------------|----------------------------------------------|----------|------|------------|

| DS90UR907QSQE | 36-pin LLP, 6.0 X 6.0 X 0.8 mm, 0.5 mm pitch | 250      | NOPB | SQA36A     |

| DS90UR907QSQ  | 36-pin LLP, 6.0 X 6.0 X 0.8 mm, 0.5 mm pitch | 1000     | NOPB | SQA36A     |

| DS90UR907QSQX | 36-pin LLP, 6.0 X 6.0 X 0.8 mm, 0.5 mm pitch | 2500     | NOPB | SQA36A     |

Note: オートモーティブ・グレード (Q) 製品は、欠陥検出の技法など、自動車市場向けの高度な製造とサポート・プロセスを採用しています。 信頼性規格については、AEC-Q100 標準で規定された要件や温度グレードに準拠します。 オートモーティブ・グレード 製品は Q の文字で識別できます。 詳細は、 http://www.national.com/automotive を参照してください。

### 絶対最大定格 (Note 1)

本データシートには軍用・航空宇宙用の規格は記載されていません。 関連する電気的信頼性試験方法の規格を参照ください。

$-0.3V \sim +2.5V$ 電源電圧 – V<sub>DDn</sub> (1.8V)  $-0.3V \sim +4.0V$ 電源電圧 - V<sub>DDIO</sub> LVCMOS 入出力電圧  $-0.3V \sim (V_{DDIO} + 0.3V)$ LVDS 入力電圧  $-0.3V \sim (V_{DDIO} + 0.3V)$ ドライバ出力電圧  $-0.3V \sim (V_{DDn} + 0.3V)$ 最大接合部温度 + 150 ℃ 保存温度範囲 - 65 °C  $\sim$  + 150 °C

36ピン LLP パッケージ

25 ℃での最大消費電力

25 ℃を上回るときのディレーティング 1/ θ <sub>JA</sub> ℃ /W 27.4 °C /W  $\theta_{JA}$  $\theta_{\rm JC}$ 4.5 °C /W

ESD 耐圧 (IEC、パワーオン時のみ )、  $R_D=330\,\Omega$ 、  $C_S = 150pF$

気中放電 (R<sub>IN+</sub>、 R<sub>IN-</sub>)

$\geq \pm 30 \text{ kV}$  $\geq \pm 6 \text{ kV}$ 接触放電 (R<sub>IN+</sub>、R<sub>IN-</sub>)

ESD 耐圧 (ISO10605)、 $R_D$  = 330 $\Omega$ 、 $X_S$  = 150 および 330pF気中放電 (R<sub>IN+</sub>、 R<sub>IN-</sub>)  $\geq \pm 15 \text{ kV}$

接触放電 (R<sub>IN+</sub>、R<sub>IN-</sub>)  $\geq \pm 8kV$

ESD 耐圧 (ISO10605)、  $R_D=2k\,\Omega$  、  $C_S=150$ pF および 330pF

気中放電 (R<sub>IN+</sub>、R<sub>IN-</sub>)  $\geq \pm 15 \text{ kV}$ 接触放電 (R<sub>IN+</sub>、R<sub>IN-</sub>)  $\geq \pm 8kV$ ESD 耐圧 (HBM)  $\geq \pm 8kV$ ESD 耐圧 (CDM)  $\geq$   $\pm$  1.25 kV

ESD 耐圧 (マシン・モデル)  $\geq$   $\pm$  250 V

ハンダ付け仕様については、 www.national.com の製品フォルダと

www.national.com/ms/MS/MS-SOLDERING.pdf を参照してく

## 推奨動作条件

|                                  | 最小値  | 標準値  | 最大値   | 単位                     |

|----------------------------------|------|------|-------|------------------------|

| 電源電圧 (V <sub>DDn</sub> )         | 1.71 | 1.8  | 1.89  | V                      |

| LVCMOS 電源電圧 $(V_{DDIO})$         | 1.71 | 1.8  | 1.89  | V                      |

| または                              |      |      |       |                        |

| LVCMOS 電源電圧 (V <sub>DDIO</sub> ) | 3.0  | 3.3  | 3.6   | V                      |

| 動作温度範囲 (TA)                      | -40  | + 25 | + 105 | $^{\circ}\!\mathbb{C}$ |

| RxCLKIN 周波数                      | 5    |      | 65    | MHz                    |

| 電源ノイズ (Note 7)                   |      |      | 100   | $mV_{P\text{-}P}$      |

### DC 電気的特性

特記のない限り、推奨動作条件での電源電圧および温度範囲に適用。(Note 2、3、4)

| Symbol             | Parameter                              | Conditi                                                      | ons                                | Pin/Freq.                    | Min                        | Тур | Max                        | Units |  |     |    |     |    |

|--------------------|----------------------------------------|--------------------------------------------------------------|------------------------------------|------------------------------|----------------------------|-----|----------------------------|-------|--|-----|----|-----|----|

| LVCMOS             | NPUT DC SPECIFICATIONS                 | 10                                                           |                                    | 10° X                        |                            |     | Fe 58                      | Co.   |  |     |    |     |    |

|                    |                                        | $V_{DDIO} = 3.0 \text{ to } 3.6 \text{V}$                    |                                    |                              | 2.2                        |     | V <sub>DDIO</sub>          | ٧     |  |     |    |     |    |

| V <sub>IH</sub>    | High Level Input Voltage               | V <sub>DDIO</sub> = 1.71 to 1.89                             | v                                  |                              | 0.65*<br>V <sub>DDIO</sub> |     | V <sub>DDIO</sub>          | v     |  |     |    |     |    |

|                    |                                        | V <sub>DDIO</sub> = 3.0 to 3.6V                              |                                    | PDB,<br>VODSEL.              | GND                        |     | 0.8                        | V     |  |     |    |     |    |

| V <sub>IL</sub>    | Low Level Input Voltage                | V <sub>DDIO</sub> = 1.71 to 1.89                             | v                                  | MAPSEL,<br>CONFIG[1:0],      | GND                        |     | 0.35*<br>V <sub>DDIO</sub> | ٧     |  |     |    |     |    |

| V                  | l1 01                                  | V - 0V V                                                     | V <sub>DDIO</sub> = 3.0<br>to 3.6V | BISTEN                       |                            |     |                            |       |  | -15 | ±1 | +15 | μА |

| I <sub>IN</sub>    | Input Current                          | $V_{IN} = 0V \text{ or } V_{DDIO}$ $V_{DDIO} = 1.7$ to 1.89V |                                    | -15                          | ±1                         | +15 | μА                         |       |  |     |    |     |    |

| FPD-LINK           | LVDS RECEIVER DC SPECI                 | FICATIONS                                                    |                                    |                              |                            |     |                            |       |  |     |    |     |    |

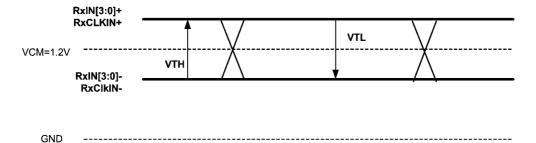

| V <sub>TH</sub>    | Differential Threshold High<br>Voltage |                                                              |                                    |                              |                            |     | +100                       |       |  |     |    |     |    |

| V <sub>TL</sub>    | Differential Threshold Low<br>Voltage  | V <sub>CM</sub> = 1.2V, Figure                               | 1                                  | 7470 V (5076C 0010           | -100                       |     |                            | mV    |  |     |    |     |    |

| IV <sub>ID</sub> I | Differential Input Voltage<br>Swing    | V <sub>DDIO</sub> = 3.3V<br>V <sub>DDIO</sub> = 1.8V         |                                    | RxIN[3:0]+/-,<br>RxCLKIN+/-, | 200                        |     | 600                        | mV    |  |     |    |     |    |

| v                  | Common Mada Valta                      |                                                              |                                    | ] [                          | 0                          | 1.2 | 2.4                        | v     |  |     |    |     |    |

| V <sub>CM</sub>    | Common Mode Voltage                    |                                                              |                                    | ]                            | 0                          | 1.2 | 1.55                       | 1 ×   |  |     |    |     |    |

| I <sub>IN</sub>    | Input Current                          |                                                              |                                    | ] [                          | -15                        | ±1  | +15                        | μА    |  |     |    |     |    |

# **DC 電気的特性** (つづき)

特記のない限り、推奨動作条件での電源電圧および温度範囲に適用。(Note 2、3、4)

| Symbol              | Parameter                                                         | Conditions                                     |                              | Pin/Freq.                | Min                             | Тур                             | Max                             | Units                           |                                 |                              |                   |  |   |   |    |

|---------------------|-------------------------------------------------------------------|------------------------------------------------|------------------------------|--------------------------|---------------------------------|---------------------------------|---------------------------------|---------------------------------|---------------------------------|------------------------------|-------------------|--|---|---|----|

| FPD-LINK            | II LVDS DRIVER DC SPECIFIC                                        | ATIONS                                         |                              |                          |                                 |                                 |                                 | 100                             |                                 |                              |                   |  |   |   |    |

|                     |                                                                   |                                                | VODSEL = 0                   |                          | ±225                            | ±300                            | ±375                            |                                 |                                 |                              |                   |  |   |   |    |

| V <sub>OD</sub>     | Differential Output Voltage                                       | $R_L = 100\Omega$ ,                            | VODSEL = 1                   | i i                      | ±350                            | ±450                            | ±550                            | mV                              |                                 |                              |                   |  |   |   |    |

| 17                  | Differential Output Voltage                                       | De-emph = disabled,<br>Figure 3                | VODSEL = 0                   |                          |                                 | 600                             | _                               | mVp-p                           |                                 |                              |                   |  |   |   |    |

| V <sub>ODp-p</sub>  | (DOUT+) - (DOUT-)                                                 | rigure 3                                       | VODSEL = 1                   |                          |                                 | 900                             |                                 | mVp-p                           |                                 |                              |                   |  |   |   |    |

| ΔV <sub>OD</sub>    | Output Voltage Unbalance                                          | R <sub>L</sub> = 100Ω, De-emph =<br>VODSEL = L | disabled,                    |                          |                                 | 1                               | 50                              | mV                              |                                 |                              |                   |  |   |   |    |

|                     | Offset Voltage - Single-ended                                     | $R_i = 100\Omega$ ,                            | VODSEL = 0                   | DOUT+,                   |                                 | 1.65                            |                                 | ٧                               |                                 |                              |                   |  |   |   |    |

| Vos                 | At TP A & B, Figure 2                                             | De-emph = disabled                             | VODSEL = 1                   | DOUT-                    |                                 | 1.575                           |                                 | ٧                               |                                 |                              |                   |  |   |   |    |

| ΔV <sub>OS</sub>    | Offset Voltage Unbalance<br>Single-ended<br>At TP A & B, Figure 2 | R <sub>L</sub> = 100Ω, De-emph =               | disabled                     |                          |                                 | 1:                              | mV                              |                                 |                                 |                              |                   |  |   |   |    |

| I <sub>os</sub>     | Output Short Circuit Current                                      | DOUT+/- = 0V,<br>De-emph = disabled            | VODSEL = 0                   |                          |                                 | -35                             |                                 | mA                              |                                 |                              |                   |  |   |   |    |

| R <sub>T</sub>      | Internal Termination Resistor                                     | 7                                              |                              |                          | 80                              |                                 | 120                             | Ω                               |                                 |                              |                   |  |   |   |    |

| SUPPLY C            | URRENT                                                            |                                                |                              |                          |                                 |                                 |                                 |                                 |                                 |                              |                   |  |   |   |    |

| I <sub>DDT1</sub>   |                                                                   | Checker Board                                  | V <sub>DD</sub> = 1.89V      | All V <sub>DD</sub> pins |                                 | 80                              | 90                              | mA                              |                                 |                              |                   |  |   |   |    |

| I <sub>DDIOT1</sub> |                                                                   | Pattern,<br>De-emph = $3 k\Omega$ ,            | De-emph = $3 k\Omega$ ,      | De-emph = $3 k\Omega$ ,  | De-emph = $3 \text{ k}\Omega$ , | De-emph = $3 \text{ k}\Omega$ , | De-emph = $3 \text{ k}\Omega$ , | De-emph = $3 \text{ k}\Omega$ , | De-emph = $3 \text{ k}\Omega$ , | V <sub>DDIO</sub> ≃<br>1.89V | V <sub>DDIO</sub> |  | 3 | 5 | mA |

| 00.011              | Supply Current                                                    | VODSEL = H, Figure<br>10                       | $V_{DDIO} = 3.6V$            | DOIO                     |                                 | 10                              | 13                              | mA                              |                                 |                              |                   |  |   |   |    |

| I <sub>DDT2</sub>   | (includes load current)<br>R <sub>1</sub> = 100Ω, f = 65MHz       | Checker Board                                  | V <sub>DD</sub> = 1.89V      | All V <sub>DD</sub> pins |                                 | 75                              | 85                              | mA                              |                                 |                              |                   |  |   |   |    |

| I <sub>DDIOT2</sub> | 10034,1-001112                                                    | Pattern,<br>De-emph = $6 \text{ k}\Omega$ ,    | V <sub>DDIO</sub> =<br>1.89V | V <sub>DDIO</sub>        |                                 | 3                               | 5                               | mA                              |                                 |                              |                   |  |   |   |    |

| 001012              |                                                                   | VODSEL = L, Figure<br>10                       | V <sub>DDIO</sub> = 3.6V     | - DDIO                   |                                 | 10                              | 13                              | mA                              |                                 |                              |                   |  |   |   |    |

| I <sub>DDZ</sub>    |                                                                   |                                                | V <sub>DD</sub> = 1.89V      | All V <sub>DD</sub> pins |                                 | 60                              | 1000                            | μА                              |                                 |                              |                   |  |   |   |    |

| I <sub>DDIOZ</sub>  | Supply Current Power-down                                         | PDB = 0V , (All other LVCMOS Inputs = 0V)      | V <sub>DDIO</sub> ≡<br>1.89V | V <sub>DDIO</sub>        |                                 | 0.5                             | 10                              | μА                              |                                 |                              |                   |  |   |   |    |

|                     |                                                                   |                                                | $V_{DDIO} = 3.6V$            |                          |                                 | 1                               | 30                              | μА                              |                                 |                              |                   |  |   |   |    |

# スイッチング特性

特記のない限り、推奨動作条件での電源電圧および温度範囲に適用。

| Symbol            | Parameter                      | Conditions        | Min   | Тур   | Max   | Units |

|-------------------|--------------------------------|-------------------|-------|-------|-------|-------|

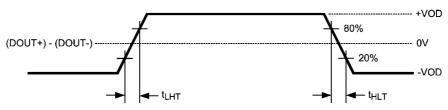

| FPD-LIN           | K LVDS INPUT                   | M1                | 12    |       |       |       |

| t <sub>RSP0</sub> | Receiver Strobe Position-bit 0 |                   | 0.66  | 1.10  | 1.54  | ns    |

| t <sub>RSP1</sub> | Receiver Strobe Position-bit 1 | 1                 | 2.86  | 3.30  | 3.74  | ns    |

| t <sub>RSP2</sub> | Receiver Strobe Position-bit 2 | RxCLKIN = 65 MHz, | 5.05  | 5.50  | 5.93  | ns    |

| t <sub>RSP3</sub> | Receiver Strobe Position-bit 3 | RxIN[3:0]         | 7.25  | 7.70  | 8.13  | ns    |

| t <sub>RSP4</sub> | Receiver Strobe Position-bit 4 | Figure 5          | 9.45  | 9.90  | 10.33 | ns    |

| t <sub>RSP5</sub> | Receiver Strobe Position-bit 5 |                   | 11.65 | 12.10 | 12.53 | ns    |

| t <sub>RSP6</sub> | Receiver Strobe Position-bit 6 | 1                 | 13.85 | 14.30 | 14.73 | ns    |

# スイッチング特性(つづき)

特記のない限り、推奨動作条件での電源電圧および温度範囲に適用。

| Symbol                                                             | Parameter                                                    | Conditions                                                                                           | Min | Тур   | Max   | Units |

|--------------------------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-----|-------|-------|-------|

| FPD-LIN                                                            | IK II LVDS OUTPUT                                            | B                                                                                                    |     |       |       |       |

| t <sub>HLT</sub>                                                   | Output Low-to-High Transition<br>Time                        | $R_L = 100\Omega$ , De-emphasis = disabled,<br>VODSEL = 0                                            |     | 200   |       | ps    |

|                                                                    | Figure 4                                                     | $R_L = 100\Omega$ , De-emphasis = disabled,<br>VODSEL = 1                                            |     | 200   |       | ps    |

| t <sub>HLT</sub> Output High-to-Low Transition<br>Time<br>Figure 4 | Time                                                         | $R_L = 100\Omega$ , De-emphasis = disabled,<br>VODSEL = 0                                            |     | 200   |       | ps    |

|                                                                    | R <sub>L</sub> = 100Ω, De-emphasis = disabled,<br>VODSEL = 1 |                                                                                                      | 200 |       | ps    |       |

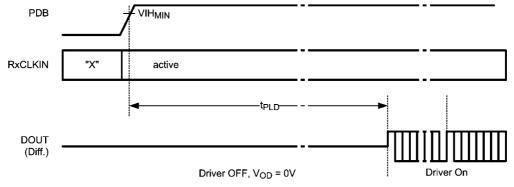

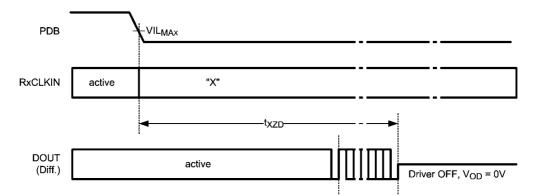

| t <sub>XZD</sub>                                                   | Ouput Active to OFF Delay,<br>Figure 7                       |                                                                                                      |     | 5     | 15    | ns    |

| t <sub>PLD</sub>                                                   | PLL Lock Time, Figure 6                                      | R <sub>L</sub> = 100Ω, ( <i>Note 5</i> )                                                             |     | 1.5   | 10    | ms    |

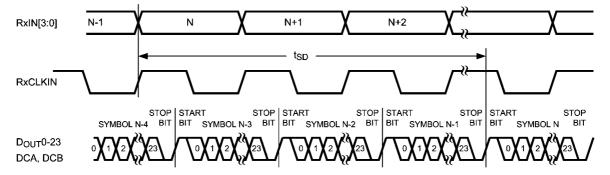

| t <sub>SD</sub>                                                    | Delay - Latency, Figure 8                                    | $R_L = 100\Omega$                                                                                    |     | 140°T | 145*T | ns    |

| t <sub>DJIT</sub>                                                  | Output Total Jitter,<br>Figure 9                             | R <sub>L</sub> = 100Ω, De-Emph = disabled,<br>RANDOM pattern, RxCLKIN = 43 & 65 MHz( <i>Note 6</i> ) |     | 0.26  |       | UI    |

| λ <sub>STXBW</sub>                                                 | Jitter Transfer                                              | RxCLKIN = 43 MHz                                                                                     |     | 2.2   |       |       |

| Function                                                           | Function -3 dB Bandwidth(Note<br>8, Note 9)                  | RxCLKIN = 65 MHz                                                                                     |     | 3     |       | MHz   |

| δ <sub>STX</sub>                                                   | Jitter Transfer                                              | RxCLKIN = 43 MHz                                                                                     | ]   | 1     |       |       |

|                                                                    | Function Peaking(Note 8, Note 9)                             | RxCLKIN = 65 MHz                                                                                     |     | 1     |       | dB    |

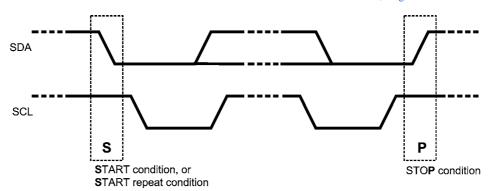

# シリアル制御バスの推奨タイミング

特記のない限り、3.3Vの電源電圧および温度範囲に適用。

| Symbol              | Parameter                              | Conditions    | Min | Тур | Max  | Units |

|---------------------|----------------------------------------|---------------|-----|-----|------|-------|

| f <sub>SCL</sub>    | CCI Clast Farmers                      | Standard Mode | 0   |     | 100  | kHz   |

| 0.0000              | SCL Clock Frequency                    | Fast Mode     | 0   |     | 400  | kHz   |

| t <sub>LOW</sub>    | COL Law Parked                         | Standard Mode | 4.7 |     |      | us    |

|                     | SCL Low Period                         | Fast Mode     | 1.3 |     |      | us    |

| t <sub>HIGH</sub>   | CCI Wish Davied                        | Standard Mode | 4.0 |     |      | us    |

|                     | SCL High Period                        | Fast Mode     | 0.6 |     |      | us    |

| t <sub>HD:STA</sub> | Hold time for a start or a             | Standard Mode | 4.0 |     |      | us    |

|                     | repeated start condition,<br>Figure 12 | Fast Mode     | 0.6 |     |      | us    |

| JUJIN .             | Set Up time for a start or a           | Standard Mode | 4.7 |     |      | us    |

|                     | repeated start condition,<br>Figure 12 | Fast Mode     | 0.6 |     |      | us    |

| t <sub>HD:DAT</sub> | Data Hold Time,                        | Standard Mode | 0   |     | 3.45 | us    |

|                     | Figure 12                              | Fast Mode     | 0   |     | 0.9  | us    |

| t <sub>SU:DAT</sub> | Data Set Up Time,                      | Standard Mode | 250 |     |      | ns    |

|                     | Figure 12                              | Fast Mode     | 100 |     |      | ns    |

| t <sub>su:sto</sub> | Set Up Time for STOP                   | Standard Mode | 4.0 |     |      | us    |

|                     | Condition, Figure 12                   | Fast Mode     | 0.6 |     |      | us    |

| t <sub>BUF</sub>    | Bus Free Time                          | Standard Mode | 4.7 |     |      | us    |

|                     | Between STOP and START,<br>Figure 12   | Fast Mode     | 1.3 |     |      | us    |

| t <sub>r</sub>      | SCL & SDA Rise Time,                   | Standard Mode |     |     | 1000 | ns    |

|                     | Figure 12                              | Fast Mode     |     |     | 300  | ns    |

| t <sub>f</sub>      | SCL & SDA Fall Time,                   | Standard Mode |     |     | 300  | ns    |

|                     | Figure 12                              | Fast mode     |     |     | 300  | ns    |

### DC/AC シリアル制御バスの特性

特記のない限り、3.3Vの電源電圧および温度範囲に適用。

| Symbol              | Parameter               | Conditions                                           | Min                       | Тур | Max                       | Units |

|---------------------|-------------------------|------------------------------------------------------|---------------------------|-----|---------------------------|-------|

| V <sub>IH</sub>     | Input High Level        | SDA and SCL                                          | 0.7*<br>V <sub>DDIO</sub> |     | V <sub>DDIO</sub>         | v     |

| V <sub>IL</sub>     | Input Low Level Voltage | SDA and SCL                                          | GND                       |     | 0.3*<br>V <sub>DDIO</sub> | ٧     |

| V <sub>HY</sub>     | Input Hysteresis        |                                                      |                           | >50 |                           | mV    |

| V <sub>OL</sub>     |                         | SDA, IOL = 1.25mA                                    | 0                         |     | 0.36                      | V     |

| l <sub>in</sub>     |                         | SDA or SCL, Vin = V <sub>DDIO</sub> or GND           | -10                       |     | +10                       | μА    |

| t <sub>R</sub>      | SDA RiseTime – READ     |                                                      |                           | 430 |                           | ns    |

| t <sub>F</sub>      | SDA Fall Time - READ    | SDA, RPU = $10k\Omega$ , Cb $\leq 400pF$ , Figure 12 |                           | 20  |                           | ns    |

| t <sub>SU:DAT</sub> | Set Up Time — READ      | Figure 12                                            |                           | 560 |                           | ns    |

| t <sub>HD:DAT</sub> | Hold Up Time — READ     | Figure 12                                            |                           | 615 |                           | ns    |

| t <sub>SP</sub>     | Input Filter            |                                                      |                           | 50  | 0                         | ns    |

| Cin                 | Input Capacitance       | SDA or SCL                                           |                           | <5  |                           | pF    |

- Note 1: 絶対最大定格は、IC に破壊が発生したり、使用不能になったり、信頼性や性能が低下する可能性のあるリミット値を示します。これは、絶対最大 定格において、または推奨動作条件に示されている動作条件を越える条件でこのデバイスが有効に機能することや品質が劣化しないことは意味して いません。推奨動作条件とは、このデバイスが有効に機能する条件を示しており、これらを超えた条件ではこのデバイスを使用しないように注意して ください

- Note 2: 電気的特性の表は、推奨動作条件で使用した場合に保証される特性を示しています。 ただし、電気的特性や注記で特に変更しまたは指定している場合はその限りではありません。 代表値は推定値であり、この値を保証しているものではありません。

- Note 3: 代表値は、 $V_{DD}=+3.3V$ 、 $T_a=+25$   $\mathbb C$  で、製品の特性を評価した時点における推奨動作条件下での最も可能性のあるパラメータの基準値を表しており、保証値ではありません。

- Note 4: デバイスのピンに流れ込む電流は正と定義されます。デバイスのピンから流れ出る電流は負と定義されます。電圧は、差動電圧であるVOD、ΔVOD、 VTH、VTL を除いてグラウンドを基準としています。

- Note 5: t<sub>PLD</sub> は、デバイスがアクティブな RxCLKIN によってパワーダウン状態から復帰したときにロック獲得までに要する時間です。

- Note 6: UI とはユニット・インターバルのことであり、シリアル化されたデータ 1 ビットの幅に相当します (1UI = 1/28\*RxCLKIN)。 UI は RxCLKIN 周波数に従って増減します。

- Note 7: PCB 上で最小限のコンデンサを使用して電源ノイズ・テストを実施しました。正弦波信号は  $V_{\mathrm{DDn}}$  (1.8V) 電源に AC 結合され、デバイスの  $V_{\mathrm{DDn}}$  ピンでは振幅 =  $100\mathrm{mVp}$ -p と測定されています。 $10\mathrm{m}$  のケーブルを使った Ser への入力と Des の出力のビット誤り率テストによると、Ser では、ノイズ周波数が 750kHz 未満であればエラーが発生しません。一方 Des では、ノイズ周波数が 400kHz 未満であればエラーが発生しません。

- Note 8: 仕様値は特性の評価により保証されている値で、量産時における試験は行っていません。

- Note 9: 仕様値は設計により保証されている値で、量産時における試験は行っていません。

# AC タイミング図およびテスト回路

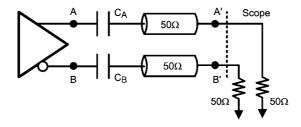

FIGURE 1. FPD-Link DC VTH/VTL Definition

FIGURE 2. Output Test Circuit

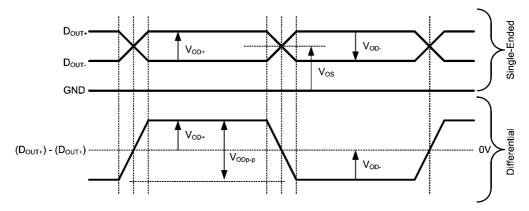

FIGURE 3. Output Waveforms

FIGURE 4. Output Transition Times

# AC タイミング図およびテスト回路(つづき)

FIGURE 6. Lock Time

FIGURE 7. Disable Time

FIGURE 8. Latency Delay

# AC タイミング図およびテスト回路(つづき) -t<sub>DJIT</sub> VOD (+) DOUT (Diff.) TxOUT\_E\_O VOD (-) t<sub>BIT</sub> (1 UI) -FIGURE 9. Output Jitter +V<sub>OD</sub> **RxCLKIN** -V<sub>OD</sub> +V<sub>OD</sub> RxIN[odd] -Vod +V<sub>OD</sub> RxIN[even] -V<sub>OD</sub> FIGURE 10. Checkerboard Data Pattern **BISTEN** VIL<sub>MAX</sub> ► tPASS PASS VOL<sub>MAX</sub> (w/ errors) Prior BIST Result Current BIST Test - Toggle on Error Result Held FIGURE 11. BIST PASS Waveform SDA thd;STA SCL tsu;sta tHIGH - tsu;dat thd;dat START STOP START REPEATED **START** FIGURE 12. Serial Control Bus Timing Diagram

# AC タイミング図およびテスト回路(つづき)

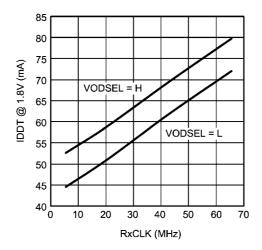

FIGURE 13. Typical IDDT (1.8V Supply) Current as a function of RxCLK

#### 機能説明

DS90UR907Q コンバータは、合計 27 ビットのデータ (24 の高速ビットと3 つの低速ビデオ制御信号)を持つ FPD-Link インタフェース (4 LVDS データ・チャネル+ 1 LVDS クロック)を単一のシリアルFPD-Link IIペア上で送信します。このシリアル・データ・ストリームには、埋め込み型クロックと、信号品質を改善してAC 結合をサポートする DC バランス情報も含まれています。このデバイスは DS90UR908Q または DS90UR906Q との使用を想定していますが、旧世代の FPD-Link II に対しても下位互換性を備えています。

DS90UR907Q は、24 ビット・カラー・モード (VS、HS、DE をシリアル・データ・ストリームにエンコード) または 18 ビット・カラー・モードで動作できます。

DS90UR907Q は、外部ピンまたはオプションのシリアル制御バスを介して構成できます。選択可能な VOD レベルや選択可能なデエンファシス・シグナル・コンディショニングのほか、ビデオ・データのランダム化、スクランブル、DC バランス化を行う FPD-Link II データ・コーディングもサポートすることにより、リンク上の信号品質を改善しています。また、ディスプレイ・データの伝送に関連した EMI を低減する機能も複数搭載しています。これには、データのランダム化やスクランブルと、システムのスペクトラム拡散 PCLK のサポートも含まれます。さらに、パ

ワーダウン・モードによる省電力機能と、自動クロック停止機能 も備えています。

シリアル制御バスとBISTモードの機能説明も参照してください。 ブロック図は、本データシートの最初の方に掲載されています。

#### データ転送

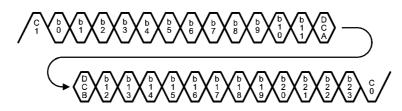

DS90UR907Q は、以下の形式で1ピクセルのデータを送信します。C1とC0は、シリアル・データ・ストリーム中の埋め込み型クロックを表しています。C1は常に Highで、C0は常にLowです。b[23:0]には、スクランブルされた RGB データが格納されます。DCBは、DC バランス化制御ビットです。DCBは、短期、長期にわたって信号ラインの DC バイアスを最小にするために使用されます。このビットは、データをそのままの極性で送るか、反転して送るかを決定します。DCA ビットは、埋め込み型データ・ストリームのデータ品質の確認に使用され、エンコードされた制御ビット(VS、HS、DE)を格納できます。DCAとDCBのどちらのコーディング方式もDS90UR907Qによって生成され、ペアとなるデシリアライザによって自動的にデコードされます。Figure 14に、PCLK サイクルごとのシリアル・データ・ストリームを示します。

Note: 各ビットは連続的にスクランブル化とバランス調整が行われるため、図のように実際のビットの値を表しません。

FIGURE 14. FPD-Link II Serial Stream

#### 動作モードと下位互換性 (CONFIG[1:0])

DS90UR907Q は、旧世代の FPD-Link II デシリアライザに対する下位互換性を備えています。 DS90C124 FPD-Link II Generation 1 デシリアライザおよび DS90UR124 FPD-Link II Generation 2デシリアライザとの下位互換性を確保するための構成モードが用意されており、それぞれの構成モードにするには、CONFIG[1:0] ピンを Table 1 に示すように設定します。この設定により、通常モードでビデオ制御信号フィルタ機能をイネーブルにするかディスエーブルにするかも決定されます。

TABLE 1. DS90UR907Q の構成モード

| CON<br>FIG1 | CON<br>FIG0 | Mode                                           | Des Device                |

|-------------|-------------|------------------------------------------------|---------------------------|

| L           | اـ          | Normal Mode, Control<br>Signal Filter disabled | DS90UR908Q,<br>DS90UR906Q |

| L           | Η           | Normal Mode, Control<br>Signal Filter enabled  | DS90UR908Q,<br>DS90UR906Q |

| Н           | L           | Backwards Compatible<br>GEN2                   | DS90UR124,<br>DS99R124    |

| Н           | Н           | Backwards Compatible<br>GEN1                   | DS90C124                  |

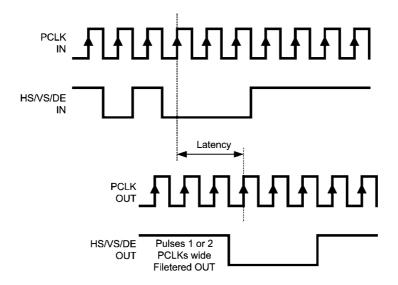

#### ビデオ制御信号フィルタ

デバイスを通常モードで動作させる場合、ビデオ制御信号 (DE、HS、VS)には以下の制約があります。

- 制御信号フィルタがイネーブルの通常モード:

DEとHS 転送される遷移は、130 クロック・サイクルごとに2回のみです。遷移パルスの長さは3 PCLK 以上必要です。

- 制御信号フィルタがディスエーブルの通常モード:

DEとHS 転送される遷移は、130 クロック・サイクルごとに2回のみです。最小遷移パルスについての制約はありません。

- VS 転送される遷移は、130 クロック・サイクルごとに1回のみです。最小パルス幅は130 クロック・サイクルです。

ビデオ制御信号は、遷移が制限された低周波信号として定義されています。制御信号のグリッチは、ビジュアル・ディスプレイのエラー原因となることがあります。この機能を利用すると、チップセットは制御信号上のあらゆる高周波ノイズを検出して、フィルタにより除去できます。Figure 15 を参照してください。

FIGURE 15. Video Control Signal Filter Wavefrom

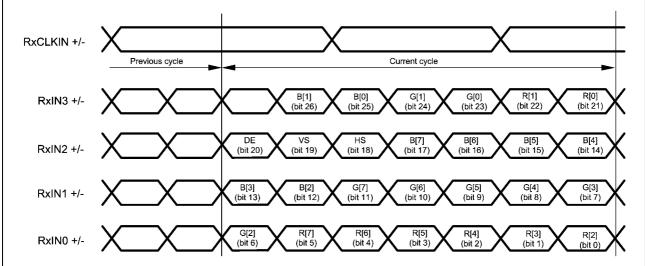

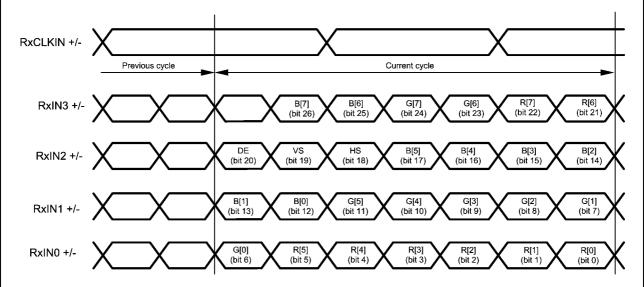

#### カラー・ビット・マッピングの選択

DS90UR907Q は、2 種類のマッピング方式 (Figure 16 に示すように RxIN[3] に LSB をマッピング、または Figure 17 に示す

ように RxIN[3] に MSB をマッピング ) によって 24 ビット・カラー (8 ビット RGB) に対応するように構成できます。マッピング方式は、MAPSEL ピンまたはレジスタによって制御できます。

FIGURE 16. 8-bit FPD-LInk Mapping: LSB's on RxIN3

FIGURE 17. 8-bit FPD-LInk Mapping: MSB's on RxIN3

#### EMI 低減機能

#### スペクトラム拡散の互換性

FPD-Link 入力の RxCLKIN は、ホスト・ソースからのスペクトラム拡散クロック (SSC) をトラッキング可能です。RxCLKIN はスペクトラム拡散を受け入れて、最大 35kHz の変調と $\pm$  0.5%、 $\pm$  1%、または $\pm$  2%の偏差 (センター拡散) をトラッキングします。RxCLKIN 入力の最大条件は、変調周波数が 35kHz、振幅偏差が $\pm$  2%(合計 4%)です。

#### 信号品質エンハンサ

### VOD の選択 (VODSEL)

DS90UR907Q の差動出力電圧は、VODSEL ピンを High に設定すれば増加できます。VODSEL が Low のときは、DC VOD は標準(デフォルト)レベルです。VODSEL を High にすると、DC VOD のレベルが増加します。増加した VOD は、きわめてノイズの高い環境や、ケーブルが長いアプリケーションで役に立ちます。デエンファシスを使用する際は、VODSEL = Hに設定して、特に大きなデエンファシス設定での過度な信号減衰を防止することを推奨します。この機能は、外部ピンまたはレジスタによって制御できます。

TABLE 2. 差動出力電圧

| Input  | Effect    |              |  |  |

|--------|-----------|--------------|--|--|

| VODSEL | VOD<br>mV | VOD<br>mVp-p |  |  |

| Н      | ±450      | 900          |  |  |

| L      | ±300      | 600          |  |  |

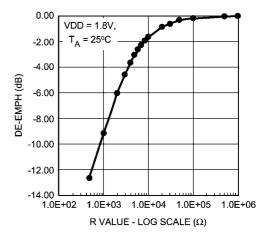

#### デエンファシス (De-Emph)

De-Emph ピンは、デバイスによって駆動されるロジック遷移から 1 ビット時間後に開始するデエンファシスの量を制御します。これは、ケーブルの伝送損失を補償するために使われるシグナル・コンディショニング機能です。標準的なスイッチング電流(デエンファシスなし)の場合や、レジスターによって制御される場合は、このピンを開放状態にしておく必要があります。デエンファシスは、このピンの抵抗 (R 値が  $0.5k\Omega \sim 1M\Omega$ ) をグラウンドに接続するか、レジスタの設定によって選択できます。デエ

ンファシスを使用する際は、VODSEL = H に設定することを推奨します。

TABLE 3. デエンファシスの抵抗値

| Resistor Value (kΩ) | De-Emphasis Setting |  |  |  |

|---------------------|---------------------|--|--|--|

| Open                | Disabled            |  |  |  |

| 0.6                 | - 12 dB             |  |  |  |

| 1.0                 | - 9 dB              |  |  |  |

| 2.0                 | - 6 dB              |  |  |  |

| 5.0                 | - 3 dB              |  |  |  |

FIGURE 18. De-Emph vs. R value

#### 省電力機能

#### パワーダウン機能 (PDB)

DS90UR907Q には、デバイスをイネーブルまたはパワーダウン 状態にするためのPDB入力ピンがあります。このピンはホストに よって制御され、ディスプレイが不要なときにリンクをディスエー ブルにすることによって消費電力を節減します。パワーダウン・ モードでは、高速ドライバ出力はいずれも VDD になり、VOD が 0V の状態になります。Note – パワーダウン・モードでは、オ プションのシリアル・バス制御レジスタは**リセット**されます。

#### クロック停止機能

DS90UR907Q は、RxCLKIN が停止した時点で低消費電力のスリープ状態に移行します。入力クロック周波数が 3MHz 未満になると、STOP 状態が検出されます。クロックは、Low 状態または High 状態のまま維持します。RxCLKIN が再開すると、デバイスは有効な入力 RxCLKIN にロックして、RGB データをデシリアライザに送信します。Note – クロック停止スリープ状態では、オプションのシリアル・バス制御レジスタ値は保持されます。

#### 1.8V または 3.3V の VDDIO 動作

DS90UR907Q のパラレル制御バスは、1.8V または 3.3V のレベル ( $V_{DDIO}$ ) で動作して、ホスト互換性を確保します。1.8V レベルでは、システムの消費電力を節減できます。

#### オプションのシリアル・バス制御

オプションのシリアル・バス制御インタフェースについては、次の項を参照してください。

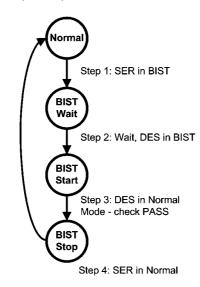

#### ビルトイン・セルフテスト (BIST)

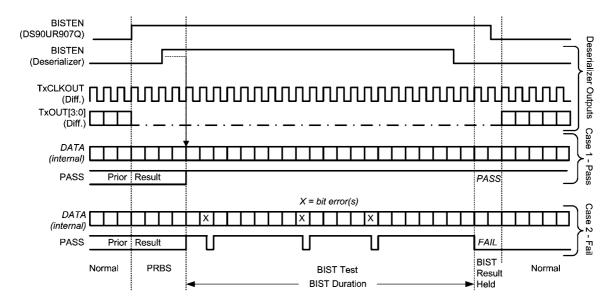

オプションの At-Speed ビルトイン・セルフテスト (BIST) 機能は、高速シリアル・リンクのテストをサポートしています。この機能は、試作段階、機器の製造、システム内テスト、システム診断で役に立ちます。BIST モードで必要なのは、DS90UR907Qとデシリアライザの BISTEN 入力ピンに対する制御と、入力クロックのみです。DS90UR907Qは、テスト・パターン (PRBS7)を出力して、リンクを高速で駆動します。デシリアライザは、PRBS7 パターンを検出して、エラーがないかどうか監視します。PASS 出力ピンの切り替えによって、1~24個のエラーがある受信ペイロードにフラグが付けられます。テスト完了後は、リセット (新規の BIST テストまたはパワーダウン )が行われるまで、テスト結果が PASS 出力に保持されます。PASS が Highの場合、エラーは検出されていません。PASS が Low の場合、1つ以上のエラーが検出されています。テスト時間は、デシリアライザのBISTENピンに印加するパルス幅によって制御できます。

この FPD-Link II デバイスとすべての世代の FPD-Link II (Gen 1/2/3) の間には、相互運用性が確保されています。 BIST モードへの移行と制御の詳細については、それぞれのデータシートを参照してください。

#### BIST シーケンスの例

BIST モードのフロー図については、Figure 19 を参照してください。

ステップ 1: Ser BISTEN = H に設定して、DS90UR907Q をBIST モードに移行させます。BIST モードは、BISTEN ピンを利用してイネーブルにします。すべてのシリアライザ・オプションでは、RxCLKIN が必要です。デシリアライザが BIST モード・パターンとコマンド (DCA コードと DCB コード )を検出すると、RGB 出力と制御信号の出力がシャットオフされます。

ステップ 2: BISTEN = H に設定して、ペアとなるデシリアライザを BIST モードに移行させます。デシリアライザが BIST モードになり、エラーがないかどうか入力シリアル・ペイロードをチェックします。ペイロードにエラー (1  $\sim$  24 個 ) が検出された場合、PASS ピンがクロック周期の半分の間 Low に切り替わります。BIST テスト中は、PASS 出力を監視、カウントして、ペイロードの誤り率を決定できます。

ステップ 3: BIST モードを停止するには、デシリアライザの BISTEN ピンを Low に設定します。デシリアライザがデータのチェックを停止し、最終テスト結果がPASSピンに保持されます。テストでエラーが検出されなかった場合は、PASS 出力が High になります。エラーが 1 つ以上検出された場合は、PASS 出力が Low になります。PASS 出力の状態は、新規の BIST が実行されるか、デバイスがリセットまたはパワーダウンされるまで保持されます。BIST 時間は、ユーザーが BISTEN 信号の時間によって制御できます。

ステップ 4: リンクを通常動作に戻すには、DS90UR907Q BISTEN 入力を Low に設定します。リンクが通常動作に復帰します。

Figure 20 に、2 つのケースにおける代表的な BIST テストの波形図を示します。ケース1はエラーが検出されなかった場合で、ケース2 は複数のエラーが検出された場合です。ほとんどの場合、リンクの堅牢性(差動信号によるデータ転送など)によりエラーは発生しにくくなっています。 そのため、エラーの発生原因となるのは、ケーブル長の大幅な延長、インターコネクトの障害、シグナル・コンディショニング強化機能(デエンファシス、VODSEL、またはデシリアライザのイコライゼーション)の削減などです。

FIGURE 19. BIST Mode Flow Diagram

#### BER の計算

ビット誤り率 (BER) のおおよその値を計算することができます。 計算には以下の情報が必要です。

- ピクセル・クロック周波数 (MHz)

- BIST 時間(秒)

- BIST テスト結果 (PASS)

BER は、24 と RxCLKIN レートとテスト時間の積で 1 を除算した結果以下になります。65MHz の RxCLKIN、10 分間 (600 秒間) のテスト、PASS と仮定した場合、BERT は  $1.07 \times 10E-12$  以下になります。

BIST モードでは、データ・ペイロード・ビットに対してチェックを行います。LOCKピンにもリンク状態が反映されます。COビットとCI ビットの復元によって、予想されたクロック信号が再構築されなかった場合、LOCKピンがLowに切り替わります。LOCKピンと At-Speed BIST PASS ピンを組み合わせれば、システム評価と性能監視のための強力なツールとなります。

FIGURE 20. BIST Waveforms

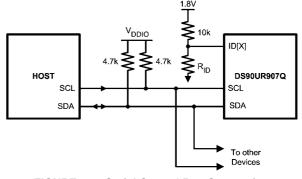

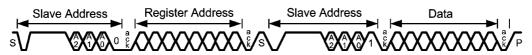

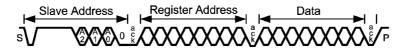

#### オプションのシリアル・バス制御

DS90UR907Q は、 $I^2$ C プロトコル互換のシリアル制御バスを使用して構成できます。デフォルトでは、 $I^2$ C reg\_0x00'h は 00'h に設定されており、すべての構成は制御 / ストラップピンによって設定されます。01'h を reg\_0x00'h に書き込むと、レジスタによる構成がイネーブル / 許可され、制御 / ストラップピンよりも優先されます。複数のアドレスがサポートされているので、複数のデバイスがシリアル制御バスを共有できます。Figure 21 を参照してください。

シリアル・バスは 3 つのピンで構成されています。SCL はシリアル・バス・クロック入力です。SDA はシリアル・バス・データ入出力信号です。SCL 信号も SDA 信号も、 $V_{DDIO}$  に接続された外付けプルアップ抵抗を必要とします。ほとんどのアプリケーションでは、 $V_{DDIO}$  に接続された 4.7k プルアップ抵抗を使用できます。抵抗値は、容量性負荷やデータ・レートの要件に応じて調整可能です。信号は High にも Low にもなります。

FIGURE 21. Serial Control Bus Connection

3つ目のピンは ID[X] ピンです。このピンは、4つのデバイス・アドレスのいずれかを設定します。以下の 2 種類の接続方法が可能です。ピンは、 $10k\Omega$  抵抗を使用して  $V_{DD}$   $(1.8V_{ODIO}$  ではない)に接続できます。または、 $10k\Omega$  プルアップ抵抗  $(V_{DD}$   $(1.8V_{ODIO}$  ではない)と、推奨値のプルダウ

ン抵抗で 3 つのアドレスを設定できます。 Table 4 を参照してください。

シリアル・バス・プロトコルは、START フェーズ、繰り返し START フェーズ、STOP フェーズによって制御されます。SDA が High のときに SCL が Low に遷移すると、START フェーズになります。 SCL が High のときに SDA も High に遷移すると、STOP フェーズになります。 Figure 22 を参照してください。

FIGURE 22. START and STOP Conditions

リモート・デバイスと通信する際は、ホスト・コントローラ(マス タ)がスレーブ・アドレスを送信して、スレーブからの応答を待 機します。この応答は、確認応答 (ACK) ビットと呼ばれます。 バス上のスレーブに送信されたアドレスが正しい場合、スレーブ は SDA バスを Low にするとマスタに確認応答 (ACK) します。 アドレスがデバイスのスレーブ・アドレスに一致しない場合、ス レーブは SDA を High にするとマスタに否定応答 (NACK) しま す。データの転送時も、バス上では ACK が行われます。マス タがデータを書き込む場合は、スレーブがデータ・バイトを正 しく受信するたびに ACK を行います。 マスタがデータを読み出 す場合は、マスタがデータ・バイトを受信するたびに ACK を 行い、次のデータ・バイトの受信が必要であることをスレーブに 通知します。マスタが読み出しを中止する場合は、マスタが最 後のデータ・バイトの受信後に NACK を行い、バス上で STOP 状態を生成します。バス上のすべての通信は、START 状態ま たは繰り返し START 状態で開始します。バス上のすべての通

信は、STOP 状態で終了します。読み出しを Figure 23 に、書き込みを Figure 24 に示します。

シリアル・バスが不要な場合、3 つのピンは開放 (NC) したままで構いません。

TABLE 4. ID[x] の抵抗値 - DS90UR907Q

| Resistor<br>RID kΩ | Address<br>7'b      | Address<br>8'b<br>0 appended<br>(WRITE) |

|--------------------|---------------------|-----------------------------------------|

| 0.47               | 7b' 110 1001 (h'69) | 8b' 1101 0010 (h'D2)                    |

| 2.7                | 7b' 110 1010 (h'6A) | 8b' 1101 0100 (h'D4)                    |

| 8.2                | 7b' 110 1011 (h'6B) | 8b' 1101 0110 (h'D6)                    |

| Open               | 7b' 110 1110 (h'6E) | 8b' 1101 1100 (h'DC)                    |

FIGURE 23. Serial Control Bus — READ

FIGURE 24. Serial Control Bus — WRITE

# TABLE 5. シリアル・バス制御レジスタ

| ADD<br>(dec) | ADD<br>(hex) | Register Name | Bit(s) | R/W | Defa<br>ult | Function     | Description                                         |  |  |

|--------------|--------------|---------------|--------|-----|-------------|--------------|-----------------------------------------------------|--|--|

| (,           | (,           |               |        |     | (bin)       |              |                                                     |  |  |

| 0 0          |              | Ser Config 1  | 7      | R/W | 0           | Reserved     | Reserved                                            |  |  |

|              |              |               | 6      | R/W | 0           | MAPSEL       | 0: LSB on RxIN3                                     |  |  |

|              |              |               |        |     |             |              | 1: MSB on RxIN3                                     |  |  |

|              |              |               | 5      | R/W | 0           | VODSEL       | 0: Low                                              |  |  |

|              |              |               |        |     |             |              | 1: High                                             |  |  |

|              |              |               | 4:2    | R/W | 00          | Reserved     | Reserved                                            |  |  |

|              |              |               | 1      | R/W | 0           | SLEEP        | Note – not the same function as PowerDown (PDB)     |  |  |

|              |              |               |        |     |             |              | 0: normal mode                                      |  |  |

|              |              |               |        |     |             |              | 1: Sleep Mode – Register settings retained.         |  |  |

|              |              |               | 0      | R/W | 0           | REG          | 0: Configurations set from control pins             |  |  |

|              |              |               |        |     |             |              | 1: Configuration set from registers (except I2C_ID) |  |  |

| 1            | 1            | Device ID     | 7      | R/W | 0           | REG ID       | 0: Address from ID[X] Pin                           |  |  |

|              |              |               |        |     |             |              | 1: Address from Register                            |  |  |

|              |              |               | 6:0    | R/W | 1101        | ID[X]        | Serial Bus Device ID, Five IDs are:                 |  |  |

|              |              |               |        |     | 000         |              | 7b '1101 000 (h'68)                                 |  |  |

|              |              |               |        |     |             |              | 7b '1101 001 (h'69)                                 |  |  |

|              |              |               |        |     |             |              | 7b '1101 010 (h'6A)                                 |  |  |

|              |              |               |        |     |             |              | 7b '1101 011 (h'6B)                                 |  |  |

|              |              |               |        |     |             |              | 7b '1101 110 (h'6E)                                 |  |  |

|              |              |               |        |     |             |              | All other addresses are <i>Reserved</i> .           |  |  |

| 2            | 2            | De-Emphasis   | 7:5    | R/W | 000         | De-E Setting | 000: set by external Resistor                       |  |  |

|              |              | Control       |        |     |             |              | 001: -1 dB                                          |  |  |

|              |              |               |        |     |             |              | 010: -2 dB                                          |  |  |

|              |              |               |        |     |             |              | 011: -3.3 dB                                        |  |  |

|              |              |               |        |     |             |              | 100: -5 dB                                          |  |  |

|              |              |               |        |     |             |              | 101: -6.7 dB                                        |  |  |

|              |              |               |        |     |             |              | 110: -9 dB                                          |  |  |

|              |              |               |        |     |             |              | 111: -12 dB                                         |  |  |

|              |              |               | 4      | R/W | 0           | De-E EN      | 0: De-Emphasis Enabled                              |  |  |

|              |              |               |        |     |             |              | 1: De-Emphasis Disabled                             |  |  |

|              |              |               | 3:0    | R/W | 000         | Reserved     | Reserved                                            |  |  |

### アプリケーション情報

#### ディスプレイ・アプリケーション

DS90UR907QとDS90UR908Q チップセットは、ホスト(グラフィック・プロセッサ)やディスプレイをインタフェースするためのものです。これは、24 ビットの色深度 (RGB888)と最大  $1024 \times 768$ のディスプレイ・フォーマットをサポートしています。RGB888 アプリケーションでは、24 色のビット (R[7:0]、G[7:0]、B[7:0]、ピクセル・クロック (PCLK)、3 つの制御ビット (VS、HS、DE)が PCLK 周波数  $5 \sim 65$ MHz のシリアル・リンク全体でサポートされています。このチップセットは、18 ビット・カラー・アプリケーションでも用いられる場合があります。このアプリケーションでは、ホストからディスプレイに  $3 \sim 6$  個の汎用信号を送信することもできます。

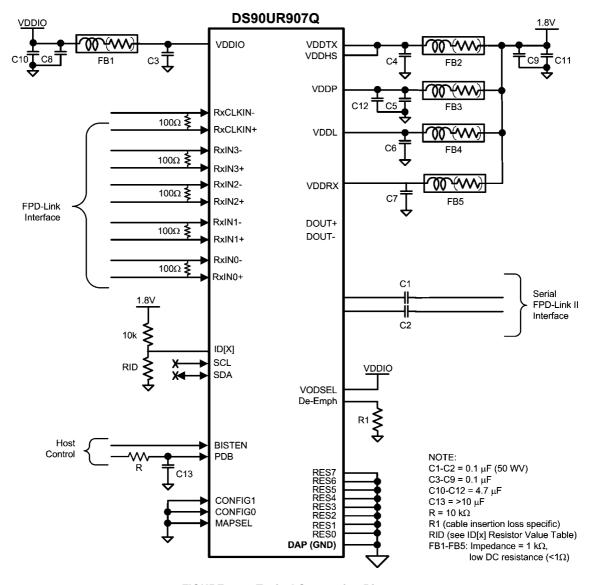

#### 代表的なアプリケーションの接続

Figure 25 に、DS90UR907Q の代表的なアプリケーションとして 65MHz、24 ビット・カラー・ディスプレイ・アプリケーションを 示します。FPD-Link インタフェースの LVDS 入力には、外付

けの 100 Ω 終端が必要です。FPD-Link II の LVDS 出力には、 ラインとの 100nF AC 結合コンデンサが必要です。 ライン・ドラ イバには終端が内蔵されています。 電源ピン付近にはバイパ ス・コンデンサを接続しなければなりません。ローカル・デバイ ス・バイパスには、最低でも4個の0.1μFコンデンサと1個の 4.7 μ Fコンデンサを使用する必要があります。システムGPO (汎 用出力)信号でPDBピンとBISTENピンを制御します。このア プリケーションでは、対になるデシリアライザ (DS90UR908Q) の 使用が想定されており、構成ピンはいずれも Low に固定され ています。この例の場合、ケーブルが長いため、VODSELピ ンは High に固定され、デエンファシス値は抵抗 R1 によって選 択されます。ホストへのインタフェースは 1.8V LVCMOS レベル に対応し、VDDIOピンも1.8Vレールに接続されています。こ の例ではオプションのシリアル・バス制御が使用されていないの で、SCL ピン、SDA ピン、ID[x] ピンは開放されたままです。 電源が安定するまでデバイスのイネーブルを遅らすことを目的 に、PDB 信号に対して遅延のためのコンデンサと抵抗が置か れています。電源ピン付近にはバイパス・コンデンサを接続し なければなりません。電源ライン上にフェライト・ビーズを配置 することにより、ノイズを効果的に抑制しています。

FIGURE 25. Typical Connection Diagram

## **アプリケーション情報**(つづき)

#### パワーオン要件と PDB ピン

VDD ( $V_{\rm DDn}$  と  $V_{\rm DDIO}$ ) の電源ランプ・スピードは、1.5ms 未満の単調上昇である必要があります。1.5ms よりも遅い場合は、コンデンサを PDB ピンに接続させて、すべての VDD が推奨動作電圧に落ち着いてから PDB がオンするようにしなければなりません。PDB ピンを  $V_{\rm DDIO}$  に接続する場合では、10k  $\Omega$  プルアップと 22uF コンデンサを GND に接続して PDB 入力信号を遅らすことを推奨します。

#### 伝送メディア

DS90UR907Q と、対になるデシリアライザのチップセットは、 PCB の配線パターンかツイストペア・ケーブルを介して、一対 一の構成で使用できます。DS90UR907Q には終端が内蔵され ており、クリーンな信号環境を提供します。LVDS のインターコネクトには、 $100\Omega$  の差動インピーダンスを使用します。差動インピーダンスの一致したケーブルとコネクタを使用して、インピーダンス不整合を最小限にします。ノイズ環境やアプリケーション要件に応じて、シールド付きケーブルまたはシールドなしケーブルを使用します。

### その他のカラー / データ・マッピング

24 ビット・アプリケーションと 18 ビット・アプリケーションでの推 奨マッピングを構成する、カラー・マッピングされたデータ・ピ ンの名称を挙げておきます。旧世代の FPD-Link II デシリアライ ザ・デバイスに接続する場合は、適切な接続が得られるように カラー・マッピングを確認することを推奨します。 Table 6 に、 DS90UR907Q と各種デシリアライザとのインタフェース例を示し ます。

TABLE 6. その他のカラー / データ・マッピング

| FPD-Link               | Bit Number                            | RGB (LSB<br>Example) | D | S90UR906Q           | DS90UR124         | DS99R124Q | DS90C124             |

|------------------------|---------------------------------------|----------------------|---|---------------------|-------------------|-----------|----------------------|

| RxIN3                  | Bit 26                                | B1                   |   | B1                  |                   | N/A       |                      |

|                        | Bit 25                                | В0                   |   | B0                  |                   |           |                      |

|                        | Bit 24                                | G1                   |   | G1                  |                   |           |                      |

|                        | Bit 23                                | G0                   |   | G0                  |                   |           |                      |

|                        | Bit 22                                | R1                   |   | R1                  |                   |           |                      |

|                        | Bit 21                                | R0                   |   | R0                  |                   |           |                      |

| RxIN2                  | Bit 20                                | DE                   |   | DE                  | ROUT20            | TxOUT2    | ROUT20               |

|                        | Bit 19                                | VS                   |   | VS                  | ROUT19            |           | ROUT19               |

|                        | Bit 18                                | HS                   |   | HS                  | ROUT18            |           | ROUT18               |

|                        | Bit 17                                | B7                   |   | В7                  | ROUT17            |           | ROUT17               |

|                        | Bit 16                                | B6                   |   | B6ROUT10            | ROUT16            |           | ROUT16               |

|                        | Bit 15                                | B5                   |   | B5                  | ROUT15            |           | ROUT15               |

|                        | Bit 14                                | B4                   |   | B4                  | ROUT14            |           | ROUT14               |

| RxIN1                  | Bit 13                                | В3                   |   | В3                  | ROUT13            | TxOUT1    | ROUT13               |

|                        | Bit 12                                | B2                   |   | B2                  | ROUT12            |           | ROUT12               |

|                        | Bit 11                                | G7                   |   | G7                  | ROUT11            |           | ROUT11               |

|                        | Bit 10                                | G6                   |   | G6                  | ROUT10            |           | ROUT10               |

|                        | Bit 9                                 | G5                   |   | G5                  | ROUT9             |           | ROUT9                |

|                        | Bit 8                                 | G4                   |   | G4                  | ROUT8             |           | ROUT8                |

|                        | Bit 7                                 | G3                   |   | G3                  | ROUT7             |           | ROUT7                |

| RxIN0                  | Bit 6                                 | G2                   |   | G2                  | ROUT6             | TxOUT0    | ROUT6                |

|                        | Bit 5                                 | R7                   |   | R7                  | ROUT5             |           | ROUT5                |

|                        | Bit 4                                 | R6                   |   | R6                  | ROUT4             |           | ROUT4                |

|                        | Bit 3                                 | R5                   |   | R5                  | ROUT3             |           | ROUT3                |

|                        | Bit 2                                 | R4                   |   | R4                  | ROUT2             |           | ROUT2                |

|                        | Bit 1                                 | R3                   |   | R3                  | ROUT1             |           | ROUT1                |

|                        | Bit 0                                 | R2                   |   | R2                  | ROUT0             |           | ROUT0                |

|                        | N/A * These bits are not supported by |                      |   |                     | ROUT23*           | OS2*      | ROUT23*              |

| * These b              |                                       |                      |   |                     | ROUT22*           | OS1*      | ROUT22*              |

| DS90UR907Q             |                                       |                      |   |                     | ROUT21*           | OS0*      | ROUT21*              |

| DS90UR907Q<br>Settings | MAPS                                  | SEL = 0              | C | ONFIG [1:0]<br>= 00 | CONFIG [1:0] = 10 |           | CONFIG [1:0]<br>= 11 |

## アプリケーション情報(つづき)

#### プリント基板と電源系の注意事項

LVDS デバイスを搭載するプリント基板は、デバイスに対してノ イズの少ない電源を供給するように、レイアウトと層構成を設計 しなければなりません。優れたレイアウトでは、不必要にノイズ を拾ったり帰還や干渉を最小にするために、高い周波数の信 号および高いレベルの入出力信号の分離を行います。 また、 2~4ミル程度の薄い誘電体材料を電源層とグラウンド層の間 に挟むと、電源系の性能を大きく改善できる場合があります。 つまり、この方式によりプリント基板の電源層の容量が増えるた め、特に高周波の電源ノイズに対するフィルタ特性を改善する 効果があり、併せて外付けバイパス・コンデンサの容量や配置 に対する条件を緩やかにします。 外付けバイパス・コンデンサ は、高周波セラミック・コンデンサとタンタル電解コンデンサの 両方を用いてください。高周波セラミック・コンデンサの値は、  $0.01 \mu$ Fから $0.1 \mu$ Fの範囲を使用します。また、タンタル・コ ンデンサの値は、 $2.2\mu$ Fから  $10\mu$ Fの範囲です。 タンタル・ コンデンサの電圧定格は、使用する電源電圧の5倍以上にし ます。

コンデンサには寄生インダクタンス分が少ない表面実装品を推奨します。1つの電源ピンに複数のコンデンサを配置する場合は、容量の小さなコンデンサの方をピン側に置きます。また大容量コンデンサをプリント基板の電源接続部分に配置してください。低周波スイッチング・ノイズを平滑化する容量は  $50\,\mu$  F から  $100\,\mu$  F の範囲が一般的です。電源ピンとグラウンド・ピンは電源層およびグラウンド層に直接接続し、またバイパス・コンデンサはコンデンサの両端に設けたビアを経由して電源層およびグラウンド層に接続することを推奨します。電源ピンまたはグラウンド・ピンからバイパス・コンデンサへ配線を行うと、電源系のインダクタンス分を増加させてしまうからです。

外付けのバイパス・コンデンサは、静電容量の温度依存性が小さい X7R 特性の、0603 などの小型チップ・コンデンサを推奨します。 寸法が小さいため、コンデンサの寄生インダクタンス分も小さいという利点があります。 なお設計の際には、通常20~30MHz の範囲にある外付けバイパス・コンデンサの共鳴周波数に注意してください。 また効果的なバイパスを行うために、複数のコンデンサを用いて、対象となる周波数に対する電源系のインピーダンスを下げる手法がしばしば使われます。 高周波のインピーダンスを下げるため、電源ピンまたはグラウンド・ピンから各層に対して2つのビアを設ける手法もよく用いられています。

デバイスによっては、内部の回路部分ごとに電源ピンとグラウンド・ピンが分離されているものがあります。電源系を分離する目的は、スイッチング・ノイズの影響を回路間で遮断するためです。このようなデバイスに対して、通常、プリント基板の層を分ける必要はありません。一般にデバイスのピン説明から、どの電源/グラウンドのペアがどの回路部分に対応するかが分かります。なお場合によっては、PLLのようなノイズに敏感な回路部分にクリーンな電源を供給するために、外部フィルタを用います。

LVDS システムのプリント基板は、電源層とグラウンド層を含む4層以上のものを採用してください。LVCMOS信号系は、LVDS信号に結合するのを防ぐため、LVDS信号系から離して配置しなければなりません。LVDSインターコネクトは一般的に、近接によってクローズド・カップリングとした100Ωの差動ラインを推奨します。クローズド・カップリングされたラインは、カップリング・ノイズはレシーバ端でコモンモードとして現れるため除去されます。またクローズド・カップリングのラインは、放射ノイズが少ない利点も備えます。

LLP スタイルのパッケージの詳細については、 ナショナル セミ コンダクターのアプリケーション・ノート AN-1187 を参照してください。

#### LVDS インターコネクトのガイドライン

詳細はアプリケーション・ノート AN-1108 と AN-905 を参照してください。

- 100Ω の結合された差動ペア配線を使用してください。

- 配線間隔には S/2S/3S ルールを適用してください。

- -S=ペア内の配線間隔

- 2S =ペア間の配線間隔

- 3S = LVCMOS 信号との間隔

- ビアの数は可能な限り抑えてください。

- 500Mbps 以上のライン速度で動作させる場合は差動用コネクタを使用してください。

- 配線のバランスを維持してください。

- ペア内のスキューを可能な限り抑えてください。

- 終端は、可能な限り TX 出力および RX 入力の近くに配置します。

LVDS に関するそのほかの一般的な設計ガイドラインは、「LVDS オーナーズ・マニュアル」として、ナショナル セミコン ダクターのウェブサイトに PDF で提供しています

(http://www.national.com/JPN/appinfo/lvds/).

# 改訂履歴

- 2010年3月30日—初回発行

- 2010年4月14日 Table 5の Addr 0[4:2] = Reserved' Addr 0[5] = VODSEL を更新

- 2010年6月22日 AC/DC 電気的特性の各リミット値を最終的に更新、Typical IDDT のグラフを追加

- 2010年7月26日 IDDT の条件を更新、FPD Link IIN のリミット値を更新

www.national.com/jpn/

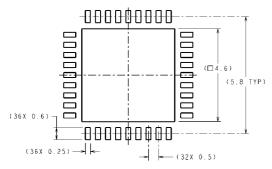

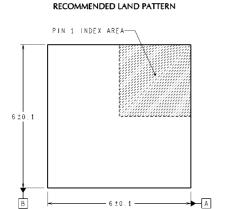

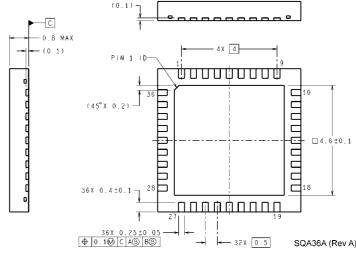

## 外形寸法図 特記のない限り inches (millimeters)

DIMENSIONS ARE IN MILLIMETERS

DIMENSIONS IN ( ) FOR REFERENCE ONLY

36-pin LLP Package (6.0 mm X 6.0 mm X 0.8 mm, 0.5 mm pitch) NS Package Number SQA36AC

このドキュメントの内容はナショナル セミコンダクター社製品の関連情報として提供されます。ナショナル セミコンダクター社は、この発行物の内容の正確性または完全性について、いかなる表明または保証もいたしません。また、仕様と製品説明を予告なく変更する権利を有します。このドキュメントはいかなる知的財産権に対するライセンスも、明示的、黙示的、禁反言による惹起、またはその他を問わず、付与するものではありません。

試験や品質管理は、ナショナル セミコンダクター社が自社の製品保証を維持するために必要と考える範囲に用いられます。政府が 課す要件によって指定される場合を除き、各製品のすべてのパラメータの試験を必ずしも実施するわけではありません。ナショナ ル セミコンダクター社は製品適用の援助や購入者の製品設計に対する義務は負いかねます。ナショナル セミコンダクター社の部品 を使用した製品および製品適用の責任は購入者にあります。ナショナル セミコンダクター社の製品を用いたいかなる製品の使用ま たは供給に先立ち、購入者は、適切な設計、試験、および動作上の安全手段を講じなければなりません。

それら製品の販売に関するナショナル セミコンダクター社との取引条件で規定される場合を除き、ナショナル セミコンダクター社 は一切の義務を負わないものとし、また、ナショナル セミコンダクター社の製品の販売か使用、またはその両方に関連する特定目的への適合性、商品の機能性、ないしは特許、著作権、または他の知的財産権の侵害に関連した義務または保証を含むいかなる表明または黙示的保証も行いません。

## 生命維持装置への使用について

ナショナル セミコンダクター社の製品は、ナショナル セミコンダクター社の最高経営責任者 (CEO) および法務部門 (GENERAL COUNSEL) の事前の書面による承諾がない限り、生命維持装置または生命維持システム内のきわめて重要な部品に使用することは認められていません。

ここで、生命維持装置またはシステムとは (a) 体内に外科的に使用されることを意図されたもの、または (b) 生命を維持あるいは 支持するものをいい、ラベルにより表示される使用法に従って適切に使用された場合に、これの不具合が使用者に身体的障害を与 えると予想されるものをいいます。重要な部品とは、生命維持にかかわる装置またはシステム内のすべての部品をいい、これの不 具合が生命維持用の装置またはシステムの不具合の原因となりそれらの安全性や機能に影響を及ぼすことが予想されるものをいい ます。

National Semiconductor とナショナル セミコンダクターのロゴはナショナル セミコンダクター コーポレーションの登録商標です。その他のブランド や製品名は各権利所有者の商標または登録商標です。

Copyright © 2011 National Semiconductor Corporation

製品の最新情報については www.national.com をご覧ください。

## ナショナル セミコンダクター ジャパン株式会社

本社/〒135-0042 東京都江東区木場 2-17-16

TEL.(03)5639-7300

技術資料(日本語/英語)はホームページより入手可能です。

www.national.com/jpn/

# ご注意

日本テキサス・インスツルメンツ株式会社(以下TIJといいます)及びTexas Instruments Incorporated(TIJの親会社、以下TIJないしTexas Instruments Incorporatedを総称してTIといいます)は、その製品及びサービスを任意に修正し、改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての製品は、お客様とTIJとの間に取引契約が締結されている場合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご注文の受諾の際に提示されるTIJの標準販売契約約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応した性能を有していること、またはお客様とTIJとの間で合意された保証条件に従い合意された仕様に対応した性能を有していることを保証します。検査およびその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計について責任を負うことはありません。TI製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。TI製部品を使用したお客様の製品及びアプリケーションについて想定されうる危険を最小のものとするため、適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明もしておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品もしくはサービスを使用することについてライセンスを与えるとか、保証もしくは是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならない場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報に一切の変更を加えること無く、かつその情報と結び付られた全ての保証、条件、制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そのような変更された情報や複製については何の義務も責任も負いません。

TIの製品もしくはサービスについてTIにより示された数値、特性、条件その他のパラメーターと異なる、あるいは、それを超えてなされた説明で当該TI製品もしくはサービスを再販売することは、当該TI製品もしくはサービスに対する全ての明示的保証、及び何らかの黙示的保証を無効にし、かつ不公正で誤認を生じさせる行為です。TIは、そのような説明については何の義務も責任もありません。

TIは、TIの製品が、安全でないことが致命的となる用途ないしアプリケーション(例えば、生命維持装置のように、TI製品に不良があった場合に、その不良により相当な確率で死傷等の重篤な事故が発生するようなもの)に使用されることを認めておりません。但し、お客様とTIの双方の権限有る役員が書面でそのような使用について明確に合意した場合は除きます。たとえTIがアプリケーションに関連した情報やサポートを提供したとしても、お客様は、そのようなアプリケーションの安全面及び規制面から見た諸問題を解決するために必要とされる専門的知識及び技術を持ち、かつ、お客様の製品について、またTI製品をそのような安全でないことが致命的となる用途に使用することについて、お客様が全ての法的責任、規制を遵守する責任、及び安全に関する要求事項を満足させる責任を負っていることを認め、かつそのことに同意します。さらに、もし万一、TIの製品がそのような安全でないことが致命的となる用途に使用されたことによって損害が発生し、TIないしその代表者がその損害を賠償した場合は、お客様がTIないしその代表者にその全額の補償をするものとします。

TI製品は、軍事的用途もしくは宇宙航空アプリケーションないし軍事的環境、航空宇宙環境にて使用されるようには設計もされていませんし、使用されることを意図されておりません。但し、当該TI製品が、軍需対応グレード品、若しくは「強化プラスティック」製品としてTIが特別に指定した製品である場合は除きます。TIが軍需対応グレード品として指定した製品のみが軍需品の仕様書に合致いたします。お客様は、TIが軍需対応グレード品として指定して収ない製品を、軍事的用途もしくは軍事的環境下で使用することは、もっぱらお客様の危険負担においてなされるということ、及び、お客様がもっぱら責任をもって、そのような使用に関して必要とされる全ての法的要求事項及び規制上の要求事項を満足させなければならないことを認め、かつ同意します。

TI製品は、自動車用アプリケーションないし自動車の環境において使用されるようには設計されていませんし、また使用されることを意図されておりません。但し、TIがISO/TS 16949の要求事項を満たしていると特別に指定したTI製品は除きます。お客様は、お客様が当該TI指定品以外のTI製品を自動車用アプリケーションに使用しても、TIは当該要求事項を満たしていなかったことについて、いかなる責任も負わないことを認め、かつ同意します。

Copyright © 2011, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社

#### 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点を遵守して下さい。 1. 熱電気

- 素手で半導体製品単体を触らないこと。どうしても触る必要がある場合は、リストストラップ等で人体からアースをとり、導電性手袋等をして取り扱うこと。

- 弊社出荷梱包単位(外装から取り出された内装及び個装)又は製品 単品で取り扱いを行う場合は、接地された導電性のテーブル上で(導 電性マットにアースをとったもの等)、アースをした作業者が行う こと。また、コンテナ等も、導電性のものを使うこと。

- マウンタやはんだ付け設備等、半導体の実装に関わる全ての装置類は、静電気の帯電を防止する措置を施すこと。

- 前記のリストストラップ・導電性手袋・テーブル表面及び実装装置 類の接地等の静電気帯電防止措置は、常に管理されその機能が確認 されていること。

#### 2. 温·湿度環境

■ 温度:0~40℃、相対湿度:40~85%で保管・輸送及び取り扱いを行うこと。(但し、結露しないこと。)

- 直射日光があたる状態で保管・輸送しないこと。

- 3. 防湿梱包

- 防湿梱包品は、開封後は個別推奨保管環境及び期間に従い基板実装すること。

- 4. 機械的衝擊

- 梱包品(外装、内装、個装)及び製品単品を落下させたり、衝撃を 与えないこと。

- 5. 熱衝撃

- はんだ付け時は、最低限260℃以上の高温状態に、10秒以上さら さないこと。(個別推奨条件がある時はそれに従うこと。)

- 6. 汚染

- はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質(硫黄、塩素等ハロゲン)のある環境で保管・輸送しないこと。

- はんだ付け後は十分にフラックスの洗浄を行うこと。(不純物含有率が一定以下に保証された無洗浄タイプのフラックスは除く。)

以上