LM22678, LM22678-Q1

JAJSAZ6M - SEPTEMBER 2008 - REVISED OCTOBER 2020

# LM22678/-Q1 使用しやすいパッケージの 42V、5A SIMPLE SWITCHER® 降圧レギュレータ

# 1 特長

- 新製品のご案内:LM61460 3V~36V、6A、低 EMI 同期整流式降圧コンバータ

- 広い入力電圧レンジ:4.5V~42V

- 内部補償機能付き電圧モード制御

- 低 ESR のセラミック・コンデンサで安定動作

- 100mΩ の N チャネル MOSFET

- 出力電圧オプション: -ADJ (最小 1.285V の出力) -5.0 (5V 固定の出力)

- ±1.5% のフィードバック・リファレンス精度

- 500kHz のスイッチング周波数

- 動作時の接合部温度範囲:-40℃~125℃

- 高精度イネーブル・ピン

- ブートストラップ・ダイオードを内蔵

- ソフトスタート内蔵

- WEBENCH® 完全対応

- LM22678-Q1 は AEC-Q100 グレード 1 準拠の車載 グレード製品

- (-40℃~+125℃の接合部温度で動作)

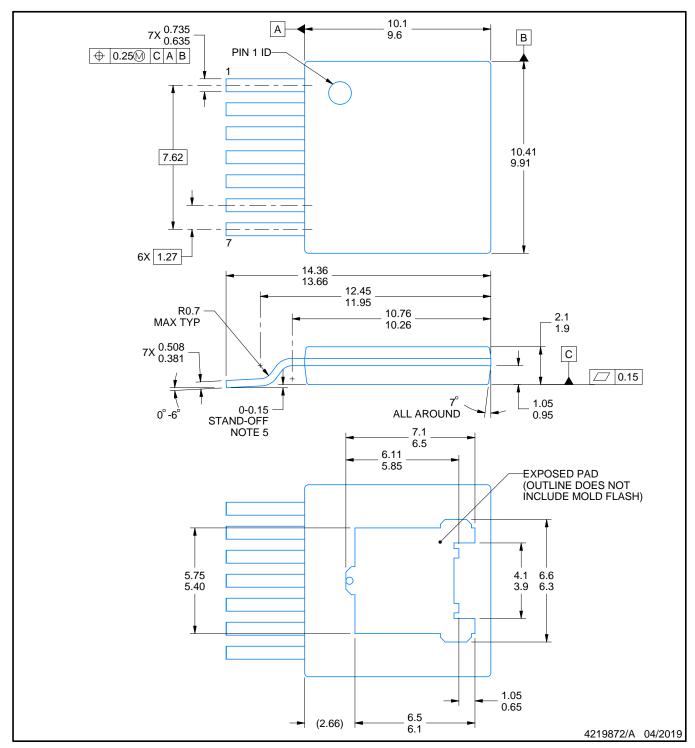

- PFM (露出パッド) パッケージ

# 2 アプリケーション

- 産業用分散電源アプリケーション

- 試験/測定機器

- 家電製品

- 広い V<sub>IN</sub> の汎用アプリケーション

#### 3 概要

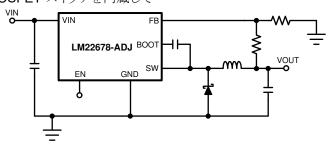

LM22678 スイッチング・レギュレータは、最小限の外付け 部品を使用して高効率高電圧の降圧レギュレータを実装 するために必要なすべての機能を備えています。この使 用しやすいレギュレータは、最大 5A の負荷電流を供給 できる 42V の N チャネル MOSFET スイッチを内蔵して

います。優れたラインおよび負荷レギュレーションと高効率 (90% 超) が特長です。電圧モード制御は最小オン時間 が短いため、入力電圧と出力電圧の比率を最も大きくでき ます。内部ループ補償により、ユーザーはループ補償部 品を計算する煩雑な作業から解放されます。 固定 5V 出 力品と可変出力電圧品を提供しています。500kHz のスイ ッチング周波数を使用するため、小型の外付け部品を使 用でき、良好な過渡応答を実現できます。高精度のイネー ブル入力により、レギュレータの制御とシステムの電源シ ーケンスが単純化されます。シャットダウン・モードでは、 本レギュレータの消費電流はわずか 25µA (標準値) で す。ソフトスタート機能 (標準値 500µs) を内蔵することで 外付け部品を減らしています。LM22678 デバイスはサー マル・シャットダウン機能と、偶発的な過負荷に対して保護 する電流制限機能も内蔵しています。

新製品の LM61460 は高効率、スタンバイ時の低静止電 流、優れた EMI 性能を実現しています。比較するには、 デバイス比較表を参照してください。WEBENCH により、 LM61460 を使用する設計を開始できます。

LM22678 デバイスは、テキサス・インスツルメンツの SIMPLE SWITCHER® ファミリの製品です。SIMPLE SWITCHER のコンセプトにより、最小限の外付け部品数 で、TIの WEBENCH 設計ツールを使用して、使いやす い完全な設計が可能になります。TIの WEBENCH ツー ルには、外付け部品の計算、電気的シミュレーション、熱 シミュレーション、デザインインを容易にする Build-It ボー ドなどの機能が含まれています。

#### 製品情報

| 型番         | パッケージ <sup>(1)</sup> | 本体サイズ (公称)               |  |  |

|------------|----------------------|--------------------------|--|--|

| LM22678    | TO-263 (7)           | 10.16mm × 9.85mm         |  |  |

| LM22678-Q1 | 10-203 (7)           | 10.10111111 ^ 9.03111111 |  |  |

利用可能なすべてのパッケージについては、このデータシートの 末尾にある注文情報を参照してください。

アプリケーション概略回路図

# **Table of Contents**

| 1 特長                                 | 1 | 7.3 Feature Description                  | 9  |

|--------------------------------------|---|------------------------------------------|----|

| 2アプリケーション                            |   | 7.4 Device Functional Modes              |    |

| 3 概要                                 |   | 8 Application and Implementation         | 14 |

| 4 Revision History                   |   | 8.1 Application Information              | 14 |

| 5 Pin Configuration and Functions    |   | 8.2 Typical Applications                 |    |

| 6 Specifications                     |   | 9 Layout                                 |    |

| 6.1 Absolute Maximum Ratings         |   | 9.1 Layout Guidelines                    | 20 |

| 6.2 Handling Ratings: LM22678        |   | 9.2 Layout Example                       |    |

| 6.3 Handling Ratings: LM22678-Q1     |   | 9.3 Thermal Considerations               |    |

| 6.4 Recommended Operating Conditions |   | 10 Device and Documentation Support      |    |

| 6.5 Thermal Information              |   | 10.1 Documentation Support               |    |

| 6.6 Electrical Characteristics       |   | 10.2 サポート・リソース                           |    |

| 6.7 Typical Characteristics          |   | 10.3ドキュメントの更新通知を受け取る方法                   |    |

| 7 Detailed Description               |   | 10.4 静電気放電に関する注意事項                       |    |

| 7.1 Overview                         |   | 10.5 用語集                                 |    |

| 7.2 Functional Block Diagram         |   | 7,7,7,7,7,7,7,7,7,7,7,7,7,7,7,7,7,7,7,7, |    |

|                                      |   |                                          |    |

|                                      |   |                                          |    |

| 4 Revision History                   |   |                                          |    |

| 貝石 | 料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。                                                                                                                                            |             |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Ch | hanges from Revision L (November 2014) to Revision M (October 2020)                                                                                                              | Page        |

| •  | 「特長」に LM61460 の箇条書き項目を追加<br>文書全体にわたって表、図、相互参照の採番方法を更新<br>タイトルを「LM22678/-Q1 42V、5A SIMPLE SWITCHER® 降圧レギュレータ、各種機能付き」から「LM226<br>使用しやすいパッケージの 42V、5A SIMPLE SWITCHER® 降圧レギュレータ」に変更 | 1<br>78/-Q1 |

|    |                                                                                                                                                                                  |             |

| Ch | hanges from Revision K (March 2013) to Revision L (November 2014)                                                                                                                | Page        |

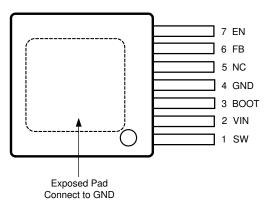

# **5 Pin Configuration and Functions**

図 5-1. 7-Pin PFM Package (Top View)

表 5-1. Pin Functions

| P                   | PIN | TYPE        | DESCRIPTION                                                       | APPLICATION INFORMATION                                                                |  |  |  |  |  |  |  |

|---------------------|-----|-------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| NAME                | NO. | 1175        | DESCRIPTION                                                       | AFFLICATION INFORMATION                                                                |  |  |  |  |  |  |  |

| воот                | 3   | I           | Bootstrap input                                                   | Provides the gate voltage for the high-side NFET.                                      |  |  |  |  |  |  |  |

| EN                  | 7   | I           | Enable input                                                      | Used to control regulator start-up and shutdown. See セクション 7.3.1.                      |  |  |  |  |  |  |  |

| EP EP — Exposed pad |     | Exposed pad | Connect to ground. Provides thermal connection to PCB. See セクシ 8. |                                                                                        |  |  |  |  |  |  |  |

| FB                  | 6   | I           | Feedback input                                                    | Feedback input to the regulator                                                        |  |  |  |  |  |  |  |

| GND                 | 4   | _           | Ground input to regulator; system common                          | System ground pin                                                                      |  |  |  |  |  |  |  |

| NC                  | 5   | _           | Not connected                                                     | Pin is not electrically connected inside chip. Pin does function as thermal conductor. |  |  |  |  |  |  |  |

| SW                  | 1   | 0           | Switch pin                                                        | Switching output of regulator                                                          |  |  |  |  |  |  |  |

| VIN                 | 2   | I           | Input voltage                                                     | Supply input to the regulator                                                          |  |  |  |  |  |  |  |

# **6 Specifications**

# 6.1 Absolute Maximum Ratings

|                                     | MIN          | MAX                 | UNIT <sup>(1)</sup> (2) |  |  |

|-------------------------------------|--------------|---------------------|-------------------------|--|--|

| VIN to GND                          |              | 43                  | V                       |  |  |

| EN Pin Voltage                      | -0.5         | 6                   | V                       |  |  |

| SW to GND (3)                       | -5           | V <sub>IN</sub>     | V                       |  |  |

| BOOT Pin Voltage                    |              | V <sub>SW</sub> + 7 | V                       |  |  |

| FB Pin Voltage                      | -0.5         | 7                   | V                       |  |  |

| Power Dissipation                   | Internally L | Internally Limited  |                         |  |  |

| Junction Temperature <sup>(4)</sup> |              | 150                 | °C                      |  |  |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the \*\*t/>\*\*D=\*\*\frac{6.4}\$ is not implied. The Recommended Operating Conditions indicate conditions at which the device is functional and should not be operated beyond such conditions.

- (2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

- (3) The absolute-maximum specification of the 'SW to GND' applies to dc voltage. An extended negative voltage limit of –10 V applies to a pulse of up to 50 ns.

- (4) For soldering specifications, refer to the application report Absolute Maximum Ratings for Soldering (SNOA549).

# 6.2 Handling Ratings: LM22678

|                    |                          |                                                                             | MIN | MAX | UNIT |

|--------------------|--------------------------|-----------------------------------------------------------------------------|-----|-----|------|

| T <sub>stg</sub>   | Storage temperature rang | е                                                                           | -65 | 150 | °C   |

| V <sub>(ESD)</sub> | Electrostatic discharge  | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup> | -2  | 2   | kV   |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

#### 6.3 Handling Ratings: LM22678-Q1

|                    |                           |                                                         | MIN             | MAX | UNIT |

|--------------------|---------------------------|---------------------------------------------------------|-----------------|-----|------|

| T <sub>stg</sub>   | Storage temperature range |                                                         | <del>-</del> 65 | 150 | °C   |

| V <sub>(ESD)</sub> | Electrostatic discharge   | Human body model (HBM), per AEC Q100-002 <sup>(1)</sup> | -2              | 2   | kV   |

(1) AEC Q100-002 indicates HBM stressing is done in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

# 6.4 Recommended Operating Conditions

|          |                            | MIN | MAX | UNIT |

|----------|----------------------------|-----|-----|------|

| $V_{IN}$ | Supply Voltage             | 4.5 | 42  | V    |

|          | Junction Temperature Range | -40 | 125 | °C   |

#### 6.5 Thermal Information

|                                                         | LM22678,<br>LM22678-Q1 |      |

|---------------------------------------------------------|------------------------|------|

| THERMAL METRIC <sup>(1)</sup> (2)                       | NDR                    | UNIT |

|                                                         | 7 PINS                 |      |

| R <sub>θJA</sub> Junction-to-ambient thermal resistance | 22                     | °C/W |

- 1) For more information about traditional and new thermal metrics, see the application report IC Package Thermal Metrics (SPRA953).

- (2) The value of R<sub>θJA</sub> for the PFM package of 22°C/W is valid if package is mounted to 1 square inch of copper. The R<sub>θJA</sub> value can range from 20 to 30°C/W depending on the amount of PCB copper dedicated to heat transfer. See application note AN-1797 (SNVA328) for more information.

# **6.6 Electrical Characteristics**

Typical values represent the most likely parametric norm at  $T_A = T_J = 25$ °C, and are provided for reference purposes only. Unless otherwise specified:  $V_{IN} = 12$  V.

|                                                                                                                                                              | PARAMETER                                                                                                                                                                                                                                                                                             | TEST CONDITIONS                                                 | MIN <sup>(1)</sup> | TYP <sup>(2)</sup> | MAX <sup>(1)</sup> | UNIT |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--------------------|--------------------|--------------------|------|--|

| LM22678                                                                                                                                                      | 3-5.0                                                                                                                                                                                                                                                                                                 |                                                                 |                    |                    |                    |      |  |

|                                                                                                                                                              |                                                                                                                                                                                                                                                                                                       | V <sub>IN</sub> = 8 V to 42 V                                   | 4.925              | 5.0                | 5.075              | V    |  |

| V <sub>FB</sub>                                                                                                                                              | Feedback Voltage  22678-ADJ  Feedback Voltage  COUTPUT VOLTAGE VERSIONS  Quiescent Current  Standby Quiescent Current  Current Limit  Output Leakage Current  (ON) Switch On-Resistance  Oscillator Frequency  Minimum Off-time  MIN Minimum On-time  Feedback Bias Current  Enable Threshold Voltage | V <sub>IN</sub> = 8 V to 42 V, −40°C ≤ T <sub>J</sub> ≤ 125°C   | 4.9                |                    | 5.1                | V    |  |

| LM22678                                                                                                                                                      | 3-ADJ                                                                                                                                                                                                                                                                                                 |                                                                 |                    |                    |                    |      |  |

|                                                                                                                                                              |                                                                                                                                                                                                                                                                                                       | V <sub>IN</sub> = 4.7 V to 42 V                                 | 1.266              | 1.285              | 1.304              |      |  |

| $V_{FB}$                                                                                                                                                     | Quiescent Current  Standby Quiescent Current  Current Limit                                                                                                                                                                                                                                           | V <sub>IN</sub> = 4.7 V to 42 V, −40°C ≤ T <sub>J</sub> ≤ 125°C | 1.259              |                    | 1.311              | V    |  |

| ALL OUT                                                                                                                                                      | TPUT VOLTAGE VERSIONS                                                                                                                                                                                                                                                                                 |                                                                 |                    |                    | <u> </u>           |      |  |

|                                                                                                                                                              | Quiaccent Current                                                                                                                                                                                                                                                                                     | V <sub>FB</sub> = 5 V                                           |                    | 3.4                |                    | m A  |  |

| IQ                                                                                                                                                           | FEMIN Minimum Off-time                                                                                                                                                                                                                                                                                | V <sub>FB</sub> = 5 V, −40°C ≤ T <sub>J</sub> ≤ 125°C           |                    |                    | 6                  | mA   |  |

| I <sub>STDBY</sub>                                                                                                                                           | Standby Quiescent Current                                                                                                                                                                                                                                                                             | EN Pin = 0 V                                                    |                    | 25                 | 40                 | μΑ   |  |

| I <sub>CL</sub>                                                                                                                                              | Current Limit                                                                                                                                                                                                                                                                                         |                                                                 | 6.0                | 7.1                | 8.4                | Λ    |  |

|                                                                                                                                                              | Current Limit                                                                                                                                                                                                                                                                                         | -40°C ≤ T <sub>J</sub> ≤ 125°C                                  | 5.75               |                    | 8.75               | Α    |  |

| I <u>L</u>                                                                                                                                                   | Output Lookaga Current                                                                                                                                                                                                                                                                                | V <sub>IN</sub> = 42 V, EN Pin = 0 V, V <sub>SW</sub> = 0 V     |                    | 0.2                | 2                  | μΑ   |  |

|                                                                                                                                                              | Output Leakage Current                                                                                                                                                                                                                                                                                | V <sub>SW</sub> = -1 V                                          |                    | 0.1                | 3                  | μA   |  |

|                                                                                                                                                              | Switch On Resistance                                                                                                                                                                                                                                                                                  |                                                                 |                    | 0.1                | 0.14               | Ω    |  |

|                                                                                                                                                              | Switch On-Resistance                                                                                                                                                                                                                                                                                  | -40°C ≤ T <sub>J</sub> ≤ 125°C                                  | 0.2                |                    | 0.2                | 12   |  |

| LM22678- VFB  ALL OUTI IQ ISTDBY ICL IL RDS(ON)                                                                                                              | Ossillator Eroquonov                                                                                                                                                                                                                                                                                  |                                                                 |                    | 500                |                    | kHz  |  |

|                                                                                                                                                              | Oscillator Frequency                                                                                                                                                                                                                                                                                  | -40°C ≤ T <sub>J</sub> ≤ 125°C                                  | 400                |                    | 600                | KΠZ  |  |

| I <sub>STDBY</sub> I <sub>CL</sub> I <sub>L</sub> R <sub>DS(ON)</sub> f <sub>O</sub> T <sub>OFFMIN</sub> T <sub>ONMIN</sub> I <sub>BIAS</sub>                | Minimum Off time                                                                                                                                                                                                                                                                                      |                                                                 |                    | 200                |                    | no   |  |

| OFFMIN                                                                                                                                                       | Will littluth On-unle                                                                                                                                                                                                                                                                                 | -40°C ≤ T <sub>J</sub> ≤ 125°C                                  | 100                |                    | 300                | ns   |  |

| T <sub>ONMIN</sub>                                                                                                                                           | Minimum On-time                                                                                                                                                                                                                                                                                       |                                                                 |                    | 100                |                    | ns   |  |

| I <sub>BIAS</sub>                                                                                                                                            | Feedback Bias Current                                                                                                                                                                                                                                                                                 | V <sub>FB</sub> = 1.3 V (ADJ Version Only)                      |                    | 230                |                    | nA   |  |

| I <sub>L</sub> Out  R <sub>DS(ON)</sub> Swi  f <sub>O</sub> Osc  T <sub>OFFMIN</sub> Min  T <sub>ONMIN</sub> Min  I <sub>BIAS</sub> Fee  V <sub>EN</sub> Ena | Enable Threshold Voltage                                                                                                                                                                                                                                                                              | Falling                                                         |                    | 1.6                |                    | V    |  |

|                                                                                                                                                              | Litable Tilleshold Voltage                                                                                                                                                                                                                                                                            | Falling, –40°C ≤ T <sub>J</sub> ≤ 125°C                         | 1.3                |                    | 1.9                | V    |  |

| V <sub>ENHYST</sub>                                                                                                                                          | Enable Threshold Hysteresis                                                                                                                                                                                                                                                                           |                                                                 |                    | 0.6                |                    | V    |  |

| I <sub>EN</sub>                                                                                                                                              | Enable Input Current                                                                                                                                                                                                                                                                                  | EN Input = 0 V                                                  |                    | 6                  |                    | μA   |  |

| T <sub>SD</sub>                                                                                                                                              | Thermal Shutdown Threshold                                                                                                                                                                                                                                                                            |                                                                 |                    | 150                |                    | °C   |  |

<sup>(1)</sup> MIN and MAX limits are 100% production tested at 25°C. Limits over the operating temperature range are ensured through correlation using Statistical Quality Control (SQC) methods. Limits are used to calculate TI's Average Outgoing Quality Level (AOQL).

<sup>(2)</sup> Typical values represent most likely parametric norms at the conditions specified and are not ensured.

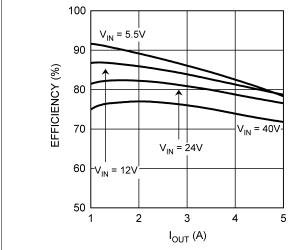

# **6.7 Typical Characteristics**

V<sub>in</sub> = 12 V, T<sub>J</sub> = 25°C (unless otherwise specified)

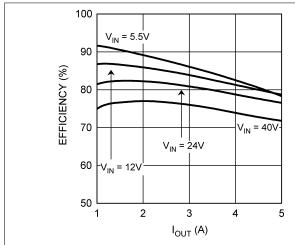

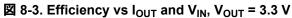

図 6-1. Efficiency vs  $I_{OUT}$  and  $V_{IN}$ ,  $V_{OUT}$  = 3.3 V

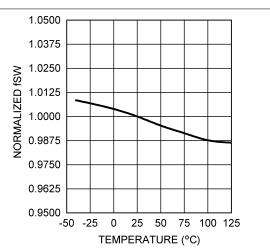

☑ 6-2. Normalized Switching Frequency vs

Temperature

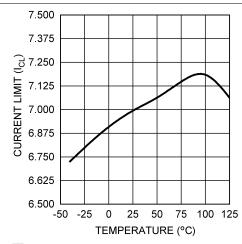

図 6-3. Current Limit vs Temperature

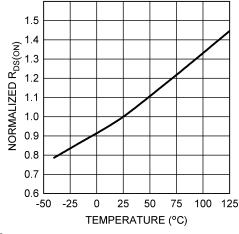

図 6-4. Normalized R<sub>DS(ON)</sub> vs Temperature

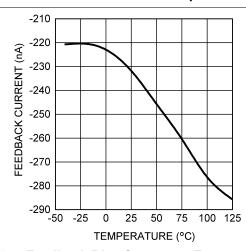

図 6-5. Feedback Bias Current vs Temperature

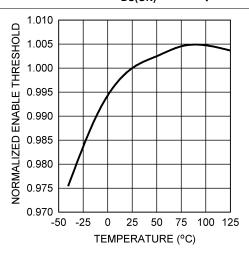

図 6-6. Normalized Enable Threshold Voltage vs Temperature

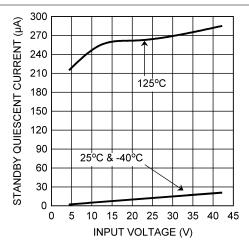

図 6-7. Standby Quiescent Current vs Input Voltage

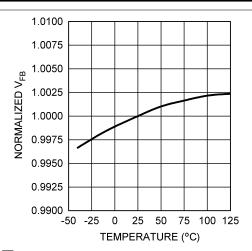

図 6-8. Normalized Feedback Voltage vs **Temperature**

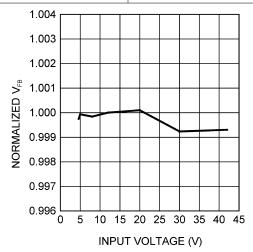

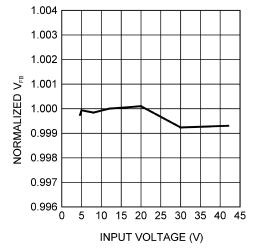

図 6-9. Normalized Feedback Voltage vs Input Voltage

# 7 Detailed Description

## 7.1 Overview

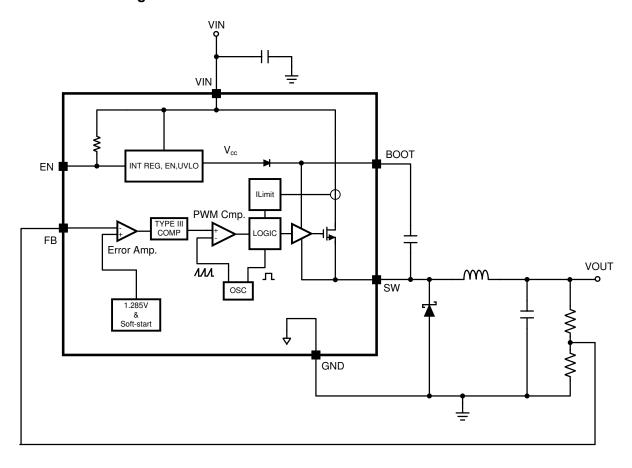

The LM22678 incorporates a voltage mode constant frequency PWM architecture. In addition, input voltage feedforward is used to stabilize the loop gain against variations in input voltage. This allows the loop compensation to be optimized for transient performance. The power MOSFET, in conjunction with the diode, produces a rectangular waveform at the switch pin, which swings from about zero volts to VIN. The inductor and output capacitor average this waveform to become the regulator output voltage. By adjusting the duty cycle of this waveform, the output voltage can be controlled. The error amplifier compares the output voltage with the internal reference and adjusts the duty cycle to regulate the output at the desired value.

The internal loop compensation of the -ADJ option is optimized for outputs of 5 V and below. If an output voltage of 5 V or greater is required, the -5.0 option can be used with an external voltage divider. The minimum output voltage is equal to the reference voltage, that is, 1.285 V (typ).

# 7.2 Functional Block Diagram

# 7.3 Feature Description

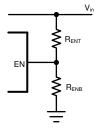

#### 7.3.1 Precision Enable and UVLO

The precision enable input (EN) is used to control the regulator. The precision feature allows simple sequencing of multiple power supplies with a resistor divider from another supply. Connecting this pin to ground or to a voltage less than 1.6 V (typ.) will turn off the regulator. The current drain from the input supply, in this state, is 25  $\mu$ A (typ.) at an input voltage of 12 V. The EN input has an internal pullup of about 6  $\mu$ A. Therefore, this pin can be left floating or pulled to a voltage greater than 2.2 V (typ) to turn the regulator on. The hysteresis on this input is about 0.6 V (typ.) above the 1.6-V (typ.) threshold. When driving the enable input, the voltage must never exceed the 6-V absolute maximum specification for this pin.

Although an internal pullup is provided on the EN pin, it is good practice to pull the input high when this feature is not used, especially in noisy environments. This can most easily be done by connecting a resistor between VIN and the EN pin. The resistor is required because the internal zener diode at the EN pin will conduct for voltages above about 6 V. The current in this zener must be limited to less than 100  $\mu$ A. A resistor of 470 k $\Omega$  will limit the current to a safe value for input voltages as high 42 V. Smaller values of resistor can be used at lower input voltages.

The LM22678 device also incorporates an input undervoltage lockout (UVLO) feature. This prevents the regulator from turning on when the input voltage is not great enough to properly bias the internal circuitry. The rising threshold is 4.3 V (typ.) while the falling threshold is 3.9 V (typ.). In some cases, these thresholds can be too low to provide good system performance. The solution is to use the EN input as an external UVLO to disable the part when the input voltage falls below a lower boundary. This is often used to prevent excessive battery discharge or early turnon during start-up. This method is also recommended to prevent abnormal device operation in applications where the input voltage falls below the minimum of 4.5 V. 又 7-1 shows the connections to implement this method of UVLO. 式 1 and 式 2 can be used to determine the correct resistor values.

$$R_{ENT} = R_{ENB} \cdot \left( \frac{V_{off}}{V_{EN}} - 1 \right)$$

(1)

$$V_{on} = V_{off} \cdot \left( \frac{V_{EN} + V_{ENHYST}}{V_{EN}} \right)$$

(2)

#### where

- V<sub>off</sub> is the input voltage where the regulator shuts off.

- V<sub>on</sub> is the voltage where the regulator turns on.

Due to the 6- $\mu$ A pullup, the current in the divider should be much larger than this. A value of 20 k $\Omega$ , for R<sub>ENB</sub> is a good first choice. Also, a zener diode may be needed between the EN pin and ground, in order to comply with the absolute maximum ratings on this pin.

図 7-1. External UVLO Connections

#### 7.3.2 Soft Start

The soft-start feature allows the regulator to gradually reach steady-state operation, thus reducing start-up stresses. The internal soft-start feature brings the output voltage up in about 500  $\mu$ s. This time is fixed and cannot be changed. Soft start is reset any time the part is shut down or a thermal overload event occurs.

#### 7.3.3 Bootstrap Supply

The LM22678 device incorporates a floating high-side gate driver to control the power MOSFET. The supply for this driver is the external bootstrap capacitor connected between the BOOT pin and SW. A good quality 10-nF ceramic capacitor must be connected to these pins with short, wide PCB traces. One reason the regulator imposes a minimum off-time is to ensure that this capacitor recharges every switching cycle. A minimum load of about 5 mA is required to fully recharge the bootstrap capacitor in the minimum off-time. Some of this load can be provided by the output voltage divider, if used.

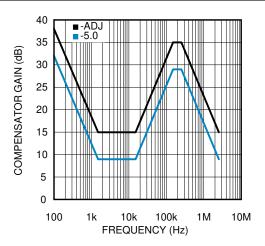

# 7.3.4 Internal Loop Compensation

The LM22678 has internal loop compensation designed to provide a stable regulator over a wide range of external power stage components.

The internal compensation of the -ADJ option is optimized for output voltages below 5 V. If an output voltage of 5 V or greater is needed, the -5.0 option with an external resistor divider can be used.

Ensuring stability of a design with a specific power stage (inductor and output capacitor) can be tricky. The LM22678 stability can be verified using the WEBENCH Designer online circuit simulation tool at WEBENCH Designer. A quick start spreadsheet can also be downloaded from the online product folder.

The complete transfer function for the regulator loop is found by combining the compensation and power stage transfer functions. The LM22678 has internal type III loop compensation, as detailed in ot in

otin

oti

$$L \cdot C_{\text{out}} \approx 1.1 \times 10^{-9}$$

Alternatively, this pole should be placed between 1.5 kHz and 15 kHz and is determined by 式 4.

$$F_{o} = \frac{1}{2\pi \cdot \sqrt{L \cdot C_{out}}}$$

(4)

The Q factor depends on the parasitic resistance of the power stage components and is not typically in the control of the designer. Of course, loop compensation is only one consideration when selecting power stage components (see \*\*D>3>\*\* 8 for more details).

図 7-2. Compensator Gain

In general, hand calculations or simulations can only aid in selecting good power stage components. Good design practice dictates that load and line transient testing should be done to verify the stability of the application. Also, Bode plot measurements should be made to determine stability margins. *AN-1889 How to Measure the Loop Transfer Function of Power Supplies* (SNVA364) shows how to perform a loop transfer function measurement with only an oscilloscope and function generator.

#### 7.4 Device Functional Modes

#### 7.4.1 Shutdown Mode

The EN pin provides electrical ON and OFF control for the LM22678 device. When VEN is below 1.6 V, the device is in shutdown mode. The current drain from the input supply, in this state, is 25  $\mu$ A (typ) at an input voltage of 12 V. The EN input has an internal pullup of about 6  $\mu$ A. The LM22678 also incorporates an input undervoltage lockout (UVLO) feature. This prevents the regulator from turning on when the input voltage is not great enough to properly bias the internal circuitry. The rising threshold is 4.3 V (typ.) while the falling threshold is 3.9 V (typ.).

#### 7.4.2 Active Mode

The LM22678 device is in active mode when VEN is above the precision enable threshold and its input voltage is above its UVLO level. The simplest way to enable the LM22678 is to connect the EN pin to VIN through a resistor. A resistor of 470 k $\Omega$  will limit the current to a safe value for input voltages as high 42 V.

#### 7.4.3 Current Limit

The LM22678 device has current limiting to prevent the switch current from exceeding safe values during an accidental overload on the output. This peak current limit is found in  $\frac{1}{2}\frac{1}{2}\frac{1}{2}$  6.6 under the heading of  $I_{CL}$ . The maximum load current that can be provided, before current limit is reached, is determined from  $\frac{1}{2}$  5.

$$I_{\text{out}}|_{\text{max}} \approx I_{\text{CL}} - \frac{(V_{\text{in}} - V_{\text{out}})}{2 \cdot L \cdot F_{\text{sw}}} \cdot \frac{V_{\text{out}}}{V_{\text{in}}}$$

(5)

#### where

L is the value of the power inductor.

When the LM22678 device enters current limit, the output voltage will drop and the peak inductor current will be fixed at  $I_{CL}$  at the end of each cycle. The switching frequency will remain constant while the duty cycle drops. The load current will not remain constant, but will depend on the severity of the overload and the output voltage.

For very severe overloads "short-circuit", the regulator changes to a low frequency current foldback mode of operation. The frequency foldback is about 1/5 of the nominal switching frequency. This will occur when the current limit trips before the minimum on-time has elapsed. This mode of operation is used to prevent inductor

current "run-away", and is associated with very low output voltages when in overload. 式 6 can be used to determine what level of output voltage will cause the part to change to low frequency current foldback.

$$V_{x} \le V_{in} \cdot F_{sw} \cdot T_{on} \cdot 1.8 \tag{6}$$

where

- F<sub>sw</sub> is the normal switching frequency.

- · V<sub>in</sub> is the maximum for the application.

If the overload drives the output voltage to less than or equal to  $V_x$ , the part will enter current foldback mode. If a given application can drive the output voltage to  $\leq V_x$ , during an overload, then a second criterion must be checked.  $\pm 7$  determines the maximum input voltage, when in this mode, before damage occurs.

$$V_{in} \le \frac{V_{sc} + 0.4}{T_{on} \cdot F_{sw} \cdot 0.36} \tag{7}$$

where

- V<sub>sc</sub> is the value of output voltage during the overload.

- F<sub>sw</sub> is the normal switching frequency.

#### **Note**

If the input voltage should exceed this value while in foldback mode, the regulator, diode, or both can be damaged.

It is important to note that the voltages in these equations are measured at the inductor. Normal trace and wiring resistance will cause the voltage at the inductor to be higher than that at a remote load. Therefore, even if the load is shorted with zero volts across its terminals, the inductor will still see a finite voltage. It is this value that should be used for  $V_x$  and  $V_{sc}$  in the calculations. In order to return from foldback mode, the load must be reduced to a value much lower than that required to initiate foldback. This load "hysteresis" is a normal aspect of any type of current limit foldback associated with voltage regulators.

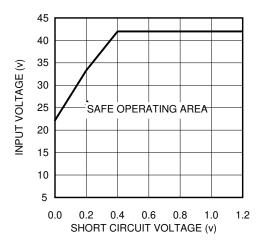

The safe operating area, when in short circuit mode, is shown in  $\boxtimes$  7-3. Operating points below and to the right of the curve represent safe operation.

図 7-3. SOA

#### 7.4.4 Thermal Protection

Internal thermal-shutdown circuitry protects the LM22678 should the maximum junction temperature be exceeded. This protection is activated at about 150°C, with the result that the regulator will shut down until the temperature drops below about 135°C.

#### 7.4.5 Duty-Cycle Limits

Ideally, the regulator would control the duty cycle over the full range of zero to one. However due to inherent delays in the circuitry, there are limits on both the maximum and minimum duty cycles that can be reliably controlled. This in turn places limits on the maximum and minimum input and output voltages that can be converted by the LM22678. A minimum on-time is imposed by the regulator to correctly measure the switch current during a current limit event. A minimum off-time is imposed in order the re-charge the bootstrap capacitor. 3 8 can be used to determine the approximate maximum input voltage for a given output voltage.

$$V_{in}|_{max} \approx \frac{V_{out} + 0.4}{T_{on} \cdot F_{sw} \cdot 1.8}$$

(8)

where

- F<sub>sw</sub> is the switching frequency.

- T<sub>ON</sub> is the minimum on-time.

Both values can be found in セクション 6.6.

The worst case occurs at the lowest output voltage. If the input voltage found in ₹ 8 is exceeded, the regulator will skip cycles; thus, effectively lowering the switching frequency. The consequences of this are higher output voltage ripple and a degradation of the output voltage accuracy.

$$V_{in}|_{min} \approx \frac{V_{out} + 0.4 + I_{out} \cdot R_L}{1 - T_{off} \cdot F_{sw} \cdot 1.8} + I_{out} \cdot R_{dson}$$

(9)

where

• The values of T<sub>OFF</sub> and R<sub>DS(ON)</sub> are found in セクション 6.6.

The worst case here occurs at the highest load. In this equation,  $R_L$  is the dc inductor resistance. Of course, the lowest input voltage to the regulator must not be less than 4.5 V (typ.).

# 8 Application and Implementation

#### Note

以下のアプリケーション情報は、TIの製品仕様に含まれるものではなく、TIではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

# 8.1 Application Information

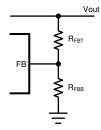

#### 8.1.1 Output Voltage Divider Selection

For output voltages between about 1.285 V and 5 V, the -ADJ option should be used, with an appropriate voltage divider as shown in 図 8-1. 式 10 can be used to calculate the resistor values of this divider.

$$R_{FBT} = \left[\frac{V_{\text{out}}}{1.285} - 1\right] \cdot R_{FBB} \tag{10}$$

A good value for  $R_{FBB}$  is 1 k $\Omega$ . This will help to provide some of the minimum load current requirement and reduce susceptibility to noise pick-up. The top of  $R_{FBT}$  should be connected directly to the output capacitor or to the load for remote sensing. If the divider is connected to the load, a local high-frequency bypass should be provided at that location.

For output voltages of 5 V, the -5.0 option should be used. In this case no divider is needed and the FB pin is connected to the output. The approximate values of the internal voltage divider are as follows:  $7.38 \text{ k}\Omega$  from the FB pin to the input of the error amplifier and  $2.55 \text{ k}\Omega$  from there to ground.

Both the -ADJ and -5.0 options can be used for output voltages greater than 5 V, by using the correct output divider. As mentioned in 2922 7.3.4, the -5.0 option is optimized for output voltages of 5 V. However, for output voltages greater than 5 V, this option may provide better loop bandwidth than the -ADJ option, in some applications. If the -5.0 option is to be used at output voltages greater than 5 V,  $\pm$  11 should be used to determine the resistor values in the output divider.

$$R_{FBT} = \frac{R_{FBB} \cdot (V_{out} - 5)}{5 + R_{FBB} \cdot 5 \times 10^{-4}}$$

(11)

Again, a value of  $R_{FBB}$  of about 1 k $\Omega$  is a good first choice.

☑ 8-1. Resistive Feedback Divider

A maximum value of 10 k $\Omega$  is recommended for the sum of R<sub>FBB</sub> and R<sub>FBT</sub> to maintain good output voltage accuracy for the -ADJ option. A maximum of 2 k $\Omega$  is recommended for the -5.0 option. For the -5.0 option, the total internal divider resistance is typically 9.93 k $\Omega$ .

In all cases the output voltage divider should be placed as close as possible to the FB pin of the LM22678 device; because this is a high impedance input and is susceptible to noise pick-up.

#### 8.1.2 Power Diode

A Schottky-type power diode is required for all LM22678 applications. Ultra-fast diodes are not recommended and may result in damage to the IC due to reverse recovery current transients. The near ideal reverse recovery characteristics and low forward voltage drop of Schottky diodes are particularly important for high input voltage and low output voltage applications common to the LM22678 device. The reverse breakdown rating of the diode should be selected for the maximum  $V_{\text{IN}}$ , plus some safety margin. A good rule of thumb is to select a diode with a reverse voltage rating of 1.3 times the maximum input voltage.

Select a diode with an average current rating at least equal to the maximum load current that will be seen in the application.

## 8.2 Typical Applications

## 8.2.1 Typical Buck Regulator Application

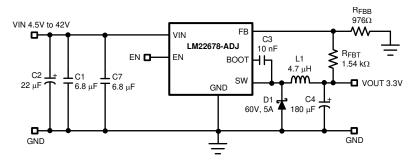

🗵 8-2 shows an example of converting an input voltage range of 5.5 V to 42 V, to an output of 3.3 V at 5 A.

図 8-2. Typical Buck Regulator Application

## 8.2.1.1 Design Requirements

| DESIGN PARAMETERS           | EXAMPLE VALUE                                           |

|-----------------------------|---------------------------------------------------------|

| Driver Supply Voltage (VIN) | 4.5 to 42 V                                             |

| Output Voltage (VOUT)       | 3.3 V                                                   |

| R <sub>FBT</sub>            | Calculated based on $R_{FBB}$ and $V_{REF}$ of 1.285 V. |

| R <sub>FBB</sub>            | 1 kΩ to 10 kΩ                                           |

| louт                        | 5 A                                                     |

#### 8.2.1.2 Detailed Design Procedure

# 8.2.1.2.1 External Components

The following guidelines should be used when designing a step-down (buck) converter with the LM22678 device.

#### 8.2.1.2.1.1 Inductor

The inductor value is determined based on the load current, ripple current, and the minimum and maximum input voltages. To keep the application in continuous conduction mode (CCM), the maximum ripple current,  $I_{RIPPLE}$ , should be less than twice the minimum load current. The general rule of keeping the inductor current peak-to-peak ripple around 30% of the nominal output current is a good compromise between excessive output voltage ripple and excessive component size and cost. Using this value of ripple current, the value of inductor (L) is calculated using  $\stackrel{\sim}{\not\sim}$  12.

$$L = \frac{(V_{in} - V_{out}) \cdot V_{out}}{0.3 \cdot I_{out} \cdot F_{sw} \cdot V_{in}}$$

(12)

#### where

- $\bullet \quad F_{sw} \text{ is the switching frequency.} \\$

- V<sub>in</sub> should be taken at its maximum value, for the given application.

式 12 provides a guide to select the value of the inductor L; the nearest standard value will then be used in the circuit.

Once the inductor is selected, the actual ripple current can be determined by  $\pm$  13.

$$\Delta I = \frac{(V_{in} - V_{out}) \cdot V_{out}}{L \cdot F_{sw} \cdot V_{in}}$$

(13)

Increasing the inductance will generally slow down the transient response but reduce the output voltage ripple. Reducing the inductance will generally improve the transient response but increase the output voltage ripple.

The inductor must be rated for the peak current,  $I_{PK}$ , in a given application, to prevent saturation. During normal loading conditions, the peak current is equal to the load current plus 1/2 of the inductor ripple current.

During an overload condition, as well as during certain load transients, the controller can trip current limit. In this case the peak inductor current is given by  $I_{CL}$ , found in  $\rlap{\ } \rlap{\ }} \rlap{\ } \rlap{\ } \rlap{\ } \rlap{\ }} \rlap{\ } \rlap{\ } \rlap{\ } \rlap{\ } \rlap{\ }} \rlap{\ } \rlap{\ } \rlap{\ }} \rlap{\ } \rlap{\ } \rlap{\ }} \rlap{\ } \rlap{\ }} \rlap{\ } \rlap{\ }} \rlap{\ }} \rlap{\ } \rlap{\ }} \rlap{\$

#### **Note**

If the inductor is not rated for the maximum expected current, it can saturate resulting in damage to the LM22678, the power diode, or both.

#### 8.2.1.2.2 Input Capacitor

The input capacitor selection is based on both input voltage ripple and RMS current. Good quality input capacitors are necessary to limit the ripple voltage at the VIN pin while supplying most of the regulator current during switch on-time. Low-ESR ceramic capacitors are preferred. Larger values of input capacitance are desirable to reduce voltage ripple and noise on the input supply. This noise can find its way into other circuitry, sharing the same input supply, unless adequate bypassing is provided. A very approximate formula for determining the input voltage ripple is shown in  $\pm$  14.

$$V_{ri} \approx \frac{I_{out}}{4 \cdot F_{sw} \cdot C_{in}}$$

(14)

#### where

V<sub>ri</sub> is the peak-to-peak ripple voltage at the switching frequency.

$$I_{\rm rms} \approx \frac{I_{\rm out}}{2}$$

(15)

The capacitor must be rated for at least this level of RMS current at the switching frequency.

All ceramic capacitors have large voltage coefficients, in addition to normal tolerances and temperature coefficients. To help mitigate these effects, multiple capacitors can be used in parallel to bring the minimum

capacitance up to the desired value. This can also help with RMS current constraints by sharing the current among several capacitors. Many times it is desirable to use an electrolytic capacitor on the input, in parallel with the ceramics. The moderate ESR of this capacitor can help to damp any ringing on the input supply caused by long power leads. This method can also help to reduce voltage spikes that may exceed the maximum input voltage rating of the LM22678 device.

It is good practice to include a high frequency bypass capacitor as close as possible to the LM22678 device. This small case size, low ESR ceramic capacitor should be connected directly to the VIN and GND pins with the shortest possible PCB traces. Values in the range of 0.47 µF to 1 µF are appropriate. This capacitor helps to provide a low impedance supply to sensitive internal circuitry. It also helps to suppress any fast noise spikes on the input supply that may lead to increased EMI.

#### 8.2.1.2.3 Output Capacitor

The output capacitor is responsible for filtering the output voltage and supplying load current during transients. Capacitor selection depends on application conditions as well as ripple and transient requirements. Best performance is achieved with a parallel combination of ceramic capacitors and a low-ESR SP™ or POSCAP™ type. Very low ESR capacitors such as ceramics reduce the output ripple and noise spikes, while higher value electrolytics or polymer provide large bulk capacitance to supply transients. Assuming very low ESR, 式 16 determines an approximation to the output voltage ripple.

$$V_{ro} \approx \frac{(V_{in} - V_{out}) \cdot V_{out}}{8 \cdot V_{in}} \cdot \frac{1}{F_{sw}^2 \cdot L \cdot C_{out}}$$

(16)

Typically, a total value of 100 µF or greater is recommended for output capacitance.

In applications with Vout less than 3.3 V, it is critical that low-ESR output capacitors are selected. This will limit potential output voltage overshoots as the input voltage falls below the device normal operating range.

#### 8.2.1.2.4 Bootstrap Capacitor

The bootstrap capacitor between the BOOT pin and the SW pin supplies the gate current to turn on the Nchannel MOSFET. The recommended value of this capacitor is 10 nF and should be a good quality, low-ESR ceramic capacitor. In some cases, it can be desirable to slow down the turnon of the internal power MOSFET in order to reduce EMI. This can be done by placing a small resistor in series with the C<sub>boot</sub> capacitor. Resistors in the range of 10  $\Omega$  to 50  $\Omega$  can be used. This technique should only be used when absolutely necessary, because it will increase switching losses and thereby reduce efficiency.

# 8.2.1.3 Application Curves

図 8-4. Normalized Feedback Voltage vs Input Voltage

# **Power Supply Recommendations**

The LM22678 device is designed to operate from an input voltage supply range between 4.5 V and 42 V. This input supply should be well regulated and able to withstand maximum input current and maintain a stable voltage. The resistance of the input supply rail should be low enough that an input current transient does not cause a high enough drop at the LM22678 supply voltage that can cause a false UVLO fault triggering and system reset. If the input supply is located more than a few inches from the LM22678 device, additional bulk capacitance may be required in addition to the ceramic bypass capacitors. The amount of bulk capacitance is not critical, but a 47  $\mu$ F or 100  $\mu$ F electrolytic capacitor is a typical choice.

# 9 Layout

# 9.1 Layout Guidelines

Board layout is critical for the proper operation of switching power supplies. First, the ground plane area must be sufficient for thermal dissipation purposes. Second, appropriate guidelines must be followed to reduce the effects of switching noise. Switch mode converters are very fast switching devices. In such cases, the rapid increase of input current combined with the parasitic trace inductance generates unwanted L di/dt noise spikes. The magnitude of this noise tends to increase as the output current increases. This noise may turn into electromagnetic interference (EMI) and can also cause problems in device performance. Therefore, care must be taken in layout to minimize the effect of this switching noise.

The most important layout rule is to keep the ac current loops as small as possible.

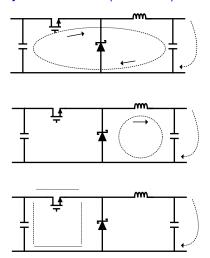

9-1 shows the current flow in a buck converter. The top schematic shows a dotted line which represents the current flow during the FET switch on-state. The middle schematic shows the current flow during the FET switch off-state.

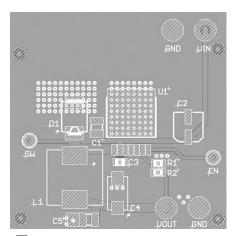

The bottom schematic shows the currents referred to as ac currents. These ac currents are the most critical because they are changing in a very short time period. The dotted lines of the bottom schematic are the traces to keep as short and wide as possible. This will also yield a small loop area reducing the loop inductance. To avoid functional problems due to layout, review the PCB layout example. Best results are achieved if the placement of the LM22678 device, the bypass capacitor, the Schottky diode,  $R_{FBB}$ ,  $R_{FBT}$ , and the inductor are placed as shown in  $\boxtimes$  9-1. In the layout shown,  $R1 = R_{FBB}$  and  $R2 = R_{FBT}$ . It is also recommended to use 2 oz copper boards or heavier to help thermal dissipation and to reduce the parasitic inductances of board traces. See *AN-1229 SIMPLE SWITCHER® PCB Layout Guidelines* (SNVA054) for more information.

図 9-1. Current Flow in a Buck Application

# 9.2 Layout Example

図 9-2. LM22678 Layout Example

#### 9.3 Thermal Considerations

The components with the highest power dissipation are the power diode and the power MOSFET internal to the LM22678 regulator. The easiest method to determine the power dissipation within the LM22678 is to measure the total conversion losses then subtract the power losses in the diode and inductor. The total conversion loss is the difference between the input power and the output power. An approximation for the power diode loss is shown in \$\preceq\$17.

$$P_{D} = I_{out} \cdot V_{D} \cdot \left[ 1 - \frac{V_{out}}{V_{in}} \right]$$

(17)

where

V<sub>D</sub> is the diode voltage drop.

An approximation for the inductor power is determined by  $\pm$  18.

$$P_{L} = I_{out}^{2} \cdot R_{L} \cdot 1.1 \tag{18}$$

where

R<sub>I</sub> is the dc resistance of the inductor.

The 1.1 factor is an approximation for the ac losses.

The regulator has an exposed thermal pad to aid power dissipation. Adding multiple vias under the device to the ground plane will greatly reduce the regulator junction temperature. Selecting a diode with an exposed pad will also aid the power dissipation of the diode. The most significant variables that affect the power dissipation of the regulator are output current, input voltage and operating frequency. The power dissipated while operating near the maximum output current and maximum input voltage can be appreciable. The junction-to-ambient thermal resistance of the LM22678 will vary with the application. The most significant variables are the area of copper in the PC board, the number of vias under the IC exposed pad and the amount of forced air cooling provided. A large continuous ground plane on the top or bottom PCB layer will provide the most effective heat dissipation. The integrity of the solder connection from the IC exposed pad to the PC board is critical. Excessive voids will greatly diminish the thermal dissipation capacity. The junction-to-ambient thermal resistance of the LM22678 PFM package is specified in \*\*Design By Insight, Not Hindsight\* (SNVA419) for more information.

# 10 Device and Documentation Support

# **10.1 Documentation Support**

#### 10.1.1 Related Documentation

- AN-2020 Thermal Design By Insight, Not Hindsight (SNVA419)

- AN-1229 SIMPLE SWITCHER® PCB Layout Guidelines (SNVA054)

- AN-1892 LM22677 Evaluation Board (SNVA366)

- AN-1889 How to Measure the Loop Transfer Function of Power Supplies (SNVA364)

#### 10.2 サポート・リソース

TI E2E<sup>™</sup> サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、該当する貢献者により、現状のまま提供されるものです。これらは TI の仕様を構成するものではなく、必ずしも TI の見解を反映したものではありません。TI の使用条件を参照してください。

# 10.3 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、ti.com のデバイス製品フォルダを開いてください。「*更新の通知を受け取る」をクリック*して登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取れます。変更の詳細については、修正されたドキュメントに含まれている改訂履歴をご覧ください。

## 10.4 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい ESD 対策をとらないと、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

## 10.5 用語集

TI 用語集 この用語集には、用語や略語の一覧および定義が記載されています。

# Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

10-Dec-2020

#### **PACKAGING INFORMATION**

| Orderable Device     | Status (1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|----------------------|------------|--------------|--------------------|------|----------------|--------------|-------------------------------|--------------------|--------------|-------------------------|---------|

| LM22678QTJ-5.0/NOPB  | ACTIVE     | TO-263       | NDR                | 7    | 1000           | RoHS & Green | SN                            | Level-1-260C-UNLIM | -40 to 125   | LM22678<br>QTJ-5.0      | Samples |

| LM22678QTJ-ADJ/NOPB  | ACTIVE     | TO-263       | NDR                | 7    | 1000           | RoHS & Green | SN                            | Level-1-260C-UNLIM | -40 to 125   | LM22678<br>QTJ-ADJ      | Samples |

| LM22678QTJE-5.0/NOPB | ACTIVE     | TO-263       | NDR                | 7    | 250            | RoHS & Green | SN                            | Level-1-260C-UNLIM | -40 to 125   | LM22678<br>QTJ-5.0      | Samples |

| LM22678QTJE-ADJ/NOPB | ACTIVE     | TO-263       | NDR                | 7    | 250            | RoHS & Green | SN                            | Level-1-260C-UNLIM | -40 to 125   | LM22678<br>QTJ-ADJ      | Samples |

| LM22678TJ-5.0/NOPB   | ACTIVE     | TO-263       | NDR                | 7    | 1000           | RoHS & Green | SN                            | Level-1-260C-UNLIM | -40 to 125   | LM22678<br>TJ-5.0       | Samples |

| LM22678TJ-ADJ/NOPB   | ACTIVE     | TO-263       | NDR                | 7    | 1000           | RoHS & Green | SN                            | Level-1-260C-UNLIM | -40 to 125   | LM22678<br>TJ-ADJ       | Samples |

| LM22678TJE-5.0/NOPB  | ACTIVE     | TO-263       | NDR                | 7    | 250            | RoHS & Green | SN                            | Level-1-260C-UNLIM | -40 to 125   | LM22678<br>TJ-5.0       | Samples |

| LM22678TJE-ADJ/NOPB  | ACTIVE     | TO-263       | NDR                | 7    | 250            | RoHS & Green | SN                            | Level-1-260C-UNLIM | -40 to 125   | LM22678<br>TJ-ADJ       | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

# PACKAGE OPTION ADDENDUM

10-Dec-2020

(5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

(6) Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE MATERIALS INFORMATION

www.ti.com 2-Oct-2020

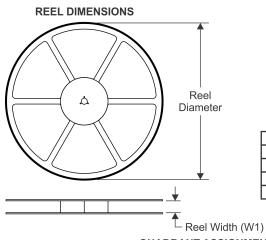

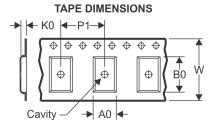

# TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

|    | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

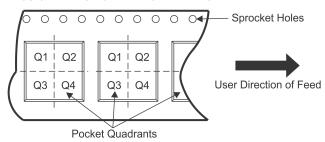

# QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| All dimensions are nominal |                 |                    |   |      |                          |                          |            |            |            |            |           |                  |

|----------------------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                     | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| LM22678QTJ-5.0/NOPB        | TO-263          | NDR                | 7 | 1000 | 330.0                    | 24.4                     | 10.6       | 15.4       | 2.45       | 12.0       | 24.0      | Q2               |

| LM22678QTJ-ADJ/NOPB        | TO-263          | NDR                | 7 | 1000 | 330.0                    | 24.4                     | 10.6       | 15.4       | 2.45       | 12.0       | 24.0      | Q2               |

| LM22678QTJE-5.0/NOPB       | TO-263          | NDR                | 7 | 250  | 178.0                    | 24.4                     | 10.6       | 15.4       | 2.45       | 12.0       | 24.0      | Q2               |

| LM22678QTJE-ADJ/NOP<br>B   | TO-263          | NDR                | 7 | 250  | 178.0                    | 24.4                     | 10.6       | 15.4       | 2.45       | 12.0       | 24.0      | Q2               |

| LM22678TJ-5.0/NOPB         | TO-263          | NDR                | 7 | 1000 | 330.0                    | 24.4                     | 10.6       | 15.4       | 2.45       | 12.0       | 24.0      | Q2               |

| LM22678TJ-ADJ/NOPB         | TO-263          | NDR                | 7 | 1000 | 330.0                    | 24.4                     | 10.6       | 15.4       | 2.45       | 12.0       | 24.0      | Q2               |

| LM22678TJE-5.0/NOPB        | TO-263          | NDR                | 7 | 250  | 178.0                    | 24.4                     | 10.6       | 15.4       | 2.45       | 12.0       | 24.0      | Q2               |

| LM22678TJE-ADJ/NOPB        | TO-263          | NDR                | 7 | 250  | 178.0                    | 24.4                     | 10.6       | 15.4       | 2.45       | 12.0       | 24.0      | Q2               |

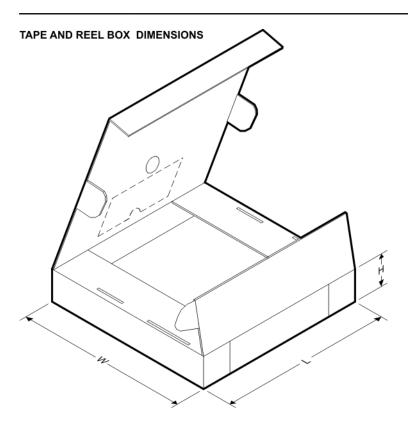

**PACKAGE MATERIALS INFORMATION**

www.ti.com 2-Oct-2020

\*All dimensions are nominal

| Device               | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |

|----------------------|--------------|-----------------|------|------|-------------|------------|-------------|--|

| LM22678QTJ-5.0/NOPB  | TO-263       | NDR             | 7    | 1000 | 367.0       | 367.0      | 35.0        |  |

| LM22678QTJ-ADJ/NOPB  | TO-263       | NDR             | 7    | 1000 | 367.0       | 367.0      | 35.0        |  |

| LM22678QTJE-5.0/NOPB | TO-263       | NDR             | 7    | 250  | 210.0       | 185.0      | 35.0        |  |

| LM22678QTJE-ADJ/NOPB | TO-263       | NDR             | 7    | 250  | 210.0       | 185.0      | 35.0        |  |

| LM22678TJ-5.0/NOPB   | TO-263       | NDR             | 7    | 1000 | 367.0       | 367.0      | 35.0        |  |

| LM22678TJ-ADJ/NOPB   | TO-263       | NDR             | 7    | 1000 | 367.0       | 367.0      | 35.0        |  |

| LM22678TJE-5.0/NOPB  | TO-263       | NDR             | 7    | 250  | 210.0       | 185.0      | 35.0        |  |

| LM22678TJE-ADJ/NOPB  | TO-263       | NDR             | 7    | 250  | 210.0       | 185.0      | 35.0        |  |

TO-263

## NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

- Features may not exist and shape may vary per different assembly sites.

Reference JEDEC registration TO-279B.

- 5. Under all conditions, leads must not be above Datum C

TO-263

NOTES: (continued)

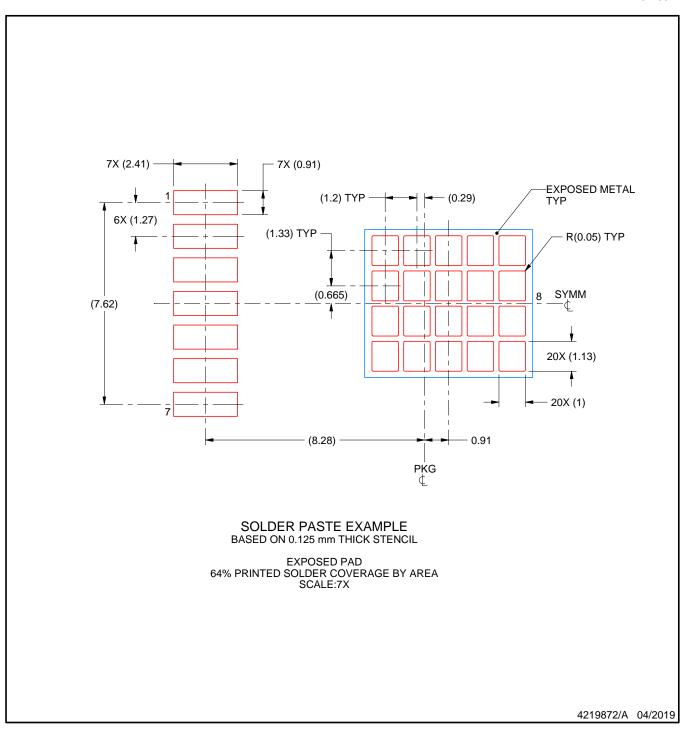

<sup>6.</sup> This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature numbers SLMA002(www.ti.com/lit/slm002) and SLMA004 (www.ti.com/lit/slma004).

<sup>7.</sup> Vias are optional depending on application, refer to device data sheet. It is recommended that vias under paste be filled, plugged or tented.

TO-263

NOTES: (continued)

<sup>8.</sup> Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations

design recommendations.

9. Board assembly site may have different recommendations for stencil design.

# 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス・デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、TI の販売条件、または ti.com やかかる TI 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、TI はそれらに異議を唱え、拒否します。

郵送先住所:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022. Texas Instruments Incorporated