# LM5125-Q1、広い入力電圧範囲、2相、車載用昇圧コントローラ、 $V_{OUT}$ トランシッキング付き

## 1 特長

- ・ 車載アプリケーション向けに AEC-Q100 認証済み

- 温度グレード 1:  $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$

- ・ **機能安全対応**

- 機能安全システムの設計に役立つ資料を利用可能

- ・ 入力電圧: 4.5V ~ 42V

- $V_{BIAS} \geq 4.5\text{V}$  または  $V_{OUT} \geq 6\text{V}$  について最低 2.5V

- ・ 出力電圧 6V ~ 60V

- 精度 2%、内部帰還抵抗

- $V_I > V_{OUT}$  のときバイパス動作

- 動的出力電圧追跡

- デジタル PWM トランシッキング (DTRK)

- アナログトランシッキング (ATRK)

- 過電圧保護 (64V, 50V, 35V, 28.5V)

- ・ 2 $\mu\text{A}$  の小さなシャットダウン  $I_Q$

- ・ 小さな動作  $I_Q$ : 1.4mA

- ・ スイッチング周波数: 100kHz ~ 2.2MHz

- 外部クロックへの同期 (SYNCIN)

- スイッチングモードを動的に選択可能 (FPWM、ダイオードエミュレーション)

- スペクトラム拡散 (DRSS)

- ・ デッドタイムを選択可能 (14ns ~ 200ns)

- ・ 電流センス抵抗、または DCR センシング

- ・ 平均インダクタ電流モニタ

- ・ 平均入力電流制限

- プログラム可能な電流制限

- 選択可能な遅延時間

- ・ パワー グッド インジケータ

- ・ プログラム可能な  $V_I$  低電圧誤動作防止 (UVLO)

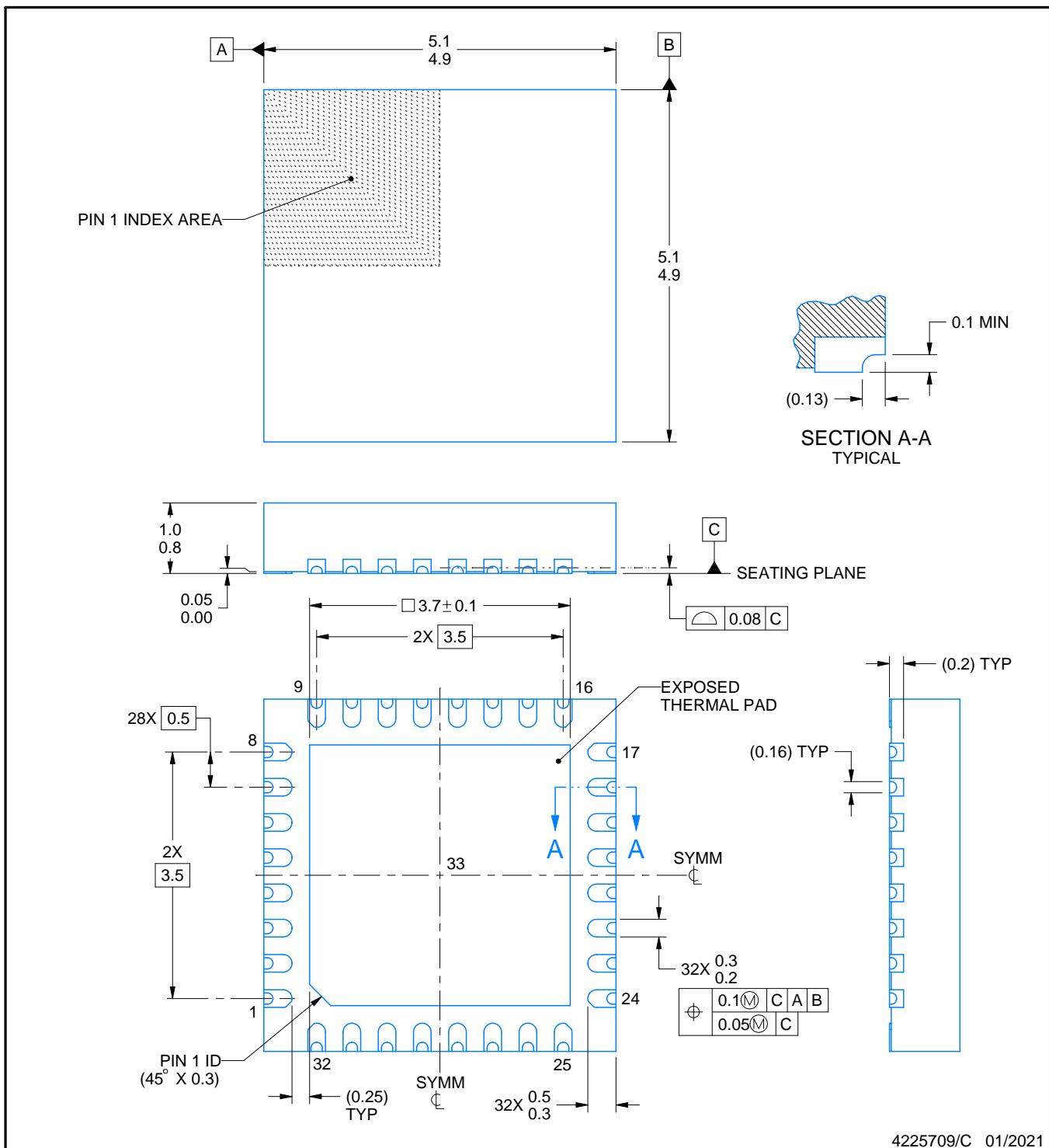

- ・ ウェッタブル フランク付きリードレス VQFN-32 パッケージ

## 2 アプリケーション

- ・ ハイエンドオーディオ電源

- ・ 電圧安定化モジュール

- ・ スタートアップ アプリケーション

## 3 説明

LM5125-Q1 は、2 相の同期整流昇圧コントローラで、このデバイスは、より低い入力電圧または等しい入力電圧に対してレギュレートされた出力電圧を供給し、消費電力を節約するため、 $V_I$  から  $V_{OUT}$  のバイパスモードにも対応しています。

アナログまたはデジタルの ATRK/DTRK 機能を使用して  $V_{OUT}$  を動的にプログラムできます。 $V_{BIAS}$  が 4.5V 未満のときは内部 VCC 電源が自動的に  $V_{BIAS}$  から  $V_{OUT}$  に切り替わるため、スタートアップ後  $V_I$  を最低 2.5V までサポートされます。固定スイッチング周波数は、RT ピンに接続された抵抗または SYNCIN クロックを使用して、100kHz と 2.2MHz の間に設定されます。スイッチングモード、FPWM、またはダイオードエミュレーションは、動作中に変更できます。

実装されている保護機能、ピーク電流制限、平均入力電流制限、平均インダクタ電流のモニタ、過電圧および低電圧保護、およびサーマルシャットダウンにより、デバイスおよびアプリケーションを保護します。

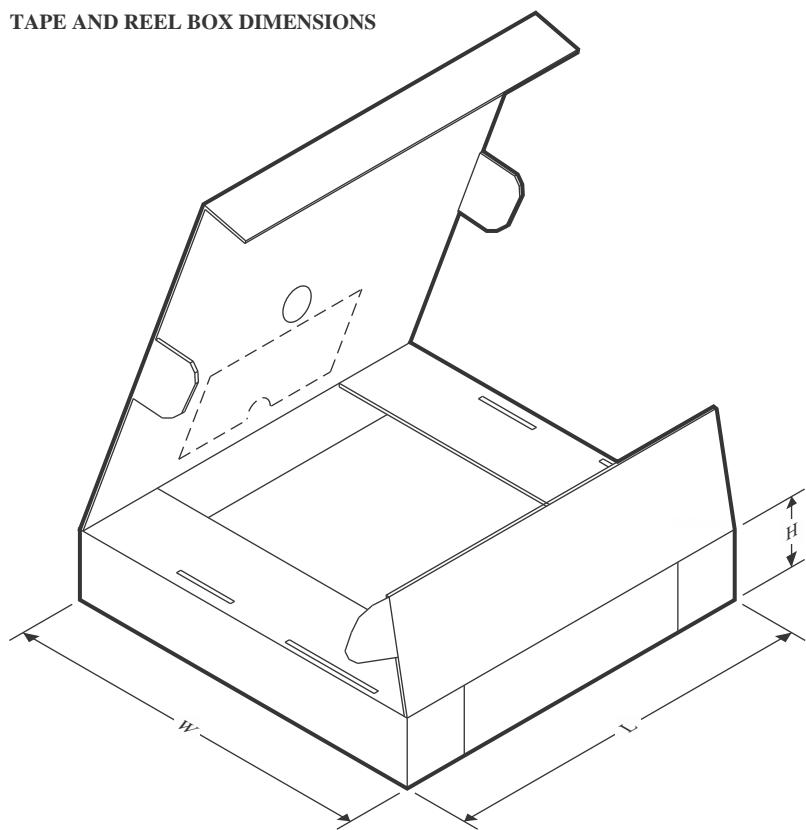

### パッケージ情報

| 部品番号      | パッケージ <sup>(1)</sup> | パッケージサイズ <sup>(2)</sup> |

|-----------|----------------------|-------------------------|

| LM5125-Q1 | RHB (VQFN, 32)       | 5mm × 5mm               |

(1) 詳細については、セクション 10 を参照してください。

(2) パッケージサイズ(長さ × 幅)は公称値であり、該当する場合はピンも含まれます。

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール(機械翻訳)を使用していることがあり、TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

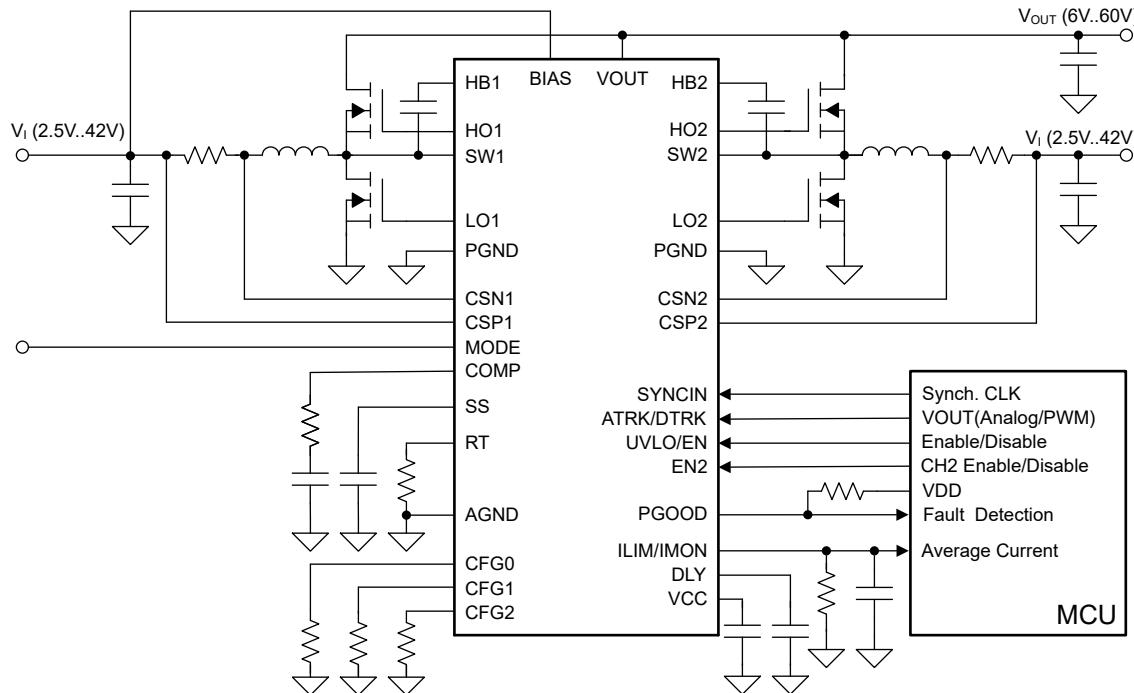

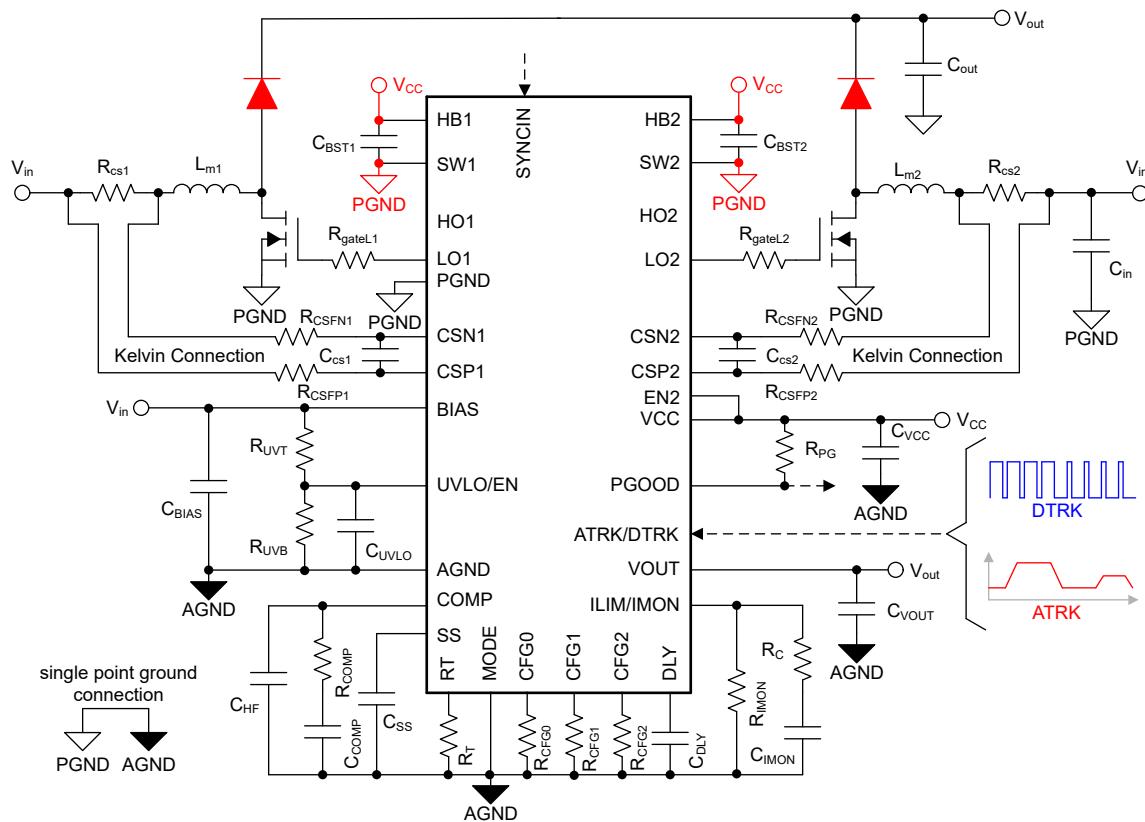

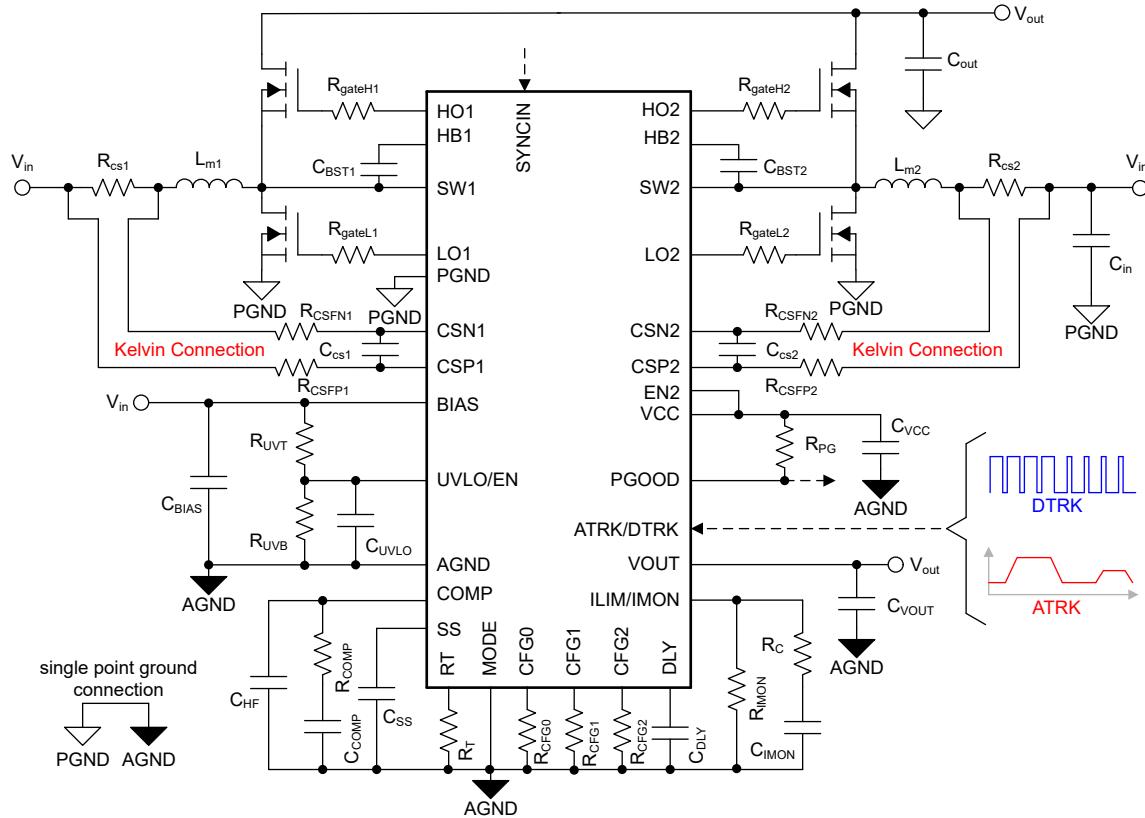

の代表的なアプリケーション

## 目次

|             |    |                        |    |

|-------------|----|------------------------|----|

| 1 特長        | 1  | 6.4 デバイスの機能モード         | 36 |

| 2 アプリケーション  | 1  | 7 アプリケーションと実装          | 37 |

| 3 説明        | 1  | 7.1 アプリケーション情報         | 37 |

| 4 ピン構成および機能 | 4  | 7.2 代表的なアプリケーション       | 40 |

| 5 仕様        | 6  | 7.3 電源に関する推奨事項         | 55 |

| 5.1 絶対最大定格  | 6  | 7.4 レイアウト              | 55 |

| 5.2 ESD 定格  | 6  | 8 デバイスおよびドキュメントのサポート   | 58 |

| 5.3 推奨動作条件  | 7  | 8.1 ドキュメントのサポート        | 58 |

| 5.4 熱に関する情報 | 7  | 8.2 ドキュメントの更新通知を受け取る方法 | 58 |

| 5.5 電気的特性   | 7  | 8.3 サポート・リソース          | 58 |

| 5.6 タイミング要件 | 13 | 8.4 商標                 | 58 |

| 5.7 代表的特性   | 14 | 8.5 静電気放電に関する注意事項      | 58 |

| 6 詳細説明      | 18 | 8.6 用語集                | 58 |

| 6.1 概要      | 18 | 9 改訂履歴                 | 58 |

| 6.2 機能ブロック図 | 19 | 10 メカニカル、パッケージ、および注文情報 | 59 |

| 6.3 機能説明    | 20 |                        |    |

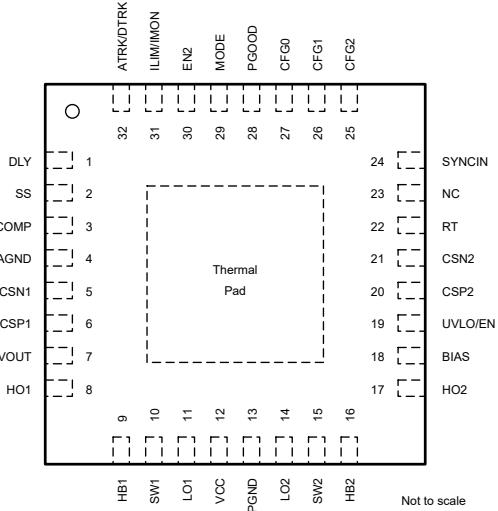

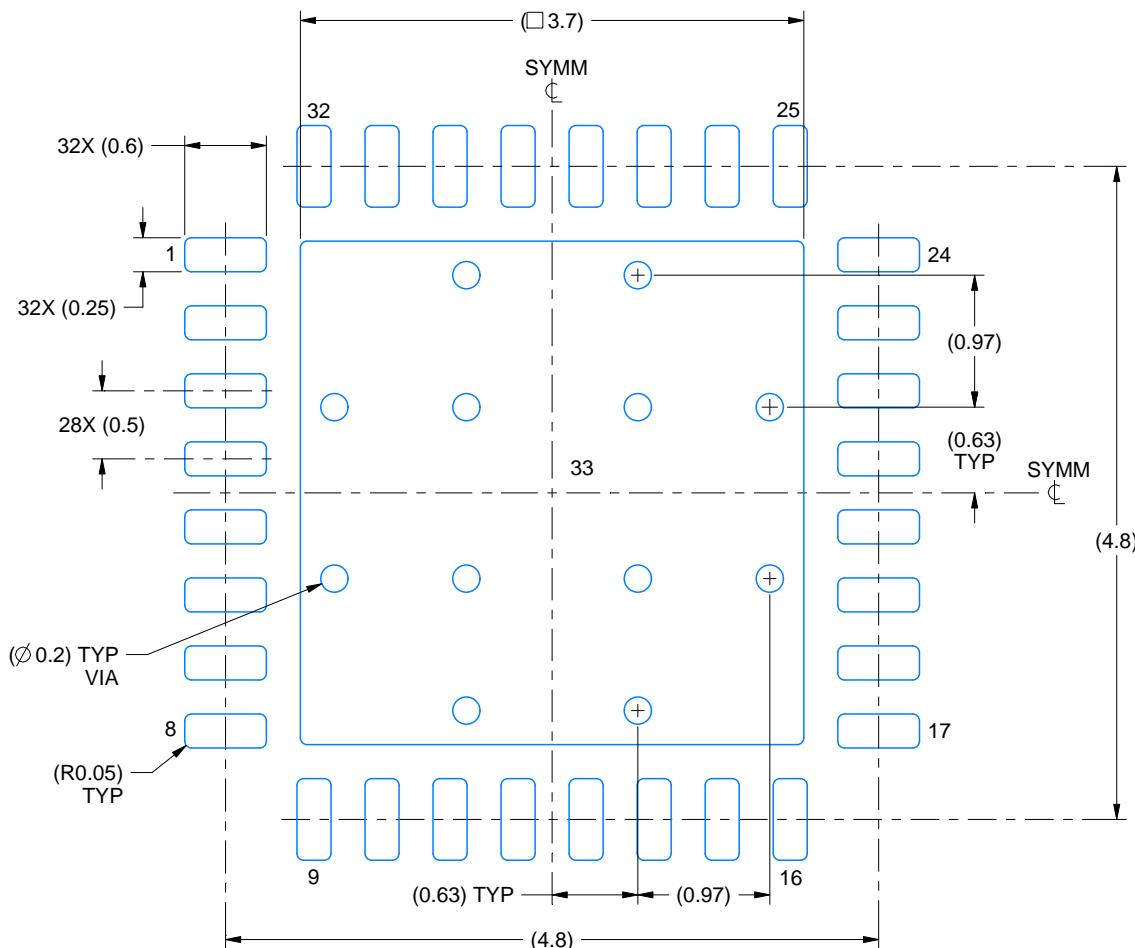

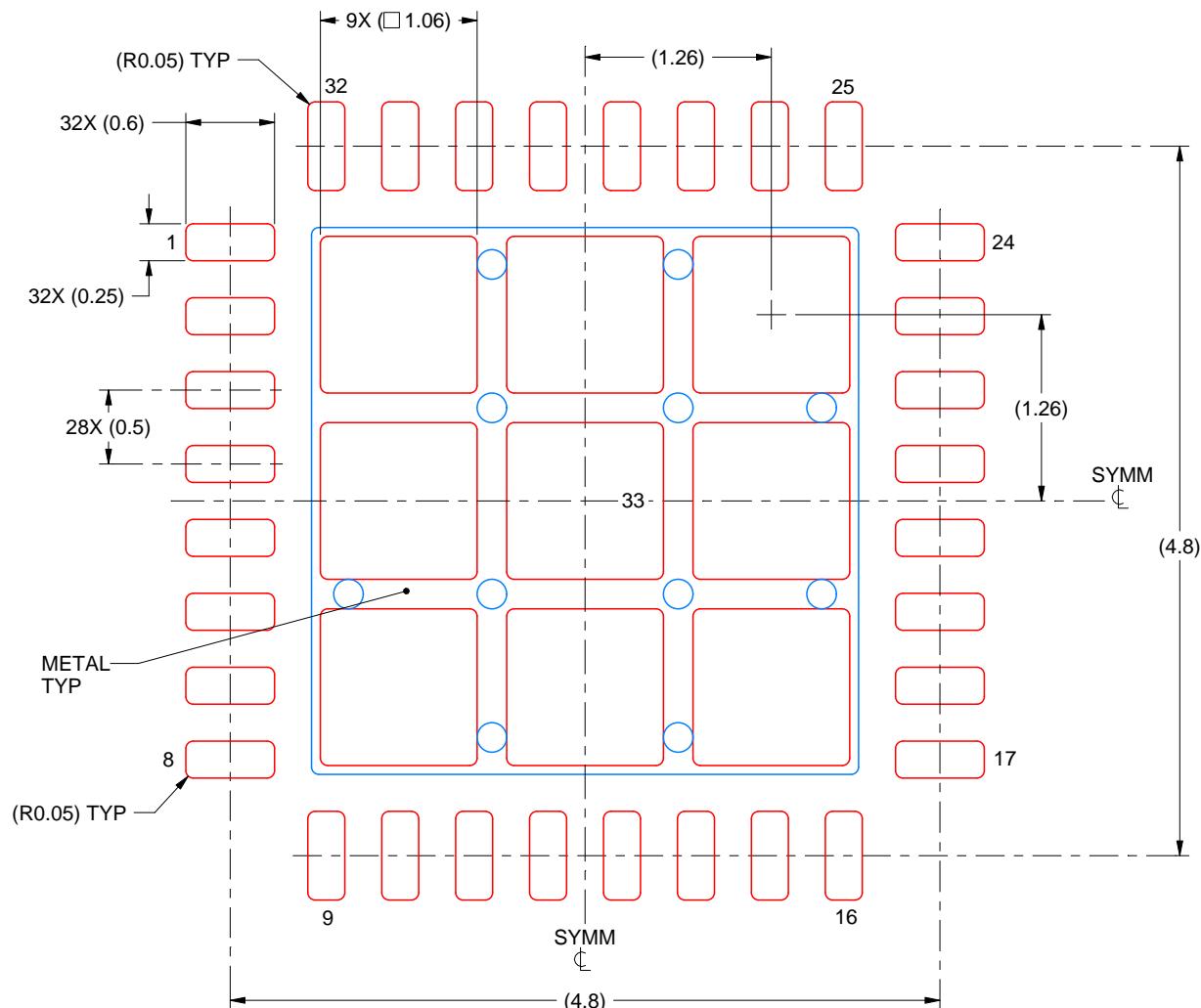

## 4 ピン構成および機能

図 4-1. LM5125-Q1 RHB パッケージ、32 ピン VQFN (上面図)

表 4-1. ピンの機能

| ピン        |    | タイプ <sup>(1)</sup> | 説明                                                                                                                                                                                                                                                        |

|-----------|----|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称        | 番号 |                    |                                                                                                                                                                                                                                                           |

| AGND      | 4  | G                  | アナログ グランドピン。広く短いバスを通して、アナログ グランド プレーンに接続します。                                                                                                                                                                                                              |

| ATRK/DTRK | 32 | I                  | 出力リギュレーションターゲットのプログラミングピン。出力電圧のリギュレーションターゲットは、ピンを抵抗経由で AGND に接続するか、ピンの推奨動作範囲内の電圧 (0.2V ~ 2.0V) で直接ピン電圧を制御することでプログラムします。起動時に 8% ~ 80% のデューティサイクルの範囲のデジタル PWM 信号が自動的に検出され、デジタル出力電圧リギュレーションが有効になります。デジタル出力電圧リギュレーションにより、推奨動作範囲内で V <sub>OUT</sub> をプログラムします。 |

| BIAS      | 18 | P                  | VCC リギュレータの電源電圧入力。1μF のローカル BIAS コンデンサを、ピンとグランドとの間に接続します。                                                                                                                                                                                                 |

| CFG0      | 27 | I/O                | デバイス構成ピン。デッド タイムを設定し、20μA の ATRK 電流を有効にします。                                                                                                                                                                                                               |

| CFG1      | 26 | I/O                | デバイス構成ピン。過電圧保護レベル、スペクトラム拡散モード、PGOOD 構成、120% ピーク電流制限ラッチ オフを設定します。                                                                                                                                                                                          |

| CFG2      | 25 | I/O                | デバイス構成ピン。デバイスが内部または外部クロックを使用しているかどうか、および過電圧保護レベルを設定します。                                                                                                                                                                                                   |

| COMP      | 3  | O                  | 内部の相互コンダクタンス エラー アンプの出力。ピンと AGND との間にループ補償部品を接続します。                                                                                                                                                                                                       |

| CSN1      | 5  | I                  | 位相 1 の電流検出アンプ入力。このピンは負の入力ピンとして動作します。                                                                                                                                                                                                                      |

| CSN2      | 21 | I                  | 位相 2 の電流検出アンプ入力。このピンは負の入力ピンとして動作します。                                                                                                                                                                                                                      |

| CSP1      | 6  | I                  | 位相 1 の電流検出アンプ入力。このピンは正の入力ピンとして動作します。内部 V <sub>I</sub> 低電圧誤動作防止回路の電源。                                                                                                                                                                                      |

| CSP2      | 20 | I                  | 位相 2 の電流検出アンプ入力。このピンは正の入力ピンとして動作します。                                                                                                                                                                                                                      |

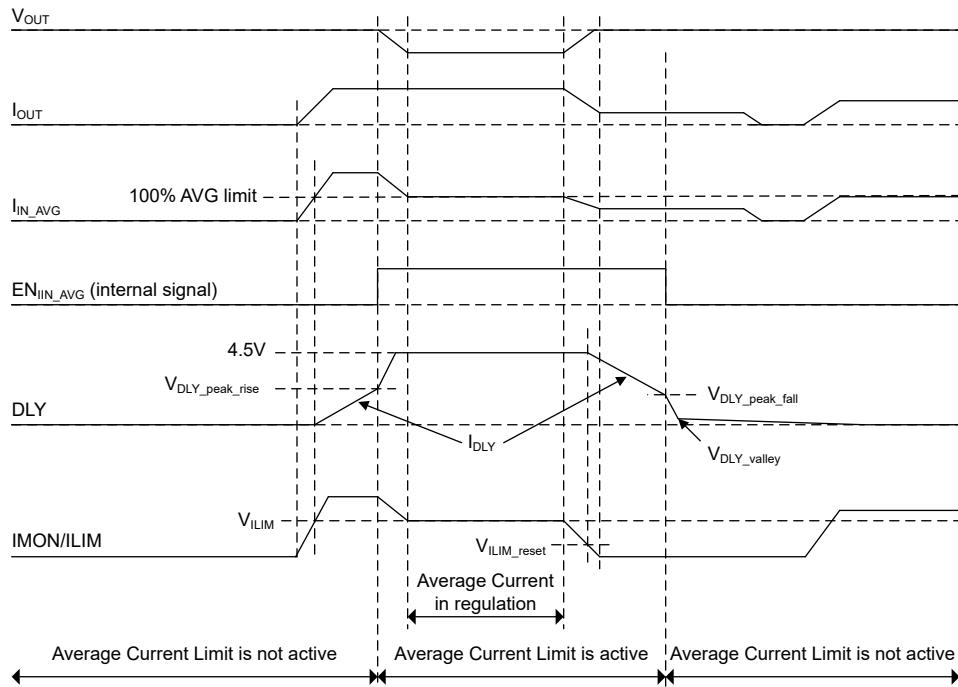

| DLY       | 1  | O                  | 平均入力電流制限遅延設定ピン。DLY と AGND の間にコンデンサを接続することで、V <sub>IMON</sub> が 1V に達したときから平均入力電流制限が有効になるまでの遅延が設定されます。                                                                                                                                                     |

| EN2       | 30 | I                  | 位相 2 のイネーブル ピン。                                                                                                                                                                                                                                           |

表 4-1. ピンの機能(続き)

| ピン        |    | タイプ <sup>(1)</sup> | 説明                                                                                                                                                                                                       |

|-----------|----|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称        | 番号 |                    |                                                                                                                                                                                                          |

| EP        | -  | G                  | パッケージの露出パッド。露出パッドは、熱抵抗を減らすために、AGNDに接続し、大きなグランドプレーンに半田付けます。                                                                                                                                               |

| HB1       | 9  | P                  | 位相 1 のブートストラップ ゲート駆動のハイサイド ドライバ電源。ブートダイオードは内部で VCC からこのピンに接続されます。このピンと SW1 との間に、0.1μF のコンデンサを接続します。                                                                                                      |

| HB2       | 16 | P                  | 位相 2 のブートストラップ ゲート駆動のハイサイド ドライバ電源。ブートダイオードは内部で VCC からこのピンに接続されます。このピンと SW2 との間に、0.1μF のコンデンサを接続します。                                                                                                      |

| HO1       | 8  | O                  | 位相 1 のハイサイド ゲートドライバ出力。短い低インダクタンスのパスを経由して、ハイサイド N チャネル MOSFET のゲートに接続します。                                                                                                                                 |

| HO2       | 17 | O                  | 位相 2 のハイサイド ゲートドライバ出力。短い低インダクタンスのパスを経由して、ハイサイド N チャネル MOSFET のゲートに接続します。                                                                                                                                 |

| ILIM/IMON | 31 | O                  | 入力電流モニタおよび平均入力電流制限設定ピン。位相 1 と位相 2 の差動電流検出電圧に比例する電流を供給します。このピンと AGND との間に抵抗を接続します。                                                                                                                        |

| LO1       | 11 | O                  | 位相 1 のローサイド ゲートドライバ出力。短い低インダクタンスのパスを経由して、ローサイド N チャネル MOSFET のゲートに接続します。                                                                                                                                 |

| LO2       | 14 | O                  | 位相 2 のローサイド ゲートドライバ出力。短い低インダクタンスのパスを経由して、ローサイド N チャネル MOSFET のゲートに接続します。                                                                                                                                 |

| モード       | 29 | I                  | DEM または FPWM を選択する動作モード選択ピン。                                                                                                                                                                             |

| NC        | 23 | -                  | 非接続ピン。このピンは GND に接続します。                                                                                                                                                                                  |

| PGND      | 13 | G                  | ローサイド ゲートドライバおよび VCC バイアス電源のパワー グランド接続ピン。                                                                                                                                                                |

| PGOOD     | 28 | O                  | オープン ドレイン出力段のパワー グッド インジケータ。CFG1 ピンの設定に基づいて、出力電圧が低電圧 レッショルドを下回るか、過電圧 レッショルドを上回ると、このピンは Low になります。このピンも Low に駆動され、故障が通知されます (パワー グッド・インジケータ (PGOOD ピン) を参照)。このピンを使用しないときは、AGND に接続するか、ピンを浮いた状態のままにしておきます。 |

| RT        | 22 | I/O                | スイッチング周波数の設定ピン。スイッチング周波数は、ピンと AGND との間の抵抗によりプログラミれます。スイッチング周波数は動作中に動的にプログラムできます。                                                                                                                         |

| SS        | 2  | O                  | ソフトスタート時間のプログラミングピン。外付けコンデンサと内部の電流ソースにより、ソフトスタート中の内部エラー アンプのリファレンス電圧のランプレートが設定されます。デバイスは、ソフトスタート時間中にダイオード エミュレーションを強制的に実行します。                                                                            |

| SW1       | 10 | I                  | 位相 1 のスイッチング ノード接続。位相 1 のハイサイド N チャネル MOSFET のソースに直接接続します。                                                                                                                                               |

| SW2       | 15 | I                  | 位相 2 のスイッチング ノード接続。位相 2 のハイサイド N チャネル MOSFET のソースに直接接続します。                                                                                                                                               |

| SYNCIN    | 24 | I                  | 外部クロック同期ピン。フリーランニング内部発振器をオーバーライドする外部クロックの入力。未使用時は SYNCIN ピンをグランドに接続します。                                                                                                                                  |

| UVLO/EN   | 19 | I                  | 低電圧誤動作防止のプログラム用ピン。このピンを抵抗デバイダを介して電源電圧に接続することで、コンバータのスタートアップおよびシャットダウン レベルをプログラムします。V <sub>UVLO-RISING</sub> より高くなると、位相 1 が有効になります。                                                                       |

| VCC       | 12 | P                  | 内部 VCC レギュレータの出力と内部 MOSFET ドライバの電源電圧入力。このピンと PGND との間に、10μF のコンデンサを接続します。                                                                                                                                |

| VOUT      | 7  | P                  | 出力電圧検出ピン。内部の帰還抵抗分圧器をピンと AGND との間に接続します。0.1μF のローカル VOUT コンデンサを、ピンとグランドとの間に接続します。                                                                                                                         |

(1) I = 入力、O = 出力、I/O = 入力または出力、G = グランド、P = 電源。

## 5 仕様

### 5.1 絶対最大定格

接合部の推奨動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|                                         |                                                        | 最小値  | 最大値                | 単位 |

|-----------------------------------------|--------------------------------------------------------|------|--------------------|----|

| 入力 <sup>(2)</sup>                       | BIAS から AGND へ                                         | -0.3 | 50                 | V  |

|                                         | UVLO/EN から AGND へ                                      | -0.3 | BIAS + 0.3         |    |

|                                         | CSPx から AGND へ                                         | -0.3 | 50                 |    |

|                                         | CSPx から CSNx へ                                         | -0.3 | 0.3                |    |

|                                         | VOUT から AGND へ                                         | -0.3 | 65                 |    |

|                                         | HBx から AGND へ                                          | -0.3 | 71                 |    |

|                                         | HBx から SWx へ                                           | -0.3 | 5.8 <sup>(3)</sup> |    |

|                                         | SWx から AGND へ                                          | -0.3 | 65                 |    |

|                                         | SWx から AGND へ (10ns)                                   | -5   | 65                 |    |

|                                         | CFG0、CFG1、CFG2、SYNCIN、ATRK/DTRK、DLY、MODE、EN2 から AGND へ | -0.3 | 5.5                |    |

| 出力 <sup>(2)</sup>                       | RT から AGND へ                                           | -0.3 | 2.5                | V  |

|                                         | PGND から AGND へ                                         | -0.3 | 0.3                |    |

|                                         | VCC から AGND へ                                          | -0.3 | 5.8 <sup>(3)</sup> |    |

|                                         | HOx から SWx へ (50ns)                                    | -1   | HBx + 0.3          |    |

|                                         | LOx から AGND へ (50ns)                                   | -1   | VCC + 0.3          | V  |

|                                         | PGOOD、SS、COMP、ILIM/IMON から AGND へ                      | -0.3 | 5.5                |    |

| 動作時の接合部温度、T <sub>J</sub> <sup>(4)</sup> |                                                        | -40  | 150                | °C |

| 保管温度、T <sub>STG</sub>                   |                                                        | -55  | 150                |    |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

- (2) 外部電圧を CFG0、CFG1、CFG2、COMP、SS、RT、LOx、HOx の各ピンに直接印加することはできません。

- (3) ピンの電圧が 5.5V を超えると、動作寿命が短くなります。

- (4) 接合部温度が高くなると、動作寿命が短くなります。接合部温度が 125°C を超えると、動作寿命が短くなります。

### 5.2 ESD 定格

|                    |      |                                            | 値              | 単位 |

|--------------------|------|--------------------------------------------|----------------|----|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM)、AEC Q100-002 準拠 <sup>(1)</sup> | ±2000          | V  |

|                    |      | デバイス帶電モデル (CDM)、AEC Q100-011 準拠            | すべてのピン<br>角のピン |    |

|                    |      |                                            | ±500<br>±750   |    |

- (1) AEC Q100-002 は、HBM ストレス試験を ANSI/ESDA/JEDEC JS-001 仕様に従って実施しなければならないと規定しています。

## 5.3 推奨動作条件

接合部の推奨動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|                                          |                                                         | 最小値 | 公称値                 | 最大値                 | 単位  |

|------------------------------------------|---------------------------------------------------------|-----|---------------------|---------------------|-----|

| $V_I$                                    | 昇圧コントローラ入力電圧 (バイアス $\geq 4.5V$ または $V_{OUT} \geq 6V$ 時) | 2.5 | 42                  | 42                  | V   |

| $V_{OUT}$                                | 昇圧コントローラ出力電圧                                            | 6   | 60                  | 60                  | V   |

| $V_{BIAS}$                               | BIAS 入力電圧                                               | 4.5 | 42                  | 42                  | V   |

| $V_{UVLO/EN}$                            | UVLO/EN 入力電圧                                            | 0   | 42                  | 42                  | V   |

| $V_{EN2}$                                | EN2 入力電圧                                                | 0   | 5.25                | 5.25                | V   |

| $V_{MODE}$                               | MODE 入力電圧                                               | 0   | 5.25                | 5.25                | V   |

| $V_{CSP1}, V_{CSN1}, V_{CSP2}, V_{CSN2}$ | 電流検出入力電圧                                                | 2.5 | 42                  | 42                  | V   |

| $V_{ATRK}$                               | ATRK 入力電圧                                               | 0.2 | 2                   | 2                   | V   |

| $V_{DTRK}$                               | DTRK 入力電圧                                               | 0   | 5.25                | 5.25                | V   |

| $V_{DLY}$                                | DLY 電圧                                                  | 0   | 5.25                | 5.25                | V   |

| $V_{PGOOD}$                              | PGOOD 電圧                                                | 0   | 5.25                | 5.25                | V   |

| $V_{ILIM/IMON}$                          | ILIM/IMON 電圧                                            | 0   | 3                   | 3                   | V   |

| $V_{SYNCIN}$                             | 同期パルス入力電圧                                               | 0   | 5.25                | 5.25                | V   |

| $f_{SW}$                                 | スイッチング周波数範囲                                             | 100 | 2200 <sup>(2)</sup> | 2200 <sup>(2)</sup> | kHz |

| $f_{SYNCIN}$                             | 同期パルス周波数範囲                                              | 100 | 2200 <sup>(2)</sup> | 2200 <sup>(2)</sup> | kHz |

| $f_{DTRK}$                               | DTRK 周波数範囲                                              | 100 | 2200                | 2200                | kHz |

| $T_J$                                    | 動作時の接合部温度                                               | -40 | 150 <sup>(3)</sup>  | 150 <sup>(3)</sup>  | °C  |

(1) 動作定格は、デバイスが機能する前提の条件です。仕様およびテスト条件については、「電気的特性」を参照してください。

(2) 最大スイッチング周波数は、 $R_{RT}$ によってプログラムされます。このデバイスは、最大 2200kHz のスイッチングをサポートします。

(3) 接合部温度が高くなると、動作寿命が短くなります。接合部温度が 125°Cを超えると、動作寿命が短くなります。

## 5.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup> |                     | LM5125-Q1  | 単位   |

|----------------------|---------------------|------------|------|

|                      |                     | RHB (VQFN) |      |

|                      |                     | 32 ピン      |      |

| $R_{qJA}$            | 接合部から周囲への熱抵抗        | 33.9       | °C/W |

| $R_{qJC(top)}$       | 接合部からケース (上面) への熱抵抗 | 24.8       | °C/W |

| $R_{qJB}$            | 接合部から基板への熱抵抗        | 14.1       | °C/W |

| $\gamma_{JT}$        | 接合部から上面への特性パラメータ    | 0.4        | °C/W |

| $\gamma_{JB}$        | 接合部から基板への特性パラメータ    | 14.0       | °C/W |

| $R_{qJC(bot)}$       | 接合部からケース (底面) への熱抵抗 | 4.3        | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション ノートを参照してください。

## 5.5 電気的特性

代表値は  $T_J = 25^\circ C$  に対応します。最小および最大の制限値は、 $T_J = -40^\circ C \sim 150^\circ C$  の範囲で適用されます。特に記述のない限り、 $V_I = V_{BIAS} = 12V$ 、 $V_{OUT} = 24V$ 、 $R_T = 14k\Omega$  です

| パラメータ                       | テスト条件                                                                           | 最小値                                                                         | 標準値 | 最大値 | 単位 |

|-----------------------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----|-----|----|

| <b>消費電流 (BIAS、VCC、VOUT)</b> |                                                                                 |                                                                             |     |     |    |

| $I_{SD}$                    | シャットダウン状態での $V_I$ 電流 (BIAS を $V_I$ に接続)。バイアス、CSP1、CSN1、CSP2、CSN2、SW1、SW2 への電流を。 | $V_{EN/UVLO} = 0V$ , $V_{OUT} = 12V$ , $T_J = -40^\circ C \sim 125^\circ C$ | 2   | 5   | μA |

## 5.5 電気的特性 (続き)

代表値は  $T_J = 25^\circ\text{C}$  に対応します。最小および最大の制限値は、 $T_J = -40^\circ\text{C} \sim 150^\circ\text{C}$  の範囲で適用されます。特に記述のない限り、 $V_I = V_{BIAS} = 12\text{V}$ 、 $V_{OUT} = 24\text{V}$ 、 $R_T = 14\text{k}\Omega$  です

| パラメータ               |                                                               | テスト条件                                                                                                                                                                            | 最小値   | 標準値 | 最大値 | 単位            |

|---------------------|---------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-----|---------------|

| $I_{SD\_BIAS}$      | シャットダウン状態でのバイアスピン電流                                           | $V_{EN/UVLO} = 0\text{V}$ 、 $V_{OUT} = 12\text{V}$ 、 $T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$                                                                            | 2     | 5   |     | $\mu\text{A}$ |

| $I_{SD\_VOUT}$      | シャットダウン状態での $V_{OUT}$ ピン電流                                    | $V_{EN/UVLO} = 0\text{V}$ 、 $V_{OUT} = 12\text{V}$ 、 $T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$                                                                            | 0.001 | 0.5 |     | $\mu\text{A}$ |

| $I_{Q\_BIAS\_FPWM}$ | アクティブ状態でのバイアスピンの静止電流、FPWM モード、内部クロック (スイッチングなし、RT、IMON 電流は除外) | 1 相、 $V_{EN/UVLO} = 2.0\text{V}$ 、 $V_{EN2} = 0\text{V}$ 、 $V_{CFG2} = 0\text{V}$ 、 $V_{ATRK} = 0.667\text{V}$ 、 $T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$                | 1.1   | 1.5 |     | $\text{mA}$   |

|                     |                                                               | 2 相、 $V_{EN/UVLO} = 2.0\text{V}$ 、 $V_{EN2} = 2\text{V}$ 、 $V_{CFG2} = 0\text{V}$ 、 $V_{ATRK} = 0.667\text{V}$ 、 $T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$                | 1.6   | 2   |     | $\text{mA}$   |

| $I_{Q\_BIAS\_DEM}$  | アクティブ状態でのバイアスピンの静止電流、DEM モード、内部クロック (スイッチングなし、RT、IMON 電流は除外)  | 1 相、 $V_{EN/UVLO} = 2.0\text{V}$ 、 $V_{EN2} = 0\text{V}$ 、 $V_{CFG2} = 0\text{V}$ 、 $V_{ATRK} = 0.667\text{V}$ 、 $T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$                | 1.1   | 1.5 |     | $\text{mA}$   |

|                     |                                                               | 2 相、 $V_{EN/UVLO} = 2.0\text{V}$ 、 $V_{EN2} = 2\text{V}$ 、 $V_{CFG2} = 0\text{V}$ 、 $V_{ATRK} = 0.667\text{V}$ 、 $T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$                | 1.6   | 2   |     | $\text{mA}$   |

| $I_{Q\_VOUT\_FPWM}$ | アクティブ状態での $V_{OUT}$ ピンの静止電流、FPWM モード、内部クロック (スイッチングなし)        | 2 相、 $V_{EN/UVLO} = 2.0\text{V}$ 、 $V_{EN2} = 2\text{V}$ 、 $V_{CFG2} = 0\text{V}$ 、 $V_{ATRK} = 0.667\text{V}$ 、 $T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$                | 250   | 300 |     | $\mu\text{A}$ |

| $I_{Q\_BIAS\_BYP}$  | バイパス状態でのバイアスピン電流 (RT および IMON 電流は除外)                          | 1 相、 $V_{EN/UVLO} = 2.0\text{V}$ 、 $V_{EN2} = 0\text{V}$ 、 $V_{CFG2} = 0\text{V}$ 、 $V_{OUT} = 12\text{V}$ 、 $T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$                    | 1     | 1.5 |     | $\text{mA}$   |

|                     | バイパス状態でのバイアスピン電流 (RT および IMON 電流は除外)                          | 2 相、 $V_{EN/UVLO} = 2.0\text{V}$ 、 $V_{EN2} = 2\text{V}$ 、 $V_{CFG2} = 0\text{V}$ 、 $V_{OUT} = 12\text{V}$ 、 $T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$                    | 1.5   | 2.0 |     | $\text{mA}$   |

| $I_{Q\_VOUT\_BYP}$  | バイパス状態の $V_{OUT}$ ピン電流                                        | 2 相、 $V_{EN/UVLO} = 2.0\text{V}$ 、 $V_{EN2} = 2\text{V}$ 、 $V_{CFG2} = 0\text{V}$ 、 $V_{OUT} = 12\text{V}$ 、 $T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$ 、HO と SW との間に抵抗なし。 | 280   | 330 |     | $\mu\text{A}$ |

| $I_{BIAS}$          | バイアスピンのバイアス電流                                                 | $V_{BIAS} = 12\text{V}$ 、 $I_{VCC} = 200\text{mA}$                                                                                                                               | 200   | 210 |     | $\text{mA}$   |

| $I_{VOUT}$          | $V_{CC}$ が $V_{OUT}$ から供給されているときの $V_{OUT}$ ピンバイアス電流          | $V_{BIAS} = 3.3\text{V}$ 、 $I_{VCC} = 200\text{mA}$                                                                                                                              | 200   | 230 |     | $\text{mA}$   |

### VCC レギュレータ (VCC)

|                        |                                           |                                                     |      |      |      |             |

|------------------------|-------------------------------------------|-----------------------------------------------------|------|------|------|-------------|

| $V_{BIAS-RISING}$      | VCC 電源を $V_{OUT}$ ピンからバイアスピンに切り替えるスレッショルド | $V_{BIAS}$ 立ち上がり                                    | 4.25 | 4.35 | 4.45 | $\text{V}$  |

| $V_{BIAS-FALLING}$     | VCC 電源をバイアスピンから $V_{OUT}$ ピンに切り替えるスレッショルド | $V_{BIAS}$ 立ち下がり                                    | 4.1  | 4.2  | 4.3  | $\text{V}$  |

| $V_{BIAS-HYS}$         | VCC 電源スレッショルドのヒステリシス                      |                                                     | 100  | 150  |      | $\text{mV}$ |

| $V_{VCC-REG1}$         | VCC レギュレーション                              | 無負荷                                                 | 4.75 | 5    | 5.25 | $\text{V}$  |

| $V_{VCC-REG2}$         | ドロップアウト時の VCC レギュレーション                    | $V_{BIAS} = 4.5\text{V}$ 、 $I_{VCC} = 110\text{mA}$ | 4    | 4.3  |      | $\text{V}$  |

| $V_{VCC-UVLO-RISING}$  | VCC UVLO スレッショルド                          | VCC 立ち上がり                                           | 3.4  | 3.5  | 3.6  | $\text{V}$  |

| $V_{VCC-UVLO-FALLING}$ | VCC UVLO スレッショルド                          | VCC 立ち下がり                                           | 3.2  | 3.3  | 3.4  | $\text{V}$  |

| $V_{VCC-UVLO-HYS}$     | VCC UVLO スレッショルドのヒステリシス                   | VCC 立ち下がり                                           |      | 215  |      | $\text{mV}$ |

| $I_{VCC-CL}$           | VCC のソース電流制限                              | $V_{VCC} = 4\text{V}$                               | 200  |      |      | $\text{mA}$ |

| <b>イネーブル (EN/UVLO)</b> |                                           |                                                     |      |      |      |             |

| $V_{EN-RISING}$        | イネーブル スレッショルド                             | EN 立ち上がり                                            | 0.50 | 0.55 | 0.6  | $\text{V}$  |

## 5.5 電気的特性 (続き)

代表値は  $T_J = 25^\circ\text{C}$  に対応します。最小および最大の制限値は、 $T_J = -40^\circ\text{C} \sim 150^\circ\text{C}$  の範囲で適用されます。特に記述のない限り、 $V_I = V_{\text{BIAS}} = 12\text{V}$ 、 $V_{\text{OUT}} = 24\text{V}$ 、 $R_T = 14\text{k}\Omega$  です。

| パラメータ                     |                    | テスト条件                                                            | 最小値   | 標準値   | 最大値   | 単位            |

|---------------------------|--------------------|------------------------------------------------------------------|-------|-------|-------|---------------|

| $V_{\text{EN-FALLING}}$   | イネーブル スレッショルド      | EN 立ち下がり                                                         | 0.40  | 0.45  | 0.50  | V             |

| $V_{\text{EN-HYS}}$       | イネーブル ヒステリシス       | EN 立ち下がり                                                         |       | 100   |       | mV            |

| $R_{\text{EN}}$           | EN プルダウン抵抗         | $V_{\text{EN}} = 0.2\text{V}$                                    | 30    | 37    | 50    | k $\Omega$    |

| $V_{\text{UVLO-RISING}}$  | UVLO スレッショルド       | UVLO 立ち上がり                                                       | 1.05  | 1.1   | 1.15  | V             |

| $V_{\text{UVLO-FALLING}}$ | UVLO スレッショルド       | UVLO 立ち下がり                                                       | 1.025 | 1.075 | 1.125 | V             |

| $V_{\text{UVLO-HYS}}$     | UVLO ヒステリシス        | UVLO 立ち下がり                                                       |       | 25    |       | mV            |

| $I_{\text{UVLO-HYS}}$     | UVLO プルダウンヒステリシス電流 | $V_{\text{UVLO}} = 0.7\text{V}$                                  | 9     | 10    | 11    | $\mu\text{A}$ |

| $I_{\text{UVLO/EN}}$      | UVLO/EN ピンのバイアス電流  | $V_{\text{UVLO/EN}} = 0.3\text{V}$ 、プルダウン抵抗 = アクティブ。             |       | 8     | 11    | $\mu\text{A}$ |

|                           |                    | $V_{\text{UVLO/EN}} = 0.7\text{V}$ 、 $10\mu\text{A}$ 電流 = アクティブ。 | 9     | 10    | 11    | $\mu\text{A}$ |

|                           |                    | $V_{\text{UVLO/EN}} = 3.3\text{V}$                               |       |       | 1     | $\mu\text{A}$ |

### CH2 イネーブル (EN2)

|                     |                        |                  |      |      |               |

|---------------------|------------------------|------------------|------|------|---------------|

| $V_{\text{EN2\_H}}$ | イネーブル 2 の High レベル入力電圧 | EN2 の立ち上がり       | 1.19 | 5.25 | V             |

| $V_{\text{EN2\_L}}$ | イネーブル 2 の Low レベル入力電圧  | EN2 の立ち下がり       | -0.3 | 0.41 | V             |

| $I_{\text{EN2}}$    | イネーブル 2 のバイアス電流        | EN1 = EN2 = 3.3V | 0.01 | 1    | $\mu\text{A}$ |

### 構成 (CFG0, CFG1, CFG2)

|                       |            |  |       |      |            |

|-----------------------|------------|--|-------|------|------------|

| $R_{\text{CFGX\_1}}$  | レベル 1 の抵抗  |  | 0     | 0.1  | k $\Omega$ |

| $R_{\text{CFGX\_2}}$  | レベル 2 の抵抗  |  | 0.496 | 0.51 | 0.526      |

| $R_{\text{CFGX\_3}}$  | レベル 3 の抵抗  |  | 1.11  | 1.15 | 1.19       |

| $R_{\text{CFGX\_4}}$  | レベル 4 の抵抗  |  | 1.81  | 1.9  | 1.93       |

| $R_{\text{CFGX\_5}}$  | レベル 5 の抵抗  |  | 2.65  | 2.7  | 2.82       |

| $R_{\text{CFGX\_6}}$  | レベル 6 の抵抗  |  | 3.71  | 3.8  | 3.94       |

| $R_{\text{CFGX\_7}}$  | レベル 7 の抵抗  |  | 4.95  | 5.1  | 5.26       |

| $R_{\text{CFGX\_8}}$  | レベル 8 の抵抗  |  | 6.29  | 6.5  | 6.68       |

| $R_{\text{CFGX\_9}}$  | レベル 9 の抵抗  |  | 8.00  | 8.3  | 8.50       |

| $R_{\text{CFGX\_10}}$ | レベル 10 の抵抗 |  | 10.18 | 10.5 | 10.81      |

| $R_{\text{CFGX\_11}}$ | レベル 11 の抵抗 |  | 12.90 | 13.3 | 13.70      |

| $R_{\text{CFGX\_12}}$ | レベル 12 の抵抗 |  | 15.71 | 16.2 | 16.69      |

| $R_{\text{CFGX\_13}}$ | レベル 13 の抵抗 |  | 19.88 | 20.5 | 21.11      |

| $R_{\text{CFGX\_14}}$ | レベル 14 の抵抗 |  | 24.15 | 24.9 | 25.65      |

| $R_{\text{CFGX\_15}}$ | レベル 15 の抵抗 |  | 29.20 | 30.1 | 31.00      |

| $R_{\text{CFGX\_16}}$ | レベル 16 の抵抗 |  | 35.40 | 36.5 | 38.60      |

### スイッチング周波数

|                      |                |                           |       |       |      |     |

|----------------------|----------------|---------------------------|-------|-------|------|-----|

| $V_{\text{RT}}$      | RT レギュレーション    |                           | 0.7   | 0.75  | 0.8  | V   |

| $f_{\text{SW1}}$     | スイッチング周波数      | $R_T = 316\text{k}\Omega$ | 85    | 100   | 115  | kHz |

| $f_{\text{SW2}}$     | スイッチング周波数      | $R_T = 14\text{k}\Omega$  | 1980  | 2200  | 2420 | kHz |

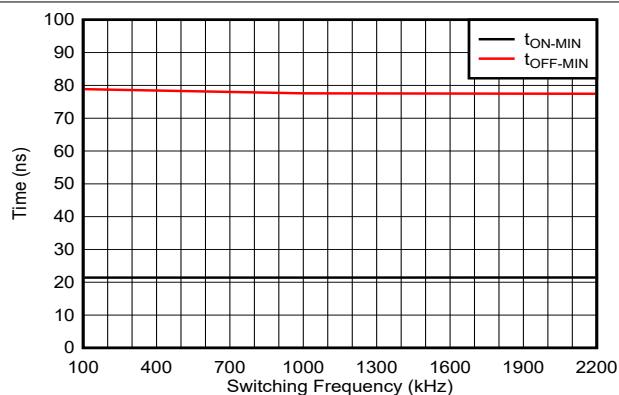

| $t_{\text{ON-MIN}}$  | 最小の制御可能なオン時間   | $R_T = 14\text{k}\Omega$  | 14    | 20    | 50   | ns  |

| $t_{\text{OFF-MIN}}$ | 最小強制オフ時間       | $R_T = 14\text{k}\Omega$  | 55    | 80    | 105  | ns  |

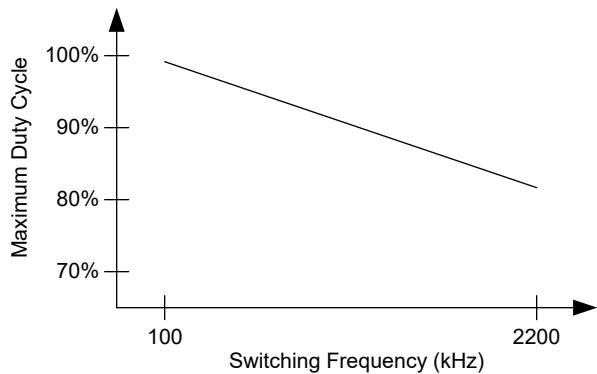

| $D_{\text{MAX1}}$    | 最大デューティ サイクル制限 | $R_T = 316\text{k}\Omega$ | 98.7% | 99.4% |      |     |

| $D_{\text{MAX2}}$    | 最大デューティ サイクル制限 | $R_T = 14\text{k}\Omega$  | 75%   | 87%   |      |     |

## 5.5 電気的特性 (続き)

代表値は  $T_J = 25^\circ\text{C}$  に対応します。最小および最大の制限値は、 $T_J = -40^\circ\text{C} \sim 150^\circ\text{C}$  の範囲で適用されます。特に記述のない限り、 $V_I = V_{\text{BIAS}} = 12\text{V}$ 、 $V_{\text{OUT}} = 24\text{V}$ 、 $R_T = 14\text{k}\Omega$  です

| パラメータ                                      |                                          | テスト条件                                       | 最小値                                      | 標準値  | 最大値   | 単位     |

|--------------------------------------------|------------------------------------------|---------------------------------------------|------------------------------------------|------|-------|--------|

| <b>同期 (SYNCIN)</b>                         |                                          |                                             |                                          |      |       |        |

|                                            | 最小 SYNCIN 周波数アクティビティ検出                   | スペクトラム拡散 = オフ                               | RT = 316kΩ                               | 60   |       | kHz    |

|                                            | SYNCIN 周波数の動作検出と RT SET のスイッチング周波数との関係   | スペクトラム拡散 = オフ                               | RT = 14kΩ ~ 210kΩ                        | -60% |       |        |

|                                            | SYNCIN 動作検出サイクル                          |                                             |                                          | 3    |       | サイクル   |

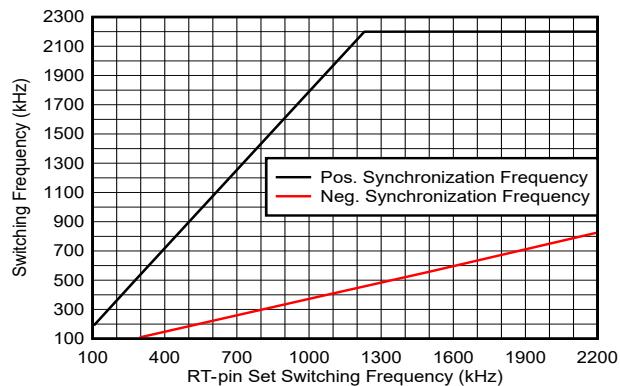

| f <sub>SYNC</sub>                          | 同期時の RT 設定周波数から の同期周波数範囲                 |                                             | 周波数は外部クロックに同期 (最小 = 100kHz、最大 = 2200kHz) | -50% | 50%   |        |

| V <sub>SYNCIN_H</sub>                      | SYNCIN の High レベル入力電圧                    | SYNCIN の立ち上がり                               | 1.19                                     | 5.25 |       | V      |

| V <sub>SYNCIN_L</sub>                      | SYNCIN の Low レベル入力電圧                     | SYNCIN の立ち下がり                               | -0.3                                     | 0.41 |       | V      |

| I <sub>SYNCIN</sub>                        | SYNCIN バイアス電流                            | SYNCIN = 3.3V                               | 0.01                                     | 1    |       | μA     |

|                                            | SYNCIN の最小プルアップ / プルダウンパルス幅              |                                             | 135                                      |      |       | ns     |

| <b>V<sub>OUT</sub> プログラミング (ATRK/DTRK)</b> |                                          |                                             |                                          |      |       |        |

| V <sub>OUT_REG</sub>                       | ATRK 電圧による V <sub>OUT</sub> レギュレーション     | ATRK = 0.2V、V <sub>I</sub> = 4.5V           | 5.88                                     | 6    | 6.12  | V      |

|                                            |                                          | ATRK = 0.4V、V <sub>I</sub> = 10V            | 11.82                                    | 12   | 12.18 | V      |

|                                            |                                          | ATRK = 0.8V                                 | 23.64                                    | 24   | 24.36 | V      |

|                                            |                                          | ATRK = 1.6V                                 | 47.28                                    | 48   | 48.72 | V      |

|                                            |                                          | ATRK = 2V                                   | 59.10                                    | 60   | 60.90 | V      |

| G <sub>DTRK</sub>                          | DTRK デューティ サイクルの V <sub>ATRK</sub> への変換率 | F <sub>DTRK</sub> = 100kHz、440kHz           | 25                                       |      |       | mV / % |

|                                            | DTRK デューティ サイクル範囲                        |                                             | 8%                                       | 80%  |       |        |

| V <sub>ATRK</sub>                          | 指定された DTRK デューティ サイクルに対する ATRK 電圧        | f <sub>DTRK</sub> = 100kHz、DC = 8%          | 0.19                                     | 0.2  | 0.21  | V      |

|                                            |                                          | f <sub>DTRK</sub> = 100kHz、DC = 40%         | 0.98                                     | 1    | 1.02  | V      |

|                                            |                                          | f <sub>DTRK</sub> = 100kHz、DC = 80%         | 1.98                                     | 2    | 2.02  | V      |

|                                            |                                          | f <sub>DTRK</sub> = 440kHz、DC = 8%          | 0.188                                    | 0.2  | 0.212 | V      |

|                                            |                                          | f <sub>DTRK</sub> = 440kHz、DC = 40%         | 0.98                                     | 1    | 1.02  | V      |

|                                            |                                          | f <sub>DTRK</sub> = 440kHz、DC = 80%         | 1.98                                     | 2    | 2.02  | V      |

| V <sub>DTRK_H</sub>                        | DTRK の High レベル入力電圧                      | DTRK の立ち上がり                                 | 1.19                                     | 5.25 |       | V      |

| V <sub>DTRK_L</sub>                        | DTRK の Low レベル入力電圧                       | DTRK の立ち下がり                                 | -0.3                                     | 0.41 |       | V      |

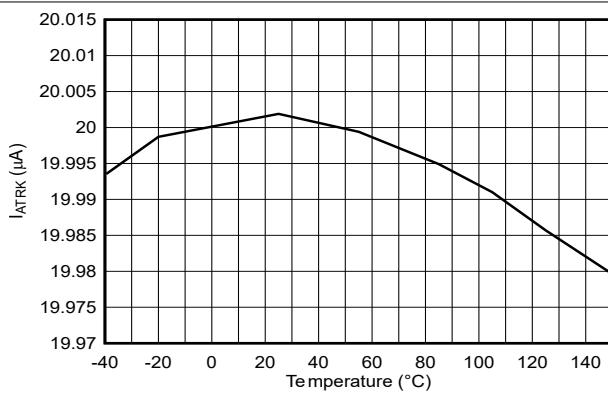

| I <sub>ATRK</sub>                          | CFG0 で起動したときのソース電流                       |                                             | 19.8                                     | 20   | 20.2  | μA     |

| I <sub>ATRK/DTRK</sub>                     | ATRK/DTRK ピンのバイアス電流                      | 20μA 電流はディスエーブル、V <sub>ATRK/DTRK</sub> = 2V | 0.01                                     | 1    |       | μA     |

|                                            | DTRK の最小プルアップ / プルダウンパルス幅                |                                             | 25                                       |      |       | ns     |

| <b>ソフトスタート (SS)</b>                        |                                          |                                             |                                          |      |       |        |

| I <sub>SS</sub>                            | ソフトスタート電流                                |                                             | 42.5                                     | 50   | 57.5  | μA     |

| V <sub>SS-DONE</sub>                       | ソフトスタート完了スレッショルド                         |                                             | 2.15                                     | 2.2  | 2.25  | V      |

| R <sub>SS</sub>                            | SS プルダウンスイッチの R <sub>DSON</sub>          |                                             | 26                                       | 70   |       | Ω      |

| V <sub>SS-DIS</sub>                        | SS 放電検出スレッショルド                           |                                             | 20                                       | 45   | 70    | mV     |

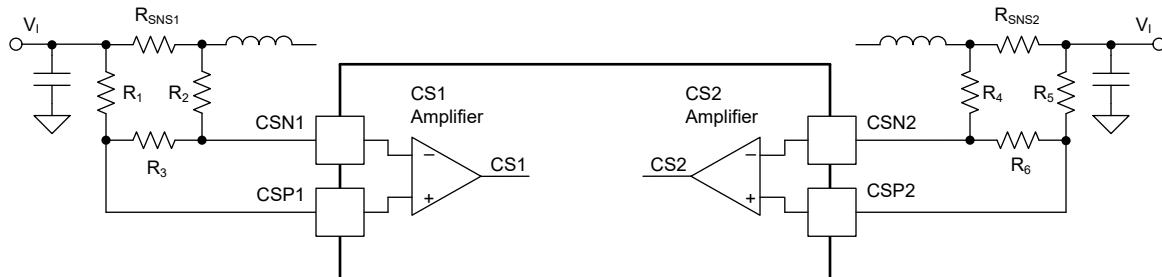

| <b>電流検出 (CSPx, CSNx)</b>                   |                                          |                                             |                                          |      |       |        |

| A <sub>CS</sub>                            | 電流センスアンプのゲイン                             | V <sub>CSP</sub> = 2.5V                     | 10                                       |      |       | V/V    |

| V <sub>CLTH</sub>                          | 正のピーク電流制限スレッショルド                         | CS 入力を基準とします                                | 54                                       | 60   | 66    | mV     |

## 5.5 電気的特性 (続き)

代表値は  $T_J = 25^\circ\text{C}$  に対応します。最小および最大の制限値は、 $T_J = -40^\circ\text{C} \sim 150^\circ\text{C}$  の範囲で適用されます。特に記述のない限り、 $V_I = V_{\text{BIAS}} = 12\text{V}$ 、 $V_{\text{OUT}} = 24\text{V}$ 、 $R_T = 14\text{k}\Omega$  です

| パラメータ                               |                                           | テスト条件                                                                                            | 最小値   | 標準値   | 最大値   | 単位                      |

|-------------------------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------|-------|-------|-------|-------------------------|

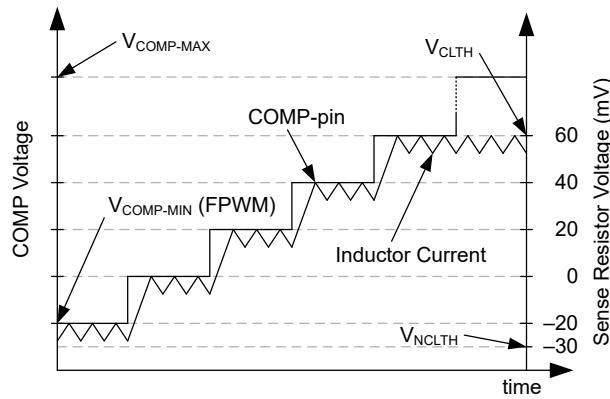

| $V_{\text{NCLTH}}$                  | 負のピーク電流制限スレッショルド                          | CS 入力、FPWM モードを基準とします                                                                            | -34   | -28   | -22   | mV                      |

| $V_{\text{ICL}}$                    | 入力電流制限                                    | CS 入力を基準とします                                                                                     | 65    | 72    | 80    | mV                      |

| $\Delta V_{\text{ICL\_CLTH}}$       | ICL と正のピーク電流スレッショルド間のデルタ電圧                |                                                                                                  | 6     | 12    |       | mV                      |

|                                     | ピーク電流制限トリップ遅延                             |                                                                                                  | 100   |       |       | ns                      |

| $V_{\text{ZCD}}$                    | ZCD スレッショルド (CSPx - CSNx)                 | CS 入力の立ち下がり、 $f_{\text{SW}} = 100\text{kHz}$ 、DEM                                                | 0     | 3     | 6     | mV                      |

| $V_{\text{ZCD}}$                    | ZCD スレッショルド (CSPx - CSNx)                 | CS 入力の立ち下がり、 $f_{\text{SW}} = 100\text{kHz}$ 、DEM、 $T_J = 0^\circ\text{C} \sim 85^\circ\text{C}$ | 0     | 3     | 5     | mV                      |

| $V_{\text{ZCD\_BYP}}$               | バイパス モードの位相 1 の ZCD スレッショルド (CSP1 – CSN1) |                                                                                                  | -6    | -2.5  | 0     | mV                      |

|                                     | バイパス モードの位相 2 の ZCD スレッショルド (CSP2 – CSN2) |                                                                                                  | -6    | -2.5  | 0     | mV                      |

| $V_{\text{SLOPE}}$                  | ピーク勾配補償アンプ                                | CS 入力を基準とし、 $f_{\text{SW}} = 100\text{kHz}$                                                      | 40    | 48    | 55    | mV                      |

| $I_{\text{CSNx}}$                   | CSNx 電流                                   | デバイスがスタンバイ状態、 $V_I = V_{\text{BIAS}} = V_{\text{OUT}} = 12\text{V}$                              |       | 1.2   |       | $\mu\text{A}$           |

| $I_{\text{CSPx}}$                   | CSPx 電流                                   | $V_{\text{BIAS}} = V_{\text{OUT}} = 12\text{V}$                                                  | 150   | 170   |       | $\mu\text{A}$           |

| $\Delta I_{\text{ph1\_ph2}}$        | ピーク インダクタ電流アンバランス (位相 1~位相 2)             | $V_{\text{CL}} = 60\text{mV}$                                                                    | -10   | 0     | 10    | %                       |

| <b>遅延付き電流モニタ / リミッタ (IMON/ILIM)</b> |                                           |                                                                                                  |       |       |       |                         |

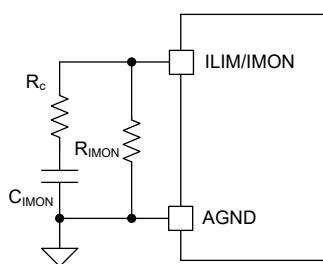

| $G_{\text{IMON}}$                   | 相互コンダクタンス ゲイン                             |                                                                                                  | 0.320 | 0.333 | 0.346 | $\mu\text{A}/\text{mV}$ |

| $I_{\text{OFFSET}}$                 | オフセット電流                                   |                                                                                                  | 3     | 4     | 5     | $\mu\text{A}$           |

| $V_{\text{ILIM}}$                   | ILIM のレギュレーション ターゲット                      |                                                                                                  | 0.93  | 1     | 1.07  | V                       |

| $V_{\text{ILIM\_th}}$               | ILIM の起動スレッショルド                           |                                                                                                  | 0.95  | 1     | 1.25  | V                       |

| $V_{\text{ILIM\_reset}}$            | DLY リセットのスレッショルド                          | ILIM の立ち下がり、 $V_{\text{ILIM}}$ を基準とする                                                            | 85%   | 88%   | 91%   |                         |

| $I_{\text{DLY}}$                    | DLY ソース / シンク電流                           |                                                                                                  | 4     | 5     | 6     | $\mu\text{A}$           |

| $V_{\text{DLY\_peak\_rise}}$        |                                           | $V_{\text{DLY}}$ 立ち上がり                                                                           | 2.45  | 2.6   | 2.75  | V                       |

| $V_{\text{DLY\_peak\_fall}}$        |                                           | $V_{\text{DLY}}$ 立ち下がり                                                                           | 2.25  | 2.4   | 2.55  | V                       |

| $V_{\text{DLY\_valley}}$            |                                           |                                                                                                  | 0.2   |       |       | V                       |

| <b>エラー アンプ (COMP)</b>               |                                           |                                                                                                  |       |       |       |                         |

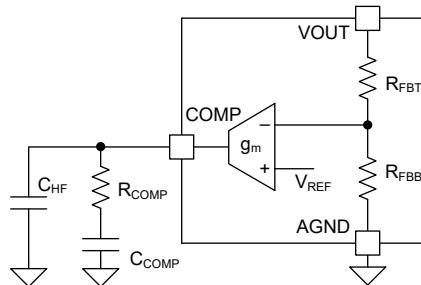

| $G_m$                               | 相互コンダクタンス                                 |                                                                                                  | 700   | 1000  | 1300  | $\mu\text{S}$           |

| $A_{\text{COMP-PWM}}$               | COMP から PWM へのゲイン                         |                                                                                                  |       | 1     |       | V/V                     |

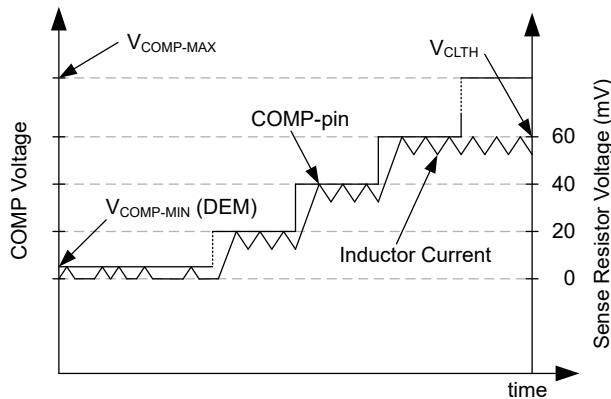

| $V_{\text{COMP-MAX}}$               | COMP 最大クランプ電圧                             | COMP 立ち上がり                                                                                       | 2.3   | 2.6   | 2.9   | V                       |

| $V_{\text{COMP-MIN}}$               | COMP 最小クランプ電圧、DEM で有効                     | COMP 立ち下がり                                                                                       | 0.38  | 0.48  | 0.55  | V                       |

|                                     | COMP 最小クランプ電圧、FPWM で有効                    | COMP 立ち下がり                                                                                       | 0.13  | 0.16  | 0.19  | V                       |

| $V_{\text{COMP-offset}}$            | 最小クランプを基準としたオフセット                         | COMP 立ち下がり                                                                                       | 0.01  | 0.03  | 0.06  | V                       |

| $I_{\text{SOURCE-MAX}}$             | 最大 COMP シンキング電流                           | $V_{\text{COMP}} = 0\text{V}$                                                                    | 90    |       |       | $\mu\text{A}$           |

| $I_{\text{SINT-MAX}}$               | 最大 COMP ソーシング電流                           | $V_{\text{COMP}} = 2.6\text{V}$                                                                  | 100   |       |       | $\mu\text{A}$           |

| <b>動作モード</b>                        |                                           |                                                                                                  |       |       |       |                         |

| $V_{\text{MODE_H}}$                 | MODE ピンの High レベル                         | FPWM                                                                                             | 1.19  | 5.25  |       | V                       |

| $V_{\text{MODE_L}}$                 | MODE ピンの Low レベル                          | DEM                                                                                              | -0.3  | 0.41  |       | V                       |

| $I_{\text{MODE}}$                   | MODE ピンのバイアス電流                            | MODE = 3.3V                                                                                      | 0.01  | 1     |       | $\mu\text{A}$           |

## 5.5 電気的特性 (続き)

代表値は  $T_J = 25^\circ\text{C}$  に対応します。最小および最大の制限値は、 $T_J = -40^\circ\text{C} \sim 150^\circ\text{C}$  の範囲で適用されます。特に記述のない限り、 $V_I = V_{\text{BIAS}} = 12\text{V}$ 、 $V_{\text{OUT}} = 24\text{V}$ 、 $R_T = 14\text{k}\Omega$  です

| パラメータ                                   |                                        | テスト条件                                          | 最小値                                            | 標準値  | 最大値  | 単位            |

|-----------------------------------------|----------------------------------------|------------------------------------------------|------------------------------------------------|------|------|---------------|

| <b>過電圧 / 低電圧監視</b>                      |                                        |                                                |                                                |      |      |               |

| $V_{\text{OVP-H}}$                      | 過電圧スレッショルド                             | $V_{\text{OUT}}$ の立ち上がり (エラー アンプのリファレンスを基準とする) | 108%                                           | 110% | 112% |               |

| $V_{\text{OVP-L}}$                      | 過電圧スレッショルド                             | $V_{\text{OUT}}$ の立ち下がり (エラー アンプのリファレンスを基準とする) | 101%                                           | 103% | 105% |               |

| $V_{\text{OVP\_max-H}}$                 | 過電圧スレッショルド                             | 64V                                            | $V_{\text{OUT}}$ の立ち上がり (エラー アンプのリファレンスを基準とする) | 63   | 64   | 65            |

|                                         |                                        | 50V                                            |                                                | 49   | 50   | 51            |

|                                         |                                        | 35V                                            |                                                | 34   | 35   | 36            |

|                                         |                                        | 28.5V                                          |                                                | 27   | 28.5 | 30            |

| $V_{\text{OVP\_max-L}}$                 | 過電圧スレッショルド                             | 64V                                            | $V_{\text{OUT}}$ の立ち下がり (エラー アンプのリファレンスを基準とする) | 62   | 63   | 64            |

|                                         |                                        | 50V                                            |                                                | 48   | 49   | 50            |

|                                         |                                        | 35V                                            |                                                | 33   | 34   | 35            |

|                                         |                                        | 28.5V                                          |                                                | 26   | 27.5 | 29            |

| $V_{\text{UVP-H}}$                      | 低電圧スレッショルド                             | $V_{\text{OUT}}$ の立ち上がり (エラー アンプのリファレンスを基準とする) | 91%                                            | 93%  | 95%  |               |

| $V_{\text{UVP-L}}$                      | 低電圧スレッショルド                             | $V_{\text{OUT}}$ の立ち下がり (エラー アンプのリファレンスを基準とする) | 88%                                            | 90%  | 92%  |               |

| <b>PGOOD</b>                            |                                        |                                                |                                                |      |      |               |

| $R_{\text{PGOOD}}$                      | PGOOD プルダウン スイッチの $R_{\text{DSON}}$    | 1mA のシンク                                       | 90                                             | 180  |      | $\Omega$      |

|                                         | 有効な PGOOD の最小 BIAS                     |                                                | 2                                              |      |      | V             |

| <b>MOSFET ドライバ (HBx, HOx, SWx, LOx)</b> |                                        |                                                |                                                |      |      |               |

|                                         | 高状態オン抵抗 (HO ドライバ)                      | 100mA シンク、HB – SW = 5V                         | 1.1                                            | 2    |      | $\Omega$      |

|                                         | Low 状態オン抵抗 (HO ドライバ)                   | 100mA ソース、HB – SW = 5V                         | 0.6                                            | 1.2  |      | $\Omega$      |

|                                         | 高状態オン抵抗 (LO ドライバ)                      | 100mA シンク、VCC = 5V                             | 1.1                                            | 2    |      | $\Omega$      |

|                                         | Low 状態オン抵抗 (LO ドライバ)                   | 100mA ソース、VCC = 5V                             | 0.7                                            | 1.4  |      | $\Omega$      |

| $V_{\text{HB-UVLO}}$                    | HB ~ SW UVLO スレッショルド                   | HB ~ SW の立ち上がり                                 | 2.85                                           | 3.05 | 3.25 | V             |

| $V_{\text{HB-UVLO}}$                    | HB ~ SW UVLO スレッショルド                   | HB ~ SW 立ち下がり                                  | 2.6                                            | 2.8  | 3    | V             |

| $V_{\text{HB-HYS}}$                     | HB ~ SW UVLO スレッショルドのヒステリシス            |                                                |                                                | 250  |      | mV            |

| $I_{\text{HB-SLEEP}}$                   | バイパス時の HB 静止電流                         | HB – SW = 5V                                   | 8                                              | 15   |      | $\mu\text{A}$ |

| $I_{\text{CP}}$                         | HB チャージ ポンプ電流は HBx ピンで利用可能             | BIAS = 4.5V、 $V_{\text{OUT}} = 6\text{V}$      | 55                                             | 75   | 100  | $\mu\text{A}$ |

| <b>デッドタイム制御</b>                         |                                        |                                                |                                                |      |      |               |

| DT1                                     | HO オフから LO オンまで、LO オフから HO オンまでのデッドタイム | 設定 1                                           | 7                                              | 14   | 30   | ns            |

| DT2                                     |                                        | 設定 2                                           | 17                                             | 30   | 50   | ns            |

| DT3                                     |                                        | 設定 3                                           | 32                                             | 50   | 75   | ns            |

| DT4                                     |                                        | 設定 4                                           | 50                                             | 75   | 110  | ns            |

| DT5                                     |                                        | 設定 5                                           | 68                                             | 100  | 140  | ns            |

| DT6                                     |                                        | 設定 6                                           | 85                                             | 125  | 180  | ns            |

| DT7                                     |                                        | 設定 7                                           | 105                                            | 150  | 215  | ns            |

| DT8                                     |                                        | 設定 8                                           | 135                                            | 200  | 285  | ns            |

| <b>サーマル シャットダウン(TSD)</b>                |                                        |                                                |                                                |      |      |               |

| $T_{\text{TSD-RISING}}$                 | サーマル シャットダウンのスレッショルド                   | 温度上昇                                           | 175                                            |      |      | °C            |

| $T_{\text{TSD-HYS}}$                    | サーマル シャットダウン ヒステリシス                    |                                                | 15                                             |      |      | °C            |

## 5.5 電気的特性 (続き)

代表値は  $T_J = 25^\circ\text{C}$  に対応します。最小および最大の制限値は、 $T_J = -40^\circ\text{C} \sim 150^\circ\text{C}$  の範囲で適用されます。特に記述のない限り、 $V_I = V_{BIAS} = 12\text{V}$ 、 $V_{OUT} = 24\text{V}$ 、 $R_T = 14\text{k}\Omega$  です

| パラメータ                    | テスト条件     | 最小値 | 標準値 | 最大値 | 単位 |

|--------------------------|-----------|-----|-----|-----|----|

| <b>タイミング</b>             |           |     |     |     |    |

| STANDBY <sub>timer</sub> | スタンバイ タイマ | 130 | 150 | 170 | μs |

## 5.6 タイミング要件

動作接合部温度範囲および推奨電源電圧範囲(特に記載のない限り)

|                   |                 |                                  | 最小値 | 公称値 | 最大値 | 単位 |

|-------------------|-----------------|----------------------------------|-----|-----|-----|----|

| <b>全体的なデバイス機能</b> |                 |                                  |     |     |     |    |

|                   | 最小時間 Low EN トグル | EN から測定した時間 H から L、L から H への切り替え | 1   |     |     | μs |

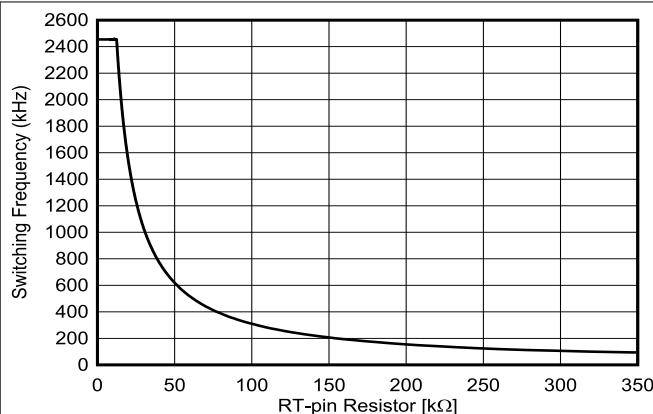

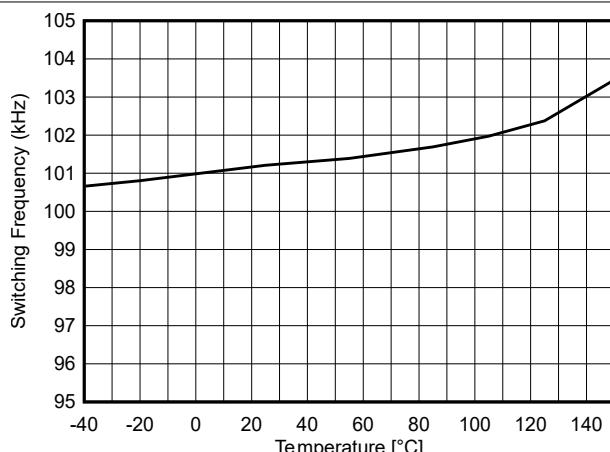

## 5.7 代表的特性

以下の条件が適用されます (特に記述のない限り)。 $T_J = 25^\circ\text{C}$ 、 $V_{BIAS} = 12\text{V}$

図 5-1. スイッチング周波数と RT 抵抗との関係

図 5-2. スイッチング周波数 (100kHz、RT = 316kΩ) と温度との関係

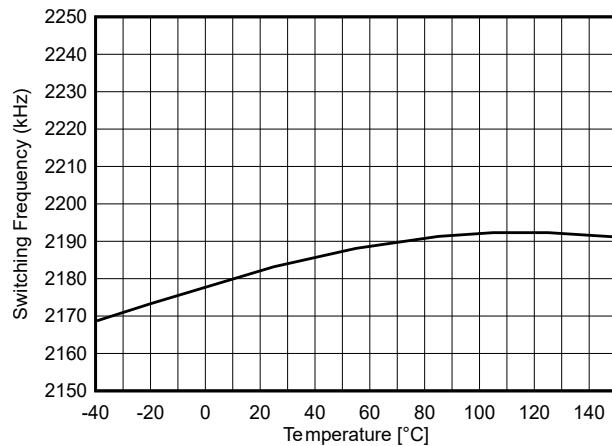

図 5-3. スイッチング周波数 (2200kHz、RT = 14kΩ) と温度との関係

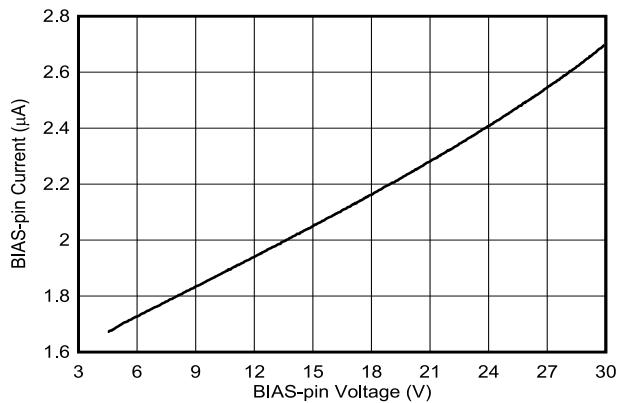

図 5-4. シャットダウン時の BIAS ピンの電流と BIAS ピンの電圧との関係

スイッチングしない

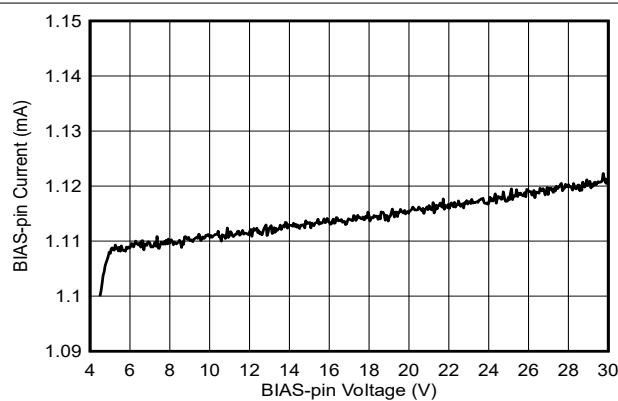

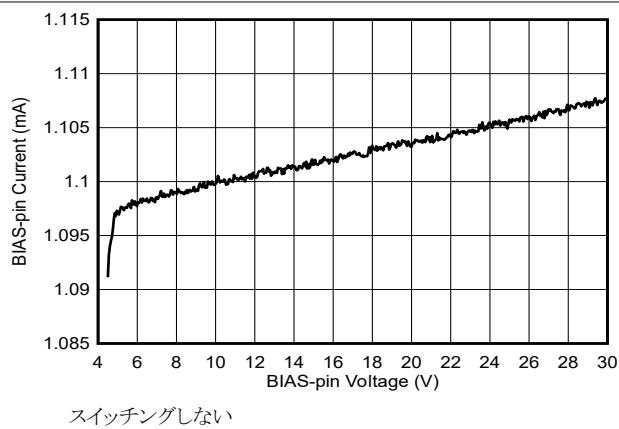

図 5-5. BIAS ピンの電流と BIAS ピンの電圧との関係 (アクティブ、1ph、DEM)

スイッチングしない

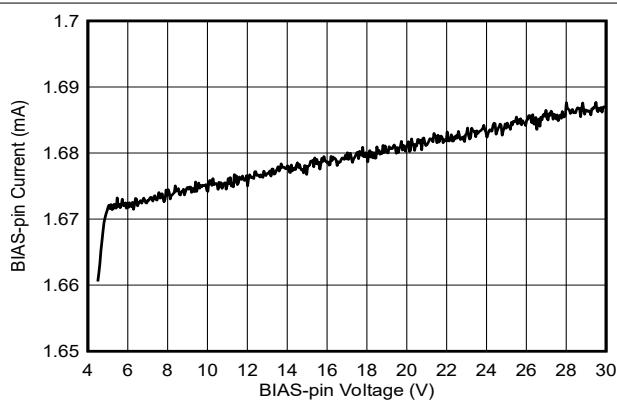

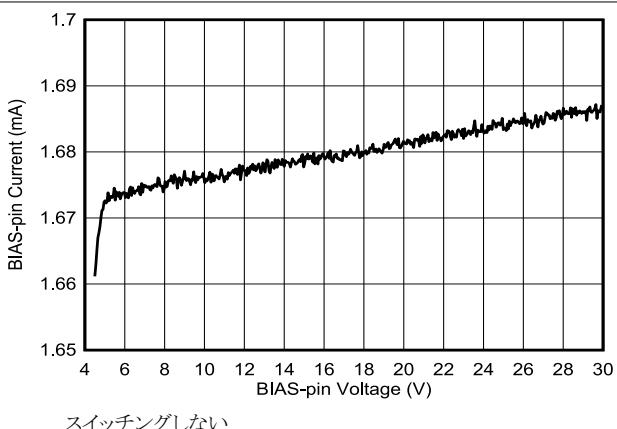

図 5-6. BIAS ピンの電流と BIAS ピンの電圧との関係 (アクティブ、2ph、DEM)

## 5.7 代表的特性 (続き)

以下の条件が適用されます (特に記述のない限り)。 $T_J = 25^\circ\text{C}$ 、 $V_{BIAS} = 12\text{V}$

スイッチングしない

図 5-7. BIAS ピンの電流と BIAS ピンの電圧との関係 (アクティブ、1ph、FPWM)

スイッチングしない

図 5-8. BIAS ピンの電流と BIAS ピンの電圧との関係 (アクティブ、2ph、FPWM)

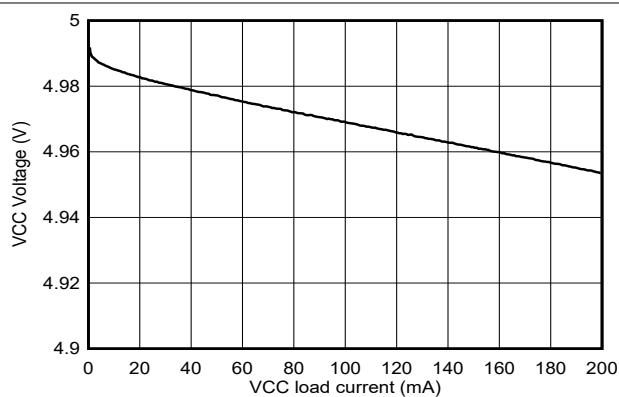

図 5-9. VCC の電圧と VCC の負荷電流との関係

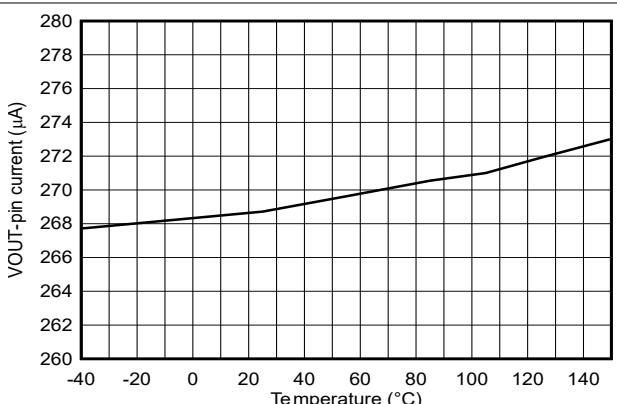

図 5-10. VOUT ピンの電流と温度との関係 (バイパス、2ph)

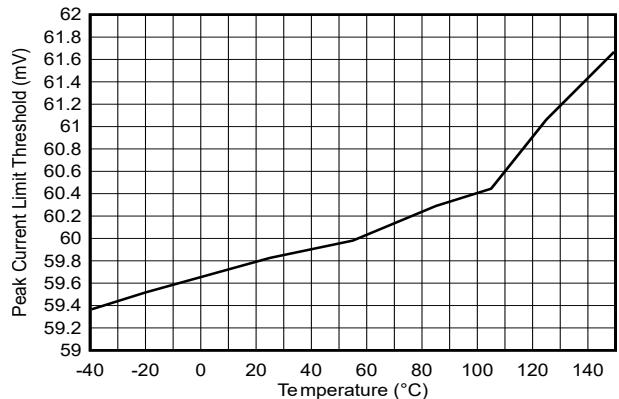

図 5-11. ピーク電流制限スレッショルド電圧  $V_{CLTH}$  と温度との関係

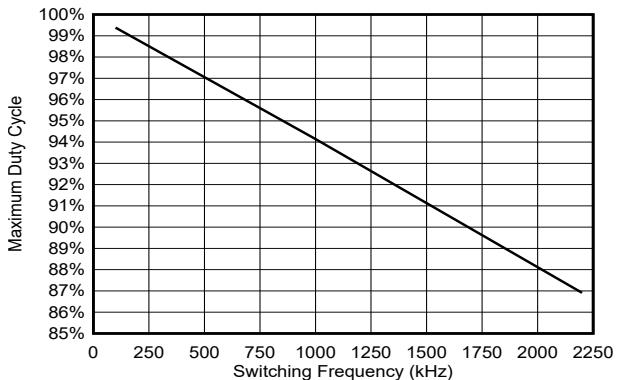

図 5-12. 最大デューティ サイクルとスイッチング周波数との関係

## 5.7 代表的特性 (続き)

以下の条件が適用されます (特に記述のない限り)。 $T_J = 25^\circ\text{C}$ 、 $V_{BIAS} = 12\text{V}$

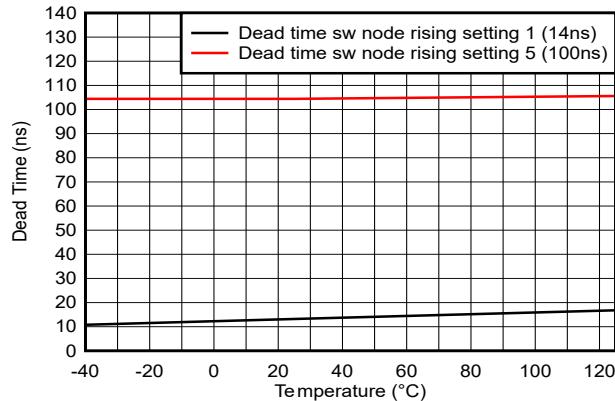

図 5-13. デッドタイムスイッチノードの立ち上がりと温度との関係

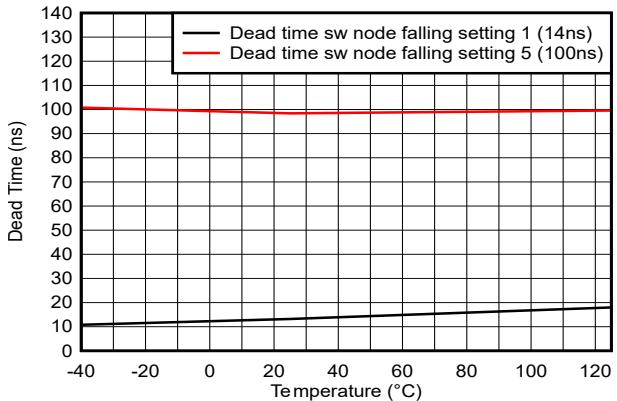

図 5-14. デッドタイムスイッチノードの立ち下がりと温度との関係

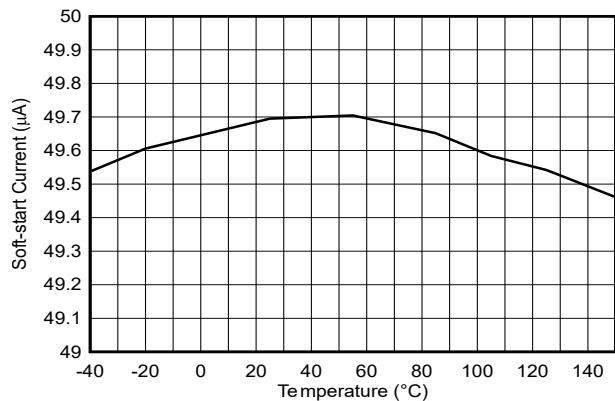

図 5-15. ソフトスタート電流と温度との関係

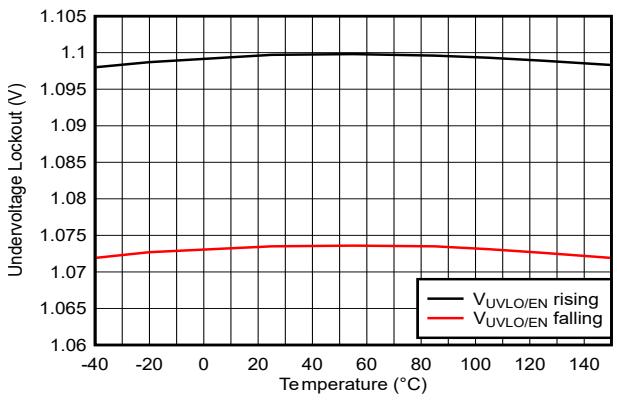

図 5-16. 低電圧誤動作防止 (UVLO) と温度との関係

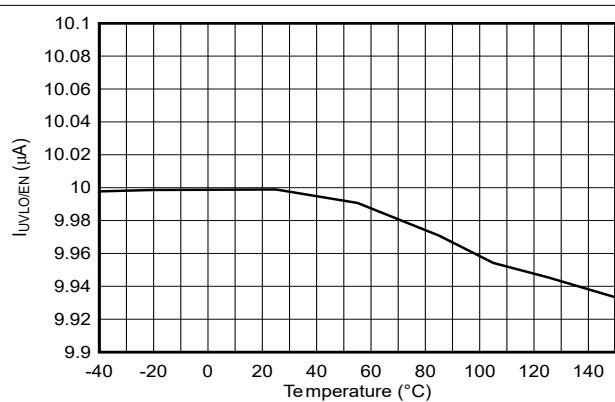

図 5-17. UVLO/EN ピンの電流と温度との関係

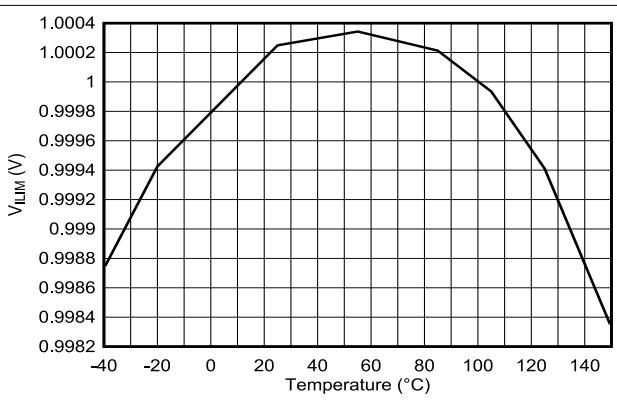

図 5-18. 平均電流制限レギュレーション電圧と温度との関係

## 5.7 代表的特性 (続き)

以下の条件が適用されます (特に記述のない限り)。 $T_J = 25^\circ\text{C}$ 、 $V_{BIAS} = 12\text{V}$

図 5-19. 最小  $t_{ON}$  および  $t_{OFF}$  時間とスイッチング周波数との関係

図 5-20. ATRK ピンの電流と温度との関係

スペクトラム拡散 = オフ

図 5-21. 同期スイッチング周波数 (SYNCIN) と RT ピン設定スイッチング周波数との関係

## 6 詳細説明

### 6.1 概要

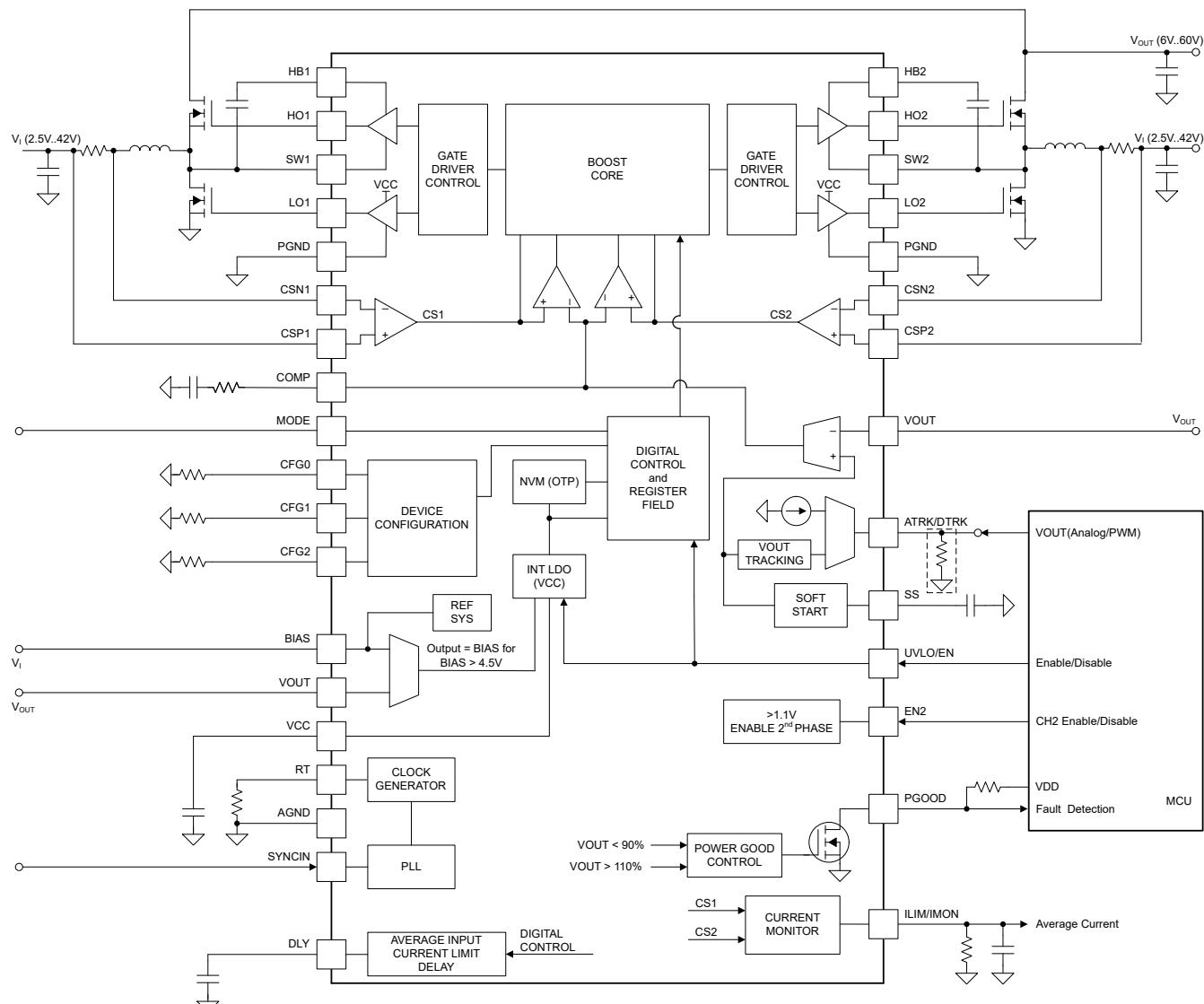

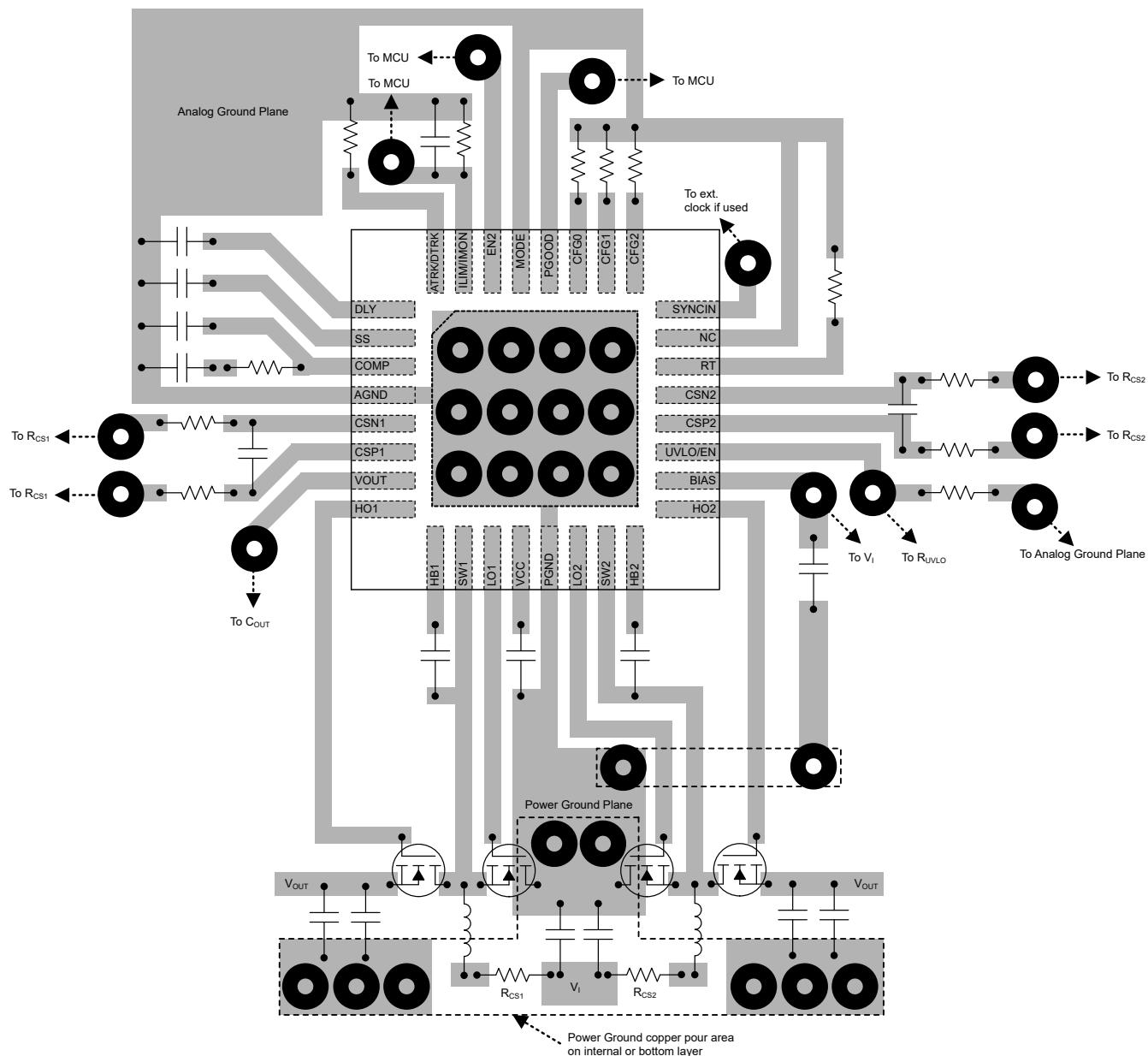

LM5125-Q1 は、入力範囲の広い 2 相昇圧コントローラです。本デバイスは入力電圧が、調整された出力電圧よりも高等しい、または低い場合に、レギュレートされた出力電圧を供給します。抵抗・デジタル間 (R2D) インターフェイスにより、のデバイス機能を簡単かつ確実に選択できます。

動作モードの **DEM** (ダイオード エミュレーション モード) と **FPWM** (強制パルス幅変調) は、動作中にオンザフライでピン選択できます。ピーク電流モード制御は、**RT** ピンで設定される固定スイッチング周波数で動作します。デュアル ランダムスペクトラム拡散動作を起動することにより、設計プロセスのどの時点でも **EMI** の低減を実現できます。

内蔵の平均電流モニタは、入力電流の監視や制限に役立ちます。動作中に出力電圧を動的に調整可能です (動的な電圧スケーリングとエンベロープ追跡)。**V<sub>OUT</sub>** は **ATRK/DTRK** ピンのアナログ基準電圧を変更するか、**ATRK/DTRK** ピンの **PWM** 入力信号を使用して調整できます。

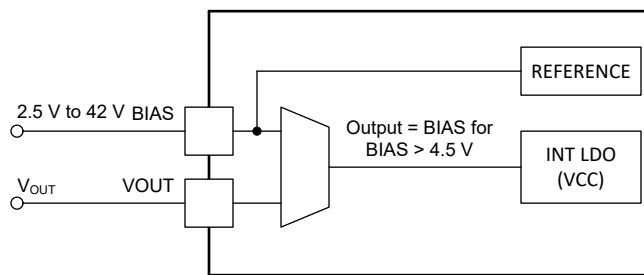

内蔵の広入力 **LDO** は、さまざまな入力および出力電圧状況下で、デバイス機能に対して確実に電源供給します。高い駆動能力と、自動およびヘッドルームによる電圧選択 (**V<sub>BIAS</sub>** または **V<sub>OUT</sub>**) により、電力損失は最小限に抑えられます。個別のバイアスピンを **V<sub>I</sub>**、**V<sub>OUT</sub>**、出力、または外部電源に接続して、デバイス内の電力損失をさらに減らすことができます。未定義のエラー処理を避けるため、常に内部電源電圧が監視されます。

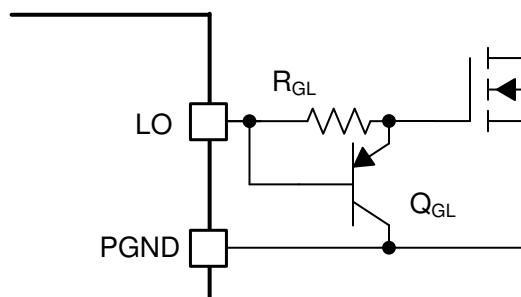

このデバイスは、ハーフ ブリッジ N チャネル MOSFET ドライバを内蔵しています。ゲート ドライバ回路は、多様な MOSFET を駆動できる高い駆動能力を備えています。このゲート ドライバには、高電圧、低ドロップアウトのブートストラップ ダイオードが内蔵されています。内部ブートストラップ回路には、負のスパイクによって注入される過電圧に対する保護機能と、低電圧誤動作防止保護機能があるため、外部パワー FET のリニア動作を防止されます。内蔵チャージ ポンプにより、バイパス モードで 100% のデューティ サイクル動作が可能になります。

内蔵の保護機能により、さまざまな故障状況で安全な動作が実現します。ブラウンアウト状態を回避するため、**V<sub>I</sub>** 低電圧誤動作防止保護機能があります。入力 UVLO スレッショルドとヒステリシスは外部の帰還デバイダにより構成されるため、さまざまな設計でブラウンアウトは回避されます。このデバイスには、出力過電圧保護機能も搭載されています。選択可能なヒップ過電流保護により、内部的なサイクル単位のピーク電流保護機能を使用して、過剰な短絡電流を防止します。デバイスにはサーマル シャットダウンが内蔵されているため、内部 VCC レギュレータの過負荷状態により生じる、熱による損傷から保護されます。すべての出力関連の故障イベントは監視され、オープンドレイン **PGOOD** ピンで通知されます。

## 6.2 機能ブロック図

図 6-1. の機能ブロック図

## 6.3 機能説明

### 6.3.1 デバイス構成 (CFG0 ピン、 CFG1 ピン、 CFG2 ピン)

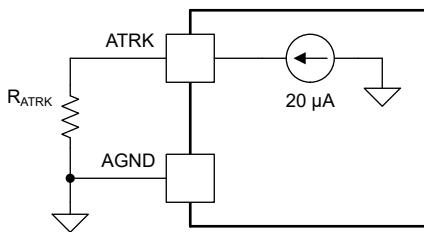

CFG ピンは、最小デッド タイム (LM5125-Q1) および ATRK/DTRK ピンの  $20\mu\text{A}$  電流を定義します。表 6-1 に示すレベルは、仕様セクションに指定された抵抗によって選択されます。 $V_{\text{OUT}}$  に抵抗をプログラムすると、 $20\mu\text{A}$  の ATRK ピン電流がオンになり、電圧トラッキングのために ATRK ピンの電流がオフになります。

表 6-1. CFG0 ピンの設定

| レベル | デッド タイム [ns] | $20\mu\text{A}$ ATRK 電流 |

|-----|--------------|-------------------------|

| 1   | 14           | オン                      |

| 2   | 30           | オン                      |

| 3   | 50           | オン                      |

| 4   | 75           | オン                      |

| 5   | 100          | オン                      |

| 6   | 125          | オン                      |

| 7   | 150          | オン                      |

| 8   | 200          | オン                      |

| 9   | 14           | オフ                      |

| 10  | 30           | オフ                      |

| 11  | 50           | オフ                      |

| 12  | 75           | オフ                      |

| 13  | 100          | オフ                      |

| 14  | 125          | オフ                      |

| 15  | 150          | オフ                      |

| 16  | 200          | オフ                      |

CFG1 ピンの設定により、 $V_{\text{OUT}}$  過電圧保護レベル、クロック ディザリング、120% の入力電流制限保護 ( $I_{\text{CL\_latch}}$ ) 動作、パワー グッド ピンの動作が定義されます。

OVP ビット 0: OVP ビット 1 および 0 は、 $V_{\text{OUT}}$  過電圧保護レベルを設定します。[00] = 64V、[01] = 50V、[10] = 35V、または [11] = 28.5V。

クロック ディザリング: デュアル ランダム スペクトラム拡散 (DRSS) クロック ディザリングをイネーブル、またはクロック ディザリングをディスエーブルします。

$I_{\text{CL\_latch}}$ :  $I_{\text{CL\_latch}}$  がイネーブルで、ピーク電流制限を 20% 超えると、デバイスはシャットダウン状態に移行します (ターンオフしてラッチされます)。 $I_{\text{CL\_latch}}$  がディスエーブルの場合、デバイスはアクティブのままで、ピーク電流制限時にインダクタ電流を制限しようとします。

$\text{PGOOD}_{\text{OVP\_enable}}$ :  $\text{PGOOD}_{\text{OVP\_enable}}$  がイネーブルのとき、 $\text{PGOOD}$  ピンは  $V_{\text{OUT}}$  が OVP (過電圧保護) を上回るか UV (低電圧) スレッショルドを下回ると Low になります。 $\text{PGOOD}_{\text{OVP\_enable}}$  がディスエーブルの場合、 $\text{PGOOD}$  ピンは  $V_{\text{OUT}}$  が UV (低電圧) スレッショルドを下回ったときのみ Low になります。

表 6-2. 過電圧保護レベルの選択

| OVP レベル | OVP ビット 1 | OVP ビット 0 |

|---------|-----------|-----------|

| 64V     | 0         | 0         |

| 50V     | 0         | 1         |

| 35V     | 1         | 0         |

| 28.5V   | 1         | 1         |

**表 6-3. CFG1 ピン設定**

| レベル | OVP ビット 0 | クロック ディザリング モード | I <sub>CL_latch</sub> | PGOOD <sub>OVP_enable</sub> |

|-----|-----------|-----------------|-----------------------|-----------------------------|

| 1   | 0         | 有効 (DRSS)       | ディセーブル                | ディセーブル                      |

| 2   | 1         | 有効 (DRSS)       | ディセーブル                | ディセーブル                      |

| 3   | 0         | 有効 (DRSS)       | ディセーブル                | 有効                          |

| 4   | 1         | 有効 (DRSS)       | ディセーブル                | 有効                          |

| 5   | 0         | 有効 (DRSS)       | 有効                    | ディセーブル                      |

| 6   | 1         | 有効 (DRSS)       | 有効                    | ディセーブル                      |

| 7   | 0         | 有効 (DRSS)       | 有効                    | 有効                          |

| 8   | 1         | 有効 (DRSS)       | 有効                    | 有効                          |

| 9   | 0         | ディセーブル          | ディセーブル                | ディセーブル                      |

| 10  | 1         | ディセーブル          | ディセーブル                | ディセーブル                      |

| 11  | 0         | ディセーブル          | ディセーブル                | 有効                          |

| 12  | 1         | ディセーブル          | ディセーブル                | 有効                          |

| 13  | 0         | ディセーブル          | 有効                    | ディセーブル                      |

| 14  | 1         | ディセーブル          | 有効                    | ディセーブル                      |

| 15  | 0         | ディセーブル          | 有効                    | 有効                          |

| 16  | 1         | ディセーブル          | 有効                    | 有効                          |

CFG2 ピンは、V<sub>OUT</sub> 過電圧保護レベル、およびデバイスが内部クロック ジェネレータと SYNCIN ピンに印加される外部クロックのどちらを使用するかを定義します。クロック同期中、クロック ディザー機能は無効化されます。

- OVP ビット 1: OVP ビット 1 および 0 は、V<sub>OUT</sub> 過電圧保護レベルを設定します。[00] = 64V、[01] = 50V、[10] = 35V、または [11] = 28.5V。

- 内部クロック: デバイスは内部クロックを使用します。

- 外部クロック: デバイスは内部クロックを使用してスタンダード アロンで使用され、外部クロックが印加されていれば、その外部クロックに同期します。

- SYNCIN: SYNCIN ピンのクロック同期機能がアクティブ (オン) か無効 (オフ) かを定義します。本デバイスは、SYNCIN がアクティブのとき、SYNCIN ピンに印加された外部クロックとのみ同期します。

- クロック ディザリング: 内部発振器を使用する場合、CFG1 ピンの設定クロック ディザリング モードに応じてクロック ディザリングを設定します。外部クロックが選択されている場合、CFG1 ピンの設定を無視して、クロック ディザリング機能は無効化されます。

**表 6-4. CFG2 ピン設定**

| レベル | OVP ビット 1 | クロック | SYNCIN | クロック ディザリング |

|-----|-----------|------|--------|-------------|

| 1   | 0         | 内部   | オフ     | CFG1 ピン     |

| 2   | 1         | 内部   | オフ     | CFG1 ピン     |

| 3   | 0         | 内部   | オフ     | CFG1 ピン     |

| 4   | 1         | 外部   | オン     | ディセーブル      |

| ≥ 5 | 0         | 外部   | オン     | ディセーブル      |

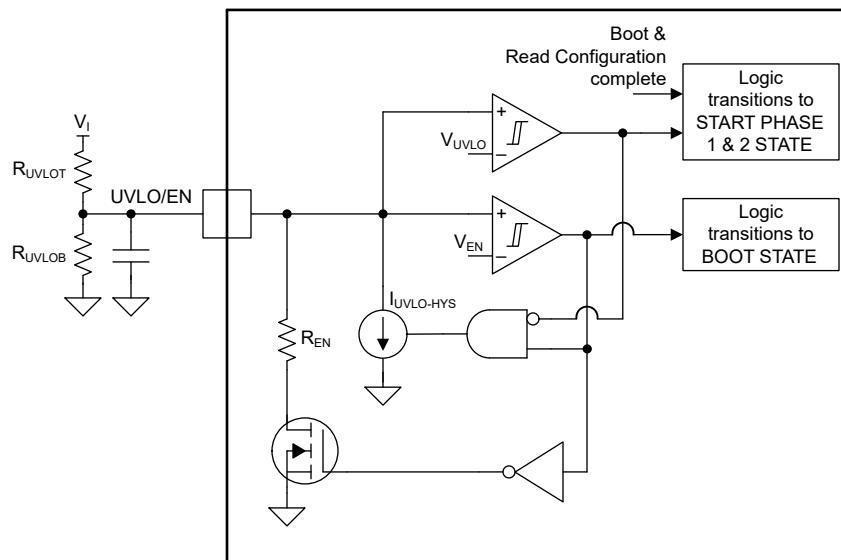

### 6.3.2 デバイスおよび位相のイネーブル / ディスエーブル (UVLO/EN、EN2)

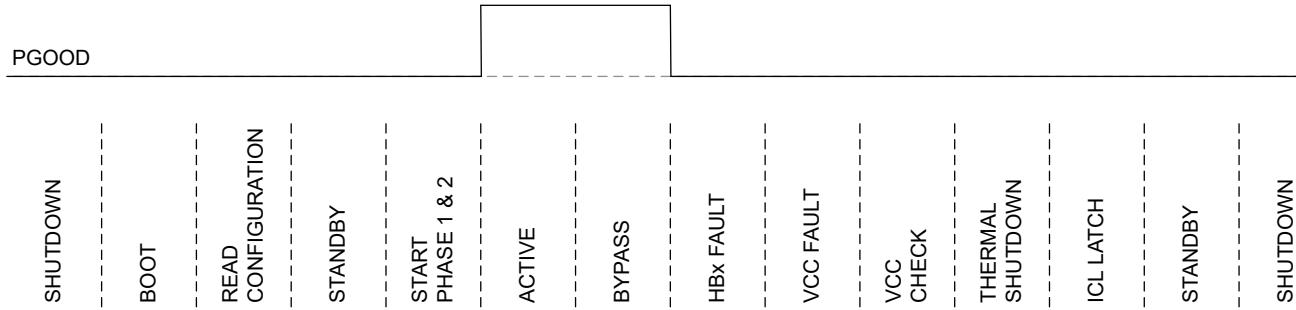

シャットダウン中、UVLO/EN ピンは内部抵抗 R<sub>EN</sub> によって Low になります。V<sub>UVLO/EN</sub> が V<sub>EN-RISING</sub> を上回ると、R<sub>EN</sub> がディスエーブルになり、I<sub>UVLO/EN</sub> (標準値 10μA) 電流ソースがイネーブルになって UVLO 機能を提供します。デバイスが起動し、構成を読み取り、STANDBY 状態に入ります (機能状態図を参照)。V<sub>UVLO/EN</sub> が V<sub>UVLO-RISING</sub> を上回ると、I<sub>UVLO/EN</sub> 電流ソースがディスエーブルになり、デバイスは開始位相 1 および 2 状態に移行し、DEM 動作中に V<sub>OUT</sub> を

上昇させるソフトスタートを実行します。ヒステリシス  $V_{EN-HYS}$  および  $V_{UVLO-HYS}$  が実装されています。式 1 と式 2 に従って、外部 UVLO 抵抗分圧器 ( $R_{UVLOT}$  と  $R_{UVLOB}$ ) を選択します。

$$R_{UVLOT} = \frac{\left(V_{ON} - \frac{V_{UVLO-RISING}}{V_{UVLO-FALLING}} \times V_{OFF}\right)}{I_{UVLO-HYS}} \quad (1)$$

$$R_{UVLOB} = \frac{V_{UVLO-FALLING} \times R_{UVLOT}}{V_{OFF} - V_{UVLO-FALLING}} \quad (2)$$

スタートアップ時または低  $V_I$  での負荷過渡時に  $V_I$  が一時的に  $V_{OFF}$  を下回る場合に備えて、UVLO コンデンサ (uvlo) が必要です。必要な UVLO コンデンサが大きい場合、追加の直列 UVLO 抵抗 ( $R_{UVLOS}$ ) を使用することで、 $I_{UVLO-HYS}$  が有効化のときに UVLO ピンの電圧を急速に上昇させることができます。

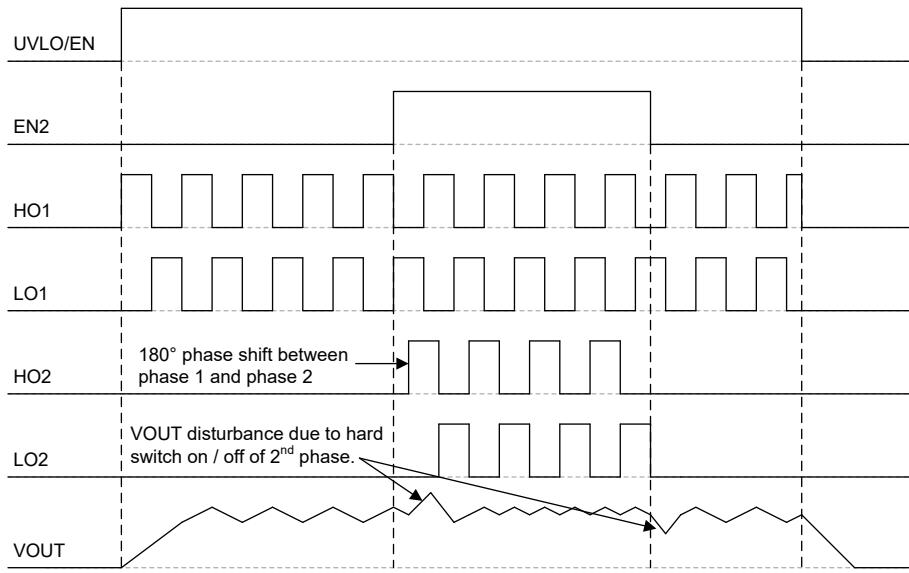

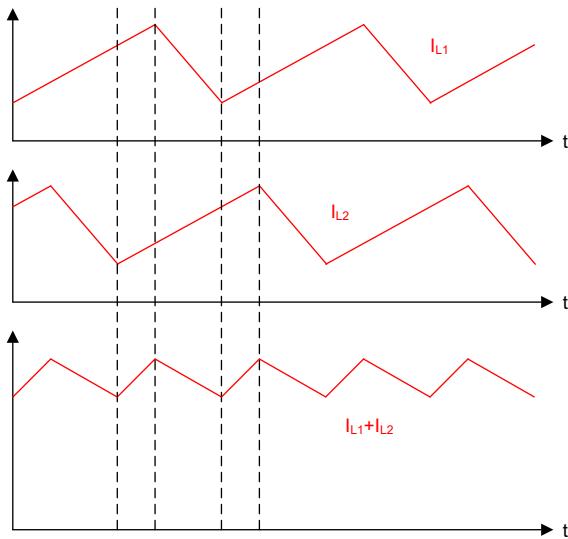

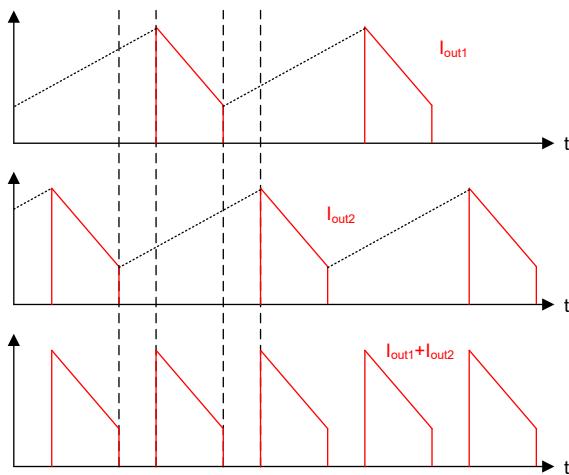

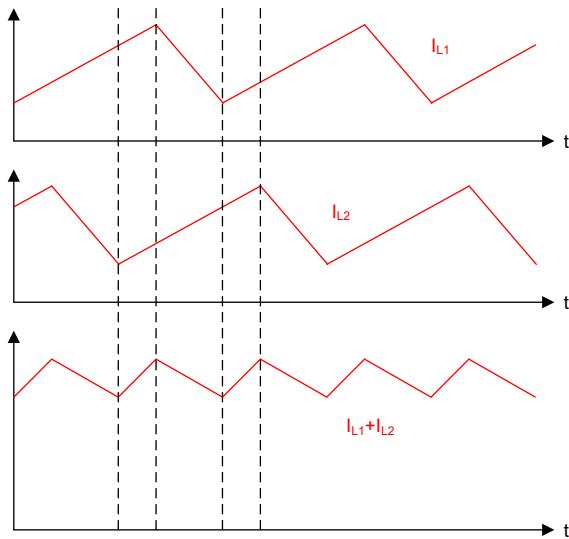

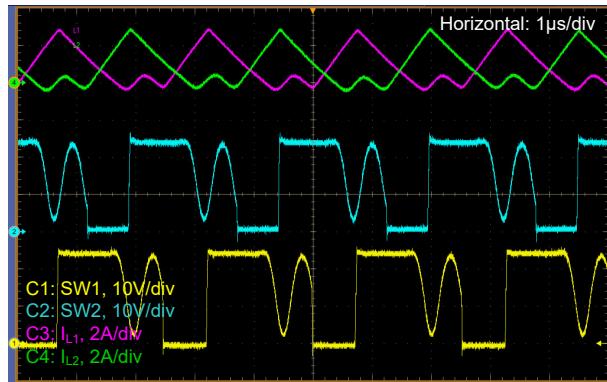

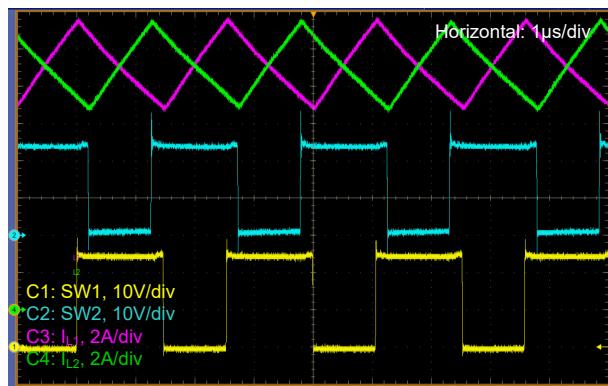

2 番目の位相は  $V_{EN2}$  が  $V_{EN2\_H}$  を上回るとイネーブルになり、 $V_{EN2}$  が  $V_{EN2\_L}$  を下回るとディスエーブルになります。スタートアップ時または動作中の 2 位相をイネーブルまたはディスエーブルにします。2 番目の位相は位相 1 に 180° 位相シフトされ、入力および出力リップルを最小限に抑えます。

UVLO/EN ピンとバイアス ピンの間の ESD ダイオードが導通しているため、UVLO/EN ピンの電圧はバイアス ピンの電圧 + 0.3V を超えることはできません (絶対最大定格を参照)。ただし、直列抵抗を使用して電流が最大 100 $\mu$ A に制限されている場合、UVLO/EN ピンに最大 42V (推奨動作条件) の高い電圧を印加できます。

図 6-2. 機能ブロック図 UVLO と EN

図 6-3. の 2 相動作

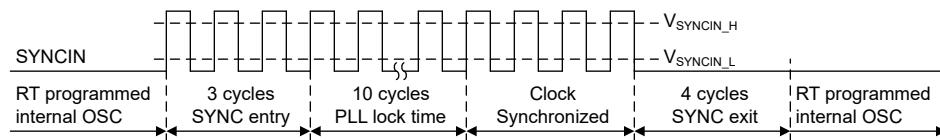

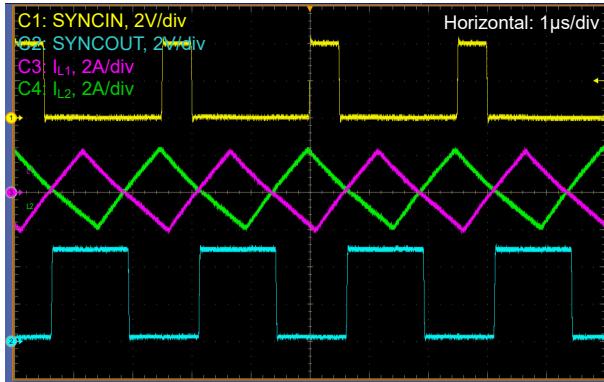

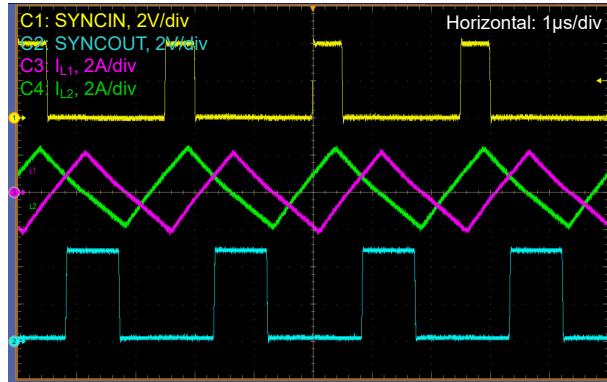

### 6.3.3 スイッチング周波数および同期 (SYNCIN)

100kHz～2.2MHz のスイッチング周波数は、RT ピンおよび AGND ピンの間に接続された RT 抵抗により設定されます。RT 抵抗は、式 4 に従って、 $14\text{k}\Omega$  と  $316\text{k}\Omega$  の間で選択されます。外部クロックを使用するように構成している場合、デバイスは RT ピンを使用して内部発振器を設定し、SYNCIN ピンに印加される外部クロックに対して ±50% 以内にスイッチング周波数を同期します。検出されるように、SYNCIN 周波数動作検出範囲 内に外部クロックを設定します。内部クロックは、SYNCIN ピンに印加された外部クロック信号の立ち上がりエッジで同期されます。外部クロック同期が選択されているとき、CFG1 ピンのスペクトラム拡散設定は無視され、クロック ディザリングはディセーブルになります。

本デバイスは常に内部クロックで起動し、START PHASE 1 および 2 と ACTIVE 状態の間に、印加される外部クロックと同期を開始します (機能状態図を参照)。本デバイスは、クロックが印加されるとすぐに外部クロックに同期し、外部クロックが停止した場合には内部クロックに戻ります。

$$f_{SW} = \frac{1}{R_{RT} \times s} + 18ns \quad (3)$$

$$R_{RT} = \left( \frac{1}{f_{SW}} - 18ns \right) \times 31.5 \frac{\text{G}\Omega}{\text{s}} \quad (4)$$

図 6-4. クロックの同期

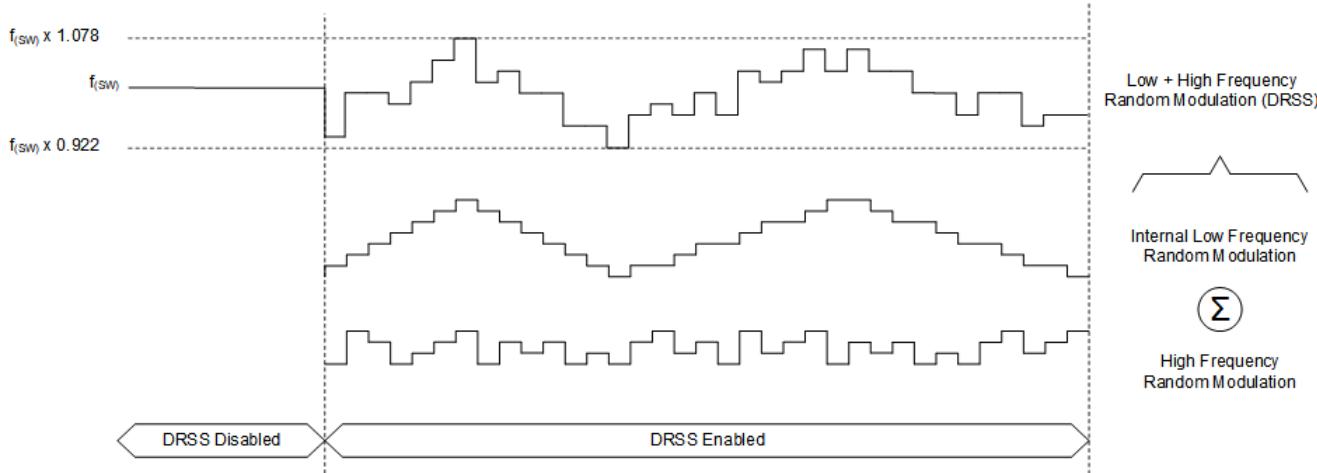

### 6.3.4 デュアルランダムスペクトラム拡散機能 (DRSS)

このデバイスにはデジタルスペクトラム拡散機能があり、広い周波数範囲にわたって電源の EMI を低減します。スペクトラム拡散は、または CFG1 ピンの設定によって有効化します。スペクトラム拡散が有効になると、内部変調器が内部クロックをディザリングします。SYNCIN ピンで印加される外部クロックを使用するようにデバイスを構成している場合、内部スペクトラム拡散は無効化されます。DRSS 機能は、低周波数の三角波変調プロファイルと、高周波数のサイクル単位のランダム変調プロファイルを組み合わせたものです。低周波数の三角波変調は低い無線周波数帯域 (AM 帯域など) で性能を向上させ、高周波のランダム変調は高い無線周波数帯域 (FM 帯域など) で性能を向上させます。さらに、可聴音が発

生する可能性を低減するために、三角波変調の周波数がさらにランダムに変調されます。スペクトラム拡散により発生する出力電圧リップルを最小限に抑えるため、ディザリングが有効な場合は、デューティサイクルをサイクル単位で調整し、ほぼ一定に維持します。

図 6-5. デュアルランダムスペクトラム拡散

### 6.3.5 動作モード (バイパス、DEM、FPWM)

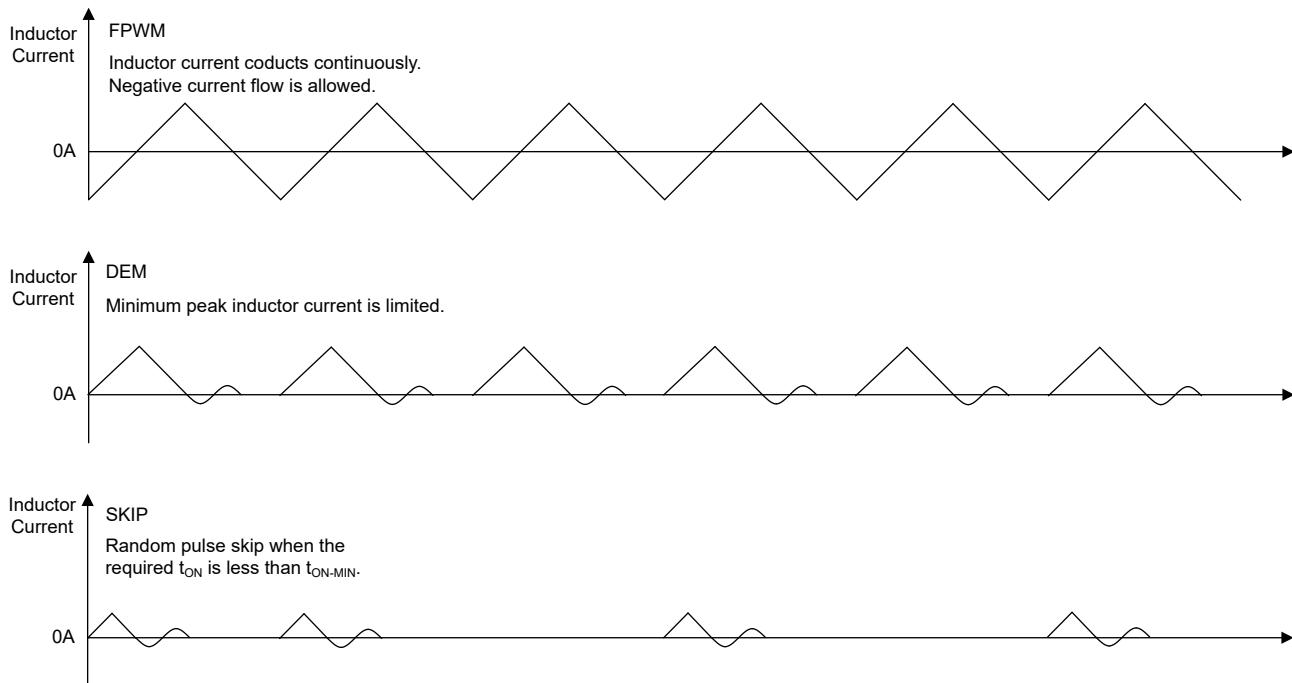

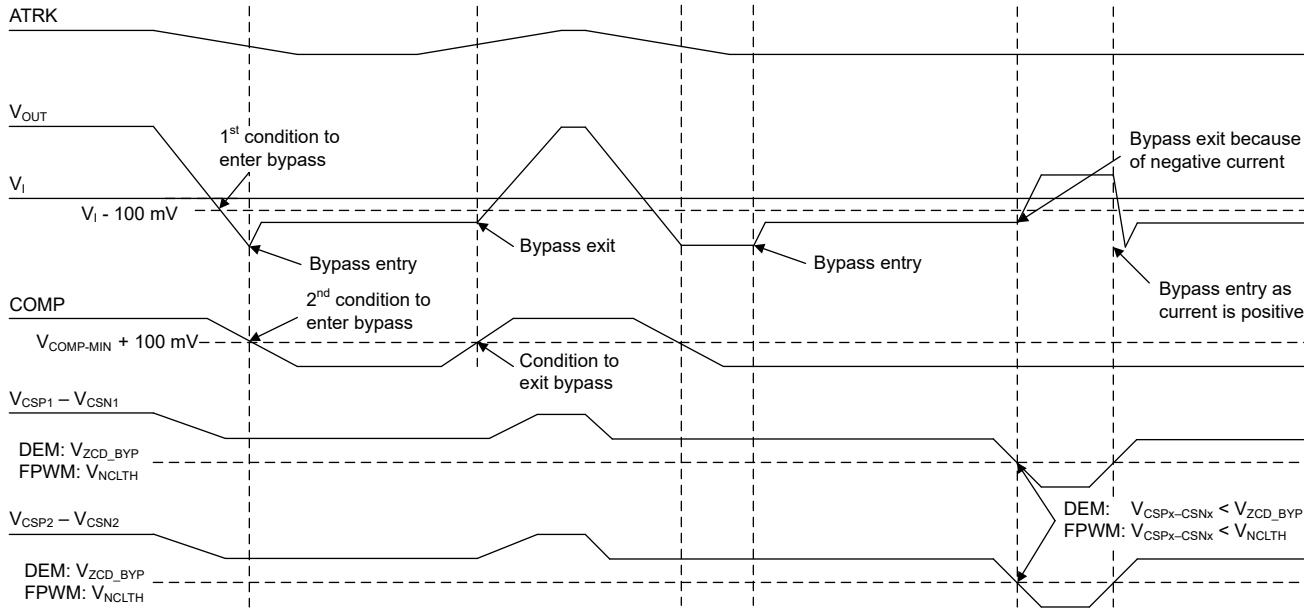

このデバイスは、バイパスモード、強制PWM(FPWM)、ダイオードエミュレーションモード(DEM)動作をサポートしています。このモードは動作中に変更でき、MODEピンの $V_{OUT} < V_I$ の場合、バイパスモードが自動的に有効になります。デバイスの動作モードは、 $V_{MODE} < 0.4V$ の場合はDEMに、 $V_{MODE} > 1.2V$ の場合はFPWMに設定されます。

表 6-5. MODE ピンの設定

| 動作モード | MODE ピン           |

|-------|-------------------|

| DEM   | $V_{MODE} < 0.4V$ |

| FPWM  | $V_{MODE} > 1.2V$ |

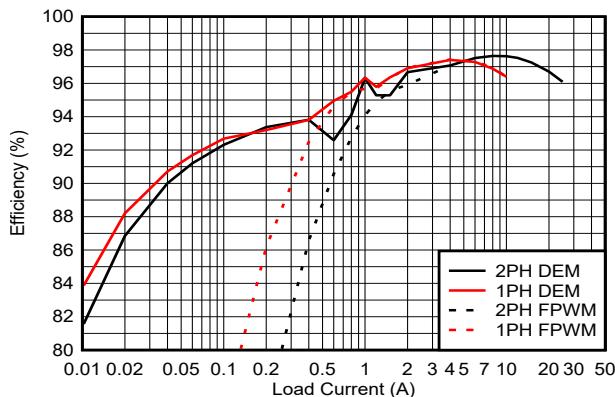

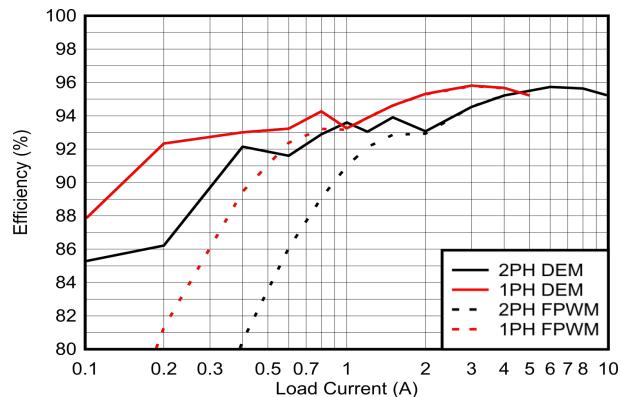

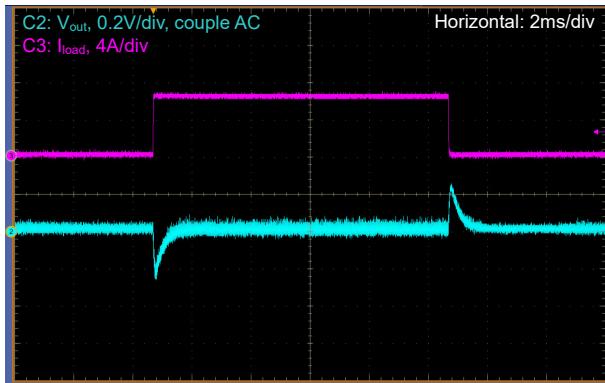

ダイオードエミュレーションモード(DEM)では、 $V_{OUT}$ から $V_I$ に電流が流れることを防ぎます。各相のSWピンの電圧は、ハイサイドのオンタイム中に監視され、ゼロ電流検出スレッショルド $V_{ZCD}$ を下回ると、ハイサイドスイッチがオフになります。このデバイスは軽負荷時には不連続導通モード(DCM)で動作し、最後にパルスをスキップして軽負荷時の効率を向上させます。両方の位相がアクティブ( $EN2 = \text{High}$ )のとき、軽負荷時には両方の位相がDCMで動作し、最後にパルスをスキップします。DEM動作では、COMPが標準460mVを下回ると、コントローラはパルスをスキップし始めます。スキップエントリポイントは、入力電流については式式5を使用し、出力電流については式式6を使用して計算。

$$I_{I\_skip} = \frac{1.5\mu \times \frac{V_I}{L}}{0.48 \times \frac{f_{SW}}{40K} + 250\mu \times R_{SNS} \times \frac{V_I}{L}} \quad (5)$$

$$I_{OUT\_skip} = \frac{\frac{V_I}{V_{OUT}} \times \frac{V_I}{L} \times 1.5\mu}{0.48 \times \frac{f_{SW}}{40K} + 250\mu \times R_{SNS} \times \frac{V_I}{L}} \quad (6)$$

強制パルス変調モード(FPWM)では、コンバータは連続導通モード(CCM)で、固定周波数によって軽負荷時にもスイッチングを継続します。このモードでは、軽負荷の過渡応答が改善されます。

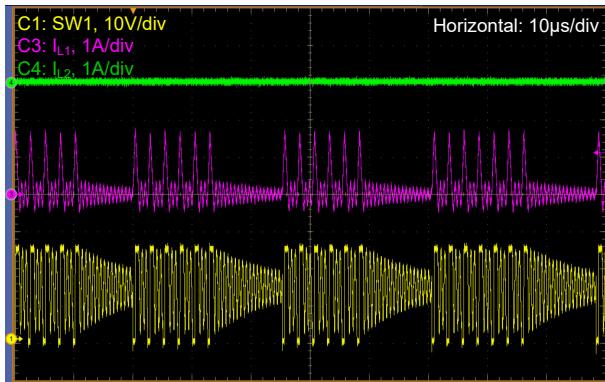

**図 6-6. 各種動作モードにおけるインダクタ電流波形**

バイパスモード (BYPASS) では、ハイサイド FET をオンにすることで、 $V_I$  を  $V_{OUT}$  (レギュレーションなし) に接続します。DEM 設定では  $V_{OUT}$  から  $V_I$  への電流の流れが防止され、FPWM 設定では  $V_{NCLTH}$  に制限されているため、 $V_I$  から  $V_{OUT}$  に流れる正電流は制御されません。内蔵チャージポンプは HOx-SWx において最小 3.75V の電圧を供給し、位相あたり 55uA ( $I_{CP}$ ) を駆動します。EN2 = Low の場合、位相 1 のハイサイド FET のみがオンになり、EN2 = High の場合、位相 1 および位相 2 のハイサイド FET がオンになります。MOSFET ゲートプルダウン抵抗を使用する場合、チャージポンプが MOSFET とプルダウン抵抗のリーク電流を駆動できることを確認します。チャージポンプが過負荷になると、 $V_{HB-UVLO}$  の最小ゲート電圧を維持するために、本デバイスはスイッチングを開始します。

表 バイパスモードの開始、終了 の条件が満たされると、本デバイスはバイパスモードに移行して終了します。

**表 6-6. バイパスモードの開始、終了**

| 動作モード    | バイパス | 条件                                                                                                                              |

|----------|------|---------------------------------------------------------------------------------------------------------------------------------|

| DEM/FPWM | 開始   | $V_{OUT} < V_I - 100mV$ および<br>$V_{COMP} < V_{COMP-MIN} + 100mV$                                                                |

| DEM      | 終了   | $V_{COMP} > V_{COMP-MIN} + 100mV$ or<br>$((V_{CSP1} - V_{CSN1}) < V_{ZCD\_BYP} \parallel (V_{CSP2} - V_{CSN2}) < V_{ZCD\_BYP})$ |

| FPWM     | 終了   | $V_{COMP} > V_{COMP-MIN} + 100mV$ or<br>$((V_{CSP1} - V_{CSN1}) < V_{NCLTH} \parallel (V_{CSP2} - V_{CSN2}) < V_{NCLTH})$       |

図 6-7. バイパス モードの開始、終了

### 6.3.6 VCC レギュレータ、BIAS (BIAS ピン、VCC ピン)

ゲートドライバは、内部の 5V VCC レギュレータから電力を供給されます。VCC レギュレータは、 $V_{BIAS} > V_{BIAS-RISING}$  の場合は BIAS ピンから電力を供給され、最大 42V をサポートし、 $V_{BIAS} < V_{BIAS-FALLING}$  の場合は VOUT ピンから電源を供給されます。リファレンスシステムは BIAS ピンから永続的な電力を供給され、電圧が 2V 未満の場合にシャットダウンできるため、BIAS ピンは 2.5V 以上の電圧 (例:  $V_I$  または 5V) に接続します。推奨される VCC コンデンサの値は 10 $\mu$ F です。

内蔵の電流制限機能により、VCC の過負荷時、または VCC ピンがグランドに短絡したときにデバイスの損傷を防止します。VCC は、最大 200mA ( $I_{VCC-CL}$ ) の電圧を供給できます。外部 MOSFET で消費される VCC 電流は、式 7 で計算できます。

$$I_{VCC} = n \times 2 \times Q_{G@5V} \times f_{SW} \quad (7)$$

ここで、

- $n$  はアクティブな位相の数です。

- $Q_{G@5V}$  は 5V のゲートソース電圧における MOSFET ゲート電荷です。

図 6-8. その場でのバイアス電源の選択

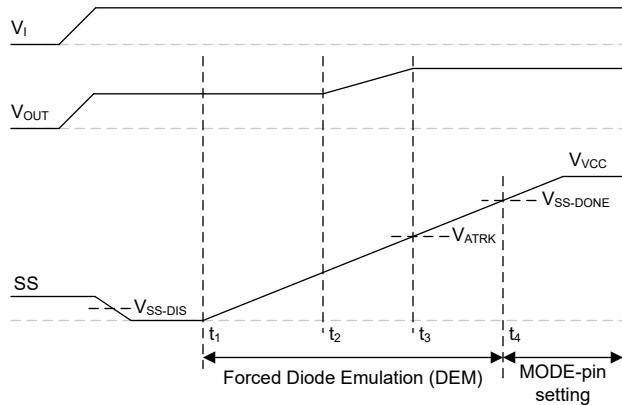

### 6.3.7 ソフトスタート (SS ピン)

開始位相 1 および 2 の状態 (FSM を参照) での起動時に、デバイスは SS ピン電圧または ATRK/DTRK ピン電圧のどちらか低い方に、エラー アンプのリファレンス電圧を調整します。安定化リファレンスにより、出力電圧  $V_{OUT}$  が次第に上

昇します。ソフトスタート中、デバイスは、ソフトスタート完了信号が生成されるまで、強制的にダイオード エミュレーションモード (DEM) を実行します。

外部ソフトスタートコンデンサは、まず  $V_{SS-DIS}$  電圧まで放電され、次に  $I_{SS}$  電流によって充電され、 $V_{SS-DONE}$  に達したときにソフトスタート完了信号が生成されます。昇圧トポロジでは、スタートアップ時に  $V_{OUT}$  が  $V_I$  と等しいため、ソフトスタート時間 ( $t_{SS}$ ) は入力電源電圧によって変化します。[ソフトスタート](#)の図では、 $t_1$  の時点でのソフトスタート電流が作動します。 $t_2$  の時点でのソフトスタート電圧は  $V_I$  電圧レベルに達し、 $V_{OUT}$  が  $t_3$  のプログラムされた  $V_{OUT}$  値に達するまで、 $V_{OUT}$  の上昇を開始します。 $SS$  ピンの電圧が  $V_{SS-DONE}$  に達すると、ソフトスタート完了信号が  $t_4$  に生成されます。 $V_{VCC}$  に達するまで、 $SS$  ピンの電圧は上昇を続け、ここでソフトスタート電流が無効になります。

$$t_{SS\_t1\_t4} = 2.2 \times \frac{C_{SS}}{I_{SS}} \quad (8)$$

$$t_{SS\_t2\_t3} = \frac{C_{SS}}{I_{SS}} \times \frac{V_{OUT} - V_I}{30} \quad (9)$$

図 6-9. ソフトスタート

### 6.3.8 $V_{OUT}$ のプログラミング (VOUT, ATRK, DTRK)

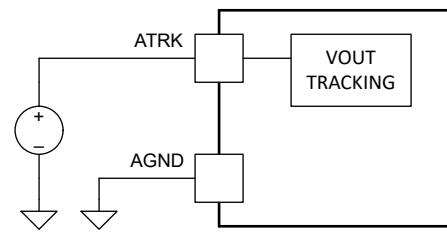

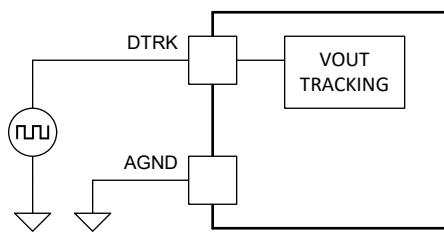

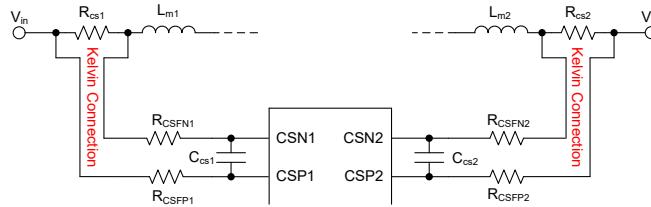

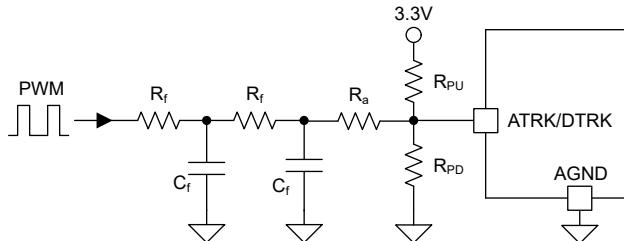

出力電圧  $V_{OUT}$  は  $V_{OUT}$  ピンで検出されます。 $V_{OUT}$  は、を使用して 6V~60V の範囲でプログラミングします。10kΩ を 100kΩ 抵抗と ATRK/DTRK ピンに接続し、0.2V~2V の電圧または 8%~80% のデューティサイクルの範囲のデジタル信号を印加します。起動時の STANDBY 状態 ([機能状態図](#)) 時に、ATRK/DTRK ピンのプログラミング方式のアナログ信号またはデジタル信号が検出されます。START PHASE 1 および 2 状態への遷移時に、ATRK/DTRK ピンのプログラミング方式はラッピングされ、動作中に変更することはできません。プログラミング方式がラッピングされる前に、DTRK 信号を検出できるよう、DTRK 信号は少なくとも 3 サイクル存在するようにします。ATRK は最大 10kHz の信号をサポートしますが、 $V_{OUT}$  が追従できるように ATRK ピンの電圧または DTRK のデューティサイクルの変更は十分に遅くする必要があります。ATRK/DTRK ピンの設定基準電圧がコンバータの帯域幅よりも高速に変化した場合、勾配補償が安定するまで、インダクタ電流はピーク電流制限を超えます。インダクタのピーク電流オーバーシュートは 90mV CSPx-CSNx センス抵抗電圧に制限されます。このデバイスは、ATRK < 0.2V または ATRK > 2V に対しても  $V_{OUT}$  の調整を試みますが、性能は持続できません。抵抗による  $V_{OUT}$  プログラミングのために、CFG0 設定で 20μA の電流を有効にします。20μA の電流は ATRK ピン経由でソースされ、目標の  $V_{OUT}$  電圧に必要な ATRK 電圧を外付け抵抗により生成します。アナログトラッキング (ATRK) またはデジタルトラッキング (DTRK) の場合、TI では 20uA の電流を無効化することを推奨します。

抵抗で  $V_{OUT}$  をプログラミングする式:

$$R_{ATRK} = \frac{V_{OUT}}{6V} \times 10 k\Omega \quad (10)$$

電圧 (ATRK) で  $V_{OUT}$  をプログラミングする式:

$$V_{OUT} = V_{ATRK} \times 30 \quad (11)$$

デジタル信号 (DTRK) で  $V_{OUT}$  をプログラミングする式:

$$V_{OUT} = 0.75 \frac{V}{\%} \times \text{Duty Cycle} \quad (12)$$

図 6-10. 抵抗による  $V_{OUT}$  のプログラミング

図 6-11. アナログ電圧による  $V_{OUT}$  のトラッキング

図 6-12. デジタル信号による  $V_{OUT}$  のトラッキング

### 6.3.9 保護

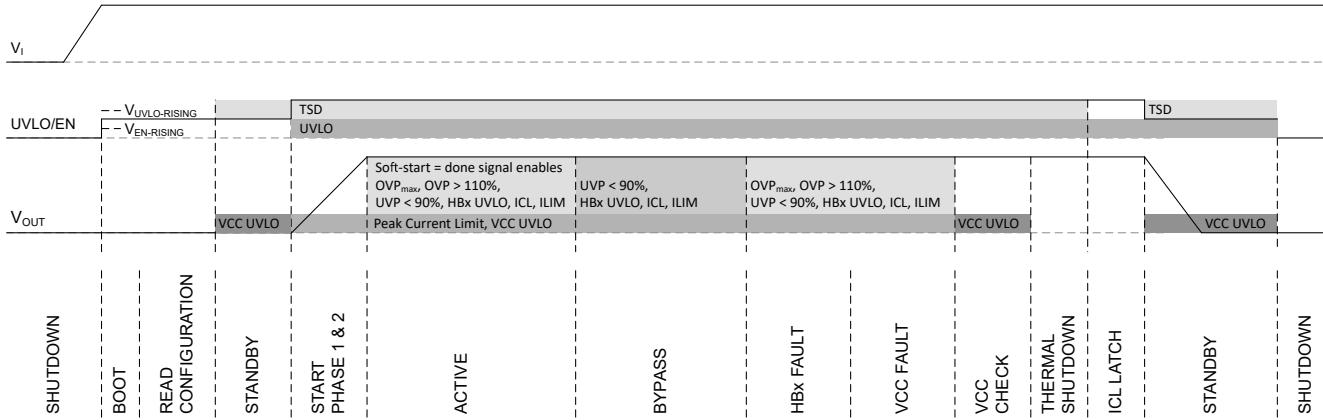

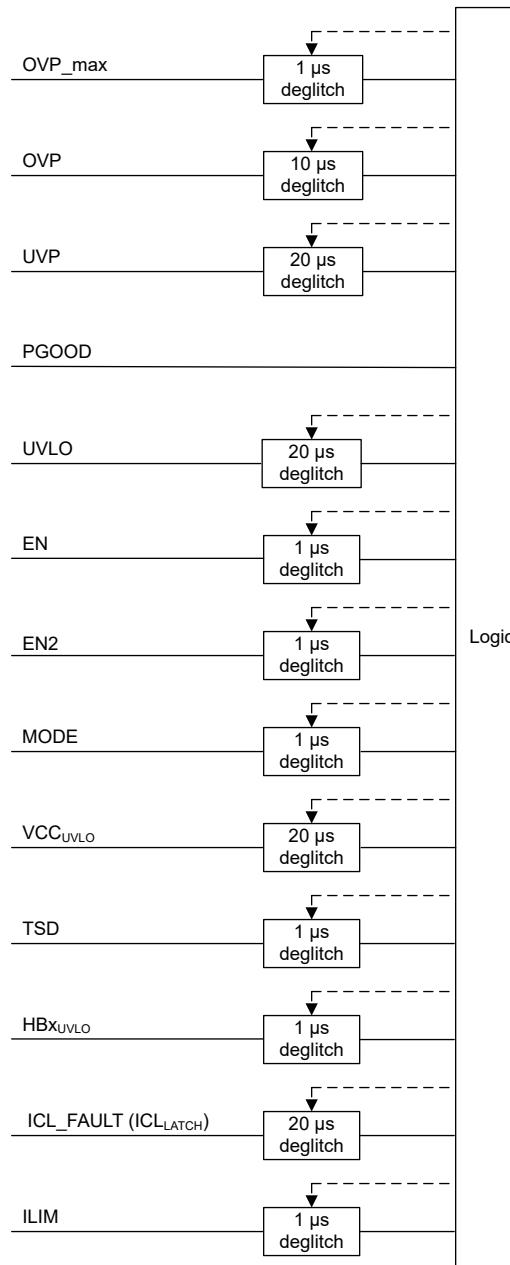

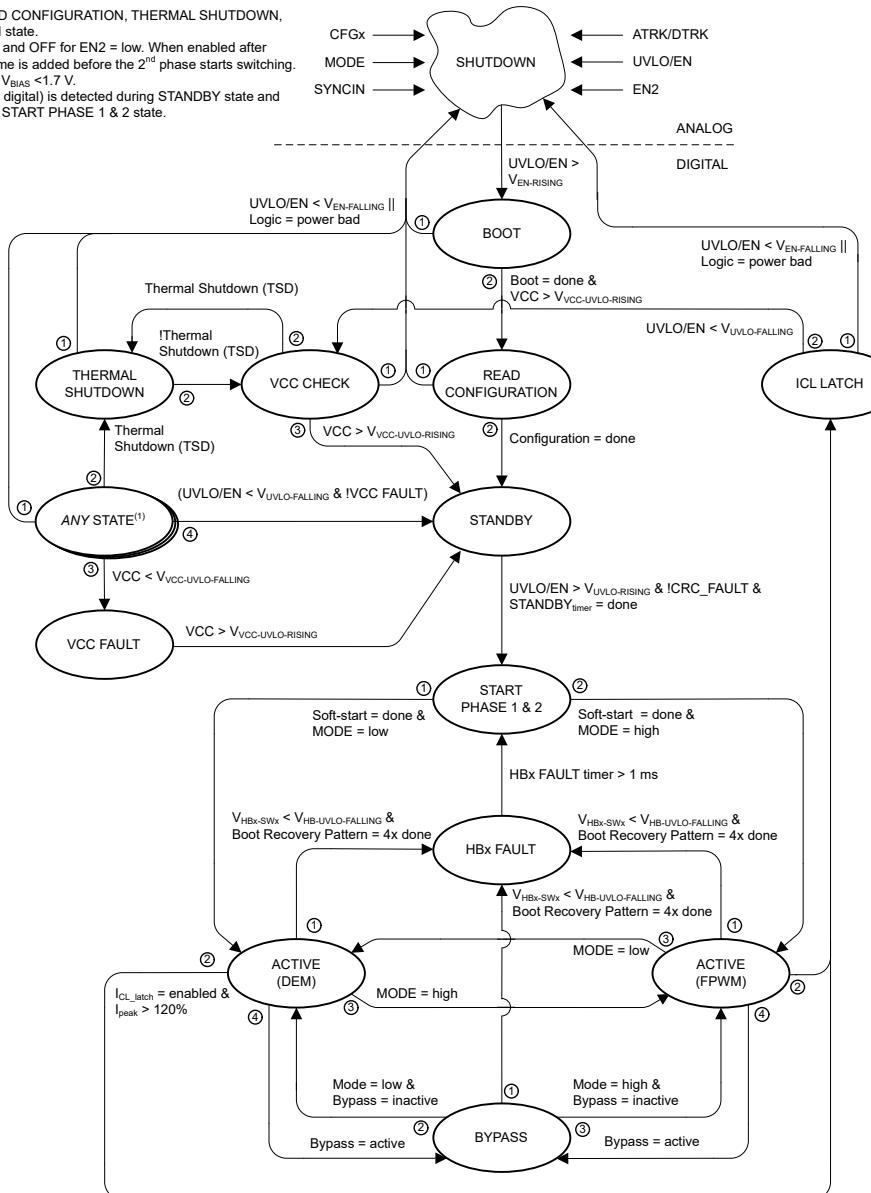

次の保護機能が実装されています。図 6-13 は、機能状態図 のどの状態でどの保護がアクティブになっているかを示します。保護は、同じ灰色のシェーディングを持つ灰色の影付きの状態でアクティブになります。たとえば、TSD は THERMAL SHUTDOWN 状態を含む STANDBY 状態でアクティブになりますが、ICL LATCH 状態ではアクティブになりません。

- 過熱時にデバイスをオフにするサーマルシャットダウン (TSD)。

- 低電圧誤動作防止 (UVLO) により、電源電圧が低いときにデバイスをオフにします。

- VCC 低電圧誤動作防止 (VCC UVLO) により、ローサイドゲートドライバ電圧が低すぎることを回避。VCC が回復するまで、デバイスはスイッチングを停止します。

- Hbx 低電圧誤動作防止 (HBx UVLO) により、ハイサイドゲートドライバ電圧が低すぎることを回避。本デバイスはリフレッシュパルスを開始します (ヒップモードのオフ時間は 512 サイクル)。詳しくは、MOSFET ドライバ、内蔵ブートダイオード、ヒップモードの故障保護 (LOx, HOx, HBx ピン) を参照してください。

- 過電圧保護 (OVP)、トリガが発生すると、 $V_{OUT}$  が目標値に戻るまで、デバイスはスイッチングを停止します。2 つの OVP が実装されています。

- $OVP_{max}$  は、プログラマブル絶対値 (通常は 64V、50V、35V、28.5V) です。

- OVP がトリガされ、 $V_{OUT}$  がプログラムされた値の 110% になるとトリガされます。

- 低電圧保護 (UVP)、トリガされると、デバイスは動作を継続しますが、PGOOD ピンは Low にプルされます。

- ピーク電流制限 (PCL) により、スイッチ電流を制限します。詳しくは、電流センス設定とスイッチピーク電流制限 (CSP1, CSP2, CSN1, CSN2) を参照してください。

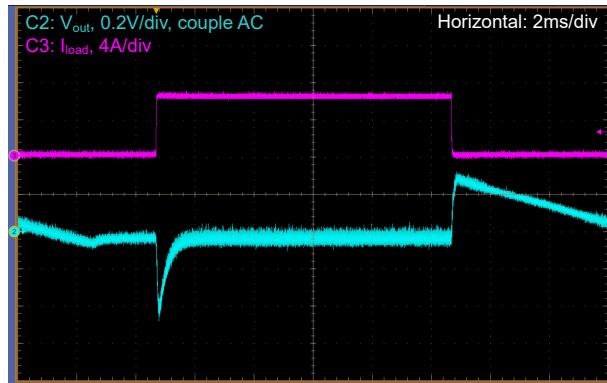

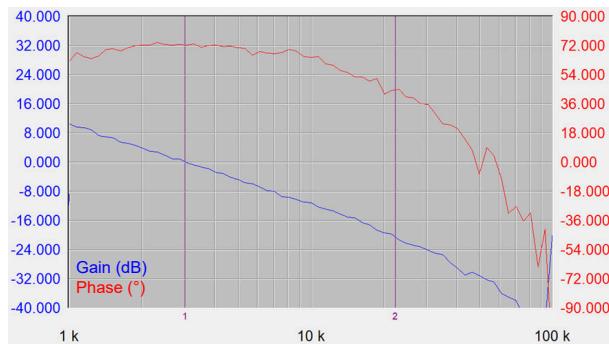

- 入力電流制限 (ICL)、スイッチのピーク電流をピーク電流制限の 120% に制限します。この保護は、 $I_{CL\_LATCH}$  プログラミングによりイネーブル / ディセーブルになります。