LP5018, LP5024

JAJSF10B-OCTOBER 2018-REVISED OCTOBER 2018

# LP50xx 18/24チャネル、12ビット、PWM超低静止電流、I<sup>2</sup>C RGB LED ドライバ

# 1 特長

# • 動作電圧範囲

- V<sub>CC</sub>範囲: 2.7V~5.5V

- EN、SDA、SCLピンは1.8V、3.3V、5Vの 電源レールに対応

- 最大出力電圧: 6V

#### • 24本の高精度、定電流シンク

- V<sub>CC</sub>の全範囲で、チャネルごとに最大25.5mA

- V<sub>CC</sub> ≥ 3.3Vのとき、チャネルごとに最大35mA

- デバイス間誤差: ±7%、チャネル間誤差: ±7%

#### 非常に低い静止電流

- シャットダウン・モード: EN LOWで最大値1μA

- パワー・セーブ・モード: EN HIGH、すべてのLED が30msを超えてオフのとき標準値10μA

- 各チャネルに12ビット、29kHzのPWMジェネレー 夕を内蔵

- チャネルごとに独立のカラー混合レジスタ

- RGB LEDモジュールごとに独立の輝度制御レジスタ

- 対数的または直線的スケールの輝度制御を選択 可能

- 3相PWMシフト方式を搭載

- 3つのプログラム可能バンク(R、G、B)により各色 をソフトウェアで簡単に制御

- 2つの外部ハードウェア・アドレス・ピンにより、最大4つのデバイスに接続可能

- ブロードキャスト・スレーブ・アドレスにより、 複数のデバイスを同時に構成可能

- 自動インクリメント機能により、1回の伝送で連続する複数のレジスタを書き込み/読み取り可能

- 最高400kHzのFast-Mode I<sup>2</sup>C速度

# 2 アプリケーション

次のような機器のLED照明、インジケータ・ライト、および装飾用ライト

- スマート・スピーカー (音声アシスタント付き)

- スマート・ホーム/家電

- ビデオ・ドアベル

- 電子スマート・ロック

- 煙感知器/熱感知器

- STB / DVR

- スマート・ルータ

- ハンドヘルド・デバイス

# 3 概要

スマート・ホームや、ヒューマン・マシン・インターフェイスを活用する他の家電機器では、高性能のRGB LEBドライバが必要となります。フラッシュ、ブリージング、追跡などのLEDアニメーション効果により、ユーザー向けの環境を大幅に改良できます。またシステム・ノイズが最小限であることは不可欠です。

LP50xxデバイスは、18または24チャネルの定電流シンク LEDドライバです。LP50xxデバイスにはカラー・ミキシング および輝度制御機能が内蔵されており、事前設定によりソ フトウェアのコーディング処理を簡素化できます。12ビッ ト、29kHzのPWMジェネレータが各チャネルに内蔵されて いるため、LEDで円滑に、鮮明な色を再現でき、可聴ノイ ズが除去されます。

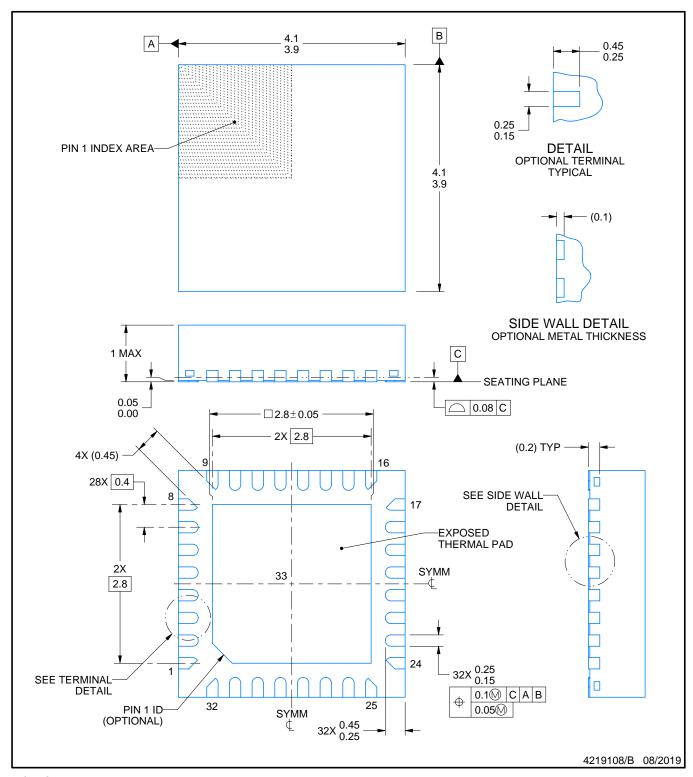

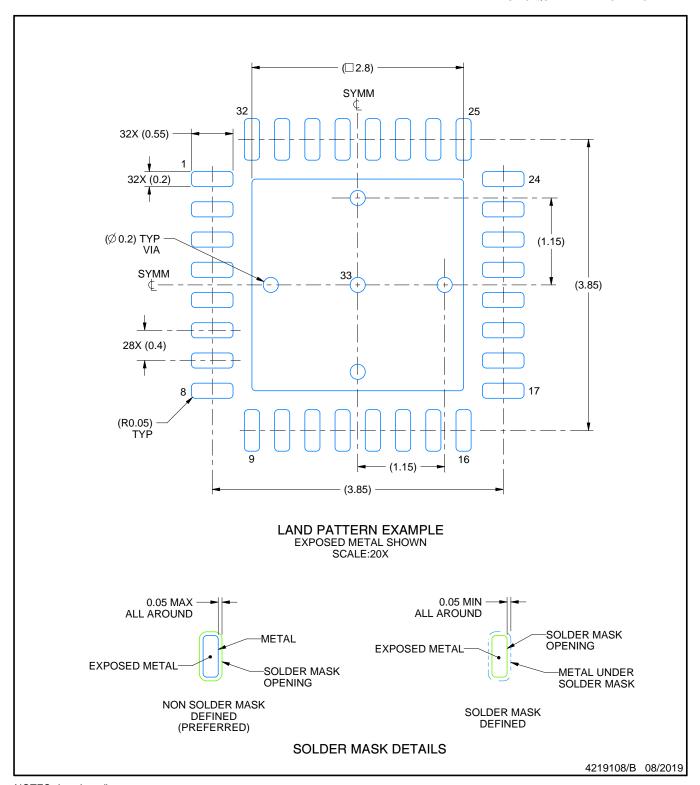

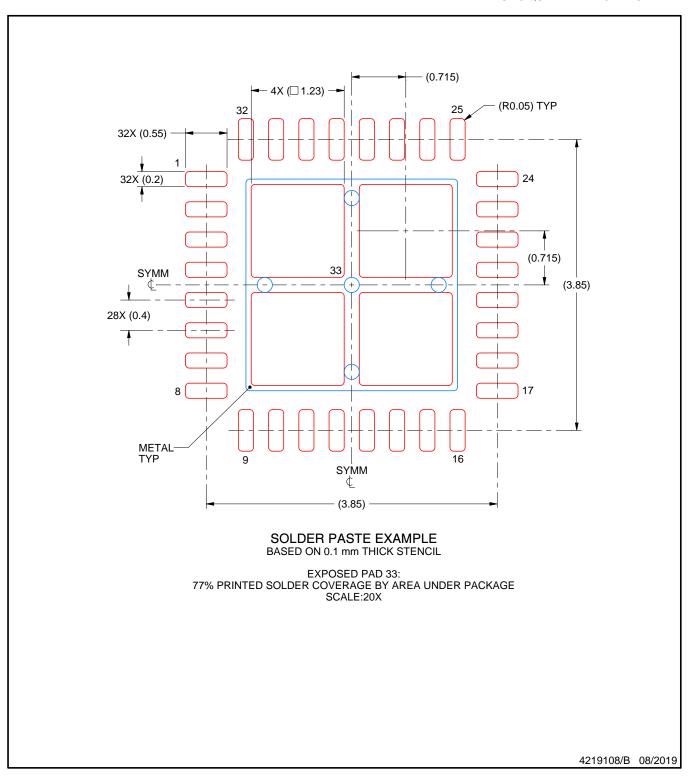

#### 製品情報<sup>(1)</sup>

| 型番     | パッケージ      | 本体サイズ(公称)        |  |  |

|--------|------------|------------------|--|--|

| LP5018 | \/OFN (22) | 4.00,0004.00,000 |  |  |

| LP5024 | VQFN (32)  | 4.00mm×4.00mm    |  |  |

(1) 提供されているすべてのパッケージについては、巻末の注文情報を参照してください。

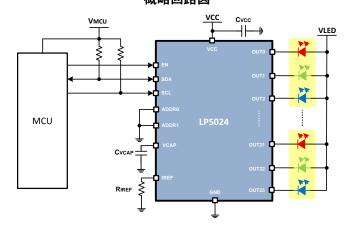

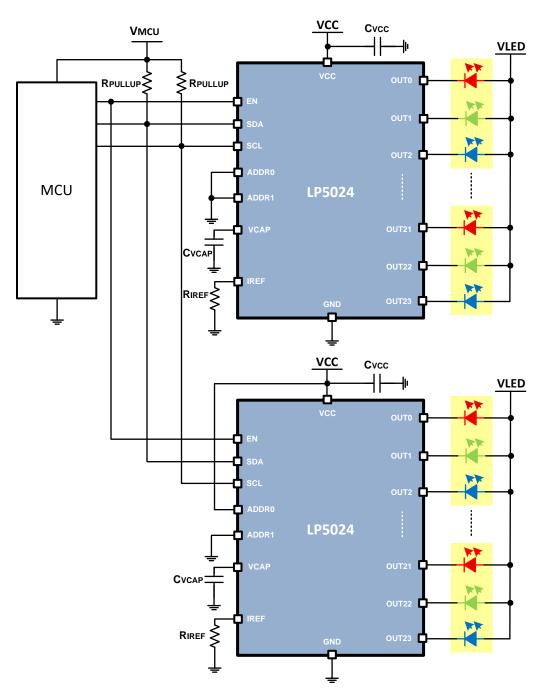

# 概略回路図

# 目次

| 1 | 特長 1                                 |    | 8.4 Device Functional Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 17 |

|---|--------------------------------------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2 | アプリケーション1                            |    | 8.5 Programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 18 |

| 3 | 概要1                                  |    | 8.6 Register Maps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 22 |

| 4 | 改訂履歴2                                | 9  | Application and Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 38 |

| 5 | 概要(続き)                               |    | 9.1 Application Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 38 |

| 6 | Pin Configuration and Functions      |    | 9.2 Typical Application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 38 |

| - | _                                    | 10 | Power Supply Recommendations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 41 |

| 7 | Specifications                       | 11 | Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

|   | 7.1 Absolute Maximum Ratings         |    | 11.1 Layout Guidelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

|   | 7.2 ESD Ratings                      |    | 11.2 Layout Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|   | 7.3 Recommended Operating Conditions | 12 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|   |                                      |    | 12.1 関連リンク                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

|   |                                      |    | 12.2 ドキュメントの更新通知を受け取る方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|   | 7.6 Timing Requirements              |    | 12.3 コミュニティ・リソース                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|   | 7.7 Typical Characteristics          |    | 12.4 商標                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

| 8 | Detailed Description                 |    | 12.5 静電気放電に関する注意事項                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|   | 8.1 Overview                         |    | 12.6 Glossary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

|   | 8.2 Functional Block Diagram         | 13 | メカニカル、パッケージ、および注文情報                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

|   | 8.3 Feature Description              | .0 | THE PARTY OF THE P |    |

# 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Revision A (October 2018) から Revision B に変更 Pa                                                    |      |  |  |

|---------------------------------------------------------------------------------------------------|------|--|--|

| Added % after 100 in Parameter for I <sub>ERR_DD</sub> and I <sub>ERR_CC</sub> under OUTPUT STAGE | 7    |  |  |

| • 変更 value of "K <sub>IREF</sub> = 100" to "K <sub>IREF</sub> = 105"                              | 16   |  |  |

| 2018年10月発行のものから更新                                                                                 | Page |  |  |

| • 量産データを用いたデータシートの初版                                                                              | 1    |  |  |

# 5 概要(続き)

LP50xxデバイスは、29kHzのスイッチング周波数、12ビットのPWM分解能で各LEDの出力を制御するため、スムーズな調光効果を達成でき、可聴周波数のノイズが排除されます。カラー・ミキシングと輝度の制御レジスタを別々に制御できるため、ソフトウェアのコーディングが明快になります。フェードイン、フェードアウト型のブリージング効果を行う際、グローバルなR、G、Bバンクの制御により、マイクロコントローラの負荷が大幅に減少します。また、LP50xxデバイスにはPWM位相シフト機能も実装されており、LEDが同時にオンになるときの入力電力バジェットを低減するために役立ちます。

LP50xxデバイスには、自動パワーセービング・モードが実装されており、非常に低い静止電流を実現しています。すべてのチャネルが30msの間オフのとき、デバイスの合計消費電力は10μAまで低下するため、LP50xxデバイスはバッテリ駆動の最終製品に適しています。

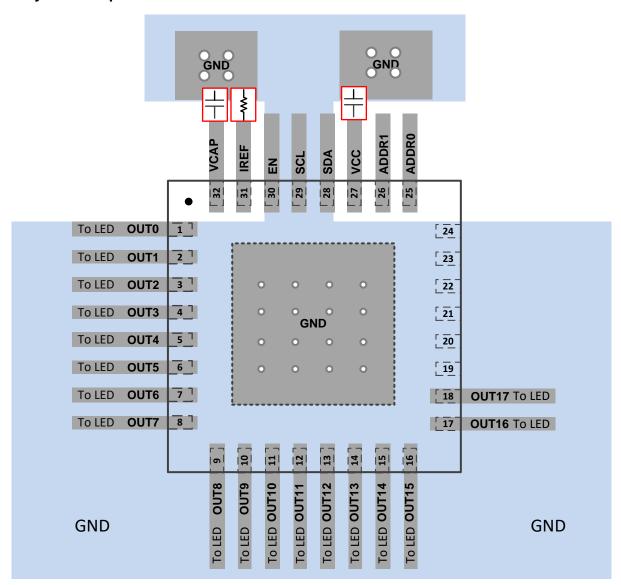

# 6 Pin Configuration and Functions

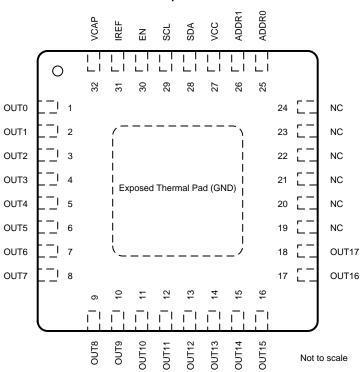

LP5018 RSM Package 32-Pin VQFN With Exposed Thermal Pad Top View

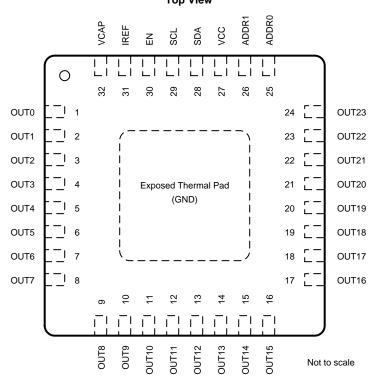

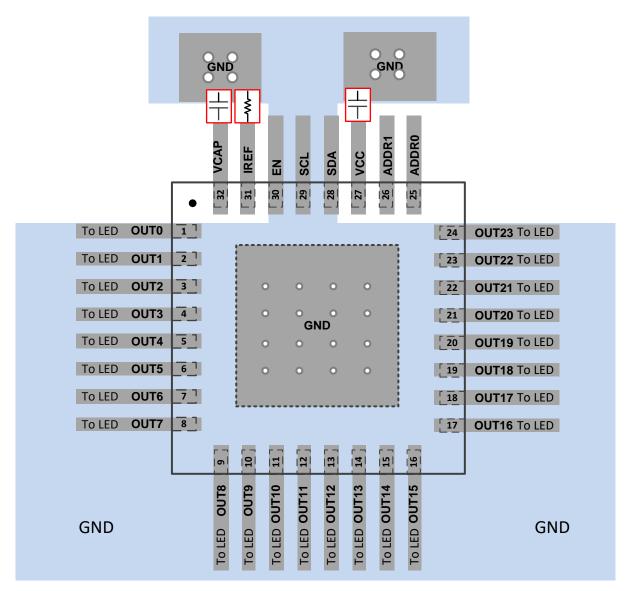

#### LP5024 RSM Package 32-Pin VQFN With Exposed Thermal Pad Top View

# **Pin Functions**

|       | PIN                       |        |     | Fill Fullctions                                                                                                                         |  |  |

|-------|---------------------------|--------|-----|-----------------------------------------------------------------------------------------------------------------------------------------|--|--|

|       | No                        | <br>O. | 1/0 | DESCRIPTION                                                                                                                             |  |  |

| NAME  | LP5018                    | LP5024 |     |                                                                                                                                         |  |  |

| ADDR0 | 25                        | 25     | _   | I <sup>2</sup> C slave-address selection pin. This pin must not be left floating.                                                       |  |  |

| ADDR1 | 26                        | 26     | _   | I <sup>2</sup> C slave-address selection pin. This pin must not be left floating.                                                       |  |  |

| EN    | 30                        | 30     | I   | Chip enable input pin                                                                                                                   |  |  |

| IREF  | 31                        | 31     | _   | Output current-reference global-setting pin                                                                                             |  |  |

| NC    | 19, 20, 21,<br>22, 23, 24 | _      | _   | No internal connection                                                                                                                  |  |  |

| OUT0  | 1                         | 1      | 0   | Current sink output 0. If not used, this pin can be left floating.                                                                      |  |  |

| OUT1  | 2                         | 2      | 0   | Current sink output 1. If not used, this pin can be left floating.                                                                      |  |  |

| OUT2  | 3                         | 3      | 0   | Current sink output 2. If not used, this pin can be left floating.                                                                      |  |  |

| OUT3  | 4                         | 4      | 0   | Current sink output 3. If not used, this pin can be left floating.                                                                      |  |  |

| OUT4  | 5                         | 5      | 0   | Current sink output 4. If not used, this pin can be left floating.                                                                      |  |  |

| OUT5  | 6                         | 6      | 0   | Current sink output 5. If not used, this pin can be left floating.                                                                      |  |  |

| OUT6  | 7                         | 7      | 0   | Current sink output 6. If not used, this pin can be left floating.                                                                      |  |  |

| OUT7  | 8                         | 8      | 0   | Current sink output 7. If not used, this pin can be left floating.                                                                      |  |  |

| OUT8  | 9                         | 9      | 0   | Current sink output 8. If not used, this pin can be left floating.                                                                      |  |  |

| OUT9  | 10                        | 10     | 0   | Current sink output 9. If not used, this pin can be left floating.                                                                      |  |  |

| OUT10 | 11                        | 11     | 0   | Current sink output 10. If not used, this pin can be left floating.                                                                     |  |  |

| OUT11 | 12                        | 12     | 0   | Current sink output 11. If not used, this pin can be left floating.                                                                     |  |  |

| OUT12 | 13                        | 13     | 0   | Current sink output 12. If not used, this pin can be left floating.                                                                     |  |  |

| OUT13 | 14                        | 14     | 0   | Current sink output 13. If not used, this pin can be left floating.                                                                     |  |  |

| OUT14 | 15                        | 15     | 0   | Current sink output 14. If not used, this pin can be left floating.                                                                     |  |  |

| OUT15 | 16                        | 16     | 0   | Current sink output 15. If not used, this pin can be left floating.                                                                     |  |  |

| OUT16 | 17                        | 17     | 0   | Current sink output 16. If not used, this pin can be left floating.                                                                     |  |  |

| OUT17 | 18                        | 18     | 0   | Current sink output 17. If not used, this pin can be left floating.                                                                     |  |  |

| OUT18 | _                         | 19     | 0   | Current sink output 18. If not used, this pin can be left floating.                                                                     |  |  |

| OUT19 | _                         | 20     | 0   | Current sink output 19. If not used, this pin can be left floating.                                                                     |  |  |

| OUT20 | _                         | 21     | 0   | Current sink output 20. If not used, this pin can be left floating.                                                                     |  |  |

| OUT21 | _                         | 22     | 0   | Current sink output 21. If not used, this pin can be left floating.                                                                     |  |  |

| OUT22 | _                         | 23     | 0   | Current sink output 22. If not used, this pin can be left floating.                                                                     |  |  |

| OUT23 | _                         | 24     | 0   | Current sink output 23. If not used, this pin can be left floating.                                                                     |  |  |

| SCL   | 29                        | 29     | I   | I <sup>2</sup> C bus clock line. If not used, this pin must be connected to GND or VCC.                                                 |  |  |

| SDA   | 28                        | 28     | I/O | I <sup>2</sup> C bus data line. If not used, this pin must be connected to GND or VCC.                                                  |  |  |

| VCAP  | 32                        | 32     | _   | Internal LDO output pin, this pin must be connected to a 1-µF capacitor to GND. Place the capacitor as close to the device as possible. |  |  |

| VCC   | 27                        | 27     | I   | Input power.                                                                                                                            |  |  |

| GND   | GND                       |        |     | Exposed thermal pad also serves the ground pin for the device.                                                                          |  |  |

# 7 Specifications

# 7.1 Absolute Maximum Ratings

over operating ambient temperature range (unless otherwise noted)<sup>(1)</sup>

|                                          | MIN   | MAX           | UNIT |

|------------------------------------------|-------|---------------|------|

| Voltage on EN, IREF, OUTx, SCL, SDA, VCC | -0.3  | 6             | V    |

| Voltage on ADDRx                         | -0.3  | VCC+0.3       | V    |

| Voltage on VCAP                          | -0.3  | 2             | V    |

| Continuous power dissipation             | Inter | nally limited |      |

| Junction temperature, T <sub>J-MAX</sub> | -40   | 125           | °C   |

| Storage temperature, T <sub>stg</sub>    | -65   | 150           | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 7.2 ESD Ratings

|                    |                         |                                                                     | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>   | ±4000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±1500 | V    |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Pins listed as ±1500

V may actually have higher performance.

# 7.3 Recommended Operating Conditions

over operating ambient temperature range (unless otherwise noted)

|                                               | MIN | MAX | UNIT |

|-----------------------------------------------|-----|-----|------|

| Input voltage on VCC                          | 2.7 | 5.5 | V    |

| Voltage on OUTx                               | 0   | 5.5 | V    |

| Voltage on ADDRx, EN, SDA, SCL                | 0   | 5.5 | V    |

| Operating ambient temperature, T <sub>A</sub> | -40 | 85  | °C   |

#### 7.4 Thermal Information

|                        |                                              | LP5018 or LP5024 |      |

|------------------------|----------------------------------------------|------------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | RSM (QFN)        | UNIT |

|                        |                                              | 32 PINS          |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 36.4             | °C/W |

| $R_{\theta JC(top)}$   | Junction-to-case (top) thermal resistance    | 34.8             | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 15.9             | °C/W |

| ΨЈТ                    | Junction-to-top characterization parameter   | 0.9              | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 16               | °C/W |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | 6.3              | °C/W |

(1) For more information about traditional and new thermal metrics, see Semiconductor and ICPackage Thermal Metrics .

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Pins listed as ±500 V may actually have higher performance.

# 7.5 Electrical Characteristics

over operating ambient temperature range (-40°C < T<sub>A</sub><85°C) (unless otherwise noted)

|                     | PARAMETER                                                                                                            | TEST CONDITIONS                                                                                                                                        | MIN         | TYP  | MAX      | UNIT |  |

|---------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------|----------|------|--|

| POWER S             | SUPPLIES (VCC)                                                                                                       | ,                                                                                                                                                      |             |      | <u>.</u> |      |  |

| √ <sub>vcc</sub>    | Supply voltage                                                                                                       |                                                                                                                                                        | 2.7         |      | 5.5      | V    |  |

|                     | Shutdown supply current                                                                                              | V <sub>EN</sub> = 0 V                                                                                                                                  |             | 0.2  | 1        |      |  |

|                     | Standby supply current                                                                                               | V <sub>EN</sub> = 3.3 V, Chip_EN = 0 (bit)                                                                                                             |             | 6    | 10       | μA   |  |

| l <sub>vcc</sub>    | Normal-mode supply current                                                                                           | With 10-mA LED current per OUTx                                                                                                                        |             | 5    | 8        | mA   |  |

| <b>V</b> 00         | Power-save mode supply current                                                                                       | V <sub>EN</sub> = 3.3 V, Chip_EN = 1 (bit),<br>Power_Save_EN = 1 (bit), all the<br>LEDs off duration > t <sub>PSM</sub>                                |             | 6    | 10       | μΑ   |  |

| V <sub>UVR</sub>    | Undervoltage restart                                                                                                 | V <sub>VCC</sub> rising                                                                                                                                |             |      | 2.5      | V    |  |

| V <sub>UVF</sub>    | Undervoltage shutdown                                                                                                | V <sub>VCC</sub> falling                                                                                                                               | 2           |      |          | V    |  |

| V <sub>UV_HYS</sub> | Undervoltage shutdown hysteresis                                                                                     |                                                                                                                                                        |             | 0.2  |          | V    |  |

|                     | STAGE (OUTx)                                                                                                         | 1                                                                                                                                                      |             |      |          |      |  |

|                     | Maximum sink current<br>(OUT0-OUTx) (For LP5024, x = 23.<br>For LP5018, x = 17.)                                     | V <sub>VCC</sub> in full range,<br>Max_Current_Option = 0 (bit), PWM<br>= 100%                                                                         |             |      | 25.5     | mA   |  |

| I <sub>MAX</sub>    | Maximum sink current (OUT0-OUTx) (For LP5024, x = 23. For LP5018, x = 17.)                                           | V <sub>VCC</sub> ≥ 3.3 V, Max_Current_Option = 1 (bit), PWM = 100%                                                                                     |             | 35   |          |      |  |

| l                   | Internal sink current limit (OUT0-OUTx) (For LP5024, x = 23. For LP5018, x = 17.)                                    | V <sub>VCC</sub> in full range,<br>Max_Current_Option = 0 (bit), V <sub>IREF</sub><br>= 0 V                                                            | 35          | 55   | 80       | mA   |  |

| I <sub>LIM</sub>    | Internal sink current limit (OUT0-OUTx) (For LP5024, x = 23. For LP5018, x = 17.)                                    | $V_{VCC} \ge 3.3V$ , Max_Current_Option=1 (bit), $V_{IREF} = 0 V$                                                                                      | 40          | 75   | 120      |      |  |

| l <sub>lkg</sub>    | Leakage current (OUT0-OUTx) (For LP5024, x = 23. For LP5018, x = 17.)                                                | PWM = 0%                                                                                                                                               |             | 0.1  | 1        | μΑ   |  |

| I <sub>ERR_DD</sub> | Device to device current error, I <sub>ERR_DD</sub> =(I <sub>AVE</sub> -I <sub>SET</sub> )/I <sub>SET</sub> ×100%    | All channels' current set to 10 mA. PWM = 100%. Already includes the V <sub>IREF</sub> and K <sub>IREF</sub> tolerance                                 | <b>-7</b> % |      | 7%       |      |  |

| I <sub>ERR_CC</sub> | Channel to channel current error, I <sub>ERR_CC</sub> =(I <sub>OUTX</sub> -I <sub>AVE</sub> )/I <sub>AVE</sub> ×100% | All channels' current set to 10 mA. PWM = 100%. Already includes the V <sub>IREF</sub> and K <sub>IREF</sub> tolerance                                 | -7%         |      | 7%       |      |  |

| V <sub>IREF</sub>   | IREF voltage                                                                                                         |                                                                                                                                                        |             | 0.7  |          | V    |  |

| K <sub>IREF</sub>   | IREF ratio                                                                                                           |                                                                                                                                                        |             | 105  |          |      |  |

| f <sub>PWM</sub>    | PWM switching frequency                                                                                              |                                                                                                                                                        | 21          | 29   |          | kHz  |  |

| $V_{SAT}$           | Output saturation voltage                                                                                            | V <sub>VCC</sub> in full range,<br>Max_Current_Option = 0 (bit), output<br>current set to 20 mA, the voltage<br>when the LED current has dropped<br>5% |             | 0.25 | 0.35     | V    |  |

|                     |                                                                                                                      | V <sub>VCC</sub> ≥ 3.3 V, Max_Current_Option<br>= 1 (bit), output current set to 20<br>mA, the voltage when the LED<br>current has dropped 5%          |             | 0.3  | 0.4      |      |  |

| LOGIC IN            | PUTS (EN, SCL, SDA, ADDRx)                                                                                           |                                                                                                                                                        |             |      |          |      |  |

| V <sub>IL</sub>     | Low level input voltage                                                                                              |                                                                                                                                                        |             |      | 0.4      | V    |  |

| V <sub>IH</sub>     | High level input voltage                                                                                             |                                                                                                                                                        | 1.4         |      |          | V    |  |

| LOGIC               | Input current                                                                                                        |                                                                                                                                                        | -1          |      | 1        | μA   |  |

| V <sub>SDA</sub>    | SDA output low level                                                                                                 | I <sub>PULLUP</sub> = 5 mA                                                                                                                             |             |      | 0.4      | V    |  |

| PROTEC              | TION CIRCUITS                                                                                                        |                                                                                                                                                        |             |      |          |      |  |

| T <sub>(TSD)</sub>  | Thermal-shutdown junction temperature                                                                                |                                                                                                                                                        |             | 160  |          | °C   |  |

# **Electrical Characteristics (continued)**

over operating ambient temperature range (-40°C <  $T_A$ <85°C) (unless otherwise noted)

|                    | PARAMETER                               | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|--------------------|-----------------------------------------|-----------------|-----|-----|-----|------|

| T <sub>(HYS)</sub> | Thermal shutdown temperature hysteresis |                 |     | 15  |     | °C   |

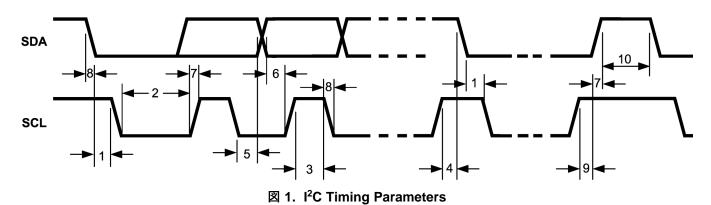

# 7.6 Timing Requirements

over operating ambient temperature range (- $40^{\circ}$ C <  $T_A$ < $85^{\circ}$ C) (unless otherwise noted)

|                   | PARAMETER                                                                               | MIN                     | TYP | MAX | UNIT |

|-------------------|-----------------------------------------------------------------------------------------|-------------------------|-----|-----|------|

| $f_{OSC}$         | Internal oscillator frequency                                                           |                         | 15  |     | MHz  |

| t <sub>PSM</sub>  | Power save mode deglitch time                                                           | 20                      | 30  | 40  | ms   |

| t <sub>EN_H</sub> | EN first rising edge until first I <sup>2</sup> C access                                |                         |     | 500 | μs   |

| t <sub>EN_L</sub> | EN first falling edge until first I <sup>2</sup> C reset                                |                         |     | 3   | μs   |

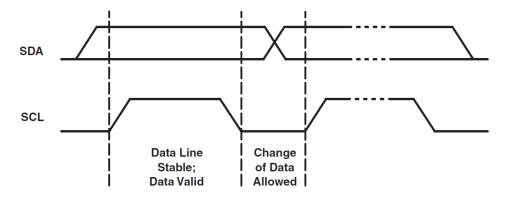

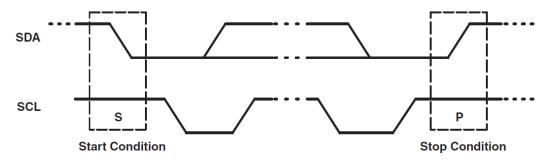

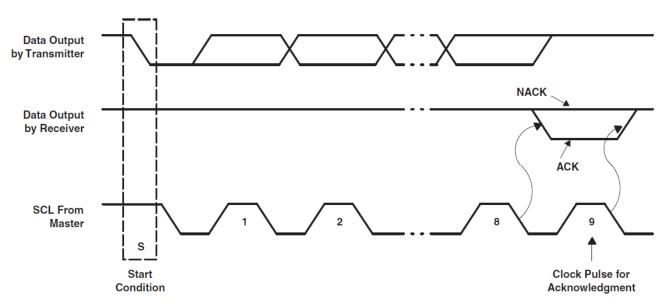

| $f_{SCL}$         | I <sup>2</sup> C clock frequency                                                        |                         |     | 400 | kHz  |

| 1                 | Hold time (repeated) START condition                                                    | 0.6                     |     |     | μs   |

| 2                 | Clock low time                                                                          | 1.3                     |     |     | μs   |

| 3                 | Clock high time                                                                         | 600                     |     |     | ns   |

| 4                 | Setup time for a repeated START condition                                               | 600                     |     |     | ns   |

| 5                 | Data hold time                                                                          | 0                       |     |     | ns   |

| 6                 | Data setup time                                                                         | 100                     |     |     | ns   |

| 7                 | Rise time of SDA and SCL                                                                | 20 + 0.1 C <sub>b</sub> |     | 300 | ns   |

| 8                 | Fall time of SDA and SCL                                                                | 15 + 0.1 C <sub>b</sub> |     | 300 | ns   |

| 9                 | Setup time for STOP condition                                                           | 600                     |     |     | ns   |

| 10                | Bus free time between a STOP and a START condition                                      | 1.3                     |     |     | μs   |

| C <sub>b</sub>    | Capacitive load parameter for each bus line Load of 1 pF corresponds to one nanosecond. | 10                      |     | 200 | pF   |

8

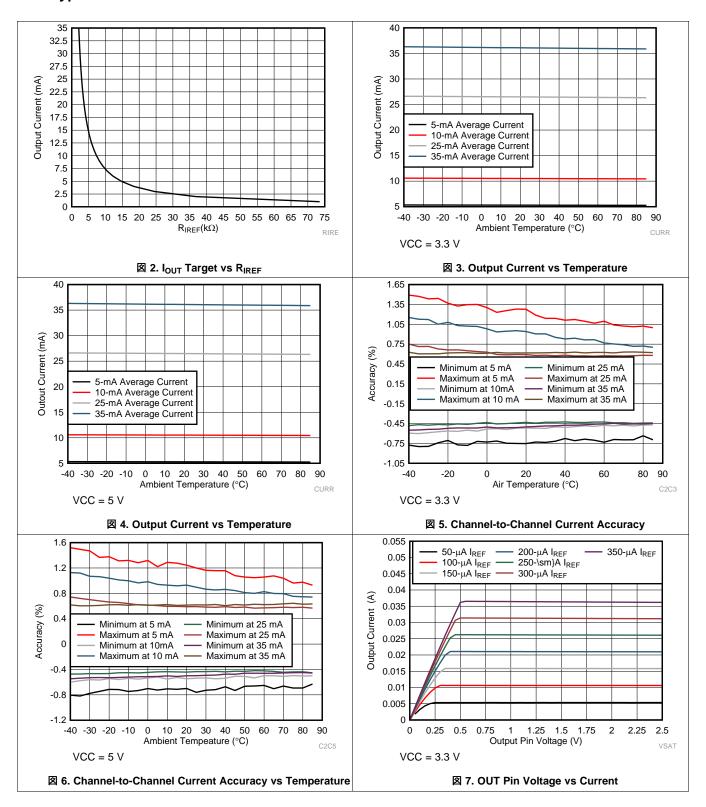

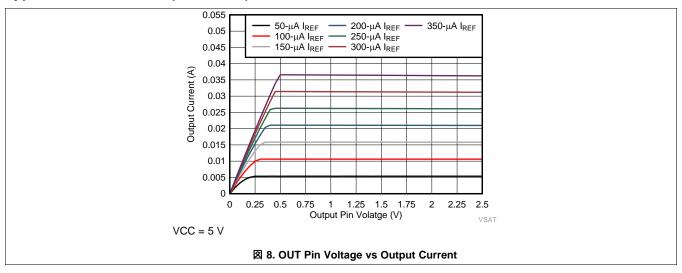

# 7.7 Typical Characteristics

# **Typical Characteristics (continued)**

# 8 Detailed Description

#### 8.1 Overview

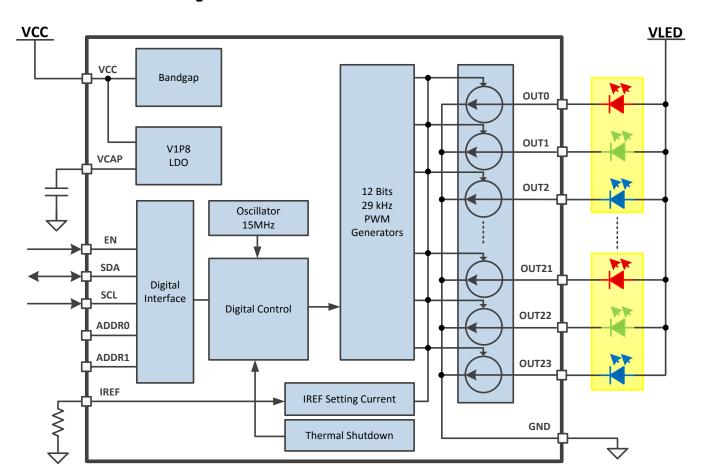

The LP50xx device is an 18- or 24-channel constant-current-sink LED driver. The LP50xx device includes all necessary power rails, an on-chip oscillator, and a two-wire serial  $I^2C$  interface. The maximum constant-current value of all channels is set by a single external resistor. Two hardware address pins allow up to four devices on the same bus. An automatic power-saving mode is implemented to keep the total current consumption under 10  $\mu$ A, which makes the LP50xx device a potential choice for battery-powered end-equipment.

The LP50xx device is optimized for RGB LEDs regarding to both live effects and software efforts. The LP50xx device controls each LED output with 12-bit PWM resolution at 29-kHz switching frequency, which helps achieve a smooth dimming effect and eliminates audible noise. The independent color-mixing and intensity-control registers make the software coding straightforward. When targeting a fade-in, fade-out type breathing effect, the global RGB bank control reduces the microcontroller loading significantly. The LP50xx device also implements a PWM phase-shifting function to help reduce the input power budget when LEDs turn on simultaneously.

# 8.2 Functional Block Diagram

#### 8.3 Feature Description

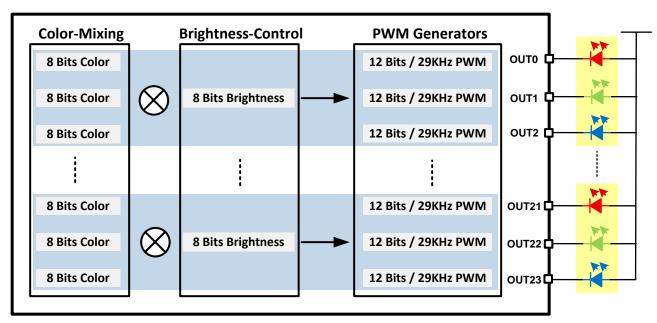

#### 8.3.1 PWM Control for Each Channel

Most traditional LED drivers are designed for the single-color LEDs, in which the high-resolution PWM generator is used for intensity control only. However, for RGB LEDs, both the color mixing and intensity control should be addressed to achieve the target effect. With the traditional solution, the users must handle the color mixing and intensity control simultaneously with a single PWM register. Several undesired effects occur: the limited dimming steps, the complex software design, and the color distortion when using a logarithmic scale control.

The LP50xx device is designed with independent color mixing and intensity control, which makes the RGB LED effects fancy and the control experience straightforward. With the inputs of the color-mixing register and the intensity-control register, the final PWM generator output for each channel is 12-bit resolution and 29-kHz dimming frequency, which helps achieve a smooth dimming effect and eliminates audible noise. See  $\blacksquare$  9.

図 9. PWM Control Scheme for Each Channel

#### 8.3.1.1 Independent Color Mixing Per RGB LED Module

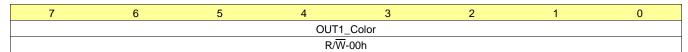

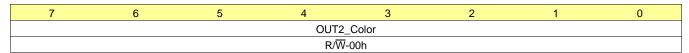

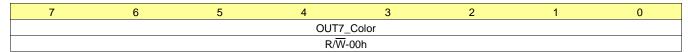

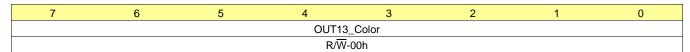

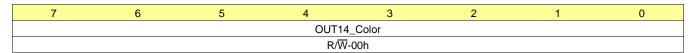

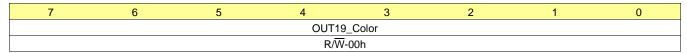

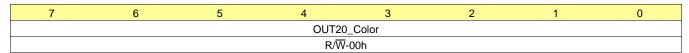

Each output channel has its own individual 8-bit color-setting register (OUTx\_COLOR). The device allows every RGB LED module to achieve >16 million ( $256 \times 256 \times 256$ ) color-mixing.

#### 8.3.1.2 Independent Intensity Control Per RGB LED Module

When color is fixed, the independent intensity-control is used to achieve accurate and flexible dimming control for every RGB LED module.

#### 8.3.1.2.1 Intensity-Control Register Configuration

Every three consecutive output channels are assigned to their respective intensity-control register (LEDx\_BRIGHTNESS). For example, OUT0, OUT1, and OUT2 are assigned to LED0\_BRIGHTNESS, so it is recommended to connect the RGB LEDs in the sequence as shown in 表 1. The LP50xx device allows 256-step intensity control for each RGB LED module, which helps achieve a smooth dimming effect.

Keeping FFh (default value) in the LED0\_BRIGHTNESS register results in 100% dimming duty cycle. With this setting, users can just configure the color mixing register by channel to achieve the target dimming effect in a single-color LED application.

# 8.3.1.2.2 Logarithmic- or Linear-Scale Intensity Control

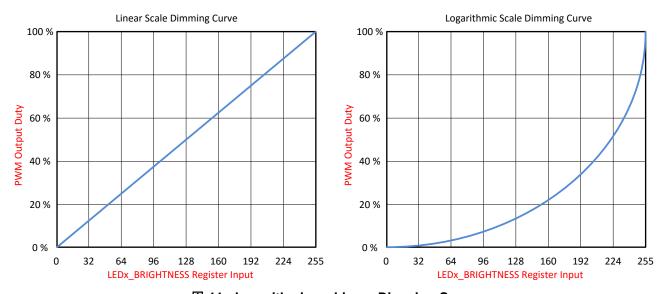

For human-eye-friendly visual performance, a logarithmic-scale dimming curve is usually implemented in LED drivers. However, for RGB LEDs, if using a single register to achieve both color mixing and intensity control, color distortion can be observed easily when using a logarithmic scale. The LP50xx device, with independent color-mixing and intensity-control registers, implements the logarithmic scale dimming control inside the intensity control function, which solves the color distortion issue effectively. See 2 10. Also, the LP50xx device allows users to configure the dimming scale either logarithmically or linearly through the global Log\_Scale\_EN register. If a special dimming curve is desired, using the linear scale with software correction is the most flexible approach. See 11.

# Brightness Control 8 Bits Brightness Linear OR Logarithmic 8 Bits Brightness Linear OR Logarithmic

図 10. Logarithmic- or Linear-Scale Intensity Control

図 11. Logarithmic vs Linear Dimming Curve

## 8.3.1.3 12-Bit, 29-kHz PWM Generator Per Channel

#### 8.3.1.3.1 PWM Generator

With the inputs of the color mixing and the intensity control, the final output PWM duty cycle is defined as the product obtained by multiplying the color-mixing register value by the related intensity-control register value. The final output PWM duty cycle has 12 bits of control accuracy, which is achieved by a 9 bits of pure PWM resolution and 3 bits of digital dithering control. For 3-bit dithering, every eighth pulse is made 1 LSB longer to increase the average value by 1 / 8th. The LP50xx device allows users to enable or disable the dithering function through the PWM\_Dithering\_EN register. When enabled (default), the output PWM duty-cycle accuracy is 12 bits. When disabled, the output PWM duty-cycle accuracy is 9 bits.

To eliminate the audible noise due to the PWM switching, the LP50xx device sets the PWM switching frequency at 29-kHz, above the 20-kHz human hearing range.

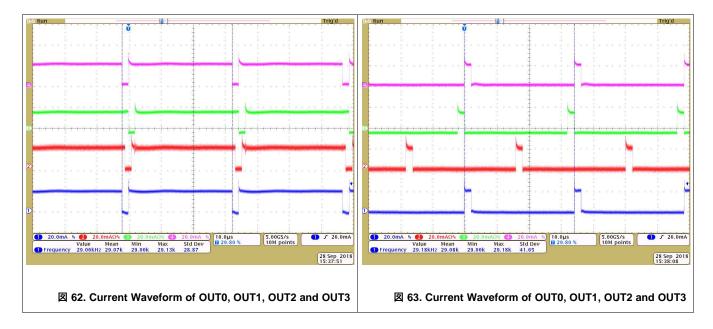

#### 8.3.1.4 PWM Phase-Shifting

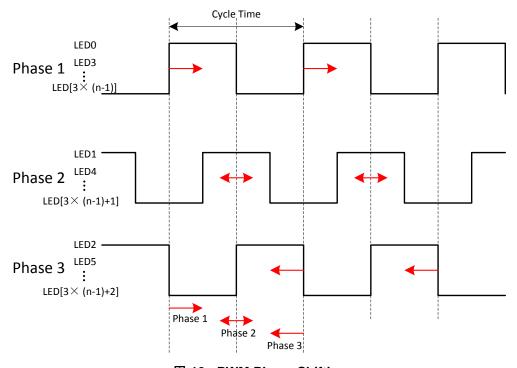

A PWM phase-shifting scheme allows delaying the time when each LED driver is active. When the LED drivers are not activated simultaneously, the peak load current from the pre-stage power supply is significantly decreased. The scheme also reduces input-current ripple and ceramic-capacitor audible ringing. LED drivers are grouped into three different phases.

- Phase 1—the rising edge of the PWM pulse is fixed. The falling edge of the pulse is changed when the duty cycle changes. Phase 1 is applied to LED0, LED3, ..., LED21.

- Phase 2—the middle point of the PWM pulse is fixed. The pulse spreads in both directions when the PWM duty cycle is increased. Phase 2 is applied to LED1, LED4, ..., LED22.

- Phase 3—the falling edge of the PWM pulse is fixed. The rising edge of the pulse is changed when the duty cycle changes. Phase 3 is applied to LED2, LED5, ..., LED23.

図 12. PWM Phase-Shifting

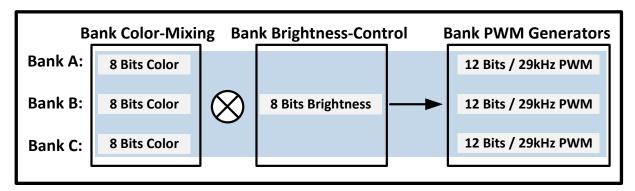

## 8.3.2 LED Bank Control

For most LED-animation effects, like blinking and breathing, all the RGB LEDs have the same lighting pattern. Instead of controlling the individual LED separately, which occupies the microcontroller resources heavily, the LP50xx device provides an easy coding approach, the LED bank control.

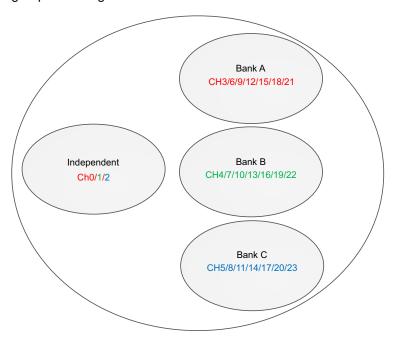

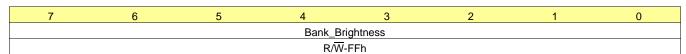

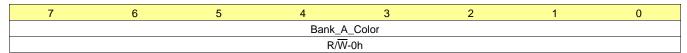

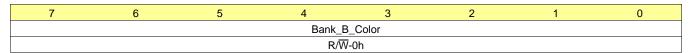

Each channel can be configured as either independent control or bank control through the LEDx\_Bank\_EN register. When LEDx\_Bank\_EN = 0 (default), the LED is controlled independently by the related color-mixing and intensity-control registers. When LEDx\_Bank\_EN = 1, the LP50xx device drives the LEDs in LED bank-control mode. The LED bank has its own independent PWM control scheme, which is the same structure as the PWM scheme of each channel. See PWM Control for Each Channel for more details. When a channel is configured in LED bank-control mode, the related color mixing and intensity control is governed by the bank control registers (BANK\_A\_COLOR, BANK\_B\_COLOR, BANK\_C\_COLOR, and BANK\_BRIGHTNESS) regardless of the inputs on its own color-mixing and intensity-control registers.

図 13. Bank PWM Control Scheme

# 表 1. Bank Number and LED Number Assignment

| OUT NUMBER          | BANK Number | RGB LED MODULE NUMBER |

|---------------------|-------------|-----------------------|

| OUT0                | Bank A      |                       |

| OUT1                | Bank B      | LED0                  |

| OUT2                | Bank C      |                       |

| OUT3                | Bank A      |                       |

| OUT4                | Bank B      | LED1                  |

| OUT5                | Bank C      |                       |

| OUT6                | Bank A      |                       |

| OUT7                | Bank B      | LED2                  |

| OUT8                | Bank C      |                       |

| OUT9                | Bank A      |                       |

| OUT10               | Bank B      | LED3                  |

| OUT11               | Bank C      |                       |

| OUT12               | Bank A      |                       |

| OUT13               | Bank B      | LED4                  |

| OUT14               | Bank C      |                       |

| OUT15               | Bank A      |                       |

| OUT16               | Bank B      | LED5                  |

| OUT17               | Bank C      |                       |

| OUT18 (LP5024 only) | Bank A      |                       |

| OUT19 (LP5024 only) | Bank B      | LED6                  |

| OUT20 (LP5024 only) | Bank C      |                       |

| OUT21 (LP5024 only) | Bank A      |                       |

| OUT22 (LP5024 only) | Bank B      | LED7                  |

| OUT23 (LP5024 only) | Bank C      |                       |

With the bank control configuration, the LP50xx device enables users to achieve smooth and live LED effects globally with an ultrasimple software effort. ☑ 14 shows an example using LED0 as an independent RGB indicator and others with group breathing effect.

図 14. Bank PWM Control Example

#### 8.3.3 Current Range Setting

The constant-current value ( $I_{SET}$ ) of all 24 channels is set by a single external resistor,  $R_{IREF}$ . The value of  $R_{IREF}$  can be calculated by  $\pm$  1.

$$R_{IREF} = K_{IREF} \times \frac{V_{IREF}}{I_{SFT}}$$

where:

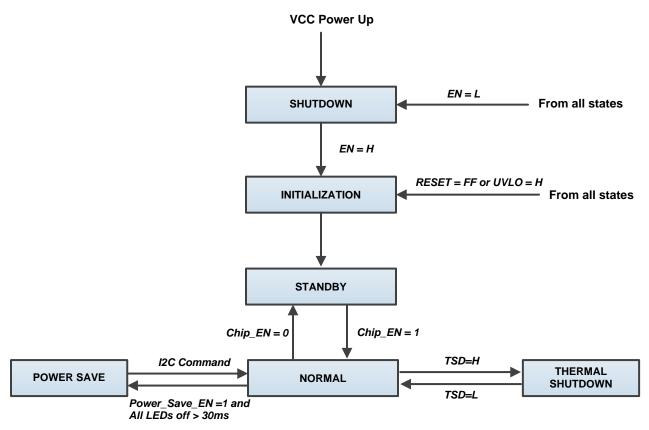

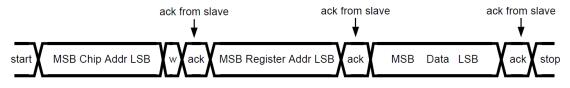

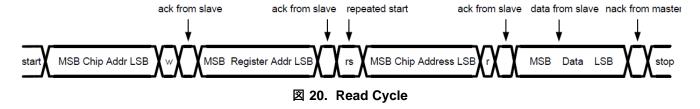

With the IREF pin floating, the output current is close to zero. With the IREF pin shorted to GND, the LP50xx device provides internal current-limit protection, and the output-channel maximum current is limited to I<sub>LIM</sub>.