# MSPM0C110x、MSPS003 ミックスド・シグナル・マイクロコントローラ

## 1 特長

- **コア**

- Arm® 32 ビット Cortex®-M0+ CPU、最大周波数 24MHz

- **動作特性**

- 拡張動作温度範囲: -40°C ~ 125°C

- 広い電源電圧範囲: 1.62V ~ 3.6V

- **メモリ**

- 最大 16KB のフラッシュ

- 1KB の SRAM

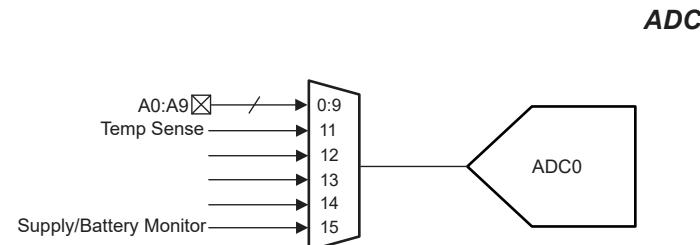

- **高性能アナログペリフェラル**

- 1 つの A/D コンバータ (ADC)、合計最大 10 本の外部チャネルを装備、VDD を電圧リファレンスとして使用して 1.7MSPS (10 ビット) または 1.5MSPS (12 ビット)

- 1.4V または 2.5V の構成可能な内部共有電圧リファレンス (VREF)

- 温度センサ内蔵

- 統合型電源監視

- **最適化された低消費電力モード**

- RUN: 87µA/MHz

- STOP: 4MHz で 609µA、32kHz で 311µA

- STANDBY: 5µA (SRAM 保持)

- SHUTDOWN: 200nA

- **インテリジェントデジタルペリフェラル**

- ADC 専用の 1 チャネル DMA コントローラ

- 最大 14 の PWM チャネルをサポートする 3 つのタイマ

- 1 つの 16 ビット高度タイマ、最大 8 個の PWM チャネルのデッドバンドをサポート

- 1 つの 16 ビット汎用タイマ、4 つのキャプチャ / コンパレータを搭載

- 1 つの 16 ビット汎用タイマ、2 つのキャプチャ / コンパレータを搭載

- ウィンドウ付きウォッチドッグタイマ

- 外部ビープ音を駆動するための 1kHz、2kHz、4kHz、または 8kHz の方形波を生成する BEEPER

- **拡張通信インターフェイス**

- 1 つの UART インターフェイス: LIN、IrDA、DALI、スマートカード、マンチェスターをサポート、STANDBY モードで低消費電力動作

- 1 つの I<sup>2</sup>C インターフェイス。FM+ (1Mbps)、SMBus、PMBus、STOP モードからのウェークアップをサポート

- 最大 12Mbps をサポートする 1 つの SPI

- **クロックシステム**

- -2% ~ +1.2% の精度 (SYSOSC) の 24MHz 発振器を内蔵

- 32kHz の低周波数発振器 (LFOSC) を内蔵

- **データの整合性**

- 巡回冗長検査 (CRC-16)

- **柔軟な I/O 機能**

- 最大 18 の GPIO

- 2 つの 5V 許容オープンドレイン IO

- **開発サポート**

- 2 ピンシリアルワイヤデバッグ (SWD)

- **パッケージオプション**

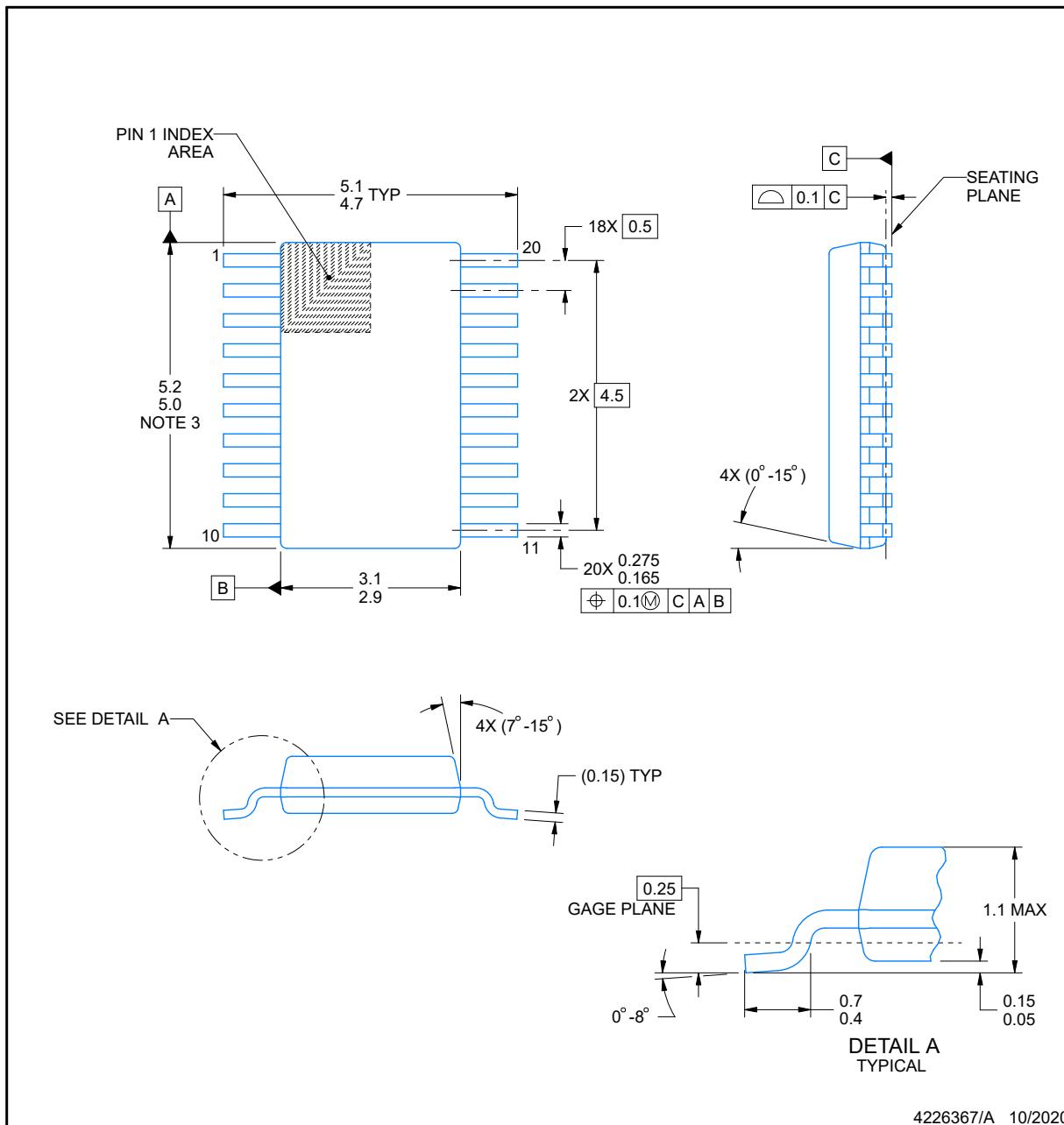

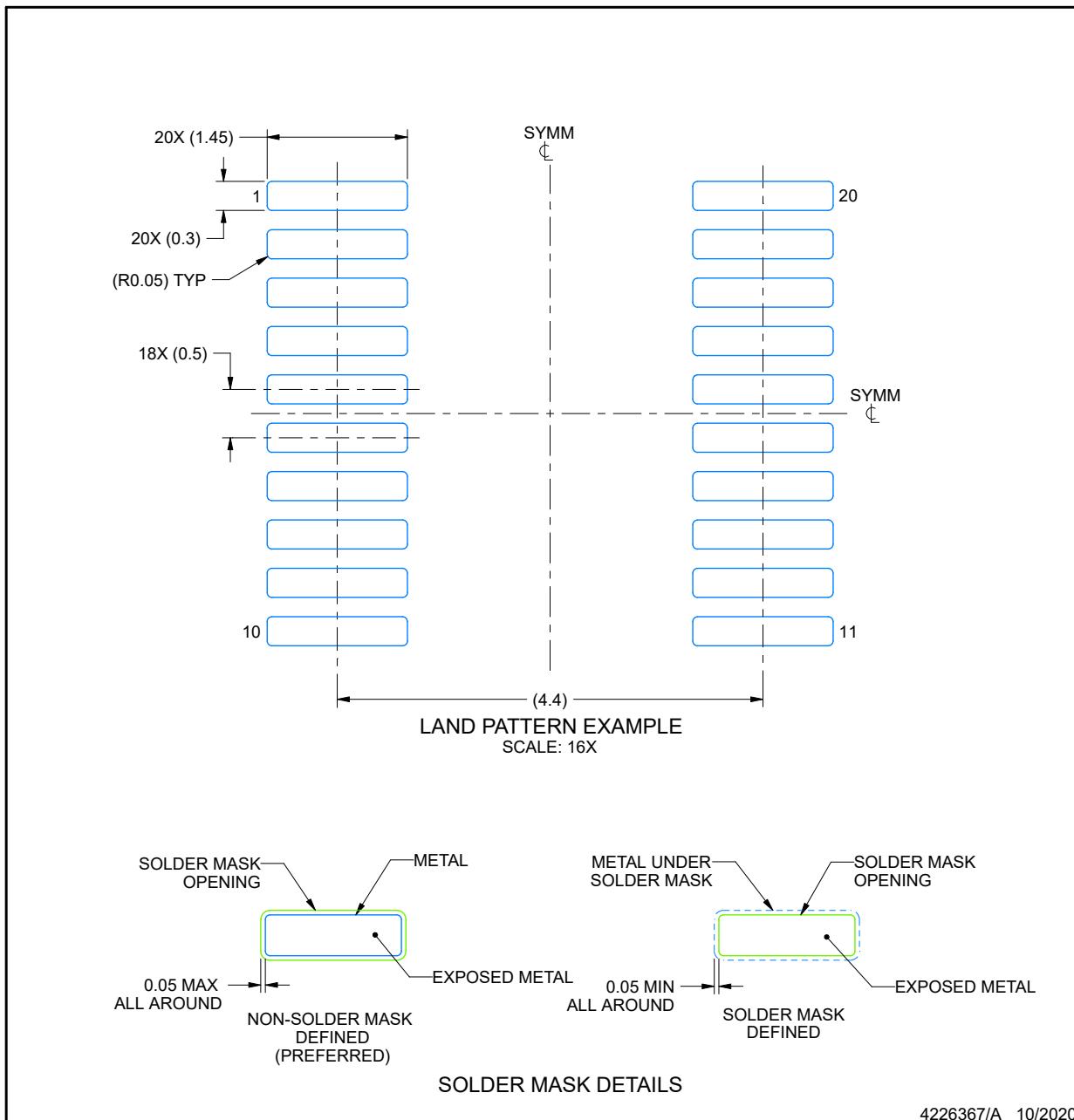

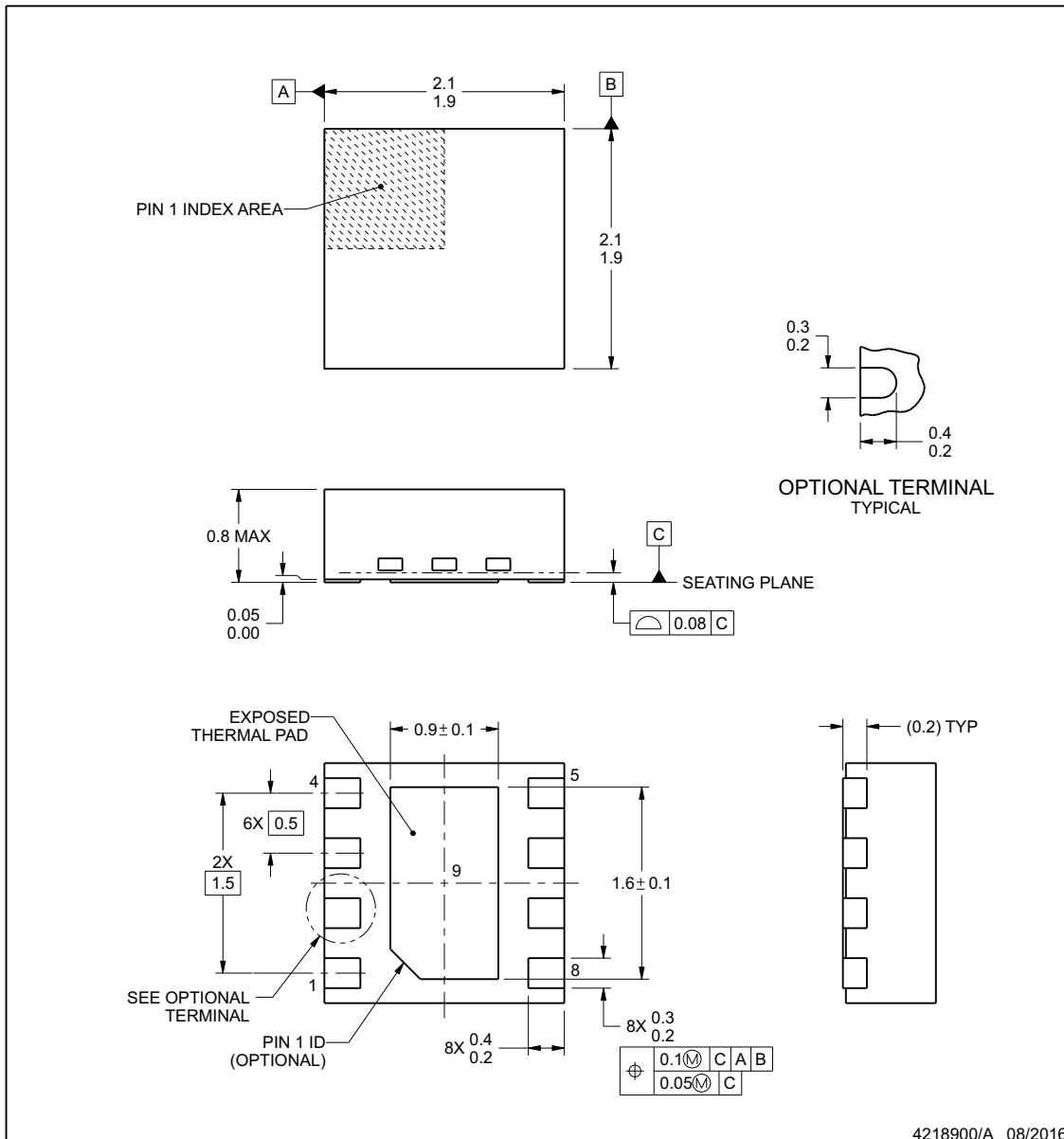

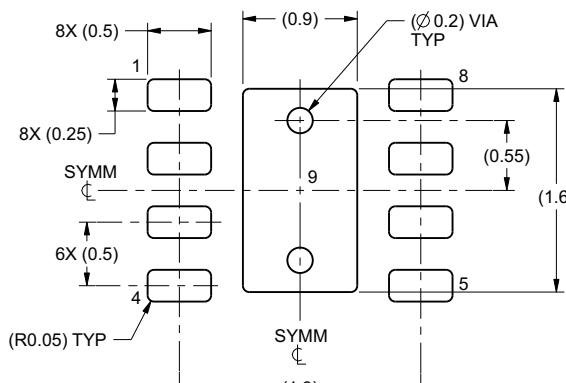

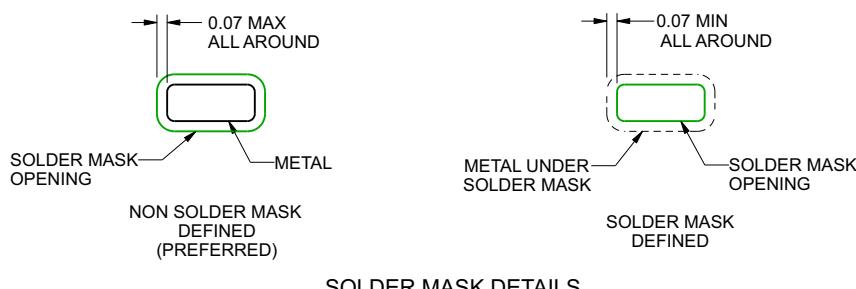

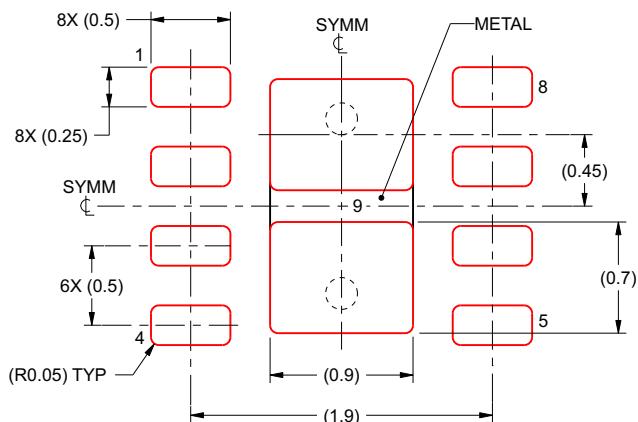

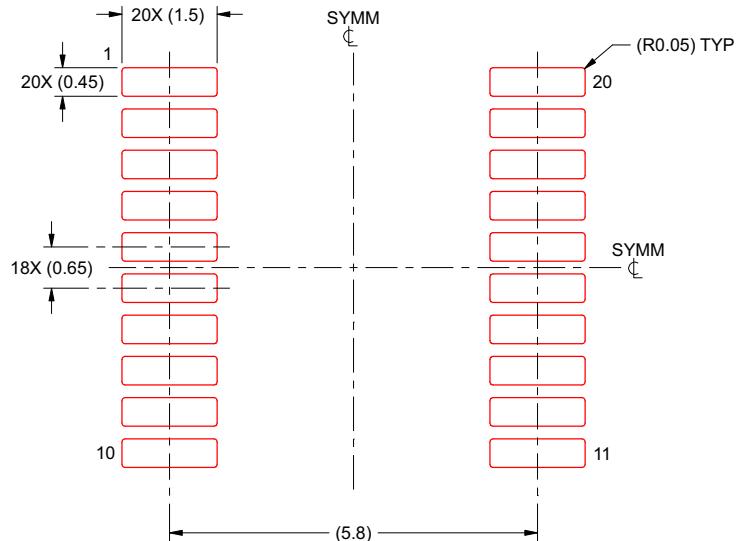

- 20 ピン TSSOP (PW)

- 20 ピン VSSOP (DGS)

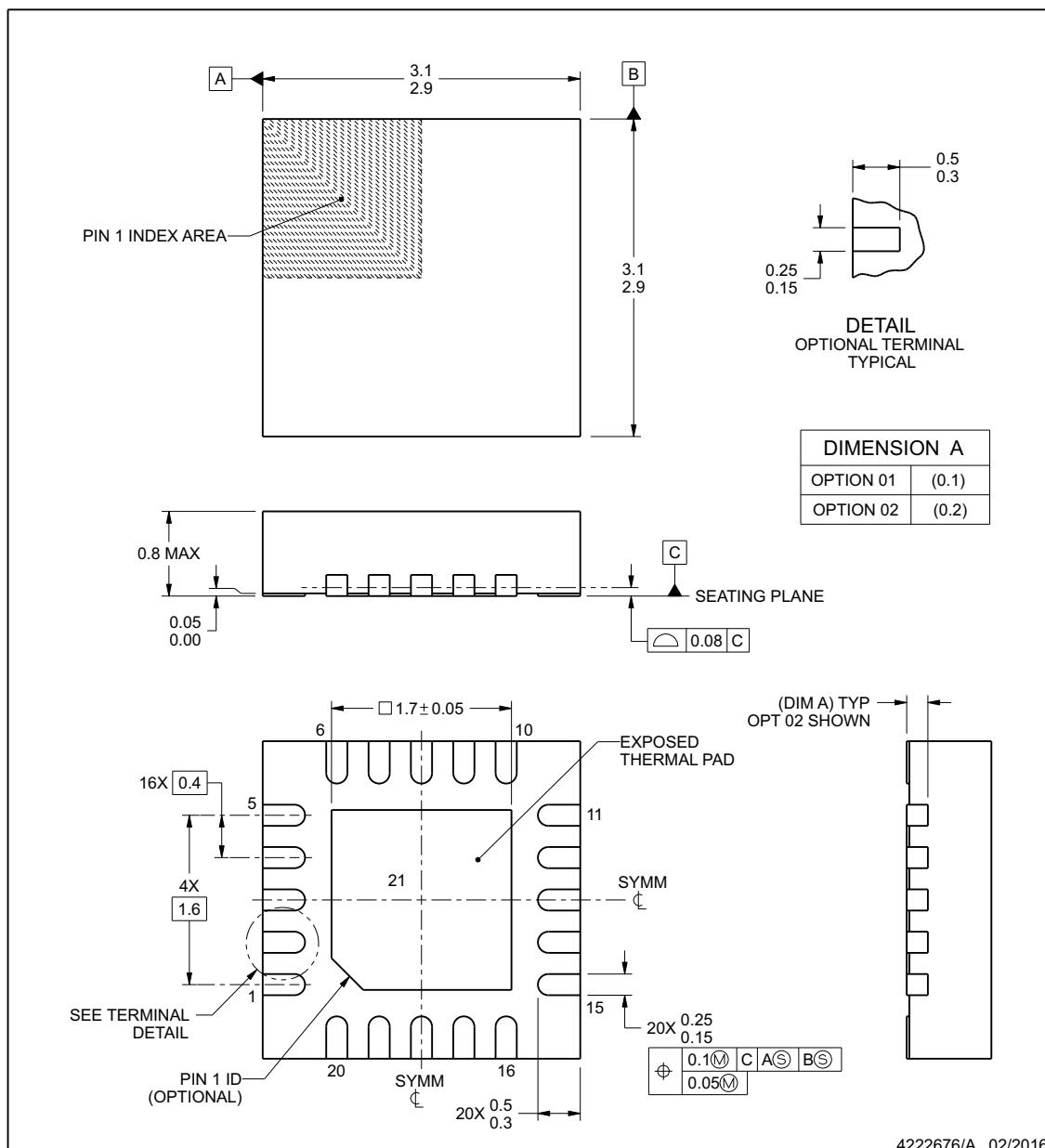

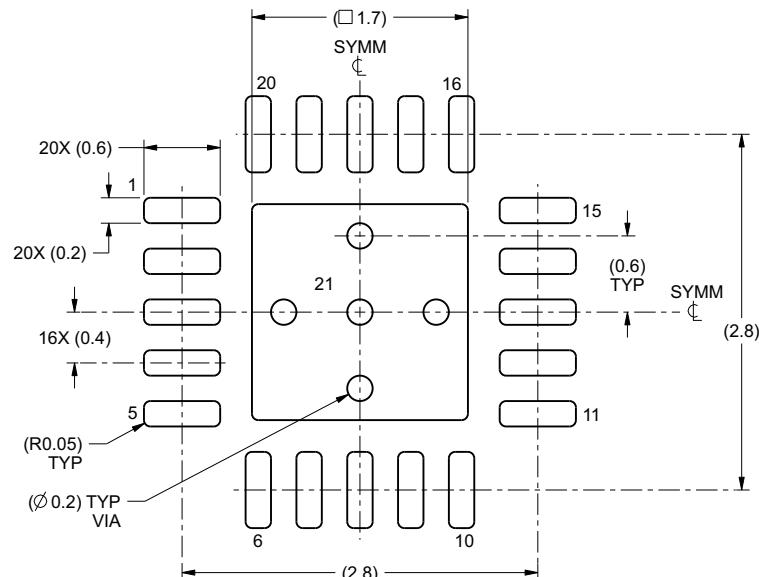

- 20 ピン WQFN (RUK)

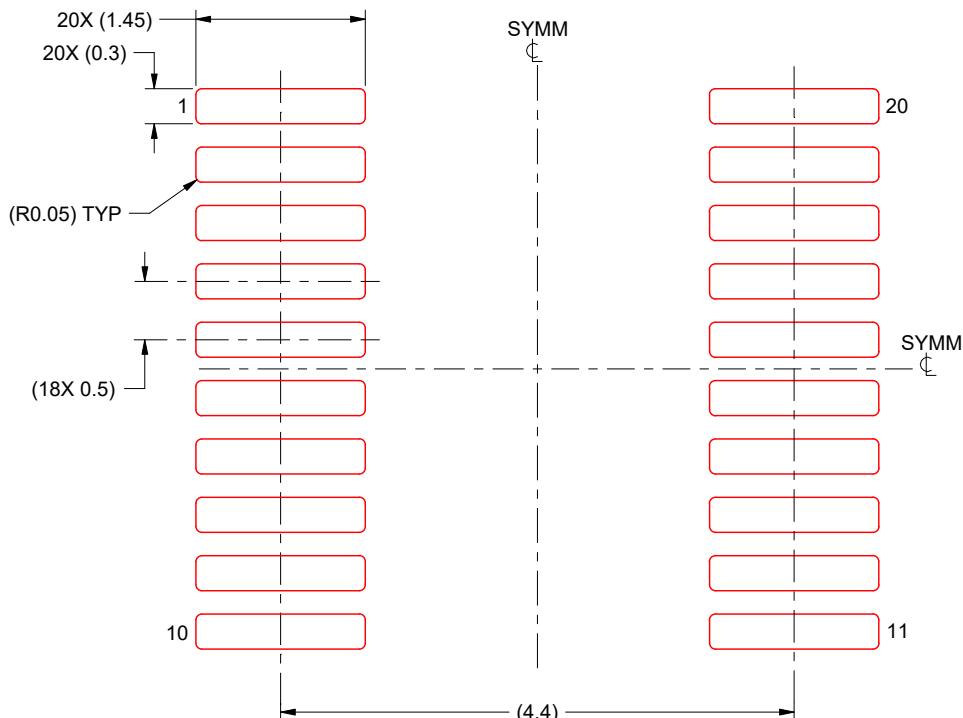

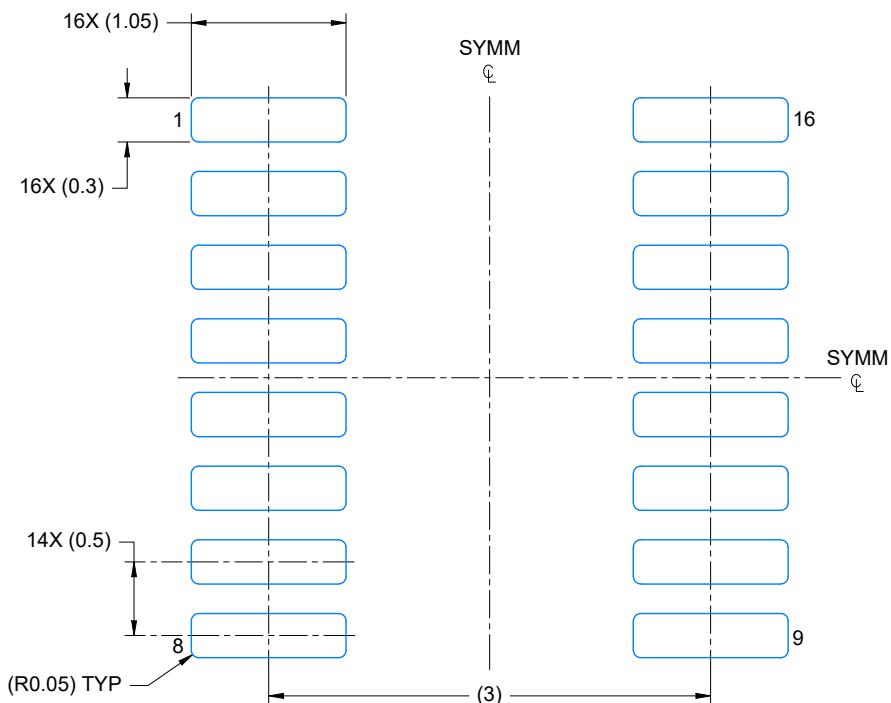

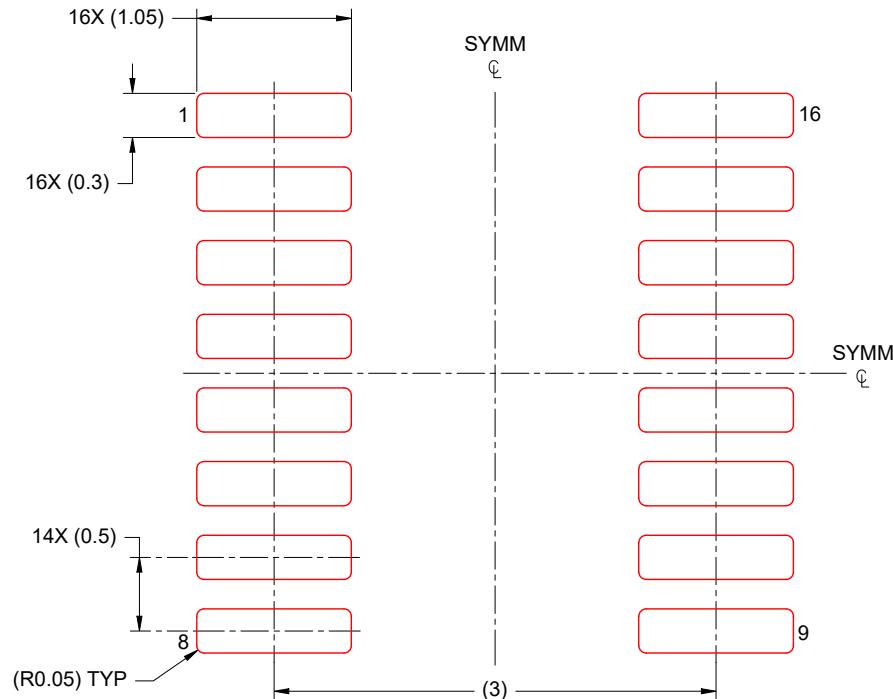

- 16 ピン SOT (DYY)

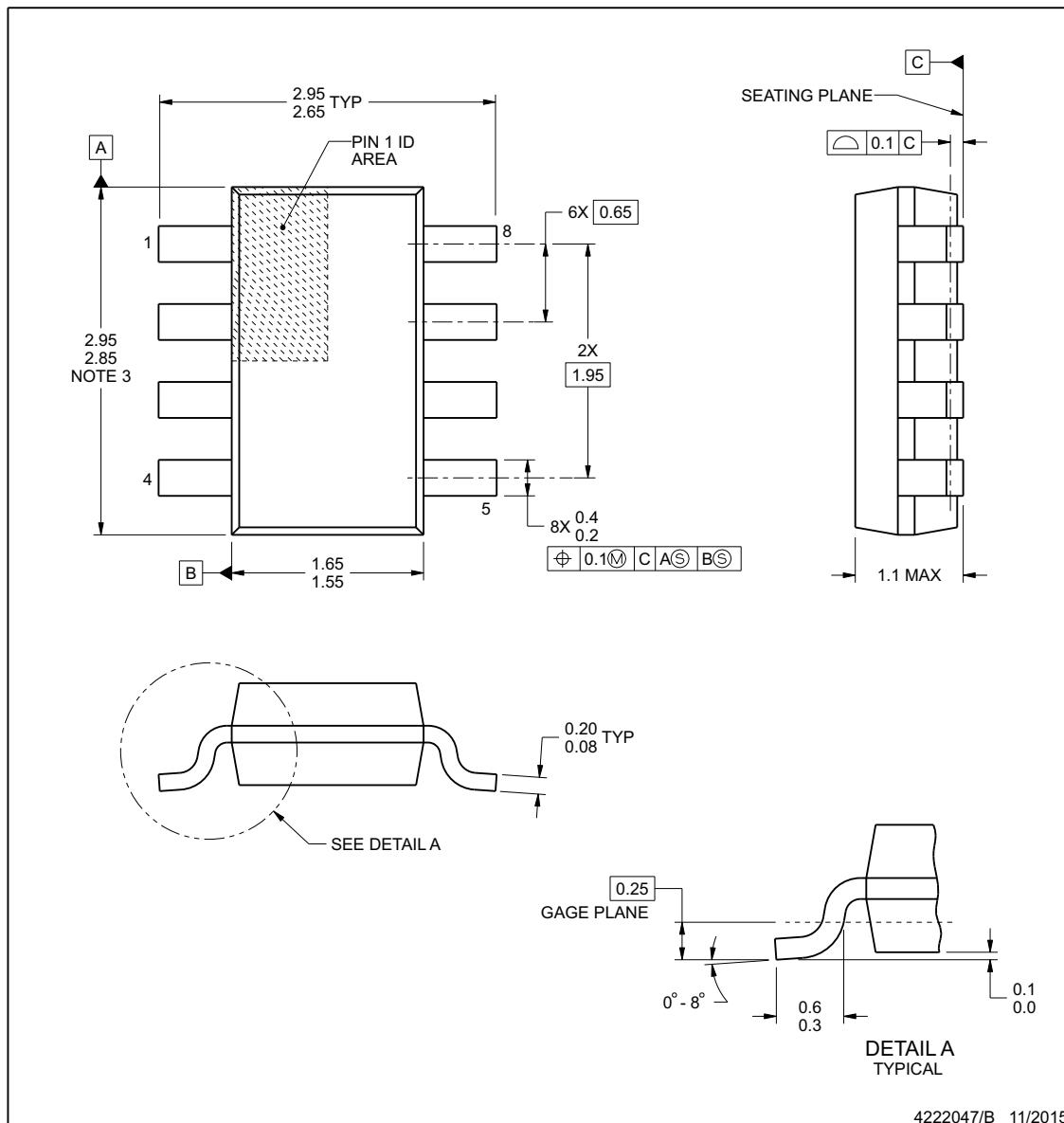

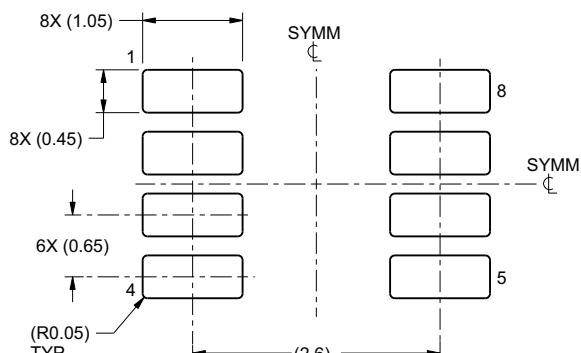

- 8 ピン SOT (DDF)

- 8 ピン WSON (DSG)

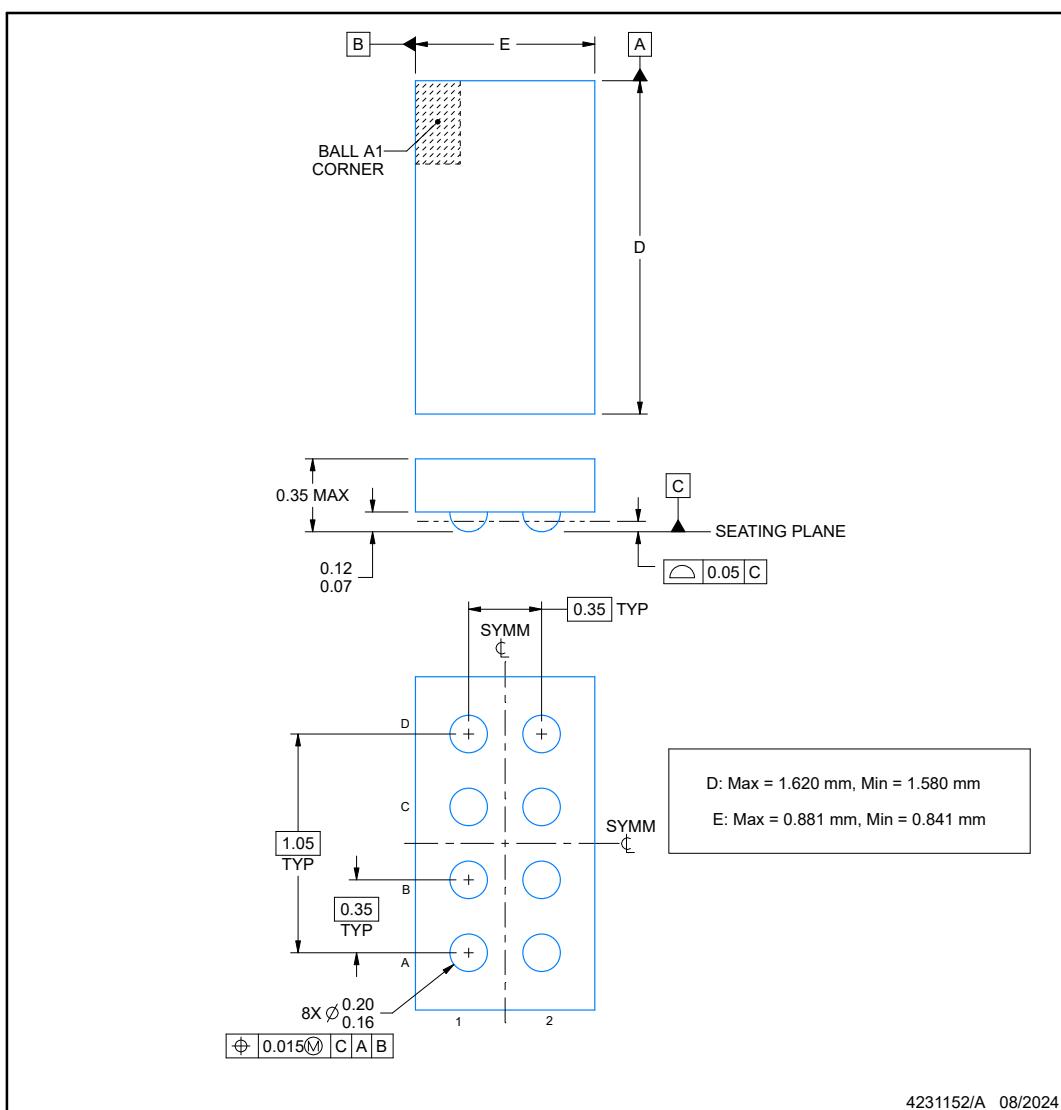

- 8 ピン DSBGA (Y CJ)

- **ファミリ製品** (「[デバイスの比較](#)」も参照)

- MSPS003F4: 16KB のフラッシュ、1KB の RAM

- MSPS003F3: 8KB のフラッシュ、1KB の RAM

- MSPM0C1104: 16KB のフラッシュ、1KB の RAM

- MSPM0C1103: 8KB のフラッシュ、1KB の RAM

- **開発キットとソフトウェア** (「[ツールとソフトウェア](#)」も参照)

- LP-MSPM0C1104 LaunchPad™ 開発キット

- MSP ソフトウェア開発キット (SDK)

## 2 アプリケーション

- バッテリ充電 / 管理

- 電源と電力供給

- パーソナル・エレクトロニクス

- ビル・セキュリティと防火

- ネットワーク接続の周辺機器とプリンタ

- グリッド・インフラストラクチャ

- スマート・メーター

- 通信モジュール

- 医療 / ヘルスケア

- 照明器具

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあります。TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

### 3 概要

MSPM0C110x マイクロコントローラ (MCU) は、最大 24MHz の周波数で動作する拡張 Arm® Cortex®-M0+ コア プラットフォームに基づく MSP 高集積超低消費電力 32 ビット MCU ファミリーの一部です。コスト最適化されたこれらの MCU は高性能アナログ ペリフェラルを統合しており、-40°C~125°C の拡張温度範囲をサポートしており、1.62V~3.6V の電源電圧で動作します。

MSPM0C110x デバイスは最大 16KB の組込みフラッシュ プログラム メモリと 1KB の SRAM を内蔵しています。これらの MCU は -2% ~ +1.2% の精度の高速オンチップ発振器を内蔵しているため、外部水晶振動子は不要です。追加機能には、1 チャネル DMA、CRC-16 アクセラレータ、各種の高性能アナログ ペリフェラル (電圧リファレンスとして VDD を含む 12 ビット 1.5Msps ADC、1 つのオンチップ温度センサなど) が含まれます。これらのデバイスは、1 つの 16 ビット高度タイマ、2 つの 16 ビット汎用タイマ、1 つのウインドウ付きウォッチドッグ タイマ、各種通信ペリフェラル (1 つの UART、1 つの SPI、1 つの I<sup>2</sup>C など) などのインテリジェントなデジタル ペリフェラルも備えています。これらの通信ペリフェラルは LIN、IrDA、DALI、マンチェスター、スマート カード、SMBus、PMBus プロトコルをサポートしています。

テキサス・インスツルメンツの MSPM0 低消費電力 MCU ファミリーは、各種のアナログおよびデジタル集積度のデバイスで構成されているため、お客様はプロジェクトのニーズを満たす MCU を見つけることができます。そのアーキテクチャと豊富な低消費電力モードは、携帯型測定アプリケーションで長いバッテリ駆動時間を実現するように最適化されています。

MSPM0C110x MCU は、広範囲にわたるハードウェアおよびソフトウェアのエコシステムによってサポートされており、リフアレンス デザインやコード サンプルを使って設計をすぐに開始できます。開発キットには、購入可能な LaunchPad™ キットとターゲット ソケット ボード用の設計ファイルが含まれています。また、テキサス・インスツルメンツは無償の MSP ソフトウェア開発キット (SDK) も提供しており、[Code Composer Studio™ IDE](#) デスクトップのコンポーネントとして利用できます。また、[TI Resource Explorer](#) ではクラウド バージョンを利用できます。MSPM0 MCU には、広範囲にわたるオンライン資料、[MSP Academy](#) によるトレーニング、[TI E2E™ サポート フォーラム](#)によるオンライン サポートも用意されています。

モジュールの詳細については、『[MSPM0 C シリーズ 24MHz マイクロコントローラ テクニカル リファレンス マニュアル](#)』を参照してください。

#### 注意

電気的な過剰ストレスや、データやコード メモリの不安定化を防止するために、デバイス レベルの ESD 仕様に従って、システム レベルの ESD 保護を適用する必要があります。詳細については、『[MSP430™ のシステム レベルの ESD に関する考慮事項](#)』を参照してください (このアプリケーション ノートの原理は MSPM0 MCU にも当てはまるため)。

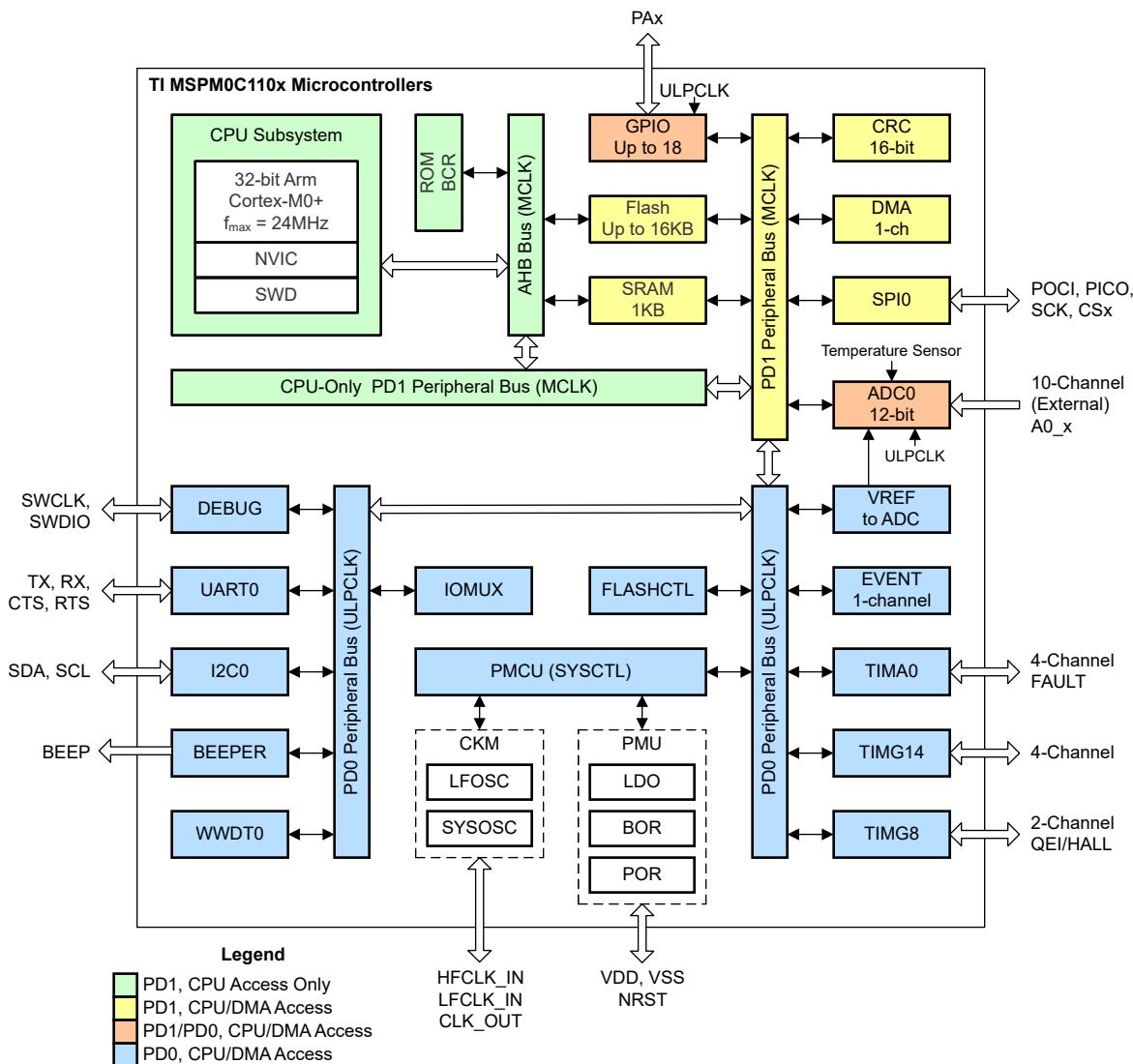

## 4 機能ブロック図

図 4-1. MSPM0C110x の機能ブロック図

## 目次

|                           |    |                               |    |

|---------------------------|----|-------------------------------|----|

| <b>1 特長</b>               | 1  | 8.4 クロック モジュール (CKM)          | 28 |

| <b>2 アプリケーション</b>         | 1  | 8.5 DMA                       | 28 |

| <b>3 概要</b>               | 2  | 8.6 イベント                      | 29 |

| <b>4 機能ブロック図</b>          | 3  | 8.7 メモリ                       | 29 |

| <b>5 デバイスの比較</b>          | 5  | 8.8 フラッシュ メモリ                 | 31 |

| <b>6 ピン構成および機能</b>        | 6  | 8.9 SRAM                      | 31 |

| 6.1 ピン配置図                 | 6  | 8.10 GPIO                     | 31 |

| 6.2 ピン属性                  | 8  | 8.11 IOMUX                    | 32 |

| 6.3 信号の説明                 | 9  | 8.12 ADC                      | 32 |

| 6.4 未使用ピンの接続              | 11 | 8.13 溫度センサ                    | 32 |

| <b>7 仕様</b>               | 12 | 8.14 VREF                     | 33 |

| 7.1 絶対最大定格                | 12 | 8.15 CRC                      | 33 |

| 7.2 ESD 定格                | 12 | 8.16 UART                     | 33 |

| 7.3 推奨動作条件                | 12 | 8.17 SPI                      | 34 |

| 7.4 熱に関する情報               | 13 | 8.18 I2C                      | 34 |

| 7.5 電源電流特性                | 14 | 8.19 WWDT                     | 35 |

| 7.6 電源シーケンス               | 15 | 8.20 タイマ (TIMx)               | 35 |

| 7.7 フラッシュ メモリの特性          | 16 | 8.21 デバイスのアナログ接続              | 37 |

| 7.8 タイミング特性               | 17 | 8.22 入力 / 出力の回路図              | 38 |

| 7.9 クロック仕様                | 17 | 8.23 シリアル ワイヤ デバッグ インターフェイス   | 38 |

| 7.10 デジタル IO              | 18 | 8.24 デバイス ファクトリ定数             | 39 |

| 7.11 ADC                  | 19 | 8.25 識別                       | 39 |

| 7.12 溫度センサ                | 21 | <b>9 アプリケーション、実装、およびレイアウト</b> | 40 |

| 7.13 VREF                 | 21 | 9.1 代表的なアプリケーション              | 40 |

| 7.14 I2C                  | 21 | <b>10 デバイスおよびドキュメントのサポート</b>  | 41 |

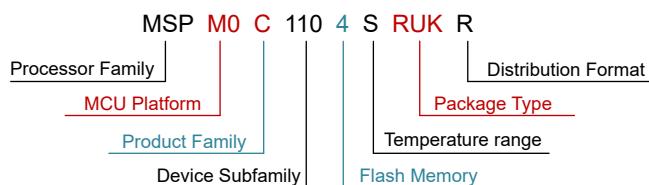

| 7.15 SPI                  | 22 | 10.1 デバイスの命名規則                | 41 |

| 7.16 UART                 | 24 | 10.2 ツールとソフトウェア               | 42 |

| 7.17 TIMx                 | 25 | 10.3 ドキュメントのサポート              | 42 |

| 7.18 ウィンドウ付きウォッチドッグの特性    | 25 | 10.4 サポート・リソース                | 43 |

| 7.19 エミュレーションおよびデバッグ      | 25 | 10.5 商標                       | 43 |

| <b>8 詳細説明</b>             | 26 | 10.6 静電気放電に関する注意事項            | 43 |

| 8.1 CPU                   | 26 | 10.7 用語集                      | 43 |

| 8.2 動作モード                 | 26 | <b>11 改訂履歴</b>                | 43 |

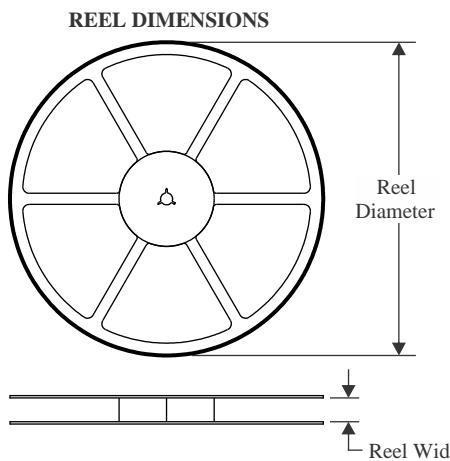

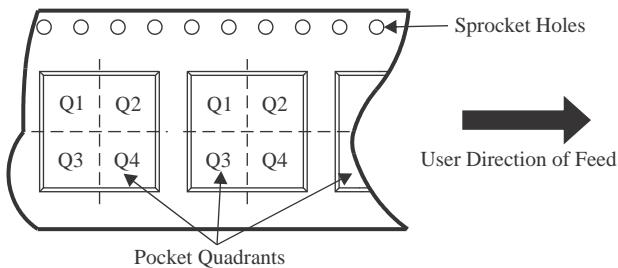

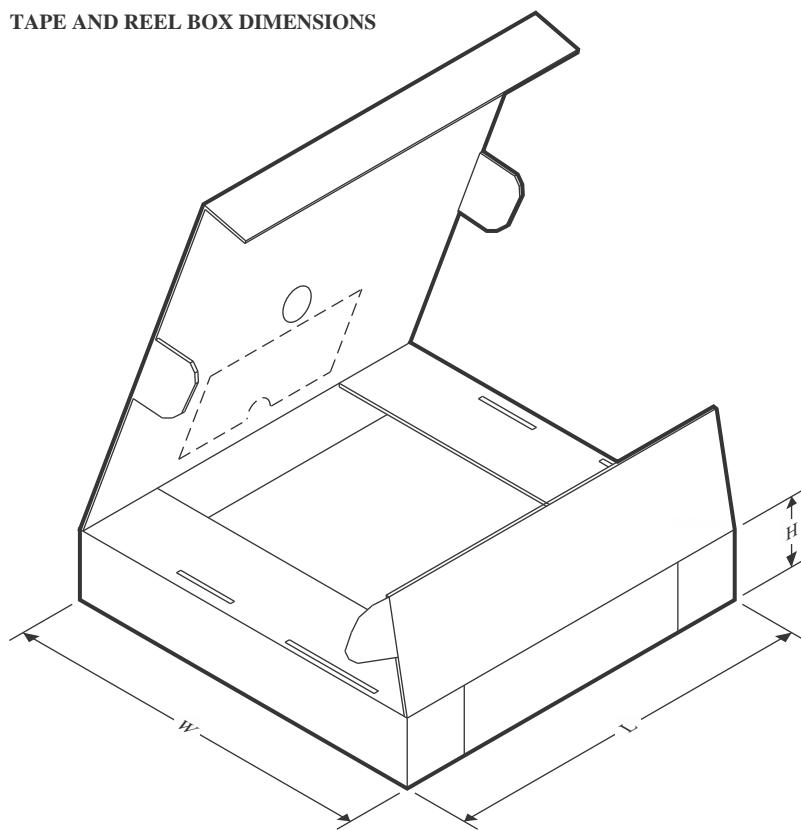

| 8.3 パワー マネジメント ユニット (PMU) | 28 | <b>12 メカニカル、パッケージ、および注文情報</b> | 44 |

## 5 デバイスの比較

**表 5-1. デバイスの比較**

| 型番 <sup>(1) (3)</sup> | フラッシュ /<br>SRAM (KB) | ADC チャネル | UART / I2C /<br>SPI | TIMG | TIMA | GPIO | 5V 許容の<br>IO | パッケージ<br>[パッケージ サイズ] <sup>(2)</sup> |

|-----------------------|----------------------|----------|---------------------|------|------|------|--------------|-------------------------------------|

| MSPS003F4SPW20R       | 16 / 1               | 9        | 1 / 1 / 1           | 2    | 1    | 17   | 2            | 20 TSSOP<br>[6.5mm × 5.0mm]         |

| MSPS003F3SPW20R       | 8 / 1                |          |                     |      |      |      |              |                                     |

| MSPM0C1104SDGS20R     | 16 / 1               | 10       | 1 / 1 / 1           | 2    | 1    | 18   | 2            | 20 VSSOP<br>[5.1mm × 4.9mm]         |

| MSPM0C1103SDGS20R     | 8 / 1                |          |                     |      |      |      |              |                                     |

| MSPM0C1104SRUKR       | 16 / 1               | 10       | 1 / 1 / 1           | 2    | 1    | 18   | 2            | 20 WQFN<br>[3mm × 3mm]              |

| MSPM0C1103SRUKR       | 8 / 1                |          |                     |      |      |      |              |                                     |

| MSPM0C1104SDYYR       | 16 / 1               | 8        | 1 / 1 / 1           | 2    | 1    | 14   | 2            | 16 SOT<br>[4.2mm × 3.26mm]          |

| MSPM0C1103SDYYR       | 8 / 1                |          |                     |      |      |      |              |                                     |

| MSPM0C1104SDSGR       | 16 / 1               | 3        | 1 / 1 / 1           | 2    | 1    | 6    | 2            | 8 WSON<br>[2mm × 2mm]               |

| MSPM0C1103SDSGR       | 8 / 1                |          |                     |      |      |      |              |                                     |

| MSPM0C1104SDDFR       | 16 / 1               | 3        | 1 / 1 / 1           | 2    | 1    | 6    | 2            | 8 SOT<br>[2.9mm × 2.8mm]            |

| MSPM0C1103SDDFR       | 8 / 1                |          |                     |      |      |      |              |                                     |

| MSPM0C1104S8YCJR      | 16 / 1               | 3        | 1 / 1 / 1           | 2    | 1    | 6    | 2            | 8 DSBGA<br>[1.6mm × 0.86mm]         |

| MSPM0C1103S8YCJR      | 8 / 1                |          |                     |      |      |      |              |                                     |

- (1) 提供中の全デバイスに関する最新の製品、パッケージ、および注文情報については、[セクション 12](#) の「付録: パッケージオプション」または [TI Web サイト](#)を参照してください。

- (2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。公差を含めたパッケージの寸法については、[セクション 12](#) の「メカニカル データ」を参照してください。

- (3) 型番の詳細については、[セクション 10.1](#) を参照してください。

## 6 ピン構成および機能

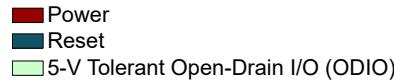

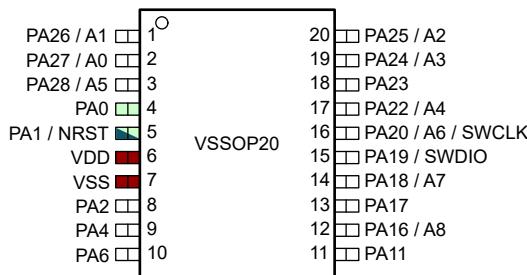

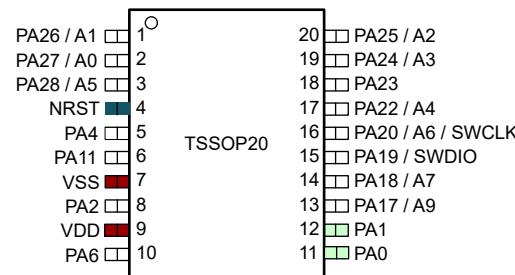

### 6.1 ピン配置図

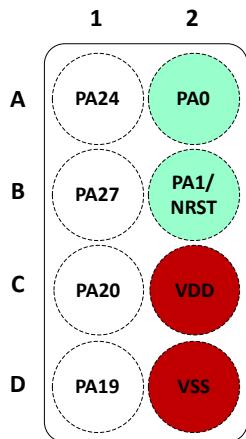

図 6-1. ピン配置図の色分け

図 6-2. 20 ピン DGS20 (VSSOP) (上面図)

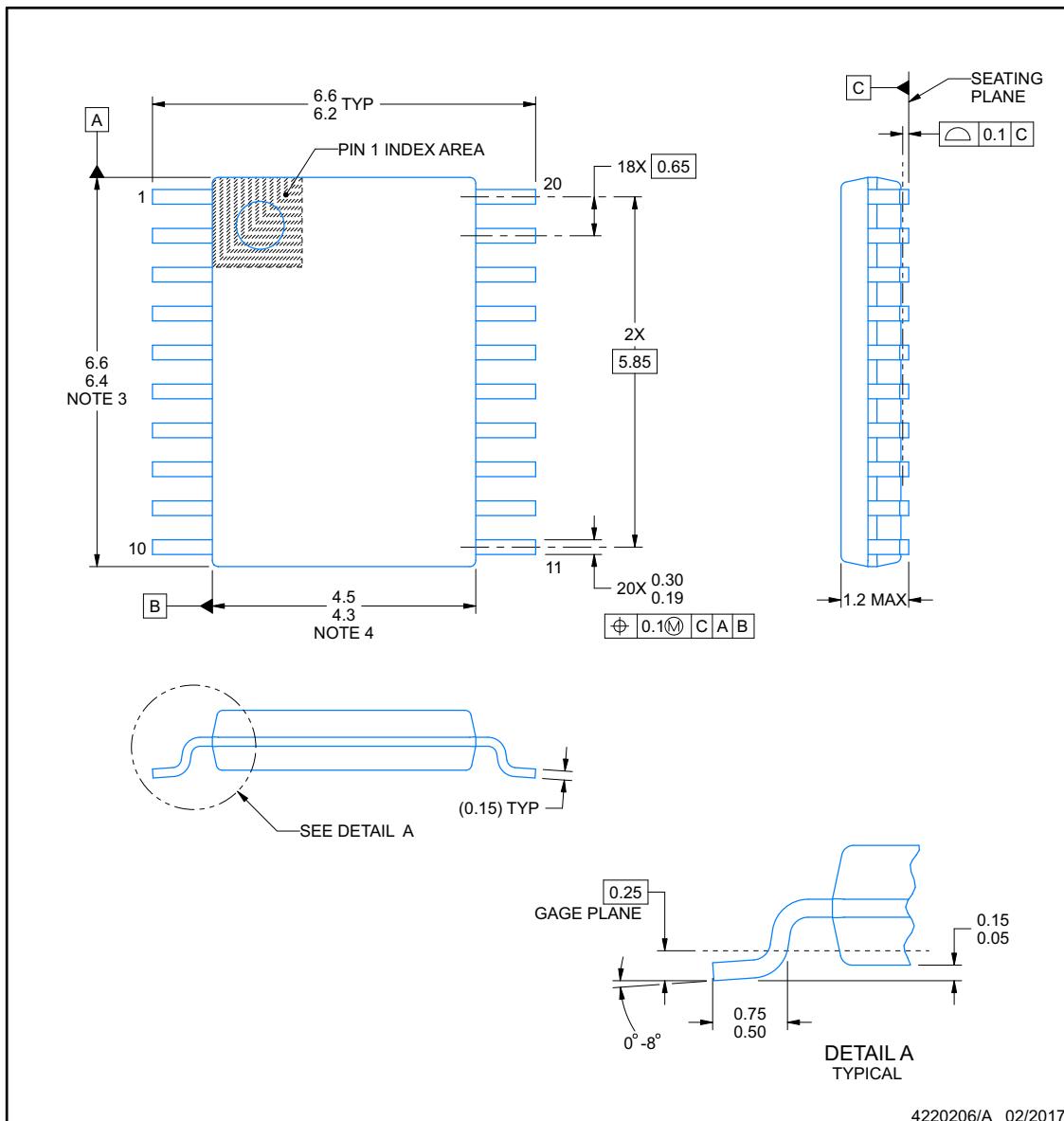

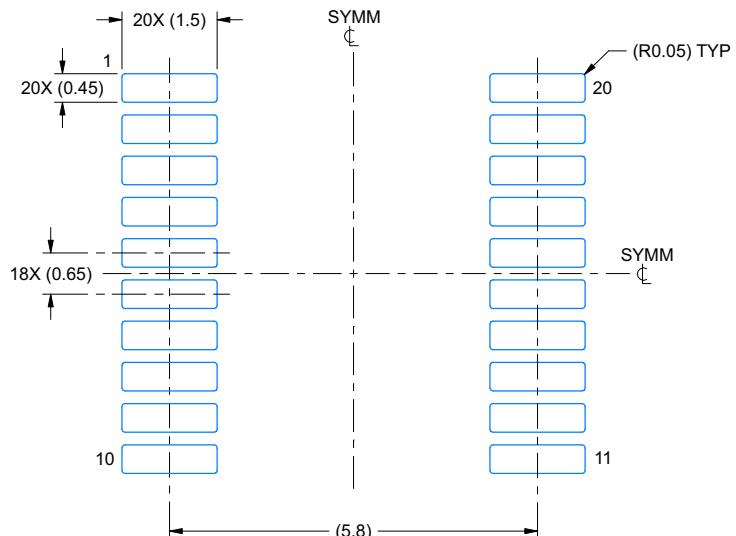

図 6-3. 20 ピン PW20 (TSSOP) (上面図)

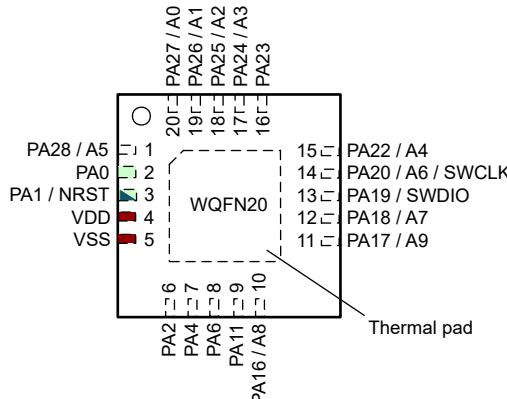

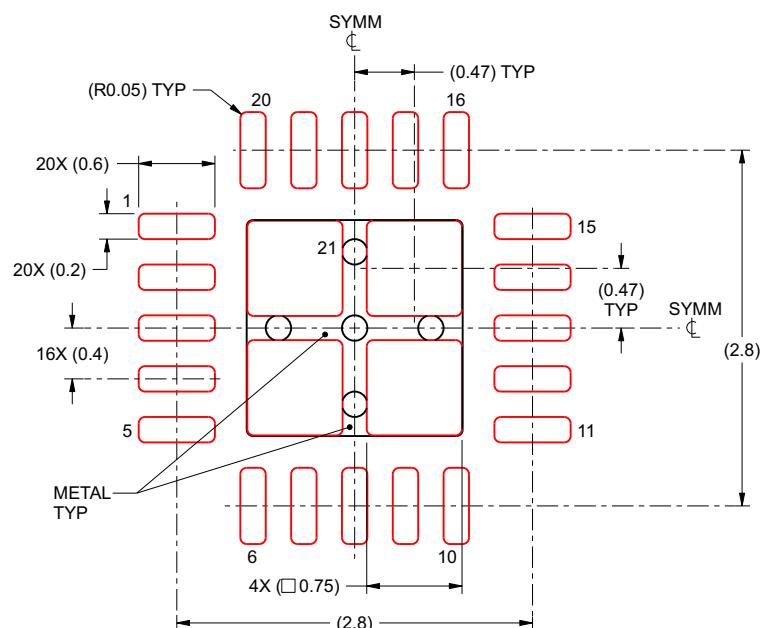

図 6-4. 20 ピン RUK (WQFN) (上面図)

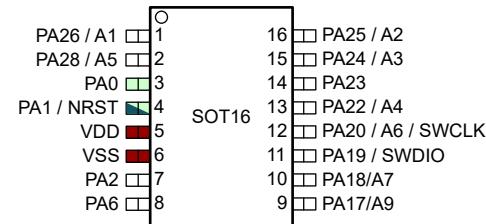

図 6-5. 16 ピン DYY (SOT) (上面図)

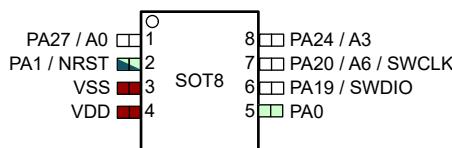

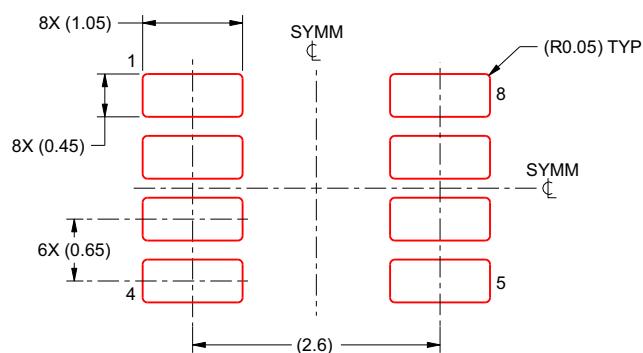

図 6-6. 8 ピン DDF (SOT) (上面図)

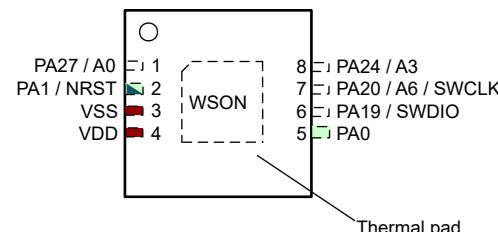

図 6-7. 8 ピン DSG (WSON) (上面図)

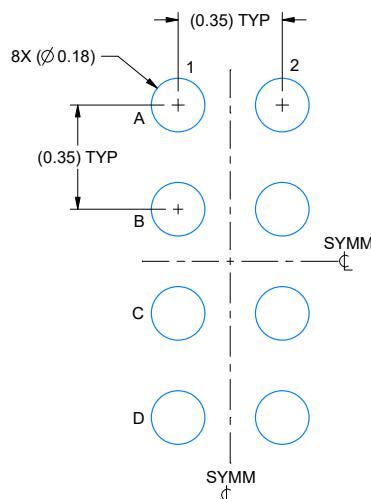

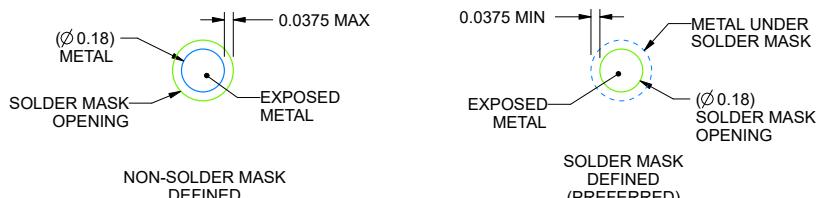

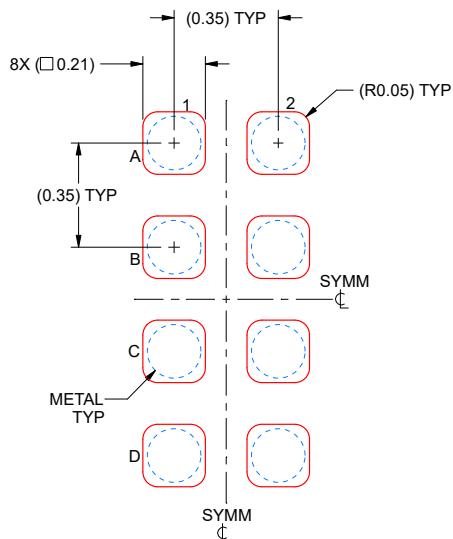

図 6-8. 8 ピン YCJ (DSBGA) (バンプを下にした図)

## 6.2 ピン属性

次の表に、各デバイス パッケージの各ピンで利用可能な機能を示します。

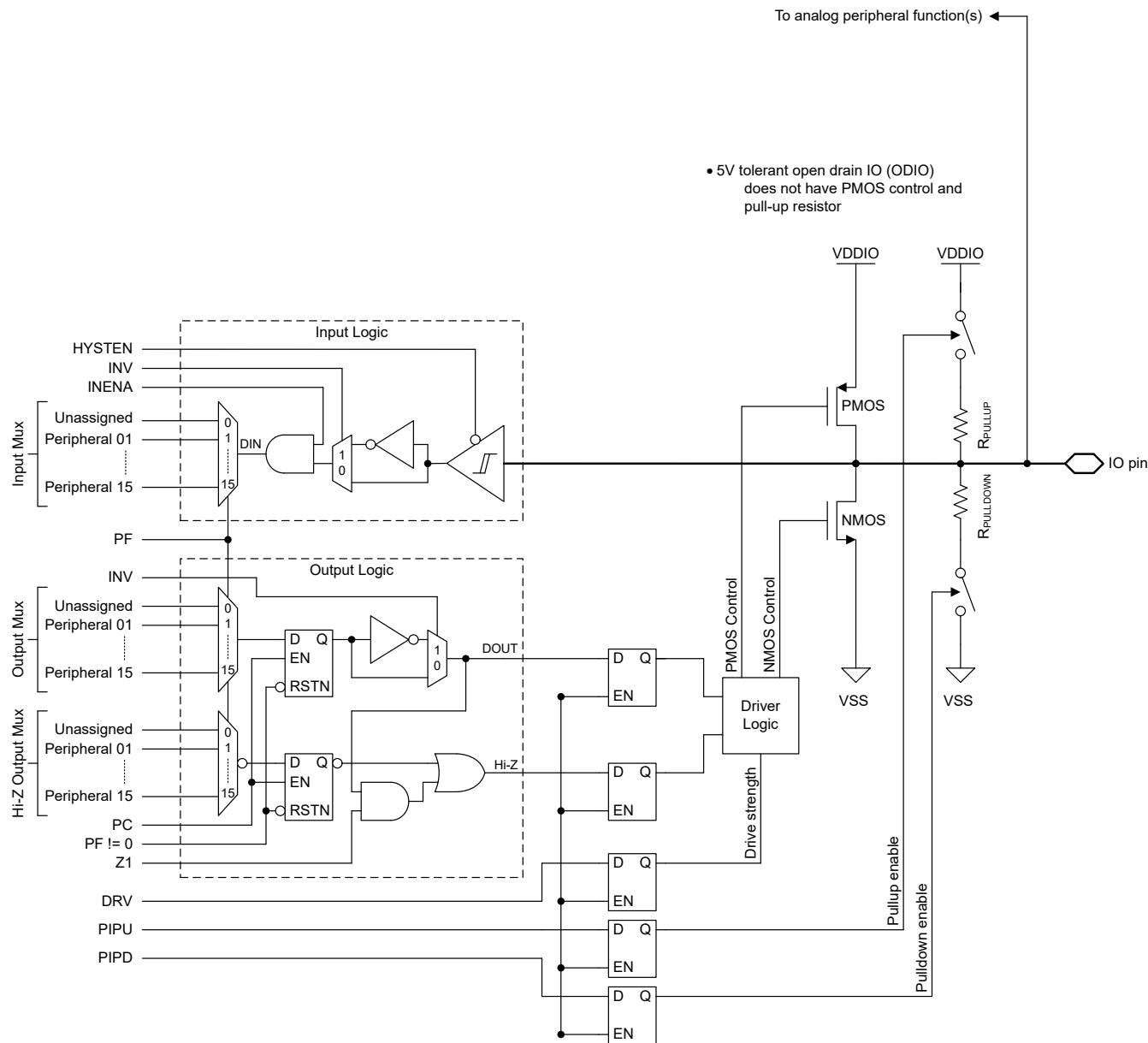

### 注

デバイス上の各デジタル I/O は、専用のピン制御管理レジスタ (PINCMx) に割り当てられており、ユーザーが PINCM.PF 制御ビットを使って必要なピン機能を設定できます。

**表 6-1. ピン属性**

| PINCM<br>x | ピン機能 |      |                                                                                       | ピン番号     |          |         |        |       |        |         |  | I/O 構造        |

|------------|------|------|---------------------------------------------------------------------------------------|----------|----------|---------|--------|-------|--------|---------|--|---------------|

|            | ピン名  | アナログ | デジタル <sup>(1)</sup>                                                                   | 20 VSSOP | 20 TSSOP | 20 WQFN | 16 SOT | 8 SOT | 8 WSON | 8 DSBGA |  |               |

| 該当なし       | VDD  |      |                                                                                       | 6        | 9        | 4       | 5      | 4     | 4      | C2      |  | 電源            |

| 該当なし       | VSS  |      |                                                                                       | 7        | 7        | 5       | 6      | 3     | 3      | D2      |  | 電源            |

| 1          | PA0  |      | BEEP [2] / I2C0_SDA [3] / TIMG8_C0 [4] / SPI0_CS1 [5] / FCC_IN [6] / TIMA_FAL1 [7]    | 4        | 11       | 2       | 3      | 5     | 5      | A2      |  | 5V 許容オーブンドレイン |

| 2          | PA1  |      | I2C0_SCL [2] / TIM8_C0 [3] / HFCLK_IN [4] / TIMA0_C1 [5]                              | 5        | 12       | 3       | 4      | 2     | 2      | B2      |  | 5V 許容オーブンドレイン |

| 該当なし       |      | NRST |                                                                                       |          | 4        |         |        |       |        |         |  | リセット          |

| 3          | PA2  |      | TIMG8_C1[2] / SPI0_CS0[3] / TIMA0_C0[4] / TIMG8_IDX[5]                                | 8        | 8        | 6       | 7      | -     | -      | -       |  | 標準            |

| 5          | PA4  |      | TIMA0_C0N[2] / SPI0_POCI[3] / LFCLK_IN[4] / HFCLK_IN[5] / TIMA0_C1N[6]                | 9        | 5        | 7       | -      | -     | -      | -       |  | 標準            |

| 7          | PA6  |      | TIMG14_C1[2] / SPI0_SCK[3] / TIMA0_C1[4] / TIMG14_C2[5] / SPI0_CS0[6] / TIMA_FAL0[7]  | 10       | 10       | 8       | 8      | -     | -      | -       |  | 標準            |

| 12         | PA11 |      | SPI0_SCK[2] / I2C0_SCL[3] / TIMA_FAL0[4]                                              | 11       | 6        | 9       | -      | -     | -      | -       |  | 標準            |

| 17         | PA16 | A8   | TIMA0_C1N[2] / SPI0_POCI[3] / TIMG14_C0[4] / FCC_IN[5]                                | 12       | -        | 10      | -      | -     | -      | -       |  | 標準            |

| 18         | PA17 | A9   | UART0_TX[2] / TIMA0_C0N[3] / SPI0_SCK[4] / TIMA0_C2[5] / SPI0_CS1[6] / TIMA0_C3[7]    | 13       | 13       | 11      | 9      | -     | -      | -       |  | 標準            |

| 19         | PA18 | A7   | UART0_RX[2] / SPI0_PICO[3] / TIMA0_C1N[4] / CLK_OUT[5] / TIMA0_C3[6] / TIMA0_C3N[7]   | 14       | 14       | 12      | 10     | -     | -      | -       |  | 標準            |

| 20         | PA19 |      | SWDIO[2] / SPI0_SCK[3] / SPI0_POCI[4] / TIMA0_C2[5] / TIMG14_C0[6] / UART0_CTS[7]     | 15       | 15       | 13      | 11     | 6     | 6      | D1      |  | 標準            |

| 21         | PA20 | A6   | SWCLK[2] / TIMA_FAL1[3] / SPI0_PICO[4] / TIMA0_C2N[5] / TIMA0_C0[6] / UART0_RTS[7]    | 16       | 16       | 14      | 12     | 7     | 7      | C1      |  | 標準            |

| 23         | PA22 | A4   | UART0_RX[2] / SPI0_POCI[3] / UART0_RTS[4] / CLK_OUT[5] / TIMA0_C1[6]                  | 17       | 17       | 15      | 13     | -     | -      | -       |  | 標準            |

| 24         | PA23 |      | UART0_TX[2] / SPI0_CS3[3] / TIMG14_C0[4] / UART0_CTS[5] / TIMA0_C3[6] / TIMG14_C1[7]  | 18       | 18       | 16      | 14     | -     | -      | -       |  | 標準            |

| 25         | PA24 | A3   | SPI0_CS2[2] / TIMG14_C1[3] / UART0_RTS[4] / TIMG14_C2[5] / TIMA0_C3N[6] / UART0_RX[7] | 19       | 19       | 17      | 15     | 8     | 8      | A1      |  | 標準            |

| 26         | PA25 | A2   | TIMG14_C3[2] / UART0_TX[3] / SPI0_PICO[4] / TIMG14_C1[5] / TIMA_FAL2[6]               | 20       | 20       | 18      | 16     | -     | -      | -       |  | 標準            |

| 27         | PA26 | A1   | TIMG8_C0[2] / UART0_RX[3] / SPI0_POCI[4] / BEEP[5] / TIMG14_C0[6] / TIMA_FAL0[7]      | 1        | 1        | 19      | 1      | -     | -      | -       |  | 標準            |

| 28         | PA27 | A0   | TIMG8_C1[2] / SPI0_CS3[3] / TIMA0_C0N[4] / UART0_TX[5] / SPI0_POCI[6] / TIMA_FAL2[7]  | 2        | 2        | 20      | -      | 1     | 1      | B1      |  | 標準            |

**表 6-1. ピン属性 (続き)**

| PINCM<br>X | ピン機能 |      |                                          |  |  |  |  | ピン番号 |          |          |         | I/O 構造 |       |        |         |    |

|------------|------|------|------------------------------------------|--|--|--|--|------|----------|----------|---------|--------|-------|--------|---------|----|

|            | ピン名  | アナログ | デジタル <sup>(1)</sup>                      |  |  |  |  |      | 20 VSSOP | 20 TSSOP | 20 WQFN | 16 SOT | 8 SOT | 8 WSON | 8 DSBGA |    |

| 29         | PA28 | A5   | TIMA0_C0[2] / UART0_RX[3] / TIMG8_IDX[4] |  |  |  |  |      | 3        | 3        | 1       | 2      | -     | -      | -       | 標準 |

(1) IOMUX 内の PINCM.PF および PINCM.PC は、ADC 入力などのアナログ機能を使用する場合は 0 に設定する必要があります。デバイス上の各デジタル I/O は、専用のピン制御管理レジスタ (PINCMx) に割り当てられており、ユーザーが PINCM.PF 制御ビットを使って必要なピン機能を設定できます。

**表 6-2. IO タイプ別のデジタル IO 機能**

| IO 構造         | 反転制御 | 駆動能力制御 | ヒステリシス制御 | プルアップ抵抗 | プルダウン抵抗 |

|---------------|------|--------|----------|---------|---------|

| 標準駆動          | Y    |        |          | Y       | Y       |

| 5V 許容オーブンドレイン | Y    |        | Y        |         | Y       |

### 6.3 信号の説明

| 機能   | 信号名     | ピン番号 <sup>(1)</sup> |          |         |        |       |        |         | ピンの種類 <sup>(2)</sup> | 説明                       |  |  |

|------|---------|---------------------|----------|---------|--------|-------|--------|---------|----------------------|--------------------------|--|--|

|      |         | 20 VSSOP            | 20 TSSOP | 20 WQFN | 16 SOT | 8 SOT | 8 WSON | 8 DSBGA |                      |                          |  |  |

| ADC  | A0      | 2                   | 2        | 20      | -      | 1     | 1      | B1      | I                    | ADC0 アナログ入力 0            |  |  |

|      | A1      | 1                   | 1        | 19      | 1      | -     | -      | -       | I                    | ADC0 アナログ入力 1            |  |  |

|      | A2      | 20                  | 20       | 18      | 16     | -     | -      | -       | I                    | ADC0 アナログ入力 2            |  |  |

|      | A3      | 19                  | 19       | 17      | 15     | 8     | 8      | A1      | I                    | ADC0 アナログ入力 3            |  |  |

|      | A4      | 17                  | 17       | 15      | 13     | -     | -      | -       | I                    | ADC0 アナログ入力 4            |  |  |

|      | A5      | 3                   | 3        | 1       | 2      | -     | -      | -       | I                    | ADC0 アナログ入力 5            |  |  |

|      | A6      | 16                  | 16       | 14      | 12     | 7     | 7      | C1      | I                    | ADC0 アナログ入力 6            |  |  |

|      | A7      | 14                  | 14       | 12      | 10     | -     | -      | -       | I                    | ADC0 アナログ入力 7            |  |  |

|      | A8      | 12                  | -        | 10      | -      | -     | -      | -       | I                    | ADC0 アナログ入力 8            |  |  |

|      | A9      | 13                  | 13       | 11      | 9      | -     | -      | -       | I                    | ADC0 アナログ入力 9            |  |  |

| クロック | CLK_OUT | 14, 17              | 14, 17   | 12, 15  | 10, 13 | -     | -      | -       | O                    | 設定可能クロック出力               |  |  |

| デバッグ | SWDIO   | 15                  | 15       | 13      | 11     | 6     | 6      | D1      | I/O                  | シリアル ワイヤ デバッグ データ入力 / 出力 |  |  |

|      | SWCLK   | 16                  | 16       | 14      | 12     | 7     | 7      | C1      | I                    | シリアル ワイヤ デバッグ入力クロック      |  |  |

| GPIO | PA0     | 4                   | 11       | 2       | 3      | 5     | 5      | A2      | I/O                  | オーブンドレイン機能を備えた汎用デジタル I/O |  |  |

|      | PA1     | 5                   | 12       | 3       | 4      | 2     | 2      | B2      | I/O                  | オーブンドレイン機能を備えた汎用デジタル I/O |  |  |

|      | PA2     | 8                   | 8        | 6       | 7      | -     | -      | -       | I/O                  | 汎用デジタル I/O               |  |  |

|      | PA4     | 9                   | 5        | 7       | -      | -     | -      | -       | I/O                  | 汎用デジタル I/O               |  |  |

|      | PA6     | 10                  | 10       | 8       | 8      | -     | -      | -       | I/O                  | 汎用デジタル I/O               |  |  |

|      | PA11    | 11                  | 6        | 9       | -      | -     | -      | -       | I/O                  | 汎用デジタル I/O               |  |  |

|      | PA16    | 12                  | -        | 10      | -      | -     | -      | -       | I/O                  | 汎用デジタル I/O               |  |  |

|      | PA17    | 13                  | 13       | 11      | 9      | -     | -      | -       | I/O                  | 汎用デジタル I/O               |  |  |

|      | PA18    | 14                  | 14       | 12      | 10     | -     | -      | -       | I/O                  | 汎用デジタル I/O               |  |  |

|      | PA19    | 15                  | 15       | 13      | 11     | 6     | 6      | D1      | I/O                  | 汎用デジタル I/O               |  |  |

|      | PA20    | 16                  | 16       | 14      | 12     | 7     | 7      | C1      | I/O                  | 汎用デジタル I/O               |  |  |

|      | PA22    | 17                  | 17       | 15      | 13     | -     | -      | -       | I/O                  | 汎用デジタル I/O               |  |  |

|      | PA23    | 18                  | 18       | 16      | 14     | -     | -      | -       | I/O                  | 汎用デジタル I/O               |  |  |

|      | PA24    | 19                  | 19       | 17      | 15     | 8     | 8      | A1      | I/O                  | 汎用デジタル I/O               |  |  |

|      | PA25    | 20                  | 20       | 18      | 16     | -     | -      | -       | I/O                  | 汎用デジタル I/O               |  |  |

|      | PA26    | 1                   | 1        | 19      | 1      | -     | -      | -       | I/O                  | 汎用デジタル I/O               |  |  |

|      | PA27    | 2                   | 2        | 20      | -      | 1     | 1      | B1      | I/O                  | 汎用デジタル I/O               |  |  |

|      | PA28    | 3                   | 3        | 1       | 2      | -     | -      | -       | I/O                  | 汎用デジタル I/O               |  |  |

| 機能               | 信号名       | ピン番号 (1)             |                    |                       |               |       |        |         | ピンの種類<br>(2) | 説明                                                          |

|------------------|-----------|----------------------|--------------------|-----------------------|---------------|-------|--------|---------|--------------|-------------------------------------------------------------|

|                  |           | 20 VSSOP             | 20 TSSOP           | 20 WQFN               | 16 SOT        | 8 SOT | 8 WSON | 8 DSBGA |              |                                                             |

| I <sup>2</sup> C | I2C0_SCL  | 5, 11                | 6                  | 3, 9                  | 4             | 2     | 2      | B2      | I/O          | I2C0 シリアル クロック                                              |

|                  | I2C0_SDA  | 4                    | 11                 | 2                     | 3             | 5     | 5      | A2      | I/O          | I2C0 シリアル データ                                               |

| 電源               | VSS       | 7                    | 7                  | 5                     | 6             | 3     | 3      | D2      | P            | グランド電源                                                      |

|                  | VDD       | 6                    | 9                  | 4                     | 5             | 4     | 4      | C2      | P            | 電源                                                          |

|                  | QFN パッド   | -                    | -                  | パッド                   | -             | -     | パッド    | -       | P            | QFN パッケージの露出サーマル パッド。V <sub>SS</sub> に接続することを推奨します。         |

| SPI              | SPI0_CS0  | 8                    | 8                  | 6                     | 7             | -     | -      | -       | I/O          | SPI0 チップ セレクト 0                                             |

|                  | SPI0_CS1  | 4, 13                | 11, 13             | 2, 11                 | 3, 9          | 5     | 5      | A2      | I/O          | SPI0 チップ セレクト 1                                             |

|                  | SPI0_CS2  | 19                   | 19                 | 17                    | 15            | 8     | 8      | A1      | I/O          | SPI0 チップ セレクト 2                                             |

|                  | SPI0_CS3  | 2, 18                | 2, 18              | 16, 20                | 14            | 1     | 1      | B1      | I/O          | SPI0 チップ セレクト 3                                             |

|                  | SPI0_SCK  | 10, 11, 13, 15       | 6, 10, 13, 15      | 8, 9, 11, 13          | 8, 9, 11      | 6     | 6      | D1      | I/O          | SPI0 クロック信号入力 – SPI ペリフェラル モード<br>クロック信号出力 – SPI コントローラ モード |

|                  | SPI0_POCI | 1, 2, 9, 12, 15, 17  | 1, 2, 5, 15, 17    | 7, 10, 13, 15, 19, 20 | 1, 11, 13     | 1, 6  | 1, 6   | D1, B1  | I/O          | SPI0 コントローラ入力 / ペリフェラル出力                                    |

|                  | SPI0_PICO | 14, 16, 20           | 14, 16, 20         | 12, 14, 18            | 10, 12, 16    | 7     | 7      | C1      | I/O          | SPI0 コントローラ出力 / ペリフェラル入力                                    |

| システム             | NRST      | 5                    | 4                  | 3                     | 4             | 2     | 2      | B2      | I            | リセット入力 (アクティブ Low)                                          |

| タイマ              | TIMA_FAL0 | 1, 10, 11            | 1, 6, 10           | 8, 9, 19              | 1, 8          | -     | -      | -       | I/O          | 高度制御タイマ フォルト 0 処理入力                                         |

|                  | TIMA_FAL1 | 4, 16                | 11, 16             | 2, 14                 | 3, 12         | 5, 7  | 5, 7   | A2, C1  | I/O          | 高度制御タイマ フォルト 1 処理入力                                         |

|                  | TIMA_FAL2 | 2, 20                | 2, 20              | 18, 20                | 16            | 1     | 1      | B1      | I/O          | 高度制御タイマ フォルト 2 処理入力                                         |

|                  | TIMA0_C0  | 2, 3, 8, 9, 13, 16   | 2, 3, 5, 8, 13, 16 | 1, 6, 7, 11, 14, 20   | 2, 7, 9, 12   | 1, 7  | 1, 7   | B1, C1  | I/O          | 高度制御タイマ 0 CCR0 キャプチャ入力 / 比較出力                               |

|                  | TIMA0_C0N | 2, 9, 13             | 2, 5, 13           | 7, 11, 20             | 9             | 1     | 1      | B1      | I/O          | 高度制御タイマ 0 CCR0 キャプチャ入力 / 比較出力 (反転)                          |

|                  | TIMA0_C1  | 5, 9, 10, 12, 14, 17 | 5, 10, 12, 14, 17  | 3, 7, 8, 10, 12, 15   | 4, 8, 10, 13  | 2     | 2      | B2      | I/O          | 高度制御タイマ 0 CCR1 キャプチャ入力 / 比較出力                               |

|                  | TIMA0_C1N | 9, 12, 14            | 5, 14              | 7, 10, 12             | 10            | -     | -      | -       | I/O          | 高度制御タイマ 0 CCR1 キャプチャ入力 / 比較出力 (反転)                          |

|                  | TIMA0_C2  | 13, 15, 16           | 13, 15, 16         | 11, 13, 14            | 9, 11, 12     | 6, 7  | 6, 7   | C1, D1  | I/O          | 高度制御タイマ 0 CCR2 キャプチャ入力 / 比較出力                               |

|                  | TIMA0_C2N | 16                   | 16                 | 14                    | 12            | 7     | 7      | C1      | I/O          | 高度制御タイマ 0 CCR2 キャプチャ入力 / 比較出力 (反転)                          |

|                  | TIMA0_C3  | 13, 14, 18, 19       | 13, 14, 18, 19     | 11, 12, 16, 17        | 9, 10, 14, 15 | 8     | 8      | A1      | I/O          | 高度制御タイマ 0 CCR3 キャプチャ入力 / 比較出力                               |

|                  | TIMA0_C3N | 14, 19               | 14, 19             | 12, 17                | 10, 15        | 8     | 8      | A1      | I/O          | 高度制御タイマ 0 CCR3 キャプチャ入力 / 比較出力 (反転)                          |

|                  | TIMG14_C0 | 1, 12, 15, 18        | 1, 15, 18          | 10, 13, 16, 19        | 1, 11, 14     | 6     | 6      | D1      | I/O          | 汎用タイマ 0 CCR0 キャプチャ入力 / 比較出力                                 |

|                  | TIMG14_C1 | 10, 18, 19, 20       | 10, 18, 19, 20     | 8, 16, 17, 18         | 8, 14, 15, 16 | 8     | 8      | A1      | I/O          | 汎用タイマ 0 CCR1 キャプチャ入力 / 比較出力                                 |

|                  | TIMG14_C2 | 10, 19               | 10, 19             | 8, 17                 | 8, 15         | 8     | 8      | A1      | I/O          | 汎用タイマ 0 CCR2 キャプチャ入力 / 比較出力                                 |

|                  | TIMG14_C3 | 20                   | 20                 | 18                    | 16            | -     | -      | -       | I/O          | 汎用タイマ 0 CCR3 キャプチャ入力 / 比較出力                                 |

|                  | TIMG8_C0  | 1, 4                 | 1, 11              | 2, 19                 | 1, 3          | 5     | 5      | A2      | I/O          | 汎用タイマ 8 CCR0 キャプチャ入力 / 比較出力                                 |

|                  | TIMG8_C1  | 2, 5, 8              | 2, 8, 12           | 3, 6, 20              | 4, 7          | 1, 2  | 1, 2   | B1, B2  | I/O          | 汎用タイマ 8 CCR1 キャプチャ入力 / 比較出力                                 |

|                  | TIMG8_IDX | 3, 8                 | 3, 8               | 1, 6                  | 2, 7          | -     | -      | -       | I            | 汎用タイマ 8 直交エンコーダ インデックス パルス入力                                |

| 機能   | 信号名       | ピン番号 <sup>(1)</sup>    |                        |                         |                        |       |        |         | ピンの種類 <sup>(2)</sup> | 説明                 |

|------|-----------|------------------------|------------------------|-------------------------|------------------------|-------|--------|---------|----------------------|--------------------|

|      |           | 20 VSSOP               | 20 TSSOP               | 20 WQFN                 | 16 SOT                 | 8 SOT | 8 WSON | 8 DSBGA |                      |                    |

| UART | UART0_TX  | 2, 13,<br>18, 20       | 2, 13,<br>18, 20       | 11,<br>16,<br>18, 20    | 9, 14,<br>16           | 1     | 1      | B1      | O                    | UART0 送信データ        |

|      | UART0_RX  | 1, 3,<br>14,<br>17, 19 | 1, 3,<br>14,<br>17, 19 | 1, 12,<br>15,<br>17, 19 | 1, 2,<br>10,<br>13, 15 | 8     | 8      | A1      | I                    | UART0 受信データ        |

|      | UART0_CTS | 15, 18                 | 15, 18                 | 13, 16                  | 11, 14                 | 6     | 6      | D1      | I                    | UART0「送信可」フロー制御入力  |

|      | UART0_RTS | 16,<br>17, 19          | 16,<br>17, 19          | 14,<br>15, 17           | 12,<br>13, 15          | 7, 8  | 7, 8   | A1, C1  | O                    | UART0「送信要求」フロー制御出力 |

| ビープ音 | ビープ音      | 1, 4                   | 1, 11                  | 2, 19                   | 1, 3                   | 5     | 5      | A2      | O                    | ビープ音出力             |

| FCC  | FCC_IN    | 4, 12                  | 11                     | 2, 10                   | 3                      | 5     | 6      | A2      | I                    | 周波数クロック カウンタ入力     |

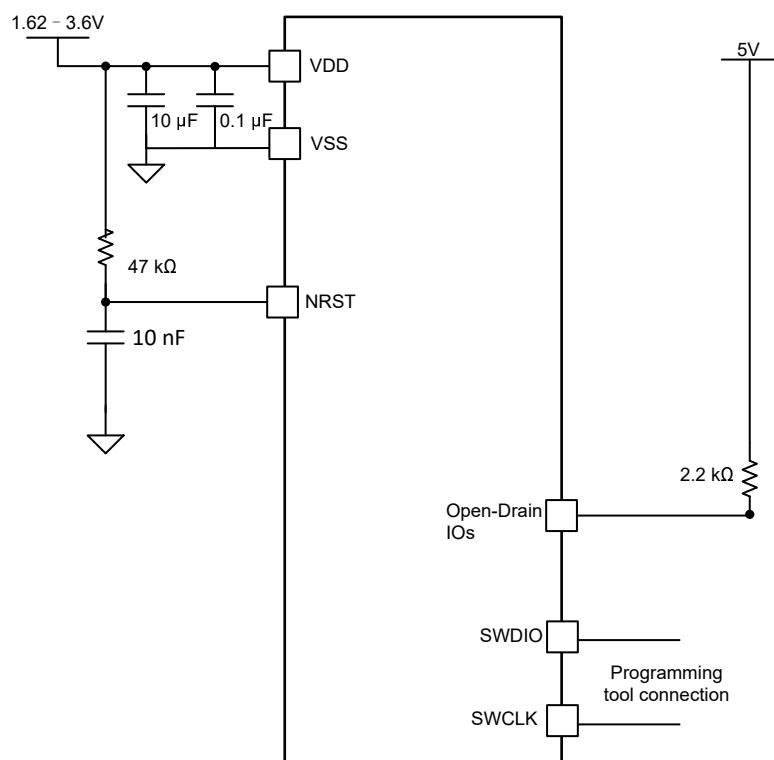

## 6.4 未使用ピンの接続

表 6-3 に、未使用ピンの正しい終端を示します。

**表 6-3. 未使用ピンの接続**

| ピン <sup>(1)</sup> | 電位   | 備考                                                                                                     |

|-------------------|------|--------------------------------------------------------------------------------------------------------|

| PAx               | オープン | 対応するピン機能を GPIO (PINCMx.PF = 0x1) に設定し、未使用のピンが Low を出力するように、または未使用のピンが内部プルアップまたはプルダウン抵抗付き入力になるように構成します。 |

| NRST              | VCC  | NRST はアクティブ Low のリセット信号です。VCC にプルアップしないと、本デバイスは起動できません。詳細については、 <a href="#">セクション 9.1</a> を参照してください。   |

(1) 汎用 I/O と共有されている機能を持つすべての未使用ピンについては、「PAx」未使用ピンの接続ガイドラインに従う必要があります。

## 7 仕様

### 7.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|                  |                  |                                                      | 最小値    | 最大値                               | 単位 |

|------------------|------------------|------------------------------------------------------|--------|-----------------------------------|----|

| VDD              | 電源電圧             | VDD ピンで                                              | -0.3   | 4.1                               | V  |

| V <sub>I</sub>   | 入力電圧             | すべての 5V 許容オープンドレインピンに印加                              | -0.3   | 5.5                               | V  |

| V <sub>I</sub>   | 入力電圧             | 任意の通常耐圧ピンに印加                                         | -0.3   | V <sub>DD</sub> + 0.3<br>(最大 4.1) | V  |

| I <sub>VDD</sub> | VDD ピンの電流        | VDD ピン (ソース) に流れ込む電流、-40°C ≤ T <sub>a</sub> ≤ 85°C   | 80     | mA                                |    |

| I <sub>VSS</sub> | VSS ピンの電流        | VSS ピン (シンク) から流れ出る電流、-40°C ≤ T <sub>a</sub> ≤ 85°C  | 80     | mA                                |    |

| I <sub>VDD</sub> | VDD ピンの電流        | VDD ピン (ソース) に流れ込む電流、-40°C ≤ T <sub>a</sub> ≤ 125°C  | 48     | mA                                |    |

| I <sub>VSS</sub> | VSS ピンの電流        | VSS ピン (シンク) から流れ出る電流、-40°C ≤ T <sub>a</sub> ≤ 125°C | 48     | mA                                |    |

| I <sub>IO</sub>  | SDIO ピンの電流       | SDIO ピンによってシンクまたはソースされる電流                            | 6      | mA                                |    |

|                  | ODIO ピンの電流       | ODIO ピンによってシンクされる電流                                  | 20     | mA                                |    |

| I <sub>b</sub>   | サポートされているダイオード電流 | PA24 を除くすべてのデバイスピンのダイオード電流                           | ±2 (2) | mA                                |    |

| T <sub>stg</sub> |                  | 保存温度                                                 | -40    | 150                               | °C |

(1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

(2) PA24 にはテスト目的で内部接続があり、このピンでは注入電流は許容されません。

### 7.2 ESD 定格

|                    |      |                                                     | 値     | 単位 |

|--------------------|------|-----------------------------------------------------|-------|----|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 に準拠、すべてのピン (1)   | ±2000 | V  |

| V <sub>(ESD)</sub> | 静電放電 | デバイス帶電モデル (CDM)、JEDEC 仕様 JESD22-C101 に準拠、すべてのピン (2) | ±500  | V  |

(1) JEDEC ドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

(2) JEDEC ドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

### 7.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                   |                                     | 最小値      | 公称値 | 最大値 | 単位  |

|-------------------|-------------------------------------|----------|-----|-----|-----|

| VDD               | 電源電圧 (2)                            | 1.62 (3) | 3.6 | 3.6 | V   |

| C <sub>VDD</sub>  | VDD と VSS の間に配置されたコンデンサ (1)         |          | 10  |     | μF  |

| T <sub>A</sub>    | 周囲温度                                | -40      | 125 | 125 | °C  |

| T <sub>J</sub>    | 最大接合部温度                             |          | 130 | 130 | °C  |

| f <sub>MCLK</sub> | MCLK、CPUCLK、ULPCLK 周波数、0 のフラッシュ待機状態 |          | 24  | 24  | MHz |

(1) C<sub>VDD</sub> は、VDD/VSS 間に、デバイスのピンにできる限り近づけて接続します。 C<sub>VDD</sub> には、容量値の誤差が ±20% までの精度の低 ESR コンデンサを使う必要があります。

(2) VDD の推奨動作範囲に関して MCLK 周波数への依存はありません。

(3) 最小 VBOR0-(min) まで機能が保証されます。

## 7.4 热に関する情報

| 热評価基準 <sup>(1)</sup> |                     | パッケージ            | 値     | 単位   |

|----------------------|---------------------|------------------|-------|------|

| $R_{\theta JA}$      | 接合部から周囲への热抵抗        | VSSOP-20 (DGS20) | 91.3  | °C/W |

| $R_{\theta JC(top)}$ | 接合部からケース (上面) への热抵抗 |                  | 29.3  | °C/W |

| $R_{\theta JB}$      | 接合部から基板への热抵抗        |                  | 48.3  | °C/W |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ    |                  | 0.7   | °C/W |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ    |                  | 47.9  | °C/W |

| $R_{\theta JC(bot)}$ | 接合部からケース (底面) への热抵抗 |                  | 該当なし  | °C/W |

| $R_{\theta JA}$      | 接合部から周囲への热抵抗        |                  | 98.2  | °C/W |

| $R_{\theta JC(top)}$ | 接合部からケース (上面) への热抵抗 | TSSOP-20 (PW20)  | 39.3  | °C/W |

| $R_{\theta JB}$      | 接合部から基板への热抵抗        |                  | 50.0  | °C/W |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ    |                  | 5.6   | °C/W |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ    |                  | 49.5  | °C/W |

| $R_{\theta JC(bot)}$ | 接合部からケース (底面) への热抵抗 |                  | 該当なし  | °C/W |

| $R_{\theta JA}$      | 接合部から周囲への热抵抗        |                  | 52.9  | °C/W |

| $R_{\theta JC(top)}$ | 接合部からケース (上面) への热抵抗 |                  | 55.5  | °C/W |

| $R_{\theta JB}$      | 接合部から基板への热抵抗        | WQFN-20 (RUK)    | 26.4  | °C/W |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ    |                  | 2.1   | °C/W |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ    |                  | 26.4  | °C/W |

| $R_{\theta JC(bot)}$ | 接合部からケース (底面) への热抵抗 |                  | 12.0  | °C/W |

| $R_{\theta JA}$      | 接合部から周囲への热抵抗        |                  | 117.1 | °C/W |

| $R_{\theta JC(top)}$ | 接合部からケース (上面) への热抵抗 |                  | 54.5  | °C/W |

| $R_{\theta JB}$      | 接合部から基板への热抵抗        |                  | 54.6  | °C/W |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ    | SOT-16 (DYY)     | 3.0   | °C/W |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ    |                  | 54.5  | °C/W |

| $R_{\theta JC(bot)}$ | 接合部からケース (底面) への热抵抗 |                  | 該当なし  | °C/W |

| $R_{\theta JA}$      | 接合部から周囲への热抵抗        |                  | 142.3 | °C/W |

| $R_{\theta JC(top)}$ | 接合部からケース (上面) への热抵抗 |                  | 65.7  | °C/W |

| $R_{\theta JB}$      | 接合部から基板への热抵抗        |                  | 62.7  | °C/W |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ    |                  | 3.2   | °C/W |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ    | SOT-8 (DDF)      | 62.5  | °C/W |

| $R_{\theta JC(bot)}$ | 接合部からケース (底面) への热抵抗 |                  | 該当なし  | °C/W |

| $R_{\theta JA}$      | 接合部から周囲への热抵抗        |                  | 70.7  | °C/W |

| $R_{\theta JC(top)}$ | 接合部からケース (上面) への热抵抗 |                  | 85.6  | °C/W |

| $R_{\theta JB}$      | 接合部から基板への热抵抗        |                  | 37.5  | °C/W |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ    |                  | 2.7   | °C/W |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ    |                  | 37.5  | °C/W |

| $R_{\theta JC(bot)}$ | 接合部からケース (底面) への热抵抗 | WSON-8 (DSG)     | 12.8  | °C/W |

## 7.4 热に関する情報 (続き)

| 热評価基準 <sup>(1)</sup> |                     | パッケージ         | 値     | 単位   |

|----------------------|---------------------|---------------|-------|------|

| $R_{\theta JA}$      | 接合部から周囲への热抵抗        | DSBGA-8 (YCJ) | 118.6 | °C/W |

| $R_{\theta JC(top)}$ | 接合部からケース (上面) への热抵抗 |               | 0.9   | °C/W |

| $R_{\theta JB}$      | 接合部から基板への热抵抗        |               | 33.2  | °C/W |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ    |               | 0.5   | °C/W |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ    |               | 33.2  | °C/W |

| $R_{\theta JC(bot)}$ | 接合部からケース (底面) への热抵抗 |               | 該当なし  | °C/W |

(1) 従来および最新の热評価基準の詳細については、『半導体および IC パッケージの热評価基準』アプリケーション レポートを参照してください。

## 7.5 電源電流特性

### 7.5.1 RUN/SLEEP モード

VDD = 3.3V。すべての入力は、0V または VDD に接続されています。出力は、電流のソースまたはシンクを行いません。すべてのペリフェラルはディセーブルです。

| パラメータ                       | MCLK                           | -40°C |      | 25°C |      | 85°C |      | 125°C |      | 単位   |        |

|-----------------------------|--------------------------------|-------|------|------|------|------|------|-------|------|------|--------|

|                             |                                | 標準値   | 最大値  | 標準値  | 最大値  | 標準値  | 最大値  | 標準値   | 最大値  |      |        |

| <b>RUN モード</b>              |                                |       |      |      |      |      |      |       |      |      |        |

| IDD <sub>RUN</sub>          | MCLK=SYSOSC、While(1)、フラッシュから実行 | 24MHz | 2.06 | 2.20 | 2.08 | 2.35 | 2.09 | 2.40  | 2.21 | 2.45 | mA     |

| IDD <sub>RUN</sub> 、MHz あたり | MCLK=SYSOSC、While(1)、フラッシュから実行 | 24MHz | 86   | 92   | 87   | 98   | 87   | 100   | 92   | 102  | μA/MHz |

| <b>SLEEP モード</b>            |                                |       |      |      |      |      |      |       |      |      |        |

| IDD <sub>SLEEP</sub>        | MCLK=SYSOSC、CPU 停止             | 24MHz | 1115 | 1256 | 1132 | 1268 | 1149 | 1380  | 1214 | 1370 | μA     |

### 7.5.2 STOP/STANDBY モード

特に記述のない限り、VDD=3.3V。すべての入力は、0V または VDD に接続されています。出力は、電流のソースまたはシンクを行いません。特に記述のないすべてのペリフェラルはディセーブルです。

| パラメータ                | ULPCLK                                    | -40°C |     | 25°C |     | 85°C |      | 125°C |      | 単位  |    |

|----------------------|-------------------------------------------|-------|-----|------|-----|------|------|-------|------|-----|----|

|                      |                                           | 標準値   | 最大値 | 標準値  | 最大値 | 標準値  | 最大値  | 標準値   | 最大値  |     |    |

| <b>STOP モード</b>      |                                           |       |     |      |     |      |      |       |      |     |    |

| IDD <sub>STOP0</sub> | SYSOSC = 24MHz、DISABLESTOP=0              | 4MHz  | 598 | 640  | 609 | 646  | 622  | 710   | 662  | 733 | μA |

| IDD <sub>STOP2</sub> | SYSOSC オフ、DISABLESTOP=1、ULPCLK=LFCCLK     | 32kHz | 305 | 343  | 311 | 346  | 324  | 359   | 364  | 430 | μA |

| <b>STANDBY モード</b>   |                                           |       |     |      |     |      |      |       |      |     |    |

| IDD <sub>STBY0</sub> | STOPCLKSTBY = 0、TIMG8、TIMG14、TIMA0 がイネーブル | 32kHz | 3.8 | 8.3  | 5.1 | 14   | 17.8 | 35.4  | 57.4 | 93  | μA |

| IDD <sub>STBY1</sub> | STOPCLKSTBY = 1、TIMG8、TIMG14、TIMA0 がイネーブル |       | 3.4 | 8.5  | 5.1 | 14   | 17.5 | 35.1  | 57   | 93  | μA |

|                      | STOPCLKSTBY=1、GPIOA イネーブル                 |       | 3.4 | 8.5  | 5.0 | 14   | 17.5 | 35.2  | 57   | 93  | μA |

### 7.5.3 SHUTDOWN モード

すべての入力は、0V または VDD に接続されています。出力は、電流のソースまたはシンクを行いません。コアレギュレータはパワーダウンされています。

| パラメータ               |                   | VDD  | -40°C |     | 25°C |     | 85°C |     | 125°C |      | 単位 |

|---------------------|-------------------|------|-------|-----|------|-----|------|-----|-------|------|----|

|                     |                   |      | 標準値   | 最大値 | 標準値  | 最大値 | 標準値  | 最大値 | 標準値   | 最大値  |    |

| IDD <sub>SHDN</sub> | SHUTDOWN モードの電源電流 | 3.3V | 140   | 320 | 200  | 350 | 428  | 932 | 1933  | 4680 | nA |

## 7.6 電源シーケンス

### 7.6.1 POR と BOR

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ                    |                                | テスト条件              | 最小値  | 標準値   | 最大値   | 単位   |    |

|--------------------------|--------------------------------|--------------------|------|-------|-------|------|----|

| dVDD/dt                  | VDD (電源電圧) のスルーレート             | 立ち上がり              |      |       | 0.1   | V/μs |    |

|                          |                                | 立ち下がり (2)          |      |       | 0.01  |      |    |

|                          |                                | 立ち下がり、STANDBY      |      |       | 0.1   | V/ms |    |

| V <sub>POR+</sub>        | パワーオンリセット電圧レベル                 | 立ち上がり (1)          | 0.92 | 1.284 | 1.59  | V    |    |

| V <sub>POR-</sub>        |                                | 立ち下がり (1)          | 0.87 | 1.236 | 1.54  | V    |    |

| V <sub>HYS, POR</sub>    | POR ヒステリシス                     | (1)                | 16   | 47    | 80    | mV   |    |

| V <sub>BOR0+, COLD</sub> | ブラウンアウトリセット電圧レベル 0 (デフォルトのレベル) | コールドスタート、立ち上がり (1) | 1.48 | 1.54  | 1.615 | V    |    |

| V <sub>BOR0+</sub>       |                                | 立ち上がり (1) (2)      | 1.57 | 1.59  | 1.61  |      |    |

| V <sub>BOR0-</sub>       |                                | 立ち下がり (1) (2)      | 1.56 | 1.57  | 1.60  |      |    |

| V <sub>BOR0, STBY</sub>  | ブラウンアウトリセット電圧レベル 0 (デフォルトのレベル) | STANDBY モード (1)    | 1.52 | 1.57  | 1.60  | V    |    |

| V <sub>BOR1+</sub>       | ブラウンアウトリセット電圧レベル 1             | 立ち上がり (1) (2)      | 2.15 | 2.17  | 2.23  | V    |    |

| V <sub>BOR1-</sub>       |                                | 立ち下がり (1) (2)      | 2.11 | 2.14  | 2.19  |      |    |

| V <sub>BOR1, STBY</sub>  | ブラウンアウトリセット電圧レベル 1             | STANDBY モード (1)    | 2.07 | 2.14  | 2.19  | V    |    |

| V <sub>BOR2+</sub>       | ブラウンアウトリセット電圧レベル 2             | 立ち上がり (1) (2)      | 2.74 | 2.77  | 2.83  | V    |    |

| V <sub>BOR2-</sub>       |                                | 立ち下がり (1) (2)      | 2.71 | 2.73  | 2.80  |      |    |

| V <sub>BOR2, STBY</sub>  | ブラウンアウトリセット電圧レベル 2             | STANDBY モード (1)    | 2.67 | 2.73  | 2.80  | V    |    |

| V <sub>BOR3+</sub>       | ブラウンアウトリセット電圧レベル 3             | 立ち上がり (1) (2)      | 2.88 | 2.96  | 3.04  | V    |    |

| V <sub>BOR3-</sub>       |                                | 立ち下がり (1) (2)      | 2.85 | 2.93  | 3.01  |      |    |

| V <sub>BOR3, STBY</sub>  | ブラウンアウトリセット電圧レベル 3             | STANDBY モード (1)    | 2.83 | 2.92  | 3.00  | V    |    |

| V <sub>HYS, BOR</sub>    | ブラウンアウトリセットのヒステリシス             | レベル 0 (1)          |      |       | 14    | 18   | mV |

|                          |                                | レベル 1~3 (1)        |      |       | 34    | 41   |    |

| T <sub>PD, BOR</sub>     | BOR 伝搬遅延                       | RUN/SLEEP/STOP モード |      |       | 10    | us   | us |

|                          |                                | STANDBY モード        |      |       | 100   | us   |    |

(1)  $|dVDD/dt| \leq 3V/s$

(2) デバイスは RUN、SLEEP、STOP モードで動作しています。

## 7.6.2 電源ランプ

図 7-1 に、パワーアップ / パワーダウン時の POR-, POR+, BOR0-, BOR0+ の関係を示します。

図 7-1. パワー サイクルの POR/BOR 条件

## 7.7 フラッシュ メモリの特性

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ                        | テスト条件                            | 最小値                            | 標準値  | 最大値 | 単位       |

|------------------------------|----------------------------------|--------------------------------|------|-----|----------|

| <b>電源</b>                    |                                  |                                |      |     |          |

| VDD <sub>PGM/ERASE</sub>     | 書き込みと消去の電源電圧                     |                                | 1.62 | 3.6 | V        |

| IDD <sub>ERASE</sub>         | 消去動作中の VDD からの電源電流               | 電源電流の差分                        |      | 2   | mA       |

| IDD <sub>PGM</sub>           | 書き込み動作中の VDD からの電源電流             | 電源電流の差分                        |      | 2.5 | mA       |

| <b>耐久性</b>                   |                                  |                                |      |     |          |

| NWEC <sub>(LOWER)</sub>      | 消去 / プログラム サイクル耐久性               |                                | 100  |     | k サイクル   |

| NE <sub>(MAX)</sub>          | 故障に至るまでの全消去動作回数 (1)              |                                | 802  |     | k 回の消去動作 |

| NW <sub>(MAX)</sub>          | セクタが消去されるまでのワード線あたりの書き込み動作回数 (1) |                                |      | 83  | 書き込み動作   |

| <b>保持</b>                    |                                  |                                |      |     |          |

| t <sub>RET_85</sub>          | フラッシュ メモリのデータ保持                  | -40°C ≤ T <sub>j</sub> ≤ 85°C  | 60   |     | 年        |

| t <sub>RET_105</sub>         | フラッシュ メモリのデータ保持                  | -40°C ≤ T <sub>j</sub> ≤ 105°C | 11.4 |     | 年        |

| t <sub>RET_130</sub>         | フラッシュ メモリのデータ保持                  | -40°C ≤ T <sub>j</sub> ≤ 130°C | 2.4  |     | 年        |

| <b>書き込みと消去のタイミング</b>         |                                  |                                |      |     |          |

| t <sub>PROG (WORD, 64)</sub> | フラッシュ ワードの書き込み時間 (2)             |                                | 40   |     | μs       |

| t <sub>PROG (SEC, 64)</sub>  | 1KB セクタの書き込み時間                   |                                | 5.1  |     | ms       |

| t <sub>ERASE (SEC)</sub>     | セクタの消去時間                         | 10k 未満の消去 / 書き込みサイクル           | 20   | 200 | ms       |

| t <sub>ERASE (BANK)</sub>    | バンクの消去時間                         | 10k 未満の消去 / 書き込みサイクル           | 22   | 220 | ms       |

- (1) ワード線を消去するまでに、許容されるワード線あたりの書き込み動作の最大回数。同じワード線への追加書き込みが必要な場合、ワード線あたりの書き込み動作の最大回数に達すると、セクタ消去が必要です。

- (2) セクタ書き込み時間は、最初のワード書き込みコマンドがトリガされてから、最後のワード書き込みコマンドが完了し、フラッシュ コントローラで割り込みフラグがセットされるまでの時間として定義されます。この時間には、セクタの書き込み中にソフトウェアが (最初のフラッシュ ワードの後に) 各フラッシュ ワードをフラッシュ コントローラに読み込むために必要な時間が含まれます。

## 7.8 タイミング特性

VDD=3.3V,  $T_a=25^\circ\text{C}$  (特に記述のない限り)

| パラメータ                            |                                                    | テスト条件              | 最小値 | 標準値 | 最大値 | 単位   |

|----------------------------------|----------------------------------------------------|--------------------|-----|-----|-----|------|

| <b>ウェークアップタイミング</b>              |                                                    |                    |     |     |     |      |

| $t_{\text{WAKE}, \text{SLEEP}}$  | SLEEP から RUN までのウェークアップ時間                          |                    | 2   |     |     | サイクル |

| $t_{\text{WAKE}, \text{STOP}}$   | STOP0 から RUN までのウェークアップ時間 (SYSOSC イネーブル)           |                    | 14  |     |     | us   |

|                                  | STOP2 から RUN までのウェークアップ時間 (SYSOSC ディセーブル)          |                    | 15  |     |     | us   |

| $t_{\text{WAKE}, \text{STBY}}$   | STANDBY から RUN までのウェークアップ時間                        |                    | 20  |     |     | us   |

| $t_{\text{WAKE}, \text{SHDN}}$   | SHUTDOWN から RUN までのウェークアップ時間                       |                    | 112 |     |     | us   |

| <b>非同期高速クロック要求タイミング</b>          |                                                    |                    |     |     |     |      |

| $t_{\text{DELAY}}$               | 非同期要求のエッジから最初の 24MHz MCLK エッジまでの遅延時間               | モードは SLEEP2        | 1.2 |     |     | us   |

|                                  |                                                    | モードは STOP2         | 1.2 |     |     | us   |

|                                  |                                                    | モードは STANDBY1      | 5.0 |     |     | us   |

| <b>スタートアップタイミング</b>              |                                                    |                    |     |     |     |      |

| $t_{\text{START}, \text{RESET}}$ | リセット / パワーアップからのデバイスのコールド スタートアップ時間 <sup>(1)</sup> |                    | 210 |     |     | us   |

| <b>NRST のタイミング</b>               |                                                    |                    |     |     |     |      |

| $t_{\text{RST}, \text{BOOTRST}}$ | BOOTRST を生成するための NRST ピンのパルス長                      | ULPCLK $\geq$ 4MHz | 2   |     |     | us   |

|                                  |                                                    | ULPCLK=32kHz       | 100 |     |     | us   |

| $t_{\text{RST}, \text{POR}}$     | POR を生成するための NRST ピンのパルス長                          |                    | 1   |     |     | s    |

(1) 起動時間は、VDD が VBOR0+ と交差 (コールド スタートアップ) した時刻から、ユーザー プログラムの最初の命令が実行された時刻までの時間として測定されます。

## 7.9 クロック仕様

### 7.9.1 システム発振器 (SYSOSC)

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ                              |                                                                 | テスト条件                                                                               | 最小値  | 標準値 | 最大値 | 単位  |

|------------------------------------|-----------------------------------------------------------------|-------------------------------------------------------------------------------------|------|-----|-----|-----|

| $f_{\text{SYSOSC}}$                | 出荷時に調整された SYSOSC 周波数                                            | SYSOSCCFG.FREQ=00 (ベース)                                                             | 24   |     |     | MHz |

| $f_{\text{SYSOSC}}$                | 内部 ROSC 抵抗使用、周波数補正ループ (FCL) イネーブル時の SYSOSC 周波数精度 <sup>(1)</sup> | SETUSEFCL=1, $T_a = 25^\circ\text{C}$                                               | -1.2 | 1.2 |     | %   |

|                                    |                                                                 | SETUSEFCL=1, $0^\circ\text{C} \leq T_a \leq 85^\circ\text{C}$                       | -1.6 | 1.4 |     |     |

|                                    |                                                                 | SETUSEFCL=1, $-40^\circ\text{C} \leq T_a \leq 125^\circ\text{C}$                    | -2   | 1.4 |     |     |

| $f_{\text{SYSOSC}}$                | 周波数補正ループ (FCL) がディセーブルのときの SYSOSC 精度、24MHz                      | SETUSEFCL=0, SYSOSCCFG.FREQ=00, $-40^\circ\text{C} \leq T_a \leq 125^\circ\text{C}$ | -2.5 | 2.5 |     | %   |

| $t_{\text{settle}, \text{SYSOSC}}$ | 目標精度に達するまでのセッティング タイム <sup>(2)</sup>                            | SETUSEFCL=1                                                                         |      |     | 30  | us  |

(1) SYSOSC の周波数補正ループ (FCL) を使うと、内部リファレンス抵抗によって SYSOSC の精度を高めることができます。SYSOSC 精度の計算方法の詳細については、テクニカル リファレンス マニュアルの「SYSOSC」のセクションを参照してください。

- (2) SYSOSC がディスエーブル状態から有効化された場合、 $t_{start, SYSOSC}$  で規定された時間内に SYSOSC 出力がデバイスに解放されます。出力が解放された時点での SYSOSC のワーストケースの精度は  $f_{settle, SYSOSC}$  によって規定されます。  $t_{settle, SYSOSC}$  で規定された時間の後、SYSOSC は目的の  $f_{SYSOSC}$  精度に収束します。

### 7.9.2 低周波数発振器 (LFOSC)

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ              |                 | テスト条件                                                   | 最小値 | 標準値   | 最大値 | 単位 |

|--------------------|-----------------|---------------------------------------------------------|-----|-------|-----|----|

| $f_{LFOSC}$        | LFOSC 周波数       |                                                         |     | 32768 |     | Hz |

| $f_{LFOSC}$        | LFOSC 精度        | $-40^{\circ}\text{C} \leq T_a \leq 125^{\circ}\text{C}$ | -5  | 5     | %   |    |

| $f_{LFOSC}$        | LFOSC 精度        | $-40^{\circ}\text{C} \leq T_a \leq 85^{\circ}\text{C}$  | -3  | 3     | %   |    |

| $I_{LFOSC}$        | LFOSC 消費電流      |                                                         |     | 300   |     | nA |

| $t_{start, LFOSC}$ | LFOSC スタートアップ時間 |                                                         |     | 1.7   |     | ms |

## 7.10 デジタル IO

### 7.10.1 電気的特性

電源電圧が推奨範囲内で、自由気流の動作温度範囲内のとき (特に記述のない限り)。

| パラメータ     |                 | テスト条件                       |                                                                                                         | 最小値      | 標準値     | 最大値 | 単位 |

|-----------|-----------------|-----------------------------|---------------------------------------------------------------------------------------------------------|----------|---------|-----|----|

| $V_{IH}$  | High レベル入力電圧    | ODIO <sup>(1)</sup>         | $VDD \geq 1.62\text{V}$                                                                                 | 0.7*VDD  |         | 5.5 | V  |

|           |                 | ODIO <sup>(1)</sup>         | $VDD \geq 2.7\text{V}$                                                                                  | 2        | 5.5     |     | V  |

|           |                 | すべての I/O<br>(ODIO とリセットを除く) | $VDD \geq 1.62\text{V}$                                                                                 | 0.7*VDD  | VDD+0.3 |     | V  |

| $V_{IL}$  | Low レベル入力電圧     | ODIO                        | $VDD \geq 1.62\text{V}$                                                                                 | -0.3     | 0.3*VDD |     | V  |

|           |                 | ODIO                        | $VDD \geq 2.7\text{V}$                                                                                  | -0.3     | 0.8     |     | V  |

|           |                 | すべての I/O<br>(ODIO とリセットを除く) | $VDD \geq 1.62\text{V}$                                                                                 | -0.3     | 0.3*VDD |     | V  |

| $V_{HYS}$ | ヒステリシス          | ODIO                        |                                                                                                         | 0.05*VDD |         |     | V  |

|           |                 | すべての I/O<br>(ODIO を除く)      |                                                                                                         | 0.1*VDD  |         |     | V  |

| $I_{lkq}$ | ハイインピーダンスのリーク電流 | SDIO <sup>(2) (3)</sup>     | $VDD = 3\text{V}$                                                                                       |          |         | 50  | nA |

| $R_{PU}$  | プルアップ抵抗         | すべての I/O<br>(ODIO を除く)      | $VIN = VSS$                                                                                             |          | 40      |     | kΩ |

| $R_{PD}$  | プルダウン抵抗         |                             | $VIN = VDD$                                                                                             |          | 40      |     | kΩ |

| $C_I$     | 入力容量            |                             | $VDD = 3.3\text{V}$                                                                                     |          | 5       |     | pF |

| $V_{OH}$  | High レベル出力電圧    | SDIO                        | $VDD \geq 2.7\text{V},  I_{OL,max}  = 6\text{mA}$                                                       | VDD-0.5  |         |     | V  |

| $V_{OH}$  | High レベル出力電圧    | SDIO                        | $VDD \geq 1.71\text{V},  I_{OL,max}  = 2\text{mA}$                                                      | VDD-0.4  |         |     | V  |

| $V_{OL}$  | Low レベル出力電圧     | SDIO                        | $VDD \geq 2.7\text{V},  I_{OL,max}  = 6\text{mA}$<br>$VDD \geq 1.71\text{V},  I_{OL,max}  = 2\text{mA}$ |          | 0.4     |     | V  |

| $V_{OL}$  | Low レベル出力電圧     | ODIO                        | $VDD \geq 2.7\text{V}, I_{OL,max} = 8\text{mA}$<br>$VDD \geq 1.71\text{V}, I_{OL,max} = 4\text{mA}$     |          | 0.5     |     | V  |

(1) I/O タイプ: ODIO = 5V 許容オープンドレイン、SDIO = 標準駆動、HSIO = 高速

(2) リーク電流は、対応するピンに VSS または VDD を印加して計測されます (特に記述のない限り)。

(3) デジタルポートピンのリーク電流は個別に計測されます。ポートピンは入力として選択され、プルアップ / プルダウン抵抗は無効化されています。

## 7.10.2 スイッチング特性

電源電圧が推奨範囲内で、自由気流の動作温度範囲内のとき (特に記述のない限り)。

| パラメータ      |                   | テスト条件             |                                              | 最小値          | 標準値 | 最大値           | 単位  |

|------------|-------------------|-------------------|----------------------------------------------|--------------|-----|---------------|-----|

| $f_{max}$  | ポート出力周波数          | SDIO (1)          | $VDD \geq 1.71V, C_L = 20pF$                 |              |     | 24            | MHz |

| $f_{max}$  | ポート出力周波数          | ODIO              | $VDD \geq 1.71V, FM^+, CL = 20pF \sim 100pF$ |              |     | 1             | MHz |

| $t_r, t_f$ | 出力立ち上がり / 立ち下がり時間 | ODIO を除くすべての出力ポート | $VDD \geq 1.71V$                             |              |     | $0.3*f_{max}$ | s   |

| $t_f$      | 出力立ち下がり時間         | ODIO              | $VDD \geq 1.71V, FM^+, CL = 20pF \sim 100pF$ | $20*VDD/5.5$ |     | 120           | ns  |

(1) I/O タイプ: ODIO = 5V 対応オープンドレイン、SDIO=標準駆動、HSIO=高速、HDIO =高駆動

## 7.11 ADC

### 7.11.1 電気的特性

電源電圧が推奨範囲内で、自由気流の動作温度範囲内のとき (特に記述のない限り)。すべての代表値は 25°Cで測定されており、すべての精度パラメータは 12 ビット分解能モードを使用して測定されています (特に記述のない限り)。

| パラメータ           |                          | テスト条件                                                                         | 最小値  | 標準値       | 最大値        | 単位      |

|-----------------|--------------------------|-------------------------------------------------------------------------------|------|-----------|------------|---------|

| $V_{in(ADC)}$   | アナログ入力電圧範囲(1)            | すべての ADC アナログ入力ピンに適用されます                                                      | 0    | $VDD$     | V          |         |

| $V_{R+}$        | 正の ADC リファレンス電圧          | $VDD$ から供給される $V_{R+}$                                                        |      | $VDD$     | V          |         |

|                 |                          | 内部リファレンス電圧 ( $V_{REF}$ ) から供給される $V_{R+}$                                     |      | $V_{REF}$ | V          |         |

| $V_{R-}$        | 負の ADC リファレンス電圧          |                                                                               | 0    |           | V          |         |

| $F_s$           | ADC サンプリング周波数            | $RES = 0x0$ (12 ビット モード)、 $VDD$ リファレンス                                        |      | 1.5       |            | Msps    |

|                 |                          | $RES = 0x1$ (10 ビット モード)、 $VDD$ リファレンス                                        |      | 1.7       |            |         |

|                 |                          | $RES = 0x2$ (8 ビット モード)、 $VDD$ リファレンス                                         |      | 2         |            |         |

| $F_s$           | ADC サンプリング周波数            | $RES = 0x0$ (12 ビット モード)、内部リファレンス                                             |      | 0.866     |            | Msps    |

|                 |                          | $RES = 0x1$ (10 ビット モード)、内部リファレンス                                             |      | 1         |            |         |

|                 |                          | $RES = 0x2$ (8 ビット モード)、内部リファレンス                                              |      | 1.2       |            |         |

| $I_{(ADC)}$     | VDD 端子に流れ込む動作電源電流        | $F_s = 1.5MSPS, V_{R+} = VDD$                                                 | 200  | 220       |            | $\mu A$ |

|                 |                          | $F_s = 0.856MSPS, V_{R+} = V_{REF} = 2.5V$ ( $V_{REF}$ 消費電力を含む)               | 220  | 250       |            |         |

| $C_{S/H}$       | ADC サンプル ホールド容量          |                                                                               | 0.22 |           | pF         |         |

| $R_{in}$        | ADC スイッチ抵抗               |                                                                               | 25   |           | k $\Omega$ |         |

| $ENOB$          | 有効ビット数                   | $VDD$ リファレンス (2)                                                              | 9.3  | 10.4      |            | ビット     |

|                 |                          | オーバー サンプリング機能付きの $VDD$ リファレンス                                                 |      | 12.2      |            |         |

|                 |                          | 内部リファレンス電圧、 $V_{R+} = V_{REF} = 2.5V$                                         | 9.4  | 9.8       |            |         |

| $SNR$           | 信号対雑音比                   | $VDD$ リファレンス (2)                                                              | 64   |           |            | dB      |

|                 |                          | オーバー サンプリング機能付きの $VDD$ リファレンス                                                 | 75   |           |            |         |

|                 |                          | 内部リファレンス電圧、 $V_{R+} = V_{REF} = 2.5V$                                         | 61   |           |            |         |

| $PSRR_{DC}$     | 電源除去比、DC                 | $VDD = VDD_{(min)} \sim VDD_{(max)}$<br>内部リファレンス電圧、 $V_{R+} = V_{REF} = 2.5V$ |      | 61        |            | dB      |

| $T_{wakeup}$    | ADC ウエークアップ時間            | 内部リファレンス電圧はオンであると仮定                                                           |      | 5         |            | us      |

| $V_{SupplyMon}$ | 電源モニタ分圧器 ( $VDD/3$ ) の精度 | ADC の入力チャネル: 電源モニタ(3)                                                         | -0.6 | +2.5      | %          |         |

| $I_{SupplyMon}$ | 電源モニタ分圧器の消費電流            | ADC の入力チャネル: 電源モニタ                                                            | 10   |           | $\mu A$    |         |

(1) 有効な変換結果を得るには、選択された ADC リファレンス電圧の範囲内 ( $V_{R+} \sim V_{R-}$ ) にアナログ入力電圧範囲が含まれている必要があります。

(2)  $VDD$  リファレンス電圧の仕様は、 $V_{R+} = VDD = 3.3V$  かつ  $V_{R-} = VSS = 0V$  の条件で測定されたものです。

(3) アナログ電源モニタ。チャネル 15 のアナログ入力は切り離されており、分圧器 ( $VDD/3$ ) と内部的に接続されています。

### 7.11.2 スイッチング特性

電源電圧が推奨範囲内で、自由気流の動作温度範囲内のとき (特に記述のない限り)。

| パラメータ                   |                             | テスト条件                                                  | 最小値   | 標準値 | 最大値 | 単位            |

|-------------------------|-----------------------------|--------------------------------------------------------|-------|-----|-----|---------------|

| $f_{ADCCLK}$            | ADC クロック周波数                 |                                                        | 12    | 24  |     | MHz           |

| $t_{ADC\ trigger}$      | ソフトウェアトリガの最小幅               |                                                        | 3     |     |     | ADCCLK のサイクル数 |

| $t_{Sample\_step}$      | サンプリング時間 (ステップ入力)           | 12 ビットモード、 $R_S = 50\Omega$ 、 $C_{pext} = 10\text{pF}$ | 0.166 |     |     | $\mu\text{s}$ |

| $t_{Sample\_SupplyMon}$ | サンプリング時間 (電源モニタ (VDD/3) あり) |                                                        | 3     |     |     | $\mu\text{s}$ |

### 7.11.3 直線性パラメータ

電源電圧が推奨範囲内で、自由気流の動作温度範囲内のとき (特に記述のない限り)。すべての代表値は 25°C で測定されており、すべての直線性パラメータは 12 ビット分解能モードを使用して測定されています (特に記述のない限り)。<sup>(1)</sup>

| パラメータ |               | テスト条件                            | 最小値  | 標準値 | 最大値  | 単位  |

|-------|---------------|----------------------------------|------|-----|------|-----|

| $E_I$ | 積分直線性誤差 (INL) | VDD リファレンス、10 ビット <sup>(2)</sup> | -1.0 |     | +1.0 | LSB |

|       |               | VDD リファレンス、12 ビット <sup>(2)</sup> | -4.0 |     | +4.0 | LSB |

| $E_D$ | 微分直線性誤差 (DNL) | VDD リファレンス、10 ビット <sup>(2)</sup> | -1.0 |     | +1.0 | LSB |

|       |               | VDD リファレンス、12 ビット <sup>(2)</sup> | -1.0 |     | +4.0 | LSB |

| $E_O$ | オフセット誤差       | VDD リファレンス、10 ビット <sup>(2)</sup> | -3   |     | 3    | mV  |

|       |               | VDD リファレンス、12 ビット <sup>(2)</sup> | -3   |     | 3    | mV  |

| $E_G$ | ゲイン誤差         | VDD リファレンス、10 ビット <sup>(2)</sup> | -5   |     | 5    | LSB |

|       |               | VDD リファレンス、12 ビット <sup>(2)</sup> | -25  |     | 25   | LSB |

(1) し総合未調整誤差 (TUE) は、次の式を使用して、 $E_I$ 、 $E_O$ 、 $E_G$  から計算できます。 $TUE = \sqrt{(E_I^2 + |E_O|^2 + E_G^2)}$

注: 上記の式が正確であるためには、すべての誤差を同じ単位 (通常は LSB) に変換する必要があります。

(2) VDD リファレンス仕様は、 $V_{R+} = VDD$  かつ  $V_{R-} = VSS = 0V$  の条件で測定されたものです。

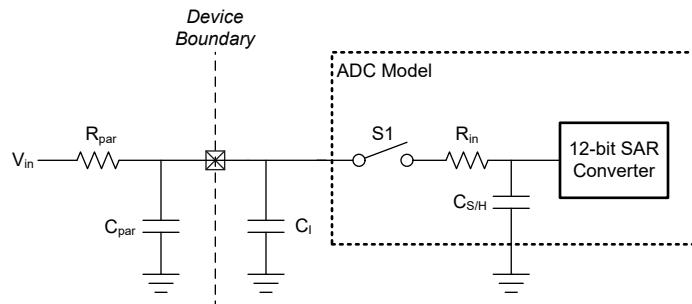

### 7.11.4 代表的な接続図

図 7-2. ADC 入力ネットワーク

1.  $R_{in}$  と  $C_{S/H}$  の値については、「[ADC 電気的特性](#)」を参照してください。

2.  $C_I$  の値については、「[デジタル IO 電気的特性](#)」を参照してください。

3.  $C_{par}$  と  $R_{par}$  は外部 ADC 入力回路の寄生容量および抵抗を表します。

次の式を使用して、ADC 変換に必要な最小サンプリング時間 (T) を求めます。

1.  $Tau = (R_{par} + R_{in}) \times C_{S/H} + R_{par} \times (C_{par} + C_I)$

2.  $K = \ln(2^n / \text{セトリング誤差}) - \ln((C_{par} + C_I) / C_{S/H})$

3.  $T$  (最小サンプリング時間) =  $K \times Tau$

## 7.12 温度センサ

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ                |                     | テスト条件                                                                            | 最小値  | 標準値  | 最大値  | 単位    |

|----------------------|---------------------|----------------------------------------------------------------------------------|------|------|------|-------|

| TS <sub>TRIM</sub>   | 出荷時調整温度 (1)         |                                                                                  | 27   | 30   | 33   | °C    |

| TS <sub>c</sub>      | 温度係数                |                                                                                  | -1.9 | -1.8 | -1.7 | mV/°C |

| t <sub>SET, TS</sub> | 温度センサのセトリング タイム (2) | ADC および VREF の構成: RES = 0 (12 ビット モード)、VRSEL = 2h (VREF = 1.4V)、ADC CHANNEL = 11 |      | 2.5  | 10   | us    |

(1) ユーザー較正により、より高い絶対精度を実現できます。

(2) これは、温度センサの測定に必要な最小 ADC サンプリング時間です。

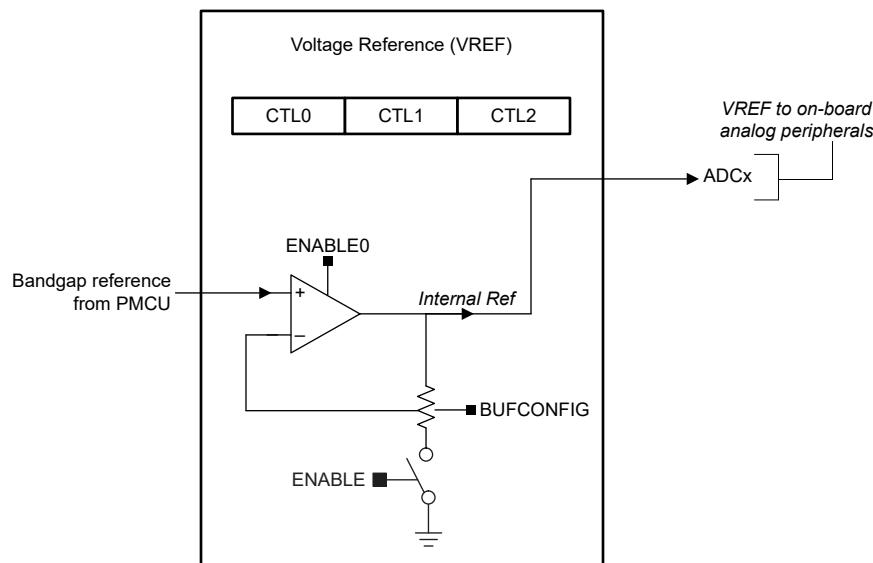

## 7.13 VREF

### 7.13.1 電圧特性

電源電圧が推奨範囲内で、自由気流の動作温度範囲内のとき (特に記述のない限り)。

| パラメータ              |                   | テスト条件         | 最小値   | 標準値 | 最大値   | 単位 |

|--------------------|-------------------|---------------|-------|-----|-------|----|

| VDD <sub>min</sub> | VREF 動作に必要な最低電源電圧 | BUFCONFIG = 1 | 1.62  |     |       | V  |

|                    |                   | BUFCONFIG = 0 | 2.7   |     |       |    |

| VREF               | リファレンス電圧の出力電圧     | BUFCONFIG = 1 | 1.378 | 1.4 | 1.421 | V  |

|                    |                   | BUFCONFIG = 0 | 2.462 | 2.5 | 2.541 |    |

### 7.13.2 電気的特性

電源電圧が推奨範囲内で、自由気流の動作温度範囲内のとき (特に記述のない限り)。

| パラメータ                |                                                           | テスト条件                                  |                                        | 最小値 | 標準値 | 最大値 | 単位     |

|----------------------|-----------------------------------------------------------|----------------------------------------|----------------------------------------|-----|-----|-----|--------|

| I <sub>VREF</sub>    | VREF の動作電源電流 (この仕様は推定値であり、IP の設計フェーズがさらに進むと、より信頼性が高くなります) | BUFCONFIG = {0, 1}、無負荷                 | BUFCONFIG = {0, 1}、無負荷。                |     | 80  | 100 | μA     |

| TC <sub>VREF</sub>   | VREF の温度係数 (1)                                            | BUFCONFIG = {0, 1}                     | BUFCONFIG = {0, 1}                     |     |     | 75  | ppm/°C |

| TC <sub>drift</sub>  | VREF の長期ドリフト                                              | 時間=1000 時間、BUFCONFIG = {0, 1}、T = 25°C | 時間=1000 時間、BUFCONFIG = {0, 1}、T = 25°C |     |     | 300 | ppm    |

| T <sub>startup</sub> | VREF 起動時間                                                 | BUFCONFIG = {0, 1}、VDD = 2.7V          | BUFCONFIG = {0, 1}、VDD = 2.7V          |     |     | 10  | us     |

(1) VREF 出力の温度係数は、TC<sub>VREFBUF</sub> と内部バンドギャップ リファレンスの温度係数の和です。

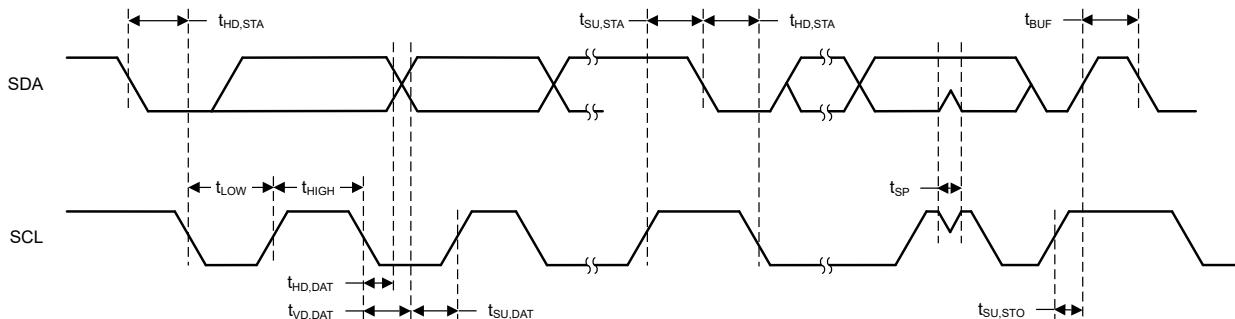

## 7.14 I2C

### 7.14.1 I2C の特性

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ               | テスト条件              | スタンダード モード      | ファスト モード | ファスト モード プラス | 単位   |     |

|---------------------|--------------------|-----------------|----------|--------------|------|-----|

|                     |                    | 最小値             | 最大値      | 最小値          | 最大値  | 最小値 |

| f <sub>I2C</sub>    | I2C 入力クロック周波数      | パワードメイン 0 の I2C | 24       | 24           | 24   | MHz |

| f <sub>SCL</sub>    | SCL クロック周波数        |                 | 100      | 400          | 1000 | kHz |

| t <sub>HD,STA</sub> | (リピート) スタート ホールド時間 |                 | 4        | 0.6          | 0.26 | us  |

| t <sub>Low</sub>    | SCL クロック Low 期間    |                 | 4.7      | 1.3          | 0.5  | us  |

### 7.14.1 I<sup>2</sup>C の特性 (続き)

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ        |                                    | テスト条件 | スタンダード モード |     | ファスト モード |     | ファスト モードプラス |     | 単位 |

|--------------|------------------------------------|-------|------------|-----|----------|-----|-------------|-----|----|

|              |                                    |       | 最小値        | 最大値 | 最小値      | 最大値 | 最小値         | 最大値 |    |

| $t_{HIGH}$   | SCL クロックの High 期間                  |       | 4          |     | 0.6      |     | 0.26        |     | us |

| $t_{SU,STA}$ | リピート スタート セットアップ時間                 |       | 4.7        |     | 0.6      |     | 0.26        |     | us |

| $t_{HD,DAT}$ | データ ホールド時間                         |       | 0          |     | 0        |     | 0           |     | ns |

| $t_{SU,DAT}$ | データ セットアップ時間                       |       | 250        |     | 100      |     | 50          |     | ns |

| $t_{SU,STO}$ | ストップ セットアップ時間                      |       | 4          |     | 0.6      |     | 0.26        |     | us |

| $t_{BUF}$    | ストップ コンディションとスタート コンディションの間のバス解放時間 |       | 4.7        |     | 1.3      |     | 0.5         |     | us |

| $t_{VD;DAT}$ | データ有効時間                            |       | 3.45       |     | 0.9      |     | 0.45        |     | us |

| $t_{VD;ACK}$ | データ有効アクリッジ時間                       |       | 3.45       |     | 0.9      |     | 0.45        |     | us |

### 7.14.2 I<sup>2</sup>C フィルタ

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ    | テスト条件                                     | 最小値 | 標準値 | 最大値 | 単位 |

|----------|-------------------------------------------|-----|-----|-----|----|

| $f_{SP}$ | 入力フィルタにより抑制されるスパイクのパルス持続時間<br>AGFSELx = 0 | 11  | 35  |     | ns |

| $f_{SP}$ | 入力フィルタにより抑制されるスパイクのパルス持続時間<br>AGFSELx = 1 | 14  | 35  |     | ns |

| $f_{SP}$ | 入力フィルタにより抑制されるスパイクのパルス持続時間<br>AGFSELx = 2 | 22  | 60  |     | ns |

| $f_{SP}$ | 入力フィルタにより抑制されるスパイクのパルス持続時間<br>AGFSELx = 3 | 35  | 90  |     | ns |

### 7.14.3 I<sup>2</sup>C のタイミング図

図 7-3. I<sup>2</sup>C タイミング図

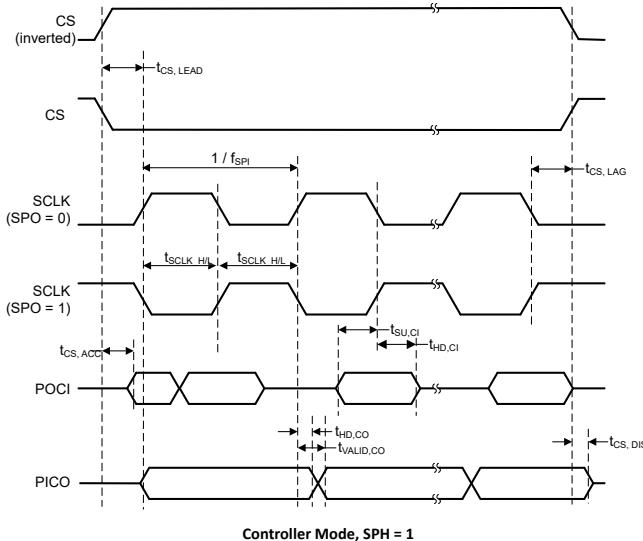

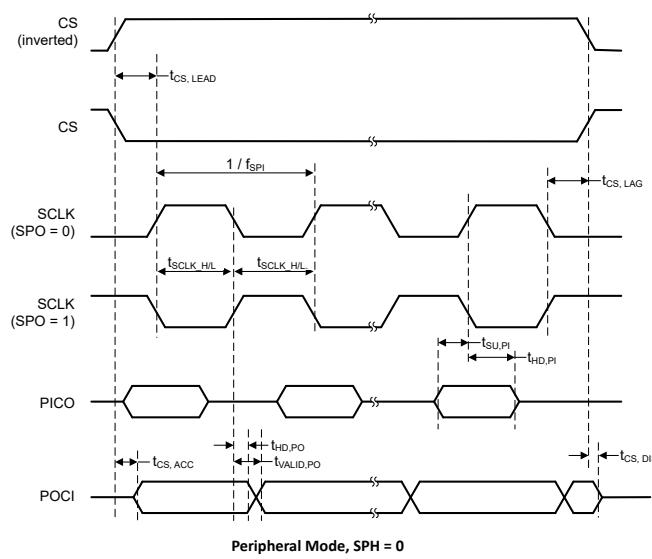

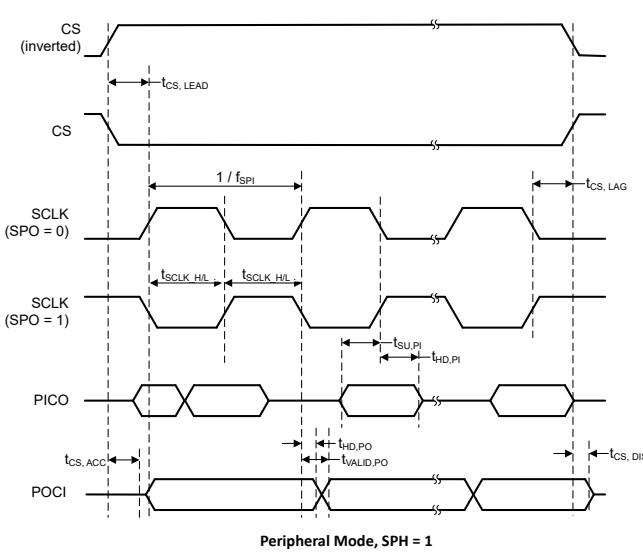

## 7.15 SPI

### 7.15.1 SPI

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ      | テスト条件                                                              | 最小値 | 標準値 | 最大値 | 単位  |

|------------|--------------------------------------------------------------------|-----|-----|-----|-----|

| <b>SPI</b> |                                                                    |     |     |     |     |

| $f_{SPI}$  | SPI クロック周波数<br>最大クロック速度 = 24MHz<br>1.62 < VDD < 3.6V<br>コントローラ モード |     |     | 12  | MHz |

### 7.15.1 SPI (続き)

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ                  |                                         | テスト条件                                               | 最小値                      | 標準値                | 最大値                      | 単位  |

|------------------------|-----------------------------------------|-----------------------------------------------------|--------------------------|--------------------|--------------------------|-----|

| $f_{\text{SPI}}$       | SPI クロック周波数                             | 最大クロック速度 = 24MHz<br>1.62 < VDD < 3.6V<br>ペリフェラル モード |                          | 12                 |                          | MHz |

| $DC_{\text{SCK}}$      | SCK のデューティ サイクル                         |                                                     | 40                       | 50                 | 60                       | %   |

| <b>コントローラ</b>          |                                         |                                                     |                          |                    |                          |     |

| $t_{\text{SCLK\_H/L}}$ | SCLK High または Low 時間                    |                                                     | $(t_{\text{SPI}/2}) - 1$ | $t_{\text{SPI}/2}$ | $(t_{\text{SPI}/2}) + 1$ | ns  |

| $t_{\text{CS.LEAD}}$   | CS 進み時間、CS アクティブからクロックまで                |                                                     | 1                        |                    |                          | ns  |

| $t_{\text{CS.LAG}}$    | CS 遅れ時間、最後のクロックから CS 非アクティブまで           |                                                     | 11                       |                    |                          | ns  |

| $t_{\text{CS.ACC}}$    | CS アクセス時間、CS アクティブから PICO データ出力まで       |                                                     |                          | 93                 |                          | ns  |

| $t_{\text{CS.DIS}}$    | CS ディセーブル時間、CS 非アクティブから PICO 高インピーダンスまで |                                                     |                          | 10                 |                          | ns  |

| $t_{\text{SU.CI}}$     | POCI 入力データのセットアップ時間<br>(1)              | 2.7 < VDD < 3.6V、遅延サンプリングがイネーブル                     |                          | 1                  |                          | ns  |

|                        |                                         | 1.62 < VDD < 2.7V、遅延サンプリングがイネーブル                    |                          | 1                  |                          |     |

| $t_{\text{SU.CI}}$     | POCI 入力データのセットアップ時間<br>(1)              | 2.7 < VDD < 3.6V、遅延サンプリングなし                         |                          | 27                 |                          | ns  |

|                        |                                         | 1.62 < VDD < 2.7V、遅延サンプリングなし                        |                          | 35                 |                          |     |

| $t_{\text{HD.CI}}$     | POCI 入力データ ホールド時間                       |                                                     | 9                        |                    |                          | ns  |

| $t_{\text{VALID.CO}}$  | PICO 出力データの有効時間 (2)                     |                                                     |                          | 10                 |                          | ns  |

| $t_{\text{HD.CO}}$     | PICO 出力データのホールド時間 (3)                   |                                                     | 1                        |                    |                          | ns  |

| <b>ペリフェラル</b>          |                                         |                                                     |                          |                    |                          |     |

| $t_{\text{CS.LEAD}}$   | CS 進み時間、CS アクティブからクロックまで                |                                                     | 8                        |                    |                          | ns  |

| $t_{\text{CS.LAG}}$    | CS 遅れ時間、最後のクロックから CS 非アクティブまで           |                                                     | 0                        |                    |                          | ns  |

| $t_{\text{CS.ACC}}$    | CS アクセス時間、CS アクティブから POC1 データ出力まで       |                                                     |                          | 50                 |                          | ns  |

| $t_{\text{CS.DIS}}$    | CS ディセーブル時間、CS 非アクティブから POC1 高インピーダンスまで |                                                     |                          | 50                 |                          | ns  |

| $t_{\text{SU.PI}}$     | PICO 入力データ セットアップ時間                     |                                                     | 2                        |                    |                          | ns  |

| $t_{\text{HD.PI}}$     | PICO 入力データ ホールド時間                       |                                                     | 1                        |                    |                          | ns  |