**TDP158** JAJSDN3F - DECEMBER 2016 - REVISED APRIL 2024

# TDP158 6Gbps、AC カップリングから TMDS™ または HDMI™ へのレベル シフタ リドライバ

# 1 特長

- AC 結合 TMDS または DisplayPort™ デュアル モー ド物理層入力から HDMI 2.0b TMDS 物理層出力へ、 最高 6Gbps のデータレートをサポート、HDMI 2.0b の電気的パラメータに適合

- DisplayPort デュアル モード規格バージョン 1.1 をサ ポート

- 4k 2k 60p および最大 WUXGA 16 ビット色深度、ま たは高リフレッシュ レート 1080p をサポート

- 固定レシーバ イコライザを最高 15.5dB にプログラム

- グローバルまたは独立の高速レーン制御、プリエンファ シスと送信スイング、スルー レート制御

- I<sup>2</sup>C またはピン ストラップによりプログラム可能

- I<sup>2</sup>C により DisplayPort リドライバとして構成可能

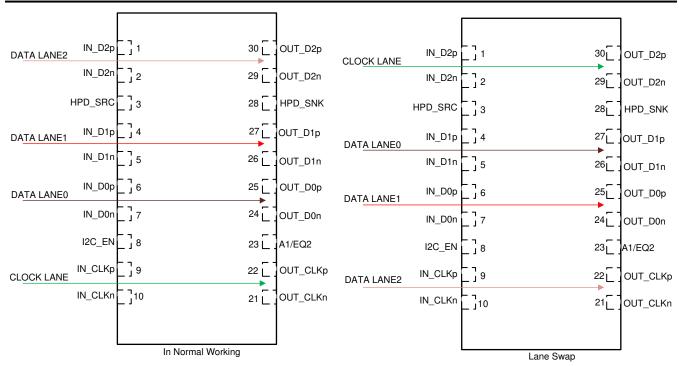

- メイン レーンのフル レーン スワップ

- 低消費電力

- アクティブ 時 6Gbps で -200mW、シャットダウン状 熊で -8mW

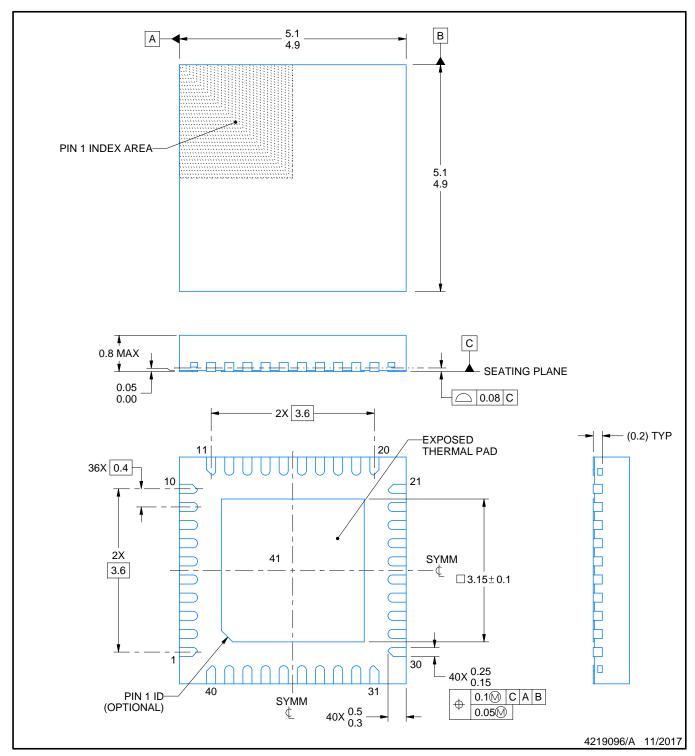

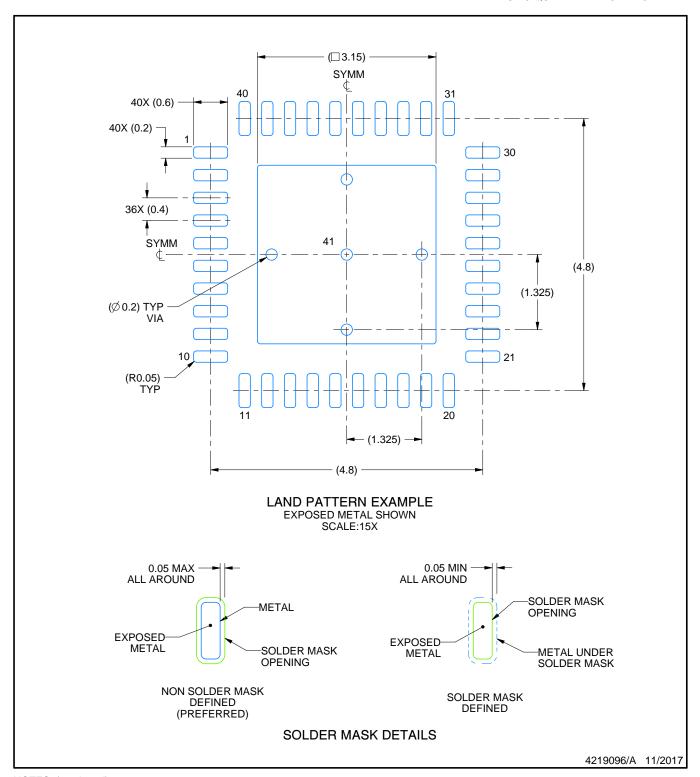

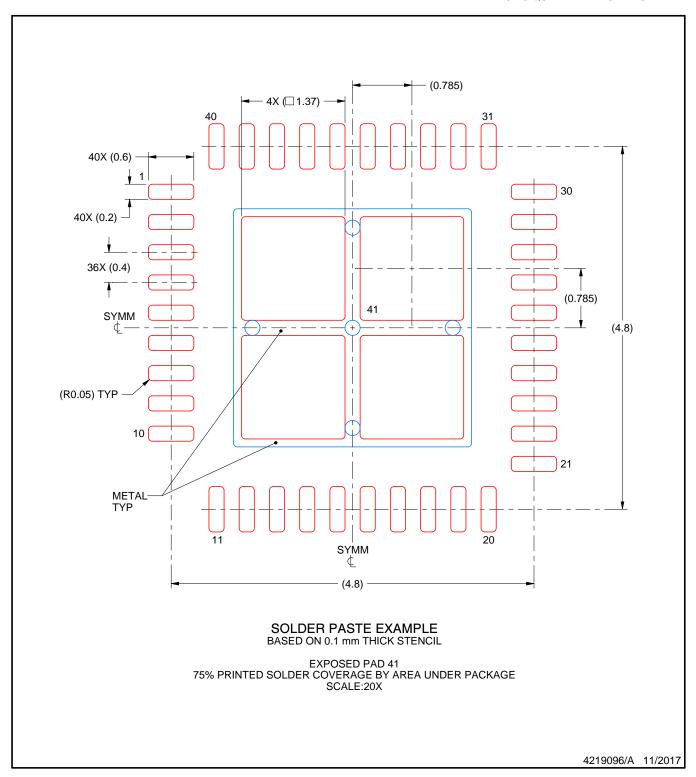

- 40 ピン、0.4mm ピッチ、5mm × 5mm、WQFN パッケ ージ、SN75DP159RSB リタイマとピン互換

# 2 アプリケーション

- ノートブック、デスクトップ、オールインワン、タブレット、 ゲーム用および産業用 PC

- オーディオまたはビデオ機器

- Blu-ray™ DVD

- ゲーム機

- HDMI アダプタまたはドングル

- ドッキング ステーション

## 3 概要

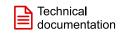

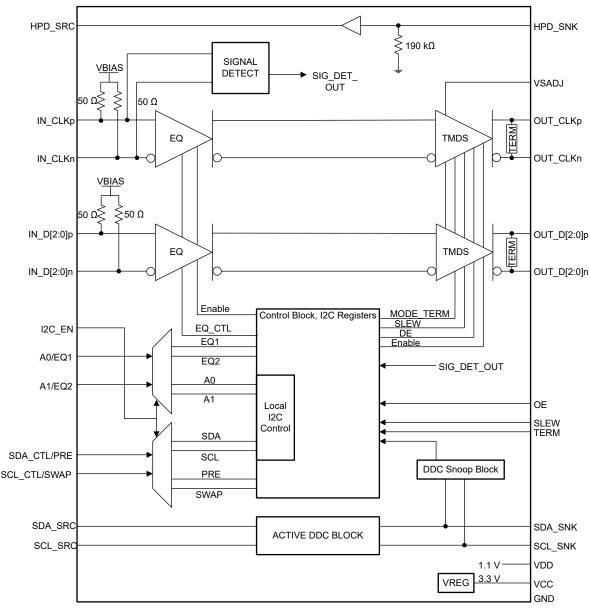

TDP158 デバイスは、AC カップリングされた HDMI 信号 から、遷移が最小化された差動信号 (TMDS) へのリドライ バであり、デジタル ビデオ インターフェイス (DVI) 1.0 お よび高解像度マルチメディア インターフェイス (HDMI) 1.4b および 2.0b の出力信号をサポートしています。 TDP158 は、4 つの TMDS チャネルと、デジタル ディス プレイ制御 (DDC) インターフェイスをサポートします。 TDP158 は、最大 6Gbps の信号速度に対応し、最高解 像度 4k 2k 60p 24 ビット/ピクセル および最大 WUXGA 16 ビット色深度、または高リフレッシュ レートの 1080p に 使用できます。TDP158 は、HDMI2.0 規格をサポートす るように構成可能です。

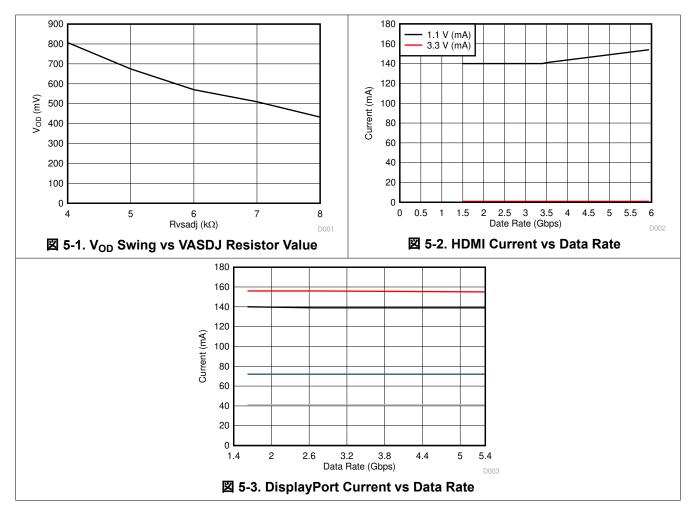

TDP158 は、 $V_{DD}$  で 1.1V、 $V_{CC}$  で 3.3V のデュアル電源 レールをサポートしているため、消費電力を削減できま す。

全体的な消費電力を低減するために、いくつかの電力管 理手法が組み込まれています。TDP158 は、I<sup>2</sup>C またはピ ン ストラップを使用して固定レシーバ EQ ゲインをサポー トし、入力ケーブルや基板のトレース長の相違を補償でき ます。

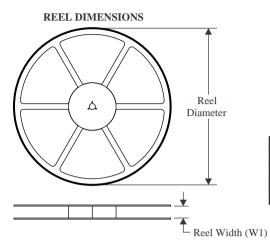

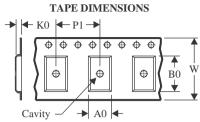

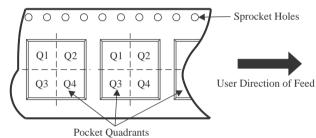

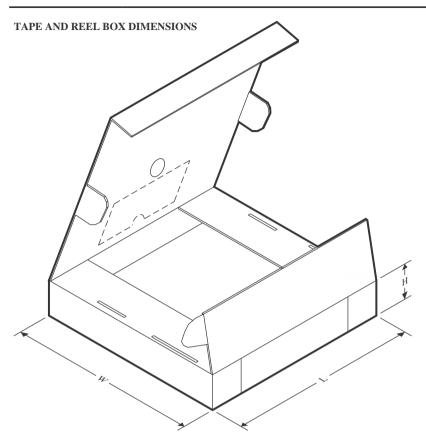

#### パッケージ情報

| 部品番号   | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|--------|----------------------|--------------------------|

| TDP158 | RSB (WQFN, 40)       | 5mm × 5mm                |

- (1) 詳細については、セクション 11 を参照してください。

- パッケージ サイズ (長さ×幅) は公称値であり、該当する場合はピ ンも含まれます。

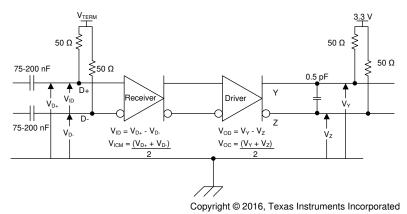

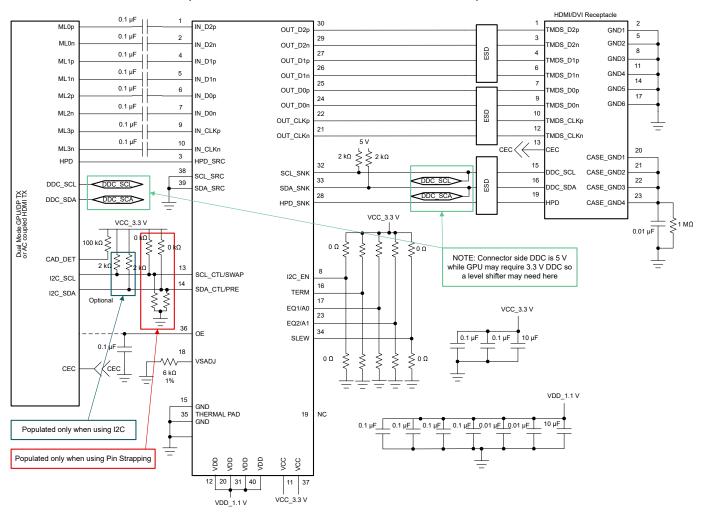

概略回路図

# **Table of Contents**

| 1 | 特長                                                       | . 1 |

|---|----------------------------------------------------------|-----|

| 2 | アプリケーション                                                 | 1   |

| 3 | 概要                                                       | . 1 |

|   | Pin Configuration and Functions                          |     |

| 5 | Specifications                                           | . 5 |

|   | 5.1 Absolute Maximum Ratings                             | . 5 |

|   | 5.2 ESD Ratings                                          | . 5 |

|   | 5.3 Recommended Operating Conditions                     | . 5 |

|   | 5.4 Thermal Information                                  |     |

|   | 5.5 Electrical Characteristics, Power Supply             | . 7 |

|   | 5.6 Electrical Characteristics, Differential Input       | . 8 |

|   | 5.7 Electrical Characteristics, TMDS Differential        |     |

|   | Output                                                   | 8   |

|   | 5.8 Electrical Characteristics, DDC, I2C, HPD, and       |     |

|   | ARC                                                      | 8   |

|   | 5.9 Electrical Characteristics, TMDS Differential        |     |

|   | Output in DP-Mode                                        |     |

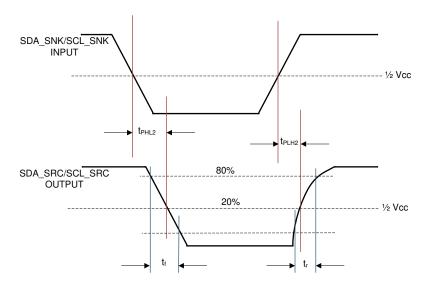

|   | 5.10 Switching Characteristics, TMDS                     |     |

|   | 5.11 Switching Characteristics, HPD                      |     |

|   | 5.12 Switching Characteristics, DDC and I <sup>2</sup> C |     |

| _ | 5.13 Typical Characteristics                             |     |

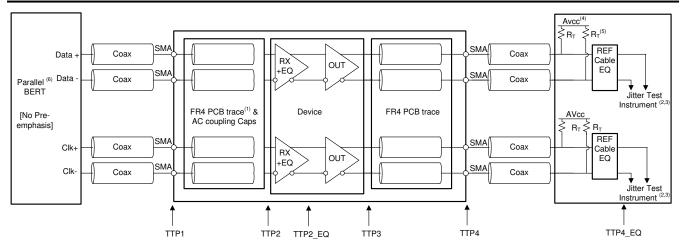

| 6 | Parameter Measurement Information                        | 12  |

| 7 Detailed Description                  | 18 |

|-----------------------------------------|----|

| 7.1 Overview                            |    |

| 7.2 Functional Block Diagram            |    |

| 7.3 Feature Description                 |    |

| 7.4 Device Functional Modes             |    |

| 7.5 Register Maps                       |    |

| 8 Application and Implementation        |    |

| 8.1 Application Information             |    |

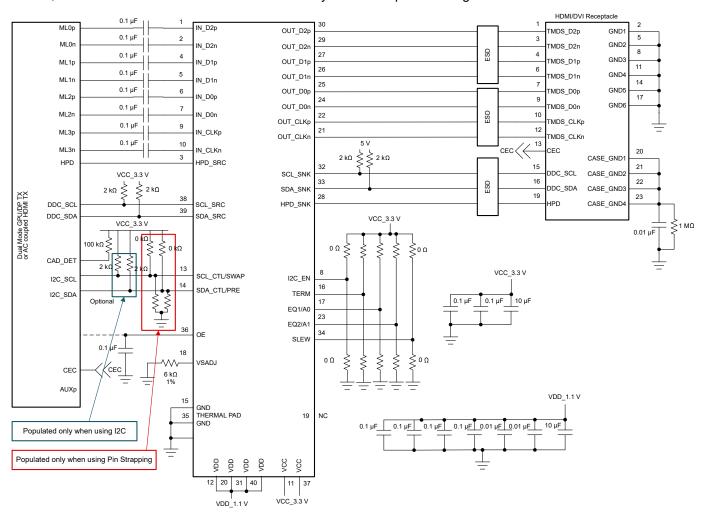

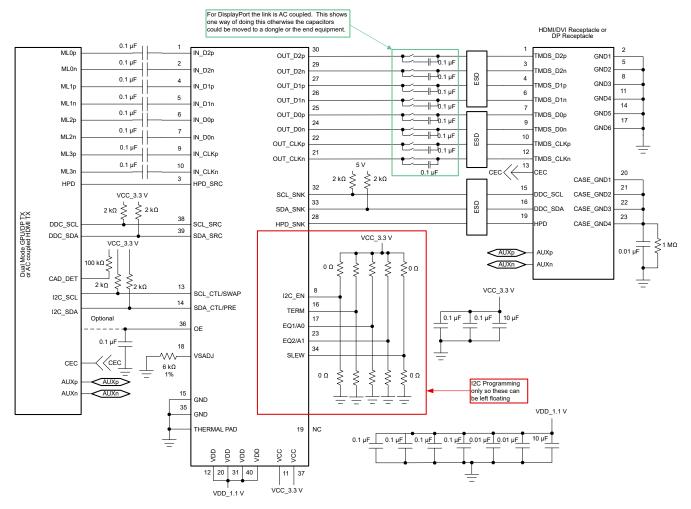

| 8.2 Typical Application                 |    |

| 8.3 Power Supply Recommendations        |    |

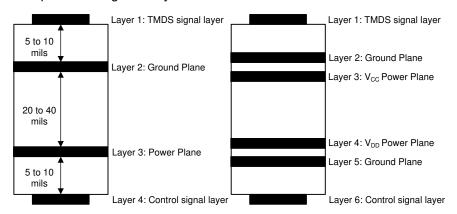

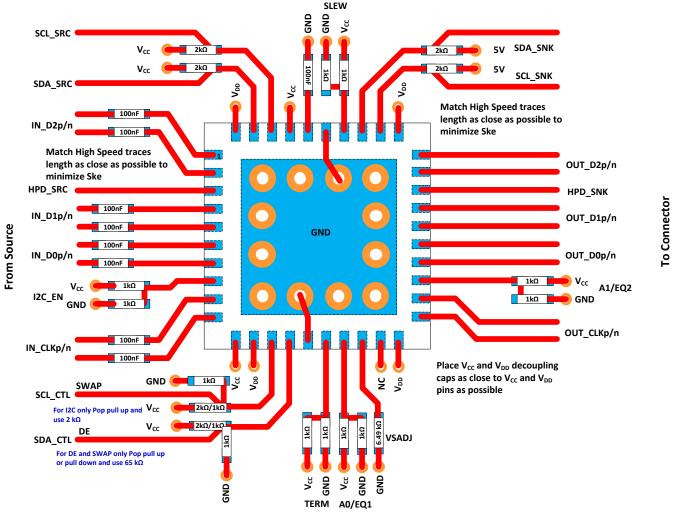

| 8.4 Layout                              | 44 |

| 9 Device and Documentation Support      |    |

| 9.1 Documentation Support               |    |

| 9.2ドキュメントの更新通知を受け取る方法                   |    |

| 9.3 サポート・リソース                           | 47 |

| 9.4 Trademarks                          | 47 |

| 9.5 静電気放電に関する注意事項                       | 47 |

| 9.6 用語集                                 | 47 |

| 10 Revision History                     | 47 |

| 11 Mechanical, Packaging, and Orderable |    |

| Information                             | 49 |

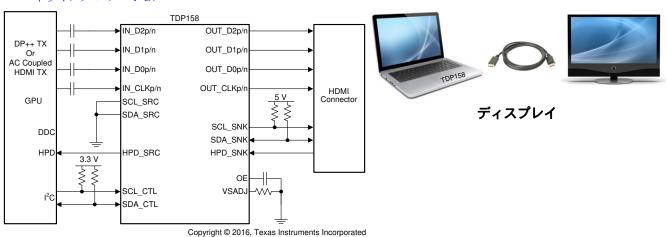

# 4 Pin Configuration and Functions

図 4-1. RSB Package, 40-Pin WQFN (Top View)

表 4-1. Pin Functions

| PIN                                                |                       | TYPE(1)                         | DESCRIPTION                         |  |  |  |

|----------------------------------------------------|-----------------------|---------------------------------|-------------------------------------|--|--|--|

| NAME                                               | NO.                   |                                 | DESCRIPTION                         |  |  |  |

|                                                    |                       |                                 | SUPPLY AND GROUND PINS              |  |  |  |

| VCC                                                | 11, 37                | Р                               | 3.3V Power Supply                   |  |  |  |

| VDD                                                | 12,20,31,40           | P 1.1V Power Supply             |                                     |  |  |  |

| GND                                                | 15, 35<br>Thermal Pad | G                               | Ground                              |  |  |  |

|                                                    | MAIN LINK INPUT PINS  |                                 |                                     |  |  |  |

| IN_D2p/n                                           | 1, 2                  | I                               | Channel 2 Differential Input        |  |  |  |

| IN_D1p/n                                           | 4, 5                  | I                               | Channel 1 Differential Input        |  |  |  |

| IN_D0p/n                                           | 6, 7                  | I                               | Channel 0 Differential Input        |  |  |  |

| IN_CLKp/n                                          | 9, 10                 | Ĺ                               | Clock Differential Input            |  |  |  |

|                                                    |                       |                                 | MAIN LINK OUTPUT PINS (FAIL SAFE)   |  |  |  |

| OUT_D2n/p                                          | 29, 30                | 0                               | TMDS Data 2 Differential Output     |  |  |  |

| OUT_D1n/p 26, 27 O TMDS Data 1 Differential Output |                       | TMDS Data 1 Differential Output |                                     |  |  |  |

| OUT_D0n/p 24, 25 O TMDS Data 0 Differential Output |                       | TMDS Data 0 Differential Output |                                     |  |  |  |

| OUT_CLKn/p                                         | 21, 22                | 0                               | TMDS Data Clock Differential Output |  |  |  |

# 表 4-1. Pin Functions (続き)

| PIN          | 400          | 表 4-1. Pin Functions (続き)                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|--------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME         | NO.          | TYPE <sup>(1)</sup>                                                                                                                  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|              |              |                                                                                                                                      | HOT PLUG DETECT AND DDC PINS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

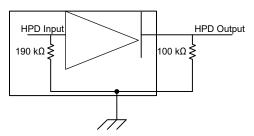

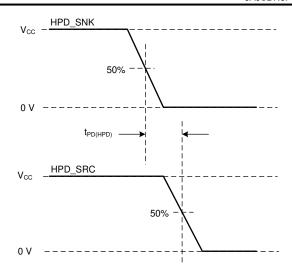

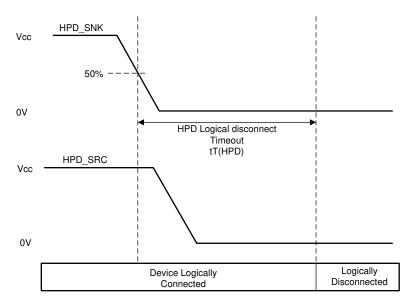

| HPD_SRC      | 3            | 0                                                                                                                                    | Hot Plug Detect Output to source side                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| HPD_SNK      | 28           | I                                                                                                                                    | Hot Plug Detect Input from sink side                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

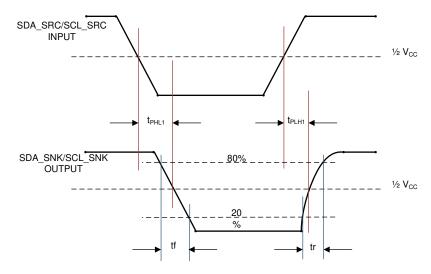

| SDA_SNK      | 33           | I/O                                                                                                                                  | Sink Side Bidirectional DDC Data Line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| SCL_SNK      | 32           | I/O                                                                                                                                  | Sink Side Bidirectional DDC Clock Line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| SDA_SRC      | 39           | I/O                                                                                                                                  | Source Side Bidirectional DDC Data Line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| SCL_SRC      | 38           | I/O                                                                                                                                  | Source Side Bidirectional DDC Clock Line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|              | CONTROL PINS |                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

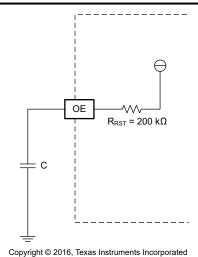

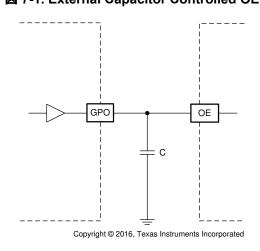

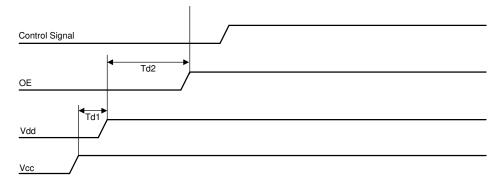

| OE           | 36           | 1                                                                                                                                    | Operation Enable/Reset Pin OE = L: Power Down Mode OE = H: Normal Operation Internal weak pullup: Resets device when transitions from H to L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| I2C_EN       | 8            | ı                                                                                                                                    | I2C_EN = High; Puts Device into I2C Control Mode I2C_EN = Low; Puts Device into Pin Strap Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

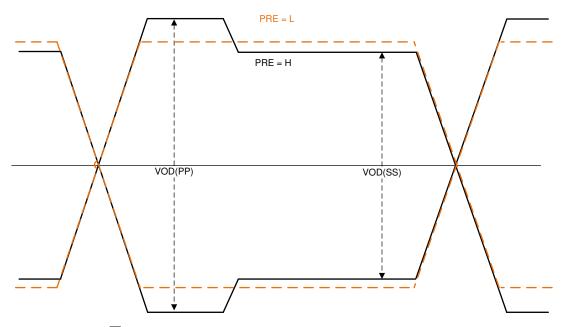

| SDA_CTL/PRE  | 14           | I2C Data Signal: When I2C_EN = High;<br>  Pre-emphasis: When I2C_EN = Low: See セクション 7.3.11<br>  DE = L: None 0dB<br>  DE = H: 3.5dB |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| SCL_CTL/SWAP | 13           | I                                                                                                                                    | I2C Clock Signal: When I2C_EN = High;<br>Lane SWAP: When I2C_EN = Low: See セクション 7.3.4 HDMI Mode Only<br>SWAP = L: Normal Operation<br>SWAP = H: Lane Swap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

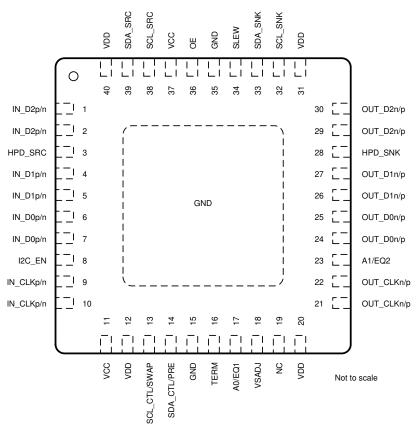

| VSADJ        | 18           | ı                                                                                                                                    | TMDS Compliant Voltage Swing Control (Nominal 6 k $\Omega$ for HDMI and DP combination; 6.49 k $\Omega$ for HDMI only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| A0/EQ1       | 17           | l<br>3 Level                                                                                                                         | Address Bit 1 for I2C Programming when I2C_EN = High EQ1 Pin Setting when I2C_EN = Low; Works in conjunction with A1/EQ2; See $\frac{t}{2}$ 7.3.5 for settings. For pin control, Low = 1k $\Omega$ pulldown resistor to GND, High = 1k $\Omega$ pullup resistor to VCC, NC = Floating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| A1/EQ2       | 23           | I<br>3 Level                                                                                                                         | Address Bit 2 for I2C Programming when I2C_EN = High EQ2 Pin Setting when I2C_EN = Low; Works in conjunction with A0/EQ1; See $\frac{t}{2}$ 7.3.5 for settings. For pin control, Low = $1k\Omega$ pulldown resistor to GND, High = $1k\Omega$ pullup resistor to VCC, NC = Floating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| SLEW         | 34           | I<br>3 Level                                                                                                                         | Clock Slew Rate Control: See $\frac{1}{2}$ 7.3.10 SLEW = L: Slowest $\cong$ 203ps SLEW = NC (Default): Mid-range 1 $\cong$ 180ps SLEW = H: Fastest $\cong$ 122ps For pin control, L = 1kΩ pulldown resistor to GND, H = 1kΩ pullup resistor to VCC, NC = Floating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

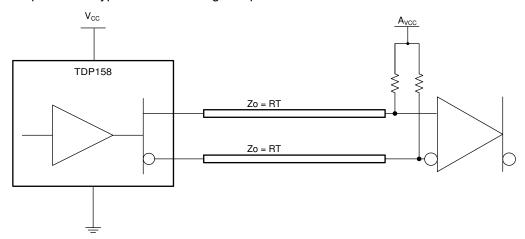

| TERM         | 16           | I<br>3 Level                                                                                                                         | Source Termination Control: See $\frac{1}{2}D = \frac{1}{2}D =$ |  |  |  |  |

| NC           | 19           | NA                                                                                                                                   | No Connect. Optionally connect 0.1µF to GND to reduce noise.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

<sup>(1)</sup> I= Input, O = Output, P = Power, G = Ground

English Data Sheet: SLLSEX2

## **5 Specifications**

# 5.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1) (2)

|                                       |                                                                                                            | MIN           | MAX  | UNIT |

|---------------------------------------|------------------------------------------------------------------------------------------------------------|---------------|------|------|

| Supply Voltage Range <sup>(3)</sup>   | VCC                                                                                                        | -0.3          | 4    | V    |

| Supply Voltage Kange                  | VDD                                                                                                        | -0.3          | 1.4  | V    |

|                                       | Main Link Input Differential Voltage (IN_Dx)                                                               | 0             | 1.56 | V    |

|                                       | Main Link Input Single Ended on Pin                                                                        | -0.3          | 1.4  | V    |

|                                       | TMDS Output ( OUT_Dx)                                                                                      | -0.3          | 4    | V    |

| ltage Range                           | HPD_SRC, VSADJ, SDA_CTL/PRE, OE, A1/<br>EQ2, A0/EQ1, TERM, I2C_EN, SLEW,<br>SCL_CTL/SWAP, SDA_SRC, SCL_SRC | -0.3          | 4    | V    |

|                                       | HDP_SNK, SDA_SNK, SCL_SNK                                                                                  | -0.3          | 6    | V    |

| Continuous power dissipation          |                                                                                                            | See セクション 5.4 |      |      |

| Storage temperature, T <sub>stg</sub> |                                                                                                            | -65           | 150  | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2) All voltage values, except differential voltages, are with respect to network ground terminal.

- (3) Tested in accordance with JEDEC Standard 22, Test Method A114-B.

# 5.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 5.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                      |                                                    |                                                                                              | MIN  | NOM MAX | UNIT |

|----------------------|----------------------------------------------------|----------------------------------------------------------------------------------------------|------|---------|------|

| V <sub>CC</sub>      | Supply Voltage Nomi                                | nal Value 3.3V for DP mode                                                                   | 3    | 3.6     | V    |

|                      | Supply Voltage Nomi                                | nal Value 3.3V for HDMI mode                                                                 | 3.13 | 3.47    | V    |

| V <sub>DD</sub>      | Supply Voltage Nomi                                | nal Value 1.1V                                                                               | 1    | 1.27    | V    |

| TJ                   | Junction temperature                               |                                                                                              | 0    | 105     | °C   |

| T <sub>A</sub>       | Operating free-air ten                             | nperature (TDP158)                                                                           | 0    | 85      | °C   |

| MAIN LIN             | K DIFFERENTIAL PINS                                |                                                                                              |      |         |      |

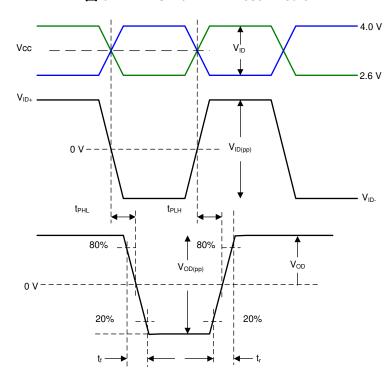

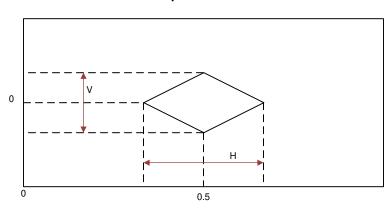

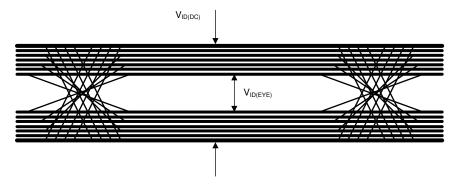

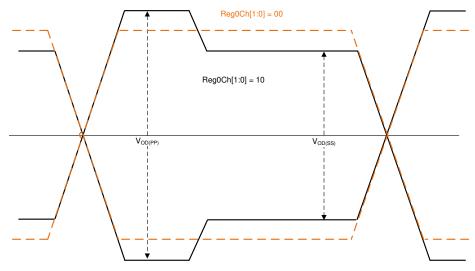

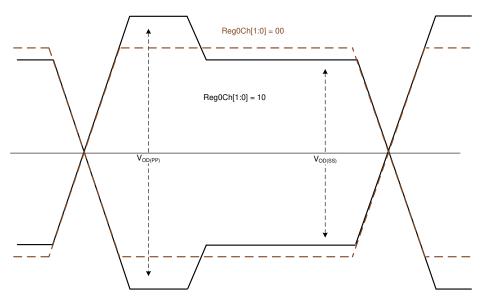

| V <sub>ID(EYE)</sub> | Peak-to-peak input differential voltage See ⊠ 6-14 |                                                                                              | 75   | 1200    | mV   |

| V <sub>ID(DC)</sub>  | The input differential                             | voltage Peak-to peak DC level, See 図 6-14                                                    | 200  | 1200    | mV   |

| V <sub>IC</sub>      | Input Common Mode                                  | Voltage (Internally Biased)                                                                  | 0.5  | 0.9     | V    |

| d <sub>R</sub>       | Data rate                                          |                                                                                              | 0.25 | 6       | Gbps |

| V <sub>SADJ</sub>    | TMDS compliant swir                                | ng voltage bias resistor (Nominal $6k\Omega$ for HDMI and $0k\Omega$ for HDMI only) $^{(1)}$ | 4.5  | 8       | kΩ   |

| DDC, I2C,            | HPD, AND CONTROL I                                 | PINS                                                                                         |      |         |      |

| V <sub>I(DC)</sub>   | DC Input Voltage                                   | HDP_SNK, SDA_SNK, SCL_SNK,                                                                   | -0.3 | 5.5     | V    |

|                      |                                                    | SDA_SRC, SCL_SRC; All other Local I2C, and control pins                                      | -0.3 | 3.6     | V    |

資料に関するフィードバック(ご意見やお問い合わせ)を送信

5

# 5.3 Recommended Operating Conditions (続き)

over operating free-air temperature range (unless otherwise noted)

|                        |                                                                                                        | MIN                   | NOM MAX               | UNIT |

|------------------------|--------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|------|

| V <sub>IL</sub>        | Low-level input voltage at DDC                                                                         |                       | 0.3 x V <sub>CC</sub> | V    |

|                        | Low-level input voltage at HPD                                                                         |                       | 0.8                   | V    |

|                        | Low-level input voltage at SDA_CTL/PRE, OE, A1/EQ2, A0/EQ1, TERM, I2C_EN, SLEW, SCL_CTL/SWAP pins only |                       | 0.3                   | V    |

| V <sub>IM</sub>        | Mid-Level input voltage at A1/EQ2, A0/EQ1, TERM, SLEW pins only                                        | 1.2                   | 1.6                   | V    |

| V <sub>IH</sub>        | High-level input voltage at OE, A1/EQ2, A0/EQ1, TERM, I2C_EN, SLEW pins only                           | 0.7 x V <sub>CC</sub> |                       | V    |

|                        | High-level input voltage at SDA_SRC, SCL_SRC, SDA_CTL/PRE, SCL_CTL/SWAP                                | 0.7 x V <sub>CC</sub> |                       | V    |

|                        | High-level input voltage at SDA_SNK, SCL_SNK                                                           | 3.2                   |                       | V    |

|                        | High-level input voltage at HPD                                                                        | 2                     |                       | V    |

| V <sub>OL</sub>        | Low-level output voltage                                                                               |                       | 0.4                   | V    |

| V <sub>OH</sub>        | High-level output voltage                                                                              | 2.4                   |                       | V    |

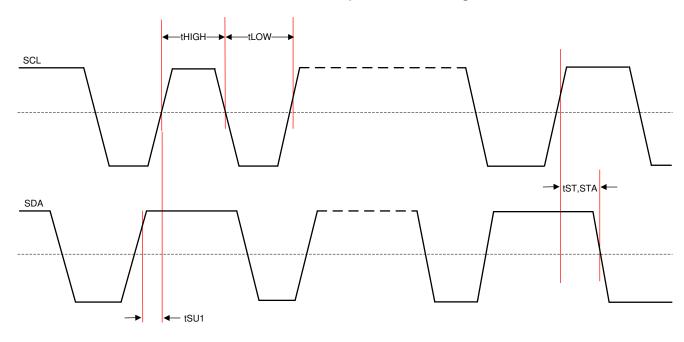

| f <sub>SCL</sub>       | SCL clock frequency fast I <sup>2</sup> C mode for local I2C control                                   |                       | 400                   | kHz  |

| C <sub>(bus,DDC)</sub> | Total capacitive load for each bus line supporting 400kHz (DDC terminals)                              |                       | 400                   | pF   |

| C <sub>(bus,I2C)</sub> | Total capacitive load for each bus line (local I2C terminals)                                          |                       | 100                   | pF   |

| d <sub>R(DDC)</sub>    | DDC Data rate                                                                                          |                       | 400                   | Kbps |

| I <sub>IH</sub>        | High level input current                                                                               | -30                   | 30                    | μA   |

| I <sub>IM</sub>        | Mid level input current                                                                                | -20                   | 20                    | μA   |

| I <sub>IL</sub>        | Low level input current                                                                                | -10                   | 10                    | μA   |

| I <sub>OZ</sub>        | High impedance output current                                                                          |                       | 10                    | μΑ   |

| R <sub>(OEPU)</sub>    | Pull up resistance on OE pin                                                                           | 150                   | 250                   | kΩ   |

<sup>(1)</sup> Reducing resistor in  $V_{SADJ}$  will increase  $V_{OD}$ , care should be taking since resistors below  $\cong 6k\Omega$  may lead to compliance failures.

#### **5.4 Thermal Information**

|                       | THERMAL METRIC(1)                            | RSB (WQFN) | UNIT |

|-----------------------|----------------------------------------------|------------|------|

|                       |                                              | 40 PINS    |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 3.7        | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 23.1       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 9.9        | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter   | 0.3        | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 3.8        | °C/W |

| $R_{\theta JC(bot)}$  | Junction-to-case (bottom) thermal resistance | 3.2        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

資料に関するフィードバック (ご意見やお問い合わせ) を送信

Copyright © 2024 Texas Instruments Incorporated