## TMS320F2803x リアルタイム・マイコン

### 1 特長

- 高効率の 32 ビット CPU (TMS320C28x)

- 60MHz (サイクル タイム 16.67ns)

- 16 ビット × 16 ビットおよび 32 ビット × 32 ビットの MAC 演算

- 16 ビット × 16 ビットのデュアル MAC

- ハーバード バス アーキテクチャ

- アトミック処理

- 高速な割り込み応答とプロセッシング

- 統合メモリプログラミング モデル

- 高いコード効率 (C/C++ およびアセンブリ)

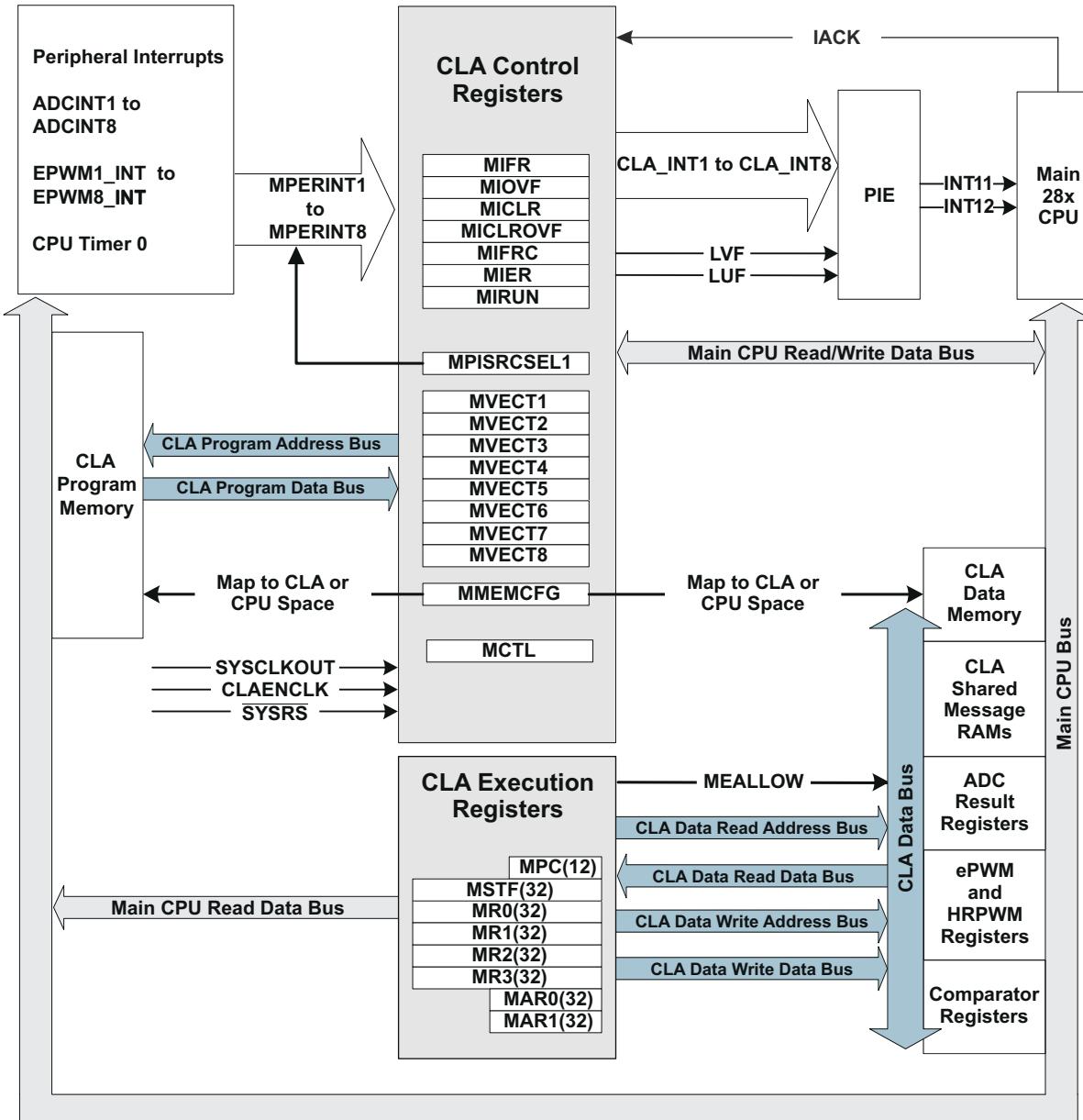

- プログラム可能な制御補償器アクセラレータ (CLA)

- 32 ビット浮動小数点演算アクセラレータ

- メイン CPU と独立にコードを実行

- エンディアンネス:リトル エンディアン

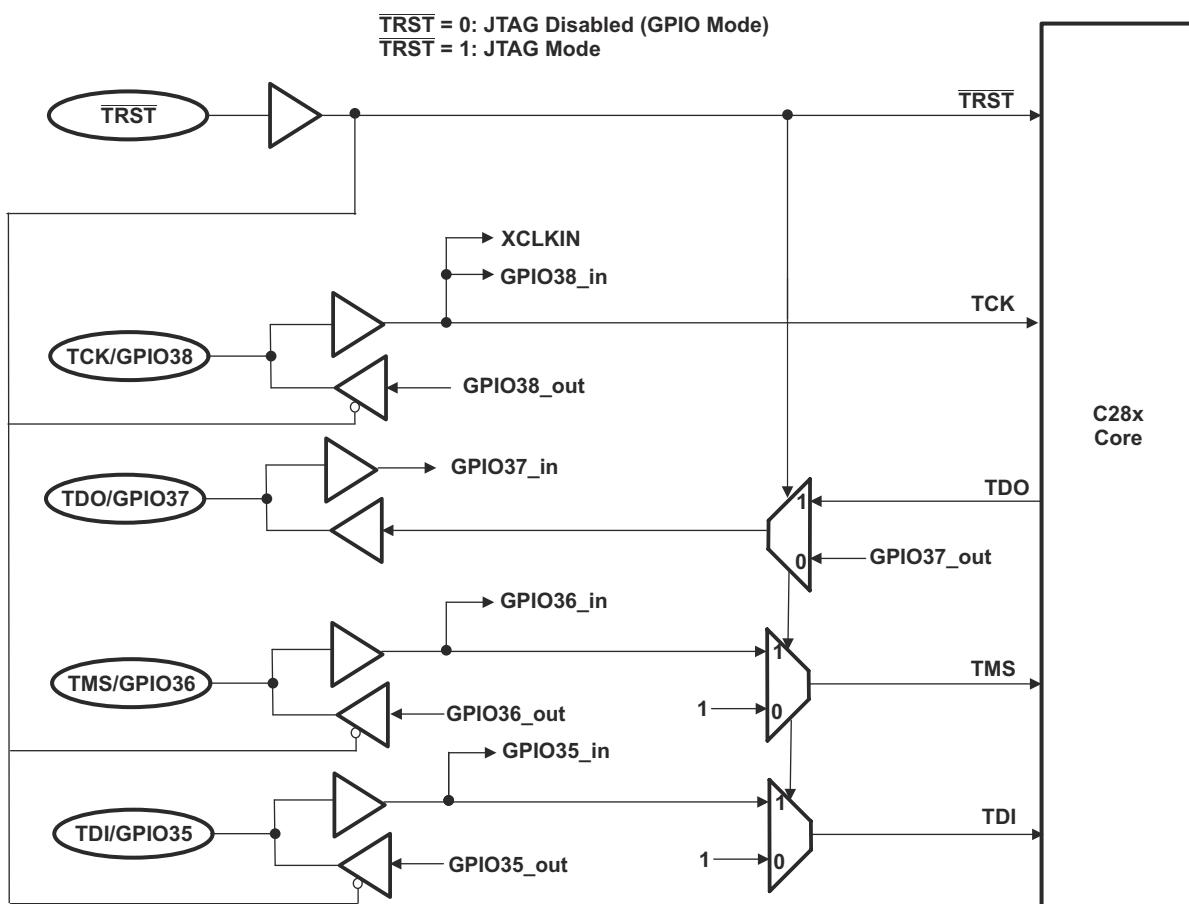

- JTAG バウンダリスキャンをサポート

- IEEE 標準 1149.1-1990 標準テスト アクセス ポートおよびバウンダリスキャンアーキテクチャ

- 低コストのデバイスおよびシステム

- 3.3 V シングル電源

- 電源シーケンス不要

- パワー オンリセットおよびブラウンアウトリセットを内蔵

- 低消費電力

- アナログ サポートピンなし

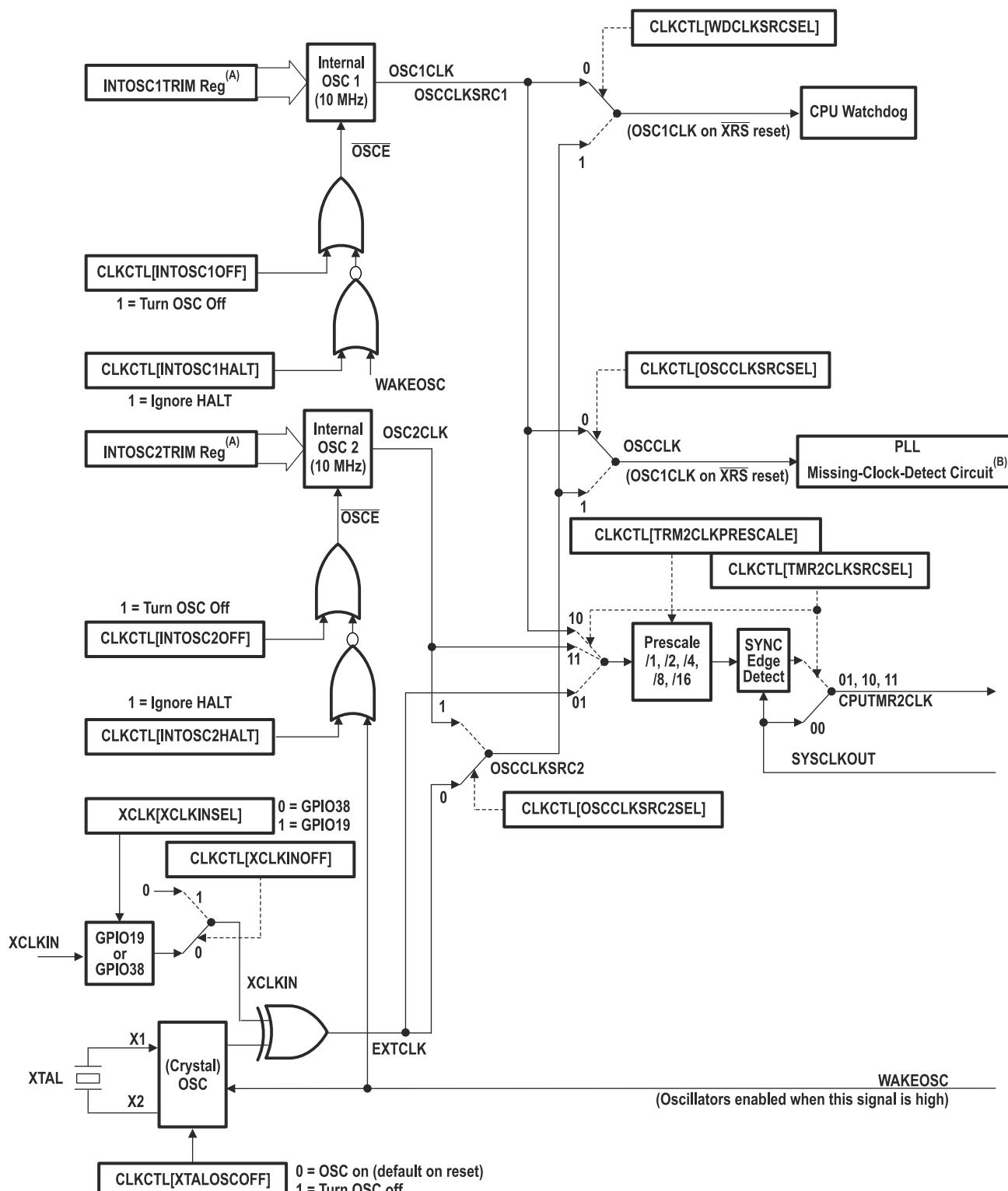

- クロック:

- 2 つの内部ゼロピン発振器

- オンチップの水晶発振器と外部クロック入力

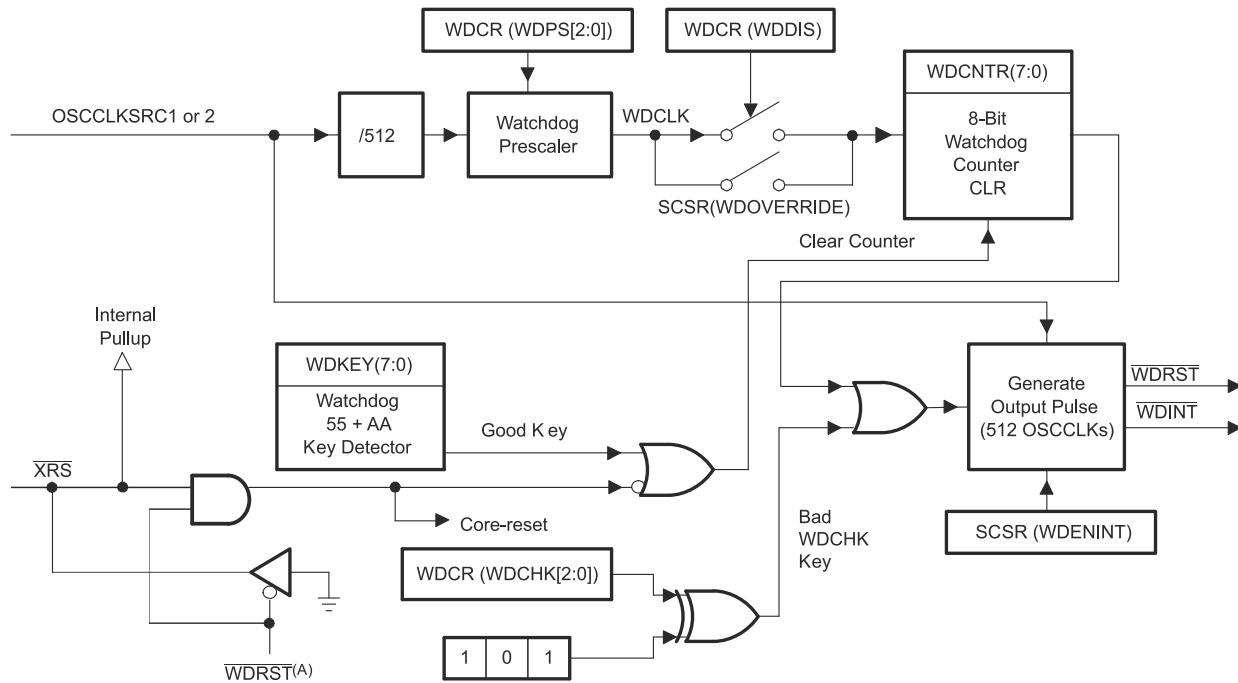

- ウオッチドッグ タイマ モジュール

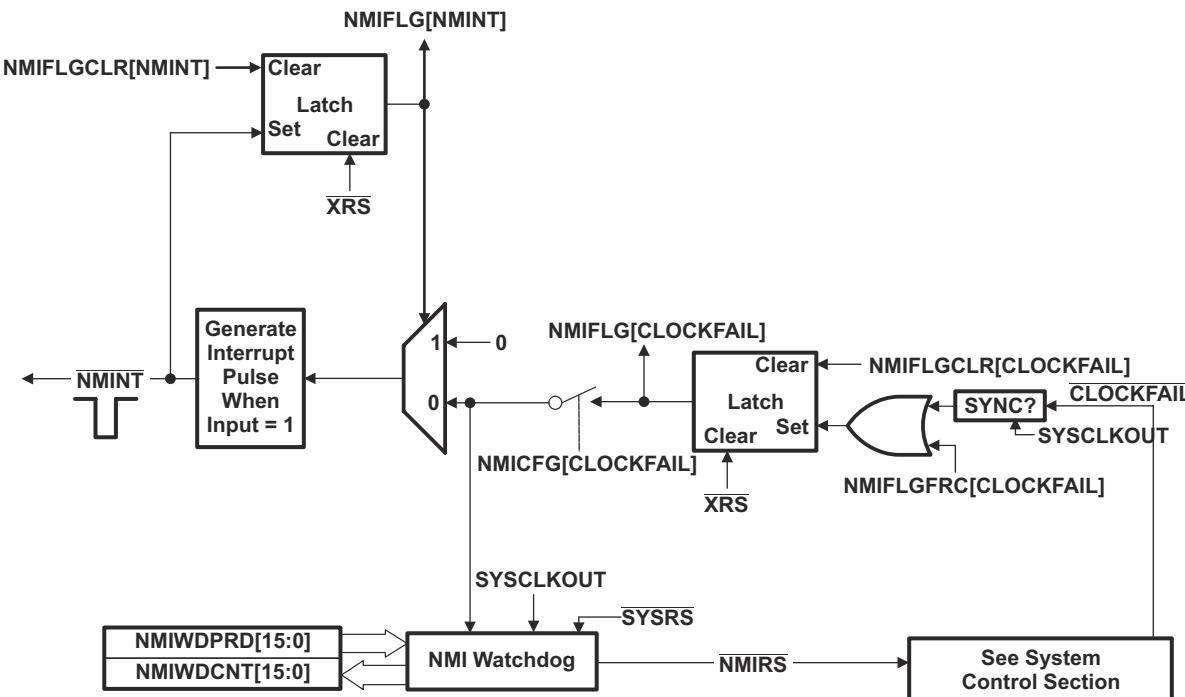

- クロック消失検出回路

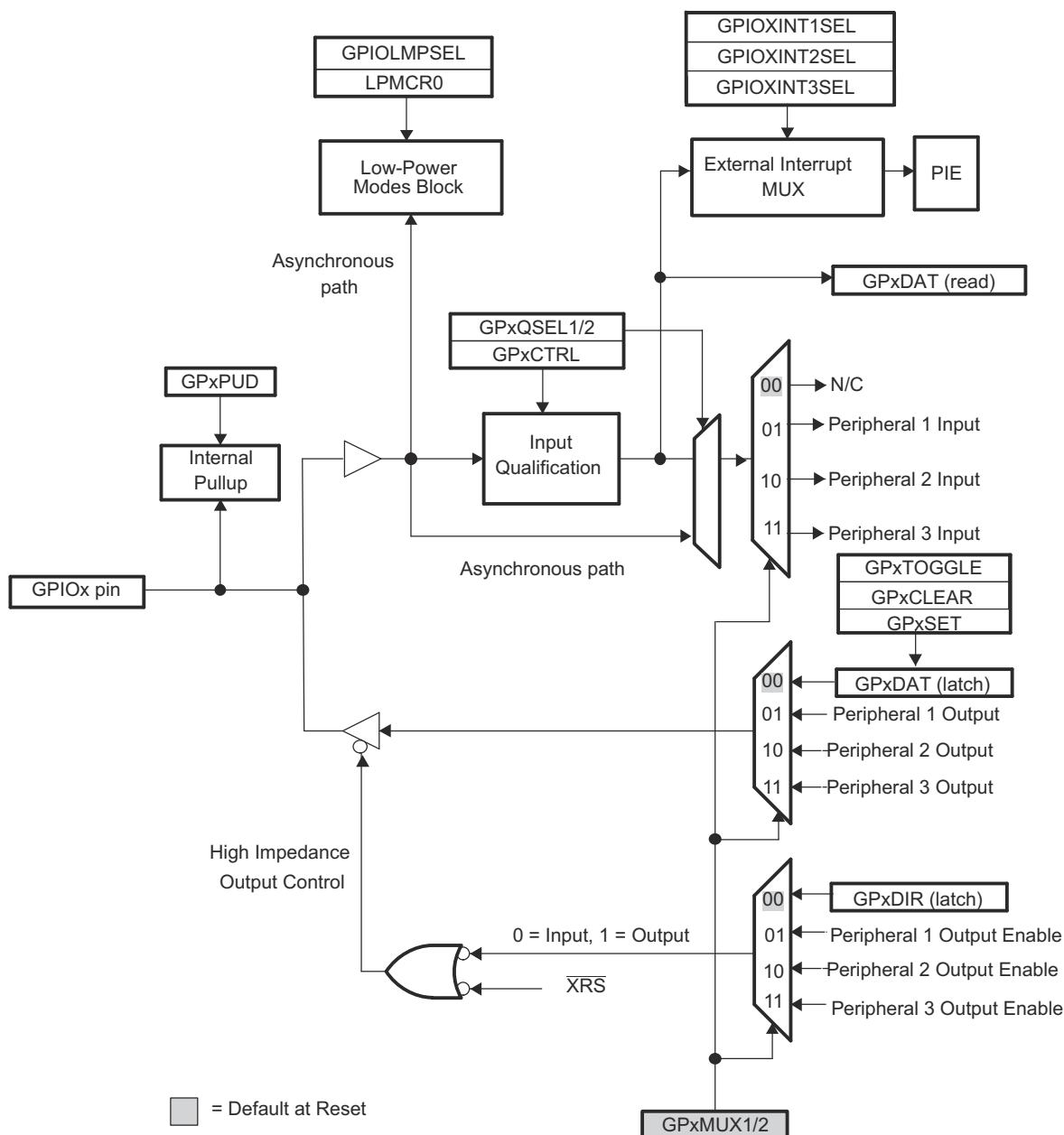

- 最大 45 の個別にプログラム可能な、多重化された、入力フィルタリング付き GPIO ピン

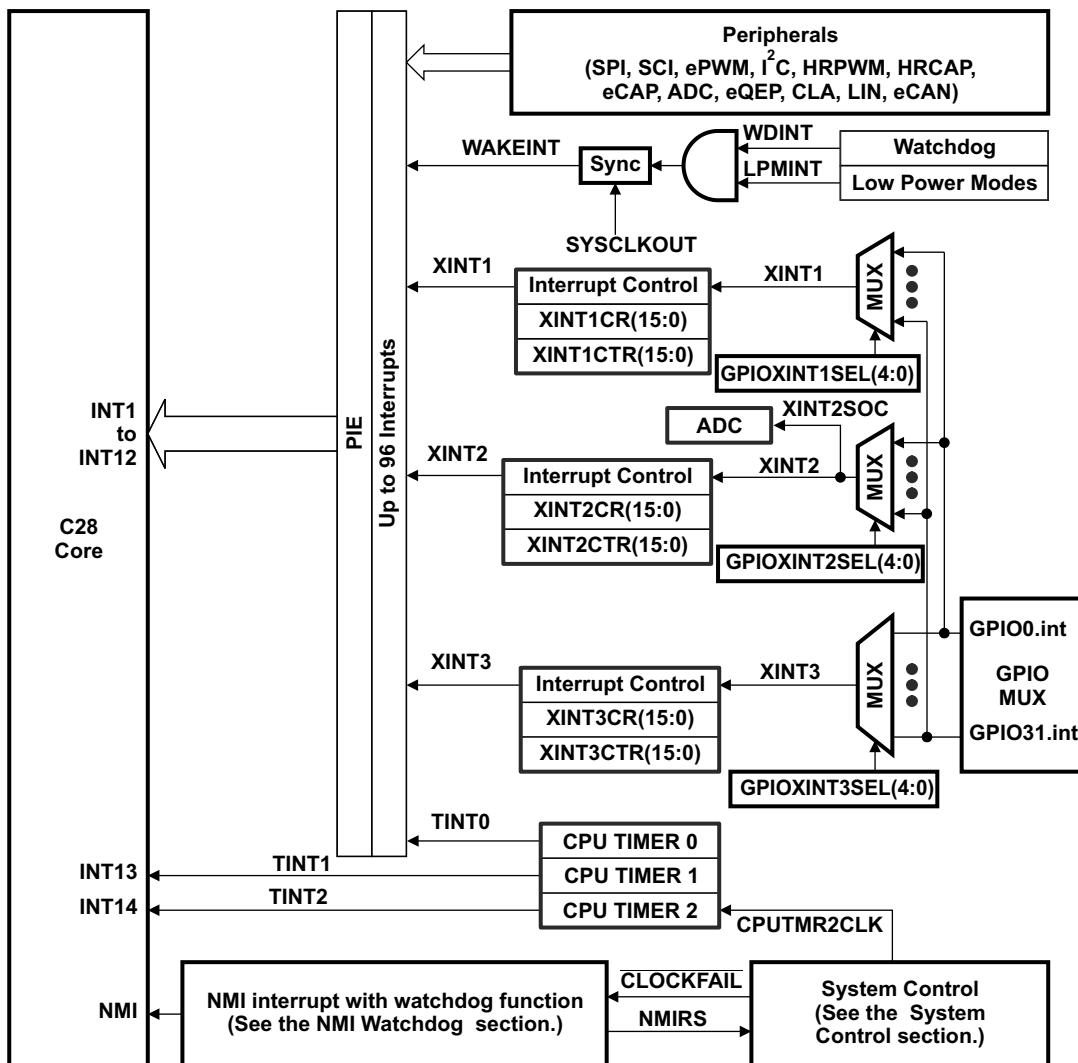

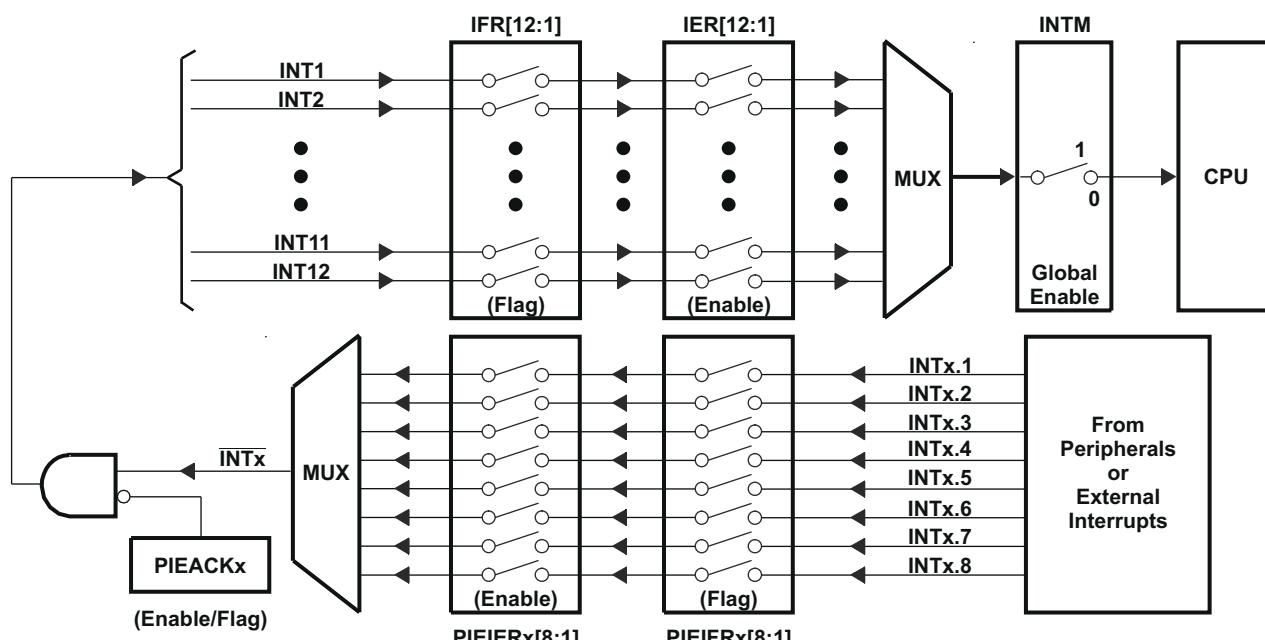

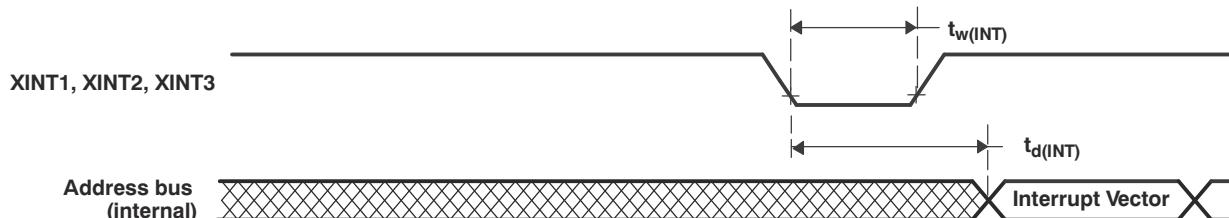

- すべてのペリフェラル割り込みをサポートするペリフェラル割り込み拡張 (PIE) ブロック

- 3 つの 32 ビット CPU タイマ

- それぞれの拡張パルス幅変調器 (ePWM) に独立の 16 ビット タイマ

- オンチップ メモリ

- フラッシュ、SARAM、OTP、ブート ROM を利用可能

- コード セキュリティ モジュール

- 128 ビットのセキュリティキーおよびロック

- セキュア メモリ ブロックを保護

- ファームウェアのリバース エンジニアリングを防止

- シリアル ポート ペリフェラル

- 1 つのシリアル通信インターフェイス (SCI) UART (Universal Asynchronous Receiver/Transmitter) モジュール

- 2 つの SPI (Serial Peripheral Interface) モジュール

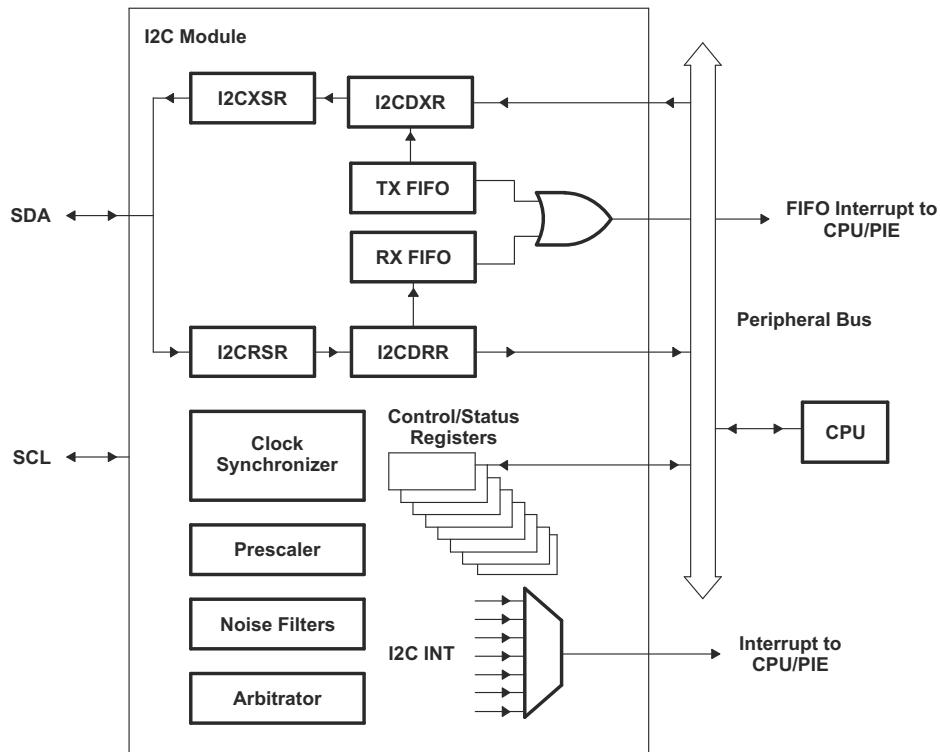

- 1 つの I2C (Inter-Integrated-Circuit) モジュール

- 1 つの LIN (Local Interconnect Network) モジュール

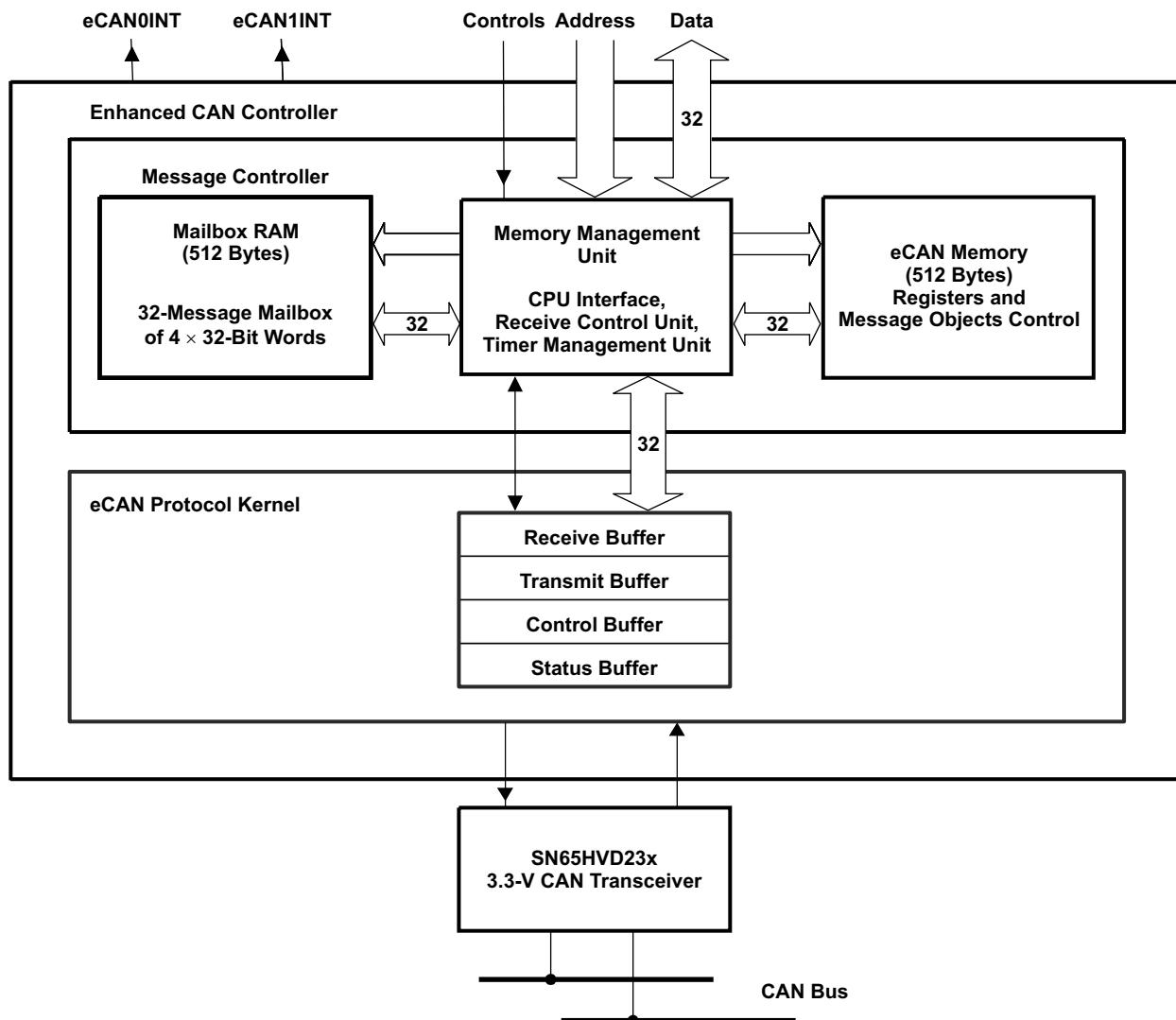

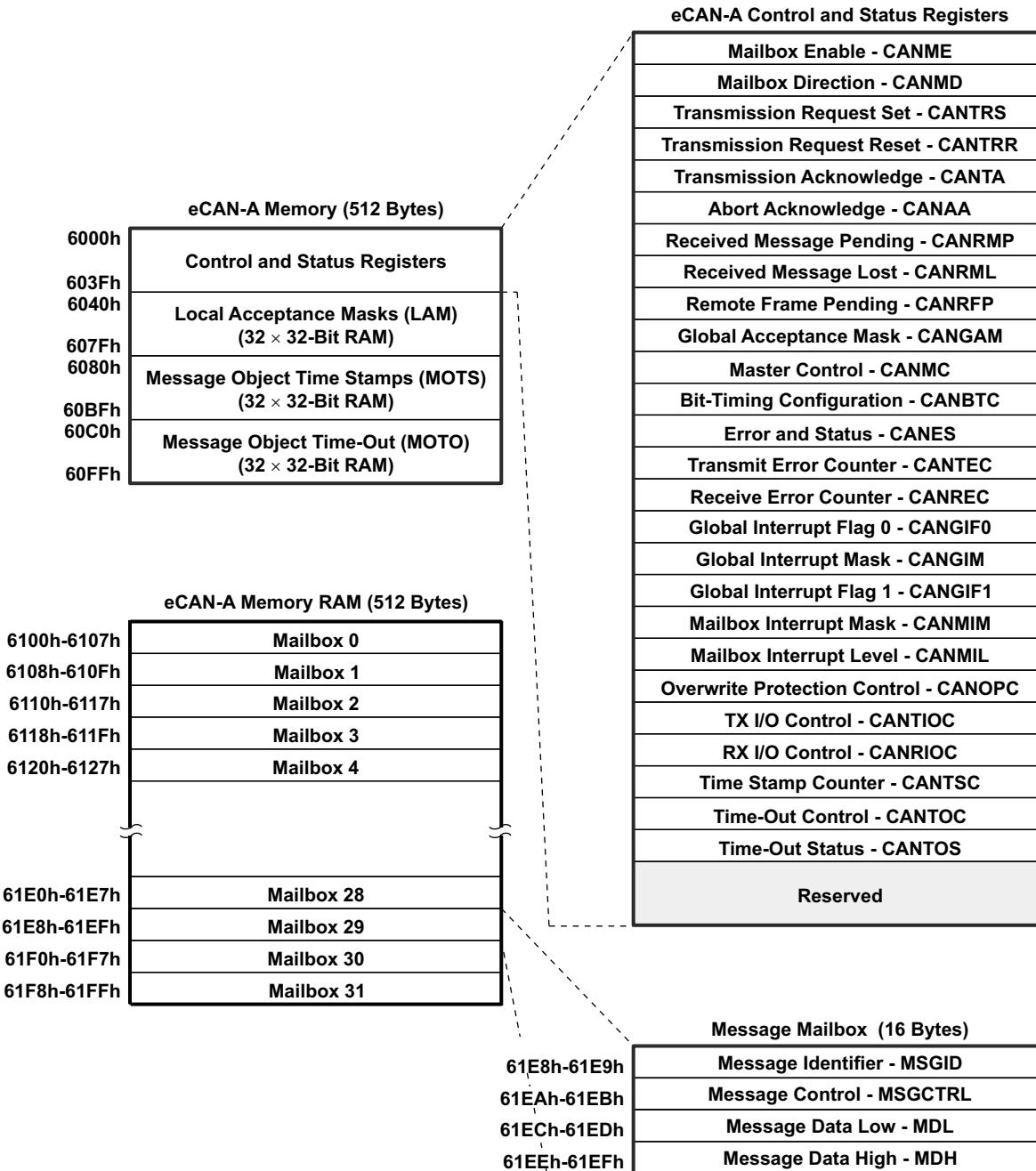

- 1 つの拡張コントローラ エリア ネットワーク (eCAN) モジュール

- 拡張制御ペリフェラル

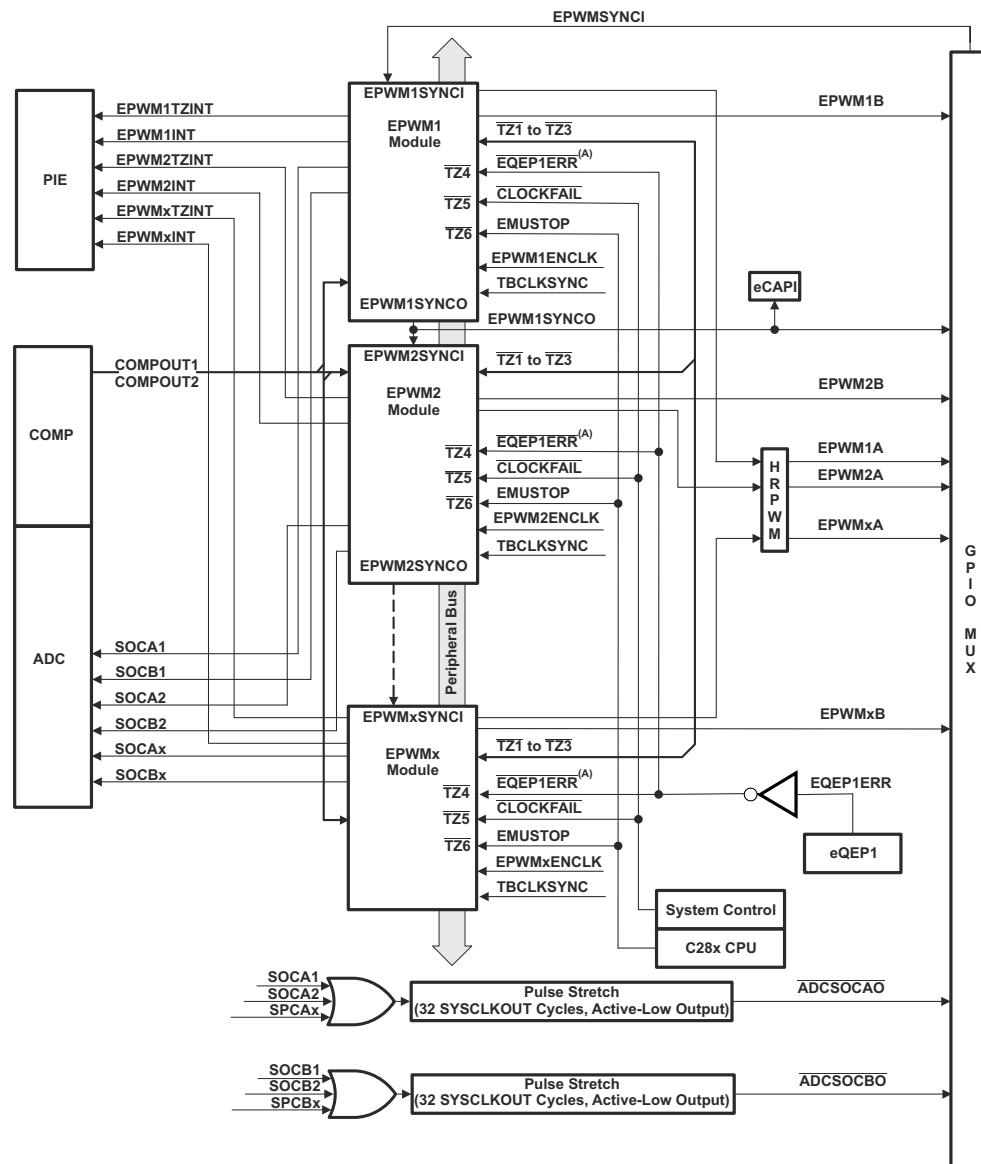

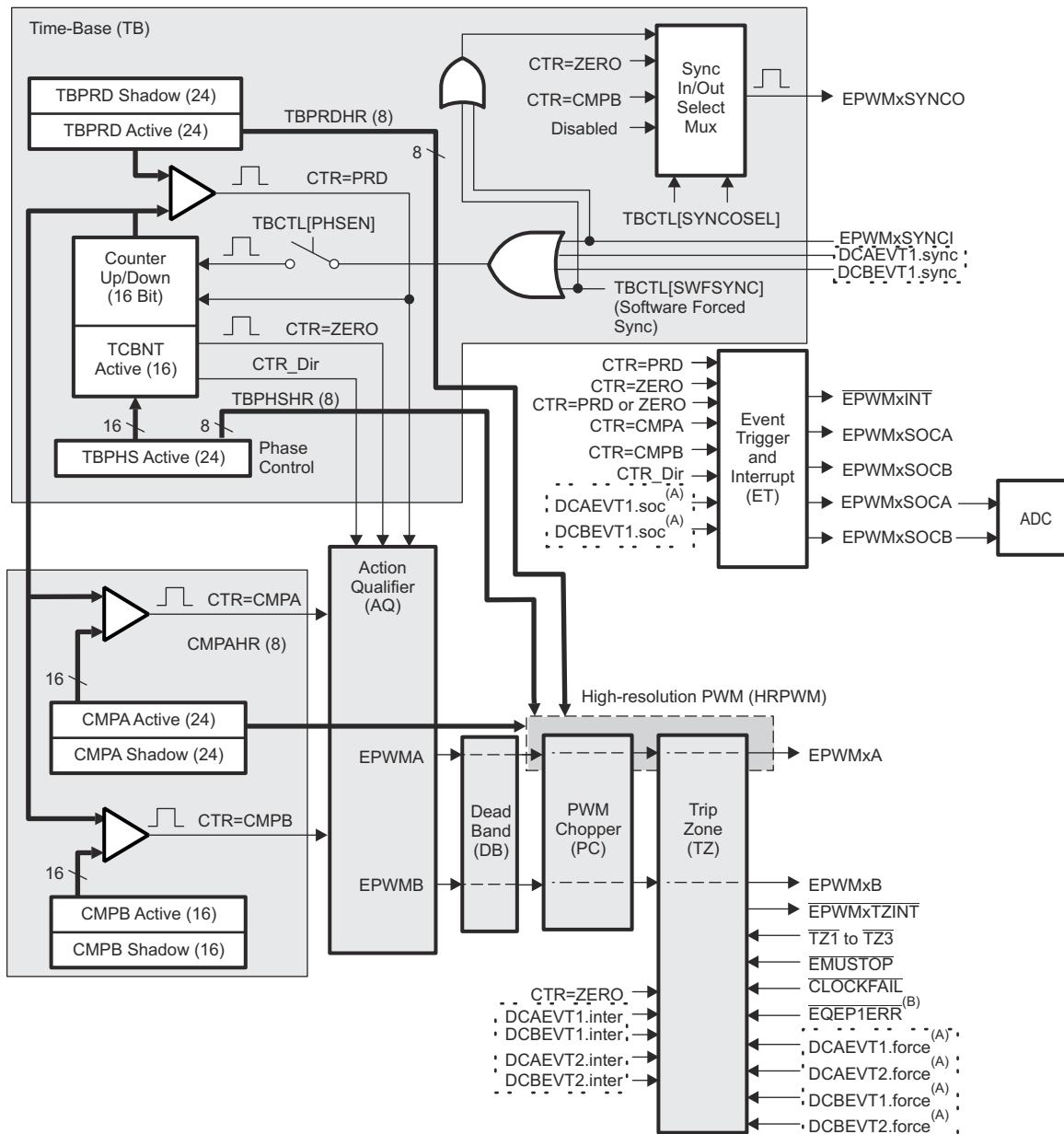

- ePWM

- 高分解能 PWM (HRPWM)

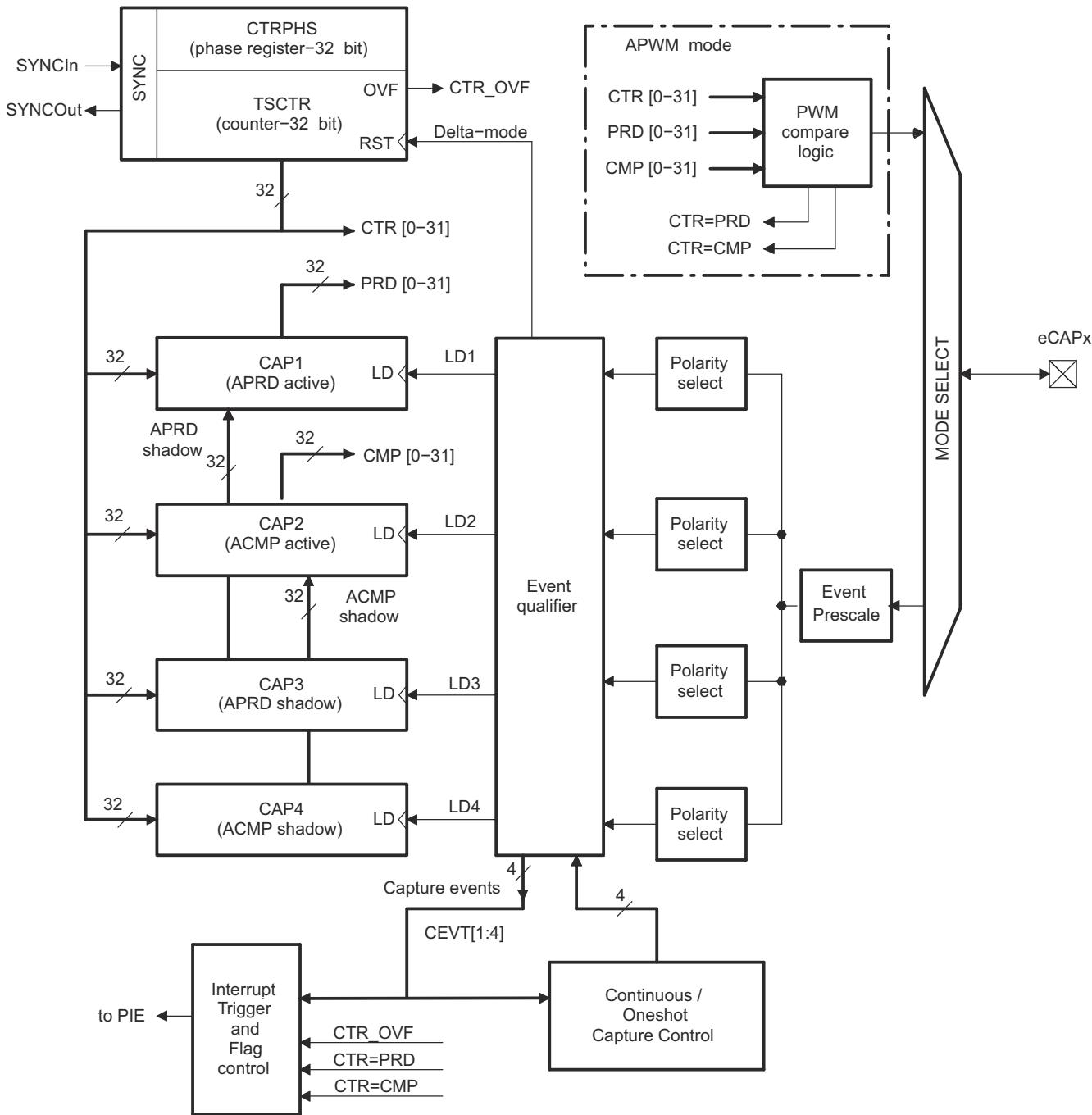

- 拡張キャプチャ (eCAP) モジュール

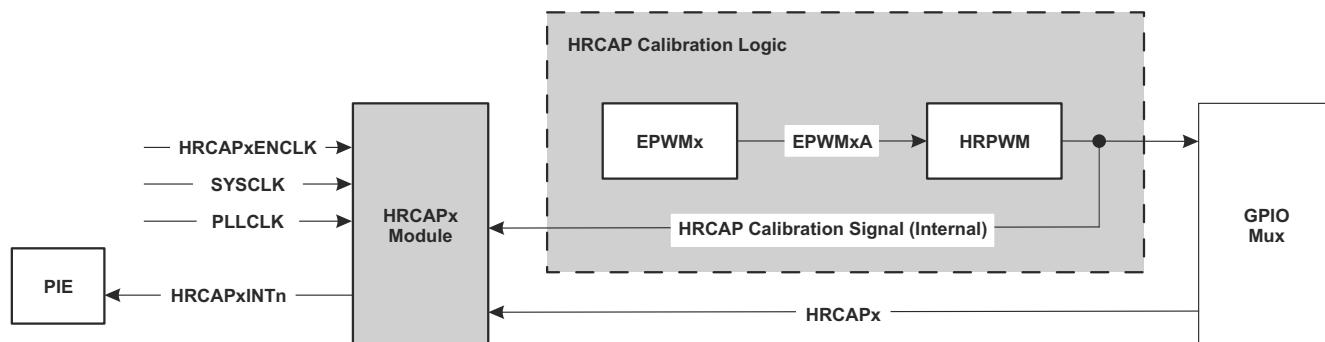

- 高分解能入力キャプチャ (HRCAP) モジュール

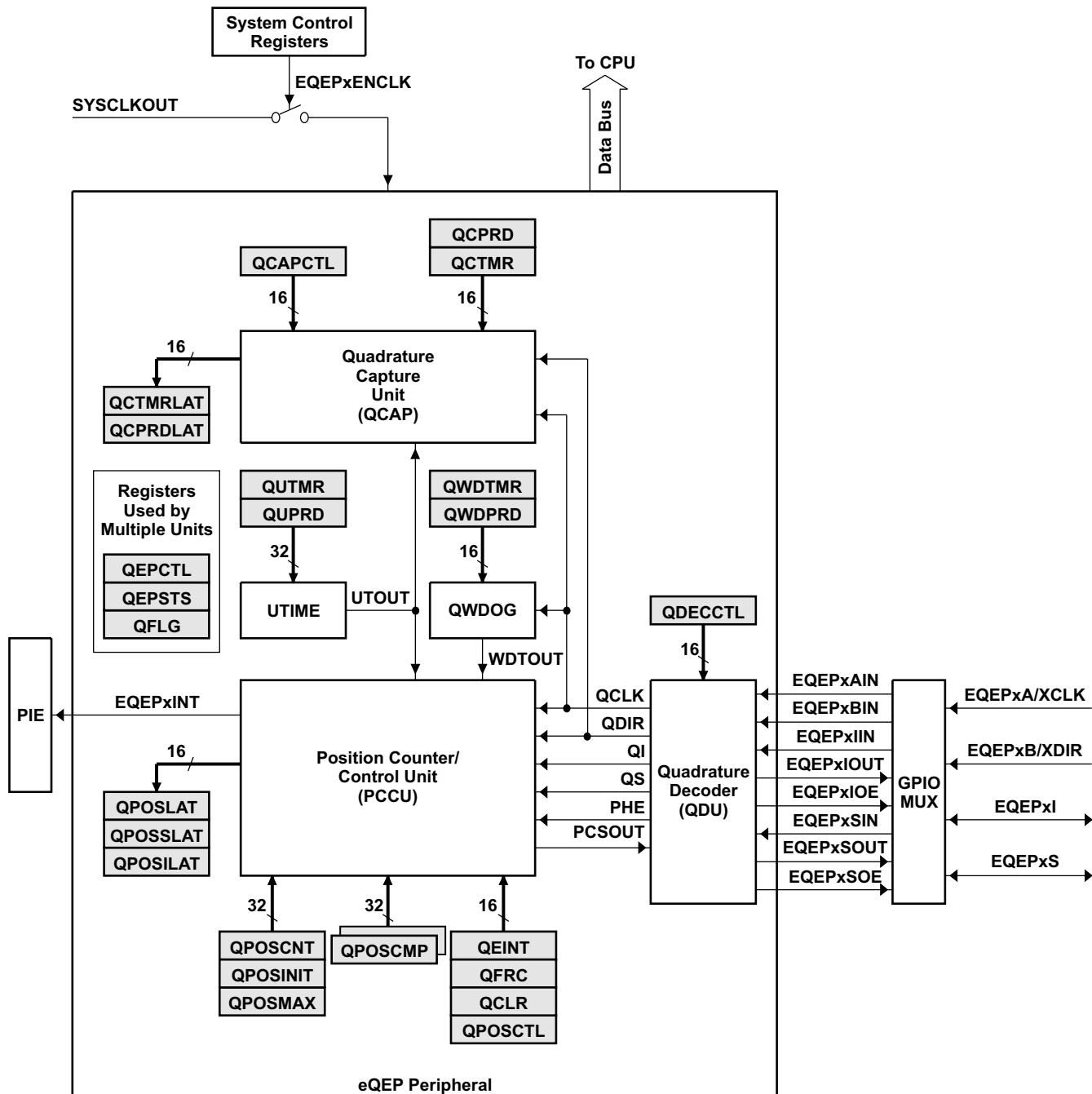

- 拡張直交エンコーダ パルス (eQEP) モジュール

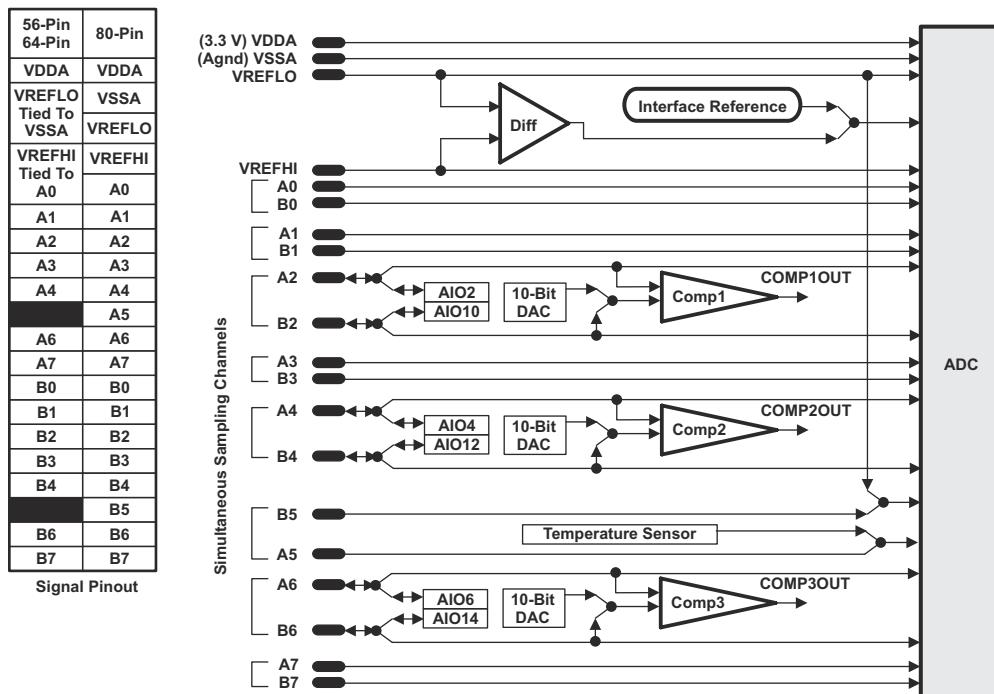

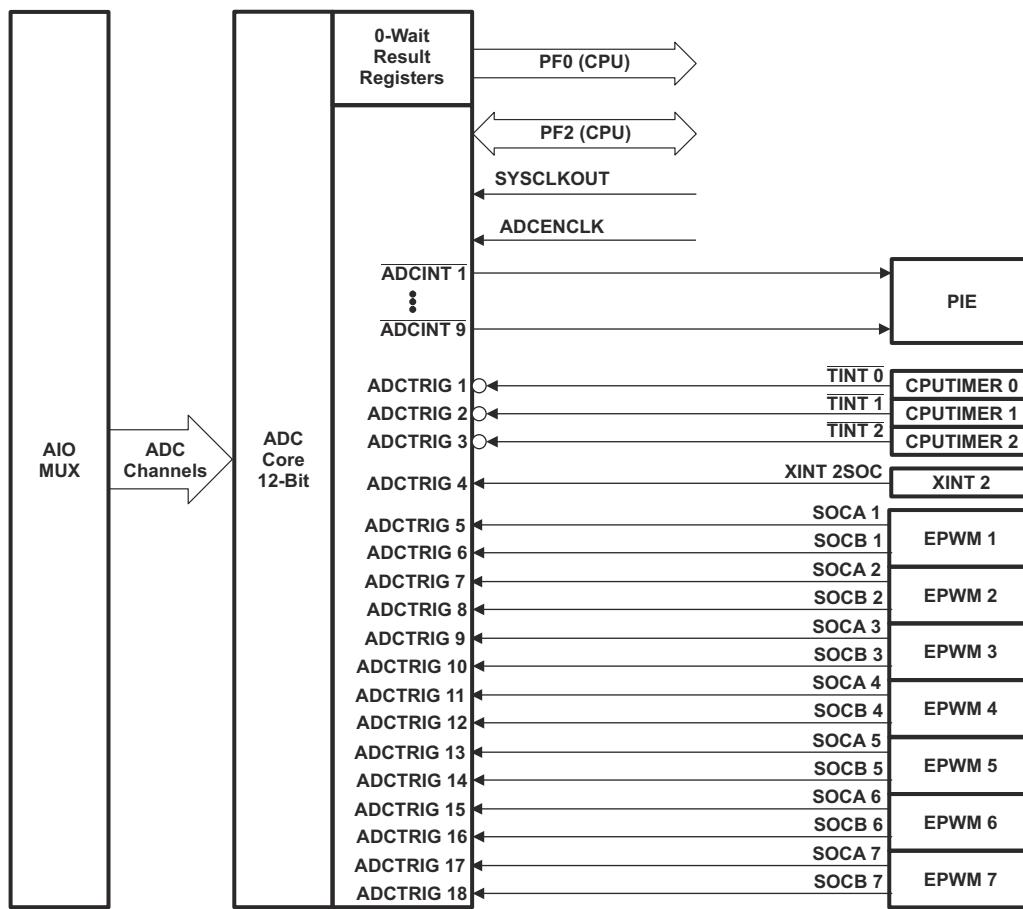

- A/D コンバータ (ADC)

- オンチップ温度センサ

- コンパレータ

- 高度なエミュレーション機能

- 分析およびブレークポイント機能

- ハードウェアによるリアルタイム デバッグ

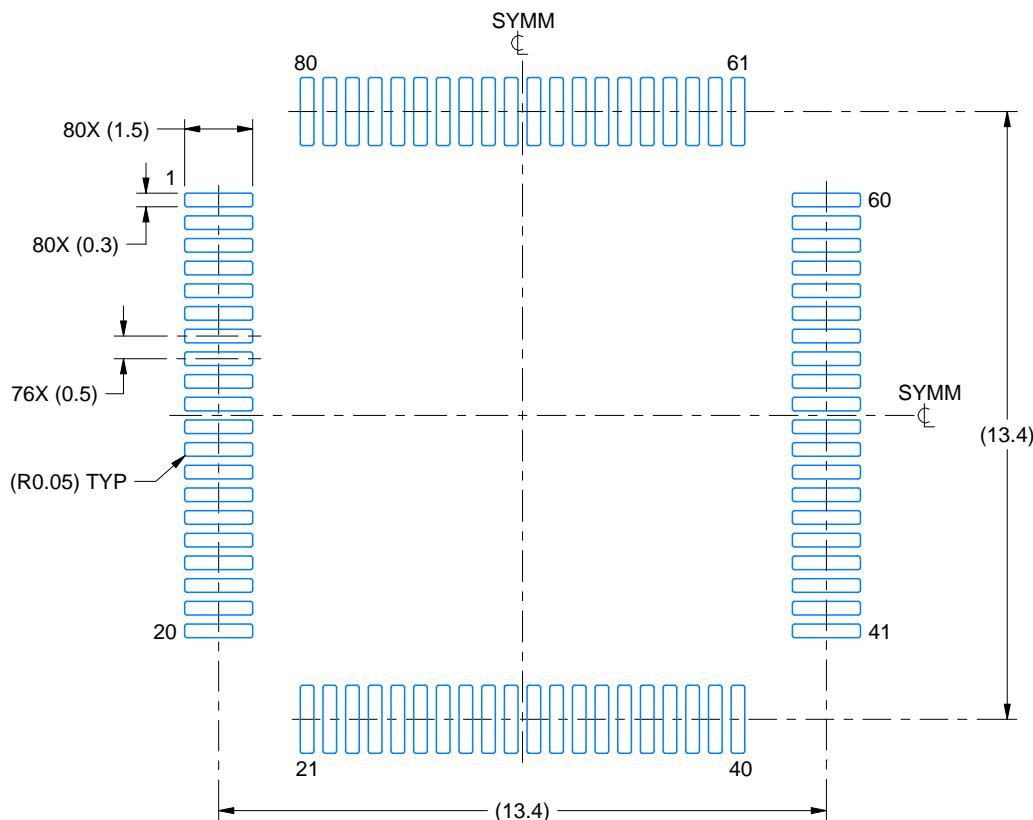

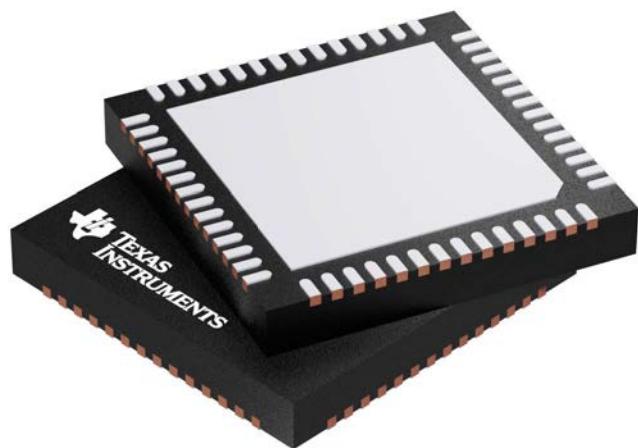

- パッケージ オプション

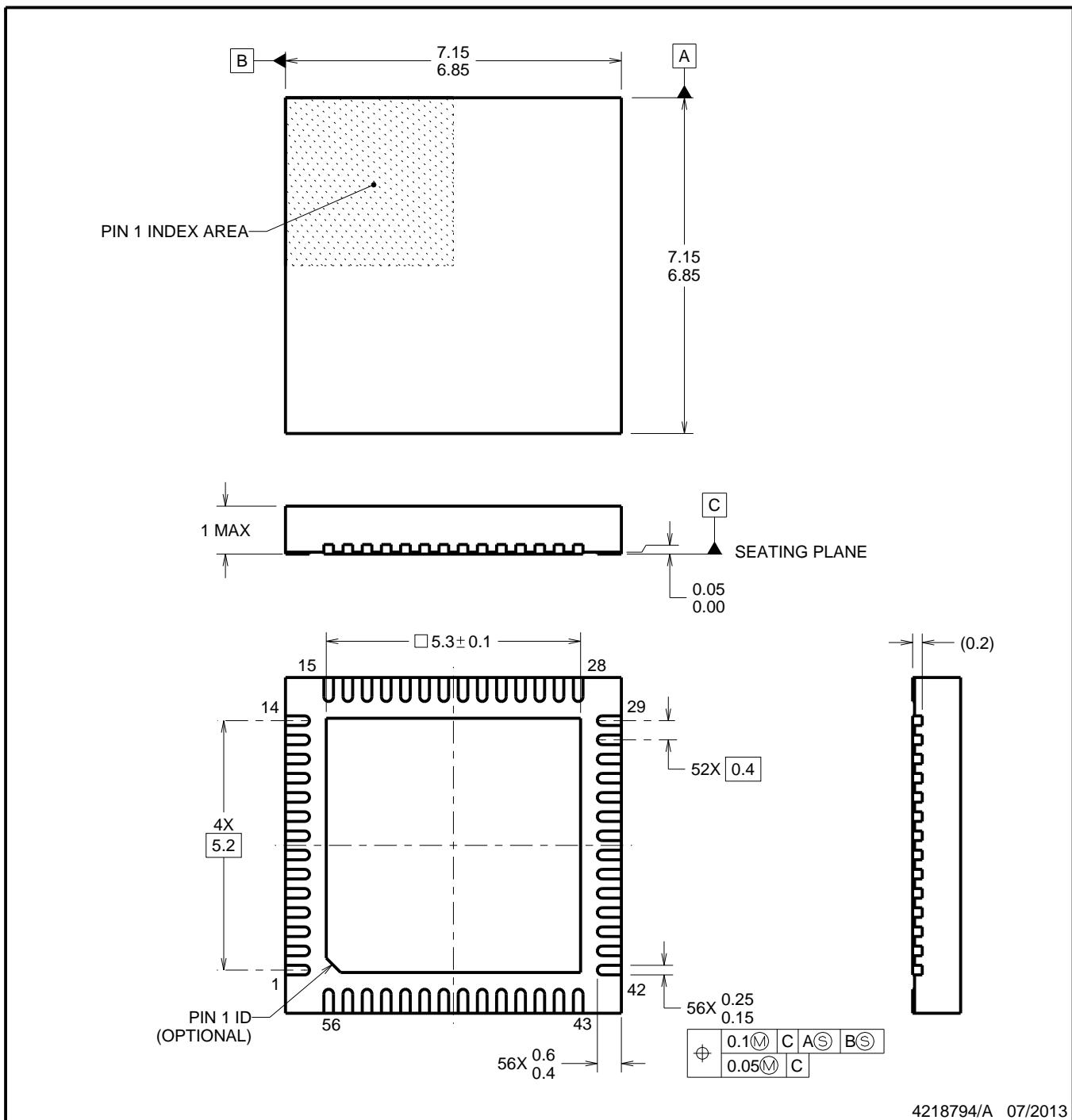

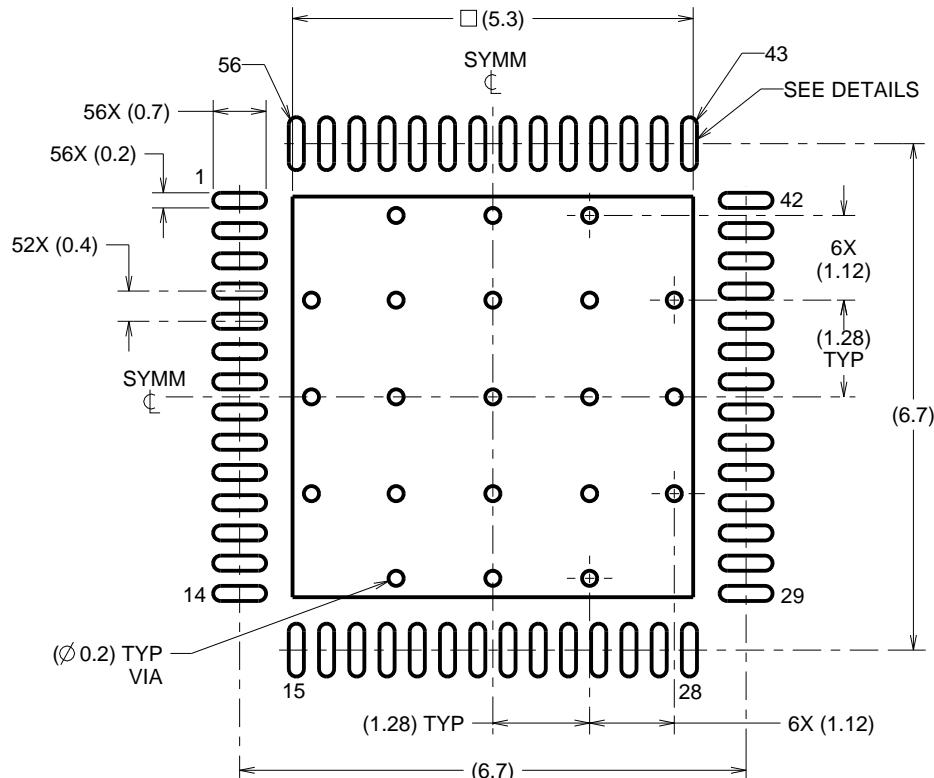

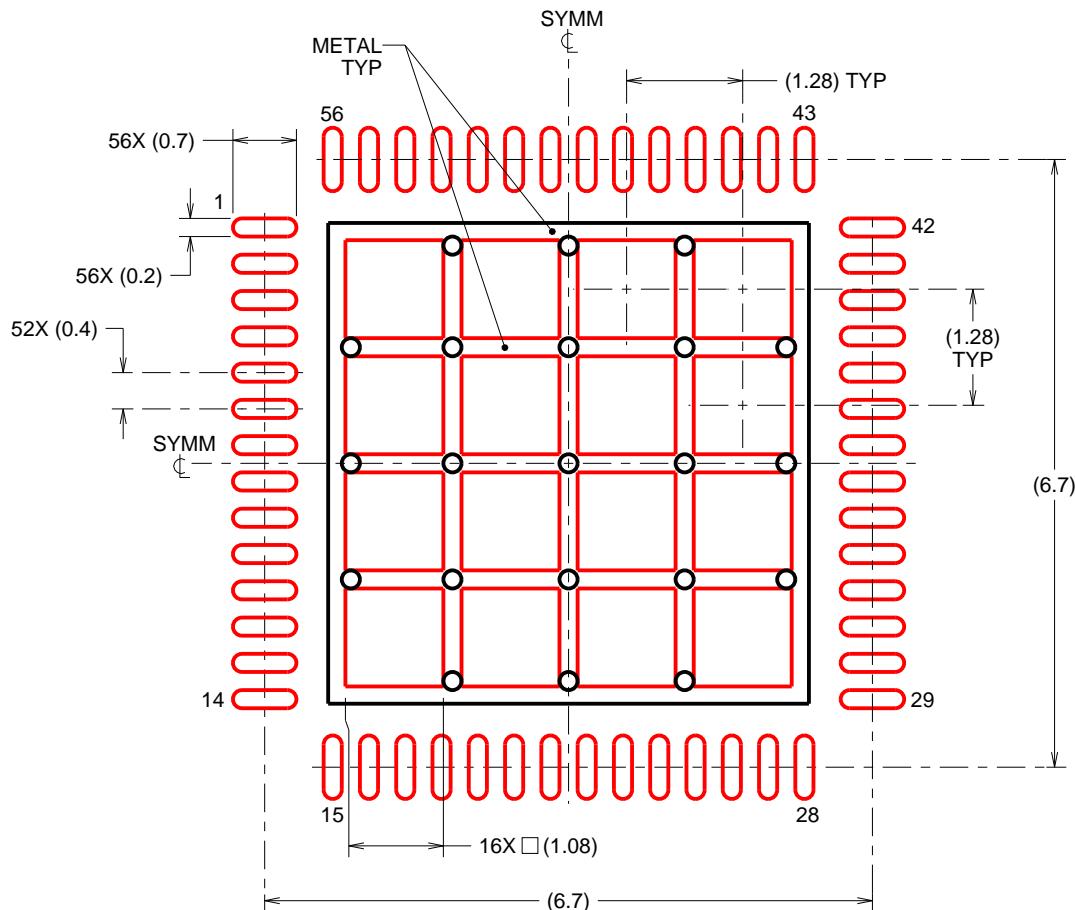

- 56 ピンの RSH 超薄型クワッド フラットパック (VQFN) (リードなし)

- 64 ピンの PAG シン クワッド フラットパック (TQFP)

- 80 ピンの PN 薄型クワッド フラットパック (LQFP)

- 温度オプション

- T:-40°C~105°C

- S:-40°C~125°C

- Q:-40°C~125°C

(車載アプリケーション用の AEC Q100 認定)

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 2 アプリケーション

- エアコン室外機

- ドア開閉装置ドライブの制御

- DC/DC コンバータ

- インバータとモーター制御

- オンボード・チャージャ (OBC) / ワイヤレス・チャージャ

- 自動仕分け機器

- 繊維機械

- 溶接機

- AC 充電 (バッテリ) ステーション

- DC 充電 (バッテリ) ステーション

- EV 充電ステーション向け電源モジュール

- ワイヤレス車両充電モジュール

- エネルギー・ストレージ電力変換システム (PCS)

- マイクロ・インバータ

- ソーラー電力オプティマイザ

- ストリング・インバータ

- AC ドライブ制御モジュール

- リニア・モーター・セグメント・コントローラ

- サーボ・ドライブの電力段モジュール

- AC 入力 BLDC モーター・ドライブ

- DC 入力 BLDC モーター・ドライブ

- 産業用 AC-DC

- 3 相 UPS

- 商用ネットワークとサーバーの PSU (電源)

- 商用テレコム整流器

## 3 概要

C2000™ 32 ビット マイクロコントローラは処理、センシング、アクチュエーションに最適化されており、リアルタイム制御アプリケーション、たとえば産業用モータードライブ、ソーラー インバータおよびデジタル電源、電気自動車および輸送機関、モーター制御、センシングおよび信号処理などにおける閉ループ性能が向上しています。C2000 ラインには最高性能の MCU とエントリ性能の MCU が含まれています。

F2803x ファミリのマイクロコントローラ (MCU) は、C28x コアと制御補償器アクセラレータ (CLA) の能力を、高度に統合された制御ペリフェラルとともに、ピン数の少ないデバイスに組み入れた製品です。このファミリは従来の C28x ベースのコードと互換性があり、アナログも高レベルで統合されています。

内蔵の電圧レギュレータにより、シングル レールでの動作が可能です。HRPWM に拡張が加えられ、デュアル エッジ制御(周波数変調)が可能になっています。内部の 10 ビット基準を持つアナログ コンパレータが追加されており、直接配線により PWM 出力を制御できます。この ADC は 0~3.3V の固定フルスケール範囲を変換し、レシオメトリックな  $V_{REFHI}$ / $V_{REFLO}$  基準電圧をサポートします。ADC インターフェイスは、オーバーヘッドが小さく、レイテンシが短くなるよう最適化されています。

C2000 MCU の詳細については、[C2000™ リアルタイム制御マイコン \(MCU\)](#) のページをご覧ください。

### 製品情報

| 部品番号 (1)        | パッケージ     | 本体サイズ           |

|-----------------|-----------|-----------------|

| TMS320F28035PN  | LQFP (80) | 12.0mm × 12.0mm |

| TMS320F28034PN  | LQFP (80) | 12.0mm × 12.0mm |

| TMS320F28033PN  | LQFP (80) | 12.0mm × 12.0mm |

| TMS320F28032PN  | LQFP (80) | 12.0mm × 12.0mm |

| TMS320F28031PN  | LQFP (80) | 12.0mm × 12.0mm |

| TMS320F28030PN  | LQFP (80) | 12.0mm × 12.0mm |

| TMS320F28035PAG | TQFP (64) | 10.0mm × 10.0mm |

| TMS320F28034PAG | TQFP (64) | 10.0mm × 10.0mm |

| TMS320F28033PAG | TQFP (64) | 10.0mm × 10.0mm |

| TMS320F28032PAG | TQFP (64) | 10.0mm × 10.0mm |

| TMS320F28031PAG | TQFP (64) | 10.0mm × 10.0mm |

| TMS320F28030PAG | TQFP (64) | 10.0mm × 10.0mm |

| TMS320F28035RSH | VQFN (56) | 7.0mm × 7.0mm   |

| TMS320F28034RSH | VQFN (56) | 7.0mm × 7.0mm   |

| TMS320F28033RSH | VQFN (56) | 7.0mm × 7.0mm   |

| TMS320F28032RSH | VQFN (56) | 7.0mm × 7.0mm   |

| TMS320F28031RSH | VQFN (56) | 7.0mm × 7.0mm   |

| TMS320F28030RSH | VQFN (56) | 7.0mm × 7.0mm   |

(1) これらのデバイスの詳細については、[メカニカル、パッケージ、および注文情報](#)を参照してください。

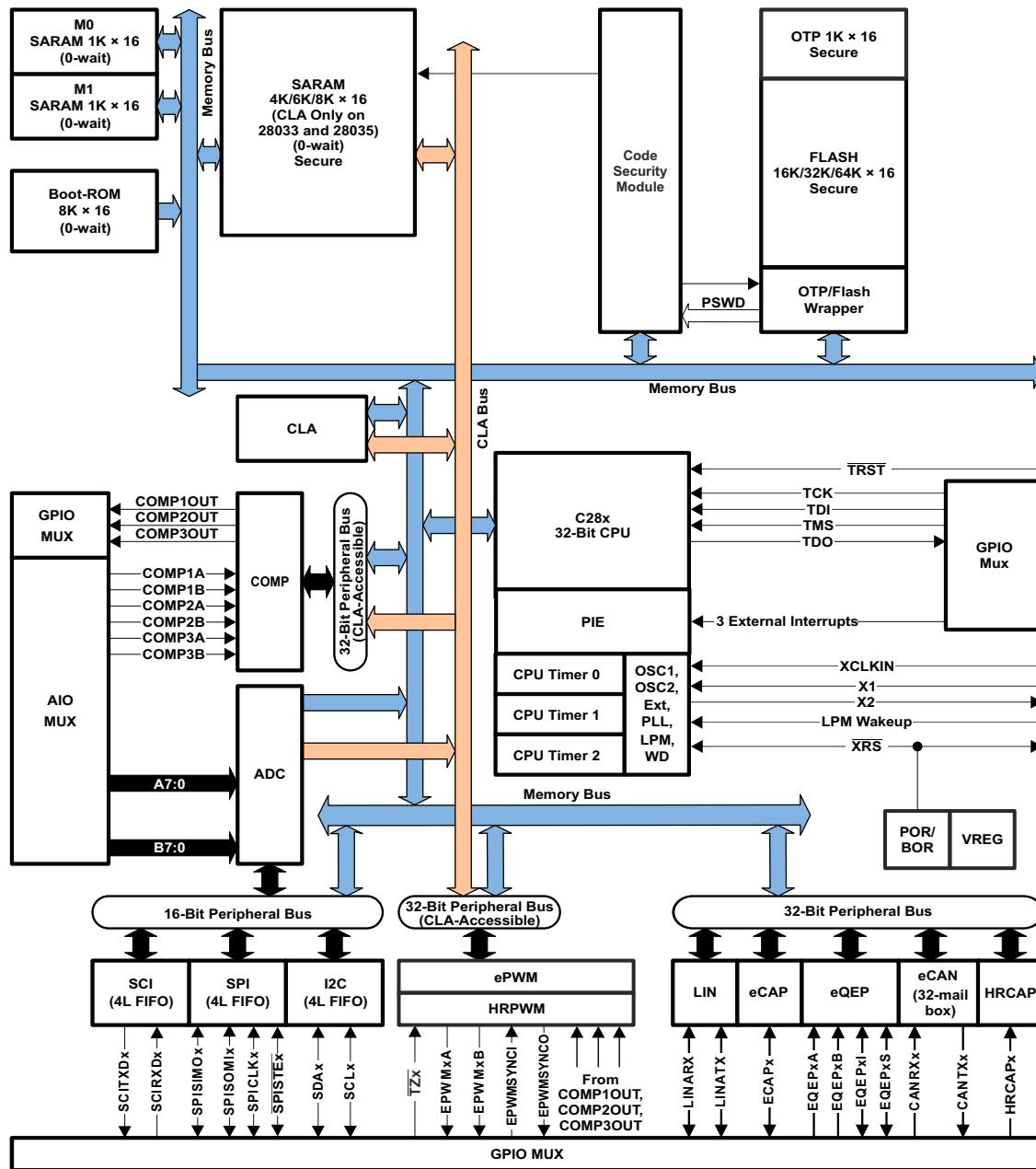

### 3.1 機能ブロック図

「機能ブロック図」に、デバイスの機能ブロック図を示します。

A. 多重化の関係で、同時にすべてのペリフェラル・ピンが利用可能なわけではありません。

図 3-1. 機能ブロック図

## 目次

|                                              |    |                                      |     |

|----------------------------------------------|----|--------------------------------------|-----|

| <b>1 特長</b>                                  | 1  | <b>6.14 フラッシュのタイミング</b>              | 39  |

| <b>2 アプリケーション</b>                            | 2  | <b>7 詳細説明</b>                        | 41  |

| <b>3 概要</b>                                  | 2  | <b>7.1 概要</b>                        | 41  |

| 3.1 機能ブロック図                                  | 4  | <b>7.2 メモリマップ</b>                    | 52  |

| <b>4 デバイスの比較</b>                             | 6  | <b>7.3 レジスタマップ</b>                   | 60  |

| 4.1 関連製品                                     | 8  | <b>7.4 デバイスエミュレーションレジスタ</b>          | 62  |

| <b>5 ピン構成と機能</b>                             | 9  | <b>7.5 VREG/BOR/POR</b>              | 63  |

| 5.1 ピン構造図                                    | 9  | <b>7.6 システムコントロール</b>                | 65  |

| 5.2 信号概要                                     | 12 | <b>7.7 低消費電力モードブロック</b>              | 73  |

| <b>6 仕様</b>                                  | 21 | <b>7.8 割り込み</b>                      | 74  |

| 6.1 絶対最大定格                                   | 21 | <b>7.9 ペリフェラル</b>                    | 79  |

| 6.2 ESD 定格 – 車載用                             | 21 | <b>8 アプリケーション、実装、およびレイアウト</b>        | 148 |

| 6.3 ESD 定格 – 民生用                             | 22 | <b>8.1 テキサス・インスツルメンツのリファレンス・デザイン</b> | 148 |

| 6.4 推奨動作条件                                   | 22 | <b>9 デバイスおよびドキュメントのサポート</b>          | 149 |

| 6.5 消費電力の概略                                  | 23 | <b>9.1 デバイスと開発ツールの命名法</b>            | 149 |

| 6.6 電気的特性                                    | 27 | <b>9.2 ツールとソフトウェア</b>                | 150 |

| 6.7 热抵抗特性                                    | 28 | <b>9.3 ドキュメントのサポート</b>               | 152 |

| 6.8 热設計の検討事項                                 | 30 | <b>9.4 サポート・リソース</b>                 | 153 |

| 6.9 MCU との JTAG デバッグプローブ接続 (信号バッ<br>ファリングなし) | 31 | <b>9.5 商標</b>                        | 153 |

| 6.10 パラメータ情報                                 | 32 | <b>9.6 静電気放電に関する注意事項</b>             | 153 |

| 6.11 テスト負荷回路                                 | 32 | <b>9.7 用語集</b>                       | 153 |

| 6.12 電源シーケンス                                 | 33 | <b>10 改訂履歴</b>                       | 153 |

| 6.13 クロック仕様                                  | 36 | <b>11 メカニカル、パッケージ、および注文情報</b>        | 155 |

|                                              |    | <b>11.1 パッケージ情報</b>                  | 155 |

## 4 デバイスの比較

表 4-1 に、TMS320F2803x デバイスの機能を示します。

表 4-1. デバイスの比較

| 機能                                       | タイプ<br>( <sup>1</sup> ) | 28030<br>28030-Q1<br>(60MHz) |                      |                      | 28031<br>28031-Q1<br>(60MHz) |                      |                      | 28032<br>28032-Q1<br>(60MHz) |                      |                      | 28033<br>28033-Q1<br>(60MHz) |                      |                      | 28034<br>28034-Q1<br>(60MHz) |                      |                      | 28035<br>28035-Q1<br>(60MHz) |                      |                      |    |

|------------------------------------------|-------------------------|------------------------------|----------------------|----------------------|------------------------------|----------------------|----------------------|------------------------------|----------------------|----------------------|------------------------------|----------------------|----------------------|------------------------------|----------------------|----------------------|------------------------------|----------------------|----------------------|----|

|                                          |                         | 80 ピン<br>PN<br>LQFP          | 64 ピン<br>PAG<br>TQFP | 56 ピン<br>RSH<br>VQFN | 80 ピン<br>PN<br>LQFP          | 64 ピン<br>PAG<br>TQFP | 56 ピン<br>RSH<br>VQFN | 80 ピン<br>PN<br>LQFP          | 64 ピン<br>PAG<br>TQFP | 56 ピン<br>RSH<br>VQFN | 80 ピン<br>PN<br>LQFP          | 64 ピン<br>PAG<br>TQFP | 56 ピン<br>RSH<br>VQFN | 80 ピン<br>PN<br>LQFP          | 64 ピン<br>PAG<br>TQFP | 56 ピン<br>RSH<br>VQFN | 80 ピン<br>PN<br>LQFP          | 64 ピン<br>PAG<br>TQFP | 56 ピン<br>RSH<br>VQFN |    |

| パッケージの種類                                 |                         | 80 ピン<br>PN<br>LQFP          | 64 ピン<br>PAG<br>TQFP | 56 ピン<br>RSH<br>VQFN | 80 ピン<br>PN<br>LQFP          | 64 ピン<br>PAG<br>TQFP | 56 ピン<br>RSH<br>VQFN | 80 ピン<br>PN<br>LQFP          | 64 ピン<br>PAG<br>TQFP | 56 ピン<br>RSH<br>VQFN | 80 ピン<br>PN<br>LQFP          | 64 ピン<br>PAG<br>TQFP | 56 ピン<br>RSH<br>VQFN | 80 ピン<br>PN<br>LQFP          | 64 ピン<br>PAG<br>TQFP | 56 ピン<br>RSH<br>VQFN | 80 ピン<br>PN<br>LQFP          | 64 ピン<br>PAG<br>TQFP | 56 ピン<br>RSH<br>VQFN |    |

| 命令サイクル                                   | -                       | 16.67ns                      |                      |                      |    |

| 制御補償器アクセラレータ (CLA)                       | 0                       | なし                           |                      |                      | なし                           |                      |                      | なし                           |                      |                      | あり                           |                      |                      | なし                           |                      |                      | あり                           |                      |                      |    |

| オンチップ フラッシュ (16 ビットワード)                  | -                       | 16K                          |                      |                      | 32K                          |                      |                      | 32K                          |                      |                      | 32K                          |                      |                      | 64K                          |                      |                      | 64K                          |                      |                      |    |

| オンチップ SARAM (16 ビットワード)                  | -                       | 6K                           |                      |                      | 8K                           |                      |                      | 10K                          |                      |                      | 10K                          |                      |                      | 10K                          |                      |                      | 10K                          |                      |                      |    |

| オンチップ フラッシュ / SARAM / OTP ブロックのコードセキュリティ | -                       | あり                           |                      |                      |    |

| ブート ROM (8K x 16)                        | -                       | あり                           |                      |                      |    |

| ワンタイム プログラマブル (OTP) ROM (16 ビットワード)      | -                       | 1K                           |                      |                      |    |

| ePWM チャネル                                | 1                       | 14                           | 12                   | 8                    | 14                           | 12                   | 8                    | 14                           | 12                   | 8                    | 14                           | 12                   | 8                    | 14                           | 12                   | 8                    | 14                           | 12                   | 8                    |    |

| eCAP 入力                                  | 0                       | 1                            |                      |                      | 1                            |                      |                      | 1                            |                      |                      | 1                            |                      |                      | 1                            |                      |                      | 1                            |                      |                      |    |

| eQEP モジュール                               | 0                       | 1                            |                      |                      | 1                            |                      |                      | 1                            |                      |                      | 1                            |                      |                      | 1                            |                      |                      | 1                            |                      |                      |    |

| ウォッチドギング タイマー                            | -                       | あり                           |                      |                      |    |

| MSPS                                     | 3                       | 2.0                          |                      |                      | 2.0                          |                      |                      | 4.6                          |                      |                      | 4.6                          |                      |                      | 4.6                          |                      |                      | 4.6                          |                      |                      |    |

| 変換時間                                     |                         | 500.00ns                     |                      |                      | 500.00ns                     |                      |                      | 216.67ns                     |                      |                      | 216.67ns                     |                      |                      | 216.67ns                     |                      |                      | 216.67ns                     |                      |                      |    |

| 12 ビット ADC                               |                         | 16                           | 14                   | 13                   | 16                           | 14                   | 13                   | 16                           | 14                   | 13                   | 16                           | 14                   | 13                   | 16                           | 14                   | 13                   | 16                           | 14                   | 13                   |    |

| 温度センサ                                    |                         | あり                           |                      |                      | あり                           |                      |                      | あり                           |                      |                      | あり                           |                      |                      | あり                           |                      |                      | あり                           |                      |                      |    |

| デュアル サンプル アンド ホールド                       |                         | あり                           |                      |                      | あり                           |                      |                      | あり                           |                      |                      | あり                           |                      |                      | あり                           |                      |                      | あり                           |                      |                      |    |

| 32 ビット CPU タイマー                          | -                       | 3                            |                      |                      | 3                            |                      |                      | 3                            |                      |                      | 3                            |                      |                      | 3                            |                      |                      | 3                            |                      |                      |    |

| 高分解能 ePWM チャネル                           | 1                       | -                            |                      |                      | -                            |                      |                      | 7                            | 6                    | 4                    | 7                            | 6                    | 4                    | 7                            | 6                    | 4                    | 7                            | 6                    | 4                    |    |

| 高分解能キャプチャ (HRCAP) モジュール                  | 0                       | -                            |                      |                      | -                            |                      |                      | 2                            | 2                    | -                    | 2                            | 2                    | -                    | 2                            | 2                    | -                    | 2                            | 2                    | -                    |    |

| DAC 内蔵コンバーティア                            | 0                       | 3                            |                      |                      | 3                            |                      |                      | 3                            |                      |                      | 3                            |                      |                      | 3                            |                      |                      | 3                            |                      |                      |    |

| I2C (Inter-Integrated Circuit)           | 0                       | 1                            |                      |                      | 1                            |                      |                      | 1                            |                      |                      | 1                            |                      |                      | 1                            |                      |                      | 1                            |                      |                      |    |

| 拡張コントローラ エリア ネットワーク (eCAN)               | 0                       | 1                            |                      |                      | 1                            |                      |                      | 1                            |                      |                      | 1                            |                      |                      | 1                            |                      |                      | 1                            |                      |                      |    |

| LIN (Local Interconnect Network)         | 0                       | 1                            |                      |                      | 1                            |                      |                      | 1                            |                      |                      | 1                            |                      |                      | 1                            |                      |                      | 1                            |                      |                      |    |

| シリアル ベリフェラル インターフェイス (SPI)               | 1                       | 2                            | 1                    | 1                    | 2                            | 1                    | 1                    | 2                            | 1                    | 1                    | 2                            | 1                    | 1                    | 2                            | 1                    | 1                    | 2                            | 1                    | 1                    |    |

| シリアル通信インターフェイス (SCI) (UART 互換)           | 0                       | 1                            |                      |                      | 1                            |                      |                      | 1                            |                      |                      | 1                            |                      |                      | 1                            |                      |                      | 1                            |                      |                      |    |

| I/O ピン数 (共有)                             | GPIO                    | -                            | 45                   | 33                   | 26                           | 45                   | 33                   | 26                           | 45                   | 33                   | 26                           | 45                   | 33                   | 26                           | 45                   | 33                   | 26                           | 45                   | 33                   | 26 |

|                                          | AIO                     | -                            | 6                    |                      |                              | 6                    |                      |                              | 6                    |                      |                              | 6                    |                      |                              | 6                    |                      |                              | 6                    |                      |    |

| 外部割り込み                                   | -                       | 3                            |                      |                      | 3                            |                      |                      | 3                            |                      |                      | 3                            |                      |                      | 3                            |                      |                      | 3                            |                      |                      |    |

| 電源電圧 (公称値)                               | -                       | 3.3V                         |                      |                      |    |

**表 4-1. デバイスの比較 (続き)**

| 機能       | タイプ<br><sup>(1)</sup>        | 28030<br>28030-Q1<br>(60MHz) |                      |                      | 28031<br>28031-Q1<br>(60MHz) |                      |                      | 28032<br>28032-Q1<br>(60MHz) |                      |                      | 28033<br>28033-Q1<br>(60MHz) |                      |                      | 28034<br>28034-Q1<br>(60MHz) |                      |                      | 28035<br>28035-Q1<br>(60MHz) |                      |                      |

|----------|------------------------------|------------------------------|----------------------|----------------------|------------------------------|----------------------|----------------------|------------------------------|----------------------|----------------------|------------------------------|----------------------|----------------------|------------------------------|----------------------|----------------------|------------------------------|----------------------|----------------------|

|          |                              | 80 ピン<br>PN<br>LQFP          | 64 ピン<br>PAG<br>TQFP | 56 ピン<br>RSH<br>VQFN | 80 ピン<br>PN<br>LQFP          | 64 ピン<br>PAG<br>TQFP | 56 ピン<br>RSH<br>VQFN | 80 ピン<br>PN<br>LQFP          | 64 ピン<br>PAG<br>TQFP | 56 ピン<br>RSH<br>VQFN | 80 ピン<br>PN<br>LQFP          | 64 ピン<br>PAG<br>TQFP | 56 ピン<br>RSH<br>VQFN | 80 ピン<br>PN<br>LQFP          | 64 ピン<br>PAG<br>TQFP | 56 ピン<br>RSH<br>VQFN | 80 ピン<br>PN<br>LQFP          | 64 ピン<br>PAG<br>TQFP | 56 ピン<br>RSH<br>VQFN |

| パッケージの種類 |                              |                              |                      |                      |                              |                      |                      |                              |                      |                      |                              |                      |                      |                              |                      |                      |                              |                      |                      |

| 温度オプション  | T:-40°C~105°C                | -                            | 28030                |                      | 28031                        |                      | 28032                |                              | 28033                |                      | 28034                        |                      | 28035                |                              |                      |                      |                              |                      |                      |

|          | S:-40°C~125°C                | -                            | 28030                |                      | 28031                        |                      | 28032                |                              | 28033                |                      | 28034                        |                      | 28035                |                              |                      |                      |                              |                      |                      |

|          | Q:-40°C~125°C <sup>(2)</sup> | -                            | 28030-Q1             | -                    | 28031-Q1                     | -                    | 28032-Q1             | -                            | 28033-Q1             | -                    | 28034-Q1                     | -                    | 28035-Q1             | -                            |                      |                      |                              |                      |                      |

- (1) タイプの違いは、ペリフェラル モジュールの機能上の主要な相違を表します。同じペリフェラル タイプのデバイス間でも、モジュールの基本的な機能には影響しないわずかな違いがあることがあります。これらのデバイス固有の相違点を、『C2000 リアルタイム制御ペリフェラル リファレンス ガイド』と『TMS320F2803x リアルタイム マイクロコントローラ テクニカル リファレンス マニュアル』に示します。

- (2) Q の文字は、車載アプリケーション向け AEC Q100 認定を表します。

## 4.1 関連製品

類似製品の詳細については、以下のリンクを参照してください。

### TMS320F2802x リアルタイム・マイクロコントローラ

F2802x シリーズは、最小のピン数とフラッシュ・メモリ・サイズの選択肢を提供します。InstaSPIN-FOC™ バージョンが利用可能です。

### TMS320F2803x リアルタイム・マイクロコントローラ

F2803x シリーズは、ピン数とメモリ・サイズの選択肢を増やします。F2803x シリーズはパラレル制御補償器アクセラレータ (CLA) オプションも採り入れています。

### TMS320F2805x リアルタイム・マイクロコントローラ

F2805x シリーズは F2803x シリーズと類似していますが、オンチップのプログラマブル・ゲイン・アンプ (PGA) を追加しています。InstaSPIN-FOC および InstaSPIN-MOTION™ バージョンが利用可能です。

### TMS320F2806x リアルタイム・マイクロコントローラ

F2806x シリーズは、浮動小数点ユニット (FPU) を内蔵した初の製品です。F2806x シリーズも、ピン数、メモリ・サイズの選択肢、ペリフェラルの数を増やします。InstaSPIN-FOC™ および InstaSPIN-MOTION™ バージョンが利用可能です。

### TMS320F2807x リアルタイム・マイクロコントローラ

F2807x シリーズは最高の性能、最大のピン数、フラッシュ・メモリ・サイズ、ペリフェラルの選択肢を提供します。F2807x シリーズは、最新世代のアクセラレータ、ePWM ペリフェラル、アナログ技術を内蔵しています。

### TMS320F28004x リアルタイム・マイクロコントローラ

F28004x シリーズは、最新世代の拡張機能を備えた F2807x シリーズの縮小版です。F28004x シリーズは、F2806x シリーズを使っておられるお客様に最適なロードマップの選択肢です。InstaSPIN-FOC およびコンフィギュラブル・ロジック・ブロック (CLB) バージョンが利用可能です。

## 5 ピン構成と機能

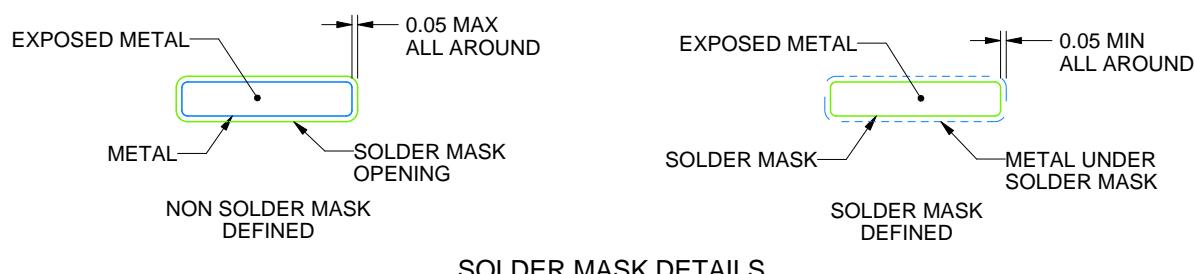

### 5.1 ピン構造図

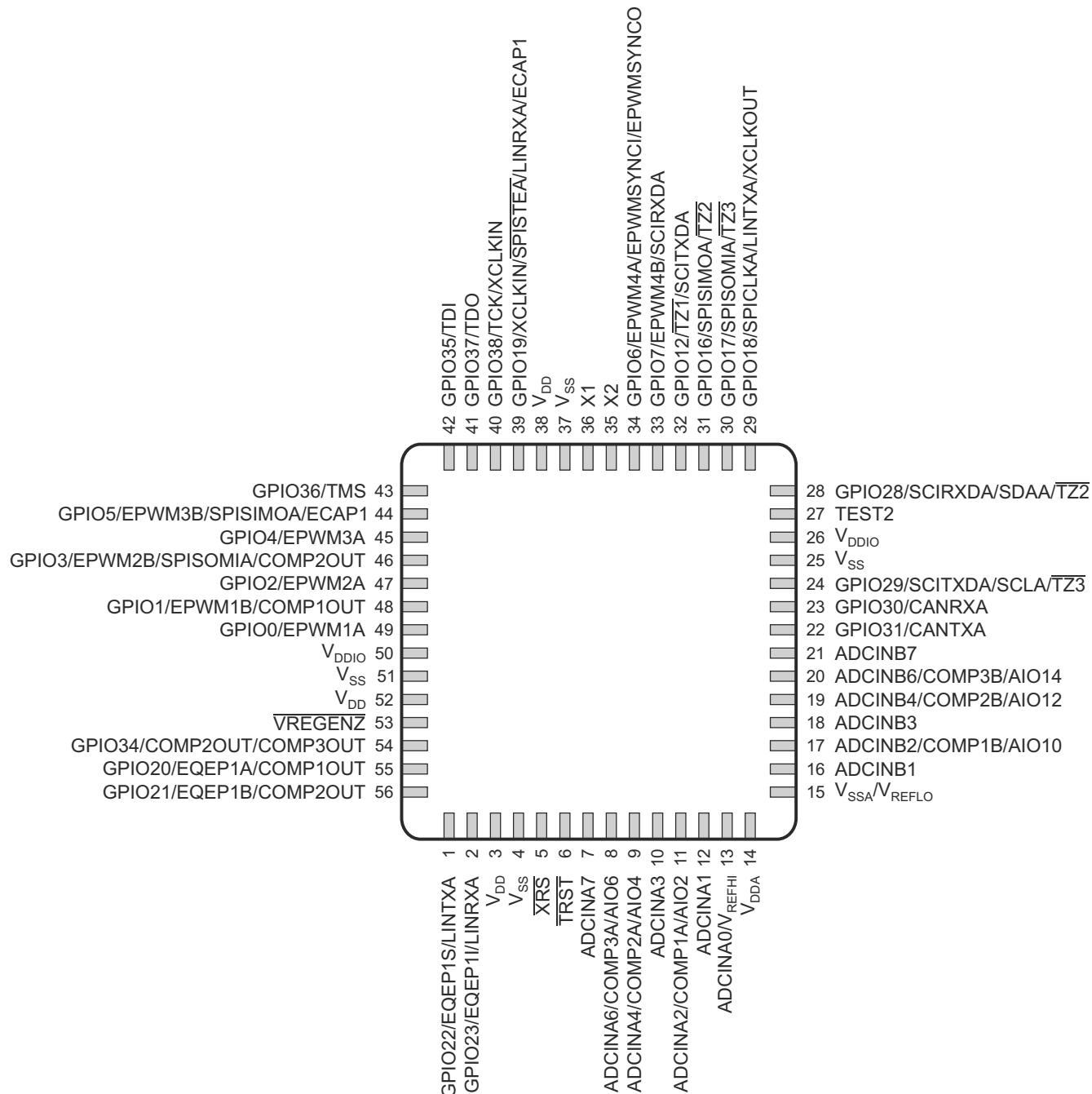

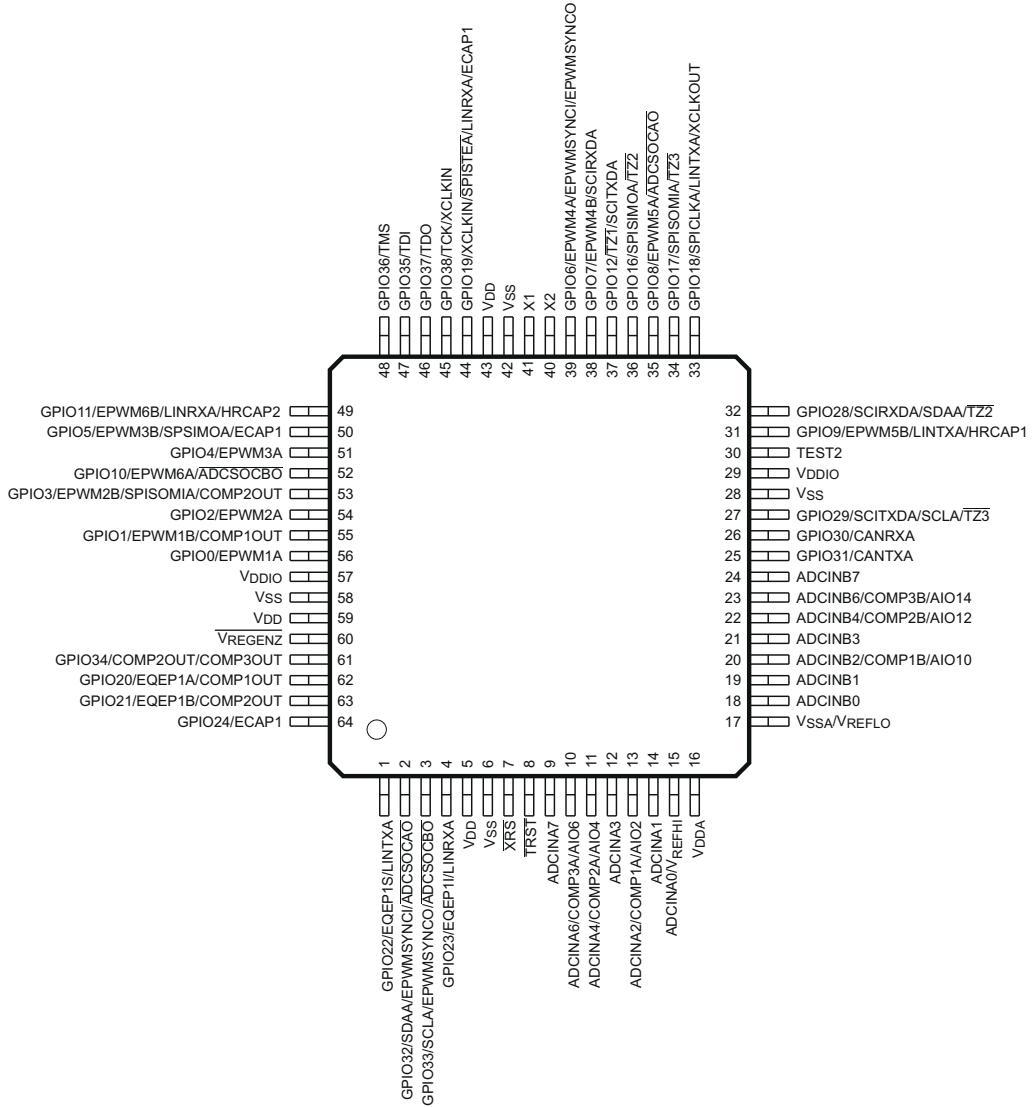

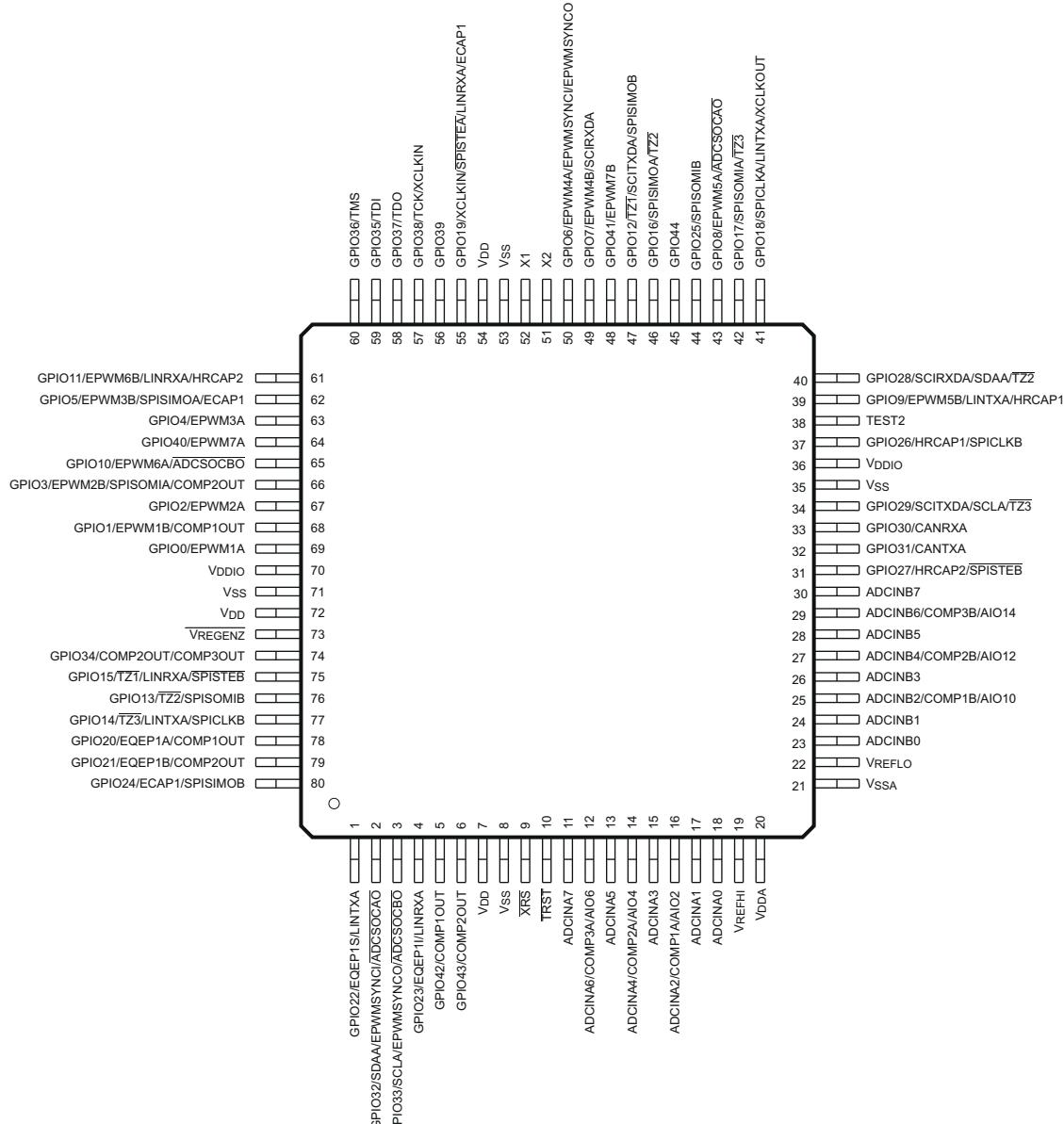

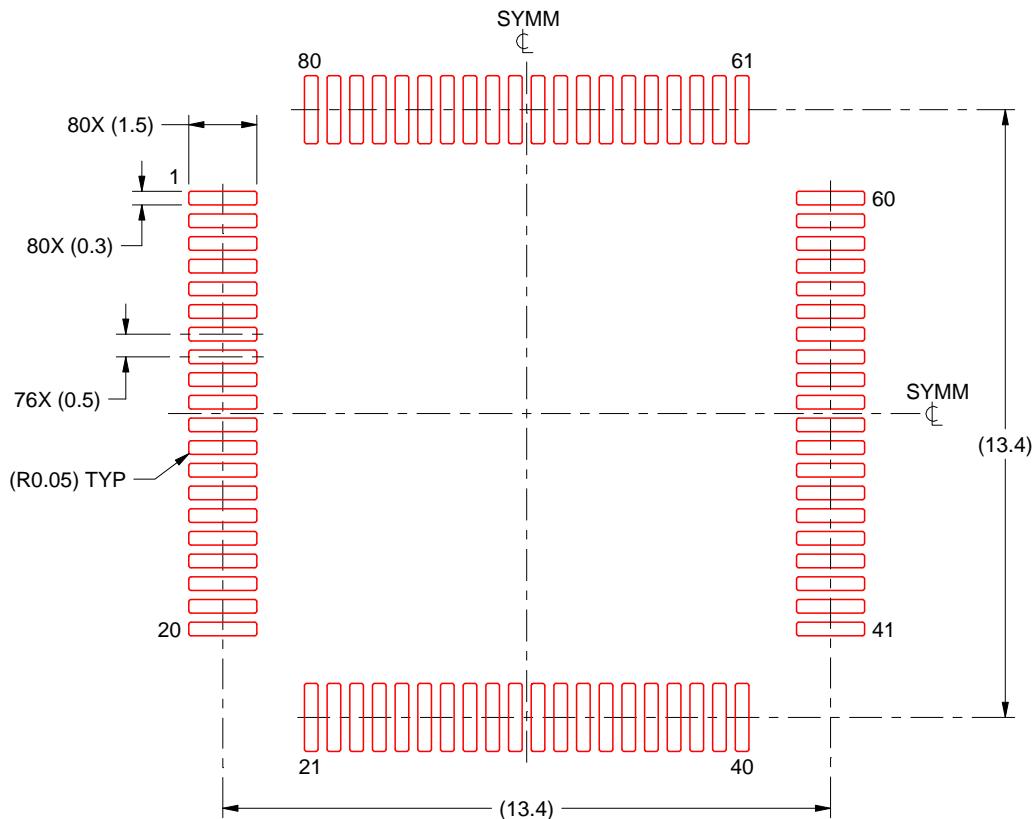

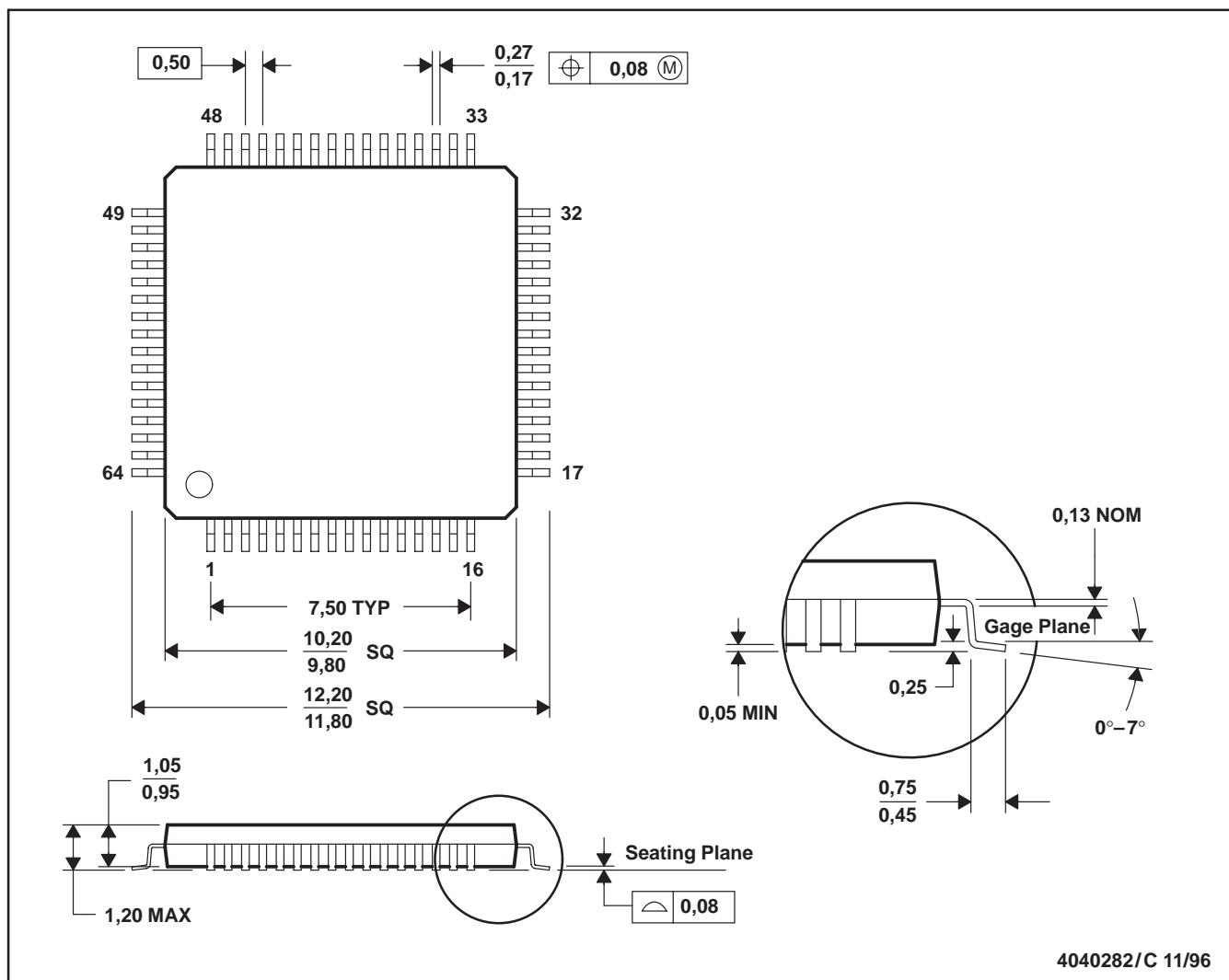

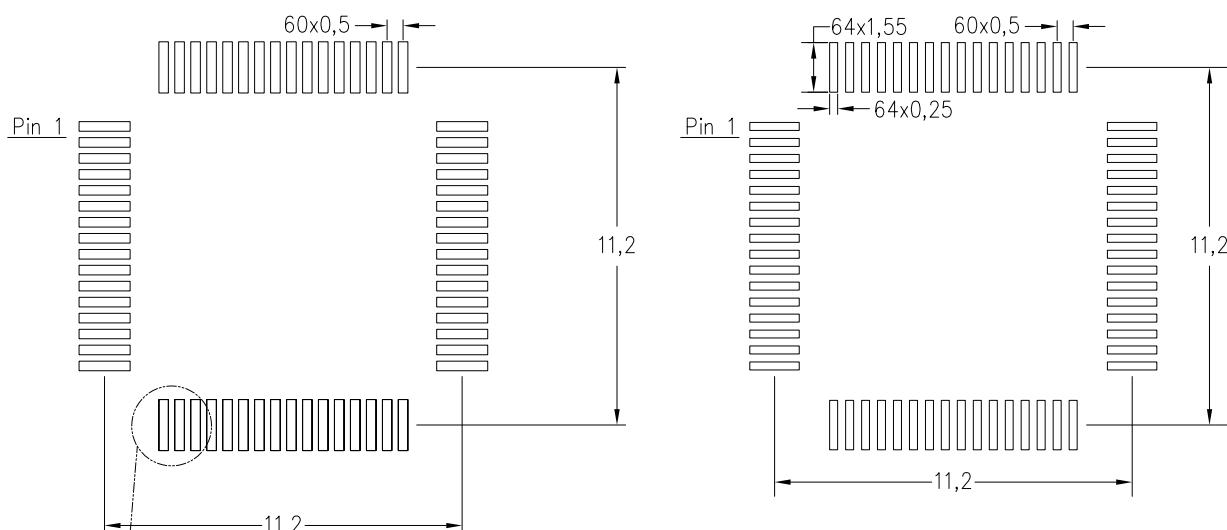

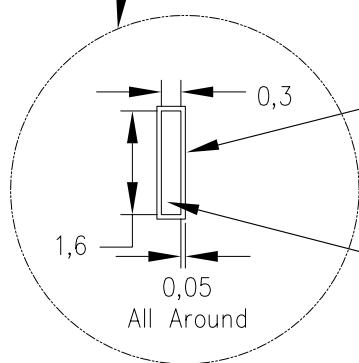

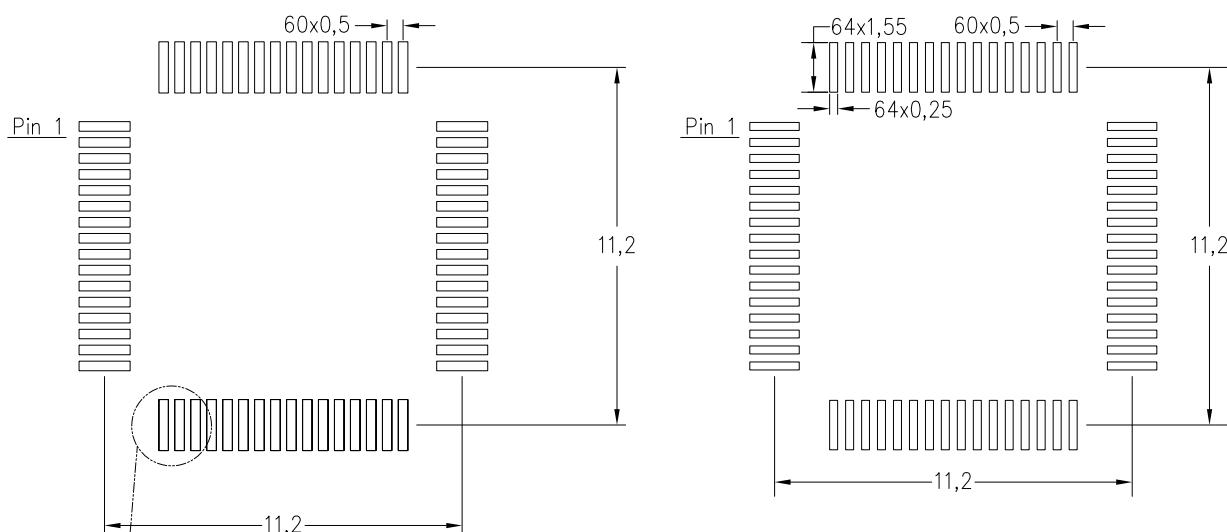

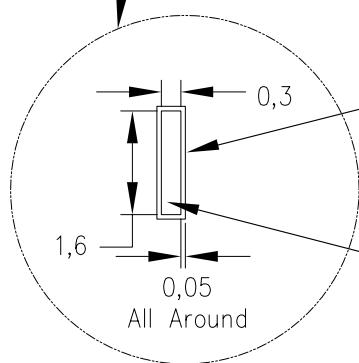

図 5-1 に、56 ピン RSH VQFN (Very Thin Quad Flat Non-leaded package) のピン配置を示します。図 5-2 に、64 ピン PAG TQFP (Thin Quad Flat Package) のピン配置を示します。図 5-3 に、80 ピン PN LQFP (Low-Profile Quad Flat Package) のピン配置を示します。

- A. この図は、56 ピン RSH パッケージの上面図を示しています。網掛けは、端子が実際にはパッケージの底面にあることを示しています。56 ピン RSH の機械的構造図については、セクション 11 を参照してください。

- B. ピン 13:56 ピン RSH デバイスでは、V<sub>REFHI</sub> と ADCINA0 は同じピンを共有しており、両方を同時に使うことはできません。

C. ピン 15:56 ピン RSH デバイスでは、V<sub>REFLO</sub> は常に V<sub>SSA</sub> に接続されています。

図 5-1. 2803x 56 ピン RSH VQFN (上面図)

- A. ピン 15:64 ピン PAG デバイスでは、V<sub>REFHI</sub> と ADCINA0 は同じピンを共有しており、両方を同時に使うことはできません。

- B. ピン 17:64 ピン PAG デバイスでは、V<sub>REFLO</sub> は常に V<sub>SSA</sub> に接続されています。

図 5-2. 2803x 64 ピン PAG TQFP (上面図)

**図 5-3. 2803x 80 ピン PN LQFP (上面図)**

## 5.2 信号概要

表 5-1 では、信号について説明します。JTAG ピンを除き、特に記述のない限り、GPIO 機能はリセット時のデフォルトです。その下に記載されているペリフェラル信号は代替機能です。一部のペリフェラル機能は、すべてのデバイスで利用できるわけではありません。詳細については、表 4-1 を参照してください。入力は 5V 許容ではありません。すべての GPIO ピンは I/O/Z であり、内部プルアップを備えています。この内部プルアップは、ピンごとに選択的に有効化 / 無効化できます。この機能は GPIO ピンにのみ適用されます。PWM ピンのプルアップはリセットしても有効化されません。他の GPIO ピンのプルアップはリセットと同時に有効化されます。AIO ピンは内部プルアップを持っていません。

### 注

オンチップ VREG を使用する場合、GPIO19、GPIO34、GPIO35、GPIO36、GPIO37、GPIO38 ピンには、電源投入時にグリッチが発生する可能性があります。この潜在的なグリッチは、ブート モード ピンが読み出される前に終了し、ブート動作には影響しません。アプリケーションでグリッチが許容されない場合、1.8V を外部から供給できます。または、ピンと外部回路の劣化の可能性を抑えるために、これらのピンとすべての外部ドライバに直列に電流制限抵抗 (470Ω など) を追加することもできます。外部 1.8V 電源を使用する場合、電源シーケンス要件はありません。ただし、I/O ピンのレベルシフト出力バッファ内の 3.3V トランジスタに、1.8V トランジスタよりも前に電力が供給される場合、出力バッファがオンすることで、電源投入時にピンにグリッチが発生する可能性があります。この挙動を回避するため、V<sub>DDIO</sub> ピンより前に V<sub>DD</sub> ピンに電力を供給し、V<sub>DDIO</sub> ピンが 0.7V に達する前に V<sub>DD</sub> ピンが確実に 0.7V に達するようにします。

表 5-1. 信号の説明

| 端子           |            |             |             | I/O/Z <sup>(1)</sup> | 説明                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------|------------|-------------|-------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称           | PN<br>ピン番号 | PAG<br>ピン番号 | RSH<br>ピン番号 |                      |                                                                                                                                                                                                                                                                                                                                                                                          |

| <b>JTAG</b>  |            |             |             |                      |                                                                                                                                                                                                                                                                                                                                                                                          |

| TRST         | 10         | 8           | 6           | I                    | 内部プルダウン付き JTAG テストリセット。TRST を High に駆動すると、本デバイスの動作の制御がスキャンシステムに渡されます。この信号が接続されていない場合、または Low に駆動されている場合、本デバイスは機能モードで動作し、テストリセット信号は無視されます。 <small>注: TRST はアクティブ High のテストピンであり、通常デバイス動作中は常に Low に維持する必要があります。このピンには外付けプルダウン抵抗が必要です。この抵抗の値は、設計に適用可能なデバッガ ポッドの駆動強度に基づいています。一般的には、2.2kΩ の抵抗を使用すれば、適切な保護が得られます。これはアプリケーション固有であるため、デバッガとアプリケーションが適切に動作するように各ターゲットボードを検証することを推奨します。(↓)</small> |

| TCK          | GPIO38 を参照 |             |             | I                    | GPIO38 を参照。内部プルアップ付き JTAG テストクロック。(↑)                                                                                                                                                                                                                                                                                                                                                    |

| TMS          | GPIO36 を参照 |             |             | I                    | GPIO36 を参照。内部プルアップ付き JTAG テスト モード選択 (TMS)。このシリアル制御入力は、TCK の立ち上がりエッジに同期して TAP コントローラに入力されます。(↑)                                                                                                                                                                                                                                                                                           |

| TDI          | GPIO35 を参照 |             |             | I                    | GPIO35 を参照。内部プルアップ付き JTAG テストデータ入力 (TDI)。TDI は、TCK の立ち上がりエッジに同期して、選択されたレジスタ (命令またはデータ) に入力されます。(↑)                                                                                                                                                                                                                                                                                       |

| TDO          | GPIO37 を参照 |             |             | O/Z                  | GPIO37 を参照。JTAG スキャン アウト、テストデータ出力 (TDO)。選択されたレジスタ (命令またはデータ) の内容は、TCK の立ち下がりエッジに同期して TDO から出力されます。(8mA 駆動)                                                                                                                                                                                                                                                                               |

| <b>フラッシュ</b> |            |             |             |                      |                                                                                                                                                                                                                                                                                                                                                                                          |

| TEST2        | 38         | 30          | 27          | I/O                  | テストピン。テキサス・インスツルメンツ用に予約済みです。未接続のままにする必要があります。                                                                                                                                                                                                                                                                                                                                            |

**表 5-1. 信号の説明 (続き)**

| 端子                  |                     |             |             | I/O/Z <sup>(1)</sup> | 説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|---------------------|---------------------|-------------|-------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 名称                  | PN<br>ピン番号          | PAG<br>ピン番号 | RSH<br>ピン番号 |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| クロック                |                     |             |             |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| XCLKOUT             | GPIO18 を参照          |             | –           | O/Z                  | GPIO18 を参照。SYSCLKOUT を基準にして生成された出力クロック。XCLKOUT は、SYSCLKOUT と同じ周波数、半分の周波数、1/4 の周波数のいずれかです。これは、XCLK レジスタのビット 1:0 (XCLKOUTDIV) で制御されます。リセット時、XCLKOUT = SYSCLKOUT/4 です。XCLKOUT 信号は、XCLKOUTDIV を 3 に設定することでオフにできます。この信号をピンに伝搬させるには、GPIO18 の MUX 制御も XCLKOUT に設定する必要があります。                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

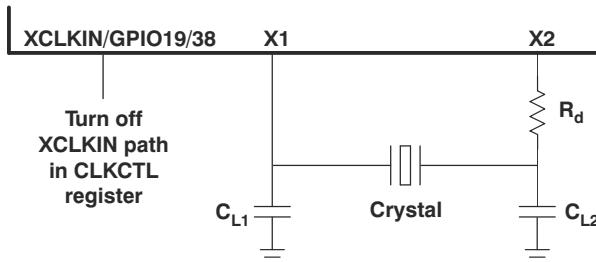

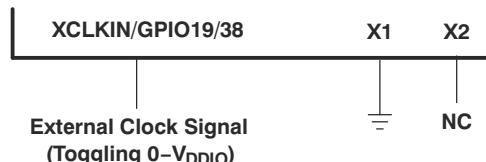

| XCLKIN              | GPIO19 と GPIO38 を参照 |             |             | I                    | GPIO19 と GPIO38 を参照。外部発振器入力。クロック ソースのピンは、XCLK レジスタの XCLKINSEL ビットで制御されます。デフォルトでは GPIO38 が選択されます。このピンには、外部 3.3V 発振器からクロックを入力します。この場合、X1 ピン (利用可能な場合) を GND に接続し、CLKCTL レジスタのビット 14 を使ってオンチップ水晶発振器を無効化する必要があります。水晶振動子 / 共振器を使用する場合、CLKCTL レジスタのビット 13 を使って XCLKIN の経路を無効化する必要があります。<br><b>注:</b> 通常デバイス動作用の外部クロックを供給するために GPIO38/TCK/XCLKIN ピンを使う設計では、JTAG コネクタを使ったデバッグ中にこの経路を無効化するための何らかの仕組みを組み込む必要があります。これは、JTAG デバッグ セッション中に作動する TCK 信号との競合を防止するためです。この間、本デバイスにクロックを供給するためにゼロピン内部発振器を使用できます。                                                                                                                                                                                                                    |  |

| X1                  | 52                  | 41          | 36          | I                    | オンチップ 1.8V 水晶発振器入力。この発振器を使用するには、X1 と X2 の間に水晶振動子またはセラミック共振器を接続する必要があります。この場合、CLKCTL レジスタのビット 13 を使って XCLKIN の経路を無効化する必要があります。このピンを使用しない場合、GND に接続する必要があります。(I)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| X2                  | 51                  | 40          | 35          | O                    | オンチップの水晶発振器出力。X1 と X2 の間に水晶振動子またはセラミック共振器を接続する必要があります。X2 を使用しない場合、未接続のままにする必要があります。(O)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| RESET               |                     |             |             |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| XRS                 | 9                   | 7           | 5           | I/O                  | デバイスリセット (入力) およびウォッチドッグリセット (出力)。これらのデバイスはパワーオンリセット (POR) およびブラウンアウトリセット (BOR) 回路を内蔵しています。電源オンまたはブラウンアウト状態の間、このピンを本デバイスは Low に駆動します。外部回路も、デバイスリセットをアサートするためにこのピンを駆動できます。ウォッチドッグリセットが発生した場合、MCU もこのピンを Low に駆動します。ウォッチドッグリセット中、XRS ピンは 512 OSCCLK サイクルのウォッチドッグリセット期間にわたって Low に駆動されます。XRS と VDDIO の間に 2.2kΩ~10kΩ の抵抗を配置する必要があります。ノイズ フィルタリングのため、XRS と VSS の間にコンデンサを配置します。容量は 100nF 以下にする必要があります。これらの値を使うことで、ウォッチドッグリセットがアサートされた際、ウォッチドッグは 512 OSCCLK サイクル以内に XRS ピンを V <sub>OL</sub> に適切に駆動できます。その原因に関係なく、デバイスリセットによって本デバイスは実行を終了します。プログラム カウンタは、位置 0x3F FFC0 に格納されたアドレスを指します。リセットが解除されると、プログラム カウンタで指定された場所から実行が開始されます。このピンの出力バッファは、内部プルアップ付きのオープンドレイン素子です。(↑) このピンを外部デバイスによって駆動する場合、オープンドレイン素子を使って駆動する必要があります。 |  |

| ADC、コンパレータ、アナログ I/O |                     |             |             |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| ADCINA7             | 11                  | 9           | 7           | I                    | ADC グループ A、チャネル 7 入力                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| ADCINA6             |                     |             |             | I                    | ADC グループ A、チャネル 6 入力                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| COMP3A              | 12                  | 10          | 8           | I                    | コンパレータ入力 3A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| AIO6                |                     |             |             | I/O                  | デジタル AIO 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| ADCINA5             | 13                  | –           | –           | I                    | ADC グループ A、チャネル 5 入力                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| ADCINA4             |                     |             |             | I                    | ADC グループ A、チャネル 4 入力                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| COMP2A              | 14                  | 11          | 9           | I                    | コンパレータ入力 2A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| AIO4                |                     |             |             | I/O                  | デジタル AIO 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

表 5-1. 信号の説明 (続き)

| 端子      |            |             |             | I/O/Z <sup>(1)</sup> | 説明                   |

|---------|------------|-------------|-------------|----------------------|----------------------|

| 名称      | PN<br>ピン番号 | PAG<br>ピン番号 | RSH<br>ピン番号 |                      |                      |

| ADCINA3 | 15         | 12          | 10          | I                    | ADC グループ A、チャネル 3 入力 |

| ADCINA2 |            |             |             | I                    | ADC グループ A、チャネル 2 入力 |

| COMP1A  | 16         | 13          | 11          | I                    | コンパレータ入力 1A          |

| AIO2    |            |             |             | I/O                  | デジタル AIO 2           |

**表 5-1. 信号の説明 (続き)**

| 端子                   |            |             |             | I/O/Z <sup>(1)</sup> | 説明                                                                                                                                                                                                                                          |

|----------------------|------------|-------------|-------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称                   | PN<br>ピン番号 | PAG<br>ピン番号 | RSH<br>ピン番号 |                      |                                                                                                                                                                                                                                             |

| ADCINA1              | 17         | 14          | 12          | I                    | ADC グループ A、チャネル 1 入力                                                                                                                                                                                                                        |

| ADCINA0              | 18         | 15          | 13          | I                    | ADC グループ A、チャネル 0 入力。<br>注: 64 ピン PAG デバイスでは、V <sub>REFHI</sub> と ADCINA0 は同じピンを共有しており、両方を同時に使うことはできません。<br>注: 56 ピン RSH デバイスでは、V <sub>REFHI</sub> と ADCINA0 は同じピンを共有しており、両方を同時に使うことはできません。                                                 |

| V <sub>REFHI</sub>   | 19         | 15          | 13          | I                    | ADC 外部基準電圧 High – ADC 外部基準電圧モードでのみ使用されます。セクション 7.9.2.1「ADC」を参照してください。<br>注: 64 ピン PAG デバイスでは、V <sub>REFHI</sub> と ADCINA0 は同じピンを共有しており、両方を同時に使うことはできません。<br>注: 56 ピン RSH デバイスでは、V <sub>REFHI</sub> と ADCINA0 は同じピンを共有しており、両方を同時に使うことはできません。 |

| ADCINB7              | 30         | 24          | 21          | I                    | ADC グループ B、チャネル 7 入力                                                                                                                                                                                                                        |

| ADCINB6              |            |             |             | I                    | ADC グループ B、チャネル 6 入力                                                                                                                                                                                                                        |

| COMP3B               | 29         | 23          | 20          | I                    | コンバレータ 入力 3B                                                                                                                                                                                                                                |

| AIO14                |            |             |             | I/O                  | デジタル AIO 14                                                                                                                                                                                                                                 |

| ADCINB5              | 28         | –           | –           | I                    | ADC グループ B、チャネル 5 入力                                                                                                                                                                                                                        |

| ADCINB4              |            |             |             | I                    | ADC グループ B、チャネル 4 入力                                                                                                                                                                                                                        |

| COMP2B               | 27         | 22          | 19          | I                    | コンバレータ 入力 2B                                                                                                                                                                                                                                |

| AIO12                |            |             |             | I/O                  | デジタル AIO12                                                                                                                                                                                                                                  |

| ADCINB3              | 26         | 21          | 18          | I                    | ADC グループ B、チャネル 3 入力                                                                                                                                                                                                                        |

| ADCINB2              |            |             |             | I                    | ADC グループ B、チャネル 2 入力                                                                                                                                                                                                                        |

| COMP1B               | 25         | 20          | 17          | I                    | コンバレータ 入力 1B                                                                                                                                                                                                                                |

| AIO10                |            |             |             | I/O                  | デジタル AIO 10                                                                                                                                                                                                                                 |

| ADCINB1              | 24         | 19          | 16          | I                    | ADC グループ B、チャネル 1 入力                                                                                                                                                                                                                        |

| ADCINB0              | 23         | 18          | –           | I                    | ADC グループ B、チャネル 0 入力                                                                                                                                                                                                                        |

| V <sub>REFLO</sub>   | 22         | 17          | 15          | I                    | ADC 外部基準電圧 Low。<br>注: 64 ピン PAG デバイスと 56 ピン RSH デバイスでは、V <sub>REFLO</sub> は常に V <sub>SSA</sub> に接続されています。                                                                                                                                   |

| <b>CPU と I/O の電源</b> |            |             |             |                      |                                                                                                                                                                                                                                             |

| V <sub>DDA</sub>     | 20         | 16          | 14          |                      | アナログ電源ピン。2.2 $\mu$ F (標準値) のコンデンサをピンの近くに接続します。                                                                                                                                                                                              |

| V <sub>SSA</sub>     | 21         | 17          | 15          |                      | アナログ グランドピン。<br>注: 64 ピン PAG デバイスと 56 ピン RSH デバイスでは、V <sub>REFLO</sub> は常に V <sub>SSA</sub> に接続されています。                                                                                                                                      |

| V <sub>DD</sub>      | 7          | 5           | 3           |                      | CPU とロジックのデジタル電源ピン。内部 VREG を使用する場合、各 V <sub>DD</sub> ピンとグラウンドとの間に 1 つの 1.2 $\mu$ F のコンデンサを接続します。より大きい値のコンデンサを使用することもできます。                                                                                                                   |

|                      | 54         | 43          | 38          |                      |                                                                                                                                                                                                                                             |

|                      | 72         | 59          | 52          |                      |                                                                                                                                                                                                                                             |

| V <sub>DDIO</sub>    | 36         | 29          | 26          |                      | デジタル I/O バッファとフラッシュメモリの電源ピン。VREG が有効化されている場合の単一電源です。各ピンに 1.2 $\mu$ F のコンデンサを接続します。実際の値は、システムの電圧レギュレーション方法によって決める必要があります。                                                                                                                    |

|                      | 70         | 57          | 50          |                      |                                                                                                                                                                                                                                             |

| V <sub>SS</sub>      | 8          | 6           | 4           |                      | デジタル グランドピン                                                                                                                                                                                                                                 |

|                      | 35         | 28          | 25          |                      |                                                                                                                                                                                                                                             |

|                      | 53         | 42          | 37          |                      |                                                                                                                                                                                                                                             |

|                      | 71         | 58          | 51          |                      |                                                                                                                                                                                                                                             |

表 5-1. 信号の説明 (続き)

| 端子                                               |            |             |             | I/O/Z <sup>(1)</sup>     | 説明                                                                                                                           |

|--------------------------------------------------|------------|-------------|-------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------|

| 名称                                               | PN<br>ピン番号 | PAG<br>ピン番号 | RSH<br>ピン番号 |                          |                                                                                                                              |

| <b>電圧レギュレータ制御信号</b>                              |            |             |             |                          |                                                                                                                              |

| VREGENZ                                          | 73         | 60          | 53          | I                        | 内部プルダウン付きの内部電圧レギュレータ (VREG) イネーブル。内部 1.8V VREG を有効化するには、VSS (Low) に直接接続します。VREG を無効化し、外部 1.8V 電源を使うには、VDDIO (High) に直接接続します。 |

| <b>GPIO およびペリフェラル信号<sup>(2)</sup></b>            |            |             |             |                          |                                                                                                                              |

| <b>GPIO0</b><br>EPWM1A<br>—<br>—                 | 69         | 56          | 49          | I/O/Z<br>O<br>—<br>—     | 汎用入出力 0<br>拡張 PWM1 出力 A および HRPWM チャネル<br>—<br>—                                                                             |

| <b>GPIO1</b><br>EPWM1B<br>—<br>COMP1OUT          | 68         | 55          | 48          | I/O/Z<br>O<br>O          | 汎用入出力 1<br>拡張 PWM1 出力 B<br>コンパレータ 1 の直接出力                                                                                    |

| <b>GPIO2</b><br>EPWM2A<br>—<br>—                 | 67         | 54          | 47          | I/O/Z<br>O               | 汎用入出力 2<br>拡張 PWM2 出力 A および HRPWM チャネル<br>—<br>—                                                                             |

| <b>GPIO3</b><br>EPWM2B<br>SPISOMIA<br>COMP2OUT   | 66         | 53          | 46          | I/O/Z<br>O<br>I/O<br>O   | 汎用入出力 3<br>拡張 PWM2 出力 B<br>SPI-A スレーブ出力、マスタ入力<br>コンパレータ 2 の直接出力                                                              |

| <b>GPIO4</b><br>EPWM3A<br>—<br>—                 | 63         | 51          | 45          | I/O/Z<br>O               | 汎用入出力 4<br>拡張 PWM3 出力 A および HRPWM チャネル<br>—<br>—                                                                             |

| <b>GPIO5</b><br>EPWM3B<br>SPISIMOA<br>ECAP1      | 62         | 50          | 44          | I/O/Z<br>O<br>I/O<br>I/O | 汎用入出力 5<br>拡張 PWM3 出力 B<br>SPI-A スレーブ入力、マスタ出力<br>拡張キャプチャ入出力 1                                                                |

| <b>GPIO6</b><br>EPWM4A<br>EPWMSYNCI<br>EPWMSYNCO | 50         | 39          | 34          | I/O/Z<br>O<br>I<br>O     | 汎用入出力 6<br>拡張 PWM4 出力 A および HRPWM チャネル<br>外部 ePWM 同期パルス入力<br>外部 ePWM 同期パルス出力                                                 |

| <b>GPIO7</b><br>EPWM4B<br>SCIRXDA<br>—           | 49         | 38          | 33          | I/O/Z<br>O<br>I          | 汎用入出力 7<br>拡張 PWM4 出力 B<br>SCI-A 受信データ<br>—                                                                                  |

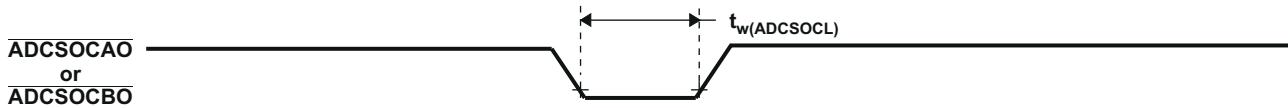

| <b>GPIO8</b><br>EPWM5A<br>—<br>ADCSOCDAO         | 43         | 35          | —           | I/O/Z<br>O<br>O          | 汎用入出力 8<br>拡張 PWM5 出力 A および HRPWM チャネル<br>—<br>ADC 変換開始 A                                                                    |

**表 5-1. 信号の説明 (続き)**

| 端子            |            |             |             | I/O/Z <sup>(1)</sup> | 説明                                                  |

|---------------|------------|-------------|-------------|----------------------|-----------------------------------------------------|

| 名称            | PN<br>ピン番号 | PAG<br>ピン番号 | RSH<br>ピン番号 |                      |                                                     |

| <b>GPIO9</b>  |            |             |             | I/O/Z                | 汎用入出力 9                                             |

| EPWM5B        | 39         | 31          | –           | O                    | 拡張 PWM5 出力 B                                        |

| LINTXA        |            |             |             | O                    | LIN 送信 A                                            |

| HRCAP1        |            |             |             | I                    | 高分解能入力キャプチャ 1                                       |

| <b>GPIO10</b> |            |             |             | I/O/Z                | 汎用入出力 10                                            |

| EPWM6A        | 65         | 52          | –           | O                    | 拡張 PWM6 出力 A および HRPWM チャネル                         |

| –             |            |             |             | O                    | –                                                   |

| ADCSOCBO      |            |             |             | O                    | ADC 変換開始 B                                          |

| <b>GPIO11</b> |            |             |             | I/O/Z                | 汎用入出力 11                                            |

| EPWM6B        | 61         | 49          | –           | O                    | 拡張 PWM6 出力 B                                        |

| LINRXA        |            |             |             | I                    | LIN 受信 A                                            |

| HRCAP2        |            |             |             | I                    | 高分解能入力キャプチャ 2                                       |

| <b>GPIO12</b> |            |             |             | I/O/Z                | 汎用入出力 12                                            |

| TZ1           |            |             |             | I                    | トリップ ゾーン入力 1                                        |

| SCITXDA       | 47         | 37          | 32          | O                    | SCI-A 送信データ                                         |

| SPISIMOB      |            |             |             | I/O                  | SPI-B スレーブ入力、マスタ出力。<br>注:SPI-B は PN パッケージでのみ利用できます。 |

| <b>GPIO13</b> |            |             |             | I/O/Z                | 汎用入出力 13                                            |

| TZ2           | 76         | –           | –           | I                    | トリップ ゾーン入力 2                                        |

| –             |            |             |             | I/O                  | –                                                   |

| SPISOMIB      |            |             |             | I/O                  | SPI-B スレーブ出力、マスタ入力                                  |

| <b>GPIO14</b> |            |             |             | I/O/Z                | 汎用入出力 14                                            |

| TZ3           | 77         | –           | –           | I                    | トリップ ゾーン入力 3                                        |

| LINRXA        |            |             |             | O                    | LIN 送信                                              |

| SPICLKB       |            |             |             | I/O                  | SPI-B クロック入出力                                       |

| <b>GPIO15</b> |            |             |             | I/O/Z                | 汎用入出力 15                                            |

| TZ1           |            |             |             | I                    | トリップ ゾーン入力 1                                        |

| LINRXA        |            |             |             | I                    | LIN 受信                                              |

| SPISTEB       | 75         | –           | –           | I/O                  | SPI-B スレーブ送信イネーブル入出力                                |

| <b>GPIO16</b> |            |             |             | I/O/Z                | 汎用入出力 16                                            |

| SPISIMOA      |            |             |             | I/O                  | SPI-A スレーブ入力、マスタ出力                                  |

| –             |            |             |             | I                    | –                                                   |

| TZ2           | 46         | 36          | 31          | I                    | トリップ ゾーン入力 2                                        |

| <b>GPIO17</b> |            |             |             | I/O/Z                | 汎用入出力 17                                            |

| SPISOMIA      |            |             |             | I/O                  | SPI-A スレーブ出力、マスタ入力                                  |

| –             |            |             |             | I                    | –                                                   |

| TZ3           | 42         | 34          | 30          | I                    | トリップ ゾーン入力 3                                        |

表 5-1. 信号の説明 (続き)

| 端子            |            |             |                                  | I/O/Z <sup>(1)</sup> | 説明                                                                                                                                                                                                                                                        |

|---------------|------------|-------------|----------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称            | PN<br>ピン番号 | PAG<br>ピン番号 | RSH<br>ピン番号                      |                      |                                                                                                                                                                                                                                                           |

| <b>GPIO18</b> |            |             |                                  | I/O/Z                | 汎用入出力 18                                                                                                                                                                                                                                                  |

| SPICLKA       |            |             |                                  | I/O                  | SPI-A クロック入出力                                                                                                                                                                                                                                             |

| LINTXA        | 41         | 33          | 29                               | O                    | LIN 送信                                                                                                                                                                                                                                                    |

| XCLKOUT       |            |             |                                  | O/Z                  | SYSCLKOUT を基準にして生成された出力クロック。XCLKOUT は、SYSCLKOUT と同じ周波数、半分の周波数、1/4 の周波数のいずれかです。これは、XCLK レジスタのビット 1:0 (XCLKOUTDIV) で制御されます。リセット時、XCLKOUT = SYSCLKOUT/4 です。XCLKOUT 信号は、XCLKOUTDIV を 3 に設定することでオフにできます。この信号をピンに伝搬させるには、GPIO18 の MUX 制御も XCLKOUT に設定する必要があります。 |

| <b>GPIO19</b> |            |             |                                  | I/O/Z                | 汎用入出力 19                                                                                                                                                                                                                                                  |

| XCLKIN        | 55         | 44          | 39                               | I/O                  | 外部発振器入力。このピンの MUX 機能は、このピンからクロック ブロックへの経路をゲート制御しません。クロック ブロックがその他のペリフェラルの機能のために使われている場合、このクロック供給経路が有効化されないように注意する必要があります。                                                                                                                                 |

| SPISTEA       |            |             |                                  | I/O                  | SPI-A スレーブ送信イネーブル入出力                                                                                                                                                                                                                                      |

| LINRXA        |            |             |                                  | I                    | LIN 受信                                                                                                                                                                                                                                                    |

| ECAP1         |            |             |                                  | I/O                  | 拡張キャプチャ入出力 1                                                                                                                                                                                                                                              |

| <b>GPIO20</b> |            |             |                                  | I/O/Z                | 汎用入出力 20                                                                                                                                                                                                                                                  |

| EQEP1A        | 78         | 62          | 55                               | I                    | 拡張 QEP1 入力 A                                                                                                                                                                                                                                              |

| –             |            |             |                                  | O                    | –                                                                                                                                                                                                                                                         |

| COMP1OUT      |            |             |                                  | O                    | コンパレータ 1 の直接出力                                                                                                                                                                                                                                            |

| <b>GPIO21</b> |            |             |                                  | I/O/Z                | 汎用入出力 21                                                                                                                                                                                                                                                  |

| EQEP1B        | 79         | 63          | 56                               | I                    | 拡張 QEP1 入力 B                                                                                                                                                                                                                                              |

| –             |            |             |                                  | O                    | –                                                                                                                                                                                                                                                         |

| COMP2OUT      |            |             |                                  | O                    | コンパレータ 2 の直接出力                                                                                                                                                                                                                                            |

| <b>GPIO22</b> |            |             |                                  | I/O/Z                | 汎用入出力 22                                                                                                                                                                                                                                                  |

| EQEP1S        | 1          | 1           | 1                                | I/O                  | 拡張 QEP1 ストローブ                                                                                                                                                                                                                                             |

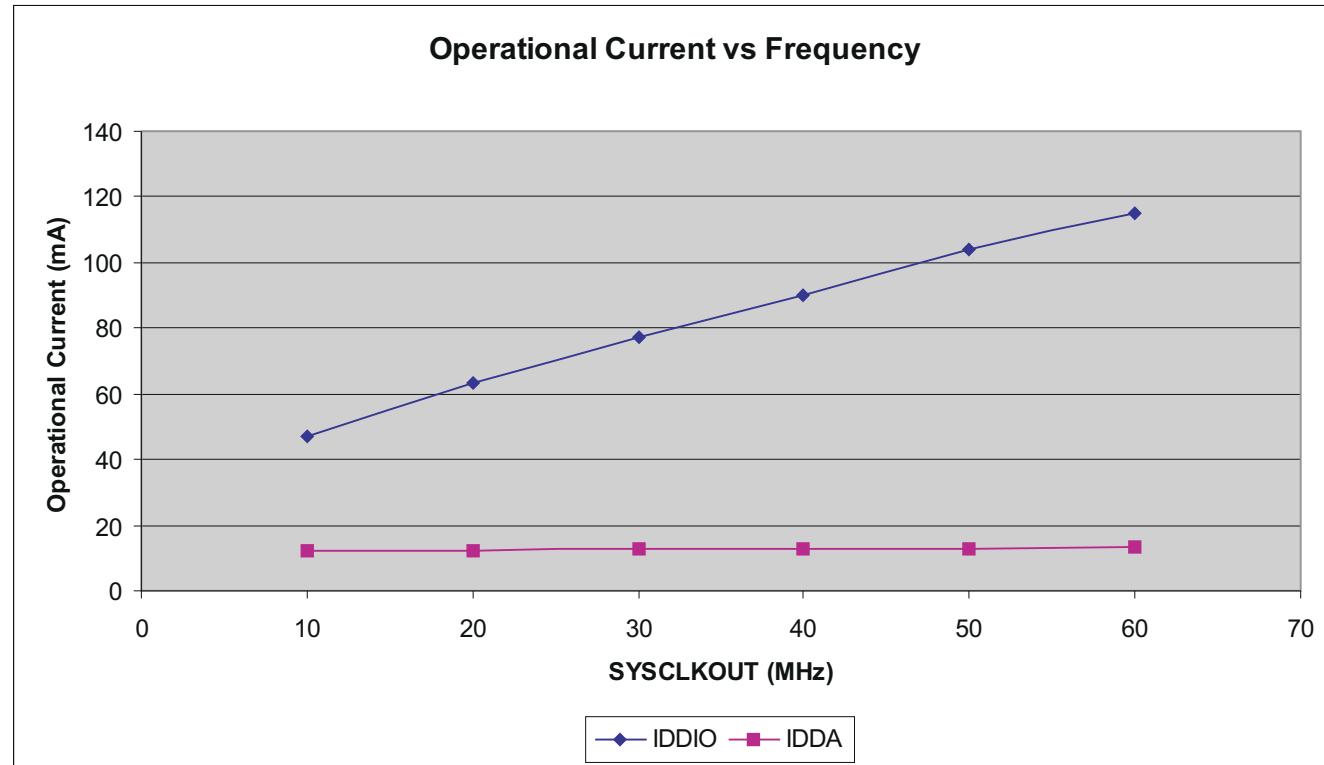

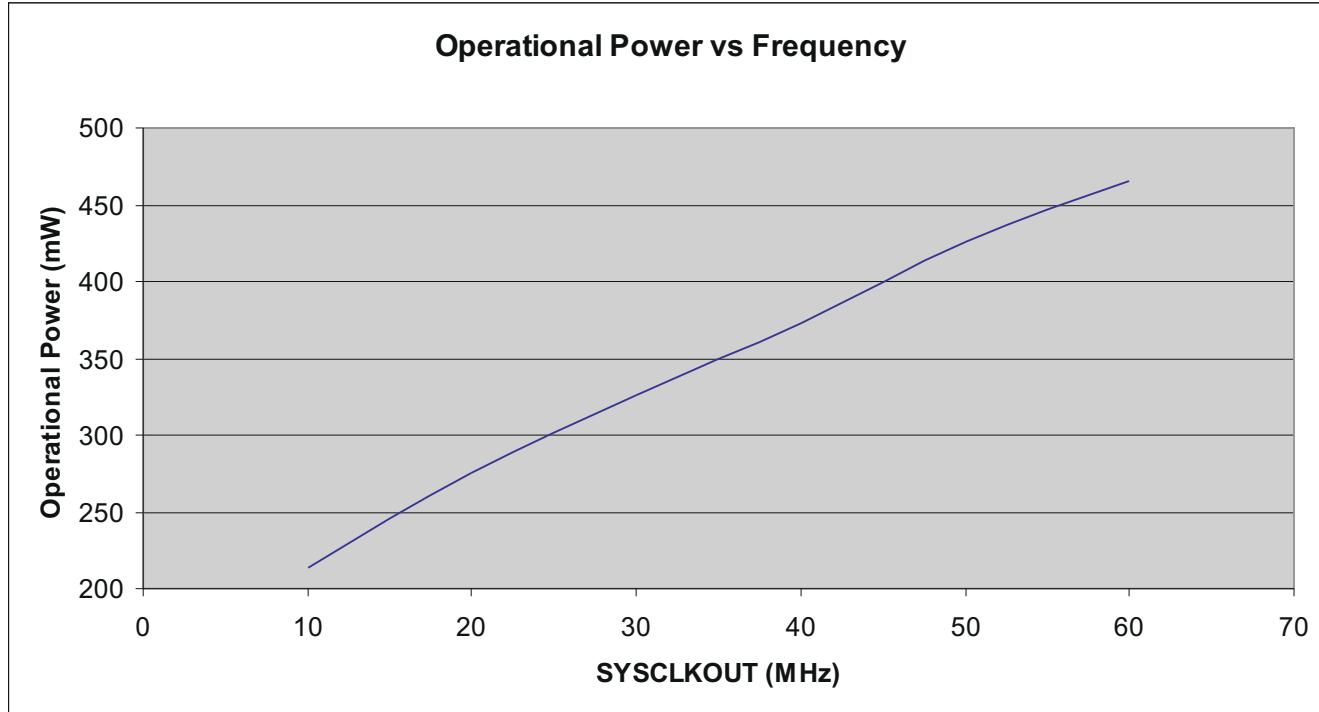

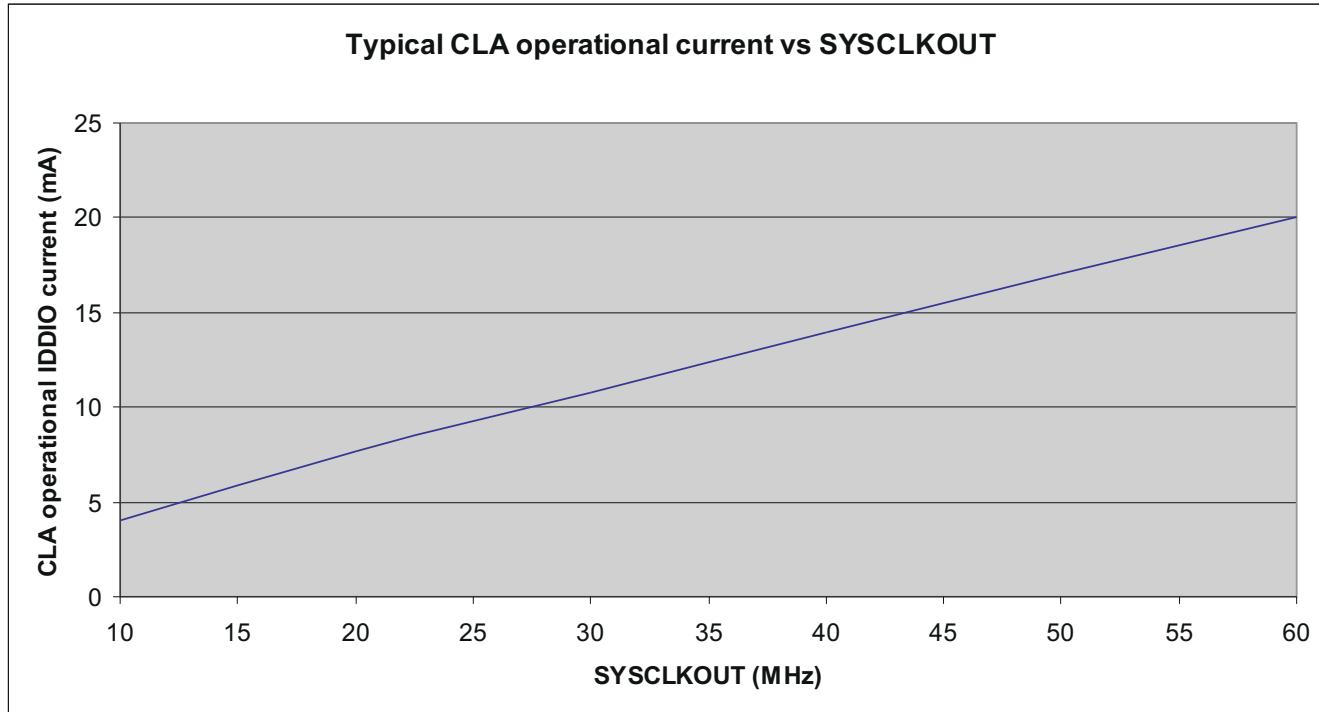

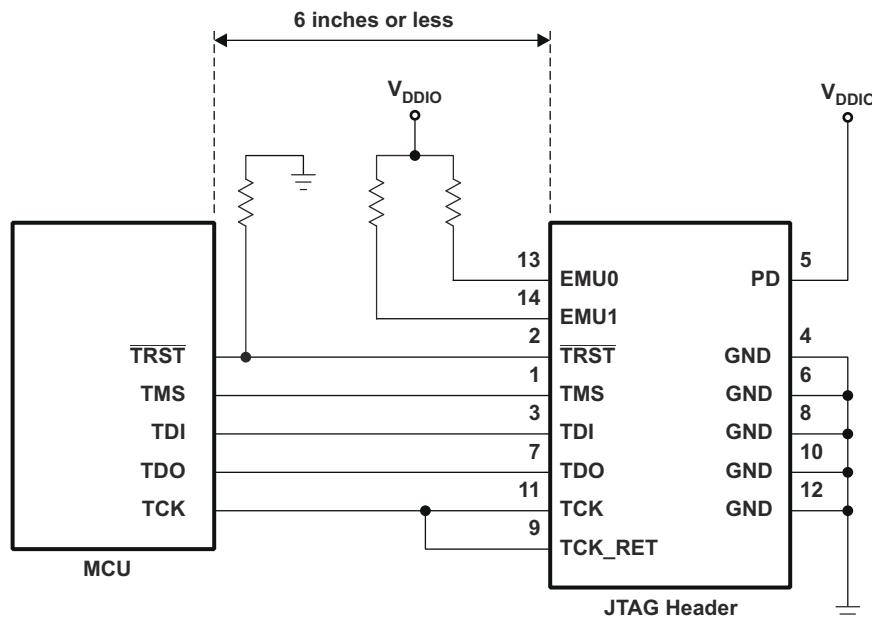

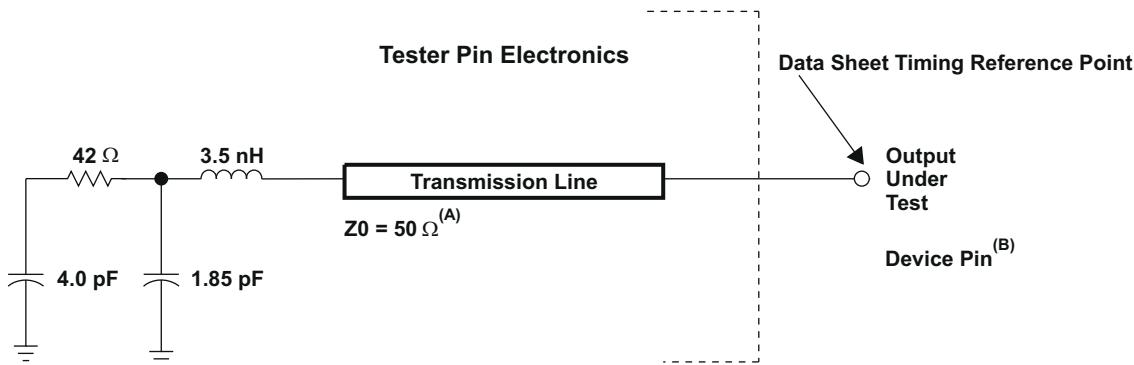

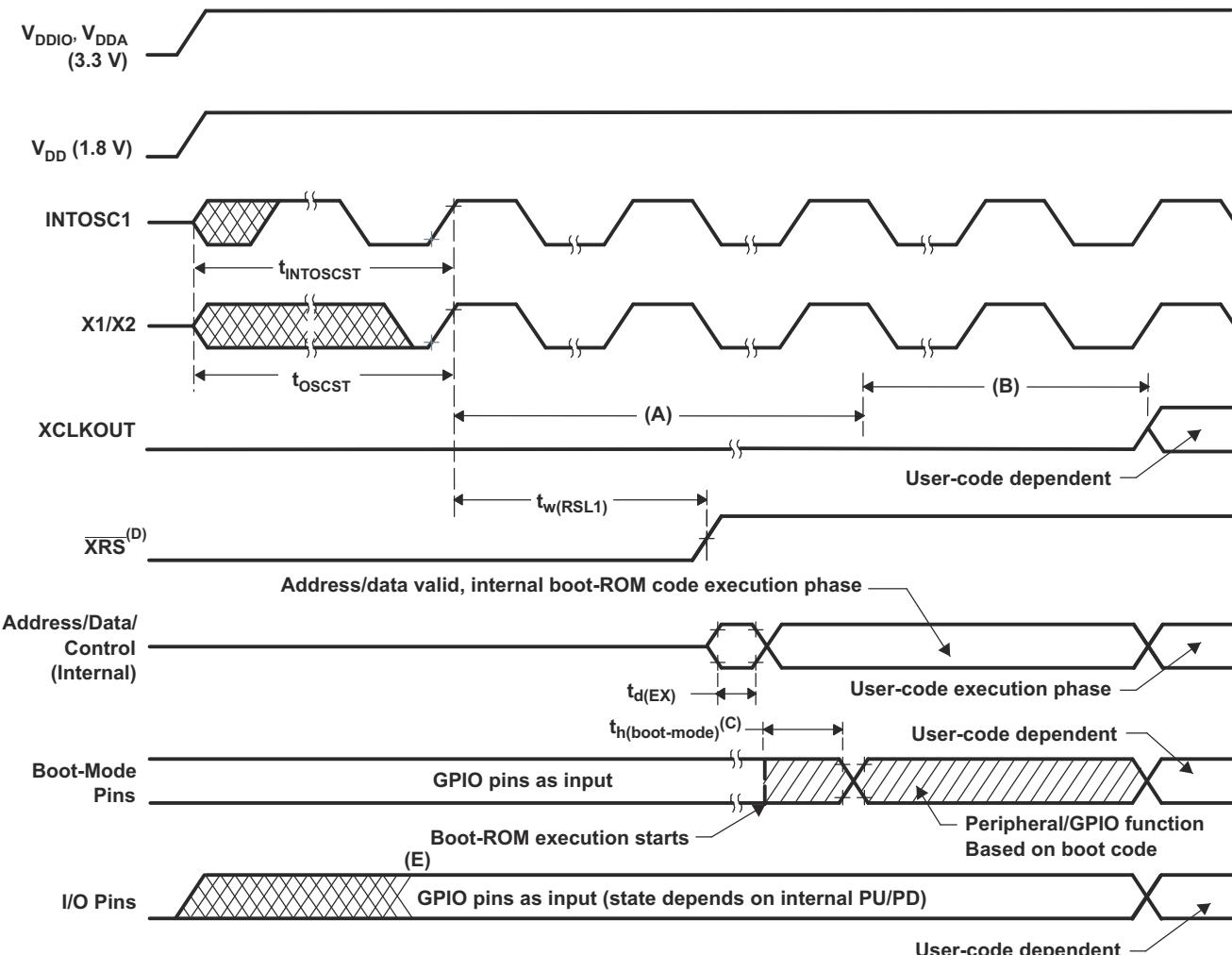

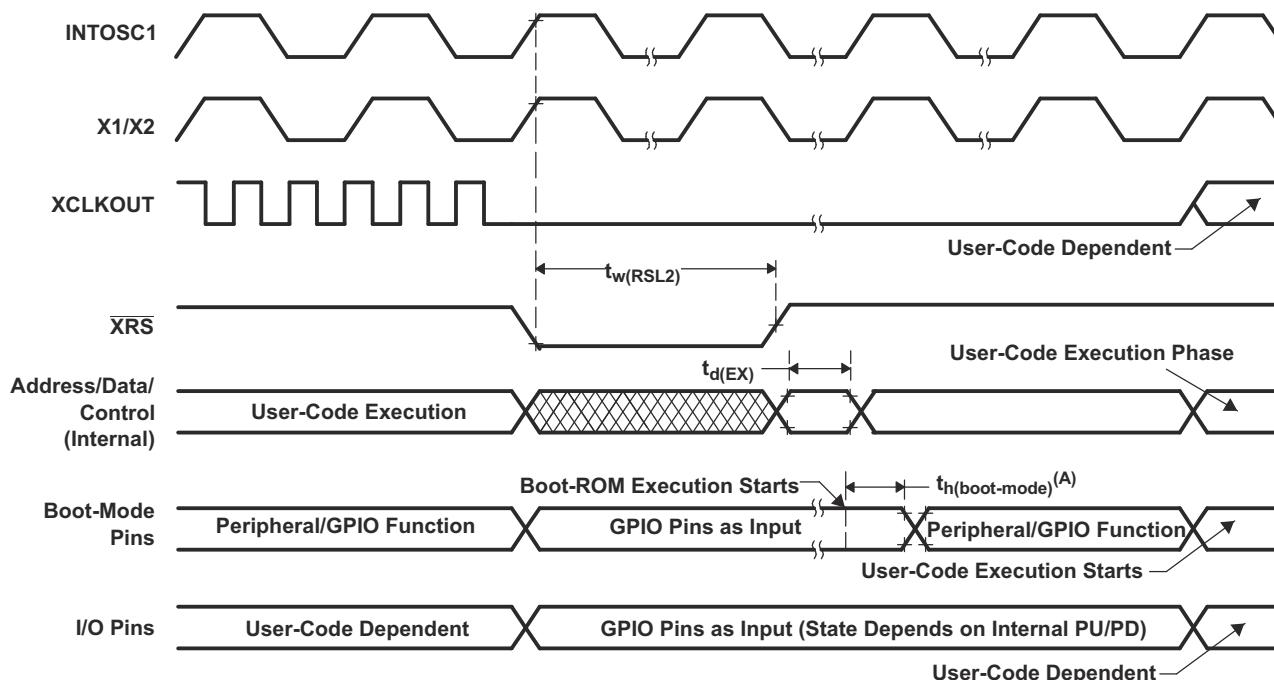

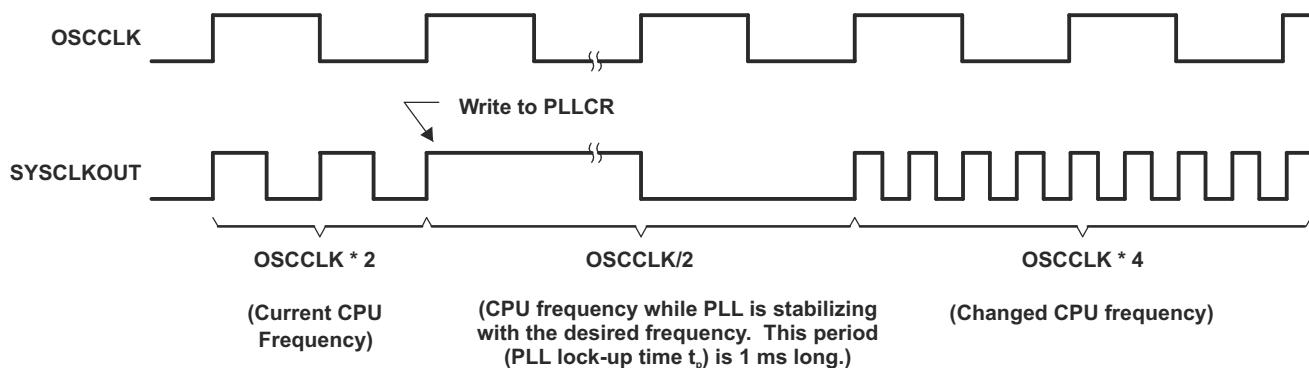

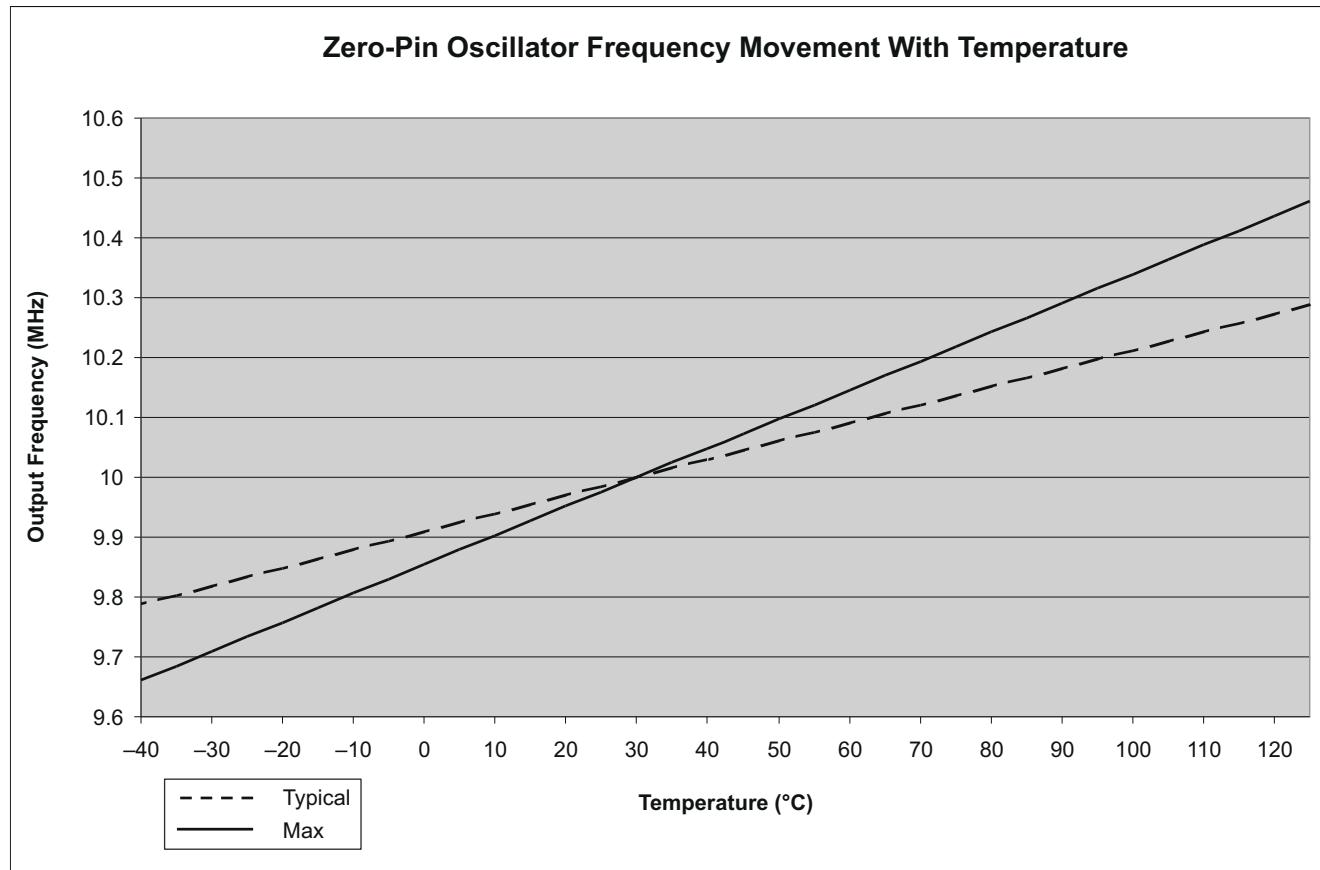

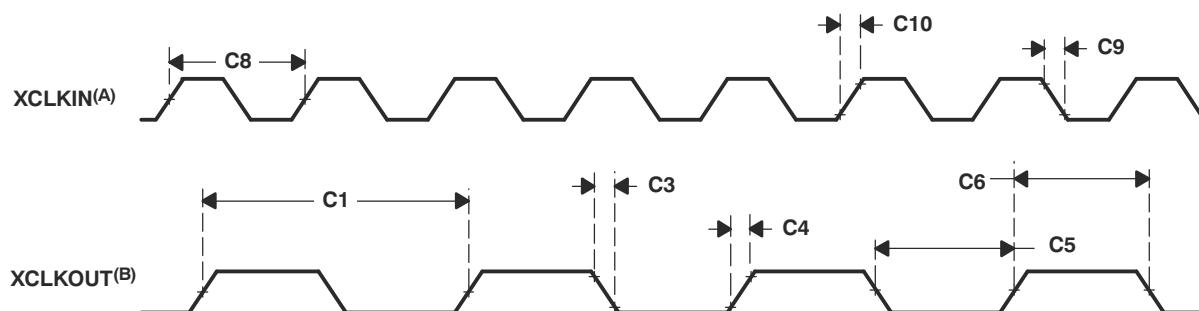

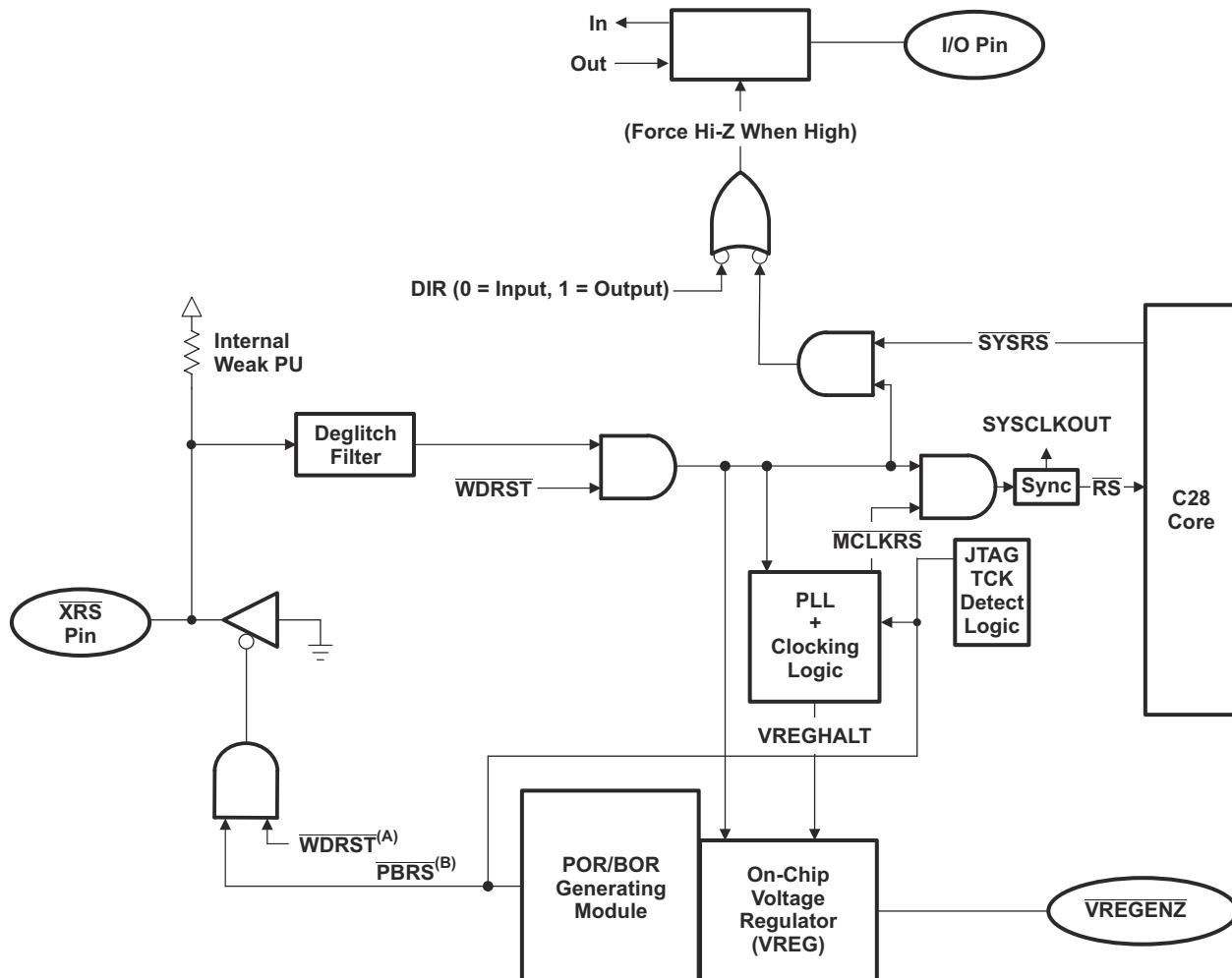

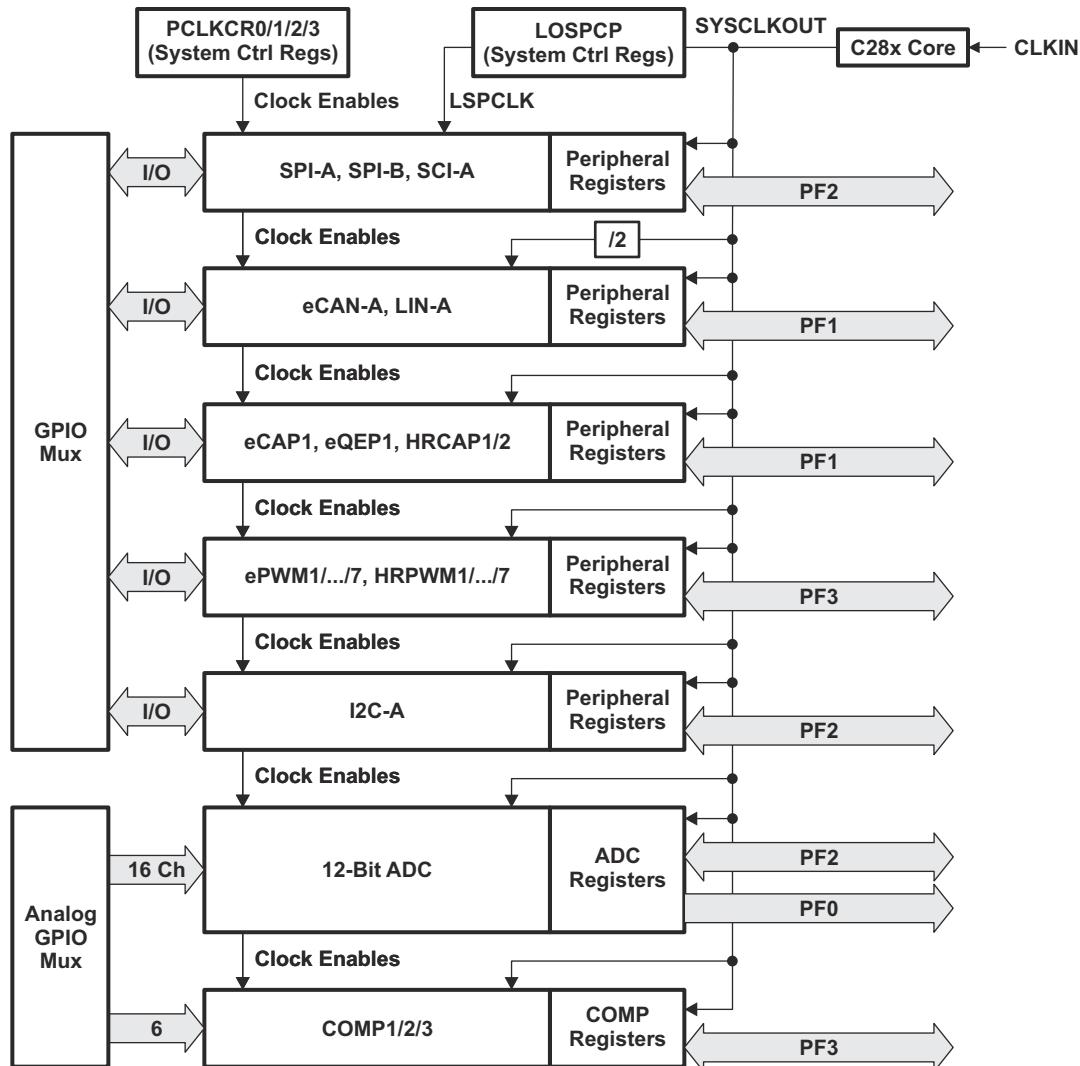

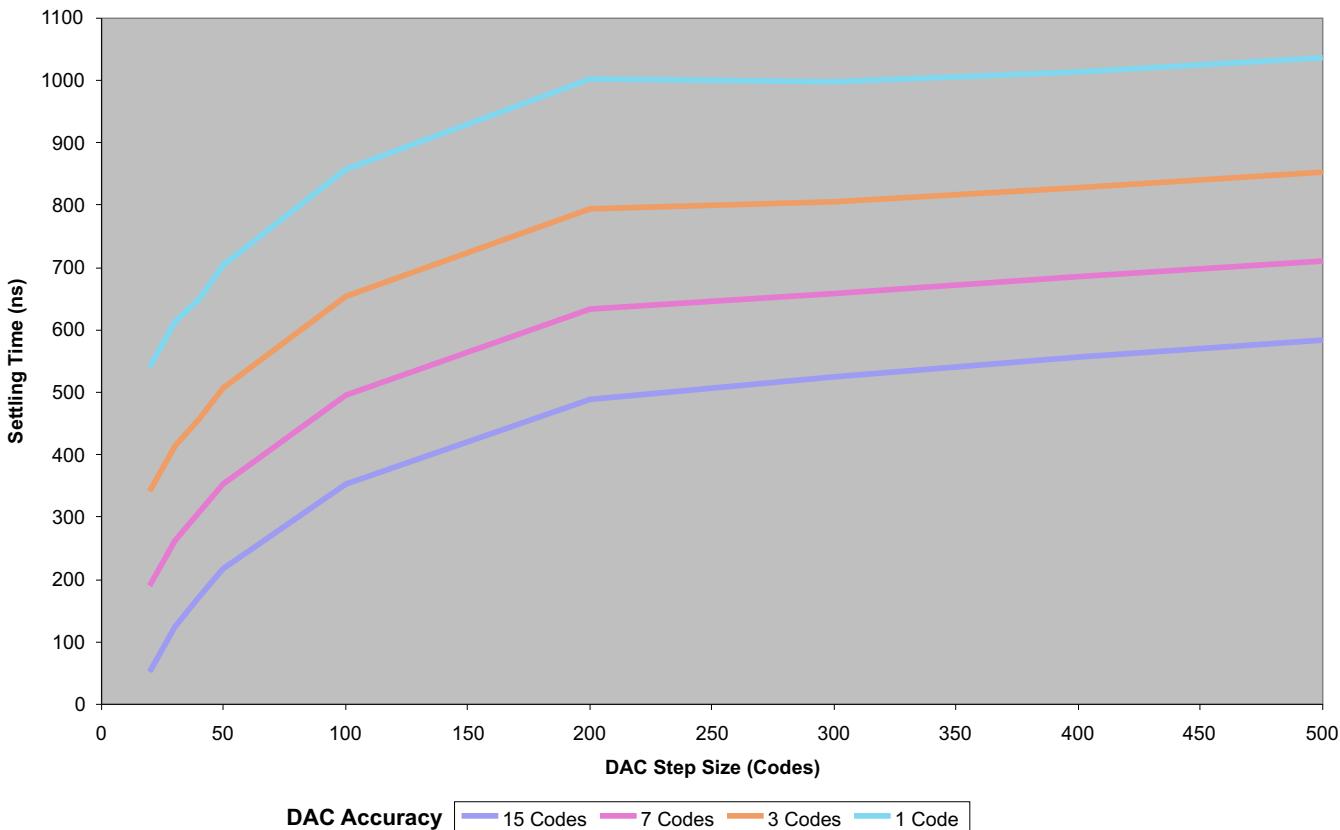

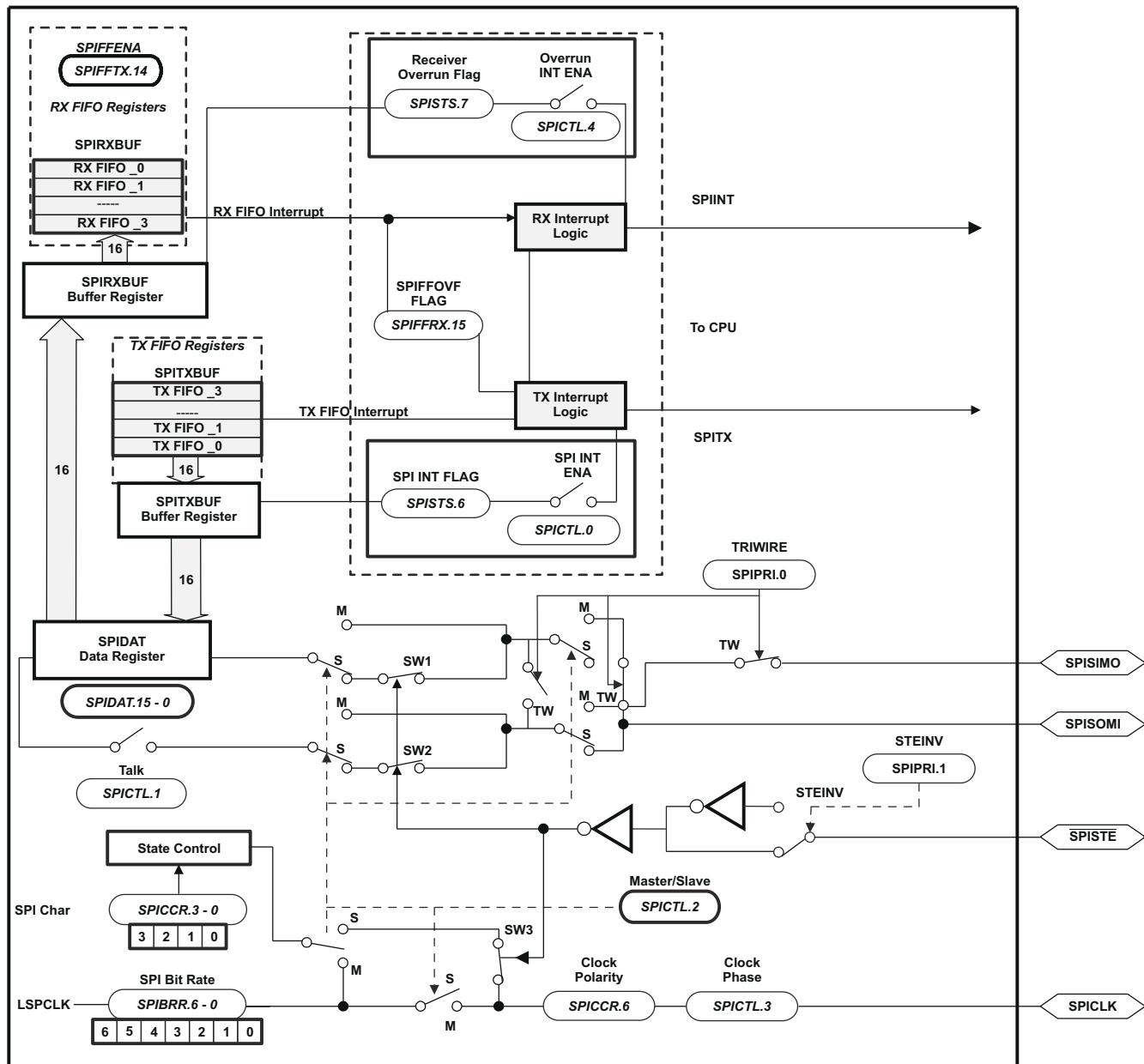

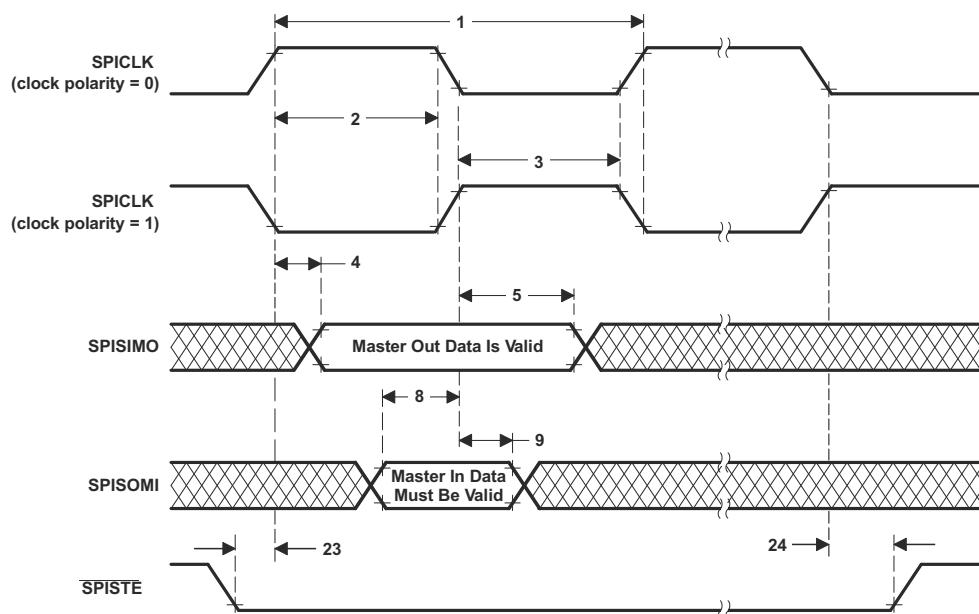

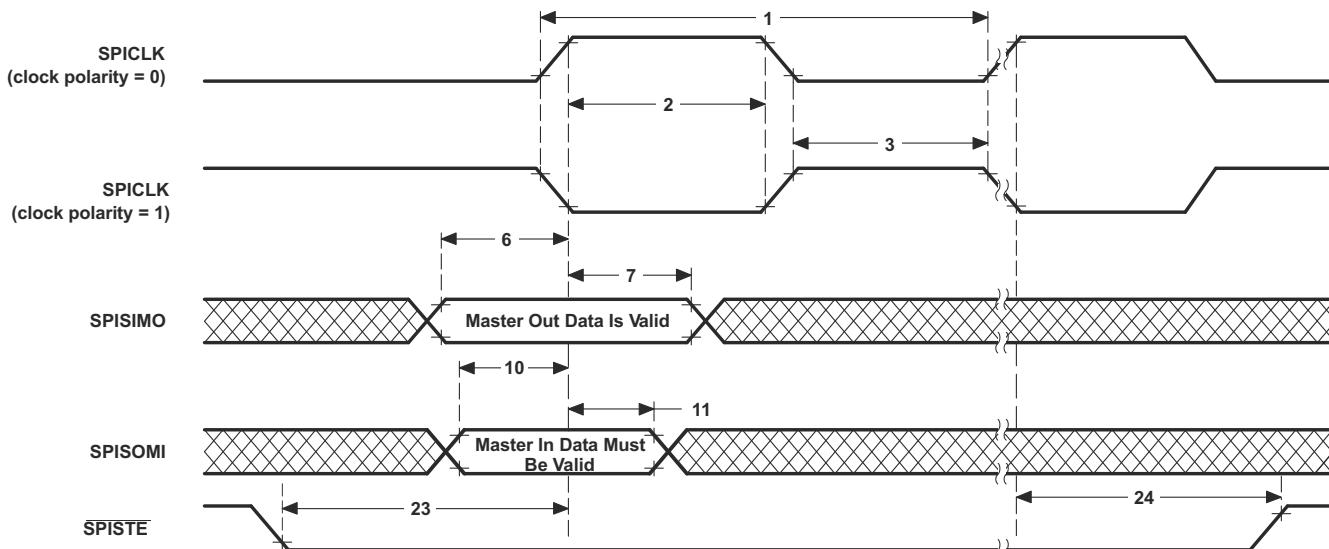

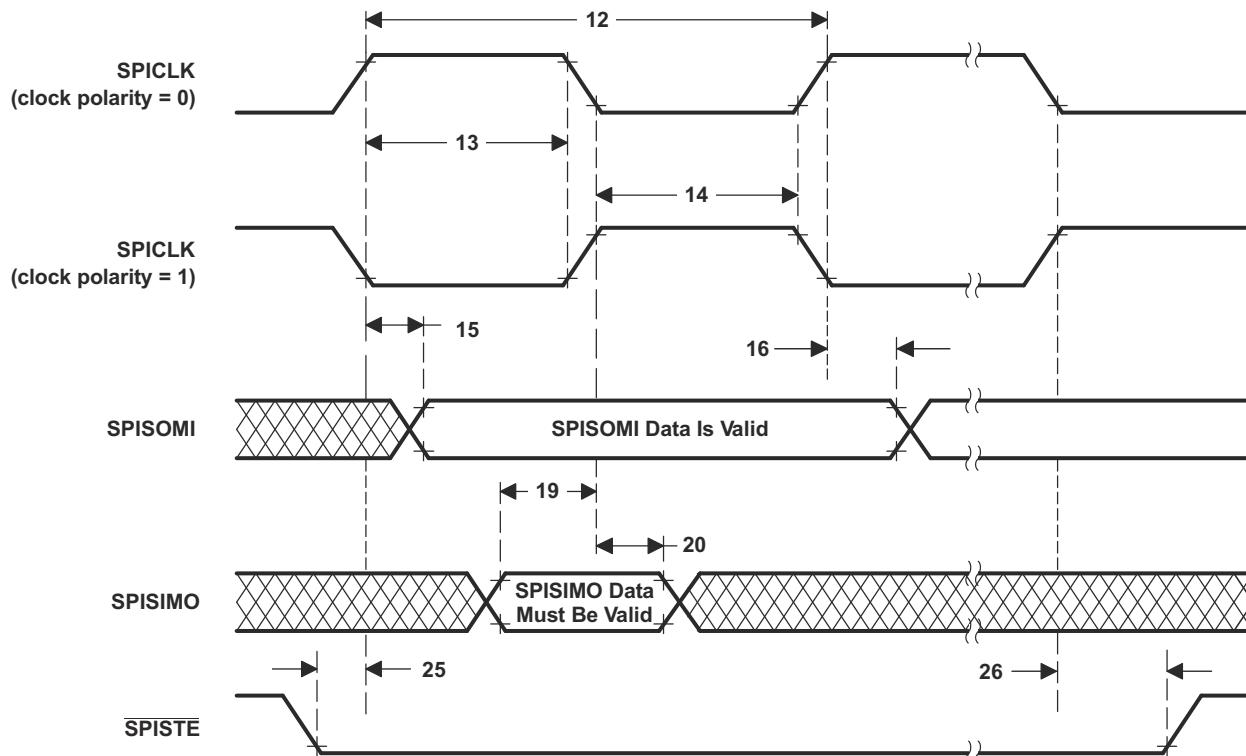

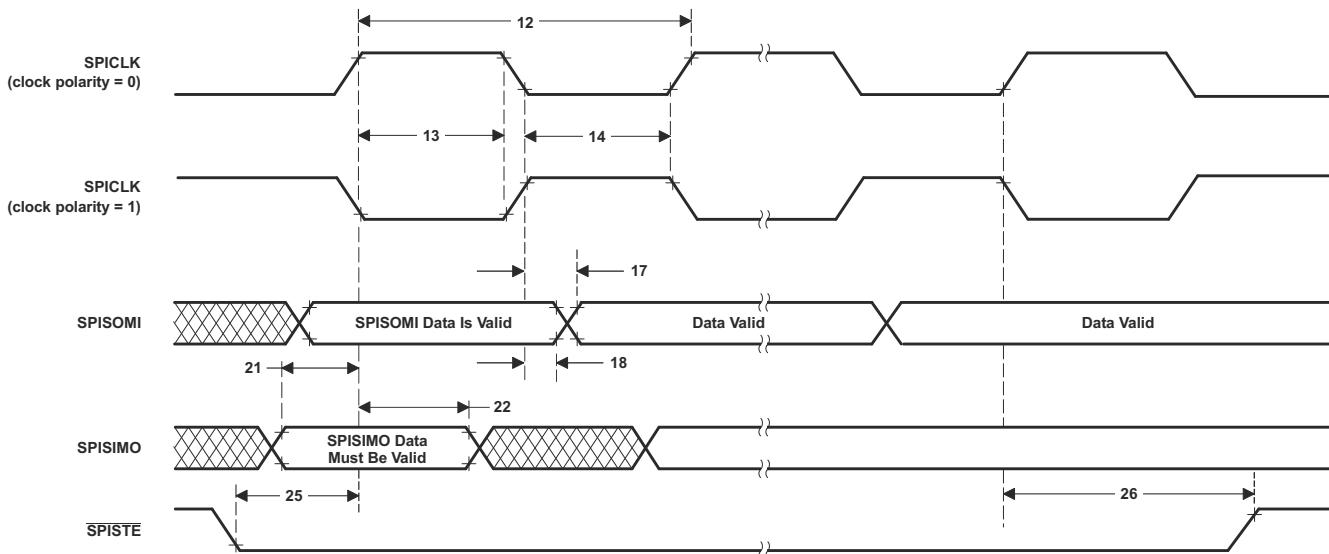

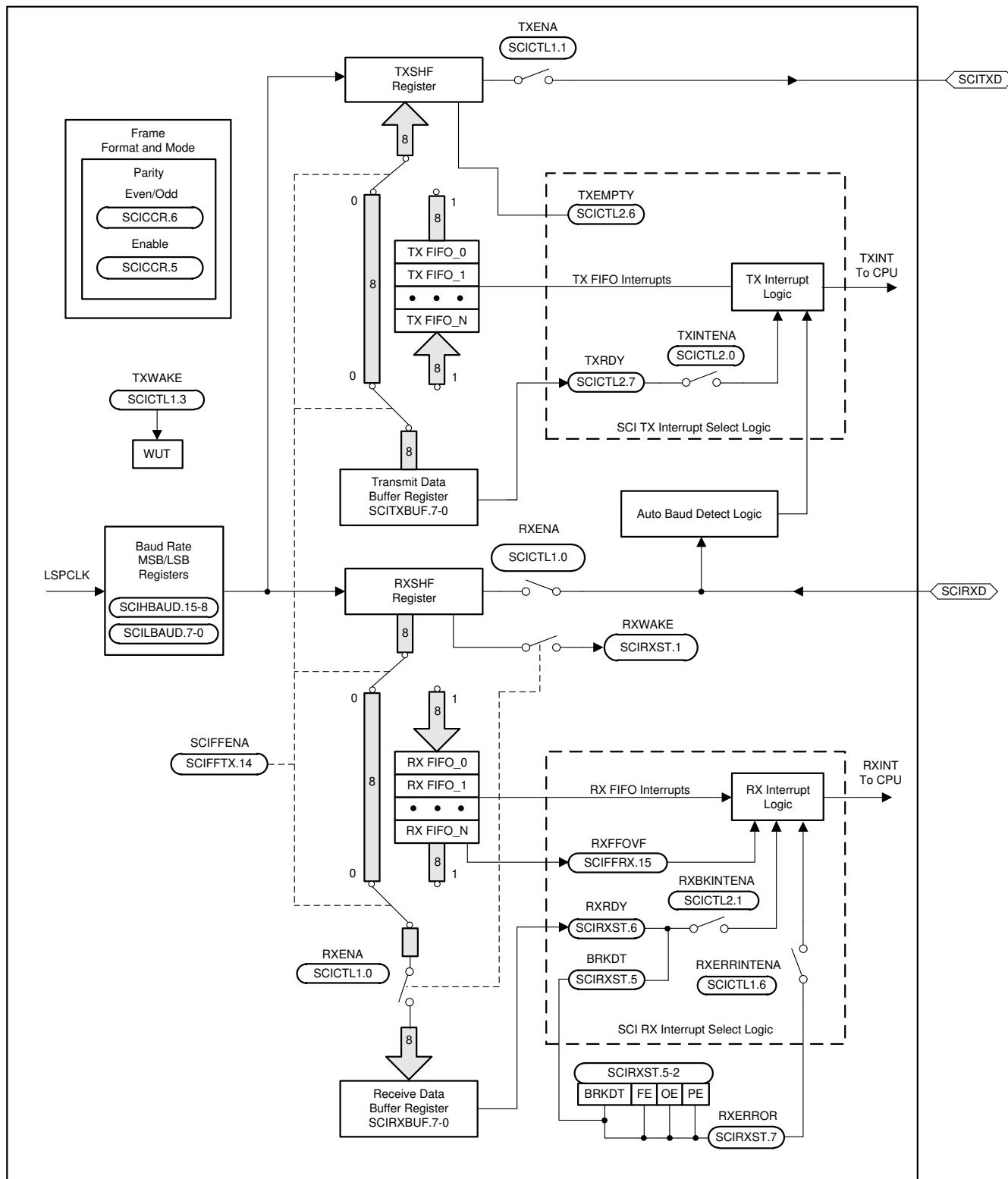

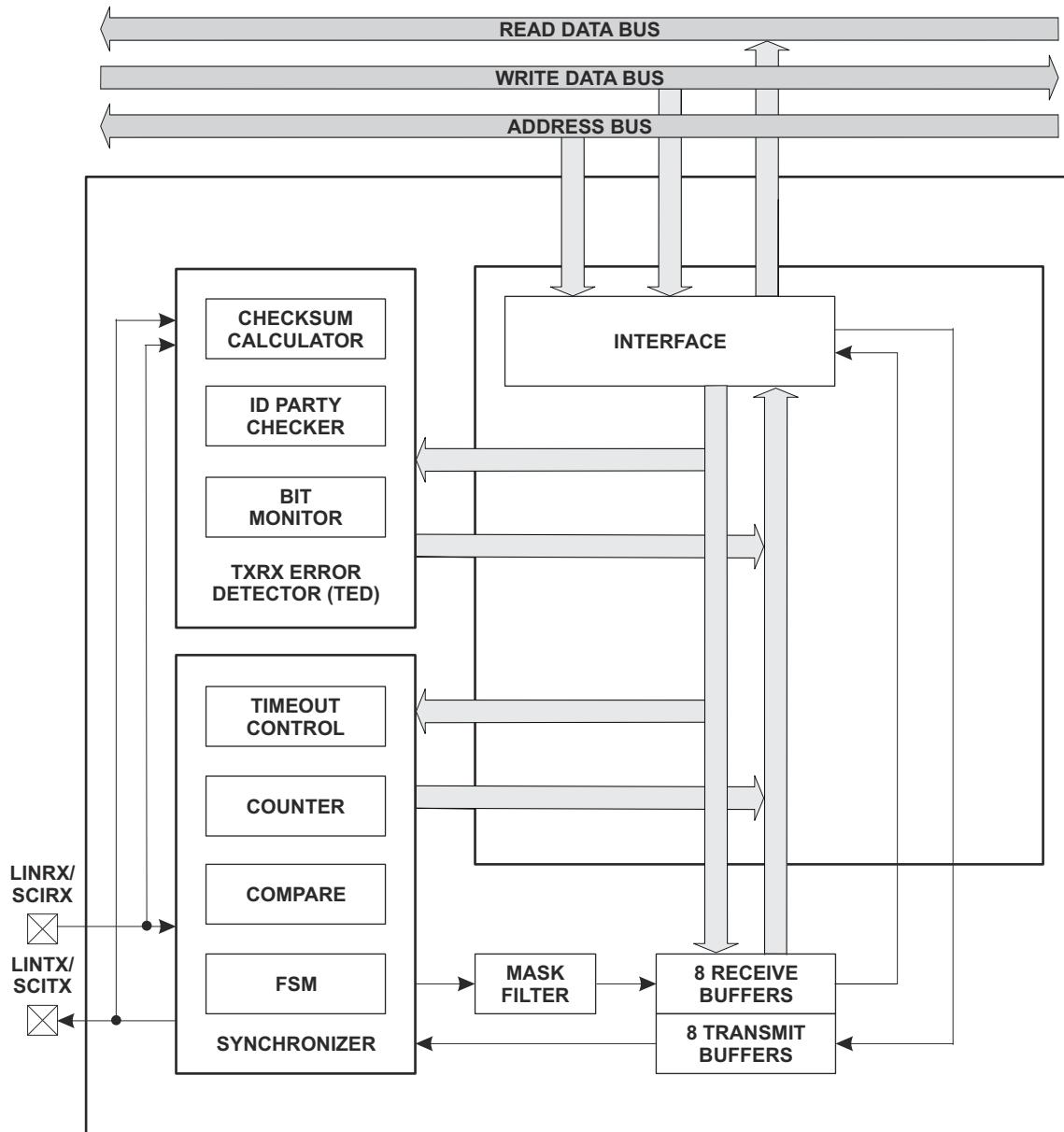

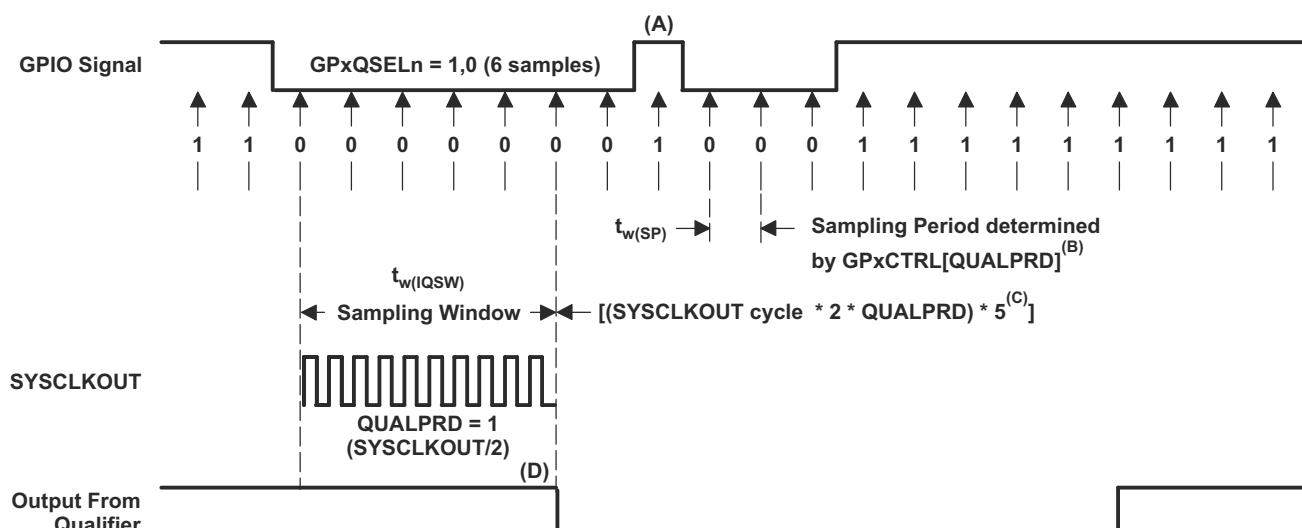

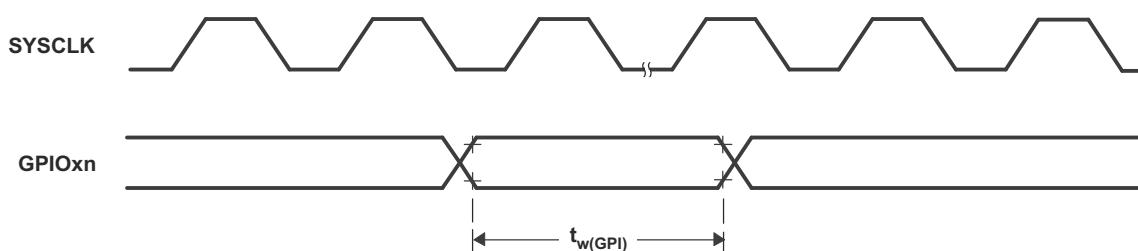

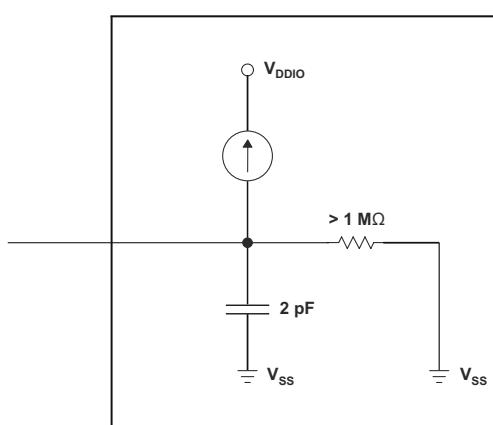

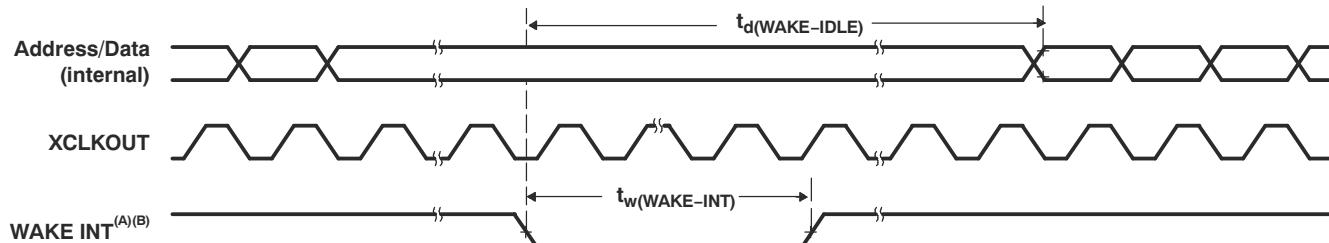

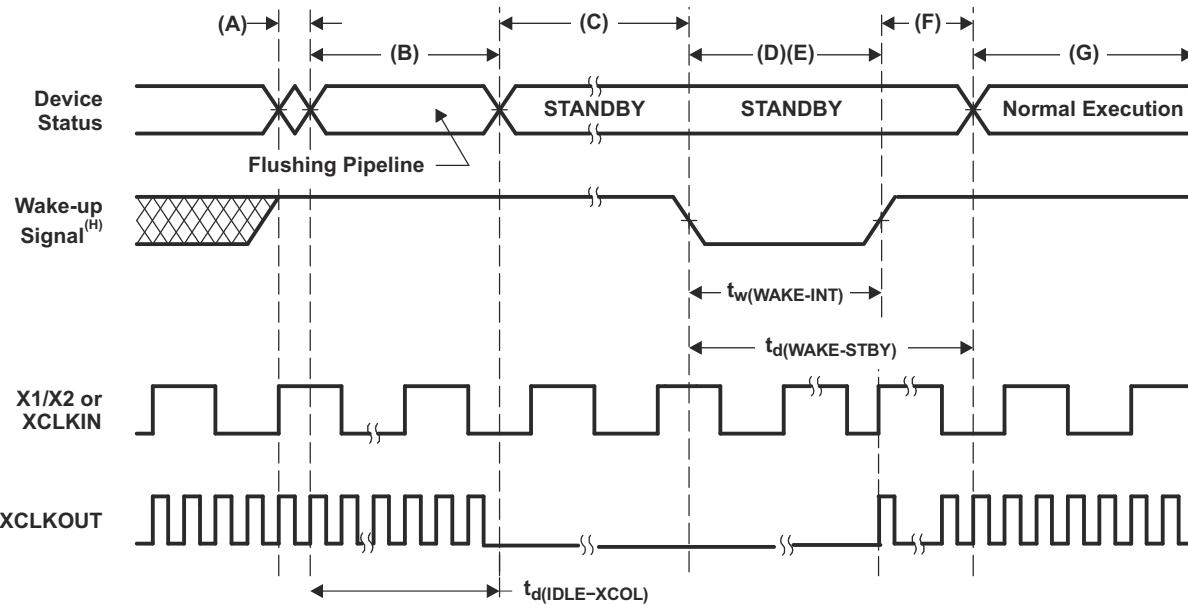

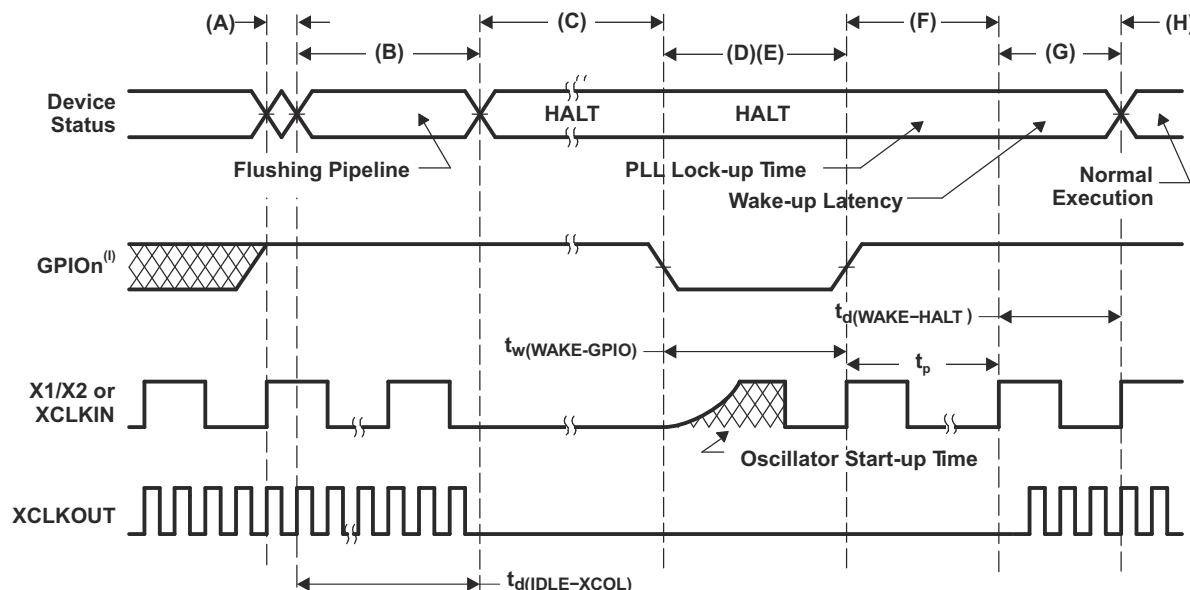

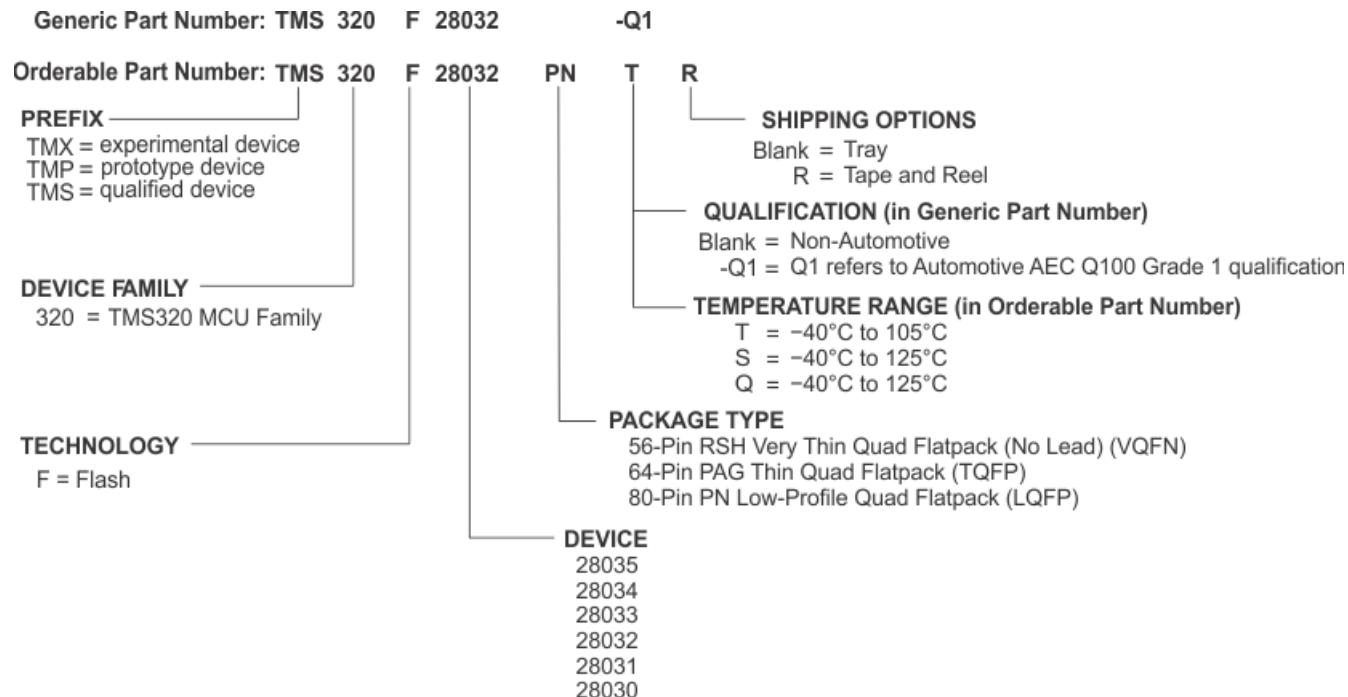

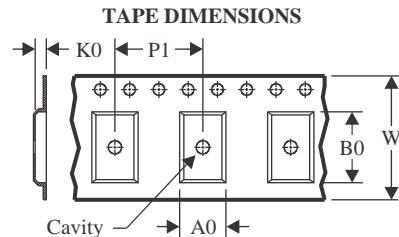

| –             |            |             |                                  | O                    | –                                                                                                                                                                                                                                                         |