参考資料

TPS2061, TPS2062, TPS2063 TPS2065, TPS2066, TPS2067

JAJSPW9K - DECEMBER 2003 - REVISED JUNE 2024

# 電流制限付き配電スイッチ

## 1 特長

- 70mΩ ハイサイド MOSFET

- 1A の連続電流

- 過熱および短絡保護

- 正確な電流制限 (最小 1.1A、最大 1.9A)

- 動作範囲:2.7V~5.5V

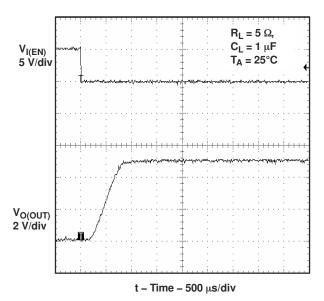

- 0.6ms の立ち上がり時間 (代表値)

- 低電圧誤動作防止

- デグリッチ フォルト レポート ( $\overline{OC}$ )

- 電源投入時の OC グリッチなし

- スタンバイ時電源電流:最大 1µA

- 双方向スイッチ

- 周囲温度範囲:-40°C~85°C

- ソフトスタート機能内蔵

- UL 認定済み:ファイル番号 E169910

## 2 アプリケーション

- 大きな容量性負荷

- 短絡保護

## 3 概要

TPS206x 配電スイッチは、大きな容量性負荷と短絡が発 生しやすいアプリケーションを対象としています。このデバ イスは、複数のパワー スイッチを 1 つのパッケージに搭載 する必要があるパワー ディストリビューション システム向け に、70mΩ N チャネル MOSFET パワー スイッチを内蔵し ています。各スイッチは、ロジックイネーブル入力によって 制御されます。ゲートドライブは、スイッチング中の電流サ ージを最小限に抑えるためにパワー スイッチの立ち上がり 時間と立ち下がり時間を制御するように設計された、内部 チャージ ポンプによって提供されています。 チャージ ポン プには外付け部品が不要で、最低 2.7V の電源で動作で

## **Table of Contents**

| 1 特長1                                              | 8.5 Enable ( <del>ENx</del> or ENx)     | 20 |

|----------------------------------------------------|-----------------------------------------|----|

| <b>2</b> アプリケーション1                                 | 8.6 Current Sense                       |    |

| 3 概要1                                              | 8.7 Overcurrent                         | 20 |

| 4 概要 (続き)                                          | 8.8 Overcurrent ( OCx)                  | 21 |

| 5 Pin Configuration and Functions4                 | 8.9 Thermal Sense                       | 21 |

| 6 Specifications6                                  | 8.10 Undervoltage Lockout               | 21 |

| 6.1 Absolute Maximum Ratings6                      | 9 Application and Implementation        | 22 |

| 6.2 Recommended Operating Conditions               | 9.1 Application Information             |    |

| 6.3 Thermal Information                            | 10 Device and Documentation Support     | 28 |

| 6.4 Electrical Characteristics                     | 10.1 Device Support                     | 28 |

| 6.5 Typical Characteristics (TPS2061, TPS2062,     | 10.2 Documentation Support              | 28 |

| TPS2065, and TPS2066)8                             | 10.3ドキュメントの更新通知を受け取る方法                  | 28 |

| 6.6 Typical Characteristics (TPS2063 & TPS2067) 11 | 10.4 サポート・リソース                          | 28 |

| 7 Parameter Measurement Information                | 10.5 Trademarks                         |    |

| 8 Detailed Description                             | 10.6 静電気放電に関する注意事項                      |    |

| 8.1 Functional Block Diagram18                     | 10.7 用語集                                |    |

| 8.2 Power Switch                                   | 11 Revision History                     |    |

| 8.3 Charge Pump                                    | 12 Mechanical, Packaging, and Orderable |    |

| 8.4 Driver                                         | Information                             | 30 |

|                                                    |                                         |    |

## 4 概要 (続き)

出力負荷が電流制限スレッショルドを超えた場合、または短絡が存在する場合、デバイスは定電流モードに切り替えて過電流 (OCx) ロジック出力を Low にすることで、出力電流を安全なレベルに制限します。連続的に大きな過負荷と短絡が発生すると、スイッチの電力散逸が増加し、接合部温度が上昇すると、熱保護回路によってスイッチがシャットオフされ、損傷を防止します。デバイスの温度が十分に低下すると、自動的にサーマル・シャットダウンからの回復が行われます。内部回路により、有効な入力電圧が印加されるまでスイッチがオフに維持されます。この配電スイッチは、電流制限を 1.5A (代表値) に設定するように設計されています。

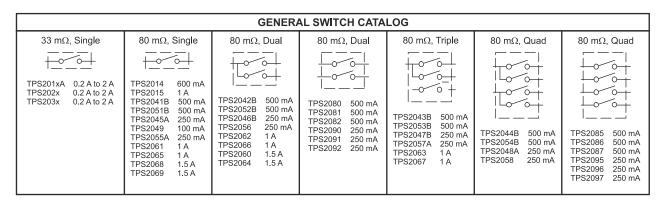

### 5 Pin Configuration and Functions

<sup>&</sup>lt;sup>†</sup> All Enable Inputs Are Active High For TPS2065, TPS2066, and TPS2067

#### 表 5-1. Pin Functions (TPS2061 and TPS2065)

|           | PINS                |         | •       |              | , |                                                                                                                    |  |

|-----------|---------------------|---------|---------|--------------|---|--------------------------------------------------------------------------------------------------------------------|--|

|           | D or DGN Package DB |         |         | DBV Package  |   | DESCRIPTION                                                                                                        |  |

| NAME      | TPS2061 TPS2065     |         | TPS2061 | 2061 TPS2065 |   |                                                                                                                    |  |

| EN        | 4                   | -       | 4       | -            | I | Enable input, logic low turns on power switch                                                                      |  |

| EN        | -                   | 4       | -       | 4            | I | Enable input, logic high turns on power switch                                                                     |  |

| GND       | 1                   | 1       | 2       | 2            |   | Ground                                                                                                             |  |

| IN        | 2, 3                | 2,3     | 5       | 5            | I | Input voltage                                                                                                      |  |

| <u>oc</u> | 5                   | 5       | 3       | 3            | 0 | Overcurrent, open-drain output, active-low                                                                         |  |

| OUT       | 6, 7, 8             | 6, 7, 8 | 1       | 1            | 0 | Power-switch output                                                                                                |  |

| PowerPAD™ | -                   | -       | -       | -            |   | Internally connected to GND; used to heat-sink the part to the circuit board traces. Must be connected to GND pin. |  |

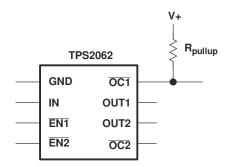

### 表 5-2. Pin Functions (TPS2062 and TPS2066)

|           | PINS    |         | PINS                                                                                                               |                                                        |   |                                                        | DESCRIPTION |

|-----------|---------|---------|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|---|--------------------------------------------------------|-------------|

| NAME      | N       | 0.      | 1/0                                                                                                                | DESCRIPTION                                            |   |                                                        |             |

|           | TPS2062 | TPS2066 |                                                                                                                    |                                                        |   |                                                        |             |

| EN1       | 3       | -       | I                                                                                                                  | Enable input, logic low turns on power switch IN-OUT1  |   |                                                        |             |

| EN2       | 4       | -       | I                                                                                                                  | Enable input, logic low turns on power switch IN-OUT2  |   |                                                        |             |

| EN1       | - 3     |         | - 3                                                                                                                |                                                        | I | Enable input, logic high turns on power switch IN-OUT1 |             |

| EN2       | - 4     |         | I                                                                                                                  | Enable input, logic high turns on power switch IN-OUT2 |   |                                                        |             |

| GND       | 1       | 1       |                                                                                                                    | Ground                                                 |   |                                                        |             |

| IN        | 2       | 2       | I                                                                                                                  | Input voltage                                          |   |                                                        |             |

| OC1       | 8       | 8       | 0                                                                                                                  | Overcurrent, open-drain output, active low, IN-OUT1    |   |                                                        |             |

| OC2       | 5       | 5       | 0                                                                                                                  | Overcurrent, open-drain output, active low, IN-OUT2    |   |                                                        |             |

| OUT1      | 7       | 7       | 0                                                                                                                  | Power-switch output, IN-OUT1                           |   |                                                        |             |

| OUT2      | 6       | 6       | 0                                                                                                                  | Power-switch output, IN-OUT2                           |   |                                                        |             |

| PowerPAD™ |         |         | Internally connected to GND; used to heat-sink the part to the circuit board traces. Must be connected to GND pin. |                                                        |   |                                                        |             |

## 表 5-3. Pin Functions (TPS2063 and TPS2067)

| PINS |          |          | I/O | DESCRIPTION                                             |  |

|------|----------|----------|-----|---------------------------------------------------------|--|

| NAME | TPS2063  | TPS2067  | 1/0 | DESCRIPTION                                             |  |

| EN1  | 3        | -        | I   | Enable input, logic low turns on power switch IN1-OUT1  |  |

| EN2  | 4        | _        | I   | Enable input, logic low turns on power switch IN1-OUT2  |  |

| EN3  | 7        | _        | I   | Enable input, logic low turns on power switch IN2-OUT3  |  |

| EN1  | _        | 3        | I   | Enable input, logic high turns on power switch IN1-OUT1 |  |

| EN2  | _        | 4        | I   | Enable input, logic high turns on power switch IN1-OUT2 |  |

| EN3  | _        | 7        | I   | Enable input, logic high turns on power switch IN2-OUT3 |  |

| GND  | 1, 5     | 1, 5     |     | Ground                                                  |  |

| IN1  | 2        | 2        | I   | Input voltage for OUT1 and OUT2                         |  |

| IN2  | 6        | 6        | I   | Input voltage for OUT3                                  |  |

| NC   | 8, 9, 10 | 8, 9, 10 |     | No connection                                           |  |

| OC1  | 16       | 16       | 0   | Overcurrent, open-drain output, active low, IN1-OUT1    |  |

| OC2  | 13       | 13       | 0   | Overcurrent, open-drain output, active low, IN1-OUT2    |  |

| OC3  | 12       | 12       | 0   | Overcurrent, open-drain output, active low, IN2-OUT3    |  |

| OUT1 | 15       | 15       | 0   | Power-switch output, IN1-OUT1                           |  |

| OUT2 | 14       | 14       | 0   | Power-switch output, IN1-OUT2                           |  |

| OUT3 | 11       | 11       | 0   | Power-switch output, IN2-OUT3                           |  |

## 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range unless otherwise noted<sup>(1)</sup>

|                                                                                        |                           | UNIT  |  |

|----------------------------------------------------------------------------------------|---------------------------|-------|--|

| Input voltage range, V <sub>I(IN)</sub> <sup>(2)</sup>                                 | -0.3 V to 6 V             |       |  |

| Output voltage range, V <sub>O(OUT)</sub> (2), V <sub>O(OUTx)</sub>                    | -0.3 V to 6 V             |       |  |

| Input voltage range, V <sub>I(EN)</sub> , V <sub>I(EN)</sub> , V <sub>I(ENx)</sub> , V | -0.3 V to 6 V             |       |  |

| Voltage range, V <sub>I( \overline{OC})</sub> , V <sub>I( \overline{OCx})</sub>        | -0.3 V to 6 V             |       |  |

| Continuous output current, I <sub>O(OUT)</sub> , I <sub>O(OUTx)</sub>                  | Internally limited        |       |  |

| Operating virtual junction temperature range                                           | -40°C to 150°C            |       |  |

|                                                                                        | Human body model          | 2 kV  |  |

| Electrostatic discharge (ESD) protection                                               | Charge device model (CDM) | 500 V |  |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## **6.2 Recommended Operating Conditions**

|                                                                                                    | MIN | MAX | UNIT |

|----------------------------------------------------------------------------------------------------|-----|-----|------|

| Input voltage, V <sub>I(IN)</sub>                                                                  | 2.7 | 5.5 | V    |

| Input voltage, V <sub>I(EN)</sub> , V <sub>I(EN)</sub> , V <sub>I(ENx)</sub> , V <sub>I(ENx)</sub> | 0   | 5.5 | V    |

| Continuous output current, I <sub>O(OUT)</sub> , I <sub>O(OUTx)</sub>                              | 0   | 1   | Α    |

| Operating virtual junction temperature, T <sub>J</sub>                                             | -40 | 125 | °C   |

### **6.3 Thermal Information**

|                       | THERMAL METRIC <sup>(1)</sup>                | · ·    | D<br>DIC) | DBV<br>(SOT-23) | DGN<br>(HVSSOP) | UNIT |

|-----------------------|----------------------------------------------|--------|-----------|-----------------|-----------------|------|

|                       |                                              | 8 PINS | 16 PINS   | 5 PINS          | 8 PINS          |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 119.3  | 81.6      | 208.6           | 53.6            | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 67.6   | 42.7      | 122.9           | 58.7            | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 59.6   | 39.1      | 37.8            | 35.5            | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter   | 20.3   | 10.4      | 14.6            | 2.7             | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 59.1   | 38.8      | 36.9            | 35.3            | °C/W |

| $R_{\theta JC(bot)}$  | Junction-to-case (bottom) thermal resistance | N/A    | N/A       | N/A             | 6.7             | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

#### 6.4 Electrical Characteristics

over recommended operating junction temperature range,  $V_{I(IN)} = 5.5 \text{ V}$ ,  $I_O = 1 \text{ A}$ ,  $V_{I(ENx)} = 0 \text{ V}$ , or  $V_{I(ENx)} = 5.5 \text{ V}$  (unless otherwise noted)

| other wide need y   |                                                                            |                                                                                                                       |                    |     |     |     |      |  |  |

|---------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------|-----|-----|-----|------|--|--|

|                     | PARAMETER TEST CONDITIONS <sup>(1)</sup>                                   |                                                                                                                       |                    | MIN | TYP | MAX | UNIT |  |  |

| POWER SWI           | тсн                                                                        |                                                                                                                       |                    |     |     |     |      |  |  |

|                     | Static drain-source on-state resistance, 5-V operation and 3.3-V operation | $V_{I(IN)} = 5 \text{ V or } 3.3 \text{ V, } I_O = 1 \text{ A, } -40^{\circ}\text{C} \le T_J \le 125^{\circ}\text{C}$ | D and DGN packages |     | 70  | 135 |      |  |  |

| F                   |                                                                            |                                                                                                                       | DBV package        |     | 95  | 140 | mΩ   |  |  |

| r <sub>DS(on)</sub> | Static drain-source on-state resistance, 2.7-V operation                   | $V_{I(IN)} = 2.7 \text{ V, } I_O = 1 \text{ A, } -40^{\circ}\text{C} \le T_J \le 125^{\circ}\text{C}$                 | D and DGN packages |     | 75  | 150 | mΩ   |  |  |

<sup>(2)</sup> All voltages are with respect to GND.

## 6.4 Electrical Characteristics (続き)

over recommended operating junction temperature range,  $V_{I(IN)} = 5.5 \text{ V}$ ,  $I_O = 1 \text{ A}$ ,  $V_{I(ENx)} = 0 \text{ V}$ , or  $V_{I(ENx)} = 5.5 \text{ V}$  (unless otherwise noted)

|                                                                                                      | PARAMETER                          |                                                                                        | TEST CONDITIONS(1)                     |                                                    | MIN  | TYP | MAX | UNIT |  |

|------------------------------------------------------------------------------------------------------|------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------|----------------------------------------------------|------|-----|-----|------|--|

|                                                                                                      |                                    | V <sub>I(IN)</sub> = 5.5 V                                                             |                                        |                                                    |      | 0.6 | 1.5 |      |  |

| t <sub>r</sub>                                                                                       | Rise time, output                  | $V_{I(IN)} = 2.7 \text{ V}$                                                            |                                        |                                                    |      | 0.4 | 1   | _    |  |

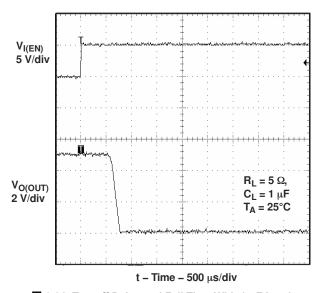

|                                                                                                      |                                    | V <sub>I(IN)</sub> = 5.5 V                                                             | $C_L = 1 \mu F, R_L = 5 \Omega, T_J =$ | $C_L = 1 \mu F, R_L = 5 \Omega, T_J = 25^{\circ}C$ |      |     | 0.5 | ms   |  |

| t <sub>f</sub>                                                                                       | Fall time, output                  | V <sub>I(IN)</sub> = 2.7 V                                                             |                                        |                                                    | 0.05 |     | 0.5 |      |  |

| ENABLE I                                                                                             | INPUT EN OR EN                     | .()                                                                                    |                                        |                                                    |      |     |     |      |  |

| V <sub>IH</sub>                                                                                      | High-level input voltage           | $2.7 \text{ V} \le \text{V}_{\text{I(IN)}} \le 5.5 \text{ V}$                          |                                        |                                                    | 2    |     |     |      |  |

| V <sub>IL</sub>                                                                                      | Low-level input voltage            | $2.7 \text{ V} \le \text{V}_{\text{I(IN)}} \le 5.5 \text{ V}$                          |                                        |                                                    |      |     | 0.8 | V    |  |

| lı                                                                                                   | Input current                      | $V_{I(ENx)} = 0 \text{ V or } 5.5 \text{ V, } V_{I(ENx)}$                              | -N <sub>V</sub> ) = 0 V or 5.5 V       |                                                    | -0.5 |     | 0.5 | μA   |  |

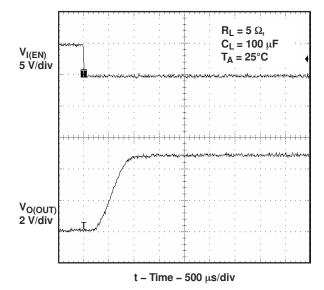

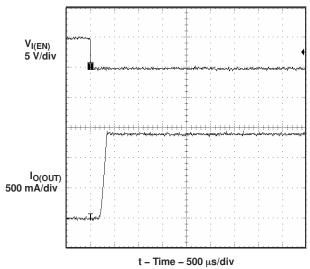

| t <sub>on</sub>                                                                                      | Turnon time                        | $C_L = 100  \mu F,  R_L = 5  \Omega$                                                   |                                        |                                                    |      |     | 3   |      |  |

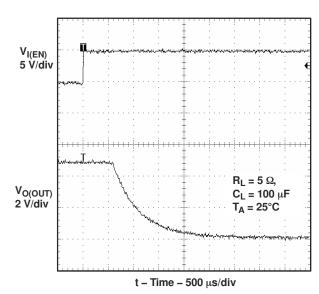

| t <sub>off</sub>                                                                                     | Turnoff time                       | $C_L = 100  \mu F,  R_L = 5  \Omega$                                                   |                                        |                                                    |      |     | 10  | ms   |  |

| CURRENT                                                                                              | T LIMIT                            |                                                                                        |                                        |                                                    |      |     |     |      |  |

|                                                                                                      |                                    | V <sub>I(IN)</sub> = 5 V, OUT connecte                                                 | ed to GND                              | T <sub>.J</sub> = 25°C                             | 1.1  | 1.5 | 1.9 |      |  |

| los                                                                                                  | Short-circuit output current       | device enabled into short-                                                             |                                        | -40°C ≤ T <sub>J</sub> ≤ 125°C                     | 1.1  | 1.5 | 2.1 | Α    |  |

| I <sub>OC</sub> (2)                                                                                  | Overcurrent trip threshold         | V <sub>I(IN)</sub> = 5 V, current ramp<br>(≤ 100 A/s) on OUT                           | TPS2063, TPS2067                       | <u> </u>                                           | 1.6  | 2.4 | 3.0 | Α    |  |

| SUPPLY (                                                                                             | CURRENT (TPS2061, TPS2065)         |                                                                                        |                                        |                                                    |      |     |     | -    |  |

|                                                                                                      |                                    | No load on OUT, V <sub>I(ENx)</sub> =                                                  | = 5.5 V.                               | T <sub>J</sub> = 25°C                              |      | 0.5 | 1   |      |  |

| Supply cui                                                                                           | rrent, low-level output            | or V <sub>I(ENx)</sub> = 0 V                                                           | ,                                      | -40°C ≤ T <sub>J</sub> ≤ 125°C                     |      | 0.5 | 5   | μA   |  |

|                                                                                                      |                                    | No load on OUT, V <sub>I(ENx)</sub>                                                    |                                        | T <sub>J</sub> = 25°C                              |      | 75  | 95  |      |  |

| Supply cur                                                                                           | rrent, high-level output           | = 0 V,<br>or V <sub>I(ENx)</sub> = 5.5 V                                               | TPS2061 TPS2065                        | -40°C ≤ T <sub>J</sub> ≤ 125°C                     |      | 75  | 95  | μA   |  |

| Leakage c                                                                                            | current                            | OUT connected to ground or V <sub>I(EN)</sub> = 0 V                                    | $H, V_{I(\overline{EN})} = 5.5 V,$     | -40°C ≤ T <sub>J</sub> ≤ 125°C                     |      | 1   |     | μΑ   |  |

| Reverse leakage current $V_{I(OUTx)} = 5.5 \text{ V}, IN = \text{ground}$ $T_J = 25^{\circ}\text{C}$ |                                    |                                                                                        |                                        | 0                                                  |      | μΑ  |     |      |  |

| SUPPLY (                                                                                             | CURRENT (TPS2062, TPS2066)         |                                                                                        |                                        |                                                    |      |     | _   |      |  |

| Supply current, low-level output                                                                     |                                    | No load on OUT, $V_{I(\overline{ENx})} = 5.5 \text{ V}$ ,                              |                                        | T <sub>J</sub> = 25°C                              |      | 0.5 | 1   | μA   |  |

| очрріу сиі                                                                                           | ment, low-level output             | or $V_{I(ENx)} = 0 V$                                                                  |                                        | -40°C ≤ T <sub>J</sub> ≤ 125°C                     |      | 0.5 | 5   | μΛ   |  |

| Supply cui                                                                                           | rrent, high-level output           | No load on OUT, $V_{I(ENx)} = 0 V$ , or $V_{I(ENx)} = 5.5 V$                           |                                        | T <sub>J</sub> = 25°C                              |      | 95  | 120 | μA   |  |

| Зирріу сиі                                                                                           | rrent, nign-level output           |                                                                                        |                                        | -40°C ≤ T <sub>J</sub> ≤ 125°C                     |      | 95  | 120 | μΑ   |  |

| Leakage c                                                                                            | current                            | OUT connected to ground, $V_{I(/ENx)} = 5.5 \text{ V}$ , or $V_{I(ENx)} = 0 \text{ V}$ |                                        | -40°C ≤ T <sub>J</sub> ≤ 125°C                     |      | 1   |     | μА   |  |

| Reverse le                                                                                           | eakage current                     | $V_{I(OUTx)} = 5.5 \text{ V}, \text{ IN} = \text{ground}$ $T_J = 25^{\circ}\text{C}$   |                                        |                                                    | 0.2  |     | μA  |      |  |

| SUPPLY (                                                                                             | CURRENT (TPS2063, TPS2067)         | •                                                                                      |                                        |                                                    |      |     |     |      |  |

| Cupply ou                                                                                            | rrent, low-level output            | No load on OUT V                                                                       | - 0 \/                                 | T <sub>J</sub> = 25°C                              |      | 0.5 | 2   |      |  |

| Supply cui                                                                                           | rrent, low-level output            | No load on OUT, V <sub>I(ENx)</sub> =                                                  | - 0 V                                  | -40°C ≤ T <sub>J</sub> ≤ 125°C                     |      | 0.5 | 10  | μA   |  |

| Cupply ou                                                                                            | rrent high level output            | No load on OUT V                                                                       | - F F \/                               | T <sub>J</sub> = 25°C                              |      | 65  | 90  |      |  |

| Supply cui                                                                                           | rrent, high-level output           | No load on OUT, V <sub>I(ENx)</sub> =                                                  | - 5.5 V                                | -40°C ≤ T <sub>J</sub> ≤ 125°C                     |      | 65  | 110 | μA   |  |

| Leakage c                                                                                            | current                            | OUT connected to ground or V <sub>I(ENx)</sub> = 0 V                                   | $I, V_{I(EN\bar{x})} = 5.5 V,$         | -40°C ≤ T <sub>J</sub> ≤ 125°C                     |      | 1   |     | μΑ   |  |

| Reverse leakage current $V_{I(OUTx)} = 5.5 \text{ V}$ , $INx = ground$ $T_J = 25 ^{\circ}C$          |                                    |                                                                                        | T <sub>J</sub> = 25°C                  |                                                    | 0.2  |     | μΑ  |      |  |

| UNDERVO                                                                                              | OLTAGE LOCKOUT (TPS2063,           | TPS2067)                                                                               |                                        | ·                                                  |      |     |     |      |  |

| Low-level                                                                                            | input voltage, IN                  |                                                                                        |                                        |                                                    | 2    |     | 2.5 | V    |  |

| Hysteresis                                                                                           | Hysteresis, IN $T_J = 25^{\circ}C$ |                                                                                        |                                        | 75                                                 |      | mV  |     |      |  |

| UNDERVO                                                                                              | OLTAGE LOCKOUT (TPS2061, 1         | TPS2062, TPS2065, TPS20                                                                | 066)                                   |                                                    |      |     |     | _    |  |

| Low-level                                                                                            | input voltage, IN                  |                                                                                        |                                        |                                                    | 2    |     | 2.6 | V    |  |

| Hysteresis                                                                                           | s, IN                              | T <sub>J</sub> = 25°C                                                                  |                                        |                                                    |      | 75  |     | mV   |  |

| OVERCU                                                                                               | RRENT OC1 and OC2                  | •                                                                                      |                                        |                                                    |      | -   |     |      |  |

| Output low                                                                                           | v voltage, V <sub>OL(OCx)</sub>    | $I_{O(\overline{OCx})} = 5 \text{ mA}$                                                 |                                        |                                                    |      | -   | 0.4 | V    |  |

| Off-state c                                                                                          | current                            | $V_{O(\overline{OCx})} = 5 \text{ V or } 3.3 \text{ V}$                                |                                        |                                                    |      |     | 1   | μA   |  |

|                                                                                                      |                                    | *O( OCX) ** ** ** ***                                                                  |                                        |                                                    | 1    |     |     |      |  |

## 6.4 Electrical Characteristics (続き)

over recommended operating junction temperature range,  $V_{I(IN)} = 5.5 \text{ V}$ ,  $I_O = 1 \text{ A}$ ,  $V_{I(ENx)} = 0 \text{ V}$ , or  $V_{I(ENx)} = 5.5 \text{ V}$  (unless otherwise noted)

| PARAMETER                      | TEST CONDITIONS <sup>(1)</sup> | MIN | TYP | MAX | UNIT |

|--------------------------------|--------------------------------|-----|-----|-----|------|

| OC deglitch                    | OCx assertion or deassertion   | 4   | 8   | 15  | ms   |

| THERMAL SHUTDOWN(3)            |                                |     |     |     |      |

| Thermal shutdown threshold     |                                | 135 |     |     | °C   |

| Recovery from thermal shutdown |                                | 125 |     |     | °C   |

| Hysteresis                     |                                |     | 10  |     | °C   |

- Pulse-testing techniques maintain junction temperature close to ambient temperature; thermal effects must be taken into account separately.

- (2) TPS2061, TSP2062, TPS2065, and TPS2066 do not have overcurrent trip threshold. Current is limited to I<sub>OS</sub> under different test condition. Check セクション 8.7 for more details.

- (3) The thermal shutdown only reacts under overcurrent conditions.

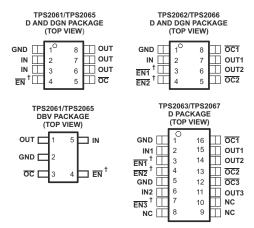

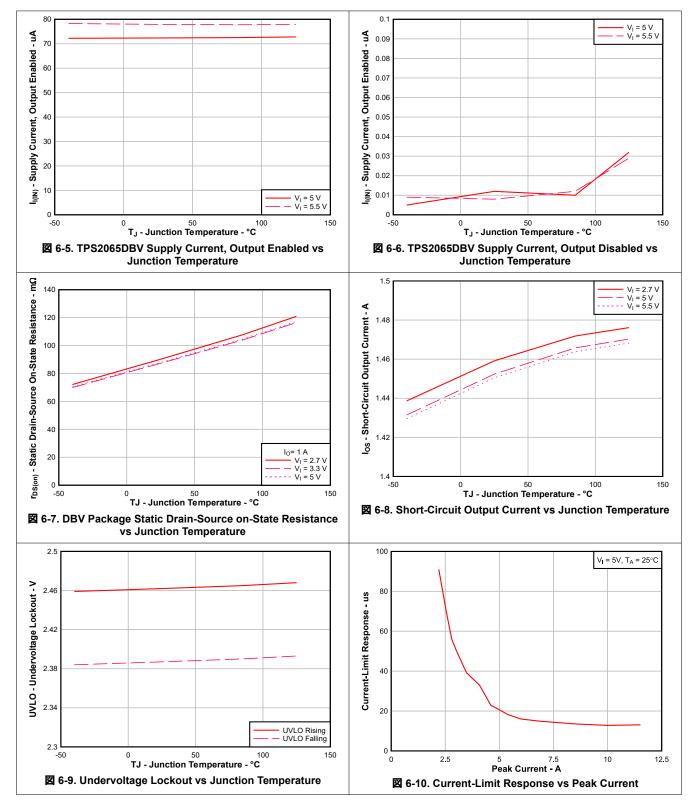

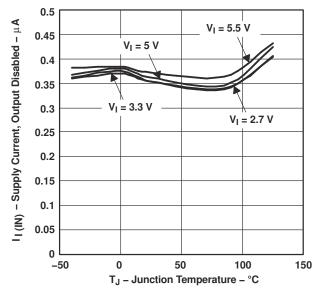

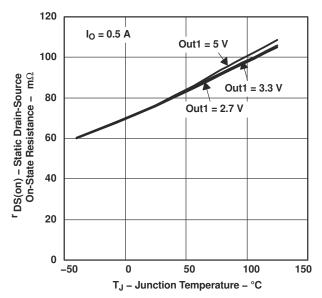

### 6.5 Typical Characteristics (TPS2061, TPS2062, TPS2065, and TPS2066)

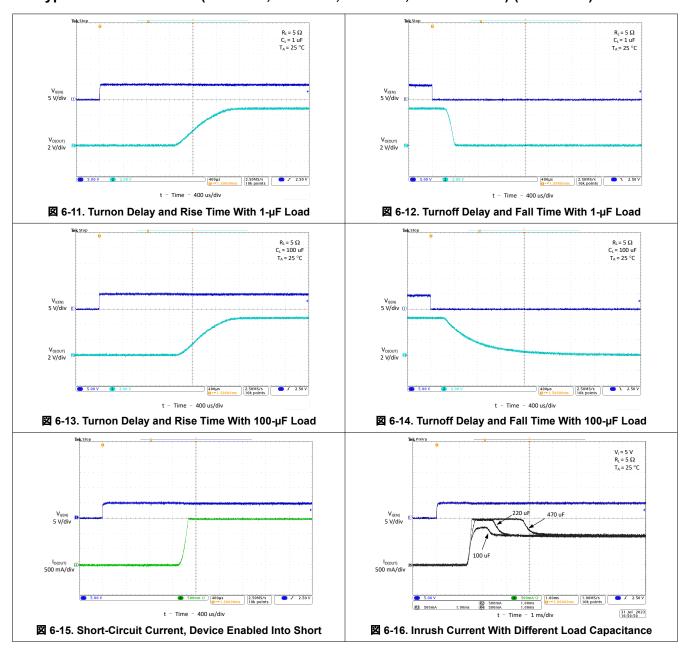

## 6.5 Typical Characteristics (TPS2061, TPS2062, TPS2065, and TPS2066) (continued)

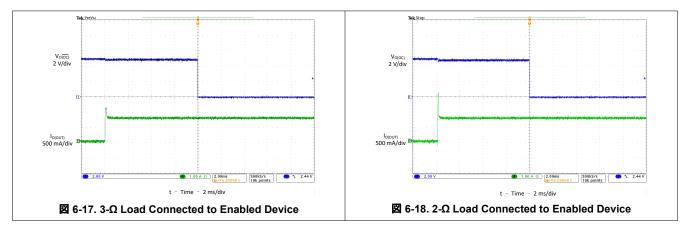

### 6.5 Typical Characteristics (TPS2061, TPS2062, TPS2065, and TPS2066) (continued)

## 6.5 Typical Characteristics (TPS2061, TPS2062, TPS2065, and TPS2066) (continued)

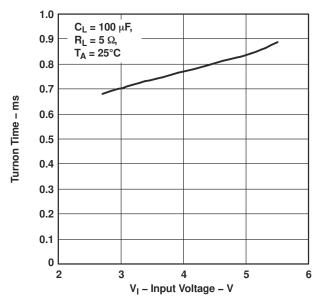

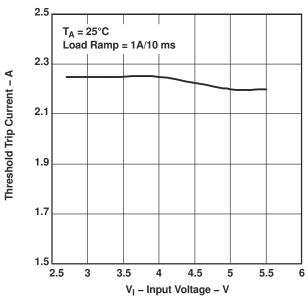

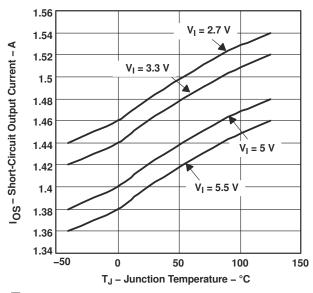

### 6.6 Typical Characteristics (TPS2063 & TPS2067)

図 6-19. TURNON TIME vs INPUT VOLTAGE

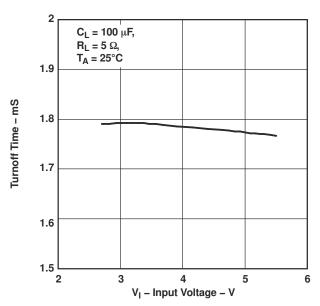

図 6-20. TURNOFF TIME vs INPUT VOLTAGE

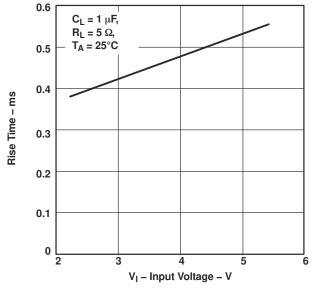

図 6-21. RISE TIME vs INPUT VOLTAGE

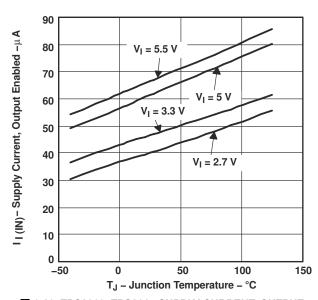

図 6-23. TPS2063, TPS2067 SUPPLY CURRENT, OUTPUT ENABLED vs JUNCTION TEMPERATURE

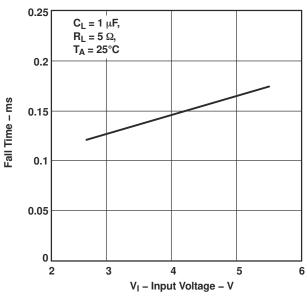

図 6-22. FALL TIME vs INPUT VOLTAGE

図 6-24. TPS2063, TPS2067 SUPPLY CURRENT, OUTPUT DISABLED vs JUNCTION TEMPERATURE

図 6-25. STATIC DRAIN-SOURCE ON-STATE RESISTANCE vs JUNCTION TEMPERATURE

図 6-27. THRESHOLD TRIP CURRENT vs INPUT VOLTAGE

図 6-26. SHORT-CIRCUIT OUTPUT CURRENT vsJUNCTION TEMPERATURE

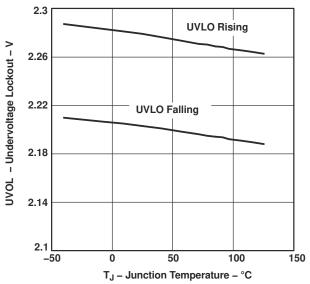

図 6-28. UNDERVOLTAGE LOCKOUT vs JUNCTION TEMPERATURE

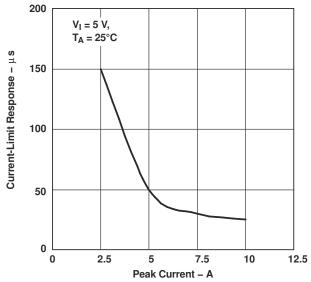

図 6-29. CURRENT-LIMIT RESPONSE vs PEAK CURRENT

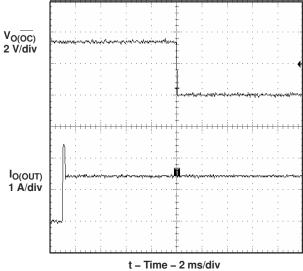

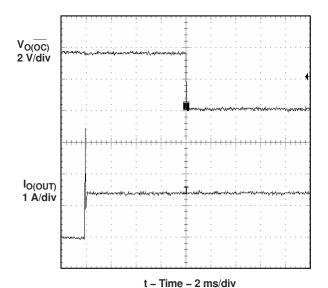

☑ 6-30. Turnon Delay and Rise Time With 1-µF Load

図 6-31. Turnoff Delay and Fall Time With 1- $\mu$ F Load

☑ 6-32. Turnon Delay and Rise Time With 100-µF Load

図 6-34. Short-Circuit Current, Device Enabled Into Short

図 6-33. Turnoff Delay and Fall Time With 100-µF Load

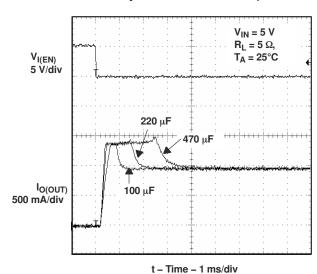

図 6-35. Inrush Current With Different Load Capacitance

図 6-36. 2-Ω Load Connected to Enabled Device

図 6-37. 1-Ω Load Connected to Enabled Device

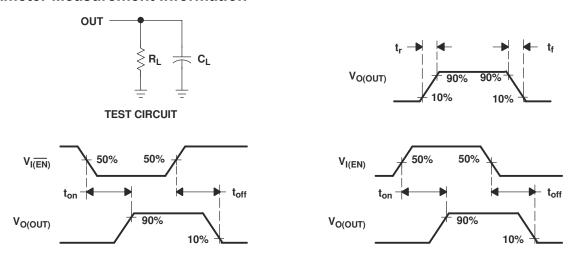

## 7 Parameter Measurement Information

**VOLTAGE WAVEFORMS**

図 7-1. Test Circuit and Voltage Waveforms

## 8 Detailed Description

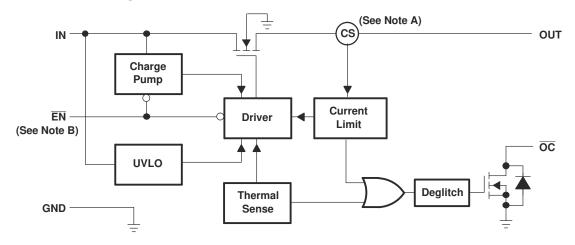

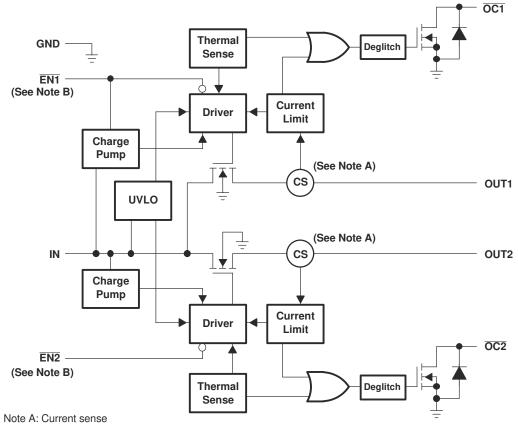

## 8.1 Functional Block Diagram

Note A: Current sense

Note B: Active low (EN) for TPS2061. Active high (EN) for TPS2065.

### 図 8-1. TPS2061 and TPS2065

Note B: Active low (ENx) for TPS2062. Active high (ENx) for TPS2066.

図 8-2. TPS2062 and TPS2066

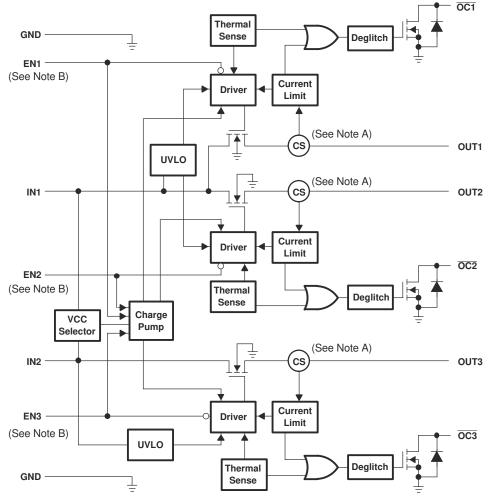

Note A: Current sense

Note B: Active low (ENx) for TPS2063; Active high (ENx) for TPS2067

図 8-3. TPS2063 and TPS2067

### 8.2 Power Switch

The power switch is an N-channel MOSFET with a low on-state resistance. Configured as a high-side switch, the power switch prevents current flow from OUT to IN and IN to OUT when disabled. The power switch supplies a minimum current of 1 A.

#### 8.3 Charge Pump

An internal charge pump supplies power to the driver circuit and provides the necessary voltage to pull the gate of the MOSFET above the source. The charge pump operates from input voltages as low as 2.7 V and requires little supply current.

### 8.4 Driver

The driver controls the gate voltage of the power switch. To limit large current surges and reduce the associated electromagnetic interference (EMI) produced, the driver incorporates circuitry that controls the rise times and fall times of the output voltage.

### 8.5 Enable ( ENx or ENx)

The logic enable disables the power switch and the bias for the charge pump, driver, and other circuitry to reduce the supply current. The supply current is reduced to less than 1  $\mu$ A when a logic high is present on  $\overline{ENx}$ , or when a logic low is present on ENx. A logic zero input on  $\overline{ENx}$ , or a logic high input on ENx restores bias to the drive and control circuits and turns the switch on. The enable input is compatible with both TTL and CMOS logic levels.

### 8.6 Current Sense

A sense FET monitors the current supplied to the load. The sense FET measures current more efficiently than conventional resistance methods. When an overload or short circuit is encountered, the current-sense circuitry sends a control signal to the driver. The driver in turn reduces the gate voltage and drives the power FET into its saturation region, which switches the output into a constant-current mode and holds the current constant while varying the voltage on the load.

#### 8.7 Overcurrent

A sense FET is employed to check for overcurrent conditions. Unlike current-sense resistors, sense FETs do not increase the series resistance of the current path. When an overcurrent condition is detected, the device maintains a constant output current and reduces the output voltage accordingly. Complete shutdown occurs only if the fault is present long enough to activate thermal limiting.

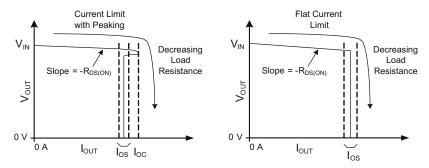

There are two kinds of current limit profiles for the TPS20xx family of devices.

The TPS2063 and TPS2067 have an output I vs V characteristic similar to the plot labeled **Current Limit with Peaking** in  $\boxtimes$  8-4. This type of limiting can be characterized by two parameters, the overcurrent trip threshold ( $I_{OC}$ ), and the short-circuit output current threshold ( $I_{OS}$ ).

The TPS2061, TPS2062, TPS2065, and TPS2066 have an output I vs V characteristic similar to the plot labeled **Flat Current Limit** in  $\boxtimes$  8-4. This type of limiting can be characterized by one parameters, the short circuit current ( $I_{OS}$ ).

図 8-4. Current Limit Profiles

## 8.7.1 Overcurrent Conditions (TPS2063 and TPS2067)

Three possible overload conditions can occur for the TPS2063 and TPS2067. In the first condition, the output has been shorted before the device is enabled or before  $V_{I(IN)}$  has been applied (see  $\boxtimes$  6-34 through  $\boxtimes$  6-36). The TPS2063 and TPS2067 senses the short and immediately switches into a constant-current output.

In the second condition, a short or an overload occurs while the device is enabled. At the instant the overload occurs, high currents may flow for a short period of time before the current-limit circuit can react. After the current-limit circuit has tripped (reached the overcurrent trip threshold  $(I_{OC})$ ), the device switches into constant-current mode and current is limited at the short-circuit output current threshold  $(I_{OS})$ .

In the third condition, the load has been gradually increased beyond the recommended operating current. The current is permitted to rise until the overcurrent trip threshold ( $I_{OC}$ ) is reached or until the thermal limit of the device is exceeded. The TPS2063 and TPS2067 are capable of delivering current up to the current-limit

threshold without damaging the device. Once the overcurrent trip threshold (I<sub>OC</sub>) has been reached, the device switches into its constant-current mode current is limited at the short-circuit output current threshold (I<sub>OS</sub>).

#### 8.7.2 Overcurrent Conditions (TPS2061, TPS2062, TPS2065, and TPS2066)

Three possible overload conditions can occur for the TPS2061, TPS2062, TPS2065 and TPS2066. In the first condition, the output has been shorted before the device is enabled or before  $V_{I(IN)}$  has been applied (see  $\boxtimes$  6-15 through  $\boxtimes$  6-18). The TPS20xx senses the short and immediately switches into a constant-current output.

In the second condition, a short or an overload occurs while the device is enabled. At the instant the overload occurs, high currents may flow for a short period of time before the current-limit circuit can react. After the short-circuit output current threshold (I<sub>OS</sub>) is reached, the device switches into constant-current mode.

In the third condition, the load has been gradually increased beyond the recommended operating current. After the short-circuit output current threshold ( $I_{OS}$ ) is reached, the device switches into constant-current mode.

### 8.8 Overcurrent ( OCx)

The  $\overline{OCx}$  open-drain output is asserted (active low) when an overcurrent or overtemperature condition is encountered. The output remains asserted until the overcurrent or overtemperature condition is removed. A 10-ms deglitch circuit prevents the  $\overline{OCx}$  signal from oscillation or false triggering. If an overtemperature shutdown occurs, the  $\overline{OCx}$  is asserted instantaneously.

#### 8.9 Thermal Sense

The TPS206x implements a thermal sensing to monitor the operating temperature of the power distribution switch. In an overcurrent or short-circuit condition the junction temperature rises. When the die temperature rises to approximately 140°C due to overcurrent conditions, the internal thermal sense circuitry turns off the switch, thus preventing the device from damage. Hysteresis is built into the thermal sense, and after the device has cooled approximately 10 degrees, the switch turns back on. The switch continues to cycle off and on until the fault is removed. The open-drain false reporting output ( $\overline{OCx}$ ) is asserted (active low) when an overtemperature shutdown or overcurrent occurs.

#### 8.10 Undervoltage Lockout

A voltage sense circuit monitors the input voltage. When the input voltage is below approximately 2 V, a control signal turns off the power switch.

## 9 Application and Implementation

注

以下のアプリケーション情報は、TIの製品仕様に含まれるものではなく、TIではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 9.1 Application Information

### 9.1.1 Power-supply Considerations

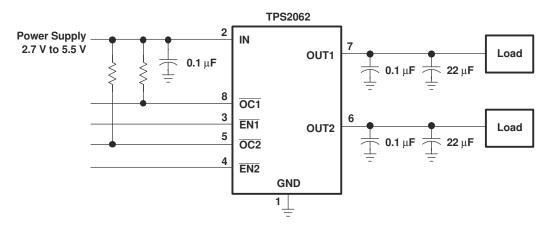

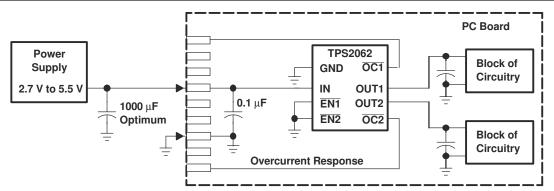

図 9-1. Typical Application

A 0.01-µF to 0.1-µF ceramic bypass capacitor between IN and GND, close to the device, is recommended. Placing a high-value electrolytic capacitor on the output pin(s) is recommended when the output load is heavy. This precaution reduces power-supply transients that may cause ringing on the input. Additionally, bypassing the output with a 0.01-µF to 0.1-µF ceramic capacitor improves the immunity of the device to short-circuit transients.

### 9.1.2 OC Response

The  $\overline{\text{OCx}}$  open-drain output is asserted (active low) when an overcurrent or overtemperature shutdown condition is encountered after a 10-ms deglitch timeout. The output remains asserted until the overcurrent or overtemperature condition is removed. Connecting a heavy capacitive load to an enabled device can cause a momentary overcurrent condition; however, no false reporting on  $\overline{\text{OCx}}$  occurs due to the 10-ms deglitch circuit. The TPS206x is designed to eliminate false overcurrent reporting. The internal overcurrent deglitch eliminates the need for external components to remove unwanted pulses.  $\overline{\text{OCx}}$  is not deglitched when the switch is turned off due to an overtemperature shutdown.

図 9-2. Typical Circuit for the OC Pin

### 9.1.3 Power Dissipation and Junction Temperature

The low on-resistance on the N-channel MOSFET allows the small surface-mount packages to pass large currents. The thermal resistances of these packages are high compared to those of power packages; it is good design practice to check power dissipation and junction temperature. Begin by determining the  $r_{DS(on)}$  of the N-channel MOSFET relative to the input voltage and operating temperature. As an initial estimate, use the highest operating ambient temperature of interest and read  $r_{DS(on)}$  from  $\boxtimes$  6-25. Using this value, the power dissipation per switch can be calculated by:

•

$$P_D = r_{DS(on)} \times I^2$$

Multiply this number by the number of switches being used. This step renders the total power dissipation from the N-channel MOSFETs.

The thermal resistance,  $R_{\theta JA}$  = 1 / (DERATING FACTOR), where DERATING FACTOR is obtained from the Dissipation Ratings Table. Thermal resistance is a strong function of the printed circuit board construction , and the copper trace area connecting the integrated circuit.

Finally, calculate the junction temperature:

•

$$T_J = P_D x R_{\theta JA} + T_A$$

#### Where:

- T<sub>A</sub>= Ambient temperature °C

- R<sub>θJA</sub> = Thermal resistance

- P<sub>D</sub> = Total power dissipation based on number of switches being used.

Compare the calculated junction temperature with the initial estimate. If they do not agree within a few degrees, repeat the calculation, using the calculated value as the new estimate. Two or three iterations are generally sufficient to get a reasonable answer.

#### 9.1.4 Thermal Protection

Thermal protection prevents damage to the IC when heavy-overload or short-circuit faults are present for extended periods of time. The TPS206x implements a thermal sensing to monitor the operating junction temperature of the power distribution switch. In an overcurrent or short-circuit condition, the junction temperature rises due to excessive power dissipation. Once the die temperature rises above a minimum of 135°C due to overcurrent conditions, the internal thermal sense circuitry turns the power switch off, thus preventing the power switch from damage. Hysteresis is built into the thermal sense circuit, and after the device has cooled approximately 10°C, the switch turns back on. The switch continues to cycle in this manner until the load fault or input power is removed. The  $\overline{OCx}$  open-drain output is asserted (active low) when an overtemperature shutdown or overcurrent occurs.

### 9.1.5 Undervoltage Lockout (UVLO)

An undervoltage lockout ensures that the power switch is in the off state at power up. Whenever the input voltage falls below approximately 2 V, the power switch is quickly turned off. The UVLO facilitates the design of hot-insertion systems where it is not possible to turn off the power switch before input power is removed. The UVLO also keeps the switch from being turned on until the power supply has reached at least 2 V, even if the switch is enabled. On reinsertion, the power switch is turned on, with a controlled rise time to reduce EMI and voltage overshoots.

#### 9.1.6 Universal Serial Bus (USB) Applications

The universal serial bus (USB) interface is a 12-Mb/s, or 1.5-Mb/s, multiplexed serial bus designed for low-to-medium bandwidth PC peripherals (for example, keyboards, printers, scanners, and mice). The four-wire USB interface is conceived for dynamic attach-detach (hot plug-unplug) of peripherals. Two lines are provided for differential data, and two lines are provided for 5-V power distribution.

USB data is a 3.3-V level signal, but power is distributed at 5 V to allow for voltage drops in cases where power is distributed through more than one hub across long cables. Each function must provide its own regulated 3.3 V from the 5-V input or its own internal power supply.

The USB specification defines the following five classes of devices, each differentiated by power-consumption requirements:

- Hosts/self-powered hubs (SPH)

- Bus-powered hubs (BPH)

- Low-power, bus-powered functions

- · High-power, bus-powered functions

- Self-powered functions

SPHs and BPHs distribute data and power to downstream functions. The TPS206x has higher current capability than required by one USB port; so, it can be used on the host side and supplies power to multiple downstream ports or functions.

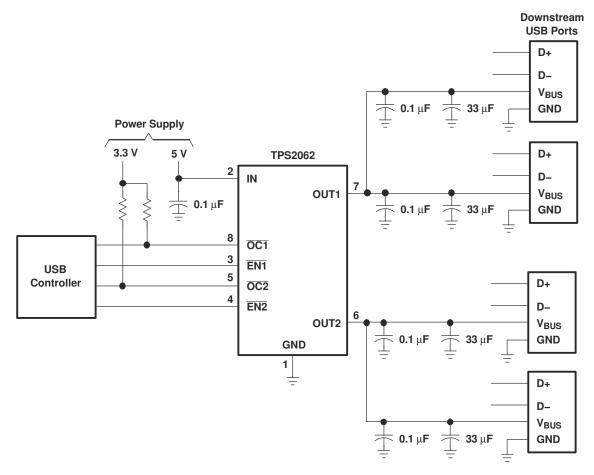

### 9.1.7 Host/Self-Powered and Bus-powered Hubs

Hosts and SPHs have a local power supply that powers the embedded functions and the downstream ports (see  $\boxtimes$  9-3). This power supply must provide from 5.25 V to 4.75 V to the board side of the downstream connection under full-load and no-load conditions. Hosts and SPHs are required to have current-limit protection and must report overcurrent conditions to the USB controller. Typical SPHs are desktop PCs, monitors, printers, and stand-alone hubs.

図 9-3. Typical Four-Port USB Host / Self-Powered Hub

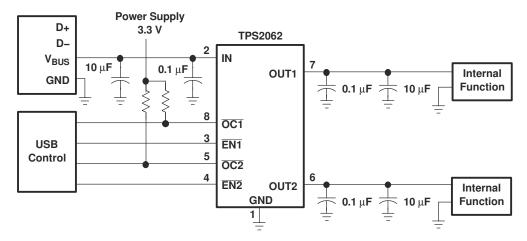

BPHs obtain all power from upstream ports and often contain an embedded function. The hubs are required to power up with less than one unit load. The BPH usually has one embedded function, and power is always available to the controller of the hub. If the embedded function and hub require more than 100 mA on power up, the power to the embedded function may need to be kept off until enumeration is completed. This can be accomplished by removing power or by shutting off the clock to the embedded function. Power switching the embedded function is not necessary if the aggregate power draw for the function and controller is less than one unit load. The total current drawn by the bus-powered device is the sum of the current to the controller, the embedded function, and the downstream ports, and it is limited to 500 mA from an upstream port.

#### 9.1.8 Low-power Bus-powered and High-Power Bus-Powered Functions

Both low-power and high-power bus-powered functions obtain all power from upstream ports; low-power functions always draw less than 100 mA; high-power functions must draw less than 100 mA at power up and can draw up to 500 mA after enumeration. If the load of the function is more than the parallel combination of 44  $\Omega$  and 10  $\mu$ F at power up, the device must implement inrush current limiting (see  $\mathbb Z$  9-4). With TPS206x, the internal functions can draw more than 500 mA, which fits the needs of some applications such as motor driving circuits.

☑ 9-4. High-Power Bus-Powered Function

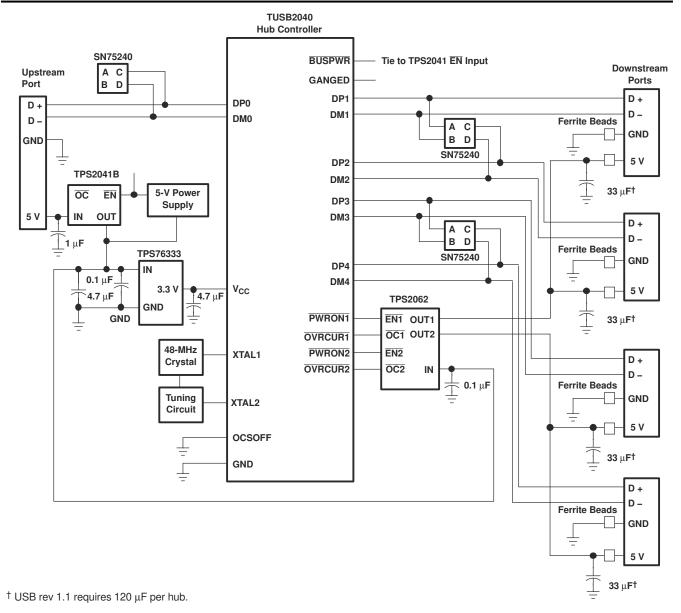

#### 9.1.9 USB Power-distribution Requirements

USB can be implemented in several ways, and, regardless of the type of USB device being developed, several power-distribution features must be implemented.

- Hosts/SPHs must:

- Current-limit downstream ports

- Report overcurrent conditions on USB V<sub>BUS</sub>

- BPHs must:

- Enable/disable power to downstream ports

- Power up at <100 mA</li>

- Limit inrush current ( $<44 \Omega$  and 10  $\mu$ F)

- Functions must:

- Limit inrush currents

- Power up at <100 mA</li>

The feature set of the TPS206x allows them to meet each of these requirements. The integrated current-limiting and overcurrent reporting is required by hosts and self-powered hubs. The logic-level enable and controlled rise times meet the need of both input and output ports on bus-powered hubs, as well as the input ports for bus-powered functions (see  $\boxed{3}$  9-5).

図 9-5. Hybrid Self / Bus-Powered Hub Implementation

### 9.1.10 Generic Hot-Plug Applications

In many applications it may be necessary to remove modules or pc boards while the main unit is still operating. These are considered hot-plug applications. Such implementations require the control of current surges seen by the main power supply and the card being inserted. The most effective way to control these surges is to limit and slowly ramp the current and voltage being applied to the card, similar to the way in which a power supply normally turns on. Due to the controlled rise times and fall times of the TPS206x, these devices can be used to provide a softer start-up to devices being hot-plugged into a powered system. The UVLO feature of the TPS206x also ensures that the switch is off after the card has been removed, and that the switch is off during the next insertion. The UVLO feature insures a soft start with a controlled rise time for every insertion of the card or module.

図 9-6. Typical Hot-Plug Implementation

By placing the TPS206x between the  $V_{CC}$  input and the rest of the circuitry, the input power reaches these devices first after insertion. The typical rise time of the switch is approximately 1 ms, providing a slow voltage ramp at the output of the device. This implementation controls system surge currents and provides a hotplugging mechanism for any device.

## 10 Device and Documentation Support

TI offers an extensive line of development tools. Tools and software to evaluate the performance of the device, generate code, and develop solutions are listed below.

### 10.1 Device Support

### 10.2 Documentation Support

### 10.3 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、www.tij.co.jp のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。 変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 10.4 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの使用条件を参照してください。

#### 10.5 Trademarks

PowerPAD<sup>™</sup> and テキサス・インスツルメンツ E2E<sup>™</sup> are trademarks of Texas Instruments. すべての商標は、それぞれの所有者に帰属します。

#### 10.6 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 10.7 用語集

テキサス・インスツルメンツ用語集 この用語集には、用語や略語の一覧および定義が記載されています。

### 11 Revision History

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

|                         | ges from Revision J (August 2023) to Revision K (June 2024)                                     | Page            |

|-------------------------|-------------------------------------------------------------------------------------------------|-----------------|

| <ul><li>「消</li></ul>    | 費電力定格」表を削除                                                                                      | 1               |

| <ul> <li>Add</li> </ul> | ded セクション 6.3                                                                                   | 6               |

| • Up                    | dated TPS2061, TPS2062, TPS2065, TPS2066 electrical characteristics, including overcurrent trip |                 |

| thre                    | eshold, high-level output supply current and undervoltage lockout                               | 6               |

| <ul> <li>Up-</li> </ul> | dated TPS2061, TPS2062, TPS2065, TPS2066 Typical Characteristics                                | <mark>8</mark>  |

| <ul> <li>Up-</li> </ul> | dated TPS2061, TPS2062, TPS2065, TPS2066 overcurrent description                                | 20              |

| • Up                    | dated セクション 8.7.1                                                                               | <mark>20</mark> |

| • Up                    | dated セクション 8.7.2                                                                               | 21              |

### Changes from Revision I (October 2009) to Revision J (August 2023)

Page

ドキュメント全体にわたって表、図、相互参照の採番方法を更新......

### www.ti.com/ja-jp

| • | Added r <sub>DS(on)</sub> for DBV package                                                                  | 6    |

|---|------------------------------------------------------------------------------------------------------------|------|

| • | Updated TPS2065DBV electrical characteristics, including overcurrent trip threshold, high-level output sup | ply  |

|   | current and undervoltage lockout                                                                           | 6    |

| • | Updated TPS2065DBV Typical Characteristics                                                                 |      |

|   | Moved overcurrent description from Application and Implementation section to Detailed Description          |      |

|   | section                                                                                                    | . 20 |

| • | Added TPS2065DBV overcurrent description                                                                   |      |

|   | ·                                                                                                          |      |

JAJSPW9K - DECEMBER 2003 - REVISED JUNE 2024

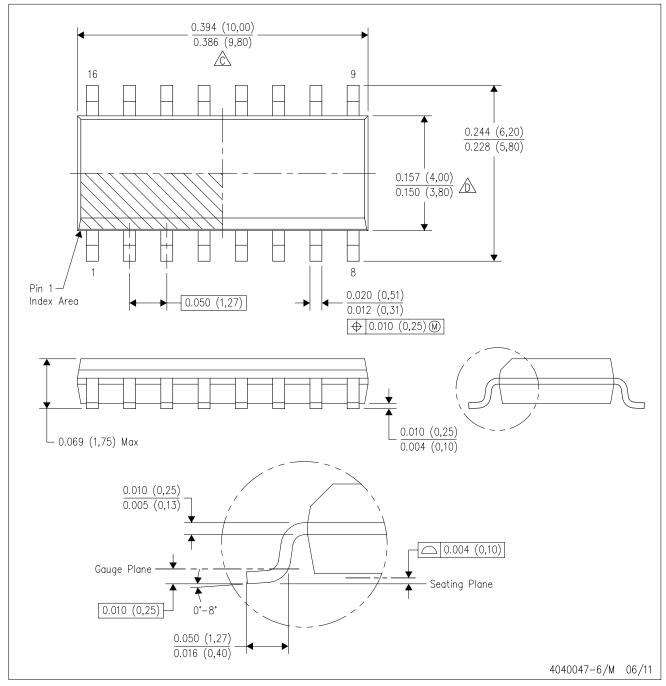

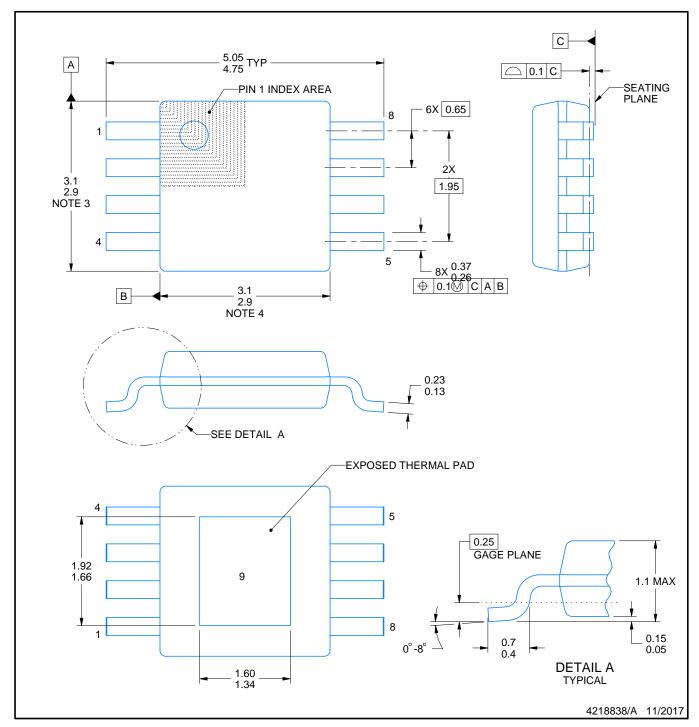

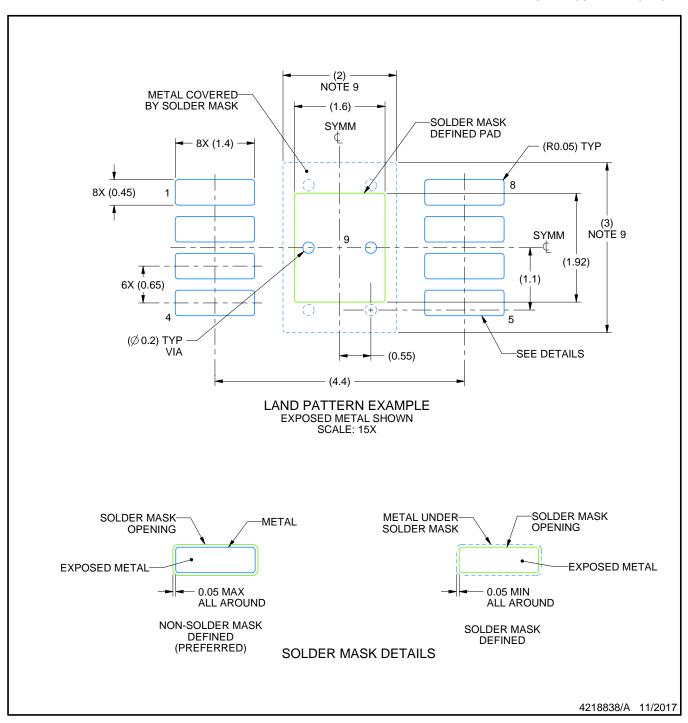

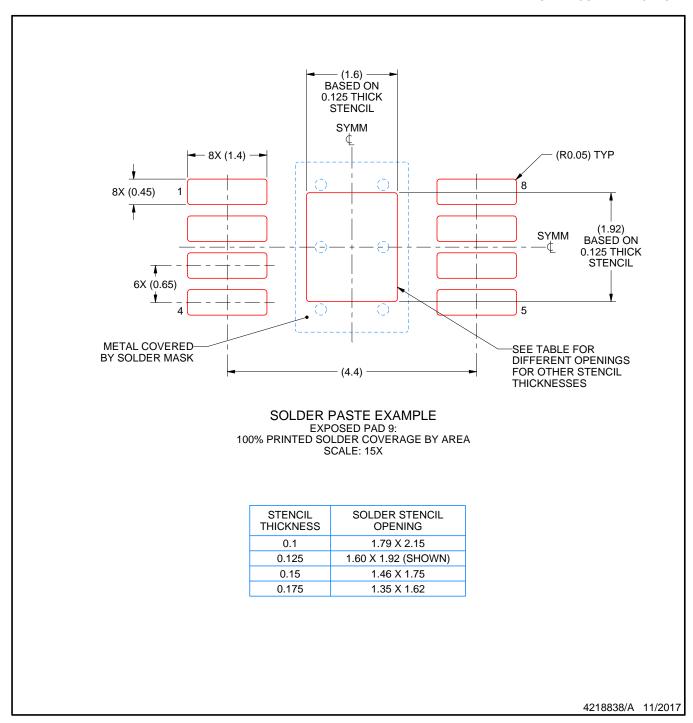

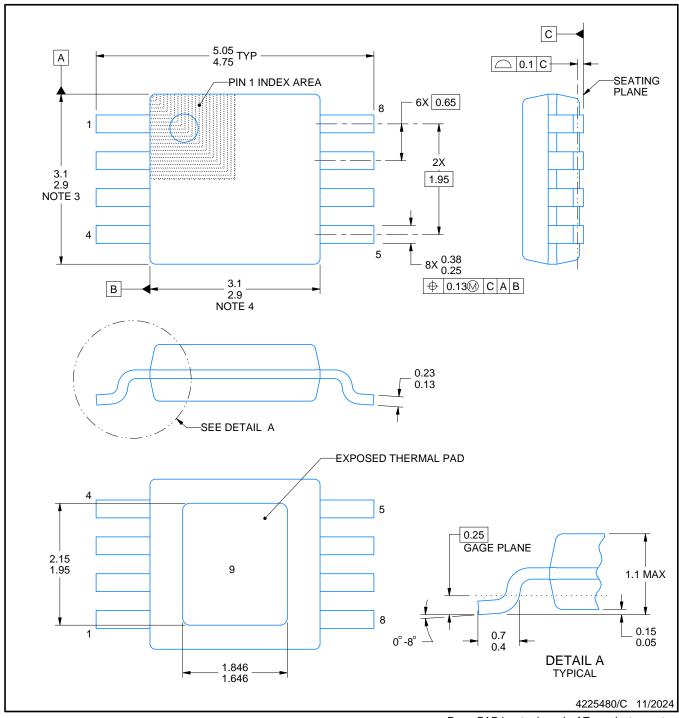

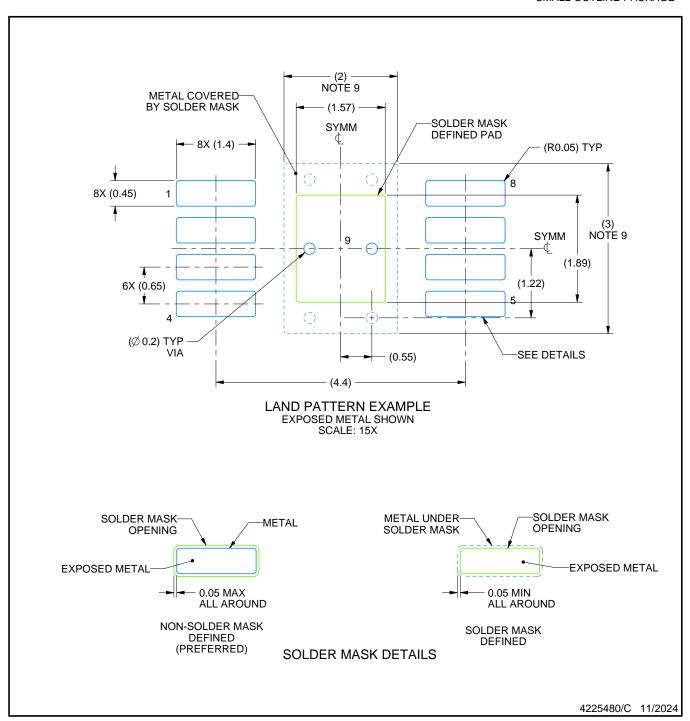

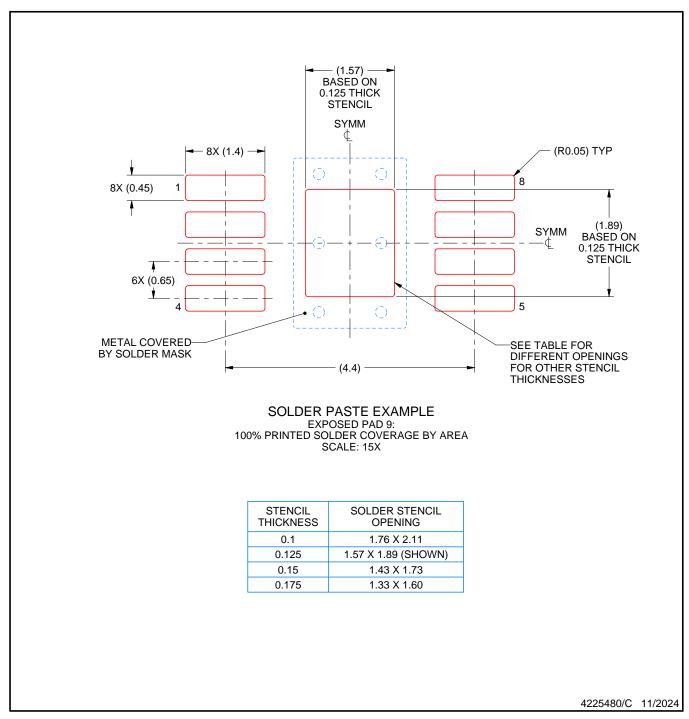

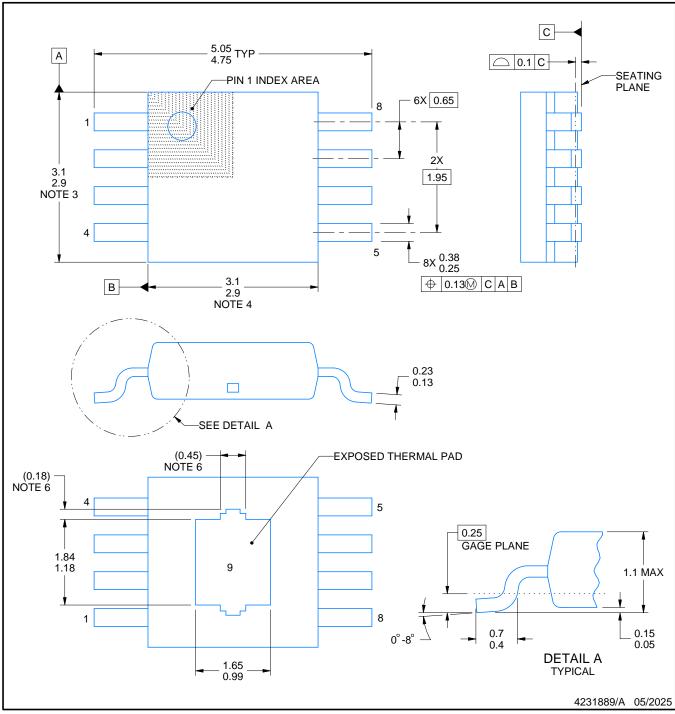

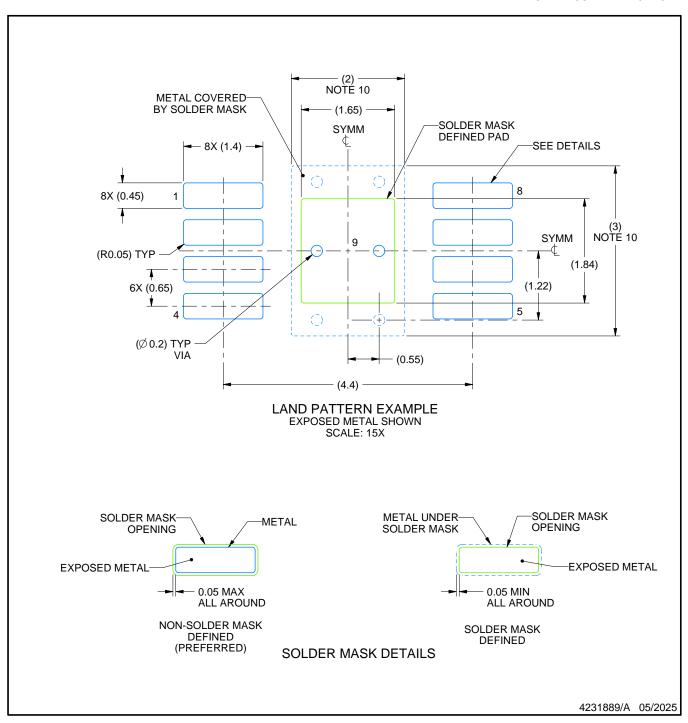

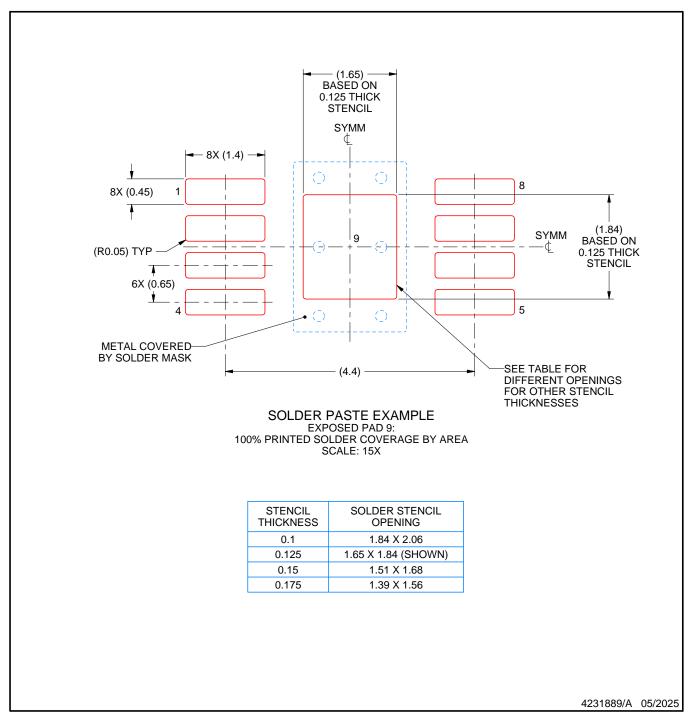

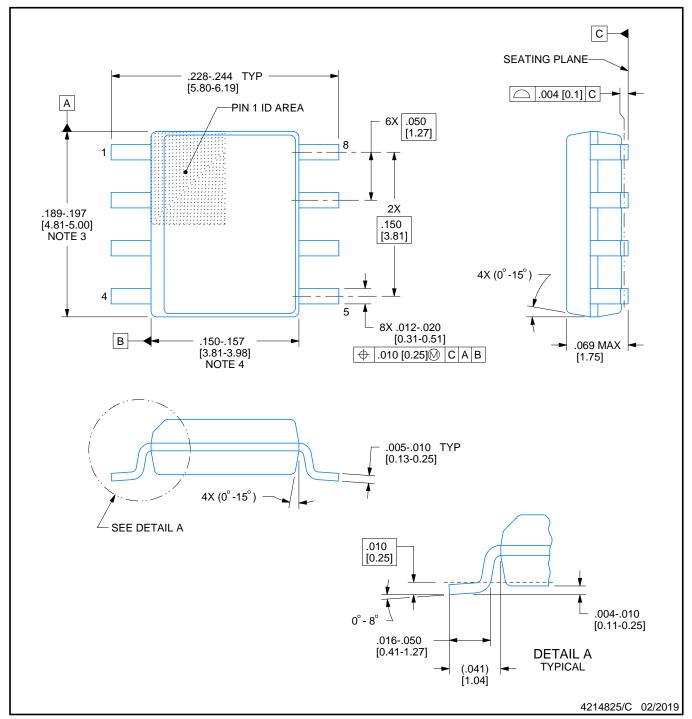

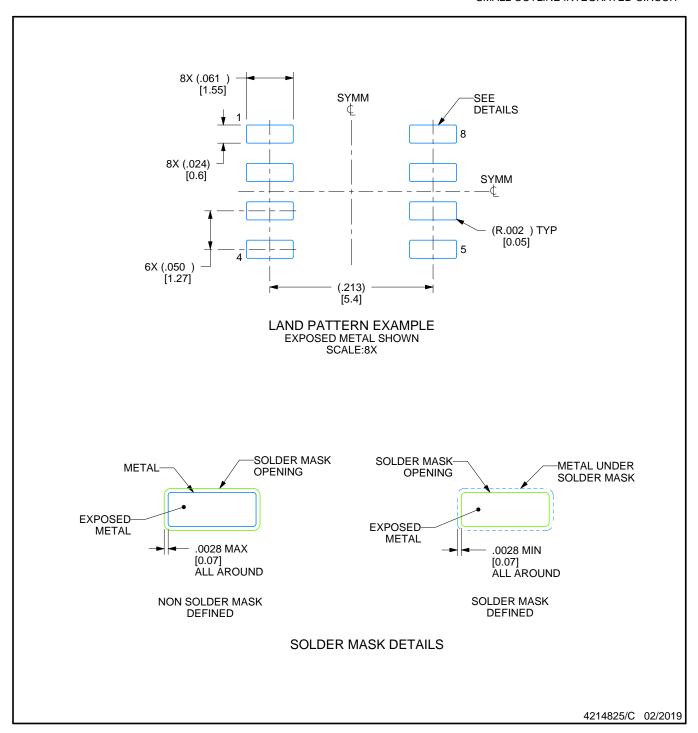

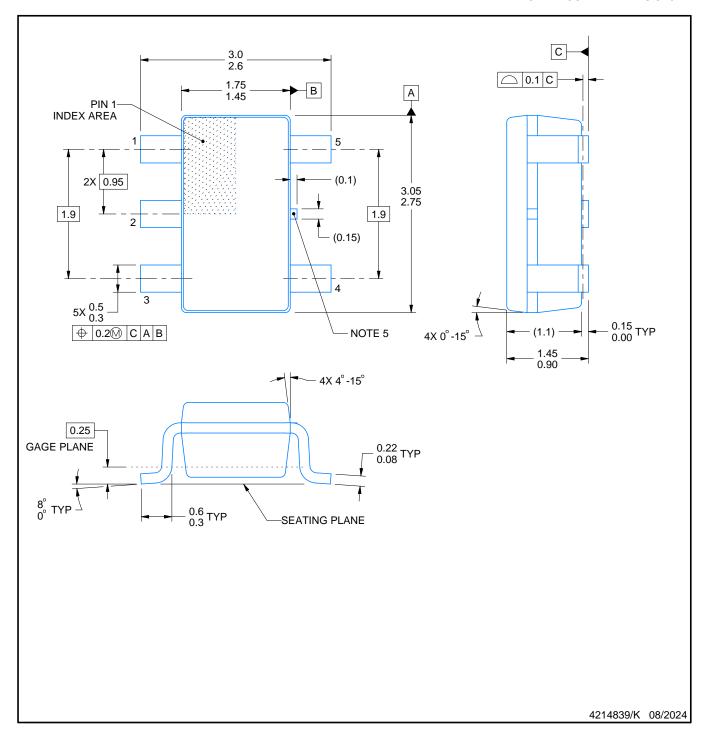

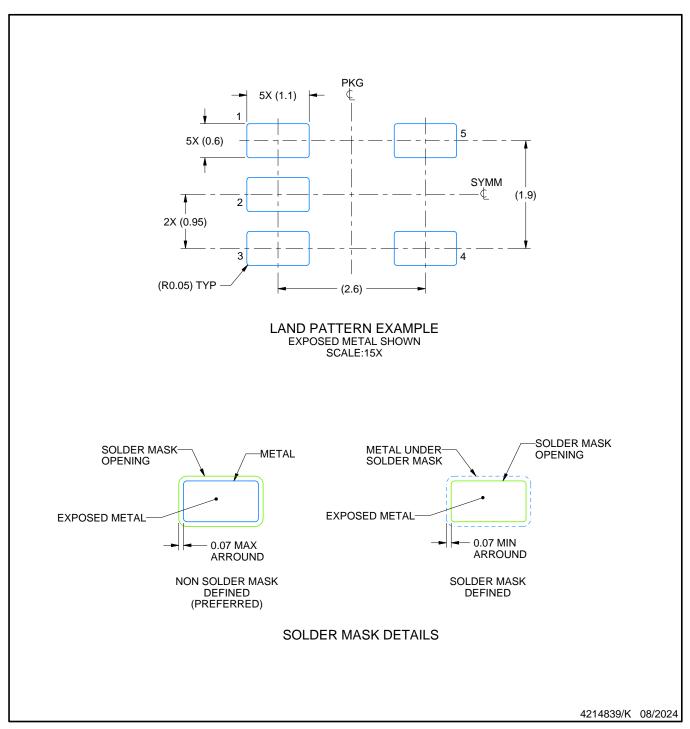

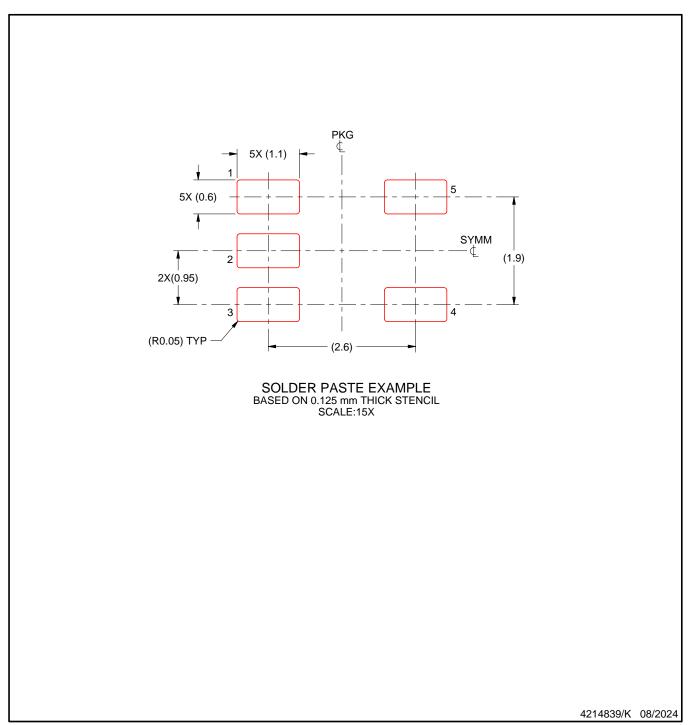

## 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

### 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、テキサス・インスツルメンツの販売条件、または ti.com やかかる テキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated www.ti.com

2-Dec-2025

## **PACKAGING INFORMATION**

| Orderable part number | Status (1) | Material type | Package   Pins   | Package qty   Carrier | <b>RoHS</b> (3) | Lead finish/<br>Ball material                         | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|------------|---------------|------------------|-----------------------|-----------------|-------------------------------------------------------|----------------------------|--------------|------------------|

| TPS2061DBVR           | Active     | Production    | SOT-23 (DBV)   5 | 3000   LARGE T&R      | Yes             | NIPDAU   SN                                           | Level-1-260C-UNLIM         | 0 to 125     | 2061             |

| TPS2061DBVR.A         | Active     | Production    | SOT-23 (DBV)   5 | 3000   LARGE T&R      | Yes             | SN                                                    | Level-1-260C-UNLIM         | 0 to 125     | 2061             |

| TPS2061DBVRG4         | Active     | Production    | SOT-23 (DBV)   5 | 3000   LARGE T&R      | Yes             | NIPDAU                                                | Level-1-260C-UNLIM         | -40 to 125   | 2061             |

| TPS2061DBVRG4.A       | Active     | Production    | SOT-23 (DBV)   5 | 3000   LARGE T&R      | Yes             | NIPDAU                                                | Level-1-260C-UNLIM         | -40 to 125   | 2061             |

| TPS2061DGNR           | Active     | Production    | HVSSOP (DGN)   8 | 2500   LARGE T&R      | Yes             | FULL NIPDAU  <br>NIPDAUAG   NIPDAU                    | Level-1-260C-UNLIM         | -40 to 125   | 2061             |

| TPS2061DGNR.A         | Active     | Production    | HVSSOP (DGN)   8 | 2500   LARGE T&R      | Yes             | FULL NIPDAU                                           | Level-1-260C-UNLIM         | -40 to 125   | 2061             |

| TPS2061DGNRG4         | Active     | Production    | HVSSOP (DGN)   8 | 2500   LARGE T&R      | Yes             | FULL NIPDAU                                           | Level-1-260C-UNLIM         | -40 to 125   | 2061             |

| TPS2061DR             | Active     | Production    | SOIC (D)   8     | 2500   LARGE T&R      | Yes             | NIPDAU                                                | Level-1-260C-UNLIM         | -40 to 125   | 2061             |

| TPS2061DR.A           | Active     | Production    | SOIC (D)   8     | 2500   LARGE T&R      | Yes             | NIPDAU                                                | Level-1-260C-UNLIM         | -40 to 125   | 2061             |

| TPS2062DGNR           | Active     | Production    | HVSSOP (DGN)   8 | 2500   LARGE T&R      | Yes             | FULL NIPDAU   Level-1-260C-UNLIM<br>NIPDAUAG   NIPDAU |                            | -40 to 125   | 2062             |

| TPS2062DGNR.A         | Active     | Production    | HVSSOP (DGN)   8 | 2500   LARGE T&R      | Yes             | FULL NIPDAU                                           | Level-1-260C-UNLIM         | -40 to 125   | 2062             |

| TPS2062DR             | Active     | Production    | SOIC (D)   8     | 2500   LARGE T&R      | Yes             | NIPDAU                                                | Level-1-260C-UNLIM         | -40 to 125   | 2062             |

| TPS2062DR.A           | Active     | Production    | SOIC (D)   8     | 2500   LARGE T&R      | Yes             | NIPDAU                                                | Level-1-260C-UNLIM         | -40 to 125   | 2062             |

| TPS2062DRG4           | Active     | Production    | SOIC (D)   8     | 2500   LARGE T&R      | Yes             | NIPDAU                                                | Level-1-260C-UNLIM         | -40 to 125   | 2062             |

| TPS2063D              | Active     | Production    | SOIC (D)   16    | 40   TUBE             | Yes             | NIPDAU                                                | Level-1-260C-UNLIM         | -40 to 125   | 2063             |

| TPS2063D.A            | Active     | Production    | SOIC (D)   16    | 40   TUBE             | Yes             | NIPDAU                                                | Level-1-260C-UNLIM         | -40 to 125   | 2063             |

| TPS2063DR             | Active     | Production    | SOIC (D)   16    | 2500   LARGE T&R      | Yes             | NIPDAU                                                | Level-1-260C-UNLIM         | -40 to 125   | 2063             |

| TPS2063DR.A           | Active     | Production    | SOIC (D)   16    | 2500   LARGE T&R      | Yes             | NIPDAU                                                | Level-1-260C-UNLIM         | -40 to 125   | 2063             |

| TPS2063DRG4           | Active     | Production    | SOIC (D)   16    | 2500   LARGE T&R      | Yes             | NIPDAU                                                | Level-1-260C-UNLIM         | -40 to 125   | 2063             |

| TPS2065DBVR           | Active     | Production    | SOT-23 (DBV)   5 | 3000   LARGE T&R      | Yes             | NIPDAU   SN                                           | Level-1-260C-UNLIM         | -40 to 125   | 2065             |

| TPS2065DBVR.A         | Active     | Production    | SOT-23 (DBV)   5 | 3000   LARGE T&R      | Yes             | NIPDAU                                                | Level-1-260C-UNLIM         | -40 to 125   | 2065             |

| TPS2065DBVR1G4.A      | Active     | Production    | SOT-23 (DBV)   5 | 3000   LARGE T&R      | -               | Call TI                                               | Call TI                    | -40 to 125   | 2065             |

| TPS2065DBVT           | Obsolete   | Production    | SOT-23 (DBV)   5 | -                     | -               | Call TI                                               | Call TI                    | -40 to 125   | 2065             |

| TPS2065DGNR           | Active     | Production    | HVSSOP (DGN)   8 | 2500   LARGE T&R      | Yes             | FULL NIPDAU  <br>NIPDAUAG   NIPDAU                    | Level-1-260C-UNLIM         | -40 to 125   | 2065             |

| TPS2065DGNR.A         | Active     | Production    | HVSSOP (DGN)   8 | 2500   LARGE T&R      | Yes             | FULL NIPDAU                                           | Level-1-260C-UNLIM         | -40 to 125   | 2065             |

| TPS2065DR             | Active     | Production    | SOIC (D)   8     | 2500   LARGE T&R      | Yes             | NIPDAU                                                | Level-1-260C-UNLIM         | -40 to 125   | 2065             |

| TPS2065DR.A           | Active     | Production    | SOIC (D)   8     | 2500   LARGE T&R      | Yes             | NIPDAU                                                | Level-1-260C-UNLIM         | -40 to 125   | 2065             |

2-Dec-2025

www.ti.com

| Orderable part number | Status<br>(1) | Material type | Package   Pins   | Package qty   Carrier | RoHS | Lead finish/<br>Ball material      | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|---------------|---------------|------------------|-----------------------|------|------------------------------------|----------------------------|--------------|------------------|

|                       | (1)           | (2)           |                  |                       | (0)  | (4)                                | (5)                        |              | (0)              |

| TPS2065DRG4           | Active        | Production    | SOIC (D)   8     | 2500   LARGE T&R      | Yes  | NIPDAU                             | Level-1-260C-UNLIM         | -40 to 125   | 2065             |

| TPS2065DRG4.A         | Active        | Production    | SOIC (D)   8     | 2500   LARGE T&R      | Yes  | NIPDAU                             | Level-1-260C-UNLIM         | -40 to 125   | 2065             |

| TPS2066DGNR           | Active        | Production    | HVSSOP (DGN)   8 | 2500   LARGE T&R      | Yes  | FULL NIPDAU  <br>NIPDAUAG   NIPDAU | Level-1-260C-UNLIM         | -40 to 125   | 2066             |

| TPS2066DGNR.A         | Active        | Production    | HVSSOP (DGN)   8 | 2500   LARGE T&R      | Yes  | FULL NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | 2066             |

| TPS2066DGNRG4         | Active        | Production    | HVSSOP (DGN)   8 | 2500   LARGE T&R      | Yes  | FULL NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | 2066             |

| TPS2066DR             | Active        | Production    | SOIC (D)   8     | 2500   LARGE T&R      | Yes  | NIPDAU                             | Level-1-260C-UNLIM         | -40 to 125   | 2066             |

| TPS2066DR.A           | Active        | Production    | SOIC (D)   8     | 2500   LARGE T&R      | Yes  | NIPDAU                             | Level-1-260C-UNLIM         | -40 to 125   | 2066             |

| TPS2066DRG4           | Active        | Production    | SOIC (D)   8     | 2500   LARGE T&R      | Yes  | NIPDAU                             | Level-1-260C-UNLIM         | -40 to 125   | 2066             |

| TPS2067D              | Active        | Production    | SOIC (D)   16    | 40   TUBE             | Yes  | NIPDAU                             | Level-1-260C-UNLIM         | -40 to 125   | 2067             |

| TPS2067D.A            | Active        | Production    | SOIC (D)   16    | 40   TUBE             | Yes  | NIPDAU                             | Level-1-260C-UNLIM         | -40 to 125   | 2067             |

| TPS2067DR             | Active        | Production    | SOIC (D)   16    | 2500   LARGE T&R      | Yes  | NIPDAU                             | Level-1-260C-UNLIM         | -40 to 125   | 2067             |

| TPS2067DR.A           | Active        | Production    | SOIC (D)   16    | 2500   LARGE T&R      | Yes  | NIPDAU                             | Level-1-260C-UNLIM         | -40 to 125   | 2067             |

| TPS2067DRG4           | Active        | Production    | SOIC (D)   16    | 2500   LARGE T&R      | Yes  | NIPDAU                             | Level-1-260C-UNLIM         | -40 to 125   | 2067             |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

## **PACKAGE OPTION ADDENDUM**

www.ti.com 2-Dec-2025

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF TPS2062, TPS2065, TPS2066:

• Automotive: TPS2062-Q1, TPS2065-Q1, TPS2066-Q1

NOTE: Qualified Version Definitions:

Automotive - Q100 devices qualified for high-reliability automotive applications targeting zero defects

www.ti.com 17-Oct-2025

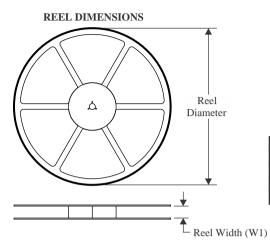

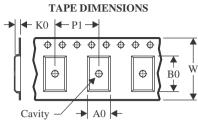

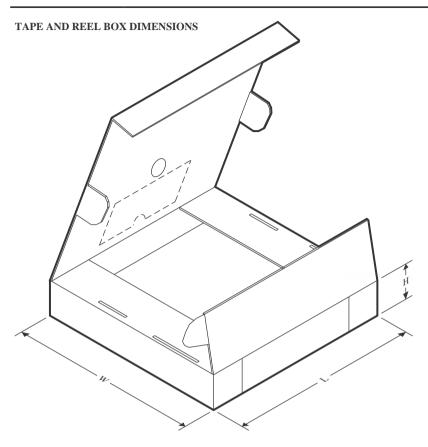

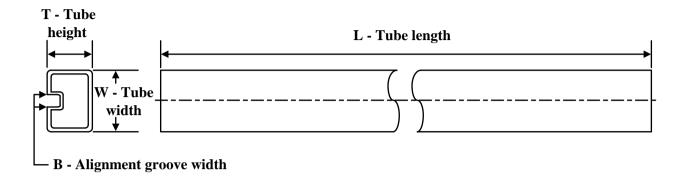

### TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

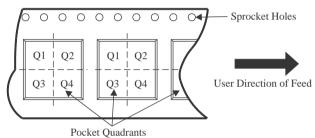

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device        | Package<br>Type | Package<br>Drawing | Pins | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------|-----------------|--------------------|------|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPS2061DBVR   | SOT-23          | DBV                | 5    | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TPS2061DBVR   | SOT-23          | DBV                | 5    | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TPS2061DBVRG4 | SOT-23          | DBV                | 5    | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TPS2061DGNR   | HVSSOP          | DGN                | 8    | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| TPS2061DR     | SOIC            | D                  | 8    | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| TPS2061DR     | SOIC            | D                  | 8    | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| TPS2062DGNR   | HVSSOP          | DGN                | 8    | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| TPS2062DR     | SOIC            | D                  | 8    | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| TPS2062DR     | SOIC            | D                  | 8    | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| TPS2063DR     | SOIC            | D                  | 16   | 2500 | 330.0                    | 16.4                     | 6.5        | 10.3       | 2.1        | 8.0        | 16.0      | Q1               |

| TPS2065DBVR   | SOT-23          | DBV                | 5    | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TPS2065DGNR   | HVSSOP          | DGN                | 8    | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |