TPS281C100

# TPS281C100x 60V、100mΩ、シングルチャネル スマート ハイサイド スイッチ

## 1 特長

- 広い動作電圧範囲:6V~60V

- 低  $R_{ON}$ :標準値  $83m\Omega$ 、最大値  $168m\Omega$

- 可変電流制限によるシステムレベルの信頼性の向上

- 1A~5A (固定 0.5A)

- 高精度電流センシング

- 標準センス モードで 1A 時に ±4%

- 高精度センス モードで 4mA 時に ±12.5%

- 64V を超える誘導性放電クランプを内蔵

- 1.5mA 未満の低静止電流

- 動作時接合部温度:-40~125℃

- 入力制御:1.8V、3.3V、5V のロジック互換

- ADC 保護のためのフォルト検出電圧スケーリングを内

- オフ状態での開路検出

- サーマル シャットダウンおよびスイング検出

- IEC61000-4-4 に準拠した強化電気的高速過渡 (EFT)

- 22nF の出力容量、DIAG\_EN を Low にした ±2kV EFT でデバイスはオフを維持

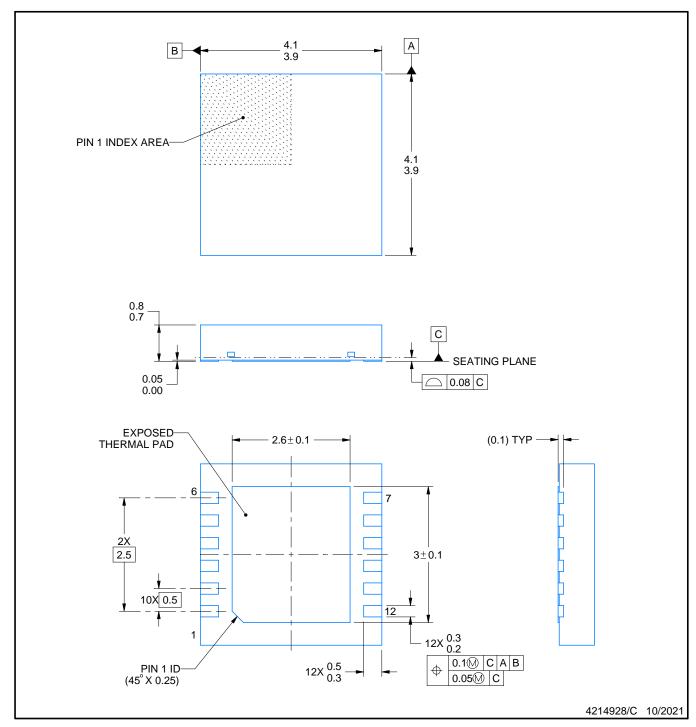

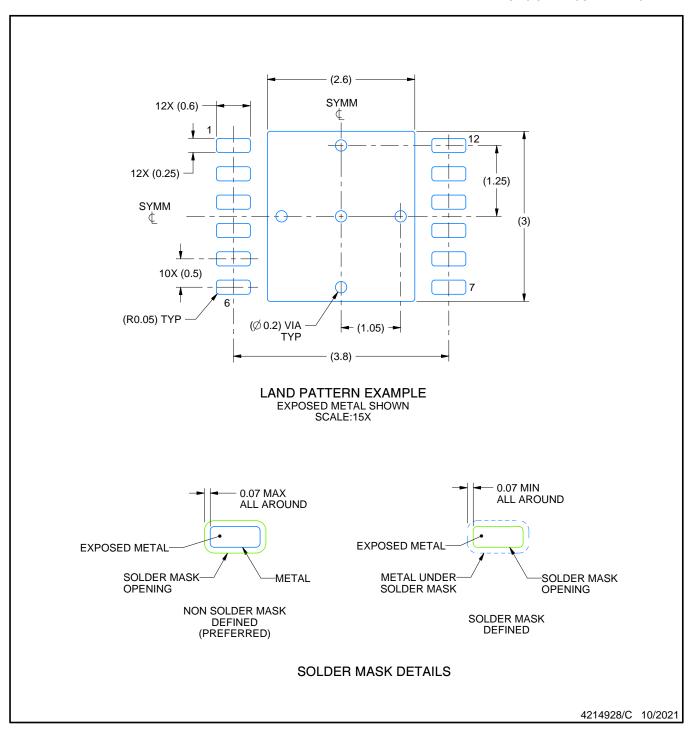

- 熱特性強化型 14 ピン TSSOP パッケージ

- 熱特性強化型 12 ピン WSON パッケージ

# 2 アプリケーション

- デジタル出力モジュール

- セーフトルクオフ (STO)

- 保持ブレーキ

- 一般的な抵抗性、誘導性、容量性負荷

## 3 概要

TPS281C100 は、産業用制御システムの要件を満たすよ うに設計された、シングル チャネル スマート ハイサイド ス イッチです。RON が低いためデバイスの電力散逸が最小 になり、広い範囲の出力負荷電流を駆動でき、最大 DC 60V の動作範囲によりシステムの堅牢性が向上します。

このデバイスには、サーマルシャットダウン、出力クラン プ、電流制限などの保護機能が内蔵されています。これら の機能により、短絡などのフォルトイベントが発生したとき のシステムの堅牢性が向上します。TPS281C100 は、可 変電流制限回路を実装しています。この回路は、大きな容 量性負荷を駆動する際に突入電流を低減し、過負荷電流 を最小化することで、システムの信頼性を向上させます。ラ ンプや高速充電の容量性負荷など、大きな突入電流の負 荷を駆動するために、TPS281C100Aでは、より高いレベ ルの許容電流を使用した突入電流期間が設定されていま す。本デバイスは、過負荷およびオープン負荷の検出な どの負荷診断機能を高めることができる高精度の負荷電 流検出機能も備えているため、よりよい予知保全が可能で す。

TPS281C100 は、小型の 14 ピン、0.65mm ピン ピッチ の 4.4mm × 5mm HTSSOP リード付きパッケージ、およ び 12 ピン、0.5mm ピンピッチの 4mm × 4mm WSON で供給され、PCBのフットプリントを最小限に抑えます。

## パッケージ情報

|  | 部品番号        | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|--|-------------|----------------------|--------------------------|

|  | TPS281C100x | DNT (WSON, 12)       | 4mm × 4mm                |

|  |             | PWP (HTSSOP、14)      | 5mm × 4.4mm              |

- 利用可能なすべてのパッケージについては、データシートの末尾 にある注文情報を参照してください。

- パッケージ サイズ (長さ×幅) は公称値であり、該当する場合はピ ンも含まれます。

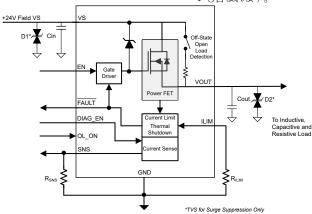

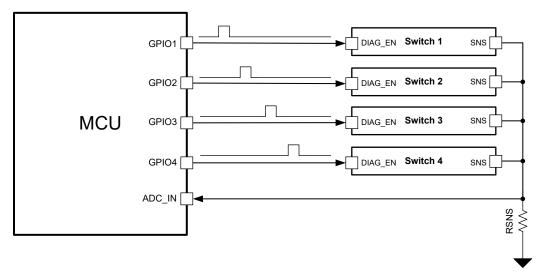

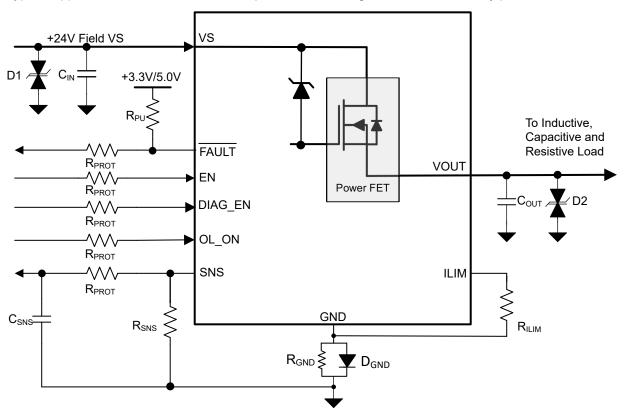

代表的なアプリケーション回路図

# **Table of Contents**

| 1 特長                                 | 1               |

|--------------------------------------|-----------------|

| 2アプリケーション                            |                 |

| 3 概要                                 | 1               |

| 4 Device Options                     |                 |

| 5 Pin Configuration and Functions    |                 |

| 6 Specifications                     | 5               |

| 6.1 Absolute Maximum Ratings         |                 |

| 6.2 ESD Ratings                      | 5               |

| 6.3 Recommended Operating Conditions |                 |

| 6.4 Thermal Information              | 6               |

| 6.5 Electrical Characteristics       |                 |

| 6.6 SNS Timing Characteristics       | 10              |

| 6.7 Switching Characteristics        | <mark>11</mark> |

| 6.8 Typical Characteristics          | 12              |

| 7 Parameter Measurement Information  |                 |

| 8 Detailed Description               | 16              |

| 8.1 Overview                         | 16              |

| 8.2 Functional Block Diagram         | 17              |

| 8.3 Device Functional Modes             | I Ö |

|-----------------------------------------|-----|

| 8.4 Working Mode                        | 18  |

| 8.5 Feature Description                 | 19  |

| 9 Application and Implementation        | 39  |

| 9.1 Application Information             | 39  |

| 9.2 Typical Application                 | 39  |

| 9.3 Power Supply Recommendations        | 42  |

| 9.4 Layout                              | 42  |

| 10 Device and Documentation Support     | 46  |

| 10.1ドキュメントの更新通知を受け取る方法                  | 46  |

| 10.2 サポート・リソース                          | 46  |

| 10.3 Trademarks                         | 46  |

| 10.4 静電気放電に関する注意事項                      | 46  |

| 10.5 用語集                                |     |

| 11 Revision History                     |     |

| 12 Mechanical, Packaging, and Orderable |     |

| Information                             | 46  |

|                                         |     |

# **4 Device Options**

| DEVICE VERSION | PART NUMBER                | CURRENT LIMIT RANGE                             | INTEGRATED CLAMP<br>FOR INDUCTIVE LOADS | INRUSH CURRENT<br>PERIOD |

|----------------|----------------------------|-------------------------------------------------|-----------------------------------------|--------------------------|

| А              | TPS281C100A <sup>(1)</sup> | 1 A to 5 A (fixed 0.5 A with ILIM short to GND) | Yes                                     | Yes                      |

| В              | TPS281C100B <sup>(1)</sup> | 1 A to 5 A (fixed 0.5 A with ILIM short to GND) | Yes                                     | No                       |

<sup>(1)</sup> Devices available in DNT package now. PWP package in preview. Contact TI for additional information.

資料に関するフィードバック(ご意見やお問い合わせ)を送信

3

Product Folder Links: *TPS281C100*English Data Sheet: SLVSH72

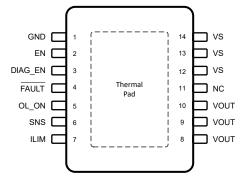

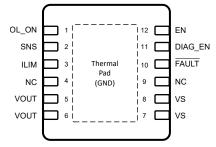

# **5 Pin Configuration and Functions**

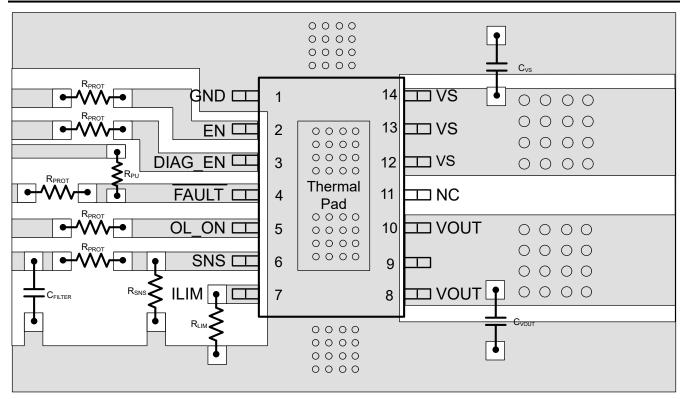

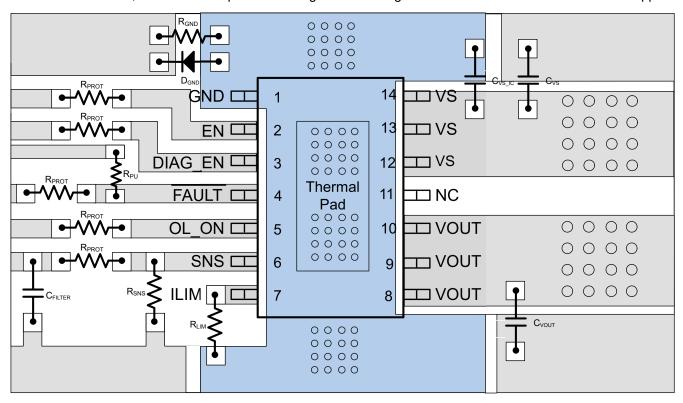

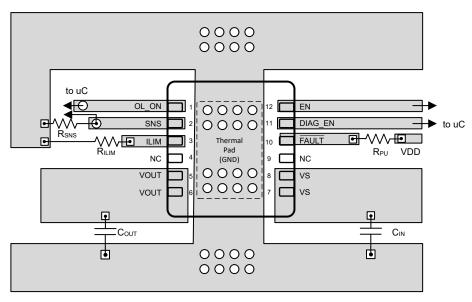

図 5-2. DNT Package, 12-Pin WSON (Top View)

図 5-1. PWP Package, 14-Pin HTSSOP (Top View)

表 5-1. Pin Functions

|         | PIN         |      | TYPE  | DESCRIPTION                                                                                                                                                                                                                                      |  |

|---------|-------------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME    | PWP         | DNT  | ITPE  | DESCRIPTION                                                                                                                                                                                                                                      |  |

| GND     | 1           | Pad  | Power | Ground of device. Connect to resistor- diode ground network to have reverse polarity protection.                                                                                                                                                 |  |

| EN      | 2           | 12   | I     | Input control for channel activation. Internal pulldown.                                                                                                                                                                                         |  |

| DIAG_EN | 3           | 11   | 1     | Enable-disable pin for diagnostics and current sensing. Internal pulldown.                                                                                                                                                                       |  |

| FAULT   | 4           | 10   | 0     | Open drain global fault output. Referred to FLT, or fault Active LOW signal.                                                                                                                                                                     |  |

| OL_ON   | 5           | 1    | 1     | Enable-disable pin for higher resolution current sense(Only available when I <sub>OUT</sub> < I <sub>Ksns2_EN</sub> ). Internal pulldown.                                                                                                        |  |

| SNS     | 6           | 2    | 0     | Analog current output corresponding to load current. Connect a resistor to GND to convert to voltage.                                                                                                                                            |  |

| ILIM    | 7           | 3    | 0     | Adjustable current limit. Connect a resistor to set the current limit. Optionally short to ground or leave pin floating to set the current limit to the default internal current limit. See the electrical characteristics for more information. |  |

| NC      | 11          | 4, 9 | N/A   | No internal connection.                                                                                                                                                                                                                          |  |

| VOUT    | 8, 9, 10    | 5, 6 | Power | Output of high side switch, connect to load.                                                                                                                                                                                                     |  |

| VS      | 12, 13, 14  | 7, 8 | Power | Power supply input.                                                                                                                                                                                                                              |  |

| Pad     | Thermal Pad | Pad  | _     | Thermal pad, internally shorted to ground.                                                                                                                                                                                                       |  |

#### **Recommended Connection for Unused Pins**

TPS281C100x is designed to provide an enhanced set of diagnostic and protection features. However, if the system design only allows for a limited number of I/O connections, some pins may be considered as optional.

表 5-2. Connections for Optional Pins

| PIN NAME                                                                                                         | CONNECTION IF NOT USED                    | IMPACT IF NOT USED                                                                                   |  |  |

|------------------------------------------------------------------------------------------------------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------|--|--|

| SNS                                                                                                              | Ground through 10-kΩ resistor             | Analog sense is not available.                                                                       |  |  |

| ILIM Float If the ILIM pin is left floating, the device will be set to the default into current-limit threshold. |                                           |                                                                                                      |  |  |

| FAULT Float                                                                                                      |                                           | If the FAULT pin is unused, the system cannot read faults from the output.                           |  |  |

|                                                                                                                  |                                           | With DIAG_EN unused, the analog sense, open-load, and short-to-supply diagnostics are not available. |  |  |

| OL_ON                                                                                                            | Ground through R <sub>PROT</sub> resistor | With OL_ON unused, the high accuracy sense mode is not available.                                    |  |  |

資料に関するフィードバック(ご意見やお問い合わせ)を送信

Copyright © 2024 Texas Instruments Incorporated

1

# 6 Specifications

## 6.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                                                 |                               | MIN  | MAX | UNIT |

|---------------------------------------------------------------------------------|-------------------------------|------|-----|------|

| Continuous supply voltage, $V_S$ with respect to IC GND: $V$                    | ersion A, B                   | -0.7 | 64  | V    |

| ontinuous supply voltage, V <sub>OUT</sub> with respect to IC GND: Version A, B |                               |      | 64  | V    |

| Transient (< 100µs) voltage at the supply pin, V <sub>S</sub> with re-          | spect to IC GND: Version A, B | -0.7 | 81  | V    |

| Enable pin voltage, V <sub>EN</sub>                                             |                               | -1   | 6   | V    |

| OL_ON pin voltage, V <sub>OL_ON</sub>                                           |                               | -1   | 6   | V    |

| DIAG_EN pin voltage, V <sub>DIAG_EN</sub>                                       |                               | -1   | 6   | V    |

| Sense pin voltage, V <sub>SNS</sub>                                             |                               | -1   | 6   | V    |

| FAULT pin voltage, V <sub>FAULT</sub>                                           |                               | -1   | 6   | V    |

| Reverse ground current, I <sub>GND</sub>                                        | V <sub>S</sub> < 0V           |      | -50 | mA   |

| Maximum junction temperature, T <sub>J</sub>                                    |                               |      | 150 | °C   |

| Storage temperature, T <sub>stg</sub>                                           |                               | -65  | 150 | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

# 6.2 ESD Ratings

|                      |                         |                                                                                          |                                 | VALUE | UNIT |

|----------------------|-------------------------|------------------------------------------------------------------------------------------|---------------------------------|-------|------|

|                      |                         | Human body model (HBM), per<br>ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>                     | All pins except VS and VOUT     | ±2000 | V    |

| V <sub>ESD</sub>     | Electrostatic discharge | Human body model (HBM), per<br>ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>                     | VS and VOUT with respect to GND | ±4000 | V    |

|                      |                         | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | All pins                        | ±750  | V    |

| V <sub>(ESD4)</sub>  | Electrostatic discharge | Contact discharge, per IEC 61000-4-2 (3)                                                 | VS and VOUT                     | ±8000 | V    |

| V <sub>(EFT)</sub>   | Electrostatic discharge | Electrical fast transient, per IEC 61000-4-4 (3)                                         | VS and VOUT                     | ±2000 | V    |

| V <sub>(surge)</sub> | Electrostatic discharge | Surge protection with 42 $\Omega$ , per IEC 61000-4-5; 1.2/50 $\mu$ s <sup>(4)</sup>     | VS and VOUT                     | ±1000 | V    |

- (1) JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process.

- (3) Tested with application circuit and supply voltage (VS) of 24V, ENx pins High (Output Enabled) and EN pins Low (Output Disabled).

- (4) Tested with application circuit and supply voltage (VS) of 24V, ENx pins High (Output Enabled) and EN pins Low (Output Disabled). External TVS at VS and VOUT required. Please refer to the IEC 61000-4-5 Surge section.

## **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted) (1)

|                       |                                       | MIN | MAX | UNIT |

|-----------------------|---------------------------------------|-----|-----|------|

| V <sub>S_OP_NOM</sub> | Nominal supply voltage                | 6.0 | 60  | V    |

| V <sub>EN</sub>       | Enable voltage                        | -1  | 5.5 | V    |

| V <sub>OL_ON</sub>    | OL_ON pin voltage, V <sub>OL_ON</sub> | -1  | 5.5 | V    |

| V <sub>DIAG_EN</sub>  | Diagnostic Enable voltage             | -1  | 5.5 | V    |

| V <sub>FAULT</sub>    | FAULT pin voltage                     | -1  | 5.5 | V    |

| V <sub>SNS</sub>      | Sense voltage                         | -1  | 5.5 | V    |

Copyright © 2024 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ) を送信

5

# 6.3 Recommended Operating Conditions (続き)

over operating free-air temperature range (unless otherwise noted) (1)

|                |                                | MIN | MAX | UNIT |

|----------------|--------------------------------|-----|-----|------|

| T <sub>A</sub> | Operating free-air temperature | -40 | 125 | °C   |

(1) All operating voltage conditions are measured with respect to device GND

### **6.4 Thermal Information**

|                        |                                              | TPS28      |              |      |

|------------------------|----------------------------------------------|------------|--------------|------|

|                        | THERMAL METRIC <sup>(1)</sup> (2)            | DNT (WSON) | PWP (HTSSOP) | UNIT |

|                        |                                              | 12 PINS    | 14 PINS      |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 36.9       | TBD          | °C/W |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance    | 24.4       | TBD          | °C/W |

| R <sub>0JB</sub>       | Junction-to-board thermal resistance         | 13.7       | TBD          | °C/W |

| $\Psi_{JT}$            | Junction-to-top characterization parameter   | 0.4        | TBD          | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 13.7       | TBD          | °C/W |

| R <sub>0JC(bot)</sub>  | Junction-to-case (bottom) thermal resistance | 1.1        | TBD          | °C/W |

- (1) For more information about traditional and new thermal metrics, see the SPRA953 application report.

- (2) The thermal parameters are based on a 4-layer PCB according to the JESD51-5 and JESD51-7 standards.

## 6.5 Electrical Characteristics

$V_S$  = 6V to 60V,  $T_A$  = -40°C to 125°C (unless otherwise noted)

|                               | PARAMETER                                                          | TEST CO                                                               | NDITIONS                                           | MIN | TYP  | MAX  | UNIT |

|-------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------|-----|------|------|------|

| VS SUPPLY                     | VOLTAGE AND CURREN                                                 | İT                                                                    | <u>'</u>                                           |     |      |      |      |

| IL <sub>NOM</sub>             | Continuous load current                                            | V <sub>EN</sub> = HI                                                  | T <sub>AMB</sub> = 85°C                            |     | 4    |      | Α    |

|                               | Total device idle state                                            | VS ≤ 60V, V <sub>EN</sub> =                                           | $T_J = -40^{\circ}\text{C to } 85^{\circ}\text{C}$ |     | 1    | 1.3  | mA   |

| I <sub>IDLE, VS</sub>         | current (including<br>MOSFET) with<br>diagnostics disabled         | $V_{DIAG\_EN} = LO, V_{OUT} = 0V$                                     | T <sub>J</sub> = 150°C                             |     |      | 1.5  | mA   |

| I <sub>IDLE,</sub><br>VS_DIAG | V <sub>S</sub> standby idle state current with diagnostics enabled | $VS \le 60V$ , $V_{EN} =$<br>LO, $V_{DIAG\_EN} = HI$ , $V_{OUT} = 0V$ |                                                    |     | 1.2  | 1.7  | mA   |

| I <sub>Q, VS</sub>            | V <sub>S</sub> quiescent current with diagnostics disabled         | V <sub>EN</sub> = V <sub>DIAG_EN</sub> = 0V                           | I <sub>OUT</sub> = 0A                              |     | 0.98 | 1.3  | mA   |

| I <sub>Q, VS_DIAG</sub>       | V <sub>S</sub> quiescent current with diagnostics enabled          | V <sub>ENx</sub> = V <sub>DIAG_EN</sub> = 0V                          | I <sub>OUT</sub> = 0A                              |     | 1.2  | 1.5  | mA   |

| I <sub>OUT(OFF,SIN</sub>      | _                                                                  | VS ≤ 60V,                                                             | $T_J = -40^{\circ}\text{C to } 85^{\circ}\text{C}$ |     | 2.1  | 2.8  | mA   |

| K)                            | Output sink current                                                | $V_{EN} = 0V$ , $V_{OUT} = 24V$ , $V_{DIAG} = 0V$                     | T <sub>J</sub> = 150°C                             |     | 2.3  | 2.6  | mA   |

|                               |                                                                    | VS ≤ 60V,                                                             | $T_J = -40$ °C to 85°C                             |     |      | 0.9  | V    |

| V <sub>OUT(OFF)</sub>         | Output floating voltage                                            | $V_{EN} = 0V$ , $V_{OUT}$ floating, $V_{DIAG} = 0V$                   | T <sub>J</sub> = 150°C                             |     |      | 0.9  | V    |

| VS UNDER                      | VOLTAGE LOCKOUT (UV                                                | LO) INPUT                                                             |                                                    |     |      | •    |      |

| V <sub>S,UVLOR</sub>          | V <sub>S</sub> undervoltage lockout rising                         | Magazired with respect to                                             | the CND pip of the device                          | 5.0 | 5.4  | 5.75 | V    |

| V <sub>S,UVLOF</sub>          | V <sub>S</sub> undervoltage lockout falling                        | nieasureu with respect to                                             | leasured with respect to the GND pin of the device |     | 4.5  | 4.85 | V    |

| VDS CLAM                      | P                                                                  |                                                                       | ·                                                  |     |      |      |      |

| \/                            | V slama valtaga                                                    | FFT ourrent = 10m ^                                                   | V <sub>S</sub> = 24V                               | 64  | 75   | 81   | V    |

| V <sub>DS,Clamp</sub>         | V <sub>DS</sub> clamp voltage                                      | FET current = 10mA                                                    | V <sub>S</sub> = 6V                                | 48  | 53   | 58   | V    |

| RON CHAR                      | ACTERISTICS                                                        | 1                                                                     | 1                                                  |     |      |      |      |

資料に関するフィードバック(ご意見やお問い合わせ)を送信

Copyright © 2024 Texas Instruments Incorporated

6

$V_S = 6V$  to 60V,  $T_A = -40$ °C to 125°C (unless otherwise noted)

|                                    | PARAMETER                                                                     | TEST CO                                                            | NDITIONS                                                          | MIN  | TYP                 | MAX                                 | UNIT               |

|------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------|------|---------------------|-------------------------------------|--------------------|

|                                    |                                                                               |                                                                    | T <sub>J</sub> = 25°C                                             |      | 83                  |                                     | mΩ                 |

| R <sub>ON</sub>                    | On-resistance                                                                 | $0.5A \le I_{OUT} \le 3A, V_S = 6V$                                | T <sub>J</sub> = 125°C                                            |      |                     | 168                                 | mΩ                 |

| 0.1                                |                                                                               | to 60V                                                             | T <sub>J</sub> = 150°C                                            | ,    |                     | 180                                 | mΩ                 |

| R <sub>ON(REV)</sub>               | On-resistance during reverse polarity                                         | 0.5A ≤ I <sub>OUT</sub> ≤ 3A, V <sub>S</sub> = –<br>24V            | $T_{J} = -40^{\circ}\text{C to } 150^{\circ}\text{C}$             |      |                     | 180                                 | mΩ                 |

| R <sub>ON_AUX</sub>                | VS to VOUT On-<br>resistance<br>High Accuracy Sense<br>Mode                   | V <sub>S</sub> = 24V, I <sub>OUT</sub> = 40 mA<br>OL_ON=DIAG_EN=5V | $T_{\rm J} = -40^{\circ}{\rm C} \ {\rm to} \ 150^{\circ}{\rm C}$  |      | 4.7                 | 12                                  | Ω                  |

| CURRENT                            | LIMIT CHARACTERISTICS                                                         | 3                                                                  |                                                                   |      |                     |                                     |                    |

|                                    |                                                                               |                                                                    | I <sub>CL, typ</sub> = 5.26A                                      |      | 52.6                |                                     | $A \times k\Omega$ |

|                                    |                                                                               |                                                                    | I <sub>CL, typ</sub> = 4.15A                                      |      | 51.9                |                                     | A × kΩ             |

| K <sub>CL</sub>                    | Current Limit Ratio                                                           |                                                                    | I <sub>CL, typ</sub> = 3.04A                                      |      | 50.8                |                                     | A × kΩ             |

|                                    |                                                                               |                                                                    | I <sub>CL, typ</sub> = 1.98A                                      |      | 49.5                |                                     | A × kΩ             |

|                                    |                                                                               |                                                                    | I <sub>CL, typ</sub> = 0.96A                                      |      | 48                  |                                     | A × kΩ             |

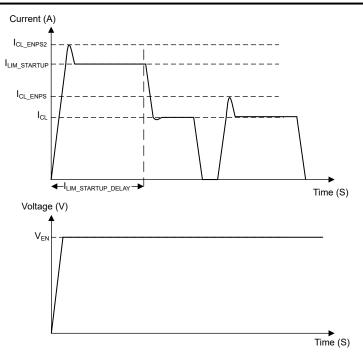

| I <sub>LIM_STARTU</sub><br>P       | Peak current limit when switch is enabled (A version)                         |                                                                    | $R_{ILIM} = 10k\Omega$ to $50k\Omega$                             |      | 2 × I <sub>CL</sub> | 6.5                                 | Α                  |

| t <sub>LIM_STARTU</sub><br>P_DELAY | Delay time for device to remain in I <sub>LIM_STARTUP</sub> level (A Version) |                                                                    |                                                                   |      |                     | 12                                  | ms                 |

|                                    |                                                                               |                                                                    | $R_{ILIM} = 50k\Omega$                                            | 0.73 | 0.96                | 1.11                                | Α                  |

|                                    |                                                                               |                                                                    | R <sub>ILIM</sub> = 25kΩ                                          | 1.5  | 1.98                | 2.3                                 | Α                  |

|                                    |                                                                               |                                                                    | $R_{ILIM} = 16.7k\Omega$                                          | 2.3  | 3.04                | 3.5                                 | Α                  |

| I <sub>CL</sub>                    | Current Limit level                                                           | Short circuit condition,                                           | R <sub>ILIM</sub> = 12.5kΩ                                        | 3.15 | 4.15                | 4.77                                | Α                  |

| CL                                 |                                                                               | V <sub>DS</sub> = 1V                                               | R <sub>ILIM</sub> = 10kΩ                                          | 4    | 5.26                | 6.3                                 | Α                  |

|                                    |                                                                               |                                                                    | $R_{ILIM}$ = GND, open, or<br>out of range(< 5kΩ, and<br>> 150kΩ) | 0.35 | 0.48                | 0.6                                 | Α                  |

| I <sub>CL_LINPK</sub>              | Overcurrent Limit<br>Threshold <sup>(1)</sup>                                 | Overload condition                                                 | R <sub>ILIM</sub> = 25kΩ                                          |      |                     | 1.5 × I <sub>CL</sub>               | Α                  |

|                                    |                                                                               |                                                                    | $R_{ILIM} = 50k\Omega$                                            |      |                     | 4 × I <sub>CL</sub>                 | Α                  |

| I <sub>CL_ENPS</sub>               | Peak current enabling into permanent short                                    |                                                                    | R <sub>ILIM</sub> = 25kΩ                                          |      |                     | 3.3 × I <sub>CL</sub>               | Α                  |

|                                    | into pormanone onore                                                          |                                                                    | R <sub>ILIM</sub> short to GND                                    |      |                     | 5.7 × I <sub>CL</sub>               | Α                  |

| I <sub>CL_ENPS2</sub>              | Peak current enabling into permanent short                                    |                                                                    | R <sub>ILIM</sub> = 10kΩ, t < ILIM_STARTUP_DELAY                  |      |                     | 2 ×<br>I <sub>LIM_START</sub><br>UP | Α                  |

| t <sub>IOS</sub>                   | Short circuit response time                                                   | VS = 24V                                                           |                                                                   |      | 0.5                 |                                     | μs                 |

| THERMAL                            | SHUTDOWN CHARACTER                                                            | RISTICS                                                            | 1                                                                 |      |                     | '                                   |                    |

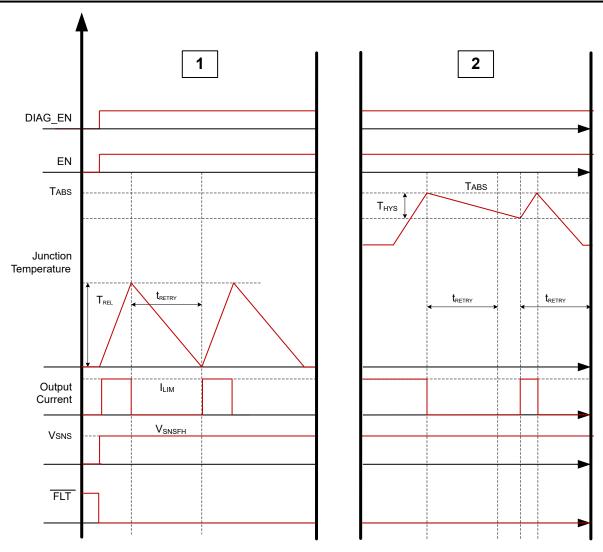

| T <sub>ABS</sub>                   | Thermal shutdown                                                              |                                                                    |                                                                   | 165  | 185                 |                                     | °C                 |

| T <sub>REL</sub>                   | Relative thermal shutdown                                                     |                                                                    |                                                                   |      | 77                  |                                     | °C                 |

| t <sub>RETRY</sub>                 | Retry time (2)                                                                | Time from fault shutdown (thermal shutdown).                       | until switch re-enable                                            |      | 2                   |                                     | ms                 |

| Fault<br>Response                  | Fault reponse to Thermal Shutdown                                             |                                                                    |                                                                   | A    | Auto-retry          |                                     |                    |

| T <sub>HYS</sub>                   | Absolute Thermal shutdown hysteresis                                          |                                                                    |                                                                   |      | 10                  |                                     | °C                 |

資料に関するフィードバック(ご意見やお問い合わせ)を送信

1

$V_S$  = 6V to 60V,  $T_A$  = -40°C to 125°C (unless otherwise noted)

|                                 | PARAMETER                                                                             | TEST (                                              | CONDITIONS                                      | MIN | TYP    | MAX | UNIT |

|---------------------------------|---------------------------------------------------------------------------------------|-----------------------------------------------------|-------------------------------------------------|-----|--------|-----|------|

| FAULT PIN                       | CHARACTERISTICS                                                                       |                                                     |                                                 |     |        |     |      |

| V <sub>FAULT</sub>              | FAULT low output voltage                                                              | I <sub>FAULT</sub> = 2.5mA                          |                                                 |     |        | 0.5 | V    |

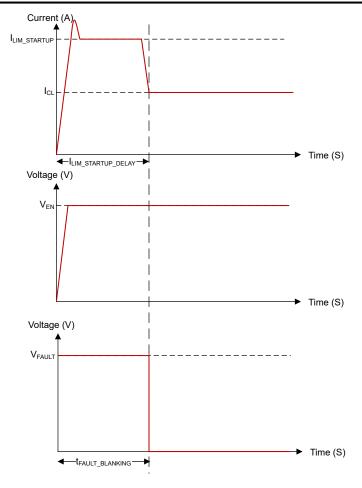

| t <sub>FAULT_BLAN</sub><br>KING | Fault blanking time<br>during startup (A and B<br>Version)                            |                                                     | $V_{DIAG\_EN} = 5V$ , $V_{EN} = 0$ to $5V$      |     |        | 12  | ms   |

| t <sub>FAULT_FLT</sub>          | Fault indication-time                                                                 | Time between fault and                              | FAULT asserting                                 |     |        | 75  | μs   |

| t <sub>FAULT_SNS</sub>          | Fault indication-time                                                                 | V <sub>DIAG_EN</sub> = 5V<br>Time between fault and | I <sub>SNS</sub> settling at V <sub>SNSFH</sub> |     |        | 106 | μs   |

| CURRENT                         | SENSE CHARACTERISTIC                                                                  | CS                                                  |                                                 |     |        |     |      |

| I <sub>KSNS2_EN</sub>           | Load current supported to enable K <sub>SNS2</sub> when in K <sub>SNS</sub> Mode      | V <sub>EN</sub> = V <sub>DIAG_EN</sub> = 5V, V      | <sub>OL_ON</sub> = GND                          | 21  | 25     | 30  | mA   |

| I <sub>KSNS2_DIS</sub>          | Load current to disable K <sub>SNS2</sub> when in K <sub>SNS2</sub> Mode              | V <sub>EN</sub> = V <sub>DIAG_EN</sub> = 5V, V      | <sub>OL_ON</sub> = GND                          | 75  | 85     | 105 | mA   |

| K <sub>SNS1</sub>               | Current sense ratio -<br>Standard Sensing<br>I <sub>OUT</sub> / I <sub>SNS</sub>      | I <sub>OUT</sub> = 1A, V <sub>OL_ON</sub> = GN      | ID                                              |     | 800    |     | A/A  |

| K <sub>SNS2</sub>               | Current sense ratio -<br>High Accuracy Sensing<br>I <sub>OUT</sub> / I <sub>SNS</sub> | I <sub>OUT</sub> = 20mA, V <sub>OL_ON</sub> =       | 5V                                              |     | 24     |     | A/A  |

|                                 |                                                                                       |                                                     | I <sub>OUT</sub> = 4A                           |     | 5      |     | mA   |

|                                 |                                                                                       |                                                     |                                                 | -4  |        | 6   | %    |

|                                 |                                                                                       |                                                     | I <sub>OUT</sub> = 3.5A                         |     | 4.375  |     | mA   |

|                                 |                                                                                       |                                                     |                                                 | -4  |        | 4   | %    |

|                                 |                                                                                       |                                                     | I <sub>OUT</sub> = 3A                           |     | 3.75   |     | mA   |

|                                 |                                                                                       |                                                     |                                                 | -4  |        | 4   | %    |

|                                 |                                                                                       |                                                     | 1 24                                            |     | 2.5    |     | mA   |

|                                 |                                                                                       |                                                     | I <sub>OUT</sub> = 2A                           | -4  |        | 4   | %    |

|                                 |                                                                                       |                                                     | . – 10                                          |     | 1.25   |     | mA   |

|                                 |                                                                                       |                                                     | I <sub>OUT</sub> = 1A                           | -4  |        | 4   | %    |

| l                               | Current sense current                                                                 | V <sub>EN</sub> = V <sub>DIAG</sub> EN =            | I <sub>OUT</sub> = 0.75A                        |     | 0.9375 |     | mA   |

| I <sub>SNS</sub>                |                                                                                       | 5V, V <sub>OL_ON</sub> = GND                        | 10UT - 0.73A                                    | -6  |        | 6   | %    |

|                                 |                                                                                       |                                                     | I - 0.5A                                        |     | 0.625  |     | mA   |

|                                 |                                                                                       |                                                     | I <sub>OUT</sub> = 0.5A                         | -6  |        | 6   | %    |

|                                 |                                                                                       |                                                     | I <sub>OUT</sub> = 250mA                        |     | 0.3125 |     | mA   |

|                                 |                                                                                       |                                                     | IOUT - ZOUITA                                   | -10 |        | 10  | %    |

|                                 |                                                                                       |                                                     | 1 - 1500- 4                                     |     | 0.1875 |     | mA   |

|                                 |                                                                                       |                                                     | I <sub>OUT</sub> = 150mA                        | -10 |        | 10  | %    |

|                                 |                                                                                       |                                                     | 1 = 60m A                                       |     | 0.075  |     | mA   |

|                                 |                                                                                       |                                                     | I <sub>OUT</sub> = 60mA                         | -25 | ,      | 25  | %    |

|                                 |                                                                                       |                                                     |                                                 |     | 0.0375 |     | mA   |

|                                 |                                                                                       |                                                     | I <sub>OUT</sub> = 30mA                         | -25 |        | 25  | %    |

$V_S = 6V$  to 60V,  $T_A = -40$ °C to 125°C (unless otherwise noted)

|                               | PARAMETER                                         | TEST CO                                                                        | NDITIONS                | MIN   | TYP    | MAX  | UNIT |

|-------------------------------|---------------------------------------------------|--------------------------------------------------------------------------------|-------------------------|-------|--------|------|------|

|                               |                                                   |                                                                                | 1 = 20m A               |       | 0.833  |      | mA   |

|                               |                                                   |                                                                                | I <sub>OUT</sub> = 20mA | -6    |        | 6    | %    |

|                               |                                                   |                                                                                | I = 10m A               |       | 0.404  |      | mA   |

|                               |                                                   |                                                                                | I <sub>OUT</sub> = 10mA | -10   |        | 10   | %    |

| 1                             | Current sense current                             | V <sub>EN</sub> = V <sub>DIAG</sub> EN =                                       | l = 4mΛ                 |       | 0.161  |      | mA   |

| SNS2                          | and accuracy for high accuracy sense mode         | 5V, V <sub>OL_ON</sub> = 5V                                                    | I <sub>OUT</sub> = 4mA  | -12.5 |        | 12.5 | %    |

|                               |                                                   |                                                                                | I - 2mA                 |       | 0.0800 |      | mA   |

|                               |                                                   |                                                                                | I <sub>OUT</sub> = 2mA  | -15   |        | 15   | %    |

|                               |                                                   |                                                                                | I <sub>OUT</sub> = 1mA  |       | 0.0395 |      | mA   |

|                               |                                                   |                                                                                | IOUT - IIIIA            | -20   |        | 20   | %    |

| SNS PIN CI                    | HARACTERISTICS                                    |                                                                                |                         |       |        | ·    |      |

|                               |                                                   | V <sub>DIAG_EN</sub> = 5V                                                      |                         | 4.5   | 5      | 5.77 | V    |

| $V_{SNSFH}$                   | V <sub>SNS</sub> fault high-level                 | V <sub>DIAG_EN</sub> = 3.3V, R <sub>SNS</sub> =O                               | pen                     | 3.3   | 3.95   | 4.4  | V    |

|                               |                                                   | V <sub>DIAG_EN</sub> = V <sub>IH</sub>                                         |                         | 2.9   | 3.2    | 3.5  | V    |

| I <sub>SNSFLT</sub>           | I <sub>SNS</sub> fault high-level                 | V <sub>DIAG_EN</sub> > V <sub>IH,DIAG_EN</sub>                                 |                         | 5.2   | 6.4    |      | mA   |

| I <sub>SNSleak</sub>          | I <sub>SNS</sub> leakage                          | V <sub>DIAG_EN</sub> = 5V, IL = 0mA                                            |                         |       |        | 1.3  | μA   |

| V                             | V <sub>S</sub> for full current sense             | V <sub>DIAG_EN</sub> = 3.3V                                                    | 5.9                     |       |        | V    |      |

| $V_{S\_ISNS}$                 | and fault functionality                           | V <sub>DIAG_EN</sub> = 5V                                                      |                         | 7.1   |        |      | V    |

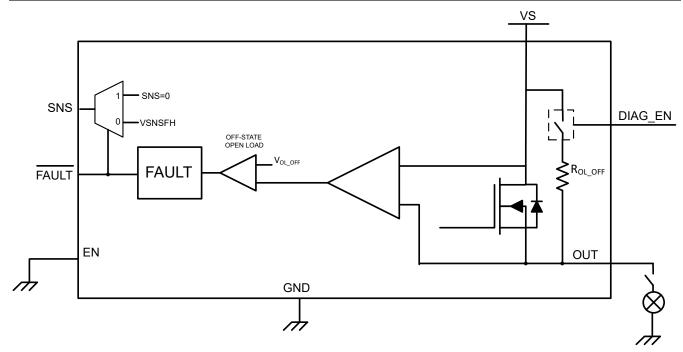

| OPEN LOA                      | D DETECTION CHARACT                               | ERISTICS                                                                       |                         |       |        |      |      |

| V <sub>OL_OFF</sub>           | OFF state open-load (OL) detection voltage        | V <sub>EN</sub> = 0V, V <sub>DIAG_EN</sub> = 5V                                |                         | 1.4   | 2      | 2.6  | V    |

|                               | OFF state open-load (OL) detection internal       |                                                                                | V <sub>S</sub> = 6V     | 110   | 133    | 150  | kΩ   |

| $R_{OL\_OFF}$                 |                                                   | $V_{EN} = 0V$ , $V_{DIAG\_EN} = 5V$                                            | V <sub>S</sub> = 24V    | 114   | 140    | 166  | kΩ   |

|                               | pull-up resistor                                  |                                                                                | V <sub>S</sub> = 48V    | 120   | 140    | 166  | kΩ   |

| t <sub>OL_OFF</sub>           | OFF state open-load (OL) detection deglitch time  | $V_{EN}$ = 0V, $V_{DIAG\_EN}$ = 5V, duration longer than $t_{OL}$ .            |                         |       | 480    | 1050 | μs   |

| t <sub>OL_OFF_1</sub>         | OL_OFF and STB indication-time from EN falling    | $V_{EN}$ = 5V to 0V, $V_{DIAG\_EN}$<br>$I_{OUT}$ = 0mA, $V_{OUT}$ = Vs - V     | = 5V<br>/ <sub>OL</sub> |       | 310    | 905  | μs   |

| t <sub>OL_OFF_2</sub>         | OL and STB indication-<br>time from DIA_EN rising | $V_{EN} = 0V$ , $V_{DIAG\_EN} = 0V$ t<br>$I_{OUT} = 0$ mA, $V_{OUT} = V_S$ - \ |                         |       |        | 1080 | μs   |

|                               | CHARACTERISTICS                                   | I                                                                              |                         | T     |        |      |      |

| V <sub>IL, OL_ON</sub>        | Input voltage low-level                           |                                                                                |                         |       |        | 8.0  | V    |

| V <sub>IH, OL_ON</sub>        | Input voltage high-level                          |                                                                                |                         | 1.5   |        |      | V    |

| V <sub>IHYS,</sub><br>OL_ON   | Input voltage hysteresis                          |                                                                                |                         |       | 282    |      | mV   |

| R <sub>OL_ON</sub>            | Internal pulldown resistor                        |                                                                                |                         | 0.7   | 1      | 1.3  | МΩ   |

| IL_OL_ON                      | Input current low-level                           | V <sub>OL_ON</sub> = -1V                                                       |                         | -25   |        | 0    | μΑ   |

| I <sub>IL, OL_ON</sub>        | Input current low-level                           | V <sub>OL_ON</sub> = 0.8V                                                      |                         | 0.6   | .8     | 1.2  | μA   |

| I <sub>IH, OL_ON</sub>        | Input current high-level                          | V <sub>OL_ON</sub> = 5V                                                        |                         | 3     | 5      | 7    | μΑ   |

| DIAG_EN P                     | IN CHARACTERISTICS                                |                                                                                |                         |       |        |      |      |

| V <sub>IL, DIAG_EN</sub>      | Input voltage low-level                           | No GND Network                                                                 |                         |       |        | 8.0  | V    |

| V <sub>IH, DIAG_EN</sub>      | Input voltage high-level                          | No GND Network                                                                 |                         | 1.5   |        |      | V    |

| V <sub>IHYS,</sub><br>DIAG_EN | Input voltage hysteresis                          |                                                                                |                         |       | 270    |      | mV   |

$V_S = 6V$  to 60V,  $T_A = -40$ °C to 125°C (unless otherwise noted)

|                          | PARAMETER                  | TEST CONDITIONS                                  | MIN | TYP | MAX | UNIT |

|--------------------------|----------------------------|--------------------------------------------------|-----|-----|-----|------|

| R <sub>DIAG_EN</sub>     | Internal pulldown resistor |                                                  | 200 | 350 | 500 | kΩ   |

| I <sub>IL, DIAG_EN</sub> | Input current low-level    | V <sub>DIAG_EN</sub> = 0.8V, V <sub>EN</sub> =0V |     | 2.9 |     | μΑ   |

| I <sub>IH, DIAG_EN</sub> | Input current high-level   | V <sub>DIAG_EN</sub> = 5V                        |     | 14  |     | μΑ   |

| EN PIN CH                | ARACTERISTICS              |                                                  |     |     |     |      |

| V <sub>IL, EN</sub>      | Input voltage low-level    | No GND Network                                   |     |     | 0.8 | V    |

| V <sub>IH, EN</sub>      | Input voltage high-level   | No GND Network                                   | 1.5 |     |     | V    |

| V <sub>IHYS, EN</sub>    | Input voltage hysteresis   |                                                  |     | 300 |     | mV   |

| R <sub>EN</sub>          | Internal pulldown resistor |                                                  | 200 | 350 | 500 | kΩ   |

| I <sub>IL, EN</sub>      | Input current low-level    | V <sub>EN</sub> = 0.8V                           |     | 2.2 |     | μΑ   |

| I <sub>IH, EN</sub>      | Input current high-level   | V <sub>EN</sub> = 5V                             |     | 14  |     | μΑ   |

<sup>(1)</sup> The maximum current output under overload condition before current limit regulation.

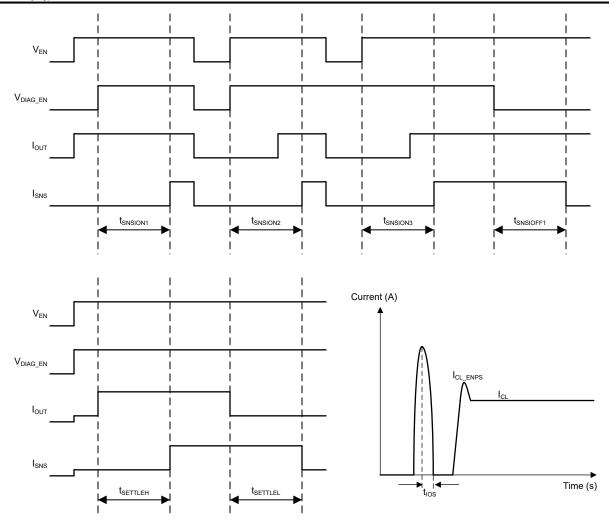

# **6.6 SNS Timing Characteristics**

$V_S$  = 6V to 60V,  $T_A$  = -40°C to 125°C (unless otherwise noted), parameters not tested in production

|                                | PARAMETER                                                                                                                                                                          | TEST CONDITIONS                                                                                                                     | MIN | TYP | MAX | UNIT |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| SNS TIMIN                      | G - CURRENT SENSE                                                                                                                                                                  |                                                                                                                                     |     |     |     |      |

| 4                              | Settling time from rising edge of DIAG_EN                                                                                                                                          | $V_{EN}$ = 5V, $V_{DIAG\_EN}$ = 0V to 5V, $V_{OL\_ON}$ = 0V, $R_{SNS}$ = 1k $\Omega$ , $I_L$ = 1A                                   |     |     | 15  | μs   |

| <sup>t</sup> snsion1           | 50% of V <sub>DIAG_EN</sub> to 90% of settled ISNS                                                                                                                                 | $V_{EN}$ = 5V, $V_{DIAG\_EN}$ = 0V to 5V,<br>$V_{OL\_ON}$ = 0V ,<br>$R_{SNS}$ = 1k $\Omega$ , $I_L$ = 50mA                          |     |     | 80  | μs   |

| t <sub>SNSION2</sub>           | Settling time from rising edge of EN and DIAG_EN 50% of V <sub>DIAG_EN</sub> V <sub>EN</sub> to 90% of settled ISNS                                                                | $V_{EN} = V_{DIAG\_EN} = 0V \text{ to } 5V$<br>$V_{S} = 24V \text{ R}_{SNS} = 1 \text{ k}\Omega, \text{ I}_{L} = 1\text{A}$         |     |     | 200 | μs   |

| t <sub>SNSION3</sub>           | Settling time from rising edge of EN 50% of V <sub>EN</sub> to 90% of settled ISNS                                                                                                 | $V_{EN}$ = 0V to 5V, $V_{DIAG\_EN}$ = 5V $R_{SNS}$ = 1k $\Omega$ , $I_L$ = 1A                                                       |     |     | 200 | μs   |

| t <sub>SNSION4</sub>           | Settling time from rising edge of OL_ON 50% of V <sub>OL_ON</sub> to 90% of settled ISNS                                                                                           | $V_{OL\_ON}$ = 0 to 5V, $V_{EN}$ = $V_{DIAG\_EN}$ = 5V $R_{SNS}$ = 1k $\Omega$ , $I_L$ = 6mA                                        |     |     | 60  | μs   |

| t <sub>SNSION5</sub>           | Settling time from falling edge of I <sub>L</sub> < I <sub>KSNS2_EN</sub> to 90% of settled ISNS                                                                                   | $V_{OL\_ON} = V_{EN} = V_{DIAG\_EN} = 5V$<br>$R_{SNS} = 1k\Omega$ , $I_L = 100mA$ to 10mA                                           |     |     | 60  | μs   |

| t <sub>SNSION6</sub>           | Settling time from Rising edge of $I_L > I_{KSNS2\_DIS.}$ to 90% of settled ISNS                                                                                                   | $V_{OL\_ON} = V_{EN} = V_{DIAG\_EN} = 5V$<br>$R_{SNS} = 1k\Omega$ , $I_L = 10m\overline{A}$ to 100mA                                |     |     | 60  | μs   |

| t <sub>KSNS2_DIS_</sub><br>DGL | Deglitch time for transition of $I_L > I_{KSNS2\_DIS.}$                                                                                                                            | $V_{OL\_ON} = V_{EN} = V_{DIAG\_EN} = 5V$<br>$R_{SNS} = 1k\Omega$ , $I_L = 10m\overline{A}$ to 100mA                                |     |     | 30  | μs   |

| t <sub>SNSIOFF</sub>           | Settling time from falling edge of DIAG_EN                                                                                                                                         | $V_{EN}$ = 5V, $V_{DIAG\_EN}$ = 5V to 0V<br>$R_{SNS}$ = 1k $\Omega$ , $R_L$ = 48 $\Omega$                                           |     |     | 20  | μs   |

| t <sub>SETTLEH</sub>           | Settling time from rising edge of load step. 50% of $V_{OL\_ON}$ to 90% of settled ISNS                                                                                            | $V_{EN} = V_{DIAG\_EN} = 5V$<br>$R_{SNS} = 1k\Omega$ , $I_{OUT} = 0.5A$ to 3A                                                       |     |     | 20  | μs   |

| t <sub>SETTLEL</sub>           | Settling time from falling edge of load step. 50% of V <sub>OL_ON</sub> to 10% of settled ISNS                                                                                     | $V_{EN} = V_{DIAG\_EN} = 5V$<br>$R_{SNS} = 1k\Omega$ , $I_{OUT} = 3A$ to 0.5A                                                       |     |     | 20  | μs   |

| t <sub>TIME</sub> OUT          | Time to indicate VSNSFH due to VS-VOUT>2V. From rising edge of EN, DIAG_EN and OL_ON 50% of V <sub>DIA_EN</sub> V <sub>EN</sub> V <sub>OL_ON</sub> to 50% of rising edge of VSNSFH | $V_{DIAG\_EN} = V_{EN} = V_{OL\_ON} = 0V \text{ to } 5V$<br>$R_{SNS} = 1k\Omega$ , $I_{OUT} = 5\text{mA}$ $C_{OUT} = 50\mu\text{F}$ |     | 245 |     | μs   |

資料に関するフィードバック(ご意見やお問い合わせ)を送信

Copyright © 2024 Texas Instruments Incorporated

10

<sup>(2)</sup> Data not tested in production.

# 6.6 SNS Timing Characteristics (続き)

$V_S$  = 6V to 60V,  $T_A$  = -40°C to 125°C (unless otherwise noted), parameters not tested in production

|                    | PARAMETER                                                                                      | TEST CONDITIONS                                                                                                                    | MIN | TYP | MAX | UNIT |

|--------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>SNSFH</sub> | Assertion time for SNSFH<br>From 50% rising edge of VSNSFH<br>to 50% of falling edge of VSNSFH | $V_{DIAG\_EN} = V_{EN} = V_{OL\_ON} = 0V \text{ to } 5V$<br>$R_{SNS} = 1k\Omega$ , $I_{OUT} = 5\text{mA } C_{OUT} = 15\mu\text{F}$ | 60  |     |     | μs   |

# **6.7 Switching Characteristics**

VS = 6V to 60V,  $T_A = -40$ °C to 125°C (unless otherwise noted),  $C_{OUT} = 22$ nF

| PARAMETER                          |                                              | TEST CONDITIONS                                                                                   | MIN        | TYP | MAX | UNIT |

|------------------------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------|------------|-----|-----|------|

| t <sub>DR</sub>                    | Turnon delay time (from delay or diagnostic) | $V_S$ = 24V, $R_L$ = 48 $\Omega$ 50% of EN to 20% of VOUT                                         |            | 17  | 45  | μs   |

| t <sub>DF</sub>                    | Turnoff delay time                           | $V_S$ = 24V, $R_L$ = 48 $\Omega$ 50% of EN to 80% of VOUT                                         | 10         | 18  | 26  | μs   |

| SR <sub>R</sub>                    | VOUT rising slew rate                        | $V_S = 24V, 20\% \text{ to } 80\% \text{ of } V_{OUT},$<br>$R_L = 48\Omega$                       | 2.3        | 3.6 | 4.6 | V/µs |

| SR <sub>F</sub>                    | VOUT falling slew rate                       | $V_S = 24V, 80\% \text{ to } 20\% \text{ of } V_{OUT},$<br>$R_L = 48\Omega$                       | 2.3        | 3.5 | 4.8 | V/µs |

| t <sub>ON</sub>                    | Turnon time                                  | $V_S$ = 24V, $R_L$ = 48 $\Omega$ 50% of EN to 80% of VOUT                                         |            | 20  | 40  | μs   |

| t <sub>OFF</sub>                   | Turnoff time                                 | $V_S$ = 24V, $R_L$ = 48 $\Omega$ 50% of EN to 20% of VOUT                                         |            | 20  | 40  | μs   |

| t <sub>ON</sub> - t <sub>OFF</sub> | Turn-on and off matching                     | 1ms ON time switch enable pulse                                                                   | -25        |     | 70  | μs   |

| $\Delta_{PWM}$                     | PWM accuracy - average load current          | 200 $\mu$ s enable pulse, V <sub>S</sub> = 24V, R <sub>L</sub> = 48 $\Omega$ F = f <sub>max</sub> | <b>–15</b> |     | 15  | %    |

資料に関するフィードバック(ご意見やお問い合わせ)を送信

11

Product Folder Links: TPS281C100 English Data Sheet: SLVSH72

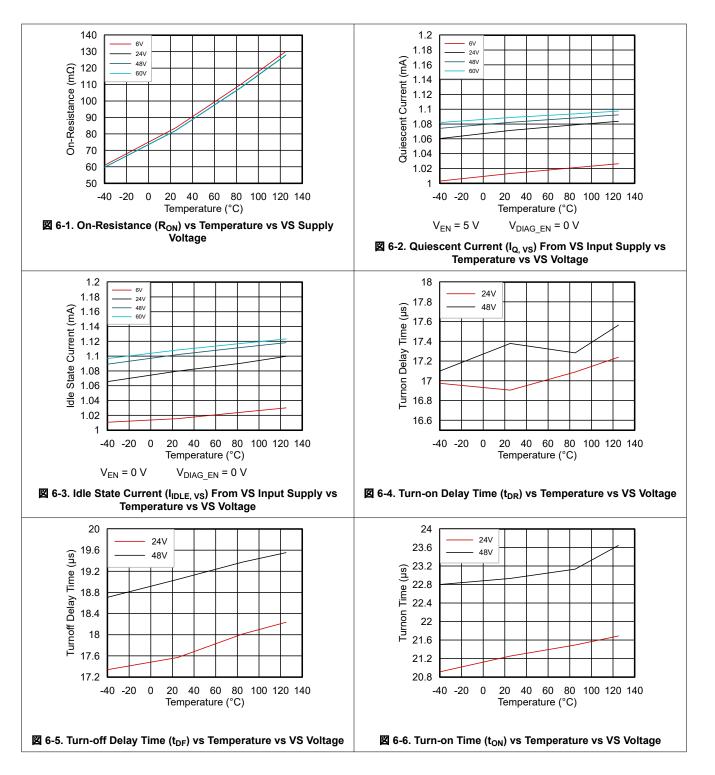

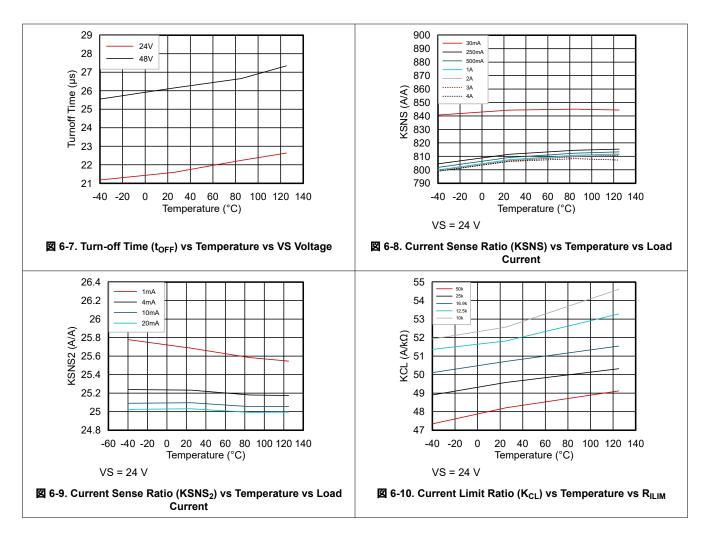

## 6.8 Typical Characteristics

# **6.8 Typical Characteristics (continued)**

13

# 7 Parameter Measurement Information

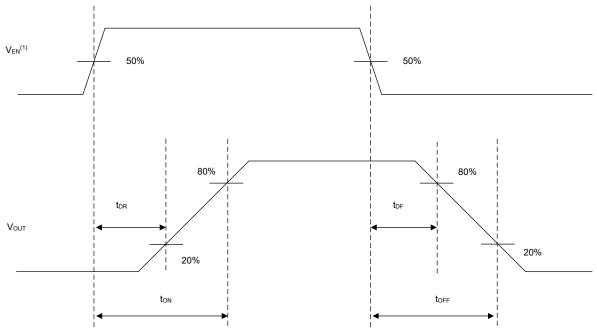

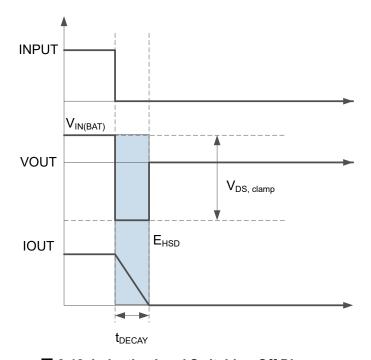

図 7-1. Parameter Definitions

(1) Rise and fall time of  $V_{\text{EN}}$  is 100 ns.

図 7-2. Switching Characteristics Definitions

資料に関するフィードバック (ご意見やお問い合わせ) を送信

Copyright © 2024 Texas Instruments Incorporated

Rise and fall times of control signals are 100 ns. Control signals include: EN, DIA\_EN.

図 7-3. SNS Timing Characteristics Definitions

15

# 8 Detailed Description

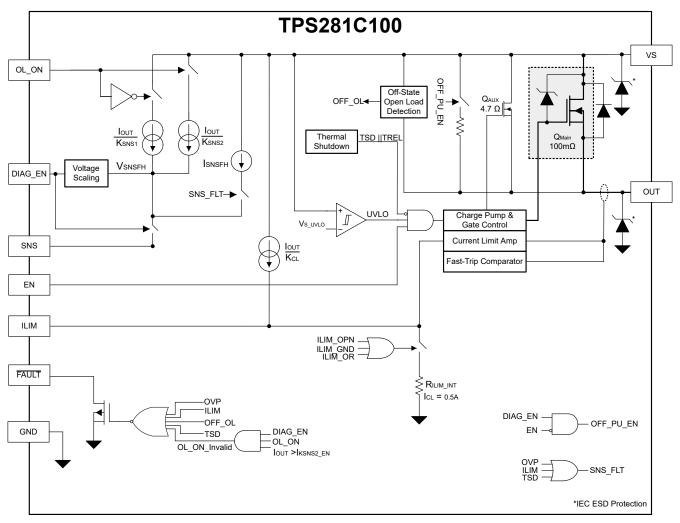

### 8.1 Overview

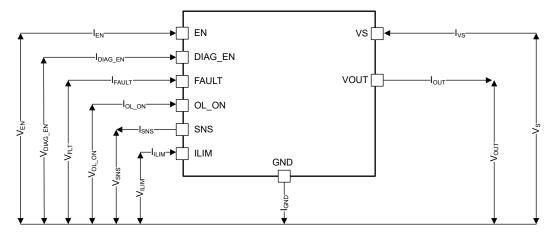

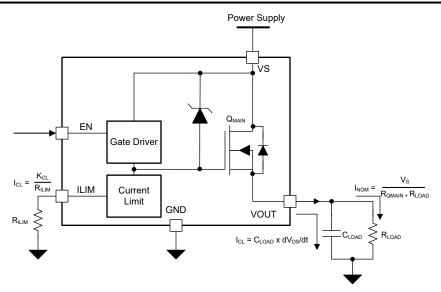

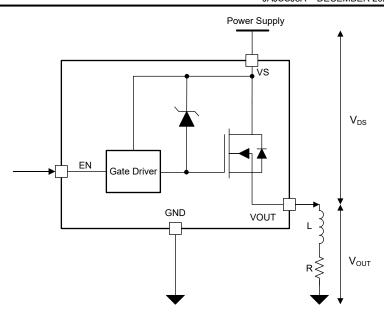

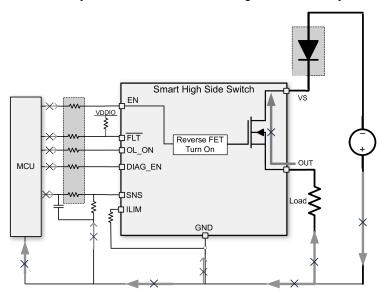

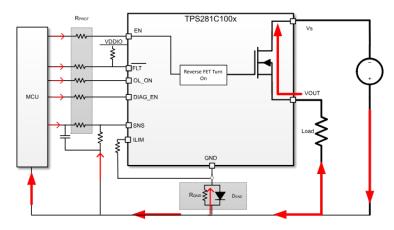

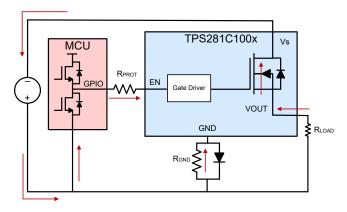

The TPS281C100 is a single-channel, fully-protected, high-side power switch with an integrated NMOS power FET and charge pump. Full diagnostics and high-accuracy current-sense features enable intelligent control of the load. Low logic high threshold,  $V_{IH}$ , of 1.5V on the input pins allow use of MCU's down to 1.8V. A programmable current-limit function greatly improves the reliability of the whole system. The device diagnostic reporting has two pins to support both digital status and analog current-sense output, both of which can be set to the high-impedance state when diagnostics are disabled, for multiplexing the MCU analog or digital interface among devices.

The digital status report is implemented with an open-drain structure on the fault pin. When a fault condition occurs, the pin is pulled down to GND. An external pullup is required to match the microcontroller supply level. High-accuracy current sensing allows a better real-time monitoring effect and more-accurate diagnostics without further calibration. A current mirror is used to source 1 /  $K_{SNS}$  of the load current, which is reflected as voltage on the SNS pin.  $K_{SNS}$  is a constant value across temperature and supply voltage. The SNS pin can also report a fault by forcing a voltage of  $V_{SNSFH}$  that scales with the diagnostic enable voltage so that the max voltage seen by the system's ADC is within an acceptable value. This removes the need for an external zener diode or resistor divider on the SNS pin.

The external high-accuracy current limit allows setting the current limit value by application. It highly improves the reliability of the system by clamping the inrush current effectively under start-up or short-circuit conditions. Also, it can save system costs by reducing PCB trace, connector size, and the preceding power-stage capacity. An internal current limit can also be implemented in this device. The lower value of the external or internal current-limit value is applied.

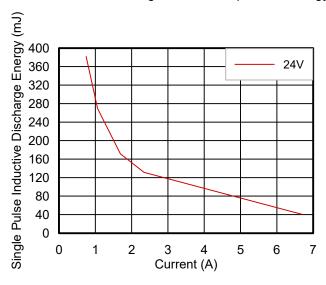

An active drain to source voltage clamp is built in to address switching off the energy of inductive loads, such as relays, solenoids, pumps, motors, and so forth. During the inductive switching-off cycle, both the energy of the power supply ( $E_{BAT}$ ) and the load ( $E_{LOAD}$ ) are dissipated on the high-side power switch itself. With the benefits of process technology and excellent IC layout, the TPS281C100x device can achieve excellent energy dissipation capacity, which can help save the external free-wheeling circuitry in most cases.

The TPS281C100x device can be used as a high-side power switch for a wide variety of resistive, inductive, and capacitive loads, including the low-wattage bulbs, LEDs, relays, solenoids, and heaters.

資料に関するフィードバック(ご意見やお問い合わせ) を送信

Copyright © 2024 Texas Instruments Incorporated

# 8.2 Functional Block Diagram

17

#### 8.3 Device Functional Modes

### 8.4 Working Mode

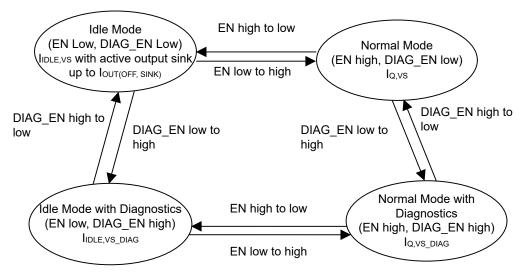

The four working modes in the device are normal mode, normal mode with diagnostics, idle mode and idle mode with diagnostics.

Normal mode is when EN is high and DIAG\_EN is low. In this mode, VS is having quiescent current of  $I_{Q,VS}$ , and the main FET is ON. With DIAG EN low, no current sense information is available through the SNS pin.

Normal mode with Diagnostics is when both EN and DIAG\_EN is high. In this mode, VS is having quiescent current of  $I_{Q,VS\_DIAG}$ , and the main FET is ON. With DIAG\_EN high, current sense information will be available through the SNS pin.

Idle mode is when both EN and DIAG\_EN low. In this mode, main FET is OFF, and VS is consuming a current of I<sub>IDLE,VS</sub>. There is extra current consumed in this state compared to the traditional shutdown state, due to having EFT detection circuitry being active. Additionally, there is a current sink at the output always active to keep the output near 0V. The output sink can sink up to I<sub>OLIT(OFF,SINK)</sub>.

Idle mode with diagnostics is when EN is low and DIAG\_EN is high. In this mode, main FET is OFF, and VS is consuming a current of I<sub>IDLE,VS\_DIAG</sub>. With DIAG\_EN high, the output pullup circuitry is active for open-load and short-to-VS detection, and there is no active output sink.

図 8-1. Work-Mode State Machine

### 8.5 Feature Description

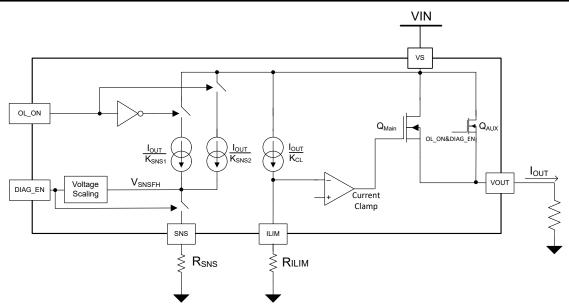

#### 8.5.1 Accurate Current Sense

The current-sense function is internally implemented, which allows a better real-time monitoring effect and more-accurate diagnostics without further calibration. A current mirror is used to source 1 /  $K_{SNS}$  of the load current, flowing out to the external resistor between the SNS pin and GND, and reflected as voltage on the SNS pin.

$K_{SNS}$  is the ratio of the output current and the sense current. The accuracy values of  $K_{SNS}$  quoted in the electrical characteristics do take into consideration temperature and supply voltage. Each device was internally calibrated while in production, so post-calibration by users is not required in most cases.

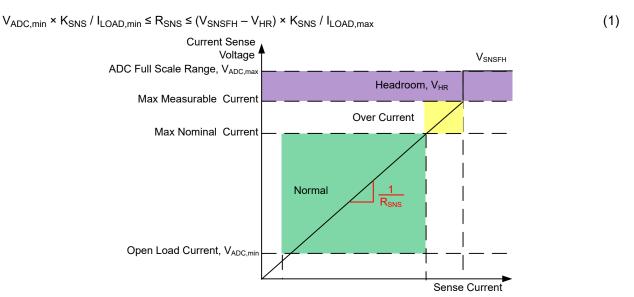

The maximum voltage out on the SNS pin is clamped to V<sub>SNSFH</sub> which is the fault voltage level. In order to make sure that this voltage is not higher than the system can tolerate, TI has correlated the voltage coming in on the DIAG\_EN pin with the maximum voltage out on the SNS pin. If DIAG\_EN is between  $V_{IH}$  and 3.3 V, the maximum output on the SNS pin will be ~3.3 V. However, if the voltage at DIAG\_EN is above 3.3 V, then the fault SNS voltage, V<sub>SNSFH</sub>, will track that voltage up to 5 V. This is done because the GPIO voltage output that is powering the diagnostics through DIAG\_EN, will be close to the maximum acceptable ADC voltage within the same microcontroller. Therefore, the sense resistor value, R<sub>SNS</sub>, can be chosen to maximize the range of currents needed to be measured by the system. The R<sub>SNS</sub> value should be chosen based on application need. The maximum usable R<sub>SNS</sub> value is bounded by the ADC minimum acceptable voltage, V<sub>ADC.min</sub>, for the smallest load current needed to be measured by the system, I<sub>LOAD,min</sub>. The minimum acceptable R<sub>SNS</sub> value has to ensure the V<sub>SNS</sub> voltage is below the V<sub>SNSFH</sub> value so that the system can determine faults. This difference between the maximum readable current through the SNS pin,  $I_{LOAD,max} \times R_{SNS}$ , and the  $V_{SNSFH}$  is called the headroom voltage, V<sub>HR</sub>. The headroom voltage is determined by the system but is important so that there is a difference between the maximum readable current and a fault condition. Therefore, the minimum RSNS value has to be the V<sub>SNSFH</sub> minus the V<sub>HR</sub> times the sense current ratio, K<sub>SNS</sub> divided by the maximum load current the system needs to measure,  $I_{LOAD,max}$ . This boundary equation can be seen in  $\pm 1$ .

図 8-2. Voltage Indication on the Current-Sense Pin

The maximum current the system wants to read,  $I_{LOAD,max}$ , needs to be below the current limit threshold because once the current limit threshold is tripped the  $V_{SNS}$  value will go to  $V_{SNSFH}$ . Additionally, currents being measured should be below 4 A to ensure that the current sense output is not saturated.

資料に関するフィードバック(ご意見やお問い合わせ)を送信

19

図 8-3. Current-Sense and Current-Limit Block Diagram

Since this scheme adapts based on the voltage coming in from the MCU. There is no need to have a zener diode on the SNS pin to protect from high voltages.

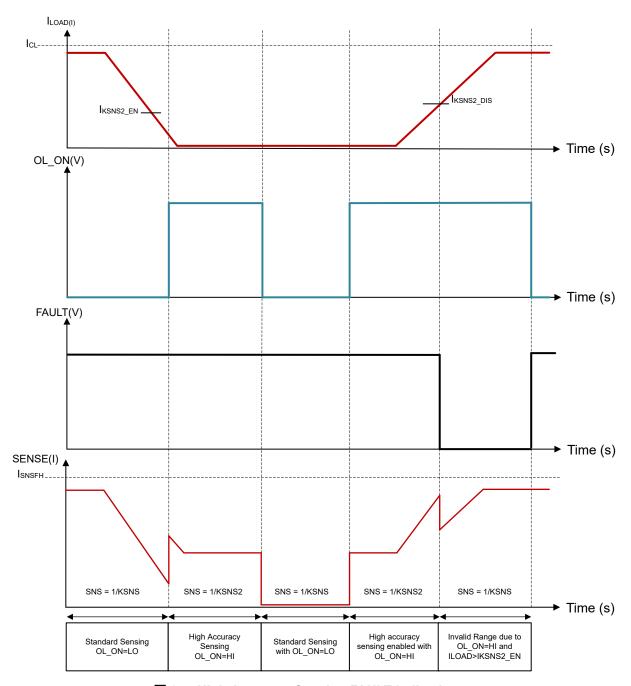

#### 8.5.1.1 High Accuracy Sense Mode

In some applications, having accurate current sensing at lower load currents can be critical to distinguish between a real load and a fault scenario such as an open load condition(Wire-Break). To address this challenge, TPS281C100 implements a high accuracy sense mode that enables customers to achieve  $\pm 12.5\%$  at 4mA load. This mode will be activated when diagnostics are enabled(DIAG\_EN=HI), OL\_ON = HI and  $I_{Load} < I_{KSNS2\_EN}$ . To achieve this high accuracy , the device increases its main path resistance to improve its sense accuracy while high accuracy sensing is active. TI recommends users to disable this accuracy sense mode by setting OL\_ON=LO if the load starts to increase beyond 20 mA. This will proactively prevent any higher power dissipation states.

In other scenarios such as a sudden load step where the system might not be fast enough to react to the change in SNS output current. For this case, in order to prevent a high-power dissipation state given by the increased resistance. TPS281C100 senses the load flowing through the VS to VOUT path to be less than  $I_{KSNS2\_DIS}$ . If the load increases beyond  $I_{KSNS2\_DIS}$  the FET resistance will revert back to its lowest resistance and high accuracy sense mode will be disabled. This will result in FAULT being asserted to signal that high accuracy sense mode has been disabled. This will ensure the lowest power dissipation when higher loads are being driven. In addition to this, the user can PWM the OL\_ON pin to disable the high resistance mode and minimize power losses further.

However, even if accuracy is achieved by the device; Depending on the current sense ratio, system ADCs can struggle to measure lower load currents accurately due to the low voltages that would need to be read by the ADC. As an example, a 6 mA  $I_{Load}$  will be represented as ~7.5 mV using RSNS=1kOhm with a current sense ratio of 800. For a 10-bit 5 V ADC the 7.5 mV output is just over 1 LSB (4.88 mV). This does not provide enough margin to accurately measure this current for the ADC and likely a higher resolution would need to be used.

Therefore, in order to enable lower ADC resolution requirements and to accurately sense low load currents when operating in high accuracy sense mode, TPS281C100 decreases its current sense ratio to 24. With a sense ratio of 24, the 6 mA  $I_{Load}$  will be represented as 250 mV using RSNS=1kOhm when operating in high accuracy sense mode. This equals to 51 LSBs of margin for the same 10-bit ADC or even for an 8-bit ADC the output would still provide > 12 LSBs of headroom.

Full Protection and Diagnostics for full device states.

表 8-1. Current Sensing Operation Modes

| Conditions                                 | EN | VOUT | OL_ON | KSNS | SNS                                      | FAULT | Behavior                                                                                                                                       | Recovery                                                                       |

|--------------------------------------------|----|------|-------|------|------------------------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| Normal                                     | L  | L    | L     | 800  | 0                                        | Hi-Z  | Normal                                                                                                                                         |                                                                                |

| Standard Sensing                           | Н  | Н    | L     | 800  | I <sub>Load</sub> /<br>K <sub>SNS</sub>  | Hi-Z  | Normal                                                                                                                                         |                                                                                |

| High Accuracy<br>Sense<br>Normal Operation | Н  | Н    | Н     | 24   | I <sub>Load</sub> /<br>K <sub>SNS2</sub> | Hi-Z  | Enables low sense ratio for high accuracy sensing and FAULT stays Hi-Z since valid condition is met I <sub>Load</sub> <i<sub>KSNS2_EN.</i<sub> |                                                                                |

| High Accuracy<br>Sense<br>Invalid Range    | Н  | Н    | Н     | 800  | I <sub>Load</sub> /<br>K <sub>SNS</sub>  | L     | FAULT is asserted signaling that high accuracy sensing is not enabled since I <sub>Load</sub> >I <sub>KSNS2_DIS</sub>                          | Clears when load falls below  I <sub>KSNS2_EN</sub> or  OL_ON is reset to  LO. |

資料に関するフィードバック(ご意見やお問い合わせ)を送信

21

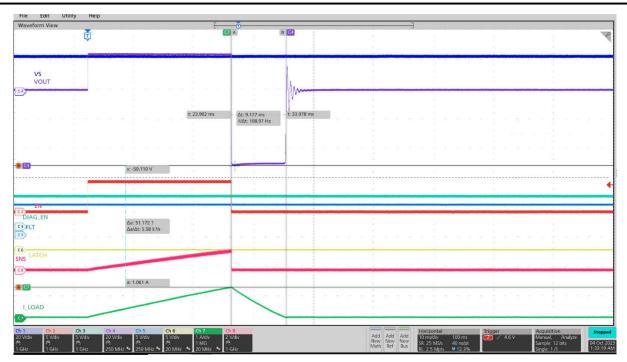

図 8-4. High Accuracy Sensing FAULT Indication

### 8.5.2 Programmable Current Limit

A high-accuracy current limit allows higher reliability, which protects the power supply during short circuit or power up. Also, it can save system costs by reducing PCB traces, connector size, and the capacity of the preceding power stage.

資料に関するフィードバック(ご意見やお問い合わせ)を送信

Copyright © 2024 Texas Instruments Incorporated

22

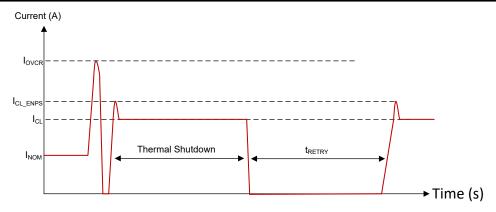

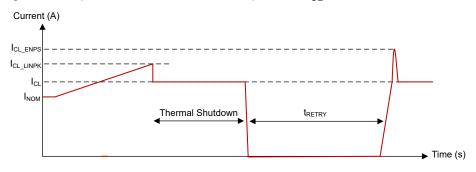

Current limit offers protection from overstressing to the load and integrated power FET. Current limit holds the current at the set value, and pulls up the SNS pin to  $V_{SNSFH}$  and asserts the  $\overline{FAULT}$  pin as diagnostic reports. The two current-limit thresholds are:

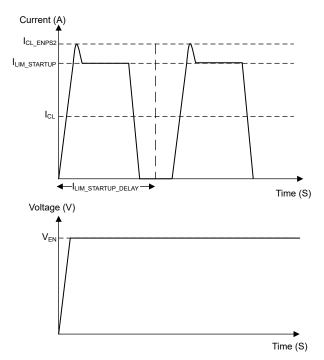

- External programmable current limit: An external resistor, R<sub>ILIM</sub>is used to set the channel current limit. When