www.tij.co.jp JAJA374

# 4.5V~18V、3A出力、FET内蔵、 同期降圧型スイッチャ(SWIFT™)

# 特長

- 高速過渡応答を可能にするD-CAP2™モード

- 低出力リップルによりセラミック出力コンデンサ を使用可能

- 幅広いV<sub>CC</sub>入力電圧範囲:4.5V~18V

- 幅広いV<sub>IN</sub>入力電圧範囲:2.0V~18V

- 出力電圧範囲: 0.76V~5.5V

- 低デューティ・サイクルのアプリケーションに対し て最適化された高効率の内蔵FET

- 120m $\Omega$  (ハイサイド) および70m $\Omega$  (ローサイド)

- 高効率、シャットダウン時10µA未満の消費電流

- 高い初期バンドギャップ・リファレンス精度

- 調整可能なソフト・スタート

- プリバイアス対応のソフト・スタート

- スイッチング周波数 (f<sub>SW</sub>):700kHz

- サイクル毎の過電流制限

- パワー・グッド出力

# アプリケーション

- 幅広い範囲の低電圧システム用アプリケーション

- 一 デジタル・テレビ用電源

- 高精細Blu-ray Disc™プレーヤー

- ニ ネットワーク・ホーム・ターミナル

- 一 デジタル・セットトップ・ボックス(STB)

# 概要

TPS54325は、適応型オン時間およびD-CAP2™モードに対応した同期バック・コンバータです。TPS54325を採用することで、各種機器の電源バス・レギュレータに対して、コスト効果が高く、部品数の少ない、低スタンバイ電流のソリューションを実現できます。TPS54325の主制御ループではD-CAP2™モード制御を使用し、外部部品なしで非常に高速な過渡応答が得られます。また、TPS54325には、POSCAP/SP-CAPなどの低ESR(等価直列抵抗)出力コンデンサだけでなく、超低ESRのセラミック・コンデンサにも対応できる、独自の回路が採用されています。TPS54325は、4.5V~18VのVCC入力、および2.0V~18VのVIN入力電源電圧により動作します。出力電圧は、0.76V~5.5Vの

SWIFT, D-CAP2, PowerPADは、テキサス・インスツルメンツの登録商標です。Blue-ray Discは、Blue-ray Disc社の登録商標です。

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ (日本TI) が英文から和文へ翻訳して作成したものです。

資料によっては正規英語版資料の更新に対応していないものがあります。 日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補 助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料を ご確認下さい。

TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

SLVS932A 翻訳版

範囲でプログラミングできます。また、調整可能なスロー・ス タート時間と、パワー·グッド機能も備えています。TPS54325 は14ピンのHTSSOPパッケージで提供され、-40℃~85℃の温 度範囲で動作するように設計されています。

# 静電気放電対策

これらのデバイスは、限定的なESD (静電破壊) 保護機能を 内蔵しています。保存時または取り扱い時に、MOSゲートに 対する静電破壊を防止するために、リード線どうしを短絡して おくか、デバイスを導電性のフォームに入れる必要があります。

### 製品情報(1)

| T <sub>A</sub> | パッケージ <sup>(2)(3)</sup> | オーダー可能な部品番号  | 出荷形態、<br>数量  | エコ・プラン            |  |

|----------------|-------------------------|--------------|--------------|-------------------|--|

| –45°C ∼ 85°C   | PowerPAD™               | TPS54325PWP  | チューブ         | Green             |  |

| _45 C ~ 65 C   | (HTSSOP) – PWP          | TPS54325PWPR | テープ・リール、3000 | (RoHS & no Sb/Br) |  |

- (1) 最新のパッケージおよびご発注情報については、このドキュメントの巻末にある「付録:パッケージ・オプション」を参照するか、 TIのWebサイト(www.ti.comまたはwww.tij.co.jp)をご覧ください。

(2) パッケージ図面、熱特性データ、記号の意味については、www.ti.com/packagingを参照してください。

(3) すべてのパッケージ・オプションがCu NIPdAuリード/ボール仕上げとなっています。

## 絶対最大定格

動作温度範囲内(特に記述のない限り)(1)

|                  |                                |                                           | VALUE              | 単位 |

|------------------|--------------------------------|-------------------------------------------|--------------------|----|

|                  |                                | V <sub>IN</sub> , V <sub>CC</sub> , EN    | <b>−</b> 0.3 ~ 20  | V  |

|                  |                                | $V_{BST}$                                 | <b>−</b> 0.3 ~ 26  | V  |

| <b>.</b> ,       | Input valtage venge            | V <sub>BST</sub> (vs SW1, SW2)            | <b>−</b> 0.3 ∼ 6.5 | V  |

| V <sub>I</sub>   | Input voltage range            | V <sub>FB</sub> , V <sub>O</sub> , SS, PG | <b>−</b> 0.3 ∼ 6.5 | V  |

|                  |                                | SW1, SW2                                  | <b>−</b> 2 ~ 20    | V  |

|                  |                                | SW1, SW2 (10 ns transient)                | −3 ~ 20            | V  |

| V                | O desidentile and many         | V <sub>REG5</sub>                         | <b>−</b> 0.3 ∼ 6.5 | V  |

| Vo               | Output voltage range           | P <sub>GND1</sub> , P <sub>GND2</sub>     | -0.3 ~ 0.3         | V  |

| $V_{diff}$       | Voltage from GND to POWERPAD   | ,                                         | -0.2 ~ 0.2         | V  |

| ECD watin a      |                                | Human Body Model (HBM)                    | 2                  | kV |

| ESD rating       | Electrostatic discharge        | Charged Device Model (CDM)                | 500                | V  |

| TJ               | Operating junction temperature | <b>−40</b> ~ 150                          | °C                 |    |

| T <sub>stg</sub> | Storage temperature            | −55 ~ 150                                 | °C                 |    |

<sup>(1)</sup> 絶対最大定格以上のストレスは、致命的なダメージを製品に与えることがあります。これはストレスの定格のみについて示してあり、 このデータシートの「推奨動作条件」に示された値を越える状態での本製品の機能動作は含まれていません。絶対最大定格の状態に 長時間置くと、本製品の信頼性に影響を与えることがあります。

#### 定格消費電力(1)

(2オンス・パターンおよび銅パッド+半田)

| パッケージ | $\theta_{	extsf{JA}}$ | T <sub>A</sub> = 25℃の<br>電力定格 | T <sub>A</sub> = 85℃の<br>電力定格 |

|-------|-----------------------|-------------------------------|-------------------------------|

| PWP   | 44.5°C/W              | 2.25 W                        | 0.9 W                         |

<sup>(1)</sup>定格は、2×2のサーマル・ビア配列を持つJEDEC高熱伝導率(High K)基板に基づいています。PowerPAD™パッケージの熱特性については、 Texas Instrumentsアプリケーション・レポート (SLMA002) を参照してください。

# 推奨動作条件

動作温度範囲内(特に記述のない限り)

|                |                                |                                       | MIN  | MAX | 単位 |

|----------------|--------------------------------|---------------------------------------|------|-----|----|

| $V_{CC}$       | Supply input voltage range     |                                       | 4.5  | 18  | V  |

| $V_{IN}$       | Power input voltage range      |                                       | 2    | 18  | V  |

|                |                                | V <sub>BST</sub>                      | -0.1 | 24  |    |

|                |                                | V <sub>BST</sub> (vs SW1, SW2)        | -0.1 | 6   |    |

|                | Input voltage range            | SS, PG                                | -0.1 | 6   |    |

| .,             |                                | EN                                    | -0.1 | 18  | V  |

| VI             |                                | V <sub>O</sub> , V <sub>FB</sub>      | -0.1 | 5.5 | V  |

|                |                                | SW1, SW2                              | -1.8 | 18  |    |

|                |                                | SW1, SW2 (10 ns transient)            | -3   | 18  |    |

|                |                                | P <sub>GND1</sub> , P <sub>GND2</sub> | -0.1 | 0.1 |    |

| Vo             | Output voltage range           | $V_{REG5}$                            | -0.1 | 6   | V  |

| Io             | Output Current range           | I <sub>VREG5</sub>                    | 0    | 10  | mA |

| T <sub>A</sub> | Operating free-air temperature |                                       | -40  | 85  | °C |

| TJ             | Operating junction temperature |                                       | -40  | 125 | °C |

# 電気的特性

動作温度範囲内(特に記述のない限り)

|                      | パラメータ                                                                                                         | テスト条件                                                                      | MIN | TYP | MAX      | 単位        |

|----------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-----|-----|----------|-----------|

| SUPPLY               | CURRENT                                                                                                       | -                                                                          |     |     | <u>'</u> |           |

| I <sub>VCC</sub>     | Operating - non-switching supply current $V_{CC}$ current, $T_A = 25^{\circ}C$ , $EN = 5$ V, $V_{FB} = 0.8$ V |                                                                            |     | 850 | 1300     | μΑ        |

| I <sub>VCCSDN</sub>  | Shutdown supply current                                                                                       | V <sub>CC</sub> current, T <sub>A</sub> = 25°C, EN = 0 V                   |     |     | 10       | μΑ        |

| LOGIC TI             | HRESHOLD                                                                                                      |                                                                            |     |     |          |           |

| V <sub>ENH</sub>     | EN high-level input voltage                                                                                   | EN                                                                         | 2   |     |          | V         |

| $V_{ENL}$            | EN low-level input voltage                                                                                    | EN                                                                         |     |     | 0.4      | V         |

| V <sub>FB</sub> VOL1 | TAGE AND DISCHARGE RESISTANC                                                                                  | E                                                                          |     |     | •        |           |

|                      |                                                                                                               | T <sub>A</sub> = 25°C, V <sub>O</sub> = 1.05 V                             | 757 | 765 | 773      |           |

| $V_{FBTH}$           | V <sub>FB</sub> threshold voltage                                                                             | $T_A = 0^{\circ}C \sim 85^{\circ}C, V_O = 1.05 V^{(1)}$                    | 753 |     | 777      | mV        |

|                      |                                                                                                               | $T_A = -40^{\circ}C \sim 85^{\circ}C, V_O = 1.05V^{(1)}$                   | 751 |     | 779      |           |

| $I_{VFB}$            | V <sub>FB</sub> input current                                                                                 | V <sub>FB</sub> = 0.8 V, T <sub>A</sub> = 25°C                             |     | 0   | ±0.1     | μΑ        |

| R <sub>Dischg</sub>  | V <sub>O</sub> discharge resistance                                                                           | EN = 0 V, V <sub>O</sub> = 0.5 V, T <sub>A</sub> = 25°C                    |     | 50  | 100      | Ω         |

| V <sub>REG5</sub> OU | ITPUT                                                                                                         |                                                                            |     |     | ·        |           |

| $V_{VREG5}$          | V <sub>REG5</sub> output voltage                                                                              | $T_A = 25$ °C, 6.0 V < $V_{CC}$ < 18 V, 0 < $I_{VREG5}$ < 5 mA             | 5.3 | 5.5 | 5.7      | V         |

| $V_{LN5}$            | Line regulation                                                                                               | 6.0 V < V <sub>CC</sub> < 18 V, I <sub>VREG5</sub> = 5 mA                  |     |     | 20       | mV        |

| $V_{LD5}$            | Load regulation                                                                                               | 0 mA < I <sub>VREG5</sub> < 5 mA                                           |     |     | 100      | mV        |

| I <sub>VREG5</sub>   | Output current                                                                                                | $V_{CC} = 6 \text{ V}, V_{REG5} = 4.0 \text{ V}, T_A = 25^{\circ}\text{C}$ |     | 70  |          | mA        |

| MOSFET               |                                                                                                               |                                                                            |     |     |          |           |

| R <sub>dsonh</sub>   | High side switch resistance                                                                                   | 25°C, V <sub>BST</sub> - SW1, SW2 = 5.5 V                                  |     | 120 |          | $m\Omega$ |

| R <sub>dsonl</sub>   | Low side switch resistance                                                                                    | 25°C                                                                       |     | 70  |          | $m\Omega$ |

| CURREN               | T LIMIT                                                                                                       |                                                                            |     |     |          |           |

| I <sub>ocl</sub>     | Current limit                                                                                                 | $T_A = -40^{\circ}C \sim 85^{\circ}C^{(1)}$                                | 3.5 | 4.1 |          | Α         |

<sup>(1)</sup> 実製品の検査は行っていません。

## 電気的特性

動作温度範囲内(特に記述のない限り)

| パラメータ                 |                                                      | マータ テスト条件                                       |      |       | MAX  | 単位 |

|-----------------------|------------------------------------------------------|-------------------------------------------------|------|-------|------|----|

| THERMA                | L SHUTDOWN                                           | •                                               |      |       | •    |    |

| +                     | The same of the defendence the selection             | Shutdown temperature (1)                        |      | 150   |      | 20 |

| T <sub>SDN</sub>      | Thermal shutdown threshold                           | Hysteresis (1)                                  |      | 25    |      | °C |

| ON-TIME               | TIMER CONTROL                                        | ·                                               | •    |       | •    |    |

| T <sub>ON</sub>       | On time                                              | V <sub>IN</sub> = 12 V, V <sub>O</sub> = 1.05 V |      | 145   |      | ns |

| T <sub>OFF(MIN)</sub> | Minimum off time                                     | $T_A = 25^{\circ}C, V_{FB} = 0.7 V$             |      | 260   |      | ns |

| SOFT ST               | ART                                                  | ·                                               |      |       |      |    |

| I <sub>SSC</sub>      | SS charge current                                    | V <sub>SS</sub> = 0 V                           | 1.4  | 2.0   | 2.6  | μΑ |

| I <sub>SSD</sub>      | SS discharge current                                 | V <sub>SS</sub> = 0.5 V                         | 0.1  | 0.2   |      | mA |

| POWER (               | GOOD                                                 |                                                 |      |       |      |    |

|                       | DO there also let                                    | V <sub>FB</sub> rising (good)                   | 85   | 90    | 95   | 0/ |

| $V_{THPG}$            | PG threshold                                         | V <sub>FB</sub> falling (fault)                 |      | 85    |      | %  |

| I <sub>PG</sub>       | PG sink current                                      | PG = 0.5 V                                      | 2.5  | 5     |      | mA |

| OUTPUT                | UNDERVOLTAGE AND OVERVOL                             | TAGE PROTECTION                                 | ·    |       | •    |    |

| V <sub>OVP</sub>      | Output OVP trip threshold                            | OVP detect                                      | 115  | 120   | 125  | %  |

| T <sub>OVPDEL</sub>   | Output OVP prop delay                                |                                                 |      | 5     |      | μs |

| V                     | Output LIVE trip throubold                           | UVP detect                                      | 65   | 70    | 75   | %  |

| $V_{UVP}$             | Output UVP trip threshold                            | Hysteresis                                      | 10   |       |      | 70 |

| T <sub>UVPDEL</sub>   | Output UVP delay                                     |                                                 |      | 0.25  |      | ms |

| T <sub>UVPEN</sub>    | Output UVP enable delay                              | Relative to soft-start time                     |      | x 1.7 |      |    |

| UVLO                  |                                                      | _                                               |      |       |      |    |

| V                     | LIVI O threehold                                     | Wake up V <sub>REG5</sub> voltage               | 3.45 | 3.70  | 3.95 | V  |

| $V_{UVLO}$            | UVLO threshold  Hysteresis V <sub>REG5</sub> voltage |                                                 | 0.15 | 0.25  | 0.35 | V  |

<sup>(1)</sup> 実製品の検査は行っていません。

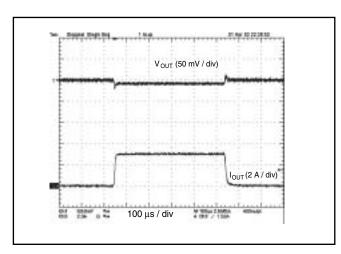

# 製品情報

# ピン配置

## 端子機能

| TERMINAL     |        |                                                                                                        |  |  |  |  |

|--------------|--------|--------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME         | NO.    | 説<br>· · · · · · · · · · · · · · · · · · ·                                                             |  |  |  |  |

| VO           | 1      | コンバータの出力に接続します。この端子はオン時間の調整のために使用されます。                                                                 |  |  |  |  |

| VFB          | 2      | コンバータのフィードバック入力。フィードバック抵抗デバイダが接続されます。                                                                  |  |  |  |  |

| VREG5        | 3      | 5.5V電源出力。コンデンサ (標準 1µF) をこの端子からGND間に接続する必要があります。                                                       |  |  |  |  |

| SS           | 4      | ソフトスタート制御端子。外付けコンデンサをこの端子とGND間に接続します。                                                                  |  |  |  |  |

| GND          | 5      | シグナルグランド端子。                                                                                            |  |  |  |  |

| PG           | 6      | オープンドレイン・パワーグット出力。                                                                                     |  |  |  |  |

| EN           | 7      | イネーブル制御入力。                                                                                             |  |  |  |  |

| PGND1, PGND2 | 8, 9   | ローサイドMOSFETのグランド・リターン。電流コンパレータの入力としても機能します。PGNDとGNDは、ICの近くで互いに強く接続する必要があります。                           |  |  |  |  |

| SW1, SW2     | 10, 11 | ハイサイドNFETおよびローサイドNFET用のスイッチ・ノード接続。電流コンパレータへの入力としても<br>機能します。                                           |  |  |  |  |

| VBST         | 12     | ハイサイドNFETゲート・ドライバの電源入力(ブースト端子)。このピンと、SW1、SW2ピンとの間に、コンデンサを接続します。VREG5ピンとVBSTピンの間には、内部でPNダイオードが接続されています。 |  |  |  |  |

| VIN          | 13     | パワー入力であり、ハイサイドNFETのドレインに接続されています。                                                                      |  |  |  |  |

| VCC          | 14     | 制御回路用の5V内部リニア・レギュレータの電源入力。                                                                             |  |  |  |  |

| PowerPAD™    | 裏側     | パッケージのサーマル・パッド。適切な放熱を実現するために、半田付けする必要があります。PGNDに接続してください。                                              |  |  |  |  |

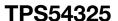

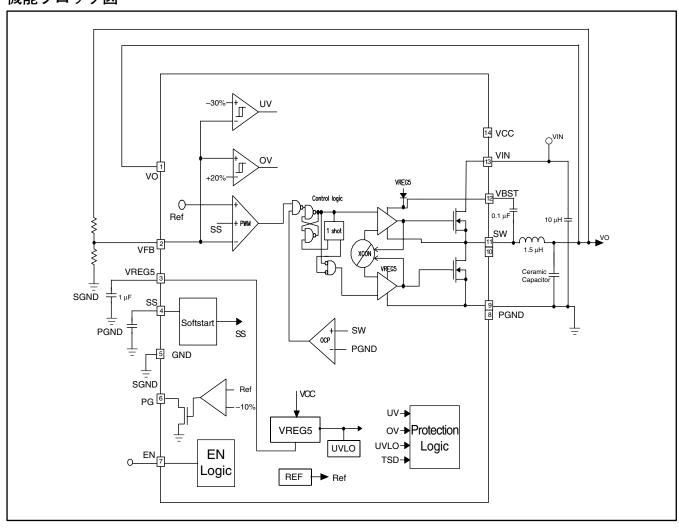

# 機能ブロック図

### 概要

TPS54325は、2つのNチャネルMOSFETを内蔵した、3Aの同期降圧型(バック)コンバータです。D-CAP2™モード制御を使用して動作します。D-CAP2™制御の高速過渡応答により、特定レベルの性能を満たすために必要な出力容量が小さくて済みます。独自の内部回路により、セラミックおよび特殊なポリマー・タイプを含めた低ESR出力コンデンサを使用可能です。

## 詳細説明

#### PWM動作

TPS54325のメイン制御ループは、独自のD-CAP2™モード制御をサポートする適応型オン時間パルス幅変調 (PWM) コントローラとなっています。D-CAP2™モード制御は、一定オン時間制御を、擬似固定周波数で外部部品数の少ない構成を可能にする内部補償回路と組み合わせたもので、低ESRコンデンサとセラミック出力コンデンサの両方を使用できます。出力にほとんどリップルがない場合でも安定して動作します。

各サイクルの開始時に、ハイサイドMOSFETがオンになります。内部のワンショット・タイマが終了すると、このMOSFETがオフになります。このワンショット・タイマの時間は、入力電圧範囲内で擬似固定周波数を維持するために、コンバータの入力電圧(VIN)と出力電圧(VO)によって設定されます。そのため、これは適応型オン時間制御と呼ばれます。帰還電圧がリファレンス電圧を下回ると、ワンショット・タイマがリセットされ、ハイサイドMOSFETが再度オンになります。出力リップルをシミュレートするために、リファレンス電圧に内部ランプが追加され、これにより、D-CAP2™モード制御からESRによる出力リップルが不要になります。

#### PWM周波数と適応型オン時間制御

TTPS54325は、適応型オン時間制御方式を採用し、専用の発振器は内蔵していません。入力電圧および出力電圧を使用してオン時間ワンショット・タイマを設定することにより、700kHzの擬似定周波数で動作します。オン時間は、入力電圧に逆比例し、出力電圧に比例するため、デューティ比がVOUT/VINのとき周波数は一定となります。

## ソフト・スタートおよびプリバイアス対応ソ フト・スタート

TPS54325は、調整可能なソフト・スタート機能を備えています。ENピンが"High"になると、SSピンとGNDの間に接続されているコンデンサの充電が2.0 $\mu$ Aの電流によって開始されます。スタートアップ中には出力電圧のスムーズな制御が維持されます。スロー・スタート時間は式(1)で計算されます。VFB電圧は0.765V、SSピンのソース電流は2 $\mu$ Aです。

Tss(ms) =

$$\frac{C6(nF) \cdot Vref}{Iss(\mu A)} = \frac{C6(nF) \cdot 0.765}{2}$$

(1)

TPS54325には、出力がプリバイアスされている状態でのスタートアップ中に、出力から電流が引き出されるのを防ぐための、独自の回路が含まれています。ソフト・スタートでプリバイアス・レベルよりも高い電圧が指定された場合(内部ソフト・スタートが帰還電圧[VFB]よりも大きくなる)、コントローラは、最初のローサイドFETゲート・ドライバ・パルスを狭いオン時間で開始することにより、ゆっくりと同期整流を起動します。次に、そのオン時間が(1-D)で示される時間と一致するまで(Dは、コンバータのデューティ・サイクル)、ローサイドFETのオン時間をサイクルごとにインクリメントします。この方式により、プリバイアス出力の初期シンクを防ぐとともに、出力電圧(VO)が立ち上がり後スムーズにレギュレーション状態まで上昇し、また、制御ループがプリバイアス・スタートアップから通常モード動作へと遷移するために十分な時間が与えられます。

### パワー・グッド

TPS54325は、パワー・グッド出力を備えています。パワー・グッド機能はソフト・スタートの終了後に起動されます。出力電圧が"目標値-10%"以上に持ち上がった場合、内部のコンパレータによりパワー・グッド状態が検出され、パワー・グッド信号が"High"になります。スタートアップ時には、パワー・グッド信号のグリッチを避けるために、ソフト・スタート時間の1.7倍の時間が経過した後でパワー・グッドが開始されます。帰還電圧が"目標値-15%"を下回った場合、内部で10μsの内部遅延の経過後、パワー・グッド信号が"Low"になります。

### 出力放電制御

TPS54325では、ENが"Low"の場合、または保護機能 (OVP、UVP、UVLO、過熱保護) によってコントローラがオフ になった場合、出力が放電されます。VOとPGNDに接続されている内部の $50\Omega$  MOSFETを使用して出力を放電します。出力に負電圧が生じることを避けるために、出力放電中は内部ローサイドMOSFETがオンになりません。

## 電流保護

TPS54325では、サイクル毎に過電流制限制御が行われます。OFF状態中に、インダクタ電流が監視されます。インダクタ電流が過電流トリップ・レベルを超えている間、OFF状態が維持されます。高精度と低コストを両立するために、温度補償付きの内部MOSFET R<sub>DS(on)</sub>センス機能がサポートされています。

インダクタ電流は、PGNDピンとSW1/SW2ピンの間の電圧によってモニタされます。過電流状態では、負荷に対する電流が出力コンデンサに対する電流を超えます。そのため、通常は出力電圧が低下します。最終的には、出力電圧が低電圧保護スレッショルドを下回り、シャットダウンされます。

## 過電圧/低電圧保護

TPS54325では、抵抗で分割された帰還電圧を監視することで、出力の過電圧と低電圧を検出しています。帰還電圧が目標電圧の120%を超過すると、OVPコンパレータの出力が"High"になり、ハイサイドMOSFETドライバがOFF、ローサイドMOSFETがONになるようにラッチされます。

帰還電圧が目標電圧の70%より低くなると、UVPコンパレータ出力が"High"になり、内部のUVP遅延カウンタが動作を開始します。250µs経過後、上側と下側の両方の内部MOSFETがOFFにラッチされます。この機能は、ソフト・スタート時間の1.7倍の時間(1.7×ソフト・スタート時間)が経過した後にイネーブルになります。

### UVLO保護

TPS54325は、 $V_{REG5}$ ピンの電圧を監視する低電圧ロックアウト保護 (UVLO) 機能を備えています。 $V_{REG5}$ 電圧がUVLOスレッショルド電圧を下回ると、TPS54325がオフになります。これは非ラッチ方式の保護です。

## 過熱シャットダウン

TPS54325は、自身の温度を監視しています。温度がスレッショルド値 (標準150°C) を超えると、デバイスがシャットダウンされます。これは非ラッチ方式の保護です。

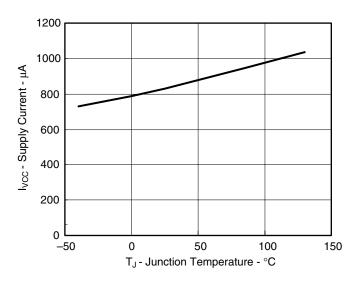

図 1. V<sub>CC</sub>消費電流 対 接合部温度

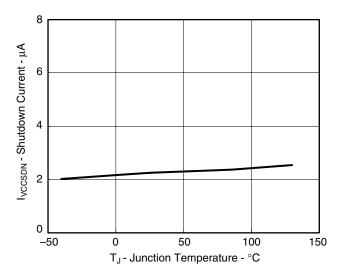

図 2. V<sub>CC</sub>シャットダウン電流 対 接合部温度

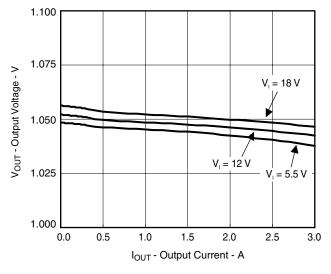

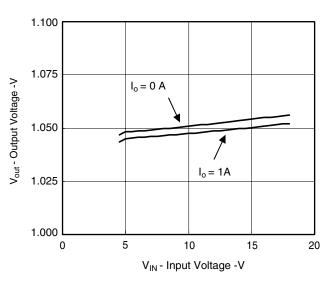

**図 4.** 1.05V出力電圧 対 入力電圧

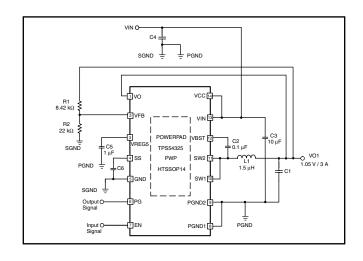

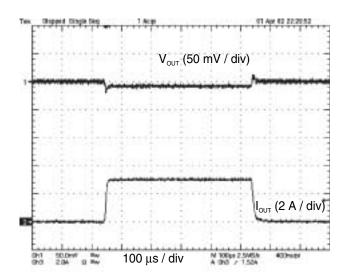

図 5.1.05V、0A~3A負荷過渡応答

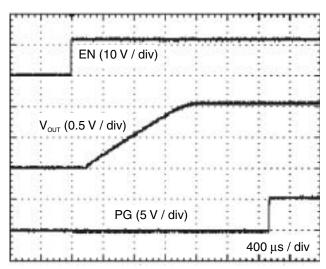

図 6. スタートアップ波形

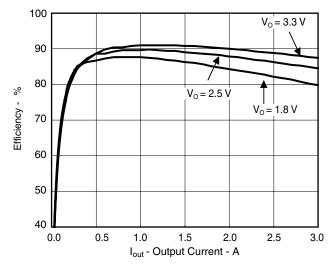

図 7. 効率 対 出力電流(V<sub>IN</sub> = 12V)

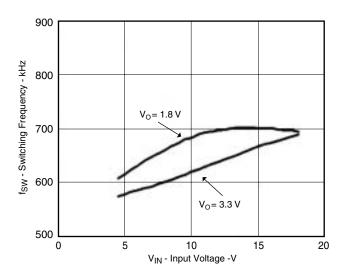

図 8. スイッチング周波数 対 入力電圧 (I<sub>O</sub> = 1A)

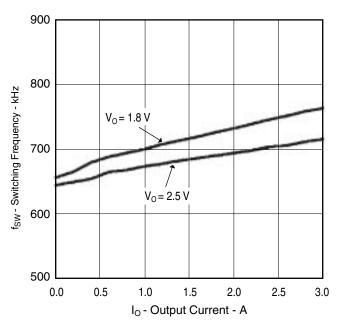

図9.スイッチング周波数 対 出力電流

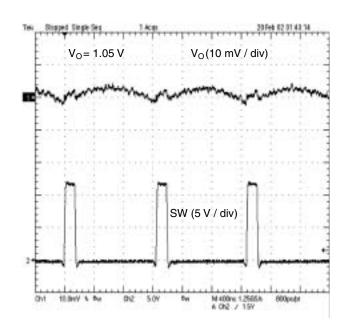

図 10. 出力電圧リップル

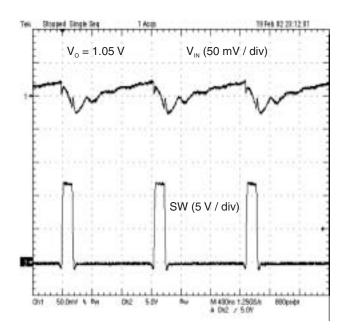

図 11. 入力電圧リップル

## 設計ガイド

## ステップ毎の設計手順

設計プロセスを開始するには、アプリケーションに対して以下のパラメータを定義する必要があります。

- 入力電圧範囲

- 出力電圧

- 出力電流

- 出力電圧リップル

- 入力電圧リップル

### 出力インダクタの選択

インダクタ値は、最大負荷で約30%のピーク・ツー・ピーク・リップル電流を提供するよう選択されます。リップル電流が大きくなると、出力リップル電圧が増加し、S/N比が向上するため、安定動作につながります。リップル電流が小さいと、出力リップル電圧が低くなります。低ESRの出力コンデンサを使用する場合、出力リップル電圧が通常は低いため、より大きなリップル電流が許容されます。係数Kindは、リップル電流のパーセンテージを表します。Kindの値が0.4を超えてはなりません。低ESR出力コンデンサを使用するときには、0.3を使用します。L1は式(2)を使って求められます。f<sub>SW</sub>には700kHzを使用します。選択したインダクタが、式(4)のピーク電流および式(5)のRMS電流の定格を満たすことを確認してください。

$$L_{O} = \frac{V_{OUT}}{V_{IN(max)}} \bullet \frac{V_{IN(max)} - V_{OUT}}{I_{OUT} \bullet f_{SW} \bullet Kind}$$

(2)

$$II_{p-p} = \frac{V_{OUT}}{V_{IN(max)}} \bullet \frac{V_{IN(max)} - V_{OUT}}{L_{O} \bullet f_{SW}}$$

(3)

$$I_{lpeak} = I_O + \frac{Il_{p-p}}{2}$$

(4)

$$I_{Lo(RMS)} = \sqrt{I_O^2 + \frac{1}{12}II_{p-p}^2}$$

(5)

#### 出力コンデンサの選択

コンデンサの値とESRによって、出力電圧リップルの大きさが決まります。セラミック出力コンデンサの使用を推奨します。式(6)~式(8)を使用して、容量値、ESR、およびRMS電流の初期見積もりを計算できます。負荷過渡が大きい場合は、リップル電流の代わりに負荷ステップを使用して最大ESRを計算します。最小 $C_0$ は、 $20\mu$ Fより大きい必要があります。

$$C_{\rm O} > \frac{1}{8 \cdot f_{\rm SW}} \cdot \left( \frac{1}{I_{\rm (ripple)}} - R_{\rm ESR} \right)$$

(6)

$$R_{ESR} < \frac{V_{O(ripple)}}{I_{l(ripple)}}$$

(7)

$$I_{CO(RMS)} = \frac{V_{OUT} \bullet (V_{IN} - V_{OUT})}{\sqrt{12} \bullet V_{IN} \bullet L_{O} \bullet f_{SW}}$$

(8)

## 入力コンデンサの選択

TPS54325には、入力デカップリング・コンデンサと、アプリケーションによってはバルク・コンデンサが必要となります。デカップリング・コンデンサには、 $10\mu$ F以上のセラミック・コンデンサを推奨します。コンデンサの電圧定格は、最大入力電圧よりも大きい必要があります。 $V_{CC}$ と $V_{IN}$ が別個である場合、 $V_{IN}$ には $10\mu$ F以上のセラミック・コンデンサを推奨します。また、 $V_{CC}$ には $0.1\mu$ F以上のセラミック・コンデンサの使用を推奨します。

## ブートストラップ・コンデンサの選択

適切な動作のためには、VBSTピンとSWピンの間に $0.1\mu$ Fのセラミック・コンデンサを接続する必要があります。セラミック・コンデンサの使用を推奨します。

#### VREG5コンデンサの選択

適切な動作のためには、VREG5ピンとGNDピンの間に $1\mu F$ のセラミック・コンデンサを接続する必要があります。セラミック・コンデンサの使用を推奨します。

### 出力電圧抵抗の選択

出力電圧は、出力ノードとVFBピンとの間の抵抗デバイダによって設定されます。公差1%以内のデバイダ抵抗を使用することを推奨します。最初は、式 (9) および式 (10) を使用して $V_{OLT}$ を計算します。

非常に軽い負荷での効率を向上させるには、より大きな値の抵抗の使用を考慮します。ただし、抵抗が大きすぎると、ノイズの影響を受けやすくなり、VFB入力電流からの電圧誤差が目立つようになります。

出力電圧が0.76V~2.5Vの場合:

$$V_{OUT} = 0.765 \bullet \left(1 + \frac{R1}{R2}\right) \tag{9}$$

出力電圧が2.5V以上の場合:

$$V_{OUT} = \left(0.763 + 0.0017 \bullet V_{OUT}\right) \bullet \left(1 + \frac{R1}{R2}\right)$$

(10)

## 熱特性について

このPowerPAD™パッケージには、外部ヒートシンクに接続するように設計された、露出したサーマル・パッドが装備されています。このサーマル・パッドは、プリント基板 (PCB) に直接半田付けする必要があります。半田付け後は、PCBをヒートシンクとして使用できます。また、サーマル・ピアを使用して、サーマル・パッドをデバイスの回路図に示された適切な銅プレーンに直接接続するか、あるいはPCB内に設計された特別なヒートシンク構造に接続することができます。この設計により、ICからの熱伝導が最適化されます。

PowerPAD™パッケージについての追加情報及びその熱放散能力の利用法については、テクニカル・ブリーフ『PowerPAD™ Thermally Enhanced Package』(TI文献番号SLMA002) およびアプリケーション・ブリーフ『PowerPAD™ Made Easy』(TI文献番号SLMA004) を参照してください。

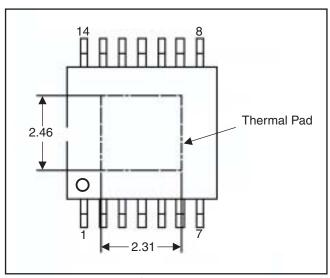

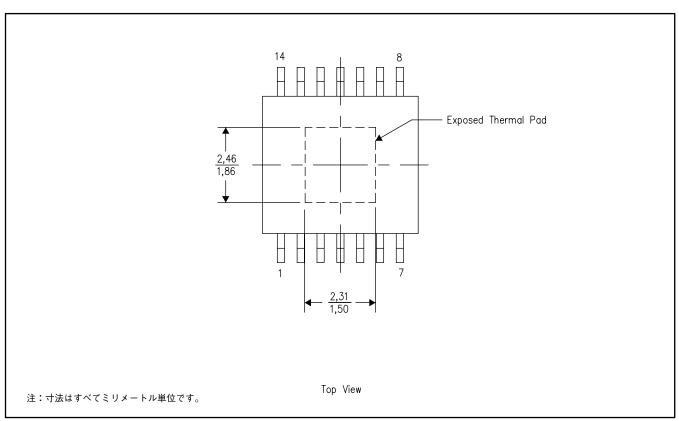

このパッケージの露出したサーマル・パッドの寸法を次の図に示します。

図12. サーマル・パッドの寸法

### レイアウトについての考慮事項

- 1. 入力スイッチング電流ループは可能な限り小さくします。

- 2. 寄生容量およびインダクタンスを低減し、放射を最小限に抑えるために、SWノードは物理的に可能な限り小さく、かつ短くします。出力とデバイスの帰還ピンとの間に、ケルビン接続を使用してください。

- 3. アナログ部品と非スイッチング部品は、スイッチング部品 から離します。

- 4. 信号グランドと電源グランドは一点接続します。

- 5. デバイスの下をスイッチング電流が流れないようにしてく ださい。

- 6. VINおよびPGNDのパターン·ラインを幅広くします。

- 7. デバイスの露出したパッドは、PGNDに半田付けする必要があります。

- 8. VREG5コンデンサは、デバイスの近くに配置し、PGNDに接続する必要があります。

- 9. 出力コンデンサは、PGNDの幅広いパターンに接続する必要があります。

- 10. 電圧帰還ループはできる限り短くし、可能であればグランド・シールドを使用します。

- 11. VFBピンに接続される電圧デバイダの下側の抵抗は、 SGNDに接続する必要があります。

- 12. VIN、SW、およびPGND接続に対しては、十分なビアを 設けることを推奨します。

- 13. VIN、SW、およびPGNDのPCBパターンは、可能な限り 幅広くします。

- 14. VINとVCCを短絡する場合、VINのパターンとVCCのパターンを幅広いパターン・ラインで接続する必要があります。

- 15. VINコンデンサは、可能な限りデバイスの近くに配置します。

## パッケージ・オプション

### 製品情報

| Orderable Device | Status (1) | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan <sup>(2)</sup>    | Lead/Ball Finish | MSL Peak Temp (3)   |

|------------------|------------|-----------------|--------------------|------|----------------|----------------------------|------------------|---------------------|

| TPS54325PWP      | ACTIVE     | HTSSOP          | PWP                | 14   | 90             | Green (RoHS &<br>no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR |

| TPS54325PWPR     | ACTIVE     | HTSSOP          | PWP                | 14   | 2000           | Green (RoHS &<br>no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR |

(1) マーケティング・ステータスは次のように定義されています。

ACTIVE:製品デバイスが新規設計用に推奨されています。

LIFEBUY:TIによりデバイスの生産中止予定が発表され、ライフタイム購入期間が有効です。

**NRND:**新規設計用に推奨されていません。デバイスは既存の顧客をサポートするために生産されていますが、TIでは新規設計にこの部品を使用することを推奨

していません。

PREVIEW:デバイスは発表済みですが、まだ生産が開始されていません。サンプルが提供される場合と、提供されない場合があります。

OBSOLETE: TIによりデバイスの生産が中止されました。

(2) エコ・プラン - 環境に配慮した製品分類プランであり、Pb-Free (RoHS)、Pb-Free (RoHS Expert) およびGreen (RoHS & no Sb/Br) があります。最新情報および製品内容の詳細については、http://www.ti.com/productcontentでご確認ください。

TBD: Pb-Free/Green変換プランが策定されていません。

Pb-Free (RoHS): TIにおける "Lead-Free" または "Pb-Free"(鉛フリー) は、6つの物質すべてに対して現在のRoHS要件を満たしている半導体製品を意味します。これには、同種の材質内で鉛の重量が0.1%を超えないという要件も含まれます。高温で半田付けするように設計されている場合、TIの鉛フリー製品は指定された鉛フリー・プロセスでの使用に適しています。

Pb-Free (RoHS Exempt): この部品は、1) ダイとパッケージの間に鉛ベースの半田バンプ使用、または 2) ダイとリードフレーム間に鉛ベースの接着剤を使用、が除外されています。それ以外は上記の様にPb-Free (RoHS) と考えられます。

**Green (RoHS & no Sb/Br):**TIにおける "Green" は、"Pb-Free"(RoHS互換) に加えて、臭素 (Br) およびアンチモン (Sb) をベースとした難燃材を含まない (均質 な材質中のBrまたはSb重量が0.1%を超えない) ことを意味しています。

(3) MSL、ピーク温度 -- JEDEC業界標準分類に従った耐湿性レベル、およびピーク半田温度です。

重要な情報および免責事項:このページに記載された情報は、記載された日付時点でのTIの知識および見解を表しています。TIの知識および見解は、第三者によって提供された情報に基づいており、そのような情報の正確性について何らの表明および保証も行うものではありません。第三者からの情報をより良く統合するための努力は続けております。TIでは、事実を適切に表す正確な情報を提供すべく妥当な手順を踏み、引き続きそれを継続してゆきますが、受け入れる部材および化学物質に対して破壊試験や化学分析は実行していない場合があります。TIおよびTI製品の供給者は、特定の情報を機密情報として扱っているため、CAS番号やその他の制限された情報が公開されない場合があります。

TIは、いかなる場合においても、かかる情報により発生した損害について、TIがお客様に1年間に販売した本書記載の問題となった TIパーツの購入価格の合計金額を超える責任は負いかねます。

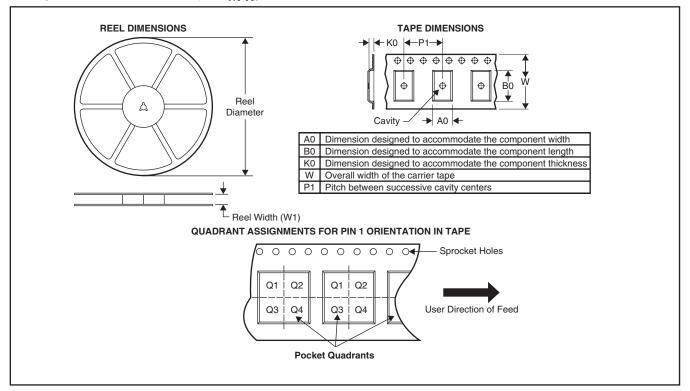

# パッケージ・マテリアル情報

## テープおよびリール・ボックス情報

#### \*All dimensions are nominal

| Device       | Package<br>Type | Package<br>Drawing | Pins | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|------|------|--------------------------|--------------------------|---------|---------|---------|------------|-----------|------------------|

| TPS54325PWPR | HTSSOP          | PWP                | 14   | 2000 | 330.0                    | 12.4                     | 7.0     | 5.6     | 1.6     | 8.0        | 12.0      | Q1               |

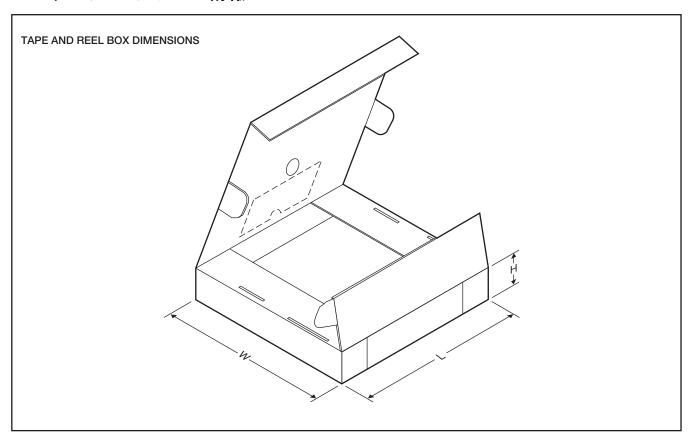

# パッケージ・マテリアル情報

#### \*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS54325PWPR | HTSSOP       | PWP             | 14   | 2000 | 346.0       | 346.0      | 29.0        |

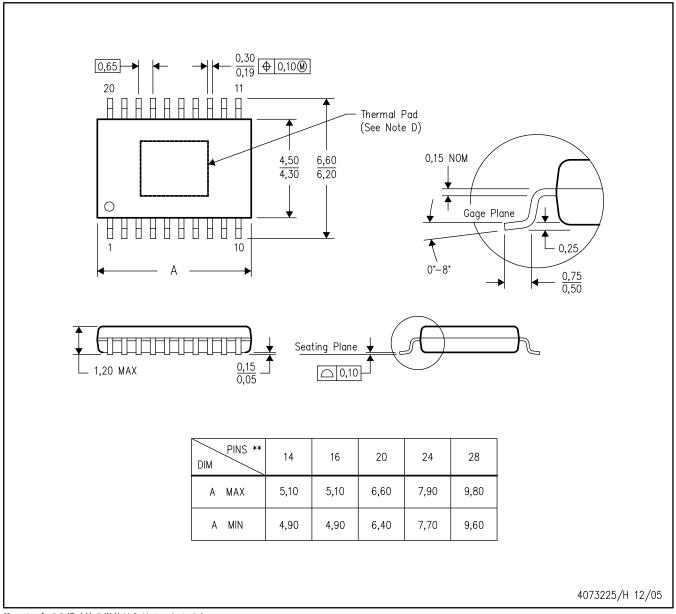

#### PWP (R-PDSO-G\*\*)

20 PINS SHOWN

- 注: A. 全ての線寸法の単位はミリメートルです。

- A. 全ての緑寸法の単位はミリメートルです。

B. 図は予告なく変更することがあります。

C. 本体寸法にはモールド・フラッシュや突起を含みません。モールド・フラッシュおよび突起は、各辺0.15を超えてはなりません。

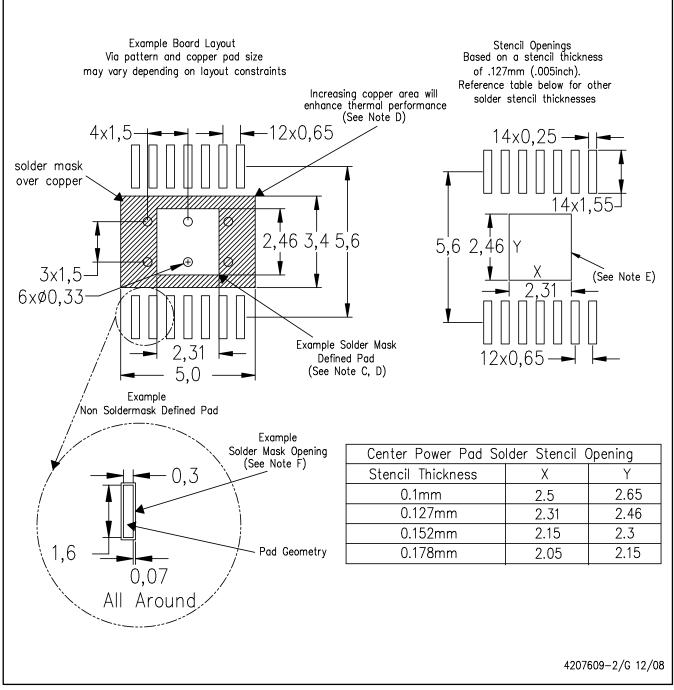

D. このパッケージは、基板上のサーマル・パッドに半田付けされるように設計されています。推奨基板レイアウトについては、テクニカル・ブリーフ『PowerPAD Thermally Enhanced Package』(TI文献番号SLMA002)を参照してください。これらのドキュメントは、ホームページwww.ti.comで入手できます。

E. JEDEC MO-153に適合しています。

## サーマルパッド・メカニカル・データ

#### PWP (R-PDSO-G14)

#### 熱特性について

このPowerPADTMパッケージには、外部ヒートシンクに直接接続するように設計された、露出したサーマル・パッドが装備されています。このサーマル・パッドは、プリント基板 (PCB) に直接半田付けする必要があります。半田付け後は、PCBをヒートシンクとして使用できます。また、サーマル・ビアを使用して、サーマル・パッドをデバイスの回路図に示された適切な銅プレーンに直接接続するか、あるいはPCB内に設計された特別なヒートシンク構造に接続することができます。この設計により、ICからの熱伝導が最適化されます。

PowerPAD<sup>TM</sup>パッケージについての追加情報及びその熱放散能力の利用法については、テクニカル・ブリーフ『PowerPAD Thermally Enhanced Package』(TI文献番号SLMA002) およびアプリケーション・ブリーフ『PowerPAD Made Easy』(TI文献番号SLMA004) を参照してください。いずれもホームページwww.ti.comで入手できます。

このパッケージの露出したサーマル・パッドの寸法を次の図に示します。

露出サーマル・パッドの寸法

#### PWP (R-PDSO-G14) PowerPAD™

- 注: A. 全ての線寸法の単位はミリメートルです。

- B. 図は予告なく変更することがあります。

- C. 中央の半田マスク定義パッドを変更しないように、回路基板組み立て図に注記を書き込んでください。

- C. 中央の中田マスク定義パットを変更しないように、回路を依組が立て図に注語を書き込んでください。

D. このパッケージは、基板上のサーマル・パッドに半田付けされるように設計されています。推奨基板レイアウトについては、テクニカル・ブリーフ

『PowerPAD Thermally Enhanced Package』(TI文献番号SLMA002、SLMA004)を参照してください。これらのドキュメントは、ホームページ

www.ti.comで入手できます。代替設計については、資料IPC-7351を推奨します。

E. レーザ切断開口部の壁面を台形にし、角に丸みを付けることで、ペーストの離れがよくなります。ステンシル設計要件については、基板組み立て

拠点にお問い合わせください。例に示したステンシル設計は、50%容積のメタルロード半田ペーストに基づいています。ステンシルに関する他の

- 推奨事項については、IPC-7525を参照してください。

- F. 信号パッド間および信号パッド周囲の半田マスク許容差については、基板組み立て拠点にお問い合わせください。

(SLVS932A)

# ご注意

日本テキサス・インスツルメンツ株式会社(以下TIJといいます)及びTexas Instruments Incorporated(TIJの親会社、以下TIJないしTexas Instruments Incorporatedを総称してTIといいます)は、その製品及びサービスを任意に修正し、改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての製品は、お客様とTIJとの間に取引契約が締結されている場合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご注文の受諾の際に提示されるTIJの標準販売契約約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応した性能を有していること、またはお客様とTIJとの間で合意された保証条件に従い合意された仕様に対応した性能を有していることを保証します。検査およびその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計について責任を負うことはありません。丁!製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。丁!製部品を使用したお客様の製品及びアプリケーションについて想定されうる危険を最小のものとするため、適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明もしておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品もしくはサービスを使用することについてライセンスを与えるとか、保証もしくは是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならない場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報に一切の変更を加えること無く、かつその情報と結び付られた全ての保証、条件、制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そのような変更された情報や複製については何の義務も責任も負いません。

TIの製品もしくはサービスについてTIにより示された数値、特性、条件その他のパラメーターと異なる、あるいは、それを超えてなされた説明で当該TI製品もしくはサービスを再販売することは、当該TI製品もしくはサービスに対する全ての明示的保証、及び何らかの黙示的保証を無効にし、かつ不公正で誤認を生じさせる行為です。TIは、そのような説明については何の義務も責任もありません。

TIは、TIの製品が、安全でないことが致命的となる用途ないしアプリケーション(例えば、生命維持装置のように、TI製品に不良があった場合に、その不良により相当な確率で死傷等の重篤な事故が発生するようなもの)に使用されることを認めておりません。但し、お客様とTIの双方の権限有る役員が書面でそのような使用について明確に合意した場合は除きます。たとえてがアプリケーションに関連した情報やサポートを提供したとしても、お客様は、そのようなアプリケーションの安全面及び規制面から見た諸問題を解決するために必要とされる専門的知識及び技術を持ち、かつ、お客様の製品について、またTI製品をそのような安全でないことが致命的となる用途に使用することについて、お客様が全ての法的責任、規制を遵守する責任、及び安全に関する要求事項を満足させる責任を負っていることを認め、かつそのことに同意します。さらに、もし万一、TIの製品がそのような安全でないことが致命的となる用途に使用されたことによって損害が発生し、TIないしその代表者がその損害を賠償した場合は、お客様がTIないしその代表者にその全額の補償をするものとします。

TI製品は、軍事的用途もしくは宇宙航空アプリケーションないし軍事的環境、航空宇宙環境にて使用されるようには設計もされていませんし、使用されることを意図されておりません。但し、当該TI製品が、軍需対応グレード品、若しくは「強化プラスティック」製品としてTIが特別に指定した製品である場合は除きます。TIが軍需対応グレード品として指定した製品のみが軍需品の仕様書に合致いたします。お客様は、TIが軍需対応グレード品として指定していない製品を、軍事的用途もしくは軍事的環境下で使用することは、もっぱらお客様の危険負担においてなされるということ、及び、お客様がもっぱら責任をもって、そのような使用に関して必要とされる全ての法的要求事項及び規制上の要求事項を満足させなければならないことを認め、かつ同意します。

TI製品は、自動車用アプリケーションないし自動車の環境において使用されるようには設計されていませんし、また使用されることを意図されておりません。但し、TIがISO/TS 16949の要求事項を満たしていると特別に指定したTI製品は除きます。お客様は、お客様が当該TI指定品以外のTI製品を自動車用アプリケーションに使用しても、TIは当該要求事項を満たしていなかったことについて、いかなる責任も負わないことを認め、かつ同意します。

Copyright © 2009, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社

## 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点を遵守して下さい。

1. 静電気

素手で半導体製品単体を触らないこと。どうしても触る必要がある 場合は、リストストラップ等で人体からアースをとり、導電性手袋 等をして取り扱うこと。

弊社出荷梱包単位(外装から取り出された内装及び個装)又は製品 単品で取り扱いを行う場合は、接地された導電性のテーブル上で(導 電性マットにアースをとったもの等)、アースをした作業者が行う こと。また、コンテナ等も、導電性のものを使うこと。

マウンタやはんだ付け設備等、半導体の実装に関わる全ての装置類は、静電気の帯電を防止する措置を施すこと。

前記のリストストラップ・導電性手袋・テーブル表面及び実装装置類の接地等の静電気帯電防止措置は、常に管理されその機能が確認されていること。

#### 2. 温·湿度環境

温度:0~40 、相対湿度:40~85%で保管・輸送及び取り扱いを行うこと。(但し、結露しないこと。)

直射日光があたる状態で保管・輸送しないこと。

3. 防湿梱包

防湿梱包品は、開封後は個別推奨保管環境及び期間に従い基板実装 すること。

4. 機械的衝擊

梱包品(外装、内装、個装)及び製品単品を落下させたり、衝撃を 与えないこと。

5. 熱衝擊

はんだ付け時は、最低限260 以上の高温状態に、10秒以上さらさないこと。(個別推奨条件がある時はそれに従うこと。)

6. 汚染

はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質(硫黄、塩素等ハロゲン)のある環境で保管・輸送しないこと。 はんだ付け後は十分にフラックスの洗浄を行うこと。(不純物含有率が一定以下に保証された無洗浄タイプのフラックスは除く。)

以上