TPS543C20

JAJSDZ4B - MARCH 2017 - REVISED MAY 2018

# TPS543C20 4V<sub>IN</sub>~14V<sub>IN</sub>、40A、スタック可能、適合型内部補償搭載の同期整流降圧型SWIFT™コンバータ

## 1 特長

- 内部で補償される高度な電流モード制御: 40A POL

- 入力電圧範囲:4V~14V

- 出力電圧範囲: 0.6V~5.5V

- 内蔵の3/0.9mΩスタック式 NexFET™電源段と、 無損失のローサイド電流センシング

- 固定周波数 外部クロックまたはSYNC出力に同期

- ピン・ストラッピングによりスイッチング周波数 をプログラム可能

- スタンドアロンで300kHz~2MHz

- スタック可能で300kHz~1MHz

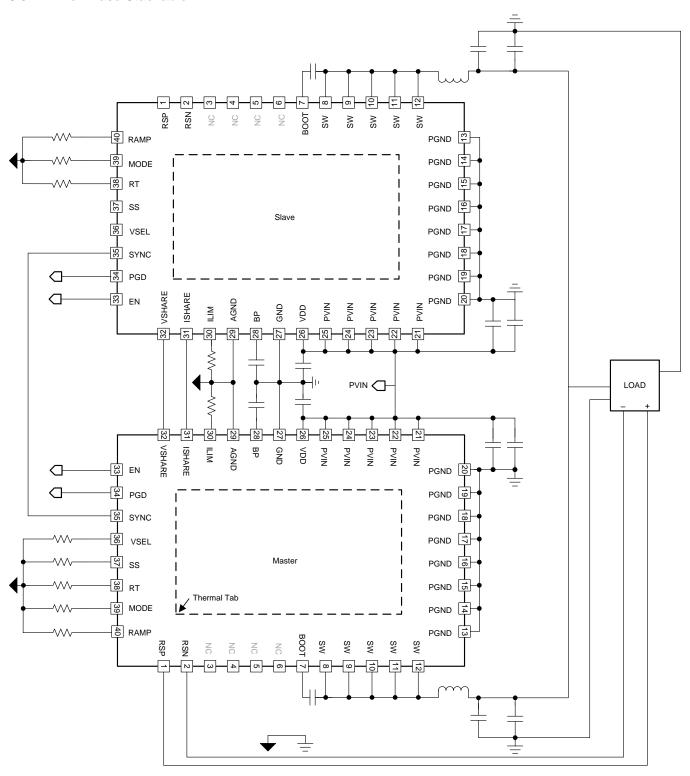

- 2xのスタックにより、電流共有、電圧共有、CLK 同期で最大80Aが可能

- ピン・ストラッピングにより基準電圧を0.6V~ 1.1Vにプログラム可能、精度0.5%

- 差動リモート・センシング

- プリバイアス出力への安全なスタートアップ

- 高精度のヒカップ電流制限

- 非同期パルス注入(API)およびボディ・ブレーキング

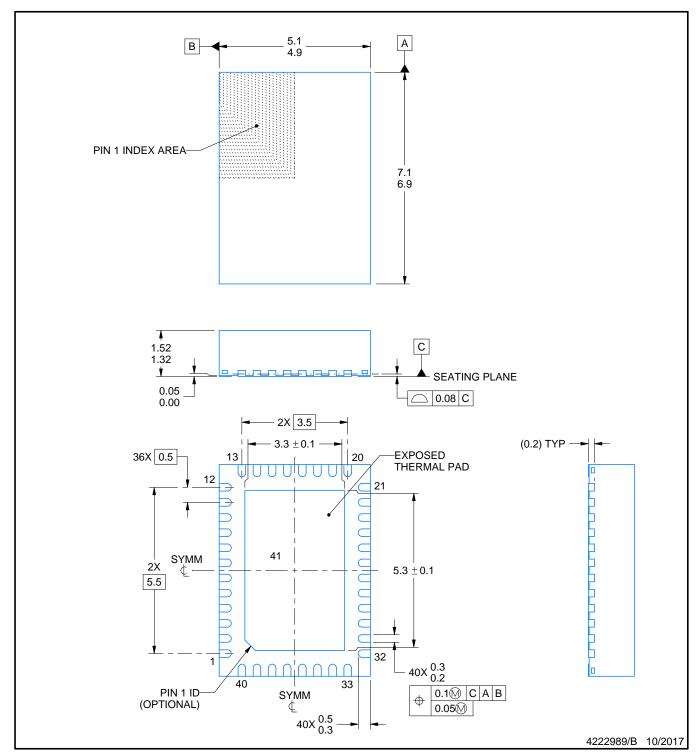

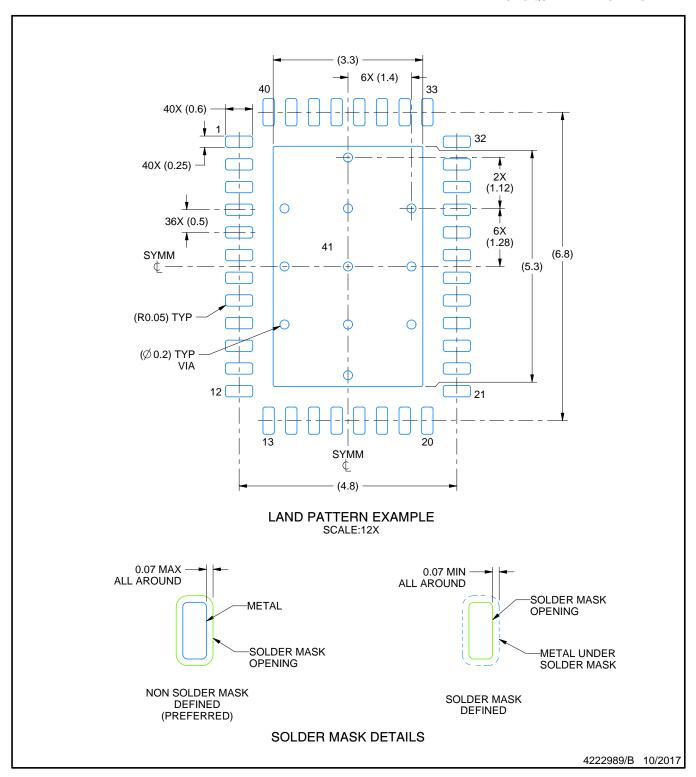

- 40ピン、5mm×7mm、0.5mmピッチ、単一サーマル・パッドのLQFNパッケージ

- WEBENCH® Power Designerにより、 TPS543C20を使用するカスタム設計を作成

# 2 アプリケーション

- 無線および有線の通信インフラストラクチャ機器

- エンタープライズ・サーバー、スイッチ、ルーター

- エンタープライズ・ストレージ、SSD

- ASIC、SoC、FPGA、DSPコア、I/Oレール

## 3 概要

TPS543C20は、EMIに敏感なPOL用に、内部で補償され、エミュレートされるピーク電流モード制御と、クロック同期可能な固定周波数変調器を採用しています。内部積分器と、直接増幅を行うランプ・トラッキング・ループにより、広い範囲の周波数について外部的な補償が必要なくなり、システムの設計が柔軟、高密度、単純になります。オプションのAPIおよびボディ・ブレーキングは、それぞれアンダーシュートとオーバーシュートを大きく低減し、過渡特性の改善に役立ちます。内蔵のNexFETTMMOSFETと低損失のスイッチングにより、高い効率が得られ、最高40Aを供給できます。レイアウトしやすいサーマル・パッドを備えた5mm×7mmのPowerStackTMパッケージで供給されます。2つのTPS543C20デバイスをスタックすると、最高80Aのポイント・オブ・ロード(POL)電流を供給できます。

#### 製品情報(1)

| 型番        | パッケージ          | 本体サイズ(公称)     |

|-----------|----------------|---------------|

| TPS543C20 | LQFN-CLIP (40) | 5.00mm×7.00mm |

1. 利用可能なすべてのパッケージについては、この データシートの末尾にある注文情報を参照してくださ い。

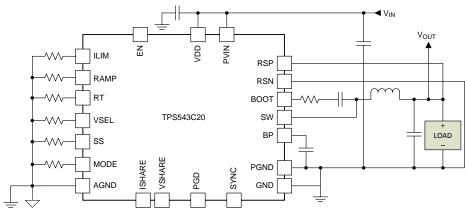

#### 概略回路図

Copyright © 2017, Texas Instruments Incorporated

**Page**

## 目次

| 1 | 特長1                             | 9  | Application and Implementation                        | 24 |

|---|---------------------------------|----|-------------------------------------------------------|----|

| 2 | アプリケーション1                       |    | 9.1 Application Information                           | 24 |

| 3 | 概要 1                            |    | 9.2 Typical Application: TPS543C20 Stand-alone Device |    |

| 4 | 改訂履歷 2                          |    | 9.3 System Example                                    | 30 |

| 5 | Device Comparison Table         | 10 | Power Supply Recommendations                          | 32 |

| 6 | Pin Configuration and Functions | 11 | Layout                                                | 33 |

| 7 | Specifications5                 |    | 11.1 Layout Guidelines                                |    |

|   | 7.1 Absolute Maximum Ratings 5  |    | 11.2 Layout Example                                   |    |

|   | 7.2 ESD Ratings                 |    | 11.3 Package Size, Efficiency and Thermal Performance |    |

|   | 7.4 Thermal Information 6       | 12 | デバイスおよびドキュメントのサポート                                    | 37 |

|   | 7.5 Electrical Characteristics  |    | <b>12.1</b> デバイス・サポート                                 |    |

|   | 7.6 Typical Characteristics11   |    | 12.2 ドキュメントの更新通知を受け取る方法                               |    |

| 8 | Detailed Description 14         |    | 12.3 コミュニティ・リソース                                      |    |

|   | 8.1 Overview                    |    | 12.4 商標                                               | 37 |

|   | 8.2 Functional Block Diagram 14 |    | 12.5 静電気放電に関する注意事項                                    | 37 |

|   | 8.3 Feature Description         |    | 12.6 Glossary                                         |    |

|   | 8.4 Device Functional Modes 15  | 13 | メカニカル、パッケージ、および注文情報                                   |    |

## 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

Revision A (September 2017) から Revision B に変更

#

| 20 | <b>117年3</b> 月発行のものから更新                                                          | Page |

|----|----------------------------------------------------------------------------------|------|

| •  | WEBENCHへのリンク 追加                                                                  | 1    |

| •  | 変更 from "DART" to "ACM" in the Detailed Description and Functional Block Diagram | 14   |

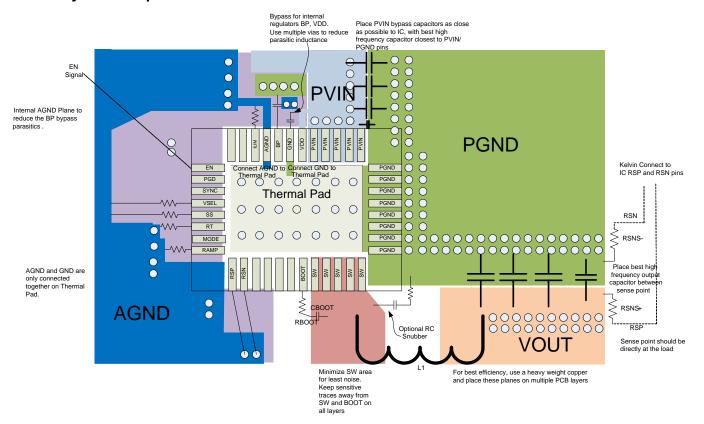

| •  | Replace figures 42 through 49 with new "Example Layout"                          | 34   |

## 5 Device Comparison Table

| DEVICE    | OUTPUT CURRENT |

|-----------|----------------|

| TPS543B20 | 25 A           |

| TPS543C20 | 40 A           |

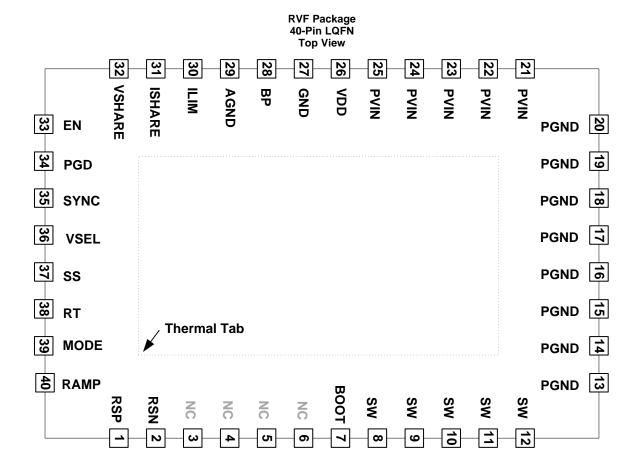

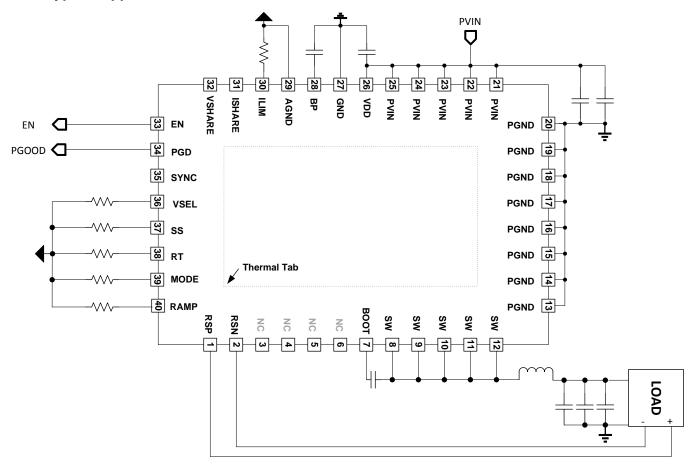

# 6 Pin Configuration and Functions

## **Pin Functions**

|         | PIN (c)     |                      |                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|---------|-------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NO.     | NAME        | I/O/P <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| 1       | RSP         | I                    | The positive input of the remote sense amplifier. Connect RSP pin to the output voltage at the load. For multi-phase configuration, the remote sense amplifier is not needed for slave devices.                                                                                                             |  |  |  |  |

| 2       | RSN         | I                    | The negative input of the remote sense amplifier. Connect RSN pin to the ground at load side. For multi-phase configuration, the remote sense amplifier is not needed for slave devices.                                                                                                                    |  |  |  |  |

| 3 – 6   | NC          |                      | Not connected                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 7       | воот        | I                    | Bootstrap pin for the internal flying high-side driver. Connect a typical 100-nF capacitor from this pin to SW. To reduce the voltage spike at SW, a BOOT resistor with a value between 1 $\Omega$ to 10 $\Omega$ may be placed in series with the BOOT capacitor to slow down turnon of the high-side FET. |  |  |  |  |

| 8 – 12  | SW          | В                    | Output of converted power. Connect this pin to the output Inductor.                                                                                                                                                                                                                                         |  |  |  |  |

| 13 – 20 | PGND        | G                    | These ground pins are connected to the return of the internal low-side MOSFET                                                                                                                                                                                                                               |  |  |  |  |

| 21 – 25 | PVIN        | I                    | Input power to the power stage. Low impedance bypassing of these pins to PGND is critical. A 10-nF to 100-nF capacitor from PVIN to PGND close to IC is required.                                                                                                                                           |  |  |  |  |

| 26      | VDD         | 1                    | Controller power supply input                                                                                                                                                                                                                                                                               |  |  |  |  |

| 27      | GND         | G                    | Ground return for the controller. This pin should be directly connected to the thermal pad on the PCB board. A 10-nF to 100-nF capacitor from PVIN to GND close to IC is required.                                                                                                                          |  |  |  |  |

| 28      | BP          | 0                    | Output of the 5 V on board regulator. This regulator powers the driver stage of the controller and must be bypassed with a minimum of 2.2 $\mu$ F to the thermal pad (power stage ground, that is, GND). Low impedance bypassing of this pin to PGND is critical.                                           |  |  |  |  |

| 29      | AGND        | G                    | GND return for internal analog circuits.                                                                                                                                                                                                                                                                    |  |  |  |  |

| 30      | ILIM        | 0                    | Current protection pin; connect a resistor from this pin to AGND sets current limit level.                                                                                                                                                                                                                  |  |  |  |  |

| 31      | ISHARE      | 1                    | Current sharing signal for multi-phase operation. Float this pin for single phase                                                                                                                                                                                                                           |  |  |  |  |

| 32      | VSHARE      | В                    | Voltage sharing signal for multi-phase operation. Float this pin for single phase.                                                                                                                                                                                                                          |  |  |  |  |

| 33      | EN          | I                    | The enable pin turns on the switcher.                                                                                                                                                                                                                                                                       |  |  |  |  |

| 34      | PGD         | 0                    | Open-drain power-good status signal which provides start-up delay after the FB voltage falls within the specified limits. After the FB voltage moves outside the specified limits, PGOOD goes low.                                                                                                          |  |  |  |  |

| 35      | SYNC        | В                    | For frequency synchronization. This pin can be configured as sync in or sync out by MODE pin and RT pin for master and slave devices.                                                                                                                                                                       |  |  |  |  |

| 36      | VSEL        | I                    | Connect a resistor from this pin to AGND to select internal reference voltage.                                                                                                                                                                                                                              |  |  |  |  |

| 37      | SS          | 0                    | Connect a resistor from this pin to AGND to select soft-start time.                                                                                                                                                                                                                                         |  |  |  |  |

| 38      | RT          | 0                    | Frequency setting pin. Connect a resistor from this pin to AGND to program the switching frequency. This pin also selects sync point for devices in stackable applications                                                                                                                                  |  |  |  |  |

| 39      | MODE        | В                    | Enable or disable API or body brake function, choose API threshold, also selects the operation mode in stackable applications                                                                                                                                                                               |  |  |  |  |

| 40      | RAMP        | В                    | Ramp level selection, with a resistor to AGND to adjust internal loop.                                                                                                                                                                                                                                      |  |  |  |  |

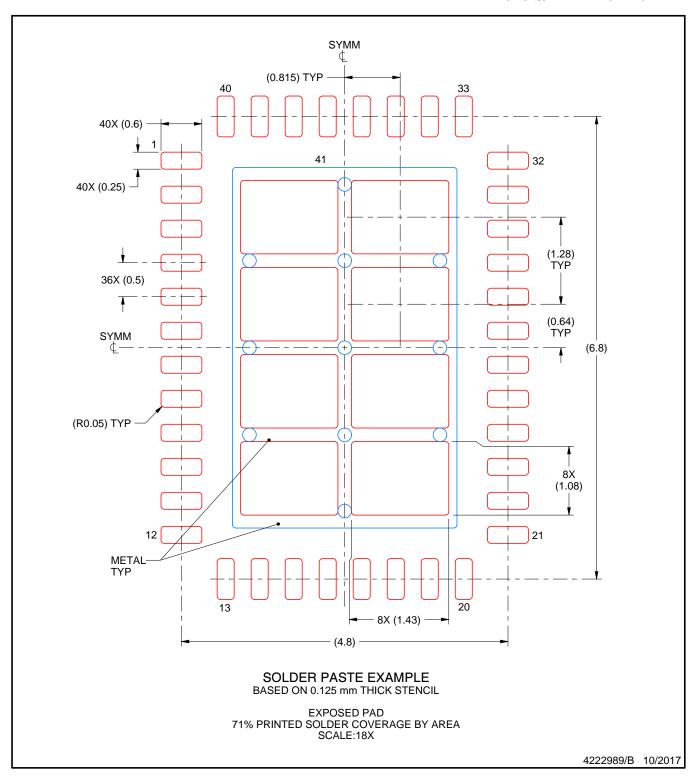

| _       | Thermal Tab | _                    | Package thermal tab, internally connected to PGND. The thermal tab must have adequate solder coverage for proper operation.                                                                                                                                                                                 |  |  |  |  |

<sup>(1)</sup> I = Input, O = Output, B = Bidirectional, P = Supply, G = Ground

## 7 Specifications

## 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)(2)

|                                             |                                            |         | MIN  | MAX  | UNIT |

|---------------------------------------------|--------------------------------------------|---------|------|------|------|

|                                             | VIN                                        |         | -0.3 | 16   |      |

| Input voltage <sup>(1)</sup> Output voltage | VIN to SW <sup>(3)</sup>                   |         |      | 20   |      |

|                                             | VDD                                        |         | -0.3 | 16   |      |

|                                             | BOOT                                       |         | -0.3 | 34.5 |      |

|                                             | DOOT to CIM                                | DC      | -0.3 | 6.5  |      |

|                                             | BOOT to SW                                 | < 10 ns | -0.3 | 7    | V    |

|                                             | VSEL, SS, MODE, RT, SYNC, EN, ISHARE, ILIM |         | -0.3 | 7    | V    |

|                                             | RSP                                        |         | -0.3 | 3.6  |      |

|                                             | RSN                                        |         | -0.3 | 0.3  |      |

|                                             | PGND, GND                                  |         | -0.3 | 0.3  |      |

|                                             | SW to PGND <sup>(3)</sup>                  | DC      | -0.3 | 20   |      |

|                                             | SW to PGND                                 | < 10 ns | -5   | 20   |      |

|                                             | BP, RAMP                                   |         | -0.3 | 7    |      |

| Output voltage                              | PGD                                        |         | -0.3 | 7    | V    |

| Output voltage PGD                          | VSHARE                                     |         | -0.3 | 3.6  |      |

| Junction tempera                            | ature, T <sub>J</sub>                      |         | -55  | 150  | °C   |

| Storage tempera                             | ture, T <sub>stg</sub>                     |         | -55  | 150  | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 7.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

| \/                 | Floatroototic disabores | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)                         | ±2500 | \/   |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±1500 | V    |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 500-V HBM is possible with the necessary precautions.

<sup>(2)</sup> All voltage values are with respect to the network ground terminal unless otherwise noted.

<sup>(3)</sup> VIN to SW and SW to PGND must not exceed 20 V.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 250-V CDM is possible with the necessary precautions.

# 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)(1)

|                       |                                            |         | MIN  | MAX                                                         | UNIT |

|-----------------------|--------------------------------------------|---------|------|-------------------------------------------------------------|------|

|                       | VIN                                        |         | 4    | 14                                                          |      |

|                       | V(N) (= Q(N)(3)                            | DC      | -0.1 | 18                                                          |      |

|                       | VIN to SW <sup>(3)</sup>                   | < 10 ns |      | 18                                                          |      |

|                       | VDD                                        |         | 4    | 16                                                          |      |

|                       | BOOT                                       |         | -0.1 | 14 18 18 18 16 23.5 5.5 6 5.5 1.7 0.1 0.1 18 18 7 7 3.6 125 |      |

|                       | DOOT to CIM                                | DC      | -0.1 |                                                             |      |

| Input voltage (2)     | BOOT to SW                                 | < 10 ns | -0.1 |                                                             | V    |

| input voltage         | VSEL, SS, MODE, RT, SYNC, EN, ISHARE, ILIM |         | -0.1 |                                                             | V    |

|                       | RSP                                        |         | -0.1 |                                                             |      |

|                       | RSN                                        |         | -0.1 | 0.1                                                         |      |

|                       | PGND, GND                                  |         | -0.1 | 0.1                                                         |      |

|                       | CW to DCND                                 | DC      | -0.1 | 18                                                          |      |

|                       | SW to FGND                                 | < 10 ns | -5   | 18                                                          |      |

| _                     | BP, RAMP                                   |         | -0.3 | 7                                                           |      |

| SW to PGND DC < 10 ns | PGD                                        |         | -0.3 | 7                                                           | V    |

|                       |                                            | -0.3    | 3.6  |                                                             |      |

| Junction temper       | rature, T <sub>J</sub>                     |         | -40  | 125                                                         | °C   |

| Storage temper        | ature, T <sub>stg</sub>                    |         | -55  | 125                                                         | °C   |

<sup>(1)</sup> Stresses beyond those listed under may cause permanent damage to the device.

## 7.4 Thermal Information

|                        |                                              | TPS543C20  |      |

|------------------------|----------------------------------------------|------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | RVF (LQFN) | UNIT |

|                        |                                              | 40 PINS    |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 28.9       | °C/W |

| $R_{\theta JC(top)}$   | Junction-to-case (top) thermal resistance    | 18.9       | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 4.1        | °C/W |

| ΨЈТ                    | Junction-to-top characterization parameter   | 1.3        | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 4.1        | °C/W |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | 1          | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

<sup>(2)</sup> All voltage values are with respect to the network ground terminal unless otherwise noted.

<sup>(3)</sup> See Layout Guidelines for VIN capacitor placement requirement to reduce MOSFET voltage stress.

# 7.5 Electrical Characteristics

|                           | PARAMETER                                                          | TEST CONDITIONS                                                         | MIN   | TYP  | MAX   | UNIT |

|---------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------|-------|------|-------|------|

| MOSFET R <sub>DS(O)</sub> | N)                                                                 |                                                                         |       |      |       |      |

| R <sub>DS(on)HS</sub>     | HS FET                                                             | VBST – VSW = 5 V, I <sub>D</sub> = 20 A, T <sub>j</sub> = 25°C          |       | 3.0  |       | mΩ   |

| R <sub>DS(on)LS</sub>     | LS FET                                                             | VDD = 5 V, I <sub>D</sub> = 20 A, T <sub>j</sub> = 25°C                 |       | 0.9  |       | mΩ   |

| t <sub>DEAD(LtoH)</sub>   | Power stage driver dead-time from Low-side off to High-side on (1) | VDD ≥ 12 V, T <sub>J</sub> = 25°C                                       |       | 12   |       | ns   |

| t <sub>DEAD(HtoL)</sub>   | Power stage driver dead-time from High-side off to Low-side on (1) | VDDN ≥ 12 V, T <sub>J</sub> = 25°C                                      |       | 15   |       | ns   |

| INPUT SUPPLY              | and CURRENT                                                        |                                                                         |       |      |       |      |

| $V_{VIN}$                 | Power stage voltage                                                |                                                                         | 4     |      | 14    |      |

| $V_{VDD}$                 | VDD supply voltage                                                 |                                                                         | 4     |      | 16    |      |

| I <sub>VDD</sub>          | VDD bias current                                                   | T <sub>A</sub> = 25°C, no load, power conversion enabled (no switching) |       | 4.3  |       | mA   |

| I <sub>VDDSTBY</sub>      | VDD standby current                                                | T <sub>A</sub> = 25°C, no load, power conversion disabled               |       | 4.3  |       | mA   |

| UNDERVOLTA                | GE LOCKOUT                                                         |                                                                         |       |      |       |      |

| V <sub>VDD_UVLO</sub>     | VDD UVLO rising threshold                                          |                                                                         |       | 3.8  |       | V    |

| V <sub>VDD_UVLO_HYS</sub> | VDD UVLO hysteresis                                                |                                                                         |       | 0.2  |       | V    |

| V <sub>VIN_UVLO</sub>     | VIN UVLO rising threshold                                          |                                                                         |       | 3.2  |       | V    |

| V <sub>VIN_UVLO_HYS</sub> | VIN UVLO hysteresis                                                |                                                                         |       | 0.2  |       | V    |

| V <sub>EN_ON_TH</sub>     | EN on threshold                                                    |                                                                         | 1.45  | 1.6  | 1.75  | V    |

| V <sub>HYS</sub>          | EN hysteresis                                                      |                                                                         | 270   | 300  | 330   | mV   |

| I <sub>EN_LKG</sub>       | EN input leakage current                                           |                                                                         | -1    | 0    | 1     | μA   |

| INTERNAL REF              | ERENCE VOLTAGE                                                     |                                                                         |       |      |       |      |

| V <sub>INTREF</sub>       | Internal REF voltage                                               | R <sub>VSEL</sub> = OPEN                                                |       | 1000 |       | mV   |

| V <sub>INTREFTOL</sub>    | Internal REF voltage tolerance                                     | $T_J = -40$ °C to 125°C                                                 | -0.5% |      | +0.5% |      |

| V <sub>INTREF_VSEL</sub>  | Internal REF voltage range                                         | Programable by VSEL (pin 36)                                            | 0.6   |      | 1.1   | V    |

| OUTPUT VOLT               | AGE                                                                |                                                                         |       |      |       |      |

| I <sub>RSP</sub>          | RSP input current                                                  | V <sub>RSP</sub> = 600 mV                                               | -1    |      | 1     | μA   |

|                           | REMOTE SENSE AMPLIFIER                                             |                                                                         | 1     |      |       |      |

| f <sub>UGBW</sub>         | Unity gain bandwidth (1)                                           |                                                                         | 5     | 8.5  |       | MHz  |

| A0                        | Open loop gain <sup>(1)</sup>                                      |                                                                         | 75    |      |       | dB   |

| SR                        | SLew rate <sup>(1)</sup>                                           |                                                                         |       | ±10  |       | V/µs |

| V <sub>ICM</sub>          | Input common mode range <sup>(1)</sup>                             |                                                                         | -0.2  |      | 1.7   | V    |

|                           |                                                                    | V <sub>RSN-VGND</sub> = 0 mV                                            | -1    |      | 1     | .,   |

| V <sub>OFFSET</sub>       | Input offset voltage <sup>(1)</sup>                                | $V_{RSN-VGND} = \pm 100 \text{ mV}$                                     | -1.9  |      | 1.9   | mV   |

<sup>(1)</sup> Specified by design. Not production tested.

# **Electrical Characteristics (continued)**

|                       | PARAMETER                                  | TES                                            | ST CONDITIONS                   | MIN TYP | MAX | UNIT |  |  |

|-----------------------|--------------------------------------------|------------------------------------------------|---------------------------------|---------|-----|------|--|--|

| SWITCHING             | G FREQUENCY                                |                                                |                                 | ·       |     |      |  |  |

|                       |                                            | V <sub>IN</sub> = 12 V, V <sub>VO</sub> = 1    | V, RT = 66.5 kΩ                 | 300     |     |      |  |  |

|                       |                                            | V <sub>IN</sub> = 12 V, V <sub>VO</sub> =      | 1 V, RT = 48.7 kΩ               | 400     |     |      |  |  |

|                       |                                            | $V_{IN} = 12 \text{ V}, V_{VO} = 12 \text{ V}$ | 1 V, RT = 39.2 kΩ               | 500     |     |      |  |  |

| _                     | V <sub>O</sub> switching frequency maximum | V <sub>IN</sub> = 12 V, V <sub>VO</sub> = 1    | V, RT = 28.0 kΩ                 | 700     |     |      |  |  |

| F <sub>SW</sub>       | frequency for multi-phase is<br>1MHz       | V <sub>IN</sub> = 12 V, V <sub>VO</sub> = 1    | V, RT = 22.6 kΩ                 | 850     |     | kHz  |  |  |

|                       |                                            | V <sub>IN</sub> = 12 V, V <sub>VO</sub> =      | 1 V, RT = 19.1 kΩ               | 1000    |     |      |  |  |

|                       |                                            | V <sub>IN</sub> = 12 V, V <sub>VO</sub> =      | 1 V, RT = 15.4 kΩ               | 1200    |     |      |  |  |

|                       |                                            | V <sub>IN</sub> = 12 V, V <sub>VO</sub> =      |                                 | 2000    |     |      |  |  |

| t <sub>ON(min)</sub>  | Minimum on-time <sup>(1)</sup>             | DRVH rising to fall                            | ing                             | 30      |     | ns   |  |  |

| t <sub>OFF(min)</sub> | Minimum off-time <sup>(1)</sup>            | DRVH falling to rising                         |                                 | 250     |     | ns   |  |  |

| ` '                   | BOOTSTRAP SWITCH                           |                                                |                                 | ·       |     |      |  |  |

| $V_{F}$               | Forward voltage                            | V <sub>BP-VBST</sub> , T <sub>A</sub> = 25°C   | C, I <sub>F</sub> = 5 mA        | 0.1     | 0.2 | V    |  |  |

| VSEL                  |                                            |                                                |                                 | ·       |     |      |  |  |

|                       |                                            | $R_{VSEL} = 0 k\Omega$                         |                                 | 0.6     |     |      |  |  |

|                       |                                            | R <sub>VSEL</sub> = 8.66 kΩ                    |                                 | 0.7     |     | V    |  |  |

|                       |                                            | R <sub>VSEL</sub> = 15.4 kΩ                    |                                 | 0.75    |     |      |  |  |

|                       |                                            | $R_{VSEL}$ = 23.7 k $\Omega$                   |                                 | 0.8     |     |      |  |  |

| \/OF!                 | latamat reference contrare                 | R <sub>VSEL</sub> = 34.8 kΩ                    |                                 | 0.85    |     |      |  |  |

| VSEL                  | Internal reference voltage                 | R <sub>VSEL</sub> = 51.1 kΩ                    |                                 | 0.9     |     |      |  |  |

|                       |                                            | R <sub>VSEL</sub> = 78.7 kΩ                    |                                 | 0.95    |     |      |  |  |

|                       |                                            | R <sub>VSEL</sub> = OPEN                       |                                 | 1       |     |      |  |  |

|                       |                                            | R <sub>VSEL</sub> = 121 kΩ                     |                                 | 1.05    |     |      |  |  |

|                       |                                            | R <sub>VSEL</sub> = 187 kΩ                     |                                 | 1.1     |     |      |  |  |

| SOFT STA              | RT                                         |                                                |                                 |         |     |      |  |  |

|                       |                                            |                                                | $R_{SS} = 0 k\Omega$            | 0.5     |     |      |  |  |

|                       |                                            |                                                | $R_{SS} = 8.66 \text{ k}\Omega$ | 1       |     |      |  |  |

|                       |                                            |                                                | $R_{SS} = 15.4 \text{ k}\Omega$ | 2       |     |      |  |  |

|                       |                                            |                                                | R <sub>SS</sub> = Open          | 4       |     |      |  |  |

|                       | On the stand time                          | V <sub>O</sub> rising from 0 V                 | $R_{SS} = 23.7 \text{ k}\Omega$ | 5       |     |      |  |  |

| t <sub>SS</sub>       | Soft-start time                            | to 95% of final set point                      | R <sub>SS</sub> = 34.8 kΩ       | 8       |     | ms   |  |  |

|                       |                                            |                                                | R <sub>SS</sub> = 51.1 kΩ       | 12      |     |      |  |  |

|                       |                                            |                                                | $R_{SS} = 78.7 \text{ k}\Omega$ | 16      |     | 1    |  |  |

|                       |                                            |                                                | R <sub>SS</sub> = 121 kΩ        | 24      |     |      |  |  |

|                       |                                            |                                                | R <sub>SS</sub> = 187 kΩ        | 32      |     |      |  |  |

| POWER OF              | N DELAY                                    |                                                |                                 | ·       |     |      |  |  |

| t <sub>PODLY</sub>    | Power-on delay time                        | Delay from enable                              | to switching                    | 512     |     | μs   |  |  |

# **Electrical Characteristics (continued)**

|                          | PARAMETER                                                                                                                                   | TEST CONDITIONS                       | MIN  | TYP   | MAX | UNIT              |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------|-------|-----|-------------------|

| PGOOD COM                | WPARATOR                                                                                                                                    |                                       |      |       |     |                   |

| Vacan                    | OV warning threshold on RSP pin, PGOOD fault threshold on rising                                                                            | VREF = 600 mV                         | 108  | 112   | 116 | %V <sub>REF</sub> |

| V <sub>PG</sub> (thresh) | UV warning threshold on RSP pin, PGOOD fault threshold on falling                                                                           | VREF = 600 mV                         | 84   | 88    | 92  | 70 V REF          |

| $V_{PGD(rise)}$          | PGOOD threshold on rising and UV warning threshold de-<br>assertion threshold at RSP pin                                                    | VREF = 600 mV                         |      | 95    |     | $%V_{REF}$        |

| $V_{PGD(fall)}$          | PGOOD threshold on falling and OV warning threshold de-<br>assertion threshold at RSP pin                                                   | VREF = 600 mV                         |      | 105   |     | %V <sub>REF</sub> |

| R <sub>PGD</sub>         | PGOOD pulldown resistance                                                                                                                   | I <sub>PGOOD</sub> = 5 mA, VRSP = 0 V | 30   | 45    | 60  | Ω                 |

|                          | PGOOD delay time                                                                                                                            | Delay for PGOOD going in              |      | 1.024 |     | ms                |

| t <sub>PGDLY</sub>       | FGOOD delay time                                                                                                                            | Delay for PGOOD coming out            |      |       | 2   | μs                |

| V <sub>PGD(OL)</sub>     | PGOOD output low level voltage at no supply voltage                                                                                         | VDD=0, I <sub>PGOOD</sub> = 80 μA     |      |       | 0.8 | V                 |

| I <sub>PGLK</sub>        | PGOOD leakage current                                                                                                                       | V <sub>PGOOD</sub> = 5 V              |      |       | 15  | μΑ                |

| CURRENT S                | SHARE ACCURACY                                                                                                                              |                                       |      |       |     |                   |

|                          | Output current sharing accuracy                                                                                                             | I <sub>OUT</sub> ≥ 20 A/phase         | -15% |       | 15% |                   |

| I <sub>SHARE(acc)</sub>  | among stackable devices, defined as the ratio of the current difference between devices to total current(sensing error only) <sup>(1)</sup> | I <sub>OUT</sub> ≤ 20 A/phase         |      | ±3    |     | А                 |

| CURRENT D                | ETECTION                                                                                                                                    |                                       |      |       |     |                   |

| $V_{\text{ILIM}}$        | V <sub>TRIP</sub> voltage range                                                                                                             | R <sub>dson</sub> sensing             | 0.1  |       | 1.2 | V                 |

|                          | Low-side FET current protection                                                                                                             | $R_{ILIM}$ = 33.2 k $\Omega$          |      | 35    |     | Α                 |

| I <sub>OCP</sub>         | threshold and tolerance                                                                                                                     | OC tolerance                          |      | ±10%  |     |                   |

|                          | Low-Side FET Current protection                                                                                                             | $R_{ILIM}$ = 23.7 k $\Omega$          |      | 25    |     | Α                 |

| I <sub>OCP</sub>         | threshold and tolerance                                                                                                                     | OC tolerance                          |      | ±15%  |     |                   |

| I <sub>OCP_N</sub>       | Negative current limit threshold                                                                                                            | Valley-point current sense            |      | -23   |     | Α                 |

| I <sub>CLMP_LO</sub>     | Clamp current at V <sub>TRIP</sub> clamp at lowest                                                                                          | 25°C, V <sub>TRIP</sub> = 0.1 V       | 5.5  | 6.5   | 7.5 | Α                 |

# **Electrical Characteristics (continued)**

|                              | PARAMETER                                                                 | TEST CONDITIONS                                                           | MIN | TYP                 | MAX  | UNIT  |  |

|------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------|-----|---------------------|------|-------|--|

| HIGH-SIDE SH                 | IORT-CIRCUIT PROTECTION                                                   |                                                                           |     |                     |      |       |  |

| I <sub>HSOC</sub>            | High-side short circuit protection fault threshold (1)                    |                                                                           |     | 60                  |      | А     |  |

| OV / UV PROT                 | ECTION                                                                    |                                                                           |     |                     |      |       |  |

| V <sub>OVP</sub>             | OVP threshold voltage                                                     | OVP detect voltage                                                        | 113 | 117                 | 121  | %VREF |  |

| t <sub>OVPDLY</sub>          | OVP response time (1)                                                     | OVP response time with 100-mV overdrive                                   |     |                     | 1    | μs    |  |

| V <sub>UVP</sub>             | UVP threshold voltage                                                     | UVP detect voltage                                                        | 79  | 83                  | 87   | %VREF |  |

| t <sub>UVPDLY</sub>          | UVP delay <sup>(1)</sup>                                                  | UVP delay                                                                 |     |                     | 1.5  | μs    |  |

| tHICDLY                      | Hiccup delay time                                                         | Regular t <sub>SS</sub> setting                                           |     | 7 × t <sub>SS</sub> |      | ms    |  |

| BP LDO REGU                  | JLATOR                                                                    |                                                                           | •   |                     |      |       |  |

| BP                           | LDO output voltage                                                        | V <sub>IN</sub> = 12 V, I <sub>LOAD</sub> = 0 to 10 mA                    | 4.5 | 5                   | 5.5  | V     |  |

| .,                           |                                                                           | Wakeup                                                                    |     | 3.32                |      |       |  |

| V <sub>BPUVLO</sub>          | BP UVLO threshold voltage                                                 | Shutdown                                                                  |     | 3.11                |      | V     |  |

| VLDO <sub>BP</sub>           | LDO low dropout voltage                                                   | V <sub>IN</sub> = 4.5 V, I <sub>LOAD</sub> = 30 mA, T <sub>A</sub> = 25°C |     |                     | 365  | mV    |  |

| I <sub>LDOMAX</sub>          | LDO overcurrent limit                                                     | V <sub>IN</sub> = 12 V, T <sub>A</sub> = 25°C                             |     | 100                 |      | mA    |  |

| SYNCHRONIZ                   | ATION                                                                     |                                                                           | •   |                     |      |       |  |

| V <sub>IH(SYNC)</sub>        | High-level input voltage                                                  |                                                                           | 2   |                     |      |       |  |

| V <sub>IL(SYNC)</sub>        | Low-level input voltage                                                   |                                                                           |     |                     | 0.8  | V     |  |

| t <sub>PSW(SYNC)</sub>       | Sync input minimum pulse width                                            |                                                                           |     |                     | 100  | ns    |  |

| _                            | Synchronization frequency                                                 |                                                                           | 300 |                     | 2000 |       |  |

| F <sub>SYNC</sub>            | Dual-phase                                                                |                                                                           | 300 |                     | 1000 | kHz   |  |

| t <sub>SYNC to SW</sub>      | Sync to SW delay tolerance, percentage from phase-to-phase <sup>(1)</sup> | F <sub>SYNC</sub> = 300 kHz to 1 MHz,                                     |     | 10%                 |      |       |  |

| t <sub>Lose_SYNC_delay</sub> | Delay when lose sync clock <sup>(1)</sup>                                 | F <sub>SYNC</sub> = 300 kHz                                               |     | 5                   |      | μs    |  |

| THERMAL SH                   |                                                                           | •                                                                         |     |                     |      |       |  |

| _                            | Built-in thermal shutdown threshold <sup>(1)</sup>                        | Shutdown temperature                                                      | 155 | 165                 |      |       |  |

| T <sub>SDN</sub>             |                                                                           | Hysteresis                                                                |     | 30                  |      | °C    |  |

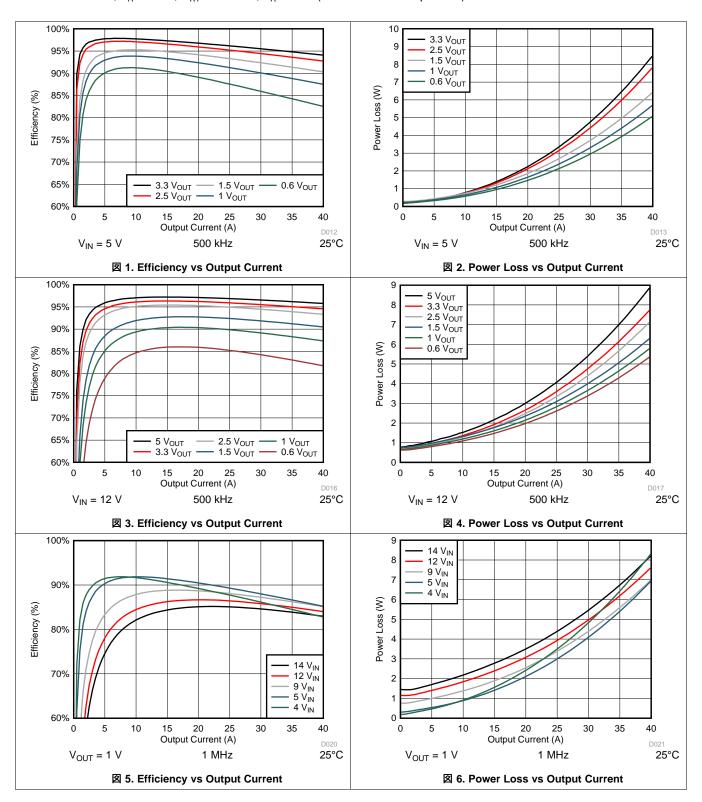

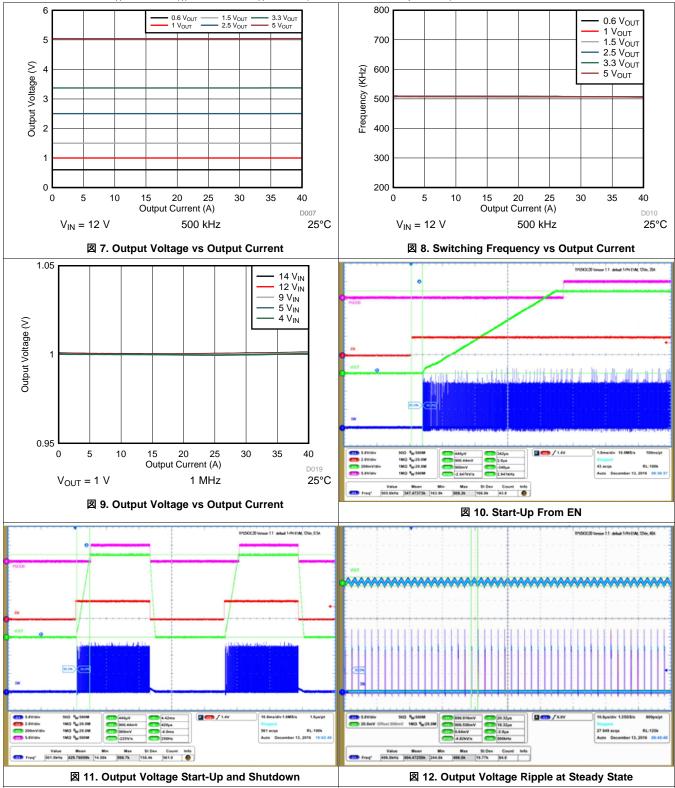

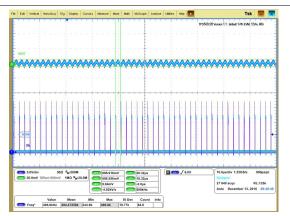

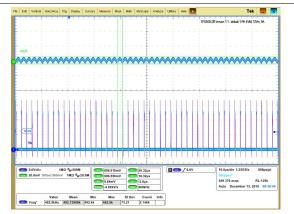

## 7.6 Typical Characteristics

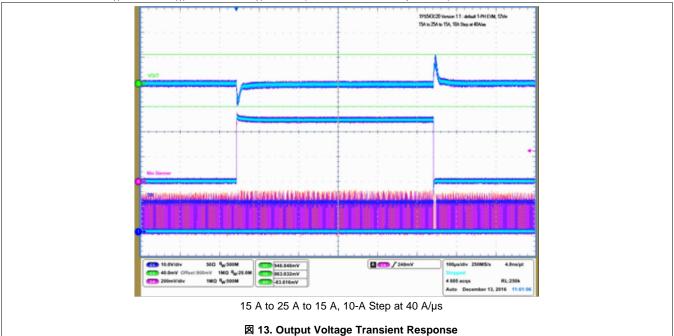

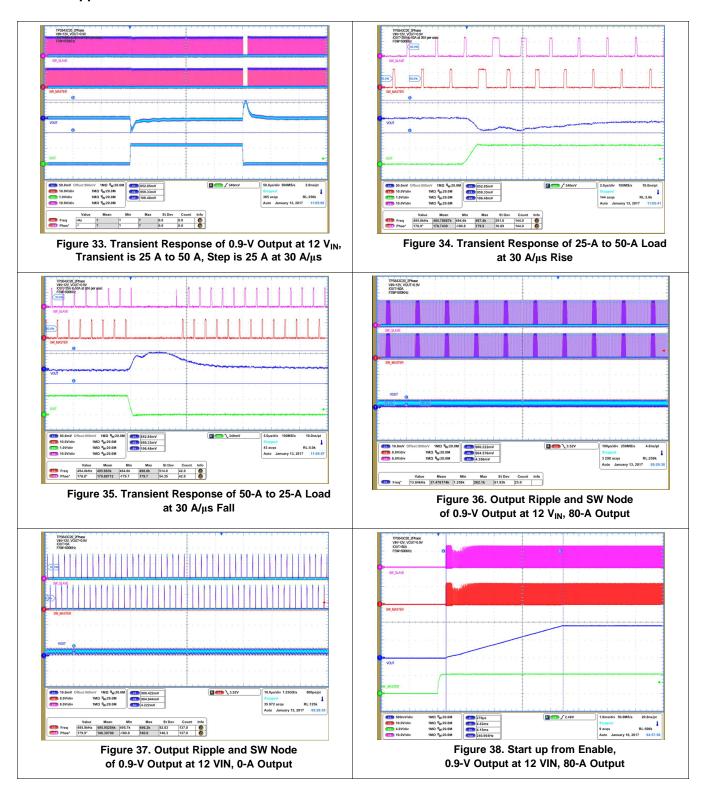

VIN = VDD = 12 V,  $T_A$  = 25°C,  $R_{RT}$  = 40.2 k $\Omega$ ,  $T_A$ = 25°C (unless otherwise specified)

## **Typical Characteristics (continued)**

VIN = VDD = 12 V,  $T_A$  = 25°C,  $R_{RT}$  = 40.2 k $\Omega$ ,  $T_A$ = 25°C (unless otherwise specified)

# **Typical Characteristics (continued)**

VIN = VDD = 12 V,  $T_A$  = 25°C,  $R_{RT}$  = 40.2 k $\Omega$ ,  $T_A$ = 25°C (unless otherwise specified)

# 8 Detailed Description

#### 8.1 Overview

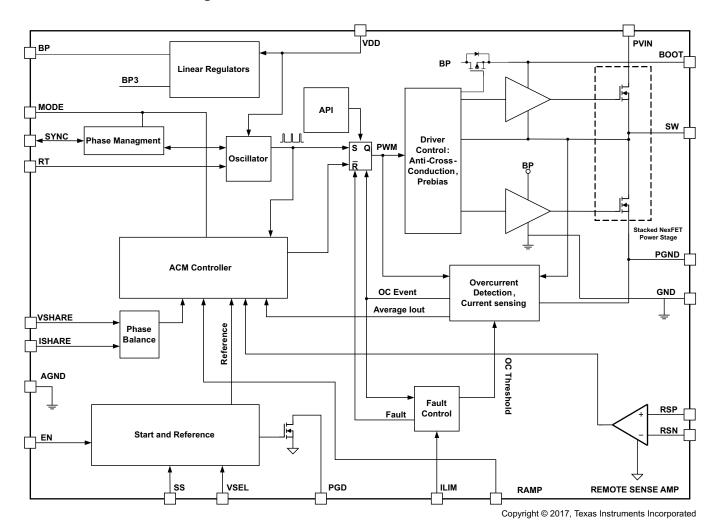

The TPS543C20 device is 40-A, high-performance, synchronous buck converter with two integrated N-channel NexFET™ power MOSFETs. These devices implement the fixed frequency non-compensation mode control. Safe pre-bias capability eliminates concerns about damaging sensitive loads. Two TPS543C20 devices can be paralleled together to provide up to 80-A load. Current sensing for over-current protection and current sharing between devices is done by sampling a small portion of the power stage current providing accurate information independent on the device temperature.

Advanced Current Mode (ACM) is an emulated peak current control topology. It supports stable static and transient operation without complex external compensation design. This control architecture includes an internal ramp generation network that emulates inductor current information, enabling the use of low ESR output capacitors such as multi-layered ceramic capacitors (MLCC). The internal ramp also creates a high signal to noise ratio for good noise immunity. The TPS543C20 has 10 ramp options (see *Ramp Selections* for detail) to optimize internal loop for various inductor and output capacitor combinations with only a simple resistor to GND. The TPS543C20 is easy to use and allows low external component count with fast load transient response. Fixed-frequency modulation also provides ease-of-filter design to overcome EMI noise.

## 8.2 Functional Block Diagram

## 8.3 Feature Description

The TPS543C20 device is a high-performance, integrated FET converter supporting current rating up to 40-A thermally. It integrates two N-channel NexFET™ power MOSFETs, enabling high power density and small PCB layout area. The drain-to-source breakdown voltage for these FETs is 20 V DC and transient. Avalanche breakdown occurs if the absolute maximum voltage rating exceeds 20 V. In order to limit the switch node ringing of the device, TI recommends adding a R-C snubber from the SW node to the PGND pins. Also a 10~100nF capacitor from VIN (Pin 25) to GND (Pin2 7) is mandatory to reduce high side FET stress. Refer to Layout Guidelines for the detailed recommendations.

The typical on-resistance (RDS(on)) for the high-side MOSFET is 3 m $\Omega$  and typical on-resistance for the low-side MOSFET is 0.9 m $\Omega$  with a nominal gate voltage (VGS) of 5 V.

#### 8.4 Device Functional Modes

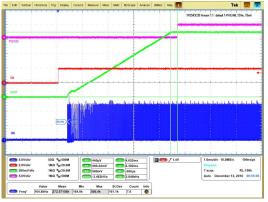

#### 8.4.1 Soft-Start Operation

In the TPS543C20 device, the soft-start time controls the inrush current required to charge the output capacitor bank during start-up. The device offers 10 selectable soft-start options ranging from 0.5 ms to 32 ms. When the device is enabled the reference voltage ramps from 0 V to the final level defined by VSEL pin strap configuration, in a given soft-start time, which can be selected by SS pin. See 表 1 for details.

| SS TIME (ms) | RESISTOR VALUE (kΩ) <sup>(1)</sup> |  |  |

|--------------|------------------------------------|--|--|

| 0.5          | 0                                  |  |  |

| 1            | 8.66                               |  |  |

| 2            | 15.4                               |  |  |

| 5            | 23.7                               |  |  |

| 4            | OPEN                               |  |  |

| 8            | 34.8                               |  |  |

| 12           | 51.1                               |  |  |

| 16           | 78.7                               |  |  |

| 24           | 121                                |  |  |

| 32           | 187                                |  |  |

表 1. SS Pin Configuration

## 8.4.2 Input and VDD Undervoltage Lockout (UVLO) Protection

The TPS543C20 provides fixed VIN and VDD undervoltage lockout threshold and hysteresis. The typical VIN turnon threshold is 3.2 V and hysteresis is 0.2 V. The typical VDD turnon threshold is 3.8 V and hysteresis is 0.2 V. No specific power-up sequence is required.

#### 8.4.3 Power Good and Enable

The TPS543C20 has power-good output that indicates logic high when output voltage is within the target. The power-good function is activated after soft-start has finished. When the soft-start ramp reaches 90% of setpoint, PGOOD detection function will be enabled. If the output voltage becomes within  $\pm 8\%$  of the target value, internal comparators detect power-good state and the power good signal becomes high after a delay. If the output voltage goes outside of  $\pm 12\%$  of the target value, the power good signal becomes low after an internal delay. The power-good output is an open-drain output and must be pulled up externally.

This part has internal pull up for EN. EN is internally pulled up to BP when EN pin is floating. EN can be pulled low through external grounding. When EN pin voltage is below its threshold, TPS543C20 enters into shutdown operation, and the minimum time for toggle EN to reset is  $5 \mu s$ .

<sup>(1)</sup> The E48 series resistors with no more than 1% tolerance are recommended.

#### 8.4.4 Voltage Reference

VSEL pin strap is used to program initial boot voltage value from 0.6 V to 1.1 V by the resistor connected from VSEL to AGND. The initial boot voltage is used to program the main loop voltage reference point. VSEL voltage settings provide TI designated discrete internal reference voltages. 表 2 lists internal reference voltage selections.

| AX 2. VOLL FIII Configuration |                                    |  |  |  |  |

|-------------------------------|------------------------------------|--|--|--|--|

| DEFAULT Vref (V)              | RESISTOR VALUE (kΩ) <sup>(1)</sup> |  |  |  |  |

| 0.6                           | 0                                  |  |  |  |  |

| 0.7                           | 8.66                               |  |  |  |  |

| 0.75 15.4                     |                                    |  |  |  |  |

| 0.8                           | 23.7                               |  |  |  |  |

| 0.85                          | 34.8                               |  |  |  |  |

| 0.9                           | 51.1                               |  |  |  |  |

| 0.95                          | 78.7                               |  |  |  |  |

| 1.0                           | OPEN                               |  |  |  |  |

| 1.05                          | 121                                |  |  |  |  |

187

表 2. VSEL Pin Configuration

1.1

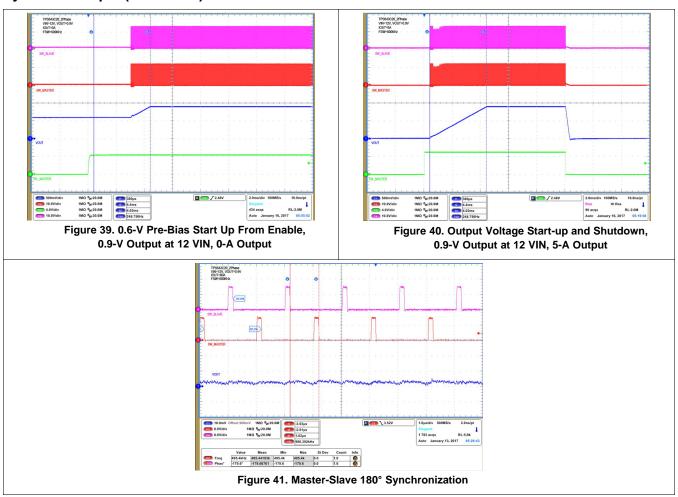

#### 8.4.5 Prebiased Output Start-up

The device prevent current from being discharged from the output during start-up, when a pre-biased output condition exists. No SW pulses occur until the internal soft-start voltage rises above the error amplifier input voltage, if the output is pre-biased. As soon as the soft-start voltage exceeds the error amplifier input, and SW pulses start, the device limits synchronous rectification after each SW pulse with a narrow on-time. The low-side MOSFET on-time slowly increases on a cycle-by-cycle basis until 128 pulses have been generated and the synchronous rectifier runs fully complementary to the high-side MOSFET. This approach prevents the sinking of current from a pre-biased output, and ensures the output voltage start-up and ramp-to regulation sequences are smooth and monotonic.

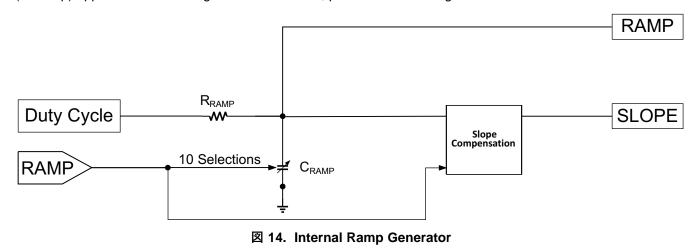

#### 8.4.6 Internal Ramp Generator

Internal ramp voltage is generated from duty cycle that contains emulated inductor ripple current information and then feed it back for control loop regulation and optimization according to required output power stage, duty ratio and switching frequency. Internal ramp amplitude is set by RAMP pin by adjusting an internal ramp generation capacitor C<sub>RAMP</sub>, selected by the resistor connected from MODE pin to GND. For best performance, we recommend ramp signal to be no more than 4 times of output ripple signal for all Low ESR output capacitor (MLCC) applications, or no more than 2 times larger than output ripple signal for regular ESR output capacitor (Pos-cap) applications. For design recommendation, please find the design tool at www.ti.com/WEBENCH.

16

The E48 series resistors with no worse than 1% tolerance are recommended

#### 8.4.6.1 Ramp Selections

RAMP pin sets internal ramp amplitude for the control loop. RAMP amplitude is determined by internal RC, selected by the resistor connected from MODE pin to GND, to optimize the control loop. See 表 3.

| 衣 3. RAMP Pin-strapping Selection |                                    |  |  |  |  |

|-----------------------------------|------------------------------------|--|--|--|--|

| C <sub>RAMP</sub> (pF)            | RESISTOR VALUE (kΩ) <sup>(1)</sup> |  |  |  |  |

| 1                                 | 0                                  |  |  |  |  |

| 1.42                              | 8.66                               |  |  |  |  |

| 1.94 15.4                         |                                    |  |  |  |  |

| 2.58                              | 23.7                               |  |  |  |  |

| 3.43                              | 34.8                               |  |  |  |  |

| 4.57                              | 51.1                               |  |  |  |  |

| 6.23                              | 78.7                               |  |  |  |  |

| 8.91                              | 121                                |  |  |  |  |

| 14.1                              | 187                                |  |  |  |  |

| 29.1                              | Open                               |  |  |  |  |

表 3. RAMP Pin-strapping Selection

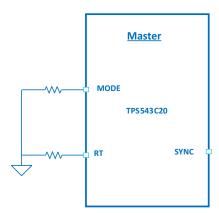

## 8.4.7 Switching Frequency

The converter supports analog frequency selections from 300 kHz to 2 MHz, for stand alone device and sync frequency from 300 kHz to 1 MHz for stackable configuration. The RT pin also sets clock sync point (SP) for the slave device.

## Switching Frequency Configuration for Stand-alone and Master Device in Stackable Configuration

図 15. Standalone: RT Pin Sets the Switching Frequency

The E48 series resistors with tolerance of 1% or less are recommended.

(1)

図 16. Stackable: Master (as Clock Master) RT Pin Sets Switching Frequency, and passes it to Slave

Resistor R<sub>RT</sub> sets the continuous switching frequence selection by

$$R_{RT} = \frac{20 \times 10^9}{f_{SW}} - \frac{f_{SW} \times 2}{2000}$$

where

- R is the resistor from RT pin to GND, in  $\Omega$

- $f_{\rm SW}$  is the desired switching frequency, in Hz

## 8.4.8 Clock Sync Point Selection

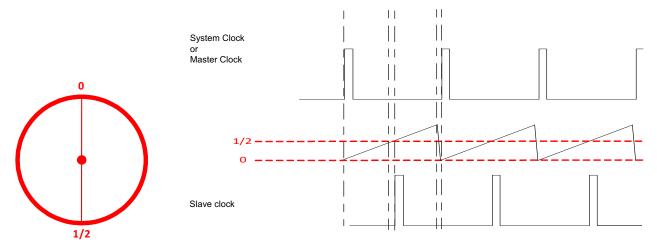

The TPS543C20 device implements an unique clock sync scheme for phase interleaving during stackable configuration. The device will receive the clock through sync pin and generate sync points for another TPS543C20 device to sync to one of them to achieve phase interleaving. Sync point options can be selected through RT pin when 1) device is configurated as master sync in, 2) device is configured as slave. See 表 5 for Control Mode Selection.

図 17. 2-Phase Stackable with 180° Clock Phase Shift

| CLOCK SYNC OPTIONS      | RESISTOR VALUE (kΩ) |  |  |

|-------------------------|---------------------|--|--|

| 0 (0° Interleaving)     | 0                   |  |  |

| 1/4 (90° Interleaving)  | 8.66                |  |  |

| 1/3 (120° Interleaving) | 15.4                |  |  |

| 2/3 (240° Interleaving) | 23.7                |  |  |

| 3/4 (270° Interleaving) | 34.8                |  |  |

| 1/2 (180° Interleaving) | OPEN                |  |  |

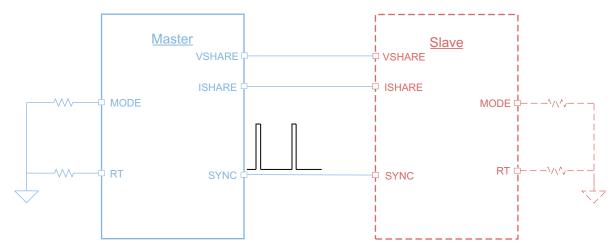

#### 8.4.9 Synchronization and Stackable Configuration

The TPS543C20 device can synchronize to an external clock which must be equal to or higher than internal frequency setting. For stand alone device, the external clock should be applied to the SYNC pin. A sudden change in synchronization clock frequency causes an associated control loop response, resulting in an overshoot or undershoot on the output voltage.

In dual phase stackable configuration:

- 1. when there is no external system clock applied, the master device will be configured as clock master, sending out pre-set switching frequency clock to slave device through SYNC pin. Slave will receive this clock as switching clock with phase interleaving.

- 2. when a system clock is applied, both master and slave devices will be configured as clock slave, they will sync to the external system clock as switching frequency with proper phase shift

#### 8.4.10 Dual-Phase Stackable Configurations

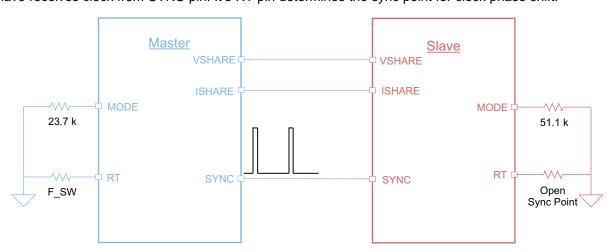

#### 8.4.10.1 Configuration 1: Master Sync Out Clock-to-Slave

- Direct SYNC, VSHARE and ISHARE connections between Master and Slave.

- Switching frequency is set by RT pin of Master, and pass to slave through SYNC pin. SYNC pin of master will be configured as sync out by it's MODE pin.

- Slave receives clock from SYNC pin. It's RT pin determines the sync point for clock phase shift.

図 18. 2-Phase Stackable with 180° Phase Shift: Master Sync Out Clock-to-Slave

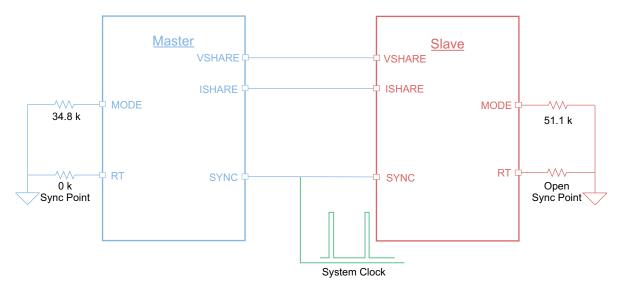

#### 8.4.10.2 Configuration 2: Master and Slave Sync to External System Clock

- Direct connection between external clock and SYNC pin of Master and Slave.

- Direct VSHARE and ISHARE connections between Master and Slave.

- SYNC pin of master will be configured as sync in by it's MODE pin.

- Master and Slave receive external system clock from SYNC pin. Their RT pin determine the sync point for clock phase shift.

図 19. 2-Phase Stackable with 180° Phase Shift: Master and Slave Sync to External System Clock

#### 8.4.11 Operation Mode

The operation mode and API/Body Brake feature is set by the MODE pin. They are selected by the resistor connected from MODE pin to GND. Mode pin sets the device to be stand-alone mode or stackable mode. In stand-alone mode, MODE pin sets the API on/off or trigger point sensitivity of API (1x stands for most sensitive and 4x stands for least sensitive). In stackable mode, the MODE pin sets the device as master or slave, as well as SYNC pin function (sync in or sync out) of the master device.

| CONTROL MODE<br>SELECTION | API/BODY BRAKE                       | RESISTOR VALUE ( $k\Omega$ ) and API/BB Threshold (1) | NOTE                                                                         |

|---------------------------|--------------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------|

|                           | API OFF<br>BB OFF                    | Open                                                  |                                                                              |

| Standalone                | API ON<br>BB OFF                     | 15.4, API = 35 mV                                     | Suma nin ta rassiva slask                                                    |

| API/body brake            | API ON BB ON (API Threshold Setting) | 121, API = 15 mV, BB = 30 mV                          | <ul><li>Sync pin to receive clock</li><li>RT pin to set frequency</li></ul>  |

| ·                         |                                      | 187, API = 25 mV, BB = 30 mV                          | ,                                                                            |

|                           |                                      | 8.66, API = 35 mV, BB = 30 mV                         |                                                                              |

|                           |                                      | 78.7, API = 45 mV, BB = 30 mV                         |                                                                              |

| (Master sync out)         |                                      | 23.7                                                  | <ul><li>Sync pin to send out clock</li><li>RT pin to set frequency</li></ul> |

| (Master sync in)          | API OFF<br>BB OFF                    | 34.8                                                  | <ul><li>Sync pin to receive clock</li><li>RT pin to set sync point</li></ul> |

| (Slave Sync In)           |                                      | 51.1                                                  | Sync pin to receive clock     RT pin to set sync point                       |

表 5. MODE Pin-Strapping Selection

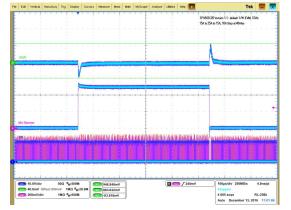

#### 8.4.12 API/BODY Brake

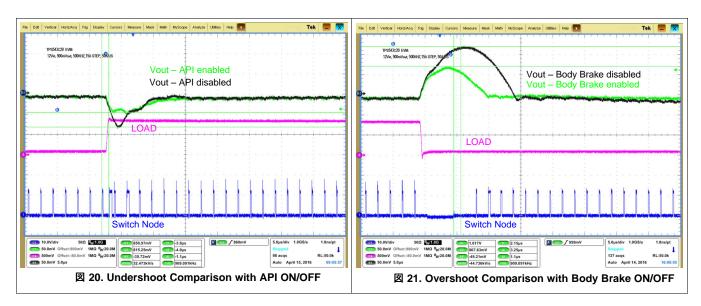

TPS543C20 is a true fixed frequency converter. The major limitation for any fixed frequency converter is that during transient load step up, the converter needs to wait for the next clock cycle to response to the load change, depending on loop bandwidth design and the timing of load transient, this delay time could cause additional output voltage drop. TPS543C20 implements a special circuitry to improve transient performance. During load step up, the converter senses both the speed and the amplitude of the output voltage change, if the output voltage change is fast and big enough, the converter will issue an additional PWM pulse before the next available clock cycle to stop output voltage from further dropping, thus reducing the undershoot voltage.

<sup>(1)</sup> The E48 series resistors with tolerance of 1% or less are recommended.

During load step down, TPS543C20 implements a body brake function, that turns off both high-side and lowside FET, and allows power to dissipate through the low-side body diode, reducing overshoot. This approach is very effective while having some impact on efficiency during transient. See 20 and 21.

#### 8.4.13 Sense and Overcurrent Protection

#### 8.4.13.1 Low-Side MOSFET Overcurrent Protection

The TPS543C20 utilizes ILIM pin to set the OCP level. The ILIM pin should be connected to AGND through the ILIM voltage setting resistor, RILIM. The ILIM terminal sources IILIM current, which is around 11.2  $\mu$ A typically at room temperature, and the ILIM level is set to the OCP ILIM voltage VILIM as shown in  $\pm$  2. In order to provide both good accuracy and cost effective solution, TPS543C20 supports temperature compensated MOSFET  $R_{DS(on)}$  sensing.

$$V_{ILIM}(mV) = R_{ILIM}(k\Omega) \times I_{ILIM}(\mu A)$$

Consider  $R_{DS(on)}$  variation vs VDD in calculation (2)

Also, TPS543C20 performs both positive and fixed negative inductor current limiting.

The inductor current is monitored by the voltage between GND pin and SW pin during the OFF time. ILIM has 1200 ppm/ $^{\circ}$ C temperature slope to compensate the temperature dependency of the R<sub>DS(on)</sub>. The GND pin is used as the positive current sensing node.

The device has cycle-by-cycle over-current limiting control. The inductor current is monitored during the OFF state and the controller maintains the OFF state during the period that the inductor current is larger than the overcurrent ILIM level.  $V_{ILIM}$  sets the Peak level of the inductor current. Thus, the load current at the overcurrent threshold,  $I_{OCP}$ , can be calculated as shown in .

$$\begin{split} &I_{\text{OCP}} = V_{\text{ILIM}} / (16 \times R_{\text{DS(on)}}) - I_{\text{IND(ripple)}} / 2 \\ &= \frac{V_{\text{ILIM}}}{16 \times R_{\text{DS(on)}}} - \frac{1}{2 \times L \times f_{\text{SW}}} \times \frac{(V_{\text{IN}} - V_{\text{OUT}}) \times V_{\text{OUT}}}{V_{\text{IN}}} \end{split}$$

where

R<sub>DS(on)</sub> is the on-resistance of the low-side MOSFET.

式 3 is valid for VDD ≥ 5 V. Use 0.58 m $\Omega$  for R<sub>DS(on)</sub> in calculation, which is the pure on-resistance for current sense.

If an overcurrent event is detected in a given switching cycle, the device increments an overcurrent counter. When the device detects three consecutive overcurrent (either high-side or low-side) events, the converter responds, entering continuous restart hiccup. In continuous hiccup mode, the device implements a 7 soft-start cycle timeout, followed by a normal soft-start attempt. When the overcurrent fault clears, normal operation resumes; otherwise, the device detects overcurrent and the process repeats.

## 8.4.13.2 High-Side MOSFET Overcurrent Protection

The device also implements a fixed high-side MOSFET overcurrent protection to limit peak current, and prevent inductor saturation in the event of a short circuit. The device detects an overcurrent event by sensing the voltage drop across the high-side MOSFET during ON state. If the peak current reaches the IHOSC level on any given cycle, the cycle terminates to prevent the current from increasing any further. High-side MOSFET overcurrent events are counted. If the devices detect three consecutive overcurrent events (high-side or low-side), the converter responds by entering continuous restart hiccup.

## 8.4.14 Output Overvoltage and Undervoltage Protection

The device includes both output overvoltage protection and output undervoltage protection capability. The devices compare the RSP pin voltage to internal selectable pre-set voltages. If the RSP voltage with respect to RSN voltage rises above the output overvoltage protection threshold, the device terminates normal switching and turns on the low-side MOSFET to discharge the output capacitor and prevent further increases in the output voltage. Then the device enters continuous restart hiccup.

If the RSP pin voltage falls below the undervoltage protection level, after soft-start has completed, the device terminates normal switching and forces both the high-side and low-side MOSFETs off, then enters hiccup time-out delay prior to restart.

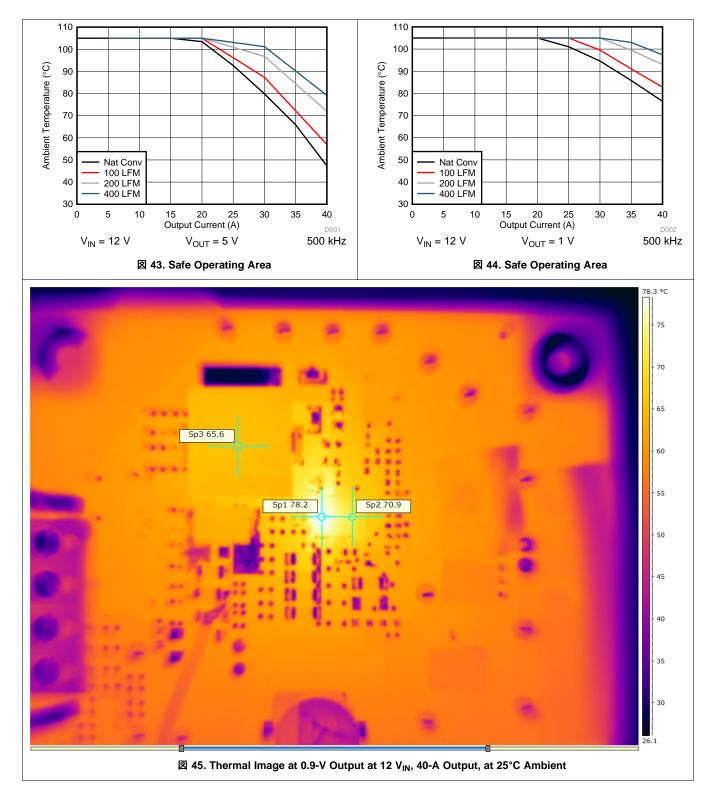

#### 8.4.15 Overtemperature Protection

An internal temperature sensor protects the devices from thermal runaway. The internal thermal shutdown threshold,  $T_{SD}$ , is fixed at 165°C typical. When the devices sense a temperature above  $T_{SD}$ , power conversion stops until the sensed junction temperature falls by the thermal shutdown hysteresis amount; then, the device starts up again.

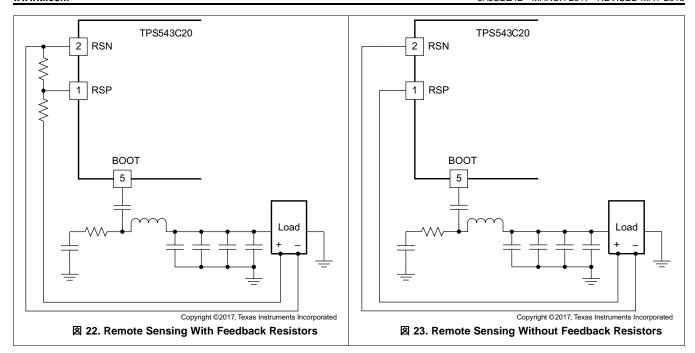

#### 8.4.16 RSP/RSN Remote Sense Function

RSP and RSN pins are used for remote sensing purpose. In the case where feedback resistors are required for output voltage programming, the RSP pin should be connected to the mid-point of the resistor divider and the RSN pin should always be connected to the load return.

In the case where feedback resistors are not required as when the VSEL programs the output voltage set point, the RSP pin should be connected to the positive sensing point of the load and the RSN pin should always be connected to the load return. RSP and RSN pins are extremely high-impedance input terminals of the true differential remote sense amplifier. The feedback resistor divider should use resistor values much less than 100 k $\Omega$ . A simple rule of thumb is to use a 10-k $\Omega$  lower divider resistor and then size the upper resistor to achieve the desired ratio.

#### 8.4.17 Current Sharing

When devices operate in dual-phase stackable application, a current sharing loop maintains the current balance between devices. Both devices share the same internal control voltage through VSHARE pin. The sensed current in each phase is compared first in a current share block by connecting ISHARE pin of each device, then the error current is added into the internal loop. The resulting voltage is compared with the PWM ramp to generate the PWM pulse.

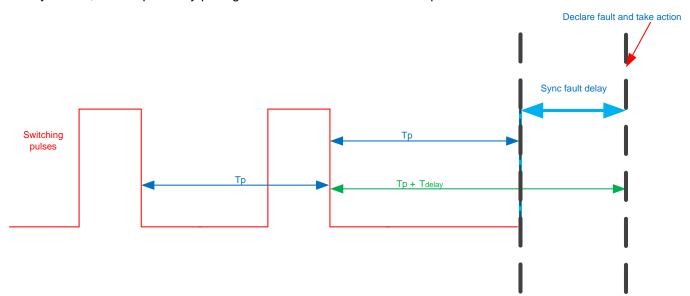

#### 8.4.18 Loss of Synchronization

During sync clock condition, each individual converter will continuously compare current falling edge and previous falling edge, if current falling edge exceeded a 1us delay versus previous pulse, converter will declare a lost sync fault, and response by pulling down ISHARE to shut down all phases.

図 24. Switching Response When Sync Clock Lost

## 9 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## 9.1 Application Information

The TPS543C20 device is a highly-integrated synchronous step-down DC/DC converter. The device is used to convert a higher DC input voltage to a lower DC output voltage, with a maximum output current of 40 A. Use the following design procedure to select key component values for this device.

## 9.2 Typical Application: TPS543C20 Stand-alone Device

Figure 25. 4.5-V to 16-V Input, 1-V Output, 40-A Converter

#### 9.2.1 Design Requirements

For this design example, use the input parameters shown in Table 6.

**Table 6. Design Example Specifications**

|                         | PARAMETER                     | TEST CONDITION                                                         | MIN | TYP | MAX  | UNIT |

|-------------------------|-------------------------------|------------------------------------------------------------------------|-----|-----|------|------|

| V <sub>IN</sub>         | Input voltage <sup>(1)</sup>  |                                                                        | 4   | 12  | 14   | V    |

| V <sub>IN(ripple)</sub> | Input ripple voltage          | I <sub>OUT</sub> = 40 A                                                |     |     | 0.4  | V    |

| V <sub>OUT</sub>        | Output voltage                |                                                                        |     | 0.9 |      | V    |

|                         | Line regulation               | 5 V ≤ V <sub>IN</sub> ≤ 14 V                                           |     |     | 0.5% |      |

|                         | Load regulation               | 0 V ≤ I <sub>OUT</sub> ≤ 40 A                                          |     |     | 0.5% |      |

| V <sub>PP</sub>         | Output ripple voltage         | I <sub>OUT</sub> = 40 A                                                |     | 20  |      | mV   |

| V <sub>OVER</sub>       | Transient response overshoot  | I <sub>STEP</sub> = 10 A                                               |     | 50  |      | mV   |

| V <sub>UNDER</sub>      | Transient response undershoot | I <sub>STEP</sub> = 10A                                                |     | 50  |      | mV   |

| I <sub>OUT</sub>        | Output current                | 5 V ≤ V <sub>IN</sub> ≤ 16 V                                           |     | 35  | 40   | Α    |

| t <sub>SS</sub>         | Soft-start time               | V <sub>IN</sub> = 12 V                                                 |     | 4   |      | ms   |

| loc                     | Overcurrent trip point (2)    |                                                                        |     | 45  |      | Α    |

| η                       | Peak efficiency               | I <sub>OUT</sub> = 20 A, V <sub>IN</sub> = 12 V, V <sub>DD</sub> = 5 V |     | 90% |      |      |

| $f_{SW}$                | Switching frequency           |                                                                        | 300 | 500 | 700  | kHz  |

- (1) Recommended electrical ratings:

- (a) Input voltage ≤ 7 V: current rating ≤ 40 A

- (b) Input voltage ≤ 11 V: current rating ≤ 35 A

- (c) Input voltage ≤ 14 V: current rating ≤ 30 A

- (2) DC overcurrent level

#### 9.2.2 Detailed Design Procedure

#### 9.2.2.1 Custom Design With WEBENCH® Tools

Click here to create a custom design using the TPS543C20 device with the WEBENCH® Power Designer.

- 1. Start by entering the input voltage (V<sub>IN</sub>), output voltage (V<sub>OUT</sub>), and output current (I<sub>OUT</sub>) requirements.

- 2. Optimize the design for key parameters such as efficiency, footprint, and cost using the optimizer dial.

- 3. Compare the generated design with other possible solutions from Texas Instruments.

The WEBENCH Power Designer provides a customized schematic along with a list of materials with real-time pricing and component availability.

In most cases, these actions are available:

- Run electrical simulations to see important waveforms and circuit performance

- Run thermal simulations to understand board thermal performance

- · Export customized schematic and layout into popular CAD formats

- Print PDF reports for the design, and share the design with colleagues

Get more information about WEBENCH tools at www.ti.com/WEBENCH.

#### 9.2.2.2 Switching Frequency Selection