# TPS6287x-Q1 2.7V ~ 6V 入力、15A、20A、25A、および 30A 車載用高速過渡同期整流式降圧コンバータ、I<sup>2</sup>C インターフェイスおよびリモートセンス搭載

## 1 特長

- 車載アプリケーション向けに AEC-Q100 認証済み

- デバイス温度グレード 1: -40°C ~ 125°C T<sub>A</sub>

- 接合部温度範囲: -40°C ~ 150°C

- 機能安全対応**

- 機能安全システムの設計に役立つ資料を利用可能

- 入力電圧範囲: 2.7V ~ 6V

- ピン互換性のあるデバイス ファミリ: 15A、20A、25A、30A

- 3 つの選択可能な出力電圧範囲: 0.4V ~ 1.675V

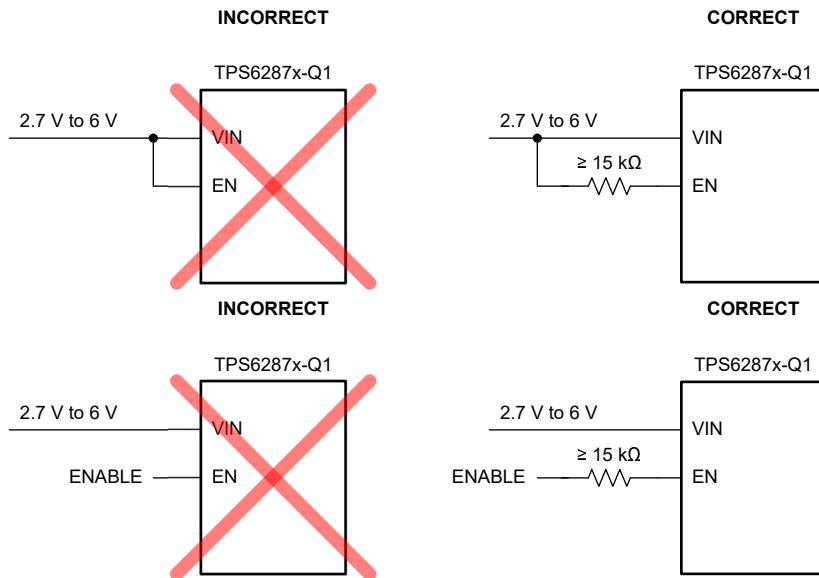

- 0.4V ~ 0.71875V (1.25mV 刻み)

- 0.4V ~ 1.0375V (2.5mV 刻み)

- 0.4V ~ 1.675V (5mV 刻み)

- 出力電圧精度: ±0.8%

- 内部電力 MOSFET: 2.6mΩ、1.5mΩ

- 可変ソフトスタート

- 外部補償

- VSEL ピンを介してスタートアップ出力電圧を選択可能

- FSEL ピンを介して 1.5MHz、2.25MHz、2.5MHz、3MHz のスイッチング周波数を選択可能

- 強制 PWM またはパワー セーブ モード動作

- 外部抵抗または I<sup>2</sup>C によるスタートアップ出力電圧の選択

- I<sup>2</sup>C 互換インターフェイス: 最高 3.4MHz

- オプションのスタック動作により、出力電流能力を向上

- 差動リモートセンス

- サーマル事前警告およびサーマル シャットダウン

- 出力放電

- オプションのスペクトラム拡散クロック供給機能を内蔵

- ウインドウ コンパレータによるパワー グッド出力

## 2 アプリケーション

- ADAS カメラ、ADAS センサ フュージョン

- サラウンド ビュー ECU

- ハイブリッドおよび再構成可能 クラスタ

- ヘッド ユニット、テレマティクス制御ユニット

## 3 説明

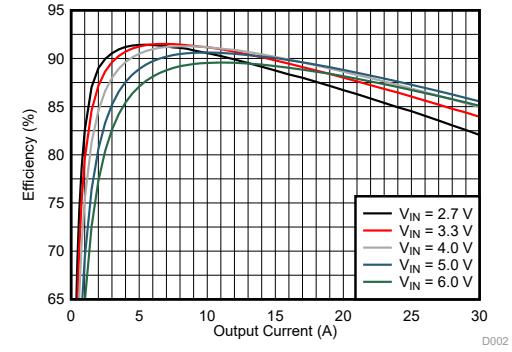

TPS62874-Q1、TPS62875-Q1、TPS62876-Q1、および TPS62877-Q1 は、I<sup>2</sup>C インターフェイスおよび差動リモートセンスを搭載したピン互換、15A、20A、25A、30A 同期整流式降圧 DC/DC コンバータのファミリです。すべてのデバイスは、高い効率と使いやすさを特長としています。

低抵抗の電源スイッチにより、高い周囲温度でも最大 30A の出力電流を供給できます。これらのデバイスをスタックモードで動作させることで、大きな出力電流を供給することや、消費電力を複数のデバイスに分散することが可能です。

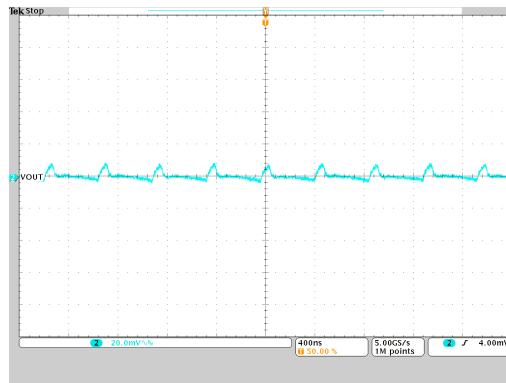

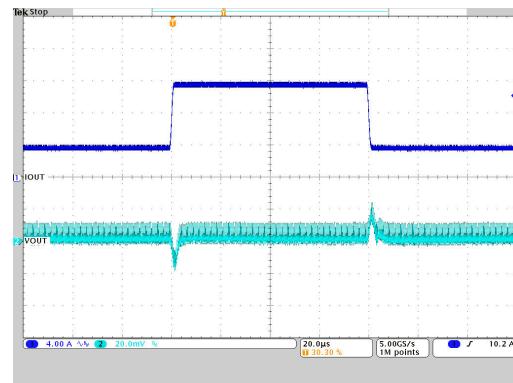

TPS6287x-Q1 ファミリは、高速過渡応答をサポートする固定周波数 DCS 制御方式を実装します。デバイスは、最大効率を達成するパワー セーブ モード、または最高の過渡性能と最小の出力電圧リップルを実現する強制 PWM モードで動作できます。

オプションのリモート センシング機能により、ポイント オブ ロードでの電圧レギュレーションが最大化され、デバイスは出力電圧範囲全体にわたって ±0.8% の DC 電圧精度を達成します。

スイッチング周波数は FSEL ピンを介して選択可能であり、1.5MHz、2.25MHz、2.5MHz、3MHz のいずれかに設定する、または同じ周波数範囲の外部クロックに同期させることができます。

I<sup>2</sup>C 互換インターフェイスを使うと、各種の制御、監視、警告機能（電圧の監視、温度に関連する警告など）を実現できます。出力電圧は、負荷の消費電力を性能ニーズに合わせて迅速に調整できます。デフォルトの起動電圧は、VSEL ピンを介して抵抗により選択できます。

## 製品情報

| 部品番号 (3)    | 電流定格 | パッケージ <sup>(1)</sup>    | パッケージ<br>サイズ <sup>(2)</sup> |

|-------------|------|-------------------------|-----------------------------|

| TPS62874-Q1 | 15A  | RZV (WQFN-FCRLF、<br>24) | 3.05mm ×<br>4.05mm          |

| TPS62875-Q1 | 20A  |                         |                             |

| TPS62876-Q1 | 25A  |                         |                             |

| TPS62877-Q1 | 30A  |                         |                             |

(1) 詳細については、[セクション 13](#) を参照してください。

(2) パッケージサイズ（長さ × 幅）は公称値であり、該当する場合はピンを含みます。

(3) 「[デバイスのオプション](#)」の表を参照してください。

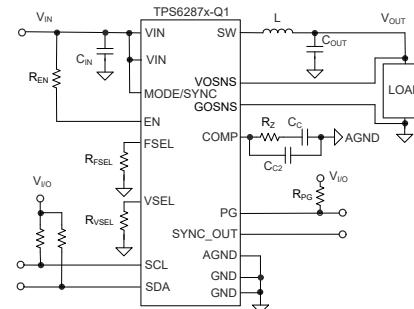

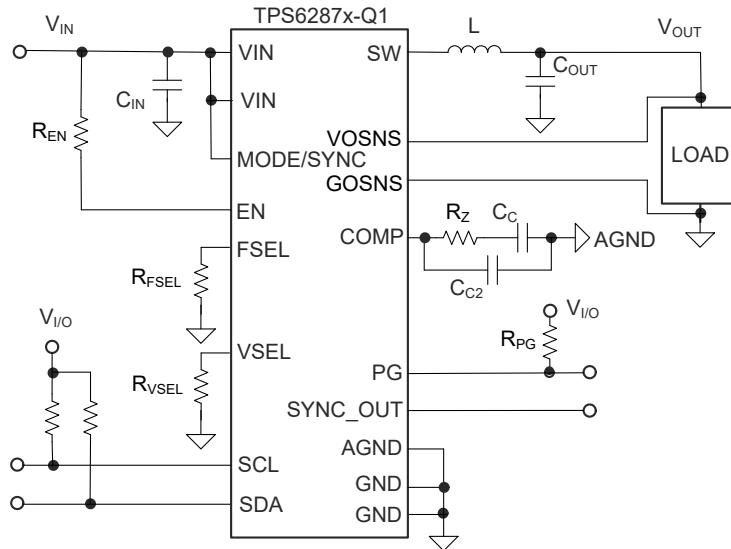

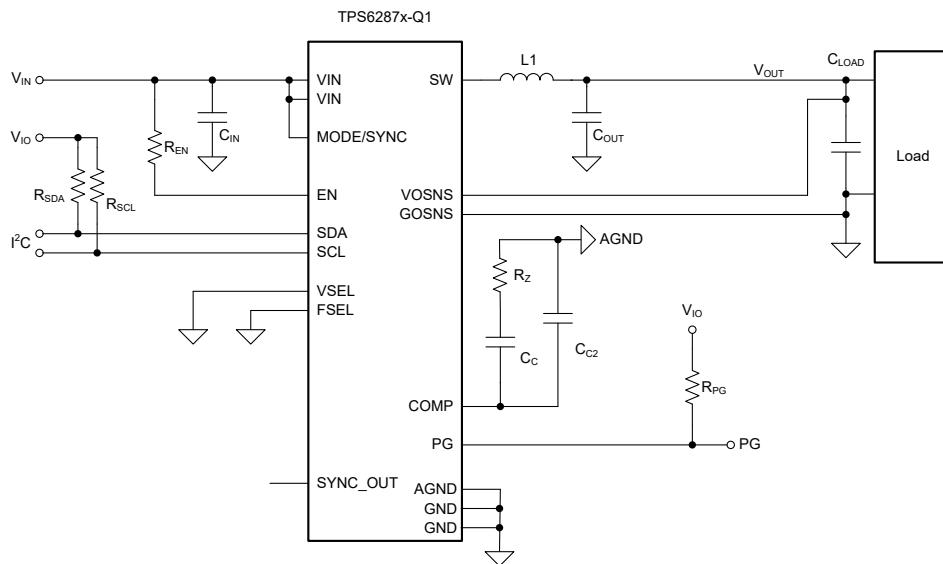

概略回路図

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                                       |    |                                                   |    |

|---------------------------------------|----|---------------------------------------------------|----|

| 1 特長                                  | 1  | 9 デバイスのレジスタ                                       | 37 |

| 2 アプリケーション                            | 1  | 10 アプリケーションと実装                                    | 43 |

| 3 説明                                  | 1  | 10.1 アプリケーション情報                                   | 43 |

| 4 デバイスのオプション                          | 3  | 10.2 代表的なアプリケーション                                 | 43 |

| 5 ピン構成および機能                           | 4  | 10.3 2つの TPS62876-Q1 をスタック構成で使用する<br>代表的なアプリケーション | 52 |

| 6 仕様                                  | 6  | 10.4 3つの TPS62876-Q1 をスタック構成で使用する<br>代表的なアプリケーション | 57 |

| 6.1 絶対最大定格                            | 6  | 10.5 設計のベストプラクティス                                 | 61 |

| 6.2 ESD 定格 - Q100                     | 6  | 10.6 電源に関する推奨事項                                   | 61 |

| 6.3 推奨動作条件                            | 6  | 10.7 レイアウト                                        | 61 |

| 6.4 熱に関する情報                           | 7  | 11 デバイスおよびドキュメントのサポート                             | 64 |

| 6.5 電気的特性                             | 7  | 11.1 ドキュメントのサポート                                  | 64 |

| 6.6 I <sup>2</sup> C インターフェイスタイミングの要件 | 11 | 11.2 ドキュメントの更新通知を受け取る方法                           | 64 |

| 6.7 代表的特性                             | 13 | 11.3 サポート・リソース                                    | 64 |

| 7 パラメータ測定情報                           | 14 | 11.4 商標                                           | 64 |

| 8 詳細説明                                | 15 | 11.5 静電気放電に関する注意事項                                | 64 |

| 8.1 概要                                | 15 | 11.6 用語集                                          | 64 |

| 8.2 機能ブロック図                           | 15 | 12 改訂履歴                                           | 64 |

| 8.3 機能説明                              | 16 | 13 メカニカル、パッケージ、および注文情報                            | 65 |

| 8.4 デバイスの機能モード                        | 32 |                                                   |    |

| 8.5 プログラミング                           | 33 |                                                   |    |

## 4 デバイスのオプション

| 部品番号               | 出力電流 | スタートアップ電圧、I <sub>2</sub> C アドレスの VSEL 設定     | SSC | デフォルトのドループ | TRANS. 非同期モード | ソフトスタート時間 |

|--------------------|------|----------------------------------------------|-----|------------|---------------|-----------|

| TPS62874QWRZVRQ1   | 15A  | VSEL ピンを 6.2kΩ の抵抗で GND に接続した場合: 0.80V, 0x44 | オフ  | オフ         | オフ            |           |

| TPS62875QWRZVRQ1   | 20A  | VSEL を GND に短絡: 0.75V, 0x45                  | オフ  | オフ         | オフ            |           |

| TPS62876QWRZVRQ1   | 25A  | VSEL を VIN に短絡: 0.875V, 0x46                 | オフ  | オフ         | オフ            |           |

| TPS62877QWRZVRQ1   | 30A  | VSEL、47kΩ を VIN に: 0.58V, 0x47               | オフ  | オフ         | オフ            |           |

| TPS62874B1QWRZVRQ1 | 15A  | VSEL ピンを 6.2kΩ の抵抗で GND に接続した場合: 0.8V, 0x44  | オフ  | オン         | オン            |           |

| TPS62875B1QWRZVRQ1 | 20A  | VSEL を GND に短絡: 0.8V, 0x45                   | オフ  | オン         | オン            |           |

| TPS62876B1QWRZVRQ1 | 25A  | VSEL を VIN に短絡: 0.875V, 0x46                 | オフ  | オン         | オン            |           |

| TPS62877B1QWRZVRQ1 | 30A  | VSEL、47kΩ を VIN に: 0.8V, 0x47                | オフ  | オン         | オン            |           |

| TPS62875B2QWRZVRQ1 | 20A  | VSEL ピンを 6.2kΩ の抵抗で GND に接続した場合: 0.85V, 0x44 | オフ  | オン         | オン            |           |

| TPS62875B3QWRZVRQ1 | 20A  | VSEL を GND に短絡: 0.75V, 0x45                  | オン  | オン         | オン            | 1ms       |

| TPS62876B3QWRZVRQ1 | 25A  | VSEL を VIN に短絡: 0.8V, 0x46                   | オン  | オン         | オン            |           |

| TPS62877B3QWRZVRQ1 | 30A  | VSEL、47kΩ を VIN に: 0.77V, 0x47               | オン  | オン         | オン            |           |

| TPS62874B4QWRZVRQ1 | 15A  | VSEL ピンを 6.2kΩ の抵抗で GND に接続した場合: 0.7V, 0x44  | オフ  | オン         | オン            |           |

| TPS62875B4QWRZVRQ1 | 20A  | VSEL を GND に短絡: 0.75V, 0x45                  | オフ  | オン         | オン            |           |

| TPS62875B5QWRZVRQ1 | 20A  | VSEL を VIN に短絡: 0.765V, 0x46                 | オフ  | オン         | オン            |           |

| TPS62875B5QWRZVRQ1 | 20A  | VSEL、47kΩ を VIN に: 0.85V, 0x47               | オフ  | オン         | オン            |           |

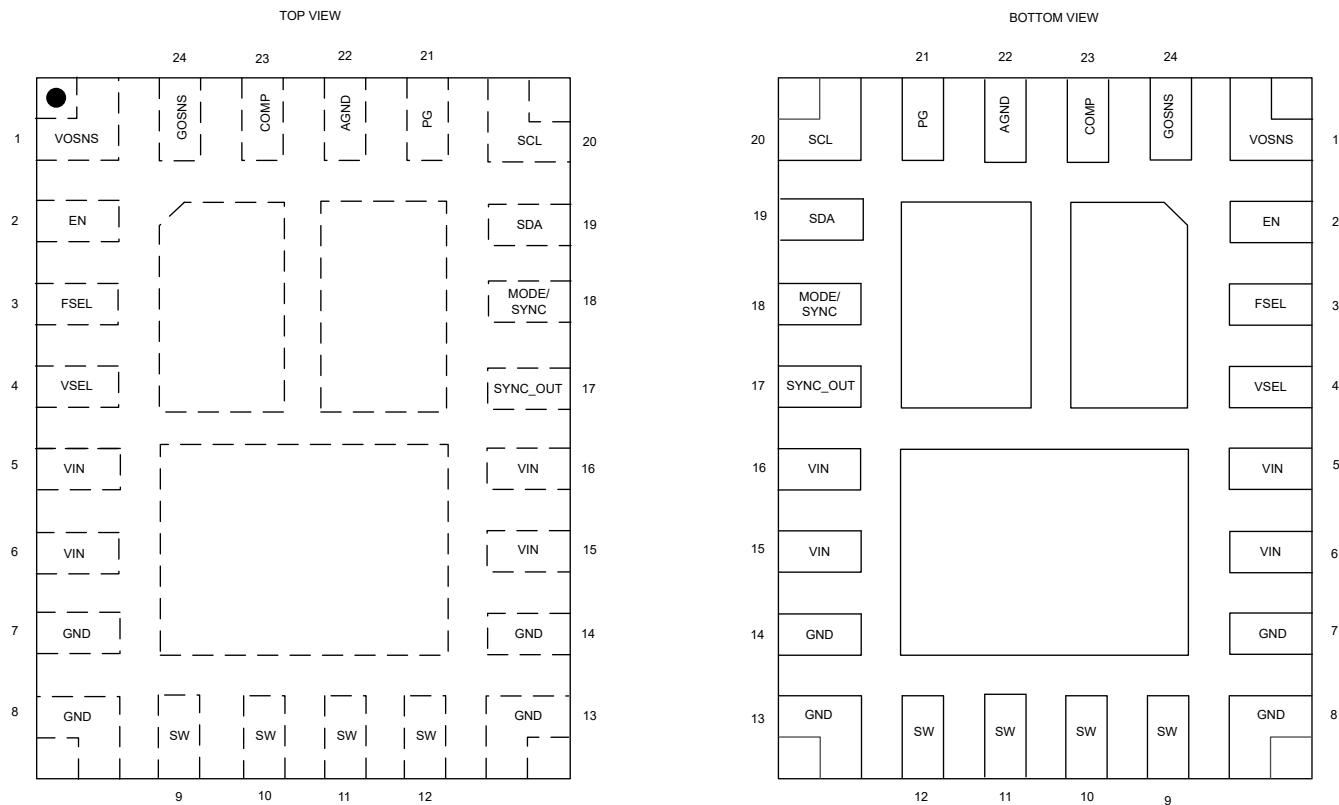

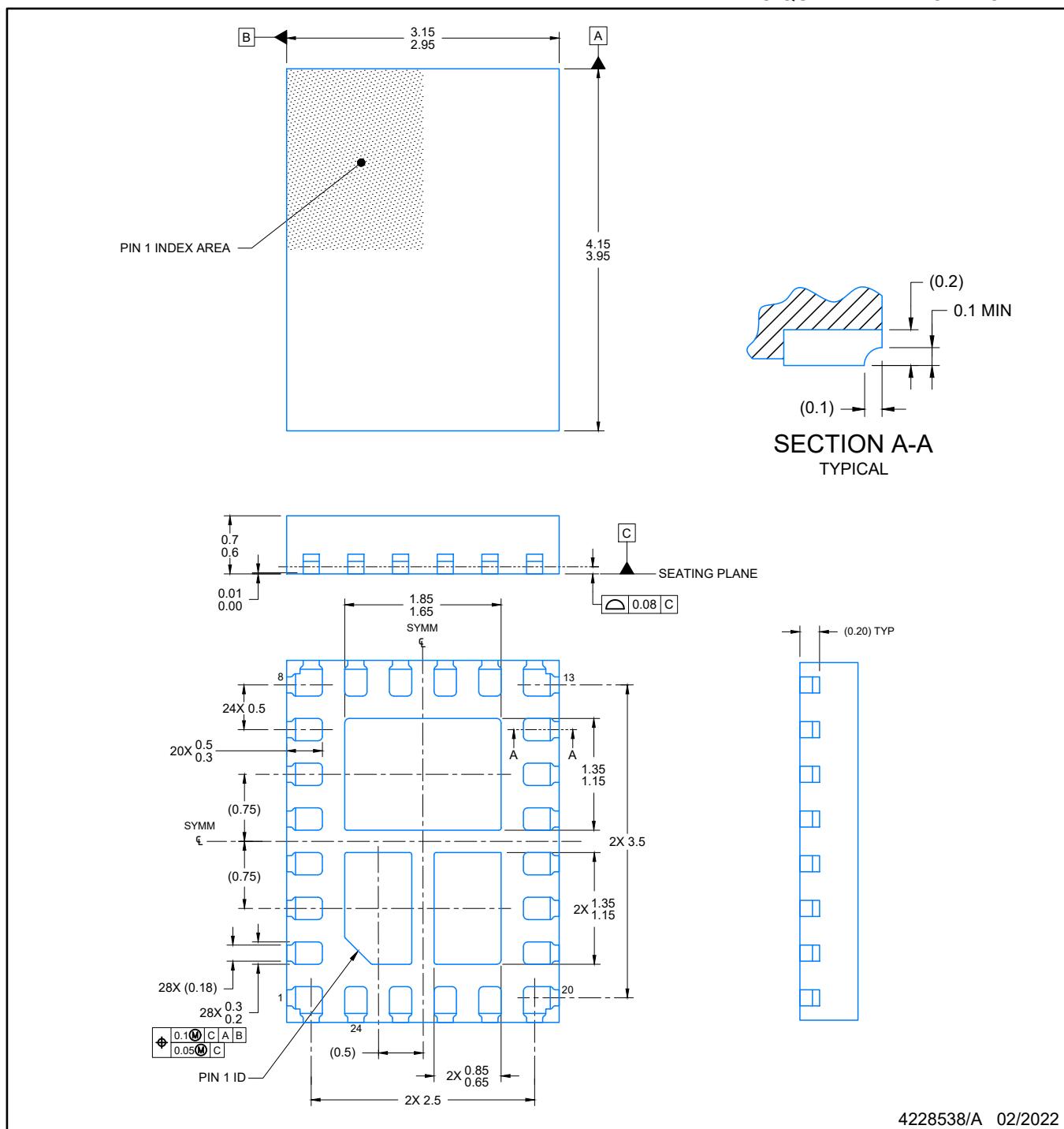

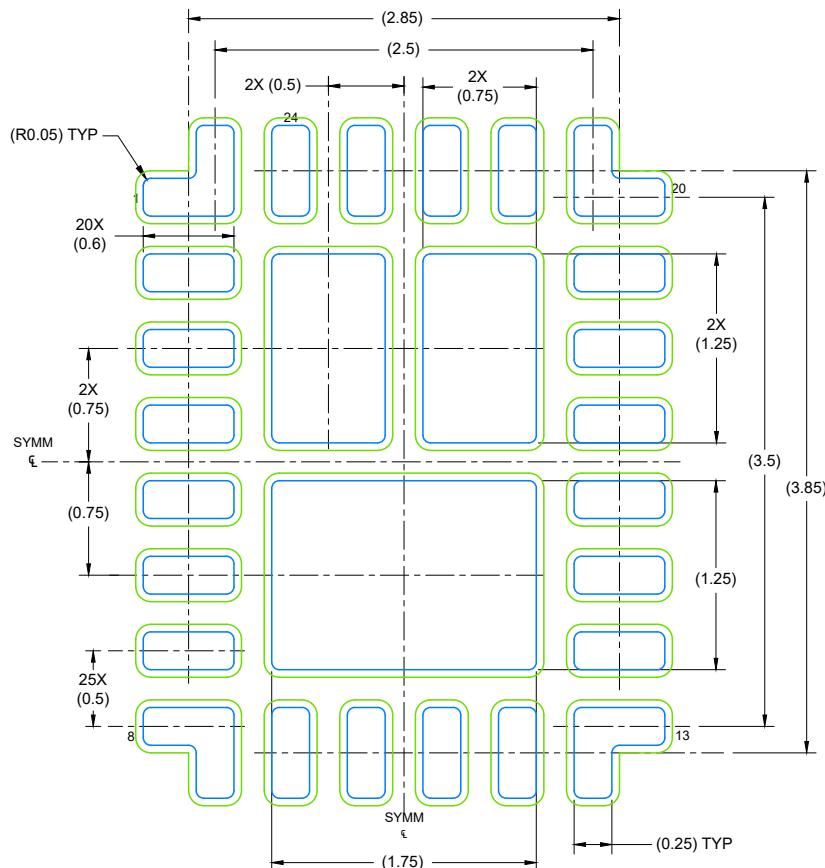

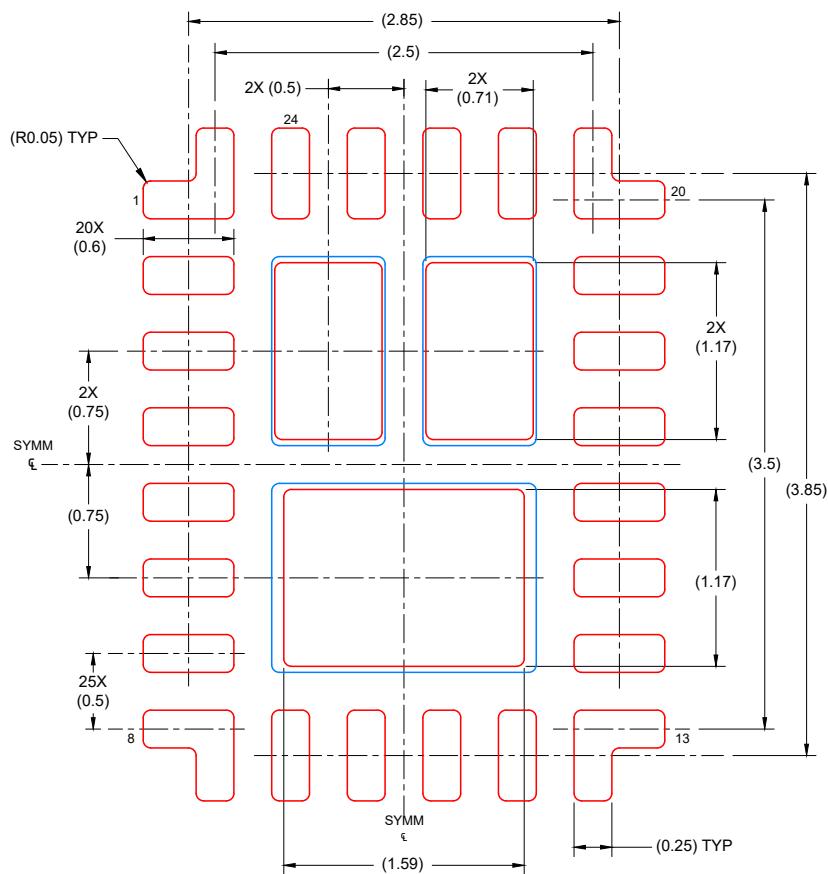

## 5 ピン構成および機能

図 5-1. RZV パッケージ 24 ピン WQFN-FCRLF

表 5-1. ピンの機能

| ピン             |       | 種類 <sup>(1)</sup> | 説明                                                                                                                                                                                                                                                           |

|----------------|-------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 番号             | 名称    |                   |                                                                                                                                                                                                                                                              |

| 1              | VOSNS | I                 | 出力電圧検出(差動出力電圧センシング)。                                                                                                                                                                                                                                         |

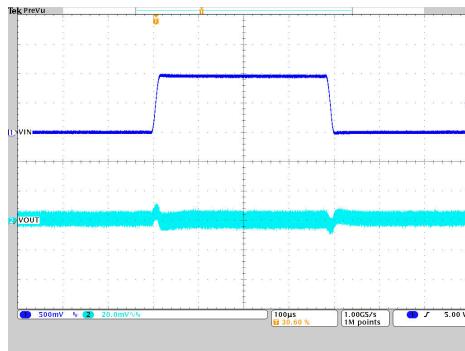

| 2              | EN    | I                 | このピンはデバイスのイネーブルピンです。このピンには、15kΩ 以上の直列抵抗を介して接続します。このピンがロジック Low レベルのときはデバイスが無効化され、ロジック High レベルのときはデバイスが有効になります。このピンを未接続のままにしないでください。<br>スタック動作を行う場合は、すべてのデバイスの EN ピンを相互に接続し、それらを電源電圧またはプロセッサの GPIO に抵抗を介して接続します。詳細については、「 <a href="#">スタック動作</a> 」を参照してください。 |

| 3              | FSEL  | I                 | 周波数選択ピン。外部同期が行われていない場合、抵抗または GND または VIN への短絡によってスイッチング周波数が決まります。周波数オプションについては、 <a href="#">セクション 8.3.6</a> を参照してください。                                                                                                                                       |

| 4              | VSEL  | I                 | スタートアップ時の出力電圧設定ピン。抵抗、または GND もしくは VIN への短絡によって、選択される出力電圧が決まります。                                                                                                                                                                                              |

| 5, 6, 15, 16   | VIN   | P                 | 電源入力。入力コンデンサを VIN と GND の間に、できるだけ近づけて接続します。                                                                                                                                                                                                                  |

| 7, 8<br>13, 14 | GND   | GND               | グランド ピン                                                                                                                                                                                                                                                      |

| 9, 10, 11, 12  | SW    | O                 | これはコンバータのスイッチ ピンであり、内部パワー MOSFET に接続されています。                                                                                                                                                                                                                  |

**表 5-1. ピンの機能 (続き)**

| ピン           |           | 種類 <sup>(1)</sup> | 説明                                                                                                                                                                                                                                                                                                                               |

|--------------|-----------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 番号           | 名称        |                   |                                                                                                                                                                                                                                                                                                                                  |

| 17           | SYNCOUT   | O                 | スタック モードでの同期用の内部クロック出力ピン。このピンはシングルデバイス動作用にフローティングのままにします。スタック動作においては、このピンをデイジーチェーンで次段のデバイスの MODE/SYNC ピンに接続します。このピンを TPS6287x-Q1 以外のデバイスの接続に使用しないでください。<br>スタートアップ時、このピンは、デバイスがスタック動作時にセカンダリ コンバータとして動作する必要があるかどうかを識別するのに使われます。このピンと GND との間に 47kΩ 抵抗を接続して、スタック動作でセカンダリ コンバータを定義します。詳細については、「 <a href="#">スタック動作</a> 」を参照してください。 |

| 18           | MODE/SYNC | I                 | このピンが Low になると、デバイスはパワーセーブ モードで動作します。ピンが High にプルされる場合、デバイスは強制 PWM モードで動作します。このピンを未接続のままにしないでください。モードピンを使用して、デバイスを外部クロックに同期することもできます。                                                                                                                                                                                            |

| 19           | SDA       | I/O               | I <sup>2</sup> C シリアル データピン。このピンをフローティングのままにしないでください。プルアップをロジック High レベルに接続します。<br>スタック動作での 2 次側デバイスの場合は GND に接続します。                                                                                                                                                                                                             |

| 20           | SCL       | I/O               | I <sup>2</sup> C シリアル クロック ピン。このピンをフローティングのままにしないでください。プルアップ抵抗をロジック High レベルに接続します。<br>スタック動作での 2 次側デバイスの場合は GND に接続します。                                                                                                                                                                                                         |

| 21           | PG        | I/O               | オープン ドレインのパワー グッド出力。「パワー グッド」でないときは低インピーダンス、「パワー グッド」のときは高インピーダンスになります。このピンはオープンのままにするか、1 つのデバイス動作で使用しない場合は GND に接続できます。<br>スタック動作では、すべてのデバイスの PG ピンを相互に接続します。スタック動作のプライマリ コンバータの PG ピンのみがオープン ドレイン出力です。スタックモードでセカンダリ コンバータとして定義されたデバイスの場合、ピンは入力ピンです。詳細については、「 <a href="#">スタック動作</a> 」を参照してください。                                |

| 22           | AGND      | GND               | アナログ グランド。GND に接続。                                                                                                                                                                                                                                                                                                               |

| 23           | COMP      | —                 | デバイス補償入力。このピンと AGND との間に抵抗とコンデンサによって、制御ループの補償が定義されます。<br>スタック動作では、スタックされたすべてのデバイスの COMP ピンを互いに接続し、共通の COMP ノードと AGND との間に抵抗とコンデンサを接続します。                                                                                                                                                                                         |

| 24           | GOSNS     | I                 | 出力グランド検出 (差動出力電圧センシング)                                                                                                                                                                                                                                                                                                           |

| 露出したサーマル パッド |           | —                 | 適切な熱抵抗と機械的安定性を実現するため、サーマル パッドは GND に半田付けする必要があります。                                                                                                                                                                                                                                                                               |

(1) I = 入力、O = 出力、P = 電源、GND = グランド

## 6 仕様

### 6.1 絶対最大定格

動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|                   |                                       | 最小値  | 最大値                   | 単位 |

|-------------------|---------------------------------------|------|-----------------------|----|

| 電圧 <sup>(2)</sup> | VIN <sup>(4)</sup>                    | -0.3 | 6.5                   | V  |

|                   | SW (DC)                               | -0.3 | V <sub>IN</sub> + 0.3 | V  |

|                   | COMP                                  | -0.3 | V <sub>IN</sub>       | V  |

|                   | SW (AC、10ns 未満) <sup>(3)</sup>        | -3   | 10                    | V  |

|                   | VOSNS                                 | -0.3 | 1.8                   | V  |

| 電圧 <sup>(2)</sup> | SCL、SDA、                              | -0.3 | 5.5                   | V  |

| 電圧 <sup>(2)</sup> | SYNC_OUT                              | -0.3 | 2                     | V  |

| 電圧 <sup>(2)</sup> | PG                                    | -0.3 | 6.5                   | V  |

| 電圧 <sup>(2)</sup> | FSEL、VSEL、EN、MODE/SYNC <sup>(4)</sup> | -0.3 | 6.5                   | V  |

| 電圧 <sup>(2)</sup> | GOSNS                                 | -0.3 | 0.3                   | V  |

| T <sub>stg</sub>  | 保存温度                                  | -65  | 150                   | °C |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

- (2) すべての電圧値は、回路のグランド端子 GND を基準としたものです。

- (3) スイッチング動作時。

- (4) このピンの電圧は、絶対最大定格 6.5V を短時間にわたって超えることができますが、8V 未満に維持する必要があります。VIN を 8V に 100ms さらすことは、室温でのデバイスの経年劣化約 8 時間に相当します。

### 6.2 ESD 定格 - Q100

|                    |       |                                                               | 値     | 単位 |

|--------------------|-------|---------------------------------------------------------------|-------|----|

| V <sub>(ESD)</sub> | 静電気放電 | 人体モデル (HBM)、AEC Q100-002 準拠 <sup>(1)</sup><br>HBM ESD 分類レベル 2 | ±2000 | V  |

| V <sub>(ESD)</sub> | 静電気放電 | デバイス帶電モデル (CDM)、AEC Q100-011、<br>CDM ESD 分類レベル C5 準拠          | ±750  | V  |

- (1) AEC Q100-002 は、HBM ストレス試験を ANSI/ESDA/JEDEC JS-001 仕様に従って実施しなければならないと規定しています。

### 6.3 推奨動作条件

動作温度範囲内 (特に記述のない限り)

|                  |                                                  | 最小値 | 公称値                                                       | 最大値                                                       | 単位 |

|------------------|--------------------------------------------------|-----|-----------------------------------------------------------|-----------------------------------------------------------|----|

| V <sub>IN</sub>  | 入力電圧範囲                                           | 2.7 | 6                                                         | 6                                                         | V  |

| V <sub>OUT</sub> | 出力電圧範囲                                           | 0.4 | 1.675V ま<br>たは (V <sub>IN</sub> –<br>1.5V) <sup>(1)</sup> | 1.675V ま<br>たは (V <sub>IN</sub> –<br>1.5V) <sup>(1)</sup> | V  |

| 電圧               | ピン SDA および SCL の公称プルアップ電圧                        | 1.2 | 5                                                         | 5                                                         | V  |

| L                | f <sub>SW</sub> = 1.5MHz の場合の実効インダクタンス           | 100 | 150                                                       | 200                                                       | nH |

| L                | f <sub>SW</sub> = 2.25MHz、2.5MHz、3MHz の実効インダクタンス | 40  | 100                                                       | 200                                                       | nH |

| C <sub>IN</sub>  | 電力入力ピンあたりの実効入力容量                                 | 10  | 22                                                        | 22                                                        | μF |

| C <sub>OUT</sub> | 実効出力キャパシタンス                                      | 47  | 47                                                        | 47                                                        | μF |

| C <sub>PAR</sub> | FSEL、VSEL ピンの寄生容量                                |     |                                                           | 100                                                       | pF |

| C <sub>PAR</sub> | SYNC_OUT ピンの寄生容量                                 |     |                                                           | 20                                                        | pF |

| R <sub>EN</sub>  | EN ピンに対するプルアップ抵抗                                 | 15  | 15                                                        | 15                                                        | kΩ |

## 6.3 推奨動作条件 (続き)

動作温度範囲内 (特に記述のない限り)

|                         |                                                            | 最小値 | 公称値 | 最大値 | 単位 |

|-------------------------|------------------------------------------------------------|-----|-----|-----|----|

| $R_{VSEL}$ 、 $R_{FSEL}$ | VSEL が GND または VIN に直接接続されていない場合の VSEL、FSEL ピンから GND への抵抗値 |     | 6.2 |     | kΩ |

| $R_{VSEL}$ 、 $R_{FSEL}$ | VSEL が GND または VIN に直接接続されていない場合の VSEL、FSEL ピンから VIN への抵抗値 |     | 47  |     | kΩ |

| $R_{VSEL}$ 、 $R_{FSEL}$ | VSEL、FSEL の抵抗の公差                                           |     |     | ±2% |    |

| $I_{SINK\_PG}$          | PG ピンのシンク電流                                                | 0   | 1   |     | mA |

| $T_J$                   | 動作時接合部温度 (2)                                               | -40 |     | 150 | °C |

(1)  $V_{OUT}$  の値が小さい値でも。

(2) 接合部温度が 125°Cを超えると、動作寿命が短くなります。

(3) 推奨される最大出力キャパシタンスは、アプリケーションの特定の動作条件によって異なります。通常は、最大数ミリファラッドの出力キャパシタンス値が可能です。

## 6.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup> | TPS6287x-Q1         | TPS6287x-Q1 | 単位   |

|----------------------|---------------------|-------------|------|

|                      | RZV (JEDEC)         | RZV (EVM)   |      |

|                      | 24 ピン               | 24 ピン       |      |

| $R_{\theta JA}$      | 接合部から周囲への熱抵抗        | 34.7        | °C/W |

| $R_{\theta JC(top)}$ | 接合部からケース (上面) への熱抵抗 | 14.9        | °C/W |

| $R_{\theta JB}$      | 接合部から基板への熱抵抗        | 6.5         | °C/W |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ    | 1.5         | °C/W |

| $\Upsilon_{JB}$      | 接合部から基板への特性パラメータ    | 6.5         | °C/W |

| $R_{\theta JC(bot)}$ | 接合部からケース (底面) への熱抵抗 | 4.8         | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション ノートを参照してください。

## 6.5 電気的特性

動作時接合部温度範囲全体( $T_J = -40^{\circ}\text{C} \sim +150^{\circ}\text{C}$ )、 $V_{IN} = 2.7\text{V} \sim 6\text{V}$ 、 $V_{IN} = 5\text{V}$ かつ  $T_J = 25^{\circ}\text{C}$  での標準値 (特に記述のない限り)。

| パラメータ               | テスト条件                                                                             | 最小値 | 標準値 | 最大値 | 単位 |

|---------------------|-----------------------------------------------------------------------------------|-----|-----|-----|----|

| <b>電源</b>           |                                                                                   |     |     |     |    |

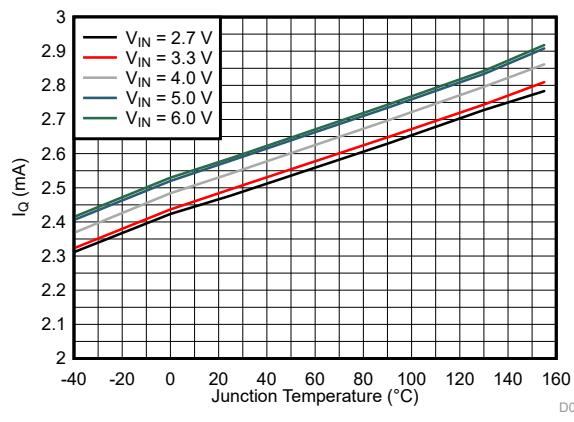

| $I_Q$               | 静止時電流<br>EN = High、 $I_{OUT} = 0\text{ mA}$ 、デバイスはスイッチングなし、MODE = Low             | 2.1 | 3.8 |     | mA |

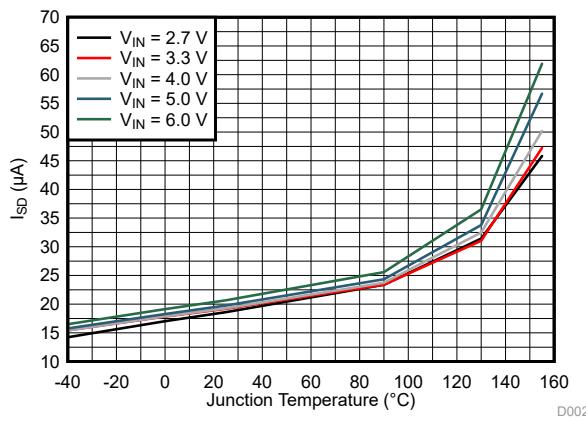

| $I_{SD}$            | シャットダウン電流<br>EN = Low、 $V_{(SW)} = 0\text{V}$ 、 $T_J = 125^{\circ}\text{C}$ での最大値 | 18  | 450 |     | μA |

| $V_{IT+}$<br>(UVLO) | 正方向の UVLO スレッショルド電圧 (VIN)                                                         | 2.5 | 2.6 | 2.7 | V  |

| $V_{IT-(UVLO)}$     | 負方向の UVLO スレッショルド電圧 (VIN)                                                         | 2.4 | 2.5 | 2.6 | V  |

| $V_{hys(UVLO)}$     | UVLO ヒステリシス電圧 (VIN)                                                               | 80  |     |     | mV |

| $V_{IT+}$<br>(OVLO) | 正方向の OVLO スレッショルド電圧 (VIN)                                                         | 6.1 | 6.3 | 6.5 | V  |

| $V_{IT-(OVLO)}$     | 負方向の OVLO スレッショルド電圧 (VIN)                                                         | 6.0 | 6.2 | 6.4 | V  |

| $V_{hys(OVLO)}$     | OVLO ヒステリシス電圧 (VIN)                                                               | 80  |     |     | mV |

## 6.5 電気的特性 (続き)

動作時接合部温度範囲全体( $T_J = -40^{\circ}\text{C} \sim +150^{\circ}\text{C}$ )、 $V_{IN} = 2.7\text{V} \sim 6\text{V}$ 。 $V_{IN} = 5\text{V}$ かつ $T_J = 25^{\circ}\text{C}$ での標準値(特に記述のない限り)。

| パラメータ          |                                               | テスト条件                                                                         | 最小値  | 標準値  | 最大値  | 単位 |

|----------------|-----------------------------------------------|-------------------------------------------------------------------------------|------|------|------|----|

| $V_{IT-(POR)}$ | 負方向のパワーオンリセットスレッショルド電圧 ( $V_{IN}$ )           |                                                                               | 1.4  |      |      | V  |

| $T_{SD}$       | サーマルシャットダウンスレッショルド温度                          | $T_J$ 立ち上がり                                                                   |      | 170  |      | °C |

|                | サーマルシャットダウンヒステリシス                             |                                                                               |      | 20   |      | °C |

| $T_W$          | 過熱警告スレッショルド温度                                 | $T_J$ 立ち上がり                                                                   |      | 150  |      | °C |

|                | 過熱警告ヒステリシス                                    |                                                                               |      | 20   |      | °C |

| 制御とインターフェイス    |                                               |                                                                               |      |      |      |    |

| $V_{IT+}$      | 正方向の入力スレッショルド電圧 (EN)                          |                                                                               | 0.97 | 1.0  | 1.03 | V  |

| $V_{IT-}$      | 負方向の入力スレッショルド電圧 (EN)                          |                                                                               | 0.87 | 0.9  | 0.93 | V  |

| $V_{hys}$      | ヒステリシス電圧 (EN)                                 |                                                                               | 95   |      |      | mV |

| $R_{(EN)}$     | GNDへの入力抵抗 (EN)                                | スタック動作でのスタートアップ時にのみアクティブになります。                                                | 1.4  | 1.8  | 3    | kΩ |

| $I_{IH}$       | Highレベル入力電流 (EN)                              | $V_{IH} = V_{IN}$ 、内部プルダウン抵抗は無効                                               |      |      | 3    | μA |

| $I_{IL}$       | Lowレベル入力電流 (EN)                               | $V_{IL} = 0\text{V}$ 、内部プルダウン抵抗は無効                                            | -200 |      |      | nA |

| $V_{IH}$       | Highレベル入力電圧 (MODE/SYNC、VSEL、FSEL、SYNC_OUT、PG) |                                                                               | 0.8  |      |      | V  |

| $V_{IL}$       | Highレベル入力電圧 (SDA、SCL)                         |                                                                               | 0.95 |      |      | V  |

| $V_{IL}$       | Lowレベル入力電圧 (MODE/SYNC、VSEL、FSEL、SYNC_OUT、PG)  |                                                                               |      | 0.4  |      | V  |

| $V_{IL}$       | Lowレベル入力電圧 (SDA、SCL)                          |                                                                               |      | 0.5  |      | V  |

| $R_{IN}$       | ピン MODE/SYNC、EN、PG で GNDとの間の入力抵抗              |                                                                               | 2    | 3    | 4    | MΩ |

| $V_{OL}$       | Lowレベル出力電圧 (SDA)                              | $I_{OL} = 9\text{mA}$                                                         |      | 0.4  |      | V  |

| $V_{OL}$       | Lowレベル出力電圧 (SDA)                              | $I_{OL} = 5\text{mA}$                                                         |      | 0.2  |      | V  |

| $I_{LKG}$      | SDA、SCLへの入力リーク電流                              | $V_{OH} = 3.3\text{V}$                                                        |      | 200  |      | nA |

| $I_{IL}$       | Lowレベル入力電圧 (MODE/SYNC)                        | $V_{IL} = 0\text{V}$                                                          | -100 | 100  |      | nA |

| $I_{IH}$       | Highレベル入力電圧 (MODE/SYNC)                       | $V_{IH} = V_{IN}$                                                             |      | 3    |      | μA |

| $I_{IL}$       | Lowレベル入力電圧 (SYNC_OUT)                         | $V_{IL} = 0\text{V}$                                                          | -230 |      |      | nA |

| $I_{IH}$       | Highレベル入力電圧 (SYNC_OUT)                        | $V_{IH} = 2\text{V}$                                                          |      | 110  |      | nA |

| $V_{OL}$       | Lowレベル出力電圧 (SYNC_OUT)                         | $I_{OL} = 1\text{mA}$                                                         |      | 0.3  |      | V  |

| $V_{OH}$       | Highレベル出力電圧 (SYNC_OUT)                        | $I_{OH} = 0.1\text{mA}$                                                       | 1.3  | 2.1  |      | V  |

| $t_{d(EN)1}$   | ENを $V_{IN}$ に接続したときのイネーブル遅延時間                | ENがHighになった時点からデバイスがスイッチングを開始する時点までを測定、 $SR_{V_{IN}} = 1\text{V}/\mu\text{s}$ |      | 200  | 600  | μs |

| $t_{d(EN)2}$   | $V_{IN}$ がすでに印加されているときのイネーブル遅延時間              | ENがHighになった時点からデバイスがスイッチングを開始する時点までを測定                                        |      | 40   | 100  | μs |

| $t_{d(Ramp)}$  | CONTROL2[1:0] = 00 の出力電圧ランプ時間                 | デバイスがスイッチングを開始してから、PG信号が立ち上がるまでの時間を測定                                         | 0.35 | 0.5  | 0.65 | ms |

|                | CONTROL2[1:0] = 01 の出力電圧ランプ時間                 |                                                                               | 0.54 | 0.77 | 1.0  | ms |

|                | CONTROL2[1:0] = 10 の出力電圧ランプ時間、デフォルト           |                                                                               | 0.7  | 1    | 1.3  | ms |

|                | CONTROL2[1:0] = 11 の出力電圧ランプ時間                 |                                                                               | 1.4  | 2    | 2.6  | ms |

## 6.5 電気的特性 (続き)

動作時接合部温度範囲全体( $T_J = -40^{\circ}\text{C} \sim +150^{\circ}\text{C}$ )、 $V_{IN} = 2.7\text{V} \sim 6\text{V}$ 。 $V_{IN} = 5\text{V}$ かつ $T_J = 25^{\circ}\text{C}$ での標準値(特に記述のない限り)。

| パラメータ                    |                                           | テスト条件                                                                                     | 最小値   | 標準値   | 最大値  | 単位  |

|--------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------|-------|-------|------|-----|

| $f_{(\text{SYNC})}$      | 同期クロック周波数範囲 (MODE/SYNC)                   | $f_{(\text{SW})\text{nom}} = 1.5\text{MHz}$ , $D_{(\text{MODE/SYNC})} = 45\% \dots 55\%$  | 1.2   | 1.8   | 1.8  | MHz |

|                          | 同期クロック周波数範囲 (MODE/SYNC)                   | $f_{(\text{SW})\text{nom}} = 2.25\text{MHz}$ , $D_{(\text{MODE/SYNC})} = 45\% \dots 55\%$ | 1.8   | 2.7   | 2.7  | MHz |

|                          | 同期クロック周波数範囲 (MODE/SYNC)                   | $f_{(\text{SW})\text{nom}} = 2.5\text{MHz}$ , $D_{(\text{MODE/SYNC})} = 45\% \dots 55\%$  | 2     | 3.0   | 3.0  | MHz |

| $f_{(\text{SYNC})}$      | 同期クロック周波数範囲 (MODE/SYNC)                   | $f_{(\text{SW})\text{nom}} = 3\text{MHz}$ , $D_{(\text{MODE/SYNC})} = 45\% \dots 55\%$    | 2.4   | 3.3   | 3.3  | MHz |

| $D_{(\text{MODE/SYNC})}$ | 同期クロック周波数のデューティ サイクル (MODE/SYNC)          |                                                                                           | 45    | 55    | 55   | %   |

|                          | SYNC_OUT での位相シフト(内部 CLK または外部 CLK を基準とする) | CONTROL2:SYNCH_OUT_PHASE = 0b0                                                            |       | 120   |      | °   |

|                          | SYNC_OUT での位相シフト(内部 CLK または外部 CLK を基準とする) | CONTROL2:SYNCH_OUT_PHASE = 0b1                                                            |       | 180   |      | °   |

|                          | 外部周波数にロックする時間                             |                                                                                           |       | 50    |      | μs  |

|                          | FSEL、VSEL が GND に直接接続されていない場合の、GND への抵抗値  |                                                                                           |       | 6.2   |      | kΩ  |

|                          | FSEL、VSEL が VIN に直接接続されていない場合の、VIN への抵抗値  |                                                                                           |       | 47    |      | kΩ  |

| $V_{T+(UVP)}$            | 正方向のパワーグッド スレッショルド電圧(出力低電圧)               |                                                                                           | 94    | 96    | 98   | %   |

| $V_{T-(UVP)}$            | 負方向のパワーグッド スレッショルド電圧(出力低電圧)               |                                                                                           | 92    | 94    | 96   | %   |

| $V_{T+(OVP)}$            | 正方向のパワーグッド スレッショルド電圧(出力過電圧)               |                                                                                           | 104   | 106   | 108  | %   |

| $V_{T-(OVP)}$            | 負方向のパワーグッド スレッショルド電圧(出力過電圧)               |                                                                                           | 102   | 104   | 106  | %   |

| $V_{OL}$                 | Low レベル出力電圧 (PG)                          | $I_{OL} = 1\text{mA}$                                                                     |       | 0.012 | 0.3  | V   |

| $I_{OH}$                 | High レベル出力電流 (PG)                         | $V_{OH} = 5\text{V}$                                                                      |       |       | 3    | μA  |

| $I_{IH}$                 | High レベル入力電流 (PG)                         | スタック動作でセカンダリ デバイスとして構成されたデバイス                                                             |       |       | 3    | μA  |

| $I_{IL}$                 | Low レベル入力電流 (PG)                          | スタック動作でセカンダリ デバイスとして構成されたデバイス                                                             |       | -1    |      | μA  |

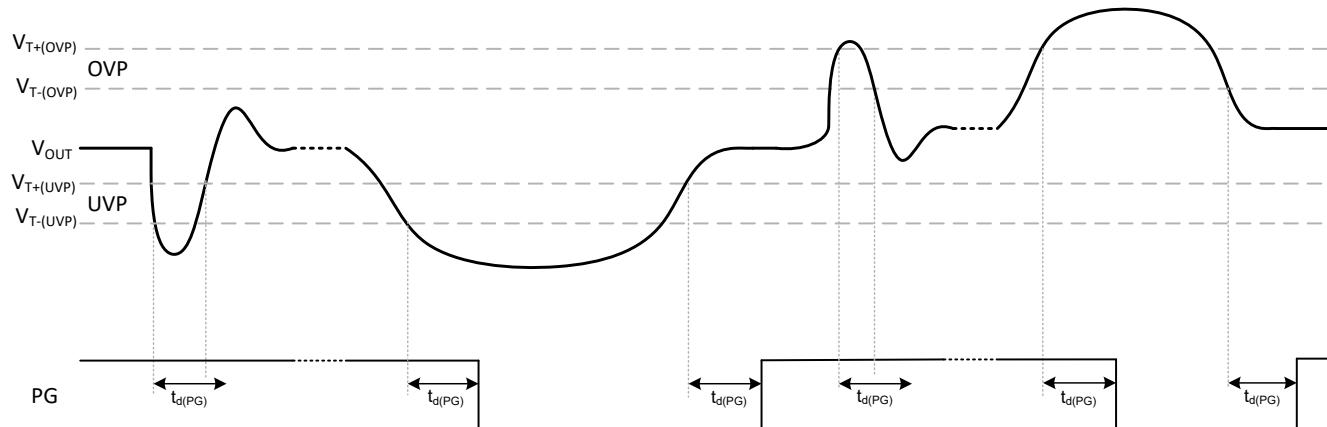

| $t_{d(\text{PG})}$       | グリッチ除去時間 (PG)                             | PG ピンの High から Low、または Low から High への遷移                                                   | 34    | 40    | 46   | μs  |

| <b>出力</b>                |                                           |                                                                                           |       |       |      |     |

| $\Delta V_{OUT}$         | 出力電圧精度                                    | $V_{IN} = V_{OUT} = 1.6\text{V}$ 、ドロップ補償は無効                                               | -0.8  | 0.8   | 0.8  | %   |

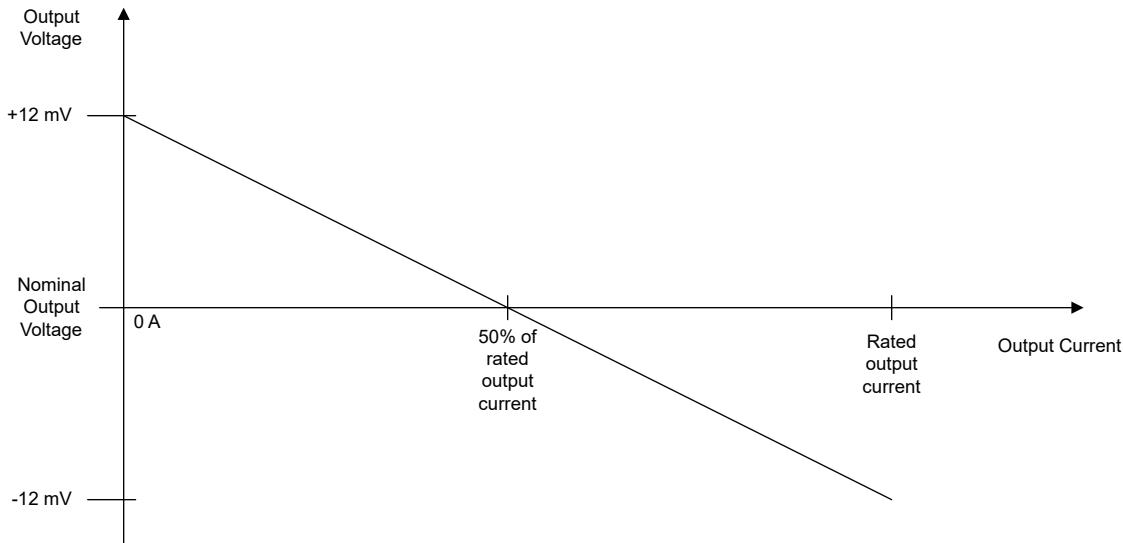

| $\Delta V_{OUT}$         | 出力電圧の電流がない状態から定格電流への変化                    | ドロップ補償は有効                                                                                 |       | ±12   |      | mV  |

|                          | ドロップ補償電圧の精度、TPS62874-Q1                   | デバイスは強制 PWM モード                                                                           | -3.75 | 3.75  | 3.75 | mV  |

|                          | ドロップ補償電圧の精度、TPS62875-Q1                   | デバイスは強制 PWM モード                                                                           | -3.5  | 3.5   | 3.5  | mV  |

|                          | ドロップ補償電圧の精度、TPS62876-Q1、TPS62877-Q1       | デバイスは強制 PWM モード                                                                           | -3    | 3     | 3    | mV  |

|                          | ライン レギュレーション                              | $I_{OUT} = 15\text{A}$ , $V_{IN} \geq V_{OUT} + 1.6\text{V}$                              | 0.02  |       |      | %/V |

| $I_{IB}$                 | 入力バイアス電流 (GOSNS)                          | $EN = \text{High}$ ; $V_{(GOSNS)} = -100\text{mV} \text{ to } 100\text{mV}$               | -60   | 3     | 3    | μA  |

## 6.5 電気的特性 (続き)

動作時接合部温度範囲全体( $T_J = -40^{\circ}\text{C} \sim +150^{\circ}\text{C}$ )、 $V_{IN} = 2.7\text{V} \sim 6\text{V}$ 。 $V_{IN} = 5\text{V}$ かつ $T_J = 25^{\circ}\text{C}$ での標準値(特に記述のない限り)。

| パラメータ           |                                 | テスト条件                                                                      | 最小値           | 標準値           | 最大値   | 単位               |

|-----------------|---------------------------------|----------------------------------------------------------------------------|---------------|---------------|-------|------------------|

| $I_{IB}$        | 入力バイアス電流 (VOSNS)                | $V_{(VOSNS)} = 1.675\text{V}$ , $V_{IN} = 6\text{V}$ 、ドロップ補償が無効            | -5.5          | 5.5           |       | $\mu\text{A}$    |

| $I_{IB}$        | 入力バイアス電流 (VOSNS)                | $V_{(VOSNS)} = 1.675\text{V}$ , $V_{IN} = 6\text{V}$ 、ドロップ補償が有効            | -13.2         | 13.2          |       | $\mu\text{A}$    |

| $V_{ICR}$       | 同相入力範囲 (GOSNS)                  |                                                                            | -100          | 100           |       | $\text{mV}$      |

| $R_{DIS}$       | 出力放電抵抗                          | $V_{OUT} \leq 1\text{V}$                                                   |               | 2.7           | 9.2   | $\Omega$         |

| $f_{SW}$        | スイッチング周波数 (SW)                  | $f_{SW} = 1.5\text{MHz}$ 、PWM動作                                            | 1.35          | 1.5           | 1.65  | $\text{MHz}$     |

|                 |                                 | $f_{SW} = 2.25\text{MHz}$ 、PWM動作                                           | 2.025         | 2.25          | 2.475 | $\text{MHz}$     |

|                 |                                 | $f_{SW} = 2.5\text{MHz}$ 、PWM動作                                            | 2.25          | 2.5           | 2.75  | $\text{MHz}$     |

|                 |                                 | $f_{SW} = 3\text{MHz}$ 、PWM動作                                              | 2.7           | 3             | 3.3   | $\text{MHz}$     |

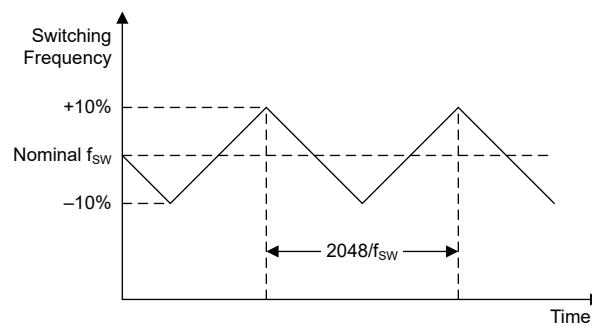

| $f_{SSC}$       | 変調周波数                           |                                                                            | $f_{SW}/2048$ |               |       | $\text{kHz}$     |

| $\Delta f_{SW}$ | スペクトラム拡散動作時のスイッチング周波数の変動        |                                                                            | $f_{SW}-10\%$ | $f_{SW}+10\%$ |       |                  |

| $gm$            | COMP ピン上の OTA の相互コンダクタンス        |                                                                            |               | 1.5           |       | $\text{mS}$      |

| $\tau$          | エミュレート電流時定数                     |                                                                            | 11.87         | 12.5          | 13.2  | $\mu\text{s}$    |

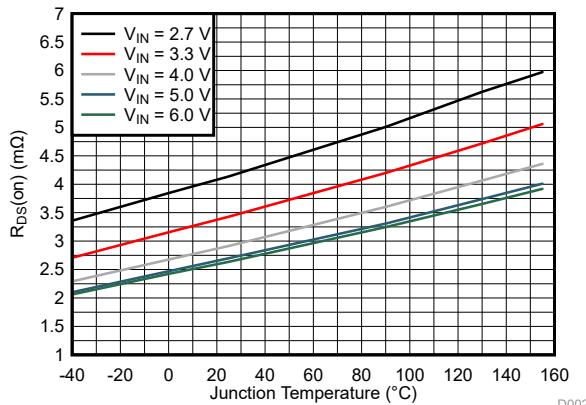

| $R_{DS(ON)}$    | ハイサイド FET の静的オン抵抗               | $V_{IN} = 3.3\text{V}$                                                     |               | 3.4           | 6.4   | $\text{m}\Omega$ |

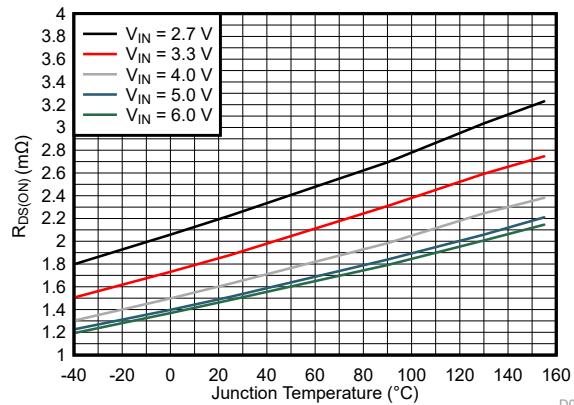

| $R_{DS(ON)}$    | ローサイド FET の静的オン抵抗               | $V_{IN} = 3.3\text{V}$                                                     |               | 1.9           | 3.6   | $\text{m}\Omega$ |

| $I_{(SW)(off)}$ | HS-FET と LS-FET がオフのときの SW ピン電流 | $V_{IN} = 6\text{V}$ , $V_{(SW)} = 0\text{V}$ , $T_J = 25^{\circ}\text{C}$ | -1.5          | 0.1           |       | $\mu\text{A}$    |

|                 | HS-FET と LS-FET がオフのときの SW ピン電流 | $V_{IN} = 6\text{V}$ , $V_{(SW)} = 6\text{V}$ , $T_J = 25^{\circ}\text{C}$ | 60            | 130           |       | $\mu\text{A}$    |

|                 | HS-FET と LS-FET がオフのときの SW ピン電流 | $V_{(SW)} = 0.4\text{V}$ , SW ピンへの電流                                       | 11            | 3000          |       | $\mu\text{A}$    |

| ILIM            | ハイサイド FET 順方向スイッチ電流制限、DC        | TPS62874-Q1                                                                | 19            | 22.5          | 26    | A                |

| ILIM            | ハイサイド FET 順方向スイッチ電流制限、DC        | TPS62875-Q1                                                                | 24            | 28.5          | 32    | A                |

| ILIM            | ハイサイド FET 順方向スイッチ電流制限、DC        | TPS62876-Q1                                                                | 29            | 34            | 39    | A                |

| ILIM            | ハイサイド FET 順方向スイッチ電流制限、DC        | TPS62877-Q1                                                                | 34            | 39            | 44    | A                |

| ILIM            | ローサイド FET 順方向スイッチ電流制限、DC        | TPS62874-Q1                                                                | 15            | 20            | 24    | A                |

| ILIM            | ローサイド FET 順方向スイッチ電流制限、DC        | TPS62875-Q1                                                                | 20            | 24.5          | 29    | A                |

| ILIM            | ローサイド FET 順方向スイッチ電流制限、DC        | TPS62876-Q1                                                                | 24.5          | 29            | 33    | A                |

| ILIM            | ローサイド FET 順方向スイッチ電流制限、DC        | TPS62877-Q1                                                                | 29.5          | 33.5          | 38    | A                |

| ILIM            | ローサイド FET 負電流制限、DC              |                                                                            |               | -10           |       | A                |

| $t_{on, min}$   | HS FET の最小オン時間                  | $V_{IN} = 3.3\text{V}$                                                     |               | 45            | 53    | ns               |

| $t_{on, min}$   | HS FET の最小オン時間                  | $V_{IN} = 5\text{V}$                                                       |               | 35            | 44    | ns               |

| $t_{off, min}$  | HS FET の最小オフ時間                  | $V_{IN} = 5\text{V}$                                                       |               | 70            | 100   | ns               |

|                 | 電力段の最大デューティサイクル                 | TPS62877-Q1 のみ                                                             |               | 45            |       | %                |

## 6.6 I<sup>2</sup>C インターフェイス タイミングの要件

| パラメータ             |                           | テスト条件                        | 最小値  | 標準値  | 最大値     | 単位 |

|-------------------|---------------------------|------------------------------|------|------|---------|----|

| $f_{SCL}$         | SCL クロック周波数               | スタンダード モード                   |      | 100  | kHz     |    |

|                   |                           | ファスト モード                     |      | 400  | kHz     |    |

|                   |                           | ファスト モード プラス                 |      | 1    | MHz     |    |

|                   |                           | 高速モード (書き込み動作)、CB – 最大 100pF |      | 3.4  | MHz     |    |

|                   |                           | 高速モード (読み取り動作)、CB – 最大 100pF |      | 3.4  | MHz     |    |

|                   |                           | 高速モード (書き込み動作)、CB – 最大 400pF |      | 1.7  | MHz     |    |

| $t_{HD}, t_{STA}$ | (繰り返し) START 条件のホールド時間    | スタンダード モード                   | 4    |      | $\mu$ s |    |

|                   |                           | ファスト モード                     | 0.6  |      | $\mu$ s |    |

|                   |                           | ファスト モード プラス                 | 0.26 |      | $\mu$ s |    |

|                   |                           | 高速度モード                       | 0.16 |      | $\mu$ s |    |

| $t_{LOW}$         | SCL クロック Low 期間           | スタンダード モード                   | 4.7  |      | $\mu$ s |    |

|                   |                           | ファスト モード                     | 1.3  |      | $\mu$ s |    |

|                   |                           | ファスト モード プラス                 | 0.5  |      | $\mu$ s |    |

|                   |                           | 高速モード、CB – 最大 100pF          | 0.16 |      | $\mu$ s |    |

|                   |                           | 高速モード、CB – 最大 400pF          | 0.32 |      | $\mu$ s |    |

| $t_{HIGH}$        | SCL クロックの High の時間        | スタンダード モード                   | 4    |      | $\mu$ s |    |

|                   |                           | ファスト モード                     | 0.6  |      | $\mu$ s |    |

|                   |                           | ファスト モード プラス                 | 0.26 |      | $\mu$ s |    |

|                   |                           | 高速モード、CB – 最大 100pF          | 0.06 |      | $\mu$ s |    |

|                   |                           | 高速モード、CB – 最大 400pF          | 0.12 |      | $\mu$ s |    |

| $t_{SU}, t_{STA}$ | 反復開始条件のセットアップ時間           | スタンダード モード                   | 4.7  |      | $\mu$ s |    |

|                   |                           | ファスト モード                     | 0.6  |      | $\mu$ s |    |

|                   |                           | ファスト モード プラス                 | 0.26 |      | $\mu$ s |    |

|                   |                           | 高速度モード                       | 0.16 |      | $\mu$ s |    |

| $t_{SU}, t_{DAT}$ | データ セットアップ時間              | スタンダード モード                   | 250  |      | ns      |    |

|                   |                           | ファスト モード                     | 100  |      | ns      |    |

|                   |                           | ファスト モード プラス                 | 50   |      | ns      |    |

|                   |                           | 高速モード、CB – 最大 100pF          | 10   |      | ns      |    |

| $t_{HD}, t_{DAT}$ | データ ホールド時間                | スタンダード モード                   | 0    | 3.45 | $\mu$ s |    |

|                   |                           | ファスト モード                     | 0    | 0.9  | $\mu$ s |    |

|                   |                           | ファスト モード プラス                 | 0    |      | $\mu$ s |    |

|                   |                           | 高速モード、CB – 最大 100pF          | 0    | 70   | ns      |    |

|                   |                           | 高速モード、CB – 最大 400pF          | 0    | 150  | ns      |    |

| $t_{RCL}$         | SDA 信号と SCL 信号の両方の立ち上がり時間 | スタンダード モード                   |      | 1000 | ns      |    |

|                   |                           | ファスト モード                     | 20   | 300  | ns      |    |

|                   |                           | ファスト モード プラス                 |      | 120  | ns      |    |

|                   |                           | 高速モード、CB – 最大 100pF          | 10   | 40   | ns      |    |

|                   |                           | 高速モード、CB – 最大 400pF          | 20   | 80   | ns      |    |

## 6.6 I<sup>2</sup>C インターフェイス タイミングの要件 (続き)

| パラメータ             |                                          | テスト条件               | 最小値                     | 標準値 | 最大値 | 単位 |

|-------------------|------------------------------------------|---------------------|-------------------------|-----|-----|----|

| $t_{FCL}$         | SDA 信号と SCL 信号の両方の立ち下がり時間 <sup>(1)</sup> | スタンダード モード          |                         | 300 |     | ns |

|                   |                                          | ファスト モード            | $20 \times V_{DD}/5.5V$ | 300 |     | ns |

|                   |                                          | ファスト モード プラス        | $20 \times V_{DD}/5.5V$ | 120 |     | ns |

|                   |                                          | 高速モード、CB – 最大 100pF | 10                      | 40  |     | ns |

|                   |                                          | 高速モード、CB – 最大 400pF | 20                      | 80  |     | ns |

| $t_{SU}, t_{STO}$ | STOP 条件のセットアップ時間                         | スタンダード モード          | 4                       |     |     | μs |

|                   |                                          | ファスト モード            | 0.6                     |     |     | μs |

|                   |                                          | ファスト モード プラス        | 0.26                    |     |     | μs |

|                   |                                          | 高速モード               | 0.16                    |     |     | μs |

| CB                | SDA および SCL の容量性負荷                       | スタンダード モード          |                         | 400 |     | pF |

|                   |                                          | ファスト モード            |                         | 400 |     | pF |

|                   |                                          | ファスト モード プラス        |                         | 550 |     | pF |

|                   |                                          | 高速モード               |                         | 400 |     | pF |

| $t_{BUF}$         | 停止条件と開始条件の間のバス フリー時間                     | スタンダード モード          | 4.7                     |     |     | μs |

|                   |                                          | ファスト モード            | 1.3                     |     |     | μs |

|                   |                                          | ファスト モード プラス        | 0.5                     |     |     | μs |

(1)  $V_{DD}$  は SDA と SCL のプルアップ電圧。

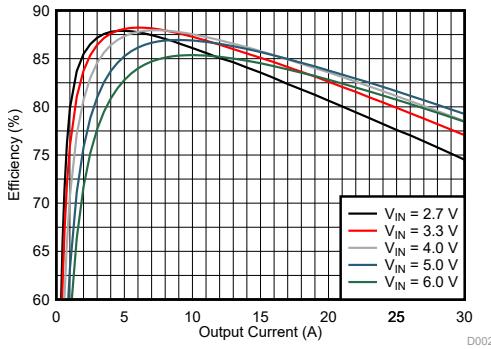

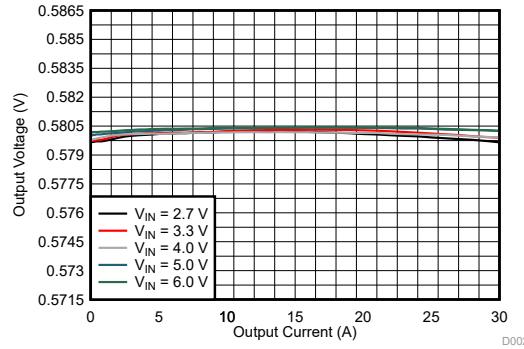

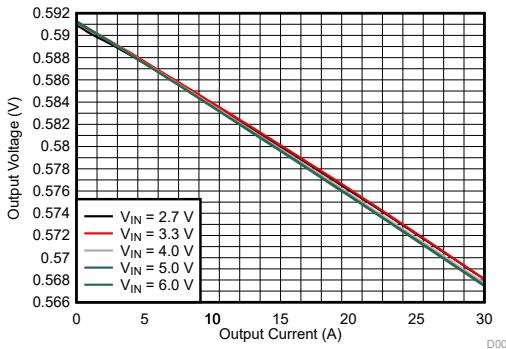

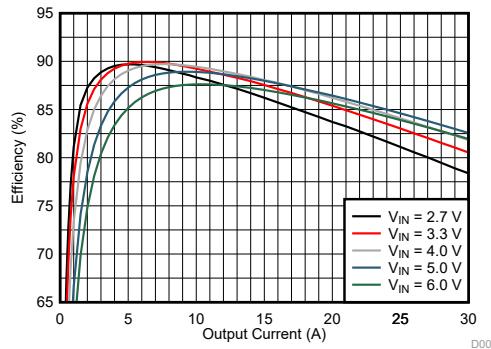

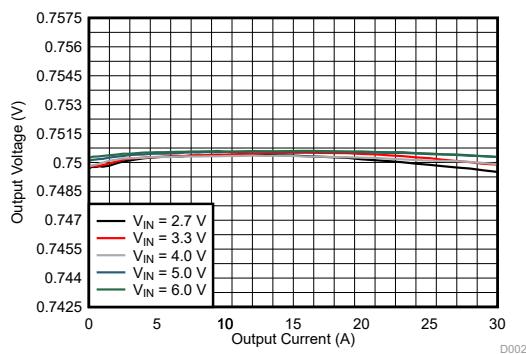

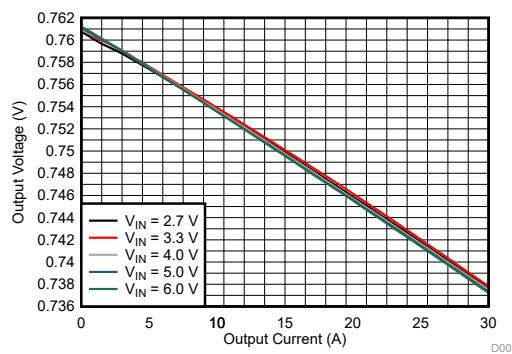

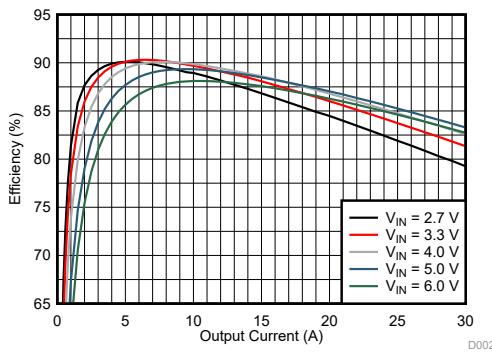

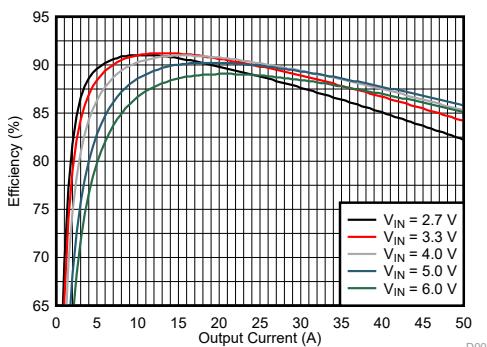

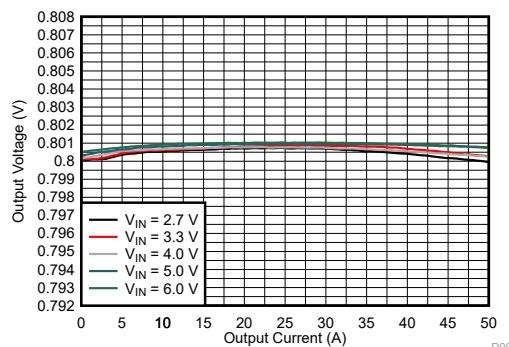

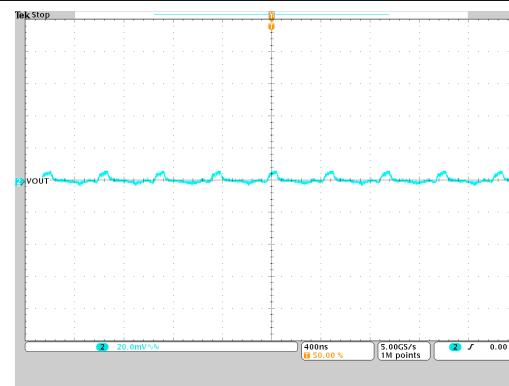

## 6.7 代表的特性

図 6-1. ハイサイド スイッチの  $R_{DS(ON)}$

図 6-2. ローサイド スイッチの  $R_{DS(ON)}$

図 6-3. シャットダウン電流と温度との関係

図 6-4. 静止電流と温度との関係

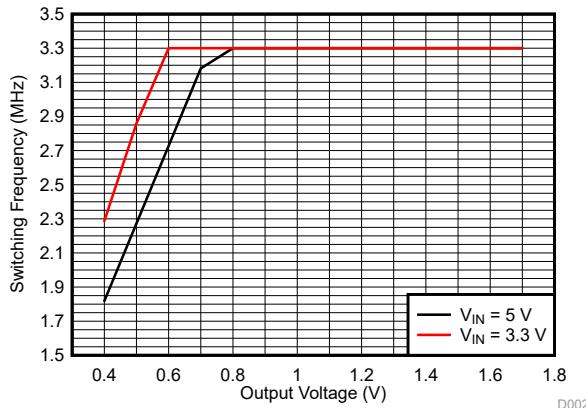

図 6-5. 最大スイッチング周波数と出力電圧との関係

図 6-6. スイッチング周波数と温度との関係

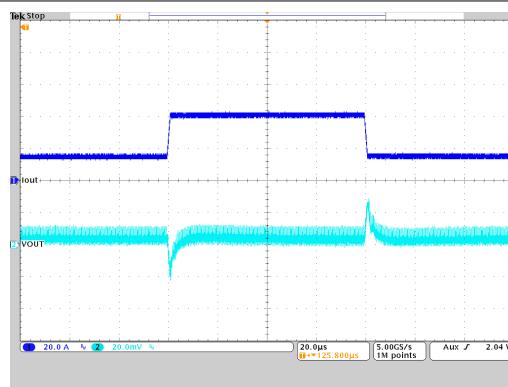

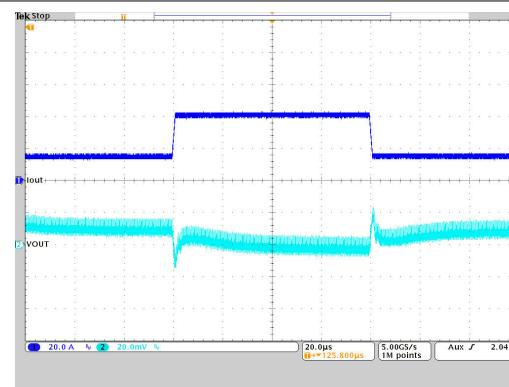

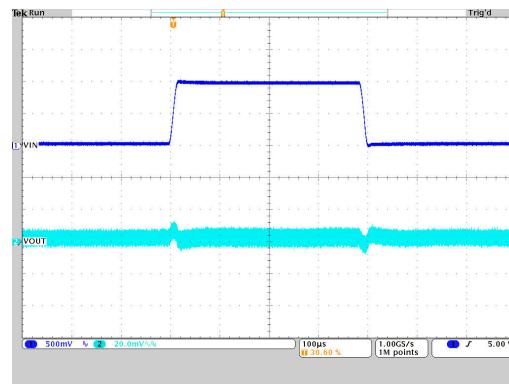

## 7 パラメータ測定情報

図 7-1. TPS6287x-Q1 の測定設定

表 7-1. 部品のリスト

| リファレンス            | 説明                                                                                                                                | メーカー                |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------|

| IC                | TPS62877QWRZVRQ1                                                                                                                  | テキサス・インスツルメンツ       |

| L                 | IHSR2525CZ-56nH                                                                                                                   | Vishay              |

| C <sub>IN</sub>   | 6 × 10 $\mu$ F / 10V; GCM21BR71A106KE22L + 2 × 4.7 $\mu$ F / 10V; LMK107BJ475MAHT                                                 | Murata, Taiyo Yuden |

| C <sub>OUT</sub>  | 2 × 22 $\mu$ F / 10V; GCM31CR71A226KE02L + 8 × 47 $\mu$ F / 6.3V; GCM32ER70J476ME19L + 3 × 100 $\mu$ F / 6.3V; GRT32ER60J107NE13L | Murata (村田製作所)      |

| C <sub>C</sub>    | 1nF                                                                                                                               | 任意                  |

| R <sub>Z</sub>    | 3.6k $\Omega$                                                                                                                     | 任意                  |

| C <sub>C2</sub>   | 4.7pF                                                                                                                             | 任意                  |

| R <sub>EN</sub>   | 22k $\Omega$                                                                                                                      | 任意                  |

| R <sub>FSEL</sub> | 0k $\Omega$ から GND へ                                                                                                              | 任意                  |

| R <sub>VSEL</sub> | 6.2k $\Omega$ or 47k $\Omega$ 、または 0k $\Omega$                                                                                    | 任意                  |

| R <sub>PG</sub>   | 100k $\Omega$                                                                                                                     | 任意                  |

## 8 詳細説明

### 8.1 概要

TPS6287x-Q1 デバイスは、車載用認定済みの同期整流降圧型（バック）DC/DC コンバータです。これらのデバイスは、高速な過渡応答と固定周波数動作を両立させた強化型 DCS-Control 方式を採用しており、低出力リップル、高い DC 精度、差動リモートセンシングと組み合わせることで、最新の高性能プロセッサのコア電源に最適な設計となっています。

このファミリに属する 4 つのデバイスは、電流定格を除いてすべて同一です。

- TPS62874-Q1 は 15A 定格のデバイスです

- TPS62875-Q1 は 20A 定格のデバイスです

- TPS62876-Q1 は 25A 定格のデバイスです

- TPS62877-Q1 は 30A 定格のデバイスです

出力電流能力をさらに高めるには、スタック内に複数のデバイスを組み合わせてください。たとえば、2 つの TPS62875-Q1 デバイスをスタックすると、40A の電流容量になります。

TPS6287x-Q1 デバイスには  $I^2C$  互換のインターフェイスが内蔵されており、動作の制御と監視が可能です。 $I^2C$  互換インターフェースを使用しない場合は、SCL ピンおよび SDA ピンを GND に接続してください。

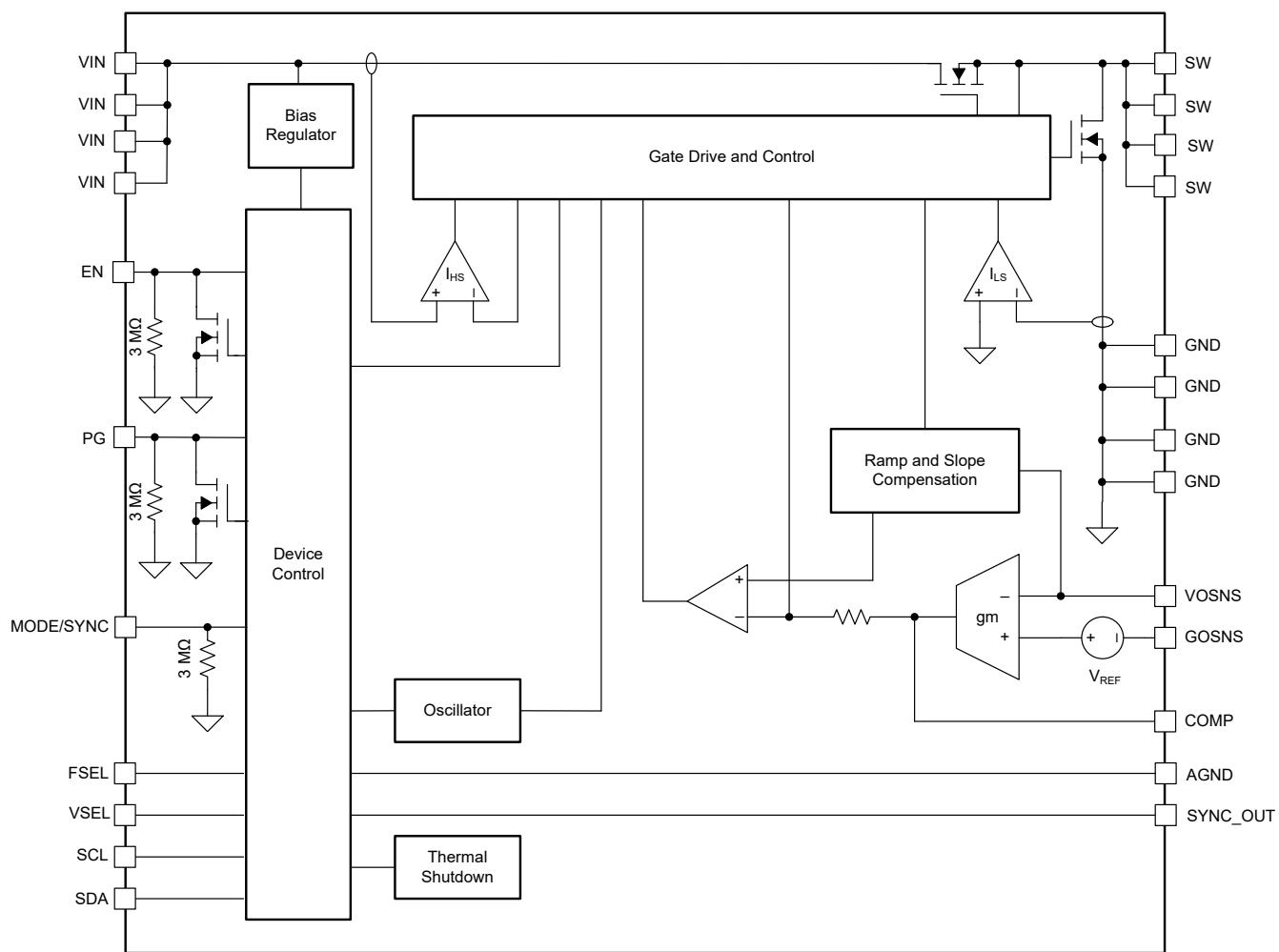

### 8.2 機能ブロック図

## 8.3 機能説明

### 8.3.1 固定周波数の DCS-Control トポロジ

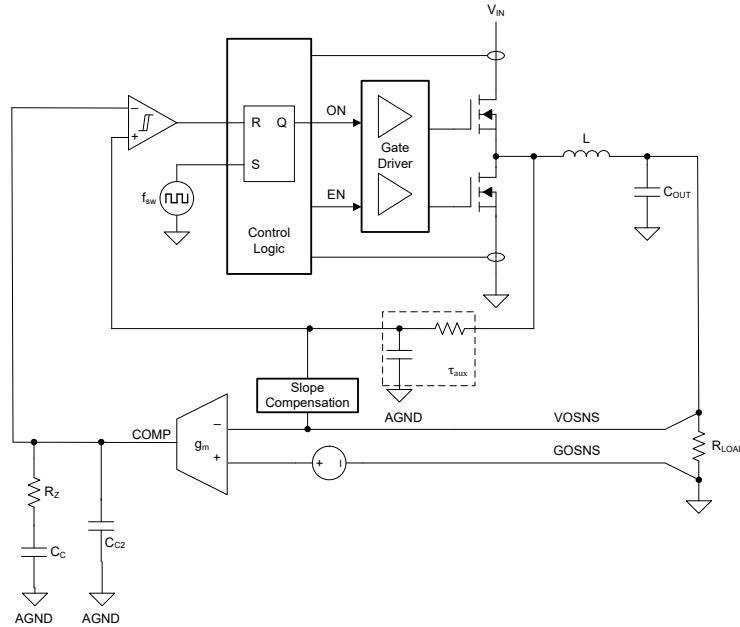

図 8-1 に、TPS6287x-Q1 デバイスで使用されている固定周波数 DCS-Control トポロジの簡略ブロック図を示します。このトポロジは、内部でエミュレートされた電流ループと外部の電圧調整ループで構成されています。

図 8-1. 固定周波数の DCS-Control トポロジ (簡略図)

### 8.3.2 強制 PWM モードとパワーセーブ モード

デバイスは、出力をレギュレートするための 3 つの方法でインダクタ電流を制御できます。

- 連続インダクタ電流を使用するパルス幅変調 (PWM-CCM)

- 不連続インダクタ電流によるパルス幅変調 (PWM-DCM)

- 不連続インダクタ電流およびパルススキップによるパルス周波数変調 (PFM - CCM)

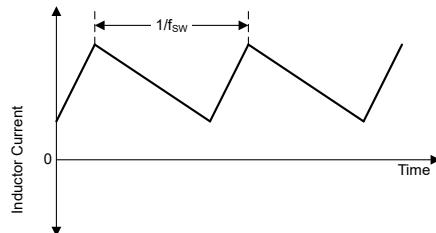

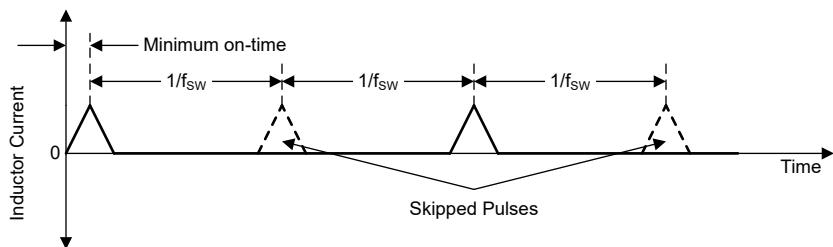

PWM-CCM 動作中、デバイスは一定の周波数でスイッチングを行い、インダクタ電流は連続的です (図 8-2 を参照)。PWM 動作は、最小の出力電圧リップルと最高の過渡性能を達成します。

図 8-2. 連続導通モード (CCM) 電流波形

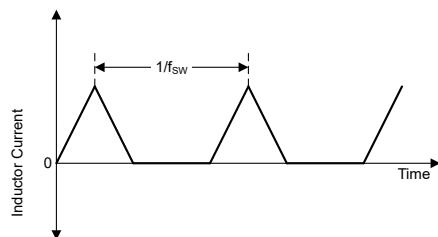

PWM-DCM 動作中、デバイスは一定の周波数でスイッチングを行い、インダクタ電流は不連続です (図 8-3 を参照)。このモードでは、デバイスはピーク インダクタ電流を制御し、選択したスイッチング周波数を維持しながら、出力のレギュレーションを維持することができます。

図 8-3. 不連続導通モード (DCM) 電流波形

PFM - DCM 動作中、デバイスはピーク インダクタ電流を一定に維持し (コンバータの最小オン時間に対応するレベル)、パルスをスキップして出力をレギュレートします (図 8-4 を参照)。PFM - DCM 動作中に発生するスイッチング パルスは、内部クロックに同期されます。

図 8-4. 不連続導通モード (PFM/DCM) 電流波形

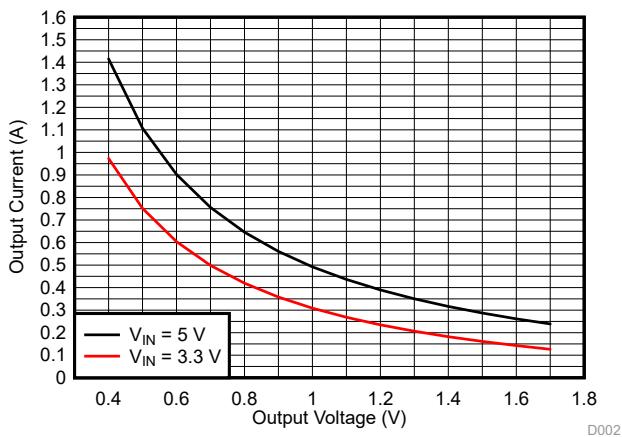

デバイスが PFM-DCM になる出力電流スレッショルドを計算するには、式 1 を使用します。

$$I_{OUT(PFM)} = \frac{(V_{IN} - V_{OUT})}{2L} t_{ON}^2 \left( \frac{V_{IN}}{V_{OUT}} \right) f_{sw} \quad (1)$$

次の図は、スレッショルド  $V_{IN}$  と  $V_{OUT}$  が、スイッチング周波数 2.25MHz の場合に、どのように変化するかを示しています。

図 8-5.  $f_{sw} = 2.25\text{MHz}$  の出力電流 PFM - DCM エントリ スレッショルド

強制 PWM モード (FPWM) とパワーセーブ モード (PSM) のどちらかを使用するようにデバイスを構成します。

- 強制 PWM モードでは、デバイスは常に PWM-CCM を使用します。

- パワーセーブモードでは、このデバイスは中負荷および高負荷で PWM-CCM、低負荷で PWM-DCM、非常に低負荷で PFM -DCM を使用します。各種動作モード間の遷移はシームレスに行われます。

表 8-1 に、本デバイスの動作モードを制御する MODE/SYNC ピンの機能表と CONTROL1 レジスタの FPWMEN ビットを示します。

表 8-1. FPWM モードとパワーセーブ モードの選択

| MODE/SYNC ピン | FPWMEN ビット | 動作モード | 注記                 |

|--------------|------------|-------|--------------------|

| 低            | 0          | PSM   | スタック構成では使用しないでください |

|              | 1          | FPWM  |                    |

| 高            | X          | FPWM  |                    |

| 同期クロック       | X          | FPWM  |                    |

### 8.3.3 非同期過渡モード(オプション)

TPS6287x -Q1 には過渡非同期モードがあり、負荷解放時の出力電圧のオーバーシュートを最小限に抑えるのに役立ちます。ハイサイド FET がオフになると、インダクタ電流の減衰は主に出力電圧によって決まり、ローサイド FET にはほとんど電圧降下が生じません。出力電圧が非常に低い場合、電流の減衰が遅いため、負荷変動時には通常、アンダーシュートよりもオーバーシュートの方が大きくなります。非同期モードでは、ローサイド FET が 6 つのスイッチング サイクルの間オフになり、その間インダクタ電流はボディダイオードを通じて減衰します。この場合、インダクタの両端に電圧が追加されるため、電流の減衰が速くなり、出力電圧のオーバーシュートは小さくなります。

### 8.3.4 高精度イネーブル

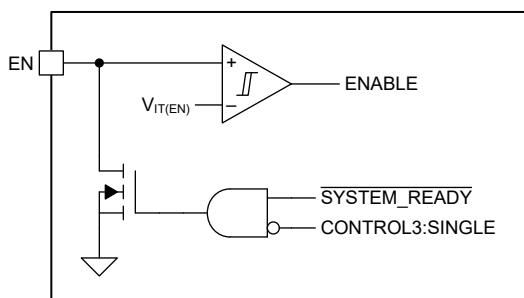

イネーブル (EN) ピンは双方向で、2 つの機能を持ちます。

- このピンは、入力として、デバイスの DC/DC コンバータを有効/無効にします。

- 出力として、このピンはスタック構成内の他のデバイスに対して SYSTEM\_READY 信号を提供します。

図 8-6. 機能ブロック図を有効にする

EN ピンに接続された内部オープンドレイントランジスタがあるため、低インピーダンスのソースからこのピンを直接駆動しないでください。代わりに、抵抗を使用して、EN ピンに流れる電流を制限します (セクション 10.1 を参照)。

VIN ピンに電源が初めて供給されると、デバイスは非揮発メモリからデフォルトのレジスタ設定を読み込み、VSEL、FSEL および SYNC\_OUT ピンの状態を読み取るまで、EN ピンを Low に保持します。また、サーマル シャットダウンや過電圧ロックアウトなどの故障が発生した場合も、デバイスは EN を Low にプルします。スタック構成では、すべてのデバイスが共通のイネーブル信号を共有します。これは、スタック内のすべてのデバイスが初期化を完了するまで、スタック内の DC/DC コンバータのスイッチングを開始できないことを意味します。同様に、スタック内の 1 つ以上のデバイスに故障が発生すると、スタック内のすべてのコンバータが無効化されます (セクション 8.3.18 を参照)。

スタンダード (非スタック) アプリケーションでは、CONTROL3 レジスタで SINGLE = 1 に設定することで、EN ピンのアクティブプルダウン機能を無効にすることができます。SINGLE = 1 の場合、故障状態は EN ピンに影響を与えません。(デバイスの初期化中は、EN ピンは常にプルダウンされることに注意してください。) スタックアプリケーションでは、SINGLE = 0 であることを確認してください。

内部 SYSTEM\_ready 信号が Low のとき (つまり、初期化が完了し、フォルト条件がないとき)、内部オープンドレイントランジスタは高インピーダンスであり、EN ピンは標準入力と同様に機能します。EN ピンが High レベルになると、デバイ

この DC/DC コンバータがイネーブルになり、Low レベルになると、デバイスの DC/DC コンバータがディセーブルされます。(I<sup>2</sup>C インターフェイスは、デバイスが初期化を完了するとすぐに有効になり、内部 ENABLE または SYSTEM\_READY 信号の状態には影響されません。)

EN ピンが Low レベルになると、デバイスは強制的にシャットダウンします。シャットダウン中、電力段の MOSFET がオフになり、内部制御回路が無効化され、デバイスの消費電流は 20 $\mu$ A (標準値) のみです。

EN ピンの立ち上がりしきい値電圧は 1.0V、立ち下がりしきい値電圧は 0.9V です。スレッショルド電圧の許容誤差は  $\pm 30mV$  であるため、EN ピンを使用して正確なオン/オフ制御を実現できます。

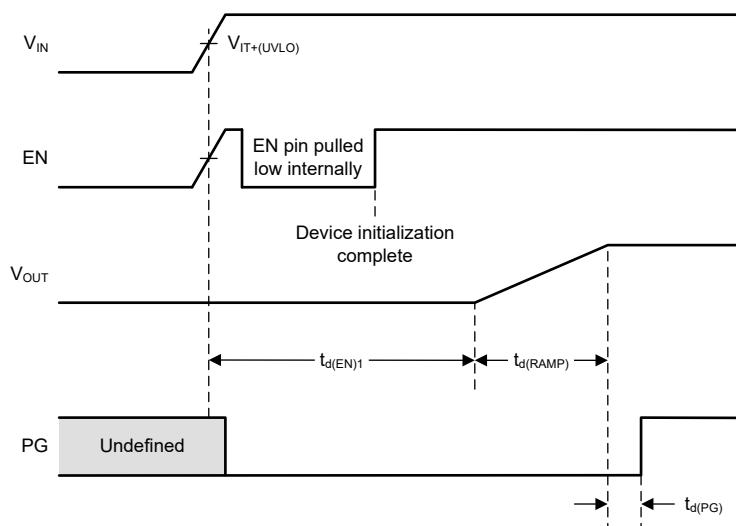

### 8.3.5 スタートアップ

V<sub>IN</sub> ピンの電圧が正方向の UVLO スレッショルドを超えると、デバイスは次のように初期化されます。

- デバイスは、EN ピンを Low にプルします。

- デバイスは、内部リファレンス電圧を無効にします。

- デバイスは VSEL、FSEL、および SYNC\_OUT ピンの状態を読み取ります。

- デバイスは、デフォルト値をデバイスのレジスタにロードします。

初期化が完了すると、デバイスは I<sup>2</sup>C 通信を有効にし、EN ピンを解放します。これで、EN ピンを制御する外部回路によってデバイスの動作が決定されます。

- EN ピンが Low の場合、デバイスは無効化されます。この状態でもレジスタへの読み書きは可能ですが、DC/DC コンバータは動作しません。

- EN ピンが High の場合、デバイスは有効になります。この状態ではレジスタへの読み書きが可能であり、EN ピンが High になってから短い遅延の後に、DC/DC コンバータが出力の立ち上げを開始します。

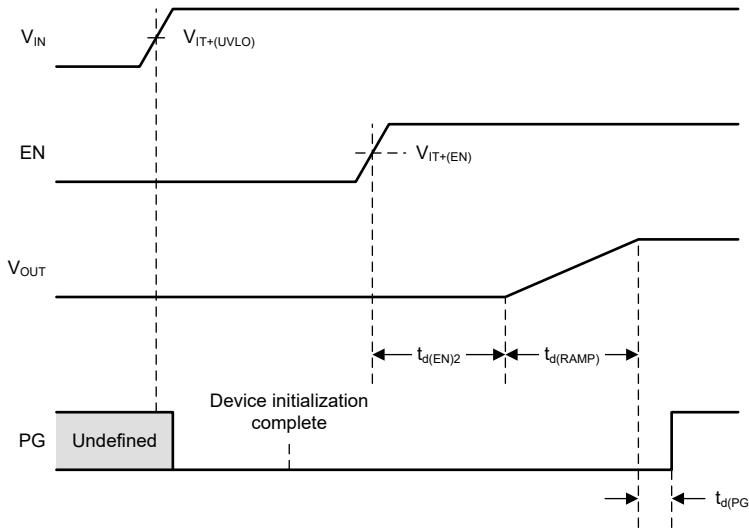

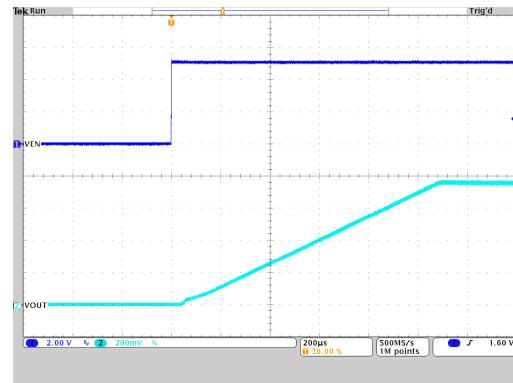

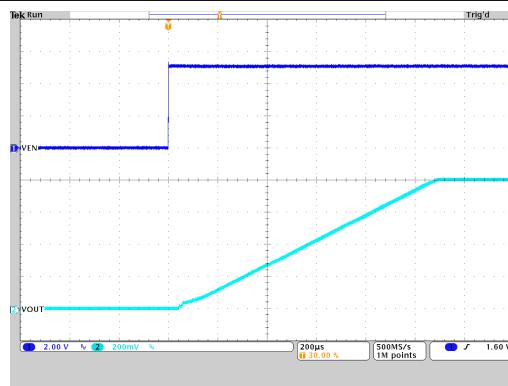

図 8-7 に、EN ピンが抵抗を経由して V<sub>IN</sub> にプルアップされたときのスタートアップ シーケンスを示します。

図 8-7. EN が V<sub>IN</sub> にプルアップされたときのスタートアップタイミング

図 8-8 に、外部信号が EN ピンに接続されている場合のスタートアップ シーケンスを示します。

図 8-8. 外部信号が EN ピンに接続されている場合のスタートアップタイミング

CONTROL2 レジスタの SSTIME[1:0] ビットを使用して、ソフトスタートランプの持続時間を選択します。

- $t_{d(RAMP)} = 500\mu s$

- $t_{d(RAMP)} = 770\mu s$  (TPS6287BxxLA0 のデフォルト)

- $t_{d(RAMP)} = 1ms$  (TPS6287BxxHA0, TPS6287BxxJE2 および TPS6287BxxVA0 のデフォルト)

- $t_{d(RAMP)} = 2ms$

デバイスがすでにソフトスタートシーケンスを開始している状態で、ユーザーが新しい出力電圧設定値 (VSET[7:0])、出力電圧範囲 (VRANGE[1:0])、またはソフトスタート時間 (SSTIME[1:0]) を設定しても、デバイスはソフトスタートシーケンスが完了するまでその新しい値を無視します。たとえば、ソフトスタート中にユーザーが VSET[7:0] の値を変更した場合、デバイスはまず、ソフトスタートシーケンス開始時点の VSET[7:0] の値に向かって出力を立ち上げ、その後、ソフトスタートが完了すると、新しい値に向かって電圧を上昇または下降させます。

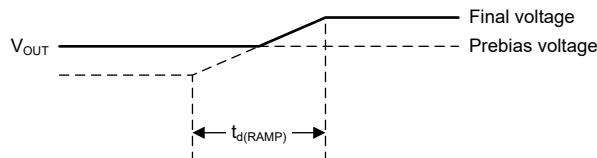

デバイスはプリバイアス出力の起動ができます。この場合、内部電圧ランプの一部のみが外部から検出されます (図 8-9 を参照)。

図 8-9. プリバイアス出力の起動

スタートアップランプ中は、他の構成設定や動作条件に関係なく、デバイスは常に DCM / PFM で動作することに注意してください。

### 8.3.6 スイッチング周波数の選択

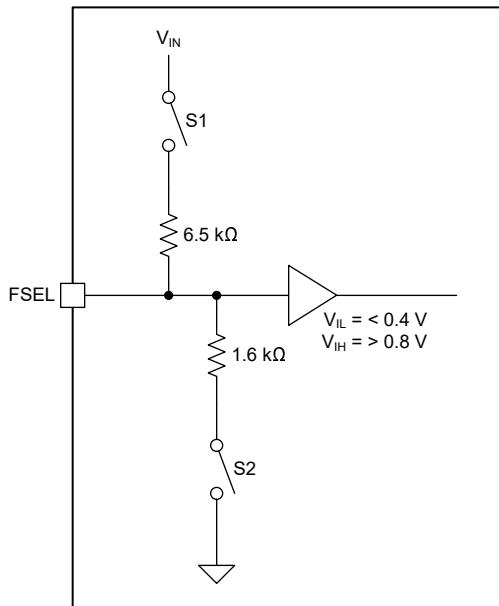

デバイスの初期化時に、デバイスの抵抗/デジタルコンバータによって FSEL ピンの状態が決定され、表 8-2 に従って DC/DC コンバータのスイッチング周波数が設定されます。

表 8-2. スイッチング周波数の選択肢

| FSEL の抵抗(1%)       | スイッチング周波数 |

|--------------------|-----------|

| GND に $6.2k\Omega$ | 1.5MHz    |

| GND への短絡           | 2.25MHz   |

| $V_{IN}$ への短絡      | 2.5MHz    |

表 8-2. スイッチング周波数の選択肢 (続き)

| FSEL の抵抗(1%)                  | スイッチング周波数 |

|-------------------------------|-----------|

| $V_{IN}$ に $47\text{k}\Omega$ | 3MHz      |

次の図は FSEL ピンの状態を検出するために使用される R2D コンバータの簡略化ブロック図を示しています (同一の回路が VSEL ピンの状態検出にも使用されます - [出力電圧設定ポイント](#)を参照)。

図 8-10. FSEL R2D コンバータの機能ブロック図

FSEL ピンの状態の検出は次のように動作します。

最上位ビット (MSB) を検出するため、回路は S1 と S2 を開き、入力バッファが FSEL ピンに HIGH または LOW レベルが接続されているかどうかを検出します。

最下位ビット (LSB) を検出する場合:

- MSB が 0 の場合、回路は S1 を閉じます。入力バッファが HIGH レベルを検出すると、 $LSB = 1$  になります。回路が LOW レベルを検出すると、 $LSB = 0$  になります。

- MSB が 1 の場合、回路は S2 を閉じます。入力バッファが LOW レベルを検出した場合、 $LSB = 0$  になります。回路が HIGH レベルを検出した場合、 $LSB = 1$  になります。

電流センシング コンパレータの伝搬遅延により、デバイスの最小オン時間が制限されます。実際には、これは、小さなデューティサイクルでデバイスがサポートできる最大スイッチング周波数が低下することを意味します。3.3V および 5V 電源を使用するデバイスの実際的な動作範囲を [図 6-5](#) に示します。

### 8.3.7 出力電圧設定

#### 8.3.7.1 出力電圧範囲

このデバイスは、3 つの電圧範囲に対応しています。CONTROL1 レジスタの VRANGE[1:0] ビットは、アクティブにする範囲を制御します ([表 8-3](#) を参照)。

表 8-3. 電圧レンジ

| VRANGE[1:0] | 電圧レンジ                     |

|-------------|---------------------------|

| 0b00        | 0.4V~0.71875V (1.25mV 刻み) |

| 0b01        | 0.4V~1.0375V (2.5mV 刻み)   |

表 8-3. 電圧レンジ (続き)

| VRANGE[1:0] | 電圧レンジ                |

|-------------|----------------------|

| 0b10        | 0.4V~1.675V (5mV 刻み) |

| 0b11        | 0.4V~1.675V (5mV 刻み) |

VRANGE[1:0] ビットの変更の後には、VSET[7:0] ビットの値が変化しない場合でも、VSET レジスタに書き込む必要があります。このシーケンスは、デバイスが新しい電圧範囲の使用を開始するために必要です。

### 8.3.7.2 出力電圧の設定ポイント

選択した範囲と一緒に、VSET レジスタの VSET[7:0] ビットは、デバイスの出力電圧設定点を制御します (表 8-4 を参照)。

表 8-4. 起動時の電圧設定

| VRANGE[1:0] | 出力電圧の設定ポイント               |

|-------------|---------------------------|

| 0b00        | 0.4V + VSET[7:0] × 1.25mV |

| 0b01        | 0.4V + VSET[7:0] × 2.5mV  |

| 0b10        | 0.4V + VSET[7:0] × 5mV    |

| 0b11        | 0.4V + VSET[7:0] × 5mV    |

初期化時に、デバイスは VSEL ピンの状態を読み取り、表 8-5 に従ってデフォルト出力電圧を選択します。VSEL ピンの、デバイスの I<sup>2</sup>C ターゲットアドレスも選択されることに注意してください (以下を参照)。デバイスバージョンおよび出力電圧設定ポイントの詳細なリストについては、デバイスのオプション表を参照してください。

表 8-5. デフォルトの出力電圧の設定ポイント

| VSEL ピン <sup>1</sup>     | VSET[7:0] | I <sup>2</sup> C デバイスアドレス | 出力電圧の設定ポイント |

|--------------------------|-----------|---------------------------|-------------|

| 6.2kΩ から GND へ           | 0x50      | 0x44                      | 800mV       |

| GND への短絡                 | 0x46      | 0x45                      | 750mV       |

| V <sub>IN</sub> への短絡     | 0x5F      | 0x46                      | 875mV       |

| 47kΩ を V <sub>IN</sub> へ | 0x24      | 0x47                      | 580mV       |

デバイスがすでにソフトスタートシーケンスを開始している状態で、新たな出力電圧設定値 (VSET[7:0])、出力電圧範囲 (VRANGE[1:0])、またはソフトスタート時間 (SSTIME[1:0]) をプログラムしても、それらの新しい設定はソフトスタートシーケンスが完了するまで無視されます。たとえば、ソフトスタート中に VSET[7:0] の値を変更した場合、デバイスはまず、ソフトスタートシーケンス開始時点での VSET[7:0] の値に向かって出力電圧を立ち上げ、その後ソフトスタートが完了してから、新しい値に向かって電圧を上げるか下げるかします。

ユーザーが EN 信号が Low の間に VSET[7:0]、VRAMP[1:0]、または SSTIME[1:0] を変更した場合、デバイスは次回ユーザーが有効化したときに新しい値を使用します。

起動時には、まず出力電圧が VSEL ピンで設定された目標値まで立ち上がり、その後、I<sup>2</sup>C インターフェイスを介してデバイスにプログラムされた新しい値に向かって、電圧が上昇または下降します。

### 8.3.7.3 デフォルト以外の出力電圧の設定ポイント

デフォルトの電圧範囲や電圧設定値の組み合わせがアプリケーションに最適でない場合は、ユーザーはデバイスを有効にする前に、I<sup>2</sup>C によってこれらの設定を変更することができます。その後、EN ピンを High にすると、デバイスは希望する起動電圧で立ち上がります。

<sup>1</sup> 信頼性の高い電圧設定を得るため、VSEL ピンに接続された浮遊電流バスが存在しないこと、および VSEL ピンと GND の間の寄生容量が 30pF 未満であることを確認します。

デバイスのランプ中にI<sup>2</sup>Cを使用してデバイス設定を変更した場合は、ランプが完了するまでの変更は無視されることに注意してください。

#### 8.3.7.4 ダイナミック電圧スケーリング

DC/DCコンバータが動作中に出力電圧の設定値を変更した場合、デバイスは新しい電圧設定に向けて制御された方法で電圧を上昇または下降させます。

CONTROL1レジスタのVRAMP[1:0]ビットは、DVS中にデバイスがある電圧から別の電圧に上昇するときのスルーレートを設定します(表8-6を参照)。

**表8-6. 動的電圧スケーリングスルーレート**

| VRAMP[1:0]  | DVSスルーレート |

|-------------|-----------|

| 0b00        | 10mV/μs   |

| 0b01        | 5mV/μs    |

| 0b10(デフォルト) | 1.25mV/μs |

| 0b11        | 0.5mV/μs  |

出力をより高い電圧に上げるには、追加の出力電流が必要になることに注意してください。そのため、DVS中、コンバータは次の式で求められる合計出力電流を生成する必要があります。

$$I_{OUT} = I_{OUT(DC)} + C_{OUT} \frac{dV_{OUT}}{dt} \quad (2)$$

ここで

- $I_{OUT}$ は、より高い電圧に上昇している間にコンバータが生成する必要がある合計電流です

- $I_{OUT(DC)}$ はDC負荷電流

- $C_{OUT}$ は合計出力キャパシタンス

- $dV_{OUT}/dt$ は出力電圧のスルーレートです(0.5mV/μs ~ 10mV/μsの範囲でプログラマブル)

正常に動作させるには、DVS中の合計出力電流がデバイスの電流制限を超えないことを確認してください。

#### 8.3.7.5 ドループ補償

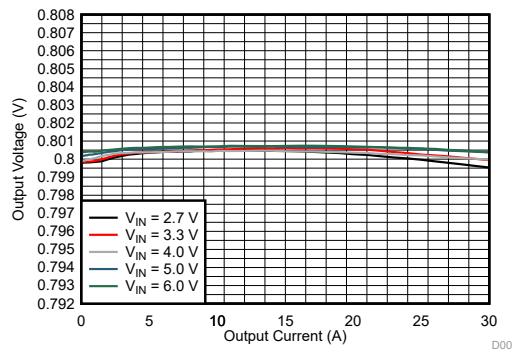

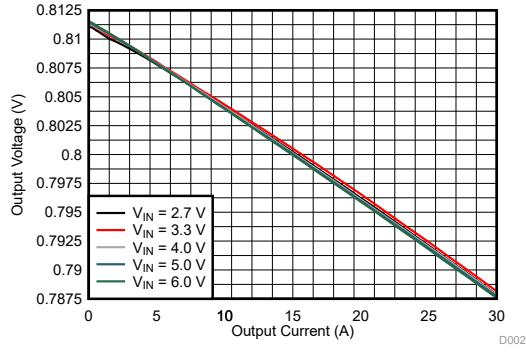

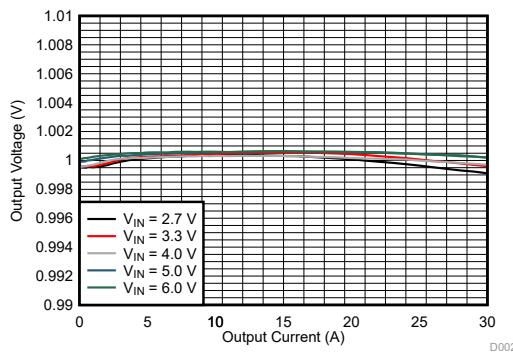

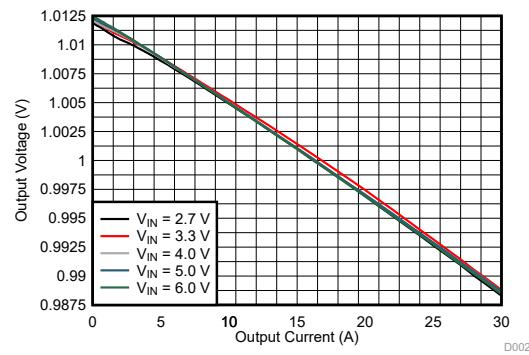

ドループ補償により、出力電流に基づいて公称出力電圧がスケーリングされます。この動作は、出力電流がない場合は出力電圧がより高い値に設定され、最大出力電流で公称値よりも小さい値に設定されるようにします。そのため、ドループ補償は負荷過渡時により大きなマージンを提供し、大きな負荷変動や負荷解除時にも出力電圧を一定の許容範囲内に保つのに役立ち、また出力容量を小さく抑えることも可能になります。電圧スケーリングは、相対値ではなく絶対値です。電圧スケーリングと出力電流の関係は、TPS6287x-Q1の出力電流バージョンは、それぞれ、15A、20A、25A、30Aの定格出力電流に基づいて依存します。その動作を図8-11のグラフに示します。ドループ補償がデフォルトで無効または有効になっている場合の特定のバージョンについては、「デバイスオプション」表を参照してください。ドループ補償は、ビットCONTROL3:DROOPENで有効化できます。ドループ補償を有効化するには、デバイスが無効化されている間に行う必要があります。有効にしないと、過渡出力電圧の偏差が発生する可能性があります。

図 8-11. 出力電流による電圧スケーリング

### 8.3.8 補償 (COMP)

COMP ピンは、外部補償ネットワークを接続するための端子です。通常のアプリケーションでは、AGND に直列接続された抵抗とコンデンサで十分であり、幅広い動作条件に対応したループ応答の最適化が可能です。

複数のデバイスをスタック構成で使用する場合、すべてのデバイスが共通の補償ネットワークを共有し、COMP ピンによって各デバイス間で電流が均等に分担されるようにします (セクション 8.3.18 を参照)。

### 8.3.9 モード選択 / クロック同期 (MODE/SYNC)

MODE/SYNC ピンに High レベルが印加されると、強制 PWM 動作が選択されます。MODE/SYNC ピンが Low レベルになると、パワーセーブ動作が選択され、デバイスは負荷条件に応じて PWM と PFM の間を自動的に遷移します。

MODE/SYNC ピンに有効なクロック信号を印加すると、デバイスはスイッチング サイクルを外部クロックに同期させ、強制 PWM 動作を自動的に選択します。

MODE/SYNC ピンは CONTROL1 レジスタの FPWMEN ビットと論理 OR されます (表 8-1 を参照)。

複数のデバイスをスタック構成で使用する場合、セカンダリデバイスの MODE/SYNC ピンはクロック信号の入力として機能します (セクション 8.3.18 を参照)。

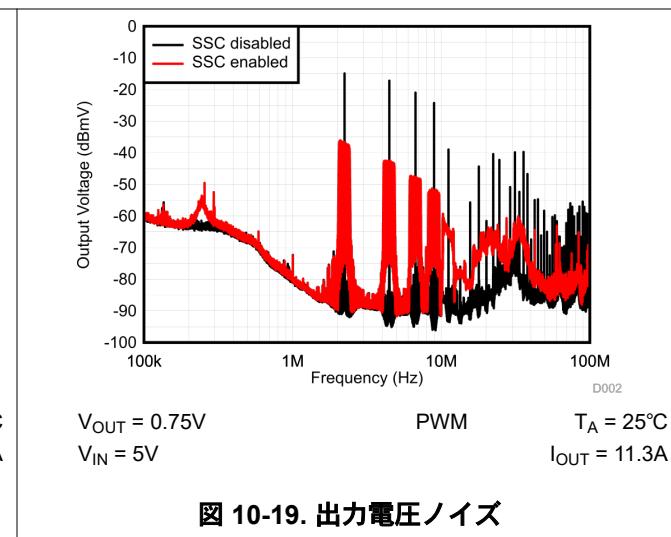

### 8.3.10 スペクトラム拡散クロック処理 (SSC)

このデバイスはスペクトラム拡散クロック機能を備え、電磁干渉 (EMI) を低減できます。SSC 機能がアクティブのとき、デバイスは公称値の  $\pm 10\%$  までスイッチング周波数を変調します。周波数変調は三角波特性を持っています (図 8-12 を参照)。

図 8-12. スペクトラム拡散クロック処理の動作

SSC 機能を使用するには、次のことを確認します。

- CONTROL1 レジスタの **SSCEN** = 1

- 強制 PWM 動作を選択 (CONTROL1 レジスタで **MODE** ピンを High または **FPWMEN** = 1)

- クロックが外部クロックに同期していない。

SSC 機能を無効化するには、CONTROL1 レジスタで **SSCEN** = 0 であることを確認します。

スタック構成の複数のデバイスで SSC 機能を使用するには、1 次コンバータが内部発振器から動作し、すべての 2 次コンバータが 1 次クロックに同期するようにします (図 8-16 を参照)。

### 8.3.11 出力放電

このデバイスには出力放電機能が備わっており、デバイスが無効化された際に出力電圧が一定の速度で低下するようにし、デバイスがオフの間も出力電圧を 0V 付近に保ちます。CONTROL1 レジスタで **DISCHEN** = 1 のとき、出力放電機能は有効にされます。出力放電機能はデフォルトで有効になっています。

有効になっている場合、デバイスは以下の条件下で出力を放電します:

- EN ピンには low レベルが印加されている

- CONTROL1 レジスタの **SWEN** = 0

- サーマル シャットダウンイベントが発生する

- UVLO イベントが発生する

- OVLO イベントが発生する

出力放電機能は、電源投入後に一度でもデバイスを有効化しない限り使用できません。電源オフ時、デバイスは供給電圧が約 1.8V を上回っている限り、出力の放電を継続します。

### 8.3.12 低電圧誤動作防止 (UVLO)

TPS6287x-Q1 には低電圧誤動作防止機能があり、電源電圧が低すぎて正常な動作ができない場合、デバイスはディスエーブルされます。UVLO 機能の負方向スレッショルドは 2.5V (標準値) です。電源電圧がこの値を下回ると、デバイスはスイッチングを停止します。CONTROL1 レジスタで **DISCHEN** = 1 の場合、出力放電をオンにします。

### 8.3.13 過電圧誤動作防止 (OVLO)

TPS6287x-Q1 には過電圧ロックアウト機能があり、電源電圧が高すぎて正常な動作ができない場合、DC/DC コンバータが無効になります。OVLO 機能の正方向スレッショルドは 6.3V (標準値) です。電源電圧がこの値を超えると、デバイスはスイッチングを停止し、CONTROL1 レジスタで **DISCHEN** = 1 に設定されている場合は、出力放電機能が有効になります。

デバイスは自動的にスイッチングを再開します。電源電圧が 6.2V (標準値) を下回ると、デバイスは新しいソフトスタートシーケンスを開始します。

### 8.3.14 過電流保護

#### 8.3.14.1 サイクル単位の電流制限

ピーク インダクタ電流がハイサイド電流制限のしきい値を超えると、デバイスはハイサイド スイッチをオフにし、ローサイド スイッチをオンにしてインダクタ電流を減少させます。デバイスは、インダクタ電流がローサイド電流制限のしきい値を下回った場合にのみ、再びハイサイド スイッチをオンにします。

なお、電流制限コンパレータの伝播遅延により、実際の電流制限スレッショルドは、電気的特性に記載された DC 値より大きくなる場合があります。実際には、次の式で電流制限を求められます。

$$I_L = I_{LIMH} + \left( \frac{V_{IN} - V_{OUT}}{L} \right) t_{pd} \quad (3)$$

ここで

- $I_L$  は、ピークインダクタ電流です

- $I_{LIMH}$  は DC で測定されるハイサイド電流制限スレッショルドです

- $V_{IN}$  は入力電圧

- $V_{OUT}$  は出力電圧です。

- $L$  は、ピーク電流レベルでの実効インダクタンスです

- $t_{pd}$  は、電流制限コンパレータの伝播遅延です (通常は 50ns)

### 8.3.14.2 ヒカップ モード

ヒカップ動作を有効にするには、CONTROL1 レジスタで **HICCUPEN = 1** であることを確認します。HICCUP 機能は、デフォルトで無効になっています。

ヒカップ動作が有効になり、ハイサイドスイッチ電流が連続 32 スイッチングサイクルでハイサイド電流制限スレッショルドを超えると、デバイスは次の動作を行います。

- 128 $\mu$ s のスイッチングを停止する。その後、デバイスは自動的にスイッチングを再開する (新しいソフトスタート シーケンスを開始)。

- STATUS レジスタの HICCUP ビットをセットする。

- PG ピンを low にします過負荷状態が解消され、デバイスが正常に起動して出力電圧をレギュレートできるまで、PG ピンは Low のまま維持されます。パワーグッド機能にはグリッチ除去回路があり、パワーグッド信号の立ち上がりエッジを 40 $\mu$ s (標準値) 遅延させることに注意してください。

ヒカップ動作は、出力過負荷状態が存在する限り、電流制限内の 32 サイクルで繰り返されます。その後、128 $\mu$ s の一時停止と、ソフトスタートが試みられます。

過負荷状態が解消されたときに STATUS レジスタを読み取ると、デバイスは HICCUP ビットをクリアします。

### 8.3.14.3 電流制限モード

電流制限モードを有効にするには、CONTROL1 レジスタで **HICCUPEN = 0** であることを確認します。

電流制限動作が有効になっているとき、過負荷状態が存在する間、デバイスはハイサイドスイッチの電流をサイクルごとに制限します。デバイスが連続 4 回以上のスイッチング サイクルにわたってハイサイド スイッチ電流を制限する場合、デバイスは STATUS レジスタで **ILIM = 1** に設定します。

過負荷状態が解消された後にユーザーが STATUS レジスタを読み取ると、デバイスは ILIM ビットをクリアします。

### 8.3.15 パワーグッド (PG)

パワーグッド (PG) ピンは双方向で、次の 2 つの機能を備えています。

- スタンドアロン構成の場合、またスタック構成の主要デバイスでは、PG ピンはコンバータまたはスタックのステータスを示すオープンドレイン出力です。

- スタック構成におけるセカンダリ デバイスでは、PG ピンは入力として機能し、ソフトスタート シーケンスが完了し、スタック内のすべてのコンバータが DCM スイッチングから CCM スイッチングに切り替え可能な状態であることを示します。

図 8-13. PG のタイミング

### 8.3.15.1 スタンドアロン、プライマリ デバイスの動作

PG ピンの主な目的は、出力電圧がレギュレート状態であるかどうかを示すことですが、PG ピンはデバイスがサーマルシャットダウン状態でも無効化状態でも示されます。表 8-7 にスタンドアロンまたはプライマリ デバイスにおける PG ピンの動作をまとめます。

表 8-7. パワーグッド機能表

| $V_{IN}$                                 | EN | $V_{OUT}$                                                 | ソフトスタート | PGBLNKDVS AND DVS_active | $T_J$          | PG        |

|------------------------------------------|----|-----------------------------------------------------------|---------|--------------------------|----------------|-----------|

| $V_{IN} < 2V$                            | X  | X                                                         | X       | X                        | X              | 未定義       |

| $V_{IT-}(UVLO) \geq V_{IN} \geq 2V$      | X  | X                                                         | X       | X                        | X              | 低         |

|                                          | L  | X                                                         | X       | X                        | X              | 低         |

|                                          | H  | X                                                         | アクティブ   | X                        | X              | 低         |

| $V_{IT-}(UVLO) < V_{IN} < V_{IT+}(OVLO)$ |    | $V_{OUT} > V_{T+(OVP)}$<br>または<br>$V_{OUT} < V_{T-(UVP)}$ | 非アクティブ  | 0                        | X              | 低         |

|                                          |    | $V_{T-(OVP)} > V_{OUT} > V_{T+(UVP)}$                     |         | 1                        | $T_J < T_{SD}$ | ハイインピーダンス |

|                                          |    | X                                                         | X       | X                        | $T_J < T_{SD}$ | ハイインピーダンス |

|                                          |    | X                                                         | X       | X                        | $T_J > T_{SD}$ | 低         |

| $V_{IN} > V_{IT+}(OVLO)$                 | X  | X                                                         | X       | X                        | X              | 低         |

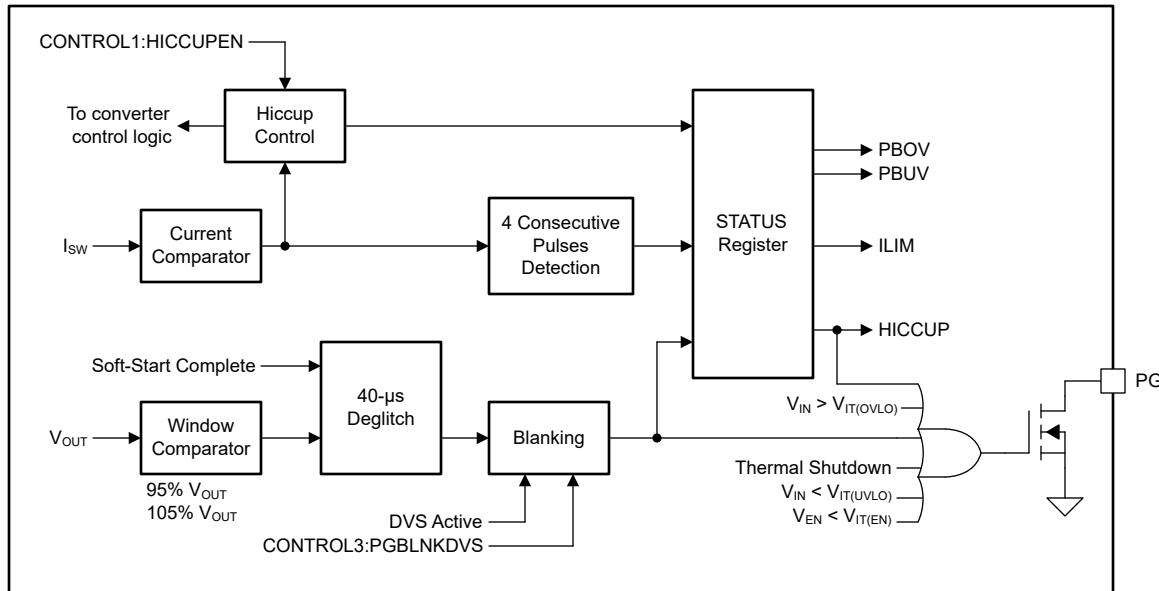

図 8-14 に、スタンドアロンまたはプライマリ デバイスのパワーグッド機能の機能ブロック図を示します。ウインドウコンパレータは出力電圧を監視し、出力電圧が公称出力電圧の 95% 未満 (標準値) または 公称電圧の 105% を上回る場合、コンパレータの出力が High になります。ウインドウコンパレータの出力はグリッチ除去されます: 標準のグリッチ除去時間は  $40\mu s$ 。その後、オープンドレインの PG ピンの駆動に使用されます。

図 8-14. パワーグッド機能のブロック図 (スタンドアロン、プライマリ デバイス)

DVS動作中に、DC/DCコンバータがある出力電圧設定から別の出力電圧設定に遷移すると、出力電圧が一時的にウインドウコンパレータの制限を超えることがあります。デバイスには、この動作を無効化する機能があります。CONTROL3レジスタで PGBLNKDVS = 1 の場合、DVS がアクティブの間、パワーグッド ウィンドウコンパレータの出力を無視します。

PG ピンは、以下の場合ウィンドウコンパレータの出力に関係なく常に Low であることに注意してください。

- デバイスがサーマルシャットダウン中

- デバイスが無効化されている

- デバイスは低電圧ロックアウト状態

- デバイスは過電圧ロックアウト状態

- デバイスがソフトスタート状態にある

- デバイスがヒップアップモード中

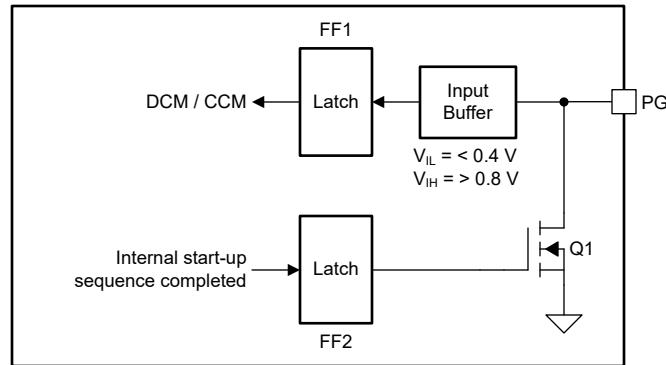

### 8.3.15.2.2 次デバイスの動作

図 8-15 は、2 次側デバイスにおけるパワーグッド機能の機能ブロック図を示しています。初期化中、デバイスは FF2 をプリセットし、これによって PG ピンがプルダウンされ、スタック内のデバイスが DCM で動作するように強制されます。デバイスが内部の起動シーケンスを完了すると、FF2 がリセットされ、Q1 がオフになります。スタック構成では、すべてのデバイスが同じ PG 信号を共有するため、スタック内のすべてのデバイスが起動を完了するまで PG ピンは Low のままになります。その場合 FF1 が設定されコンバータが CCM で動作します FF1 と FF2 はプリセットされており、コンバータが無効になるたびに (EN ピン、EN ビット、熱シャットダウン、または UVLO による) DCM が許可されるようになっています。

図 8-15. パワーグッド機能のブロック図 (2 次側デバイス)

### 8.3.16 リモートセンス

このデバイスには VOSNS と GOSNS の 2 つのピンがあり、出力電圧をリモートで検出できます。リモートセンシングにより、コンバータはポイント・オブ・ロードで出力電圧を直接検出し、出力電圧レギュレーションの精度を向上できます。

スタック構成では、プライマリ デバイスの VOSNS および GOSNS を必ず負荷接続点に直接接続する必要があります。セカンダリ デバイスの場合は、VOSNS ピンと GOSNS ピンをローカル出力コンデンサに接続するか、または両方のピンを AGND に接続します (セクション 8.3.18 を参照)。

### 8.3.17 热警告およびシャットダウン

このデバイスは、2 レベルの過熱検出機能を備えています。

接合部温度が過熱警告スレッショルド 150°C (標準値) を上回ると、デバイスは STATUS レジスタの TWARN ビットを設定します。接合部温度が 130°C (標準値) の TWARN スレッショルドを下回った後に STATUS レジスタを読み取ると、デバイスは TWARN ビットをクリアします。

接合部温度が 170°C (標準値) のサーマル シャットダウンのスレッショルドを上回ると、デバイスは次の動作を行います。

- スイッチングを停止する

- EN ピンをプルダウンする (CONTROL3 レジスタで SINGLE = 0 の場合)

- 出力放電を有効にする (CONTROL1 レジスタで DISCHEN = 1 の場合)

- STATUS レジスタの TSHUT ビットをセットする

- PG ピンを low にします

接合部温度が 150°C (標準値) のサーマル シャットダウンのスレッショルドを下回ると、デバイスは次の動作を行います。

- 新しいソフトスタート シーケンスから開始して、再度スイッチングを開始する

- EN ピンをハイインピーダンス状態に設定する

- PG ピンをハイインピーダンス状態に設定する

接合部温度が 150°C (標準値) の TSHUT スレッショルドを下回った後に STATUS レジスタを読み取ると、デバイスは TSHUT ビットをクリアします。

すべてのデバイスが共通のイネーブル信号を共有するスタック構成では、1 つのデバイスのサーマル シャットダウン条件により、スタック全体が無効化されます。熱いデバイスが冷却されると、スタック全体が自動的に再びスイッチングを開始します。

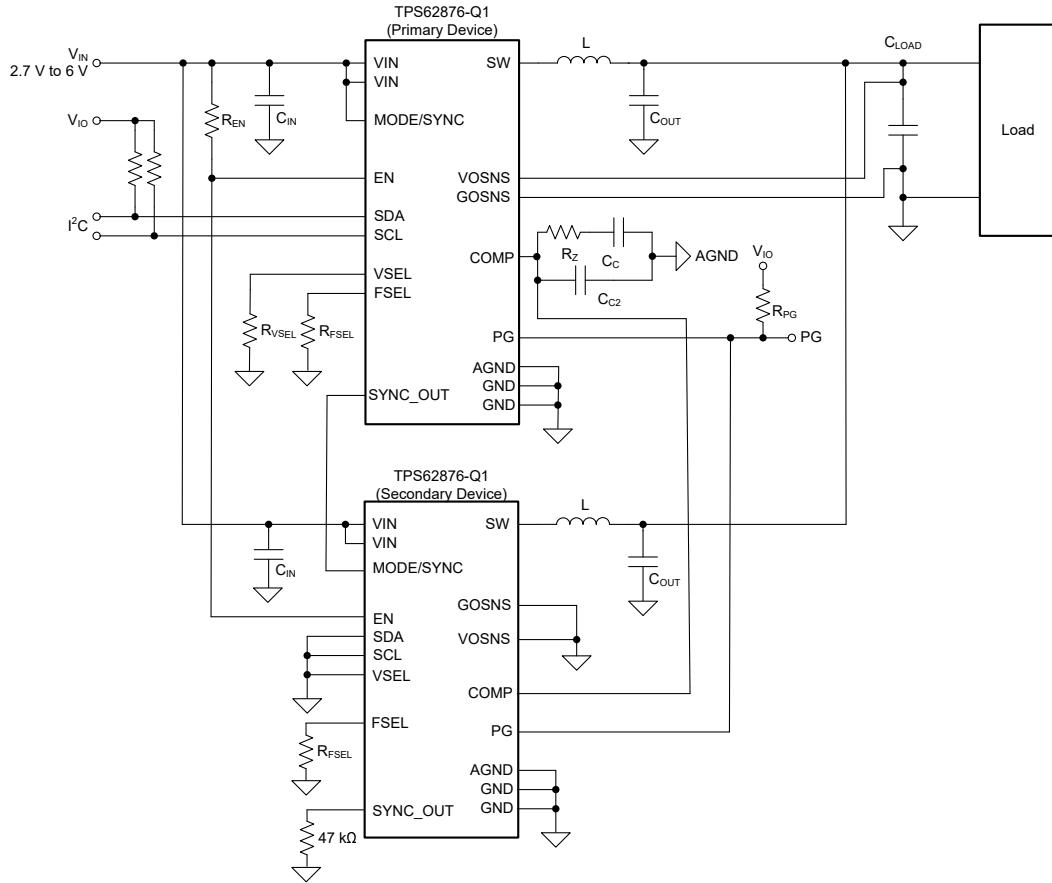

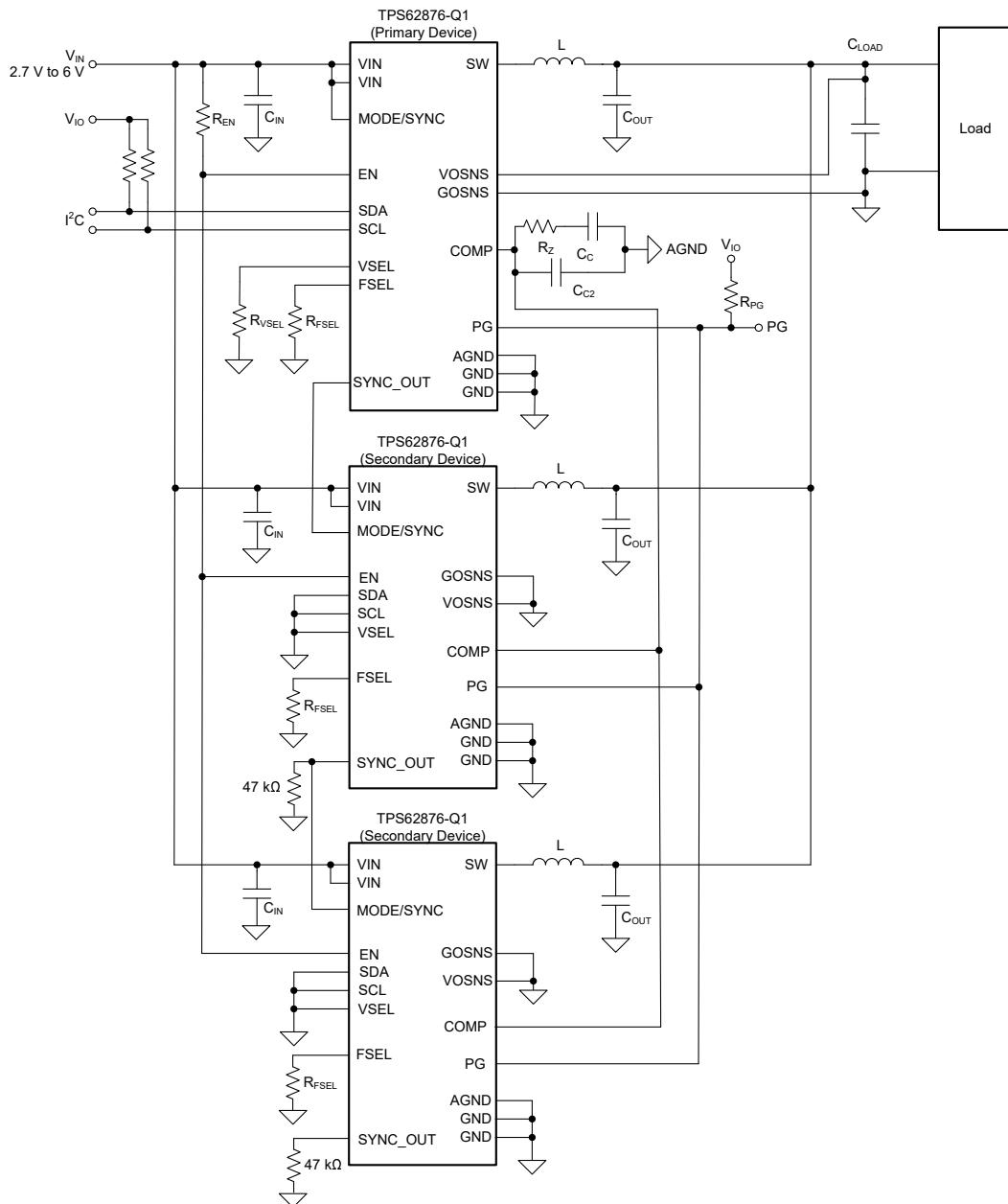

### 8.3.18 スタック動作

複数の TPS6287x-Q1 または デバイスを「スタック」と呼ばれる構成で並列接続することで、出力電流能力を高めたり、デバイスの接合部温度を下げたりすることができます。スタックは、1 つのプライマリデバイスと 1 つ以上のセカンダリデバイスで構成されます。初期化中に、各デバイスは SYNCOUT ピンを監視し、自身が 1 次側デバイスとして動作すべきか、それとも 2 次側デバイスとして動作すべきかを判断します。

- SYNCOUT ピンとグランドの間に  $47\text{k}\Omega$  の抵抗が接続されている場合、そのデバイスは 2 次側デバイスとして動作します

- SYNCOUT ピンがハイインピーダンス状態の場合、そのデバイスは 1 次側デバイスとして動作します

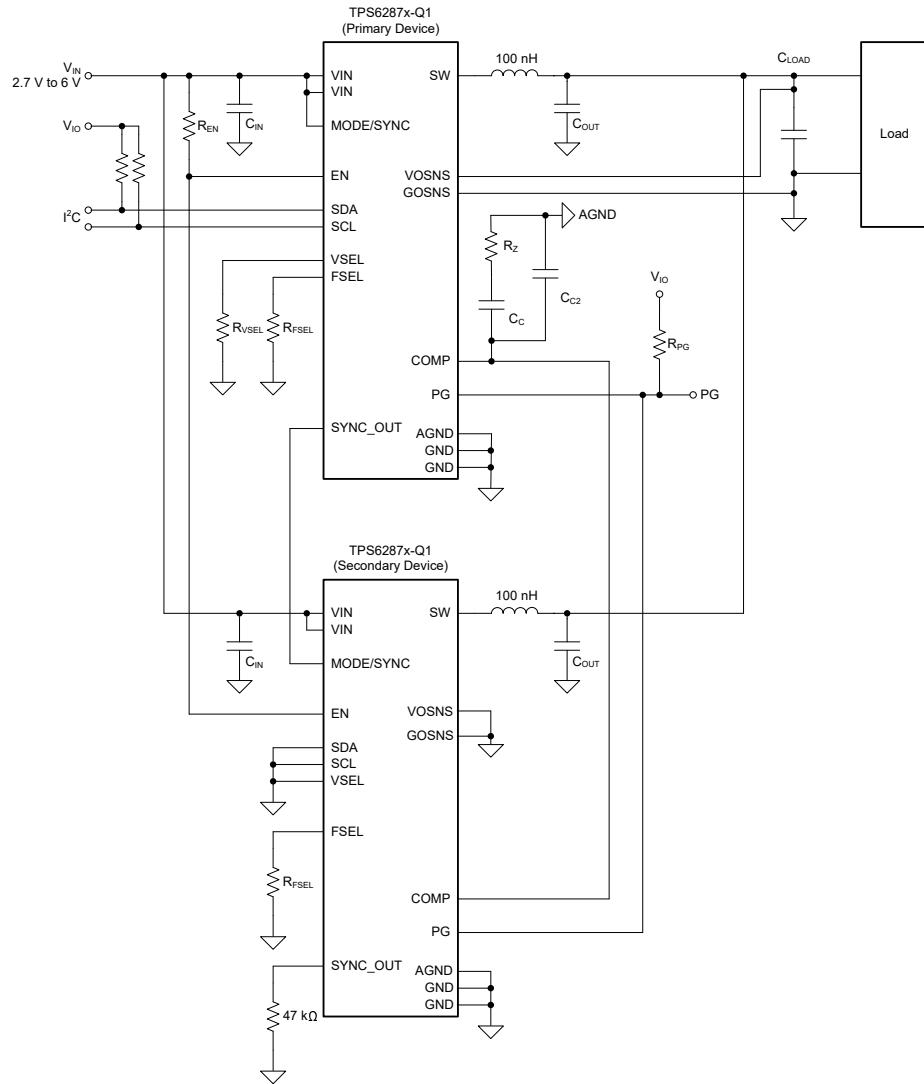

図 8-16 に、2 つの TPS6287x-Q1 デバイスをスタックした推奨相互接続を示します。

図 8-16. 2 個の TPS6287x-Q1 デバイスをスタックした構成

注意すべき重要なポイントは次のとおりです。

- スタック内のすべてのデバイスは共通のイネーブル信号を共有しています。この信号は、 $15\text{k}\Omega$  以上の抵抗でプルアップする必要があります。

- スタック内のすべてのデバイスは、共通のパワー グッド信号を共有します。

- スタック内のすべてのデバイスは共通の補償信号を共有します。

- すべてのセカンダリ デバイスは、SYNC\_OUT ピンとグランドの間に  $47\text{k}\Omega$  抵抗を接続する必要があります。

- 各デバイスのリモート センス ピン (VOSNS および GOSNS) は接続する必要があります (これらのピンをフローティングのままにしないでください)。

- プライマリ デバイスの VOSNS および GOSNS は、負荷のコンデンサに接続する必要があります

- セカンダリ デバイスの VOSNS と GOSNS は、デバイスの出力コンデンサに接続するか、または両方のピンを AGND に接続することもできます。

- 各デバイスは、同じスイッチング周波数に設定する必要があります。

- 1 次側デバイスは、強制 PWM 動作に設定する必要があります (2 次側デバイスは自動的に強制 PWM 動作に設定されます)。

- スタック構成は、外部クロックとの同期またはスペクトラム拡散クロック処理をサポートできます。

- デフォルトの出力電圧の設定には、1 次側デバイスの VSEL ピンのみが使用されます。2 次側デバイスの VSEL ピンのは使用しないため、グランドに接続する必要があります。

- セカンダリ デバイスの SDA および SCL ピンは使わず、グランドに接続する必要があります。

- スタック構成ではデイジーチェーン接続されたクロック信号を使用し、各デバイスは隣接するデバイスに対して約 120° の位相差を持ってスイッチング動作を行います。クロック信号をデイジーチェーン接続するには、1 次側デバイスの SYNCOUT ピンを最初の 2 次側デバイスの MODE/SYNC ピンに接続します。最初の 2 次側デバイスの SYNCOUT ピンを、2 番目の 2 次側デバイスの MODE/SYNC ピンに接続します。スタック内のすべてのデバイスに対してこの接続方式を続行し、デバイスをデイジーチェーン接続します。

- CONTROL2:SYNC\_OUT\_PHASE = 1 によって、1 次側デバイスから最初の 2 次側デバイスへ 180° の位相シフトが設定されます。利用可能な OTP スピンの全リストについては、デバイスのオプション表を参照してください。

- ヒップ過電流保護は、スタック構成で使用しないでください。

スタック構成では、共通イネーブル信号は **SYSTEM\_READY** 信号としても機能します (セクション 8.3.4 を参照)。デバイスの起動時またはフォルトの発生時に、スタック内の各デバイスが EN ピンを Low にすることができます。そのため、すべてのデバイスがスタートアップ シーケンスを完了し、フォルトがない場合のみ、スタックが有効になります。いずれか 1 つのデバイスに故障が発生した場合、その故障状態が存在している限り、スタック全体が無効化します。

起動中、イネーブル信号 (SYSTEM\_READY) が Low になっている間、1 次側デバイスは COMP ピンを Low にします。イネーブル信号が High になると、1 次側デバイスが COMP ピンを能動的に制御し、スタック内のすべてのデバイスがその COMP 電圧に従います。起動時に、スタック内の各デバイスが、ピンが初期化される間、PG ピンを Low にします。初期化が完了すると、スタック内の 2 次側の各デバイスは PG ピンを高インピーダンス状態にし、PG 信号の状態は 1 次側デバイスのみが制御します。PG ピンは、スタックが立ち上がりシーケンスを完了し、出力電圧が規定範囲内に達したときに High になります。スタック内の 2 次側デバイスは、パワーグッド信号の立ち上がりエッジを検出すると、DCM 動作から CCM 動作に切り替わります。スタックが正常に起動すると、プライマリ デバイスは通常の方法でパワーグッド信号を制御します。スタック構成では、個々のデバイスにのみ影響する故障と、すべてのデバイスに影響する他の故障があります。たとえば、1 つのデバイスが電流制限に入った場合、そのデバイスのみが影響を受けます。しかし、1 つのデバイスにサーマル シャットダウンまたは低電圧誤動作防止イベントが発生すると、共有のイネーブル (SYSTEM\_READY) 信号により、すべてのデバイスが無効化されます。

## スタック動作中の機能

デバイス機能の一部はスタック動作中は使用できないか、プライマリ コンバータでのみ使用できます。表 8-8 に、スタック動作時に使用できる機能をまとめます。

**表 8-8. スタック動作中の機能**

| 機能                        | プライマリ デバイス | セカンダリ デバイス | 注記                 |

|---------------------------|------------|------------|--------------------|

| UVLO                      | あり         | あり         | 共通のイネーブル信号         |

| OVLO                      | あり         | あり         | 共通のイネーブル信号         |

| OCP - 電流制限                | あり         | あり         | 個人向け               |

| OCP - ヒップ OCP             | なし         | なし         | スタック操作中は使用しないでください |

| サーマル シャットダウン              | あり         | あり         | 共通のイネーブル信号         |

| パワーグッド (ウインドウ コンパレーター)    | あり         | なし         | プライマリ デバイスのみ       |

| I <sup>2</sup> C インターフェイス | あり         | なし         | プライマリ デバイスのみ       |

**表 8-8. スタック動作中の機能 (続き)**

| 機能       | プライマリ デバイス          | セカンダリ デバイス | 注記                                 |

|----------|---------------------|------------|------------------------------------|

| DVS      | I <sup>2</sup> C 経由 | なし         | プライマリ デバイスのみで制御される電圧ループ            |

| SSC      | I <sup>2</sup> C 経由 | なし         | プライマリ デバイスからセカンダリ デバイスへのデイジーチェーン接続 |

| SYNC     | あり                  | あり         | 1 次側デバイスに適用される同期クロック               |

| 高精度イネーブル | なし                  | なし         | バイナリイネーブルのみ                        |

| 出力放電     | あり                  | あり         | セカンダリ デバイスでは常に有効になっています            |

## スタック動作中の故障処理

スタック構成では、個々のデバイスにのみ影響する故障と、すべてのデバイスに影響するその他の故障があります。たとえば、1 つのデバイスが電流制限に入った場合、そのデバイスのみが影響を受けます。しかし、1 つのデバイスにサーマルシャットダウンまたは低電圧誤動作防止イベントが発生すると、共有のイネーブル (SYSTEM\_READY) 信号により、すべてのデバイスが無効化されます。表 8-9 に、TPS6287x-Q1 デバイスのスタック動作中のフォルト処理を示します。

**表 8-9. スタック動作中の故障処理**

| 故障状態                         | デバイスの応答                   | システムの応答                                                   |

|------------------------------|---------------------------|-----------------------------------------------------------|

| UVLO                         |                           |                                                           |

| OVLO                         | イネーブル信号が Low にプルされる       | 新しいソフトスタート                                                |

| サーマル シャットダウン                 |                           |                                                           |

| 電流制限                         | イネーブル信号は High に維持される      | エラー アンプがクランプされる                                           |

| MODE/SYNC に印加された外部 CLK が失敗する | SYNC_OUT と電力段が内部発振器に切り換わる | システムは動作を継続しますが、2 次側デバイスへのクロック信号が失われた場合、スイッチング周波数は同期されません。 |

## 8.4 デバイスの機能モード

### 8.4.1 パワーオン リセット

電源電圧が POR スレッショルド未満のときに、デバイスは POR モードで動作します。

POR モードでは、どの機能も利用できず、デバイスのレジスタの内容は無効です。

デバイスは、電源電圧が POR スレッショルドを上回ると、POR モードを終了して UVLO モードに移行します。

### 8.4.2 低電圧誤動作防止

電源電圧が POR スレッショルドと UVLO スレッショルドの間にあるとき、デバイスは UVLO モードで動作します。

デバイスが POR モードから UVLO モードに移行した場合、利用できる機能はありません。デバイスがスタンバイモードから UVLO モードに移行する場合は、出力放電機能が利用可能です。デバイスのレジスタの内容は UVLO モードで有効です。

電源電圧が POR スレッショルドを下回ると、デバイスは UVLO モードを終了し、POR モードに移行します。電源電圧が UVLO スレッショルドを上回ると、デバイスは UVLO モードを終了し、スタンバイモードに移行します。

### 8.4.3 スタンバイ

デバイスは、電源電圧が UVLO スレッショルドを超え、初期化が完了するとスタンバイ モードで動作します<sup>2</sup> 次の条件のいずれかが当てはまります。

- EN ピンには low レベルが印加されている。

- CONTROL1 レジスタの SWEN = 0。

- デバイスの接合部温度がサーマル シャットダウンのスレッショルドよりも高くなっている。

- 電源電圧が OVLO スレッショルドを超えている。

スタンバイモードでは、以下の機能が使用できます。

- I<sup>2</sup>C インターフェイス

- 出力放電

- パワー グッド

電源電圧が UVLO スレッショルドを下回ると、デバイスはスタンバイモードから UVLO モードに移行します。次のすべての条件が満たされると、デバイスはスタンバイモードを終了し、オンモードに移行します。

- EN ピンには high レベルが印加されている。

- CONTROL1 レジスタの SWEN = 1。

- デバイスの接合部温度がサーマル シャットダウンのスレッショルドよりも低くなっている。

- 電源電圧が OVLO スレッショルドを下回っている。

### 8.4.4 オン

電源電圧が UVLO スレッショルドより高く、次のすべての条件が成立する場合、デバイスはオンモードで動作します。

- EN ピンには high レベルが印加されている

- CONTROL1 レジスタの SWEN = 1

- デバイスの接合部温度がサーマル シャットダウンのスレッショルドよりも低くなっている

- 電源電圧が OVLO スレッショルドを下回っている

すべての機能はオンモードで使用できます。

電源電圧が UVLO スレッショルドを下回ると、デバイスはオン モードを維持し、UVLO モードに移行します。以下のいずれかの条件に該当する場合、本デバイスはオン モードを終了し、スタンバイ モードに移行します。

- EN ピンには low レベルが印加されている

- CONTROL1 レジスタの SWEN = 0

- デバイスの接合部温度がサーマル シャットダウンのスレッショルドよりも高くなっている

- 電源電圧が OVLO スレッショルドを超えている

## 8.5 プログラミング

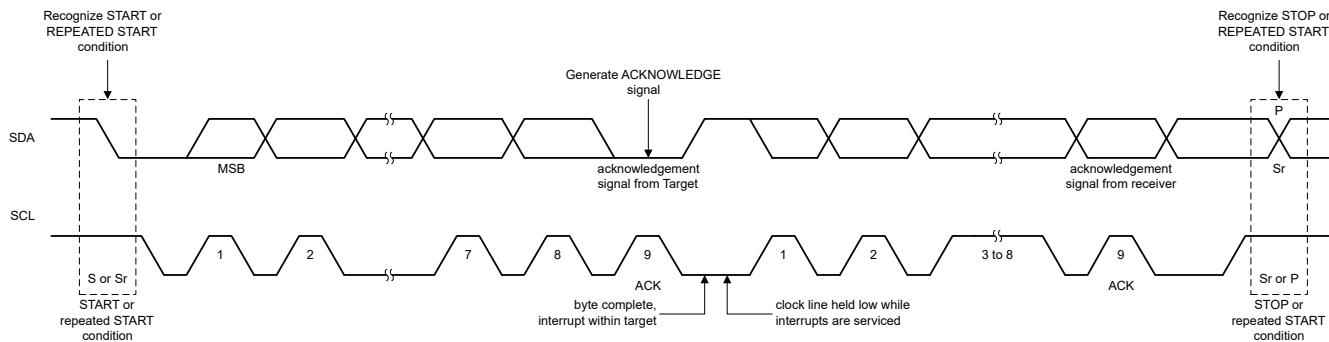

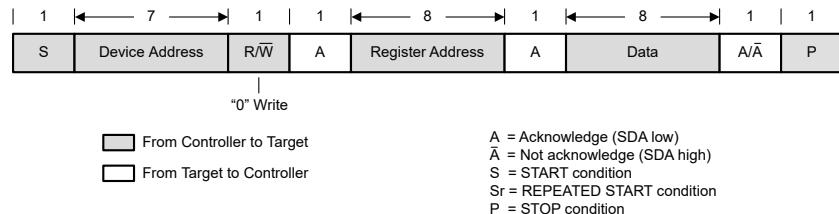

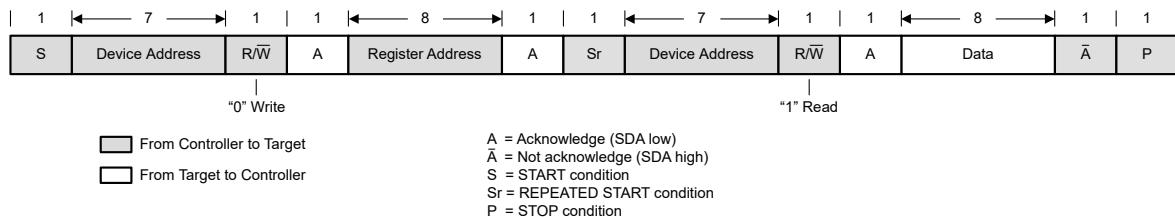

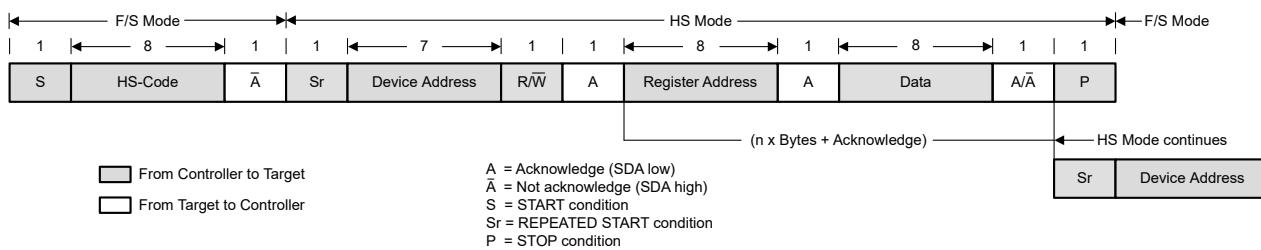

### 8.5.1 シリアルインターフェイスの説明

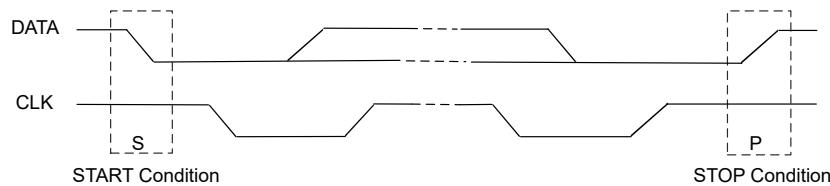

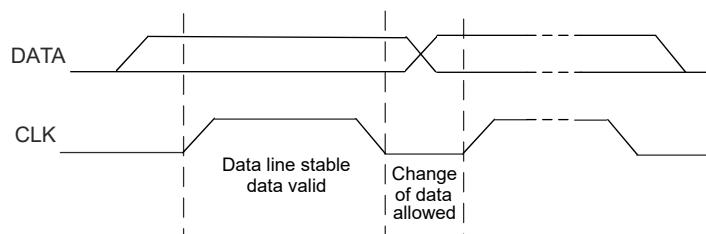

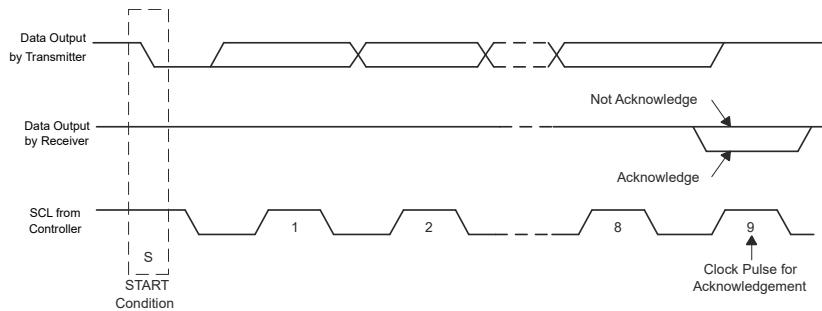

I<sup>2</sup>C<sup>TM</sup> C は、Philips Semiconductor (現在の NXP Semiconductors) によって開発された 2 線式シリアル インターフェースです (2014 年 4 月 4 日付の I<sup>2</sup> C-Bus 仕様とユーザーマニュアル改訂 6 を参照)。バスは、プルアップ構造を持つデータライン (SDA) とクロック・ライン (SCL) で構成されます。バスが アイドルのときは、SDA ラインと SCL ラインの両方が High にプルされます。I<sup>2</sup>C 互換のデバイスはすべて、オープンドレインの I/O ピンである SDA および SCL を介して I<sup>2</sup>C バスに接続します。コントローラ (通常はマイクロコントローラまたはデジタル信号プロセッサ) がバスを制御します。コントローラは SCL 信号とデバイス アドレスを生成します。コントローラは、データ転送の開始と停止を示す特定の条件も生成します。ターゲットはコントローラ デバイスの制御に従ってバス上、データを受信または送信します。