# TPS65219 パワー マネジメント IC (PMIC)、3 つの降圧回路と 4 つの LDO、産業 アプリケーション向け

## 1 特長

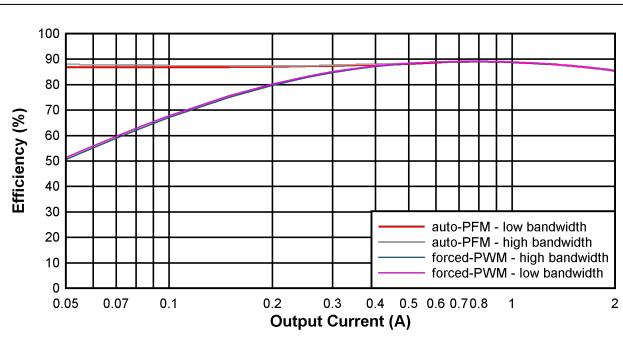

- 最大 2.3MHz のスイッチング周波数で動作する、3 つの降圧コンバータ。

- 1 つの VIN: 2.5V~5.5V,  $I_{OUT}$ : 3.5A,  $V_{OUT}$ : 0.6V ~ 3.4V

- 2 つの VIN: 2.5V~5.5V,  $I_{OUT}$ : 2A,  $V_{OUT}$ : 0.6V ~ 3.4V

- 4 つのリニア レギュレータ:

- 2x VIN: 1.5V~5.5V,  $I_{OUT}$ : 400mA,  $V_{OUT}$ : 0.6V ~ 3.4V (ロード スイッチ / バイパス モードとして構成可能、SD カードをサポート)

- 2x VIN: 2.2V~5.5V,  $I_{OUT}$ : 300mA,  $V_{OUT}$ : 1.2V ~ 3.3V (ロード スイッチとして構成可能)

- 3 つの降圧コンバータすべてで、動的な電圧スケーリングを実現

- 低 IQ/PFM、PWM モード (擬似固定周波数)

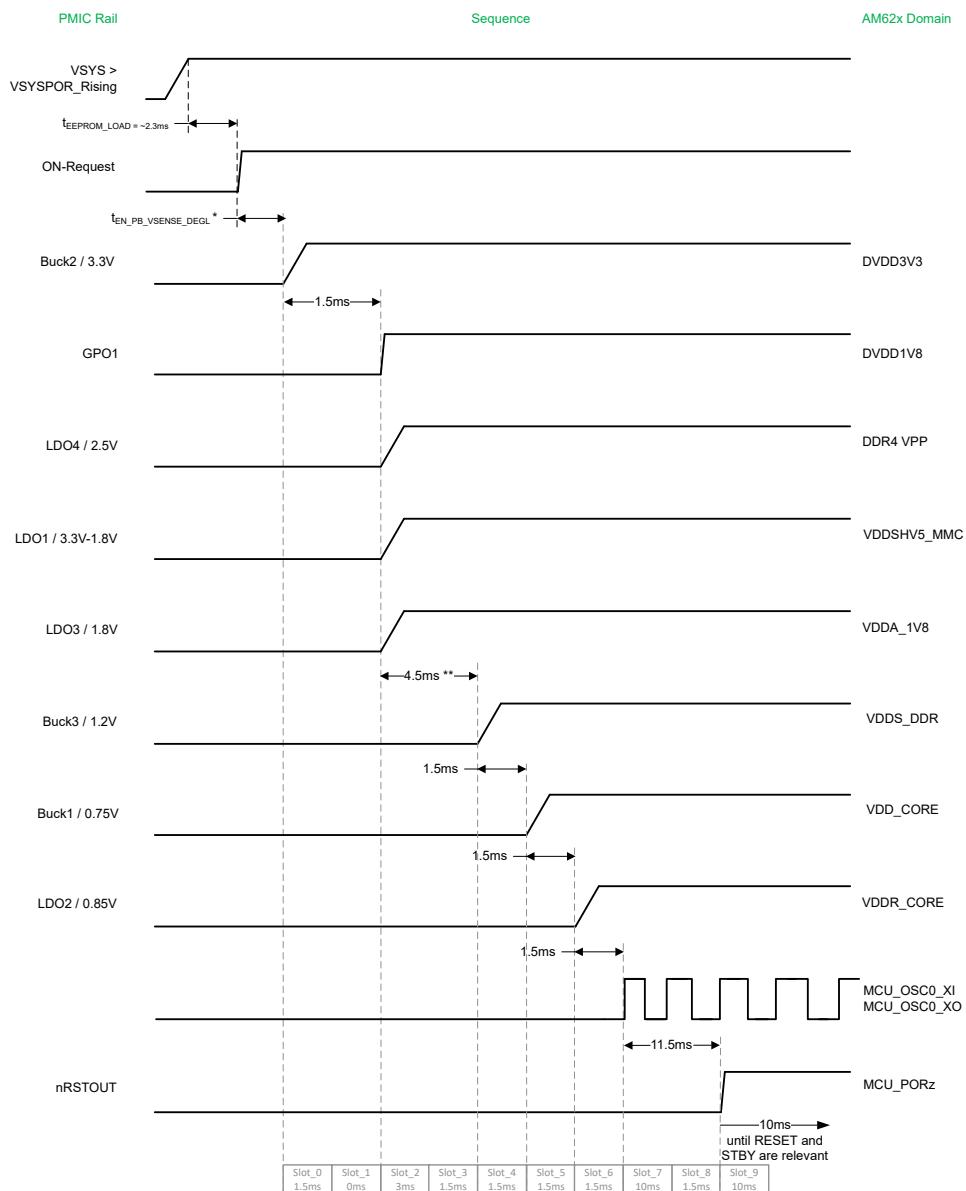

- 電源シーケンスとデフォルト電圧をプログラム可能

- I<sup>2</sup>C インターフェイス。標準、ファースト モード、ファースト モード+ をサポート

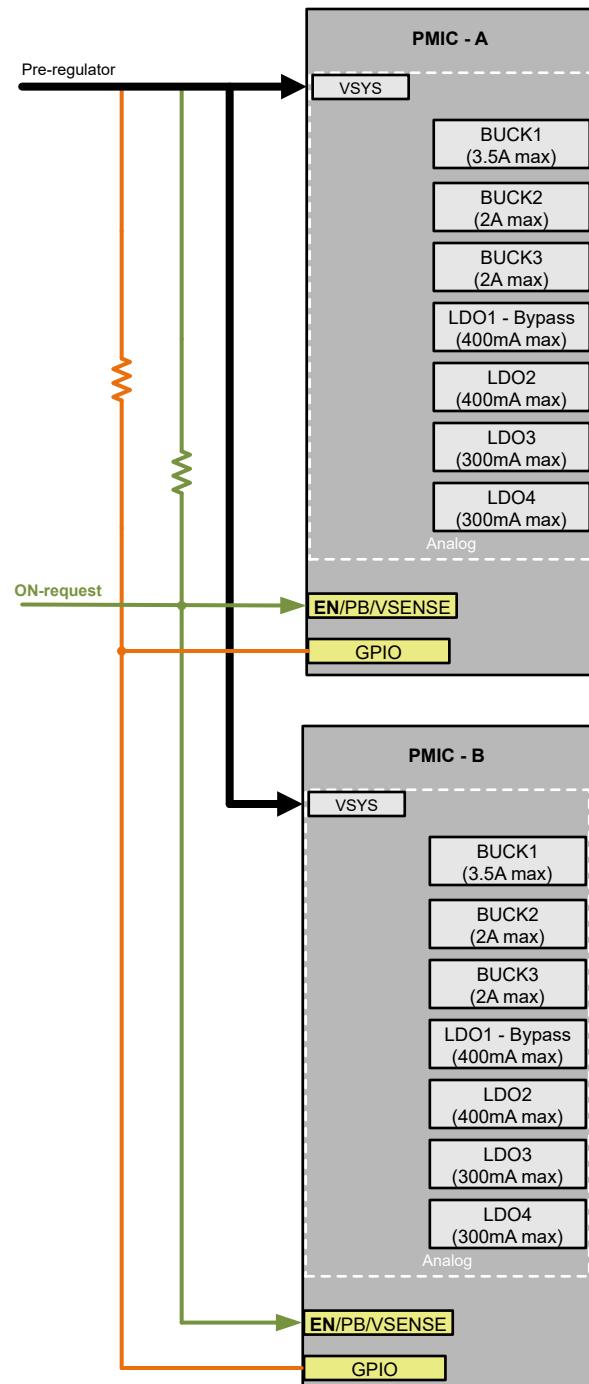

- 14 本以上のレールを備えたシステム (マルチ PMIC 構成で 2 台の TPS65219 デバイス) をサポートするように設計

- 2 つの GPO、1 つの GPIO、3 つのマルチファンクション ピン

- EEPROM プログラマビリティ

## 2 アプリケーション

- 消費電力が低い産業用 MPU および MCU (AM62x、AM64x、AM243x など)

- HMI

- PLC

- 産業用 PC

- ビル セキュリティ

- HVAC

- ビデオ監視

- データコンセントレータ

- スマートメーター

- 保護リレー

- メディカル モニタと診断

- 画像処理

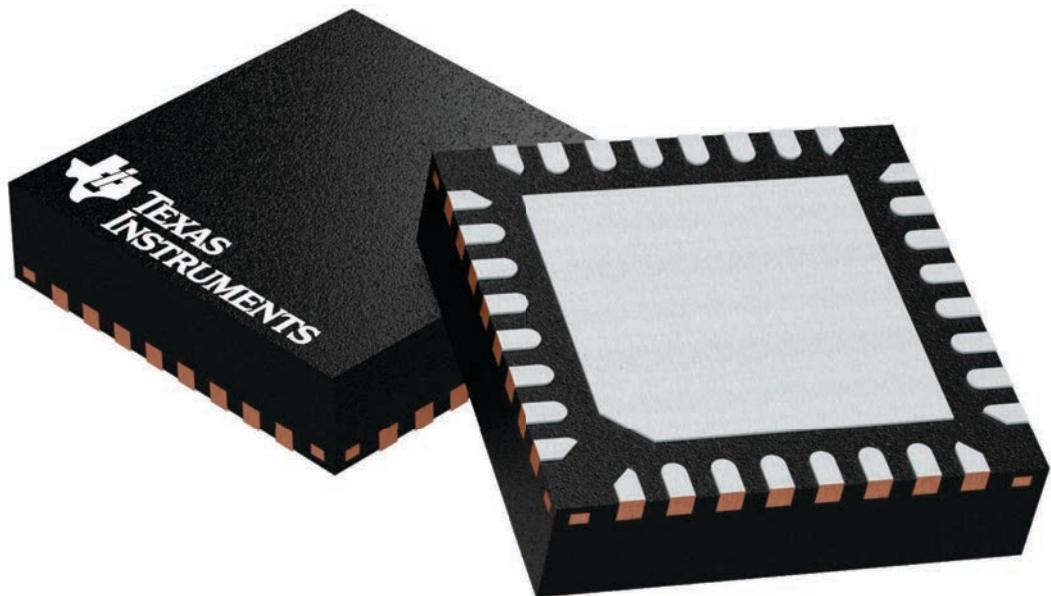

## 3 説明

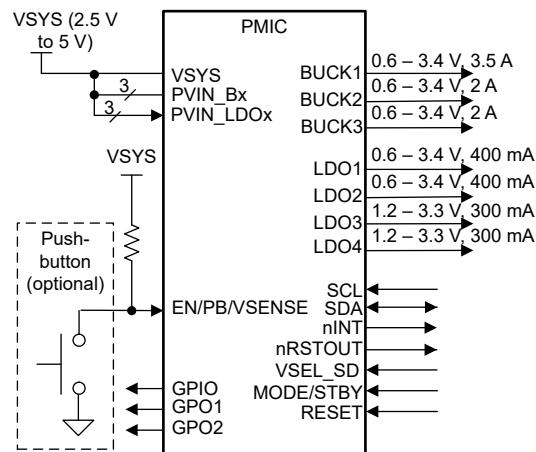

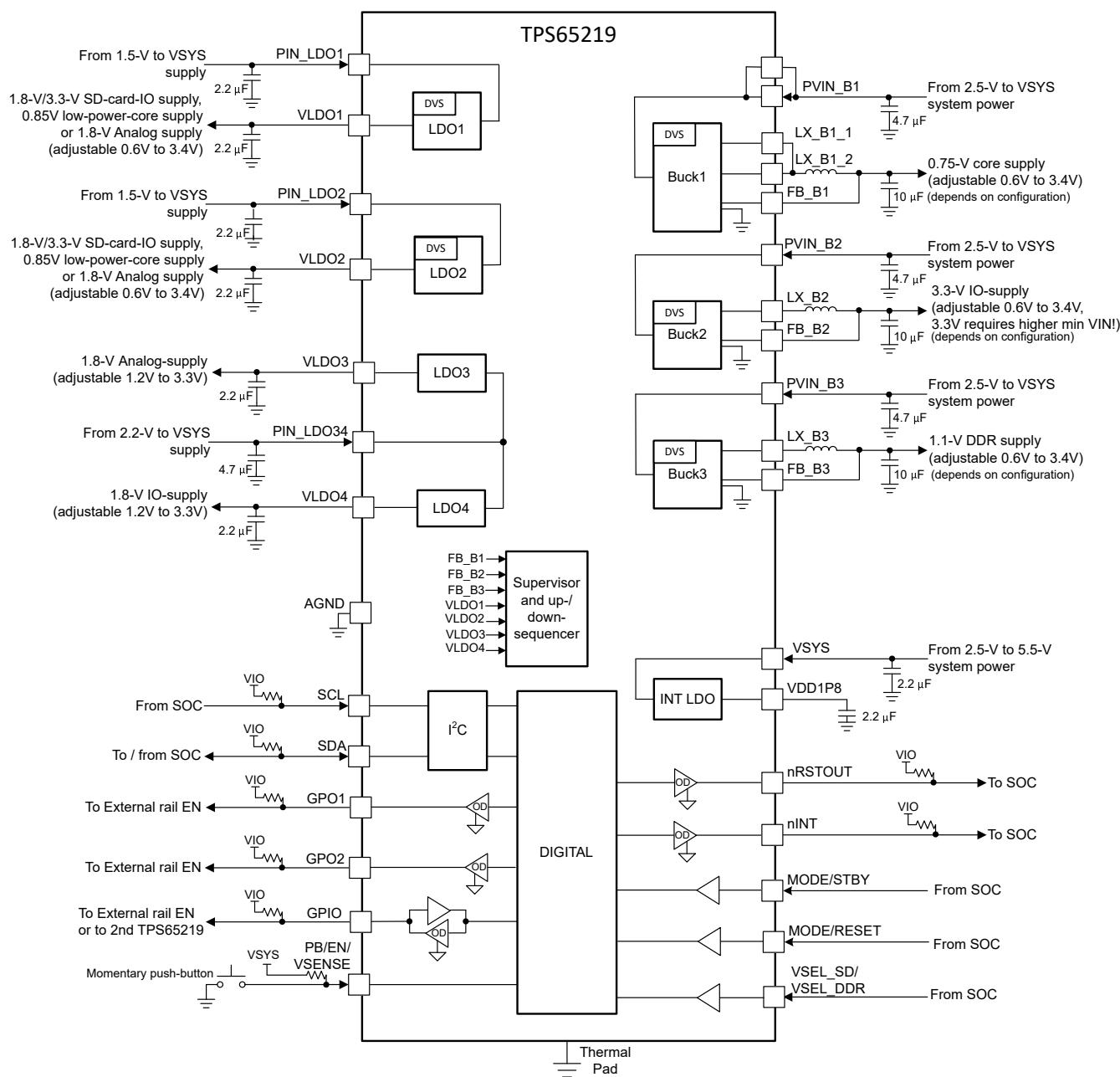

TPS65219 は、携帯機器および据置型機器アプリケーションに搭載されている、さまざまな SoC に電源を供給するように設計されたパワー マネジメント IC (PMIC) です。このデバイスは、-40°C~+105°C の周囲温度範囲で特性が規定されているため、さまざまな産業用アプリケーションに最適な PMIC です。このデバイスは、3 つの同期整流式降圧 DC/DC コンバータと 4 つのリニア レギュレータを内蔵しています。

この DC/DC コンバータは、1x 3.5A と 2x 2A 電源で供給可能です。コンバータには、スイッチング モード構成に応じて、小型の 470nH インダクタ、4.7μF 入力容量、レールあたり最小 10μF の出力容量が必要です。

2 つの LDO が 0.6V ~ 3.4V の出力電圧範囲で 400mA の出力電流をサポートします。これらの LDO は、バイパス モードをサポートし、負荷スイッチとして動作し、動作中に電圧を変化させることができます。他の 2 つの LDO は、1.2V ~ 3.3V の出力電圧範囲において 300mA の出力電流をサポートします。これらの LDO は、負荷スイッチ モードもサポートしています。

I<sup>2</sup>C インターフェイス、IO、GPIO、マルチファンクション ピン (MFP) は、さまざまな SoC にシームレスに接続します。

### パッケージ情報

| 部品番号     | パッケージ           | パッケージ サイズ (公称)  |

|----------|-----------------|-----------------|

| TPS65219 | RSM (32 ピン QFN) | 4.00mm × 4.00mm |

| TPS65219 | RHB (32 ピン QFN) | 5.00mm × 5.00mm |

アプリケーション概略図

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

English Data Sheet: [SLVSGA0](#)

## 目次

|                                                                                                                      |          |                               |            |

|----------------------------------------------------------------------------------------------------------------------|----------|-------------------------------|------------|

| <b>1 特長</b>                                                                                                          | <b>1</b> | <b>7 詳細説明</b>                 | <b>28</b>  |

| <b>2 アプリケーション</b>                                                                                                    | <b>1</b> | 7.1 概要                        | 28         |

| <b>3 説明</b>                                                                                                          | <b>1</b> | 7.2 機能ブロック図                   | 29         |

| <b>4 デバイスの比較</b>                                                                                                     | <b>3</b> | 7.3 機能説明                      | 30         |

| <b>5 ピン構成および機能</b>                                                                                                   | <b>4</b> | 7.4 デバイスの機能モード                | 54         |

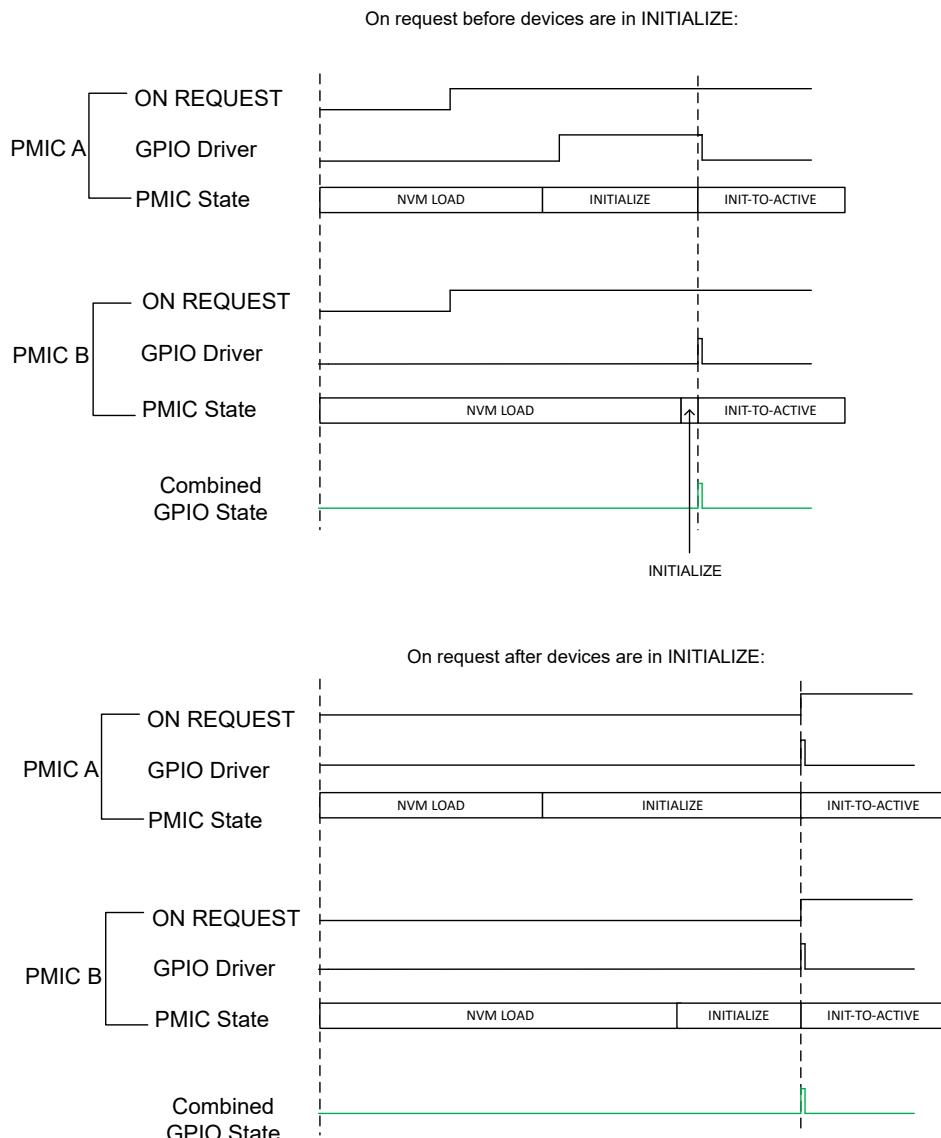

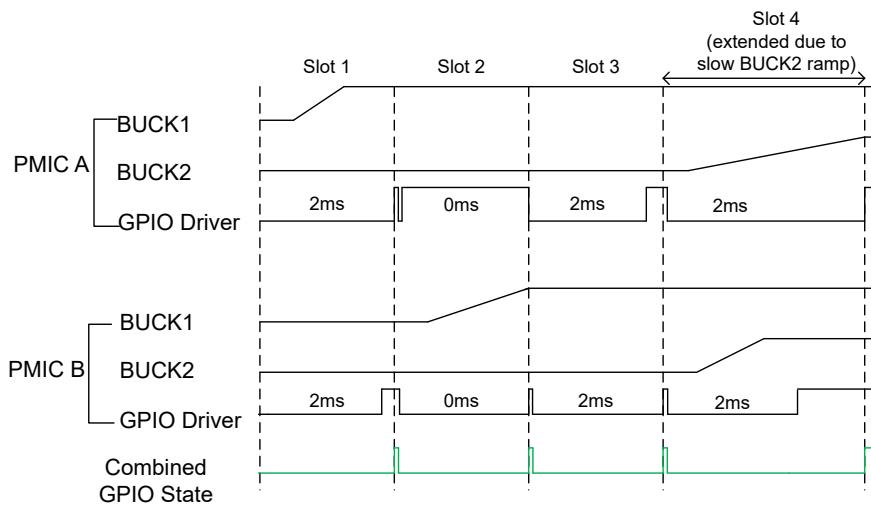

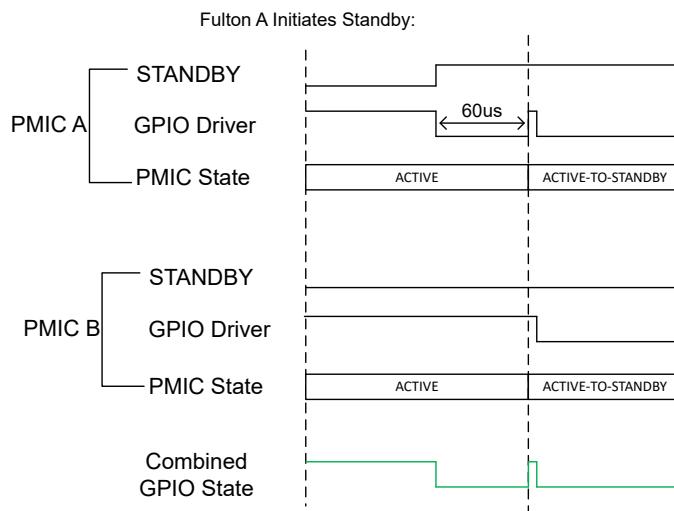

| <b>6 仕様</b>                                                                                                          | <b>8</b> | 7.5 マルチ PMIC 動作               | 60         |

| 6.1 絶対最大定格                                                                                                           | 8        | 7.6 ユーザー レジスタ                 | 64         |

| 6.2 ESD 定格                                                                                                           | 8        | 7.7 デバイスのレジスタ                 | 65         |

| 6.3 推奨動作条件                                                                                                           | 8        | <b>8 アプリケーションと実装</b>          | <b>140</b> |

| 6.4 熱に関する情報                                                                                                          | 10       | 8.1 アプリケーション情報                | 140        |

| 6.5 システム制御スレッショルド                                                                                                    | 10       | 8.2 代表的なアプリケーション              | 140        |

| 6.6 BUCK1 コンバータ                                                                                                      | 12       | 8.3 電源に関する推奨事項                | 147        |

| 6.7 BUCK2、BUCK3 コンバータ                                                                                                | 14       | 8.4 レイアウト                     | 148        |

| 6.8 汎用 LDO (LDO1、LDO2)                                                                                               | 17       | <b>9 デバイスおよびドキュメントのサポート</b>   | <b>150</b> |

| 6.9 汎用 LDO (LDO3、LDO4)                                                                                               | 19       | 9.1 ドキュメントの更新通知を受け取る方法        | 150        |

| 6.10 GPIO とマルチファンクションピン (EN/PB/<br>VSENSE、nRSTOUT、nINT、GPO1、GPO2、<br>GPIO、MODE/RESET、MODE/STBY、VSEL_SD/<br>VSEL_DDR) | 21       | 9.2 サポート・リソース                 | 150        |

| 6.11 電圧と温度の監視                                                                                                        | 22       | 9.3 商標                        | 150        |

| 6.12 I <sup>2</sup> C インターフェイス                                                                                       | 23       | 9.4 静電気放電に関する注意事項             | 150        |

| 6.13 代表的特性                                                                                                           | 26       | 9.5 用語集                       | 150        |

|                                                                                                                      |          | <b>10 改訂履歴</b>                | <b>150</b> |

|                                                                                                                      |          | <b>11 メカニカル、パッケージ、および注文情報</b> | <b>152</b> |

## 4 デバイスの比較

表 4-1 に、事前構成済みの注文可能な部品番号 (OPN) と推奨アプリケーション使用事例の簡単な要約を示します。この表には、新しい設計をサポートする提供中の販促用品リソースも掲載されています。アプリケーションノートでは、特定のプロセッサおよびマイコンの要件を満たすために、TPS65219 PMIC の電力およびデジタルリソースを使用する方法について説明しています。注文可能なデフォルトの不揮発性メモリ (NVM) レジスタ設定の詳細については、技術参考書 (TRM) に記載されています。

TPS6521905 は、デフォルトですべての電源レールがオフになっている、ユーザーがプログラム可能なバージョンで、各種プロセッサまたは SoC の電力要件を満たすようにプログラムできます。

**表 4-1. TI のプロセッサとマイコンのデバイス比較表**

| デバイス名          | プロセッサ/マイコン                 | アプリケーション使用事例 |        |                 | 販促用品                                                |                                                                                                                                                            |

|----------------|----------------------------|--------------|--------|-----------------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                |                            | Vin          | メモリ    | VDD_CORE        | TRM                                                 | アプリケーションノート                                                                                                                                                |

| TPS6521901     | AM62x、AM62x SIP、AM64       | 5V           | DDR4   | 0.75V           | SLVUCH3                                             | <ul style="list-style-type: none"> <li>AM62 <a href="#">SLVAFD0</a></li> <li>AM64 <a href="#">SLVAE9</a></li> <li>AM243 <a href="#">SLVAFK3</a></li> </ul> |

| TPS6521902     | AM62x、AM62x SIP、AM64       | 3.3V または 5V  | LPDDR4 | 0.75V           | SLVUCLO                                             |                                                                                                                                                            |

| TPS6521903 (1) | AM62x、AM62x SIP、AM64       | 3.3V または 5V  | DDR4   | 0.75V           | SLVUCJ2                                             |                                                                                                                                                            |

| TPS6521904 (1) | AM62x、AM62x SIP、AM64、AM243 | 3.3V または 5V  | DDR4   | 0.85V           | SLVUCL1                                             |                                                                                                                                                            |

| TPS6521907     | AM62x、AM62x SIP、AM64、AM243 | 5V           | DDR4   | 0.85V           | SLVUCL9                                             |                                                                                                                                                            |

| TPS6521908     | AM62x、AM62x SIP、AM64、AM243 | 3.3V または 5V  | LPDDR4 | 0.85V           | SLVUCM0                                             |                                                                                                                                                            |

| TPS6521909     | AM62A、AM67                 | 5V           | LPDDR4 | 0.85V または 0.75V | SLVUCZ4                                             |                                                                                                                                                            |

| TPS6521910     | AM62A、AM67                 | 5V           | LPDDR4 | 0.85V または 0.75V | SLVUD09                                             |                                                                                                                                                            |

| TPS652190C     | NXP I.MX 8M Plus           | 3.3V         | DDR4   | 0.85            | SLVUCV3                                             | <a href="#">SLVAFQ2</a>                                                                                                                                    |

| TPS6521940     | NXP I.MX93                 | 5V           | LPDDR4 | 0.85V           | SLVUD41                                             | <a href="#">TIDA-050087</a>                                                                                                                                |

| TPS6521905     | ユーザー プログラマブルバージョン          | 任意           | 任意     | 任意              | <a href="#">『TPS65219 不揮発性メモリ (NVM) プログラミングガイド』</a> |                                                                                                                                                            |

(1) PMIC 付き AM62B スターターキットには、デフォルトで TPS6521904 が搭載されており、VDD\_CORE = 0.85V をサポートしています。このハードウェアは、TPS6521903 PMIC を使用して、VDD\_CORE = 0.75V をサポートするように変更することもできます。

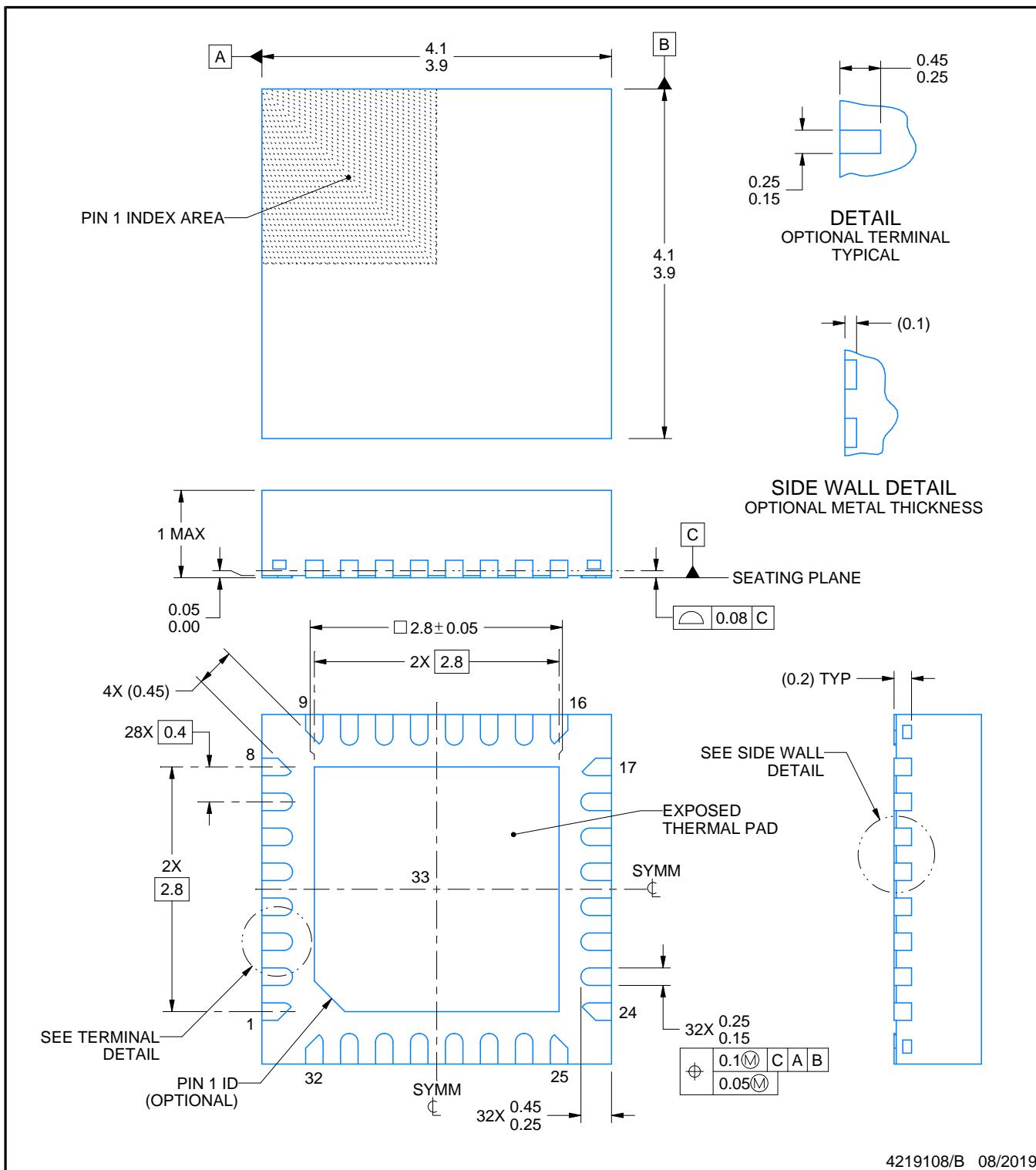

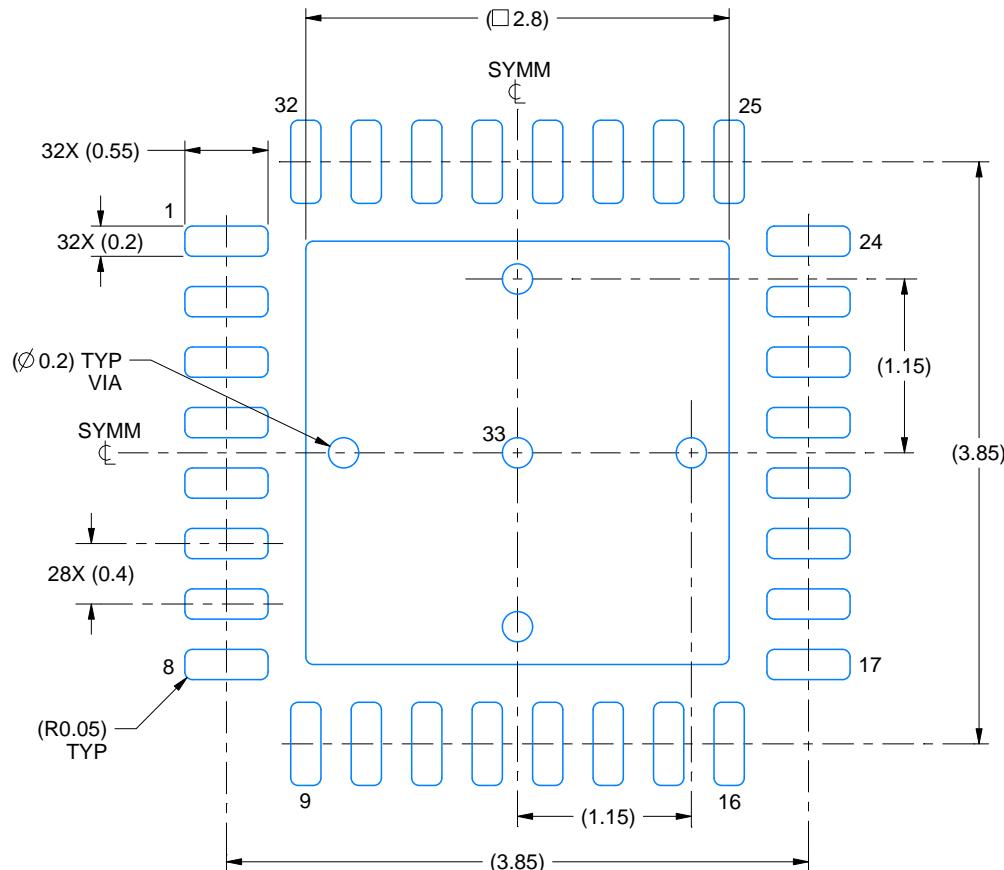

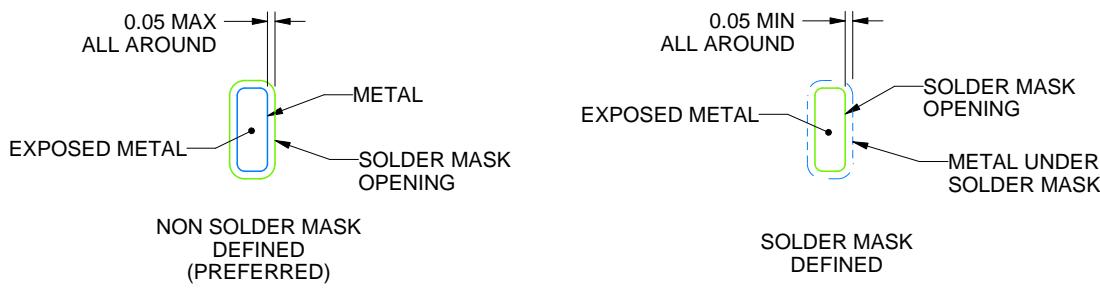

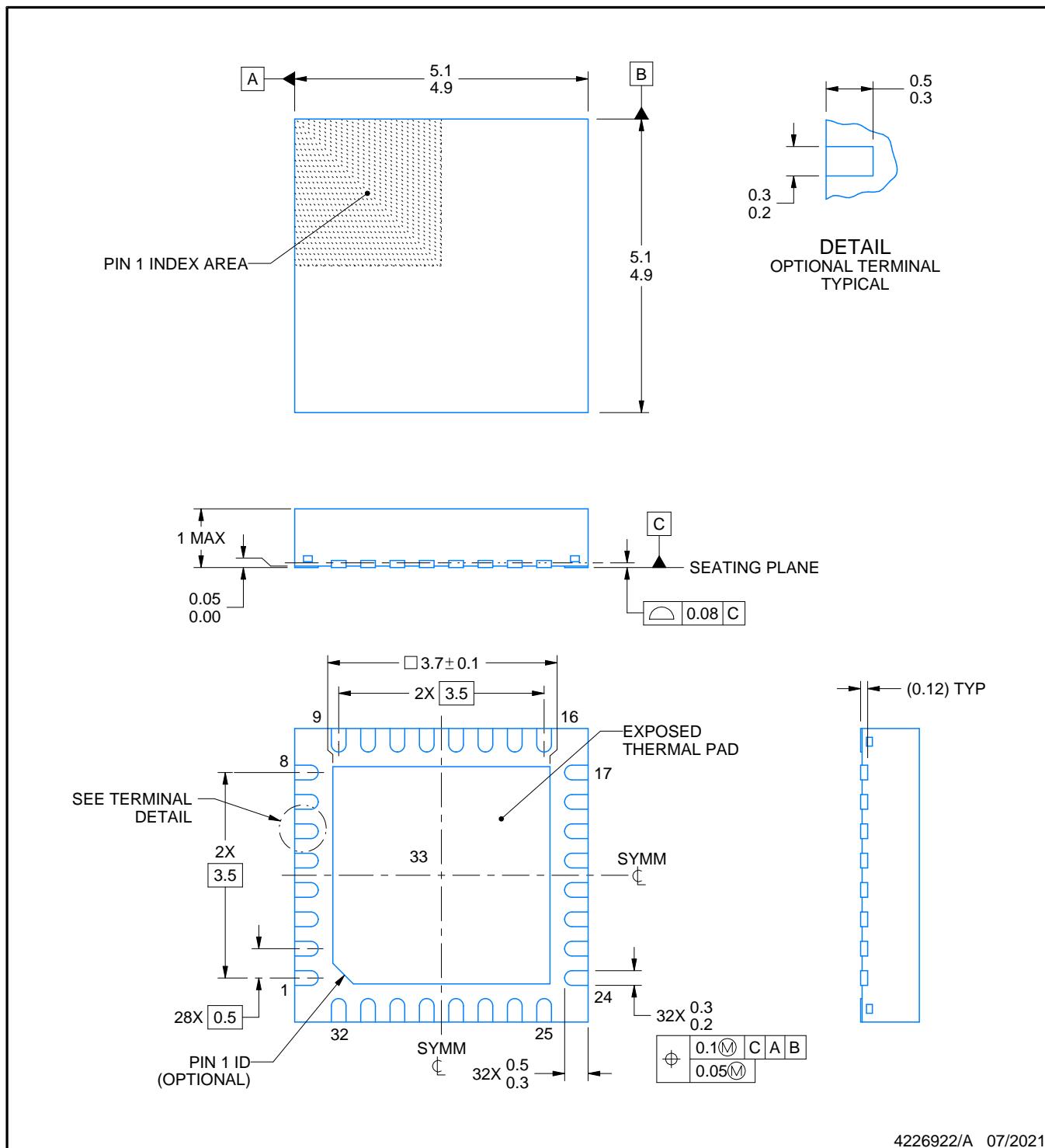

## 5 ピン構成および機能

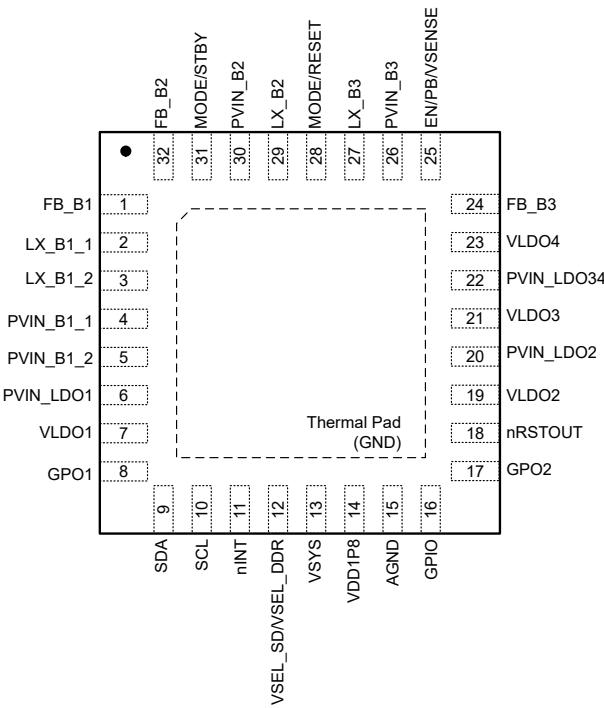

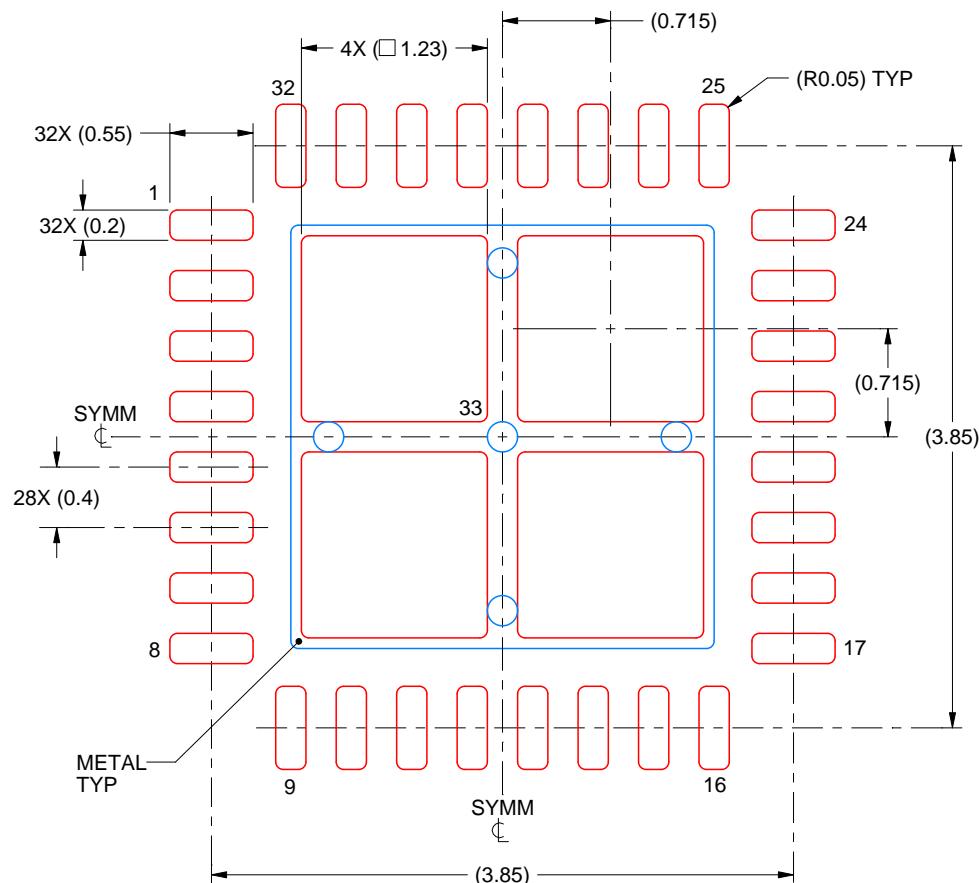

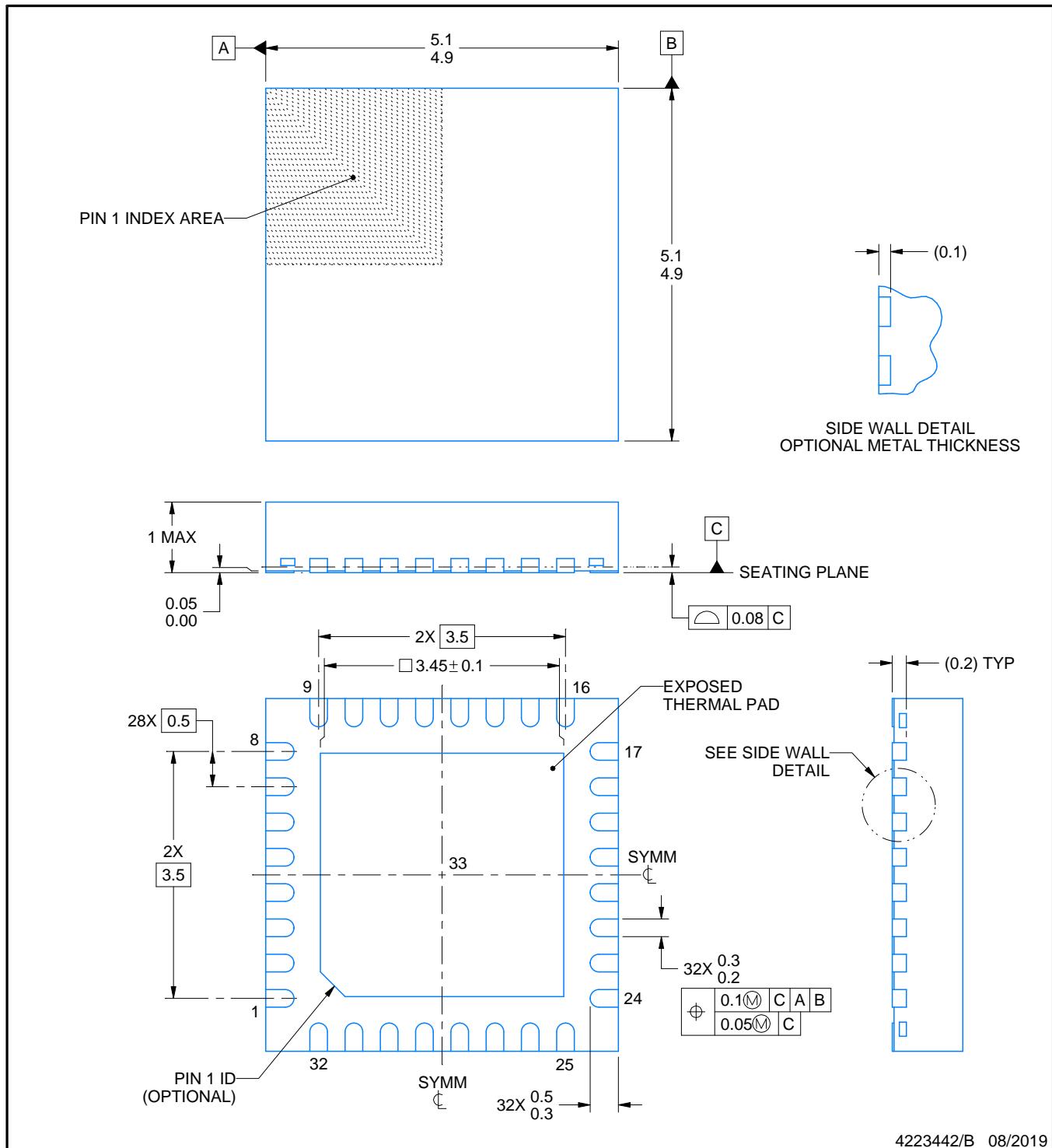

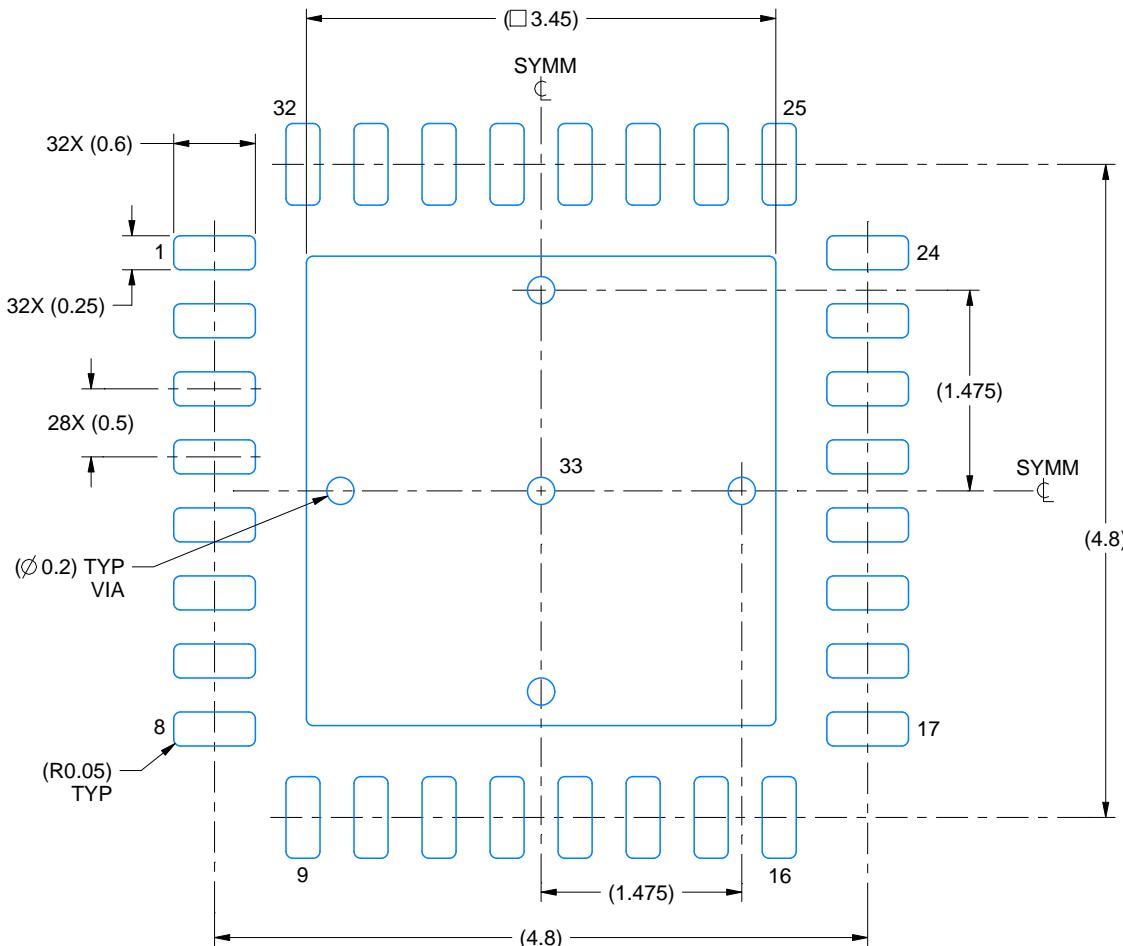

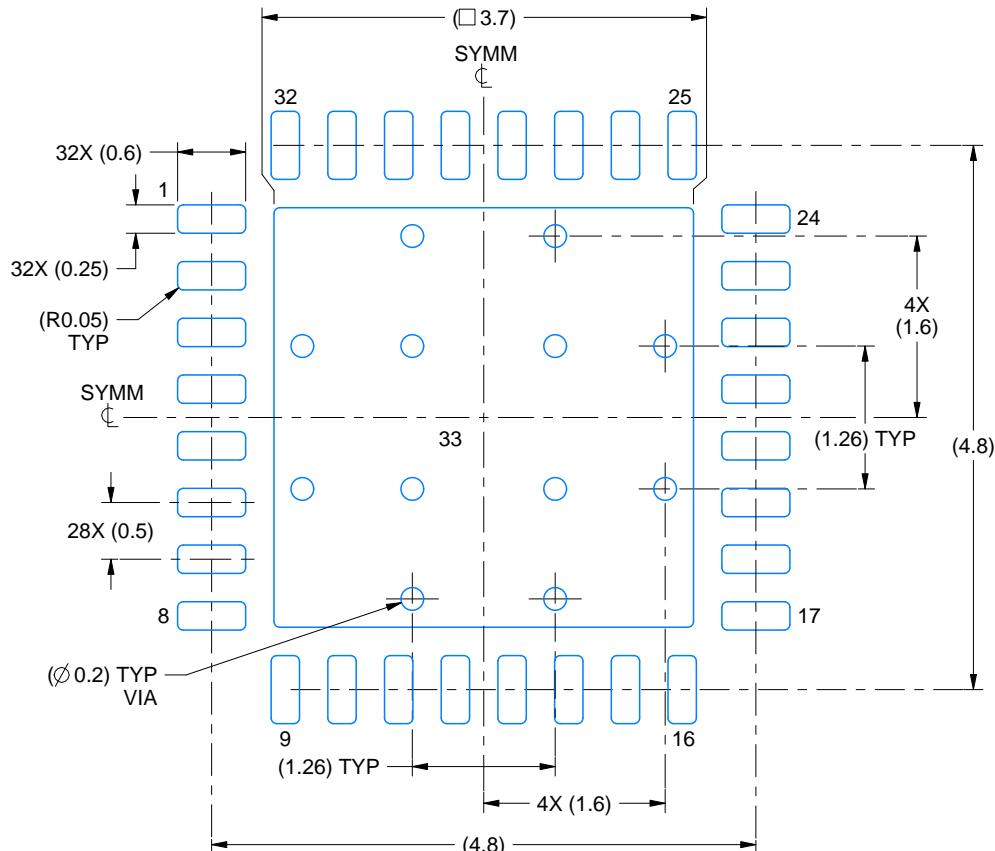

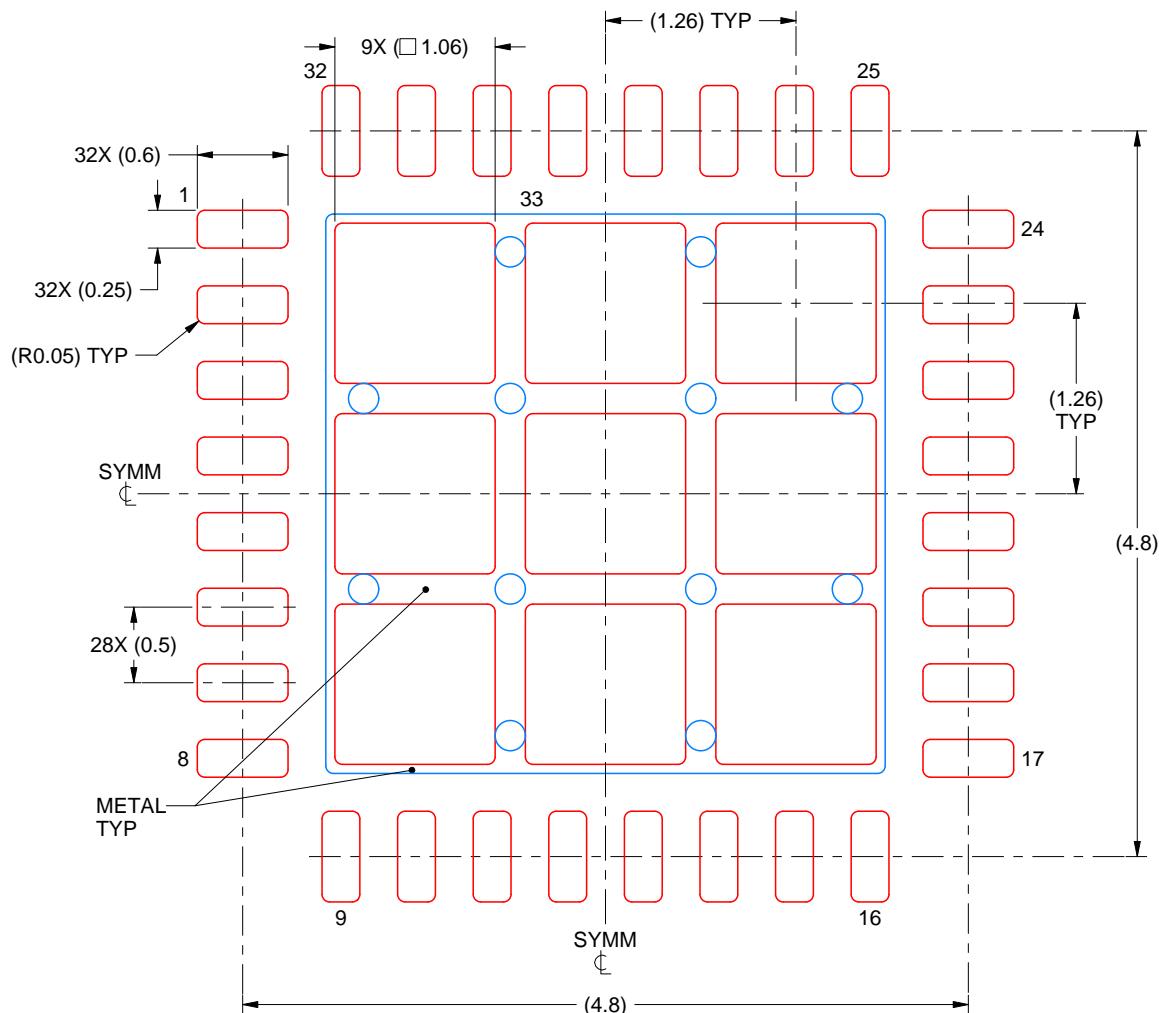

図 5-1. RHB パッケージ、32 ピン QFN (上面図)

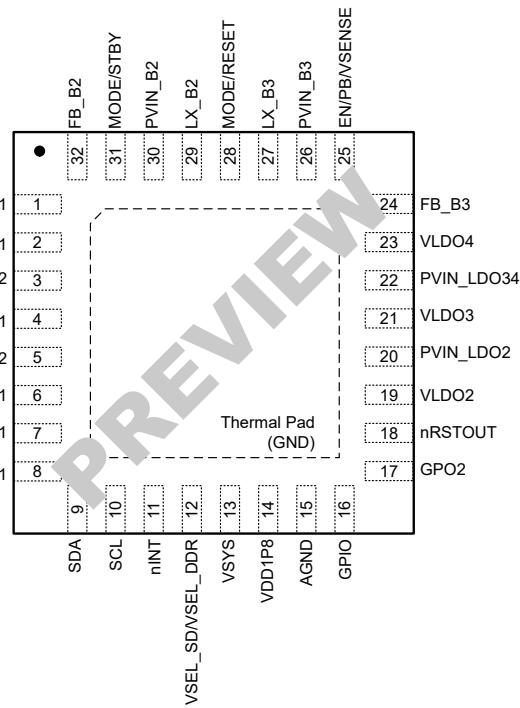

図 5-2. RSM パッケージ、32 ピン QFN (上面図)

表 5-1. ピンの機能

| ピン名              | ピン番号 | タイプ | 説明                                                                                                        | 使用しない場合は接続 (出力レールを恒久的に無効化する必要があります) |

|------------------|------|-----|-----------------------------------------------------------------------------------------------------------|-------------------------------------|

| <b>FB_B1</b>     | 1    | I   | Buck1 のフィードバック入力 Buck1 出力フィルタに接続します。公称出力電圧は EEPROM によって構成されます。                                            | GND に接続                             |

| <b>LX_B1_1</b>   | 2    | PWR | Buck1 用スイッチピン。Buck1 コンデンサの片側を、このピンに接続します。                                                                 | フローティング状態のままにします。                   |

| <b>LX_B1_2</b>   | 3    | PWR | Buck1 用の 2 番目スイッチピン。Buck1 コンデンサの片側を、このピンに接続します。LX_B1_1 に接続します。                                            | フローティング状態のままにします。                   |

| <b>PVIN_B1_1</b> | 4    | PWR | BUCK1 の電源入力。4.7 $\mu$ F 以上のセラミックコンデンサを使用して、このピンをバイパスして接地します。PVIN_B1_1 ピンの電圧は、VSYS ピンの電圧を超えないようにする必要があります。 | VSYS に接続                            |

| <b>PVIN_B1_2</b> | 5    | PWR | BUCK1 の 2 番目の電源入力。このピンはピン 4 のバイパスコンデンサを共有しています。PVIN_B1_2 ピンの電圧は、VSYS ピンの電圧を超えないようにする必要があります。              | VSYS に接続                            |

| <b>PVIN_LDO1</b> | 6    | PWR | LDO1 の電源入力。PVIN_LDO1 ピンの電圧は、VSYS ピンの電圧を超えないようにする必要があります。                                                  | VSYS に接続                            |

| <b>VLDO1</b>     | 7    | PWR | LDO1 の出力電圧公称出力電圧は EEPROM によって構成されます。2.2 $\mu$ F 以上のセラミックコンデンサを使用して、このピンをバイパスして接地します。                      | フローティング状態のままにします。                   |

**表 5-1. ピンの機能 (続き)**

| ピン名                          | ピン番号 | タイプ | 説明                                                                                                                                                                                                       | 使用しない場合は接続 (出力レールを恒久的に無効化する必要があります) |

|------------------------------|------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| <b>GPO1</b>                  | 8    | O   | 汎用オープンドレイン出力。パワーアップおよびパワーダウンシーケンスで、外部レールを有効にするように構成できます。                                                                                                                                                 | フローティング状態のままにします。                   |

| <b>SDA</b>                   | 9    | I/O | I <sup>2</sup> Cシリアルポート用のデータピン。I <sup>2</sup> Cのロジックレベルは、外部プルアップ電圧に依存します。                                                                                                                                | VIOに接続                              |

| <b>SCL</b>                   | 10   | I   | I <sup>2</sup> Cシリアルポート用のクロックピン。I <sup>2</sup> Cのロジックレベルは、外部プルアップ電圧に依存します。                                                                                                                               | VIOに接続                              |

| <b>nINT</b>                  | 11   | O   | 割り込み要求出力。オープンドレインドライバは故障状態時に Lowになります。ビットがクリアされると解除されます                                                                                                                                                  | フローティング状態のままにします。                   |

| <b>VSEL_SD/<br/>VSEL_DDR</b> | 12   | I   | マルチファンクションピン:<br>VSEL_SDとして構成:SDカードIO電圧の選択。<br>SoCに接続されます。1.8Vと、LDO1またはLDO2上のレジスタベースの VOUTとの間の電圧変化をトリガします。極性を設定可能です。<br>VSEL_DDRとして構成:DDR電圧の選択。ハードウェアド プルアップ(1.35V)、プルダウン(レジスタベースの VOUT)またはフローティング(1.2V) | 該当なし(GNDに接続)                        |

| <b>VSYS</b>                  | 13   | PWR | リファレンスシステムの入力電源ピン。このピンは2.2μF以上のセラミックコンデンサを使用してグランドにバイパスします(PVINコンデンサと共有可能)。                                                                                                                              | 該当なし                                |

| <b>VDD1P8</b>                | 14   | PWR | 内部基準電圧社内使用限定。2.2μF以上のセラミックコンデンサを使用して、このピンをバイパスして接地します。                                                                                                                                                   | 該当なし                                |

| <b>AGND</b>                  | 15   | GND | アナログGND用グランド端子                                                                                                                                                                                           | 該当なし                                |

| <b>GPIO</b>                  | 16   | I/O | GPO構成:汎用オープンドレイン出力。パワーアップおよびパワーダウンシーケンスで、外部レールを有効にするように構成できます。<br>GPIO構成:<br>I/Oの同期。2つ以上のTPS65219の同期に使用します。ピンはレベルセンシティブです。                                                                               | フローティング状態のままにします。                   |

| <b>GPO2</b>                  | 17   | O   | 汎用オープンドレイン出力。パワーアップおよびパワーダウンシーケンスで、外部レールを有効にするように構成できます。                                                                                                                                                 | フローティング状態のままにします。                   |

| <b>nRSTOUT</b>               | 18   | O   | SoCへのリセット出力。シーケンサで制御。アクティブおよびスタンバイ状態で High。                                                                                                                                                              | フローティング状態のままにします。                   |

| <b>VLDO2</b>                 | 19   | PWR | LDO2の出力電圧公称出力電圧は EEPROMによって構成されます。2.2μF以上のセラミックコンデンサを使用して、このピンをバイパスして接地します。                                                                                                                              | フローティング状態のままにします。                   |

| <b>PVIN_LDO2</b>             | 20   | PWR | LDO2の電源入力。2.2μF以上のセラミックコンデンサを使用して、このピンをバイパスして接地します。<br>PVIN_LDO2ピンの電圧は、VSYSピンの電圧を超えないようにする必要があります。                                                                                                       | VSYSに接続                             |

| <b>VLDO3</b>                 | 21   | PWR | LDO3の出力電圧公称出力電圧は EEPROMによって構成されます。2.2μF以上のセラミックコンデンサを使用して、このピンをバイパスして接地します。                                                                                                                              | フローティング状態のままにします。                   |

| <b>PVIN_LDO34</b>            | 22   | PWR | LDO3およびLDO4の電源入力。4.7μF以上のセラミックコンデンサを使用して、このピンをバイパスして接地します。<br>PVIN_LDO34ピンの電圧は、VSYSピンの電圧を超えないようにする必要があります。                                                                                               | VSYSに接続                             |

表 5-1. ピンの機能 (続き)

| ピン名                      | ピン番号 | タイプ | 説明                                                                                                                                                                                                                                                                                                                            | 使用しない場合は接続 (出力レールを恒久的に無効化する必要があります)                        |

|--------------------------|------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| <b>VLDO4</b>             | 23   | PWR | LDO4 の出力電圧公称出力電圧は EEPROM で設定されます。2.2 $\mu$ F 以上のセラミックコンデンサを使用してこのピンをグラウンドにバイパスします。                                                                                                                                                                                                                                            | フローティング状態のままにします。                                          |

| <b>FB_B3</b>             | 24   | I   | Buck3 のフィードバック入力 Buck3 出力フィルタに接続します。公称出力電圧は EEPROM によって構成されます。                                                                                                                                                                                                                                                                | GND に接続                                                    |

| <b>EN/PB/<br/>VSENSE</b> | 25   | I   | オンリクエスト入力。<br>EN として設定: デバイスイネーブルピン、High レベルはオン要求、Low レベルはオフ要求です。<br>PB として設定: プッシュボタンモニタ入力。600ms の Low レベルはオン要求、8s の Low レベルはオフ要求です。<br>VSENSE として設定: 電源障害コンバータ入力。入力からブリッジレギュレータに接続された抵抗分圧器を使用して検出電圧を設定し、このピンを接地します。ブリッジレギュレータの立ち上がり/立ち下がり電圧を検出し、オン/オフ要求をトリガします。<br>このピンは、PB 構成では待機時間、EN および VSENSE 構成ではデグリッチ時間でエッジセンシティブです。 | N/A (EN として構成して VSYS に接続)                                  |

| <b>PVIN_B3</b>           | 26   | PWR | BUCK3 の電源入力。4.7 $\mu$ F 以上のセラミックコンデンサを使用して、このピンをバイパスして接地します。<br>PVIN_B3 ピンの電圧は、VSYS ピンの電圧を超えないようにする必要があります。                                                                                                                                                                                                                   | VSYS に接続                                                   |

| <b>LX_B3</b>             | 27   | PWR | Buck3 用スイッチピン。Buck3 コンデンサの片側を、このピンに接続します。                                                                                                                                                                                                                                                                                     | フローティング状態のままにします。                                          |

| <b>モード / リセット</b>        | 28   | I   | マルチファンクションピン:<br>モードとして構成: SoC またはハードワイヤードのプルアップ/ダウンに接続されます。降圧コンバータを強制的に PWM に設定するか、PFM モードでの自動移行を許可します。<br>RESET として設定: SoC に接続されます。ウォームリセットまたはコールドリセットを強制します (構成可能)。ウォームリセットは出力電圧のデフォルトにリセットし、コールドリセットは無効化されているすべてのレールをシーケンスして再度パワーアップします。<br>極性を設定可能です。<br>このピンはモード構成ではレベルセンシティブで、リセット構成ではエッジセンシティブです。                     | 該当なし (構成に応じて High または Low に接続、「PFM とリセット (MODE/RESET)」を参照) |

| <b>LX_B2</b>             | 29   | PWR | Buck2 用スイッチピン。Buck2 コンデンサの片側を、このピンに接続します。                                                                                                                                                                                                                                                                                     | フローティング状態のままにします。                                          |

| <b>PVIN_B2</b>           | 30   | PWR | BUCK2 の電源入力。4.7 $\mu$ F 以上のセラミックコンデンサを使用して、このピンをバイパスして接地します。<br>PVIN_B2 ピンの電圧は、VSYS ピンの電圧を超えないようにする必要があります。                                                                                                                                                                                                                   | VSYS に接続                                                   |

**表 5-1. ピンの機能 (続き)**

| ピン名          | ピン番号     | タイプ | 説明                                                                                                                                                                                                                            | 使用しない場合は接続 (出力レールを恒久的に無効化する必要があります)                                 |

|--------------|----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| モード/スタンバイ    | 31       | I   | <p>マルチファンクション ピン:<br/>モードとして構成:<br/>SoC またはハードワイヤードのプルアップ/ダウンに接続されます。降圧コンバータを強制的に PWM に設定するか、PFM モードでの自動移行を許可します。<br/>STBY として設定: 低消費電力モード コマンドで、選択されたレールを無効化します。<br/>モードとスタンバイの両方の機能を組み合わせることができます。<br/>ピンはレベル センシティブです。</p> | 該当なし (構成に応じて High または Low に接続、「PWM/PFM および低消費電力モード (MODE/STBY)」を参照) |

| <b>FB_B2</b> | 32       | I   | Buck2 のフィードバック入力 Buck2 出力フィルタに接続します。公称出力電圧は EEPROM によって構成されます。                                                                                                                                                                | GND に接続                                                             |

| <b>PGND</b>  | PowerPad | GND | 電源グランド。電気および熱伝導を最大化するために、露出したパッドを TPS65219 直下の複数のインターフェクトビアによってプリント基板の連続接地面に接続します。                                                                                                                                            | 該当なし                                                                |

## 6 仕様

### 6.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

| POS   |                  |                                                             | 最小値  | 最大値           | 単位 |

|-------|------------------|-------------------------------------------------------------|------|---------------|----|

| 1.1.1 | 入力電圧             | VSYS                                                        | -0.3 | 6             | V  |

| 1.1.2 | 入力電圧             | PVIN_B1, PVIN_B2, PVIN_B3, PVIN_LDO1, PVIN_LDO2, PVIN_LDO34 | -0.3 | 6             | V  |

| 1.1.3 | 入力電圧対降圧用 VSYS    | VSYS を超える PVIN_B1, PVIN_B2, PVIN_B3 最大電圧                    |      | 200           | mV |

| 1.1.4 | 入力電圧対 LDO 用 VSYS | VSYS を超える PVIN_LDO1, PVIN_LDO2, PVIN_LDO34 最大電圧             |      | 20            | mV |

| 1.1.5 | 入力電圧             | FB_B1, FB_B2, FB_B3                                         | -0.3 | 6             | V  |

| 1.1.6 | 入力電圧             | EN/PB/VSENSE, MODE/STBY, MODE/RESET, VSEL_SD/VSEL_DDR       | -0.3 | 6             | V  |

| 1.2.1 | 出力電圧             | LX_B1, LX_B2, LX_B3                                         | -0.3 | 0.3V, 最大 6V   | V  |

| 1.2.2 | 出力電圧             | 最大 10ns の LX_B1, LX_B2, LX_B3 スパイク                          | -2   | 10            | V  |

| 1.2.3 | 出力電圧             | GPO1, GPO2, GPIO                                            | -0.3 | 6             | V  |

| 1.2.4 | 出力電圧             | VLDO1, VLDO2, VLDO3, VLDO4                                  | -0.3 | + 0.3V, 最大 6V | V  |

| 1.2.5 | 出力電圧             | VDD1P8                                                      | -0.3 | 2             | V  |

| 1.2.6 | 出力電圧             | SDA, SCL                                                    | -0.3 | 6             | V  |

| 1.2.7 | 出力電圧             | nINT, nRSTOUT                                               | -0.3 | 6             | V  |

| 1.4.1 | 動作時の接合部温度、 $T_J$ |                                                             | -40  | 125           | °C |

| 1.4.2 | 保管温度、 $T_{stg}$  |                                                             | -40  | 150           | °C |

- (1) 「絶対最大定格」の範囲を超える動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗示するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用した場合、本デバイスは完全に機能するとは限らず、このことが本デバイスの信頼性、機能、性能に影響を及ぼし、本デバイスの寿命を縮める可能性があります。

### 6.2 ESD 定格

| POS |             |                |                                                                   | 値     | 単位 |

|-----|-------------|----------------|-------------------------------------------------------------------|-------|----|

| 2.1 | $V_{(ESD)}$ | 静電放電、人体モデル     | 人体モデル (HBM), ANSI/ESDA/JEDEC JS-001 に準拠、すべてのピン <sup>(1)</sup>     | ±2000 | V  |

| 2.2 | $V_{(ESD)}$ | 静電放電、デバイス帶電モデル | デバイス帶電モデル (CDM), ANSI/ESDA/JEDEC JS-002 に準拠、すべてのピン <sup>(2)</sup> | ±500  | V  |

- (1) JEDEC ドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

(2) JEDEC ドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

### 6.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

| POS   |            |      | 最小値                | 公称値 | 最大値 | 単位 |

|-------|------------|------|--------------------|-----|-----|----|

| 3.1.1 | $V_{VSYS}$ | 入力電圧 | 2.5 <sup>(1)</sup> |     | 5.5 | V  |

## 6.3 推奨動作条件 (続き)

自由気流での動作温度範囲内 (特に記述のない限り)

| POS     |                                                                                                      |                                                                                                                                                  | 最小値 | 公称値    | 最大値     | 単位      |

|---------|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------|---------|---------|

| 3.1.2   | $V_{PVIN\_B1}$ 、 $V_{PVIN\_B2}$ 、<br>$V_{PVIN\_B3}$<br>$V_{LX\_B1}$ 、 $V_{LX\_B2}$ 、<br>$V_{LX\_B3}$ | BUCKx ピン                                                                                                                                         |     | 2.5    | 5.5 (2) | V       |

| 3.1.3   | $\Delta V_{VSYS\_PVIN\_Bx}$                                                                          | $V_{PVIN\_Bx}$ が $V_{VSYS}$ を超える可能性がある電圧                                                                                                         |     |        | 0       | mV      |

| 3.1.4   | $\Delta V_{VSYS\_PVIN\_LDO1,LDO2}$                                                                   | $V_{PVIN\_LDO1}$ または $V_{PVIN\_LDO2}$ が $V_{VSYS}$ を超える可能性がある電圧                                                                                  |     |        | 0       | mV      |

| 3.1.5   | $\Delta V_{VSYS\_VLDO34}$                                                                            | $V_{VSYS}$ が LDO 出力電圧 (VLDO3、VLDO4) を超える可能性がある電圧、 $V_{VSYS} = 2.5V \sim 3.45V$ 、<br>LDO モード                                                      |     | 150    |         | mV      |

| 3.1.6   | $\Delta V_{VSYS\_VLDO34}$                                                                            | $V_{VSYS}$ が LDO 出力電圧 (VLDO3、VLDO4) を超える可能性がある電圧、 $V_{VSYS} = \text{LDO モードで } 3.45V \sim 5.5V$ または $V_{VSYS} = \text{LSW モードで } 2.5V \sim 5.5V$ |     | 該当なし   |         | mV      |

| 3.1.7   | $C_{PVIN\_B1}$ 、 $C_{PVIN\_B2}$ 、<br>$C_{PVIN\_B3}$                                                  | BUCKx 入力キャパシタンス                                                                                                                                  | 3.9 | 4.7    |         | $\mu F$ |

| 3.1.8   | $L_{B1}$ 、 $L_{B2}$ 、 $L_{B3}$                                                                       | BUCKx 出力インダクタンス                                                                                                                                  | 330 | 470    | 611     | nH      |

| 3.1.9a  | $C_{OUT\_B1}$ 、 $C_{OUT\_B2}$ 、<br>$C_{OUT\_B3}$                                                     | BUCKx 出力容量、強制 PWM または自動 PFM、<br>低帯域幅ケース                                                                                                          |     | 10     | 75      | $\mu F$ |

| 3.1.10a | $C_{OUT\_B1}$ 、 $C_{OUT\_B2}$ 、<br>$C_{OUT\_B3}$                                                     | BUCKx 出力容量、強制 PWM または自動 PFM、<br>高帯域幅ケース                                                                                                          |     | 30     | 220     | $\mu F$ |

| 3.1.11  | $V_{FB\_B1}$ 、 $V_{FB\_B2}$ 、<br>$V_{FB\_B3}$                                                        | BUCKx FB ピン                                                                                                                                      | 0   |        | 5.5 (2) | V       |

| 3.1.12  | $V_{PVIN\_LDO1}$ 、 $V_{PVIN\_LDO2}$                                                                  | LDO 入力電圧                                                                                                                                         | 1.5 |        | 5.5 (2) | V       |

| 3.1.13  | $V_{PVIN\_LDO1}$ 、 $V_{PVIN\_LDO2}$                                                                  | バイパス モードでの LDO 入力電圧                                                                                                                              | 1.5 |        | 3.6     | V       |

| 3.1.14  | $V_{PVIN\_LDO1}$ 、 $V_{PVIN\_LDO2}$                                                                  | $V_{PVIN\_LDOx}$ とバイパス モードで構成された $V_{VLDOx}$ との間の許容デルタ                                                                                           |     | -200   | 200     | mV      |

| 3.1.15  | $V_{VLDO1}$ 、 $V_{VLDO2}$                                                                            | LDO 出力電圧範囲                                                                                                                                       |     | 0.6    | 3.4     | V       |

| 3.1.16  | $C_{PVIN\_LDO1}$ 、 $C_{PVIN\_LDO2}$                                                                  | LDO 入力容量                                                                                                                                         | 1.6 | 2.2    |         | $\mu F$ |

| 3.1.17  | $C_{VLDO1}$ 、 $C_{VLDO2}$                                                                            | LDO 出力キャパシタンス                                                                                                                                    | 1.6 | 2.2    | 20      | $\mu F$ |

| 3.1.18  | $V_{PVIN\_LDO3}$ 、 $V_{PVIN\_LDO4}$                                                                  | LDO 入力電圧                                                                                                                                         | 2.2 |        | 5.5 (2) | V       |

| 3.1.19  | $V_{VLDO3}$ 、 $V_{VLDO4}$                                                                            | LDO 出力電圧範囲                                                                                                                                       | 1.2 |        | 3.3     | V       |

| 3.1.20  | $C_{PVIN\_LDO34}$                                                                                    | LDO 入力容量                                                                                                                                         | 2.2 | 4.7    |         | $\mu F$ |

| 3.1.21  | $C_{VLDO3}$ 、 $C_{VLDO4}$                                                                            | LDO 出力キャパシタンス                                                                                                                                    | 1.6 | 2.2    | 30 (3)  | $\mu F$ |

| 3.1.22  | $V_{VDD1P8}$                                                                                         | VDD1P8 ピン                                                                                                                                        | 0   |        | 1.8     | V       |

| 3.1.23  | $C_{VDD1P8}$                                                                                         | 内部レギュレータのデカッピング容量                                                                                                                                | 1   | 2.2    | 4       | $\mu F$ |

| 3.1.24  | $C_{VSYS}$                                                                                           | $V_{VSYS}$ 入力デカッピング容量                                                                                                                            | 1   | 2.2    |         | $\mu F$ |

| 3.1.25  | $V_{nINT}$ 、 $V_{nRSTOUT}$                                                                           | デジタル出力                                                                                                                                           | 0   |        | 3.4     | V       |

| 3.1.26  | $V_{GPO1}$ 、 $V_{GPO2}$ 、 $V_{GPIO}$                                                                 | デジタル出力                                                                                                                                           | 0   |        | 5.5 (2) | V       |

| 3.1.27  | $V_{SCL}$ 、 $V_{SDA}$                                                                                | I <sup>2</sup> C インターフェイス                                                                                                                        | 0   |        | 3.4     | V       |

| 3.1.28  | $V_{EN/PB/SENSE}$ 、 $V_{MODE/STBY}$ 、<br>$V_{MODE/RESET}$ 、<br>$V_{VSEL\_SD/VSEL/DDR}$               | デジタル入力                                                                                                                                           | 0   |        | 5.5 (2) | V       |

| 3.2.1   | $t_{VSYS\_RAMP\_RISE}$                                                                               | 入力電圧立ち上がりランプ時間、入力電圧はブリレギュレータで制御されます。 $V_{VSYS} = V_{PVIN\_Bx} = V_{PVIN\_LDOx} = 0V \sim 5V$                                                     | 0.1 | 600000 |         | ms      |

## 6.3 推奨動作条件 (続き)

自由気流での動作温度範囲内 (特に記述のない限り)

| POS   |                        |                                                                           | 最小値 | 公称値    | 最大値 | 単位 |

|-------|------------------------|---------------------------------------------------------------------------|-----|--------|-----|----|

| 3.2.2 | $t_{VSYS\_RAMP\_FALL}$ | 入力電圧立ち下がりランプ時間、 $V_{VSYS} = V_{PVIN\_Bx} = V_{PVIN\_LDOx} = 5V \sim 2.5V$ | 0.4 | 600000 | ms  |    |

| 3.3.1 | $T_A$                  | 自由空気での動作温度                                                                | -40 | 105    | °C  |    |

| 3.3.2 | $T_J$                  | 動作時接合部温度                                                                  | -40 | 125    | °C  |    |

- (1) EEPROM プログラミング用、 $VSYS$  (最小) = 3.3V

- (2)  $VSYS$  を超えないようにしてください

- (3) 低速ランプ モード。高速ランプは最大 15 $\mu$ F をサポート

## 6.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup> |                     | TPS65219                 | TPS65219                 | 単位   |

|----------------------|---------------------|--------------------------|--------------------------|------|

|                      |                     | RHB (QFN)                | RSM (QFN)                |      |

|                      |                     | 32 ピン、5x5mm <sup>2</sup> | 32 ピン、4x4mm <sup>2</sup> |      |

| $R_{\Theta JA}$      | 接合部から周囲への熱抵抗        | 31.3                     | 31.9                     | °C/W |

| $R_{\Theta JC(top)}$ | 接合部からケース (上面) への熱抵抗 | 20.4                     | 25.6                     | °C/W |

| $R_{\Theta JB}$      | 接合部から基板への熱抵抗        | 10.9                     | 10.5                     | °C/W |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ    | 0.3                      | 0.3                      | °C/W |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ    | 10.8                     | 10.5                     | °C/W |

| $R_{\Theta JC(bot)}$ | 接合部からケース (底面) への熱抵抗 | 2.8                      | 2.9                      | °C/W |

- (1) 従来および新しい熱評価基準値の詳細については、アプリケーション レポート『半導体および IC パッケージの熱評価基準値』、SPRA953 を参照してください。

## 6.5 システム制御スレッショルド

自由気流での動作温度範囲内 (特に記述のない限り)。電圧レベルはデバイスの AGND グランドを基準としています。

| POS          | パラメータ                  | テスト条件                                | 最小値                                                                                                                   | 標準値   | 最大値  | 単位            |    |

|--------------|------------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-------|------|---------------|----|

| <b>電気的特性</b> |                        |                                      |                                                                                                                       |       |      |               |    |

| 4.1.1        | $VSYS$                 | 動作入力電圧                               | 2.5                                                                                                                   | 5.5   | 5.5  | V             |    |

| 4.1.2        | $VSYS_{POR\_Rising}$   | $VSYS$ POR 立ち上がりスレッショルド              | $VSYS$ ピンで測定、トリムされない                                                                                                  | 2.2   | 2.5  | V             |    |

| 4.1.3        | $VSYS_{UVLO\_Falling}$ | $VSYS$ UVLO 立ち下がりスレッショルド             | $VSYS$ ピンで測定、トリム済み                                                                                                    | 2.175 | 2.25 | V             |    |

| 4.1.4        | $VSYS_{POR\_Hyst}$     | $VSYS$ UVLO/POR ヒステリシス               | $VSYS_{POR\_Rising\_untrimmed}$<br>$VSYS_{UVLO\_Falling\_trimmed}$                                                    | 130   |      | mV            |    |

| 4.1.5        | $V_{VSYS\_OVP\_Rise}$  | $VSYS$ OVP 上昇スレッショルド、トリム済み           | $VSYS$ ピンで測定、トリム済み                                                                                                    | 5.9   | 6.1  | V             |    |

| 4.1.6        | $V_{VSYS\_OVP\_Fall}$  | $VSYS$ OVP 下降スレッショルド、トリム済み           | $VSYS$ ピンで測定、トリム済み                                                                                                    | 5.7   | 5.95 | V             |    |

| 4.1.7        | $V_{VSYS\_OVP\_Hyst}$  | $VSYS$ OVP ヒステリシス                    | $VSYS_{OVP\_Rising\_trimmed}$<br>$VSYS_{OVP\_falling\_trimmed}$                                                       | 100   | 140  | 180           | mV |

| 4.1.8        | $V_{VDD1P8}$           | VDD1P8 電圧                            |                                                                                                                       | 1.7   | 1.8  | 1.9           | V  |

| 4.2.1a       | $I_{INITIALIZE}$       | 初期化状態での消費電流、 $25^{\circ}\text{C}$ の時 | $VSYS$ ピンと $PVIN\_x$ ピンからの結合電流。 $VSYS = PVIN\_Bx = PVIN\_LDOx = 5V$ 。すべてのモニタがオフになっています。<br>$T_J = 25^{\circ}\text{C}$ | 15    | 22   | $\mu\text{A}$ |    |

## 6.5 システム制御スレッショルド (続き)

自由気流での動作温度範囲内 (特に記述のない限り)。電圧レベルはデバイスの AGND グランドを基準としています。

| POS            | パラメータ                      | テスト条件                                                                                                                                                                                                                                                           | 最小値                                                           | 標準値 | 最大値 | 単位 |

|----------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-----|-----|----|

| 4.2.1b         | $I_{\text{INITIALIZE}}$    | 初期化状態、<br>40°C~125°C の消費電流<br><br>VSYS ピンと PVIN_x ピンからの結合電流。VSYS = PVIN_Bx = PVIN_LDOx = 5V。すべてのモニタがオフ。<br>$T_J = -40^{\circ}\text{C} \sim 125^{\circ}\text{C}$                                                                                                 |                                                               | 15  | 35  | μA |

| 4.2.2a         | $I_{\text{ACTIVE}}$        | アクティブ状態での消費電流、すべてのレールがオン、25°C 時<br><br>VSYS ピンと PVIN_x ピンからの結合電流。VSYS = PVIN_Bx = PVIN_LDOx = 5V。すべての出力はオン、すべての LDO は LDO モード、降圧コンバータは PFM モードです。無負荷<br>$T_J = 25^{\circ}\text{C}$                                                                              |                                                               | 250 | 290 | μA |

| 4.2.2b         | $I_{\text{ACTIVE}}$        | アクティブ状態での消費電流、すべてのレールがオン、<br>-40°C~125°C<br><br>VSYS ピンと PVIN_x ピンからの結合電流。VSYS = PVIN_Bx = PVIN_LDOx = 5V。すべての出力はオン、すべての LDO は LDO モード、降圧コンバータは PFM モードです。無負荷<br>$T_J = -40^{\circ}\text{C} \sim 125^{\circ}\text{C}$                                           |                                                               | 250 | 430 | μA |

| 4.2.3a         | $I_{\text{STBY}}$          | スタンバイ状態での消費電流、LDO1 のみオン、25°C 時<br><br>VSYS ピンと PVIN_x ピンからの結合電流。VSYS = PVIN_Bx = PVIN_LDOx = 5V。LDO モードで LDO1 のみオン。無負荷<br>$T_J = 25^{\circ}\text{C}$                                                                                                            |                                                               | 105 | 125 | μA |

| 4.2.3b         | $I_{\text{STBY}}$          | スタンバイ状態での消費電流、LDO1 のみオン、-40°C~125°C<br><br>VSYS ピンと PVIN_x ピンからの結合電流。VSYS = PVIN_Bx = PVIN_LDOx = 5V。LDO モードで LDO1 のみオン。無負荷<br>$T_J = -40^{\circ}\text{C} \sim 125^{\circ}\text{C}$                                                                             |                                                               | 105 | 150 | μA |

| 4.2.4a         | $I_{\text{STBY}}$          | スタンバイ状態での消費電流、すべてのレールがオン、25°C で VMON がオン<br><br>VSYS ピンと PVIN_x ピンからの結合電流。VSYS = PVIN_Bx = PVIN_LDOx = 5V。すべての出力はオン、すべての LDO は LDO モード、降圧コンバータは PFM モードです。無負荷出力電圧モニタがオン、VSYS モニタ (UV/OVP) がオン。<br>$T_J = 25^{\circ}\text{C}$                                    |                                                               | 250 | 290 | μA |

| 4.2.4b         | $I_{\text{STBY}}$          | アクティブ状態での消費電流、すべてのレールがオン、VMON がオン、<br>-40°C~125°C<br><br>VSYS ピンと PVIN_x ピンからの結合電流。VSYS = PVIN_Bx = PVIN_LDOx = 5V。すべての出力はオン、すべての LDO は LDO モード、降圧コンバータは PFM モードです。無負荷出力電圧モニタがオン、VSYS モニタ (UV/OVP) がオン。<br>$T_J = -40^{\circ}\text{C} \sim 125^{\circ}\text{C}$ |                                                               | 250 | 430 | μA |

| <b>タイミング要件</b> |                            |                                                                                                                                                                                                                                                                 |                                                               |     |     |    |

| 4.3.1          | $t_{\text{OFF\_TO\_INIT}}$ | VSYS が VSYS_POR を超えてから初期化状態に入るまでの時間で、EEPROM の読み取りを含み、オン要求の準備が完了するまでの時間                                                                                                                                                                                          | VSYS が VSYS_POR を超えてから初期化状態に入るまでの時間。HOT と RV によって制御されるオン要求の実行 |     | 3.2 | ms |

## 6.5 システム制御スレッショルド (続き)

自由気流での動作温度範囲内 (特に記述のない限り)。電圧レベルはデバイスの AGND グランドを基準としています。

| POS    | パラメータ                    |                                                             | テスト条件 | 最小値 | 標準値                                                      | 最大値 | 単位 |

|--------|--------------------------|-------------------------------------------------------------|-------|-----|----------------------------------------------------------|-----|----|

| 4.3.2a | $t_{TIMEOUT\_UV}$        | ランプアップ時にレールが UV スレッショルドに達しない場合の UV 検出                       |       |     | $t_{RAMP + sample}$<br>および<br>グリッヂ<br>除去時<br>間の終<br>了    |     |    |

| 4.3.2b | $t_{TIMEOUT\_UV\_SLOT}$  | ランプアップ時にレールが UV スレッショルドに達しない場合のタイムアウトは、マルチ PMIC 構成にのみ適用されます |       |     | スロット<br>延長時<br>間の終<br>了<br>(3ms、<br>4ms、ま<br>たは<br>13ms) |     |    |

| 4.3.3  | $t_{TIMEOUT\_Discharge}$ | スタンバイからアクティブ状態に遷移するときにレールを放電できない場合のタイムアウト                   |       | 72  | 80                                                       | 88  | ms |

## 6.6 BUCK1 コンバータ

自由気流での動作温度範囲内 (特に記述のない限り)

| POS          | パラメータ                   |                                                            | テスト条件                                                                                                   | 最小値   | 標準値  | 最大値 | 単位      |

|--------------|-------------------------|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------|------|-----|---------|

| <b>電気的特性</b> |                         |                                                            |                                                                                                         |       |      |     |         |

| 5.1.1a       | $V_{IN\_BUCK1}$         | 入力電圧 <sup>(1)</sup>                                        | 降圧電源電圧、最大 VSYS                                                                                          | 2.5   | 5.5  |     | V       |

| 5.1.1b       | $V_{OUT\_BUCK1}$        | 降圧出力電圧の設定可能範囲                                              | 出力電圧は $0.6V \leq V_{OUT} \leq 1.4V$ の場合は 25mV 単位、 $1.4V < V_{OUT} \leq 3.4V$ の場合は 100mV 単位で構成可能         | 0.6   | 3.4  |     | V       |

| 5.1.2a       | $I_{Q\_BUCK1}$          | 25°C、PFM、低 BW ケースでの静止電流                                    | PFM、BUCK1 有効、無負荷、 $V_{IN} = 5.0V$ 、 $V_{OUT} = 1.2V$ 、 $T_J = 25^{\circ}C$                              | 10    | 13   |     | $\mu A$ |

| 5.1.2b       | $I_{Q\_BUCK1}$          | 静止電流 -40°C~125°C、PFM、低 BW ケース                              | PFM、BUCK1 有効、無負荷、 $V_{IN} = 5.0V$ 、 $V_{OUT} = 1.2V$ 、 $T_J = -40^{\circ}C~125^{\circ}C$                | 15    | 44   |     | $\mu A$ |

| 5.1.2c       | $I_{Q\_BUCK1}$          | 静止電流 -40°C~150°C、PFM、低 BW ケース                              | PFM、BUCK1 有効、無負荷、 $V_{IN} = 5.0V$ 、 $V_{OUT} = 1.2V$ 、 $T_J = -40^{\circ}C~150^{\circ}C$                | 20    | 63   |     | $\mu A$ |

| 5.1.3a       | $V_{HEADROOM\_PWM}$     | 入力から出力への電圧レベル <sup>(2)</sup>                               | 最大負荷時のコーナー ケース $I_{OUT} = 2.5A$                                                                         | 500   |      |     | mV      |

| 5.1.3b       | $V_{HEADROOM\_PWM}$     | $I_{OUT} = I_{OUT\_MAX}$ <sup>(2)</sup> での入力から出力への電圧ヘッドルーム | $I_{OUT} = I_{OUT\_MAX}$ でのコーナー ケース                                                                     | 700   |      |     | mV      |

| 5.1.4        | $V_{OUT\_STEP\_LOW}$    | 出力電圧ステップ                                                   | $0.6V \leq V_{OUT} \leq 1.4V$                                                                           | 25    |      |     | mV      |

| 5.1.5        | $V_{OUT\_STEP\_HIGH}$   | 出力電圧ステップ                                                   | $1.5V \leq V_{OUT} \leq 3.4V$                                                                           | 100   |      |     | mV      |

| 5.1.6a       | $V_{OUT\_ACC\_DC\_PWM}$ | 強制 PWM モード、低および高 BW ケースでの DC 出力電圧精度                        | $I_{OUT} = I_{OUT\_MAX}$ 、 $V_{OUT} \geq 0.7V~3.4V$ 、 $V_{IN} \sim V_{OUT} > 700$ mV<br>強制 PWM、低 BW ケース | -1.5% | 1.5% |     |         |

| 5.1.6b       | $V_{OUT\_ACC\_DC\_PWM}$ | 強制 PWM モード、低および高 BW ケースでの DC 出力電圧精度                        | $I_{OUT} = I_{OUT\_MAX}$ 、 $V_{OUT} = 0.6V~0.7V$ 、 $V_{IN} \sim V_{OUT} > 700$ mV<br>強制 PWM、低 BW ケース    | -10   | 10   |     | mV      |

## 6.6 BUCK1 コンバータ (続き)

自由気流での動作温度範囲内 (特に記述のない限り)

| POS    | パラメータ                   | テスト条件                                                                                                  | 最小値                                                                                                                                                               | 標準値   | 最大値  | 単位   |           |

|--------|-------------------------|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|------|-----------|

| 5.1.6c | $V_{OUT\_ACC\_DC\_PFM}$ | $I_{OUT} = 1mA$ 、<br>$V_{OUT} = 0.6V \sim 3.4V$ 、<br>$V_{IN} \sim V_{OUT} > 500 mV$<br>自動 PFM、低 BW ケース | -3.0%                                                                                                                                                             | 3.5%  |      |      |           |

| 5.1.7  | $R_{FB\_INPUT}$         | フィードバック入力インピーダンス                                                                                       | コンバータ有効                                                                                                                                                           | 2.3   | 3.75 | 5.0  | $M\Omega$ |

| 5.2.1a | $V_{LOAD\_REG\_PWM}$    | DC 負荷レギュレーション、強制 PWM、低 BW ケース                                                                          | $V_{IN} = 5.0V$ 、 $V_{OUT} = 1.2V$ 、<br>$I_{OUT} = 0 \sim I_{OUT\_MAX}$ 、<br>強制 PWM、低 BW ケース、 $C_{OUT} = 40\mu F$                                                 | 0.1   | 0.16 |      | %/A       |

| 5.2.2a | $V_{LINE\_REG}$         | DC ライン レギュレーション、強制 PWM、低 BW ケース                                                                        | $V_{IN} = 3.3V \sim 5.5V$ 、<br>$V_{OUT} = 1.2V$ 、<br>$I_{OUT} = 1mA$ および $I_{OUT\_MAX}$<br>強制 PWM、低 BW ケース、 $C_{OUT} = 40\mu F$                                   | 0.1   | 0.16 |      | %/V       |

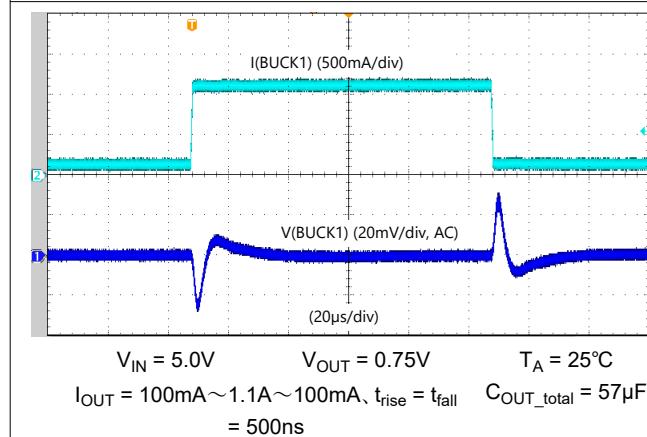

| 5.2.3a | $V_{LOAD\_TRANSIENT}$   | 負荷過渡、 $V_{OUT} = 0.75V$ 、自動 PFM、高 BW ケース                                                               | $V_{IN} = 5.0V$ 、 $V_{OUT} = 0.75V$ 、<br>$I_{OUT} = 100mA \sim 1100mA \sim 100mA$ 、<br>$t_R = t_F = 500ns$ 、<br>自動 PFM、高 BW ケース、 $C_{OUT} = 80\mu F$              | -27.5 | 27.5 |      | $mV$      |

| 5.2.3b | $V_{LOAD\_TRANSIENT}$   | 負荷過渡、 $V_{OUT} = 0.75V$ 、強制 PWM、高 BW ケース                                                               | $V_{IN} = 5.0V$ 、 $V_{OUT} = 0.75V$ 、<br>$I_{OUT} = 100mA \sim 1100mA \sim 100mA$ 、<br>$t_R = t_F = 500ns$ 、<br>強制 PWM、高 BW ケース、 $C_{OUT} = 80\mu F$              | -27.5 | 27.5 |      | $mV$      |

| 5.2.4a | $V_{LOAD\_TRANSIENT}$   | 負荷過渡、 $V_{OUT} = 1.8V$ 、自動 PFM、低 BW ケース                                                                | $V_{IN} = 5.0V$ 、 $V_{OUT} = 1.8V$ 、<br>$I_{OUT} = 1mA \sim 1A \sim 1mA$ 、<br>$t_R = t_F = 1\mu s$ 、<br>自動 PFM、 $C_{OUT} = 40\mu F$                               | -90   | 90   |      | $mV$      |

| 5.2.4b | $V_{LOAD\_TRANSIENT}$   | 負荷過渡、 $V_{OUT} = 1.8V$ 、強制 PWM、低 BW ケース                                                                | $V_{IN} = 5.0V$ 、 $V_{OUT} = 1.8V$ 、<br>$I_{OUT} = 1mA \sim 1A \sim 1mA$ 、<br>$t_R = t_F = 1\mu s$ 、<br>強制 PWM、 $C_{OUT} = 40\mu F$                               | -60   | 60   |      | $mV$      |

| 5.2.5a | $V_{LINE\_TRANSIENT}$   | ライントランジエント、 $V_{OUT} = 1.2V$ 、強制 PWM、低 BW ケース                                                          | $50\mu s$ で $V_{IN} = 3.3V$ から $5.5V$ 、<br>$V_{OUT} = 1.2V$ 、 $I_{OUT} = 1mA$ および<br>$I_{OUT\_MAX}$ 、<br>強制 PWM、低 BW ケース、 $C_{OUT} = 40\mu F$                     | -50   | 50   |      | $mV$      |

| 5.2.6a | $V_{RIPPLE\_PP\_PWM}$   | 強制 PWM モード、低 BW ケース                                                                                    | $V_{IN} = 5.0V$ 、 $V_{OUT} = 2.5V$ 、<br>強制 PWM、低 BW ケース、 $C_{OUT} = 40\mu F$ 、 $X5R$ 、 $ESR = 10m\Omega$ 、<br>$L = 470nH$ 、 $DCR = 50m\Omega$<br>$I_{OUT} = 1A$   | 10    | 20   |      | $mV_{PP}$ |

| 5.2.6b | $V_{RIPPLE\_PP\_PFM}$   | 自動 PFM モード、低 BW ケース                                                                                    | $V_{IN} = 5.0V$ 、 $V_{OUT} = 2.5V$ 、<br>自動 PFM、低 BW ケース、 $C_{OUT} = 40\mu F$ 、 $X5R$ 、 $ESR = 10m\Omega$ 、<br>$L = 470nH$ 、 $DCR = 50m\Omega$<br>$I_{OUT} = 20mA$ | 20    | 40   |      | $mV_{PP}$ |

| 5.3.1  | $I_{OUT\_MAX}$          | 最大動作電流                                                                                                 |                                                                                                                                                                   |       | 3.5  |      | A         |

| 5.3.2  | $I_{CURRENT\_LIMIT}$    | ピーク電流制限                                                                                                | シミュレーションでは $V_{IN} = 2.5V \sim 5.5V$                                                                                                                              | 4.6   | 5.7  | 6.9  | A         |

| 5.3.3  | $I_{REV\_CUR\_LIMIT}$   | 逆方向ピーク電流制限                                                                                             | シミュレーションでは $V_{IN} = 2.5V \sim 5.5V$                                                                                                                              | -2.0  | -1.5 | -1.0 | A         |

## 6.6 BUCK1 コンバータ (続き)

自由気流での動作温度範囲内 (特に記述のない限り)

| POS    | パラメータ               |                                 | テスト条件                        | 最小値 | 標準値 | 最大値 | 単位        |

|--------|---------------------|---------------------------------|------------------------------|-----|-----|-----|-----------|

| 5.3.4a | $R_{DS0N\_HS}$      | ハイサイド MOSFET オン抵抗、5V 電源         | ピン間で測定された、 $V_{IN} = 5V$     |     | 70  |     | $m\Omega$ |

| 5.3.4b | $R_{DS0N\_HS}$      | ハイサイド MOSFET オン抵抗、3.3V 電源       | ピン間で測定された、 $V_{IN} = 3.3V$   |     | 80  |     | $m\Omega$ |

| 5.3.5a | $R_{DS0N\_LS}$      | ローサイド MOSFET オン抵抗、5V 電源         | ピン間で測定された、 $V_{IN} = 5V$     |     | 40  |     | $m\Omega$ |

| 5.3.5b | $R_{DS0N\_LS}$      | ローサイド MOSFET オン抵抗、3.3V 電源       | ピン間で測定された、 $V_{IN} = 3.3V$   |     | 50  |     | $m\Omega$ |

| 5.3.6  | $R_{DISCHARGE}$     | 出力放電抵抗                          | コンバータが無効な場合のみアクティブ           | 60  | 125 | 200 | $\Omega$  |

| 5.4.1  | $L_{SW}$            | 出力インダクタンス                       | $DCR = \text{最大 } 50m\Omega$ | 330 | 470 | 611 | $nH$      |

| 5.4.2a | $C_{OUT}$           | 低 BW ケース用自動 PFM または強制 PWM の出力容量 | $ESR = \text{最大 } 10m\Omega$ | 10  |     | 75  | $\mu F$   |

| 5.4.3a | $C_{OUT\_HIGH\_BW}$ | 高 BW ケース用自動 PFM または強制 PWM の出力容量 | $ESR = \text{最大 } 10m\Omega$ | 30  |     | 220 | $\mu F$   |

### タイミング要件

|        |                   |                                 |                                   |      |      |      |            |

|--------|-------------------|---------------------------------|-----------------------------------|------|------|------|------------|

| 5.5.1  | $t_{RAMP}$        | 強制 PWM、低 BW ケースでのランプ時間          | 残留電圧なしと仮定した場合、有効化から目標値の 98% までの時間 | 0.3  | 1.65 | ms   |            |

| 5.5.2a | $DVFS\_RISE\_QFF$ | 強制 PWM の DVFS タイミング要件、立ち上がりスロープ | 0.6V~1.4V の DVFS 電圧調整中のステップ持続時間   | 2.9  | 3.2  | 3.5  | $mV/\mu s$ |

| 5.5.2c | $DVFS\_FALL$      | 強制 PWM の DVFS タイミング要件、立ち下がりスロープ | 1.4V~0.6V の DVFS 電圧調整中のステップ持続時間   | 0.45 | 0.53 | 0.61 | $mV/\mu s$ |

### スイッチング特性

|        |          |                               |                                                                                       |     |  |     |

|--------|----------|-------------------------------|---------------------------------------------------------------------------------------|-----|--|-----|

| 5.6.1a | $f_{sw}$ | スイッチング周波数、強制 PWM、高または低 BW ケース | 強制 PWM、 $V_{IN} = 3.3V \sim 5V$ 、 $V_{OUT} = 0.8V \sim 1.8V$ 、 $I_{OUT} = 1A \sim 3A$ | 2.3 |  | MHz |

|--------|----------|-------------------------------|---------------------------------------------------------------------------------------|-----|--|-----|

- (1)  $P_{VIN\_Bx}$  は VSYS を超えてはなりません

- (2) DC レギュレーションのみを指します。過渡応答には、より大きなヘッドルームが必要になる場合があります。ヘッドルームが小さい場合、擬似固定周波数において周波数変動が増加します。

## 6.7 BUCK2、BUCK3 コンバータ

自由気流での動作温度範囲内 (特に記述のない限り)

| POS          | パラメータ             |                               | テスト条件                                                                                           | 最小値 | 標準値 | 最大値 | 単位      |

|--------------|-------------------|-------------------------------|-------------------------------------------------------------------------------------------------|-----|-----|-----|---------|

| <b>電気的特性</b> |                   |                               |                                                                                                 |     |     |     |         |

| 6.1.1a       | $V_{IN\_BUCK23}$  | 入力電圧 <sup>(1)</sup>           | 降圧電源電圧、最大 VSYS                                                                                  | 2.5 | 5.5 |     | $V$     |

| 6.1.1b       | $V_{OUT\_BUCK23}$ | 降圧出力電圧の設定可能範囲                 | 出力電圧は $0.6V \leq V_{OUT} \leq 1.4V$ の場合は 25mV 単位、 $1.4V < V_{OUT} \leq 3.4V$ の場合は 100mV 単位で構成可能 | 0.6 | 3.4 |     | $V$     |

| 6.1.2a       | $I_{Q\_BUCK23}$   | 25°C での静止電流、PFM               | PFM、BUCKx 有効、無負荷、 $V_{IN} = 5.0V$ 、 $V_{OUT} = 1.2V$ 、 $T_J = 25^\circ C$                       | 10  | 13  |     | $\mu A$ |

| 6.1.2b       | $I_{Q\_BUCK23}$   | 静止電流 -40°C~125°C、PFM、低 BW ケース | PFM、BUCKx 有効、無負荷、 $V_{IN} = 5.0V$ 、 $V_{OUT} = 1.2V$ 、 $T_J = -40^\circ C \sim 125^\circ C$     | 15  | 43  |     | $\mu A$ |

| 6.1.2c       | $I_{Q\_BUCK23}$   | 静止電流 -40°C~150°C、PFM、低 BW ケース | PFM、BUCKx 有効、無負荷、 $V_{IN} = 5.0V$ 、 $V_{OUT} = 1.2V$ 、 $T_J = -40^\circ C \sim 150^\circ C$     | 20  | 63  |     | $\mu A$ |

## 6.7 BUCK2、BUCK3 コンバータ (続き)

自由気流での動作温度範囲内 (特に記述のない限り)

| POS    | パラメータ                   | テスト条件                                                      | 最小値                                                                                                                                                  | 標準値   | 最大値  | 単位  |    |

|--------|-------------------------|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-----|----|

| 6.1.3a | $V_{HEADROOM\_PWM}$     | 入力から出力への電圧レベル <sup>(2)</sup>                               | 最大負荷時のコーナー ケース $I_{OUT} = I_{OUT\_MAX}$ の 85%                                                                                                        | 500   |      | mV  |    |

| 6.1.3b | $V_{HEADROOM\_PWM}$     | $I_{OUT} = I_{OUT\_MAX}$ <sup>(2)</sup> での入力から出力への電圧ヘッドルーム | $I_{OUT} = I_{OUT\_MAX}$ でのコーナーケース                                                                                                                   | 700   |      | mV  |    |

| 6.1.4  | $V_{OUT\_STEP\_LOW}$    | 出力電圧ステップ Buck2 と Buck3                                     | $0.6V \leq V_{OUT} \leq 1.4V$                                                                                                                        | 25    |      | mV  |    |

| 6.1.5  | $V_{OUT\_STEP\_HIGH}$   | 出力電圧ステップ Buck2、Buck3                                       | $1.5V \leq V_{OUT} \leq 3.4V$                                                                                                                        | 100   |      | mV  |    |

| 6.1.6a | $V_{OUT\_ACC\_DC\_PWM}$ | 強制 PWM モード、低および高 BW ケースでの DC 出力電圧精度                        | $I_{OUT} = I_{OUT\_MAX}$ 、<br>$V_{OUT} \geq 0.7V \sim 3.4V$ 、<br>$V_{IN} \sim V_{OUT} > 700mV$<br>強制 PWM、低 BW ケース                                    | -1.5% | 1.5% |     |    |

| 6.1.6b | $V_{OUT\_ACC\_DC\_PWM}$ | 強制 PWM モード、低および高 BW ケースでの DC 出力電圧精度                        | $I_{OUT} = I_{OUT\_MAX}$ 、<br>$V_{OUT} = 0.6V \sim 0.7V$ 、<br>$V_{IN} \sim V_{OUT} > 700mV$<br>強制 PWM、低 BW ケース                                       | -10   | 10   | mV  |    |

| 6.1.6c | $V_{OUT\_ACC\_DC\_PFM}$ | 自動 PFM モード、低および高 BW ケースでの DC 出力電圧精度                        | $I_{OUT} = 1mA$ 、<br>$V_{OUT} = 0.6V \sim 3.4V$ 、<br>$V_{IN} \sim V_{OUT} > 500 mV$<br>自動 PFM、低 BW ケース                                               | -3.0% | 3.5% |     |    |

| 6.1.9  | $R_{FB\_INPUT}$         | フィードバック入力インピーダンス                                           | コンバータ有効                                                                                                                                              | 2.3   | 3.75 | 5.0 | MΩ |

| 6.2.1a | $V_{LOAD\_REG\_PWM}$    | DC 負荷レギュレーション、強制 PWM、低 BW ケース                              | $V_{IN} = 5.0V$ 、 $V_{OUT} = 1.2V$ 、<br>$I_{OUT} = 0 \sim I_{OUT\_MAX}$ 、<br>強制 PWM、低 BW ケース                                                         | 0.1   | 0.16 | %/A |    |

| 6.2.2a | $V_{LINE\_REG}$         | DC ライン レギュレーション、強制 PWM、低 BW ケース                            | $V_{IN} = 3.3V \sim 5.5V$ 、<br>$V_{OUT} = 1.2V$ 、<br>$I_{OUT} = 1mA$ および $I_{OUT\_MAX}$<br>強制 PWM、低 BW ケース、 $C_{OUT} = 40\mu F$                      | 0.1   | 0.16 | %/V |    |

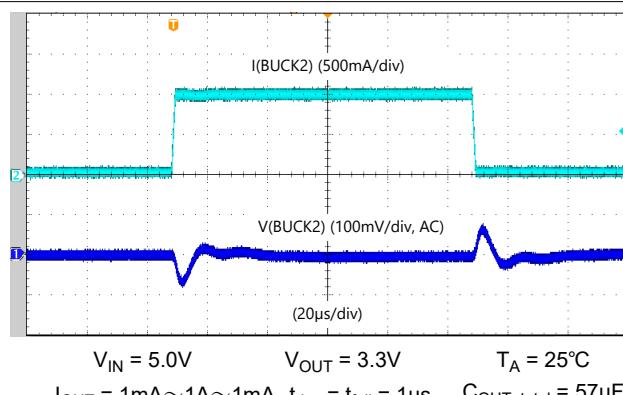

| 6.2.3a | $V_{LOAD\_TRANSIENT}$   | 負荷過渡、 $V_{OUT} = 0.75V$ 、自動 PFM、高 BW ケース                   | $V_{IN} = 5.0V$ 、 $V_{OUT} = 0.75V$ 、<br>$I_{OUT} = 100mA \sim 1100mA \sim 100mA$ 、<br>$t_R = t_F = 500ns$ 、<br>自動 PFM、高 BW ケース、 $C_{OUT} = 80\mu F$ | -27.5 | 27.5 | mV  |    |

| 6.2.3b | $V_{LOAD\_TRANSIENT}$   | 負荷過渡、 $V_{OUT} = 0.75V$ 、強制 PWM、高 BW ケース                   | $V_{IN} = 5.0V$ 、 $V_{OUT} = 0.75V$ 、<br>$I_{OUT} = 100mA \sim 1100mA \sim 100mA$ 、<br>$t_R = t_F = 500ns$ 、<br>強制 PWM、高 BW ケース、 $C_{OUT} = 80\mu F$ | -27.5 | 27.5 | mV  |    |

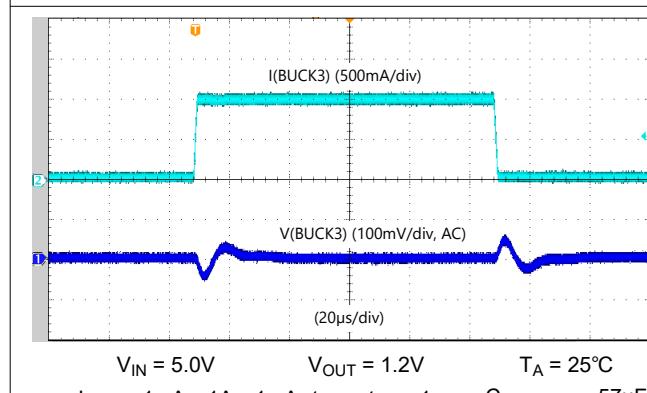

| 6.2.4a | $V_{LOAD\_TRANSIENT}$   | 負荷過渡、 $V_{OUT} = 1.8V$ 、自動 PFM、低 BW ケース                    | $V_{IN} = 5.0V$ 、 $V_{OUT} = 1.8V$ 、<br>$I_{OUT} = 1mA \sim 1A \sim 1mA$ 、<br>$t_R = t_F = 1\mu s$ 、<br>自動 PFM、 $C_{OUT} = 40\mu F$                  | -90   | 90   | mV  |    |

| 6.2.4b | $V_{LOAD\_TRANSIENT}$   | 負荷過渡、 $V_{OUT} = 1.8V$ 、強制 PWM、低 BW ケース                    | $V_{IN} = 5.0V$ 、 $V_{OUT} = 1.8V$ 、<br>$I_{OUT} = 1mA \sim 1A \sim 1mA$ 、<br>$t_R = t_F = 1\mu s$ 、<br>強制 PWM、 $C_{OUT} = 40\mu F$                  | -60   | 60   | mV  |    |

| 6.2.5a | $V_{LINE\_TRANSIENT}$   | ライントランジエント、 $V_{OUT} = 1.2V$ 、強制 PWM、低 BW ケース              | $50\mu s$ で $V_{IN} = 3.3V$ から $5.5V$ 、<br>$V_{OUT} = 1.2V$ 、 $I_{OUT} = 1mA$ および $I_{OUT\_MAX}$ 、<br>強制 PWM、低 BW ケース、 $C_{OUT} = 40\mu F$           | -50   | 50   | mV  |    |

## 6.7 BUCK2、BUCK3 コンバータ (続き)

自由気流での動作温度範囲内 (特に記述のない限り)

| POS    | パラメータ                        | テスト条件                                                                                                                                                                                             | 最小値                                                       | 標準値  | 最大値  | 単位               |    |

|--------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|------|------|------------------|----|

| 6.2.6a | $V_{\text{RIPPLE\_PP\_PWM}}$ | $V_{\text{IN}} = 5.0\text{V}$ 、 $V_{\text{OUT}} = 2.5\text{V}$ 、強制 PWM、低 BW ケース、 $C_{\text{OUT}} = 40\mu\text{F}$ 、X5R、ESR = 10mΩ、 $L = 470\text{nH}$ 、DCR = 50mΩ、 $I_{\text{OUT}} = 1\text{A}$   |                                                           | 10   | 20   | mV <sub>PP</sub> |    |

| 6.2.6b | $V_{\text{RIPPLE\_PP\_PFM}}$ | $V_{\text{IN}} = 5.0\text{V}$ 、 $V_{\text{OUT}} = 2.5\text{V}$ 、自動 PFM、低 BW ケース、 $C_{\text{OUT}} = 40\mu\text{F}$ 、X5R、ESR = 10mΩ、 $L = 470\text{nH}$ 、DCR = 50mΩ、 $I_{\text{OUT}} = 20\text{mA}$ |                                                           | 20   | 40   | mV <sub>PP</sub> |    |

| 6.3.1  | $I_{\text{OUT\_MAX}}$        | 最大動作電流                                                                                                                                                                                            |                                                           |      | 2.0  | A                |    |

| 6.3.2  | $I_{\text{CURRENT\_LIMIT}}$  | ピーク電流制限                                                                                                                                                                                           | シミュレーションでは $V_{\text{IN}} = 2.5\text{V} \sim 5.5\text{V}$ | 3.1  | 3.9  | 4.7              | A  |

| 6.3.3  | $I_{\text{REV\_CUR\_LIMIT}}$ | 逆方向ピーク電流制限                                                                                                                                                                                        | シミュレーションでは $V_{\text{IN}} = 2.5\text{V} \sim 5.5\text{V}$ | -2.0 | -1.5 | -1.0             | A  |

| 6.3.4a | $R_{\text{DSON\_HS}}$        | ハイサイド MOSFET オン抵抗、5V 電源                                                                                                                                                                           | ピン間で測定された、 $V_{\text{IN}} = 5\text{V}$                    |      | 110  | mΩ               |    |

| 6.3.4b | $R_{\text{DSON\_HS}}$        | ハイサイド MOSFET オン抵抗、3.3V 電源                                                                                                                                                                         | ピン間で測定された、 $V_{\text{IN}} = 3.3\text{V}$                  |      | 135  | mΩ               |    |

| 6.3.5a | $R_{\text{DSON\_LS}}$        | ローサイド MOSFET オン抵抗、5V 電源                                                                                                                                                                           | ピン間で測定された、 $V_{\text{IN}} = 5\text{V}$                    |      | 110  | mΩ               |    |

| 6.3.5b | $R_{\text{DSON\_LS}}$        | ローサイド MOSFET オン抵抗、3.3V 電源                                                                                                                                                                         | ピン間で測定された、 $V_{\text{IN}} = 3.3\text{V}$                  |      | 130  | mΩ               |    |

| 6.3.6  | $R_{\text{DISCHARGE}}$       | 出力放電抵抗                                                                                                                                                                                            | コンバータが無効な場合のみアクティブ                                        | 60   | 125  | 200              | Ω  |

| 6.4.1  | $L_{\text{SW}}$              | 出力インダクタンス                                                                                                                                                                                         | DCR = 最大 50mΩ                                             | 330  | 470  | 611              | nH |

| 6.4.2a | $C_{\text{OUT}}$             | 低 BW ケース用自動 PFM または強制 PWM の出力容量                                                                                                                                                                   | ESR = 最大 10mΩ                                             |      | 10   | 75               | μF |

| 6.4.3a | $C_{\text{OUT\_HIGH\_BW}}$   | 高 BW ケース用自動 PFM または強制 PWM の出力容量                                                                                                                                                                   | ESR = 最大 10mΩ                                             |      | 30   | 220              | μF |

### タイミング要件

|        |                    |                                |                                  |     |      |     |       |

|--------|--------------------|--------------------------------|----------------------------------|-----|------|-----|-------|

| 6.5.1  | $t_{\text{RAMP}}$  | 疑似固定周波数モードでのランプ時間              | 残留電圧なしと仮定した場合、有効化から目標値の 98%までの時間 | 0.3 | 1.65 | ms  |       |

| 6.5.2a | $DVFS\_SLOPE\_QFF$ | 強制 PWM、低 BW ケースでの DVFS タイミング要件 | 0.6V～1.4V の DVFS 電圧調整中のステップ持続時間  | 2.9 | 3.2  | 3.5 | mV/μs |

### スイッチング特性

|        |                 |                                 |                                                                                                                                                        |      |      |      |       |

|--------|-----------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| 6.5.2c | $DVFS\_FALL$    | 強制 PWM の DVFS タイミング要件、立ち下がりスロープ | 1.4V～0.6V の DVFS 電圧調整中のステップ持続時間                                                                                                                        | 0.45 | 0.53 | 0.61 | mV/μs |

| 6.6.1a | $f_{\text{sw}}$ | スイッチング周波数、強制 PWM、高または低 BW ケース   | 強制 PWM、 $V_{\text{IN}} = 3.3\text{V} \sim 5\text{V}$ 、 $V_{\text{OUT}} = 0.8\text{V} \sim 1.8\text{V}$ 、 $I_{\text{OUT}} = 1\text{A} \sim 1.8\text{A}$ |      | 2.3  |      | MHz   |

- (1)  $P_{\text{VIN\_Bx}}$  は  $V_{\text{SYS}}$  を超えてはなりません

- (2) DC レギュレーションのみを指します。過渡応答には、より大きなヘッドルームが必要になる場合があります。ヘッドルームが小さい場合、擬似固定周波数において周波数変動が増加します。

## 6.8 汎用 LDO (LDO1、LDO2)

自由気流での動作温度範囲内 (特に記述のない限り)

| POS          | パラメータ                    | テスト条件                                                 | 最小値                                                                                            | 標準値 | 最大値  | 単位                  |          |

|--------------|--------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------|-----|------|---------------------|----------|

| <b>電気的特性</b> |                          |                                                       |                                                                                                |     |      |                     |          |

| 7.1.1        | $V_{IN\_LDO}$            | 入力電圧 (LDO モード) <sup>(1)</sup>                         | LDO モード、最大 VSYS                                                                                | 1.5 | 5.5  | V                   |          |

| 7.1.2        | $V_{IN\_LDO\_BYP}$       | 入力電圧 (バイパス モード) <sup>(1) (5)</sup>                    | バイパス モード、最大 VSYS                                                                               | 1.5 | 3.4  | V                   |          |

| 7.1.3        | $V_{IN\_LDO\_LSW}$       | 入力電圧 (LSW モード) <sup>(1)</sup>                         | LSW モード、最大 VSYS                                                                                | 1.5 | 5.5  | V                   |          |

| 7.1.4        | $V_{OUT\_LDO}$           | LDO 出力電圧の設定可能範囲                                       | LDO モード、50mV 刻み、 $V_{IN} - V_{OUT} > 300\text{mV}$                                             | 0.6 | 3.4  | V                   |          |

| 7.1.5        | $V_{OUT\_LDO\_BYP}$      | バイパス モードでの LDO 出力電圧の構成可能範囲                            | バイパス モード、構成可能な $V_{OUT}$ 範囲 (50mV ステップ)                                                        | 1.5 | 3.4  | V                   |          |

| 7.1.6        | $V_{OUT\_STEP}$          | 出力電圧ステップ                                              | LDO モード、 $0.6V \leq V_{OUT} \leq 3.4V$                                                         | 50  |      | mV                  |          |

| 7.1.7        | $V_{DROPOUT}$            | ドロップアウト電圧                                             | $V_{IN_{min}} \leq V_{IN} \leq V_{IN_{max}}, I_{OUT} = 400\text{mA}$                           | 150 | 300  | mV                  |          |

| 7.1.8        | $V_{OUT\_ACCURACY\_H}$   | 電圧リファレンス、DC 負荷、ラインレギュレーション、プロセス、温度の変動を含む、総合 DC 出力電圧精度 | LDO モード、 $V_{IN} - V_{OUT} > 300\text{mV}, V_{OUT} \geq 1V$                                    | -1% | 1%   |                     |          |

| 7.1.9        | $V_{OUT\_ACCURACY\_L}$   | 電圧リファレンス、DC 負荷、ラインレギュレーション、プロセス、温度の変動を含む、総合 DC 出力電圧精度 | LDO モード、 $V_{IN} - V_{OUT} > 300\text{mV}, V_{OUT} < 1V$                                       | -10 | 10   | mV                  |          |

| 7.1.10       | $R_{BYPASS\_H}$          | バイパス抵抗、高出力電圧                                          | $2.5V \leq V_{IN} \leq 3.6V, V_{IN} \leq VSYS, I_{OUT} = 400\text{mA}$ 、バイパス モード               | 200 |      | $\text{m}\Omega$    |          |

| 7.1.11       | $R_{BYPASS\_L}$          | バイパス抵抗、低出力電圧                                          | $1.5V \leq V_{IN} \leq 2.5V, V_{IN} \leq VSYS, I_{OUT} = 400\text{mA}$ 、バイパス モード               | 250 |      | $\text{m}\Omega$    |          |

| 7.1.12       | $R_{LSW\_H}$             | LSW 抵抗、高出力電圧                                          | $2.5V \leq V_{IN} \leq 5.5V, V_{IN} \leq VSYS, I_{OUT} = 400\text{mA}$ 、LSW モード                | 200 |      | $\text{m}\Omega$    |          |

| 7.1.13       | $R_{LSW\_L}$             | LSW 抵抗、低出力電圧                                          | $1.5V \leq V_{IN} \leq 2.5V, V_{IN} \leq VSYS, I_{OUT} = 400\text{mA}$ 、LSW モード                | 250 |      | $\text{m}\Omega$    |          |

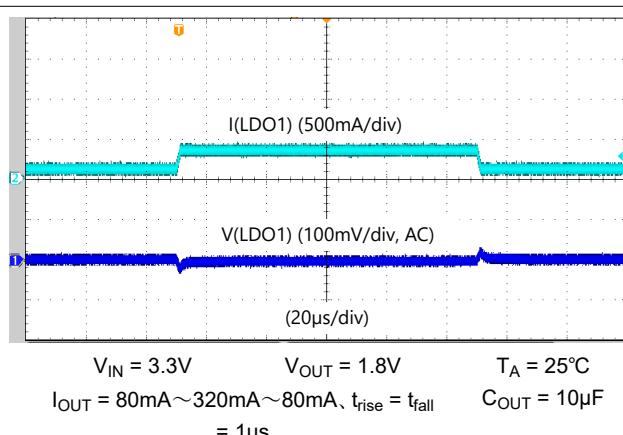

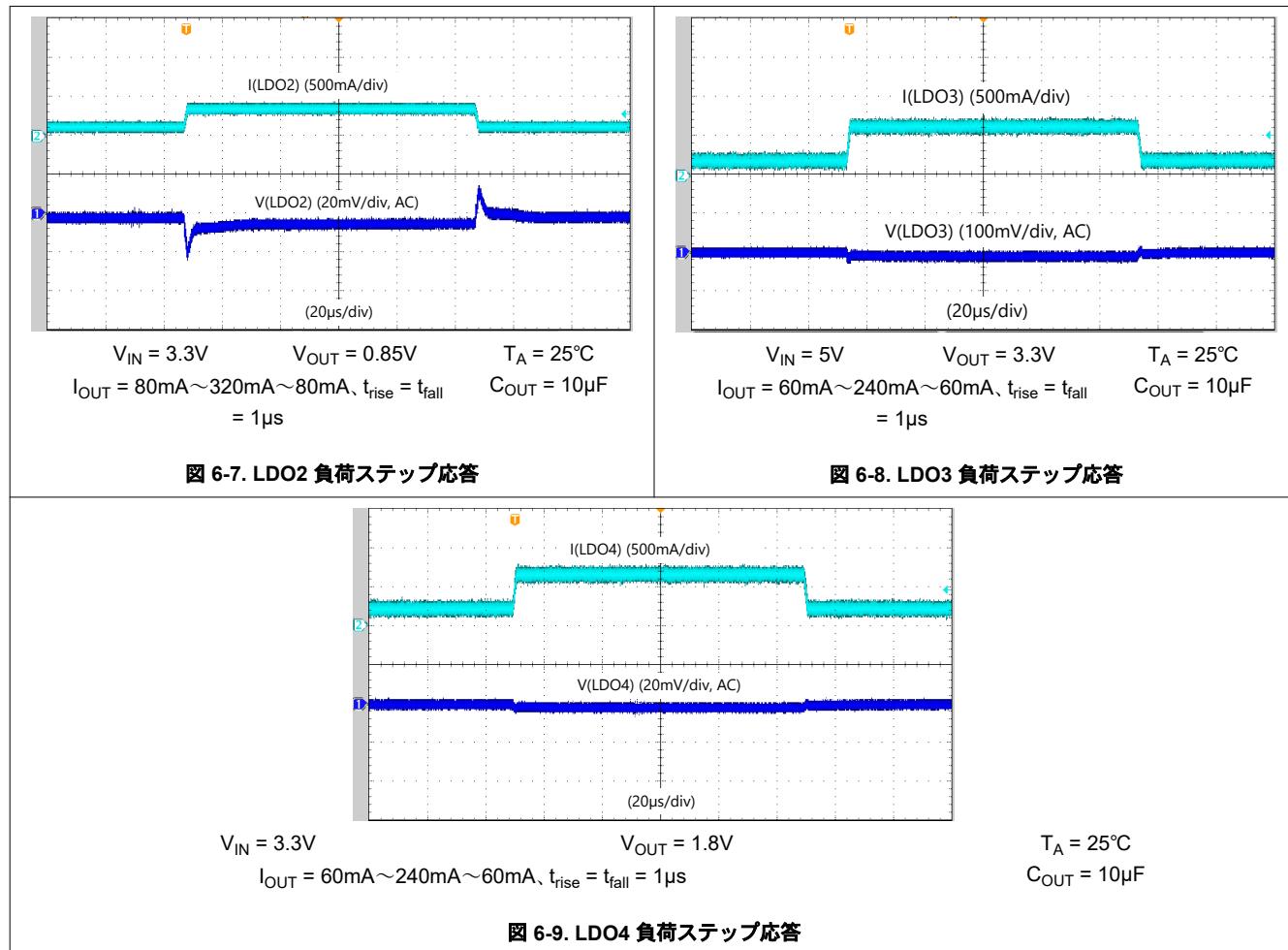

| 7.2.1        | $V_{LOAD\_TRANSIENT}$    | 過渡負荷レギュレーション、 $\Delta V_{OUT}$                        | $I_{OUT} = I_{OUT\_MAX}$ の 20%~80%~20%、 $t_r = t_f = 1\mu\text{s}$                             | -35 | 35   | mV                  |          |

| 7.2.2        | $V_{LINE\_TRANSIENT}$    | 過渡ライン レギュレーション                                        | $V_{IN}$ ステップ = 600 mV <sub>PP</sub> 、 $t_R = t_F = 10\mu\text{s}$ 、LDO はドロップアウト状態ではない、LDO モード | -25 | 25   | mV                  |          |

| 7.2.3        | $NOISE_{RMS}$            | RMS ノイズ                                               | $100\text{Hz} < f \leq 100\text{kHz}, V_{IN} = 3.3V, V_{OUT} = 1.8V, I_{OUT} = 300\text{mA}$   | 600 |      | $\mu\text{V}_{RMS}$ |          |

| 7.2.4        | $V_{RIPPLE}$             | 電圧リップル                                                |                                                                                                | 5   |      | $\text{mV}_{PP}$    |          |

| 7.3.1        | $I_{OUT\_MAX}$           | 出力電流                                                  | $V_{PVIN\_LDO_{min}} \leq V_{IN} \leq V_{PVIN\_LDO_{max}}$ 、LDO-、bypass-、LSW-モードに適用            | 400 |      | mA                  |          |

| 7.3.2        | $I_{CURRENT\_LIMIT}$     | 短絡電流制限                                                | $V_{IN} = 3.6V, V_{OUT} = 0V$                                                                  | 600 | 980  | 1600                | mA       |

| 7.3.3        | $I_{IN\_RUSH\_LDO}$      | LDO 突入電流                                              | LDO-モード、最大 20 $\mu\text{F}$ の負荷を VLDOx に接続、 $I_{OUT} = 0\text{mA}$ または 400mA                   |     | 1500 |                     | mA       |

| 7.3.4        | $I_{IN\_RUSH\_LDO\_BYP}$ | バイパス モードでの LDO 突入電流                                   | バイパス モード、最大 50- $\mu\text{F}$ の負荷を VLDOx に接続                                                   |     | 1500 |                     | mA       |

| 7.3.5        | $I_{IN\_RUSH\_LDO\_LSW}$ | LSW モードでの LDO 突入電流                                    | LSW モード、最大 50- $\mu\text{F}$ の負荷を VLDOx に接続                                                    |     | 1500 |                     | mA       |

| 7.3.6        | $R_{DISCHARGE}$          | LDO 出力でのプルダウン放電抵抗                                     | コンバータが無効な場合のみアクティブ。LDO、バイパス、LSW モードに適用                                                         | 100 | 200  | 300                 | $\Omega$ |

## 6.8 汎用 LDO (LDO1、LDO2) (続き)

自由気流での動作温度範囲内 (特に記述のない限り)

| POS     | パラメータ                      | テスト条件                                            | 最小値                                                                                    | 標準値 | 最大値  | 単位                      |

|---------|----------------------------|--------------------------------------------------|----------------------------------------------------------------------------------------|-----|------|-------------------------|

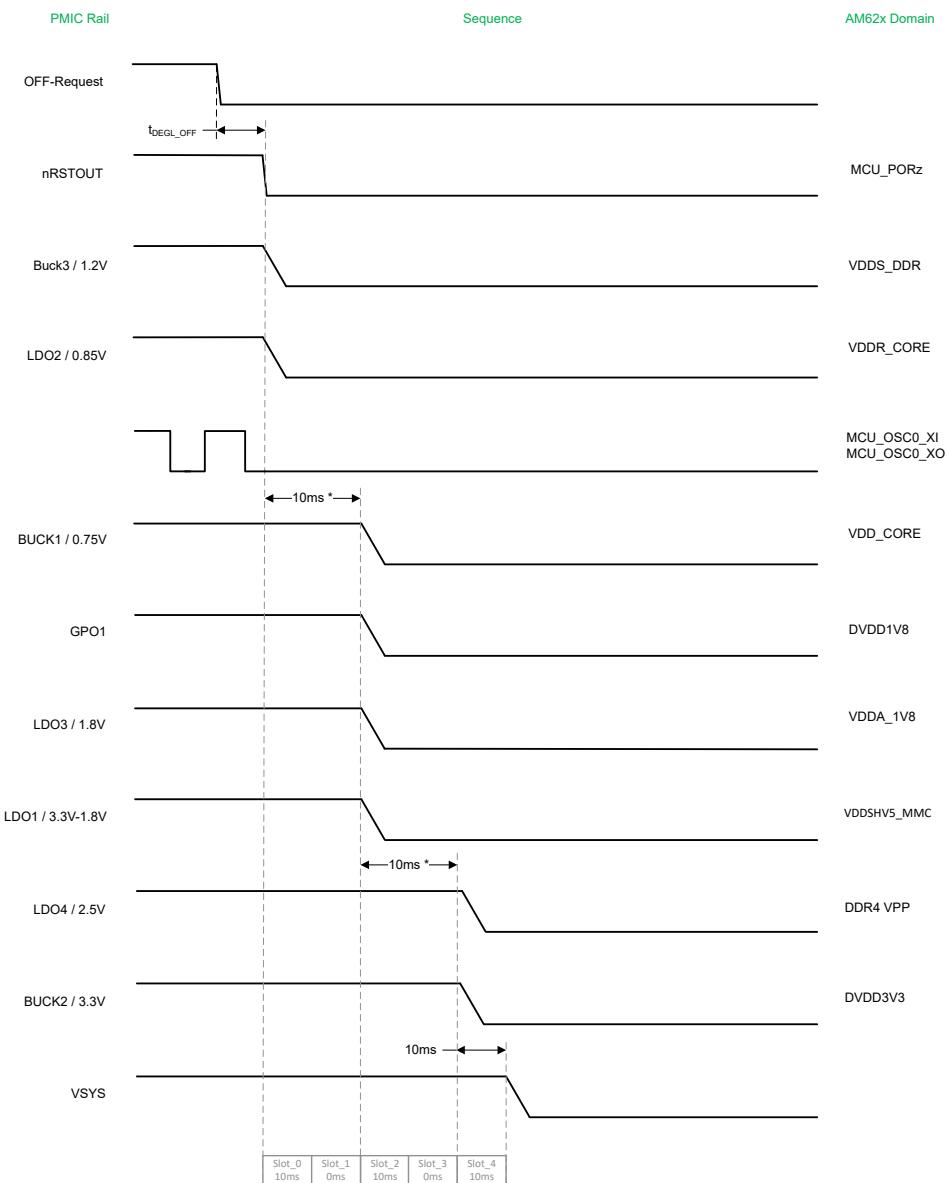

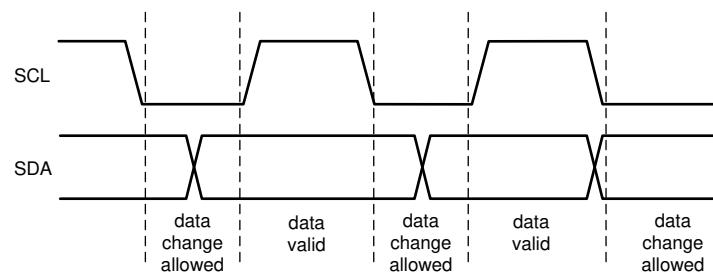

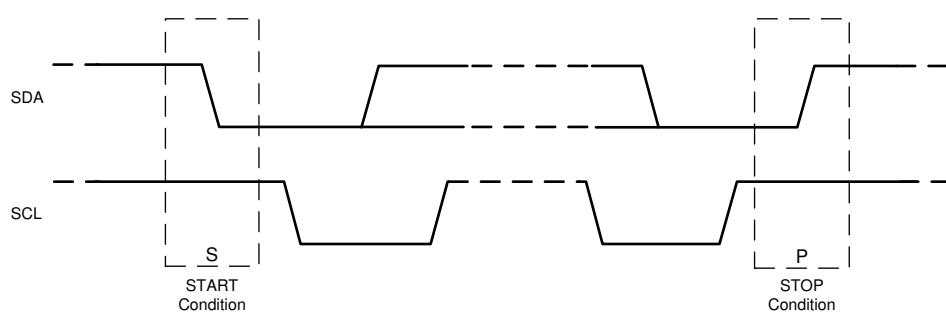

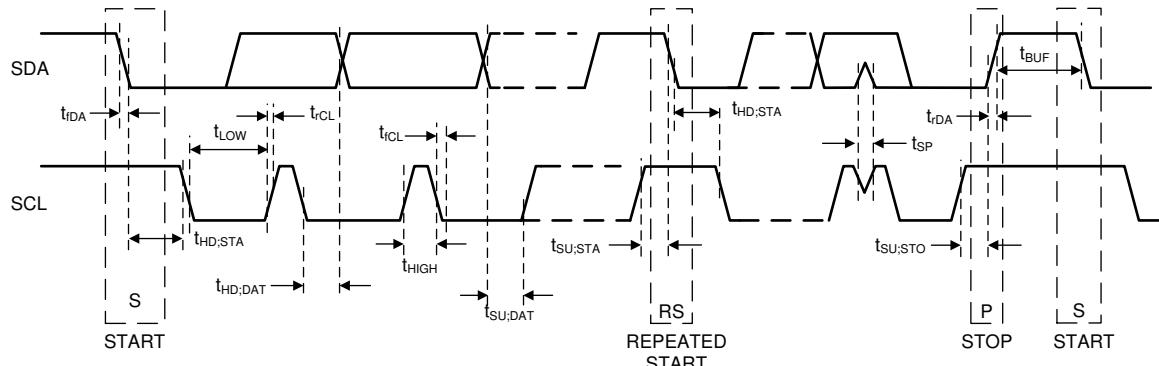

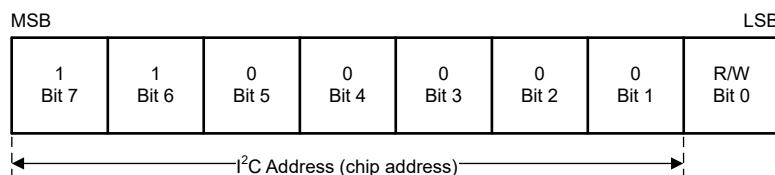

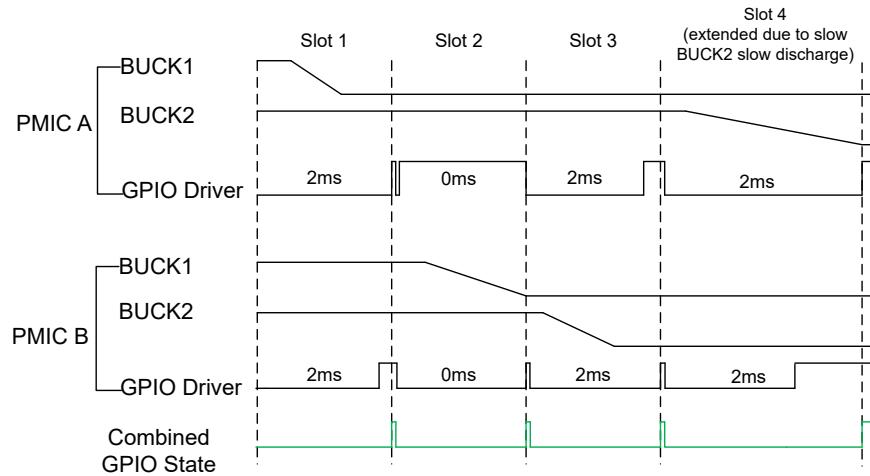

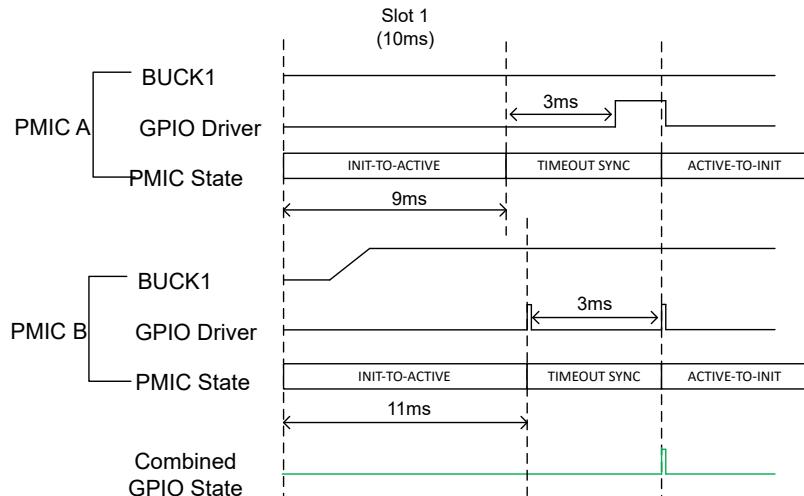

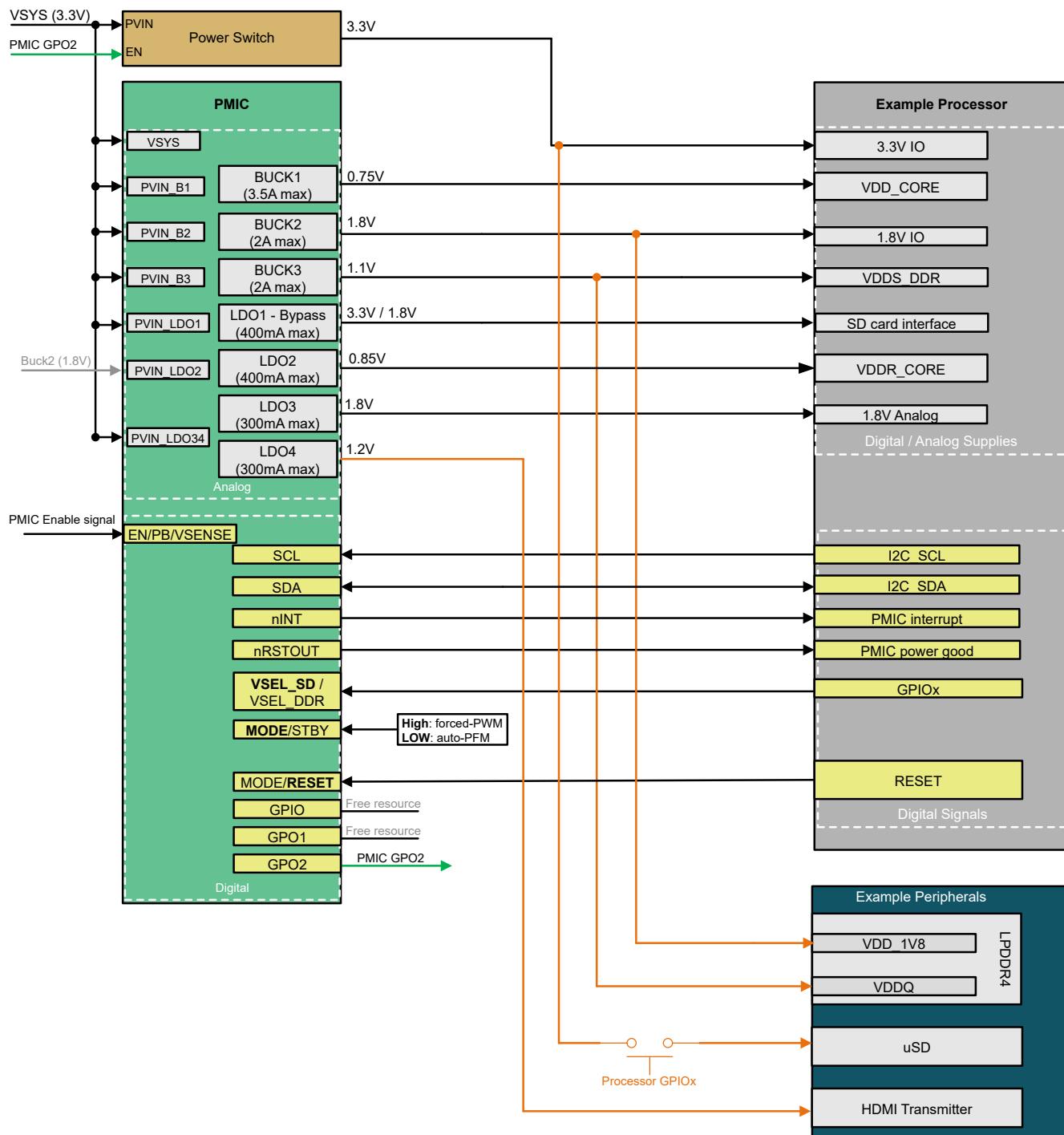

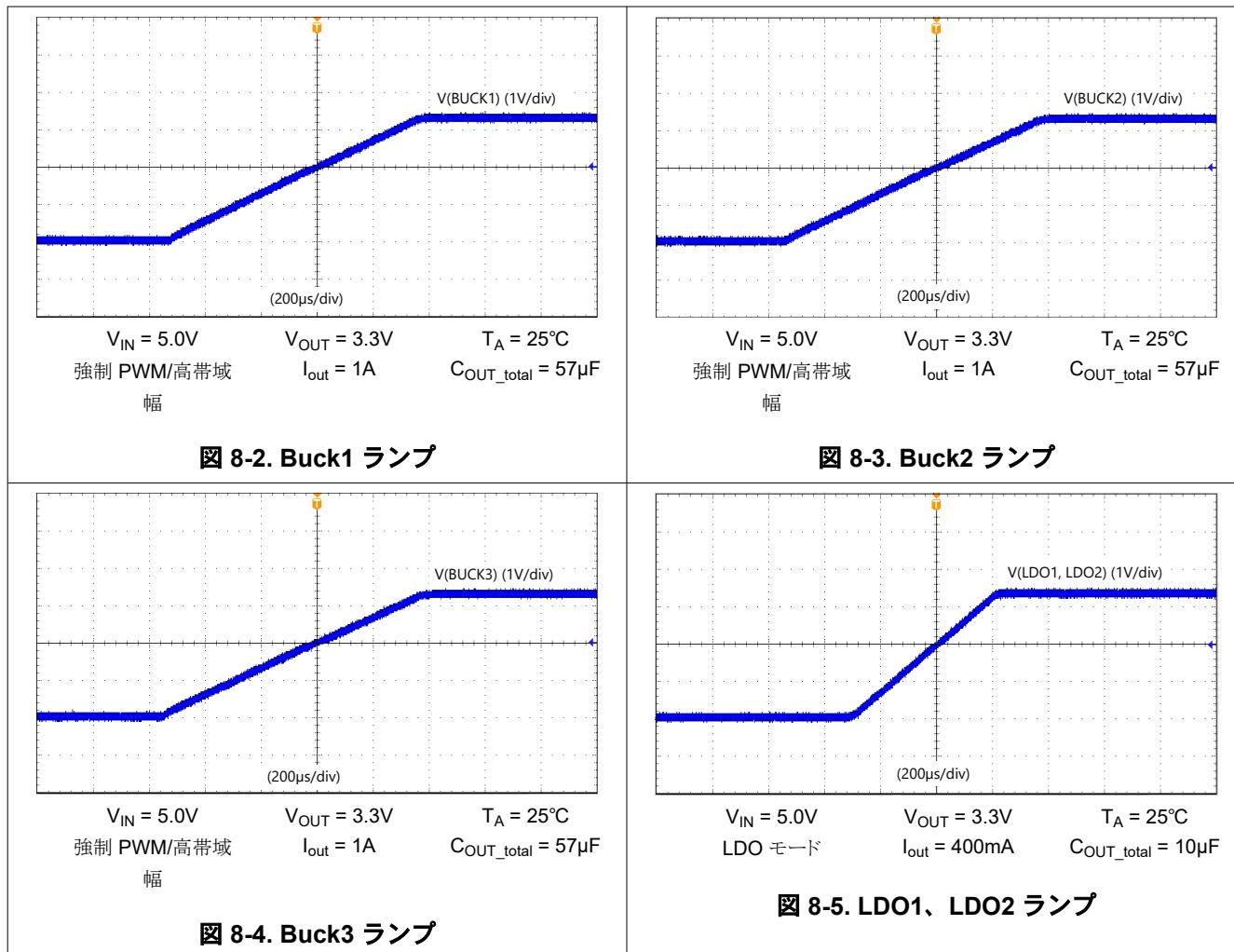

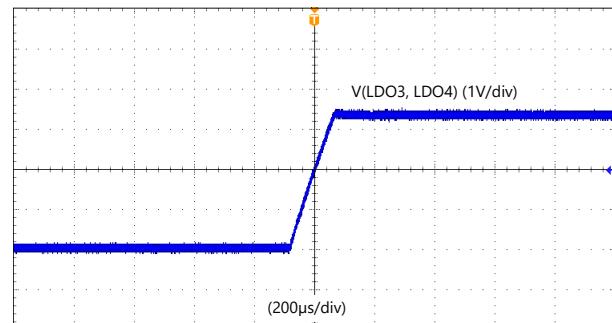

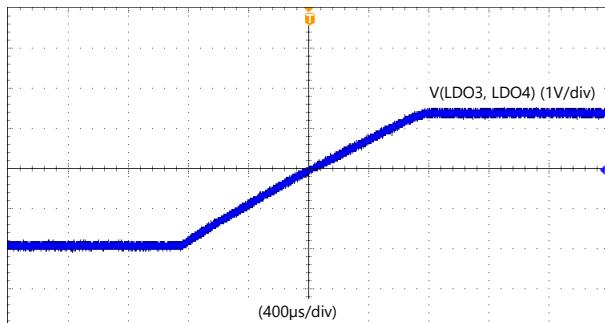

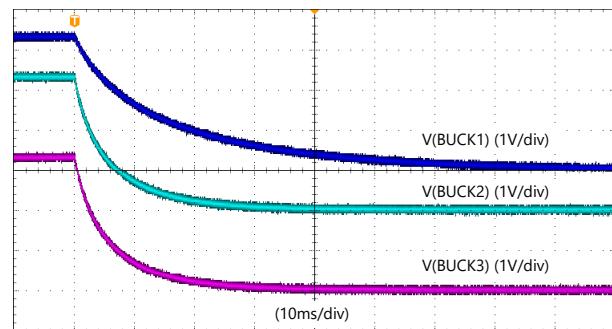

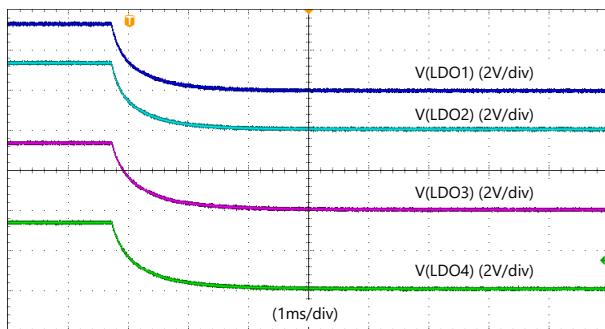

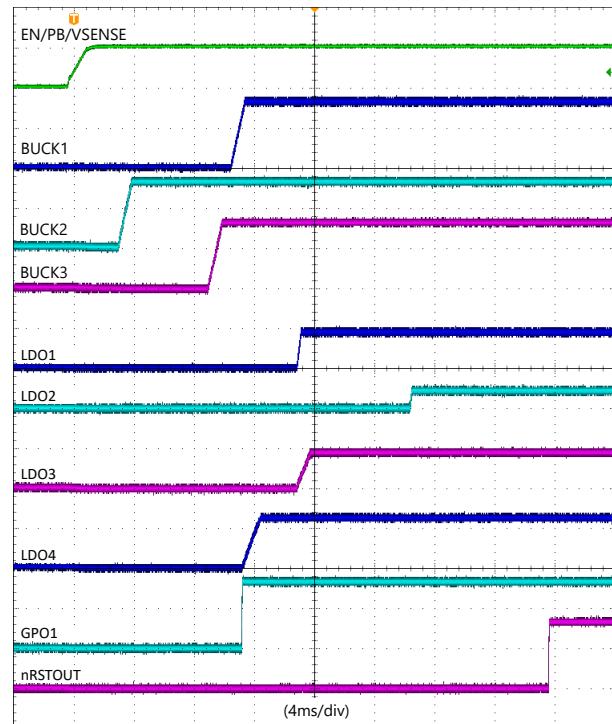

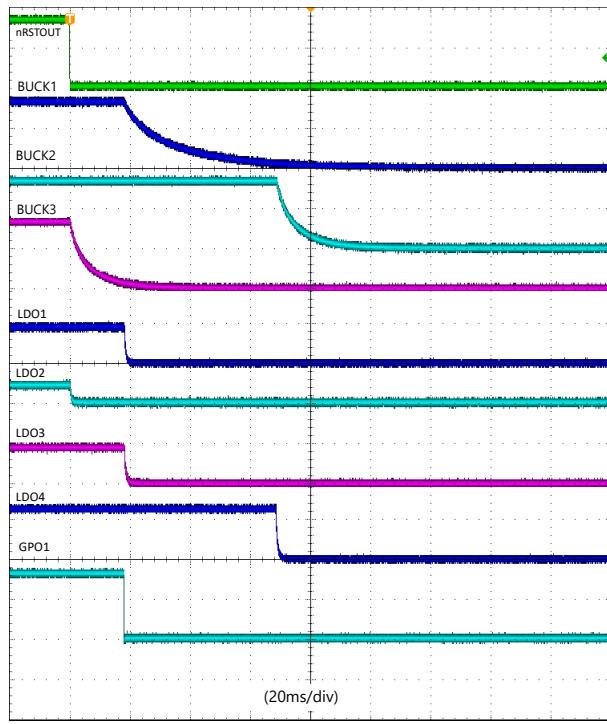

| 7.3.7a  | $I_{Q\_ACTIVE\_LDO}$       | 25°C、<br>LDO モード時のアクティブ状態での静止電流                  | LDO モード、 $I_{OUT} = 0\text{mA}$ 、<br>$T_J = 25^\circ\text{C}$                          | 50  | 62   | $\mu\text{A}$           |