# TPSM336xx-Q1、車載、3V ~ 36V 入力、1V ~ 7V 出力、0.6A、1A、および 2A、HotRod™ QFN パッケージの同期整流 ZEN 1 降圧コンバータ電源モジュール

## 1 特長

- 車載アプリケーション用に AEC-Q100 認定取得済み:

- 温度グレード 1: -40°C ~ +125°C, TA

- **機能安全対応**

- 機能安全システムの設計に役立つ資料を利用可能

- 同期整流、降圧 DC/DC 車載モジュール:

- パワー MOSFET、コントローラ、AEC-Q200 認証済みインダクタ、C<sub>BOOT</sub> コンデンサを内蔵

- 接合部温度範囲: 内蔵インダクタと C<sub>BOOT</sub> を含む -40°C ~ 150°C

- 固定スイッチング周波数 (2.2MHz)

- 連続出力電流: 0.6A、1A、2A

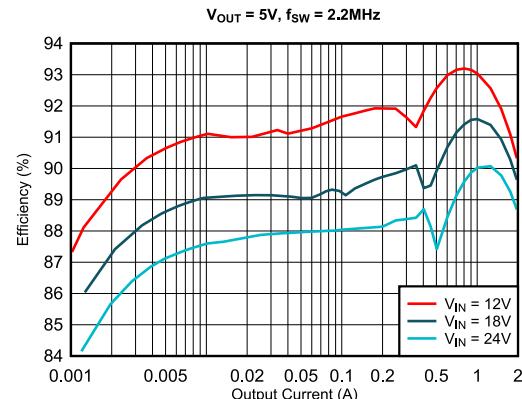

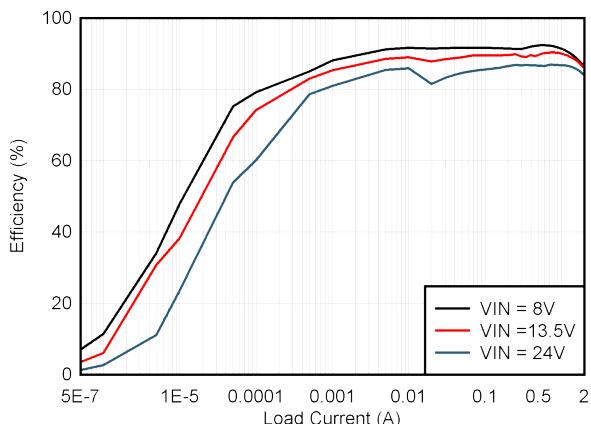

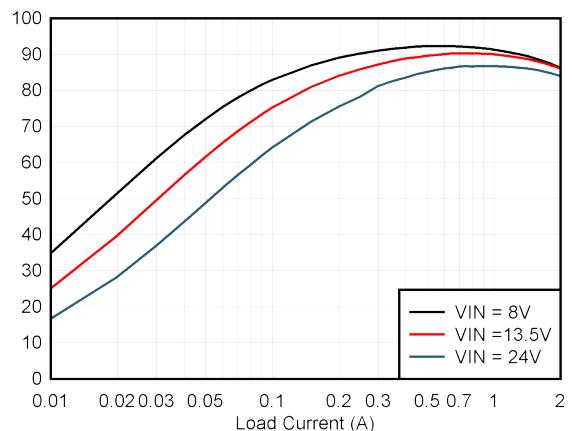

- 全負荷範囲にわたって極めて高い効率を実現:

- ピーク効率は V<sub>IN</sub> = 12V, V<sub>OUT</sub> = 5V で 93.2%、V<sub>IN</sub> = 24V, V<sub>OUT</sub> = 5V のときに 90% です

- 13.5V<sub>IN</sub> で 1.2μA の超低非スイッチング I<sub>Q</sub>、および Q<sub>AV</sub> および 300nA の低シャットダウン電流

- ZEN 1 スイッチャ

- デュアルランダムスペクトラム拡散機能 - DRSS

- C<sub>BOOT</sub> と HotRod™ の各パッケージを内蔵

- ピン選択可能な FPWM および自動モード

- CISPR 25 Class 5 準拠

- 出力電圧オプション:

- 固定出力バリアント: 3.3V または 5V の V<sub>OUT</sub>

- 可変出力電圧: 1V ~ 7V

- **WEBENCH® Power Designer** により、TPSM336xx-Q1 を使用するカスタム設計を作成

## 2 アプリケーション

- パワーステアリング

- オンボードチャージャ

- 車載ライティング

- 車載用カメラ

## 3 説明

TPSM336xx-Q1 は、0.6A、1A または 2A、36V 入力、車載用の同期降圧 DC/DC パワー ジュールで、フリップチップ オン リード パッケージ、統合型パワー MOSFET、AEC-Q100 認定の内蔵インダクタ、ブート コンデンサをコンパクトで使いやすいパッケージに統合しています。小型 HotRod QFN パッケージにより、放熱性能が向上し、高い周囲温度での動作が確保できます。拡散スペクトラムは優れた EMI 性能を実現します。本デバイスは、3.3V および 5V をサポートする 2 つの固定出力電圧オプションで利用可能です。本デバイスは、フィードバック デバイダにより 1V から 7V までの出力に設定でき、MODE/SYNC ピンを介して自動または強制 PWM モードで動作します。このでデバイスは、3.3V および 5V 固定出力設計に必要な 4 つの外付け部品だけで、PCB レイアウトと設計が簡素化されます。

本デバイスは、常時オンの車載アプリケーションの低スタンバイ電力要件を満たすように設計されています。自動モードは、軽負荷動作時の周波数フォールドバックを可能にするため、軽負荷効率を高めることができます。DRSS を使用して、入力 EMI フィルタの外部部品を低減します。ZEN 1 スイッチャの機能により、本デバイスは低 EMI アプリケーションをサポートできます。

### パッケージ情報

| 部品番号 <sup>(1)</sup> | パッケージ <sup>(2)</sup> | パッケージ サイズ <sup>(3)</sup> |

|---------------------|----------------------|--------------------------|

| TPSM33620-Q1        |                      |                          |

| TPSM33610-Q1        | RDN (QFN-FCMOD、11)   | 4.50mm × 3.50mm × 2mm    |

| TPSM33606-Q1        |                      |                          |

(1) 「[デバイス比較表](#)」を参照してください。

(2) 詳細については、[セクション 11](#) を参照してください。

(3) パッケージ サイズ(長さ × 幅 × 高さ)は公称値であり、該当する場合はピンも含まれます。

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール(機械翻訳)を使用していることがあり、TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

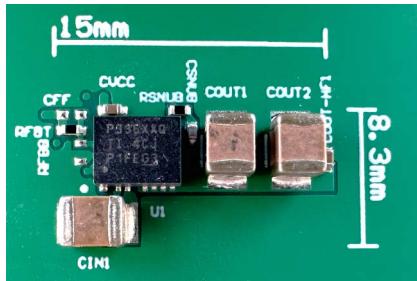

標準的な EVM レイアウト設計サイズ (15mm × 8.3mm)

効率と出力電流との関係

## 目次

|                    |           |                               |           |

|--------------------|-----------|-------------------------------|-----------|

| <b>1 特長</b>        | <b>1</b>  | <b>8 アプリケーションと実装</b>          | <b>25</b> |

| <b>2 アプリケーション</b>  | <b>1</b>  | <b>8.1 アプリケーション情報</b>         | <b>25</b> |

| <b>3 説明</b>        | <b>1</b>  | <b>8.2 代表的なアプリケーション</b>       | <b>26</b> |

| <b>4 デバイス比較表</b>   | <b>4</b>  | <b>8.3 設計のベスト プラクティス</b>      | <b>34</b> |

| <b>5 ピン構成および機能</b> | <b>5</b>  | <b>8.4 電源に関する推奨事項</b>         | <b>34</b> |

| <b>6 仕様</b>        | <b>6</b>  | <b>8.5 レイアウト</b>              | <b>34</b> |

| 6.1 絶対最大定格         | 6         | <b>9 デバイスおよびドキュメントのサポート</b>   | <b>37</b> |

| 6.2 ESD 定格         | 6         | 9.1 デバイス サポート                 | 37        |

| 6.3 推奨動作条件         | 6         | 9.2 ドキュメントのサポート               | 37        |

| 6.4 熱に関する情報        | 7         | 9.3 ドキュメントの更新通知を受け取る方法        | 38        |

| 6.5 電気的特性          | 7         | 9.4 サポート・リソース                 | 38        |

| 6.6 代表的特性          | 9         | 9.5 商標                        | 38        |

| <b>7 詳細説明</b>      | <b>10</b> | 9.6 静電気放電に関する注意事項             | 38        |

| 7.1 概要             | 10        | 9.7 用語集                       | 38        |

| 7.2 機能ブロック図        | 11        | <b>10 改訂履歴</b>                | <b>38</b> |

| 7.3 機能説明           | 12        | <b>11 メカニカル、パッケージ、および注文情報</b> | <b>40</b> |

| 7.4 デバイスの機能モード     | 20        |                               |           |

## 4 デバイス比較表

| デバイス         | 発注用部品番号 <sup>(1)</sup> | 出力電圧       | 出力電流 | スペクトラム拡散 |

|--------------|------------------------|------------|------|----------|

| TPSM33620-Q1 | TPSM33620S5QRDNRQ1     | 5V 固定/可変   | 2A   | あり       |

|              | TPSM33620S3QRDNRQ1     | 3.3V 固定/可変 |      | あり       |

|              | TPSM336203QRDNRQ1      | 3.3V 固定/可変 |      | なし       |

| TPSM33610-Q1 | TPSM33610S5QRDNRQ1     | 5V 固定/可変   | 1A   | あり       |

|              | TPSM33610S3QRDNRQ1     | 3.3V 固定/可変 |      | あり       |

| TPSM33606-Q1 | TPSM33606S3QRDNRQ1     | 3.3V 固定/可変 | 0.6A | あり       |

|              | TPSM33606S5QRDNRQ1     | 5V 固定/可変   |      | あり       |

(1) デバイスの発注用製品型番の詳細については、[セクション 9.1.3](#) を参照してください。

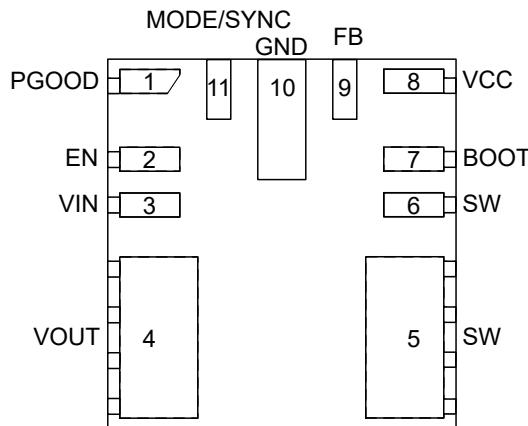

## 5 ピン構成および機能

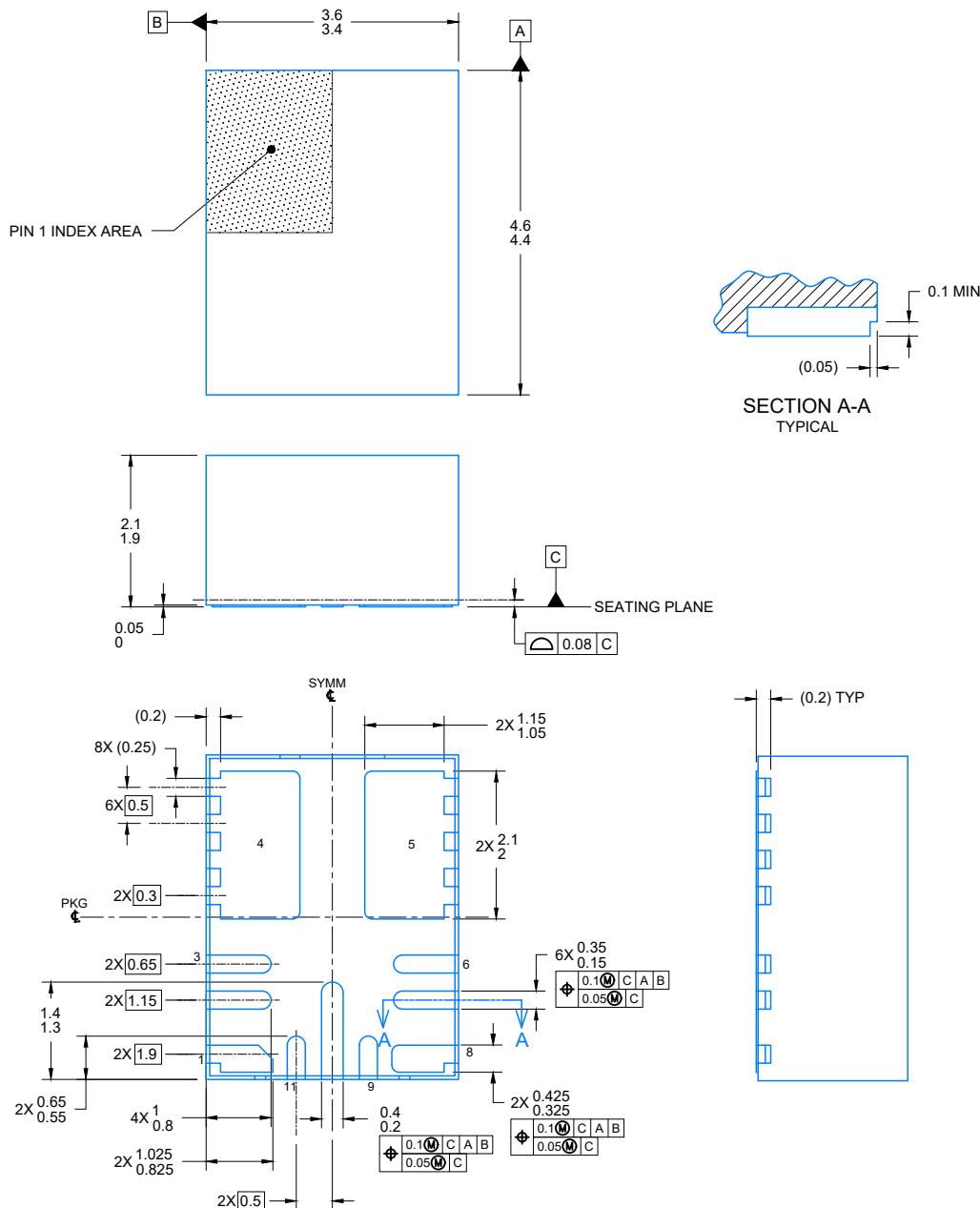

図 5-1. RDN パッケージ、11 ピン QFN-FCMOD、上面図(すべてのバリエント)

### ピンの機能

| 番号   | ピン<br>名称  | タイプ <sup>(1)</sup> | 説明                                                                                                                                                                                                                                                                                                |

|------|-----------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | PGOOD     | A                  | パワー グッド モニタ。帰還電圧が指定したウインドウしきい値を超えた場合に Low にアサートするオープンドレイン出力。優れたブルアップ電圧には、10kΩ ~ 100kΩ のブルアップ抵抗が必要です。使用しない場合、このピンはオープンのままにすることも GND に接続することもできます。High = パワー OK、Low = フォルト。EN = Low にすると、PGOOD ピンは Low になります。                                                                                       |

| 2    | EN        | A                  | 高精度イネーブル入力ピン。High = オン、Low = オフ。高精度イネーブルを使うと、このピンを調整可能な UVLO として使用できます。VIN に直接接続できます。オープンドレインまたはオープンコレクタデバイスを使用して、このピンを GND に接続することで、本モジュールをターンオフできます。VIN、このピン、GND の間に外部分圧回路を配置することで、外部 UVLO を生成することができます。このピンをフローティングにしないでください。                                                                  |

| 3    | VIN       | P                  | 入力電源電圧。入力電源をこれらのピンに接続します。このピンと GND の間に、高品質のバイパスコンデンサをモジュールにごく近付けて直接接続します。入力コンデンサの配置例については、セクション 8.5.2 を参照してください。                                                                                                                                                                                  |

| 4    | VOUT      | P                  | 出力電圧。このピンは、内部のフィルタリング回路に接続されています。ピンを出力負荷に接続し、このピンと GND との間に外部出力コンデンサを接続します。固定出力オプションが利用可能です。固定出力バリアントの場合は、FB ピンを VOUT に接続します。詳細は、セクション 4 をご覧ください。                                                                                                                                                 |

| 5, 6 | SW        | P                  | 電源モジュールのスイッチノード。このピンに外部部品を配置したり、信号に接続したりしないでください。ノイズや EMI の問題を防止するため、これらのピンに配置する銅の量は最小限に抑える必要があります。                                                                                                                                                                                               |

| 7    | BOOT      | P                  | 内部ハイサイドドライバ回路のブートストラップピン。このピンからモジュール内の SW に 100nF のブートストラップコンデンサが内部接続されており、これによってブートストラップ電圧が供給されています。                                                                                                                                                                                             |

| 8    | VCC       | P                  | 内部 LDO 出力。内部制御回路への電源として使用されます。外部負荷に接続しないでください。パワー グッド フラグのロジック電源として使用できます。このピンと GND との間に高品質の 1μF コンデンサを接続します。                                                                                                                                                                                     |

| 9    | FB        | A                  | 帰還入力。可変出力の場合は、出力電圧の帰還抵抗分圧回路の中間点にこのピンを接続します。帰還分圧器の上側抵抗 ( $R_{FBT}$ ) を目的のレギュレーション点 (VOUT) に接続します。帰還分圧器の下側抵抗 ( $R_{FBB}$ ) を GND に接続します。帰還抵抗分圧器に接続する場合、ノイズの結合を防止するため、この FB パターンをできるだけ短くかつ小さくします。帰還抵抗の配置については、セクション 8.5.2 をご覧ください。固定出力設定の場合は、FB/VOUT ピン 9 を直接 VOUT ピン 4 に接続します。オープン状態、GND への接続は禁止です。 |

| 10   | GND       | G                  | 電源グランドピン。システムグランドに接続。短くかつ広いパターンで $C_{IN}$ に接続します。                                                                                                                                                                                                                                                 |

| 11   | MODE/SYNC | A                  | 本デバイスは、MODE/SYNC ピンの電圧に基づいて、ユーザーが自動/FPWM動作を選択できます。この部品は、外部クロックに同期させることもできます。クロックは、適用する外部クロックの立ち上がりエッジでトリガれます。このピンをフローティングにしないでください。                                                                                                                                                               |

(1) A = アナログ、P = 電源、G = グランド

## 6 仕様

### 6.1 絶対最大定格

制限値は、 $T_J = -40^{\circ}\text{C} \sim 150^{\circ}\text{C}$  の範囲全体に適用されます (特に注記のない限り)。<sup>(1)</sup>

|      |                            | 最小値  | 最大値 | 単位 |

|------|----------------------------|------|-----|----|

| 入力電圧 | VIN から GND へ               | -0.3 | 40  | V  |

|      | BOOT から SW へ               | -0.3 | 5.5 | V  |

|      | MODE/SYNC から GND へ         | -0.3 | 5.5 | V  |

|      | EN から GND へ                | -0.3 | 40  | V  |

|      | FB から GND へ                | -0.3 | 16  | V  |

|      | PG から GND へ                | 0    | 20  | V  |

| 出力電圧 | VCC から GND へ               | -0.3 | 5.5 | V  |

|      | SW から GND へ <sup>(2)</sup> | -0.3 | 40  | V  |

|      | VOUT から GND へ              | -0.3 | 16  | V  |

| 入力電流 | PG                         | —    | 10  | mA |

| 温度   | $T_J$ 、接合部温度               | -40  | 150 | °C |

| 温度   | $T_{stg}$ 、保管温度            | -65  | 150 | °C |

- (1) 絶対最大定格を超えた動作は、デバイスに恒久的な損傷を与える可能性があります。絶対最大定格は、これらの条件において、または 推奨動作条件に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用した場合、本デバイスは完全に機能するとは限らず、このことが本デバイスの信頼性、機能、性能に影響を及ぼし、本デバイスの寿命を縮める可能性があります。

- (2) このピンには、PGND より 2V 低い値から VIN より 2V 高い値までの電圧を最大 200ns の間 (デューティサイクルは 0.01% 以下) 印加できます。

### 6.2 ESD 定格

|             |                                            | 値     | 単位 |

|-------------|--------------------------------------------|-------|----|

| $V_{(ESD)}$ | 人体モデル (HBM)、AEC Q100-002 準拠 <sup>(1)</sup> | ±2000 | V  |

|             | 荷電デバイス モデル (CDM)、AEC Q100-011 準拠           | ±1000 | V  |

- (1) AEC Q100-002 は、HBM ストレス試験を ANSI/ESDA/JEDEC JS-001 仕様に従って実施しなければならないと規定しています。

### 6.3 推奨動作条件

制限値は  $T_J = -40^{\circ}\text{C} \sim 150^{\circ}\text{C}$  の範囲全体に適用されます (特に注記のない限り)。

|      |                                         | 最小値 | 公称値 | 最大値 | 単位  |

|------|-----------------------------------------|-----|-----|-----|-----|

| 入力電圧 | VIN (起動後の入力電圧範囲)                        | 3   | 36  | 36  | V   |

| 出力電圧 | 出力電圧調整範囲 <sup>(1)</sup>                 | 1   | 7   | 7   | V   |

| 出力電流 | TPSM33620-Q1 の $I_{OUT}$ <sup>(2)</sup> | 0   | 2   | 2   | A   |

| 出力電流 | TPSM33610-Q1 の $I_{OUT}$ <sup>(2)</sup> | 0   | 1   | 1   | A   |

| 出力電流 | TPSM33606-Q1 の $I_{OUT}$ <sup>(2)</sup> | 0   | 0.6 | 0.6 | A   |

| 周波数  | スイッチング周波数                               | 2.1 | 2.2 | 2.3 | MHz |

| 周波数  | SYNC によって設定される $f_{sw}$                 | 1.9 | 2.5 | 2.5 | MHz |

| 温度   | 動作時の接合部温度、 $T_J$                        | -40 | 150 | 150 | °C  |

- (1) いかなる条件下でも、出力電圧は 0V を下回ってはなりません。

- (2) スイッチング周波数が高い、または周囲温度が高い状態で動作している場合、最大連続 DC 電流が低下する場合があります。詳細については、「代表的特性」セクションを参照してください。

## 6.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup>        |                             | TPSM33620-Q1/ TPSM33610-Q1/<br>TPSM33606-Q1 | 単位   |

|-----------------------------|-----------------------------|---------------------------------------------|------|

|                             |                             | RDN (QFN-FCMOD)                             |      |

|                             |                             | 11 ピン                                       |      |

| $R_{\theta JA}$             | 接合部から周囲への熱抵抗 (TPSM33625EVM) | 22                                          | °C/W |

| $R_{\theta JA}$             | 接合部から周囲への熱抵抗 (JESD 51-7)    | 54.1                                        | °C/W |

| $R_{\theta JC(\text{top})}$ | 接合部からケース (上面)への熱抵抗          | 52.1                                        | °C/W |

| $R_{\theta JB}$             | 接合部から基板への熱抵抗                | 16.6                                        | °C/W |

| $\Psi_{JT}$                 | 接合部から上面への特性パラメータ            | 8.1                                         | °C/W |

| $\Psi_{JB}$                 | 接合部から基板への特性パラメータ            | 16.3                                        | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーションノートを参照してください。この表に示す  $R_{\theta JA}$  の値は他のパッケージとの比較にのみ有効であり、設計目的に使用することはできません。この値は JESD 51-7 に従って計算されており、4 層 JEDEC 基板上でシミュレーションされています。この値は、実際のアプリケーションで得られた性能を表すものではありません。

## 6.5 電気的特性

制限値は、 $T_J = -40^{\circ}\text{C} \sim 150^{\circ}\text{C}$ 、 $V_{IN} = 13.5\text{V}$ 、 $V_{OUT} = 3.3\text{V}$ 、 $F_{SW} = 2.2\text{MHz}$  の範囲で適用されます (特に注記がない限り)。最小値および最大値の制限値は、量産テストを通して、または設計により規定されています。標準値は最も一般的なパラメータ基準値を表しており、参考目的にのみ提供されています。

| パラメータ               | テスト条件                            | 最小値                                                                          | 標準値   | 最大値   | 単位    |

|---------------------|----------------------------------|------------------------------------------------------------------------------|-------|-------|-------|

| <b>電源電圧</b>         |                                  |                                                                              |       |       |       |

| $V_{IN}$            | 入力電圧立ち上がりスレッショルド                 | 起動前                                                                          | 3.2   | 3.35  | 3.5   |

|                     |                                  | 動作開始後                                                                        | 2.45  | 2.7   | 3     |

| $I_{Q\_VIN}$        | 入力動作静止電流 (スイッチングなし)              | $T_A = 25^{\circ}\text{C}$ 、 $V_{EN} = 3.3\text{V}$ 、 $V_{FB} = 1.5\text{V}$ |       | 1.2   | μA    |

| $I_{SDN\_VIN}$      | $VIN$ のシャットダウン時静止電流              | $V_{EN} = 0\text{V}$ 、 $T_A = 25^{\circ}\text{C}$                            |       | 0.3   | μA    |

| <b>イネーブル</b>        |                                  |                                                                              |       |       |       |

| $V_{EN\_RISE}$      | EN 電圧立ち上がりスレッショルド                |                                                                              | 1.16  | 1.23  | 1.3   |

| $V_{EN\_FALL}$      | EN 電圧立ち下がりスレッショルド                |                                                                              | 0.81  | 0.9   | 0.97  |

| $V_{EN\_HYS}$       | EN 電圧ヒステリシス                      |                                                                              | 0.275 | 0.353 | 0.404 |

| $V_{EN\_WAKE}$      | EN ウエークアップ スレッショルド               |                                                                              | 0.5   | 0.7   | 1     |

| $I_{LKG-EN}$        | イネーブル ピン入力リーク電流                  | $V_{EN} = V_{IN} = 24\text{V}$                                               |       | 10    | nA    |

| <b>内部 LDO VCC</b>   |                                  |                                                                              |       |       |       |

| $V_{CC}$            | 内部 LDO VCC 出力電圧                  | $V_{FB} = 0\text{V}$ 、 $I_{VCC} = 1\text{mA}$                                | 3.1   | 3.3   | 3.5   |

| <b>FEEDBACK</b>     |                                  |                                                                              |       |       |       |

| $V_{FB}$            | 内部リファレンス電圧精度                     | $V_{IN}$ レンジ全体、 $V_{OUT} = 1\text{V}$ 、FPWM モード、 $F_{SW} = 2.2\text{MHz}$    | 0.99  | 1     | 1.01  |

| $V_{OUT\_ACC\_3V3}$ | 固定 3.3V $V_{OUT}$ 調整オプションの出力電圧精度 | $V_{IN}$ レンジ全体、FPWM モード、 $F_{SW} = 2.2\text{MHz}$                            | 3.27  | 3.3   | 3.33  |

| $V_{OUT\_ACC\_5V0}$ | 固定 5V $V_{OUT}$ 調整オプションの出力電圧精度   | $V_{IN}$ レンジ全体、FPWM モード、 $F_{SW} = 2.2\text{MHz}$                            | 4.95  | 5     | 5.05  |

| $I_{FB}$            | FB ピンへの入力電流                      | 可変構成、 $V_{FB} = 1\text{V}$                                                   |       | 10    | nA    |

| <b>電流制限</b>         |                                  |                                                                              |       |       |       |

| $I_{L\_HS}$         | ハイサイド スイッチ電流制限値 (TPSM33620-Q1)   | デューティ サイクルを 0% に近付ける                                                         | 3.4   | 4     | 4.6   |

| $I_{L\_LS}$         | ローサイド スイッチ電流制限値 (TPSM33620-Q1)   |                                                                              | 1.9   | 2.2   | 2.53  |

| $I_{L\_NEG}$        | 負の電流制限値 (TPSM33620-Q1)           |                                                                              | -1    | -0.8  | -0.6  |

| $I_{L\_HS}$         | ハイサイド スイッチ電流制限値 (TPSM33610-Q1)   | デューティ サイクルを 0% に近付ける                                                         | 1.7   | 2     | 2.3   |

| $I_{L\_LS}$         | ローサイド スイッチ電流制限値 (TPSM33610-Q1)   |                                                                              | 0.85  | 1.1   | 1.4   |

| $I_{L\_NEG}$        | 負の電流制限値 (TPSM33610-Q1)           |                                                                              | -1    | -0.8  | -0.6  |

| $I_{L\_HS}$         | ハイサイド スイッチ電流制限値 (TPSM33606-Q1)   | デューティ サイクルを 0% に近付ける                                                         | 1.5   | 1.8   | 2.1   |

## 6.5 電気的特性 (続き)

制限値は、 $T_J = -40^\circ\text{C} \sim 150^\circ\text{C}$ 、 $V_{IN} = 13.5\text{V}$ 、 $V_{OUT} = 3.3\text{V}$ 、 $F_{SW} = 2.2\text{MHz}$  の範囲で適用されます (特に注記がない限り)。最小値および最大値の制限値は、量産テストを通して、または設計により規定されています。標準値は最も一般的なパラメータ基準値を表しており、参考目的にのみ提供されています。

| パラメータ               |                                                | テスト条件                                                   | 最小値  | 標準値  | 最大値  | 単位  |

|---------------------|------------------------------------------------|---------------------------------------------------------|------|------|------|-----|

| $I_{L\_LS}$         | ローサイド スイッチ電流制限値 (TPSM33606-Q1)                 |                                                         | 0.85 | 1.1  | 1.4  | A   |

| $I_{L\_NEG}$        | 負の電流制限値 (TPSM33606-Q1)                         |                                                         | -1   | -0.8 | -0.6 | A   |

| $I_{ZC}$            | ゼロクロスの電流制限値                                    | 自動モード                                                   | 80   |      |      | mA  |

| $V_{HICCUP}$        | 下回るとモジュールはヒップモードに移行する FB ピンの電圧                 | ソフトスタート中以外                                              | 0.4  |      |      | V   |

| $t_W$               | 短絡待機時間 (ソフトスタートの前の「ヒップ」時間) <sup>(1)</sup>      |                                                         | 30   | 50   | 75   | ms  |

| <b>ソフトスタート</b>      |                                                |                                                         |      |      |      |     |

| $t_{SS}$            | 最初の SW パルスから $V_{REF}$ が設定点の 90% に達するまでの時間     | $V_{IN} \geq 4.2\text{V}$                               | 2    | 3.5  | 4.6  | ms  |

| <b>パワー グッド</b>      |                                                |                                                         |      |      |      |     |

| $PG_{OV}$           | PG の上限 - 立ち上がり                                 | $V_{OUT}$ 設定の %                                         | 104  | 108  | 111  | %   |

| $PG_{UV}$           | PG の下限 - 立ち下がり                                 | $V_{OUT}$ 設定の %                                         | 89   | 91   | 94.2 | %   |

| $PG_{HYS}$          | OV の PG 上限スレッショルド ヒステリシス                       | $V_{OUT}$ 設定の %                                         | 1.8  | 2    | 2.4  | %   |

|                     | UV の PG 上限スレッショルド ヒステリシス                       | $V_{OUT}$ 設定の %                                         | 1.8  | 3    | 4.7  | %   |

| $V_{IN\_PG\_VALID}$ | 有効な PG 出力の入力電圧                                 | $R_{PGD\_PU} = 10\text{k}\Omega$ , $V_{EN} = 0\text{V}$ |      | 1.5  |      | V   |

| $V_{PG\_LOW}$       | Low レベル PG 機能出力電圧                              | PG ピンに 2mA のプルアップを接続、 $V_{EN} = 3.3\text{V}$            |      | 0.4  |      | V   |

| $t_{PG\_FLT\_RISE}$ | PG High 信号までの遅延時間                              |                                                         | 1.35 | 2.5  | 4    | ms  |

| $t_{RESET\_FILTER}$ | 立ち下がりエッジでの PGOOD グリッチ除去遅延                      |                                                         | 25   | 47   | 75   | μs  |

| $R_{PGD}$           | PGOOD オン抵抗                                     | $V_{EN} = 3.3\text{V}$ , 200μA のプルアップ電流                 |      | 100  |      | Ω   |

| $R_{PGD}$           | PGOOD オン抵抗                                     | $V_{EN} = 0\text{V}$ , 200μA のプルアップ電流                   |      | 100  |      | Ω   |

| <b>スイッチング周波数</b>    |                                                |                                                         |      |      |      |     |

| $f_{SW}$            | スイッチング周波数                                      |                                                         | 2.1  | 2.2  | 2.3  | MHz |

| $f_{SYNC\_RANGE}$   | SYNC によるスイッチング周波数範囲                            |                                                         | 1.9  |      | 2.5  | MHz |

| $\Delta f_C$        | 内部発振器のスペクトラム拡散による周波数の増加 / 減少                   | デュアル ランダム スペクトラム拡散                                      |      | ±4   |      | %   |

| <b>同期</b>           |                                                |                                                         |      |      |      |     |

| $V_{MODE\_L}$       | SYNC/MODE 入力電圧の Low レベル スレッショルド                |                                                         | 1    |      |      | V   |

| $V_{MODE\_H}$       | SYNC/MODE 入力電圧の High レベル スレッショルド               |                                                         |      | 1.6  |      | V   |

| $t_{PULSE\_H}$      | パルスとして認識されるのに必要な High の継続時間                    |                                                         | 100  |      |      | ns  |

| $t_{PULSE\_L}$      | パルスとして認識されるのに必要な Low の継続時間                     |                                                         | 100  |      |      | ns  |

| $t_B$               | 立ち上がりまたは立ち下がりエッジの後の EN のブランкиング <sup>(1)</sup> |                                                         | 4    | 28   |      | μs  |

| $t_{SYNC}$          | 有効なクロック信号として認識されるための HIGH/LOW レベル パルスの最大期間     |                                                         |      | 6    |      | μs  |

| <b>電力段</b>          |                                                |                                                         |      |      |      |     |

| $V_{BOOT\_UVLO}$    | ハイサイド スイッチがオフになる BOOT ピンの電圧 (SW 基準)            |                                                         | 2.1  |      |      | V   |

| $t_{ON\_MIN}$       | HS スイッチ ON の最小パルス幅 <sup>(1)</sup>              | FPWM モード、 $V_{OUT} = 1\text{V}$ , $I_{OUT} = 1\text{A}$ | 65   | 75   |      | ns  |

| $t_{ON\_MAX}$       | HS スイッチ ON の最大パルス幅 <sup>(1)</sup>              | ドロップアウト時の HS タイムアウト                                     | 6    | 9    | 13   | μs  |

| $t_{OFF\_MIN}$      | HS スイッチ OFF の最小パルス幅                            | $V_{IN} = 4\text{V}$ , $I_{OUT} = 1\text{A}$            | 60   | 85   |      | ns  |

| $R_{DSON-HS}$       | ハイサイド MOSFET オン抵抗                              | 負荷 = 1A                                                 | 132  | 260  |      | mΩ  |

| $R_{DSON-LS}$       | ローサイド MOSFET オン抵抗                              | 負荷 = 1A                                                 | 75   | 140  |      | mΩ  |

(1) パラメータは、設計、統計分析、相関パラメータの製造試験によって規定されています。実製品の検査は行っていません。

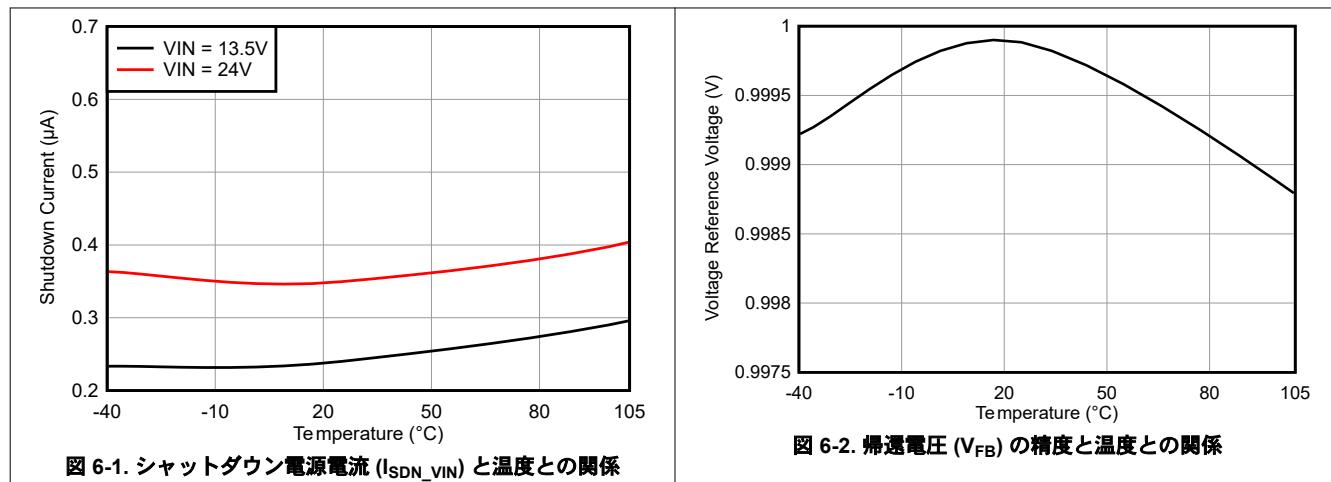

## 6.6 代表的特性

特記のない限り、次の条件が適用されます。 $T_A = 25^\circ\text{C}$ 、 $V_{IN} = 13.5\text{V}$ 。

図 6-1. シャットダウン電源電流 ( $I_{SDN\_VIN}$ ) と温度との関係

図 6-2. 帰還電圧 ( $V_{FB}$ ) の精度と温度との関係

## 7 詳細説明

### 7.1 概要

TPSM336xx-Q1 は、3V～36V の電源電圧で動作する使いやすい同期降圧 DC/DC 電源モジュールです。このデバイスは、3.3V および 5V の電源レールからの降圧変換を意図しており、外部の帰還抵抗分圧回路により出力を最大 7V までの調整することができます。電源コントローラ、インダクタ、MOSFET を内蔵することにより、TPSM336xx-Q1 は、非常に小さな設計サイズでありながら、最大 2A の DC 負荷電流を高効率、超低 J 自己消費電流でご提供します。このデバイスは実装が簡単になるように設計されていますが、対象アプリケーションに応じて使用を最適化する柔軟性があります。制御ループ補償は不要で、設計時間の短縮と外部部品点数の減少につながります。

TPSM336xx-Q1 は、幅広いデューティ比にわたって 2.2MHz の固定スイッチング周波数で動作します。最小オン時間またはオフ時間が目的のデューティ比をサポートできない場合は、スイッチング周波数が自動的に低下し、出力電圧レギュレーションが維持されます。さらに、遅延リリース機能を備えた PGOOD 出力機能により、多くのアプリケーションでリセットスーパーバイザを不要にできます。

TPSM336xx-Q1 のパワーモジュールには、ノイズに敏感なアプリケーションにより EMI 性能を向上させる特定の機能が組み込まれています。

- フリップチップ オンリード (FCOL) 技術およびピン配置設計を採用したように設計されたパッケージは、放射 EMI を低減するシールド付きスイッチノードレイアウトを可能にします。

- デュアルランダムスペクトラム拡散 (DRSS) により、ピーク放射を低減します。

- インダクタとブートコンデンサの統合

これらの機能を組み合わせることでコモンモードチョーク、シールド、入力フィルタインダクタが不要になり、EMI/EMC 低減対策の複雑さとコストを大幅に削減することができます。

TPSM336xx-Q1 モジュールには、堅牢なシステム要件に必要な基本的保護機能も内蔵されています。

- 電源レールのシーケンシングと障害報告用のオープンドレイン PGOOD インジケータ

- 以下の機能を提供するヒステリシス付き高精度イネーブル入力

- プログラム可能なライン低電圧誤動作防止 (UVLO)

- リモートオン/オフ特性

- プリバイアス負荷への単調起動を備えた内部固定出力電圧ソフトスタート

- サイクル単位のピーク電流制限とバレー電流制限によるヒップアップモード過電流保護

- 自動回復機能付きサーマルシャットダウン。

これらの機能により、幅広い範囲のアプリケーションに対応した柔軟で使いやすいプラットフォームを可能にします。ピン配置はレイアウトが単純になるよう設計されており、必要な外付け部品はほとんどありません。レイアウト例については、[セクション 8.5](#) を参照してください。

このデバイスは、ウェッタブル フランクメッキによる超小型デバイスで、4.50mm×3.50mm の強化型 HotRod QFN パッケージで供給され、光学検査を迅速に行えます。

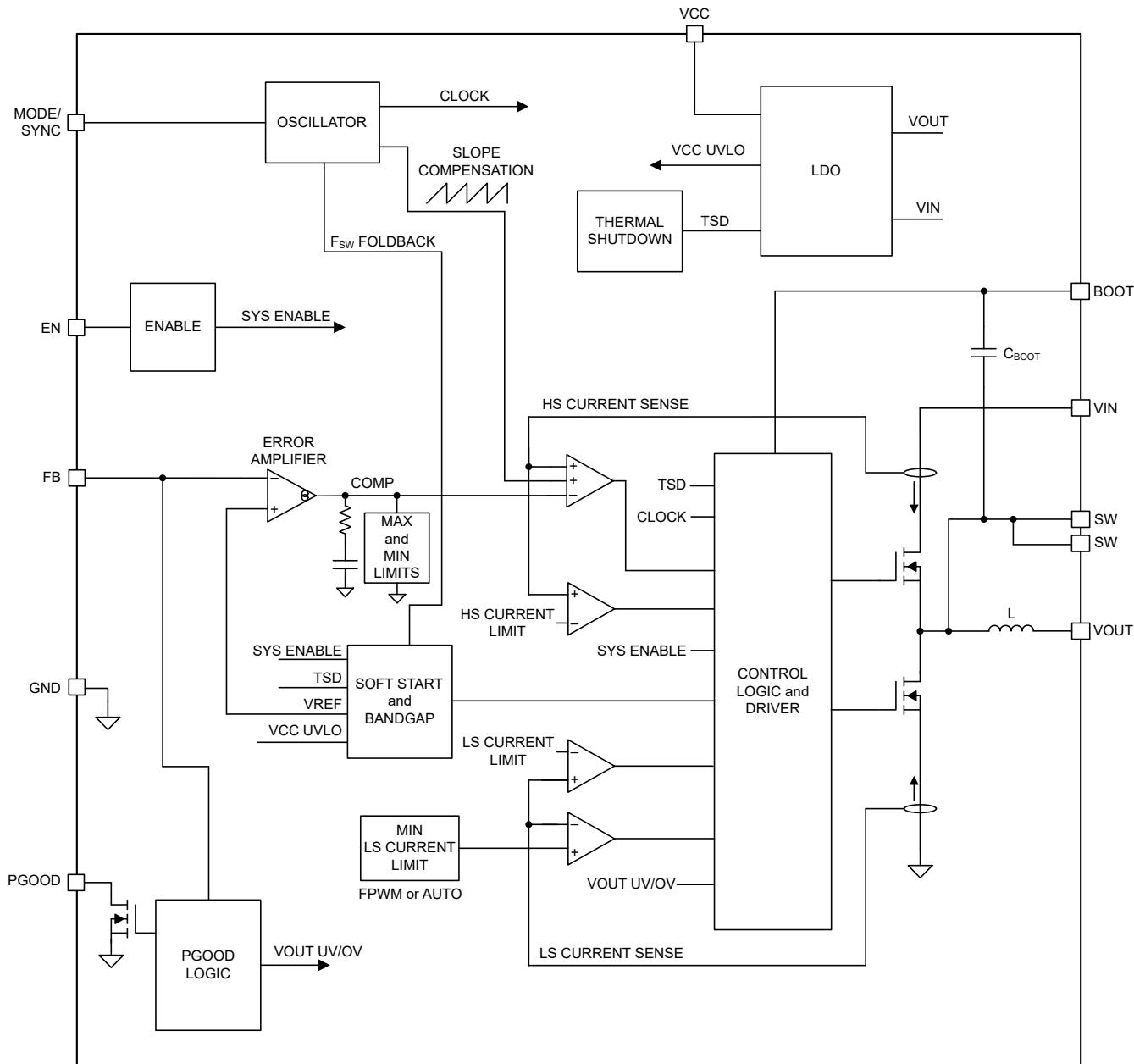

## 7.2 機能ブロック図

## 7.3 機能説明

### 7.3.1 入力電圧範囲

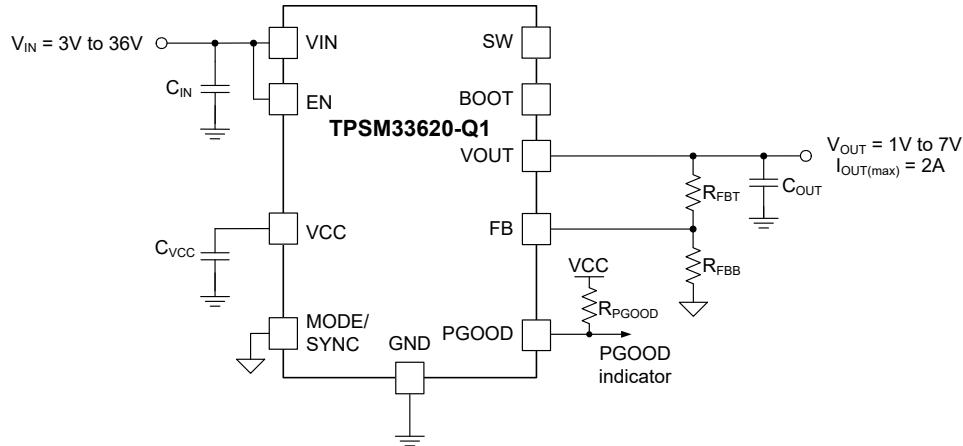

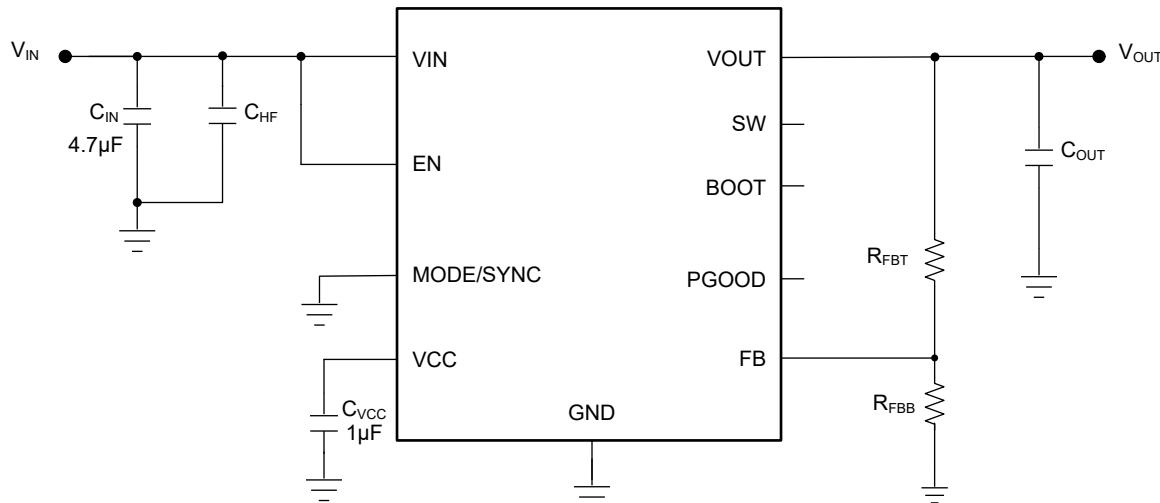

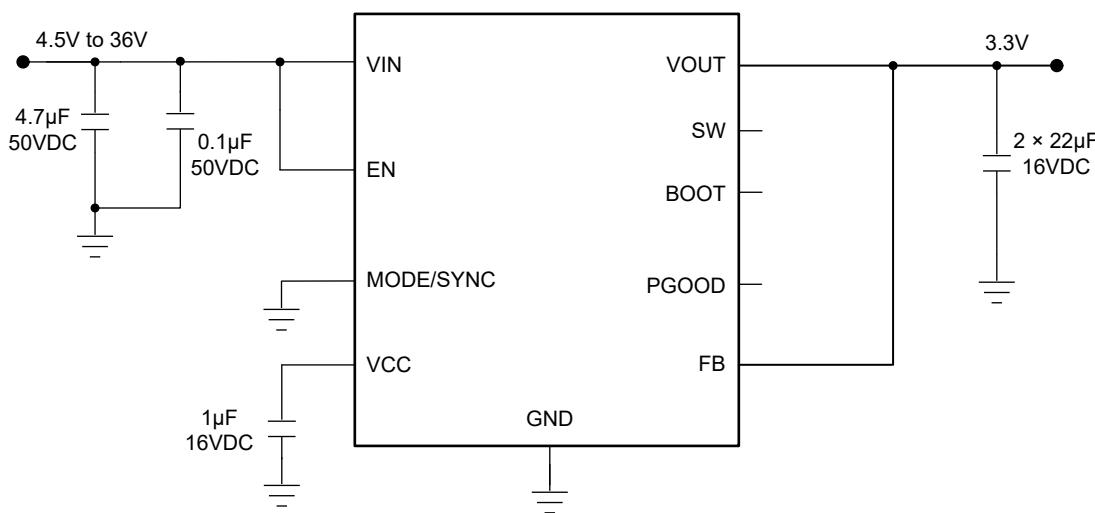

本 TPSM336xx-Q1 デバイスは、3V～36V の定的な入力電圧範囲に対応しており、たとえば標準的な 12V～36V の入力電源レールからの降圧変換を目的としています。図 7-1 の回路図に、単一の入力電源を使用して TPSM336xx-Q1 ベースの降圧レギュレータを実装するために必要なすべての部品を示します。

図 7-1. 入力電圧動作範囲が 3V～36V の場合の TPSM336xx-Q1 回路図

ラインまたは負荷過渡イベントの間、VIN ピンの電圧が絶対最大定格 (40V) を超えないように特に注意してください。絶対最大定格を超える VIN ピンでの電圧リンクは、IC に損傷を与える可能性があります。

### 7.3.2 出力電圧の選択

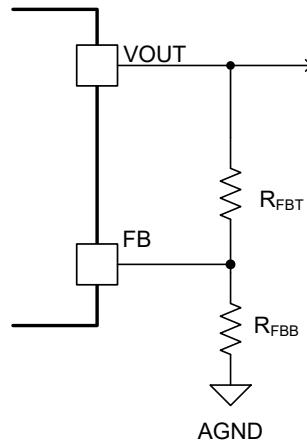

#### 7.3.2.1 可変出力電圧バリエント

TPSM336xx-Q1 は、起動時に帰還経路の抵抗を検出することで、固定出力電圧と可変出力電圧のどちらが必要かを判断します。固定 3.3V または 5V のオプションとは異なる出力電圧を希望する場合、TPSM336xx-Q1 の出力電圧を 2 つの外付け抵抗 ( $R_{FBT}$ ,  $R_{FBB}$ ) によって設定します。 $R_{FBT}$  は、VOUT (レギュレーション点) と FB ピン間に接続します。 $R_{FBB}$  は、FB ピンと AGND の間に接続します。

TPSM336xx-Q1 の可変出力電圧の範囲は 7V に対して 1V です。パワー モジュールが希望する出力電圧に確実に調整されるように、 $R_{FBT}$  と  $R_{FBB}$  を並列接続した場合の抵抗値は、式 3 に示す通り、その最小値を 5kΩ (標準値)、最大値を 10kΩ (標準値)にしてください。式 2 および 式 3 を、 $R_{FBT}$  の値を決定するための出発点として使用します。各種出力電圧に対応する抵抗値の一覧は、表 7-1 を参照してください。

$$5\text{k}\Omega < R_{FBT} \parallel R_{FBB} \leq 10\text{k}\Omega \quad (1)$$

$$R_{FBT}[\text{k}\Omega] = R_{FBB}[\text{k}\Omega] \times \left( \frac{V_{OUT}[\text{V}]}{1\text{V}} - 1 \right) \quad (2)$$

$$R_{FBT}[\text{k}\Omega] \leq 10\text{k}\Omega \times \frac{V_{OUT}[\text{V}]}{1\text{V}} \quad (3)$$

可変出力オプションの場合、 $R_{FBT}$  と並列にフィードフォワード コンデンサ  $C_{FF}$  を追加すれば、過渡応答の最適化に利用します。詳細については、「 $C_{FF}$  の選択」を参照してください。固定出力バリエントの場合、抵抗分圧回路もフィードフォワード コンデンサ  $C_{FF}$  も追加する必要はありません。

図 7-2. 可変出力バリアントの出力電圧の設定

表 7-1. 各種出力電圧に対する帰還抵抗の推奨値

| V <sub>OUT</sub> (V) | R <sub>FBT</sub> (kΩ) <sup>(1)</sup> | R <sub>FBB</sub> (kΩ) |

|----------------------|--------------------------------------|-----------------------|

| 3.3                  | 33.2                                 | 14.3                  |

| 5.0                  | 49.9                                 | 12.4                  |

| 7                    | 69.8                                 | 11.5                  |

(1) 1%の標準抵抗値に基づいた R<sub>FBT</sub> および R<sub>FBB</sub>

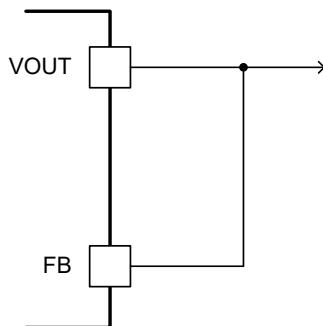

### 7.3.2.2 固定出力電圧バリアント

TPSM336xx-Q1 を固定出力設定 (外付け抵抗なし) で使用する場合、単に FB および VOUT ピンにを出力調整ポイントに直接接するだけです。3.3V または 5V 固定出力オプションは、工場出荷時に個々デバイスに固有のプログラムが済んでいます。固定出力バリアントの詳細については、[セクション 4](#) を参照してください。

図 7-3. 固定出力バリアントの出力電圧の設定

### 7.3.3 イネーブル、起動、およびシャットダウン

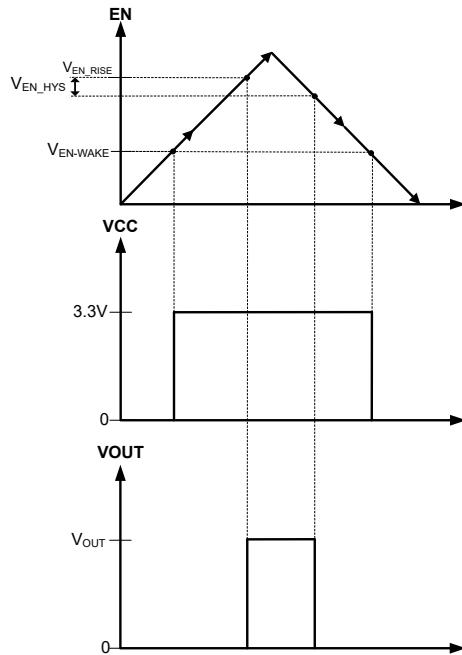

EN ピンの電圧によって、TPSM336xx-Q1 の起動またはリモートシャットダウンを制御します。EN ピンの電圧が V<sub>EN\_WAKE</sub> 未満である限り、本デバイスはシャットダウン状態を維持します。EN ピンの電圧が V<sub>EN\_WAKE</sub> を上回ると、本デバイスはスタンバイモードに移行し、内部 LDO が起動して VCC を生成します。EN の電圧がさらに上昇し、V<sub>EN\_RISE</sub> に近づくと、本デバイスは最終的にスイッチングを開始し、ソフトスタートによる起動モードに移行します。本デバイスのシャットダウンプロセス中に、EN 入力電圧の測定値が (V<sub>EN\_RISE</sub> - V<sub>EN\_HYST</sub>) を下回ると、レギュレータはスイッチングを停止し、デバイススタンバイモードに戻ります。EN ピンの電圧が V<sub>EN\_WAKE</sub> を下回ると、本デバイスは確実にシャットダウンされます。リモート高精度制御が不要な場合、高電圧に対応した EN 入力ピンを VIN 入力ピンに直接接続できます。EN 入力ピンをフローティングにすることはできません。

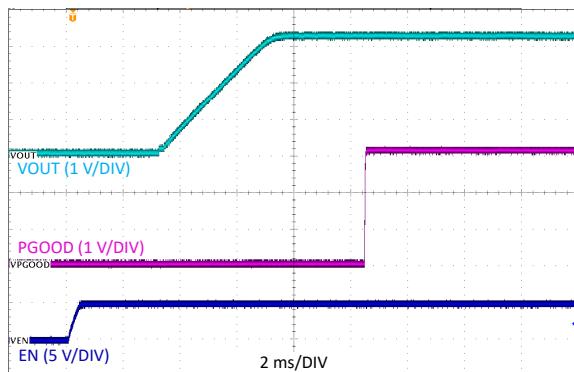

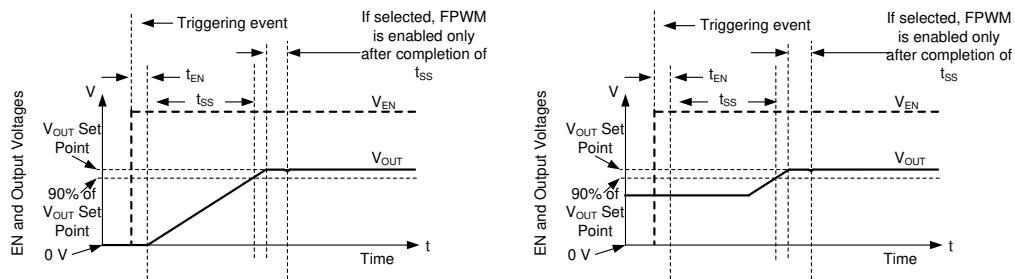

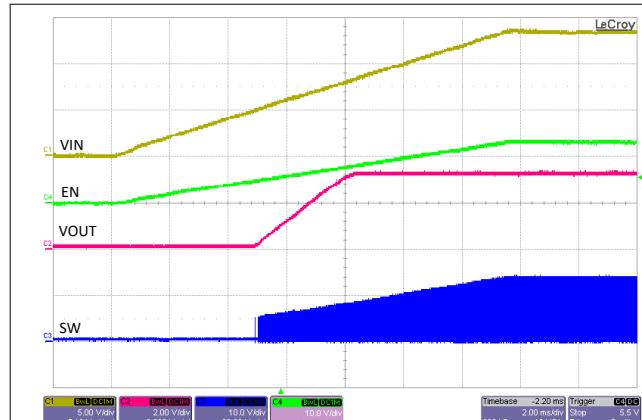

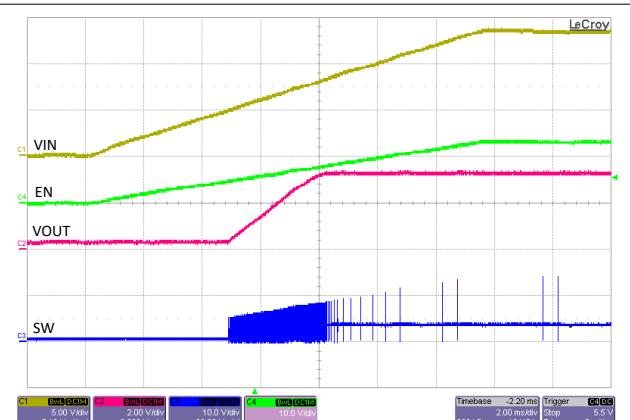

各種の EN しきい値 パラメータとそれらの値については、「電気的特性」に記載されています。図 7-4 に、高精度イネーブルの動作を示し、図 7-5 に、アプリケーションでの代表的なリモート EN の起動波形を示します。EN が High になってから約 1ms の遅延の後、出力電圧はソフトスタートで上がり始め、約 3.5ms ( $t_{ss}$ ) 後にほぼ最終値に達します。約 2.5ms ( $t_{PG\_FLT\_RISE}$ ) の遅延の後、PGOOD フラグが High になります。起動中、ソフトスタート時間が経過するまで、本デバイスは FPWM モードに移行できません。この時間は、EN の立ち上がりエッジから測定されます。

図 7-4. 高精度イネーブルの動作

図 7-5. イネーブルによる起動、 $V_{IN} = 24V$ 、 $V_{OUT} = 3.3V$

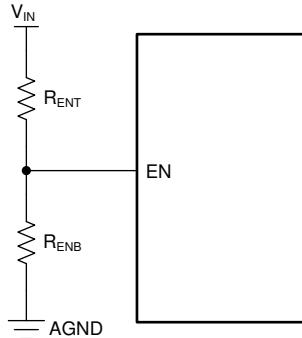

### 7.3.3.1 EN ピンによる外部 UVLO

場合によっては、本デバイスが内部的に備えているものとは異なる入力 UVLO レベルが必要とされることがあります。このニーズは、セクション 7.3.3 に示す回路を使うことで実現できます。本デバイスがオンする入力電圧を  $V_{ON}$ 、オフする入力電圧を  $V_{OFF}$  と表します。最初に、 $R_{ENB}$  の値を  $10k\Omega \sim 100k\Omega$  の範囲で選択し、次に、式 4 および 式 5 を使って  $R_{ENT}$  と  $V_{OFF}$  をそれぞれ計算します。

図 7-6. 外部 UVLO アプリケーション用のセットアップ

$$R_{ENT} = \left( \frac{V_{ON}}{V_{EN\_RISE}} - 1 \right) \times R_{ENB} \quad (4)$$

$$V_{OFF} = V_{ON} \times \left( 1 - \frac{V_{EN\_HYS}}{V_{EN\_RISE}} \right) \quad (5)$$

ここで、

- $V_{ON}$  は  $V_{IN}$  のターンオン電圧、

- $V_{OFF}$  は  $V_{IN}$  のターンオフ電圧です。

その他の用語については、「[電気的特性](#)」の表を参照してください。

### 7.3.4 外部クロック同期

1つのシステムの中で複数のレギュレータの動作を同期させ、特定のシステム レベル性能を実現することは、魅力的な機能です。TPSM336xx-Q1 の MODE/SYNC ピンにより、電源設計者は本デバイスを共通の外部クロックに同期させることができます。デバイスの同期によって、MODE/SYNC ピンに供給されるクロック信号はデバイスのスイッチングと同相になります。外部クロック同期は、すべての大きなグリッチを除去するフェーズ ロック ループ (PLL) を使用して実装されます。TPSM336xx-Q1 に流れ込んだ外部クロックは、内部の自走クロックに置き換わりますが、周波数フォールドバック動作には影響しません。出力電圧は引き続き適切にレギュレートされます。同期信号が入力されている場合、本デバイスは FPWM モードに維持され、軽負荷時には CCM で動作します。

TPSM336xx-Q1 の MODE/SYNC 入力ピンは次の選択可能な 3 つのモードのいずれかで動作できます：

- 自動モード：パルス周波数変調 (PFM) 動作は、軽負荷時に有効化されるので、ダイオード エミュレーションは、インダクタを通じて流れる逆電流を防止します。

- FPWM モード：ダイオード エミュレーションは無効化されるので、電流はインダクタを逆方向に流れることができます。これにより、負荷電流が流れなくても最大周波数で動作できます。

- SYNC モード：内部クロックは MODE/SYNC ピンに印加された外部信号にロックされます。出力電圧を最大周波数で制御でき、最小オフ時間または最小オン時間によって制限されない限り、クロック周波数は、MODE/SYNC ピンに印加された信号の周波数に一致します。デバイスが SYNC モードの間、デバイスは FPWM モードのように動作します。ダイオード エミュレーションが無効化されるため、無負荷でも MODE/SYNC ピンに印加される周波数に合わせることができます。

### 7.3.4.1 パルス依存 MODE/SYNC ピン制御

本デバイスによる 1 つ以上の動作モードを必要とするほとんどのシステムは、マイクロプロセッサなどのデジタル回路によって制御されます。これらのシステムは、動的な信号は簡単に生成できますが、マルチレベル信号を生成するのは不得意です。パルス依存 MODE/SYNC ピン制御は、これらのシステムに有効です。パルス依存 MODE/SYNC ピン制御を開始するには、有効な同期信号を印加する必要があります。表 7-2 に、パルス依存モード選択設定の概要を示します。

表 7-2. パルス依存モード選択の設定

| MODE/SYNC 入力    | モード                         |

|-----------------|-----------------------------|

| $> V_{MODE\_H}$ | FPWM (工場出荷時にスペクトラム拡散機能を設定)  |

| $< V_{MODE\_L}$ | 自動モード (工場出荷時にスペクトラム拡散機能を設定) |

| 同期クロック          | SYNC モード                    |

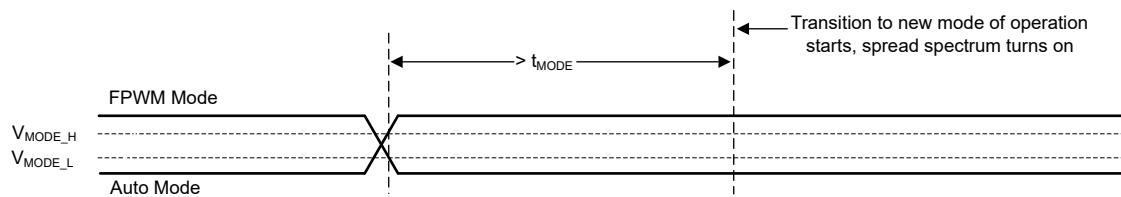

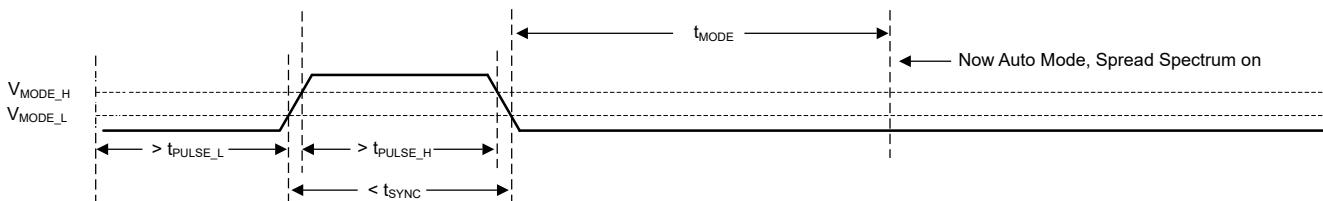

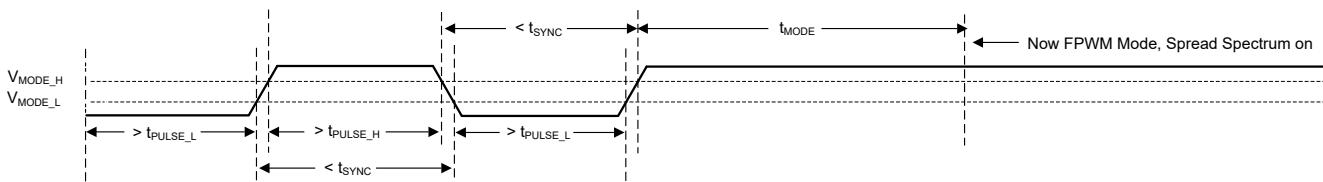

図 7-7 に、パルス依存 MODE/SYNC 制御中の自動モードと FPWM モードとの間の遷移を示します。本デバイスは、最小  $12.5\mu s$  の  $t_{MODE}$  の時間の後に新しい動作モードに遷移します。図 7-7 と図 7-8 に詳細を示します。

図 7-7. 自動モードと FPWM モードとの間の遷移

MODE/SYNC 電圧が一定のまま  $t_{MODE}$  より長い時間が経過すると、本デバイスは（工場出荷時の設定が有効化されている場合）スペクトラム拡散をオンにして、自動モードと FPWM モードのどちらかに移行し、MODE/SYNC はパルス依存方式で動作し続けます。

図 7-8. 同期モードから自動モードへの遷移

図 7-9. 同期モードから FPWM モードへの遷移

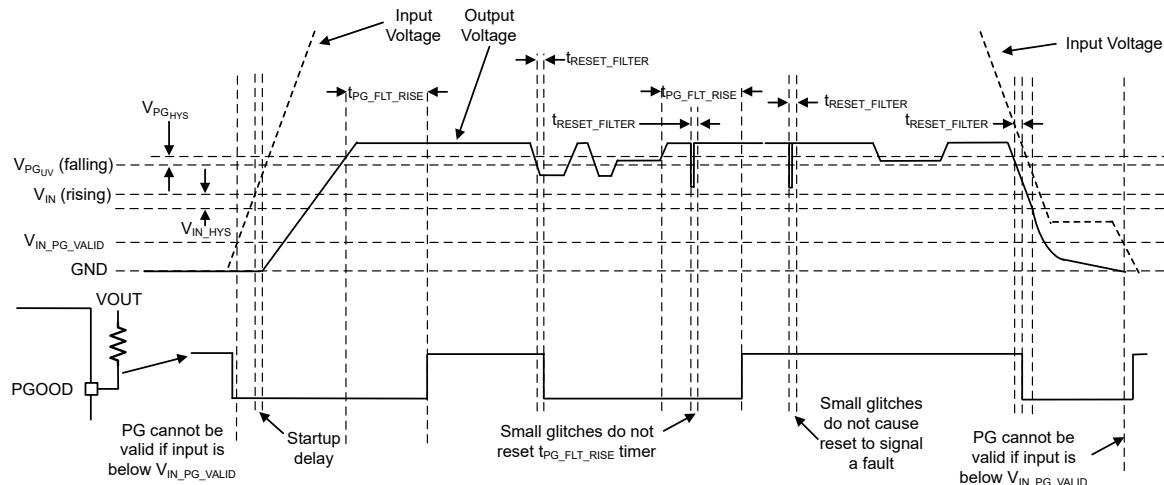

### 7.3.5 パワー グッド出力動作

TPSM336xx-Q1 の PGOOD ピンを使ったパワー グッド機能は、出力電圧が安定化範囲を外れたときはすぐにシステムマイクロプロセッサをリセットするために使用できます。通常の起動中だけでなく、デバイス フォルト条件（電流制限、サーマル シャットダウンなど）の際も、このオープン ドレイン出力は Low に維持されます。グリッチ フィルタは、出力電圧の短時間の変動（ラインおよび負荷過渡時など）に対するフラグの誤動作を防止します。 $t_{RESET\_FILTER}$  よりも短い出力電圧変動では、パワー グッド フラグは立ちません。図 7-10 に、パワー グッド動作を分かりやすく図示します。表 7-3 に、PGOOD 動作の詳細な内訳を示します。ここで、 $V_{PGUV}$  は  $V_{OUT}$ （目的の安定化出力電圧）と  $PG_{UV}$  の積、 $V_{PGHYS}$  は

$V_{OUT}$  と  $PG_{HYS}$  の積として定義されます。ここで、 $PG_{UV}$  と  $PG_{HYS}$  はどちらも「電気的特性」に記載されています。最初の起動時に、 $V_{EN\_RISE}$  がトリガされてからパワー グッドに High のフラグが立つまでに生じる総遅延時間は 6ms (標準値) です。この遅延は本デバイスの起動時にのみ発生し、パワー グッド機能のその他の通常動作中は発生しません。 $EN$  が Low にプルされると、パワー グッド フラグ出力も Low に強制されます。 $EN$  が Low であれば、入力電圧が (最大  $V_{IN\_PG\_VALID}$  が 1.5V 以上) である限り、パワー グッドは有効です。

パワー グッド出力回路はオープンドレインの N チャネル MOSFET で構成されており、適切なロジック電源に接続された外付けプルアップ抵抗を必要とします。希望に応じて、適切な抵抗を介して  $PGOOD$  を  $V_{CC}$  または  $V_{OUT}$  にプルアップします。この機能が不要な場合、 $PGOOD$  ピンをオープンにし、またはグランドに接続できます。このピンに流れ込む電流は、4mA 以下に制限します。

図 7-10. パワー グッド動作 (OV イベントは含まれません)

表 7-3. PGOOD のフォルト条件 (Low にプル)

| フォルト条件の開始                                          | 異常状態が終了しました <sup>(1)</sup>                                                               |

|----------------------------------------------------|------------------------------------------------------------------------------------------|

| $V_{OUT} < V_{PG_{UV}}$ かつ $t > t_{RESET\_FILTER}$ | 出力電圧がレギュレートされている。<br>$V_{PG_{UV}} + V_{PG_{HYS}} < V_{OUT} - V_{PG_{UV}} - V_{PG_{HYS}}$ |

| $V_{OUT} > V_{PG_{ov}}$ かつ $t > t_{RESET\_FILTER}$ | 出力電圧がレギュレートされている。                                                                        |

| $T_J > T_{SDN}$                                    | $T_J < T_{SDN} - T_{HYST}$ かつ出力電圧が調整されている                                                |

| $EN < V_{EN\_RISE} - V_{EN\_HYS}$                  | $EN > V_{EN\_RISE}$ かつ出力電圧が調整されている                                                       |

(1) 障害状態が終了した後、 $PGOOD$  出力が解放される前に  $t_{PGOOD\_ACT}$  が経過する必要があります。

### 7.3.6 内部 LDO、VCC、VOUT/FB 入力

TPSM336xx-Q1 では、内部 LDO 出力と VCC ピンを使用してすべての内部電源を供給しています。起動中、VCC は瞬間に通常の動作電圧を超えた後、通常の動作電圧まで低下します。

### 7.3.7 ブートストラップ電圧および $V_{BOOT-UVLO}$ (BOOT 端子)

HS スイッチを確実にターンオンさせるため、ハイサイドスイッチドライバ回路には、VIN よりも高いバイアス電圧が必要です。BOOT と SW の間には 0.1μF の内部コンデンサが接続されており、BOOT 端子の電圧を (SW + VCC) まで昇圧するためのチャージ ポンプとして機能します。物理的な設計サイズを最小化するため、TPSM336xx-Q1 のダイにはブートダイオードが内蔵されています。ブート レールには UVLO 設定が備わっています。この UVLO のしきい値は  $V_{BOOT-UVLO}$  ですが、標準設定値は 2.1V です。ブートコンデンサが、SW ピンを基準として、この電圧を超えて充電されていない場合、本デバイスは充電シーケンスを開始し、ハイサイド素子をターンオンしようとする前にローサイド スイッチをターンオンします。

### 7.3.8 スペクトラム拡散

スペクトラム拡散は、固定周波数で動作する部品よりも広範囲の周波数帯域にピークを拡散することにより、特定の周波数によるピーク放射に対する影響を低減します。TPSM336xx-Q1 は、スイッチング周波数の最初のいくつかの高調波からの低周波伝導放射を低減するように設計された変調パターンを実装しています。このパターンは、FM 帯域に落ちる可能性があり、フィルタ処理が難しい高調波を低減させるのにも役立ちます。これらの高調波はしばしば、スイッチノードとインダクタの周囲の電界によって環境と結合します。TPSM336xx-Q1 は±4%の周波数拡散を採用しており、FM および TV 帯域全体にエネルギーをスムーズに拡散できます。このデバイスには、デュアル ランダム スペクトラム拡散(DRSS)機能が実装されています。DRSS は、三角波の周波数拡散パターンと疑似ランダム周波数ホッピングを組み合わせたものです。これらの組み合わせにより、スペクトラム拡散は、次のとおりエネルギー拡散に非常に効果的です：

- 低速三角波パターンによる基本スイッチング高調波

- スイッチング周波数に疑似ランダムジャンプを付加した高周波ハーモニクス

DRSS の利点は、基本周波数偏差が小さく、高域の周波数で等価高調波減衰が得られることです。この利点により、変調周波数で生じる入力電流と出力電圧リップルの量が低減されます。また、TPSM336xx-Q1 では、ユーザーがスペクトラム拡散変調パターンに起因する出力電圧リップルをさらに低減できます。

スペクトラム拡散は、本デバイスのクロックが本来の周波数で自走している間に限り利用できます。以下のいずれかの条件がスペクトラム拡散に優先する場合、スペクトラム拡散はオフになります：

- 低い入力電圧での動作 一ドロップアウトする動作条件 - により、クロック速度が低下している場合。

- 自動モードで軽負荷によりクロック速度が低下した場合。FPWM モードで動作している場合、無負荷であってもスペクトラム拡散が有効となっている可能性があるので、注意してください。

- 入出力電圧比が大きいため、クロック速度が低下しました場合。オン時間が最小オン時間に達した場合にこの動作モードが想定されます。[電気的特性](#) を参照してください。

- クロックが外部クロックに同期している。

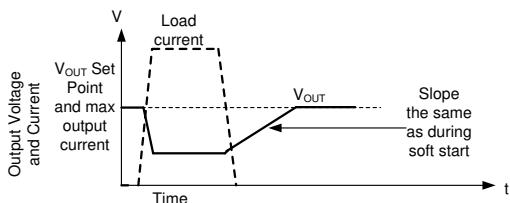

### 7.3.9 ソフトスタートとドロップアウトからの回復

TPSM336xx-Q1 を使用して設計する場合、[図 7-11](#) および [図 7-12](#) に示すように、ドロップアウトからの回復とソフトスタートに起因する出力電圧の上昇は、2 つの個別の動作条件として考慮します。ソフトスタートは、以下のいずれかの条件によってトリガれます。

- デバイスの VIN ピンに電力が供給され、低電圧ロックアウトが解除されました。

- 本デバイスをオンにするために EN が使われました。

- 過熱保護によるシャットダウンから回復した。

ソフトスタートがトリガされた後、パワー モジュールは以下の動作を実行します。

- 出力電圧を制御するためにパワー モジュールで使われる基準電圧が、ゆっくりと上昇します。その結果、出力電圧が(それまで 0V だった場合)、 $t_{ss}$  の時間をかけて目的の値の 90% に達します。

- 動作モードが自動動作モードに設定され、ローサイド MOSFET のダイオード エミュレーション モードがアクティブになります。これにより、出力を Low にしなくても起動できます。この説明は、プリバイアス スタートアップ時に出力に電圧がすでに存在している場合にも当てはまります。

図 7-11. プリバイアス電圧の有無によるソフトスタート

### 7.3.9.1 ドロップアウトからの回復

出力電圧の低下が数 % を超えると常に、出力電圧はゆっくり上昇します。この条件は、本書ではドロップアウトからの正常な回復と呼ばれ、ソフトスタートとは以下の 2 つの重要な点で異なります。

- 基準電圧は、現在の出力電圧を実現するために必要な値よりも約 1% 高い値に設定される。

- 本デバイスが **FPWM** に設定されている場合、ドロップアウトからの回復中は **FPWM** モードで動作し続けます。外部電源によって出力電圧が突然プルアップされた場合、は出力をプルダウンする場合があります。通常動作中に存在するすべての保護機能は作動しており、出力が高い電圧またはグランドに短絡した場合の致命的な障害を防止していることに注意します。

図 7-12. ドロップアウトからの回復

出力電圧の低下が、高負荷と低入力電圧のどちらによるものであっても、出力がその設定点を下回る原因となっている条件が解消された後、起動時と同じ速度で出力は上昇します。図 7-12 に、この挙動の例を示します。

### 7.3.10 過電流保護(ヒカップモード)

TPSM336xx-Q1 は、ハイサイド (HS) MOSFET とローサイド (LS) MOSFET の両方でサイクル バイ サイクル電流制限回路をすることで、過電流状態から保護されます。内蔵のインダクタ電流が、スイッチングサイクルごとに、ハイサイドおよびローサイドの電流制限しきい値と比較されます。過電流状態の間、スイッチング周波数の低下に伴って出力電圧が低下します。

ハイサイド MOSFET 過電流保護機能は、代表的なピーク電流モード制御方式で実装されています。HS スイッチ電流は、短いブランкиング時間の後に HS がオンになると検出されます。固定電流設定点と、内部誤差アンプ ループ出力からスロープ補償を引いた値のどちらか小さい方と HS スイッチ電流が、スイッチング サイクルごとに比較されます。内部誤差アンプ ループ出力には最大値があり、スロープ補償はデューティ サイクルに対応して大きくなるため、デューティ サイクルが 35% より大きい場合、デューティ サイクルが大きくなると HS 電流制限値は下がります。

LS スイッチがオンになると、LS スイッチを流れる電流も検出され、監視されます。ハイサイド デバイスと同様にローサイド デバイスは、内部誤差アンプ ループによって制御されるターンオフ限界値を持っています。ローサイド デバイスの場合、発振器が正常に新しいスイッチング サイクルを開始したとしても、電流がこの値を超えるとターンオフは禁止されます。また、ハイサイド デバイスと同様に、ターンオフ電流に許容される高さに限界があります。これをローサイド電流制限と呼びます。LS 電流制限を超えた場合、LS MOSFET はオン状態を維持し、HS スイッチはターンオンしません。LS 電流がこの制限値を下回ると、LS スイッチはオフになり、HS 素子が最後にオンになってから 1 クロック周期以上が経過しさえすれば、HS スイッチは再度オンになります。

電流制限中に短絡が発生して FB 入力の電圧が約 0.4V ( $V_{HICUP}$ ) を下回ると、本デバイスはヒカップ モードに入ります。このモードでは、本デバイスは  $t_W$  または約 50ms の間スイッチングを停止し、その後、ソフトスタートを使って通常の再起動を行います。短絡状態が続く場合、本デバイスは電流制限内で約 5ms (標準値) 動作した後、再度シャットダウンします。短絡状態が持続する限り、このサイクルが繰り返されます。

### 7.3.11 サーマルシャットダウン

サーマル シャットダウンは、本デバイスの接合部温度が 168°C (標準値) を超えると内部スイッチをオフにすることで、総電力損失を制限します。サーマル シャットダウンは、158°C (最小値) 未満ではトリガされません。サーマル シャットダウン

が発生した後、ヒステリシスにより、接合部温度が約 153°C (標準値) に低下するまで、本デバイスはスイッチングできません。接合部温度が 153°C (標準値) を下回ると、TPSM336xx-Q1 は再度ソフトスタートを試みます。

接合部温度が上昇して、TPSM336xx-Q1 がシャットダウンされても、電力は VCC に供給され続けます。高い接合部温度のせいで本デバイスが無効化されると同時に、VCC の短絡による過熱を防止するため、VCC に電力を供給する LDO の電流制限値が低減されます。サーマル シャットダウン時の LDO の供給電流はわずか数ミリアンペアです。

## 7.4 デバイスの機能モード

### 7.4.1 シャットダウンモード

EN ピンは、本デバイスの電気的オン / オフ制御に使用できます。EN ピンの電圧が 0.7V (標準値) を下回ると、パワーモジュールは電圧を出力しなくなり、本デバイスはシャットダウン モードに入ります。シャットダウン モードでは、通常、静止電流が 300nA まで低下します。

### 7.4.2 スタンバイ モード

内部 LDO の EN スレッショルドは、出力の EN スレッショルドよりも低い値です。EN ピンの電圧が 1V (最大値) より高く、かつ出力電圧の高精度イネーブル スレッショルドより低い場合、内部 LDO は VCC 電圧を 3.3V (標準値) にレギュレートします。EN ピンの電圧が高精度イネーブルしきい値を上回らない限り、SW ノードの内部パワー MOSFET はオフのままでです。TPSM336xx-Q1 は UVLO 保護も動作します。

### 7.4.3 アクティブ モード

EN ピンの電圧が  $V_{EN\_RISE}$  を上回っており、かつ  $V_{IN}$  が  $V_{IN}(\text{min})$  を上回っていて、なおかつその他のフォルト条件が存在しない場合、TPSM336xx-Q1 は必ずアクティブ モードになっています。この動作を可能にする最も簡単な方法は、EN ピンを  $V_{IN}$  に接続することです。これにより、印加された入力電圧が最小  $V_{IN}(\text{min})$  を超えると自動的に起動できます。

TPSM336xx-Q1 は、負荷電流、入力電圧、出力電圧に応じて次の 5 つのモードのいずれかになります：

- 連続導通モード (CCM)。負荷電流がインダクタリップル電流の 1/2 より大きいときには、固定周波数 ( $f_{SW}$ ) の連続導通モードになります。

- 自動モード - 軽負荷動作時: パルス周波数変調 (PFM)。非常に軽い負荷で  $f_{SW}$  が低下した場合。

- FPWM モード - 軽負荷動作: 不連続導通モード (DCM)。負荷電流がインダクタリップル電流の 1/2 未満である場合。

- 最小オン時間: 入力電圧が高くかつ出力電圧が低い場合に、レギュレーションを維持するため、 $f_{SW}$  が低下します。

- ドロップアウト モード: 電圧低下を最小限に抑えるため、 $f_{SW}$  が低下します。

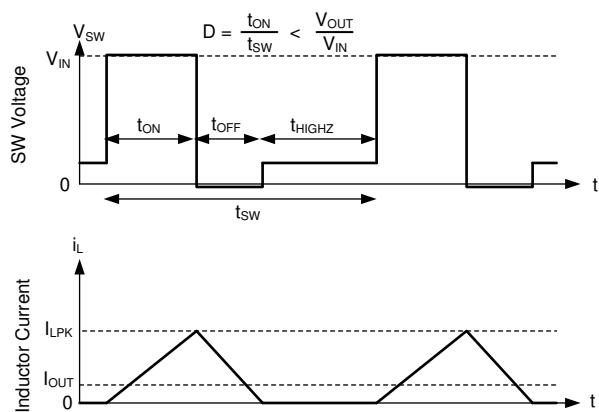

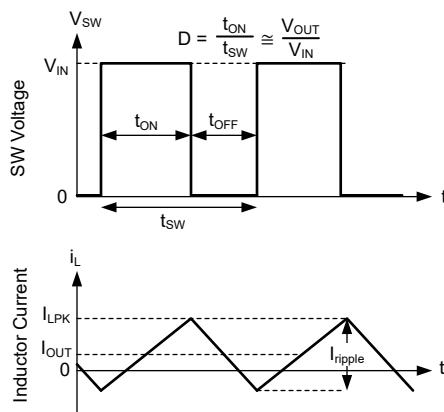

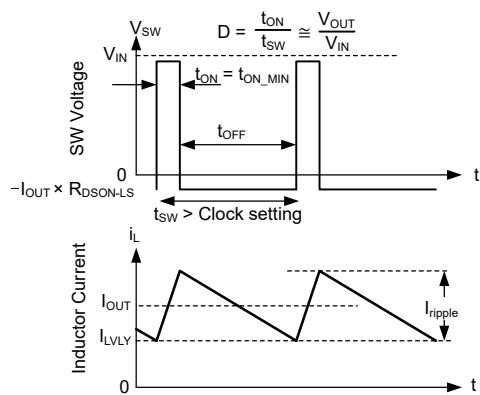

#### 7.4.3.1 CCM モード

以下の TPSM336xx-Q1 の動作説明については、「[機能ブロック図](#)」を参照してください。CCM では、TPSM336xx-Q1 は、各種デューティサイクル (D) で内蔵ハイサイド (HS) およびローサイド (LS) スイッチをオンにすることで、出力電圧のレギュレーションを実現します。HS スイッチのオン時間の間、SW ピンの電圧 ( $V_{SW}$ ) は  $V_{IN}$  の付近までスイングし、インダクタ電流は線形的な傾きで増加します。HS スイッチは、制御ロジックによってオフにされます。HS スイッチのオフ時間 ( $t_{OFF}$ ) の間、LS スイッチはオンにされます。インダクタ電流は LS スイッチを通して放電され、LS スイッチの両端の電圧降下によって  $V_{SW}$  をグランドの下まで強制的にスイングさせます。一定の出力電圧を維持するため、降圧モジュールのコンバータループはデューティサイクルを調整します。D は、HS スイッチのオン時間をスイッチング周期で割った値として次のように定義されます。

$$D = T_{ON} \div T_{SW} \quad (6)$$

損失が無視される理想的な降圧モジュール コンバータでは、次のように D は出力電圧に比例し、入力電圧に反比例します。

$$D = V_{OUT} \div V_{IN} \quad (7)$$

#### 7.4.3.2 自動モード – 軽負荷動作

軽負荷時、TPSM336xx-Q1 は 2 つの動作を行うことができます。自動モード動作と呼ばれる動作を使うと、負荷が重い際の通常電流モードと高効率の軽負荷動作との間を継ぎ目なく移行できます。FPWM モードと呼ばれるもう 1 つの動作では、無負荷時でも最大周波数が維持されます。TPSM336xx-Q1 がどのモードで動作するかは、このファミリから選定したバリエントによって異なります。周波数を外部信号に同期させる場合、すべてのデバイスは FPWM モードで動作することに注意します。

自動モードでの軽負荷動作を採用しているのは、TPSM336xx-Q1 だけです。軽負荷動作では、効率を向上させるため次の 2 つの手法が使われます。

- DCM 動作が可能なダイオード エミュレーション (図 7-13 を参照)

- 周波数低減 (図 7-14 を参照)

これら 2 つの機能は、同時に動作することで軽負荷時の効率を向上させますが、互いに独立して機能しています。

##### 7.4.3.2.1 ダイオード エミュレーション

ダイオード エミュレーションは、インダクタを流れる逆電流を防止します。固定ピーク インダクタ電流の場合、レギュレートするために周波数をより低くする必要がある可能性があります。ダイオード エミュレーションは、周波数が下がった際のリップル電流も制限します。固定ピーク電流では、出力電流がゼロに向かって低下するにつれて、レギュレーションを維持するために周波数をゼロに近い値まで下げます。

自動モードでは、SW ノード電流がゼロに近づくとローサイド素子はオフになります。その結果、出力電流が CCM で発生する可能性があるインダクタリップルの 1/2 未満になると、本デバイスは DCM で動作します。これは、ダイオード エミュレーションが機能しているということと等価です。

図 7-13. PFM 動作

自動モードでは、TPSM336xx-Q1 は最小ピーク インダクタ電流設定値を持っています。入力電圧を一定にした状態で、電流値が下がると、オン時間は一定になります。その後、周波数を調整することで、レギュレーションが達成されます。この動作モードを PFM モード レギュレーションと呼びます。

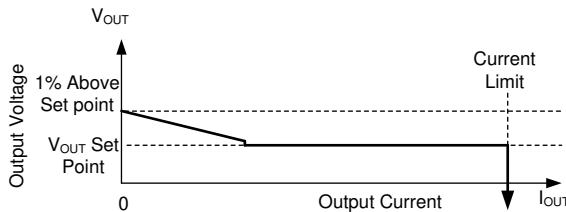

##### 7.4.3.2.2 周波数低減

TPSM336xx-Q1 は、出力電圧が高くなるとすぐに周波数を下げます。この機能は、内部誤差アンプ補償出力 (内部信号 COMP) が Low でありかつ VOUT/FB のレギュレーション設定点と VOUT/FB に印加される電圧との間にオフセットが存在する場合、常に有効化されます。結果的に、自動モードでの軽負荷の間、通常動作の場合よりも出力インピーダンスが大きくなります。本デバイスが完全に無負荷である場合、出力電圧は約 1% 高くなるはずです。

自動モードでは、本デバイスの出力電流が定格電流の約 1/10 を下回ると、降圧コンバータが完全に無負荷になった際に出力電圧が 1% 高くなるように出力抵抗が増大します。

図 7-14. 定常状態の出力電圧と自動モードの出力電流との関係

PFM動作では、PFM検出回路を動作させるために、出力電圧に小さな正のDCオフセットが必要となります。PFMの周波数が低いほど、 $V_{OUT}$ に必要なDCオフセットは大きくなります。 $V_{OUT}$ でのDCオフセットが許容できない場合、 $V_{OUT}$ に接続したダミー負荷またはFPWMモードを使うことで、このオフセットを低減または除去できます。

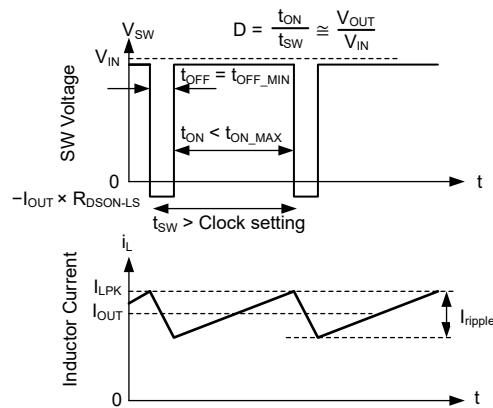

#### 7.4.3.3 FPWMモード - 軽負荷動作

FPWMモードでは、出力の負荷が軽い間、周波数が維持されます。周波数を維持するため、インダクタを流れる逆電流が制限されます。負電流制限回路により、逆電流が制限されます。負電流制限値については、「電気的特性」を参照してください。

FPWMモードでは、 $I_{OUT}$ が $I_{ripple}$ の半分未満でも連続導通(CCM)が可能です。

図 7-15. FPWMモード動作

デバイスの種類にかかわらず、FPWMモードでは、軽負荷時であっても最小オン時間指示できるほど出力電圧が高ければ、依然として周波数を低減できるため、出力をプルアップする必要があるフォルト中も良好に動作できます。

#### 7.4.3.4 最小オン時間(高入力電圧)での動作

入出力電圧比が所与のクロック設定によるチップの最小オン時間よりも短いオン時間を要求した場合でも、TPSM336xx-Q1は引き続き出力電圧の調整を続けます。この動作は、バレー電流制御を使用して実行されます。補償回路は常に最大ピークインダクタ電流と最大バレーインダクタ電流の両方を指示します。何らかの理由でバレー電流を超過した場合、補償回路によって決定された値をバレー電流が下回るまで、クロックサイクルは延長されます。本パワー モジュールが電流制限動作をしていない場合、最大バレー電流はピークインダクタ電流よりも高く設定され、ピーク電流のみを使ったリギュレーションに失敗しない限りバレー制御が使われることがないようにしています。補償回路が指示したピークコマンドをインダクタピーク電流値が上回るほど、出力電圧に対する入力電圧の比が高すぎる場合、出力電圧をリギュレートするのに十分な速さではハイサイド素子をオフにすることはできません。結果的に、補償回路はピーク電流とバレー電流の両方を

小さくします。補償回路によって十分小さい電流が選択されると、バレー電流は、補償回路が指示した電流に一致します。これらの条件では、ローサイド素子がオンに維持され、目的のバレー電流をインダクタ電流が下回るまで、次のクロックサイクルは開始されません。オン時間は最小値に固定されているため、このタイプの動作は、コンスタント オンタイム (COT) 制御方式を採用したデバイスの動作と似ています。図 7-16 を参照してください。

バレー制御モードでは、ピーク インダクタ電流ではなく、最小インダクタ電流が制御されます。

図 7-16. バレー電流モード動作

#### 7.4.3.5 ドロップアウト

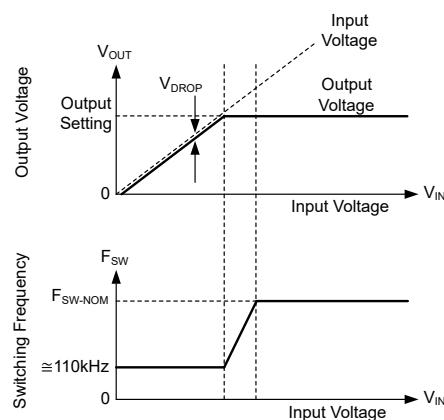

ドロップアウト動作とは、必要なデューティサイクルを達成するために周波数を下げ、入力電圧に対する出力電圧の比を任意の値に制御することです。与えられたクロック周波数において、デューティサイクルは最小オフ時間によって制限されます。クロック周波数が維持される場合、図 7-18 に示すように、この制限値に達した後、出力電圧が低下する可能性があります。TPSM336xx-Q1 は、出力電圧が下がるのを許容するのではなく、クロックサイクルが終わっても必要なピークインダクタ電流が達成されるまでハイサイドスイッチのオン時間を延長します。必要なピークインダクタ電流に達すると、または所定の最大オン時間 ( $t_{ON-MAX}$ 、約 9μs) が経過すると、クロックは新しいサイクルを開始できます。その結果、最小オフ時間の存在に起因して、選択されたクロック周波数において必要なデューティサイクルが達成できない場合、レギュレーションを維持するために周波数が低下します。図 7-17 に示すように、 $t_{ON-MAX}$  のオン時間を使っても出力電圧をレギュレートできないほど入力電圧が低い場合、出力電圧は入力電圧よりもわずかに ( $V_{DROP}$ ) 低い値に下がります。ドロップアウトからの回復の詳細については、セクション 7.3.9.1 を参照してください。

出力電圧および周波数と入力電圧との関係: 入力電圧と出力電圧設定値との差がほとんどない場合、本 IC はレギュレーションを維持するために周波数を下げます。入力電圧が低すぎて、約 110kHz で目的の出力電圧を供給できない場合、入力電圧は出力電圧に追従します。

図 7-17. ドロップアウト時の周波数と出力電圧

ドロップアウト中のスイッチング波形。インダクタ電流は、目的のピーク値に達するのに通常のクロックよりも長い時間を要します。その結果、周波数は低下します。この周波数の低下は  $t_{ON-MAX}$  によって制限されます。

図 7-18. ドロップアウト波形

## 8 アプリケーションと実装

---

### 注

以下のアプリケーション情報は、テキサス・インスツルメンツの製品仕様に含まれるものではなく、テキサス・インスツルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。また、お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

---

### 8.1 アプリケーション情報

TPSM336xx-Q1 では、わずか数個の外部部品を使用するだけで、幅広い範囲の電源電圧を固定出力電圧に変換できます。TPSM336xx-Q1 の設計プロセスを迅速化および効率化する場合、[WEBENCH](#) の回路設計と選定シミュレーションサービスのオンラインソフトウェアを利用すれば、設計手順を繰り返し活用し包括的な部品データベースにアクセスして完全な設計を生成することができます。以下のセクションでは、TPSM336xx-Q1 パワー モジュールを設定するための設計手順について解説します。

すでに説明したように、TPSM336xx-Q1 は、高精度イネーブル、UVLO、PGOOD インジケータなど、システム設計要件を満たすためのオプション機能もいくつか内蔵しています。以下に示す詳細なアプリケーション回路では、各種の使用事例に適した TPSM336xx-Q1 の設定方法を紹介しています。詳細については、[『TPSM33620QEVM EVM 評価基板 EVM ユーザー ガイド』](#)を参照してください。

---

### 注

以下のアプリケーション情報に記載されているすべての容量値は、特に記述のない限り実効値を指しています。実効値は、定格値や銘板値ではなく、DC バイアスおよび温度における実際の容量として定義されます。X7R 以上の誘電体を使用した、高品質で低 ESR のセラミックコンデンサを全体にわたって使用してください。値の大きいセラミックコンデンサは、すべて、通常の許容誤差と温度効果に加えて、電圧係数が大きくなります。DC バイアスを印加すると、静電容量は大幅に低下します。この点については、ケース サイズが大きく、より高い電圧定格のものが望ましいです。これらの影響を軽減するために、複数のコンデンサを並列に使用すれば、最小実効静電容量を必要な値まで大きくすることができます。この対策により、個別のコンデンサの RMS 電流要件も緩和されます。実効静電容量の最小値を確実に実現するために、コンデンサ バンクのバイアスおよび温度変動を慎重に検討する必要があります。

---

## 8.2 代表的なアプリケーション

図 8-1 に、TPSM336xx-Q1 の代表的なアプリケーション回路を示します。本デバイスは、幅広い外付け部品とシステムパラメータで機能するように設計されています。しかし内部補償は、特定の範囲のスイッチング周波数と出力容量に対して最適化されています。

図 8-1. アプリケーション回路例 (TPSM336xx-Q1)

表 8-1. 調整可能な出力 TPSM33620-Q1 における外付け部品の標準値

| f <sub>sw</sub> (kHz) | V <sub>OUT</sub> (V) | 公称 C <sub>OUT</sub> (定格容量) | R <sub>FBT</sub> <sup>(1)</sup> (kΩ) | R <sub>FB<sub>B</sub></sub> <sup>(1)</sup> (kΩ) | C <sub>IN</sub>   | C <sub>VCC</sub> | C <sub>FF</sub> |

|-----------------------|----------------------|----------------------------|--------------------------------------|-------------------------------------------------|-------------------|------------------|-----------------|

| 2200                  | 3.3                  | 2 × 22µF                   | 33.2                                 | 14.3                                            | 4.7µF + 1 × 100nF | 1µF              | 10pF            |

| 2200                  | 5                    | 2 × 22µF                   | 49.9                                 | 12.4                                            | 4.7µF + 1 × 100nF | 1µF              | 10pF            |

(1) 上記の範囲外の R<sub>FBT</sub> と R<sub>FB<sub>B</sub></sub> の値については、セクション 7.3.2 を参照してください。

表 8-2. 固定出力 TPSM33620-Q1 における外付け部品の標準値

| f <sub>sw</sub> (kHz) | V <sub>OUT</sub> (V) | 公称 C <sub>OUT</sub> (定格容量) | R <sub>FBT</sub> (kΩ) | R <sub>FB<sub>B</sub></sub> (kΩ) | C <sub>IN</sub>   | C <sub>VCC</sub> | C <sub>FF</sub> <sup>(1)</sup> |

|-----------------------|----------------------|----------------------------|-----------------------|----------------------------------|-------------------|------------------|--------------------------------|

| 2200                  | 3.3                  | 2 × 22µF                   | 0                     | DNP                              | 4.7µF + 1 × 100nF | 1µF              | DNP                            |

| 2200                  | 5                    | 2 × 22µF                   | 0                     | DNP                              | 4.7µF + 1 × 100nF | 1µF              | DNP                            |

(1) DNP = 自動入力されません

表 8-3. 固定出力 TPSM33610/06-Q1 の一般的な外部コンポーネントの値

| デバイス         | V <sub>OUT</sub> (V) <sup>(1)</sup> | 公称 C <sub>OUT</sub> (定格容量) | C <sub>IN</sub>   | C <sub>VCC</sub> (µF) | C <sub>FF</sub> <sup>(2)</sup> |

|--------------|-------------------------------------|----------------------------|-------------------|-----------------------|--------------------------------|

| TPSM33610-Q1 | 3.3                                 | 1 × 22µF                   | 4.7µF + 1 × 100nF | 1                     | DNP                            |

| TPSM33606-Q1 | 5                                   | 1 × 22µF                   | 4.7µF + 1 × 100nF | 1                     | DNP                            |

(1) 固定出力構成では R<sub>FBT</sub> は短く、rfbb<sub>FB<sub>B</sub></sub> は DNP です

(2) DNP = 自動入力されません

### 8.2.1 設計要件

「[詳細な設計手順](#)」では、表 8-4 に従って、部品を設計および選択する手順を説明します。

表 8-4. 詳細設計パラメータ

| 設計パラメータ   | 数値の例       |

|-----------|------------|

| 入力電圧      | 4.5V ~ 36V |

| 出力電圧      | 3.3V       |

| 最大出力電流    | 0A~2A      |

| スイッチング周波数 | 2.2MHz(固定) |

### 8.2.2 詳細な設計手順

図 8-2 に、次の設計手順と部品の選定について説明しています。

図 8-2. 3.3V VOUT の設計例

#### 8.2.2.1 WEBENCH® ツールによるカスタム設計

ここをクリックすると、WEBENCH® Power Designer により、TPSM336xx-Q1 デバイスを使用するカスタム設計を作成できます。

- 最初に、入力電圧 (VIN)、出力電圧 (VOUT)、出力電流 (IOUT) の要件を入力します。

- オプティマイザのダイヤルを使用して、効率、占有面積、コストなどの主要なパラメータについて設計を最適化します。

- 生成された設計を、テキサス・インスツルメンツが提供する他の方式と比較します。WEBENCH Power Designer では、カスタマイズされた回路図と部品リストを、リアルタイムの価格と部品の在庫情報と併せて参照できます。

通常、次の操作を実行可能です。

- 電気的なシミュレーションを実行し、重要な波形と回路の性能を確認する

- 熱シミュレーションを実行し、基板の熱特性を把握する

- カスタマイズされた回路図やレイアウトを、一般的な CAD フォーマットで出力する

- 設計のレポートを PDF で印刷し、設計を共有する

WEBENCH ツールの詳細は、[www.ti.com/ja-jp/WEBENCH](http://www.ti.com/ja-jp/WEBENCH) でご覧になれます。

#### 8.2.2.2 出力電圧の設定

このデバイスは固定、可変デバイスです。固定 3.3V の出力電圧を希望する場合、ユーザーは VOUT/FB ピンを出力コンデンサに直接接続することができます。3.3V または 5V 固定出力オプションは、工場で個々のデバイスごとに固有の調整が行われます。固定出力電圧バリエントの選択については [セクション 4](#) を参照してください。可変出力電圧を希望する場合は、抵抗分圧回路で希望出力電圧を設定することができます。帰還抵抗値の選択方法の詳細については、[セクション 7.3.2](#) および [セクション 7.3.2.1](#) を参照してください。

### 8.2.2.3 入力コンデンサの選択

TPSM336xx-Q1 には、最小入力容量として 4.7μF が必要です。バイパス機能を向上させるため、並列に 0.1μF コンデンサを追加することを推奨します。十分な電圧および温度定格を持つ高品質のセラミック タイプ コンデンサが必要です。入力コンデンサの電圧定格は、最大入力電圧よりも高い必要があります。セラミックコンデンサの印加電圧に対するディレーティングを補償するために、最大入力電圧の 2 倍の電圧を定格とする、複数のコンデンサを並列に配置することを推奨します。この設計では、4.7μF と 0.1μF の 50V 定格のコンデンサを使用します。

多くの場合、入力にセラミックと並列に電解コンデンサを使用することが推奨されます。これは、長い配線またはパターンを使って入力電源をレギュレータに接続する場合に特に当てはまります。このコンデンサに中程度の ESR を持つコンデンサを使うことは、長い電源配線によって生じる入力電源のリギングを減衰させるのに有効です。この追加コンデンサの使用は、インピーダンスの非常に高い入力電源によって生じる電圧低下の防止にも有効です。

考慮すべき入力コンデンサの部品番号の例については、[表 8-5](#) を参照してください。

**表 8-5. 推奨入力コンデンサ**

| メーカー <sup>(1)</sup> | 誘電  | 部品番号                 | ケース サイズ | コンデンサ特性 |                       |

|---------------------|-----|----------------------|---------|---------|-----------------------|

|                     |     |                      |         | 定格電圧(V) | 容量(μF) <sup>(2)</sup> |

| TDK                 | X7R | C3225X7R1H475K2 50AB | 1210    | 50      | 4.7                   |

| Wurth               | X7R | 885012209048         | 1210    | 50      | 4.7                   |

| Murata (村田製<br>作所)  | X5R | GRM155R61H104M E14D  | 0402    | 50      | 0.1                   |

| Chemi-Con           | 電解  | EMVY500ADA101M HA0G  | HA0     | 50      | 100                   |

(1) この表に記載されているコンデンサの入手可能性、材料組成、RoHS および鉛フリーのステータス、製造プロセスの要件については、コンデンサのサプライヤにお問い合わせください。「サードパーティ製品に関する免責事項」をご覧ください。

(2) 銘板の容量値(実効値は、印加された DC 電圧および温度に基づいて低いです)。

### 8.2.2.4 出力コンデンサの選択

3.3V 出力の場合、TPSM336xx-Q1 が正常に動作するためには、最低でも 40μF 以上の実効的な出力容量が必要です。セラミック コンデンサを使用する場合は、DC バイアスと温度変動の影響を考慮する必要があります。リップル電圧を低減するため、または過渡的な負荷要件を持つアプリケーションのために、出力容量を追加することもできます。

実際には、過渡応答とループ位相マージンに最も影響を与えるのは出力コンデンサです。負荷過渡テストおよびボード線図は、特定の設計を検証する最善の方法であり、アプリケーションを量産に移行する前に必ず完了する必要があります。必要な出力容量に加えて、出力ノードに小さなセラミック コンデンサを配置すると、高周波ノイズの低減に役立ちます。ケースサイズの小さな 1nF~100nF レンジのセラミックコンデンサは、インダクタや基板の寄生成分に起因する出力ノードのスパイクを低減するのに非常に役立ちます。

合計出力容量の最大値は、設計値の約 10 倍、または 1000μF のどちらか小さい方に制限します。出力容量の値が大きいと、レギュレータのスタートアップ動作やループの安定性に悪影響を及ぼす可能性があります。ここに記載した値よりも大きい値を使用する必要がある場合、全負荷でのスタートアップおよびループ安定性を慎重に検討する必要があります。

この設計例では、22μF、16V、1210 ケース サイズのセラミックコンデンサ 2 個を選定します。これらのコンデンサの実効容量の合計値は 3.3V で約 40μF です。出力コンデンサの選定例については、[セクション 6.3](#) を参照してください。

### 8.2.2.5 VCC

VCC ピンは、レギュレータの制御回路に電力を供給するために使用される内部 LDO の出力です。この出力を適切に動作させるには、VCC と GND との間に 1μF、16V のセラミックコンデンサを接続する必要があります。一般に、この出力に負荷として外部回路を接続できません。ただし、この出力は、パワー グッド機能のプルアップに電力を供給するために使

えます（「パワー グッド出力の動作」を参照）。この場合では、 $10\text{k}\Omega \sim 100\text{k}\Omega$  の範囲の抵抗値が適切な選択となります。VCC の公称出力電圧は 3.3V です。限界値については、「電気的特性」を参照してください。

#### 8.2.2.6 $C_{FF}$ の選択

場合によっては、 $R_{FBT}$  の両端にフィードフォワード コンデンサを接続して、負荷過渡応答やループ位相マージンを改善できます。『内部的に補正される、フィードフォワード コンデンサを持つ DC-DC コンバータの過渡応答の最適化』アプリケーション レポートは、フィードフォワード コンデンサの実験に役立ちます。

可変出力電圧設定の場合、帰還検出回路の性質上、希望する出力電圧が確実に達成されるように、 $C_{FF}$  の値を制限する必要があります。 $C_{FF}$  が確実に最大値を下回るように、次の 式 8 に従ってください。

$$C_{FF} < C_{OUT} \times \frac{\sqrt{V_{OUT}}}{1.2 \times 10^6} \quad (8)$$

#### 8.2.2.7 パワー グッド信号

出力電圧が存在し、かつレギュレートされていることを示すパワー グッド信号が必要なアプリケーションでは、PGOOD ピンと有効な電圧源との間に接続されたプルアップ 抵抗を使用する必要があります。この電圧源として、たとえば VCC または VOUT を使用できます。

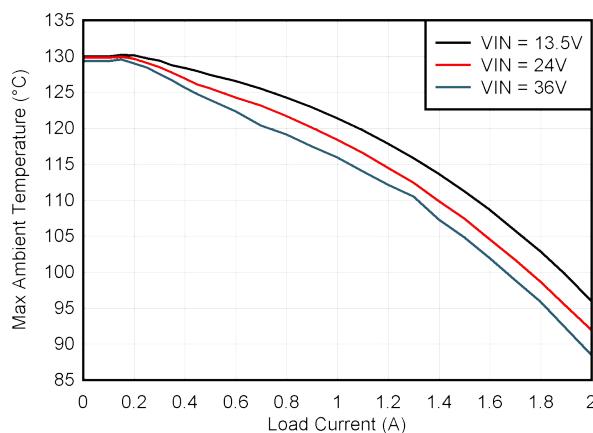

#### 8.2.2.8 最大周囲温度

他の電力変換デバイスと同様に、TPSM336xx-Q1 は動作中に内部で電力を消費します。この消費電力の影響により、パワー モジュールの内部温度が周囲温度よりも高くなります。内部ダイおよびインダクタ温度 ( $T_J$ ) は、周囲温度、電力損失、本モジュールと PCB の組み合わせの実効熱抵抗  $R_{\theta JA}$  の関数です。TPSM336xx-Q1 の最大接合部温度は、 $150^\circ\text{C}$  に制限する必要があります。この制限により、モジュールの最大消費電力が制限され、それに伴って負荷電流も制限されます。式 9 に、重要なパラメータ間の関係を示します。周囲温度 ( $T_A$ ) が高いほど、また、 $R_{\theta JA}$  が大きいほど、利用可能な最大出力電流が低減されます。パワー モジュールの効率は、このデータシートに示す曲線を使用して推定できます。いずれかの曲線に目的の動作条件が見つからない場合は、補間によって効率を推定できます。または、目的のアプリケーション要件に合わせて EVM を調整し、効率を直接測定することもできます。 $R_{\theta JA}$  の正確な値を推定するのは、より困難です。最後に、EVM でのベンチ解析によって得られた安全動作領域曲線とモジュールのサーマル画像から、出力電力能力に関する知見を得ることができます。これらの曲線は、本データシートの「アプリケーション曲線」セクションに記載されています。

『半導体および IC パッケージの熱評価基準』アプリケーション ノート で述べているように、「熱に関する情報」セクションに記載されている値は、設計目的では無効で、アプリケーションの熱性能の推定には使用することはできません。この表に報告されている値は、実際のアプリケーションではめったに見られない特定の一連の条件で測定されたものです。

$$I_{OUT, max} = \frac{(T_J - T_A)}{R_{\theta JA}} \times \frac{\eta}{(1 - \eta)} \times \frac{1}{V_{OUT}} \quad (9)$$

ここで、

$\eta$  は効率です。

実効  $R_{\theta JA}$  (TPSM33625EVM =  $22^\circ\text{C/W}$ ) は重要なパラメータであり、以下のような多くの要因に依存します。

- 消費電力

- 空気温度、フロー

- PCB 面積

- 銅箔ヒートシンク面積

- パッケージの下にあるサーマル リビアの数

- 隣接する部品の配置

上の IC の電力損失は、全体の電力損失からインダクタの DC 抵抗に起因する損失を減算したものです。総合的な電力損失は、特定の動作条件と温度に対する WEBENCH 回路や選定シミュレーションサービスを使用して概算できます。

優れた熱 PCB 設計および特定のアプリケーション環境における  $R_{\theta JA}$  を推定するためのガイドとして、以下の資料をご参照ください。

- 『AN-2020 過去ではなく、現在の議見による熱設計』アプリケーションノート

- 『AN-1520 露出パッド パッケージで最良の熱抵抗を実現するための基板レイアウト ガイド』アプリケーションノート

- 『半導体および IC パッケージの熱評価基準』アプリケーション レポート

- PCB 温度計算ツール

#### 8.2.2.9 その他の接続

- MODE/SYNC ピンを外部クロックに接続すると、本デバイスは強制的に同期動作に入ります。MODE/SYNC ピンを Low に接続すると、本デバイスは軽負荷時に PFM モードで動作できます。MODE/SYNC ピンを High に接続すると、本デバイスは FPWM モードに移行し、負荷電流にかかわらず最大周波数で動作できます。

- EN ピンに抵抗分圧器回路を追加することで、高精度の入力低電圧誤動作防止 (UVLO) を実現できます。

- 固定出力電圧設定の場合、VOUT/FB ピンを FB に接続します。

- VCC ピンと PGND の間に、本デバイスに近付けて、 $1\mu F$  のコンデンサを配置します。

- パワー グッド信号を生成するため、PGOOD ピンと有効な電圧源との間にプルアップ抵抗を接続します。

### 8.2.3 アプリケーション曲線

図 8-3. 自動モード効率 (ログ)、3.3VOUT、2.2MHz

図 8-4. FPWM モード効率 (ログ)、3.3VOUT、2.2MHz

図 8-5. 最大周囲温度と負荷電流との関係 (TPSM33620QEVM の解析)、3.3VOUT、2.2MHz

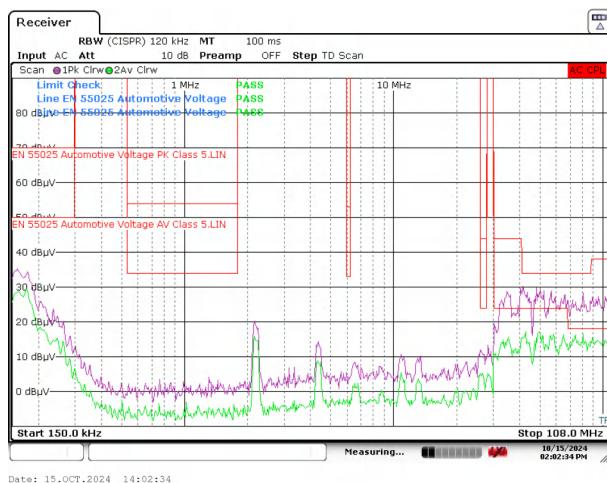

図 8-6. CISPR 25、CE スキャン 150kHz–108MHz、(紫: ピーク、緑: AVG)、12VIN、3.3VOUT、2.2MHz、2A 負荷電流

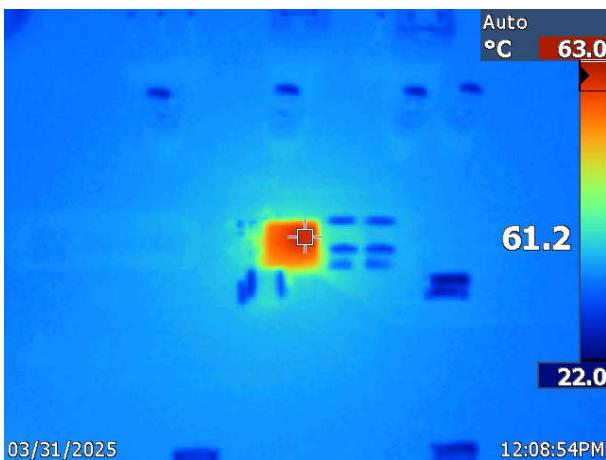

図 8-7. サーマルキャプチャ、13.5VIN、3.3VOUT、2.2MHz、2A 負荷電流

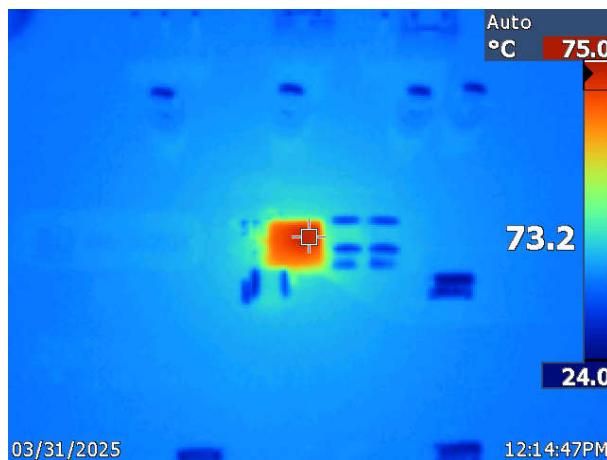

図 8-8. サーマルキャプチャ、36VIN、3.3VOUT、2.2MHz、2A 負荷電流

### 8.2.3 アプリケーション曲線(続き)

図 8-9. 起動、12VIN、3.3VOUT、2.2MHz、2A 負荷電流

図 8-10. 起動、12VIN、3.3VOUT、2.2MHz、0A 負荷電流

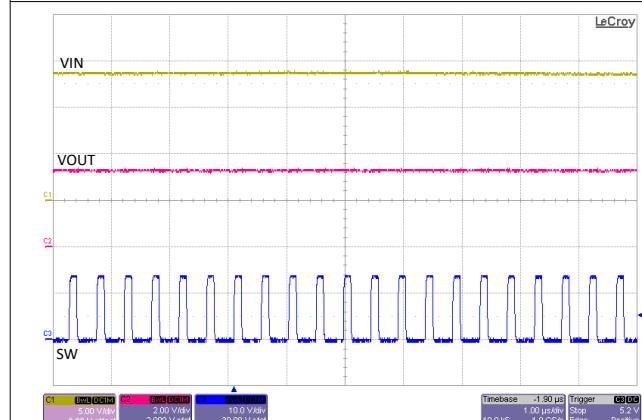

図 8-11. SW ノード、12VIN、3.3VOUT、2.2MHz、2A 負荷電流

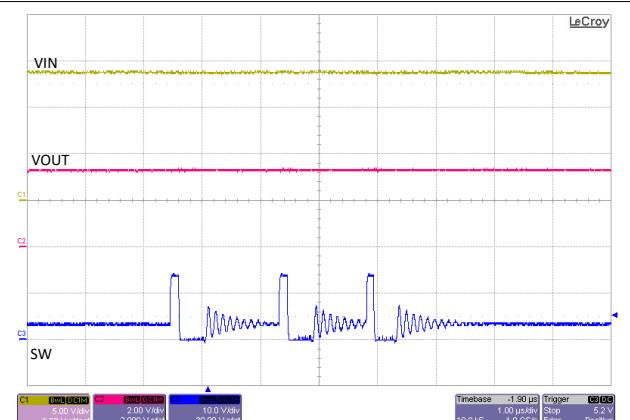

図 8-12. SW ノード、12VIN、3.3VOUT、2.2MHz、0A 負荷電流

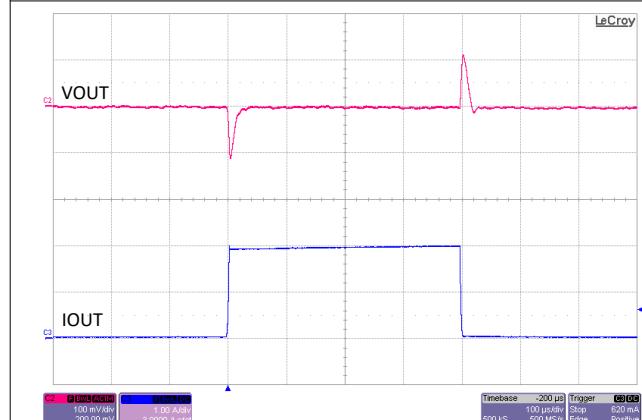

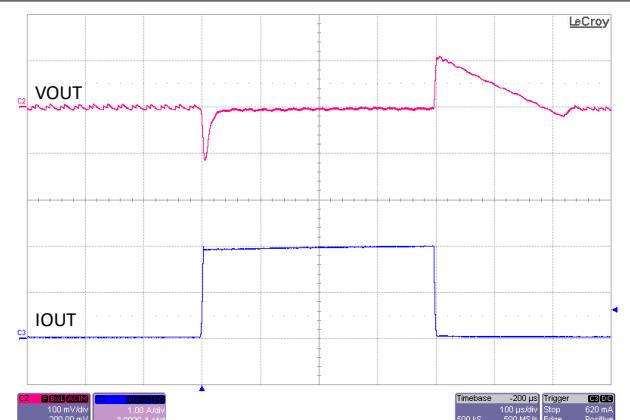

図 8-13. 負荷過渡、12VIN、3.3VOUT、2.2MHz (FPWM)、0A ~ 2A、

1A/μs、COUT = 2 x 22μF

図 8-14. 負荷過渡、12VIN、3.3VOUT、2.2MHz (Auto)、0A ~ 2A、

1A/μs、COUT = 2 x 22μF

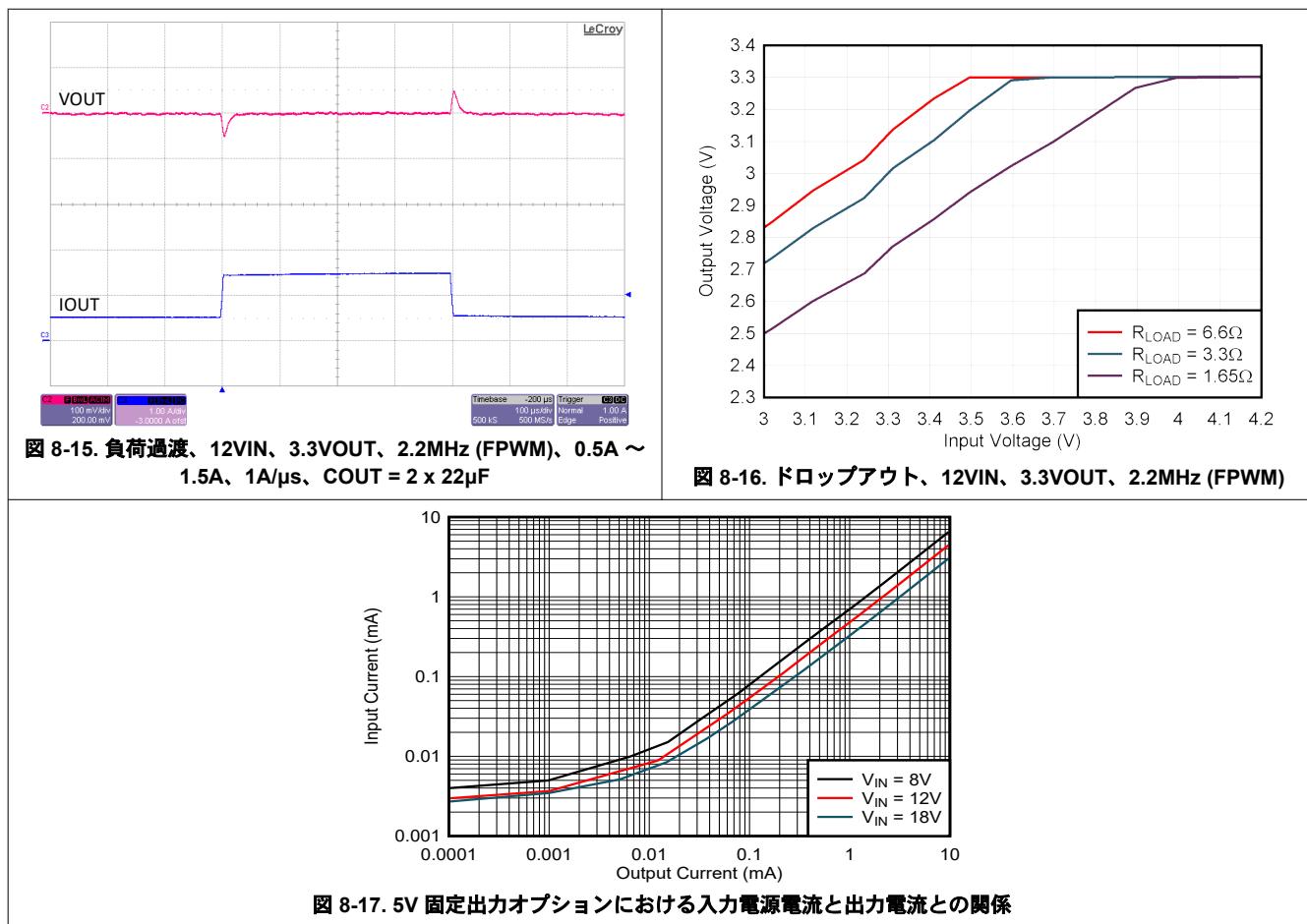

### 8.2.3 アプリケーション曲線(続き)

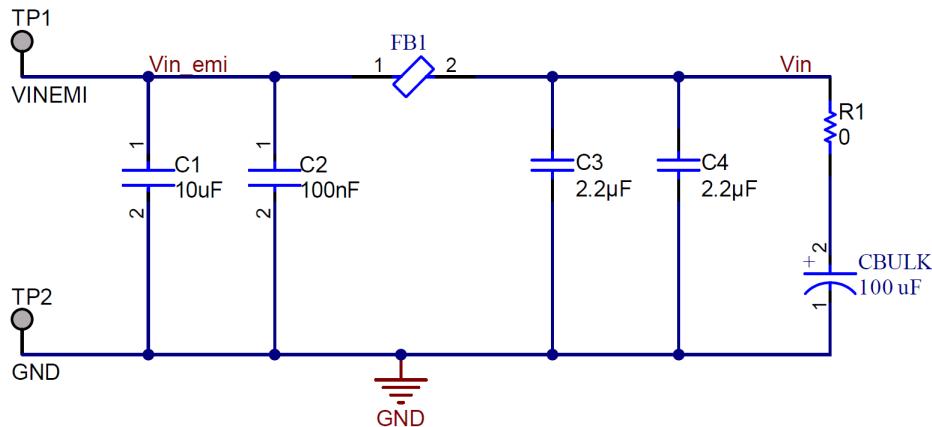

図 8-18. 標準入力 EMI フィルタ

## 8.3 設計のベスト プラクティス

- 絶対最大定格を超過してはなりません。

- 推奨動作条件を超過してはなりません。

- ESD 定格を超過してはなりません。

- EN 入力をフローティングにしないでください。

- 出力電圧が入力電圧を超えないように、またグランドを下回らないようにしてください。

- 設計を量産用に確定する前に、このデータシートに記載されているすべてのガイドラインと推奨事項に従ってください。テキサス インストゥルメンツのアプリケーション エンジニアが、設計および PCB レイアウトの評価をサポートして、プロジェクトの成功を支援します。

## 8.4 電源に関する推奨事項

TPSM336xx-Q1 の降圧モジュールは、3V ~ 36V の広い入力電圧範囲で動作するよう設計されています。入力電源の特性は、このデータシートの **絶対最大定格** と **推奨動作条件** に適合していかなければなりません。また、入力電源は、負荷時 レギュレータ回路に必要な入力電流を供給できる必要があります。平均入力電流を見積るには、式 10 を使用します。

$$I_{IN} = \frac{V_{OUT} \times I_{OUT}}{V_{IN} \times \eta} \quad (10)$$

ここで、

$\eta$  = 効率

モジュールが高インピーダンスを持つ長い配線や PCB パターンを経由して入力電源に接続されている場合は、安定した性能が実現されていることを確認してください。入力ケーブルの寄生インダクタンスと抵抗は、モジュールの動作に悪影響を及ぼすことがあります。具体的には、寄生インダクタンスと低 ESR のセラミック入力コンデンサの組み合わせにより、低減衰共振回路が形成され、入力電源のオン / オフが繰り返されるたびに不安定性と電圧過渡のどちらかまたは両方が発生する可能性があります。寄生抵抗により、負荷過渡中に入力電圧が低下する場合があります。モジュールが最小入力電圧に近い値で動作している場合、この低下によって UVLO が誤って起動され、システムがリセットされる可能性があります。

こうした問題を解決する最善策は、入力電源からモジュールまでの距離を短くして、電解入力コンデンサをセラミックと並列に使用することです。中程度の ESR を持つ電解コンデンサは、入力共振回路の振動を減衰させ、入力のすべてのオーバーシュートまたはアンダーシュートを低減するのに役立ちます。通常、入力並列ダンピングには  $47\mu F$ ~ $100\mu F$  の静電容量で十分であり、大きな負荷トランジエント(負荷過渡)のときも入力電圧を安定した状態に保持に寄与します。代表的な ESR は  $0.1\Omega$ ~ $0.4\Omega$  であり、ほとんどの入力回路構成で十分な減衰を実現します。

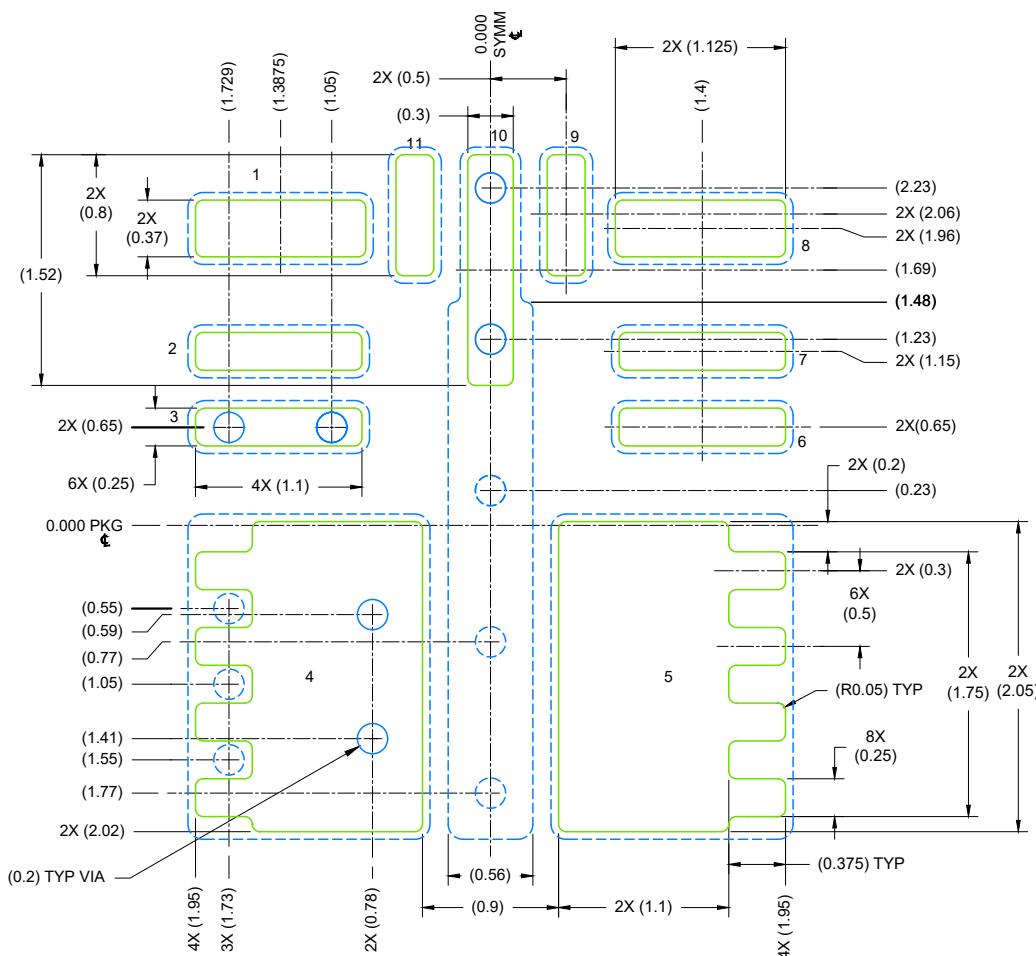

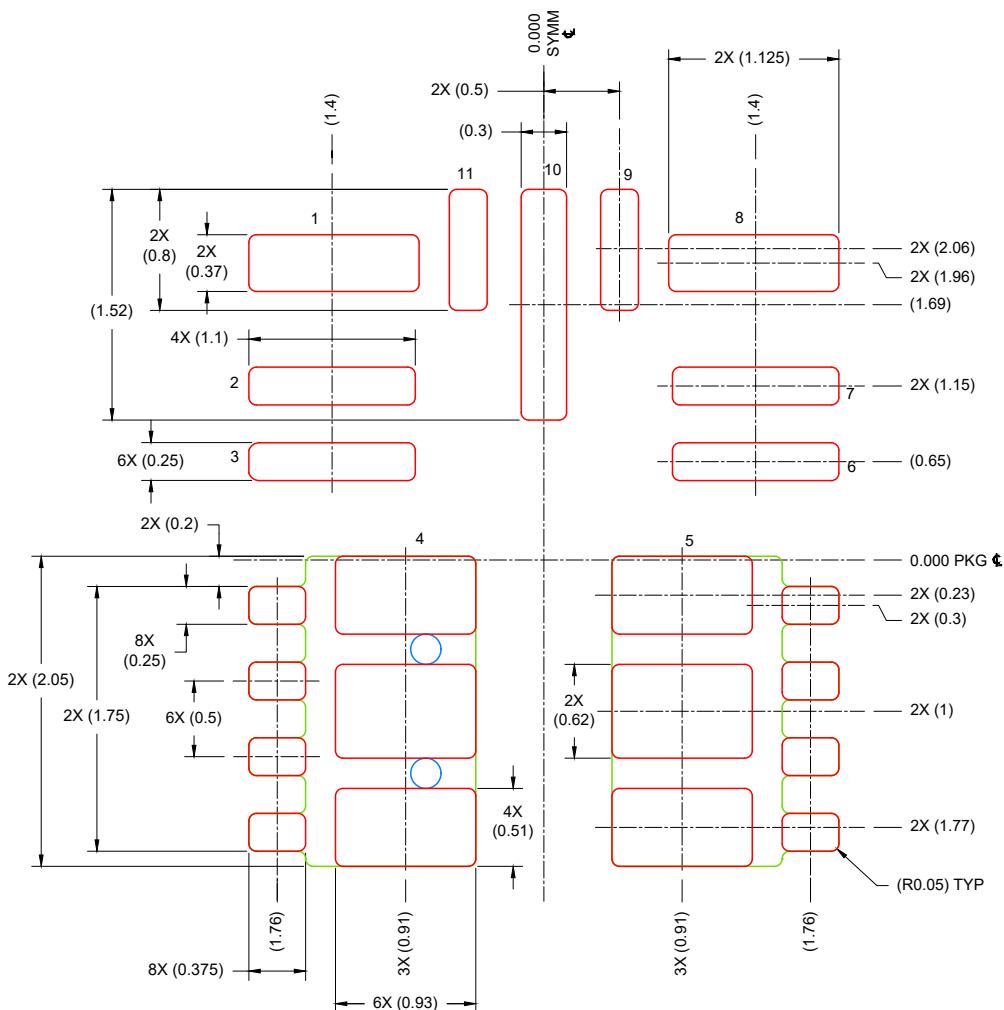

## 8.5 レイアウト

スイッチング電源の性能は、部品の選択だけでなく PCB のレイアウトにも依存します。最高の電力変換性能と最高の熱性能を実現しながら、不要な EMI の生成を最小限に抑える PCB を設計するため、以下のガイドラインを使います。

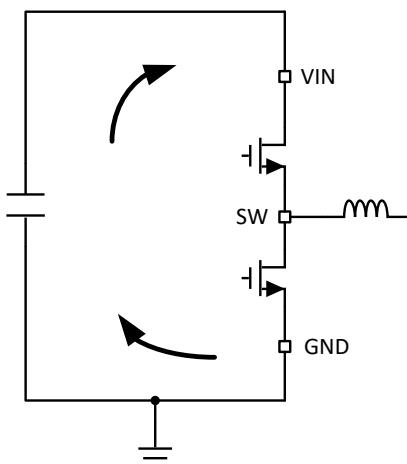

### 8.5.1 レイアウトのガイドライン

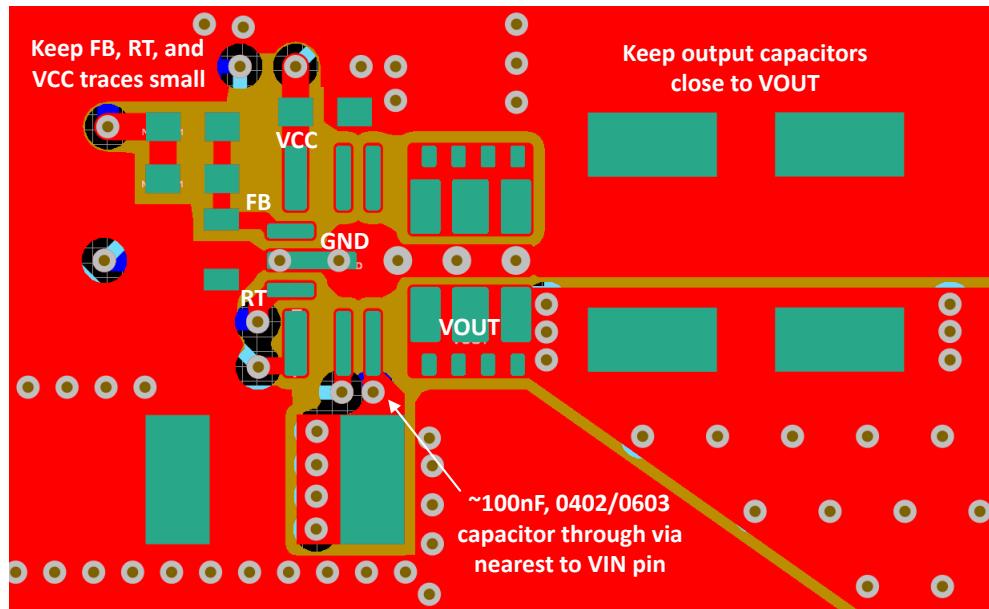

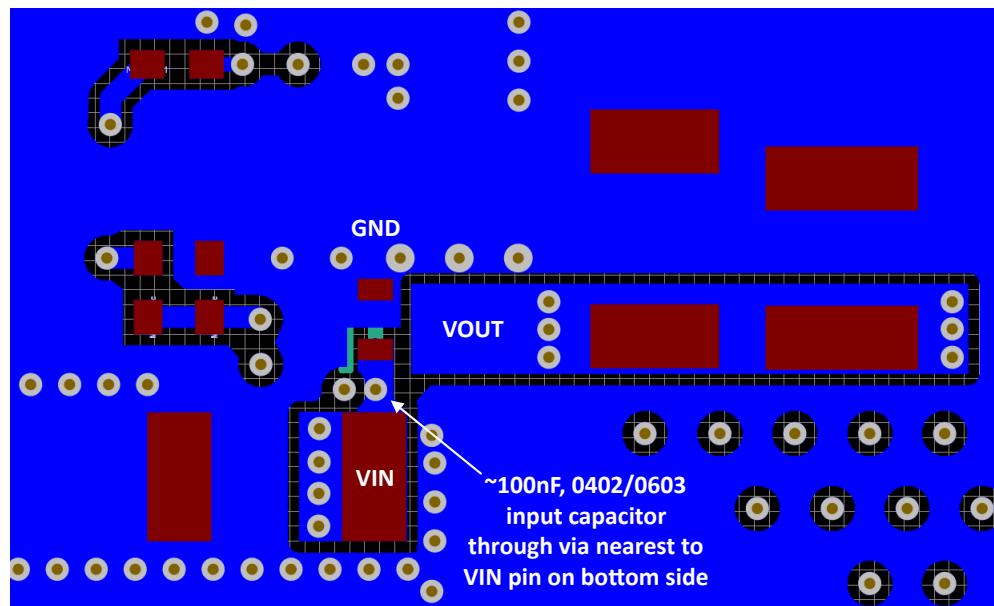

DC/DC モジュールの PCB レイアウトは、設計の最高の性能を実現するために重要です。PCB レイアウトが不適切な場合、適正な回路図設計の動作の妨げとなる可能性があります。モジュールが適切にレギュレートしている場合でも、PCB レイアウトが不適切では、堅牢な設計と量産できない設計という違いが生じる可能性があります。さらに、レギュレータの EMI 性能は、PCB レイアウトの影響を大きく受けます。降圧コンバータ モジュールにおける PCB の最も重要な機能は、入力コンデンサと電源グランドによって形成されるループです (図 8-19 を参照)。このループには、パターンのインダクタンスに応答して大きな過渡電圧を発生させる可能性がある大きな過渡電流が流れます。これらの望ましくない過渡電圧は、パワー モジュールの正常な動作を妨げます。このことから、このループ内のパターンは広く短くして、ループ領域をできる限り小さくし、寄生インダクタンスを低減する必要があります。レイアウト例に、TPSM336xx-Q1 の重要部品の推奨レイアウトを示します。

- 入力コンデンサは、VIN および GND ピンにできる限り近づけて配置してください。VIN および GND ピンは隣接しているため、入力コンデンサを簡単に配置できます。

2. **VCC** のバイパスコンデンサは、**VCC** ピンの近くに配置します。このコンデンサは、本デバイスの近くに配置し、短く広いパターンで **VCC** および **GND** ピンに配線する必要があります。

3. 帰還分圧器は、本デバイスの **FB** ピンのできるだけ近くに配置します。 $R_{FBB}$ 、 $R_{FBT}$ 、 $C_{FF}$  は、使用する場合、本デバイスに物理的に近付けて配置します。**FB** および **GND** への接続は、短くする必要があり、かつ本デバイスのそれらのピンに近付ける必要があります。**V<sub>OUT</sub>** への接続は、多少長くなつてもかまいません。ただし、後者のパターンは、レギュレータの帰還経路に静電容量結合する可能性があるすべてのノイズ源 (**SW** ノードなど) の近くには配線しないでください。

4. 内層の 1 つを使って、少なくとも 1 つのグランドプレーンを配置します。このプレーンは、ノイズシールドと放熱経路として機能します。

5. **VIN**、**V<sub>OUT</sub>**、**GND** には広いパターンを使います。パワー モジュールの入力または出力経路でのすべての電圧降下を低減し、効率を最大化するため、これらの配線はできるだけ広くかつ真っすぐにする必要があります。

6. 適切なヒートシンクのために十分な PCB 領域を確保します。最大負荷電流と周囲温度に見合った低  $R_{θJA}$  を実現するため、十分な大きさの銅面積を確保する必要があります。PCB の上層と下層は 2 オンス銅箔とし、最低でも 1 オンス以上とする必要があります。PCB 設計に複数の銅層を使用している場合は(推奨設計)、これらのサーマルビアも内部層の熱拡散グランドプレーンに接続することができます。

7. 複数のビアを使用して、パワー プレーンを内部の層に接続します。

8. EMI の重要なアプリケーションとレイアウトのガイドラインについては、[TPSM33620-Q1 EMI エンジニアリング ボードの EMI レポートアプリケーション ノート](#) を参照してください。

その他の重要なガイドラインについては、以下の PCB レイアウト資料を参照してください。

- スイッチング電源レイアウトのガイドラインアプリケーション レポート

- [Simple Switcher PCB レイアウトガイドラインアプリケーション レポート](#)

- [『独自電源の構築 - レイアウトの考慮事項』セミナー](#)

図 8-19. 高速エッジを持つ電流ループ

#### 8.5.1.1 グランドと熱に関する考慮事項

テキサス インストゥルメンツでは、中間層の 1 つをソリッド グランド プレーンとして使用することを推奨しています。グランド プレーンは敏感な回路やパターンのシールドとして機能するだけでなく、制御回路の低ノイズ基準電位を提供します。バイパス コンデンサの隣にあるビアを使用して、**GND** ピンをグランド プレーンに接続します。**GND**、**VIN**、**SW** パターンをグランド プレーンの片側に制約します。グランド プレーンのもう片方はノイズが非常に少ないため、ノイズの影響を受けやすい配線に使用します。

**GND** ピンの近くに十分な面積の銅箔を配置することで、適切なデバイスヒートシンクを設けることを推奨します。レイアウト例については、[図 8-20](#) を参照してください。システムのグランド プレーンでは、効率の高い放熱のために、レイヤの上下に出来る限り多くの銅を使用します。4 つの層の銅厚が上からそれぞれ 2 オンス、1 オンス、1 オンス、2 オンスとなっている 4 層基板を使用します。

1. 2oz

2. 1oz

3. 1oz

4. 2oz

十分な厚さの銅箔と適切なレイアウトを備えた 4 層基板は、低インピーダンスの電流導通、適切なシールド効果、低熱抵抗を実現します。

### 8.5.2 レイアウト例

図 8-20. レイアウトの上層の例

図 8-21. レイアウトの下層の例

## 9 デバイスおよびドキュメントのサポート

### 9.1 デバイス サポート

#### 9.1.1 サード・パーティ製品に関する免責事項

サード・パーティ製品またはサービスに関するテキサス・インスツルメンツの出版物は、単独またはテキサス・インスツルメンツの製品、サービスと一緒に提供される場合に關係なく、サード・パーティ製品またはサービスの適合性に関する是認、サード・パーティ製品またはサービスの是認の表明を意味するものではありません。

#### 9.1.2 開発サポート

##### 9.1.2.1 WEBENCH® ツールによるカスタム設計

ここをクリックすると、WEBENCH® Power Designer により、TPSM336xx-Q1 デバイスを使用するカスタム設計を作成できます。

- 最初に、入力電圧 (VIN)、出力電圧 (VOUT)、出力電流 (IOUT) の要件を入力します。

- オプティマイザのダイヤルを使用して、効率、占有面積、コストなどの主要なパラメータについて設計を最適化します。

- 生成された設計を、テキサス・インスツルメンツが提供する他の方式と比較します。WEBENCH Power Designer では、カスタマイズされた回路図と部品リストを、リアルタイムの価格と部品の在庫情報と併せて参照できます。

通常、次の操作を実行可能です。

- 電気的なシミュレーションを実行し、重要な波形と回路の性能を確認する

- 熱シミュレーションを実行し、基板の熱特性を把握する

- カスタマイズされた回路図やレイアウトを、一般的な CAD フォーマットで出力する

- 設計のレポートを PDF で印刷し、設計を共有する

WEBENCH ツールの詳細は、[www.ti.com/ja-jp/WEBENCH](http://www.ti.com/ja-jp/WEBENCH) でご覧になれます。

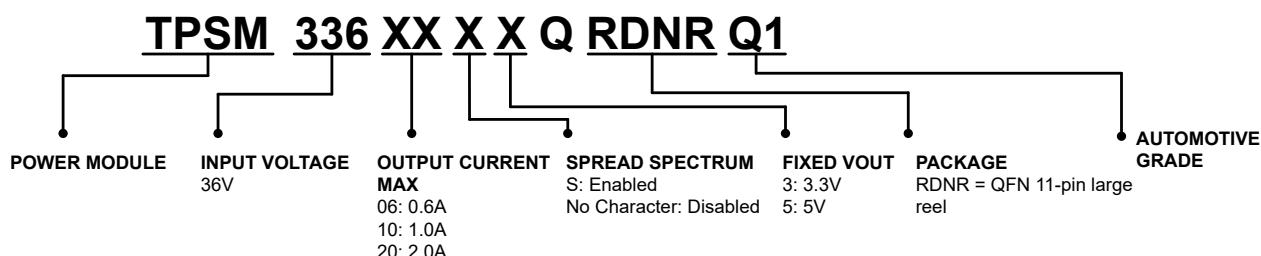

#### 9.1.3 デバイスの命名規則

図 9-1 に、TPSM336xx-Q1 のデバイス命名規則を示します。各バリエントの特長については、セクション 4 を参照してください。他のオプションの詳細と提供状況については、テキサス・インスツルメンツの販売代理店またはテキサス・インスツルメンツの E2E フォーラムにお問い合わせください。

図 9-1. デバイスの命名規則

## 9.2 ドキュメントのサポート

### 9.2.1 関連資料

関連資料については、以下を参照してください。

- テキサス・インスツルメンツ、『過去ではなく、現在の識見による熱設計』アプリケーション レポート

- テキサス・インスツルメンツ、『露出パッド パッケージで最良の熱抵抗を実現するための基板レイアウト ガイド』アプリケーション ノート

- テキサス・インスツルメンツ、『半導体および IC パッケージの熱評価基準』アプリケーション ノート

- テキサス・インスツルメンツ、『PCB 熱計算ツール』、デザインリソース

- テキサス・インスツルメンツ、『[TPSM33620-Q1 EMI エンジニアリング ボードの EMI レポート](#)』アプリケーション ノート

- テキサス・インスツルメンツ、『[スイッチング電源 レイアウトガイドライン](#)』アプリケーション ノート

- テキサス・インスツルメンツ、『[Simple Switcher PCB レイアウトガイドライン](#)』アプリケーション ノート

- テキサス・インスツルメンツ、『[独自電源の構築 - レイアウトの考慮事項](#)』セミナー

### 9.3 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 9.4 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの[使用条件](#)を参照してください。

### 9.5 商標

HotRod™ and テキサス・インスツルメンツ E2E™ are trademarks of Texas Instruments.

WEBENCH® is a registered trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

### 9.6 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 9.7 用語集

[テキサス・インスツルメンツ用語集](#) この用語集には、用語や略語の一覧および定義が記載されています。

## 10 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| <b>Changes from Revision C (September 2025) to Revision D (November 2025)</b> | <b>Page</b> |

|-------------------------------------------------------------------------------|-------------|

| • タイトルに ZEN 1 の文言を追加.....                                                     | 0           |

| • 「超低 EMI 要件向けの設計」を「ZEN 1 スイッチャ」に変更.....                                      | 1           |

| • ZEN 1 スイッチャの機能に言及する文を追加.....                                                | 1           |

| <b>Changes from Revision B (July 2025) to Revision C (September 2025)</b> | <b>Page</b> |

|---------------------------------------------------------------------------|-------------|

| • TPSM33610-Q1 から製品レビューの注を削除.....                                         | 1           |

| • <a href="#">デバイス比較表</a> で、すべてのデバイスのステータスを「製品レビュー」から「量産データ」に変更.....      | 4           |

---

| <b>Changes from Revision A (June 2025) to Revision B (July 2025)</b> | <b>Page</b> |

|----------------------------------------------------------------------|-------------|

| • TPSM33606-Q1 から製品レビューの注を削除.....                                    | 1           |

| • デバイス比較表の TPSM33606S5QRDNRQ1 から製品レビューの注を削除.....                     | 4           |

---

## 11 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins          | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|-------------------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| TPSM33606S3QRDNRQ1    | Active        | Production           | QFN-FCMOD<br>(RDN)   11 | 3000   LARGE T&R      | Yes         | SN                                   | Level-2-260C-1 YEAR               | -40 to 150   | 33606S3Q            |

| TPSM33606S5QRDNRQ1    | Active        | Production           | QFN-FCMOD<br>(RDN)   11 | 3000   LARGE T&R      | Yes         | SN                                   | Level-2-260C-1 YEAR               | -40 to 150   | 33606S5Q            |

| TPSM33610S3QRDNRQ1    | Active        | Production           | QFN-FCMOD<br>(RDN)   11 | 3000   LARGE T&R      | Yes         | SN                                   | Level-2-260C-1 YEAR               | -40 to 150   | 33610S3Q            |

| TPSM33610S5QRDNRQ1    | Active        | Production           | QFN-FCMOD<br>(RDN)   11 | 3000   LARGE T&R      | Yes         | SN                                   | Level-2-260C-1 YEAR               | -40 to 150   | 33610S5Q            |

| TPSM336203QRDNRQ1     | Active        | Production           | QFN-FCMOD<br>(RDN)   11 | 3000   LARGE T&R      | Yes         | SN                                   | Level-2-260C-1 YEAR               | -40 to 150   | 336203Q             |

| TPSM33620S3QRDNRQ1    | Active        | Production           | QFN-FCMOD<br>(RDN)   11 | 3000   LARGE T&R      | Yes         | SN                                   | Level-2-260C-1 YEAR               | -40 to 150   | 33620S3Q            |

| TPSM33620S5QRDNRQ1    | Active        | Production           | QFN-FCMOD<br>(RDN)   11 | 3000   LARGE T&R      | Yes         | SN                                   | Level-2-260C-1 YEAR               | -40 to 150   | 33620S5Q            |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

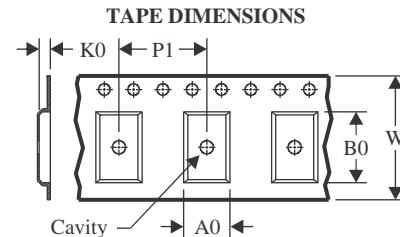

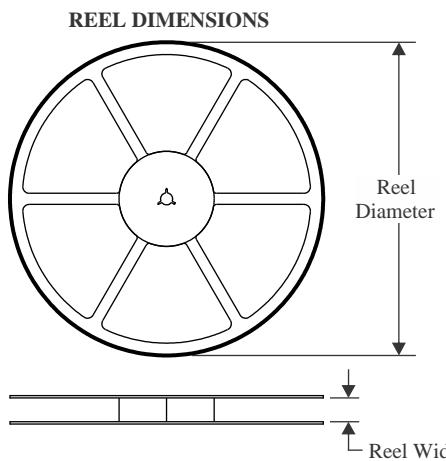

**TAPE AND REEL INFORMATION**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

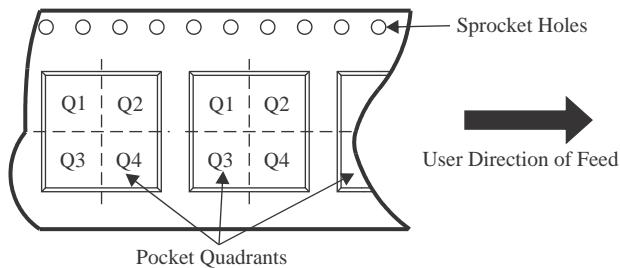

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device             | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|--------------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| TPSM33606S3QRDNRQ1 | QFN-FCMOD    | RDN             | 11   | 3000 | 330.0              | 12.4               | 3.8     | 4.8     | 2.3     | 8.0     | 12.0   | Q1            |

| TPSM33606S5QRDNRQ1 | QFN-FCMOD    | RDN             | 11   | 3000 | 330.0              | 12.4               | 3.8     | 4.8     | 2.3     | 8.0     | 12.0   | Q1            |

| TPSM33610S3QRDNRQ1 | QFN-FCMOD    | RDN             | 11   | 3000 | 330.0              | 12.4               | 3.8     | 4.8     | 2.3     | 8.0     | 12.0   | Q1            |

| TPSM33610S5QRDNRQ1 | QFN-FCMOD    | RDN             | 11   | 3000 | 330.0              | 12.4               | 3.8     | 4.8     | 2.3     | 8.0     | 12.0   | Q1            |

| TPSM336203QRDNRQ1  | QFN-FCMOD    | RDN             | 11   | 3000 | 330.0              | 12.4               | 3.8     | 4.8     | 2.3     | 8.0     | 12.0   | Q1            |

| TPSM33620S3QRDNRQ1 | QFN-FCMOD    | RDN             | 11   | 3000 | 330.0              | 12.4               | 3.8     | 4.8     | 2.3     | 8.0     | 12.0   | Q1            |

| TPSM33620S5QRDNRQ1 | QFN-FCMOD    | RDN             | 11   | 3000 | 330.0              | 12.4               | 3.8     | 4.8     | 2.3     | 8.0     | 12.0   | Q1            |

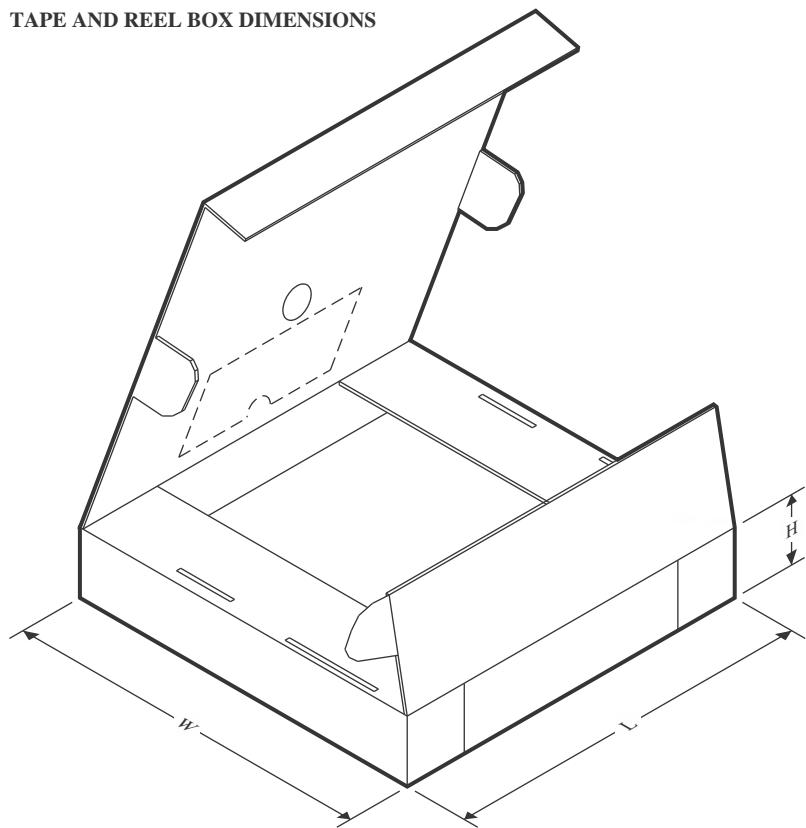

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device             | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPSM33606S3QRDNRQ1 | QFN-FCMOD    | RDN             | 11   | 3000 | 367.0       | 367.0      | 38.0        |

| TPSM33606S5QRDNRQ1 | QFN-FCMOD    | RDN             | 11   | 3000 | 367.0       | 367.0      | 38.0        |

| TPSM33610S3QRDNRQ1 | QFN-FCMOD    | RDN             | 11   | 3000 | 367.0       | 367.0      | 38.0        |

| TPSM33610S5QRDNRQ1 | QFN-FCMOD    | RDN             | 11   | 3000 | 367.0       | 367.0      | 38.0        |

| TPSM336203QRDNRQ1  | QFN-FCMOD    | RDN             | 11   | 3000 | 367.0       | 367.0      | 38.0        |

| TPSM33620S3QRDNRQ1 | QFN-FCMOD    | RDN             | 11   | 3000 | 367.0       | 367.0      | 38.0        |

| TPSM33620S5QRDNRQ1 | QFN-FCMOD    | RDN             | 11   | 3000 | 367.0       | 367.0      | 38.0        |

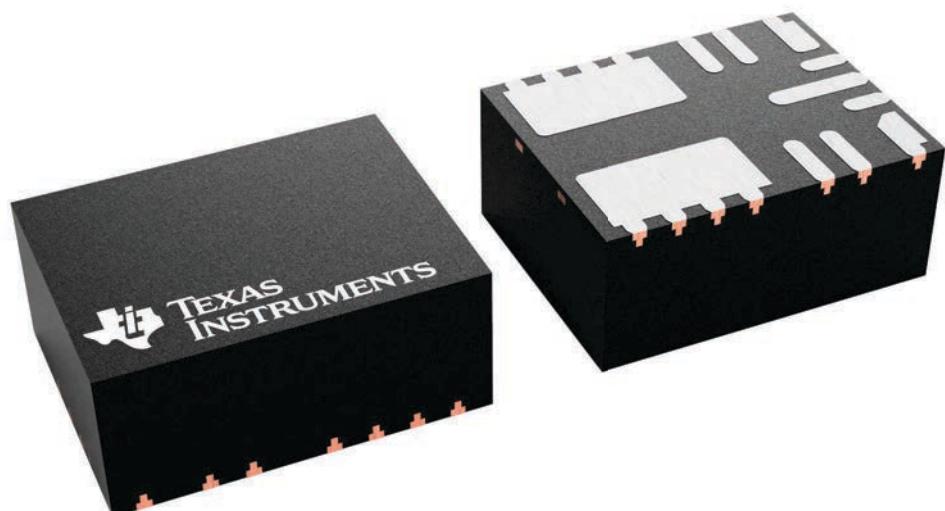

# GENERIC PACKAGE VIEW

RDN 11

QFN-FCMOD - 2.1 mm max height

3.5 x 4.5, 0.5 mm pitch

PLASTIC QUAD FLATPACK - NO LEAD

This image is a representation of the package family, actual package may vary.

Refer to the product data sheet for package details.

4231226/A

## **PACKAGE OUTLINE**

RDN0011B

## **QFN-FCMOD - 2.1 mm max height**

## **PLASTIC QUAD FLAT PACK- NO LEAD**

4231197/B 08/2025

## **NOTES:**

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. The package thermal pad must be soldered to the printed circuit board for optimal thermal and mechanical performance.

PLASTIC QUAD FLAT PACK- NO LEAD

4231197/B 08/2025

NOTES: (continued)

4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 ([www.ti.com/lit/slua271](http://www.ti.com/lit/slua271))

5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

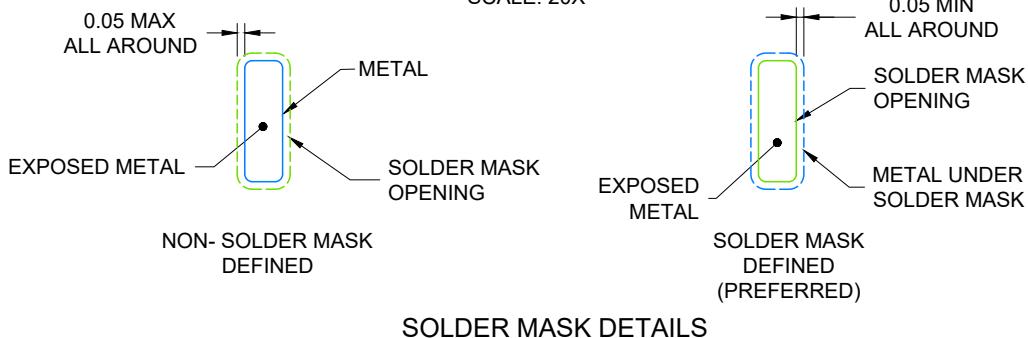

# EXAMPLE STENCIL DESIGN

## QFN-FCMOD - 2.1 mm max height

RDN0011B

PLASTIC QUAD FLAT PACK- NO LEAD

SOLDER PASTE EXAMPLE

BASED ON 0.1 mm THICK STENCIL

PIN 4 & 5:

72% SOLDER COVERAGE BY AREA

SCALE: 20X

4231197/B 08/2025

NOTES: (continued)

- Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2026, Texas Instruments Incorporated

最終更新日：2025 年 10 月