# UCC14131-Q1 車載用 1.5W、12V $V_{IN}$ / 12V $V_{OUT}$ 、15V $V_{IN}$ / 15V $V_{OUT}$ 、高密度、 5kV<sub>RMS</sub> 超の絶縁型 DC/DC モジュール

## 1 特長

- 絶縁変圧器付きの完全統合型高密度絶縁型 DC/DC モジュール

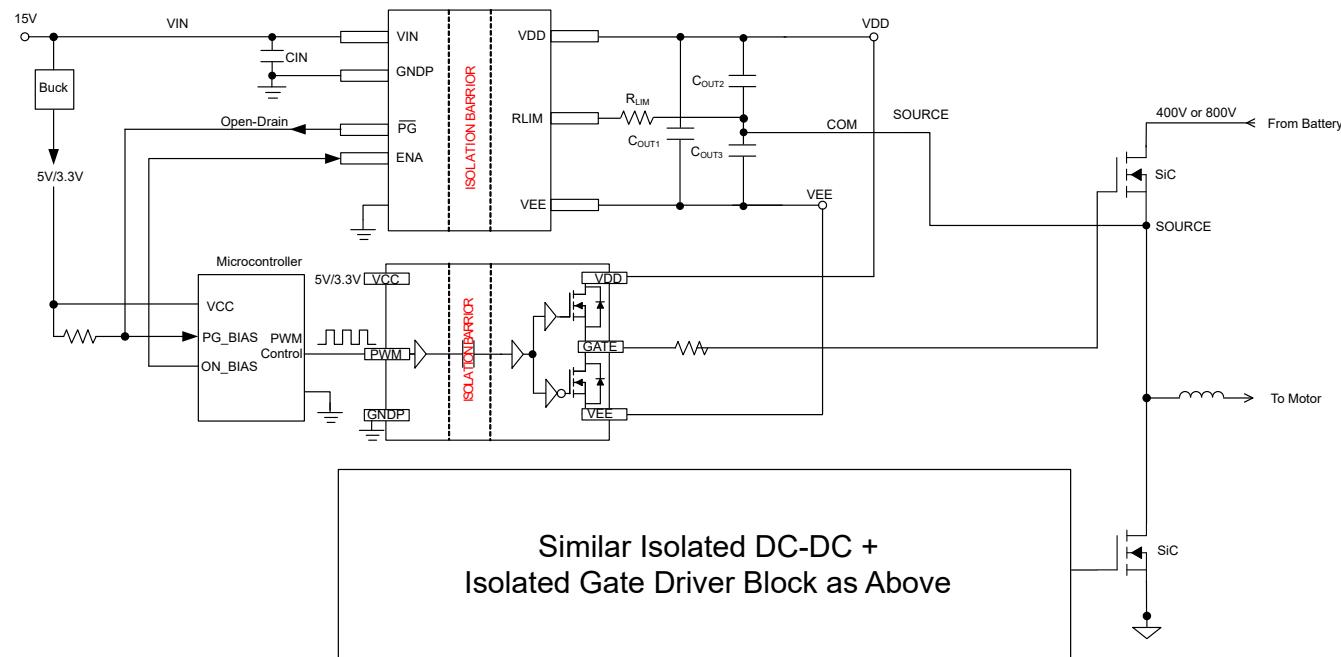

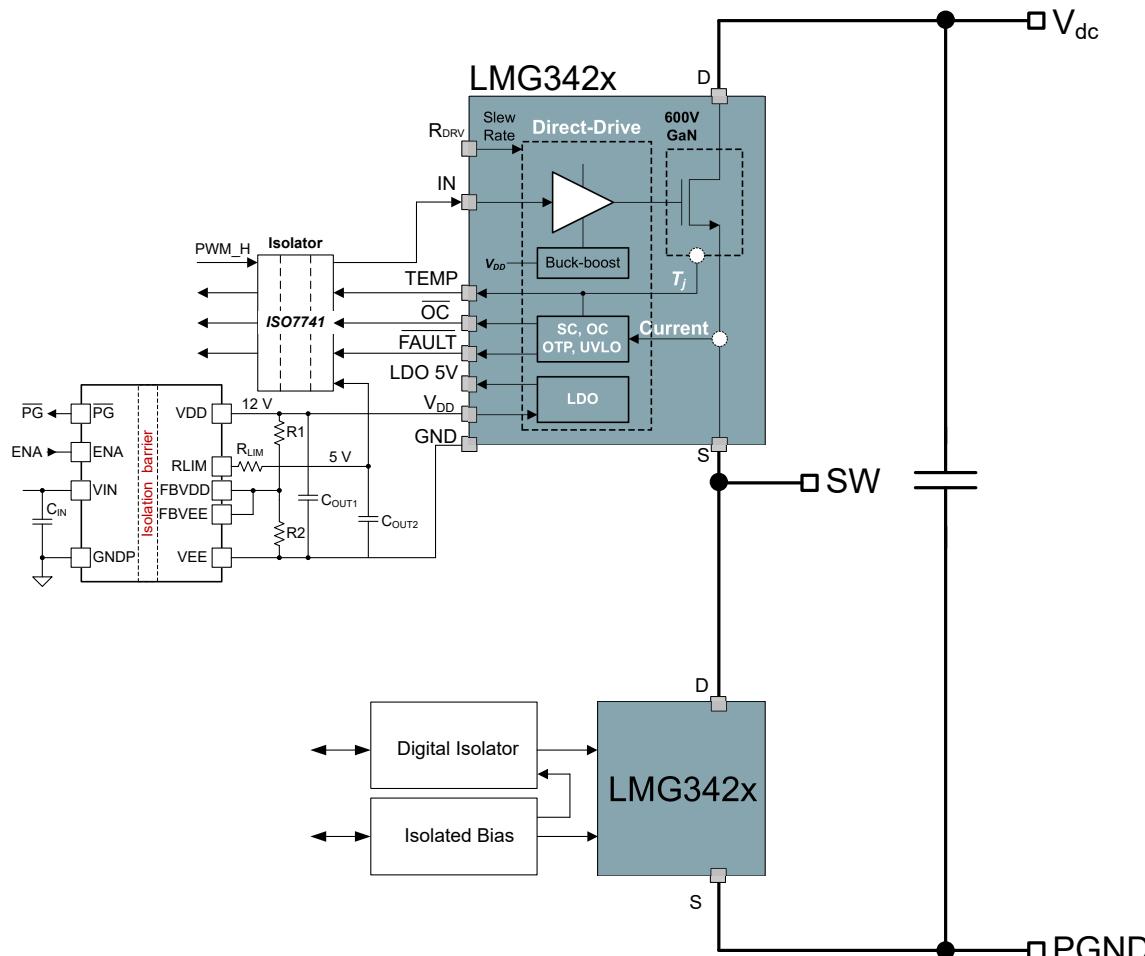

- 以下のものを駆動する絶縁型 DC/DC: IGBT、GaN、SiC、Si MOSFET

- 入力電圧範囲: 10V ~ 18V、絶対最大定格 32V

- $T_A \leq 105^{\circ}\text{C}$  で 1.5W の出力電力

- $T_A = 105^{\circ}\text{C}$  で、 $10V < V_{IN} < 18V$  に対して 1.0W の出力電力

- (抵抗を使用した) 可変シングルまたはデュアル出力電圧により、動作範囲の全体にわたって  $\pm 1.3\%$  未満のレギュレーション精度を実現

- スペクトラム拡散変調と内蔵変圧器により、低い電磁放射を実現

- イネーブル、パワー・グッド、UVLO、OVLO、ソフトスタート、短絡、電力制限、低電圧、過電圧、過熱からの保護

- CMTI  $> 150\text{kV}/\mu\text{s}$

- 車載アプリケーション向けに AEC-Q100 認定済み

- 温度グレード 1:  $-40^{\circ}\text{C} \leq T_J \leq 150^{\circ}\text{C}$

- 温度グレード 1:  $-40^{\circ}\text{C} \leq T_A \leq 125^{\circ}\text{C}$

- 機能安全規格に対応**

- 機能安全システム設計に役立つ資料を利用可能

- 安全関連の認証計画:

- DIN EN IEC 60747-17 (VDE 0884-17) に準拠した強化絶縁耐圧: 7071VPK

- UL1577 に準拠した絶縁耐圧: 5000V<sub>RMS</sub> (1 分間)

- CQC GB4943.1 準拠の強化絶縁

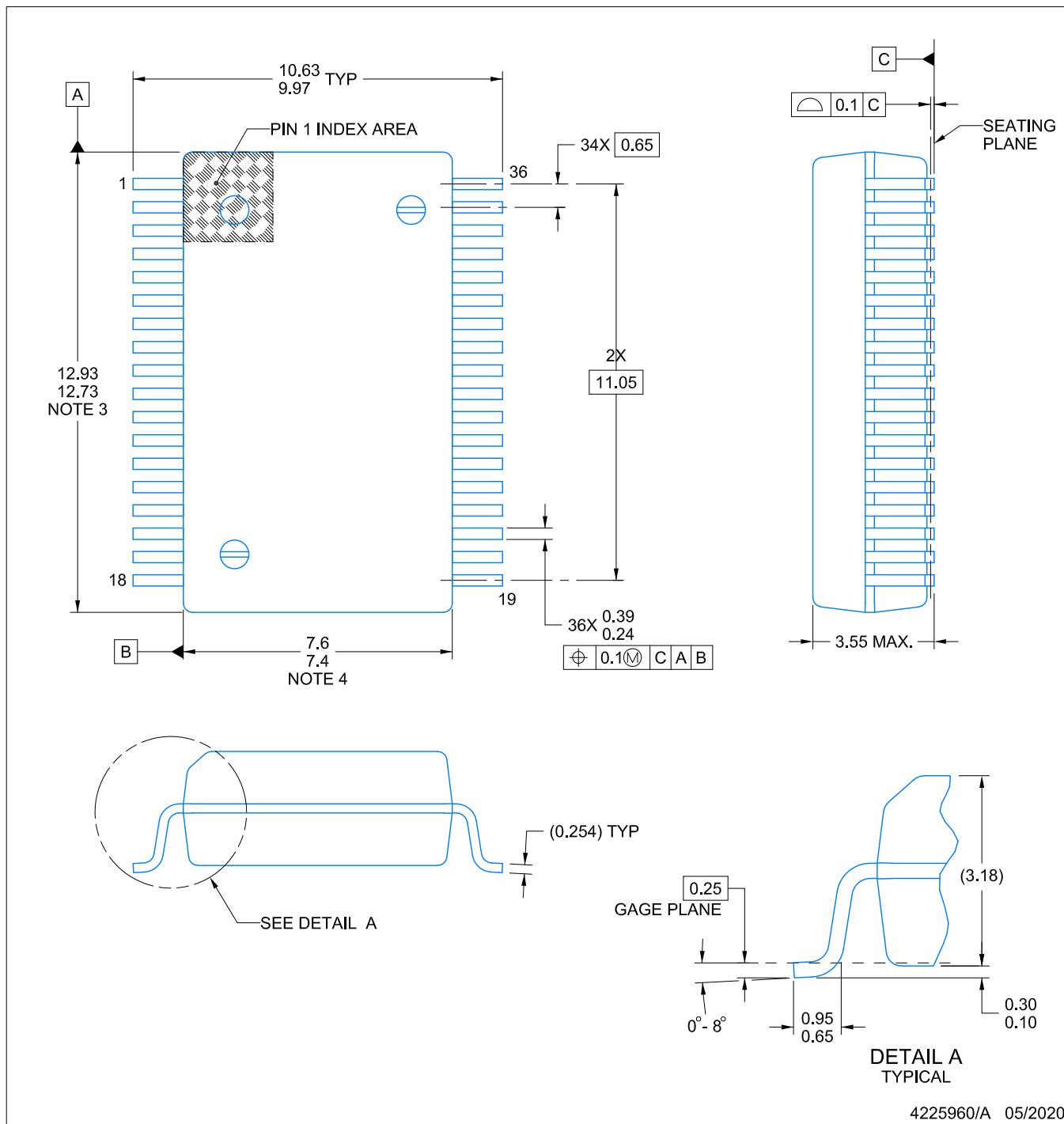

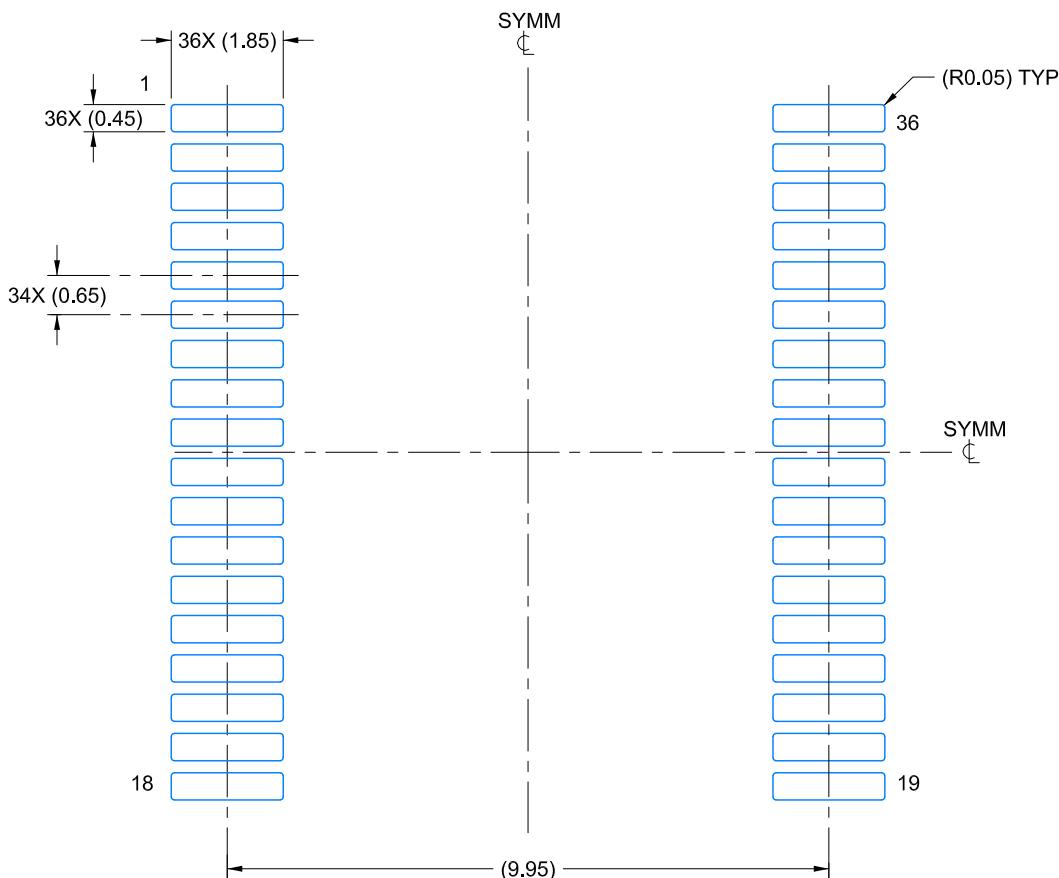

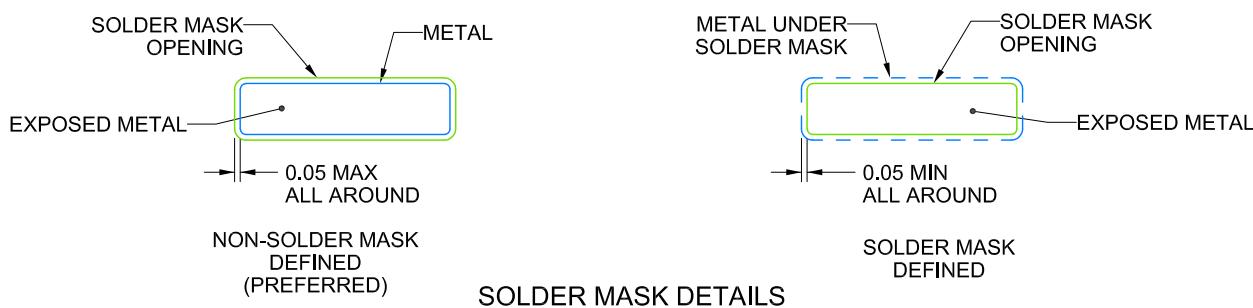

- 36 ピンのワイド SSOP パッケージ

## 2 アプリケーション

- ハイブリッド、電気自動車、およびパワー・トレーン・システム (EV/HEV)

- インバータおよびモーター制御

- オンボード・チャージャ (OBC) およびワイヤレス・チャージャ

- 車載用 DC/DC コンバータ

- グリッド・インフラ

- EV 充電ステーション向け電源モジュール

- DC 充電 (バッテリ) ステーション

- ストリーミング・インバータ

- モーター・ドライブ

- 産業用の輸送

- 商用サーバーの PSU (電源)

## 3 概要

UCC14131-Q1 は、GaN、IGBT、SiC、または Si ゲート・ドライバへの電力供給を目的として設計された車載認定済み高絶縁電圧 DC/DC 電源モジュールです。UCC14131-Q1 は、変圧器と DC/DC コントローラを独自のアーキテクチャで統合して非常に低い放射で高効率を実現しています。GaN および Si MOSFET の駆動用 12V レギュレーション済みの入力から絶縁型の 12V 出力、および 15V レギュレーション済みの入力から絶縁型の 15V または 18V 出力を供給して、SiC MOSFET または IGBT のドライバ回路にバイアスを供給できます。高精度により優れたチャネル拡張を実現し、パワー・デバイスのゲートに過大なストレスを与えることなくシステム効率を向上させます。

UCC14131-Q1 は、高効率で、最大 1.5 W (標準値) の絶縁出力電力を供給します。必要な外付け部品が最小限で、オンチップのデバイス保護機能が内蔵されており、入力低電圧誤動作防止、過電圧誤動作防止、出力電圧パワーグッド・コンバーティ、過熱シャットダウン、ソフトスタート・タイムアウト、可変絶縁正負出力電圧、イネーブル・ピン、オープン・ドレイン出力パワーグッド・ピンなどの追加機能を備えています。

### パッケージ情報

| 発注型番 (1)        | パッケージ         | 本体サイズ (公称)      |

|-----------------|---------------|-----------------|

| UCC14131QDWNRQ1 | DWN (SSOP、36) | 12.83mm × 7.5mm |

(1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

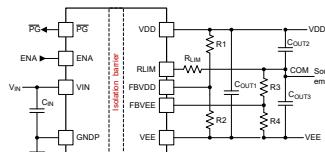

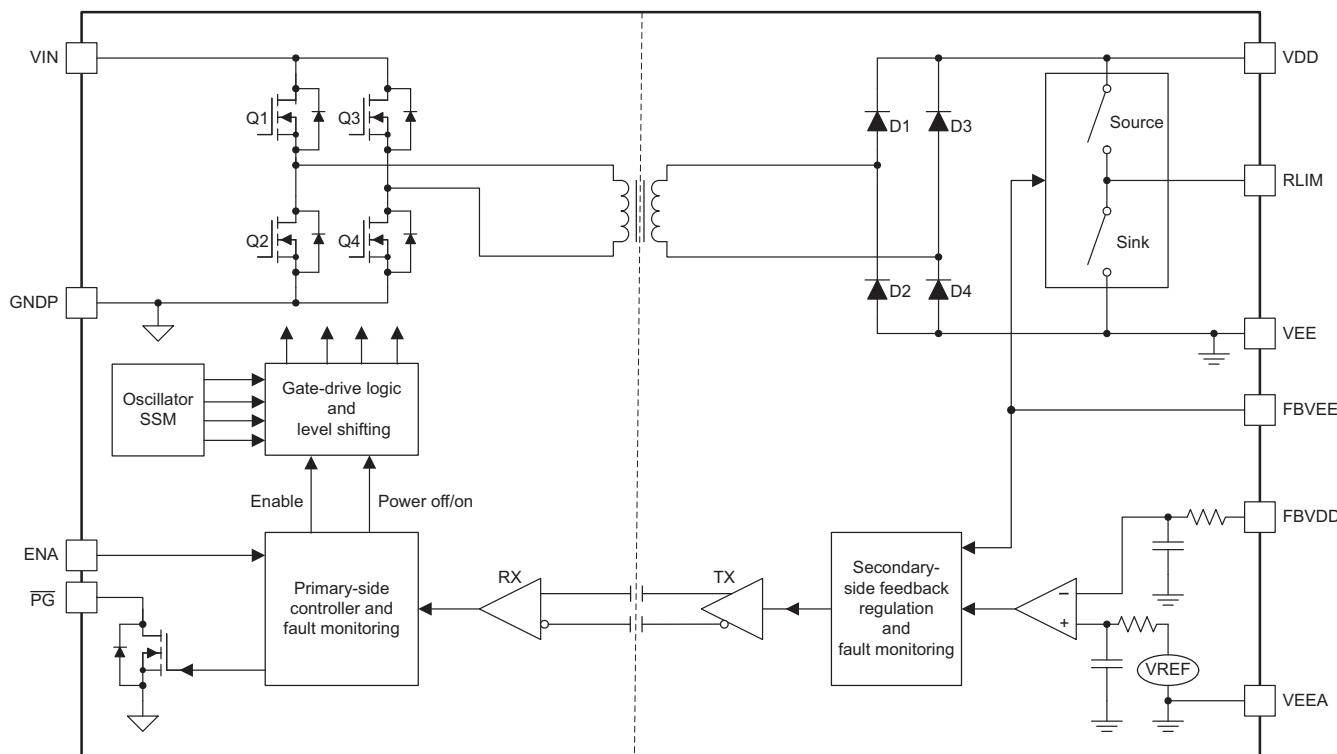

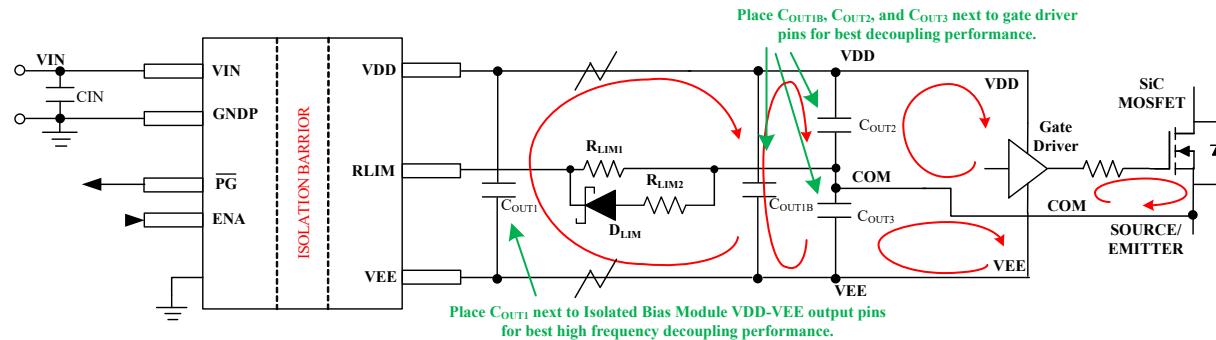

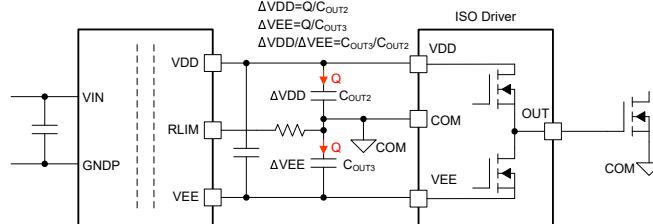

### アプリケーション概略図

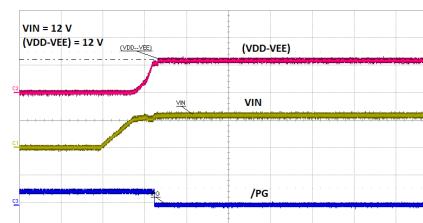

### 代表的な電源投入シーケンス

英語版の TI 製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、必ず最新版の英語版をご参照ください。

## Table of Contents

|                                                |           |                                                                            |           |

|------------------------------------------------|-----------|----------------------------------------------------------------------------|-----------|

| <b>1 特長</b> .....                              | <b>1</b>  | 11.2 Functional Block Diagram.....                                         | <b>18</b> |

| <b>2 アプリケーション</b> .....                        | <b>1</b>  | 11.3 Feature Description.....                                              | <b>19</b> |

| <b>3 概要</b> .....                              | <b>1</b>  | 11.4 Device Functional Modes.....                                          | <b>28</b> |

| <b>4 Revision History</b> .....                | <b>2</b>  | <b>12 Application and Implementation</b> .....                             | <b>29</b> |

| <b>5 Device Comparison</b> .....               | <b>3</b>  | 12.1 Application Information.....                                          | <b>29</b> |

| <b>6 Pin Configuration and Functions</b> ..... | <b>4</b>  | 12.2 Typical Application.....                                              | <b>29</b> |

| <b>7 Specifications</b> .....                  | <b>6</b>  | 12.3 System Examples.....                                                  | <b>42</b> |

| 7.1 Absolute Maximum Ratings.....              | 6         | 12.4 Power Supply Recommendations.....                                     | <b>44</b> |

| 7.2 ESD Ratings.....                           | 6         | 12.5 Layout.....                                                           | <b>44</b> |

| 7.3 Recommended Operating Conditions.....      | 6         | <b>13 Device and Documentation Support</b> .....                           | <b>51</b> |

| 7.4 Thermal Information.....                   | 6         | 13.1 Documentation Support.....                                            | <b>51</b> |

| 7.5 Insulation Specifications.....             | 7         | 13.2 ドキュメントの更新通知を受け取る方法.....                                               | <b>51</b> |

| 7.6 Electrical Characteristics.....            | 8         | 13.3 サポート・リソース.....                                                        | <b>51</b> |

| 7.7 Safety Limiting Values.....                | 10        | 13.4 Trademarks.....                                                       | <b>51</b> |

| <b>8 Safety-Related Certifications</b> .....   | <b>12</b> | 13.5 静電気放電に関する注意事項.....                                                    | <b>51</b> |

| <b>9 Insulation Characteristics</b> .....      | <b>12</b> | 13.6 用語集.....                                                              | <b>51</b> |

| <b>10 Typical Characteristics</b> .....        | <b>13</b> | <b>14 Mechanical, Packaging, and Orderable</b><br><b>Information</b> ..... | <b>52</b> |

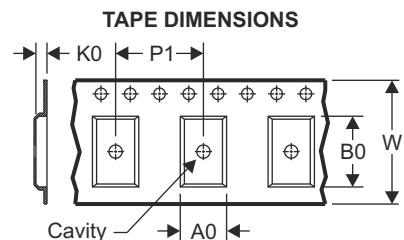

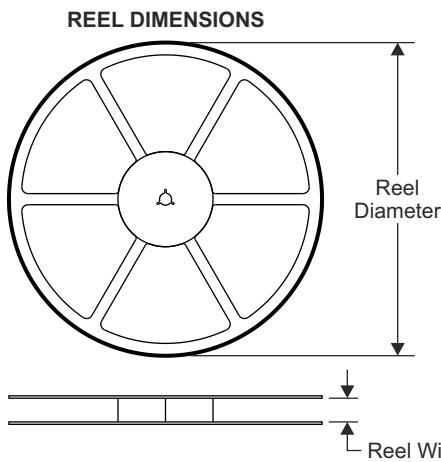

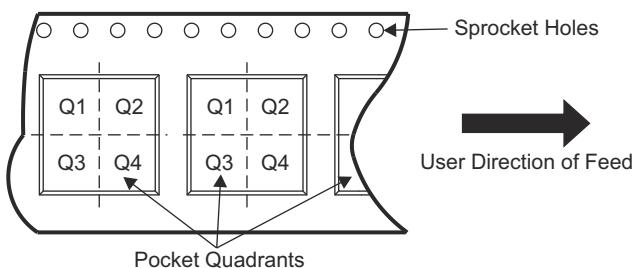

| <b>11 Detailed Description</b> .....           | <b>17</b> | <b>15 Tape and Reel Information</b> .....                                  | <b>53</b> |

| 11.1 Overview.....                             | 17        |                                                                            |           |

## 4 Revision History

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| <b>Changes from Revision * (April 2023) to Revision A (August 2023)</b> | <b>Page</b> |

|-------------------------------------------------------------------------|-------------|

| • UCC14131-Q1 の初回リリース.....                                              | <b>1</b>    |

## 5 Device Comparison

**表 5-1. Device Comparison Table**

| DEVICE NAME | V <sub>VIN</sub> Range | Output (VDD-VEE)<br>Adjustable Range | Typical power | Isolation rating |

|-------------|------------------------|--------------------------------------|---------------|------------------|

| UCC14240-Q1 | 21 V to 27 V           | 15 V to 25 V                         | 2 W           | Basic            |

| UCC14241-Q1 | 21 V to 27 V           | 15 V to 25 V                         | 2 W           | Reinforced       |

| UCC14140-Q1 | 8 V to 18 V            | 15 V to 25 V                         | 1 W           | Basic            |

|             | 10.8 V to 13.2 V       | 15 V to 25 V                         | 1.5 W         |                  |

| UCC14141-Q1 | 8 V to 18 V            | 15 V to 25 V                         | 1 W           | Reinforced       |

|             | 10.8 V to 13.2 V       | 15 V to 25 V                         | 1.5 W         |                  |

| UCC14340-Q1 | 13.5 V to 16.5 V       | 15 V to 25 V                         | 1.5 W         | Basic            |

| UCC14341-Q1 | 13.5 V to 16.5 V       | 15 V to 25 V                         | 1.5 W         | Reinforced       |

| UCC14130-Q1 | 12 V to 15 V           | 12 V to 15 V                         | 1.5 W         | Basic            |

|             | 15 V to 18 V           | 15 V to 18 V                         | 1.5 W         |                  |

|             | 10 V to 18 V           | 10 V to 12 V                         | 1 W           |                  |

|             | 14 V to 18 V           | 10 V to 18 V                         | 1 W           |                  |

| UCC14131-Q1 | 12 V to 15 V           | 12 V to 15 V                         | 1.5 W         | Reinforced       |

|             | 15 V to 18 V           | 15 V to 18 V                         | 1.5 W         |                  |

|             | 10 V to 18 V           | 10 V to 12 V                         | 1 W           |                  |

|             | 14 V to 18 V           | 10 V to 18 V                         | 1 W           |                  |

| UCC15240-Q1 | 21 V to 27 V           | 15 V to 25 V                         | 2.5 W         | Basic            |

| UCC15241-Q1 | 21 V to 27 V           | 15 V to 25 V                         | 2.5 W         | Reinforced       |

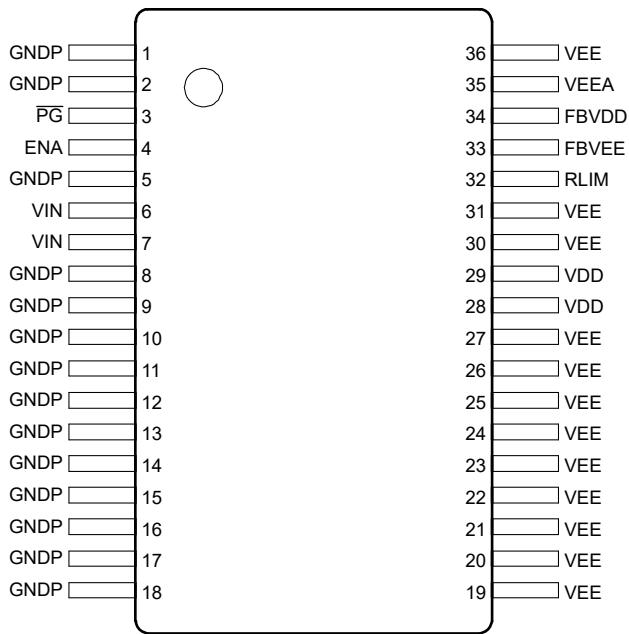

## 6 Pin Configuration and Functions

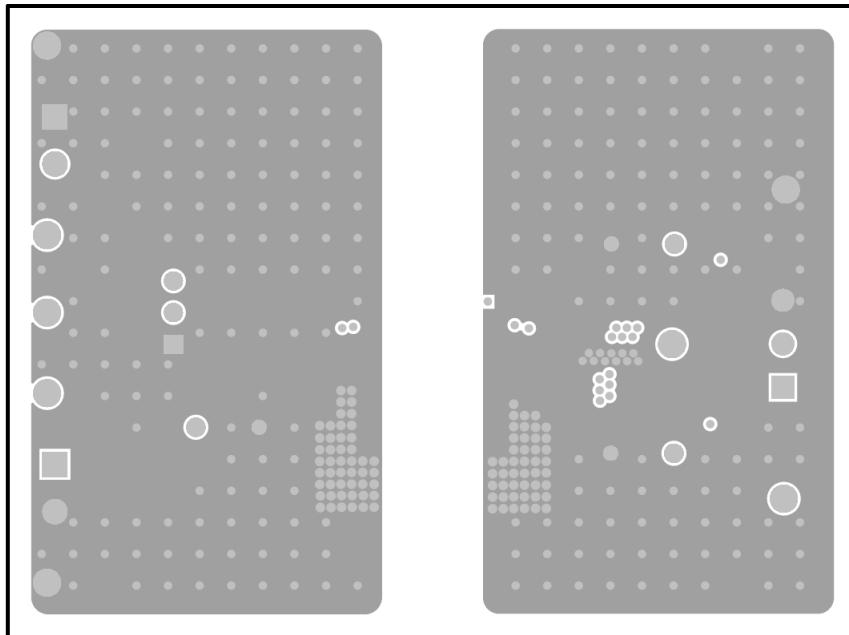

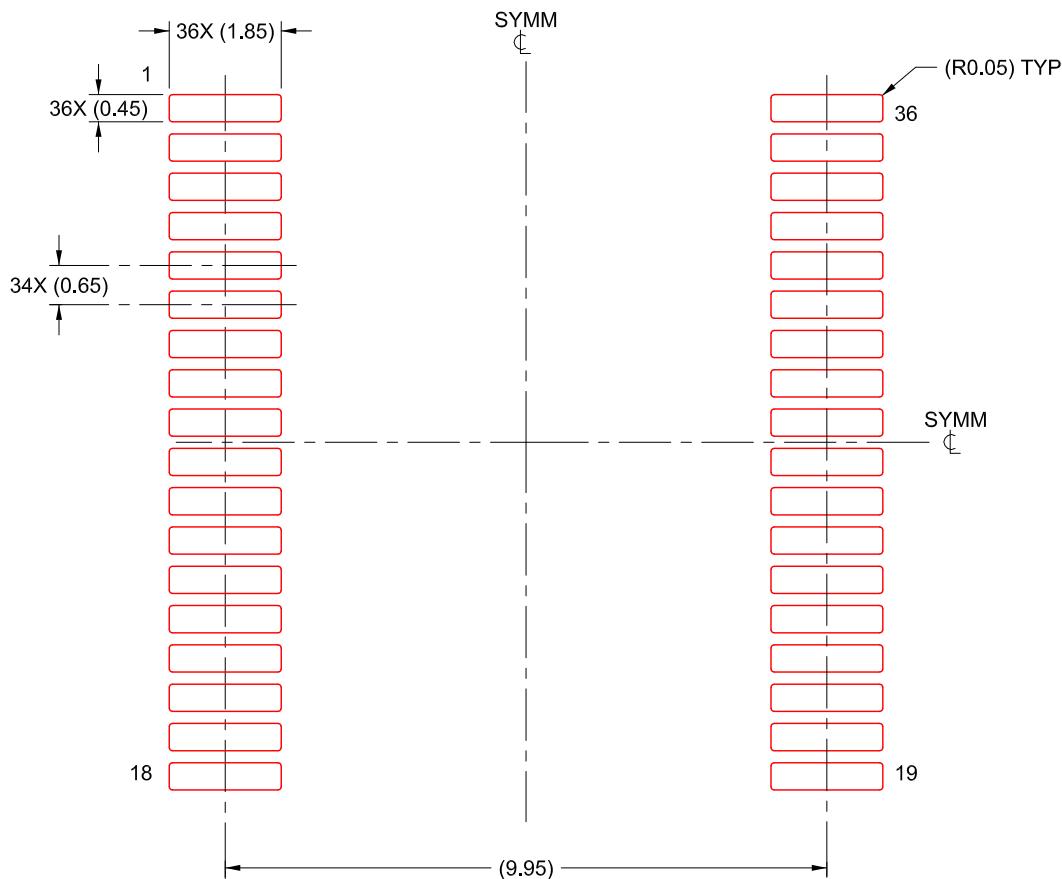

図 6-1. DWN Package, 36-Pin SSOP (Top View)

表 6-1. Pin Functions

| PIN  |                                                   | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                           |

|------|---------------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME | NO.                                               |                     |                                                                                                                                                                                                                                                                                                                                       |

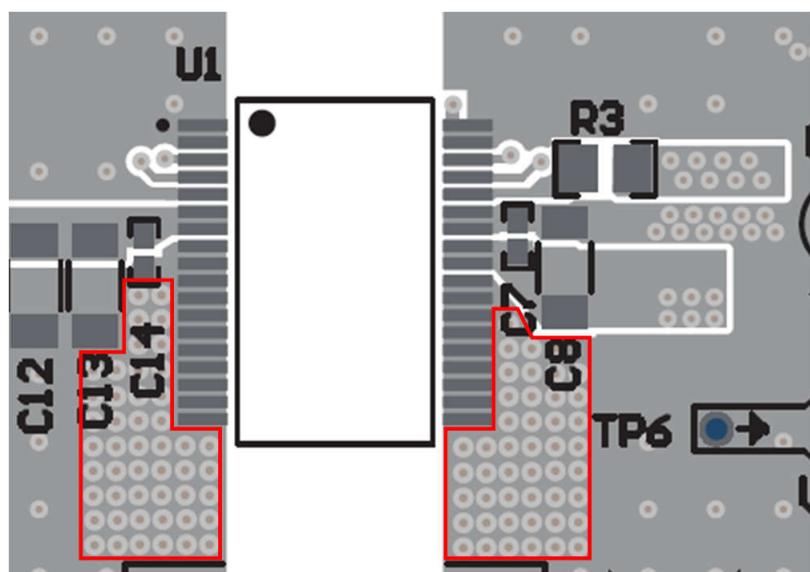

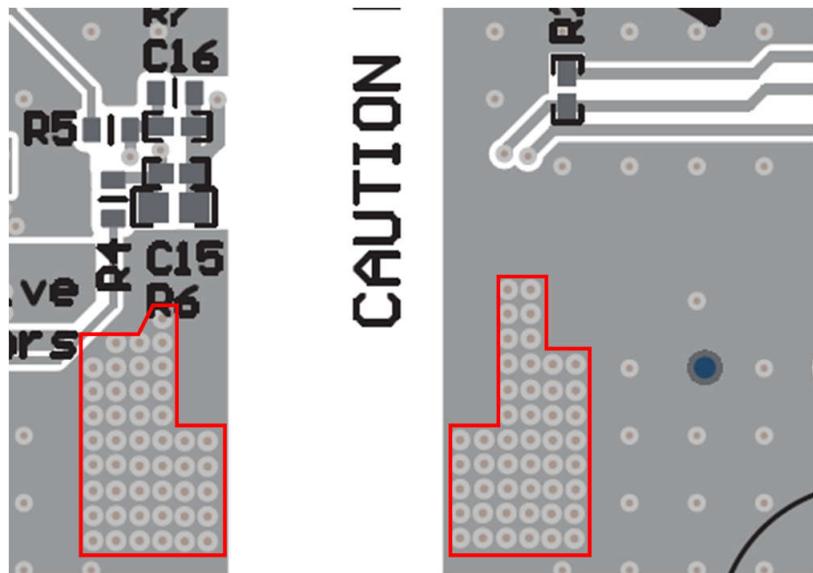

| GNDP | 1, 2, 5, 8, 9, 10, 11, 12, 13, 14, 15, 16, 17, 18 | G                   | Primary-side ground connection for VIN. PIN 1,2, and 5 are analog ground. PIN 8, 9, 10, 11, 12, 13, 14, 15, 16, 17, and 18 are power ground. Place several vias to copper pours for thermal relief. See <i>Layout Guidelines</i> section.                                                                                             |

| PG   | 3                                                 | O                   | Active low power-good open-drain output pin. PG remains low when ( $V_{VIN\_UVLOP} \leq V_{VIN} \leq V_{VIN\_OVLOP}$ ); ( $V_{VDD\_UVP} \leq V_{FBVDD} \leq V_{VDD\_OVP}$ ); ( $V_{VEE\_UVP} \leq V_{FBVEE} \leq V_{VEE\_OVP}$ ); $T_{J\_Primary} \leq TSHUTP_{PRIMARY\_RISE}$ ; and $T_{J\_secondary} \leq TSHUTS_{SECONDARY\_RISE}$ |

| ENA  | 4                                                 | I                   | Enable pin. Forcing ENA LOW disables the device. Pull HIGH to enable normal device functionality. 5.5-V recommended maximum.                                                                                                                                                                                                          |

| VIN  | 6, 7                                              | P                   | Primary input voltage. PIN 6 is for analog input, and PIN 7 is for power input. For PIN 7, connect two 10- $\mu$ F ceramic capacitor from power VIN PIN 7 to power GNDP PIN 8. Connect a 0.1- $\mu$ F high-frequency bypass ceramic capacitor close to PIN 7 and PIN 8.                                                               |

| VEE  | 19, 20, 21, 22, 23, 24, 25, 26, 27, 30, 31, 36    | G                   | Secondary-side reference connection for VDD and COM. The VEE pins are used for the high current return paths.                                                                                                                                                                                                                         |

**表 6-1. Pin Functions (continued)**

| PIN   |        | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------|--------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME  | NO.    |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

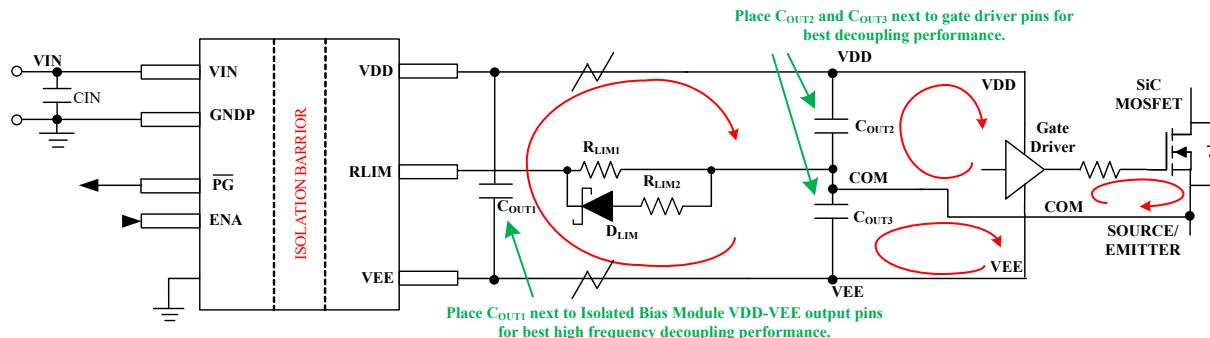

| VDD   | 28, 29 | P                   | Secondary-side isolated output voltage from transformer. Connect a 10- $\mu$ F and a parallel 0.1- $\mu$ F ceramic capacitor from VDD to VEE. The 0.1- $\mu$ F ceramic capacitor is the high frequency bypass and must be next to the IC pins.                                                                                                                                                                                                                                                                 |

| RLIM  | 32     | P                   | Secondary-side second isolated output voltage resistor to limit the source current from VDD to COM node, and the sink current from COM to VEE. Connect a resistor from RLIM to COM to regulate the (COM – VEE) voltage. See <a href="#">RLIM Resistor Selection</a> for more detail.                                                                                                                                                                                                                           |

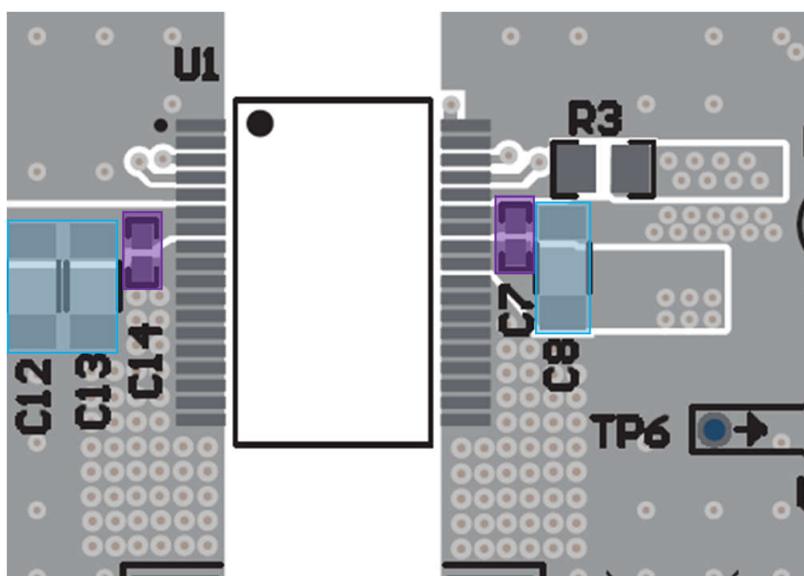

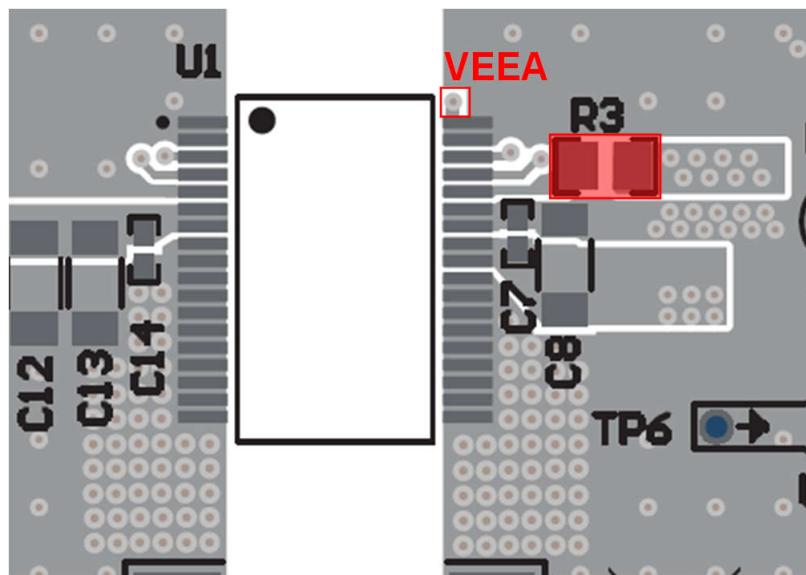

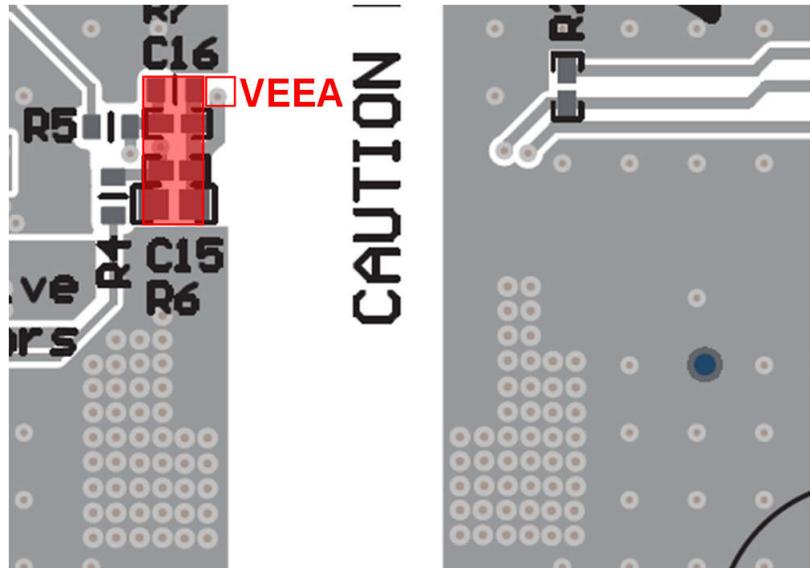

| FBVEE | 33     | I                   | Feedback (COM – VEE) output voltage sense pin used to adjust the output (COM – VEE) voltage. Connect a resistor divider from COM to VEE so that the midpoint is connected to FBVEE, and the equivalent FBVEE voltage when regulating is 2.5 V. Add a 330-pF ceramic capacitor for high frequency decoupling in parallel with the low-side feedback resistor. The 330-pF ceramic capacitor for high frequency bypass must be next to the FBVEE and VEEA IC pins on top layer or back layer connected with vias. |

| FBVDD | 34     | I                   | Feedback (VDD – VEE) output voltage sense pin and to adjust the output (VDD – VEE) voltage. Connect a resistor divider from VDD to VEE so that the midpoint is connected to FBVDD, and the equivalent FBVDD voltage when regulating is 2.5 V. Add a 330-pF ceramic capacitor for high frequency decoupling in parallel with the low-side feedback resistor. The 330-pF ceramic capacitor for high frequency bypass must be next to the FBVDD and VEEA IC pins on top layer or back layer connected with vias.  |

| VEEA  | 35     | G                   | Secondary-side analog sense reference connection for the noise sensitive analog feedback inputs, FBVDD and FBVEE. Connect the low-side feedback resistors and high frequency decoupling filter capacitor close to the VEEA pin and respective feedback pin FBVDD or FBVEE. Connect to secondary-side gate drive lowest voltage reference, VEE. Use a single point connection and place the high frequency decoupling ceramic capacitor close to the VEEA pin. See <a href="#">Layout Guidelines</a> section.   |

(1) P = power, G = ground, I = input, O = output

## 7 Specifications

### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

| Parameter                       |                                                                                                          | MIN  | TYP | MAX   | UNIT |

|---------------------------------|----------------------------------------------------------------------------------------------------------|------|-----|-------|------|

|                                 | VIN to GNDP                                                                                              | -0.3 |     | 32    | V    |

|                                 | ENA, PG to GNDP                                                                                          | -0.3 |     | 7     | V    |

|                                 | VDD, VEE, RLIM, FBVDD, FBVEE to VEE                                                                      | -0.3 |     | 32    | V    |

| P <sub>OUT_VDD_MAX</sub>        | Total (VDD-VEE) output power at T <sub>A</sub> =25°C                                                     |      |     | 2.5   | W    |

| I <sub>RLM_MAX_RMS_SOURCE</sub> | Max RLIM pin rms current sourcing from VDD to RLIM.<br>(16% average run time over lifetime of 24,500 hr) |      |     | 0.125 | A    |

| I <sub>RLM_MAX_RMS_SINK</sub>   | Max RLIM pin rms current sinking from RLIM to VEE.<br>(16% average run time over lifetime of 24,500 hr)  |      |     | 0.125 | A    |

| T <sub>J</sub>                  | Operating junction temperature range                                                                     | -40  |     | 150   | °C   |

| T <sub>stg</sub>                | Storage temperature                                                                                      | -65  |     | 150   | °C   |

- (1) Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions*. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 7.2 ESD Ratings

|                    |                         |                                                          | VALUE | UNIT |

|--------------------|-------------------------|----------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> | Electrostatic discharge | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup>  | ±2000 | V    |

|                    |                         | Charged-device model (CDM), per AEC Q100-011 Section 7.2 | ±500  | V    |

- (1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

### 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

| PIN                                        |                                    | MIN              | TYP | MAX     | UNIT |

|--------------------------------------------|------------------------------------|------------------|-----|---------|------|

| V <sub>VIN</sub>                           | Primary-side input voltage to GNDP | 9 <sup>(1)</sup> | 12  | 18      | V    |

| V <sub>ENA</sub>                           | Enable to GNDP                     | 0                |     | 5.5     | V    |

| V <sub>PG</sub>                            | Powergood to GNDP                  | 0                |     | 5.5     | V    |

| V <sub>VDD</sub>                           | VDD to VEE                         | 10               |     | 18      | V    |

| V <sub>VEE</sub>                           | COM to VEE                         | 2.5              |     | VDD-VEE | V    |

| V <sub>FBVDD</sub> ,<br>V <sub>FBVEE</sub> | FBVDD, FBVEE to VEE                | 0                | 2.5 | 5.5     | V    |

| T <sub>A</sub>                             | Ambient temperature                | -40              |     | 125     | °C   |

| T <sub>J</sub>                             | Junction temperature               | -40              |     | 150     | °C   |

- (1) See the V<sub>VIN\_UVLOP\_RISING</sub> and V<sub>VIN\_UVLOP\_FALLING</sub> electrical characteristics for the minimum operational V<sub>VIN</sub>. Because V<sub>VIN\_UVLOP\_FALLING</sub> < 8V, V<sub>VIN</sub> can operate at 8 V as long as V<sub>VIN</sub> > V<sub>VIN\_UVLOP\_RISING</sub> during start up.

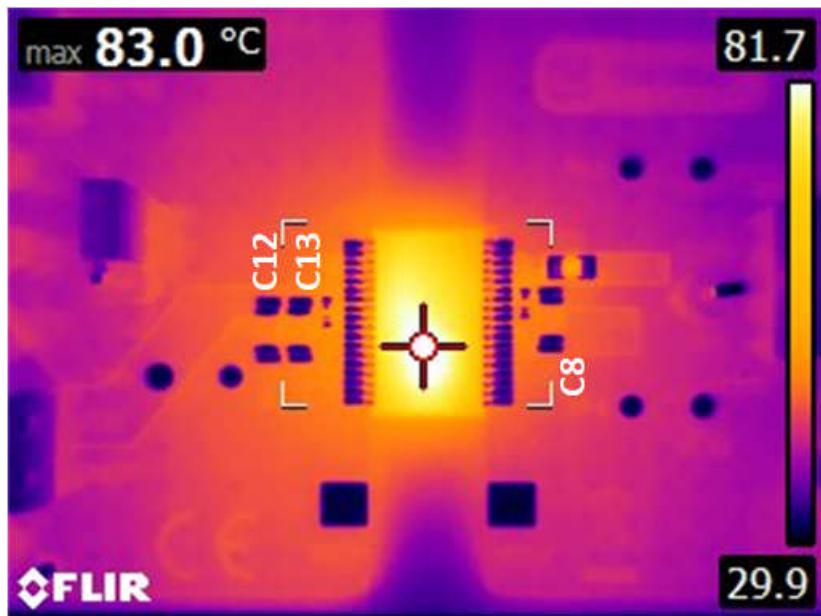

### 7.4 Thermal Information

| THERMAL METRIC <sup>(1)</sup> |                                           | DWN (SSOP) | UNIT |

|-------------------------------|-------------------------------------------|------------|------|

|                               |                                           | 36 PINS    |      |

| R <sub>θJA</sub>              | Junction-to-ambient thermal resistance    | 52.3       | °C/W |

| R <sub>θJC(top)</sub>         | Junction-to-case (top) thermal resistance | 28.5       | °C/W |

| R <sub>θJB</sub>              | Junction-to-board thermal resistance      | 25.9       | °C/W |

| THERMAL METRIC <sup>(1)</sup> |                                                | DWN (SSOP) | UNIT |

|-------------------------------|------------------------------------------------|------------|------|

|                               |                                                | 36 PINS    |      |

| $\Psi_{JA}$                   | Junction-to-ambient characterization parameter | 29.5       | °C/W |

| $\Psi_{JT}$                   | Junction-to-top characterization parameter     | 16.6       | °C/W |

| $\Psi_{JB}$                   | Junction-to-board characterization parameter   | 25.6       | °C/W |

| $R_{\theta JC(bot)}$          | Junction-to-case (bottom) thermal resistance   | –          | °C/W |

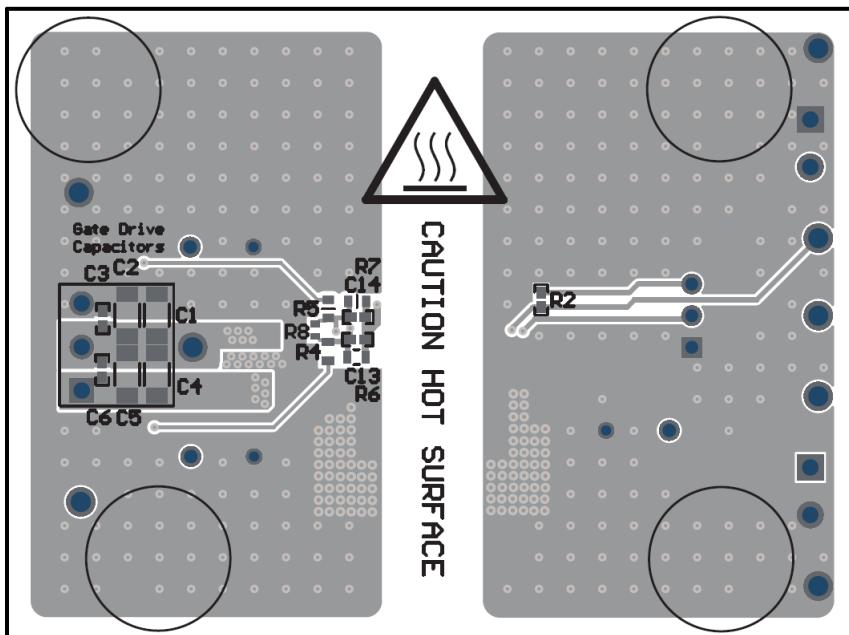

- (1) The thermal resistances (R) are based on JEDEC board, and the characterization parameters ( $\Psi$ ) are based on the EVM described in the Layout section. For more information about traditional and new thermal metrics, see the [Semiconductor and IC Package Thermal Metrics](#) application report.

## 7.5 Insulation Specifications

| PARAMETER      |                                   | TEST CONDITIONS                                                         | VALUE  | UNIT |

|----------------|-----------------------------------|-------------------------------------------------------------------------|--------|------|

| <b>GENERAL</b> |                                   |                                                                         |        |      |

| CLR            | External clearance <sup>(1)</sup> | Shortest terminal-to-terminal distance through air                      | > 8    | mm   |

| CPG            | External creepage <sup>(1)</sup>  | Shortest terminal-to-terminal distance across the package surface       | > 8    | mm   |

| DTI            | Distance through the insulation   | Minimum internal gap (internal clearance – transformer power isolation) | > 120  | μm   |

|                |                                   | Minimum internal gap (internal clearance – capacitive signal isolation) | > 15.4 |      |

| CTI            | Comparative tracking index        | DIN EN 60112 (VDE 0303-11); IEC 60112                                   | > 600  | V    |

|                | Material group                    | According to IEC 60664-1                                                | I      |      |

|                | Overvoltage category              | Rated mains voltage ≤ 300 VRMS                                          | I-IV   |      |

|                |                                   | Rated mains voltage ≤ 600 VRMS                                          | I-IV   |      |

|                |                                   | Rated mains voltage ≤ 1000 VRMS                                         | III    |      |

### DIN V VDE V 0884-11:2017-01 (Planned Certification Targets) <sup>(2)</sup>

|            |                                                      |                                                                                                                                                                                                |             |           |

|------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------|

| $V_{IORM}$ | Maximum repetitive peak isolation voltage            | AC voltage (bipolar)                                                                                                                                                                           | 1414        | $V_{PK}$  |

| $V_{IOWM}$ | Maximum working isolation voltage                    | AC voltage (sine wave) Time dependent dielectric breakdown (TDDB) test                                                                                                                         | 1000        | $V_{RMS}$ |

|            |                                                      | DC voltage                                                                                                                                                                                     | 1414        | $V_{DC}$  |

| $V_{IOTM}$ | Maximum transient isolation voltage                  | $V_{TEST} = V_{IOTM}$ , $t = 60s$ (qualification); $V_{TEST} = 1.2 \times V_{IOTM}$ , $t = 1s$ (100% production)                                                                               | 7071        | $V_{PK}$  |

| $V_{IMP}$  | Maximum impulse voltage <sup>(3)</sup>               | Tested in air, 1.2/50-μs waveform per IEC 62368-1                                                                                                                                              | 7692        | $V_{PK}$  |

| $V_{IOSM}$ | Maximum surge isolation voltage <sup>(3)</sup>       | Tested in oil (qualification test), 1.2/50 μs waveform per IEC 62368-1                                                                                                                         | 10000       | $V_{PK}$  |

| qpd        | Apparent charge <sup>(4)</sup>                       | Method a: After I/O safety test subgroup 2/3, $V_{ini} = V_{IOTM}$ , $t_{ini} = 60 s$ ; $V_{pd(m)} = 1.2 \times V_{IORM} = 1442 V_{PK}$ , $t_m = 10 s$                                         | ≤ 5         | pC        |

|            |                                                      | Method a: After environmental tests subgroup 1, $V_{ini} = V_{IOTM}$ , $t_{ini} = 60 s$ ; $V_{pd(m)} = 1.6 \times V_{IORM} = 2262 V_{PK}$ , $t_m = 10 s$                                       | ≤ 5         | pC        |

|            |                                                      | Method b1: At routine test (100% production) and preconditioning (type test) $V_{ini} = 1.2 \times V_{IOTM}$ , $t_{ini} = 1 s$ ; $V_{pd(m)} = 1.5 \times V_{IORM} = 1803 V_{PK}$ , $t_m = 1 s$ | ≤ 5         | pC        |

| $C_{IO}$   | Barrier capacitance, input to output <sup>(5)</sup>  | $V_{IO} = 0.4 \sin(2\pi ft)$ , $f = 1 \text{ MHz}$                                                                                                                                             | < 3.5       | pF        |

| $R_{IO}$   | Isolation resistance, input to output <sup>(5)</sup> | $V_{IO} = 500 \text{ V}$ , $T_A = 25^\circ\text{C}$                                                                                                                                            | $> 10^{12}$ | Ω         |

|            |                                                      | $V_{IO} = 500 \text{ V}$ , $100^\circ\text{C} \leq T_A \leq 125^\circ\text{C}$                                                                                                                 | $> 10^{11}$ | Ω         |

|            |                                                      | $V_{IO} = 500 \text{ V}$ at $TS = 150^\circ\text{C}$                                                                                                                                           | $> 10^9$    | Ω         |

|            | Pollution degree                                     |                                                                                                                                                                                                | 2           |           |

|            | Climatic category                                    |                                                                                                                                                                                                | 40/125/21   |           |

| PARAMETER                                     |                             | TEST CONDITIONS                                                                                                                                                                           | VALUE | UNIT             |

|-----------------------------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------|

| <b>UL 1577 (Planned Certification Target)</b> |                             |                                                                                                                                                                                           |       |                  |

| V <sub>ISO</sub>                              | Withstand isolation voltage | V <sub>TEST</sub> = V <sub>ISO</sub> = 5000 V <sub>RMS</sub> , t = 60 s (qualification)<br>V <sub>TEST</sub> = 1.2 × V <sub>ISO</sub> = 6000 V <sub>RMS</sub> , t = 1 s (100% production) | 5000  | V <sub>RMS</sub> |

- (1) Creepage and clearance requirements should be applied according to the specific equipment isolation standards of an application. Care should be taken to maintain the creepage and clearance distance of a board design to ensure that the mounting pads of the isolator on the printed-circuit board do not reduce this distance. Creepage and clearance on a printed-circuit board become equal in certain cases. Techniques such as inserting grooves and/or ribs on a printed-circuit board are used to help increase these specifications.

- (2) This coupler is suitable for *safe electrical insulation* only within the maximum operating ratings. Compliance with the safety ratings shall be ensured by means of suitable protective circuits.

- (3) Testing is carried out in air or oil to determine the intrinsic surge immunity of the isolation barrier

- (4) Apparent charge is electrical discharge caused by a partial discharge (pd).

- (5) All pins on each side of the barrier tied together creating a two-terminal device

## 7.6 Electrical Characteristics

Over operating temperature range ( $-40^{\circ}\text{C} \leq T_J \leq 150^{\circ}\text{C}$ ),  $8\text{ V} \leq V_{\text{VIN}} \leq 18\text{ V}$ ,  $C_{\text{IN}} = 20\text{ }\mu\text{F}$ ,  $C_{\text{OUT}} = 10\text{ }\mu\text{F}$ ,  $V_{\text{ENA}} = 5\text{ V}$ ,  $R_{\text{LIM}} = 1\text{ k}\Omega$  unless otherwise noted. All typical values at  $T_J = 25^{\circ}\text{C}$  and  $V_{\text{VIN}} = 12\text{ V}$ .

| PARAMETER                                                                |                                                         | TEST CONDITIONS                                                                                                        | MIN  | TYP | MAX  | UNIT |

|--------------------------------------------------------------------------|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|------|-----|------|------|

| <b>INPUT SUPPLY (Primary-side. All voltages with respect to GNDP)</b>    |                                                         |                                                                                                                        |      |     |      |      |

| V <sub>VIN</sub>                                                         | Input voltage range <sup>(1)</sup>                      | Primary-side input voltage to GNDP, 1-W output power                                                                   | 8    | 12  | 18   | V    |

| I <sub>VINQ_OFF</sub>                                                    | VIN quiescent current, disabled                         | V <sub>ENA</sub> = 0 V; V <sub>VIN</sub> = 8 V - 18 V                                                                  |      | 600 |      | μA   |

| I <sub>VIN_ON_NO_LOAD</sub>                                              | VIN operating current, enabled, No Load                 | V <sub>ENA</sub> = 5 V; V <sub>VIN</sub> = 8 V - 18 V; (VDD-VEE) = 12-V regulating; I <sub>VDD-VEE</sub> = 0 mA        |      | 40  |      | mA   |

| I <sub>VIN_ON_FULL_LOAD</sub>                                            | VIN operating current, enabled, Full Load               | V <sub>ENA</sub> = 5 V; V <sub>VIN</sub> = 10 V - 18 V; (VDD-VEE) = 12-V regulating; I <sub>VDD-VEE</sub> = 83 mA      |      | 200 |      | mA   |

| I <sub>VIN_ON_FULL_LOAD</sub>                                            | VIN operating current, enabled, Full Load               | V <sub>ENA</sub> = 5 V; V <sub>VIN</sub> = 10.8 V - 13.2 V; (VDD-VEE) = 12-V regulating; I <sub>VDD-VEE</sub> = 125 mA |      | 270 |      | mA   |

| <b>UVLO COMPARATOR (Primary-side. All voltages with respect to GNDP)</b> |                                                         |                                                                                                                        |      |     |      |      |

| V <sub>VIN_UVLO_RISING</sub>                                             | VIN undervoltage lockout rising threshold               | VIN rising                                                                                                             | 7.8  | 8.2 | 8.5  | V    |

| V <sub>VIN_UVLO_FALLING</sub>                                            | VIN under-voltage lockout falling threshold             | VIN falling                                                                                                            | 7    | 7.4 | 7.7  | V    |

| <b>OVLO COMPARATOR (Primary-side. All voltages with respect to GNDP)</b> |                                                         |                                                                                                                        |      |     |      |      |

| V <sub>VIN_OVLO_RISE</sub>                                               | VIN over-voltage lockout rising threshold               | VIN rising                                                                                                             | 20.9 | 22  | 23.1 | V    |

| V <sub>VIN_OVLO_FALLING</sub>                                            | VIN over-voltage lockout falling threshold              | VIN falling                                                                                                            | 19   | 20  | 21   | V    |

| <b>THERMAL SHUTDOWN (Primary side)</b>                                   |                                                         |                                                                                                                        |      |     |      |      |

| TSHUTP <sub>PRIMARY_RISE</sub>                                           | Primary-side over-temperature shutdown rising threshold | First time at power-up T <sub>j</sub> needs to be < 140 °C to turnon                                                   | 150  | 160 | 170  | °C   |

| TSHUTP <sub>PRIMARY_HYST</sub>                                           | Primary-side over-temperature shutdown hysteresis       |                                                                                                                        | 15   | 20  | 25   | °C   |

| <b>ENA INPUT PIN (Primary-side. All voltages with respect to GNDP)</b>   |                                                         |                                                                                                                        |      |     |      |      |

| V <sub>EN_IR</sub>                                                       | Input voltage rising threshold, logic HIGH              | Rising edge                                                                                                            |      | 2.1 |      | V    |

| V <sub>EN_IF</sub>                                                       | Input voltage falling threshold, logic LOW              | Falling edge                                                                                                           |      | 0.8 |      | V    |

| I <sub>EN</sub>                                                          | Enable Pin Input Current                                | V <sub>EN</sub> = 5.0 V                                                                                                | 5    | 18  |      | μA   |

| <b>POWERGOOD (Primary-side. All voltages with respect to GNDP)</b>       |                                                         |                                                                                                                        |      |     |      |      |

Over operating temperature range ( $-40^{\circ}\text{C} \leq T_J \leq 150^{\circ}\text{C}$ ),  $8\text{ V} \leq V_{\text{VIN}} \leq 18\text{ V}$ ,  $C_{\text{IN}} = 20\text{ }\mu\text{F}$ ,  $C_{\text{OUT}} = 10\text{ }\mu\text{F}$ ,  $V_{\text{ENA}} = 5\text{ V}$ ,  $R_{\text{LIM}} = 1\text{ k}\Omega$  unless otherwise noted. All typical values at  $T_J = 25^{\circ}\text{C}$  and  $V_{\text{VIN}} = 12\text{ V}$ .

| PARAMETER                                                                      | TEST CONDITIONS                                                                                      | MIN                                                                                                                                                                                  | TYP    | MAX         | UNIT          |

|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------|---------------|

| $V_{\text{PG\_OUT\_LO}}$                                                       | PG output-low saturation voltage                                                                     |                                                                                                                                                                                      |        | 0.5         | V             |

| $I_{\text{PG\_OUT\_HI}}$                                                       | PG Leakage current                                                                                   |                                                                                                                                                                                      |        | 5           | $\mu\text{A}$ |

| <b>Primary-side Control (Primary-side. All voltages with respect to GNDP)</b>  |                                                                                                      |                                                                                                                                                                                      |        |             |               |

| $F_{\text{SW}}$                                                                | Switching frequency                                                                                  | $V_{\text{VIN}} = 12\text{ V}$ ; $V_{\text{ENA}} = 5\text{ V}$ ; $(\text{VDD}-\text{VEE}) = 12\text{ V}$                                                                             |        | 20.5        | MHz           |

| $F_{\text{SSM}}$                                                               | Frequency of Spread Spectrum Modulation (SSM) triangle waveform                                      | Only during primary-side startup starting after $V_{\text{IN}} > \text{UVLOP}$ , and $\text{EN} = \text{HIGH}$ ; $F_{\text{SS\_BURST\_P}} = 1/8\text{ }\mu\text{s} = 125\text{ kHz}$ |        | 90          | kHz           |

| SSM Percentage change of $F_{\text{CARRIER}}$                                  | SSM Percent change of carrier frequency during Spread Spectrum Modulation (SSM) by triangle waveform | Only during primary-side startup starting after $V_{\text{IN}} > \text{UVLOP}$ , and $\text{EN} = \text{HIGH}$ ; $F_{\text{SS\_BURST\_P}} = 1/8\text{ }\mu\text{s} = 125\text{ kHz}$ |        | 5           | %             |

| $t_{\text{SOFT\_START\_TIME\_OUT}}$                                            | Primary-side soft-start time-out                                                                     | Timer begins when $V_{\text{IN}} > \text{UVLOP}$ and $\text{ENA} = \text{High}$ and reset when Powergood pin indicates Good                                                          |        | 28.4        | ms            |

| <b>VDD OUTPUT VOLTAGE (Secondary-side. All voltages with respect to VEE)</b>   |                                                                                                      |                                                                                                                                                                                      |        |             |               |

| $V_{\text{VDD\_RANGE}}$                                                        | (VDD – VEE) Output voltage range                                                                     |                                                                                                                                                                                      | 10     | 18          | V             |

| $V_{\text{VDD\_DC\_ACCURACY}}$                                                 | (VDD – VEE) Output voltage DC regulation accuracy                                                    | Secondary-side (VDD – VEE) output voltage, over load, line and temperature range, externally adjust with external resistor divider                                                   | -1.3   | 1.3         | %             |

| <b>VDD REGULATION (Secondary-side. All voltages with respect to VEE)</b>       |                                                                                                      |                                                                                                                                                                                      |        |             |               |

| $V_{\text{FBVDD\_REF}}$                                                        | Feedback regulation reference voltage for (VDD – VEE)                                                | (VDD – VEE) output in regulation                                                                                                                                                     | 2.4675 | 2.5         | 2.5325        |

| <b>COM OUTPUT VOLTAGE (Secondary-side. All voltages with respect to VEE)</b>   |                                                                                                      |                                                                                                                                                                                      |        |             |               |

| $V_{\text{VEE\_RANGE}}$                                                        | (COM – VEE) Output voltage range                                                                     | Secondary-side (COM – VEE), adjust with external resistor divider                                                                                                                    | 2.5    | (VDD – VEE) | V             |

| $V_{\text{VEE\_DC\_ACCURACY}}$                                                 | (COM – VEE) Output voltage DC regulation accuracy                                                    | Secondary-side (COM – VEE) output voltage, over load, line and temperature range, externally adjust with external resistor divider                                                   | -1.3   | 1.3         | %             |

| <b>COM REGULATION (Secondary-side. All voltages with respect to VEE)</b>       |                                                                                                      |                                                                                                                                                                                      |        |             |               |

| $V_{\text{FBVEE\_REF}}$                                                        | Feedback regulation reference voltage for (COM – VEE)                                                | (COM – VEE) output in regulation                                                                                                                                                     | 2.4675 | 2.5         | 2.5325        |

| $V_{\text{RLIM\_SHORT\_CHRG\_CMP\_RISE}}$                                      | RLIM Short Charge comparator rising threshold to exit PWM                                            | Rising threshold                                                                                                                                                                     |        | 0.73        | V             |

| $t_{\text{RLIM\_SHORT\_CHRG\_ON\_TIME}}$                                       | On-Time during RLIM pin Short Charge PWM mode                                                        | RLIM pin $< 0.645\text{ V}$ , while FBVEE pin $< 2.48\text{ V}$                                                                                                                      |        | 1.2         | us            |

| $t_{\text{RLIM\_SHORT\_CHRG\_OFF\_TIME}}$                                      | Off-Time during RLIM pin Short Charge PWM mode                                                       | RLIM pin $< 0.645\text{ V}$ , while FBVEE pin $< 2.48\text{ V}$                                                                                                                      |        | 5           | us            |

| <b>VDD UVLOS COMPARATOR (Secondary-side. All voltages with respect to VEE)</b> |                                                                                                      |                                                                                                                                                                                      |        |             |               |

| $V_{\text{VDD\_UVLO\_RISE}}$                                                   | (VDD – VEE) undervoltage lockout rising threshold                                                    | Voltage at FBVDD                                                                                                                                                                     |        | 0.9         | V             |

| $V_{\text{VDD\_UVLO\_HYST}}$                                                   | (VDD – VEE) undervoltage lockout hysteresis                                                          | Voltage at FBVDD                                                                                                                                                                     |        | 0.2         | V             |

| <b>VDD OVLOS COMPARATOR (Secondary-side. All voltages with respect to VEE)</b> |                                                                                                      |                                                                                                                                                                                      |        |             |               |

| $V_{\text{VDD\_OVLOS\_RISE}}$                                                  | (VDD – VEE) over-voltage lockout rising threshold                                                    | Voltage from VDD to VEE, rising                                                                                                                                                      | 29.45  | 31          | 32.55         |

| $V_{\text{VDD\_OVLOS\_FALL}}$                                                  | (VDD – VEE) over-voltage lockout falling threshold                                                   | Voltage from VDD to VEE, falling                                                                                                                                                     | 27.55  | 29          | 30.45         |

Over operating temperature range ( $-40^{\circ}\text{C} \leq T_J \leq 150^{\circ}\text{C}$ ),  $8\text{ V} \leq V_{\text{VIN}} \leq 18\text{ V}$ ,  $C_{\text{IN}} = 20\text{ }\mu\text{F}$ ,  $C_{\text{OUT}} = 10\text{ }\mu\text{F}$ ,  $V_{\text{ENA}} = 5\text{ V}$ ,  $R_{\text{LIM}} = 1\text{ k}\Omega$  unless otherwise noted. All typical values at  $T_J = 25^{\circ}\text{C}$  and  $V_{\text{VIN}} = 12\text{ V}$ .

| PARAMETER                                                                                            | TEST CONDITIONS                                                                                         | MIN                                                                         | TYP   | MAX  | UNIT  |

|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------|------|-------|

| <b>SOFT-START (Secondary-side. All voltages with respect to VEE)</b>                                 |                                                                                                         |                                                                             |       |      |       |

| $t_{\text{blankout}}$                                                                                | Blank out time after soft start before $\overline{\text{PG}}$ for (VDD-VEE) UVP and (COM-VEE) UVP & OVP |                                                                             | 3     |      | ms    |

| <b>(VDD – VEE) UVP, UNDER -VOLTAGE PROTECTION (Secondary-side. All voltages with respect to VEE)</b> |                                                                                                         |                                                                             |       |      |       |

| $V_{\text{VDD\_UVP\_RISE}}$                                                                          | (VDD – VEE) under-voltage protection rising threshold, $V_{\text{UVP}} = V_{\text{REF}} \times 90\%$    |                                                                             | 2.175 | 2.25 | 2.3   |

| $V_{\text{VDD\_UVP\_HYST}}$                                                                          | (VDD – VEE) under-voltage protection hysteresis                                                         |                                                                             | 25    |      | mV    |

| <b>(VDD – VEE) OVP, OVER-VOLTAGE PROTECTION (Secondary-side. All voltages with respect to VEE)</b>   |                                                                                                         |                                                                             |       |      |       |

| $V_{\text{VDD\_OVP\_RISE}}$                                                                          | (VDD – VEE) over-voltage protection rising threshold, $V_{\text{OVP}} = V_{\text{REF}} \times 110\%$    |                                                                             | 2.7   | 2.75 | 2.825 |

| $V_{\text{VDD\_OVP\_HYST}}$                                                                          | (VDD – VEE) over-voltage protection hysteresis                                                          |                                                                             | 25    |      | mV    |

| <b>(COM – VEE) UVP, UNDER -VOLTAGE PROTECTION (Secondary-side. All voltages with respect to VEE)</b> |                                                                                                         |                                                                             |       |      |       |

| $V_{\text{VEE\_UVP\_RISE}}$                                                                          | (COM – VEE) under-voltage protection rising threshold, $V_{\text{UVP}} = V_{\text{REF}} \times 90\%$    |                                                                             | 2.175 | 2.25 | 2.3   |

| $V_{\text{VEE\_UVP\_HYST}}$                                                                          | (COM – VEE) under-voltage protection hysteresis                                                         |                                                                             | 25    |      | mV    |

| <b>(COM – VEE) OVP, OVER-VOLTAGE PROTECTION (Secondary-side. All voltages with respect to VEE)</b>   |                                                                                                         |                                                                             |       |      |       |

| $V_{\text{VEE\_OVP\_RISE}}$                                                                          | (COM – VEE) over-voltage protection rising threshold, $V_{\text{OVP}} = V_{\text{REF}} \times 110\%$    |                                                                             | 2.7   | 2.75 | 2.825 |

| $V_{\text{VEE\_OVP\_HYST}}$                                                                          | (COM – VEE) over-voltage protection hysteresis                                                          |                                                                             | 25    |      | mV    |

| <b>THERMAL SHUTDOWN(Secondary side)</b>                                                              |                                                                                                         |                                                                             |       |      |       |

| $T_{\text{SHUTS}}_{\text{SECONDAR Y\_RISE}}$                                                         | Secondary -side over-temperature shutdown rising threshold                                              | First time at power-up $T_J$ needs to be $< 140^{\circ}\text{C}$ to turnon. | 150   | 160  | 170   |

| $T_{\text{SHUTS}}_{\text{SECONDAR Y\_HYST}}$                                                         | Secondary-side over-temperature shutdown hysteresis                                                     |                                                                             | 15    | 20   | 25    |

| <b>CMTI (Common Mode Transient Immunity)</b>                                                         |                                                                                                         |                                                                             |       |      |       |

| CMTI                                                                                                 | Common Mode Transient Immunity                                                                          | Positive VEE with respect to GNDP                                           | 150   |      | V/ns  |

|                                                                                                      |                                                                                                         | Negative VEE with respect to GNDP                                           |       | -150 | V/ns  |

| <b>INTEGRATED TRANSFORMER</b>                                                                        |                                                                                                         |                                                                             |       |      |       |

| N                                                                                                    | Transformer effective turns ratio                                                                       | Secondary side to primary side                                              | 1.51  |      | -     |

(1)  $V_{\text{VIN}}$  needs to be above  $V_{\text{VIN\_UVLOP\_RISING}}$  first before it operates with the minimum input voltage.

## 7.7 Safety Limiting Values

| PARAMETER | TEST CONDITIONS                          | MAX                                                                                                                                                                          | UNIT |                    |

|-----------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------|

| $I_S$     | Safety input or output current (VDD-VEE) | $R_{\theta JA} = 53^{\circ}\text{C/W}$ , $V_{\text{VIN}} = 18\text{ V}$ , $T_J = 150^{\circ}\text{C}$ , $T_A = 25^{\circ}\text{C}$ , $P_{\text{OUT}} = 1.5\text{ W}$ (1) (2) | 216  | mA                 |

|           |                                          | $R_{\theta JA} = 53^{\circ}\text{C/W}$ , $V_{\text{VIN}} = 8\text{ V}$ , $T_J = 150^{\circ}\text{C}$ , $T_A = 25^{\circ}\text{C}$ , $P_{\text{OUT}} = 1.2\text{ W}$ (1) (2)  | 449  | mA                 |

| $P_S$     | Safety input or output power (VDD-VEE)   | $R_{\theta JA} = 53^{\circ}\text{C/W}$ , $T_J = 150^{\circ}\text{C}$ , $T_A = 25^{\circ}\text{C}$ (1) (2)                                                                    | 2.36 | W                  |

| $T_S$     | Safety temperature                       | (1) (2)                                                                                                                                                                      | 150  | $^{\circ}\text{C}$ |

- (1) The maximum safety temperature,  $T_S$ , has the same value as the maximum junction temperature,  $T_J$ , specified for the device. The  $I_S$  and  $P_S$  parameters represent the safety current and safety power respectively. The maximum limits of  $I_S$  and  $P_S$  should not be exceeded. These limits vary with the ambient temperature,  $T_A$ .

- (2) The junction-to-air thermal resistance,  $R_{\theta JA}$ , in the Thermal Information table is that of a device installed on a high-K test board for leaded surface-mount packages. Use these equations to calculate the value for each parameter:  $T_J = T_A + R_{\theta JA} \times P$ , where  $P$  is the

power dissipated in the device.  $TJ(max) = TS = TA + R_{\theta JA} \times PS$ , where  $TJ(max)$  is the maximum allowed junction temperature.  $PS = IS \times VI$ , where  $VI$  is the maximum input voltage.

## 8 Safety-Related Certifications

| VDE                                                                                                                                                                                                        | UL                                                          | CQC                                                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| Plan to certify according to DIN EN IEC 60747-17 (VDE 0884-17)                                                                                                                                             | Plan to certify under UL 1577 Component Recognition Program | Plan to certify according to GB4943.1                                                                         |

| Reinforced insulation Maximum transient isolation voltage, 7071 V <sub>PK</sub> ; Maximum repetitive peak isolation voltage, 1414 V <sub>PK</sub> ; Maximum surge isolation voltage, 10000 V <sub>PK</sub> | Single protection, 5000 V <sub>RMS</sub>                    | Reinforced insulation, Altitude $\leq$ 5000 m, Tropical Climate, 700 V <sub>RMS</sub> maximum working voltage |

| Certificate number: (planned)                                                                                                                                                                              | File number: (planned)                                      | Certificate number: (planned)                                                                                 |

## 9 Insulation Characteristics

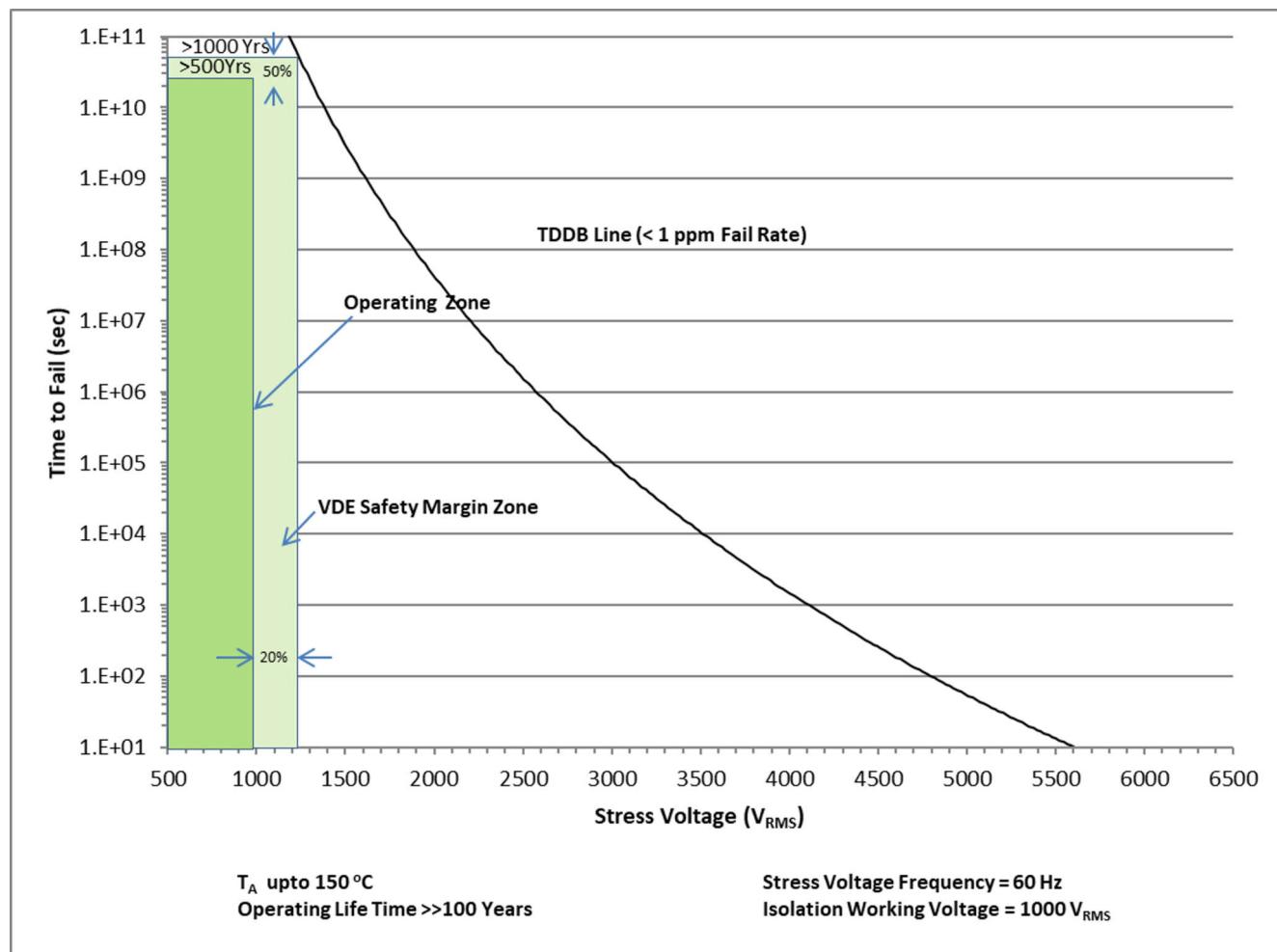

Insulation lifetime projection data is collected by using industry-standard Time Dependent Dielectric Breakdown (TDDB) test method. In this test, all pins on each side of the barrier are tied together creating a two-terminal device and high voltage applied between the two sides; The insulation breakdown data is collected at various high voltages switching at 60 Hz over temperature. For reinforced insulation, VDE standard requires the use of TDDB projection line with failure rate of less than 1 part per million (ppm). Even though the expected minimum insulation lifetime is 20 years at the specified working isolation voltage, VDE reinforce certification requires additional safety margin of 20% for working voltage and 50% for lifetime which translates into minimum required insulation lifetime of 30 years at a working voltage that's 20% higher than the specified value. The TDDB projection line shows the intrinsic capability of the isolation barrier to withstand high voltage stress over its lifetime. Based on the TDDB data, the intrinsic capability of the insulation is 1000 V<sub>RMS</sub> with a lifetime  $\gg$ 100 years.

图 9-1. TDDB: Insulation Lifetime Projection for 1000 Vrms Working Voltage.

## 10 Typical Characteristics

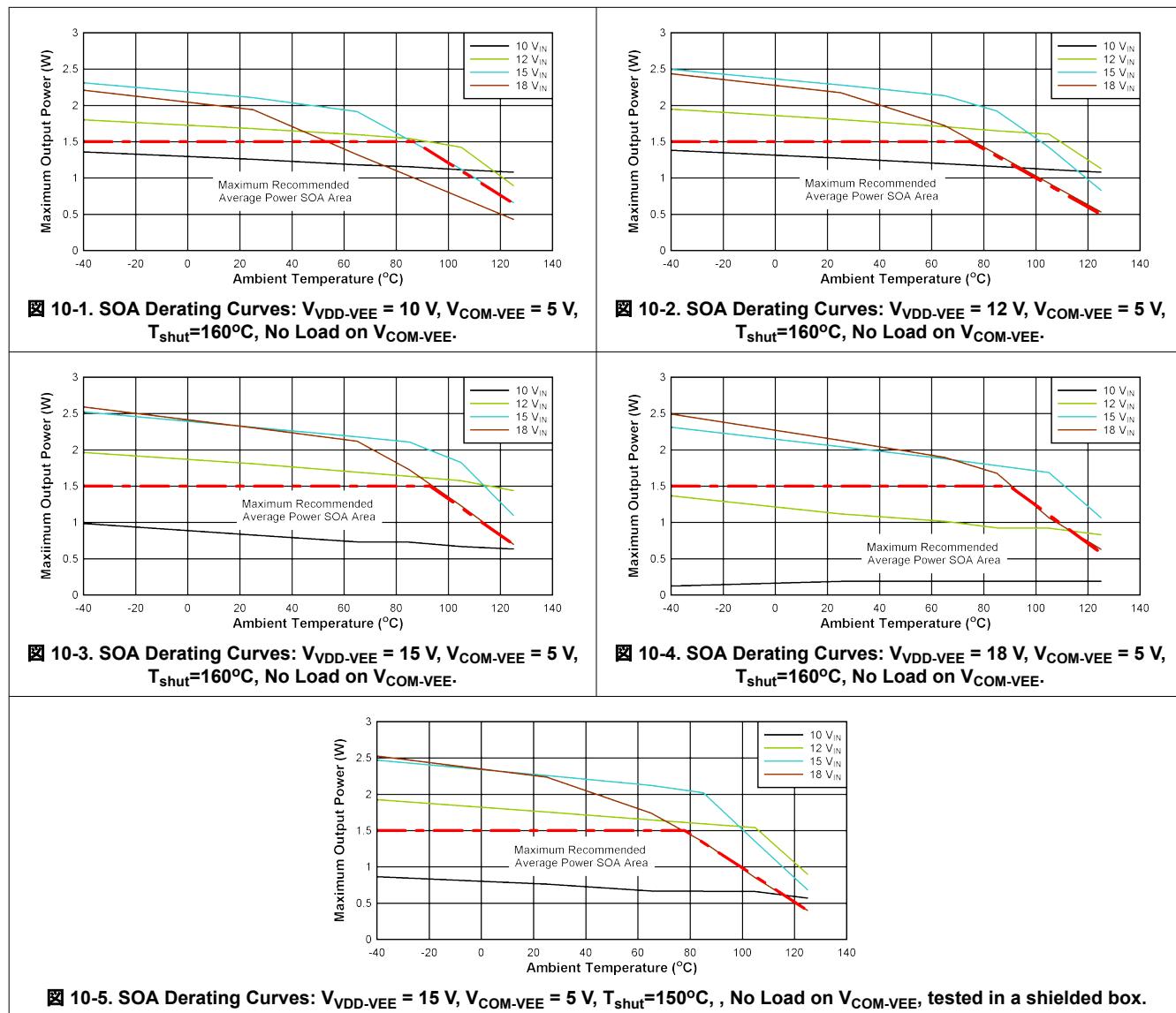

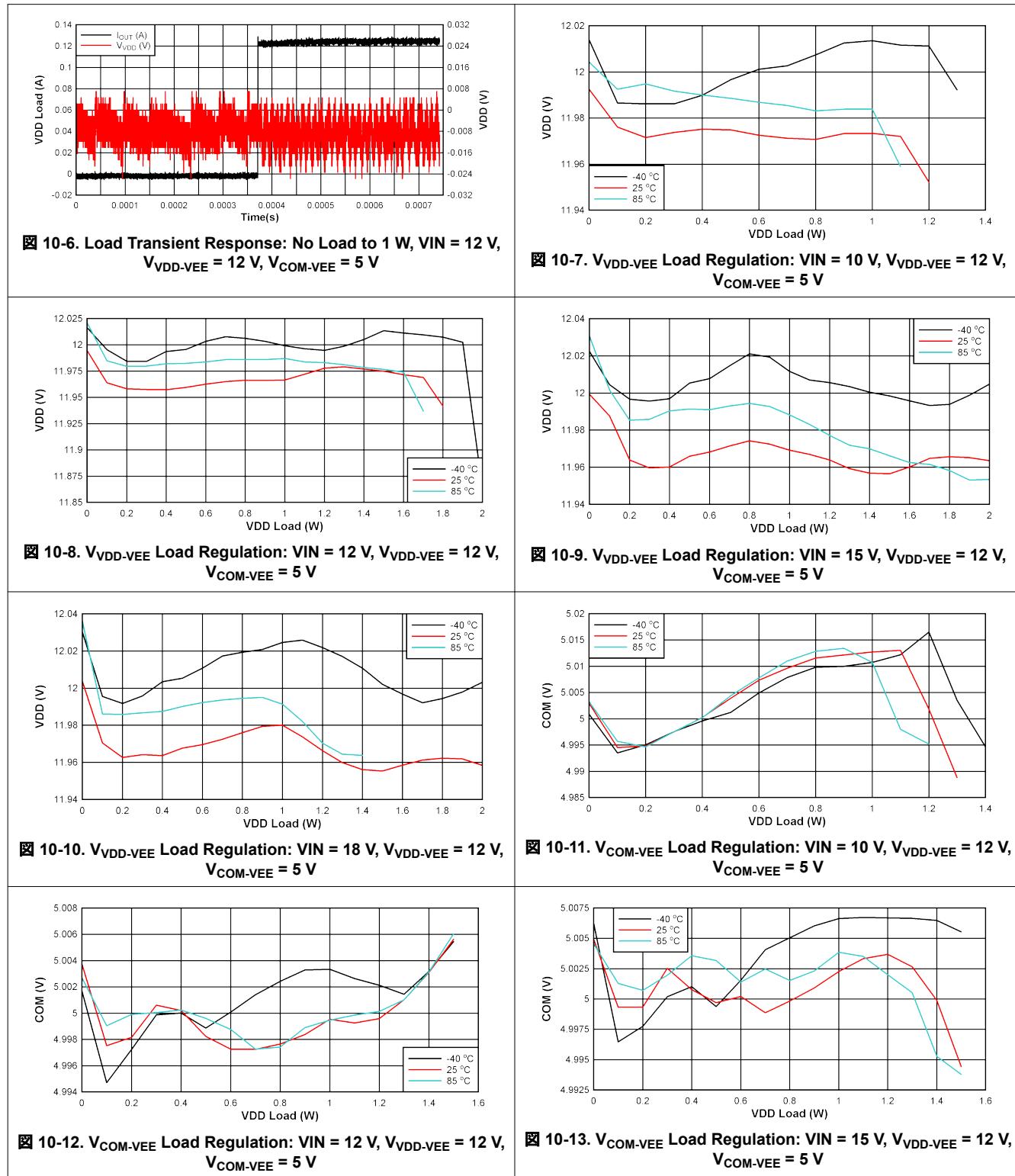

The maximum recommended average power safe operating area (SOA) at each  $V_{IN}$  is determined by the lower value of the 1.5 W limit (dotted line) and the corresponding thermal derating curve (solid line) at that input voltage. It is not recommended to operate at an ambient temperature higher than 125°C. The thermal derating power is acquired with an evaluation board similar to the EVM shown in the Application and Implementation section.  $T_{shut}$  represents the primary-side over-temperature shutdown rising threshold. As shown in the Electrical Characteristics table, the typical  $T_{shut}$  value is 160°C, and minimal  $T_{shut}$  value is 150°C. The SOA derating curve with both  $T_{shut} = 160^\circ\text{C}$  and 150°C are provided below. The SOA curves under four common  $V_{DD-VEE}$  settings, 10V, 12V, 15V, and 18V are characterized. In each SOA curve, the input voltage is swept from 10V to 18V. To represent a worst-case condition with  $T_{shut} = 150^\circ\text{C}$ , the test is done in a shielded box to block circulating air in the thermal chamber.

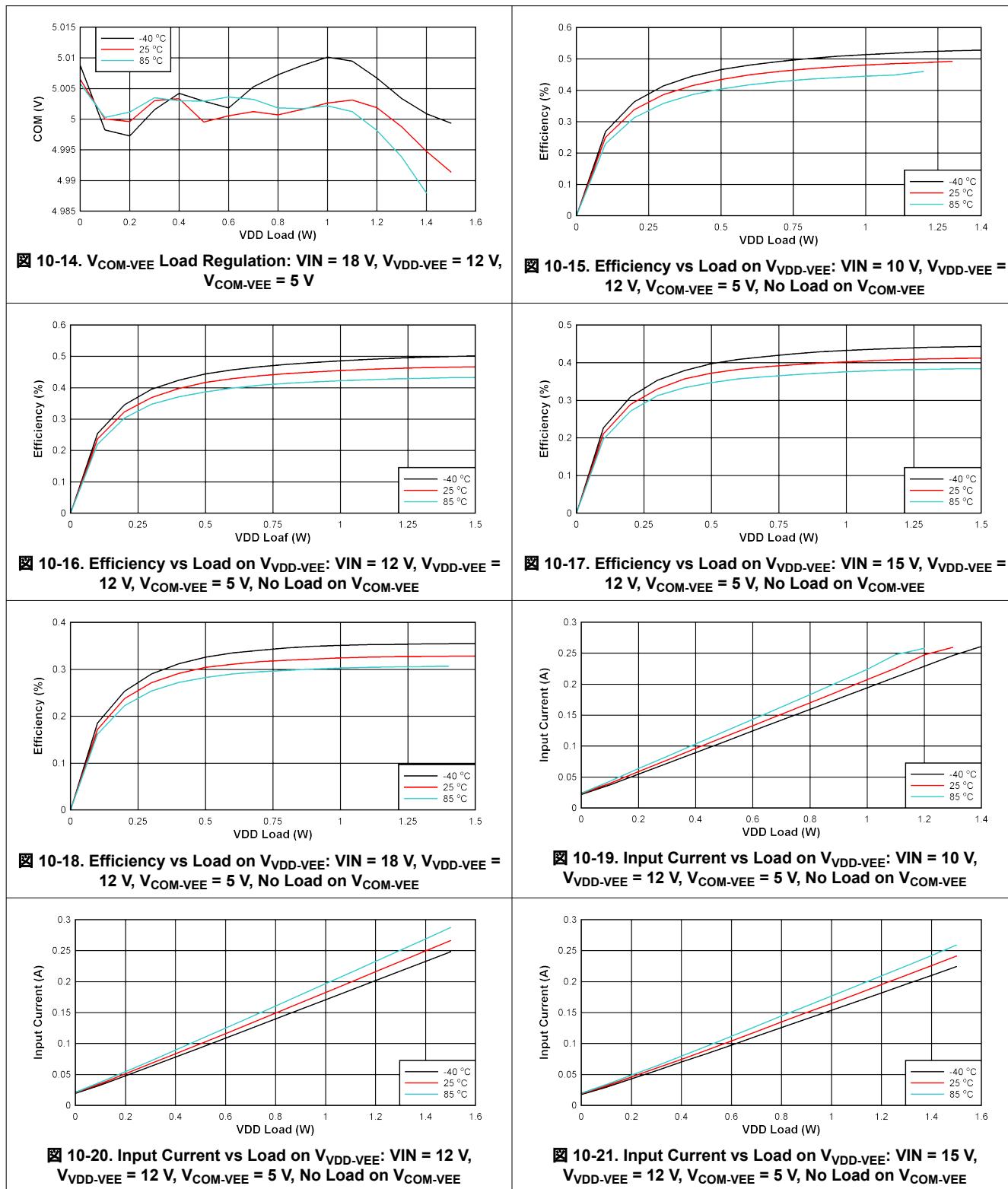

## 10 Typical Characteristics (continued)

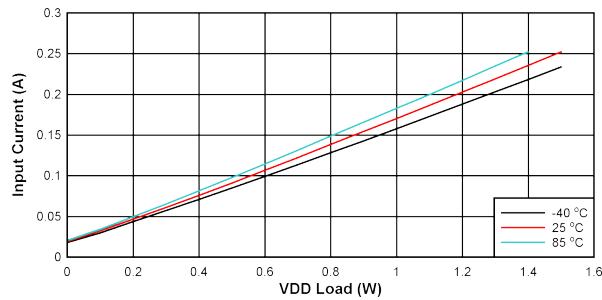

## 10 Typical Characteristics (continued)

## 10 Typical Characteristics (continued)

图 10-22. Input Current vs Load on  $V_{VDD-VEE}$ :  $V_{IN} = 18$  V,  $V_{VDD-VEE} = 12$  V,  $V_{COM-VEE} = 5$  V, No Load on  $V_{COM-VEE}$

## 11 Detailed Description

### 11.1 Overview

UCC14131-Q1 device is suitable for applications that have limited board space and require more integration. These devices are also suitable for very-high voltage applications, where power transformers meeting the required isolation specifications are bulky and expensive. The low-profile, low-center of gravity, and low weight provides a higher vibration tolerance than systems using large bulky transformers. The device is easy-to-use and provides flexibility to adjust both positive and negative output voltages as needed when optimizing the gate voltage for maximum efficiency while protecting gate oxide from over-stress with its tight voltage regulation accuracy.

The device integrates a high-efficiency, low-emissions isolated DC/DC converter for powering the gate drive of GaN, SiC or IGBT power devices in traction inverter motor drives, on-board-charger (OBC), server telecom rectifiers, industrial motor drives, or other high voltage DC/DC converters. This DC/DC converter provides greater than 1.5 W of power.

The integrated DC/DC converter uses switched mode operation and proprietary circuit techniques to reduce power losses and boost efficiency. Specialized control mechanisms, clocking schemes, and the use of an on-chip transformer provide high efficiency and low radiated emissions.

The integrated transformer provides power delivery throughout a wide temperature range while maintaining a 5000-V<sub>RMS</sub> isolation, and an 1000-V<sub>RMS</sub> continuous working voltage. The low isolation capacitance of the transformer provides high CMTI allowing fast dv/dt switching and higher switching frequencies, while emitting less noise.

The VIN supply is provided to the primary-side power controller that switches the input stage connected to the integrated transformer. Power is transferred to the secondary-side output stage, and regulated to a level set by the resistor divider connected between the (VDD – VEE) pin and the FBVDD pin with respect to the VEE pin. The output voltage is adjustable with external resistor divider allowing a wide (VDD – VEE) range.

For optimal performance ensure to maintain the V<sub>VIN</sub> input voltage within the recommended operating voltage range. Do not exceed the absolute maximum voltage rating to avoid over-stressing the input pins.

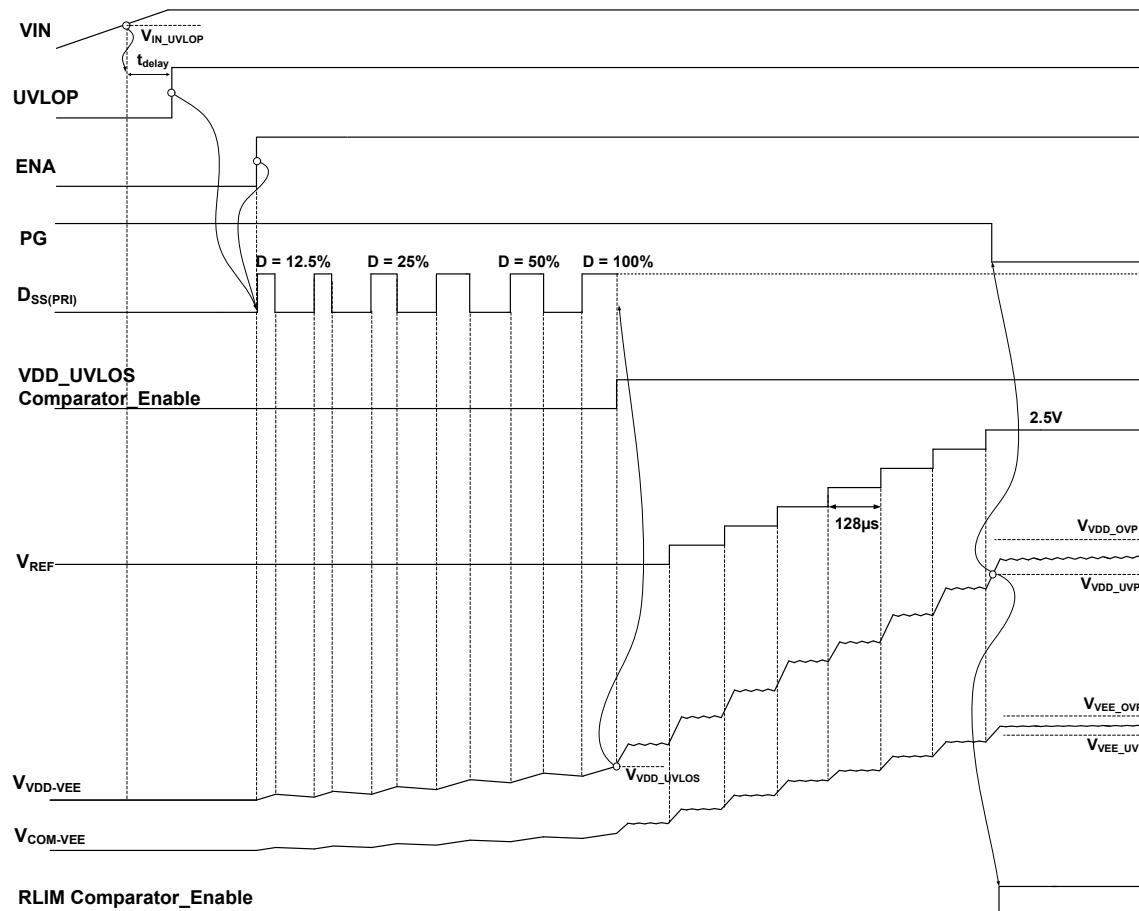

A fast hysteretic feedback burst control loop monitors (VDD – VEE) and ensures the output voltage is kept within the hysteresis with low overshoots and undershoots during load and line transients. The burst control loop enables efficient operation across full load and allows a wide output voltage adjustability throughout the whole V<sub>VIN</sub> range. The undervoltage lockout (UVLO) protection monitors the input voltage pin, VIN, with hysteresis and input filter ensuring robust system performance under noisy conditions. The overvoltage lockout (OVLO) protection monitors the input voltage pin, VIN, protects against over-voltage stress by disabling switching and reducing the internal peak voltage. Controlled soft-start timing, provided throughout the full power-up time, limits the peak input inrush current while charging the output capacitor and load.

The UCC14131-Q1 can provide dual outputs, for example, 12-V and 5-V outputs, using VEE as the common reference point. With this configuration, it is suitable for used together to GaN power stages, such as LMG3422R030 to provide the gate driver power, and the 5-V needed for the digital isolator.

The UCC14131-Q1 can also provide a second output rail, (COM – VEE), that is used as a negative bias for the gate drivers, allowing quicker turn-off switching for the IGBTs, and also to protect from unwanted turn-on during fast switching of SiC devices. (COM – VEE) has a simple, yet fast and efficient bias controller to ensure the positive and negative rails are regulated during the PWM switching. In this case, COM pin is used as the common reference point. The COM pin connects to the source of SiC device or emitter of an IGBT device. An external current limiting resistor allows the designer to program the sink and source current peak according to the needs of the gate drive system.

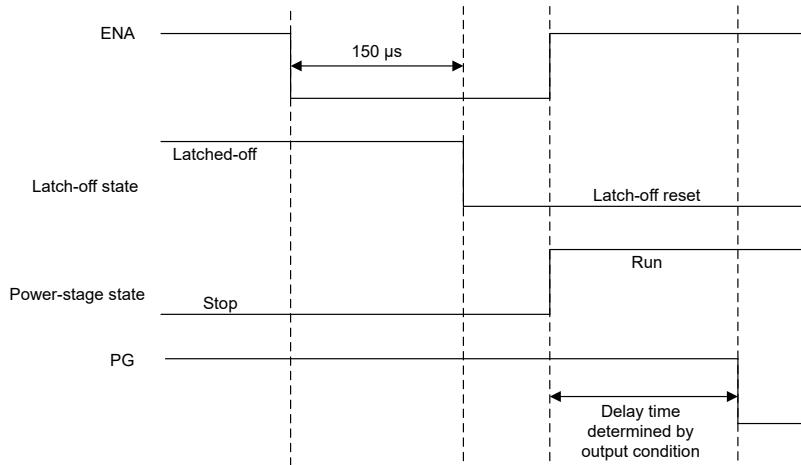

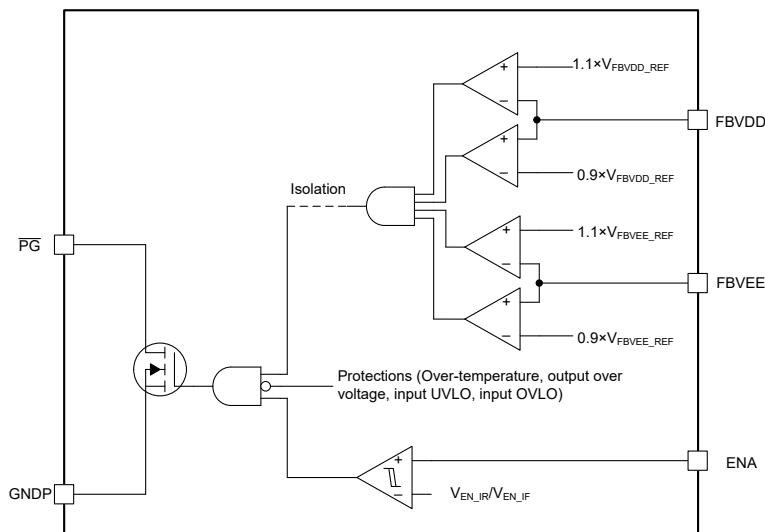

A fault protection and powergood status pin provides a mechanism for the host controller to monitor the status of the DC/DC converter and provide proper sequencing of power and PWM control signals to the gate driver. Fault protection includes undervoltage, overvoltage, over-temperature shutdown, and isolated channel communication interface watchdog timer.

A typical soft-start ramp-up time is approximately  $t_{SOFT\_START\_TIME\_OUT}$  ms, but varies based on input voltage, output voltage, output capacitance, and load. If either output is shorted or over-loaded, the device is not able to power-up within the  $t_{SOFT\_START\_TIME\_OUT}$ -ms soft-start watch-dog-timer protection time, the device latches off for protection. The latch can be reset by toggling the ENA pin or powering  $V_{VIN}$  down and up.

The output load must be kept low until start-up is complete and  $\overline{PG}$  pin becomes low. When powering up, do not apply a heavy load to (VDD – VEE) or (COM – VEE) outputs until the  $\overline{PG}$  pin has indicated power is good to avoid problems providing the power to ramp-up the voltage.

TI recommends to use the  $\overline{PG}$  status indicator as a trigger point to start the PWM signal into the gate driver.  $\overline{PG}$  output removes any ambiguity as to when the outputs are ready by providing a robust closed loop indication of when both (VDD – VEE) and (COM – VEE) outputs have reached their regulation threshold within  $\pm 10\%$ .

Do not allow the host to begin PWM to gate driver until after  $\overline{PG}$  goes low. This action typically occurs less than  $t_{SOFT\_START\_TIME\_OUT}$  ms after  $V_{VIN} > V_{VIN\_UVLOP}$  and ENA goes high. The  $\overline{PG}$  status output indicates the power is good after soft-start of (VDD – VEE) and (COM – VEE) and are within  $\pm 10\%$  of regulation.

If the host is not monitoring  $\overline{PG}$ , then ensure that the host does not begin PWM to gate driver until 35 ms after  $V_{VIN} > V_{VIN\_UVLOP}$  and ENA goes high in order to allow enough time for power to be good after soft-start of VDD and VEE.

## 11.2 Functional Block Diagram

## 11.3 Feature Description

### 11.3.1 Power Stage Operation

The UCC14131-Q1 module uses an active full-bridge inverter on the primary-side and a passive full-bridge rectifier on the secondary-side. The small integrated transformer has a relatively high carrier frequency to reduce the size for integrating into the 36-pin SSOP package. The power stage carrier frequency operates within 12 MHz to 18 MHz. The power stage carrier frequency is determined by input voltage with a feed-forward control: when  $V_{VIN}$  is 12 V, the frequency is 18 MHz; when  $V_{VIN}$  is 18 V, the frequency is 12 MHz; when  $V_{VIN}$  is between 12 V and 18 V, the frequency reduces gradually from 18 MHz to 12 MHz as  $V_{VIN}$  voltage rises. Spread spectrum modulation, SSM, is used to reduce emissions. ZVS operation is maintained to reduce switching power losses.

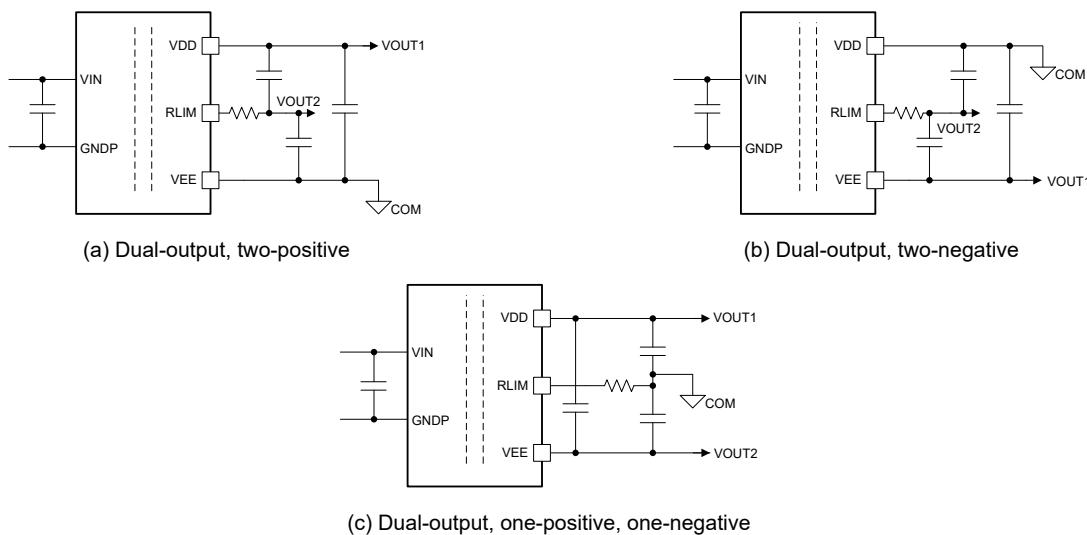

The UCC14131-Q1 module creates two regulated outputs. It can be configured as a single output converter, VDD to VEE only, or a dual-output converter, VDD to VEE and COM to VEE. Even though the module uses VEE as the reference point to create two positive output voltages, the outputs can use COM as the reference point and become a positive and a negative output.

These two outputs are controlled independently through hysteresis control. Furthermore, the VDD-VEE is the main output, and COM to VEE uses the main output as its input to create a second regulated output voltage.

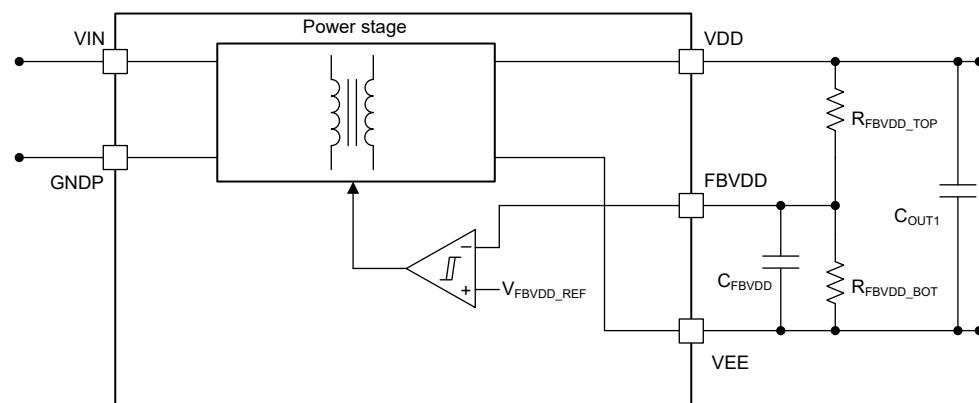

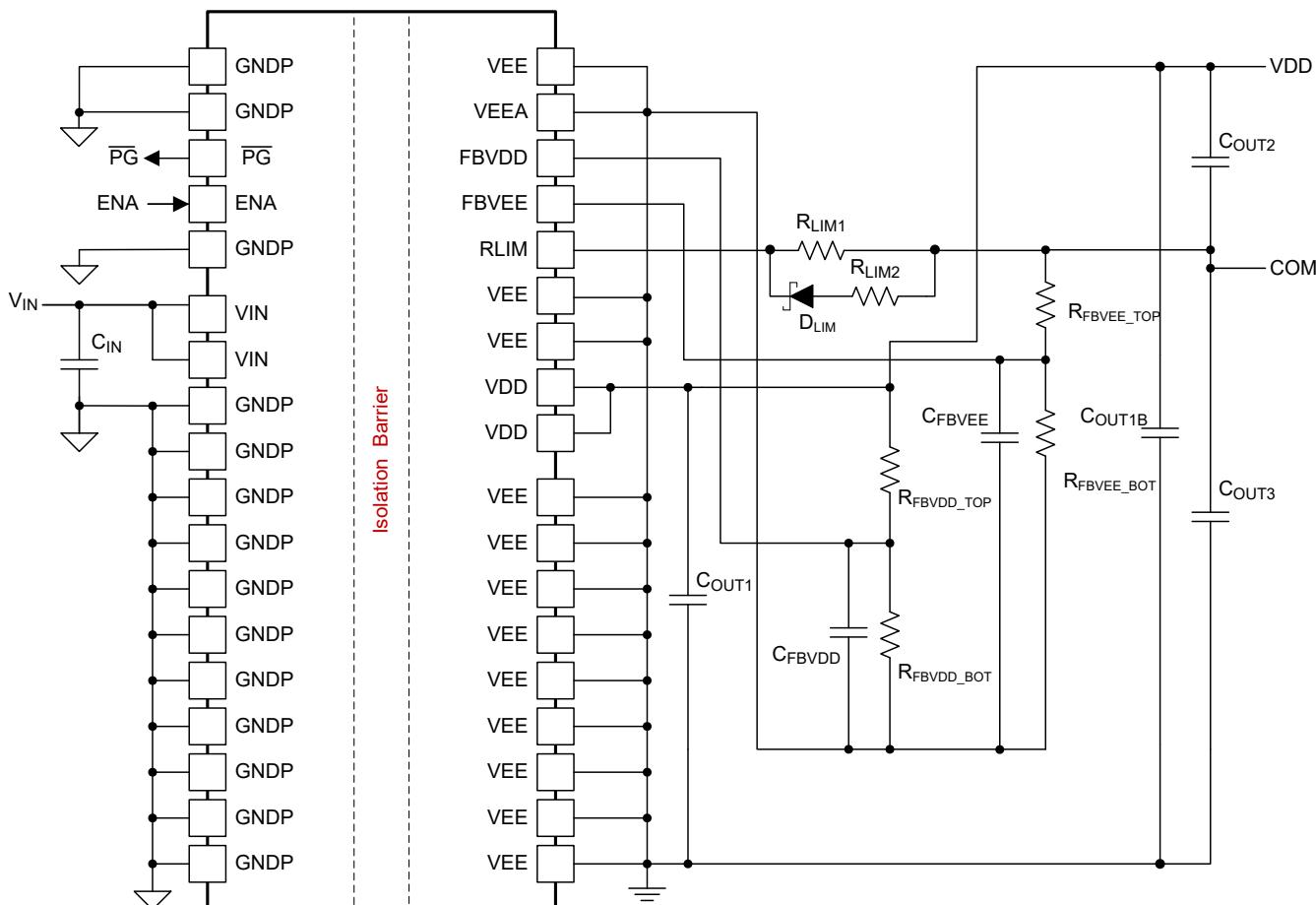

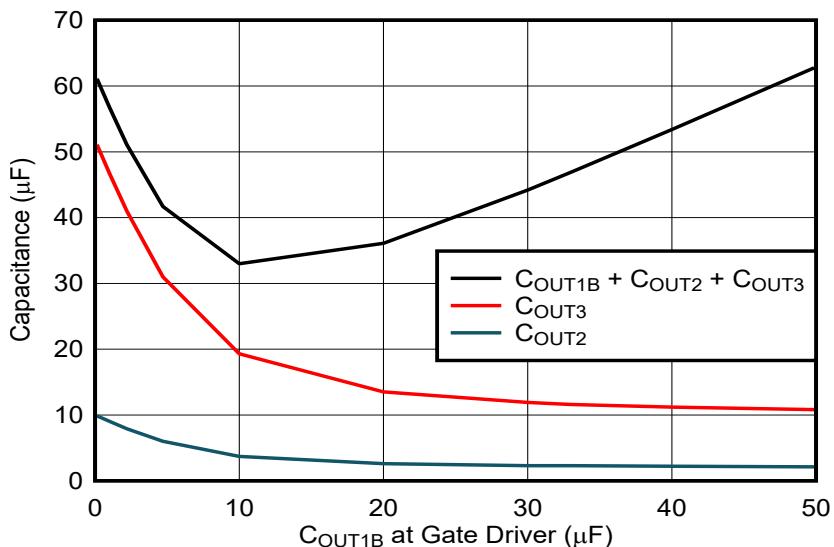

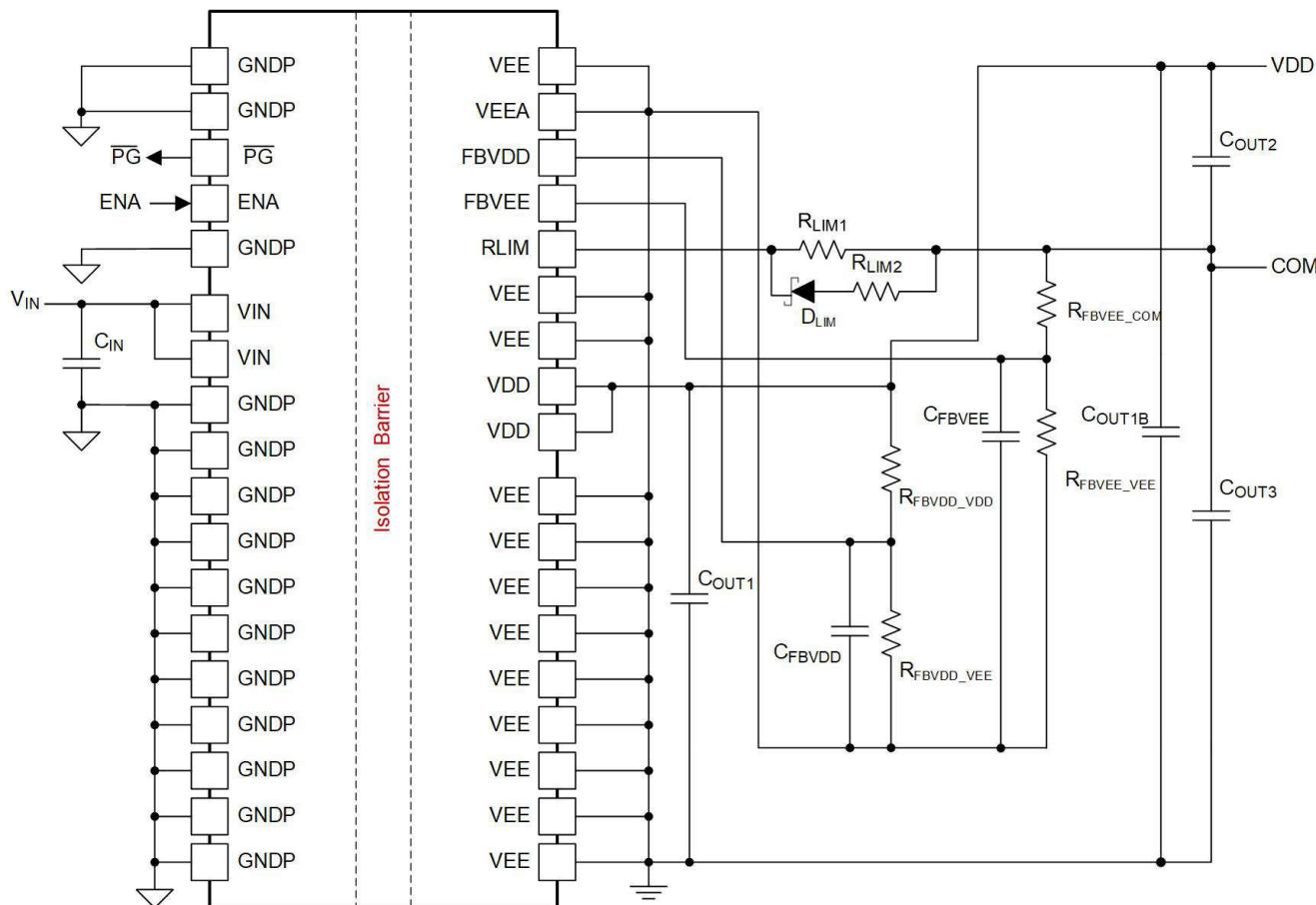

#### 11.3.1.1 VDD-VEE Voltage Regulation

The VDD-VEE output is the main output of the module. The power stage operation is determined by the sensed VDD-VEE voltage on FBVDD pin. As shown in [图 11-1](#), the VDD-VEE voltage is sensed through a voltage divider  $R_{FBVDD\_TOP}$  and  $R_{FBVDD\_BOT}$ . When FBVDD voltage stays below the turn-off threshold, roughly 10 mV above the  $V_{FBVDD\_REF}$ , the power stage operates, delivers power to the secondary side and makes the VDD-VEE output voltage rise. After the output reaches the turn-off threshold, the power stage turns off. Output voltage drops because of the load current. After the output voltage drops below the turn-on threshold, roughly 10 mV below the  $V_{FBVDD\_REF}$ , the power stage is turned on again. With the accurate voltage reference and hysteresis control, the VDD-VEE output voltage can be regulated with high accuracy. To improve the noise immunity, a small capacitor of 330 pF should be added between FBVDD and VEE pins. Excessive capacitor slows down the hysteresis loop and can cause excessive output voltage ripple or even stability issue.

[图 11-1. VDD-VEE Voltage Regulation](#)

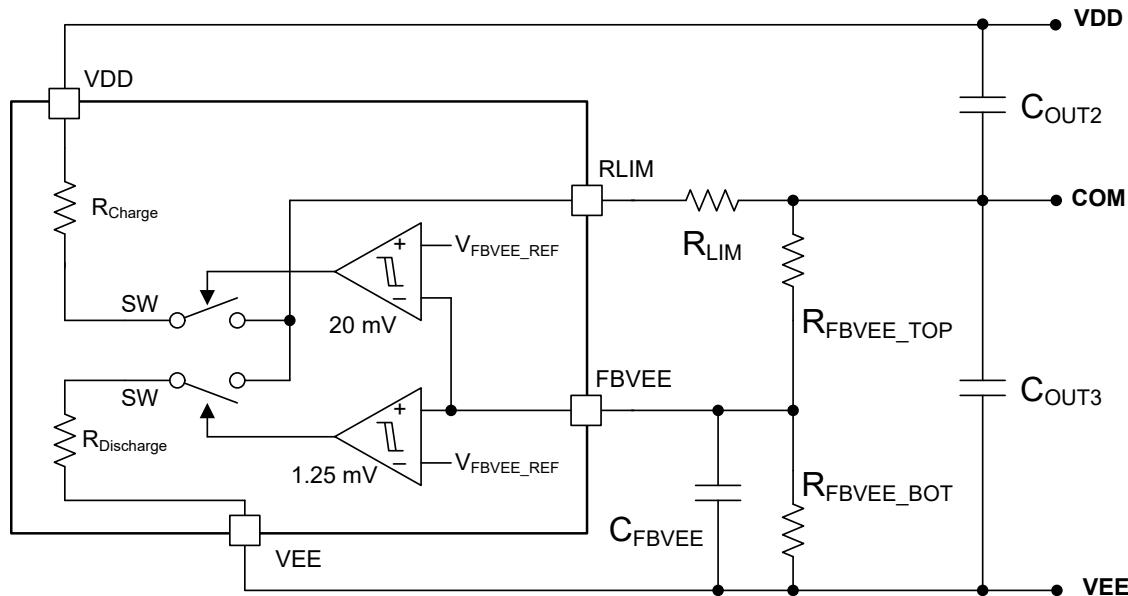

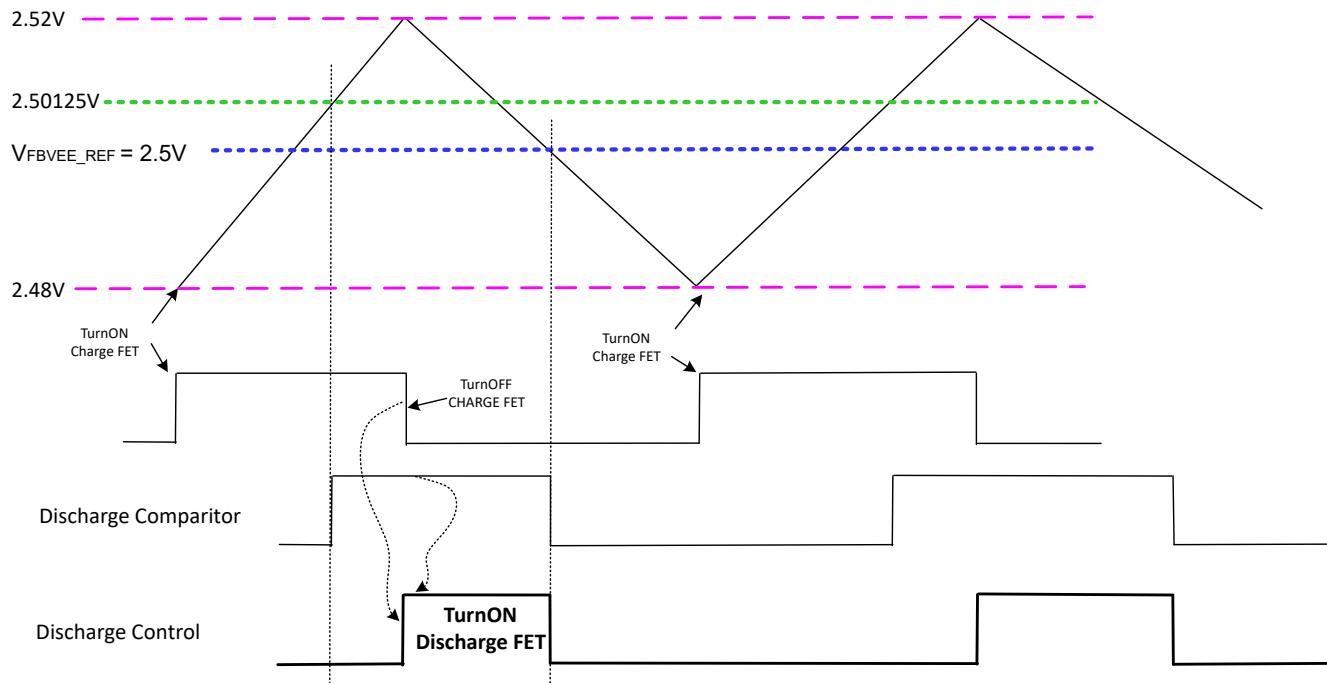

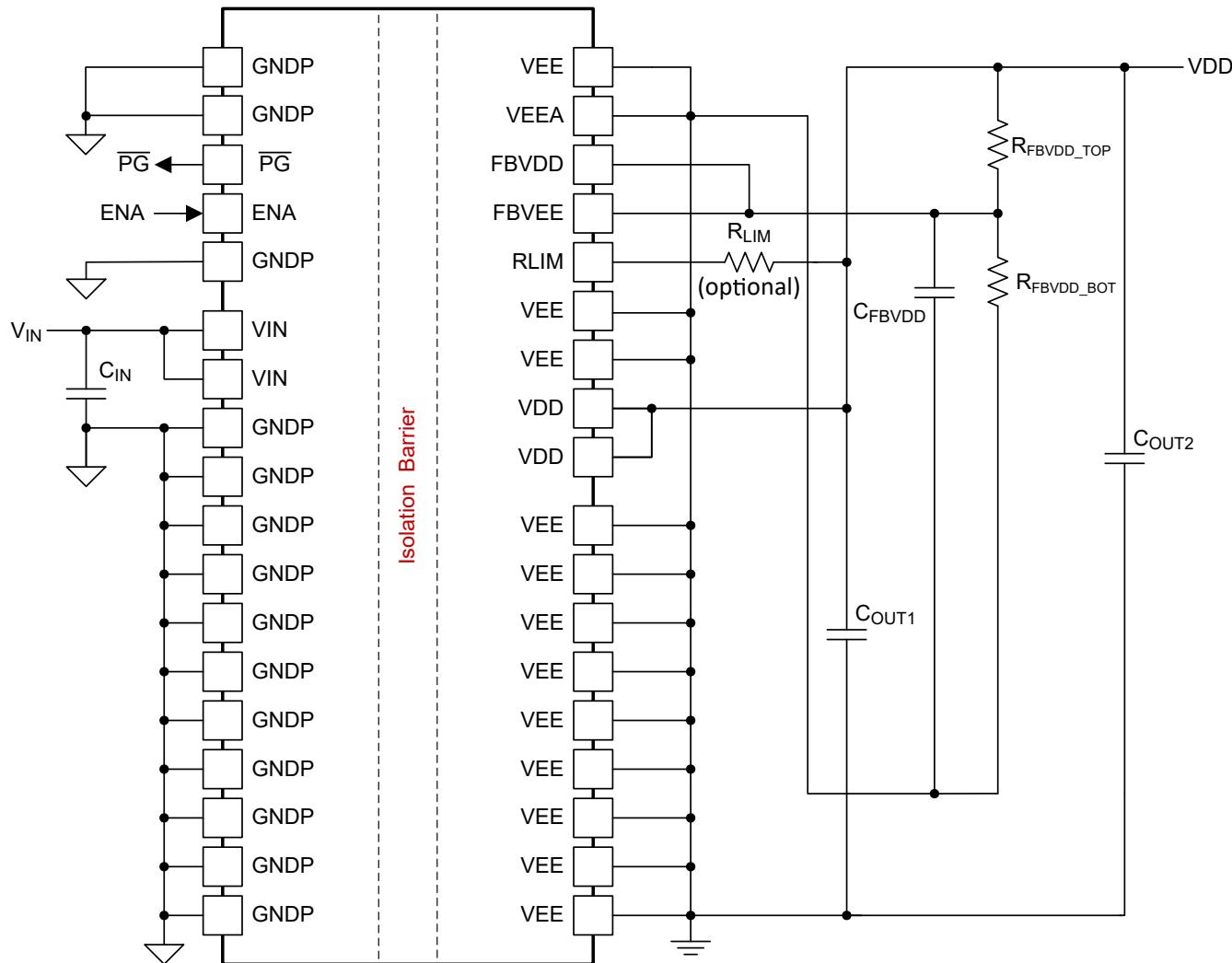

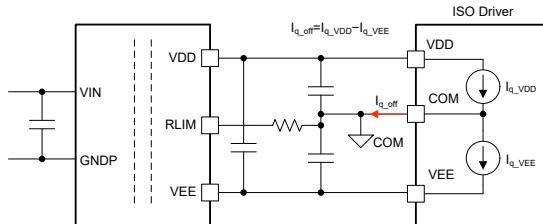

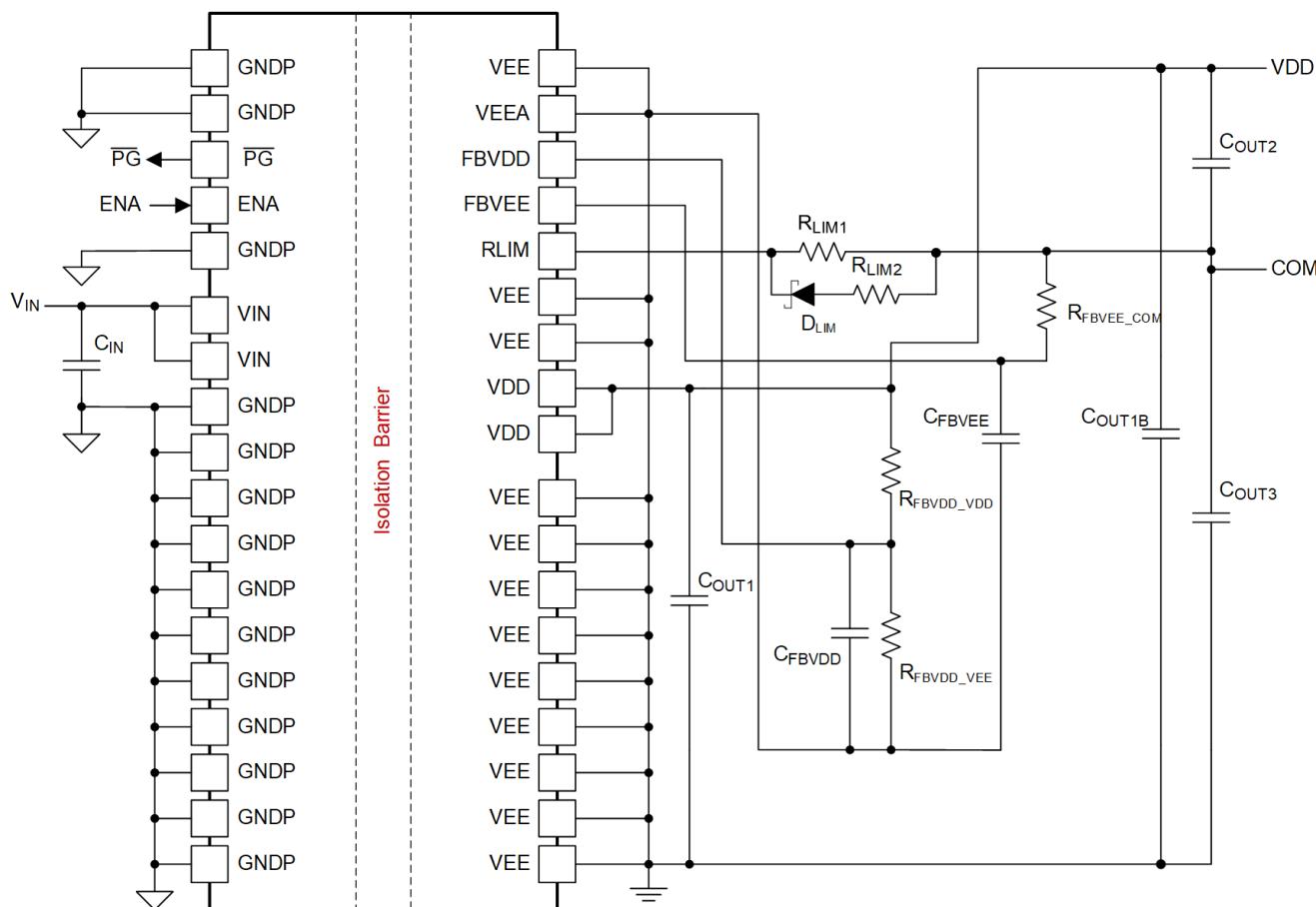

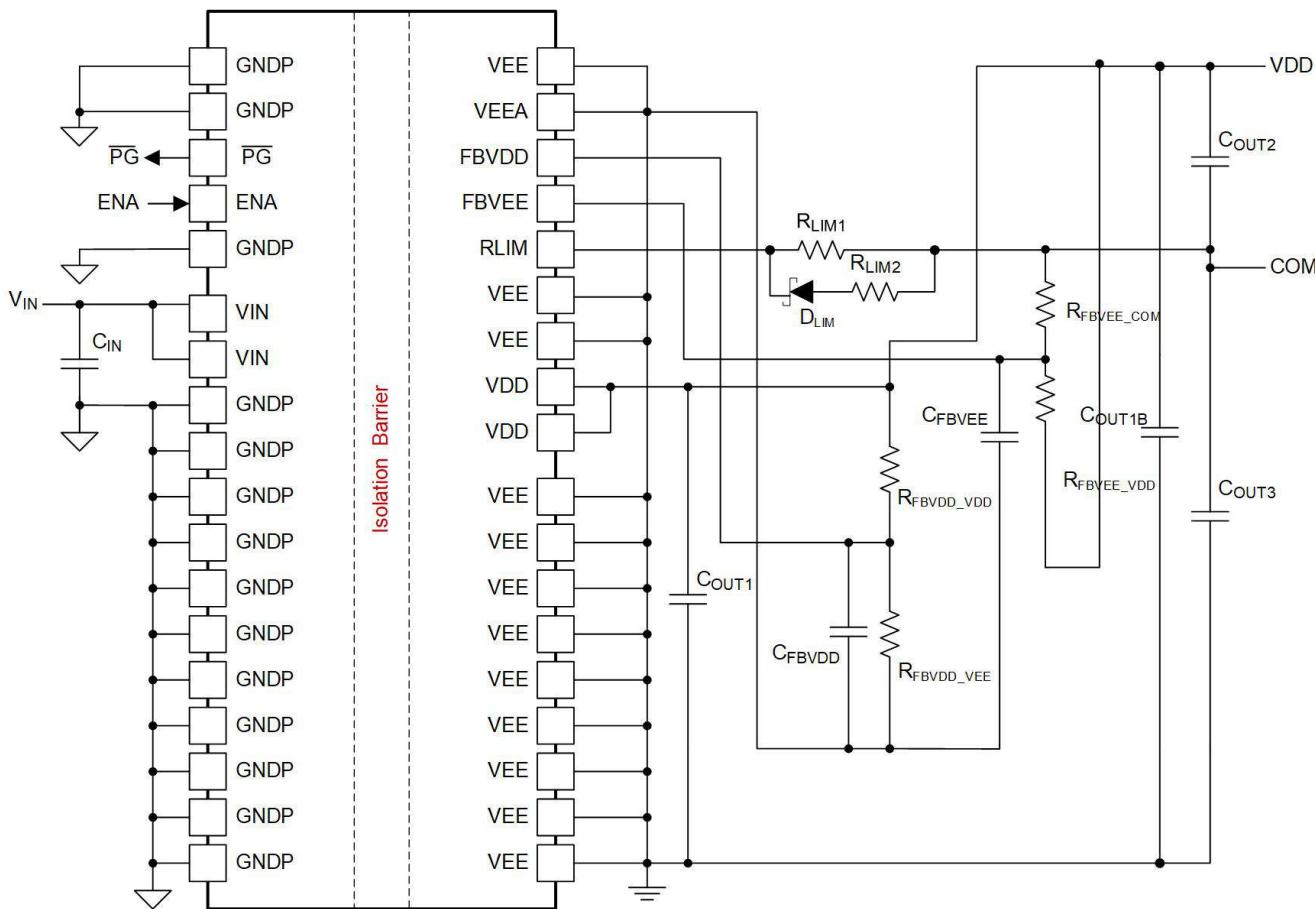

### 11.3.1.2 COM-VEE Voltage Regulation

COM-VEE output takes VDD-VEE output as its input and creates a regulated output voltage. It can be considered as an LDO output from VDD-VEE, though the operation principle is not quite the same. Given its input voltage is VDD-VEE, the maximum output voltage from COM to VEE is the voltage between VDD and VEE.

The COM-VEE output regulator stage uses the internal high-side or low-side FETs in series with the external current-limit resistor ( $R_{LIM}$ ) to charge or discharge the COM-VEE output voltage. The hysteresis control is used to control the switching instance of the two FETs, to achieve an accurately regulated COM-VEE voltage. As shown in [图 11-2](#), the COM-VEE output voltage is sensed through the voltage divider  $R_{FBVEE\_TOP}$  and  $R_{FBVEE\_BOT}$  on FBVEE pin. TI recommends a 330-pF capacitor on FBVEE pin to filter out the switching frequency noise. When the voltage on FBVEE is below the charging threshold, 20 mV below the  $V_{FBVEE\_REF}$ , the charging resistor is kept on and discharging resistor is kept off. COM-VEE output voltage rises. After FBVEE voltage reaches the stop charging threshold, 20 mV above the  $V_{FBVEE\_REF}$ , the charging resistor is turned off. Output voltage rise stops. When the charging resistor is turned off, the discharge resistor is controlled by another hysteresis controller, based on FBVEE pin voltage, with the same reference voltage  $V_{FBVEE\_REF}$ , and 20-mV of hysteresis.

The COM-VEE output regulator stage will protect from having the high-side FET stay ON for a long time during a COM to VEE short. This protection feature is implemented by monitoring the RLIM-pin voltage and controlling the high-side FET duty-ratio. When the COM pin voltage is lower than 0.645 V while the FBVEE voltage is below 2.48 V, the hysteretic control of the COM-VEE regulator is overridden by an approximately 20 % duty-ratio control on high-side FET, with a typical on-time of  $t_{RLIM\_SHORT\_CHRG\_ON\_TIME}$  and off-time of  $t_{RLIM\_SHORT\_CHRG\_OFF\_TIME}$  in each duty cycle. When the COM pin voltage is higher than  $V_{RLIM\_SHORT\_CHRG\_CMP\_RISE}$ , the duty ratio control is disabled and the hysteretic control resumes to normal operation.

**图 11-2. COM-VEE Voltage Regulation**

FIG 11-3. COM-VEE Voltage Regulation Diagram

#### 11.3.1.3 Power Handling Capability

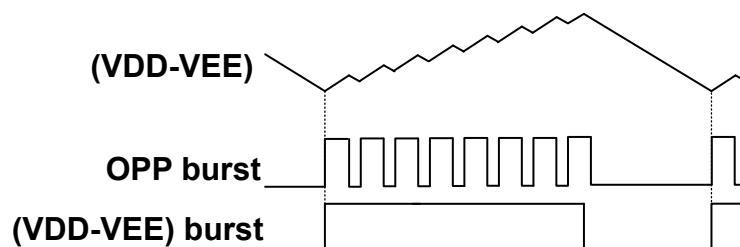

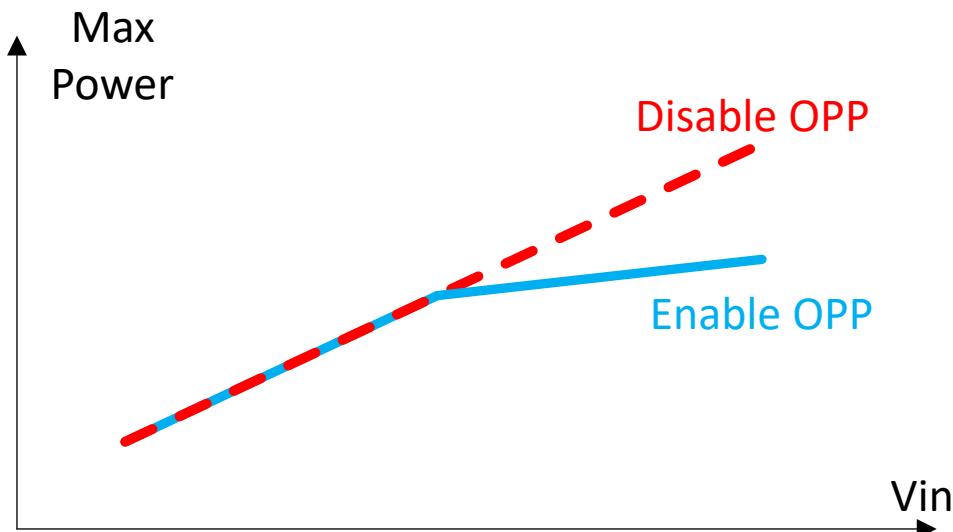

The maximum power handling capability is determined by both circuit operation and thermal condition. For a given output voltage, the maximum power increases with input voltage before triggering the thermal protection. An over-power-protection (OPP) is implemented to limit maximum output power and reduces power stage RMS current at high input voltage. The OPP is implemented by a feed-forward control from the input voltage to the OPP burst duty cycle ( $D_{OPP}$ ). The  $D_{OPP}$  adds a "baby" burst within the on-time of "Mama" burst from the main feedback loop for the (VDD-VEE) regulation. When the input voltage increases, the  $D_{OPP}$  reduces automatically to limit the averaged output power.

At high ambient temperature, the thermal performance determines the maximum power and safe operating area (SOA). A protective thermal shut-down is triggered after overtemperature is detected. The high-efficiency and optimized thermal design for transformer and silicon provide a high power handling capability at high ambient temperature in a small package.

FIG 11-4. Diagram of Over-Power-Protection with baby burst

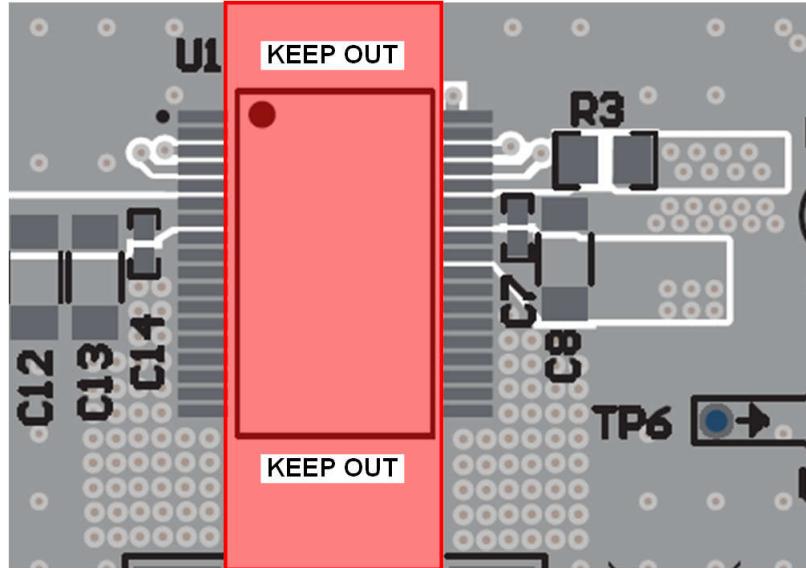

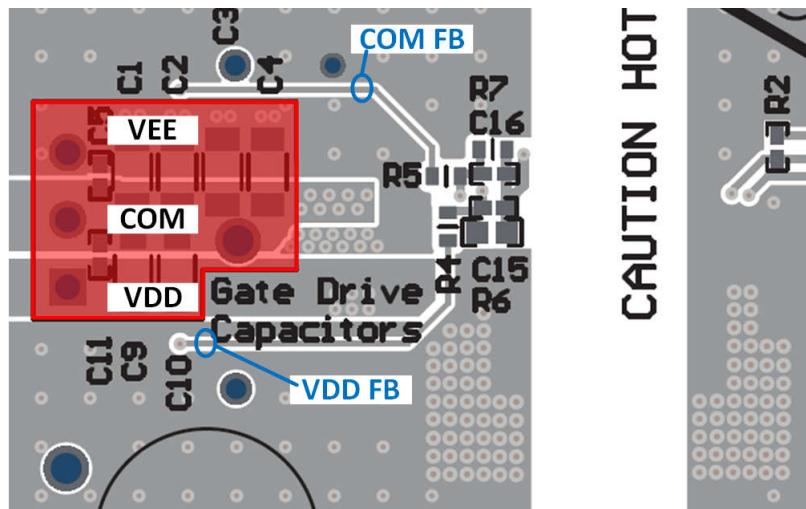

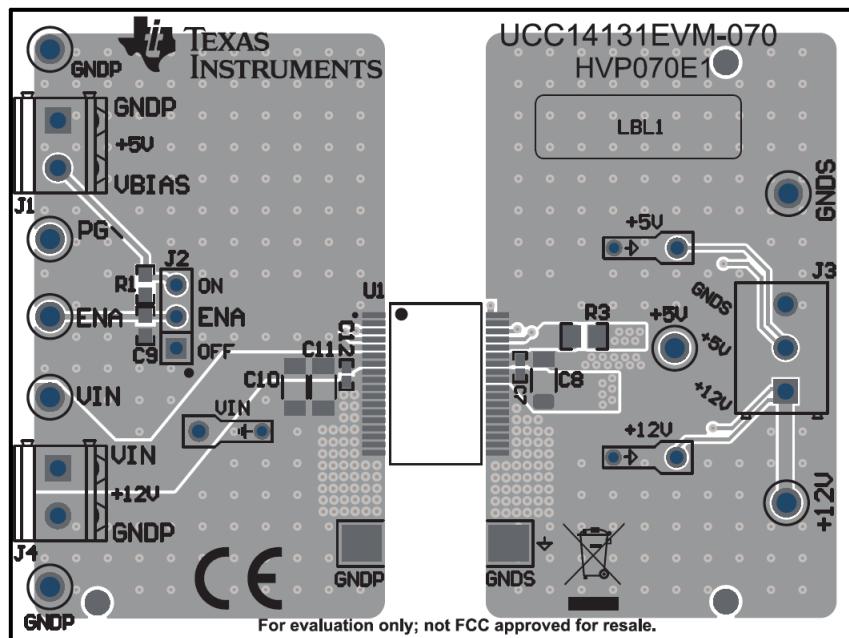

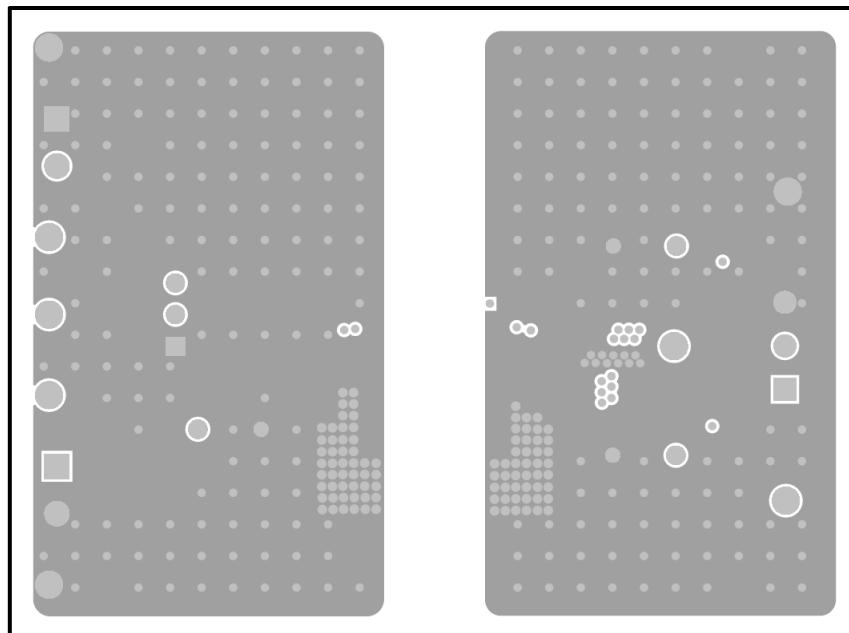

### 11.3.2 Output Voltage Soft Start