# UCC27289 3A、120V ハーフブリッジ・ドライバ、8V UVLO および負電圧対応付き

## 1 特長

- ハイサイド / ローサイド構成の 2 つの N チャネル MOSFET を駆動

- イネーブル / ディセーブル機能付き、DRC パッケージ

- ディセーブル時の低い消費電流 (7μA)

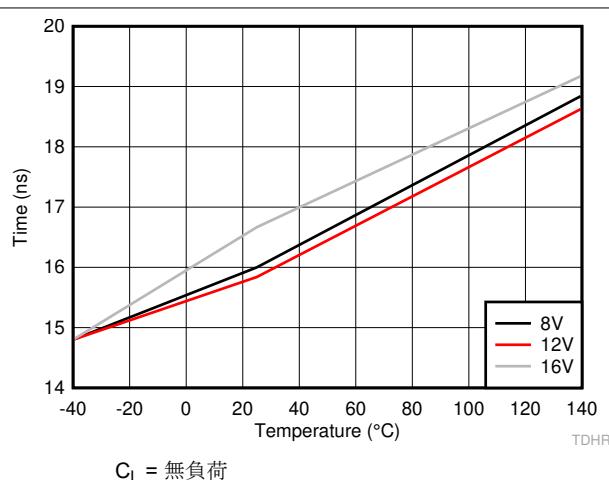

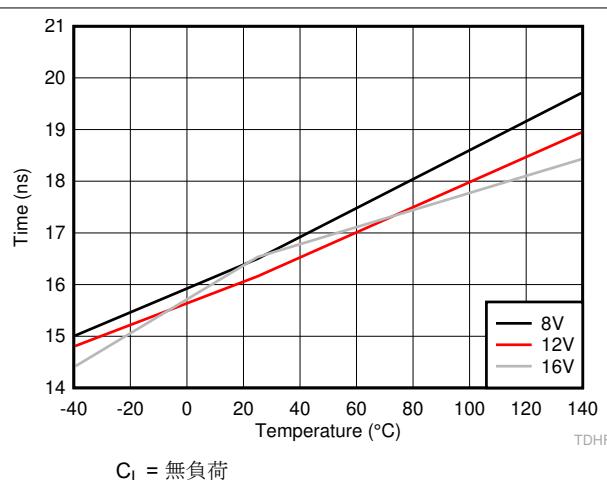

- 16ns (標準値) の伝搬遅延

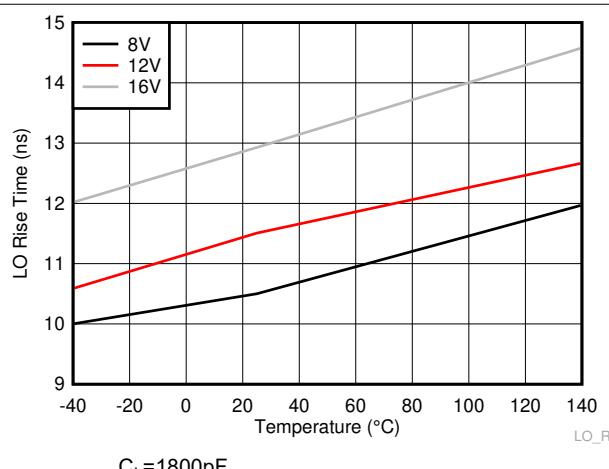

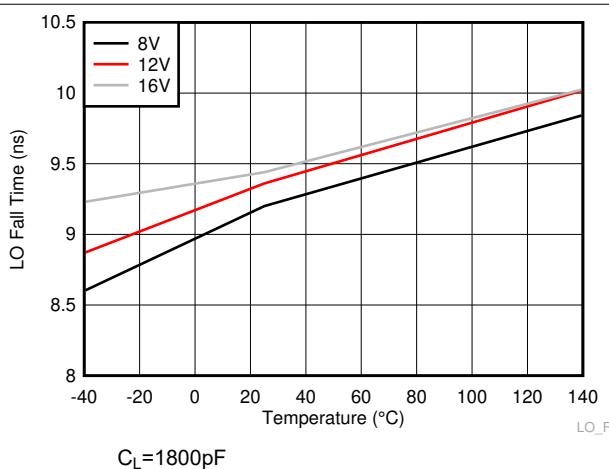

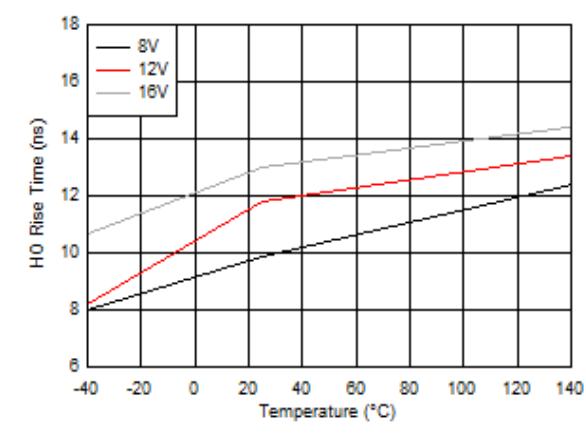

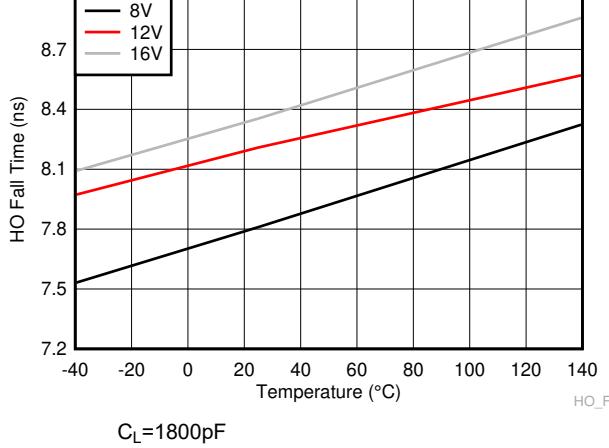

- 立ち上がり時間 12ns、立ち下がり時間 10ns (標準値、1800pF 負荷時)

- 1ns (標準値) の遅延マッチング

- 100V ブートストラップ・ダイオード内蔵

- 8V (標準値) の低電圧誤動作防止

- 入力で扱える絶対最大負電圧: -5V

- HS で扱える絶対最大負電圧: -14V

- ピーク出力電流: ±3A

- 絶対最大ブート電圧: 120V

- 入力は互いに独立しており、VDD とも独立

- 両方のチャネルに低電圧誤動作防止

- 接合部温度 -40°C~140°C で動作を規定

## 2 アプリケーション

- 商用ネットワークおよびサーバーの PSU (電源)

- 商用テレコム整流器

- DC 入力 BLDC モーター駆動

- 太陽光マイクロ・インバータ

- 試験および計測機器

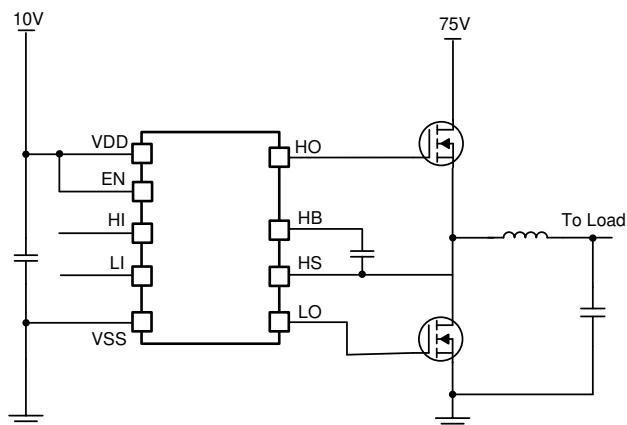

### アプリケーション概略図

## 3 説明

UCC27289 は、100V の最大スイッチ・ノード (HS) 電圧定格を持つ堅牢な N チャネル MOSFET ドライバです。ハーフブリッジまたは同期整流降圧構成に基づくトポロジで 2 つの N チャネル MOSFET を制御できます。UCC27289 は、ピーク・ソース電流およびピーク・シンク電流が 3A であり、プルアップおよびプルダウン抵抗も小さいため、MOSFET のミラー・プラトー遷移中のスイッチング損失を最小限に抑えて大電力 MOSFET を駆動できます。各入力が電源電圧と無関係であるため、UCC27289 はアナログ・コントローラともデジタル・コントローラとも組み合わせて使用できます。2 つの入力は互いに完全に独立しているため、必要があれば、オーバーラップした入力によって、2 つの出力をオーバーラップさせることができます。イネーブルおよびディセーブル機能により、ドライバの消費電力を低減してシステムの柔軟性をさらに高めるとともに、システム内のフォルト・イベントに応答できます。

入力ピンと HS ピンは、大きい負の電圧に耐えられるため、システムの堅牢性が強化されます。伝搬遅延が短く、遅延マッチング仕様によりデッドタイムの要件が最小化されるため、システム効率が向上します。

ハイサイドとローサイド両方のドライバ段に低電圧誤動作防止 (UVLO) 機能があり、VDD 電圧が指定のスレッショルドを下回ると、出力が強制的に LOW になります。内蔵のブートストラップ・ダイオードにより、多くのアプリケーションでは別の外付けダイオードが不要になるため、基板面積の削減とシステム・コストの低減に役立ちます。UCC27289 は、複数のパッケージで供給され、過酷な環境での堅牢性やコンパクトなアプリケーションでの部品密度などのシステム要件に対応可能です。

### 製品情報

| 部品番号        | パッケージ (サイズ) <sup>(1)</sup> |

|-------------|----------------------------|

| UCC27289D   | SOIC8 (6mm × 5mm)          |

| UCC27289DRC | SON10 (3mm × 3mm)          |

| UCC27289DRM | SON8 (4mm × 4mm)           |

| UCC27289DPR | SON10 (4mm × 4mm)          |

(1) 利用可能なパッケージについては、このデータシートの末尾にある注文情報を参照してください。

## 目次

|                    |           |                               |           |

|--------------------|-----------|-------------------------------|-----------|

| <b>1 特長</b>        | <b>1</b>  | 7.3 機能説明                      | <b>13</b> |

| <b>2 アプリケーション</b>  | <b>1</b>  | 7.4 デバイスの機能モード                | <b>15</b> |

| <b>3 説明</b>        | <b>1</b>  | <b>8 アプリケーションと実装</b>          | <b>17</b> |

| <b>4 改訂履歴</b>      | <b>2</b>  | 8.1 アプリケーション情報                | <b>17</b> |

| <b>5 ピン構成および機能</b> | <b>3</b>  | 8.2 代表的なアプリケーション              | <b>18</b> |

| <b>6 仕様</b>        | <b>4</b>  | <b>9 電源に関する推奨事項</b>           | <b>26</b> |

| 6.1 絶対最大定格         | 4         | <b>10 レイアウト</b>               | <b>27</b> |

| 6.2 ESD 定格         | 4         | 10.1 レイアウトのガイドライン             | <b>27</b> |

| 6.3 推奨動作条件         | 4         | 10.2 レイアウト例                   | <b>27</b> |

| 6.4 熱に関する情報        | 5         | <b>11 デバイスおよびドキュメントのサポート</b>  | <b>28</b> |

| 6.5 電気的特性          | 5         | 11.1 ドキュメントの更新通知を受け取る方法       | <b>28</b> |

| 6.6 スイッチング特性       | 6         | 11.2 サポート・リソース                | <b>28</b> |

| 6.7 代表的特性          | 8         | 11.3 商標                       | <b>28</b> |

| <b>7 詳細説明</b>      | <b>13</b> | 11.4 静電気放電に関する注意事項            | <b>28</b> |

| 7.1 概要             | 13        | 11.5 用語集                      | <b>28</b> |

| 7.2 機能ブロック図        | 13        | <b>12 メカニカル、パッケージ、および注文情報</b> | <b>28</b> |

## 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| <b>Changes from Revision * (December 2020) to Revision A (May 2022)</b>         | <b>Page</b> |

|---------------------------------------------------------------------------------|-------------|

| ・ 「電気的特性」で、ピーク・プルアップ / プルダウン電流の標準値を $+2.5A/-3.5A$ から $\pm 3A$ に更新               | <b>5</b>    |

| ・ 「電気的特性」で、 $I_{HBS}$ の標準リーコンデンサ電流を $5.0\mu A$ に更新し、テスト電圧を $110V$ から $100V$ に更新 | <b>5</b>    |

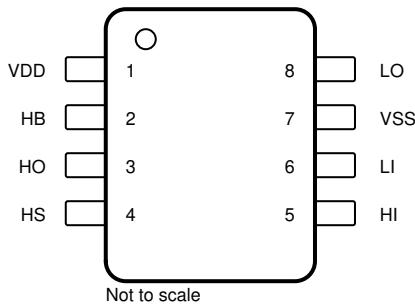

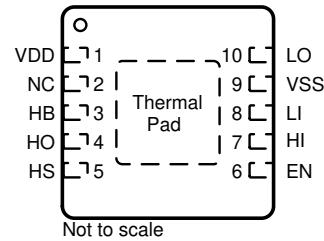

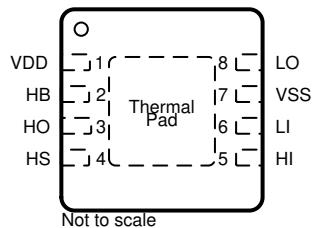

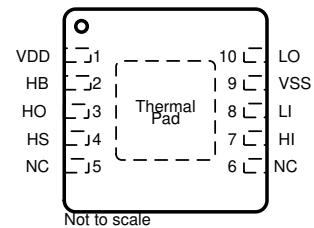

## 5 ピン構成および機能

図 5-1. D パッケージ 8 ピン SOIC 上面図

図 5-2. DRC パッケージ 10 ピン SON 上面図

図 5-3. DRM パッケージ 8 ピン SON 上面図

図 5-4. DPR パッケージ 10 ピン SON 上面図

## ピンの機能

| 名称  | ピン  |      |      |      | I/O <sup>(1)</sup> | 説明                                                                                                                                                                                                                                                  |

|-----|-----|------|------|------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | DRC | DRM  | DPR  | D    |                    |                                                                                                                                                                                                                                                     |

| EN  | 6   | 該当なし | 該当なし | 該当なし | I                  | イネーブル入力。このピンを High にすると、ドライバはイネーブルになります。フローティング状態または Low にプルされると、ドライバはディセーブルになります。1nF のフィルタ・コンデンサは、高ノイズ・システムに推奨されます。                                                                                                                                |

| HB  | 3   | 2    | 2    | 2    | P                  | ハイサイド・ブートストラップ電源。ブートストラップ・ダイオードはオンチップですが、VDD からブートストラップ電源を生成するには外部ブートストラップ・コンデンサが必要です。ブートストラップ・コンデンサの正側と外部ダイオードのカソードをこのピンに接続します。外部ダイオードは 100V (最小) 定格にする必要があります。より電圧定格の高いダイオードも使用できます。HB バイパス・コンデンサの標準推奨値は 0.1μF で、この値は主にハイサイド MOSFET のゲート電荷に依存します。 |

| HI  | 7   | 5    | 7    | 5    | I                  | ハイサイド入力。                                                                                                                                                                                                                                            |

| HO  | 4   | 3    | 3    | 3    | O                  | ハイサイド出力。使用する場合は、ハイサイド・パワー MOSFET のゲート、または外部ゲート抵抗の一方の端に接続します。                                                                                                                                                                                        |

| HS  | 5   | 4    | 4    | 4    | P                  | ハイサイド・ソース接続。ハイサイド・パワー MOSFET のソースに接続します。ブートストラップ・コンデンサの負側をこのピンに接続します。                                                                                                                                                                               |

| LI  | 8   | 6    | 8    | 6    | I                  | ローサイド入力                                                                                                                                                                                                                                             |

| LO  | 10  | 8    | 10   | 8    | O                  | ローサイド出力。使用する場合は、ローサイド・パワー MOSFET のゲート、または外部ゲート抵抗の一方の端に接続します。                                                                                                                                                                                        |

| NC  | 2   | 該当なし | 5, 6 | 該当なし | -                  | 内部未接続。                                                                                                                                                                                                                                              |

| VDD | 1   | 1    | 1    | 1    | P                  | ローサイド・ゲート・ドライバへの正電源。このピンを VSS にデカッピングします。デカッピング・コンデンサの標準値は 1μF です。外部ブート・ダイオードを使用する場合は、アノードをこのピンに接続します。直列抵抗をブート・ダイオードと直列に使用する場合は、直列ブート抵抗の一方の端をこのピンに接続し、抵抗のもう一方の端を外部ブート・ダイオードのアノードに接続する必要があります。                                                       |

| VSS | 9   | 7    | 9    | 7    | G                  | デバイスの負電源端子で、一般にシステム・グランドです。                                                                                                                                                                                                                         |

### ピンの機能 (続き)

| ピン       |     |     |     |      | I/O <sup>(1)</sup> | 説明                                                                      |

|----------|-----|-----|-----|------|--------------------|-------------------------------------------------------------------------|

| 名称       | DRC | DRM | DPR | D    |                    |                                                                         |

| サーマル・パッド | -   | -   | -   | 該当なし | -                  | 熱性能を向上させるため、大きな熱質量パターン (一般に IC のグランド・プレーン) に接続します。これのみ VSS に電気的に接続できます。 |

(1) P = 電源、G = グランド、I = 入力、O = 出力、I/O = 入力/出力

## 6 仕様

### 6.1 絶対最大定格

すべての電圧は V<sub>SS</sub> を基準にしています<sup>(1) (2)</sup>

|                                                   |                    |                            | 最小値                   | 最大値                   | 単位 |

|---------------------------------------------------|--------------------|----------------------------|-----------------------|-----------------------|----|

| V <sub>DD</sub>                                   | 電源電圧               |                            | -0.3                  | 20                    | V  |

| V <sub>EN</sub> 、V <sub>HI</sub> 、V <sub>LI</sub> | EN、HI、LI の入力電圧     |                            | -5                    | 20                    | V  |

| V <sub>LO</sub>                                   | LO の出力電圧           | DC                         | -0.3                  | V <sub>DD</sub> + 0.3 | V  |

|                                                   |                    | パルス < 100ns <sup>(3)</sup> | -2                    | V <sub>DD</sub> + 0.3 |    |

| V <sub>HO</sub>                                   | HO の出力電圧           | DC                         | V <sub>HS</sub> - 0.3 | V <sub>HB</sub> + 0.3 | V  |

|                                                   |                    | パルス < 100ns <sup>(3)</sup> | V <sub>HS</sub> - 2   | V <sub>HB</sub> + 0.3 |    |

| V <sub>HS</sub>                                   | HS の電圧             | DC                         | -10                   | 100                   | V  |

|                                                   |                    | パルス < 100ns <sup>(3)</sup> | -14                   | 100                   |    |

| V <sub>HB</sub>                                   | HB の電圧             |                            | -0.3                  | 120                   | V  |

| V <sub>HB-HS</sub>                                | HS を基準とした HB の電圧   |                            | -0.3                  | 20                    | V  |

| T <sub>J</sub>                                    | 動作時接合部温度           |                            | -40                   | 150                   | °C |

|                                                   | リード温度 (ハンダ付け、10 秒) |                            |                       | 300                   | °C |

| T <sub>stg</sub>                                  | 保存温度               |                            | -65                   | 150                   | °C |

- (1) 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみについて示しており、このデータシートの「推奨動作条件」に示された値を越える状態で本製品が正常に動作することを暗黙的に示すものではありません。絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

- (2) すべての電圧は V<sub>SS</sub> を基準にしています。電流は、指定されたピンに流れ込む方向が正、ピンから流れ出る方向が負です。

- (3) 値は特性評価のみで検証されます。

### 6.2 ESD 定格

|                    |       |                                                          | 値     | 単位 |

|--------------------|-------|----------------------------------------------------------|-------|----|

| V <sub>(ESD)</sub> | 静電気放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 <sup>(1) (2)</sup> 準拠 | ±2000 | V  |

|                    |       | デバイス帯電モデル (CDM)、JEDEC 仕様 JESD22-C101 <sup>(3)</sup> 準拠   | ±1500 |    |

(1) JEDEC ドキュメント JEP155 には、500V HBM であれば標準的な ESD 制御プロセスで安全な製造が可能であると記載されています。

(2) ピン HS、HB、HO の定格は 500V HBM です

(3) JEDEC ドキュメント JEP157 には、250V CDM であれば標準的な ESD 制御プロセスで安全な製造が可能であると記載されています。

### 6.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                                                   |                                     | 最小値 | 公称値             | 最大値             | 単位 |

|---------------------------------------------------|-------------------------------------|-----|-----------------|-----------------|----|

| V <sub>DD</sub>                                   | 電源電圧                                | 8   | 12              | 16              | V  |

| V <sub>EN</sub> 、V <sub>HI</sub> 、V <sub>LI</sub> | 入力電圧                                | 0   |                 | V <sub>DD</sub> |    |

| V <sub>LO</sub>                                   | ローサイド出力電圧                           | 0   |                 | V <sub>DD</sub> |    |

| V <sub>HO</sub>                                   | ハイサイド出力電圧                           |     | V <sub>HS</sub> | V <sub>HB</sub> |    |

| V <sub>HS</sub>                                   | HS の電圧 <sup>(1)</sup>               | -8  |                 | 100             | V  |

|                                                   | HS の電圧 (パルス < 100ns) <sup>(1)</sup> | -12 |                 | 100             |    |

自由気流での動作温度範囲内 (特に記述のない限り)

|          |              | 最小値          | 公称値 | 最大値           | 単位   |

|----------|--------------|--------------|-----|---------------|------|

| $V_{HB}$ | HB の電圧       | $V_{HS} + 8$ |     | $V_{HS} + 16$ | V    |

| $V_{sr}$ | HS の電圧スルーレート |              |     | 50            | V/ns |

| $T_J$    | 動作時接合部温度     | -40          |     | 140           | °C   |

(1)  $V_{HB-HS} < 16V$  (HS を基準とした HB の電圧は 16V 未満とする必要があります)

## 6.4 熱に関する情報

| 熱評価基準 (1)                                | UCC27289 |      |       |       | 単位   |

|------------------------------------------|----------|------|-------|-------|------|

|                                          | DRC      | DRM  | DPR   | D     |      |

|                                          | 10 ピン    | 8 ピン | 10 ピン | 8 ピン  |      |

| $R_{\theta JA}$ 接合部から周囲への熱抵抗             | 47.3     | 43.3 | 43.0  | 118.3 | °C/W |

| $R_{\theta JC(top)}$ 接合部からケース (上面) への熱抵抗 | 50.3     | 37.7 | 33.0  | 53.6  | °C/W |

| $R_{\theta JB}$ 接合部から基板への熱抵抗             | 21.3     | 19.2 | 19.0  | 63.1  | °C/W |

| $\Psi_{JT}$ 接合部から上面への熱特性パラメータ            | 1.0      | 0.8  | 0.6   | 10.7  | °C/W |

| $\Psi_{JB}$ 接合部から基板への熱特性パラメータ            | 21.2     | 19.2 | 19.0  | 62.1  | °C/W |

| $R_{\theta JC(bot)}$ 接合部からケース (底面) への熱抵抗 | 4.4      | 6.3  | 6.2   | n/a   | °C/W |

(1) 热評価基準の詳細については、アプリケーション・レポート『半導体および IC パッケージの熱評価基準』、SPRA953 を参照してください。

## 6.5 電気的特性

$V_{DD} = V_{EN} = V_{HB} = 12V$ 、 $V_{HS} = V_{SS} = 0V$ 、LO または HO は無負荷、 $T_J = -40°C \sim +140°C$  (特に記述のない限り)

| パラメータ                                       | テスト条件                         | 最小値  | 代表値  | 最大値 | 単位 |

|---------------------------------------------|-------------------------------|------|------|-----|----|

| <b>供給電流</b>                                 |                               |      |      |     |    |

| $I_{DD}$ VDD 静止電流                           | $V_{LI} = V_{HI} = 0$         | 0.36 | 0.45 |     | mA |

| $I_{DDO}$ VDD 動作電流                          | $f = 500kHz$ , $C_{LOAD} = 0$ | 2.2  | 4.5  |     | mA |

| $I_{HB}$ HB 静止電流                            | $V_{LI} = V_{HI} = 0V$        | 0.2  | 0.4  |     | mA |

| $I_{HBO}$ HB 動作電流                           | $f = 500kHz$ , $C_{LOAD} = 0$ | 2.5  | 4    |     | mA |

| $I_{HBS}$ HB から VSS への静止電流                  | $V_{HS} = V_{HB} = 100V$      | 5.0  | 50   |     | μA |

| $I_{HBSO}$ HB から VSS への動作電流 <sup>(1)</sup>  | $f = 500kHz$ , $C_{LOAD} = 0$ | 0.1  |      |     | mA |

| $I_{DD\_DIS}$ ドライバがディセーブルの場合 $I_{DD}$       | $V_{EN} = 0$                  | 7.0  |      |     | μA |

| <b>イネーブル</b>                                |                               |      |      |     |    |

| $V_{EN}$ ドライバをイネーブルにするための EN ピンの電圧スレッショルド   |                               | 1.54 | 2.0  |     | V  |

| $V_{DIS}$ ドライバをディセーブルにするための EN ピンの電圧スレッショルド |                               | 0.7  | 1.21 |     | V  |

| $V_{ENHYS}$ イネーブル・ピンのヒステリシス                 |                               | 0.3  |      |     | V  |

| $R_{EN}$ EN ピン内部プルダウン抵抗                     |                               | 250  |      |     | kΩ |

| <b>入力</b>                                   |                               |      |      |     |    |

| $V_{HIT}$ 入力立ち上がりスレッショルド (HI および LI)        |                               | 1.9  | 2.1  | 2.4 | V  |

| $V_{LIT}$ 入力立ち下がりスレッショルド (HI および LI)        |                               | 0.9  | 1.1  | 1.3 | V  |

| $V_{IHYS}$ 入力電圧ヒステリシス (HI および LI)           |                               | 1.0  |      |     | V  |

| $R_{IN}$ 入力プルダウン抵抗 (HI および LI)              |                               | 100  | 250  | 350 | kΩ |

| <b>低電圧駆動動作防止 (UVLO)</b>                     |                               |      |      |     |    |

| $V_{DDR}$ VDD 立ち上がりスレッショルド                  |                               | 6.5  | 7.0  | 7.8 | V  |

| $V_{DDF}$ VDD 立ち下がりスレッショルド                  |                               | 5.7  | 6.5  | 7.3 | V  |

$V_{DD} = V_{EN} = V_{HB} = 12V$ 、 $V_{HS} = V_{SS} = 0V$ 、LO または HO は無負荷、 $T_J = -40^{\circ}C \sim +140^{\circ}C$  (特に記述のない限り)

| パラメータ                 | テスト条件                         | 最小値                                             | 代表値   | 最大値  | 単位       |   |

|-----------------------|-------------------------------|-------------------------------------------------|-------|------|----------|---|

| $V_{DDHYS}$           | $V_{DD}$ スレッショルド・ヒステリシス       |                                                 | 0.5   |      | V        |   |

| $V_{HBR}$             | HS ピンを基準とした HB 立ち上がりスレッショルド   |                                                 | 5.5   | 6.3  | 7.1      | V |

| $V_{HBF}$             | HS ピンを基準とした HB 立ち下がりスレッショルド   |                                                 | 5.0   | 5.8  | 6.6      | V |

| $V_{HBHYS}$           | HB スレッショルド・ヒステリシス             |                                                 | 0.5   |      | V        |   |

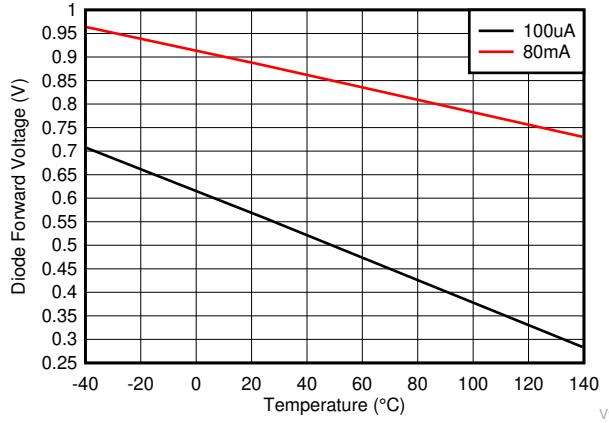

| <b>ブートストラップ・ダイオード</b> |                               |                                                 |       |      |          |   |

| $V_F$                 | 低電流順方向電圧                      | $I_{VDD-HB} = 100\mu A$                         | 0.65  | 0.85 | V        |   |

| $V_{FI}$              | 高電流順方向電圧                      | $I_{VDD-HB} = 80mA$                             | 0.85  | 1.0  | V        |   |

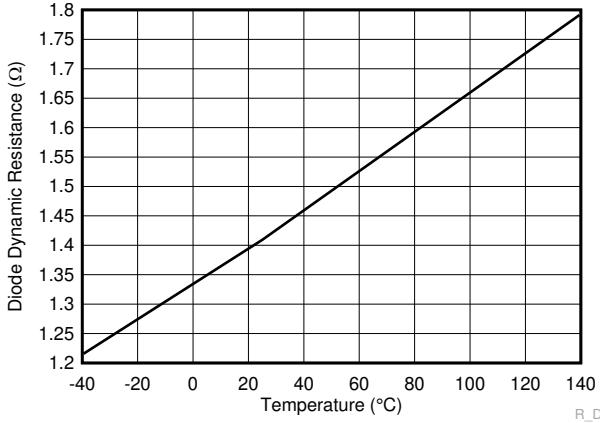

| $R_D$                 | 動的抵抗、 $\Delta V_F / \Delta I$ | $I_{VDD-HB} = 100mA$ および $80mA$                 | 1.5   | 2.5  | $\Omega$ |   |

| <b>LO ゲート・ドライバ</b>    |                               |                                                 |       |      |          |   |

| $V_{LOL}$             | Low レベル出力電圧                   | $I_{LO} = 100mA$                                | 0.085 | 0.4  | V        |   |

| $V_{LOH}$             | High レベル出力電圧                  | $I_{LO} = -100mA$ 、 $V_{LOH} = V_{DD} - V_{LO}$ | 0.13  | 0.42 | V        |   |

| ピーク・ブルアップ電流 (1)       |                               | $V_{LO} = 0V$                                   |       | 3.0  | A        |   |

| ピーク・ブルダウン電流 (1)       |                               | $V_{LO} = 12V$                                  |       | 3.0  | A        |   |

| <b>HO ゲート・ドライバ</b>    |                               |                                                 |       |      |          |   |

| $V_{HOL}$             | Low レベル出力電圧                   | $I_{HO} = 100mA$                                | 0.1   | 0.4  | V        |   |

| $V_{HOH}$             | High レベル出力電圧                  | $I_{HO} = -100mA$ 、 $V_{HOH} = V_{HB} - V_{HO}$ | 0.13  | 0.42 | V        |   |

| ピーク・ブルアップ電流 (1)       |                               | $V_{HO} = 0V$                                   |       | 3.0  | A        |   |

| ピーク・ブルダウン電流 (1)       |                               | $V_{HO} = 12V$                                  |       | 3.0  | A        |   |

(1) 量産品のパラメータはテストしていません

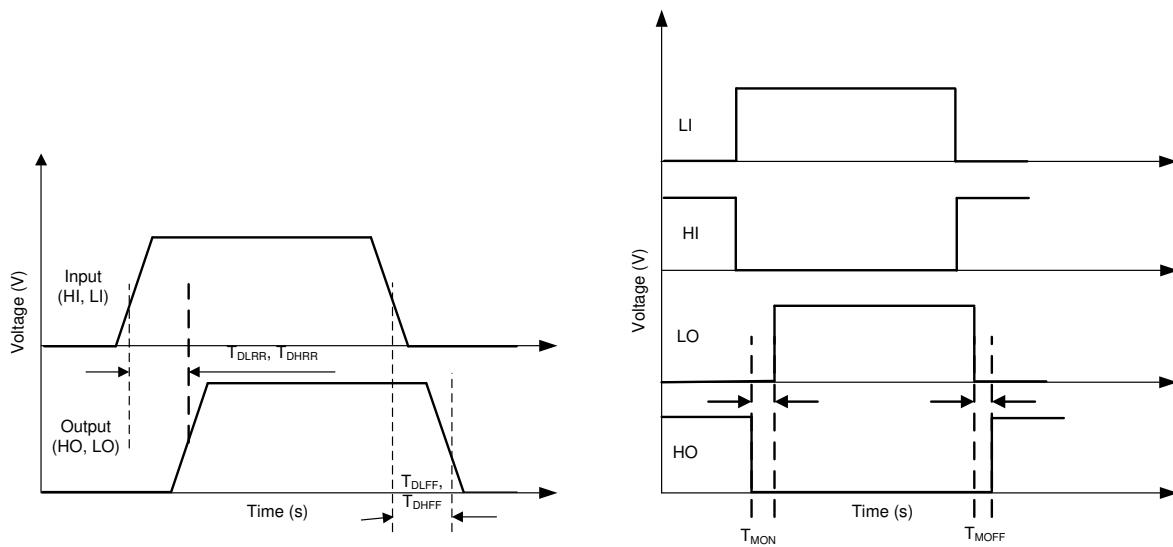

## 6.6 スイッチング特性

$V_{DD} = V_{HB} = 12V$ 、 $V_{HS} = V_{SS} = 0V$ 、LO または HO は無負荷、 $T_J = -40^{\circ}C \sim +140^{\circ}C$  (特に記述のない限り)

| パラメータ                     | テスト条件                             | 最小値                             | 標準値  | 最大値 | 単位      |

|---------------------------|-----------------------------------|---------------------------------|------|-----|---------|

| <b>伝搬遅延</b>               |                                   |                                 |      |     |         |

| $t_{DLFF}$                | $V_{LI}$ 立ち下がりから $V_{LO}$ 立ち下がりまで | 図 6-1 を参照                       | 16   | 30  | ns      |

| $t_{DHFF}$                | $V_{HI}$ 立ち下がりから $V_{HO}$ 立ち下がりまで | 図 6-1 を参照                       | 16   | 30  | ns      |

| $t_{DLRR}$                | $V_{LI}$ 立ち上がりから $V_{LO}$ 立ち上がりまで | 図 6-1 を参照                       | 16   | 30  | ns      |

| $t_{DHRR}$                | $V_{HI}$ 立ち上がりから $V_{HO}$ 立ち上がりまで | 図 6-1 を参照                       | 16   | 30  | ns      |

| <b>遅延マッチング</b>            |                                   |                                 |      |     |         |

| $t_{MON}$                 | LO がオンになってから HO がオフになるまで          | 図 6-1 を参照                       | 1    | 7   | ns      |

| $t_{MOFF}$                | LO がオフになってから HO がオンになるまで          | 図 6-1 を参照                       | 1    | 7   | ns      |

| <b>出力の立ち上がりおよび立ち下がり時間</b> |                                   |                                 |      |     |         |

| $t_R$                     | LO、HO の立ち上がり時間                    | $C_{LOAD} = 1800pF$ 、10%~90%    | 12   |     | ns      |

| $t_F$                     | LO、HO の立ち下がり時間                    | $C_{LOAD} = 1800pF$ 、90%~10%    | 10   |     | ns      |

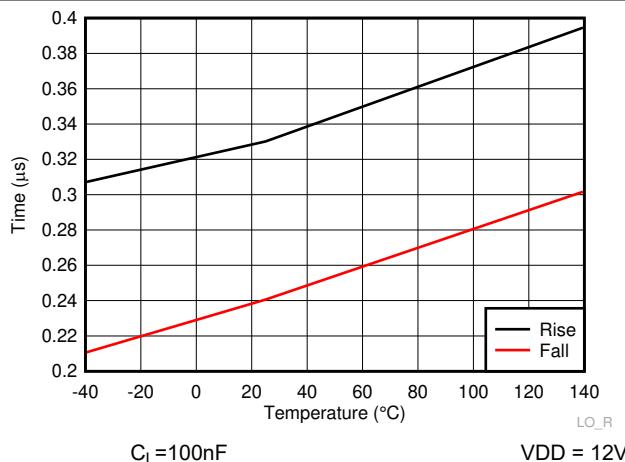

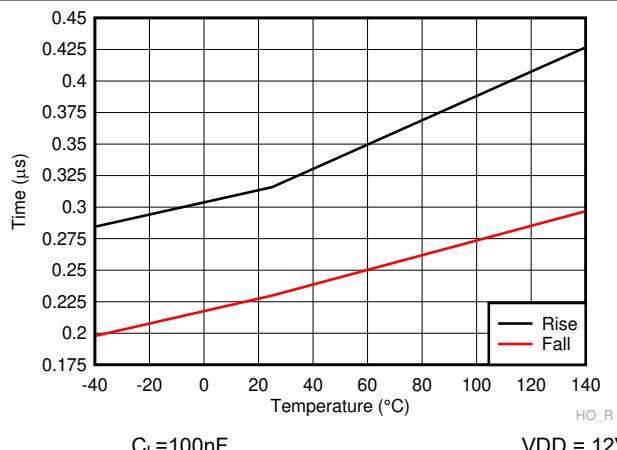

| $t_R$                     | LO、HO (3V~9V) の立ち上がり時間            | $C_{LOAD} = 0.1\mu F$ 、30%~70%  | 0.33 | 0.6 | $\mu s$ |

| $t_F$                     | LO、HO (3V~9V) の立ち下がり時間            | $C_{LOAD} = 0.1\mu F$ 、70%~30%  | 0.23 | 0.6 | $\mu s$ |

| <b>その他</b>                |                                   |                                 |      |     |         |

| $T_{PW,min}$              | 出力を変化させる最小入力パルス幅                  |                                 | 20   |     | ns      |

| ブートストラップ・ダイオードのターンオフ時間(1) |                                   | $I_F = 20mA$ 、 $I_{REV} = 0.5A$ | 50   |     | ns      |

(1) 量産品のパラメータはテストしていません

図 6-1. タイミング図

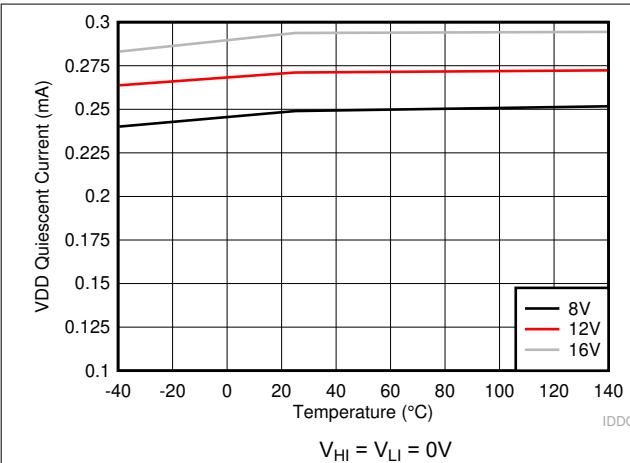

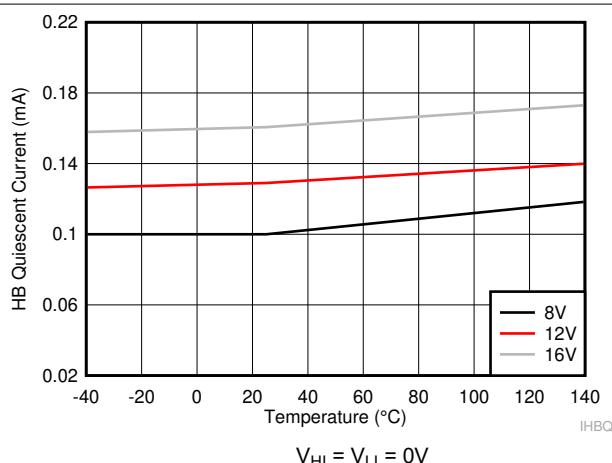

## 6.7 代表的特性

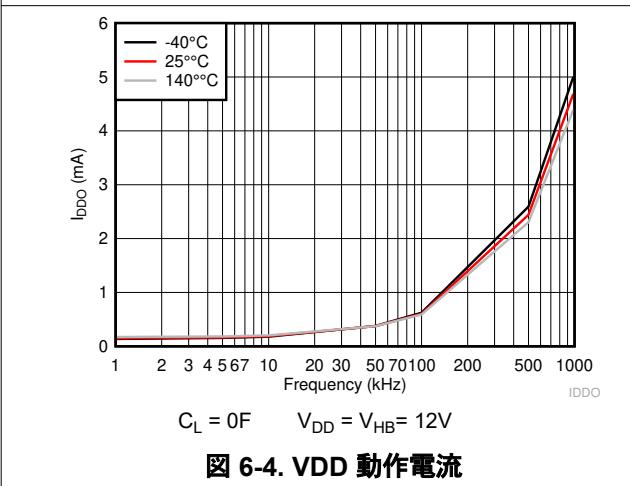

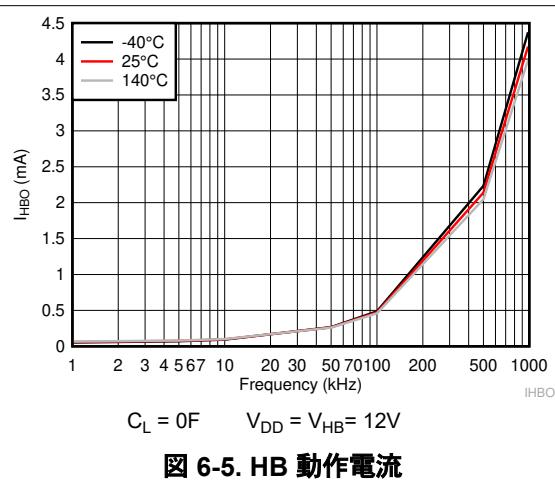

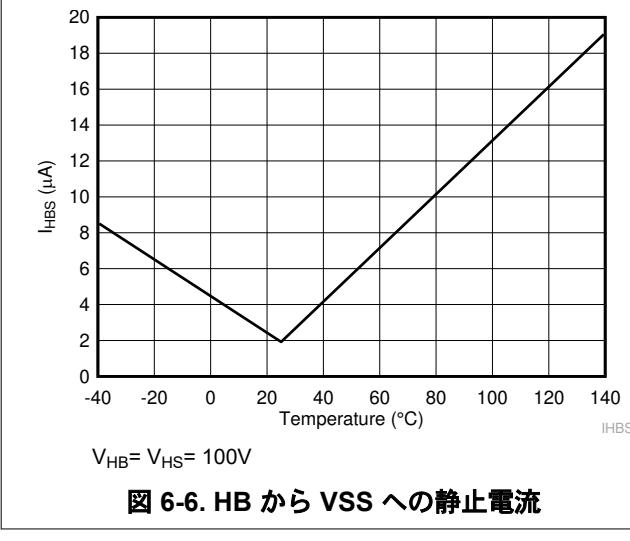

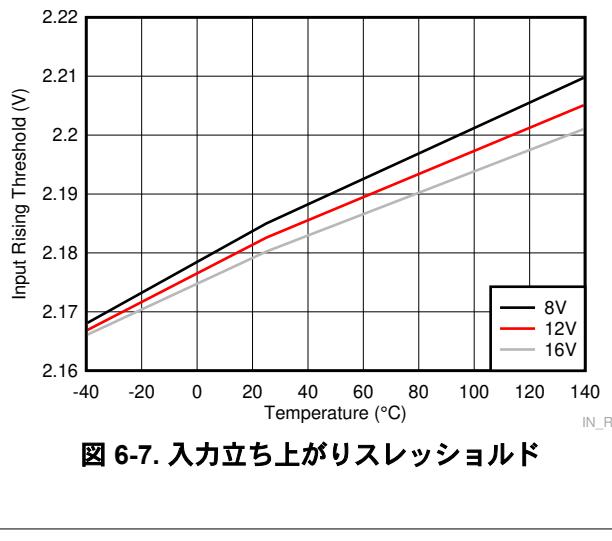

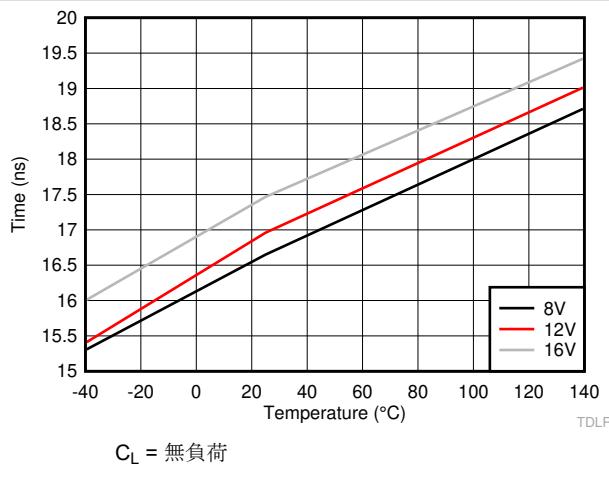

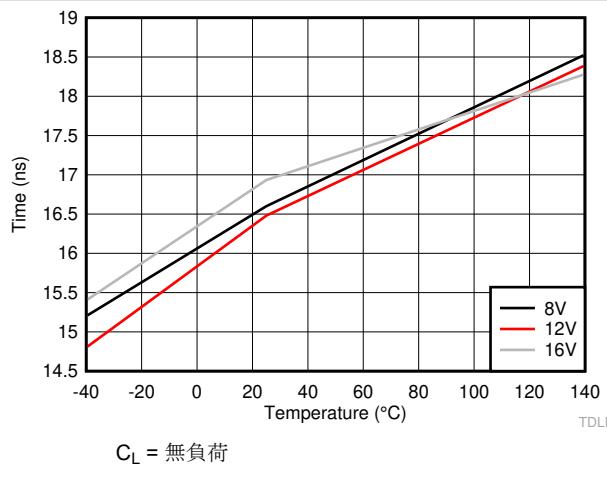

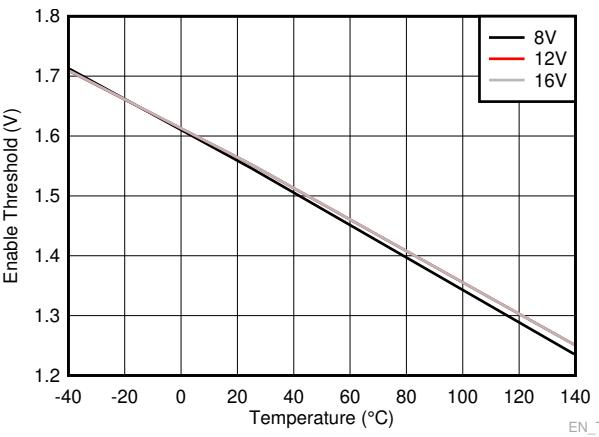

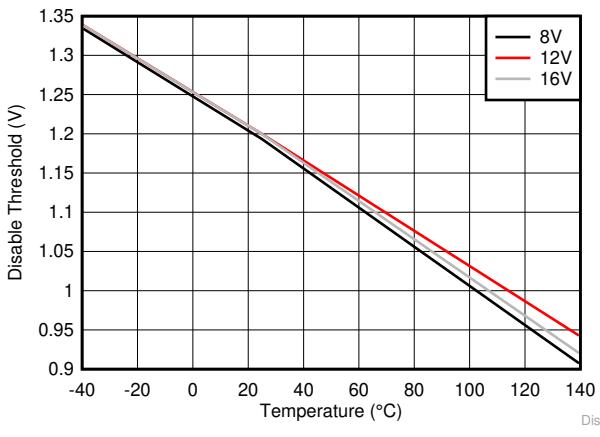

特に記述のない限り、 $V_{VDD} = V_{HB} = 12V$ 、 $V_{HS} = V_{VSS} = 0V$ 、出力は無負荷

図 6-2. VDD 静止時電流

図 6-3. HB 静止時電流

$C_L = 0F$   $V_{DD} = V_{HB} = 12V$

図 6-4. VDD 動作電流

$C_L = 0F$   $V_{DD} = V_{HB} = 12V$

図 6-5. HB 動作電流

$V_{HB} = V_{HS} = 100V$

図 6-6. HB から VSS への静止電流

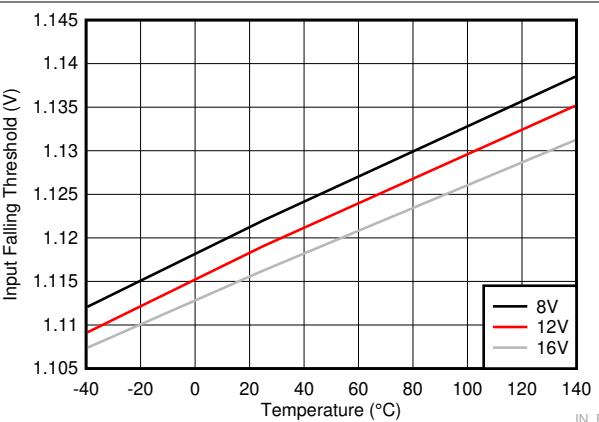

図 6-7. 入力立ち上がりリスレッショルド

図 6-8. 入力立ち下がりスレッショルド

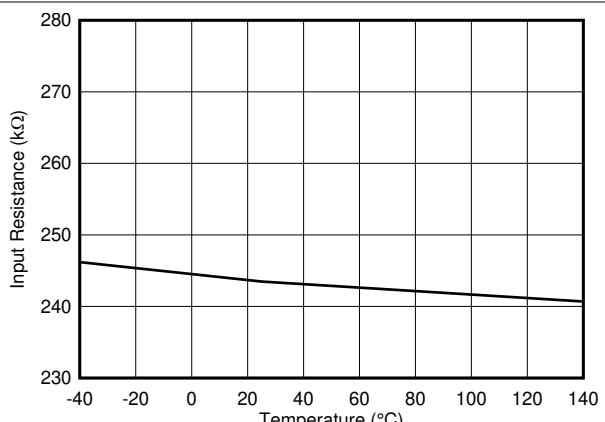

図 6-9. 入力プルダウン抵抗

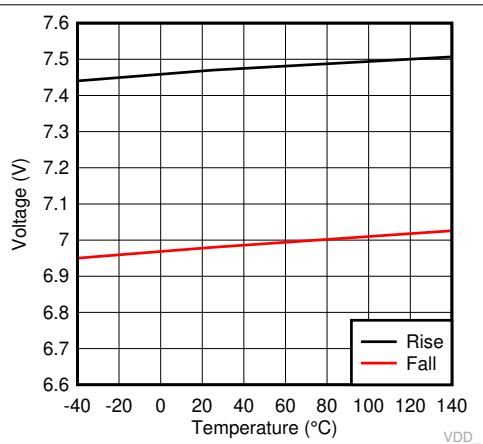

図 6-10. VDD UVLO スレッショルド

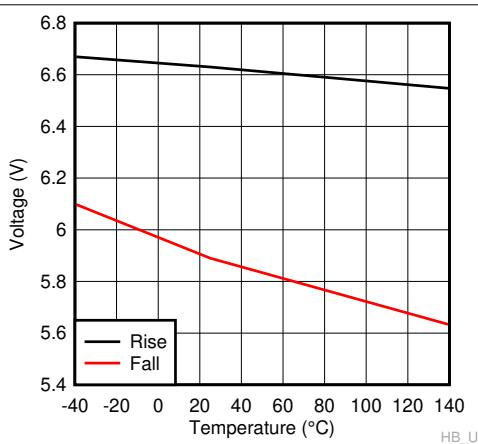

図 6-11. HB UVLO スレッショルド

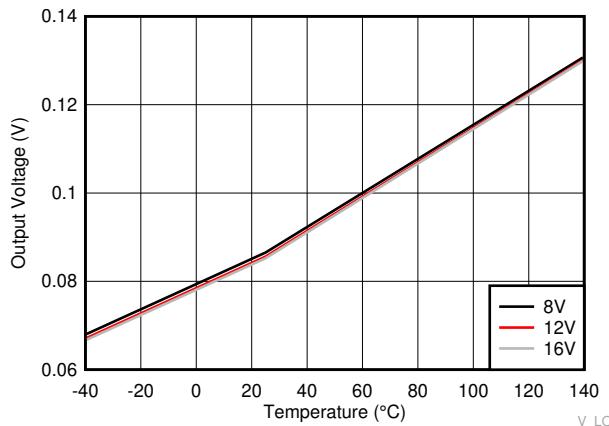

$I_O = 100\text{mA}$

図 6-12. LO LOW 出力電圧 (V<sub>LOL</sub>)

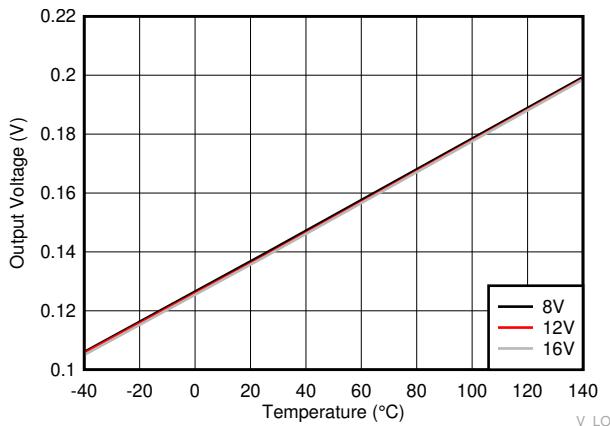

$I_O = -100\text{mA}$

図 6-13. LO HIGH 出力電圧 (V<sub>LOH</sub>)

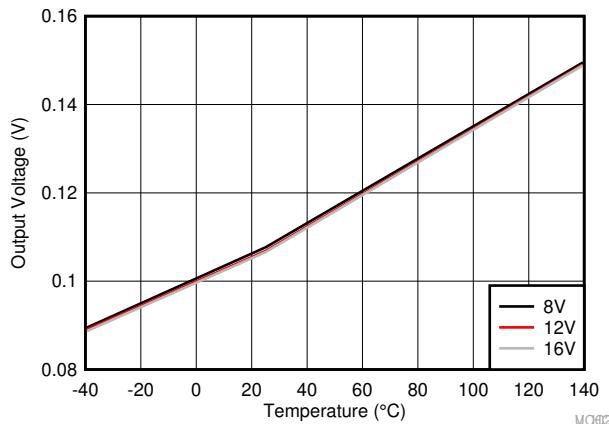

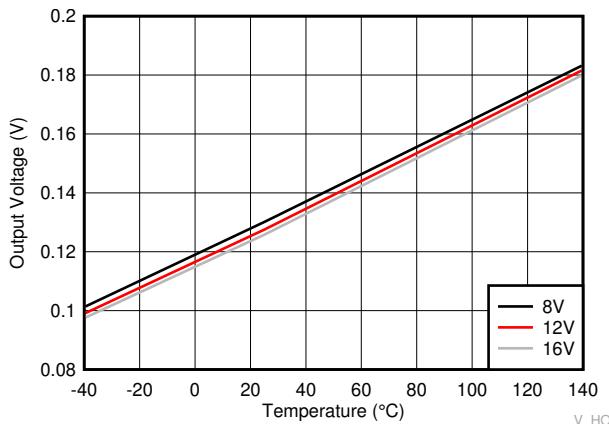

図 6-14. HO LOW 出力電圧 (V<sub>HOL</sub>)図 6-15. HO HIGH 出力電圧 (V<sub>HOH</sub>)

図 6-16. LO 立ち上がり時間

図 6-17. LO 立ち下がり時間

図 6-18. HO 立ち上がり時間

図 6-19. HO 立ち下がり時間

図 6-20. LO 立ち上がりおよび立ち下がり時間

図 6-21. HO 立ち上がりおよび立ち下がり時間

図 6-22. HO 立ち上がり伝搬遅延 (TDHRR)

図 6-23. HO 立ち下がり伝搬遅延 (TDHFF)

図 6-24. LO 立ち上がり伝搬遅延 (TDLRR)

図 6-25. LO 立ち下がり伝搬遅延 (TDLFF)

図 6-26. イネーブル・スレッショルド

図 6-27. ディセーブル・スレッショルド

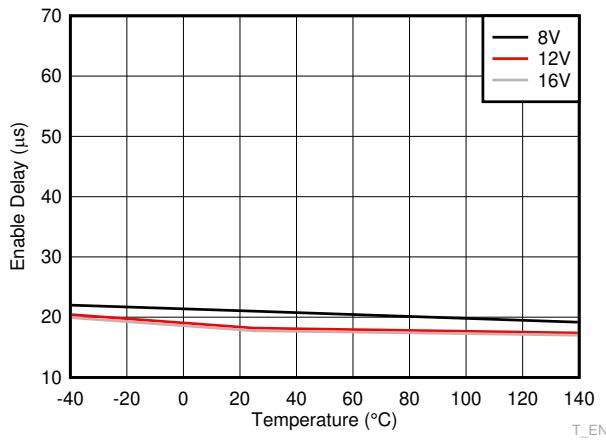

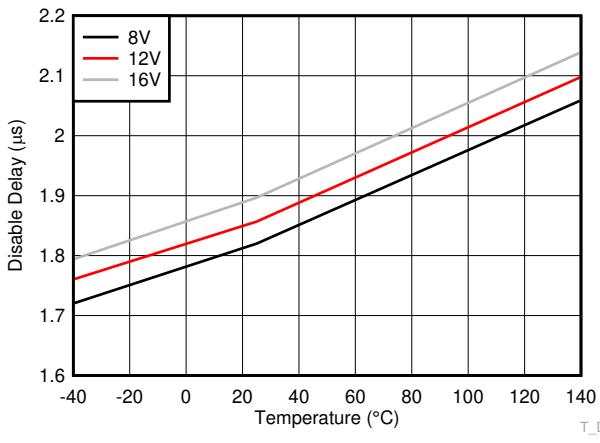

図 6-28. イネーブル遅延

図 6-29. ディセーブル遅延

図 6-30. ブート・ダイオードの順方向電圧降下

図 6-31. ブート・ダイオードの動的抵抗

## 7 詳細説明

### 7.1 概要

UCC27289 は、同期整流式降圧型またはハーフブリッジの構成においてハイサイドとローサイド両方の N チャネル FET を駆動するよう設計された高電圧ゲート・ドライバです。2 つの出力は、TTL 互換の入力信号によって独立して制御されます。また、信号が UCC27289 のターンオンおよびターンオフ・スレッショルド仕様を満たしている限り、このデバイスは入力で CMOS タイプの制御信号でも動作できます。フローティング・ハイサイド・ドライバは、VSS に関して最大 100V の HS 電圧で動作できます。UCC27289 デバイスには、外部のハイサイド・ゲート・ドライバのブートストラップ・コンデンサを充電するための内部ブートストラップ・ダイオードがあります。アプリケーションで必要な場合は、外部ブート・ダイオードを使用できます。堅牢なレベル・シフタにより、消費電力を抑えながら高速で動作し、制御ロジックからハイサイド・ゲート・ドライバへのクリーンなレベル遷移を実現します。ローサイドとハイサイド両方の電源レールに低電圧誤動作防止機能 (UVLO) が搭載されています。

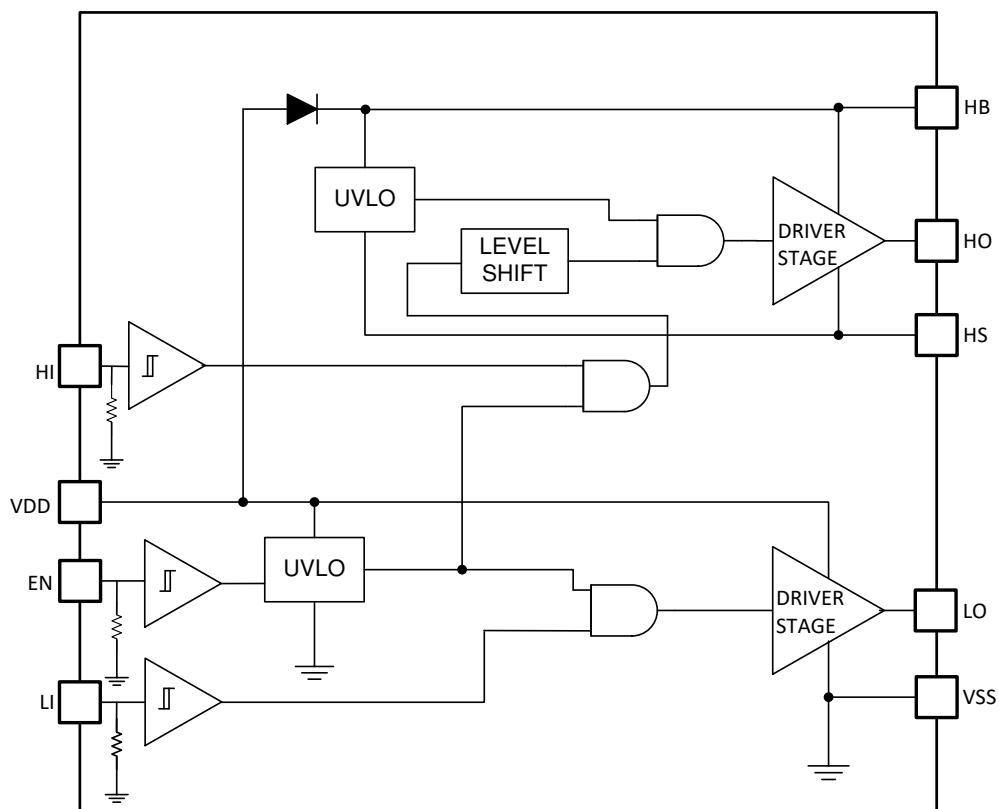

### 7.2 機能ブロック図

Copyright © 2020, Texas Instruments Incorporated

### 7.3 機能説明

#### 7.3.1 イネーブル

DRC パッケージのデバイスにはイネーブル (EN) ピンがあります。EN ピンの電圧がスレッショルド電圧を上回っている場合のみ、出力がアクティブになります。EN ピンがフローティング状態のままになっているか、グランドにプルダウンされている場合、出力は Low に保持されます。250kΩ の内部抵抗により、EN ピンを VSS ピンに接続します。そのため、EN ピンをフローティングにすると、デバイスはディセーブルされます。また、EN ピンを外部でグランドにプルダウンすると、デバイスはディセーブルされます。EN ピンを使用しない場合は、ピンを VDD ピンに接続することを推奨します。プルアップ抵抗を使用する必要がある場合は、強力なプルアップ抵抗を推奨します。12V の電源電圧の場合、10kΩ のプルアップをお勧めします。ノイズが発生しやすいアプリケーションでは、小さなフィルタ・コンデンサである 1nF を、デバイスにできる限り近づけて EN ピンと VSS ピンの間に接続する必要があります。EN ピンにアナログまたはデジタル・コントローラの出力ビ

ンを接続して、デバイスをイネーブルまたはディセーブルできます。ヒステリシスが組み込まれているため、わずらわしい出力のトリップやチャタリングを防止できます。

### 7.3.2 起動と UVLO

ハイサイドおよびローサイドのドライバ段は、電源電圧 ( $V_{DD}$ ) およびブートストラップ・コンデンサ電圧 ( $V_{HB-HS}$ ) を監視する UVLO 保護回路を備えています。UVLO 回路は、外部 MOSFET をターンオンするのに十分な電源電圧が得られるまで、各出力を禁止します。UVLO ヒステリシスが組み込まれており、電源電圧変動時のチャタリングを防止します。デバイスの  $V_{DD}$  ピンに電源電圧が印加されると、 $V_{DD}$  が UVLO スレッショルド (通常は 7.0V) を超えるまで両方の出力が LOW に保持されます。ブートストラップ・コンデンサの UVLO 状態 ( $V_{HB-HS}$ ) の場合は、ハイサイド出力 (HO) のみがディセーブルされます。

表 7-1. VDD UVLO ロジック動作

| 条件 ( $V_{HB-HS} > V_{HBR}$ )                  | HI | LI | HO | LO |

|-----------------------------------------------|----|----|----|----|

| デバイス起動時に、 $V_{DD}-V_{SS} < V_{DDR}$           | H  | L  | L  | L  |

|                                               | L  | H  | L  | L  |

|                                               | H  | H  | L  | L  |

|                                               | L  | L  | L  | L  |

| デバイス起動後に、 $V_{DD}-V_{SS} < V_{DDR} - V_{DDH}$ | H  | L  | L  | L  |

|                                               | L  | H  | L  | L  |

|                                               | H  | H  | L  | L  |

|                                               | L  | L  | L  | L  |

表 7-2. HB UVLO ロジック動作

| 条件 ( $V_{DD} > V_{DDR}$ )                 | HI | LI | HO | LO |

|-------------------------------------------|----|----|----|----|

| デバイス起動時に、 $V_{HB-HS} < V_{HBR}$           | H  | L  | L  | L  |

|                                           | L  | H  | L  | H  |

|                                           | H  | H  | L  | H  |

|                                           | L  | L  | L  | L  |

| デバイス起動後に、 $V_{HB-HS} < V_{HBR} - V_{HBH}$ | H  | L  | L  | L  |

|                                           | L  | H  | L  | H  |

|                                           | H  | H  | L  | H  |

|                                           | L  | L  | L  | L  |

### 7.3.3 入力段

2 つの入力は互いに独立して動作します。2 つの入力はオーバーラップする可能性があり、出力は入力信号に追従するものとします。独立しているため、单一入力のゲート・ドライバに比べて 2 つの出力を完全に制御できます。本デバイスには固定時間グリッチ除去フィルタが実装されていないため、伝搬遅延と遅延マッチングが犠牲になることはありません。言い換えると、デッドタイムは組み込まれていません。2 つの出力間のデッド・タイムが必要な場合は、マイコンを使用してこの値をプログラムする必要があります。入力信号にノイズが発生し、入力がオーバーラップする可能性がある場合、出力は入力に追従するものとし、貫通電流が発生する可能性があります。このような状況を回避するために、ゲート・ドライバ入力 HI および LI の前面に小さな入力フィルタを実装する必要があります。各入力は電源電圧と無関係であるため、デジタル・コントローラとアナログ・コントローラのどちらの出力にも接続できます。入力は広いスルーレートの信号を受け付け、入力は負電圧に耐えられるため、堅牢性が向上します。ドライバの入力に小さなフィルタを配置すると、すでに説明したように、ノイズが発生しやすいアプリケーションでシステムの堅牢性をさらに向上させることができます。入力には、標準値 250k $\Omega$  のプルダウン抵抗が内蔵されています。したがって、入力がフローティングのとき、出力は Low に保持されます。

### 7.3.4 レベル・シフタ

レベル・シフト回路は、VSS を基準とする信号であるハイサイド入力から、スイッチ・ノード (HS ピン) を基準とするハイサイド・ドライバ段へのインターフェイスです。レベル・シフトにより、HS ピンを基準とする HO 出力を制御できます。レベル・シフタによって生じる遅延は可能な限り低く保たれており、このデバイスは、優れた伝搬遅延特性、およびローサイド・ドライ

バ出力との遅延マッチングを実現します。遅延マッチングが小さいため、電力段は、より短いデッドタイムで動作できます。デッドタイムの短縮は、高い効率が必要なアプリケーションでは非常に重要です。

### 7.3.5 出力段

出力段は、レベル・シフタ出力からパワー・トレンイン内のパワー MOSFET へのインターフェイスです。両方の出力で高いスルーレート、低い抵抗、高いピーク電流能力を実現しているため、パワー MOSFET の効率的なスイッチングが可能です。ローサイド出力段は **VSS** を基準とし、ハイサイドは **HS** を基準とします。このデバイスの出力段は堅牢で、100ns にわたって **-2V** 過渡というような過酷な環境に対応できます。このデバイスは、出力での正の過渡にも耐えられます。このデバイスの出力段は、プルアップ構造を採用しており、パワー・スイッチのターンオン遷移のミラー・ブロート領域において、最も必要なときに最大のピーク・ソース電流を供給します。デバイスの出力プルアップおよびプルダウン構造は、トータルポール NMOS-PMOS 構造です。

### 7.3.6 負の電圧過渡

ほとんどのアプリケーションでは、外部ローサイド・パワー MOSFET のボディ・ダイオードが **HS** ノードをグランドにクランプします。場合によっては、基板の容量とインダクタンスに起因して、**HS** ノードがグランドより数 V 低い電圧まで過渡的にスイングする可能性があり、外部ローサイド MOSFET のボディ・ダイオードがこのスイングをクランプするのが間に合わないこともあります。UCC27289 と組み合わせて使用する場合には、**HS** ノードは、仕様に違反しない限り、またこのセクションで説明した条件に従う限り、グランドを下回る値までスイングできます。

**HS** は常に **HO** より低い電位にする必要があります。**HO** を規定の条件よりも負にすると、寄生トランジスタがアクティブになります。**HB** 電源から過剰な電流が流れる可能性があります。その結果、デバイスが損傷する可能性があります。**LO** と **VSS** についても同じ関係があります。必要に応じて、**HO** と **HS** の間、または **LO** と **VSS** の間にショットキー・ダイオードを外部に配置することにより、この種の過渡現象からデバイスを保護できます。ダイオードを有効にするために、デバイスのピンのできるだけ近くにダイオードを配置する必要があります。

**HB** と **HS** の間の動作電圧は、必ず 16V 以下になっている必要があります。したがって、**HS** ピンの過渡電圧が **-5V** になる場合、**HB** を 16V 未満に維持するためには、**VDD** (および **HB**) は理想的には 11V に制限されます。通常は、**HS** が負にスイングする場合、**HB** は **HS** に即座に追従するため、**HB** と **HS** の間の電圧はそれほどオーバーシュートしない可能性があります。ゲート・ドライバ・デバイスを適切に動作させるには、**HB** から **HS** へ、および **VDD** から **VSS** への低 ESR バイパス・コンデンサが不可欠です。直列インダクタンスを最小限に抑えるため、コンデンサはデバイスのリード直近に配置する必要があります。**LO** と **HO** からのピーク電流は非常に大きい可能性があります。バイパス・コンデンサと直列インダクタンスは、デバイスのリードにおいて、電圧リンクを引き起こします。信頼性の高い動作を実現するには、このリンクを回避する必要があります。

アプリケーション・ボードの設計やその他の動作パラメータの状況によっては、**HS** ピンだけでなく入力ピンなど他のピンについても、グランドを下回る方向に過渡的にスイングする場合があります。このような動作条件に対応するために、UCC27289 の入力ピンは、**-5V** を扱うことができるようになっています。レイアウトやその他の設計上の制約によって、出力 **HO** および **LO** でも過渡電圧が発生することがあります。したがって、UCC27289 ゲート・ドライバは、出力ピンで **-2V** 100ns の過渡電圧を扱うこともできるようになっています。

## 7.4 デバイスの機能モード

このデバイスは、通常モードおよび UVLO モードで動作します。UVLO 動作モードの詳細については、「[起動と UVLO](#)」を参照してください。通常モードでは、**V<sub>DD</sub>** および **V<sub>HB-HS</sub>** が UVLO スレッショルドを上回っているとき、出力段は **EN**、**HI**、および **LI** ピンの状態に依存します。入力状態がフローティングの場合、出力 **HO** および **LO** は **LOW** になります。次の真理値表は、デバイスがイネーブル (**EN** ピンが **HIGH** にプルアップされた状態) のときに適用されます。

表 7-3. 通常モード動作での入出力ロジック

| <b>HI</b> | <b>LI</b> | <b>HO</b> (1) | <b>LO</b> (2) |

|-----------|-----------|---------------|---------------|

| H         | H         | H             | H             |

| L         | H         | L             | H             |

| H         | L         | H             | L             |

| L         | L         | L             | L             |

表 7-3. 通常モード動作での入出力ロジック (続き)

| HI      | LI      | HO <sup>(1)</sup> | LO <sup>(2)</sup> |

|---------|---------|-------------------|-------------------|

| フローティング | L       | L                 | L                 |

| フローティング | H       | L                 | H                 |

| L       | フローティング | L                 | L                 |

| H       | フローティング | H                 | L                 |

| フローティング | フローティング | L                 | L                 |

(1) HO は HS を基準として測定されます

(2) LO は VSS を基準として測定されます

## 8 アプリケーションと実装

### 注

以下のアプリケーション情報は、TI の製品仕様に含まれるものではなく、TI ではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 8.1 アプリケーション情報

多くの電子機器やアプリケーションは、ますます多くの電力を消費するようになっています。これらのアプリケーションは、全体のサイズも小型化しています。大電力と小型化の両方を実現する 1 つの方法は、効率を改善するとともに、電力損失を最適に分散することです。これらのアプリケーションの多くは、パワー MOSFET を採用しており、ますます高い周波数でスイッチングされています。パワー MOSFET を高いスイッチング周波数で動作させるとともに、関連するスイッチング損失を低減するために、コントローラの PWM 出力と、パワー半導体デバイス（パワー MOSFET、IGBT、SiC FET、GaN FET など）のゲートとの間に強力なゲート・ドライバを採用します。これらのアプリケーションの多くは、電源半導体デバイスが最適にターンオンおよびターンオフされるようにするために、適切な UVLO 保護を必要とします。また、PWM コントローラがスイッチング・デバイスのゲートを直接駆動できない場合、ゲート・ドライバが不可欠です。デジタル電源の登場に伴って、デジタル・コントローラからの PWM 信号は多くの場合、3.3V のロジック信号であり、パワー・スイッチを正常にターンオンできないので、この状況がよく発生します。パワー・デバイスを完全にターンオンし、導通損失を最小限にし、スイッチング損失を最小限にするために、3.3V 信号をゲート駆動電圧（たとえば 12V または 5V）に昇圧するレベル・シフト回路が必要です。トーテムポール配置の NPN/PNP バイポーラ・トランジスタをベースとする従来のバッファ・ドライブ回路は、レベル・シフト機能および低電圧誤動作防止保護がないので、デジタル電源においては不十分であることがわかつています。ゲート・ドライバは、レベル・シフト機能とバッファ・ドライブ機能の両方を効果的に組み合わせています。ゲート・ドライバは、（大電流ドライバ・デバイスを物理的にパワー・スイッチの近くに配置することにより）高周波スイッチング・ノイズの影響を最小化し、ゲート・ドライブ・トランジスタを駆動し、フローティング・パワー・デバイス・ゲートを制御するなど、他の問題も解決します。これにより、ゲート電荷の電力損失をコントローラ IC からゲート・ドライバに移動することで、コントローラの消費電力および熱ストレスを低減できます。

UCC27289 ゲート・ドライバは、単一のデバイスで高電圧（100V）、小さい遅延（16ns）、優れた駆動能力（±3A）を実現します。このフローティング・ハイサイド・ドライバは、最大 100V のスイッチ・ノード電圧で動作できます。これにより、ハーフブリッジ、フルブリッジ、同期整流降圧、同期整流昇圧、アクティブ・クランプの各トポロジで N チャネル MOSFET を制御できます。UCC27289 ゲート・ドライバ IC にはブートストラップ・ダイオードが内蔵されているので、ほとんどのアプリケーションでは外部ブート・ダイオードが不要で、VDD 電圧からハイサイド・バイアスを生成できます。これにより、ユーザーは基板レイアウトを最適化し、部品コストを削減できます。外部ブートストラップ・ダイオードを使用する場合は、ファースト・リカバリで順方向電圧降下の小さいショットキー・ダイオードが必要です。各チャネルは、それぞれの入力ピン（HI および LI）で制御されるため、出力のオン・オフ状態を柔軟に制御できます。

MOSFET などのスイッチング・パワー・デバイスには、スイッチング損失と導通損失という 2 つの主な損失要素があります。導通損失は、デバイスを流れる電流とデバイスのオン抵抗によって支配されます。スイッチング損失は、スイッチング・デバイスのゲート電荷、スイッチング・デバイスのゲート電圧、スイッチング周波数によって支配されます。動作スイッチング周波数が高いアプリケーションでは、スイッチング損失がシステム全体の効率に影響を及ぼすようになります。このようなアプリケーションでは、スイッチング損失を低減するために、ゲート電圧を低くすることが不可欠です。ゲート電圧はゲート・ドライバ IC の電源電圧によって決定されるため、ゲート・ドライバ IC はこのようなアプリケーションではより低い電源電圧で動作する必要があります。UCC27289- ゲート・ドライバの UVLO レベルは標準値 7.0V であるため、バイアス電圧を 12V から 10V へ、あるいはさらに 9.5V にまで下げる必要があるアプリケーションに最適です。HB UVLO は VDD UVLO よりも低いので、ブートストラップ・ダイオードの電圧降下によってこの低いバイアス電圧での動作が抑止されることはありません。UVLO には十分なヒステリシスが設けられているため、チャタリングや不要なトリップを防止し、システムの堅牢性を向上させることができます。

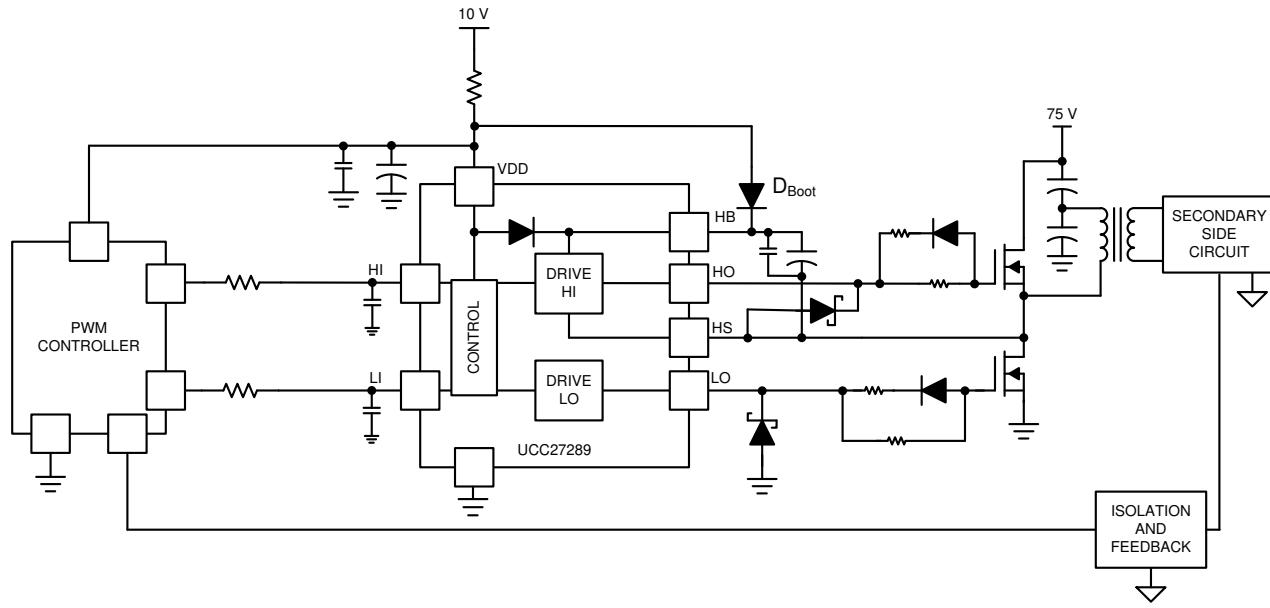

## 8.2 代表的なアプリケーション

Copyright © 2020, Texas Instruments Incorporated

図 8-1. 代表的なアプリケーション

### 8.2.1 設計要件

次の表に、システム・パラメータを示します。UCC27289 は、これらとの組み合わせにより正常に動作します。

表 8-1. 設計要件

| パラメータ                              | 値           |

|------------------------------------|-------------|

| MOSFET                             | CSD19535KTT |

| 最大入力電圧、 $V_{in}$                   | 75V         |

| 動作バイアス電圧、 $V_{DD}$                 | 10V         |

| スイッチング周波数、 $F_{sw}$                | 300kHz      |

| 所定の $V_{DD}$ での FET の総ゲート電荷、 $Q_G$ | 52nC        |

| MOSFET 内部ゲート抵抗、 $R_{GFET\_Int}$    | 1.4         |

| 最大デューティ・サイクル、 $D_{Max}$            | 0.5         |

| ゲート・ドライバ                           | UCC27289    |

### 8.2.2 詳細な設計手順

#### 8.2.2.1 ブートストラップおよび $V_{DD}$ コンデンサの選択

通常の動作では、ブートストラップ・コンデンサは、 $V_{HB-HS}$  電圧を UVLO スレッショルドよりも高く維持する必要があります。ブートストラップ・コンデンサ  $\Delta V_{HB}$  の最大許容ドロップは 式 1 で計算します。

$$\Delta V_{HB} = V_{DD} - V_{DH} - V_{HBL} \\ = (10V - 1V - (7.1V - 0.5V)) = 2.4V \quad (1)$$

ここで

- $V_{DD}$  はゲート・ドライバ・デバイスの電源電圧

- $V_{DH}$  はブートストラップ・ダイオードの順方向電圧降下

- $V_{HBL}$  は HB の立ち下がりスレッショルド ( $V_{HBR(max)} - V_{HBH}$ )

この例では、ブートストラップ・コンデンサの両端で許容される電圧降下は **2.4V** です。

一般に、ブートストラップ・コンデンサおよび **VDD** コンデンサのリップル電圧は、できるだけ小さくすることを推奨します。民生用、産業用、車載用の多くのアプリケーションでは、**0.5V** のリップル値を使用します。

**式 2** を使用して、スイッチング・サイクルごとに必要な、ブートストラップ・コンデンサからの総電荷量を推定します。

$$\begin{aligned} Q_{\text{TOTAL}} &= Q_G + I_{\text{HBS}} \times \left( \frac{D_{\text{MAX}}}{f_{\text{SW}}} \right) + \left( \frac{I_{\text{HB}}}{f_{\text{SW}}} \right) \\ &= 52 \text{ nC} + 0.083 \text{ nC} + 1.33 \text{ nC} = 53.41 \text{ nC} \end{aligned} \quad (2)$$

ここで

- $Q_G$  は MOSFET の総ゲート電荷量

- $I_{\text{HBS}}$  はデータシートに記載された HB から VSS へのリーク電流

- $D_{\text{MAX}}$  はコンバータの最大デューティ・サイクル

- $I_{\text{HB}}$  はデータシートに記載された HB 静止電流

計算された総電荷量は **53.41nC** です。

次に、**式 3** を使用して、ブートストラップ・コンデンサの最小値を推定します。

$$C_{\text{BOOT}(\text{min})} = \frac{Q_{\text{TOTAL}}}{\Delta V_{\text{HB}}} = \frac{53.41 \text{ nC}}{2.4 \text{ V}} = 22.25 \text{ nF} \quad (3)$$

計算されたブートストラップ・コンデンサの推奨値は、**22.25nF** です。この容量値は、フル・バイアス電圧で必要であることに注意する必要があります。実際には、さまざまな過渡条件によって電力段がパルスをスキップできるように、ブートストラップ・コンデンサの値を計算値より大きくする必要があります。この例では、**100nF** のブートストラップ・コンデンサを使用することを推奨します。また、十分なマージンを確保するとともに、ブートストラップ・コンデンサを HB および HS ピンのできるだけ近くに配置することを推奨します。さらに、高周波ノイズをフィルタリングするために、小型、**0402**、小容量、**1000pF** コンデンサをメインのバイパス・コンデンサと並列に配置します。

このアプリケーションでは、次の仕様の  $C_{\text{BOOT}}$  コンデンサを選択します。**0.1μF, 25V, X7R**

原則として、ローカル **VDD** バイパス・コンデンサは、ブートストラップ・コンデンサよりも大きい値にする必要があります（通常は、ブートストラップ・コンデンサの値の **10 倍**）。このアプリケーションでは、次の仕様の  $C_{\text{VDD}}$  コンデンサを選択します。**1μF, 25V, X7R**

$C_{\text{VDD}}$  コンデンサは、ゲート・ドライバの **VDD** ピンと **VSS** ピンの間に配置します。ブートストラップ・コンデンサと同様に、小型で値の小さいコンデンサをメインのバイパス・コンデンサと並列に配置します。このアプリケーションでは、高周波ノイズをフィルタリングするために、メイン・バイパス・コンデンサと並列に **0402, 1000pF** の容量を選択します。

ブートストラップおよびバイアス・コンデンサは、**X7R** 誘電体またはそれ以上のセラミック・タイプである必要があります。印加される最大電圧の少なくとも **2 倍** の電圧定格を持つコンデンサを選択します。ほとんどのセラミック・コンデンサはバイアスされると大幅に容量が低下するので、この値を選択してください。この値を選ぶことによって、システムの長期的な信頼性も向上します。

### 8.2.2.2 外部ブートストラップ・ダイオードと直列抵抗

UCC27289 は、ハイサイド・バイアスを生成して HO を正常に動作させるのに必要な、ブートストラップ・ダイオードを内蔵しています。このダイオードの特性は、効率的で信頼性の高い動作を実現するために重要です。外部ブートストラップ・ダイオードが必要な場合は、ダイオードの特性として、逆電圧処理機能、反復的ピーク順方向電流、順方向電圧降下、順回復および逆回復時間、動的抵抗を考慮します。UCC27289 は **100V** 定格のゲート・ドライバであるため、外部ブートストラップ・ダイオードは **100V** 以上の定格とする必要があります。ピーク順方向電流定格は、ハイサイドとローサイドのデューティ・サイクル、ブートストラップ・コンデンサの値、ブートストラップ・コンデンサで許容される電圧リップルなど、複数のシステム・パラメータに依存します。一般に、ブートストラップ・コンデンサの充電中の電力損失を低減するために、順方向電圧降下の小さいダイオードが推奨されます。ショットキー・ダイオードは順方向電圧降下が小さいため、UCC27289 と組み合わ

せて使用できます。考慮すべき動的特性は、ダイオードの回復時間と蓄積された電荷です。ほとんどのアプリケーションには、順回復および逆回復時間が 50ns 未満のダイオードが適しています。

特に、例えば 1MHz を超える非常に高いスイッチング周波数のアプリケーションでは、また、ローサイドの最小パルス幅が非常に小さい場合、特に、大きいブートストラップ・コンデンサ値を選択した場合は、ダイオードのピーク順方向電流が非常に大きくなり、ピーク逆電流も非常に大きくなる可能性があります。このようなアプリケーションでは、ブートストラップ・ダイオードとしてショットキー・ダイオードを使用することをお勧めします。MURS210 ダイオードは、ここで説明したアプリケーション例で動作します。

### 8.2.2.3 ドライバの電力損失の推定

UCC27289 などのゲート・ドライバ・デバイスの総電力損失は、ゲート・ドライバ・デバイスのさまざまな機能ブロックにおける電力損失の合計です。これらの電力損失の要素について、このセクションで説明します。

- 式 4 は、静止電流 ( $I_{DD}$  および  $I_{HB}$ ) が静的電力損失  $P_{QC}$  に与える影響を記述しています。

$$P_{QC} = (V_{DD} \times I_{DD}) + (V_{DD} - V_{DH}) \times I_{HB} \\ = 10 \text{ V} \times 0.4 \text{ mA} + 9 \text{ V} \times 0.4 \text{ mA} = 7.6 \text{ mW} \quad (4)$$

ここには示されていませんが、より安全側の近似をするためには、上記の式に無負荷動作電流  $I_{DD0}$  および  $I_{HBO}$  を加算します。

- 式 5 は、ハイサイドからローサイドへのリーク電流 ( $I_{HBS}$ ) がレベル・シフタ損失 ( $P_{IHBS}$ ) に与える影響を記述しています。

$$P_{IHBS} = V_{HB} \times I_{HBS} \times D = 85 \text{ V} \times 50 \mu\text{A} \times 0.5 = 2.12 \text{ mW} \quad (5)$$

ここで

- $D$  はハイサイド MOSFET のデューティ・サイクル

- $V_{HB}$  は、入力電圧とブートストラップ・コンデンサの両端の電圧との合計です。

- 式 6 は、MOSFET のゲート電荷 ( $Q_G$ ) が動的損失  $P_{QG}$  に与える影響を記述しています。

$$P_{QG} = 2 \times V_{DD} \times Q_G \times f_{SW} \times \frac{R_{GD\_R}}{R_{GD\_R} + R_{GATE} + R_{GFET\ (int)}} \\ = 2 \times 10 \text{ V} \times 52 \text{ nC} \times 300 \text{ kHz} \times 0.74 = 0.23 \text{ W} \quad (6)$$

ここで

- $Q_G$  は MOSFET の総ゲート電荷量

- $f_{SW}$  はスイッチング周波数

- $R_{GD\_R}$  はプルアップおよびプルダウン抵抗の平均値

- $R_{GATE}$  は外部ゲート駆動抵抗

- $R_{GFET\ (int)}$  はパワー MOSFET の内部ゲート抵抗です

この例では、外部ゲート抵抗が存在しないと仮定します。ドライバ出力セクションの最大プルアップおよびプルダウン抵抗の平均値は約  $4\Omega$  です。アプリケーションの値を代入して、ゲート電荷による動的損失を計算します。この場合、この値は  $230\text{mW}$  です。

- 式 7 は、各スイッチング・サイクルのレベル・シフタ寄生電荷 ( $Q_P$ ) が、ハイサイド・スイッチング中の動的損失 ( $P_{LS}$ ) に与える影響を記述しています。

$$P_{LS} = V_{HB} \times Q_P \times f_{SW} \quad (7)$$

この例ではわかりやすくするために、寄生電荷  $Q_P$  の値が  $1\text{nC}$  であると仮定します。値を代入すると、レベル・シフタの動的損失として  $25.5\text{mW}$  が得られます。この推定値は、レベル・シフタの動的損失としては非常に大きい値です。

すべての損失を合計すると、ゲート・ドライバの総損失は、 $265.22\text{mW}$  になります。この例に示すように、ほとんどのアプリケーションでは、ゲート電荷による動的損失がゲート・ドライバ・デバイスの総電力損失の大部分を占めます。ブートストラップ

プ・ダイオードを含むゲート・ドライバの場合、ブートストラップ・ダイオードの損失も推定する必要があります。ダイオードの順方向導通損失は、平均順方向電圧降下と平均順方向電流の積として計算されます。

式 8 は、与えられた周囲温度に対して、デバイスの最大許容電力損失を推定するものです。

$$P_{MAX} = \frac{(T_J - T_A)}{R_{\theta JA}} \quad (8)$$

ここで

- $P_{MAX}$  はゲート・ドライバ・デバイスで許容される最大消費電力

- $T_J$  は動作時の推奨最高接合部温度

- $T_A$  はゲート・ドライバ・デバイスの周囲温度

- $R_{\theta JA}$  は接合部から周囲への熱抵抗

アプリケーションでゲート・ドライバ・デバイスの接合部温度をより正確に推定するには、まずケース温度を正確に測定し、次に特定のアプリケーションでの消費電力を決定することを推奨します。その後、 $\Psi_{JT}$  を使用して接合部温度を計算します。接合部温度を推定し、アプリケーションでの周囲温度を測定した後、 $\theta_{JA(effective)}$  を計算します。次に、プロジェクトの開発中に設計パラメータ（外部ゲート抵抗やパワー MOSFET の値など）が変化した場合、 $\theta_{JA(effective)}$  を使用して、これらの変化がゲート・ドライバ・デバイスの接合部温度にどのように影響するかを推定します。

「[熱に関する情報](#)」表に、ドライバ・パッケージの熱評価基準の概要を示します。熱に関する情報表の詳細については、『[半導体およびICパッケージの熱評価基準](#)』アプリケーション・レポートを参照してください。

#### 8.2.2.4 外付けゲート抵抗の選択

UCC27289 などの大電流ゲート・ドライバを使用する高周波スイッチング電源アプリケーションでは、寄生インダクタンス、寄生容量、大電流ループによって、パワー MOSFET のゲートにノイズやリングが発生する可能性があります。多くの場合、このリングとノイズを抑制するために外部ゲート抵抗を使用します。一部のアプリケーションでは、ゲート・ドライバ・デバイスの負荷であるゲート電荷が、ゲート・ドライバのピーク出力電流能力よりも大幅に大きくなります。このようなアプリケーションでは、外部ゲート抵抗によりゲート・ドライバのピーク出力電流を制限できます。レイアウトまたはアプリケーションの条件により可能である場合は、外部ゲート抵抗を用意することを推奨します。

式 9 を使って、ドライバのハイサイド・プルアップ電流を計算します。

$$I_{OHH} = \frac{V_{DD} - V_{DH}}{R_{HOH} + R_{GATE} + R_{GFET(int)}} \quad (9)$$

ここで

- $I_{OHH}$  はハイサイドのピーク・プルアップ電流

- $V_{DH}$  はブートストラップ・ダイオードの順方向電圧降下

- $R_{HOH}$  はゲート・ドライバの内部ハイサイド・プルアップ抵抗。値はデータシートに直接記載されているか、テスト条件 ( $R_{HOH} = V_{HOH}/I_{HO}$ ) から計算できます。

- $R_{GATE}$  はドライバ出力とパワー MOSFET ゲートの間に接続される外部ゲート抵抗

- $R_{GFET(int)}$  は MOSFET のデータシートに記載されている MOSFET の内部ゲート抵抗

式 10 を使って、ドライバのハイサイド・シンク電流を計算します。

$$I_{OLH} = \frac{V_{DD} - V_{DH}}{R_{HOL} + R_{GATE} + R_{GFET(int)}} \quad (10)$$

ここで

- $R_{HOL}$  はゲート・ドライバの内部ハイサイド・プルダウン抵抗

式 11 を使って、ドライバのローサイド・ソース電流を計算します。

$$I_{OHL} = \frac{V_{DD}}{R_{LOH} + R_{GATE} + R_{GFET(int)}} \quad (11)$$

ここで

- $R_{LOH}$  はゲート・ドライバの内部ローサイド・プルアップ抵抗

式 12 を使って、ドライバのローサイド・シンク電流を計算します。

$$I_{OLL} = \frac{V_{DD}}{R_{LOL} + R_{GATE} + R_{GFET(int)}} \quad (12)$$

ここで

- $R_{LOL}$  はゲート・ドライバの内部ローサイド・プルダウン抵抗

ゲート・ドライバのハイサイドおよびローサイド・チャネルのピーク電流定格は、いずれも  $\pm 3A$  です。これらの式は、必要に応じてピーク電流を低減するのに役立ちます。図 8-1 に示すように、外付けゲート抵抗と逆並列にダイオードと抵抗の組み合わせを設けることにより、立ち下がり時間の値とは異なる立ち上がり時間の値を設定できます。一般的に、外部ゲート抵抗の最適な値または構成を選択するのは、反復的なプロセスです。外部ゲート抵抗の選択の詳細については、『ゲート・ドライバ向けの外部ゲート抵抗設計ガイド』を参照してください。

### 8.2.2.5 遅延およびパルス幅

PWM、ドライバ、および電力段で発生する合計遅延は、主として電流制限応答の遅延ですが、他にもいくつかの原因を考慮する必要があります。また、ドライバ間の遅延の違いも考慮する必要があります。この場合、トポロジによってはさまざまな問題が発生する可能性があります。同期整流降圧トポロジのスイッチングでは、クロス導通および過剰なボディ・ダイオード導通を避けるため、ハイサイド・スイッチとローサイド・スイッチの間のデッドタイムを慎重に選択する必要があります。

どのような動作条件でも、ハイサイドとローサイドのパルス幅に不均衡が生じた場合、トランジスタのボルト秒不均衡がブリッジ・トポロジに影響を及ぼす可能性があります。UCC27289 デバイスは、プロセスおよび温度変動全体にわたって、最大伝搬遅延が 30ns、遅延マッチングが 7ns であり、これは業界でもトップクラスの性能です。

入力パルス幅が非常に小さい場合には、出力が入力信号に十分に追従しない可能性があるため、ゲート・ドライバ・デバイスでは、小さい入力パルス幅に対する性能が重要な考慮事項になります。コントローラからの PWM 出力信号は、定常状態では比較的広くなる可能性がありますが、以下の動作条件では非常に小さい幅のパルスが発生することがあります。

- ソフトスタート期間

- 大きな負荷過渡

- 短絡状態

小さい幅のパルスは、ゲート・ドライバ・デバイスへの入力信号として現れるので、ゲート・ドライバ・デバイスは、これらの小さい幅の信号に適切に応答する必要があります。

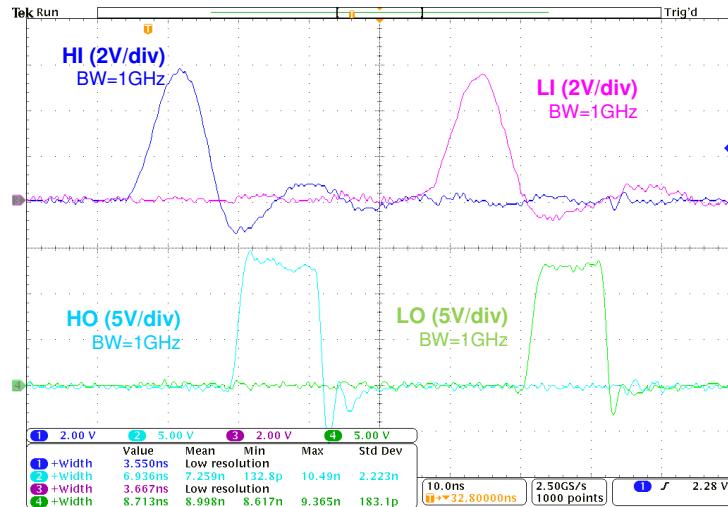

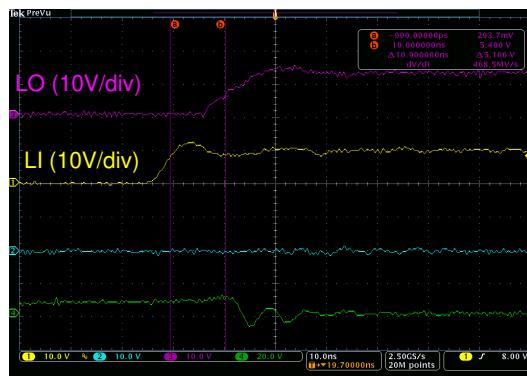

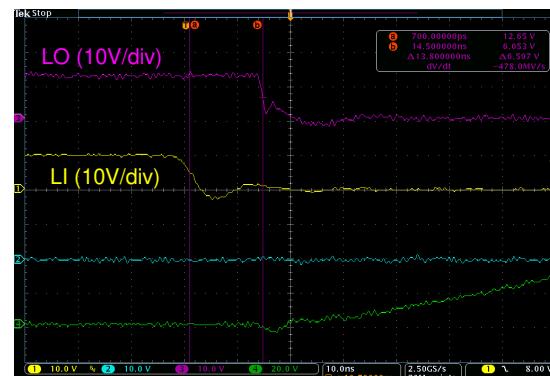

図 8-2 は、入力パルス幅が非常に小さい場合であっても、UCC27289 デバイスが信頼性の高い出力パルスを生成することを示しています。入力パルス幅が非常に小さい場合でも、伝搬遅延と遅延マッチングは影響を受けません。

図 8-2. 入力および出力パルス幅

### 8.2.2.6 VDD および入力フィルタ

スイッチング電源アプリケーションの中には、非常にノイズの多いものもあります。ノイズは、入力 (ゲート・ドライバ・デバイスの HI ピンと LI ピン) でのグランド・バウンスおよびレンギングによって発生することがあります。このような状況を緩和するために、UCC27289 は、負の入力電圧処理能力と広い入力スレッショルド・ヒステリシスを備えています。これらの機能が十分でない場合、アプリケーションに入力フィルタが必要になる可能性があります。ゲート・ドライバ・デバイスの入力でノイズをフィルタリングするには、 $10\Omega$  抵抗および  $47\text{pF}$  コンデンサなどの小さいフィルタで十分です。この RC フィルタは遅延を発生させるので、慎重に検討する必要があります。バイアス電源に高周波ノイズが発生すると、ゲート・ドライバ・デバイスの性能に問題が発生する可能性があります。このノイズをフィルタリングするには、図 8-1 に示すように、VDD ピンと直列に  $1\Omega$  の抵抗を使用することを推奨します。この抵抗は、電流制限素子としても機能します。バイアス・レールで短絡が発生した場合、この抵抗は開路となり、さらなる損傷を防止します。この抵抗は、開発フェーズ中の設計のデバッグにも役立ちます。

### 8.2.2.7 過渡保護

前のセクションで説明したように、大電力でスイッチング周波数の高い電源は、本質的にノイズが多くなります。回路の  $dV/dt$  および  $di/dt$  が大きいと、HO、LO、HS などのさまざまなピンで負電圧が発生する可能性があります。このデバイスは、仕様表に記載されているように、これらのすべてのピンで負電圧を許容します。回路の寄生成分が非常に大きな負のスイングを引き起こす場合、回路に追加の保護が必要になることがあります。このような場合は、高速動作かつ低リーク・タイプのショットキー・ダイオードを使用する必要があります。このダイオードは、ゲート・ドライバ・デバイスのピンでの過剰な負電圧をクランプする効果を発揮するために、できるだけゲート・ドライバ・デバイスのピンに近づけて配置する必要があります。低リークのツェナー・ダイオードを使用すれば、出力ピンまたは電源ピンの過電圧によるドライバ・デバイスの損傷の可能性を回避できます。電圧を  $16\text{V}$  の最大推奨値未満にクランプするためには、多くの場合、 $15\text{V}$  のツェナー・ダイオードで十分です。

### 8.2.3 アプリケーション曲線

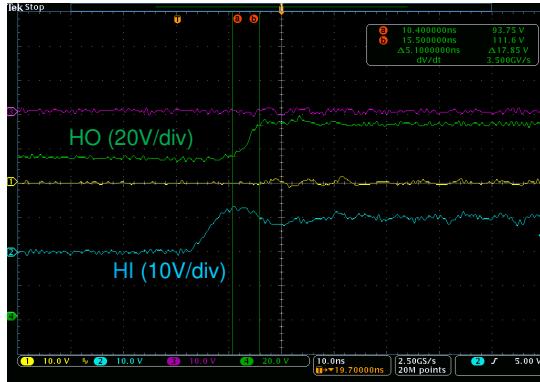

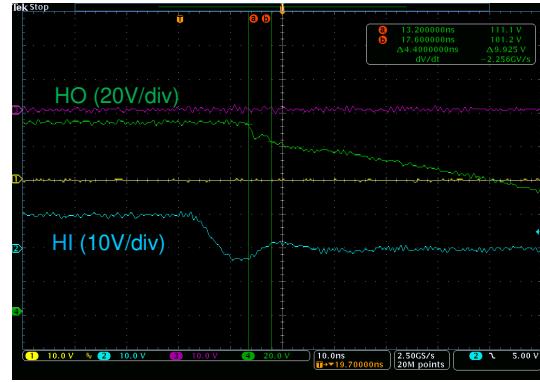

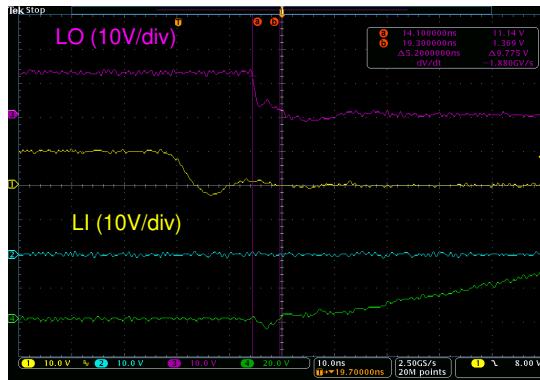

電源のスイッチング損失を最小限に抑えるには、パワー MOSFET のターンオンおよびターンオフをできるだけ高速にすむ必要があります。ドライバの駆動電流能力が高いほど、スイッチングは高速になります。したがって、UCC27289- は、高い駆動電流能力と低抵抗の出力段を備えるように設計されています。ゲート・ドライバ・デバイスの駆動能力をテストする一般的な方法の 1 つは、重負荷でテストすることです。出力の立ち上がり時間と立ち下がり時間により、ゲート・ドライバ・デバイスの駆動能力がわかります。大きいコンデンサを使用して駆動強度を測定する場合は、負荷コンデンサと直列に抵抗を配置しないでください。ピーク電流能力は、グラフの立ち上がりおよび立ち下がり曲線に沿って最も速い  $dV/dt$  を使って推定できます。この方法は、2 つ以上のゲート・ドライバ・デバイスの性能比較にも役立ちます。

アプリケーションに類似した環境で UCC27289 をテストしました。以下に示す波形は、無負荷の同期整流降圧コンバータを使用して生成したものです。スイッチング周波数  $100\text{kHz}$ 、入力電圧  $100\text{V}$  に設定しました。UCC27289 は  $2\Omega$  の外付

け抵抗で BSC16DN250NS3 を駆動しました。すべての波形はシングルエンド・プローブを使用して測定しました。図 8-3 および 図 8-4 は、それぞれ HO の立ち上がり時間および立ち下がり時間を示しています。図 8-5 および 図 8-6 は、それぞれ LO の立ち上がり時間および立ち下がり時間を示しています。内部ブートストラップ・ダイオードおよび外部ブートストラップ・コンデンサにより、ハイサイド・バイアスを生成しました。

セクション 8.2.2.5 で説明しているように、伝搬遅延は、多くのアプリケーションで信頼性の高い動作を実現するために重要な役割を果たします。図 8-7 および 図 8-8 は、UCC27289 の LO 立ち上がりおよび立ち下がりの伝搬遅延を示します。HO 出力についても同様の伝搬遅延が観測されました。

$V_{DD}=12V$ ,  $HS=100V$

図 8-3. HO 立ち上がり時間

$V_{DD}=12V$ ,  $HS=100V$

図 8-4. HO 立ち下がり時間

$V_{DD}=12V$ ,  $HS=100V$

図 8-5. LO 立ち上がり時間

$V_{DD}=12V$ ,  $HS=100V$

図 8-6. LO 立ち下がり時間

$V_{DD} = 12V$

図 8-7. ターンオン伝搬遅延

$V_{DD} = 12V$

図 8-8. ターンオフ伝搬遅延

$V_{DD}=10V, V_{in}=100V$

$C_L = 1nF$

Ch1=HI Ch2=LI Ch3=HO Ch4=LO

図 8-9. 負電圧入力

## 9 電源に関する推奨事項

UCC27289 の推奨バイアス電源電圧範囲は、8V～16V です。この範囲の下限は、 $V_{DD}$  電源回路ブロックの内部低電圧誤動作防止 (UVLO) 保護機能 (標準値 7.0V) によって決まります。この範囲の上限は、 $V_{VDD}$  の推奨最大電圧定格である 16V によって決まります。 $VDD$  ピンの電圧は、推奨最大電圧よりも低くすることを推奨します。

UVLO 保護機能は、ヒステリシス機能も備えています。これは、デバイスが通常モードで動作し始めた後に  $VDD$  電圧が低下した場合、電圧の低下がヒステリシス仕様値  $V_{DDHYS}$  を超えない限り、デバイスは通常モードで動作を継続することを意味します。電圧の低下がヒステリシスの仕様値を超える場合、デバイスはシャットダウンします。したがって、8V またはそれに近い範囲の電圧で動作しているときは、デバイスのシャットダウンがトリガされないように、補助電源出力の電圧リップルを UCC27289 のヒステリシス仕様値よりも小さくする必要があります。

UCC27289 には、EN ピンによるイネーブル / ディセーブル機能があります。したがって、EN ピンの信号はできるだけクリーンにする必要があります。EN ピンを使用しない場合は、ピンを  $VDD$  ピンに接続することを推奨します。抵抗を介して EN ピンをプルアップする場合、プルアップ抵抗を強くする必要があります。ノイズが発生しやすいアプリケーションでは、X7R 0402 1nF などの小型コンデンサを使用して EN ピンをフィルタすることを推奨します。

同様に、 $VDD$  ピンと GND ピンの間にもバイパス・コンデンサを配置する必要があります。このコンデンサは、デバイスにできる限り近づけて配置する必要があります。低 ESR の表面実装型セラミック・コンデンサを推奨します。 $VDD$  と GND の間に 2 つのコンデンサを使用することを推奨します。1 つは小容量のセラミック表面実装コンデンサで、高周波フィルタリングのために  $VDD$  と GND ピンのすぐ近くに配置します。もう 1 つはデバイスのバイアス要件に対応する大容量の表面実装コンデンサです。同様に、HO ピンから供給される電流パルスは HB ピンから電源を得ています。したがって、HB と HS の間に 2 個のコンデンサを推奨します。1 つは高周波フィルタ用の小容量小型コンデンサで、もう 1 つは HO パルスを供給するための大容量コンデンサです。

ノイズが非常に支配的で、PWB (プリント配線基板) にスペースがあるアプリケーションでは、小さな RC フィルタを入力に配置することを推奨します。これにより、設計全体の性能を向上できます。このようなアプリケーションでは、パワー MOSFET の外部ゲート抵抗用のプレースホルダも使用することをお勧めします。この抵抗を使用すると、駆動能力だけでなく、HS のスルーレートも制御でき、ハイサイド回路の性能に影響を及ぼします。外部ゲート抵抗の両端にダイオードを設ける場合は、ダイオードと直列に抵抗を使用することを推奨します。これにより、立ち下がり時間をさらに制御できます。

モーター・ドライブなどの電源アプリケーションでは、システム全体にわたって多くの過渡現象が存在します。この結果、ゲート・ドライバ・デバイスのほぼすべてのピンで過電圧および低電圧スパイクが発生することがあります。設計の堅牢性を高めるため、HO および LO ピンにクランプ・ダイオードを使用することを推奨します。パワー MOSFET の寄生ダイオードを使用したくない場合は、HS ピンに外部クランプ・ダイオードを付けることを推奨します。このダイオードは、高電圧大電流タイプ (MOSFET と同じ定格) で、非常に高速な動作を必要とします。これらのダイオードの温度範囲全体でのリークは、最小限に抑える必要があります。

過大な負の HS 電圧が発生することがほぼ確実である電源アプリケーションでは、HS ピンとスイッチ・ノードの間に小さな抵抗を配置することを推奨します。この抵抗は、ドライバ・デバイスへの電流をある程度制限するのに役立ちます。この抵抗は、ハイサイド・ドライブ能力に影響を与えるため、慎重に検討する必要があります。

## 10 レイアウト

### 10.1 レイアウトのガイドライン

ハイサイドおよびローサイドのゲート・ドライバの最適な性能を実現するには、プリント配線基板 (PWB) のレイアウト・ガイドラインに従うことを考慮する必要があります。

- 低 ESR/ESL コンデンサを VDD ピンと HB ピンの間、および HB ピンと HS ピンの間にデバイスの近くで接続して、外部 MOSFET のターンオン時に VDD ピンと HB ピンから引き出される大きいピーク電流に備える必要があります。

- 上側の MOSFET のドレインでの大きい電圧過渡を防止するために、低 ESR の電解コンデンサと高品質のセラミック・コンデンサをハイサイド MOSFET のドレインとグランド (VSS) の間に接続する必要があります。

- スイッチ・ノード (HS) ピンでの大きな負の過渡を防止するため、ハイサイド MOSFET のソースとローサイド MOSFET (同期整流器) のソースとの間の寄生インダクタンスを最小限に抑える必要があります。

- スイッチング・ノイズのグランド・プレーンへの結合を最小限に抑えるため、HS プレーンとグランド (VSS) プレーンの重なりは、できるだけ小さくする必要があります。

- デバイスの熱性能を向上させるために、サーマル・パッドを大きな重い銅プレーンに接続する必要があります。一般に、サーマル・パッドは、デバイスの VSS と同じグランド・プレーンに接続されています。このパッドは VSS ピンのみに接続することを推奨します。

- 接地に関する注意事項:

- グランド接続を設計する際の最優先事項は、MOSFET のゲートを充電および放電する大きいピーク電流を、最小の物理的領域内に限定することです。このように限定することによって、ループのインダクタンスが小さくなり、MOSFET のゲート端子のノイズ問題が最小限に抑えられます。ゲート・ドライバは、可能な限り MOSFET の近くに配置します。

- 2 番目の考慮事項は、ブートストラップ・コンデンサ、ブートストラップ・ダイオード、ローカル・グランド基準バイパス・コンデンサ、ローサイド MOSFET ボディ・ダイオードを含む大電流パスです。ブートストラップ・コンデンサは、VDD バイパス・コンデンサからブートストラップ・ダイオードを通って、サイクルごとに再充電されます。この再充電は短い時間間隔で発生し、大きなピーク電流を必要とします。回路基板上でこのループの長さと面積を最小化することは、動作の信頼性を確保する上で重要です。

### 10.2 レイアウト例

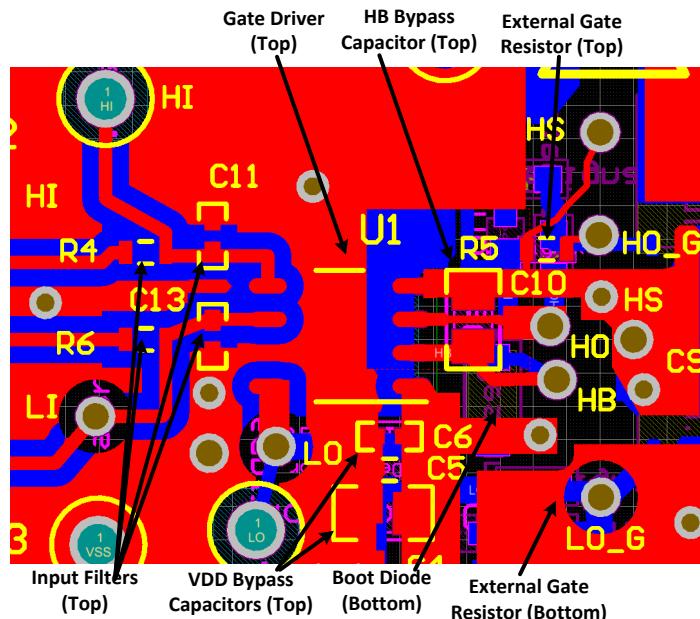

図 10-1. レイアウト例

## 11 デバイスおよびドキュメントのサポート

### 11.1 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[ti.com](http://ti.com) のデバイス製品フォルダを開いてください。「更新の通知を受け取る」をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取れます。変更の詳細については、修正されたドキュメントに含まれている改訂履歴をご覧ください。

### 11.2 サポート・リソース

**TI E2E™ サポート・フォーラム**は、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、該当する貢献者により、現状のまま提供されるものです。これらは TI の仕様を構成するものではなく、必ずしも TI の見解を反映したものではありません。[TI の使用条件](#)を参照してください。

### 11.3 商標

TI E2E™ is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

### 11.4 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい ESD 対策をとらないと、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 11.5 用語集

#### TI 用語集

この用語集には、用語や略語の一覧および定義が記載されています。

## 12 メカニカル、パッケージ、および注文情報

以下のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに対して提供されている最新のデータです。このデータは予告なく変更されることがあります、ドキュメントが改訂される場合もあります。本データシートのブラウザ版については、左側のナビゲーションをご覧ください。

**PACKAGING INFORMATION**

| Orderable part number        | Status<br>(1) | Material type<br>(2) | Package   Pins  | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|------------------------------|---------------|----------------------|-----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| <a href="#">UCC27289D</a>    | Active        | Production           | SOIC (D)   8    | 75   TUBE             | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | U289                |

| UCC27289D.A                  | Active        | Production           | SOIC (D)   8    | 75   TUBE             | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | U289                |

| <a href="#">UCC27289DR</a>   | Active        | Production           | SOIC (D)   8    | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | U289                |

| UCC27289DR.A                 | Active        | Production           | SOIC (D)   8    | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | U289                |

| <a href="#">UCC27289DRCR</a> | Active        | Production           | VSON (DRC)   10 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | U289                |

| UCC27289DRCR.A               | Active        | Production           | VSON (DRC)   10 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | U289                |

| <a href="#">UCC27289DRMR</a> | Active        | Production           | VSON (DRM)   8  | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | U289                |

| UCC27289DRMR.A               | Active        | Production           | VSON (DRM)   8  | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | U289                |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

---

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

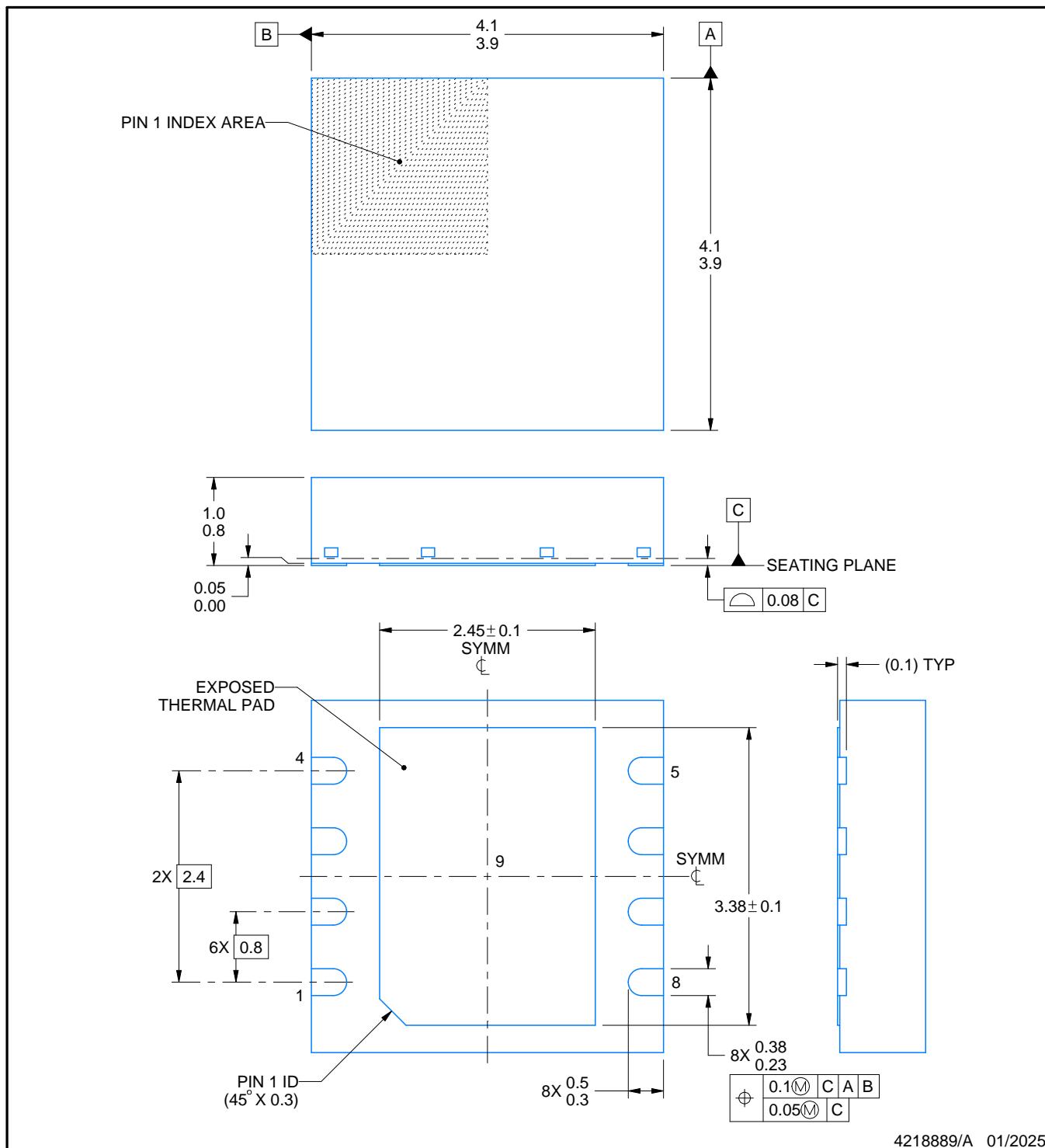

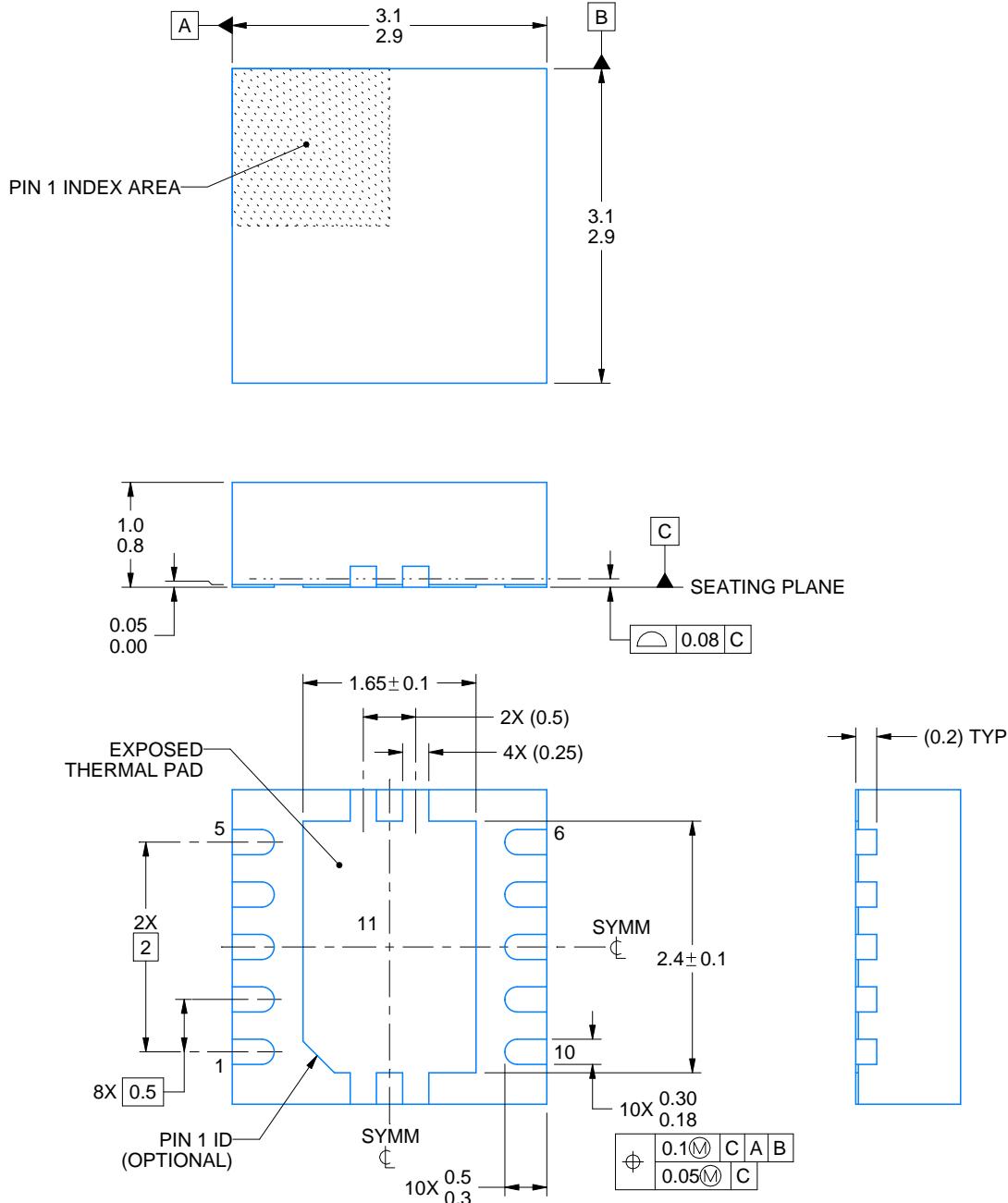

# PACKAGE OUTLINE

DRM0008A

VSON - 1 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

4218889/A 01/2025

## NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

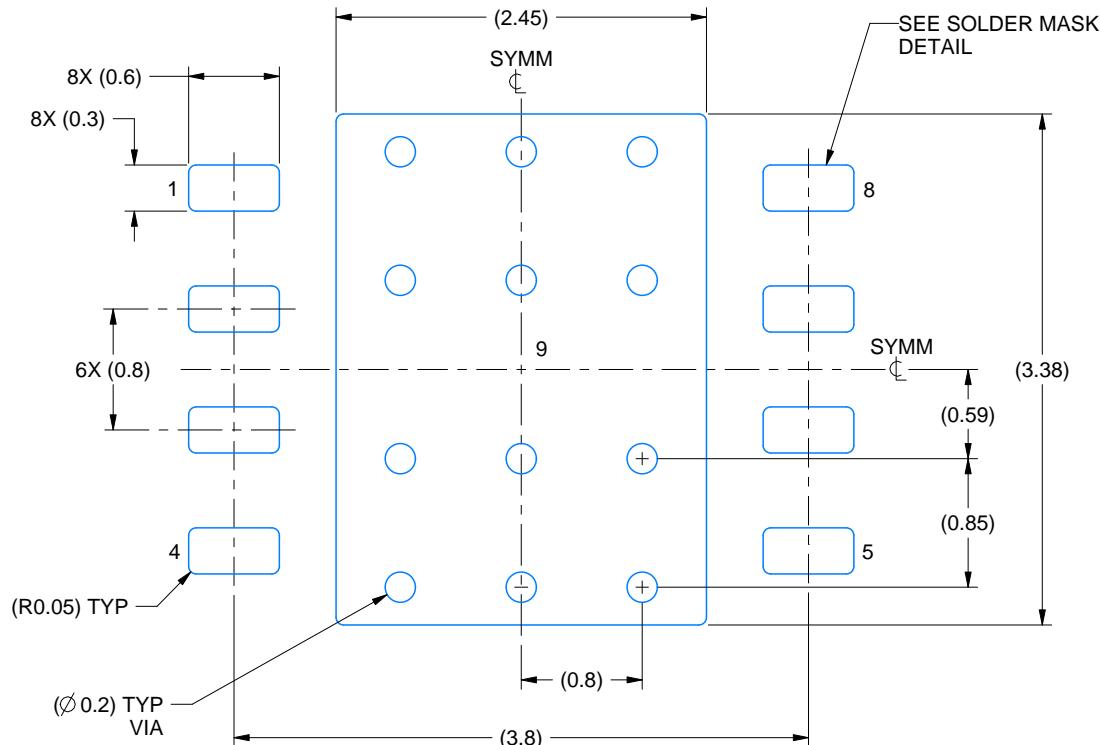

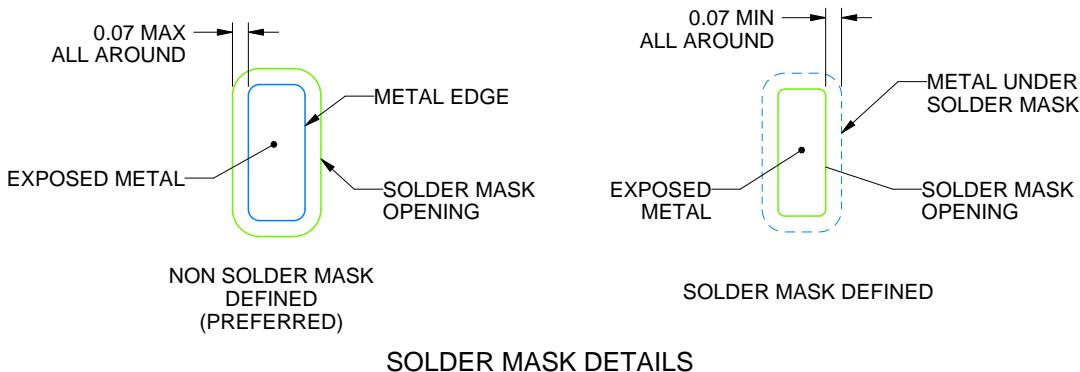

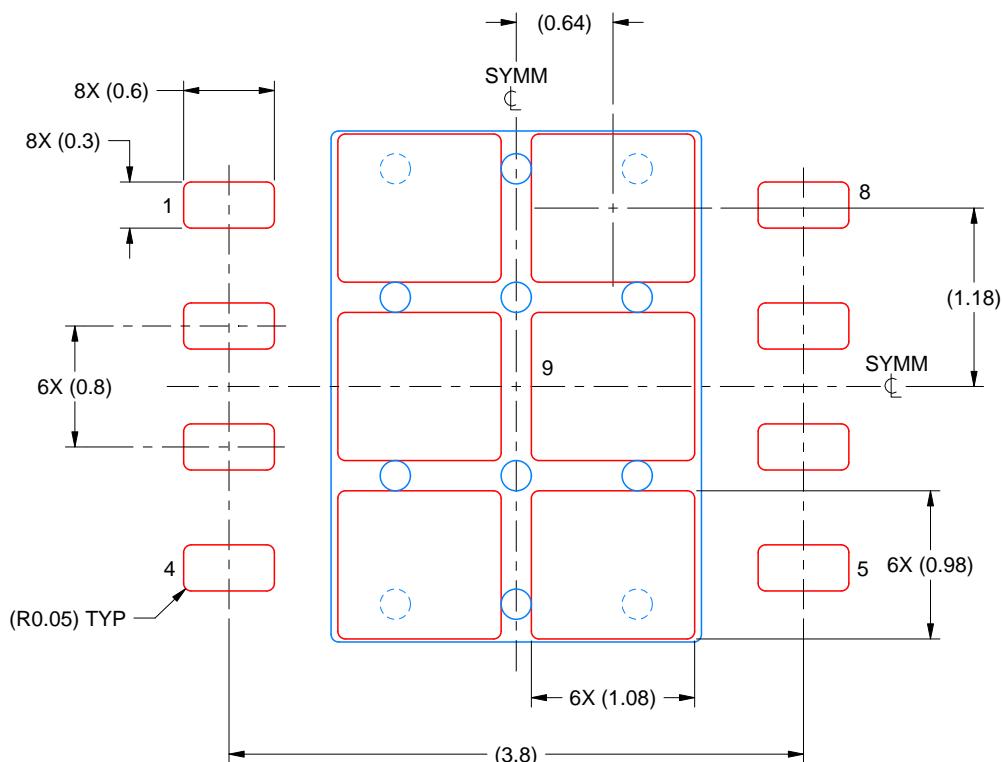

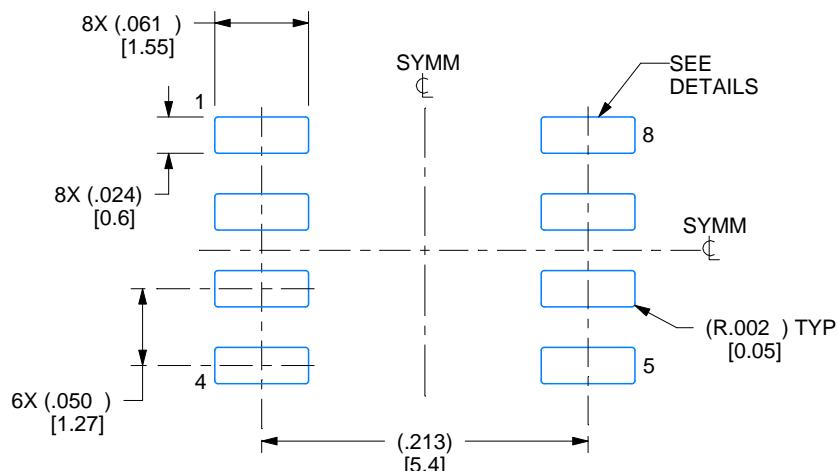

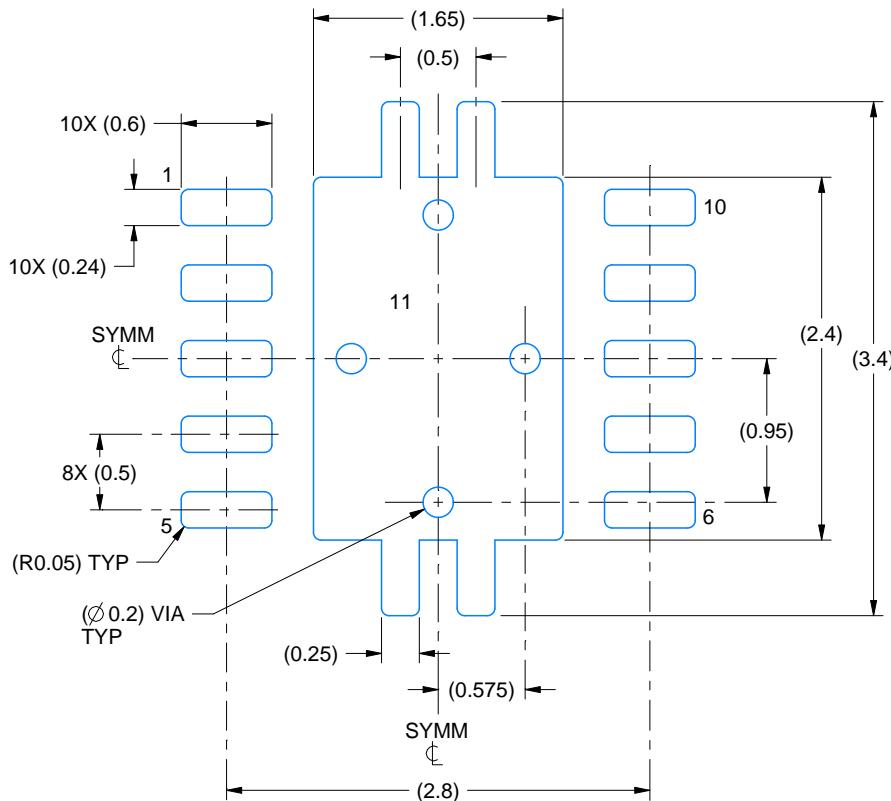

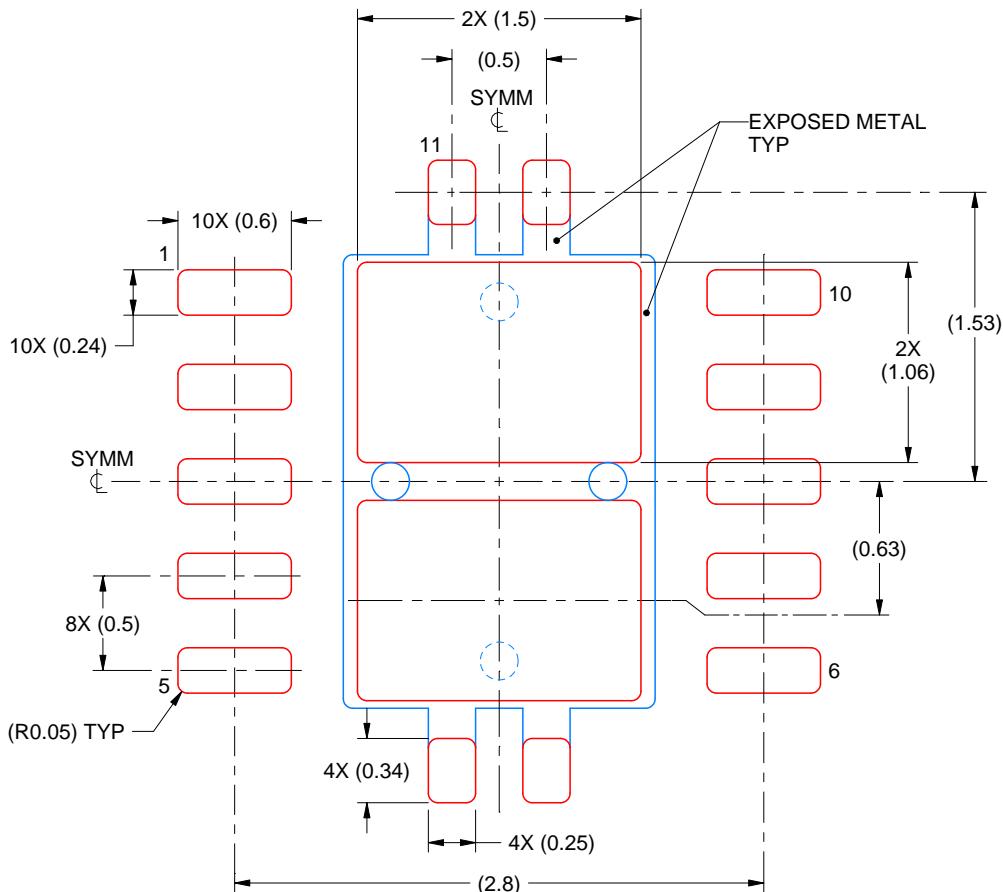

## EXAMPLE BOARD LAYOUT

**DRM0008A**

## VSON - 1 mm max height

### PLASTIC SMALL OUTLINE - NO LEAD

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE: 20X

4218889/A 01/2025

#### NOTES: (continued)

4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 ([www.ti.com/lit/slua271](http://www.ti.com/lit/slua271)).

5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

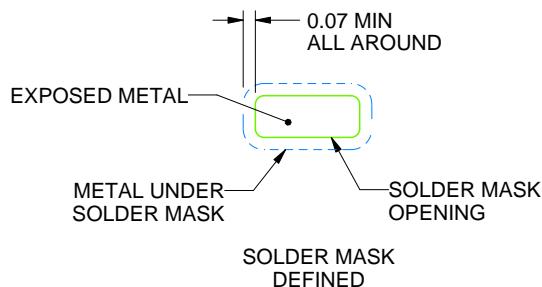

# EXAMPLE STENCIL DESIGN

DRM0008A

VSON - 1 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

SOLDER PASTE EXAMPLE

BASED ON 0.125 MM THICK STENCIL

SCALE: 20X

EXPOSED PAD 9

77% PRINTED SOLDER COVERAGE BY AREA UNDER PACKAGE

4218889/A 01/2025

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

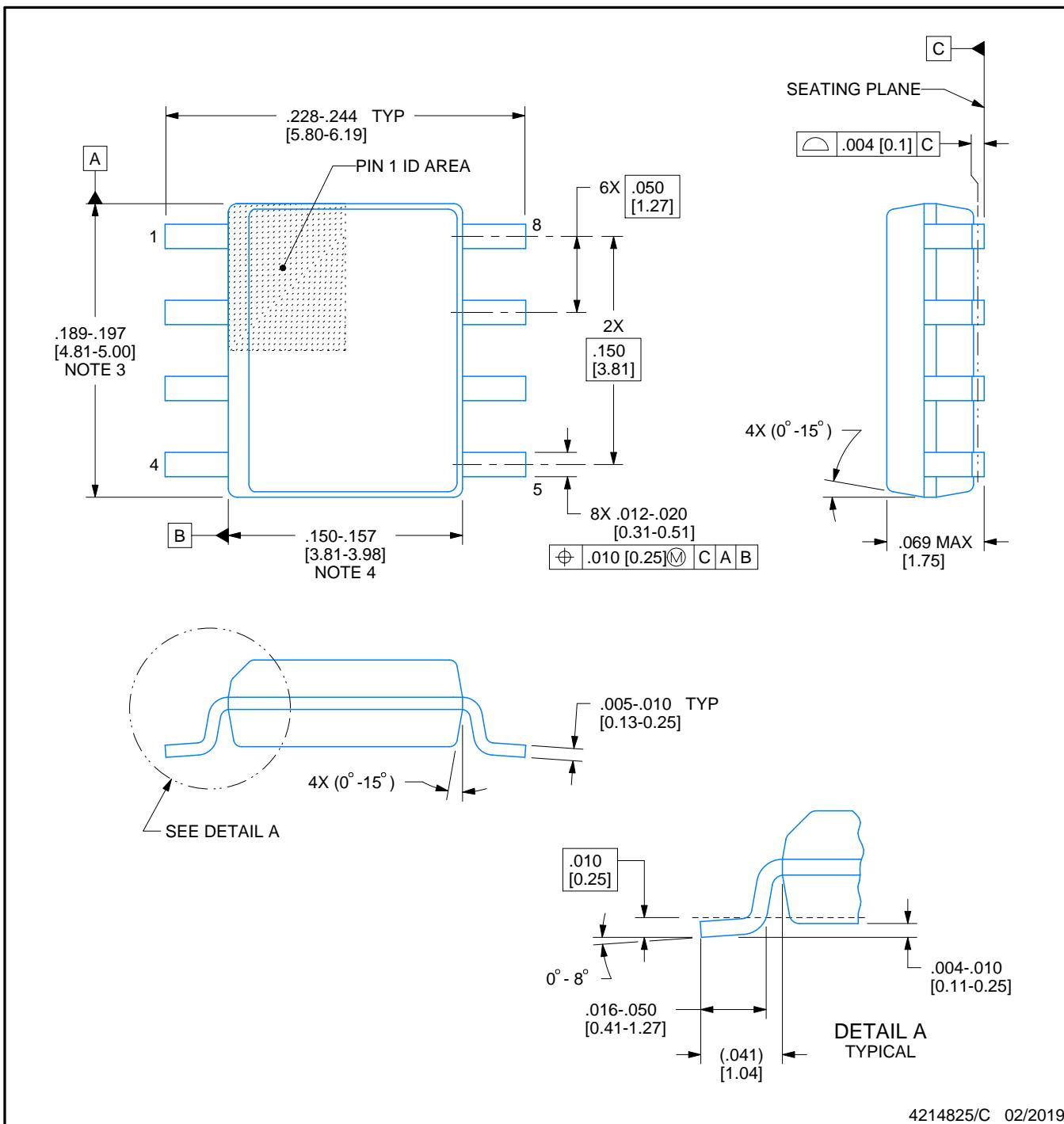

# PACKAGE OUTLINE

## SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

### NOTES:

1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

4. This dimension does not include interlead flash.

5. Reference JEDEC registration MS-012, variation AA.

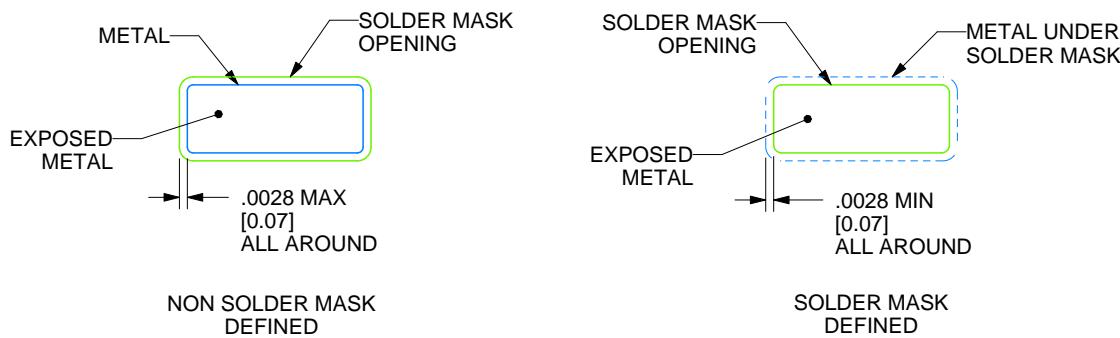

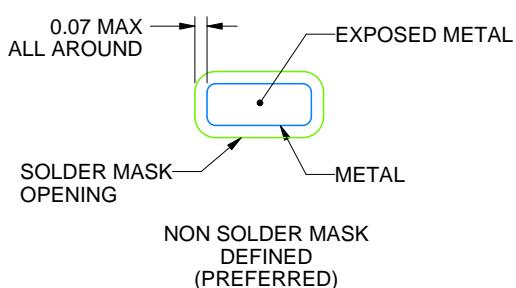

# EXAMPLE BOARD LAYOUT

D0008A

SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE:8X

SOLDER MASK DETAILS

4214825/C 02/2019

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

# EXAMPLE STENCIL DESIGN

D0008A

SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

SOLDER PASTE EXAMPLE

BASED ON .005 INCH [0.125 MM] THICK STENCIL

SCALE:8X

4214825/C 02/2019

NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

9. Board assembly site may have different recommendations for stencil design.

# GENERIC PACKAGE VIEW

## DRC 10

## VSON - 1 mm max height

3 x 3, 0.5 mm pitch

PLASTIC SMALL OUTLINE - NO LEAD

This image is a representation of the package family, actual package may vary.

Refer to the product data sheet for package details.

4226193/A

DRC0010J

# PACKAGE OUTLINE

VSON - 1 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

4218878/B 07/2018

NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. The package thermal pad must be soldered to the printed circuit board for optimal thermal and mechanical performance.

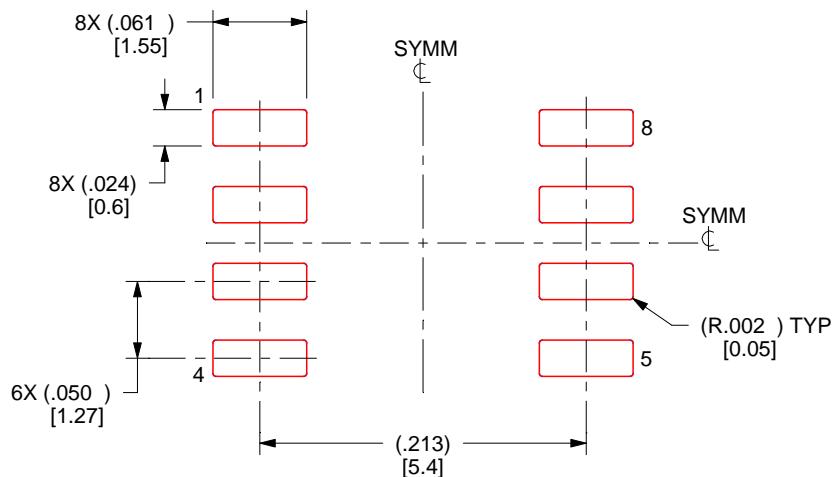

# EXAMPLE BOARD LAYOUT

DRC0010J

VSON - 1 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE:20X

SOLDER MASK DETAILS

4218878/B 07/2018

NOTES: (continued)

4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 ([www.ti.com/lit/slua271](http://www.ti.com/lit/slua271)).

5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

# EXAMPLE STENCIL DESIGN

DRC0010J

VSON - 1 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

SOLDER PASTE EXAMPLE

BASED ON 0.125 mm THICK STENCIL

EXPOSED PAD 11:

80% PRINTED SOLDER COVERAGE BY AREA

SCALE:25X

4218878/B 07/2018

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月