UCC28750 JAJSOG3 - DECEMBER 2023

# UCC28750 オフライン アプリケーション向け、2 次側安定化 (SSR) 機能搭載、電流 モード フライバック コントローラ

# 1 特長

- 内部スロープ補償による安定した連続導通モード (CCM) 動作

- 65kHz または 100kHz の固定周波数動作

- フォトカプラによる 2 次側安定化 (SSR) 機能

- 周波数フォールドバックとバースト モードによる 軽負荷時の効率の向上

- 周波数ディザリングによる EMI 性能の向上

- ゲート ソース / シンク能力: 300mA/500mA

- 4ms の内部ソフト スタート

- 堅牢な保護機能:

- 過電圧および低電圧誤動作防止

- 出力過電力保護 (OPP)

- 出力短絡 (OSC) 保護

- 出力過電圧 (OVP) 保護

- サイクル単位のピーク過電流制限

- FLT ピンでの外部過熱、過電圧保護 (OTP、 OVP)、ブラウンアウト検出

- 内部サーマル シャットダウン

# 2 アプリケーション

- 絶縁型オフライン AC/DC 電源

- 電化製品

- バッテリ・パックとチャージャ

- 小型家電製品

- 主な家電製品

- グリッド・インフラ

- 電気メーター

- ストリング・インバータ

- マイクロインバータ

- 電力供給

- 12V 出力、サーバー向け PSU (電源)

# 3 概要

UCC28750 は、フォトカプラを使用する、高性能、 低スタンバイ電力、コスト効率の優れたオフライン フライバック コンバータ アプリケーション向けに 最適化された、高集積電流モード、連続導通対応の PWM コントローラです。軽負荷の状況では周波数フ ォールドバックおよびバースト モードに移行し、軽 負荷時の効率を向上させます。UCC28750 で使用さ れているバースト モード アルゴリズムは、最小実 効スイッチング周波数を制御して、軽負荷状況におけ る可聴ノイズを防止します。周波数ディザリングによ り EMI 性能が向上します。これは、通常動作、周波 数フォールドバック動作、および電力昇圧動作でアク ティブになります。

UCC28750 は保護機能を搭載しており、最小限の外 付け部品で堅牢なコンバータ設計を実現できます。出 力過電力保護 (OPP) とサイクル単位の過電流制 限により、負荷段および電力段の部品を電気的ストレ スから保護します。過電圧および低電圧誤動作防止 (OVLO および UVLO) により、望ましくない入力状態 でのスイッチングを防止します。FLT ピンは、デバイ ス バリアントに応じて、ライン ブラウンアウトの検 出および保護機能、または外部過熱および過電圧保護 機能を備えています。FLT ピンは、デバイス バリア ントに関係なく、ピンをグランドにプルダウンして外 部制御でデバイスをディセーブルにする目的にも使用 されます。

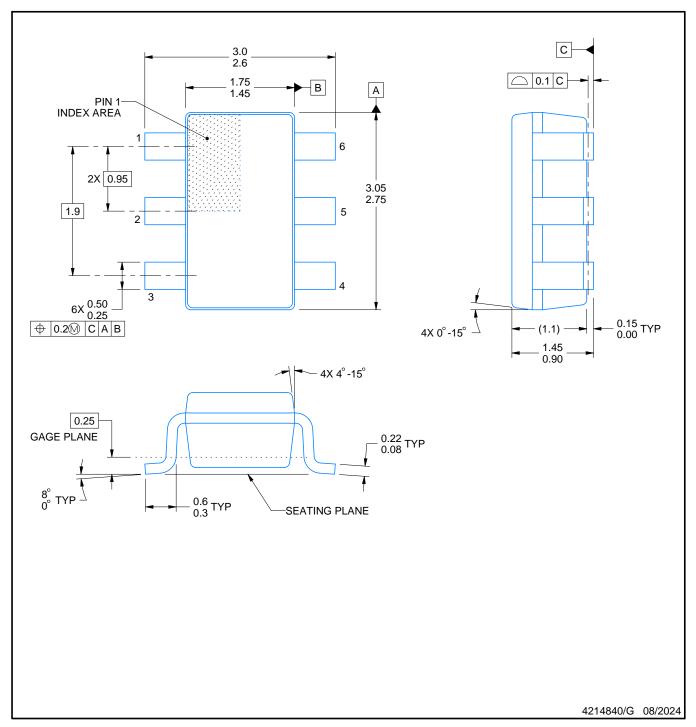

#### 爋品情報

|          | Security IN          |             |

|----------|----------------------|-------------|

| 部品番号     | パッケージ <sup>(1)</sup> | 本体サイズ (公称)  |

| UCC28750 | DBV (SOT23-6)        | 2.9mm×1.6mm |

(1) 利用可能なパッケージについては、このデータシートの末尾 にある注文情報を参照してください。

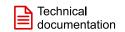

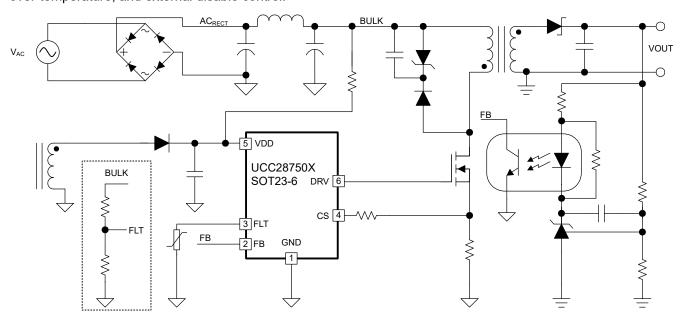

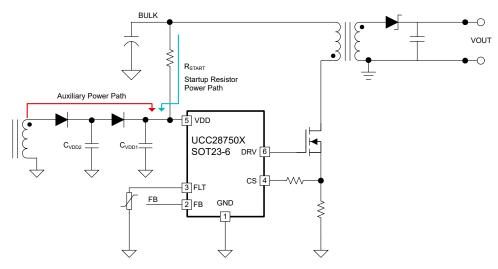

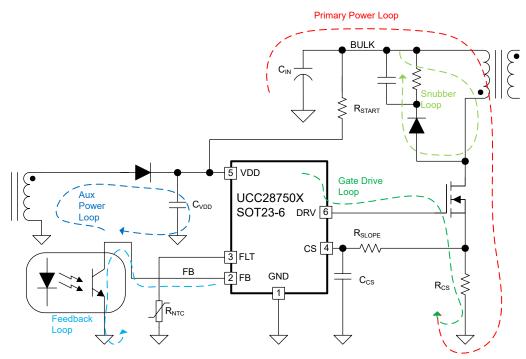

図 3-1. 代表的なアプリケーションの図

# **Table of Contents**

| 1 特長                                 | 1              | 7.4 Feature Description                 | 18 |

|--------------------------------------|----------------|-----------------------------------------|----|

| 2 アプリケーション                           |                | 7.5 Device Functional Modes             |    |

| 3 概要                                 |                | 8 Application and Implementation        | 29 |

| 4 Device Comparison                  | 3              | 8.1 Application Information             | 29 |

| 5 Pin Configuration and Functions    | 4              | 8.2 Typical Application                 |    |

| 6 Specifications                     | <mark>5</mark> | 8.3 Power Supply Recommendations        | 42 |

| 6.1 Absolute Maximum Ratings         | <mark>5</mark> | 8.4 Layout                              | 43 |

| 6.2 ESD Ratings                      | <mark>5</mark> | 9 Device and Documentation Support      | 45 |

| 6.3 Recommended Operating Conditions | <mark>5</mark> | 9.1 Documentation Support               | 45 |

| 6.4 Thermal Information              | 5              | 9.2 ドキュメントの更新通知を受け取る方法                  | 45 |

| 6.5 Electrical Characteristics       | <mark>6</mark> | 9.3 サポート・リソース                           | 45 |

| 6.6 Switching Characteristics        | 8              | 9.4 Trademarks                          | 45 |

| 6.7 Timing Requirements              | 8              | 9.5 静電気放電に関する注意事項                       | 45 |

| 6.8 Typical Characteristics          | 10             | 9.6 用語集                                 | 45 |

| 7 Detailed Description               | 12             | 10 Revision History                     | 45 |

| 7.1 Overview                         | 12             | 11 Mechanical, Packaging, and Orderable |    |

| 7.2 Functional Block Diagram         | 13             | Information                             | 46 |

| 7.3 Detailed Pin Descriptions        | 14             |                                         |    |

Product Folder Links: UCC28750

# **4 Device Comparison**

# **Device Comparison**

| PART NUMBER | SWITCHING FREQUENCY | PROTECTION RESPONSE | FAULT PIN MODE    |

|-------------|---------------------|---------------------|-------------------|

| UCC287501   | 65kHz               | Auto-Restart        | Brown Out         |

| UCC287502   | 65kHz               | Auto-Restart        | OVP, External NTC |

| UCC287503   | 65kHz               | Latching            | Brown Out         |

| UCC287504   | 65kHz               | Latching            | OVP, External NTC |

| UCC287505   | 100kHz              | Auto-Restart        | Brown Out         |

| UCC287506   | 100kHz              | Auto-Restart        | OVP, External NTC |

| UCC287507   | 100kHz              | Latching            | Brown Out         |

| UCC287508   | 100kHz              | Latching            | OVP, External NTC |

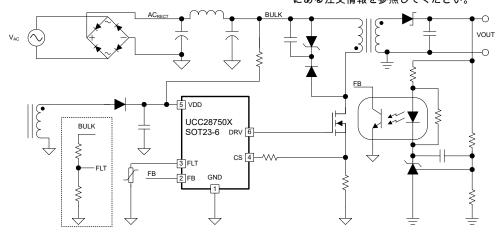

# **5 Pin Configuration and Functions**

図 5-1. Top-view of DBV package (6 pins)

表 5-1. Pin Descriptions

| PIN  |     | TYPE(1) | PECCENTION                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME | NO. | ITPE    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                          |

| GND  | 1   | G       | Ground return for the controller. Connect this pin to the primary-side ground of the converter using a low-impedance path.                                                                                                                                                                                                                                                                                                           |

| FB   | 2   | I       | Voltage feedback pin with internal DC bias. Typically, connect this pin to the collector of an opto-coupler device to provide isolated voltage feedback from the secondary side of the converter.                                                                                                                                                                                                                                    |

| FLT  | 3   | I       | Fault sensing pin. Implement over-temperature protection by connecting an NTC resistor between this pin and GND. Connecting a resistor or Zener diode from a rectified auxiliary winding voltage can also implement output voltage overvoltage protection. Implement brownout detection by using a resistor divider from the bulk voltage to the FLT pin. Pulling this pin below the disable threshold disables switching operation. |

| CS   | 4   | I       | Current-sense and slope-compensation input pin. Connect this pin to the source lead of the flyback power MOSFET and the external current sensing resistor. An optional series resistor between the CS pin and source of the power MOSFET can be used to adjsut the amplitude of the controller's internal slope compensation.                                                                                                        |

| VDD  | 5   | Р       | Bias supply pin for the controller. Typically connect this pin the output of an auxiliary bias winding from the flyback transformer, and to a resistor network from the line voltage to provide bias at start-up. Other bias schemes that do not violate the pin ratings of the device are permissible.                                                                                                                              |

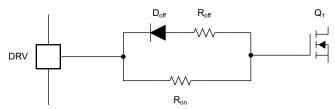

| DRV  | 6   | 0       | Low-side gate-driver output optimized to drive low-cost silicon MOSFETs with up to 300 mA peak pull-up and 500 mA peak pull-down capability. A series gate resistor can be used to slow the turn-on and turn-off of the MOSFET to control high-frequency EMI.                                                                                                                                                                        |

<sup>(1)</sup> I = Input, O = Output, I/O = Input or Output, G = Ground, P = Power.

# **6 Specifications**

# 6.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted)(1)

|                  |                          | MIN        | MAX                    | UNIT |

|------------------|--------------------------|------------|------------------------|------|

| VDD              | VDD input voltage range  | -0.3       | 30                     | V    |

| DRV              | DRV output voltage range | -0.3       | V <sub>VDD</sub> + 0.3 | V    |

| CS               | CS pin voltage           | -0.3       | 5.5                    | V    |

| FB               | FB pin voltage           | -0.3       | 5.5                    | V    |

|                  | FB pin source current    | Internally | limited                | mA   |

| FLT              | FLT pin voltage range    | -0.3       | 5.5                    | V    |

| FLI              | FLT pin sink current     | 0          | 5                      | mA   |

| TJ               | Junction temperature     | -40        | 125                    | °C   |

| T <sub>stg</sub> | Storage temperature      | -65        | 150                    | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                                       |                    |                         |                                                                                     | VALUE | UNIT |

|---------------------------------------|--------------------|-------------------------|-------------------------------------------------------------------------------------|-------|------|

| \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |                    | Electrostatio discharge | Human body model (HBM), per ANSI/ESDA/<br>JEDEC JS-001, all pins <sup>(1)</sup>     | ±2000 | V    |

| \(\rac{1}{V}\)                        | V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JS-002, all pins <sup>(2)</sup> | ±500  | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# **6.3 Recommended Operating Conditions**

Over operating free-air temperature range (unless otherwise noted)

|     |                             | MIN  | TYP MAX | UNIT |

|-----|-----------------------------|------|---------|------|

| VDD | Operating VDD input voltage | 10   | 26      | V    |

| DRV | DRV output voltage range    | -0.3 | 12      | V    |

| cs  | CS pin voltage              | -0.3 | 0.9     | V    |

| FB  | FB pin voltage              | -0.3 | 2.6     | V    |

| FLT | FLT pin voltage range       | -0.3 | 4       | V    |

| GND | GND pin voltage             | -0.3 | 0.3     | V    |

| TJ  | Junction temperature        | -40  | 125     | °C   |

# **6.4 Thermal Information**

|                       |                                            | UCC28750         |      |

|-----------------------|--------------------------------------------|------------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>              | PKG DBV (SOT-23) | UNIT |

|                       |                                            | 6 PINS           |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance     | 231.1            | °C/W |

| R <sub>θJC(top)</sub> | Junction-to-case (top) thermal resistance  | 158.9            | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance       | 117.2            | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter | 94.9             | °C/W |

Product Folder Links: UCC28750

資料に関するフィードバック(ご意見やお問い合わせ)を送信

|             | THERMAL METRIC(1)                            | UCC28750<br>PKG DBV (SOT-23) | UNIT |

|-------------|----------------------------------------------|------------------------------|------|

|             |                                              | 6 PINS                       |      |

| $\Psi_{JB}$ | Junction-to-board characterization parameter | 116.9                        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## **6.5 Electrical Characteristics**

Unless otherwise specified, VDD = 20 V;  $V_{FB}$  = 2.3 V;  $V_{FLT}$  = 2 V;  $T_A$  = 25 °C;  $C_{DRV}$  = 1000 pF

|                                 | PARAMETER                                                              | TEST CONDITIONS                                                                                               | MIN  | TYP  | MAX  | UNIT |

|---------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------|------|------|------|

| VDD PIN                         |                                                                        | ·                                                                                                             |      |      |      |      |

| V <sub>uvlo(on)</sub>           | VDD undervoltage-lockout turn-on voltage (rising)                      | -40°C < T <sub>J</sub> < 125°C                                                                                | 14.3 | 15.3 | 16.3 | V    |

| $V_{\text{uvlo(off)}}$          | VDD undervoltage-lockout turn-off voltage (falling)                    | -40°C < T <sub>J</sub> < 125°C                                                                                | 8    | 9    | 10   | V    |

| V <sub>ovlo</sub> (1)           | VDD overvoltage-lockout threshold                                      | V <sub>FB</sub> = 2.3 V                                                                                       | 26   | 28   | 30   | V    |

| V <sub>por</sub> <sup>(1)</sup> | Power-on reset level (latch-off fault unlatches, IC reset)             |                                                                                                               |      | 5    |      | V    |

| I <sub>VDD(start)</sub>         | Start-up controller bias current                                       | V <sub>VDD</sub> = 14 V                                                                                       |      | 5    | 10   | μΑ   |

| 1                               | Operating controller bigs current                                      | UCC287501/2/3/4 (65 kHz) f <sub>SW</sub> = 65<br>kHz<br>C <sub>DRV</sub> = 1000 pF<br>V <sub>FB</sub> = 2.3 V |      | 1.8  | 2.5  | mA   |

| IVDD(on)                        | Operating controller bias current                                      | UCC287505/6/7/8 (100 kHz) f <sub>SW</sub> = 100 kHz<br>C <sub>DRV</sub> = 1000 pF<br>V <sub>FB</sub> = 2.3 V  |      | 2    | 2.7  | mA   |

| I <sub>VDD(wait)</sub> (1)      | Wait state bias current                                                | FB Pin bias current subracted from value                                                                      |      | 360  |      | μΑ   |

| I <sub>VDD(fault)</sub> (1)     | Fault state controller bias current                                    | FB Pin bias current subracted from value                                                                      |      | 360  |      | μΑ   |

| I <sub>VDD(dis)</sub> (1)       | Disabled state controller bias current                                 | V <sub>FLT</sub> = 0 V                                                                                        |      | 250  |      | μΑ   |

| FB PIN <sup>(1)</sup>           |                                                                        |                                                                                                               |      |      | ,    |      |

| R <sub>FB</sub>                 | Pull-up resistor                                                       |                                                                                                               |      | 10   |      | kΩ   |

| V <sub>FB(offset)</sub>         | Internal offset of V <sub>FB</sub>                                     |                                                                                                               |      | 8.0  |      | V    |

| G <sub>FB</sub>                 | FB pin to CS pin ratio                                                 |                                                                                                               |      | 2    |      | V/V  |

| I <sub>FB(short)</sub>          | FB pin short circuit current                                           |                                                                                                               |      | 0.5  |      | mA   |

| V0 <sub>peak</sub>              | Feedback voltage pin threshold to clamp maximum switching frequency    |                                                                                                               |      | 3.0  |      | V    |

| V1 <sub>norm</sub>              | Feedback voltage threshold to operate at the fixed switching frequency |                                                                                                               |      | 2.6  |      | V    |

| V2 <sub>foldback</sub>          | Feedback voltage pin threshold to linearly lower switching frequency   |                                                                                                               |      | 2.0  |      | V    |

| V3 <sub>burst</sub>             | Feedback voltage pin threshold to enter burst mode                     |                                                                                                               |      | 1.2  |      | V    |

| V4 <sub>stop</sub>              | Feedback voltage pin threshold to stop switching                       |                                                                                                               |      | 1.1  |      | V    |

| V <sub>open</sub>               | Feedback voltage open loop                                             |                                                                                                               |      | 5    |      | V    |

| $V_{\rm opp}$                   | Feedback voltage which starts the over-power protection fault timer    | Duty cycle > 60-%                                                                                             |      | 2.6  |      | V    |

| DRV PIN (1)                     |                                                                        |                                                                                                               |      |      | '    |      |

| I <sub>source(pk)</sub> (1)     | Peak driver source current                                             |                                                                                                               |      | 300  |      | mA   |

Unless otherwise specified, VDD = 20 V;  $V_{FB}$  = 2.3 V;  $V_{FLT}$  = 2 V;  $T_A$  = 25 °C;  $C_{DRV}$  = 1000 pF

|                                             | PARAMETER                                                                                                                                                    | TEST CONDITIONS                                                           | MIN  | TYP | MAX  | UNIT |

|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------|-----|------|------|

| I <sub>sink(pk)</sub> (1)                   | Peak driver sink current                                                                                                                                     |                                                                           |      | 500 |      | mA   |

| R <sub>OL</sub> (1)                         | Pull-down resistance (off-state)                                                                                                                             | VDD = V <sub>UVLO(off)</sub> + 100 mV <sub>.</sub> I <sub>DRV</sub> =1 mA |      | 5   |      | Ω    |

|                                             |                                                                                                                                                              | VDD = 20 V                                                                |      | 12  |      | V    |

| V <sub>DRV(clamp)</sub> <sup>(1)</sup>      | DRV voltage clamp                                                                                                                                            | VDD = V <sub>uvlo(off)</sub> + 100 mV                                     | 8    |     |      | V    |

| FLT PIN                                     |                                                                                                                                                              | uvio(oii)                                                                 |      |     |      |      |

|                                             | Voltage on FLT pin which causes the                                                                                                                          |                                                                           |      |     |      |      |

| V <sub>brownout</sub> (1)                   | controller to stop switching when a brownout event is detected                                                                                               |                                                                           |      | 1.4 |      | V    |

| I <sub>brownout</sub> (1)                   | Current source which changes the threshold of V <sub>brownout</sub> after a brown-in event, providing hysteresis                                             |                                                                           |      | 4   |      | μΑ   |

| FLT <sub>hyst(brownout)</sub> (1)           | Hysteresis on FLT pin for the brownout threshold. The FLT pin must cross V <sub>brownout</sub> + FLT <sub>hyst(brownout)</sub> to enable switching operation |                                                                           |      | 50  |      | mV   |

| V <sub>FLT(open)</sub> (1)                  | Voltage on FLT pin when nothing is connected                                                                                                                 | UCC287502/4/6/8                                                           |      | 2.3 |      | V    |

| $V_{FLT(ovp)}$                              | Voltage on FLT pin which causes the controller to stop switching when an overvoltage event occurs                                                            |                                                                           | 3.8  | 4.1 | 4.3  | V    |

| FLT <sub>hyst(ovp)</sub> (1)                | Hyteresis on FLT pin for the overvoltage protection threshold                                                                                                |                                                                           |      | 100 |      | mV   |

| I <sub>FLT(ovp, clamp)</sub> <sup>(1)</sup> | Current sink that is enabled during the OVP fault                                                                                                            |                                                                           |      | 500 |      | μΑ   |

| I <sub>FLT(tsd)</sub> <sup>(1)</sup>        | Current source out of the pin into an NTC resistor for external over-temperature fault                                                                       |                                                                           |      | 100 |      | μА   |

| V <sub>FLT(tsd)</sub> (1)                   | Voltage on FLT pin which causes the controller to stop switching when an overtemperature even occurs                                                         |                                                                           | 0.95 | 1   | 1.05 | V    |

| FLT <sub>hyst(tsd)</sub> (1)                | Hysteresis on FLT pin for the thermal shutdown theshold                                                                                                      |                                                                           |      | 200 |      | mV   |

| $V_{FLT(dis)}$                              | Voltage on FLT pin which causes the controller to stop switching when the pin is pulled below the threshold                                                  |                                                                           | 0.45 | 0.5 | 0.55 | V    |

| FLT <sub>hyst(dis)</sub> (1)                | Hysteresis on FLT pin for the disable theshold                                                                                                               |                                                                           |      | 100 |      | mV   |

| t <sub>prop(dis)</sub> <sup>(1)</sup>       | Propagation from the time when the disable fault occurs to the time when the controller stops switching                                                      |                                                                           |      | 1   |      | μs   |

| CS PIN AND INTE                             | ERNAL SLOPE-COMPENSATION (1)                                                                                                                                 |                                                                           |      |     |      |      |

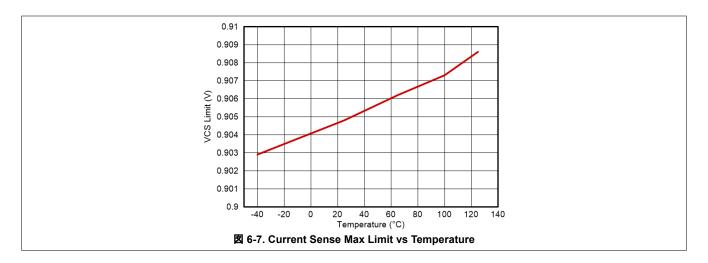

| V <sub>CS(limit)</sub>                      | CS peak current limit voltage                                                                                                                                | V <sub>FB</sub> > V0 <sub>Norm</sub>                                      |      | 900 |      | mV   |

| V <sub>CS(min)</sub>                        | CS peak current limit voltage                                                                                                                                | V <sub>FB</sub> < V3 <sub>Burst</sub>                                     |      | 200 |      | mV   |

| t <sub>ontime(min)</sub>                    | $\begin{array}{l} \text{Minimum on time possible, this} \\ \text{is a sum of the } t_{prop(ocl)} \text{ and} \\ t_{leb} \text{ specifications} \end{array}$  |                                                                           |      | 310 |      | ns   |

| t <sub>prop(ocl)</sub>                      | Current limit propagation delay                                                                                                                              |                                                                           |      | 60  |      | ns   |

| t <sub>leb</sub>                            | Leading edge blanking time                                                                                                                                   |                                                                           |      | 250 |      | ns   |

| $t_{ss}$                                    | Soft-start time                                                                                                                                              |                                                                           |      | 4.3 |      | ms   |

| I <sub>ramp(slope)</sub>                    | Slope compensation current ramp amplitude                                                                                                                    | V <sub>FB</sub> = 2.3 V                                                   |      | 100 |      | μA   |

Unless otherwise specified, VDD = 20 V;  $V_{FB}$  = 2.3 V;  $V_{FLT}$  = 2 V;  $T_A$  = 25 °C;  $C_{DRV}$  = 1000 pF

|                         | PARAMETER                                                 | TEST CONDITIONS | MIN TYP | MAX | UNIT |

|-------------------------|-----------------------------------------------------------|-----------------|---------|-----|------|

| T <sub>shut</sub>       | Internal die temperature that will stop device operation  |                 | 160     | )   | °C   |

| T <sub>shut(hyst)</sub> | Thermal shutdown hysteresis                               |                 | 20      | )   | °C   |

| T <sub>shut(rec)</sub>  | Internal die temperature to recover from thermal shutdown |                 | 140     | )   | °C   |

<sup>(1)</sup> Specified by design, not production tested.

# 6.6 Switching Characteristics

Unless otherwise specified, VDD = 20 V; V<sub>FB</sub> = 2.3 V; V<sub>FLT</sub> = 2 V; T<sub>A</sub> = 25 °C; C<sub>DRV</sub> = 1000 pF

|                            | PARAMETER                                | TEST CONDITIONS                                                                                                    | MIN                  | TYP | MAX | UNIT |

|----------------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------|----------------------|-----|-----|------|

| DRV PIN (1)                |                                          |                                                                                                                    |                      |     | '   |      |

| t <sub>rise</sub>          | Drive voltage rise time                  | VDD > 12 V, 10-90% Rise time C <sub>LOAD</sub> = 1000 pF                                                           | 120                  |     |     | ns   |

| t <sub>fall</sub>          | Drive voltage fall time                  | 90-10% Fall time C <sub>LOAD</sub> = 1000 pF                                                                       | 20                   |     |     | ns   |

| OSCILLATOR A               | AND FREQUENCY FOLDBACK                   |                                                                                                                    |                      |     |     |      |

| $f_{sw}$                   |                                          | UCC287501/2/3/4 (65 kHz version)<br>V <sub>FB</sub> = 3.5 V                                                        |                      | 130 |     | kHz  |

|                            |                                          | UCC287505/6/7/8 (100 kHz version)<br>V <sub>FB</sub> = 3.5 V                                                       | 200                  |     |     | kHz  |

|                            |                                          | V1 <sub>norm</sub> < V <sub>FB</sub>                                                                               | Frequency Increase   |     |     | kHz  |

|                            | Switching frequency                      | UCC287501/2/3/4<br>-40°C < T <sub>J</sub> < 125°C<br>V2 <sub>foldback</sub> < V <sub>FB</sub> < V1 <sub>norm</sub> | 56                   | 65  | 73  | kHz  |

|                            |                                          | UCC287505/6/7/8<br>-40°C < T <sub>J</sub> < 125°C<br>V2 <sub>foldback</sub> < V <sub>FB</sub> < V1 <sub>norm</sub> | 87                   | 100 | 113 | kHz  |

|                            |                                          | V3 <sub>burst</sub> < V <sub>FB</sub> < V2 <sub>foldback</sub>                                                     | Frequency Foldback   |     | kHz |      |

|                            |                                          | V4 <sub>stop</sub> < V <sub>FB</sub> < V3 <sub>burst</sub>                                                         | 25                   |     |     | kHz  |

|                            |                                          | V <sub>FB</sub> < V <sub>burst</sub>                                                                               | Burst Mode Operation |     |     | kHz  |

| D <sub>max</sub>           | Max Duty Cycle                           |                                                                                                                    | 80                   |     |     | %    |

| f <sub>dither(range)</sub> | Frequency modulation (EMI dither) range  |                                                                                                                    | ± 5                  |     |     | %    |

| T <sub>dither</sub>        | Frequency modulation period (EMI dither) | From peak to peak f <sub>sw</sub>                                                                                  | 4.4                  |     |     | ms   |

<sup>(1)</sup> Specified by design, not production tested.

# 6.7 Timing Requirements

Unless otherwise specified, VDD = 20 V; V<sub>FB</sub> = 2.3 V; V<sub>FLT</sub> = 2 V; T<sub>A</sub> = 25 °C; C<sub>DRV</sub> = 1000 pF

| PARAMETER                  |                                                                                                       | TEST CONDITIONS                                    | MIN | TYP | MAX | UNIT   |  |

|----------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------|-----|-----|-----|--------|--|

| PROTECTIONS <sup>(1)</sup> |                                                                                                       |                                                    |     |     |     |        |  |

| VDD <sub>delay(ovlo)</sub> | Switching cycles required to trigger over-voltage lockout                                             | V <sub>VDD</sub> = 29 V<br>V <sub>FB</sub> = 2.3 V |     | 3   |     | cycles |  |

| t <sub>opp</sub>           | Duration that V <sub>FB</sub> must be at or above the V <sub>opp</sub> threshold to trigger the fault | V <sub>FB</sub> = 3 V, Duty cycle > 60 %           | 80  | 85  | 90  | ms     |  |

| t <sub>brownout</sub>      | Amount of time the brownout threshold must be active to trigger the brownout fault                    |                                                    |     | 44  |     | ms     |  |

| FLT <sub>delay(ovp)</sub>  | Delay from the time the FLT over-<br>voltage fault occurs to when the<br>controller stops switching   | V <sub>FLT</sub> = 4.1 V                           |     | 3   |     | cycles |  |

資料に関するフィードバック(ご意見やお問い合わせ)を送信

Copyright © 2023 Texas Instruments Incorporated

Unless otherwise specified, VDD = 20 V;  $V_{FB}$  = 2.3 V;  $V_{FLT}$  = 2 V;  $T_A$  = 25 °C;  $C_{DRV}$  = 1000 pF

| PARAMETER                 |                                                                                                  | TEST CONDITIONS                             | MIN T | YP MAX | UNIT   |

|---------------------------|--------------------------------------------------------------------------------------------------|---------------------------------------------|-------|--------|--------|

| FLT <sub>delay(tsd)</sub> | Delay from the time the FLT thermal shutdown fault occurs to when the controller stops switching | V <sub>FLT</sub> = 0.9 V                    |       | 32     | cycles |

| CS <sub>oscp(delay)</sub> | Number of cycles of output short circuit condition to trigger the fault                          | $V_{CS} \ge V_{CS(limit)}$ during $t_{leb}$ |       | 8      | cycles |

| T <sub>shut(delay)</sub>  | Number of switching cycles once internal temperature reaches threshold to trigger fault          | T <sub>J</sub> > 160 °C                     |       | 32     | cycles |

<sup>(1)</sup> Specified by design, not production tested.

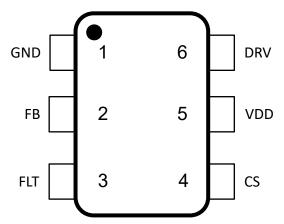

# 6.8 Typical Characteristics

# **6.8 Typical Characteristics (continued)**

# 7 Detailed Description

# 7.1 Overview

UCC28750 is a flyback controller which provides high-performance voltage regulation using an optocoupler feedback from the secondary-side. A control law allows a high efficiency across the entire load range, enabling both discontinuous-conduction mode (DCM) and continuous-conduction mode (CCM) designs. Frequency dithering lowers the EMI energy and helps ease with EMI standards compliance. The programmable FLT pin makes the controller adaptable to various protection requirements such as brown in/out, over-voltage, over-temperature, and external disable control.

図 7-1. The UCC28750 in a flyback design

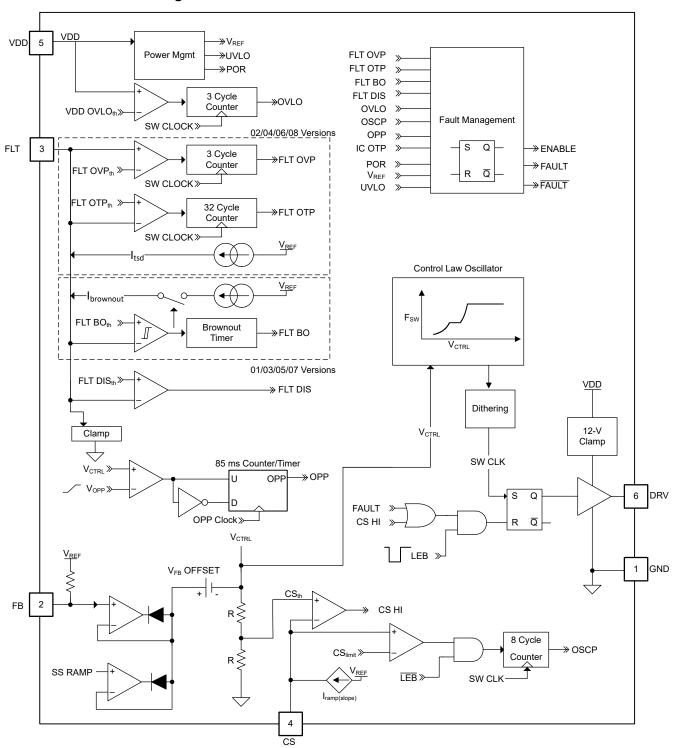

# 7.2 Functional Block Diagram

図 7-2. Functional Block Diagram

## 7.3 Detailed Pin Descriptions

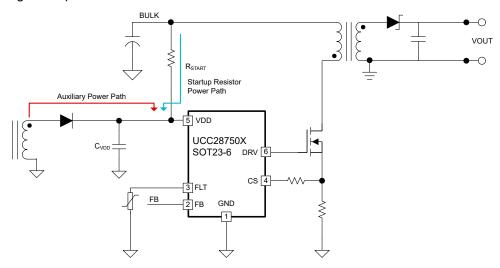

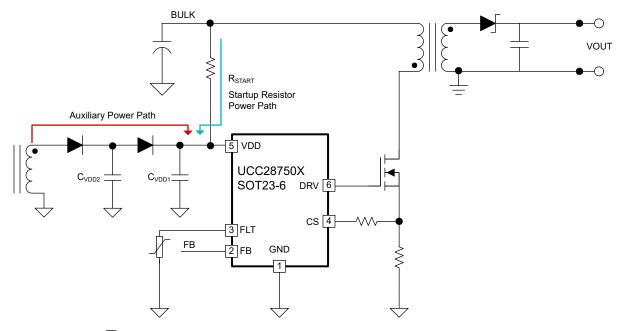

## 7.3.1 VDD - Input Bias

The VDD pin provides the bias to the controller, powering the internal references, regulators, and the undervoltage lockout (UVLO) circuit. The VDD pin is typically powered through a resistor network connected to the rectified bulk voltage and later an auxiliary winding in an AC/DC flyback application or a separate, active source outside of AC/DC applications. The VDD pin has a wide range of operation from a turn on of 15.3V,  $V_{uvlo(on)}$ , to a turn off of 9V,  $V_{uvlo(off)}$ , and a max voltage of 28V,  $V_{ovlo}$ . The VDD pin has low startup current, decreasing startup time and lowering the power loss of the trickle charging network used in AC/DC flyback applications.

In addition to the  $C_{VDD}$  capacitors shown in figures  $\boxtimes$  7-3 and  $\boxtimes$  7-4, bypass capacitors can be added for additional filtering at the pin.

図 7-3. Biasing paths in a flyback application

図 7-4. Biasing path using two diodes to split the VDD capacitance

Refer to セクション 8.2.3.5 in the design guide to size the VDD pin capacitance.

#### 7.3.2 DRV - Gate Drive Out

The DRV pin is the output of the internal gate drive of the UCC28750 controller, and is connected to the gate pin of a MOSFET switching device, typically with a series resistor. The DRV pin drives a MOSFET gate with a sink/source current of 500mA and 300mA, respectively. The DRV signal is powered through VDD, but is clamped to 12V.

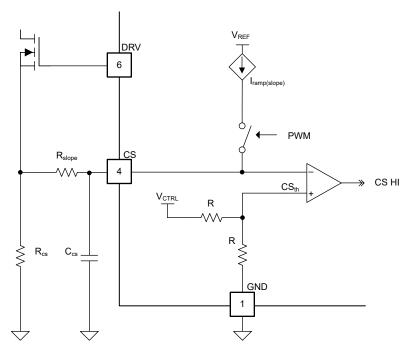

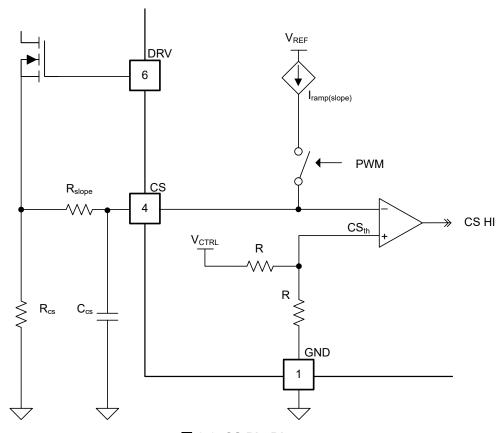

#### 7.3.3 CS - Current Sensing

The current sensing pin, CS, is an input pin which translates the primary switching device's current information into a voltage to be compared to the internal control voltage. The CS pin has a range of 200mV, V<sub>CS(min)</sub>, to 900mV, V<sub>CS(limit)</sub>. The generated current sense threshold is the control voltage (V<sub>CTRL</sub>) divided down by a gain of 2V/V, G<sub>FB</sub>.

図 7-5. Current Sensing Pin Circuit

An internal slope compensation ramp,  $I_{ramp(slope)}$ , programmed through an external series resistor  $R_{slope}$  enables stable operation in a continuous-conduction-mode (CCM) by removing the unwanted effect of sub-harmonic oscillation when the duty cycle is above 50%.

An internal leading-edge blanking circuit blinds the controller from noise during the turn-on edge of a MOSFET. If additional filtering is required a capacitor from the CS pin to GND can be used. The time constant of the RC filter cannot be similar to the leading edge blanking time of 250ns, as the additional filtering can lead to more power being delivered than designed due to delays in sensing. In addition to delivering more power, heavy filtering on the CS pin does not allow the criteria to be met for the short-circuit protection response. The criteria for a short-circuit pulse is that the CS pin voltage is greater than 900mV, V<sub>CS(limit)</sub>, during the leading edge blanking time.

A small capacitor with a value of 10pF to 50pF is recommended on C<sub>CS</sub>.

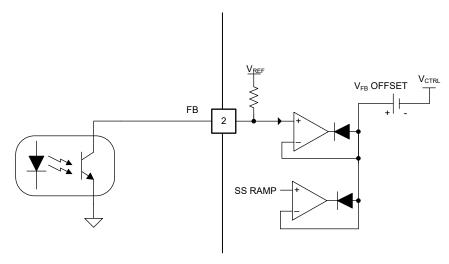

### 7.3.4 FB - Feedback

The Feedback (FB) pin connects to the collector of an analog optocoupler output transistor and carries information about the system output state. Internally, the FB node is pulled up to  $V_{REF}$  by the  $R_{FB}$  resistor. This interaction of the pull up resistor and the output current from the optocoupler output transistor work together to create a control voltage. The current sense threshold reference  $CS_{th}$  is created by offsetting the FB pin voltage by 0.8V,  $V_{FB(offset)}$ , then divided down by a factor of 2V/V,  $G_{FB}$ .

The control voltage directly determines the converter switching frequency and peak primary current limit. More detail is provided in the  $29 \times 3 \times 7.4.2$  section of the data sheet.

図 7-6. Feedback pin schematic drawing

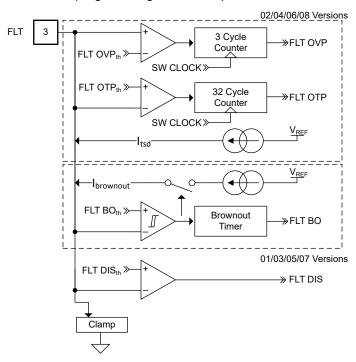

#### 7.3.5 FLT - Fault

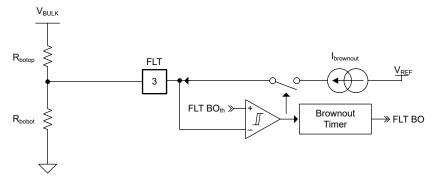

The FLT pin is a programmable protection pin that shuts down the device in unwanted conditions. The UCC28750 device has two versions of the FLT pin: a programmable brown-in/brown-out detection version, and over-temperature and over-voltage version. All versions of the device can disable the system by pulling the FLT pin below 0.5V,  $V_{FLT(dis)}$ . There is no delay in exiting the disable state when the FLT pin is raised above the  $V_{FLT(dis)}$  threshold.

The brown-in/out fault detection monitors the rectified bulk voltage in a flyback application and stops switching operation when the line voltage drops below a programmed threshold longer than 45ms, t<sub>brown-out</sub>. The brown-out fault resumes switching operation immediately when the FLT pin voltage goes above the brown-out threshold and does not wait for a new VDD fault cycle.

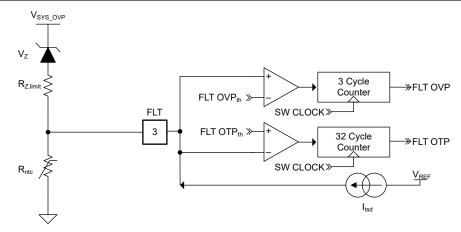

The overvoltage protection fault triggers when the FLT pin rises above  $V_{FLT(ovp)}$  for three consecutive switching cycles. Care is required when designing the overvoltage circuit such that the current going into the FLT pin does not exceed 5mA. If the FLT pin voltage drops below 1.0V,  $V_{FLT(tsd)}$ , for 32 switching cycles then the overtemperature protection response is triggered.

The FLT pin can be left floating, or open, for only the UCC287502/4/6/8 variants. If the pin is left floating in UCC287501/3/5/7 variants that have the brown-out feature the device does not start up as the FLT pin is in a disable state. At startup with the brown-out configuration there is no current sourced from the FLT pin to raise the pin voltage above protection levels.

More information on the operation and programming of the FLT pin is found in section セクション 7.4.4.

図 7-7. FLT Pin Block Diagram

#### 7.3.6 GND - Ground Return

The GND pin is the external return pin, and provides a reference point for the internal circuitry and the gate drive of the device.

資料に関するフィードバック(ご意見やお問い合わせ) を送信

## 7.4 Feature Description

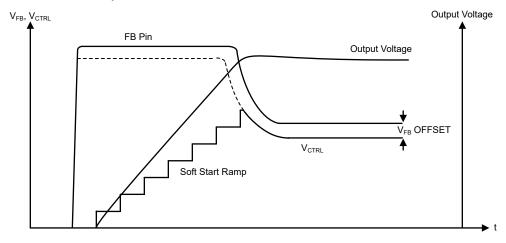

#### 7.4.1 Soft Start

The UCC28750 includes a soft start feature to lower the peak current during the start-up phase. At the beginning of a normal startup operation the output voltage of the system is zero, and the capacitors at the output are discharged. In this scenario the FB pin is pulled up to the internal  $V_{REF}$  value. In a controller without a soft start feature, the controller switches at the highest power mode. The soft-start feature limits the stresses on the system and switching devices by clamping the internal FB voltage during the start-up phase to a stepping ramp. Now, the output voltage can rise in a controlled manner.

The internal soft-start ramp is compared to the FB pin voltage, and as long as the internal ramp is lower than the FB pin voltage, the internal ramp is in control of the power delivery level. As the output voltage increases to the programmed level, the FB pin decreases and takes control instead of the internal soft start ramp. The full ramp time of soft start is fixed internally to 4.3ms, t<sub>ss</sub>.

図 7-8. Softstart Ramp on Startup

## 7.4.2 Control Law

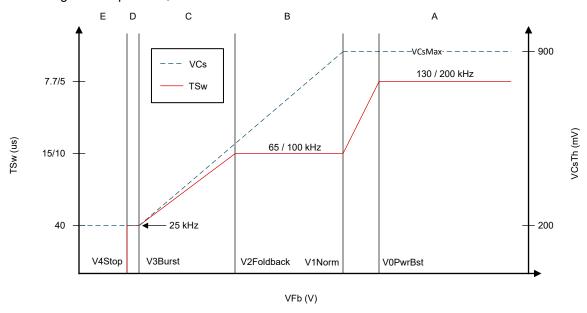

UCC28750 is a fixed frequency controller under normal operating conditions, but modulates the switching frequency and CS thresholds at higher and lighter loads, providing a momentary boost of power for high loads and increased efficiency at light loads. The frequency control law uses alternating amplitude and frequency modulating regions in conjunction with an amplitude modulated current sense threshold to achieve regulation at varying conditions.

There are five regions of operation, referred to as section A-E in **☒** 7-9.

図 7-9. UCC28750 Control Law

- Region A: This region is the power boost region in which the frequency increased to the maximum of 130/200kHz (based on the device variant) and the current sense threshold is fixed to the V<sub>CS(limit)</sub> of 900mV.

- 2. Region B: This is the normal operating region, where the switching frequency is fixed to 65/100kHz, but the current sensing threshold is amplitude modulated to provide the necessary power required by the application load.

- 3. Region C: This is the frequency foldback region, where the switching frequency and current sensing threshold are being lowered, to accommodate lower power requirements and lower switching losses.

- 4. Region D, E: These two regions are the burst mode operation of the controller. When the FB voltage is lower than 1.2V,V3Burst, but higher than 1.1V, V4Stop, the controller continues to switch but at the lowest current sensing threshold and frequency. When the FB pin voltage is below V4Stop, the controller stops switching operation. Without switching the FB pin rises as the output voltage drops, and the controller resumes switching operation.

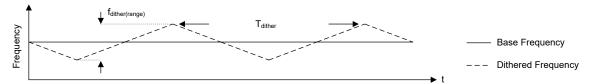

## 7.4.3 Frequency Dithering

Frequency dithering, also known as frequency swapping, frequency hopping, frequency jitter, is a concept to modulate the primary switching frequency by a small amount to spread the EMI energy, lowering EMI peaks. UCC28750 modulates the primary switching frequency by superimposing a triangular frequency onto the switching frequency, shifting the switching frequency by 5%,  $f_{dither(range)}$ , over a period of 240Hz,  $T_{dither}$ .

図 7-10. Frequency Dithering of a Fixed Frequency

### 7.4.4 Fault Protections

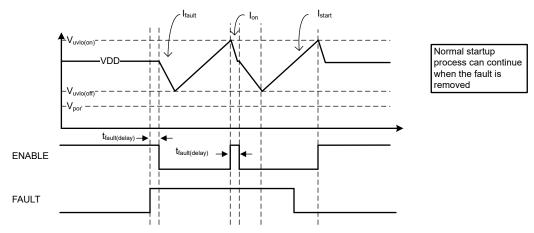

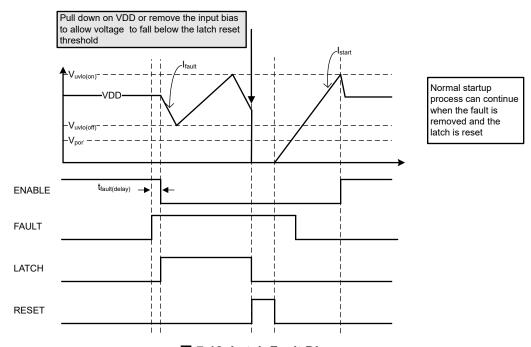

UCC28750 includes a set of protection features, both internally fixed and externally programmable. These faults are designed to protect the device and the system application. UCC28750 has latches and auto-restart options for the protection responses. In a latched device when a fault is detected UCC28750 does not resume switching operation, even if all faults are removed, until the VDD pin voltage is brought below 5V,  $V_{por}$ , and then up to the turn on threshold of 15.3V,  $V_{uvlo(on)}$ . In the auto-restart response the device resumes switching operation every startup cycle. The a fault is detected again the controller re-enters the fault state. If all faults are removed prior to a startup cycle then the controller resumes normal operation.

The faults are listen below:

- VDD under and overvoltage lockout

- · Internal overtemperature shutdown

- Output overpower protection (OPP) with internal compensation

- Output short circuit protection (OSCP)

- FLT pin protections

- Input line brown-in/out detection

- Overvoltage protection

- External overtemperature protection

- Controllable disable/shutdown

図 7-11. Auto-Restart Fault Diagram

図 7-12. Latch Fault Diagram

### 7.4.4.1 VDD Overvoltage and Undervoltage Lockout

UCC28750 operates over a wide input voltage range, and has protections to enable safe operation. The device does not start switching operation until the input voltage, VDD, reaches above 15.3V,  $V_{uvlo(on)}$ , threshold. UCC28750 continues to operate until the input voltage reaches either 9V,  $V_{uvlo(off)}$ , or 28V,  $V_{ovlo}$ . The upper limit to the operation range is defined as the over-voltage lockout threshold. In the UVLO case, the device stops switching immediately. In the OVLO case, the device stops switching operation and triggers a protection response after the input voltage goes above the  $V_{ovlo}$  threshold for three consecutive switching cycles.

### 7.4.4.2 Internal Overtemperature Protection

The device has an internal temperature threshold, which disables the part once the internal die has reached  $160^{\circ}\text{C}$  and is qualified after 32 switching cycles. The thermal shutdown threshold has a large hysteresis of  $20^{\circ}\text{C}$ . Once the fault clear temperature of  $140^{\circ}\text{C}$  is reached the part can resume normal switching operation. If the device is a latched version, then the VDD pin voltage needs to be brought below 5V,  $V_{por}$ , to have the device resume switching operation.

資料に関するフィードバック(ご意見やお問い合わせ)を送信

### 7.4.4.3 Output Overpower Protection

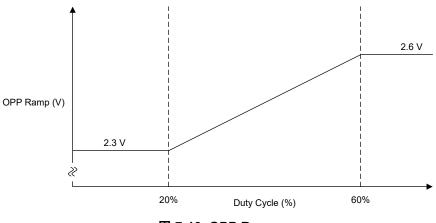

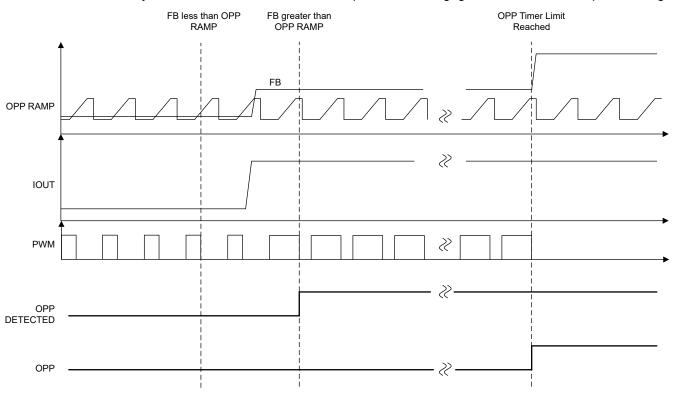

The output power-protection is a line-compensated, feedback based protection to limit the output power of the system application. The FB pin voltage is compared to a ramp that is generated based on the switch on-time, the duty cycle, of each switching event. When the FB pin voltage is greater than the ramp at the negative edge of the internal PWM signal, the OPP timer increases. If the FB pin voltage is less than the OPP threshold, the timer decreases. When the timer reaches the OPP time,  $t_{\rm opp}$ , of 85ms the fault is engaged and the device stops switching.

図 7-13. OPP Ramp

In  $\boxtimes$  7-14, the output load in an application is increased which causes the control loop to increase the FB pin voltage. The increase in FB pin voltage indicates the need to deliver more power to maintain regulation. Once the FB pin is above the OPP ramp and OPP is detected, the internal OPP timer starts counting towards the t<sub>opp</sub> limit of 85ms. Eventually the OPP timer is reached and the protection is engaged and the device stops switching.

図 7-14. Load Step Causing OPP

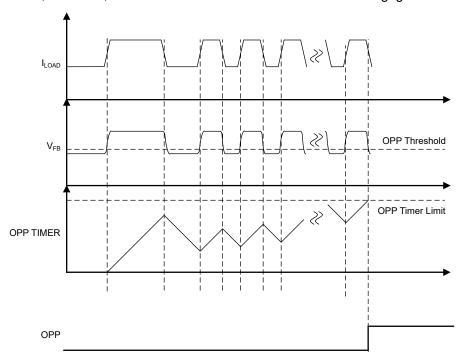

$\boxtimes$  7-15 shows how the timer operation works, with a load condition that is not as long as  $t_{opp}$  initially, but with repetitive high load pulses the overpower protection can still engage. In an application that requires momentary power boosts, the time of the power boost pulse must be shorter than the time without a power boost to not engage OPP. Otherwise, over time, the internal timer reaches the 85ms limit to engage OPP.

図 7-15. OPP Timer Increasing to the OPP Timer Limit

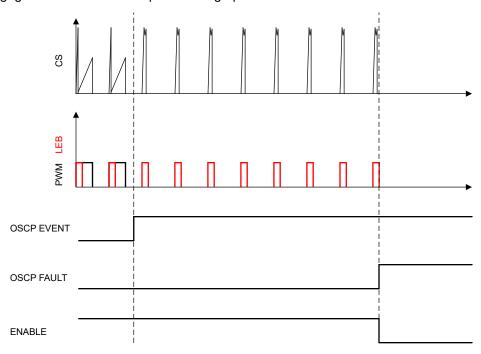

# 7.4.4.4 Output Short-Circuit Protection

In the event of an output short circuit, the UCC28750 can protect the system by quickly shutting down. During a short-circuit event, the current sense sees a sharp rise during the switch on-time, and a very shallow negative slope during the off-time of the switching cycle. The UCC28750 is turned on for a minimum amount of time for every switching cycle due to the leading edge blanking (LEB) feature and internal logic delays. If the CS pin is above the maximum CS threshold during the leading edge blanking time for eight cycles, the output short-circuit protection is engaged and the device stops switching operation.

図 7-16. Output Short-Circuit Protection Diagram

#### 7.4.4.5 FLT Pin Protections

The FLT pin is a programmable fault pin and changes operation basedo on the UCC28750 variant, whether the device is a brown-out or over-temperature/over-voltage version.

図 7-17. FLT Pin Brown-out Configuration Example

The brown-out variant is a fault method to control the turn-on and turn-off thresholds of the system application. Once the system has crossed the turn-on (also known as brown-in) threshold, the UCC28750 turns on an offset current, typically  $4\mu$ A, which makes the thresholds programmable. The offset current is turned on only after the bulk voltage passes the brown-in threshold first. The FLT pin voltage must cross the  $V_{brown-out}$  threshold for  $t_{brown-out}$  for the brown-out fault to trigger. The time required to trigger the fault disqualifies any short term false triggering events from incorrectly triggering the brown-out. The FLT pin has a clamp internally that prevents the FLT pin from reaching dangerous levels if the application requires the brownout feature and has a wide input range requirement (such as a 100V,AC to 400V,AC operating range).

Programming the brown-in and brown-out thresholds is a matter of choosing the desired voltage divider resistor values:

$$V_{bi} = \frac{\left(V_{\text{brownout}} + 50 \text{mV}\right) \times \left(R_{\text{botop}} + R_{\text{bobot}}\right)}{R_{\text{bobot}}} \tag{1}$$

$$V_{\text{bo}} = \frac{\left(V_{\text{brownout}}\right) \times \left(R_{\text{botop}} + R_{\text{bobot}}\right) - I_{\text{brownout}} \times R_{\text{bobot}} \times R_{\text{botop}}}{R_{\text{bobot}}}$$

(2)

## Where:

- V<sub>bi</sub> is the programmed brown-in input voltage level

- V<sub>bo</sub> is the resultant brown-out input voltage level

- V<sub>brown-out</sub> is the FLT pin's brown-out threshold, 1.4V

- R<sub>bobot</sub> is the bottom resistor in the voltage divider

- R<sub>botop</sub> is the top equivalent resistor in the voltage divider

- I<sub>brown-out</sub> is the offset current enabled once the input voltage passes the V<sub>bi</sub> level

図 7-18. FLT Pin Overvoltage/Overtemperature Configuration Example

The programmable over-voltage and over-temperature features are available in the UCC28750 variants. The overvoltage protection fault is triggered when the FLT pin voltage crosses 4V,  $V_{FLT(ovp)}$ , for three consecutive switching cycles, similar as the three switching cycles required for OVLO. In  $\boxtimes$  7-18,  $V_{SYS\_OVP}$  is a voltage source that can be used to triggeer the protection outside of the device VDD and system output voltage. If the overvoltage is configured with a Zener diode, then the following restriction applies:

$$V_{\text{SYS OVP}} > V_Z - V_{\text{FLT(ovp)}}$$

(3)

#### Where:

- V<sub>Z</sub> is the breakdown voltage of the Zener diode

- V<sub>SYS OVP</sub> is a user defined location that is susceptible to over-voltage and is used to turn off the UCC28750

Care must be take that the current going into the FLT pin from the Zener diode's breakdown does not exceed 5mA. Therefore a current limiting resistor is recommended if a Zener diode is use for overvoltage protection on the FLT pin.

A different method can be applied as long as the voltage stays within the FLT pin's voltage rating.

The overtemperature fault is triggered when the FLT pin voltage crosses the 1V,  $V_{FLT(tsd)}$ , overtemperature threshold for 32 switching cycles,  $FLT_{delay(tsd)}$ . Finally, the disable threshold of 0.5V , $V_{FLT(dis)}$ , stops switching operation immediately immediately.

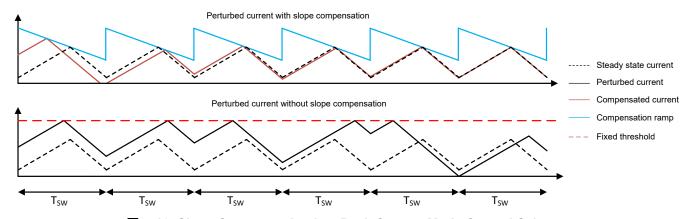

# 7.4.5 Slope Compensation

The UCC28750 device is a peak-current mode control device which offers high efficiency while overcoming drawbacks from voltage-mode control devices. However, when the application requires switching with a duty cycle greater than 50%, the application can suffer from an instability called sub-harmonic oscillation. Z 7-19 shows what can happen to the switching operation and inductor current of a peak current mode control scheme. The perturbed current, without a compensated ramp, cannot return to a normal steady state operation. By adding a ramp onto the fixed threshold, this phenomenon is resolved.

The slope compensation ramp is programmed through a series resistor on the CS pin, and is shown in more detail in  $292 \times 8.2.3.3$ .

図 7-19. Slope Compensation in a Peak Current Mode Control Scheme

資料に関するフィードバック(ご意見やお問い合わせ)を送信

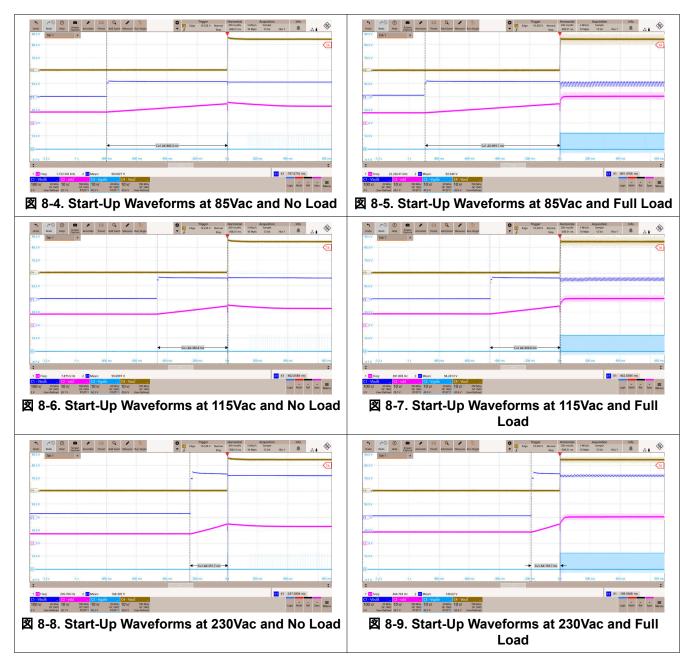

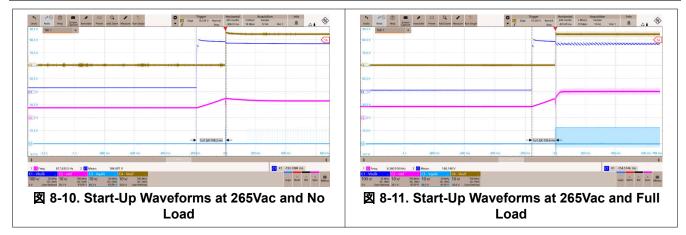

### 7.5 Device Functional Modes

#### 7.5.1 Off

At an initial startup phase, the device is in the off state while the voltage at the VDD pin is below the  $V_{uvlo(on)}$  voltage of 15.3 V. In this state the device's features and circuitry are disabled, and the device's current consumption is only the quiescent current,  $I_{VDD(start)}$ , of 5  $\mu$ A. Once the VDD pin voltages crosses the turn on threshold, the device enters in to the startup phase. If a fault occurs, or the system application is shutting down, the device remains on until the VDD pin voltage falls below  $V_{uvlo(off)}$ .

### 7.5.2 Startup

When the UCC28750's VDD pin voltage reaches the turn-on threshold, the device enters into the startup state and begins to deliver power to the output. In this state the internal control voltage is clamped to a fixed ramp, enabling a controlled rise in the output voltage while lowering current stresses on the switching devices. After the soft start ramp is finished rising, or the FB pin voltage falls below the soft start ramp, is the startup state finished. All of the fault features are still enabled during this time, and can cause the device to enter into a fault state.

## 7.5.3 On

Once finished with the startup state, the device enteres the on state. In this state all of the features of the control law are enabled. The control loop of the system application takes over as the main feedback signal for the control voltage. The FB pin voltage determines the switching operation of the device, and decides if the controller operates in the burst mode, frequency foldback, fixed frequency, or power boost modes, as seen in the  $t = 2 \times 3 \times 7.4.2$  section.

## 7.5.4 Fault

The fault state is entered when the UCC28750 devices recognizes one of the numerous faults available, as seen in t = 2.5 = 2.7.4.4. When a fault is triggered, the device stop switching operation, and begins to sink a fault current of 350  $\mu$ A. This fault current causes the VDD pin voltage to drop to the  $V_{uvlo(off)}$  voltage, turning off the device and resetting the fault logic states. Once the device crosses the turn on voltage,  $V_{uvlo(on)}$ , the startup phase begins and if the fault is removed then normal operation resumes. If the device is a latched variant (UCC287501/3/5/7), then the switching operation cannot resume until the VDD pin voltage is brought below the 5 V,  $V_{por}$ , power-on reset threshold. Refer to figures below for expected operation waveforms in a fault state.

To have the correctly VDD cycle as shown in the fault diagrams a restriction on the startup resistors is placed, where  $R_{START}$  is the startup resistor network shown in  $\pm 2 > 3 > 7.3.1$ .

$$\frac{V_{\text{bulk,max}}}{I_{\text{fault}}} < R_{\text{start}} \tag{4}$$

#### 7.5.5 Disabled

The disabled state is a low-power state that is entered by bringing the FLT pin voltage below the  $V_{flt(dis)}$  threshold of 0.5 V, available in all variants of the UCC28750 device. In this state the device current consumption drops to 250  $\mu$ A, and switching operation is stopped. The device resumes normal operation, if no other faults are present, once the FLT pin voltage exceeds 0.5 V. A logic level MOSFET can be used with a control signal from another source to bring the FLT pin voltage below the 0.5-V threshold.

Because the device consumes less current in the disabled state, extra care must be taken with the selection of the start up trickle charge resistors if that biasing scheme is used as shown in 2.7-3 and 2.7-4. If the startup resistors are too small and do not meet the criteria of 3.5, the amount of current through the biasing path can be greater than the current that the device consumes. This leads to the VDD pin voltage rising and causing an over stress event on the VDD pin. A Zener diode can be put from VDD to GND as a safety clamp.

$$\frac{V_{\text{bulk,max}}}{I_{\text{dis}}} < R_{\text{start}} \tag{5}$$

資料に関するフィードバック(ご意見やお問い合わせ)を送信

Copyright © 2023 Texas Instruments Incorporated

# 8 Application and Implementation

注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes, as well as validating and testing their design implementation to confirm system functionality.

## 8.1 Application Information

The UCC28750 device is an optimized AC-DC flyback controller that uses secondary side regulation through an optocoupler interface and peak-current mode control to tightly regulate the output voltage. The information from the optocoupler interface determines the voltage at the FB pin, which controls the mode of operation. Under light loads the UCC28750 switches at a lower frequency, entering burst mode if the load is light enough. At higher loads the device switches at the fixed frequency, 65kHz or 100kHz, depending on the UCC28750 variant. The UCC28750 has duty cycle capabilities greater than 50%, and the integrated slope compensation allows the application to make full use of both continuous and discontinuous conduction modes of operation.

# 8.2 Typical Application

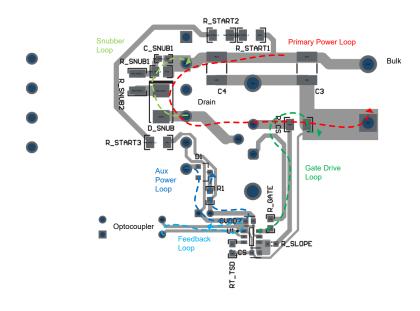

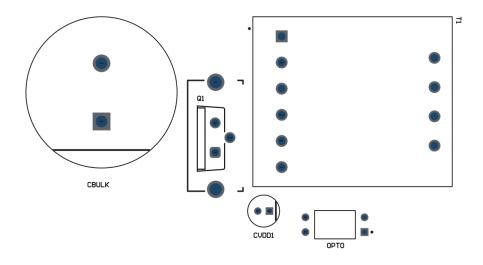

図 8-1. Typical Application Diagram

# 8.2.1 Application

The typical application of the UCC28750 is an off-line flyback power supply up to 70W. A trickle charge resistor network and an auxiliary winding provide the bias from startup to normal operation to the controller. The auxiliary winding provides information of the ouput voltage, which can be used for over-voltage protection. The FLT pin is programmed to provide over-temperature protection to an expected hotspot on the printed circuit board, such as the transformer.

# 8.2.2 Design Requirements

表 8-1. Design Parameters

| PARAMETER              | AX 0-1. Design Farameters  PARAMETER Conditions MIN TYP MAX UNIT |        |         |       |       |  |  |  |  |

|------------------------|------------------------------------------------------------------|--------|---------|-------|-------|--|--|--|--|

| PARAMETER              | Conditions                                                       | IVIIIV | IIF     | IVIAA | UNII  |  |  |  |  |

| Input Requirements     |                                                                  |        |         |       |       |  |  |  |  |

| Input Line Voltage     |                                                                  | 90     | 120/240 | 265   | V, AC |  |  |  |  |

| Minimum Bulk Voltage   |                                                                  |        | 90      |       | V, DC |  |  |  |  |

| Input Line Frequency   |                                                                  | 47     | 50/60   | 63    | Hz    |  |  |  |  |

| Output Requirements    |                                                                  |        |         |       |       |  |  |  |  |

| Output Voltage         | VIN = Min to max, lout = No load<br>to Full load                 |        | 24      |       | V     |  |  |  |  |

| Output Current         | VIN = Min to max                                                 | 0      |         | 2.5   | А     |  |  |  |  |

| Output Voltage Ripple  | Steady state                                                     |        | 1       |       | %     |  |  |  |  |

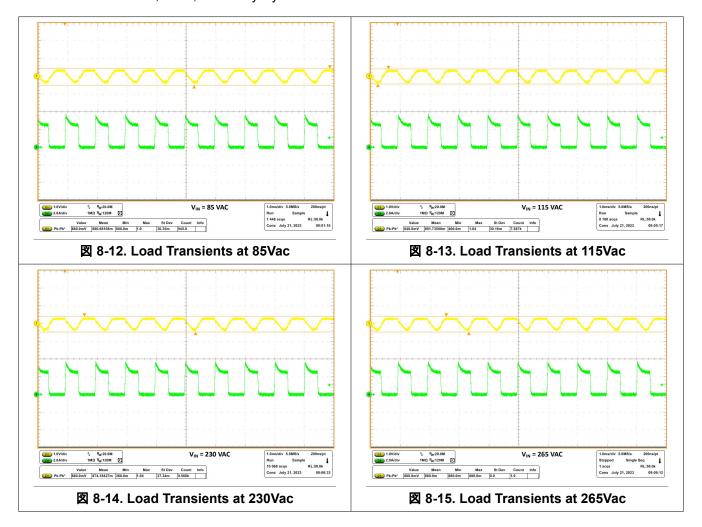

|                        | Load transient 10% to 90% of maximum current                     |        | 5       |       | %     |  |  |  |  |

| System Characteristics |                                                                  |        |         |       |       |  |  |  |  |

| Switching Frequency    | VIN = Min to max, Max output current                             |        | 65      |       | kHz   |  |  |  |  |

| Switching Frequency    | VIN = Min to max, Min output current                             |        | 25      |       | kHz   |  |  |  |  |

## 8.2.3 Detailed Design Procedure

### 8.2.3.1 Input Bulk Capacitance with Minimum Bulk Voltage

The bulk capacitance can consist of a set of one or more capacitors connected in parallel, often with some inductance between them to suppress differential mode noise. Input EMI filter design is outside the scope of this data sheet and is not discussed.

The mimimum bulk voltage valley,  $V_{\text{bulk,min}}$ , is dependent on the total input capacitance value used in the power stage design. The input capacitor is chosen to maintain an acceptable input voltage ripple. The ripple is largest at the minimum input line at the largest output power scenario. Therefore, the input bulk capacitance is based on the a wanted  $V_{\text{bulk,min}}$  at the max power.

The input power can be estimated by taking the maximum output power and dividing the result by the estimated efficiency.

$$P_{\rm in} = \frac{V_{\rm out} \times I_{\rm out,max}}{\eta} \tag{6}$$

$$C_{\text{bulk}} = \frac{2P_{\text{in}} \times \left(\frac{1}{4} + \frac{1}{2\pi} \arcsin\left(\frac{V_{\text{bulk,min}}}{(\sqrt{2}VIN_{\text{min}})}\right)\right)}{\left(\sqrt{2}VIN_{\text{min}}\right)^2 - \left(V_{\text{bulk min}}\right)^2}$$

(7)

#### Where

- V<sub>bulk.min</sub> is the minimum DC bulk voltage

- VIN<sub>min</sub> is the minimum AC voltage applied to the flyback application

For this design, the result from taking the design requirements and the plugging in those values to  $\pm$  6 and  $\pm$  7, a recommended minimum of 110 $\mu$ F for the bulk input capacitance.

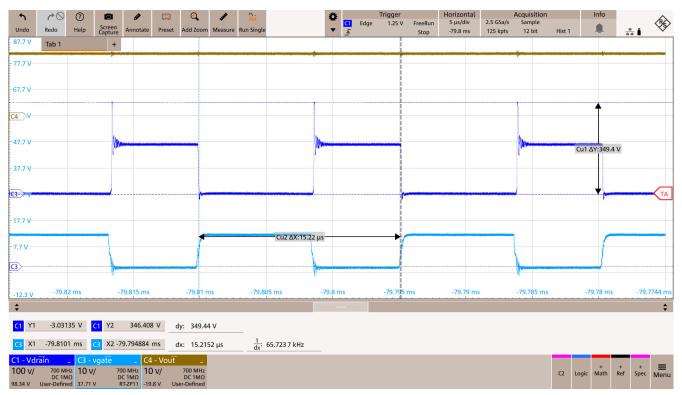

#### 8.2.3.2 Transformer Turns Ratio and Inductance

The transformer design process starts with selecting a switching frequency and maximum duty cycle. With the UCC287502, the switching frequency is set to 65kHz for the max load operation. The maximum duty cycle can safely be chosen to be above 50% as the UCC28750 is a flexible controller capable of DCM and CCM operation while handling sub-harmonic oscillation with the internal slope compensation feature.

$$D_{\text{max,initial}} = 65\%$$

(8)

With the maximum duty cycle for the design set, the secondary to primary transformer turns ratio,  $N_S$  to  $N_P$ , can be chosen by using the boundary mode condition equations to simplify the design process. The turns ratio selection is an iterative process, and the primary switching MOSFET device maximim drain-to-source voltage must be accounted for when designing the transformer.

The turns ratio is initially chosen by using the minimum input voltage and the maximum duty cycle value. This scenario has the highest average current the transformer and switching device must handle, and is why in most of the equations use this worst case for determining the inductance and turns ratio of the transformer. Setting  $N_P$  to 1 turn, the secondary turns in the turns ratio is determined with  $\vec{x}$  9

$$N_S = \frac{V_o \times (1 - D_{\text{max,initial}})}{V_{\text{bulk min}} \times D_{\text{max,initial}}}$$

(9)

The 650V drain-to-source ( $V_{DS}$ ) rated MOSFET is a popular device used in flyback topologies, especially those with a universal input requirement (80V,AC to 265V,AC). The reflected voltage, the voltage seen by the transformer during the secondary conduction time, must be below the MOSFET  $V_{DS}$  rating, with additional margin for the leakage spike. The leakage spike is additional ringing that occurs in flyback designs due to the MOSFET output capacitance and transformer leakage inductance.

$$V_{\text{margin}} = 0.8 \times V_{\text{DS}} \tag{10}$$

$$V_{\text{reflected}} = V_{\text{bulk,max}} + \frac{N_P}{N_S} \times V_o$$

(11)

$$V_{\text{reflected}} < V_{\text{margin}}$$

(12)

Combining 式 10, 式 11, 式 12, and solving for the turns ratio results in a constraint for the turns ratio:

$$\frac{N_P}{N_S} < \frac{V_{\text{margin}} - V_{\text{bulk,max}}}{V_o} \tag{13}$$

A turns ratio of 1:6 is chosen for this design concept. The duty cycle can be iterated on and a new maximum duty cycle,  $D_{max}$ , can be selected with the new turns ratio, and comes out to be around 65%, which is what the max was initially set to.

$$D_{\text{max}} = \frac{V_o}{\frac{N_S}{N_P} \times V_{\text{bulk,min}} + V_o} \tag{14}$$

With the selected turns ratio, maximum duty cycle, input range, and output power range, the magnetizing inductance value can be calculated using equation ₹ 15, and comes out to be approximately 480µH. The equation for the inductance is derived by using the boundary mode equations and equating the average input power equal to the average output power, with a factor for the efficiency.

$$L = \frac{V_{\text{bulk,min}}^2 \times D_{\text{max}}^2 \times T_{\text{sw}} \times \eta}{2 \times P_{\text{out,max}} \times K_{\text{ccm}}}$$

(15)

### Where

- η as the assumed efficiency of the flyback

- T<sub>sw</sub> as the normal operation switching period

- $-\$  In this case 15  $\mu s$  , as the device variant for this application design is a 65 kHz variant

- K<sub>ccm</sub> is factor from 0.1 to 1 that determines the percentage of output max output power at the boundary condition that the flyback enters into the CCM state

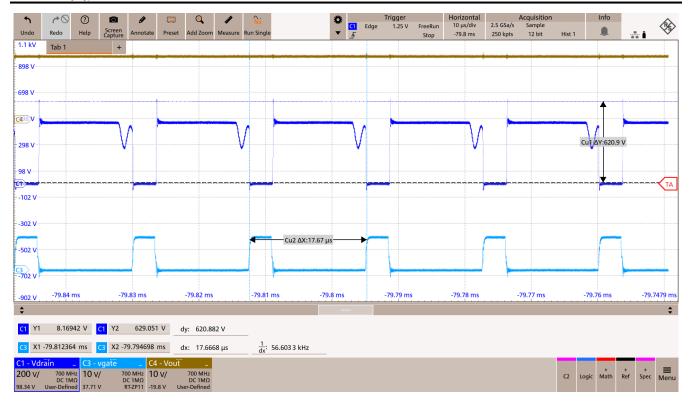

# 8.2.3.3 Current Sense and Slope Compensation Network

The CS pin consists of a network of current sensing resistors and the slope compensation components. For designs with a maximum duty cycle less than 50%, the slope compensation network is not necessary, and thus the current sensing resistor is a calculation based on just the maximum peak current and the maximum threshold on the CS pin. The current sensing resistors connected from the source of the MOSFET to the ground control the maximum peak current of the power stage. The CS pin maximum threshold is 900mV, and a small margin is used to have a more robust design.

図 8-2. CS Pin Diagram

$$R_{\rm CS} = \frac{0.8 \times V_{\rm CS,max}}{i_{\rm pk}} \tag{16}$$

Because UCC28750 can operate in CCM and DCM, the boundary mode equation for  $i_{pk}$  is used as a starting point for selecting the current sense resistor value, with  $R_{CS}$  initially selected with a nominal value of 420m $\Omega$ .

$$I_{\rm pk} = \frac{V_{\rm bulk,min} \times D_{\rm max} \times T_{\rm sw}}{L} \tag{17}$$

In a design with the duty cycle greater than 50% slope compensation must be used to avoid sub-harmonic isolation. UCC28750 has an internal ramp that helps remedy this issue. A resistor is added between the CS pin and the current sense resistor which programs the amount value of the ramp. In a peak-current current scheme, adding a ramp that is equal to half of the slope of the flyback transformer during the off-time of the switching device removes instability. The slope,  $S_{\rm off}$ , with units Amps per second, and reflected to the primary side, during the off time of the primary switching MOSFET is shown in  $\pm$  18.

$$S_{\text{off}} = \frac{V_o \frac{N_P}{N_S}}{L} \tag{18}$$

UCC28750 has a current source that ramps to  $100\mu A$  at the device's maximum duty cycle of 80%. Therefore the ramp amplitude is a ratio of the max level and the calculated duty cycle of the design. The term  $i_{slope}$  has units of Amps per second, just like  $S_{off}$ .

$$i_{\text{slope}} = \frac{i_{\text{ramp}}}{D_{\text{max}} \times T_{\text{sw}}} \tag{19}$$

Where  $i_{ramp}$  is the 100 $\mu$ A amplitude of the slope compensation current during the fixed frequency (65/100 kHz) region in the control law.

The value of the R<sub>slope</sub> resistor is half of the S<sub>off</sub> value divided by the i<sub>slope</sub>.

$$R_{\text{slope}} = \frac{\frac{1}{2} \times S_{\text{off}}}{i_{\text{slope}}} \tag{20}$$

With a slope compensation resistor in place, the CS pin voltage needs to be re-evaluated to make sure that full power delivery is still possible at the minimum input voltage and highest load. The ramp that is generated from  $R_{slope}$  causes the CS pin threshold to be reached earlier than expected, if the  $R_{CS}$  stays the same as calculated from  $\pm$  16.

$$V_{\text{CS,with slope comp}} = R_{\text{slope}} \times \left( i_{\text{slope}} \times D_{\text{max}} \times T_{\text{sw}} \right) + R_{\text{CS}} \times I_{\text{pk}}$$

(21)

$$V_{\text{CS,with slope comp}} < 0.8 \times V_{\text{CS,max}}$$

(22)

$V_{CS,with\ slope\ comp}$ , the addition of the peak current, represented as a voltage, and the ramp from the slope compensation current source, can go above the threshold set in  $\pm$  22. The slope compensation resistor is changed to be lowered, rather than the current sense changing to accommodate the value from  $\pm$  20, as adding too much of a ramp can change the control mode from peak-current mode control to effectively voltage mode control.

式 21 is modified to solve for  $R_{slope}$  with  $R_{CS}$  locked from the initial value of 420m $\Omega$ , the new  $R_{slope}$  is 1k $\Omega$ .

## 8.2.3.4 Output Capacitors

The output capacitor value is determined by two factors in a power supply design: steady state ripple voltage and the output transient voltage response. The capacitor values for the transient response are typically specified as a load step from no load to full load of the power supply design.

$$C_{\text{out}} = \frac{I_{\text{step}} \times t_{\text{response}}}{\Delta V_{\text{out}}}$$

(23)

#### Where

- I<sub>step</sub> is the largest step in load current

- t<sub>response</sub> is the approximate response time

- ΔV<sub>out</sub> is the allowable output voltage change

$$t_{\text{response}} = \frac{0.33}{f_c} + T_{\text{sw}} \tag{24}$$

#### Where

- f<sub>c</sub> is the approximate crossover frequency, typically set to one-tenth the switching frequency

- T<sub>sw</sub> is the switching period expected at the initial load condition before the load step

The ripple voltage in steady state has two major contributors: the change in the output voltage due to the charge and discharge of the output capacitors in every switching cycle, and the step in the output voltage due to the equivalent series resistor of the capacitors. An additional margin is placed on the ESR calculation to account for variance and aging of the

$$ESR \le \frac{V_{\text{ripple}}}{i_{\text{pk,max}} \times N_{\text{PS}}} \times 50 \%$$

(25)

$$C_{\text{ripple}} = \frac{I_{\text{out,max}} \times D_{\text{max}}}{V_{\text{ripple}} \times f_{\text{sw}}}$$

(26)

#### Where

- V<sub>ripple</sub> is the allowable voltage ripple for a design

- N<sub>PS</sub> is the primary to secondary turns ratio

- I<sub>out.max</sub> is the maximum output load current

- i<sub>pk, max</sub> is the primary side maximum peak current of the transformer

The final output capacitor value is the larger of the  $C_{out}$  and  $C_{ripple}$  values. The estimated crossover frequency largely determines the value of capacitance to use. For example, a crossover frequency of 2.5kHz suggests to use  $900\mu F$ , while a 6.5kHz crossover is much lower capacitance, about  $350\mu F$ . Use multiple capacitors to lower the equivalent ESR and get the actual capacitance close to the nameplate capacitance. Multiple capacitors increase robustness by accounting for DC derating and temperature rating fluctuations in the capacitance value.

## 8.2.3.5 VDD Capacitance, C<sub>VDD</sub>

The capacitance on VDD needs to supply the device operating current until the output of the converter reaches the target minimum operating voltage. At this time the auxiliary winding can sustain the voltage to the UCC28750. The input VDD capacitance is determind by the on current of the controller and the output voltage rise time of the application. The VDD capacitor must be able to keep the VDD pin voltage above 9V,  $V_{uvlo(off)}$ , until the output voltage reflected to the auxiliary can take over as the primary bias to the controller.

The soft start feature in UCC28750 does not ramp to full power deliver in the first steps, therefore a conservative 2ms addition is placed into 式 27 to help size the input capacitors.

A split diode and capacitor network can be used in flyback designs to lower the initial startup time, but still have a path for a bulk capacitance on the device's input put, as shown  $299 \times 7.3.1$  and reproduced here for ease of use.

図 8-3. Split Diode Biasing Scheme for Use With Startup Resistors

The first capacitor,  $C_{VDD1}$ , is determined by the startup resistor value and the desired turn-on time. The startup resistor values are constrained by power loss and fault requirements as mentioned in  $29.3 \times 10^{-5}$  7.5.4.

For a design with a typical one second start time, and a startup resistor network with an sum resistance of  $1.2M\Omega$  after adding in additional margin. The resulting  $C_{VDD1}$  value is approximatly  $6\mu F$ . The nearest standard value is  $6.8\mu F$ .