**UCC28781**

JAJSMZ6 - DECEMBER 2021

# UCC28781 ゼロ電圧スイッチング・フライバック・コントロー 専用同期整流ゲート・ドライブ付き

### 1 特長

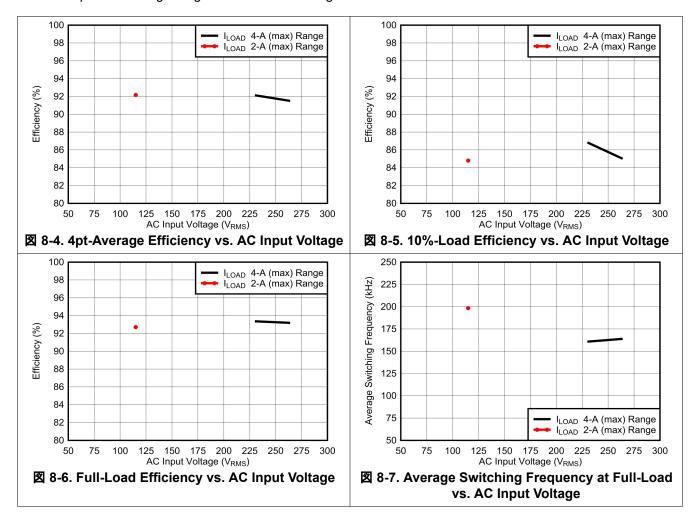

- スイッチング周波数:> 500kHz

- 93%を超えるピーク効率を実現

- 45mW 未満のスタンバイ電力を実現

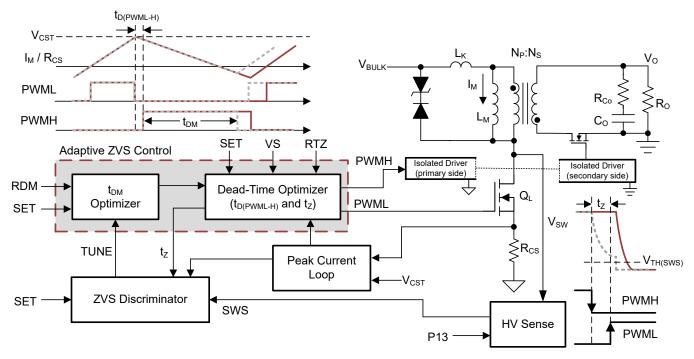

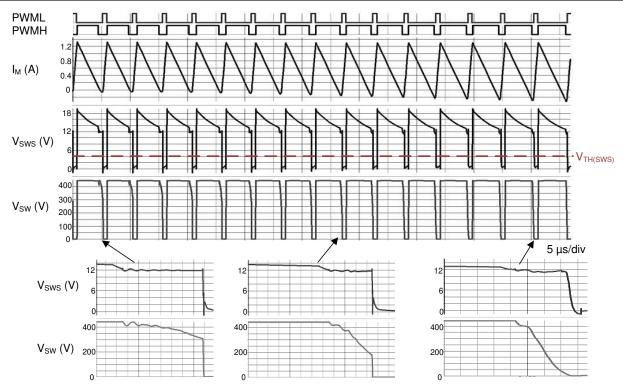

- ゼロ電圧スイッチング (ZVS) とデッドタイム最適 化のための適応型制御

- 過渡応答も可聴ノイズも犠牲にしない EMI 周波数 ディザリング

- プログラム可能な適応型バースト・モード (ABM) (内部補償付き)

- Xコンデンサの放電能力

- 過熱、過電圧、出力短絡、過電流、過電力、ピ ン・フォルト保護機能

- 自動回復フォルト応答

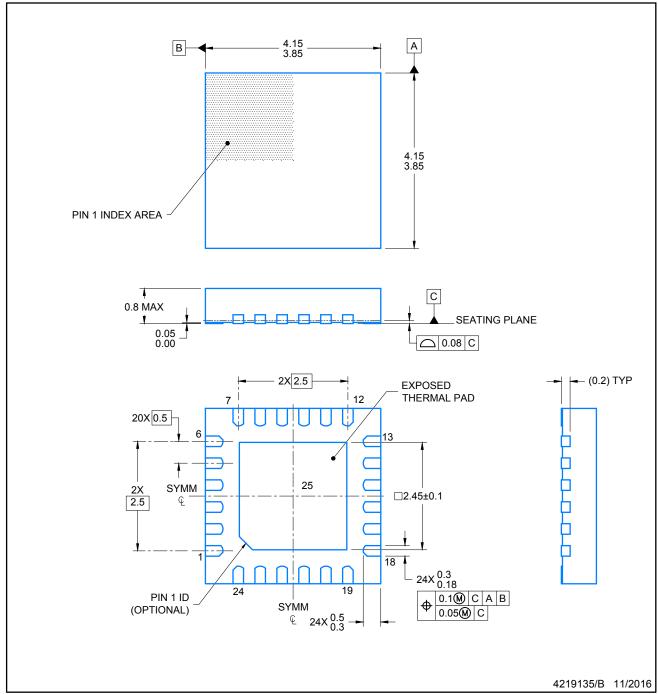

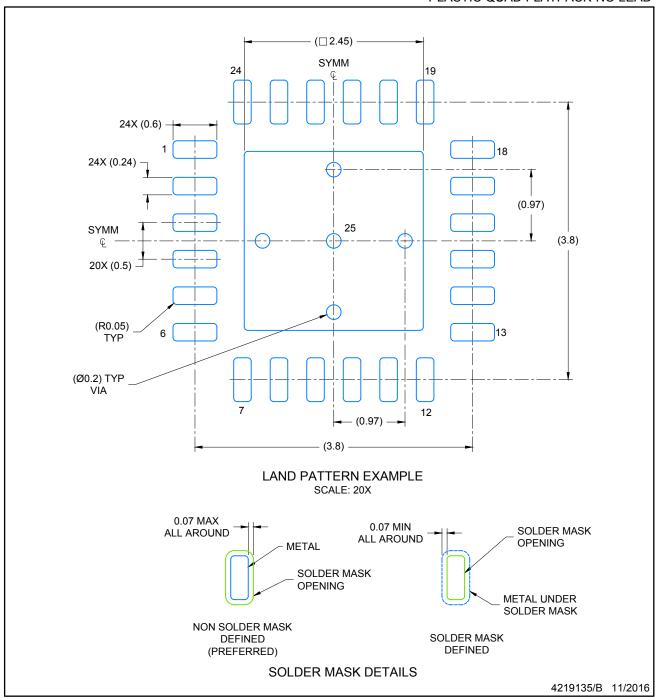

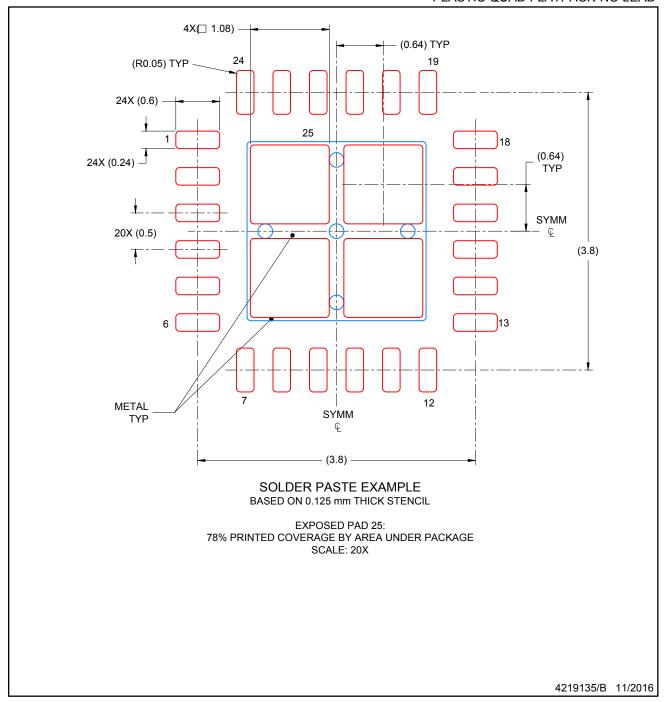

- 4mm × 4mm の 24 ピン QFN パッケージ

#### 2 アプリケーション

- サウンドバー

- スマート・スピーカ

- 商用ネットワークとサーバーの PSU

- 家電製品のバッテリ・チャージャ

- 商用バッテリ・チャージャ

- 產業用 AC-DC

### 3 説明

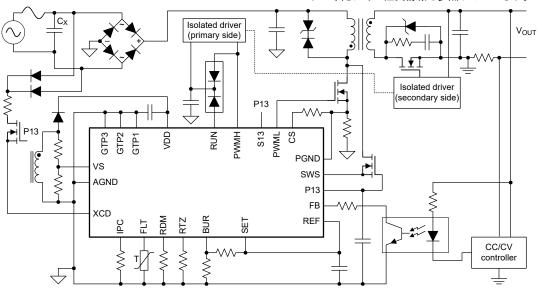

UCC28781 は、ゼロ電圧スイッチング (ZVS) コント ローラで、非常に高いスイッチング周波数で使用でき るため、トランスのサイズを最小化し、高い電力密度 を実現できます。

直接同期整流 (SR) 制御により、コントローラは SR FET を直接駆動して効率を最大化し、設計を簡素化 できるため、個別の SR コントローラを必要としませ ん。(絶縁型アプリケーションの場合は、絶縁型ゲー ト・ドライバ IC が必要です。)

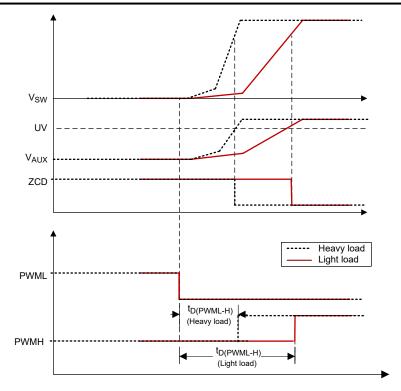

ZVS 用の適応型デッドタイム制御を使用すると、ス イッチング損失と EMI を最小限に抑えることができ ます。この設計により、コントローラは全動作範囲に わたって非常に高い変換効率を実現します。

プログラム可能な適応型バースト・モード (ABM) により、コントローラのスタンバイ・モードへの移行 および終了を柔軟に制御し、軽負荷および無負荷の状 況でスタンバイ電力を最適化できます。また、ABM はリップルの低減と可聴ノイズの最小化にも役立ちま す。

このコントローラには、自動再起動 (再試行) 応答を 備えた複数の保護モードがあります。

#### 製品情報

| 部品番号     | パッケージ <sup>(1)</sup> | 本体サイズ           |

|----------|----------------------|-----------------|

| UCC28781 | WQFN (24)            | 4.00mm × 4.00mm |

利用可能なすべてのパッケージについては、このデータシー トの末尾にある注文情報を参照してください。

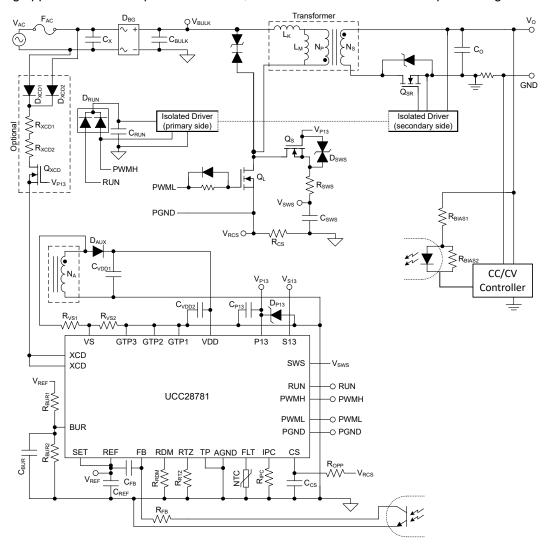

アプリケーション概略

### **Table of Contents**

| 1 特長                                 | 1              | 7.4 Device Functional Modes             | 36               |

|--------------------------------------|----------------|-----------------------------------------|------------------|

| 2 アプリケーション                           |                | 8 Application and Implementation        | 57               |

| 3 説明                                 |                | 8.1 Application Information             | 57               |

| 4 Revision History                   | <mark>2</mark> | 8.2 Typical Application Circuit         |                  |

| 5 Pin Configuration and Functions    | 3              | 9 Power Supply Recommendations          | 67               |

| 6 Specifications                     | 6              | 10 Layout                               | 68               |

| 6.1 Absolute Maximum Ratings         | 6              | 10.1 Layout Guidelines                  | 68               |

| 6.2 ESD Ratings                      | 6              | 10.2 Layout Example                     | <mark>7</mark> 1 |

| 6.3 Recommended Operating Conditions | 7              | 11 Device and Documentation Support     | <mark>7</mark> 6 |

| 6.4 Thermal Information              | 7              | 11.1 Documentation Support              | 76               |

| 6.5 Electrical Characteristics       | 7              | 11.2 サポート・リソース                          | <mark>7</mark> 6 |

| 6.6 Typical Characteristics          | 13             | 11.3 Trademarks                         | <mark>7</mark> 6 |

| 7 Detailed Description               | 16             | 11.4 静電気放電に関する注意事項                      | <b>7</b> 6       |

| 7.1 Overview                         |                | 11.5 用語集                                | <mark>76</mark>  |

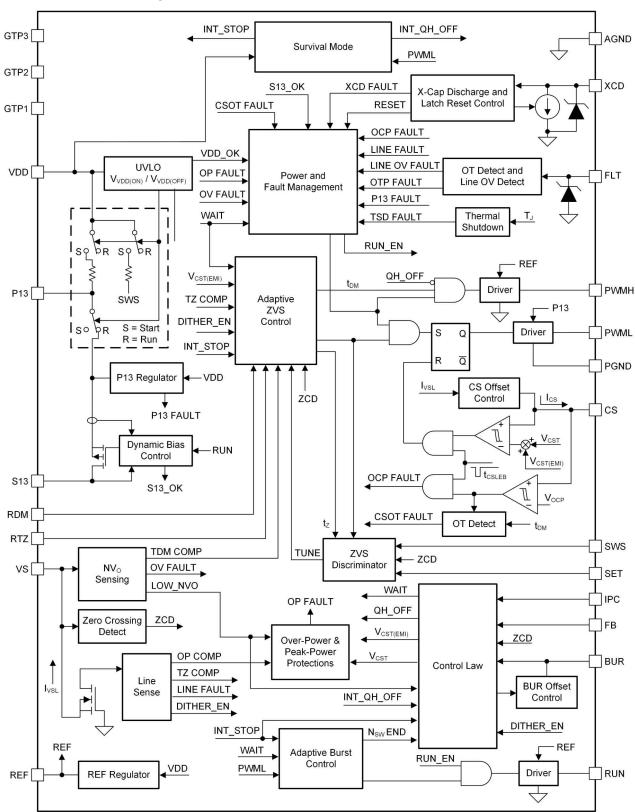

| 7.2 Functional Block Diagram         | 18             | 12 Mechanical, Packaging, and Orderable |                  |

| 7.3 Detailed Pin Description         | 19             | Information                             | <mark>77</mark>  |

|                                      |                |                                         |                  |

## **4 Revision History**

| DATE          | REVISION | NOTES            |

|---------------|----------|------------------|

| December 2021 | *        | Initial release. |

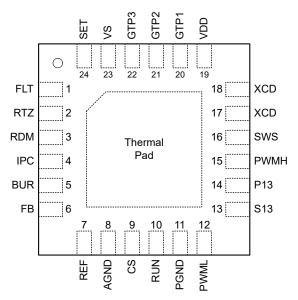

## **5 Pin Configuration and Functions**

図 5-1. RTW Package, 24-Pin WQFN (Top View)

表 5-1. Pin Functions

|      | 双 5-1. PIII FUIICUONS |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|------|-----------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| P    | PIN                   | TYPE(1) | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| NAME | NO.                   |         | DECORN HON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

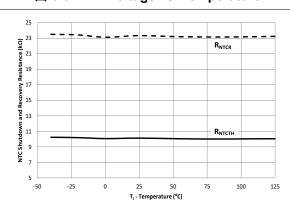

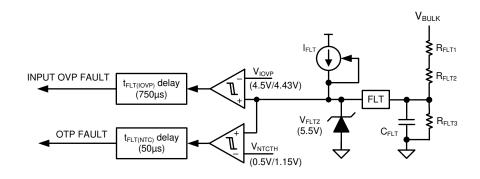

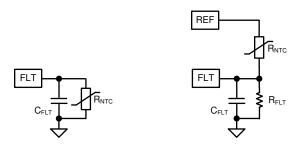

| FLT  | 1                     | I       | The controller enters into the fault state if the FLT-pin voltage is pulled above 4.5 V or below 0.5 V. A 50-µA current source interfaces directly with an external NTC (negative temperature coefficient) thermistor to AGND pin for remote temperature sensing. The current source is active during the run state and inactive during the wait state. A 50-µs fault delay allows a filter capacitor to be placed on the FLT pin without false triggering the 0.5-V OTP fault when the controller enters into a run state from a wait state. Alternatively, a high-resistance voltage divider can be used to sense the bulk input capacitor voltage for line-OVP detection, and a 750-µs fault delay helps to prevent false triggering the 4.5-V input line-OVP from a short-duration bulk capacitor voltage overshoot during line surge and ESD strike events. When FLT-pin voltage is used for line-OVP detection, the external OTP can be implemented on CS pin. |  |  |  |  |

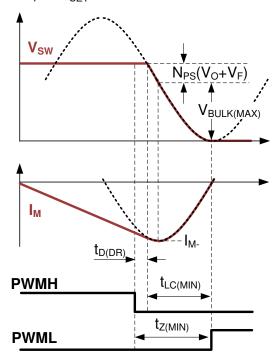

| RTZ  | 2                     | I       | A resistor between this pin and AGND pin programs an adaptive delay for transition to zero voltage from the turn-off edge of the PWMH signal to the turn-on edge of the PWML signal. Parasitic capacitance between this pin and any other net, including AGND, must be minimized to avoid noise coupling and its effect on the dead-time calculation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| RDM  | 3                     | I       | A resistor between this pin and AGND pin programs a synthesized demagnetization time used to control the on-time of the PWMH signal to achieve zero voltage switching on the primary switch. The controller applies a voltage on this pin that varies with the output voltage derived from the VS pin signal. Parasitic capacitance between this pin and any other net, including AGND, must be minimized to avoid noise coupling and its effect on the internal PWMH on-time calculation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

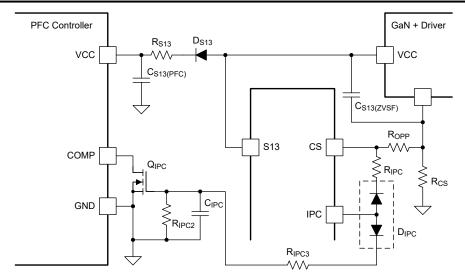

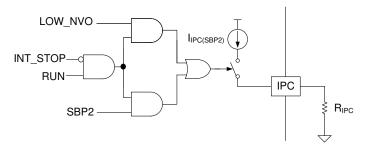

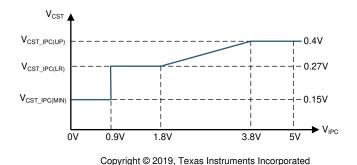

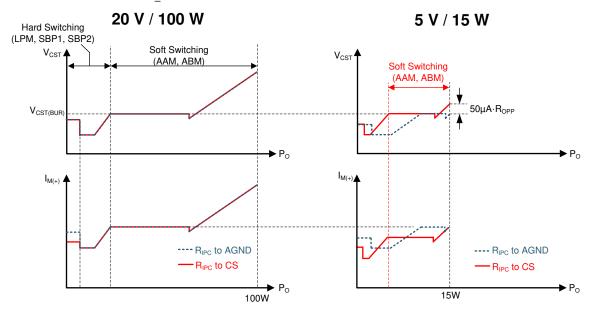

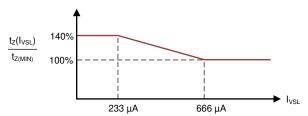

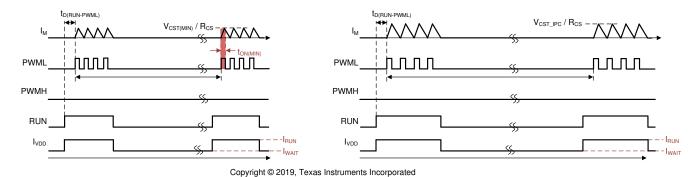

| IPC  | 4                     | I       | This pin is an intelligent power control (IPC) pin to optimize the converter efficiency. A 50- $\mu$ A current source directly interfaces with a resistor (R <sub>IPC</sub> ) to AGND pin to program an increase in the peak current level at very light load; the burst frequency can be further reduced, helping to achieve low standby power and tiny-load power. If the IPC pin is connected to AGND without R <sub>IPC</sub> , the peak current level in very light load is set to a minimum level for the output ripple or audible noise sensitive designs. R <sub>IPC</sub> can also be connected between this pin and the CS pin or IPC pin can be directly connected to CS pin, so the 50- $\mu$ A IPC current can create an output voltage dependent offset voltage on the CS pin for reducing output ripple in adaptive burst mode and improving light-load efficiency at lower output voltage level of a wide output voltage range design.               |  |  |  |  |

### 表 5-1. Pin Functions (continued)

| Р    | 'IN | <b></b> (1)         | 表 5-1. PIN Functions (continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------|-----|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME | NO. | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

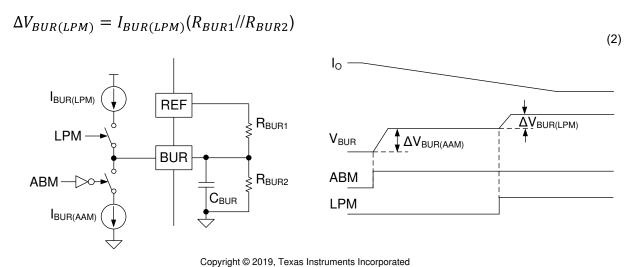

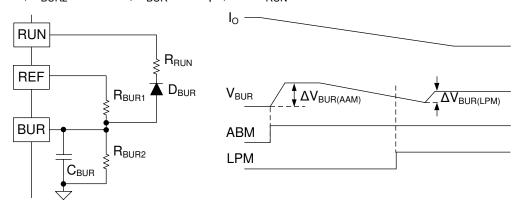

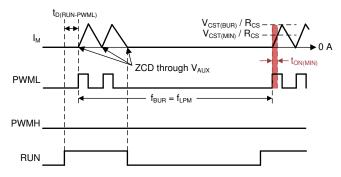

| BUR  | 5   | ı                   | This pin is used to program the burst threshold of the converter at light load. A resistor divider between REF and AGND is used to set a voltage at BUR to determine the peak current level when the converter enters adaptive burst mode (ABM). In addition, the Thevenin resistance on BUR is used to activate offset voltages for smooth mode transitions. A 2.7-µA pull up current increases the peak current threshold when the converter enters low-power mode (LPM) from ABM. A 5-µA pull down current reduces the peak current threshold when the converter enters into high-power mode (adaptive amplitude modulation, AAM) from ABM.                                                                                                                                                                                                                                                                                                                |

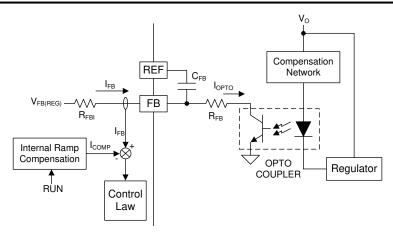

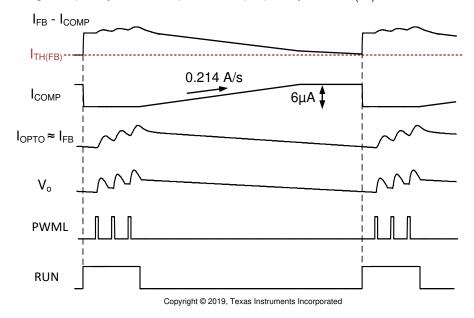

| FB   | 6   | I                   | A current signal is coupled to this pin to close the converter regulation feedback loop. This pin presents a 4.25-V output that is designed to have 0-μA to 75-μA current pulled out of the pin corresponding to the converter operating from full-power to zero-power conditions. A 220-pF filter capacitor between FB pin and REF pin is recommended to desensitize the feedback signal from noise interference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

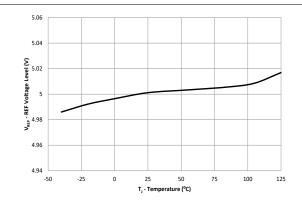

| REF  | 7   | 0                   | This pin is a 5-V reference output that requires a 0.22-µF ceramic bypass capacitor to the AGND pin. This reference is used to power internal circuits and can supply a limited external load current. Pulling this pin low shuts down PWM action and initiates a VDD restart.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| AGND | 8   | G                   | Analog ground and the ground return of PWMH and RUN drivers. Return all analog control signals to this ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

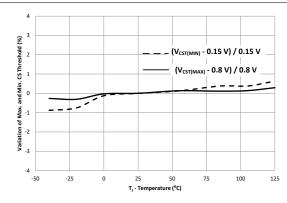

| CS   | 9   | ı                   | This is the current-sense input pin. This pin couples to the current-sense resistor through a line-compensation resistor to control the peak primary current in each switching cycle. An internal current source on this pin, proportional to the converter's input voltage, creates an offset voltage across the line-compensation resistor to balance the over-power protection (OPP) threshold level across input line. The CS pin can also provide an alternative OTP function, when the FLT pin is being used for the line input-OVP. A small-signal diode in series with an NTC resistor is connected between PWMH pin and CS pin to form the OTP detection. When PWMH is high, the NTC resistor and the line-compensation resistor become a resistor divider from 5 V and creates a temperature dependent voltage on CS pin. When CS pin voltage is higher than 1.2 V in PWMH on state for 2 consecutive cycles, the OTP fault on CS pin is triggered. |

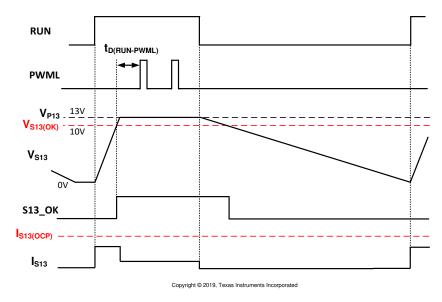

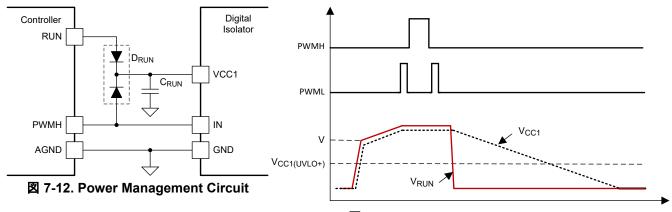

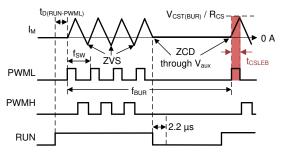

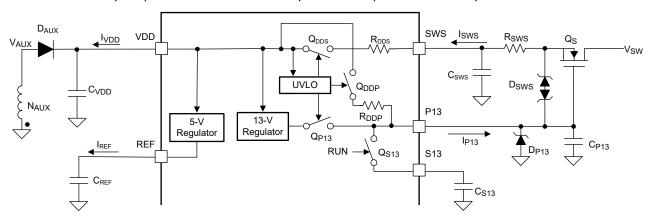

| RUN  | 10  | 0                   | This output pin is high when the controller is in the run state. This output is low during start-up, wait, and fault states. A 2.2-µs timer delays the initiation of PWML switching after this pin has gone high and S13-pin voltage is above its 10-V power-good threshold. The pull-up driving capability of both RUN and PWMH pins allows bias power management of a digital isolator through a common-cathode small-signal diode, so the power consumption can be reduced in the wait state.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

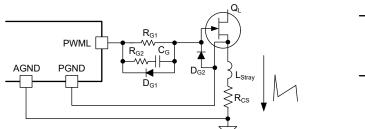

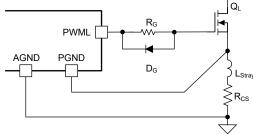

| PGND | 11  | G                   | Low-side ground return of the PWML driver to the primary switch. The internal level shifter allows the common return impedance to be eliminated and improves higher frequency operation by decoupling the additional voltage spike on the current-sense resistor and layout parasitic inductance of the gate driving loop. For a silicon (Si) power FET, this pin can be connected to the source for a smaller gate driving loop. For a GaN power IC with a logic PWM input, this pin can be connected to AGND. For a GaN-based gate-injection transistor (GIT), this pin can be directly connected to the separate source pin of a GIT GaN device, which enhances the turn-off speed.                                                                                                                                                                                                                                                                        |

| PWML | 12  | 0                   | Primary switch gate driver output. The high-current capability (-0.5A/+1.9A) of PWML enables driving of a silicon power MOSFET with higher capacitive loading, a GIT GaN with continuous on-state current, or a GaN power IC with logic input. The maximum voltage level of PWML is clamped to the P13 pin voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| S13  | 13  | 0                   | S13 is a switched bias-voltage source coupled to P13 through an internal 2.8-Ω switch controlled by the RUN pin. When RUN is high, the S13 decoupling capacitor is charged up to 13 V by an internal current limiter. The S13 pin voltage must increase above 10 V to initiate PWML switching. When RUN is low, S13 is discharged by its load. The power-on delay of any device powered by S13 must be less than 2 μs to be responsive to PWML. A 22-nF ceramic capacitor between S13 and the driver ground is recommended. S13 can also perform power management on a PFC controller at the same time through a diode, such that PFC can be disabled at very light-load condition.                                                                                                                                                                                                                                                                           |

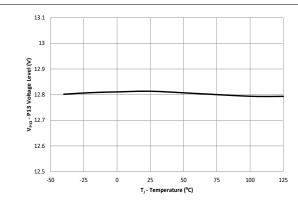

| P13  | 14  | 0                   | P13 is a regulated 13-V bias-voltage source derived from V <sub>VDD</sub> . During V <sub>VDD</sub> startup, P13 pin is connected to the VDD pin internally, so an external high-voltage depletion MOSFET, such as BSS126, can provide controlled startup current to charge the VDD capacitor. After the initial startup, P13 recovers back to 13-V regulation. A 1-µF ceramic bypass capacitor is required from P13 to AGND. A 20-V Zener diode between P13 and AGND is recommended to protect this pin from overstress, such as if the connection between this pin and the depletion MOSFET gate is fail-open or if line surge energy is coupled to this pin.                                                                                                                                                                                                                                                                                               |

### 表 5-1. Pin Functions (continued)

| P              | PIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                     | 表 5-1. Pin Functions (continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME           | NO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| PWMH           | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0                   | PWM output signal used to control the gate of a secondary-side synchronous rectifier (SR) MOSFET through an external isolating gate driver. The driving capability is designed to bias a level-shifting isolator through a small-signal diode, or can also transmit the signal to secondary-side driving circuitry through a pulse transformer. The maximum voltage level of PWMH is clamped to REF.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

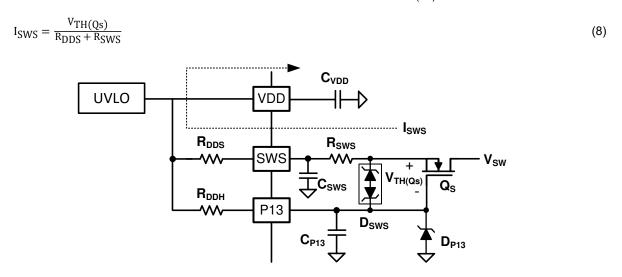

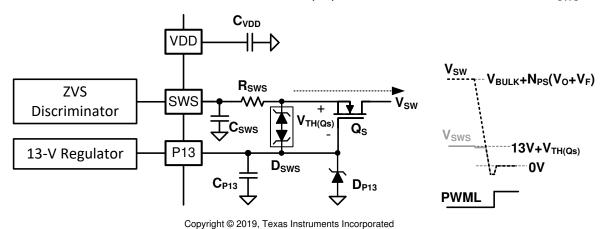

| sws            | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | I                   | This sensing input is used to monitor the switch-node voltage as it nears zero volts in normal operation for ZVS auto-tuning. The source of a high-voltage depletion-mode MOSFET, such as BSS126, is coupled to this pin through a current-limiting resistor so only the useful switching characteristic below 15 V is monitored. During start-up, this pin is connected to the VDD pin internally to allow the depletion-mode MOSFET to provide start-up current. The external current-limit resistor and a small bidirectional TVS across gate and source should be added to protect the $V_{\rm GS}$ from potential abnormal voltage stress. The resistor should be higher than 500 $\Omega$ and less than 820 $\Omega$ . The clamping voltage of TVS should be less than the MOSFET voltage rating but greater than 15 V. Moreover, the resistor and a 22-pF ceramic capacitor between the SWS pin and the bulk input capacitor ground form a small sensing delay to help the internal detection circuit to identify the ZVS characteristic correctly.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

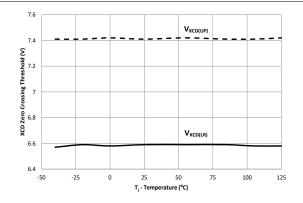

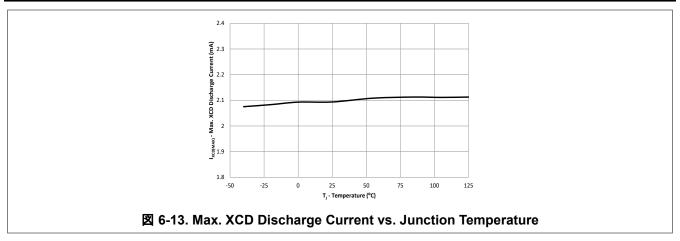

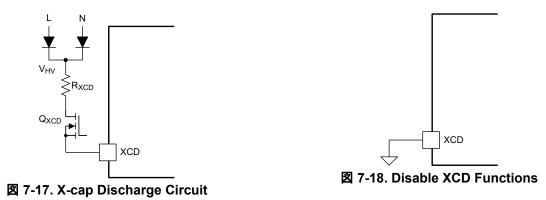

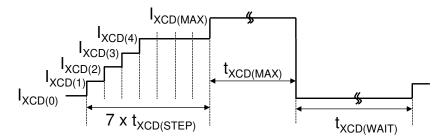

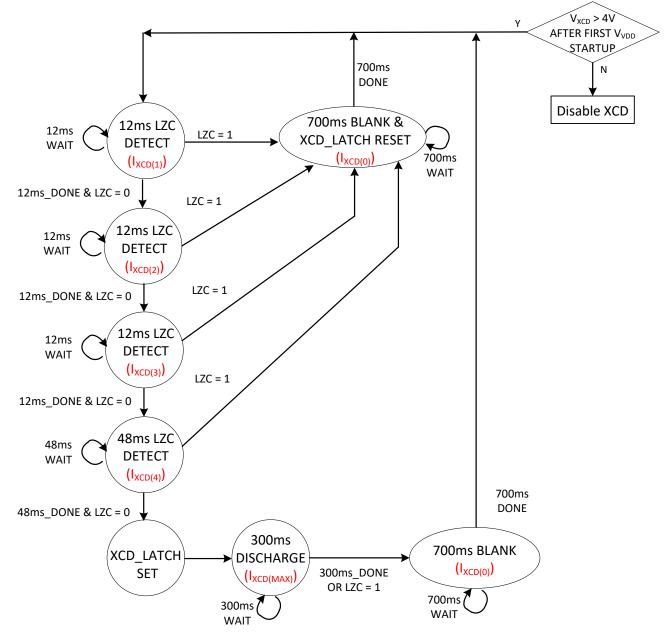

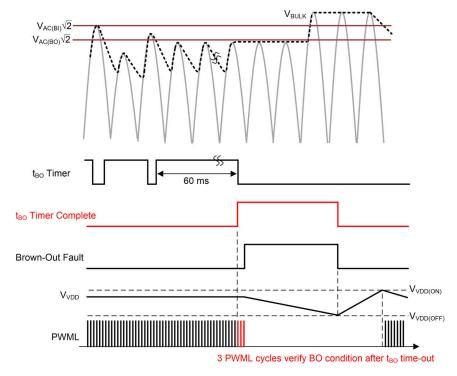

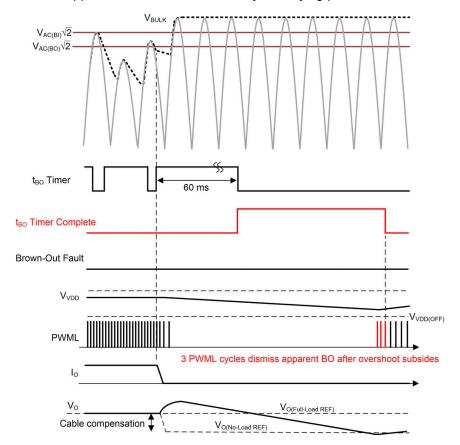

| XCD            | <ul> <li>(LZC) threshold of 6.5 V on XCD is used to detect AC-line presence. When LZC is not detect an 84-ms test period, the discharge current is enabled for a maximum period of 300 ms follow by a no-current blanking time of 700 ms. When AC-line recovers and LZC is detected again, controller can reset the fault state almost immediately and will attempt to restart without waiting fully discharge the bulk input capacitor. For the auto-recovery fault protections, if the controllong 1.5-s auto-recovery fault state, LZC can reset the timer and speed up the restart attempt. The redundant XCD pins help to provide the X-cap discharge function even when one pin is in fair condition. To form the discharge path, an anode of two high-voltage diode rectifiers is connected to each X-cap terminal, the two diode cathodes are connected together to a 26-kΩ high-voltage current-limiting resistance, and the drain-to-source connection of a high-voltage depletion MC couples the resistance to the XCD pins. Two series 13-kΩ SMD resistors in 1206 size can be as the current limiting device, and share the potential transient voltage from the AC-line. A 60 rated MOSFET such as BSS126 is needed as the high voltage blocking device. The MOSFE connected to the P13 pin, so the XCD pins can obtain enough signal headroom for LZC determined.</li> </ul> |                     | X-cap Discharge input pins with 2-mA maximum discharge current capability. A line zero-crossing (LZC) threshold of 6.5 V on XCD is used to detect AC-line presence. When LZC is not detected within an 84-ms test period, the discharge current is enabled for a maximum period of 300 ms followed by a no-current blanking time of 700 ms. When AC-line recovers and LZC is detected again, the controller can reset the fault state almost immediately and will attempt to restart without waiting to fully discharge the bulk input capacitor. For the auto-recovery fault protections, if the controller is in 1.5-s auto-recovery fault state, LZC can reset the timer and speed up the restart attempt. The two redundant XCD pins help to provide the X-cap discharge function even when one pin is in fail-open condition. To form the discharge path, an anode of two high-voltage diode rectifiers is connected to each X-cap terminal, the two diode cathodes are connected together to a 26-k $\Omega$ high-voltage current-limiting resistance, and the drain-to-source connection of a high-voltage depletion MOSFET couples the resistance to the XCD pins. Two series 13-k $\Omega$ SMD resistors in 1206 size can be used as the current limiting device, and share the potential transient voltage from the AC-line. A 600-V rated MOSFET such as BSS126 is needed as the high voltage blocking device. The MOSFET gate is connected to the P13 pin, so the XCD pins can obtain enough signal headroom for LZC detection. If the X-cap discharge function is not needed, XCD pins must be connected to AGND pin to disable the function, and the diode-resistor-MOSFET path must be removed. |

| VDD            | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Р                   | Controller bias power input. A ceramic capacitor with 10-µF or 15-µF capacitance is recommended, and the minimum voltage rating is 25 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| GTP1           | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | G                   | Ground This Pin. This pin must be connected to AGND for proper operation of the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| GTP2           | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | G                   | Ground This Pin. This pin must be connected to AGND for proper operation of the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| GTP3           | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | G                   | Ground This Pin. This pin must be connected to AGND for proper operation of the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

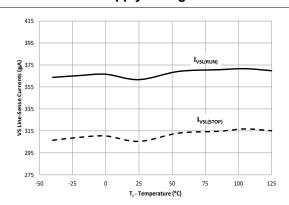

| VS             | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | I                   | This voltage-sensing input pin is coupled to an auxiliary winding of the converter's transformer via a resistor divider. The pin and associated external resistors are used to monitor the output and input voltages and switching edges of the converter at different moments within each switching cycle. Parasitic capacitance between VS and any net, including AGND, must be minimized to avoid adverse effects on output voltage sensing, edge detection, and the dead-time calculation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SET            | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | I                   | This pin is used to configure the controller to be optimized for gallium nitride (GaN) power FETs or silicon (Si) power FETs on the primary side. Depending on the setting, it will optimize parameters of the ZVS control loop, dead-time adjustment, and protection features. When pulled high to REF pin, it is optimized for Si FETs. When pulled low to AGND, it is optimized for GaN FETs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Thermal<br>Pad |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | G                   | The thermal pad (TP) must be connected to AGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

<sup>(1)</sup> I = input, O = output, I/O = input or output, FB = feedback, G = ground, P = power

### **6 Specifications**

### **6.1 Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted) (1)

|                                                                                                                              |                                                                      | MIN   | MAX           | UNIT |

|------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-------|---------------|------|

|                                                                                                                              | VDD                                                                  |       | 38            |      |

|                                                                                                                              | sws                                                                  | -6    | 38            |      |

| Input Voltage  Output Voltage                                                                                                | SWS (transient, negative pulse width of 20 ns max., duty cycle ≤ 1%) | -10   | 38            |      |

|                                                                                                                              | VDD-SWS                                                              | -20   | 38            |      |

|                                                                                                                              | CS                                                                   | -0.3  | 3.6           |      |

| Input Voltage                                                                                                                | VS                                                                   | -0.75 | 7             | V    |

|                                                                                                                              | VS (transient, 100 ns max.)                                          | -1    | 7             |      |

|                                                                                                                              | PGND                                                                 | -1    | 4             |      |

|                                                                                                                              | PGND (transient, 25 ns max.)                                         |       | 5             |      |

|                                                                                                                              | RTZ, BUR, SET, RDM, IPC, FLT, FB                                     | -0.3  | 7             |      |

| Output Voltage                                                                                                               | XCD                                                                  | -0.3  | 30            |      |

| Output Voltage                                                                                                               | REF, PWMH, RUN                                                       | -0.3  | 7             | V    |

| Output voltage                                                                                                               | P13, S13, PWML                                                       | -0.3  | 20            | V    |

|                                                                                                                              | REF, P13, RTZ, RDM, IPC                                              |       | Self–limiting |      |

|                                                                                                                              | S13 (average)                                                        |       | 15            |      |

|                                                                                                                              | VS                                                                   |       | 2             |      |

|                                                                                                                              | VS (transient, 100 ns max.)                                          |       | 2.5           |      |

| Source Current                                                                                                               | FB                                                                   |       | 1             | mA   |

|                                                                                                                              | RUN (continuous)                                                     |       | 5             |      |

|                                                                                                                              | PWML (continuous)                                                    |       | 50            |      |

|                                                                                                                              | PWMH (continuous)                                                    |       | 10            |      |

|                                                                                                                              | CS (transient, 30 ns max.)                                           |       | 1             |      |

|                                                                                                                              | RUN (continuous)                                                     |       | 8             |      |

|                                                                                                                              | PWML (continuous)                                                    |       | 50            |      |

| Input Voltage  VS VS PC PC RT XC Output Voltage  P1 RE S1 VS VS VS Source Current FB RL PV PV CS RI RV SV SINK Current SV XC | PWMH (continuous)                                                    |       | 10            | mA   |

|                                                                                                                              | SWS                                                                  |       | Self–limiting | IIIA |

|                                                                                                                              | XCD                                                                  |       | 25            |      |

|                                                                                                                              | FLT                                                                  |       | 0.3           |      |

| Operating junction                                                                                                           | on temperature, T <sub>J</sub>                                       | -40   | 150           | °C   |

| Storage tempera                                                                                                              | iture, T <sub>stg</sub>                                              | -65   | 150           | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

### 6.2 ESD Ratings

|                    |                         |                                                                     | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------|-------|------|

| V                  | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>1</sup>     | ±2000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per ANSI/ESDA/JEDEC JS-002 <sup>2</sup> | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                  |                                | MIN  | NOM MAX | UNIT |

|------------------|--------------------------------|------|---------|------|

| V <sub>VDD</sub> | Bias supply operating voltage  | 14   | 34      | V    |

| C <sub>VDD</sub> | VDD capacitor                  | 10   |         | μF   |

| C <sub>P13</sub> | P13 bypass capacitor           | 1    |         | μF   |

| C <sub>REF</sub> | REF bypass capacitor           | 0.22 |         | μF   |

| TJ               | Operating junction temperature | -40  | 140     | °C   |

### **6.4 Thermal Information**

|                       |                                              | UCC28781   |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>1</sup>                  | RTW (WQFN) | UNIT |

|                       |                                              | 24 PINS    |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 43.1       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 31.6       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 20.3       | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.5        | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 20.3       | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 5.7        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

### **6.5 Electrical Characteristics**

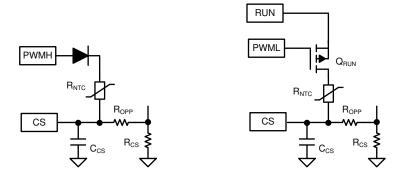

Unless otherwise stated:  $V_{VDD}$  = 20 V,  $R_{RDM}$  = 115 k $\Omega$ ,  $R_{RTZ}$  = 140 k $\Omega$ ,  $V_{BUR}$  = 1.2 V,  $V_{SET}$  = 0 V,  $R_{NTC}$  = 50 k $\Omega$ ,  $V_{VS}$  = 4 V,  $V_{SWS}$  = 0 V,  $I_{FB}$  = 0  $\mu$ A,  $C_{PWML}$  = 0 pF,  $C_{PWMH}$  = 0 pF,  $C_{REF}$  = 0.22  $\mu$ F,  $C_{P13}$  = 1  $\mu$ F, and -40°C <  $T_{J}$  =  $T_{A}$  < 125°C

|                         | PARAMETER                                               | TEST CONDITIONS                                                          | MIN   | TYP  | MAX   | UNIT |

|-------------------------|---------------------------------------------------------|--------------------------------------------------------------------------|-------|------|-------|------|

| VDD INPUT               |                                                         |                                                                          |       |      |       |      |

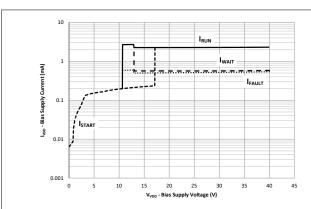

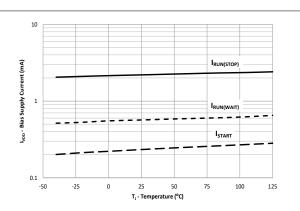

| I <sub>RUN(STOP)</sub>  | Supply current, run state                               | No switching                                                             | 0.88  | 2.2  | 2.66  | mA   |

| I <sub>RUN(SW)</sub>    | Supply current, run state                               | Switching, I <sub>VSL</sub> = 0 µA                                       | 2.45  | 3    | 3.55  | mA   |

| I <sub>WAIT</sub>       | Supply current, wait state                              | I <sub>FB</sub> = -85 μA, I <sub>VDD</sub> only                          | 465   | 540  | 658   | μA   |

| I <sub>START</sub>      | Supply current, start state                             | $V_{VDD} = V_{VDD(ON)}$ - 100 mV, $V_{VS} = 0$ V                         | 150   | 235  | 301   | μA   |

| I <sub>FAULT</sub>      | Supply current, fault state                             | fault state                                                              |       | 500  | 630   | μA   |

| I <sub>VDD(LIMIT)</sub> | VDD startup current limit during startup                | $V_{VDD}$ increasing, $V_{SWS}$ - $V_{VDD}$ = 1 V,<br>$V_{VDD}$ = 16.5 V | 1.2   | 2    | 2.53  | mA   |

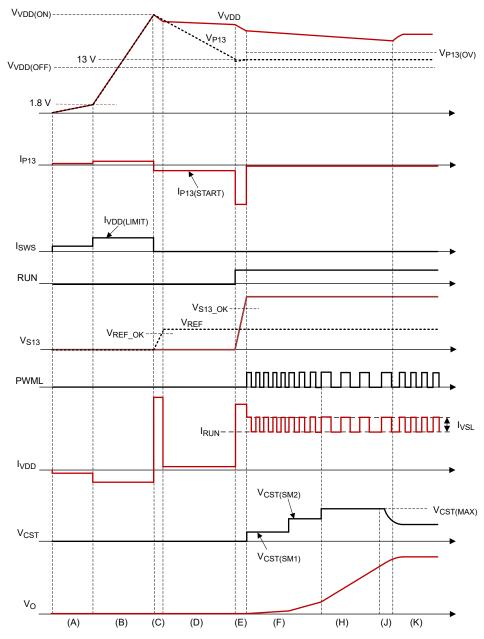

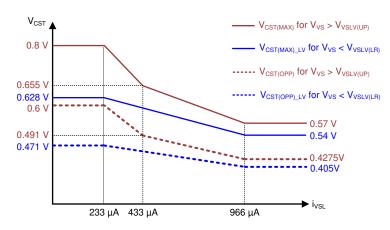

| V <sub>VDD(ON)</sub>    | VDD turnon threshold                                    | V <sub>VDD</sub> increasing                                              | 16.2  | 17   | 17.91 | V    |

| V <sub>VDD(OFF)</sub>   | VDD turnoff threshold                                   | V <sub>VDD</sub> decreasing                                              | 9.94  | 10.6 | 11.17 | V    |

| V <sub>VDD(PCT)</sub>   | Offset to power cycle for long output voltage overshoot | Offset above $V_{VDD(OFF)}$ , $I_{FB} = -85 \mu A$                       | 1.54  | 2.2  | 2.98  | V    |

| P13 OUTPUT              | •                                                       |                                                                          |       |      |       |      |

| V <sub>P13</sub>        | P13 voltage level including load regulation             | 0 mA to 60 mA out of P13, run state,<br>V <sub>VDD</sub> = 20 V          | 12.0  | 12.8 | 13.6  | V    |

| I <sub>P13(START)</sub> | Max sink current of P13 pin during startup              | V <sub>P13</sub> = 14 V                                                  | 1.53  | 2.2  | 3.04  | mA   |

| I <sub>P13(MAX)</sub>   | Current sourcing limit of P13 pin                       | P13 shorted to AGND, V <sub>VDD</sub> = 20 V                             | 103.3 | 133  | 160   | mA   |

| VR13 <sub>(LINE)</sub>  | Line regulation of V <sub>P13</sub>                     | V <sub>VDD</sub> = 15 V to 35 V                                          | -6    | 2    | 8.7   | mV   |

| V <sub>P13(OV)</sub>    | Over voltage fault threshold above V <sub>P13</sub>     |                                                                          | 1.35  | 2    | 2.54  | V    |

Copyright © 2023 Texas Instruments Incorporated

Submit Document Feedback

|                                      | PARAMETER                                                                        | TEST CONDITIONS                                                                                        | MIN   | TYP  | MAX   | UNIT |

|--------------------------------------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-------|------|-------|------|

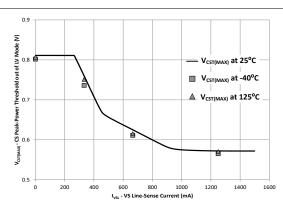

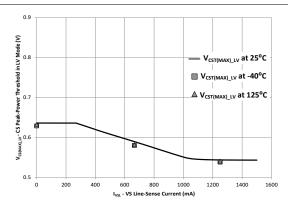

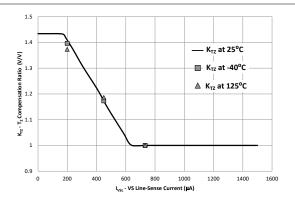

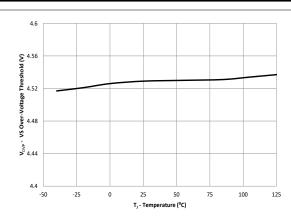

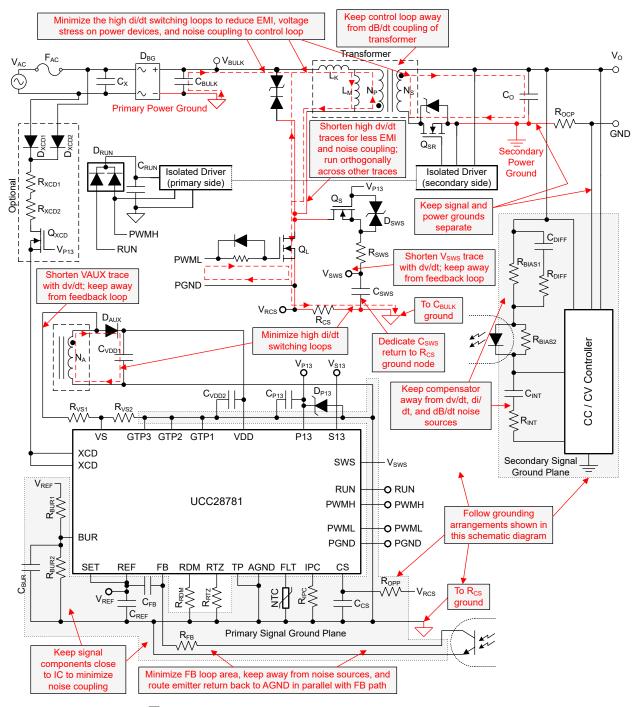

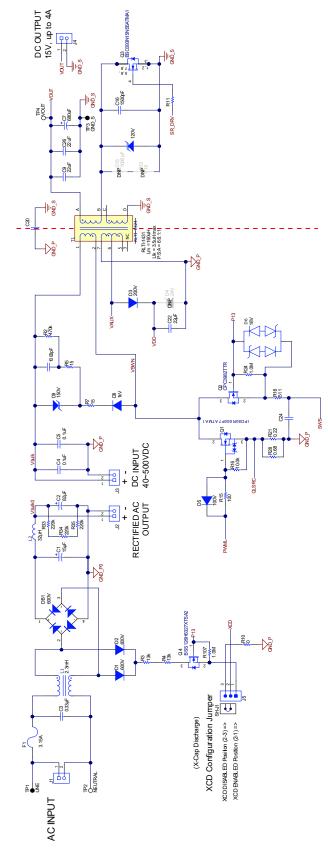

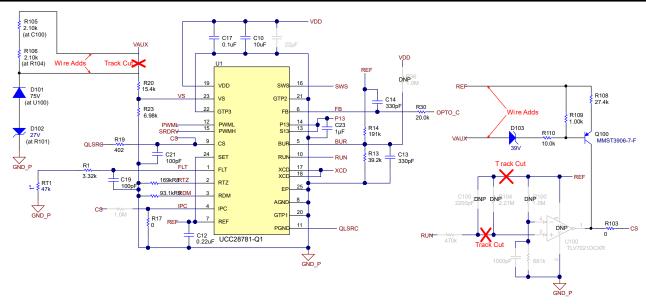

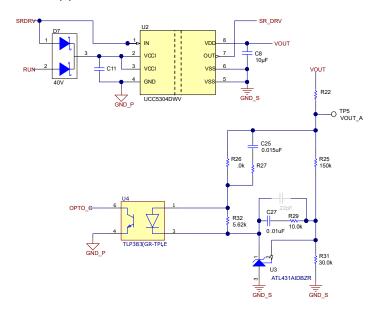

| R <sub>P13</sub>                     | Dropout resistance of P13 regulator switch between VDD and P13 pins              | (V <sub>VDD</sub> - V <sub>P13</sub> ) / 30 mA, V <sub>VDD</sub> = 11 V,<br>30 mA out of P13           | 8.5   | 13   | 22.7  | Ω    |