## UCCx8C4x BiCMOS、低消費電力、電流モード PWM コントローラ

### 1 特長

- UCx84x および UCx84xA ファミリとピン互換の機能強化代替品

- 動作周波数: 最大 1MHz

- 50 $\mu$ A のスタートアップ電流、最大 100 $\mu$ A

- 小さい動作電流: 2.3mA ( $f_{osc} = 52\text{kHz}$  時)

- 高速なサイクルごとの過電流制限: 35ns

- ピーク駆動電流:  $\pm 1\text{A}$ 。レールツーレール出力

- 25ns の立ち上がり時間

- 20ns の立ち下がり時間

- $\pm 1\%$  の精度の 2.5V エラー アンプ基準電圧

- トリムされた発振器放電電流

- 低電圧誤動作防止保護

- VSSOP-8 パッケージにより基板面積を最小化

### 2 アプリケーション

- スイッチ モード電源

- 汎用シングルエンド DC/DC またはオフライン絶縁型電源コンバータ

- 基板実装のパワー モジュール

### 3 概要

UCCx8C4x ファミリは、高性能の電流モード PWM コントローラです。UCCx8C4x は、業界標準の UCx84xA ファミリおよび UCx84x ファミリの PWM コントローラとピン互換で、機能強化された BiCMOS 版です。BiCMOS テクノロジにより消費電力が低減され、効率が向上し、電流検出および発振器周波数も高速化しています。

さらに、バッテリ駆動のシステムで使用するために、スタートアップ電圧が 7V と低いバージョンとして、UCCx8C40 および UCCx8C41 を用意しています。UCC28C4x シリーズは -40°C ~ 125°C での動作が規定されており、UCC38C4x シリーズは 0°C ~ 85°C での動作が規定されています。

このファミリは、固定周波数のピーク電流モード電源を制御するために必要な機能を提供し、以下の性能上の利点があります。このデバイスは、1MHz までの高い周波数で動作するため、高速のアプリケーションに適しています。トリムされた放電電流により、UCCx8C4x ファミリと比較して、最大デューティ サイクルとデッドタイムの制限をより正確にプログラムできます。スタートアップ時および動作時の電流の低減によってスタートアップ時の損失が最小化され、動作時の消費電力も低いため、効率が向上しています。また、このデバイスは、電流検出から出力までの遅延時間が 35ns と高速で、パワー スイッチにおける過負荷保護にも優れています。また、 $\pm 1\text{A}$  のピーク出力電流能力と、立ち上がりおよび立ち下がり時間の短縮により、外部の大きい MOSFET を直接駆動できます。

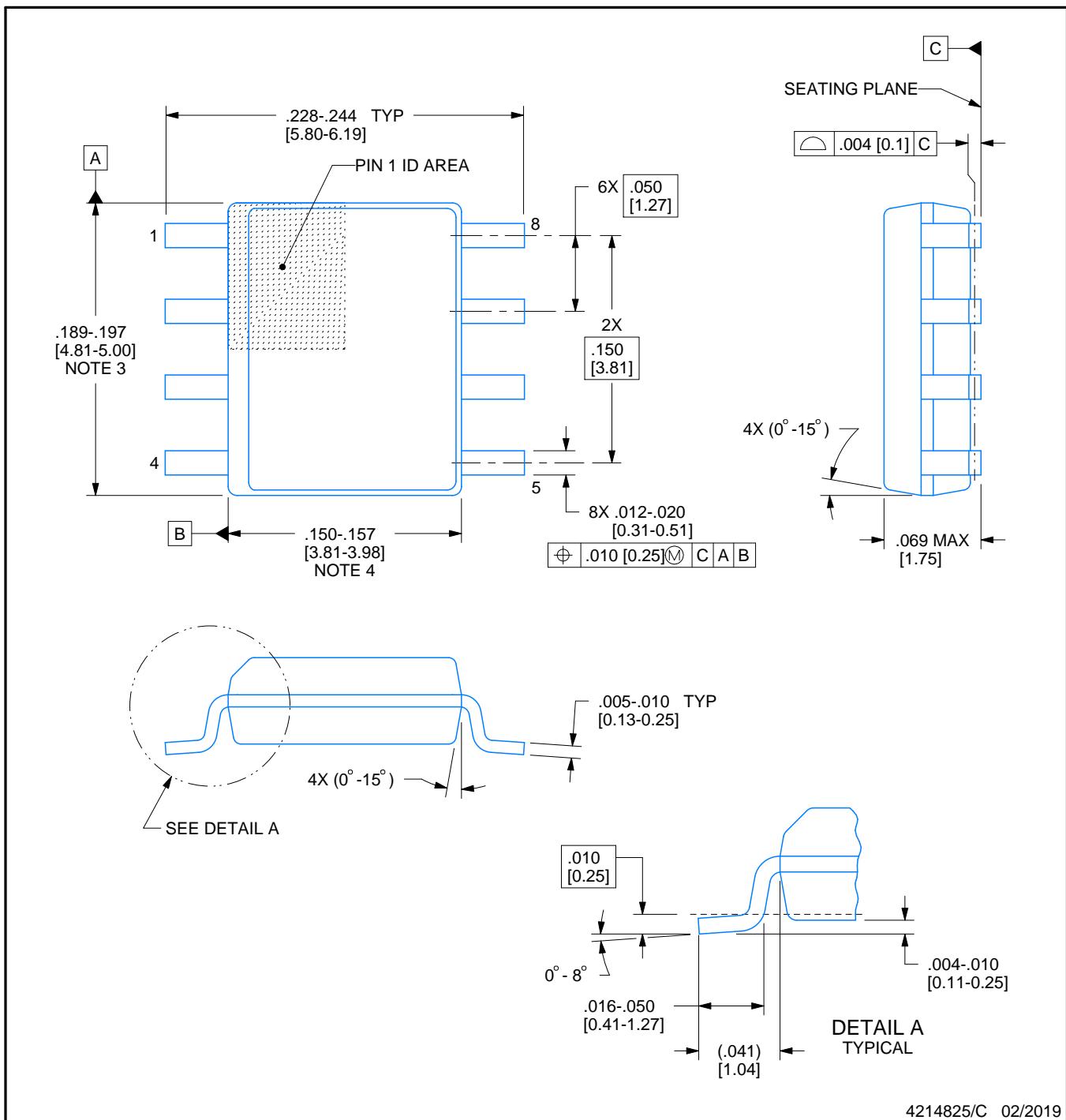

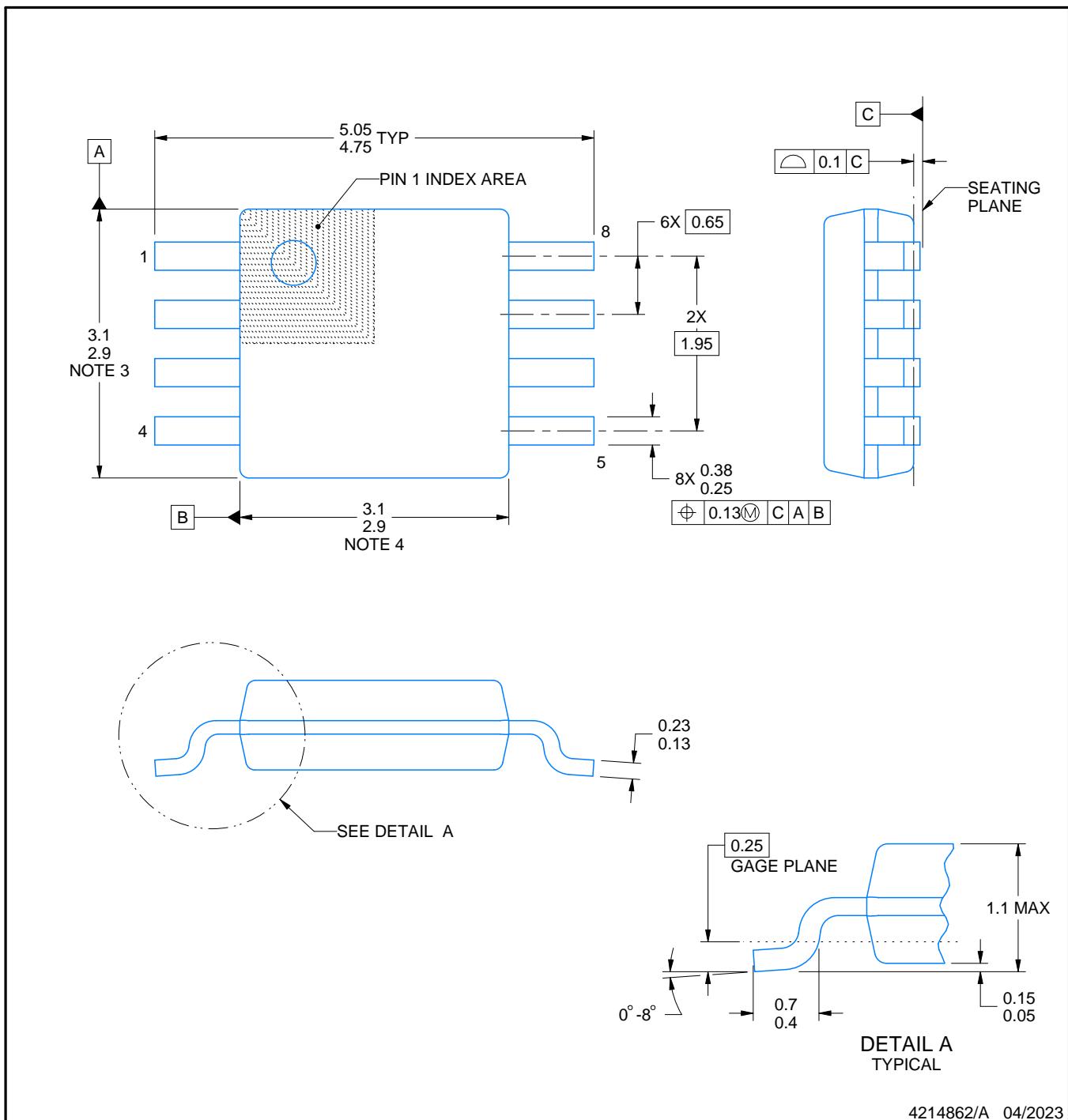

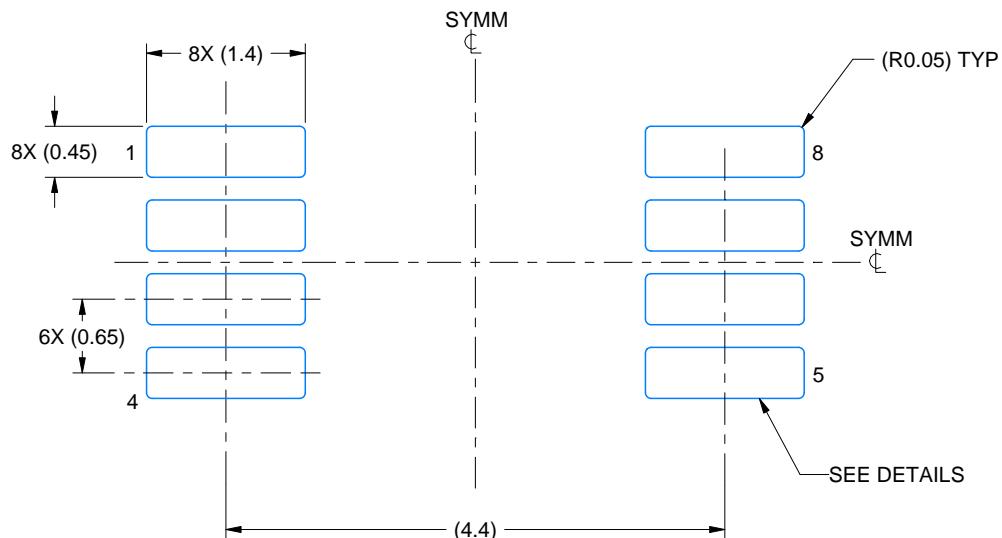

UCCx8C4x ファミリは、8 ピン VSSOP (DGK) および 8 ピン SOIC (D) パッケージで供給されます。

#### 製品情報

| 部品番号     | パッケージ (1) | 本体サイズ (公称)      |

|----------|-----------|-----------------|

| UCC28C4x | SOIC (8)  | 3.91mm × 4.90mm |

| UCC38C4x | VSSOP (8) | 3.00mm × 3.00mm |

(1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

Copyright © 2016, Texas Instruments Incorporated

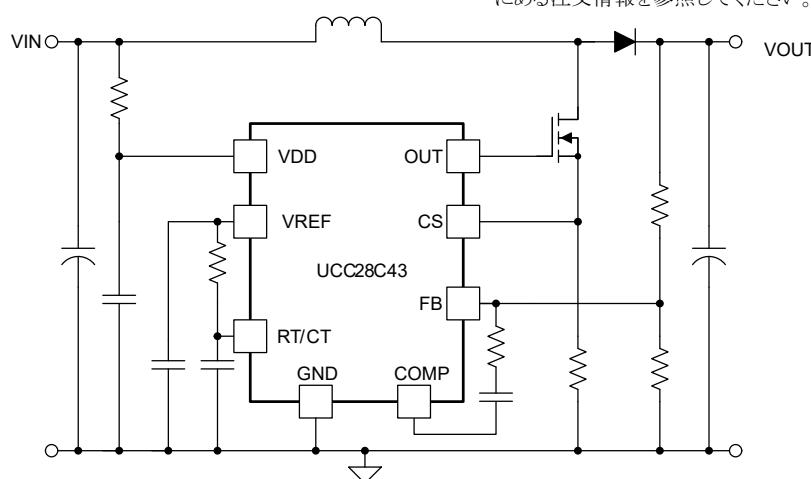

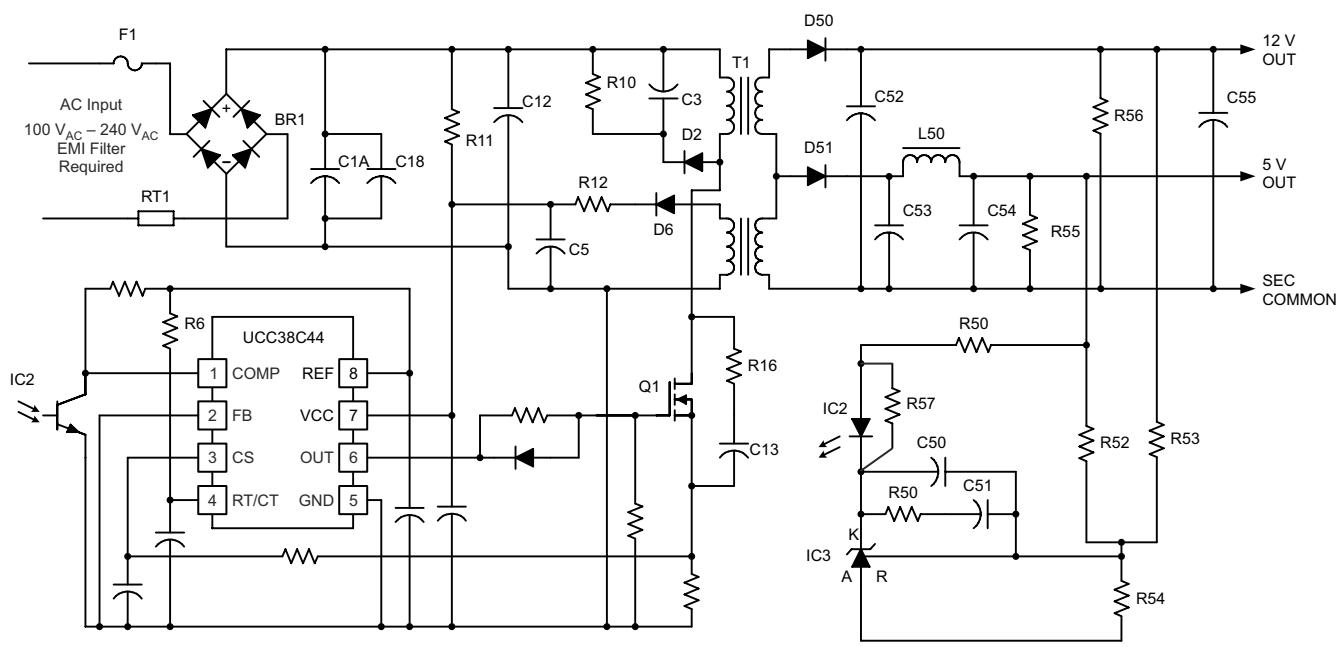

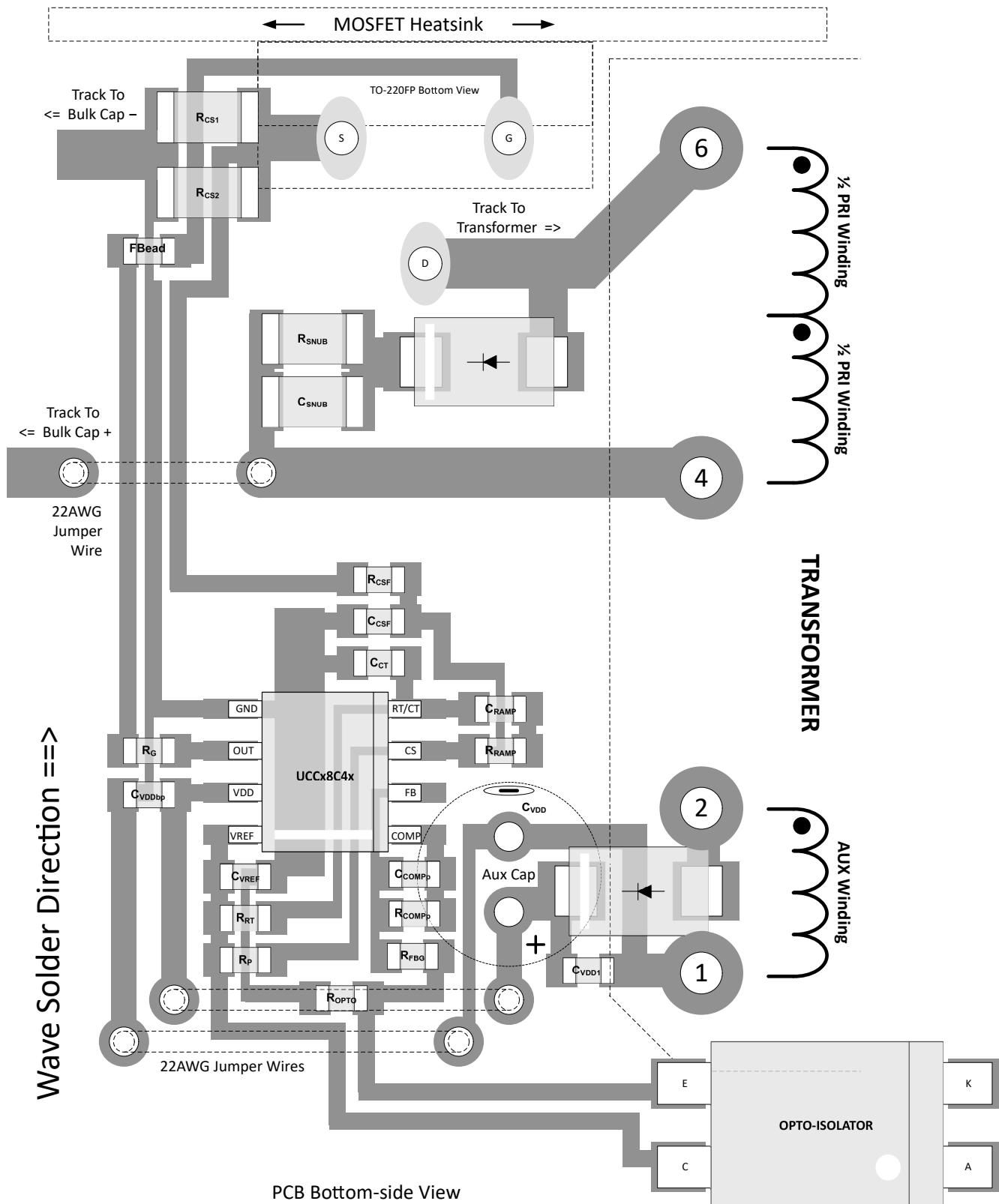

アプリケーション概略図

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあります。TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|             |    |                        |    |

|-------------|----|------------------------|----|

| 1 特長        | 1  | 7.4 デバイスの機能モード         | 26 |

| 2 アプリケーション  | 1  | 8 アプリケーションと実装          | 27 |

| 3 概要        | 1  | 8.1 アプリケーション情報         | 27 |

| 4 デバイス比較表   | 3  | 8.2 代表的なアプリケーション       | 29 |

| 5 ピン構成および機能 | 4  | 8.3 電源に関する推奨事項         | 41 |

| 6 仕様        | 5  | 8.4 レイアウト              | 41 |

| 6.1 絶対最大定格  | 5  | 9 デバイスおよびドキュメントのサポート   | 45 |

| 6.2 ESD 定格  | 6  | 9.1 デバイス サポート          | 45 |

| 6.3 推奨動作条件  | 6  | 9.2 ドキュメントのサポート        | 45 |

| 6.4 熱に関する情報 | 7  | 9.3 ドキュメントの更新通知を受け取る方法 | 45 |

| 6.5 電気的特性   | 7  | 9.4 サポート・リソース          | 45 |

| 6.6 代表的特性   | 10 | 9.5 商標                 | 46 |

| 7 詳細説明      | 14 | 9.6 静電気放電に関する注意事項      | 46 |

| 7.1 概要      | 14 | 9.7 用語集                | 46 |

| 7.2 機能ブロック図 | 15 | 10 改訂履歴                | 46 |

| 7.3 機能説明    | 15 | 11 メカニカル、パッケージ、および注文情報 | 46 |

## 4 デバイス比較表

| UVLO                                            |                                                  |                                               | 接合部温度<br>( $T_J$ ) (°C) | 最大デューティ<br>サイクル |

|-------------------------------------------------|--------------------------------------------------|-----------------------------------------------|-------------------------|-----------------|

| 14.5V でターンオン<br>9V でターンオフ<br>(オンライン アプリケーション向け) | 8.4V でターンオン<br>7.6V でターンオフ<br>(DC/DC アプリケーション向け) | 7V でターンオン<br>6.6V でターンオフ<br>(バッテリ アプリケーション向け) |                         |                 |

| UCC28C42                                        | UCC28C43                                         | UCC28C40                                      | -40~125                 | 100%            |

| UCC38C42                                        | UCC38C43                                         | UCC38C40                                      | 0~85                    |                 |

| UCC28C44                                        | UCC28C45                                         | UCC28C41                                      | -40~125                 | 50%             |

| UCC38C44                                        | UCC38C45                                         | UCC38C41                                      | 0~85                    |                 |

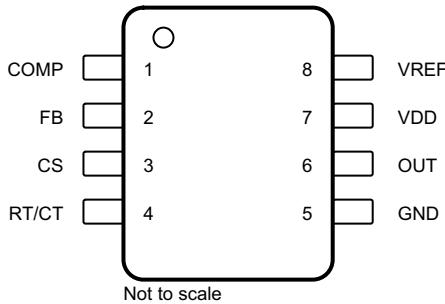

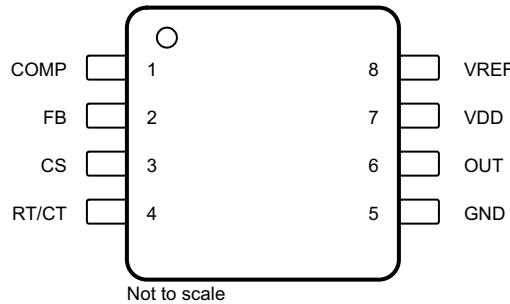

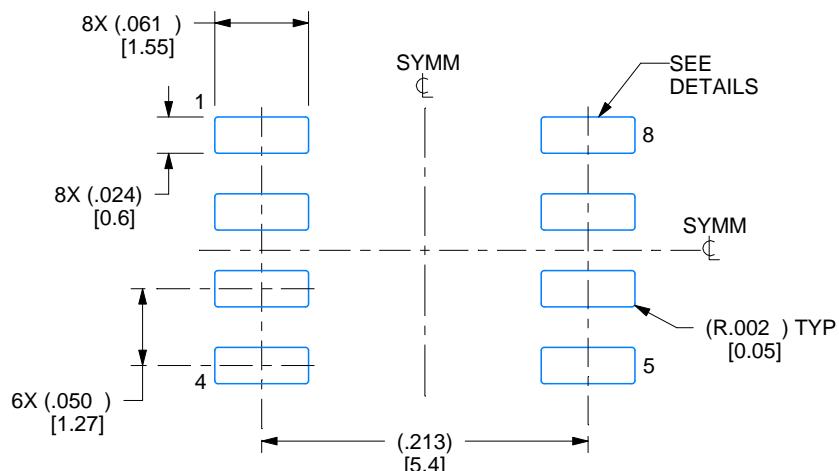

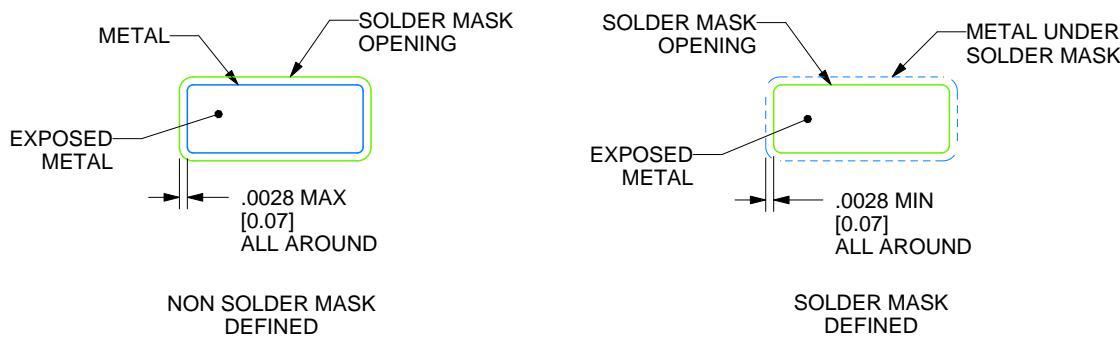

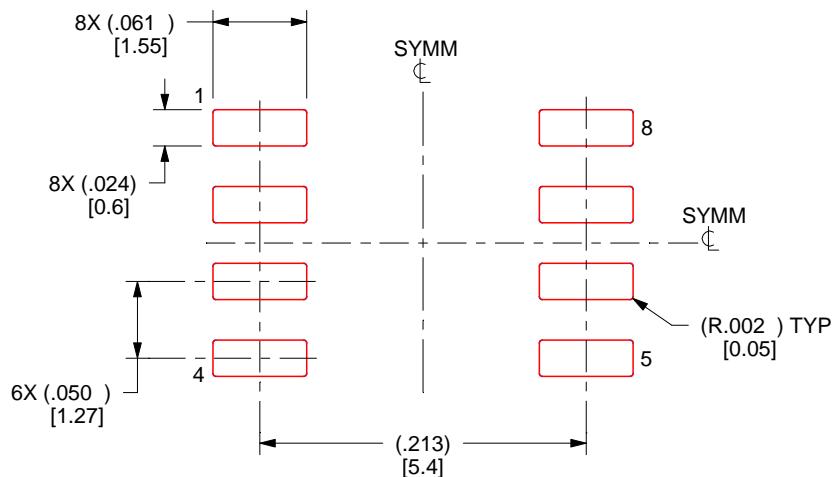

## 5 ピン構成および機能

図 5-1. D パッケージ、8 ピン SOIC (上面図)

図 5-2. DGK パッケージ、8 ピン VSSOP (上面図)

表 5-1. ピンの機能

| ピン    |    | 種類 <sup>(1)</sup> | 説明                                                                                                                                                                                                                                                                                                                                                  |

|-------|----|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称    | 番号 |                   |                                                                                                                                                                                                                                                                                                                                                     |

| COMP  | 1  | O                 | このピンは、補償のためのエラー アンプの出力として機能します。また、2 次側と 1 次側の間の絶縁境界越しに光アイソレータ経由でエラー信号を送信するために 2 次側エラー アンプを利用することで、COMP ピンは制御ポートとしてしばしば使用されます。エラー アンプは内部的に電流制限されるため、ユーザーは COMP を外部で GND に強制的に接続することでゼロ デューティ サイクルを指定できます。                                                                                                                                            |

| CS    | 3  | I                 | 1 次側電流検出ピン。電流検出ピンは、PWM コンバレータへの非反転入力です。電流検出抵抗に接続します。この信号は、エラー アンプの出力電圧に比例する信号と比較されます。PWM はこの信号を使用して、OUT スイッチの導通を終了します。電圧ランプをこのピンに適用して、電圧モード制御構成でデバイスを動作させることができます。                                                                                                                                                                                  |

| FB    | 2  | I                 | このピンはエラー アンプの反転入力です。FB を使用してパワー コンバータの電圧帰還ループを制御し、安定性を確保します。エラー アンプの非反転入力は、内部的に $2.5V \pm 1\%$ に調整されています。                                                                                                                                                                                                                                           |

| GND   | 5  | —                 | 出力ドライバ段とロジック レベル コントローラ部のグランドリターン ピン。                                                                                                                                                                                                                                                                                                               |

| OUT   | 6  | O                 | オンチップ駆動段の出力。OUT は、MOSFET を直接駆動することを目的としています。UCCx8C40、UCCx8C42、UCCx8C43 の OUT ピンは、発振器と同じ周波数でスイッチングされ、100% に近いデューティ サイクルで動作できます。UCCx8C41、UCCx8C44、UCCx8C45 では、内部 T フリップ フロップにより、OUT の周波数は発振器の周波数の半分になります。これにより、最大デューティ サイクルが 50% 未満に制限されます。最大 1A のピーク電流が、このピンからソースおよびシンクされます。VDD がターンオン スレッショルドを下回ると、OUT はアクティブに Low に保持されます。                         |

| RT/CT | 4  | I/O               | 固定周波数発振器の設定ポイント。このピンから、タイミング抵抗 ( $R_{RT}$ ) を VREF に、タイミング コンデンサ ( $C_{CT}$ ) を GND に接続して、スイッチング周波数を設定します。最高の性能を得るには、タイミング コンデンサからデバイスの GND へのリードができるだけ短く、直線的にします。可能であれば、タイミング コンデンサと他のすべての機能に別々のグランド配線を使用します。UCCx8C40、UCCx8C42、UCCx8C43 のゲート駆動のスイッチング周波数 ( $f_{sw}$ ) は $f_{osc}$ に等しく、UCCx8C41、UCCx8C44、UCCx8C45 のスイッチング周波数は $f_{osc}$ の半分に等しいです。 |

| VDD   | 7  | I                 | デバイスに電力を供給するアナログ コントローラ バイアス入力。合計 VDD 電流は、静止 VDD 電流と平均 OUT 電流の和です。このピンには、最小のパターン長で GND に直接接続されたバイパスコンデンサ (通常 $0.1\mu F$ ) が必要です。VDD には、設計で使用するメイン スイッチング FET のゲート容量の 10 倍以上の追加容量が必要です。                                                                                                                                                              |

| VREF  | 8  | O                 | 5V のリファレンス電圧。VREF は、タイミング抵抗を経由して発振器のタイミング コンデンサに充電電流を供給するために使用されます。リファレンスの安定性のため、セラミック コンデンサをピンのできるだけ近くに接続して VREF を GND にバイパスすることが重要です。 $0.1\mu F$ 以上のセラミックが必要です。VREF の外部負荷に、追加の VREF バイパスが必要です。                                                                                                                                                    |

(1) I = 入力、O = 出力、G = グランド

## 6 仕様

### 6.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り) <sup>(1)</sup> <sup>(2)</sup>

|                                     |                  | 最小値  | 最大値 | 単位   |

|-------------------------------------|------------------|------|-----|------|

| 入力電圧                                | VDD              | 20   |     | V    |

| 入力電流                                | IVDD             | 30   |     | mA   |

| 出力駆動電流 (ピーク)                        |                  | ±1   |     | A    |

| 出力エネルギー (容量性負荷)、E <sub>OUT</sub>    |                  | 5    |     | μJ   |

| アナログ入力電圧                            | COMP、CS、FB、RT/CT | -0.3 | 6.3 | V    |

| 出力ドライバ電圧                            | OUT              | -0.3 | 20  |      |

| リファレンス電圧                            | VREF             | 7    |     |      |

| エラー アンプの出力シンク電流                     | COMP             | 10   |     | mA   |

| 総合許容損失 ( $T_A = 25^\circ\text{C}$ ) | D パッケージ          | 72.3 |     | °C/W |

|                                     | DGK パッケージ        | 98.1 |     |      |

| リード温度 (半田付け、10 秒)、T <sub>LEAD</sub> |                  | 300  |     | °C   |

| 動作時の接合部温度、T <sub>J</sub>            |                  | -55  | 150 | °C   |

| 保管温度、T <sub>stg</sub>               |                  | -65  | 150 | °C   |

- (1) 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみについて示しており、このデータシートのセクション 6.3 に示された値を超える状態で本製品が正常に動作することを暗黙的に示すものではありません。絶対最大定格の状態が長時間続くと、デバイスの信頼性に影響を与える可能性があります。

- (2) すべての電圧は GND ピンを基準にしています。電流は、指定されたピンに流れ込む方向が正、ピンから流れ出る方向が負です。

## 6.2 ESD 定格

|             |      | 値                                                      | 単位         |

|-------------|------|--------------------------------------------------------|------------|

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>   | $\pm 2500$ |

|             |      | デバイス帶電モデル (CDM)、JEDEC 仕様 JESD22-C101 準拠 <sup>(2)</sup> | $\pm 1500$ |

(1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

(2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

## 6.3 推奨動作条件

自由空気での動作温度範囲内 (特に記述のない限り)

|                 |                                       | 最小値      | 最大値 | 単位  |

|-----------------|---------------------------------------|----------|-----|-----|

| $V_{VDD}$       | 入力電圧                                  |          | 18  | V   |

| $V_{OUT}$       | 出力ドライバ電圧                              |          | 18  | V   |

| $V_{REF}$       | 外部回路からの最大連続電圧                         |          | 5.5 | V   |

| $I_{OUT}$       | 平均出力ドライバ電流 (ソースおよびシンク) <sup>(1)</sup> |          | 200 | mA  |

| $I_{OUT(VREF)}$ | リファレンス出力電流 (ソース) <sup>(1)</sup>       |          | 20  | mA  |

| $T_J$           | 動作時接合部温度 <sup>(1)</sup>               | UCC28C4x | -40 | 125 |

|                 |                                       | UCC38C4x | 0   | 85  |

(1) テキサス・インストルメンツは、この表に規定された条件を超えて長時間にわたって本デバイスを動作させないことを推奨します。

## 6.4 热に関する情報

| 热評価基準 <sup>(1)</sup>  |                   | UCC28C4x, UCC38C4x |                | 単位   |

|-----------------------|-------------------|--------------------|----------------|------|

|                       |                   | D<br>(SOIC)        | DGK<br>(VSSOP) |      |

|                       |                   | 8 ピン               | 8 ピン           |      |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗      | 128.9              | 176.4          | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース(上面)への熱抵抗 | 71.7               | 67.3           | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗      | 72.3               | 98.1           | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への特性パラメータ  | 23.4               | 11.1           | °C/W |

| Ψ <sub>JB</sub>       | 接合部から基板への特性パラメータ  | 71.5               | 91.5           | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーションレポートを参照してください。

## 6.5 電気的特性

V<sub>VDD</sub> = 15V <sup>(1)</sup>、R<sub>RT</sub> = 10kΩ、C<sub>CT</sub> = 3.3nF、C<sub>VDD</sub> = 0.1μF、出力は無負荷、UCC28C4x の場合 T<sub>J</sub> = -40°C~125°C、UCC38C4x の場合 T<sub>J</sub> = 0°C~85°C (特に記述のない限り)。

| パラメータ             | テスト条件                    | 最小値                                                                | 代表値                    | 最大値  | 単位    |

|-------------------|--------------------------|--------------------------------------------------------------------|------------------------|------|-------|

| リファレンス            |                          |                                                                    |                        |      |       |

| V <sub>VREF</sub> | V <sub>REF</sub> 電圧、初期精度 | T <sub>J</sub> = 25°C、I <sub>OUT</sub> = 1mA                       | 4.9                    | 5    | 5.1   |

|                   | ライン レギュレーション             | V <sub>VDD</sub> = 12V~18V                                         | 0.2                    | 20   | mV    |

|                   | 負荷レギュレーション               | 1mA~20mA                                                           | 3                      | 25   | mV    |

|                   | 温度安定性                    | (2) を参照してください。                                                     | 0.2                    | 0.4  | mV/°C |

|                   | 総出力変動                    | (2) を参照してください。                                                     | 4.82                   | 5.18 | V     |

|                   | V <sub>REF</sub> ノイズ電圧   | 10Hz~10kHz、T <sub>J</sub> = 25°C、(2) を参照                           | 50                     |      | μV    |

|                   | 長期的安定性                   | 1000 時間、T <sub>J</sub> = 125°C、(2) を参照                             | 5                      | 25   | mV    |

| I <sub>VREF</sub> | 出力短絡電流(ソース電流)            |                                                                    | 30                     | 45   | 55    |

| 発振器               |                          |                                                                    |                        |      |       |

| f <sub>osc</sub>  | 初期精度                     | T <sub>J</sub> = 25°C、(3) を参照                                      | 50.5                   | 53   | 55    |

|                   | 電圧安定性                    | 12V ≤ V <sub>VDD</sub> ≤ 18V                                       | 0.2%                   | 1%   |       |

|                   | 温度安定性                    | T <sub>J(MIN)</sub> ~T <sub>J(MAX)</sub> 、(2) を参照                  | 1%                     | 2.5% |       |

|                   | 振幅                       | RT/CT ピンのピークツーピーク電圧                                                | 1.9                    |      | V     |

|                   | 放電電流                     | T <sub>J</sub> = 25°C、V <sub>RT/CT</sub> = 2V、(4) を参照              | 7.7                    | 8.4  | 9     |

|                   |                          | V <sub>RT/CT</sub> = 2V、(4) を参照                                    | 7.2                    | 8.4  | 9.5   |

| エラー アンプ           |                          |                                                                    |                        |      |       |

| V <sub>FB</sub>   | 帰還入力電圧、初期精度              | V <sub>COMP</sub> = 2.5V、T <sub>J</sub> = 25°C                     | 2.475                  | 2.5  | 2.525 |

|                   | 帰還入力電圧、全変動               | V <sub>COMP</sub> = 2.5V                                           | 2.45                   | 2.5  | 2.55  |

| I <sub>FB</sub>   | 入力バイアス電流(ソース電流)          | V <sub>FB</sub> = 5V                                               | 0.1                    | 2    | μA    |

| A <sub>VOL</sub>  | 開ループ電圧ゲイン                | 2V ≤ V <sub>OUT</sub> ≤ 4V                                         | 65                     | 90   | dB    |

|                   | ユニティ ゲイン 帯域幅             | (2) を参照してください。                                                     | 1                      | 1.5  | MHz   |

| PSRR              | 電源除去比                    | 12V ≤ V <sub>VDD</sub> ≤ 18V                                       | 60                     |      | dB    |

|                   | 出力シンク電流                  | V <sub>FB</sub> = 2.7V、V <sub>COMP</sub> = 1.1V                    | 2                      | 14   | mA    |

|                   | 出力ソース電流                  | V <sub>FB</sub> = 2.3V、V <sub>COMP</sub> = 5V                      | 0.5                    | 1    | mA    |

|                   | 出力ソース電流(2)               | V <sub>FB</sub> ≤ 2.3V、V <sub>COMP</sub> = 0V                      |                        | 5.5  | mA    |

| VOH               | High レベル COMP 電圧         | V <sub>FB</sub> = 2.3V、R <sub>COMP</sub> = 15kΩ を COMP と GND の間に接続 | V <sub>REF</sub> - 0.2 |      | V     |

$V_{VDD} = 15V$  (1)、 $R_{RT} = 10k\Omega$ 、 $C_{CT} = 3.3nF$ 、 $C_{VDD} = 0.1\mu F$ 、出力は無負荷、UCC28C4x の場合  $T_J = -40^{\circ}C \sim 125^{\circ}C$ 、UCC38C4x の場合  $T_J = 0^{\circ}C \sim 85^{\circ}C$  (特に記述のない限り)。

| パラメータ               | テスト条件                                                        | 最小値 | 代表値 | 最大値 | 単位 |

|---------------------|--------------------------------------------------------------|-----|-----|-----|----|

| VOL Low レベル COMP 電圧 | $V_{FB} = 2.7V$ 、 $R_{COMP} = 15k\Omega$ を COMP と VREF の間に接続 | 0.1 | 1.1 |     | V  |

$V_{VDD} = 15V$  (1)、 $R_{RT} = 10k\Omega$ 、 $C_{CT} = 3.3nF$ 、 $C_{VDD} = 0.1\mu F$ 、出力は無負荷、UCC28C4x の場合  $T_J = -40^{\circ}C \sim 125^{\circ}C$ 、UCC38C4x の場合  $T_J = 0^{\circ}C \sim 85^{\circ}C$  (特に記述のない限り)。

| パラメータ           |                    | テスト条件                                       | 最小値  | 代表値  | 最大値  | 単位       |

|-----------------|--------------------|---------------------------------------------|------|------|------|----------|

| 電流検出            |                    |                                             |      |      |      |          |

| $A_{CS}$        | ゲイン                | (5) (6) を参照                                 | 2.85 | 3    | 3.15 | V/V      |

| $V_{CS}$        | 最大入力信号             | $V_{FB} < 2.4V$                             | 0.9  | 1    | 1.1  | V        |

| $PSRR$          | 電源除去比              | $V_{VDD} = 12V \sim 18V$ (2) (5)            |      | 70   |      | dB       |

| $I_{CS}$        | 入力バイアス電流 (ソース電流)   |                                             |      | 0.1  | 2    | $\mu A$  |

| $t_D$           | CS から出力までの遅延       |                                             |      | 35   | 70   | ns       |

|                 | COMP から CS へのオフセット | $V_{CS} = 0V$                               |      | 1.15 |      | V        |

| 出力              |                    |                                             |      |      |      |          |

| $V_{OUT(low)}$  | $R_{DS(on)}$ プルダウン | $I_{SINK} = 200mA$                          | 5.5  | 15   |      | $\Omega$ |

| $V_{OUT(high)}$ | $R_{DS(on)}$ プルアップ | $I_{SOURCE} = 200mA$                        |      | 10   | 25   | $\Omega$ |

| $t_{RISE}$      | 立ち上がり時間            | $T_J = 25^{\circ}C, C_{OUT} = 1nF$          |      | 25   | 50   | ns       |

| $t_{FALL}$      | 立ち下がり時間            | $T_J = 25^{\circ}C, C_{OUT} = 1nF$          |      | 20   | 40   | ns       |

| 低電圧誤動作防止        |                    |                                             |      |      |      |          |

| $V_{DD_{ON}}$   | 開始スレッショルド          | UCCx8C42、UCCx8C44                           | 13.5 | 14.5 | 15.5 | V        |

|                 |                    | UCCx8C43、UCCx8C45                           | 7.8  | 8.4  | 9    |          |

|                 |                    | UCCx8C40、UCCx8C41                           | 6.5  | 7    | 7.5  |          |

| $V_{DD_{OFF}}$  | 最小動作電圧             | UCCx8C42、UCCx8C44                           | 8    | 9    | 10   | V        |

|                 |                    | UCCx8C43、UCCx8C45                           | 7    | 7.6  | 8.2  |          |

|                 |                    | UCCx8C40、UCCx8C41                           | 6.1  | 6.6  | 7.1  |          |

| PWM             |                    |                                             |      |      |      |          |

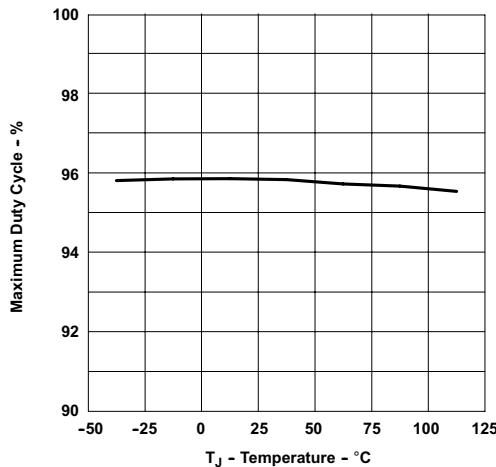

| $D_{MAX}$       | 最大デューティ サイクル       | UCCx8C42、UCCx8C43、UCCx8C40、 $V_{FB} < 2.4V$ | 94%  | 96%  |      |          |

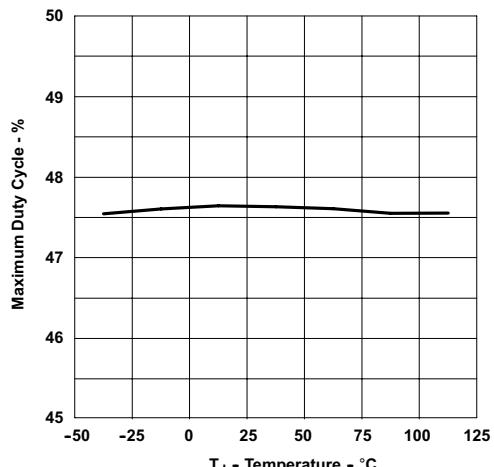

|                 |                    | UCCx8C44、UCCx8C45、UCCx8C41、 $V_{FB} < 2.4V$ | 47%  | 48%  |      |          |

| $D_{MIN}$       | 最小デューティ サイクル       | $V_{FB} > 2.6V$                             |      |      | 0%   |          |

| 電源電流            |                    |                                             |      |      |      |          |

| $I_{START-UP}$  | スタートアップ電流          | $V_{VDD} = V_{DD_{ON}} - 0.5V$              | 50   | 100  |      | $\mu A$  |

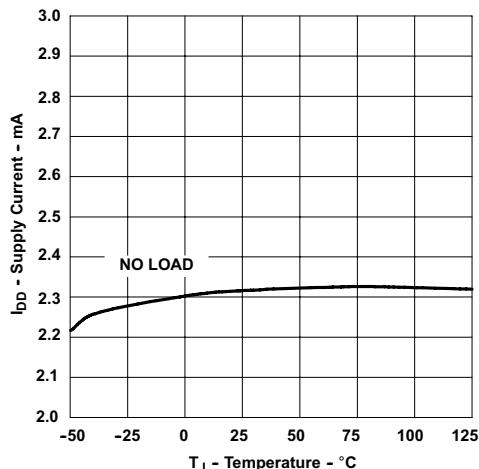

| $I_{VDD}$       | 動作電源電流             | $V_{FB} = V_{CS} = 0V$                      |      | 2.3  | 3    | mA       |

- (1)  $V_{VDD}$  は、開始スレッショルドより高く調整してから、15.5V に設定します。

- (2) 設計により規定されています。実製品の検査は行っていません。

- (3) UCCx8C41、UCCx8C44、UCCx8C45 の出力周波数は発振器周波数の半分です。

- (4) 発振器の放電電流は、VREF に接続された  $R_{RT} = 10k\Omega$  を使って測定されます。

- (5)  $V_{FB} = 0V$  の条件で、ラッチのトリップポイントで測定されたパラメータ。

- (6) ゲインは  $A_{CS} = \Delta V_{COMP}/\Delta V_{CS}$  で定義され、 $0V \leq V_{CS} \leq 900mV$  です。

## 6.6 代表的特性

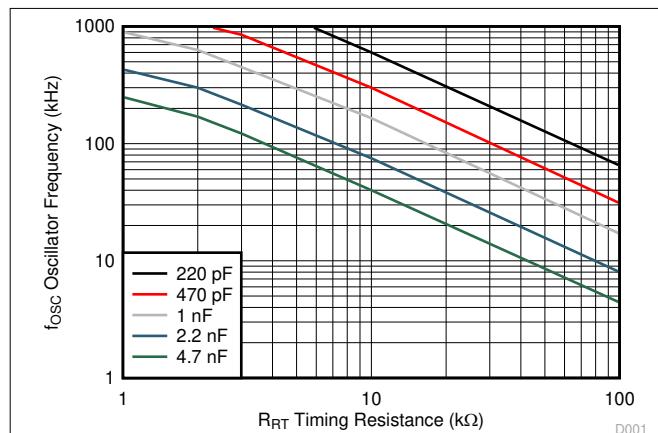

図 6-1. 発振器の周波数とタイミング抵抗および容量との関係

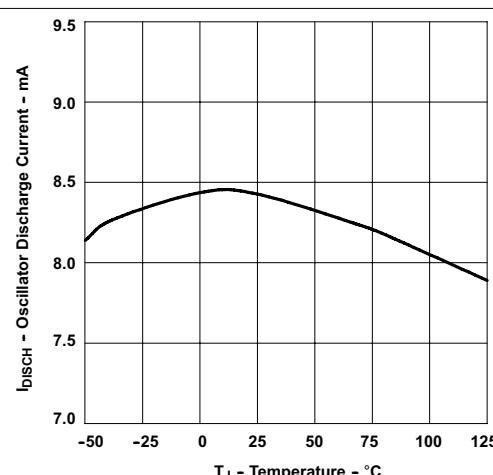

図 6-2. 発振器の放電電流と温度との関係

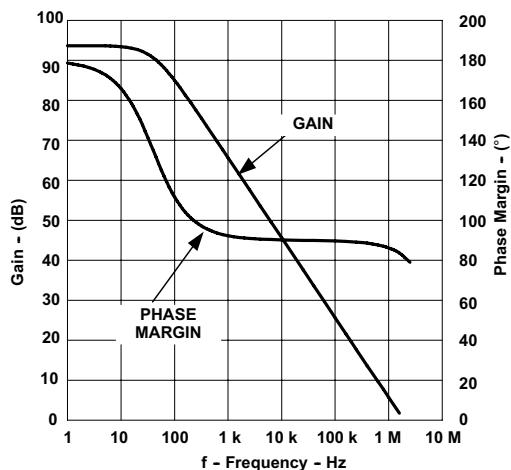

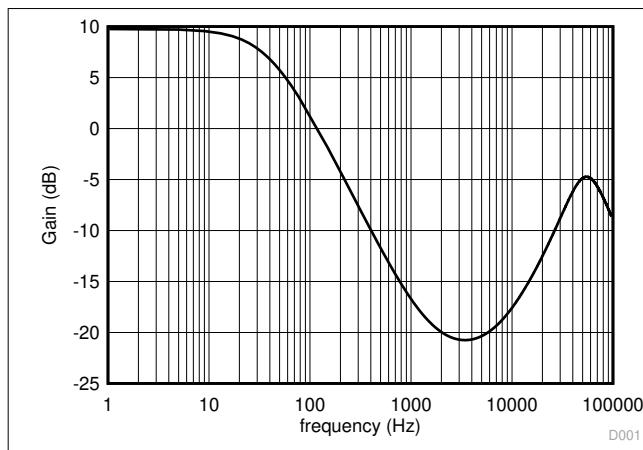

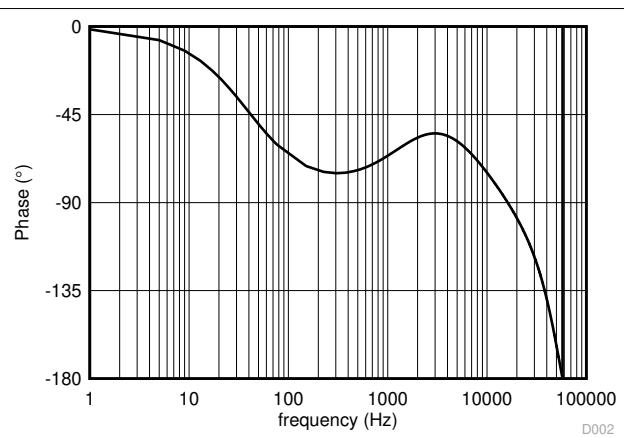

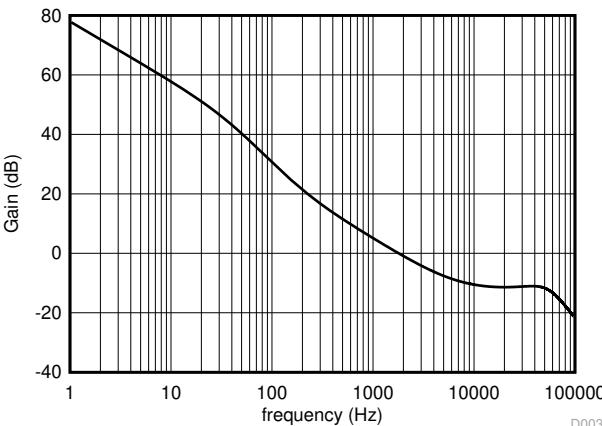

図 6-3. エラー アンプの周波数応答

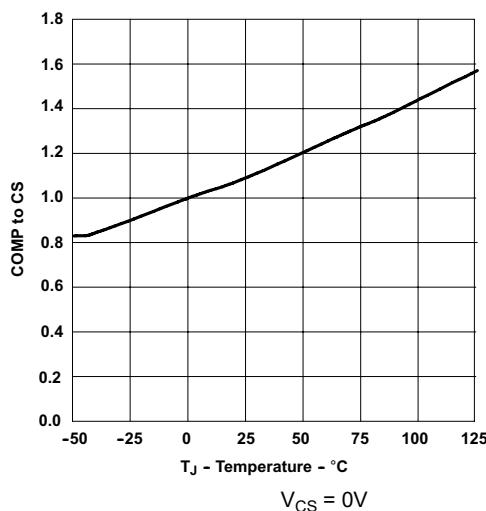

図 6-4. COMP-CS オフセット電圧と温度との関係

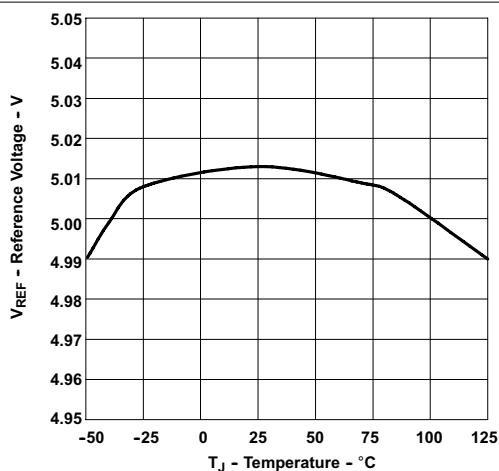

図 6-5. 基準電圧と温度との関係

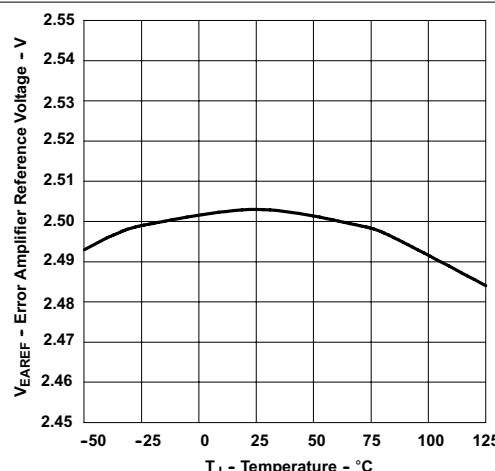

図 6-6. エラー アンプの基準電圧と温度との関係

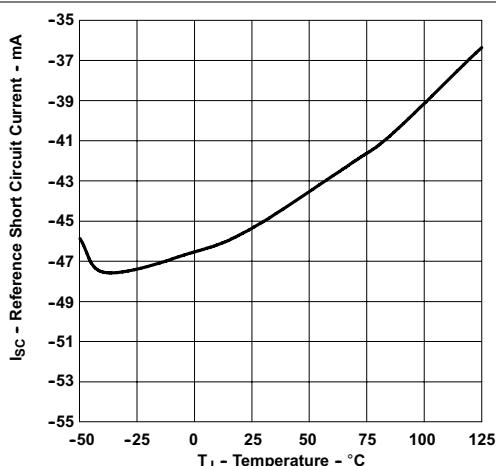

図 6-7. 基準電圧の短絡電流と温度との関係

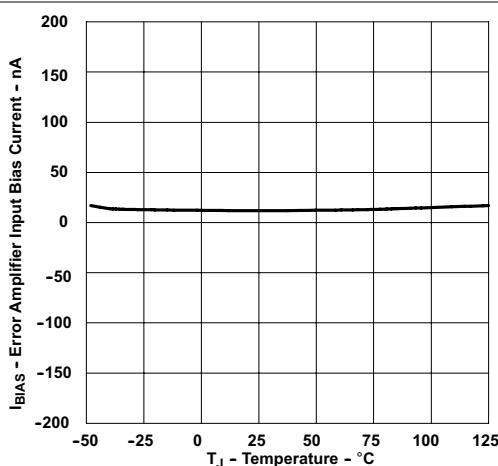

図 6-8. エラー アンプの入力バイアス電流と温度との関係

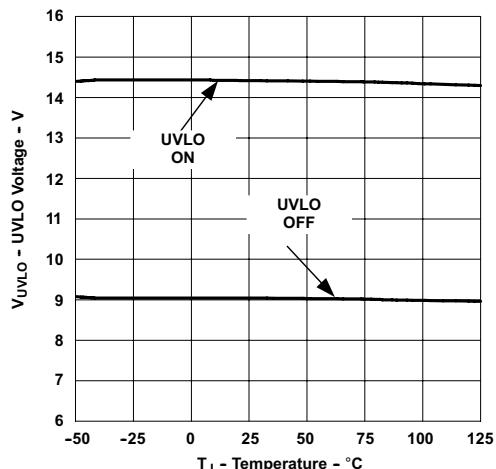

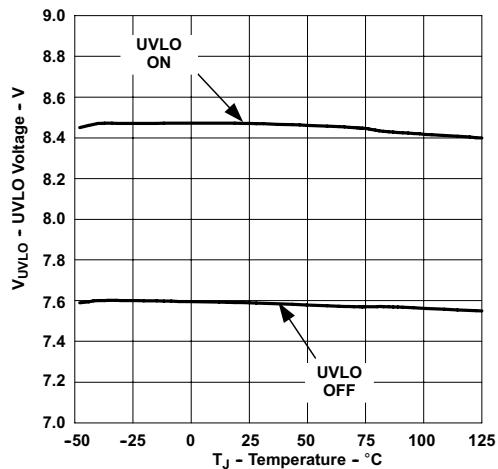

図 6-9. 低電圧誤動作防止と温度との関係

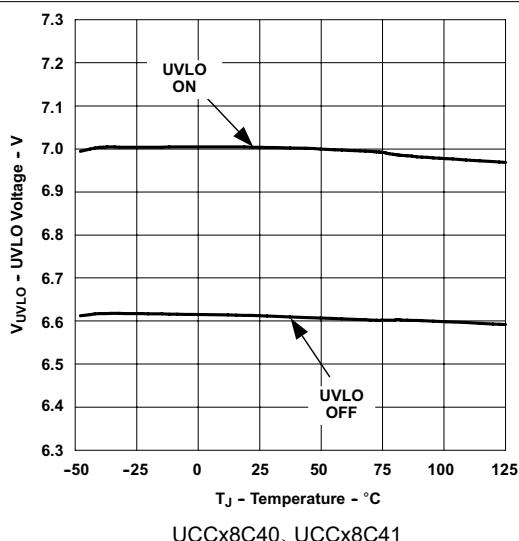

図 6-10. 低電圧誤動作防止と温度との関係

図 6-11. 低電圧誤動作防止と温度との関係

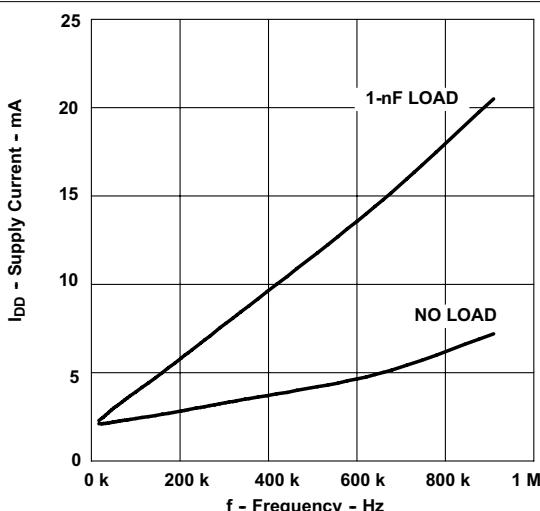

図 6-12. 消費電流と発振器周波数との関係

図 6-13. 電源電流と温度との関係

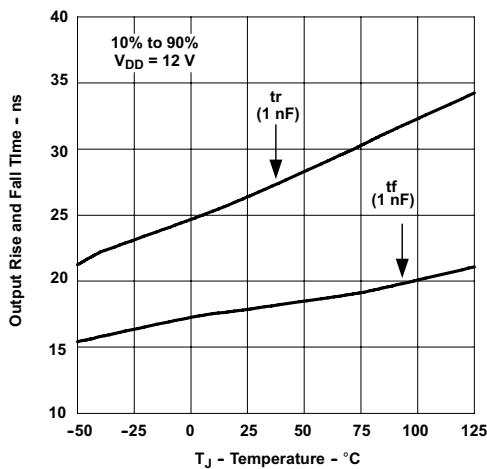

図 6-14. 出力の立ち上がりおよび立ち下がり時間と温度との関係

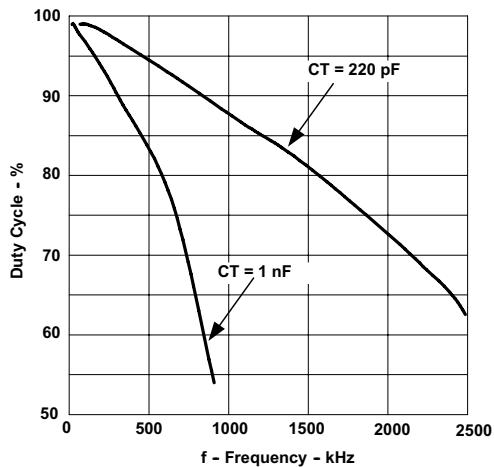

図 6-15. 最大デューティ サイクルと発振器周波数との関係

図 6-16. 最大デューティ サイクルと温度との関係 (最大デューティ サイクルが 100% のデバイス)

図 6-17. 最大デューティ サイクルと温度との関係 (最大デューティ サイクルが 50% のデバイス)

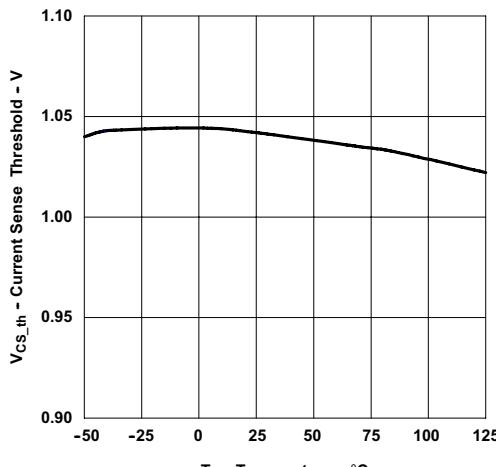

図 6-18. 電流検出スレッショルド電圧と温度との関係

図 6-19. 電流検出から出力までの遅延時間と温度との関係

## 7 詳細説明

### 7.1 概要

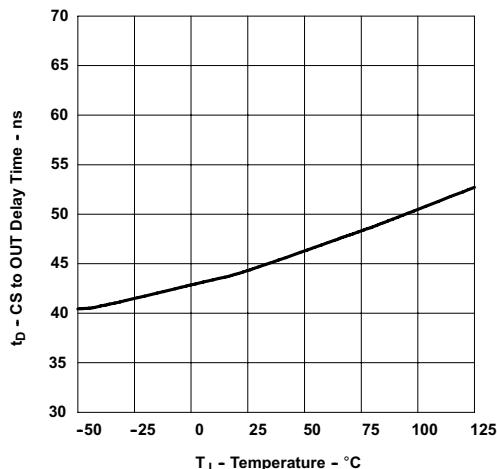

UCCx8C4x シリーズの制御 IC には、AC-DC または DC-DC 固定周波数の電流モード制御スキーマを最小限の外付け部品で実装するために必要な機能が搭載されています。保護回路には、低電圧誤動作防止 (UVLO) と電流制限が含まれます。内部回路では、スタートアップ電流が  $100\mu\text{A}$  未満で、エラー アンプ入力で高精度のリファレンス電圧がトリムされて正確性を実現します。ラッチ動作を保証するロジック、電流制限御の機能を持つパルス幅変調 (PWM) コンパレータ、および高いピーク電流をソースまたはシンクするように設計された出力段が内蔵されています。出力段は N チャネル MOSFET の駆動に適しており、オフ状態では Low になります。発振器には、最大デューティ サイクルとデッドタイム制限を正確に設定できる放電電流調整機能が備わっているため、本デバイスは高速アプリケーションに適しています。

このシリーズに属する製品間の主な違いは、UVLO スレッショルド、許容可能な周囲温度範囲、最大デューティ サイクルです。UVLO スレッショルドの標準値は、UCCx8C42 および UCCx8C44 デバイスでは  $14.5\text{V}$  (オン) と  $9\text{V}$  (オフ) で、オフラインの AC-DC アプリケーションに理想的です。UCCx8C43 および UCCx8C45 デバイスは、対応する標準スレッショルドが  $8.4\text{V}$  (オン) と  $7.6\text{V}$  (オフ) で、DC-DC アプリケーションで使用されるレギュレートされた入力電圧での使用に理想的です。UCCx8C40 と UCCx8C41 は、スタートアップ スレッショルドが  $7\text{V}$ 、ターンオフ スレッショルドが  $6.6\text{V}$  (オフ) であるため、バッテリ駆動のアプリケーションに適しています。UCCx8C40、UCCx8C42、UCCx8C43 デバイスは、 $100\%$  に近いデューティ サイクルで動作します。UCCx8C41、UCCx8C44、UCCx8C45 は、1 クロック サイクルおきに出力をオフにするトグル フリップ フロップを内部に追加することで、 $0\% \sim 50\%$  のデューティ サイクルを実現しています。UCC28C4x シリーズは  $-40^\circ\text{C} \sim 125^\circ\text{C}$  での動作が規定されており、UCC38C4x シリーズは  $0^\circ\text{C} \sim 85^\circ\text{C}$  での動作が規定されています。

UCC28C4x および UCC38C4x シリーズは、バイポーラの UC284x、UC384x、UC284xA、UC384xA ファミリとピン互換の、性能を向上させた代替品です。この新しいシリーズは、類似の機能を持つ従来のバイポーラ デバイスとその他の競合 BiCMOS デバイスと比較して、性能が向上しています。これらの改善は通常、旧製品の定格仕様の限度値をより厳しくするという形で行われるため、ドロップイン機能は維持されます。これらの改善により、新規設計では、従来のデバイスと比較して、部品点数を低減させ、回路性能を向上させることができます。

## 7.2 機能ブロック図

UCCx8C41、UCCx8C44、UCCx8C45 のみで使われているトグル フリップ フロップ

## 7.3 機能説明

BiCMOS 設計は、従来のバイポーラ デバイスでは実現できなかった高い周波数での動作を可能にします。第 1 に、従来のデバイスの約半分の時間で外部パワー スイッチを駆動するため、出力段が再設計されました。第 2 に、内部発振器はより堅牢であり、周波数が上がっても変動が小さくなっています。このように発振器が高速であるため、このデバイスは高速アプリケーションに適しています。また、放電電流調整機能により、最大デューティ サイクルおよびデッドタイム制限値を正確に設定できます。また、電流検出から出力までの遅延は 45ns (標準値) に保たれています。電流検出のこのような遅延時間は、パワー スイッチの優れた過負荷保護特性をもたらします。このデバイスの小さいスタートアップ電流は、スタートアップ抵抗での定常状態での消費電力を最小化し、小さい動作電流は動作中の効率を最大化し、オフライン回路、DC 入力回路、バッテリ駆動回路のいずれを動作させる場合でも、回路全体の効率を向上させます。これらの機能を組み合わせることで、高い周波数で確実に動作できるデバイスを実現しています。

表 7-1. 向上した主要パラメータ

| パラメータ             | UCCx8C4x         | UCx84x |

|-------------------|------------------|--------|

| 50 kHz 時の消費電流     | 2.3mA            | 11mA   |

| スタートアップ電流         | 50µA             | 1mA    |

| 過電流伝搬遅延           | 50ns             | 150ns  |

| 基準電圧精度            | ±1%              | ±2%    |

| エラー アンプ基準電圧精度     | ± 25mV           | ± 80mV |

| 最大発振器周波数          | > 1MHz           | 500kHz |

| 出力立ち上がり / 立ち下がり時間 | 25ns             | 50ns   |

| UVLO ターンオン精度      | ± 1V             | ± 1.5V |

| 最小パッケージ オプション     | VSSOP-8 (MSOP-8) | SOIC-8 |

## 7.3.1 ピンの詳細説明

### 7.3.1.1 COMP

UCCx8C4x ファミリのエラー アンプは 1.5MHz のユニティ ゲイン帯域幅を持っています。COMP 端子は、ソース電流とシンク電流の両方に対応できます。エラー アンプは内部的に電流制限されているため、COMP を外部から GND に接続することでゼロ デューティ サイクルを指定できます。

### 7.3.1.2 FB

FB は、エラー アンプの反転入力です。エラー アンプへの非反転入力は内部で  $2.5V \pm 1\%$  に調整されています。FB を使用してパワー コンバータの電圧帰還ループを制御し、安定性を確保します。最大の安定性を得るため、FB リードの長さはできるだけ短くし、FB の浮遊容量をできるだけ少なくします。

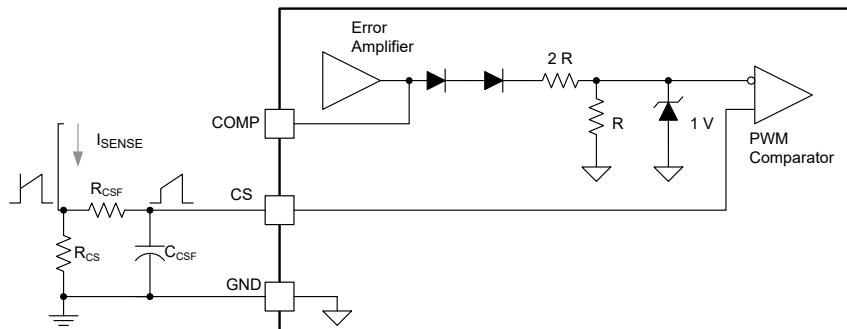

### 7.3.1.3 CS

UCCx8C4x の電流センス入力は、PWM コンパレータに直接接続します。CS は、MOSFET のソース電流検出抵抗に接続します。PWM はこの信号を使用して、OUT スイッチの導通を終了します。電圧ランプをこのピンに適用して、電圧モード制御構成でデバイスを動作させるか、勾配補償を追加できます。リーディング エッジノイズによる誤トリガを防止するため、RC 電流検出フィルタが必要なことがあります。電流検出アンプのゲインは、通常  $3V/V$  です。

### 7.3.1.4 RT/CT

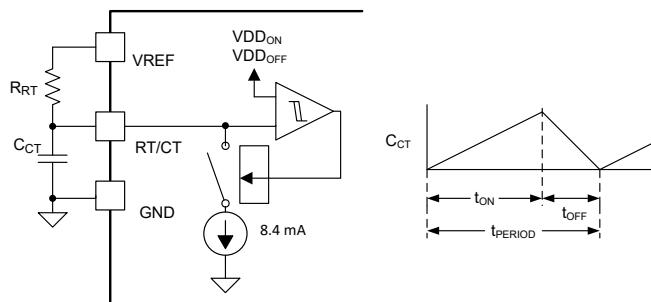

内部発振器は、タイミング コンデンサ ( $C_{CT}$ ) とタイミング抵抗 ( $R_{RT}$ ) を使用して、発振器の周波数と最大デューティ サイクルをプログラムします。動作周波数は、「発振器周波数とタイミング抵抗および容量との関係」の曲線に基づいてプログラムできます。これらのグラフでは、タイミング コンデンサを選択すると、タイミング抵抗を求めることができます。タイミング コンデンサには温度係数がフラットなものを選択してください。ほとんどの COG や NPO タイプのコンデンサは、この条件を満たします。このコンバータの場合、110kHz のスイッチングで動作するように、 $R_{RT}$  と  $C_{CT}$  として  $15.4k\Omega$  と  $1000pF$  が選択されています。

### 7.3.1.5 GND

GND は、グランドに戻る信号と電力です。信号がスイッチング電流の影響を受けないように、信号のリターン パスと大電流のゲートドライバ パスは分離することをお勧めします。

### 7.3.1.6 OUT

UCCx8C4x の大電流出力段は、従来のデバイスの約半分の時間で外部パワー スイッチを駆動するように再設計されています。パワー MOSFET を直接駆動するため、トーテムポール OUT ドライバは最大 1A のピーク電流をシンクまたはソースします。UCCx8C40、UCCx8C42、UCCx8C43 デバイスの OUT は、発振器と同じ周波数でスイッチングし、100% に近いデューティ サイクルで動作できます。UCCx8C41、UCCx8C44、UCCx8C45 では、内部 T フリップ フロップにより、OUT のスイッチング周波数は発振器の半分になります。これにより、UCCx8C41、UCCx8C44、UCCx8C45 の最大デューティ サイクルは 50% 未満に制限されます。

UCCx8C4x ファミリは、上側レールに対するインピーダンスが  $10\Omega$  (標準値) を示し、グランドに対するインピーダンスが  $5.5\Omega$  (標準値) を示す独自のトーテムポールドライバを備えています。このようにローサイド スイッチのインピーダンスが小さいため、パワー MOSFET のターンオフ損失を最小限に抑えることができます。一方、ハイサイド スイッチのより大きいターンオン インピーダンスは、多くの高速出力整流器の逆方向回復特性とよく調和することを目的としています。立ち上がりエッジと立ち下がりエッジの遷移時間 (電圧が 10% から 90% まで変化する時間) の標準値はそれぞれ 25ns と 20ns です。

バイポーラトランジスタと並列接続された低インピーダンス MOS 構造 (BiCMOS 構造) は、トーテムポール出力構造からなります。このようにシリコンをより効率的に利用することで、高速な遷移と完全なレール ツー レール電圧スイングに加えて、必要とされる大きなピーク電流を実現します。さらに、出力段は自己バイアスであり、低電圧誤動作防止タイプの場合はアクティブ Low です。VDD 電源電圧が印加されていないときに、出力を High にしようとするとき、出力はアクティブに Low をプルします。この状況は、ドライバ負荷としてパワー MOSFET を使って、最初に電源を投入した際にしばしば発生します。

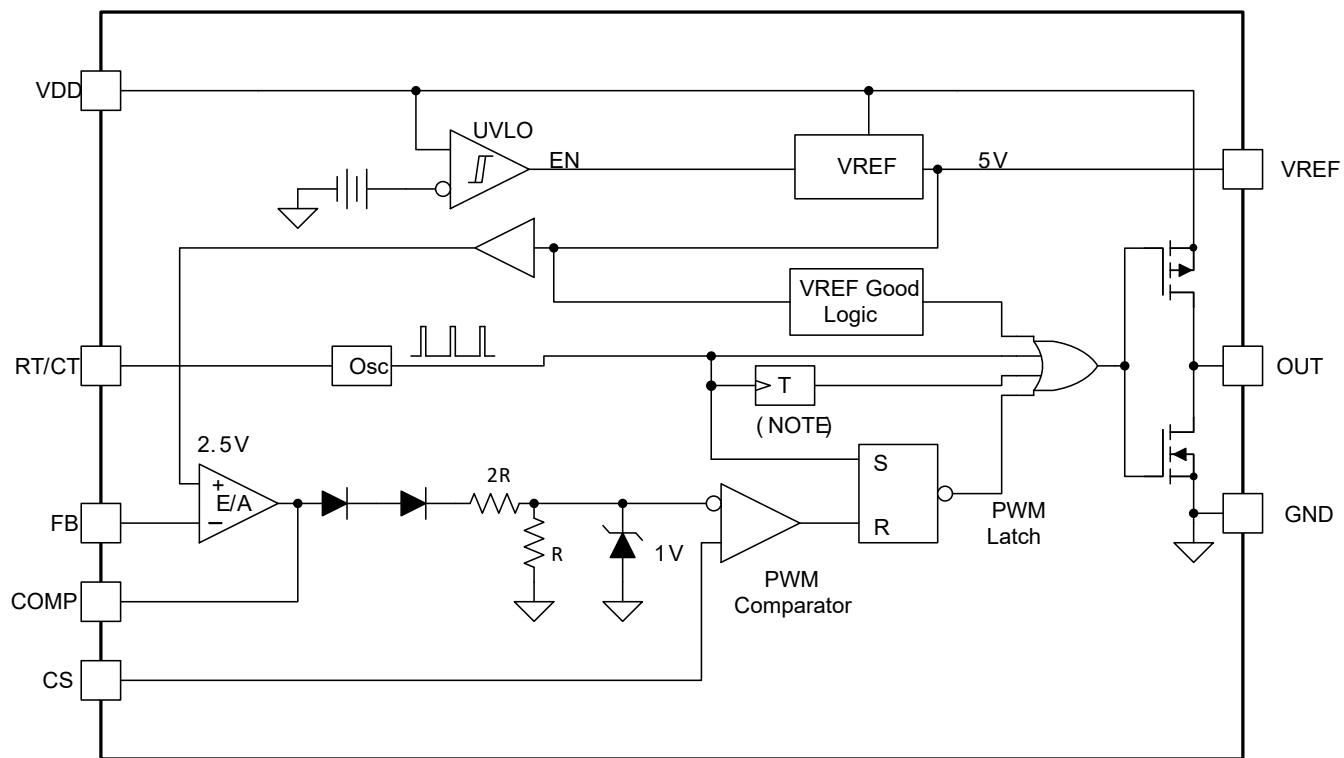

### 7.3.1.7 VDD

VDD は、このデバイスの電源入力接続です。通常動作では、電流制限抵抗を経由して VDD に電力を供給します。存在する可能性がある過渡電圧を含めて、電源電圧の絶対最大定格値は 20V です。この電圧を超えると、デバイスが損傷する可能性があります。これは、入力バイアスピニに最大 30V を印加しても耐えられた従来のバイポーラ デバイスとは対照的です。また、本デバイスには内部クランプが内蔵されていないため、20V のレベルを超える可能性がある外部電源から VDD ピンを保護する必要があります。すべてのラインおよび負荷条件の下で、補助巻線 NA からのスタートアップおよびブートストラップ電源電圧を 20V 未満に抑えることができない場合、VDD と GND の間にツェナー保護ダイオードを接続します。ブートストラップ電源のインピーダンスと配置によっては、ツェナーに流れ込む電流を制限するため、補助巻線と直列に抵抗  $R_{VDD}$  を追加する必要がある可能性があります (図 7-1 を参照)。すべての許容誤差と温度を含めて、最小ツェナー電圧が UVLO 上側ターンオン スレッショルドの最大値よりも大きくなるようにします。ノイズに関連する問題が発生しないように、GND との間に接続されたセラミック バイパスコンデンサで VDD をフィルタ処理します。VDD ピンは、GND ピンのできるだけ近くでデカップリングする必要があります。

図 7-1. VDD 保護

VDD 動作電流の公称値はわずか 2.3mA ですが、OUT 電流次第で、総電源電流はより大きくなります。合計 VDD 電流は、静止 VDD 電流と平均 OUT 電流の合計です。動作周波数と MOSFET ゲート電荷 ( $Q_g$ ) が判明していれば、式 1 から平均 OUT 電流を計算できます。

$$I_{OUT} = Q_g \times f_{SW} \quad (1)$$

### 7.3.1.8 VREF

VREF はエラー アンプの電圧リファレンスで、IC 内にある他の多くの内部回路でも使用されます。UCCx8C4x ファミリの場合、5V リファレンス電圧の公差は  $\pm 1\%$  です。高速スイッチング ロジックは、ロジック電源として VREF を使用します。リファレンス電圧は内部で  $2.5V \pm 1\%$  に分圧され、エラー アンプの非反転入力に接続されることで、出力電圧を正確にリギュレートします。リファレンス電圧は、過電流制限スレッショルドに加えて、発振器上側および下側スレッショルドなどの機能の内部バイアスピニに設定します。出力短絡電流は 55mA (最大値) です。デバイスの過熱と損傷を防止するため、スイッチングを終了させる手段として VREF をグランドにプルすることはしないでください。リファレンス電圧の安定性を確保し、高速スイッチング過渡によるノイズの問題を防止するため、IC パッケージの近くにセラミック コンデンサを配置して、VREF を GND にバイパスします。0.1μF 以上のセラミック コンデンサが必要です。リファレンスの外部負荷には、追加の VREF バイパスが必要です。セラミック コンデンサに加えて電解コンデンサも使用できます。

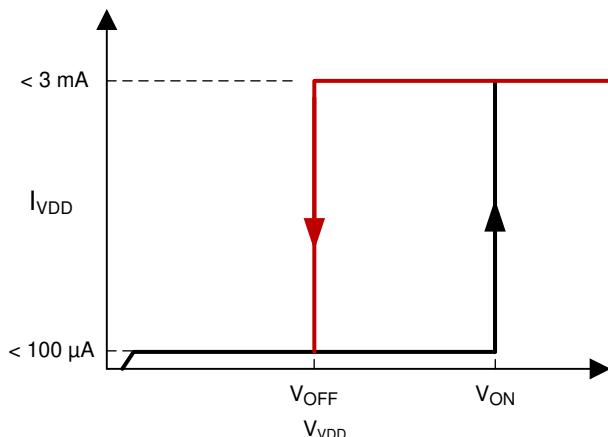

### 7.3.2 低電圧誤動作防止

ターンオンおよびターンオフ スレッショルドがそれぞれ (14.5V および 9V)、(8.4V および 7.6V)、(7V および 6.6V) である 3 組の UVLO スレッショルドが利用できます。最初の組み合わせは主にオフライン 48V 分散電源アプリケーション向けであり、ヒステリシスが広いため、コンバータをより低い周波数で動作させることができ、ソフトスタート時間をより長くできます。2 番目の UVLO の組み合わせは、通常 12VDC 入力で動作する高周波数 DC/DC コンバータに理想的です。最も新しい 3 番目の組み合わせは、バッテリ駆動およびポータブル アプリケーションに対応するために追加されました。[表 7-2](#) に、デバイスごとの最大デューティサイクルと UVLO スレッショルドを示します。

表 7-2. UVLO オプション

| 最大デューティサイクル (%) | UVLO オン (V) | UVLO オフ (V) | 部品番号     |

|-----------------|-------------|-------------|----------|

| 100             | 14.5        | 9           | UCCx8C42 |

| 100             | 8.4         | 7.6         | UCCx8C43 |

| 100             | 7           | 6.6         | UCCx8C40 |

| 50              | 14.5        | 9           | UCCx8C44 |

| 50              | 8.4         | 7.6         | UCCx8C45 |

| 50              | 7           | 6.6         | UCCx8C41 |

UVLO 中、IC の電源電流は  $100\mu\text{A}$  未満です。ターンオン スレッショルドを超えた後、本デバイスの電源電流は最大  $3\text{mA}$  (標準値は  $2.3\text{mA}$ ) まで増加します。このようにスタートアップ電流が小さいため、電源設計者は最適なスタートアップ抵抗値を選択し、より効率的な設計を行うことができます。部品コストの低減が効率の最大化に優先すアプリケーションでは、 $2.3\text{mA}$  (標準値) の小さい動作電流を生かすことで、電源トランジスタのブートストラップ巻線と整流器を必要としないで、(+) レールに接続された 1 本の抵抗を通して制御デバイスが直接動作できます。また、この場合の始動および動作抵抗は、1 次側スイッチング MOSFET を駆動するのに十分な電流を通す必要があります。この電流は、小型デバイスで数  $\text{mA}$  に達する可能性があります。

図 7-2. UVLO のオンおよびオフのプロファイル

### 7.3.3 $\pm 1\%$ の内部基準電圧

2.5V の BiCMOS 内部基準電圧には改良された設計が採用されており、量産トリミングにより室温で  $\pm 1\%$ 、全温度範囲で  $\pm 2\%$  の初期精度を実現しています。この基準電圧を使うことで、追加デバイスにより超高精度を実現する必要があるアプリケーション以外では、外部基準電圧を不要にできます。この基準電圧は、制御デバイスと出力が同じコモンを基準とする非絶縁型 DC/DC アプリケーションに役立ちます。1 次側バイアス巻線を観察することで、または降圧派生回路の出力インダクタの巻線によって、絶縁境界の 1 次側をレギュレートするオフライン設計にも、この基準電圧は応用できます。

### 7.3.4 電流センスと過電流制限

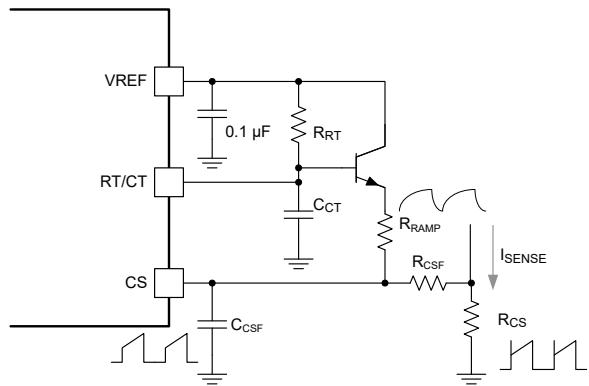

外部直列抵抗 ( $R_{CS}$ ) が電流を検出して、CS ピンの入力電圧に変換します。CS ピンは、PWM コンパレータへの非反転入力です。本デバイスは、エラー アンプの出力電圧に比例する信号と CS 入力を比較します。電流検出アンプのゲインは、通常  $3V/V$  です。ピーク  $I_{SENSE}$  電流は、式 2 を使って計算されます。

$$I_{SENSE} = \frac{V_{CS}}{R_{CS}} \quad (2)$$

$V_{CS}$  の標準値は  $1V$  です。2 次側ダイオードの逆回復特性(等価容量性負荷と回路の寄生インピーダンス)に起因するスイッチング過渡を抑制するため、時定数が小さい RC フィルタ ( $R_{CSF}$ ,  $C_{CSF}$ ) が必要な場合もあります。このフィルタの時定数は、コンバータのスイッチング時間よりも大幅に短くする必要があります。

図 7-3. 電流検出回路図

PWM コンパレータで実行されるサイクル単位のパルス幅変調は、実質的にエラー アンプ出力を電流検出入力と比較します。これは、電圧と電圧の直接の比較ではありません。PWM コンパレータに接続する前に、エラー アンプの出力ネットワークには、抵抗分圧回路と直列に接続された 2 つのダイオードが組み込まれているためです。2 つのダイオードの電圧降下は、低いアンプ出力でゼロ デューティ サイクルを実現できるオフセット電圧を追加します。 $2R/R$  の抵抗分圧器のおかげで、 $2.5V$  非反転入力電圧を中心としてより対称性に優れた、より広いエラー アンプ出力スイングを簡単に利用できます。

エラー アンプからの PWM コンパレータ入力に関連した  $1V$  ツエナー ダイオードは、デバイス設計における実際のダイオードではなく、最大電流検出入力振幅が  $1V$  (標準値) であることを示すものです。このスレッショルドに達すると、エラー アンプの出力電圧に関係なく、サイクル単位の電流制限が行われ、出力パルスは  $35ns$  (標準値) 以内に打ち切られます。この電流制限スレッショルドの最小値は  $0.9V$  であり、最大値は  $1.1V$  です。このパラメータの許容誤差に加えて、電流検出抵抗(電流検出回路)の精度も考慮する必要があります。すべてのパワー半導体および磁気部品の定格とワーストケース条件を検討する際は、1 次側および 2 次側電流のワーストケースを考慮に入れることが推奨します。

### 7.3.5 放電電流の変動の低減

UCCx8C4x コントローラの発振器には、最大デューティサイクルと動作周波数を正確に設定するための放電電流調整機能が備わっています。基本動作では、タイミングコンデンサ ( $C_{CT}$ ) は、デバイス基準電圧 (VREF) に接続されたタイミング抵抗 ( $R_{RT}$ ) によって作られた電流源によって充電されます。発振器の設計には、タイミングコンデンサの電圧の振幅を監視するためのコンパレータが含まれます。指数関数的に成形された波形は、発振器の上側スレッショルド (3V) を表す特定の振幅までタイミングコンデンサを充電します。コントローラがこのレベルに達すると、グランドへの内部電流シンクがターンオンし、コンデンサは放電を開始します。この放電は、電流シンクがターンオフする、発振器の下側スレッショルド (0.7V) に達するまで続きます。次に、タイミングコンデンサは再び充電を開始し、新しいスイッチングサイクルが始まります。

図 7-4. 発振回路

本デバイスがタイミングコンデンサを放電させる間、抵抗  $R_{RT}$  は引き続き  $C_{CT}$  を充電しようと試みます。最大デューティサイクルを規定するのは、これらの 2 つの電流のまさにその比 (放電電流対充電電流) です。 $C_{CT}$  の放電期間中、本デバイスの出力は常にオフしています。これは、一般にデッドタイムと呼ばれる、スイッチが確実にオフする最小時間を表します。正確な最大デューティサイクルを設定するには、「最大デューティサイクルと発振器周波数との関係」に記載されている情報を使用して、最大デューティサイクルと発振器周波数との関係を調べます。 $R_{RT}$  と  $C_{CT}$  の値を調整することで、与えられた周波数に対して任意の値の最大デューティサイクルを設定できます。 $R_{RT}$  の値を選択した後、「発振器周波数とタイミング抵抗および容量との関係」の曲線を使用して、発振器のタイミング容量を求めます。ただし、抵抗では、より細かい刻み (通常 1%) の値の素子が入手できるのに対して、コンデンサでは、5% の刻みの値の素子しか入手できないため、最初に最も近いコンデンサの値を選択してから、タイミング抵抗の値を計算する方が、より実用的な場合があります。

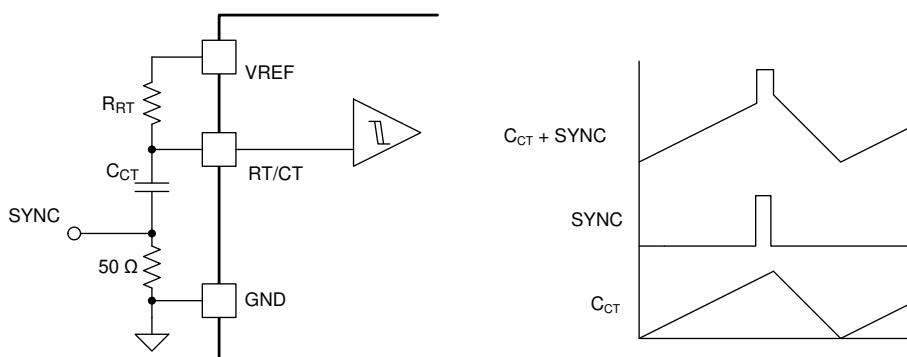

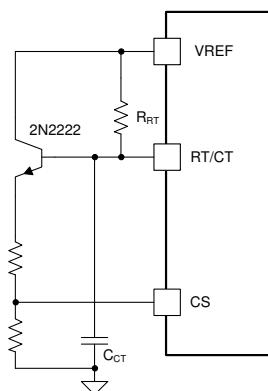

### 7.3.6 発振器の同期

同期を達成する最良の方法は、発振器の内部上側スレッショルドを上回るようにタイミングコンデンサ電圧を引き上げることです。 $C_{CT}$  と直列に、一方が GND に接続された小さな抵抗を配置します。この抵抗は同期パルスの入力として機能し、同期パルスによって  $C_{CT}$  の電圧が発振器の内部上限スレッショルドより高くなります。PWM は、同期パルスが発生するまで、 $R_{RT}$  と  $C_{CT}$  で設定された周波数で動作できます。この方式には、勾配補償にローカルランプを使用できるなど、いくつかの利点があります。UCCx8C4x の発振器は、同期パルスストリームより低い周波数に設定する必要があります。通常は、抵抗の両端に 0.5V パルスを印加した状態で 20% に設定します。

Copyright © 2016, Texas Instruments Incorporated

図 7-5. 発振器同期回路

### 7.3.7 ソフトスタートのタイミング制御

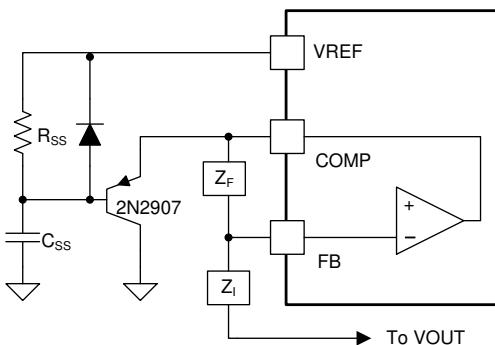

ソフトスタートタイミングとは、実効デューティサイクルをゼロから徐々に増やすことで、適切に制御された方法でコンバータ出力を徐々に増やす手法です。PWMが始動した後、エラー アンプの反転入力が Low になることで、エラー アンプの出力を High にするように指示します。アンプの出力段は 1mA (標準値) をソースできます。これは、ほとんどの高インピーダンス補償ネットワークを駆動するのに十分な大きさですが、大きな負荷を高速で駆動するには十分とは言えません。ソフトスタートタイミングは、PNPトランジスタを通してエラー アンプ出力に接続された、1μF を超えるかなり大きな値のコンデンサ ( $C_{SS}$ ) を充電することで実現されます (図 7-6 を参照)。

図 7-6. ソフトスタートの実装

コンデンサに流れ込む、アンプの充電電流を制限することは、エラー アンプ出力の  $dv/dt$  を制限することと言い換えることができます。PWM コンパレータ入力の一方は徐々に上昇するため、これは、電流モード制御システムの 1 次側電流の最大変化率に直接相当します。COMP ピンの電圧が制御された速度で上昇するように  $R_{SS}$  と  $C_{SS}$  の値を選択することで、電力段によって供給されるピーク電流を制限する必要があります。ソフトスタート期間が完了した後も、コンデンサは VREF まで充電し続けるため、実質的に PNPトランジスタは回路の考察から外れます。ソフトスタートタイミングは、電圧モード制御システムというよりも電流モード制御システムにおいて、しばしば望ましい機能を提供します。電流モードでは、ソフトスタートはピーク スイッチ電流の立ち上がりを制御します。電圧モード制御では、ソフトスタートは、1 次側電流にもランプアップ レートにも関係なく、デューティサイクルを徐々に増加させます。

抵抗  $R_{SS}$  とダイオードの目的は、通常動作時において、ソフトスタート期間が完了してコンデンサが完全に充電された後、エラー アンプ経路からソフトスタートコンデンサを切り離すことです。抵抗と並列に接続された任意のダイオードは、VREF を Low に強制する UVLO 条件を PWM が通過するたびに、ソフトスタート期間を強制します。ダイオードがない場合、短時間の電源喪失またはブランクアウトの間、コンデンサは充電されたままとなり、VDD が再度印加されても、本デバイスはソフトスタート機能を有効化しません。

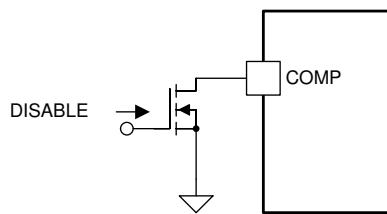

### 7.3.8 イネーブルおよびディセーブル

必要とされる再起動の種類に応じて、UCCx8C4x デバイスを有効化または無効化する方法は複数あります。2 つの基本的な手法は、外部トランジスタを使用して、エラー アンプの出力を Low ( $< 2V_{BE}$ ) にプルする方法と、電流検出入力を High ( $> 1.1V$ ) にプルする方法のどちらかです。ディセーブル信号を印加すると、PWM コンパレータの出力は High になります。PWM ラッチはリセットドミナントなので、COMP 端子または CS ピンのシャットダウン状態が解消されて、その次のクロックサイクルまで、出力は Low に維持されます。ソフトスタート期間なしで再起動させるためのもう 1 つの選択肢は、サイクル単位の電流制限スレッショルドより高い電位に電流検出入力をプルすることです。基準電圧と電流検出入力の間に接続された、ロジック レベルの P チャネル FET が、そのために使えます。

図 7-7. ディセーブル回路

### 7.3.9 スロープ補償

電流モード制御では、50% を超えるデューティ サイクルでループ全体を安定させる上で、スロープ補償が必要です。最大デューティ サイクルが 50% 未満のアプリケーションでは、スロープ補償は必須ではありませんが、やはり安定性を向上させます。スロープ補償は、実際に検出された 1 次側電流に発振器波形の一部を注入することで実現されます。これらの 2 つの信号は、フィルタ コンデンサの電流検出入力 (CS) の接続部で足し合わされます。発振器の負荷を最小限に抑えるため、コレクタを基準電圧に接続した小型トランジスタでタイミング コンデンサ波形をバッファすることを推奨します。

図 7-8. スロープ補償回路

### 7.3.10 電圧モード

特定のアプリケーションでは、さまざまな理由から、制御方式として電圧モード制御が選択される場合があります。電圧モード制御は、すべての電流モードコントローラ (特に UCCx8C4x ファミリ製品) を使って簡単に実現できます。実装を行うには、PWM コンパレータの 1 つの入力でもある電流検出ピン (CS) に入力する 0V/0.9V のこぎり波信号を生成する必要があります。この信号は、PWM コンパレータのもう一方の入力の、分圧されたエラー アンプ出力電圧と比較されます。エラー アンプ出力が変化すると、のこぎり波と交差する時刻が変化し、生成されるパルス幅が変化します。これは、誤差電圧に比例する幅のパルスを生成する簡単な方法です。

発振器のタイミング コンデンサ ( $C_{CT}$ ) の波形の一部を使用することで、電圧モード制御を実装できます。この値を分圧し、電流検出ピンに入力できます (図 7-9 を参照)。発振器のタイミング部品は、線形のこぎり波形にできるだけ近づくように選択する必要があります。指数関数的に充電されるとはいえ、大きいタイミング抵抗値と小さいタイミング容量値を使うことで、より直線的な形状の波形を近似できます。発振器のタイミング部品が抵抗分圧回路の負荷の影響を受けないように、バッファとして小さなトランジスタを使います。発振器の下側タイミング スレッショルドのオフセットのせいで、DC 阻止コンデンサが追加されています。

図 7-9. 電流モード PWM を電圧モード PWM として使用

## 7.4 デバイスの機能モード

### 7.4.1 通常動作

通常動作モードでは、ピーク電流モードまたは電圧モード制御で本コントローラを使用できます。コンバータがピーク電流モードで動作しているとき、コントローラはコンバータのピーク電流とデューティサイクルをレギュレートします。電圧モード制御で使用すると、本コントローラはパワー コンバータのデューティサイクルをレギュレートします。内蔵のエラー アンプと外部のフィードバック回路を使用すると、システムのピーク電流とデューティサイクルをレギュレートできます。

### 7.4.2 UVLO モード

システムのスタートアップ時に、VDD 電圧は 0V から上昇を開始します。VDD 電圧が対応するターンオン スレッショルドに達するまで、IC は UVLO モードで動作します。UVLO モード動作中、VREF ピンの電圧は生成されません。VDD が 1V を上回り、かつターンオン スレッショルドを下回っている場合、VREF ピンはアクティブに Low にプルされます。この挙動により、UVLO モードを示すロジック信号として VREF を使うことができます。VDD へのバイアス電圧が UVLO-OFF スレッショルドを下回ると、PWM スイッチングは停止し、VREF は 0V に戻ります。UVLO-ON スレッショルドより高い電圧を VDD ピンに印加することで、本デバイスを再起動できます。

## 8 アプリケーションと実装

### 注

以下のアプリケーション情報は、TI の製品仕様に含まれるものではなく、TI ではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

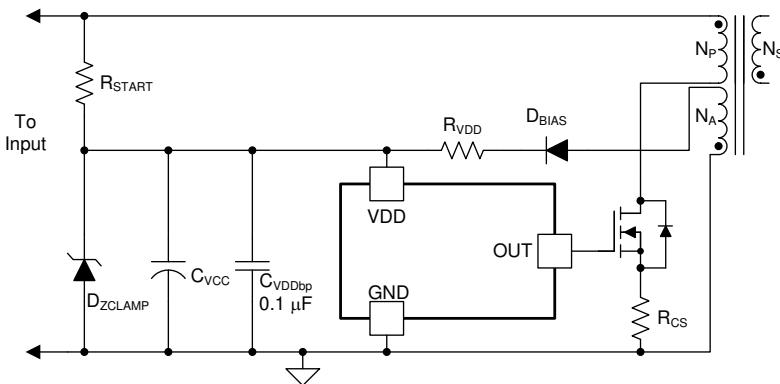

### 8.1 アプリケーション情報

UCCx8C4x コントローラは、ピーク電流モードのパルス幅変調器です。これらのコントローラにはオンボード アンプが搭載されており、絶縁型および非絶縁型の電源設計に使用できます。オンボードのトータル ポール ゲート ドライバは、1A のピーク電流を供給できます。この高速 PWM は、最大 1MHz のスイッチング周波数で動作できます。図 8-1 に、UCC38C44 を使用した代表的なオフライン アプリケーションを示します。

図 8-1. 代表的なオフライン アプリケーション

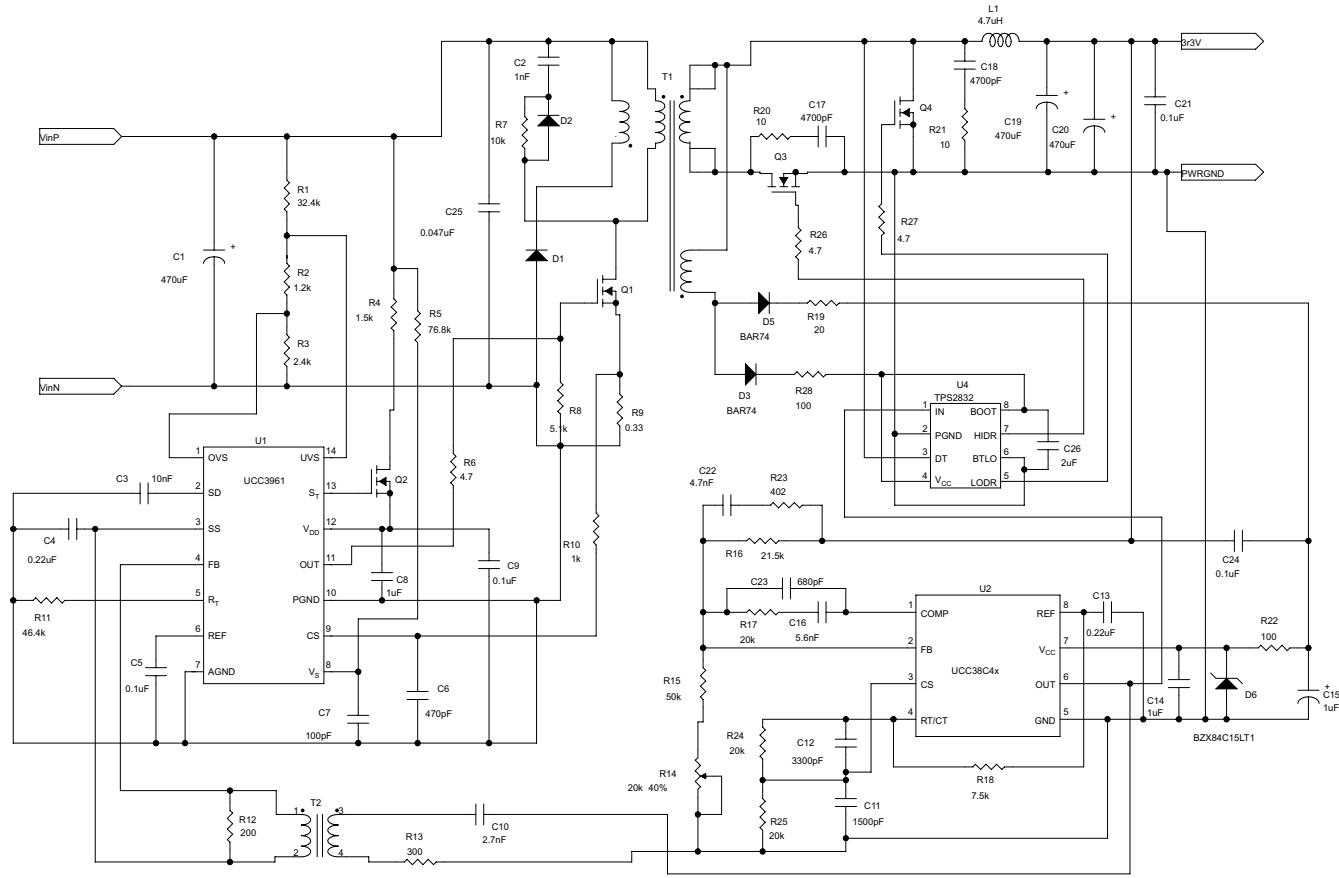

図 8-2 に、同期整流機能付きフォワード コンバータを示します。このアプリケーションは、85% (10A 時) を上回る効率で 48V を 3.3V に変換します。2 次側コントローラとして UCC38C42、1 次側スタートアップ制御デバイスとして UCC3961 を使用しています。

Copyright © 2016, Texas Instruments Incorporated

図 8-2. UCC38C42 を 2 次側コントローラとして使用した、同期整流機能付きフォワード コンバータ

## 8.2 代表的なアプリケーション

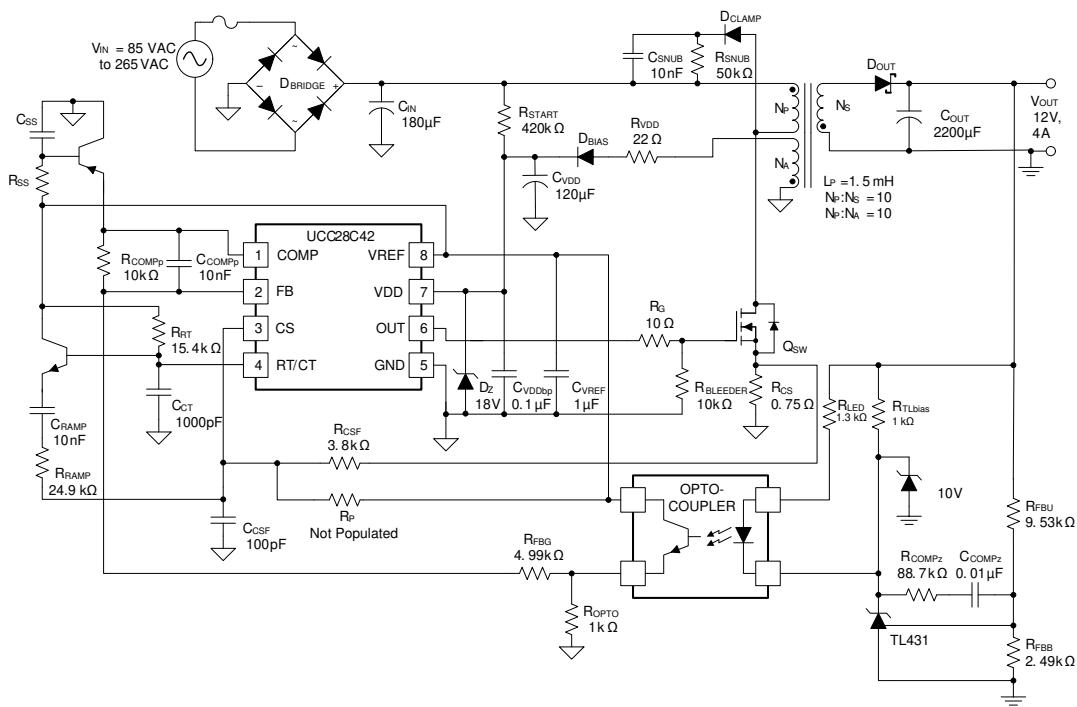

オフライン フライバック コンバータでの UCC28C42 コントローラの代表的なアプリケーションを、図 8-3 に示します。本コントローラは、1 次インダクタの電流ランプを検出する小さな電流検出抵抗を内蔵した内部電流制御ループを使用しています。この電流検出抵抗は、インダクタの電流波形を、1 次側 PWM コンパレータに直接入力される電圧信号に変換します。この内部ループによって、入力電圧の変化に対する応答が決定されます。外部電圧制御ループでは、出力電圧の一部を、エラー アンプの入力におけるリファレンス電圧と比較します。オフライン絶縁型アプリケーションで使用する場合、絶縁出力の電圧フィードバックは、2 次側のエラー アンプと、TL431 などの調整可能な電圧リファレンスを使用して実現されます。この誤差信号は、コレクタが VREF ピンに接続され、エミッタが FB に接続されている光アイソレータを使用して、1 次側と 2 次側の絶縁境界をまたぐものです。外側の電圧制御ループによって、負荷の変化に対する応答が決定されます。

Copyright © 2016, Texas Instruments Incorporated

図 8-3. 代表的なアプリケーション設計の回路図

### 8.2.1 設計要件

ユニバーサル AC 入力から 12V の出力電圧で 48W を供給できるオフライン フライバック コンバータの標準的な性能要件を、表 8-1 に示します。この設計では、連続電流モード PWM コンバータでピーク 1 次電流制御を使用します。

表 8-1. 設計パラメータ

| パラメータ               | テスト条件     | 最小値                                                                 | 公称値     | 最大値 | 単位               |   |

|---------------------|-----------|---------------------------------------------------------------------|---------|-----|------------------|---|

| V <sub>IN</sub>     | 入力電圧      | 85                                                                  | 115/230 | 265 | V <sub>RMS</sub> |   |

| f <sub>LINE</sub>   | ライン周波数    | 47                                                                  | 50/60   | 63  | Hz               |   |

| V <sub>OUT</sub>    | 出力電圧      | I <sub>VOUT(min)</sub> ≤ I <sub>VOUT</sub> ≤ I <sub>VOUT(max)</sub> | 11.75   | 12  | 12.25            | V |

| V <sub>RIPPLE</sub> | 出力リップル電圧  | I <sub>VOUT(min)</sub> ≤ I <sub>VOUT</sub> ≤ I <sub>VOUT(max)</sub> |         | 100 | mVpp             |   |

| I <sub>VOUT</sub>   | 出力電流      | 0                                                                   | 4       |     | A                |   |

| f <sub>sw</sub>     | スイッチング周波数 |                                                                     | 110     |     | kHz              |   |

| η                   | 効率        |                                                                     | 85%     |     |                  |   |

## 8.2.2 詳細な設計手順

ここでは、オンラインのユニバーサル入力連続電流モード (CCM) フライバックコンバータを設計する手順の概要を示します。設計の手順で参照されている部品名については、図 8-3 を参照してください。

### 8.2.2.1 入力バルク容量と最小バルク電圧

バルク容量は、並列に接続された 1 個以上のコンデンサから構成され、多くの場合は、差動モードの伝導ノイズを抑制するために、コンデンサ間にインダクタンスを配置します。入力コンデンサの値によって、最小バルク電圧が設定されます。最小の入力容量を使用してバルク電圧を低く設定すると、ピークの 1 次側電流が大きくなり、MOSFET スイッチ、トランジスタ、および出力コンデンサのストレスが増加します。大きな入力コンデンサを使用してバルク電圧を高く設定すると、入力ソースからのピーク電流が大きくなり、コンデンサ自体が物理的に大きくなります。サイズと部品のストレスを調整すると、許容される最小入力電圧が決定されます。1 次側バルク容量の必要な合計値 ( $C_{IN}$ ) は、コンバータの電力レベル ( $P_{OUT}$ )、効率目標 ( $\eta$ )、最小入力電圧 ( $V_{IN(min)}$ ) に基づき、式 3 を使用して、許容される最小バルク電圧レベル ( $V_{BULK(min)}$ ) を維持するように選択されます。

$$C_{IN} = \frac{2 \times P_{IN} \times \left( 0.25 + \frac{1}{\pi} \times \arcsin \left( \frac{V_{BULK(min)}}{\sqrt{2} \times V_{IN(min)}} \right) \right)}{(2 \times V_{IN(min)}^2 - V_{BULK(min)}^2) \times f_{LINE(min)}} \quad (3)$$

ここで、

- $V_{IN(min)}$  は最小 AC 入力電圧 (85VRMS) の RMS 値です。この入力の最小ライン周波数は  $f_{LINE(min)}$  と表記され、47Hz です。

式 3 に基づいて、最小バルク電圧 75V を実現するには、コンバータ効率を 85% と想定すると、バルクコンデンサを 126μF より大きくする必要があります。この設計では、部品の許容誤差と効率の推定値を考慮して、180μF を使っています。

### 8.2.2.2 トランジスタの巻線比と最大デューティサイクル

トランジスタの設計は、特定のアプリケーションに適したスイッチング周波数を選択することから始まります。UCC28C42 は最大 1MHz のスイッチングが可能ですが、コンバータ全体のサイズ、スイッチング損失、コア損失、システム互換性、通信周波数帯域との干渉などを考慮して、一般的に使用すべき最適な周波数が決まります。このオンラインコンバータでは、トランジスタのサイズと EMI フィルタのサイズを最小化しながら許容可能な損失を維持するための折衷案として、スイッチング周波数 ( $f_{SW}$ ) を 110kHz に選択します。

トランジスタの 1 次側と 2 次側の巻線比 ( $N_{PS}$ ) は、要求される MOSFET の電圧定格と、2 次側ダイオードの電圧定格に基づいて選択できます。最大入力電圧は 265VRMS なので、式 4 に示すようにピークバルク入力電圧を計算できます。

$$V_{BULK(max)} = \sqrt{2} \times V_{IN(max)} \approx 375 \text{ V} \quad (4)$$

システムのコストを最小限に抑えるため、どこでも入手可能な 650V MOSFET が選択されています。ドレインの最大電圧ストップを定格値の 80% までディレーティングし、最大バルク入力電圧の 30% までのリークインダクタンス電圧スパイクを許容できるようにするには、式 5 に示すように、反射出力電圧を 130V 未満にする必要があります。

$$V_{REFLECTED} = 0.8 \times (V_{DS(rated)} - 1.3 \times V_{BULK(max)}) = 130.2 \text{ V} \quad (5)$$

12V 出力の 1 次側と 2 次側のトランジスタの最大巻線比 ( $N_{PS}$ ) は、次の式で選択できます。

$$N_{PS} = \frac{V_{REFLECTED}}{V_{OUT}} = 10.85 \quad (6)$$

この設計例では、 $N_{PS} = 10$  の巻線比を使用します。

補助巻線を使用して、コントローラにバイアス電圧を供給します。安定した動作のため、ターンオン後にバイアス電圧を  $VDD$  の最小動作電圧よりも高く維持する必要があります。この設計で選択されたコントローラ  $VDD$  動作電圧の最小値は  $10V$  です。最小動作レベルよりも高いが、IC 内の損失が小さく維持される  $12V$  のバイアス電圧をサポートするように、補助巻線を選択します。1 次と補助の巻線比 ( $N_{PA}$ ) は、式 7 で計算できます。

$$N_{PA} = N_{PS} \times \frac{V_{OUT}}{V_{BIAS}} = 10 \quad (7)$$

出力ダイオードには、出力電圧に反射入力電圧を加えた値と等しい電圧ストレスが発生します。

$$V_{DIODE} = \frac{V_{BULK(\max)}}{N_{PS}} + V_{OUT} = 49.5 \text{ V} \quad (8)$$

リンギングによる電圧スパイクに対応するため、定格ブロッキング電圧が  $60V$  を超えるショットキー ダイオードを推奨します。このダイオードの順方向電圧降下 ( $V_F$ ) は  $0.6V$  と推定されます。

高いピーク電流を回避するため、この設計のフライバック コンバータは連続導通モードで動作します。 $N_{PS}$  が決まると、最大デューティサイクル ( $D_{MAX}$ ) は、CCM フライバック コンバータの伝達関数を使用して計算できます。

$$\frac{V_{OUT} + V_F}{V_{BULK(\min)}} = \left( \frac{1}{N_{PS}} \right) \times \left( \frac{D_{MAX}}{1 - D_{MAX}} \right) \quad (9)$$

$$D_{MAX} = \frac{N_{PS} \times (V_{OUT} + V_F)}{V_{BULK(\min)} + N_{PS} \times (V_{OUT} + V_F)} = 0.627 \quad (10)$$

最大デューティサイクルが  $50\%$  を超え、設計がオフライン (AC 入力) アプリケーションなので、このアプリケーションには UCC28C42 が最適です。

### 8.2.2.3 トランスのインダクタンスとピーク電流

この設計例では、CCM 条件に基づいてトランスの磁化インダクタンスを選択します。コンバータができるだけ広い動作範囲にわたって、不連続電流モードに移行せず、CCM を維持できるよう、インダクタンスの値を選択します。これによって、大電流の発生による損失を最小化し、出力リップルも減らすことができます。この例のトランスの設計では、インダクタンスのサイズを調整して、コンバータが CCM 動作に移行するとき約  $10\%$  の負荷と最小バルク電圧を確保し、出力リップルを最小限に抑えます。

CCM フライバックのインダクタ ( $L_P$ ) は、式 11 を使用して計算できます。

$$L_P = \frac{1}{2} \times \frac{\left( V_{BULK(\min)} \right)^2 \times \left( \frac{N_{PS} \times V_{OUT}}{V_{BULK(\min)} + N_{PS} \times V_{OUT}} \right)^2}{0.1 \times P_{IN} \times f_{SW}} \quad (11)$$

ここで、

- $P_{IN}$  は、最大出力電力 ( $P_{OUT}$ ) を目標効率 ( $\eta$ ) で除算することで概算されます。

- $f_{SW}$  はコンバータのスイッチング周波数です。

UCC28C42 の場合、スイッチング周波数は発振器の周波数と等しく、 $110\text{kHz}$  に設定されています。 $f_{SW}$  に  $110\text{kHz}$  を選択することで、磁気素子のサイズとスイッチング損失の折り合いを付けることができ、EN55022 の  $150\text{kHz}$  の下限よりも低い位置に第 1 高調波が設定されます。したがって、トランスのインダクタンスは約  $1.8\text{mH}$  とする必要があります。この設計では、磁化インダクタンス  $L_P$  の値として  $1.5\text{mH}$  のインダクタンスを選択しています。

計算されたインダクタの値とスイッチング周波数に基づいて、MOSFET と出力ダイオードの電流ストレスを計算できます。

CCM フライバックの 1 次側 MOSFET のピーク電流は、式 12 に示すように計算できます。

$$I_{PK_{MOSFET}} = \frac{P_{IN}}{V_{BULK(min)} \times \frac{N_{PS} \times V_{OUT}}{V_{BULK(min)} + (N_{PS} \times V_{OUT})}} + \left( \frac{V_{BULK(min)} \times \frac{N_{PS} \times V_{OUT}}{V_{BULK(min)} + (N_{PS} \times V_{OUT})}}{2 \times L_m} \times \frac{\frac{N_{PS} \times V_{OUT}}{V_{BULK(min)} + (N_{PS} \times V_{OUT})}}{f_{SW}} \right) \quad (12)$$

MOSFET のピーク電流は 1.36A です。式 13 に示すように、MOSFET の RMS 電流は 0.97A と計算されます。したがって、1 次側スイッチとして使用するため、IRFB9N65A を選択します。

$$I_{RMS_{MOSFET}} = \sqrt{\frac{D_{MAX}^3}{3} \times \left( \frac{V_{BULK(min)}}{L_p \times f_{SW}} \right)^2 - \left( \frac{D_{MAX}^2 \times I_{PK_{MOSFET}} \times V_{BULK(min)}}{L_p \times f_{SW}} \right) + (D_{MAX} \times I_{PK_{MOSFET}}^2)} \quad (13)$$

出力ダイオードのピーク電流は、2 次側に反射される MOSFET のピーク電流と等しくなります。

$$I_{PK_{DIODE}} = N_{PS} \times I_{PK_{MOSFET}} = 13.634 \text{ A} \quad (14)$$

ダイオードの平均電流は合計出力電流 (4A) と等しいので、必要な 60V 定格と 13.6A のピーク電流要件と組み合わせ、出力ダイオードとして 48CTQ060-1 が選択されています。

#### 8.2.2.4 出力コンデンサ

合計出力容量は、出力電圧リップルの要件に基づいて選択します。この設計では、0.1% の電圧リップルを想定しています。0.1% のリップル要件に基づいて、式 15 を使用してコンデンサの値を選択できます。

$$C_{OUT} \geq \frac{I_{OUT} \times \frac{N_{PS} \times V_{OUT}}{V_{BULK(min)} + N_{PS} \times V_{OUT}}}{0.001 \times V_{OUT} \times f_{SW}} = 1865 \mu\text{F} \quad (15)$$

設計では、デバイスの公差を考えて、2200μF のコンデンサが選択されています。

### 8.2.2.5 電流検出ネットワーク

電流検出ネットワークは、1次側電流検出抵抗 ( $R_{CS}$ )、フィルタリング部品  $R_{CSF}$  および  $C_{CSF}$ 、オプションの  $R_P$  で構成されます。通常、直流検出信号には、メインパワー MOSFET のターンオンに関連する大きな振幅のリーディングエッジスパイク、出力整流器の逆回復、および寄生容量の充電と放電などの他の要因が含まれています。したがって、 $C_{CSF}$  と  $R_{CSF}$  はローパスフィルタを形成し、リーディングエッジのスパイクを抑制する耐性を持ちます。このコンバータでは、 $C_{CSF}$  が選択されています。

$R_P$  を使用しない場合、 $R_{CS}$  は、1V に規定されている CS ピンの最大振幅に基づいて、トランジスタの 1 次側の最大ピーケー電流を設定します。1 次側のピーケー電流を 1.36A にするには、 $R_{CS}$  に  $0.75\Omega$  の抵抗を選択します。

CS の高い電流検出スレッショルドにより、システムのノイズ耐性が向上しますが、電流検出抵抗での損失も大きくなります。これらの電流検出損失は、 $R_P$  を使用してオフセット電圧を電流センス信号に注入することで最小化できます。 $R_P$  および  $R_{CSF}$  は、電流検出信号からコントローラのリファレンス電圧 ( $V_{VREF}$ ) までの分圧抵抗回路を形成し、電流検出電圧にオフセットを追加します。この技法でも、サイクル単位の過電流保護を含めた電流モード制御を実現できます。必要なオフセット値 ( $V_{OFFSET}$ ) を計算するには、式 16 を使用します。

$$V_{OFFSET} = \frac{R_{CSF}}{R_{CSF} + R_P} \times V_{REF} \quad (16)$$

$R_P$  抵抗を追加した後、それに応じて  $R_{CS}$  の値を調整します。

### 8.2.2.6 ゲートドライブ抵抗

$R_G$  は、パワー スイッチ ( $Q_{SW}$ ) のゲートドライバ抵抗です。この抵抗の値は、EMI 準拠テストや効率テストと合わせて選択する必要があります。 $R_G$  に大きな抵抗値を使用すると、MOSFET のターンオンとターンオフが低速になります。スイッチング速度が遅いと、EMI は減少しますが、スイッチング損失が増加します。スイッチング損失と EMI 性能との間のトレードオフは、慎重に検討する必要があります。この設計では、ゲート駆動抵抗として  $10\Omega$  の抵抗が選択されています。

### 8.2.2.7 VREF コンデンサ

高精度の 5V リファレンス電圧は、いくつかの重要な機能を実行します。リファレンス電圧は内部で 2.5V に分圧され、エラー アンプの非反転入力に接続されることで、出力電圧を正確にレギュレートします。またリファレンス電圧は、内部バイアス電流やスレッショルドを設定し、発振器の上限と下限のスレッショルドなどの機能も果たします。したがって、リファレンス電圧は、セラミックコンデンサでバイパスする必要があります。このコンバータには、 $1\mu F$ 、16V のセラミックコンデンサを選択しました。このコンデンサをプリント基板の物理的なレイアウトに配置するときは、対応する VREF ピンと GND ピンにできるだけ近づける必要があります。

### 8.2.2.8 RT/CT

内部発振器は、タイミングコンデンサ ( $C_{CT}$ ) とタイミング抵抗 ( $R_{RT}$ ) を使用して、発振器の周波数と最大デューティサイクルをプログラムします。動作周波数は、「発振器周波数とタイミング抵抗および容量との関係」の曲線に基づいてプログラムできます。これらのグラフでは、タイミングコンデンサを選択すると、タイミング抵抗を求めることができます。タイミングコンデンサには温度係数がフラットなものを選択してください。ほとんどの COG や NPO タイプのコンデンサは、この条件を満たします。このコンバータの場合、110kHz のスイッチングで動作するように、 $R_{RT}$  と  $C_{CT}$  として  $15.4k\Omega$  と  $1000pF$  が選択されています。

### 8.2.2.9 スタートアップ回路

スタートアップ時に、IC は高電圧バルクから高電圧抵抗 ( $R_{START}$ ) を介して直接電力を受け取ります。スタートアップ抵抗の選択は、電力損失とスタートアップ時間との間のトレードオフです。最小入力電圧で  $R_{START}$  を流れる電流は、UVLO 条件での VDD 電流（最大値で  $100\mu A$ ）を上回る必要があります。 $R_{START}$  には  $420k\Omega$  の抵抗が選択されており、低ライン条件で  $250\mu A$  のスタートアップ電流を供給します。高ラインでの高い電圧要件と電力定格を満たすため、スタートアップ抵抗は、直列接続された 2 本の  $210k\Omega$  抵抗で物理的に構成されています。

VDD が UVLO-ON スレッショルドを超えて充電されると、UCC28C42 は最大動作電流の消費を開始します。VDD コンデンサは、スタートアップ時に、出力がレギュレートされたレベルに達するまで、電圧が UVLO-OFF スレッショルドを下回ることを防止するために十分なエネルギーを供給する必要があります。バルク容量が大きいと、より多くのエネルギーを保持できますが、起動時間が遅くなります。この設計では、十分なエネルギーを供給し、スタートアップ時間を約 7 秒に維持するため、 $120\mu F$  のコンデンサが選択されています。スタートアップを速めるには、バルク コンデンサの値を減らすか、 $R_{START}$  抵抗をより小さい値に変えます。

### 8.2.2.10 電圧帰還補償

帰還補償は閉ループ制御とも呼ばれ、定常状態の誤差を低減または除去し、システムのパラメータの変化に対する感度を低減して、目的の周波数範囲全体にわたってシステムのゲインまたは位相を変更し、小信号負荷の乱れやノイズがシステム性能に及ぼす影響を減らして、不安定なシステムから安定したシステムを生み出すことができます。摂動があったとしても、最終的にその摂動が消滅する場合、システムは安定します。ピーク電流モード フライバックは、外部電圧帰還ループを使用してコンバータを安定させます。電圧ループを十分に補償するには、電力段の開ループ パラメータを決定する必要があります。

#### 8.2.2.10.1 電力段の極とゼロ

固定周波数フライバックを補償するための最初のステップは、コンバータが連続導通モード (CCM) と不連続導通モード (DCM) のどちらかを確認することです。1 次側インダクタンス ( $L_P$ ) が、DCM モード動作と CCM モード動作の境界のインダクタンスであるクリティカル インダクタンス ( $L_{Pcrit}$ ) より大きい場合、コンバータは CCM で動作します。

$$L_P > L_{Pcrit}, \text{ then CCM} \quad (17)$$

$$L_{Pcrit} = \frac{R_{OUT} \times (N_{PS})^2}{2 \times f_{SW}} \times \left( \frac{V_{IN}}{V_{IN} + V_{OUT} \times N_{PS}} \right)^2 \quad (18)$$

入力電圧範囲全体にわたって、選択したインダクタの値はクリティカル インダクタよりも大きくなります。したがって、コンバータは CCM で動作し、補償ループは CCM フライバックの式に基づいて設計する必要があります。

電流から電圧への変換は、グランド基準の  $R_{CS}$  と、内部電流検出ゲイン  $A_{CS} = 3$  を設定する内部 2R/R 抵抗分圧器とを使用して、外部的に行われます。これらの内部抵抗の正確な値は重要ではありません。しかし、IC は分圧抵抗比を厳密に制御できるため、実際の抵抗値の変動に関係なく、互いに相対的な値が維持されます。

式 19 に示すピーク電流モード制御 CCM フライバック コンバータの固定周波数電圧制御ループの DC 開ループ ゲイン ( $G_0$ ) は、出力負荷 ( $R_{OUT}$ )、1 次側と 2 次側の巻線比 ( $N_{PS}$ )、最大デューティ サイクル ( $D$ 、式 20 で計算されます) を最初に使うことで概算されます。

$$G_0 = \frac{R_{OUT} \times N_{PS}}{R_{CS} \times A_{CS}} \times \frac{1}{\frac{(1-D)^2}{\tau_L} + (2 \times M) + 1} \quad (19)$$

式 19 で、D は式 20、 $\tau_L$  は式 21、M は式 22 で計算されます。

$$D = \frac{N_{PS} \times V_{OUT}}{V_{BULKmin} + (N_{PS} \times V_{OUT})} \quad (20)$$

$$\tau_L = \frac{2 \times L_P \times f_{SW}}{R_{OUT} \times (N_{PS})^2} \quad (21)$$

$$M = \frac{V_{OUT} \times N_{PS}}{V_{BULKmin}} \quad (22)$$

この設計では、出力電圧 ( $V_{OUT}$ ) が 12V で 48W のコンバータは、出力負荷 ( $R_{OUT}$ ) に対応し、全負荷時に  $3\Omega$  と等しくなります。最大デューティサイクルが 0.627、電流検出抵抗が  $0.75\Omega$ 、1 次側と 2 次側の巻線比  $N_{PS}$  が 10 の場合、開ループゲインは 3.082、すなわち  $9.776\text{dB}$  と計算されます。

CCM フライバックには注目対象として 2 つのゼロがあります。ESR と出力容量は、左半面ゼロ ( $\omega_{ESRz}$ ) を電力段に与え、このゼロの周波数 ( $f_{ESRz}$ ) は式 23 と式 24 で計算されます。

$$\omega_{ESRz} = \frac{1}{R_{ESR} \times C_{OUT}} \quad (23)$$

$$f_{ESRz} = \frac{1}{2 \times \pi \times R_{ESR} \times C_{OUT}} \quad (24)$$

出力容量が  $2200\mu\text{F}$  で、合計 ESR が  $43\text{m}\Omega$  なら、 $f_{ESRz}$  のゼロは  $1.682\text{kHz}$  にあります。

CCM フライバック コンバータは、伝達関数の右半面 (RHP) にゼロが存在します。RHP のゼロは、周波数の増加による立ち上がりゲイン振幅が左半面のゼロと同じ  $20\text{dB/dec}$  ですが、リードの代わりに  $90^\circ$  の位相ラグが追加されます。この位相ラグは、ループ全体の帯域幅を制限する傾向があります。RHP ゼロ ( $\omega_{RHPz}$ ) の周波数位置 ( $f_{RHPz}$ )、は、出力負荷、デューティサイクル、1 次側インダクタンス ( $L_P$ )、1 次側と 2 次側の巻線比 ( $N_{PS}$ ) の関数です。

$$\omega_{RHPz} = \frac{R_{OUT} \times (1 - D)^2 \times (N_{PS})^2}{L_P \times D} \quad (25)$$

$$f_{RHPz} = \frac{R_{OUT} \times (1 - D)^2 \times (N_{PS})^2}{2 \times \pi \times L_P \times D} \quad (26)$$

入力電圧が高く、負荷が軽くなるほど、右半面のゼロ周波数は増加します。設計では一般に、右半面のゼロ周波数が最も小さくなるワーストケースを考慮し、入力が最小で負荷が最大の状況でも、コンバータが補償を行える必要があります。75V DC 入力で 1 次インダクタンスが  $1.5\text{mH}$  の場合、RHP のゼロ周波数 ( $f_{RHPz}$ ) は最大デューティサイクル、全負荷時で  $7.07\text{kHz}$  になります。

電力段には、1 つの支配的な極 ( $\omega_{P1}$ ) が、低い周波数 ( $f_{P1}$ ) の対象領域に存在します。この周波数は、デューティサイクル  $D$ 、出力負荷、出力容量に関係しており、式 28 のように計算されます。また、コンバータのスイッチング周波数の半分の周波数に二重極 ( $f_{P2}$ ) が存在します（この周波数は式 30 で計算されます）。この例では、極  $f_{P1}$  は  $40.37\text{Hz}$ 、 $f_{P2}$  は  $55\text{kHz}$  です。

$$\omega_{P1} = \frac{\frac{(1 - D)^3}{\tau_L} + 1 + D}{R_{OUT} \times C_{OUT}} \quad (27)$$

$$f_{P1} = \frac{\frac{(1 - D)^3}{\tau_L} + 1 + D}{2 \times \pi \times R_{OUT} \times C_{OUT}} \quad (28)$$

$$\omega_{P2} = \pi \times f_{SW} \quad (29)$$

$$f_{P2} = \frac{f_{SW}}{2} \quad (30)$$

### 8.2.2.10.2 スロープ補償

勾配補償は、デューティサイクルが 50% を超える場合に発生の可能性のある、大信号の分数調波不安定性です。この場合、1 次側インダクタの立ち上がり電流勾配が、2 次側の立ち下がり電流勾配と一致しない可能性があります。分数調波の発振によって出力電圧リップルが増加し、コンバータの電力処理能力が制限される可能性もあります。

勾配補償の目標は、理想的な品質係数 ( $Q_P$ ) を、スイッチング周波数の半分において 1 に等しくすることです。 $Q_P$  は式 31 で計算されます。

$$Q_P = \frac{1}{\pi \times [M_C \times (1 - D) - 0.5]} \quad (31)$$

ここで、

- $D$  は 1 次側スイッチのデューティサイクルです。

- $M_C$  は勾配補償係数であり、式 32 で定義されます。

$$M_C = \frac{S_e}{S_n} + 1 \quad (32)$$

ここで、

- $S_e$  は補償ランプ勾配です。

- $S_n$  はインダクタの立ち上がり勾配です。

勾配補償の最適な目標は、 $Q_P$  を 1 にすることです。式 32 を再編成すると、勾配補償の理想的な値が決定されます。

$$M_{ideal} = \frac{\frac{1}{\pi} + 0.5}{1 - D} \quad (33)$$

この設計で十分な勾配補償を行うには、 $D$  が最大値の 0.627 に達したとき、 $M_C$  を 2.193 にする必要があります。

**CS** ピンでのインダクタの立ち上がり勾配 ( $S_n$ ) は、式 34 で計算されます。

$$S_n = \frac{V_{INmin} \times R_{CS}}{L_p} = 0.038 \frac{V}{\mu s} \quad (34)$$

補償スロープ ( $S_e$ ) は、式 35 で計算されます。

$$S_e = (M_C - 1) \times S_n = 44.74 \frac{mV}{\mu s} \quad (35)$$

補償スロープは、 $R_{RAMP}$  と  $R_{CSF}$  によってシステムに追加されます。 $C_{RAMP}$  は、電流検出にオフセットを追加しなくても、発振器の電圧ランプが使えるようにする AC カップリング コンデンサです。高周波短絡を近似するため、開始点として 10nF などの値を選択し、必要に応じて調整を加えます。抵抗  $R_{RAMP}$  および  $R_{CSF}$  は、発振器の充電勾配から分割電圧を形成し、この比例ランプを **CS** ピンに注入して勾配補償を追加します。 $R_{RAMP}$  の値を、 $R_{RT}$  抵抗よりも大幅に大きくすると、内部発振器の負荷がダウンして周波数シフトが起きることを避けられます。発振器の充電勾配は、式 37 に示すように、 $RT/CT$  のごり波のピークツーピーク電圧 ( $V_{OSCpp}$ ) である 1.9V と、最小オン時間を使用して計算されます。

$$t_{ONmin} = \frac{D}{f_{SW}} \quad (36)$$

$$S_{OSC} = \frac{V_{OSC_{pp}}}{t_{ONmin}} = \frac{1.9 \text{ V}}{5.7 \mu\text{s}} = 333 \frac{\text{mV}}{\mu\text{s}} \quad (37)$$

44.74mV/μs の補償勾配を実現するため、式 38 を使って  $R_{CSF}$  が計算されます。この設計では、 $R_{ramp}$  に 24.9kΩ、 $R_{CSF}$  に 3.8kΩ の抵抗が選択されています。

$$R_{CSF} = \frac{R_{RAMP}}{\frac{S_{OSC}}{S_e} - 1} \quad (38)$$

### 8.2.2.10.3 開ループゲイン

電力段の極とゼロを計算し、勾配補償を決定してから、CCM フライバック コンバータの出力段の開ループ ゲインと位相を、周波数の関数としてプロットできます。電力段の伝達関数は式 39 で特性付けできます。

$$H_{OPEN}(s) = G_0 \times \frac{\left(1 + \frac{s(f)}{\omega_{ESRz}}\right) \times \left(1 - \frac{s(f)}{\omega_{RHPz}}\right)}{1 + \frac{s(f)}{\omega_{P1}}} \times \frac{1}{1 + \frac{s(f)}{\omega_{P2} \times Q_P} + \frac{s(f)^2}{(\omega_{P2})^2}} \quad (39)$$

開ループ ゲインと位相のボード線図は、式 40 を使用してプロットできます。

$$\text{Gain}_{OPEN}(s) = 20 \times \log(|H_{OPEN}(s)|) \quad (40)$$

図 8-4 と図 8-5 を参照してください。

図 8-4. コンバータの開ループ ボード線図 - ゲイン

図 8-5. コンバータの開ループ ボード線図 - 位相

### 8.2.2.10.4 補償ループ

補償ループの設計では、動作範囲全体にわたって安定したシステムを作り上げるために必要なゲイン、極、ゼロを設計できるよう、適切な部品を選択する必要があります。ループは TL431、フォトカプラー、エラー アンプという 3 つの異なる部分で構成されます。これらの各段を電力段と組み合わせることで、安定した堅牢なシステムが実現できます。

優れた過渡応答を得るには、最終的な設計の帯域幅をできるだけ大きくする必要があります。CCM フライバックの帯域幅  $f_{BW}$  は、RHP ゼロ周波数の 1/4 に制限されます。式 41 より、約 1.77kHz と計算されます。

$$f_{BW} = \frac{f_{RHPz}}{4} \quad (41)$$

$f_{BW}$  での開ループ電力段のゲインは、式 40 で計算でき、ボード線図（図 8-4）でも観測できます。この値は -19.55dB で、 $f_{BW}$  での位相は -58° です。

補償ループの 2 次側部分では、まずレギュレートされた定常状態の出力電圧を確立します。レギュレートされた出力電圧を設定するため、TL431 可変高精度シャントレギュレータは、高精度の電圧リファレンスと内部オペアンプを搭載しているので、絶縁型コンバータの 2 次側での使用に理想的です。コンバータの出力端子から TL431 の REF ピンまでの分圧抵抗は、目的の消費電力に基づいて選択します。TL431 の REF 入力電流はわずか  $2\mu A$  なので、 $1mA$  の分圧電流 ( $I_{FB\_REF}$ ) に合わせて抵抗を選択すると、誤差が最小限に抑えられます。上側の分圧器抵抗 ( $R_{FBU}$ ) は、次の式を使用して計算します。

$$R_{FBU} = \frac{V_{OUT} - REF_{TL431}}{I_{FB\_REF}} \quad (42)$$

TL431 の基準電圧 ( $REF_{TL431}$ ) は  $2.495V$  (標準値) です。 $R_{FBU}$  として  $9.53k\Omega$  の抵抗を選択します。出力電圧を  $12V$  に設定するため、 $R_{FBB}$  に  $2.49k\Omega$  を使用します。

$$R_{FBB} = \frac{REF_{TL431}}{V_{OUT} - REF_{TL431}} \times R_{FBU} \quad (43)$$

適切な位相マージンを得るには、補償器ゼロ ( $f_{COMPz}$ ) が必要であり、これを目的の帯域幅の  $1/10$  に配置する必要があります。

$$f_{COMPz} = \frac{f_{BW}}{10} \quad (44)$$

$$\omega_{COMPz} = 2 \times \pi \times f_{COMPz} \quad (45)$$

このコンバータでは、 $f_{COMPz}$  を約  $177Hz$  に設定する必要があります。直列抵抗 ( $R_{COMPz}$ ) およびコンデンサ ( $C_{COMPz}$ ) を TL431 のカソードと REF の間に配置することで、補償器ゼロの位置が設定されます。 $C_{COMPz}$  を  $0.01\mu F$  に設定すると、 $R_{COMPz}$  は次の式で計算されます。

$$R_{COMPz} = \frac{1}{\omega_{COMPz} \times C_{COMPz}} \quad (46)$$

$R_Z$  に標準値  $88.7k\Omega$ 、 $C_Z$  に  $0.01\mu F$  を使用すると、 $179Hz$  の位置にゼロが配置されます。

図 8-3において、 $R_{TLbias}$  はツェナー ダイオード ( $D_{REG}$ ) から供給されるレギュレート済み電圧から、TL431 にカソード電流を供給します。動作を確実にするため、 $10V$  ツェナーと、 $R_{TLbias}$  として  $1k\Omega$  の抵抗を使用することで、 $10mA$  の電流で TL431 をバイアスします。

補償ループの TL431 の部分のゲインは、式 47 で計算されます。

$$G_{TL431}(s) = \left( R_{COMPz} + \frac{1}{s(f) \times C_{ZCOMPz}} \right) \times \frac{1}{R_{FBU}} \quad (47)$$

右半面ゼロまたは ESR ゼロのうち、どちらか低い方の周波数に補償極が必要です。前の分析によれば、右半面ゼロ ( $f_{RHPz}$ ) は  $7.07kHz$ 、ESR ゼロ ( $f_{ESRz}$ ) は  $1.68kHz$  です。したがって、この設計では補償極を  $1.68kHz$  に設定する必要があります。フォトカプラには、周波数上の特性評価が困難な寄生極が含まれているため、フォトカプラには  $1k\Omega$  のブル

ダウン抵抗 ( $R_{OPTO}$ ) がセットアップされ、これによって寄生フォトカプラの極は、この設計が対象とする範囲の外に移動します。

必要な補償極は、 $R_{COMPp}$  および  $C_{COMPp}$  を使用して 1 次側エラー アンプに追加できます。 $R_{COMPp}$  に  $10\text{k}\Omega$  を選択すると、 $C_{COMPp}$  に必要な値は式 48 で決定されます。

$$C_{COMPp} = \frac{1}{2 \times \pi \times f_{ESRZ} \times R_{COMPp}} = 9.46 \text{ nF} \quad (48)$$

補償極を  $1.59\text{kHz}$  に設定するため、 $C_{COMPp}$  には  $10\text{nF}$  のコンデンサを使用します。

要求される帯域幅を得て、必要に応じてループ ゲインを調整するため、1 次側エラー アンプに DC ゲインを追加する必要があります。 $R_{FBG}$  に  $4.99\text{k}\Omega$  を使用すると、エラー アンプの DC ゲインを 2 に設定できます。この時点では、式 49 を使って、補償ループのエラー アンプ段のゲイン伝達関数 ( $G_{EA}(s)$ ) を特性化できます。

$$G_{EA}(s) = \left( \frac{R_{COMPp}}{R_{FBG}} \right) \times \left( \frac{1}{1 + s(f) \times C_{COMPp} \times R_{COMPp}} \right) \quad (49)$$

目的の周波数範囲で電流伝達率 (CTR) の標準値が 100% であるフォトカプラを使用すると、 $CTR = 1$  になります。それによって、フォトカプラ段の伝達関数 ( $G_{OPTO}(s)$ ) は式 50 を使って求まります。

$$G_{OPTO}(s) = \frac{CTR \times R_{OPTO}}{R_{LED}} \quad (50)$$

フォトカプラの内部ダイオードへのバイアス抵抗 ( $R_{LED}$ ) と、光エミッタへのプレダウン抵抗 ( $R_{OPTO}$ ) を使用して、絶縁境界をまたぐゲインを設定します。 $R_{OPTO}$  はすでに  $1\text{k}\Omega$  に設定されていますが、 $R_{LED}$  の値はまだ決定されていません。

合計閉ループ ゲイン ( $G_{TOTAL}(s)$ ) は、開ループの電力段 ( $H_o(s)$ )、光ゲイン ( $G_{OPTO}(s)$ )、エラー アンプのゲイン ( $G_{EA}(s)$ )、TL431 段のゲイン ( $G_{TL431}(s)$ ) の組み合わせです (式 51 を参照)。

$$G_{TOTAL}(s) = |H_{OPEN}(s)| \times |G_{OPTO}(s)| \times |G_{EA}(s)| \times |G_{TL431}(s)| \quad (51)$$

$R_{LED}$  に必要な値を選択して、目的のクロスオーバー周波数 ( $f_{BW}$ ) を実現できます。目的のクロスオーバー周波数で合計ループ ゲインを 1 に設定し、式 51 を再整理することで、 $R_{LED}$  に最適な値を式 52 のように決定できます。

$$R_{LED} \leq |H_{OPEN}(s)| \times |CTR \times C_{OPTO}| \times |G_{EA}(s)| \times |G_{TL431}(s)| \quad (52)$$

$R_{LED}$  の要件には、 $1.3\text{k}\Omega$  の抵抗が適しています。

補償ループの構造に基づいて、補償ループ全体の伝達関数は式 53 に示すように記述されます。

$$G_{CLOSED}(s) = H_{OPEN}(s) \times \left( \frac{CTR \times R_{OPTO}}{R_{LED}} \right) \times \left( \frac{R_{COMPp}}{R_{FBG}} \right) \times \left( \frac{1}{1 + (s \times C_{COMPp} \times R_{COMPp})} \right) \\ \times \left( \frac{R_{COMPz} + \left( \frac{1}{s \times C_{COMPz}} \right)}{R_{FBU}} \right) \quad (53)$$

最終的な閉ループ ボード線図を、図 8-6 と図 8-7 に示します。このコンバータのクロスオーバー周波数は約  $1.8\text{kHz}$  で、位相マージンは約  $67^\circ$  です。

システムの安定性を保証するため、部品の公差を含め、すべてのコーナー ケースにわたってループの安定性をチェックすることをお勧めします。

図 8-6. コンバータの閉ループのボード線図 - ゲイン

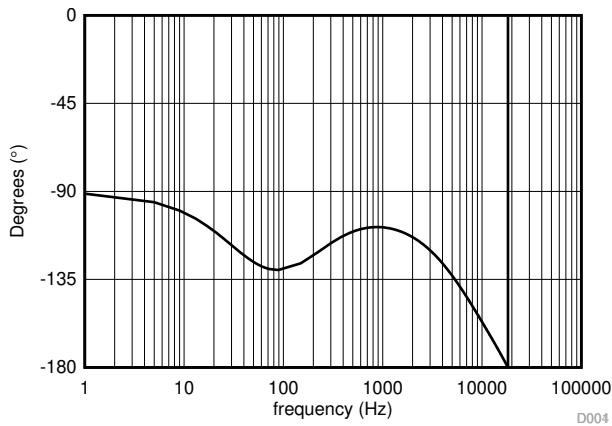

図 8-7. コンバータの閉ループのボード線図 - 位相

### 8.2.3 アプリケーション曲線

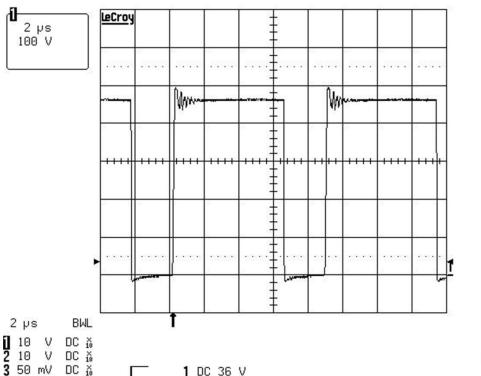

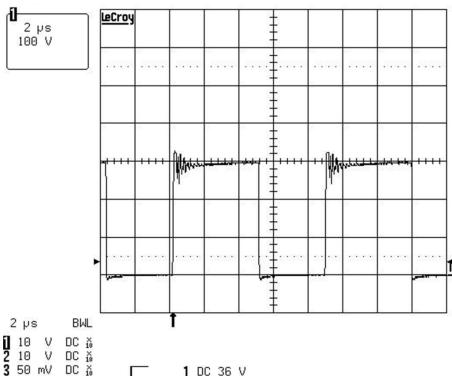

図 8-8. AC 240V 入力での 1 次側 MOSFET のドレン - ソース間電圧 (100V/div)

図 8-9. AC 120V 入力での 1 次側 MOSFET のドレン - ソース間電圧 (100V/div)

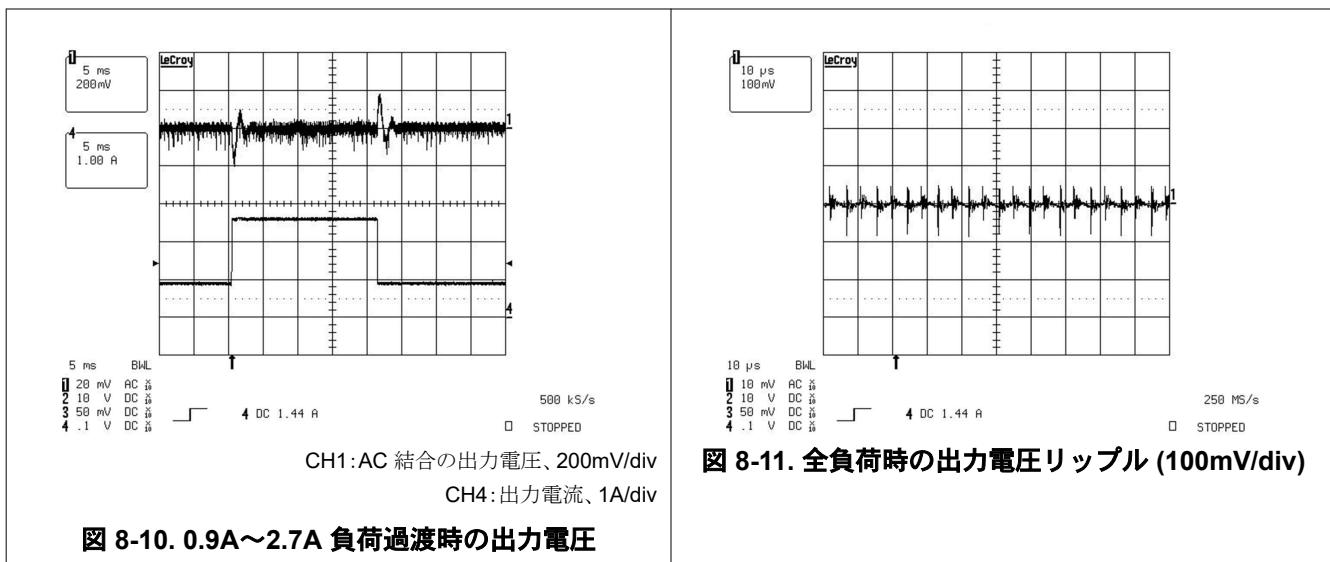

図 8-10. 0.9A～2.7A 負荷過渡時の出力電圧

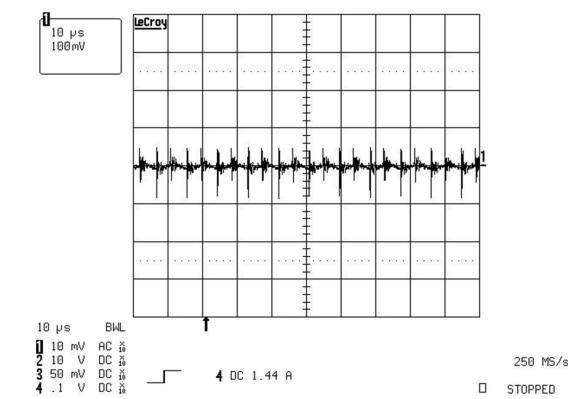

図 8-11. 全負荷時の出力電圧リップル (100mV/div)

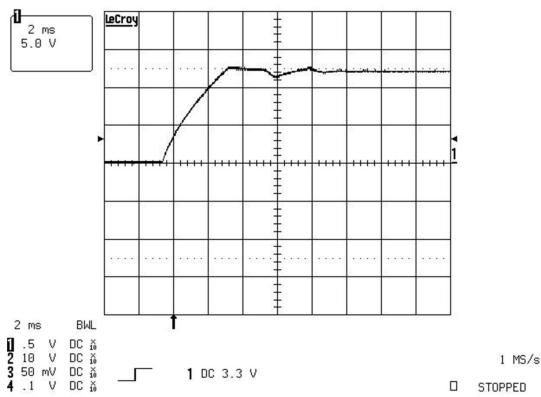

図 8-12. 全負荷スタートアップ時の出力電圧動作 (5V/div)

## 8.3 電源に関する推奨事項

存在する可能性がある過渡電圧を含めて、UCC28C42 の電源電圧の絶対最大定格値は 20V です。この電圧を超えると、デバイスが損傷する可能性があります。この損傷リスクは、最大 30V に耐えられた従来のバイポーラ デバイスとは対照的です。そのため、GND ピンのできるだけ近くで電源ピンをデカッピングする必要があります。

本デバイスにはクランプが内蔵されていないため、20V のレベルを超える可能性がある外部電源から電源ピンを保護する必要があります。

リーディング エッジ ノイズによる誤トリガを防止するため、CS に RC 電流検出フィルタが必要な場合があります。RC フィルタの時定数は、最小オン時間パルス幅を十分に下回るようにします。

高速スイッチング過渡によるノイズの問題を防止するため、IC パッケージの近くにセラミック コンデンサを配置して、VREF をグランドにバイパスします。0.1μF 以上のセラミック コンデンサが必要です。リファレンスの外部負荷には、追加の VREF バイパスが必要です。セラミック コンデンサに加えて電解コンデンサも使用できます。

## 8.4 レイアウト

### 8.4.1 レイアウトのガイドライン

#### 8.4.1.1 事前の注意事項

高周波電源では、プリント基板を入念にレイアウトする必要があります。デバイス スイッチング速度および動作周波数が上がるにつれて、コンバータのレイアウトはますます重要になります。

この 8 ピン デバイスは、ロジックおよび電源接続のためのグランドを 1 つのみ備えています。そのため、ゲート駆動電流パルスは、制御回路が基準として使っている同じグランドを流れざるを得ません。したがって、相互接続のインダクタンスができるだけ小さくする必要があります。つまり、デバイス (ゲートドライバ) 回路を、それが駆動している MOSFET の近くに配置する必要があります。これは、ノイズを発生させる部品からエラー アンプと帰還経路を遠ざける必要性と矛盾する可能性があります。

PWM 制御のプリント基板レイアウトで最も重要な 1 つの要素は、タイミング コンデンサの配置です。電源バイパス コンデンサと基準バイパス コンデンサの位置はどちらも重要ですが、タイミング コンデンサの配置はもっと重要です。プリント回路の長い配線のインダクタンスまたは、大電力スイッチング ノイズに近づくことによるピックアップ ノイズに起因する  $C_{CT}$  波形のノイズ スパイクは、さまざまな動作上の問題を引き起こします。難問は、ノイズ スパイクに起因する発振器のプリトリガによる動作周波数の間違いから、やはりノイズ スパイクに起因する周波数のジャンプとデューティ サイクルの変動まで、さまざまです。タイミング コンデンサの配置は、レイアウト上の最も重要な考慮事項として扱う必要があります。直列インダクタンスの増加を最小限に抑えるため、プリント基板の配線をできるだけ短く保ちます。

#### 8.4.1.2 フィードバック配線

フィードバック配線は、インダクタやノイズの多い電源の配線とできるだけ離すようにします。また、フィードバック配線はできるだけ直接的に、多少太くすることを検討してください。これら 2 つはトレードオフになることもあります、どちらかを選ぶ必要があるときは、EMI や他のノイズ源から遠ざけることのほうが重要です。可能なら、PCB 上でインダクタと反対側の面にフィードバック配線を置き、両方の間にグランド プレーンで分離されるようにします。

#### 8.4.1.3 バイパス コンデンサ

値の小さいセラミック バイパス コンデンサを使用する場合は、デバイスの VDD ピンのできるだけ近くに配置する必要があります。これにより、配線のインダクタンスの影響を可能な限り排除し、よりクリーンな電圧電源を内部デバイス レールに供給できます。表面実装コンデンサを使用すると、リード長が短くなり、スルーホール部品によって生成される事実上のアンテナにノイズが結び付く可能性が低くなります。

#### 8.4.1.4 補償部品

安定性を最大限に高めるには、IC の近くに外部補償部品を配置する必要があります。FB リードはできるだけ短くし、FB 浮遊容量はできるだけ小さくします。フィルタコンデンサについての説明と同じ理由で、テキサス・インスツルメンツは表面実装部品を推奨します。これらの部品は、スイッチングノイズの大きい配線にあまり近付けないようにします。

#### 8.4.1.5 配線とグランドプレーン

すべての電源(大電流)配線はできるだけ短く、直線的で、太くします。標準的な PCB 基板では、配線の絶対最小値をアンペアあたり 15mil (0.381mm) にすることをお勧めします。インダクタ、出力コンデンサ、出力ダイオードは、可能な限り互いに近く配置します。これにより、電源配線に大きなスイッチング電流が流れても EMI が放射されることを低減できます。これによつてリードインダクタンスと抵抗も減少するので、電圧誤差を引き起こすノイズスパイク、リング、抵抗性損失も減少します。

IC、入力コンデンサ、出力コンデンサ、出力ダイオードのグランドは、該当する場合、グランドプレーンに直接、かつ互いに近接して接続します。PCB の両側にグランドプレーンを配置することも推奨されます。これにより、グランドループの誤差を低減するとともに、インダクタから放射される EMI をより多く吸収し、ノイズを低減できます。2 層より多い多層基板の場合、グランドプレーンを使用して電源プレーン(電源配線と部品が配置されているプレーン)と信号プレーン(帰還や補償とその部品が配置されているプレーン)を分離し、性能を向上させることができます。多層基板では、配線や異なるプレーンを接続するためにビアを使用する必要があります。その配線があるプレーンから別のプレーンに大電流を流す場合、電流 200mA ごとに 1 個の標準ビアを使用することを推奨します。

スイッチング電流ループが同じ方向に流れるように部品を配置します。スイッチングレギュレータの動作方法により、2つの電力状態があります。1つはスイッチがオンのとき、もう1つはスイッチがオフのときです。いずれの状態でも、現在導通している電源部品によって電流ループが形成されます。2つの状態のそれぞれで、電流ループが同じ方向に導通するように、電源部品を配置します。これにより、2つの半サイクル間の配線による磁界の反転を防止し、放射 EMI を低減できます。

#### 8.4.2 レイアウト例

図 8-13. UCCx8C4x のレイアウト例

## 9 デバイスおよびドキュメントのサポート

### 9.1 デバイス サポート

#### 9.1.1 サード・パーティ製品に関する免責事項

サード・パーティ製品またはサービスに関するテキサス・インスツルメンツの出版物は、単独またはテキサス・インスツルメンツの製品、サービスと一緒に提供される場合に関係なく、サード・パーティ製品またはサービスの適合性に関する是認、サード・パーティ製品またはサービスの是認の表明を意味するものではありません。

### 9.2 ドキュメントのサポート

#### 9.2.1 関連資料

関連資料については、以下を参照してください。

『UC384x による低コストの電流モード制御』(SLUA143)

### 9.3 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 9.4 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの使用条件を参照してください。

## 9.5 商標

テキサス・インスツルメンツ E2E™ is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

## 9.6 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことをお勧めします。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

## 9.7 用語集

### テキサス・インスツルメンツ用語集

この用語集には、用語や略語の一覧および定義が記載されています。

## 10 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision H (September 2022) to Revision I (June 2024) | Page |

|--------------------------------------------------------------------|------|

| • 「電気的特性」セクションに COMP ピンの短絡電流を追加.....                               | 7    |

| Changes from Revision G (January 2017) to Revision H (September 2022) | Page |

|-----------------------------------------------------------------------|------|

| • -40°C~105°Cを -40°C~125°C、0°C~70°Cを 0°C~85°Cに変更.....                 | 1    |

| • 「製品情報」から PDIP パッケージを削除.....                                         | 1    |

| • 「デバイス比較」表の $T_J$ の範囲を更新 .....                                       | 3    |

| • 「ピン構成」から PDIP パッケージを削除.....                                         | 4    |

| • 「絶対最大定格」表から PDIP パッケージを削除 .....                                     | 5    |

| • 「絶対最大定格」表の総合許容損失の値を更新 .....                                         | 5    |

| • 「推奨動作条件」の $V_{REF}$ の外部回路からの最大連続電圧を追加 .....                         | 6    |

| • 「推奨動作条件」表の $T_J$ の最大値を更新 .....                                      | 6    |

| • 「熱に関する情報」の熱抵抗のすべての数値を更新 .....                                       | 7    |

| • 「電気的特性」セクションを更新.....                                                | 7    |

| Changes from Revision F (August 2016) to Revision G (January 2017) | Page |

|--------------------------------------------------------------------|------|

| • $V_{REFLECTED}$ の式を変更。.....                                      | 30   |

| • $D_{MAX}$ の式を変更。.....                                            | 30   |

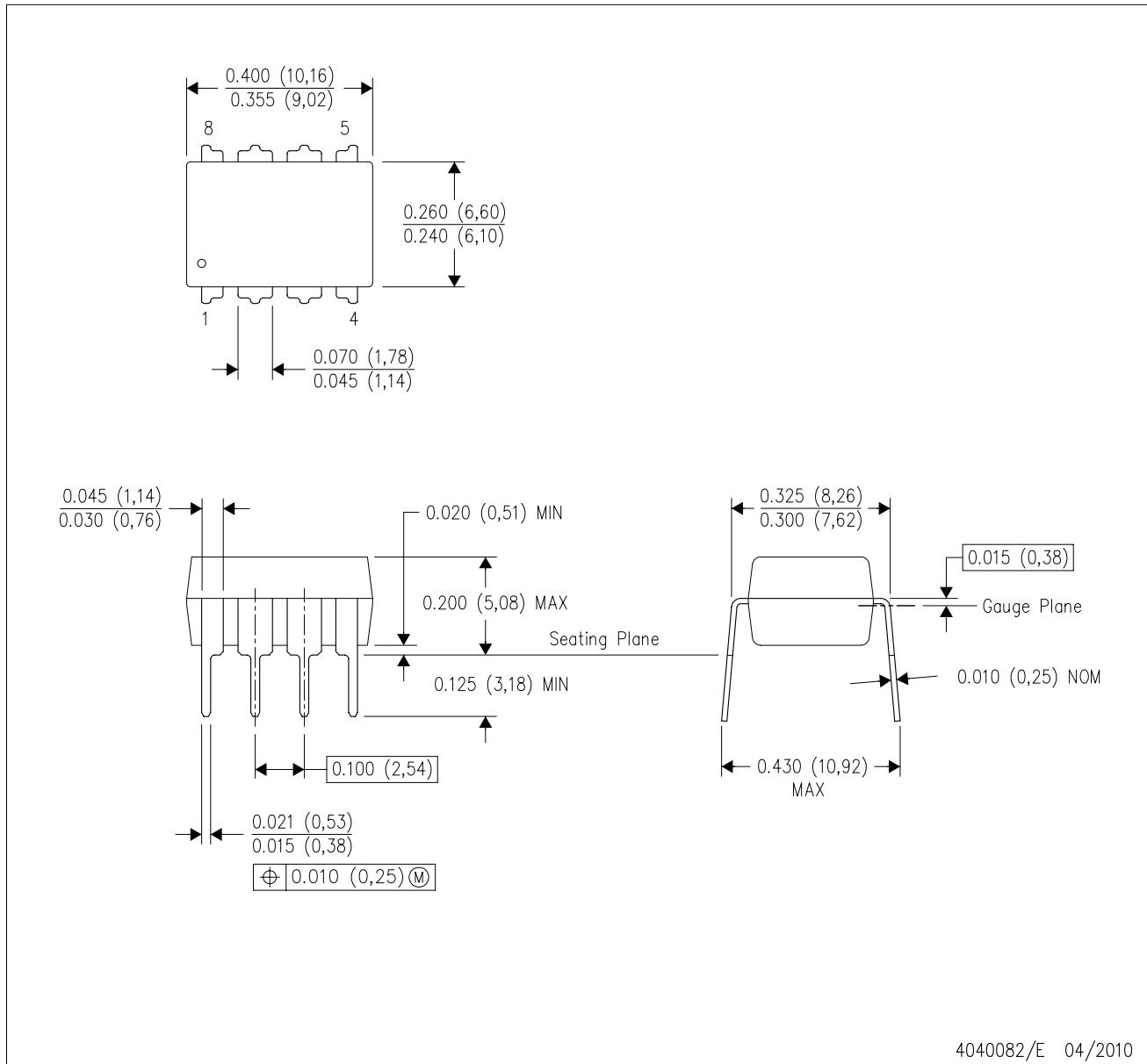

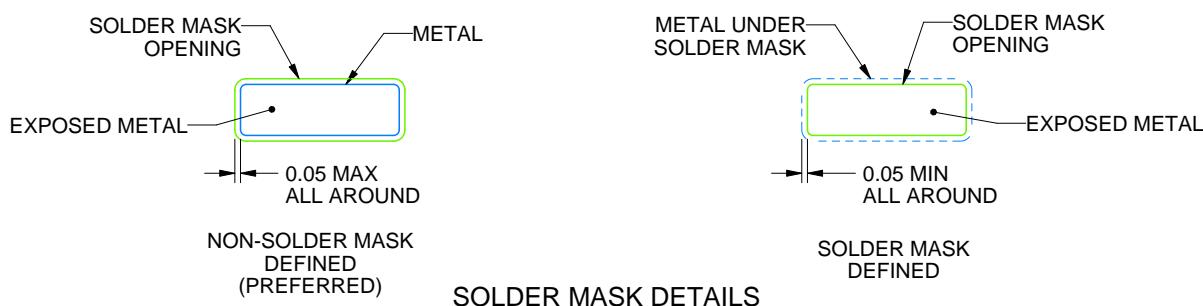

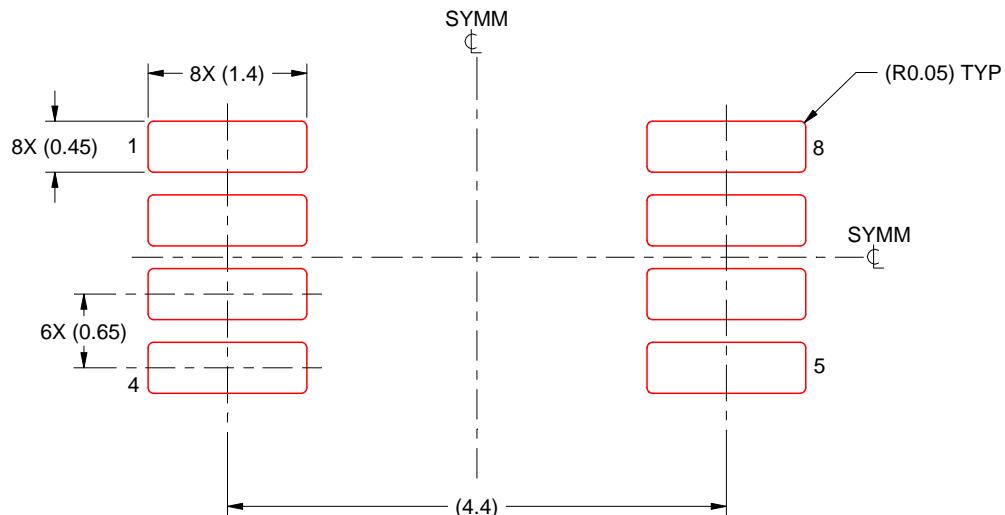

## 11 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報はそのデバイスについて利用可能な最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用されている場合は、左側のナビゲーションを参照してください。

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ（データシートを含みます）、設計リソース（リファレンス デザインを含みます）、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている テキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかる テキサス・インスツルメンツ製品の関連資料などのいづれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2024, Texas Instruments Incorporated

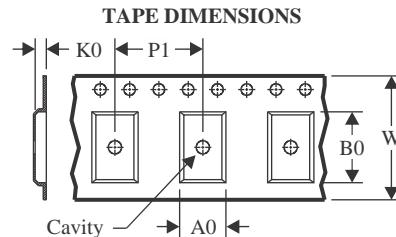

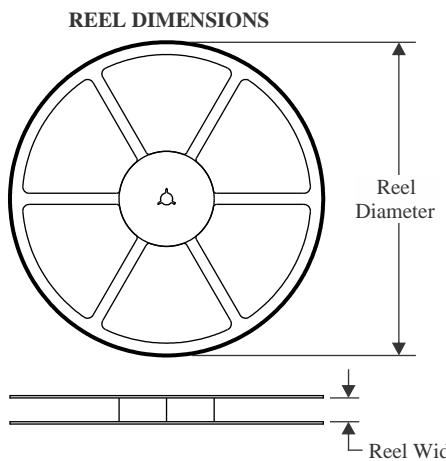

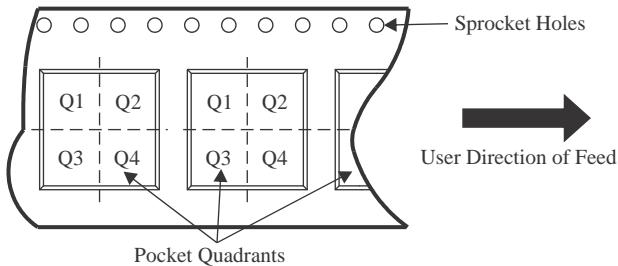

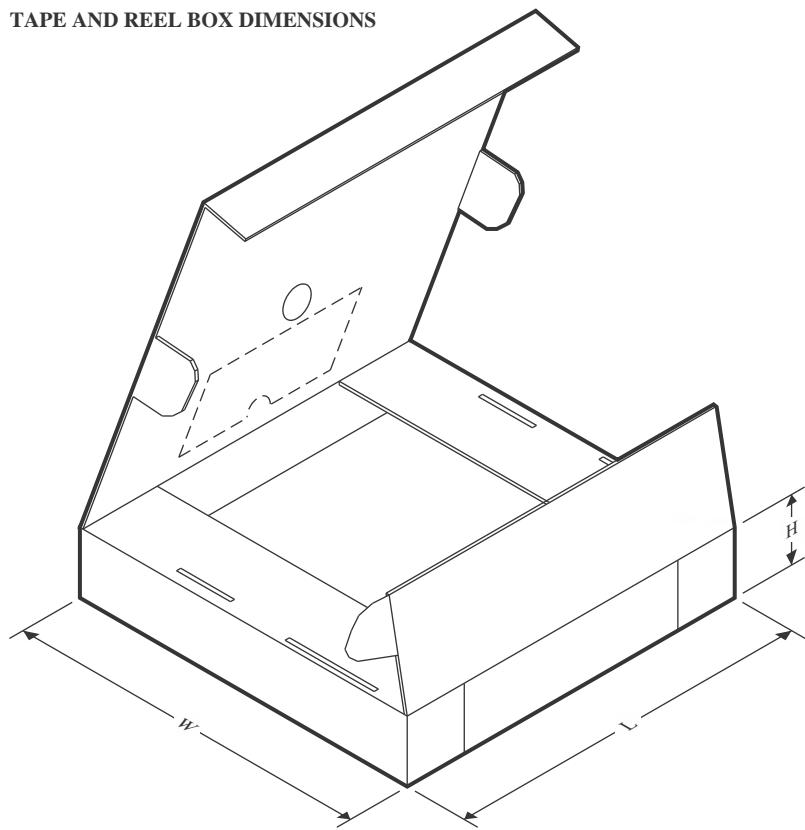

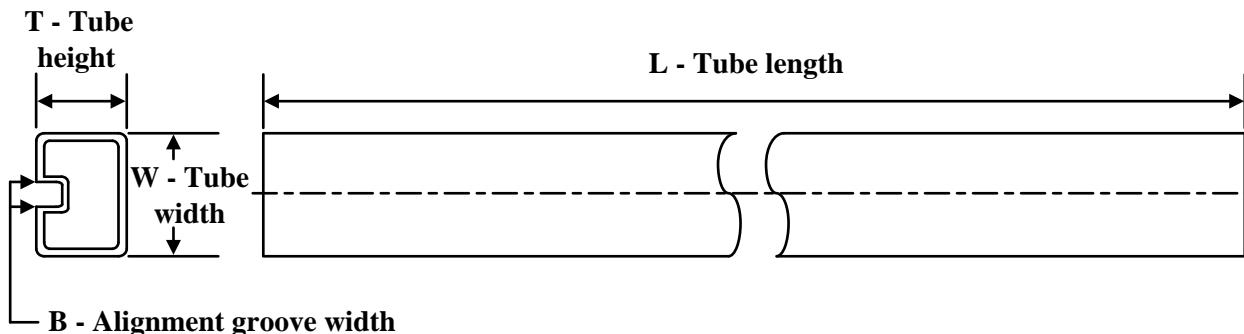

**PACKAGING INFORMATION**

| Orderable part number            | Status<br>(1) | Material type<br>(2) | Package   Pins  | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|----------------------------------|---------------|----------------------|-----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| <a href="#">UCC28C40D</a>        | Obsolete      | Production           | SOIC (D)   8    | -                     | -           | Call TI                              | Call TI                           | -40 to 125   | 28C40               |

| <a href="#">UCC28C40DGK</a>      | Obsolete      | Production           | VSSOP (DGK)   8 | -                     | -           | Call TI                              | Call TI                           | -40 to 125   | 28C40               |

| <a href="#">UCC28C40DGKR</a>     | Active        | Production           | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | (28C40, 2C40)       |

| <a href="#">UCC28C40DGKR.A</a>   | Active        | Production           | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | (28C40, 2C40)       |

| <a href="#">UCC28C40DGKRG4</a>   | Active        | Production           | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | 2C40                |

| <a href="#">UCC28C40DGKRG4.A</a> | Active        | Production           | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | 2C40                |

| <a href="#">UCC28C40DR</a>       | Active        | Production           | SOIC (D)   8    | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 28C40               |

| <a href="#">UCC28C40DR.A</a>     | Active        | Production           | SOIC (D)   8    | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 28C40               |

| <a href="#">UCC28C41D</a>        | Obsolete      | Production           | SOIC (D)   8    | -                     | -           | Call TI                              | Call TI                           | -40 to 125   | 28C41               |

| <a href="#">UCC28C41DGKR</a>     | Active        | Production           | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes         | Call TI   Nipdau                     | Level-2-260C-1 YEAR               | -40 to 125   | (28C41, 2C41)       |

| <a href="#">UCC28C41DGKR.A</a>   | Active        | Production           | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | (28C41, 2C41)       |

| <a href="#">UCC28C41DR</a>       | Active        | Production           | SOIC (D)   8    | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 28C41               |

| <a href="#">UCC28C41DR.A</a>     | Active        | Production           | SOIC (D)   8    | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 28C41               |

| <a href="#">UCC28C42DGKR</a>     | Active        | Production           | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes         | Call TI   Nipdau                     | Level-2-260C-1 YEAR               | -40 to 125   | (28C42, 2C42)       |

| <a href="#">UCC28C42DGKR.A</a>   | Active        | Production           | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | (28C42, 2C42)       |

| <a href="#">UCC28C42DR</a>       | Active        | Production           | SOIC (D)   8    | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 28C42               |

| <a href="#">UCC28C42DR.A</a>     | Active        | Production           | SOIC (D)   8    | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 28C42               |

| <a href="#">UCC28C42DRG4</a>     | Active        | Production           | SOIC (D)   8    | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 28C42               |

| <a href="#">UCC28C43DGKR</a>     | Active        | Production           | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes         | Call TI   Nipdau                     | Level-2-260C-1 YEAR               | -40 to 125   | (28C43, 2C43)       |

| <a href="#">UCC28C43DGKR.A</a>   | Active        | Production           | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | (28C43, 2C43)       |

| <a href="#">UCC28C43DGKRG4</a>   | Active        | Production           | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | (28C43, 2C43)       |

| <a href="#">UCC28C43DR</a>       | Active        | Production           | SOIC (D)   8    | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 28C43               |

| <a href="#">UCC28C43DR.A</a>     | Active        | Production           | SOIC (D)   8    | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 28C43               |

| <a href="#">UCC28C43DRG4</a>     | Active        | Production           | SOIC (D)   8    | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 28C43               |

| <a href="#">UCC28C44DGKR</a>     | Active        | Production           | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | (28C44, 2C44)       |

| <a href="#">UCC28C44DGKR.A</a>   | Active        | Production           | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | (28C44, 2C44)       |

| <a href="#">UCC28C44DGKRG4</a>   | Active        | Production           | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | 2C44                |

| <a href="#">UCC28C44DGKRG4.A</a> | Active        | Production           | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | 2C44                |

| <a href="#">UCC28C44DR</a>       | Active        | Production           | SOIC (D)   8    | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 28C44               |

| Orderable part number        | Status<br>(1) | Material type<br>(2) | Package   Pins  | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|------------------------------|---------------|----------------------|-----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| UCC28C44DR.A                 | Active        | Production           | SOIC (D)   8    | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 28C44               |

| UCC28C44DRG4                 | Active        | Production           | SOIC (D)   8    | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 28C44               |

| <a href="#">UCC28C45DGKR</a> | Active        | Production           | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | (28C45, 2C45)       |

| UCC28C45DGKR.A               | Active        | Production           | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | (28C45, 2C45)       |

| <a href="#">UCC28C45DR</a>   | Active        | Production           | SOIC (D)   8    | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 28C45               |

| UCC28C45DR.A                 | Active        | Production           | SOIC (D)   8    | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 28C45               |

| UCC28C45DRG4                 | Active        | Production           | SOIC (D)   8    | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 28C45               |

| <a href="#">UCC38C40DGK</a>  | Active        | Production           | VSSOP (DGK)   8 | 80   TUBE             | Yes         | NIPDAUAG                             | Level-2-260C-1 YEAR               | 0 to 85      | 38C40               |

| UCC38C40DGK.A                | Active        | Production           | VSSOP (DGK)   8 | 80   TUBE             | Yes         | NIPDAUAG                             | Level-2-260C-1 YEAR               | 0 to 85      | 38C40               |

| <a href="#">UCC38C40DGKR</a> | Active        | Production           | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes         | Call TI   Nipdaug                    | Level-2-260C-1 YEAR               | 0 to 85      | 38C40               |

| UCC38C40DGKR.A               | Active        | Production           | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes         | Call TI                              | Level-2-260C-1 YEAR               | 0 to 85      | 38C40               |

| <a href="#">UCC38C40DR</a>   | Active        | Production           | SOIC (D)   8    | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | 0 to 85      | 38C40               |

| UCC38C40DR.A                 | Active        | Production           | SOIC (D)   8    | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | 0 to 85      | 38C40               |

| <a href="#">UCC38C41DGK</a>  | Active        | Production           | VSSOP (DGK)   8 | 100   TUBE            | Yes         | NIPDAUAG                             | Level-2-260C-1 YEAR               | 0 to 85      | 38C41               |

| UCC38C41DGK.A                | Active        | Production           | VSSOP (DGK)   8 | 100   TUBE            | Yes         | NIPDAUAG                             | Level-2-260C-1 YEAR               | 0 to 85      | 38C41               |

| <a href="#">UCC38C41DR</a>   | Active        | Production           | SOIC (D)   8    | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | 0 to 85      | 38C41               |

| UCC38C41DR.A                 | Active        | Production           | SOIC (D)   8    | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | 0 to 85      | 38C41               |

| UCC38C41DRG4                 | Active        | Production           | SOIC (D)   8    | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | 0 to 85      | 38C41               |

| <a href="#">UCC38C42D</a>    | Obsolete      | Production           | SOIC (D)   8    | -                     | -           | Call TI                              | Call TI                           | 0 to 85      | 38C42               |

| <a href="#">UCC38C42DGK</a>  | Active        | Production           | VSSOP (DGK)   8 | 100   TUBE            | Yes         | NIPDAUAG                             | Level-2-260C-1 YEAR               | 0 to 85      | 38C42               |