# ADC32RF72 デュアルチャネル、1.5GSPS、16ビットRFサンプリングADC

## 1 特長

- 16ビット、デュアルチャネル、1.5GSPS ADC

- ノイズスペクトル密度:-163.7dBFS/Hz

- 熱ノイズ:75.6dBFS

- ノイズ指数:14.4dB

- シングルコア(非インターリーブ)ADCアーキテクチャ

- アパーチャジッタ:40fs

- バッファ付きアナログ入力

- 入力フルスケール:1.44Vpp (4.1dBm)

- フルパワー入力帯域幅(-3dB):1.8GHz

- 超低クローズイン残留位相ノイズ:

- -140dBc/Hz (1GHzの10kHzオフセット時)

- スペクトル性能( $f_{IN} = 1\text{GHz}$ , -1dBFS時):

- SNR<sub>flat</sub>:72.1dBFS

- HD2, 3:68dBc

- 非HD2, 3:93dBFS

- 192タップ/チャネルプログラマブルFIRイコライザフィルタ

- 12ビットフラクショナル遅延フィルタ

- デジタルダウンコンバータ(DDC)

- 最大8つのDDC

- 複素数出力:/2, /3, /4, /5から/32768のデシメーション

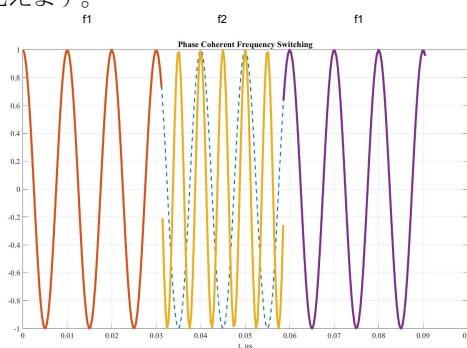

- 48ビットNCOによる位相コヒーレント周波数ホッピング

- 高速周波数ホッピング:<1μs

- JESD204B/Cシリアルデータインターフェイス

- 最大レーン速度:24.75Gbps

- コードエラーレート(CER):1E-15エラー/サンプル

- 消費電力:1.5W/チャネル(1.5GSPS)

## 2 アプリケーション

- フェーズドアレイレーダー

- ウェハー検査

- スペクトルアナライザ

- ソフトウェア無線(SDR)

- 電子戦

- 高速デジタイザ

- ケーブルインフラストラクチャ

- 通信インフラ

## 3 説明

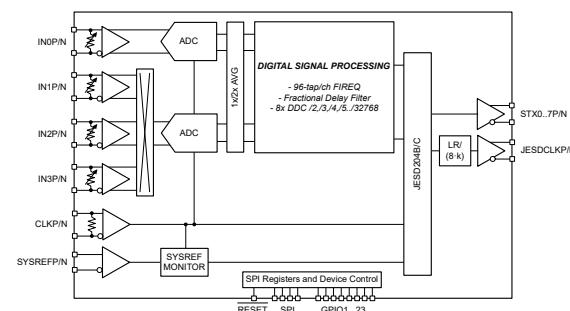

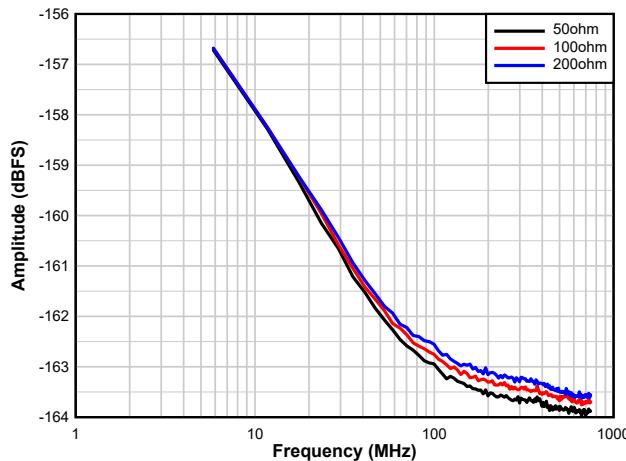

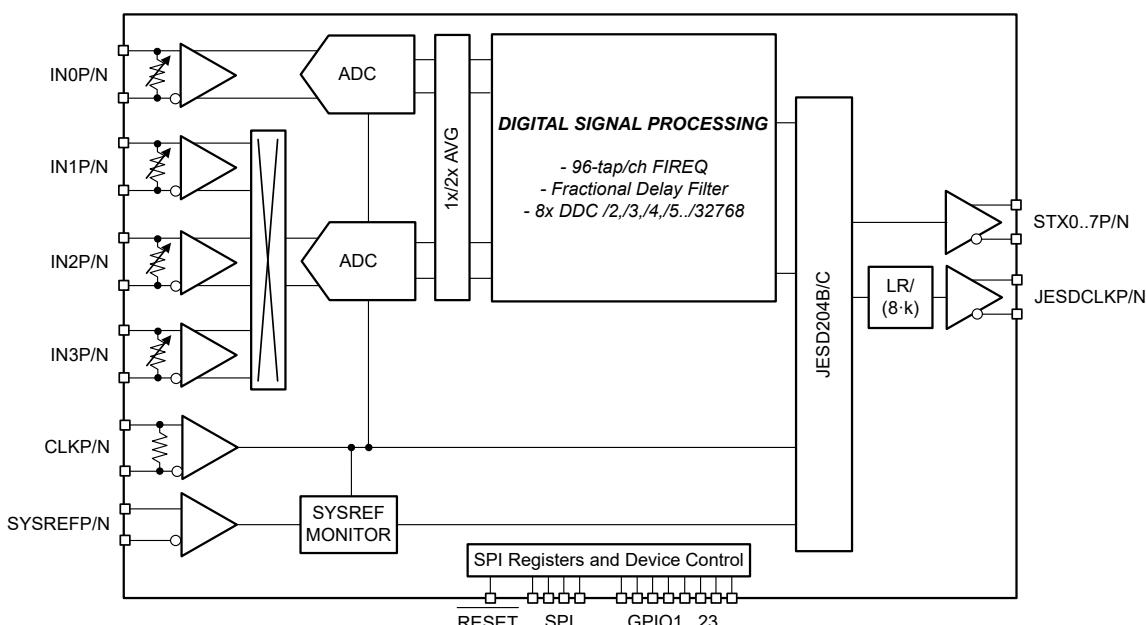

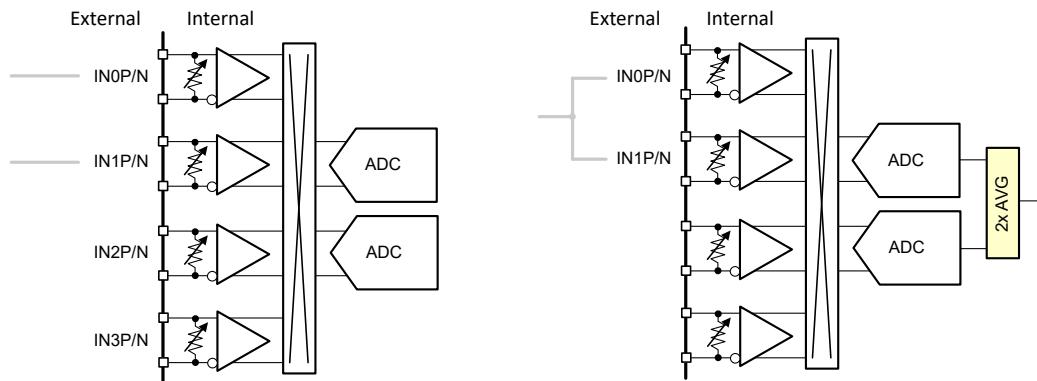

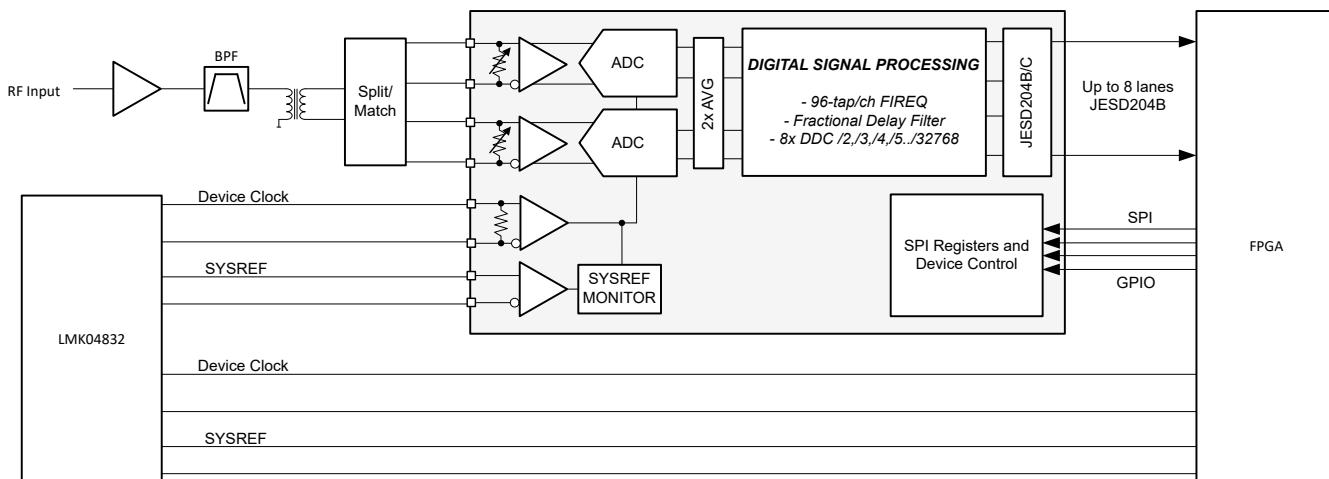

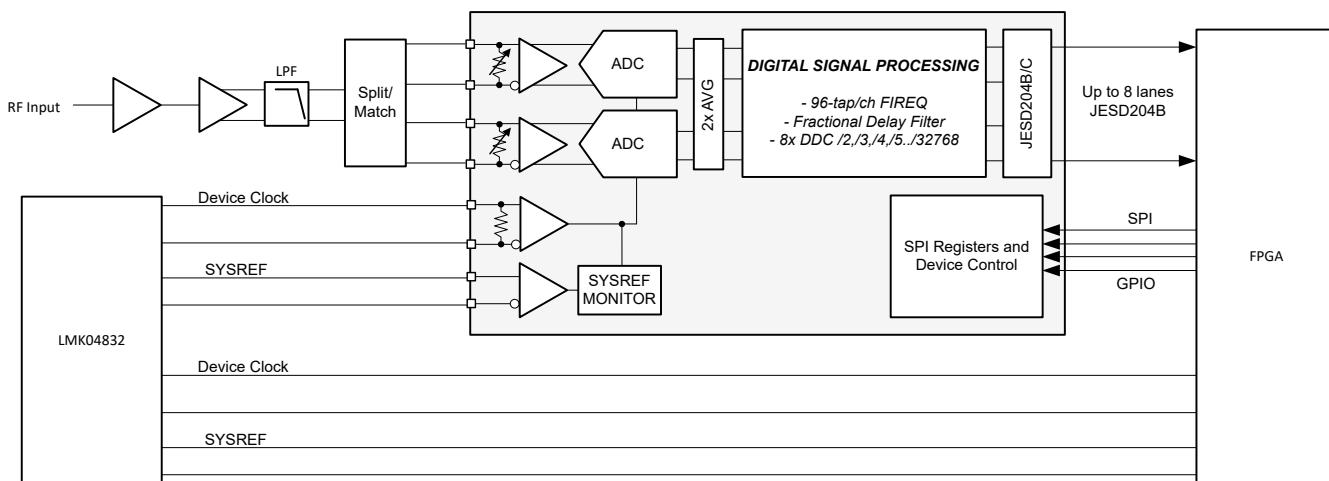

ADC32RF72は、16ビット、1.5GSPS(非インターリーブ)、デュアルチャネルA/Dコンバータ(ADC)です。このデバイスは、最高の信号対雑音比(SNR)を実現するよう設計されており、-163.7dBFS/Hzのノイズスペクトル密度を備えています。内部平均化モードを使用すると、NSDを-166.2dBFS/Hzまで減少させることができます。バッファ付きアナログ入力は、1.8GHz(-3dB)のフルパワー入力帯域幅で、50、100、および200Ωのプログラム可能な内部終端インピーダンスをサポートしています。このデバイスでは、IN0に加えてIN1/2/3から1つの入力を選択できます。

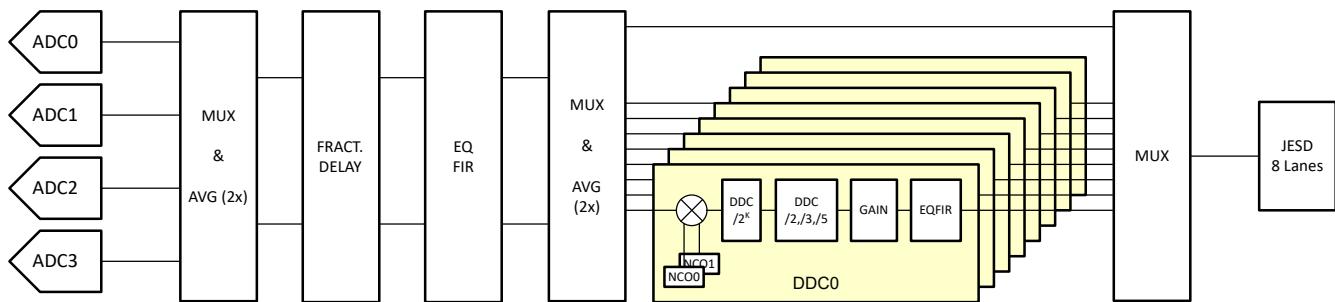

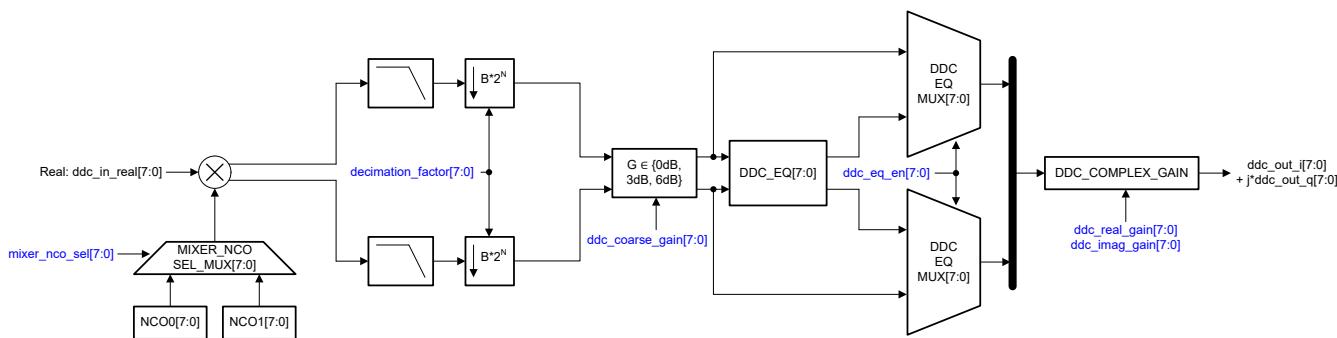

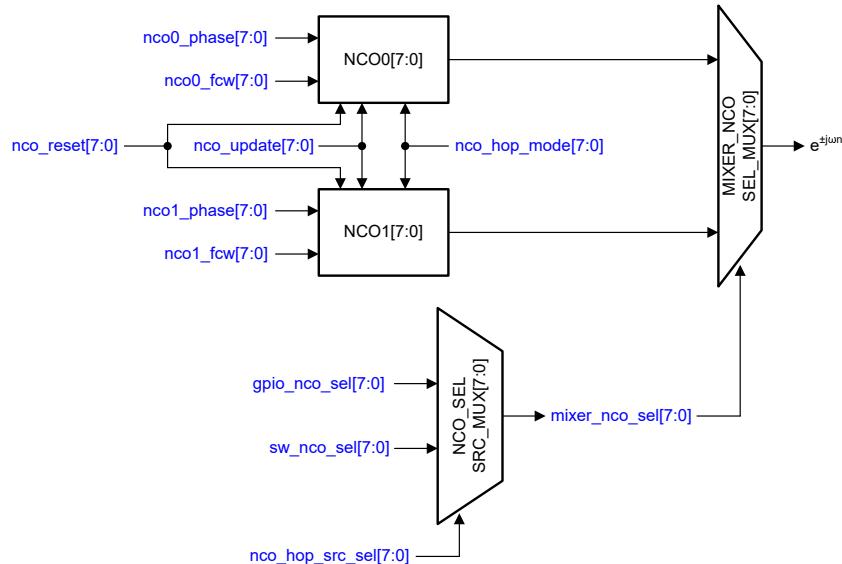

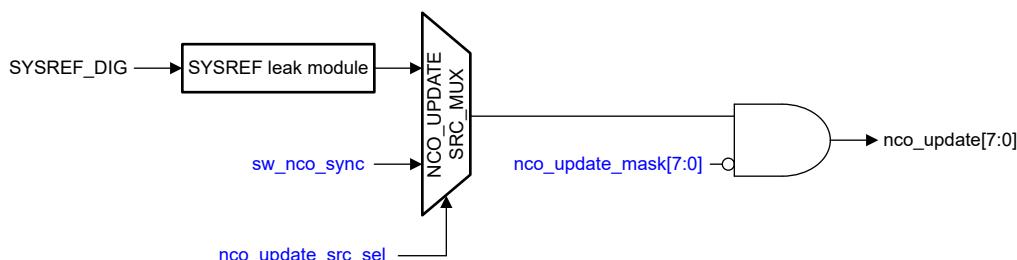

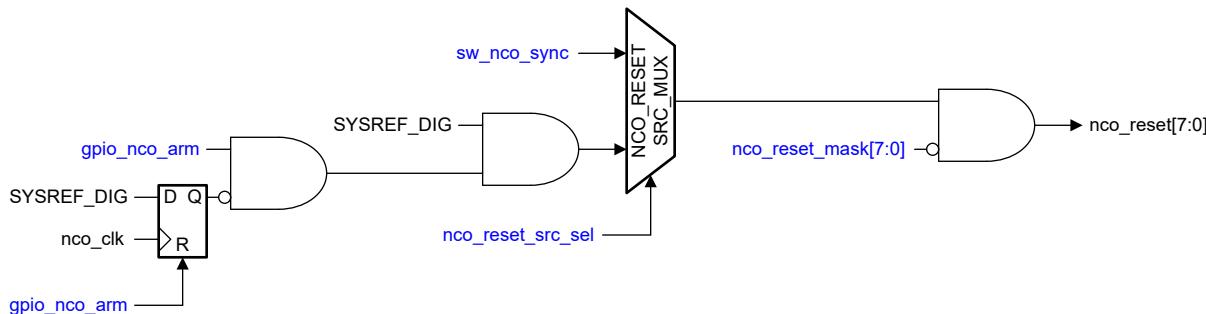

このデバイスには、イコライゼーション用の192タップ/チャネルのプログラマブルFIRフィルタ、12ビットの非整数遅延フィルタ、複数のデジタルダウンコンバータ(DDC)など、いくつかのデジタル処理機能を搭載しています。8つのDDCが/2, /3, /5から/32768までのデシメーション係数をサポートしています。48ビットNCOは位相コヒーレント周波数ホッピングをサポートしています。

ADC32RF72は、JESD204B/Cシリアルデータインターフェイスをサポートし、最大24.75Gbpsのインターフェイスレートを使用します。電力効率の優れたADCアーキテクチャは、1.5GSPSで1.5W/chの消費電力を実現し、低サンプリングレートで電力スケーリングを実現します。

### パッケージ情報

| 部品番号      | パッケージ <sup>(1)</sup> | パッケージサイズ <sup>(2)</sup> |

|-----------|----------------------|-------------------------|

| ADC32RF72 | FCCSP                | 13.8mm × 13.8mm         |

(1) 詳細については、セクション11を参照してください。

(2) パッケージサイズ(長さ×幅)は公称値であり、該当する場合はピンも含まれます。

### デバイスの比較

| 部品番号      | チャネル数 |

|-----------|-------|

| ADC32RF72 | 2     |

| ADC34RF72 | 4     |

ブロック図

## 目次

|                    |  |           |                                      |           |

|--------------------|--|-----------|--------------------------------------|-----------|

| <b>1 特長</b>        |  | <b>1</b>  | <b>7.4 デバイスの機能モード</b>                | <b>56</b> |

| <b>2 アプリケーション</b>  |  | <b>1</b>  | <b>7.5 プログラミング</b>                   | <b>58</b> |

| <b>3 説明</b>        |  | <b>1</b>  | <b>8 アプリケーションと実装</b>                 | <b>60</b> |

| <b>4 ピン構成および機能</b> |  | <b>3</b>  | <b>8.1 アプリケーション情報</b>                | <b>60</b> |

| <b>5 仕様</b>        |  | <b>7</b>  | <b>8.2 代表的なアプリケーション: スペクトル アナライザ</b> | <b>60</b> |

| 5.1 絶対最大定格         |  | 7         | 8.3 代表的なアプリケーション: 時間ドメインデジタイザ        | 63        |

| 5.2 ESD 定格         |  | 7         | 8.4 初期化セットアップ                        | 65        |

| 5.3 推奨動作条件         |  | 7         | 8.5 電源に関する推奨事項                       | 66        |

| 5.4 熱に関する情報        |  | 8         | 8.6 レイアウト                            | 67        |

| 5.5 電気的特性 - 消費電力   |  | 8         | <b>9 デバイスおよびドキュメントのサポート</b>          | <b>69</b> |

| 5.6 電気的特性 - DC 仕様  |  | 9         | 9.1 ドキュメントのサポート                      | 69        |

| 5.7 電気的特性 - AC 仕様  |  | 10        | 9.2 ドキュメントの更新通知を受け取る方法               | 69        |

| 5.8 タイミング要件        |  | 11        | 9.3 サポート・リソース                        | 69        |

| 5.9 代表的特性          |  | 12        | 9.4 商標                               | 69        |

| <b>6 パラメータ測定情報</b> |  | <b>18</b> | 9.5 静電気放電に関する注意事項                    | 69        |

| <b>7 詳細説明</b>      |  | <b>19</b> | 9.6 用語集                              | 69        |

| 7.1 概要             |  | 19        | <b>10 改訂履歴</b>                       | <b>69</b> |

| 7.2 機能ブロック図        |  | 19        | <b>11 メカニカル、パッケージ、および注文情報</b>        | <b>70</b> |

| 7.3 機能説明           |  | 20        |                                      |           |

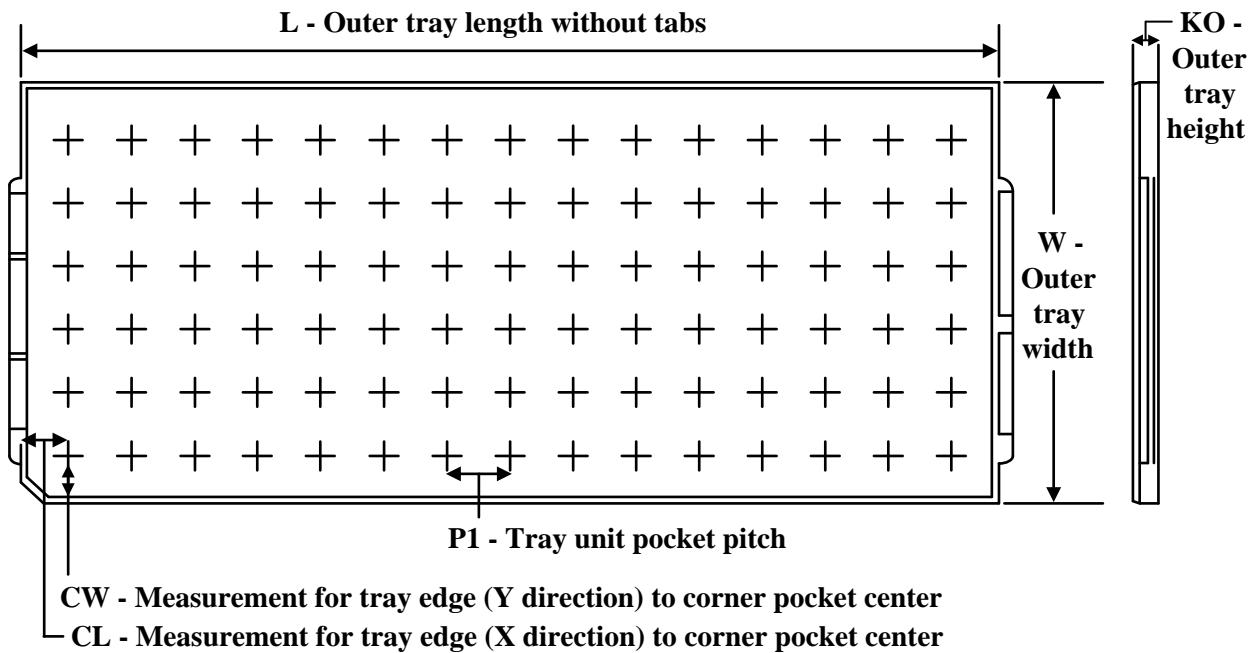

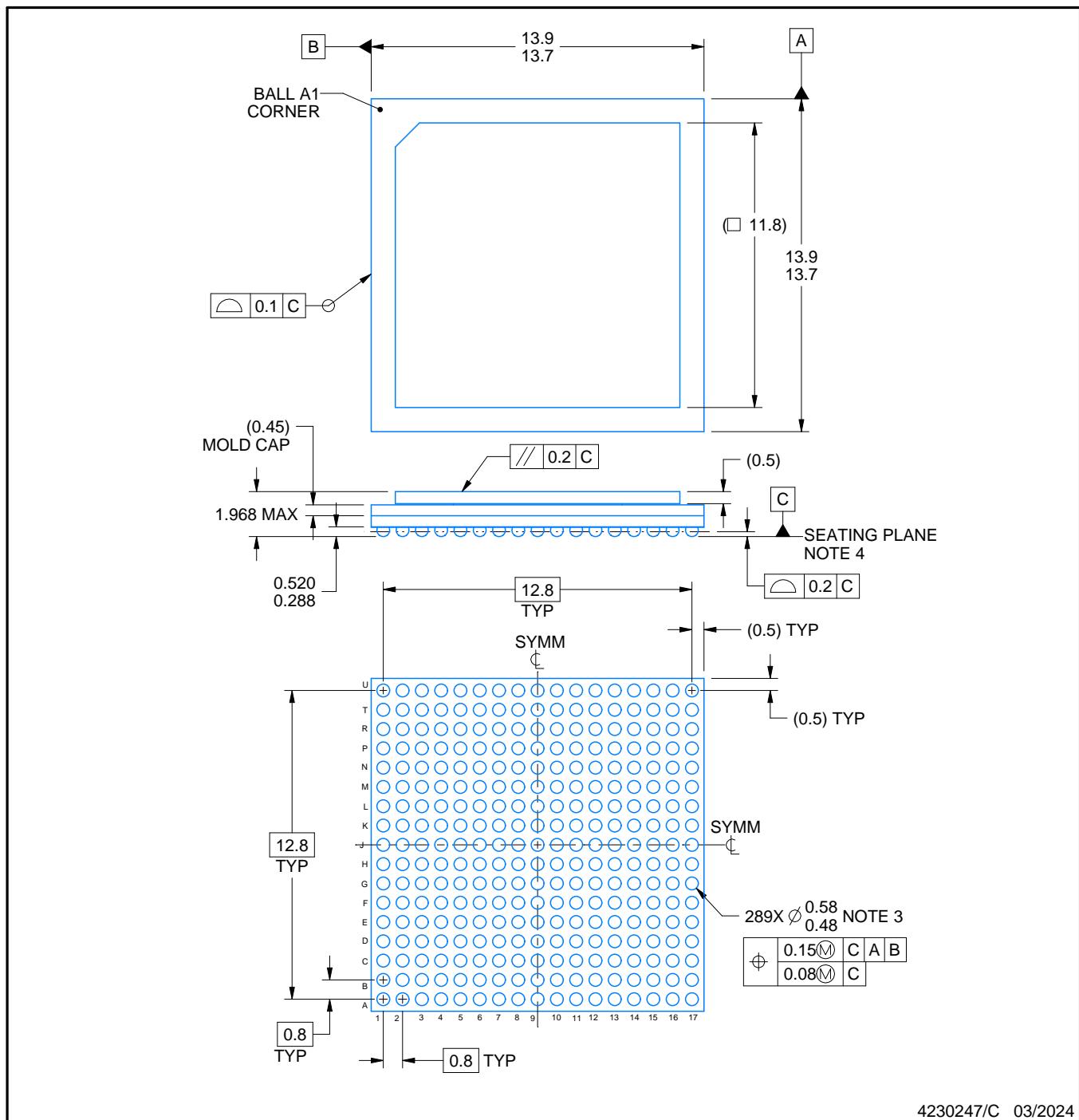

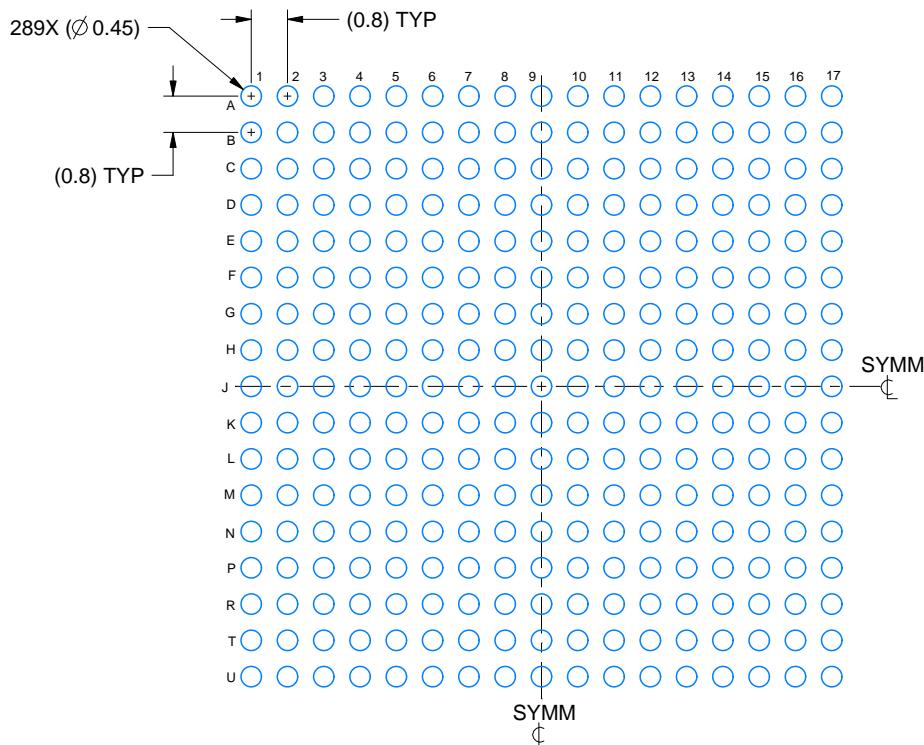

## 4 ピン構成および機能

|   | 1              | 2        | 3        | 4        | 5              | 6        | 7                          | 8         | 9         | 10        | 11        | 12        | 13      | 14      | 15      | 16      | 17             |   |

|---|----------------|----------|----------|----------|----------------|----------|----------------------------|-----------|-----------|-----------|-----------|-----------|---------|---------|---------|---------|----------------|---|

| A | GND            | STX5N    | STX5P    | STX6N    | STX6P          | GND      | STX7N                      | STX7P     | GND       | STX3P     | STX3N     | GND       | STX2P   | STX2N   | STX1P   | STX1N   | GND            | A |

| B | STX4P          | GND      | AVDD12   | AVDD12   | AVDD12         | AVDD12   | AVDD12                     | AVDD12    | AVDD12    | AVDD12    | AVDD12    | AVDD12    | AVDD12  | AVDD12  | AVDD12  | GND     | STX0P          | B |

| C | STX4N          | GPIO15   | LVDS029N | LVDS026N | LVDS023N       | LVDS021N | LVDS018N                   | DVDD09    | JESDCLKN  | GND       | LVDS02N   | LVDS05N   | LVDS07N | LVDS10N | LVDS13N | GPIO22  | STX0N          | C |

| D | GND            | GPIO16   | LVDS029P | LVDS026P | LVDS023P       | LVDS021P | LVDS018P                   | DVDD09    | JESDCLKP  | GND       | LVDS02P   | LVDS05P   | LVDS07P | LVDS10P | LVDS13P | GPIO23  | GND            | D |

| E | LVDS<br>DCLK1P | LVDS031N | LVDS028N | LVDS025N | LVDS022N       | LVDS020N | LVDS017N                   | DVDD09    | AVDD18    | GND       | LVDS01N   | LVDS04N   | LVDS06N | LVDS09N | LVDS12N | LVDS15N | LVDS<br>DCLK0P | E |

| F | LVDS<br>DCLK1N | LVDS031P | LVDS028P | LVDS025P | LVDS022P       | LVDS020P | LVDS017P                   | DVDD09    | AVDD12    | GND       | LVDS01P   | LVDS04P   | LVDS06P | LVDS09P | LVDS12P | LVDS15P | LVDS<br>DCLK0N | F |

| G | LVDS<br>FCLK1P | LVDS030N | LVDS027N | LVDS024N | GND            | LVDS019N | LVDS016N                   | DVDD09    | GND       | GND       | LVDS00N   | LVDS03N   | GND     | LVDS08N | LVDS11N | LVDS14N | LVDS<br>FCLK0P | G |

| H | LVDS<br>FCLK1N | LVDS030P | LVDS027P | LVDS024P | AVDD18         | LVDS019P | LVDS016P                   | DVDD09    | GND       | GND       | LVDS00P   | LVDS03P   | AVDD18  | LVDS08P | LVDS11P | LVDS14P | LVDS<br>FCLK0N | H |

| J | RESET          | GPIO12   | GPIO9    | SYNC     | NC             | GND      | GND                        | DVDD09    | GND       | GND       | GND       | GND       | AVDD18  | NC      | GPIO3   | SEN     | GPIO19         | J |

| K | NC             | GPIO13   | GPIO10   | GPIO1    | NC             | GND      | GND                        | DVDD09    | GND       | GND       | GND       | GND       | DVDD09  | NC      | SCLK    | GPIO17  | GPIO20         | K |

| L | NC             | GPIO14   | SDOUT    | GPIO8    | AVDD<br>GPIO18 | DVDD09   | DVDD09                     | DVDD09    | DVDD09    | DVDD09    | DVDD09    | DVDD09    | DVDD09  | GPIO2   | SDIO    | GPIO18  | GPIO21         | L |

| M | GND            | GND      | AVDD12   | AVDD12   | GND            | AVDD18   | GND                        | AVDD12    | GND       | GND       | AVDD12    | GND       | AVDD18  | AVDD12  | AVDD12  | GND     | GND            | M |

| N | AVDD18         | GND      | AVDD12   | AVDD12   | GND            | AVDD18   | TIME<br>STAMP <sub>P</sub> | AVDD12    | GND       | GND       | AVDD12    | GND       | AVDD18  | AVDD12  | AVDD12  | GND     | AVDD18         | N |

| P | IN2N           | GND      | AVDD12   | AVDD12   | GND            | AVDD18   | TIME<br>STAMP <sub>N</sub> | AVDD12    | GND       | GND       | AVDD12    | GND       | AVDD18  | AVDD12  | AVDD12  | GND     | IN0P           | P |

| R | IN2P           | GND      | AVDD12   | AVDD12   | GND            | AVDD18   | GND                        | GND       | GND       | GND       | AVDD12    | GND       | AVDD18  | AVDD12  | AVDD12  | GND     | IN0N           | R |

| T | AVDD18         | GND      | AVDD18   | AVDD18   | GND            | GND      | VCM                        | AVDDCLK18 | AVDDCLK12 | AVDDCLK12 | AVDDCLK18 | VCM       | GND     | AVDD18  | AVDD18  | GND     | AVDD18         | T |

| U | GND            | GND      | IN3N     | IN3P     | GND            | SYSREFN  | SYSREFP                    | GND       | CLKN      | CLKP      | GND       | AVDDCLK12 | GND     | IN1N    | IN1P    | GND     | GND            | U |

|   | 1              | 2        | 3        | 4        | 5              | 6        | 7                          | 8         | 9         | 10        | 11        | 12        | 13      | 14      | 15      | 16      | 17             |   |

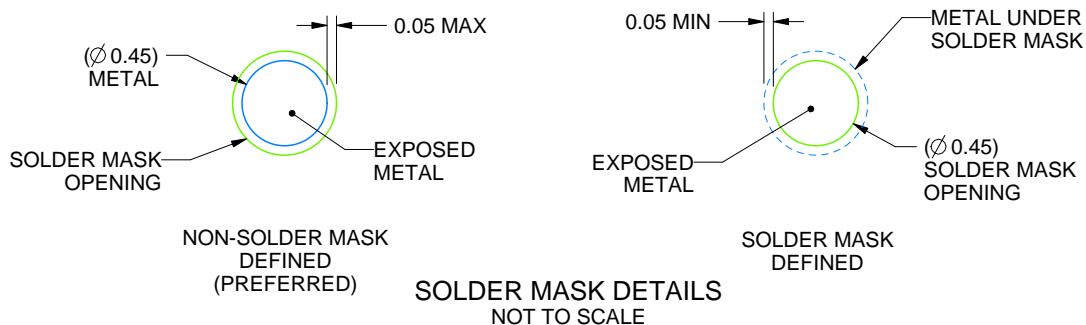

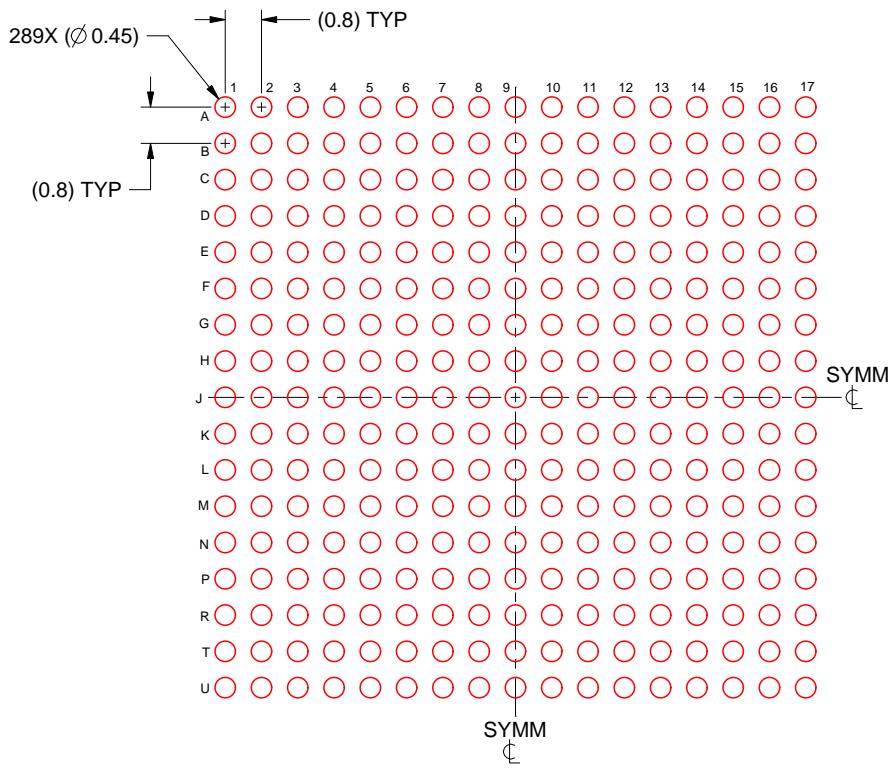

図 4-1. 289 ポールフリップチップ BGA

(上面図)

表 4-1. ピンの機能

| ピン                         |                                                                                                                                                                                                                                                                                                                        | タイプ <sup>(1)</sup> | 説明                                                                                                                                                          |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称                         | 番号                                                                                                                                                                                                                                                                                                                     |                    |                                                                                                                                                             |

| AVDD12                     | B3、B4、B5、B6、B7、B8、B9、<br>B10、B11、B12、B13、B14、<br>B15、F9、M3、M4、M8、M11、<br>M14、<br>M15、N3、N4、N8、N11、N14、<br>N15、P3、P4、P8、P11、P14、<br>P15、R3、R4、R14、R15                                                                                                                                                                   | P                  | アナログ 1.2V 電源。低ノイズ LDO を推奨。                                                                                                                                  |

| AVDDCLK12                  | T9、T10、U12                                                                                                                                                                                                                                                                                                             | P                  | クロック電源、1.2V。低ノイズ LDO を推奨                                                                                                                                    |

| AVDD18                     | E9、H5、H13、J13、M6、M13、<br>N1、N6、N13、N17、P6、P13、<br>R6、R13、T1、T3、T4、T14、<br>T15、<br>T17                                                                                                                                                                                                                                  | P                  | アナログ 1.8V 電源。低ノイズ LDO を推奨                                                                                                                                   |

| AVDDCLK18                  | T8、T11                                                                                                                                                                                                                                                                                                                 | P                  | クロック電源、1.8V。低ノイズ LDO を推奨                                                                                                                                    |

| AVDDGPIO18                 | L5                                                                                                                                                                                                                                                                                                                     | P                  | GPIO ピン用 1.8V 電源。                                                                                                                                           |

| CLKN、<br>CLKP              | U9、U10                                                                                                                                                                                                                                                                                                                 | I                  | 差動クロック入力。内部差動 100Ω 終端および 0.7V の同相電圧への自己バイアス。外部で AC 結合する必要があります。                                                                                             |

| DVDD09                     | C8、D8、E8、F8、G8、H8、J8、<br>K8、K13、L6、L7、L8、<br>L9、L10、L11、L12、L13                                                                                                                                                                                                                                                        | P                  | デジタル電源、0.9V。スイッチング DC/DC レギュレータを推奨します。                                                                                                                      |

| GND                        | A1、A6、A9、A12、A17、B2、<br>B16、<br>C10、D1、D10、D17、E10、<br>F10、G5、G9、G10、G13、H9、<br>H10、<br>J6、J7、J9、J10、J11、J12、K6、<br>K7、K9、K10、K11、K12、M1、<br>M2、M5、M7、M9、M10、M12、<br>M16、M17、N2、N5、N9、N10、<br>N12、N16、P2、P5、P9、P10、<br>P12、P16、R2、R5、R7、R8、<br>R9、R10、R11、R12、R16、T2、<br>T5、T6、T13、T16、U1、U2、<br>U5、U8、U11、U13、U16、U17 | G                  | グランド、0V                                                                                                                                                     |

| GPIO1、<br>GPIO2、<br>GPIO3  | K4、<br>L14、<br>J15                                                                                                                                                                                                                                                                                                     | I/O                | GPIO ピンは、SPI 書き込みにより異なる機能を割り当てることができます。 <a href="#">セクション 7.5.1</a> を参照してください。                                                                              |

| GPIO8、<br>GPIO9、<br>GPIO10 | L4、<br>J3、<br>K3、                                                                                                                                                                                                                                                                                                      | I/O                |                                                                                                                                                             |

| GPIO12～GPIO23              | J2、K2、L2、C2、<br>D2、K16、L16、J17、K17、<br>L17、C16、D16                                                                                                                                                                                                                                                                     | I/O                |                                                                                                                                                             |

| IN0N、IN0P                  | R17、P17                                                                                                                                                                                                                                                                                                                | I                  | 差動アナログ入力、チャネル 0。内部プログラム可能な 50Ω、100Ω および 200Ω 終端。                                                                                                            |

| IN1N、<br>IN1P              | U14、U15                                                                                                                                                                                                                                                                                                                | I                  | 差動アナログ入力、チャネル 1。内部プログラム可能な 50Ω、100Ω および 200Ω 終端。                                                                                                            |

| IN2N、IN2P                  | P1、R1                                                                                                                                                                                                                                                                                                                  | I                  | 差動アナログ入力、チャネル 2。内部プログラム可能な 50Ω、100Ω および 200Ω 終端。                                                                                                            |

| IN3N、IN3P                  | U3、U4                                                                                                                                                                                                                                                                                                                  | I                  | 差動アナログ入力、チャネル 3。内部プログラム可能な 50Ω、100Ω および 200Ω 終端。                                                                                                            |

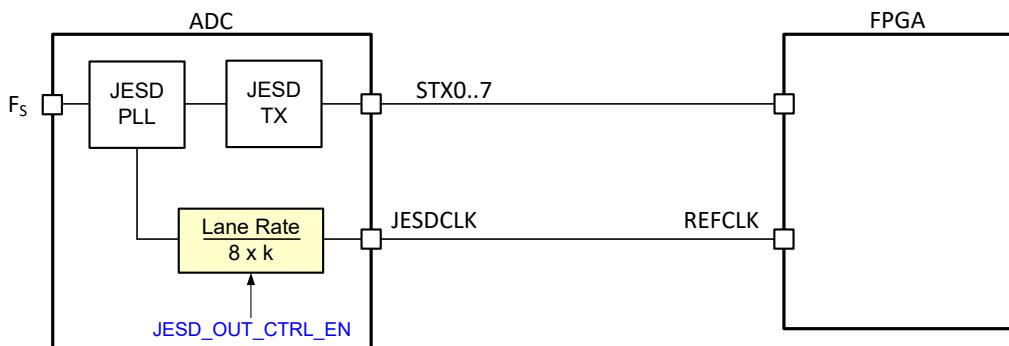

| JESDCLKN、<br>JESDCLKP      | C9、D9                                                                                                                                                                                                                                                                                                                  | O                  | 差動 JESD 出力クロック。LVDS ロジックレベル。SerDes レーン レートを (8x k) で除算するように構成できます。デフォルトでは、この機能はパワーダウンされ、ピンをフローティングのままにできます。この出力クロックは内部の SerDes PLL から直接生成され、確定的レイテンシはありません。 |

| LVDSCLK0N、<br>LVDSCLK0P    | F17、E17                                                                                                                                                                                                                                                                                                                | O                  | 差動 LVDS ビットクロック出力。<br>現在ソフトウェアではサポートされていません。「未接続」のままにします                                                                                                    |

| LVDSCLK1N、<br>LVDSCLK1P    | F1、E1                                                                                                                                                                                                                                                                                                                  | O                  | 差動 LVDS フレームクロック出力。<br>現在ソフトウェアではサポートされていません。「未接続」のままにします                                                                                                   |

| LVDSFCLK0N、<br>LVDSFCLK0P  | H17、G17                                                                                                                                                                                                                                                                                                                | O                  | 差動 LVDS フレームクロック出力。<br>現在ソフトウェアではサポートされていません。「未接続」のままにします                                                                                                   |

| LVDSFCLK1N、<br>LVDSFCLK1P  | H1、G1                                                                                                                                                                                                                                                                                                                  | O                  |                                                                                                                                                             |

**表 4-1. ピンの機能 (続き)**

| 名称                    | ピン番号    | タイプ <sup>(1)</sup> | 説明                                                    |

|-----------------------|---------|--------------------|-------------------------------------------------------|

| LVDSD0N、<br>LVDSD0P   | G11、H11 | O                  |                                                       |

| LVDSD1N、<br>LVDSD1P   | E11、F11 | O                  |                                                       |

| LVDSD2N、<br>LVDSD2P   | C11、D11 | O                  |                                                       |

| LVDSD3N、<br>LVDSD3P   | G12、H12 | O                  |                                                       |

| LVDSD4N、<br>LVDSD4P   | E12、F12 | O                  |                                                       |

| LVDSD5N、<br>LVDSD5P   | C12、D12 | O                  |                                                       |

| LVDSD6N、<br>LVDSD6P   | E13、F13 | O                  |                                                       |

| LVDSD7N、<br>LVDSD7P   | C13、D13 | O                  |                                                       |

| LVDSD8N、<br>LVDSD8P   | G14、H14 | O                  |                                                       |

| LVDSD9N、<br>LVDSD9P   | E14、F14 | O                  |                                                       |

| LVDSD10N、<br>LVDSD10P | C14、D14 | O                  |                                                       |

| LVDSD11N、<br>LVDSD11P | G15、H15 | O                  |                                                       |

| LVDSD12N、<br>LVDSD12P | E15、F15 | O                  |                                                       |

| LVDSD13N、<br>LVDSD13P | C15、D15 | O                  |                                                       |

| LVDSD14N、<br>LVDSD14P | G16、H16 | O                  | LVDS 出力インターフェイス<br>現在ソフトウェアではサポートされていません。「未接続」のままにします |

| LVDSD15N、<br>LVDSD15P | E16、F16 | O                  |                                                       |

| LVDSD16N、<br>LVDSD16P | G7、H7   | O                  |                                                       |

| LVDSD17N、<br>LVDSD17P | E7、F7   | O                  |                                                       |

| LVDSD18N、<br>LVDSD18P | C7、D7   | O                  |                                                       |

| LVDSD19N、<br>LVDSD19P | G6、H6   | O                  |                                                       |

| LVDSD20N、<br>LVDSD20P | E6、F6   | O                  |                                                       |

| LVDSD21N、<br>LVDSD21P | C6、D6   | O                  |                                                       |

| LVDSD22N、<br>LVDSD22P | E5、F5   | O                  |                                                       |

| LVDSD23N、<br>LVDSD23P | C5、D5   | O                  |                                                       |

| LVDSD24N、<br>LVDSD24P | G4、H4   | O                  |                                                       |

| LVDSD25N、<br>LVDSD25P | E4、F4   | O                  |                                                       |

| LVDSD26N、<br>LVDSD26P | C4、D4   | O                  |                                                       |

| LVDSD27N、<br>LVDSD27P | G3、H3   | O                  |                                                       |

| LVDSD28N、<br>LVDSD28P | E3、F3   | O                  |                                                       |

表 4-1. ピンの機能 (続き)

| ピン                        |                     | タイプ <sup>(1)</sup> | 説明                                                                          |

|---------------------------|---------------------|--------------------|-----------------------------------------------------------------------------|

| 名称                        | 番号                  |                    |                                                                             |

| LVDS2D9N、<br>LVDS2D9P     | C3、D3               | O                  |                                                                             |

| LVDS3D0N、<br>LVDS3D0P     | G2、H2               | O                  | LVDS 出力インターフェイス<br>現在ソフトウェアではサポートされていません。「未接続」のままにします                       |

| LVDS3D1N、<br>LVDS3D1P     | E2、F2               | O                  |                                                                             |

| NC                        | J5、J14、K1、K5、K14、L1 | -                  | 接続しない                                                                       |

| RESET                     | J1                  | I                  | ハードウェアリセットアクティブ Low。このピンには、AVDD18 に接続された内部 10kΩ プルアップ抵抗があります。               |

| SCLK                      | K15                 | I                  | シリアルインターフェースクロック入力。このピンには内部 10kΩ プルダウン抵抗があります。                              |

| SDIO                      | L15                 | I/O                | シリアルインターフェイスデータ入出力。このピンには内部 10kΩ プルダウン抵抗があります。                              |

| SDOUT                     | L3                  | O                  | シリアルインターフェイスデータ出力。                                                          |

| SEN                       | J16                 | I                  | シリアルインターフェースのイネーブル。アクティブ Low。このピンには、AVDD18 に接続された内部 10kΩ プルアップ抵抗があります。      |

| STX0N、STX0P               | C17、B17             | O                  | 差動、高速シリアル JESD204B/C 出力データインターフェイス、レーン 0                                    |

| STX1N、STX1P               | A16、A15             | O                  | 差動、高速シリアル JESD204B/C 出力データインターフェイス、レーン 1                                    |

| STX2N、STX2P               | A14、A13             | O                  | 差動、高速シリアル JESD204B/C 出力データインターフェイス、レーン 2                                    |

| STX3N、STX3P               | A11、A10             | O                  | 差動、高速シリアル JESD204B/C 出力データインターフェイス、レーン 3                                    |

| STX4N、STX4P               | C1、B1               | O                  | 差動、高速シリアル JESD204B/C 出力データインターフェイス、レーン 4                                    |

| STX5N、STX5P               | A2、A3               | O                  | 差動、高速シリアル JESD204B/C 出力データインターフェイス、レーン 5                                    |

| STX6N、STX6P               | A4、A5               | O                  | 差動、高速シリアル JESD204B/C 出力データインターフェイス、レーン 6                                    |

| STX7N、STX7P               | A7、A8               | O                  | 差動、高速シリアル JESD204B/C 出力データインターフェイス、レーン 7                                    |

| SYNC                      | J4                  | I                  | JESD アクティブ Low SYNC 入力。SYNC が Low で、デバイスが構成されると、デバイスは K 文字を JESD レーンに送信します。 |

| SYSREFN、<br>SYSREFP       | U6、U7               | I                  | 差動 SYSREF 入力 (100Ω 差動終端、1.2V に自己バイアス)。AC および DC カッピングがサポートされます。             |

| TIMESTAMPN、<br>TIMESTAMPP | P7、N7               | I                  | 現在ソフトウェアではサポートされていません。GND に接続できます。                                          |

| VCM                       | T7、T12              | O                  | 同相電圧リファレンス出力。2 つのピンは内部で短絡されています。                                            |

(1) I = 入力、O = 出力、I/O = 入力または出力、G = グランド、P = 電源。

## 5 仕様

### 5.1 絶対最大定格

動作周囲温度範囲内 (特に記述のない限り)<sup>(1)</sup>

| パラメータ                 | テスト条件                                   | 最小値  | 最大値 | 単位 |

|-----------------------|-----------------------------------------|------|-----|----|

| 電源電圧範囲、AVDD18         |                                         | -0.5 | 2.1 |    |

| 電源電圧範囲、AVDD12         |                                         | -0.3 | 1.4 |    |

| 電源電圧範囲、AVDDCLK18      |                                         | -0.5 | 2.1 |    |

| 電源電圧範囲、AVDDCLK12      |                                         | -0.3 | 1.4 |    |

| 電源電圧範囲、DVDD09         |                                         | -0.3 | 1.2 |    |

| 電源電圧範囲、AVDDGPIO18     |                                         | -0.5 | 2.1 |    |

| 入力ピンに印加される電圧          | IN0P/N, IN1P/N, IN2P/N, IN3P/N          | -0.5 | 2.1 | V  |

|                       | CLKP/N                                  | -0.3 | 1.4 |    |

|                       | SYSREFP/N, Timestampp/N                 | -0.3 | 2.1 |    |

|                       | GPIO1..23, RESET, SCLK, SEN, SDIO, SYNC | -0.5 | 2.1 |    |

| 接合部温度、T <sub>J</sub>  |                                         |      | 125 |    |

| 保管温度、T <sub>stg</sub> |                                         | -65  | 150 | °C |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

### 5.2 ESD 定格

|                    |      |                                                            | 値    | 単位 |

|--------------------|------|------------------------------------------------------------|------|----|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM) ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>       | 1000 | V  |

|                    |      | デバイス帯電モデル (CDM), ANSI/ESDA/JEDEC JS-002 に準拠 <sup>(2)</sup> | 150  |    |

- (1) JEDEC ドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

(2) JEDEC ドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

### 5.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                |              |  | 最小値   | 公称値 | 最大値                | 単位 |

|----------------|--------------|--|-------|-----|--------------------|----|

| AVDD18         | 1.8V アナログ電源  |  | 1.75  | 1.8 | 1.85               |    |

| AVDD12         | 1.2V アナログ電源  |  | 1.175 | 1.2 | 1.225              |    |

| AVDDCLK18      | 1.8 V クロック電源 |  | 1.75  | 1.8 | 1.85               | V  |

| AVDDCLK12      | 1.2 V クロック電源 |  | 1.175 | 1.2 | 1.225              |    |

| DVDD09         | 0.9V デジタル電源  |  | 0.875 | 0.9 | 0.925              |    |

| AVDDGPIO18     | 1.8V GPIO 電源 |  | 1.75  | 1.8 | 1.85               |    |

| T <sub>A</sub> | 外気温度での動作時    |  | -40   | 105 |                    |    |

| T <sub>J</sub> | 動作時接合部温度     |  |       |     | 110 <sup>(1)</sup> | °C |

- (1) この接合部温度を超えて長時間使用すると、デバイスの時間あたりの故障回数 (FIT) レートが上昇する可能性があります。

## 5.4 热に関する情報

| 热評価基準 <sup>(1)</sup>  |                   | ADC32RF72 | 単位   |

|-----------------------|-------------------|-----------|------|

|                       |                   | ANH (BGA) |      |

|                       |                   | 289 ポール   |      |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗      | 15.4      | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース(上面)への熱抵抗 | 0.5       | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗      | 4.2       | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への特性パラメータ  | 0.1       | °C/W |

| Ψ <sub>JB</sub>       | 接合部から基板への特性パラメータ  | 4.1       | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体およびICパッケージの熱評価基準』アプリケーションノートを参照してください。

## 5.5 電気的特性 - 消費電力

最大値と最小値は、自由気流での動作温度範囲および公称電源電圧について規定されています。特に記述のない限り、標準値は T<sub>A</sub> = 25°C、ADC サンプリングレート = 1.5GSPS、DDC バイパスモード、50% クロックデューティサイクル、公称電源電圧、-1dBFS 差動入力で規定されています。

| パラメータ                   |                     | テスト条件                     | 最小値  | 標準値  | 最大値 | 単位 |

|-------------------------|---------------------|---------------------------|------|------|-----|----|

| I <sub>AVDD18</sub>     | 電源電流、1.8V アナログ電源    | バイパスモード<br>LMFS = 4-2-1-1 | 315  | 350  |     | mA |

| I <sub>AVDD12</sub>     | 電源電流、1.2V アナログ電源    |                           | 915  | 1100 |     |    |

| I <sub>AVDDCLK18</sub>  | 電源電流、1.8V クロック電源    |                           | 50   | 75   |     |    |

| I <sub>AVDDCLK12</sub>  | 電源電流、1.2V クロック電源    |                           | 50   | 75   |     |    |

| I <sub>DVDD09</sub>     | 電源電流、0.9V デジタル電源    |                           | 1450 | 1800 |     |    |

| I <sub>AVDDGPIO18</sub> | 電源電流、1.8V GPIO 電源   |                           | 5    |      |     |    |

| P <sub>DIS</sub>        | 消費電力                |                           | 3.1  |      |     | W  |

| <b>パワーダウンモード</b>        |                     |                           |      |      |     |    |

| P <sub>DIS</sub>        | 高速パワーダウンモードの消費電力    | 高速ウェークアップ時間               | 2.0  |      |     | W  |

| P <sub>DIS</sub>        | グローバルパワーダウンモードの消費電力 |                           | 0.4  |      |     |    |

## 5.6 電気的特性 - DC 仕様

最大値と最小値は、自由気流での動作温度範囲および公称電源電圧について規定されています。特に記述のない限り、標準値は  $T_A = 25^\circ\text{C}$ 、ADC サンプリングレート = 1.5GSPS、DDC バイパスモード、50% クロックデューティサイクル、公称電源電圧、-1dBFS 差動入力で規定されています。

| パラメータ                                                   |                                 | テスト条件                                | 最小値                   | 標準値            | 最大値   | 単位            |

|---------------------------------------------------------|---------------------------------|--------------------------------------|-----------------------|----------------|-------|---------------|

| <b>DC 精度</b>                                            |                                 |                                      |                       |                |       |               |

|                                                         | ミッキング コードなし                     |                                      | 16                    |                |       | ビット           |

| DNL                                                     | 微分非直線性                          | $f_{IN} = 10\text{MHz}$              | 0.3                   |                |       | LSB           |

| INL                                                     | 積分非直線性                          | $f_{IN} = 10\text{MHz}$              | 2.5                   |                |       | LSB           |

| $V_{OS\_ERR}$                                           | オフセット誤差                         |                                      | 0.9                   |                |       | %FSR          |

| $GAIN_{ERR}$                                            | ゲイン誤差                           |                                      | 1.0                   |                |       | %FSR          |

| $GAIN_{Matching}$                                       | チャネル間のゲインマッチング                  |                                      | 0.1                   |                |       | dB            |

| <b>ADC アナログ入力 (IN0P/N、IN1P/N、IN2P/N、IN3P/N)</b>         |                                 |                                      |                       |                |       |               |

| FS                                                      | 入力フルスケール                        | 差動                                   | 1.4375                |                |       | Vpp           |

| $V_{ICM}$                                               | 入力同相電圧                          |                                      | 1.25                  | 1.35           | 1.45  | V             |

| $Z_{IN}$                                                | 差動入力インピーダンス                     | 差動、100MHz                            | 100                   |                |       | $\Omega$      |

| $V_{OCM}$                                               | 出力同相電圧                          |                                      | 1.35                  |                |       | V             |

| BW                                                      | アナログ入力帯域幅 (-3dB)                |                                      | 1.8                   |                |       | GHz           |

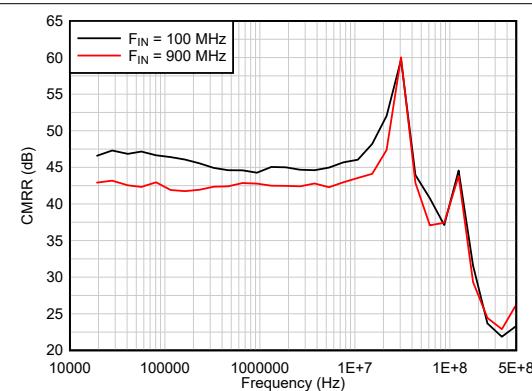

| CMRR                                                    | 同相除去比                           | $f_{IN} = 100\text{MHz}$             | 30                    |                |       | dB            |

| <b>クロック入力 (CLKP/N)</b>                                  |                                 |                                      |                       |                |       |               |

| 入力クロック周波数                                               |                                 |                                      | 500                   | 1500           |       | MHz           |

| $V_{ID}$                                                | 差動入力電圧                          |                                      | 0.6                   | 2.0            | 2.8   | Vpp           |

| $V_{ICM}$                                               | 入力同相電圧                          |                                      | 0.7                   |                |       | V             |

| $Z_{IN}$                                                | 差動入力インピーダンス                     | 差動、1.5GHz                            | 100                   |                |       | $\Omega$      |

| クロック デューティ サイクル                                         |                                 |                                      | 30                    | 50             | 70    | %             |

| <b>SYSREF 入力 (SYSREFP/N)</b>                            |                                 |                                      |                       |                |       |               |

| $V_{ID}$                                                | 差動入力電圧                          |                                      | 350                   | 450            | 800   | mVpp          |

| $V_{ICM}$                                               | 入力同相電圧                          |                                      | 1.05                  | 1.2            | 1.325 | V             |

| <b>デジタル入力 (GPIO1..23, RESET, SCLK, SEN, SDIO, SYNC)</b> |                                 |                                      |                       |                |       |               |

| $V_{IH}$                                                | High レベル入力電圧                    |                                      | 1.15                  |                |       | V             |

| $V_{IL}$                                                | Low レベル入力電圧                     |                                      |                       | 0.65           |       | V             |

| $I_{IH}$                                                | High レベル入力電流                    |                                      | -250                  | 250            |       | $\mu\text{A}$ |

| $I_{IL}$                                                | Low レベル入力電流                     |                                      | -250                  | 250            |       | $\mu\text{A}$ |

| $C_I$                                                   | 入力容量                            |                                      |                       | 2              |       | pF            |

| <b>デジタル出力 (SDIO, SDOUT)</b>                             |                                 |                                      |                       |                |       |               |

| $V_{OH}$                                                | High レベル出力電圧                    | $I_{LOAD} = -400\mu\text{A}$         | AVDDG<br>PIO18<br>0.1 | AVDDG<br>PIO18 |       | V             |

| $V_{OL}$                                                | Low レベル出力電圧                     | $I_{LOAD} = 400\mu\text{A}$          |                       |                | 0.1   | V             |

| <b>CML SERDES 出力:STX[0..7]P/N</b>                       |                                 |                                      |                       |                |       |               |

| $V_{OD}$                                                | SerDes トランスマッタ出力振幅              | 差動ピークツーピーク                           | 950                   |                |       | mVpp          |

| $V_{OCM}$                                               | SerDes トランスマッタ出力同相モード           |                                      | 450                   |                |       | mV            |

| $Z_{TX}$                                                | SerDes トランスマッタのシングルエンド終端インピーダンス |                                      | 50                    |                |       | $\Omega$      |

|                                                         | トランスマッタ短絡電流                     | -0.25V ~ 1.45V の任意の電圧に短絡されたトランスマッタピン | -100                  | 100            |       | mA            |

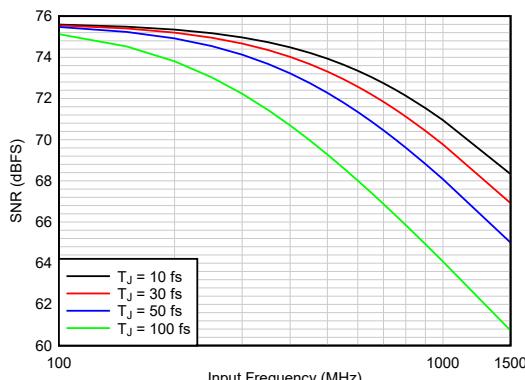

## 5.7 電気的特性 - AC 仕様

最大値と最小値は、自由気流での動作温度範囲および公称電源電圧について規定されています。特に記述のない限り、標準値は  $T_A = 25^\circ\text{C}$ 、ADC サンプリングレート = 1.5GSPS、 $100\Omega$  終端、DDC バイパスモード、50% クロックデューティサイクル、公称電源電圧、-1dBFS 差動入力で規定されています。

| パラメータ                                |                                         | テスト条件                                                                                | 最小値 <sup>(2)</sup> | 標準値  | 最大値 | 単位      |

|--------------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------|--------------------|------|-----|---------|

| <b>AC 精度</b>                         |                                         |                                                                                      |                    |      |     |         |

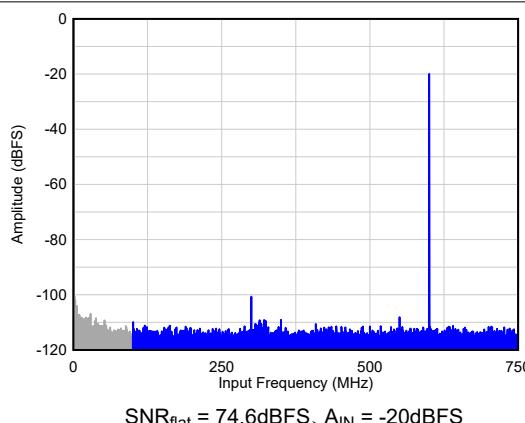

| NSD <sub>flat</sub>                  | ノイズ スペクトル密度                             | $f_{\text{IN}} = 600\text{MHz}$ , $A_{\text{IN}} = -20\text{dBFS}$                   | -163.7             |      |     | dBFS/Hz |

| NF                                   | ノイズ指数 ( $100\Omega$ 終端)                 | $f_{\text{IN}} = 600\text{MHz}$ , $A_{\text{IN}} = -20\text{dBFS}$                   | 14.4               |      |     | dB      |

| SNR                                  | 信号対雑音比                                  | $f_{\text{IN}} = 100\text{MHz}$                                                      | 73.0               |      |     | dBFS    |

| SNR <sub>flat</sub> <sup>(1)</sup>   | ナイキストゾーン内の 100MHz から FS/2 で測定された信号 対雑音比 | $f_{\text{IN}} = 100\text{MHz}$                                                      | 72.0               | 75.3 |     | dBFS    |

|                                      |                                         | $f_{\text{IN}} = 600\text{MHz}$                                                      | 73.4               |      |     |         |

|                                      |                                         | $f_{\text{IN}} = 600\text{MHz}$ , $A_{\text{IN}} = -20\text{dBFS}$                   | 75.5               |      |     |         |

|                                      |                                         | $f_{\text{IN}} = 900\text{MHz}$                                                      | 72.1               |      |     |         |

|                                      |                                         | $f_{\text{IN}} = 1.4\text{GHz}$                                                      | 69.0               |      |     |         |

| SINAD <sub>flat</sub> <sup>(1)</sup> | 信号対雑音歪み比                                | $f_{\text{IN}} = 100\text{MHz}$                                                      | 74.3               |      |     | dBFS    |

| ENOB                                 | 有効ビット数                                  | $f_{\text{IN}} = 100\text{MHz}$                                                      | 11.8               |      |     | ビット     |

| THD                                  | 全高調波歪み (最初の 5 つの 高調波)                   | $f_{\text{IN}} = 100\text{MHz}$                                                      | 82                 |      |     | dBc     |

|                                      |                                         | $f_{\text{IN}} = 600\text{MHz}$                                                      | 74                 |      |     |         |

|                                      |                                         | $f_{\text{IN}} = 900\text{MHz}$                                                      | 68                 |      |     |         |

|                                      |                                         | $f_{\text{IN}} = 1.4\text{GHz}$                                                      | 57                 |      |     |         |

| HD2                                  | 2 次高調波歪み                                | $f_{\text{IN}} = 100\text{MHz}$                                                      | 74                 | 88   |     | dBc     |

|                                      |                                         | $f_{\text{IN}} = 600\text{MHz}$                                                      | 77                 |      |     |         |

|                                      |                                         | $f_{\text{IN}} = 900\text{MHz}$                                                      | 74                 |      |     |         |

|                                      |                                         | $f_{\text{IN}} = 1.4\text{GHz}$                                                      | 64                 |      |     |         |

| HD3                                  | 3 次高調波歪み                                | $f_{\text{IN}} = 100\text{MHz}$                                                      | 74                 | 83   |     | dBc     |

|                                      |                                         | $f_{\text{IN}} = 600\text{MHz}$                                                      | 77                 |      |     |         |

|                                      |                                         | $f_{\text{IN}} = 900\text{MHz}$                                                      | 68                 |      |     |         |

|                                      |                                         | $f_{\text{IN}} = 1.4\text{GHz}$                                                      | 58                 |      |     |         |

| Non HD2,3                            | スプリアス フリー ダイナミック レンジ (HD2 と HD3 を除く)    | $f_{\text{IN}} = 100\text{MHz}$                                                      | 80                 | 95   |     | dBFS    |

|                                      |                                         | $f_{\text{IN}} = 600\text{MHz}$                                                      | 90                 |      |     |         |

|                                      |                                         | $f_{\text{IN}} = 900\text{MHz}$                                                      | 93                 |      |     |         |

|                                      |                                         | $f_{\text{IN}} = 1.4\text{GHz}$                                                      | 79                 |      |     |         |

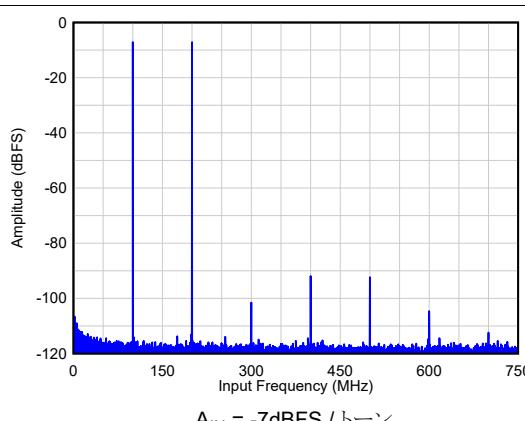

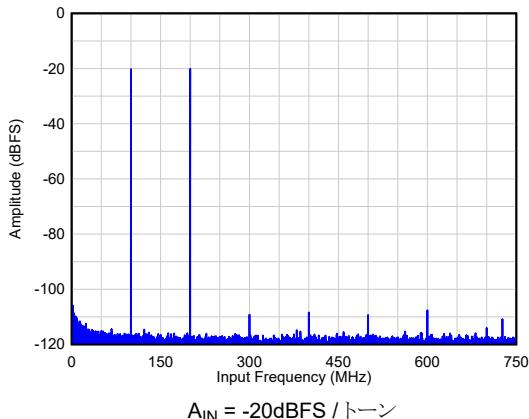

| IMD3                                 | 2 トーンの相互変調歪み                            | $f_1 = 100\text{MHz}$ , $f_2 = 200\text{MHz}$ , $A_{\text{IN}} = -7\text{dBFS/tone}$ | 89                 |      |     | dBFS    |

|                                      |                                         | $f_1 = 0.9\text{GHz}$ , $f_2 = 1.0\text{GHz}$ , $A_{\text{IN}} = -7\text{dBFS/tone}$ | 76                 |      |     |         |

(1) SNR<sub>flat</sub> および NSD<sub>flat</sub> の詳細な説明については、[セクション 6](#) を参照してください。

(2) SNR<sub>flat</sub>、HD3、および非 HD2,3 の最小値は最終テストで規定されています。HD2 はベンチ特性評価により規定されています。

## 5.8 タイミング要件

最大値と最小値は、自由気流での動作温度範囲および公称電源電圧について規定されています。特に記述のない限り、標準値は  $T_A = 25^\circ\text{C}$ 、ADC サンプリングレート = 1.5GSPS、DDC バイパスモード、50% クロックデューティサイクル、公称電源電圧、-1dBFS 差動入力で規定されています。

| パラメータ                                               | テスト条件                                      | 最小値                                                               | 公称値   | 最大値   | 単位            |

|-----------------------------------------------------|--------------------------------------------|-------------------------------------------------------------------|-------|-------|---------------|

| <b>ADC タイミング仕様</b>                                  |                                            |                                                                   |       |       |               |

| $t_{AD}$                                            | アパーーチャ遅延                                   |                                                                   | 0.15  |       | ns            |

|                                                     | アパーーチャ遅延の変動                                |                                                                   | 0.05  |       | ns            |

| $T_A$                                               | アパーーチャジッタ                                  |                                                                   | 40    |       | fs            |

| CER                                                 | コード エラー レート                                |                                                                   | 1e-15 |       | エラー / サンプル    |

|                                                     | ウェークアップ時間                                  | 高速パワーダウン終了後 (JESD はアクティブのまま) 有効なデータまでの時間 (SNR はデータシートの値から 2dB 以内) |       | 5     | μs            |

| <b>レイテンシ:<math>t_{PD} + t_{ADC}</math></b>          |                                            |                                                                   |       |       |               |

| $t_{PD}$                                            | 伝搬遅延                                       |                                                                   | 1     |       | ns            |

| $t_{ADC}$                                           | サンプリングの瞬間から JESD 出力までの ADC レイテンシ           | DDC バイパス、LMFS = 8411                                              | 524   |       | ADC クロック サイクル |

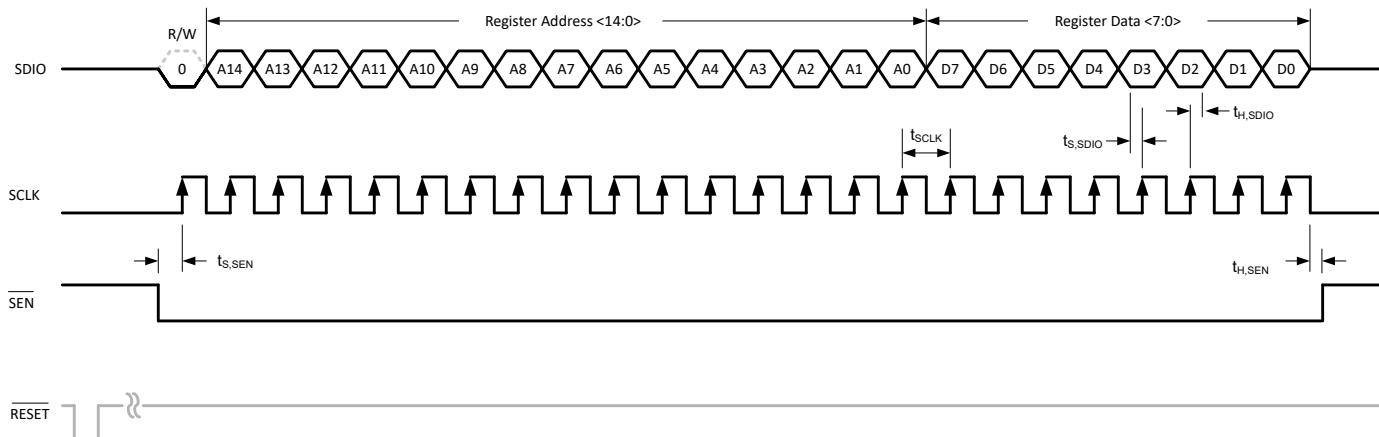

| <b>シリアル プログラミング インターフェイス (SCLK, SEN, SDIO) - 入力</b> |                                            |                                                                   |       |       |               |

| $f_{CLK(SCLK)}$                                     | シリアル クロック周波数                               |                                                                   | 1     | 50    | MHz           |

| $t_{S(SEN)}$                                        | SCLK の立ち上がりエッジへの SEN                       |                                                                   | 10    |       | ns            |

| $t_{H(SEN)}$                                        | SCLK の立ち上がりエッジからの SEN                      |                                                                   | 10    |       | ns            |

| $t_{SU(SDIO)}$                                      | SCLK の立ち上がりエッジへの SDIO                      |                                                                   | 10    |       | ns            |

| $t_{H(SDIO)}$                                       | SCLK の立ち上がりエッジからの SDIO                     |                                                                   | 10    |       | ns            |

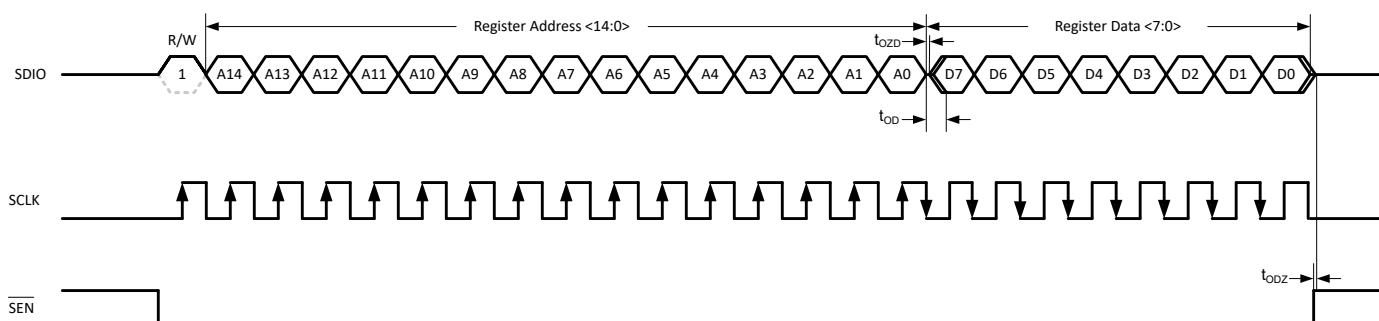

| <b>シリアルプログラミングインターフェイス (SDIO, SDOUT) - 出力</b>       |                                            |                                                                   |       |       |               |

| $t_{(OZD)}$                                         | SDIO トライステートから駆動へ                          |                                                                   | 10    |       | ns            |

| $t_{(ODZ)}$                                         | SDIO データからトライステートへ                         |                                                                   | 14    |       | ns            |

| $t_{(OD)}$                                          | SDIO は SCLK の立ち下がりエッジから有効                  |                                                                   | 10    |       | ns            |

| <b>タイミング:SYSREFP/N</b>                              |                                            |                                                                   |       |       |               |

| $t_{s(SYSREF)}$                                     | セットアップ時間、SYSREFP/N 有効から CLKP/N の立ち上がりエッジまで |                                                                   | 50    |       | ps            |

| $t_{h(SYSREF)}$                                     | ホールド時間、SYSREFP/N 有効から CLKP/N の立ち上がりエッジまで   |                                                                   | 50    |       | ps            |

| <b>CML SerDes 出力:STX[0..7]P/N</b>                   |                                            |                                                                   |       |       |               |

| $f_{Serdes}$                                        | SerDes ビットレート                              |                                                                   | 4.0   | 24.75 | Gbps          |

| $R_J$                                               | ランダム ジッタ                                   |                                                                   | 0.45  |       | ps            |

| $D_J$                                               | 確定的ジッタ                                     |                                                                   | 12.5  |       | ps            |

| $T_J$                                               | 総ジッタ、ピークツーピーク                              |                                                                   | 19.7  |       | ps            |

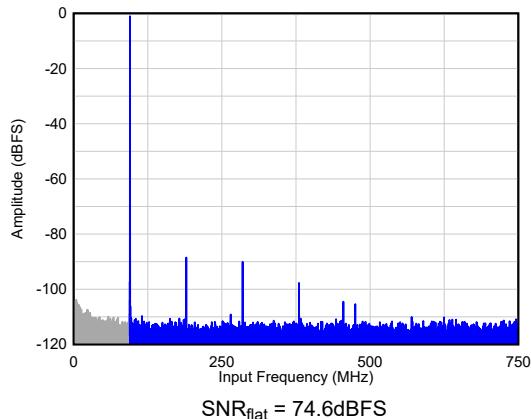

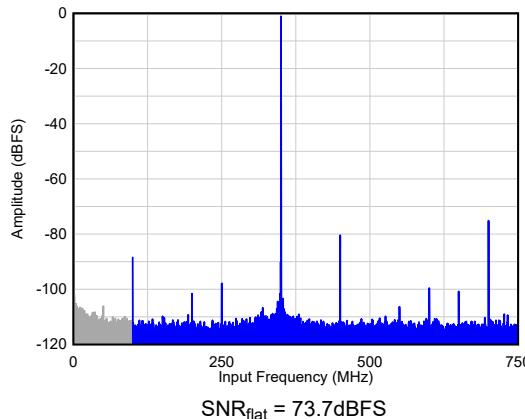

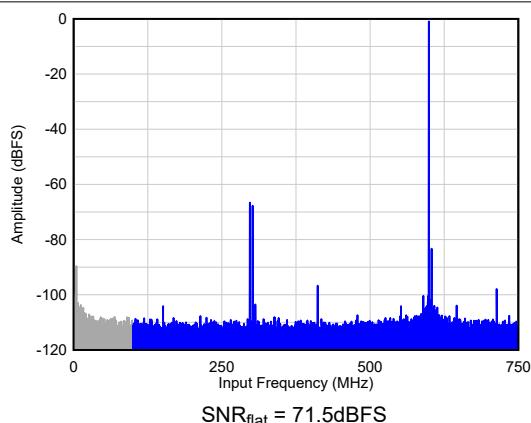

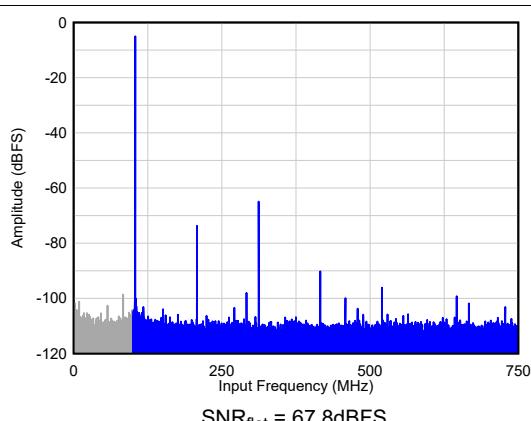

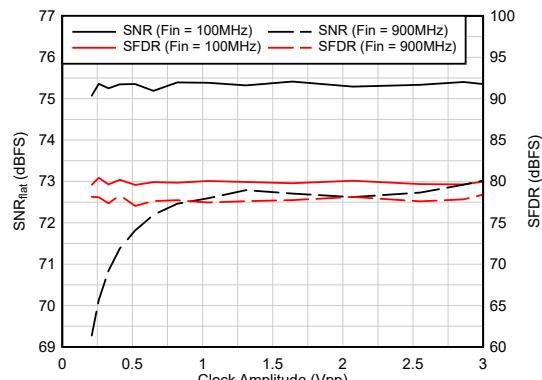

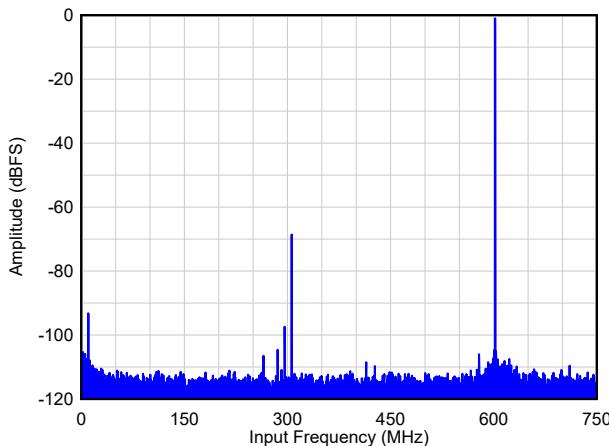

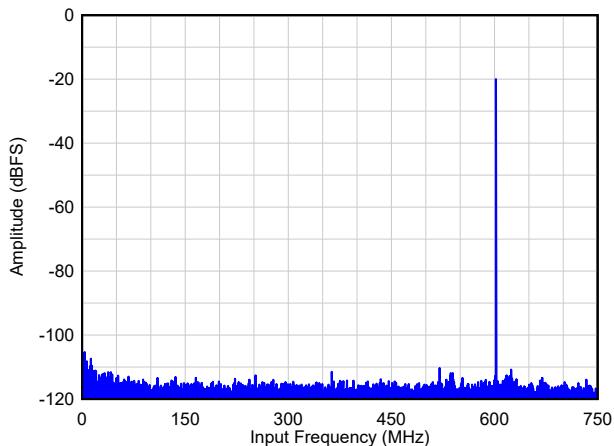

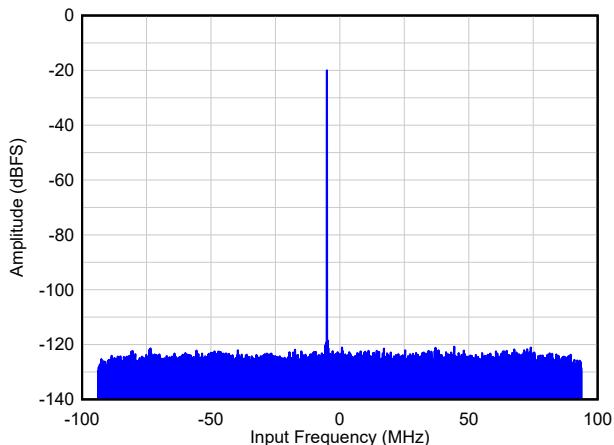

## 5.9 代表的特性

特に記述のない限り、標準値は  $T_A = 25^\circ\text{C}$ 、ADC サンプリングレート = 1.5GSPS、50% クロックデューティサイクル、公称電源、-1dBFS 差動入力、 $100\Omega$  終端で規定されています

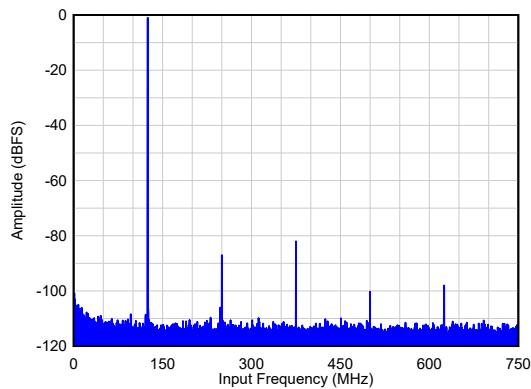

図 5-1.  $F_{\text{IN}} = 100\text{MHz}$  でのシングル トーン FFT

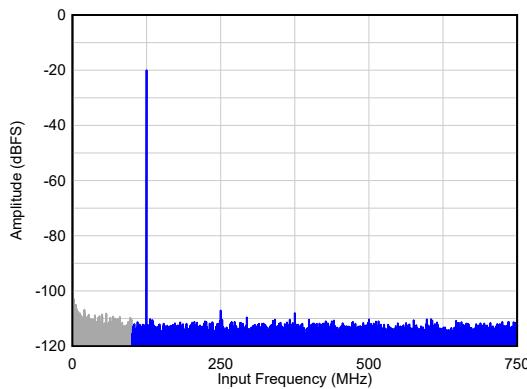

図 5-2.  $F_{\text{IN}} = 300\text{MHz}$  でのシングル トーン FFT

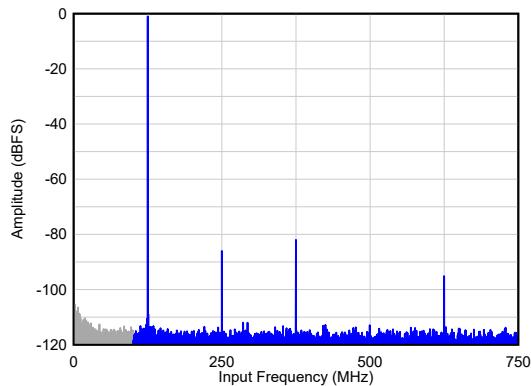

図 5-3.  $F_{\text{IN}} = 900\text{MHz}$  でのシングル トーン FFT

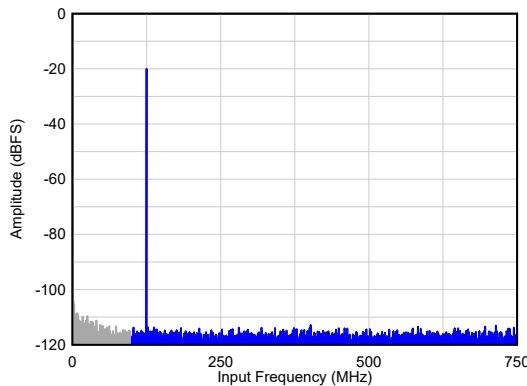

図 5-4.  $F_{\text{IN}} = 900\text{MHz}$  でのシングル トーン FFT

図 5-5.  $F_{\text{IN}} = 1400\text{MHz}$  でのシングル トーン FFT

図 5-6.  $F_{\text{IN}} = 100/200\text{MHz}$  での 2 トーン FFT

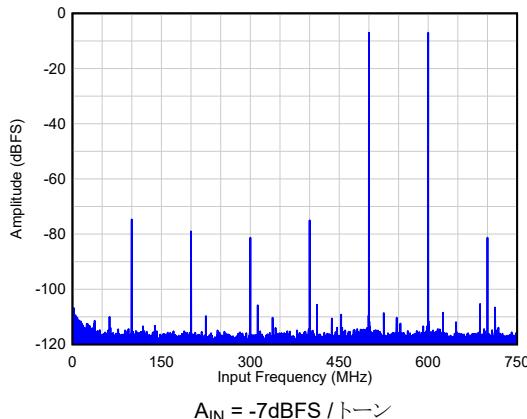

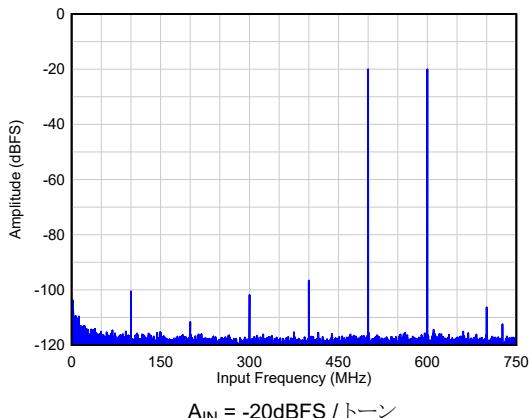

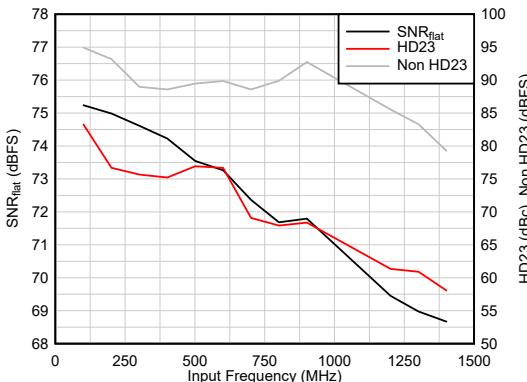

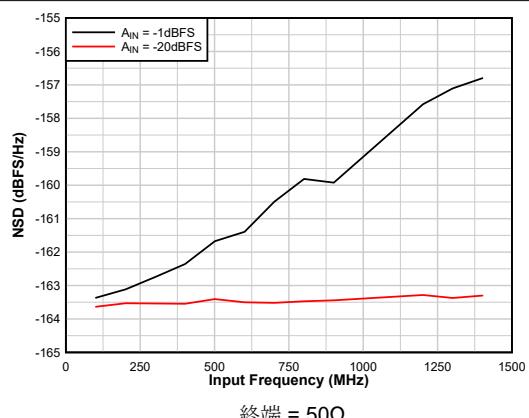

## 5.9 代表的特性 (続き)

特に記述のない限り、標準値は  $T_A = 25^\circ\text{C}$ 、ADC サンプリングレート = 1.5GSPS、50% クロックデューティサイクル、公称電源、-1dBFS 差動入力、 $100\Omega$  終端で規定されています

図 5-7.  $F_{IN} = 100/200\text{MHz}$  での 2 トーン FFT

図 5-8.  $F_{IN} = 900/1000\text{MHz}$  での 2 トーン FFT

図 5-9.  $F_{IN} = 900/1000\text{MHz}$  での 2 トーン FFT

図 5-10. AC 性能と  $F_{IN}$  との関係

図 5-11. NSD 性能と  $F_{IN}$  との関係

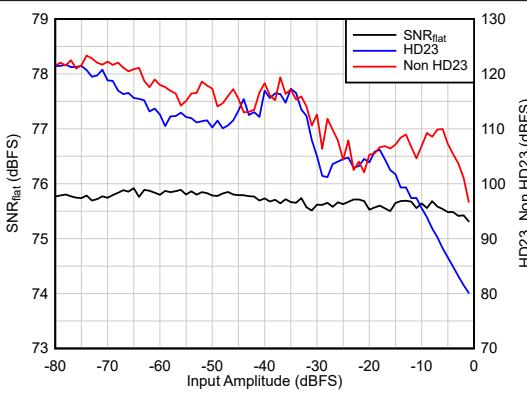

図 5-12. AC 性能と  $A_{IN}$  との関係

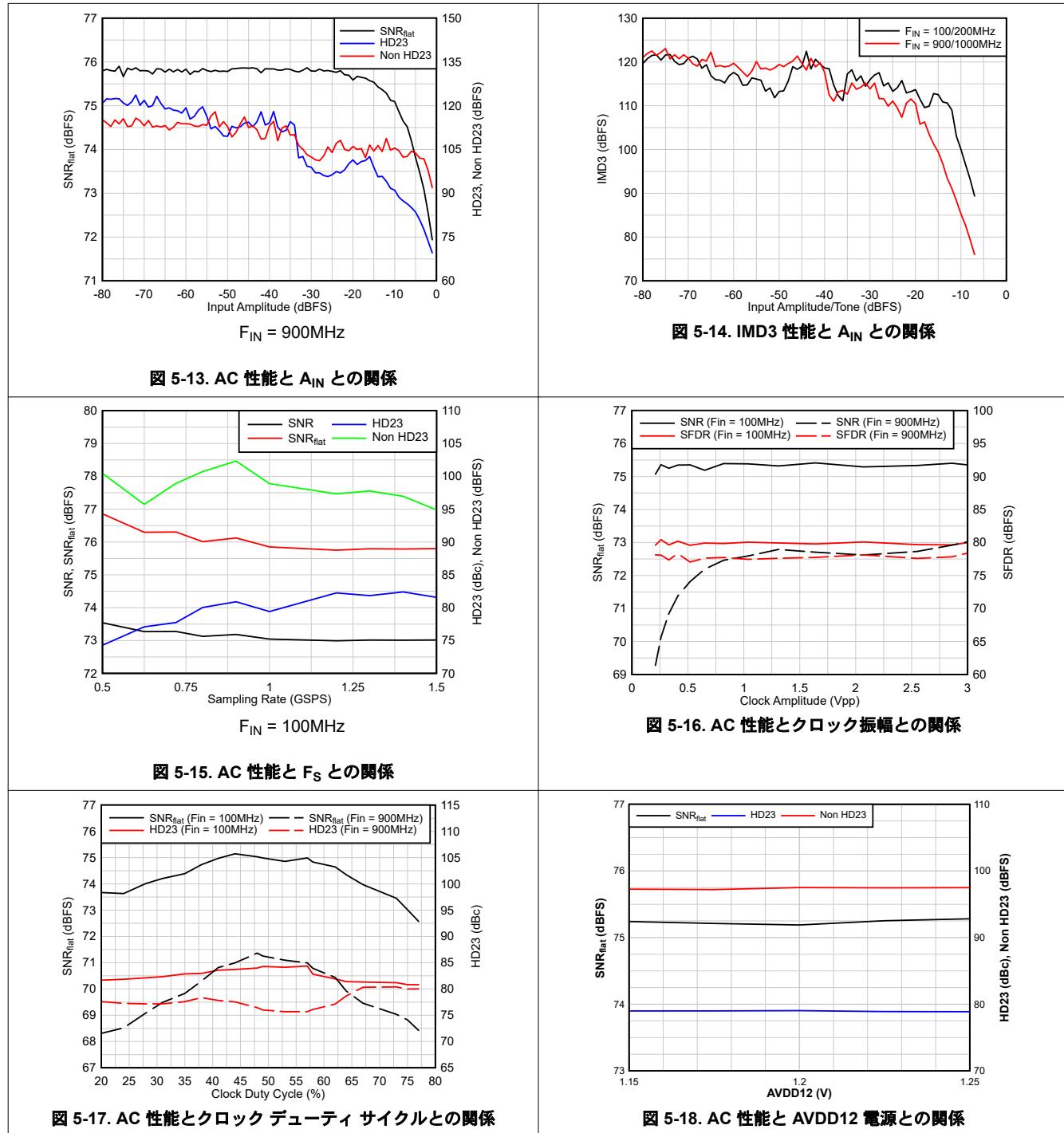

## 5.9 代表的特性 (続き)

特に記述のない限り、標準値は  $T_A = 25^\circ\text{C}$ 、ADC サンプリングレート = 1.5GSPS、50% クロックデューティサイクル、公称電源、-1dBFS 差動入力、 $100\Omega$  終端で規定されています

## 5.9 代表的特性 (続き)

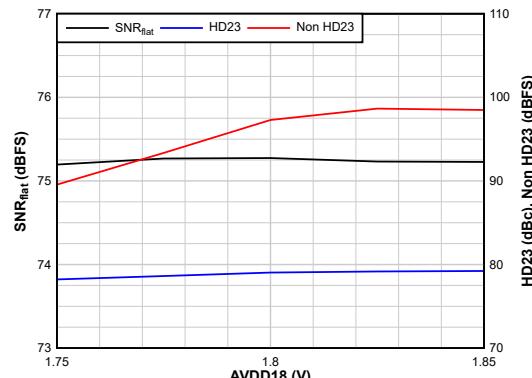

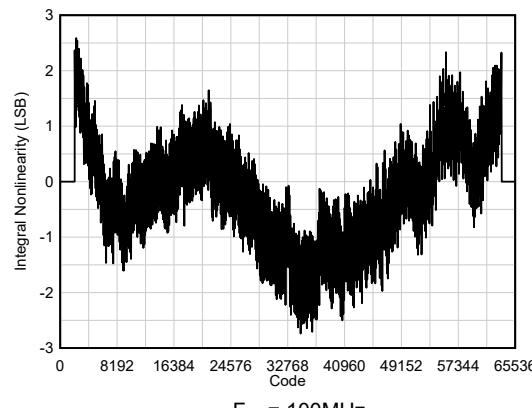

特に記述のない限り、標準値は  $T_A = 25^\circ\text{C}$ 、ADC サンプリングレート = 1.5GSPS、50% クロックデューティサイクル、公称電源、-1dBFS 差動入力、 $100\Omega$  終端で規定されています

図 5-19. AC 性能と AVDD18 電源との関係

図 5-20. AC 性能と温度との関係

図 5-21. INL とコードとの関係

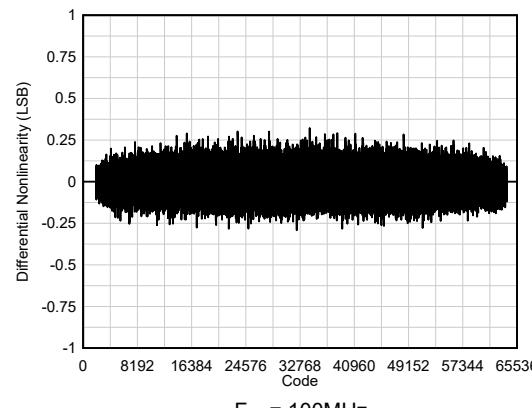

図 5-22. DNL とコードとの関係

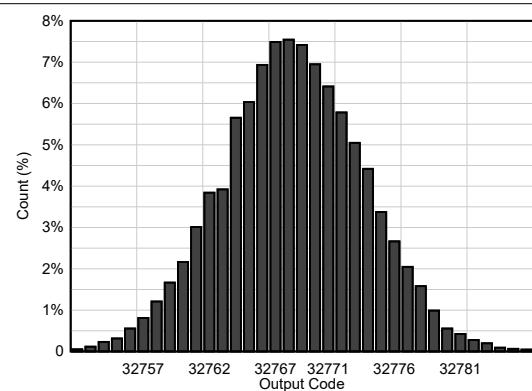

図 5-23. アイドルチャネルのヒストグラム

図 5-24. CMRR

## 5.9 代表的特性 (続き)

特に記述のない限り、標準値は  $T_A = 25^\circ\text{C}$ 、ADC サンプリングレート = 1.5GSPS、50% クロックデューティサイクル、公称電源、-1dBFS 差動入力、 $100\Omega$  終端で規定されています

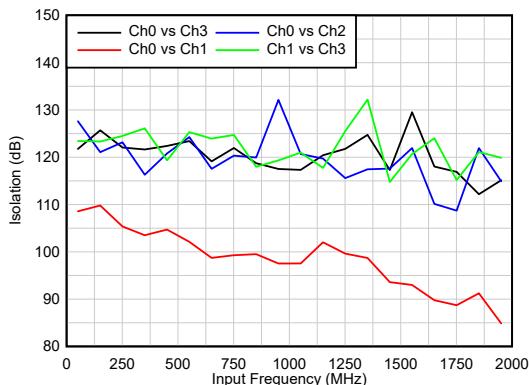

図 5-25. チャネル分離

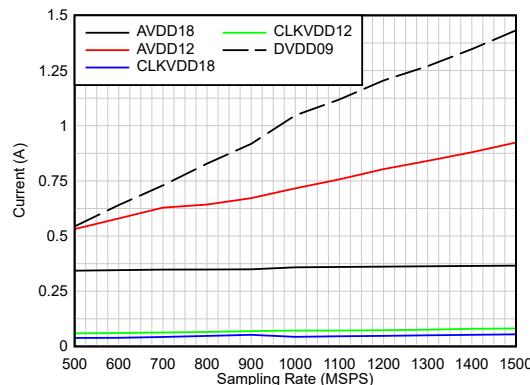

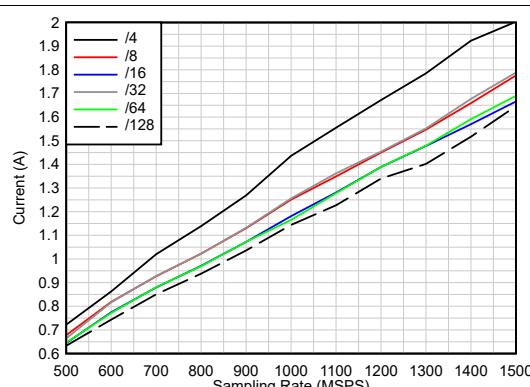

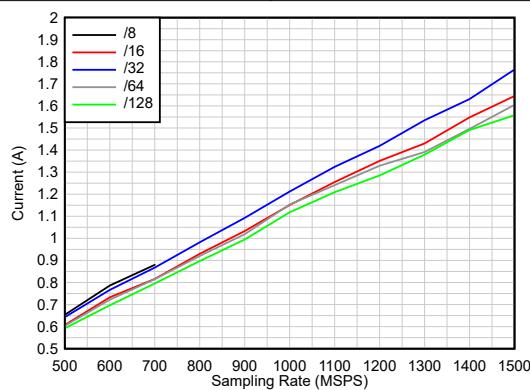

LMFS = 4-2-1-1

図 5-26. 電流とサンプリングレートとの関係

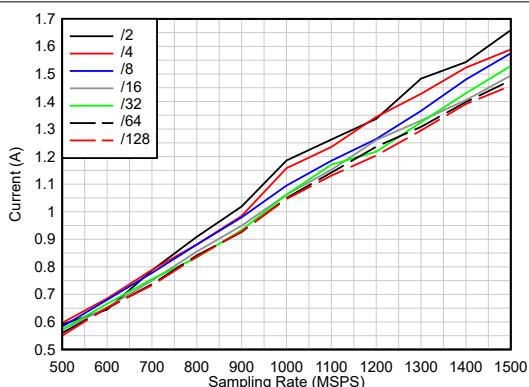

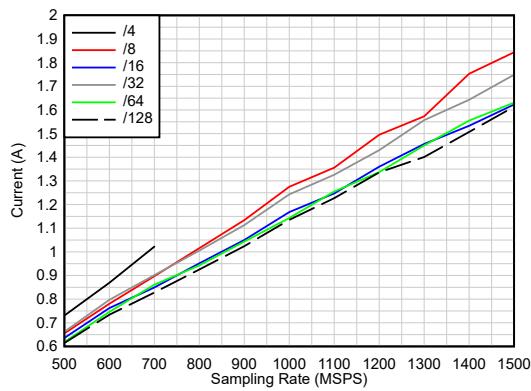

デュアル バンド、LMFS = 8-4-1-1

図 5-27. DVDD09 電流とデシメーションとの関係

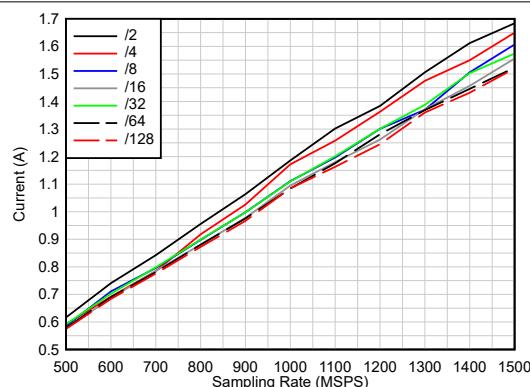

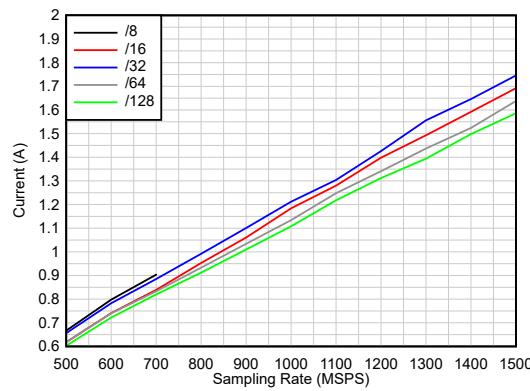

デュアル バンド、LMFS = 4-4-2-1

図 5-28. DVDD09 電流とデシメーションとの関係

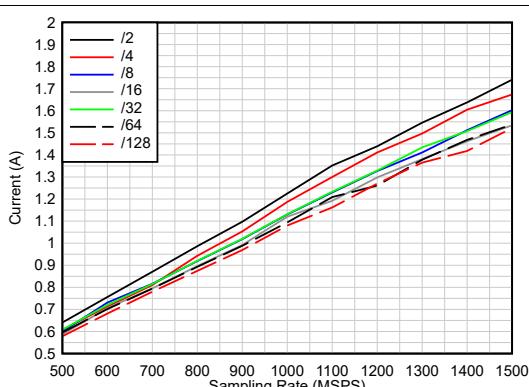

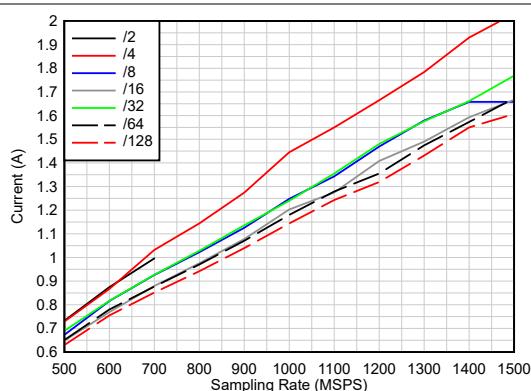

クワッド バンド、LMFS = 8-8-2-1

図 5-29. DVDD09 電流とデシメーションとの関係

クワッド バンド、LMFS = 4-8-4-1

図 5-30. DVDD09 電流とデシメーションとの関係

## 5.9 代表的特性 (続き)

特に記述のない限り、標準値は  $T_A = 25^\circ\text{C}$ 、ADC サンプリングレート = 1.5GSPS、50% クロックデューティサイクル、公称電源、-1dBFS 差動入力、 $100\Omega$  終端で規定されています

図 5-31. DVDD09 電流とデシメーションとの関係

クワッド バンド、LMFS = 1-8-16-1

オクタル バンド、LMFS = 8-16-4-1

オクタル バンド、LMFS = 4-16-8-1

オクタル バンド、LMFS = 2-16-16-1

図 5-35. DVDD09 電流とデシメーションとの関係

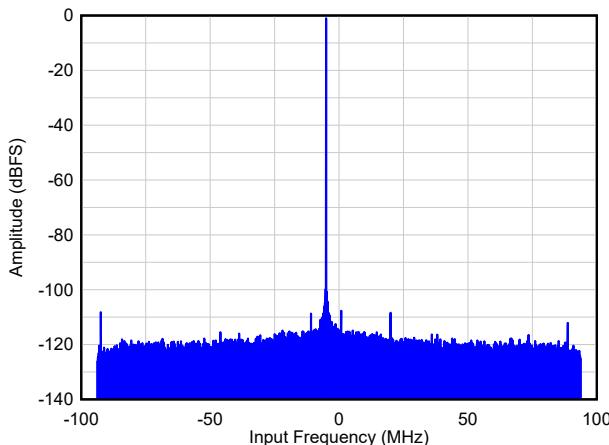

## 6 パラメータ測定情報

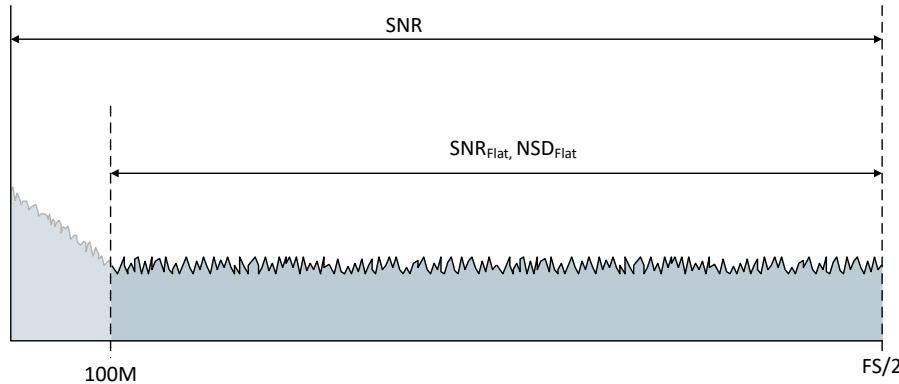

ADC32RF72 には、コーナー周波数が約 100MHz の 1/f ノイズがあります。高性能および RF サンプリングアプリケーションの真のノイズフロアをより的確に説明できるように、ADC のノイズ性能は以下の 2 つの方法で規定されています。

信号対雑音比: 1/F ノイズを含むフルナイキストゾーンで測定

$\text{SNR}_{\text{flat}}, \text{NSD}_{\text{flat}}$ : 100MHz から FS/2 (750MHz) までの平坦なノイズ領域で測定

測定帯域幅を 100MHz ずつ狭くすると (0Hz ではなく 100MHz から開始)、ナイキストゾーン全体で平坦で均一なノイズがあると仮定すると、信号対雑音比が約 0.6dB ( $10\log(750\text{MHz}/650\text{MHz}) = 10\log(0.06) = 0.62\text{dB}$ ) 改善されます。

図 6-1. SNR (DC から FS/2) と  $\text{SNR}_{\text{flat}}$  (100MHz から FS/2) との関係

$\text{NSD}_{\text{flat}} = -163.7\text{dBFS/Hz}$  と仮定

$\text{SNR}_{\text{flat}}$  は次のように計算します:

$$-(-163.7\text{dBFS/Hz} + 10\log(650\text{MHz})) = -(-163.7 + 88.1)\text{dBFS} = 75.6\text{dBFS} \quad (1)$$

1/F ノイズは約 76.4dBFS です。解像度の帯域幅が約 6MHz の 1/f ノイズ測定値を 図 6-2 に示します。1/F ノイズを含むフルナイキストゾーンの信号対雑音比は次のように計算されます:

$$\text{SNR}_{1/f} + \text{SNR}_{\text{flat}} =$$

$$\text{SNR}_{1/f} + \text{SNR}_{\text{flat}} = 10\log\sqrt{\left(10\frac{-\text{SNR}_{1/f}}{20}\right)^2 + \left(10\frac{-\text{SNR}_{\text{flat}}}{20}\right)^2} = 10\log\sqrt{\left(10\frac{-76.4}{20}\right)^2 + \left(10\frac{-75.6}{20}\right)^2} = 73\text{dBFS} \quad (2)$$

図 6-2. 1/f ノイズ測定

## 7 詳細説明

### 7.1 概要

ADC32RF72 は、16 ビット、1.5GSPS (非インターリーブ)、デュアル チャネル A/D コンバータ (ADC) です。このデバイスは、信号対雑音比 (SNR) を最大化し、-163.7dBFS/Hz のノイズスペクトル密度を実現します。2 つの ADC 入力に入力信号を供給するとき、内部デジタル平均化を使用して、NSD を -166.2dBFS/Hz に改善できます。このデバイスでは、ADC0 と、残りの 3 つの ADC チャネルのいずれかを選択できます。パッケージの同じ側にある 2 つの ADC チャネル (ADC0/1) を選択すると、2x の平均化を行えます。パッケージの反対側にある 2 つの ADC チャネル (ADC0/2) を選択すると、最適な絶縁を実現できます。

アナログ信号入力はバッファされ、 $50\Omega$ 、 $100\Omega$ 、 $200\Omega$  のプログラム可能な内部終端インピーダンスをサポートします。最大出力の入力帯域幅は 1.8GHz (-3dB) であり、このデバイスは DC から L バンドまでの入力周波数の直接 RF サンプリングをサポートしています。ADC32RF72 は、高性能のレーダーアプリケーションのサポートのために、残留位相ノイズが小さくなるように設計されています。

このデバイスには、イコライゼーション用の 192 タップ/チャネルのプログラマブル FIR フィルタ、12 ビットの非整数遅延フィルタ、複数のデジタルダウントコンバータ (DDC) など、いくつかのデジタル処理機能を搭載しています。8 つのデジタルダウントコンバータがあり、 $/2$ 、 $/3$ 、 $/5$  のデシメーション係数をサポートしています。48 ビット NCO は位相コヒーレント周波数ホッピングをサポートしています。NCO 周波数制御に GPIO ピンを使用すると、 $1\mu\text{s}$  未満で周波数ホッピングを実現できます。デジタルダウントコンバータは、 $/2$  複素デシメーションの広帯域モードから、 $/32768$  の複素デシメーションの狭帯域幅チャネルまで、広い瞬時帯域幅 (IBW) の要件をサポートしています。最終  $/2$  デシメーション段は、プログラム可能なフィルタ係数を特徴としています。

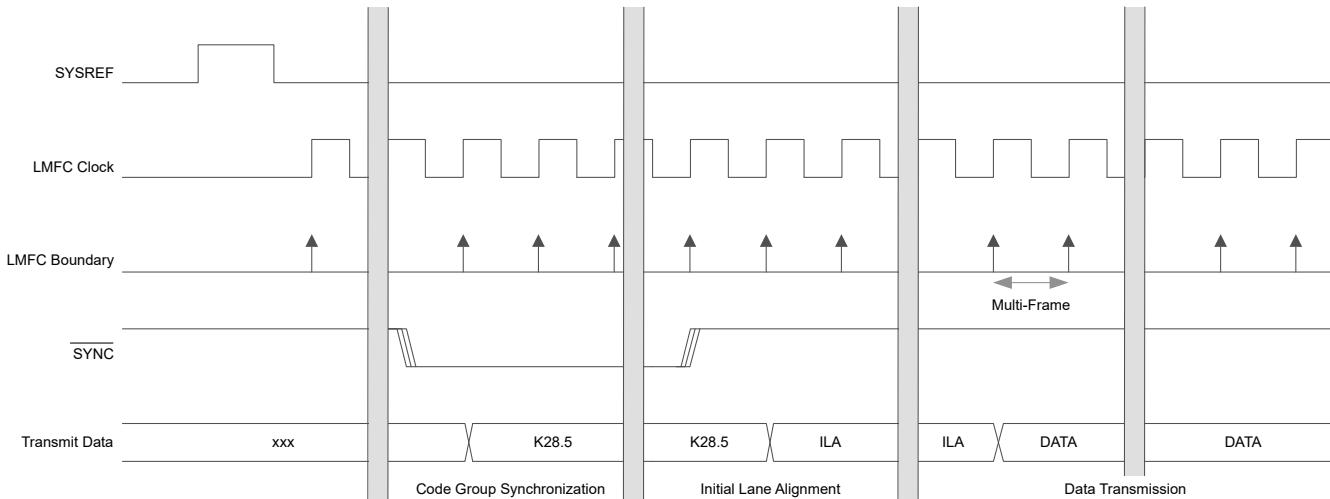

このデバイスは、64b/66b および 8b/10b エンコーディングを使用する JESD204B シリアルデータインターフェイス、最大 24.75Gbps のデータレートを使用するサブクラス 1 の確定的レイテンシをサポートしています。両方のインターフェイスオプションを使用すると、ADC32RF7x はフルスペクトル (DDC バイパス) とデシメーションデータの両方を出力できます。さらに、SerDes PLL (レーンレート / (8x k)) を FPGA に出力することで、システムクロックを簡素化できます。

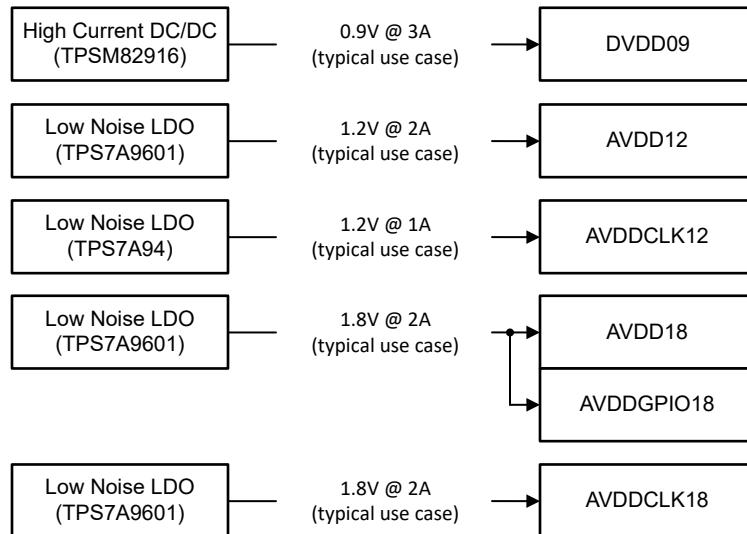

このデバイスには 3 種類の電源レールが必要です:(1.8V、1.2V、0.9V) を供給できます。

### 7.2 機能ブロック図

ブロック図

## 7.3 機能説明

### 7.3.1 アナログ入力

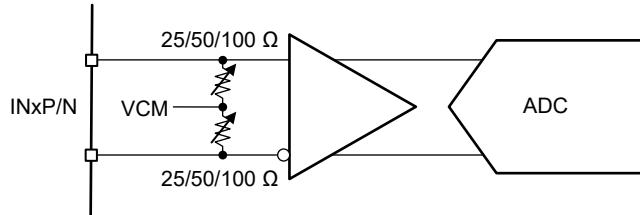

ADC32RF72 のアナログ入力には内部バッファがあり、サンプリングコンデンサを外部入力回路から絶縁します。アナログ入力には、プログラム可能な差動分割終端があり、内部バイアスを備えています(図 7-1 を参照)。差動終端は、SPI レジスタへの書き込みにより、差動 50Ω、100Ω、200Ω を選択できます。アナログ入力の AC 結合と DC 結合の両方がサポートされています。

図 7-1. アナログ入力(内部)電気回路

次のパラメータをプログラムできます:

表 7-1. 入力終端のプログラミング ( $x = 0, 1, 2, 3$ )

| システムパラメータ名            | サイズ(ビット) | デフォルト | リセット | 説明                                                     |

|-----------------------|----------|-------|------|--------------------------------------------------------|

| ADC{x}_INPUT_TERM_SEL | 2        | 0     | R/W  | ADC{x} 入力終端設定を選択<br>0:50Ω 差動<br>1:100Ω 差動<br>2:200Ω 差動 |

#### 7.3.1.1 入力帯域幅

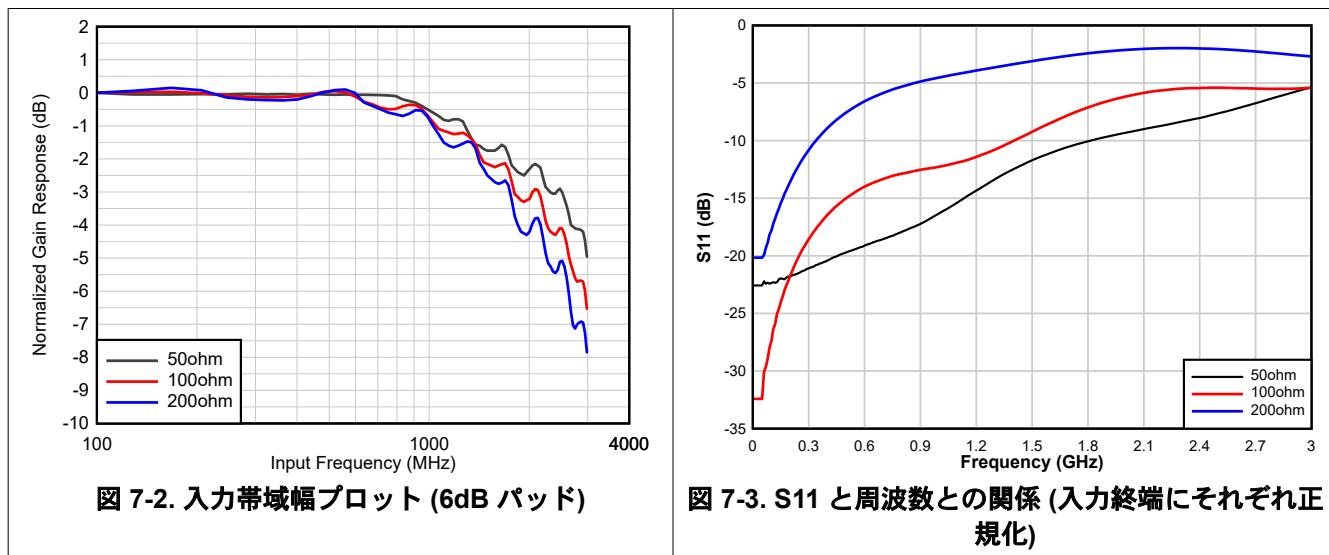

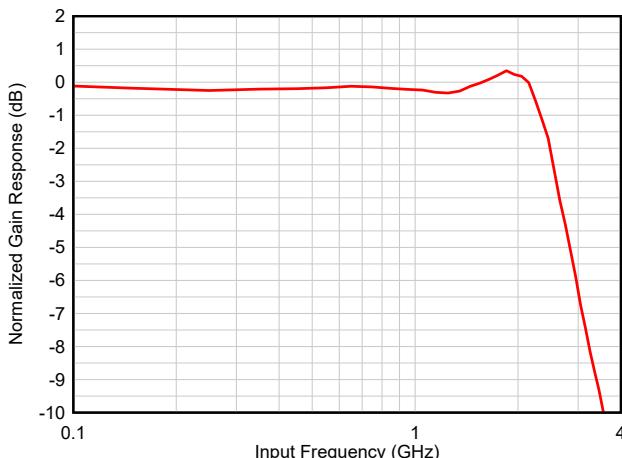

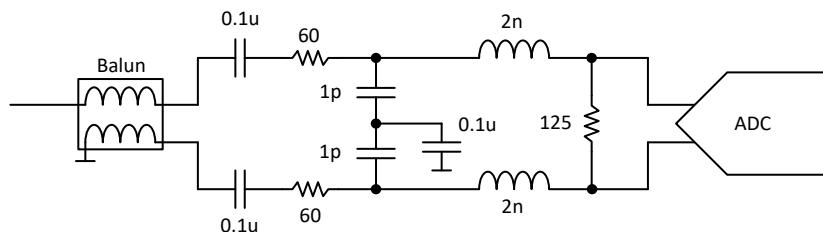

図 7-2 に、内部の 50Ω、100Ω、200Ω の差動終端に対する入力帯域幅 (-3dB) と、S11 の応答を示します(図 7-2)。100Ω を終端した場合、入力帯域幅は約 1.8GHz (-3dB) です。図 7-4 は、図 7-5 の外部整合回路網を使用した 100Ω 終端がある周波数応答を示します。

図 7-2. 入力帯域幅プロット (6dB パッド)

図 7-3. S11 と周波数との関係(入力終端にそれぞれ正規化)

図 7-4. 入力帯域幅プロット

図 7-5. 外部マッチング回路網

### 7.3.1.2 バックグラウンドキャリブレーション

ADC32RF72 は内部バックグラウンドキャリブレーションを使用して、温度範囲全体にわたって高い AC 性能を維持します。キャリブレーションは定期的に実行され、ユーザー制御または入力信号などは必要ありません。キャリブレーション中は、信号オフセットに対する小さな変化(約 30LSB)が観測されます。このキャリブレーションは、SPI 書き込みまたは GPIO 制御を使用した測定中の外乱を回避するために停止できます。

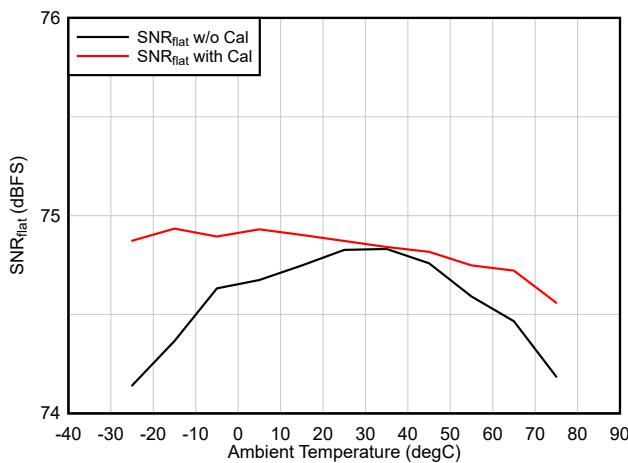

$F_{IN} = 100\text{MHz}$ ,  $A_{IN} = -1\text{dBFS}$ ,  $25^\circ\text{C}$  でキャリブレーション

図 7-6. SNR<sub>flat</sub> と温度とキャリブレーションとの関係

### 7.3.2 ADC チャネルの選択とパワー ダウン モード

4 つの異なる ADC チャネル (Ch0 ~ 3) が使用可能ですが、チャネル 0 は常にイネーブルにする必要があります。ユーザーは、以下に示すシステム パラメータのチャネルイネーブル制御を使用して、残りの 3 つのいずれかを選択できます。これは静的な構成で、電源投入時に設定する必要があります。

このデバイスは、GPIO ピンまたは SPI レジスタ書き込みで制御できる 3 種類のパワーダウン モードをサポートしています。

- 高速パワーダウン: 個別チャネルのパワーダウンで、ウェークアップ時間が短くなりますが、消費電力が大きくなります。JESD インターフェイスはアクティブのままであります。

- パワーダウン: 個別チャネルのパワーダウン。JESD インターフェイスは調整可能であり、未使用レーンをパワーダウンできます。

- グローバル パワーダウン: チップ全体のパワーダウンにより、消費電力を最小限に抑えます (アクション呼び出しによりイネーブルされます)。

**表 7-2. パワーダウン モードの比較**

| パワーダウン モード   | ウェークアップ時間           | 消費電力 (typ) | コメント                        |

|--------------|---------------------|------------|-----------------------------|

| 高速パワーダウン     | ~5 us               | ~2.0 W     | JESD インターフェイスはアクティブのままであります |

| グローバル パワーダウン | JESD インターフェイスに依存します | ~0.4 W     | JESD インターフェイスはパワーダウンされています  |

パワーダウン モードは次のパラメータを使用してプログラムできます:

**表 7-3. パワーダウン モードのプログラミング**

| システムパラメータ名         | サイズ | デフォルト | アクセス権 | 説明                                                                                                                                                                                                                          |

|--------------------|-----|-------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADC_EN_BITMAP      | 4   | 3     | R/W   | 4 つの ADC のうち 2 つを選択します。<br>3:チャネル 0 および 1 がアクティブです。<br>5:チャネル 0 および 2 がアクティブです。<br>9:チャネル 0 および 3 がアクティブです。                                                                                                                 |

| ADC_CH_PDN_VAL     | 4   | 0     | R/W   | 個別の ADC チャネル パワーダウン設定。各 ADC には 1 ビットがあります。このビットをセットすると、対応するチャネルがパワーダウンします。この設定を有効にするには、ADC_CH_PDN_SRC_SEL を 1 に設定する必要があります。<br>ビット 0:ADC0 パワーダウン制御。<br>ビット 1:ADC1 パワーダウン制御。<br>ビット 2:ADC2 パワーダウン制御。<br>ビット 3:ADC3 パワーダウン制御。 |

| ADC_CH_PDN_SRC_SEL | 1   | 0     | R/W   | チャネルのパワーダウン信号が GPIO から供給されるか、SPI から供給されるかを選択します。<br>0:チャネルのパワーダウンは GPIO からです。<br>1:チャネルのパワーダウンは ADC_CH_PDN_VAL からです。                                                                                                        |

| ADC_CH_PDN_MODE    | 1   | 0     | R/W   | チャネルのパワーダウンモードを選択します。<br>0:通常の PDN (各チャネルの消費電力が最小)。<br>1:高速 PDN (電源投入時間が短縮されますが、消費電力が増加)。                                                                                                                                   |

### 7.3.3 サンプリングクロック入力

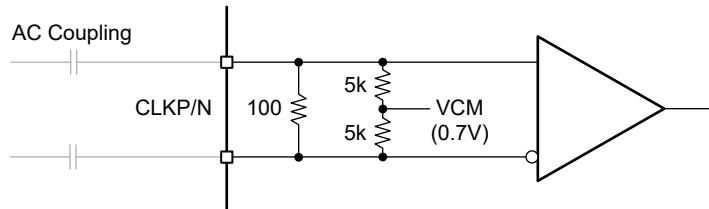

クロック入力には  $V_{CM} = 0.7V$  の自己バイアスを備えた  $100\Omega$  の差動終端が内蔵されており、外部 AC 結合が可能です（図 7-7 を参照）。

図 7-7. 内部サンプリングクロック回路

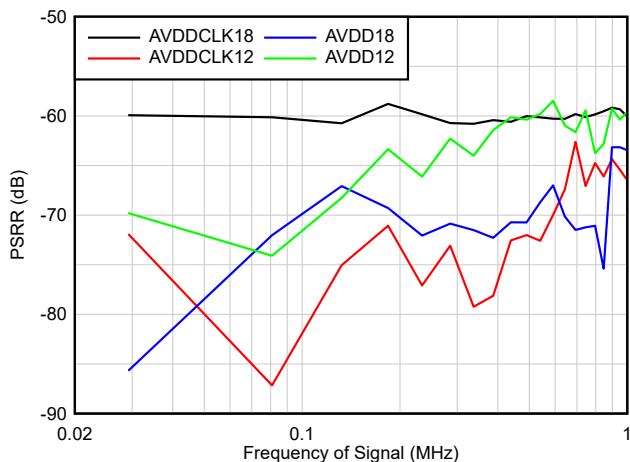

内部サンプリングクロックパスは、残留位相ノイズへの影響が非常に小さくなるように設計されています。サンプリングクロック回路には、最高の性能を得るために、専用の低ノイズ電源が必要です。内部アーチャクロックの位相ノイズは、クロックの振幅からも影響を受けます。最高の性能を得るために、クロック振幅を  $1V_{pp}$  より大きくする必要があります。

表 7-4. 1GHz の内部アーチャクロックノイズ

| 周波数オフセット (MHz) | 位相ノイズ (dbc/Hz) | 振幅ノイズ (dbc/Hz) |

|----------------|----------------|----------------|

| 0.001          | -130           | -139           |

| 0.01           | -140           | -149           |

| 0.1            | -150           | -155           |

| 1              | -155           | -159           |

次のパラメータをプログラムできます：

表 7-5. クロックレジスタのプログラミング

| システム パラメータ<br>名称 | サイズ | デフォルト | リセット | 説明                                    |

|------------------|-----|-------|------|---------------------------------------|

| ADC_CLK_FREQ_HZ  | 33  | 0     | R/W  | サンプリングクロック周波数 (Hz) を示す 33 ビットの符号なし数値。 |

### 7.3.4 SYSREF

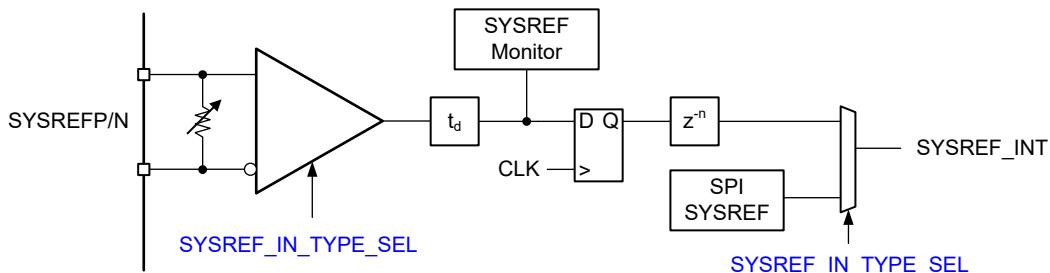

SYSREF 入力信号はマルチチップの同期に使用され、内部 LMFC カウンタをリセットします。デバイスは SYSREF 信号を予期して準備する必要があります。デバイスは準備後の最初の SYSREF エッジに敏感です。

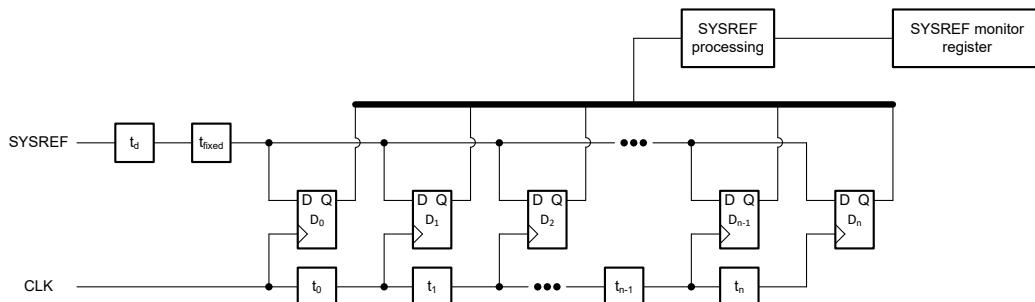

内部 SYSREF キャプチャには、図 7-8 に示すように、プログラマブルなアナログ遅延  $t_d$ 、SYSREF モニタ、プログラマブルなデジタル整数クロックサイクル遅延  $z^n$  が含まれています。

図 7-8. SYSREF 入力内部パス

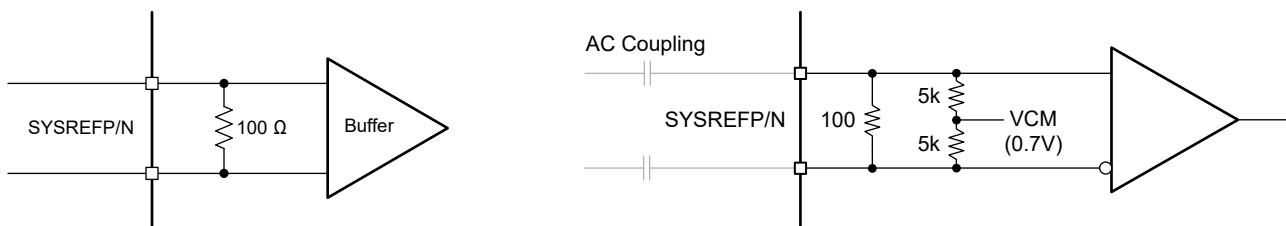

図 7-9 に示すように、SYSREF 入力信号は AC 結合または DC 結合することができます (SPI レジスタオプションで選択)。SYSREF 入力には、DC 結合用の  $100\Omega$  終端と、AC 結合を使用するときの内部バイアスがあります。

図 7-9. SYSREF 入力回路とエッジ アライメント (左側 : DC 結合、右側 : AC 結合)

次のパラメータをプログラムできます:

表 7-6. SYSREF 構成プログラミング

| システム パラメータ<br>名称   | サイズ | デフォルト | リセット | 説明                                                                                                              |

|--------------------|-----|-------|------|-----------------------------------------------------------------------------------------------------------------|

| SYSREF_IN_TYPE_SEL | 2   | 0     | R/W  | 入力 SYSREF のタイプを選択:<br>0:DC 結合 LVDS SYSREF 入力。<br>1:AC 結合 SYSREF 入力。<br>2:未使用。<br>3:SPI 書き込みを使用して内部生成された SYSREF。 |

| SYSREF_DIG_DEL     | 8   | 0     | R/W  | CLK のクロックサイクルにおけるデジタル SYSREF 内部遅延 ( $z^n$ )。<br>0...255: 使用前にデジタル SYSREF に適用されるデバイスクロックサイクル遅延数。                 |

### 7.3.4.1 SYSREF モニタ

SYSREF モニタは、入力 SYSREF 信号をアナログ遅延を含むサンプリングクロックのコピーでラッチすることにより、入力 SYSREF 信号を ADC サンプリングクロックと比較します。ラッチされた出力は SYSREF 处理ブロックを介して内部で処理され、最終的な出力がユーザーに提供されます。ラッチされたフロップ出力を使用して、CLK と SYSREF の立ち上がりエッジの間に十分なマージンがあるかどうかを確認します（セットアップ時間およびホールド時間）。セットアップおよびホールド違反が検出された場合、プログラマブル遅延  $t_d$  を使用して SYSREF 遅延を調整し、CLK と SYSREF の間に十分なマージンを確保して SYSREF が適切にラッチされるようにします。

図 7-10. SYSREF 検出回路

次のパラメータをプログラムできます：

表 7-7. SYSREF 構成プログラミング

| システム パラメータ<br>名称         | サイズ | デフォルト | アクセス<br>権 | 説明                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------|-----|-------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYSREF_MONITOR_NUM_POLLS | 8   | 1     | R/W       | SYSREF_MONITOR_OUT が更新される前に検出される、SYSREF 立ち上がりエッジの数を設定します。より高い値の SYSREF_MONITOR_NUM_POLLS を使用すると、SYSREF エッジの拡散を測定できます。これは、SYSREF_MONITOR_NUM_POLLS SYSREF の立ち上がりエッジが観測されるまで、各フロップ出力は以前のすべての出力と OR 結合されるためです。<br>1...255:SYSREF_MONITOR_OUT が更新される前に観測される SYSREF 立ち上がりエッジの数。                                                                                                                                                  |

| SYSREF_MONITOR_TD_COARSE | 4   | 0     | R/W       | $t_d$ ブロック内の粗い遅延 (45ps) の数を設定します。                                                                                                                                                                                                                                                                                                                                                                                           |

| SYSREF_MONITOR_TD_FINE   | 4   | 0     | R/W       | $t_d$ ブロックに細かい遅延を設定します。<br>$td\_fine = (\text{floor}(\text{SYSREF\_MONITOR\_TD\_FINE}/2)*15\text{ps}) + ((\text{SYSREF\_MONITOR\_TD\_FINE}\%2)*4\text{ps})$                                                                                                                                                                                                                                                                 |

| SYSREF_MONITOR_OUT       | 8   | 0     | R         | SYSREF モニタ出力。ビット 0 は最も早い CLK エッジに対応し、ビット 7 は最新の CLK エッジに対応します。<br>SYSREF_MONITOR_OUT は次のいずれかの状態にのみ存在し、次のように解釈できます：<br>状態 0: 1つ以上のゼロの後に 1つ以上のゼロが続きます。SYSREF 遷移の立ち上がりが SYSREF モニタウンドウに表示され、セットアップおよびホールド違反が検出されます。SYSREF_LAT は、すべてのゼロまたはすべての 1 が観測されるまで遅延する必要があります。<br>状態 1: すべてゼロ。CLK は SYSREF_LAT に先行し、SYSREF_LAT は次の CLK 立ち上がりエッジで適切にラッチされます。<br>状態 2: すべての CLK は SYSREF_LAT より遅れ、SYSREF_LAT は現在の CLK 立ち上がりエッジで適切にラッチされます。 |

### 7.3.5 デジタルシグナルプロセッサ(DSP) 機能

このデバイスには、デジタル信号処理ブロック内にいくつかの異なるデジタル機能が搭載されています：

- 12ビットの分数遅延で、1つのサンプリングクロックサイクル範囲、遅延ステップサイズが  $1/(2^{12} * t_{CLK})$

- チャネルごとに最大 96 タップのイコライゼーションが可能な、プログラマブル FIR フィルタ

- $/2$ 、 $/3$ 、 $/5$  から  $/32768$  までのデシメーション係数をサポートする複数のデジタルダウンコンバータ(DDC)

- デシメーション後のイコライゼーション用の追加のプログラマブル FIR フィルタ

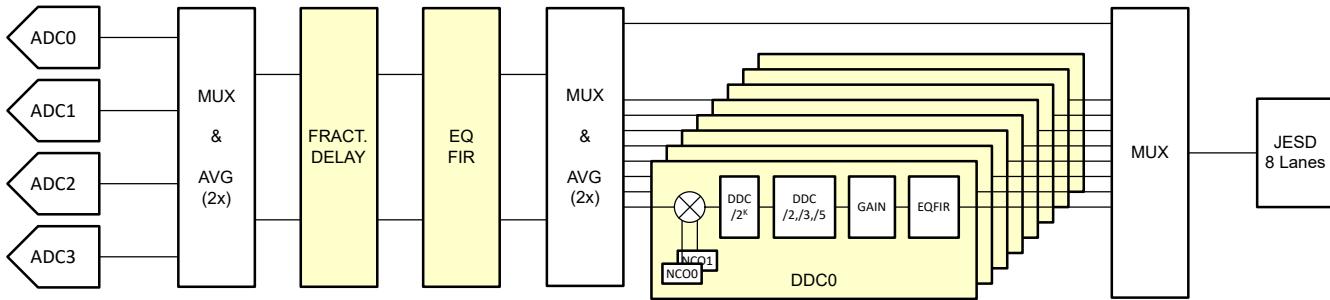

図 7-11. デジタル信号処理チェーン

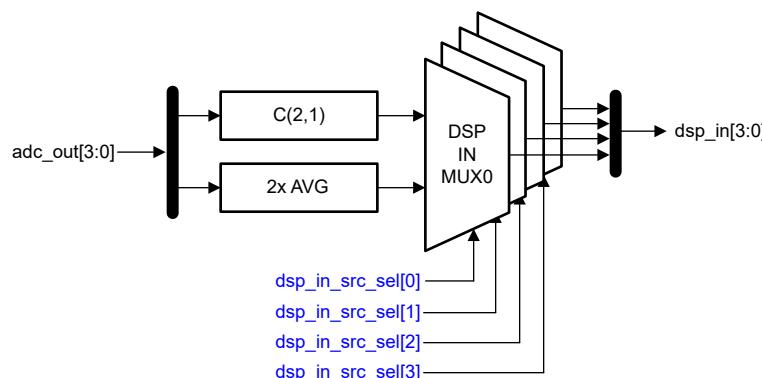

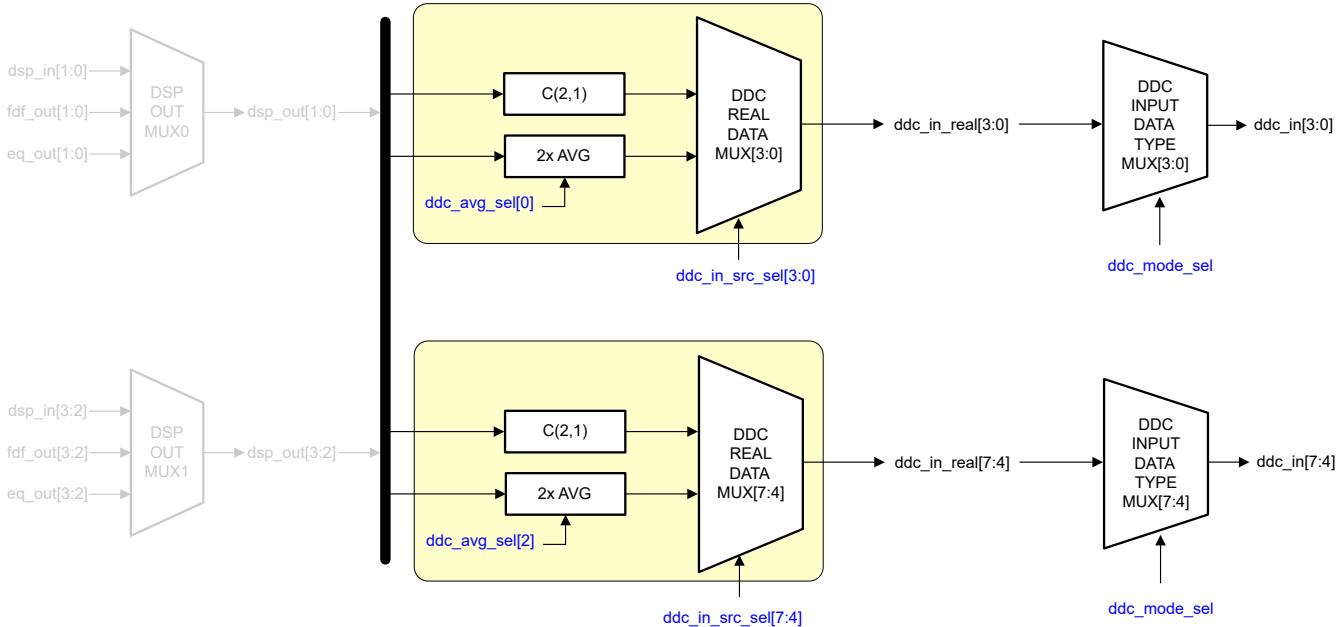

### 7.3.5.1 DSP 入力マルチプレクサ

図 7-12 に示すように、DSP ブロックの入力には 4 つのデジタルマルチプレクサがあります。バスは `adc_out[3:0]` を基準とし、各インデックスは特定の ADC の固有の出力ストリームを表します。たとえば、ADC0 の出力は `adc_out[0]` です。各 `DSP_IN` マルチプレクサの出力は、DSP ブロックのシングル DSP 入力データストリームに対応します。DSP 入力データストリームの集計セットは、`dsp_in[3:0]` と呼ばれます。`dsp_in[0]` は 0 番目の DSP 入力データストリームに対応します。各 DSP 入力データストリームは、次のいずれかから供給できます：

- 2 つの `adc_out` ストリームのいずれか (`adc_out[0]` とその他のいずれか 1 つ)。これは  $C(2,1)$  と表記されます。

- 2 つの `adc_out` ストリームの平均。

#### 注

命名法  $C(n,k)$  は、 $n$  個の異なる項目を含む集合から  $k$  個の項目を選択する可能性のある組み合わせを表しています。

たとえば、`adc_out={adc0,adc1,adc2,adc3}` という集合があるとすれば、この集合から 2 つの項目を選択する方法は以下の 6 つとなります： $C(\text{adc\_out},2)=\{\{\text{ADC0,ADC1}\},\{\text{ADC0,ADC2}\},\{\text{ADC0,ADC3}\},\{\text{ADC1,ADC2}\},\{\text{ADC1,ADC3}\},\{\text{ADC2,ADC3}\}\}$

図 7-12. DSP 入力マルチプレクサの概要

次のパラメータをプログラムできます：

表 7-8. DSP 入力マルチプレクサ構成のプログラミング ( $x = 0, 1, 2, 3$ )

| システムパラメータ名                     | サイズ | デフォルト      | アクセス権 | 説明                                                                                                                                                                                                                                                                                                 |

|--------------------------------|-----|------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <code>DSP_IN_SRC_SEL{x}</code> | 4   | 0, 1, 2, 3 | R/W   | DSP ブロックへの <code>dsp_in[0..3]</code> 入力データストリームの入力データソースを選択します。<br>0:ADC0 データ。<br>1:ADC1 データ。<br>2:ADC2 データ。<br>3:ADC3 データ。<br>4:ADC0 と ADC1 の 2 倍平均。<br>5:ADC0 と ADC2 の 2 倍平均。<br>6:ADC0 と ADC3 の 2 倍平均。<br>7:ADC1 と ADC2 の 2 倍平均。<br>8:ADC1 と ADC3 の 2 倍平均。<br>9:ADC2 と ADC3 の 2 倍平均。<br>その他:未使用 |

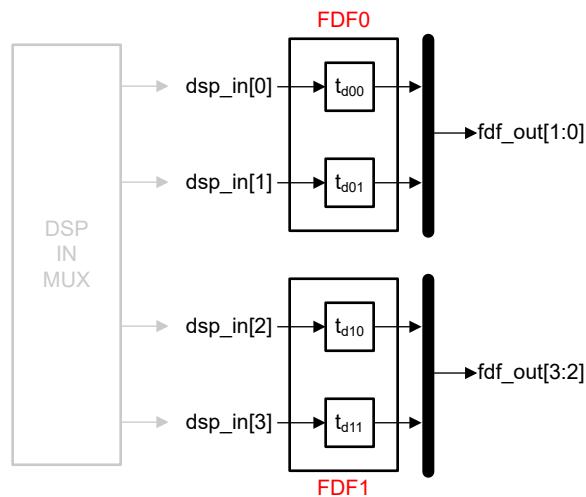

### 7.3.5.2 非整数遅延

このデバイスには、DSP 入力マルチプレクサ後にオプションのプログラマブル 12 ビット非整数デジタル遅延が含まれています（図 7-13 を参照）。2 つの独立したデジタル非整数遅延ブロック（FDF0 および FDF1）があります。各 FDF ブロックは 2 つの入力ストリーム（`dsp_in[1:0]` または `dsp_in[3:2]`）に接続されており、各入力ストリームには、`dsp_in[1:0]` の場合は  $t_{d00}$  および  $t_{d01}$ 、`dsp_in[3:2]` 場合は  $t_{d10}$  および  $t_{d11}$  のプログラマブル非整数遅延値があります。FDF ブロックは合計 4 つのデータストリーム（`fdf_out[3:0]`）を出力し、各出力ストリームは個別の非整数遅延入力ストリームに対応します。

非整数遅延は周波数全体で線形位相を持つ実時間遅延の実装です。非整数遅延は以下のように計算します：

非整数遅延 [サンプリング クロック周期] = 遅延 /  $4096 \times T_S$  (サンプリング周期)。

図 7-13. 非整数遅延機能

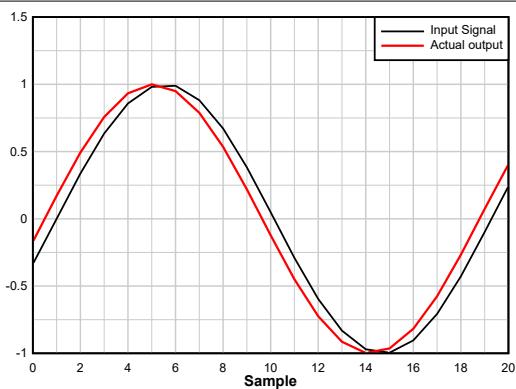

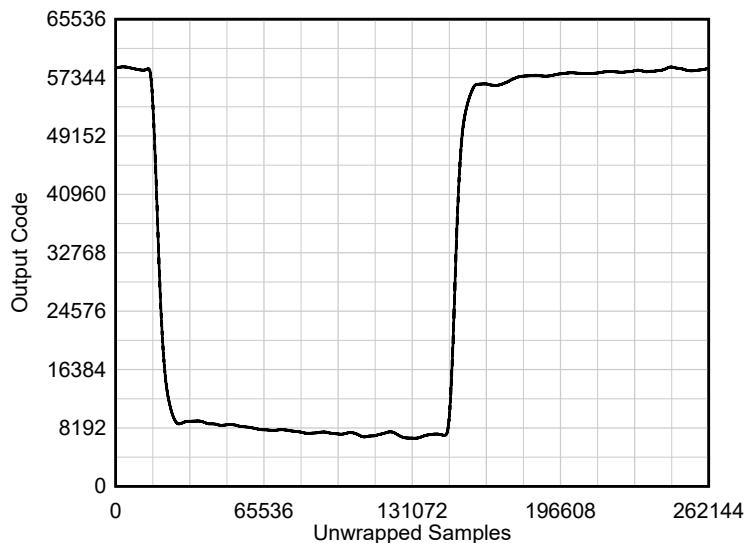

たとえば、図 7-14 に示すように、2048 の設定は 1/2 クロックサイクル遅延と等しくなります。振幅誤差は -80dB 未満です（目的の遅延に対して）。

図 7-14. 非整数遅延 = 1/2 クロックサイクル

(遅延設定 = 2048)

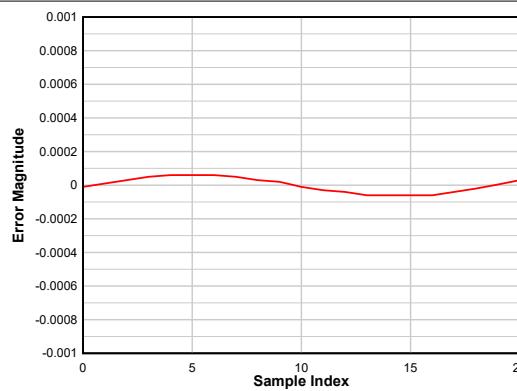

図 7-15. 誤差の大きさ

(目的の波形と実際の波形との関係)

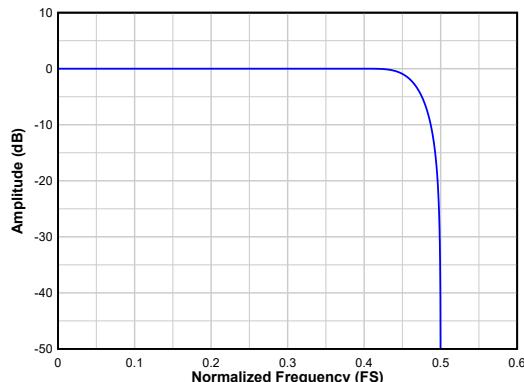

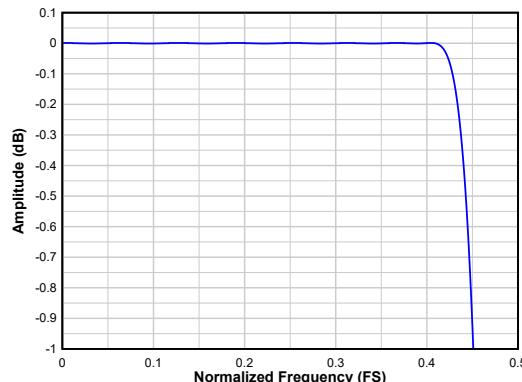

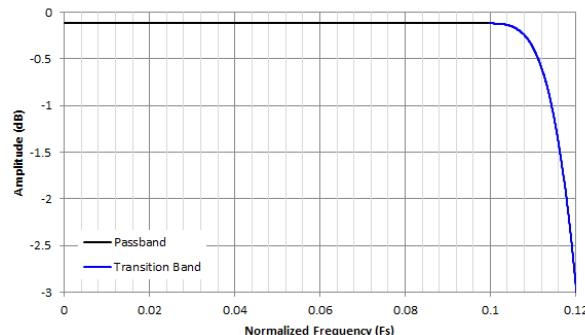

非整数遅延は SPI レジスタへの書き込みにより構成され、プログラムされた遅延は内部的にフィルタ係数に変換されます。図 7-16 と 図 7-17 はフィルタ応答を示しています。パスバンドはナイキストゾーンの約 85% です。非整数遅延の再プログラミングでは、フィルタ係数の更新に最大 2 $\mu$ sかかる場合があります。

図 7-16. 非整数遅延 FIR のフィルタ応答

図 7-17. 非整数遅延 FIR のフィルタ応答 (ズーム)

非整数遅延は次のパラメータを使用してプログラムできます：

表 7-9. 非整数遅延構成のプログラミング

| システムパラメータ名           | サイズ | デフォルト | アクセス権 | 説明                                         |

|----------------------|-----|-------|-------|--------------------------------------------|

| FDF0_DELAY_VAL_0_LSB | 8   | 0     | R/W   | FDF0 への 0 番目の入力データストリームの非整数遅延値のビット [7:0]。  |

| FDF0_DELAY_VAL_0_MSB | 4   | 0     | R/W   | FDF0 への 0 番目の入力データストリームの非整数遅延値のビット [11:8]。 |

| FDF0_DELAY_VAL_1_LSB | 8   | 0     | R/W   | FDF0 への 1 番目の入力データストリームの非整数遅延値のビット [7:0]。  |

| FDF0_DELAY_VAL_1_MSB | 4   | 0     | R/W   | FDF0 への 1 番目の入力データストリームの非整数遅延値のビット [11:8]。 |

| FDF1_DELAY_VAL_0_LSB | 8   | 0     | R/W   | FDF1 への 0 番目の入力データストリームの非整数遅延値のビット [7:0]。  |

| FDF1_DELAY_VAL_0_MSB | 4   | 0     | R/W   | FDF1 への 0 番目の入力データストリームの非整数遅延値のビット [11:8]。 |

| FDF1_DELAY_VAL_1_LSB | 8   | 0     | R/W   | FDF1 への 1 番目の入力データストリームの非整数遅延値のビット [7:0]。  |

| FDF1_DELAY_VAL_1_MSB | 4   | 0     | R/W   | FDF1 への 1 番目の入力データストリームの非整数遅延値のビット [11:8]。 |

### 7.3.5.3 イコライゼーション用のプログラム可能な FIR フィルタ

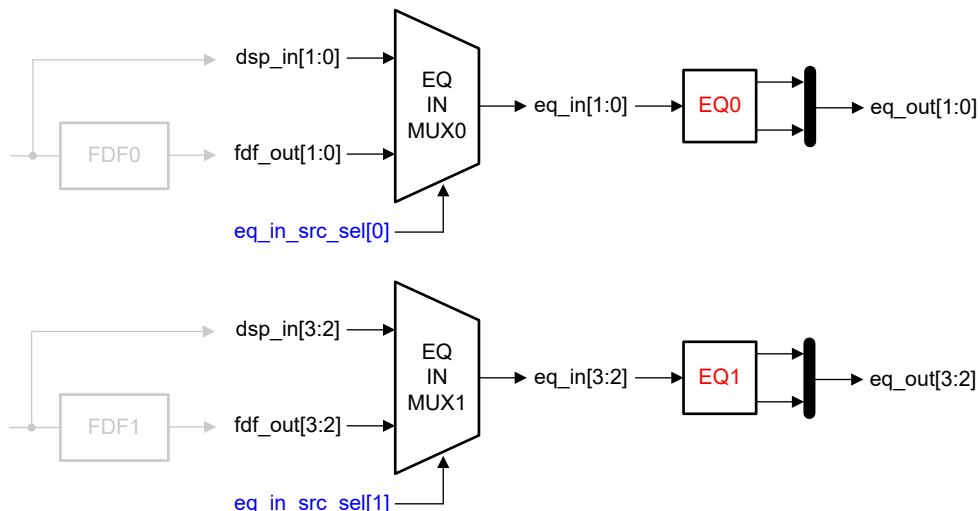

ADC32RF7x にはイコライザ (EQ) と呼ばれるプログラマブル FIR フィルタ ブロックが内蔵されています。図 7-18 に示すように、非整数遅延フィルタ (FDF0/1) の出力に配置された 2 つの EQ ブロック (EQ0 および EQ1) があります。各 EQ ブロックは、`dsp_in` から直接、または先行する FDF ブロックから、入力データ ストリームを供給できます。合計 4 つの出力データストリーム (`eq_out[3:0]`) があり、各出力ストリームは異なるフィルタ処理済み入力ストリームに対応します。

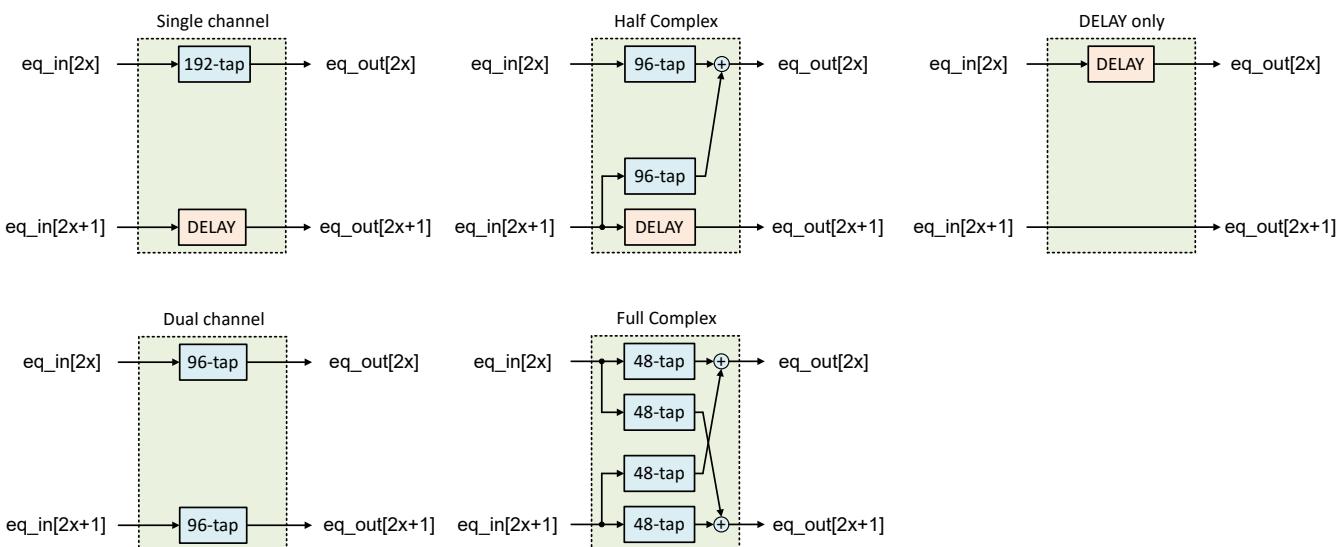

2 つのイコライザ (EQ0/EQ1) には 2 つの入力ストリームで共有される最大 192 タップ (16 ビット) が含まれます。

図 7-18. FIR イコライザの構成

図 7-19 に示すように、各 EQ は EQFIR ごとに最大 192 タップの複数の異なる構成をサポートします。

図 7-19. EQ0 (x=0) および EQ1 (x=1) の FIR イコライザの構成

消費電力はサンプリングレートおよび使用するタップ数に応じて直線的にスケーリングされます。未使用的タップは 0 に設定できます。

デジタルイコライザは次のパラメータを使用してプログラムできます：

**表 7-10. EQ{x} 構成プログラミング (x= 0,1)**

| システムパラメータ名       | サイズ  | デフォルト | アクセス権 | 説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------|------|-------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EQ{x}_IN_SRC_SEL | 1    | 0     | R/W   | EQ{x} 入力データソースを選択します。<br>0:DSP_IN[2x+1, 2x] からの EQ{x} 入力。<br>1:FDF_OUT[2x+1, 2x] からの EQ{x} 入力。                                                                                                                                                                                                                                                                                                                                                                                       |

| EQ{x}_MODE_SEL   | 3    | 0     | R/W   | EQ{x} モードを選択します。<br>0:シングルチャネルモード。<br>1:デュアルチャネルモード。<br>2:半複素モード。<br>3:完全複素モード。<br>4:遅延のみモード。                                                                                                                                                                                                                                                                                                                                                                                        |

| EQ{x}_DEL_VAL    | 8    | 0     | R/W   | EQ{x} 遅延値。この設定の影響は EQ{x} モードに依存します。<br>0...255:EQ{x} がプログラマブル遅延を使用するモードであるときに適用されるデバイスクロックサイクル遅延数。                                                                                                                                                                                                                                                                                                                                                                                   |

| EQ{x}_NUM_TAPS   | 8    | 0     | R/W   | 特定のモードで EQ{x} が使用するタップ数。シングルチャネルモードのときは任意の値に設定できます。デュアルチャネルモードと半複素モードでも必要です。完全複素モードでは 4 で割り切れる必要があります。<br>1...192:EQ{x} で使用されるタップ数。                                                                                                                                                                                                                                                                                                                                                  |

| EQ{x}_TAPS       | 3072 | 0     | R/W   | EQ{x} ブロックの 192 タップを設定します。<br>シングルチャネルモード: eq_input[2x] には最大 192 タップが適用されます。<br>デュアルチャネルモード: eq_input ごとに最大 96 タップ。最初の 96 タップは eq_input[2x] に適用されます。2 番目の 96 タップは eq_input[2x+1] に適用されます。<br>半複素モード: eq_input ごとに最大 96 タップ。最初の 96 タップは eq_input[2x] に適用されます。2 番目の 96 タップは eq_input[2x+1] に適用されます。<br>完全複素モード: eq_input ごとに最大 96 タップ。最初の 96 タップは eq_input[2x] に適用され、それらのタップの最初の 48 は eq_output[2x] に適用されます。2 番目の 96 タップは eq_input[2x+1] に適用され、それらのタップの最初の 48 は eq_output[2x] に適用されます。 |

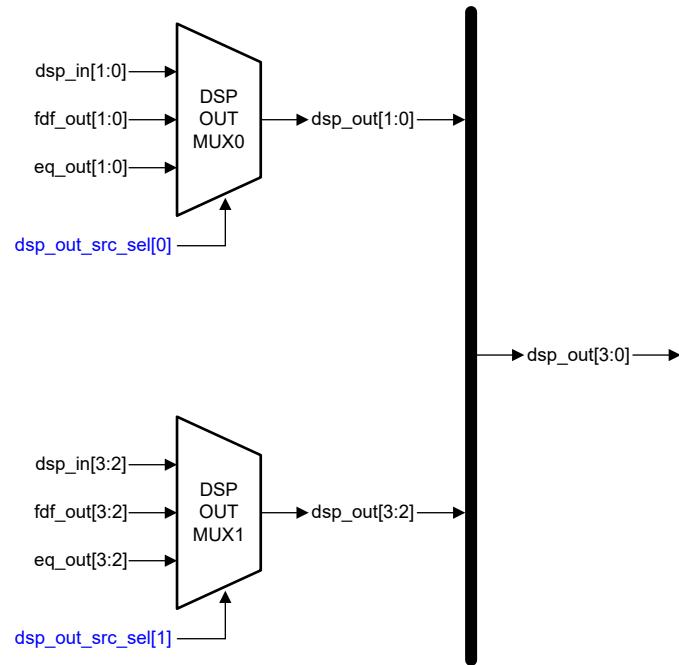

### 7.3.5.4 DSP 出力マルチプレクサ

DSP の出力では DDC より前にいくつかの異なるマルチプレクサが利用可能です。

図 7-20. DSP 出力マルチプレクサ

次のパラメータをプログラムできます:

表 7-11. DDC プログラミングに対する入力の選択 (x = 0 または 1)

| システムパラメータ名         | サイズ | デフォルト | アクセス権 | 説明                                                                                                                                                                              |

|--------------------|-----|-------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DSP_OUT_SRC_SEL{x} | 2   | 0     | R/W   | DSP ブロックから DSP_OUT_MUX{x} の出力データソースを選択します。<br>0: dsp_in[2x+1,2x] は DSP_OUT_MUX{x} の出力。<br>1: fdf_out[2x+1,2x] は DSP_OUT_MUX{x} の出力。<br>2: eq_out[2x+1,2x] は DSP_OUT_MUX{x} の出力。 |

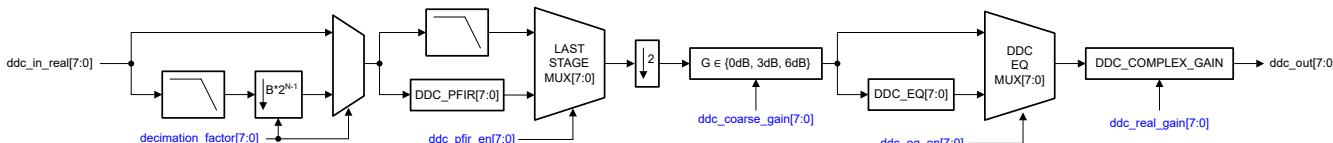

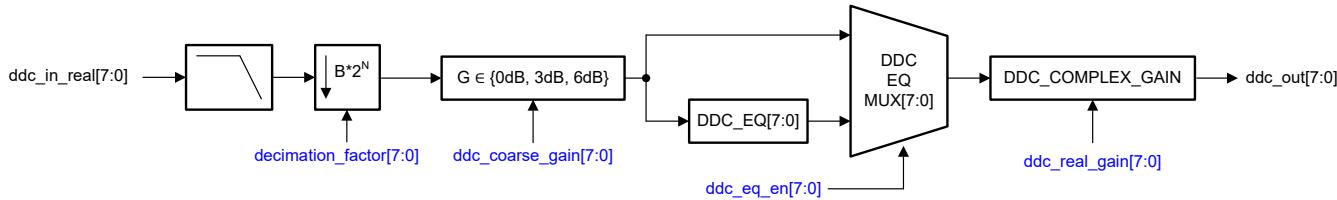

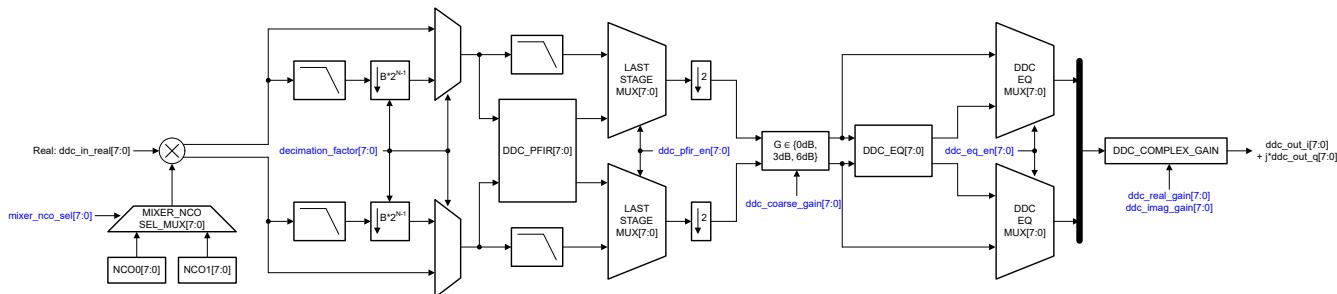

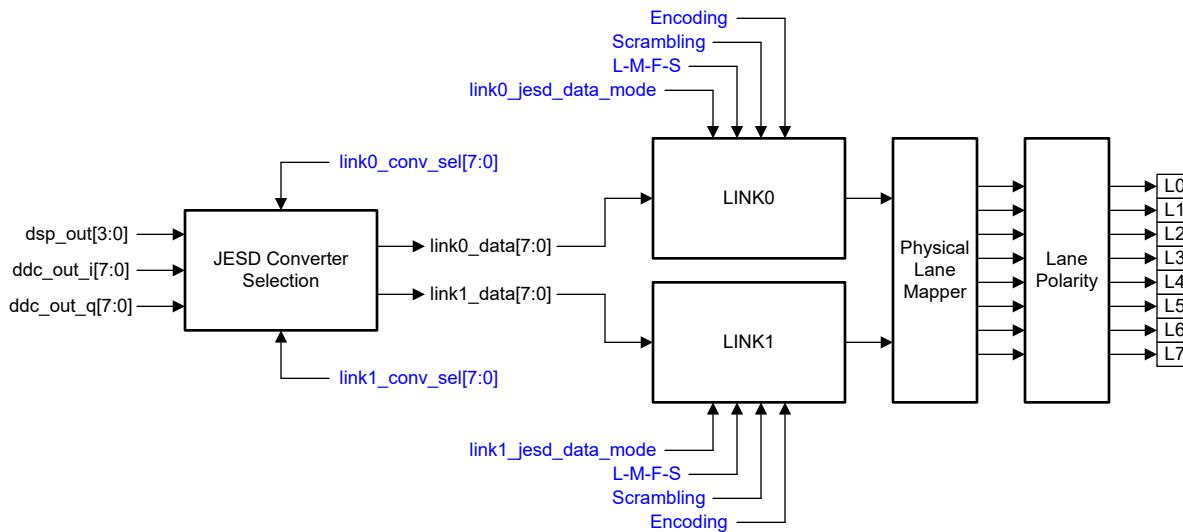

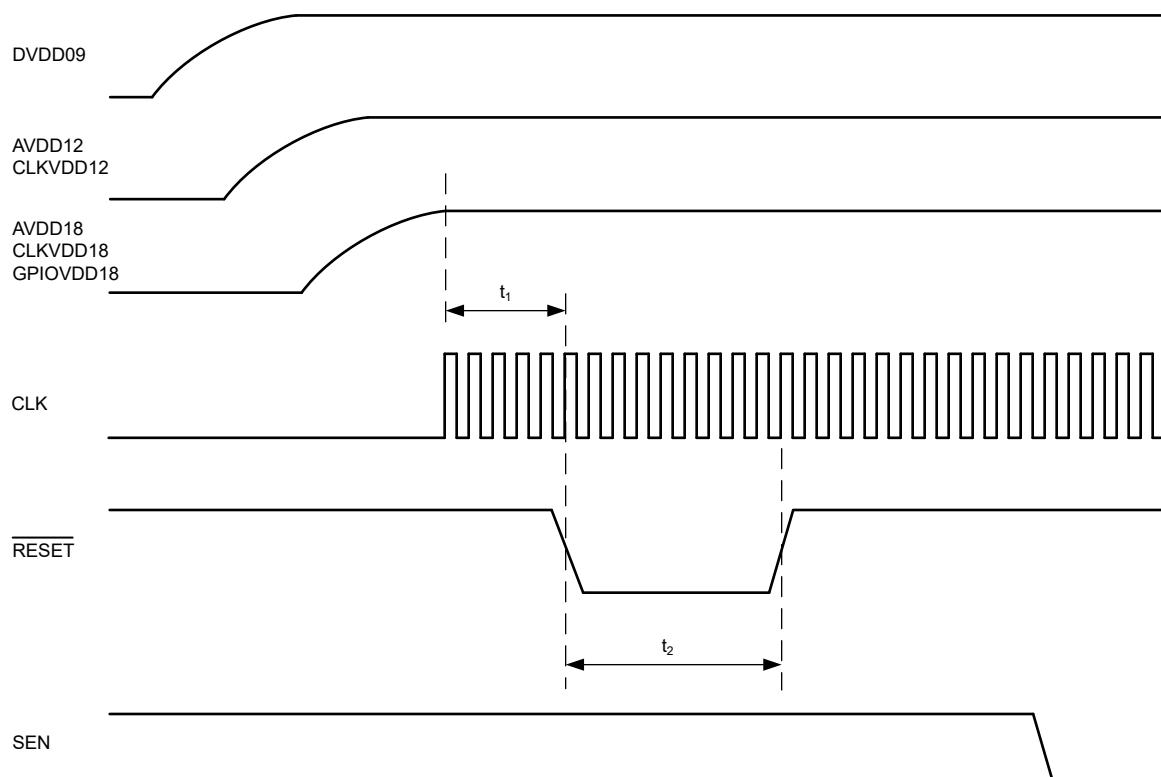

### 7.3.5.5 デジタルダウンコンバータ (DDC)