# 超低ノイズ 24ビット A/Dコンバータ

## 特 長

- 24ビット、ミッシング・コードなし

- すべてのデータ・レートおよびPGAゲインにおいて

- 23ビットのノイズ・フリー分解能(最大)

- $\pm 0.0010\%$ の非直線性誤差(最大)

- データ出力周波数: 30kSPS(最大)

- 高速チャネル・サイクリング

- 18.6ビットのノイズ・フリー(有効ビット 21.3)

1.45kHz時

- シングルサイクルでセトリングするワンショット変換

- フレキシブルな入力マルチプレクサ センサー検出機能つき

- 4差動入力(ADS1256のみ)

- 8シングルエンド入力(ADS1256のみ)

- チョッパ安定型入力バッファ

- 低ノイズPGA: 27nV入力換算ノイズ

- 自己およびシステム・キャリブレーションすべてのPGAゲイン設定に対して

- 5V印加可能なSPI™互換シリアル・インターフェイス

- アナログ電源電圧: 5V

- デジタル電源電圧: 1.8Vから3.6V

- 電力消費

- 38mWの低消費電力ノーマル・モード時

- 0.4mW スタンバイ・モード時

## ア プ リ ケ シ ョ ン

- ウエイ・スケール

- 科学用機器

- 産業用プロセス制御

- 医療機器

- 試験および測定

## 解 説

ADS1255およびADS1256は、非常に低ノイズの24ビットA/Dコンバータ(アナログ-トゥ-デジタル・コンバータ)です。両デバイスともに、非常に困難なアプリケーションに対して、完璧な高分解能測定ソリューションを提供します。

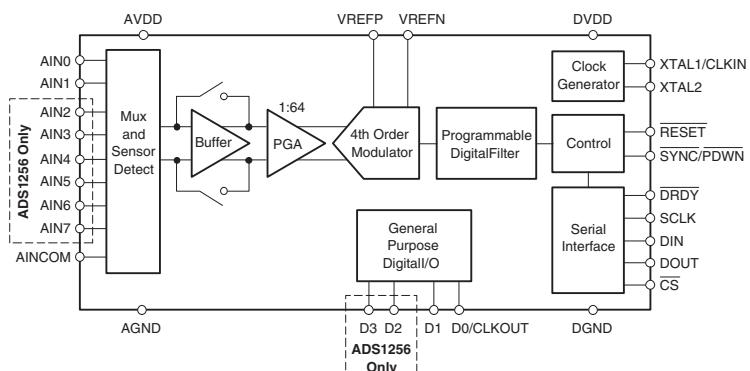

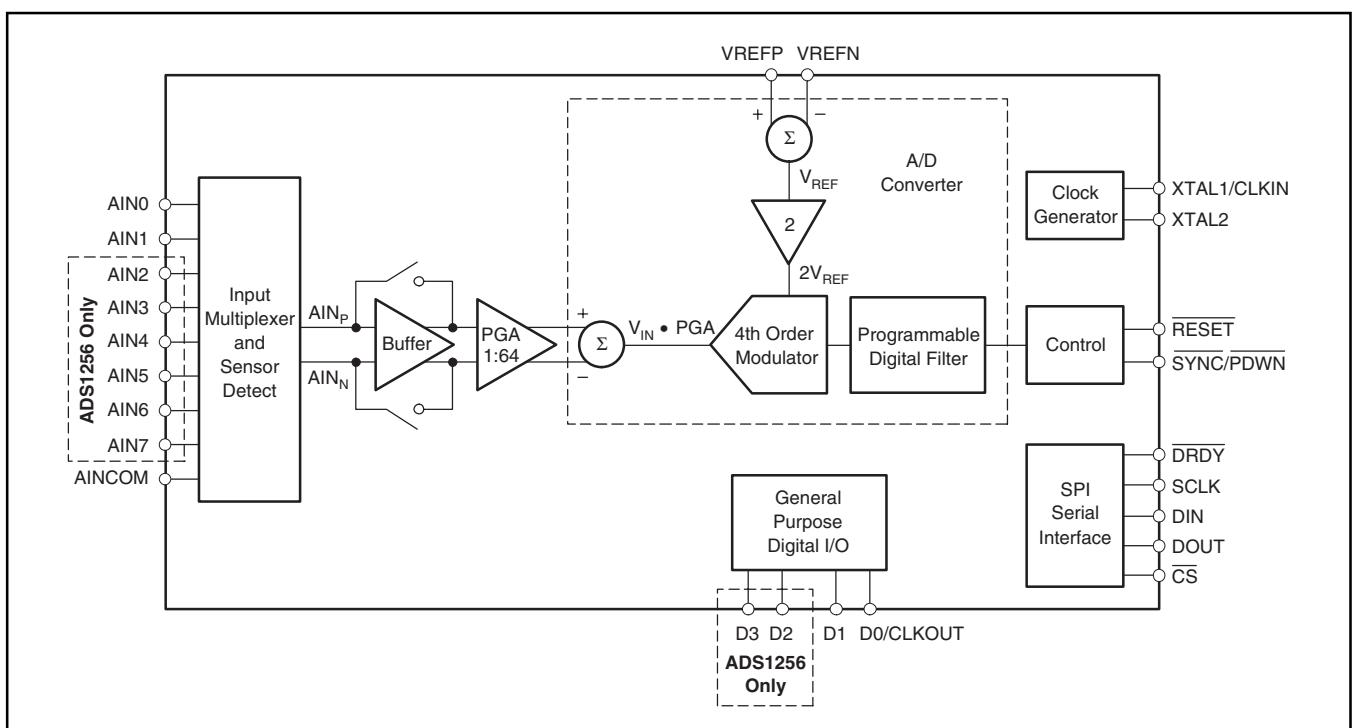

コンバータ部分は4次のデルタ-シグマ( $\Delta\Sigma$ )変調器と、それに続くプログラマブル・デジタル・フィルタで構成されています。フレキシブルな入力マルチプレクサは、差動あるいはシングルエンドの信号を取り扱うことができます。また、入力マルチプレクサには、外部センサーが正しく接続されているか検証する回路が含まれています。選択可能な入力バッファにより入力インピーダンスは十分高く、低ノイズのプログラマブル・ゲイン・アンプ(PGA)により、1から64のバイナリ・ステップのゲインが得られます。また、プログラマブル・フィルタにより、最大23ビットのノイズ・フリーな分解能と最高30kHzのデータ・レート(データ変換周波数、単位はSPS)の間で、ユーザは最適な選択ができます。さらに両デバイスは、多重化された入力を高速チャネル・サイクリングで測定し、わずか1回のサイクル(シングル・サイクル)でセトリングするワンショット変換も実行できます。

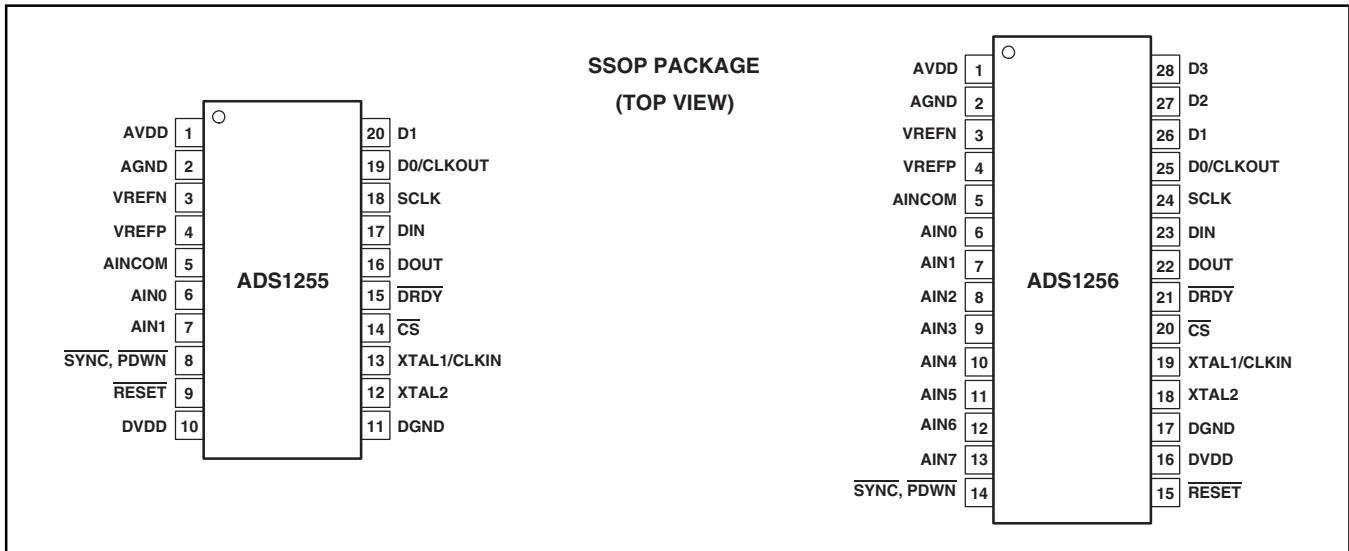

交信はSPI互換のシリアル・インターフェイスで行われ、2線式の接続で動作します。また、内蔵のキャリブレーション回路により、全PGAゲイン設定のオフセットとゲイン誤差に対する、自己およびシステムの両キャリブレーションをサポートします。さらに、双方向デジタルI/Oおよびクロック出力ドライバが、一般目的用に提供されています。ADS1255のパッケージはSSOP-20であり、ADS1256はSSOP-28になります。

SWIFT、PowerPAD、SpActおよびBurr-Brownは、テキサス・インスツルメンツの商標です。

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ(日本TI)が英文から和文へ翻訳して作成したものです。

資料によっては正規英語版資料の更新に対応していないものがあります。

日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。

TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

## 注文情報(1)

| PRODUCT | PACKAGE-LEAD | PACKAGE DESIGNATOR | PACKAGE MARKING | ORDERING NUMBER | TRANSPORT MEDIA, QUANTITY |

|---------|--------------|--------------------|-----------------|-----------------|---------------------------|

| ADS1255 | SSOP-20      | DB                 | ADS1255IDB      | ADS1255IDBT     | Tape and Reel, 250        |

|         |              |                    |                 | ADS1255IDBR     | Tape and Reel, 1000       |

| ADS1256 | SSOP-28      | DB                 | ADS1256IDB      | ADS1256IDBT     | Tape and Reel, 250        |

|         |              |                    |                 | ADS1256IDBR     | Tape and Reel, 1000       |

(1) 最新の仕様およびパッケージに関する情報は、弊社ウェブサイトのwww.ti.comを参照願います。

## 絶対最大定格

over operating free-air temperature range unless otherwise noted<sup>(1)</sup>

|                                   | ADS1255, ADS1256                                           | UNIT               |   |

|-----------------------------------|------------------------------------------------------------|--------------------|---|

| AVDD to AGND                      | −0.3 to +6                                                 | V                  |   |

| DVDD to DGND                      | −0.3 to +3.6                                               | V                  |   |

| AGND to DGND                      | −0.3 to +0.3                                               | V                  |   |

| Input Current                     | 100, Momentary                                             | mA                 |   |

|                                   | 10, Continuous                                             | mA                 |   |

| Analog inputs to AGND             | −0.3 to AVDD + 0.3                                         | V                  |   |

| Digital inputs                    | DIN, SCLK, CS, RESET,<br>SYNC/PDWN,<br>XTAL1/CLKIN to DGND | −0.3 to +6         | V |

|                                   | D0/CLKOUT, D1, D2, D3<br>to DGND                           | −0.3 to DVDD + 0.3 | V |

| Maximum Junction Temperature      | +150                                                       | °C                 |   |

| Operating Temperature Range       | −40 to +105                                                | °C                 |   |

| Storage Temperature Range         | −60 to +150                                                | °C                 |   |

| Lead Temperature (soldering, 10s) | +300                                                       | °C                 |   |

(1) 上記の絶対最大定格以上のストレスを加えると、デバイスが永久破壊することがあります。また、デバイスを絶対最大定格の状態に長時間さらすと、その信頼性が低下することがあります。これらはストレスのみに関する定格であり、推奨動作条件を超える状態でのデバイスの機能動作を含むものではありません。

## 静電気放電対策

静電気放電はわずかな性能の低下から完全なデバイスの故障に至るまで、様々な損傷を与えます。すべての集積回路は、適切なESD保護方法を用いて、取扱いと保存を行うようにして下さい。高精度の集積回路は、損傷に対して敏感であり、極めてわずかなパラメータの変化により、デバイスに規定された仕様に適合しなくなる場合があります。

# 電氣的特性

All specifications at  $-40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ , AVDD = +5V, DVDD = +1.8V,  $f_{\text{CLKIN}} = 7.68\text{MHz}$ , PGA = 1, and  $V_{\text{REF}} = +2.5\text{V}$ , unless otherwise noted.

| PARAMETER                                                               | TEST CONDITIONS                                                            | MIN         | TYP                              | MAX          | UNIT                          |

|-------------------------------------------------------------------------|----------------------------------------------------------------------------|-------------|----------------------------------|--------------|-------------------------------|

| <b>Analog Inputs</b>                                                    |                                                                            |             |                                  |              |                               |

| Full-scale input voltage ( $\text{AIN}_P - \text{AIN}_N$ )              |                                                                            |             | $\pm 2V_{\text{REF}}/\text{PGA}$ |              | V                             |

| Absolute input voltage ( $\text{AIN}0\text{-}7, \text{AINCOM}$ to AGND) | Buffer off                                                                 | AGND - 0.1  | AVDD + 0.1                       |              | V                             |

|                                                                         | Buffer on                                                                  | AGND        | AVDD - 2.0                       |              | V                             |

| Programmable gain amplifier                                             |                                                                            | 1           | 64                               |              |                               |

|                                                                         | Buffer off, PGA = 1, 2, 4, 8, 16                                           | 150/PGA     |                                  |              | $\text{k}\Omega$              |

| Differential input impedance                                            | Buffer off, PGA = 32, 64                                                   |             | 4.7                              |              | $\text{k}\Omega$              |

|                                                                         | Buffer on, $f_{\text{DATA}} \leq 50\text{Hz}^{(1)}$                        |             | 80                               |              | $\text{M}\Omega$              |

| Sensor detect current sources                                           | SDCS[1:0] = 01                                                             |             | 0.5                              |              | $\mu\text{A}$                 |

|                                                                         | SDCS[1:0] = 10                                                             |             | 2                                |              | $\mu\text{A}$                 |

|                                                                         | SDCS[1:0] = 11                                                             |             | 10                               |              | $\mu\text{A}$                 |

| <b>System Performance</b>                                               |                                                                            |             |                                  |              |                               |

| Resolution                                                              |                                                                            | 24          |                                  |              | Bit                           |

| No missing codes                                                        | All data rates and PGA settings                                            | 24          |                                  |              | Bit                           |

| Data rate ( $f_{\text{DATA}}$ )                                         | $f_{\text{CLKIN}} = 7.68\text{MHz}$                                        | 2.5         | 30,000                           |              | SPS <sup>(2)</sup>            |

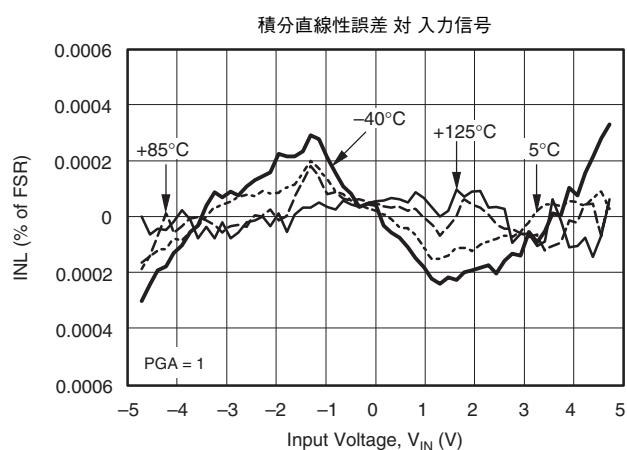

| Integral nonlinearity                                                   | Differential input, PGA = 1                                                |             | $\pm 0.0003$                     | $\pm 0.0010$ | %FSR <sup>(3)</sup>           |

|                                                                         | Differential input, PGA = 64                                               |             | $\pm 0.0007$                     |              | %FSR                          |

| Offset error                                                            | After calibration                                                          |             | On the level of the noise        |              |                               |

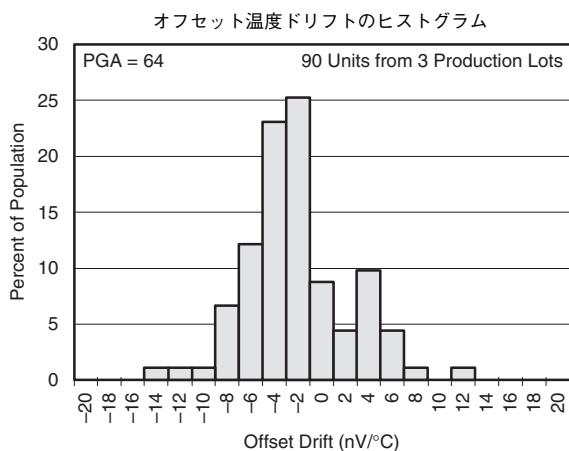

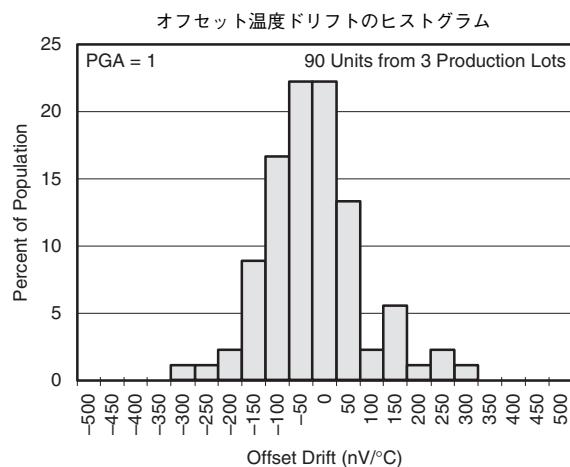

| Offset drift                                                            | PGA = 1                                                                    |             | ±100                             |              | $\text{nV}/^{\circ}\text{C}$  |

|                                                                         | PGA = 64                                                                   |             | ±4                               |              | $\text{nV}/^{\circ}\text{C}$  |

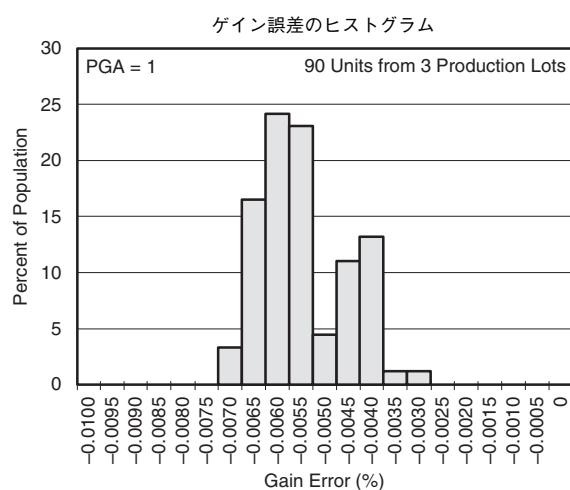

| Gain error                                                              | After calibration, PGA = 1, Buffer on                                      |             | ±0.005                           |              | %                             |

|                                                                         | After calibration, PGA = 64, Buffer on                                     |             | ±0.03                            |              | %                             |

| Gain drift                                                              | PGA = 1                                                                    |             | ±0.8                             |              | $\text{ppm}/^{\circ}\text{C}$ |

|                                                                         | PGA = 64                                                                   |             | ±0.8                             |              | $\text{ppm}/^{\circ}\text{C}$ |

| Common-mode rejection                                                   | $f_{\text{CM}}^{(4)} = 60\text{Hz}, f_{\text{DATA}} = 30\text{kSPS}^{(5)}$ | 95          | 110                              |              | dB                            |

| Noise                                                                   |                                                                            |             | See Noise Performance Tables     |              |                               |

| AVDD power-supply rejection                                             | $\pm 5\% \Delta$ in AVDD                                                   | 60          | 70                               |              | dB                            |

| DVDD power-supply rejection                                             | $\pm 10\% \Delta$ in DVDD                                                  |             | 100                              |              | dB                            |

| <b>Voltage Reference Inputs</b>                                         |                                                                            |             |                                  |              |                               |

| Reference input voltage ( $V_{\text{REF}}$ )                            | $V_{\text{REF}} = \text{VREFP} - \text{VREFN}$                             | 0.5         | 2.5                              | 2.6          | V                             |

| Negative reference input (VREFN)                                        | Buffer off                                                                 | AGND - 0.1  | VREFP - 0.5                      |              | V                             |

|                                                                         | Buffer on <sup>(6)</sup>                                                   | AGND        | VREFP - 0.5                      |              | V                             |

| Positive reference input (VREFP)                                        | Buffer off                                                                 | VREFN + 0.5 | AVDD + 0.1                       |              | V                             |

|                                                                         | Buffer on <sup>(6)</sup>                                                   | VREFN + 0.5 | AVDD - 2.0                       |              | V                             |

| Voltage reference impedance                                             | $f_{\text{CLKIN}} = 7.68\text{MHz}$                                        |             | 18.5                             |              | $\text{k}\Omega$              |

| <b>Digital Input/Output</b>                                             |                                                                            |             |                                  |              |                               |

| $V_{\text{IH}}$                                                         | DIN, SCLK, XTAL1/CLKIN, SYNC/PDWN, CS, RESET                               | 0.8 DVDD    | 5.25                             |              | V                             |

|                                                                         | D0/CLKOUT, D1, D2, D3                                                      | 0.8 DVDD    | DVDD                             |              | V                             |

| $V_{\text{IL}}$                                                         |                                                                            | DGND        | 0.2 DVDD                         |              | V                             |

| $V_{\text{OH}}$                                                         | $I_{\text{OH}} = 5\text{mA}$                                               | 0.8 DVDD    |                                  |              | V                             |

| $V_{\text{OL}}$                                                         | $I_{\text{OL}} = 5\text{mA}$                                               |             | 0.2 DVDD                         |              | V                             |

| Input hysteresis                                                        |                                                                            |             | 0.5                              |              | V                             |

| Input leakage                                                           | $0 < V_{\text{DIGITAL INPUT}} < DVDD$                                      |             |                                  | ±10          | $\mu\text{A}$                 |

| Master clock rate                                                       | External crystal between XTAL1 and XTAL2                                   | 2           | 7.68                             | 10           | MHz                           |

|                                                                         | External oscillator driving CLKIN                                          | 0.1         | 7.68                             | 10           | MHz                           |

## 電気的特性(続き)

All specifications at  $-40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ , AVDD = +5V, DVDD = +1.8V,  $f_{\text{CLKIN}} = 7.68\text{MHz}$ , PGA = 1, and  $V_{\text{REF}} = +2.5\text{V}$ , unless otherwise noted.

| PARAMETER                | TEST CONDITIONS                               | MIN  | TYP | MAX  | UNIT               |

|--------------------------|-----------------------------------------------|------|-----|------|--------------------|

| <b>Power-Supply</b>      |                                               |      |     |      |                    |

| AVDD                     |                                               | 4.75 |     | 5.25 | V                  |

| DVDD                     |                                               | 1.8  |     | 3.6  | V                  |

| AVDD current             | Power-down mode                               |      | 2   |      | $\mu\text{A}$      |

|                          | Standby mode                                  |      | 20  |      | $\mu\text{A}$      |

|                          | Normal mode, PGA = 1, Buffer off              |      | 7   | 10   | mA                 |

|                          | Normal mode, PGA = 64, Buffer off             |      | 16  | 22   | mA                 |

|                          | Normal mode, PGA = 1, Buffer on               |      | 13  | 19   | mA                 |

|                          | Normal mode, PGA = 64, Buffer on              |      | 36  | 50   | mA                 |

| DVDD current             | Power-down mode                               |      | 2   |      | $\mu\text{A}$      |

|                          | Standby mode, CLKOUT off, DVDD = 3.3V         |      | 95  |      | $\mu\text{A}$      |

|                          | Normal mode, CLKOUT off, DVDD = 3.3V          |      | 0.9 | 2    | mA                 |

| Power dissipation        | Normal mode, PGA = 1, Buffer off, DVDD = 3.3V |      | 38  | 57   | mW                 |

|                          | Standby mode, DVDD = 3.3V                     |      | 0.4 |      | mW                 |

| <b>Temperature Range</b> |                                               |      |     |      |                    |

| Specified                |                                               | -40  |     | +85  | $^{\circ}\text{C}$ |

| Operating                |                                               | -40  |     | +105 | $^{\circ}\text{C}$ |

| Storage                  |                                               | -60  |     | +150 | $^{\circ}\text{C}$ |

(1) 入力インピーダンスに関する詳細な情報は、本文を参照願います。

(2) SPS = サンプル/秒

(3) FSR = フルスケール・レンジ =  $4V_{\text{REF}}/\text{PGA}$

(4)  $f_{\text{CM}}$ は同相入力信号の周波数。

(5) デジタル・フィルタのノッチ周波数を60Hz( $f_{\text{DATA}} = 60\text{SPS}, 30\text{SPS}, 15\text{SPS}, 10\text{SPS}, 5\text{SPS}$ , あるいは2.5SPS)にすると、この周波数での同相除去比はさらに改善されます。

(6) バッファ・オン時の基準電圧入力範囲は、自己キャリブレーションあるいはゲイン自己キャリブレーションを実施した場合に限ります。

## ピン配置

## ピン機能

| NAME        | TERMINAL NO.       | ANALOG/DIGITAL INPUT/OUTPUT                  | DESCRIPTION                                          |

|-------------|--------------------|----------------------------------------------|------------------------------------------------------|

|             | ADS1255    ADS1256 |                                              |                                                      |

| AVDD        | 1    1             | Analog                                       | Analog power supply                                  |

| AGND        | 2    2             | Analog                                       | Analog ground                                        |

| VREFN       | 3    3             | Analog input                                 | Negative reference input                             |

| VREFP       | 4    4             | Analog input                                 | Positive reference input                             |

| AINCOM      | 5    5             | Analog input                                 | Analog input common                                  |

| AIN0        | 6    6             | Analog input                                 | Analog input 0                                       |

| AIN1        | 7    7             | Analog input                                 | Analog input 1                                       |

| AIN2        | —    8             | Analog input                                 | Analog input 2                                       |

| AIN3        | —    9             | Analog input                                 | Analog input 3                                       |

| AIN4        | —    10            | Analog input                                 | Analog input 4                                       |

| AIN5        | —    11            | Analog input                                 | Analog input 5                                       |

| AIN6        | —    12            | Analog input                                 | Analog input 6                                       |

| AIN7        | —    13            | Analog input                                 | Analog input 7                                       |

| SYNC/PDWN   | 8    14            | Digital input <sup>(1)(2)</sup> : active low | Synchronization / power down input                   |

| RESET       | 9    15            | Digital input <sup>(1)(2)</sup> : active low | Reset input                                          |

| DVDD        | 10    16           | Digital                                      | Digital power supply                                 |

| DGND        | 11    17           | Digital                                      | Digital ground                                       |

| XTAL2       | 12    18           | Digital <sup>(3)</sup>                       | Crystal oscillator connection                        |

| XTAL1/CLKIN | 13    19           | Digital/Digital input <sup>(2)</sup>         | Crystal oscillator connection / external clock input |

| CS          | 14    20           | Digital input <sup>(1)(2)</sup> : active low | Chip select                                          |

| DRDY        | 15    21           | Digital output: active low                   | Data ready output                                    |

| DOUT        | 16    22           | Digital output                               | Serial data output                                   |

| DIN         | 17    23           | Digital input <sup>(1)(2)</sup>              | Serial data input                                    |

| SCLK        | 18    24           | Digital input <sup>(1)(2)</sup>              | Serial clock input                                   |

| D0/CLKOUT   | 19    25           | Digital IO <sup>(4)</sup>                    | Digital I/O 0 / clock output                         |

| D1          | 20    26           | Digital IO <sup>(4)</sup>                    | Digital I/O 1                                        |

| D2          | —    27            | Digital IO <sup>(4)</sup>                    | Digital I/O 2                                        |

| D3          | —    28            | Digital IO <sup>(4)</sup>                    | Digital I/O 3                                        |

### (1) シュミット・トリガーのデジタル入力。

(2) 5Vを印加可能なデジタル入力。

(3) 外部クロック入力をXTAL1/CLKINに印加するときは、このピンをオープンにする。

(4) デジタルI/Oを入力に設定する場合、このピンはショミット・トリガーのデジタル入力。

# パラメータ測定資料

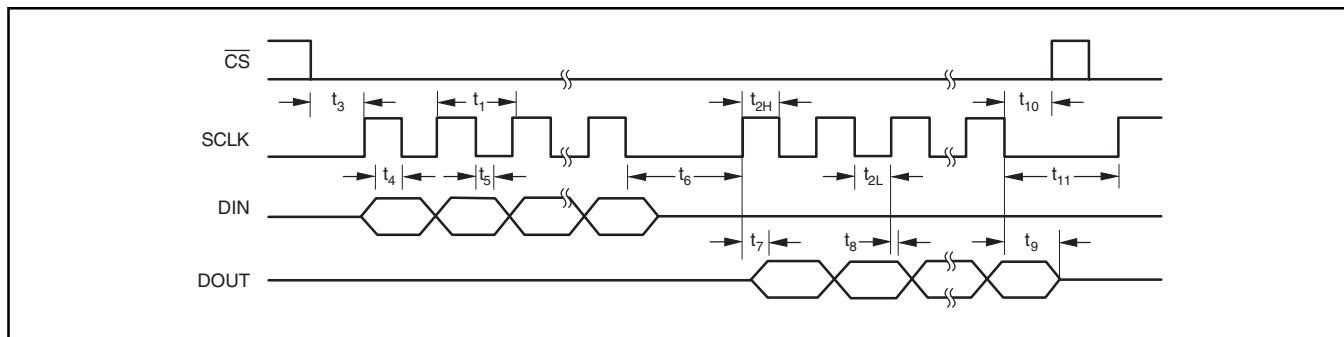

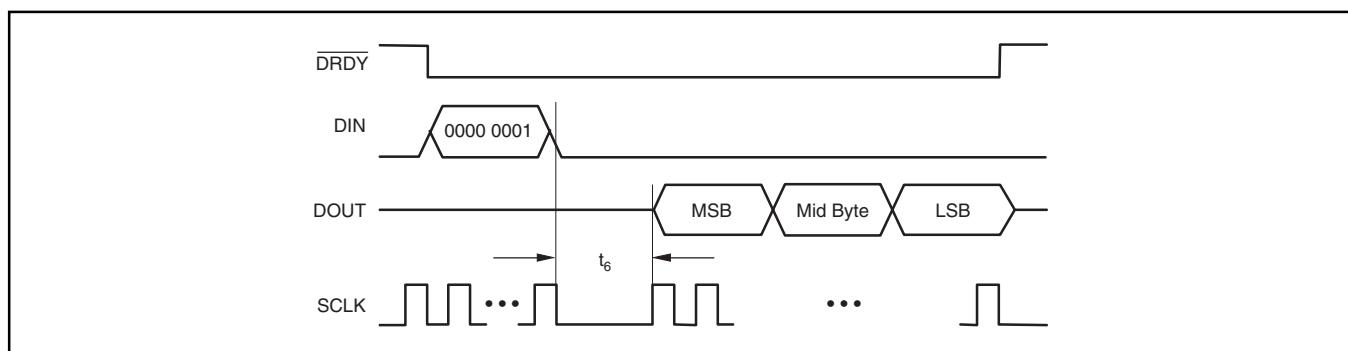

図1. シリアル・インターフェイスのタイミング

## タイミング特性(図1)

| SYMBOL   | DESCRIPTION                                                                                                                | MIN                                                             | MAX                                  | UNIT                 |

|----------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--------------------------------------|----------------------|

| $t_1$    | SCLK period                                                                                                                | 4                                                               | 10                                   | $\tau_{CLKIN}^{(1)}$ |

|          |                                                                                                                            |                                                                 |                                      | $\tau_{DATA}^{(2)}$  |

| $t_{2H}$ | SCLK pulse width: high                                                                                                     | 200                                                             | 9                                    | ns                   |

|          |                                                                                                                            |                                                                 |                                      | $\tau_{DATA}$        |

| $t_{2L}$ | SCLK pulse width: low                                                                                                      | 200                                                             |                                      | ns                   |

| $t_3$    | $\overline{CS}$ low to first SCLK: setup time <sup>(3)</sup>                                                               | 0                                                               |                                      | ns                   |

| $t_4$    | Valid DIN to SCLK falling edge: setup time                                                                                 | 50                                                              |                                      | ns                   |

| $t_5$    | Valid DIN to SCLK falling edge: hold time                                                                                  | 50                                                              |                                      | ns                   |

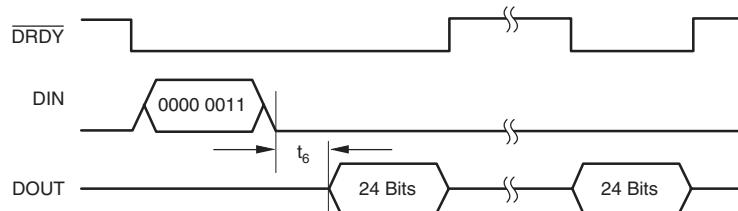

| $t_6$    | Delay from last SCLK edge for DIN to first SCLK rising edge for DOUT: RDATA, RDATAC, RREG Commands                         | 50                                                              |                                      | $\tau_{CLKIN}$       |

| $t_7$    | SCLK rising edge to valid new DOUT: propagation delay <sup>(4)</sup>                                                       | 50                                                              |                                      | ns                   |

| $t_8$    | SCLK rising edge to DOUT invalid: hold time                                                                                | 0                                                               |                                      | ns                   |

| $t_9$    | Last SCLK falling edge to DOUT high impedance<br>NOTE: DOUT goes high impedance immediately when $\overline{CS}$ goes high | 6                                                               | 10                                   | $\tau_{CLKIN}$       |

| $t_{10}$ | $\overline{CS}$ low after final SCLK falling edge                                                                          | 0                                                               |                                      | ns                   |

| $t_{11}$ | Final SCLK falling edge of command to first SCLK rising edge of next command.                                              | RREG, WREG, RDATA                                               | 4                                    | $\tau_{CLKIN}$       |

|          |                                                                                                                            | RDATAC, RESET, SYNC                                             | 24                                   | $\tau_{CLKIN}$       |

|          |                                                                                                                            | RDATAC, STANDBY, SELFOCAL, SY-SOCAL, SELFGCAL, SYSGCAL, SELFCAL | Wait for $\overline{DRDY}$ to go low |                      |

(1)  $\tau_{CLKIN}$  = マスター・クロック周期 =  $1/f_{CLKIN}$

(2)  $\tau_{DATA}$  = 出力データ周期 =  $1/f_{DATA}$

(3)  $\overline{CS}$ はローレベルに固定可。

(5) DOUT負荷 =  $20pF \parallel 100k\Omega$ 対DGND。

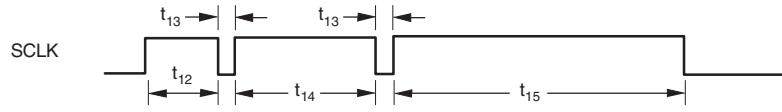

図2. SCLKリセット・タイミング

### タイミング特性(図2)

| SYMBOL   | DESCRIPTION                           | MIN  | MAX  | UNIT                 |

|----------|---------------------------------------|------|------|----------------------|

| $t_{12}$ | SCLK reset pattern, first high pulse  | 300  | 500  | $\tau_{CLKIN}^{(1)}$ |

| $t_{13}$ | SCLK reset pattern, low pulse         | 5    |      | $\tau_{CLKIN}$       |

| $t_{14}$ | SCLK reset pattern, second high pulse | 550  | 750  | $\tau_{CLKIN}$       |

| $t_{15}$ | SCLK reset pattern, third high pulse  | 1050 | 1250 | $\tau_{CLKIN}$       |

(1)  $\tau_{CLKIN}$  = マスター・クロック周期 =  $1/f_{CLKIN}$

図3.  $\overline{RESET}$ および $\overline{SYNC/PDWN}$ タイミング

### タイミング特性(図3)

| SYMBOL   | DESCRIPTION                                               | MIN | MAX | UNIT                 |

|----------|-----------------------------------------------------------|-----|-----|----------------------|

| $t_{16}$ | $\overline{RESET}$ , $\overline{SYNC/PDWN}$ , pulse width | 4   |     | $\tau_{CLKIN}^{(1)}$ |

(1)  $\tau_{CLKIN}$  = マスター・クロック周期 =  $1/f_{CLKIN}$

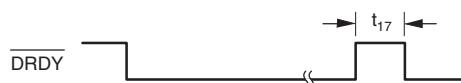

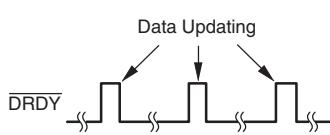

図4.  $\overline{DRDY}$ 更新タイミング

### タイミング特性(図4)

| SYMBOL   | DESCRIPTION                                                                                   | MIN | MAX | UNIT                 |

|----------|-----------------------------------------------------------------------------------------------|-----|-----|----------------------|

| $t_{17}$ | Conversion data invalid while being updated ( $\overline{DRDY}$ shown with no data retrieval) | 16  |     | $\tau_{CLKIN}^{(1)}$ |

(1)  $\tau_{CLKIN}$  = マスター・クロック周期 =  $1/f_{CLKIN}$

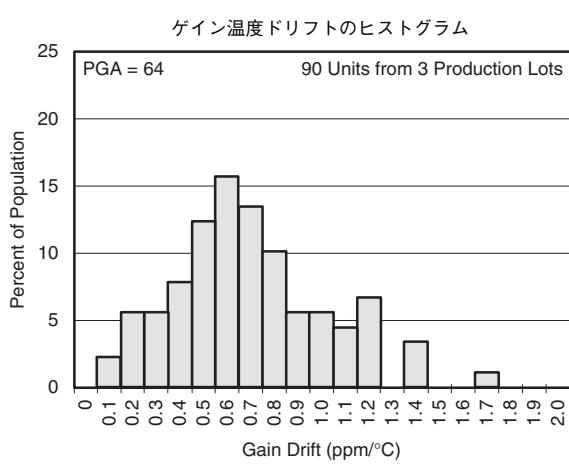

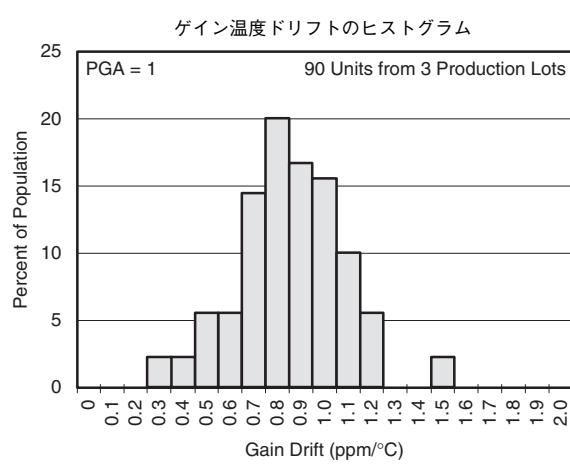

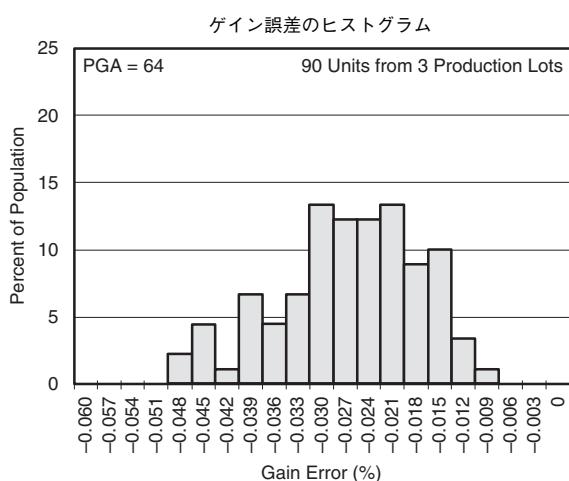

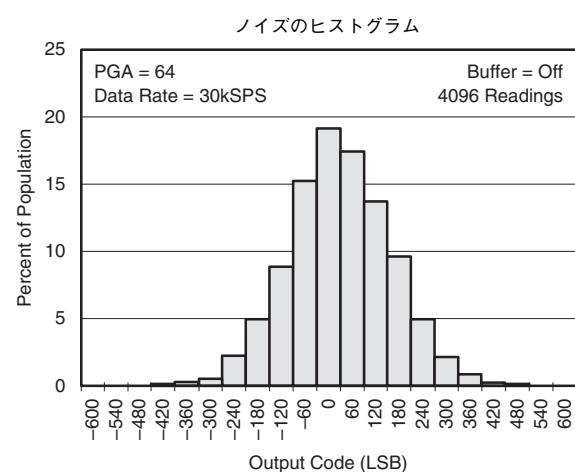

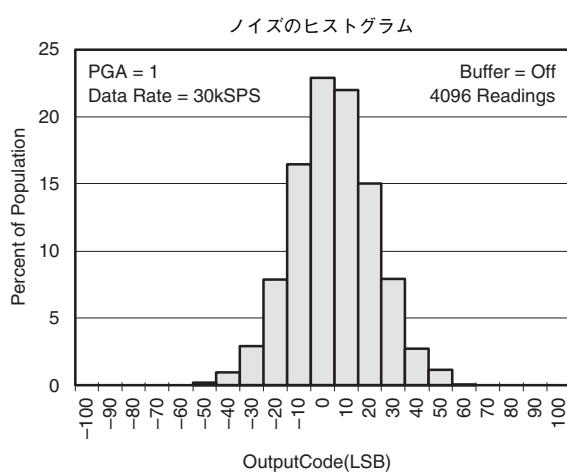

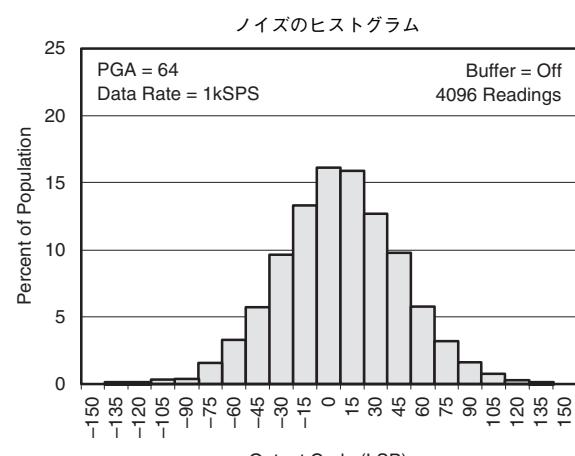

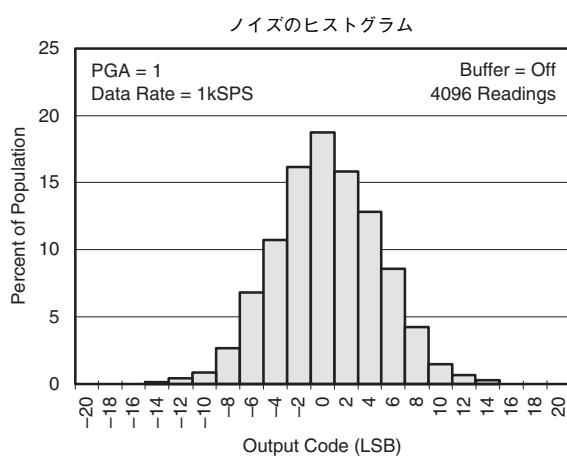

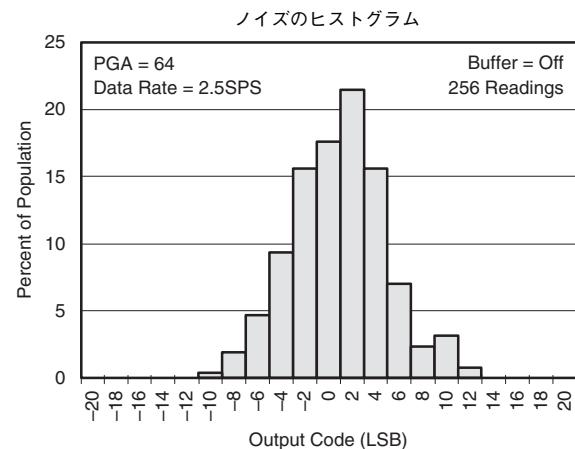

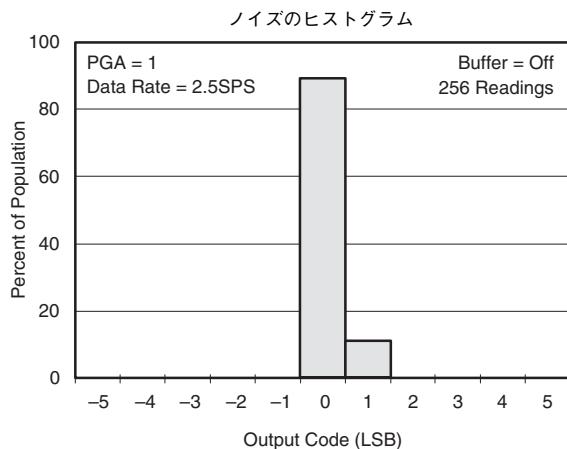

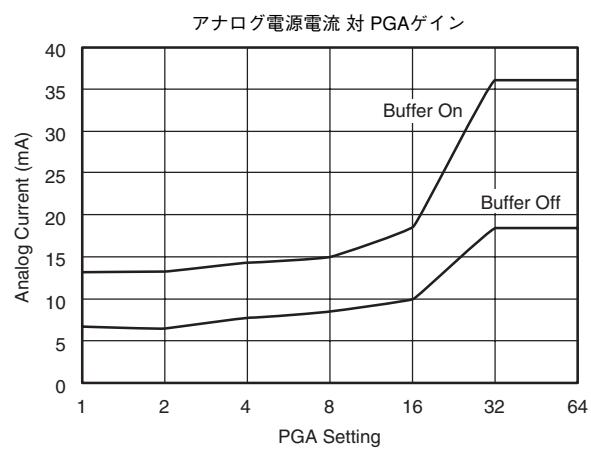

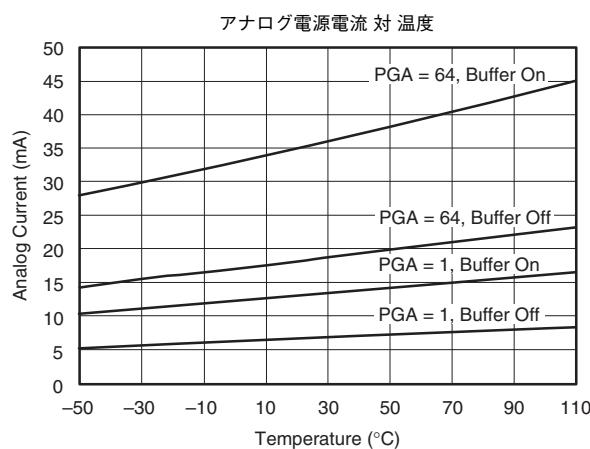

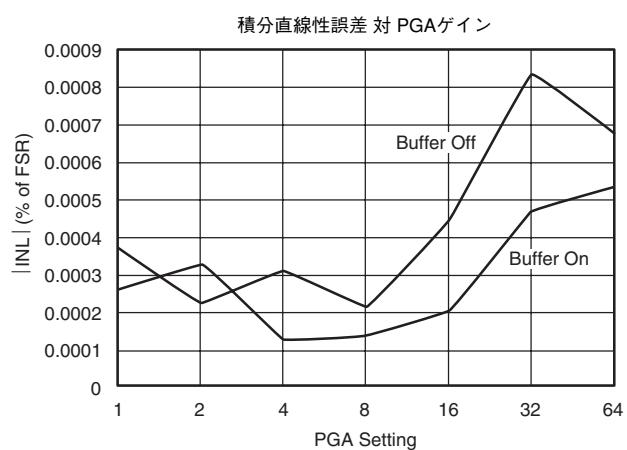

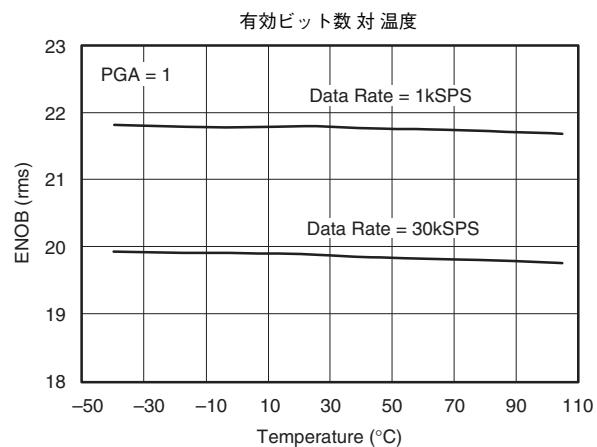

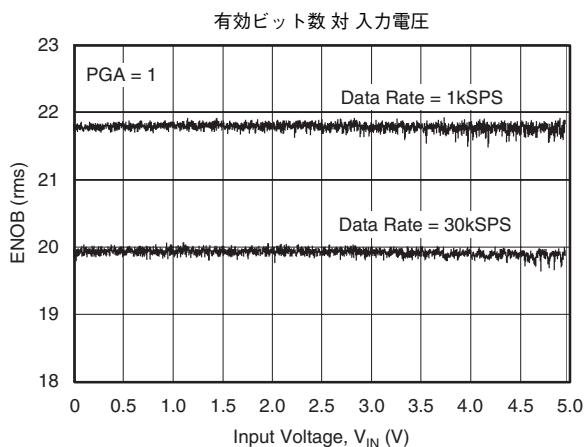

# 代表的特性

$T_A = +25^\circ\text{C}$ , AVDD = 5V, DVDD = 1.8V,  $f_{\text{CLKIN}} = 7.68\text{MHz}$ , PGA = 1, and  $V_{\text{REF}} = 2.5\text{V}$ , unless otherwise noted.

## 代表的特性(続き)

$T_A = +25^\circ\text{C}$ , AVDD = 5V, DVDD = 1.8V,  $f_{\text{CLKIN}} = 7.68\text{MHz}$ , PGA = 1, and  $V_{\text{REF}} = 2.5\text{V}$ , unless otherwise noted.

## 代表的特性(続き)

$T_A = +25^\circ\text{C}$ ,  $\text{AVDD} = 5\text{V}$ ,  $\text{DVDD} = 1.8\text{V}$ ,  $f_{\text{CLKIN}} = 7.68\text{MHz}$ ,  $\text{PGA} = 1$ , and  $\text{V}_{\text{REF}} = 2.5\text{V}$ , unless otherwise noted.

## 概要

ADS1255およびADS1256は、非常に低ノイズなA/Dコンバータです。ADS1255は、1差動入力あるいは2シングルエンド入力をサポートし、2つの一般目的用デジタルI/Oがあります。ADS1256は、4差動入力あるいは8シングルエンド入力をサポートし、4つの一般目的用デジタルI/Oがあります。その他の点では両デバイスは同じであるため、ADS1255/6としてまとめて本データシートで述べております。

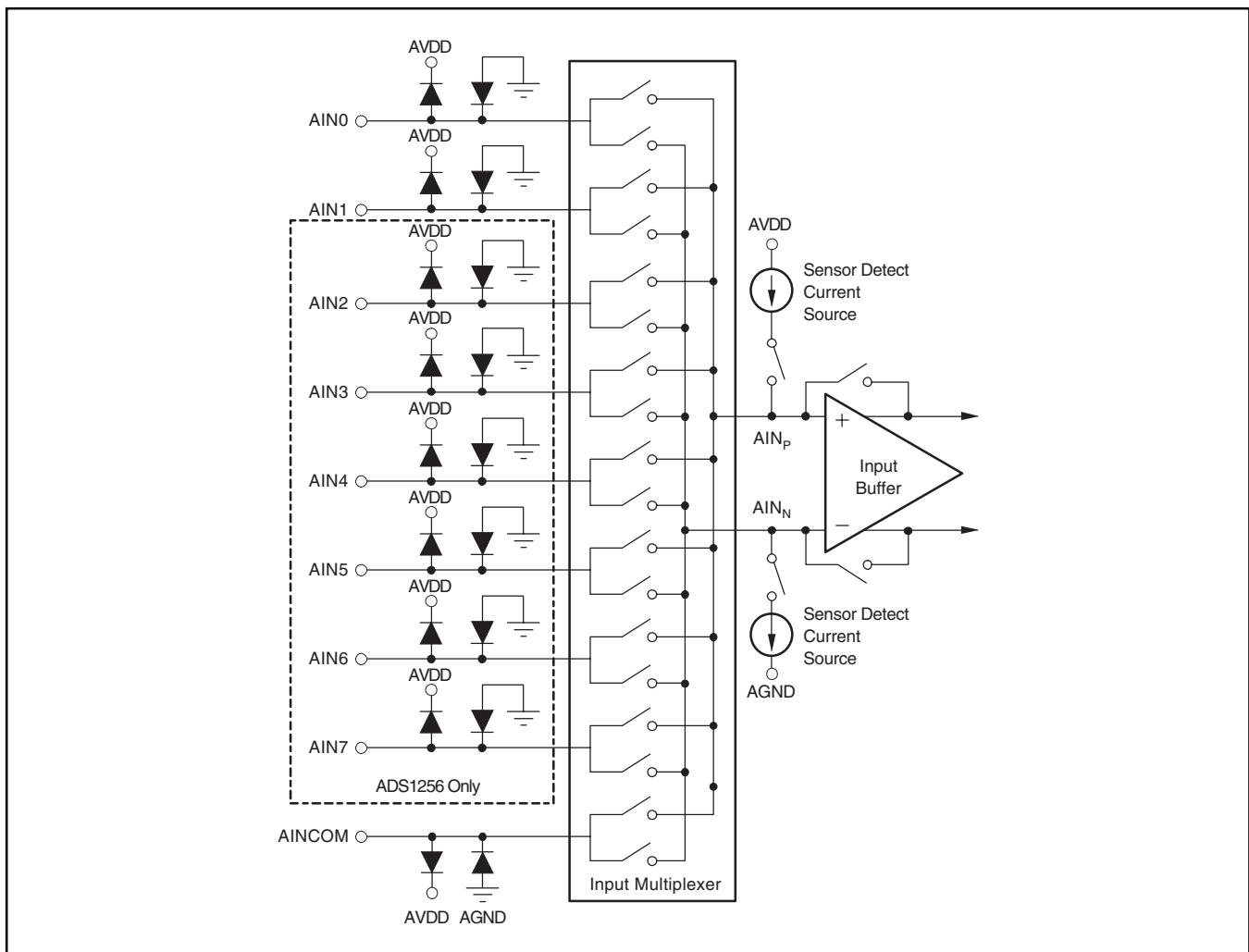

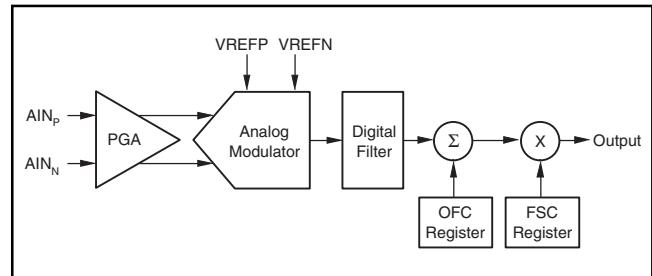

図5にADS1256のブロック図を示します。入力マルチプレクサにより、どの入力ピンをA/Dコンバータに接続するか選択します。また、入力マルチプレクサ内の選択可能な電流源により、外部センサーの開放あるいは短絡状態がチェックできます。オンチップの入力バッファは選択可能であり、最大80MΩの入力インピーダンスにより、入力に接続する外部回路の負荷を大幅に低減します。低ノイズのPGAは、1, 2, 4, 8, 16, 32、あるいは64のゲインを提供します。ADS1255/6のA/Dコンバータは、4次のデルタシグマ( $\Delta\Sigma$ )変調器と、それに続くプログラマブル・デジタル・フィルタで構成されています。

この変調器は、増幅された差動入力信号 $V_{IN} = (AIN_P - AIN_N)$ を差動基準電圧 $V_{REF} = (VREFP - VREFN)$ に対して測定します。差動基準電圧は内部的に2倍に拡大され、フルスケールの入力範囲は $\pm 2V_{REF}$ になります(PGA = 1のとき)。

デジタル・フィルタは変調器の出力信号を受け、低ノイズのデジタル信号を出力します。フィルタのデータ・レート(データ変換周波数)は2.5SPSから30kSPSで可変であり、分解能と変換速度のトレードオフができます。

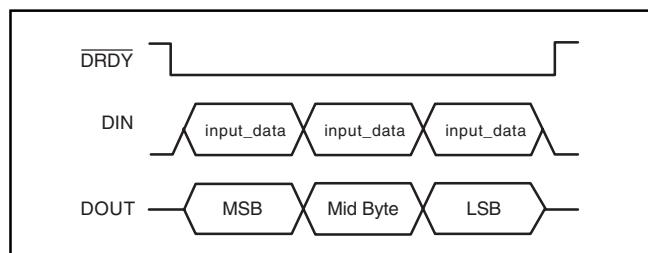

通信はSPI互換のシリアル・インターフェイスによって、ADS1255/6を制御する単純なコマンドのセットで行われます。オンチップのレジスタは、入力マルチプレクサ、センサー検出用電

流源、入力バッファのイネーブル、PGAゲイン、データ・レートなどの各種の設定情報を格納します。クロック源は、外部の水晶発振器あるいはクロック発振器のいずれかを使用できます。一般目的用デジタルI/Oは、最大4ピンまでの静的なリード/ライト制御を行います。そのうちの1ピンは、プログラマブルなクロック出力にも使用できます。

## ノイズ特性

ADS1255/6は、データ・レートとPGAゲイン設定の調整を最適化して得られる、傑出したノイズ特性を提供します。データ・レートを下げてアベレージング回数を増すと、それに相応してノイズは低減します。低レベル信号を測定する場合、PGAにより入力換算ノイズは低くなります。表1から表6に、外部で入力を短絡したときの代表的なノイズ特性を要約します。これら全6表に次の条件を適用しています。すなわち、 $T = +25^\circ\text{C}$ ,  $\text{AVDD} = 5\text{V}$ ,  $\text{DVDD} = 1.8\text{V}$ ,  $\text{V}_{REF} = 2.5\text{V}$ , および $f_{CLKIN} = 7.68\text{MHz}$ です。表1から表3では、デバイスの入力バッファをイネーブルにしています。表1は入力換算電圧ノイズを実効値で表しています。また、表2は分解能有効ビット数(ENOB)を示し、ノイズのデータを表1から使用しています。有効ビット数の定義は次の通りです。

$$\text{ENOB} = \frac{1n(\text{FSR}/\text{RME Noise})}{1n(2)}$$

ここでFSRはフルスケール・レンジです。表3は分解能ノイズ・フリー・ビットを示します。これはENOBと同じ式で計算しますが、ノイズを実効値の代わりにピーク・ツー・ピーク値で表しています。表4から表6は同様のノイズのデータを示しますが、入力バッファがディスエーブルになっています。

図5. ブロック図

| DATA RATE (SPS) | PGA    |       |       |       |       |       |       |

|-----------------|--------|-------|-------|-------|-------|-------|-------|

|                 | 1      | 2     | 4     | 8     | 16    | 32    | 64    |

| 2.5             | 0.247  | 0.156 | 0.080 | 0.056 | 0.043 | 0.037 | 0.033 |

| 5               | 0.301  | 0.175 | 0.102 | 0.076 | 0.061 | 0.045 | 0.044 |

| 10              | 0.339  | 0.214 | 0.138 | 0.106 | 0.082 | 0.061 | 0.061 |

| 15              | 0.401  | 0.264 | 0.169 | 0.126 | 0.107 | 0.085 | 0.073 |

| 25              | 0.494  | 0.305 | 0.224 | 0.149 | 0.134 | 0.102 | 0.093 |

| 30              | 0.533  | 0.335 | 0.245 | 0.176 | 0.138 | 0.104 | 0.106 |

| 50              | 0.629  | 0.393 | 0.292 | 0.216 | 0.168 | 0.136 | 0.122 |

| 60              | 0.692  | 0.438 | 0.321 | 0.233 | 0.184 | 0.146 | 0.131 |

| 100             | 0.875  | 0.589 | 0.409 | 0.305 | 0.229 | 0.170 | 0.169 |

| 500             | 1.946  | 1.250 | 0.630 | 0.648 | 0.497 | 0.390 | 0.367 |

| 1000            | 2.931  | 1.891 | 1.325 | 1.070 | 0.689 | 0.512 | 0.486 |

| 2000            | 4.173  | 2.589 | 1.827 | 1.492 | 0.943 | 0.692 | 0.654 |

| 3750            | 5.394  | 3.460 | 2.376 | 1.865 | 1.224 | 0.912 | 0.906 |

| 7500            | 7.249  | 4.593 | 3.149 | 2.436 | 1.691 | 1.234 | 1.187 |

| 15,000          | 9.074  | 5.921 | 3.961 | 2.984 | 2.125 | 1.517 | 1.515 |

| 30,000          | 10.728 | 6.705 | 4.446 | 3.280 | 2.416 | 1.785 | 1.742 |

表1. 入力換算ノイズ(μV, 実効値) 入力バッファがオン

| DATA RATE (SPS) | PGA  |      |      |      |      |      |      |

|-----------------|------|------|------|------|------|------|------|

|                 | 1    | 2    | 4    | 8    | 16   | 32   | 64   |

| 2.5             | 25.3 | 24.9 | 24.9 | 24.4 | 23.8 | 23.0 | 22.2 |

| 5               | 25.0 | 24.8 | 24.5 | 24.0 | 23.3 | 22.7 | 21.8 |

| 10              | 24.8 | 24.5 | 24.1 | 23.5 | 22.9 | 22.3 | 21.3 |

| 15              | 24.6 | 24.2 | 23.4 | 23.1 | 22.2 | 21.4 | 21.0 |

| 25              | 24.3 | 24.0 | 22.7 | 22.0 | 21.0 | 20.3 | 20.7 |

| 30              | 24.2 | 23.8 | 23.3 | 22.8 | 22.1 | 21.5 | 20.5 |

| 50              | 23.9 | 23.6 | 23.0 | 22.5 | 21.8 | 21.1 | 20.3 |

| 60              | 23.8 | 23.4 | 22.9 | 22.4 | 21.7 | 21.0 | 20.2 |

| 100             | 23.4 | 23.0 | 22.5 | 22.0 | 21.4 | 20.8 | 19.8 |

| 500             | 22.3 | 21.9 | 21.5 | 20.9 | 20.3 | 19.6 | 18.7 |

| 1000            | 21.7 | 21.3 | 20.8 | 20.2 | 19.8 | 19.2 | 18.3 |

| 2000            | 21.2 | 20.9 | 20.4 | 19.7 | 19.3 | 18.8 | 17.9 |

| 3750            | 20.8 | 20.5 | 20.0 | 19.4 | 19.0 | 18.4 | 17.4 |

| 7500            | 20.4 | 20.1 | 19.6 | 19.0 | 18.5 | 17.9 | 17.0 |

| 15,000          | 20.1 | 19.7 | 19.3 | 18.7 | 18.2 | 17.7 | 16.7 |

| 30,000          | 19.8 | 19.5 | 19.1 | 18.5 | 18.0 | 17.4 | 16.5 |

表2. 有効ビット数(ENOB, 実効値) 入力バッファがオン

| DATA RATE (SPS) | PGA  |      |      |      |      |      |      |

|-----------------|------|------|------|------|------|------|------|

|                 | 1    | 2    | 4    | 8    | 16   | 32   | 64   |

| 2.5             | 23.0 | 22.6 | 22.1 | 21.7 | 21.3 | 20.8 | 19.7 |

| 5               | 22.3 | 22.4 | 21.9 | 21.3 | 20.7 | 20.3 | 19.3 |

| 10              | 22.3 | 22.0 | 21.6 | 21.0 | 20.4 | 19.9 | 18.9 |

| 15              | 22.0 | 21.7 | 21.3 | 20.7 | 20.1 | 19.3 | 18.7 |

| 25              | 21.7 | 21.4 | 21.1 | 20.5 | 19.7 | 19.2 | 18.5 |

| 30              | 21.8 | 21.3 | 20.8 | 20.4 | 19.8 | 19.0 | 18.1 |

| 50              | 21.3 | 21.1 | 20.4 | 19.9 | 19.4 | 18.8 | 17.9 |

| 60              | 21.3 | 20.9 | 20.5 | 19.8 | 19.3 | 18.8 | 17.8 |

| 100             | 20.9 | 20.7 | 20.2 | 19.6 | 19.1 | 18.5 | 17.4 |

| 500             | 20.1 | 19.6 | 19.1 | 18.6 | 18.0 | 17.3 | 16.3 |

| 1000            | 19.0 | 18.6 | 18.1 | 17.5 | 17.2 | 16.5 | 15.6 |

| 2000            | 18.5 | 18.1 | 17.8 | 17.0 | 16.6 | 16.1 | 15.3 |

| 3750            | 18.1 | 17.8 | 17.3 | 16.6 | 16.2 | 15.7 | 14.7 |

| 7500            | 17.7 | 17.3 | 16.9 | 16.2 | 15.8 | 15.3 | 14.4 |

| 15,000          | 17.3 | 17.0 | 16.5 | 15.9 | 15.5 | 14.9 | 13.9 |

| 30,000          | 17.1 | 16.7 | 16.4 | 15.9 | 15.4 | 14.6 | 13.8 |

表3. ノイズ・フリー分解能(ビット, 実効値) 入力バッファがオン

| DATA RATE (SPS) | PGA    |       |       |       |       |       |       |

|-----------------|--------|-------|-------|-------|-------|-------|-------|

|                 | 1      | 2     | 4     | 8     | 16    | 32    | 64    |

| 2.5             | 0.247  | 0.149 | 0.097 | 0.058 | 0.036 | 0.031 | 0.027 |

| 5               | 0.275  | 0.176 | 0.109 | 0.070 | 0.046 | 0.039 | 0.038 |

| 10              | 0.338  | 0.201 | 0.129 | 0.084 | 0.063 | 0.048 | 0.047 |

| 15              | 0.401  | 0.221 | 0.150 | 0.109 | 0.070 | 0.063 | 0.057 |

| 25              | 0.485  | 0.279 | 0.177 | 0.136 | 0.093 | 0.076 | 0.076 |

| 30              | 0.559  | 0.315 | 0.202 | 0.142 | 0.107 | 0.093 | 0.082 |

| 50              | 0.644  | 0.390 | 0.238 | 0.187 | 0.129 | 0.108 | 0.103 |

| 60              | 0.688  | 0.417 | 0.281 | 0.204 | 0.134 | 0.109 | 0.111 |

| 100             | 0.815  | 0.530 | 0.360 | 0.233 | 0.169 | 0.123 | 0.122 |

| 500             | 1.957  | 1.148 | 0.772 | 0.531 | 0.375 | 0.276 | 0.259 |

| 1000            | 2.803  | 1.797 | 1.191 | 0.940 | 0.518 | 0.392 | 0.365 |

| 2000            | 4.025  | 2.444 | 1.615 | 1.310 | 0.700 | 0.526 | 0.461 |

| 3750            | 5.413  | 3.250 | 2.061 | 1.578 | 0.914 | 0.693 | 0.625 |

| 7500            | 7.017  | 4.143 | 2.722 | 1.998 | 1.241 | 0.914 | 0.857 |

| 15,000          | 8.862  | 5.432 | 3.378 | 2.411 | 1.569 | 1.149 | 1.051 |

| 30,000          | 10.341 | 6.137 | 3.873 | 2.775 | 1.805 | 1.313 | 1.211 |

表4. 入力換算ノイズ(μV, 実効値) 入力バッファがオフ

| DATA RATE (SPS) | PGA  |      |      |      |      |      |      |

|-----------------|------|------|------|------|------|------|------|

|                 | 1    | 2    | 4    | 8    | 16   | 32   | 64   |

| 2.5             | 25.3 | 25.0 | 24.6 | 24.4 | 24.0 | 23.2 | 22.5 |

| 5               | 25.1 | 24.8 | 24.5 | 24.1 | 23.7 | 22.9 | 22.0 |

| 10              | 24.8 | 24.6 | 24.2 | 23.8 | 23.2 | 22.6 | 21.7 |

| 15              | 24.6 | 24.4 | 24.0 | 23.4 | 23.1 | 22.2 | 21.4 |

| 25              | 24.3 | 24.1 | 23.8 | 23.1 | 22.7 | 22.0 | 21.0 |

| 30              | 24.1 | 23.9 | 23.6 | 23.1 | 22.5 | 21.7 | 20.9 |

| 50              | 23.9 | 23.6 | 23.3 | 22.7 | 22.2 | 21.5 | 20.5 |

| 60              | 23.8 | 23.5 | 23.1 | 22.5 | 22.1 | 21.5 | 20.4 |

| 100             | 23.5 | 23.2 | 22.7 | 22.4 | 21.8 | 21.3 | 20.3 |

| 500             | 22.3 | 22.1 | 21.6 | 21.2 | 20.7 | 20.1 | 19.2 |

| 1000            | 21.8 | 21.4 | 21.0 | 20.3 | 20.2 | 19.6 | 18.7 |

| 2000            | 21.2 | 21.0 | 20.6 | 19.9 | 19.8 | 19.2 | 18.4 |

| 3750            | 20.8 | 20.6 | 20.2 | 19.6 | 19.4 | 18.8 | 17.9 |

| 7500            | 20.4 | 20.2 | 19.8 | 19.3 | 18.9 | 18.4 | 17.5 |

| 15,000          | 20.1 | 19.8 | 19.5 | 19.0 | 18.6 | 18.1 | 17.2 |

| 30,000          | 19.9 | 19.6 | 19.3 | 18.8 | 18.4 | 17.9 | 17.0 |

表5. 有効ビット数(ENOB, 実効値) 入力バッファがオフ

| DATA RATE (SPS) | PGA  |      |      |      |      |      |      |

|-----------------|------|------|------|------|------|------|------|

|                 | 1    | 2    | 4    | 8    | 16   | 32   | 64   |

| 2.5             | 23.0 | 22.4 | 22.0 | 21.9 | 21.3 | 21.1 | 20.0 |

| 5               | 22.4 | 22.1 | 21.9 | 21.5 | 21.2 | 20.4 | 19.4 |

| 10              | 22.3 | 22.1 | 21.7 | 21.5 | 20.8 | 20.3 | 19.2 |

| 15              | 22.0 | 21.8 | 21.4 | 20.8 | 20.6 | 19.9 | 19.0 |

| 25              | 21.8 | 21.7 | 21.1 | 20.7 | 20.3 | 19.5 | 18.6 |

| 30              | 21.6 | 21.4 | 21.1 | 20.4 | 20.0 | 16.4 | 18.5 |

| 50              | 21.3 | 21.3 | 20.7 | 20.1 | 19.8 | 19.1 | 18.2 |

| 60              | 21.2 | 21.0 | 20.6 | 20.1 | 19.8 | 19.1 | 18.1 |

| 100             | 21.1 | 20.5 | 20.3 | 19.9 | 19.5 | 19.0 | 17.9 |

| 500             | 20.0 | 19.7 | 19.3 | 18.9 | 18.3 | 17.8 | 16.9 |

| 1000            | 19.0 | 18.7 | 18.4 | 17.7 | 17.5 | 16.9 | 15.9 |

| 2000            | 18.5 | 18.3 | 17.9 | 17.4 | 17.0 | 16.4 | 15.6 |

| 3750            | 18.1 | 17.8 | 17.5 | 17.0 | 16.7 | 16.1 | 15.2 |

| 7500            | 17.7 | 17.6 | 17.0 | 16.6 | 16.2 | 15.7 | 14.8 |

| 15,000          | 17.4 | 17.1 | 16.8 | 16.3 | 15.9 | 15.3 | 14.4 |

| 30,000          | 17.1 | 17.0 | 16.6 | 16.0 | 15.6 | 15.0 | 14.4 |

表6. ノイズ・フリー分解能(ビット, 実効値) 入力バッファがオフ

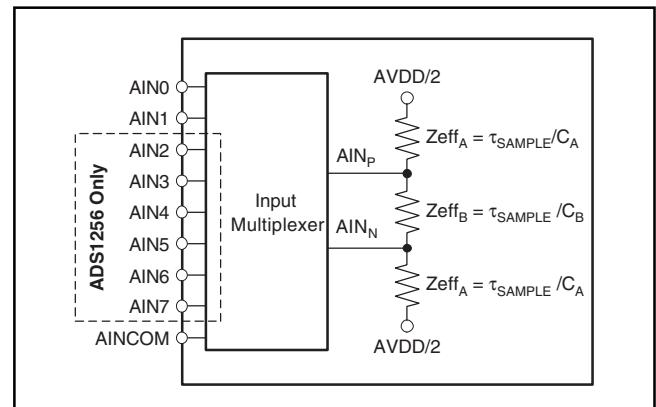

## 入力マルチプレクサ

図6に入力マルチプレクサの単純化した図を示します。このブロックはフレキシブルなので、全アナログ入力ピンはA/Dコンバータの差動入力のどちら側にも接続できます。すなわち、全ピンは正入力( $AIN_P$ )を選択でき、同様に全ピンは負入力( $AIN_N$ )も選択できます。入力ピンの選択はマルチプレクサ・レジスタが制御します。

ADS1256は9つのアナログ入力を提供します。この9入力は、4つの独立した差動入力、8つのシングルエンド入力、あるいは差動およびシングルエンドの組合せに設定できます。

ADS1255は3つのアナログ入力を提供します。この3入力は、1つの差動入力、あるいは2つのシングルエンド入力に設定できます。ADS1255の入力をプログラムする場合、入力マルチプレクサ・レジスタのプログラミングは使える入力だけを選ぶ必要があります。

一般に、入力ピンの選択に制約はありません。

しかし、最適なアナログ特性を得るには、下記の項目を推奨します。

1.  $AIN_0$ から $AIN_7$ で差動測定するには、近傍の入力を使用するのが望ましいです。例えば、 $AIN_0$ と $AIN_1$ を使用します。 $AIN_{COM}$ は使用しません。

2. シングルエンド測定では $AIN_{COM}$ をコモン入力として使い、 $AIN_0$ から $AIN_7$ はシングルエンド入力に使用します。

3. 使用しないアナログ入力はフローティングにしておきます。このようにするとリーコンデンサが最小になります。

ESDダイオードはアナログ入力を保護します。これらのダイオードがオンしないように、入力ピンにかかる電圧をAGNDより100mV以上低くせず、また同様に、AVDDより100mV以上高くしないようにしなければなりません。すなわち、 $-100mV < (AIN_0 - 7 \text{ および } AIN_{COM}) < AVDD + 100mV$ とします。

ADS1255/6をシングルエンド測定に使用する場合、コモン入力 $AIN_{COM}$ を必ずしもグランドに接続する必要がないことに注意してください。例えば、 $AIN_{COM}$ は+2.5Vのような基準電圧の中点や、AVDDにさえも接続できます。

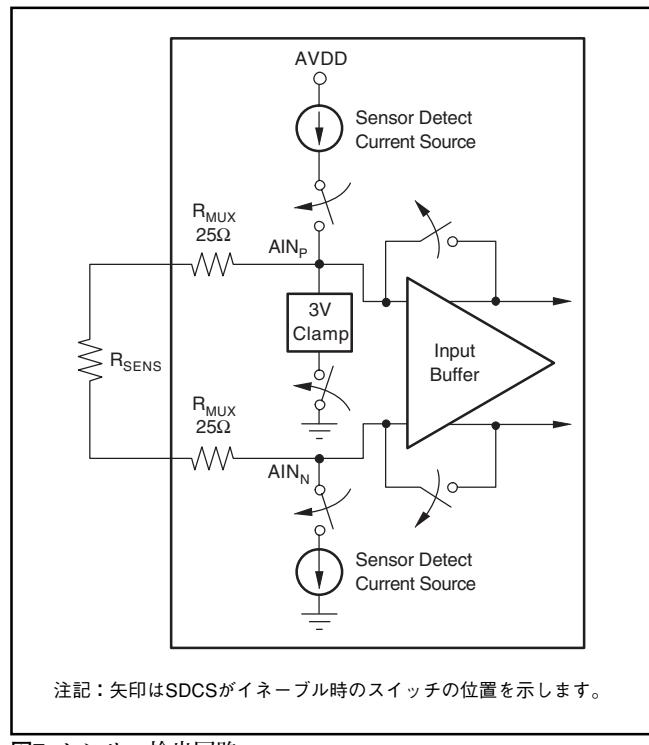

## 開放/短絡センサー検出

センサー検出用電流源(SDCS)は、ADS1255/6に接続された外部センサーの接続チェックに使用できます。SDCSをイネーブルにすると、およそ $0.5\mu A$ ,  $2\mu A$ , あるいは $10\mu A$ の電流( $I_{SDC}$ )を入力マルチプレクサ経由でセンサーに供給します。ADCONレジスタのSDCSビットがSDCSをイネーブルにし、 $I_{SDC}$ の値を設定します。

SDCSをイネーブルにすると、ADS1255/6はBUFENビットの

図6. 入力マルチプレクサの単純化した図

設定にかかわらず、自動的にアナログ入力バッファをオンします。このようにして、入力回路がSDCSの負荷になるのを防止します。AIN<sub>P</sub>は3Vより低くして、バッファの絶対入力範囲以下でなければなりません。この条件を満たすように、AIN<sub>P</sub>が3Vを超えると、3Vクランプ回路がAIN<sub>P</sub>からAGNDへ電流を引き始めます。このクランプは、SDCSがイネーブルの場合にのみ働くことにご注意願います。

図7はADS1255/6の入力回路構造を単純化した図であり、外部センサーを2入力ピン間の抵抗モデル( $R_{SENS}$ )で表しています。SDCSがイネーブルになると、一方のSDCSはAIN<sub>P</sub>に接続された入力ピンに $I_{SDC}$ を供給し、他方のSDCSはAIN<sub>N</sub>に接続された入力ピンから $I_{SDC}$ を引きります。2個の25Ωの直列抵抗 $R_{MUX}$ は、ADS1255/6の内部抵抗のモデルです。SDCSがイネーブル時に測定される信号は電圧降下IRの総和に等しく、 $I_{SDC} \times (2R_{MUX} + R_{SENS})$ になります。センサーが短絡(すなわち $R_{SENS} = 0$ )の場合でも、SDCSがイネーブルならば、小信号( $I_{SDC} \times 2R_{MUX}$ )がADS1255/6によって測定されます。

図7. センサー検出回路

### アナログ入力バッファ

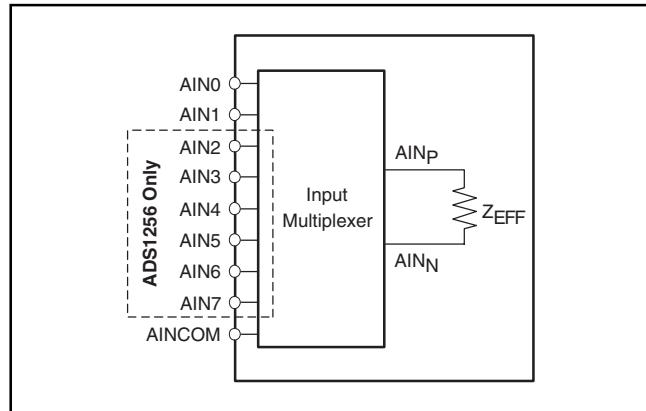

ADS1255/6は、低ドリフトのチョッパ安定型バッファをSTATUSレジスタのBUFENビットでイネーブルにして、入力インピーダンスを飛躍的に増加できます。バッファがイネーブル時の入力インピーダンスは、図8に示すような抵抗モデルでできます。表7に $Z_{EFF}$ の値を異なるデータ・レートについて列記します。入力インピーダンスはCLKIN周波数と反比例します。例えば、 $F_{CLKIN}$ が3.84MHzに半減すると、データ・レートが50SPSの $Z_{EFF}$ は80MΩから160MΩへ2倍になります。

図8. 実効インピーダンス バッファがオン時

| DATA RATE (SPS) | $Z_{EFF}$ (MΩ) |

|-----------------|----------------|

| 30,000          | 10             |

| 15,000          | 10             |

| 7,500           | 10             |

| 3,750           | 10             |

| 2,000           | 10             |

| 1,000           | 20             |

| 500             | 40             |

| 100             | 40             |

| 60              | 40             |

| ≤ 50            | 80             |

NOTE:  $f_{CLKIN} = 7.68\text{MHz}$ .

表7. 入力インピーダンス バッファがオン時

バッファがイネーブルのとき、アナログ入力の電圧(電気的特性で「絶対入力電圧」と記したもの)は、グランドを基準にしてAGNDからAVDD - 2.0Vの間でなければなりません。この範囲を超えると、特性の中で特にADS1255/6の直線性が悪化します。それと同じ電圧範囲(AGNDからAVDD - 2.0V)を基準電圧入力に印加して、バッファがオン時の自己ゲイン・キャリブレーションを行います。

### プログラマブル・ゲイン・アンプ(PGA)

ADS1255/6は非常に高分解能のA/Dコンバータです。この特性を十分に実現するため、低ノイズPGAは入力信号が小さい場合に、より高い分解能を提供します。最高の分解能を得るには、PGAゲインをできるだけ大きく設定します。このゲイン設定は、測定する入力信号の最大値に依存します。ADS1255/6のフルスケール入力電圧は、 $\pm 2V_{REF}/\text{PGA}$ になります。表8は、異なるPGAゲイン設定時( $V_{REF} = 2.5\text{V}$ )のフルスケール入力電圧を示します。例として、測定する最大信号が1.0Vとすると、最適なPGAゲイン設定は4になります。このとき、フルスケール入力電圧は1.25Vです。これ以上の高いPGAゲインは、1.0Vの入力信号を取り扱えないので使用できません。

PGAはADCONレジスタで制御されます。PGAゲインの変更後はA/Dコンバータの再キャリブレーションをお奨めします。自己

| PGA SETTING | FULL-SCALE INPUT VOLTAGE ( $V_{REF} = 2.5V$ ) |

|-------------|-----------------------------------------------|

| 1           | $\pm 5V$                                      |

| 2           | $\pm 2.5V$                                    |

| 4           | $\pm 1.25V$                                   |

| 8           | $\pm 0.625V$                                  |

| 16          | $\pm 312.5mV$                                 |

| 32          | $\pm 156.25mV$                                |

| 64          | $\pm 78.125mV$                                |

表8. フルスケール入力電圧 対 PGAゲイン設定

キャリブレーションに要する時間は、PGAゲイン設定によります。この詳細は「キャリブレーション」の節を参照願います。アナログ電流と入力インピーダンスは、PGAゲイン設定の関数で変化します(バッファがディスエーブルの場合)。

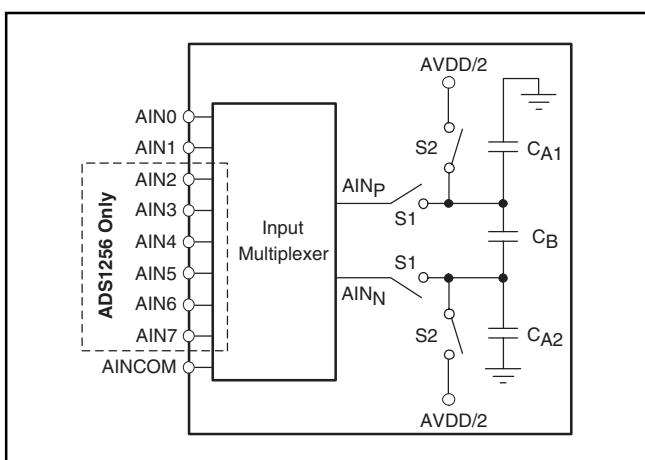

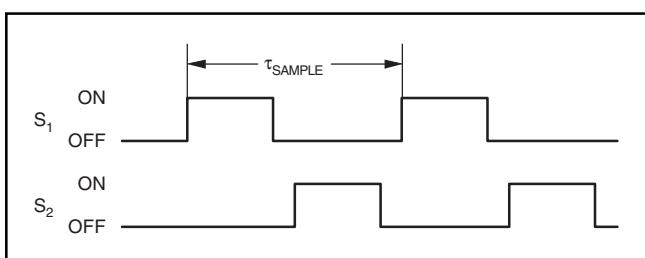

### 変調器の入力回路

ADS1255/6の変調器は、繰り返し充電される内部コンデンサを用いて入力信号を測定します。図9は、入力バッファがディスエーブル時のADS1255/6の単純化した入力回路図を示します。図10は、図9のスイッチのオン/オフ・タイミングを示します。S1は入力をサンプリングする期間に閉じます。S1が閉じると、 $C_{A1}$ は $AIN_P$ に充電され、 $C_{A2}$ は $AIN_N$ に充電され、さらに $C_B$ は( $AIN_P - AIN_N$ )に充電されます。放電期間では、S1が最初に開き、次にS2が閉じます。すると、 $C_{A1}$ と $C_{A2}$ はおよそ $AVDD/2$ に放電され、 $C_B$ は0Vに放電されます。この2期間のサンプル/放電サイクル

は、 $\tau_{SAMPLE}$ の周期で繰り返されます。この時間は、表9に示すPGAゲイン設定の関数になります。ここで、コンデンサの値は、 $C_{A1} = C_{A2} = C_A$ および $C_B$ です。

入力コンデンサに充電すると、ADS1255/6の入力をドライブするセンサーから過渡電流が引かれます。この電流の平均値は実効インピーダンス $Z_{EFF}$ の計算に使用でき、 $Z_{EFF} = V_{IN}/I_{AVERAGE}$ になります。図11は、図9のコンデンサとスイッチをその実効インピーダンスに置き換えた入力回路を示します。これらのインピーダンスはCLKIN周波数に反比例します。例えば、 $f_{CLKIN}$ が半分になると、インピーダンスは2倍になります。これはまた、PGAのゲイン設定によっても変化します。表10に、バッファはオフ、 $f_{CLKIN} = 7.68MHz$ 時の実効インピーダンスの値を列記します。

| PGA SETTING | $\tau_{SAMPLE}^{(1)}$ | $C_A$ | $C_B$ |

|-------------|-----------------------|-------|-------|

| 1           | $f_{CLKIN}/4$ (521ns) | 2.1pF | 2.4pF |

| 2           | $f_{CLKIN}/4$ (521ns) | 4.2pF | 4.9pF |

| 4           | $f_{CLKIN}/4$ (521ns) | 8.3pF | 9.7pF |

| 8           | $f_{CLKIN}/4$ (521ns) | 17pF  | 19pF  |

| 16          | $f_{CLKIN}/4$ (521ns) | 33pF  | 39pF  |

| 32          | $f_{CLKIN}/2$ (260ns) | 33pF  | 39pF  |

| 64          | $f_{CLKIN}/2$ (260ns) | 33pF  | 39pF  |

(1)  $\tau_{SAMPLE}$ は $f_{CLKIN} = 7.68MHz$ の場合

表9. 入力サンプリング時間 $\tau_{SAMPLE}$ ,  $C_A$ , および $C_B$ 対PGAゲイン設定

図9. 単純化した入力構造 バッファがオフ時

図11. アナログ入力の実効インピーダンス バッファがオフ時

図10. 図9のS1およびS2のスイッチ・タイミング

| PGA SETTING | $Z_{EFF A}$ (k $\Omega$ ) | $Z_{EFF B}$ (k $\Omega$ ) |

|-------------|---------------------------|---------------------------|

| 1           | 260                       | 220                       |

| 2           | 130                       | 110                       |

| 4           | 65                        | 55                        |

| 8           | 33                        | 28                        |

| 16          | 16                        | 14                        |

| 32          | 8                         | 7                         |

| 64          | 8                         | 7                         |

NOTE:  $f_{CLKIN} = 7.68MHz$

表10. アナログ入力の実効インピーダンス バッファがオフ時

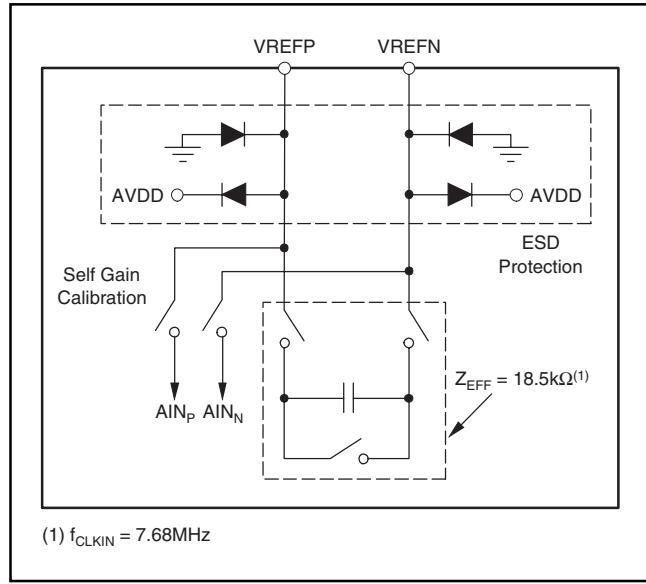

## 基準電圧入力(VREFP, VREFN)

ADS1255/6のA/Dコンバータ用の基準電圧は、VREFPとVREFN間の差動電圧、すなわち $V_{REF} = VREFP - VREFN$ になります。基準電圧入力はアナログ入力に類似した構造を使用しています。その回路を図12に示します。負荷はスイッチド・キャパシタで表されるので、 $f_{CLKIN} = 7.68\text{MHz}$ のとき、 $18.5\text{k}\Omega$ の実効インピーダンス( $Z_{EFF}$ )にモデル化できます。この基準電圧入力の実効インピーダンスの温度係数は、 $35\text{ppm}/\text{°C}$ になります。

図12. 単純化した基準電圧入力回路

ESDダイオードは基準電圧入力を保護します。これらのダイオードがオンしないようにするには、基準電圧入力ピンにかかる電圧がAGNDを100mVより下回らないようにします。また同様に、AVDDを100mVより上回らないようにします。すなわち：

$$-100\text{ mV} < (\text{VREFPあるいはVREFN}) < \text{AVDD} + 100\text{ mV}$$

自己ゲイン・キャリブレーションの間は、入力マルチプレクサの全スイッチがオープンになります。VREFNは内部的に $AIN_N$ に接続され、VREFPは $AIN_P$ に接続されます。入力バッファは、キャリブレーションの間にディスエーブルあるいはイネーブルにできます。入力バッファがディスエーブルの場合、自己ゲイン・キャリブレーションの間、基準電圧入力ピンは図9の回路をドライブします。この負荷の増加によるゲイン誤差を防止するため、基準電圧入力ピンをドライブする回路には、適当なドライブ能力がなければなりません。入力バッファがイネーブルの場合、基準電圧入力ピンの負荷はもっと軽くなります。しかし、自己あるいは自己ゲイン・キャリブレーションの間、入力バッファによりVREFPおよびVREFNの許容電圧範囲が制限されます。これは、適正なゲイン・キャリブレーションを行うには、基準電圧入力ピンはバッファの規定入力電圧範囲内である必要があるからです。

基準電圧が高精度であることが、ADS1255/6の特性が最善になる基本条件です。基準電圧にノイズおよび温度ドリフトがあると、システム全体の特性は低下します。低ノイズの設定(すなわち、低データ・レート)で動作して基準電圧による特性低下を防止する場合、基準電圧の供給回路およびそのレイアウトに十分注意することが特に重要です。

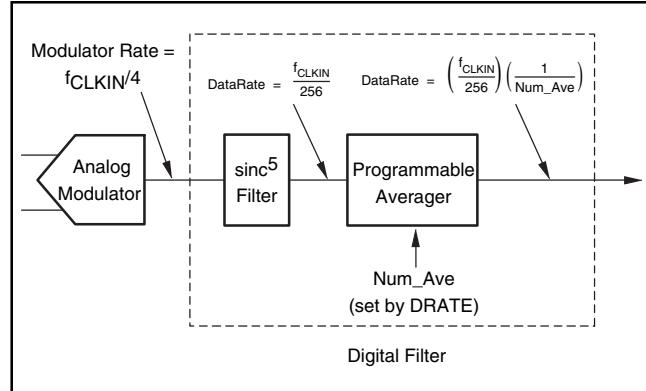

## デジタル・フィルタ

プログラマブルなローパス・デジタル・フィルタは変調器出力を受け取り、高分解能のデジタル信号を出力します。フィルタリングの量を調整すると、分解能とデータ・レートのトレードオフができます。すなわち、高分解能にはフィルタ量を増やし、高速変換にはフィルタ量を減らします。フィルタは2つの区分からなり、固定フィルタの次にプログラマブル・フィルタが続きます。図13はアナログ変調器とデジタル・フィルタのブロック図を示します。データはアナログ変調器から $f_{CLKIN}/4$ の周波数でフィルタに供給されます。固定フィルタは、デシメーション値が64の5次のsincフィルタであり、 $f_{CLKIN}/256$ の周波数でデータを出力します。フィルタの2段目はプログラマブル・アベレージャ(1次のsincフィルタ)であり、平均化の回数はDRATEレジスタで指定されます。データ・レートは平均化数(Num\_Ave)の関数になり、式(1)で与えられます。

$$\text{データ・レート} = \left( \frac{f_{CLKIN}}{256} \right) \left( \frac{1}{\text{Num\_Ave}} \right) \quad (1)$$

図13. アナログ変調器とデジタル・フィルタのブロック図

表11は、DRATEレジスタ設定の各16について、 $f_{CLKIN} = 7.68\text{MHz}$ 時の平均化の回数とそれに相当するデータ・レートを示します。ここで、データ・レートがCLKIN周波数そのものに比例することに注意願います。例えば、 $f_{CLKIN}$ を $7.68\text{MHz}$ から $3.84\text{MHz}$ に半減すると、 $DR[7:0] = 11110000$ のデータ・レートが $30,000\text{SPS}$ から $15,000\text{SPS}$ に半減します。

| D RATE<br>DR[7:0] | NUMBER OF AVERAGES FOR<br>PROGRAMMABLE FILTER<br>(Num_Ave) | DATA RATE <sup>(1)</sup><br>(SPS) |

|-------------------|------------------------------------------------------------|-----------------------------------|

| 11110000          | 1 (averager bypassed)                                      | 30,000                            |

| 11100000          | 2                                                          | 15,000                            |

| 11010000          | 4                                                          | 7500                              |

| 11000000          | 8                                                          | 3750                              |

| 10110000          | 15                                                         | 2000                              |

| 10100001          | 30                                                         | 1000                              |

| 10010010          | 60                                                         | 500                               |

| 10000010          | 300                                                        | 100                               |

| 01110010          | 500                                                        | 60                                |

| 01100011          | 600                                                        | 50                                |

| 01010011          | 1000                                                       | 30                                |

| 01000011          | 1200                                                       | 25                                |

| 00110011          | 2000                                                       | 15                                |

| 00100011          | 3000                                                       | 10                                |

| 00010011          | 6000                                                       | 5                                 |

| 00000011          | 12,000                                                     | 2.5                               |

(1) for  $f_{CLKIN} = 7.68\text{MHz}$ .

表11. D RATEレジスタの各設定での平均化の回数とデータ・レート

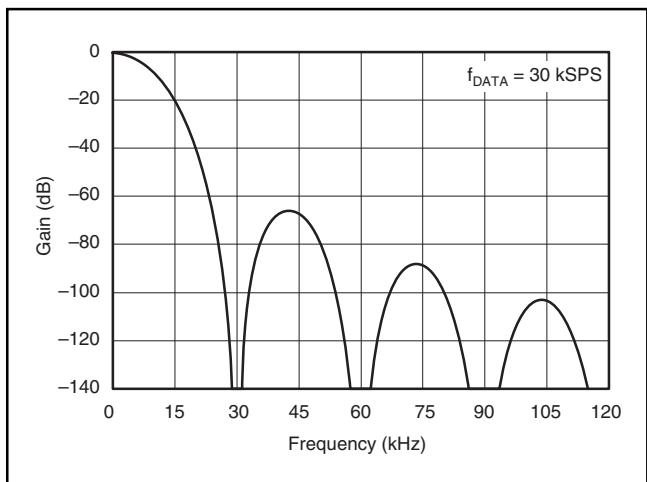

図14. データ・レート = 30kSPSの周波数応答

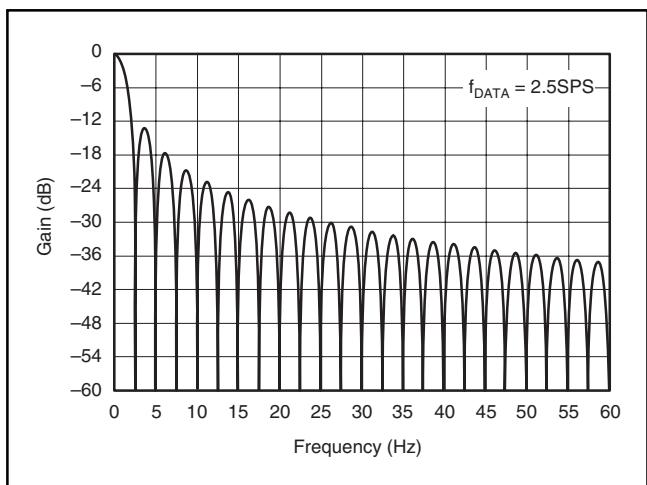

図15. データ・レート = 2.5SPSの周波数応答

## 周波数応答

ローパス・デジタル・フィルタは、ADS1255/6の全体の周波数応答を設定します。フィルタの応答は固定とプログラマブルの両フィルタ段の応答の積であり、式(2)で与えられます。

$$|H(f)| = |H_{\text{sinc}5}(f)| \cdot |H_{\text{Averager}}(f)| = \left| \frac{\sin\left(\frac{256\pi \cdot f}{f_{CLKIN}}\right)}{64 \cdot \sin\left(\frac{4\pi \cdot f}{f_{CLKIN}}\right)} \right|^5 \cdot \left| \frac{\sin\left(\frac{256\pi \cdot \text{Num\_Ave} \cdot f}{f_{CLKIN}}\right)}{\text{Num\_Ave} \cdot \sin\left(\frac{256\pi \cdot f}{f_{CLKIN}}\right)} \right| \quad (2)$$

デジタル・フィルタは変調器出力のノイズを減衰します。これには、ADS1255/6内で発生したノイズと、ADS1255/6の入力信号にある外部ノイズが含まれます。プログラマブル・フィルタの平均化の回数を変更してフィルタリングを調整すると、フィルタの帯域幅が変わります。平均化の回数を増やすと帯域幅が狭まり、より多くのノイズが減衰します。

ローパス・フィルタには、データ出力周波数(データ・レート)およびその倍数にノッチ(すなわちゼロ)があります。その周波数では、フィルタのゲインが0になります。これは、特定の干渉信号を除去する場合に役立ちます。例として、60Hz(およびその高調波)を除去するには、データ・レートを2.5SPS, 5SPS, 10SPS, 15SPS, 30SPS, あるいは60SPSに設定します。このフィルタ特性を説明するため、図14と図15にデータ・レートの上下限である30kSPSおよび2.5SPSの各応答を示します。表12は、異なるデータ・レート設定についての、第1ノッチ周波数および-3dB帯域幅の要約です。

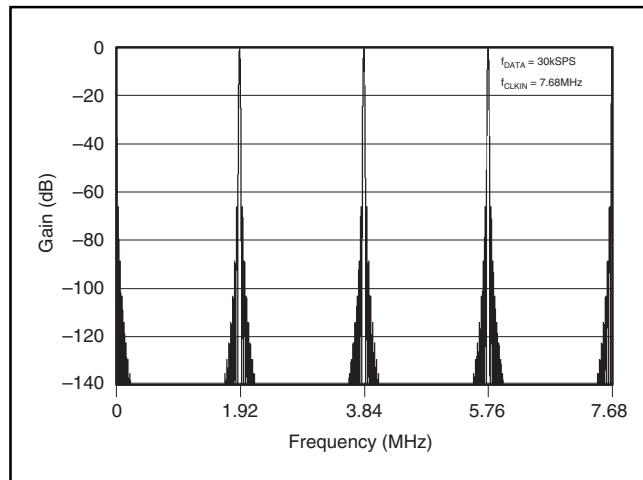

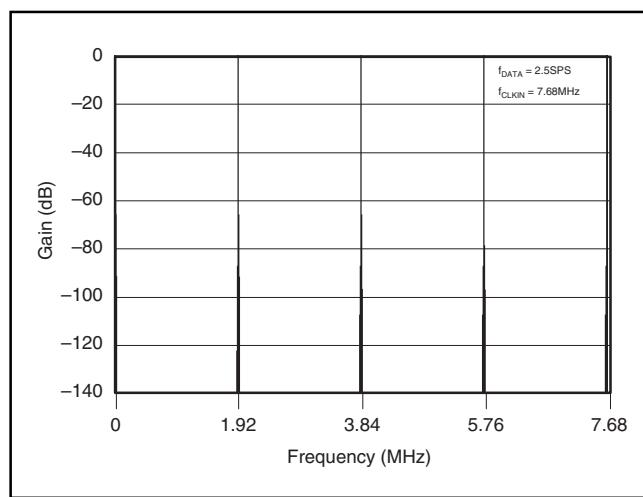

デジタル・フィルタのローパス特性は、変調器周波数 $f_{CLKIN}/4$ の倍数で繰り返し現われます。図16と図17は、データ・レートの上下限である30kSPSおよび2.5SPSについて、7.68MHzまでプロットした応答を示します。その特性がDC, 1.92MHz, 3.84MHz, 5.76MHz, 7.68MHzの付近においていかに等しいか注意願います。デジタル・フィルタは、この応答が繰り返される周波数ま

| DATA RATE<br>(SPS) | FIRST NOTCH<br>(Hz) | -3dB BANDWIDTH<br>(Hz) |

|--------------------|---------------------|------------------------|

| 30,000             | 30,000              | 6106                   |

| 15,000             | 15,000              | 4807                   |

| 7500               | 7500                | 3003                   |

| 3750               | 3750                | 1615                   |

| 2000               | 2000                | 878                    |

| 1000               | 1000                | 441                    |

| 500                | 500                 | 221                    |

| 100                | 100                 | 44.2                   |

| 60 <sup>(1)</sup>  | 60                  | 26.5                   |

| 50 <sup>(2)</sup>  | 50                  | 22.1                   |

| 30 <sup>(1)</sup>  | 30                  | 13.3                   |

| 25 <sup>(2)</sup>  | 25                  | 11.1                   |

| 15 <sup>(1)</sup>  | 15                  | 6.63                   |

| 10 <sup>(3)</sup>  | 10                  | 4.42                   |

| 5 <sup>(3)</sup>   | 5                   | 2.21                   |

| 2.5 <sup>(3)</sup> | 2.5                 | 1.1                    |

NOTE:  $f_{CLKIN} = 7.68\text{MHz}$ .

(1) Notch at 60Hz.

(2) Notch at 50Hz.

(3) Notch at 50Hz and 60Hz.

表12. 第1ノッチ周波数および-3dBフィルタ帯域幅

図16. 7.68MHzまでの周波数応答 データ・レート = 30kSPS時

図17. 7.68MHzまでの周波数応答 データ・レート = 2.5SPS時

で、ADS1255/6入力における高周波ノイズを減衰します。もし、この周波数より高い大きなノイズが入力にあれば、外付けのフィルタで除去するようにします。幸運なことにADS1255/6の場合には、「アプリケーション」節に示すように、単純なRCフィルタで除去できます(図25参照)。

### セトリング・タイム

ADS1255/6は、高速セトリングに最適化されたデジタル・フィルタが特長です。そのセトリング・タイム(アナログ入力におけるステップ変化が、フィルタを通って伝播するのに要する時間)を、異なるデータ・レートについて表13に示します。以下の節ではフィルタのセトリング能力に注目し、変換プロセスを制御する種々の方法を示します。

### 同期によるセトリング・タイム

SYNC/PDWNピンにより、変換タイミングを直接制御できます。アナログ入力を変えた後で(詳細は「同期」の節を参照)、単にSyncコマンドの実行すなわち、SYNC/PDWNピンをストローブするだけです。SYNC/PDWNがハイになると、今までの変換を

| DATA RATE (SPS) | SETTLING TIME ( $t_{18}$ ) (ms) |

|-----------------|---------------------------------|

| 30,000          | 0.21                            |

| 15,000          | 0.25                            |

| 7500            | 0.31                            |

| 3750            | 0.44                            |

| 2000            | 0.68                            |

| 1000            | 1.18                            |

| 500             | 2.18                            |

| 100             | 10.18                           |

| 60              | 16.84                           |

| 50              | 20.18                           |

| 30              | 33.51                           |

| 25              | 40.18                           |

| 15              | 66.84                           |

| 10              | 100.18                          |

| 5               | 200.18                          |

| 2.5             | 400.18                          |

NOTE:  $f_{CLKIN} = 7.68\text{MHz}$ .

表13. セトリング・タイム 対 データ・レート

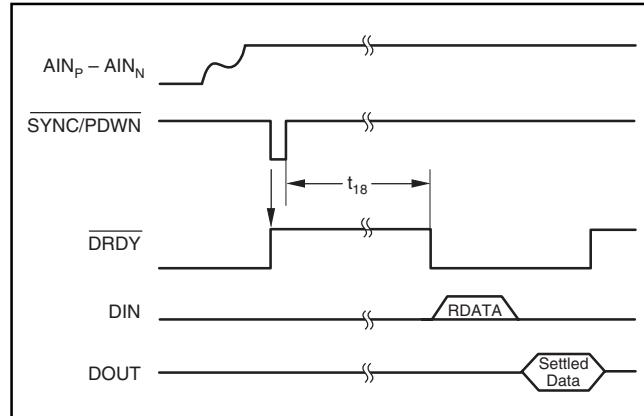

終了し、デジタル・フィルタが再スタートし、新しい変換が始まります。SYNC/PDWNがローになると、すぐにDRDY出力がハイになり、変換の間ハイを続けます。セトリング・タイム $t_{18}$ が過ぎると、DRDYがローになり、データ出力ができる事を示します。ADS1255/6はシングル・サイクルでセトリングするので、同期後のデータ読み出しの無視や棄却は不要です。図18は、同期に続くデータ取りこみのシーケンスを示します。

図18. 同期後のデータ検索

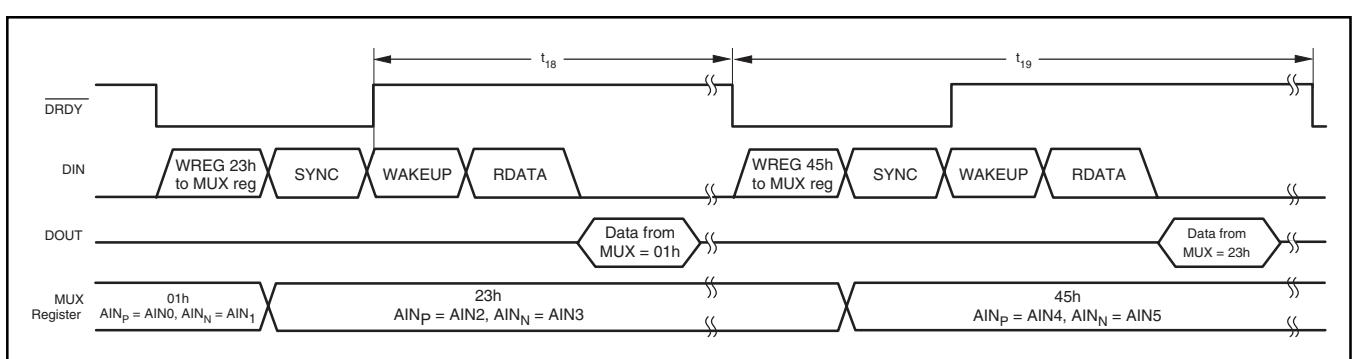

### 入力マルチプレクサ使用時のセトリング・タイム

入力を循環的に切り換える(サイクル切り換え)最も効率的な方法は、DRDYがローになった直後にマルチプレクサの設定(マルチプレクサ・レジスタMUXへのWREGコマンドを使用)を変更することです。次に、マルチプレクサを切り換えた後、SYNCおよびWAKEUPの両コマンドにより変換プロセスを再始動し、RDATAコマンドでデータを取りこみます。データ読み込み前にマルチプレクサを切り換えると、ADS1255/6は即座に新しい入力

チャンネルの測定を始められます。この効率の良い入力サイクルを図19に示します。

1. ステップ1: DRDYがローになると、データ取り込みに対する準備ができたことを示し、マルチプレクサ・レジスタMUXをWREGコマンドで更新します。例えば、MUXを23hに設定すると、 $AIN_P = AIN_2, AIN_N = AIN_3$ になります。

2. ステップ2: SYNCコマンドおよびその直後に続くWAKEUPコマンドにより変換プロセスを再始動します。このとき、両コマンド間でタイミング仕様の $t_{11}$ を確保するよう注意します。

3. ステップ3: RDATAコマンドを用いて、前の変換データを読み取ります。

4. ステップ4: DRDYが再びローになると、このサイクルを繰り返し、最初にマルチプレクサ・レジスタを更新し、次に前のデータを読み取ります。

入力マルチプレクサをサイクル切り換える場合の、実際の全体のスループット( $1/t_{19}$ )を表14に示します。スループットの値( $1/t_{19}$ )は、マルチプレクサが3バイトのWREGコマンドで切り換えられ、かつ $f_{SCLK} = f_{CLKIN}/4$ であることが前提です。

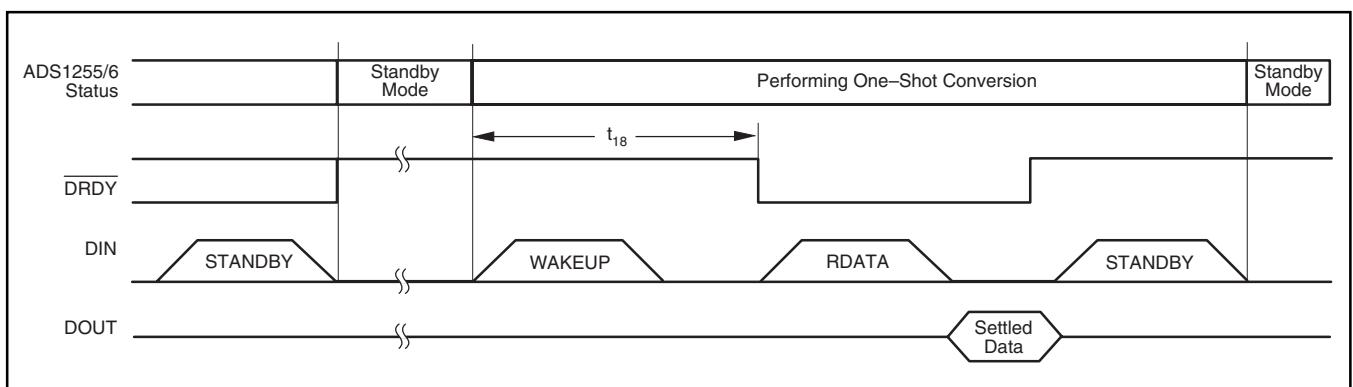

#### ワンショット・モード使用時のセトリング・タイム

ADS1255/6は、STANBYコマンドを使ってワンショット変換を行うと、その電力消費を極度に低減できます。このシーケンスを図20に示します。まず、スタンバイ・モード時にWAKEUPコマンドを実行してワンショット変換を始めます。次に、セトリング・タイム $t_{18}$ の後、DRDYがローになって変換が完了したことを

示すと、RDATAコマンドでデータが読み取れます。ADS1255/6はシングル・サイクルでセトリングするので、データの無視や棄却は必要ありません。このデータ・リード・サイクルに続いて別のSTANBYコマンドを実行し、電力消費を低減します。次の測定の準備ができたら、再度WAKEUPコマンドで始まるサイクルを繰り返します。

| DATA RATE (SPS) | CYCLING THROUGHPUT ( $1/t_{19}$ ) (Hz) |

|-----------------|----------------------------------------|

| 30,000          | 4374                                   |

| 15,000          | 3817                                   |

| 7500            | 3043                                   |

| 3750            | 2165                                   |

| 2000            | 1438                                   |

| 1000            | 837                                    |

| 500             | 456                                    |

| 100             | 98                                     |

| 60              | 59                                     |

| 50              | 50                                     |

| 30              | 30                                     |

| 25              | 25                                     |

| 15              | 15                                     |

| 10              | 10                                     |

| 5               | 5                                      |

| 2.5             | 2.5                                    |

NOTE:  $f_{CLKIN} = 7.68\text{MHz}$ .

表14. 入力マルチプレクサ・サイクリングのスループット

図19. ADS1256の入力マルチプレクサのサイクリング

図20. STANBYコマンドによるワンショット変換

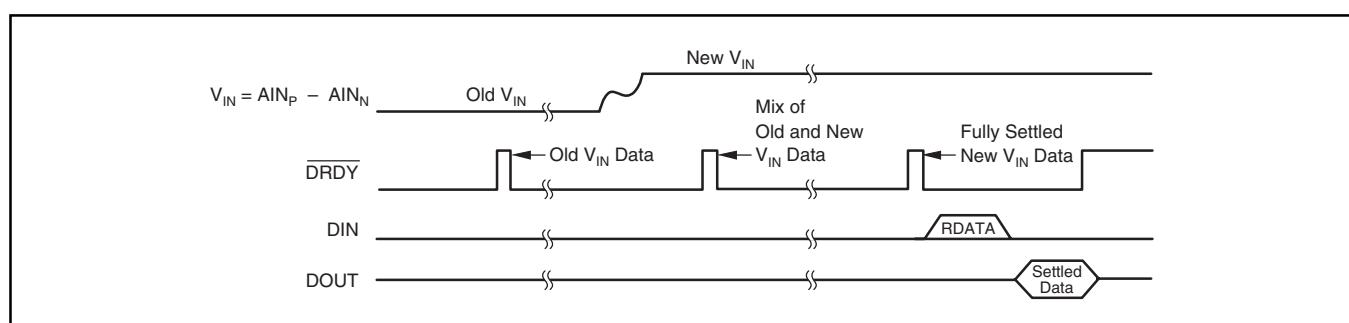

## 連続変換時のセトリング・タイム

ADS1255/6は、同期、入力マルチプレクサ切り換え、あるいはスタンバイ・モードからのWAKEUPの後で、アナログ入力を連続変換します。この変換は $\overline{\text{DRDY}}$ の立ち下りエッジで行われます。連続変換の間は、セトリング・タイムは表15に示す $\overline{\text{DRDY}}$ の周期の観点から考えると便利です。 $\overline{\text{DRDY}}$ の周期はデータ・レートの逆数になります。

連続変換の間に入力信号がステップ変化をした場合、同期動作による新しい変換を始めるよう推奨します。さもないと、次のデータは前と現在のデータが結合したものになってしまふので、これを棄却する必要があります。図21は、この状況におけるリードバックの例を示します。

| INPUT SIGNAL $V_{\text{IN}}$<br>( $A_{\text{IN}_P} - A_{\text{IN}_N}$ )             | IDEAL OUTPUT CODE <sup>(1)</sup> |

|-------------------------------------------------------------------------------------|----------------------------------|

| $\geq \frac{+2V_{\text{REF}}}{\text{PGA}}$                                          | 7FFFFFFh                         |

| $\frac{+2V_{\text{REF}}}{\text{PGA}(2^{23} - 1)}$                                   | 000001h                          |

| 0                                                                                   | 000000h                          |

| $\frac{-2V_{\text{REF}}}{\text{PGA}(2^{23} - 1)}$                                   | FFFFFFFFFFh                      |

| $\leq \frac{-2V_{\text{REF}}}{\text{PGA}} \left( \frac{2^{23}}{2^{23} - 1} \right)$ | 800000h                          |

(1) ノイズ、INL、オフセット、およびゲイン誤差の影響を除きます。

表16. 理想出力コード 対 入力信号

| DATA RATE<br>(SPS) | SETTLING TIME<br>( $\overline{\text{DRDY}}$ Periods) |

|--------------------|------------------------------------------------------|

| 30,000             | 5                                                    |

| 15,000             | 3                                                    |

| 7500               | 2                                                    |

| 3750               | 1                                                    |

| 2000               | 1                                                    |

| 1000               | 1                                                    |

| 500                | 1                                                    |

| 100                | 1                                                    |

| 60                 | 1                                                    |

| 50                 | 1                                                    |

| 30                 | 1                                                    |

| 25                 | 1                                                    |

| 15                 | 1                                                    |

| 10                 | 1                                                    |

| 5                  | 1                                                    |

| 2.5                | 1                                                    |

表15. データ・セトリング遅延 対 データ・レート

## データ・フォーマット

ADS1255/6は、24ビット、2の補数のバイナリ・フォーマットでデータを出力します。LSBには $2V_{\text{REF}}/(2^{23} - 1)$ の重みがあります。正のフルスケール入力の出力コードは7FFFFFFhになり、負のフルスケール入力の出力コードは800000hになります。フルスケールを超える信号の場合、これらのコードで出力がクリップします。表16に、異なる入力信号に関する理想出力コードを要約します。

## 一般目的用デジタルI/O(D0-D3)

ADS1256には4本のデジタルI/Oピン(一般目的用I/OピンあるいはGPIOピン)があり、ADS1255のそれは2本です。すべてのデジタルI/Oピンは、IOレジスタによって個々に入力あるいは出力に設定できます。IOレジスタのDIRビットは、各ピンを入力あるいは出力のいずれかに定義し、また同レジスタのDIOビットは各ピンの状態を制御します。IOレジスタをリードバックすると、そのDIRビットによって、デジタルI/Oピンが入出力のいずれに設定されているかわかります。デジタルI/Oピンが入力に設定されていると、IOレジスタはこれらのピン状態の読み込に使用されます。また、デジタルI/Oピンが出力に設定されていると、DIOビットは出力値を設定します。ADS1255にはデジタルI/OピンのD2とD3がありません。したがって、それらの動作を制御するIOレジスタのビットを設定しても、ADS1255にはなんら影響がありません。

スタンバイおよびパワーダウン・モードの間も、デジタルI/Oピンはアクティブのままであります。それが出力に設定されていると、デジタルI/Oピンの負荷をドライブし続けます。デジタルI/Oピンが入力に設定されている場合は、外部からドライブしてフローティング状態を避け、過剰な電力消費を防止しなければなりません。

デジタルI/Oピンは、パワーアップ(電源投入)あるいはリセット後、D0/CLKOUTを除いて入力に設定されます。D0/CLKOUTはクロック出力としてイネーブルになります。デジタルI/Oピンを使用しない場合は、入力に設定してグランドに接続するか、あるいは出力に設定します。このようにして、過剰な電力消費を防止します。

図21.  $V_{\text{IN}}$ のステップ変化(連続変換時、データ・レート≤3750SPS)

## クロック出力(D0/CLKOUT)

クロック出力ピンは、マイクロコントローラのような他のデバイスへのクロック供給に使用できます。このクロックは、ADCONレジスタのCLK1およびCLK0を用いて、 $f_{CLKIN}$ ,  $f_{CLKIN}/2$ , あるいは $f_{CLKIN}/4$ の周波数で動作するように設定できます。ここで、出力クロックをイネーブルにして外部負荷をドライブすると、デジタルの電力消費が増加することに注意願います。スタンバイ・モードは、クロック出力の状態に影響しません。つまり、スタンバイがイネーブルされてスタンバイ・モードになっても、クロック出力は自走し続けます。クロック出力が不要ならば、パワー・アップあるいはリセットの後で、ADCONレジスタに書き込んでディスエーブルにします。

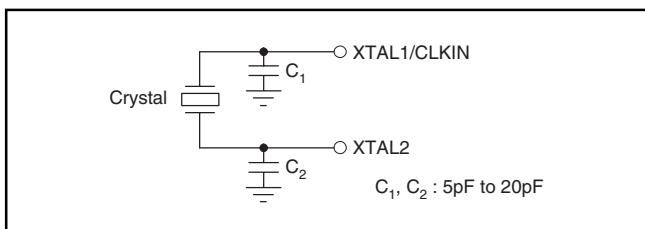

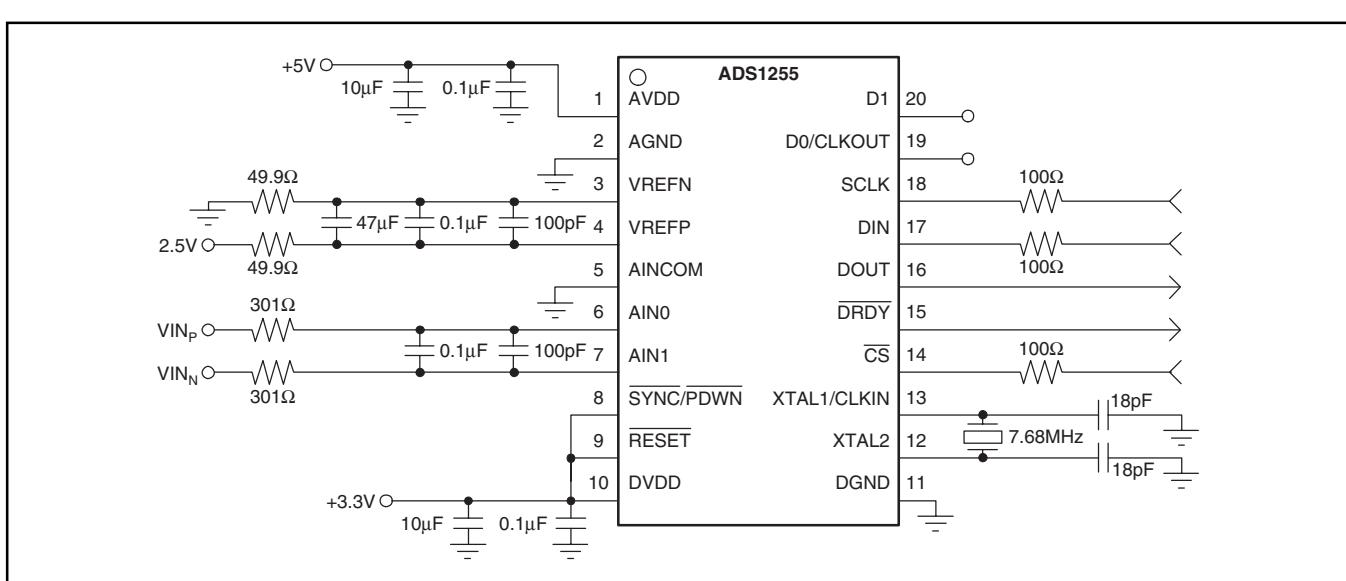

## クロックの生成

ADS1255/6の主クロック源は、外付けの水晶あるいはクロック発生回路を使用します。クロックを水晶で生成する場合、スタートアップ動作と安定した周波数を得るために、図22のような外付けのコンデンサが必要になります。水晶は表17の2種類をお奨めします。水晶の長いリードを最小にして、ADS1255/6のピンの極力近くに配置します。セラミック共振子に関する情報は、アプリケーション・ノートSBAA104, “Using Ceramic Resonator with the ADS1255/6 (セラミック共振子のADS1255/6での使用法)” をwww.ti.comからダウンロードして参照願います。

図22. 水晶の接続

| MANUFACTURER | FREQUENCY | PART NUMBER |

|--------------|-----------|-------------|

| Citizen      | 7.68MHz   | CIA/53383   |

| ECS          | 8.0MHz    | ECS-80-5-4  |

表17. お奨めする水晶

水晶を使用する場合は、XTAL1/CLKINピンあるいはXTAL2ピンのいずれも、外部のロジックのドライブに使用してはなりません。他のデバイスがクロック源を必要とするならば、D0/CLKOUTピンがそれに使えます。外付けのクロック発生回路を使用する場合は、そのクロックをXTAL1/CLKINピンに供給し、XTAL2ピンはフローティングにします。また、この外付けクロック発生回路が、きれいなクロック波形を供給するように注意します。クロックにオーバーシュートやグリッチがあると、全体の特性が悪化します。

## キャリブレーション

ADS1255/6に内蔵のキャリブレーション回路は、オフセットおよびゲイン誤差を最小にします。図23にキャリブレーション回路のブロック図を示します。オフセット誤差は、オフセット・キャリブレーション・レジスタ(OFC)で補正され、同様にフルスケール誤差は、フルスケール・キャリブレーション・レジスタ(FSC)で補正されます。この各レジスタは24ビット構成であり、読み取りと書き込みが可能です。

図23. キャリブレーション・ブロック図

キャリブレーション後のADS1255/6の出力は、式(3)のようになります。

$$\text{Output} = \left( \frac{\text{PGA} \cdot V_{IN}}{2V_{REF}} - \frac{\text{OFC}}{\alpha} \right) \text{FSC} \cdot \beta \quad (3)$$

ここで、 $\alpha$ と $\beta$ はデータ・レート設定により表18のよう、OFCおよびFSCの理想値(アナログ特性が完全であると仮定した値)とともに変化します。OFCは2の補数のバイナリであり、-8,388,608から8,388,607の範囲の値をとります。また、FSCは単極性であり、0から16,777,215の範囲です。

ADS1255/6は、PGAのゲイン設定にかかわらず、次のコマンドを使用して自己およびシステムの両キャリブレーションをサポートします。すなわち、SEFOCAL, SELFGCAL, SELFCAL, SYSOCAL, およびSYSGCALの5コマンドです。キャリブレーションはいつでもできますが、多くのアプリケーションの場合、ADS1255/6のドリフト特性は十分低く、1回のキャリブレーションで間に合います。キャリブレーションが始まるとDRDYはハイになります。データがセトリングしてレディになるまでハイを続けます。したがって、キャリブレーション後にデータを棄却する必要はありません。また、パワー・アップの後で基準電圧が安定したときに、自己キャリブレーション・コマンドを実行することを強く推奨します。リセット後については、ADS1255/6は自動的に自己キャリブレーションを行います。データ・レートの変更時もキャリブレーションを実行しなければなりません。バッファの設定あるいはPGAゲインの変更時も、キャリブレーションを実行すべきです。

| DATA RATE<br>(SPS) | $\alpha$            | $\beta$ | IDEAL OFC           | IDEAL FSC           |

|--------------------|---------------------|---------|---------------------|---------------------|

| 30,000             | 400000 <sub>H</sub> | 1.8639  | 000000 <sub>H</sub> | 44AC08 <sub>H</sub> |

| 15,000             | 400000 <sub>H</sub> | 1.8639  | 000000 <sub>H</sub> | 44AC08 <sub>H</sub> |

| 7500               | 400000 <sub>H</sub> | 1.8639  | 000000 <sub>H</sub> | 44AC08 <sub>H</sub> |

| 3750               | 400000 <sub>H</sub> | 1.8639  | 000000 <sub>H</sub> | 44AC08 <sub>H</sub> |

| 2000               | 3C0000 <sub>H</sub> | 1.7474  | 000000 <sub>H</sub> | 494008 <sub>H</sub> |

| 1000               | 3C0000 <sub>H</sub> | 1.7474  | 000000 <sub>H</sub> | 494008 <sub>H</sub> |

| 500                | 3C0000 <sub>H</sub> | 1.7474  | 000000 <sub>H</sub> | 494008 <sub>H</sub> |

| 100                | 4B0000 <sub>H</sub> | 2.1843  | 000000 <sub>H</sub> | 3A99A0 <sub>H</sub> |

| 60                 | 3E8000 <sub>H</sub> | 1.8202  | 000000 <sub>H</sub> | 4651F3 <sub>H</sub> |

| 50                 | 4B0000 <sub>H</sub> | 2.1843  | 000000 <sub>H</sub> | 3A99A0 <sub>H</sub> |

| 30                 | 3E8000 <sub>H</sub> | 1.8202  | 000000 <sub>H</sub> | 4651F3 <sub>H</sub> |

| 25                 | 4B0000 <sub>H</sub> | 2.1843  | 000000 <sub>H</sub> | 3A99A0 <sub>H</sub> |

| 15                 | 3E8000 <sub>H</sub> | 1.8202  | 000000 <sub>H</sub> | 4651F3 <sub>H</sub> |

| 10                 | 5DC000 <sub>H</sub> | 2.7304  | 000000 <sub>H</sub> | 2EE14C <sub>H</sub> |

| 5                  | 5DC000 <sub>H</sub> | 2.7304  | 000000 <sub>H</sub> | 2EE14C <sub>H</sub> |

| 2.5                | 5DC000 <sub>H</sub> | 2.7304  | 000000 <sub>H</sub> | 2EE14C <sub>H</sub> |

表18. 異なるデータ・レート設定に対するキャリブレーション値

### 自己キャリブレーション

自己キャリブレーションは、内部のオフセットおよびゲインの両誤差を補正します。自己キャリブレーションの間、適当なキャリブレーション信号が内部でアナログ入力に印加されます。

SELFOCALは自己オフセット・キャリブレーションを実行します。アナログ入力のAIN<sub>P</sub>およびAIN<sub>N</sub>は、外部の信号源から分離され、AVDD/2に接続されます。自己オフセット・キャリブレーションに要する時間については、表19の異なるデータ・レートの値を参照願います。キャリブレーション時間は、ADS1255/6のほとんどのタイミングと同様に、直接f<sub>CLKIN</sub>に比例します。自己オフセット・キャリブレーションを行うと、OFCレジスタの内容が更新されます。

SELCALは自己ゲイン・キャリブレーションを実行します。アナログ入力のAIN<sub>P</sub>およびAIN<sub>N</sub>は、外部の信号源から分離さ

れ、AIN<sub>P</sub>は内部でVREFPに接続され、AIN<sub>N</sub>はVREFNに接続されます。自己ゲイン・キャリブレーションは、すべてのPGAゲイン設定で実行できます。また、ADS1255/6のゲイン・キャリブレーションは、PGAゲインが高い場合でも、「代表的特性」の節で示したように優れています。入力バッファを使用する場合、自己ゲイン・キャリブレーションの間、基準電圧入力の同相範囲が限定されます。基準電圧入力がバッファ入力に接続されるため、基準電圧がアナログ入力電圧範囲の仕様内である必要があるからです。VREFPあるいはVREFNがバッファのアナログ入力範囲 (AVDD - 2.0V) を超える場合は、自己ゲイン・キャリブレーション中にバッファをオフしなければなりません。別の方としては、システム・ゲイン・キャリブレーションを使用するか、ゲイン係数を直接FSCレジスタに書き込みます。各種のデータ・レートおよびPGAゲインについて、表20に自己ゲイン・キャリブレー

| DATA RATE<br>(SPS) | SELF OFFSET CALIBRATION AND<br>SYSTEM OFFSET CALIBRATION TIME |

|--------------------|---------------------------------------------------------------|

| 30,000             | 387μs                                                         |

| 15,000             | 453μs                                                         |

| 7500               | 587μs                                                         |

| 3750               | 853μs                                                         |

| 2000               | 1.3ms                                                         |

| 1000               | 2.3ms                                                         |

| 500                | 4.3ms                                                         |

| 100                | 20.3ms                                                        |

| 60                 | 33.7ms                                                        |

| 50                 | 40.3ms                                                        |

| 30                 | 67.0ms                                                        |

| 25                 | 80.3ms                                                        |

| 15                 | 133.7ms                                                       |

| 10                 | 200.3ms                                                       |

| 5                  | 400.3ms                                                       |

| 2.5                | 800.3ms                                                       |

NOTE: For f<sub>CLKIN</sub> = 7.68MHz.

表19. 自己オフセットおよびシステム・オフセットによるキャリブレーション時間

| DATA RATE<br>(SPS) | PGA SETTING |       |       |         |            |

|--------------------|-------------|-------|-------|---------|------------|

|                    | 1           | 2     | 4     | 8       | 16, 32, 64 |

| 30,000             | 417μs       | 417μs | 451μs | 517μs   | 651μs      |

| 15,000             | 484μs       | 484μs | 484μs | 551μs   | 551μs      |

| 7500               | 617μs       | 617μs | 617μs | 617μs   | 751μs      |

| 3750               |             |       |       | 884     |            |

| 2000               |             |       |       | 1.4ms   |            |

| 1000               |             |       |       | 2.4ms   |            |

| 500                |             |       |       | 4.5ms   |            |

| 100                |             |       |       | 21.0ms  |            |

| 60                 |             |       |       | 34.1ms  |            |

| 50                 |             |       |       | 41.7ms  |            |

| 30                 |             |       |       | 67.8ms  |            |

| 25                 |             |       |       | 83.0ms  |            |

| 15                 |             |       |       | 135.3ms |            |

| 10                 |             |       |       | 207.0ms |            |

| 5                  |             |       |       | 413.7ms |            |

| 2.5                |             |       |       | 827.0ms |            |

NOTE: For f<sub>CLKIN</sub> = 7.68MHz.

表20. 自己ゲイン・キャリブレーション時間

ションに要する時間を示します。自己ゲイン・キャリブレーションを実行すると、FSCレジスタが更新されます。

SELF CALは、最初に自己オフセット、次に自己ゲインのキャリブレーションを実行します。アナログ入力は、自己キャリブレーションの間、外部の信号源から分離されます。自己キャリブレーションで入力バッファを使用する場合、上述したように基準電圧入力の同相範囲を必ず観察します。各種のデータ・レートについて、表21に自己キャリブレーションに要する時間を示します。自己キャリブレーションを実行すると、OFCおよびFSCの両レジスタが更新されます。

| DATA RATE<br>(SPS) | PGA SETTING |       |       |       |            |

|--------------------|-------------|-------|-------|-------|------------|

|                    | 1           | 2     | 4     | 8     | 16, 32, 64 |

| 30,000             | 596μs       | 596μs | 692μs | 696μs | 892μs      |

| 15,000             | 696μs       | 696μs | 696μs | 762μs | 896μs      |

| 7500               | 896μs       | 896μs | 896μs | 896μs | 1029μs     |

| 3750               |             |       |       |       | 1.3ms      |

| 2000               |             |       |       |       | 2.0ms      |

| 1000               |             |       |       |       | 3.6ms      |

| 500                |             |       |       |       | 6.6ms      |

| 100                |             |       |       |       | 31.2ms     |

| 60                 |             |       |       |       | 50.9ms     |

| 50                 |             |       |       |       | 61.8ms     |

| 30                 |             |       |       |       | 101.3ms    |

| 25                 |             |       |       |       | 123.2ms    |

| 15                 |             |       |       |       | 202.1ms    |

| 10                 |             |       |       |       | 307.2ms    |

| 5                  |             |       |       |       | 613.8ms    |

| 2.5                |             |       |       |       | 1227.2ms   |

NOTE: For  $f_{CLKIN} = 7.68\text{MHz}$ .

表21. 自己キャリブレーション時間

### システム・キャリブレーション

システム・キャリブレーションは、SYSOCALおよびSYSGCALのコマンドを用いて、内部と外部のオフセットおよびゲインの両誤差を補正します。システム・キャリブレーションの間、ユーザは適当なキャリブレーション信号を入力に印加しなければなりません。

SYSOCALは、システム・オフセット・キャリブレーションを実行します。このとき、ユーザは入力差動信号を0にしなければなりません。すると、ADS1255/6はシステムのオフセットをなくす値を計算します。このシステム・オフセット・キャリブレーションに要する時間を、異なるデータ・レートについて表19に示します。この時間が自己オフセット時間に等しいことに注意願います。システム・オフセット・キャリブレーションを実行すると、OFCレジスタが更新されます。

SYSGCALはシステム・ゲイン・キャリブレーションを実行します。このとき、ユーザはフルスケールの入力信号をADS1255/6に供給する必要があります。すると、ADS1255/6はシステムのゲイン誤差をなくす値を計算します。システム・ゲイン・キャリブレーションは、フルスケール入力電圧の80%以上の入力を補正できます。しかし、システム・ゲイン・キャリブレーションでは、フルス

| DATA RATE<br>(SPS) | SYSTEM GAIN CALIBRATION TIME |

|--------------------|------------------------------|

| 30,000             | 417μs                        |

| 15,000             | 484μs                        |

| 7500               | 617μs                        |

| 3750               | 884μs                        |

| 2000               | 1.4ms                        |

| 1000               | 2.4ms                        |

| 500                | 4.4ms                        |

| 100                | 20.4ms                       |

| 60                 | 33.7ms                       |

| 50                 | 40.4ms                       |

| 30                 | 67.0ms                       |

| 25                 | 80.4ms                       |

| 15                 | 133.7ms                      |

| 10                 | 200.4ms                      |

| 5                  | 400.4ms                      |

| 2.5                | 800.4ms                      |

NOTE: For  $f_{CLKIN} = 7.68\text{MHz}$ .

表22. システム・ゲイン・キャリブレーション時間

ケール入力電圧を絶対超えないようにします。このシステム・ゲイン・キャリブレーションに要する時間を、異なるデータ・レートについて表22に示します。システム・ゲイン・キャリブレーションを実行すると、FSCレジスタが更新されます。

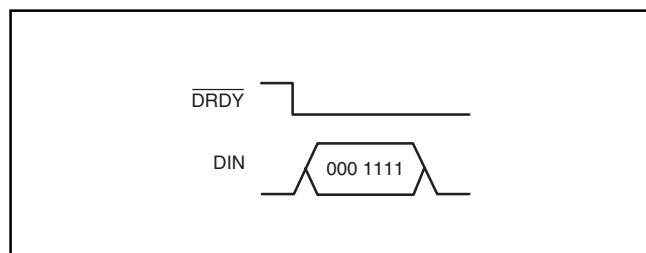

### 自動キャリブレーション

自動キャリブレーションをイネーブル(ADCONレジスタのACALビットによる)にすると、データ・レート、PGAゲイン設定、あるいはバッファの状態を変更する書き込みコマンド(WREG)の完了後、ADS1255/6は自動的に自己キャリブレーションを開始します。

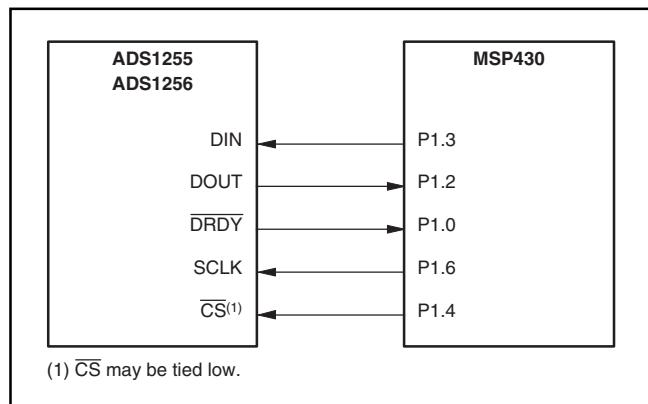

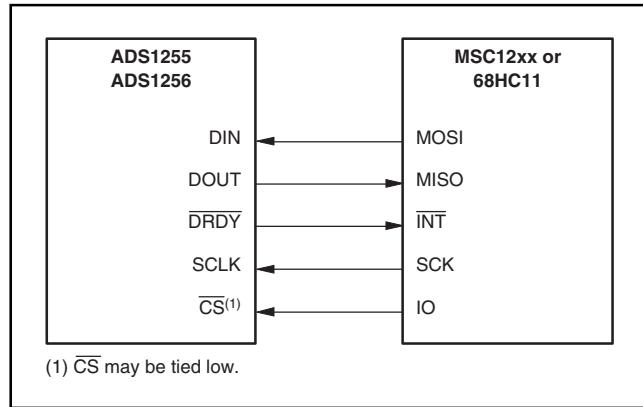

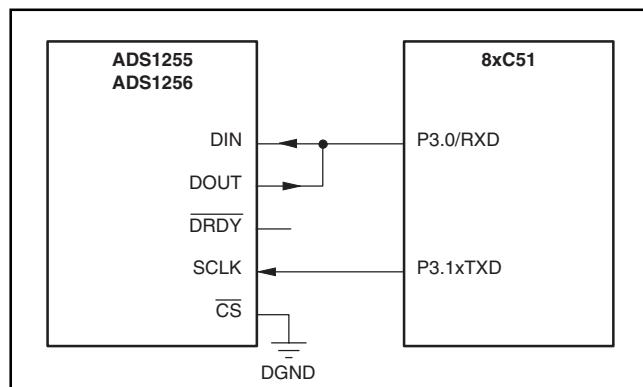

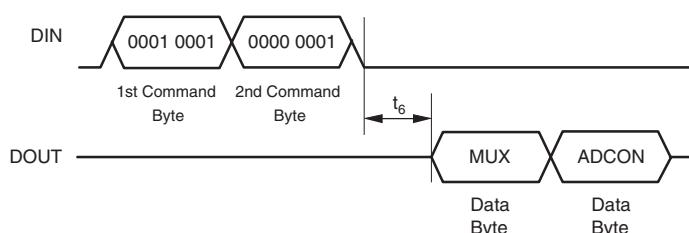

### シリアル・インターフェイス

シリアル・インターフェイスは、 $\overline{CS}$ , SCLK, DIN, およびDOUTの4個の信号で構成され、これによりコントローラはADS1255/6と交信できます。プログラマブル機能は、チップに内蔵のレジスタで制御されます。データは、シリアル・インターフェイス経由で、これらのレジスタへの書き込み、およびレジスタからの読み取りがなされます。

$\overline{CS}$ の出力ラインは、いつ変換が終了したかを示すステータス信号として使用されます。DRDYは新しいデータが準備できるとローになります。ADS1255/6とのインターフェイスに関するタイミング図は、「タイミング特性(図1)」にあります。

### チップ・セレクト( $\overline{CS}$ )

チップ・セレクト( $\overline{CS}$ )入力により、複数デバイスがシリアル・インターフェイス上にある場合でも、ADS1255/6を個別に選択できます。シリアル・インターフェイスで交信している期間、 $\overline{CS}$ はローのままでなければなりません。 $\overline{CS}$ がハイになると、シリアル・インターフェイスはリセットされ、DOUTがハイ・インピーダンスになります。 $\overline{CS}$ は常時ローに固定することもできます。

## シリアル・クロック(SCLK)

シリアル・クロック(SCLK)はシミュット・トリガー入力であり、ADS1255/6の入力ピンのDIN、および出力ピンのDOUTにおけるデータのクロックに使用されます。SCLK入力にヒステリシスがあるとは言っても、SCLKを極力クリーンに保ち、グリッチによってデータが誤ってシフトしないように防止することを推奨します。SCLKが $\overline{\text{DRDY}}$ の32周期分ローであると、シリアル・インターフェイスはリセットされ、次のSCLKパルスによって新しい交信サイクルが開始されます。このタイムアウトは、シリアル・インターフェイスの伝送が遮断されたとき、交信の回復に使用できます。また、SCLKが特殊なパターンになると、チップはリセットされます。この手順に関する詳細は、「リセット」の節を参照願います。

## データ入力(DIN)およびデータ出力(DOUT)

データ入力ピン(DIN)は、SCLKとともにデータをADS1255/6に送るのに使用されます。データ出力ピン(DOUT)は、SCLKとともにデータをADS1255/6から読み出すのに使用されます。DINのデータはSCLKの立ち下りエッジでADS1255/6にシフト・インされ、DOUTのデータはSCLKの立ち上りエッジでシフト・アウトされます。DOUTは、使用されないときはハイ・インピーダンスになるので、DINとDOUTは互いに接続でき、また、双方向バスによるドライブもできます。

注意：DINとDOUTを互いに接続している場合、RDATACコマンドを実行してはなりません。

## データ・レディ( $\overline{\text{DRDY}}$ )

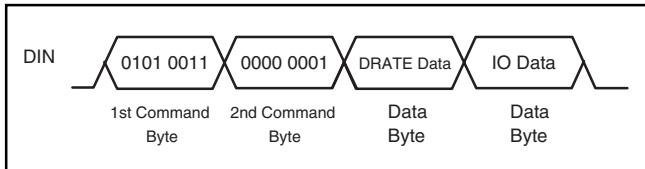

$\overline{\text{DRDY}}$ はステータス信号として使用され、変換データの読み込みに対する準備ができたことを知らせます。新しい変換データが読み込み可能になると、 $\overline{\text{DRDY}}$ がローになります。データの24ビットすべてが、リード・データ(RDATA)コマンドあるいはリード・データ・コンティニュアス(RDATAC)コマンドでリード・バックされると、 $\overline{\text{DRDY}}$ はリセットされてハイになります。また、新しい変換データに更新(アップデート)されたときもハイになります。この更新期間はデータが正しくないので、データをリードしてはなりません。データがリードされなければ、 $\overline{\text{DRDY}}$ は図24に示すように、更新の間はハイであり続けます。