ADS8331, ADS8332

JAJS517E - DECEMBER 2009 - REVISED AUGUST 2016

# ADS833x 低消費電力、16ビット、500kSPS、4/8チャネル、 ユニポーラ入力、シリアル・インターフェイス内蔵A/Dコンバータ

# 1 特長

- 低消費電力で柔軟な電源電圧範囲:

- 2.7V~5.5Vのアナログ電源

- 8.7mW (オート・ナップ・モード、VA = 2.7V、 VBD = 1.65Vで250kSPS)

- 14.2mW (VA = 2.7V, VBD = 1.65V℃ 500kSPS)

- 最大500kSPSのサンプリング・レート

- 非常に優れたDC性能:

- 2.7VにおいてINL標準値±1.2 LSB、 最大値±2 LSB

- 2.7VにおいてDNL標準値±0.6 LSB、 最大値-1/1.5 LSB

- 動作温度範囲で16ビットのNMC

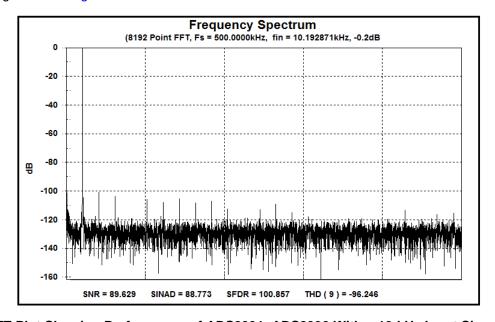

- 5V、f<sub>IN</sub> = 1kHzでの非常に優れたAC性能:

- 91.5dB SNR、101dB SFDR、-100dB THD

- 柔軟なアナログ入力の配置:

- 4/8チャネルMUX内蔵、ブレークアウト機能付き

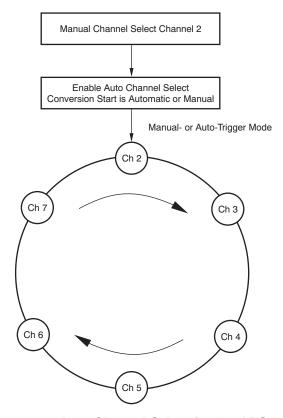

- 自動または手動でのチャネル選択およびトリガ

- その他のハードウェア機能:

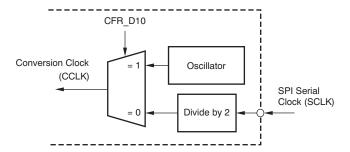

- 変換クロック(CCLK)内蔵

- ソフトウェア/ハードウェア・リセット

- ステータス、極性をプログラム可能なEOC/INT

- デイジー・チェーン・モード

- グローバルCONVST (CSから独立)

- ディープ、ナップ、およびオート・ナップ・パワーダ ウン・モード

- SPI™/DSP互換のシリアル・インターフェイス

- 独立したI/O電源: 1.65V~VA

- 最大40MHzのSCLK (VA = VBD = 5V)

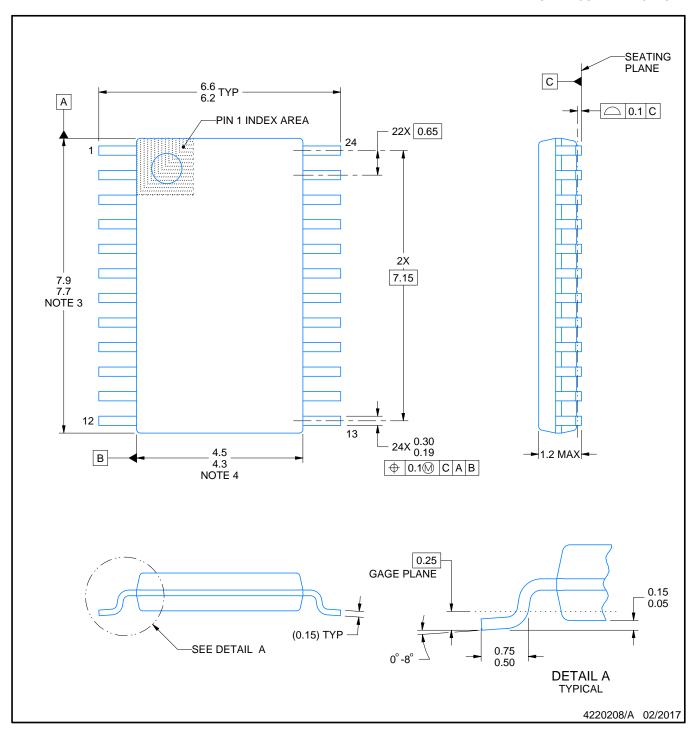

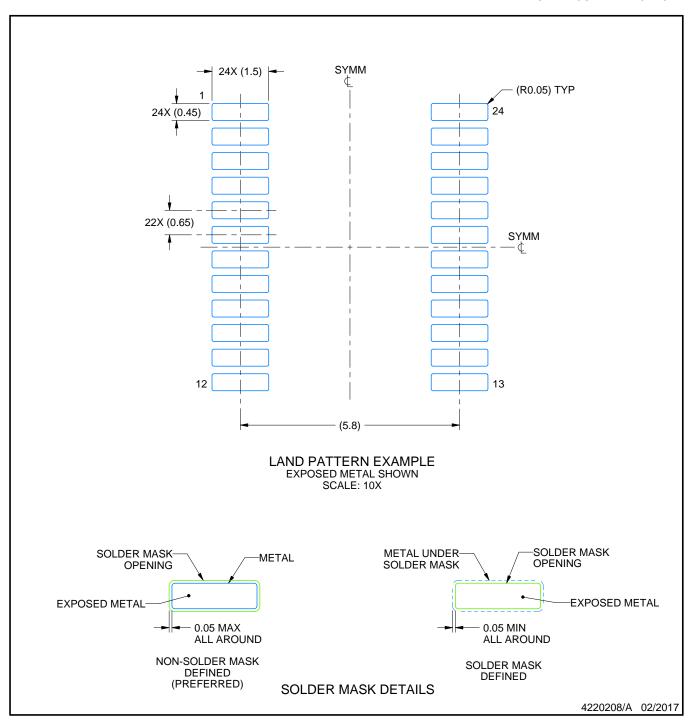

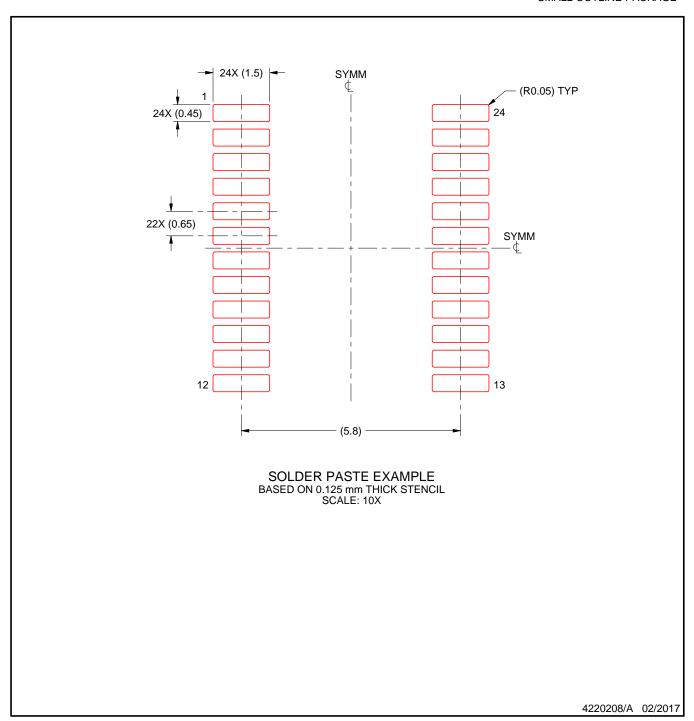

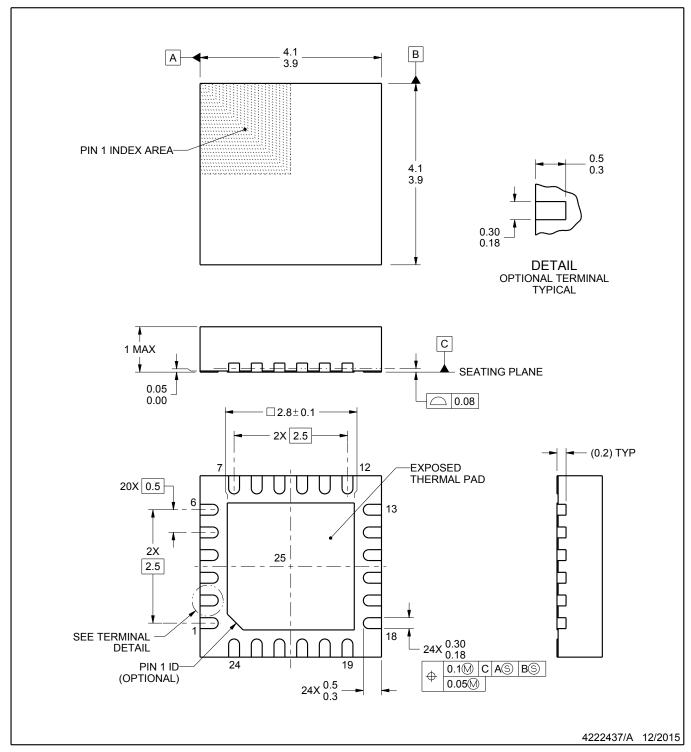

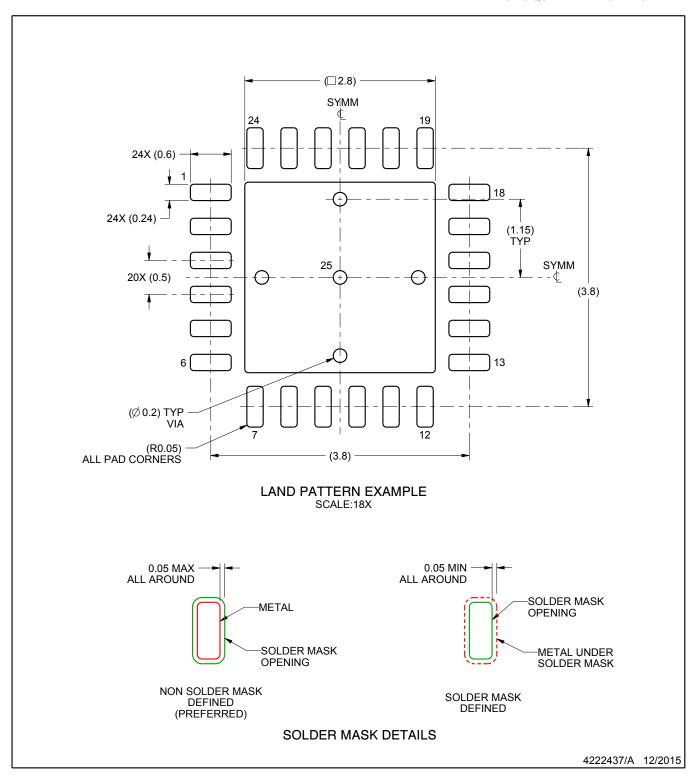

- 24ピンの4mm×4mm VQFNおよび24ピンTSSOP パッケージ

### 2 アプリケーション

- 通信

- トランスデューサ・インターフェイス

- 医療機器

- 磁力計

- 産業用プロセス制御

- データ収集システム

- 自動テスト機器

### 3 概要

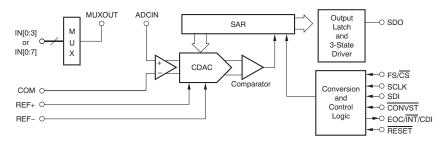

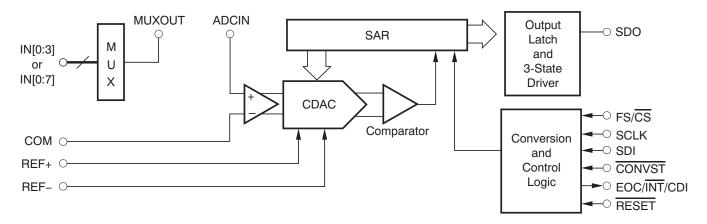

ADS8331は低消費電力、16ビット、500kSPS(サンプル/秒)のA/Dコンバータ(ADC)で、ユニポーラの4対1マルチプレクサ(MUX)入力を備えています。このデバイスには、サンプル/ホールド機能を備えた電荷再配分方式の16ビットSAR (逐次比較型) ADCが搭載されています。

ADS8332は同じコアをベースとし、ユニポーラの8対1 入力MUXが内蔵されています。どちらのデバイスも、高速で広い電圧範囲に対応するシリアル・インターフェイスが搭載されており、複数のコンバータを使用するときにはディジー・チェーン動作が可能です。

これらのコンバータは24ピンの4×4 VQFNおよび24ピン TSSOPパッケージで供給され、-40℃~85℃の工業用温 度範囲で仕様が完全に規定されています。

#### 製品情報(1)

| 型番      | パッケージ      | 本体サイズ(公称)     |

|---------|------------|---------------|

| ADC022v | VQFN (24)  | 4.00mm×4.00mm |

| ADS833x | TSSOP (24) | 7.80mm×4.40mm |

(1) 利用可能なすべてのパッケージについては、このデータシートの末 尾にある注文情報を参照してください。

#### ブロック図

| <br> |

|------|

| `/~  |

| , Y. |

|      |

| 1   | 特長 1                                                   |        | 9.2 Functional Block Diagram   | 20   |

|-----|--------------------------------------------------------|--------|--------------------------------|------|

| 2   | アプリケーション1                                              |        | 9.3 Feature Description        | 20   |

| 3   | 概要1                                                    |        | 9.4 Device Functional Modes    | 22   |

| 4   | 改訂履歴                                                   |        | 9.5 Programming                | 29   |

| 5   | Companion Products 3                                   | 10     | Application and Implementation | 37   |

| -   | •                                                      |        | 10.1 Application Information   | 37   |

| 6   | Device Comparison                                      |        | 10.2 Typical Applications      | 41   |

| 7   | Pin Configuration and Functions 4                      | 11     | Power Supply Recommendations   |      |

| 8   | Specifications6                                        | 12     |                                |      |

|     | 8.1 Absolute Maximum Ratings 6                         |        | 12.1 Layout Guidelines         |      |

|     | 8.2 ESD Ratings 6                                      |        | 12.2 Layout Example            |      |

|     | 8.3 Recommended Operating Conditions6                  | 13     | デバイスおよびドキュメントのサポート             |      |

|     | 8.4 Thermal Information                                | 13     | 13.1 ドキュメントのサポート               |      |

|     | 8.5 Electrical Characteristics: VA = 2.7 V             |        | 13.2 関連リンク                     |      |

|     | 8.6 Electrical Characteristics: VA = 5 V               |        | 13.3 ドキュメントの更新通知を受け取る方法        |      |

|     | 8.7 Timing Requirements: VA = 2.7 V 11                 |        | 13.4 コミュニティ・リソース               |      |

|     | 8.8 Timing Characteristics: VA = 5 V 12                |        | 13.5 商標                        |      |

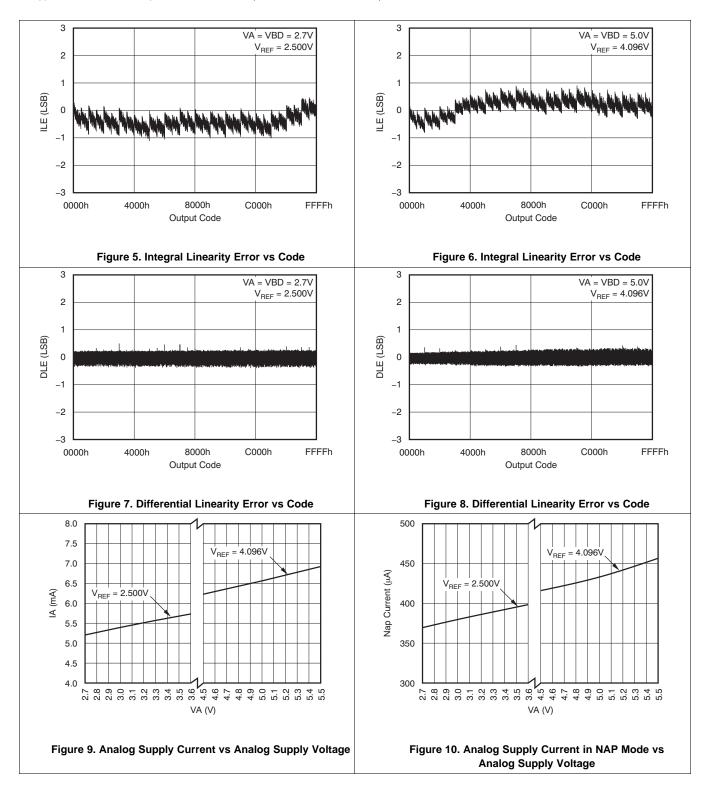

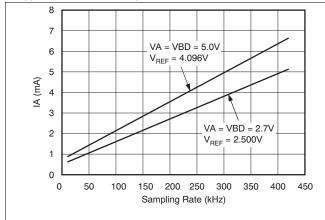

|     | 8.9 Typical Characteristics: DC Performance 14         |        | 13.6 静電気放電に関する注意事項             |      |

|     | 8.10 Typical Characteristics: AC Performance 17        |        | 13.7 Glossary                  |      |

| 9   | Detailed Description 20                                | 4.4    |                                |      |

|     | 9.1 Overview                                           | 14     | メカニカル、パッケージ、および注文情報            | 48   |

|     | <b>没訂履歴</b><br>番号末尾の英字は改訂を表しています。その改訂履歴は英語版            | に準じて   | こいます。                          |      |

| evi | sion D (October 2015) から Revision E に変更                |        |                                | Page |

| C   | Changed VA parameter maximum specification in Recomme. | nded O | perating Conditions table      | 6    |

|     |                                                        |        |                                |      |

| evi | sion C (May 2012) から Revision D に変更                    |        |                                | Page |

「ESD定格」表、「機能説明」セクション、「デバイスの機能モード」セクション、「アプリケーションと実装」セクション、「電源に関 する推奨事項」セクション、「レイアウト」セクション、「デバイスおよびドキュメントのサポート」セクション、「メカニカル、パッケー

Revision B (December 2010) から Revision C に変更

Deleted 4-channel and 8-channel rows from 14-Bit Pseudo-Diff resolution in Low-Power, High-Speed, SAR

Revision A (November 2010) から Revision B に変更

**Page**

# **5 Companion Products**

| Part number | Name                                                                                                 |

|-------------|------------------------------------------------------------------------------------------------------|

| REF3240     | 4.096V 4ppm/°C, 100uA SOT23-6 Series (Bandgap) Voltage Reference                                     |

| DAC8562     | 16-bit, dual-channel, low-power, ultra-low glitch, buffered voltage output DAC with 2.5V,4ppm/°C ref |

| DAC8568     | 16-bit, octal-channel, ultra-low glitch, voltage output DAC with 2.5V, 2ppm/°C internal reference    |

| LM5160      | Wide Input 65V, 1.5A Synchronous Step-Down DC-DC Conv                                                |

| OPA2348     | 1MHz, 45uA, RRIO, Dual Op Amp                                                                        |

# 6 Device Comparison

| RESOLUTION | CHANNELS | f <sub>S</sub> ≤ 250 kSPS | 250 kSPS < f <sub>S</sub> ≤ 500 kSPS | 500 kSPS < f <sub>S</sub> ≤ 1 MSPS |

|------------|----------|---------------------------|--------------------------------------|------------------------------------|

| 18 bits    | 8        | _                         | ADS8698                              | _                                  |

| TO DIES    | 4        | _                         | ADS8694                              | _                                  |

|            | 0        | ADS8344                   | ADS8688                              |                                    |

|            | 8        | ADS8345                   | ADS8688A                             | _                                  |

| 16 bits    |          | ADS8341                   | ADS8684                              |                                    |

|            | 4        | ADS8342                   | ADS8684A                             | _                                  |

|            |          | ADS8343                   |                                      |                                    |

|            | 8        | TLC3548                   | AD20670                              |                                    |

| 4.4 6.95   | 0        | TLC3578                   | ADS8678                              | _                                  |

| 14 bits    | 4        | TLC3544                   | - ADS8674                            | AD67262                            |

|            | 4        | TLC3574                   |                                      | ADS7263                            |

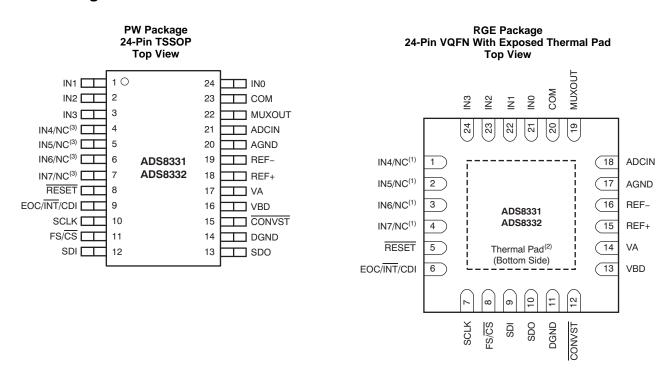

# 7 Pin Configuration and Functions

- (1) NC = No internal connection (ADS8331 only).

- (2) Connect thermal pad to analog ground.

- (3) NC = No internal connection (ADS8331 only).

# Pin Functions: ADS8331

| PIN    |       |      | 1/0 | DESCRIPTION                                                   |  |  |

|--------|-------|------|-----|---------------------------------------------------------------|--|--|

| NAME   | TSSOP | VQFN | 1/0 | DESCRIPTION                                                   |  |  |

| ADCIN  | 21    | 18   | I   | ADC input                                                     |  |  |

| AGND   | 20    | 17   | _   | Analog ground                                                 |  |  |

| DGND   | 14    | 11   | _   | Digital interface ground                                      |  |  |

| COM    | 23    | 20   | I   | Common ADC input (usually connected to AGND)                  |  |  |

| CONVST | 15    | 12   | I   | Conversion start. Freezes sample and hold, starts conversion. |  |  |

# Pin Functions: ADS8331 (continued)

| PIN                 |         |       | 1/0   | DECODINE                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|---------------------|---------|-------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME                | TSSOP   | VQFN  | 1/0   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| EOC/INT/CDI         | 9       | 6     | O/O/I | Status output. If programmed as end-of-conversion (EOC), this pin is low (default) when a conversion is in progress. If programmed as an interrupt (INT), this pin is low (default) after the end of conversion and returns high after FS/CS goes low. The polarity of EOC or INT is programmable.  This pin can also be used as a chain data input (CDI) when operated in daisy-chain mode. |  |  |

| FS/CS               | 11      | 8     | - 1   | Frame sync signal for DSP (such as TMS320™ DSP) or chip select input for SPI.                                                                                                                                                                                                                                                                                                                |  |  |

| IN <sub>[0:3]</sub> | 1-3, 24 | 21-24 | - 1   | Mux inputs                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| NC                  | 4-7     | 1-4   | _     | No connection                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| MUXOUT              | 22      | 19    | 0     | Mux output                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| REF+                | 18      | 15    | I     | External reference input                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| REF-                | 19      | 16    | _     | External reference ground (connect to AGND through an individual via on the printed-circuit-board)                                                                                                                                                                                                                                                                                           |  |  |

| RESET               | 8       | 5     | 1     | External reset (active low)                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| SCLK                | 10      | 7     | I     | SPI clock for serial interface                                                                                                                                                                                                                                                                                                                                                               |  |  |

| SDI                 | 12      | 9     | 1     | SPI serial data in                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| SDO                 | 13      | 10    | 0     | SPI serial data out                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| VA                  | 17      | 14    | _     | Analog supply, 2.7 V to 5.5 V                                                                                                                                                                                                                                                                                                                                                                |  |  |

| VBD                 | 16      | 13    | _     | Digital interface supply                                                                                                                                                                                                                                                                                                                                                                     |  |  |

# **Pin Functions: ADS8332**

| PIN                 |         | 1/0            | DESCRIPTION |                                                                                                                                                                                                                                                                                                                                                                                              |  |

|---------------------|---------|----------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME                | TSSOP   | VQFN           | I/O         | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                  |  |

| ADCIN               | 21      | 18             | I           | ADC input                                                                                                                                                                                                                                                                                                                                                                                    |  |

| AGND                | 20      | 17             | _           | Analog ground                                                                                                                                                                                                                                                                                                                                                                                |  |

| DGND                | 14      | 11             | _           | Digital interface ground                                                                                                                                                                                                                                                                                                                                                                     |  |

| COM                 | 23      | 20             | I           | Common ADC input (usually connected to AGND)                                                                                                                                                                                                                                                                                                                                                 |  |

| CONVST              | 15      | 12             | Ι           | Conversion start. Freezes sample and hold, starts conversion.                                                                                                                                                                                                                                                                                                                                |  |

| EOC/INT/CDI         | 9       | 6              | O/O/I       | Status output. If programmed as end-of-conversion (EOC), this pin is low (default) when a conversion is in progress. If programmed as an interrupt (INT), this pin is low (default) after the end of conversion and returns high after FS/CS goes low. The polarity of EOC or INT is programmable.  This pin can also be used as a chain data input (CDI) when operated in daisy-chain mode. |  |

| FS/CS               | 11      | 8              | - 1         | Frame sync signal for DSP (such as TMS320™ DSP) or chip select input for SPI.                                                                                                                                                                                                                                                                                                                |  |

| IN <sub>[0:7]</sub> | 1-7, 24 | 1-4, 21-<br>24 | I           | Mux inputs                                                                                                                                                                                                                                                                                                                                                                                   |  |

| MUXOUT              | 22      | 19             | 0           | Mux output                                                                                                                                                                                                                                                                                                                                                                                   |  |

| REF+                | 18      | 15             | I           | External reference input                                                                                                                                                                                                                                                                                                                                                                     |  |

| REF-                | 19      | 16             | _           | External reference ground (connect to AGND through an individual via on the printed-circuit-board)                                                                                                                                                                                                                                                                                           |  |

| RESET               | 8       | 5              | I           | External reset (active low)                                                                                                                                                                                                                                                                                                                                                                  |  |

| SCLK                | 10      | 7              | - 1         | SPI clock for serial interface                                                                                                                                                                                                                                                                                                                                                               |  |

| SDI                 | 12      | 9              | I           | SPI serial data in                                                                                                                                                                                                                                                                                                                                                                           |  |

| SDO                 | 13      | 10             | 0           | SPI serial data out                                                                                                                                                                                                                                                                                                                                                                          |  |

| VA                  | 17      | 14             | _           | Analog supply, 2.7 V to 5.5 V                                                                                                                                                                                                                                                                                                                                                                |  |

| VBD                 | 16      | 13             | _           | Digital interface supply                                                                                                                                                                                                                                                                                                                                                                     |  |

# 8 Specifications

### 8.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                                                |                                               | MIN                   | MAX                                  | UNIT |

|------------------------------------------------|-----------------------------------------------|-----------------------|--------------------------------------|------|

|                                                | IN <sub>X</sub> , MUXOUT, ADCIN, REF+ to AGND | -0.3                  | VA + 0.3                             |      |

|                                                | COM, REF- to AGND                             | -0.3                  | 0.3                                  |      |

| Voltage                                        | VA to AGND                                    | -0.3                  | 7                                    | V    |

|                                                | VBD to DGND                                   | -0.3                  | 7                                    |      |

|                                                | AGND to DGND                                  | -0.3                  | 0.3                                  |      |

| Digital input                                  | voltage to DGND                               | -0.3                  | VBD + 0.3                            | V    |

| Digital output                                 | voltage to DGND                               | -0.3                  | VBD + 0.3                            | ٧    |

| 4 × 4                                          | Power dissipation                             | (T <sub>J</sub> Max - | W                                    |      |

| VQFN-24<br>Package                             | R <sub>θJA</sub> thermal impedance            |                       | 47                                   | °C/W |

| TSSOP-24                                       | Power dissipation                             | (T <sub>J</sub> Max   | – T <sub>A</sub> ) / θ <sub>JA</sub> | W    |

| Package                                        | R <sub>0JA</sub> thermal impedance            |                       | 47                                   | °C/W |

| Operating free-air temperature, T <sub>A</sub> |                                               | -40                   | 85                                   | °C   |

| Junction tem                                   | Junction temperature, T <sub>J</sub> Max      |                       | 150                                  | °C   |

| Storage temp                                   | perature range, T <sub>stg</sub>              | -65                   | 150                                  | °C   |

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated is not implied. Exposure to absolutemaximum-rated conditions for extended periods may affect device reliability.

# 8.2 ESD Ratings

|                    |                         |                                                                     | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±500  | V    |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 8.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|     |                        | MIN  | NOM | MAX      | UNIT |

|-----|------------------------|------|-----|----------|------|

| VA  | Analog supply voltage  | 2.7  | 3   | 5.5      | V    |

| VBD | Digital supply voltage | 1.65 | 3   | VA + 0.2 | V    |

### 8.4 Thermal Information

|                      |                                              | ADS        | ADS833x    |      |  |  |

|----------------------|----------------------------------------------|------------|------------|------|--|--|

|                      | THERMAL METRIC <sup>(1)</sup>                | RGE (VQFN) | PW (TSSOP) | UNIT |  |  |

|                      |                                              | 24 PINS    | 24 PINS    |      |  |  |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 31.9       | 78.3       | °C/W |  |  |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 29.2       | 12.1       | °C/W |  |  |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 8.7        | 33.8       | °C/W |  |  |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.3        | 0.3        | °C/W |  |  |

| ΨЈВ                  | Junction-to-board characterization parameter | 8.7        | 33.5       | °C/W |  |  |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 2.25       | NA         | °C/W |  |  |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

# 8.5 Electrical Characteristics: VA = 2.7 V

at  $T_A = -40$ °C to 85°C, VA = 2.7 V, VBD = 1.65 V to 2.7 V,  $V_{REF} = 2.5$  V, and  $f_{SAMPLE} = 500$  kSPS (unless otherwise noted)

|                      | PARAMETER                                      | TEST C                                          | ONDITIONS            | MIN        | TYP   | MAX        | UNIT               |  |

|----------------------|------------------------------------------------|-------------------------------------------------|----------------------|------------|-------|------------|--------------------|--|

| ANALOG               | INPUT                                          |                                                 |                      |            |       |            |                    |  |

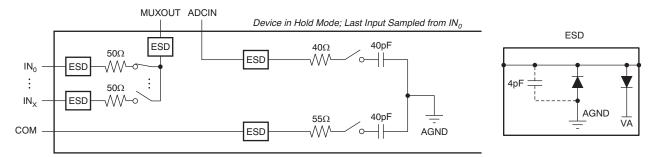

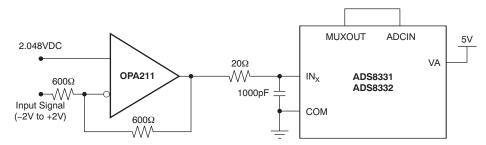

|                      | Full-scale input voltage (1)                   | IN <sub>X</sub> – COM, ADCIN – CO               | M                    | 0          |       | $V_{REF}$  | V                  |  |

|                      | Al                                             | IN <sub>X</sub> , ADCIN                         |                      | AGND - 0.2 |       | VA + 0.2   | , ,                |  |

|                      | Absolute input voltage                         | СОМ                                             | СОМ                  |            |       | AGND + 0.2 | V                  |  |

|                      | Input capacitance                              | ADCIN                                           |                      |            | 40    | 45         | pF                 |  |

|                      | Input leakage current                          | Unselected ADC input                            |                      |            | ±1    |            | nA                 |  |

| SYSTEM               | PERFORMANCE                                    |                                                 |                      |            |       |            |                    |  |

|                      | Resolution                                     |                                                 |                      |            | 16    |            | Bits               |  |

|                      | No missing codes                               |                                                 |                      | 16         |       |            | Bits               |  |

| INII                 | Integral linearity                             | ADS8331I, ADS8332I                              |                      | -3         | ±2    | 3          | LSB <sup>(2)</sup> |  |

| INL                  | Integral linearity                             | ADS8331IB, ADS8332IB                            |                      | -2         | ±1.2  | 2          | LODY               |  |

| DNL                  | Differential linearity                         | ADS8331I, ADS8332I                              |                      | -1         | ±0.6  | 2          | LSB <sup>(2)</sup> |  |

| DINL                 | Differential linearity                         | ADS8331IB, ADS8332IB                            |                      | -1         | ±0.6  | 1.5        | LOBY               |  |

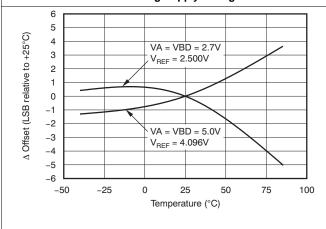

| Eo                   | Offset error <sup>(3)</sup>                    |                                                 |                      | -0.5       | ±0.15 | 0.5        | mV                 |  |

|                      | Offset error drift                             |                                                 |                      |            | ±1    |            | PPM/°C             |  |

|                      | Offset error matching                          |                                                 |                      | -0.2       |       | 0.2        | mV                 |  |

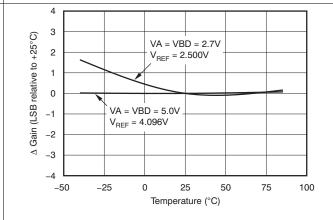

| E <sub>G</sub>       | Gain error                                     |                                                 |                      | -0.25      | -0.06 | 0.25       | %FSR               |  |

|                      | Gain error drift                               |                                                 |                      |            | ±0.4  |            | PPM/°C             |  |

|                      | Gain error matching                            |                                                 |                      | -0.003     |       | 0.003      | %FSR               |  |

|                      | Transition noise                               |                                                 |                      |            | 28    |            | μV RMS             |  |

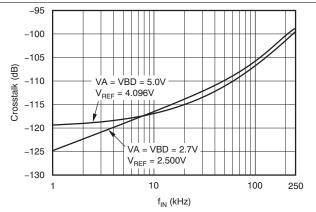

| PSRR                 | Power-supply rejection ratio                   |                                                 |                      |            | 74    |            | dB                 |  |

| SAMPLIN              | NG DYNAMICS                                    |                                                 |                      |            |       |            |                    |  |

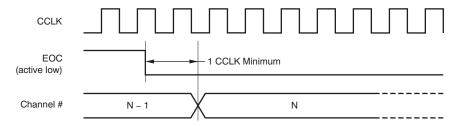

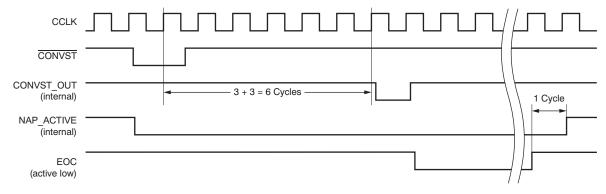

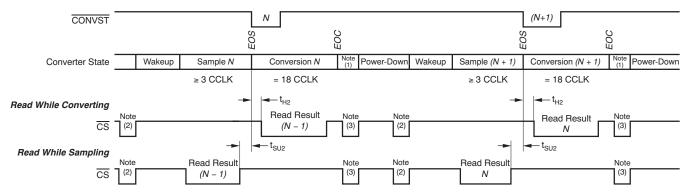

| t <sub>CONV</sub>    | Conversion time                                |                                                 |                      |            | 18    |            | CCLK               |  |

| t <sub>SAMPLE1</sub> | A aguicition time                              | Manual-trigger mode                             |                      | 3          |       |            | CCLK               |  |

| t <sub>SAMPLE2</sub> | Acquisition time                               | Auto-trigger mode                               |                      |            | 3     |            | CCLK               |  |

|                      | Throughput rate                                |                                                 |                      |            |       | 500        | kSPS               |  |

| DYNAMIC              | C CHARACTERISTICS                              |                                                 |                      |            |       |            |                    |  |

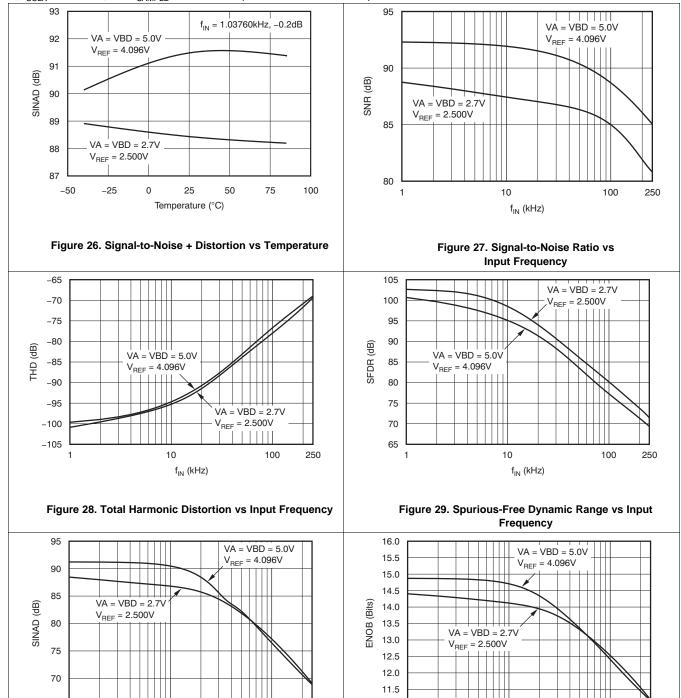

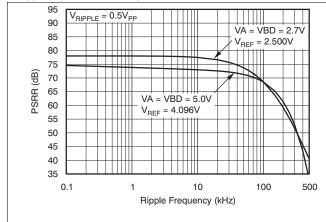

| THD                  | Total harmonic distortion (4)                  | $V_{IN} = 2.5 V_{PP}$ at 1 kHz                  |                      |            | -101  |            | dB                 |  |

| טווו                 | Total Harmonic distortion **                   | $V_{IN} = 2.5 V_{PP}$ at 10 kHz                 |                      |            | -95   |            | uБ                 |  |

|                      |                                                | $V_{IN} = 2.5 V_{PP}$ at 1 kHz                  | ADS8331I, ADS8332I   |            | 88    |            |                    |  |

| SNR                  | Signal-to-noise ratio                          | VIN = 2.5 VPP at 1 KHZ                          | ADS8331IB, ADS8332IB |            | 89    |            | dB                 |  |

| SINIX                | Signal-to-noise ratio                          | $V_{IN} = 2.5 V_{PP}$ at 10 kHz                 | ADS8331I, ADS8332I   |            | 86.5  |            | uБ                 |  |

|                      |                                                | V <sub>IN</sub> = 2.5 V <sub>PP</sub> at 10 K12 | ADS8331IB, ADS8332IB |            | 87.5  |            |                    |  |

|                      |                                                | $V_{IN} = 2.5 V_{PP}$ at 1 kHz                  | ADS8331I, ADS8332I   |            | 87.5  |            |                    |  |

| SINAD                | Signal to point a distortion                   | VIN = 2.3 VPP at 1 KHZ                          | ADS8331IB, ADS8332IB |            | 88.5  |            | ٩D                 |  |

| SINAD                | Signal-to-noise + distortion                   | \/ - 2.5.\/ ot 10.k∐z                           | ADS8331I, ADS8332I   |            | 86    |            | dB                 |  |

|                      |                                                | $V_{IN} = 2.5 V_{PP}$ at 10 kHz                 | ADS8331IB, ADS8332IB |            | 87    |            |                    |  |

| SFDR                 | V <sub>IN</sub> = 2.5 V <sub>PP</sub> at 1 kHz |                                                 |                      |            | 103   |            | dB                 |  |

| JI DK                | Spurious-free dynamic range                    | $V_{IN} = 2.5 V_{PP}$ at 10 kHz                 |                      |            | 98    |            | ub                 |  |

|                      | Crosstalk                                      | $V_{IN} = 2.5 V_{PP}$ at 1 kHz                  |                      |            | 125   |            | dB                 |  |

|                      | CIUSSIAIK                                      | $V_{IN} = 2.5 V_{PP}$ at 100 kHz                |                      |            | 108   |            | ub                 |  |

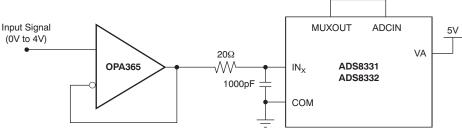

| -                    | 3 dB small signal bandwidth                    | IN <sub>X</sub> – COM with MUXOUT               | tied to ADCIN        |            | 17    |            | MU-                |  |

|                      | –3-dB small-signal bandwidth                   | ADCIN – COM                                     |                      |            | 30    |            | MHz                |  |

<sup>(1)</sup> Ideal input span; does not include gain or offset error.

<sup>(3)</sup> Measured relative to an ideal full-scale input (IN<sub>X</sub> – COM) of 2.5 V when VA = 2.7 V.

(4) Calculated on the first nine harmonics of the input frequency.

# **Electrical Characteristics: VA = 2.7 V (continued)**

at  $T_A = -40$ °C to 85°C, VA = 2.7 V, VBD = 1.65 V to 2.7 V,  $V_{REF} = 2.5$  V, and  $f_{SAMPLE} = 500$  kSPS (unless otherwise noted)

|                 | PARAME                            | TER                    | TEST CONDITIONS                                                                                                              | MIN        | TYP         | MAX        | UNIT |

|-----------------|-----------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------|------------|-------------|------------|------|

| CLOCK           | (                                 |                        |                                                                                                                              |            |             | ·          |      |

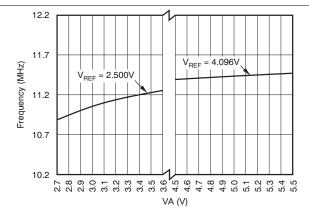

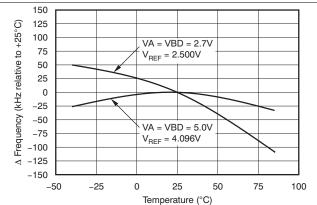

|                 | Internal conver                   | rsion clock            |                                                                                                                              | 10.5       | 11          | 12.2       | MHz  |

|                 | 0011/                             |                        | Used as I/O clock only                                                                                                       |            |             | 25         | MHz  |

|                 | SCLK external                     | serial clock           | Used as both I/O clock and conversion clock                                                                                  | 1          |             | 21         | MHz  |

| EXTER           | NAL VOLTAGE R                     | EFERENCE INPUT         |                                                                                                                              |            |             |            |      |

|                 | Input                             | (REF+) - (REF-)        |                                                                                                                              | 1.2        |             | 2.525      |      |

| $V_{REF}$       | reference<br>range <sup>(5)</sup> | (REF-) - AGND          |                                                                                                                              | -0.1       |             | 0.1        | V    |

|                 | Resistance (6)                    | *                      | Reference input                                                                                                              |            | 20          |            | kΩ   |

| DIGITA          | L INPUT/OUTPUT                    | Г                      |                                                                                                                              | II.        |             |            |      |

|                 | Logic family                      |                        |                                                                                                                              |            | CMOS        |            |      |

| .,              | 18.1.1.                           |                        | 1.65 V < VBD < 2.5 V                                                                                                         | 0.8 × VBD  |             | VBD + 0.3  | .,   |

| $V_{IH}$        | High-level inpu                   | it voitage             | 2.5 V ≤ VBD ≤ VA                                                                                                             | 0.65 × VBD |             | VBD + 0.3  | V    |

| .,              | 1 1 1                             |                        | 1.65 < VBD < 2.5 V                                                                                                           | -0.3       |             | 0.1 × VBD  | .,   |

| $V_{IL}$        | Low-level inpu                    | t voltage              | 2.5 V ≤ VBD ≤ VA                                                                                                             | -0.3       |             | 0.25 × VBD | V    |

| l <sub>l</sub>  | Input current                     |                        | V <sub>IN</sub> = VBD or DGND                                                                                                | -1         |             | 1          | μА   |

| Cı              | Input capacitar                   | nce                    |                                                                                                                              |            | 5           |            | pF   |

| V <sub>OH</sub> | High-level outp                   | out voltage            | VA ≥ VBD ≥ 1.65V, I <sub>O</sub> = 100 μA                                                                                    | VBD - 0.6  |             | VBD        | V    |

| V <sub>OL</sub> | Low-level outp                    | ut voltage             | $VA \ge VBD \ge 1.65 \text{ V}, I_O = -100 \mu\text{A}$                                                                      | 0          |             | 0.4        | V    |

| Co              | SDO pin capad                     | citance                | Hi-Z state                                                                                                                   |            | 5           |            | pF   |

| C <sub>L</sub>  | Load capacitar                    | nce                    |                                                                                                                              |            |             | 30         | pF   |

|                 | Data format                       |                        |                                                                                                                              | Stra       | aight binar | у          |      |

| POWER           | R-SUPPLY REQUI                    | IREMENTS               |                                                                                                                              |            |             |            |      |

| VA              | Analog supply                     | voltage <sup>(5)</sup> |                                                                                                                              | 2.7        |             | 3.6        | V    |

| VBD             | Digital I/O supp                  | ply voltage            |                                                                                                                              | 1.65       |             | VA + 0.2   | V    |

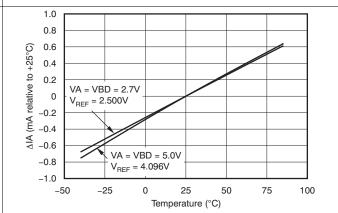

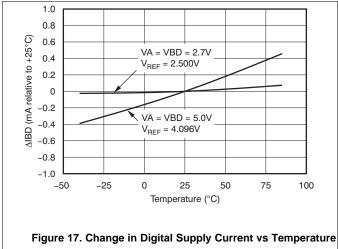

|                 |                                   |                        | f <sub>SAMPLE</sub> = 500 kSPS                                                                                               |            | 5.2         | 6.5        | mA   |

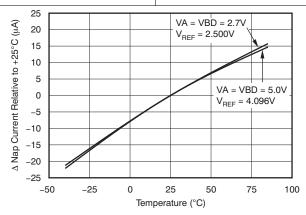

| IA              | Analog gunnly                     | ourrant                | f <sub>SAMPLE</sub> = 250 kSPS in Auto-NAP mode                                                                              |            | 3.2         |            | ША   |

| IA              | Analog supply                     | current                | Nap mode, SCLK = VBD or DGND                                                                                                 |            | 325         | 400        | μА   |

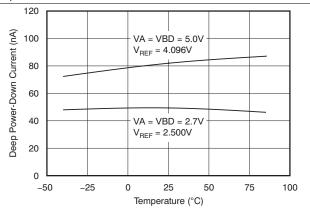

|                 |                                   |                        | Deep PD mode, SCLK = VBD or DGND                                                                                             |            | 50          | 250        | nA   |

| IBD             | Digital I/O augu                  | nhy ourrant            | f <sub>SAMPLE</sub> = 500 kilobytes per second                                                                               |            | 0.1         | 0.4        | mΛ   |

| טסו             | Digital I/O sup                   | pry current            | f <sub>SAMPLE</sub> = 250 kSPS in Auto-NAP mode                                                                              |            | 0.05        |            | mA   |

|                 |                                   |                        | VA = 2.7 V, VBD = 1.65 V, f <sub>SAMPLE</sub> = 500 kSPS                                                                     |            | 14.2        | 18.2       |      |

|                 | Power dissipation                 |                        | $\label{eq:VA} \mbox{VA} = 2.7\mbox{V, VBD} = 1.65 \mbox{ V, } \mbox{f}_{\mbox{SAMPLE}} = 250 \mbox{ kSPS in Auto-NAP mode}$ |            | 8.72        |            | mW   |

| TEMPE           | RATURE RANGE                      |                        |                                                                                                                              |            |             |            |      |

| T <sub>A</sub>  | Operating free                    | -air temperature       |                                                                                                                              | -40        |             | 85         | °C   |

<sup>(5)</sup> The ADS8331, ADS8332 operates with VA from 2.7 V to 5.5 V, and V<sub>REF</sub> between 1.2 V and VA. However, the device may not meet the specifications listed in the *Electrical Characteristics* when VA is from 3.6 V to 4.5 V.

(6) Can vary ±30%.

### 8.6 Electrical Characteristics: VA = 5 V

at  $T_A = -40$ °C to 85°C, VA = 5 V, VBD = 1.65 V to 5 V,  $V_{REF} = 4.096$  V, and  $f_{SAMPLE} = 500$  kSPS (unless otherwise noted)

|                              | PARAMETER                     | TEST CO                                    | NDITIONS                | MIN        | TYP   | MAX        | UNIT               |  |

|------------------------------|-------------------------------|--------------------------------------------|-------------------------|------------|-------|------------|--------------------|--|

| ANALOG I                     | NPUT                          |                                            |                         |            |       |            |                    |  |

|                              | Full-scale input voltage (1)  | IN <sub>X</sub> – COM, ADCIN               | I – COM                 | 0          |       | $V_{REF}$  | V                  |  |

|                              | Abaduta input valtaga         | IN <sub>X</sub> , ADCIN                    |                         | AGND - 0.2 |       | VA + 0.2   | V                  |  |

|                              | Absolute input voltage        | СОМ                                        |                         | AGND - 0.2 |       | AGND + 0.2 | V                  |  |

|                              | Input capacitance             | ADCIN                                      |                         |            | 40    | 45         | pF                 |  |

|                              | Input leakage current         | Unselected ADC in                          | put                     |            | ±1    |            | nA                 |  |

| SYSTEM P                     | ERFORMANCE                    |                                            |                         |            |       |            |                    |  |

|                              | Resolution                    |                                            |                         |            | 16    |            | Bits               |  |

|                              | No missing codes              |                                            |                         | 16         |       |            | Bits               |  |

| INL                          | Integral linearity            | ADS8331I, ADS833                           | 321                     | -3         | ±2    | 3          | LSB <sup>(2)</sup> |  |

|                              | integral intearty             | ADS8331IB, ADS8                            | 332IB                   | -2         | ±1    | 2          |                    |  |

| DNL                          | Differential linearity        | ADS8331I, ADS833                           | 321                     | -1         | ±1    | 2          | LSB <sup>(2)</sup> |  |

| DIVL                         | -                             | ADS8331IB, ADS8                            | 332IB                   | -1         | ±0.5  | 1.5        | LOD                |  |

| Eo                           | Offset error <sup>(3)</sup>   |                                            |                         | -1         | ±0.23 | 1          | mV                 |  |

|                              | Offset error drift            |                                            |                         |            | ±1    |            | PPM/°C             |  |

|                              | Offset error matching         |                                            |                         | -0.125     |       | 0.125      | mV                 |  |

| E <sub>G</sub>               | Gain error                    |                                            |                         | -0.25      | -0.06 | 0.25       | %FSR               |  |

|                              | Gain error drift              |                                            |                         |            | ±0.02 |            | PPM/°C             |  |

|                              | Gain error matching           |                                            |                         | -0.003     |       | 0.003      | %FSR               |  |

|                              | Transition noise              |                                            |                         |            | 30    |            | μV RMS             |  |

| PSRR                         | Power-supply rejection ratio  |                                            |                         |            | 78    |            | dB                 |  |

| SAMPLING                     | DYNAMICS                      |                                            |                         |            |       |            |                    |  |

| t <sub>CONV</sub>            | Conversion time               |                                            |                         |            | 18    |            | CCLK               |  |

| t <sub>SAMPLE1</sub>         | Acquisition time              | Manual-trigger mod                         | le                      | 3 3        |       |            | CCLK               |  |

| t <sub>SAMPLE2</sub>         | 7 toquiolilon timo            | Auto-trigger mode                          |                         |            |       |            | OOLIT              |  |

|                              | Throughput rate               |                                            |                         |            |       | 500        | kSPS               |  |

| DYNAMIC                      | CHARACTERISTICS               |                                            |                         | 1          |       |            |                    |  |

|                              |                               | $V_{IN} = 4.096 V_{PP}$ at                 | 1 kHz                   |            | -100  |            |                    |  |

| THD                          | Total harmonic distortion (4) | $V_{IN} = 4.096 V_{PP}$ at                 | ADS8331I,<br>ADS8332I   |            | -94   |            | dB                 |  |

|                              |                               | 10 kHz                                     | ADS8331IB,<br>ADS8332IB |            | -95   |            |                    |  |

|                              |                               | V <sub>IN</sub> = 4.096 V <sub>PP</sub> at | ADS8331I,<br>ADS8332I   |            | 90.5  |            |                    |  |

| SNR                          | Signal-to-noise ratio         | 1 kHz                                      | ADS8331IB,<br>ADS8332IB |            | 91.5  |            | dB                 |  |

|                              |                               | $V_{IN} = 4.096 V_{PP}$ at                 | 10 kHz                  |            | 88    |            |                    |  |

|                              |                               | $V_{IN} = 4.096 V_{PP}$ at                 | ADS8331I,<br>ADS8332I   |            | 90    |            |                    |  |

| SINAD                        | Signal-to-noise + distortion  | 1 kHz                                      | ADS8331IB,<br>ADS8332IB |            | 91    |            | dB                 |  |

|                              |                               | $V_{IN} = 4.096 V_{PP}$ at                 | 1                       |            | 87    |            |                    |  |

| CEDB                         | Spurious-free dynamic range   | $V_{IN} = 4.096 V_{PP}$ at                 | 1 kHz                   |            | 101   |            | <b>ال</b>          |  |

| SFDR                         | Spurious-free dynamic range   | $V_{IN} = 4.096 V_{PP}$ at                 | 10 kHz                  |            | 96    |            | dB                 |  |

|                              | Crosstelle                    | $V_{IN} = 4.096 V_{PP}$ at                 | 1 kHz                   |            | 119   |            | ۲ <u>۰</u>         |  |

|                              | Crosstalk                     | $V_{IN} = 4.096 V_{PP}$ at                 | 100 kHz                 |            | 107   |            | dB                 |  |

|                              | –3-dB small-signal bandwidth  | IN <sub>X</sub> – COM with MU<br>ADCIN     | JXOUT tied to           |            | 22    |            | MHz                |  |

| -5-db smail-signal bandwidth |                               | ADCIN – COM                                |                         | 40         |       |            |                    |  |

Ideal input span; does not include gain or offset error. LSB means least significant bit.

<sup>(2)</sup>

Measured relative to an ideal full-scale input ( $IN_X$  – COM) of 4.096 V when VA = 5 V. Calculated on the first nine harmonics of the input frequency.

# **Electrical Characteristics: VA = 5 V (continued)**

at  $T_A = -40$ °C to 85°C, VA = 5 V, VBD = 1.65 V to 5 V,  $V_{REF} = 4.096$  V, and  $f_{SAMPLE} = 500$  kSPS (unless otherwise noted)

|                 | PARAMETE                   | R                   | TEST CONDITIONS                                                              | MIN        | TYP          | MAX        | UNIT |  |

|-----------------|----------------------------|---------------------|------------------------------------------------------------------------------|------------|--------------|------------|------|--|

| CLOCK           |                            |                     |                                                                              |            |              |            |      |  |

|                 | Internal conversion        | n clock frequency   |                                                                              | 10.9       | 11.5         | 12.6       | MHz  |  |

|                 |                            |                     | Used as I/O clock only                                                       |            |              | 40         |      |  |

|                 | SCLK external serial clock |                     | Used as both I/O clock and conversion clock                                  | 1          |              | 21         | MHz  |  |

| EXTERN          | AL VOLTAGE REFERI          | ENCE INPUT          |                                                                              |            |              |            |      |  |

|                 | Input reference            | (REF+) - (REF-)     |                                                                              | 1.2        | 4.096        | 4.2        | V    |  |

| $V_{REF}$       | range <sup>(5)</sup>       | (REF-) - AGND       |                                                                              | -0.1       |              | 0.1        | V    |  |

|                 | Resistance (6)             |                     | Reference input                                                              |            | 20           |            | kΩ   |  |

| DIGITAL         | INPUT/OUTPUT               |                     |                                                                              |            |              |            |      |  |

|                 | Logic family               |                     |                                                                              |            | CMOS         |            |      |  |

|                 |                            |                     | 1.65 < VBD < 2.5 V                                                           | 0.8 × VBD  |              | VBD + 0.3  |      |  |

| $V_{IH}$        | High-level input vo        | oltage              | 2.5 V ≤ VBD ≤ VA                                                             | 0.65 × VBD |              | VBD + 0.3  | V    |  |

|                 |                            |                     | 1.65 < VBD < 2.5 V                                                           | -0.3       |              | 0.1 × VBD  |      |  |

| $V_{IL}$        | Low-level input vo         | Itage               | 2.5 V ≤ VBD ≤ VA                                                             | -0.3       |              | 0.25 × VBD | V    |  |

| I <sub>I</sub>  | Input current              |                     | V <sub>IN</sub> = VBD or DGND                                                | -1         |              | 1          | μA   |  |

| C <sub>I</sub>  | Input capacitance          |                     |                                                                              |            | 5            |            | pF   |  |

| V <sub>OH</sub> | High-level output v        | /oltage             | VA ≥ VBD ≥ 1.65 V, I <sub>O</sub> = 100 μA                                   | VBD - 0.6  |              | VBD        | V    |  |

| V <sub>OL</sub> | Low-level output v         | oltage              | VA ≥ VBD ≥ 1.65 V, I <sub>O</sub> = −100 μA                                  | 0          |              | 0.4        | V    |  |

| Co              | SDO pin capacitar          | nce                 | Hi-Z state                                                                   |            | 5            |            | pF   |  |

| C <sub>L</sub>  | Load capacitance           |                     |                                                                              |            |              | 30         | pF   |  |

|                 | Data format                |                     |                                                                              | Str        | aight binary |            |      |  |

| POWER-          | SUPPLY REQUIREME           | NTS                 |                                                                              |            |              |            |      |  |

| VA              | Analog supply volt         | tage <sup>(5)</sup> |                                                                              | 4.5        | 5            | 5.5        | V    |  |

| VBD             | Digital I/O supply         | voltage             |                                                                              | 1.65       |              | VA + 0.2   | V    |  |

|                 | ,                          |                     | f <sub>SAMPLE</sub> = 500 kSPS                                               |            | 6.6          | 7.75       |      |  |

|                 |                            |                     | f <sub>SAMPLE</sub> = 250 kSPS in Auto-NAP mode                              |            | 4.2          |            | mA   |  |

| IA              | Analog supply cur          | rent                | Nap mode, SCLK = VBD or DGND                                                 |            | 390          | 500        | μА   |  |

|                 |                            |                     | Deep PD mode, SCLK = VBD or DGND                                             |            | 80           | 250        | nA   |  |

|                 |                            |                     | f <sub>SAMPLE</sub> = 500 kSPS                                               |            | 1.2 2        |            |      |  |

| IBD             | Digital I/O supply         | current             | f <sub>SAMPLE</sub> = 250 kSPS in Auto-NAP mode                              |            | 0.7          |            | mA   |  |

|                 | Down diagin - 41           |                     | VA = 5 V, VBD = 5 V, f <sub>SAMPLE</sub> = 500<br>kSPS                       |            | 39           | 48.75      | \A/  |  |

|                 | Power dissipation          |                     | VA = 5 V, VBD = 5 V, f <sub>SAMPLE</sub> = 250<br>kSPS in Auto-NAP mode 24.5 |            | 24.5         |            | mW   |  |

| TEMPER          | ATURE RANGE                |                     | '                                                                            |            |              | J.         |      |  |

| T <sub>A</sub>  | Operating free-air         | temperature         |                                                                              | -40        |              | 85         | °C   |  |

|                 |                            |                     |                                                                              |            |              |            |      |  |

<sup>(5)</sup> The ADS8331, ADS8332 operates with VA from 2.7 V to 5.5 V, and V<sub>REF</sub> between 1.2 V and VA. However, the device may not meet the specifications listed in the *Electrical Characteristics* when VA is from 3.6 V to 4.5 V.

(6) Can vary ±30%.

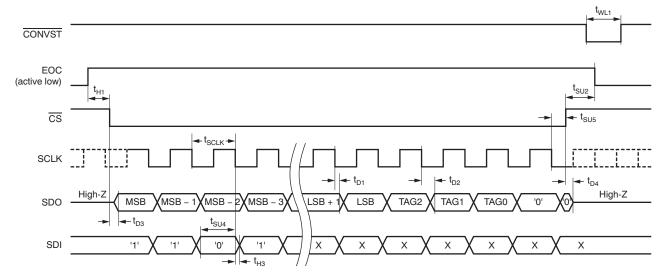

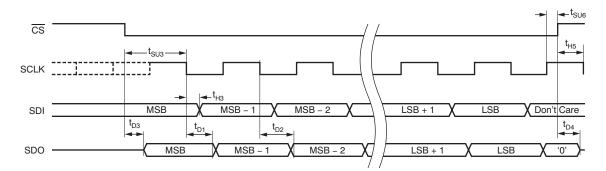

# 8.7 Timing Requirements: VA = 2.7 V

at  $T_A = -40$ °C to 85°C, VA = 2.7 V, and VBD = 1.65 V (unless otherwise noted)<sup>(1)(2)</sup>

| ,,                              |                                                                                               | ,                                                   | MIN  | NOM | MAX                  | UNIT    |

|---------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------|------|-----|----------------------|---------|

|                                 | Francisco con considera electric CCLIV                                                        | External, f <sub>CCLK</sub> = 1/2 f <sub>SCLK</sub> | 0.5  |     | 10.5                 | N 41 1- |

| f <sub>CCLK</sub>               | Frequency, conversion clock, CCLK                                                             | Internal                                            | 10.5 | 11  | 12.2                 | MHz     |

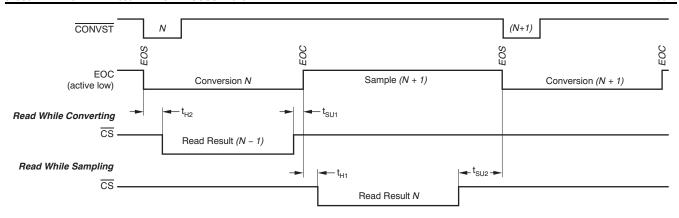

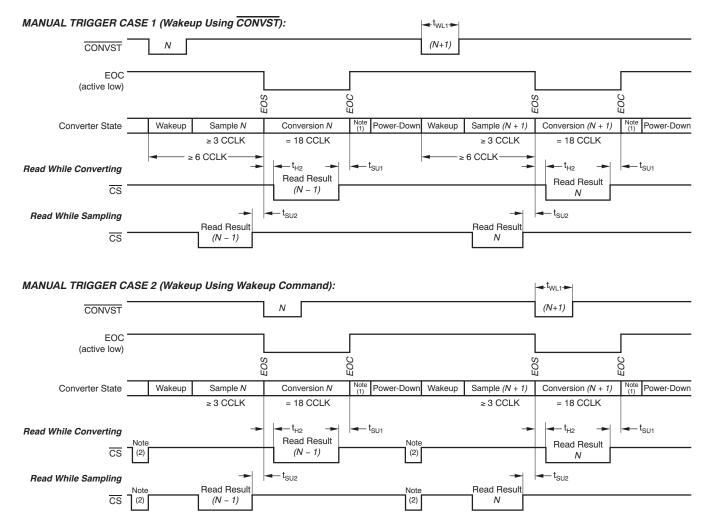

| t <sub>SU1</sub>                | Setup time, rising edge of $\overline{\text{CS}}$ to $\text{EOC}^{(3)}$                       | Read while converting                               | 1    |     |                      | CCLK    |

| t <sub>H1</sub>                 | CS hold time with respect to EOC (3)                                                          | Read while sampling                                 | 25   |     |                      | ns      |

| t <sub>WL1</sub>                | Pulse duration, CONVST low                                                                    |                                                     | 40   |     |                      | ns      |

| t <sub>WH1</sub>                | Pulse duration, CS high                                                                       |                                                     | 40   |     |                      | ns      |

| t <sub>SU2</sub>                | Setup time, rising edge of $\overline{\text{CS}}$ to EOS                                      | Read while sampling                                 | 25   |     |                      | ns      |

| t <sub>H2</sub>                 | CS hold time with respect to EOS                                                              | Read while converting                               | 25   |     |                      | ns      |

| t <sub>SU3</sub>                | Setup time, falling edge of $\overline{\text{CS}}$ to first falling edge of SCLK              |                                                     | 14   |     |                      | ns      |

| t <sub>WL2</sub>                | Pulse duration, SCLK low                                                                      |                                                     | 17   |     | $t_{SCLK} - t_{WH2}$ | ns      |

| t <sub>WH2</sub>                | Pulse duration, SCLK high                                                                     |                                                     | 12   |     | $t_{SCLK} - t_{WL2}$ | ns      |

|                                 | Cycle time, SCLK                                                                              | I/O clock only                                      | 40   |     |                      |         |

|                                 |                                                                                               | I/O and conversion clocks                           | 47.6 |     | 1000                 |         |

| t <sub>SCLK</sub>               |                                                                                               | I/O clock, daisy-chain mode                         | 40   |     |                      | ns      |

|                                 |                                                                                               | I/O and conversion clocks, daisy-chain mode         | 47.6 |     | 1000                 |         |

| t <sub>D1</sub>                 | Delay time, falling edge of SCLK to SDO invalid                                               | 10-pF load                                          | 8    |     |                      | ns      |

| t <sub>D2</sub>                 | Delay time, falling edge of SCLK to SDO valid                                                 | 10-pF load                                          |      |     | 35                   | ns      |

| t <sub>D3</sub>                 | Delay time, falling edge of $\overline{\text{CS}}$ to SDO valid, SDO MSB output               | 10-pF load                                          |      |     | 35                   | ns      |

| t <sub>SU4</sub>                | Setup time, SDI to falling edge of SCLK                                                       |                                                     | 8    |     |                      | ns      |

| t <sub>H3</sub>                 | Hold time, SDI to falling edge of SCLK                                                        |                                                     | 8    |     |                      | ns      |

| t <sub>D4</sub>                 | Delay time, rising edge of $\overline{\text{CS}}$ to SDO 3-state                              | 10-pF load                                          |      |     | 15                   | ns      |

| t <sub>SU5</sub>                | Setup time, last falling edge of SCLK before rising edge of $\overline{\text{CS}}$            | •                                                   | 15   |     |                      | ns      |

| t <sub>H4</sub>                 | Hold time, last falling edge of SCLK before rising edge of $\overline{\text{CS}}$             |                                                     |      |     |                      | ns      |

| t <sub>SU6</sub> <sup>(4)</sup> | Setup time, rising edge of SCLK to rising edge of $\overline{\text{CS}}$                      |                                                     |      |     |                      | ns      |

| t <sub>H5</sub> <sup>(4)</sup>  | Hold time, rising edge of SCLK to rising edge of $\overline{\text{CS}}$                       |                                                     | 2    |     |                      | ns      |

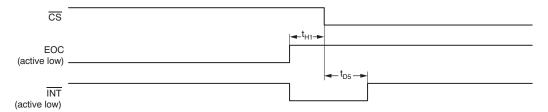

| t <sub>D5</sub>                 | Delay time, falling edge of $\overline{\text{CS}}$ to deactivation of $\overline{\text{INT}}$ | 10-pF load                                          |      |     | 40                   | ns      |

All input signals are specified with  $t_r = t_f = 1.5$  ns (10% to 90% of VBD) and timed from a voltage level of  $(V_{IL} + V_{IH}) / 2$ .

See the timing diagrams.

The EOC and EOS signals are the inverse of each other.

Applies to the 5th or 17th rising SCLK when sending 4-bit or 16-bit commands, respectively, to the ADS8331, ADS8332.

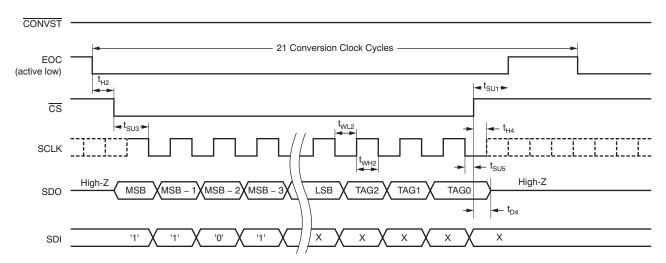

# 8.8 Timing Characteristics: VA = 5 V

at  $T_A = -40$ °C to 85°C, and VA = VBD = 5 V (unless otherwise noted)<sup>(1)(2)</sup>

|                                 |                                                                                               |                                                     | MIN  | TYP MAX                              | UNIT    |

|---------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------|------|--------------------------------------|---------|

|                                 | Francisco de la CCLIA                                                                         | External, f <sub>CCLK</sub> = 1/2 f <sub>SCLK</sub> | 0.5  | 10.5                                 | N 41 1- |

| f <sub>CCLK</sub>               | Frequency, conversion clock, CCLK                                                             | Internal                                            | 10.9 | 11.5 12.6                            | MHz     |

| t <sub>SU1</sub>                | Setup time, rising edge of $\overline{\text{CS}}$ to $\text{EOC}^{(3)}$                       | Read while converting                               | 1    |                                      | CCLK    |

| t <sub>H1</sub>                 | CS hold time with respect to EOC (3)                                                          | Read while sampling                                 | 20   |                                      | ns      |

| t <sub>WL1</sub>                | Pulse duration, CONVST low                                                                    |                                                     | 40   |                                      | ns      |

| t <sub>WH1</sub>                | Pulse duration, CS high                                                                       |                                                     | 40   |                                      | ns      |

| t <sub>SU2</sub>                | Setup time, rising edge of $\overline{\text{CS}}$ to EOS                                      | Read while sampling                                 | 20   |                                      | ns      |

| t <sub>H2</sub>                 | CS hold time with respect to EOS                                                              | Read while converting                               | 20   |                                      | ns      |

| t <sub>SU3</sub>                | Setup time, falling edge of $\overline{\text{CS}}$ to first falling edge of SCLK              |                                                     | 8    |                                      | ns      |

| t <sub>WL2</sub>                | Pulse duration, SCLK low                                                                      |                                                     | 12   | t <sub>SCLK</sub> - t <sub>WH2</sub> | ns      |

| t <sub>WH2</sub>                | Pulse duration, SCLK high                                                                     |                                                     | 11   | t <sub>SCLK</sub> - t <sub>WL2</sub> | ns      |

|                                 | Cycle time, SCLK                                                                              | I/O clock only                                      | 25   |                                      |         |

|                                 |                                                                                               | I/O and conversion clocks                           | 47.6 | 1000                                 | ı       |

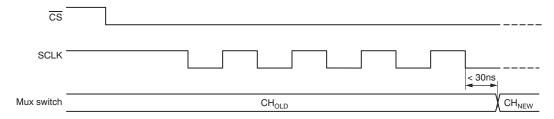

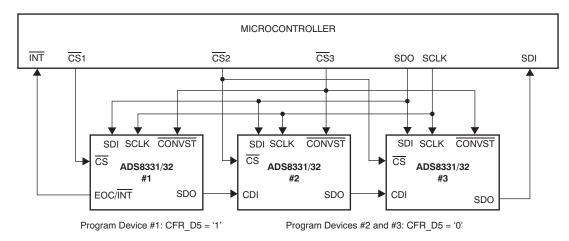

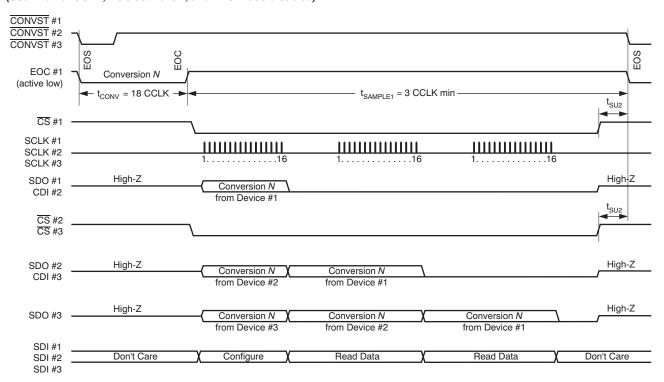

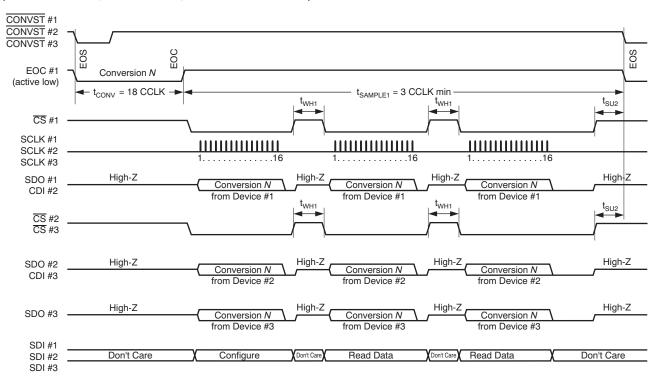

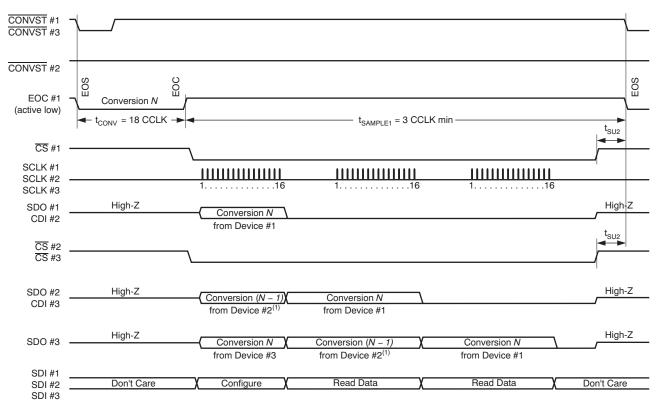

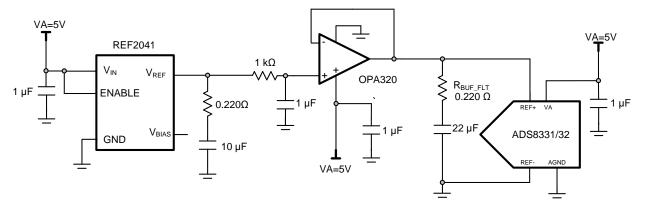

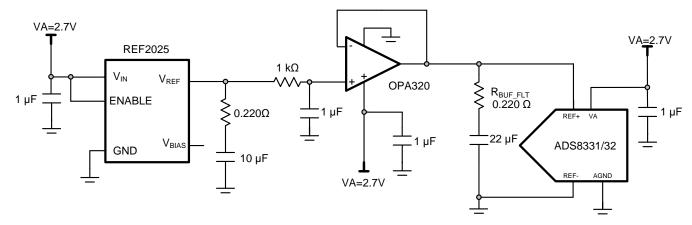

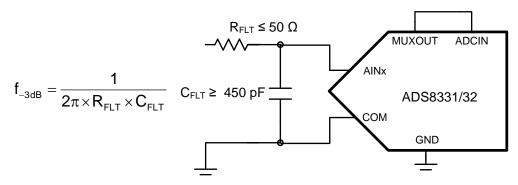

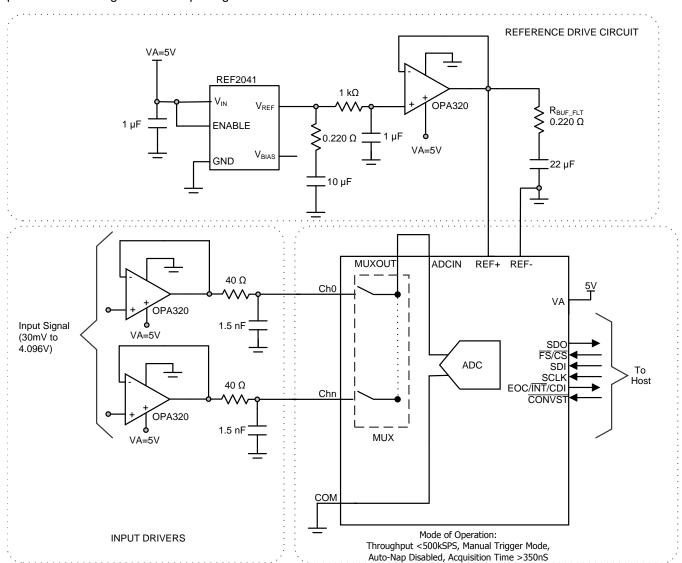

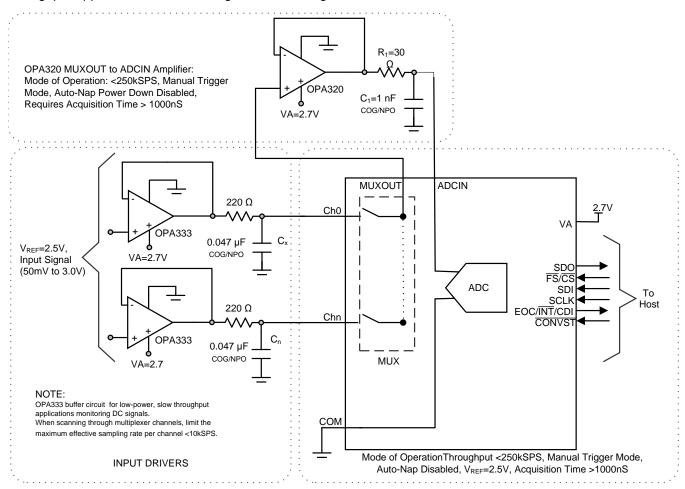

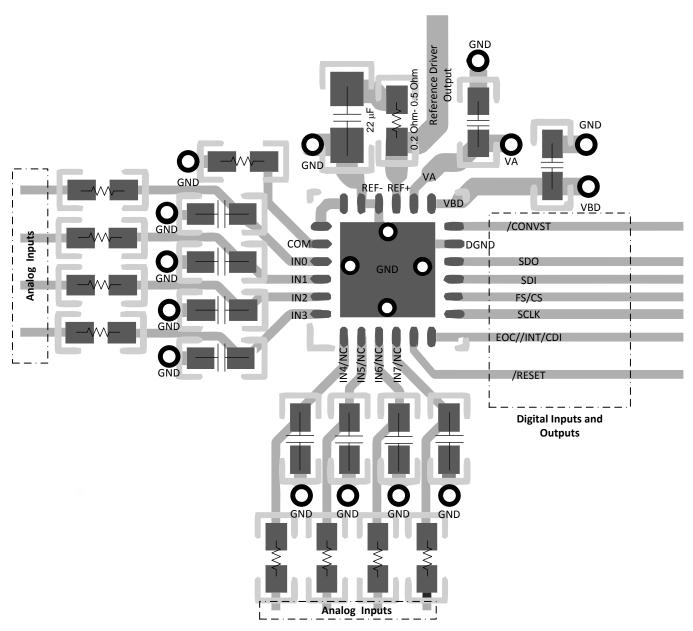

| $t_{\text{SCLK}}$               |                                                                                               | I/O clock, daisy-chain mode                         | 25   |                                      | ns      |