# AFEEx3004W 10 ビット、12 ビット、クワッド電圧および電流出力、10 ビット ADC、スマート AFE、DSBGA パッケージ

## 1 特長

- 柔軟な構成でプログラム可能な電圧または電流出力:

- 電圧出力:

- 1LSB DNL

- 1×、1.5×、2×、3×、4× のゲイン

- 電流出力:

- 1LSB INL および DNL (8 ビット)

- 25µA ~ 250µA のユニポーラおよびバイポーラ出力範囲オプション

- 10 ビット ADC 入力

- 2LSB INL, 1LSB DNL

- すべてのチャネルでコンパレータ モードをプログラム可能

- VDD オフ時はハイインピーダンス出力

- ハイインピーダンスまたは抵抗性プルダウンのパワーダウンモード

- 50MHz SPI 互換インターフェイス

- I<sup>2</sup>C、SPI、PMBus<sup>®</sup> インターフェイスを自動検出

- 1.62V V<sub>IH</sub> (V<sub>DD</sub> = 5.5V の場合)

- 汎用入出力 (GPIO) をさまざまな機能に構成可能

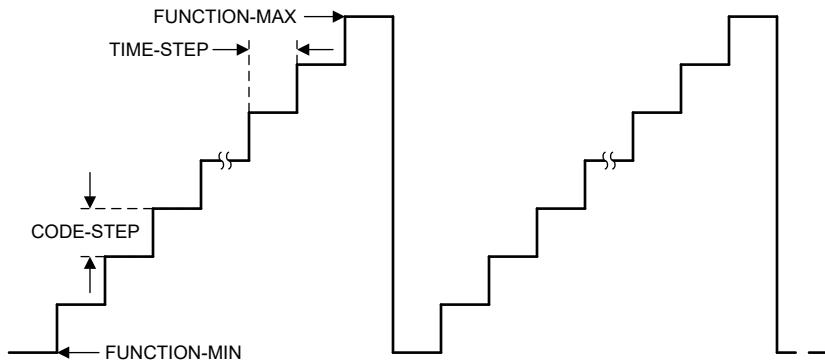

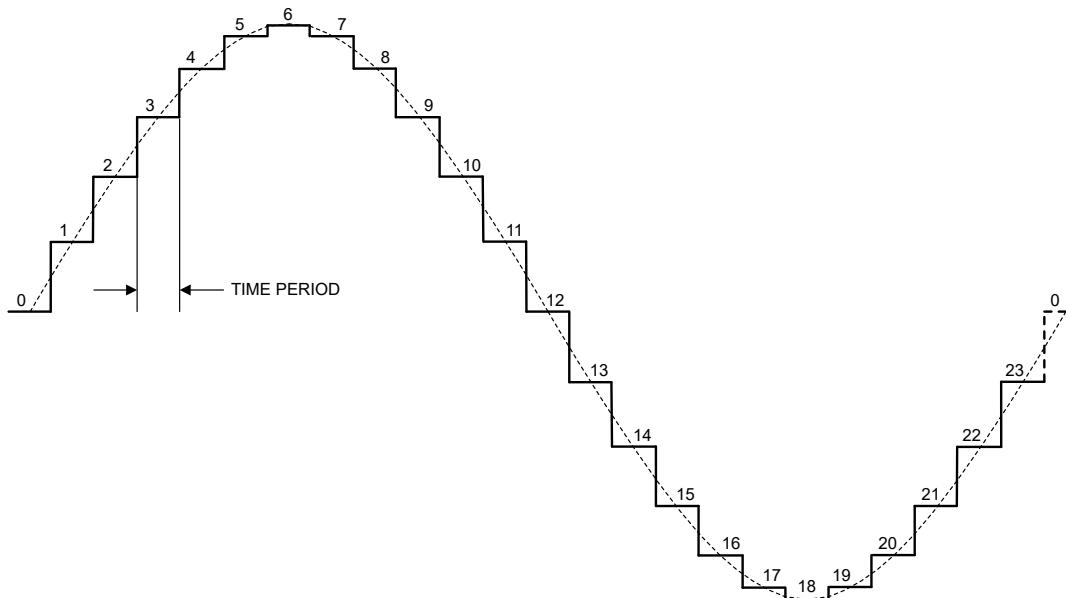

- あらかじめ定義された波形生成: 正弦波、三角波、のこぎり波

- ユーザーがプログラム可能な不揮発性メモリ (NVM)

- 基準電圧として、内部、外部または電源を使用可能

- 広い動作範囲:

- 電源: 1.8V ~ 5.5V

- 温度範囲: -40°C ~ +125°C

- 超小型パッケージ: 16 ピン DSBGA (1.76mm × 1.76mm)

## 2 アプリケーション

- 光学モジュール

- 標準的ノート PC

## 3 説明

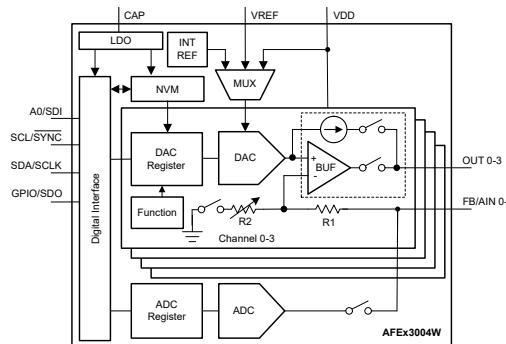

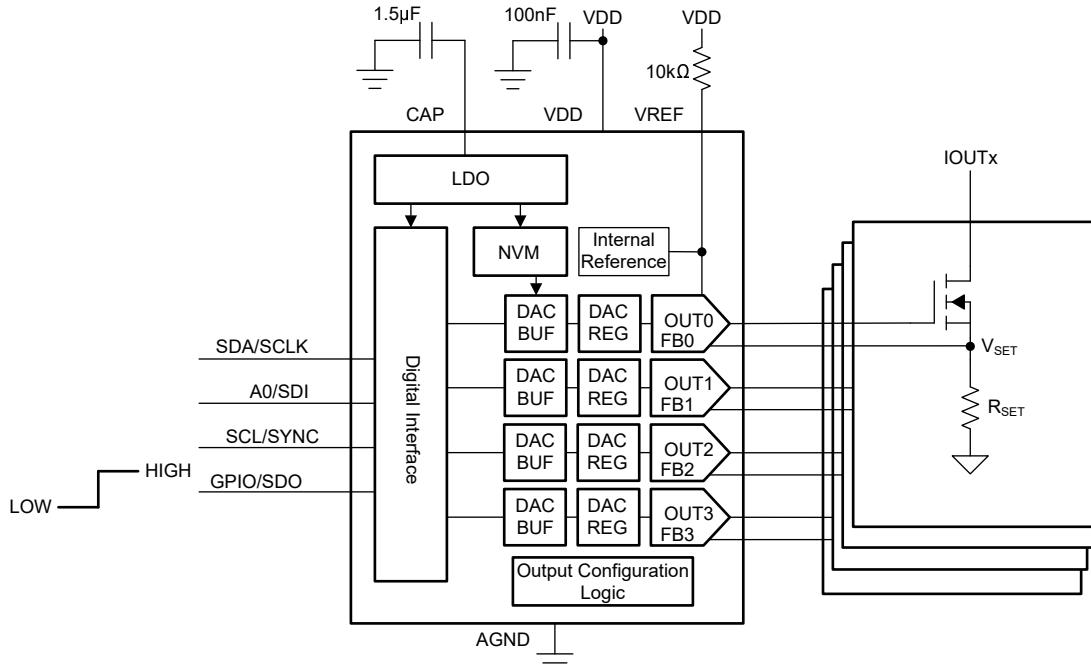

10 ビット AFE53004W および 12 ビット AFE63004W (AFEEx3004W) は、4 チャネル、超低消費電力のスマートアナログ フロントエンド (AFE) デバイス ファミリです。これらのデバイスは、1 つの共有 10 ビット アナログ/デジタルコンバータ (ADC) と 4 つの独立したチャネルを備えています。各チャネルは、バッファ付き電圧出力の D/A コンバータ (DAC)、プログラム可能な電流出力 DAC、または共有 ADC への入力として個別に構成可能です。このデバイスは、ハイインピーダンスのパワーダウン モードと、電源オフ状態でのハイインピーダンス出力をサポートしています。アナログ出力は、プログラマブルなコンパレータおよび電流シンクとして使用するためのフォース センス オプションを備えています。このスマート AFE は、多機能 GPIO、関数生成、NVM によって、プロセッサレスアプリケーションや設計の再利用を実現できます。I<sup>2</sup>C、PMBus、SPI を自動的に検出します。また、内部リファレンスを搭載しています。

スマート AFE の柔軟性と機能セットを、超小型パッケージと超低動作電力と組み合わせることで、これらのデバイスは小型のバッテリ駆動システムに最適です。

## 製品情報

| 部品番号      | 分解能    | パッケージ <sup>(1)</sup> |

|-----------|--------|----------------------|

| AFE53004W | 10 ビット | YBH (DSBGA、16)       |

| AFE63004W | 12 ビット |                      |

(1) 詳細については、セクション 11 を参照してください。

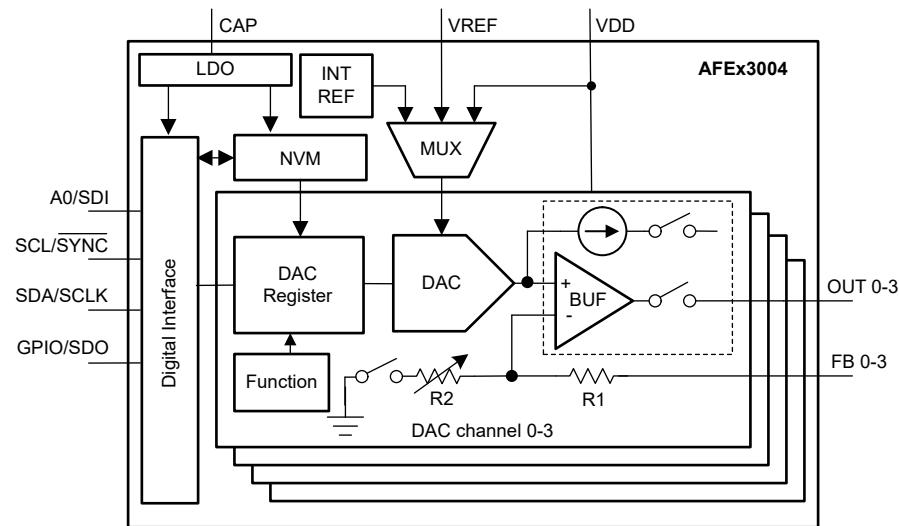

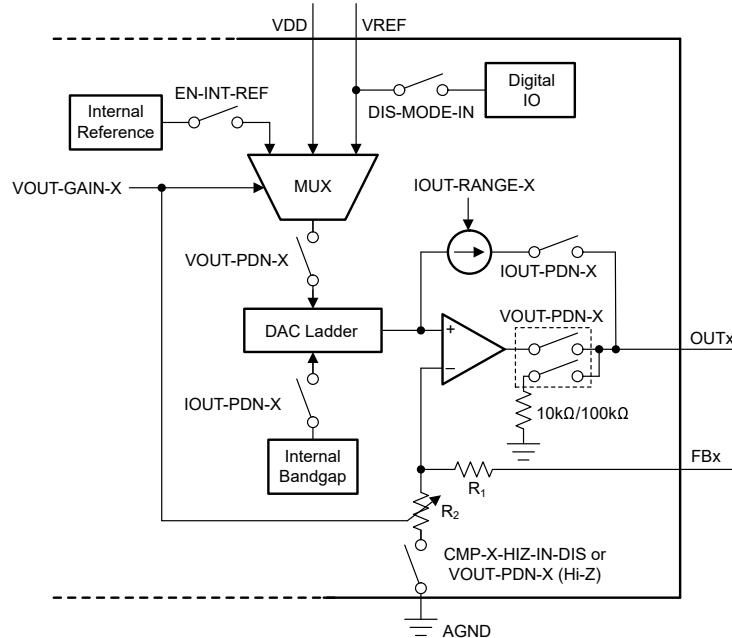

概略ブロック図

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                                                                            |    |                                                                                  |    |

|----------------------------------------------------------------------------|----|----------------------------------------------------------------------------------|----|

| <b>1 特長</b>                                                                | 1  | 7.8 DAC-X-DATA レジスタ (アドレス = 19h、1Ah、<br>1Bh、1Ch) [リセット = 0000h].....             | 73 |

| <b>2 アプリケーション</b>                                                          | 1  | 7.9 ADC-CONFIG-TRIG レジスタ (アドレス = 1Dh) [リ<br>セット = 0000h].....                    | 74 |

| <b>3 説明</b>                                                                | 1  | 7.10 ADC-DATA レジスタ (アドレス = 1Eh) [リセット =<br>0000h].....                           | 75 |

| <b>4 ピン構成および機能</b>                                                         | 3  | 7.11 COMMON-CONFIG レジスタ (アドレス = 1Fh) [リ<br>セット = 0FFFh].....                     | 75 |

| <b>5 仕様</b>                                                                | 5  | 7.12 COMMON-TRIGGER レジスタ (アドレス = 20h)<br>[リセット = 0000h].....                     | 77 |

| 5.1 絶対最大定格                                                                 | 5  | 7.13 COMMON-DAC-TRIG レジスタ (アドレス = 21h)<br>[リセット = 0000h].....                    | 78 |

| 5.2 ESD 定格                                                                 | 5  | 7.14 GENERAL-STATUS レジスタ (アドレス = 22h) [リ<br>セット = 00h、DEVICE-ID、VERSION-ID]..... | 79 |

| 5.3 推奨動作条件                                                                 | 5  | 7.15 CMP-STATUS レジスタ (アドレス = 23h) [リセット<br>= 0000h].....                         | 80 |

| 5.4 熱に関する情報                                                                | 5  | 7.16 GPIO-CONFIG レジスタ (アドレス = 24h) [リセット<br>= 0000h].....                        | 80 |

| 5.5 電気的特性、電圧出力                                                             | 6  | 7.17 DEVICE-MODE-CONFIG レジスタ (アドレス =<br>25h) [リセット = 0000h].....                 | 82 |

| 5.6 電気的特性、電流出力                                                             | 8  | 7.18 INTERFACE-CONFIG レジスタ (アドレス = 26h)<br>[リセット = 0000h].....                   | 82 |

| 5.7 電気的特性、コンパレータ モード                                                       | 9  | 7.19 SRAM-CONFIG レジスタ (アドレス = 2Bh) [リセッ<br>ト = 0000h].....                       | 83 |

| 5.8 電気的特性、ADC 入力                                                           | 9  | 7.20 SRAM-DATA レジスタ (アドレス = 2Ch) [リセット =<br>0000h].....                          | 83 |

| 5.9 電気的特性、一般論                                                              | 11 | 7.21 DAC-X-DATA-8BIT レジスタ (アドレス = 40h、<br>41h、42h、43h) [リセット = 0000h].....       | 84 |

| 5.10 タイミング要件、I <sup>2</sup> C 標準モード                                        | 12 | 7.22 BRDCAST-DATA レジスタ (アドレス = 50h) [リセッ<br>ト = 0000h].....                      | 84 |

| 5.11 タイミング要件、I <sup>2</sup> C 高速モード                                        | 12 | 7.23 PMBUS ページ レジスタ [リセット = 0300h].....                                          | 84 |

| 5.12 タイミング要件、I <sup>2</sup> C 高速モード プラス                                    | 12 | 7.24 PMBUS-OP-CMD-X レジスタ [リセット = 0000h].....                                     | 85 |

| 5.13 タイミング要件、SPI 書き込み動作                                                    | 13 | 7.25 PMBUS-CML レジスタ [リセット = 0000h].....                                          | 85 |

| 5.14 タイミング要件、SPI 読み出しおよびデイジーチェ<br>ーン動作 (FSDO = 0)                          | 13 | 7.26 PMBUS バージョン レジスタ [リセット = 2200h].....                                        | 85 |

| 5.15 タイミング要件、SPI 読み出しおよびデイジーチェ<br>ーン動作 (FSDO = 1)                          | 13 | <b>8 アプリケーションと実装</b> .....                                                       | 87 |

| 5.16 タイミング要件、GPIO                                                          | 15 | 8.1 アプリケーション情報.....                                                              | 87 |

| 5.17 タイミング図                                                                | 15 | 8.2 代表的なアプリケーション.....                                                            | 87 |

| 5.18 代表的特性:電圧出力                                                            | 17 | 8.3 電源に関する推奨事項.....                                                              | 91 |

| 5.19 代表的特性:電流出力                                                            | 22 | 8.4 レイアウト.....                                                                   | 91 |

| 5.20 代表的特性:ADC                                                             | 26 | <b>9 デバイスおよびドキュメントのサポート</b> .....                                                | 92 |

| 5.21 代表的特性:コンパレータ                                                          | 28 | 9.1 ドキュメントのサポート.....                                                             | 92 |

| 5.22 代表的特性:総則                                                              | 29 | 9.2 ドキュメントの更新通知を受け取る方法.....                                                      | 92 |

| <b>6 詳細説明</b>                                                              | 30 | 9.3 サポート・リソース.....                                                               | 92 |

| 6.1 概要                                                                     | 30 | 9.4 商標.....                                                                      | 92 |

| 6.2 機能ブロック図                                                                | 31 | 9.5 静電気放電に関する注意事項.....                                                           | 92 |

| 6.3 機能説明                                                                   | 32 | 9.6 用語集.....                                                                     | 92 |

| 6.4 デバイスの機能モード                                                             | 34 | <b>10 改訂履歴</b> .....                                                             | 92 |

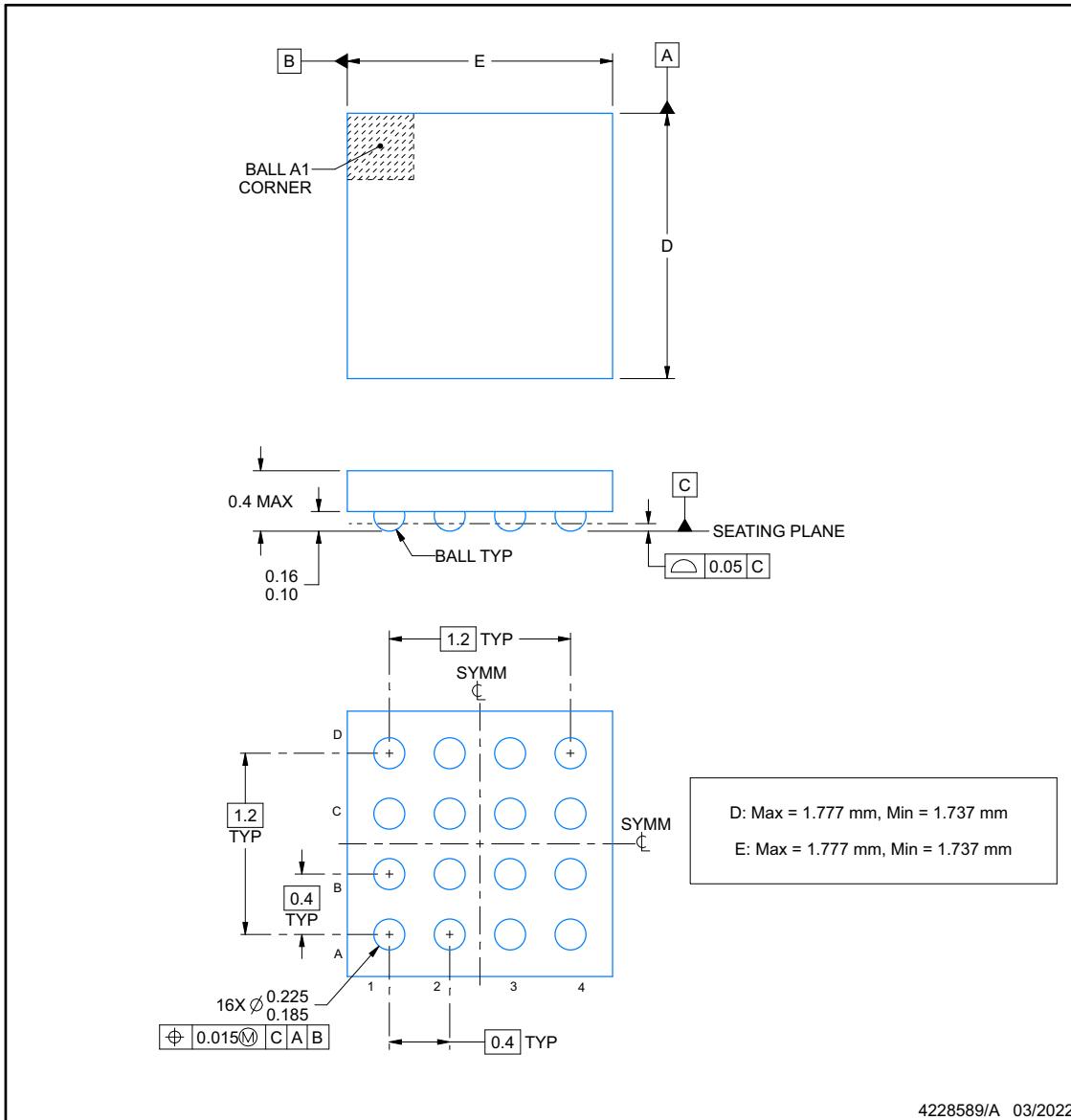

| 6.5 プログラミング                                                                | 52 | <b>11 メカニカル、パッケージ、および注文情報</b> .....                                              | 93 |

| <b>7 レジスタ マップ</b>                                                          | 62 |                                                                                  |    |

| 7.1 NOP レジスタ (アドレス = 00h) [リセット = 0000h]                                   | 67 |                                                                                  |    |

| 7.2 DAC-X-MARGIN-HIGH レジスタ (アドレス = 01h、<br>07h、0Dh、13h) [リセット = 0000h]     | 67 |                                                                                  |    |

| 7.3 DAC-X-MARGIN-LOW レジスタ (アドレス = 02h、<br>08h、0Eh、14h) [リセット = 0000h]      | 67 |                                                                                  |    |

| 7.4 DAC-X-VOUT-CMP-CONFIG レジスタ (アドレス =<br>03h、09h、0Fh、15h) [リセット = 0000h]  | 68 |                                                                                  |    |

| 7.5 DAC-X-IOUT-MISC-CONFIG レジスタ (アドレス =<br>04h、0Ah、10h、16h) [リセット = 0000h] | 69 |                                                                                  |    |

| 7.6 DAC-X-CMP-MODE-CONFIG レジスタ (アドレス =<br>05h、0Bh、11h、17h) [リセット = 0000h]  | 69 |                                                                                  |    |

| 7.7 DAC-X-FUNC-CONFIG レジスタ (アドレス = 06h、<br>0Ch、12h、18h) [リセット = 0000h]     | 70 |                                                                                  |    |

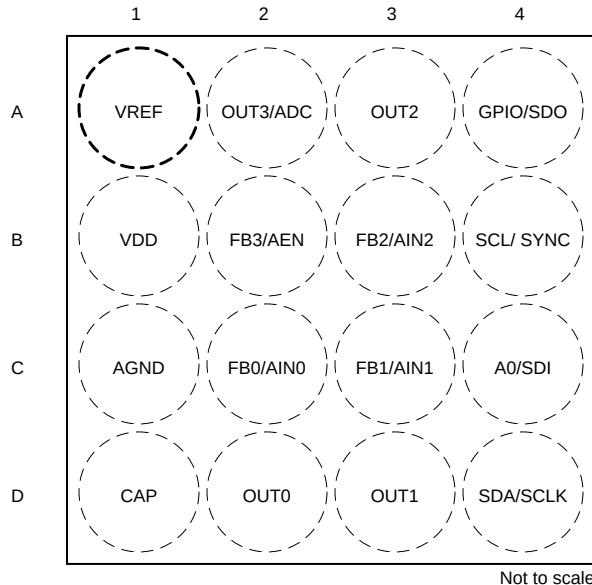

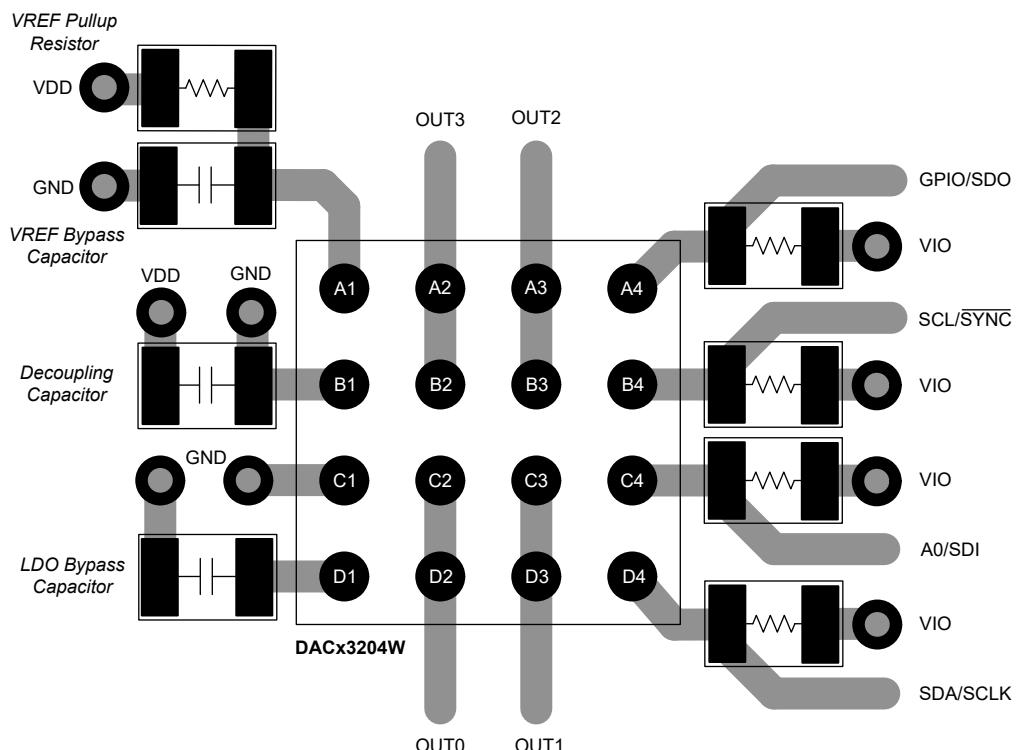

## 4 ピン構成および機能

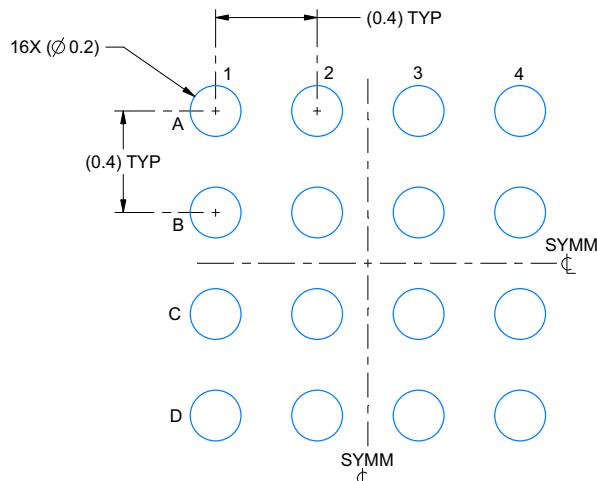

図 4-1. YBH パッケージ、16 ピン DSBGA (上面図)

表 4-1. ピンの機能

| 番号 | ピン<br>名称 | タイプ     | 説明                                                                                                                                                                                                 |

|----|----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1 | VREF     | 電源      | 外部基準電圧入力ピン (1)VREF と AGND の間にコンデンサ (おおよそ 0.1μF) を接続します。<br>外部基準電圧を使用しない場合は、VDD にプルアップ抵抗を使用します。このピンは、VDD より前に上昇させないでください。外部基準電圧を使用する場合は、必ず VDD の後にリファレンス電圧が上昇します。                                   |

| A2 | OUT3/ADC | 出力      | 電圧または電流出力モードでの DAC チャネル 3 からのアナログ出力。ADC モードで ADC チャネル 3 への入力。                                                                                                                                      |

| A3 | OUT2     | 出力      | DAC チャネル 2 からのアナログ出力。ADC モードでは接続なし、フローティングのままにします。                                                                                                                                                 |

| A4 | GPIO/SDO | 入力 / 出力 | LDAC、PD、PROTECT、RESET、SDO、STATUS として構成可能な汎用入出力。STATUS および SDO の場合、外部プルアップ抵抗を使用してピンを IO 電圧に接続します。使用しない場合は、外部抵抗を使用して GPIO ピンを VDD または AGND に接続します。このピンは、VDD より前にランプアップすることができます。                     |

| B1 | VDD      | 電源      | 電源電圧。                                                                                                                                                                                              |

| B2 | FB3/AEN  | 入力      | チャネル 3 の電圧フィードバックピン。電圧出力モードでは、閉ループアンプ出力の場合は OUT3 に接続します。電流出力モードでは、リーク電流を最小限に抑えるため、FB3 ピンを未接続のままにします。ADC モードでは、プルアップ抵抗を使用して VDD に接続します。                                                             |

| B3 | FB2/AIN2 | 入力      | チャネル 2 の電圧フィードバックピン。電圧出力モードでは、閉ループアンプ出力の場合は OUT2 に接続します。電流出力モードでは、リーク電流を最小限に抑えるため、FB2 ピンを未接続のままにします。ADC モードでは、ADC チャネル 2 への入力を行います。                                                                |

| B4 | SCL/SYNC | 出力      | I <sup>2</sup> C シリアルインターフェースクロックまたは SPI チップセレクト入力。これを外付けプルアップ抵抗を使用して IO 電圧に接続します。このピンは、VDD より前にランプアップすることができます。                                                                                   |

| C1 | AGND     | グランド    | デバイスの全回路のグランド基準点。                                                                                                                                                                                  |

| C2 | FB0/AINO | 入力      | チャネル 0 の電圧フィードバックピン。電圧出力モードでは、閉ループアンプ出力の場合は OUT0 に接続します。電流出力モードでは、リーク電流を最小限に抑えるため、FB0 ピンを未接続のままにします。ADC モードでは、ADC チャネル 0 への入力を行います。                                                                |

| C3 | FB1/AIN1 | 入力      | チャネル 1 の電圧フィードバックピン。電圧出力モードでは、閉ループアンプ出力の場合は OUT1 に接続します。電流出力モードでは、リーク電流を最小限に抑えるため、FB1 ピンを未接続のままにします。ADC モードでは、ADC チャネル 1 への入力を行います。                                                                |

| C4 | A0/SDI   | 入力      | I <sup>2</sup> C または SPI のシリアルデータ入力のアドレス構成ピン。<br>A0 の場合、アドレス構成のためにこのピンを VDD、AGND、SDA、SCL のいずれかに接続します (セクション 6.5.2.2.1)。<br>SDI の場合は、このピンをプルアップする必要も、プルダウンする必要もありません。このピンは、VDD より前にランプアップすることができます。 |

| D1 | CAP      | 電源      | 内部 LDO の外部バイパスコンデンサ。CAP と AGND の間にコンデンサ (おおよそ 1.5μF) を接続します。                                                                                                                                       |

**表 4-1. ピンの機能 (続き)**

| ピン |          | タイプ     | 説明                                                                                                                                    |

|----|----------|---------|---------------------------------------------------------------------------------------------------------------------------------------|

| 番号 | 名称       |         |                                                                                                                                       |

| D2 | OUT0     | 出力      | DAC チャネル 0 からのアナログ出力。ADC モードでは接続なし、フローティングのままにします。                                                                                    |

| D3 | OUT1     | 出力      | DAC チャネル 1 からのアナログ出力。ADC モードでは接続なし、フローティングのままにします。                                                                                    |

| D4 | SDA/SCLK | 入力 / 出力 | 双方向 I <sup>2</sup> C シリアル データ バスまたは SPI クロック入力。このピンは、I <sup>2</sup> C モードでは外付けプルアップ抵抗を使用して IO 電圧に接続します。このピンは、VDD より前にランプアップすることができます。 |

## 5 仕様

### 5.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|           |                                                  | 最小値  | 最大値            | 単位 |

|-----------|--------------------------------------------------|------|----------------|----|

| $V_{DD}$  | 電源電圧、 $V_{DD}$ から AGND へ                         | -0.3 | 6              | V  |

|           | デジタル入力から AGND へ                                  | -0.3 | $V_{DD} + 0.3$ | V  |

|           | $V_{OUTx}$ または $A_{INx}$ または $V_{FBx}$ から AGND へ | -0.3 | $V_{DD} + 0.3$ | V  |

| $V_{REF}$ | 外部リファレンス電圧、 $V_{REF}$ から AGND へ                  | -0.3 | $V_{DD} + 0.3$ | V  |

|           | OUTx、VDD、AGND ピンを除く任意のピンに流れ込む電流                  | -10  | 10             | mA |

| $T_J$     | 接合部温度                                            | -40  | 150            | °C |

| $T_{stg}$ | 保存温度                                             | -65  | 150            | °C |

(1) 「絶対最大定格」を超えた動作は、デバイスに恒久的な損傷を与える可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用した場合、本デバイスは完全に機能するとは限らず、このことが本デバイスの信頼性、機能、性能に影響を及ぼし、本デバイスの寿命を縮める可能性があります。

### 5.2 ESD 定格

|             |      | 値                                                                | 単位 |

|-------------|------|------------------------------------------------------------------|----|

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 に準拠、すべてのピン <sup>(1)</sup>     | V  |

|             |      | デバイス帯電モデル (CDM)、ANSI/ESDA/JEDEC JS-002 に準拠、すべてのピン <sup>(2)</sup> |    |

(1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

(2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

### 5.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|           |                                      | 最小値  | 公称値      | 最大値     | 単位 |

|-----------|--------------------------------------|------|----------|---------|----|

| $V_{DD}$  | グランド (AGND) への正の電源電圧                 | 1.7  | 5.5      | V       |    |

| $V_{REF}$ | グランドへの外部基準電圧 (AGND)                  | 1.7  | $V_{DD}$ | V       |    |

| $V_{IH}$  | デジタル入力高電圧、 $1.7V < V_{DD} \leq 5.5V$ | 1.62 |          | V       |    |

| $V_{IL}$  | デジタル入力低電圧                            |      | 0.4      | V       |    |

| $C_{CAP}$ | CAP ピンの外部コンデンサ                       | 0.5  | 15       | $\mu F$ |    |

| $T_A$     | 周囲温度                                 | -40  | 125      | °C      |    |

### 5.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup>        |                     | AFEx3004W   | 単位   |

|-----------------------------|---------------------|-------------|------|

|                             |                     | YBH (DSBGA) |      |

|                             |                     | 16 ピン       |      |

| $R_{\theta JA}$             | 接合部から周囲への熱抵抗        | 81.2        | °C/W |

| $R_{\theta JC(\text{top})}$ | 接合部からケース (上面) への熱抵抗 | 0.3         | °C/W |

| $R_{\theta JB}$             | 接合部から基板への熱抵抗        | 20.3        | °C/W |

| $\Psi_{JT}$                 | 接合部から上面への特性パラメータ    | 0.2         | °C/W |

| $\Psi_{JB}$                 | 接合部から基板への特性パラメータ    | 20.3        | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション レポートを参照してください。

## 5.5 電気的特性、電圧出力

すべての最小/最大仕様は  $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$  で、標準仕様は  $T_A = 25^\circ\text{C}$ 、 $1.7V \leq V_{DD} \leq 5.5V$ 、DAC リファレンスは  $VDD$  に接続、ゲイン =  $1 \times$ 、DAC 出力ピン (OUT) には抵抗負荷 ( $R_L = 5\text{k}\Omega \sim \text{AGND}$ ) および容量負荷 ( $C_L = 200\text{pF} \sim \text{AGND}$ )、およびデジタル入力は  $VDD$  または  $\text{AGND}$  です (特に明記しない限り)

| パラメータ                        | テスト条件                                                                               | 最小値                                                                                                                                                                                                                                                             | 標準値      | 最大値                          | 単位   |

|------------------------------|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------------------|------|

| <b>安定動作</b>                  |                                                                                     |                                                                                                                                                                                                                                                                 |          |                              |      |

| 分解能                          | AFE63004W                                                                           | 12                                                                                                                                                                                                                                                              |          |                              | ビット  |

|                              | AFE53004W                                                                           | 10                                                                                                                                                                                                                                                              |          |                              |      |

| INL                          | AFE63004W                                                                           | -5                                                                                                                                                                                                                                                              | 5        | -1.25                        | LSB  |

|                              | AFE53004W                                                                           | 1.25                                                                                                                                                                                                                                                            |          |                              |      |

| DNL                          | 微分非直線性 <sup>(1)</sup>                                                               | -1                                                                                                                                                                                                                                                              | 1        | 1                            | LSB  |

| ゼロコード誤差 <sup>(4)</sup>       | コード 0d を DAC に入力、外部リファレンス電圧、 $V_{DD} = 5.5V$                                        | 6                                                                                                                                                                                                                                                               | 12       | mV                           |      |

|                              | コード 0d を DAC に入力、内部 $V_{REF}$ 、ゲイン = $4 \times$ 、 $V_{DD} = 5.5V$                   | 6                                                                                                                                                                                                                                                               | 15       |                              |      |

| ゼロコード誤差の温度係数 <sup>(4)</sup>  |                                                                                     | $\pm 10$                                                                                                                                                                                                                                                        |          | $\mu\text{V}/^\circ\text{C}$ |      |

| オフセット誤差 <sup>(4) (6)</sup>   | $1.7V \leq V_{DD} < 2.7V$ 、 $V_{FB}$ ピンを $V_{OUT}$ に短絡、DAC コード:12 ビット分解能の場合は 32d    | -0.75                                                                                                                                                                                                                                                           | 0.3      | 0.75                         | %FSR |

|                              | $2.7V \leq V_{DD} \leq 5.5V$ 、 $V_{FB}$ ピンを $V_{OUT}$ に短絡、DAC コード:12 ビット分解能の場合は 32d | -0.5                                                                                                                                                                                                                                                            | 0.25     | 0.5                          |      |

| オフセット誤差の温度係数 <sup>(4)</sup>  | $V_{FB}$ ピンを $V_{OUT}$ に短絡、DAC コード:12 ビット分解能の場合は 32d、10 ビット分解能の場合は 8d               | $\pm 0.0003$                                                                                                                                                                                                                                                    |          | %FSR/°C                      |      |

| ゲイン誤差 <sup>(4)</sup>         | エンドポイントコード間:12 ビット分解能の場合は 32d ~ 4064d、10 ビット分解能の場合は 8d ~ 1016d                      | -0.5                                                                                                                                                                                                                                                            | 0.25     | 0.5                          | %FSR |

| ゲイン誤差の温度係数 <sup>(4)</sup>    | エンドポイントコード間:12 ビット分解能の場合は 32d ~ 4064d、10 ビット分解能の場合は 8d ~ 1016d                      | $\pm 0.0008$                                                                                                                                                                                                                                                    |          | %FSR/°C                      |      |

| フルスケール誤差 <sup>(4) (6)</sup>  | $1.7V \leq V_{DD} < 2.7V$ 、フルスケールの DAC                                              | -1                                                                                                                                                                                                                                                              | 1        | 0.5                          | %FSR |

|                              | $2.7V \leq V_{DD} \leq 5.5V$ 、フルスケールの DAC                                           | -0.5                                                                                                                                                                                                                                                            | 0.25     |                              |      |

| フルスケール誤差の温度係数 <sup>(4)</sup> | フルスケールでの DAC                                                                        | $\pm 0.0008$                                                                                                                                                                                                                                                    |          | %FSR/°C                      |      |

| <b>出力</b>                    |                                                                                     |                                                                                                                                                                                                                                                                 |          |                              |      |

| 出力電圧                         | リファレンス電圧を $V_{DD}$ に接続                                                              | 0                                                                                                                                                                                                                                                               | $V_{DD}$ | V                            |      |

| $C_L$                        | 容量性負荷 <sup>(2)</sup>                                                                | $R_L = \text{無限}$ 、位相マージン = $30^\circ$                                                                                                                                                                                                                          |          | 200                          | pF   |

|                              |                                                                                     | 位相マージン = $30^\circ$                                                                                                                                                                                                                                             |          | 1000                         |      |

| 短絡電流                         |                                                                                     | $V_{DD} = 1.7V$ 、フルスケール出力を $\text{AGND}$ に短絡またはゼロスケール出力を $V_{DD}$ に短絡                                                                                                                                                                                           | 15       | mA                           |      |

|                              |                                                                                     | $V_{DD} = 2.7V$ 、フルスケール出力を $\text{AGND}$ に短絡またはゼロスケール出力を $V_{DD}$ に短絡                                                                                                                                                                                           | 50       |                              |      |

|                              |                                                                                     | $V_{DD} = 5.5V$ 、フルスケール出力を $\text{AGND}$ に短絡またはゼロスケール出力を $V_{DD}$ に短絡                                                                                                                                                                                           | 60       |                              |      |

| 出力電圧ヘッドルーム <sup>(2)</sup>    |                                                                                     | $V_{DD}$ まで (DAC 出力無負荷、内部リファレンス = $1.21V$ )、 $V_{DD} \geq 1.21V \times \text{ゲイン} + 0.2V$                                                                                                                                                                       | 0.2      | %FSR                         | V    |

|                              |                                                                                     | $V_{DD}$ および $\text{AGND} \sim$ ( $\text{DAC}$ 出力無負荷、 $V_{DD}$ での外部リファレンス電圧 (ゲイン = $1 \times$ )、 $V_{REF}$ ピンは $V_{DD}$ と短絡していません)                                                                                                                              | 0.8      |                              |      |

|                              |                                                                                     | $V_{DD}$ および $\text{AGND} \sim (V_{DD} = 5.5V \text{ で } I_{LOAD} = 10\text{mA}, V_{DD} = 2.7V \text{ で } I_{LOAD} = 3\text{mA}, V_{DD} = 1.8V \text{ で } I_{LOAD} = 1\text{mA})$ 、 $V_{DD}$ での外部リファレンス (ゲイン = $1 \times$ )、 $V_{REF}$ ピンは $V_{DD}$ に短絡されていません) | 10       |                              |      |

## 5.5 電気的特性、電圧出力 (続き)

すべての最小/最大仕様は  $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$  で、標準仕様は  $T_A = 25^\circ\text{C}$ 、 $1.7V \leq V_{DD} \leq 5.5V$ 、DAC リファレンスは  $VDD$  に接続、ゲイン =  $1 \times$ 、DAC 出力ピン (OUT) には抵抗負荷 ( $R_L = 5\text{k}\Omega \sim \text{AGND}$ ) および容量負荷 ( $C_L = 200\text{pF} \sim \text{AGND}$ )、およびデジタル入力は  $VDD$  または  $\text{AGND}$  です (特に明記しない限り)

| パラメータ                     |                                      | テスト条件                                                                                                                                     | 最小値  | 標準値 | 最大値                            | 単位               |  |  |

|---------------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------|-----|--------------------------------|------------------|--|--|

| $Z_o$                     | $V_{FB}$ DC 出力インピーダンス <sup>(3)</sup> | DAC 出力イネーブル、内部リファレンス (ゲイン = $1.5 \times$ または $2 \times$ )、または $V_{DD}$ での外部リファレンス電圧 (ゲイン = $1 \times$ )、 $V_{REF}$ ピンは $V_{DD}$ に短絡していません | 400  | 500 | 600                            | $\text{k}\Omega$ |  |  |

|                           |                                      | DAC 出力イネーブル、内部 $V_{REF}$ 、ゲイン = $3 \times$ または $4 \times$                                                                                 | 325  | 400 | 485                            |                  |  |  |

| 電源除去比 (DC)                |                                      | 内部 $V_{REF}$ 、ゲイン = $2 \times$ 、ミッドスケールでの DAC、 $V_{DD} = 5\text{V} \pm 10\%$                                                              | 0.25 |     | mV/V                           |                  |  |  |

| ダイナミック性能                  |                                      |                                                                                                                                           |      |     |                                |                  |  |  |

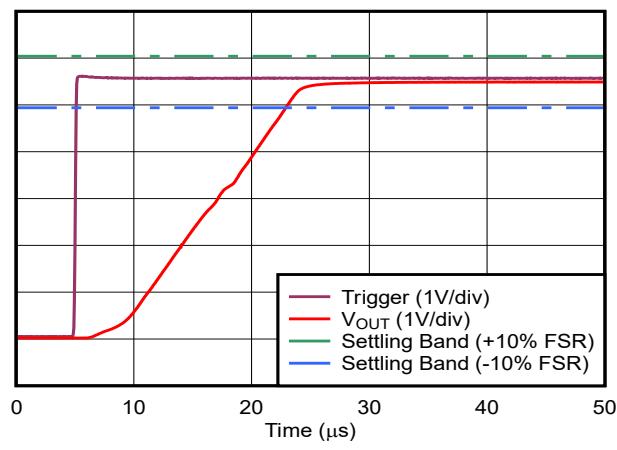

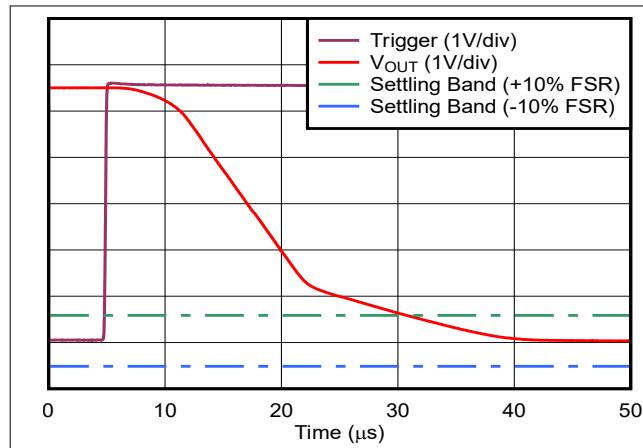

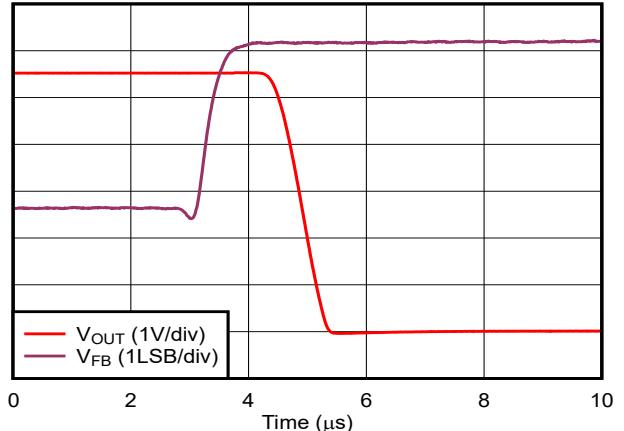

| $t_{sett}$                | 出力電圧セッティング時間                         | 1/4 から 3/4 へのスケール、3/4 から 1/4 へのスケールで 10% FSR にセッティング、 $V_{DD} = 5.5\text{V}$                                                              | 20   |     | $\mu\text{s}$                  |                  |  |  |

|                           |                                      | 1/4 から 3/4 へのスケール、3/4 から 1/4 へのスケールで 10% FSR にセッティング、 $V_{DD} = 5.5\text{V}$ 、内部 $V_{REF}$ 、ゲイン = $4 \times$                              | 25   |     |                                |                  |  |  |

| スルー レート                   |                                      | $V_{DD} = 5.5\text{V}$                                                                                                                    | 0.3  |     | $\text{V}/\mu\text{s}$         |                  |  |  |

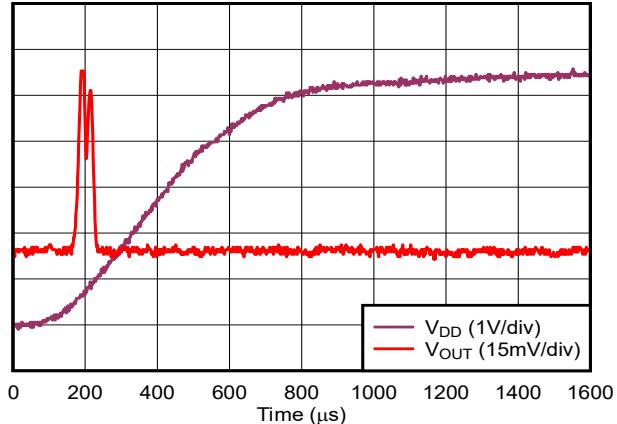

|                           | 電源オン時のグリッチ振幅                         | スタートアップ時 (DAC 出力ディセーブル)                                                                                                                   | 75   |     | $\text{mV}$                    |                  |  |  |

|                           |                                      | スタートアップ時 (DAC 出力無効)、 $R_L = 100\text{k}\Omega$                                                                                            | 200  |     |                                |                  |  |  |

| 出力イネーブルのグリッチ振幅            |                                      | DAC 出力を無効化して有効にする (DAC レジスタがゼロスケール)、 $R_L = 100\text{k}\Omega$                                                                            | 250  |     | $\text{mV}$                    |                  |  |  |

| $V_n$                     | 出力ノイズ電圧 (ピークツーピーク)                   | $f = 0.1\text{Hz} \sim 10\text{Hz}$ 、ミッドスケールでの DAC、 $V_{DD} = 5.5\text{V}$                                                                | 50   |     | $\mu\text{V}_{PP}$             |                  |  |  |

|                           |                                      | 内部 $V_{REF}$ 、ゲイン = $4 \times$ 、 $f = 0.1\text{Hz} \sim 10\text{Hz}$ 、ミッドスケールでの DAC、 $V_{DD} = 5.5\text{V}$                               | 90   |     |                                |                  |  |  |

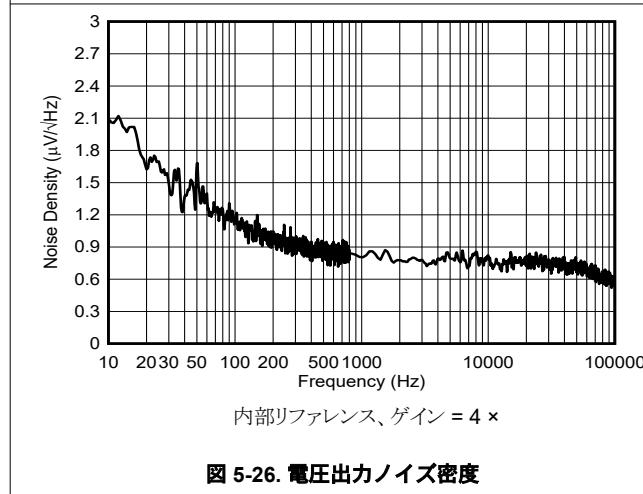

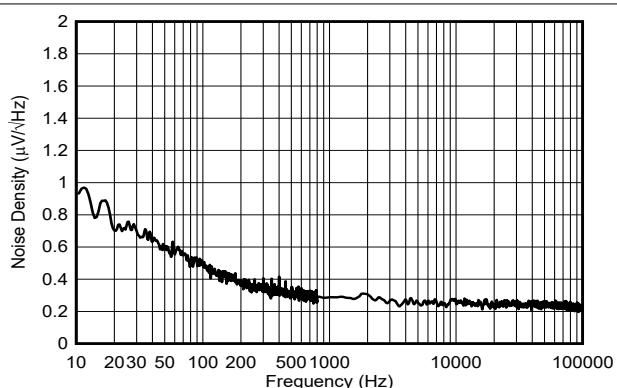

|                           | 出力ノイズ 密度                             | $f = 1\text{kHz}$ 、ミッドスケールでの DAC、 $V_{DD} = 5.5\text{V}$                                                                                  | 0.35 |     | $\mu\text{V}/\sqrt{\text{Hz}}$ |                  |  |  |

|                           |                                      | 内部 $V_{REF}$ 、ゲイン = $4 \times$ 、 $f = 1\text{kHz}$ 、ミッドスケールでの DAC、 $V_{DD} = 5.5\text{V}$                                                 | 0.9  |     |                                |                  |  |  |

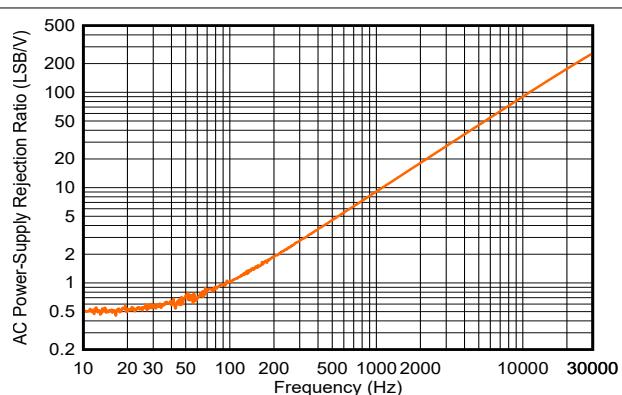

| 電源除去比 (ac) <sup>(3)</sup> |                                      | 内部 $V_{REF}$ 、ゲイン = $4 \times$ 、電源電圧に重ね合わせた 200mV 50Hz または 60Hz 正弦波、ミッドスケールでの DAC                                                         | -68  |     | $\text{dB}$                    |                  |  |  |

| コード書き換えによるグリッチ インバ尔斯      |                                      | ミッドスケール付近で $\pm 1\text{LSB}$ の変化 (フィードスルーを含む)                                                                                             | 10   |     | $\text{nV}\cdot\text{s}$       |                  |  |  |

| コード書き換えによるグリッチ インバ尔斯振幅    |                                      | ミッドスケール付近で $\pm 1\text{LSB}$ の変化 (フィードスルーを含む)                                                                                             | 15   |     | $\text{mV}$                    |                  |  |  |

| 電源                        |                                      |                                                                                                                                           |      |     |                                |                  |  |  |

| $I_{DD}$                  | $VDD$ に流れる電流 <sup>(4) (5)</sup>      | 通常動作、フルスケールでの DAC、デジタルピンは静的、 $V_{DD}$ での外部リファレンス電圧ですが、 $V_{REF}$ ピンは $V_{DD}$ に短絡していません                                                   | 35   | 50  | $\mu\text{A}/\text{ch}$        |                  |  |  |

- (1) DAC 出力を無負荷の状態で測定しています。外部リファレンス電圧と内部リファレンス  $V_{DD} \geq 1.21 \times \text{ゲイン} + 0.2\text{V}$  の場合、エンドポイントコードの間: 12 ビット分解能の場合は  $32d \sim 4064d$ 、10 ビット分解能の場合は  $8d \sim 1016d$ 。

- (2) 設計と特性評価による仕様で、製造テストは未実施。

- (3) 内部リファレンスを使用する場合、リファレンス値に対して 200mV のヘッドルームで規定。

- (4) DAC 出力を無負荷の状態で測定しています。

- (5) 総消費電力は、 $I_{DD} \times (\text{電源オンされるチャネルの合計数}) + (\text{スリープ モード電流})$  で計算されます。

- (6) DAC チャネルが長期的に IOUT モードに構成されてから、VOUT モードに切り換わると、VOUT モードにパラメータドリフトを表示できます。

## 5.6 電気的特性、電流出力

すべての最小および最大値は  $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$  で、標準値は  $T_A = 25^\circ\text{C}$ 、 $1.7\text{V} \leq V_{DD} \leq 5.5\text{V}$ 、 $\pm 250\mu\text{A}$  出力範囲、およびデジタル入力が VDD または AGND の場合です (特に明記しない限り)

| パラメータ                       | テスト条件                                                                                                                             | 最小値                                                        | 標準値       | 最大値 | 単位                     |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----------|-----|------------------------|

| <b>安定動作</b>                 |                                                                                                                                   |                                                            |           |     |                        |

| 分解能                         |                                                                                                                                   | 8                                                          |           |     | ビット                    |

| INL                         | 積分非直線性<br>その場合は 0d ~ 255d の DAC コード                                                                                               | -1                                                         | 1         | 1   | LSB                    |

| DNL                         | 微分非直線性<br>その場合は 0d ~ 255d の DAC コード                                                                                               | -1                                                         | 1         | 1   | LSB                    |

| オフセット エラー                   | DAC 出力範囲: $\pm 25\mu\text{A}, \pm 50\mu\text{A}, \pm 125\mu\text{A}, \pm 250\mu\text{A}$ 、ミッドスケールの DAC                            |                                                            | $\pm 1$   |     | %FSR                   |

| ゲイン誤差                       | DAC 出力範囲: $\pm 25\mu\text{A}, \pm 50\mu\text{A}, \pm 125\mu\text{A}, \pm 250\mu\text{A}$ 。DAC コードは 0d ~ 255d                      |                                                            | $\pm 1.3$ |     | %FSR                   |

| <b>出力</b>                   |                                                                                                                                   |                                                            |           |     |                        |

| 出力コンプライアンス電圧 <sup>(1)</sup> | DAC 出力範囲: $\pm 25\mu\text{A}, \pm 50\mu\text{A}, \pm 125\mu\text{A}, \pm 250\mu\text{A}$ , $V_{DD}$ および AGND へ                    | 400                                                        |           |     | mV                     |

| $Z_o$                       | $I_{OUT}$ DC 出力インピーダンス <sup>(2)</sup>                                                                                             | 60                                                         |           |     | MΩ                     |

|                             | 電源除去比 (DC)                                                                                                                        | 0.23                                                       |           |     | LSB/V                  |

| <b>ダイナミック性能</b>             |                                                                                                                                   |                                                            |           |     |                        |

| $t_{sett}$                  | 出力電流セッティング時間<br>1/4 から 3/4 スケール、および 3/4 から 1/4 へのスケールで 1LSB にセッティング、8 ビット分解能、 $V_{DD} = 5.5\text{V}$ 、OUTx ピンの同相電圧は $V_{DD}/2$ です | 60                                                         |           |     | μs                     |

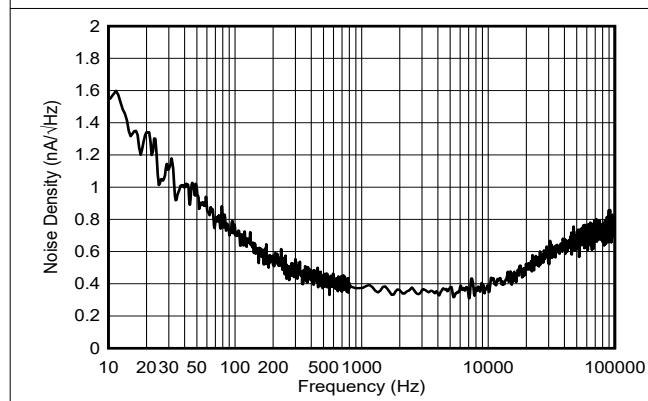

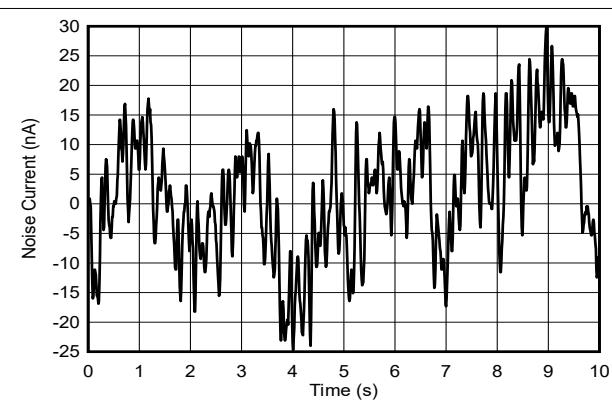

| $V_n$                       | 出力ノイズ電流 (ピークツーピーク)<br>$V_{DD} = 5.5\text{V}, \pm 250\mu\text{A}$ の出力範囲                                                            | 150                                                        |           |     | nA <sub>PP</sub>       |

|                             | 出力ノイズ 密度<br>$f = 1\text{kHz}$ 、ミッドスケールの DAC、 $V_{DD} = 5.5\text{V}$ 、出力範囲 $\pm 250\mu\text{A}$                                    | 1                                                          |           |     | nA/ $\sqrt{\text{Hz}}$ |

|                             | 電源除去比 (ac) <sup>(3)</sup>                                                                                                         | 0.65                                                       |           |     | LSB/V                  |

| <b>電源</b>                   |                                                                                                                                   |                                                            |           |     |                        |

| $I_{DD}$                    | VDD に流れる電流 <sup>(3) (4)</sup>                                                                                                     | 通常動作、フルスケールでの DAC、 $\pm 25\mu\text{A}$ の出力範囲、デジタル ピンの静電容量  | 42        | 50  | μA/ch                  |

|                             |                                                                                                                                   | 通常動作、フルスケールでの DAC、 $\pm 50\mu\text{A}$ の出力範囲、デジタル ピンの静電容量  | 56        | 70  |                        |

|                             |                                                                                                                                   | 通常動作、フルスケールでの DAC、 $\pm 125\mu\text{A}$ の出力範囲、デジタル ピンの静電容量 | 98        | 120 |                        |

|                             |                                                                                                                                   | 通常動作、フルスケールでの DAC、 $\pm 250\mu\text{A}$ の出力範囲、デジタル ピンの静電容量 | 167       | 200 |                        |

(1) DAC コード 0d と 255d の間で測定。

(2) 設計と特性評価による仕様で、製造テストは未実施。

(3)  $V_{DD}$  に流れる電流は、OUTx ピンに供給またはシンクされる負荷電流を考慮していません。 $V_{REF}$  ピンは  $V_{DD}$  に接続されます。

(4) 総消費電力は、 $I_{DD} \times (\text{電源オンされるチャネルの合計数}) + (\text{スリープ モード電流})$  で計算されます。

## 5.7 電気的特性、コンパレータモード

すべての最小および最大値は  $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$  で、標準値は  $T_A = 25^\circ\text{C}$ 、 $1.7V \leq V_{DD} \leq 5.5V$ 、DAC リファレンスは  $VDD$  に接続、ゲイン =  $1 \times$  電圧出力モード、DAC 出力ピン (OUT) には抵抗負荷 ( $R_L = 5\text{k}\Omega \sim \text{AGND}$ ) および容量負荷 ( $C_L = 200\text{pF} \sim \text{AGND}$ )、およびデジタル入力は  $VDD$  または  $\text{AGND}$  です (特に明記しない限り)

| パラメータ                         | テスト条件                                                                                                                                                  | 最小値                                                                                                                                                                                                                    | 標準値                           | 最大値      | 単位 |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------|----|

| <b>安定動作</b>                   |                                                                                                                                                        |                                                                                                                                                                                                                        |                               |          |    |

| オフセット誤差 <sup>(1) (2)</sup>    | $1.7V \leq V_{DD} \leq 5.5V$ 、ミッドスケールの DAC、Hi-Z のコンパレータ入力、外部基準電圧で動作する DAC。                                                                             | -6                                                                                                                                                                                                                     | 0                             | 6        | mV |

| オフセット誤差の時間ドリフト <sup>(1)</sup> | $V_{DD} = 5.5V$ 、外部リファレンス電圧、 $T_A = 125^\circ\text{C}$ 、Hi-Z モードの FB、フルスケールの DAC、0V の $V_{FB}$ または ゼロスケールの DAC、1.84V の $V_{FB}$ 、10 年間の連続動作に対してドリフトを規定 |                                                                                                                                                                                                                        | 4                             |          | mV |

| <b>出力</b>                     |                                                                                                                                                        |                                                                                                                                                                                                                        |                               |          |    |

| 入力電圧                          | $V_{REF}$ を $V_{DD}$ に接続、 $V_{FB}$ 抵抗ネットワークをグランドに接続します                                                                                                 | 0                                                                                                                                                                                                                      |                               | $V_{DD}$ | V  |

|                               | $V_{REF}$ を $V_{DD}$ に接続、 $V_{FB}$ 抵抗ネットワークをグランドから切断                                                                                                   | 0                                                                                                                                                                                                                      | $V_{DD} \times (1/3 - 1/100)$ |          |    |

| $V_{OL}$                      | ロジック Low 出力電圧                                                                                                                                          | $I_{LOAD} = 100\mu\text{A}$ 、オープンドレインモードで出力                                                                                                                                                                            | 0.1                           |          | V  |

| <b>ダイナミック性能</b>               |                                                                                                                                                        |                                                                                                                                                                                                                        |                               |          |    |

| $t_{resp}$                    | 出力応答時間                                                                                                                                                 | DAC はミッドスケールで 10 ビットの分解能、FB 入力は Hi-Z、FB ノードでの遷移ステップは ( $V_{DAC} - 2\text{LSB}$ ) から ( $V_{DAC} + 2\text{LSB}$ )、遷移時間は出力の 10% から 90% の間に測定、出力電流は $100\mu\text{A}$ 、コンパレータ出力はプッシュプルモードに設定、DAC 出力での負荷コンデンサは $25\text{pF}$ | 10                            |          | μs |

- (1) 設計と特性評価による仕様で、製造テストは未実施。

(2) この仕様には、DAC の総合未調整誤差 (TUE) は含まれていません。

## 5.8 電気的特性、ADC 入力

すべての最小値と最大値は  $-40^\circ\text{C} \leq T_A \leq +125^\circ\text{C}$  で、標準値は  $T_A = 25^\circ\text{C}$ 、 $1.7V \leq VDD \leq 5.5V$ 、リファレンスは  $VDD$  に接続、ゲイン =  $1 \times$ 、デジタル入力は  $VDD$  または  $\text{AGND}$  で (特に明記しない限り)、容量性負荷 ( $C_L = 200\text{pF}$  対  $\text{AGND}$ )、デジタル入力は  $VDD$  または  $\text{AGND}$  で (特に明記しない限り)

| パラメータ                          | テスト条件                                     | 最小値  | 標準値      | 最大値 | 単位   |

|--------------------------------|-------------------------------------------|------|----------|-----|------|

| <b>安定動作</b>                    |                                           |      |          |     |      |

| 分解能                            |                                           | 10   |          |     | ビット  |

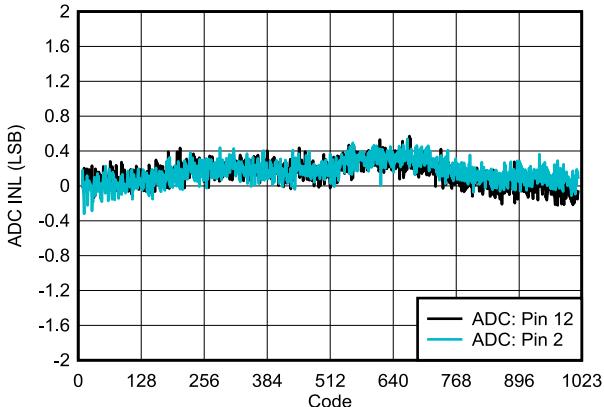

| INL 積分非直線性 <sup>(1) (2)</sup>  |                                           | -2   | 2        |     | LSB  |

| DNL 微分非直線性 <sup>(1) (2)</sup>  |                                           | -1   | 1        |     | LSB  |

| オフセット誤差 <sup>(1) (2) (3)</sup> | $1.7V \leq V_{DD} < 5.5V$                 | -5   | 0        | +5  | mV   |

|                                | $2.7V \leq V_{DD} \leq 5.5V$              | -5   | 0        | +5  |      |

| ゲイン誤差 <sup>(1) (2) (3)</sup>   |                                           | -1   | 1        |     | %FSR |

| <b>入力</b>                      |                                           |      |          |     |      |

| 入力電圧範囲                         | 外部 $V_{REF} = V_{DD}$ 、 $V_{FB}$ 減衰は 1 です | 0    | $V_{DD}$ |     | V    |

| <b>ダイナミック性能</b>                |                                           |      |          |     |      |

| データレート <sup>(2)</sup>          | ADC 平均化設定は 4 サンプル                         | 1406 | 2008     |     | SPS  |

| サンプリング コンデンサ                   |                                           |      | 10       |     | pF   |

- (1) 外部リファレンス電圧と内部リファレンス  $VDD \geq 1.21 \times \text{ゲイン} + 0.2V$  の場合、エンドポイントコードの間: 10 ビット分解能の場合は  $8d \sim 1016d$

(2) 設計と特性評価による仕様で、製造テストは未実施。

- (3) ミッドスケール、Hi-Z 入力構成、外部リファレンスを使用してアナログ入力で測定。

## 5.9 電気的特性、一般論

すべての最小および最大値は  $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$  で、標準値は  $T_A = 25^\circ\text{C}$ 、 $1.7\text{V} \leq V_{DD} \leq 5.5\text{V}$ 、DAC リファレンスは  $VDD$  に接続、ゲイン =  $1 \times$  (電圧出力モード)、または  $\pm 250\mu\text{A}$  出力範囲 (電流出力モード)、DAC 出力ピン (OUT) には電圧出力モードの抵抗負荷 ( $R_L = 5\text{k}\Omega \sim \text{AGND}$ ) および容量負荷 ( $C_L = 200\text{pF} \sim \text{AGND}$ )、およびデジタル入力は  $VDD$  または  $\text{AGND}$  です (特に明記しない限り)

| パラメータ                                   | テスト条件                                                                                                      | 最小値                                                                                                                          | 標準値     | 最大値   | 単位                    |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|---------|-------|-----------------------|

| <b>内部リファレンス</b>                         |                                                                                                            |                                                                                                                              |         |       |                       |

| 初期精度                                    | $T_A = 25^\circ\text{C}$                                                                                   | 1.1979                                                                                                                       | 1.212   | 1.224 | V                     |

| リファレンス出力の温度係数 <sup>(1) (2)</sup>        |                                                                                                            |                                                                                                                              | 50      |       | ppm/ $^\circ\text{C}$ |

| <b>EXTERNAL REFERENCE</b>               |                                                                                                            |                                                                                                                              |         |       |                       |

| $V_{REF}$ 入力インピーダンス <sup>(1) (3)</sup>  |                                                                                                            |                                                                                                                              | 192     |       | k $\Omega$ -ch        |

| <b>EEPROM</b>                           |                                                                                                            |                                                                                                                              |         |       |                       |

| 耐久性 <sup>(1)</sup>                      | $-40^\circ\text{C} \leq T_A \leq +85^\circ\text{C}$                                                        | 20000                                                                                                                        |         |       | サイクル                  |

|                                         | $T_A = 125^\circ\text{C}$                                                                                  | 1000                                                                                                                         |         |       |                       |

| データ保持期間 <sup>(1)</sup>                  | $T_A = 25^\circ\text{C}$                                                                                   | 50                                                                                                                           |         |       | 年                     |

| EEPROM プログラミング書き込みサイクル時間 <sup>(1)</sup> |                                                                                                            |                                                                                                                              | 200     |       | ms                    |

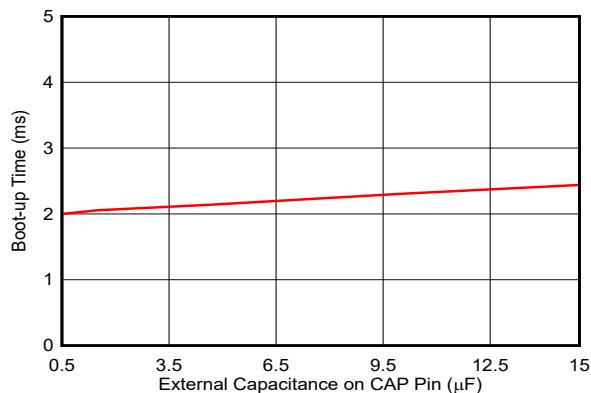

| デバイスのブートアップ時間 <sup>(1)</sup>            | 電源有効 ( $V_{DD} \geq 1.7\text{V}$ ) から出力有効状態 (EEPROM にプログラムされた出力状態) までに要する時間、CAP ピンの $0.5\mu\text{F}$ コンデンサ |                                                                                                                              | 5       |       | ms                    |

| <b>デジタル入力</b>                           |                                                                                                            |                                                                                                                              |         |       |                       |

| デジタル フィードスルー                            | 電圧出力モード、ミッドスケールでの DAC 静的出力、高速モード プラス、SCL トグル                                                               | 20                                                                                                                           |         |       | nV-s                  |

| ピン容量 1                                  | ピンごと                                                                                                       | 10                                                                                                                           |         |       | pF                    |

| <b>電源</b>                               |                                                                                                            |                                                                                                                              |         |       |                       |

| $I_{DD}$                                | $VDD$ に流れる電流                                                                                               | スリープ モード、内部リファレンスはパワーダウン、 $5.5\text{V}$ での外部リファレンス電圧                                                                         |         | 28    | $\mu\text{A}$         |

| $I_{DD}$                                | $VDD$ に流れる電流 <sup>(1)</sup>                                                                                | スリープ モード、内部リファレンス イネーブル、内部リファレンスを流れる追加電流                                                                                     |         | 10    | $\mu\text{A}$         |

| $I_{DD}$                                | $VDD$ に流れる電流 <sup>(1)</sup>                                                                                | すべてのチャネル イネーブル、内部リファレンス イネーブル、チャネルごとに内部リファレンスを流れる追加電流                                                                        |         | 12.5  | $\mu\text{A}$         |

| <b>ハイインピーダンス出力</b>                      |                                                                                                            |                                                                                                                              |         |       |                       |

| $I_{LEAK}$                              | $V_{OUTX}$ および $V_{FBX}$ に流れる電流                                                                            | DAC はハイインピーダンス出力モード、 $1.7\text{V} \leq V_{DD} \leq 5.5\text{V}$                                                              | 10      |       | nA                    |

|                                         |                                                                                                            | $V_{DD} = 0\text{V}$ 、 $V_{OUT} \leq 1.5\text{V}$ 、 $V_{DD}$ と $\text{AGND} = 0.1\mu\text{F}$ の間のデカップリング コンデンサ               | 200     |       | nA                    |

|                                         |                                                                                                            | $V_{DD} = 0\text{V}$ 、 $1.5\text{V} < V_{OUT} \leq 5.5\text{V}$ 、 $V_{DD}$ と $\text{AGND} = 0.1\mu\text{F}$ の間のデカップリング コンデンサ | 500     |       | nA                    |

|                                         |                                                                                                            | $V_{DD}$ と $\text{AGND}$ の間の $100\text{k}\Omega$ 、 $V_{OUT} \leq 1.25\text{V}$ 、OUT ピンの $10\text{k}\Omega$ の直列抵抗             | $\pm 2$ |       | $\mu\text{A}$         |

- (1) 設計と特性評価による仕様で、製造テストは未実施。

- (2)  $-40^\circ\text{C}$  および  $125^\circ\text{C}$  で測定し、勾配を計算しています。

- (3) DAC チャネルのインピーダンスは並列に接続されています。

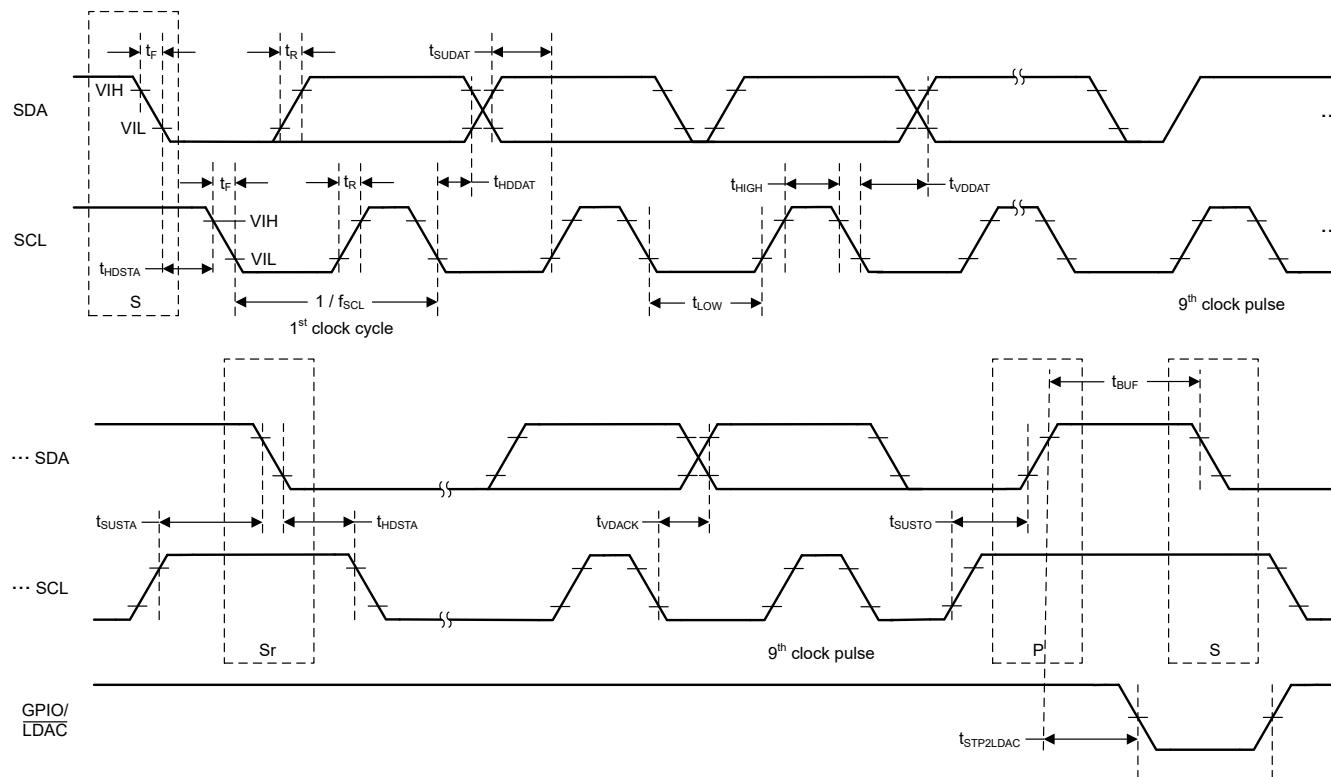

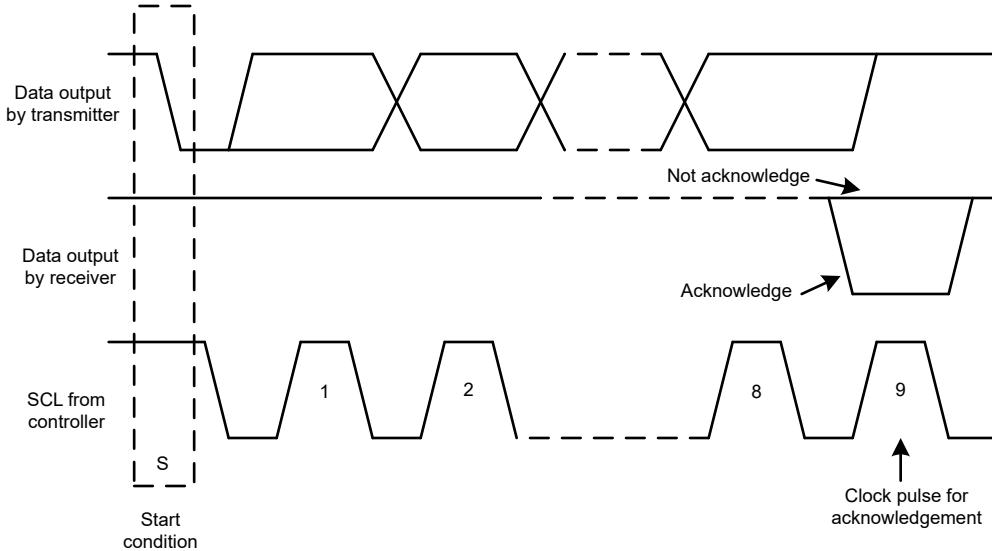

## 5.10 タイミング要件、I<sup>2</sup>C 標準モード

すべての入力信号は、V<sub>IIL</sub> から V<sub>pull-up</sub> の 70%、1.7V ≤ V<sub>DD</sub> ≤ 5.5V、−40°C ≤ T<sub>A</sub> ≤ +125°C、1.7V ≤ V<sub>pull-up</sub> ≤ V<sub>DD</sub> まででタイミング設定されます

|                    |                                                                            | 最小値  | 公称値 | 最大値  | 単位  |

|--------------------|----------------------------------------------------------------------------|------|-----|------|-----|

| f <sub>SCL</sub>   | SCL 周波数                                                                    |      |     | 100  | kHz |

| t <sub>BUF</sub>   | 停止条件と始動条件の間のバス解放時間                                                         | 4.7  |     |      | μs  |

| t <sub>HDSTA</sub> | リピート スタート後のホールド時間                                                          | 4    |     |      | μs  |

| t <sub>SUSTA</sub> | 繰り返しスタートのセットアップ時間                                                          | 4.7  |     |      | μs  |

| t <sub>SUSTO</sub> | STOP 条件のセットアップ時間                                                           | 4    |     |      | μs  |

| t <sub>HDDAT</sub> | データ ホールド時間                                                                 | 0    |     |      | ns  |

| t <sub>SUDAT</sub> | データ セットアップ時間                                                               | 250  |     |      | ns  |

| t <sub>LOW</sub>   | SCL クロックの Low 期間                                                           | 4700 |     |      | ns  |

| t <sub>HIGH</sub>  | SCL クロックの High 期間                                                          | 4000 |     |      | ns  |

| t <sub>F</sub>     | クロック / データの立ち下がり時間                                                         |      |     | 300  | ns  |

| t <sub>R</sub>     | クロック / データの立ち上がり時間                                                         |      |     | 1000 | ns  |

| t <sub>VDDAT</sub> | データ有効時間、R = 360Ω、C <sub>trace</sub> = 23pF、C <sub>probe</sub> = 10pF       |      |     | 3.45 | μs  |

| t <sub>VDACK</sub> | データ有効アクリシッジ時間、R = 360Ω、C <sub>trace</sub> = 23pF、C <sub>probe</sub> = 10pF |      |     | 3.45 | μs  |

## 5.11 タイミング要件、I<sup>2</sup>C 高速モード

すべての入力信号は、V<sub>IIL</sub> から V<sub>pull-up</sub> の 70%、1.7V ≤ V<sub>DD</sub> ≤ 5.5V、−40°C ≤ T<sub>A</sub> ≤ +125°C、1.7V ≤ V<sub>pull-up</sub> ≤ V<sub>DD</sub> まででタイミング設定されます

|                    |                                                                            | 最小値  | 公称値 | 最大値 | 単位  |

|--------------------|----------------------------------------------------------------------------|------|-----|-----|-----|

| f <sub>SCL</sub>   | SCL 周波数                                                                    |      |     | 400 | kHz |

| t <sub>BUF</sub>   | 停止条件と始動条件の間のバス解放時間                                                         | 1.3  |     |     | μs  |

| t <sub>HDSTA</sub> | リピート スタート後のホールド時間                                                          | 0.6  |     |     | μs  |

| t <sub>SUSTA</sub> | 繰り返しスタートのセットアップ時間                                                          | 0.6  |     |     | μs  |

| t <sub>SUSTO</sub> | STOP 条件のセットアップ時間                                                           | 0.6  |     |     | μs  |

| t <sub>HDDAT</sub> | データ ホールド時間                                                                 | 0    |     |     | ns  |

| t <sub>SUDAT</sub> | データ セットアップ時間                                                               | 100  |     |     | ns  |

| t <sub>LOW</sub>   | SCL クロックの Low 期間                                                           | 1300 |     |     | ns  |

| t <sub>HIGH</sub>  | SCL クロックの High 期間                                                          | 600  |     |     | ns  |

| t <sub>F</sub>     | クロック / データの立ち下がり時間                                                         |      |     | 300 | ns  |

| t <sub>R</sub>     | クロック / データの立ち上がり時間                                                         |      |     | 300 | ns  |

| t <sub>VDDAT</sub> | データ有効時間、R = 360Ω、C <sub>trace</sub> = 23pF、C <sub>probe</sub> = 10pF       |      |     | 0.9 | μs  |

| t <sub>VDACK</sub> | データ有効アクリシッジ時間、R = 360Ω、C <sub>trace</sub> = 23pF、C <sub>probe</sub> = 10pF |      |     | 0.9 | μs  |

## 5.12 タイミング要件、I<sup>2</sup>C 高速モード プラス

すべての入力信号は、V<sub>IIL</sub> から V<sub>pull-up</sub> の 70%、1.7V ≤ V<sub>DD</sub> ≤ 5.5V、−40°C ≤ T<sub>A</sub> ≤ +125°C、1.7V ≤ V<sub>pull-up</sub> ≤ V<sub>DD</sub> まででタイミング設定されます

|                    |                    | 最小値  | 公称値 | 最大値 | 単位  |

|--------------------|--------------------|------|-----|-----|-----|

| f <sub>SCL</sub>   | SCL 周波数            |      |     | 1   | MHz |

| t <sub>BUF</sub>   | 停止条件と始動条件の間のバス解放時間 | 0.5  |     |     | μs  |

| t <sub>HDSTA</sub> | リピート スタート後のホールド時間  | 0.26 |     |     | μs  |

| t <sub>SUSTA</sub> | 繰り返しスタートのセットアップ時間  | 0.26 |     |     | μs  |

| t <sub>SUSTO</sub> | STOP 条件のセットアップ時間   | 0.26 |     |     | μs  |

| t <sub>HDDAT</sub> | データ ホールド時間         | 0    |     |     | ns  |

| t <sub>SUDAT</sub> | データ セットアップ時間       | 50   |     |     | ns  |

| t <sub>LOW</sub>   | SCL クロックの Low 期間   | 0.5  |     |     | μs  |

| t <sub>HIGH</sub>  | SCL クロックの High 期間  | 0.26 |     |     | μs  |

すべての入力信号は、V<sub>I</sub>L から V<sub>pull-up</sub> の 70%、1.7V ≤ V<sub>DD</sub> ≤ 5.5V、−40°C ≤ T<sub>A</sub> ≤ +125°C、1.7V ≤ V<sub>pull-up</sub> ≤ V<sub>DD</sub> まででタイミング設定されます

|                    |                                                                           | 最小値 | 公称値 | 最大値  | 単位 |

|--------------------|---------------------------------------------------------------------------|-----|-----|------|----|

| t <sub>F</sub>     | クロック / データの立ち下がり時間                                                        |     |     | 120  | ns |

| t <sub>R</sub>     | クロック / データの立ち上がり時間                                                        |     |     | 120  | ns |

| t <sub>VDDAT</sub> | データ有効時間、R = 360Ω、C <sub>trace</sub> = 23pF、C <sub>probe</sub> = 10pF      |     |     | 0.45 | μs |

| t <sub>VDACK</sub> | データ有効アノリジジ時間、R = 360Ω、C <sub>trace</sub> = 23pF、C <sub>probe</sub> = 10pF |     |     | 0.45 | μs |

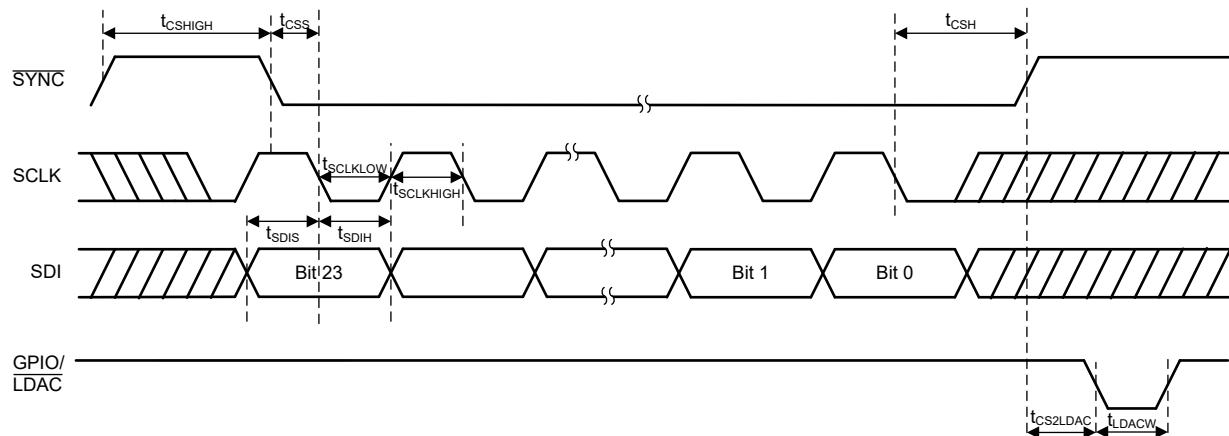

### 5.13 タイミング要件、SPI 書き込み動作

すべての入力信号は t<sub>r</sub> = t<sub>f</sub> = 1V/ns (V<sub>IO</sub> の 10% ~ 90%) で規定され、(V<sub>I</sub>L + V<sub>I</sub>H) / 2、1.7V ≤ V<sub>IO</sub> ≤ 5.5V、1.7V ≤ V<sub>DD</sub> ≤ 5.5V、および −40°C ≤ T<sub>A</sub> ≤ +125°C の電圧レベルからタイミングが規定されています

|                        |                                                     | 最小値 | 公称値 | 最大値 | 単位  |

|------------------------|-----------------------------------------------------|-----|-----|-----|-----|

| f <sub>SCLK</sub>      | シリアル クロック周波数                                        |     |     | 50  | MHz |

| t <sub>SCLKHIGH</sub>  | SCLK High 時間                                        | 9   |     |     | ns  |

| t <sub>SCLKLOW</sub>   | SCLK Low 時間                                         | 9   |     |     | ns  |

| t <sub>SDIS</sub>      | SDI のセットアップ時間                                       | 8   |     |     | ns  |

| t <sub>SDIH</sub>      | SDI のホールド時間                                         | 8   |     |     | ns  |

| t <sub>css</sub>       | CS から SCLK 立ち下がりエッジまでのセットアップ時間                      | 18  |     |     | ns  |

| t <sub>CSH</sub>       | SCLK 立ち下がりエッジから CS 立ち上がりエッジまで                       | 10  |     |     | ns  |

| t <sub>CSHIGH</sub>    | CS High 時間                                          | 50  |     |     | ns  |

| t <sub>DACWAIT</sub>   | 同じチャネルのシーケンシャル DAC の更新待機時間 (後続の LDAC 立ち下がりエッジまでの時間) | 2   |     |     | μs  |

| t <sub>BCASTWAIT</sub> | ブロードキャスト DAC の更新待機時間 (後続の LDAC 立ち下がりエッジまでの時間)       | 2   |     |     | μs  |

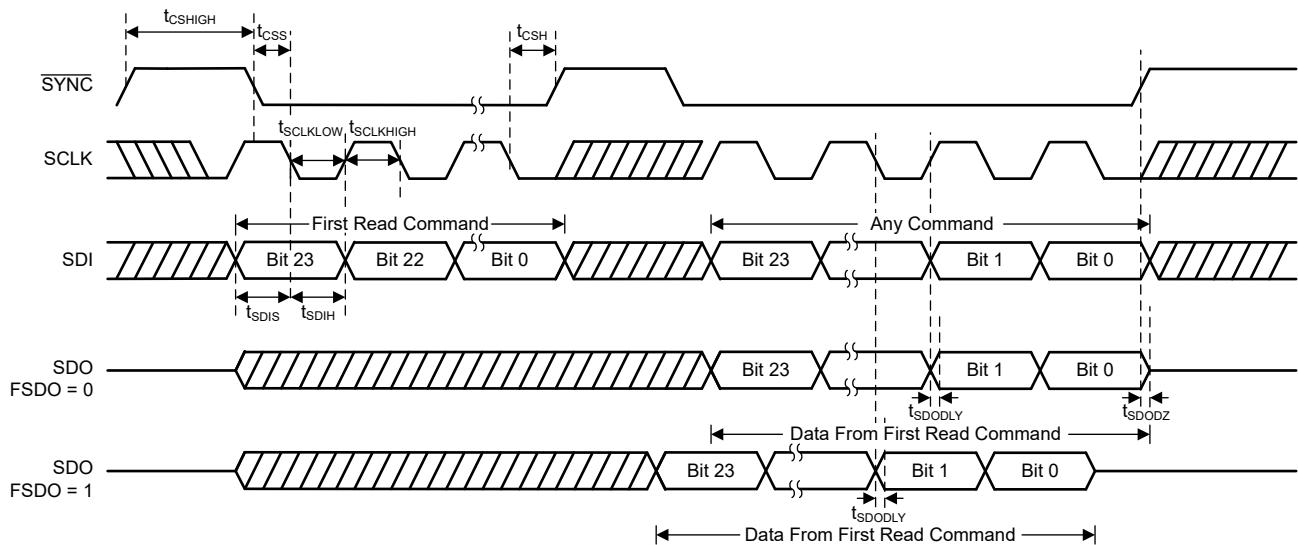

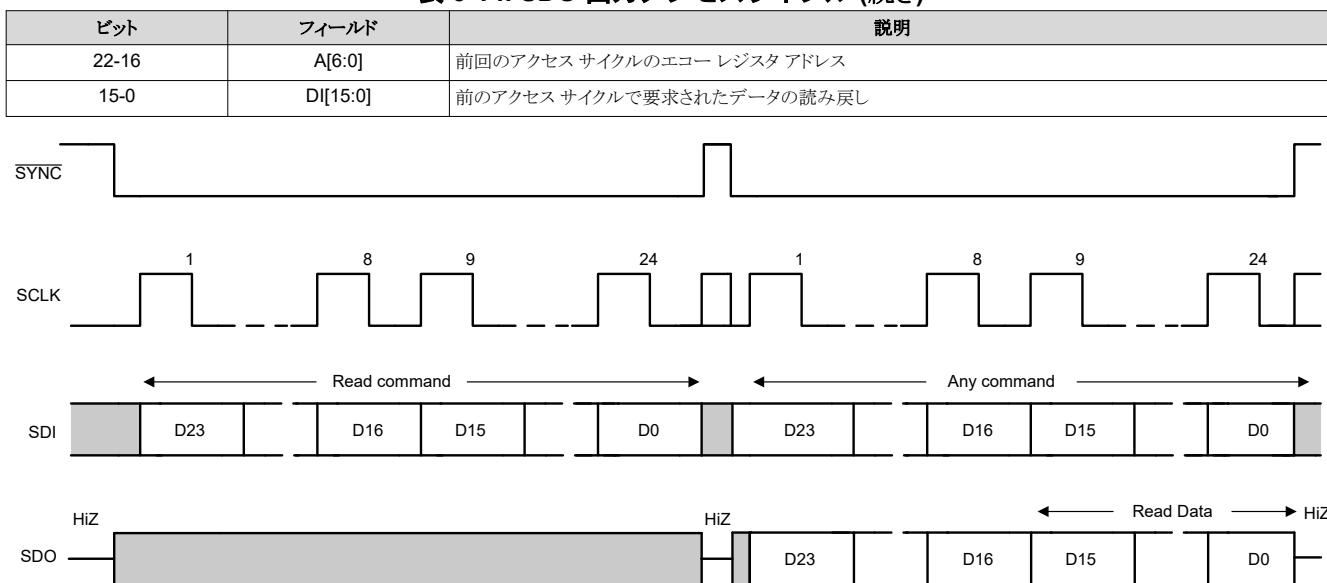

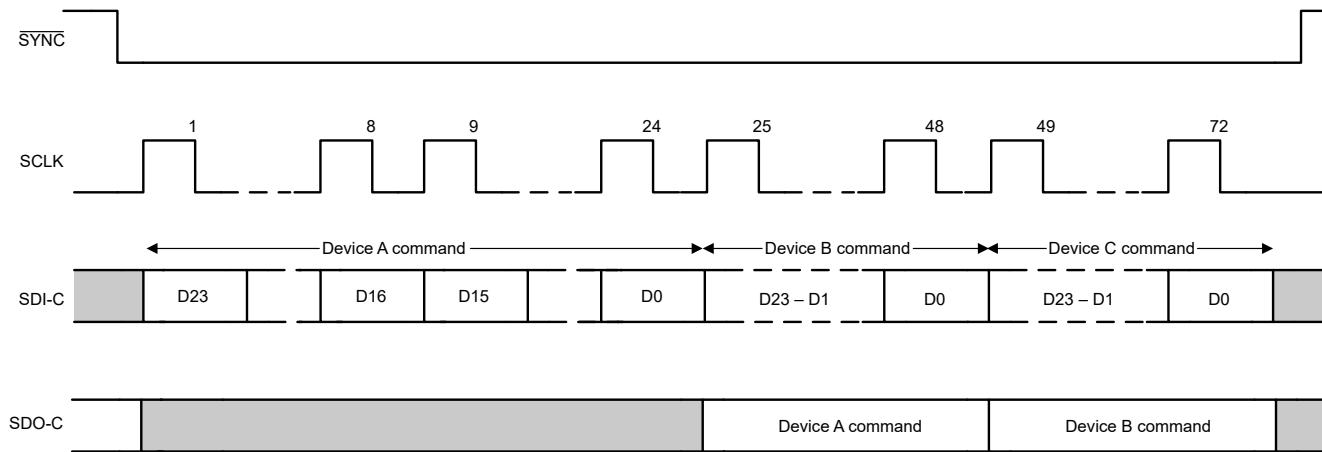

### 5.14 タイミング要件、SPI 読み出しおよびデイジー チェーン動作 (FSDO = 0)

すべての入力信号は t<sub>r</sub> = t<sub>f</sub> = 1V/ns (V<sub>IO</sub> の 10% ~ 90%) で規定され、(V<sub>I</sub>L + V<sub>I</sub>H) / 2、1.7V ≤ V<sub>IO</sub> ≤ 5.5V、1.7V ≤ V<sub>DD</sub> ≤ 5.5V、−40°C ≤ T<sub>A</sub> ≤ +125°C、および FSDO = 0

|                       |                                                                             | 最小値 | 公称値 | 最大値  | 単位  |

|-----------------------|-----------------------------------------------------------------------------|-----|-----|------|-----|

| f <sub>SCLK</sub>     | シリアル クロック周波数                                                                |     |     | 1.25 | MHz |

| t <sub>SCLKHIGH</sub> | SCLK High 時間                                                                | 350 |     |      | ns  |

| t <sub>SCLKLOW</sub>  | SCLK Low 時間                                                                 | 350 |     |      | ns  |

| t <sub>SDIS</sub>     | SDI のセットアップ時間                                                               | 8   |     |      | ns  |

| t <sub>SDIH</sub>     | SDI のホールド時間                                                                 | 8   |     |      | ns  |

| t <sub>css</sub>      | SYNC から SCLK 立ち下がりエッジまでのセットアップ時間                                            | 400 |     |      | ns  |

| t <sub>CSH</sub>      | SCLK 立ち下がりエッジから SYNC 立ち上がりエッジまで                                             | 400 |     |      | ns  |

| t <sub>CSHIGH</sub>   | SYNC High 時間                                                                | 1   |     |      | μs  |

| t <sub>SDODLY</sub>   | SCLK 立ち上がりエッジから SDO 立ち下がりエッジまで、I <sub>OL</sub> ≤ 5mA、C <sub>L</sub> = 20pF。 |     |     | 300  | ns  |

### 5.15 タイミング要件、SPI 読み出しおよびデイジー チェーン動作 (FSDO = 1)

すべての入力信号は t<sub>r</sub> = t<sub>f</sub> = 1V/ns (V<sub>IO</sub> の 10% ~ 90%) で規定され、(V<sub>I</sub>L + V<sub>I</sub>H) / 2、1.7V ≤ V<sub>IO</sub> ≤ 5.5V、1.7V ≤ V<sub>DD</sub> ≤ 5.5V、−40°C ≤ T<sub>A</sub> ≤ +125°C、および FSDO = 1

|                       |              | 最小値 | 公称値 | 最大値 | 単位  |

|-----------------------|--------------|-----|-----|-----|-----|

| f <sub>SCLK</sub>     | シリアル クロック周波数 |     |     | 2.5 | MHz |

| t <sub>SCLKHIGH</sub> | SCLK High 時間 | 175 |     |     | ns  |

すべての入力信号は  $t_r = t_f = 1V/ns$  ( $V_{IO}$  の 10% ~ 90%) で規定され、 $(V_{IL} + V_{IH}) / 2$ 、

$1.7V \leq V_{IO} \leq 5.5V$ 、 $1.7V \leq V_{DD} \leq 5.5V$ 、 $-40^\circ C \leq T_A \leq +125^\circ C$ 、および  $FSDO = 1$

|               |                                                                    | 最小値 | 公称値 | 最大値 | 単位 |

|---------------|--------------------------------------------------------------------|-----|-----|-----|----|

| $t_{SCLKLOW}$ | SCLK Low 時間                                                        |     | 175 |     | ns |

| $t_{SDIS}$    | SDI のセットアップ時間                                                      |     | 8   |     | ns |

| $t_{SDIH}$    | SDI のホールド時間                                                        |     | 8   |     | ns |

| $t_{CSS}$     | SYNC から SCLK 立ち下がりエッジまでのセットアップ時間                                   |     | 300 |     | ns |

| $t_{CSH}$     | SCLK 立ち下がりエッジから SYNC 立ち上がりエッジまで                                    |     | 300 |     | ns |

| $t_{CSHIGH}$  | SYNC High 時間                                                       |     | 1   |     | μs |

| $t_{SDODLY}$  | SCLK 立ち上がりエッジから SDO 立ち下がりエッジまで、 $I_{OL} \leq 5mA$ 、 $C_L = 20pF$ 。 |     |     | 300 | ns |

## 5.16 タイミング要件、GPIO

すべての入力信号は  $t_f = t_r = 1V/ns$  ( $V_{IO}$  の 10% ~ 90%) で規定され、 $(V_{IL} + V_{IH}) / 2$ 、

$1.7V \leq V_{IO} \leq 5.5V$ 、 $1.7V \leq V_{DD} \leq 5.5V$ 、および  $-40^\circ C \leq T_A \leq +125^\circ C$  の電圧レベルからタイミングが規定されています

|                |                                                     | 最小値 | 公称値 | 最大値 | 単位      |

|----------------|-----------------------------------------------------|-----|-----|-----|---------|

| $t_{GPIHIGH}$  | GPI High 時間                                         |     | 2   |     | $\mu s$ |

| $t_{GPILOW}$   | GPI Low 時間                                          |     | 2   |     | $\mu s$ |

| $t_{GPAWGD}$   | LDAC 立ち下がりエッジから DAC 更新までの遅延                         |     |     | 2   | $\mu s$ |

| $t_{CS2LDAC}$  | SYNC 立ち上がりエッジから LDAC 立ち下がりエッジまで                     | 1   |     |     | $\mu s$ |

| $t_{STP2LDAC}$ | I <sup>2</sup> C ストップ ビット立ち上がりエッジから LDAC 立ち下がりエッジまで | 1   |     |     | $\mu s$ |

| $t_{LDACW}$    | LDAC Low 時間                                         | 2   |     |     | $\mu s$ |

## 5.17 タイミング図

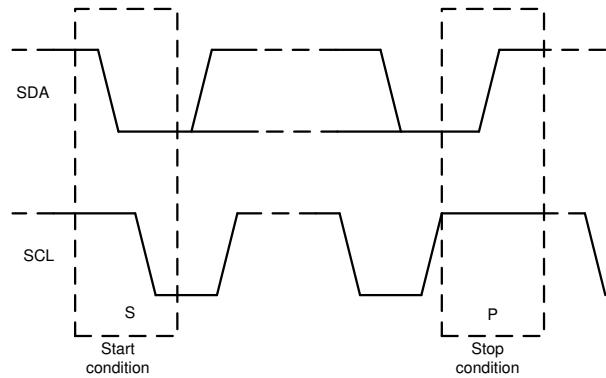

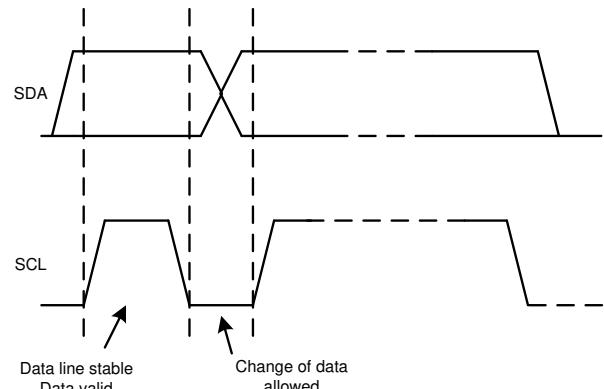

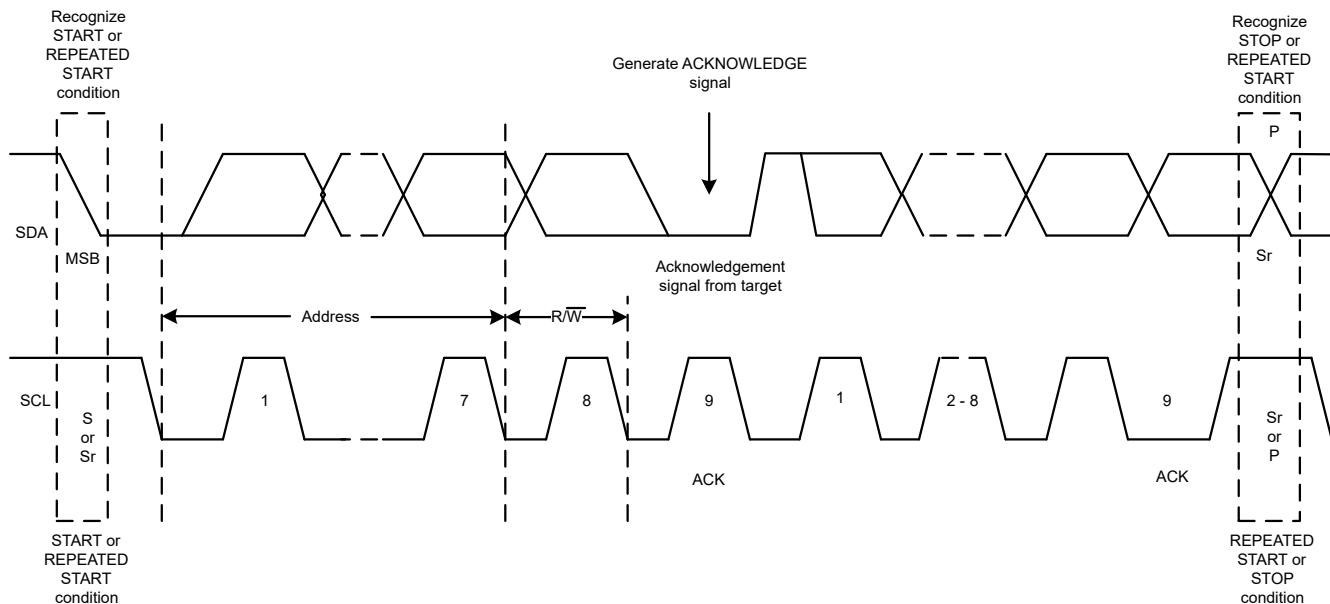

図 5-1. I<sup>2</sup>C のタイミング図

図 5-2. SPI 書き込みタイミング図

図 5-3. SPI 読み出しのタイミング図

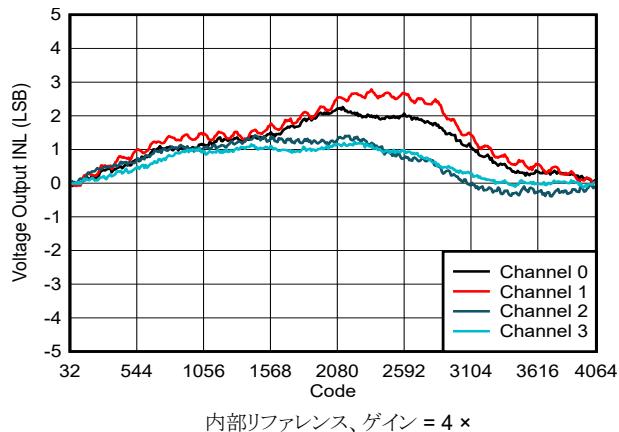

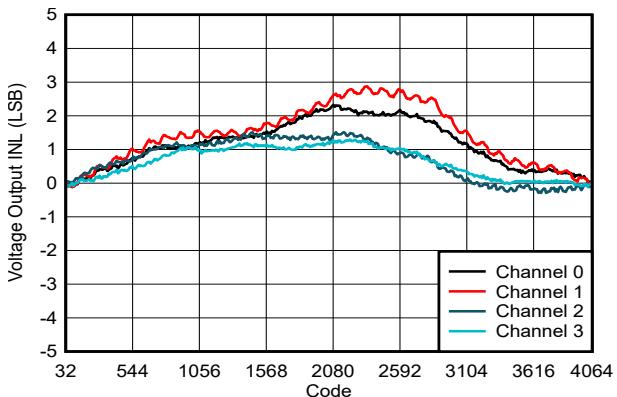

## 5.18 代表的特性：電圧出力

$T_A = 25^\circ\text{C}$ 、 $V_{DD} = 5.5\text{V}$ 、外部リファレンス =  $5.5\text{V}$ 、ゲイン =  $1 \times$ 、12 ビット分解能、DAC 出力は無負荷時 (特に記述のない限り)

図 5-4. 電圧出力 INL とデジタル入力コードとの関係

図 5-5. 電圧出力 INL とデジタル入力コードとの関係

図 5-6. 電圧出力 INL と温度との関係

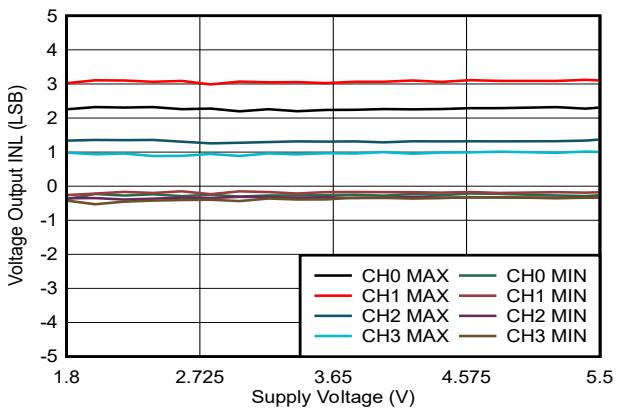

図 5-7. 電圧出力 INL と電源電圧との関係

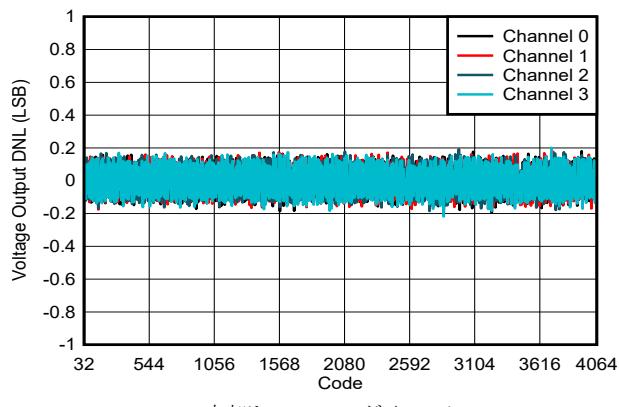

図 5-8. 電圧出力 DNL とデジタル入力コードとの関係

図 5-9. 電圧出力 DNL とデジタル入力コードとの関係

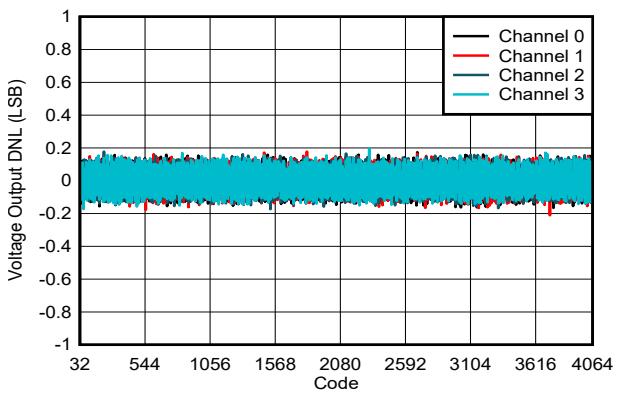

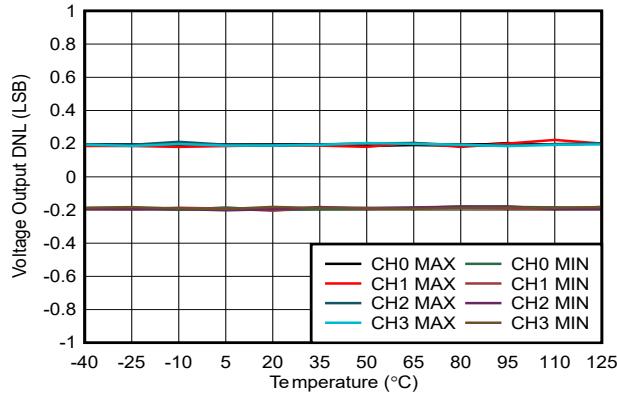

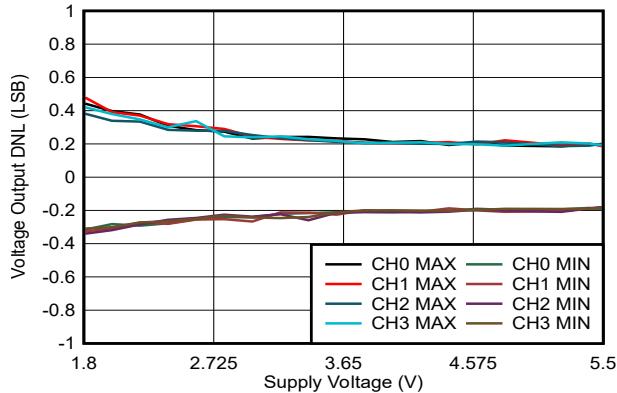

## 5.18 代表的特性：電圧出力 (続き)

$T_A = 25^\circ\text{C}$ 、 $V_{DD} = 5.5\text{V}$ 、外部リファレンス =  $5.5\text{V}$ 、ゲイン =  $1 \times$ 、12 ビット分解能、DAC 出力は無負荷時 (特に記述のない限り)

図 5-10. 電圧出力 DNL と温度との関係

図 5-11. 電圧出力 DNL と電源電圧との関係

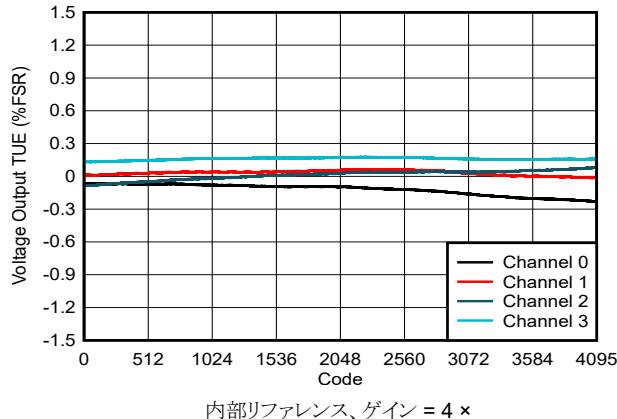

内部リファレンス、ゲイン =  $4 \times$

図 5-12. 電圧出力 TUE とデジタル入力コードとの関係

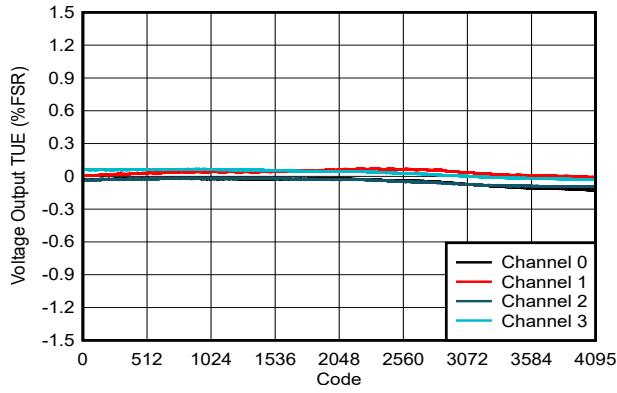

図 5-13. 電圧出力 TUE とデジタル入力コードとの関係

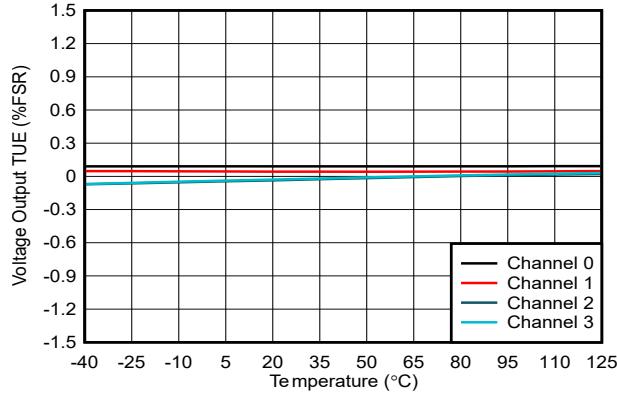

ミッドスケールでの DAC チャネル

図 5-14. 電圧出力 TUE と温度との関係

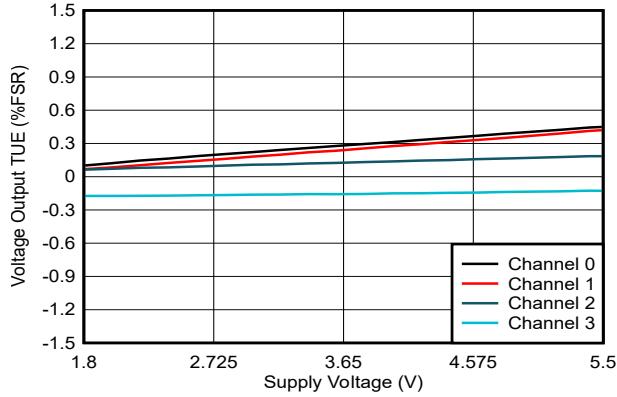

ミッドスケールでの DAC チャネル

図 5-15. 電圧出力 TUE と電源電圧との関係

## 5.18 代表的特性：電圧出力 (続き)

$T_A = 25^\circ\text{C}$ ,  $V_{DD} = 5.5\text{V}$ , 外部リファレンス =  $5.5\text{V}$ , ゲイン =  $1 \times$ , 12 ビット分解能、DAC 出力は無負荷時 (特に記述のない限り)

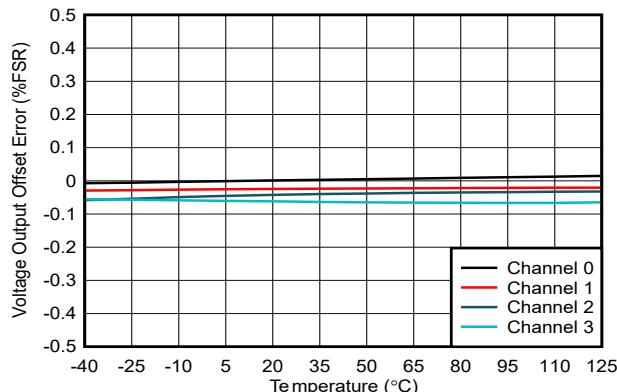

図 5-16. 電圧出力オフセット誤差と温度との関係

図 5-17. 電圧出力ゲイン誤差と温度との関係

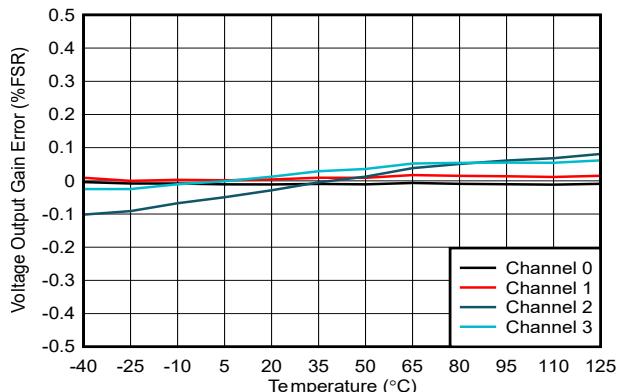

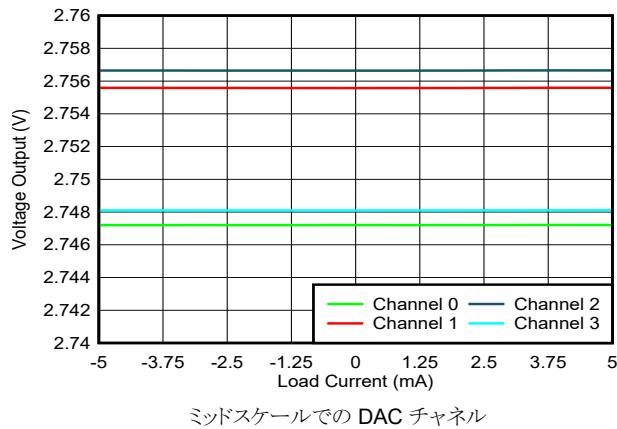

図 5-18. 電圧出力と負荷電流との関係

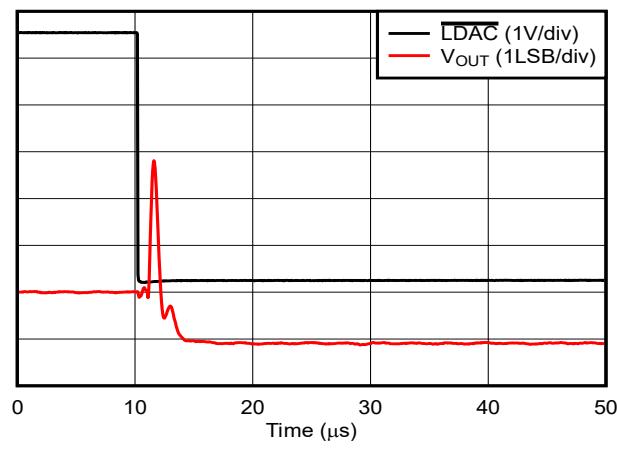

図 5-19. 電圧出力コードからコードへのグリッチ - 立ち上がりエッジ

図 5-20. 電圧出力のコード間グリッチ：立ち下がりエッジ

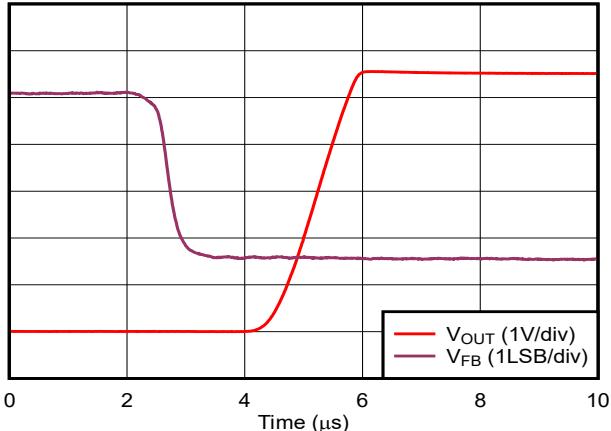

図 5-21. 出力電圧セッティング時間：立ち上がりエッジ

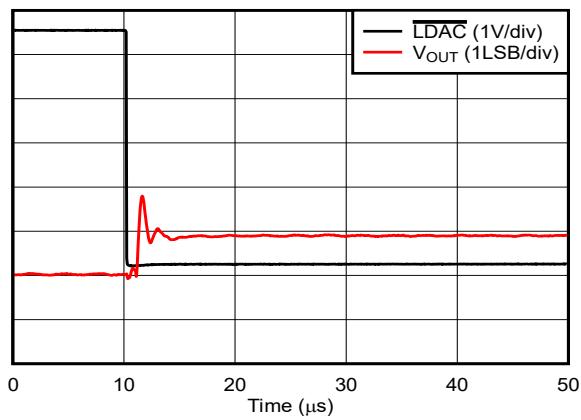

## 5.18 代表的特性：電圧出力 (続き)

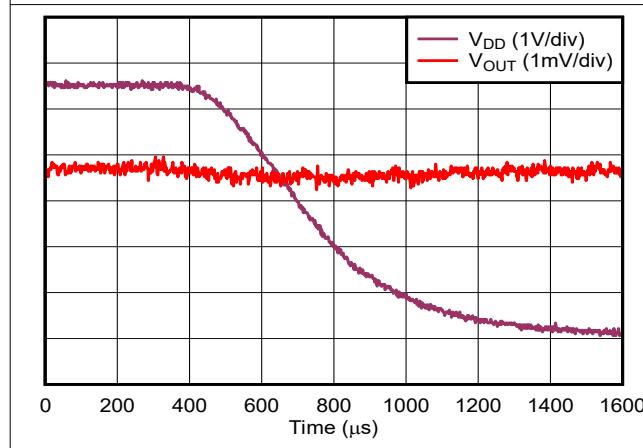

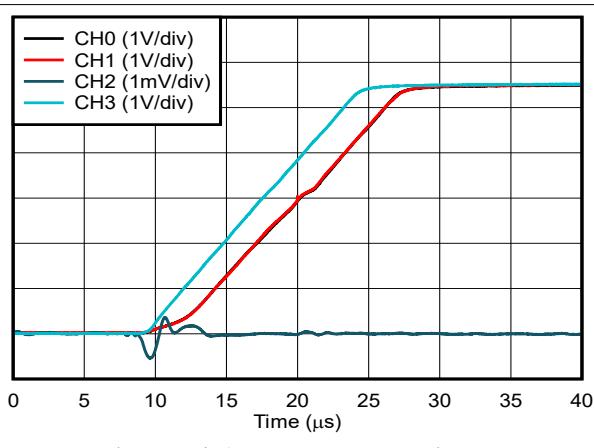

$T_A = 25^\circ\text{C}$ 、 $V_{DD} = 5.5\text{V}$ 、外部リファレンス =  $5.5\text{V}$ 、ゲイン =  $1 \times$ 、12 ビット分解能、DAC 出力は無負荷時 (特に記述のない限り)

図 5-22. 出力電圧セッティング時間：立ち下がりエッジ

図 5-23. 電圧出力パワーオン グリッチ

図 5-24. 電圧出力パワーオフ グリッチ

図 5-25. 電圧出力チャネル間クロストーク

図 5-26. 電圧出力ノイズ密度

図 5-27. 電圧出力ノイズ密度

## 5.18 代表的特性：電圧出力 (続き)

$T_A = 25^\circ\text{C}$ 、 $V_{DD} = 5.5\text{V}$ 、外部リファレンス =  $5.5\text{V}$ 、ゲイン =  $1 \times$ 、12 ビット分解能、DAC 出力は無負荷時 (特に記述のない限り)

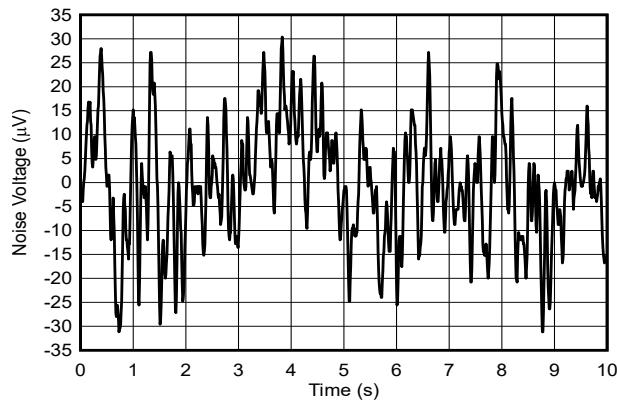

図 5-28. 電圧出力フリッカーノイズ

図 5-29. 電圧出力フリッカーノイズ

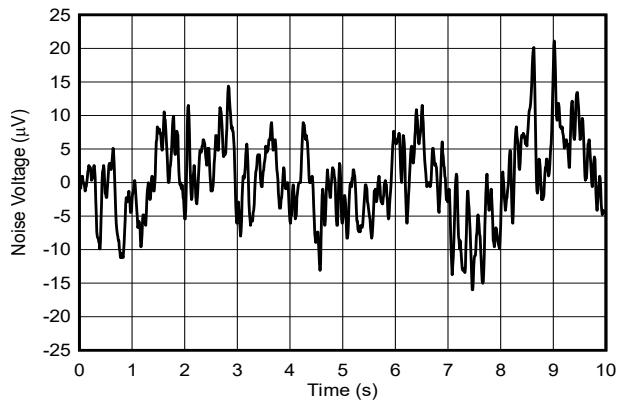

図 5-30. 電圧出力 AC PSRR と周波数との関係

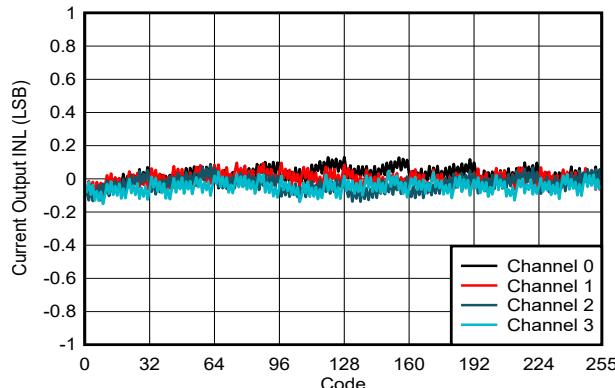

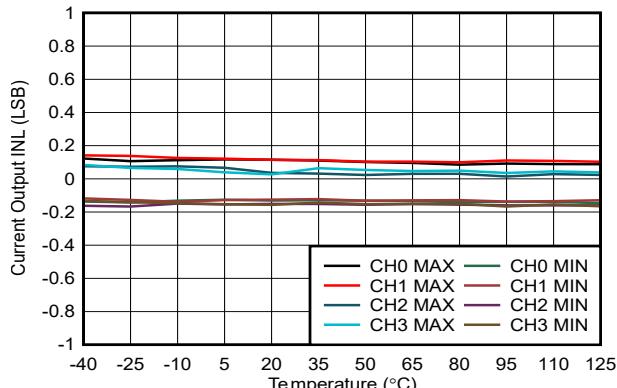

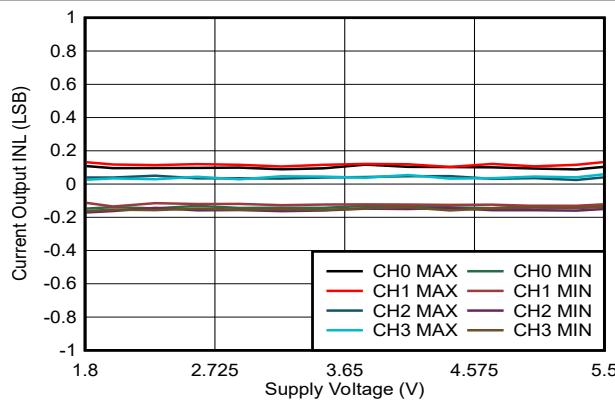

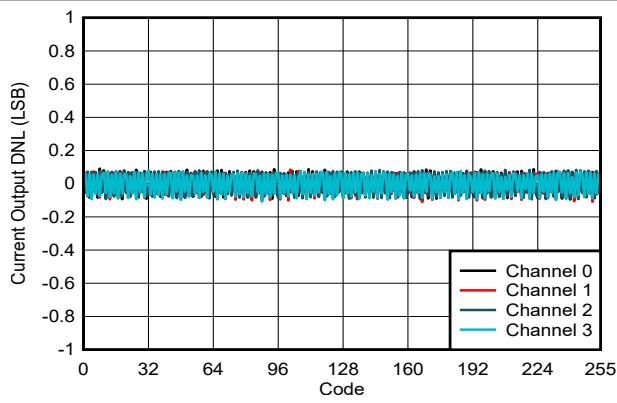

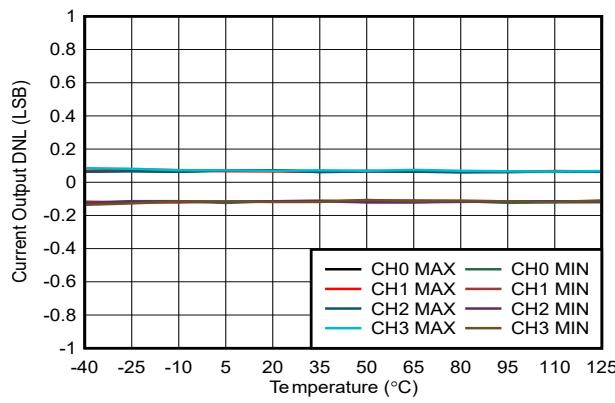

## 5.19 代表的特性：電流出力

$T_A = 25^\circ\text{C}$ 、 $V_{DD} = 5.5\text{V}$ 、出力範囲： $\pm 250\mu\text{A}$  (特に記述のない限り)

図 5-31. 電流出力 INL とデジタル入力コードとの関係

図 5-32. 電流出力 INL と温度との関係

図 5-33. 電流出力 INL と電源電圧との関係

図 5-34. 電流出力 DNL とデジタル入力コードとの関係

図 5-35. 電流出力 DNL と温度との関係

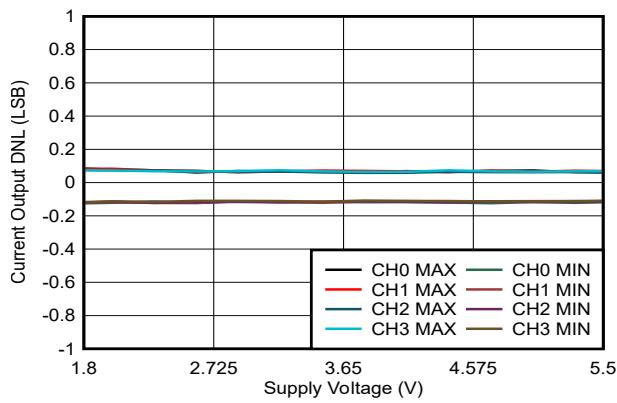

図 5-36. 電流出力 DNL と電源電圧との関係

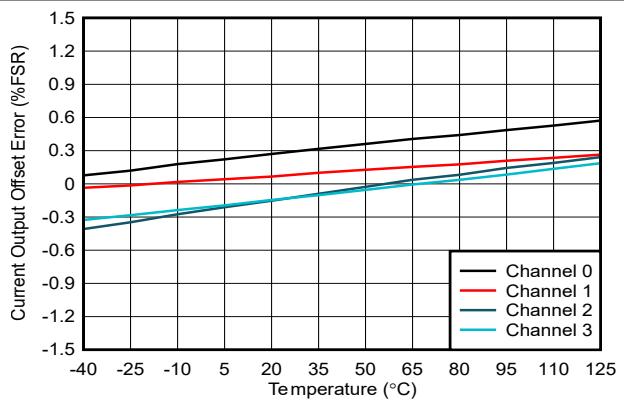

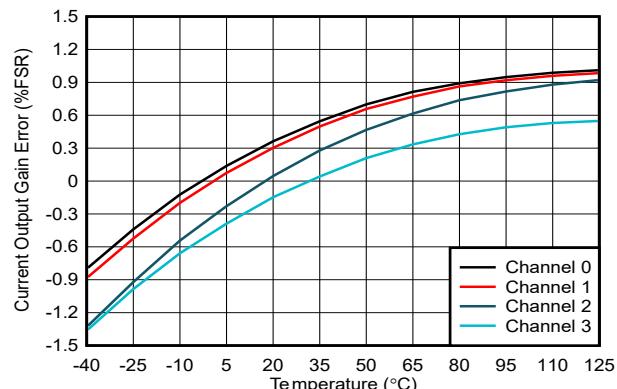

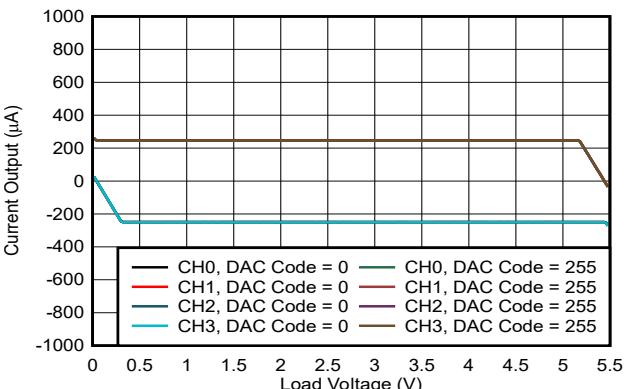

## 5.19 代表的特性：電流出力 (続き)

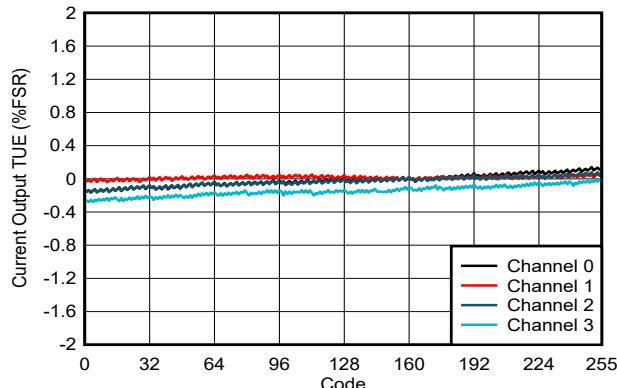

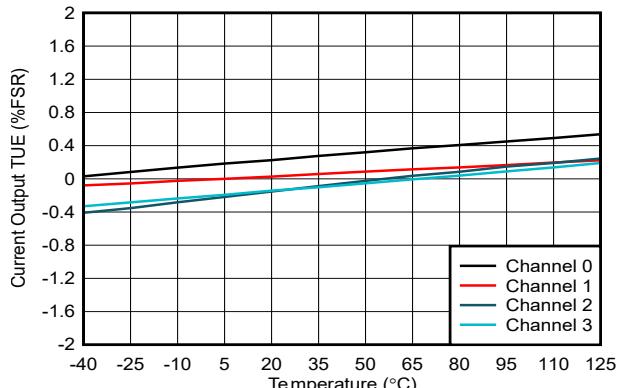

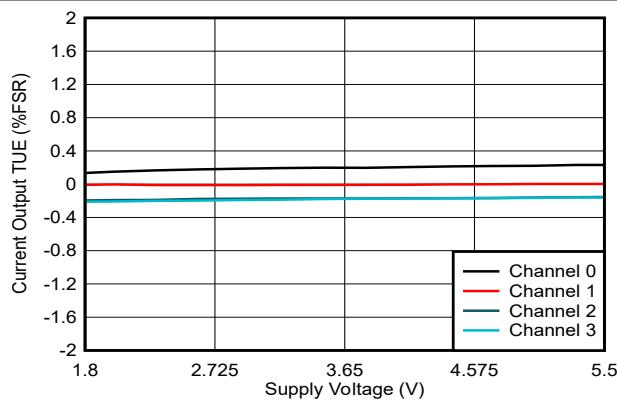

$T_A = 25^\circ\text{C}$ 、 $V_{DD} = 5.5\text{V}$ 、出力範囲： $\pm 250\mu\text{A}$  (特に記述のない限り)

図 5-37. 電流出力 TUE とデジタル入力コードとの関係

ミッドスケールでの DAC チャネル

図 5-38. 電流出力 TUE と温度との関係

ミッドスケールでの DAC チャネル

図 5-39. 電流出力 TUE と電源電圧との関係

図 5-40. 電流出力オフセット誤差と温度との関係

図 5-41. 電流出力ゲイン誤差と温度との関係

図 5-42. 電流出力と負荷電圧との関係

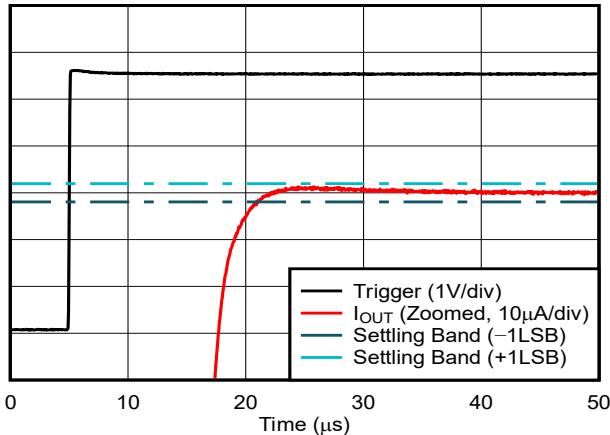

## 5.19 代表的特性：電流出力 (続き)

$T_A = 25^\circ\text{C}$ 、 $V_{DD} = 5.5\text{V}$ 、出力範囲： $\pm 250\mu\text{A}$  (特に記述のない限り)

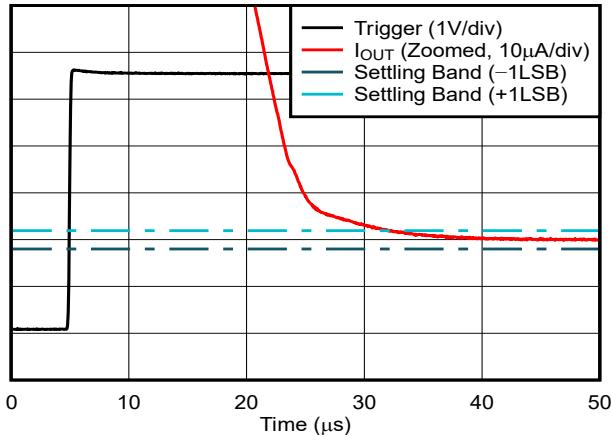

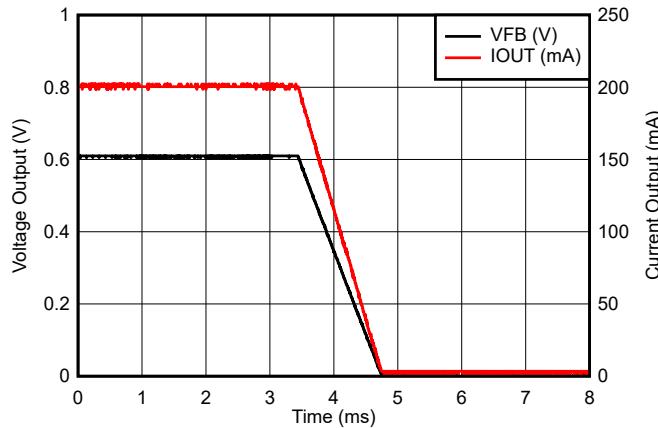

図 5-43. 電流出力セッティング時間：立ち上がりリエッジ ( $\frac{1}{4} \sim \frac{3}{4}$  スケール)

図 5-44. 電流出力セッティング時間：立ち下がりリエッジ ( $\frac{3}{4} \sim \frac{1}{4}$  スケール)

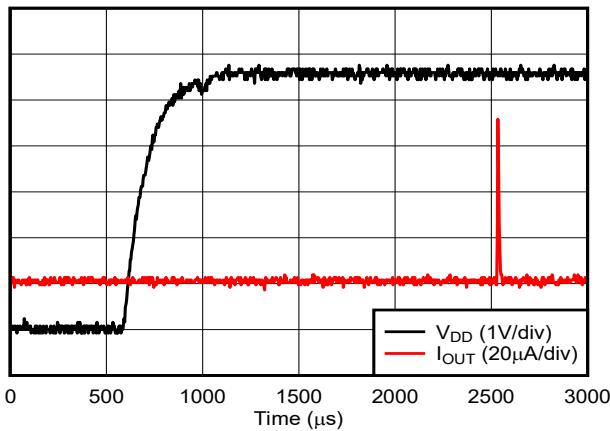

ミッドスケールでの DAC (0 $\mu\text{A}$ )、EEPROM に保存

図 5-45. 電流出力パワーオン グリッチ

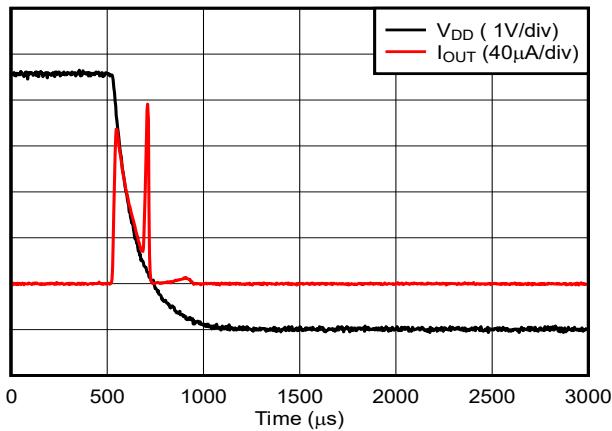

ミッドスケールでの DAC (0 $\mu\text{A}$ )

図 5-46. 電流出力電源オフ グリッチ

## 5.19 代表的特性：電流出力 (続き)

$T_A = 25^\circ\text{C}$ 、 $V_{DD} = 5.5\text{V}$ 、出力範囲： $\pm 250\mu\text{A}$  (特に記述のない限り)

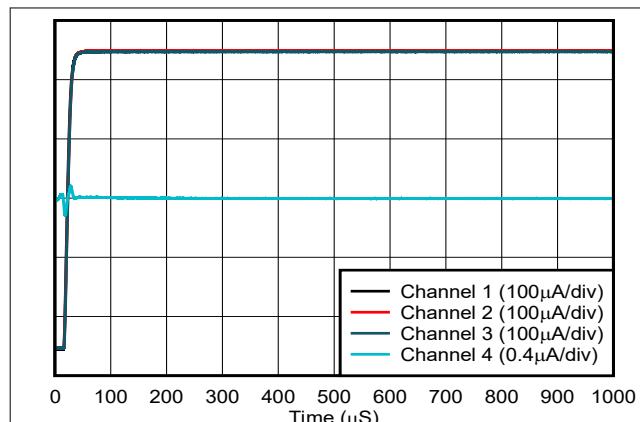

チャネル 4 は常駐し、他のすべてのチャネルは干渉です

図 5-47. 電流出力チャネル間クロストーク

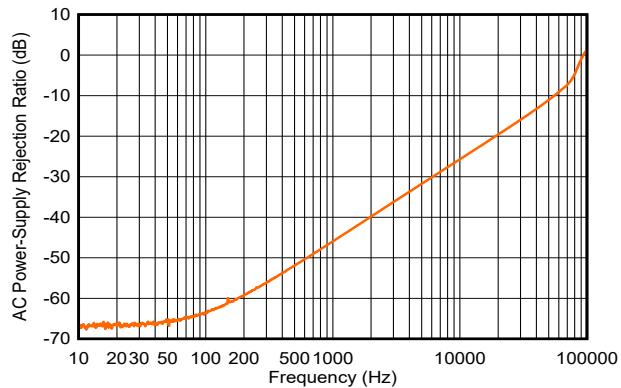

図 5-48. 電流出力 AC PSRR と周波数との関係

図 5-49. 電流出力ノイズ密度

$f = 0.1\text{Hz} \sim 10\text{Hz}$

図 5-50. 電流出力フリッカー ノイズ

## 5.20 代表的特性：ADC

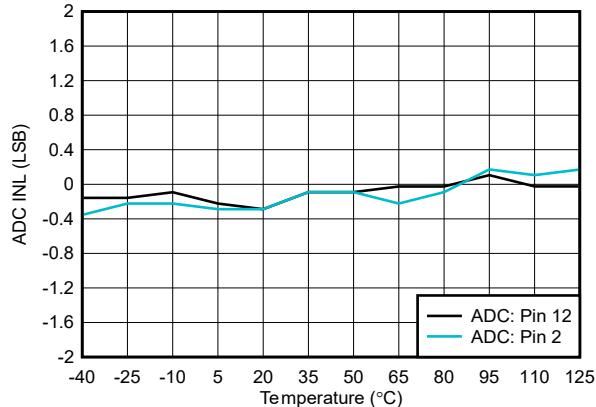

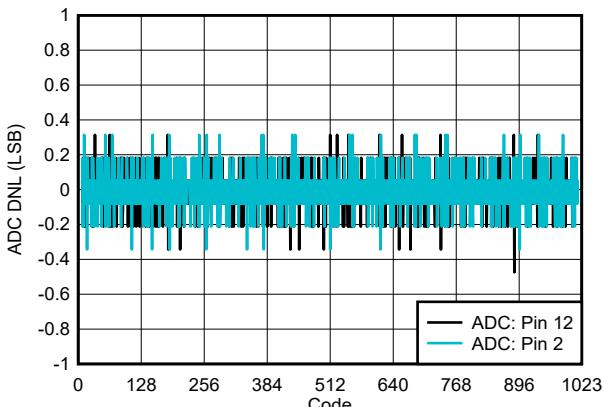

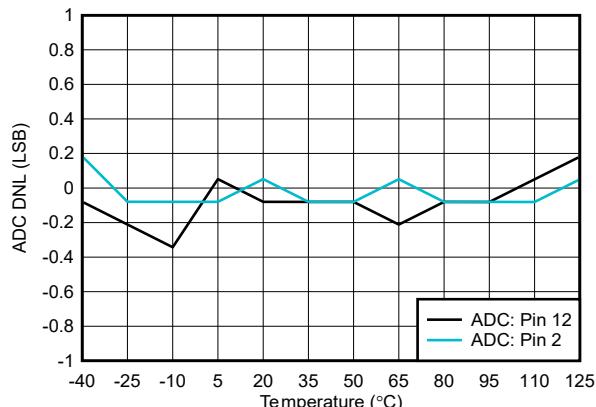

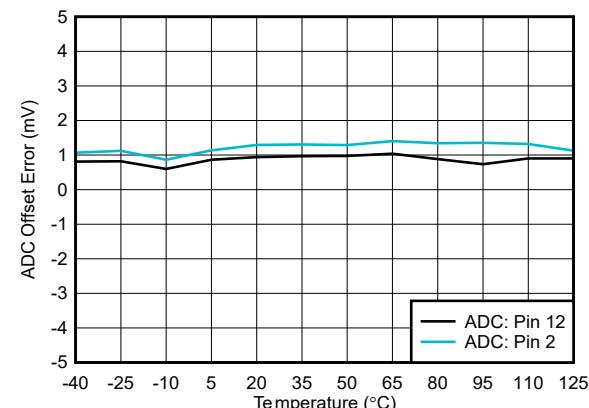

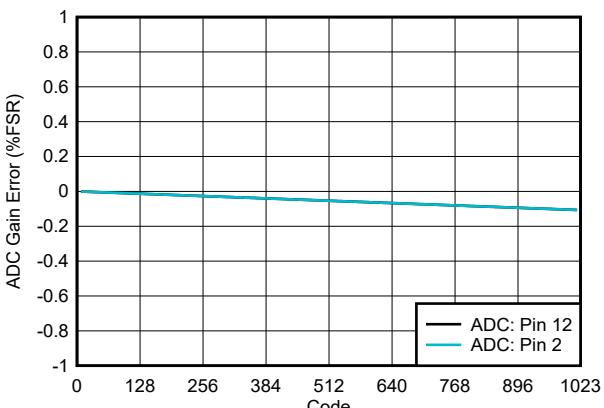

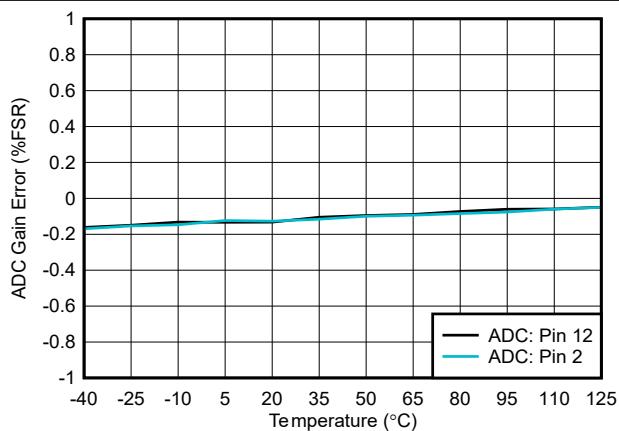

$T_A = 25^\circ\text{C}$  の場合、 $V_{DD} = 5.5\text{V}$ 、外部のリファレンス =  $5.5\text{V}$ 、ゲイン =  $1 \times$ 、10 ビット分解能、ハイインピーダンス入力 (特に記述のない限り)

図 5-51. ADC INL とデジタル出力コードとの関係

図 5-52. ADC INL と温度との関係

図 5-53. ADC DNL とデジタル出力コードとの関係

図 5-54. ADC DNL と温度との関係

図 5-55. ADC オフセット誤差と温度との関係

図 5-56. ADC ゲイン誤差とデジタル出力コードとの関係

## 5.20 代表的特性：ADC (続き)

$T_A = 25^\circ\text{C}$  の場合、 $V_{DD} = 5.5\text{V}$ 、外部のリファレンス = 5.5V、ゲイン = 1 ×、10 ビット分解能、ハイインピーダンス入力 (特に記述のない限り)

図 5-57. ADC ゲイン誤差と温度との関係

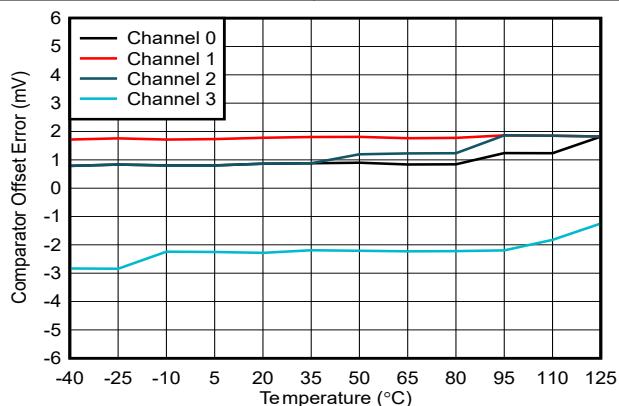

## 5.21 代表的特性：コンパレータ

$T_A = 25^\circ\text{C}$ ,  $V_{DD} = 5.5\text{V}$  で、外部リファレンス = 5.5V、ゲイン = 1x、12 ビット分解能、FBx ピン (Hi-Z モード)、DAC 出力は無負荷 (特に記述のない限り)

図 5-60. コンパレータ オフセット誤差と温度との関係

## 5.22 代表的特性：総則

$T_A = 25^\circ\text{C}$  の場合、 $V_{DD} = 5.5\text{V}$ 、DAC 出力は無負荷 (特に記述のない限り)

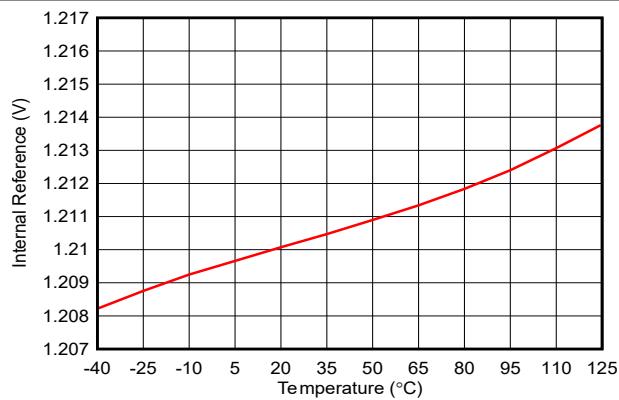

内部リファレンス

図 5-61. 内部リファレンスと温度との関係

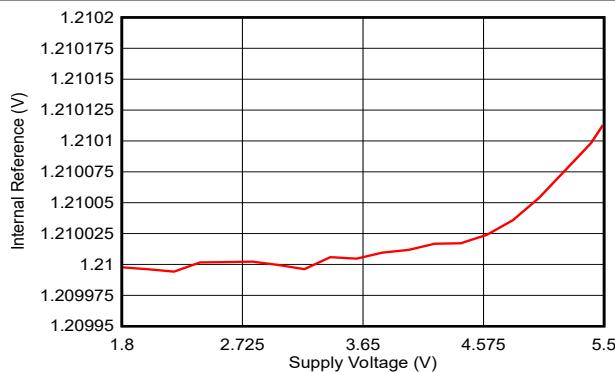

内部リファレンス

図 5-62. 内部リファレンスと電源電圧との関係

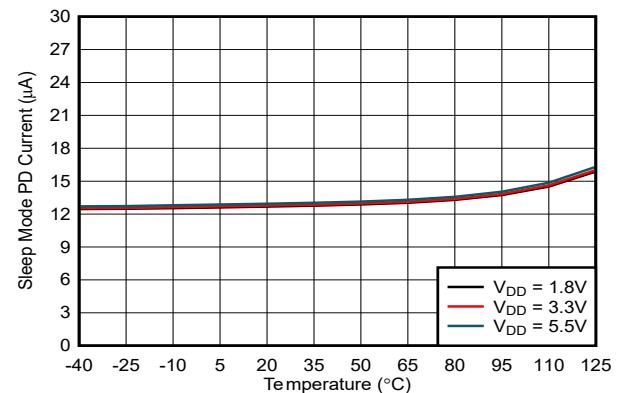

スリープ モード、内部リファレンス ディスエーブル

図 5-63. パワーダウン電流と温度との関係

図 5-64. ブートアップ時間と CAP ピンの容量との関係

## 6 詳細説明

### 6.1 概要

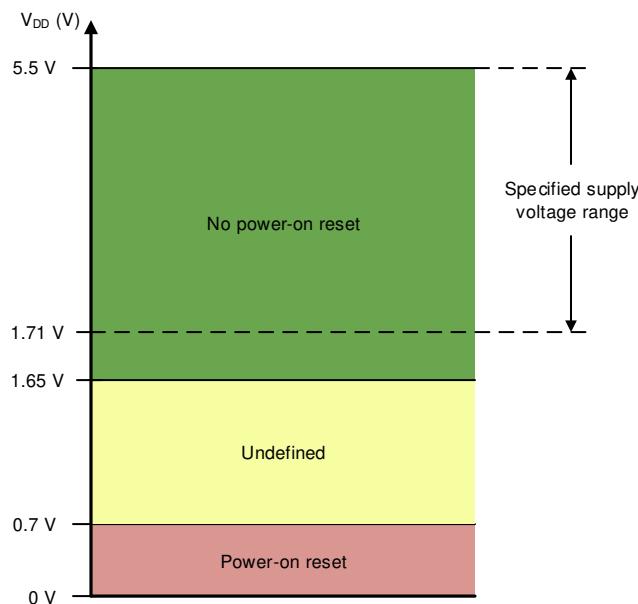

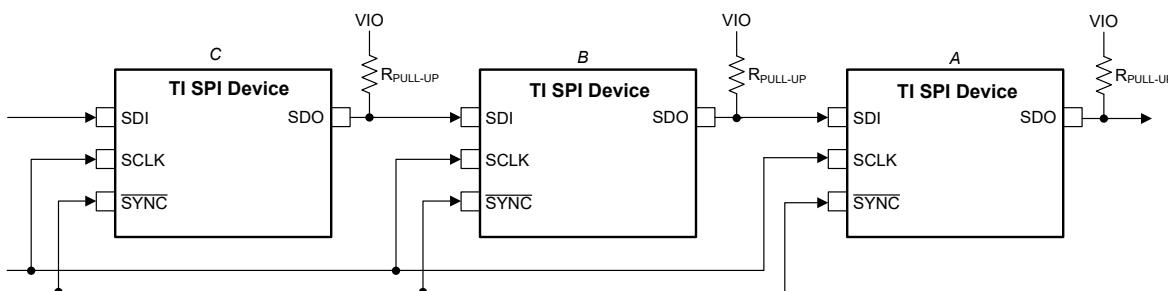

10 ビット AFE53004W および 12 ビット AFE63004W (AFEx3004W) は、単一の超小型 WCSP でアナログ機能とデジタル機能の独自の組み合わせを提供する 4 チャネルのスマート アナログ フロントエンド (AFE) デバイスのピン互換ファミリです。AFE のアナログ チャネルは、10 ビット (AFE53004W) または 12 ビット (AFE63004W) のバッファ付き電圧出力、8 ビットのユニポーラまたはバイポーラの電流出力、10 ビットのアナログ/デジタル コンバータ (ADC) に多重化されたアナログ入力として、個別に構成できます。このスマート AFE は不揮発性メモリ (NVM)、内部リファレンス、自動検出可能な SPI または I<sup>2</sup>C インターフェイス、I<sup>2</sup>C モードでの PMBus 互換性、フォースセンス出力、および汎用入力を内蔵しています。これらのデバイスはデフォルトで Hi-Z パワーダウン モードをサポートしており、NVM を使用して 10kΩ-GND または 100kΩ-GND に設定できます。また、VDD がオフのときはアナログ出力は Hi-Z になります。AFEx3004W にはパワー オン リセット (POR) 回路があり、すべてのレジスタがデフォルト設定、または NVM を使用してユーザーがプログラムした設定から確実に開始されます。AFEx3004W は、内部リファレンス、外部リファレンス、またはリファレンスとして電源を使用して動作し、1.8V ~ 5.5V のフルスケール出力を提供します。

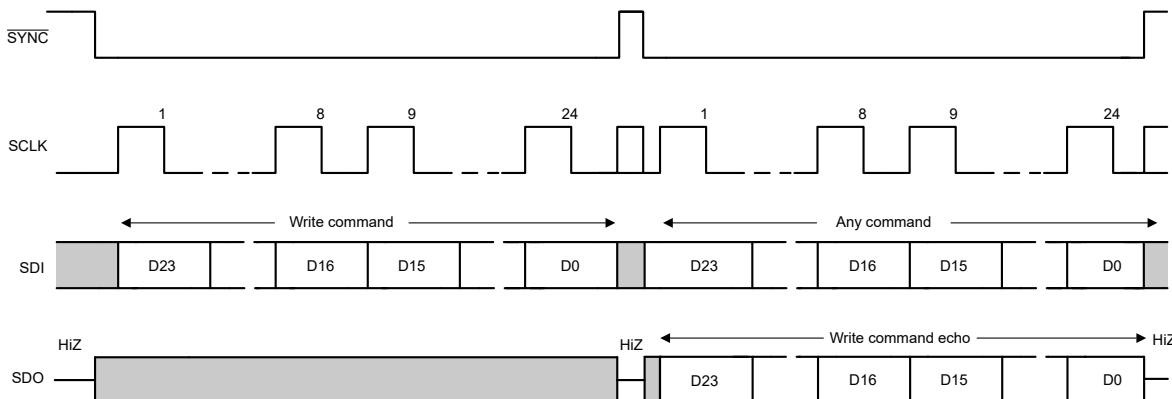

AFEx3004W デバイスは、I<sup>2</sup>C 標準モード (100Kbps)、高速モード (400Kbps)、高速モード プラス (1Mbps) をサポートします。I<sup>2</sup>C インターフェイスは、A0 ピンを使用して 4 つのターゲット アドレスで構成できます。これらのデバイスは、オン/オフ、マージン high または low などの特定の PMBus コマンドもサポートしています。SPI モードでは、デフォルトで最大 50MHz の SCLK 入力を持つ 3 線式インターフェイスをサポートしています。GPIO 入力は、NVM で SDO として構成して、SPI 読み取り機能を実現できます。GPIO 入力は、LDAC、PD、STATUS、FAULT-DUMP、RESET、または PROTECT 機能としても構成できます。

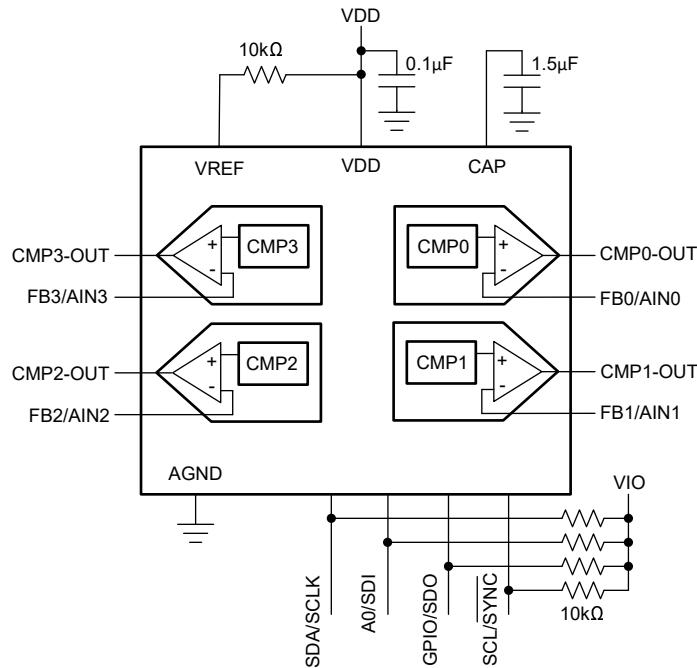

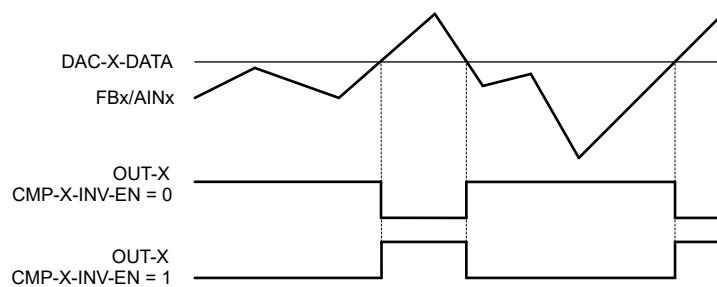

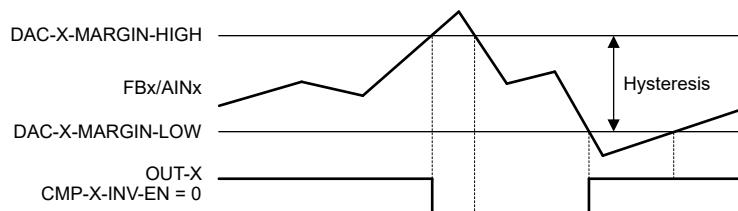

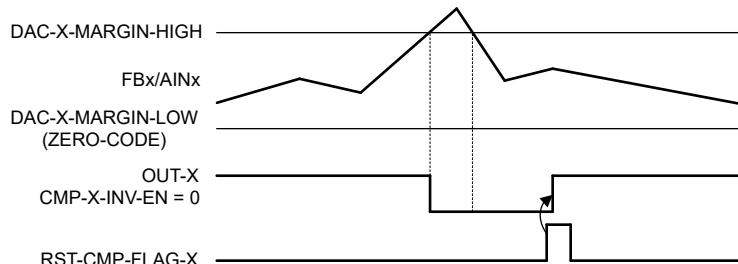

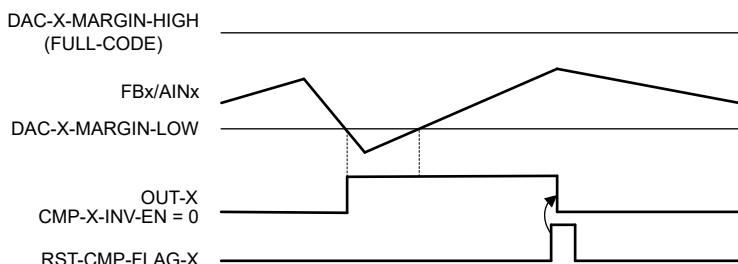

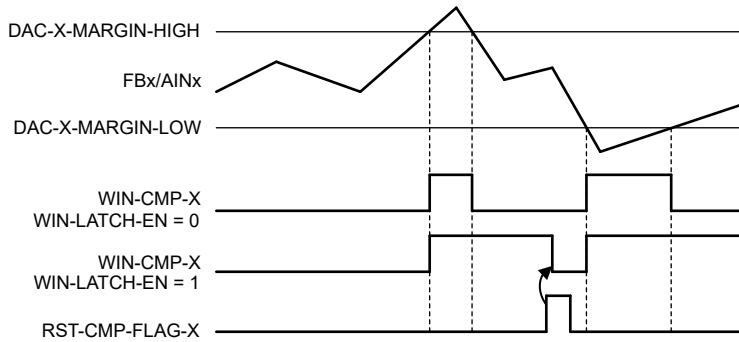

また、AFEx3004W はデジタル スルーレート制御機能を備えており、正弦および余弦、三角波、のこぎり 波などの標準的な波形生成をサポートしています。これらのデバイスは、三角波またはのこぎり波と FB ピンの組み合わせにより、パルス幅変調 (PWM) 出力を生成できます。アナログ チャネルのフォース センス出力は、プログラマブル コンバレータとして使用できます。コンバレータ モードでは、プログラマブル ヒステリシス、ラッチ コンバレータ、ウインドウ コンバレータ、NVM へのフォルトダンプが可能です。

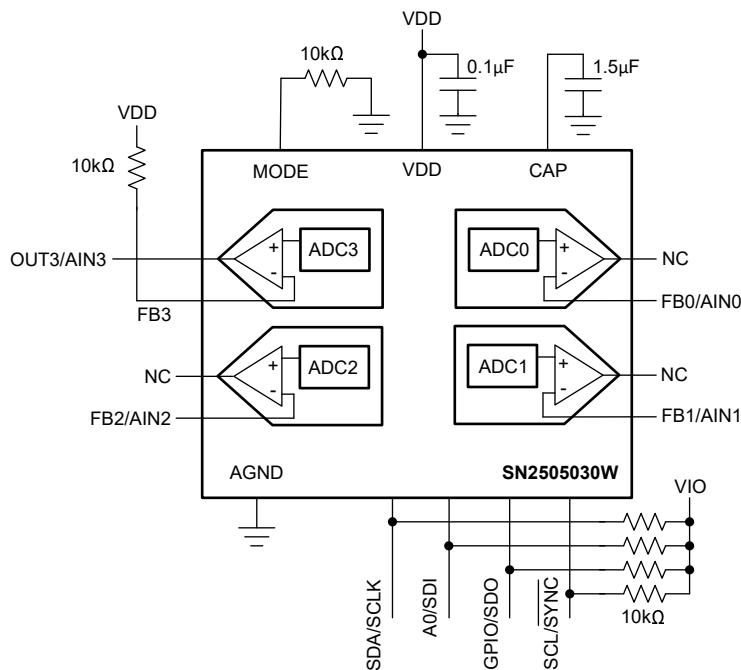

## 6.2 機能ブロック図

図 6-1. ADC デバイスの機能図を無効化

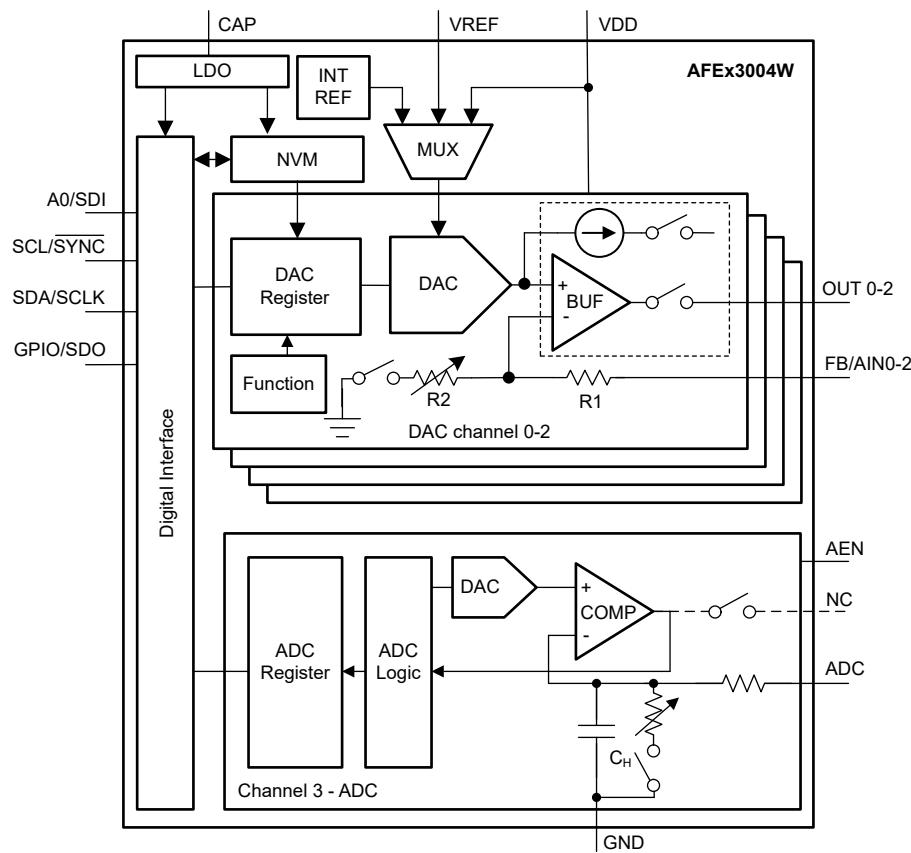

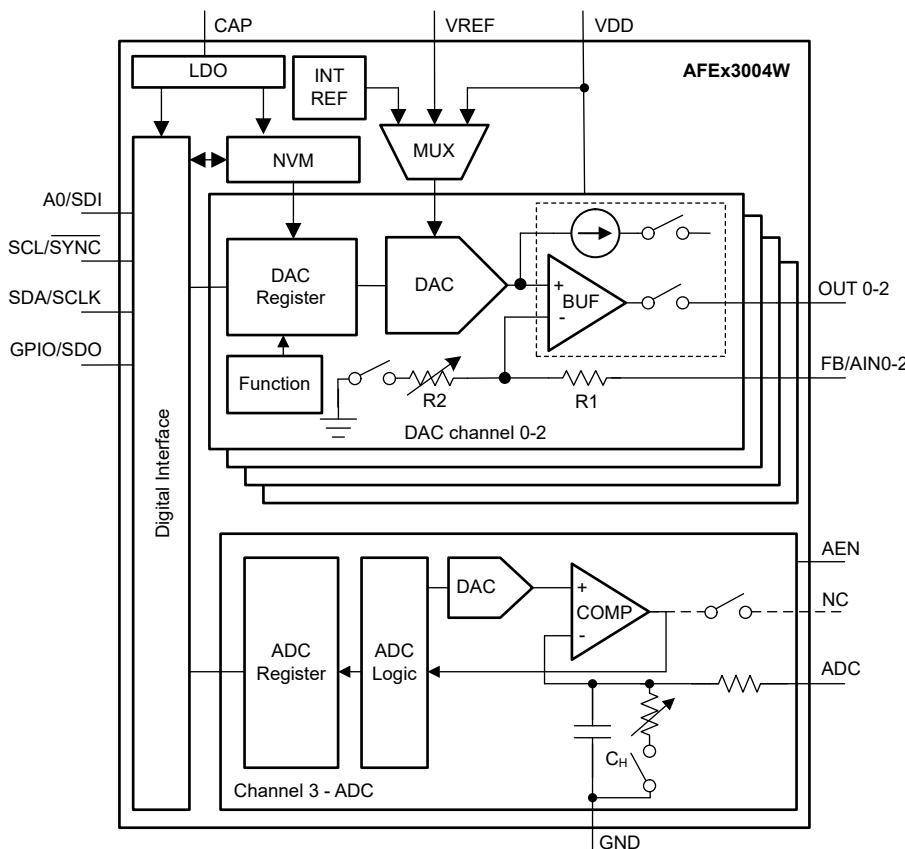

図 6-2. 有効化された ADC デバイスの機能図

## 6.3 機能説明

### 6.3.1 スマートアナログフロントエンドコンバーター(AFE)アーキテクチャ

AFEx3004W DAC チャンネルはストリング アーキテクチャで構成され、電圧出力アンプと外部 FB ピンおよび電圧/電流コンバータが構成されています。セクション 6.2 に、ブロック図内の DAC アーキテクチャを示します。この DAC アーキテクチャは、1.8V から 5.5V の電源で動作します。AFE の内部基準電圧は 1.21V です。VREF ピンで外部リファレンス、電源をリファレンスとして、内部基準電圧 (ゲインを設定可能) を選択するオプションがあります。電圧出力モードはこれら 3 つのリファレンス オプションのいずれかを使用し、DAC チャンネルごとに個別に構成できます。電流出力モードでは、内部バンド ギヤップを使用して電流出力を生成します。電圧出力モードと電流出力モードはどちらも、プログラム可能な複数の出力範囲に対応しています。

AFEx3004W は、チャネル 3 に 10 ビットの逐次比較レジスタ (SAR) ADC を内蔵しています。チャネル 3 が ADC モードに設定されている場合は、他のすべてのアナログ チャンネルを ADC 入力として構成できます。ADC リファレンスはチャネルごとに個別に構成でき、DAC 構成で同じリファレンス オプションを使用できます。次の図に、ADC が有効になっている AFE アーキテクチャを示します。

図 6-3. 有効化された ADC デバイスの機能図

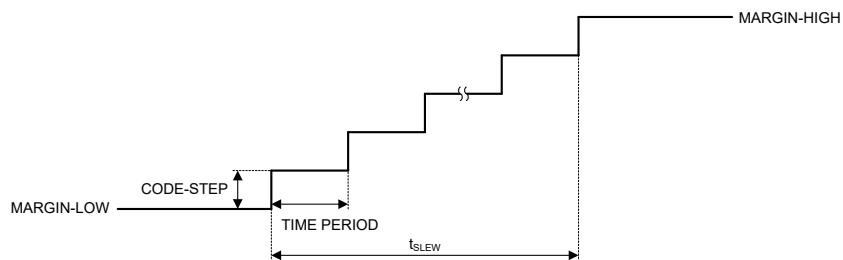

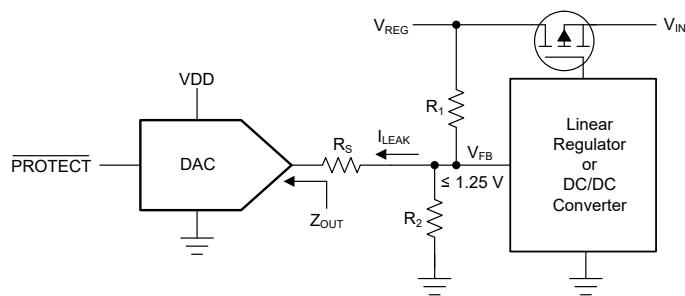

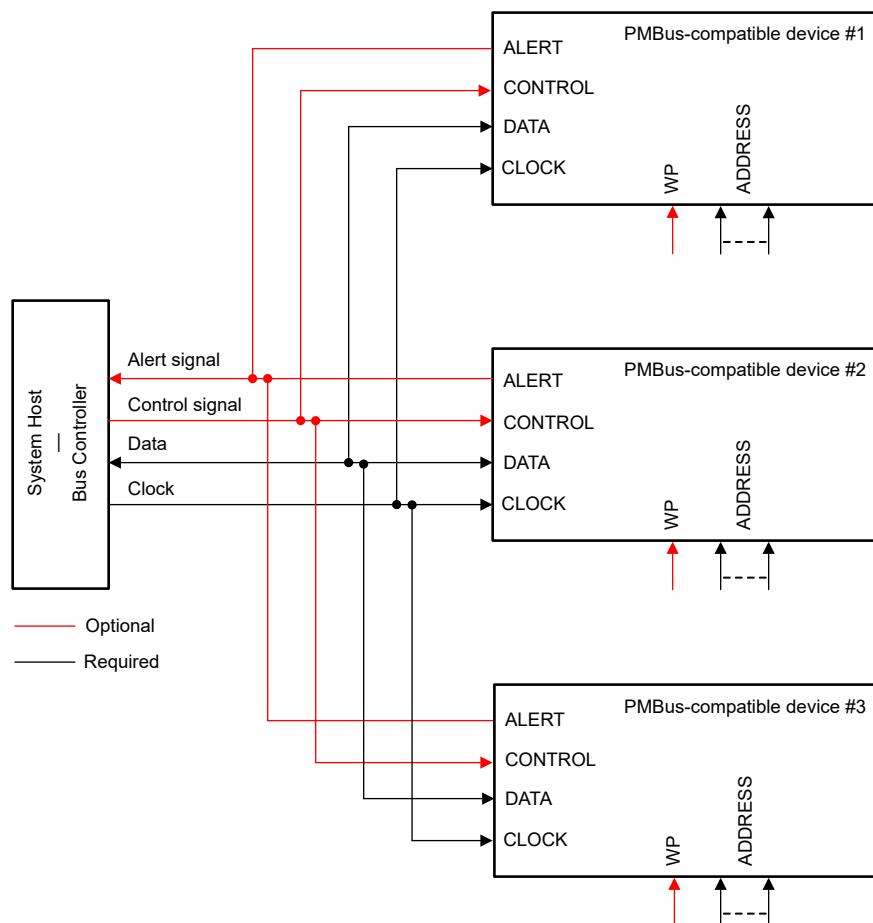

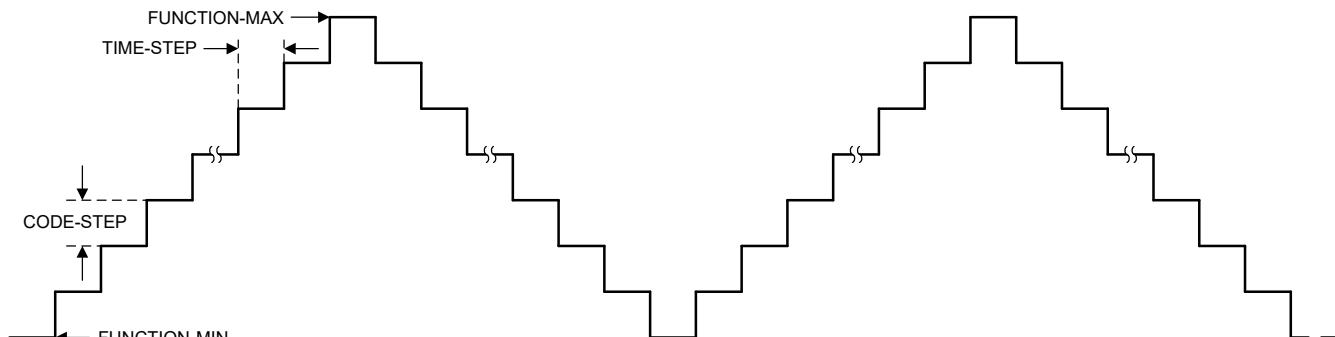

AFEx3004W デバイスは、VDD がオフのときはハイインピーダンス出力をサポートするため、最大 1.25V の強制電圧で出力ピンで非常に低いリーク電流を維持できます。また、アナログ出力ピンは、デフォルトで高インピーダンス モードで起動します。パワーアップ モードを  $10k\Omega$ -GND または  $100k\Omega$ -GND に変更するには、COMMON-CONFIG レジスタの対応する VOUT-PDN-X フィールドをプログラムし、これらのビットをデバイス NVM にロードします。