## BQ25630 I<sup>2</sup>C 制御シングルセル 5A 降圧チャージャ、USB-C 検出機能付き

### 1 特長

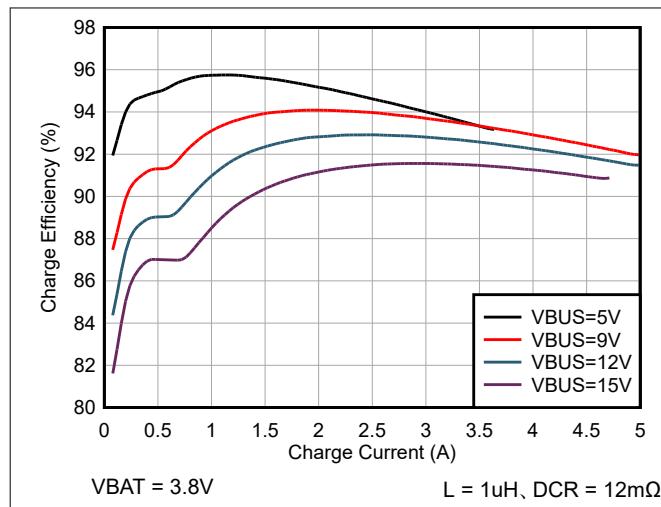

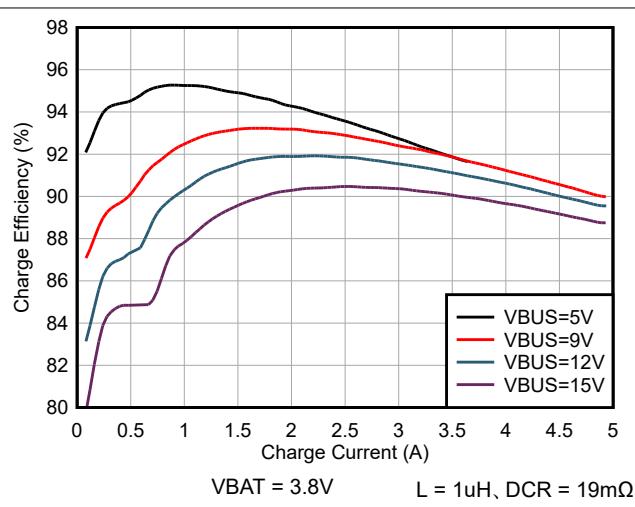

- シングルセルバッテリ向けの高効率 5A、1.5MHz、同期スイッチング モード降圧チャージャ

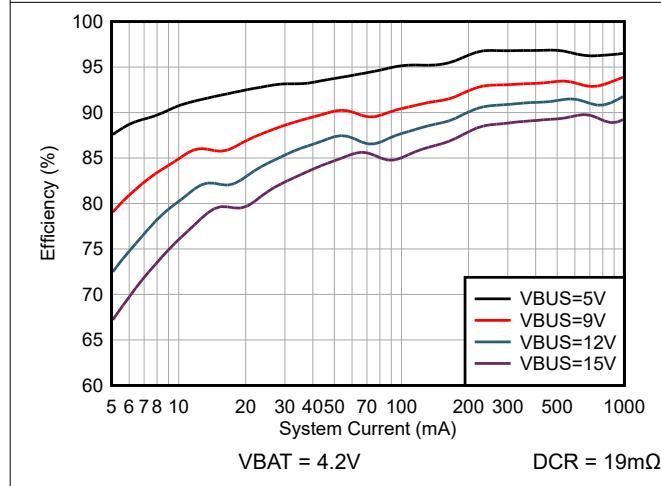

- 5V 入力から 90% を上回る効率で 10mA の出力電流を供給

- 20mA 刻みの最大 5A の充電電流

- 10mA 刻みの 30 ~ 1000mA の充電終端

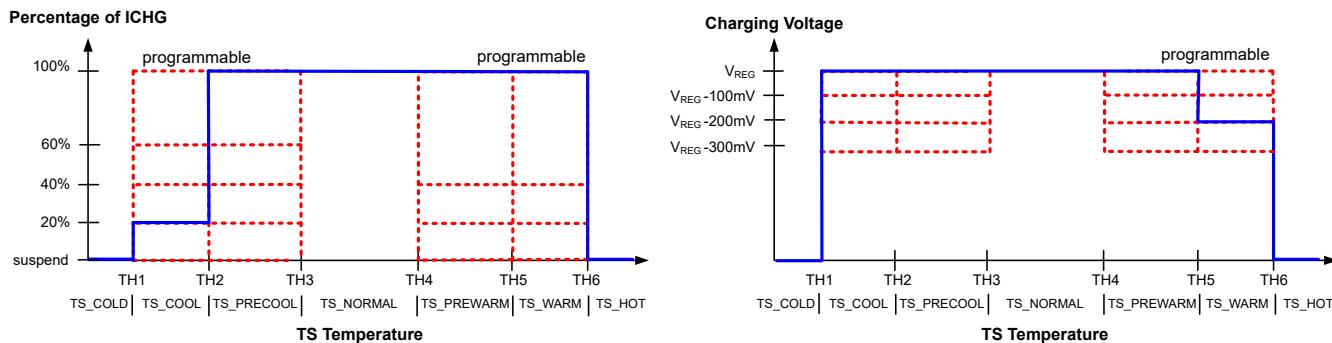

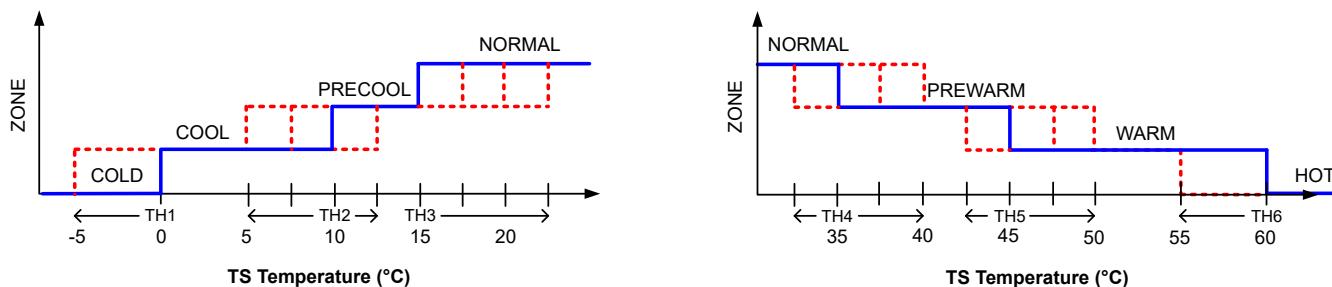

- 高度に設定可能な JEITA プロファイルにより、温度範囲全体にわたって安全に充電

- 完全統合型 CC コントローラ、デュアル ロール パワー (DRP), Try.SNK, Try.SRC

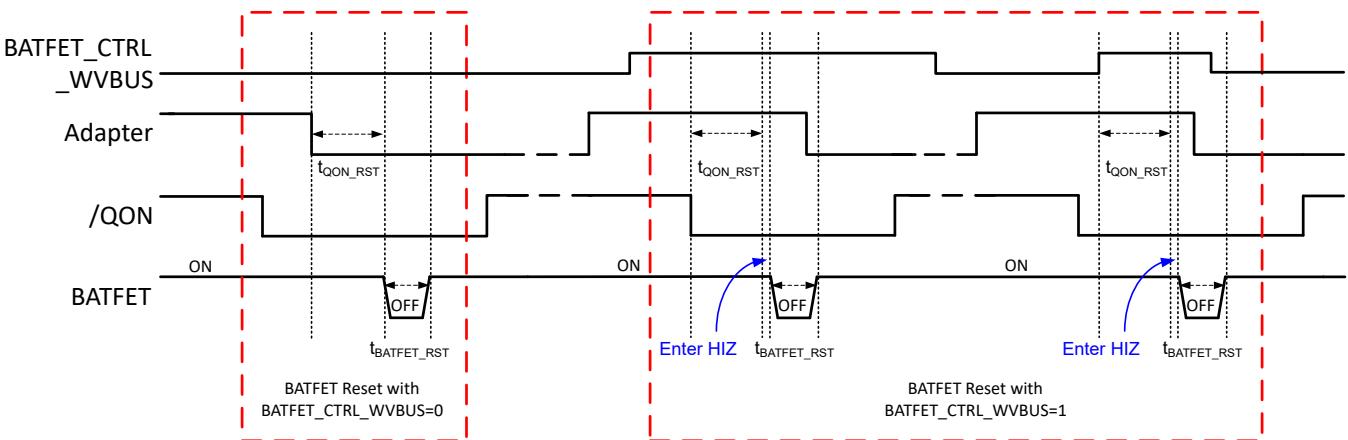

- BATFET 制御によりシャットダウン、出荷モード、完全システムリセットをサポート

- バッテリのみモードで 1.5µA の静止電流

- 出荷モードで 0.15µA のバッテリリーク電流

- シャットダウン モードで 0.1µA のバッテリリーク電流

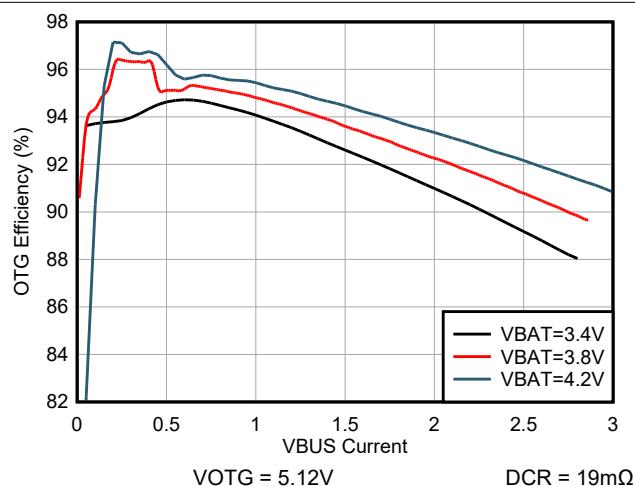

- USB On-The-Go (OTG) と SRC (直列共振コンバータ) モードをサポート

- 3.84V ~ 9.6V の出力による逆方向モード

- プログラマブル制限機能: 最大 3.2A

- 幅広い入力電源をサポート

- 3.9V ~ 18V の広い入力動作電圧範囲、26V の絶対最大入力電圧

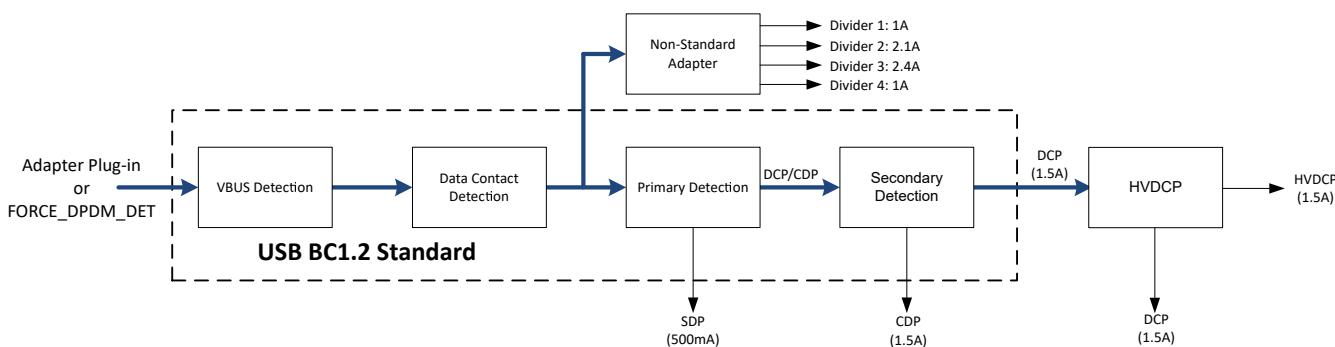

- USB Type-C 入力、USB BC1.2、HVDCCP、非標準アダプタをサポート

- 10mA から 3.2A までの IINDPM 範囲をサポート

- 10mA までの低消費電力入力ソース用の API (入力からの代替電源) モード

- バッテリ電圧を自動的に追従する VINDPM

- 入力電流オプティマイザ (ICO) により、アダプタの過負荷を引き起こさずに入力電力を最大化

- 7mΩ の BATFET による高効率のバッテリ動作

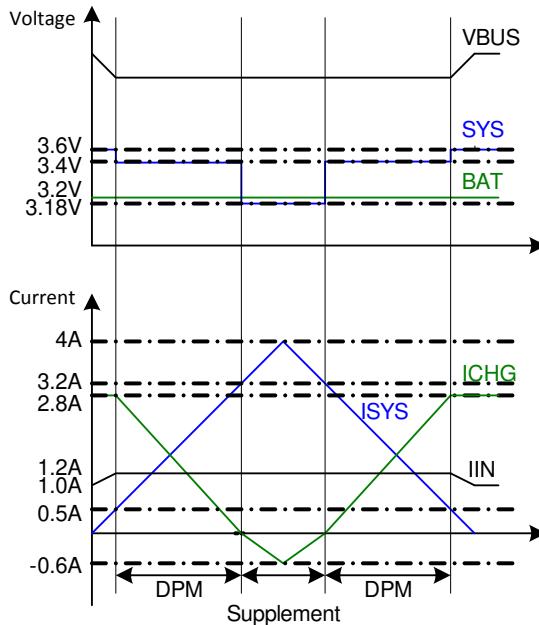

- Narrow VDC (NVDC) パワー パス管理

- 消耗したバッテリまたはバッテリ未接続でもシステムを即時オン

- アダプタが全負荷になったときのバッテリ補完

- フレキシブルな自律または I<sup>2</sup>C 制御モード

- 電圧、電流、温度を監視するための 12 ビット ADC を内蔵

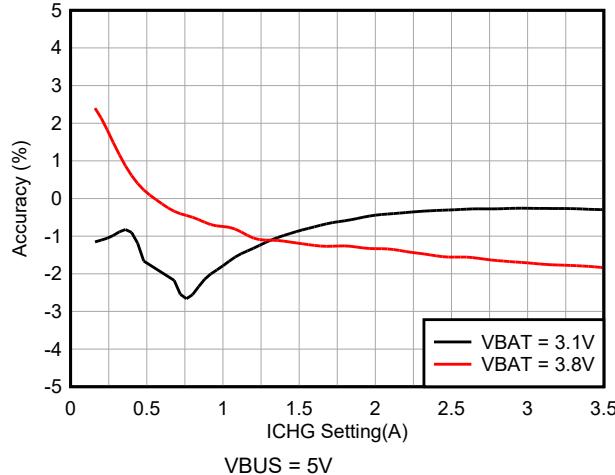

- 高い精度

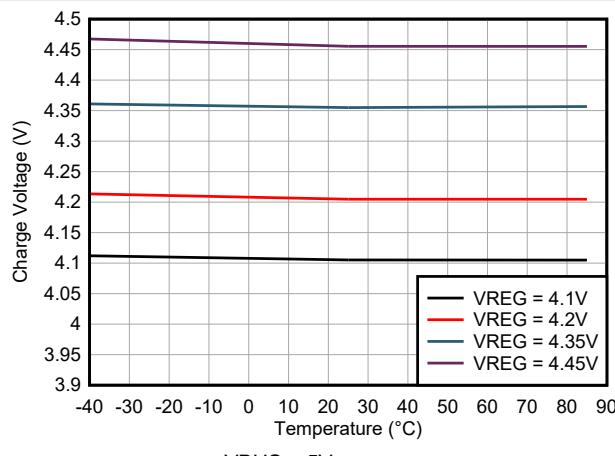

– ±0.5% の充電電圧レギュレーション

– ±5% の充電電流レギュレーション

– ±5% の入力電流レギュレーション

### 2 アプリケーション

### 3 説明

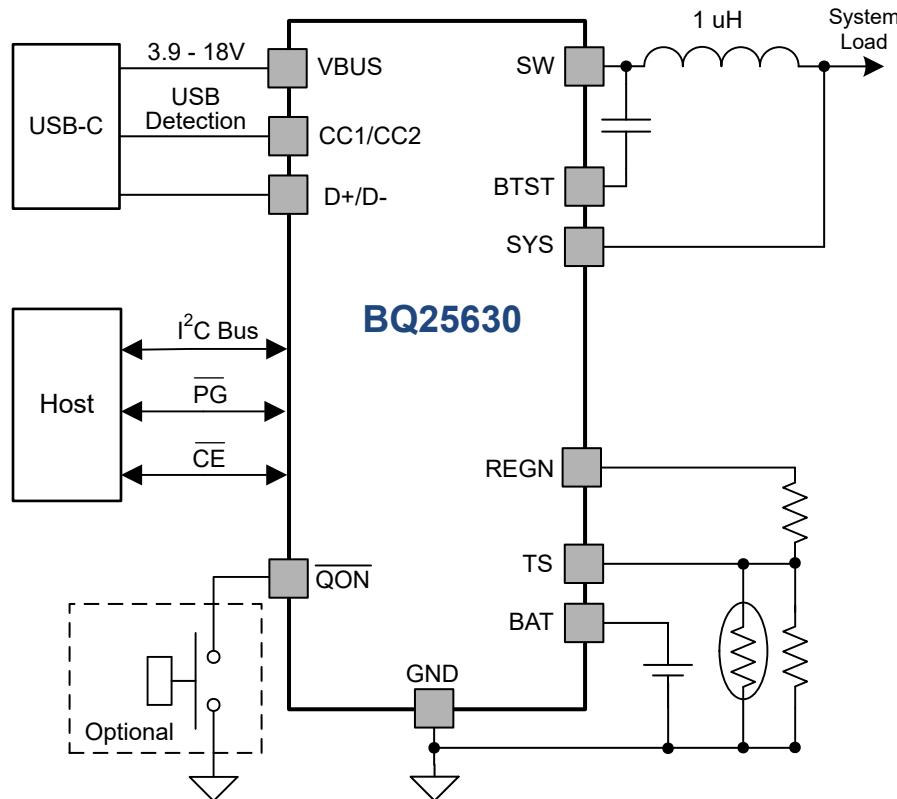

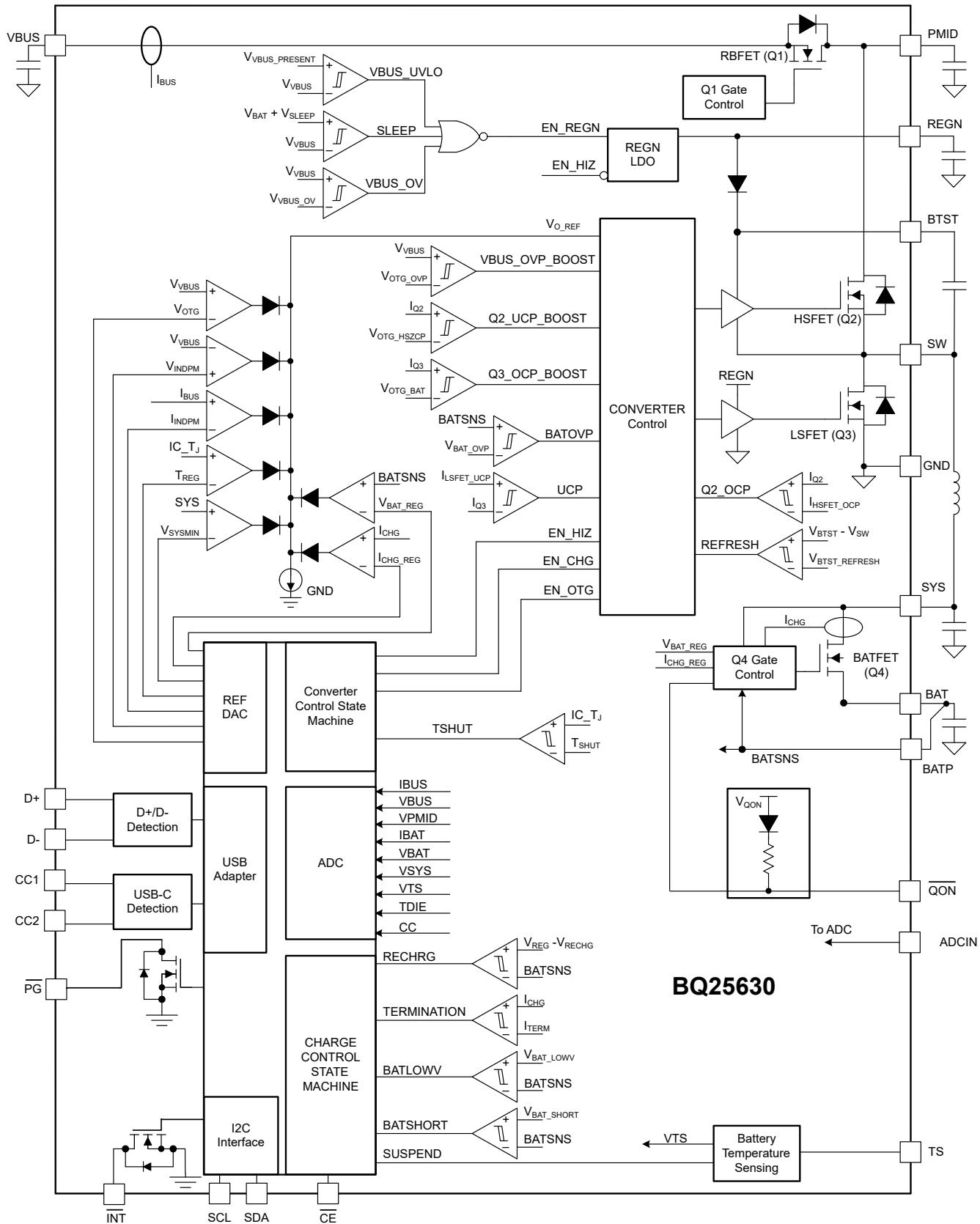

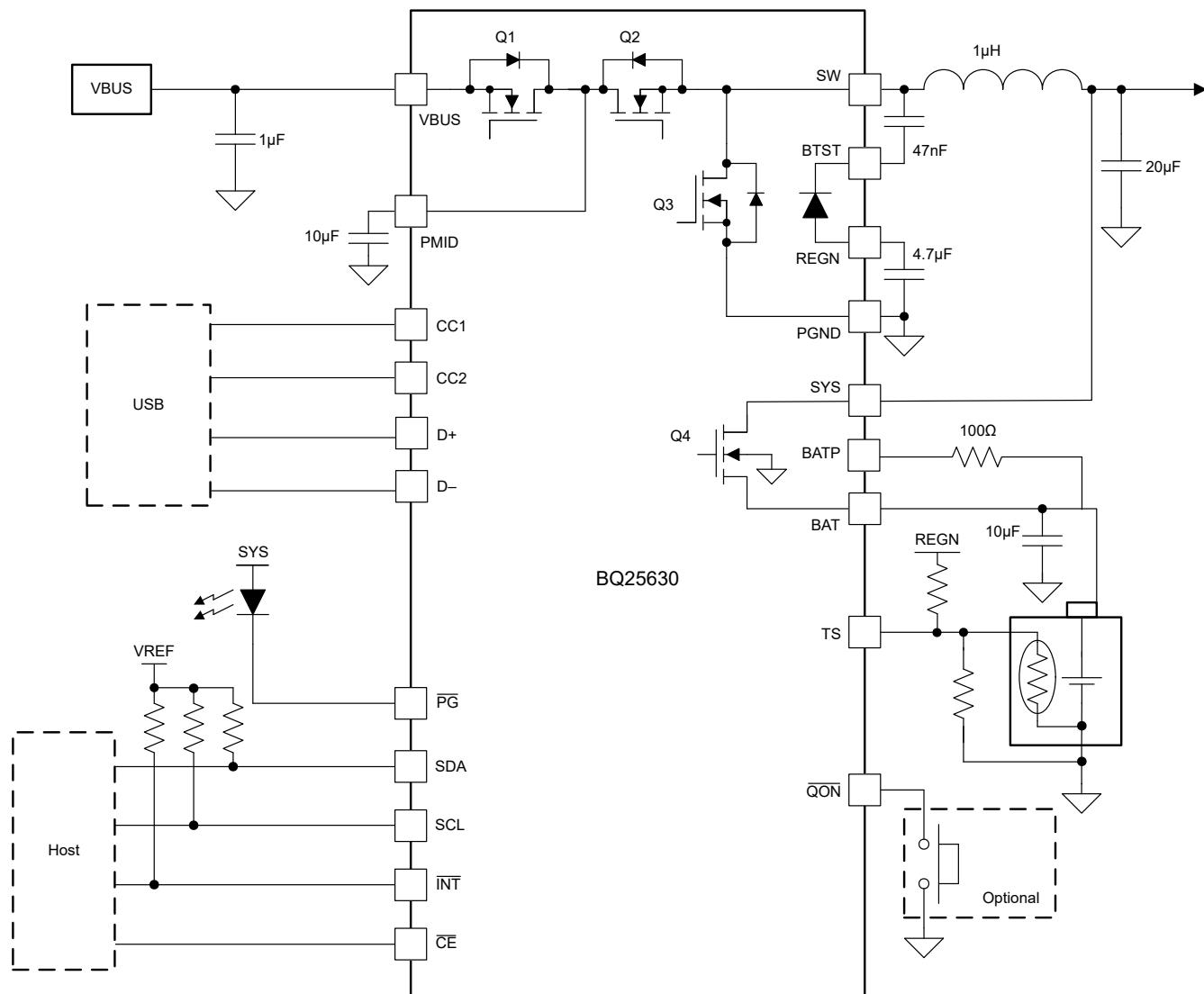

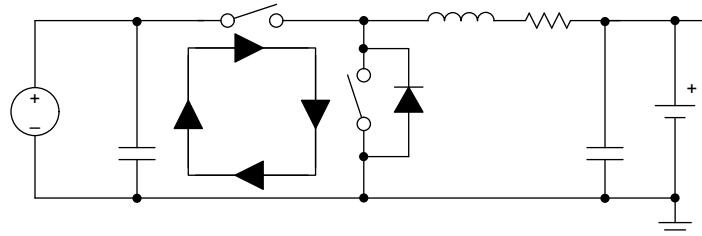

BQ25630 は、シングルセルリチウムイオン / リチウムポリマー バッテリ用の高度に統合された 5A スイッチモード バッテリ充電管理およびシステム パワー パス管理デバイスです。この設計では、内蔵電流検出、ループ補償、入力逆電流ブロック FET (Q1)、スイッチング FET (Q2 および Q3)、およびシステムとバッテリの間にあるバッテリ FET (Q4) を高度に統合しています。このデバイスは、Try.SNK および Try.SRC をサポートするデュアル ロール電源対応の USB Type-C コントローラを内蔵しています。システム電圧が設定可能な最小値を下回らないように、BQ25630 は NVDC パワー パス管理機能を使用してシステム電圧をバッテリ電圧よりわずかに高い値にレギュレートします。低インピーダンスのパワー パスは効率を最適化し、バッテリ充電時間を短縮し、放電フェーズ中のバッテリ寿命を延長します。また、非常に小さい 0.15µA の出荷モード電流はバッテリの保存性を高めます。

### パッケージ情報

| 部品番号    | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|---------|----------------------|--------------------------|

| BQ25630 | YBG (DSBGA 30)       | 2.3mm × 2.4mm            |

(1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

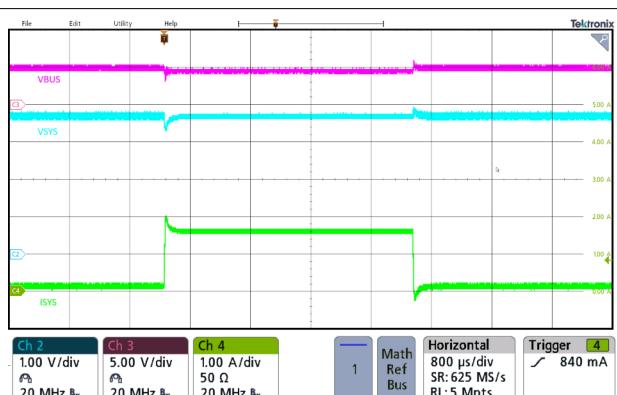

BQ25630 のアプリケーション概略図

## 目次

|                    |           |                               |           |

|--------------------|-----------|-------------------------------|-----------|

| <b>1 特長</b>        | <b>1</b>  | 8.5 プログラミング                   | <b>46</b> |

| <b>2 アプリケーション</b>  | <b>1</b>  | 8.6 レジスタ マップ                  | <b>49</b> |

| <b>3 説明</b>        | <b>1</b>  | <b>9 アプリケーションと実装</b>          | <b>87</b> |

| <b>4 概要 (続き)</b>   | <b>4</b>  | 9.1 アプリケーション情報                | <b>87</b> |

| <b>5 デバイスの比較</b>   | <b>5</b>  | 9.2 代表的なアプリケーション              | <b>88</b> |

| <b>6 ピン構成および機能</b> | <b>6</b>  | 9.3 電源に関する推奨事項                | <b>92</b> |

| <b>7 仕様</b>        | <b>8</b>  | 9.4 レイアウト                     | <b>92</b> |

| 7.1 絶対最大定格         | 8         | <b>10 デバイスおよびドキュメントのサポート</b>  | <b>94</b> |

| 7.2 ESD 定格         | 8         | 10.1 デバイス サポート                | <b>94</b> |

| 7.3 推奨動作条件         | 8         | 10.2 ドキュメントのサポート              | <b>94</b> |

| 7.4 熱に関する情報        | 9         | 10.3 ドキュメントの更新通知を受け取る方法       | <b>94</b> |

| 7.5 電気的特性          | 9         | 10.4 サポート・リソース                | <b>94</b> |

| 7.6 タイミング要件        | 19        | 10.5 商標                       | <b>94</b> |

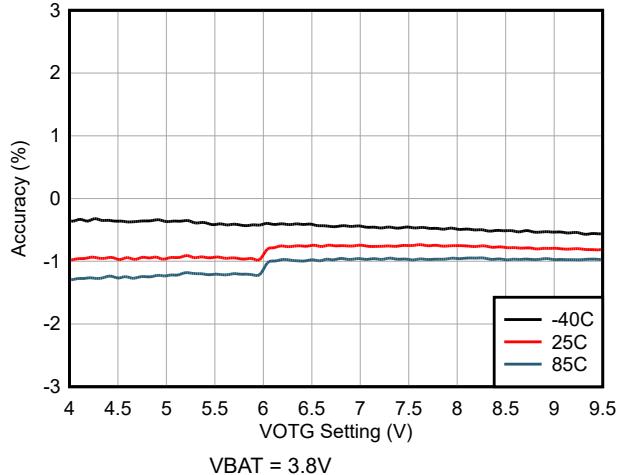

| 7.7 代表的特性          | 21        | 10.6 静電気放電に関する注意事項            | <b>94</b> |

| <b>8 詳細説明</b>      | <b>23</b> | 10.7 用語集                      | <b>94</b> |

| 8.1 概要             | 23        | <b>11 改訂履歴</b>                | <b>94</b> |

| 8.2 機能ブロック図        | 24        | <b>12 メカニカル、パッケージ、および注文情報</b> | <b>95</b> |

| 8.3 機能説明           | 25        | 12.1 付録:パッケージ オプション           | <b>96</b> |

| 8.4 デバイスの機能モード     | 43        | 12.2 メカニカル データ                | <b>99</b> |

## 4 概要 (続き)

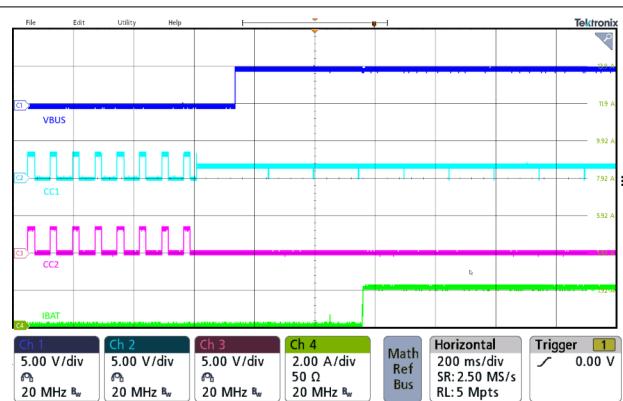

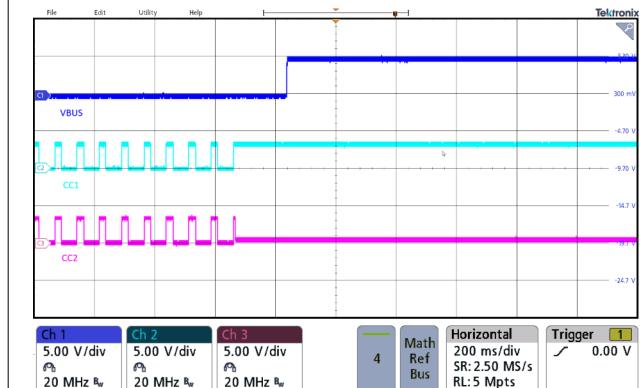

BQ25630 は、標準の USB ホストポート、USB 充電ポート、USB-C アダプタ、USB 準拠の可変高電圧アダプタなど、幅広い入力ソースをサポートしています。このデバイスは、最大 15Wまでの USB-C 検出に対応した USB Type-C コントローラ (CC1/CC2) を内蔵しており、検出結果に基づいて電流制限を設定します。このデバイスは、Try.SNK および Try.SRC を備えたデュアルロールパワーをサポートします。このデバイスには、内蔵の D+/D- USB アダプタ検出インターフェイスを使用した BC1.2 検出機能も含まれています。BQ25630 は、入力電流および電圧のレギュレーションにより、USB2.0 および USB3.0 の電力仕様に準拠しています。さらに、入力電流オプティマイザ (ICO) は、入力ソースの過負荷なしで最大電力点の検出をサポートします。また、このデバイスは最大 3.2A までの定電流制限による USB On-the-Go (OTG) の動作電力定格仕様にも合致しています。

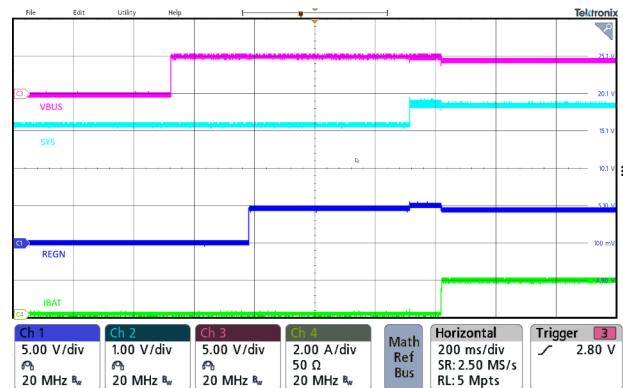

パワー パス管理により、システムはバッテリ電圧より少し高くなるように、かつプログラム可能な最低システム電圧より低くならないようにレギュレートされます。この機能により、システムはバッテリが完全に消耗したとき、または取り外したときでも、動作を継続できます。入力の電流または電圧が制限値に達すると、パワー パス管理機能が自動的に充電電流を低下させます。システム負荷が引き続き増大すると、電力パスはシステムの電力要件が満たされるまで、バッテリを放電します。この補助モードにより入力ソースの過負荷を防止します。

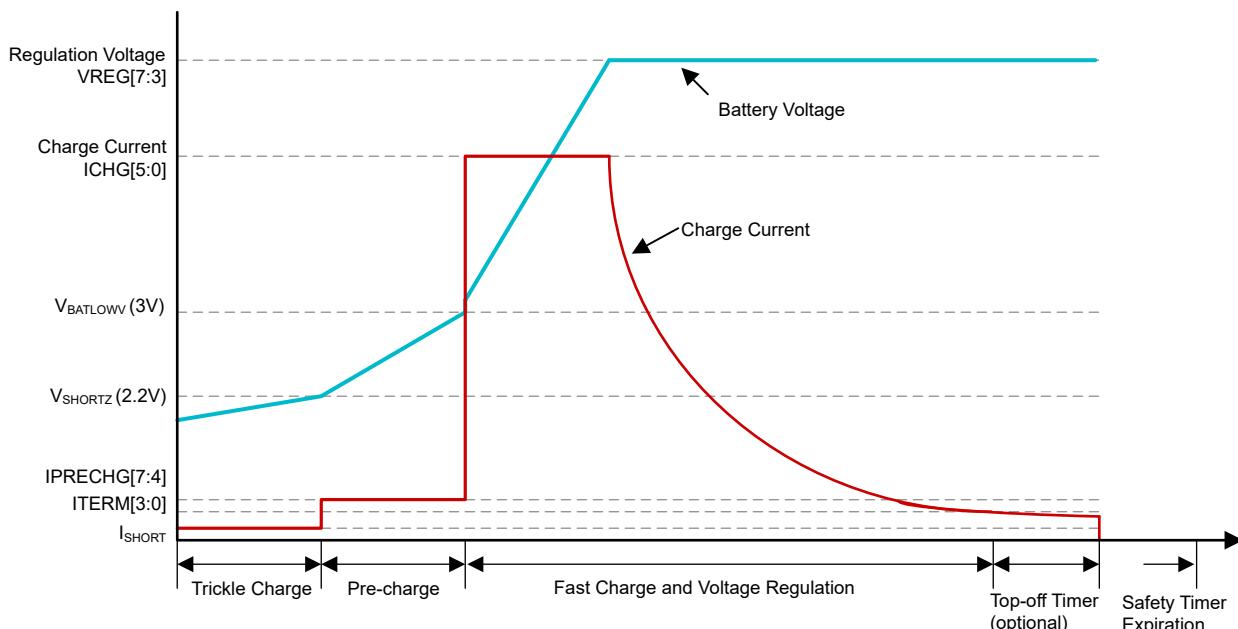

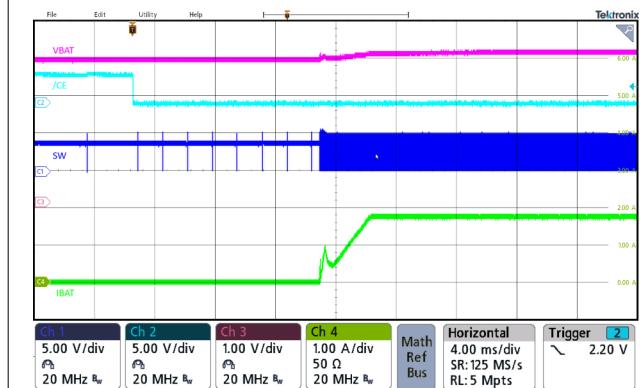

このデバイスは、ホスト制御なしで、充電サイクルの開始から完了までを実行できます。バッテリ電圧を検知することで、このデバイスは 4 種類の段階 (トリクル充電、予備充電、定電流 (CC) 充電、定電圧 (CV) 充電) でバッテリを充電します。充電サイクルの終わりに、充電電流があらかじめ設定されたスレッショルドを下回り、かつバッテリ電圧が再充電スレッショルドを上回ると、充電器は自動的に処理を終了します。TS ピンの COOL、PRECOOL、NORMAL、WARM および PREWARM 温度ゾーンでは、終端がサポートされています。十分に充電された電圧がプログラム可能な再充電スレッショルドを下回ると、充電器は自動的に新しい充電サイクルを開始します。

この充電器は、バッテリの負温度係数 (NTC) サーミスタ監視、充電安全タイマ、過電圧および過電流保護など、バッテリ充電とシステム運用のための多様な安全機能を備えています。接合部温度がプログラム可能なスレッショルド値を超えると、サーマル レギュレーションにより充電電流が低下します。その他の安全機能としては、充電モードと OTG 昇圧モードでのバッテリ温度センシング、サーマル シャットダウン、入力 UVLO および過電圧保護を装備しています。このデバイスには、湿気によるポート腐食を防止するための、液体検出および腐食軽減機能も内蔵されています。PG 出力は、良好な電源が存在し、プログラム可能な PG\_TH 値を上回っているかどうかを示します。INT 出力は、フォルトの発生とステータスの変化を即座にホストに通知します。

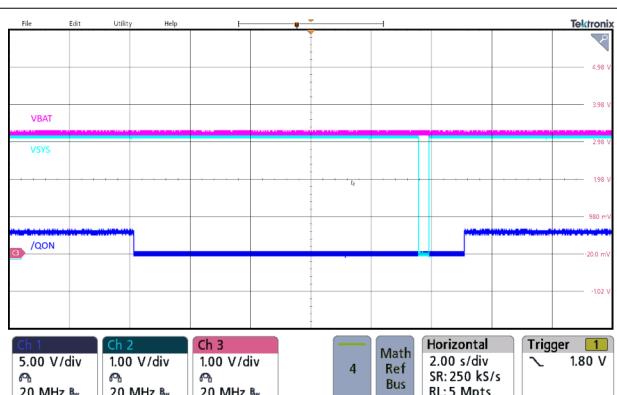

このデバイスには、充電電流と入力 / バッテリ / システム (VBUS、BAT、SYS、TS) 電圧を監視するための、12 ビットのアナログ / デジタル コンバータ (ADC) も搭載されています。QON ピンは、出荷モードおよびスタンバイ モードから復帰するための BATFET イネーブルおよびリセット制御を提供します。

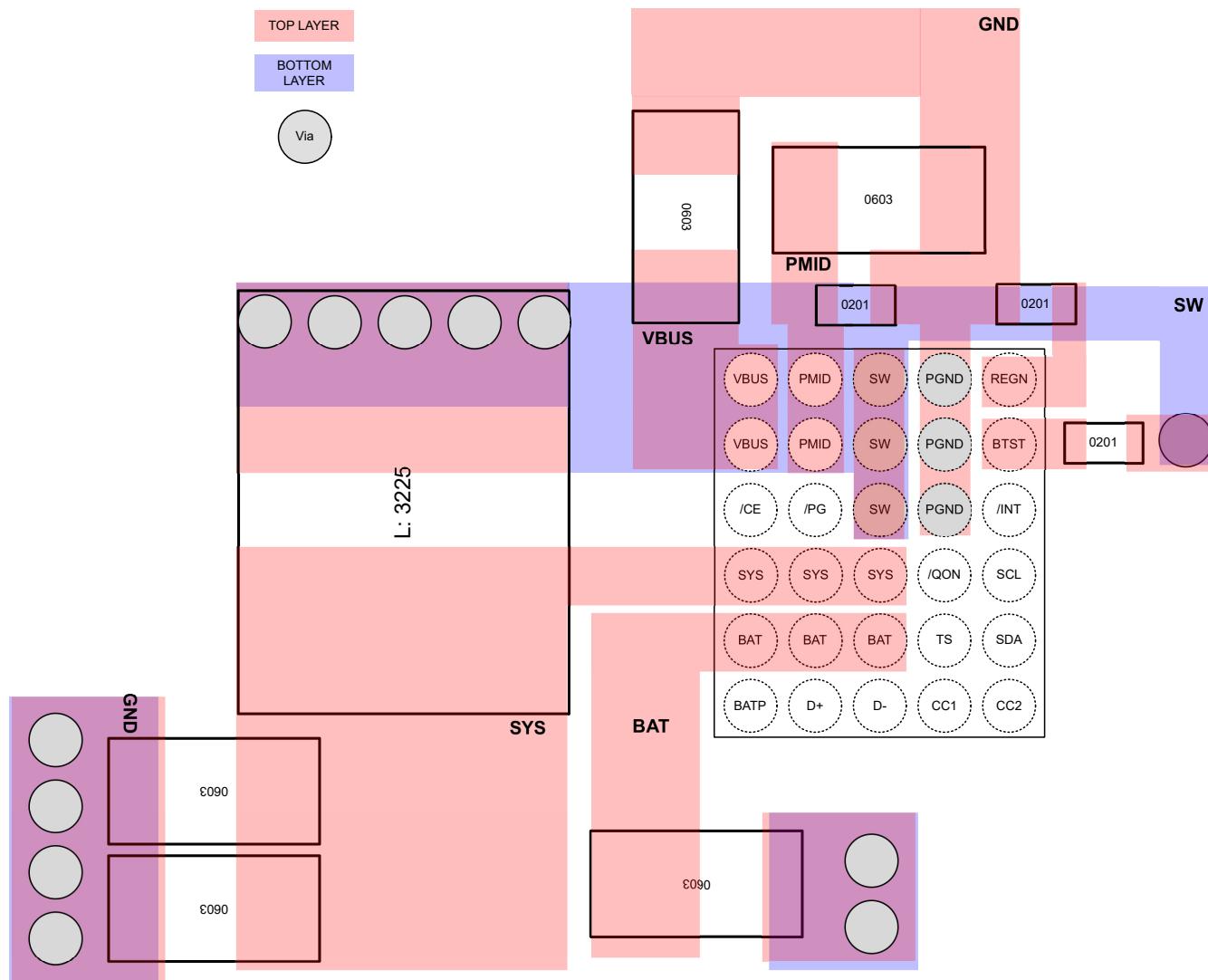

BQ25630 は 30 ポール、2.3mm×2.4mm の DSBGA、パッケージで供給されます。

## 5 デバイスの比較

**表 5-1. デバイスの比較**

| 機能                | BQ25630              | BQ25638              | BQ25898              |

|-------------------|----------------------|----------------------|----------------------|

| 入力電圧範囲            | 3.9V ~ 18V           | 3.9V ~ 18V           | 3.9V ~ 14V           |

| 最大充電電流            | 5A                   | 5A                   | 4A                   |

| USB-C 検出          | SNK のみ、SRC のみ、DRP    | なし                   | なし                   |

| D+/D- BC1.2 をサポート | あり                   | なし                   | なし                   |

| ILIM ピン           | なし                   | あり                   | あり                   |

| TS プロファイル         | 7ゾーン フレキシブル JEITA    | 7ゾーン フレキシブル JEITA    | 3ゾーン JEITA           |

| バッテリの静止電流         | 1.5µA                | 1.5µA                | 32µA                 |

| パッケージ             | 2.3 x 2.4mm DSBGA 30 | 2.0 x 2.4mm DSBGA 30 | 2.8 x 2.5mm DSBGA 42 |

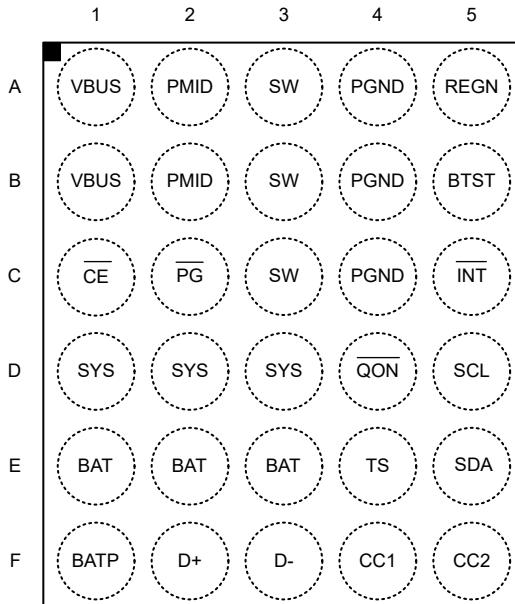

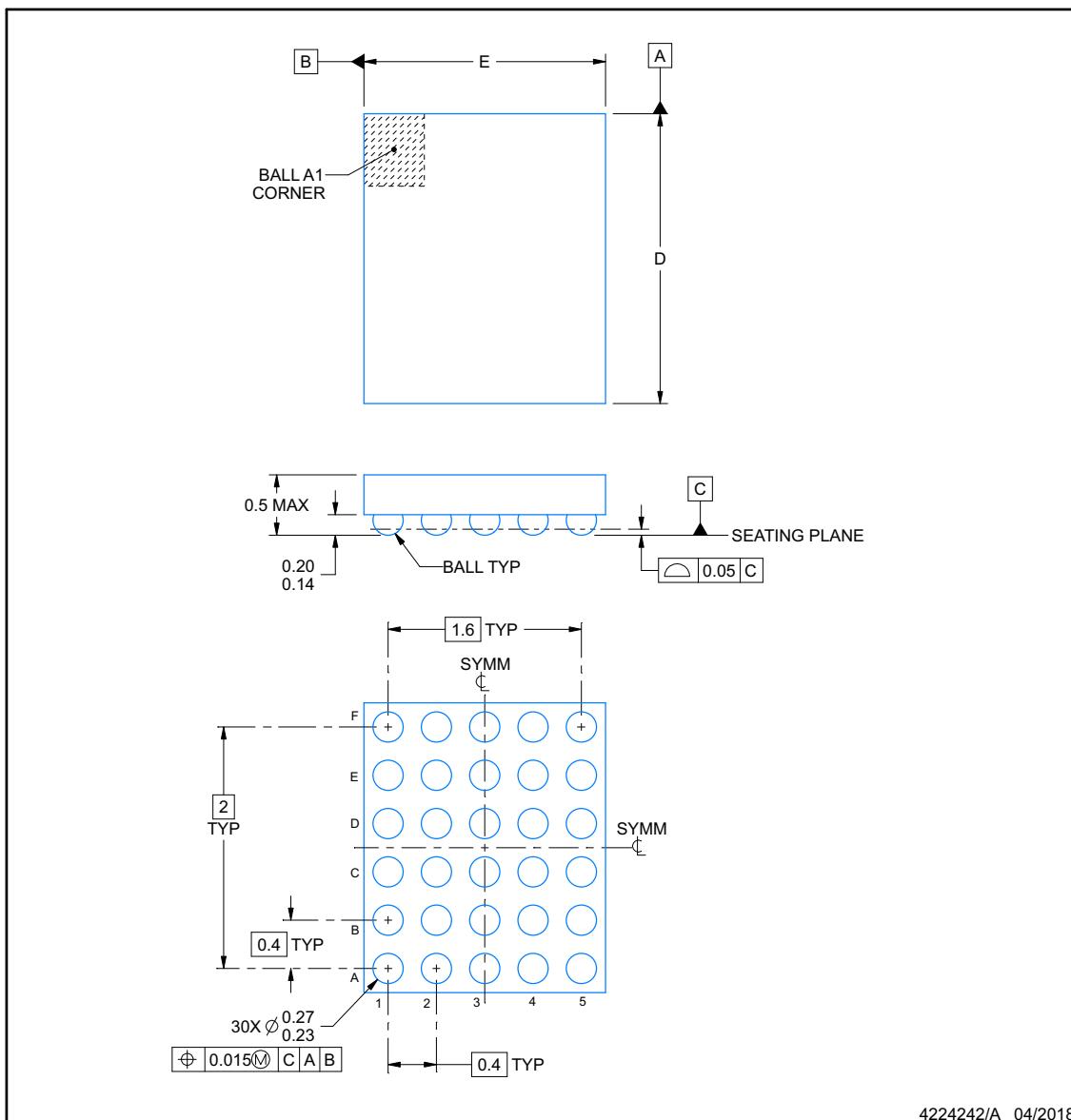

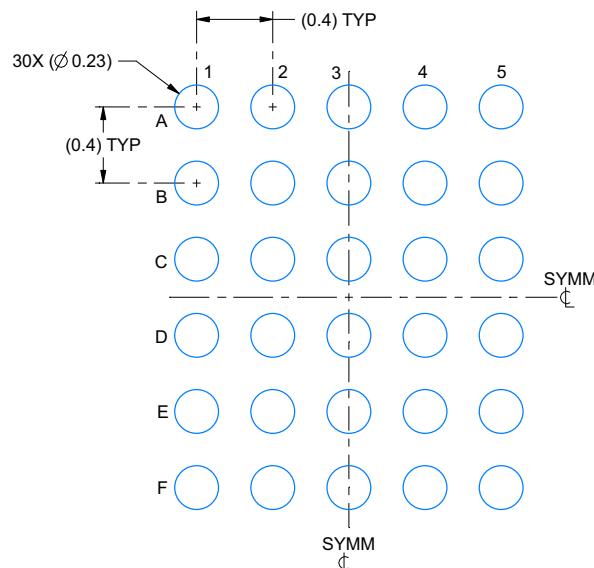

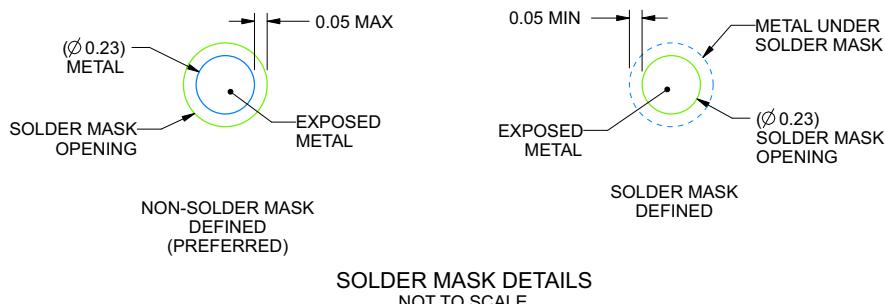

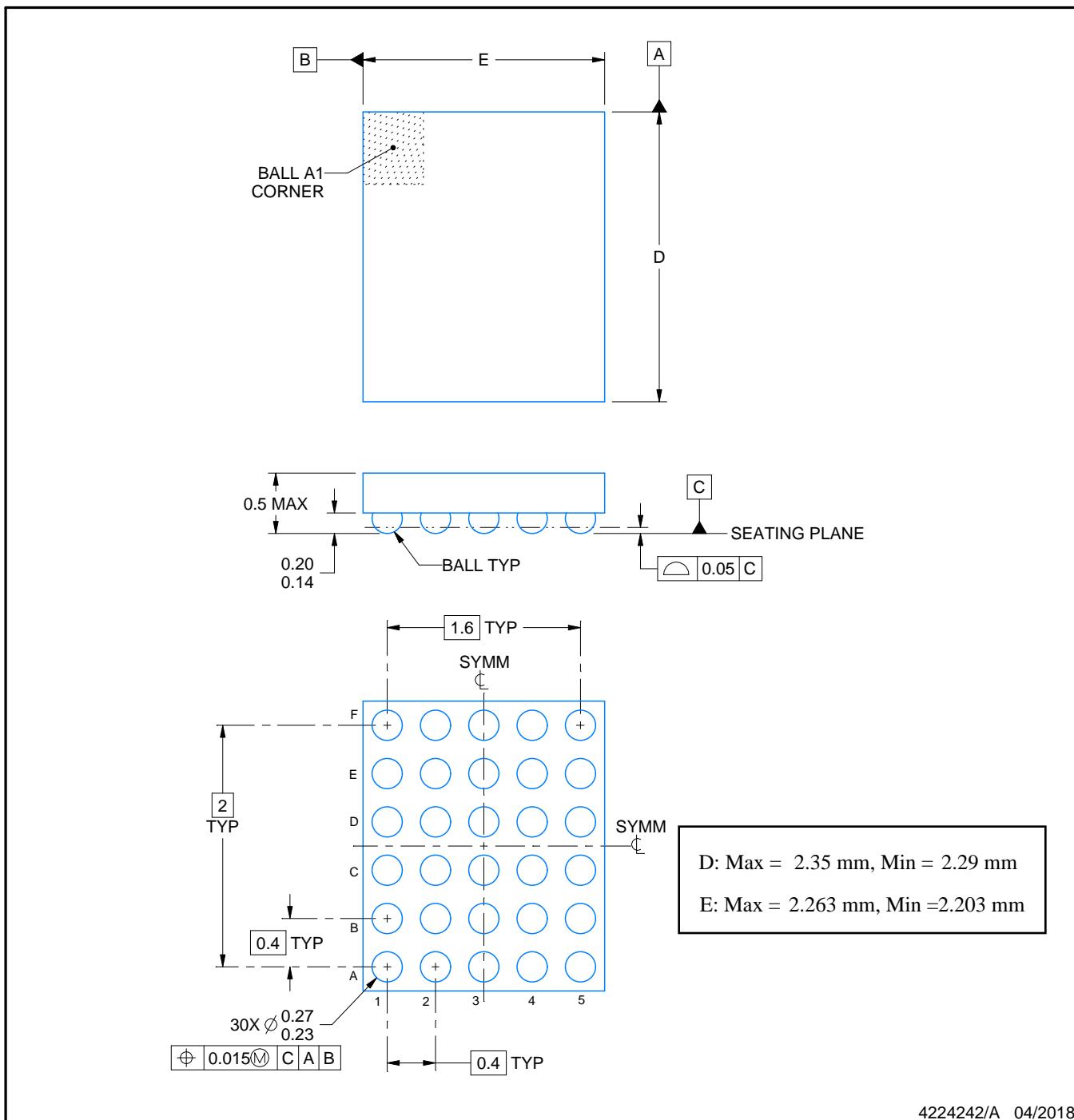

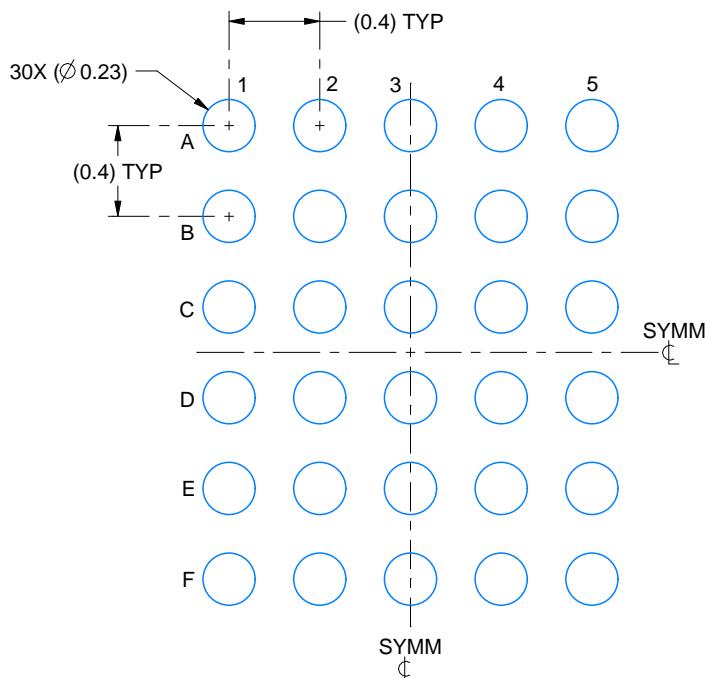

## 6 ピン構成および機能

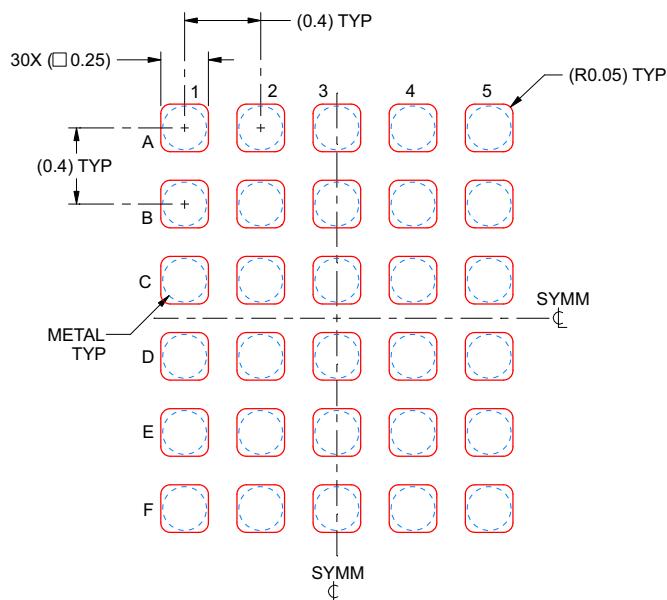

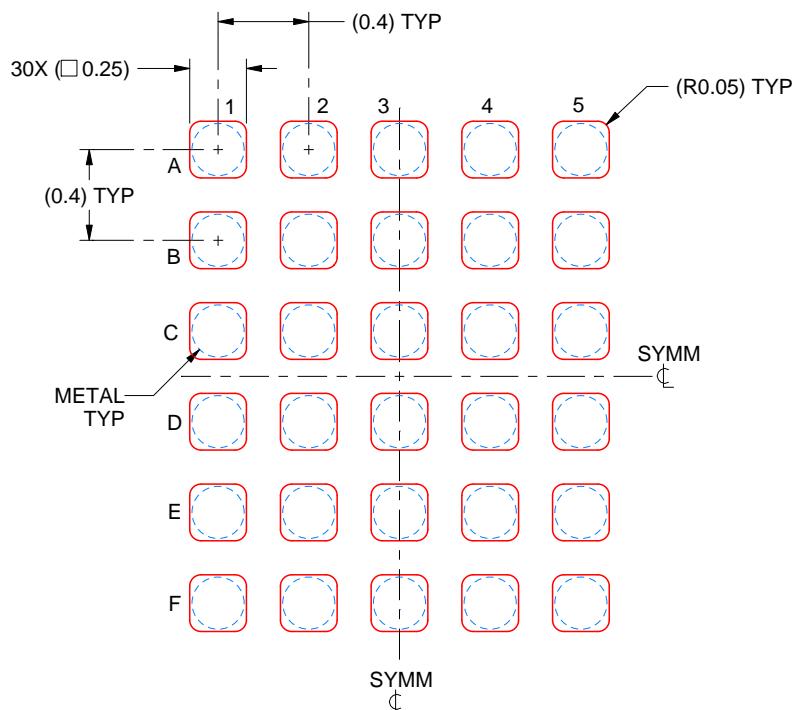

図 6-1. BQ25630 ピン配置

表 6-1. ピンの機能

| ピン   |    | タイプ <sup>(1)</sup> | 説明                                                                                                                               |

|------|----|--------------------|----------------------------------------------------------------------------------------------------------------------------------|

| 名称   | 番号 |                    |                                                                                                                                  |

| BAT  | E1 | P                  | バッテリパック接続の正端子 - 内部 BATFET は SYS と BAT の間に接続されます。BAT ピンと GND の近くに、10μF のセラミックコンデンサを接続します。                                         |

|      | E2 |                    |                                                                                                                                  |

|      | E3 |                    |                                                                                                                                  |

| BATP | F1 | AI                 | 正バッテリ電圧センス - バッテリ正極端子にケルビン接続します。このピンとバッテリの正端子の間に 100Ω の直列抵抗を配置します。                                                               |

| BTST | B5 | P                  | PWM ハイサイドドライバ電源 - 内部では、BTST はブートストラップダイオードのカソードに接続されています。47nF ブートストラップコンデンサを SW から BTST に接続します。                                  |

| CE   | C1 | DI                 | アクティブ Low 充電イネーブルピン - EN_CHG ビットが 1かつ CE ピンが Low の場合、バッテリ充電が有効になります。CE ピンは High または Low にする必要があります。フローティングのままにしないでください。          |

| D+   | F2 | AIO                | 正の USB データライン - D+/D- に基づく USB ホスト / 充電ポート検出。この検出には、データ接触検出 (DCD)、BC1.2 における一次検出および二次検出、ならびに非標準アダプタの検出が含まれます。                    |

| D-   | F3 | AIO                | 負の USB データライン - D+/D- ベースの USB ホスト / 充電ポートの検出。この検出には、データ接触検出 (DCD)、BC1.2 における一次検出および二次検出、ならびに非標準アダプタの検出が含まれます。                   |

| CC1  | F4 | AIO                | Type-C 構成チャネル 1) - USB-C コネクタの向き判定、接続検出、接続解除、および電流能力の判定に使用されます。                                                                  |

| CC2  | F5 | AIO                | Type-C 構成チャネル 2) - USB-C コネクタの向き判定、接続検出、接続解除、および電流能力の判定に使用されます。                                                                  |

| INT  | C5 | DO                 | オープンドレイン アクティブ Low 割り込み出力 - 10kΩ 抵抗を経由して、INT ピンをロジックレールに接続します。INT ピンは、充電器デバイスのステータスおよび故障を通知するため、アクティブ Low の 256μs パルスをホストに送信します。 |

| PG   | C2 | DO                 | オープンドレインのアクティブ Low パワーグッドインジケーター - 2.2kΩ の抵抗を介してプルアップレールに接続します。LOW は、PG_TH を上回る有効な入力ソースを示します。                                    |

**表 6-1. ピンの機能 (続き)**

| ピン   |    | タイプ <sup>(1)</sup> | 説明                                                                                                                                                                                                                                        |

|------|----|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称   | 番号 |                    |                                                                                                                                                                                                                                           |

| PGND | A4 | P                  | グランドリターン                                                                                                                                                                                                                                  |

|      | B4 |                    |                                                                                                                                                                                                                                           |

|      | C4 |                    |                                                                                                                                                                                                                                           |

| PMID | A2 | P                  | <b>MOSFET 接続のブロッキング</b> —合計入力容量を考慮し、VBUS には $1\mu\text{F}$ を配置し、残りは PMID に、可能な限り IC の近くに配置します。標準値: $10\mu\text{F}$ を $0.1\mu\text{F}$ セラミックコンデンサと並列に接続します。                                                                                |

|      | B2 |                    |                                                                                                                                                                                                                                           |

| QON  | D4 | DI                 | <b>BATFET イネーブル</b> またはシステム電源リセット制御入力 — Low にプルして、出荷モードまたはスタンバイモードからウェークアップします、または Low に保持してシステムリセット。このピンには、デフォルトの high ロジックを維持するための内部ブルアップが内蔵されています。                                                                                     |

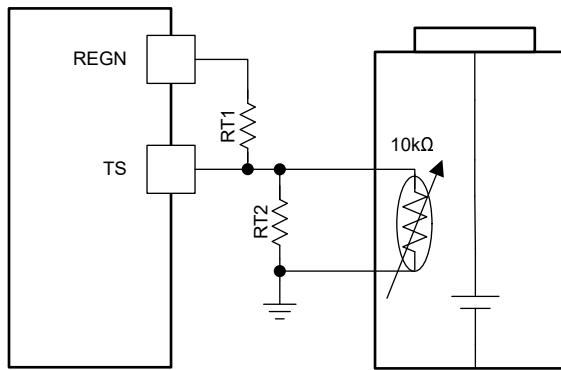

| REGN | A5 | P                  | 内部リニアレギュレータの出力 — 内部では、REGN はブートストラップダイオードのアノードに接続されています。REGN とパワー グランドの間に、定格電圧 $10\text{V}$ 以上の $4.7\mu\text{F}$ セラミックコンデンサを接続してください。このコンデンサは IC の近くに配置する必要があります。REGN LDO の出力は、内部 MOSFET のゲート駆動電圧として使用されるほか、外付け TS ピンのサーミスタのバイアスにも使用されます。 |

| SCL  | D5 | DI                 | <b>I<sup>2</sup>C インターフェイス クロック</b> — $10\text{k}\Omega$ 抵抗を経由して SCL をロジック レールに接続します。                                                                                                                                                     |

| SDA  | E5 | DIO                | <b>I<sup>2</sup>C インターフェイス データ</b> — $10\text{k}\Omega$ 抵抗を経由して SDA をロジック レールに接続します。                                                                                                                                                      |

| SW   | A3 | P                  | 出力インダクタに接続するスイッチングノード — 内部的に、SW は n チャネル HSFET のソースおよび n チャネル LSFET のドレインに接続されています。SW と BTST の間に $47\text{nF}$ のブートストラップコンデンサを接続します。                                                                                                      |

|      | B3 |                    |                                                                                                                                                                                                                                           |

|      | C3 |                    |                                                                                                                                                                                                                                           |

| SYS  | D1 | P                  | 充電器の出力電圧からシステム — 降圧コンバータの出力をシステムに接続するポイントです。内部 BATFET は SYS と BAT の間に接続されます。SYS ピンの近くに $20\mu\text{F}$ を接続します。                                                                                                                            |

|      | D2 |                    |                                                                                                                                                                                                                                           |

|      | D3 |                    |                                                                                                                                                                                                                                           |

| TS   | E4 | AI                 | 温度認定電圧入力 — 負の温度係数サーミスタを接続します。TS ピンのバイアスリファレンスからの抵抗分圧によって温度ウインドウをプログラムしますを TS に、その後 GND に接続します。TS ピンの電圧が範囲外になると、充電は一時停止されます。 $103\text{AT-2 } 10\text{k}\Omega$ サーミスタを推奨します。                                                               |

| VBUS | A1 | P                  | チャージャの入力電圧 — 内蔵の n チャネル逆流防止 MOSFET (RBFET) は、VBUS をソース側として、VBUS と PMID の間に接続されています。VBUS と GND の間に $1\mu\text{F}$ のセラミックコンデンサを、できるだけ IC の近くに配置します。                                                                                         |

|      | B1 |                    |                                                                                                                                                                                                                                           |

(1) AI = アナログ入力、AO = アナログ入出力、AIO = アナログ入力出力、DI = デジタル入力、DO = デジタル出力、DIO = デジタル入出力、P = 電源

## 7 仕様

### 7.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|                     |                                                    |  | 最小値       | 最大値 | 単位 |

|---------------------|----------------------------------------------------|--|-----------|-----|----|

| 電圧範囲 (GND を基準とした場合) | VBUS (コンバータのスイッチングなし)                              |  | -2        | 26  | V  |

|                     | PMID (コンバータのスイッチングなし)                              |  | -0.3      | 26  | V  |

|                     | BAT、SYS (コンバータのスイッチングなし)                           |  | -0.3      | 6   | V  |

|                     | SW                                                 |  | -2 (50ns) | 21  | V  |

|                     | BATP, CE, D+, D-, INT, PG, QON, REGN, SCL, SDA, TS |  | -0.3      | 6   | V  |

|                     | CC1, CC2                                           |  | -0.3      | 26  | V  |

| 差動電圧                | BTST-SW                                            |  | -0.3      | 6   | V  |

|                     | PMID-VBUS                                          |  | -0.3      | 6   | V  |

|                     | SYS-BAT                                            |  | -0.3      | 6   | V  |

| 出力シンク電流             | INT, PG                                            |  |           | 6   | mA |

| T <sub>J</sub>      | 接合部温度                                              |  | -40       | 150 | °C |

| T <sub>stg</sub>    | 保存温度                                               |  | -55       | 150 | °C |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

### 7.2 ESD 定格

|                    |      |                                                                | 値     | 単位 |

|--------------------|------|----------------------------------------------------------------|-------|----|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 に準拠、すべてのピン <sup>(1)</sup>   | ±2000 | V  |

|                    |      | デバイス帯電モデル (CDM)、JEDEC 仕様 JESD22-C101 に準拠、すべてのピン <sup>(2)</sup> | ±250  |    |

- (1) JEDEC ドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

(2) JEDEC ドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

### 7.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                   |                                          | 最小値  | 公称値 | 最大値 | 単位 |

|-------------------|------------------------------------------|------|-----|-----|----|

| V <sub>VBUS</sub> | 入力電圧                                     | 3.9  | 18  | 18  | V  |

| V <sub>BAT</sub>  | バッテリ電圧                                   |      |     | 4.8 | V  |

| I <sub>VBUS</sub> | 入力電流                                     |      |     | 3.2 | A  |

| I <sub>SW</sub>   | 出力電流 (SW)                                |      |     | 5.0 | A  |

| I <sub>BAT</sub>  | 高速充電電流                                   |      |     | 5.0 | A  |

|                   | RMS 放電電流 (連続)                            |      |     | 7   | A  |

|                   | ピーク放電電流 (最大 50ms)                        |      |     | 9   | A  |

| I <sub>REGN</sub> | 最大 REGN 電流、V <sub>VBUS</sub> ≤ 18V       |      |     | 20  | mA |

| I <sub>REGN</sub> | 最大 REGN 電流、18V ≤ V <sub>VBUS</sub> ≤ 28V |      |     | 8.5 | mA |

| T <sub>A</sub>    | 周囲温度                                     | -40  |     | 85  | °C |

| T <sub>J</sub>    | 接合部温度                                    | -40  |     | 125 | °C |

| L <sub>SW</sub>   | スイッチング レギュレータ用インダクタ                      | 0.68 |     | 2.2 | μH |

| C <sub>VBUS</sub> | VBUS コンデンサ (定格低下なし)                      | 1    |     |     | μF |

自由気流での動作温度範囲内 (特に記述のない限り)

|                   |                                           | 最小値 | 公称値 | 最大値 | 単位 |

|-------------------|-------------------------------------------|-----|-----|-----|----|

| C <sub>PMID</sub> | PMID コンデンサ (定格低下なし)                       | 10  |     |     | μF |

| C <sub>SYS</sub>  | SYS コンデンサ (定格低下なし)                        | 20  |     |     | μF |

| C <sub>BAT</sub>  | BAT コンデンサ (定格低下なし)                        | 10  |     |     | μF |

| C <sub>SYS</sub>  | NVM_EN_MIN_CSYS = 1 での実効 SYS 容量 (電圧定格低下後) | 1.5 |     |     | μF |

## 7.4 热に関する情報

| 热評価基準 <sup>(1)</sup>  |                           | BQ25630     | 単位   |

|-----------------------|---------------------------|-------------|------|

|                       |                           | YBG (DSBGA) |      |

|                       |                           | 30 ピン       |      |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗 (BQ25630EVM) | 21.4        | °C/W |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗              | 60          | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース (上面) への熱抵抗       | 0.3         | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗              | 12.4        | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への特性パラメータ          | 0.2         | °C/W |

| Ψ <sub>JB</sub>       | 接合部から基板への特性パラメータ          | 12.4        | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーションレポートを参照してください。

## 7.5 電気的特性

V<sub>VBUS\_UVLOZ</sub> < V<sub>VBUS</sub> < V<sub>VBUS\_OVP</sub>、T<sub>J</sub> = -40°C ~ +125°C、標準値は T<sub>J</sub> = 25°C (特に記述がない限り)

| パラメータ                   | テスト条件                                              | 最小値                                                                                               | 標準値 | 最大値 | 単位 |

|-------------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------|-----|-----|----|

| <b>静止時電流</b>            |                                                    |                                                                                                   |     |     |    |

| I <sub>Q_BAT</sub>      | バッテリ専用モードでの静止バッテリ電流 (BAT、SYS、SW)                   | VBAT = 4V、VBUS なし、BATFET 有効、I2C 有効、ADC 無効、CC 無効、システムはバッテリ駆動。-40°C < T <sub>J</sub> < 60°C         | 1.5 | 3.1 | μA |

| I <sub>Q_BAT_SNK</sub>  | SNK のみ通知する CC を備えたバッテリ専用モードでの静止バッテリ電流 (BAT、SYS、SW) | VBAT = 4V、VBUS なし、BATFET 有効、I2C 有効、ADC 無効、SNK のみ通知する CC、システムはバッテリ駆動。-40°C < T <sub>J</sub> < 60°C | 2.1 | 4.0 | μA |

| I <sub>Q_BAT_SRC</sub>  | SRC のみ通知する CC を備えたバッテリ専用モードでの静止バッテリ電流 (BAT、SYS、SW) | VBAT = 4V、VBUS なし、BATFET 有効、I2C 有効、ADC 無効、SRC のみ通知する CC、システムはバッテリ駆動。-40°C < T <sub>J</sub> < 60°C | 25  | 30  | μA |

| I <sub>Q_BAT_DRP</sub>  | DRP を通知する CC を備えたバッテリ専用モードでの静止バッテリ電流 (BAT、SYS、SW)  | VBAT = 4V、VBUS なし、BATFET 有効、I2C 有効、ADC 無効、DRP を通知する CC、システムはバッテリ駆動。-40°C < T <sub>J</sub> < 60°C  | 25  | 30  | μA |

| I <sub>Q_BAT_ADC</sub>  | ADC 有効化を備えたバッテリ専用モードでの静止バッテリ電流 (BAT、SYS、SW)        | VBAT = 4V、VBUS なし、BATFET 有効、I2C 有効、ADC 有効、システムはバッテリ駆動。-40°C < T <sub>J</sub> < 60°C               | 260 |     | μA |

| I <sub>Q_BAT_SD</sub>   | 充電器がシャットダウン モードのときの静止バッテリ電流 (BAT)                  | VBAT = 4V、VBUS なし、BATFET 無効、I2C 無効、シャットダウン モード、ADC 無効、T <sub>J</sub> < 60°C                       | 100 | 200 | nA |

| I <sub>Q_BAT_SHIP</sub> | 充電器が出荷モードのときの静止バッテリ電流 (BAT)                        | VBAT = 4V、VBUS なし、BATFET 無効、I2C 無効、出荷モード、ADC 無効、T <sub>J</sub> < 60°C                             | 150 | 300 | nA |

$V_{VBUS\_UVLOZ} < V_{VBUS} < V_{VBUS\_OVP}$ ,  $T_J = -40^\circ\text{C} \sim +125^\circ\text{C}$ , 標準値は  $T_J = 25^\circ\text{C}$  (特に記述がない限り)

| パラメータ                 |                                                  | テスト条件                                                                                                                                 | 最小値  | 標準値  | 最大値  | 単位 |

|-----------------------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|------|------|------|----|

| $I_{Q\_BAT\_STANDBY}$ | 充電器がスタンバイモードのときの静止バッテリ電流 (BAT)                   | $V_{BAT} = 4\text{V}$ , $CC\_DIS = 1$ , $V_{BUS}$ なし, BATFET 無効, I <sub>C</sub> 有効, スタンバイモード, CC 無効, ADC 無効, $T_J < 60^\circ\text{C}$ |      | 1.3  | 2.5  | μA |

| $I_{Q\_VBUS}$         | 静止入力電流 (VBUS)                                    | $V_{BUS} = 5\text{V}$ , $V_{BAT} = 4\text{V}$ , 充電無効, コンバータスイッチング, ISYS = 0A, PFM 有効, TS フロート                                         |      | 450  |      | μA |

| $I_{SD\_VBUS}$        | ハイインピーダンスでの静止入力電流 (VBUS)                         | $V_{BUS} = 5\text{V}$ , $V_{BAT} = 4\text{V}$ , ハイインピーダンスマード, ADC 無効, DIS_CC = 1                                                      |      | 5    | 20   | μA |

|                       |                                                  | $V_{BUS} = 15\text{V}$ , $V_{BAT} = 4\text{V}$ , ハイインピーダンスマード, ADC 無効, DIS_CC = 1                                                     |      | 20   | 35   | μA |

|                       |                                                  | $V_{BUS} = 5\text{V}$ , $V_{BAT} = 4\text{V}$ , ハイインピーダンスマード, ADC 無効, DIS_CC = 0                                                      |      | 5    | 25   | μA |

| $I_{Q\_OTG}$          | 昇圧 OTG / SRC モードでの静止バッテリ電流 (BAT, SYS, SW)        | $V_{BAT} = 4\text{V}$ , $V_{BUS} = 5\text{V}$ , OTG モード有効, コンバータスイッチング, PFM 有効, $I_{VBUS} = 0\text{A}$ , TS フロート, TS_IGNORE = 1       |      | 250  |      | μA |

| <b>VBUS / VBAT 電源</b> |                                                  |                                                                                                                                       |      |      |      |    |

| $V_{VBUS\_OP}$        | VBUS の動作範囲                                       |                                                                                                                                       | 3.9  | 18   |      | V  |

| $V_{VBUS\_UVLO}$      | I <sub>C</sub> をオフにする VBUS 立ち下がり、バッテリなし          | VBUS 立ち下がり                                                                                                                            | 3.0  | 3.15 | 3.3  | V  |

| $V_{VBUS\_UVLOZ}$     | アクティブ I <sub>C</sub> の VBUS 立ち上がり、バッテリなし         | VBUS 立ち上がり                                                                                                                            | 3.2  | 3.35 | 3.5  | V  |

| $V_{VBUS\_OVP}$       | VBUS 過電圧立ち上がりスレッショルド                             | VBUS 立ち上がり, $V_{BUS\_OVP} = 0$                                                                                                        | 6.1  | 6.5  | 6.7  | V  |

|                       |                                                  | VBUS 立ち上がり, $V_{BUS\_OVP} = 1$                                                                                                        | 18.5 | 18.8 | 19.1 | V  |

| $V_{VBUS\_OVPZ}$      | VBUS 過電圧立ち下がりスレッショルド                             | VBUS 立ち下がり, $V_{BUS\_OVP} = 0$                                                                                                        | 5.8  | 6.0  | 6.2  | V  |

|                       |                                                  | VBUS 立ち下がり, $V_{BUS\_OVP} = 1$                                                                                                        | 17.6 | 17.8 | 18.3 | V  |

| $V_{SLEEP}$           | スリープモードの立ち下がりスレッショルド                             | ( $V_{BUS} - V_{BAT}$ ), VBUS 立ち下がり                                                                                                   | 9    | 45   | 85   | mV |

| $V_{SLEEPZ}$          | スリープモードの立ち上がりスレッショルド                             | ( $V_{BUS} - V_{BAT}$ ), VBUS 立ち上がり                                                                                                   | 115  | 220  | 340  | mV |

| $V_{BAT\_UVLOZ}$      | アクティブ I <sub>C</sub> の BAT 電圧、BATFET をオン、VBUS なし | VBAT 立ち上がり                                                                                                                            | 2.3  | 2.4  | 2.5  | V  |

| $V_{BAT\_UVLO}$       | I <sub>C</sub> をオフにする BAT 電圧、BATFET をオフ、VBUS なし  | VBAT 立ち下がり, $V_{BAT\_UVLO} = 0$                                                                                                       | 2.1  | 2.2  | 2.3  | V  |

|                       |                                                  | VBAT 立ち下がり, $V_{BAT\_UVLO} = 1$                                                                                                       | 1.7  | 1.8  | 1.9  | V  |

| $V_{BAT\_OTG}$        | OTG モードを有効にする BAT 電圧の立ち上がりスレッショルド                | VBAT 立ち上がり, $V_{BAT\_OTG\_MIN} = 00$                                                                                                  | 3.1  | 3.2  | 3.3  | V  |

|                       |                                                  | VBAT 立ち上がり, $V_{BAT\_OTG\_MIN} = 01$                                                                                                  | 2.9  | 3.0  | 3.1  | V  |

|                       |                                                  | VBAT 立ち上がり, $V_{BAT\_OTG\_MIN} = 10$                                                                                                  | 2.7  | 2.8  | 2.9  | V  |

|                       |                                                  | VBAT 立ち上がり, $V_{BAT\_OTG\_MIN} = 11$                                                                                                  | 2.5  | 2.6  | 2.7  | V  |

| $V_{BAT\_OTGZ}$       | OTG モードを無効にする BAT 電圧の立ち下がりスレッショルド                | VBAT 立ち下がり, $V_{BAT\_OTG\_MIN} = 00$                                                                                                  | 2.9  | 3.0  | 3.1  | V  |

|                       |                                                  | VBAT 立ち下がり, $V_{BAT\_OTG\_MIN} = 01$                                                                                                  | 2.7  | 2.8  | 2.9  | V  |

|                       |                                                  | VBAT 立ち下がり, $V_{BAT\_OTG\_MIN} = 10$                                                                                                  | 2.5  | 2.6  | 2.7  | V  |

|                       |                                                  | VBAT 立ち下がり, $V_{BAT\_OTG\_MIN} = 11$                                                                                                  | 2.3  | 2.4  | 2.5  | V  |

| <b>パワー パス管理</b>       |                                                  |                                                                                                                                       |      |      |      |    |

| $V_{SYS\_REG\_ACC}$   | 標準的なシステム電圧レギュレーション                               | ISYS = 0A, $V_{BAT} > VSYSMIN$ , 充電無効。VBAT を上回るオフセット                                                                                  |      | 50   |      | mV |

|                       |                                                  | ISYS = 0A, $V_{BAT} < VSYSMIN$ , 充電無効。VSYSMIN を上回るオフセット                                                                               |      | 230  |      | mV |

| $V_{SYSMIN\_RNG}$     | VSYSMIN レジスタの範囲                                  |                                                                                                                                       | 2.56 | 4.0  |      | V  |

$V_{VBUS\_UVLOZ} < V_{VBUS} < V_{VBUS\_OVP}$ ,  $T_J = -40^{\circ}\text{C} \sim +125^{\circ}\text{C}$ , 標準値は  $T_J = 25^{\circ}\text{C}$  (特に記述がない限り)

| パラメータ                   | テスト条件                                       | 最小値                                                                                                                          | 標準値  | 最大値  | 単位 |

|-------------------------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------|------|----|

| $V_{SYSMIN\_REG\_STEP}$ | $V_{SYSMIN}$ レジスタ ステップ サイズ                  |                                                                                                                              | 80   |      | mV |

| $V_{SYSMIN\_REG\_ACC}$  | 最小 DC システム電圧出力                              | $ISYS = 0\text{A}, V_{BAT} < V_{SYSMIN} = B00\text{h}$<br>(3.52V)、充電無効                                                       | 3.52 | 3.75 | V  |

| $V_{SYS\_SHORT}$        | 強制 PFM に移行する VSYS 短絡電圧の立ち下がりスレッショルド         |                                                                                                                              | 0.9  |      | V  |

| $V_{SYS\_SHORTZ}$       | 強制 PFM を終了する VSYS 短絡電圧の立ち上がりスレッショルド         |                                                                                                                              | 1.1  |      | V  |

| <b>バッテリ チャージャ</b>       |                                             |                                                                                                                              |      |      |    |

| $V_{REG\_RANGE}$        | 標準的な充電電圧レギュレーション範囲                          |                                                                                                                              | 3.50 | 4.80 | V  |

| $V_{REG\_STEP}$         | 標準的な充電電圧ステップ                                |                                                                                                                              | 10   |      | mV |

| $V_{REG\_ACC}$          | 充電電圧精度                                      | $T_J = 25^{\circ}\text{C}, V_{REG} = 4.2\text{V}$                                                                            | -0.3 | 0.3  | %  |

|                         |                                             | $T_J = -10^{\circ}\text{C} \sim 65^{\circ}\text{C}, V_{REG} = 4.2\text{V}$                                                   | -0.5 | 0.5  | %  |

| $I_{CHG\_RANGE}$        | 標準的な充電電流レギュレーション範囲                          |                                                                                                                              | 0.08 | 5.04 | A  |

| $I_{CHG\_STEP}$         | 標準的な充電電流レギュレーションステップ                        |                                                                                                                              | 20   |      | mA |

| $I_{CHG\_ACC}$          | 標準的な充電電流精度                                  | $V_{BAT} = 3.1\text{V} \text{ または } 3.8\text{V}, I_{CHG} = 1760\text{mA}, T_J = -10^{\circ}\text{C} \sim 65^{\circ}\text{C}$ | -5   | 5    | %  |

|                         |                                             | $V_{BAT} = 3.1\text{V} \text{ または } 3.8\text{V}, I_{CHG} = 1040\text{mA}, T_J = -10^{\circ}\text{C} \sim 65^{\circ}\text{C}$ | -6   | 6    | %  |

|                         |                                             | $V_{BAT} = 3.1\text{V} \text{ または } 3.8\text{V}, I_{CHG} = 480\text{mA}, T_J = -10^{\circ}\text{C} \sim 65^{\circ}\text{C}$  | -10  | 10   | %  |

| $I_{PRECHG\_RANGE}$     | 標準的なプリチャージ電流範囲                              |                                                                                                                              | 40   | 1000 | mA |

| $I_{PRECHG\_STEP}$      | 標準的なプリチャージ電流ステップ                            |                                                                                                                              | 20   |      | mA |

| $I_{PRECHG\_ACC}$       | $V_{BAT}$ が $V_{SYSMIN}$ 設定未満のときのプリチャージ電流精度 | $V_{BAT} = 2.5\text{V}, I_{PRECHG} = 480\text{mA}, T_J = -10^{\circ}\text{C} \sim 65^{\circ}\text{C}$                        | -10  | 10   | %  |

|                         |                                             | $V_{BAT} = 2.5\text{V}, I_{PRECHG} = 200\text{mA}, T_J = -10^{\circ}\text{C} \sim 65^{\circ}\text{C}$                        | -10  | 10   | %  |

|                         |                                             | $V_{BAT} = 2.5\text{V}, I_{PRECHG} = 100\text{mA}, T_J = -10^{\circ}\text{C} \sim 65^{\circ}\text{C}$                        | -30  | 30   | %  |

|                         |                                             | $V_{BAT} = 2.5\text{V}, I_{PRECHG} = 40\text{mA}, T_J = -10^{\circ}\text{C} \sim 65^{\circ}\text{C}$                         | -70  | 70   | %  |

| $I_{TERM\_RANGE}$       | 代表的な終端電流範囲                                  |                                                                                                                              | 30   | 1000 | mA |

| $I_{TERM\_STEP}$        | 代表的な終端電流ステップ                                |                                                                                                                              | 10   |      | mA |

| $I_{TERM\_ACC}$         | 終了電流の精度                                     | $I_{TERM} = 30\text{mA}, T_J = -10^{\circ}\text{C} \sim 65^{\circ}\text{C}$                                                  | -70  | 70   | %  |

|                         |                                             | $I_{TERM} = 100\text{mA}, T_J = -10^{\circ}\text{C} \sim 65^{\circ}\text{C}$                                                 | -10  | 20   | %  |

|                         |                                             | $I_{TERM} = 200\text{mA}, T_J = -10^{\circ}\text{C} \sim 65^{\circ}\text{C}$                                                 | -5   | 15   | %  |

| $I_{LIM\_API\_RANGE}$   | 入力モードからの代替電力における標準的な電流制限範囲                  |                                                                                                                              | 10   | 100  | mA |

| $I_{LIM\_API\_STEP}$    | 入力モードからの代替電力における標準的な電流制限ステップ                |                                                                                                                              | 2.5  |      | mA |

| $I_{LIM\_API\_ACC}$     | 入力モードからの代替電力における標準的な電流制限精度                  | $V_{BUS} = 5\text{V}, API\_ILIM} = 100\text{mA}$                                                                             | -10  | 10   | %  |

| $V_{BAT\_SHORTZ}$       | プリチャージを開始するバッテリ短絡電圧の立ち上がりスレッショルド            | VBAT 立ち上がり                                                                                                                   | 2.25 |      | V  |

| $V_{BAT\_SHORT}$        | プリチャージを停止するバッテリ短絡電圧の立ち下がりスレッショルド            | VBAT 立ち下がり、 $VBAT\_UVLO = 0$                                                                                                 | 2.05 |      | V  |

$V_{VBUS\_UVLOZ} < V_{VBUS} < V_{VBUS\_OVP}$ 、 $T_J = -40^{\circ}\text{C} \sim +125^{\circ}\text{C}$ 、標準値は  $T_J = 25^{\circ}\text{C}$  (特に記述がない限り)

| パラメータ                    |                                   | テスト条件                                                                                              | 最小値  | 標準値  | 最大値  | 単位 |

|--------------------------|-----------------------------------|----------------------------------------------------------------------------------------------------|------|------|------|----|

| $V_{BAT\_SHORT}$         | プリチャージを停止するバッテリ短絡電圧の立ち下がりスレッショルド  | $V_{BAT}$ 立ち下がり、 $V_{BAT\_UVLO} = 1$                                                               |      | 1.85 |      | V  |

| $I_{BAT\_SHORT}$         | バッテリ短絡トリクル充電電流                    | $V_{BAT} < V_{BAT\_SHORTZ}$ , $ITRICKLE = 0$ , $T_J = -10^{\circ}\text{C} \sim 65^{\circ}\text{C}$ | 6    | 20   | 34   | mA |

|                          |                                   | $V_{BAT} < V_{BAT\_SHORTZ}$ , $ITRICKLE = 1$ , $T_J = -10^{\circ}\text{C} \sim 65^{\circ}\text{C}$ | 64   | 80   | 102  | mA |

| $V_{BAT\_LOWV}$          | 高速充電を開始するバッテリ Low 立ち上がりの電圧スレッショルド | $BATLOWV = 00$                                                                                     | 2.9  | 3.0  | 3.1  | V  |

|                          | 高速充電を開始するバッテリ Low 立ち下がりの電圧スレッショルド | $BATLOWV = 00$                                                                                     | 2.7  | 2.8  | 2.9  | V  |

| $V_{RECHG}$              | $V_{REG}$ 未満のバッテリ再充電スレッショルド       | $V_{BAT}$ 立ち下がり、 $V_{RECHG} = 0$                                                                   |      | 100  |      | mV |

|                          |                                   | $V_{BAT}$ 立ち下がり、 $V_{RECHG} = 1$                                                                   |      | 200  |      | mV |

| $I_{PMID\_LOAD}$         | PMID 放電負荷電流                       |                                                                                                    | 20   |      |      | mA |

| $I_{BAT\_LOAD}$          | バッテリ放電負荷電流                        |                                                                                                    | 20   |      |      | mA |

| $I_{SYS\_LOAD}$          | システム放電負荷電流                        |                                                                                                    | 20   |      |      | mA |

| <b>BATFET</b>            |                                   |                                                                                                    |      |      |      |    |

| $V_{SUPPZ}$              | 補完モードを終了する $SYS < BAT$ スレッショルド    |                                                                                                    |      | 5    |      | mV |

| $R_{BATFET}$             | SYS から BAT への MOSFET オン抵抗         |                                                                                                    |      | 7    | 12   | mΩ |

| <b>バッテリ保護</b>            |                                   |                                                                                                    |      |      |      |    |

| $V_{BAT\_OVP}$           | バッテリ過電圧の立ち上がりスレッショルド              | $V_{REG}$ の割合として表示                                                                                 | 103  | 104  | 105  | %  |

| $V_{BAT\_OVPZ}$          | バッテリ過電圧立ち下がりスレッショルド               | $V_{REG}$ の割合として表示                                                                                 | 101  | 102  | 103  | %  |

| $I_{BATFET\_OCP}$        | BATFET 過電圧の立ち上がりスレッショルド           |                                                                                                    | 7    |      |      | A  |

| $I_{BAT\_PK}$            | バッテリ放電ピーク電流の立ち上がりスレッショルド          | $IBAT\_PK = 00$                                                                                    | 3    |      |      | A  |

|                          |                                   | $IBAT\_PK = 01$                                                                                    | 6    |      |      | A  |

|                          |                                   | $IBAT\_PK = 10$                                                                                    | 9    |      |      | A  |

| <b>入力電圧 / 電流レギュレーション</b> |                                   |                                                                                                    |      |      |      |    |

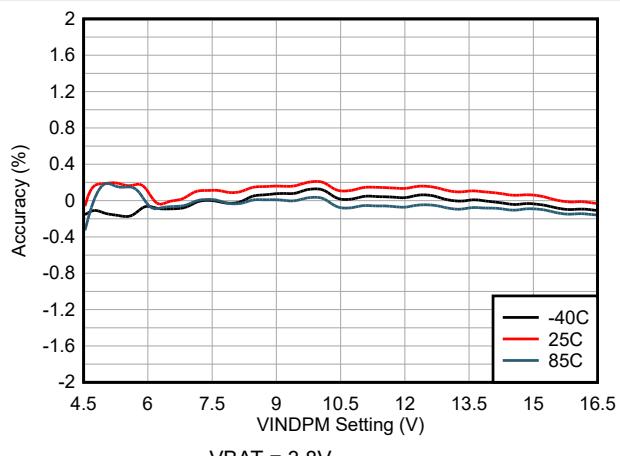

| $V_{INDPM\_RANGE}$       | 標準的な入力電圧レギュレーション範囲                |                                                                                                    | 3.8  | 16.8 |      | V  |

| $V_{INDPM\_STEP}$        | 標準的な入力電圧レギュレーションステップ              |                                                                                                    |      | 40   |      | mV |

| $V_{INDPM\_ACC}$         | 入力電圧レギュレーション精度                    | $V_{INDPM} = 4.6\text{V}$                                                                          | -3   | 3    |      | %  |

|                          |                                   | $V_{INDPM} = 8\text{V}$                                                                            | -3   | 3    |      | %  |

|                          |                                   | $V_{INDPM} = 16\text{V}$                                                                           | -2   | 2    |      | %  |

| $V_{INDPM\_BAT\_TRACK}$  | バッテリトラッキング $V_{INDPM}$ の精度        | $V_{BAT} = 3.9\text{V}$ , $V_{INDPM\_BAT\_TRACK} = 1$ , $V_{INDPM} = 4\text{V}$                    | 3.95 | 4.1  | 4.2  | V  |

| $I_{INDPM\_RANGE}$       | 標準的な入力電流レギュレーション範囲                |                                                                                                    | 0.1  | 3.2  |      | A  |

| $I_{INDPM\_STEP}$        | 標準的な入力電流レギュレーションステップ              |                                                                                                    |      | 10   |      | mA |

| $I_{INDPM\_ACC}$         | 入力電流のレギュレーション精度                   | $I_{INDPM} = 500\text{mA}$ , $V_{BUS} = 5\text{V}$                                                 | 415  | 475  | 500  | mA |

|                          |                                   | $I_{INDPM} = 900\text{mA}$ , $V_{BUS} = 5\text{V}$                                                 | 750  | 825  | 900  | mA |

|                          |                                   | $I_{INDPM} = 1500\text{mA}$ , $V_{BUS} = 5\text{V}$                                                | 1350 | 1425 | 1500 | mA |

| <b>USB TYPE C</b>        |                                   |                                                                                                    |      |      |      |    |

$V_{VBUS\_UVLOZ} < V_{VBUS} < V_{VBUS\_OVP}$ ,  $T_J = -40^{\circ}\text{C} \sim +125^{\circ}\text{C}$ , 標準値は  $T_J = 25^{\circ}\text{C}$  (特に記述がない限り)

| パラメータ             | テスト条件                                       | 最小値   | 標準値  | 最大値  | 単位 |

|-------------------|---------------------------------------------|-------|------|------|----|

| $V_{SAFE5V}$      | 5V での USB-C の安全動作電圧。                        | 4.75  | 5.5  | 5.5  | V  |

| $V_{SAFE0V}$      | 「0V」での USB-C の安全動作電圧。                       | 0     | 0.8  | 0.8  | V  |

| $V_{CC\_OVP\_TH}$ | $V_{CC\_OVP}$ コンパレータ スレッショルド、 $CC\_OVP = 0$ | 立ち上がり | 3.53 | 3.63 | V  |

|                   |                                             | 立ち下がり | 3.43 | 3.53 | V  |

|                   | $V_{CC\_OVP}$ コンパレータ スレッショルド、 $CC\_OVP = 1$ | 立ち上がり | 5.9  | 6.1  | V  |

|                   |                                             | 立ち下がり | 5.7  | 5.9  | V  |

| $R_D$             | SNK または DRP モードでのプルダウン抵抗                    | 4.6   | 5.1  | 5.6  | kΩ |

#### Type-C シンク (Rd プルダウン)

|                       |                                                                    |                                                                     |       |      |   |

|-----------------------|--------------------------------------------------------------------|---------------------------------------------------------------------|-------|------|---|

| $V_{SNK\_DISCONNECT}$ | VBUS が 5V のとき Attached.SNK から Unattached.SNK に遷移するためのスレッショルドの有効範囲。 |                                                                     | 0.8   | 3.67 | V |

| $V_{SNK\_RDB}$        | デッド バッテリ Rd クランプ                                                   | VBAT < VBAT_UVLO の場合、接続されている SRC はデフォルトの電流供給能力 (500mA/900mA) を提示します | 0.25  | 1.5  | V |

|                       |                                                                    | VBAT < VBAT_UVLO の場合、接続されている SRC は中レベルの電流供給能力 (1.5A) を提示します         | 0.45  | 1.5  |   |

|                       |                                                                    | VBAT < VBAT_UVLO の場合、接続されている SRC は高レベルの電力供給能力 (3A) を提示します           | 0.88  | 2.18 |   |

| $V_{SNK\_RD\_RA}$     | Ra を示すケーブルを検出する SNK として構成した場合の Rd の両端の電圧                           | VBAT > VBAT_OTG, CC_MODE = 00b                                      | -0.25 | 0.2  | V |

| $V_{SNK\_RD\_DEF}$    | SNK として構成された場合に、デフォルトの電流供給能力 (500mA/900mA) を持つ SRC を検出する Rd 両端の電圧  | VBAT > VBAT_OTG, CC_MODE = 00b                                      | 0.25  | 0.61 | V |

| $V_{SNK\_RD\_MED}$    | SNK として構成された場合に、中レベルの電流供給能力 (1.5A) を持つ SRC を検出する Rd 両端の電圧          | VBAT > VBAT_OTG, CC_MODE = 00b                                      | 0.7   | 1.16 | V |

| $V_{SNK\_RD\_HI}$     | SNK として構成された場合に、高レベルの電流供給能力 (3A) を持つ SRC を検出する Rd 両端の電圧            | VBAT > VBAT_OTG, CC_MODE = 00b                                      | 1.31  | 2.04 | V |

#### Type-C ソース (Rp プルアップ)

|                    |                                                     |                                   |     |     |     |    |

|--------------------|-----------------------------------------------------|-----------------------------------|-----|-----|-----|----|

| $I_{SRC\_RP\_DEF}$ | SRC として提示する場合、デフォルトの電流供給能力 (500mA/900mA) 向けプルアップ電流源 | $RP\_VALUE = 00b, CC\_MODE = 01b$ | 64  | 80  | 96  | μA |

| $I_{SRC\_RP\_MED}$ | SRC として提示する場合、中レベルの電流供給能力 (1.5A) 向けプルアップ電流源         | $RP\_VALUE = 01b, CC\_MODE = 01b$ | 166 | 180 | 194 | μA |

| $I_{SRC\_RP\_HI}$  | SRC として提示する場合、高レベルの電流供給能力 (3A) 向けプルアップ電流源           | $RP\_VALUE = 10b, CC\_MODE = 01b$ | 304 | 330 | 356 | μA |

#### 液体検出

|           |                     |                |       |  |   |

|-----------|---------------------|----------------|-------|--|---|

| $V_{LQD}$ | 液体を検出する立ち上がりスレッショルド | $VLQD = 1100b$ | 1.600 |  | V |

|-----------|---------------------|----------------|-------|--|---|

#### D+ / D- 検出

|                    |                 |                                                          |      |   |     |    |

|--------------------|-----------------|----------------------------------------------------------|------|---|-----|----|

| $V_{D+D-0MV\_SRC}$ | D+/D- 電圧源 (0mV) | $I_{D+} < 1\text{mA}, DP\_DAC = 001$ または $DM\_DAC = 001$ | -150 | 0 | 150 | mV |

|--------------------|-----------------|----------------------------------------------------------|------|---|-----|----|

$V_{V_{BUS\_UVLOZ}} < V_{V_{BUS}} < V_{V_{BUS\_OVP}}$ 、 $T_J = -40^\circ\text{C} \sim +125^\circ\text{C}$ 、標準値は  $T_J = 25^\circ\text{C}$  (特に記述がない限り)

| パラメータ                        |                                                              | テスト条件                                                                            | 最小値   | 標準値   | 最大値              | 単位            |

|------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------|-------|-------|------------------|---------------|

| $V_{D+D-600mV\_SRC}$         | D+/D- 電圧源 (600mV)                                            | $I_{D+} < 1\text{mA}$ , DP_DAC = 010 または<br>$I_{D-} < 1\text{mA}$ , DM_DAC = 010 | 400   | 600   | 800              | mV            |

| $V_{D+D-650mV\_SRC}$         | D+/D- 電圧源 (650mV)                                            |                                                                                  | 638   | 650   | 700              | mV            |

| $V_{D+D-1p2V\_SRC}$          | D+/D- 電圧源 (1.2V)                                             | $I_{D+} < 1\text{mA}$ , DP_DAC = 011 または<br>$I_{D-} < 1\text{mA}$ , DM_DAC = 011 | 1.075 | 1.2   | 1.325            | V             |

| $V_{D+D-2p0V\_SRC}$          | D+/D- 電圧源 (2.0V)                                             | $I_{D+} < 1\text{mA}$ , DP_DAC = 100 または<br>$I_{D-} < 1\text{mA}$ , DM_DAC = 100 | 1.875 | 2.0   | 2.125            | V             |

| $V_{D+D-2p7V\_SRC}$          | D+/D- 電圧源 (2.7V)                                             | $I_{D+} < 1\text{mA}$ , DP_DAC = 101 または<br>$I_{D-} < 1\text{mA}$ , DM_DAC = 101 | 2.575 | 2.7   | 2.825            | V             |

| $V_{D+D-3p3V\_SRC}$          | D+/D- 電圧源 (3.3V)                                             | $I_{D+} < 1\text{mA}$ , DP_DAC = 110 または<br>$I_{D-} < 1\text{mA}$ , DM_DAC = 110 | 3.1   | 3.3   | 3.5              | V             |

| $I_{D+10uA\_SRC}$            | D+ 電流源 (10 $\mu\text{A}$ )                                   |                                                                                  | 7     | 10    | 13               | $\mu\text{A}$ |

| $I_{D+D-100uA\_SNK}$         | D+/D- 電流シンク (100 $\mu\text{A}$ )                             |                                                                                  | 50    | 90    | 150              | $\mu\text{A}$ |

| $V_{D+D-0P325}$              | 二次側検出の D+/D- コンパレータ<br>スレッショルド                               |                                                                                  | 250   | 400   |                  | mV            |

| $V_{D+0P8}$                  | データ接触検出の D+ コンパレータ<br>スレッショルド                                |                                                                                  | 775   | 850   | 925              | mV            |

| $R_{D-19K}$                  | グランドへの D- 抵抗 (19k $\Omega$ )                                 | $V_{D-} = 500\text{mV}$                                                          | 14.25 | 24.8  |                  | k $\Omega$    |

| $I_{D+D-LKG}$                | D+/D- へのリーク電流                                                | ハイインピーダンスモード                                                                     | -1    | 1     |                  | $\mu\text{A}$ |

| $V_{D+D-2p8}$                | 非標準アダプタの D+/D- コンパレータ<br>スレッショルド                             |                                                                                  | 2.55  | 2.85  |                  | V             |

| $V_{D+D-2p0}$                | 非標準アダプタの D+/D- コンパレータ<br>スレッショルド                             |                                                                                  | 1.85  | 2.15  |                  | V             |

| サーマル レギュレーションおよびサーマル シャットダウン |                                                              |                                                                                  |       |       |                  |               |

| $T_{REG}$                    | 接合部温度レギュレーション精度                                              | TREG = 1                                                                         | 120   |       | $^\circ\text{C}$ |               |

|                              |                                                              | TREG = 0                                                                         | 60    |       | $^\circ\text{C}$ |               |

| $T_{SHUT}$                   | サーマル シャットダウン立ち上がりスレッショルド                                     | 温度上昇                                                                             | 150   |       | $^\circ\text{C}$ |               |

| $T_{SHUT\_HYS}$              | サーマル シャットダウンの立ち下がり<br>ヒステリシス                                 | $T_{SHUT\_HYS}$ による温度低下                                                          | 30    |       | $^\circ\text{C}$ |               |

| サーミスタ コンパレータ(充電モード)          |                                                              |                                                                                  |       |       |                  |               |

| $V_{TS\_COLD}$               | TS_COOL から TS_COLD へ遷移する TH1 コンパレータ用 TS ピン立ち上がり電圧スレッショルド。    | TS ピンのバイアス基準に対する割合<br>(103AT 使用時で $-5^\circ\text{C}$ ), TS_TH1 = 0               | 74.75 | 75.25 | 75.75            | %             |

|                              |                                                              | TS ピンのバイアス基準に対する割合<br>(103AT 使用時で $0^\circ\text{C}$ ), TS_TH1 = 1                | 72.75 | 73.25 | 73.75            | %             |

| $V_{TS\_COLDZ}$              | TS_COLD から TS_COOL へ遷移する TH1 コンパレータ用 TS ピン立ち上がり電圧スレッショルド。    | TS ピンのバイアス基準に対する割合<br>(103AT 使用時で $-2.5^\circ\text{C}$ ), TS_TH1 = 0             | 73.75 | 74.25 | 74.75            | %             |

|                              |                                                              | TS ピンのバイアス基準に対する割合<br>(103AT 使用時で $2.5^\circ\text{C}$ ), TS_TH1 = 1              | 71.75 | 72.25 | 72.75            | %             |

| $V_{TS\_COOL}$               | TS_PRECOOL から TS_COOL へ遷移する TH2 コンパレータ用 TS ピン立ち上がり電圧スレッショルド。 | TS ピンのバイアス基準に対する割合<br>(103AT 使用時で $5^\circ\text{C}$ ), TS_TH2 = 0                | 70.25 | 70.75 | 71.25            | %             |

|                              |                                                              | TS ピンのバイアス基準に対する割合<br>(103AT 使用時で $7.5^\circ\text{C}$ ), TS_TH2 = 1              | 69.25 | 69.75 | 70.25            | %             |

|                              |                                                              | TS ピンのバイアス基準に対する割合<br>(103AT 使用時で $10^\circ\text{C}$ ), TS_TH2 = 2               | 67.75 | 68.25 | 68.75            | %             |

|                              |                                                              | TS ピンのバイアス基準に対する割合<br>(103AT 使用時で $12.5^\circ\text{C}$ ), TS_TH2 = 3             | 66.25 | 66.75 | 67.25            | %             |

$V_{VBUS\_UVLOZ} < V_{VBUS} < V_{VBUS\_OVP}$ ,  $T_J = -40^\circ\text{C} \sim +125^\circ\text{C}$ , 標準値は  $T_J = 25^\circ\text{C}$  (特に記述がない限り)

| パラメータ              |                                                                | テスト条件                                                             | 最小値   | 標準値   | 最大値   | 単位 |

|--------------------|----------------------------------------------------------------|-------------------------------------------------------------------|-------|-------|-------|----|

| $V_{TS\_COOLZ}$    | TS_COOL から TS_PRECOOL へ遷移する TH2 コンバレータ用 TS ピン立ち下がり電圧スレッショルド。   | TS ピンのバイアス基準に対する割合 (103AT 使用時で $7.5^\circ\text{C}$ ), TS_TH2 = 0  | 69.25 | 69.75 | 70.25 | %  |

|                    |                                                                | TS ピンのバイアス基準に対する割合 (103AT 使用時で $10^\circ\text{C}$ ), TS_TH2 = 1   | 67.75 | 68.25 | 68.75 | %  |

|                    |                                                                | TS ピンのバイアス基準に対する割合 (103AT 使用時で $12.5^\circ\text{C}$ ), TS_TH2 = 2 | 66.25 | 66.75 | 67.25 | %  |

|                    |                                                                | TS ピンのバイアス基準に対する割合 (103AT 使用時で $15^\circ\text{C}$ ), TS_TH2 = 3   | 64.75 | 65.25 | 65.75 | %  |

| $V_{TS\_PRECOOL}$  | TS_NORMAL から TS_PRECOOL へ遷移する TH3 コンバレータ用 TS ピン立ち上がり電圧スレッショルド。 | TS ピンのバイアス基準に対する割合 (103AT 使用時で $15^\circ\text{C}$ ), TS_TH3 = 0   | 64.75 | 65.25 | 65.75 | %  |

|                    |                                                                | TS ピンのバイアス基準に対する割合 (103AT 使用時で $17.5^\circ\text{C}$ ), TS_TH3 = 1 | 63.25 | 63.75 | 64.25 | %  |

|                    |                                                                | TS ピンのバイアス基準に対する割合 (103AT 使用時で $20^\circ\text{C}$ ), TS_TH3 = 2   | 61.75 | 62.25 | 62.75 | %  |

|                    |                                                                | TS ピンのバイアス基準に対する割合 (103AT 使用時で $22.5^\circ\text{C}$ ), TS_TH3 = 3 | 60.25 | 60.75 | 61.25 | %  |

| $V_{TS\_PRECOOLZ}$ | TS_PRECOOL から TS_NORMAL へ遷移する TH3 コンバレータ用 TS ピン立ち下がり電圧スレッショルド。 | TS ピンのバイアス基準に対する割合 (103AT 使用時で $17.5^\circ\text{C}$ ), TS_TH3 = 0 | 63.25 | 63.75 | 64.25 | %  |

|                    |                                                                | TS ピンのバイアス基準に対する割合 (103AT 使用時で $20^\circ\text{C}$ ), TS_TH3 = 1   | 61.75 | 62.25 | 62.75 | %  |

|                    |                                                                | TS ピンのバイアス基準に対する割合 (103AT 使用時で $22.5^\circ\text{C}$ ), TS_TH3 = 2 | 60.25 | 60.75 | 61.25 | %  |

|                    |                                                                | TS ピンのバイアス基準に対する割合 (103AT 使用時で $25^\circ\text{C}$ ), TS_TH3 = 3   | 58.5  | 59.00 | 59.5  | %  |

| $V_{TS\_PREWARM}$  | TS_NORMAL から TS_PREWARM へ遷移する TH4 コンバレータ用 TS ピン立ち下がり電圧スレッショルド。 | TS ピンのバイアス基準に対する割合 (103AT 使用時で $32.5^\circ\text{C}$ ), TS_TH4 = 0 | 53.25 | 53.75 | 54.25 | %  |

|                    |                                                                | TS ピンのバイアス基準に対する割合 (103AT 使用時で $35^\circ\text{C}$ ), TS_TH4 = 1   | 51.50 | 52.00 | 52.50 | %  |

|                    |                                                                | TS ピンのバイアス基準に対する割合 (103AT 使用時で $37.5^\circ\text{C}$ ), TS_TH4 = 2 | 49.5  | 50    | 50.5  | %  |

|                    |                                                                | TS ピンのバイアス基準に対する割合 (103AT 使用時で $40^\circ\text{C}$ ), TS_TH4 = 3   | 47.75 | 48.25 | 48.75 | %  |

| $V_{TS\_PREWARMZ}$ | TS_PREWARM から TS_NORMAL へ遷移する TH4 コンバレータ用 TS ピン立ち上がり電圧スレッショルド。 | TS ピンのバイアス基準に対する割合 (103AT 使用時で $30^\circ\text{C}$ ), TS_TH4 = 0   | 55.00 | 55.50 | 56.00 | %  |

|                    |                                                                | TS ピンのバイアス基準に対する割合 (103AT 使用時で $32.5^\circ\text{C}$ ), TS_TH4 = 1 | 53.25 | 53.75 | 54.25 | %  |

|                    |                                                                | TS ピンのバイアス基準に対する割合 (103AT 使用時で $35^\circ\text{C}$ ), TS_TH4 = 2   | 51.50 | 52.00 | 52.50 | %  |

|                    |                                                                | TS ピンのバイアス基準に対する割合 (103AT 使用時で $37.5^\circ\text{C}$ ), TS_TH4 = 3 | 49.50 | 50.00 | 50.50 | %  |

| $V_{TS\_WARM}$     | TS_PREWARM から TS_WARM へ遷移する TH5 コンバレータ用 TS ピン立ち下がり電圧スレッショルド。   | TS ピンのバイアス基準に対する割合 (103AT 使用時で $42.5^\circ\text{C}$ ), TS_TH5 = 0 | 46.00 | 46.50 | 47.00 | %  |

|                    |                                                                | TS ピンのバイアス基準に対する割合 (103AT 使用時で $45^\circ\text{C}$ ), TS_TH5 = 1   | 44.25 | 44.75 | 45.25 | %  |

|                    |                                                                | TS ピンのバイアス基準に対する割合 (103AT 使用時で $47.5^\circ\text{C}$ ), TS_TH5 = 2 | 42.50 | 43.00 | 43.50 | %  |

|                    |                                                                | TS ピンのバイアス基準に対する割合 (103AT 使用時で $50^\circ\text{C}$ ), TS_TH5 = 3   | 40.75 | 41.25 | 41.75 | %  |

$V_{VBUS\_UVLOZ} < V_{VBUS} < V_{VBUS\_OVP}$ 、 $T_J = -40^\circ\text{C} \sim +125^\circ\text{C}$ 、標準値は  $T_J = 25^\circ\text{C}$  (特に記述がない限り)

| パラメータ                  |                                                              | テスト条件                                                                         | 最小値   | 標準値   | 最大値              | 単位  |

|------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------|-------|-------|------------------|-----|

| $V_{TS\_WARMZ}$        | TS_WARM から TS_PREWARM へ遷移する TH5 コンバレータ用 TS ピン立ち上がり電圧スレッショルド。 | TS ピンのバイアス基準に対する割合 (103AT 使用時で $40^\circ\text{C}$ )、 $TS\_TH5 = 0$            | 47.75 | 48.25 | 48.75            | %   |

|                        |                                                              | TS ピンのバイアス基準に対する割合 (103AT 使用時で $42.5^\circ\text{C}$ )、 $TS\_TH5 = 1$          | 46.00 | 46.50 | 47.00            | %   |

|                        |                                                              | TS ピンのバイアス基準に対する割合 (103AT 使用時で $45^\circ\text{C}$ )、 $TS\_TH5 = 2$            | 44.25 | 44.75 | 45.25            | %   |

|                        |                                                              | TS ピンのバイアス基準に対する割合 (103AT 使用時で $47.5^\circ\text{C}$ )、 $TS\_TH5 = 3$          | 42.50 | 43.00 | 43.50            | %   |

| $V_{TS\_HOT}$          | TS_WARM から TS_HOT に遷移する TH6 コンバレータ用 TS ピン立ち下がり電圧スレッショルド。     | TS ピンのバイアス基準に対する割合 (103AT 使用時で $55^\circ\text{C}$ )、 $TS\_TH6 = 0$            | 37.25 | 37.75 | 38.25            | %   |

|                        |                                                              | TS ピンのバイアス基準に対する割合 (103AT 使用時で $60^\circ\text{C}$ )、 $TS\_TH6 = 1$            | 34.00 | 34.50 | 35.00            | %   |

| $V_{TS\_HOTZ}$         | TS_HOT から TS_WARM に遷移する TH6 コンバレータ用 TS ピン立ち上がり電圧スレッショルド。     | TS ピンのバイアス基準に対する割合 (103AT 使用時で $52.5^\circ\text{C}$ )、 $TS\_TH6 = 0$          | 39.00 | 39.50 | 40.00            | %   |

|                        |                                                              | TS ピンのバイアス基準に対する割合 (103AT 使用時で $57.5^\circ\text{C}$ )、 $TS\_TH6 = 1$          | 35.75 | 36.25 | 36.75            | %   |

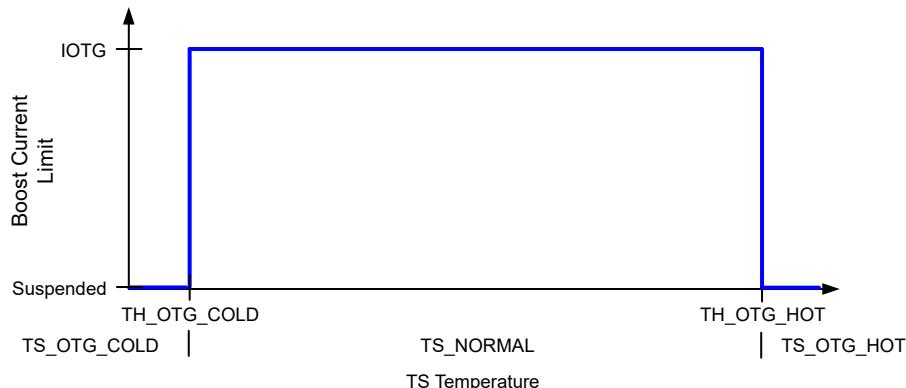

| サーミスタ コンバレータ (OTG モード) |                                                              |                                                                               |       |       |                  |     |

| $V_{TS\_OTG\_COLD}$    | TS_OTG_NORMAL から TS_OTG_COLD へ遷移する TS ピン立ち上がり電圧スレッショルド。      | TS ピンのバイアス基準に対する割合 (103AT 使用時で $-20^\circ\text{C}$ )、 $TS\_TH\_OTG\_COLD = 0$ | 79.50 | 80.00 | 80.50            | %   |

|                        |                                                              | TS ピンのバイアス基準に対する割合 (103AT 使用時で $-10^\circ\text{C}$ )、 $TS\_TH\_OTG\_COLD = 1$ | 76.50 | 77.00 | 77.50            | %   |

| $V_{TS\_OTG\_COLDZ}$   | TS_OTG_COLD から TS_OTG_NORMAL へ遷移する TS ピン立ち下がり電圧スレッショルド。      | TS ピンのバイアス基準に対する割合 (103AT 使用時で $-15^\circ\text{C}$ )、 $TS\_TH\_OTG\_COLD = 0$ | 78.00 | 78.50 | 79.00            | %   |

|                        |                                                              | TS ピンのバイアス基準に対する割合 (103AT 使用時で $-5^\circ\text{C}$ )、 $TS\_TH\_OTG\_COLD = 1$  | 74.75 | 75.25 | 75.75            | %   |

| $V_{TS\_OTG\_HOT}$     | TS_OTG_NORMAL から TS_OTG_HOT へ遷移する TS ピン立ち下がり電圧スレッショルド。       | TS ピンのバイアス基準に対する割合 (103AT 使用時で $55^\circ\text{C}$ )、 $TS\_OTG\_HOT = 00$      | 37.25 | 37.75 | 38.25            | %   |

|                        |                                                              | TS ピンのバイアス基準に対する割合 (103AT 使用時で $60^\circ\text{C}$ )、 $TS\_OTG\_HOT = 01$      | 34.00 | 34.50 | 35.00            | %   |

|                        |                                                              | TS ピンのバイアス基準に対する割合 (103AT 使用時で $65^\circ\text{C}$ )、 $TS\_OTG\_HOT = 10$      | 30.75 | 31.25 | 31.75            | %   |

| $V_{TS\_OTG\_HOTZ}$    | TS_OTG_HOT から TS_OTG_NORMAL へ遷移する TS ピン立ち上がり電圧スレッショルド。       | TS ピンのバイアス基準に対する割合 (103AT 使用時で $52.5^\circ\text{C}$ )、 $TS\_OTG\_HOT = 00$    | 39.00 | 39.50 | 40.00            | %   |

|                        |                                                              | TS ピンのバイアス基準に対する割合 (103AT 使用時で $57.5^\circ\text{C}$ )、 $TS\_OTG\_HOT = 01$    | 35.75 | 36.25 | 36.75            | %   |

|                        |                                                              | TS ピンのバイアス基準に対する割合 (103AT 使用時で $62.5^\circ\text{C}$ )、 $TS\_OTG\_HOT = 10$    | 32.50 | 33.00 | 33.50            | %   |

| スイッチング コンバータ           |                                                              |                                                                               |       |       |                  |     |

| $f_{SW}$               | PWM スイッチング周波数                                                | オシレータの周波数                                                                     | 1.35  | 1.5   | 1.65             | MHz |

| MOSFET オン抵抗            |                                                              |                                                                               |       |       |                  |     |

| $R_{Q1\_ON}$           | VBUS から PMID へのオン抵抗                                          | $T_J = -40^\circ\text{C} \sim 85^\circ\text{C}$ (標準値は $25^\circ\text{C}$ 未満)  | 15    | 20    | $\text{m}\Omega$ |     |

$V_{VBUS\_UVLOZ} < V_{VBUS} < V_{VBUS\_OVP}$ ,  $T_J = -40^\circ\text{C} \sim +125^\circ\text{C}$ , 標準値は  $T_J = 25^\circ\text{C}$  (特に記述がない限り)

| パラメータ                |                                                    | テスト条件                                                                                          | 最小値  | 標準値  | 最大値 | 単位               |

|----------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------|------|------|-----|------------------|

| $R_{Q2\_ON}$         | PMID と SW 間における降圧ハイサイド スイッチング MOSFET のオン抵抗         | $T_J = -40^\circ\text{C} \sim 85^\circ\text{C}$ (標準値は $25^\circ\text{C}$ 未満)                   |      | 20   | 27  | $\text{m}\Omega$ |

| $R_{Q3\_ON}$         | SW と PGND の間の降圧ローサイド スイッチング MOSFET のオン抵抗           | $T_J = -40^\circ\text{C} \sim 85^\circ\text{C}$ (標準値は $25^\circ\text{C}$ 未満)                   |      | 14   | 18  | $\text{m}\Omega$ |

| <b>OTG モード コンバータ</b> |                                                    |                                                                                                |      |      |     |                  |

| $V_{OTG\_RANGE}$     | 標準的な OTG モードの電圧レギュレーション範囲                          |                                                                                                |      | 3.84 | 9.6 | V                |

| $V_{OTG\_STEP}$      | 標準的な OTG モードの電圧レギュレーションステップ                        |                                                                                                |      | 20   |     | $\text{mV}$      |

| $V_{OTG\_ACC}$       | OTG モードの電圧レギュレーション精度                               | $\text{IVBUS} = 0\text{A}, V_{OTG} = 9\text{V}, T_J = -20^\circ\text{C} \sim 65^\circ\text{C}$ | -2   | 2    | %   |                  |

| $V_{OTG\_ACC}$       | OTG モードの電圧レギュレーション精度                               | $\text{IVBUS} = 0\text{A}, V_{OTG} = 5\text{V}, T_J = -20^\circ\text{C} \sim 65^\circ\text{C}$ | -3   | 3    | %   |                  |

| $I_{OTG\_RANGE}$     | 標準的な OTG モードの電流レギュレーション範囲                          |                                                                                                |      | 0.1  | 3.2 | A                |

| $I_{OTG\_STEP}$      | 標準的な OTG モードの電流レギュレーションステップ                        |                                                                                                |      | 10   |     | $\text{mA}$      |

| $I_{OTG\_ACC}$       | OTG モードの電流レギュレーション精度                               | $I_{OTG} = 1.8\text{A}, T_J = -20^\circ\text{C} \sim 65^\circ\text{C}$                         | -3.5 | 3.5  | %   |                  |

|                      |                                                    | $I_{OTG} = 1.5\text{A}, T_J = -20^\circ\text{C} \sim 65^\circ\text{C}$                         | -5   | 5    | %   |                  |

|                      |                                                    | $I_{OTG} = 1.0\text{A}, T_J = -20^\circ\text{C} \sim 65^\circ\text{C}$                         | -10  | 10   | %   |                  |

| $V_{OTG\_UVP}$       | PMID での OTG モードの低電圧立ち下がりスレッショルド                    |                                                                                                |      | 3.4  |     | V                |

| <b>REGN LDO</b>      |                                                    |                                                                                                |      |      |     |                  |

| $V_{REGN}$           | REGN LDO 出力電圧                                      | $V_{VBUS} = 5\text{V}, I_{REGN} = 20\text{mA}$                                                 | 4.4  | 4.6  |     | V                |

|                      |                                                    | $V_{VBUS} = 9\text{V}, I_{REGN} = 20\text{mA}$                                                 | 4.8  | 5.0  | 5.2 | V                |

| $V_{REGNZ\_OK}$      | REGN 不良判定の立ち下がりスレッショルド                             | コンバータがスイッチング                                                                                   | 3.2  |      |     | V                |

|                      |                                                    | コンバータのスイッチングなし                                                                                 | 2.3  |      |     | V                |

| $I_{REGN\_LIM}$      | REGN LDO 電流制限                                      | $V_{VBUS} = 5\text{V}, V_{REGN} = 4.3\text{V}$                                                 | 20   |      |     | $\text{mA}$      |

| <b>PG スレッショルド</b>    |                                                    |                                                                                                |      |      |     |                  |

| $PG\_TH$             | $\overline{PG}$ ピンのプルダウンを解放する VBUS 電圧立ち下がりスレッショルド  | $PG\_TH = 000\text{b}$                                                                         | 3.7  |      |     | V                |

|                      |                                                    | $PG\_TH = 001\text{b}$                                                                         | 7.4  |      |     | V                |

|                      |                                                    | $PG\_TH = 010\text{b}$                                                                         | 8.0  |      |     | V                |

|                      |                                                    | $PG\_TH = 011\text{b}$                                                                         | 10.4 |      |     | V                |

|                      |                                                    | $PG\_TH = 100\text{b}$                                                                         | 11.0 |      |     | V                |

|                      |                                                    | $PG\_TH = 101\text{b}$                                                                         | 13.4 |      |     | V                |

|                      |                                                    | $PG\_TH = 110\text{b}$                                                                         | 14.0 |      |     | V                |

| $PG\_THz$            | $\overline{PG}$ ピンのプルダウンを有効にする VBUS 電圧立ち上がりスレッショルド | $PG\_TH = 000\text{b}$                                                                         | 3.9  |      |     | V                |

|                      |                                                    | $PG\_TH = 001\text{b}$                                                                         | 7.9  |      |     | V                |

|                      |                                                    | $PG\_TH = 010\text{b}$                                                                         | 8.5  |      |     | V                |

|                      |                                                    | $PG\_TH = 011\text{b}$                                                                         | 10.9 |      |     | V                |

|                      |                                                    | $PG\_TH = 100\text{b}$                                                                         | 11.5 |      |     | V                |

|                      |                                                    | $PG\_TH = 101\text{b}$                                                                         | 13.9 |      |     | V                |

|                      |                                                    | $PG\_TH = 110\text{b}$                                                                         | 14.5 |      |     | V                |

| <b>ADC 測定の精度と性能</b>  |                                                    |                                                                                                |      |      |     |                  |

$V_{VBUS\_UVLOZ} < V_{VBUS} < V_{VBUS\_OVP}$ ,  $T_J = -40^\circ\text{C} \sim +125^\circ\text{C}$ , 標準値は  $T_J = 25^\circ\text{C}$  (特に記述がない限り)

| パラメータ                          |                                               | テスト条件                   | 最小値  | 標準値   | 最大値 | 単位  |

|--------------------------------|-----------------------------------------------|-------------------------|------|-------|-----|-----|

| $t_{ADC\_CONV}$                | 変換時間、各測定                                      | ADC_SAMPLE = 00         |      | 24    |     | ms  |

|                                |                                               | ADC_SAMPLE = 01         |      | 12    |     | ms  |

|                                |                                               | ADC_SAMPLE = 10         |      | 6     |     | ms  |

|                                |                                               | ADC_SAMPLE = 11         |      | 3     |     | ms  |

| ADC_RES                        | 有効分解能                                         | ADC_SAMPLE = 00         | 11   | 12    |     | ビット |

|                                |                                               | ADC_SAMPLE = 01         | 10   | 11    |     | ビット |

|                                |                                               | ADC_SAMPLE = 10         | 9    | 10    |     | ビット |

|                                |                                               | ADC_SAMPLE = 11         | 8    | 9     |     | ビット |

| $V_{BAT\_LOWV\_ADC}$           | アダプタが存在しない状態で ADC を動作させる最小バッテリ電圧、立ち上がりスレッショルド |                         |      | 2.7   |     | V   |

| $V_{BAT\_LOWV\_ADCZ}$          | アダプタが存在しない状態で ADC を動作させる最小バッテリ電圧、立ち下がりスレッショルド |                         |      | 2.5   |     | V   |

| <b>ADC の測定範囲と LSB</b>          |                                               |                         |      |       |     |     |

| IBUS_ADC                       | ADC バス電流の読み取り値 (順方向と OTG の両方)                 | 範囲                      | -5   | 5     | A   |     |

|                                |                                               | LSB                     |      | 2.5   |     | mA  |

| VBUS_ADC                       | ADC VBUS 電圧の読み取り値                             | 範囲                      | 0    | 20    | V   |     |

|                                |                                               | LSB                     |      | 5     |     | mV  |

| VPMID_ADC                      | ADC PMID 電圧の読み取り値                             | 範囲                      | 0    | 20    | V   |     |

|                                |                                               | LSB                     |      | 5     |     | mV  |

| VBAT_ADC                       | ADC BAT 電圧の読み取り値                              | 範囲                      | 0    | 5     | V   |     |

|                                |                                               | LSB                     |      | 1.25  |     | mV  |

| VBAT_ADC                       | ADC BAT 電圧の読み取り精度                             | 4V での精度、ADC_SAMPLE = 00 | -0.5 | 0.5   | %   |     |

| CC1_ADC                        | CC1 電圧の読み取り値                                  | 範囲                      | 0    | 5     | V   |     |

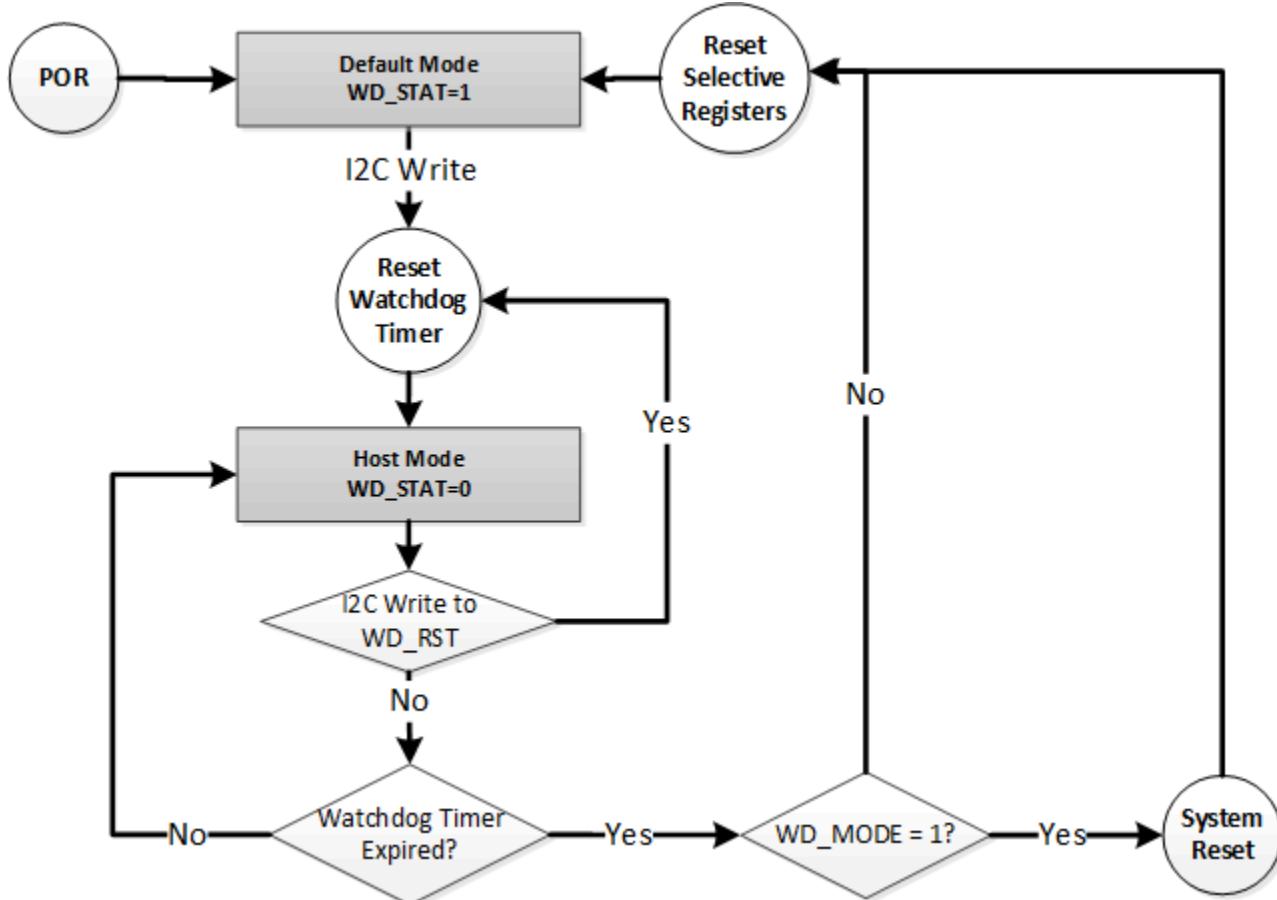

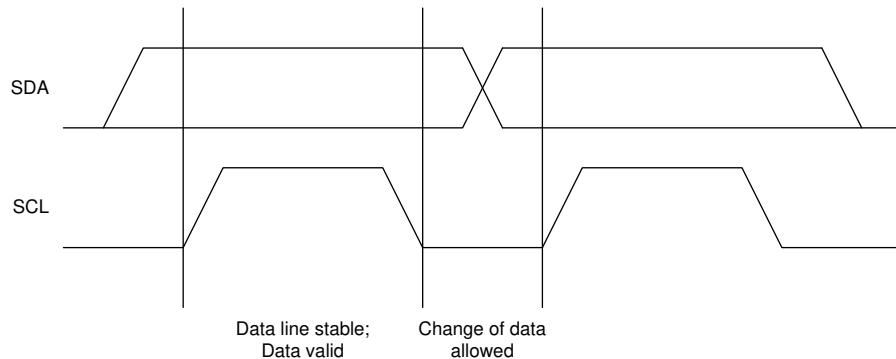

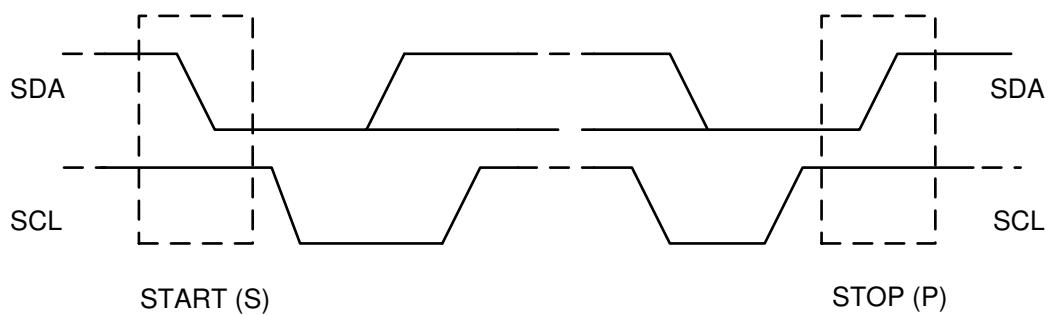

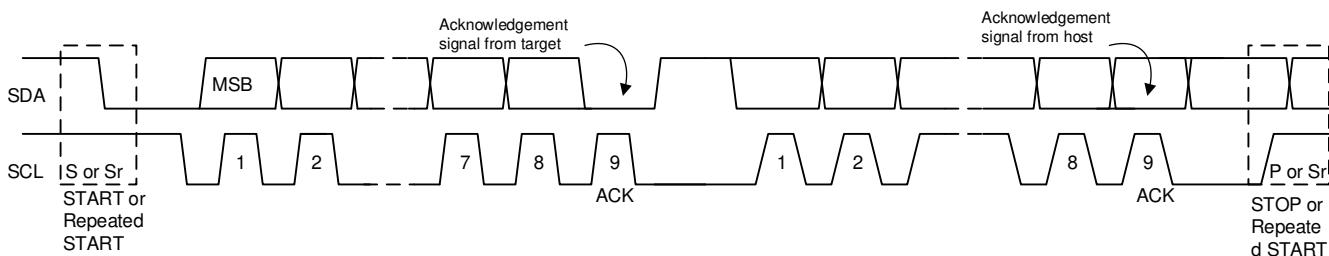

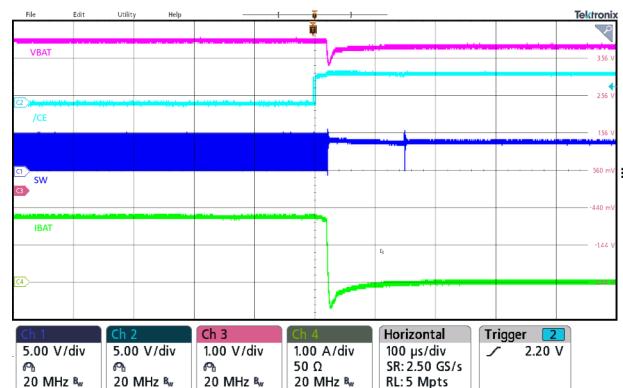

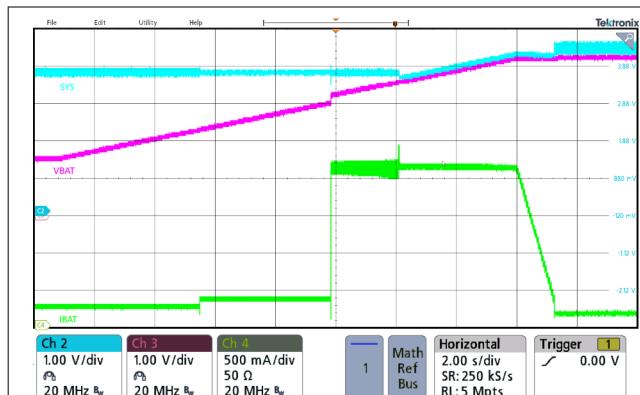

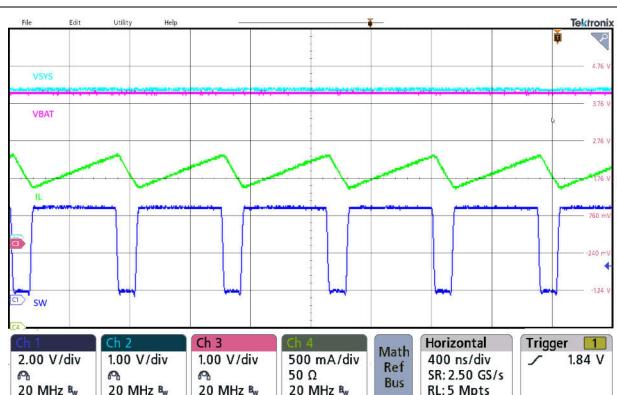

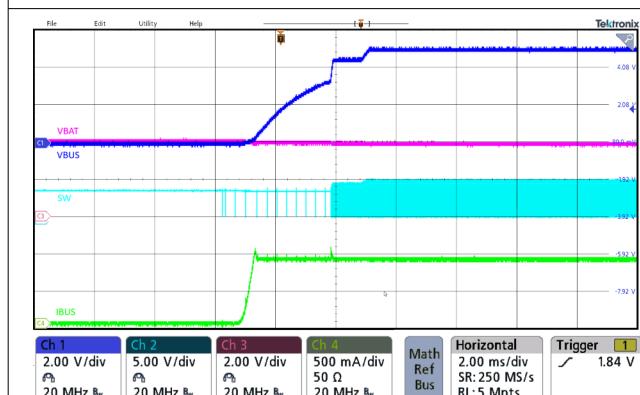

|                                |                                               | LSB                     |      | 1.25  |     | mV  |