# **CDCE949-Q1 : プログラマブル 4-PLL VCXO クロック シンセサイザ 1.8V、2.5V、 3.3V LVC MOS 出力**

## 1 特長

- 車載アプリケーション用に認定済み

- プログラマブル クロック ジェネレータ ファミリ製品

- CDCE913/CDCEL913: 1 PLL、3 出力

- CDCE925/CDCEL925: 2 PLL、5 出力

- CDCE937/CDCEL937: 3 PLL、7 出力

- **CDCE949: 4 PLL、9 出力**

- システム内プログラミングおよび EEPROM

- シリアル プログラミングが可能な揮発性レジスタ

- 不揮発性 EEPROM に顧客設定を保存

- 非常に柔軟なクロックドライバ

- 3 つのユーザ定義可能な制御入力 [S0/S1/S2] を、SSC 選択、周波数切り替え、出力イネーブル、電源オフなどに使用可能

- ビデオ、オーディオ、USB、IEEE1394、RFID 用の高精度クロックを生成し、TI DaVinci™、OMAP™、DSP を使用して使用する共通クロック周波数を生成します

- Bluetooth™、WLAN、イーサネット、および GPS です

- SSC 変調をプログラム可能

- 0ppm クロック生成が可能

- 出力周波数を最高 230MHz まで選択可能

- 柔軟な入力クロック設定

- 外部水晶振動子: 8MHz ~ 32MHz

- オンチップ VCXO: 引き込み範囲: ±150ppm

- シングルエンドの LVC MOS: 最高 160MHz

- 低ノイズの PLL コア

- PLL ループ フィルタコンポーネントを内蔵

- 非常に短いジッタ時間 (標準値 60ps)

- 独立した出力供給ピン

- 3.3V および 2.5V

- 1.8V デバイス電源

- JESD 78、Class I 準拠で 100mA のラッチアップ性能

- 広い温度範囲: -40°C ~ 125°C

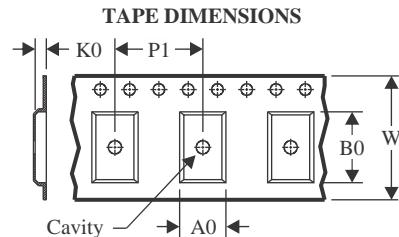

- TSSOP パッケージ

- 開発およびプログラミング キットにより PLL の設計およびプログラムが容易 (TI ClockPro)

## 2 アプリケーション

- セットトップ ボックス (STB)、ハイビジョン テレビ (HDTV)、プリンタ、DVD プレーヤー、DVD レコーダー

## 3 説明

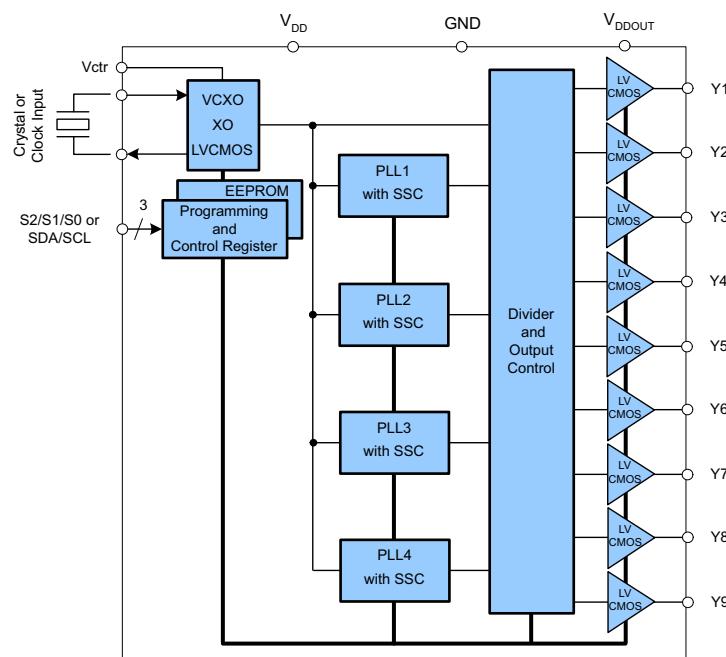

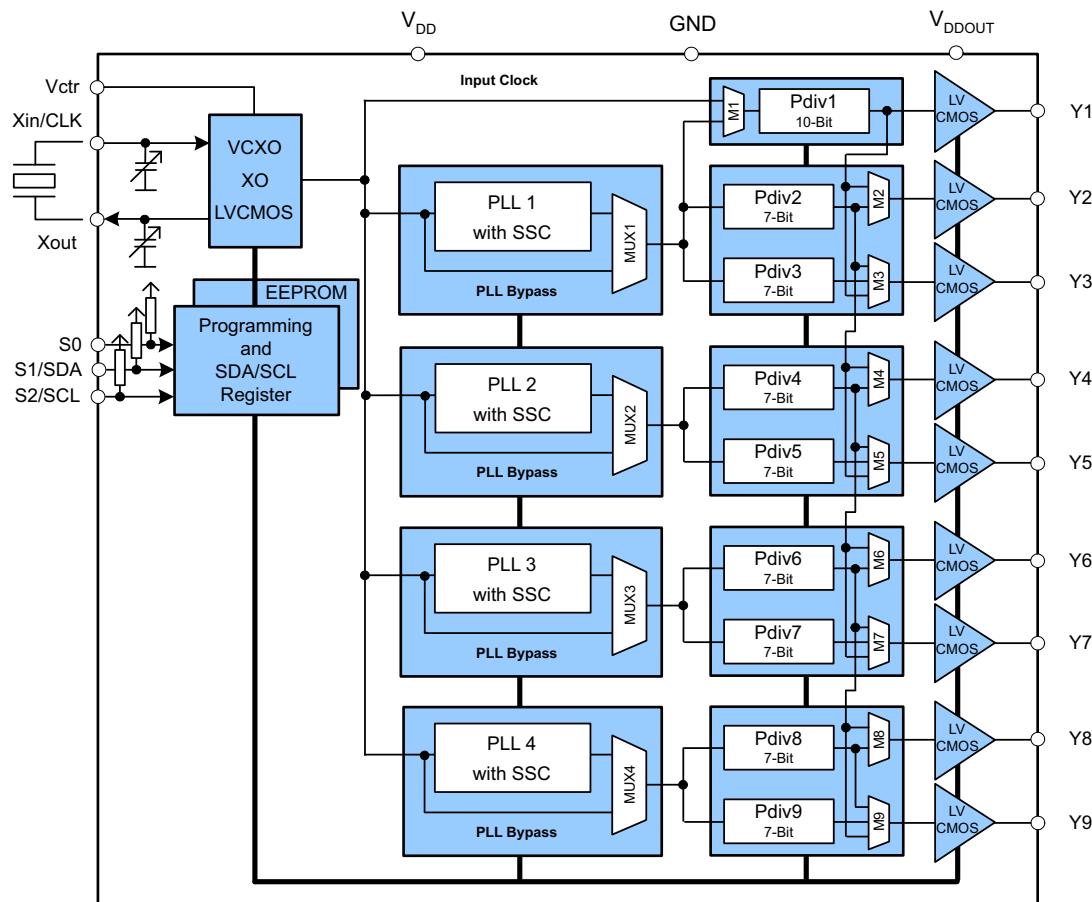

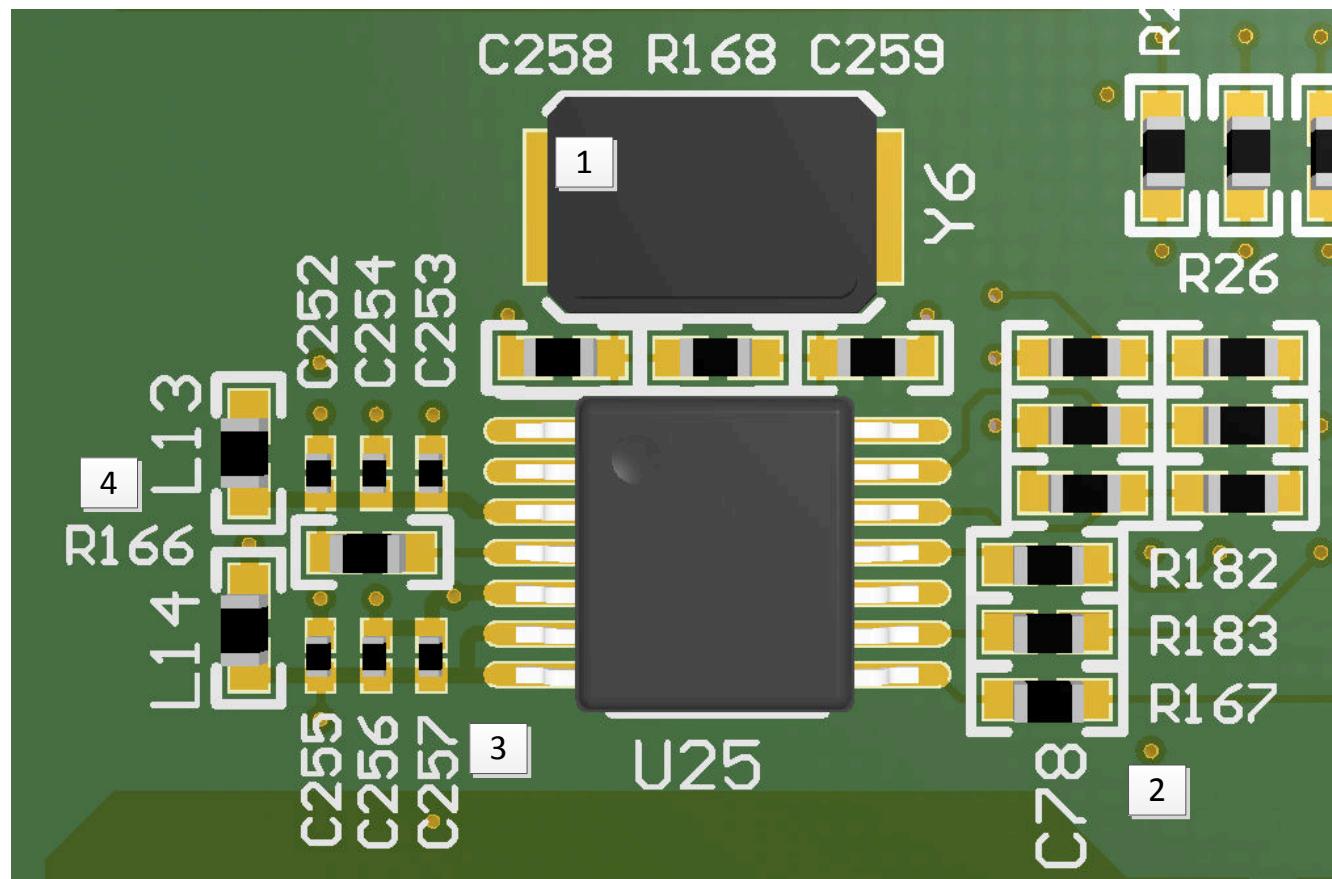

CDCE949-Q1 は、モジュラー PLL ベースの低コストで高性能なプログラマブル クロック シンセサイザ、マルチプライヤ、およびディバイダです。これらのデバイスは、単一の入力周波数から最大 9 個の出力クロックを生成します。それぞれの出力は、最大 4 つの個別に設定可能な PLL を使用し、システム内で最高 230MHz まで、どのような周波数にでもプログラムできます。

CDCE949-Q1 には 2.5V ~ 3.3V の独立した出力電源ピン  $V_{DDOUT}$  があります。

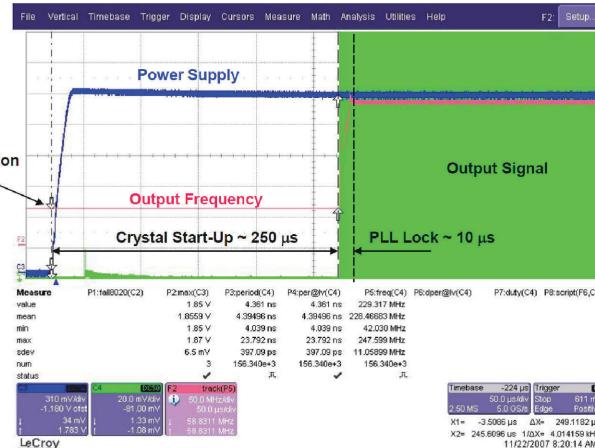

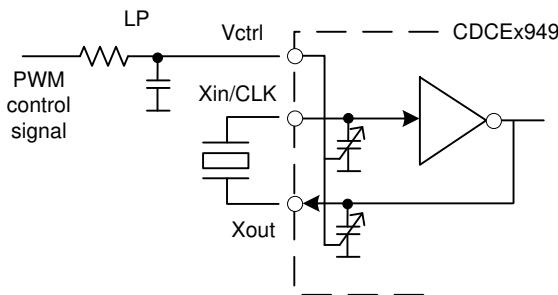

入力には外付けの水晶振動子、または LVC MOS クロック信号を接続できます。外付けの水晶振動子を使用する場合、ほとんどのアプリケーションではオンチップの負荷コンデンサだけで十分です。負荷コンデンサの値は、0 ~ 20pF の範囲でプログラム可能です。さらに、オンチップの VCXO を選択でき、出力周波数と外部の制御信号、すなわち PWM 信号とを同期できます。

大きな M/N 分周比により、ゼロ ppm のオーディオまたはビデオ、ネットワーク (WLAN、BlueTooth™、イーサネット、GPS)、またはインターフェイス (USB、IEEE1394、メモリスティック) の 0ppm のクロックを、たとえば 27MHz の基準入力周波数から生成できます。

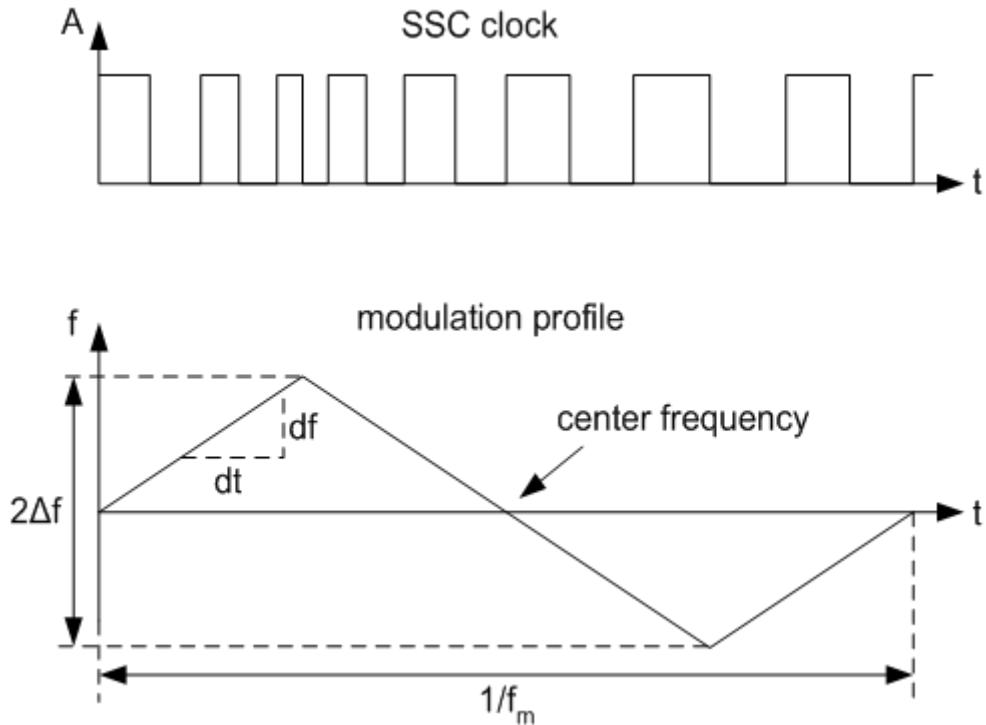

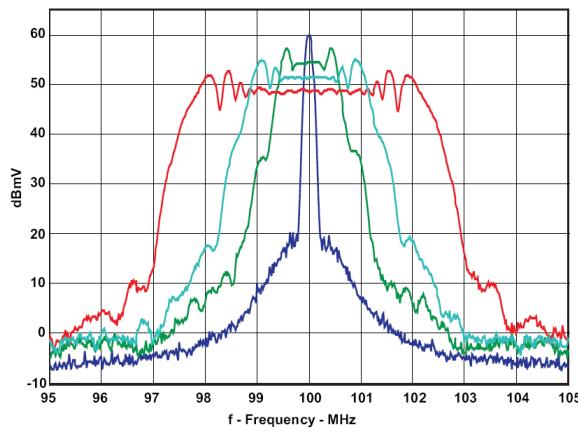

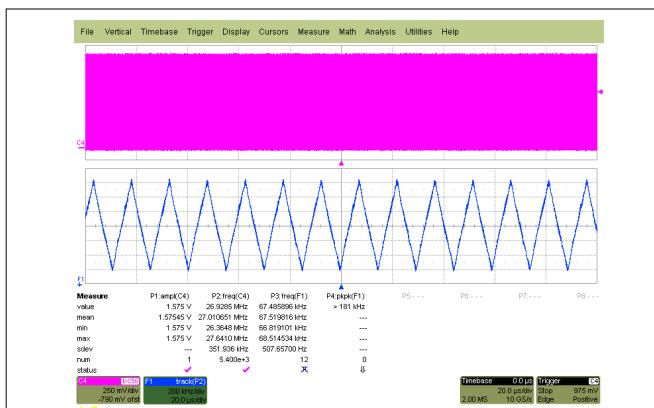

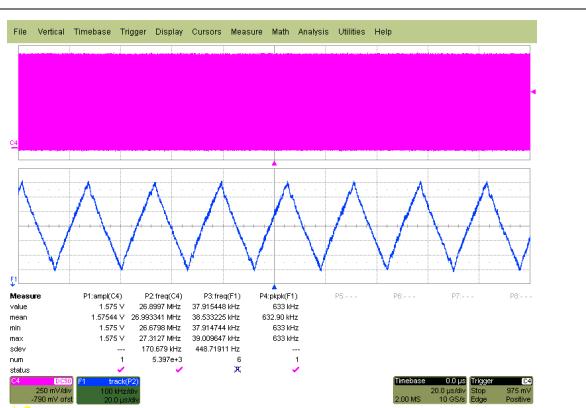

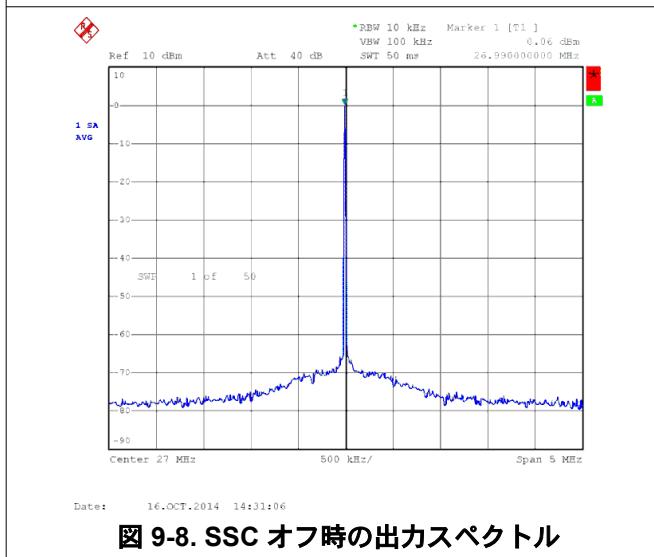

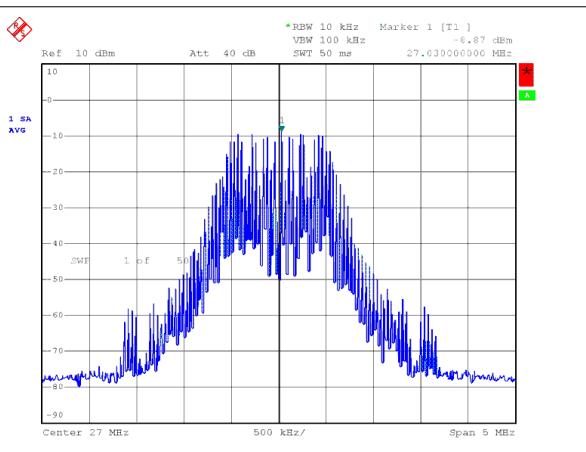

すべての PLL は SCC (拡散スペクトラム クロッキング) をサポートします。センタースプレッドおよびダウンスプレッドクロッキングの SSC を使用できます。この技法は、電磁気的干渉 (EMI) を低減するために一般的です。

PLL 周波数と分周値の設定に基づいて内部のループ フィルタコンポーネントを自動的に調整することにより、高い安定性を実現し、各 PLL のジッタ伝達特性を最適化します。

このデバイスは不揮発性 EEPROM プログラミングをサポートしており、アプリケーションに合わせて簡単にカスタマイズできます。CDCE949-Q1 は、工場出荷時にあらかじめデフォルト設定済みです (「デフォルトのデバイス構成」セクションを参照)。各種のアプリケーション構成に応じて PCB 組み立て前に再プログラム可能したり、システム内プログラムにより再プログラムしたりできます。すべてのデバイス設定は、2 線式シリアル インターフェイスの SDA/SCL バスでプログラムできます。

3 つのプログラム可能な制御入力 S0、S1、S2 を使用して、周波数の選択、SSC パラメータの変更による EMI の低減、PLL バイパス、電源オフ、出力ディセーブル機能と

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

して low レベルと TRI-STATE のどちらを選択するかなど、動作のさまざまな要因を制御できます。

CDCE949-Q1 は 1.8V 環境で動作します。このデバイスは、-40°C~125°C の温度範囲で動作します。

**表 3-1. パッケージ情報**

| デバイス       | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|------------|----------------------|--------------------------|

| CDCE949-Q1 | PW (TSSOP, 24)       | 7.8mm × 6.4mm            |

(1) 詳細については、[セクション 12](#) を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンを含みます。

## 目次

|                           |    |                         |    |

|---------------------------|----|-------------------------|----|

| 1 特長                      | 1  | 7.4 デバイスの機能モード          | 17 |

| 2 アプリケーション                | 1  | 7.5 プログラミング             | 19 |

| 3 説明                      | 1  | 8 レジスタ マップ              | 20 |

| 4 ピンの機能                   | 4  | 8.1 SDA および SCL レジスタ    | 20 |

| 5 仕様                      | 5  | 8.2 構成レジスタ              | 20 |

| 5.1 絶対最大定格                | 5  | 9 アプリケーションと実装           | 29 |

| 5.2 ESD 定格                | 5  | 9.1 アプリケーション情報          | 29 |

| 5.3 熱抵抗特性                 | 5  | 9.2 代表的なアプリケーション        | 29 |

| 5.4 推奨動作条件                | 6  | 9.3 電源に関する推奨事項          | 33 |

| 5.5 推奨される Crystal/VCXO 仕様 | 6  | 9.4 レイアウト               | 33 |

| 5.6 EEPROM 仕様             | 6  | 10 デバイスおよびドキュメントのサポート   | 35 |

| 5.7 電気的特性                 | 7  | 10.1 ドキュメントのサポート        | 35 |

| 5.8 タイミング要件               | 8  | 10.2 ドキュメントの更新通知を受け取る方法 | 35 |

| 5.9 タイミング図                | 9  | 10.3 サポート・リソース          | 35 |

| 5.10 代表的特性                | 10 | 10.4 商標                 | 35 |

| 6 パラメータ測定情報               | 11 | 10.5 静電気放電に関する注意事項      | 35 |

| 7 詳細説明                    | 12 | 10.6 用語集                | 35 |

| 7.1 概要                    | 12 | 11 改訂履歴                 | 36 |

| 7.2 機能ブロック図               | 13 | 12 メカニカル、パッケージ、および注文情報  | 36 |

| 7.3 機能説明                  | 13 |                         |    |

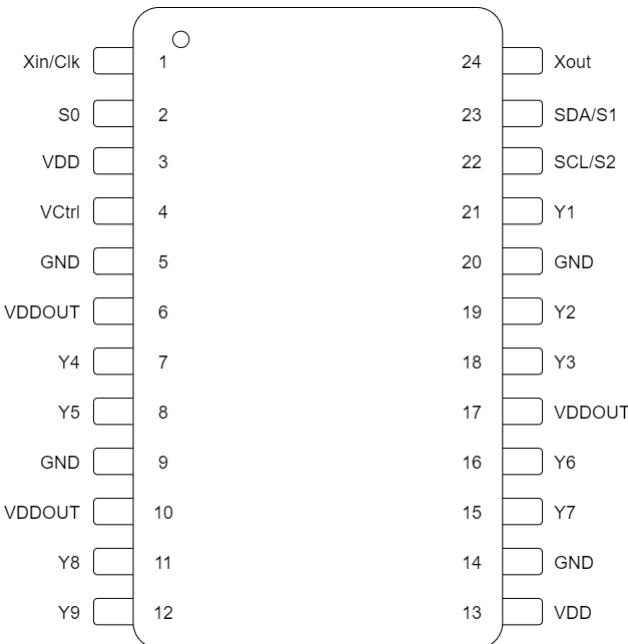

## 4 ピンの機能

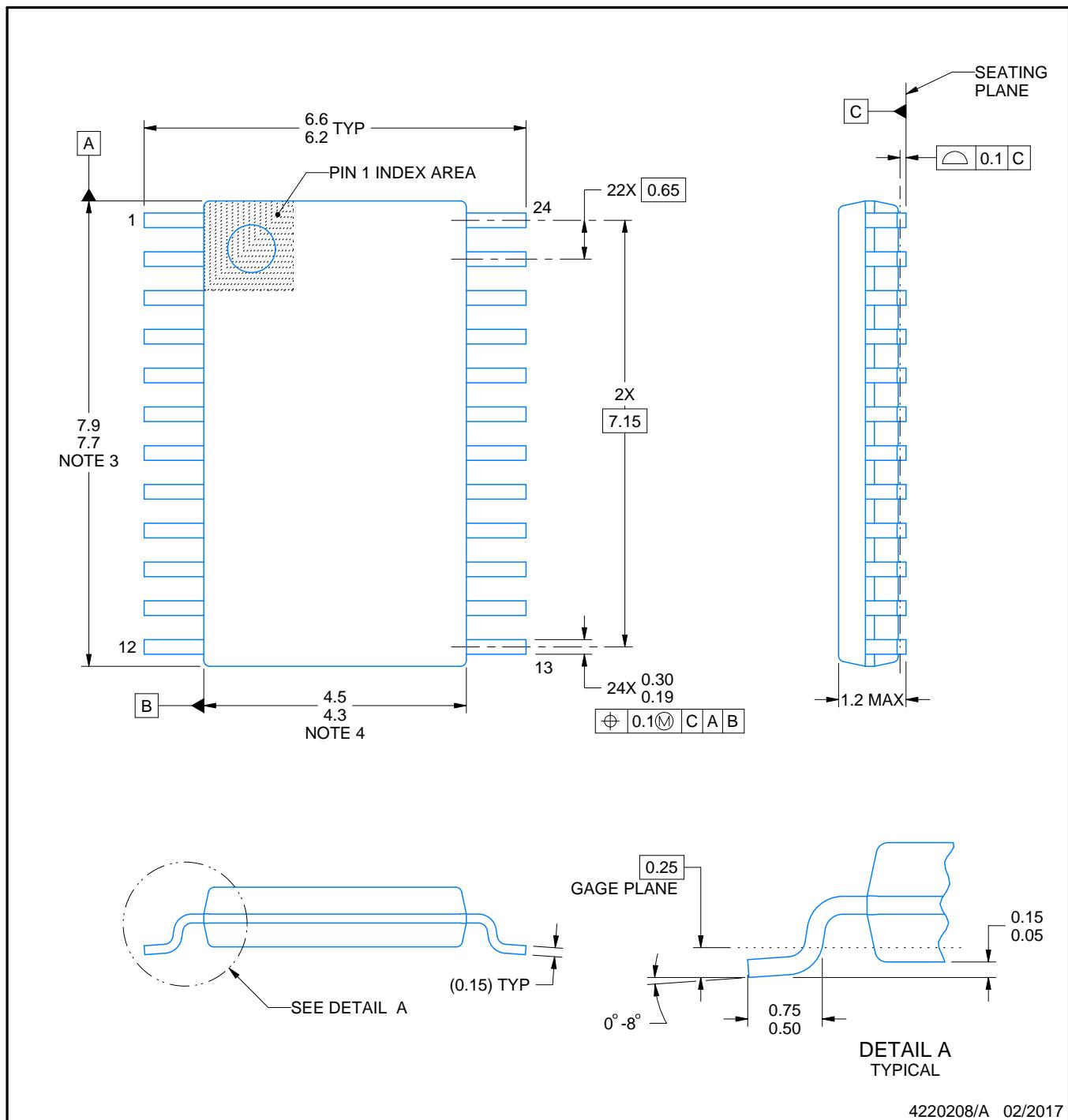

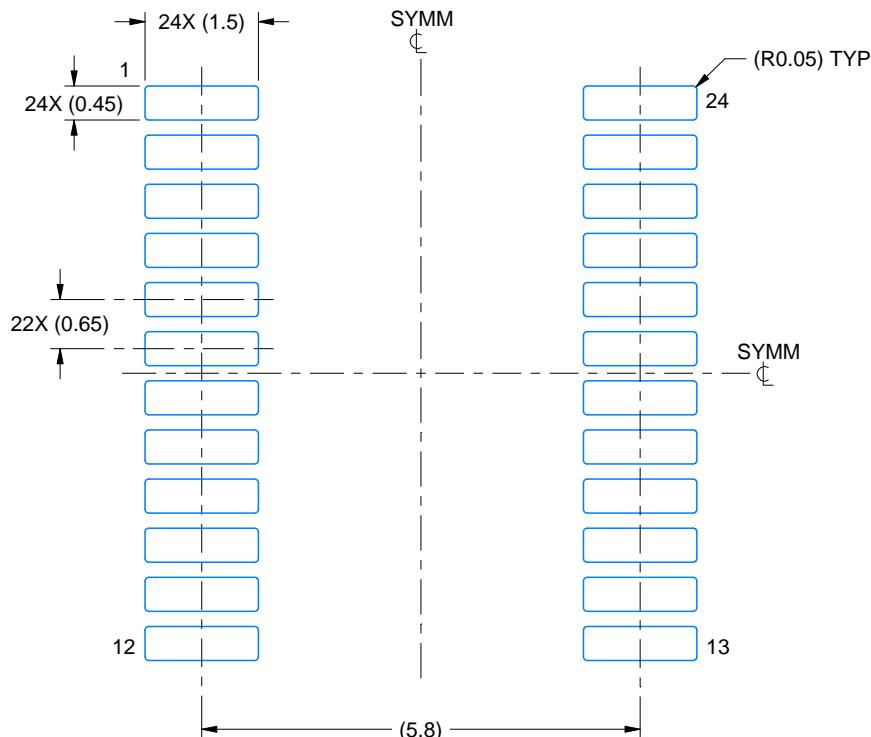

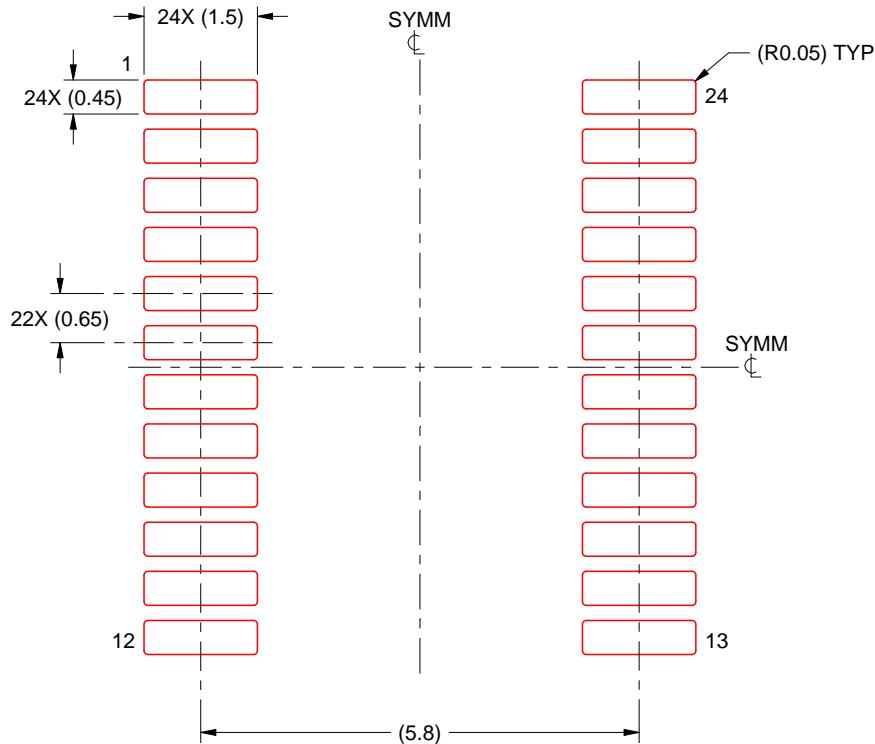

図 4-1. PW パッケージ 24 ピン TSSOP 上面図

表 4-1. ピンの機能

| 端子                 | 番号        | タイプ <sup>(1)</sup> | 説明                                                                                                                          |

|--------------------|-----------|--------------------|-----------------------------------------------------------------------------------------------------------------------------|

| GND                | 5、9、14、20 | G                  | グランド                                                                                                                        |

| S0                 | 2         | I                  | ユーザーがプログラム可能な制御入力 S0、LVC MOS 入力、内部プルアップ 500kΩ                                                                               |

| SCL/S2             | 22        | I                  | <b>SCL:</b> シリアル クロック入力 (デフォルト構成)、LVC MOS、内部プルアップ 500kΩ、または<br><b>S2:</b> ユーザーがプログラム可能な制御入力、LVC MOS 入力、内部プルアップ 500kΩ        |

| SDA/S1             | 23        | I/O, I             | <b>SDA:</b> 双方向シリアル データ入出力 (デフォルト構成)、LVC MOS、内部プルアップ 500kΩ、ま<br>たは<br><b>S1:</b> ユーザーがプログラム可能な制御入力、LVC MOS 入力、内部プルアップ 500kΩ |

| V <sub>Ctrl</sub>  | 4         | I                  | VCXO 制御電圧 (未使用時はオープンまたはプルアップのままにする)                                                                                         |

| V <sub>DD</sub>    | 3、13      | P                  | デバイスの 1.8V 電源                                                                                                               |

| V <sub>DDOUT</sub> | 6、10、17   | P                  | すべての出力の 3.3V または 2.5V 電源                                                                                                    |

| Y1                 | 21        | O                  | LVC MOS 出力                                                                                                                  |

| Y2                 | 19        | O                  |                                                                                                                             |

| Y3                 | 18        | O                  |                                                                                                                             |

| Y4                 | 7         | O                  |                                                                                                                             |

| Y5                 | 8         | O                  |                                                                                                                             |

| Y6                 | 16        | O                  |                                                                                                                             |

| Y7                 | 15        | O                  |                                                                                                                             |

| Y8                 | 11        | O                  |                                                                                                                             |

| Y9                 | 12        | O                  |                                                                                                                             |

| Xin/CLK            | 1         | I                  | 水晶発振器入力または LVC MOS クロック入力 (SDA/SCL バスで選択可能)                                                                                 |

| Xout               | 24        | O                  | 水晶発振器出力 (未使用時はオープンまたはプルアップのままにします)                                                                                          |

(1) I = 入力、O = 出力、P = 電源、G = グランド

## 5 仕様

### 5.1 絶対最大定格

自由空気での動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|           |                                  | 値                        | 単位 |

|-----------|----------------------------------|--------------------------|----|

| $V_{DD}$  | 電源電圧範囲                           | -0.5~2.5                 | V  |

| $V_I$     | 入力電圧範囲 <sup>(2) (3)</sup>        | -0.5 ~ $V_{DD} + 0.5$    | V  |

| $V_O$     | 出力電圧範囲 <sup>(2)</sup>            | -0.5 ~ $V_{DDOUT} + 0.5$ | V  |

| $I_I$     | 入力電流 ( $V_I < 0, V_I > V_{DD}$ ) | 20                       | mA |

| $I_O$     | 連続出力電流                           | 50                       | mA |

| $T_{stg}$ | 保管温度範囲                           | -65~150                  | °C |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。絶対最大定格は、これらの条件において、または推奨動作条件に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用した場合、本デバイスは完全に機能するとは限らず、このことが本デバイスの信頼性、機能、性能に影響を及ぼし、本デバイスの寿命を縮める可能性があります。

- (2) 入力と出力のクランプ電流の定格を順守しても、入力と出力の負電圧の定格を超えることができます。

- (3) SDA と SCL は、「推奨動作条件」の表に記載されているように、最大 3.6V まで動作できます。

### 5.2 ESD 定格

|             |                                                | 値          | 単位 |

|-------------|------------------------------------------------|------------|----|

| $V_{(ESD)}$ | 人体モデル (HBM)、AEC Q100-002 準拠 <sup>(1)</sup>     | $\pm 2000$ | V  |

|             | デバイス帶電モデル (CDM)、AEC Q100-011 準拠 <sup>(2)</sup> | $\pm 1000$ |    |

- (1) AEC Q100-002 は、HBM ストレス試験を ANSI / ESDA / JEDEC JS-001 仕様に従って実施しなければならないと規定しています。

- (2) コーナー ピンのデバイス帶電モデルの ESD 定格は 750V です。

### 5.3 热抵抗特性

| パラメータ <sup>(1)</sup> |              | 気流<br>(lfm) | °C/W |

|----------------------|--------------|-------------|------|

| $\theta_{JA}$        | 熱抵抗、接合部-周囲間  | 0           | 91   |

|                      |              | 150         | 75   |

|                      |              | 200         | 74   |

|                      |              | 250         | 73   |

|                      |              | 500         | 65   |

| $\theta_{JC}$        | 熱抵抗、接合部-ケース間 | —           | 27   |

| $\theta_{JB}$        | 熱抵抗、接合部-基板間  | —           | 52   |

| $R_{\theta JT}$      | 熱抵抗、接合部-上面間  | —           | 0.5  |

| $R_{\theta JB}$      | 熱抵抗、接合部-底面間  | —           | 50   |

- (1) パッケージの熱インピーダンスは、JESD 51 および JEDEC2S2P (high-k 基板) に従って計算しています。

## 5.4 推奨動作条件

|                                   |                      | 最小値                                       | 公称値                   | 最大値 | 単位 |

|-----------------------------------|----------------------|-------------------------------------------|-----------------------|-----|----|

| V <sub>DD</sub>                   | デバイス電源電圧             | 1.7                                       | 1.8                   | 1.9 | V  |

| V <sub>DD(OUT)</sub>              | 出力 Yx 電源電圧           | 2.3                                       |                       | 3.6 | V  |

| V <sub>IL</sub>                   | Low レベル入力電圧 LVC MOS  |                                           | 0.3 × V <sub>DD</sub> |     | V  |

| V <sub>IH</sub>                   | High レベル入力電圧 LVC MOS | 0.7 × V <sub>DD</sub>                     |                       |     | V  |

| V <sub>I(thresh)</sub>            | 入力電圧スレッショルド LVC MOS  | 0.5 × V <sub>DD</sub>                     |                       |     | V  |

| V <sub>IS</sub>                   | 入力電圧範囲 S0            | 0                                         | 1.9                   |     | V  |

|                                   | 入力電圧範囲 S1、S2、SDA、SCL | V <sub>Ithresh</sub> = 0.5V <sub>DD</sub> | 0                     | 3.6 |    |

| V <sub>ICLK</sub>                 | 入力電圧範囲 VCLK          | 0                                         | 1.9                   |     | V  |

| I <sub>OH</sub> / I <sub>OL</sub> | 出力電流                 | V <sub>DDout</sub> = 3.3V                 |                       | ±12 | mA |

|                                   |                      | V <sub>DDout</sub> = 2.5V                 |                       | ±10 | mA |

|                                   |                      | V <sub>DDout</sub> = 1.8V                 |                       | ±8  | mA |

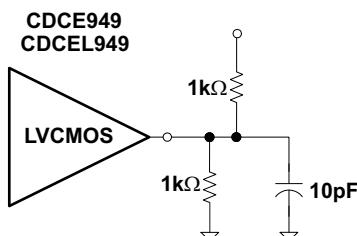

| C <sub>L</sub>                    | 出力負荷 LVC MOS         |                                           | 10                    |     | pF |

| T <sub>J</sub>                    | 動作時接合部温度             | -40                                       | 125                   |     | °C |

## 5.5 推奨される Crystal/VCXO 仕様

|                                |                                                           | 最小値  | 公称値             | 最大値 | 単位  |

|--------------------------------|-----------------------------------------------------------|------|-----------------|-----|-----|

| f <sub>Xtal</sub>              | 水晶振動子の入力周波数範囲 (基本波モード) <sup>(1)</sup>                     | 8    | 27              | 32  | MHz |

| ESR                            | 等価直列抵抗                                                    |      |                 | 100 | Ω   |

| f <sub>PR</sub>                | 引き込み範囲 (0V ≤ Vctrl <sub>Ctrl</sub> ≤ 1.8V) <sup>(2)</sup> | ±120 | ±150            |     | ppm |

| V <sub>(Ctrl)</sub>            | 周波数制御電圧                                                   | 0    | V <sub>DD</sub> |     | V   |

| C <sub>0</sub> /C <sub>1</sub> | プル能力比率                                                    |      | 220             |     |     |

| C <sub>L</sub>                 | XIN と XOUT のオンチップ負荷容量                                     | 0    | 20              |     | pF  |

- (1) VCXO の構成と水晶振動子に関する推奨事項の詳細については、『CDCE (L) 9xx ファミリの VCXO アプリケーション ガイドライン』アプリケーション ノートを参照してください。

- (2) 引き込み範囲は、水晶振動子のタイプ、オンチップの水晶振動子の負荷容量、PCB の浮遊容量によって異なります。±120ppm の範囲は、『CDCE (L) 9xx ファミリの VCXO アプリケーション ガイドライン』アプリケーション ノートに記載されている水晶振動子に適用されます。

## 5.6 EEPROM 仕様

|       |                             | 最小値  | 標準値 | 最大値 | 単位   |

|-------|-----------------------------|------|-----|-----|------|

| EEcyc | EEPROM の EEcyc プログラミング サイクル | 1000 |     |     | サイクル |

| EEret | EEret データ保持                 | 10   |     |     | 年    |

## 5.7 電気的特性

(特に注記のない限り) 接合の推奨動作温度範囲以上

| パラメータ                                                     |                                        | テスト条件                                                 | 最小値          | 標準値<br><sup>(1)</sup> | 最大値  | 単位      |

|-----------------------------------------------------------|----------------------------------------|-------------------------------------------------------|--------------|-----------------------|------|---------|

| <b>全般的なパラメータ</b>                                          |                                        |                                                       |              |                       |      |         |

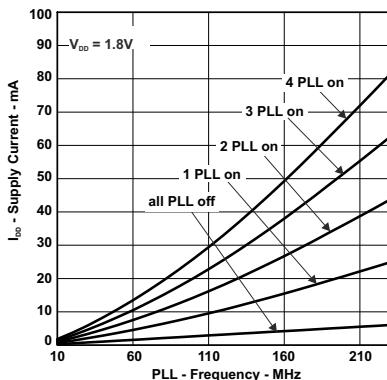

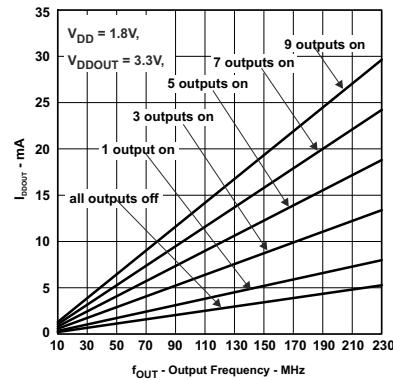

| $I_{DD}$                                                  | 消費電流 (図 5-2 を参照)                       | すべての出力がオフ、 $f_{CLK} = 27MHz$ , $f_{VCO} = 135MHz$     | すべての PLL がオン | 38                    | mA   |         |

|                                                           |                                        | PLL ごと                                                |              | 9                     |      |         |

| $I_{DD(OUT)}$                                             | 消費電流 (図 5-3 を参照)                       | 無負荷、すべての出力がオン、 $f_{OUT} = 27MHz$ , $V_{DDOUT} = 3.3V$ |              | 4                     |      | mA      |

| $I_{DD(PD)}$                                              | パワー ダウン電流。SDA/SCL を除くすべての回路はパワードウンします。 | $f_{IN} = 0MHz$ , $V_{DD} = 1.9V$                     |              | 50                    |      | $\mu A$ |

| $V_{(PUC)}$                                               | 電源オン制御回路の電源電圧 $V_{DD}$ スレッショルド         |                                                       |              | 0.85                  | 1.45 | V       |

| $f_{VCO}$                                                 | PLL の VCO 周波数範囲                        |                                                       |              | 80                    | 230  | MHz     |

| $f_{OUT}$                                                 | LVC MOS 出力周波数                          |                                                       |              | 230                   |      | MHz     |

| <b>LVC MOS パラメータ</b>                                      |                                        |                                                       |              |                       |      |         |

| $V_{IK}$                                                  | LVC MOS 入力電圧                           | $V_{DD} = 1.7V$ , $I_I = -18mA$                       |              | -1.2                  |      | V       |

| $I_I$                                                     | LVC MOS 入力電流                           | $V_I = 0V$ または $V_{DD}, V_{DD} = 1.9V$                |              | $\pm 5$               |      | $\mu A$ |

| $I_{IH}$                                                  | S0/S1/S2 の LVC MOS 入力電流                | $V_I = V_{DD}, V_{DD} = 1.9V$                         |              | 5                     |      | $\mu A$ |

| $I_{IL}$                                                  | S0/S1/S2 の LVC MOS 入力電流                | $V_I = 0V, V_{DD} = 1.9V$                             |              | -4                    |      | $\mu A$ |

| $C_I$                                                     | Xin/clk での入力容量                         | $V_{ICLK} = 0V$ 、または $V_{DD}$                         |              | 6                     | pF   |         |

|                                                           | Xout の入力容量                             | $V_{IXout} = 0V$ または $V_{DD}$                         |              | 2                     |      |         |

|                                                           | S0, S1, S2 での入力キャパシタンス                 | $V_{IN} = 0V$ または $V_{DD}$                            |              | 3                     |      |         |

| <b><math>V_{DDOUT} = 3.3V</math> – モードの LVC MOS パラメータ</b> |                                        |                                                       |              |                       |      |         |

| $V_{OH}$                                                  | LVC MOS high レベル出力電圧                   | $V_{DDOUT} = 3V, I_{OH} = -0.1mA$                     | 2.9          | V                     |      |         |

|                                                           |                                        | $V_{DDOUT} = 3V, I_{OH} = -8mA$                       | 2.4          |                       |      |         |

|                                                           |                                        | $V_{DDOUT} = 3V, I_{OH} = -12mA$                      | 2.2          |                       |      |         |

| $V_{OL}$                                                  | LVC MOS low レベル出力電圧                    | $V_{DDOUT} = 3V, I_{OL} = 0.1mA$                      | 0.1          | V                     |      |         |

|                                                           |                                        | $V_{DDOUT} = 3V, I_{OL} = 8mA$                        | 0.5          |                       |      |         |

|                                                           |                                        | $V_{DDOUT} = 3V, I_{OL} = 12mA$                       | 0.8          |                       |      |         |

| $t_{PLH}, t_{PHL}$                                        | 伝搬遅延                                   | PLL バイパス                                              | 3.2          |                       | ns   |         |

| $t_r/t_f$                                                 | 立ち上がりおよび立ち下がり時間                        | $V_{DDOUT} = 3.3V$ (20% ~ 80%)                        | 0.6          |                       | ns   |         |

| $t_{jilt(cc)}$                                            | サイクル間ジッタ <sup>(2) (3)</sup>            | 1 個の PLL スイッチング、Y2 から Y3 へ                            | 60           | 90                    | ps   |         |

|                                                           |                                        | 4 個の PLL スイッチング、Y2 から Y9 へ                            | 120          | 170                   |      |         |

| $t_{jilt(per)}$                                           | ピーク ツー ピーク周期ジッタ <sup>(2) (3)</sup>     | 1 個の PLL スイッチング、Y2 から Y3 へ                            | 70           | 100                   | ps   |         |

|                                                           |                                        | 4 個の PLL スイッチング、Y2 から Y9 へ                            | 130          | 180                   |      |         |

| $t_{sk(o)}$                                               | 出力スキュー <sup>(4)</sup>                  | $f_{OUT} = 50MHz, Y1 から Y3$                           |              | 60                    | ps   |         |

|                                                           |                                        | $f_{OUT} = 50MHz, Y2 から Y5$ または $Y6$ から $Y9$          |              | 160                   |      |         |

| $odc$                                                     | 出力デューティ サイクル <sup>(5)</sup>            | $f_{VCO} = 100MHz, Pdiv = 1$                          | 45           | 55                    | %    |         |

## 5.7 電気的特性 (続き)

(特に注記のない限り) 接合の推奨動作温度範囲以上

| パラメータ                                                |                                    | テスト条件                                                     | 最小値                | 標準値<br><sup>(1)</sup> | 最大値 | 単位 |

|------------------------------------------------------|------------------------------------|-----------------------------------------------------------|--------------------|-----------------------|-----|----|

| <b>V<sub>DDOUT</sub> = 2.5V – モードの LVC MOS パラメータ</b> |                                    |                                                           |                    |                       |     |    |

| V <sub>OH</sub>                                      | LVC MOS high レベル出力電圧               | V <sub>DDOUT</sub> = 2.3V, I <sub>OH</sub> = -0.1mA       | 2.2                |                       |     | V  |

|                                                      |                                    | V <sub>DDOUT</sub> = 2.3V, I <sub>OH</sub> = -6mA         | 1.7                |                       |     |    |

|                                                      |                                    | V <sub>DDOUT</sub> = 2.3V, I <sub>OH</sub> = -10mA        | 1.6                |                       |     |    |

| V <sub>OL</sub>                                      | LVC MOS low レベル出力電圧                | V <sub>DDOUT</sub> = 2.3V, I <sub>OL</sub> = 0.1mA        |                    | 0.1                   |     | V  |

|                                                      |                                    | V <sub>DDOUT</sub> = 2.3V, I <sub>OL</sub> = 6mA          |                    | 0.5                   |     |    |

|                                                      |                                    | V <sub>DDOUT</sub> = 2.3V, I <sub>OL</sub> = 10mA         |                    | 0.7                   |     |    |

| t <sub>PLH</sub> , t <sub>PHL</sub>                  | 伝搬遅延                               | PLL バイパス                                                  |                    | 3.4                   |     | ns |

| t <sub>r/t<sub>f</sub></sub>                         | 立ち上がりおよび立ち下がり時間                    | V <sub>DDOUT</sub> = 2.5V (20% ~ 80%)                     |                    | 0.8                   |     | ns |

| t <sub>jit(cc)</sub>                                 | サイクル間ジッタ <sup>(2) (3)</sup>        | 1 個の PLL スイッチング、Y2 から Y3 へ                                | 60                 | 90                    |     | ps |

|                                                      |                                    | 4 個の PLL スイッチング、Y2 から Y9 へ                                | 120                | 170                   |     |    |

| t <sub>jit(per)</sub>                                | ピーク ツー ピーク周期ジッタ <sup>(2) (3)</sup> | 1 個の PLL スイッチング、Y2 から Y3 へ                                | 70                 | 100                   |     | ps |

|                                                      |                                    | 4 個の PLL スイッチング、Y2 から Y9 へ                                | 130                | 180                   |     |    |

| t <sub>sk(o)</sub>                                   | 出力スキュー <sup>(4)</sup>              | f <sub>OUT</sub> = 50MHz, Y1 から Y3                        |                    | 60                    |     | ps |

|                                                      |                                    | F <sub>OUT</sub> = 50MHz, Y2 から Y5 または Y6 から Y9           |                    | 160                   |     |    |

| odc                                                  | 出力デューティ サイクル <sup>(5)</sup>        | f <sub>VCO</sub> = 100MHz, Pdiv = 1                       | 45                 | 55                    | %   |    |

| <b>SDA/SCL パラメータ</b>                                 |                                    |                                                           |                    |                       |     |    |

| V <sub>IK</sub>                                      | SCL および SDA 入力クランプ電圧               | V <sub>DD</sub> = 1.7V, I <sub>I</sub> = -18mA            |                    | -1.2                  |     | V  |

| I <sub>IH</sub>                                      | SCL および SDA 入力電流                   | V <sub>I</sub> = V <sub>DD</sub> , V <sub>DD</sub> = 1.9V |                    | ±10                   |     | μA |

| V <sub>IH</sub>                                      | SDA/SCL 入力高電圧 <sup>(6)</sup>       |                                                           | 0.7V <sub>DD</sub> |                       |     | V  |

| V <sub>IL</sub>                                      | SDA/SCL 入力低電圧 <sup>(6)</sup>       |                                                           | 0.3V <sub>DD</sub> |                       |     | V  |

| V <sub>OL</sub>                                      | SDA low レベル出力電圧                    | I <sub>OL</sub> = 3mA, V <sub>DD</sub> = 1.7V             |                    | 0.2V <sub>DD</sub>    |     | V  |

| C <sub>I</sub>                                       | SCL/SDA 入力容量                       | V <sub>I</sub> = 0V または V <sub>DD</sub>                   | 3                  | 10                    | pF  |    |

(1) すべての標準値は、それぞれの公称 V<sub>DD</sub> における値です。

(2) 10000 サイクル。

(3) ジッタは、デバイスの構成によって異なります。データは次の条件で取得されます。1-PLL:f<sub>IN</sub> = 27MHz, Y2/3 = 27MHz、(Y2 で測定)、4-PLL:f<sub>IN</sub> = 27MHz, Y2/3 = 27MHz、(Y2 で測定)、Y4/5 = 16.384MHz, Y6/7 = 74.25MHz, Y8/9 = 48MHz。

(4) t<sub>sk(o)</sub> 仕様は、出力の各バシクが等しい負荷に対してのみ有効で、出力は同じ分周器から生成されます。立ち上がりエッジ(t<sub>r</sub>)でサンプリングされたデータです。

(5) ODC は、出力の立ち上がり時間と立ち下がり時間(t<sub>r</sub>/t<sub>f</sub>)に依存します。

(6) SDA と SCL ピンは 3.3V 許容です。

### 5.8.1 CLK\_IN のタイミング要件

電源電圧が推奨範囲内で、自由気流の動作温度範囲内のとき

|                                 |                                     |              | 最小値 | 公称値 | 最大値 | 単位  |

|---------------------------------|-------------------------------------|--------------|-----|-----|-----|-----|

| f <sub>(CLK)</sub>              | LVC MOS クロック入力周波数                   | PLL バイパス モード | 0   | 160 |     | MHz |

|                                 |                                     | PLL モード      | 8   | 160 |     |     |

| t <sub>r</sub> / t <sub>f</sub> | 立ち上がり/立ち下がり時間 CLK 信号 (20% ~ 80%)    |              |     | 3   |     | ns  |

| duty <sub>CLK</sub>             | V <sub>DD</sub> /2 でのデューティ サイクル CLK |              | 40% | 60% |     |     |

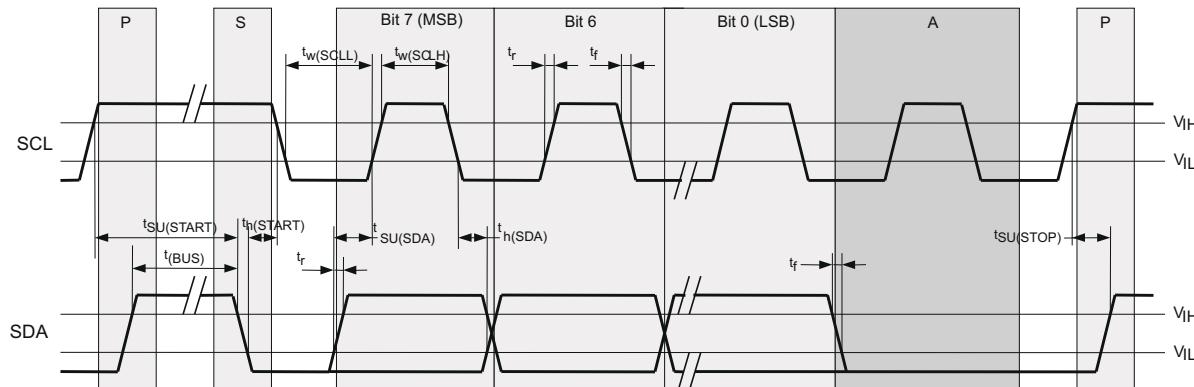

## 5.8.2 SDA/SCL のタイミング要件

図 5-1 参照

|                 | SCL クロック周波数                           | スタンダード モード |      | ファスト モード |     | 単位  |

|-----------------|---------------------------------------|------------|------|----------|-----|-----|

|                 |                                       | 最小値        | 最大値  | 最小値      | 最大値 |     |

| $f_{(SCL)}$     | SCL クロック周波数                           | 0          | 100  | 0        | 400 | kHz |

| $t_{su(START)}$ | スタートセットアップ時間 (SCL high から SDA low まで) | 4.7        |      | 0.6      |     | μs  |

| $t_h(START)$    | START ホールド時間 (SDA low から SDA low まで)  | 4          |      | 0.6      |     | μs  |

| $t_w(SCLL)$     | SCL low パルス期間                         | 4.7        |      | 1.3      |     | μs  |

| $t_w(SCLH)$     | SCL high パルスの期間                       | 4          |      | 0.6      |     | μs  |

| $t_h(SDA)$      | SDA ホールド時間 (SCL low から SDA 有効の間)      | 0          | 3.45 | 0        | 0.9 | μs  |

| $t_{su(SDA)}$   | SDA のセットアップ時間                         | 250        |      | 100      |     | ns  |

| $t_r$           | SCL/SDA 入力立ち上がり時間                     |            |      | 1000     |     | ns  |

| $t_f$           | SCL/SDA 入力立ち下がり時間                     |            |      | 300      |     | ns  |

| $t_{su(STOP)}$  | STOP のセットアップ時間                        | 4.0        |      | 0.6      |     | μs  |

| $t_{BUF}$       | STOP 条件と START 条件の間のバスフリー時間           | 4.7        |      | 1.3      |     | μs  |

## 5.9 タイミング図

### 5.9.1 SDA/SCL シリアル制御インターフェイスのタイミング図

図 5-1. SDA/SCL シリアル制御インターフェイスのタイミング図

## 5.10 代表的特性

図 5-2. 消費電流と PLL 周波数との関係

図 5-3. 出力電流と出力周波数との関係

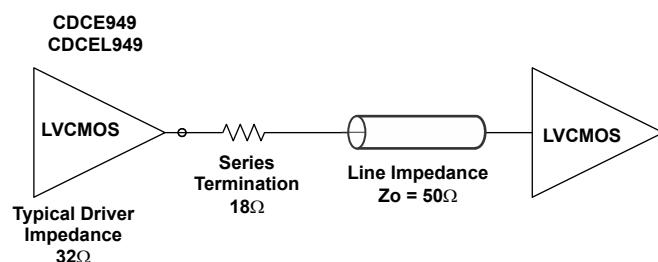

## 6 パラメータ測定情報

図 6-1. テスト負荷

図 6-2. 50Ω 基板環境のテスト負荷

## 7 詳細説明

### 7.1 概要

CDCE949-Q1 デバイスは、モジュラー PLL ベースの低コストで高性能なプログラマブル クロック シンセサイザ、マルチ プライヤ、およびディバイダです。これらのデバイスは、単一の入力周波数から最大 9 個の出力クロックを生成します。それぞれの出力は、内蔵の 4 つの構成可能 PLL を使用して、230MHz までの任意のクロック周波数にシステム内でプログラム可能です。CDCE949-Q1 には 2.5V または 3.3V の出力電源ピン VDDOUT があります。

入力には外付けの水晶振動子、または LVC MOS クロック信号を接続できます。外付けの水晶振動子を使用する場合、ほとんどのアプリケーションではオンチップの負荷コンデンサだけで十分です。負荷コンデンサの値は、0~20pF の範囲でプログラム可能です。さらに、選択可能なオンチップ VCXO により、出力周波数と外部の制御信号、すなわち PWM 信号とを同期できます。

大きな M/N 分周比により、オーディオまたはビデオ、ネットワーク (WLAN、BlueTooth イーサネット、GPS)、またはインターフェイス (USB、IEEE1394、メモリスティック) の 0ppm のクロックを、たとえば 27MHz の基準入力周波数から生成できます。

すべての PLL は SCC (拡散スペクトラム クロッキング)をサポートします。SSC は、センター スプレッドおよびダウン スプレッド クロッキングを使用でき、これは電磁気的干渉 (EMI) を低減するための一般的な技法です。

PLL 周波数と分周値の設定に基づいて内部のループ フィルタ コンポーネントを自動的に調整することにより、高い安定性を実現し、各 PLL のジッタ伝達特性を最適化します。

このデバイスは不揮発性の EEPROM のプログラミングをサポートしているため、アプリケーションを簡単にカスタマイズできます。デバイスは工場出荷時にあらかじめデフォルト設定済みです。(デフォルトのデバイス設定を参照)各種のアプリケーション構成に応じて PCB 組み立て前に再プログラム可能したり、システム内プログラミングにより再プログラムしたりできます。すべてのデバイス設定は、2 線式シリアル インターフェイスの SDA/SCL バスでプログラムできます

3 つのプログラム可能な制御入力 S0、S1、S2 を使用して、周波数の選択による SSC パラメータの変更による EMI の低減、PLL バイパス、電源オフ、出力ディセーブル機能として low レベルと TRI-STATE のどちらを選択するなど、動作のさまざまな要因を制御できます。

CDCE949-Q1 は 1.8V 環境で動作します。CDCE949-Q1 は、-40°C~85°Cで動作特性が規定されています。

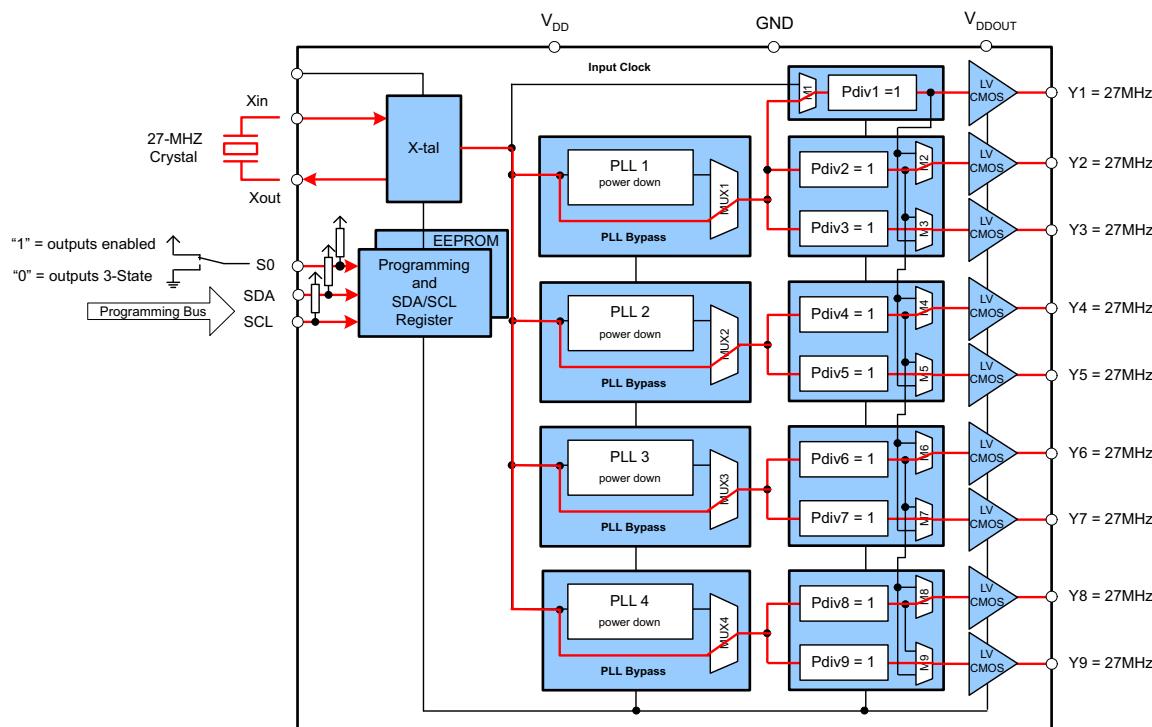

## 7.2 機能ブロック図

図 7-1. 機能ブロック図

## 7.3 機能説明

### 7.3.1 制御端子の構成

CDCE949 には、ユーザー定義可能な 3 つの制御端子 (S0, S1, S2) があり、デバイス設定を外部から制御できます。端子は、次のいずれかの機能を実行するようにプログラムできます。

- スペクトラム拡散クロック処理の選択: スプレッドタイプとスプレッド量の選択

- 周波数の選択: 2 つのユーザー定義周波数のいずれか間での切り替え

- 出力状態の選択: 出力構成とパワーダウン制御

ユーザーは、最大 8 つの異なるコントロール設定を事前定義できます。[表 7-1](#) と [表 7-2](#) は、これらの設定について説明します。

表 7-1. コントロール端末定義

| 外部制御ビット   | PLL1 の設定   |         |              | PLL2 の設定   |         |              | PLL3 の設定   |         |              | PLL4 の設定   |         |              | Y1 の設定          |

|-----------|------------|---------|--------------|------------|---------|--------------|------------|---------|--------------|------------|---------|--------------|-----------------|

| コントローラの機能 | PLL 周波数の選択 | SSC の選択 | 出力 Y2/Y3 の選択 | PLL 周波数の選択 | SSC の選択 | 出力 Y4/Y5 の選択 | PLL 周波数の選択 | SSC の選択 | 出力 Y6/Y7 の選択 | PLL 周波数の選択 | SSC の選択 | 出力 Y8/Y9 の選択 | 出力 Y1 および電源オフ選択 |

**表 7-2. PLLx 設定 (PLL ごとに個別に選択可能) <sup>(1)</sup>**

| SSCx [3 ビット] |   |   | 中心      | 下へ      |

|--------------|---|---|---------|---------|

| 0            | 0 | 0 | 0% (オフ) | 0% (オフ) |

| 0            | 0 | 1 | ±0.25%  | -0.25%  |

| 0            | 1 | 0 | ±0.5%   | -0.5%   |

| 0            | 1 | 1 | ±0.75%  | -0.75%  |

| 1            | 0 | 0 | ±1.0%   | -1.0%   |

| 1            | 0 | 1 | ±1.25%  | -1.25%  |

| 1            | 1 | 0 | ±1.5%   | -1.5%   |

| 1            | 1 | 1 | ±2.0%   | -2.0%   |

| 周波数の選択 <sup>(2)</sup> |            |

|-----------------------|------------|

| FSX                   | 機能         |

| 0                     | Frequency0 |

| 1                     | Frequency1 |

| 出力選択 <sup>(3)</sup> (Y2 ... Y9) |        |

|---------------------------------|--------|

| YxYx                            | 機能     |

| 0                               | State0 |

| 1                               | State1 |

(1) センター/ダウ nsプレッド、Frequency0/1、State0/1 は PLLx 構成レジスタでユーザー定義可能です。

(2) Frequency0 および Frequency1 には、指定された  $f_{VCO}$  範囲内の任意の周波数を指定できます。

(3) State0/1 の選択は、対応する PLL モジュールの両方の出力で有効であり、パワーダウン、3-ステート、low、またはアクティブにすることができます

**表 7-3. Y1 の設定 <sup>(1)</sup>**

| Y1 選択 |        |

|-------|--------|

| Y1    | 機能     |

| 0     | ステート 0 |

| 1     | 状態 1   |

(1) ステート 0 とステート 1 は汎用コンフィグレーション レジスターでユーザー定義可能で、パワーダウン、3-ステート、low、またはアクティブにすることができます。

CDCE949 の S1/SDA および S2/SCL ピンはデュアル機能ピンです。デフォルト構成では、ピンはシリアルインターフェイスの SDA/SCL として定義されています。EEPROM の適切なビットを設定することで、ピンを制御ピン (S1/S2) としてプログラムできます。制御レジスタ (バイト 02 のビット [6]) の変更は、その変更が EEPROM に書き込まれるまで無効になることに注意してください。

ピンを制御ピンとして設定すると、シリアル プログラミング インターフェイスは使用できなくなります。ただし、 $V_{DDOUT}$  が GND に強制的に接続されると、S1 と S2 の 2 つの制御ピンは、一時的にシリアル プログラミング ピン (SDA/SCL) として機能します。

S0 は複数使用ピンではなく、このピンは制御ピンのみです。

### 7.3.2 デフォルトのデバイス設定

CDCE949-Q1 の内部 EEPROM は、図 7-2 に示すように事前構成されています。入力周波数はデフォルトで出力に渡されます。デフォルト設定は、電源供給後、または電源オフ/オン シーケンスの後に、デバイスの EEPROM が別のアプリケーション構成に再プログラムされるまで表示されます。新しいレジスタ設定は、シリアル SDA/SCL インターフェイスを使用してプログラムされます。

図 7-2. デフォルト構成

表 7-4 に、制御端子レジスタ（外部制御ピン）のデフォルト設定を示します。通常動作時は、8 つのレジスタ設定すべてが利用可能ですが、デフォルト構成では、最初の 2 つの設定（0 と 1）のみを S0 で選択できます。S1 と S2 はデフォルトモードのプログラミングピンとして構成されているため、S1 と S2 は S0 で選択できます。

表 7-4. 制御端子レジスタの工場出荷時デフォルト設定

| 外部制御ピン <sup>(1)</sup>  |                        |    | Y1     | PLL1 の設定            |       |        | PLL2 の設定            |       |        | PLL3 の設定            |       |        | PLL4 の設定            |       |        |

|------------------------|------------------------|----|--------|---------------------|-------|--------|---------------------|-------|--------|---------------------|-------|--------|---------------------|-------|--------|

|                        |                        |    | 出力選択   | 周波数選択               | SSC選択 | 出力選択   |

| S2                     | S1                     | S0 | Y1     | FS1                 | SSC1  | Y2Y3   | FS2                 | SSC2  | Y4Y5   | FS3                 | SSC3  | Y6Y7   | FS4                 | SSC4  | Y8Y9   |

| SCL (I <sup>2</sup> C) | SDA (I <sup>2</sup> C) | 0  | 3 ステート | f <sub>VCO1_0</sub> | オフ    | 3 ステート | f <sub>VCO2_0</sub> | オフ    | 3 ステート | f <sub>VCO3_0</sub> | オフ    | 3 ステート | f <sub>VCO4_0</sub> | オフ    | 3 ステート |

| SCL (I <sup>2</sup> C) | SDA (I <sup>2</sup> C) | 1  | 有効     | f <sub>VCO1_0</sub> | オフ    | 有効     | f <sub>VCO2_0</sub> | オフ    | 有効     | f <sub>VCO3_0</sub> | オフ    | 有効     | f <sub>VCO4_0</sub> | オフ    | 有効     |

- (1) デフォルトモードでは、それぞれプログラムされている場合、S1 と S2 はシリアルプログラミングインターフェイス SDA/SCL として動作します。このモードでは、ピンには制御ピン機能はありませんが、S1 = 0 および S2 = 0 の場合と内部的に解釈されます。ただし、S0 は制御ピンであり、デフォルトモードでは（上記で事前定義したとおり）すべての出力をオンまたはオフに切り替えます。

### 7.3.3 SDA/SCL シリアルインターフェイス

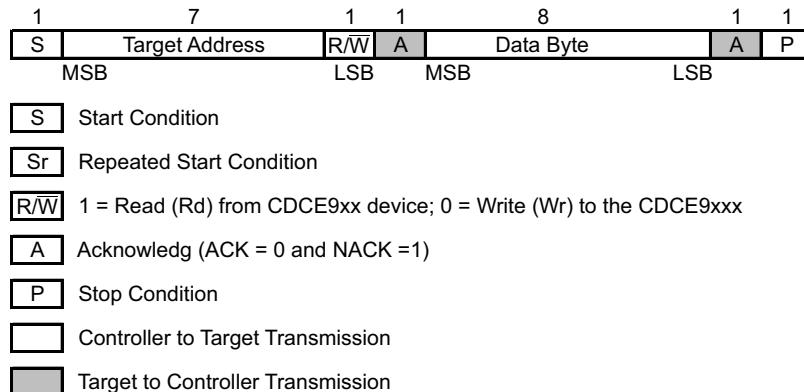

CDCE949 は 2 線式シリアル SDA/SCL バス上でターゲットデバイスとして動作し、一般的な SMBus または I<sup>2</sup>C™ 仕様と互換性があります。このデバイスは、標準モード転送（最大 100kbps）と高速モード転送（最大 400kbps）で動作し、7 ビットアドレッシングをサポートしています。

CDC9xx の S1/SDA および S2/SCL ピンはデュアル機能ピンです。デフォルト構成では、ピンを SDA/SCL シリアルプログラミングインターフェイスとして使用します。対応する EEPROM 設定のバイト 02、ビット [6] を変更することで、汎用制御ピン S1 および S2 としてこのピンを再プログラムできます。

### 7.3.4 データプロトコル

このデバイスは、バイト書き込みとバイト読み取り、ブロック書き込みとブロック読み取りの各動作をサポートしています。

バイト書き込み/読み取り動作の場合、システムコントローラはアドレス指定されたバイトに個別にアクセスできます。

ブロック書き込み/読み出し動作の場合、バイトは最小バイトから最上位バイト(最上位ビットが先頭)まで順次アクセスされ、任意の完全なバイトが転送された後で停止できます。読み出すバイト数は、汎用構成レジスタのバイト数フィールドで定義されます。ブロック読み取り命令の間、読み取りサイクルを正しく完了するには、バイトカウントで定義されているバイト数全体を読み出す必要があります。

バイトがデバイスに送信されると、そのバイトは内部レジスタに書き込まれ、直ちに有効になります。これは、バイト書き込みシーケンスでもブロック書き込みシーケンスでも、転送された各バイトに適用されます。

EEPROM の書き込みサイクルが開始された場合、内部レジスタが EEPROM に書き込まれます。データは、プログラミング シーケンス (バイト読み取りまたはブロック読み取り) 中に読み出すことができます。プログラミング ステータスは、EEPIP バイト 01-ビット [6] で監視できます。EEPROM プログラミングを開始する前に、CLKIN を LOW にします。EEPROM プログラミングの間、CLKIN を LOW に保持する必要があります。EEWRITE バイト 06-ビット [0] を使用して EEPROM プログラミングを開始した後、EEPIP が 0 として読み戻されるまで、デバイス レジスタに書き込みを行わないでください。

インデックス付きバイトのオフセットは、表 7-6 で説明されているように、コマンドコードでエンコードされます。

**表 7-5. ターゲット レシーバ アドレス (7 ビット)**

| デバイス             | A6       | A5       | A4       | A3       | A2       | A1 <sup>(1)</sup> | A0 <sup>(1)</sup> | R/W        |

|------------------|----------|----------|----------|----------|----------|-------------------|-------------------|------------|

| CDCE913/CDCEL913 | 1        | 1        | 0        | 0        | 1        | 0                 | 1                 | 1/0        |

| CDCE925/CDCEL925 | 1        | 1        | 0        | 0        | 1        | 0                 | 0                 | 1/0        |

| CDCE937/CDCEL937 | 1        | 1        | 0        | 1        | 1        | 0                 | 1                 | 1/0        |

| <b>CDCE949</b>   | <b>1</b> | <b>1</b> | <b>0</b> | <b>1</b> | <b>1</b> | <b>0</b>          | <b>0</b>          | <b>1/0</b> |

- (1) アドレス ビット A0 および A1 は、SDA/SCL バス (バイト 01、ビット [1:0]) 経由でプログラムできます。これにより、同じ SDA/SC L バスに接続された最大 4 つのデバイスをアドレス指定できます。アドレス バイトの最下位ビットは、書き込みまたは読み取り動作を指定します。

**表 7-6. コマンド コードの定義**

| ビット   | 説明                                                   |

|-------|------------------------------------------------------|

| 7     | 0 = ブロック読み取りまたはブロック書き込み動作<br>1 = バイト読み取りまたはバイト書き込み動作 |

| (6:0) | バイト読み取り、ブロック読み取り、バイト書き込み、ブロック書き込み動作のバイト オフセット。       |

### 7.3.5 PLL マルチプライヤ/デバイダの定義

与えられた入力周波数 ( $f_{IN}$ ) で、CDCE949 の出力周波数 ( $f_{OUT}$ ) は次の式で計算できます。

$$f_{OUT} = \frac{f_{IN}}{P_{div}} \times \frac{N}{M}$$

ここで、

$M$  (1 ~ 511) および  $N$  (1 ~ 4095) は PLL の倍増器/分周器の値です。

$P_{div}$  (1 ~ 127) は出力分周器です。

各 PLL の目標 VCO 周波数 ( $f_{VCO}$ ) は、次のように計算できます。

$$f_{VCO} = f_{IN} \times \frac{N}{M}$$

PLL は分数分周器として動作し、次のマルチプライヤ/デバイダ設定が必要です

$N$

$$P = 4 - \text{int}(\log_2 \frac{N}{M}) \quad \{\text{if } P < 0 \text{ then } P = 0\}$$

$$Q = \text{int}(\frac{N'}{M})$$

$$R = N' - M \times Q$$

ここで

$$N' = N \times 2^P;$$

$$N \geq M;$$

$$80\text{MHz} < f_{VCO} > 230\text{MHz}.$$

例 1: $f_{IN} = 27\text{MHz}$ ,  $M = 1$ ,  $N = 4$ ,  $P_{div} = 2$  の場合

$$\rightarrow f_{OUT} = 54\text{MHz};$$

$$\rightarrow f_{VCO} = 108\text{MHz};$$

$$\rightarrow P = 4 - \text{int}(\log_2 4) = 4 - 2 = 2;$$

$$\rightarrow N' = 4 \times 2^2 = 16;$$

$$\rightarrow Q = \text{int}(16) = 16;$$

$$\rightarrow R = 16 - 16 = 0;$$

例 2: $f_{IN} = 27\text{MHz}$ ,  $M = 2$ ,  $N = 11$ ,  $P_{div} = 2$  の場合

$$\rightarrow f_{OUT} = 75.25\text{MHz};$$

$$\rightarrow f_{VCO} = 148.50\text{MHz};$$

$$\rightarrow P = 4 - \text{int}(\log_2 5.5) = 4 - 2 = 2;$$

$$\rightarrow N' = 11 \times 2^2 = 44;$$

$$\rightarrow Q = \text{int}(22) = 22;$$

$$\rightarrow R = 44 - 44 = 0;$$

TI ClockPro™ ソフトウェアを使用するときは、 $P$ 、 $Q$ 、 $R$ 、 $N'$  の値が自動的に計算されます。

## 7.4 デバイスの機能モード

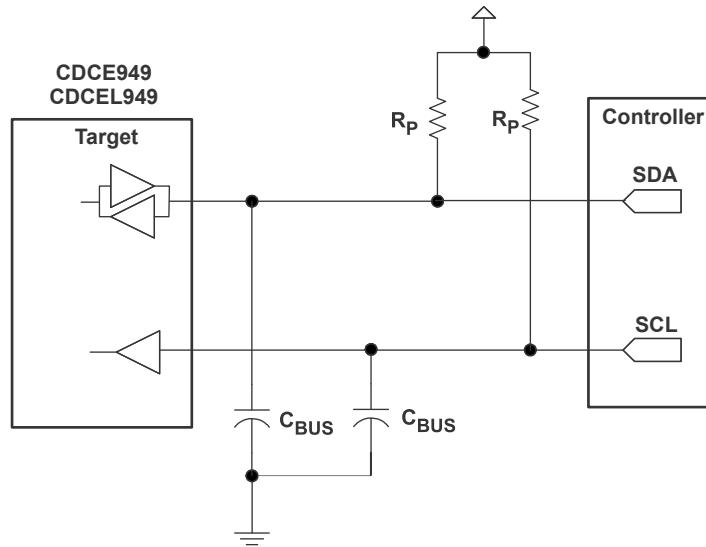

### 7.4.1 SDA/SCL ハードウェアインターフェイス

図 7-3 に、CDCE949-Q1 クロック シンセサイザを SDA/SCL シリアル インターフェイス バスに接続する方法を示します。複数のデバイスをバスに接続できますが、多くのデバイスを接続すると速度を低減できます (400kHz の最大値)。

プルアップ抵抗値 ( $R_P$ ) は、電源電圧、バス容量、接続デバイス数に依存することに注意してください。推奨プルアップ値は  $4.7\text{k}\Omega$  です。プルアップ値は、出力段の  $V_{OLmax} = 0.4\text{V}$  における  $3\text{mA}$  の最小シンク電流を満たす必要があります (詳細については、SMBus または I<sup>2</sup>C バスの仕様を参照してください)。

図 7-3. SDA/SCL ハードウェア インターフェイス

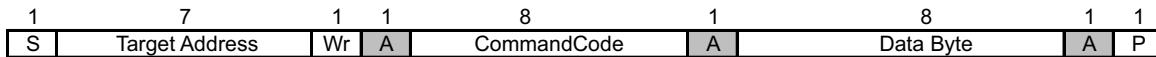

## 7.5 プログラミング

### 7.5.1 汎用プログラミングシーケンス

図 7-4. 汎用プログラミングシーケンス

### 7.5.2 バイト書き込みのプログラミングシーケンス

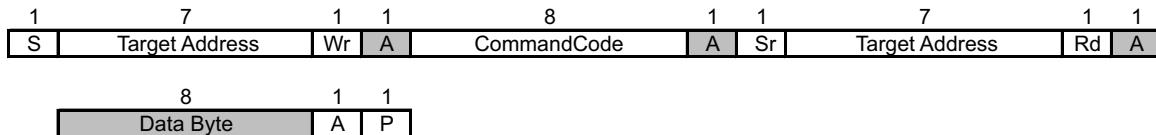

図 7-5. バイト書き込みプロトコル

### 7.5.3 バイト読み取りのプログラミングシーケンス

図 7-6. バイト読み取りプロトコル

### 7.5.4 ブロック書き込みのプログラミングシーケンス

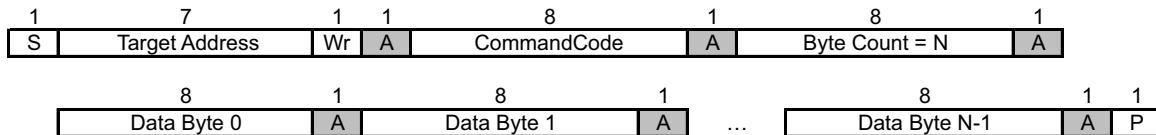

データバイト 0 ビット [7:0] は、リビジョンコードおよびベンダ識別用に予約されています。これらのビットは内部テスト目的で使用されるため、上書きしてはなりません。

図 7-7. ブロック書き込みプログラミング

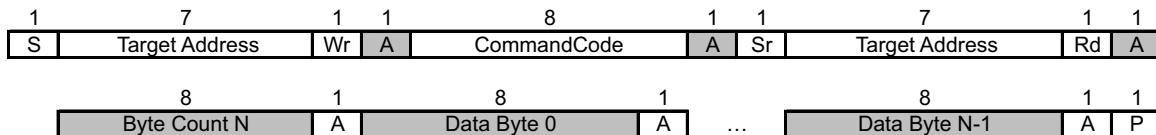

### 7.5.5 ブロック読み取りのプログラミングシーケンス

図 7-8. ブロック読み取りプロトコル

## 8 レジスタ マップ

### 8.1 SDA および SCL レジスタ

クロック入力、制御ピン、PLL、および出力段はユーザーが構成可能です。以下の表と説明に、CDCE949-Q1 のプログラマブル機能を示します。すべての設定は、SDA/SCL バスを使用してデバイスに手動で書き込むことも、TI ClockPro ソフトウェアを使用して簡単にプログラムすることもできます。TI ClockPro ソフトウェアを使用すると、ユーザーはすべての設定を迅速に行い、最小のジッタで、最適な性能を実現する目的で値を自動的に計算することができます。

表 8-1. SDA/SCL レジスタ

| アドレス オフセット | レジスタの説明     | 表                     |

|------------|-------------|-----------------------|

| 00h        | 汎用構成レジスタ    | <a href="#">表 8-3</a> |

| 10h        | PLL1 構成レジスタ | <a href="#">表 8-4</a> |

| 20h        | PLL2 構成レジスタ | <a href="#">表 8-5</a> |

| 30h        | PLL3 構成レジスタ | <a href="#">表 8-6</a> |

| 40h        | PLL4 構成レジスタ | <a href="#">表 8-7</a> |

### 8.2 構成レジスタ

以下のページの構成レジスタの表で説明されている灰色でハイライトされたビットは、制御端子レジスタに属します。ユーザーは、最大 8 つの異なるコントロール設定を事前定義できます。これらの設定は、外部制御ピン S0、S1、S2 によって選択できます（「制御端子の構成」セクションを参照）。

表 8-2. 構成レジスタ、外部制御端子

| 外部制御ピン                   | Y1 | PLL1 の設定 |        |       | PLL2 の設定 |        |       | PLL3 の設定 |        |       | PLL4 の設定 |        |       |         |        |

|--------------------------|----|----------|--------|-------|----------|--------|-------|----------|--------|-------|----------|--------|-------|---------|--------|

|                          |    | 周波数選択    | SSC 選択 | 出力選択  |         |        |

| S2                       | S1 | S0       | Y1     | FS1   | SSC1     | Y2Y3   | FS2   | SSC2     | Y4Y5   | FS3   | SSC3     | Y6Y7   | FS4   | SSC4    | Y8Y9   |

| 0                        | 0  | 0        | Y1_0   | FS1_0 | SSC1_0   | Y2Y3_0 | FS2_0 | SSC2_0   | Y4Y5_0 | FS3_0 | SSC3_0   | Y6Y7_0 | FS4_0 | SSC4_0  | Y8Y9_0 |

| 0                        | 0  | 1        | Y1_1   | FS1_1 | SSC1_1   | Y2Y3_1 | FS2_1 | SSC2_1   | Y4Y5_1 | FS3_1 | SSC3_1   | Y6Y7_1 | FS4_1 | SSC4_1  | Y8Y9_1 |

| 0                        | 1  | 0        | Y1_2   | FS1_2 | SSC1_2   | Y2Y3_2 | FS2_2 | SSC2_2   | Y4Y5_2 | FS3_2 | SSC3_2   | Y6Y7_2 | FS4_2 | SSC4_2  | Y8Y9_2 |

| 0                        | 1  | 1        | Y1_3   | FS1_3 | SSC1_3   | Y2Y3_3 | FS2_3 | SSC2_3   | Y4Y5_3 | FS3_3 | SSC3_3   | Y6Y7_3 | FS4_3 | SSC4_3  | Y8Y9_3 |

| 1                        | 0  | 0        | Y1_4   | FS1_4 | SSC1_4   | Y2Y3_4 | FS2_4 | SSC2_4   | Y4Y5_4 | FS3_4 | SSC3_4   | Y6Y7_4 | FS4_4 | SSC4_4  | Y8Y9_4 |

| 1                        | 0  | 1        | Y1_5   | FS1_5 | SSC1_5   | Y2Y3_5 | FS2_5 | SSC2_5   | Y4Y5_5 | FS3_5 | SSC3_5   | Y6Y7_5 | FS4_5 | SSC4_5  | Y8Y9_5 |

| 1                        | 1  | 0        | Y1_6   | FS1_6 | SSC1_6   | Y2Y3_6 | FS2_6 | SSC2_6   | Y4Y5_6 | FS3_6 | SSC3_6   | Y6Y7_6 | FS4_6 | SSC4_6  | Y8Y9_6 |

| 1                        | 1  | 1        | Y1_7   | FS1_7 | SSC1_7   | Y2Y3_7 | FS2_7 | SSC2_7   | Y4Y5_7 | FS3_7 | SSC3_7   | Y6Y7_7 | FS4_7 | SSC4_7  | Y8Y9_7 |

| アドレスオフセット <sup>(1)</sup> |    |          | 04h    | 13h   | 10h-12h  | 15h    | 23h   | 20h-22h  | 25h    | 33h   | 30h-32h  | 35h    | 43h   | 40h-42h | 45h    |

(1) アドレス オフセットとは、以降のページの構成レジスタのバイト アドレスを指します。

#### 8.2.1 汎用構成レジスタ

表 8-3. 汎用構成レジスタ

| オフセット <sup>(1)</sup> | ビット <sup>(2)</sup> | 略称   | デフォルト <sup>(3)</sup> | 説明                                                      |

|----------------------|--------------------|------|----------------------|---------------------------------------------------------|

| 00h                  | 7                  | E_EL | xb                   | デバイス識別 (読み出し専用): 1 は CDCE949 (3.3V)、0 は CDCEL949 (1.8V) |

|                      | 6:4                | RID  | Xb                   | リビジョンの識別番号 (読み出し専用)                                     |

|                      | 3:0                | VID  | 1h                   | ベンダー識別番号 (読み出し専用)                                       |

表 8-3. 汎用構成レジスタ (続き)

| オフセット <sup>(1)</sup> | ビット <sup>(2)</sup> | 略称          | デフォルト <sup>(3)</sup> | 説明                                                                                                                                                                                      |

|----------------------|--------------------|-------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01h                  | 7                  | -           | 0b                   | 予約済み - 常に 0 を書き込みます                                                                                                                                                                     |

|                      | 6                  | EEPIP       | 0b                   | EEPROM プログラミング ステータス 0–EEPROM のプログラミングが完了<br>(4): (読み出し専用)<br>1–EEPROM はプログラミング モードです                                                                                                   |

|                      | 5                  | EELOCK      | 0b                   | EEPROM データを永続的にロック 0 - EEPROM はロックされていません<br>1 - EEPROM は永続的にロックされます                                                                                                                    |

|                      | 4                  | PWDN        | 0b                   | デバイスの電源オフ (S0/S1/S2 設定を上書き、構成レジスタ設定は変更されません)<br>注: EEPROM で PWDN を 1 に設定することはできません。<br>0 – デバイス アクティブ (すべての PLL およびすべての出力がイネーブル)<br>1 – デバイスのパワーダウン (すべての PLL はパワーダウン状態、すべての出力は 3 ステート) |

|                      | 3:2                | INCLK       | 00b                  | 入力クロックの選択:<br>00 – X-tal<br>01 – VCXO<br>11 – 予約済み                                                                                                                                      |

|                      | 1:0                | I2C_ADR     | 00b                  | ターゲット レシーバのアドレスのプログラム可能なアドレス ビット A0 および A1                                                                                                                                              |

|                      | 02h                | M1          | 1b                   | 出力 Y1 のクロック ソースの選択:<br>0 – 入力クロック<br>1 – PLL1 クロック                                                                                                                                      |

| 03h                  | 6                  | SPICON      | 0b                   | ピン 22/23 の動作モード選択 <sup>(6)</sup><br>0 – シリアル プログラミング インターフェイス SDA (ピン 23) および SCL (ピン 22)<br>1 – 制御ピン S1 (ピン 23) および S2 (ピン 22)                                                         |

|                      | 5:4                | Y1_ST1      | 11b                  | Y1 - ステート 0/1 の定義 (Y1_ST1 および Y1_ST0 に適用)                                                                                                                                               |

|                      | 3:2                | Y1_ST0      | 01b                  | 00 – デバイスの電源オフ (すべての PLL が電源オフになり、すべての出力が 3 ステート)<br>01-Y1 は<br>ディセーブルから 3 ステートに 10-Y1 はディセーブルから low<br>11-Y1 はイネーブル (通常動作)                                                             |

|                      | 1:0                | Pdiv1 [9:8] | 001h                 | 10 ビット Y1 出力分周器 Pdiv1:<br>0 分周器のリセットおよびスタンバイ、<br>1 対 1023 の分周器の値                                                                                                                        |

|                      | 7:0                | Pdiv1 [7:0] |                      |                                                                                                                                                                                         |

| 04h                  | 7                  | Y1_7        | 0b                   | Y1_x 状態の選択 <sup>(7)</sup><br>0 – ステート 0 (Y1 によって定義済み - ステート 0 定義 [Y1_ST0] で定義済み)<br>1 – ステート 1 (Y1-ステート 1 定義 [Y1_ST1] で定義済み)                                                            |

|                      | 6                  | Y1_6        | 0b                   |                                                                                                                                                                                         |

|                      | 5                  | Y1_5        | 0b                   |                                                                                                                                                                                         |

|                      | 4                  | Y1_4        | 0b                   |                                                                                                                                                                                         |

|                      | 3                  | Y1_3        | 0b                   |                                                                                                                                                                                         |

|                      | 2                  | Y1_2        | 0b                   |                                                                                                                                                                                         |

|                      | 1                  | Y1_1        | 1b                   |                                                                                                                                                                                         |

|                      | 0                  | Y1_0        | 0b                   |                                                                                                                                                                                         |

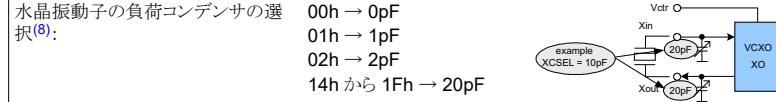

| 05h                  | 7:3                | XCSEL       | 0Ah                  | 水晶振動子の負荷コンデンサの選択 <sup>(8)</sup> :<br>00h → 0pF<br>01h → 1pF<br>02h → 2pF<br>14h から 1Fh → 20pF                                                                                           |

|                      | 2:0                | —           | 0b                   | 予約済み。0 以外は書かないでください。                                                                                                                                                                    |

| 06h                  | 7:1                | BCOUNT      | 50h                  | 7 ビットのバイト カウント (次のブロック読み取り転送でこのデバイスから送信されるバイト数を定義します。読み出しサイクルを正しく完了するには、すべてのバイトを読み出す必要があります。)                                                                                           |

|                      | 0                  | EEWRITE     | 0b                   | EEPROM 書き込みサイクルの開始 <sup>(4) (9)</sup><br>0 – EEPROM 書き込みサイクルなし<br>1 – EEPROM 書き込みサイクルを開始 (内部構成レジスタを EEPROM に保存)                                                                         |

| 07h-0Fh              | —                  | —           | 0h                   | 予約済み。0 以外は書かないでください                                                                                                                                                                     |

- (1) 「50h」を超えるデータを書き込むと、デバイスの機能に悪影響を及ぼす可能性があります。

- (2) すべてのデータは、MSB ファーストで転送されます。

- (3) カスタム設定が使用されていない場合。

- (4) EEPROM プログラミング中、プログラミング シーケンスが完了するまで、SDA/SCL バスを使用してデバイスにデータを送信することはできません。ただし、データは、プログラミング シーケンス (バイト読み取りまたはブロック読み取り) 中に読み取ることができます。

- (5) このビットが EEPROM の high にセットされている場合、EEPROM の実際のデータは永続的にロックされ、それ以上プログラムすることはできません。ただし、データは SDA/SC L バスを使用して内部レジスタに書き込むことで、デバイスの機能をその場で変更できます。ただし、新しいデータを EEPROM に保存することはできません。EELOCK は、EEPROM に書き込まれた場合にのみ有効です

- (6) 制御ピンの選択は、EEPROMに書き込まれた場合にのみ有効です。EEPROMに書き込まれると、シリアルプログラミングピンは使用できなくなります。ただし、 $V_{DDOUT}$ が強制的にGNDに設定されると、2つの制御ピンS1とS2が一時的にシリアルプログラミングピン(SDA/SCL)として動作し、2つのターゲットレシーバアドレスビットはA0=0およびA1=0にリセットされます。

- (7) これらは制御端子レジスタのビットです。ユーザーは、最大8つの異なる制御設定を事前定義できます。その後、外部制御ピンS0、S1、S2を使用してこれらの設定を選択できます。

- (8) 最高のクロック性能を実現するには、内部負荷コンデンサ( $C_1, C_2$ )を使用する必要があります。数個のpFで $C_L$ の微調整を行う場合にのみ、外付けコンデンサを使用します。 $C_L$ の値は、分解能1pFで、水晶振動子の総負荷範囲は0pF～20pFです。 $C_L$ が20pFより大きい場合は、追加の外付けコンデンサを使用します。また、デバイスの入力容量を考慮する必要があります。これにより、選択した $C_L$ に1.5pF(6pF//2pF)が追加されます。VCXOの構成と水晶の推奨事項の詳細については、アプリケーションノートSCAA085を参照してください。

- (9) 注: EEPROM書き込みビットは最後に送信される必要があります。これにより、すべての内部レジスタの内容がEEPROMに書き込まれたことを検証できます。EEWRITEサイクルは、EEWRITEビットの立ち上がりエッジで開始されます。静的レベルのhighでは、EEPROMの書き込みサイクルはトリガされません。プログラミングの完了後にEEWRITEビットをlowにリセットする必要があります。プログラミングステータスは、EEPIPを読み出して監視できます。EELOCKがhighに設定されている場合、EEPROMのプログラミングはできません。

## 8.2.2 PLL1 構成レジスタ

表 8-4. PLL1 構成レジスタ

| オフセット <sup>(1)</sup> | ビット <sup>(2)</sup> | 略称           | デフォルト <sup>(3)</sup> | 説明                                                                                                                                                                                                                                            |

|----------------------|--------------------|--------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10h                  | 7:5                | SSC1_7 [2:0] | 000b                 | SSC1:PLL1 SSC の選択 (変調量) <sup>(4)</sup>                                                                                                                                                                                                        |

|                      | 4:2                | SSC1_6 [2:0] | 000b                 |                                                                                                                                                                                                                                               |

|                      | 1:0                | SSC1_5 [2:1] | 000b                 |                                                                                                                                                                                                                                               |

| 11h                  | 7                  | SSC1_5 [0]   | 000b                 | ダウン<br>000 (オフ)<br>001 – 0.25%<br>010 – 0.5%<br>011 – 0.75%<br>100 – 1.0%<br>101 – 1.25%<br>110 – 1.5%<br>111 – 2.0%<br>センター<br>000 (オフ)<br>001 ± 0.25%<br>010 ± 0.5%<br>011 ± 0.75%<br>100 ± 1.0%<br>101 ± 1.25%<br>110 ± 1.5%<br>111 ± 2.0% |

|                      | 6:4                | SSC1_4 [2:0] | 000b                 |                                                                                                                                                                                                                                               |

|                      | 3:1                | SSC1_3 [2:0] | 000b                 |                                                                                                                                                                                                                                               |

|                      | 0                  | SSC1_2 [2]   | 000b                 |                                                                                                                                                                                                                                               |

| 12h                  | 7:6                | SSC1_2 [1:0] | 000b                 | FS1_x:PLL1 周波数選択 <sup>(4)</sup>                                                                                                                                                                                                               |

|                      | 5:3                | SSC1_1 [2:0] | 000b                 |                                                                                                                                                                                                                                               |

|                      | 2:0                | SSC1_0 [2:0] | 000b                 |                                                                                                                                                                                                                                               |

| 13h                  | 7                  | FS1_7        | 0b                   | FS1_x:PLL1 周波数選択 <sup>(4)</sup><br>0 – $f_{VCO1\_0}$ (PLL1_0 – 乗算器/分周器の値によって事前定義)<br>1 – $f_{VCO1\_1}$ (PLL1_1 – 乗算器/分周器の値によって事前定義)                                                                                                           |

|                      | 6                  | FS1_6        | 0b                   |                                                                                                                                                                                                                                               |

|                      | 5                  | FS1_5        | 0b                   |                                                                                                                                                                                                                                               |

|                      | 4                  | FS1_4        | 0b                   |                                                                                                                                                                                                                                               |

|                      | 3                  | FS1_3        | 0b                   |                                                                                                                                                                                                                                               |

|                      | 2                  | FS1_2        | 0b                   |                                                                                                                                                                                                                                               |

|                      | 1                  | FS1_1        | 0b                   |                                                                                                                                                                                                                                               |

|                      | 0                  | FS1_0        | 0b                   |                                                                                                                                                                                                                                               |

| 14h                  | 7                  | MUX1         | 1b                   | PLL1 マルチブレクサ:<br>0 – PLL1<br>1 – PLL1 バイパス (PLL1 はパワーダウン中)                                                                                                                                                                                    |

|                      | 6                  | M2           | 1b                   | 出力 Y2 マルチブレクサ:<br>0 – Pdiv1<br>1 – Pdiv2                                                                                                                                                                                                      |

|                      | 5:4                | M3           | 10b                  | 出力 Y3 マルチブレクサ:<br>00 – Pdiv1-分周器<br>01 – Pdiv2-分周器<br>10 – Pdiv3-分周器<br>11 – 預約済み                                                                                                                                                             |

|                      | 3:2                | Y2Y3_ST1     | 11b                  | Y2、Y3-ステート 0/1 定義:<br>00 – Y2/Y3 ディセーブルから 3-ステート (PLL1 はパワーダウン中)<br>01 – Y2/Y3 ディセーブルから 3-ステート (PLL1 オン) 10 – Y2/Y3 ディセーブル<br>から low (PLL1 オン)<br>11 – Y2/Y3 イネーブル (通常動作、PLL1 オン)                                                             |

|                      | 1:0                | Y2Y3_ST0     | 01b                  |                                                                                                                                                                                                                                               |

| 15h                  | 7                  | Y2Y3_7       | 0b                   | Y2Y3_x の出力状態の選択 <sup>(4)</sup><br>0 – ステート 0 (Y2Y3_ST0 で定義)<br>1 – ステート 1 (Y2Y3_ST1 で定義)                                                                                                                                                      |

|                      | 6                  | Y2Y3_6       | 0b                   |                                                                                                                                                                                                                                               |

|                      | 5                  | Y2Y3_5       | 0b                   |                                                                                                                                                                                                                                               |

|                      | 4                  | Y2Y3_4       | 0b                   |                                                                                                                                                                                                                                               |

|                      | 3                  | Y2Y3_3       | 0b                   |                                                                                                                                                                                                                                               |

|                      | 2                  | Y2Y3_2       | 0b                   |                                                                                                                                                                                                                                               |

|                      | 1                  | Y2Y3_1       | 1b                   |                                                                                                                                                                                                                                               |

|                      | 0                  | Y2Y3_0       | 0b                   |                                                                                                                                                                                                                                               |

**表 8-4. PLL1 構成レジスタ (続き)**

| オフセット <sup>(1)</sup> | ビット <sup>(2)</sup> | 略称             | デフォルト <sup>(3)</sup> | 説明                                                                                                                                                                                                                    |  |

|----------------------|--------------------|----------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 16h                  | 7                  | SSC1DC         | 0b                   | PLL1 SSC ダウン/センターの選択:<br>0 – 下<br>1 – 中央                                                                                                                                                                              |  |

|                      | 6:0                | Pdiv2          | 01h                  | 7 ビット Y2 出力分周器 Pdiv2:<br>0 – リセットおよびスタンバイ<br>1 ~ 127 – 分周器の値                                                                                                                                                          |  |

| 17h                  | 7                  | —              | 0b                   | 予約済み。0 以外は書かないでください                                                                                                                                                                                                   |  |

|                      | 6:0                | Pdiv3          | 01h                  | 7 ビット Y3 出力分周器 Pdiv3:<br>0 – リセットおよびスタンバイ<br>1 ~ 127 – 分周器の値                                                                                                                                                          |  |

| 18h                  | 7:0                | PLL1_0N [11:4] | 004h                 | PLL1_0:周波数 $f_{VCO1\_0}$<br>の 30 ビット マルチプライヤ/分周器値 (詳細については、「PLL マルチプライヤ/分周器の定義」を参照)                                                                                                                                   |  |

| 19h                  | 7:4                | PLL1_0N [3:0]  |                      |                                                                                                                                                                                                                       |  |

|                      | 3:0                | PLL1_0R [8:5]  | 000h                 |                                                                                                                                                                                                                       |  |

| 1Ah                  | 7:3                | PLL1_0R[4:0]   |                      |                                                                                                                                                                                                                       |  |

|                      | 2:0                | PLL1_0Q [5:3]  | 10h                  |                                                                                                                                                                                                                       |  |

| 1Bh                  | 7:5                | PLL1_0Q [2:0]  |                      |                                                                                                                                                                                                                       |  |

|                      | 4:2                | PLL1_0P [2:0]  | 010b                 |                                                                                                                                                                                                                       |  |

|                      | 1:0                | VCO1_0_RANGE   | 00b                  | $f_{VCO1\_0}$ 範囲の選択:<br>00 – $f_{VCO1\_0} < 125\text{MHz}$<br>01 – $125\text{MHz} \leq f_{VCO1\_0} < 150\text{MHz}$<br>10 – $150\text{MHz} \leq f_{VCO1\_0} < 175\text{MHz}$<br>11 – $f_{VCO1\_0} \geq 175\text{MHz}$ |  |

| 1Ch                  | 7:0                | PLL1_1N [11:4] | 004h                 | PLL1_1:周波数 $f_{VCO1\_1}$<br>の 30 ビット マルチプライヤ/分周器値 (詳細については、「PLL マルチプライヤ/分周器の定義」の段落を参照)                                                                                                                                |  |

| 1Dh                  | 7:4                | PLL1_1N [3:0]  |                      |                                                                                                                                                                                                                       |  |

|                      | 3:0                | PLL1_1R [8:5]  | 000h                 |                                                                                                                                                                                                                       |  |

| 1Eh                  | 7:3                | PLL1_1R[4:0]   |                      |                                                                                                                                                                                                                       |  |

|                      | 2:0                | PLL1_1Q [5:3]  | 10h                  |                                                                                                                                                                                                                       |  |

| 1Fh                  | 7:5                | PLL1_1Q [2:0]  |                      |                                                                                                                                                                                                                       |  |

|                      | 4:2                | PLL1_1P [2:0]  | 010b                 |                                                                                                                                                                                                                       |  |

|                      | 1:0                | VCO1_1_RANGE   | 00b                  | $f_{VCO1\_1}$ 範囲の選択:<br>00 – $f_{VCO1\_1} < 125\text{MHz}$<br>01 – $125\text{MHz} \leq f_{VCO1\_1} < 150\text{MHz}$<br>10 – $150\text{MHz} \leq f_{VCO1\_1} < 175\text{MHz}$<br>11 – $f_{VCO1\_1} \geq 175\text{MHz}$ |  |

- (1) 50h を超えるデータを書き込むと、デバイスの機能に悪影響を及ぼす可能性があります。

- (2) すべてのデータは、MSB ファーストで転送されます。

- (3) カスタム設定を使用しない限り

- (4) ユーザーは、最大 8 つの異なる制御設定を事前定義できます。通常のデバイス動作では、外部制御ピン S0、S1、S2 によりこれらの設定を選択できます。

### 8.2.3 PLL2 構成レジスタ

**表 8-5. PLL2 構成レジスタ**

| オフセット <sup>(1)</sup> | ビット <sup>(2)</sup> | 略称           | デフォルト <sup>(3)</sup> | 説明                                                                                                                                                                                                                                                                                              |  |

|----------------------|--------------------|--------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 20h                  | 7:5                | SSC2_7 [2:0] | 000b                 | SSC2:PLL2 SSC の選択 (変調量) <sup>(4)</sup><br><br>ダウン<br>000 (オフ)<br>001 – 0.25%<br>010 – 0.5%<br>011 – 0.75%<br>100 – 1.0%<br>101 – 1.25%<br>110 – 1.5%<br>111 – 2.0%<br><br>センター<br>000 (オフ)<br>001 ± 0.25%<br>010 ± 0.5%<br>011 ± 0.75%<br>100 ± 1.0%<br>101 ± 1.25%<br>110 ± 1.5%<br>111 ± 2.0% |  |

|                      | 4:2                | SSC2_6 [2:0] | 000b                 |                                                                                                                                                                                                                                                                                                 |  |

|                      | 1:0                | SSC2_5 [2:1] | 000b                 |                                                                                                                                                                                                                                                                                                 |  |

|                      | 7                  | SSC2_5 [0]   | 000b                 |                                                                                                                                                                                                                                                                                                 |  |

|                      | 6:4                | SSC2_4 [2:0] |                      |                                                                                                                                                                                                                                                                                                 |  |

|                      | 3:1                | SSC2_3 [2:0] |                      |                                                                                                                                                                                                                                                                                                 |  |

|                      | 0                  | SSC2_2 [2]   |                      |                                                                                                                                                                                                                                                                                                 |  |

| 22h                  | 7:6                | SSC2_2 [1:0] | 000b                 |                                                                                                                                                                                                                                                                                                 |  |

|                      | 5:3                | SSC2_1 [2:0] |                      |                                                                                                                                                                                                                                                                                                 |  |

|                      | 2:0                | SSC2_0 [2:0] |                      |                                                                                                                                                                                                                                                                                                 |  |

**表 8-5. PLL2 構成レジスタ (続き)**

| オフセット <sup>(1)</sup> | ビット <sup>(2)</sup> | 略称             | デフォルト <sup>(3)</sup> | 説明                                                                                                                                                                            |

|----------------------|--------------------|----------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23h                  | 7                  | FS2_7          | 0b                   | FS2_x:PLL2 周波数選択 <sup>(4)</sup><br>0 – $f_{VCO2\_0}$ (PLL2_0 – 乗算器/分周器の値によって事前定義)<br>1 – $f_{VCO2\_1}$ (PLL2_1 – 乗算器/分周器の値によって事前定義)                                           |

|                      | 6                  | FS2_6          | 0b                   |                                                                                                                                                                               |

|                      | 5                  | FS2_5          | 0b                   |                                                                                                                                                                               |

|                      | 4                  | FS2_4          | 0b                   |                                                                                                                                                                               |

|                      | 3                  | FS2_3          | 0b                   |                                                                                                                                                                               |

|                      | 2                  | FS2_2          | 0b                   |                                                                                                                                                                               |

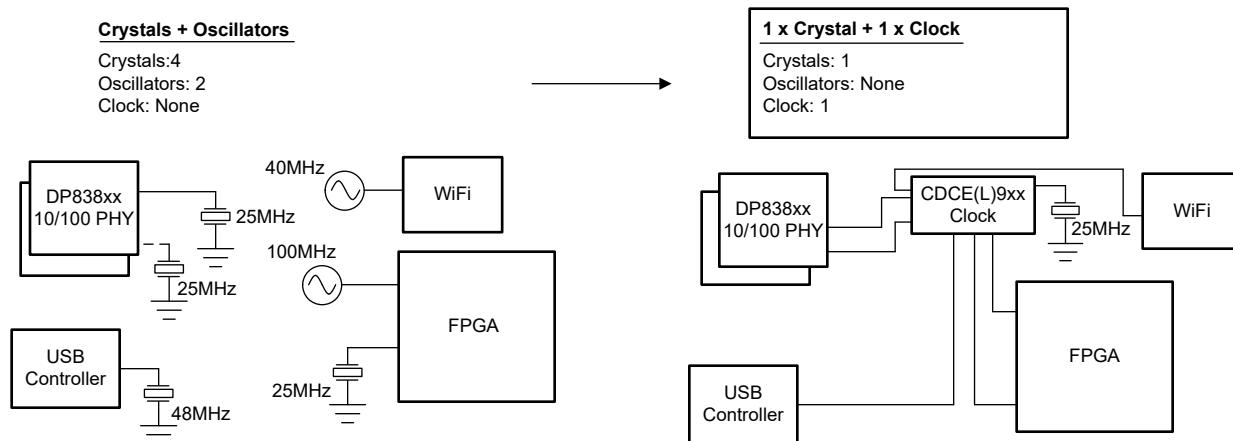

|                      | 1                  | FS2_1          | 0b                   |                                                                                                                                                                               |