# DAC39RF20 : 22GSPS、または44GSPS、16ビット、シングルおよびデュアルチャネル、マルチナイキストD/Aコンバータ(DAC)、JESD204Cインターフェイス付き

## 1 特長

- 16ビット、マルチナイキストD/Aコア

- DACサンプルレート:

- NRZ、RFモード: 22GSPS

- DES2xL、DES2xHモード: 44GSPS

- 最大入力データレート:

- 12ビット、デュアルチャネル: 21GSPS/Ch

- 16ビット、デュアルチャネル: 15.75GSPS/Ch

- 16ビット、シングルチャネル: 22GSPS

- 出力周波数範囲: 18GHz超

- $f_{OUT} = 10\text{GHz}$ 、DES2xLモードで高性能を発揮

- ノイズフロア(小信号): -170dBFS/Hz

- SFDR(-0.1dBFS): -55dBc

- IMD3(各トーン-7dBFS): -60dBc

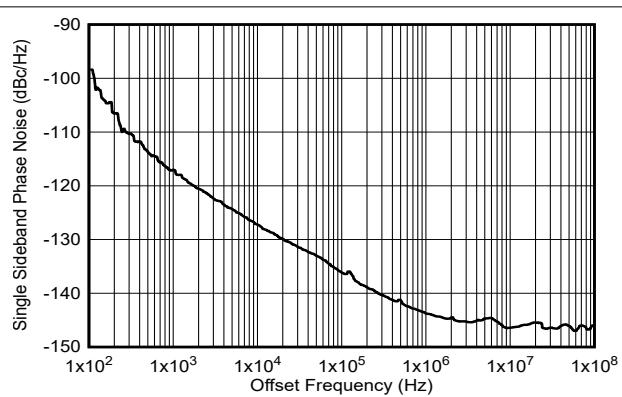

- 付加位相ノイズ、10kHzオフセット: -132dBc/Hz

- DACクロック生成のPLL/VCOオプション

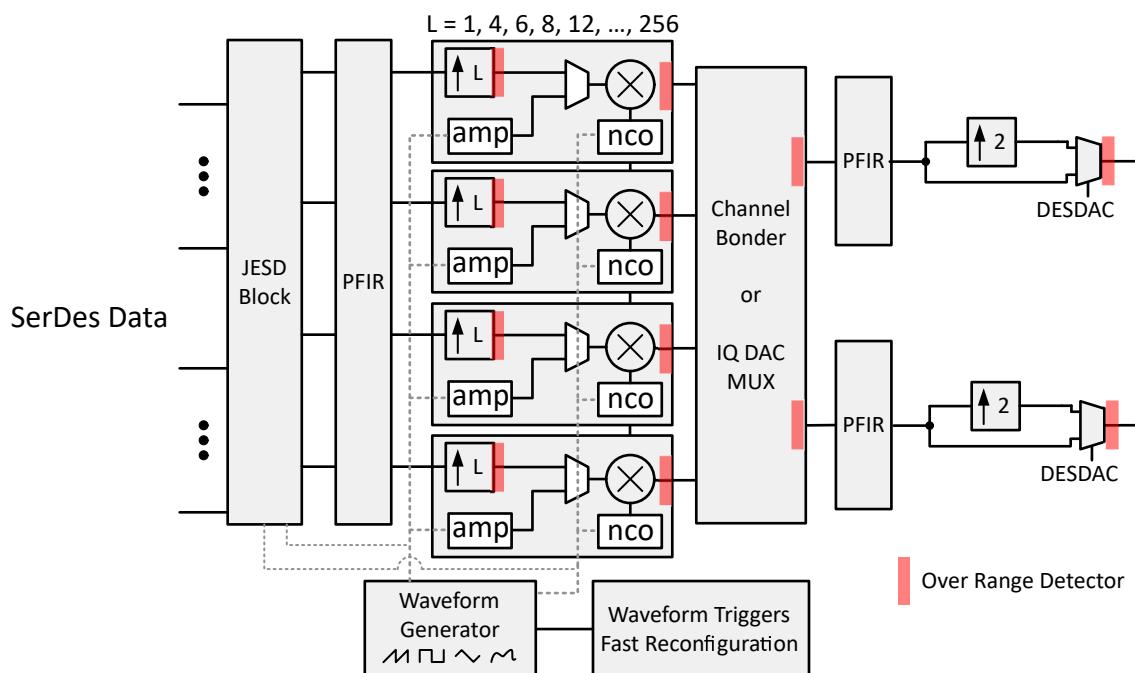

- 4つのデジタルアップコンバータ(DUC)を内蔵

- 補間: 1倍、4倍、6倍、8倍 ~ 256倍

- I/Q出力用の複素ベースバンドDUC

- ダイレクトRFサンプリングに適した、複素数から実数へのアップコンバージョン

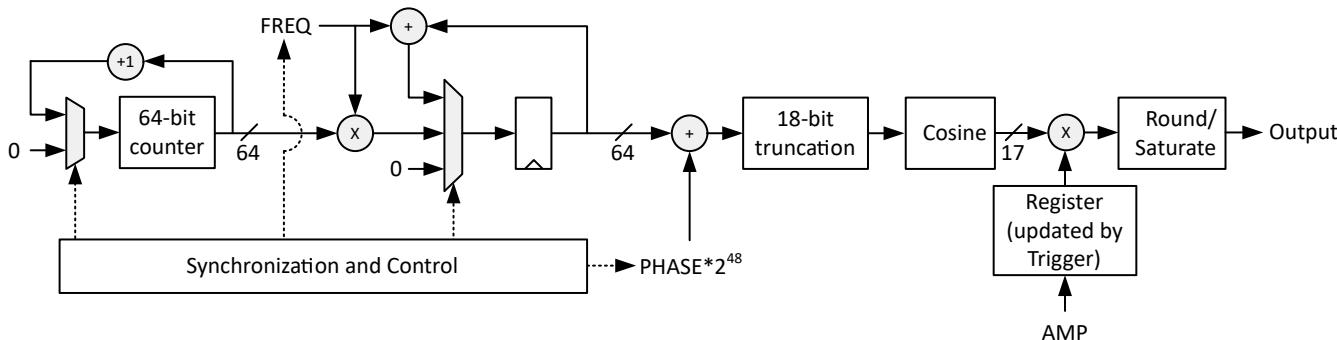

- 64ビットの周波数分解能NCO

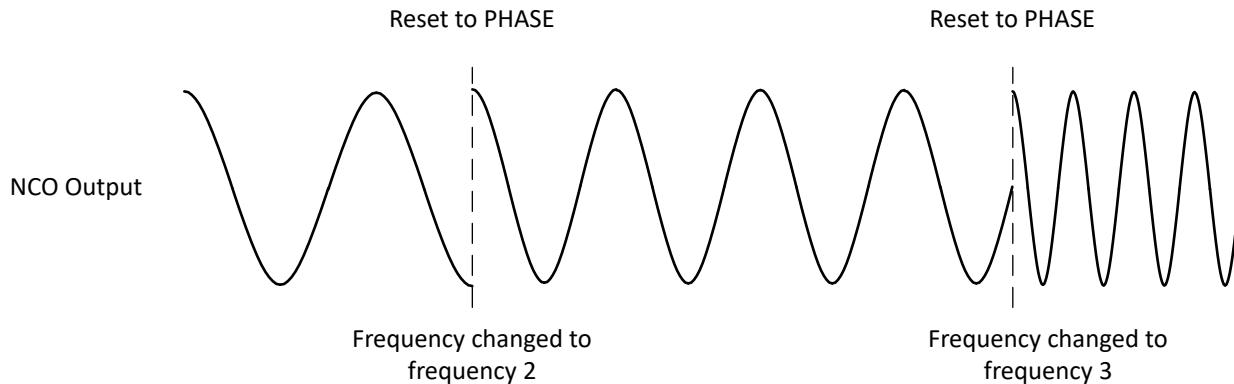

- 周波数ホッピングを使用した位相連続、同期、リセットの各オプション

- DUC入力またはDAC入力でのプログラマブルFIRイコライザ

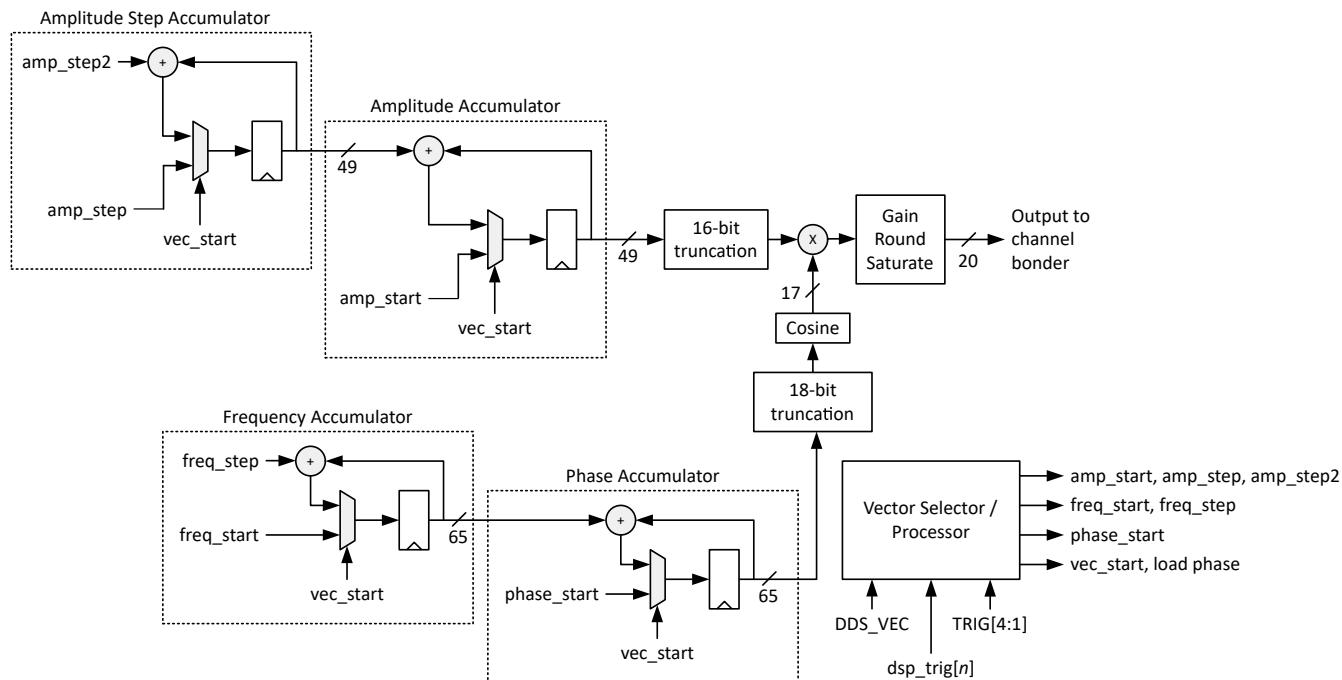

- 直接デジタル合成(DDS)

- 4つの区分線形波形ジェネレータ

- 16個の事前保存波形

- 合計256個のベクトル

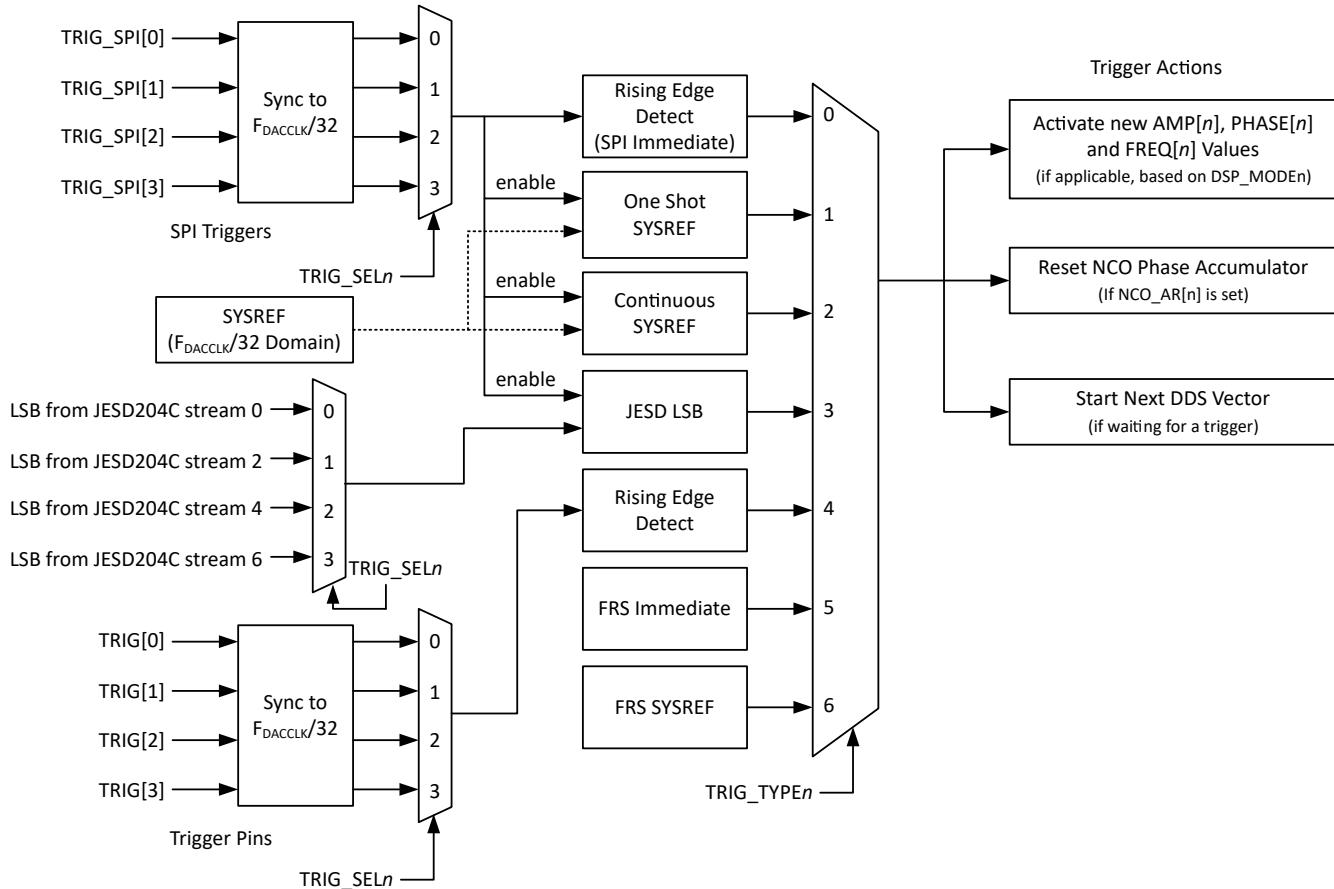

- 自動または同期の外部トリガ

- 周波数、振幅、位相インターフェイスストリーミング

- JESD204Cインターフェイス

- 最大32.5Gbpsで最大16レーン

- Class C-S、Subclass-1互換

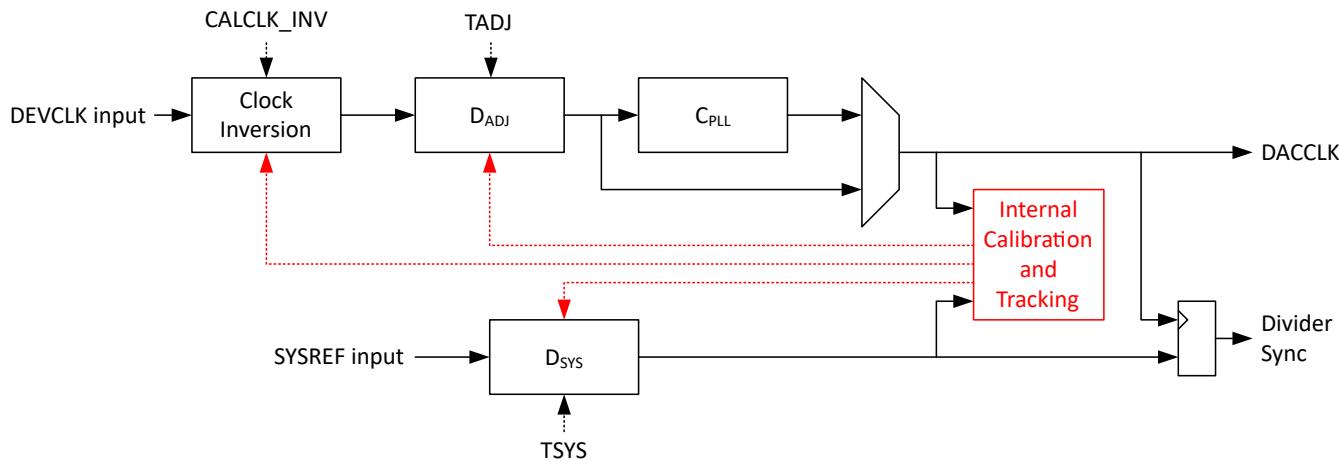

- クロックおよびSYSREF自動キャリブレーションおよびトラッキング

## 2 アプリケーション

- 衛星通信(SATCOM)

- フェーズドアレイアンテナシステム

- 合成開口レーダー(SAR)励振器

- ワイヤレス通信テスター

## • 任意波形ジェネレータ(AWG)

## 3 説明

DAC39RF20は、16ビット分解能のシングルおよびデュアルチャネルD/Aコンバータ(DAC)です。外部のフルレートクロックを使用する場合、これらのデバイスはシングルエッジサンプリングモード(NRZおよびRF)で22GSPS、デュアルエッジサンプリングモード(DES2XL、DES2XH)で44GSPSをサポートします。内部PLL/VCOを使用する場合、これらのデバイスはシングルエッジサンプリングモード(NRZおよびRF)で17GSPS、デュアルエッジサンプリングモード(DES2XL、DES2XH)で34GSPSをサポートします。これらのデバイスは、直接RFサンプリングまたは複素ベースバンド信号生成のいずれかに対して、非補間または補間D/Aとして使用できます。2つのチャネルの最大入力データレートは、21GSPS(12ビット分解能)または15.75GSPS(16ビット分解能)です。1つのチャネルの最大レートは、22GSPS(16ビット分解能)です。このデバイスは、10GHz帯域幅を超える信号を20GHzを超える周波数で生成でき、これにより、Ku帯域幅を介した直接サンプリングが可能になります。

## パッケージ情報

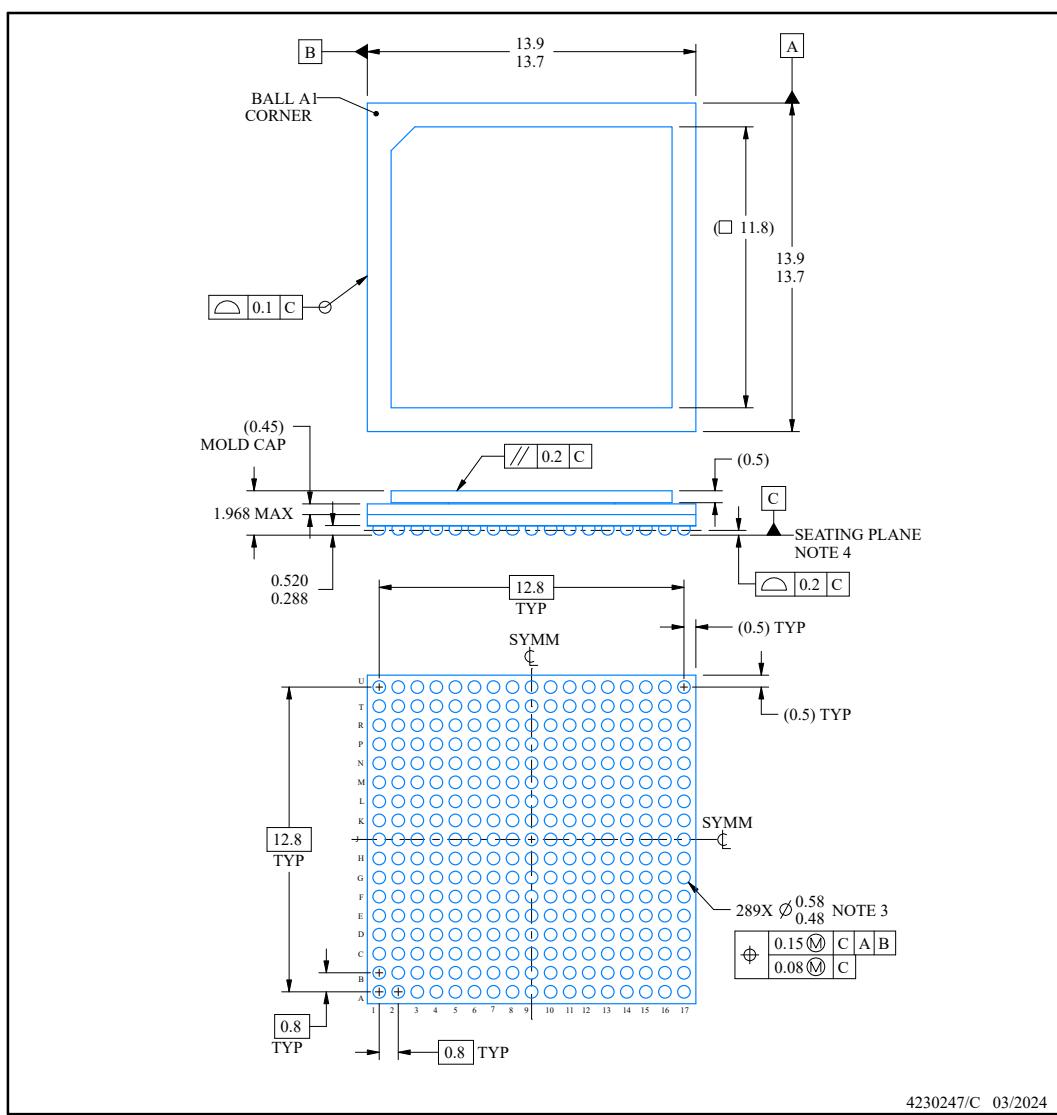

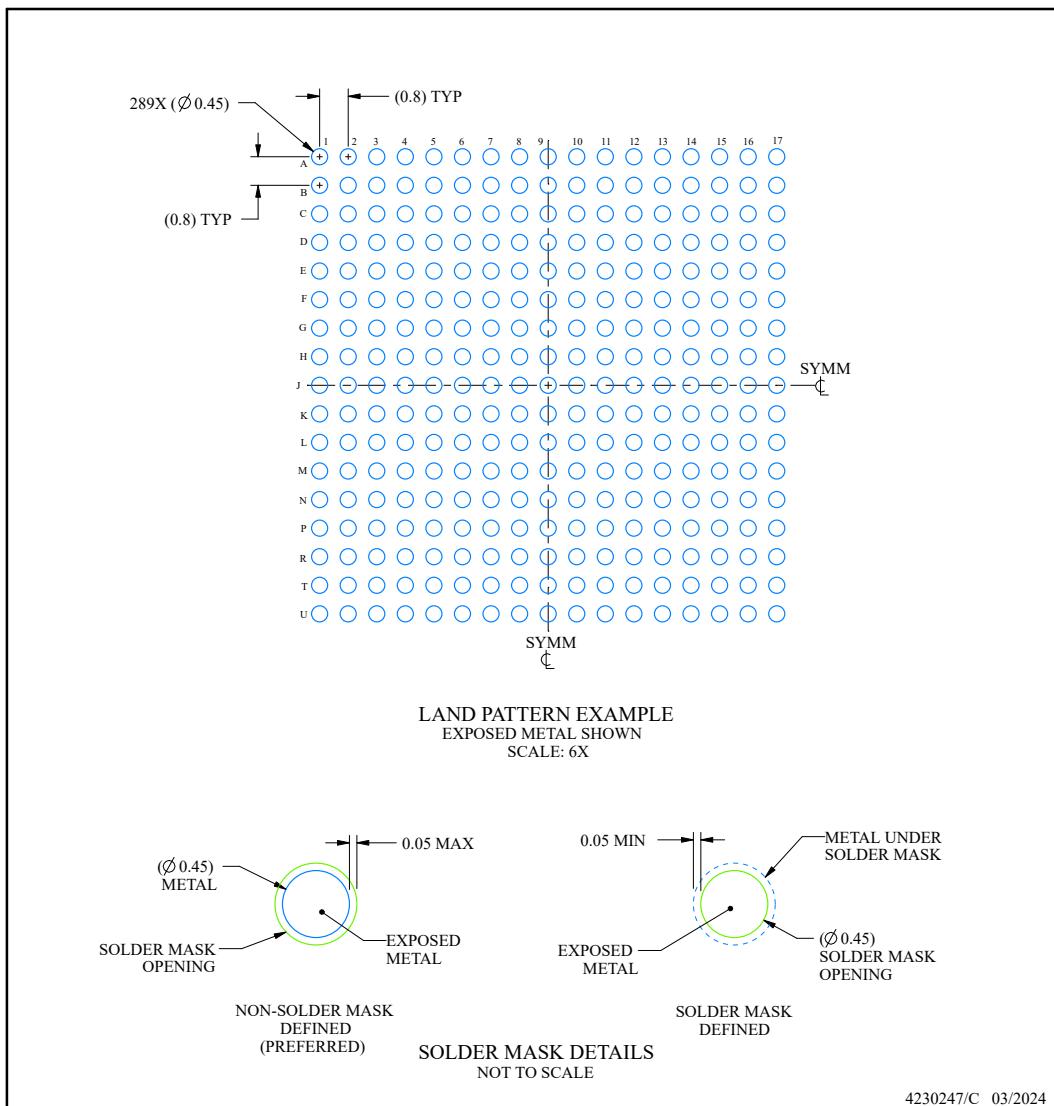

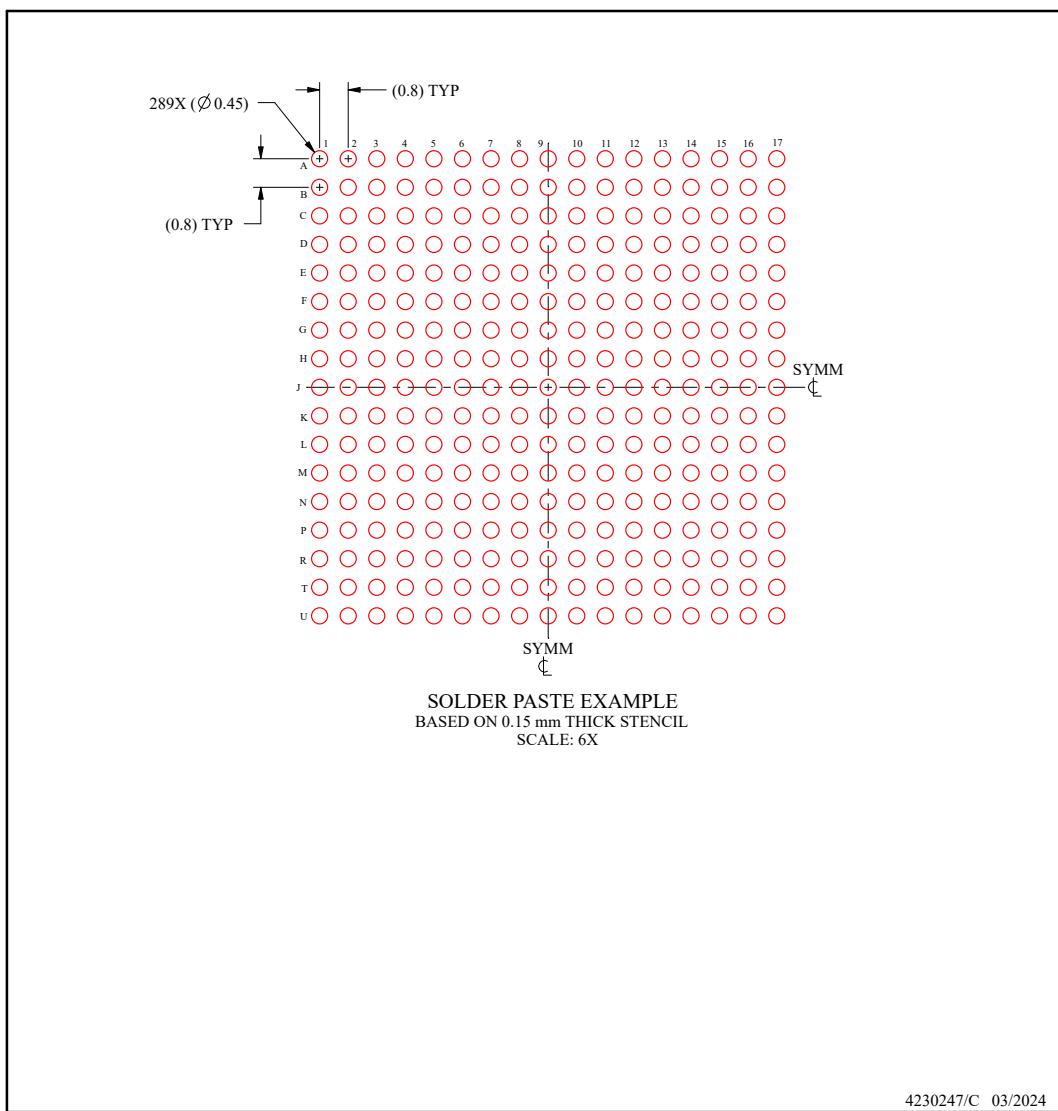

| 部品番号      | パッケージ <sup>(1)</sup> | パッケージサイズ <sup>(2)</sup>    |

|-----------|----------------------|----------------------------|

| DAC39RF20 | FCCSP(289ポール)        | 13.8mm × 13.8mm × 0.8mmピッチ |

(1) 詳細については、[セクション12](#)を参照してください。

(2) パッケージサイズ(長さ×幅)は公称値であり、該当する場合はピンを含みます。

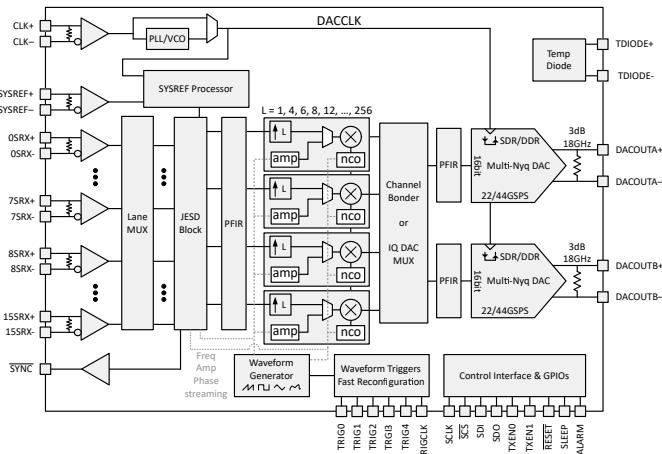

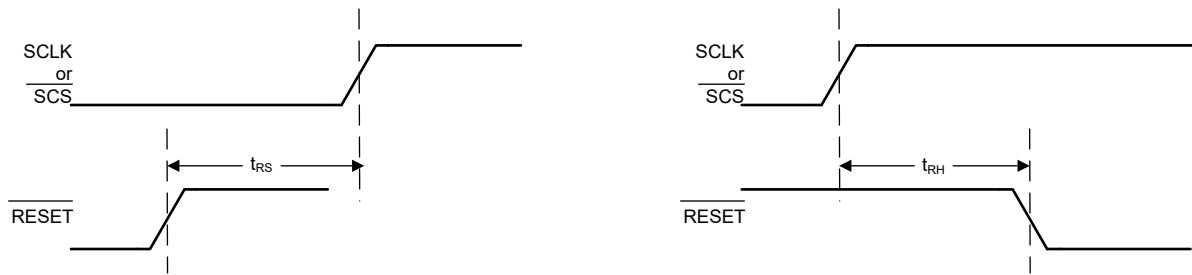

ブロック図

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール(機械翻訳)を使用していることがあり、TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.comで必ず最新の英語版をご参照くださいますようお願いいたします。

English Data Sheet: [SBASA08](#)

## 4 デバイスの比較

| 特長/仕様                                          |              | DAC39RF20 ジェネレーション 1                                         | DAC39RF2x ジェネレーション 2                                         |

|------------------------------------------------|--------------|--------------------------------------------------------------|--------------------------------------------------------------|

| PLL/VCO                                        | $F_{DACCLK}$ | $8.125\text{GHz} \leq F_{DACCLK} \leq 17\text{GHz}$          | $0.8\text{GHz} \leq F_{DACCLK} \leq 22\text{GHz}$            |

|                                                | PLL 出力分周器    | 1x のみ                                                        | 1、2、4、8 または 16x                                              |

|                                                | CPLL_MPY     | 8~99                                                         | 6~256                                                        |

|                                                | 位相ノイズ        |                                                              | $100\text{kHz} \leq F_{OFFSET} \leq 10\text{MHz}$ の間で 5dB 良好 |

|                                                | マルチデバイス同期    | なし                                                           | あり                                                           |

| $F_{DACCLK} < 10\text{GHz}$ の SYSREF Windowing |              | なし                                                           | あり                                                           |

| タイムスタンプ出力                                      |              | なし                                                           | あり                                                           |

| SPI 読み取り可能温度センサー                               |              | なし(温度ダイオード利用可能)                                              | あり                                                           |

| SerDes 信号検出器の喪失                                |              | なし                                                           | あり                                                           |

| 最大 SPI クロック周波数                                 |              | 15MHz                                                        | > 50MHz(ターゲット)                                               |

| DDS ストリーミングトリガー                                |              | AMP = 0                                                      | AMP = 0 および PHASE[0]= 1                                      |

| SOFT_RESET                                     |              | アドレス範囲 0x0080 から 0x00FE のレジスタを正しくクリアしていません。外部の RESET を使用します。 | 固定                                                           |

| HD2                                            |              |                                                              | 10 から 20dB まで改善されました                                         |

## 目次

|                            |     |                                          |     |

|----------------------------|-----|------------------------------------------|-----|

| <b>1 特長</b>                | 1   | 8.3 レジスタ マップ                             | 120 |

| <b>2 アプリケーション</b>          | 1   | 8.3.1 Standard_SPI-3.1 レジスタ              | 121 |

| <b>3 説明</b>                | 1   | 8.3.2 システム レジスタ                          | 124 |

| <b>4 デバイスの比較</b>           | 2   | 8.3.3 トリガ レジスタ                           | 132 |

| <b>5 ピン構成および機能</b>         | 4   | 8.3.4 CPLL_AND_CLOCK レジスタ                | 136 |

| <b>6 仕様</b>                | 9   | 8.3.5 SYSREF レジスタ                        | 140 |

| 6.1 絶対最大定格                 | 9   | 8.3.6 JESD204C のレジスタ                     | 146 |

| 6.2 ESD 定格                 | 9   | 8.3.7 JESD204C_Advanced のレジスタ            | 151 |

| 6.3 推奨動作条件                 | 10  | 8.3.8 SerDes_Equalizer レジスタ              | 181 |

| 6.4 熱に関する情報                | 10  | 8.3.9 SerDes_Eye-Scan レジスタ               | 189 |

| 6.5 電気的特性 - DC 仕様          | 11  | 8.3.10 SerDes_Lane_Status レジスタ           | 192 |

| 6.6 電気的特性 - AC 仕様          | 13  | 8.3.11 SerDes_PLL レジスタ                   | 194 |

| 6.7 電気的特性 - 消費電力           | 24  | 8.3.12 DAC_and_Analog_Configuration レジスタ | 196 |

| 6.8 タイミング要件                | 26  | 8.3.13 データバスレジスタ                         | 199 |

| 6.9 スイッチング特性               | 27  | 8.3.14 NCO_and_Mixer レジスタ                | 205 |

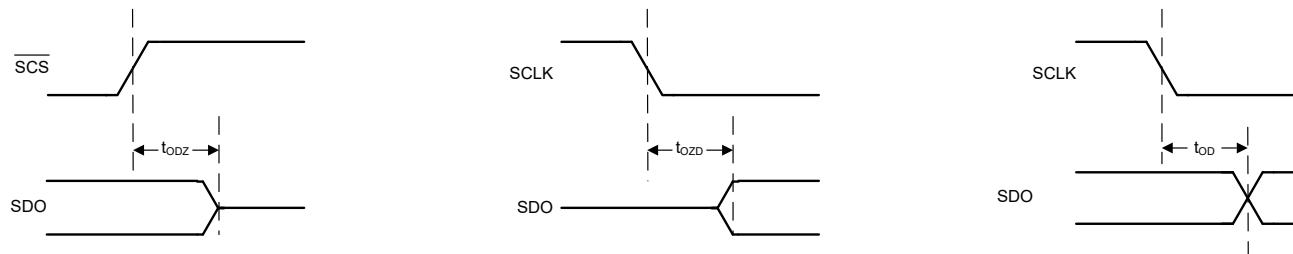

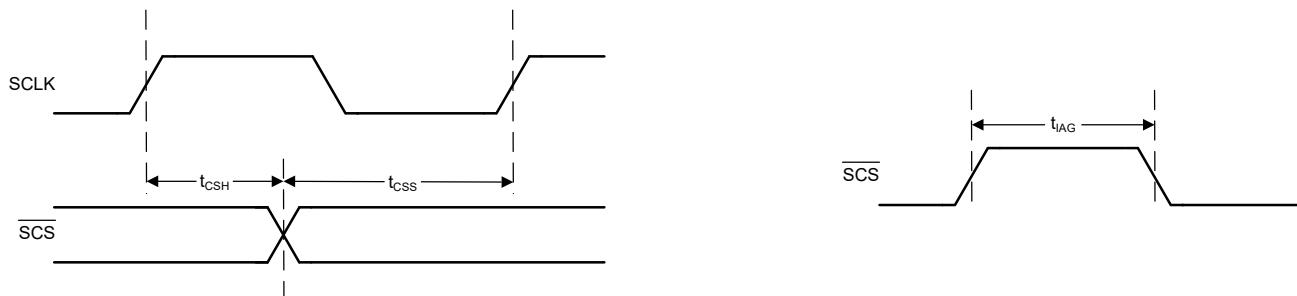

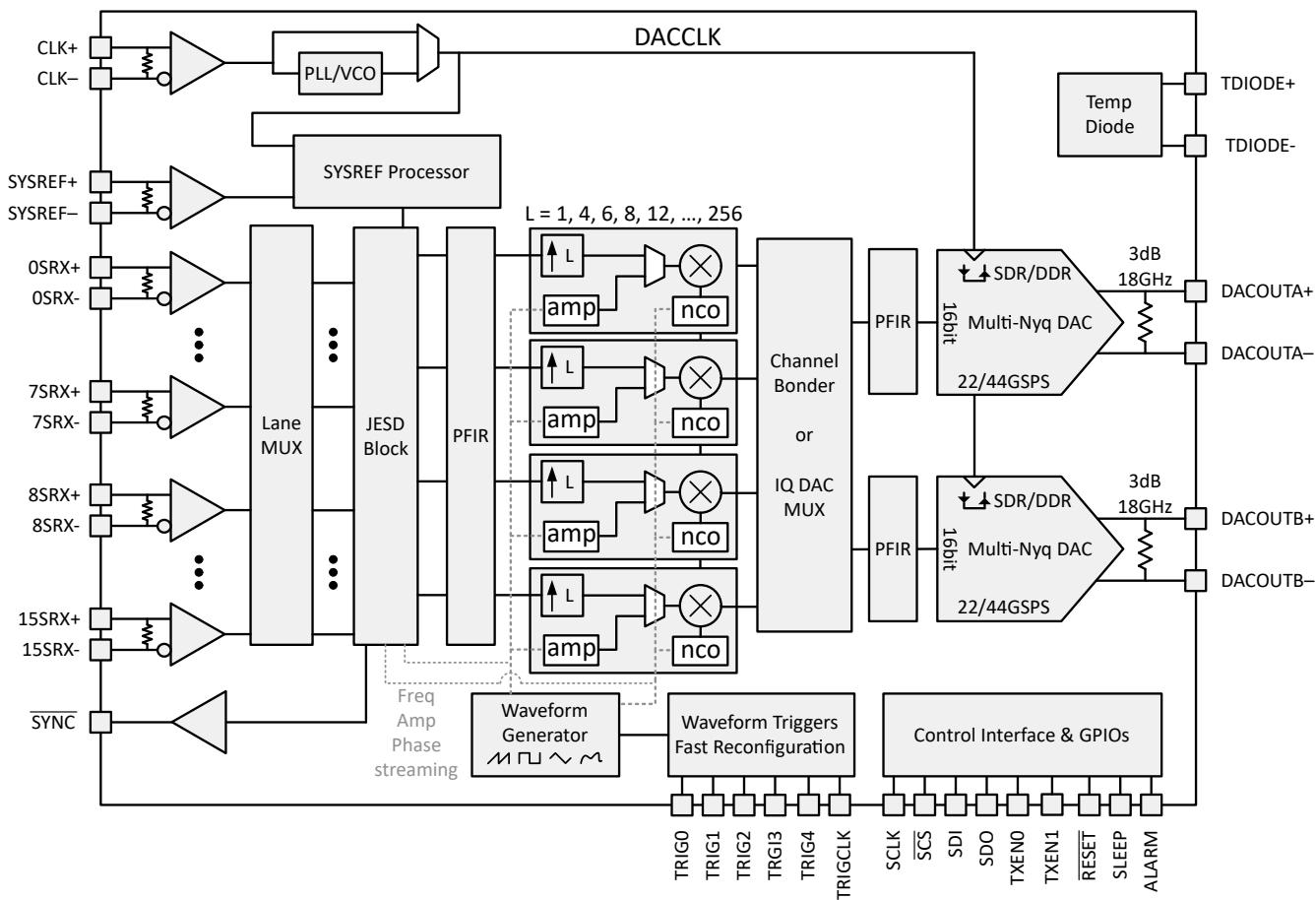

| 6.10 SPI インターフェイスのタイミング図   | 29  | 8.3.15 アラーム レジスタ                         | 218 |

| <b>7 詳細説明</b>              | 30  | 8.3.16 Fuse_Control レジスタ                 | 222 |

| 7.1 概要                     | 30  | 8.3.17 Fuse_Backed レジスタ                  | 223 |

| 7.2 機能ブロック図                | 31  | 8.3.18 DDS_Vector_Mode レジスタ              | 226 |

| 7.3 機能説明                   | 32  | 8.3.19 Programmable_FIR レジスタ             | 231 |

| 7.3.1 DAC 出力モード            | 32  | <b>9 アプリケーションと実装</b>                     | 235 |

| 7.3.2 DAC コア               | 35  | 9.1 アプリケーション情報                           | 235 |

| 7.3.3 DEM とディザリング          | 37  | 9.1.1 起動手順                               | 235 |

| 7.3.4 オフセット調整              | 38  | 9.1.2 矩形波モードの帯域幅最適化                      | 236 |

| 7.3.5 クロッキング サブシステム        | 38  | 9.2 代表的なアプリケーション: Ku バンド レーダー トラ         | 235 |

| 7.3.6 デジタル信号処理ブロック         | 41  | シスミッタ                                    | 237 |

| 7.3.7 Serdes 物理層           | 74  | 9.2.1 設計要件                               | 237 |

| 7.3.8 JESD204C インターフェイス    | 80  | 9.2.2 詳細な設計手順                            | 238 |

| 7.3.9 データバス レイテンシ          | 103 | 9.2.3 アプリケーション曲線                         | 238 |

| 7.3.10 複数デバイスの同期と決定論的レイテンシ | 105 | 9.3 電源に関する推奨事項                           | 240 |

| 7.3.11 リンクのリセット            | 110 | 9.3.1 パワーアップ / ダウン シーケンス                 | 242 |

| 7.3.12 アラーム生成              | 110 | 9.4 レイアウト                                | 242 |

| 7.3.13 ミュート機能              | 111 | 9.4.1 レイアウトのガイドラインと例                     | 242 |

| 7.4 デバイスの機能モード             | 113 | <b>10 デバイスおよびドキュメントのサポート</b>             | 250 |

| 7.4.1 電力モード                | 113 | 10.1 ドキュメントのサポート                         | 250 |

| <b>8 プログラミング</b>           | 116 | 10.1.1 関連資料                              | 250 |

| 8.1 標準 SPI インターフェイスを使用     | 116 | 10.2 ドキュメントの更新通知を受け取る方法                  | 250 |

| 8.1.1 SCS                  | 116 | 10.3 サポート・リソース                           | 250 |

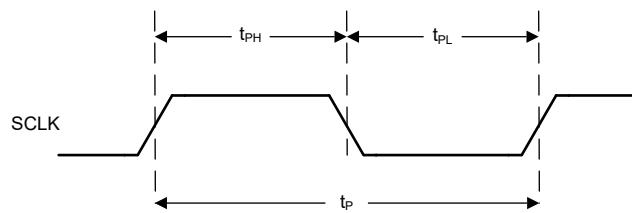

| 8.1.2 SCLK                 | 116 | 10.4 商標                                  | 250 |

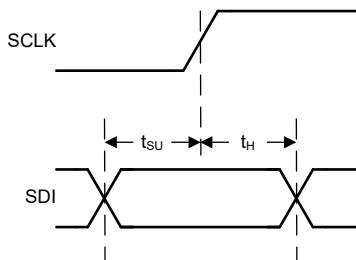

| 8.1.3 SDI                  | 116 | 10.5 静電気放電に関する注意事項                       | 250 |

| 8.1.4 SDO                  | 116 | 10.6 用語集                                 | 250 |

| 8.1.5 シリアル インターフェイス プロトコル  | 116 | <b>11 改訂履歴</b>                           | 250 |

| 8.1.6 ストリーミング モード          | 117 | <b>12 メカニカル、パッケージ、および注文情報</b>            | 250 |

| 8.2 高速再構成インターフェイスの使用       | 117 |                                          |     |

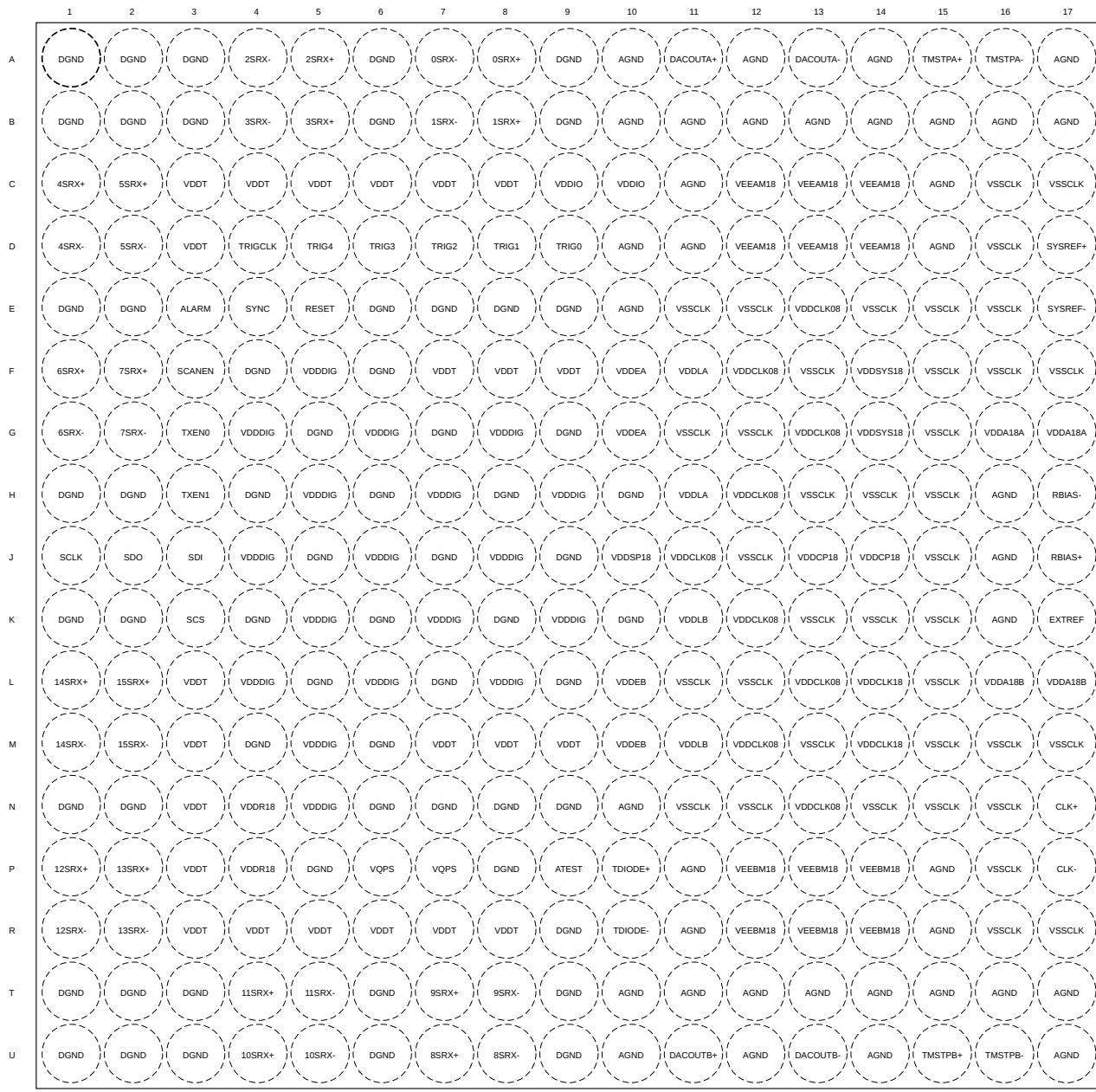

## 5 ピン構成および機能

図 5-1. ANH0289A パッケージ、289 ポールフリップチップ CSP、0.8mm ピッチ（上面図）

**表 5-1. ピンの機能**

| ピン                         |     | タイプ | 説明                                                                                                                                                                  |

|----------------------------|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称                         | なし  |     |                                                                                                                                                                     |

| <b>複数の DAC 出力</b>          |     |     |                                                                                                                                                                     |

| DACOUTA-                   | A13 | O   | DAC チャネル A アナログ出力 負端子。指定された性能を維持するために、出力電圧が DAC のコンプライアンス電圧に適合する必要があります。                                                                                            |

| DACOUTA+                   | A11 | O   | DAC チャネル A アナログ出力 正端子。指定された性能を維持するために、出力電圧が DAC のコンプライアンス電圧に適合する必要があります。                                                                                            |

| DACOUTB-                   | U13 | O   | DAC チャネル B アナログ出力 負端子。指定された性能を維持するために、出力電圧が DAC のコンプライアンス電圧に適合する必要があります。                                                                                            |

| DACOUTB+                   | U11 | O   | DAC チャネル B アナログ出力 正端子。指定された性能を維持するために、出力電圧が DAC のコンプライアンス電圧に適合する必要があります。                                                                                            |

| <b>差動クロックおよび SYSREF 入力</b> |     |     |                                                                                                                                                                     |

| CLK-                       | P17 | I   | デバイスクロック入力 負端子。CLK+ と CLK- の間には、100Ω の内部差動終端があります。この入力は自己バイアス形式であり、クロックソースと AC 結合する必要があります。                                                                         |

| CLK+                       | N17 | I   | デバイスクロック入力 正端子。CLK+ と CLK- の間には、100Ω の内部差動終端があります。この入力は自己バイアス形式であり、クロックソースと AC 結合する必要があります。                                                                         |

| SYSREF-                    | E17 | I   | 差動 JESD204C SYSREF 入力 負端子。SYSREF+ と SYSREF- の間には、100Ω の内部差動終端があります。この入力は、AC 結合されている場合、自己バイアスされます。DC 結合されている場合、入力の共通モード電圧は、 <b>推奨動作条件</b> の $V_{CMi}$ 仕様を満たす必要があります。 |

| SYSREF+                    | D17 | I   | 差動 JESD204C SYSREF 入力 負端子。SYSREF+ と SYSREF- の間には、100Ω の内部差動終端があります。                                                                                                 |

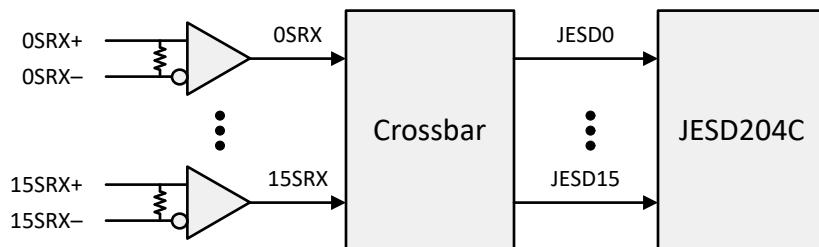

| <b>SerDes インターフェイス</b>     |     |     |                                                                                                                                                                     |

| 0SRX-                      | A7  | I   | Serdes レーン 0 負入力。0SRX+ への 100Ω の内部終端を含みます。                                                                                                                          |

| 0SRX+                      | A8  | I   | Serdes レーン 0 正入力。0SRX- への 100Ω 内部終端を含みます。                                                                                                                           |

| 1SRX-                      | B7  | I   | Serdes レーン 1 負入力。1SRX+ への 100Ω の内部終端を含みます。                                                                                                                          |

| 1SRX+                      | B8  | I   | Serdes レーン 1 正入力。1SRX- への 100Ω 内部終端を含みます。                                                                                                                           |

| 2SRX-                      | A4  | I   | Serdes レーン 2 負入力。2SRX+ への 100Ω の内部終端を含みます。                                                                                                                          |

| 2SRX+                      | A5  | I   | Serdes レーン 2 正入力。2SRX- への 100Ω 内部終端を含みます。                                                                                                                           |

| 3SRX-                      | B4  | I   | Serdes レーン 3 負入力。3SRX+ への 100Ω の内部終端を含みます。                                                                                                                          |

| 3SRX+                      | B5  | I   | Serdes レーン 3 正入力。3SRX- への 100Ω 内部終端を含みます。                                                                                                                           |

| 4SRX-                      | D1  | I   | Serdes レーン 4 負入力。4SRX+ への 100Ω の内部終端を含みます。                                                                                                                          |

| 4SRX+                      | C1  | I   | Serdes レーン 4 正入力。4SRX- への 100Ω 内部終端を含みます。                                                                                                                           |

| 5SRX-                      | D2  | I   | Serdes レーン 5 負入力。5SRX+ への 100Ω の内部終端を含みます。                                                                                                                          |

| 5SRX+                      | C2  | I   | Serdes レーン 5 正入力。5SRX- への 100Ω 内部終端を含みます。                                                                                                                           |

| 6SRX-                      | G1  | I   | Serdes レーン 6 負入力。6SRX+ への 100Ω の内部終端を含みます。                                                                                                                          |

| 6SRX+                      | F1  | I   | Serdes レーン 6 正入力。6SRX- への 100Ω 内部終端を含みます。                                                                                                                           |

| 7SRX-                      | G2  | I   | Serdes レーン 7 負入力。7SRX+ への 100Ω の内部終端を含みます。                                                                                                                          |

| 7SRX+                      | F2  | I   | Serdes レーン 7 正入力。7SRX- への 100Ω 内部終端を含みます。                                                                                                                           |

| 8SRX-                      | U8  | I   | Serdes レーン 8 負入力。8SRX+ への 100Ω の内部終端を含みます。                                                                                                                          |

| 8SRX+                      | U7  | I   | Serdes レーン 8 正入力。8SRX- への 100Ω 内部終端を含みます。                                                                                                                           |

| 9SRX-                      | T8  | I   | Serdes レーン 9 負入力。9SRX+ への 100Ω の内部終端を含みます。                                                                                                                          |

| 9SRX+                      | T7  | I   | Serdes レーン 9 正入力。9SRX- への 100Ω 内部終端を含みます。                                                                                                                           |

| 10SRX-                     | U5  | I   | Serdes レーン 10 負入力。10SRX+ への 100Ω の内部終端を含みます。                                                                                                                        |

| 10SRX+                     | U4  | I   | Serdes レーン 10 正入力。10SRX- への 100Ω 内部終端を含みます。                                                                                                                         |

| 11SRX-                     | T5  | I   | Serdes レーン 11 負入力。11SRX+ への 100Ω の内部終端を含みます。                                                                                                                        |

| 11SRX+                     | T4  | I   | Serdes レーン 11 正入力。11SRX- への 100Ω 内部終端を含みます。                                                                                                                         |

| 12SRX-                     | R1  | I   | Serdes レーン 12 負入力。12SRX+ への 100Ω の内部終端を含みます。                                                                                                                        |

| 12SRX+                     | P1  | I   | Serdes レーン 12 正入力。12SRX- への 100Ω 内部終端を含みます。                                                                                                                         |

| 13SRX-                     | R2  | I   | Serdes レーン 13 負入力。13SRX+ への 100Ω の内部終端を含みます。                                                                                                                        |

| 13SRX+                     | P2  | I   | Serdes レーン 13 正入力。13SRX- への 100Ω 内部終端を含みます。                                                                                                                         |

| 14SRX-                     | M1  | I   | Serdes レーン 14 負入力。14SRX+ への 100Ω の内部終端を含みます。                                                                                                                        |

表 5-1. ピンの機能 (続き)

| ピン                                                 |          | タイプ | 説明                                                                                          |

|----------------------------------------------------|----------|-----|---------------------------------------------------------------------------------------------|

| 名称                                                 | なし       |     |                                                                                             |

| 14SRX+                                             | L1       | I   | Serdes レーン 14 正入力。14SRX+ への 100Ω 内部終端を含みます。                                                 |

| 15SRX-                                             | M2       | I   | Serdes レーン 15 負入力。15SRX+ への 100Ω の内部終端を含みます。                                                |

| 15SRX+                                             | L2       | I   | Serdes レーン 15 正入力。15SRX- への 100Ω 内部終端を含みます。                                                 |

| <b>GPIO 機能</b>                                     |          |     |                                                                                             |

| ALARM                                              | E3       | O   | マスクされていない内部アラームが検出されると、ALARM ピンがアサートされます。アラームマスクは、ALM_MASK レジスタによってセットされます。プルアップまたはプルダウンなし。 |

| RESET                                              | E5       | I   | デバイスリセット入力、アクティブ「低」。電源を入れた後でトグルする必要があります。内部プルアップ。                                           |

| SCANEN                                             | F3       | I   | TI 専用、接続しなくともかまいません。内部プルダウン。                                                                |

| SCLK                                               | J1       | I   | シリアルプログラミングインターフェイス(SPI)クロック入力。プルアップまたはプルダウンなし。                                             |

| SCS                                                | K3       | I   | シリアルプログラミングインターフェイス(SPI)デバイス選択入力、「低」でアクティブ。内部プルアップ。                                         |

| SDI                                                | J3       | I   | シリアルプログラミングインターフェイス(SPI)データ入力。プルアップまたはプルダウンなし。                                              |

| SDO                                                | J2       | O   | シリアルプログラミングインターフェイス(SPI)データ出力。SPI データを読み出さないときは高インピーダンスになります。プルアップまたはプルダウンなし。               |

| SYNC                                               | E4       | I/O | JESD204C SYNC 出力、アクティブ「低」。入力として使用される場合はプルアップがアクティブ。                                         |

| TRIG0                                              | D9       | I   | インターフェイスボール 0 をトリガーします。FR インターフェースのデータ入力 0 としても使用されます。内部プルダウン。                              |

| TRIG1                                              | D8       | I   | インターフェイスボール 1 をトリガーします。FR インターフェースのデータ入力 1 としても使用されます。内部プルダウン。                              |

| TRIG2                                              | D7       | I   | インターフェイスボール 2 をトリガーします。FR インターフェースのデータ入力 2 としても使用されます。内部プルダウン。                              |

| TRIG3                                              | D6       | I   | インターフェイスボール 3 をトリガーします。FR インターフェースのデータ入力 3 としても使用されます。内部プルダウン。                              |

| TRIG4                                              | D5       | I   | インターフェイスボール 4 をトリガーします。FR インターフェイスのチップ選択入力としても使用されます。内部プルダウン。                               |

| TRIGCLK                                            | D4       | I/O | トリガーインターフェイスロック。FR インターフェイスの入力クロック、またはトリガーインターフェイスの出力クロックとして使用されます。内部プルダウン。                 |

| TXEN0                                              | G3       | I   | DAC 出力をミュートにする、または APP スリープに移行するためのピン制御(TX_EN_SEL を参照)。「送信の有効化」も参照してください。内部プルアップ。           |

| TXEN1                                              | H3       | I   | DAC 出力をミュートにする、または APP スリープに移行するためのピン制御(TX_EN_SEL を参照)。「送信の有効化」も参照してください。内部プルアップ。           |

| <b>アナログ機能</b>                                      |          |     |                                                                                             |

| ATEST                                              | P9       | O   | アナログテストピン。未使用時は、切断したままにできます。                                                                |

| EXTREF                                             | K17      | I/O | 基準電圧の出力または入力は、EXTREF_EN レジスタフィールドで設定されます。内部リファレンスを使用する場合、0.1μF を介して、ボールを AGND に接続する必要があります。 |

| RBIAS-                                             | H17      | O   | フルスケール出力電流バイアスは、この端子と RBIAS+ との間をつなぐレジスタによって設定されます。                                         |

| RBIAS+                                             | J17      | O   | フルスケール出力電流バイアスは、この端子と RBIAS- との間をつなぐレジスタによって設定されます。                                         |

| TDIODE+                                            | P10      | I   | 温度ダイオードの正端子(外部回路で検出される)                                                                     |

| TDIODE-                                            | R10      | I   | 温度ダイオードの負端子(外部回路で検出される)                                                                     |

| TMSTPA+                                            | A15      | O   | 予約済み。                                                                                       |

| TMSTPA -                                           | A16      | O   | 予約済み。                                                                                       |

| TMSTPB+                                            | U15      | O   | 予約済み。                                                                                       |

| TMSTPB -                                           | U16      | O   | 予約済み。                                                                                       |

| <b>電源</b>                                          |          |     |                                                                                             |

| <b>注</b>                                           |          |     |                                                                                             |

| 電源ピンごとに低 ESL 0.1μF デカップリングコンデンサを 1 つずつ使用することを推奨します |          |     |                                                                                             |

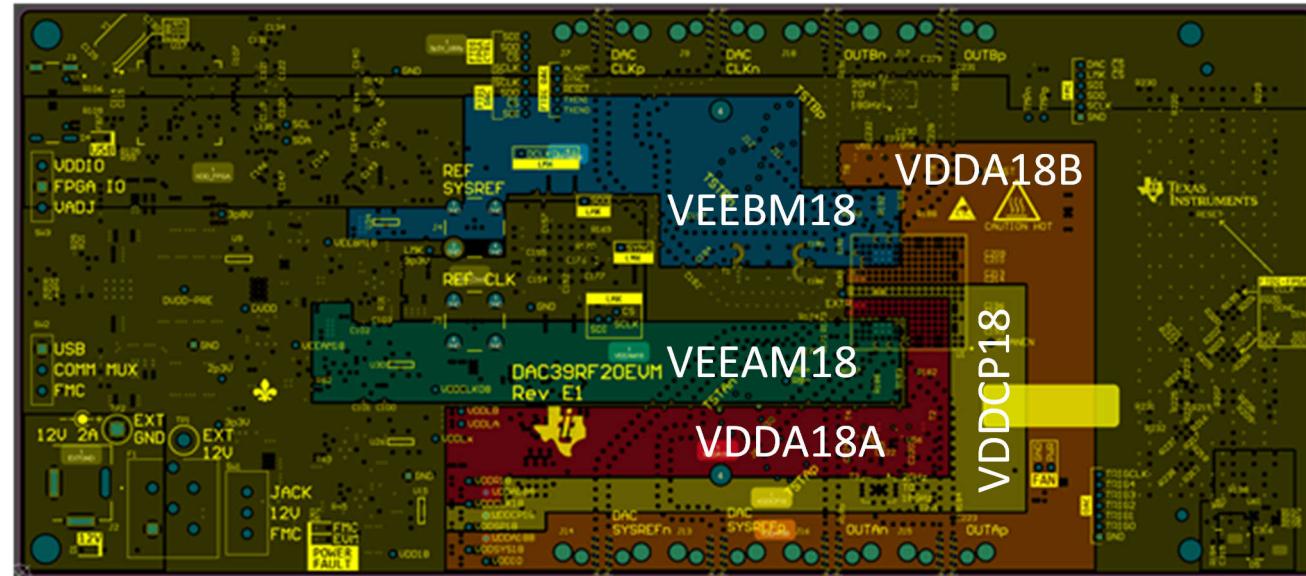

| VDDA18A                                            | G16, G17 | I   | DAC チャネル A の 1.8V 電源電圧。VDDA18B と組み合わせることができますですが、チャネル間クロストーク(XTALK)が低下する可能性があります。           |

| VDDA18B                                            | L16, L17 | I   | DAC チャネル B の 1.8V 電源電圧。VDDA18A と組み合わせることができますですが、チャネル間クロストーク(XTALK)が低下する可能性があります。           |

**表 5-1. ピンの機能 (続き)**

| ピン       |                                                                                                                                                                                                                                                  | タイプ | 説明                                                                                                                                                                          |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称       | なし                                                                                                                                                                                                                                               |     |                                                                                                                                                                             |

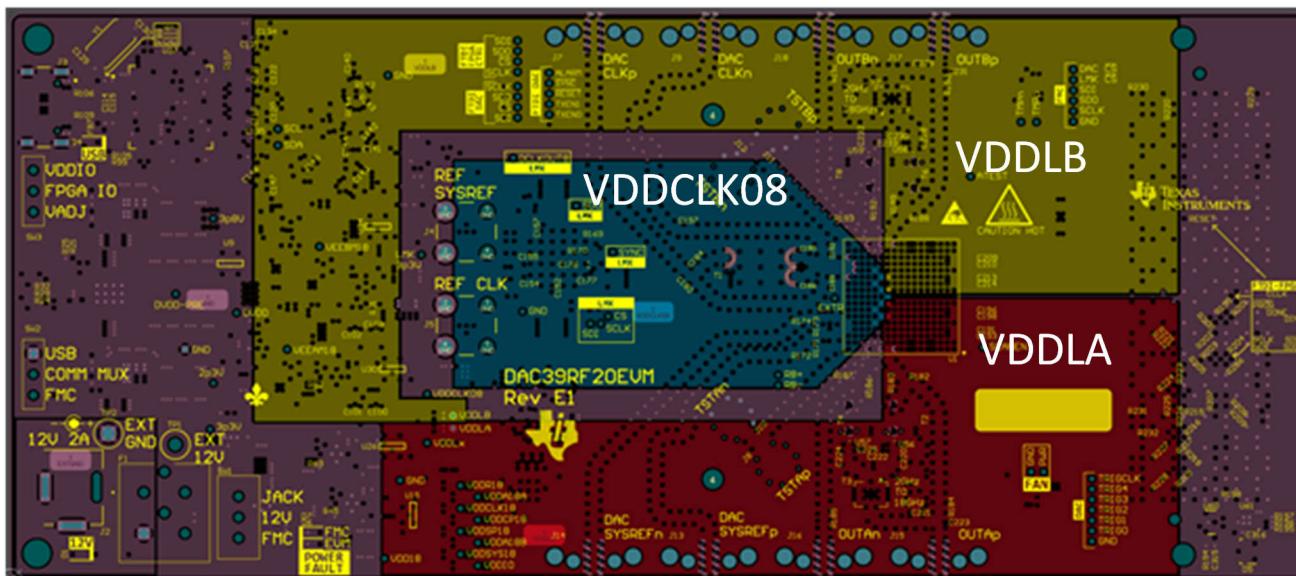

| VDDCLK08 | J11, F12, H12, K12, M12, E13, G13, L13, N13                                                                                                                                                                                                      | I   | 内部サンプリングクロック分配バスの電源電圧 0.8V。この電源でノイズやスパーズが発生すると、位相ノイズ性能 $j$ が低下する可能性があります。最高の性能を得るために、VDDDIG と VDDLA/B を分離することをお勧めします。                                                       |

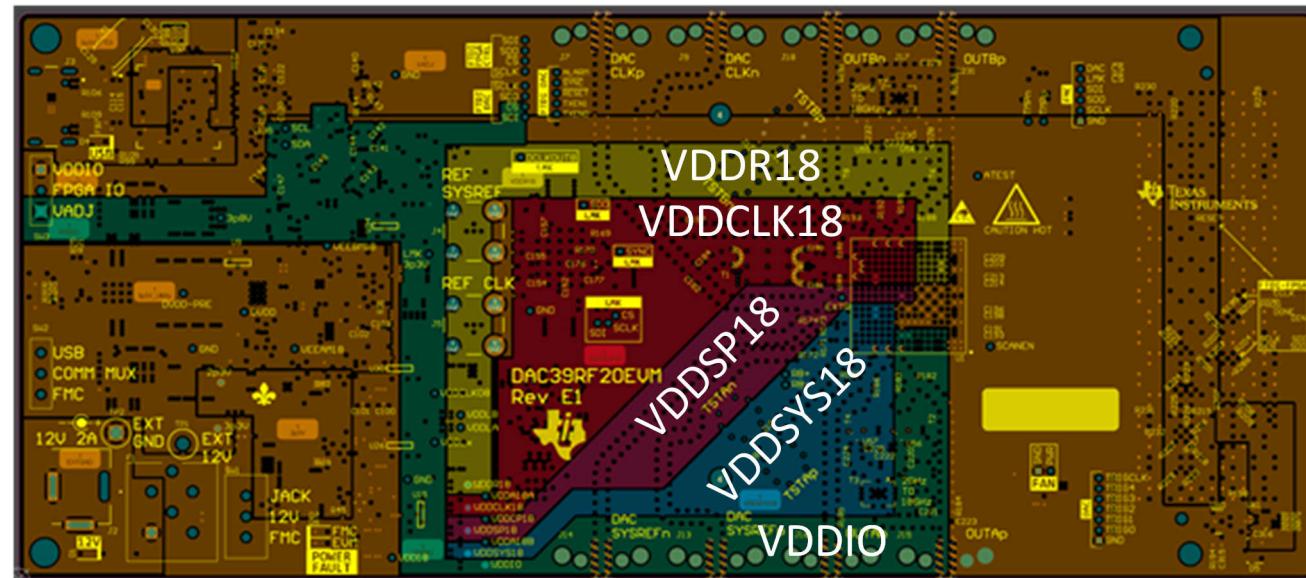

| VDDCLK18 | L14, M14                                                                                                                                                                                                                                         | I   | クロック(CLK+/-)入力バッファの 1.8V 電源電圧。この電源でノイズやスパーズが発生すると、位相ノイズ性能 $j$ が低下する可能性があります。                                                                                                |

| VDDCP18  | J13, J14                                                                                                                                                                                                                                         | I   | データコンバータ PLL 1.8V 電源。                                                                                                                                                       |

| VDDDIG   | G4, J4, L4, F5, H5, K5, M5, N5, G6, J6, L6, H7, K7, G8, J8, L8, H9, K9                                                                                                                                                                           | I   | デジタルブロック用 電源電圧 0.8V。最高の性能を得るために、VDDLA/B と VDDCLK を分離することをお勧めします。                                                                                                            |

| VDDEA    | F10, G10                                                                                                                                                                                                                                         | I   | チャネル A DAC エンコーダの電源電圧 0.8V。最高の性能を得るために、VDDDIG から分離することをお勧めします。VDDEB との組み合わせ可能。                                                                                              |

| VDDEB    | L10, M10                                                                                                                                                                                                                                         | I   | チャネル B DAC エンコーダの電源電圧 0.8V。最高の性能を得るために、VDDDIG から分離することをお勧めします。VDDEA との組み合わせ可能。                                                                                              |

| VDDIO    | C9, C10                                                                                                                                                                                                                                          | I   | CMOS 入力および出力端子用 1.8V 電源。                                                                                                                                                    |

| VDDLA    | F11, H11                                                                                                                                                                                                                                         | I   | チャネル A の DAC アナログラッチ用電源電圧 0.8V。最適なチャネル間クロストーク(XTALK)を得るために、VDDLB とは分離します。最高の性能を得るために、VDDDIG から分離する必要があります。                                                                  |

| VDDLB    | K11, M11                                                                                                                                                                                                                                         | I   | チャネル B の DAC アナログラッチ用電源電圧 0.8V。最適なチャネル間クロストーク(XTALK)を得るために、VDDLA とは分離します。最高の性能を得るために、VDDDIG から分離する必要があります。                                                                  |

| VDDR18   | N4, P4                                                                                                                                                                                                                                           | I   | SerDes レシーバ用 1.8V 電源電圧。                                                                                                                                                     |

| VDDSP18  | J10                                                                                                                                                                                                                                              | I   | SerDes PLL 1.8V 電源。                                                                                                                                                         |

| VDDSYS18 | F14, G14                                                                                                                                                                                                                                         | I   | SYSREF(SYSREF+/-)入力バッファの 1.8V 電源電圧。通常動作時に SYSREF が無効になっている場合、VDDCLK18 と組み合わせることができます。稼働中、SYSREF が連続的に動作する場合は、ノイズおよびスパーのカッピングや位相ノイズ性能の低下を回避するため、この電源を VDDCLK18 と分離する必要があります。 |

| VDDT     | C3, D3, L3, M3, N3, P3, R3, C4, R4, C5, R5, C6, R6, C7, F7, M7, R7, C8, F8, M8, R8, F9, M9                                                                                                                                                       | I   | SerDes 終端の電源電圧 0.8V。                                                                                                                                                        |

| VEEAM18  | C12, D12, C13, D13, C14, D14                                                                                                                                                                                                                     | I   | チャネル A の DAC 電流源バイアスの -1.8V 電源電圧。VEEBM18 と組み合わせることができます。チャネル間クロストーク(XTALK)の質が低下する可能性があります。                                                                                  |

| VEEBM18  | P12, R12, P13, R13, P14, R14                                                                                                                                                                                                                     | I   | チャネル B の DAC 電流源バイアスの -1.8V 電源電圧。VEEAM18 と組み合わせることができます。チャネル間クロストーク(XTALK)の質が低下する可能性があります。                                                                                  |

| VQPS     | P6, P7                                                                                                                                                                                                                                           | I   | TI 専用。通常動作時は DGND に接続できます。                                                                                                                                                  |

| グランド     |                                                                                                                                                                                                                                                  |     |                                                                                                                                                                             |

| AGND     | A10, B10, D10, E10, N10, T10, U10, B11, C11, D11, P11, R11, T11, B12, A12, T12, U12, B13, T13, A14, B14, T14, U14, B15, C15, D15, P15, R15, T15, B16, H16, J16, K16, T16, A17, B17, T17, U17                                                     | -   | アナログ グランド。                                                                                                                                                                  |

| DGND     | A1, B1, E1, H1, K1, N1, T1, U1, A2, B2, E2, H2, K2, N2, T2, U2, A3, B3, T3, U3, F4, H4, K4, M4, G5, J5, L5, P5, A6, B6, E6, F6, H6, K6, M6, N6, T6, U6, E7, G7, J7, L7, N7, E8, H8, K8, N8, P8, A9, B9, E9, G9, J9, L9, N9, R9, T9, U9, H10, K10 | -   | デジタル グランド。                                                                                                                                                                  |

表 5-1. ピンの機能 (続き)

| ピン     |                                                                                                                                                                                              | タイプ | 説明         |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------|

| 名称     | なし                                                                                                                                                                                           |     |            |

| VSSCLK | E11, G11, L11, N11, E12, G12, J12, L12, N12, F13, H13, K13, M13, E14, H14, K14, N14, E15, F15, G15, H15, J15, K15, L15, M15, N15, C16, D16, E16, F16, M16, N16, P16, R16, C17, F17, M17, R17 | -   | クロック グランド。 |

## 6 仕様

### 6.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

| パラメータ                                                                              | テスト条件                                                                             | 最小値  | 最大値           | 単位 |

|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|------|---------------|----|

| 電源電圧範囲                                                                             | 電源電圧範囲、VDDA18A、VDDA18B <sup>(2)</sup>                                             | -0.3 | 2.45          | V  |

|                                                                                    | 電源電圧範囲、VEEAM18、VEEBM18 <sup>(2)</sup>                                             | -2.0 | 0.3           | V  |

|                                                                                    | 入力電圧範囲、VDDCLK18、VDDSYS18、VDDSP18、VDDCP18 <sup>(3)</sup>                           | -0.3 | 2.45          | V  |

|                                                                                    | 電源電圧範囲、VDDLB、VDDLA、VDDCLK08 <sup>(3)</sup>                                        | -0.3 | 1.0           | V  |

|                                                                                    | 電源電圧範囲、VDDIO、VQPS、VDDR18 <sup>(4)</sup>                                           | -0.3 | 2.45          | V  |

|                                                                                    | 電源電圧範囲、VDDDIG、VDDEB、VDDEA、VDDT <sup>(4)</sup>                                     | -0.3 | 1.0           | V  |

| AGND、DGND、VSSCLK を任意に組み合わせた際の電圧                                                    | AGND、DGND、VSSCLK を任意に組み合わせた際の電圧                                                   | -0.1 | 0.1           | V  |

| 入力ピンに印加される電圧                                                                       | CLK+、CLK- <sup>(3)</sup>                                                          | -0.3 | VDDCLK18+0.3  | V  |

|                                                                                    | SYSREF+、SYSREF- <sup>(3)</sup>                                                    | -0.3 | VDDSYS18+0.3  |    |

|                                                                                    | [0:15]SRX-/+ <sup>(4)</sup>                                                       | -0.3 | VDDT + 0.2    |    |

|                                                                                    | SCLK、SCS、SDI、RESET、SYNC、SCANEN、TXEN[0:1]、FRDI[0:3]、FRCLK、FRCS、SYNC <sup>(4)</sup> | -0.3 | VDDIO+0.3     |    |

|                                                                                    | EXTREF <sup>(2)</sup>                                                             | -0.3 | VDDA18A + 0.3 |    |

| 出力ピンの電圧                                                                            | DACOUTA+、DACOUTA- <sup>(2)</sup>                                                  | -0.3 | VDDA18A + 0.5 | V  |

|                                                                                    | DACOUTB+、DACOUTB- <sup>(2)</sup>                                                  | -0.3 | VDDA18B + 0.5 |    |

|                                                                                    | ATEST <sup>(2)</sup>                                                              | -0.3 | VDDA18B + 0.3 |    |

|                                                                                    | RBIAS-/+ <sup>(2)</sup>                                                           | -0.3 | VDDA18A + 0.3 |    |

|                                                                                    | SDI、SDO、ALARM <sup>(4)</sup>                                                      | -0.3 | VDDIO + 0.3   |    |

| ピーク入力電流(任意の入力)                                                                     |                                                                                   | -20  | 20            | mA |

| ピーク合計入力電流(強制的に出入りする全電流の絶対値の合計、ただし電源電流、DACOUTA+、DACOUTA-、DACOUTB+ および DACOUTB- を除く) |                                                                                   |      | 30            | mA |

| 接合部温度、T <sub>J</sub>                                                               |                                                                                   |      | 150           | °C |

| 保管温度、T <sub>stg</sub>                                                              |                                                                                   | -65  | 150           | °C |

(1) 「絶対最大定格」を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これらはあくまでもストレス定格であり、**推奨動作条件**に示されている条件を超える当該の条件またはその他のいかなる条件下での、デバイスの正常な動作を保証するものではありません。絶対最大定格の状態が長時間続くと、デバイスの信頼性に影響を与える可能性があります。

(2) AGND に対して測定。

(3) VSSCLK に対して測定。

(4) DGND に対して測定。

### 6.2 ESD 定格

|                    |      | 値                                                                | 単位  |

|--------------------|------|------------------------------------------------------------------|-----|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 に準拠、すべてのピン <sup>(1)</sup>     | 500 |

|                    |      | デバイス帶電モデル (CDM)、ANSI/ESDA/JEDEC JS-002 に準拠、すべてのピン <sup>(2)</sup> | 250 |

(1) JEDEC ドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

(2) JEDEC ドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

## 6.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                    |                         |                                                                | 最小値   | 公称値                | 最大値   | 単位                    |

|--------------------|-------------------------|----------------------------------------------------------------|-------|--------------------|-------|-----------------------|

| 電源電圧範囲             |                         | VDDA18A、VDDA18B <sup>(1)</sup>                                 | 1.71  | 1.8                | 1.89  | V                     |

|                    |                         | VEEAM18、VEEBM18 <sup>(1)</sup>                                 | -1.89 | -1.8               | -1.71 | V                     |

|                    |                         | VDDCLK18、VDDSYS18、VDDSP18、VDDCP18 <sup>(2)</sup>               | 1.71  | 1.8                | 1.89  | V                     |

|                    |                         | VDDL8、VDDLA、VDDCLK08 <sup>(2)</sup>                            | 0.76  | 0.8                | 0.84  | V                     |

|                    |                         | VDDIO、VDDR18 <sup>(3)</sup>                                    | 1.71  | 1.8                | 1.89  | V                     |

|                    |                         | VQPS <sup>(3)</sup>                                            | 0     | 0                  | 1.89  | V                     |

| V <sub>CMI</sub>   | 入力同相電圧                  | VDDDIG、VDDEB、VDDEA、VDDT <sup>(3)</sup>                         | 0.76  | 0.8                | 0.84  | V                     |

|                    |                         | CLK+、CLK- <sup>(2) (4)</sup>                                   |       | 0.4                |       | V                     |

| V <sub>ID</sub>    | 入力作動ピークツーピーク電圧          | SYSREF+、SYSREF- <sup>(2) (4)</sup>                             |       | 0.4                | 0.5   | V                     |

|                    |                         | SYSREF+ から SYSREF -                                            | 400   | 1000               | 2000  | mV <sub>PP-DIFF</sub> |

|                    |                         | CLK+ から CLK- ～、f <sub>CLK</sub> < 3GHz <sup>(6)</sup>          | 800   | 1000               | 2000  | mV <sub>PP-DIFF</sub> |

|                    |                         | CLK+ から CLK- ～、3GHz < f <sub>CLK</sub> < 12GHz <sup>(6)</sup>  | 800   | 1000               | 1400  | mV <sub>PP-DIFF</sub> |

|                    |                         | CLK+ から CLK- ～、12GHz < f <sub>CLK</sub> < 17GHz <sup>(6)</sup> | 800   | 1000               | 1800  | mV <sub>PP-DIFF</sub> |

|                    |                         | CLK+ から CLK- ～、f <sub>CLK</sub> > 17GHz <sup>(6)</sup>         | 800   | 1000               | 2000  | mV <sub>PP-DIFF</sub> |

| DC <sub>MIN</sub>  | DACCLK+/- デューティサイクルの最小値 | CLK+/- デューティサイクルの最小値                                           |       | 45                 |       | %                     |

| DC <sub>MAX</sub>  | DACCLK+/- デューティサイクルの最大値 | CLK+/- デューティサイクルの最大値                                           |       | 55                 |       | %                     |

| T <sub>A</sub>     | 自由空気での動作温度              |                                                                | -40   | 85                 | °C    |                       |

| T <sub>J</sub>     | 推奨動作時接合部温度              |                                                                |       | 105 <sup>(5)</sup> | °C    |                       |

| T <sub>J-MAX</sub> | 動作時定格最大接合部温度            | 動作時定格最大接合部温度                                                   |       | 125                |       | °C                    |

(1) AGND に対して測定。

(2) VSSCLK に対して測定。

(3) DGND に対して測定。

(4) CLK+/- と SYSREF+/- は、最適な同相電圧へと弱く自己バイアスされます。CLK+/- は、常にクロックソースに AC 結合します。可能な場合は、SYSREF+/- をクロックソースに AC 結合することを推奨します。

(5) ダイは、T<sub>j</sub> = 150 °C での動作、および

T<sub>j</sub> = 113°C(100,000POH で 118°C)での最大 150,000POH の連続稼働によるデバイスおよびダイメタライゼーション劣化を想定して設計されています。T<sub>j</sub> = 105 °C の接合部温度を超えて長時間使用すると、パッケージの故障率(FIT)が上昇する可能性があります。

(6) 位相ノイズを最適化するには、クロック振幅を範囲の上限に近づける必要があります。

## 6.4 热に関する情報

| 熱評価基準 <sup>(1)</sup>  |                   | 13.8mm x 13.8mm FCCSP | 単位   |

|-----------------------|-------------------|-----------------------|------|

|                       |                   | 289 ピン                |      |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗      | 15.3                  | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース(上面)への熱抵抗 | 1.3                   | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗      | 4.3                   | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への特性パラメータ  | 0.5                   | °C/W |

| Ψ <sub>JB</sub>       | 接合部から基板への特性パラメータ  | 4.0                   | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション レポートを参照してください。

## 6.5 電気的特性 - DC 仕様

特に明記されていない限り、 $T_A = +25^\circ\text{C}$  での標準値、動作時接合部温度範囲における最小値および最大値、標準電源電圧、 $f_{\text{CLK}} = 22\text{GHz}$ 、外部クロックモード、 $I_{\text{FS\_SWITCH}} = 20\text{mA}$ 、シングルトーン振幅 =  $-0.1\text{dBFS}$ 、 $f_{\text{OUT}} = 2897\text{MHz}$ 、NRZ モード、ディザリングおよび DEM 有効、64b/66b エンコード。

| パラメータ                                                  |                     | テスト条件                                                                                                                                   | 最小値 | 標準値     | 最大値 | 単位                               |

|--------------------------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----|---------|-----|----------------------------------|

| <b>DC 精度</b>                                           |                     |                                                                                                                                         |     |         |     |                                  |

| ビット                                                    | DAC コア分解能           |                                                                                                                                         | 16  | 16      |     | ビット                              |

| DNL                                                    | 微分非直線性              |                                                                                                                                         |     | $\pm 4$ |     | LSB                              |

| INL                                                    | 積分非直線性              |                                                                                                                                         |     | $\pm 6$ |     | LSB                              |

| $R_{\text{TD}}_{\text{DRIFT}}$                         | 温度による内部終端抵抗ドリフト     |                                                                                                                                         |     | .02     |     | $\Omega/\text{^\circ C}$         |

| <b>DAC アナログ出力(DACOUTA+、DACOUTA-、DACOUTB+、DACOUTB-)</b> |                     |                                                                                                                                         |     |         |     |                                  |

| $I_{\text{FS\_SWITCH}}$                                | フルスケール出力電流を切り替えました  | RBIAS+ から RBIAS- への $3.6\text{k}\Omega$ の抵抗、COARSE_CUR_A / COARSE_CUR_B = 0xF および FINE_CUR_A / FINE_CUR_B = 0x10 (デフォルト)、Current_2x = 1 |     | 40      |     | mA                               |

| $I_{\text{FS\_SWITCH}}$                                | フルスケール出力電流を切り替えました  | RBIAS+ から RBIAS- への $3.6\text{k}\Omega$ の抵抗、COARSE_CUR_A / COARSE_CUR_B = 0xF および FINE_CUR_A / FINE_CUR_B = 0x10 (デフォルト)、Current_2x = 0 |     | 20      |     | mA                               |

|                                                        |                     | RBIAS+ から RBIAS- への $3.6\text{k}\Omega$ の抵抗、COARSE_CUR_A / COARSE_CUR_B = 0x0 および FINE_CUR_A / FINE_CUR_B = 0x10 (デフォルト)、Current_2x = 0 |     | 2       |     |                                  |

| $I_{\text{STATIC}}$                                    | ピンごとの静的出力電流         | RBIAS+ から RBIAS- への $3.6\text{k}\Omega$ の抵抗、COARSE_CUR_A / COARSE_CUR_B = 0xF および FINE_CUR_A / FINE_CUR_B = 0x10 (デフォルト)                |     | 4.7     |     | mA                               |

| $I_{\text{FSDRIFT}}$                                   | フルスケール出力電流の温度ドリフト   | RBIAS+ から RBIAS- への $3.6\text{k}\Omega$ の抵抗、COARSE_CUR_A / COARSE_CUR_B = 0xF および FINE_CUR_A / FINE_CUR_B = 0x10 (デフォルト)                |     | 1       |     | $\mu\text{A}/\text{^\circ C}$    |

|                                                        |                     |                                                                                                                                         |     | 65      |     | PPM/ $^\circ\text{C}$            |

| $I_{\text{FSERROR}}$                                   | フルスケール 電流誤差         | RBIAS+ から RBIAS- への $3.6\text{k}\Omega$ の抵抗、COARSE_CUR_A / COARSE_CUR_B = 0xF および FINE_CUR_A / FINE_CUR_B = 0x10 (デフォルト)                |     | $\pm 1$ |     | %                                |

| $V_{\text{COMP}}$                                      | 出力コンプライアンス電圧範囲      | DACOUTA+、DACOUTA-、DACOUTB+、DACOUTB- から AGND の間で測定                                                                                       | 1.3 | 2.3     |     | V                                |

| $R_{\text{TERM}}$                                      | 出力差動終端抵抗            |                                                                                                                                         | 100 |         |     | $\Omega$                         |

| $R_{\text{TERMDRIFT}}$                                 | 出力差動終端抵抗温度係数        |                                                                                                                                         | -5  |         |     | $\text{m}\Omega/\text{^\circ C}$ |

|                                                        |                     |                                                                                                                                         | -50 |         |     | PPM/ $^\circ\text{C}$            |

| <b>クロックと SYSREF 入力(CLK+、CLK-、SYSREF+、SYSREF-)</b>      |                     |                                                                                                                                         |     |         |     |                                  |

| $R_{\text{T}}$                                         | 内部差動終端抵抗            |                                                                                                                                         | 100 |         |     | $\Omega$                         |

| $C_{\text{IN}}$                                        | 内部差動入力容量            |                                                                                                                                         | 0.5 |         |     | $\text{pF}$                      |

| <b>基準電圧</b>                                            |                     |                                                                                                                                         |     |         |     |                                  |

| $V_{\text{REF}}$                                       | リファレンス出力電圧          |                                                                                                                                         | 0.9 |         |     | V                                |

| $V_{\text{REF-DRIFT}}$                                 | 温度によるリファレンス出力電圧ドリフト |                                                                                                                                         | 45  |         |     | $\text{ppm}/\text{^\circ C}$     |

## 6.5 電気的特性 - DC 仕様 (続き)

特に明記されていない限り、 $T_A = +25^\circ\text{C}$  での標準値、動作時接合部温度範囲における最小値および最大値、標準電源電圧、 $f_{\text{CLK}} = 22\text{GHz}$ 、外部クロックモード、 $I_{\text{FS\_SWITCH}} = 20\text{mA}$ 、シングルトーン振幅 = -0.1dBFS、 $f_{\text{OUT}} = 2897\text{MHz}$ 、NRZ モード、ディザリングおよび DEM 有効、64b/66b エンコード。

| パラメータ                                                                             |                               | テスト条件                                                                                                                                                                | 最小値           | 標準値           | 最大値         | 単位            |

|-----------------------------------------------------------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------|-------------|---------------|

| $I_{\text{REF}}$                                                                  |                               | リファレンス出力電流の最大供給量                                                                                                                                                     | 100           |               | nA          |               |

| <b>JESD204C SERDES インターフェイス([15:0]SRX+/-)</b>                                     |                               |                                                                                                                                                                      |               |               |             |               |

| $V_{\text{SRDIFF}}$                                                               | SerDes レシーバ入力振幅               |                                                                                                                                                                      | 50            | 1200          |             | mVppdiff      |

| $V_{\text{SRCOM}}$                                                                | SerDes 入力標準モード <sup>(2)</sup> |                                                                                                                                                                      |               | 450           |             | mV            |

| $Z_{\text{SRdiff}}$                                                               | SerDes 内部差動終端                 |                                                                                                                                                                      | 80            | 100           | 120         | $\Omega$      |

| <b>CMOS インターフェイス(SCLK、SCS、SDI、SDO、RESET、TRIG[0:4]、TRIGCLK、SYNC、TXENABLE[0:1])</b> |                               |                                                                                                                                                                      |               |               |             |               |

| $I_{\text{IH}}$                                                                   | High レベル入力電流(プルダウン付き)         | TRIG[0..4] <sup>(3)</sup> 、TRIGCLK <sup>(3)</sup> 、SCANEN <sup>(1)</sup>                                                                                             |               | 200           |             | $\mu\text{A}$ |

| $I_{\text{IH}}$                                                                   | High レベル入力電流(プルダウンなし)         | SDS、RESET、SYNC、TXEN[0:1]、SDI、SCLK <sup>(1)</sup>                                                                                                                     |               |               | 2           | $\mu\text{A}$ |

| $I_{\text{IL}}$                                                                   | Low レベル入力電圧(プルダウン付き)          | SDS、RESET、SYNC、TXEN[0:1] <sup>(1)</sup>                                                                                                                              | -100          |               |             | $\mu\text{A}$ |

| $I_{\text{IL}}$                                                                   | Low レベル入力電圧(プルダウンなし)          | SCANEN、SDI、SCLK <sup>(1)</sup>                                                                                                                                       | -20           |               |             | $\mu\text{A}$ |

| $C_{\text{I}}$                                                                    | 入力容量                          | 入力容量                                                                                                                                                                 | 3             |               | $\text{pF}$ |               |

| $V_{\text{IH}}$                                                                   | High レベル入力電圧                  | SCLK、SCS、SDI、RESET、SCANEN、TXEN[0:1]、SYNC、TRIG[0..4]、TRIGCLK                                                                                                          | 0.7 x VDDIO18 |               |             | V             |

| $V_{\text{IL}}$                                                                   | Low レベル入力電圧                   |                                                                                                                                                                      |               | 0.3 x VDDIO18 |             | V             |

| $V_{\text{OH}}$                                                                   | High レベル出力電圧                  | $I_{\text{LOAD}} = -400\text{uA}$                                                                                                                                    | 1.55          |               |             | V             |

| $V_{\text{OL}}$                                                                   | Low レベル出力電圧                   | $I_{\text{LOAD}} = 400\text{uA}$                                                                                                                                     |               | 0.2           |             | V             |

| <b>温度ダイオードの特性(TDIODE+、TDIODE-)</b>                                                |                               |                                                                                                                                                                      |               |               |             |               |

| $\Delta V_{\text{BE}}$                                                            | 温度ダイオードの電圧スロープ                | 100 $\mu\text{A}$ の強制順方向電流。オフセット電圧 ( $0^\circ\text{C}$ で約 0.792V) はプロセスによって異なるため、各部品ごとに測定する必要があります。デバイスの自己発熱を最小限に抑えるため、デバイスの電源をオフにするか、PD ピンをアサートしてオフセット測定を行う必要があります。 |               | -1.45         |             | mV/°C         |

- (1) 接続デバイスに IO 電源電圧オフセットはありません。

- (2) Serdes トランスマッタからの AC 結合を推奨します。

- (3) TRIG[0..3] および TRIGCLK は入力として使用する場合、プルダウンがあります。出力として使用される場合、プルダウンは無効になります。

## 6.6 電気的特性 - AC 仕様

特に明記されていない限り、 $T_A = +25^\circ\text{C}$  での標準値、動作時接合部温度範囲における最小値および最大値、標準電源電圧、 $f_{\text{CLK}} = 22\text{GHz}$  (外部クロックモード)、 $I_{\text{FS\_SWITCH}} = 20\text{mA}$ 、シングルトーン振幅 = -0.1dBFS、ディザリングおよび DEM 有効、64b/66b エンコード。

| パラメータ                        |                                                                                                              | テスト条件                                                          | 最小値 | 標準値 | 最大値 | 単位  |

|------------------------------|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-----|-----|-----|-----|

| モード別パラメータ                    |                                                                                                              |                                                                |     |     |     |     |

| $f_{\text{DACCLK}}$          | NRZ の DAC クロックレート<br>= $f_{\text{SAMPLE}}$ 、および DES2XL/H モードの RF モード<br>= $f_{\text{SAMPLE}}/2$              |                                                                |     | 22  |     | GHz |

| BW                           | アナログ出力帯域幅 (-3dB)                                                                                             | $\sin x/x$ 応答を除く。使用可能な周波数範囲は、-3dB ポイントを超える可能性があります。            |     | 18  |     | GHz |

| クロストーク                       | チャネル A (DACOUTA+/-) とチャネル B (DACOUTB+/-) の間の絶縁、被害チャネルの $f_{\text{OUT}} = -25\text{MHz}$ オフセット、デュアルチャネルデバイス限定 | $f_{\text{OUT}} = 97\text{MHz}$ 、NRZ モード                       | 90  |     |     | dBc |

|                              |                                                                                                              | $f_{\text{OUT}} = 2897\text{MHz}$ 、NRZ モード                     | 75  |     |     | dBc |

|                              |                                                                                                              | $f_{\text{OUT}} = 5897\text{MHz}$ 、NRZ モード                     | 70  |     |     | dBc |

|                              |                                                                                                              | $f_{\text{OUT}} = 8897\text{MHz}$ 、NRZ モード                     | 66  |     |     | dBc |

|                              |                                                                                                              | $f_{\text{OUT}} = 13103\text{MHz}$ 、RF モード                     | 60  |     |     | dBc |

|                              |                                                                                                              | $f_{\text{OUT}} = 16103\text{MHz}$ 、RF モード                     | 55  |     |     | dBc |

|                              |                                                                                                              | $f_{\text{OUT}} = 19103\text{MHz}$ 、RF モード                     | 50  |     |     | dBc |

| DAC 出力時間ドメインの特性              |                                                                                                              |                                                                |     |     |     |     |

| $t_{\text{RISE}}$            | 10% から 90% <sup>(1)</sup>                                                                                    | JMODE 0、1x 補間                                                  | 18  |     |     | ps  |

| $t_{\text{FALL}}$            | 90% から 10% <sup>(1)</sup>                                                                                    | JMODE 0、1x 補間                                                  | 18  |     |     | ps  |

| $f_{\text{CLK}}$ 固定スプリアス     | 1GHz のフルスケールのサイン波と比較                                                                                         | NRZ モード、 $f_{\text{OUT}} = \text{DC}$ (中間コード)、DEM/ディザリング オフ    | 50  |     |     | dBc |

|                              |                                                                                                              | NRZ モード、 $f_{\text{OUT}} = \text{DC}$ (中間コード)、DEM/ディザリング オン    | 50  |     |     | dBc |

|                              |                                                                                                              | DES2XL モード、 $f_{\text{OUT}} = \text{DC}$ (中間コード)、DEM/ディザリング オフ | 50  |     |     | dBc |

|                              |                                                                                                              | DES2XL モード、 $f_{\text{OUT}} = \text{DC}$ (中間コード)、DEM/ディザリング オン | 50  |     |     | dBc |

| $2 * f_{\text{CLK}}$ 固定スプリアス | 1GHz のフルスケールのサイン波と比較                                                                                         | DES2XL モード、 $f_{\text{OUT}} = \text{DC}$ (中間コード)、DEM/ディザリング オフ | 50  |     |     | dBc |

|                              |                                                                                                              | DES2XL モード、 $f_{\text{OUT}} = \text{DC}$ (中間コード)、DEM/ディザリング オン | 50  |     |     | dBc |

## 6.6 電気的特性 - AC 仕様 (続き)

特に明記されていない限り、 $T_A = +25^\circ\text{C}$  での標準値、動作時接合部温度範囲における最小値および最大値、標準電源電圧、 $f_{\text{CLK}} = 22\text{GHz}$ (外部クロックモード)、 $I_{\text{FS\_SWITCH}} = 20\text{mA}$ 、シングルトーン振幅 = -0.1dBFS、ディザリングおよび DEM 有効、64b/66b エンコード。

| パラメータ                                        |                                                         | テスト条件                                                                                                         | 最小値  | 標準値 | 最大値 | 単位  |

|----------------------------------------------|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------|-----|-----|-----|

| <b>22GSPS GSPS, JMODE 2, 4x Int, NRZ モード</b> |                                                         |                                                                                                               |      |     |     |     |

| $P_{\text{OUT}}$                             | 100Ω 負荷への出力電力 <sup>(2)</sup>                            | $f_{\text{OUT}} = 97\text{MHz}$                                                                               | 1.0  |     |     | dBm |

|                                              |                                                         | $f_{\text{OUT}} = 2897\text{MHz}$                                                                             | 0.6  |     |     | dBm |

|                                              |                                                         | $f_{\text{OUT}} = 2897\text{MHz}, I_{\text{FS\_SWITCH}} = 40\text{mA}$                                        | 6.6  |     |     | dBm |

|                                              |                                                         | $f_{\text{OUT}} = 5897\text{MHz}$                                                                             | -0.5 |     |     | dBm |

|                                              |                                                         | $f_{\text{OUT}} = 8897\text{MHz}$                                                                             | -3.5 |     |     | dBm |

|                                              |                                                         | $f_{\text{OUT}} = 8897\text{MHz}, I_{\text{FS\_SWITCH}} = 40\text{mA}$                                        | 2.5  |     |     | dBm |

| SFDR                                         | 0 - $F_{\text{DACCLK}}/2$ の間でのスプリアス フリー ダイナミックレンジ(SFDR) | $f_{\text{OUT}} = 97\text{MHz}$                                                                               | -74  |     |     | dBc |

|                                              |                                                         | $f_{\text{OUT}} = 2897\text{MHz}$                                                                             | -56  |     |     | dBc |

|                                              |                                                         | $f_{\text{OUT}} = 2897\text{MHz}, I_{\text{FS\_SWITCH}} = 40\text{mA}$                                        | -53  |     |     | dBc |

|                                              |                                                         | $f_{\text{OUT}} = 5897\text{MHz}$                                                                             | -44  |     |     | dBc |

|                                              |                                                         | $f_{\text{OUT}} = 8897\text{MHz}$                                                                             | -36  |     |     | dBc |

|                                              |                                                         | $f_{\text{OUT}} = 8897\text{MHz}, I_{\text{FS\_SWITCH}} = 40\text{mA}$                                        | -45  |     |     | dBc |

| HD2                                          | 2 次高調波(HD2)、0 - $F_{\text{DACCLK}}/2$                   | $f_{\text{OUT}} = 97\text{MHz}$                                                                               | -81  |     |     | dBc |

|                                              |                                                         | $f_{\text{OUT}} = 2897\text{MHz}$                                                                             | -56  |     |     | dBc |

|                                              |                                                         | $f_{\text{OUT}} = 2897\text{MHz}, I_{\text{FS\_SWITCH}} = 40\text{mA}$                                        | -55  |     |     | dBc |

|                                              |                                                         | $f_{\text{OUT}} = 5897\text{MHz}$                                                                             | -44  |     |     | dBc |

|                                              |                                                         | $f_{\text{OUT}} = 8897\text{MHz}$                                                                             | -36  |     |     | dBc |

|                                              |                                                         | $f_{\text{OUT}} = 8897\text{MHz}, I_{\text{FS\_SWITCH}} = 40\text{mA}$                                        | -38  |     |     | dBc |

| HD3                                          | 3 次高調波(HD3)、0 - $F_{\text{DACCLK}}/2$                   | $f_{\text{OUT}} = 97\text{MHz}$                                                                               | -74  |     |     | dBc |

|                                              |                                                         | $f_{\text{OUT}} = 2897\text{MHz}$                                                                             | -75  |     |     | dBc |

|                                              |                                                         | $f_{\text{OUT}} = 2897\text{MHz}, I_{\text{FS\_SWITCH}} = 40\text{mA}$                                        | -60  |     |     | dBc |

|                                              |                                                         | $f_{\text{OUT}} = 5897\text{MHz}$                                                                             | -70  |     |     | dBc |

|                                              |                                                         | $f_{\text{OUT}} = 8897\text{MHz}$                                                                             | -54  |     |     | dBc |

|                                              |                                                         | $f_{\text{OUT}} = 8897\text{MHz}, I_{\text{FS\_SWITCH}} = 40\text{mA}$                                        | -60  |     |     | dBc |

| SFDR <sub>NONHD2</sub><br>3                  | 非 HD2/3 SFDR、0 - $F_{\text{DACCLK}}/2$                  | $f_{\text{OUT}} = 97\text{MHz}$                                                                               | -98  |     |     | dBc |

|                                              |                                                         | $f_{\text{OUT}} = 2897\text{MHz}$                                                                             | -94  |     |     | dBc |

|                                              |                                                         | $f_{\text{OUT}} = 2897\text{MHz}, I_{\text{FS\_SWITCH}} = 40\text{mA}$                                        | -94  |     |     | dBc |

|                                              |                                                         | $f_{\text{OUT}} = 5897\text{MHz}$                                                                             | -71  |     |     | dBc |

|                                              |                                                         | $f_{\text{OUT}} = 8897\text{MHz}$                                                                             | -74  |     |     | dBc |

|                                              |                                                         | $f_{\text{OUT}} = 8897\text{MHz}, I_{\text{FS\_SWITCH}} = 40\text{mA}$                                        | -74  |     |     | dBc |

| IMD3                                         | 3 次 2 トーン相互変調歪み                                         | $f_{\text{OUT}} = 97 \pm 10\text{MHz}, -7\text{dBFS}/\text{トーン}$                                              | -80  |     |     | dBc |

|                                              |                                                         | $f_{\text{OUT}} = 2897 \pm 10\text{MHz}, -7\text{dBFS}/\text{トーン}$                                            | -75  |     |     | dBc |

|                                              |                                                         | $f_{\text{OUT}} = 2897 \pm 10\text{MHz}, -7\text{dBFS}/\text{トーン} \wedge I_{\text{FS\_SWITCH}} = 40\text{mA}$ | -65  |     |     | dBc |

|                                              |                                                         | $f_{\text{OUT}} = 5897 \pm 10\text{MHz}, -7\text{dBFS}/\text{トーン}$                                            | -75  |     |     | dBc |

|                                              |                                                         | $f_{\text{OUT}} = 8897 \pm 10\text{MHz}, -7\text{dBFS}/\text{トーン}$                                            | -65  |     |     | dBc |

|                                              |                                                         | $f_{\text{OUT}} = 8897 \pm 10\text{MHz}, -7\text{dBFS}/\text{トーン} \wedge I_{\text{FS\_SWITCH}} = 40\text{mA}$ | -70  |     |     | dBc |

## 6.6 電気的特性 - AC 仕様 (続き)

特に明記されていない限り、 $T_A = +25^\circ\text{C}$  での標準値、動作時接合部温度範囲における最小値および最大値、標準電源電圧、 $f_{\text{CLK}} = 22\text{GHz}$  (外部クロックモード)、 $I_{\text{FS\_SWITCH}} = 20\text{mA}$ 、シングルトーン振幅 = -0.1dBFS、ディザリングおよび DEM 有効、64b/66b エンコード。

| パラメータ |                                     | テスト条件                                                                                                                                           | 最小値  | 標準値 | 最大値 | 単位      |

|-------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|---------|

| NSD   | ノイズスペクトル密度、大信号、サイン波出力、DEM/ディザリング オン | $f_{\text{OUT}}$ からの $f_{\text{OUT}} = 97\text{MHz}$ 、70MHz オフセット                                                                               | -160 |     |     | dBc/Hz  |

|       |                                     | $f_{\text{OUT}}$ からの $f_{\text{OUT}} = 2897\text{MHz}$ 、70MHz オフセット                                                                             | -158 |     |     | dBc/Hz  |

|       |                                     | $V = 2897\text{MHz}$ 、 $f_{\text{OUT}}$ からの 70MHz オフセット、 $I_{\text{FS\_SWITCH}} = 40\text{mA}$                                                  | -158 |     |     | dBc/Hz  |

|       |                                     | $f_{\text{OUT}}$ からの $f_{\text{OUT}} = 5897\text{MHz}$ 、70MHz オフセット                                                                             | -156 |     |     | dBc/Hz  |

|       |                                     | $f_{\text{OUT}}$ からの $f_{\text{OUT}} = 8897\text{MHz}$ 、70MHz オフセット                                                                             | -152 |     |     | dBc/Hz  |

|       |                                     | $f_{\text{OUT}} = 8897\text{MHz}$ 、 $f_{\text{OUT}}$ からの 70MHz オフセット、 $I_{\text{FS\_SWITCH}} = 40\text{mA}$                                     | -152 |     |     | dBc/Hz  |

| NSD   | ノイズスペクトル密度、大信号、サイン波出力、DEM/ディザリング 無効 | $f_{\text{OUT}}$ からの $f_{\text{OUT}} = 97\text{MHz}$ 、70MHz オフセット                                                                               | -170 |     |     | dBc/Hz  |

|       |                                     | $f_{\text{OUT}}$ からの $f_{\text{OUT}} = 2897\text{MHz}$ 、70MHz オフセット                                                                             | -168 |     |     | dBc/Hz  |

|       |                                     | $f_{\text{OUT}} = 2897\text{MHz}$ 、 $f_{\text{OUT}}$ からの 70MHz オフセット、 $I_{\text{FS\_SWITCH}} = 40\text{mA}$                                     | -168 |     |     | dBc/Hz  |

|       |                                     | $f_{\text{OUT}}$ からの $f_{\text{OUT}} = 5897\text{MHz}$ 、70MHz オフセット                                                                             | -166 |     |     | dBc/Hz  |

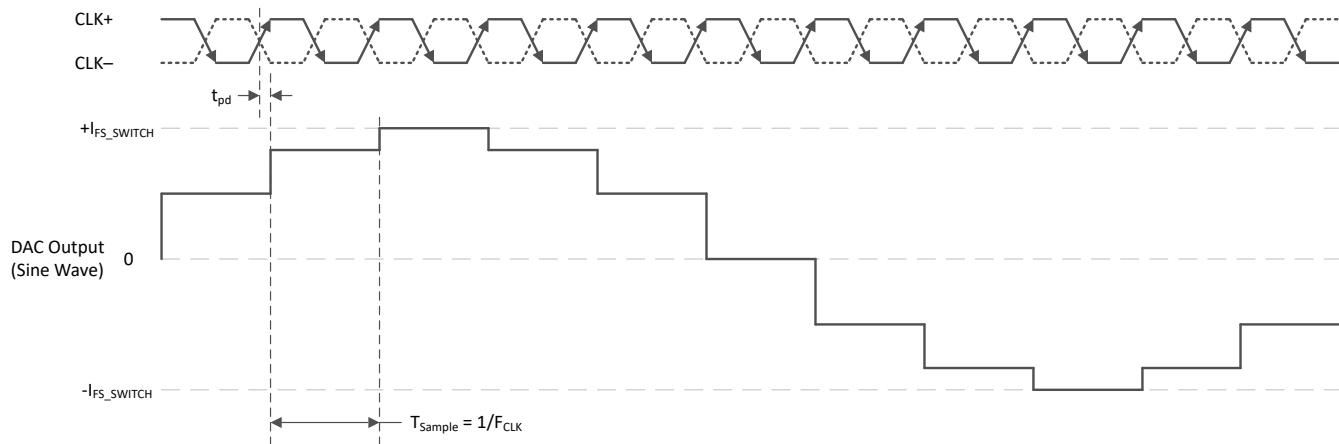

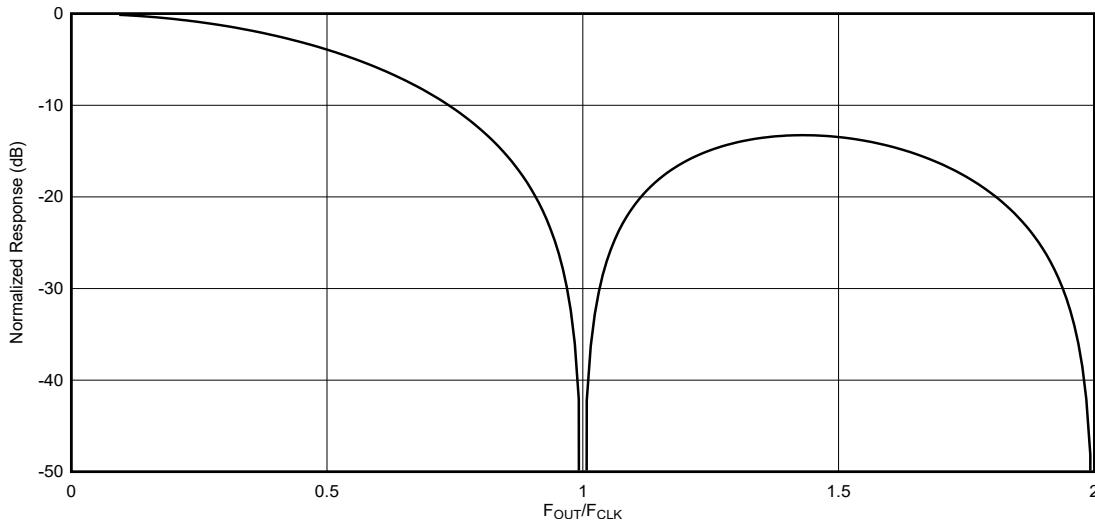

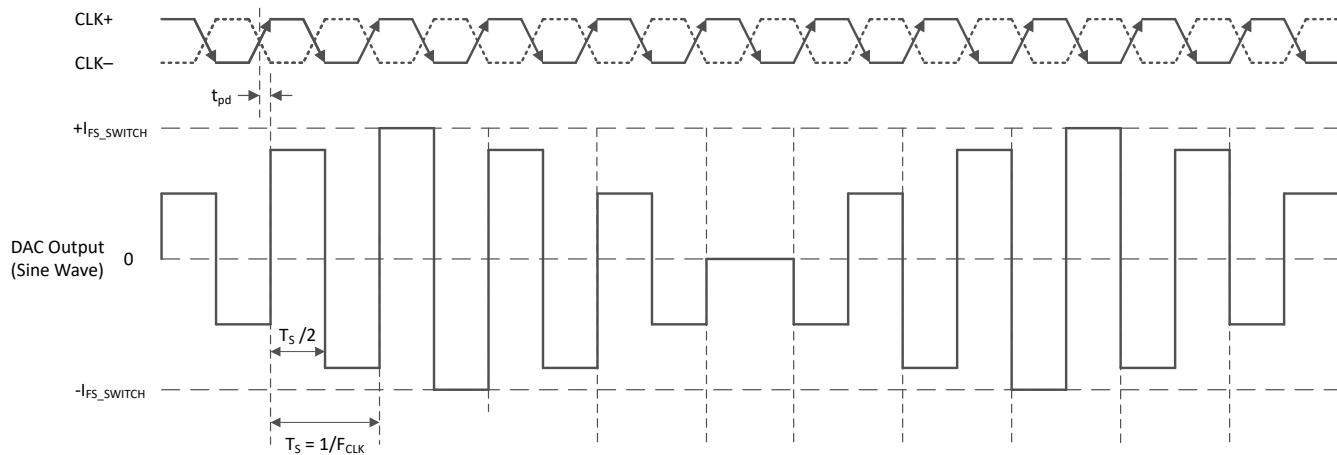

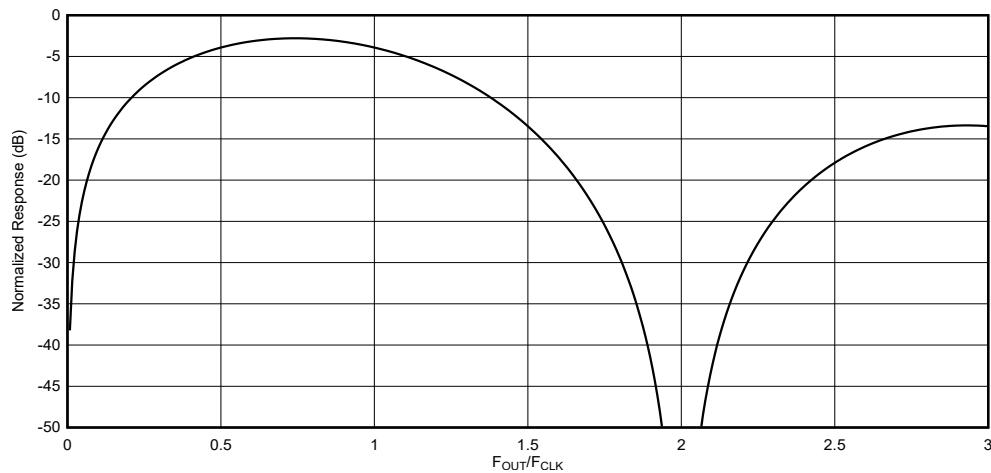

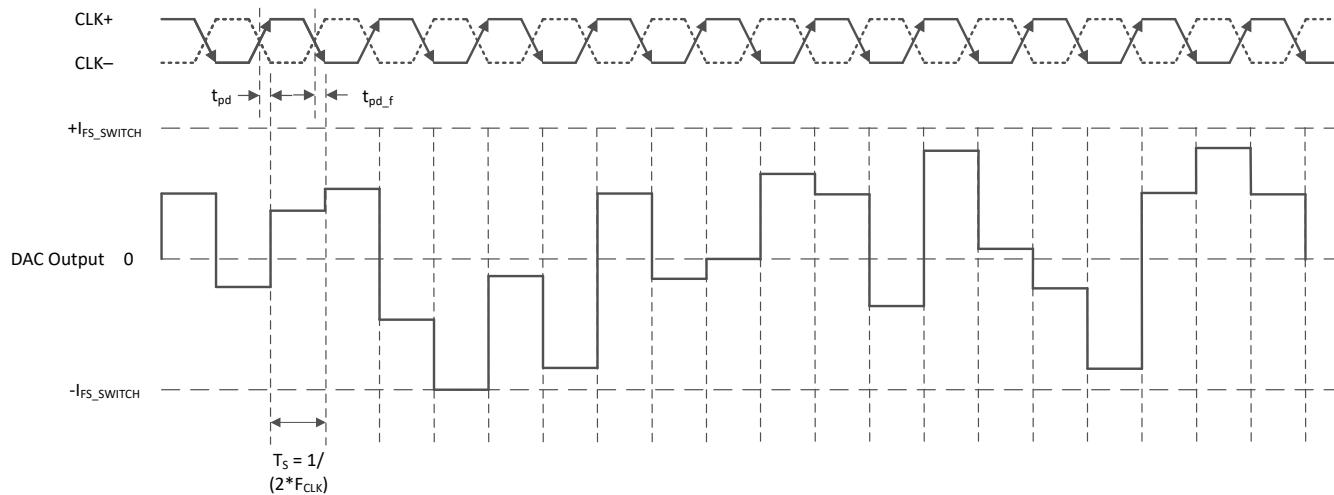

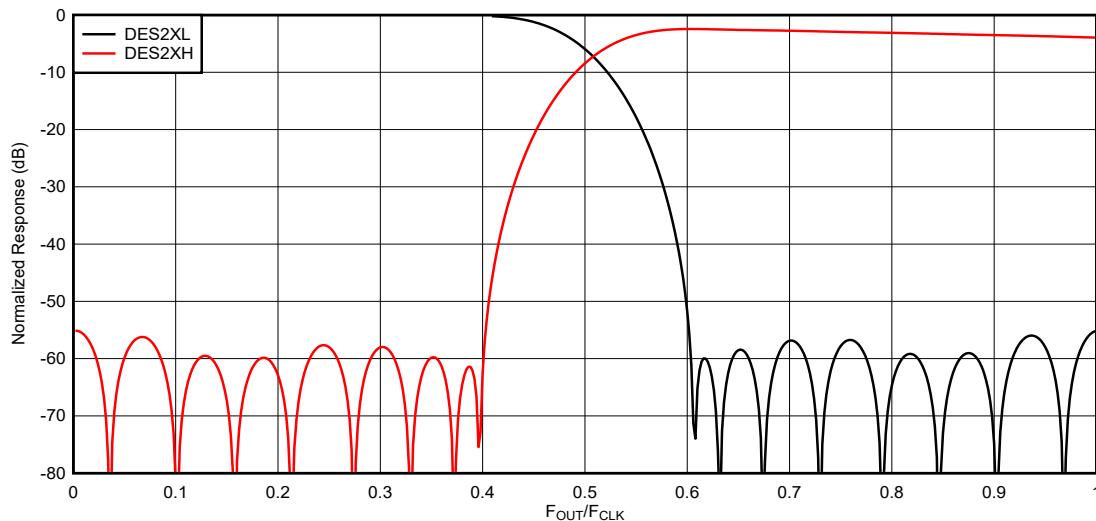

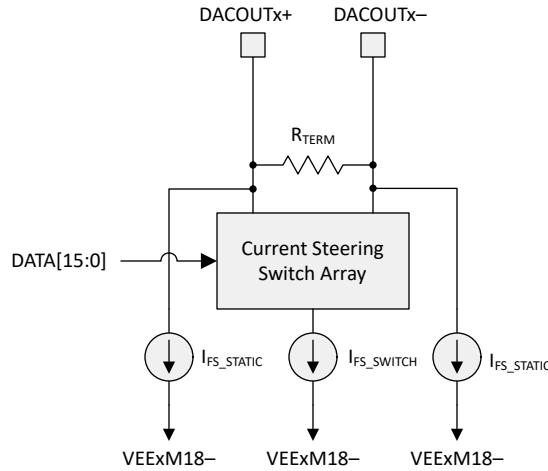

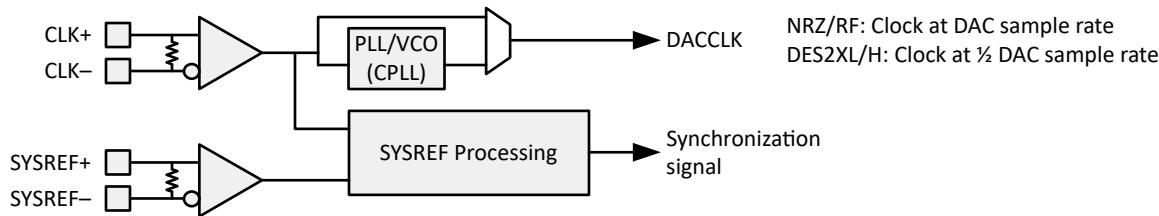

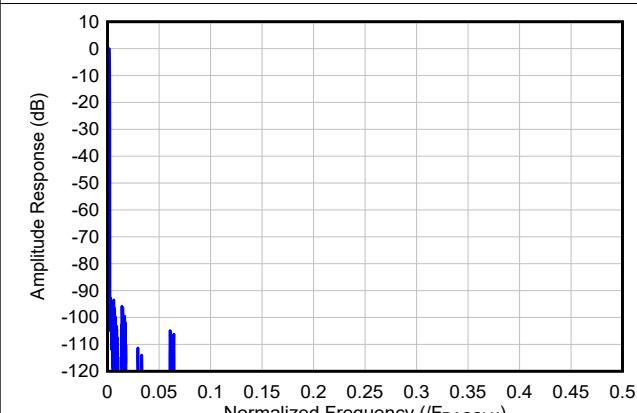

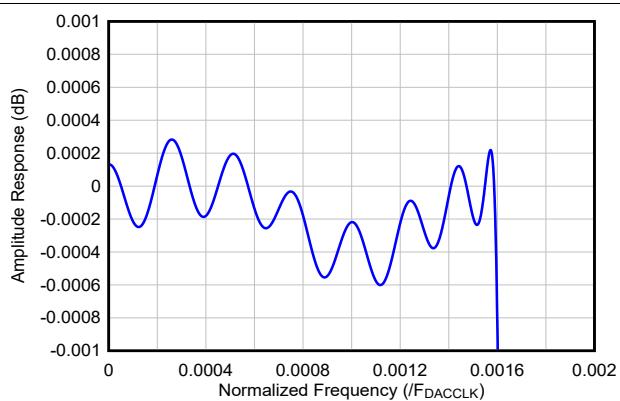

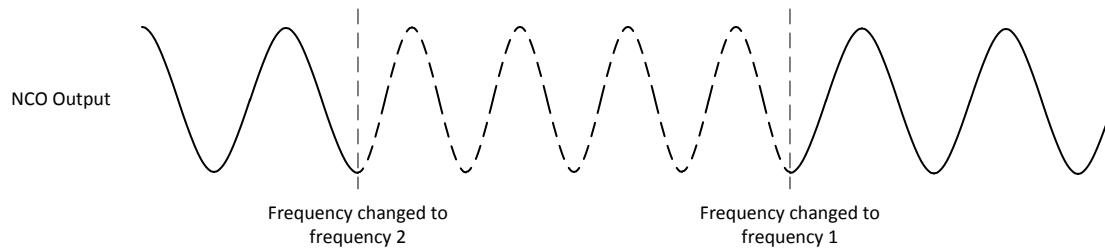

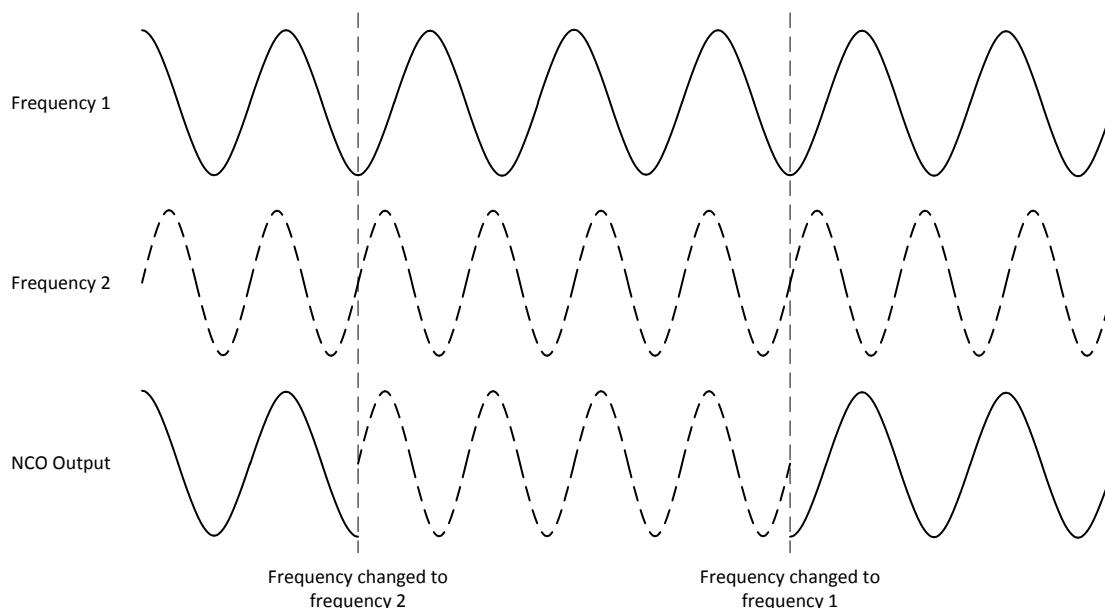

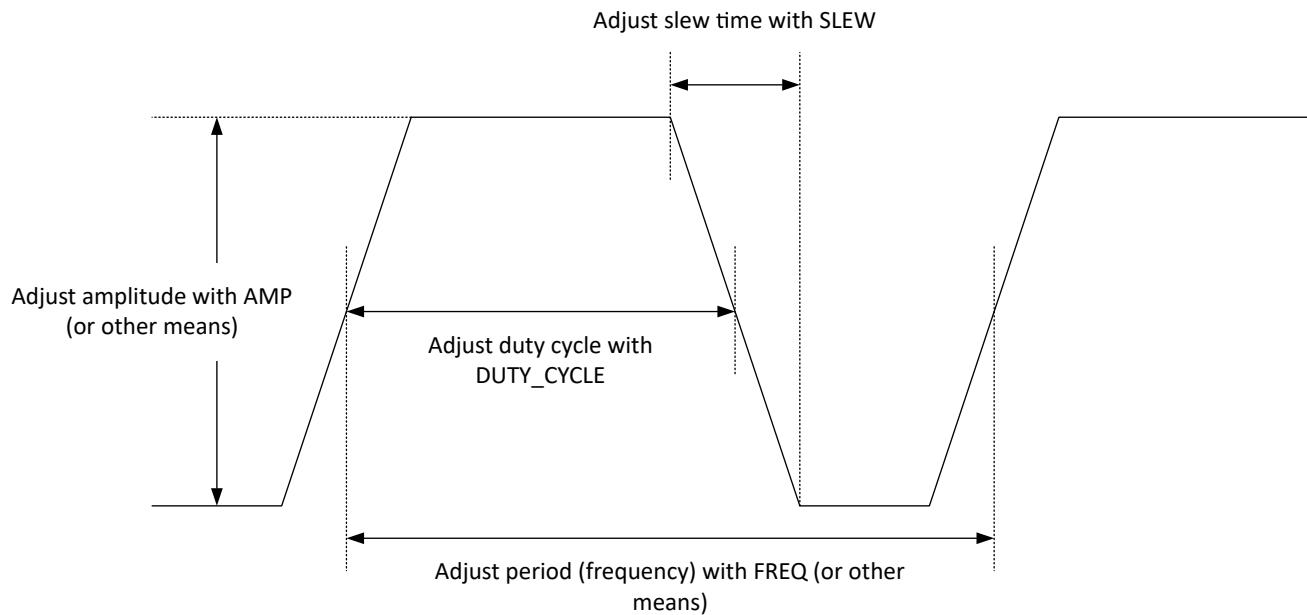

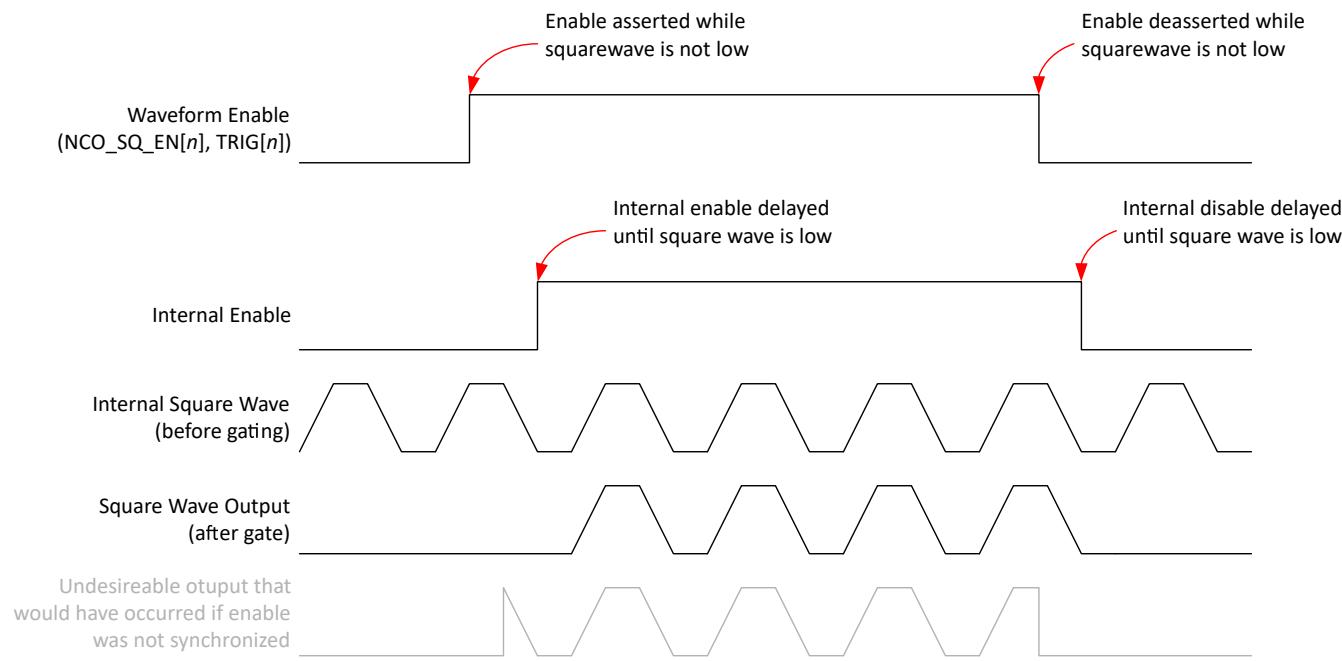

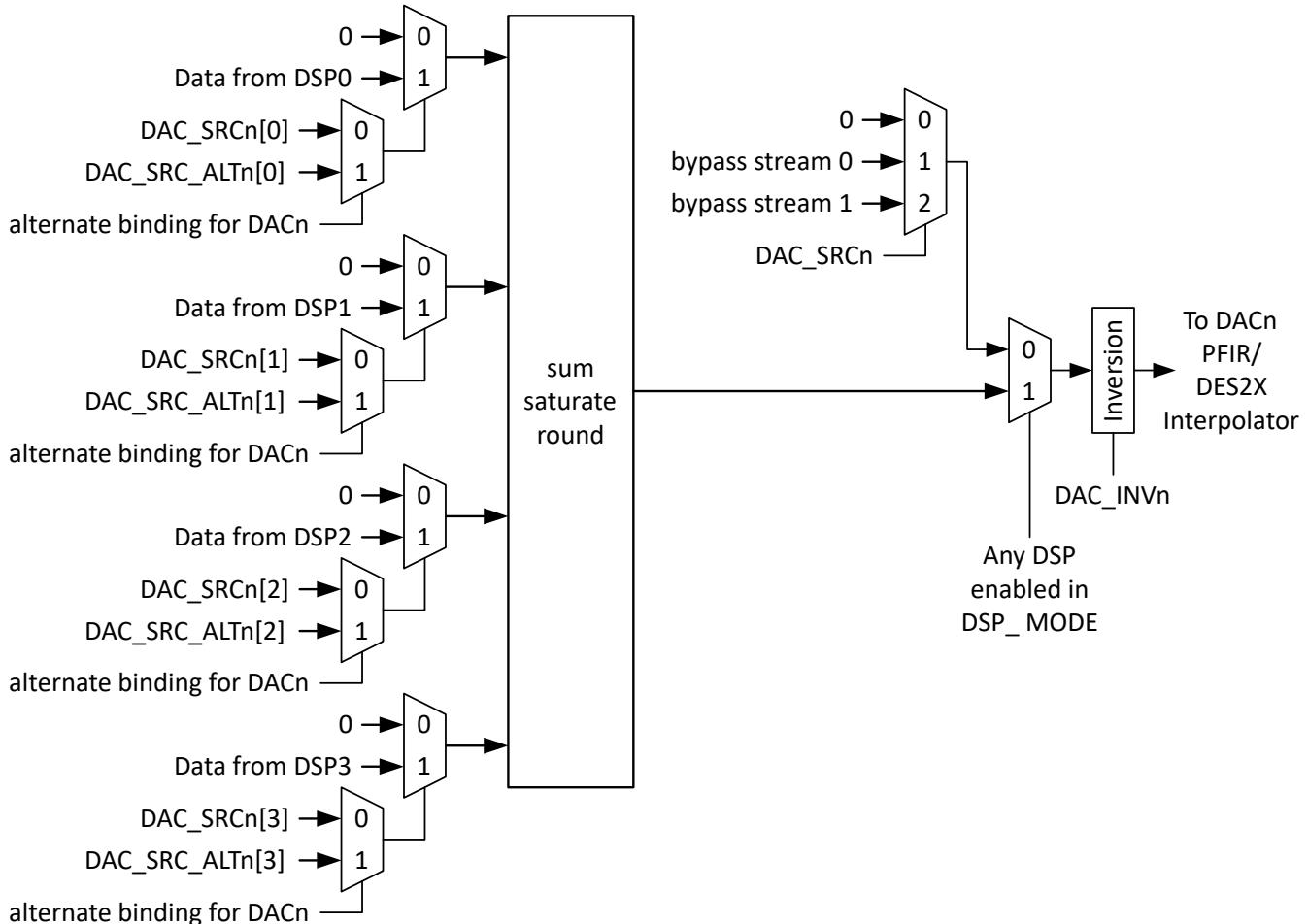

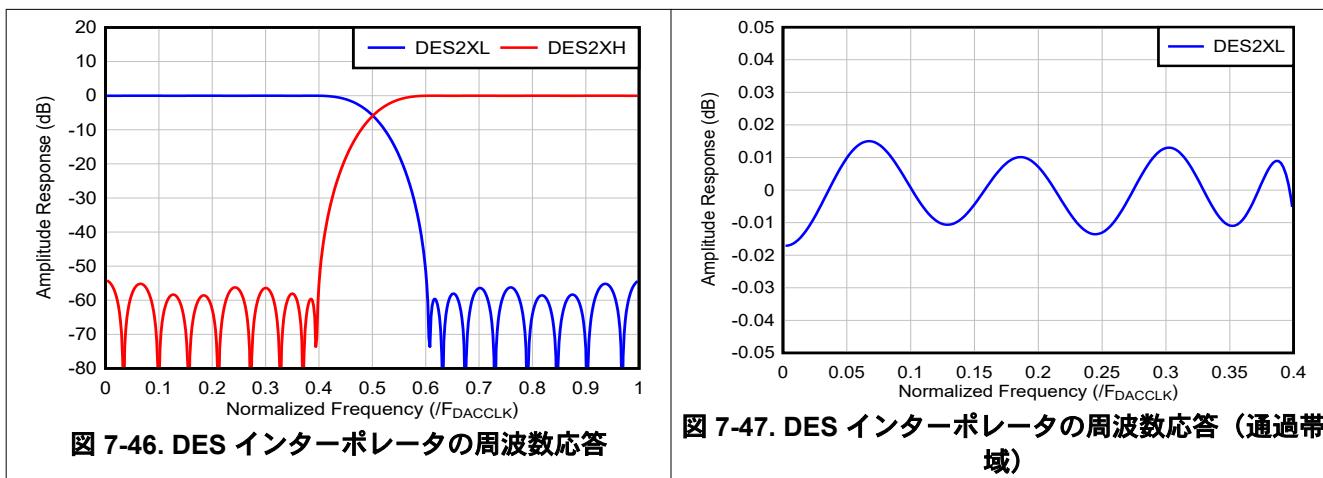

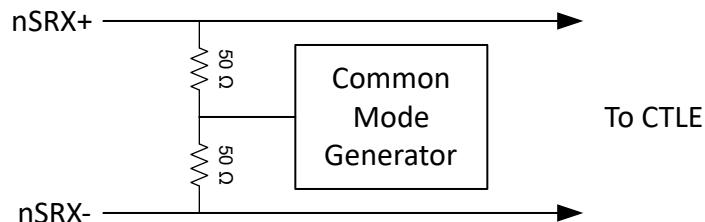

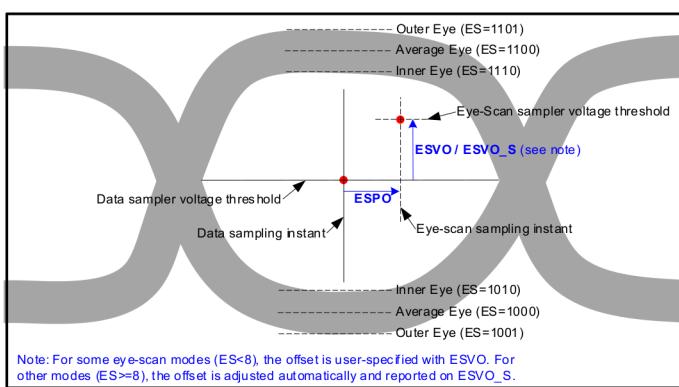

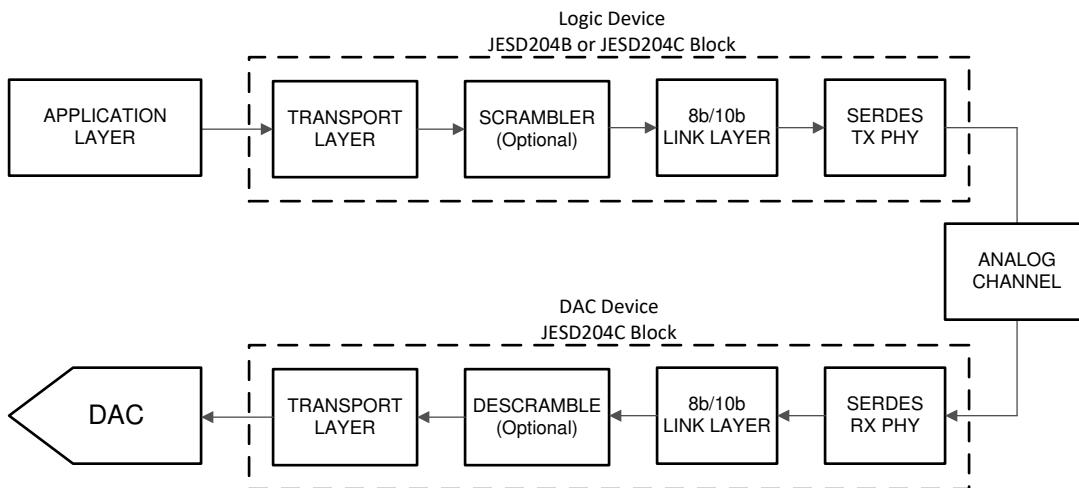

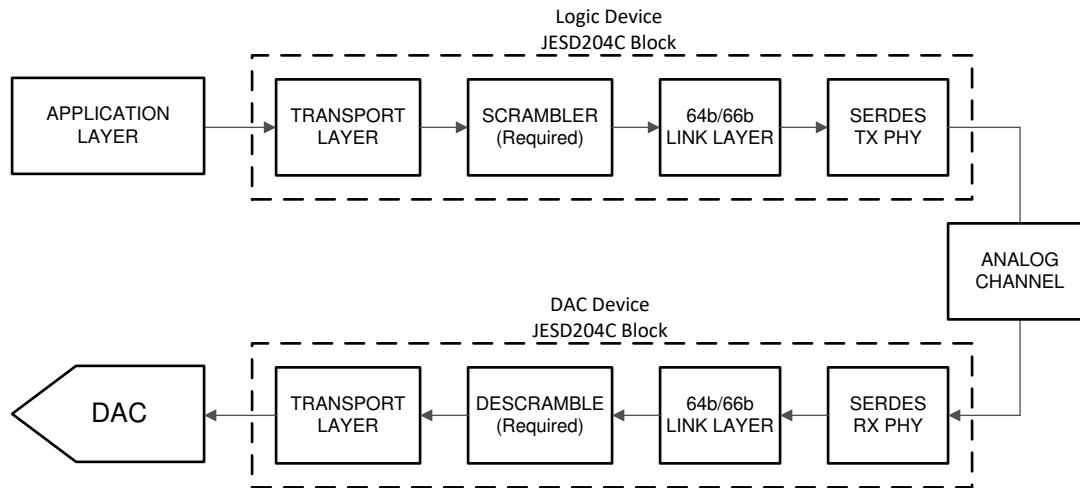

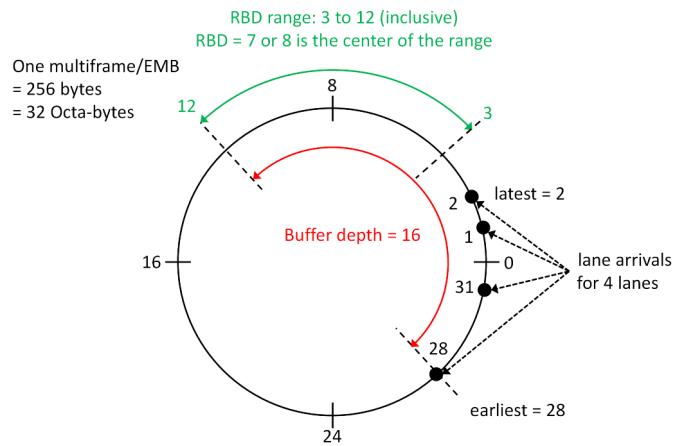

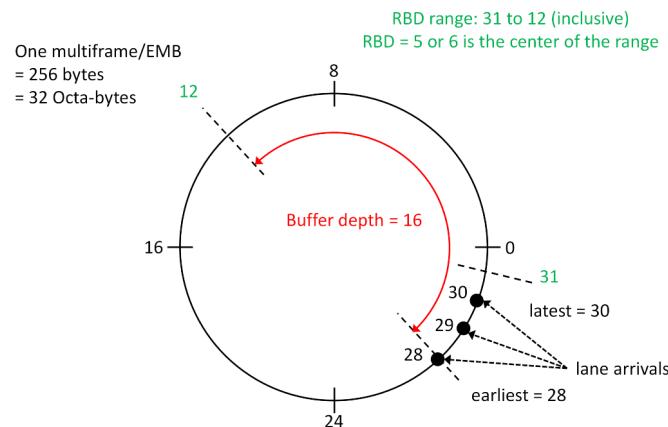

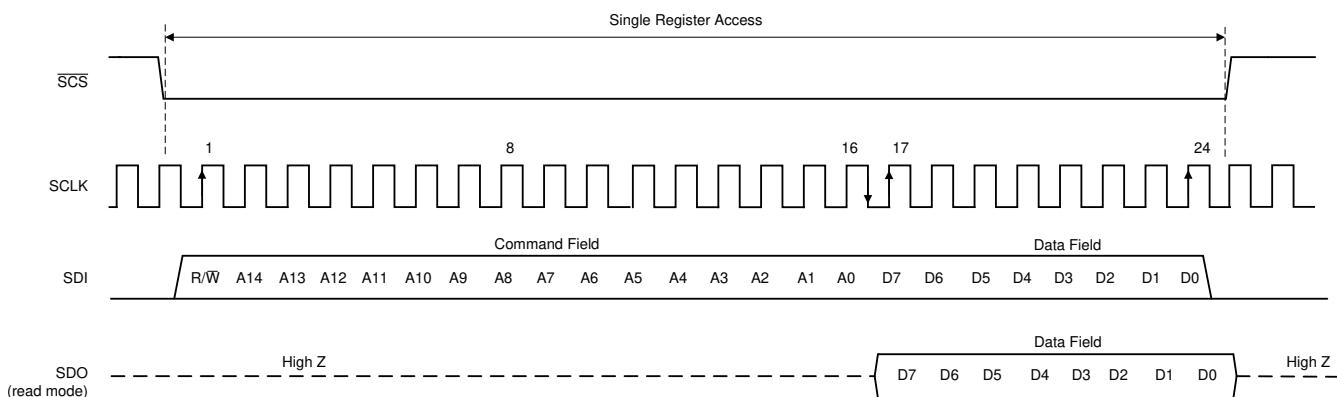

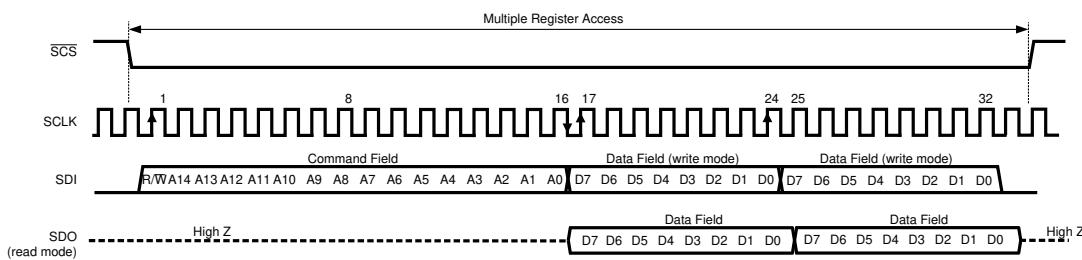

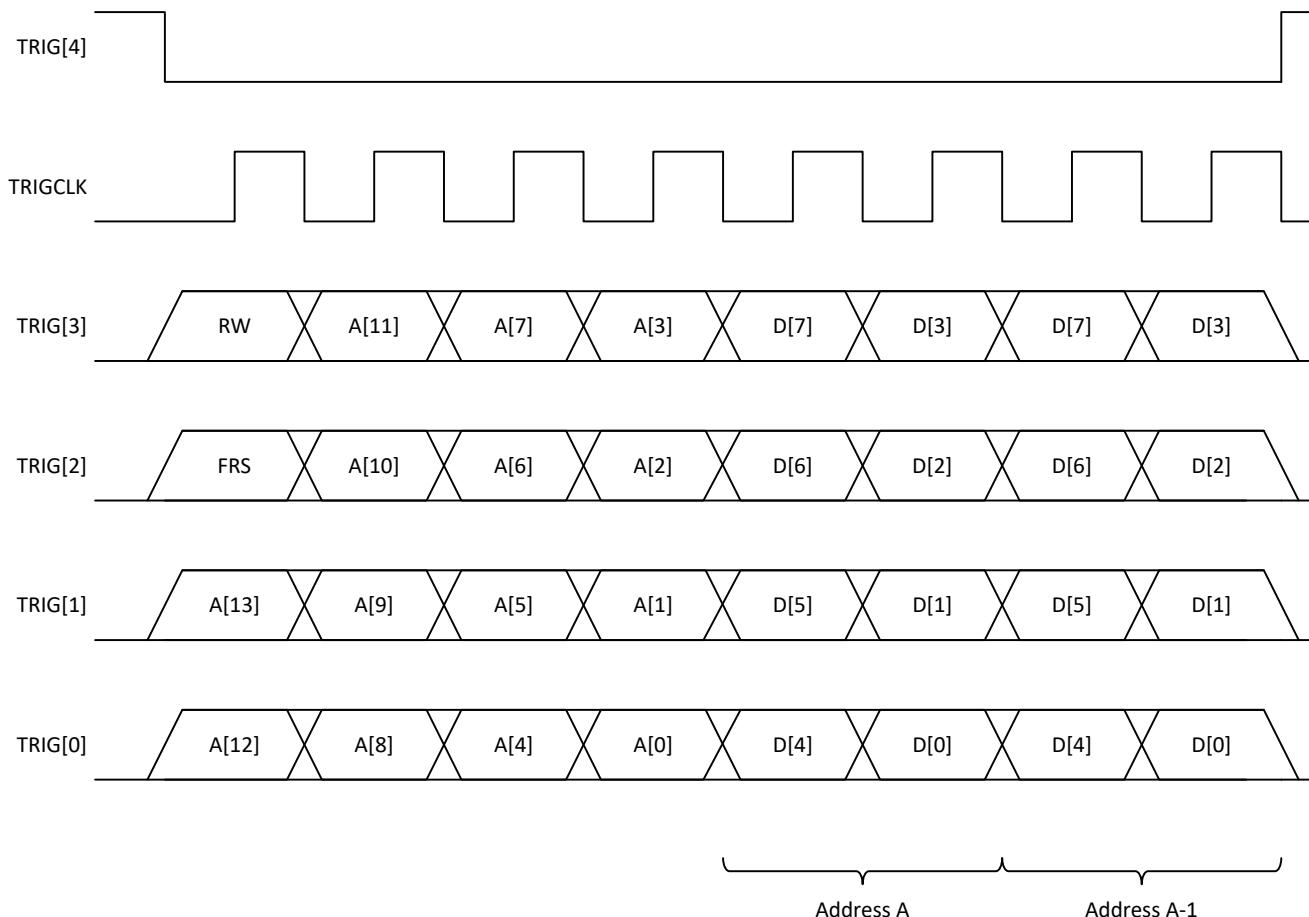

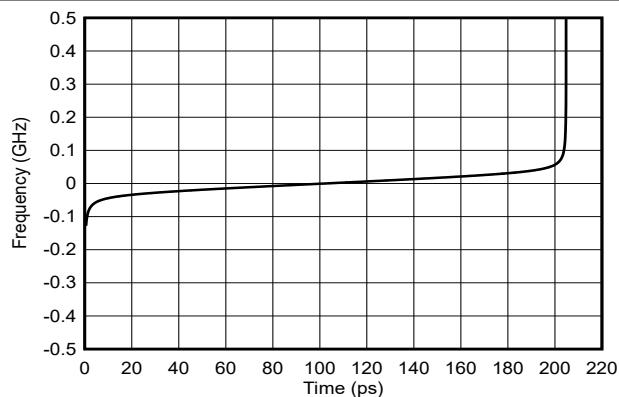

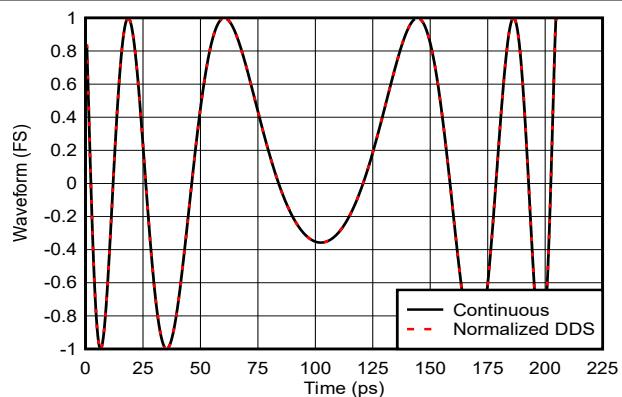

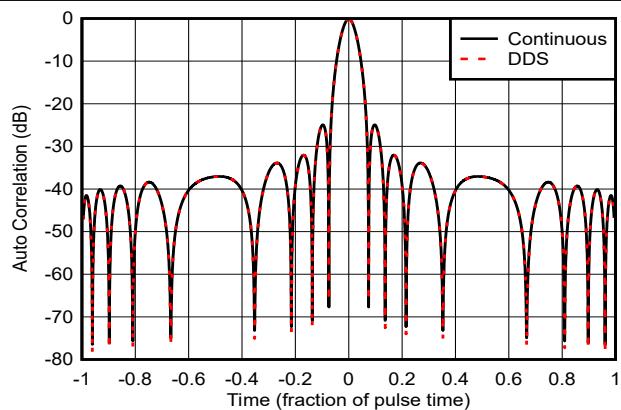

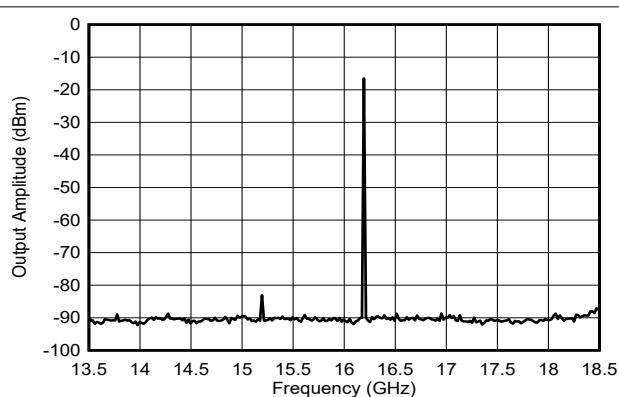

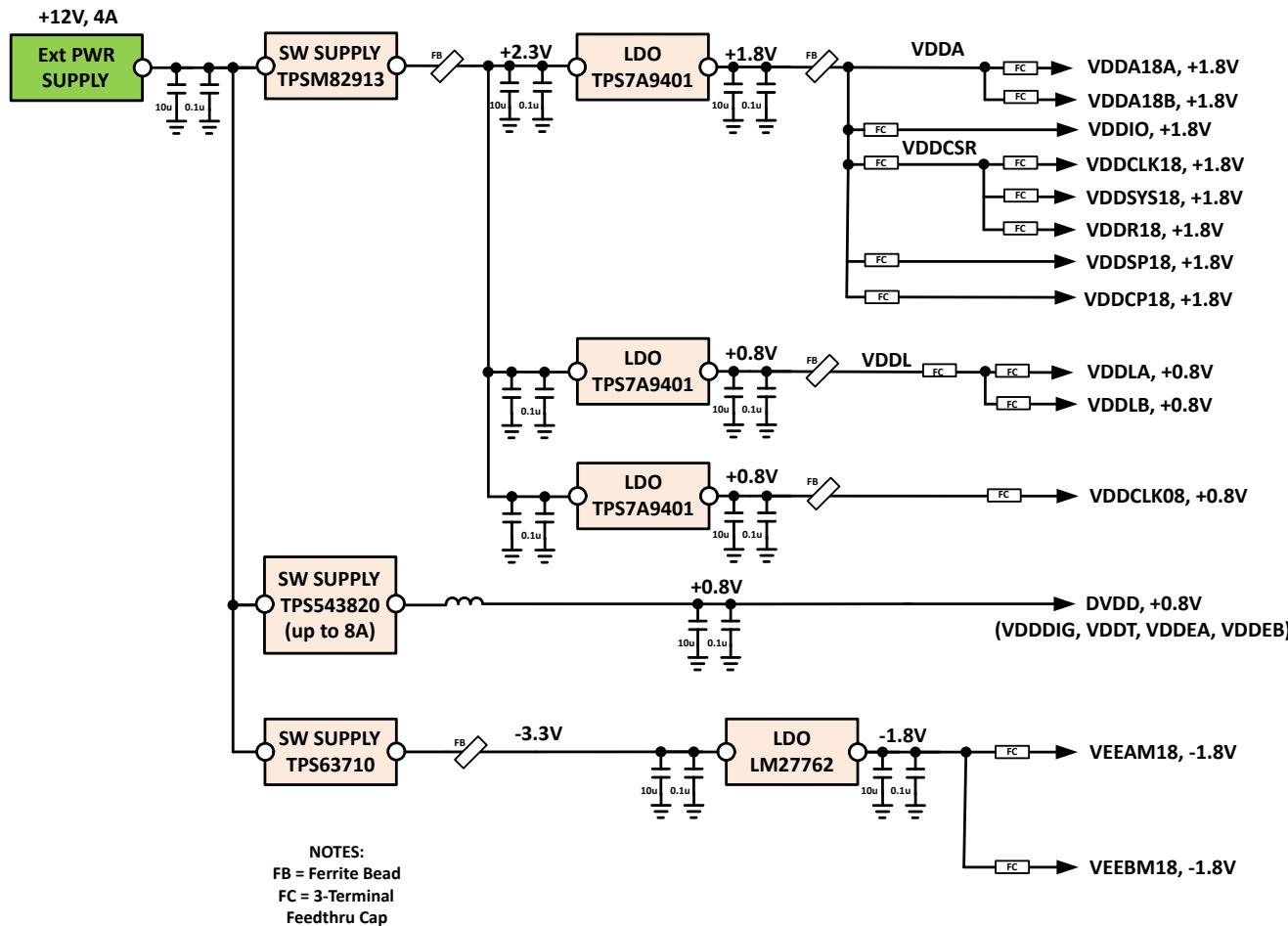

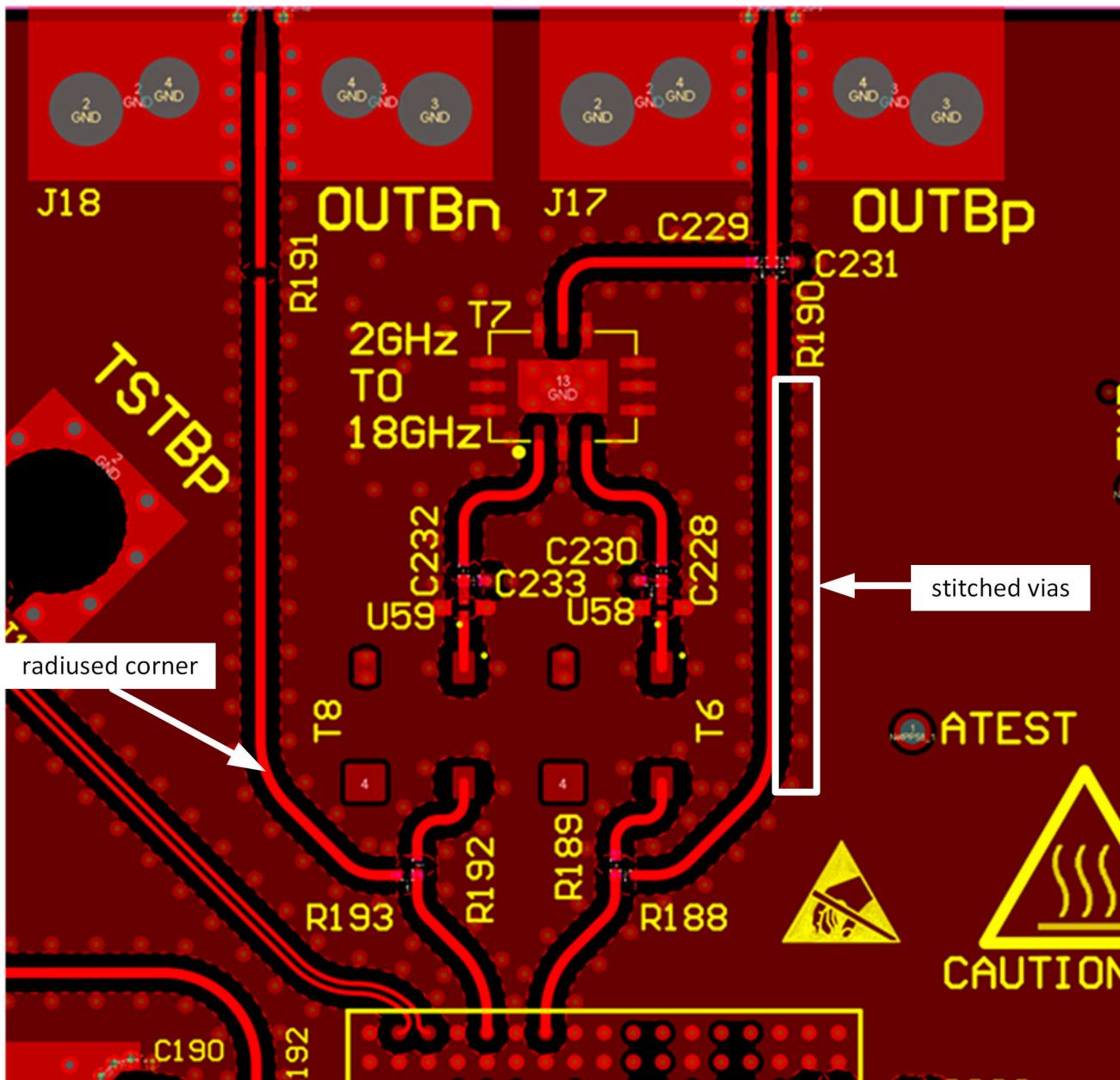

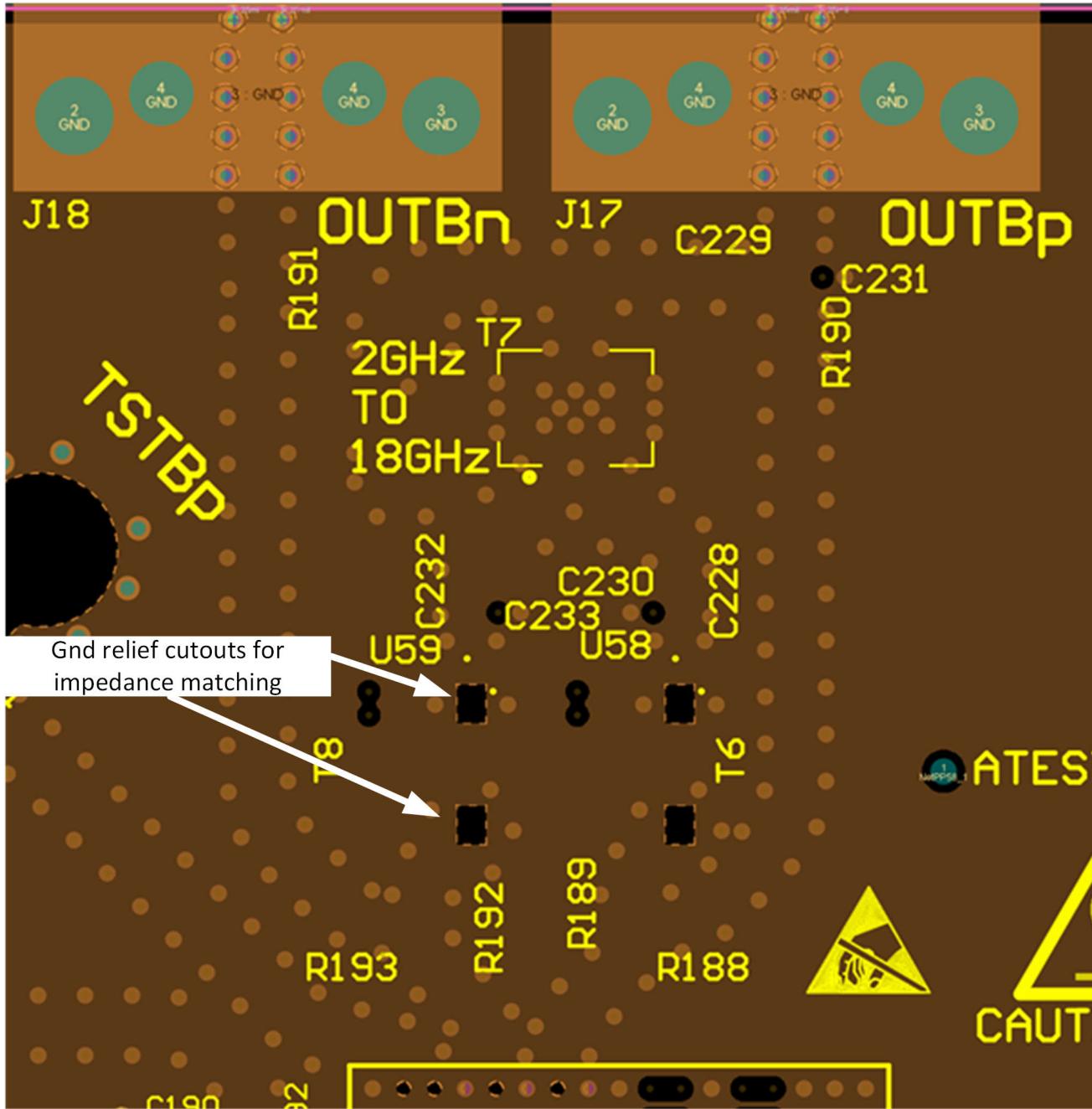

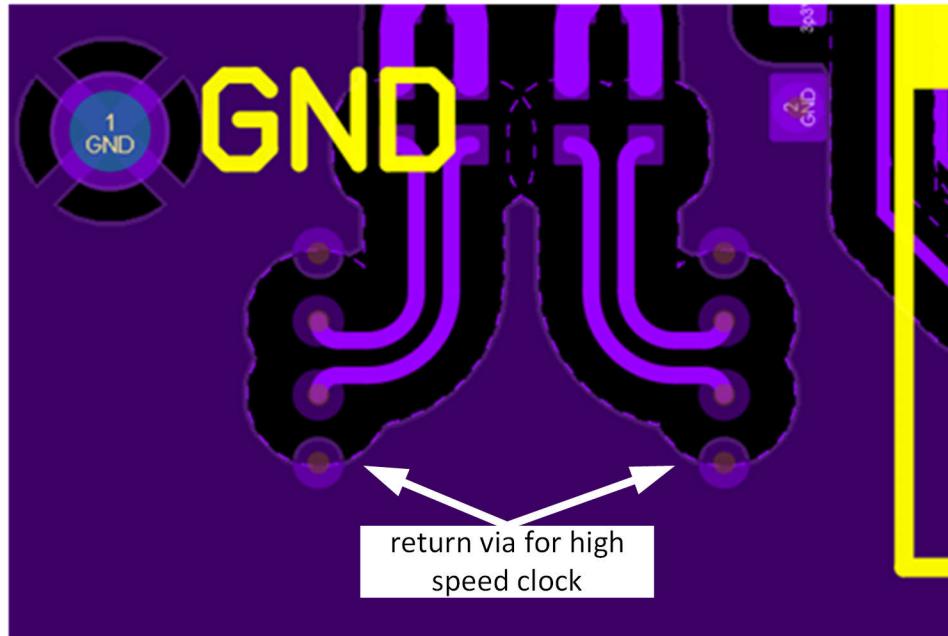

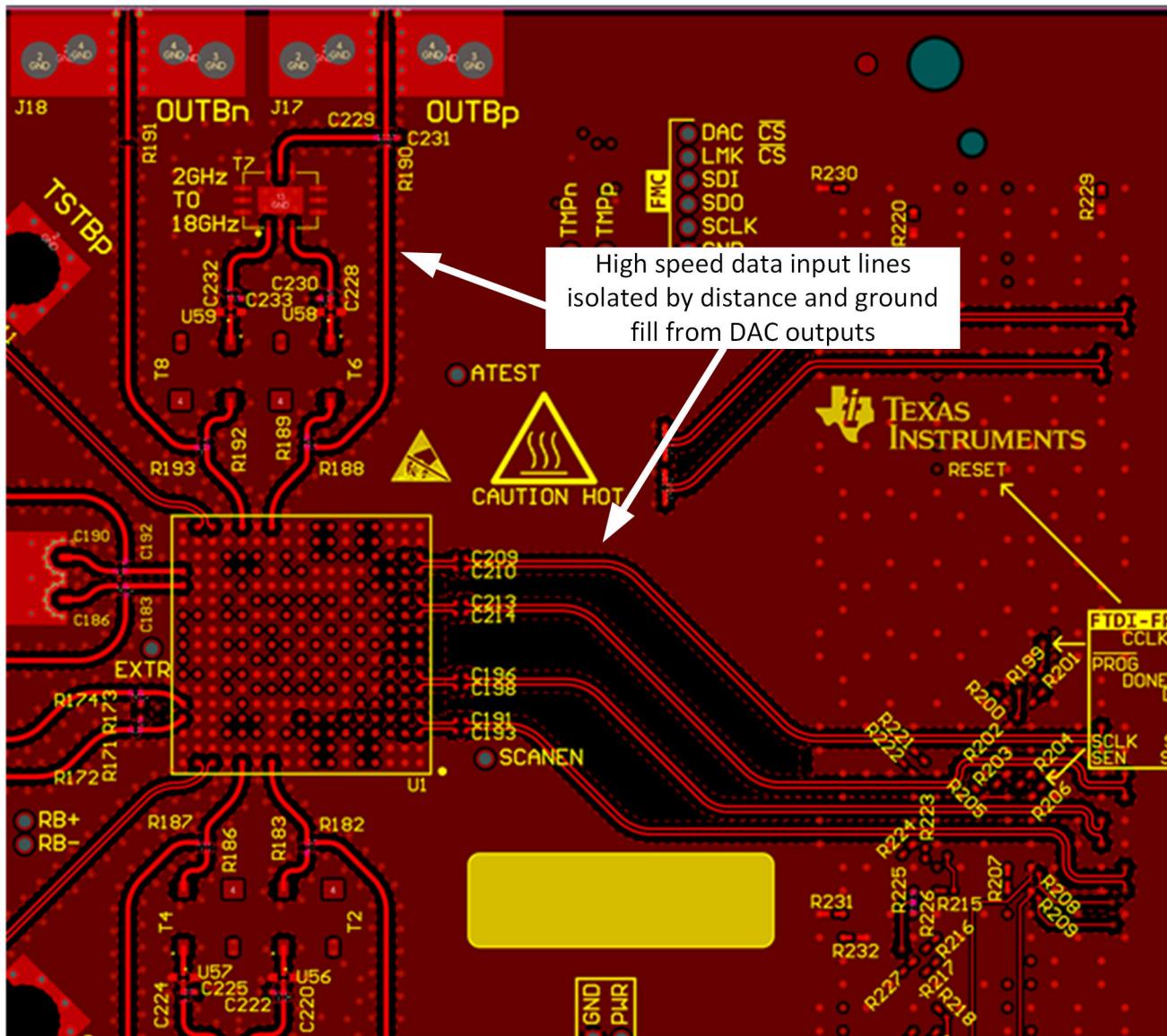

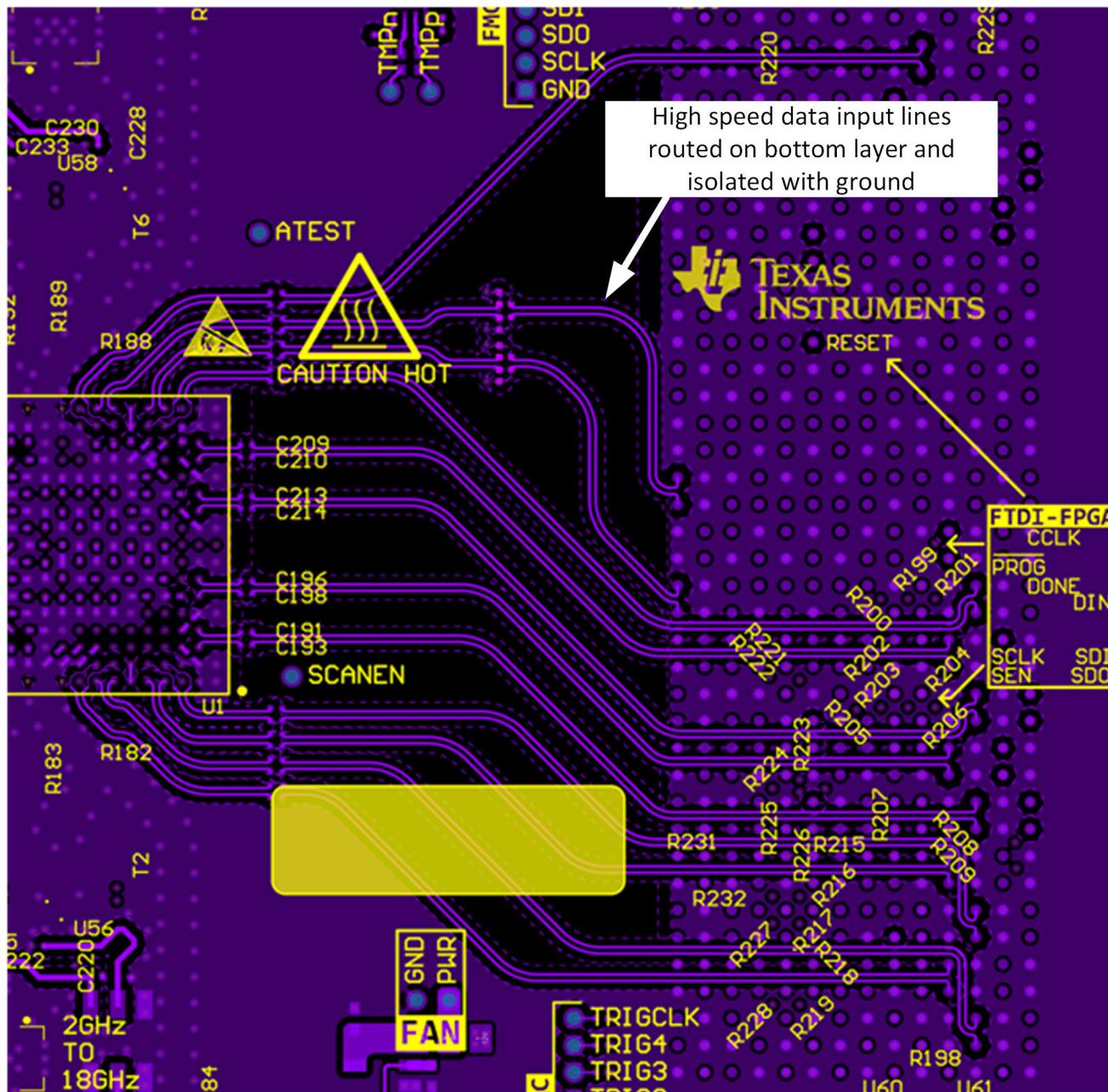

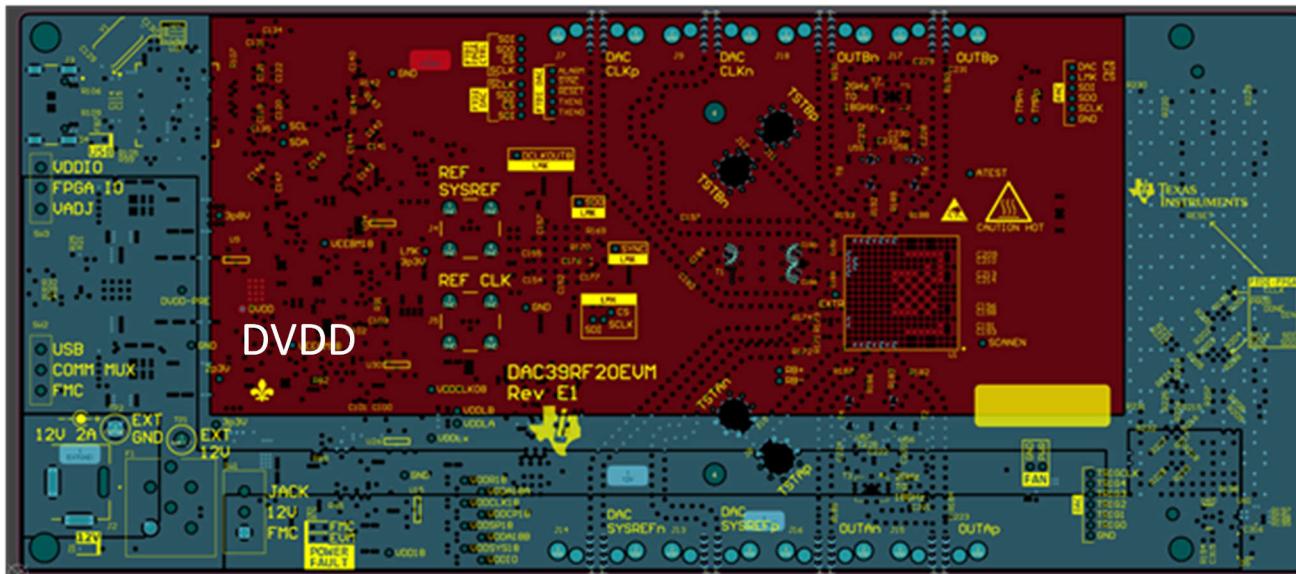

|       |                                     | $f_{\text{OUT}} = 8897\text{MHz}$ 、 $f_{\text{OUT}}$ からの 70MHz オフセット                                                                            | -160 |     |     | dBc/Hz  |