# DACx1416 16 チャネル、12/14/16 ビット、高電圧出力 DAC、 内部リファレンス付き

## 1 特長

- 性能

- 16 ビット分解能で単調性を規定

- INL: 16 ビット分解能で  $\pm 1$ LSB 以下

- TUE (総合未調整誤差): FSR 最大値  $\pm 0.1\%$

- 2.5V の高精度内部リファレンスを搭載

- 初期精度:  $\pm 2.5\text{mV}$  (最大値)

- 低いドリフト:  $5\text{ppm}/^\circ\text{C}$  (標準値)

- 柔軟な出力構成

- 出力電圧範囲:  $\pm 2.5\text{V}$ ,  $\pm 5\text{V}$ ,  $\pm 10\text{V}$ ,  $\pm 20\text{V}$ , 0V~5V, 0V~10V, 0V~20V, または 0V~40V

- 差動出力モード

- 高い駆動能力: 電源レールから 1.5V で  $\pm 25\text{mA}$

- 3 つの専用 A-B トグル ピンによるディザリング信号生成

- アナログ温度出力

- センサ ゲイン:  $-4\text{mV}/^\circ\text{C}$

- 50MHz SPI 互換のシリアルインターフェース

- 4 線式モード、1.7V~5.5V で動作

- デイジーチェーン動作

- CRC エラー チェック

- 温度範囲:  $-40^\circ\text{C} \sim +125^\circ\text{C}$

- 小型パッケージ

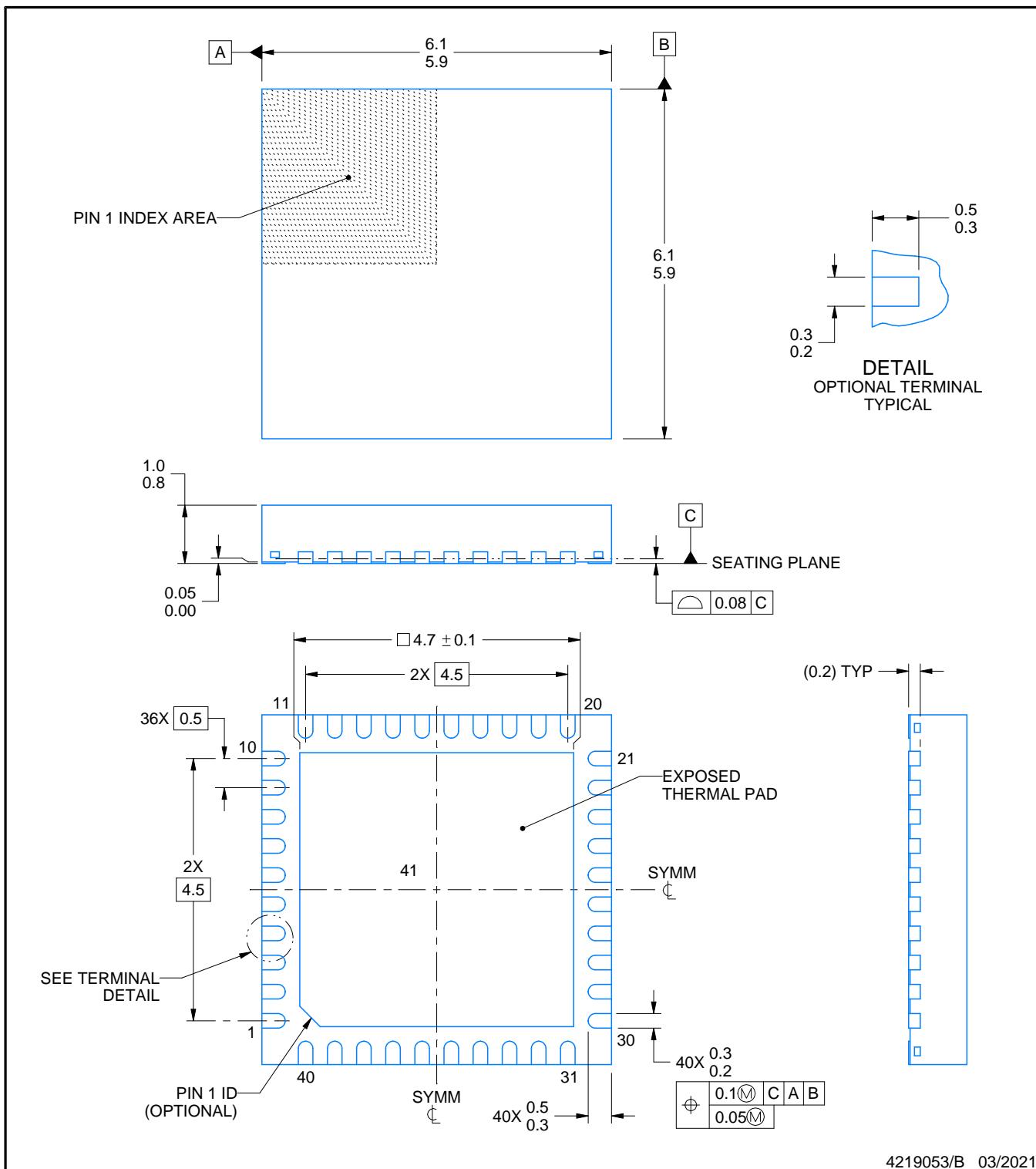

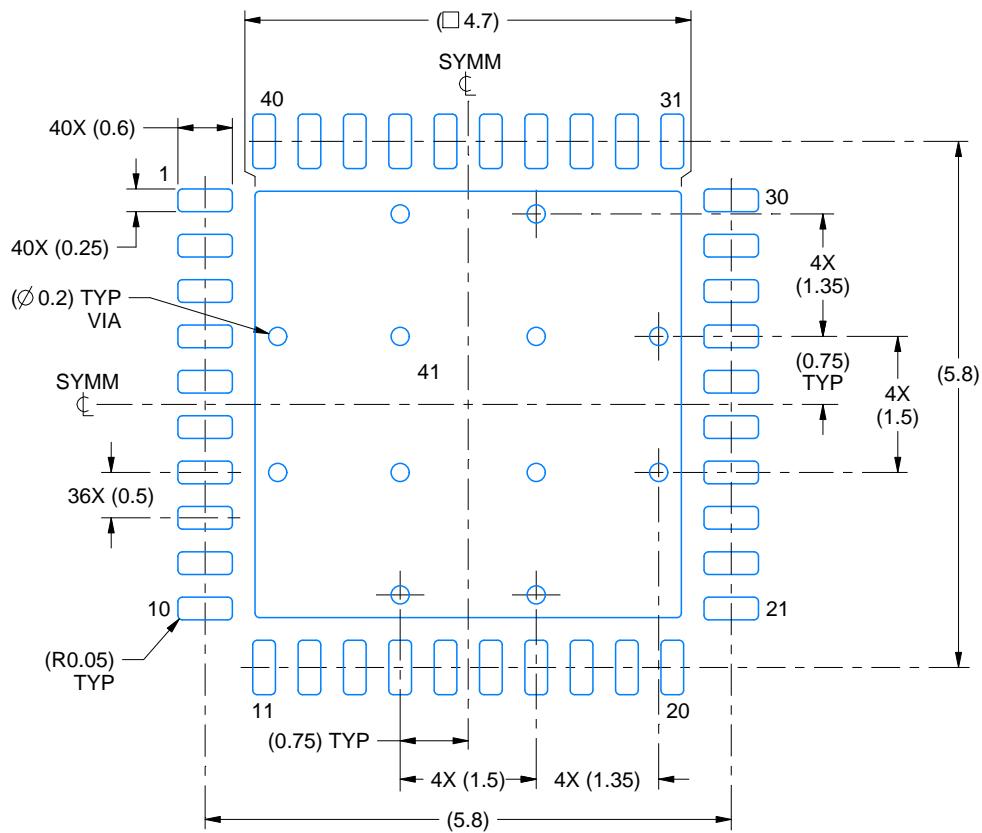

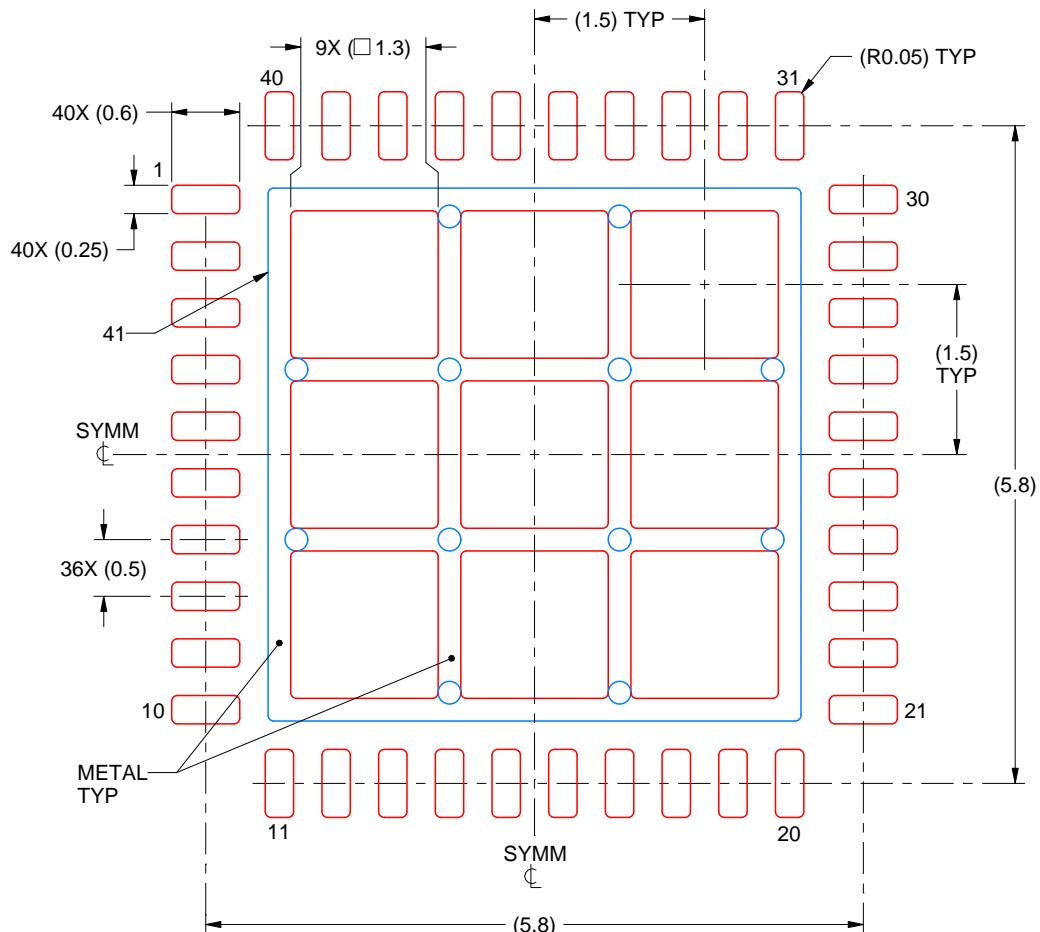

- 6mm × 6mm、40 ピン VQFN

## 2 アプリケーション

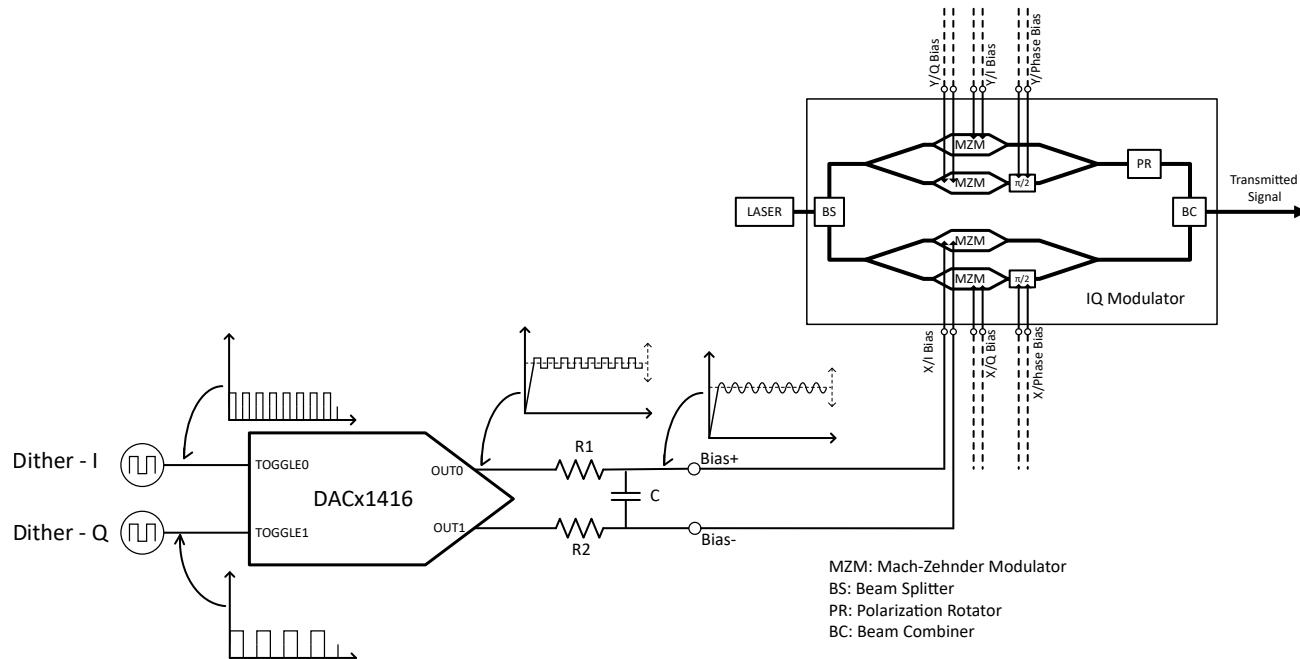

- DC (データセンター) 間の相互接続 (長距離、海底)

- DC (データセンター) 間の相互接続 (都市)

- 光学モジュール

- 半導体試験装置

- 実験室およびフィールド向け計測機器

- データ アクイジション (DAQ)

## 3 説明

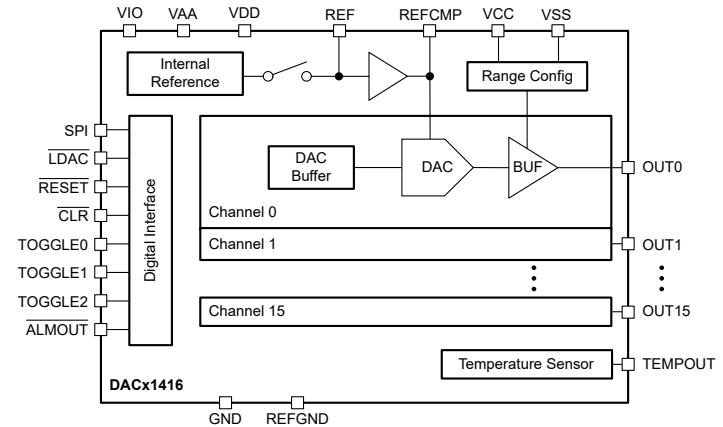

12 ビットの DAC61416、14 ビットの DAC71416、16 ビットの DAC81416 (DACx1416) は、16 チャネルのバッファ付き高電圧出力 D/A コンバータ (DAC) のピン互換ファミリです。DACx1416 には、低ドリフト、2.5V の内部リファレンスが搭載されており、ほとんどのアプリケーションでは外付けの精度リファレンスが不要になります。これらのデバイスは単調性が保証されており、 $\pm 1$ LSB INL の高い直線性を提供します。

出力構成をユーザーが選択可能で、フルスケールのバイポーラ出力電圧の  $\pm 20\text{V}$ ,  $\pm 10\text{V}$ ,  $\pm 5\text{V}$ ,  $\pm 2.5\text{V}$ 、およびフルスケールのユニポーラ出力電圧の 40V, 20V, 10V, 5V を使用できます。各 DAC チャネルのフルスケール出力範囲は別々にプログラム可能です。内蔵された DAC 出力バッファは最大  $25\text{mA}$  のシンクおよびソースが可能であり、追加のオペアンプの必要性を減らします。チャネルの各ペアは、オフセット較正付きの差動出力を供給するように構成可能です。3 つの専用 A-B トグル ピンにより、最大 3 つの周波数についてディザリング信号を生成できます。

DACx1416 にはパワー オン リセット (POR) 回路が組み込まれており、電源オン時に DAC 出力をグランドに接続します。デバイスのレジスタが動作用に正しく構成されるまで、出力がこの状態に維持されます。

DACx1416 への通信は、1.7V~5.5V での動作をサポートする 4 線式シリアルインターフェイスにより行われます。

## 製品情報

| 部品番号     | 分解能    | パッケージ (1)      |

|----------|--------|----------------|

| DAC61416 | 12 ビット | RHA (VQFN, 40) |

| DAC71416 | 14 ビット |                |

| DAC81416 | 16 ビット |                |

(1) 詳細については、[セクション 11](#) を参照してください。

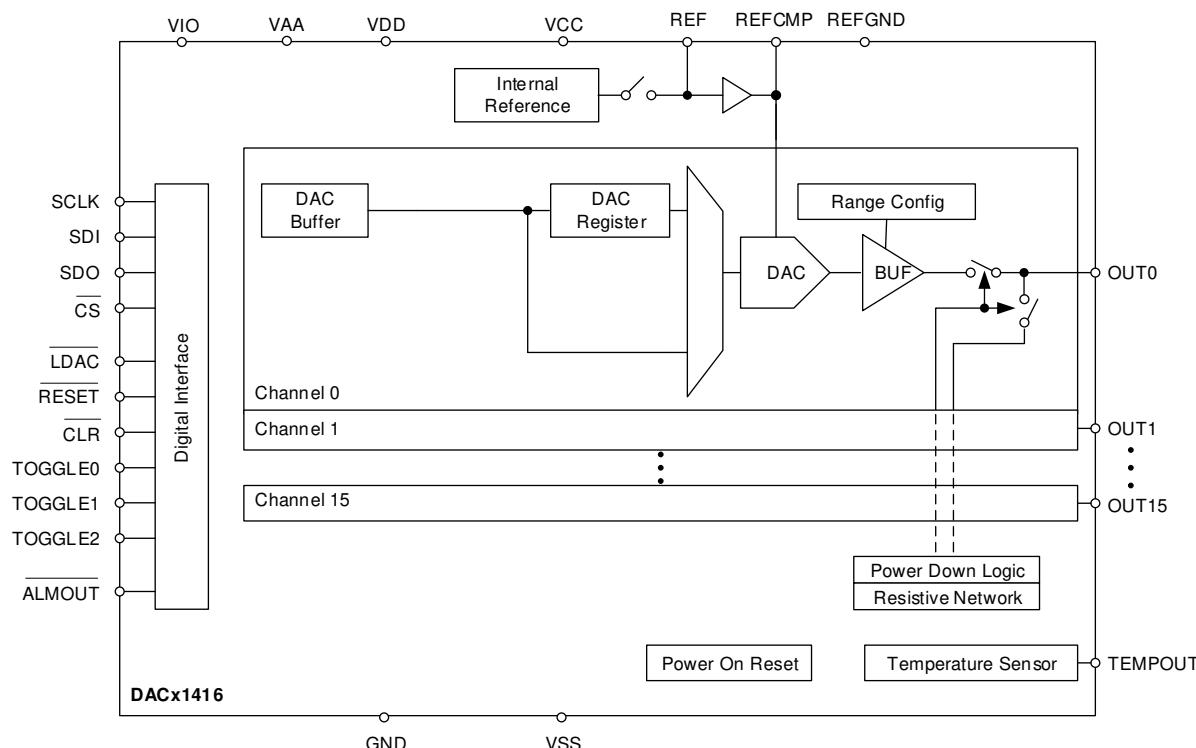

機能ブロック図

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、[ti.com](http://ti.com) で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                |    |                        |    |

|----------------|----|------------------------|----|

| 1 特長           | 1  | 6.5 プログラミング            | 33 |

| 2 アプリケーション     | 1  | 7 レジスタ マップ             | 37 |

| 3 説明           | 1  | 8 アプリケーションと実装          | 51 |

| 4 ピン構成および機能    | 2  | 8.1 アプリケーション情報         | 51 |

| 5 仕様           | 5  | 8.2 代表的なアプリケーション       | 51 |

| 5.1 絶対最大定格     | 5  | 8.3 電源に関する推奨事項         | 54 |

| 5.2 ESD 定格     | 5  | 8.4 レイアウト              | 54 |

| 5.3 推奨動作条件     | 5  | 9 デバイスおよびドキュメントのサポート   | 56 |

| 5.4 熱に関する情報    | 6  | 9.1 デバイス サポート          | 56 |

| 5.5 電気的特性      | 6  | 9.2 ドキュメントのサポート        | 56 |

| 5.6 タイミング要件    | 12 | 9.3 ドキュメントの更新通知を受け取る方法 | 56 |

| 5.7 タイミング図     | 15 | 9.4 サポート・リソース          | 56 |

| 5.8 代表的特性      | 16 | 9.5 商標                 | 56 |

| 6 詳細説明         | 27 | 9.6 静電気放電に関する注意事項      | 56 |

| 6.1 概要         | 27 | 9.7 用語集                | 56 |

| 6.2 機能ブロック図    | 27 | 10 改訂履歴                | 56 |

| 6.3 機能説明       | 28 | 11 メカニカル、パッケージ、および注文情報 | 57 |

| 6.4 デバイスの機能モード | 31 |                        |    |

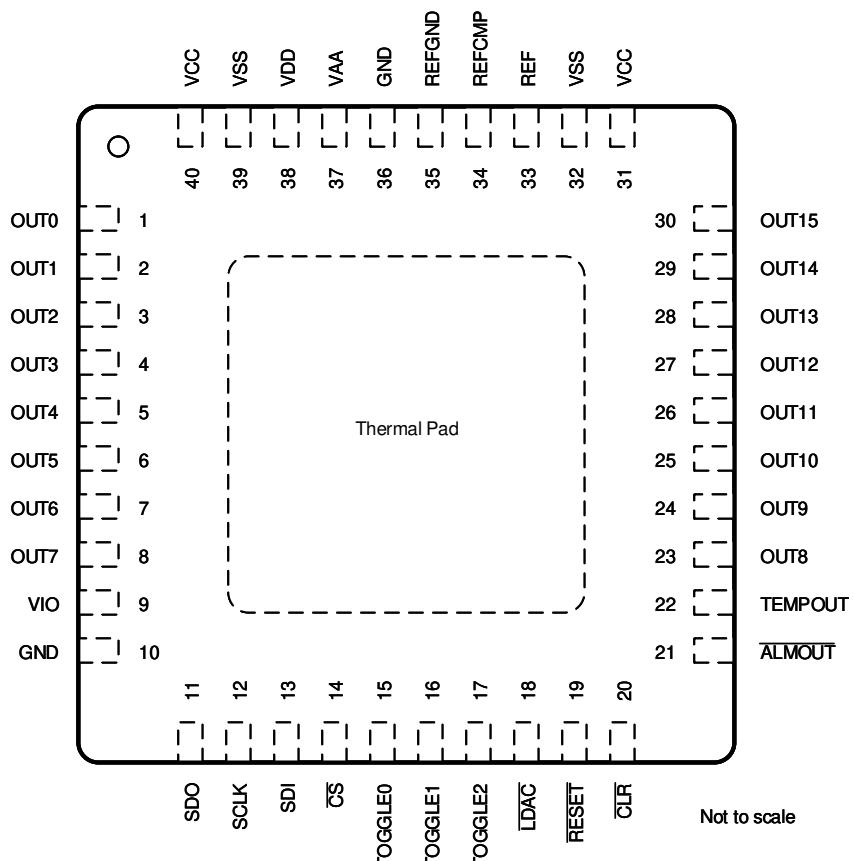

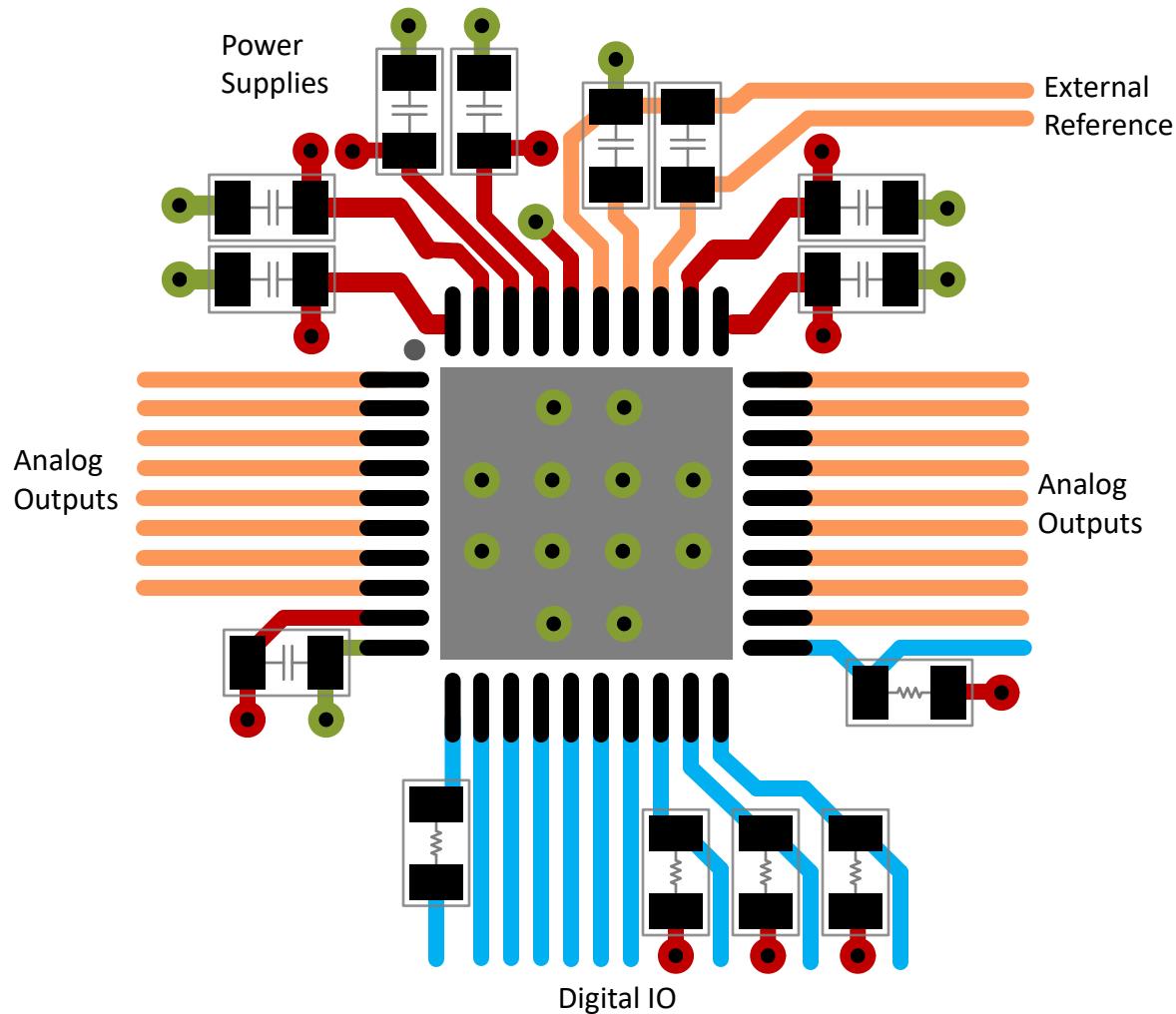

## 4 ピン構成および機能

図 4-1. RHA パッケージ、40 ピン VQFN、上面図

**表 4-1. ピンの機能**

| 番号     | ピン<br>名称 | タイプ     | 説明                                                                                                                                                                                               |

|--------|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | OUT0     | 出力      | チャネル 0 アナログ DAC 出力電圧。                                                                                                                                                                            |

| 2      | OUT1     | 出力      | チャネル 1 アナログ DAC 出力電圧。                                                                                                                                                                            |

| 3      | OUT2     | 出力      | チャネル 2 アナログ DAC 出力電圧。                                                                                                                                                                            |

| 4      | OUT3     | 出力      | チャネル 3 アナログ DAC 出力電圧。                                                                                                                                                                            |

| 5      | OUT4     | 出力      | チャネル 4 アナログ DAC 出力電圧。                                                                                                                                                                            |

| 6      | OUT5     | 出力      | チャネル 5 アナログ DAC 出力電圧。                                                                                                                                                                            |

| 7      | OUT6     | 出力      | チャネル 6 アナログ DAC 出力電圧。                                                                                                                                                                            |

| 8      | OUT7     | 出力      | チャネル 7 アナログ DAC 出力電圧。                                                                                                                                                                            |

| 9      | VIO      | 電源      | IO 消費電圧。(1.7V~5.5V)。このピンは、デバイスの I/O 動作電圧を設定します。                                                                                                                                                  |

| 10, 36 | GND      | グランド    | デバイスの全回路のグランド基準点。                                                                                                                                                                                |

| 11     | SDO      | 出力      | シリアル インターフェイス データ出力。SDO-EN ビットを設定して、動作前に SDO ピンをイネーブルにします。データは、FSDO ビットで指定されたとおりに、SCLK ピンの立ち上がりエッジまたは立ち下がりエッジで入力シフトレジスタからクロックアウトされます (デフォルトは立ち上がりエッジ)。                                           |

| 12     | SCLK     | 入力      | シリアル インターフェイス クロック。                                                                                                                                                                              |

| 13     | SDI      | 入力      | シリアル インターフェイスのデータ入力。データは SCLK ピンの各立ち下がりエッジで入力シフトレジスタにクロックされます。                                                                                                                                   |

| 14     | CS       | 入力      | アクティブ Low のシリアル データをイネーブルにします。この入力は、シリアル データのフレーム同期信号です。信号が low になると、シリアル インターフェイス入力シフトレジスタがイネーブルになります。                                                                                          |

| 15     | TOGGLE0  | 入力      | ピン 0 をトグルします。各 DAC に関連付けられた 2 つの DAC データレジスタ間を切り替えるため、トグル動作に設定された DAC 出力用の制御信号。ロジック Low では DAC 出力がレジスタ A に設定された値に更新されます。ロジック High では DAC 出力がレジスタ B に設定された値に更新されます。未使用の場合、TOGGLE0 ピンはグラウンドに接続します。 |

| 16     | TOGGLE1  | 入力      | ピン 1 をトグルします。各 DAC に関連付けられた 2 つの DAC データレジスタ間を切り替えるため、トグル動作に設定された DAC 出力用の制御信号。ロジック Low では DAC 出力がレジスタ A に設定された値に更新されます。ロジック High では DAC 出力がレジスタ B に設定された値に更新されます。未使用の場合、TOGGLE1 ピンはグラウンドに接続します。 |

| 17     | TOGGLE2  | 入力      | ピン 2 をトグルします。各 DAC に関連付けられた 2 つの DAC データレジスタ間を切り替えるため、トグル動作に設定された DAC 出力用の制御信号。ロジック Low では DAC 出力がレジスタ A に設定された値に更新されます。ロジック High では DAC 出力がレジスタ B に設定された値に更新されます。未使用の場合、TOGGLE2 ピンはグラウンドに接続します。 |

| 18     | LDAC     | 入力      | アクティブ Low 同期信号。LDAC ピンが Low のとき、同期モードに構成されたチャネルの DAC 出力は同時に更新されます。使用しない場合は VIO に接続します。                                                                                                           |

| 19     | RESET    | 入力      | アクティブ Low のリセット入力。このピンがロジック Low になると、デバイスはパワーオン リセット イベントを発生させます。                                                                                                                                |

| 20     | CLR      | 入力      | アクティブ Low クリア入力。このピンがロジック Low になると、すべての DAC 出力がクリアコードにクリアされます。使用しない場合は VIO に接続します。                                                                                                               |

| 21     | ALMOUT   | 出力      | ALMOUT はオープンドレインのアラーム出力です。V <sub>IO</sub> を超えない電圧に接続する外付け 10kΩ プルアップ抵抗が必要です。                                                                                                                     |

| 22     | TEMPOUT  | 出力      | アナログ温度モニタ出力。                                                                                                                                                                                     |

| 23     | OUT8     | 出力      | チャネル 8 アナログ DAC 出力電圧。                                                                                                                                                                            |

| 24     | OUT9     | 出力      | チャネル 9 アナログ DAC 出力電圧。                                                                                                                                                                            |

| 25     | OUT10    | 出力      | チャネル 10 アナログ DAC 出力電圧。                                                                                                                                                                           |

| 26     | OUT11    | 出力      | チャネル 11 アナログ DAC 出力電圧。                                                                                                                                                                           |

| 27     | OUT12    | 出力      | チャネル 12 アナログ DAC 出力電圧。                                                                                                                                                                           |

| 28     | OUT13    | 出力      | チャネル 13 アナログ DAC 出力電圧。                                                                                                                                                                           |

| 29     | OUT14    | 出力      | チャネル 14 アナログ DAC 出力電圧。                                                                                                                                                                           |

| 30     | OUT15    | 出力      | チャネル 15 アナログ DAC 出力電圧。                                                                                                                                                                           |

| 31, 40 | VCC      | 電源      | 出力用正のアナログ電源 (9V ~ 41.5V)。                                                                                                                                                                        |

| 32, 39 | VSS      | 電源      | 出力用負のアナログ電源 (-21.5V~0V)。                                                                                                                                                                         |

| 33     | REF      | 入力 / 出力 | 外部リファレンスで動作する場合のデバイスへの基準入力。内部リファレンスを使用する場合、このピンは基準出力電圧ピンとなります。150nF のコンデンサをグラウンドに接続します。                                                                                                          |

| 34     | REFCMP   | 入力 / 出力 | 基準補償コンデンサの接続。REFCMP と REFGND の間に 330pF のコンデンサを接続します。                                                                                                                                             |

| 35     | REFGND   | グランド    | 内部リファレンスのグラウンド基準点。                                                                                                                                                                               |

| 37     | VAA      | 電源      | アナログ消費電圧 (4.5V~5.5V)。このピンは、必ず VDD ピンと同じ電位にする必要があります。                                                                                                                                             |

表 4-1. ピンの機能 (続き)

| ピン      |         | タイプ | 説明                                                                                    |

|---------|---------|-----|---------------------------------------------------------------------------------------|

| 番号      | 名称      |     |                                                                                       |

| 38      | VDD     | 電源  | デジタル電源電圧 (4.5V ~ 5.5V)。このピンは、必ず VAA ピンと同じ電位にする必要があります。                                |

| サーマルパッド | サーマルパッド | —   | サーマルパッドはパッケージの底面に配置されています。このサーマルパッドは、複数のビアを使用して内部の任意の PCB グランドプレーンに接続し、優れた熱特性を実現できます。 |

## 5 仕様

### 5.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|           |                       | 最小値            | 最大値            | 単位 |

|-----------|-----------------------|----------------|----------------|----|

| 電源電圧      | $V_{DD}$ から GND       | -0.3           | 6              | V  |

|           | $V_{IO}$ から GND       | -0.3           | 6              | V  |

|           | $V_{CC}$ から GND       | -0.3           | 44             | V  |

|           | $V_{SS}$ から GND       | -22            | 0.3            | V  |

|           | REFGND から GND へ       | -0.3           | 0.9            | V  |

|           | $V_{DD} \sim V_{AA}$  | -0.3           | 0.3            | V  |

|           | $V_{CC}$ から $V_{SS}$  | -0.3           | 44             | V  |

| ピン電圧      | DAC 出力から GND へ        | $V_{SS} - 0.3$ | $V_{CC} + 0.3$ | V  |

|           | TEMPOUT から GND        | -0.3           | $V_{DD} + 0.3$ | V  |

|           | REF および REFCMP から GND | -0.3           | $V_{DD} + 0.3$ | V  |

|           | デジタル入力から GND へ        | -0.3           | $V_{IO} + 0.3$ | V  |

|           | SDO から GND            | -0.3           | $V_{IO} + 0.3$ | V  |

|           | ALARMOUT から GND       | -0.3           | 6              | V  |

| $T_J$     | 動作時接合部温度              | -40            | 150            | °C |

| $T_{stg}$ | 保存温度                  | -60            | 150            | °C |

(1) 「絶対最大定格」の範囲外の動作は、デバイスに恒久的な損傷を与える可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用した場合、本デバイスは完全に機能するとは限らず、このことが本デバイスの信頼性、機能、性能に影響を及ぼし、本デバイスの寿命を縮める可能性があります。

### 5.2 ESD 定格

|             |      |                                                         | 値          | 単位 |

|-------------|------|---------------------------------------------------------|------------|----|

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>    | $\pm 1000$ | V  |

|             |      | 荷電デバイス モデル (CDM)、JEDEC 仕様 JESD22-C101 準拠 <sup>(2)</sup> | $\pm 500$  |    |

(1) JEDEC ドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

(2) JEDEC ドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

### 5.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                             |                             | 最小値   | 公称値      | 最大値      | 単位 |

|-----------------------------|-----------------------------|-------|----------|----------|----|

| $V_{AA}$ <sup>(1)</sup>     | アナログ電源電圧                    | 4.5   | 5.5      | 5.5      | V  |

| $V_{DD}$ <sup>(1)</sup>     | デジタル電源電圧                    | 4.5   | 5.5      | 5.5      | V  |

| $V_{IO}$                    | IO 電源                       | 1.7   | 5.5      | 5.5      | V  |

| $V_{CC}$                    | 出力バッファの正の電源電圧               | 9     | 41.5     | 41.5     | V  |

| $V_{SS}$ <sup>(2)</sup>     | 出力バッファの負の電源電圧               | -21.5 | 0        | 0        | V  |

| $V_{CC} - V_{SS}$           | 出力バッファの電源電圧範囲               | 9     | 43       | 43       | V  |

|                             | デジタル入力電圧                    | 0     | $V_{IO}$ | $V_{IO}$ | V  |

| $V_{REFIN}$                 | $V_{REFGND}$ に対するリファレンス入力電圧 | 2.49  | 2.5      | 2.51     | V  |

| $V_{REFGND}$ <sup>(3)</sup> | REFGND ピン電圧                 | 0     | 0        | 0.6      | V  |

自由気流での動作温度範囲内 (特に記述のない限り)

|                |          | 最小値 | 公称値 | 最大値 | 単位 |

|----------------|----------|-----|-----|-----|----|

| T <sub>A</sub> | 動作時の周囲温度 | -40 |     | 125 | °C |

- (1) V<sub>AA</sub> と V<sub>DD</sub> が同じ電位にあることを確認します。

- (2) V<sub>SS</sub> は、すべての DAC 出力がユニポーラの場合のみ GND に接続されます。

- (3) V<sub>REFGND</sub> が GND に接続されていない場合は、バッファ付きソースを使用して V<sub>REFGND</sub> を駆動します。

## 5.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup>  |                     | DACx1416   | 単位   |

|-----------------------|---------------------|------------|------|

|                       |                     | RHA (VQFN) |      |

|                       |                     | 40 ピン      |      |

| R <sub>ΘJA</sub>      | 接合部から周囲への熱抵抗        | 26.8       | °C/W |

| R <sub>ΘJC(top)</sub> | 接合部からケース (上面) への熱抵抗 | 14.1       | °C/W |

| R <sub>ΘJB</sub>      | 接合部から基板への熱抵抗        | 3.4        | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への特性パラメータ    | 0.2        | °C/W |

| Ψ <sub>JB</sub>       | 接合部から基板への特性パラメータ    | 3.4        | °C/W |

| R <sub>ΘJC(bot)</sub> | 接合部からケース (底面) への熱抵抗 | 0.7        | °C/W |

- (1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション レポートを参照してください。

## 5.5 電気的特性

特に記載がない限り、最小/最大仕様は T<sub>A</sub> = -40°C ~ +125°C、代表値仕様は T<sub>A</sub> = 25°C、V<sub>CC</sub> = 9V ~ 41.5V、V<sub>SS</sub> = -21.5V ~ 0V、V<sub>DD</sub> = V<sub>AA</sub> = 4.5V ~ 5.5V、V<sub>REFIN</sub> = 2.5V、V<sub>IO</sub> = 1.7 V ~ 5.5 V、DAC 出力は無負荷、デジタル入力は V<sub>IO</sub> または GND における条件です

| パラメータ               |          | テスト条件                               | 最小値   | 標準値    | 最大値  | 単位   |

|---------------------|----------|-------------------------------------|-------|--------|------|------|

| 安定動作 <sup>(1)</sup> |          |                                     |       |        |      |      |

| INL                 | 分解能      | DAC81416                            | 16    |        |      | ビット  |

|                     |          | DAC71416                            | 14    |        |      |      |

|                     |          | DAC61416                            | 12    |        |      |      |

| DNL                 | 積分非直線性   | DAC81416、0V~40V および ±2.5V を除くすべての範囲 | -1    | ±0.5   | 1    | LSB  |

|                     |          | DAC81416、0V ~ 40V、±2.5V 範囲に対応       | -2    | ±1     | 2    |      |

|                     |          | DAC71416、すべての範囲                     | -1    | ±0.5   | 1    |      |

|                     |          | DAC61416、すべての範囲                     | -1    | ±0.5   | 1    |      |

| TUE                 | 微分非直線性   | DAC81416、16 ビット単調性を指定               | -1    | ±0.5   | 1    | LSB  |

|                     |          | DAC71416、14 ビット単調性を指定               | -1    | ±0.5   | 1    |      |

|                     |          | DAC61416、12 ビット単調性を指定               | -1    | ±0.5   | 1    |      |

| ユニポーラ オフセット誤差       | 総合未調整誤差  | すべての範囲、±2.5V を除く                    | -0.1  | ±0.01  | 0.1  | %FSR |

|                     |          | ±2.5 範囲                             | -0.2  | ±0.02  | 0.2  |      |

| ユニポーラ ゼロ コード誤差      |          | すべてのユニポーラ レンジ                       | -0.03 | ±0.015 | 0.03 | %FSR |

|                     |          | すべてのユニポーラ レンジ                       | 0     | 0.04   | 0.1  |      |

| バイポーラ ゼロ誤差          |          | すべてのバイポーラ レンジ                       | -0.2  | ±0.02  | 0.2  | %FSR |

|                     |          | 全範囲                                 | -0.2  | ±0.075 | 0.2  |      |

| ゲイン誤差               | フルスケール誤差 | すべての範囲、±2.5V を除く                    | -0.1  | ±0.02  | 0.1  | %FSR |

|                     |          | ±2.5 範囲                             | -0.2  | ±0.02  | 0.2  |      |

## 5.5 電気的特性 (続き)

特に記載がない限り、最小/最大仕様は  $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ 、代表値仕様は  $T_A = 25^\circ\text{C}$ 、 $V_{CC} = 9\text{V} \sim 41.5\text{V}$ 、 $V_{SS} = -21.5\text{V} \sim 0\text{V}$ 、 $V_{DD} = V_{AA} = 4.5\text{V} \sim 5.5\text{V}$ 、 $V_{REFIN} = 2.5\text{V}$ 、 $V_{IO} = 1.7\text{V} \sim 5.5\text{V}$ 、DAC 出力は無負荷、デジタル入力は  $V_{IO}$  または  $\text{GND}$  における条件です

| パラメータ |                    | テスト条件                                        | 最小値 | 標準値 | 最大値 | 単位               |

|-------|--------------------|----------------------------------------------|-----|-----|-----|------------------|

|       | ユニポーラ オフセット誤差のドリフト | すべてのユニポーラ レンジ                                |     | ±2  |     | ppm (対 FSR) / °C |

|       | バイポーラ ゼロ誤差のドリフト    | すべてのバイポーラ レンジ                                |     | ±2  |     | ppm (対 FSR) / °C |

|       | ゲインドリフト            | 全範囲                                          |     | ±2  |     | ppm (対 FSR) / °C |

|       | 時間の経過に伴う出力電圧ドリフト   | $T_A = 40^\circ\text{C}$ 、フルスケール コード、1900 時間 |     | 5   |     | ppm (対 FSR)      |

## 5.5 電気的特性 (続き)

特に記載がない限り、最小/最大仕様は  $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ 、代表値仕様は  $T_A = 25^\circ\text{C}$ 、 $V_{CC} = 9\text{V} \sim 41.5\text{V}$ 、 $V_{SS} = -21.5\text{V} \sim 0\text{V}$ 、 $V_{DD} = V_{AA} = 4.5\text{V} \sim 5.5\text{V}$ 、 $V_{REFIN} = 2.5\text{V}$ 、 $V_{IO} = 1.7\text{V} \sim 5.5\text{V}$ 、DAC 出力は無負荷、デジタル入力は  $V_{IO}$  または  $\text{GND}$  における条件です

| パラメータ                        |                        | テスト条件                                                                                                                                                                              | 最小値  | 標準値        | 最大値 | 単位                      |

|------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------|-----|-------------------------|

| <b>差動モード性能<sup>(1)</sup></b> |                        |                                                                                                                                                                                    |      |            |     |                         |

| TUE                          | 総合未調整誤差                | 全範囲                                                                                                                                                                                | -0.1 | $\pm 0.01$ | 0.1 | %FSR                    |

|                              |                        | $\pm 2.5$ 範囲                                                                                                                                                                       | -0.2 | $\pm 0.02$ | 0.2 |                         |

|                              | 同相モード誤差                | すべてのバイポーラ範囲、ミッドスケール コード                                                                                                                                                            | -0.1 | $\pm 0.01$ | 0.1 | %FSR                    |

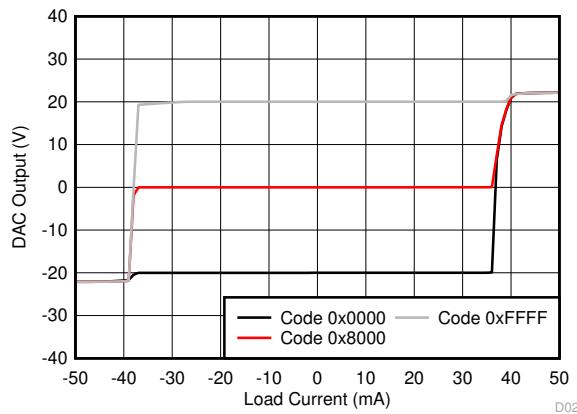

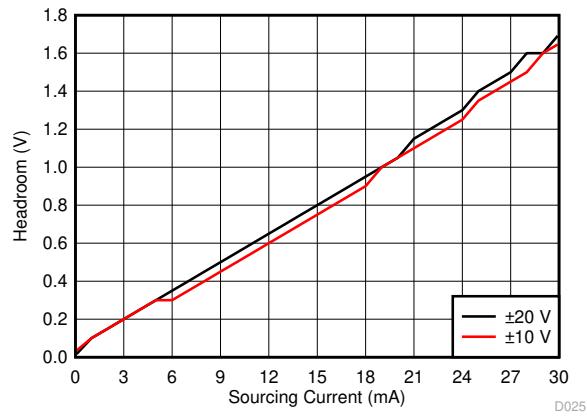

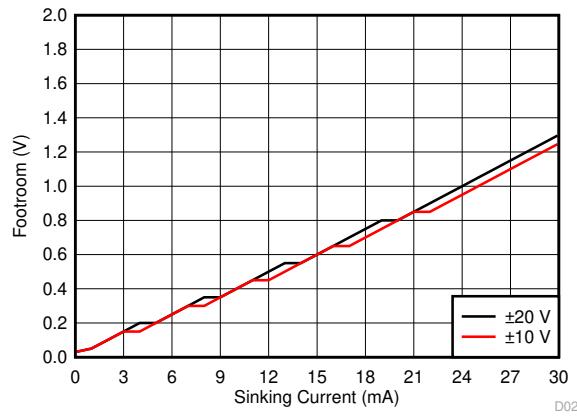

| <b>出力特性</b>                  |                        |                                                                                                                                                                                    |      |            |     |                         |

|                              | 出力電圧ヘッドルーム             | $V_{SS}$ および $V_{CC}$<br>( $-10\text{mA} \leq I_{OUT} \leq 10\text{mA}$ )                                                                                                          | 1    |            |     | V                       |

|                              |                        | $V_{SS}$ および $V_{CC}$<br>( $-15\text{mA} \leq I_{OUT} \leq 15\text{mA}$ )                                                                                                          | 1.5  |            |     |                         |

|                              | 短絡電流 <sup>(2)</sup>    | フルスケール出力を $V_{SS}$ に短絡                                                                                                                                                             | 40   |            |     | mA                      |

|                              |                        | $V_{CC}$ に短絡したゼロスケール出力                                                                                                                                                             | 40   |            |     |                         |

|                              | ロード レギュレーション           | ミッドスケール コード、 $-15\text{mA} \leq I_{OUT} \leq 15\text{mA}$                                                                                                                          | 70   |            |     | $\mu\text{V}/\text{mA}$ |

|                              | 最大容量性負荷 <sup>(3)</sup> | $R_{LOAD} = \text{開}$                                                                                                                                                              | 0    |            | 1   | nF                      |

|                              | DC 出力インピーダンス           | ミッドスケール コード                                                                                                                                                                        | 0.05 |            |     | $\Omega$                |

|                              |                        | フルスケール コード                                                                                                                                                                         | 40   |            |     |                         |

| <b>ダイナミック性能</b>              |                        |                                                                                                                                                                                    |      |            |     |                         |

|                              | 出力電圧セトリング時間            | $\frac{1}{4} \sim \frac{3}{4}$ スケールおよび $\frac{3}{4} \sim \frac{1}{4}$ スケール のセトリング タイム ( $\pm 1\text{LSB}$ 、 $\pm 10\text{V}$ レンジ、 $R_L = 5\text{k}\Omega$ 、 $C_L = 200\text{pF}$ ) | 12   |            |     | $\mu\text{s}$           |

|                              | スルーレート                 | 0V ~ 5V の範囲                                                                                                                                                                        | 1    |            |     | $\text{V}/\mu\text{s}$  |

|                              |                        | その他のすべての出力範囲                                                                                                                                                                       | 4    |            |     |                         |

|                              | 電源オン時のグリッチ振幅           | アクティブな DAC 出力までのパワーダウン、 $\pm 20\text{V}$ 範囲、ミッドスケール コード、 $R_L = 5\text{k}\Omega$ 、 $C_L = 200\text{pF}$                                                                            | 0.3  |            |     | V                       |

|                              | 出力ノイズ電圧                | 0.1Hz~10Hz、ミッドスケール コード、0V ~ 5V 範囲                                                                                                                                                  | 15   |            |     | $\mu\text{V}_{PP}$      |

|                              | 出力ノイズ 密度               | 1kHz、ミッドスケール コード、0V ~ 5V 範囲                                                                                                                                                        | 78   |            |     | $\text{nV}/\text{Hz}$   |

| PSRR-AC                      | 電源 AC 除去比              | ミッドスケール コード、周波数 = 60Hz、振幅 = 200mV <sub>PP</sub> を $V_{DD}$ 、 $V_{CC}$ または $V_{SS}$ に重畠                                                                                             | 1    |            |     | LSB/V                   |

| PSRR-DC                      | 電源 DC 除去比              | ミッドスケール コード、 $V_{DD} = 5\text{V} \pm 5\%$ 、 $V_{CC} = 20\text{V}$ 、 $V_{SS} = -20\text{V}$                                                                                         | 1    |            |     | LSB/V                   |

|                              |                        | ミッドスケール コード、 $V_{DD} = 5\text{V}$ 、 $V_{CC} = 20\text{V} \pm 5\%$ 、 $V_{SS} = -20\text{V}$                                                                                         | 1    |            |     |                         |

|                              |                        | ミッドスケール コード、 $V_{DD} = 5\text{V}$ 、 $V_{CC} = 20\text{V}$ 、 $V_{SS} = -20\text{V} \pm 5\%$                                                                                         | 1    |            |     |                         |

|                              | コード書き換えによるグリッチ インパルス   | 主要なキャリア付近での 1LSB 変化、0V ~ 5V 範囲                                                                                                                                                     | 4    |            |     | nV-s                    |

|                              | チャネル間 AC クロストーク        | 0V ~ 5V の範囲、測定チャネルはミッドスケール、他のすべてのチャネルはフルスケール スイング                                                                                                                                  | 4    |            |     | nV-s                    |

## 5.5 電気的特性 (続き)

特に記載がない限り、最小/最大仕様は  $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ 、代表値仕様は  $T_A = 25^\circ\text{C}$ 、 $V_{CC} = 9\text{V} \sim 41.5\text{V}$ 、 $V_{SS} = -21.5\text{V} \sim 0\text{V}$ 、 $V_{DD} = V_{AA} = 4.5\text{V} \sim 5.5\text{V}$ 、 $V_{REFIN} = 2.5\text{V}$ 、 $V_{IO} = 1.7\text{V} \sim 5.5\text{V}$ 、DAC 出力は無負荷、デジタル入力は  $V_{IO}$  または  $\text{GND}$  における条件です

| パラメータ |                 | テスト条件                                               | 最小値 | 標準値  | 最大値 | 単位   |

|-------|-----------------|-----------------------------------------------------|-----|------|-----|------|

|       | チャネル間 DC クロストーク | 0V ~ 5V の範囲、測定チャネルはミッドスケール、他のすべてのチャネルはフルスケール        |     | 0.25 |     | LSB  |

|       | デジタル フィードスルー    | 0V から 5V までの範囲、ミッドスケールコード、 $f_{SCLK} = 1\text{MHz}$ |     | 1    |     | nV-s |

## 5.5 電気的特性 (続き)

特に記載がない限り、最小/最大仕様は  $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ 、代表値仕様は  $T_A = 25^\circ\text{C}$ 、 $V_{CC} = 9\text{V} \sim 41.5\text{V}$ 、 $V_{SS} = -21.5\text{V} \sim 0\text{V}$ 、 $V_{DD} = V_{AA} = 4.5\text{V} \sim 5.5\text{V}$ 、 $V_{REFIN} = 2.5\text{V}$ 、 $V_{IO} = 1.7\text{V} \sim 5.5\text{V}$ 、DAC 出力は無負荷、デジタル入力は  $V_{IO}$  または  $\text{GND}$  における条件です

| パラメータ             |                    | テスト条件                                           | 最小値                 | 標準値            | 最大値                 | 単位                          |

|-------------------|--------------------|-------------------------------------------------|---------------------|----------------|---------------------|-----------------------------|

| <b>外部リファレンス入力</b> |                    |                                                 |                     |                |                     |                             |

| $V_{REFIN}$       | 基準入力電圧範囲           | $V_{REFGND}$ 向け                                 | 2.49                | 2.5            | 2.51                | V                           |

|                   | 基準入力電流             |                                                 |                     | 50             |                     | $\mu\text{A}$               |

|                   | リファレンス入力インピーダンス    |                                                 |                     | 50             |                     | $\text{k}\Omega$            |

|                   | 基準入力容量             |                                                 |                     | 20             |                     | $\text{pF}$                 |

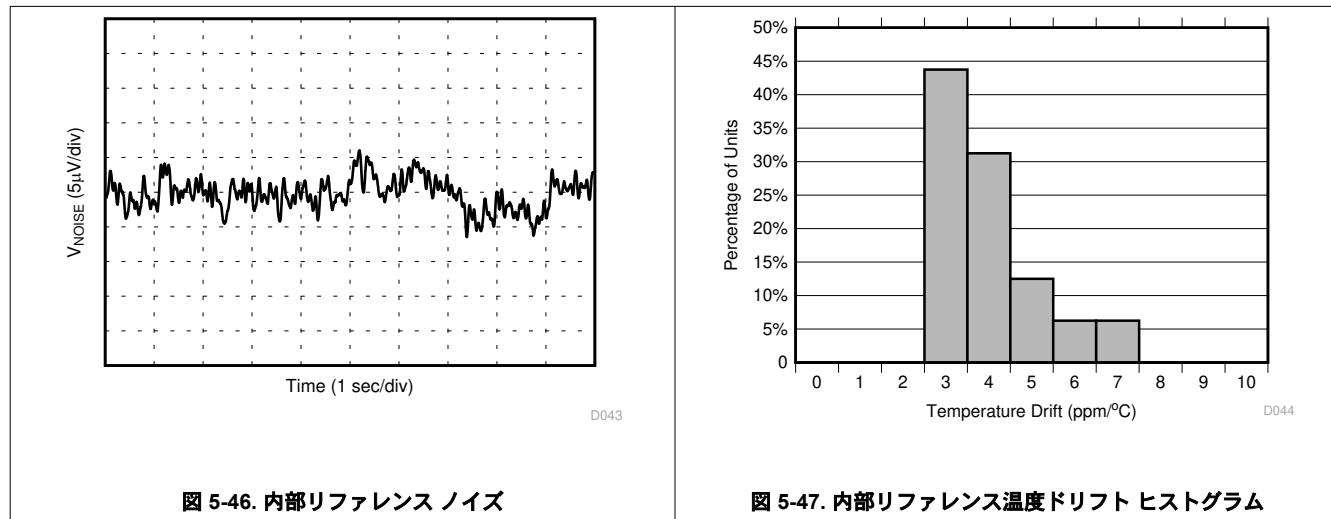

| <b>内部リファレンス</b>   |                    |                                                 |                     |                |                     |                             |

| $V_{REFOUT}$      | 基準出力電圧範囲           | $T_A = 25^\circ\text{C}$                        | 2.4975              | 2.5025         |                     | V                           |

|                   | リファレンス出力のドリフト      |                                                 |                     | 5              | 15                  | $\text{ppm}/^\circ\text{C}$ |

|                   | リファレンス出力インピーダンス    |                                                 |                     | 0.1            |                     | $\Omega$                    |

|                   | リファレンス出力ノイズ        | 0.1Hz ~ 10Hz                                    |                     | 12             |                     | $\mu\text{V}_{\text{PP}}$   |

|                   | リファレンス出力ノイズ密度      | 10kHz, $\text{REF}_{\text{LOAD}} = 10\text{nF}$ |                     | 150            |                     | $\text{nV}/\text{Hz}$       |

|                   | リファレンス負荷電流         |                                                 |                     | 5              |                     | $\text{mA}$                 |

|                   | 基準負荷レギュレーション       | ソース                                             |                     | 80             |                     | $\mu\text{V}/\text{mA}$     |

|                   | 基準ライン レギュレーション     |                                                 |                     | 20             |                     | $\mu\text{V}/\text{V}$      |

|                   | 温度によるリファレンス出力のドリフト | $T_A = 25^\circ\text{C}, 1900$ 時間               |                     | 250            |                     | $\mu\text{V}$               |

|                   | 基準温度ヒステリシス         | 最初のサイクル                                         |                     | $\pm 700$      |                     | $\mu\text{V}$               |

|                   |                    | 追加サイクル                                          |                     | $\pm 50$       |                     |                             |

| <b>デジタル入出力</b>    |                    |                                                 |                     |                |                     |                             |

| $V_{IH}$          | High レベル入力電圧       |                                                 | $0.7 \times V_{IO}$ |                |                     | V                           |

| $V_{IL}$          | Low レベル入力電圧        |                                                 |                     |                | 0.3 $\times V_{IO}$ | V                           |

|                   | 入力電流               |                                                 |                     | $\pm 2$        |                     | $\mu\text{A}$               |

|                   | 入力ピン容量             |                                                 |                     | 2              |                     | $\text{pF}$                 |

| $V_{OH}$          | High レベル出力電圧       | $I_{OH} = 0.2\text{mA}$                         |                     | $V_{IO} - 0.2$ |                     | V                           |

| $V_{OL}$          | Low レベル出力電圧        | $I_{OL} = 0.2\text{mA}$                         |                     |                | 0.4                 | V                           |

|                   | 出力ピンの容量            |                                                 |                     |                | 5                   | $\text{pF}$                 |

| <b>アラーム出力</b>     |                    |                                                 |                     |                |                     |                             |

|                   | 出力ピンの容量            |                                                 |                     | 5              |                     | $\text{pF}$                 |

| $V_{OL}$          | Low レベル出力電圧        | $I_{LOAD} = -0.2\text{mA}$                      |                     |                | 0.4                 | V                           |

| <b>温度出力</b>       |                    |                                                 |                     |                |                     |                             |

| $V_{TEMPOUT, 0C}$ | 0°Cでの出力電圧オフセット     |                                                 |                     | 1.34           |                     | V                           |

|                   | センサのゲイン            |                                                 |                     | -4             |                     | $\text{mV}/^\circ\text{C}$  |

## 5.5 電気的特性 (続き)

特に記載がない限り、最小/最大仕様は  $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ 、代表値仕様は  $T_A = 25^\circ\text{C}$ 、 $V_{CC} = 9\text{V} \sim 41.5\text{V}$ 、 $V_{SS} = -21.5\text{V} \sim 0\text{V}$ 、 $V_{DD} = V_{AA} = 4.5\text{V} \sim 5.5\text{V}$ 、 $V_{REFIN} = 2.5\text{V}$ 、 $V_{IO} = 1.7\text{V} \sim 5.5\text{V}$ 、DAC 出力は無負荷、デジタル入力は  $V_{IO}$  または  $\text{GND}$  における条件です

| パラメータ       |                | テスト条件                                                                 | 最小値 | 標準値  | 最大値 | 単位            |

|-------------|----------------|-----------------------------------------------------------------------|-----|------|-----|---------------|

| <b>電源要件</b> |                |                                                                       |     |      |     |               |

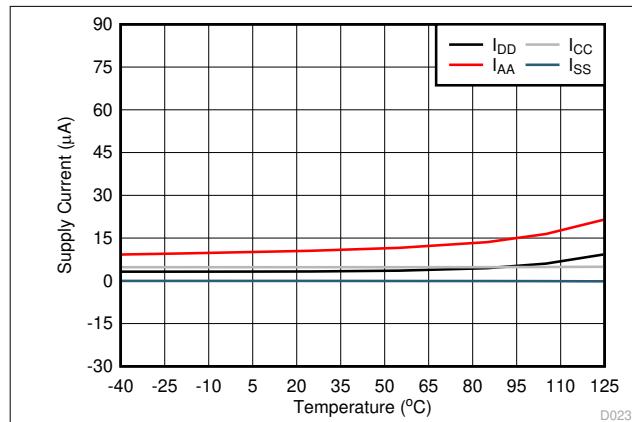

| $I_{DD}$    | $V_{DD}$ 消費電流  | アクティブ モード、内部リファレンスがイネーブル、フルスケール コード、 $\pm 20\text{V}$ の出力範囲、SPI が静的   |     | 0.05 | 0.5 | mA            |

|             |                | アクティブ モード、内部リファレンスがディスエーブル、フルスケール コード、 $\pm 20\text{V}$ の出力範囲、SPI が静的 |     | 0.05 | 0.5 | mA            |

|             |                | パワーダウン モード                                                            |     | 0.05 | 0.5 | mA            |

| $I_{AA}$    | $V_{AA}$ 消費電流  | アクティブ モード、内部リファレンスがイネーブル、フルスケール コード、 $\pm 20\text{V}$ の出力範囲、SPI が静的   |     | 20   | 30  | mA            |

|             |                | アクティブ モード、内部リファレンスがディスエーブル、フルスケール コード、 $\pm 20\text{V}$ の出力範囲、SPI が静的 |     | 18   | 28  | mA            |

|             |                | パワーダウン モード                                                            |     | 2    | 85  | $\mu\text{A}$ |

| $I_{CC}$    | $V_{CC}$ 消費電流  | アクティブ モード、内部リファレンスがイネーブル、フルスケール コード、 $\pm 20\text{V}$ の出力範囲、SPI が静的   |     | 10   | 25  | mA            |

|             |                | アクティブ モード、内部リファレンスがディスエーブル、フルスケール コード、 $\pm 20\text{V}$ の出力範囲、SPI が静的 |     | 10   | 25  | mA            |

|             |                | パワーダウン モード                                                            |     | 10   | 30  | $\mu\text{A}$ |

| $I_{SS}$    | $V_{SS}$ 消費電流  | アクティブ モード、内部リファレンスがイネーブル、フルスケール コード、 $\pm 20\text{V}$ の出力範囲、SPI が静的   |     | -15  | -10 | mA            |

|             |                | アクティブ モード、内部リファレンスがディスエーブル、フルスケール コード、 $\pm 20\text{V}$ の出力範囲、SPI が静的 |     | -15  | -10 | mA            |

|             |                | パワーダウン モード                                                            |     | -30  | -10 | $\mu\text{A}$ |

| $I_{IO}$    | $V_{IO}$ の電源電流 | 50MHz での SCLK と SDI のトグル                                              |     | 350  | 500 | $\mu\text{A}$ |

- (1) エンドポイントはコード間にフィットします。16 ビット: コード 256 ~ 65280、14 ビット: コード 128 ~ 16256、12 ビット: コード 32 ~ 4064。

- (2) 一時的な過負荷状態保護。電流制限時には、接合部温度が規定値を超える可能性があります。規定された最大接合部温度を超える動作は、デバイスの信頼性を損なう可能性があります。

- (3) 設計と特性評価による仕様で、製造テストは未実施。

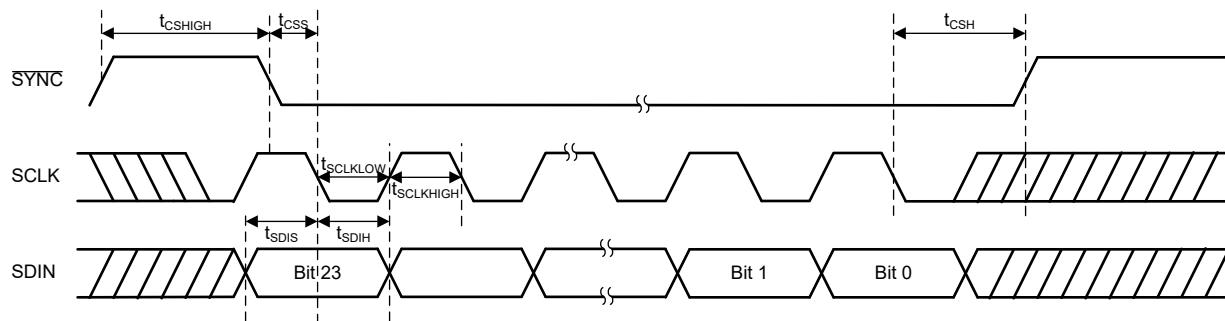

## 5.6 タイミング要件

自由気流での動作温度範囲内 (特に記述のない限り)

|                                                  |                                             | 最小値                       | 公称値 | 最大値 | 単位      |

|--------------------------------------------------|---------------------------------------------|---------------------------|-----|-----|---------|

| <b>シリアルインターフェース - 書き込み操作</b>                     |                                             |                           |     |     |         |

| $f_{(SCLK)}$                                     | シリアル クロック周波数                                | $V_{IO} = 1.7V \sim 2.7V$ |     | 25  | MHz     |

|                                                  |                                             | $V_{IO} = 2.7V \sim 5.5V$ |     | 50  |         |

| $t_{SCLKHIGH}$                                   | SCLK High 時間                                | $V_{IO} = 1.7V \sim 2.7V$ | 20  |     | ns      |

|                                                  |                                             | $V_{IO} = 2.7V \sim 5.5V$ | 10  |     |         |

| $t_{SCLKLOW}$                                    | SCLK Low 時間                                 | $V_{IO} = 1.7V \sim 2.7V$ | 20  |     | ns      |

|                                                  |                                             | $V_{IO} = 2.7V \sim 5.5V$ | 10  |     |         |

| $t_{SDIS}$                                       | SDI のセットアップ時間                               | $V_{IO} = 1.7V \sim 2.7V$ | 10  |     | ns      |

|                                                  |                                             | $V_{IO} = 2.7V \sim 5.5V$ | 5   |     |         |

| $t_{SDIH}$                                       | SDI のホールド時間                                 | $V_{IO} = 1.7V \sim 2.7V$ | 10  |     | ns      |

|                                                  |                                             | $V_{IO} = 2.7V \sim 5.5V$ | 5   |     |         |

| $t_{CSS}$                                        | $\overline{CS}$ から SCLK 立ち下がりエッジまでのセットアップ時間 | $V_{IO} = 1.7V \sim 2.7V$ | 30  |     | ns      |

|                                                  |                                             | $V_{IO} = 2.7V \sim 5.5V$ | 15  |     |         |

| $t_{CSH}$                                        | SCLK 立ち下がりエッジから $\overline{CS}$ 立ち上がりエッジまで  | $V_{IO} = 1.7V \sim 2.7V$ | 10  |     | ns      |

|                                                  |                                             | $V_{IO} = 2.7V \sim 5.5V$ | 5   |     |         |

| $t_{CSHIGH}$                                     | $\overline{CS}$ High 時間                     | $V_{IO} = 1.7V \sim 2.7V$ | 50  |     | ns      |

|                                                  |                                             | $V_{IO} = 2.7V \sim 5.5V$ | 25  |     |         |

| $t_{DACKWAIT}$                                   | シーケンシャル DAC 更新の待機時間                         | $V_{IO} = 1.7V \sim 2.7V$ | 2.4 |     | $\mu s$ |

|                                                  |                                             | $V_{IO} = 2.7V \sim 5.5V$ | 2.4 |     |         |

| $t_{BCASTWAIT}$                                  | ブロードキャスト DAC 更新待機時間                         | $V_{IO} = 1.7V \sim 2.7V$ | 4   |     | $\mu s$ |

|                                                  |                                             | $V_{IO} = 2.7V \sim 5.5V$ | 4   |     |         |

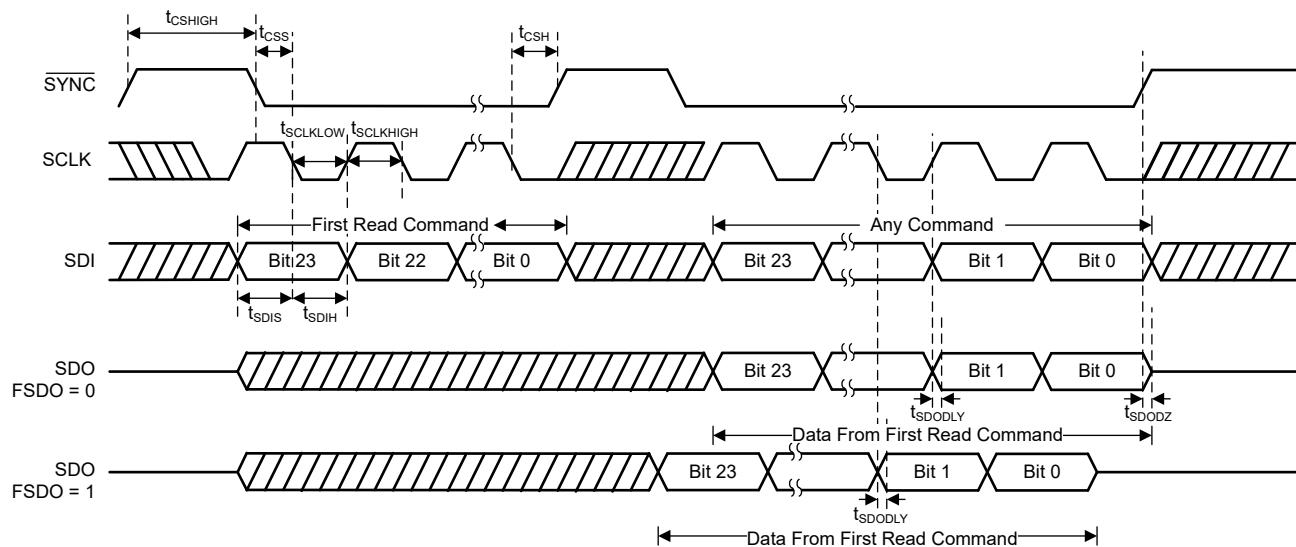

| <b>シリアルインターフェース – 読み出しおよびデイジーチェーン動作、FSDO = 0</b> |                                             |                           |     |     |         |

| $f_{(SCLK)}$                                     | シリアル クロック周波数                                | $V_{IO} = 1.7V \sim 2.7V$ |     | 15  | MHz     |

|                                                  |                                             | $V_{IO} = 2.7V \sim 5.5V$ |     | 20  |         |

| $t_{SCLKHIGH}$                                   | SCLK High 時間                                | $V_{IO} = 1.7V \sim 2.7V$ | 33  |     | ns      |

|                                                  |                                             | $V_{IO} = 2.7V \sim 5.5V$ | 25  |     |         |

| $t_{SCLKLOW}$                                    | SCLK Low 時間                                 | $V_{IO} = 1.7V \sim 2.7V$ | 33  |     | ns      |

|                                                  |                                             | $V_{IO} = 2.7V \sim 5.5V$ | 25  |     |         |

| $t_{SDIS}$                                       | SDI のセットアップ時間                               | $V_{IO} = 1.7V \sim 2.7V$ | 10  |     | ns      |

|                                                  |                                             | $V_{IO} = 2.7V \sim 5.5V$ | 5   |     |         |

| $t_{SDIH}$                                       | SDI のホールド時間                                 | $V_{IO} = 1.7V \sim 2.7V$ | 10  |     | ns      |

|                                                  |                                             | $V_{IO} = 2.7V \sim 5.5V$ | 5   |     |         |

| $t_{CSS}$                                        | $\overline{CS}$ から SCLK 立ち下がりエッジまでのセットアップ時間 | $V_{IO} = 1.7V \sim 2.7V$ | 30  |     | ns      |

|                                                  |                                             | $V_{IO} = 2.7V \sim 5.5V$ | 20  |     |         |

| $t_{CSH}$                                        | SCLK 立ち下がりエッジから $\overline{CS}$ 立ち上がりエッジまで  | $V_{IO} = 1.7V \sim 2.7V$ | 8   |     | ns      |

|                                                  |                                             | $V_{IO} = 2.7V \sim 5.5V$ | 5   |     |         |

| $t_{CSHIGH}$                                     | $\overline{CS}$ high 時間                     | $V_{IO} = 1.7V \sim 2.7V$ | 50  |     | ns      |

|                                                  |                                             | $V_{IO} = 2.7V \sim 5.5V$ | 25  |     |         |

| $t_{SDOZD}$                                      | SDO トライステート状態から駆動へ                          | $V_{IO} = 1.7V \sim 2.7V$ | 0   | 20  | ns      |

|                                                  |                                             | $V_{IO} = 2.7V \sim 5.5V$ | 0   | 20  |         |

## 5.6 タイミング要件 (続き)

自由気流での動作温度範囲内 (特に記述のない限り)

|              |          |                           | 最小値 | 公称値 | 最大値 | 単位 |

|--------------|----------|---------------------------|-----|-----|-----|----|

| $t_{SDODLY}$ | SDO 出力遅延 | $V_{IO} = 1.7V \sim 2.7V$ | 0   |     | 35  | ns |

|              |          | $V_{IO} = 2.7V \sim 5.5V$ | 0   |     | 20  |    |

## 5.6 タイミング要件 (続き)

自由気流での動作温度範囲内 (特に記述のない限り)

|                                                   |                                                                      |                           | 最小値 | 公称値 | 最大値 | 単位 |

|---------------------------------------------------|----------------------------------------------------------------------|---------------------------|-----|-----|-----|----|

| <b>シリアル インターフェース – 読み出しおよびデイジーチェーン動作、FSDO = 1</b> |                                                                      |                           |     |     |     |    |

| $f_{SCLK}$                                        | シリアル クロック周波数                                                         | $V_{IO} = 1.7V \sim 2.7V$ |     | 25  | MHz |    |

|                                                   |                                                                      | $V_{IO} = 2.7V \sim 5.5V$ |     | 35  |     |    |

| $t_{SCLKHIGH}$                                    | SCLK High 時間                                                         | $V_{IO} = 1.7V \sim 2.7V$ | 20  |     | ns  |    |

|                                                   |                                                                      | $V_{IO} = 2.7V \sim 5.5V$ | 14  |     |     |    |

| $t_{SCLKLOW}$                                     | SCLK Low 時間                                                          | $V_{IO} = 1.7V \sim 2.7V$ | 20  |     | ns  |    |

|                                                   |                                                                      | $V_{IO} = 2.7V \sim 5.5V$ | 14  |     |     |    |

| $t_{SDIS}$                                        | SDI のセットアップ時間                                                        | $V_{IO} = 1.7V \sim 2.7V$ | 10  |     | ns  |    |

|                                                   |                                                                      | $V_{IO} = 2.7V \sim 5.5V$ | 5   |     |     |    |

| $t_{SDIH}$                                        | SDI のホールド時間                                                          | $V_{IO} = 1.7V \sim 2.7V$ | 10  |     | ns  |    |

|                                                   |                                                                      | $V_{IO} = 2.7V \sim 5.5V$ | 5   |     |     |    |

| $t_{CSS}$                                         | $\overline{CS}$ から SCLK 立ち下がりエッジまでのセットアップ時間                          | $V_{IO} = 1.7V \sim 2.7V$ | 30  |     | ns  |    |

|                                                   |                                                                      | $V_{IO} = 2.7V \sim 5.5V$ | 20  |     |     |    |

| $t_{CSH}$                                         | SCLK 立ち下がりエッジから CS 立ち上がりエッジまで                                        | $V_{IO} = 1.7V \sim 2.7V$ | 8   |     | ns  |    |

|                                                   |                                                                      | $V_{IO} = 2.7V \sim 5.5V$ | 5   |     |     |    |

| $t_{CSHIGH}$                                      | $\overline{CS}$ high 時間                                              | $V_{IO} = 1.7V \sim 2.7V$ | 50  |     | ns  |    |

|                                                   |                                                                      | $V_{IO} = 2.7V \sim 5.5V$ | 25  |     |     |    |

| $t_{SDOZD}$                                       | SDO トライステート状態から駆動へ                                                   | $V_{IO} = 1.7V \sim 2.7V$ | 0   | 20  | ns  |    |

|                                                   |                                                                      | $V_{IO} = 2.7V \sim 5.5V$ | 0   | 20  |     |    |

| $t_{SDODLY}$                                      | SDO 出力遅延                                                             | $V_{IO} = 1.7V \sim 2.7V$ | 0   | 35  | ns  |    |

|                                                   |                                                                      | $V_{IO} = 2.7V \sim 5.5V$ | 0   | 20  |     |    |

| <b>デジタル ロジック</b>                                  |                                                                      |                           |     |     |     |    |

| $t_{LOGDLY}$                                      | $\overline{CS}$ 立ち上がりエッジから LDAC または $\overline{CLR}$ 立ち下がりエッジまでの遅延時間 | $V_{IO} = 1.7V \sim 2.7V$ | 40  |     | ns  |    |

| $t_{LOGDLY}$                                      | $CS$ 立ち上がりエッジから LDAC または $\overline{CLR}$ 立ち下がりエッジまでの遅延時間            | $V_{IO} = 2.7V \sim 5.5V$ | 20  |     |     |    |

| $t_{LDAC}$                                        | LDAC Low 時間                                                          | $V_{IO} = 1.7V \sim 2.7V$ | 20  |     | ns  |    |

|                                                   |                                                                      | $V_{IO} = 2.7V \sim 5.5V$ | 10  |     |     |    |

| $t_{CLR}$                                         | $\overline{CLR}$ Low 時間                                              | $V_{IO} = 1.7V \sim 2.7V$ | 20  |     | ns  |    |

|                                                   |                                                                      | $V_{IO} = 2.7V \sim 5.5V$ | 10  |     |     |    |

| $t_{RESET}$                                       | POR リセット遅延                                                           | $V_{IO} = 1.7V \sim 2.7V$ |     | 1   | ms  |    |

|                                                   |                                                                      | $V_{IO} = 2.7V \sim 5.5V$ |     | 1   |     |    |

| $f_{TOGGLE}$                                      | TOGGLE 周波数                                                           | $V_{IO} = 1.7V \sim 2.7V$ |     | 100 | kHz |    |

|                                                   |                                                                      | $V_{IO} = 2.7V \sim 5.5V$ |     | 100 |     |    |

## 5.7 タイミング図

図 5-1. シリアル インターフェース書き込みタイミング図

図 5-2. シリアル レジスタ読み取りタイミング図

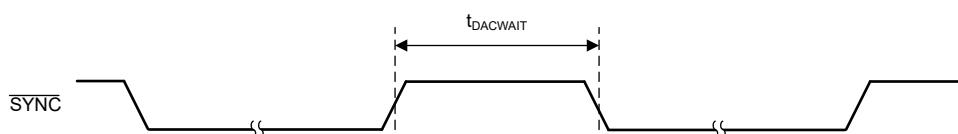

図 5-3. 更新モードでの DAC 待機時間

## 5.8 代表的特性

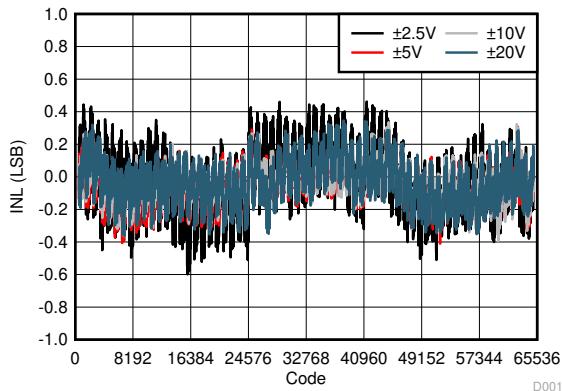

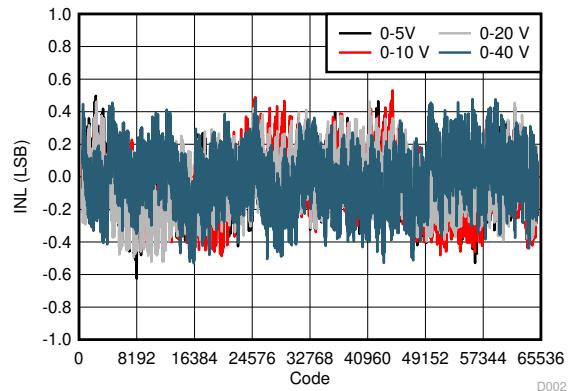

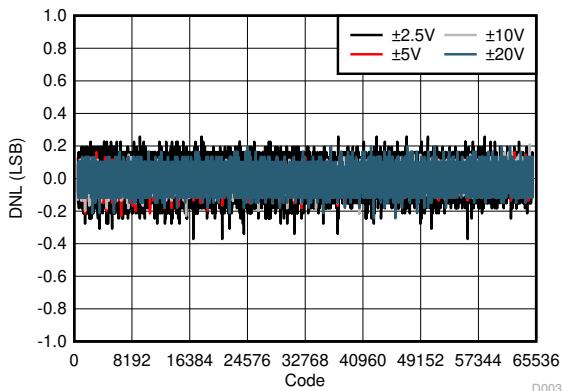

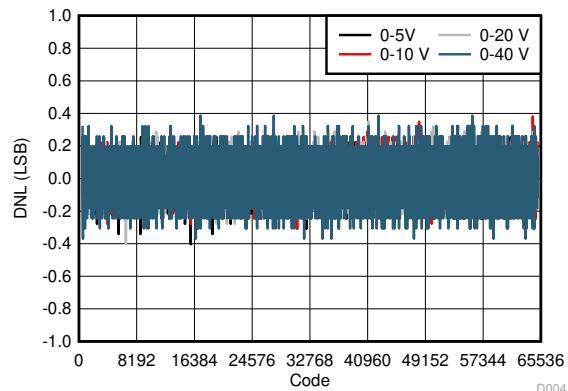

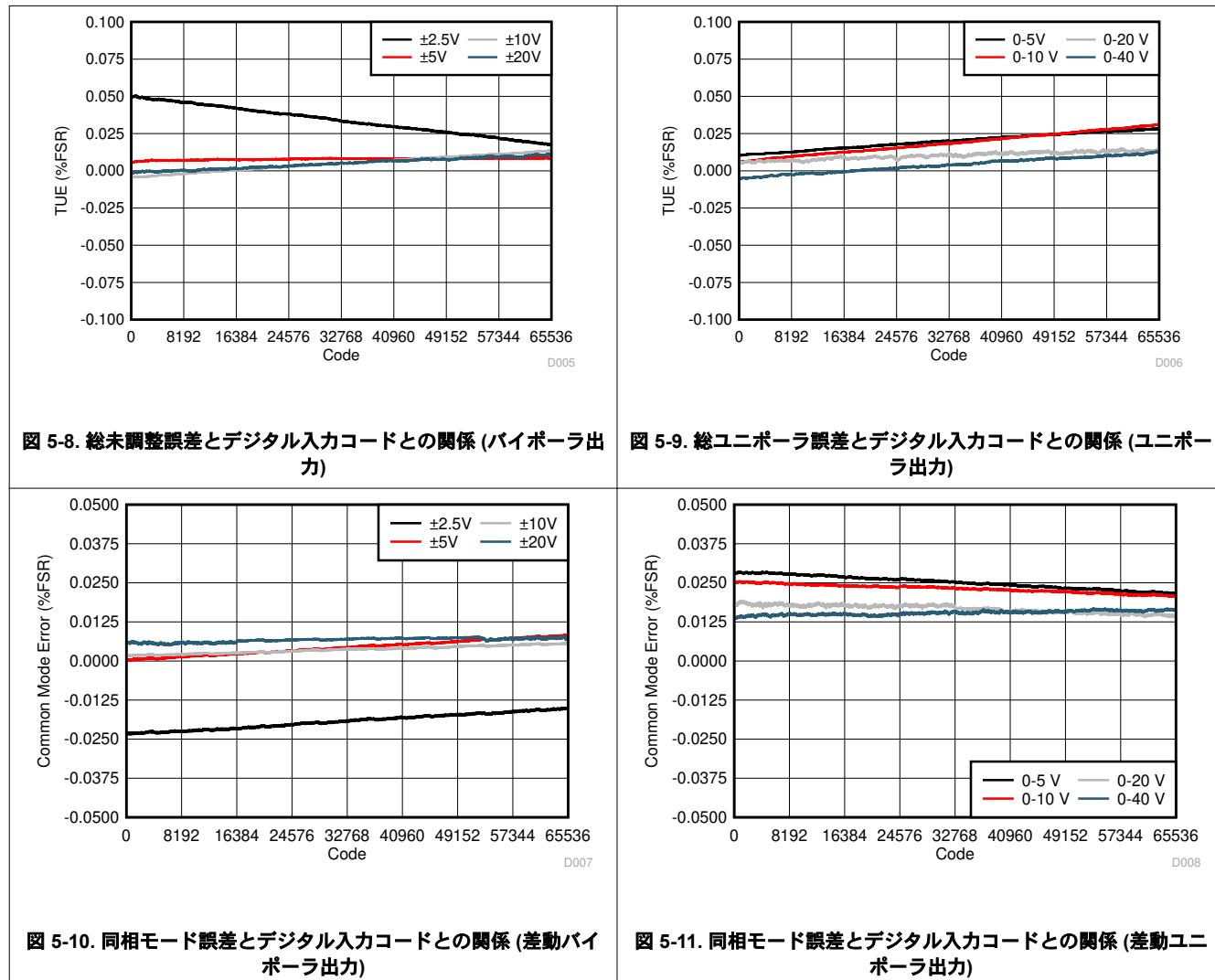

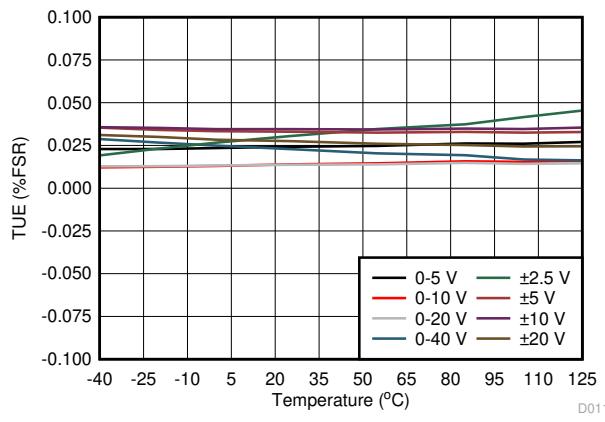

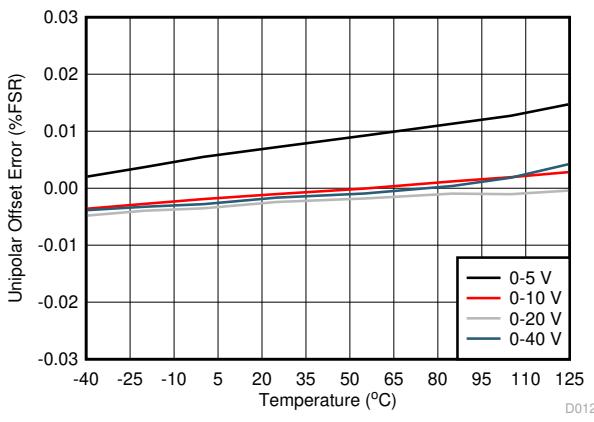

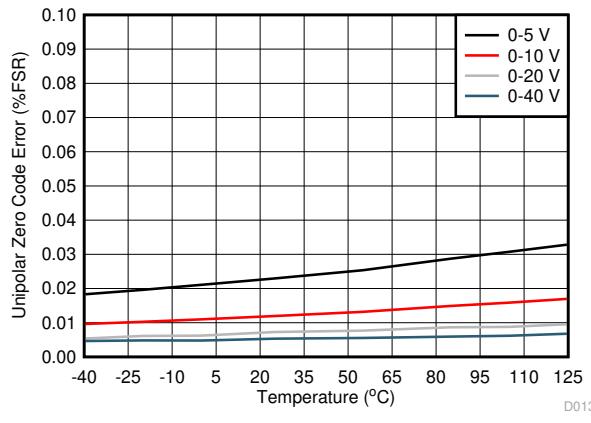

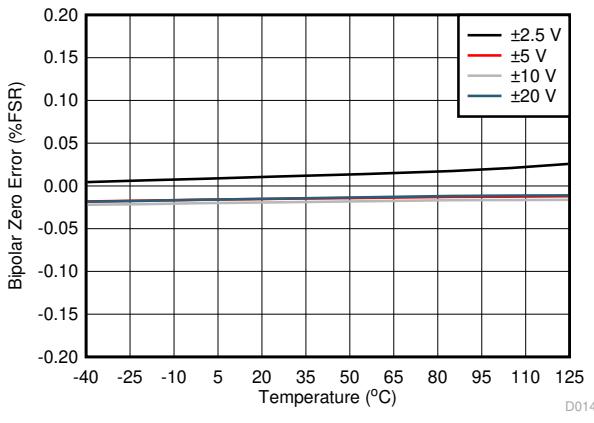

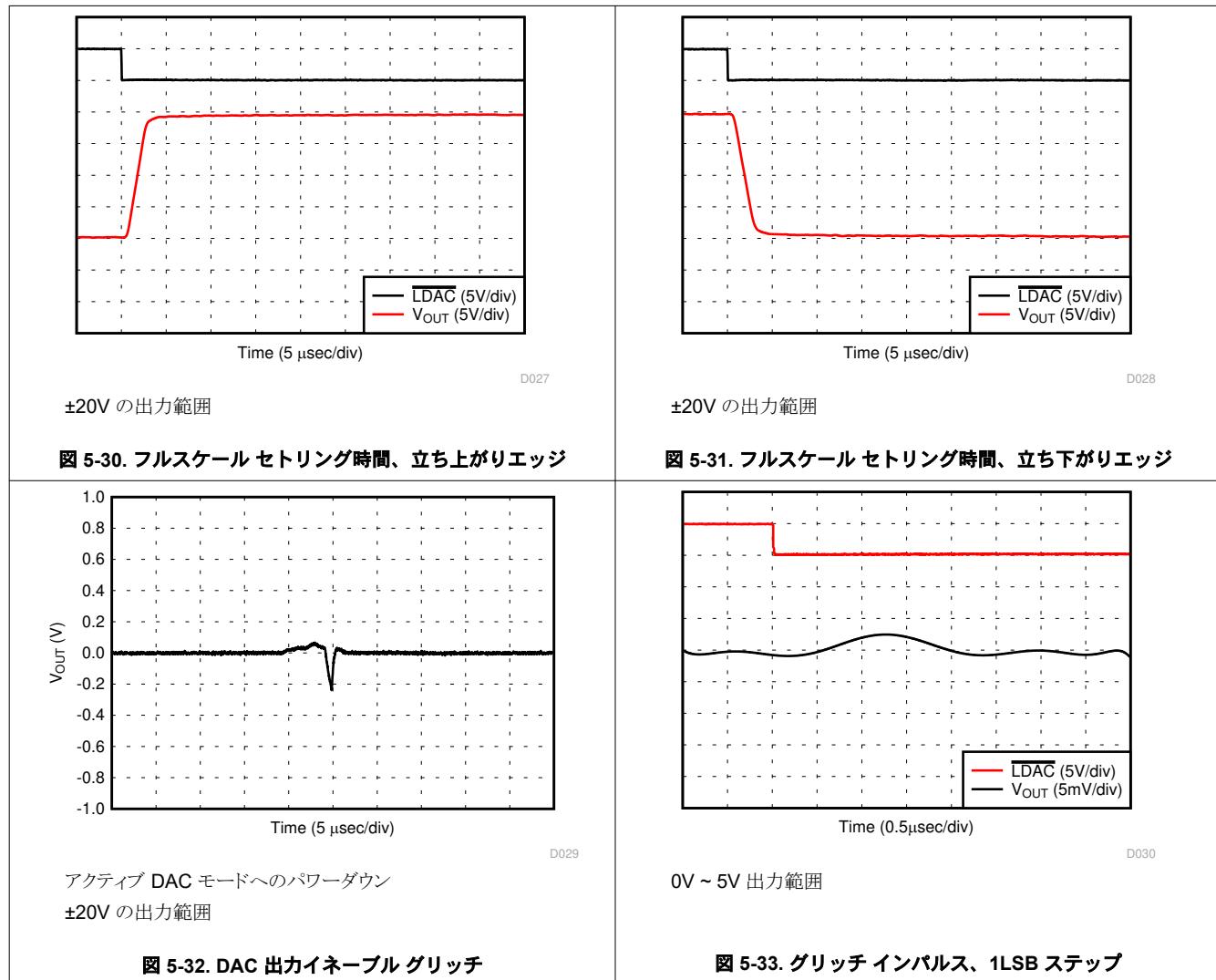

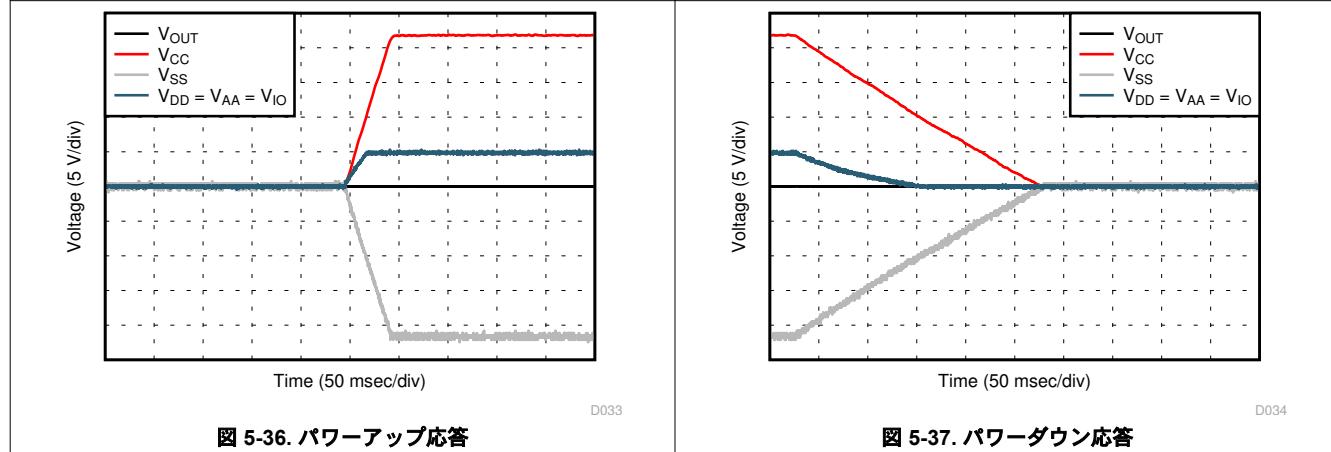

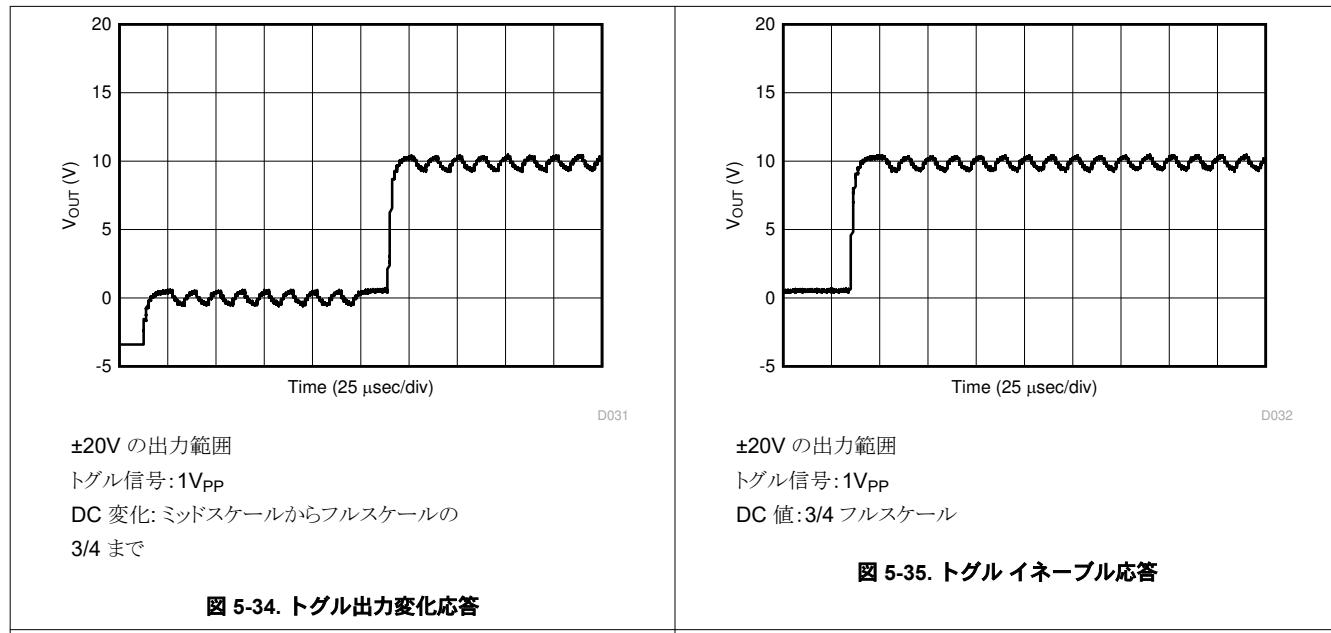

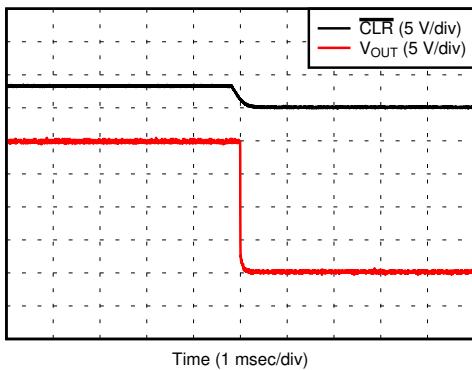

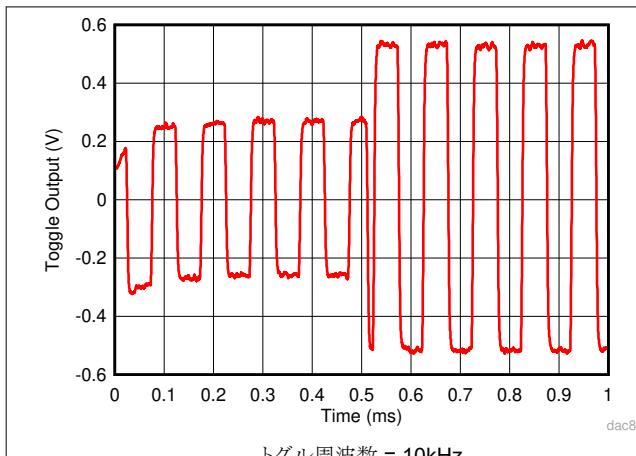

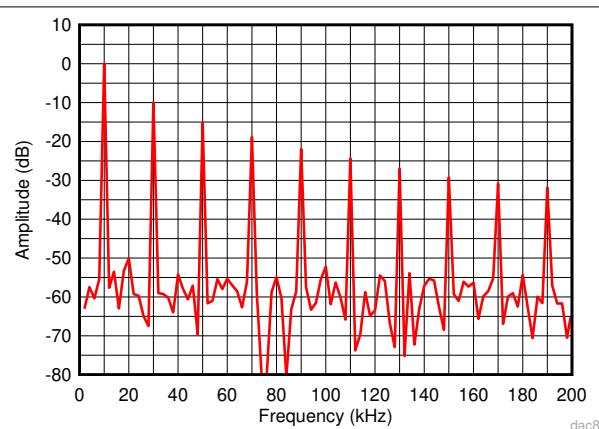

$T_A = 25^\circ\text{C}$ 、 $V_{DD} = V_{AA} = 5\text{V}$ 、 $V_{REFIN} = 2.5\text{V}$ 、ユニポーラ範囲の場合:  $V_{SS} = 0\text{V}$  かつ DAC 範囲に対して  $V_{CC} \geq V_{MAX} + 1.5\text{V}$ 、バイポーラ範囲の場合:  $V_{SS} \leq V_{MIN} - 1.5\text{V}$  かつ  $V_{CC} \geq V_{MAX} + 1.5\text{V}$  の場合に DAC 範囲となり、特に記載がない限り DAC 出力は無負荷とします

図 5-4. 積分非直線性誤差とデジタル入力コードとの関係 (バイポーラ出力)

図 5-5. 積分直線性誤差とデジタル入力コードとの関係 (ユニポーラ出力)

図 5-6. 微分直線性誤差とデジタル入力コードとの関係 (バイポーラ出力)

図 5-7. 微分直線性誤差とデジタル入力コードとの関係 (ユニポーラ出力)

## 5.8 代表的特性 (続き)

$T_A = 25^\circ\text{C}$ 、 $V_{DD} = V_{AA} = 5\text{V}$ 、 $V_{REFIN} = 2.5\text{V}$ 、ユニポーラ範囲の場合:  $V_{SS} = 0\text{V}$  かつ DAC 範囲に対して  $V_{CC} \geq V_{MAX} + 1.5\text{V}$ 、バイポーラ範囲の場合:  $V_{SS} \leq V_{MIN} - 1.5\text{V}$  かつ  $V_{CC} \geq V_{MAX} + 1.5\text{V}$  の場合に DAC 範囲となり、特に記載がない限り DAC 出力は無負荷とします

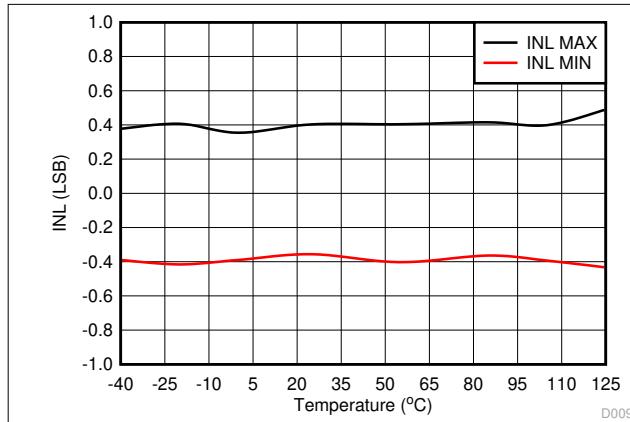

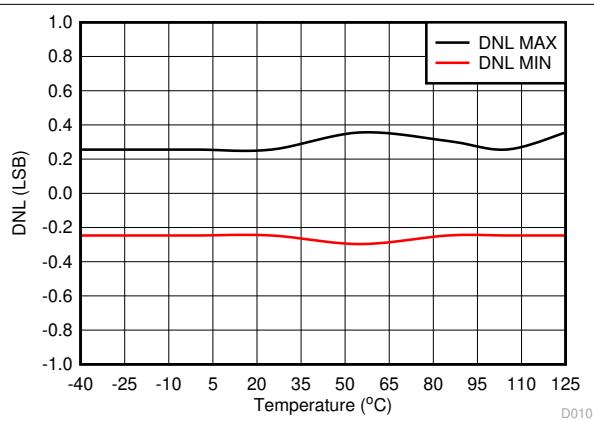

## 5.8 代表的特性 (続き)

$T_A = 25^\circ\text{C}$ 、 $V_{DD} = V_{AA} = 5\text{V}$ 、 $V_{REFIN} = 2.5\text{V}$ 、ユニポーラ範囲の場合:  $V_{SS} = 0\text{V}$ かつDAC範囲に対して  $V_{CC} \geq V_{MAX} + 1.5\text{V}$ 、バイポーラ範囲の場合:  $V_{SS} \leq V_{MIN} - 1.5\text{V}$ かつ  $V_{CC} \geq V_{MAX} + 1.5\text{V}$ の場合にDAC範囲となり、特に記載がない限りDAC出力は無負荷とします

±20V の出力範囲

図 5-12. 積分直線性誤差と温度との関係

±20V の出力範囲

図 5-13. 微分直線性誤差と温度との関係

図 5-14. 総未調整誤差と温度との関係

図 5-15. ユニポーラ オフセット誤差と温度との関係

図 5-16. ユニポーラ ゼロ コード誤差と温度との関係

図 5-17. バイポーラ ゼロ誤差と温度との関係

## 5.8 代表的特性 (続き)

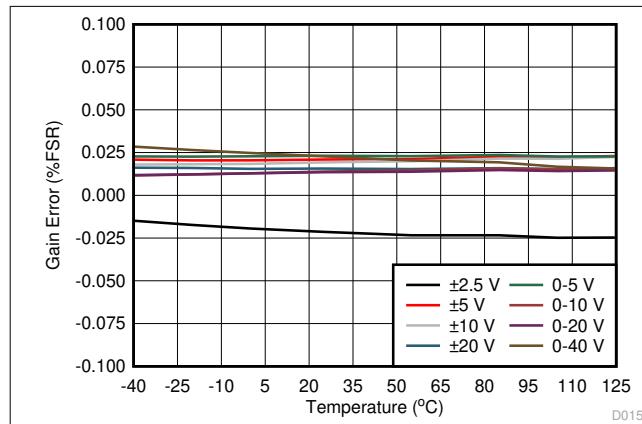

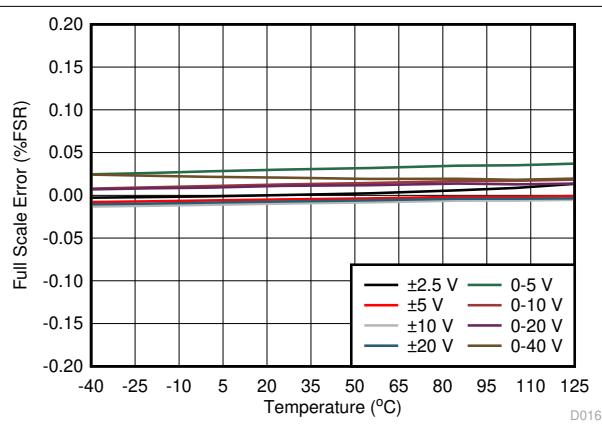

$T_A = 25^\circ\text{C}$ 、 $V_{DD} = V_{AA} = 5\text{V}$ 、 $V_{REFIN} = 2.5\text{V}$ 、ユニポーラ範囲の場合:  $V_{SS} = 0\text{V}$  かつ DAC 範囲に対して  $V_{CC} \geq V_{MAX} + 1.5\text{V}$ 、バイポーラ範囲の場合:  $V_{SS} \leq V_{MIN} - 1.5\text{V}$  かつ  $V_{CC} \geq V_{MAX} + 1.5\text{V}$  の場合に DAC 範囲となり、特に記載がない限り DAC 出力は無負荷とします

図 5-18. ゲイン誤差と温度との関係

図 5-19. フルスケール誤差と温度との関係

図 5-20. 同相モード誤差と温度との関係

(差動バイポーラ出力)

図 5-21. 同相モード誤差と温度との関係

(差動ユニポーラ出力)

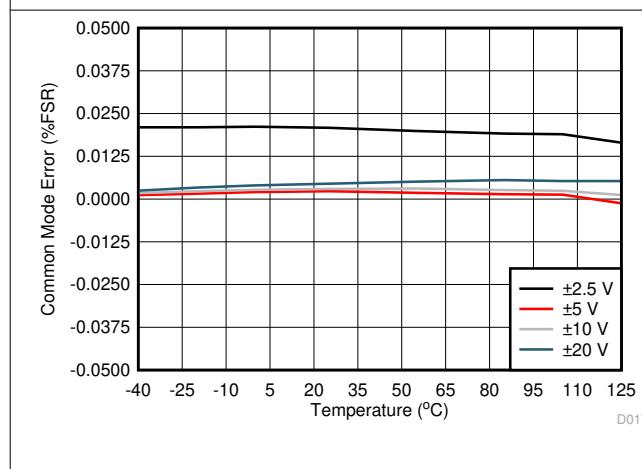

## 5.8 代表的特性 (続き)

$T_A = 25^\circ\text{C}$ 、 $V_{DD} = V_{AA} = 5\text{V}$ 、 $V_{REFIN} = 2.5\text{V}$ 、ユニポーラ範囲の場合:  $V_{SS} = 0\text{V}$  かつ DAC 範囲に対して  $V_{CC} \geq V_{MAX} + 1.5\text{V}$ 、バイポーラ範囲の場合:  $V_{SS} \leq V_{MIN} - 1.5\text{V}$  かつ  $V_{CC} \geq V_{MAX} + 1.5\text{V}$  の場合に DAC 範囲となり、特に記載がない限り DAC 出力は無負荷とします

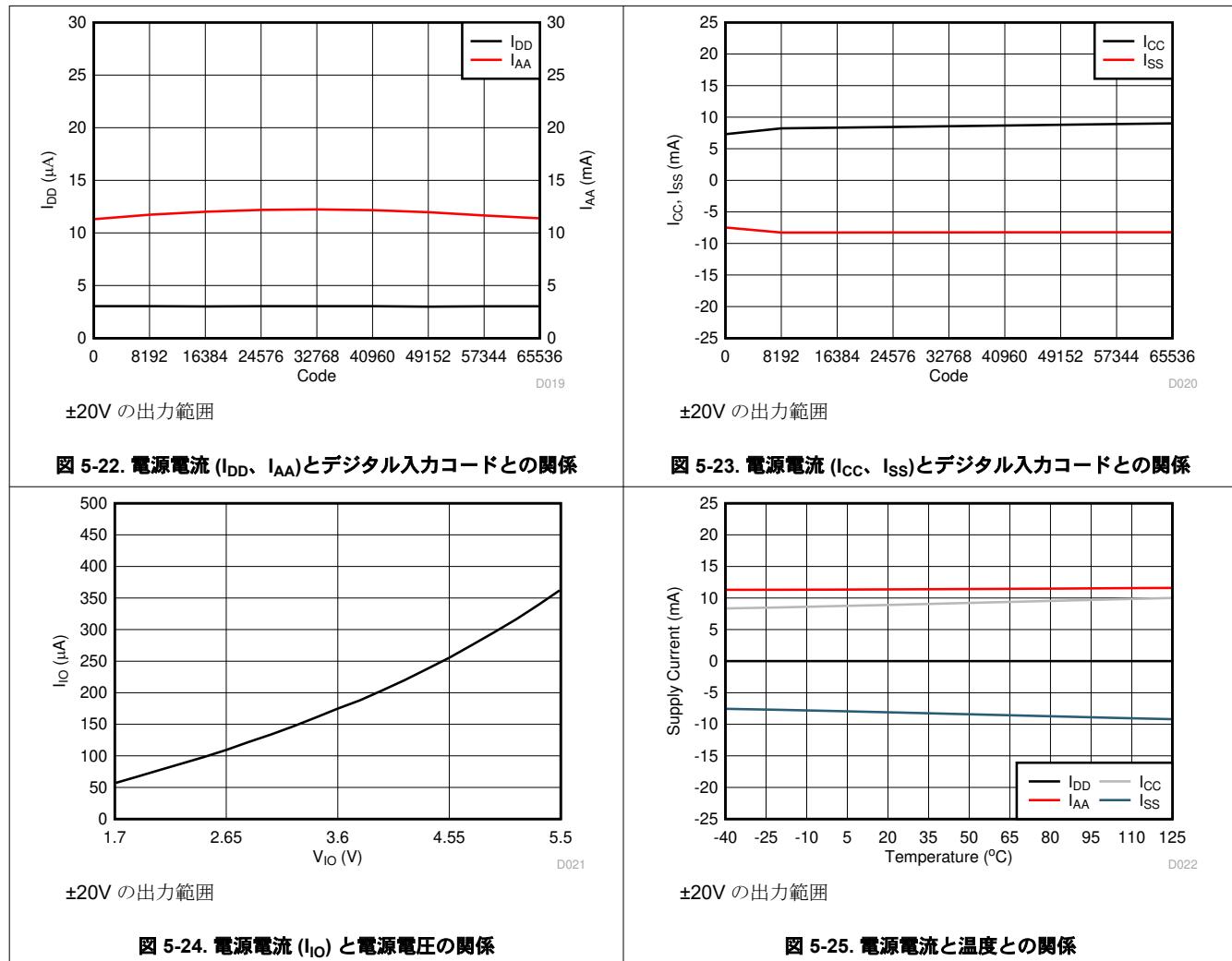

## 5.8 代表的特性 (続き)

$T_A = 25^\circ\text{C}$ 、 $V_{DD} = V_{AA} = 5\text{V}$ 、 $V_{REFIN} = 2.5\text{V}$ 、ユニポーラ範囲の場合:  $V_{SS} = 0\text{V}$  かつ DAC 範囲に対して  $V_{CC} \geq V_{MAX} + 1.5\text{V}$ 、バイポーラ範囲の場合:  $V_{SS} \leq V_{MIN} - 1.5\text{V}$  かつ  $V_{CC} \geq V_{MAX} + 1.5\text{V}$  の場合に DAC 範囲となり、特に記載がない限り DAC 出力は無負荷とします

±20V の出力範囲

図 5-26. パワーダウン電流と温度との関係

±20V の出力範囲

図 5-27. ソースおよびシンク振幅

フルスケールコード

図 5-28.  $V_{CC}$  ヘッドルームとソース電流との関係

ゼロコード

図 5-29.  $V_{SS}$  フットルームとシンク電流との関係

## 5.8 代表的特性 (続き)

$T_A = 25^\circ\text{C}$ 、 $V_{DD} = V_{AA} = 5\text{V}$ 、 $V_{REFIN} = 2.5\text{V}$ 、ユニポーラ範囲の場合:  $V_{SS} = 0\text{V}$  かつ DAC 範囲に対して  $V_{CC} \geq V_{MAX} + 1.5\text{V}$ 、バイポーラ範囲の場合:  $V_{SS} \leq V_{MIN} - 1.5\text{V}$  かつ  $V_{CC} \geq V_{MAX} + 1.5\text{V}$  の場合に DAC 範囲となり、特に記載がない限り DAC 出力は無負荷とします

## 5.8 代表的特性 (続き)

$T_A = 25^\circ\text{C}$ 、 $V_{DD} = V_{AA} = 5\text{V}$ 、 $V_{REFIN} = 2.5\text{V}$ 、ユニポーラ範囲の場合:  $V_{SS} = 0\text{V}$  かつ DAC 範囲に対して  $V_{CC} \geq V_{MAX} + 1.5\text{V}$ 、バイポーラ範囲の場合:  $V_{SS} \leq V_{MIN} - 1.5\text{V}$  かつ  $V_{CC} \geq V_{MAX} + 1.5\text{V}$  の場合に DAC 範囲となり、特に記載がない限り DAC 出力は無負荷とします

## 5.8 代表的特性 (続き)

$T_A = 25^\circ\text{C}$ 、 $V_{DD} = V_{AA} = 5\text{V}$ 、 $V_{REFIN} = 2.5\text{V}$ 、ユニポーラ範囲の場合:  $V_{SS} = 0\text{V}$  かつ DAC 範囲に対して  $V_{CC} \geq V_{MAX} + 1.5\text{V}$ 、バイポーラ範囲の場合:  $V_{SS} \leq V_{MIN} - 1.5\text{V}$  かつ  $V_{CC} \geq V_{MAX} + 1.5\text{V}$  の場合に DAC 範囲となり、特に記載がない限り DAC 出力は無負荷とします

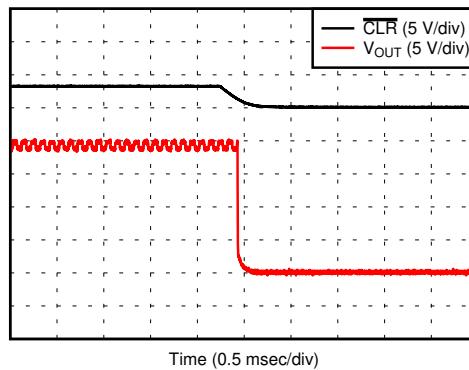

±20V の出力範囲

フルスケール コードから 0V まで

図 5-38. クリア コマンド応答

±20V の出力範囲

トグル信号: 1V<sub>PP</sub>

20V での DC 値

図 5-39. トグル モードでのクリア コマンド応答

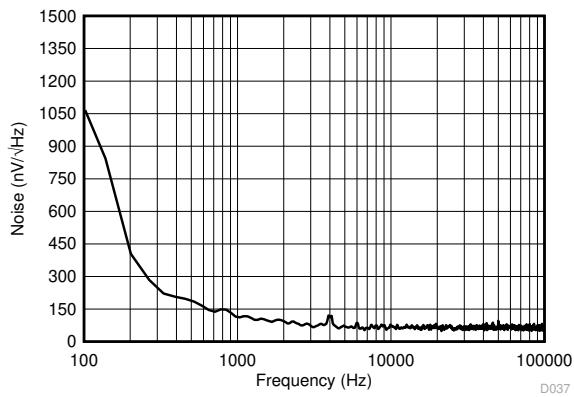

0V ~ 5V 出力範囲

ミッドスケール コード

図 5-40. DAC の出力ノイズ密度と周波数との関係

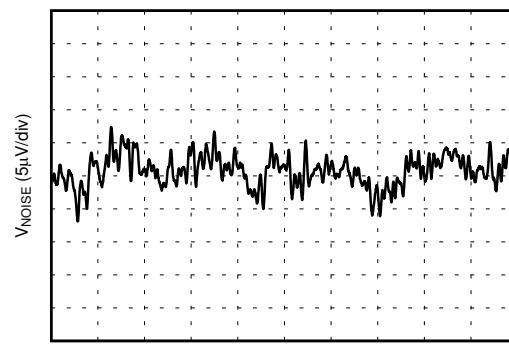

0V ~ 5V 出力範囲

ミッドスケール コード

図 5-41. DAC 出力ノイズ

## 5.8 代表的特性 (続き)

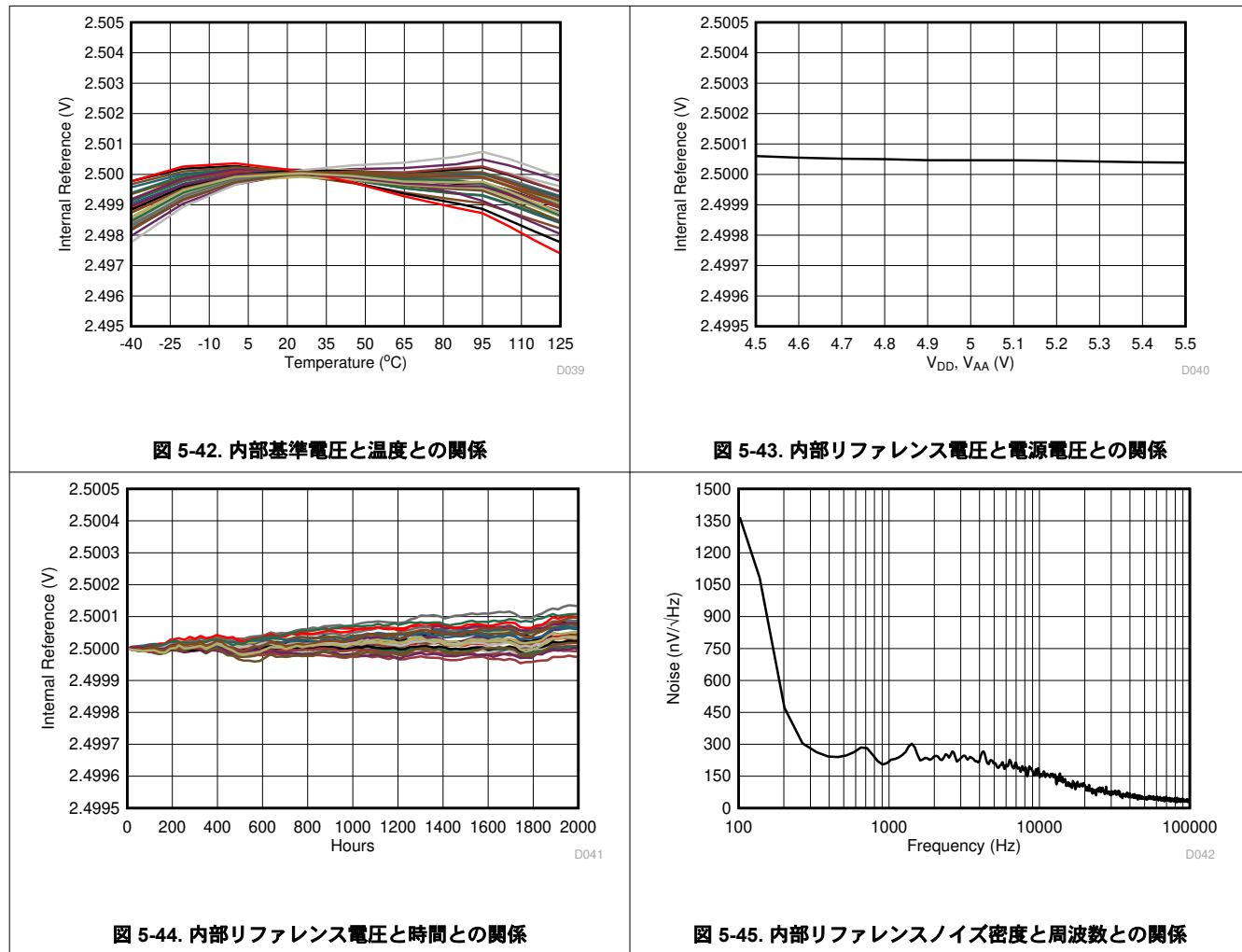

$T_A = 25^\circ\text{C}$ 、 $V_{DD} = V_{AA} = 5\text{V}$ 、 $V_{REFIN} = 2.5\text{V}$ 、ユニポーラ範囲の場合:  $V_{SS} = 0\text{V}$  かつ DAC 範囲に対して  $V_{CC} \geq V_{MAX} + 1.5\text{V}$ 、バイポーラ範囲の場合:  $V_{SS} \leq V_{MIN} - 1.5\text{V}$  かつ  $V_{CC} \geq V_{MAX} + 1.5\text{V}$  の場合に DAC 範囲となり、特に記載がない限り DAC 出力は無負荷とします

## 5.8 代表的特性 (続き)

$T_A = 25^\circ\text{C}$ 、 $V_{DD} = V_{AA} = 5\text{V}$ 、 $V_{REFIN} = 2.5\text{V}$ 、ユニポーラ範囲の場合:  $V_{SS} = 0\text{V}$  かつ DAC 範囲に対して  $V_{CC} \geq V_{MAX} + 1.5\text{V}$ 、バイポーラ範囲の場合:  $V_{SS} \leq V_{MIN} - 1.5\text{V}$  かつ  $V_{CC} \geq V_{MAX} + 1.5\text{V}$  の場合に DAC 範囲となり、特に記載がない限り DAC 出力は無負荷とします

図 5-46. 内部リファレンス ノイズ

図 5-47. 内部リファレンス温度ドリフト ヒストグラム

## 6 詳細説明

### 6.1 概要

DACx1416 は、16 チャネル、バッファ付き、高電圧出力の D/A コンバータ (DAC) ファミリで、16 ビット、14 ビット、12 ビットの分解能に対応し、ピン互換性があります。DACx1416 には、2.5V 内部リファレンスが含まれています。出力構成をユーザーが選択可能で、フルスケールのバイポーラ出力電圧の  $\pm 20V$ 、 $\pm 10V$ 、 $\pm 5V$ 、 $\pm 2.5V$ 、およびフルスケールのユニポーラ出力電圧の  $40V$ 、 $20V$ 、 $10V$ 、 $5V$  を使用できます。各 DAC チャネルのフルスケール出力範囲は別々にプログラム可能です。さらに、各 DAC チャネルのペアは差動出力を提供するように設定できます。3 つの専用 A-B トグル ピンにより、最大 3 つの周波数についてディザ信号を生成できます。

DACx1416 は 5 系統の電源電圧で動作します:  $V_{DD}$ 、 $V_{AA}$ 、 $V_{CC}$ 、 $V_{SS}$  および  $V_{IO}$ 。

- $V_{DD}$  および  $V_{AA}$  は、DAC、内部基準電圧、その他の低電圧部品のデジタル電源およびアナログ電源です。 $V_{DD}$  と  $V_{AA}$  を同じ電位に設定します。

- $V_{CC}$  および  $V_{SS}$  は、DAC 出力アンプ用の正電源および負電源です。

- $V_{IO}$  は、デジタル入力および出力のロジック レベルを設定します。

DACx1416 との通信は、スタンドアロン動作およびデイジーチェーン動作をサポートする 4 線式シリアル インターフェースを介して行われます。オプションのフレームエラー チェックにより、DACx1416 のシリアル インターフェースはさらに堅牢性が高められます。

DACx1416 にはパワー オン リセット (POR) 回路が組み込まれており、電源オン時に DAC 出力をグランドに接続します。デバイスのレジスタが動作用に正しく構成されるまで、出力がこの状態に維持されます。

### 6.2 機能ブロック図

## 6.3 機能説明

### 6.3.1 デジタル/アナログ コンバータ (DAC) アーキテクチャ

DACx1416 の各出力チャネルは、R-2R ラダー アーキテクチャと、その後段に配置されたレール ツー レール動作が可能な出力バッファ アンプで構成されています。出力アンプは、 $V_{CC}$  または  $V_{SS}$  から 1.5V のヘッドルームを確保しつつ、25mA を駆動し、デバイスの規定された TUE 特性を維持します。各チャネルのフルスケール出力電圧は、以下の範囲に個別に設定できます：

- -20V ~ +20V

- -10V ~ +10V

- -5V ~ +5V

- -2.5V ~ +2.5V

- 0V ~ 40V

- 0V ~ 20V

- 0V ~ 10V

- 0V ~ 5V

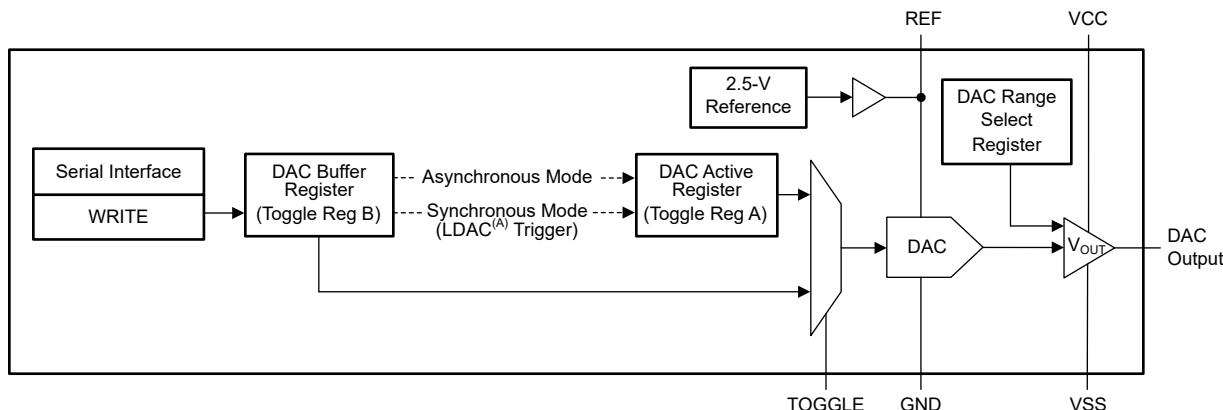

図 6-1 に、DAC アーキテクチャのブロック図を示します。

A. DAC トリガは、LDAC ビットに 1 を書き込むか、同期モードで  $\overline{LDAC}$  ピンによって生成されます。非同期モードでは、DAC ラッチは透過します。

図 6-1. DACx1416 DAC のブロック図

#### 6.3.1.1 DAC の伝達関数

入力データは、すべての出力範囲においてストレート バイナリ形式で各 DAC データレジスタに書き込まれます。DAC 伝達関数は式 1 で与えられます。

$$V_{OUT} = \left( \frac{CODE}{2^n} \times FSR \right) + V_{MIN} \quad (1)$$

ここで

- CODE は、DAC レジスタにロードされるバイナリコードの 10 進数換算値です。CODE 範囲は  $0 \sim 2^n - 1$  です。

- $n$  は DAC の分解能 (ビット数) です。12 ビット (DAC61416)、14 ビット (DAC71416)、または 16 ビット (DAC81416) のいずれかです。

- FSR は DAC フルスケール レンジです。選択した DAC 出力範囲にわたって、 $V_{MAX} - V_{MIN}$  に等しくなります。

- $V_{MIN}$  は、選択された DAC 出力範囲の最小電圧です。

### 6.3.1.2 DAC レジスタ構造

DAC データ レジスタに書き込まれたデータは、最初に DAC バッファ レジスタに格納されます。DAC バッファ レジスタからアクティブ DAC レジスタへのデータ転送は、即時に行われるよう設定することも（非同期モード）、DAC トリガ信号によって開始することも（同期モード）可能です。DAC アクティブ レジスタが更新されると、DAC 出力は新しい値に変わります。

電源投入またはリセット後、すべての DAC レジスタはゼロコードに設定され、DAC 出力アンプはパワーダウンし、DAC 出力はグランドにクランプされます。

#### 6.3.1.2.1 DAC レジスタの同期および非同期更新

各 DAC チャネルの更新モードは、対応する SYNC-EN ビットの状態によって決まります。非同期モードでは、DAC データ レジスタへの書き込みにより、CS の立ち上がりエッジで DAC のアクティブ レジスタと DAC 出力が即座に更新されます。同期モードでは、DAC データ レジスタに書き込んでも DAC 出力は自動的には更新されません。代わりに、更新はトリガ イベントの後にのみ行われます。DAC トリガ信号は、LDAC ビットまたは LDAC ピンによって生成されます。同期更新モードでは、複数の DAC 出力を同時に更新することができます。両方の更新モードにおいて、DAC 出力の更新間に最小で 2.4 $\mu$ s の待機時間が必要です。

#### 6.3.1.2.2 ブロードキャスト DAC レジスタ

DAC ブロードキャスト レジスタを使用すると、1 回のレジスタ書き込みで複数の DAC 出力を同じ値に同時更新できます。ブロードキャスト動作は、すべての DAC チャネルがシングルエンド モードで動作している場合にのみ可能です。1 つ以上の出力が差動モードに設定されている場合、ブロードキャスト コマンドは無視されます。

各 DAC チャネルは、対応する DAC-BRDCAST-EN ビットを設定することで、ブロードキャスト コマンドによって更新されるか、影響を受けないかを構成できます。BRDCAST レジスタへの書き込みにより、ブロードキャスト動作に設定された DAC チャネルは、それぞれの DAC バッファ レジスタをこの値に更新します。DAC 出力は、同期モードの設定に従ってブロードキャスト値に更新されます。

#### 6.3.1.2.3 DAC 動作のクリア

DAC 出力は、CLR ピンを使用してクリア モードに設定されます。クリア モードでは、各 DAC データ チャネルは、表 6-1 に示すそれぞれの構成に関連付けられたクリア コードに設定されます。CLR ピンがロジック Low になると、すべての DAC チャンネルは、それぞれのバッファおよびアクティブ レジスタの内容をクリア コードにリセットし、同期設定に関係なくアナログ出力をその値に設定します。

**表 6-1. DAC 値をクリアし**

| ユニポーラまたはバイポーラレンジ | 差動モード | クリア コード     |

|------------------|-------|-------------|

| ユニポーラ            | なし    | ゼロ コード      |

| ユニポーラ            | あり    | ミッドスケール コード |

| バイポーラ            | なし    | ミッドスケール コード |

| バイポーラ            | あり    | ミッドスケール コード |

DAC がトグル モードで動作している場合、クリア コマンドにより両方のトグル レジスタがクリア値に設定されます。

### 6.3.2 内部リファレンス

DAx1416 には、温度ドリフトが典型値で 5 ppm/°C の高精度 2.5V バンドギャップ リファレンスが内蔵されています。内部リファレンスは REF ピンから外部に利用可能です。外部負荷を駆動するには、高インピーダンス入力の外部バッファ アンプが必要です。

ノイズ フィルタリングのため、リファレンス出力と GND の間に最小 150nF のコンデンサを配置することを推奨します。REFCMP ピンと REFGND の間に補償用コンデンサ（代表値 330pF）を接続します。

内部リファレンスをパワーダウンすることで、外部リファレンスからの動作もサポートされます。REF ピンに外部リファレンスを印加します。

### 6.3.3 デバイスリセットオプション

#### 6.3.3.1 パワーオンリセット(POR)

DACx1416 にはパワーオンリセット機能が含まれています。電源が確立した後、POR イベントが発行されます。POR により、すべてのレジスタがデフォルト値に初期化され、1ms の POR 遅延後にのみデバイスとの通信が有効になります。POR イベント後、デバイスはパワーダウンモードに設定され、すべての DAC チャネルと内部リファレンスがパワーダウンし、DAC 出力ピンは内部 10kΩ 抵抗を介してグランドに接続されます。

#### 6.3.3.2 ハードウェアリセット

デバイス ハードウェアリセットイベントは、RESET ピンの最小 500ns のロジック Low によって開始されます。ハードウェアリセットにより、POR イベントが開始されます。

#### 6.3.3.3 ソフトウェアリセット

デバイスのソフトウェアリセットイベントは、TRIGGER レジスタの SOFT-RESET に予約コード 0x1010 を書き込むことで開始されます。ソフトウェアリセットコマンドは、命令の CS 立ち上がりエッジでトリガれます。ソフトウェアリセットにより、POR イベントが開始されます。

### 6.3.4 過熱保護

デバイスは DAC チャネル密度が高く、駆動能力も大きいため、消費電力がデバイス温度に与える影響を十分に理解し、デバイス温度が最大接合温度を超えないように注意します。

#### 6.3.4.1 アナログ温度センサ : TEMPOUT ピン

DACx1416 にはアナログ温度モニタが搭載されており、バッファなし出力電圧はデバイスの接合温度に反比例します。TEMPOUT ピンの出力電圧の温度勾配は  $-4\text{mV/}^{\circ}\text{C}$  で、1.34V オフセットは式 2 で説明します。

$$V_{\text{TEMPOUT}} = \left( \frac{-4 \text{ mV}}{^{\circ}\text{C}} \times T \right) + 1.34 \text{ V} \quad (2)$$

ここで

- T はデバイスの接合温度 ( $^{\circ}\text{C}$ ) です。

- $V_{\text{TEMPOUT}}$  は温度モニタ出力電圧です。

#### 6.3.4.2 サーマルシャットダウン

DACx1416 にはサーマルシャットダウン機能が組み込まれており、ダイ温度が  $140^{\circ}\text{C}$  を超えると作動します。サーマルシャットダウンが発生すると TEMP-ALM ビットがセットされ、すべての DAC 出力がパワーダウンしますが、内部リファレンスは動作を継続します。ALMOUT ピンは、TEMPALM-EN ビットを設定することでサーマルシャットダウン状態を監視するように構成できます。サーマルシャットダウンがトリガされると、デバイスの温度が低下してもシャットダウン状態を維持します。

デバイスが通常動作に戻るためには、ダイ温度が  $140^{\circ}\text{C}$  を下回る必要があります。通常動作を再開するには、DAC チャネルがパワーダウンモードの間に、ALM-RESET ビットを使用してサーマルアラームをクリアする必要があります。

## 6.4 デバイスの機能モード

### 6.4.1 トグル モード

デバイス内の各 DAC は、トグル モードで動作するように個別に設定できます。トグル モードの DAC チャネルは 2 つの DAC レジスタ (レジスタ A とレジスタ B) を備えており、これら 2 つの値を繰り返し切り替えるように設定できます。DACx1416 のトグルモード動作は、DAC 出力にディザ信号を導入したり、周期信号を生成したり、ON/OFF 信号を実装したりするように設定できます。そのほかにもいくつかの用途に対応しています。

トグル レジスタを更新するには、次のシーケンスを使用します：

1. DAC チャネルを同期モードに設定し、そのチャネルのトグル モードを無効にします

2. 目的のレジスタ A の値を DAC データ レジスタに書き込みます

3. DAC トリガ信号を発行してレジスタ A をロードします

4. 目的のレジスタ B の値を DAC データ レジスタに書き込みます

5. トグル モードを有効にしてレジスタ B をロードします

両方のレジスタにデータがロードされた後、3 つの TOGGLE[2:0] ピンのいずれかを使用して、トグル動作に設定された DAC を、外部クロックまたは論理信号を用いて、それぞれの DAC 固有レジスタ 2 つの内容の間で切り替えます。TOGGLE ピンがロジック Low の場合、DAC 出力はレジスタ A で設定された値に更新されます。ロジック High の場合、DAC 出力はレジスタ B で設定された値に更新されます。3 つの TOGGLE[2:0] ピンにより、DACx1416 は最大 3 種類のトグル レートで動作するオプションを持ちます。

さらに、このデバイスは SOFTTOGGLE-EN ビットを設定することで、ソフトウェア制御によるトグル動作を行うように構成できます。このモードでは、3 つの AB-TOG[2:0] ビットのいずれかをトグル制御信号として使用します。AB-TOG ビットを 1 に設定するとレジスタ B が有効になり、このビットを 0 にクリアするとレジスタ A が有効になります。

### 6.4.2 差動モード

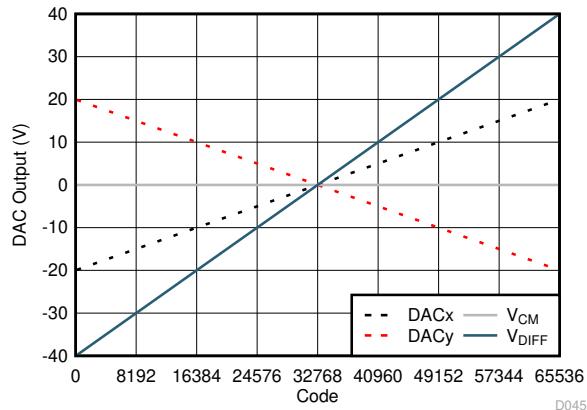

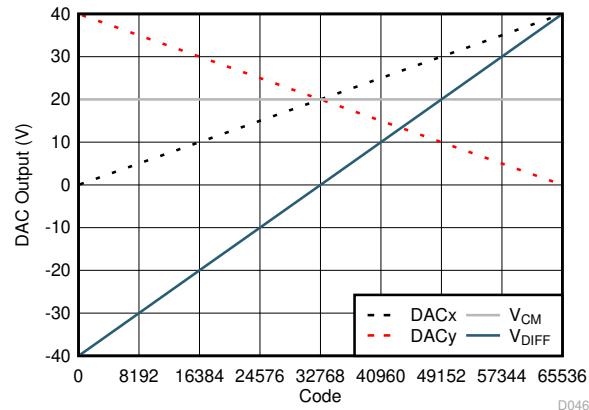

デバイス内の各 DAC ペアは、それぞれ独立して差動出力ペアとして動作するように設定できます。DACx-y ペアの差動出力は、DACx チャネルに書き込むことで更新されます。正しく動作させるためには、差動モードを有効にする前に、2 つの DAC ペアを同じ出力範囲に設定します。[図 6-2](#) と [図 6-3](#) に、それぞれ  $\pm 20V$  および  $40V$  動作に構成された DAC 差動ペアの理想的な差動出力電圧 ( $V_{DIFF}$ ) と同相電圧 ( $V_{CM}$ ) を示します。

差動出力として構成した後、DACx トグル レジスタを更新することでトグル動作できるように DACx-y ペアを設定します。[セクション 6.4.1](#) を参照します。

2 つの差動信号の間で不均衡があると、同相モード誤差と振幅誤差が発生します。このデバイスにはオフセット レジスタが組み込まれており、ユーザーは DACx-y 差動ペアの DACy チャネルに電圧オフセットを導入して、2 つのチャネル間の DC オフセット誤差を補償できます。オフセット補償により、約  $\pm 0.2\%$  の FSR 調整ウィンドウが得られます。オフセット レジスタを更新した後で、差動 DAC データ レジスタを書き換えます。

図 6-2. 差動バイポーラ出力 (16 ビット) :

$\pm 20V$  の出力範囲

図 6-3. 差動ユニポーラ出力 (16 ビット) :

0V ~ 40V の出力範囲

#### 6.4.3 パワーダウン モード

DACx1416 の DAC 出力アンプおよび内部リファレンスのパワーダウン状態は、PWDWN レジスタを通じて個別に設定および監視されます。DAC チャネルをパワーダウン モードに設定すると、出力アンプが無効化され、内部  $10\text{ k}\Omega$  抵抗を介して出力ピンがグランドにクランプされます。

DAC がパワーダウンに入っても DAC データ レジスタはクリアされないため、通常動作に戻った際に同じ出力電圧へ復帰できます。パワーダウン モード中は、DAC データ レジスタは更新できます。

電源投入またはリセット後、すべての DAC チャネルと内部リファレンスはパワーダウン モードになります。DEV-PWDWN ビットを使用して、デバイス全体をパワーダウン モードまたはアクティブ モードに設定します。

## 6.5 プログラミング

DACx1416 ファミリのデバイスは、柔軟な 4 線式シリアルインターフェースを介して制御され、多くのマイクロコントローラや DSP コントローラで使用される SPI タイプのインターフェイスと互換性があります。このインターフェイスにより DACx1416 のレジスタへアクセスでき、書き込み動作において複数デバイスをデイジタルチェーン接続するように構成できます。DACx1416 には、ノイズの多い環境で SPI データ通信の完全性を検証するためのオプションのエラー チェック モードが組み込まれています。

### 6.5.1 スタンドアロン動作

シリアルインターフェイスのアクセスサイクルは、**CS** ピンを **Low** にすることで開始されます。シリアルクロック **SCLK** は連続クロックでもゲート付きクロックでも使用できます。**SDI** データは、**SCLK** の立ち下がりエッジに同期します。通常のシリアルインターフェイスアクセスサイクルは、エラー チェックが無効の場合 24 ビット、有効の場合 32 ビットの長さとなります。したがって、**CS** ピンは少なくとも 24 回または 32 回の **SCLK** 立ち下がりエッジの間 **Low** の状態を維持する必要があります。**CS** ピンが **High** にデアサートされると、アクセスサイクルは終了します。アクセスサイクルが最小クロックエッジよりも短い場合、通信は無視されます。アクセスサイクルに最小クロックエッジ数を超えるビットが含まれている場合、デバイスは最初の 24 ビットまたは 32 ビットのみを使用します。**CS** ピンが **High** のとき、**SCLK** および **SDI** 信号はブロックされ、**SDO** はハイインピーダンス (Hi-Z) 状態になります。

エラー チェックが無効のアクセスサイクル (24 ビットの場合) では、**SDI** に入力される最初のバイトが、リクエストが読み取りコマンドか書き込みコマンドかを識別する命令サイクルおよびアクセスする 6 ビットのアドレスとなります。サイクルの最後の 16 ビットは、データサイクルを形成します。

**表 6-2. シリアルインターフェイスアクセスサイクル**

| ビット   | フィールド    | 説明                                                                                                       |

|-------|----------|----------------------------------------------------------------------------------------------------------|

| 23    | RW       | アドレス指定されたレジスタに対する読み取りまたは書き込みコマンドとして通信を識別します。 <b>R/W = 0</b> は書き込み動作を設定します。 <b>R/W = 1</b> は読み取り動作を設定します。 |

| 22    | x        | ドントケアビット。                                                                                                |

| 21-16 | A[5:0]   | レジスタアドレス。読み取りまたは書き込み操作中にアクセスするレジスタを指定します。                                                                |

| 15-0  | DI[15:0] | データサイクルビット。書き込みコマンドの場合、データサイクルのビットはアドレス A[5:0] のレジスタに書き込まれる値となります。読み取りコマンドの場合、データサイクルのビットは「無効」値となります。    |

読み取り操作を行うには、まず **SDO-EN** ビットを設定して **SDO** ピンを有効化する必要があります。読み取り操作は、読み取りコマンドのアクセスサイクルを発行することで開始されます。読み取りコマンドの後、要求されたデータを取得するために、2 回目のアクセスサイクルを発行する必要があります。データは、**FSDO** ビットに応じて、**SCLK** の立ち下がりエッジまたは立ち上がりエッジのいずれかの **SDO** ピンでクロック出力されます。

**表 6-3. SDO 出力アクセスサイクル**

| ビット   | フィールド    | 説明                               |

|-------|----------|----------------------------------|

| 23    | RW       | 前回のアクセスサイクルから <b>RW</b> をエコーします。 |

| 22    | x        | 前回のアクセスサイクルのビット 22 をエコーします。      |

| 21-16 | A[5:0]   | 前回のアクセスサイクルのアドレスをエコーします。         |

| 15-0  | DO[15:0] | 前のアクセスサイクルで要求されたデータの読み戻し。        |

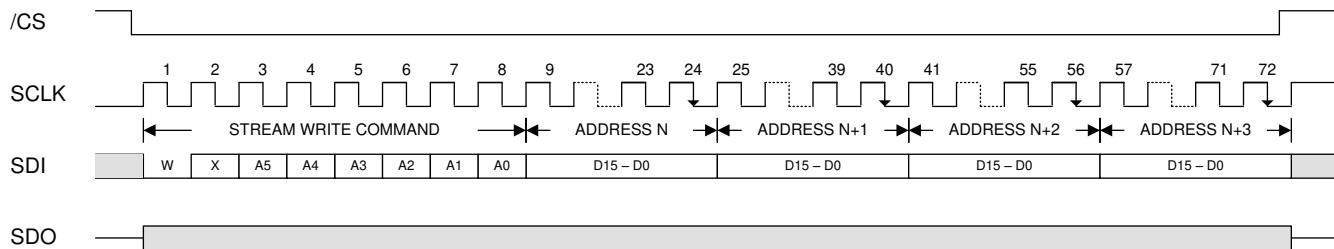

### 6.5.1.1 ストリーミング モード動作

16 チャネルのデータレジスタを更新するには大量のデータをデバイスに送信する必要があるため、このデバイスはストリーミング モードをサポートしています。ストリーミング モードでは、各データレジスタごとに命令コマンドを与えることなく、DAC データレジスタを書き込むことができます。ストリーミング モードは、STR-EN ビットを設定することで有効になります。イネーブルになると、 $\overline{CS}$  をアクティブに保持して、デバイスに新しいデータをシフトし続けることで、ストリーミング動作が実装されます。STR-EN ビットをイネーブルにすると、SDO ピンはディスエーブルになります。

命令サイクルには開始アドレスが含まれます。デバイスはこのアドレスへの書き込みを開始し、 $\overline{CS}$  がアサートされている間、アドレスを自動的にインクリメントします。最後の DAC データレジスタアドレスに達して、 $\overline{CS}$  がアサートされたままの場合、このアドレスのデータは新しいデータで上書きされます。

図 6-4. シリアル インターフェースのストリーミング サイクル

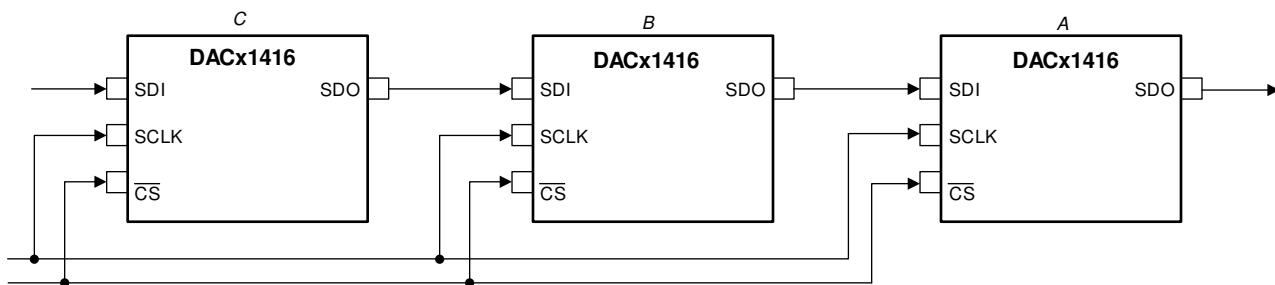

### 6.5.2 デイジーチェーン動作

複数の DACx1416 デバイスを含むシステムでは、SDO ピンを使用してそれらをデイジーチェーン接続することができます。デイジーチェーン動作を開始する前に、SDO-EN ビットを設定して SDO ピンを有効にする必要があります。シリアルインターフェイスラインの数を減らす場合に、デイジーチェーン動作が役立ちます。

$\overline{CS}$  ピンの最初の立ち下がりエッジで動作サイクルが開始されます。 $\overline{CS}$  ピンが Low のまま 24 パルスを超える SCLK パルスが印加されると、シフトレジスタ内のデータがリップル アウトし、FSDO ビットの設定に従って SCLK の立ち下がりエッジまたは立ち上がりエッジで SDO ピンからクロックアウトされます。最初のデバイスの SDO 出力をチェーン内の次のデバイスの SDI 入力に接続することで、複数デバイスのインターフェイスが構築されます。システム内の各デバイスは 24 のクロック パルスを必要とします。その結果、クロック サイクルの合計数は  $24 \times N$  に等しくする必要があります。ここで  $N$  は、デイジーチェーンに含まれる DACx1416 デバイスの総数です。すべてのデバイスへのシリアル転送が完了すると、 $\overline{CS}$  信号が High になります。この操作により、SPI シフトレジスタから各デバイスの内部レジスタへデータが転送され、さらに入力シフトレジスタへデータがクロックインされるのを防ぎます。ストリーミング モード中は、デイジーチェーン動作はサポートされていません。

図 6-5. デイジーチェーンのレイアウト

### 6.5.3 フレームエラー チェック

DACx1416 をノイズの多い環境で使用する場合、エラー チェックを利用して、デバイスとホスト プロセッサ間の SPI データ通信の完全性を確認します。この機能を有効にするには、**CRC-EN** ビットをセットします。

エラー チェック方式は、**CRC-8-ATM (HEC)** 多項式  $x^8 + x^2 + x + 1$  (つまり 100000111) に基づいています。エラー チェックがイネーブルの場合、シリアル インターフェイスのアクセス サイクル幅は 32 ビットです。常の 24 ビット SPI データには、ホスト プロセッサによって 8 ビットの CRC 多項式が付加され、デバイスに送信されます。すべてのシリアル インターフェイスの読み戻し動作において、CRC 多項式は 32 ビット サイクルの一部として SDO ピンから出力されます。

**表 6-4. エラー チェック付きシリアル インターフェイス アクセス サイクル**

| ビット   | フィールド     | 説明                                                                                                        |

|-------|-----------|-----------------------------------------------------------------------------------------------------------|

| 31    | RW        | アドレス指定されたレジスタに対する読み取りまたは書き込みコマンドとして通信を識別します。R/W = 0 は書き込み動作を設定します。R/W = 1 は読み取り動作を設定します。                  |

| 30    | CRC-ERROR | 予約済みビット。ゼロに設定します。                                                                                         |

| 29-24 | A[5:0]    | レジスタ アドレス。読み取りまたは書き込み操作中にアクセスするレジスタを指定します。                                                                |

| 23-8  | DI[15:0]  | データ サイクル ビット。書き込みコマンドの場合、データ サイクルのビットはアドレス A[5:0] のレジスタに書き込まれる値となります。読み取りコマンドの場合、データ サイクルのビットは「無効」値となります。 |

| 7-0   | CRC       | 8 ビット CRC 多項式。                                                                                            |

DACx1416 は、CS の立ち上がりエッジで 32 ビットのアクセス サイクルをデコードし、CRC の余りを計算します。エラーがない場合、CRC の余りはゼロとなり、データはデバイスに受け入れられます。

CRC チェックに失敗した書き込み操作の場合、そのデータはデバイスによって無視されます。書き込みコマンドの後、2 回目のアクセスサイクルを実行し、SDO ピン上のエラー チェック結果 (CRC-ERROR ビット) を確認します。

CRC エラーが発生すると、STATUS レジスタの CRC-ALM ビットが 1 にセットされます。CRC エラーを監視するには、CRCALM-EN ビットを設定して ALMOUT ピンを構成します。

**表 6-5. 書き込み動作エラー チェック サイクル**

| ビット   | フィールド     | 説明                                       |

|-------|-----------|------------------------------------------|

| 31    | RW        | 前回のアクセスサイクルから RW をエコーします (RW = 0)。       |

| 30    | CRC-ERROR | CRC エラーが検出された場合は 1 を返し、それ以外の場合は 0 を返します。 |

| 29-24 | A[5:0]    | 前回のアクセス サイクルのアドレスをエコーします。                |

| 23-8  | DO[15:0]  | 前回のアクセス サイクルのエコー データ。                    |

| 7-0   | CRC       | ビット 31:8 の計算された CRC 値。                   |

読み出し操作の後には、要求されたデータを SDO ピンで取得するために 2 回目のアクセス サイクルを行う必要があります。読み取りコマンドによるエラー チェック結果 (CRC-ERROR ビット) は SDO ピンに出力されます。

書き込み動作が CRC チェックに失敗した場合と同様に、ステータス レジスタの CRC-ALM ビットが 1 に設定され、ALMOUT ピンが CRC アラート用に構成されている場合は Low に設定されます。

**表 6-6. 読み取り動作エラー チェック サイクル**

| ビット   | フィールド     | 説明                                       |

|-------|-----------|------------------------------------------|

| 31    | RW        | 前回のアクセスサイクルから RW をエコーします (RW = 1)。       |

| 30    | CRC-ERROR | CRC エラーが検出された場合は 1 を返し、それ以外の場合は 0 を返します。 |

| 29-24 | A[5:0]    | 前回のアクセス サイクルのアドレスをエコーします。                |

| 23-8  | DO[15:0]  | 前のアクセス サイクルで要求されたデータの読み戻し。               |

表 6-6. 読み取り動作エラー チェック サイクル (続き)

| ビット | フィールド | 説明                     |

|-----|-------|------------------------|

| 7-0 | CRC   | ビット 31:8 の計算された CRC 値。 |

## 7 レジスタ マップ

デバイスのメモリマップ レジスタを、表 7-1 に示します。表 7-1 に記載されていないすべてのレジスタ オフセット アドレスは予約済み領域と見なされます。これらの予約済みレジスタ内容を変更しないでください。

**表 7-1. DACx1416 のレジスタ**

| オフセット | 略称          | レジスタ名                          | セクション |

|-------|-------------|--------------------------------|-------|

| 00h   | NOP         | NOP レジスタ                       | 表示    |

| 01h   | DEVICEID    | Device ID レジスタ                 | 表示    |

| 02h   | STATUS      | ステータス レジスタ                     | 表示    |

| 03h   | SPICONFIG   | SPI 構成レジスタ                     | 表示    |

| 04h   | GENCONFIG   | 全般構成レジスタ                       | 表示    |

| 05h   | BRDCONFIG   | ブロードキャスト構成レジスタ                 | 表示    |

| 06h   | SYNCCONFIG  | 同期構成レジスタ                       | 表示    |

| 07h   | TOGGCONFIG0 | DAC[15:8]トグル構成レジスタ             | 表示    |

| 08h   | TOGGCONFIG1 | DAC[7:0]トグル構成レジスタ              | 表示    |

| 09h   | DACPWDWN    | DAC パワーダウン レジスタ                | 表示    |

| 0Ah   | DACRANGE0   | DAC[15:12] 範囲レジスタ              | 表示    |

| 0Bh   | DACRANGE1   | DAC[11:8] 範囲レジスタ               | 表示    |

| 0Ch   | DACRANGE2   | DAC[7:4] 範囲レジスタ                | 表示    |

| 0Dh   | DACRANGE3   | DAC[3:0] 範囲レジスタ                | 表示    |

| 0Eh   | TRIGGER     | Trigger レジスタ                   | 表示    |

| 0Fh   | BRDCAST     | ブロードキャスト データ レジスタ              | 表示    |

| 10h   | DAC0        | DAC0 データ レジスタ                  | 表示    |

| 11h   | DAC1        | DAC1 データ レジスタ                  | 表示    |

| 12h   | DAC2        | DAC2 データ レジスタ                  | 表示    |

| 13h   | DAC3        | DAC3 データ レジスタ                  | 表示    |

| 14h   | DAC4        | DAC4 データ レジスタ                  | 表示    |

| 15h   | DAC5        | DAC5 データ レジスタ                  | 表示    |

| 16h   | DAC6        | DAC6 データ レジスタ                  | 表示    |

| 17h   | DAC7        | DAC7 データ レジスタ                  | 表示    |

| 18h   | DAC8        | DAC8 データ レジスタ                  | 表示    |

| 19h   | DAC9        | DAC9 データ レジスタ                  | 表示    |

| 1Ah   | DAC10       | DAC10 データ レジスタ                 | 表示    |

| 1Bh   | DAC11       | DAC11 データ レジスタ                 | 表示    |

| 1Ch   | DAC12       | DAC12 データ レジスタ                 | 表示    |

| 1Dh   | DAC13       | DAC13 データ レジスタ                 | 表示    |

| 1Eh   | DAC14       | DAC14 データ レジスタ                 | 表示    |

| 1Fh   | DAC15       | DAC15 データ レジスタ                 | 表示    |

| 20h   | OFFSET0     | DAC[14-15, 12-13] 差動オフセット レジスタ | 表示    |

| 21h   | OFFSET1     | DAC[10-11, 8-9] 差動オフセット レジスタ   | 表示    |

| 22h   | OFFSET2     | DAC[6-7, 4-5] 差動オフセット レジスタ     | 表示    |

| 23h   | OFFSET3     | DAC[2-3, 0-1] 差動オフセット レジスタ     | 表示    |

表の小さなセルに収まるように、複雑なビット アクセス タイプを記号で表記しています。表 7-2 に、このセクションでアクセス タイプに使用しているコードを示します。

表 7-2. アクセス タイプ コード

| アクセス タイプ         | コード | 説明                                                                                                            |

|------------------|-----|---------------------------------------------------------------------------------------------------------------|

| 読み取りタイプ          |     |                                                                                                               |

| R                | R   | 読み出し                                                                                                          |

| 書き込みタイプ          |     |                                                                                                               |

| W                | W   | 書き込み                                                                                                          |

| リセットまたはデフォルト値    |     |                                                                                                               |

| -n               |     | リセット後の値またはデフォルト値                                                                                              |

| レジスタ アレイ変数       |     |                                                                                                               |

| i, j, k, l, m, n |     | これらの変数がレジスタ名、オフセット、またはアドレスで使用される場合、その変数はレジスタが繰り返しレジスタのグループの一部であるレジスタ配列の値を参照します。レジスタグループは階層構造を形成し、アレイは式で表されます。 |

| y                |     | この変数がレジスタ名、オフセット、またはアドレスで使用される場合、その変数はレジスタ配列の値を参照します。                                                         |

## 7.1 NOP レジスタ (オフセット = 00h) [リセット = 0000h]

図 7-1 に、NOP を示し、表 7-3 に、その説明を示します。

概略表に戻ります。

図 7-1. NOP レジスタ

|      |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|------|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| 15   | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| NOP  |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| W-0h |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

表 7-3. NOP レジスタ フィールドの説明

| ビット  | フィールド | タイプ | リセット | 説明                                 |

|------|-------|-----|------|------------------------------------|

| 15-0 | NOP   | W   | 0h   | 動作なし。適切な無動作コマンドの場合は 0000h を書き込みます。 |

## 7.2 DEVICEID レジスタ (オフセット = 01h) [リセット = ----h]

DEVICEID は 図 7-2 に示され、表 7-4 に記載されています。

概略表に戻ります。

図 7-2. DEVICEID レジスタ

|          |    |    |    |    |    |           |   |  |  |

|----------|----|----|----|----|----|-----------|---|--|--|

| 15       | 14 | 13 | 12 | 11 | 10 | 9         | 8 |  |  |

| DEVICEID |    |    |    |    |    |           |   |  |  |

| R----h   |    |    |    |    |    |           |   |  |  |

| 7        | 6  | 5  | 4  | 3  | 2  | 1         | 0 |  |  |

| DEVICEID |    |    |    |    |    | VERSIONID |   |  |  |

| R----h   |    |    |    |    |    |           |   |  |  |

| R-0h     |    |    |    |    |    |           |   |  |  |

表 7-4. DEVICEID レジスタ フィールドの説明

| ビット  | フィールド     | タイプ | リセット | 説明                                                         |