**DRV3946-Q1** JAJSSJ6 – DECEMBER 2023

# DRV3946-Q1 電流レギュレーション、クランプ、診断機能搭載、デュアル チャネル 車載用ソレノイドドライバ

## 1 特長

- 車載アプリケーション向けに AEC-Q100 認定済み

- 温度グレード 1:-40℃~+125℃、T♪

- 機能安全準拠予定

- 機能安全アプリケーション向けに開発

- 今後、ASIL C までの ISO 26262 システム設計 を支援するドキュメントが入手可能

- 車載 EV 接触器リレーとソレノイド制御の各アプ リケーションをターゲットとする高集積ソレノイ ドドライバ

- 電源、電流レギュレーション、診断、安全機能 の統合

- 構成可能なピーク/ホールド電流設定による高 効率ソレノイド駆動

- 電源、インターフェイス、ドライバ、モニタの 内蔵セルフ テストおよび診断機能

- 冗長電源、ローサイドおよびハイサイドドラ イバ、2次側監視ロジックにより信頼性の高い 動作を実現するアーキテクチャ

- 動作範囲:最大 28V (絶対最大定格 40V)

- 改良型ハーフブリッジ内蔵

- 充電、還流、クランプ用途

- 代表値 R<sub>DS(ON)</sub>: 37mΩ (ローサイド)、57mΩ (ハイサイド)

- クランプ回路内蔵による迅速なターンオフ機能

- ハイサイド クランプと冗長ローサイド クラン

- 1 線式接続によるローサイド負荷制御

- 外部ハイサイド スイッチにより冗長シャット オフが可能

- ±5% 精度のローサイドおよびハイサイド電流セン ス

- アナログ負荷電流帰還ピン (IPROPI)

- 内部制御モード:

- 閉ループ PWM 電流レギュレーション

- 構成可能なピーク時間、ピーク電流、ホールド 電流

- 外部制御モード:

- 固定 PWM 周波数でデューティ サイクルを変

- 固定デューティ サイクルで PWM 周波数を変 動

- CRC 搭載 4 線式アドレス指定可能 24 ビット SPI

- 同じ SPI 上で複数のデバイスを動作可能

- 複数のデバイスへコマンドをブロードキャスト 可能

- 包括的な保護機能と診断機能:

- デバイス内蔵セルフ テスト

- 負荷監視による開路/短絡の検出

- ドライバのオン/オフ中の制御喪失の検出

- 低電流または低電圧時に強制リレーがオープン

- 冗長ピン シャットオフ

- nFAULT ピンによるフォルト通知

# 2 アプリケーション

- EV 接触器リレー

- ピークおよびホールド ソレノイド

- オン / オフ リレー

- 比例ソレノイド

- バッテリ切り離しユニット (BDU)

- バッテリ ジャンクション ボックス (BJB)

- パワー ディストリビューション ボックス (PDB)

- アクティブ サスペンション システム

- 車両制御ユニット (VCU)

### パッケージ情報

| 部品番号 (1)   | パッケージ       | パッケージ サイズ<br>(公称) <sup>(2)</sup> |

|------------|-------------|----------------------------------|

| DRV3946-Q1 | HTSSOP (28) | 9.7 mm × 4.4 mm                  |

- (1) 利用可能なすべてのパッケージについては、データシートの 末尾にある注文情報を参照してください。

- パッケージ サイズ (長さ×幅) は公称値であり、該当する場合 はピンも含まれます。

### 製品情報

| 主要な機能                         |

|-------------------------------|

| 2 個のソレノイドを高効率で駆動可能            |

| オン抵抗の低い電力段                    |

| 迅速なターンオフを可能にするクランプ回路          |

| 閉ループ PWM 電流レギュレーション           |

| ピーク電流とホールド電流とタイミング パラメータを構成可能 |

| 最大 20kHz の PWM 周波数オプション       |

| 包括的なオン / オフ状態診断               |

| アドレス指定可能な 24 ビット SPI          |

### 3 概要

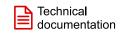

DRV3946-Q1 は、EV バッテリ管理システムの接触器リレーなど、車載アプリケーション用の 2 つのソレノイドを駆動する高集積ソリューションです。電源、電流センシングと電流レギュレーション、構成可能なピーク / ホールド電流と関連タイミング、診断機能と保護機能を搭載しています。また、従来のディスクリート ソレノイドドライバに比べて性能を向上させる複数の独自機能も搭載しています。これらの機能には、負荷電流を迅速に放電するための内蔵冗長クランプ回路、アドレス指定可能な SPI、オン抵抗の低いスイッチを備えた変更型ハーフブリッジドライバ段が含まれます。

このデバイスは、1線式のローサイド接続でソレノイド負荷を制御し、(共有可能な)外部ハイサイドスイッチと組み合わせることで、冗長シャットオフ機能を実現できます。内蔵スイッチは、充電、還流、クランプを実行します。このデバイスは、内部および外部の電流制御モードをサポートしています。PWM 周波数は構成可能で、自動疑似ランダム周波数生成および波形整形を使用した低周波数ディザリングが追加されています。内部PWM電流制御ループは、MCU電流制御ループが不要なため、ソフトウェア開発の労力削減につながります。DRV3946-Q1は柔軟な電流制御パラメータをサポートしており、広範な種類のソレノイドをサポートしています。ピーク電流とホールド電流、および対応するタイミングパラメータが構成可能なため、システムレベルで省電力を実現できます。

DRV3946-Q1 は機能安全準拠を目標としており、リレー制御と意図しない動作の防止を目的として、ASIL-C 定格の機能安全を目標にしています。このデバイスは、開放および短絡検出のための負荷の継続的な監視、オンおよびオフ状態診断、電圧監視、短絡保護、高電圧定格 IO などの包括的な保護および診断機能をサポートしています。

アドレス指定可能な SPI により、1 つの共有 SPI バスで複数のデバイスを制御できます。必要なマイコン リソースの削減に加えて、アドレス指定可能な SPI にはブロードキャスト コマンド構造が組み込まれており、共有アドレス指定バス上のすべてのデバイスが、ある特定のアクションを同時に行うことができます。SPI には、CRC、アドレス読み戻し機能、各種バス フォルト検出メカニズムなど、複数の堅牢性機能が組み込まれています。

概略回路図

### **Table of Contents**

| 1 特長 1              | 5 Mechanical, Packaging, and Orderable Information 3 |

|---------------------|------------------------------------------------------|

| 2 アプリケーション1         |                                                      |

| 3 概要2               | 5.2 Tape and Reel Information5                       |

| 4 Revision History3 | ·                                                    |

# 4 Revision History

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| DATE          | REVISION | NOTES           |

|---------------|----------|-----------------|

| December 2023 | *        | Initial Release |

# 5 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

資料に関するフィードバック(ご意見やお問い合わせ)を送信

3

### 5.1 Package Option Addendum

### **Packaging Information**

| Orderable<br>Device | Status <sup>(1)</sup> | Package Type | Package<br>Drawing | Pins | Package Qty | Eco Plan <sup>(2)</sup> | Lead/Ball<br>Finish <sup>(6)</sup> | MSL Peak<br>Temp <sup>(3)</sup> | Op Temp (°C) | Device<br>Marking <sup>(4) (5)</sup> |

|---------------------|-----------------------|--------------|--------------------|------|-------------|-------------------------|------------------------------------|---------------------------------|--------------|--------------------------------------|

| DRV3946QPW<br>PRQ1  | ACTIVE                | HTSSOP       | PWP                | 28   | 2500        | RoHS & Green            | NIPDAU                             | Level-3-260C-1<br>68 HR         | -40 to 125   | 3946                                 |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PRE\_PROD Unannounced device, not in production, not available for mass market, nor on the web, samples not available.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

OBSOLETE: TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material).

- (3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead/Ball Finish Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

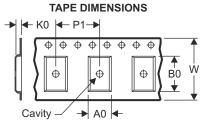

# 5.2 Tape and Reel Information

|    | D: 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                  |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

|    |                                                           |

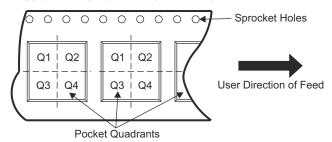

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| Device         | Package<br>Type | Package<br>Drawing | Pins | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|----------------|-----------------|--------------------|------|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| DRV3946QPWPRQ1 | HTSSOP          | PWP                | 28   | 2500 | 330.0                    | 16.4                     | 6.75       | 10.1       | 1.8        | 12.0       | 16.0      | Q1               |

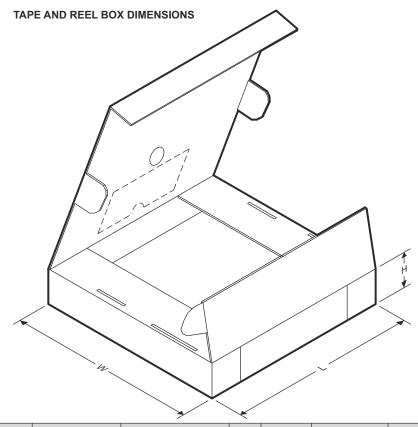

| Device         | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| DRV3946QPWPRQ1 | HTSSOP       | PWP             | 28   | 2500 | 356.0       | 356.0      | 35.0        |

English Data Sheet: SLVSHN6

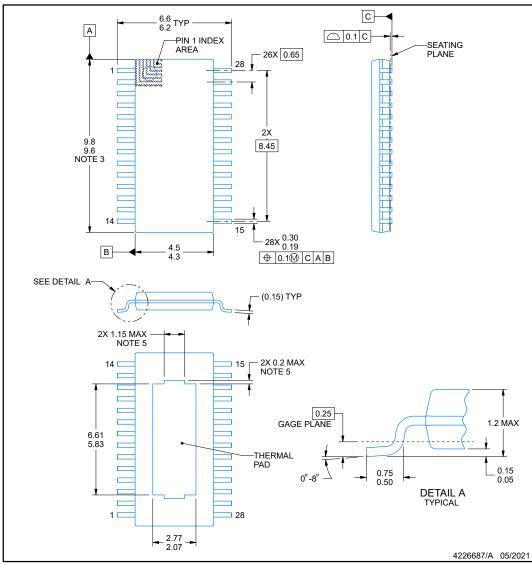

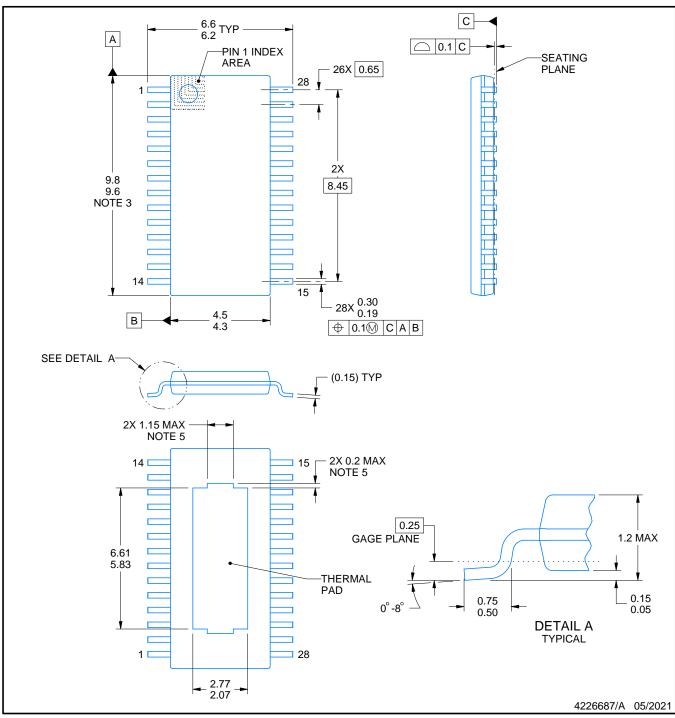

# **PWP0028T**

### **PACKAGE OUTLINE**

# PowerPAD<sup>™</sup> TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

#### NOTES:

PowerPAD is a trademark of Texas Instruments.

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

This drawing is subject to change without notice.

This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

4. Reference JEDEC registration MO-153.

5. Features may differ or may not be present.

Copyright © 2024 Texas Instruments Incorporated

資料に関するプイード、ドラク(C) 意見やお同い合わせ) を送信

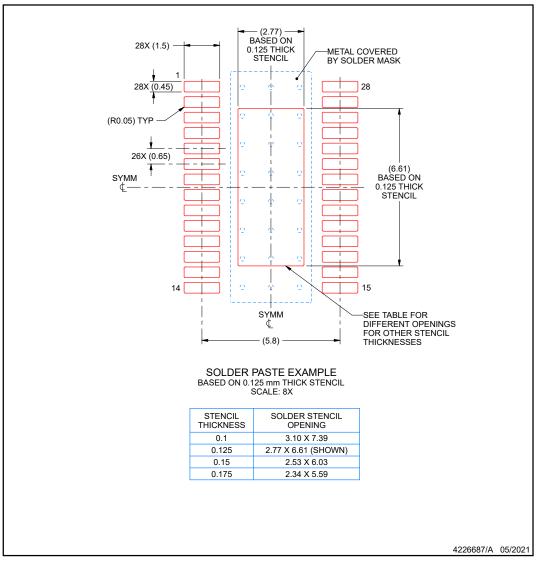

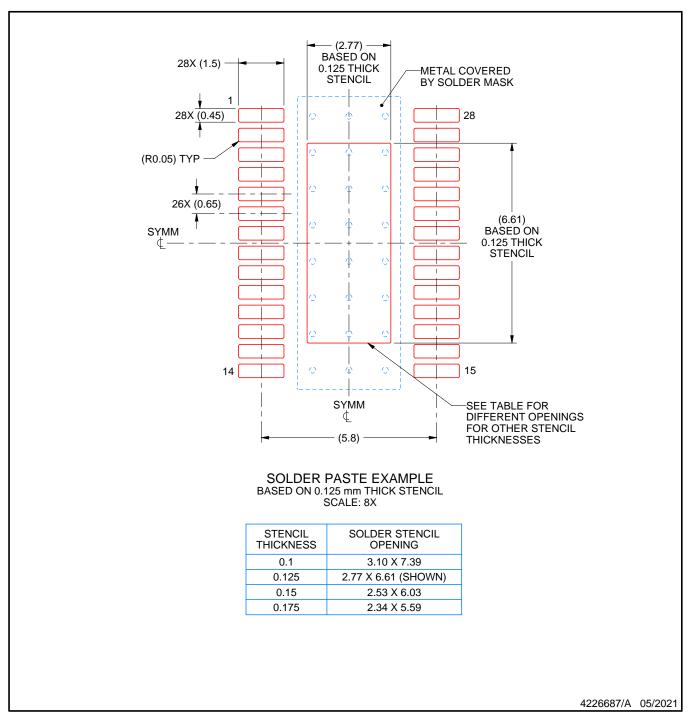

### **EXAMPLE STENCIL DESIGN**

# **PWP0028T**

# PowerPAD<sup>™</sup> TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 11. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

12. Board assembly site may have different recommendations for stencil design.

www.ti.com 17-Dec-2023

### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|-------------------------|---------|

| DRV3946QPWPRQ1   | ACTIVE | HTSSOP       | PWP                | 28   | 2500           | RoHS & Green | NIPDAU                        | Level-3-260C-168 HR | -40 to 125   | 3946                    | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

4.4 x 9.7, 0.65 mm pitch

SMALL OUTLINE PACKAGE

This image is a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

# PowerPAD<sup>™</sup> TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

### NOTES:

PowerPAD is a trademark of Texas Instruments.

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

4. Reference JEDEC registration MO-153.

- 5. Features may differ or may not be present.

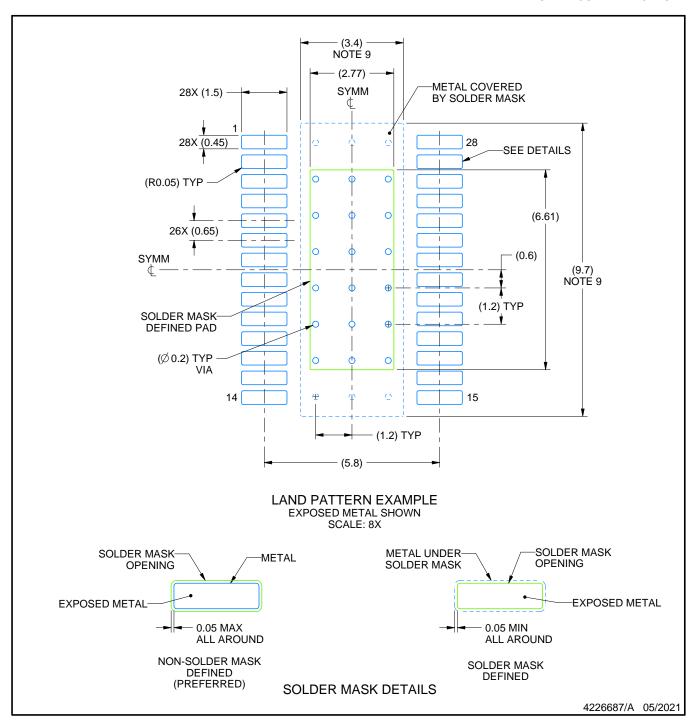

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 6. Publication IPC-7351 may have alternate designs.

- 7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

- 8. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature numbers SLMA002 (www.ti.com/lit/slma002) and SLMA004 (www.ti.com/lit/slma004).

- 9. Size of metal pad may vary due to creepage requirement.

- Vias are optional depending on application, refer to device data sheet. It is recommended that vias under paste be filled, plugged or tented.

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 11. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 12. Board assembly site may have different recommendations for stencil design.

### 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス・デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあら ゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TIの製品は、TIの販売条件、または ti.com やかかる TI 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、TIはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated