# DRV8000-Q1 ドア制御用高集積、多機能ドライバ

## 1 特長

- 車載アプリケーション用に AEC-Q100 認定済み:

- 温度グレード 1:-40°C~+125°C, T<sub>A</sub>

- **機能安全準拠予定**

- 機能安全アプリケーション向けに開発

- ISO26262 システム設計を支援するためのドキュメント

- ASIL Dまでのインテグリティレベル

- ASIL Bまでのハードウェア安全度

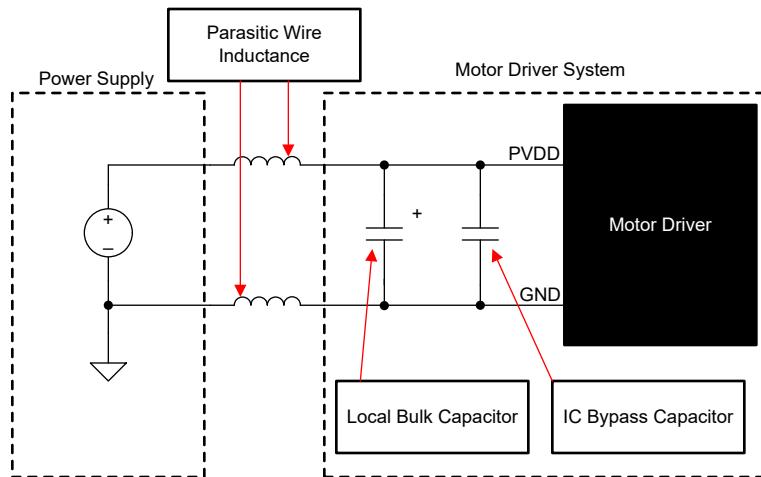

- 5V~35V(絶対最大定格 40V)動作範囲

- Hブリッジまたはデュアルチャネルハーフブリッジゲートドライバ

- スマートゲートドライブアーキテクチャ

- 100% PWMに対応するトリプラー充電ポンプ

- 同相モードの広い電流シャントアンプ

- 1個の統合ハーフブリッジ、I<sub>OUT</sub>最大 8A (R<sub>DSON HS</sub> + LS FET = 155mΩ)

- 1個の統合ハーフブリッジ、I<sub>OUT</sub>最大 7A (R<sub>DSON HS</sub> + LS FET = 185mΩ)

- 2個の統合ハーフブリッジ、I<sub>OUT</sub>最大 4A (R<sub>DSON HS</sub> + LS FET = 440mΩ)

- 2個の統合ハーフブリッジ、I<sub>OUT</sub>最大 1.3A (R<sub>DSON HS</sub> + LS FET = 1540mΩ)

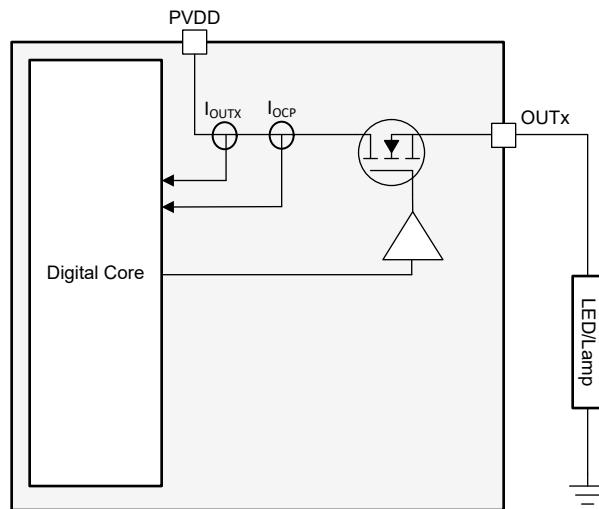

- 1個の構成可能な内蔵ハイサイドドライバをランプまたはLEDドライバとして使用、最大 I<sub>OUT</sub> 1.5/0.5A (R<sub>DSON</sub> = 0.4/1.2Ω)

- 5個の0.5/0.25A負荷用のハイサイドドライバを内蔵 (R<sub>DSON</sub>=1.2Ω)

- 1つの外部MOSFETゲートドライバ、エレクトロクロミックガラス充電用

- 1つのエレクトロクロミックガラス放電用ローサイドFET内蔵

- ハイサイドドライバ用の内部10ビットPWMジェネレータ

- すべてのハイサイドドライバは、幅広いLEDモジュールを駆動するための低電流または高電流のスレッシュホールド定電流モードをサポートしています

- 1個のヒータ用外部MOSFETゲートドライバ

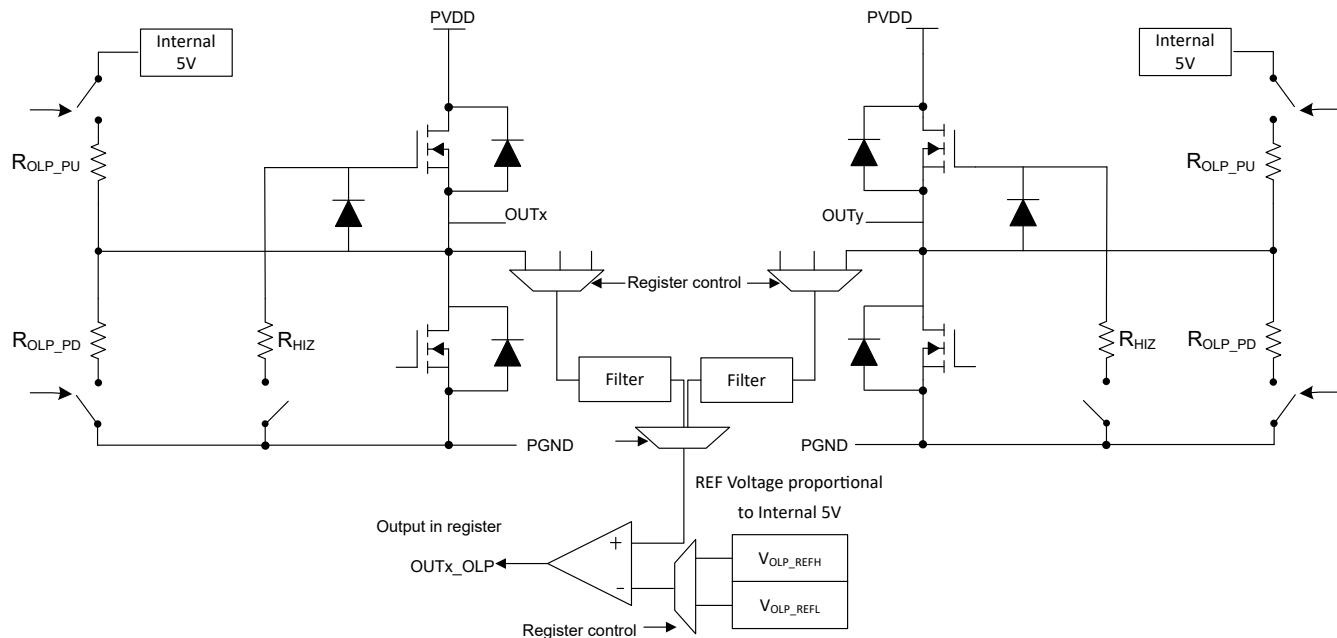

- オフライン開放負荷診断

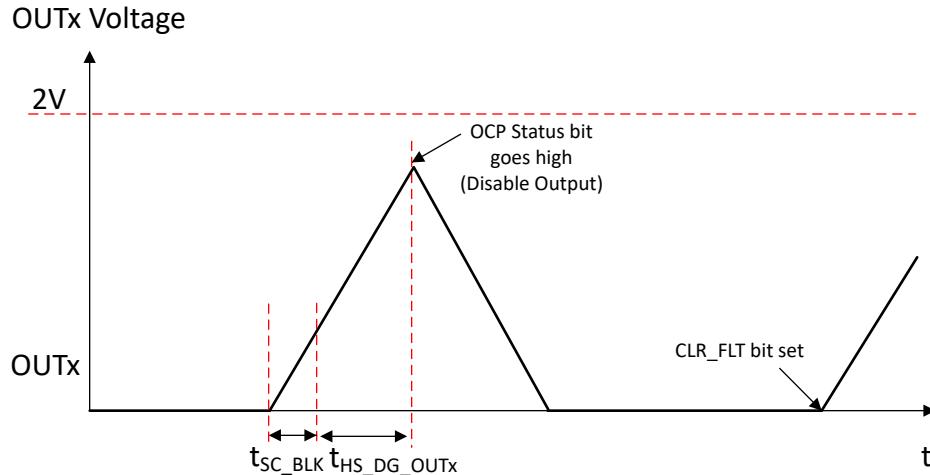

- 短絡検出に適した低 R<sub>DSON</sub> MOSFET の V<sub>DS</sub>監視

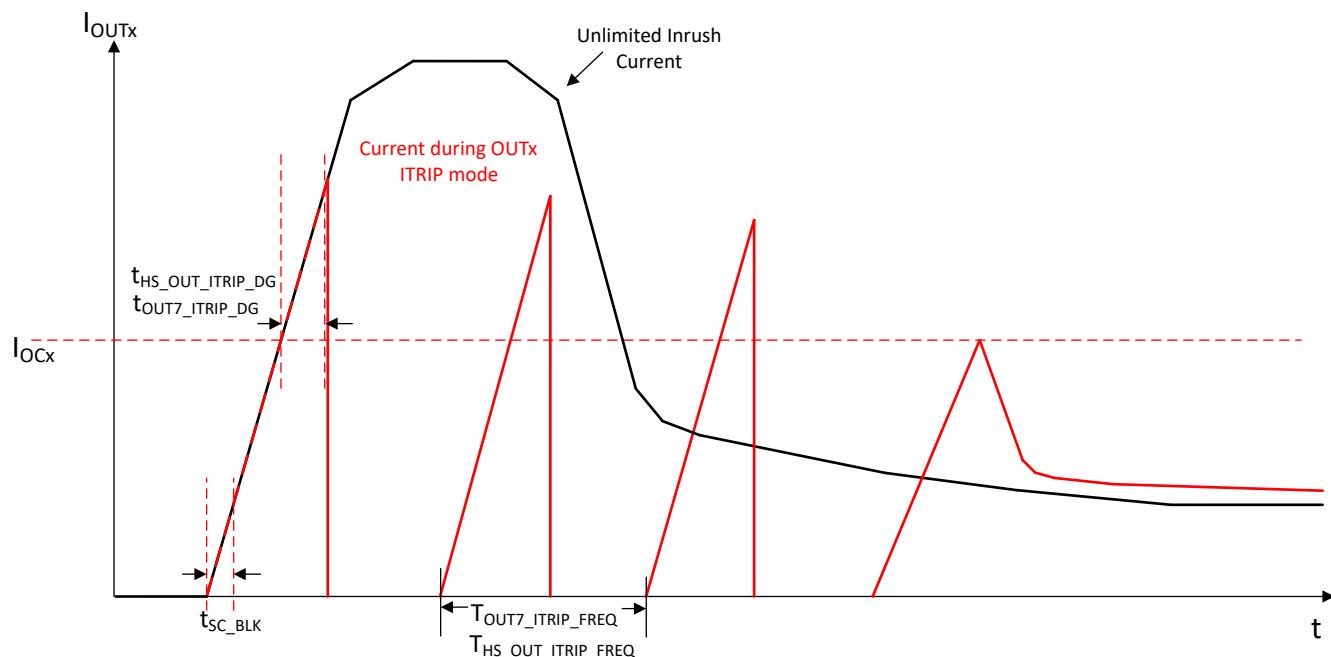

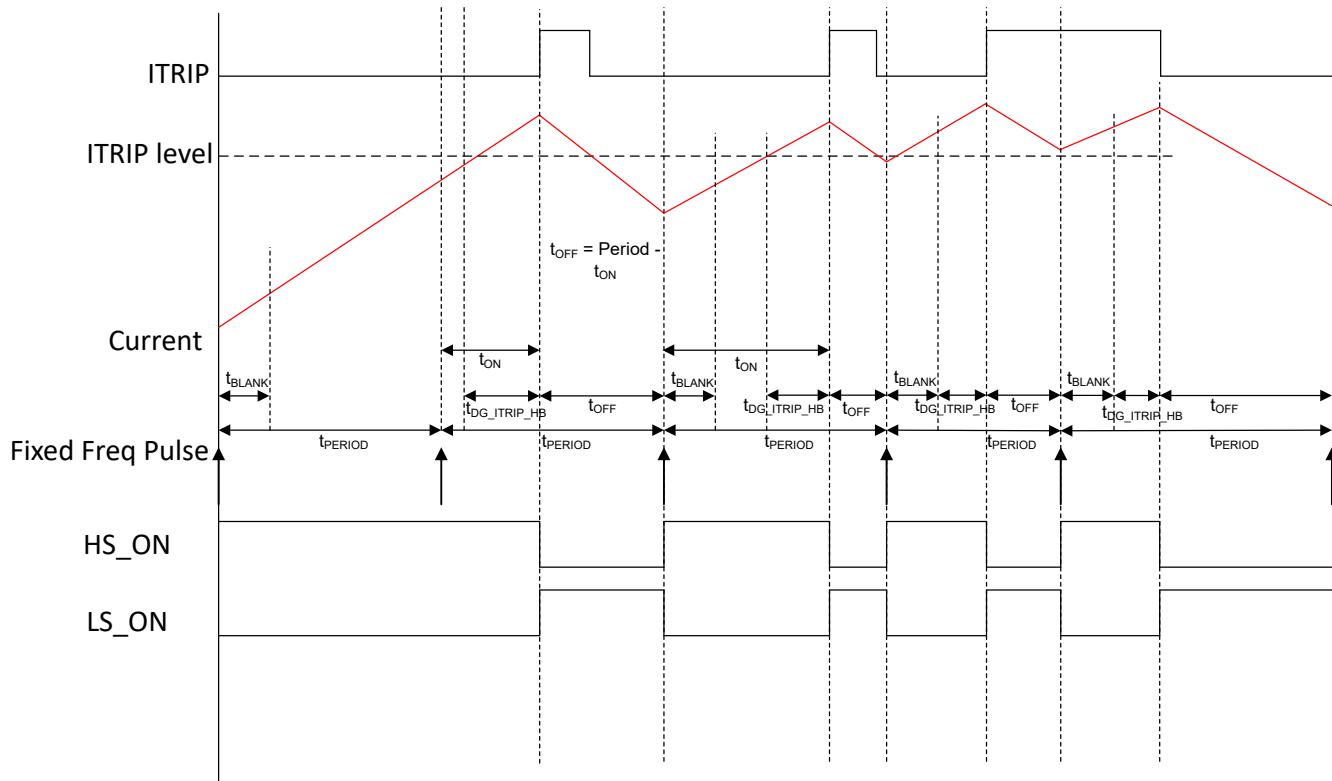

- 統合ドライバ出力は電流調整機能付き(ISTRIP)

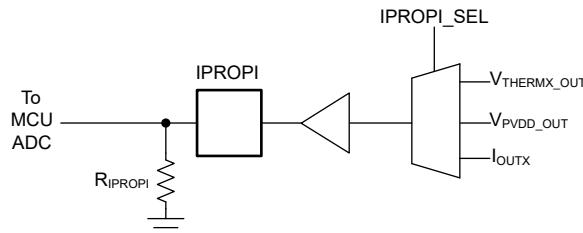

- 多重化可能なセンス出力(IPROPI)

- 比例電流出力(IPROPI)付きの内部電流検出

- 複数の熱クラスタによる高度なダイ温度モニタリング

- モーターの電源電圧モニター

- 設定可能な障害動作を備えた保護および診断機能

- オフ状態とオン状態の両方で負荷診断を行い、開放負荷および短絡を検出

- 過電流および過熱保護

- **デバイス比較表**

## 2 アプリケーション

- **ドアモジュール**

- **車体制御モジュール**

- **ゾーン型モジュール**

## 3 説明

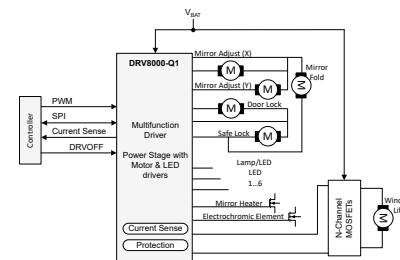

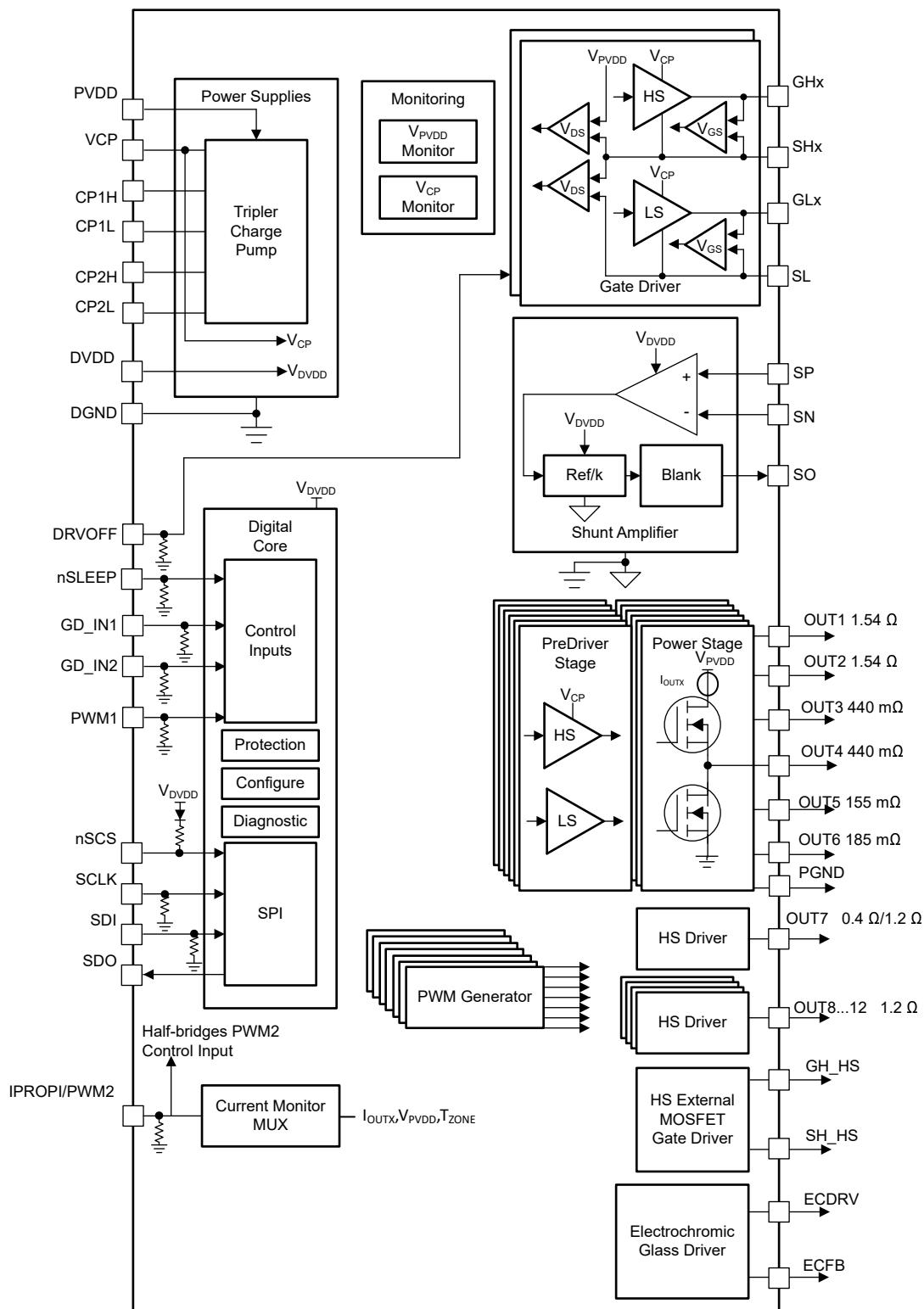

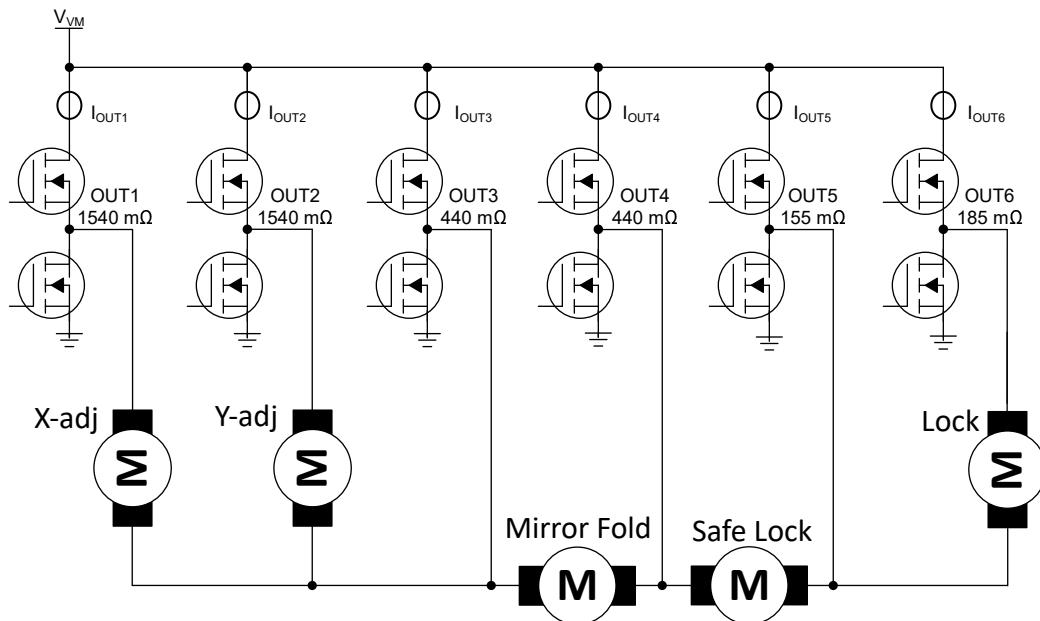

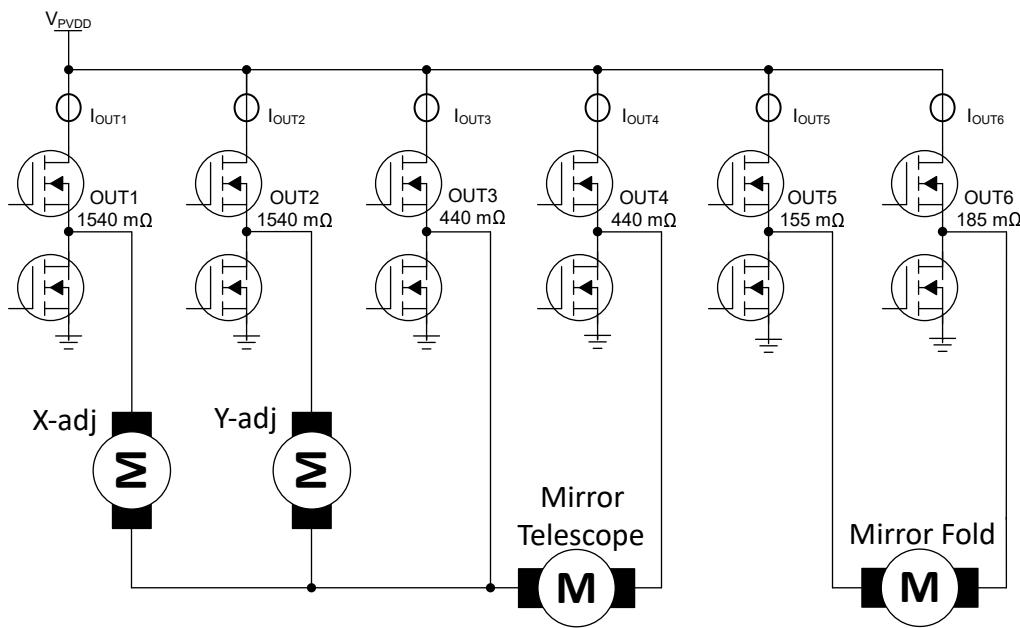

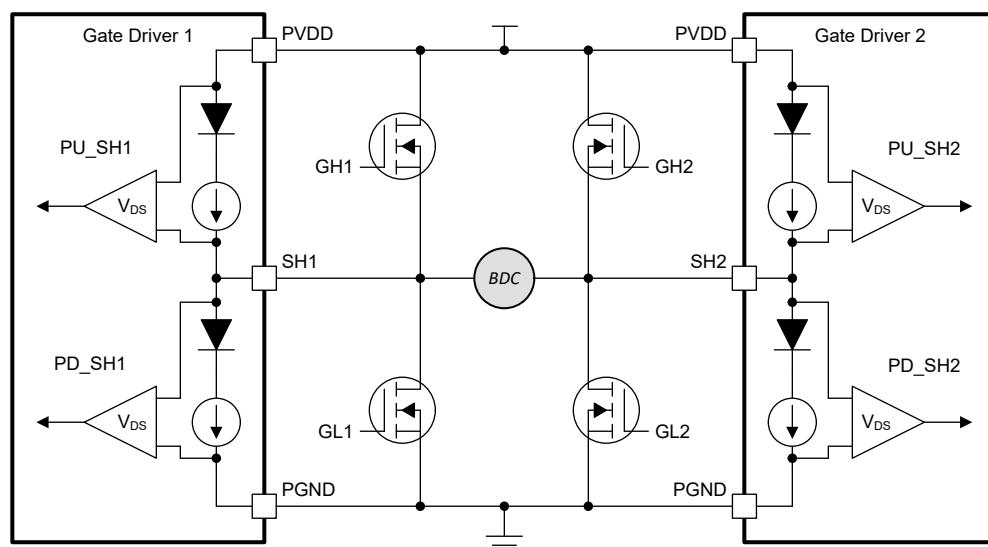

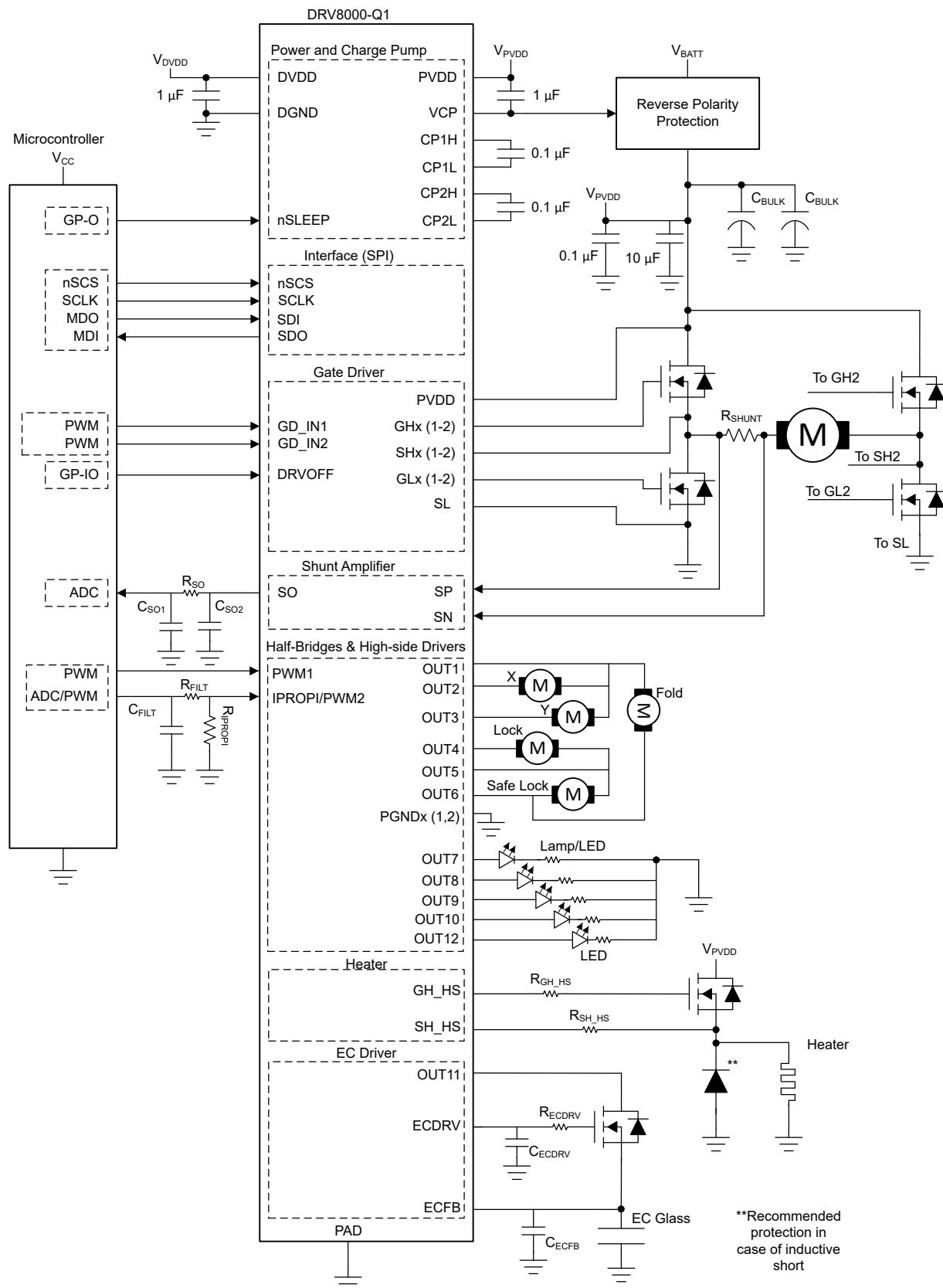

DRV8000-Q1 デバイスには、モーター(誘導性)、抵抗性および容量性負荷の駆動と診断、ランプまたは LED の駆動、加熱素子やエレクトロクロミック素子などの特殊な負荷用 MOSFET の駆動など、複数のドア制御固有の機能が内蔵されています。これらのドライバには、過電圧および低電圧モニタリング、オフラインでの開放負荷および短絡診断、ゾーンベースの温度モニタリングおよびシャットダウン保護などのオフラインおよびアクティブ診断用の保護機能が含まれています。このデバイスは、2つのハーフブリッジゲートドライバ、6つの統合ハーフブリッジ(2つのハイサイド代替モード)、6つの統合ハイサイドドライバ、ヒータ用の外部ハイサイドゲートドライバ1つ、エレクトロクロミック充電用の外部ハイサイドゲートドライバ1つ、エレクトロクロミック負荷放電用の統合ローサイドドライバ1つを搭載しています。ハーフブリッジ、ハイサイド、ヒータ、ゲートドライバは、PWM入力制御構成、センシング、診断、デバイスシステム保護機能を備えています。各ハイサイドドライバに対して、専用のプログラマブルな内部 PWM ジェネレータがあります。すべての内蔵ドライバで比例電流センスピン出力を利用できるほか、ゲートドライバ用の堅牢で柔軟な電流シャントアンプも利用可能です。

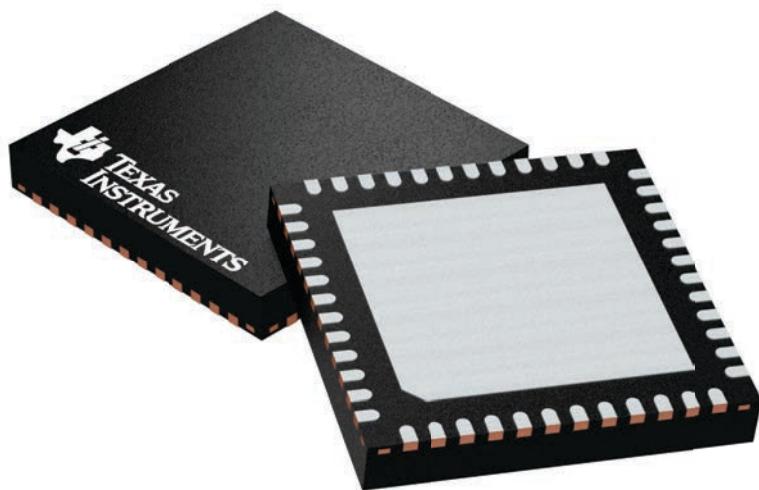

### パッケージ情報

| 部品番号       | パッケージ <sup>(1)</sup> | パッケージサイズ <sup>(2)</sup> |

|------------|----------------------|-------------------------|

| DRV8000-Q1 | RGZ (VQFN, 48)       | 7mm × 7mm               |

(1) 詳細については、[セクション 12](#)を参照してください。

(2) パッケージサイズ(長さ×幅)は公称値であり、該当する場合はピンも含まれます。

概略回路図

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール(機械翻訳)を使用していることがあり、TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.comで必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                         |    |                            |     |

|-------------------------|----|----------------------------|-----|

| 1 特長                    | 1  | 7.5 プログラミング                | 86  |

| 2 アプリケーション              | 1  | 8 DRV8000-Q1 レジスタ マップ      | 89  |

| 3 説明                    | 1  | 8.1 DRV8000-Q1_STATUS レジスタ | 92  |

| 4 デバイスの比較               | 3  | 8.2 DRV8000-Q1_CNFG レジスタ   | 102 |

| 5 ピン構成および機能             | 4  | 8.3 DRV8000-Q1_CTRL レジスタ   | 142 |

| 6 仕様                    | 7  | 9 アプリケーションと実装              | 152 |

| 6.1 絶対最大定格              | 7  | 9.1 アプリケーション情報             | 152 |

| 6.2 ESD 定格 (車載機器)       | 8  | 9.2 代表的なアプリケーション           | 152 |

| 6.3 推奨動作条件              | 8  | 9.3 電源に関する推奨事項             | 156 |

| 6.4 熱に関する情報 (RGZ パッケージ) | 8  | 9.4 レイアウト                  | 156 |

| 6.5 電気的特性               | 9  | 10 デバイスおよびドキュメントのサポート      | 159 |

| 6.6 タイミング要件             | 26 | 10.1 ドキュメントの更新通知を受け取る方法    | 159 |

| 6.7 代表的特性               | 28 | 10.2 サポート・リソース             | 159 |

| 7 詳細説明                  | 29 | 10.3 商標                    | 159 |

| 7.1 概要                  | 29 | 10.4 静電気放電に関する注意事項         | 159 |

| 7.2 機能ブロック図             | 30 | 10.5 用語集                   | 159 |

| 7.3 外付け部品               | 30 | 11 改訂履歴                    | 159 |

| 7.4 機能説明                | 32 | 12 メカニカル、パッケージ、および注文情報     | 160 |

## 4 デバイスの比較

**表 4-1. デバイスの比較**

| 型番          | H ブリッジゲートドライバ | ハーフブリッジドライバ | ハイサイドドライバ | ランプ / LED HS ドライバ | EC ゲートドライバ | ヒータ HS ゲートドライバ | 電流シャントアンプ | パッケージ                    |

|-------------|---------------|-------------|-----------|-------------------|------------|----------------|-----------|--------------------------|

| DRV8000-Q1  | 1x            | 6x          | 5x        | 1x                | 1x         | 1x             | 1x        | 7x7 QFN-48<br>ウェッタブルフランク |

| DRV8000E-Q1 | 1x            | 6x          | 5x        | 1x                | 1x         | 1x             | 1x        | 7x7 QFN-48<br>ウェッタブルフランク |

| DRV8001-Q1  | X             | 6x          | 5x        | 1x                | 1x         | 1x             | X         | 6x6 QFN-40<br>ウェッタブルフランク |

| DRV8002-Q1  | 1x            | 6x          | 5x        | 1x                | X          | X              | 1x        | 7x7 QFN-48<br>ウェッタブルフランク |

**表 4-2. デバイス注文情報**

| デバイス        | 量産開始前の型番          | 発注用製品型番          | EVM           |

|-------------|-------------------|------------------|---------------|

| DRV8000-Q1  | PDRV8000QWRGZRQ1  | DRV8000QWRGZRQ1  | DRV8000-Q1EVM |

|             | P2DRV8000QWRGZRQ1 |                  |               |

| DRV8000E-Q1 | PDRV8000EQWRGZRQ1 | DRV8000EQWRGZRQ1 | DRV8000-Q1EVM |

| DRV8001-Q1  | PDRV8001QWRHARQ1  | DRV8001QWRHARQ1  | DRV8001-Q1EVM |

| DRV8002-Q1  | PDRV8002QRGZRQ1   | DRV8002QWRGZRQ1  | DRV8000-Q1EVM |

|             | P2DRV8002QWRGZRQ1 |                  |               |

選択の検討事項:

- DRV8000E-Q1 は High でオフ状態の抵抗と独立ハーフブリッジゲートドライバを搭載しており、低消費電力ブラシ付きモーターの開放負荷検出用に最適化されています。

- DRV8001-Q1 は H ブリッジゲートドライバが不要な小型パッケージのアプリケーション用に最適化されています。

- DRV8002-Q1 は、サイドミラーを使用せず、DRV8000/E-Q1 とピン互換のアプリケーション用に最適化されています。

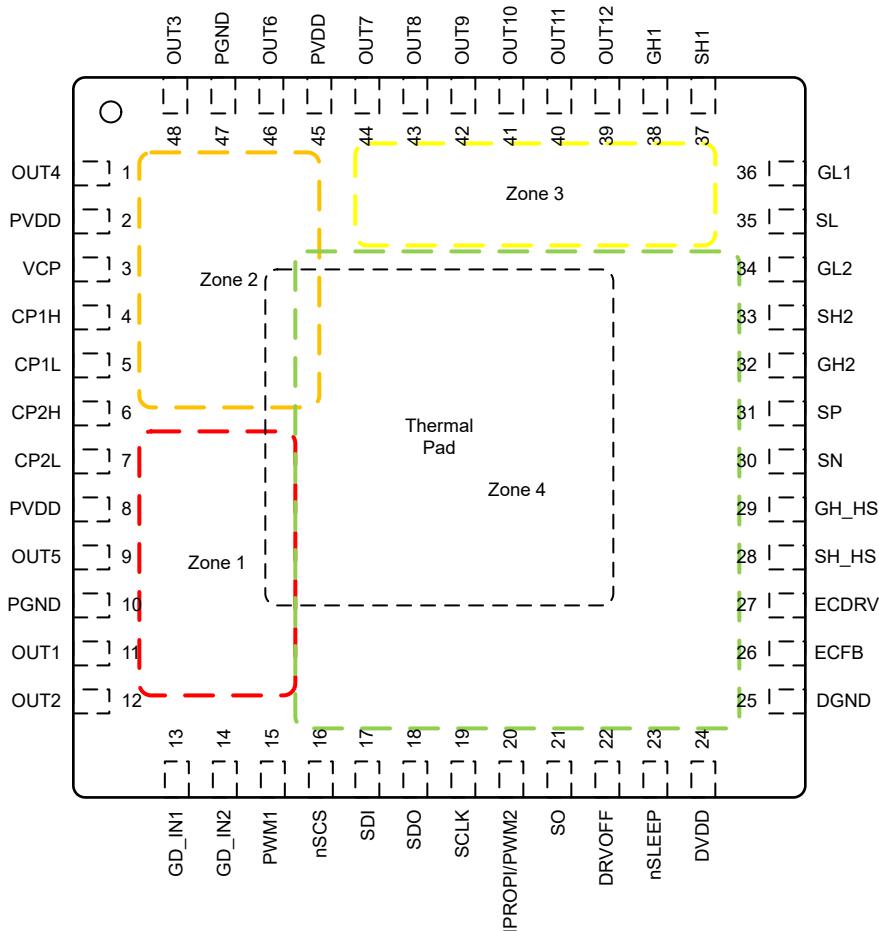

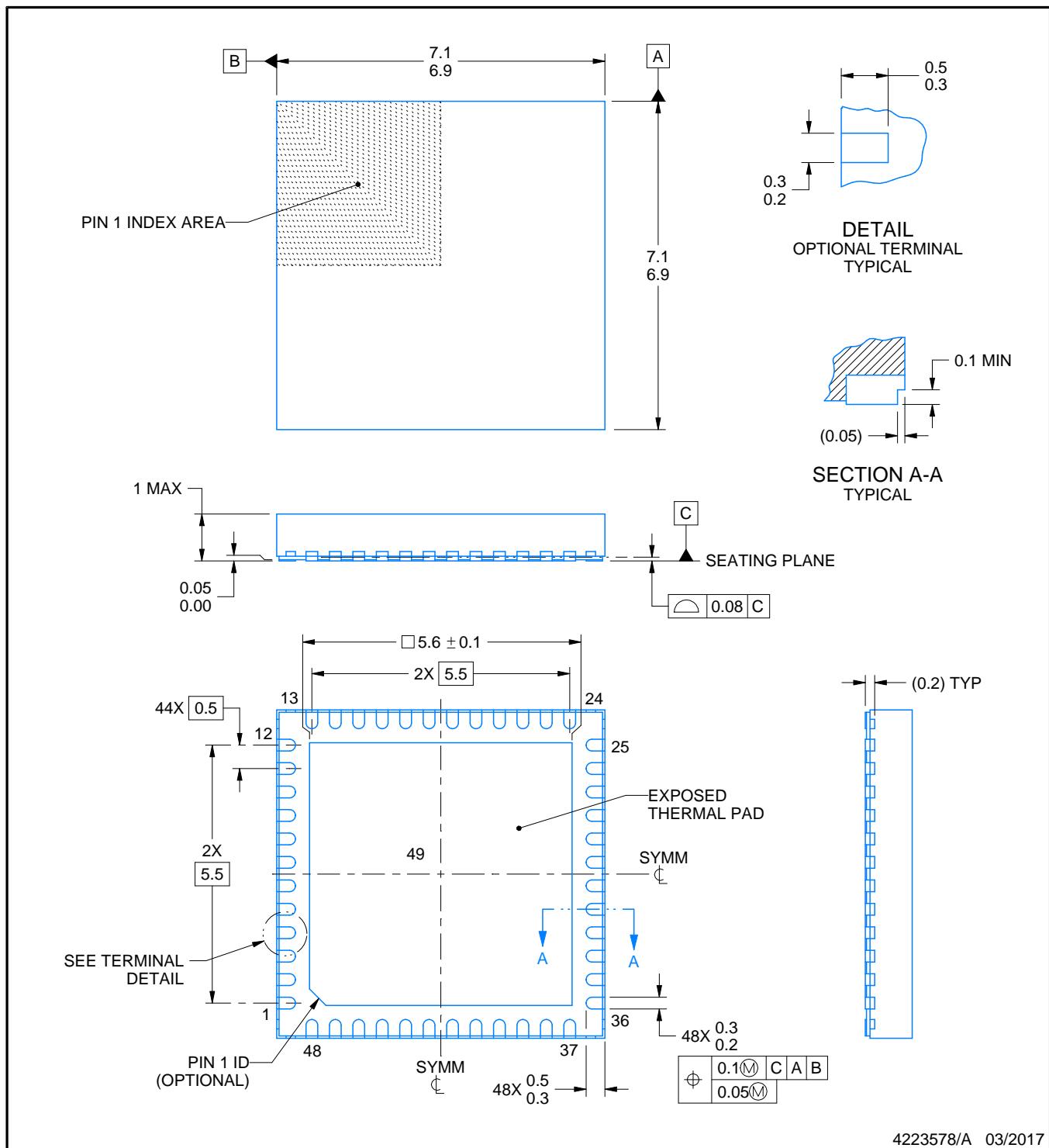

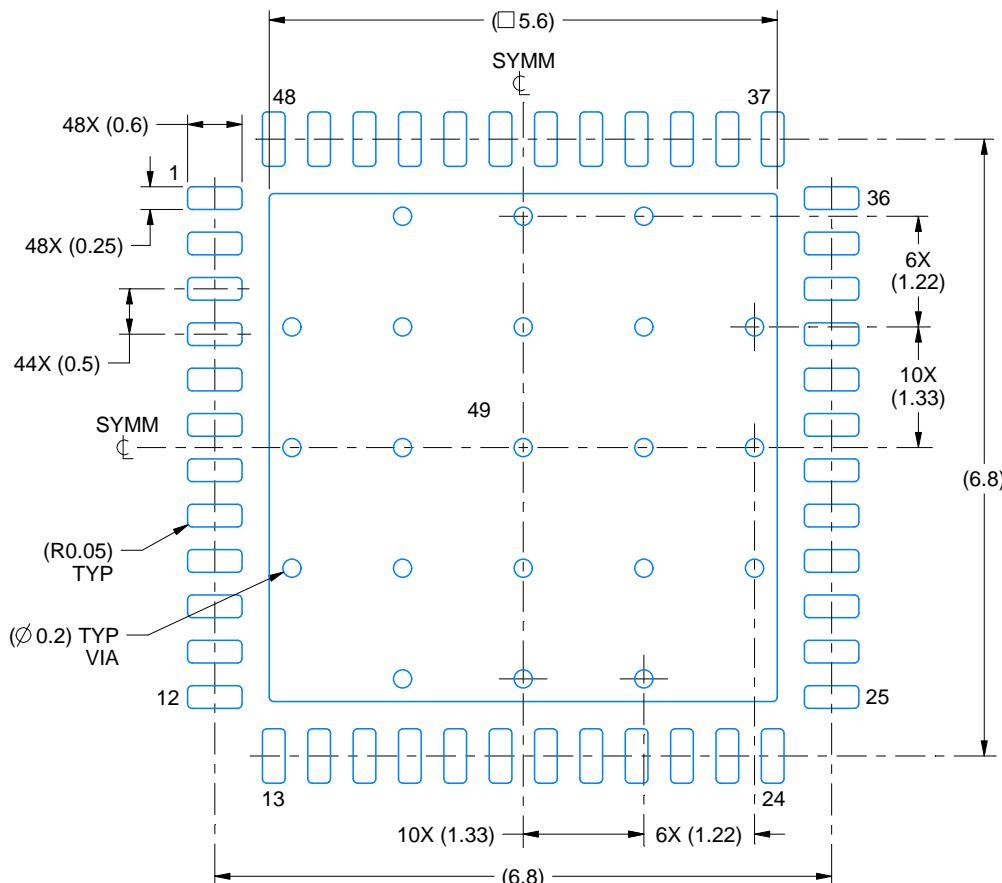

## 5 ピン構成および機能

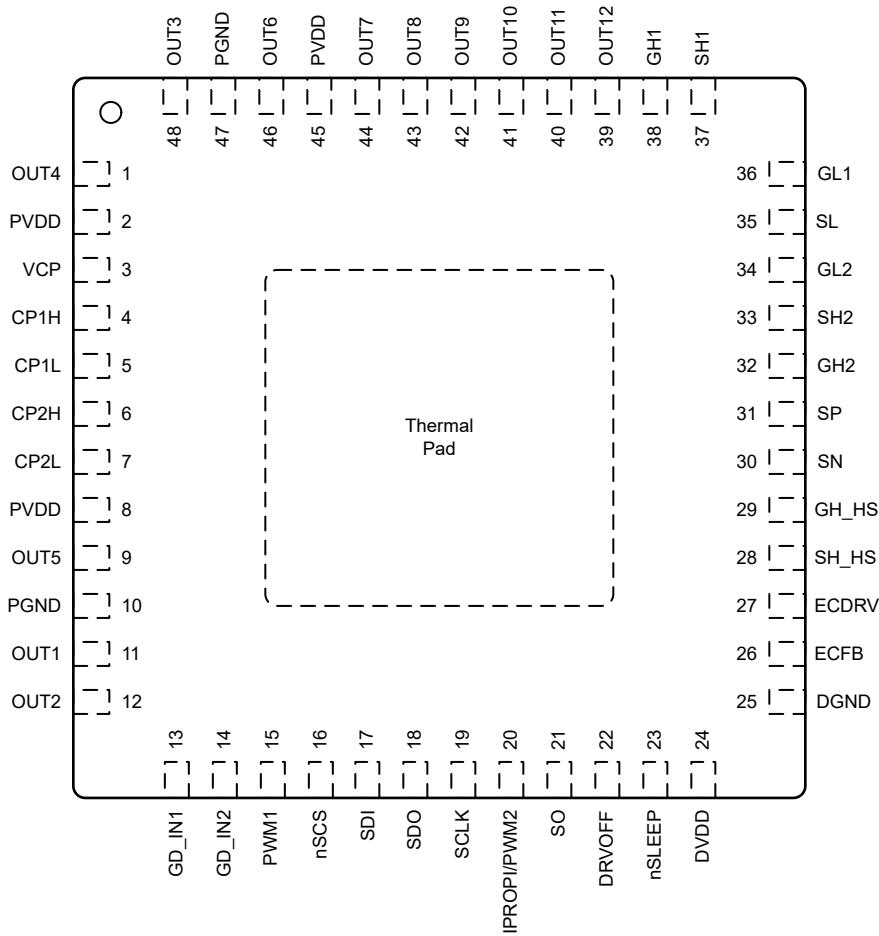

図 5-1. VQFN (RGZ) 48 ピン パッケージおよびピン機能 (上面図)

表 5-1. ピンの機能

| ピン |      | I/O <sup>(1)</sup> | タイプ  | 説明                                                                                                |

|----|------|--------------------|------|---------------------------------------------------------------------------------------------------|

| 番号 | 名称   |                    |      |                                                                                                   |

| 1  | OUT4 | O                  | 電源   | 440mΩ ハーフ ブリッジ出力 4。                                                                               |

| 2  | PVDD | I                  | 電源   | デバイスドライバ電源入力。ブリッジ電源に接続します。PVDD ピンと GND ピンの間に 0.1μF の PVDD 定格セラミックコンデンサと 10μF 以上のローカル バルク容量を接続します。 |

| 3  | VCP  | I/O                | 電源   | チャージポンプ出力。1μF、16V セラミックコンデンサを VCP ピンと PVDD ピンの間に接続します。                                            |

| 4  | CP1H | I/O                | 電源   | チャージポンプのスイッチングノード。100nF、PVDD 定格セラミックコンデンサを CP1H ピンと CP1L ピンの間に接続します。                              |

| 5  | CP1L | I/O                | 電源   |                                                                                                   |

| 6  | CP2H | I/O                | 電源   | チャージポンプのスイッチングノード。100nF、PVDD 定格セラミックコンデンサを CP2H ピンと CP2L ピンの間に接続します。                              |

| 7  | CP2L | I/O                | 電源   |                                                                                                   |

| 8  | PVDD | I                  | 電源   | デバイスドライバ電源入力。ブリッジ電源に接続します。PVDD ピンと GND ピンの間に 0.1μF の PVDD 定格セラミックコンデンサと 10μF 以上のローカル バルク容量を接続します。 |

| 9  | OUT5 | O                  | 電源   | 155mΩ ハーフ ブリッジ出力 5。                                                                               |

| 10 | PGND | I/O                | グランド | デバイスのグランド。システムグランドに接続。                                                                            |

**表 5-1. ピンの機能(続き)**

| ピン |             | I/O <sup>(1)</sup> | タイプ  | 説明                                                                                                                |

|----|-------------|--------------------|------|-------------------------------------------------------------------------------------------------------------------|

| 番号 | 名称          |                    |      |                                                                                                                   |

| 11 | OUT1        | O                  | 電源   | 1.54Ω ハーフブリッジ出力 1。                                                                                                |

| 12 | OUT2        | O                  | 電源   | 1.54Ω ハーフブリッジ出力 2。                                                                                                |

| 13 | GD_IN1      | I                  | デジタル | ゲートドライバ ハーフブリッジおよび H ブリッジ制御入力 1。                                                                                  |

| 14 | GD_IN2      | I                  | デジタル | ゲートドライバ ハーフブリッジおよび H ブリッジ制御入力 2。                                                                                  |

| 15 | PWM1        | I                  | デジタル | エレクトロクロミックおよびゲートドライバを除くすべてのドライバを制御するための PWM 入力 1。                                                                 |

| 16 | nSCS        | I                  | デジタル | シリアル チップ選択。このピンのロジック LOW により、シリアル インターフェイス通信が可能になります。内部プルアップ抵抗。                                                   |

| 17 | SDI         | I                  | デジタル | シリアル データ入力。データは、SCLK ピンの立ち下がりエッジでキャプチャされます。内部プルダウン抵抗。                                                             |

| 18 | SDO         | O                  | デジタル | シリアル データ出力。データは、SCLK ピンの立ち上がりエッジでシフト アウトされます。プッシュプル出力。                                                            |

| 19 | SCLK        | I                  | デジタル | シリアル クロック入力。シリアル データは、このピンの対応する立ち上がりおよび立ち下がりエッジでシフト アウトおよびキャプチャされます。内部プルダウン抵抗。                                    |

| 20 | IPROPI/PWM2 | I/O                | アナログ | センス出力は、ドライバ負荷電流フィードバック、PVDD 電圧フィードバック、またはサマーマル クラスタ温度フィードバックのいずれかから多重化されます。ハーフブリッジドライバの 2 番目の PWM ピン入力としても構成できます。 |

| 21 | SO          | O                  | アナログ | シャントアンプ出力。                                                                                                        |

| 22 | DRVOFF      | I                  | アナログ | ゲートドライバのシャットダウン パス。ハイサイドおよびローサイド両方のゲートドライバ出力をプルダウンするためのロジック High 信号。内部プルダウン抵抗。                                    |

| 23 | nSLEEP      | I                  | アナログ | デバイスイネーブルピン。デバイスをシャットダウンし、スリープ モードに移行するロジック Low。内部プルダウン抵抗。                                                        |

| 24 | DVDD        | I                  | 電源   | デバイスのロジック / デジタル出力電源入力。1.0μF、6.3V セラミック コンデンサを DVDD ピンと GND ピンの間に接続することを推奨します。                                    |

| 25 | DGND        | I/O                | グランド | デバイスのグランド。システム グランドに接続。                                                                                           |

| 26 | ECFB        | I/O                | 電源   | EC 制御用として、ピンは電圧モニタ入力および高速放電ローサイドスイッチとして使用されます。EC 駆動機能を使用しない場合は、このピンを 10kΩ 抵抗を介して GND に接続します。                      |

| 27 | ECDRV       | O                  | アナログ | EC 制御では、ピンは EC 電圧調整用の外部 MOSFET のゲートを制御します                                                                         |

| 28 | SH_HS       | I                  | アナログ | ハイサイドヒータ MOSFET のソース ピン、ヒータ負荷への出力。ハイサイド MOSFET のソースに接続します。                                                        |

| 29 | GH_HS       | O                  | アナログ | ヒータ MOSFET 用ゲートドライバ出力。ハイサイド MOSFET のゲートに接続します。                                                                    |

| 30 | SN          | I                  | アナログ | アンプのマイナス入力。シャント抵抗のマイナス端子に接続します。<br>シャントアンプの入力に、追加のフィルタリングを行うことは推奨されません。                                           |

| 31 | SP          | I                  | アナログ | アンプのプラス入力。シャント抵抗のプラス端子に接続します。<br>シャントアンプの入力に、追加のフィルタリングを行うことは推奨されません。                                             |

| 32 | GH2         | O                  | アナログ | ハイサイド ゲートドライバ出力。ハイサイド MOSFET のゲートに接続します。クロスオーバー遷移タイミングへの影響を与えるため、ゲート駆動直列抵抗は推奨されません。                               |

| 33 | SH2         | I                  | アナログ | ハイサイドソース センス入力。ハイサイド MOSFET ソースに接続します。                                                                            |

| 34 | GL2         | O                  | アナログ | ローサイド ゲートドライバ出力。ローサイド MOSFET のゲートに接続します。                                                                          |

| 35 | SL          | I                  | アナログ | ローサイド MOSFET ゲートドライブ センス機能とパワーリターン。ローサイド MOSFET グランドリターンへの低インピーダンスバスにより、システム グランドに接続します。                          |

| 36 | GL1         | O                  | アナログ | ローサイド ゲートドライバ出力。ローサイド MOSFET のゲートに接続します。                                                                          |

| 37 | SH1         | I                  | アナログ | ハイサイドソース センス入力。ハイサイド MOSFET ソースに接続します。                                                                            |

表 5-1. ピンの機能 (続き)

| ピン |       | I/O <sup>(1)</sup> | タイプ  | 説明                                                                                                |

|----|-------|--------------------|------|---------------------------------------------------------------------------------------------------|

| 番号 | 名称    |                    |      |                                                                                                   |

| 38 | GH1   | O                  | 電源   | ハイサイド ゲートドライバ出力。ハイサイド MOSFET のゲートに接続します。クロスオーバー遷移タイミングへの影響を与えるため、ゲート駆動直列抵抗は推奨されません。               |

| 39 | OUT12 | O                  | 電源   | 1.2Ω ハイサイド ドライバ出力 12。ローサイド負荷に接続します。                                                               |

| 40 | OUT11 | O                  | 電源   | 1.2Ω ハイサイド ドライバ出力 11。EC 駆動用の SC 保護スイッチとして構成できます。ローサイド負荷に接続します。                                    |

| 41 | OUT10 | O                  | 電源   | 1.2Ω ハイサイド ドライバ出力 10。ローサイド負荷に接続します。                                                               |

| 42 | OUT9  | O                  | 電源   | 1.2Ω ハイサイド ドライバ出力 9。ローサイド負荷に接続します。                                                                |

| 43 | OUT8  | O                  | 電源   | 1.2Ω ハイサイド ドライバ出力 8。ローサイド負荷に接続します。                                                                |

| 44 | OUT7  | O                  | 電源   | 構成可能な $R_{DS(ON)}$ (400mΩ/1200mΩ) を搭載したハイサイド ドライバ出力。ローサイド負荷に接続します。                                |

| 45 | PVDD  | I                  | 電源   | デバイスドライバ電源入力。プリッジ電源に接続します。PVDD ピンと GND ピンの間に 0.1μF の PVDD 定格セラミックコンデンサと 10μF 以上のローカル バルク容量を接続します。 |

| 46 | OUT6  | O                  | 電源   | 185mΩ ハーフ プリッジ出力 6。                                                                               |

| 47 | PGND  | I/O                | グランド | デバイスのグランド。システム グランドに接続。                                                                           |

| 48 | OUT3  | O                  | 電源   | 440mΩ ハーフ プリッジ出力 3。                                                                               |

(1) I = 入力、O = 出力

## 6 仕様

### 6.1 絶対最大定格

動作温度範囲外 (特に記述のない限り)<sup>(1)</sup>

|                                                                                          |                                                         | 最小値                                                   | 最大値                     | 単位   |

|------------------------------------------------------------------------------------------|---------------------------------------------------------|-------------------------------------------------------|-------------------------|------|

| 電源ピン電圧                                                                                   | PVDD                                                    | -0.3                                                  | 40                      | V    |

| 電源過渡電圧ランプ                                                                                | PVDD                                                    |                                                       | 2                       | V/μs |

| デジタル ロジック電源電圧ランプ                                                                         | DVDD                                                    |                                                       | 2                       | V/μs |

| グランドピン間の電圧差                                                                              | GND、PGND                                                | -0.3                                                  | 0.3                     | V    |

| チャージポンプピン電圧                                                                              | VCP                                                     | -0.3                                                  | PVDD + 15               | V    |

| チャージポンプハイサイドピン電圧                                                                         | CP1H                                                    | V <sub>PVDD</sub> - 0.3                               | V <sub>VCP</sub> + 0.3  | V    |

| チャージポンプハイサイドピン電圧                                                                         | CP2H                                                    | V <sub>PVDD</sub> - 0.6                               | V <sub>VCP</sub> + 0.3  | V    |

| チャージポンプローサイドピン電圧                                                                         | CP1L、CP2L                                               | -0.3                                                  | V <sub>PVDD</sub> + 0.3 | V    |

| デジタルレギュレータピン電圧                                                                           | DVDD                                                    | -0.3                                                  | 5.75                    | V    |

| ロジックピン電圧                                                                                 | GD_INx、PWM1、IPROPI/PWM2、<br>DRVOFF、nSLEEP、SCLK、SDI、nSCS | -0.3                                                  | 5.75                    | V    |

| 出力ロジックピン電圧                                                                               | SDO                                                     | -0.3                                                  | V <sub>DVDD</sub> + 0.3 | V    |

| 出力ピン電圧                                                                                   | OUT1-OUT12                                              | -0.3                                                  | V <sub>PVDD</sub> + 0.9 | V    |

| 出力電流                                                                                     | OUT1-OUT12、ECFB、ECDRV                                   | 内部的に制限                                                | 内部的に制限                  | A    |

| ヒータおよびエレクトロクロミック MOSFET ゲート駆動ピン電圧                                                        | GH_HS                                                   | V <sub>SH_HS</sub> - 0.3<br>~ V <sub>SH_HS</sub> + 13 | V <sub>VCP</sub> + 0.3  | V    |

| ヒータおよびエレクトロクロミック MOSFET ソースピン電圧                                                          | SH_HS、ECFB、ECDRV                                        | -0.3                                                  | V <sub>PVDD</sub> + 0.3 | V    |

| ハイサイドドライバおよびヒーター MOSFET ソースピンの最大エネルギー消費、T <sub>J</sub> = 25 °C、L <sub>LOAD</sub> < 100μH | OUT7-OUT12、SH_HS                                        | -                                                     | 1                       | mJ   |

| ハイサイドゲートドライブピン電圧                                                                         | GHx <sup>(2)</sup>                                      | -2                                                    | V <sub>VCP</sub> + 0.3  | V    |

| 過渡 1μs ハイサイドゲートドライブピン電圧                                                                  | GHx <sup>(2)</sup>                                      | -5                                                    | V <sub>VCP</sub> + 0.3  | V    |

| SHx を基準とするハイサイドゲートドライブピン電圧                                                               | GHx <sup>(2)</sup>                                      | -0.3                                                  | 13.5                    | V    |

| ハイサイドセンスピン電圧                                                                             | SHx <sup>(2)</sup>                                      | -2                                                    | 40                      | V    |

| 過渡 1μs ハイサイドセンスピン電圧                                                                      | SHx <sup>(2)</sup>                                      | -5                                                    | 40                      | V    |

| ローサイドゲートドライブピン電圧                                                                         | GLx <sup>(2)</sup>                                      | -2                                                    | 13.5                    | V    |

| 過渡 1μs ローサイドゲートドライブピン電圧                                                                  | GLx <sup>(2)</sup>                                      | -3                                                    | 13.5                    | V    |

| SL を基準とするローサイドゲートドライブピン電圧                                                                | GLx <sup>(2)</sup>                                      | -0.3                                                  | 13.5                    | V    |

| ローサイドセンスピン電圧                                                                             | SL <sup>(2)</sup>                                       | -2                                                    | 2                       | V    |

| 過渡 1μs のローサイドセンスピン電圧                                                                     | SL <sup>(2)</sup>                                       | -3                                                    | 3                       | V    |

| ゲート駆動電流                                                                                  | GHx、GLx                                                 | 内部的に制限                                                | 内部的に制限                  | A    |

| アンプ入力ピン電圧                                                                                | SN、SP                                                   | -2                                                    | V <sub>VCP</sub> + 0.3  | V    |

| 過渡 1μs アンプ入力ピン電圧                                                                         | SN、SP                                                   | -5                                                    | V <sub>VCP</sub> + 0.3  | V    |

| アンプ入力差動電圧                                                                                | SN、SP                                                   | -5.75                                                 | 5.75                    | V    |

| アンプ出力ピン電圧                                                                                | SO                                                      | -0.3                                                  | V <sub>DVDD</sub> + 0.3 | V    |

| 周囲温度、T <sub>A</sub>                                                                      |                                                         | -40                                                   | 125                     | °C   |

| 接合部温度、T <sub>J</sub>                                                                     |                                                         | -40                                                   | 150                     | °C   |

| 保管温度、T <sub>stg</sub>                                                                    |                                                         | -65                                                   | 150                     | °C   |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

(2) GHx, SHx, GLx, SL に対する PVDD は、40V を超えないようにしてください。PVDD が 35V を超える場合、GHx, SHx, GLx, SL の負電圧は、この定格を超えないように制限する必要があります。PVDD が 35V 未満の場合、GHx, SHx, GLx, SL の完全な負定格が利用可能です。

## 6.2 ESD 定格 (車載機器)

|             |                                                     |                                                             | 値                           | 単位           |

|-------------|-----------------------------------------------------|-------------------------------------------------------------|-----------------------------|--------------|

| $V_{(ESD)}$ | 静電放電                                                | 人体モデル (HBM), AEC Q100-002 HBM ESD <sup>(1)</sup> 分類レベル 2 準拠 | PVDD, OUT1~OUT12, ECFB, GND | $\pm 4000$ V |

|             |                                                     |                                                             | その他のすべてのピン                  | $\pm 2000$   |

|             | 荷電デバイス モデル (CDM), AEC Q100-011 CDM ESD 分類レベル C4B 準拠 | 角のピン                                                        | $\pm 750$                   | V            |

|             |                                                     |                                                             | その他のピン                      | $\pm 500$    |

(1) AEC Q100-002 は、HBM ストレス試験を ANSI/ESDA/JEDEC JS-001 仕様に従って実施しなければならないと規定しています。

## 6.3 推奨動作条件

動作温度範囲内 (特に記述のない限り)

|                |                                   |                                                  | 最小値 | 公称値              | 最大値 | 単位 |

|----------------|-----------------------------------|--------------------------------------------------|-----|------------------|-----|----|

| $V_{PVDD}$     | 電源電圧                              | PVDD                                             | 5   | 35               | V   |    |

| $I_{HS}^{(1)}$ | ハイサイド平均ゲートドライブ電流                  | GHx                                              | 0   | 15               | mA  |    |

| $I_{LS}^{(1)}$ | ローサイド平均ゲートドライブ電流                  | GLx                                              | 0   | 15               | mA  |    |

| $V_{DVDD}$     | ロジック入力電圧                          | DVDD                                             | 3.1 | 5.5              | V   |    |

| $V_{DIN}$      | デジタル入力電圧                          | GD_INx, PWM1, IPROPI/PWM2, DRVOFF, SO, SCLK, SDI | 0   | 5.5              | V   |    |

| $I_{DOUT}$     | デジタル出力電流                          | SDO                                              | 0   | 5                | mA  |    |

| $f_{PWM}$      | 入力 PWM 周波数                        | PWM1, IPROPI/PWM2                                | 0   | 25               | kHz |    |

| $V_{IPROPI}$   | $V_{PVDD} > 7\text{ V}$ のアナログ出力電圧 | IPROPI (IPROPI/PWM2 ピン)                          | 0   | 5.2              | V   |    |

| $V_{IPROPI}$   | $V_{PVDD} < 7\text{ V}$ のアナログ出力電圧 | IPROPI (IPROPI/PWM2 ピン)                          | 0   | $V_{PVDD} - 1.8$ | V   |    |

| $I_{SO}$       | シャントアンプ出力電流                       | SO                                               | 0   | 5                | mA  |    |

| $T_A$          | 動作時周囲温度                           |                                                  | -40 | 125              | °C  |    |

| $T_J$          | 動作時接合部温度                          |                                                  | -40 | 150              | °C  |    |

(1) 消費電力および温度の制限に従う必要があります。

## 6.4 热に関する情報 (RGZ パッケージ)

| 熱評価基準 <sup>(1)</sup> |                     | RGZ パッケージ | 単位   |

|----------------------|---------------------|-----------|------|

| $R_{\theta JA}$      | 接合部から周囲への熱抵抗        | 23.3      | °C/W |

| $R_{\theta JC(top)}$ | 接合部からケース (上面) への熱抵抗 | 11.7      | °C/W |

| $R_{\theta JB}$      | 接合部から基板への熱抵抗        | 7.0       | °C/W |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ    | 0.1       | °C/W |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ    | 7.0       | °C/W |

| $R_{\theta JC(bot)}$ | 接合部からケース (底面) への熱抵抗 | 1.3       | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション ノートを参照してください。

## 6.5 電気的特性

5 V  $\leq V_{PVDD} \leq 35$  V、3.1 V  $\leq V_{DVDD} \leq 5.5$  V、-40°C  $\leq T_J \leq 150$ °C (特に記述のない限り)。標準的な制限は、 $V_{PVDD} = 13.5$  V、 $V_{DVDD} = 5$  V および  $T_J = 25$ °C に対して適用されます。

| パラメータ                                       | テスト条件                                | 最小値                                                                                                | 標準値                    | 最大値                   | 単位          |

|---------------------------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------|------------------------|-----------------------|-------------|

| <b>電源 (DVDD、VCP、PVDD)</b>                   |                                      |                                                                                                    |                        |                       |             |

| $I_{PVDDQ}$                                 | $PVDD$ スリープ モード電流                    | $V_{PVDD} = 13.5$ V, $nSLEEP = 0$ V, $-40 \leq T_J \leq 85$ °C                                     |                        | 3.5                   | 5.5 $\mu$ A |

| $I_{DVDDQ}$                                 | $DVDD$ スリープ モード電流                    | $V_{PVDD} = 13.5$ V, $nSLEEP = 0$ V, $-40 \leq T_J \leq 85$ °C                                     |                        | 3                     | 4 $\mu$ A   |

| $I_{PVDD}$                                  | $PVDD$ アクティブ モード電流                   | $V_{PVDD} = 13.5$ V, $nSLEEP = V_{DVDD}$                                                           |                        | 8.7                   | 14.5 mA     |

| $I_{PVDD}$                                  | $PVDD$ アクティブモード電流、低減オプション。           | $V_{PVDD} = 13.5$ V, $nSLEEP = V_{DVDD}$ 、ダブルモードのチャージポンプ。                                          |                        | 7                     | 11.5 mA     |

| $I_{DVDD}$                                  | $DVDD$ アクティブ モード電流                   | $SDO = 0$ V                                                                                        |                        | 5                     | 8.5 mA      |

| $I_{DVDD}$                                  | $DVDD$ アクティブモード電流、低減オプション            | $SDO = 0$ V、ダブルモードのチャージポンプ。                                                                        |                        | 3.3                   | 7 mA        |

| $I_{PVDD\_CP\_DIS}$                         | $PVDD$ チャージポンプ無効モード電流                | $V_{PVDD} = 13.5$ V, $DIS\_CP = 1$ , $EN\_GD = 0$ , $HEAT\_EN = 0$ , $EC\_ON = 0$ , $OUTx\_EN = 0$ |                        | 1.2                   | 4.5 mA      |

| $I_{DVDD\_CP\_DIS}$                         | $DVDD$ チャージポンプ無効モード電流                | $V_{PVDD} = 13.5$ V, $DIS\_CP = 1$ , $EN\_GD = 0$ , $HEAT\_EN = 0$ , $EC\_ON = 0$ , $OUTx\_EN = 0$ |                        | 3.4                   | 8.5 mA      |

| $t_{WAKE}$                                  | ターンオン時間                              | $nSLEEP = V_{DVDD}$ でアクティブ モード                                                                     |                        | 670                   | $\mu$ s     |

| $t_{SLEEP}$                                 | ターンオフ時間                              | $nSLEEP = 0$ V でスリープ モード                                                                           |                        | 1                     | ms          |

| $t_{DRVOFF\_FLT_R}$                         | $DRVOFF$ 信号がアサートされるまでのフィルタ時間         | $DRVOFF = 0$ V ~ $V_{DVDD}$                                                                        |                        | 15                    | $\mu$ s     |

| $f_{VDD}$                                   | デジタル発信器のスイッチング周波数                    | 拡散スペクトラムの 1 次周波数                                                                                   | 12.83                  | 14.25                 | 15.68 MHz   |

| $f_{VDD}$                                   | デジタル発振器のスペクトラム拡散範囲                   | 主要周波数のセンタースプレッド                                                                                    | -7                     | 7                     | %           |

| $V_{VCP}$                                   | $PVDD$ を基準とするチャージポンプ レギュレータ電圧        | $V_{PVDD} \geq 9$ V, $I_{VCP} \leq 20$ mA                                                          | 9.5                    | 10.5                  | 12.5 V      |

| $V_{VCP}$                                   | $PVDD$ を基準とするチャージポンプ レギュレータ電圧        | $V_{PVDD} = 7$ V, $I_{VCP} \leq 15$ mA                                                             | 8.5                    | 9                     | 12 V        |

| $V_{VCP}$                                   | $PVDD$ を基準とするチャージポンプ レギュレータ電圧        | $V_{PVDD} = 5$ V, $I_{VCP} \leq 12$ mA                                                             | 6.8                    | 7.5                   | 11 V        |

| $t_{CP\_tran}$                              | ダブルモードとトリプルモード間のチャージポンプ遷移時間          |                                                                                                    |                        | 300                   | $\mu$ s     |

| $t_{CP\_EN}$                                | イネーブルコマンド後のチャージポンプのターンオン時間。初期化を含みます。 |                                                                                                    |                        | 500                   | 550 $\mu$ s |

| $I_{VCP\_LIM}$                              | チャージポンプの出力電流制限                       | $V_{PVDD} = 13.5$ V, $C_{FLY1} = C_{FLY2} = 100$ nF, $C_{VCP} = 1$ $\mu$ F、チャージポンプ起動時の突入電流         |                        | 500                   | mA          |

| $f_{VCP}$                                   | チャージポンプのスイッチング周波数                    | 拡散スペクトラムの 1 次周波数                                                                                   | 400                    |                       | kHz         |

| <b>論理レベル入力 (INx, nSLEEP, SCLK, SDI, など)</b> |                                      |                                                                                                    |                        |                       |             |

| $V_{IL}$                                    | 入力ロジック Low 電圧                        | $DRVOFF$ 、 $GD\_INx$ 、 $PWM1$ 、 $IPROPI$ / $PWM2$ 、 $nSLEEP$ 、 $SCLK$ 、 $SDI$                      | 0.3                    | $V_{DVDD} \times 0.3$ | V           |

| $V_{IH}$                                    | 入力ロジック High 電圧                       | $DRVOFF$ 、 $GD\_INx$ 、 $PWM1$ 、 $IPROPI$ / $PWM2$ 、 $nSLEEP$ 、 $SCLK$ 、 $SDI$                      | $V_{DVDD} \times 0.7$  | 5.5                   | V           |

| $V_{HYS}$                                   | 入力ヒステリシス                             | $DRVOFF$ 、 $GD\_INx$ 、 $PWM1$ 、 $IPROPI$ / $PWM2$ 、 $nSLEEP$ 、 $SCLK$ 、 $SDI$                      | $V_{DVDD} \times 0.15$ |                       | V           |

| $I_{IL}$                                    | 入力ロジック Low 電流                        | $V_{DIN} = 0$ V、 $DRVOFF$ 、 $GD\_INx$ 、 $PWM1$ 、 $IPROPI$ / $PWM2$ 、 $nSLEEP$ 、 $SCLK$ 、 $SDI$     | -5                     | 5                     | $\mu$ A     |

## 6.5 電気的特性 (続き)

5 V  $\leq$   $V_{PVDD}$   $\leq$  35 V、3.1 V  $\leq$   $V_{DVDD}$   $\leq$  5.5 V、-40°C  $\leq$   $T_J$   $\leq$  150°C (特に記述のない限り)。標準的な制限は、 $V_{PVDD} = 13.5V$ 、 $V_{DVDD} = 5V$  および  $T_J = 25^{\circ}\text{C}$  に対して適用されます。

| パラメータ                              |                  | テスト条件                                                                                                                                                           | 最小値               | 標準値  | 最大値  | 単位               |

|------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------|------|------------------|

| $I_{IL}$                           | 入力ロジック Low 電流    | $V_{DIN} = 0V$ 、nSCS                                                                                                                                            |                   | 25   | 50   | $\mu\text{A}$    |

| $I_{IH}$                           | 入力ロジック High 電流   | $V_{DIN} = V_{DVDD}$ 、nSCS                                                                                                                                      | -5                |      | 5    | $\mu\text{A}$    |

| $I_{IH}$                           | 入力ロジック High 電流   | $V_{DIN} = V_{DVDD}$ 、DRVOFF、GD_INx、<br>PWM1、IPROPI/PWM2、nSLEEP、<br>SCLK、SDI                                                                                    |                   | 25   | 50   | $\mu\text{A}$    |

| $R_{PD}$                           | 入力プルダウン抵抗        | GND、DRVOFF、GD_INx、PWM1、<br>IPROPI/PWM2、nSLEEP、SCLK、SDI ～                                                                                                        | 140               | 200  | 260  | $\text{k}\Omega$ |

| $R_{PU}$                           | 入力プルアップ抵抗        | DVDD、nSCS ～接続                                                                                                                                                   | 140               | 200  | 265  | $\text{k}\Omega$ |

| <b>プッシュプル出力 SDO</b>                |                  |                                                                                                                                                                 |                   |      |      |                  |

| $V_{OL}$                           | 出力ロジック Low 電圧    | $I_{OD} = 5\text{mA}$                                                                                                                                           |                   | 0.5  |      | V                |

| $V_{OH}$                           | ロジック High 出力電圧   | $I_{OD} = -5\text{mA}$ 、SDO                                                                                                                                     | $DVDD \times 0.8$ |      |      | V                |

| <b>ゲートドライバ (GHx, GLx, SHx, SL)</b> |                  |                                                                                                                                                                 |                   |      |      |                  |

| $V_{GHx\_L}$                       | GHx Low レベル出力電圧  | $I_{DRVN\_HS} = I_{STRONG}$ 、 $I_{GHx} = 1\text{mA}$ 、 $GHx \sim SHx$                                                                                           | 0                 | 0.25 |      | V                |

| $V_{GLx\_L}$                       | GLx Low レベル出力電圧  | $I_{DRVN\_LS} = I_{STRONG}$ 、 $I_{GLx} = 1\text{mA}$ 、 $GLx \sim SL$                                                                                            | 0                 | 0.25 |      | V                |

| $V_{GHx\_H}$                       | GHx High レベル出力電圧 | $I_{DRVP\_HS} = I_{HOLD}$ 、 $I_{GHx} = 1\text{mA}$ 、 $VCP \sim GHx$                                                                                             | 0                 | 0.25 |      | V                |

| $V_{GLx\_H}$                       | GLx High レベル出力電圧 | $I_{DRVP\_LS} = I_{HOLD}$ 、 $I_{GLx} = 1\text{mA}$ 、 $10.5V \leq V_{PVDD} \leq V_{PVDD\_OV}$ 、 $GLx \sim SL$ 。<br>$V_{PVDD} > V_{PVDD\_OV}$ の場合、ゲートドライバはオフになります | 9.35              | 10.5 | 12.5 | V                |

## 6.5 電気的特性 (続き)

5 V  $\leq$   $V_{PVDD}$   $\leq$  35 V、3.1 V  $\leq$   $V_{DVDD}$   $\leq$  5.5 V、-40°C  $\leq$   $T_J$   $\leq$  150°C (特に記述のない限り)。標準的な制限は、 $V_{PVDD} = 13.5$  V、 $V_{DVDD} = 5$  V および  $T_J = 25$  °C に対して適用されます。

| パラメータ       | テスト条件                                                 | 最小値  | 標準値 | 最大値  | 単位 |

|-------------|-------------------------------------------------------|------|-----|------|----|

| $I_{DRV_P}$ | IDRVP_x = 0000b、 $V_{GSx} = 3$ V、 $V_{PVDD} \geq 7$ V | 0.2  | 0.5 | 0.83 | mA |

|             | IDRVP_x = 0001b、 $V_{GSx} = 3$ V、 $V_{PVDD} \geq 7$ V | 0.5  | 1   | 1.6  | mA |

|             | IDRVP_x = 0010b、 $V_{GSx} = 3$ V、 $V_{PVDD} \geq 7$ V | 1.3  | 2   | 2.8  | mA |

|             | IDRVP_x = 0011b、 $V_{GSx} = 3$ V、 $V_{PVDD} \geq 7$ V | 2.1  | 3   | 4    | mA |

|             | IDRVP_x = 0100b、 $V_{GSx} = 3$ V、 $V_{PVDD} \geq 7$ V | 2.9  | 4   | 5.3  | mA |

|             | IDRVP_x = 0101b、 $V_{GSx} = 3$ V、 $V_{PVDD} \geq 7$ V | 3.7  | 5   | 6.45 | mA |

|             | IDRVP_x = 0110b、 $V_{GSx} = 3$ V、 $V_{PVDD} \geq 7$ V | 4.45 | 6   | 7.65 | mA |

|             | IDRVP_x = 0111b、 $V_{GSx} = 3$ V、 $V_{PVDD} \geq 7$ V | 5.5  | 7   | 9    | mA |

|             | IDRVP_x = 1000b、 $V_{GSx} = 3$ V、 $V_{PVDD} \geq 7$ V | 5.6  | 8   | 10.2 | mA |

|             | IDRVP_x = 1001b、 $V_{GSx} = 3$ V、 $V_{PVDD} \geq 7$ V | 8.8  | 12  | 15.2 | mA |

|             | IDRVP_x = 1010b、 $V_{GSx} = 3$ V、 $V_{PVDD} \geq 7$ V | 11.6 | 16  | 20.4 | mA |

|             | IDRVP_x = 1011b、 $V_{GSx} = 3$ V、 $V_{PVDD} \geq 7$ V | 16   | 20  | 25.4 | mA |

|             | IDRVP_x = 1100b、 $V_{GSx} = 3$ V、 $V_{PVDD} \geq 7$ V | 17.6 | 24  | 30.4 | mA |

|             | IDRVP_x = 1101b、 $V_{GSx} = 3$ V、 $V_{PVDD} \geq 7$ V | 24   | 31  | 40   | mA |

|             | IDRVP_x = 1110b、 $V_{GSx} = 3$ V、 $V_{PVDD} \geq 7$ V | 28   | 48  | 62   | mA |

|             | IDRVP_x = 1111b、 $V_{GSx} = 3$ V、 $V_{PVDD} \geq 7$ V | 46   | 62  | 78   | mA |

## 6.5 電気的特性 (続き)

5 V  $\leq$   $V_{PVDD}$   $\leq$  35 V、3.1 V  $\leq$   $V_{DVDD}$   $\leq$  5.5 V、-40°C  $\leq$   $T_J$   $\leq$  150°C (特に記述のない限り)。標準的な制限は、 $V_{PVDD} = 13.5$  V、 $V_{DVDD} = 5$  V および  $T_J = 25$  °C に対して適用されます。

| パラメータ                          |                       | テスト条件                                                                   | 最小値  | 標準値 | 最大値  | 単位 |

|--------------------------------|-----------------------|-------------------------------------------------------------------------|------|-----|------|----|

| $I_{DRVN}$                     | ピーク ゲート電流 (シンク)       | IDRVN_x = 0000b、 $V_{GSx} = 3$ V、 $V_{PVDD} \geq 7$ V                   | 0.07 | 0.5 | 0.85 | mA |

|                                |                       | IDRVN_x = 0001b、 $V_{GSx} = 3$ V、 $V_{PVDD} \geq 7$ V                   | 0.23 | 1   | 1.7  | mA |

|                                |                       | IDRVN_x = 0010b、 $V_{GSx} = 3$ V、 $V_{PVDD} \geq 7$ V                   | 0.7  | 2   | 3.2  | mA |

|                                |                       | IDRVN_x = 0011b、 $V_{GSx} = 3$ V、 $V_{PVDD} \geq 7$ V                   | 1.2  | 3   | 4.6  | mA |

|                                |                       | IDRVN_x = 0100b、 $V_{GSx} = 3$ V、 $V_{PVDD} \geq 7$ V                   | 1.75 | 4   | 5.9  | mA |

|                                |                       | IDRVN_x = 0101b、 $V_{GSx} = 3$ V、 $V_{PVDD} \geq 7$ V                   | 2.4  | 5   | 7.2  | mA |

|                                |                       | IDRVN_x = 0110b、 $V_{GSx} = 3$ V、 $V_{PVDD} \geq 7$ V                   | 3    | 6   | 8.5  | mA |

|                                |                       | IDRVN_x = 0111b、 $V_{GSx} = 3$ V、 $V_{PVDD} \geq 7$ V                   | 3.6  | 7   | 9.8  | mA |

|                                |                       | IDRVN_x = 1000b、 $V_{GSx} = 3$ V、 $V_{PVDD} \geq 7$ V                   | 4.3  | 8   | 11   | mA |

|                                |                       | IDRVN_x = 1001b、 $V_{GSx} = 3$ V、 $V_{PVDD} \geq 7$ V                   | 7.3  | 12  | 16   | mA |

|                                |                       | IDRVN_x = 1010b、 $V_{GSx} = 3$ V、 $V_{PVDD} \geq 7$ V                   | 10.6 | 16  | 20.4 | mA |

|                                |                       | IDRVN_x = 1011b、 $V_{GSx} = 3$ V、 $V_{PVDD} \geq 7$ V                   | 14   | 20  | 25.3 | mA |

|                                |                       | IDRVN_x = 1100b、 $V_{GSx} = 3$ V、 $V_{PVDD} \geq 7$ V                   | 17.8 | 24  | 30.2 | mA |

|                                |                       | IDRVN_x = 1101b、 $V_{GSx} = 3$ V、 $V_{PVDD} \geq 7$ V                   | 23.8 | 31  | 40.2 | mA |

|                                |                       | IDRVN_x = 1110b、 $V_{GSx} = 3$ V、 $V_{PVDD} \geq 7$ V                   | 27   | 48  | 63   | mA |

|                                |                       | IDRVN_x = 1111b、 $V_{GSx} = 3$ V、 $V_{PVDD} \geq 7$ V                   | 45   | 62  | 79   | mA |

| $I_{HOLD}$                     | ゲート プルアップ ホールド電流      | ゲートホールド ソース電流、 $V_{GSx} = 3$ V                                          | 5    | 16  | 30   | mA |

| $I_{STRONG}$                   | ゲート ブルダウン強電流          | $V_{GSx} = 3$ V、 $I_{DRV} = 0.5 \sim 12$ mA                             | 30   | 62  | 100  | mA |

| $I_{STRONG}$                   | ゲート ブルダウン強電流          | $V_{GSx} = 3$ V、 $I_{DRV} = 16 \sim 62$ mA                              | 45   | 128 | 200  | mA |

| $R_{PDSA\_LS}$                 | ローサイド セミアクティブゲートブルダウン | $GLx \sim SL$ 、 $V_{GSx} = 3$ V                                         |      | 1.8 |      | kΩ |

| $R_{PDSA\_LS}$                 | ローサイド セミアクティブゲートブルダウン | $GLx \sim SL$ 、 $V_{GSx} = 1$ V                                         |      | 5   |      | kΩ |

| $R_{PD\_HS}$                   | ハイサイド パッシブ ゲートブルダウン抵抗 | $GHx \sim SHx$                                                          |      | 150 |      | kΩ |

| $R_{PD\_LS}$                   | ローサイド パッシブ ゲートブルダウン抵抗 | $GLx \sim SL$                                                           |      | 150 |      | kΩ |

| $I_{SHx}$                      | スイッチ ノード センス リーク電流    | $SHx \sim$ 流入、 $SHx = PVDD \leq 28$ V $GHx - SHx = 0$ V、 $nSLEEP = 0$ V | -5   | 0   | 20   | μA |

| ゲートドライバタイミング ( $GHx$ 、 $GLx$ ) |                       |                                                                         |      |     |      |    |

| $t_{PDR\_LS}$                  | ローサイド立ち上がり伝搬遅延        | $GLx$ への入力の立ち上がり                                                        |      | 300 | 850  | ns |

| $t_{PDF\_LS}$                  | ローサイド立ち下がり伝搬遅延        | $GLx$ への入力の立ち下がり                                                        |      | 300 | 600  | ns |

| $t_{PDR\_HS}$                  | ハイサイド立ち上がり伝搬遅延        | $GHx$ への入力の立ち上がり                                                        |      | 300 | 600  | ns |

| $t_{PDF\_HS}$                  | ハイサイド立ち下がり伝搬遅延        | $GHx$ への入力の立ち上がり                                                        |      | 300 | 600  | ns |

## 6.5 電気的特性 (続き)

5 V  $\leq$   $V_{PVDD}$   $\leq$  35 V、3.1 V  $\leq$   $V_{DVDD}$   $\leq$  5.5 V、-40°C  $\leq$   $T_J$   $\leq$  150°C (特に記述のない限り)。標準的な制限は、 $V_{PVDD} = 13.5V$ 、 $V_{DVDD} = 5V$  および  $T_J = 25^\circ C$  に対して適用されます。

| パラメータ         |                  | テスト条件                                    | 最小値 | 標準値 | 最大値 | 単位 |

|---------------|------------------|------------------------------------------|-----|-----|-----|----|

| $t_{DEAD}$    | 内部ハンドシェイク デッドタイム | $GLx/GHx$ 10% 立ち下がりから $GHx/GLx$ 10%立ち上がり |     |     | 350 | ns |

| $t_{DEAD\_D}$ | 挿入可能なデジタル デッドタイム | $VGS\_TDEAD = 00b$ 、ハンドシェイクのみ            |     |     | 0   | μs |

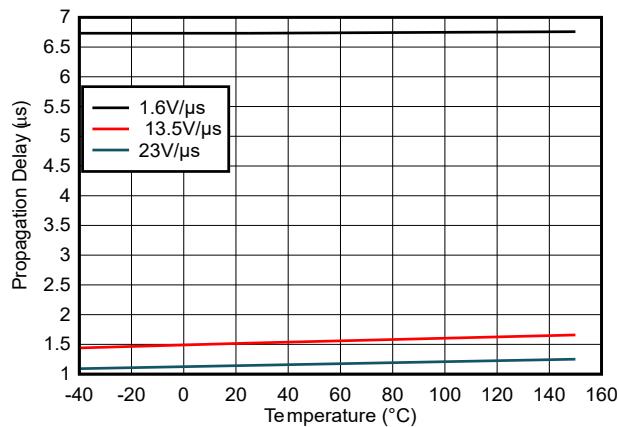

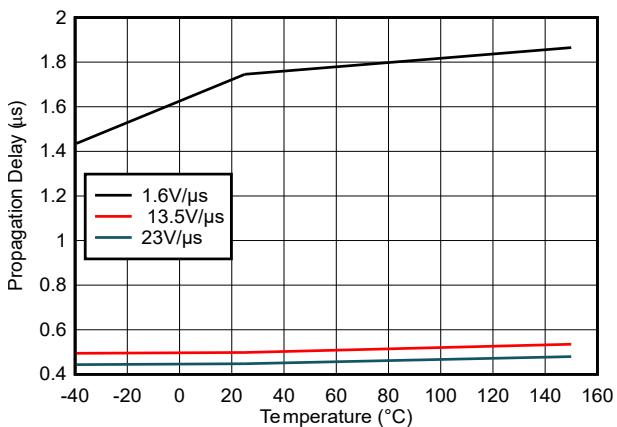

|               |                  | $VGS\_TDEAD = 01b$                       | 1.6 | 2   | 2.4 | μs |

|               |                  | $VGS\_TDEAD = 10b$                       | 3.4 | 4   | 4.6 | μs |

|               |                  | $VGS\_TDEAD = 11b$                       | 6   | 8   | 10  | μs |

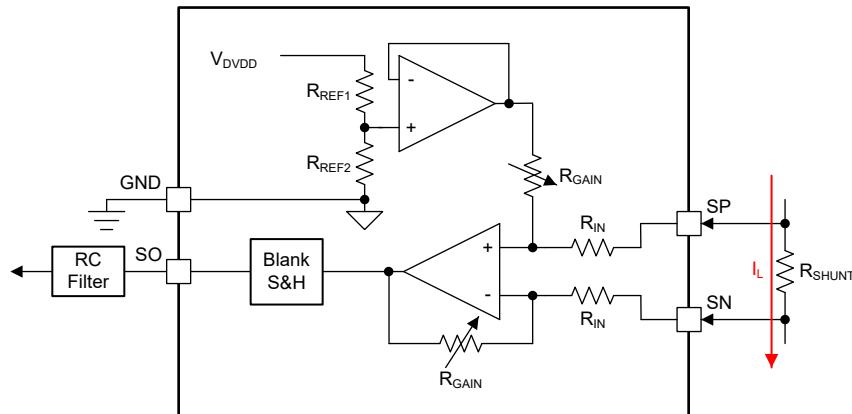

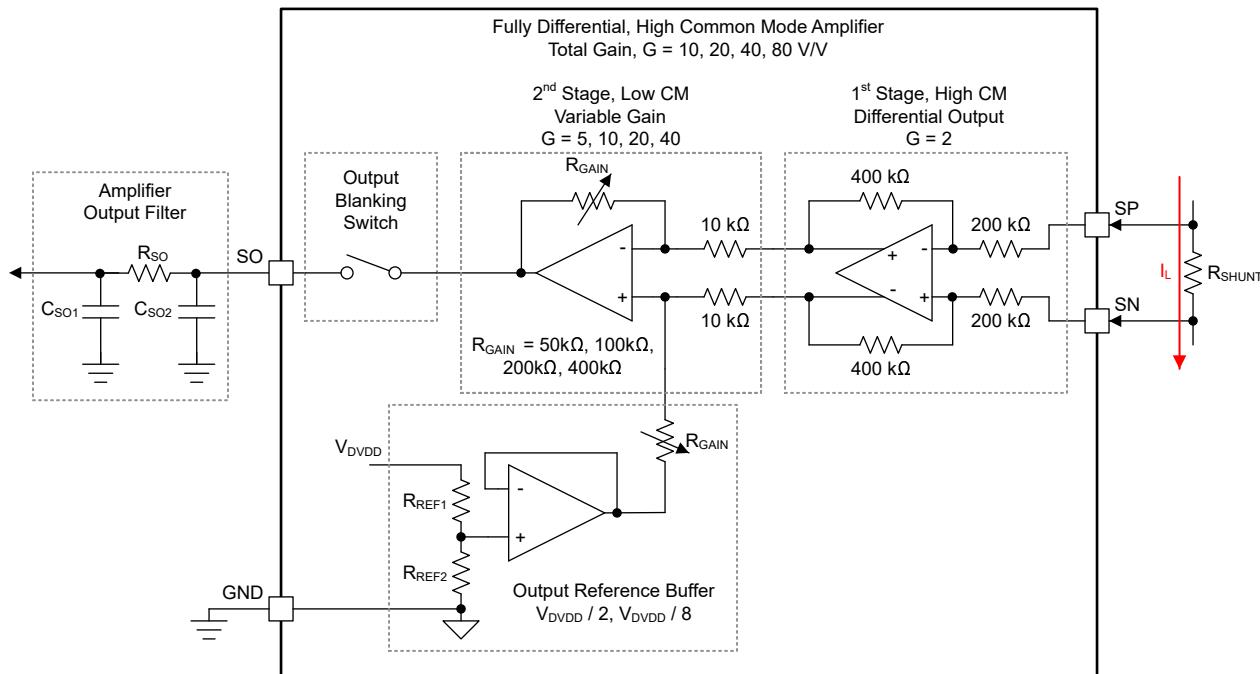

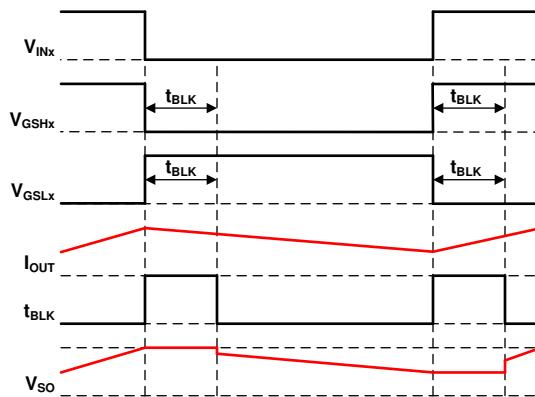

### 電流シャントアンプ (SN、SO、SP)

|                 |                                           |                                                           |      |                          |                                          |  |

|-----------------|-------------------------------------------|-----------------------------------------------------------|------|--------------------------|------------------------------------------|--|

| $V_{COM}$       | コモン モード入力範囲                               |                                                           | -2   | $V_{PVDD} + \frac{2}{2}$ | V                                        |  |

| $G_{CSA}$       | 検出アンプのゲイン                                 | $CSA\_GAIN = 00b$                                         | 9.75 | 10                       | 10.25                                    |  |

|                 |                                           | $CSA\_GAIN = 01b$                                         | 19.5 | 20                       | 20.5                                     |  |

|                 |                                           | $CSA\_GAIN = 10b$                                         | 38.8 | 40                       | 41.2                                     |  |

|                 |                                           | $CSA\_GAIN = 11b$                                         | 77.6 | 80                       | 82.4                                     |  |

| $t_{SET}$       | $\pm 1\%$ までのセンスアンプセッティングタイム              | $V_{SO\_STEP} = 1.5V$ 、 $G_{CSA} = 10V/V$ $C_{SO} = 60pF$ |      |                          | 2.2                                      |  |

|                 |                                           | $V_{SO\_STEP} = 1.5V$ 、 $G_{CSA} = 20V/V$ $C_{SO} = 60pF$ |      |                          | 2.2                                      |  |

|                 |                                           | $V_{SO\_STEP} = 1.5V$ 、 $G_{CSA} = 40V/V$ $C_{SO} = 60pF$ |      |                          | 2.2                                      |  |

|                 |                                           | $V_{SO\_STEP} = 1.5V$ 、 $G_{CSA} = 80V/V$ $C_{SO} = 60pF$ |      |                          | 3                                        |  |

| $t_{BLK\_CSA}$  | センスアンプ出力ブランディング時間<br>(ゲートドライバ TDRIVE の %) | $CSA\_BLK = 000b$                                         |      |                          | %                                        |  |

|                 |                                           | $CSA\_BLK = 001b$                                         |      |                          | 25                                       |  |

|                 |                                           | $CSA\_BLK = 010b$                                         |      |                          | 37.5                                     |  |

|                 |                                           | $CSA\_BLK = 011b$                                         |      |                          | 50                                       |  |

|                 |                                           | $CSA\_BLK = 100b$                                         |      |                          | 62.5                                     |  |

|                 |                                           | $CSA\_BLK = 101b$                                         |      |                          | 75                                       |  |

|                 |                                           | $CSA\_BLK = 110b$                                         |      |                          | 87.5                                     |  |

|                 |                                           | $CSA\_BLK = 111b$                                         |      |                          | 100                                      |  |

| $t_{SLEW\_CSA}$ | 出力スルーレート                                  | $C_{SO} = 60pF$                                           |      |                          | 2.5                                      |  |

| $V_{BIAS}$      | 出力電圧バイアス                                  | $V_{SPx} = V_{SNx} = 0V$ 、 $CSA\_DIV = 0b$                |      |                          | $V_{DVDD} / 2$                           |  |

|                 |                                           | $V_{SPx} = V_{SNx} = 0V$ 、 $CSA\_DIV = 1b$                |      |                          | $V_{DVDD} / 8$                           |  |

| $V_{LINEAR}$    | リニア出力電圧範囲                                 | $V_{DVDD} = 3.3V = 5V$                                    | 0.25 | $V_{DVDD} - 0.25$        | V                                        |  |

| $V_{OFF}$       | 入力オフセット電圧                                 | $V_{SPx} = V_{SNx} = 0V$ 、 $T_J = 25^\circ C$             | -1   |                          | 1 mV                                     |  |

| $V_{OFF\_D}$    | 入力オフセット電圧ドリフト                             | $V_{SPx} = V_{SNx} = 0V$                                  |      |                          | $\pm 10 \text{ } \mu V/\text{ }^\circ C$ |  |

| $I_{BIAS}$      | 入力バイアス電流                                  | $V_{SPx} = V_{SNx} = 0V$                                  |      |                          | 100 μA                                   |  |

| $I_{BIAS\_OFF}$ | 入力バイアス電流オフセット                             | $I_{SPx} - I_{SNx}$                                       |      |                          | 100 μA                                   |  |

| $CMRR$          | 同相除去比                                     | DC、 $-40 \leq T_J \leq 125^\circ C$                       | 72   | 90                       | dB                                       |  |

|                 |                                           | DC、 $-40 \leq T_J \leq 150^\circ C$                       | 69   | 90                       | dB                                       |  |

|                 |                                           | 20kHz                                                     |      |                          | 80                                       |  |

| $PSRR$          | 電源除去比                                     | PVDD~SOx, DC                                              |      |                          | 100                                      |  |

|                 |                                           | PVDD~SOx, 20kHz                                           |      |                          | 90                                       |  |

|                 |                                           | PVDD~SOx, 400kHz                                          |      |                          | 70                                       |  |

## 6.5 電気的特性 (続き)

5 V  $\leq$   $V_{PVDD}$   $\leq$  35 V、3.1 V  $\leq$   $V_{DVDD}$   $\leq$  5.5 V、-40°C  $\leq$   $T_J$   $\leq$  150°C (特に記述のない限り)。標準的な制限は、 $V_{PVDD} = 13.5V$ 、 $V_{DVDD} = 5V$  および  $T_J = 25^{\circ}\text{C}$  に対して適用されます。

| パラメータ              | テスト条件                                 | 最小値                                                            | 標準値   | 最大値   | 単位    |

|--------------------|---------------------------------------|----------------------------------------------------------------|-------|-------|-------|

| <b>ゲートドライバ保護回路</b> |                                       |                                                                |       |       |       |

| $V_{CP\_UV}$       | チャージポンプ低電圧スレッショルド                     | $V_{VCP} - V_{PVDD}, V_{VCP}$ 立ち下がり<br>$V_{CP\_UV\_MODE} = 0b$ | 4     | 4.75  | 5.5   |

|                    |                                       | $V_{VCP} - V_{PVDD}, V_{VCP}$ 立ち下がり<br>$V_{CP\_UV\_MODE} = 1b$ | 5.5   | 6.25  | 7     |

| $t_{CP\_UV\_DG}$   | チャージポンプ低電圧グリッチ除去時間                    |                                                                | 8     | 10    | 12.75 |

| $V_{CP\_SO}$       | チャージポンプのトリプラからダブルへの切り替えスレッショルド        | $V_{PVDD}$ 立ち上がり                                               | 17.75 | 18.75 | 19.75 |

| $V_{CP\_SO}$       | チャージポンプのトリプラからダブルへの切り替えスレッショルド        | $V_{PVDD}$ 立ち下がり                                               | 16.75 | 17.75 | 18.75 |

| $t_{CP\_SO\_HYS}$  | チャージポンプのトリプラからダブルへのスレッショルドヒステリシス      |                                                                |       | 1.15  | V     |

| $t_{CP\_SO\_DG}$   | チャージポンプのトリプラからダブルへの切り替えスレッショルド グリッチ除去 |                                                                | 8     | 10    | 12.75 |

| $V_{GS\_CLP}$      | ハイサイドドライバ VGS 保護クランプ                  |                                                                | 12.5  | 15    | 17    |

| $V_{GS\_LVL}$      | ゲート電圧監視スレッショルド                        | $V_{GHx} - V_{SHx}, V_{GLx} - V_{PGND}, VGS\_LVL = 0b$         | 1.1   | 1.4   | 1.75  |

|                    |                                       | $V_{GHx} - V_{SHx}, V_{GLx} - V_{PGND}, VGS\_LVL = 1b$         | 0.75  | 1     | 1.2   |

| $t_{GS\_FLT\_DG}$  | $V_{GS}$ 障害監視グリッチ除去時間                 |                                                                | 1.5   | 2     | 2.75  |

| $t_{GS\_HS\_DG}$   | $V_{GS}$ ハンドシェイク監視グリッチ除去時間            |                                                                |       | 210   | ns    |

| $t_{DRIVE}$        | $V_{GS}$ および $V_{DS}$ 監視ブランкиング時間     | $VGS\_TDRV = 000b$                                             | 1.5   | 2     | 2.5   |

|                    |                                       | $VGS\_TDRV = 001b$                                             | 3.25  | 4     | 4.75  |

|                    |                                       | $VGS\_TDRV = 010b$                                             | 6     | 8     | 10    |

|                    |                                       | $VGS\_TDRV = 011b$                                             | 10    | 12    | 14    |

|                    |                                       | $VGS\_TDRV = 100b$                                             | 14    | 16    | 18    |

|                    |                                       | $VGS\_TDRV = 101b$                                             | 20    | 24    | 28    |

|                    |                                       | $VGS\_TDRV = 110b$                                             | 28    | 32    | 36    |

|                    |                                       | $VGS\_TDRV = 111b$                                             | 80    | 96    | 120   |

## 6.5 電気的特性 (続き)

5 V  $\leq$  V<sub>PVDD</sub>  $\leq$  35 V、3.1 V  $\leq$  V<sub>DVDD</sub>  $\leq$  5.5 V、-40°C  $\leq$  T<sub>J</sub>  $\leq$  150°C (特に記述のない限り)。標準的な制限は、V<sub>PVDD</sub> = 13.5V、V<sub>DVDD</sub> = 5V および T<sub>J</sub> = 25°C に対して適用されます。

| パラメータ                                                                                | テスト条件                            | 最小値   | 標準値   | 最大値   | 単位 |

|--------------------------------------------------------------------------------------|----------------------------------|-------|-------|-------|----|

| V <sub>DS_LVL</sub><br><br>V <sub>DS</sub> 過電流保護スレッショルド<br>(DRV800x-Q1 独立ハーフブリッジモード) | VDS_LVL_x = 0000b、BRG_MODE = 00b | 0.050 | 0.062 | 0.074 | V  |

|                                                                                      | VDS_LVL_x = 0001b、BRG_MODE = 00b | 0.070 | 0.084 | 0.098 | V  |

|                                                                                      | VDS_LVL_x = 0010b、BRG_MODE = 00b | 0.089 | 0.105 | 0.123 | V  |

|                                                                                      | VDS_LVL_x = 0011b、BRG_MODE = 00b | 0.108 | 0.127 | 0.147 | V  |

|                                                                                      | VDS_LVL_x = 0100b、BRG_MODE = 00b | 0.128 | 0.148 | 0.170 | V  |

|                                                                                      | VDS_LVL_x = 0101b、BRG_MODE = 00b | 0.147 | 0.169 | 0.195 | V  |

|                                                                                      | VDS_LVL_x = 0110b、BRG_MODE = 00b | 0.166 | 0.191 | 0.218 | V  |

|                                                                                      | VDS_LVL_x = 0111b、BRG_MODE = 00b | 0.185 | 0.212 | 0.243 | V  |

|                                                                                      | VDS_LVL_x = 1000b、BRG_MODE = 00b | 0.278 | 0.318 | 0.363 | V  |

|                                                                                      | VDS_LVL_x = 1001b、BRG_MODE = 00b | 0.372 | 0.425 | 0.483 | V  |

|                                                                                      | VDS_LVL_x = 1010b、BRG_MODE = 00b | 0.466 | 0.532 | 0.605 | V  |

|                                                                                      | VDS_LVL_x = 1011b、BRG_MODE = 00b | 0.562 | 0.638 | 0.725 | V  |

|                                                                                      | VDS_LVL_x = 1100b、BRG_MODE = 00b | 0.655 | 0.745 | 0.847 | V  |

|                                                                                      | VDS_LVL_x = 1101b、BRG_MODE = 00b | 0.942 | 1.066 | 1.208 | V  |

|                                                                                      | VDS_LVL_x = 1110b、BRG_MODE = 00b | 1.322 | 1.494 | 1.692 | V  |

|                                                                                      | VDS_LVL_x = 1111b、BRG_MODE = 00b | 1.890 | 2.132 | 2.411 | V  |

## 6.5 電気的特性 (続き)

5 V  $\leq$  V<sub>PVDD</sub>  $\leq$  35 V、3.1 V  $\leq$  V<sub>DVDD</sub>  $\leq$  5.5 V、-40°C  $\leq$  T<sub>J</sub>  $\leq$  150°C (特に記述のない限り)。標準的な制限は、V<sub>PVDD</sub> = 13.5V、V<sub>DVDD</sub> = 5V および T<sub>J</sub> = 25°C に対して適用されます。

| パラメータ               | テスト条件                         | 最小値                                                               | 標準値  | 最大値   | 単位   |    |

|---------------------|-------------------------------|-------------------------------------------------------------------|------|-------|------|----|

| V <sub>DS_LVL</sub> | VDS_LVL_x = 0000b             | 0.051                                                             | 0.06 | 0.069 | V    |    |

|                     | VDS_LVL_x = 0001b             | 0.068                                                             | 0.08 | 0.092 | V    |    |

|                     | VDS_LVL_x = 0010b             | 0.085                                                             | 0.10 | 0.115 | V    |    |

|                     | VDS_LVL_x = 0011b             | 0.102                                                             | 0.12 | 0.138 | V    |    |

|                     | VDS_LVL_x = 0100b             | 0.119                                                             | 0.14 | 0.161 | V    |    |

|                     | VDS_LVL_x = 0101b             | 0.136                                                             | 0.16 | 0.184 | V    |    |

|                     | VDS_LVL_x = 0110b             | 0.153                                                             | 0.18 | 0.207 | V    |    |

|                     | VDS_LVL_x = 0111b             | 0.17                                                              | 0.2  | 0.23  | V    |    |

|                     | VDS_LVL_x = 1000b             | 0.255                                                             | 0.3  | 0.345 | V    |    |

|                     | VDS_LVL_x = 1001b             | 0.35                                                              | 0.4  | 0.45  | V    |    |

|                     | VDS_LVL_x = 1010b             | 0.44                                                              | 0.5  | 0.56  | V    |    |

|                     | VDS_LVL_x = 1011b             | 0.52                                                              | 0.6  | 0.68  | V    |    |

|                     | VDS_LVL_x = 1100b             | 0.61                                                              | 0.7  | 0.79  | V    |    |

|                     | VDS_LVL_x = 1101b             | 0.88                                                              | 1    | 1.12  | V    |    |

|                     | VDS_LVL_x = 1110b             | 1.2                                                               | 1.4  | 1.6   | V    |    |

|                     | VDS_LVL_x = 1111b             | 1.75                                                              | 2    | 2.25  | V    |    |

| t <sub>DS_DG</sub>  | V <sub>DS</sub> 過電流保護グリッチ除去時間 | VDS_DG = 00b                                                      | 0.75 | 1     | 1.5  | μs |

|                     |                               | VDS_DG = 01b                                                      | 1.5  | 2     | 2.5  | μs |

|                     |                               | VDS_DG = 10b                                                      | 3.25 | 4     | 4.75 | μs |

|                     |                               | VDS_DG = 11b                                                      | 6    | 8     | 10   | μs |

| I <sub>OLD_PU</sub> | オフライン診断用電流ソース                 | プルアップ電流                                                           |      | 3.5   | mA   |    |

| I <sub>OLD_PD</sub> | オフライン診断用電流ソース                 | プルダウン電流                                                           |      | 4     | mA   |    |

| R <sub>OLD</sub>    | オフライン オープン負荷抵抗検出スレッショルド       | V <sub>DS_LVL</sub> = 1.4V、5V $\leq$ V <sub>PVDD</sub> $\leq$ 18V |      | 22    | 50   | kΩ |

|                     |                               | V <sub>DS_LVL</sub> = 1.4V、5V $\leq$ V <sub>PVDD</sub> $\leq$ 37V |      | 22    | 105  | kΩ |

|                     |                               | V <sub>DS_LVL</sub> = 2V、5V $\leq$ V <sub>PVDD</sub> $\leq$ 18V   |      | 10    | 25   | kΩ |

|                     |                               | V <sub>DS_LVL</sub> = 2V、5V $\leq$ V <sub>PVDD</sub> $\leq$ 37V   |      | 10    | 50   | kΩ |

### ヒーター MOSFET ドライバ

|                               |                      |                                                                                              |                                                                          |    |    |   |

|-------------------------------|----------------------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|----|----|---|

| I <sub>GH_HS_HEAT</sub>       | 平均充電電流               | T <sub>J</sub> = 25°C                                                                        | 50                                                                       | mA |    |   |

| R <sub>GL_HEAT</sub>          | オン抵抗(放電段)            | T <sub>J</sub> = 25°C                                                                        | 15                                                                       | 20 | 25 | Ω |

| R <sub>GL_HEAT</sub>          | オン抵抗(放電段)            | T <sub>J</sub> = 125°C                                                                       | 28                                                                       | 36 | Ω  |   |

| V <sub>GH_HS_HIGH</sub>       | GH_HS の High レベル出力電圧 | V <sub>PVDD</sub> = 5V、I <sub>CP</sub> = 15mA                                                | V <sub>SH_HS</sub> + 6                                                   | V  |    |   |

| V <sub>GH_HS_HIGH</sub>       | GH_HS の High レベル出力電圧 | V <sub>PVDD</sub> = 13.5V、I <sub>CP</sub> = 15mA                                             | V <sub>SH_HS</sub> + V <sub>SH_HS</sub> + 8 10 V <sub>SH_HS</sub> + 11.5 | V  |    |   |

| I <sub>HEAT_SH_ST_BY_LK</sub> | SH_HS のリーク電流スタンバイ    |                                                                                              | 25                                                                       | μA |    |   |

| R <sub>GS_HEAT</sub>          | パッシブ ゲート クランプ抵抗      |                                                                                              | 150                                                                      | kΩ |    |   |

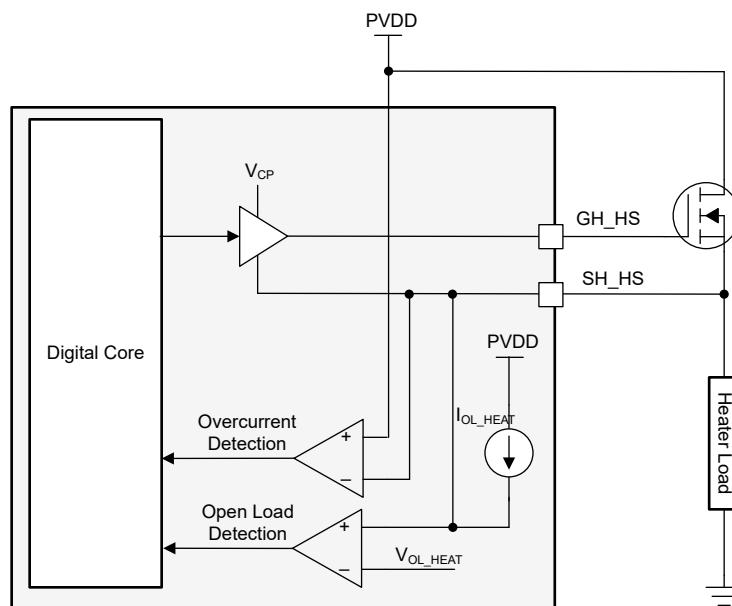

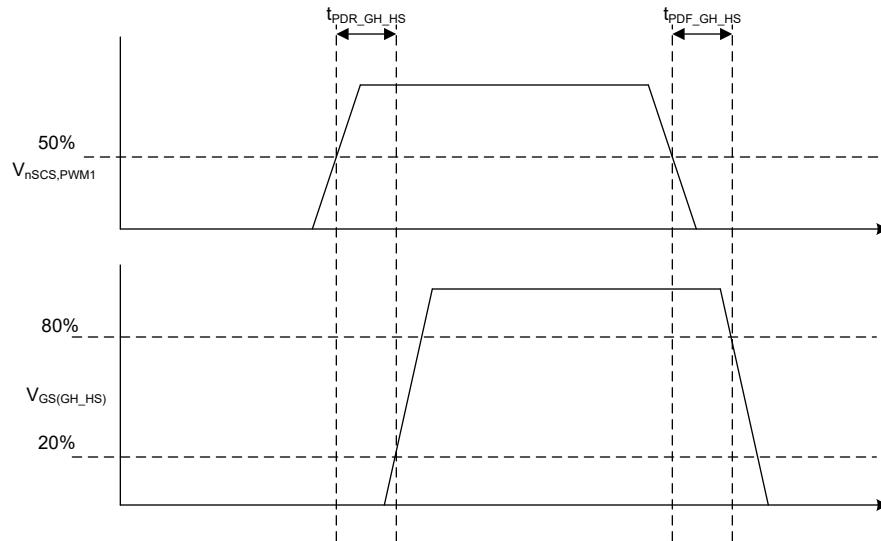

| t <sub>PDR_GH_HS</sub>        | GH_HS の立ち上がり伝搬遅延     | V <sub>PVDD</sub> = 13.5V、R <sub>G</sub> = 0Ω、C <sub>G</sub> = 2.7nF                         | 0.6                                                                      | μs |    |   |

| t <sub>PDF_GH_HS</sub>        | GH_HS の立ち下がり伝搬遅延     | V <sub>PVDD</sub> = 13.5V、V <sub>SH_HS</sub> = 0V、R <sub>G</sub> = 0Ω、C <sub>G</sub> = 2.7nF | 0.5                                                                      | μs |    |   |

| t <sub>RISE_GH_HS</sub>       | 立ち上がり時間(スイッチ モード)    | V <sub>PVDD</sub> = 13.5V、V <sub>SH_HS</sub> = 0V、R <sub>G</sub> = 0Ω、C <sub>G</sub> = 2.7nF | 300                                                                      | ns |    |   |

| t <sub>FALL_GH_HS</sub>       | 立ち下がり時間(スイッチ モード)    | V <sub>PVDD</sub> = 13.5V、V <sub>SH_HS</sub> = 0V、R <sub>G</sub> = 0Ω、C <sub>G</sub> = 2.7nF | 170                                                                      | ns |    |   |

## 6.5 電気的特性 (続き)

5 V  $\leq$   $V_{PVDD}$   $\leq$  35 V、3.1 V  $\leq$   $V_{DVDD}$   $\leq$  5.5 V、-40°C  $\leq$   $T_J$   $\leq$  150°C (特に記述のない限り)。標準的な制限は、 $V_{PVDD} = 13.5V$ 、 $V_{DVDD} = 5V$  および  $T_J = 25^\circ C$  に対して適用されます。

| パラメータ                                            | テスト条件                                | 最小値                                                                                       | 標準値   | 最大値   | 単位        |

|--------------------------------------------------|--------------------------------------|-------------------------------------------------------------------------------------------|-------|-------|-----------|

| <b>ヒーター保護回路</b>                                  |                                      |                                                                                           |       |       |           |

| $V_{DS\_LVL\_HEAT}$                              | ヒーター用 MOSFET の $V_{DS}$ 過電流保護スレッショルド | HEAT_VDS_LVL = 0000b                                                                      | 0.050 | 0.06  | 0.07      |

|                                                  |                                      | HEAT_VDS_LVL = 0001b                                                                      | 0.067 | 0.08  | 0.093     |

|                                                  |                                      | HEAT_VDS_LVL = 0010b                                                                      | 0.085 | 0.10  | 0.115     |

|                                                  |                                      | HEAT_VDS_LVL = 0011b                                                                      | 0.102 | 0.12  | 0.138     |

|                                                  |                                      | HEAT_VDS_LVL = 0100b                                                                      | 0.119 | 0.14  | 0.161     |

|                                                  |                                      | HEAT_VDS_LVL = 0101b                                                                      | 0.136 | 0.16  | 0.184     |

|                                                  |                                      | HEAT_VDS_LVL = 0110b                                                                      | 0.153 | 0.18  | 0.207     |

|                                                  |                                      | HEAT_VDS_LVL = 0111b                                                                      | 0.17  | 0.2   | 0.23      |

|                                                  |                                      | HEAT_VDS_LVL = 1000b                                                                      | 0.204 | 0.240 | 0.276     |

|                                                  |                                      | HEAT_VDS_LVL = 1001b                                                                      | 0.238 | 0.280 | 0.322     |

|                                                  |                                      | HEAT_VDS_LVL = 1010b                                                                      | 0.272 | 0.320 | 0.368     |

|                                                  |                                      | HEAT_VDS_LVL = 1011b                                                                      | 0.306 | 0.360 | 0.414     |

|                                                  |                                      | HEAT_VDS_LVL = 1100b                                                                      | 0.340 | 0.400 | 0.460     |

|                                                  |                                      | HEAT_VDS_LVL = 1101b                                                                      | 0.374 | 0.440 | 0.506     |

|                                                  |                                      | HEAT_VDS_LVL = 1110b                                                                      | 0.476 | 0.560 | 0.644     |

|                                                  |                                      | HEAT_VDS_LVL = 1111b                                                                      | 0.85  | 1     | 1.15      |

| $t_{DS\_HEAT\_DG}$                               | $V_{DS}$ 過電流保護グリッチ除去時間               | HEAT_VDS_DG = 00b                                                                         | 0.75  | 1     | $\mu s$   |

|                                                  |                                      | HEAT_VDS_DG = 01b                                                                         | 1.5   | 2     | $\mu s$   |

|                                                  |                                      | HEAT_VDS_DG = 10b                                                                         | 3.25  | 4     | 4.75      |

|                                                  |                                      | HEAT_VDS_DG = 11b                                                                         | 6     | 8     | $\mu s$   |

| $t_{DS\_HEAT\_BLK}$                              | $V_{DS}$ 過電流保護ブランкиング時間              | HEAT_VDS_BLK = 00b                                                                        | 3.25  | 4     | $\mu s$   |

|                                                  |                                      | HEAT_VDS_BLK = 01b                                                                        | 6     | 8     | $\mu s$   |

|                                                  |                                      | HEAT_VDS_BLK = 10b                                                                        | 13    | 16    | 19        |

|                                                  |                                      | HEAT_VDS_BLK = 11b                                                                        | 27    | 32    | 37        |

| $V_{OL\_HEAT}$                                   | 開放負荷スレッショルド電圧                        | $V_{SH\_HS} = 0V$                                                                         | 1.8   | 2     | V         |

| $I_{OL\_HEAT}$                                   | プルアップ電流ソースの開放負荷診断が有効化                | $V_{SH\_HS} = 0V$ 、 $V_{SHheater} = 4.5V$                                                 |       | 1     | mA        |

| $t_{OL\_HEAT}$                                   | ヒーター MOSFET の開放負荷フィルタ時間              |                                                                                           |       | 2     | ms        |

| <b>エレクトロクロミック ドライバ</b>                           |                                      |                                                                                           |       |       |           |

| $R_{DSON\_ECFB}$                                 | EC 放電用ローサイド MOSFET のオン抵抗             | $V_{PVDD} = 13.5V$ 、 $T_J = 25^\circ C$ 、 $I_{ECFB} = \pm 0.25A$<br>$ECFB\_LS\_EN = 1b$   |       | 1375  | $m\Omega$ |

| $R_{DSON\_ECFB}$                                 | EC 放電用ローサイド MOSFET のオン抵抗             | $V_{PVDD} = 13.5V$ 、 $T_J = 150^\circ C$ 、 $I_{ECFB} = \pm 0.125A$<br>$ECFB\_LS\_EN = 1b$ |       | 2500  | $m\Omega$ |

| $I_{OC\_ECFB}$                                   | ローサイド MOSFET の過電流スレッショルド             | $V_{PVDD} = 13.5V$ 、 $I_{ECFB}$ 電流シンク                                                     | 0.5   | 1     | A         |

| $t_{DG\_OC\_ECFB}$                               | 過電流シャットダウン グリッチ除去時間                  | $V_{PVDD} < 20V$ 、 $I_{ECFB}$ 電流シンク                                                       | 40    |       | $\mu s$   |

|                                                  |                                      | $V_{PVDD} > 20V$ 、 $I_{ECFB}$ 電流シンク                                                       | 15    |       | $\mu s$   |

| $dV_{ECFB}/dt$                                   | ECFB およびローサイド MOSFET のスルーレート         | $V_{PVDD} = 13.5V$ 、 $R_{load} = 64\Omega$ を $P_{VDD}$ に接続                                | 7     |       | $V/\mu s$ |

| $I_{OL\_ECFB\_LS}$                               | 放電中の EC の開放負荷検出スレッショルド               | $EC\_OLEN = 1b$ 、 $ECFB\_LS\_EN = 1b$                                                     | 10    | 20    | 32        |

| Copyright © 2026 Texas Instruments Incorporated  |                                      |                                                                                           |       |       |           |

| 資料に関するフィードバック(ご意見やお問い合わせ)を送信                     |                                      |                                                                                           |       |       |           |

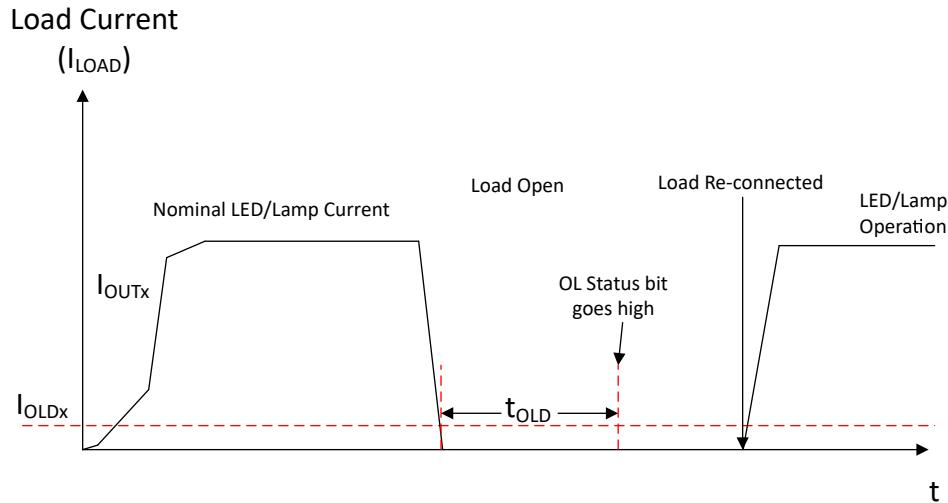

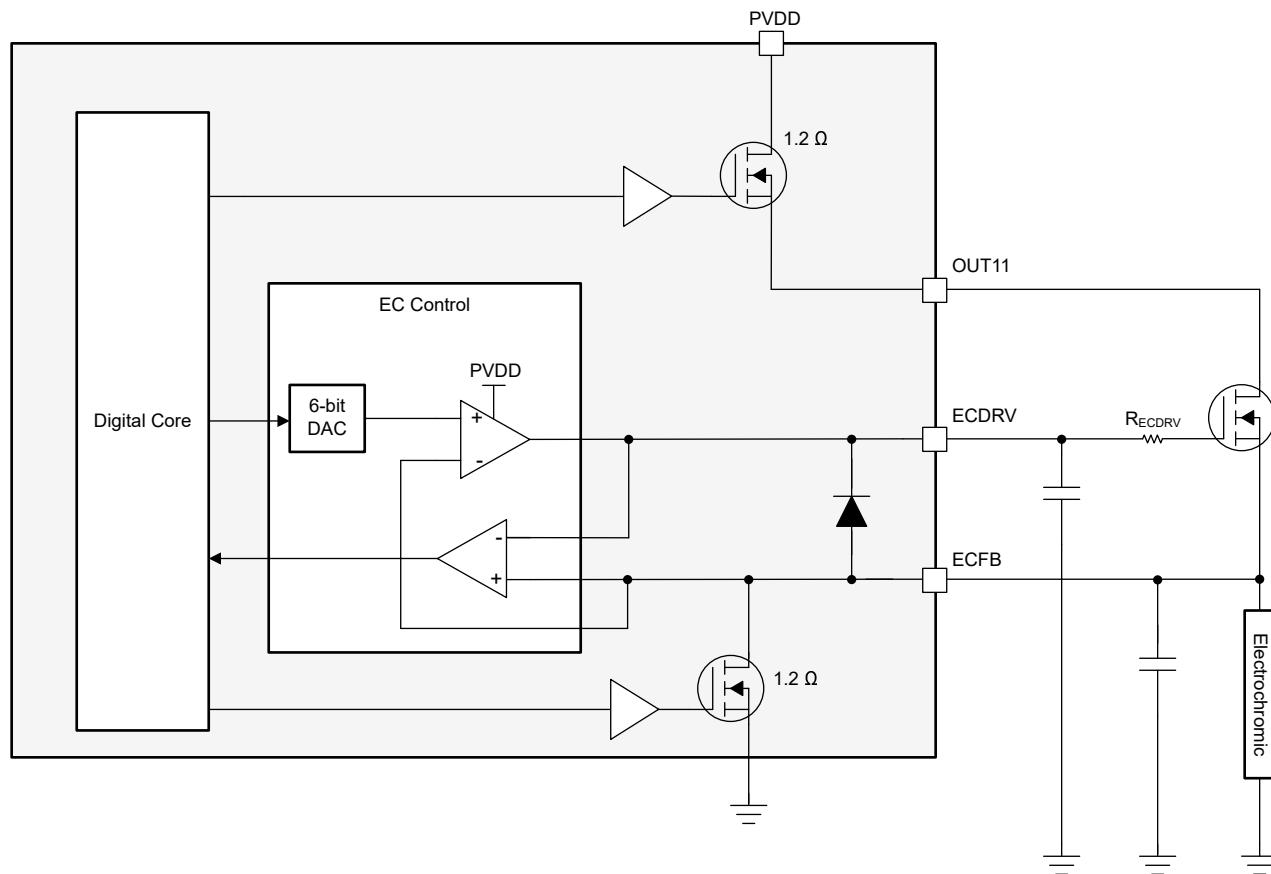

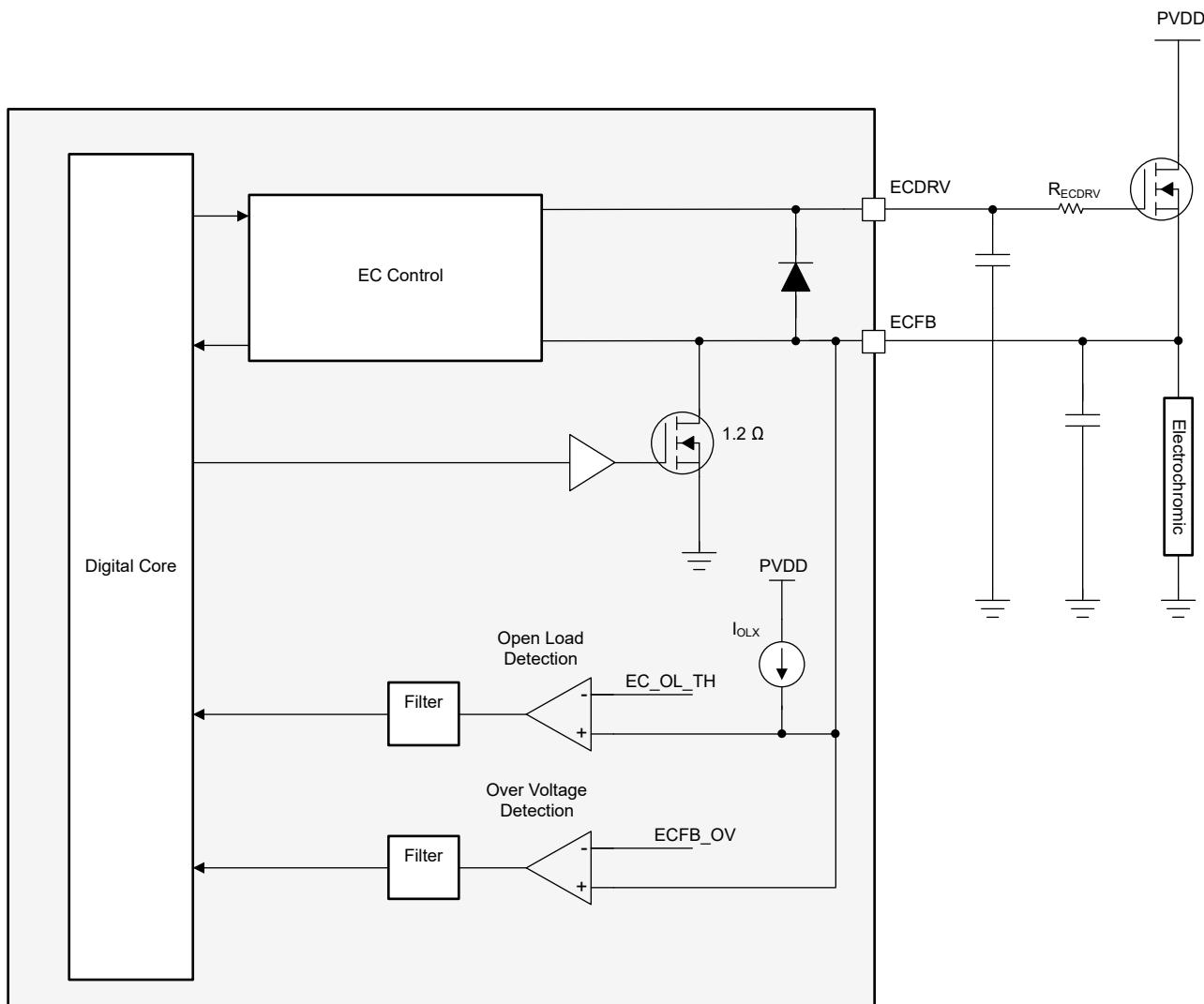

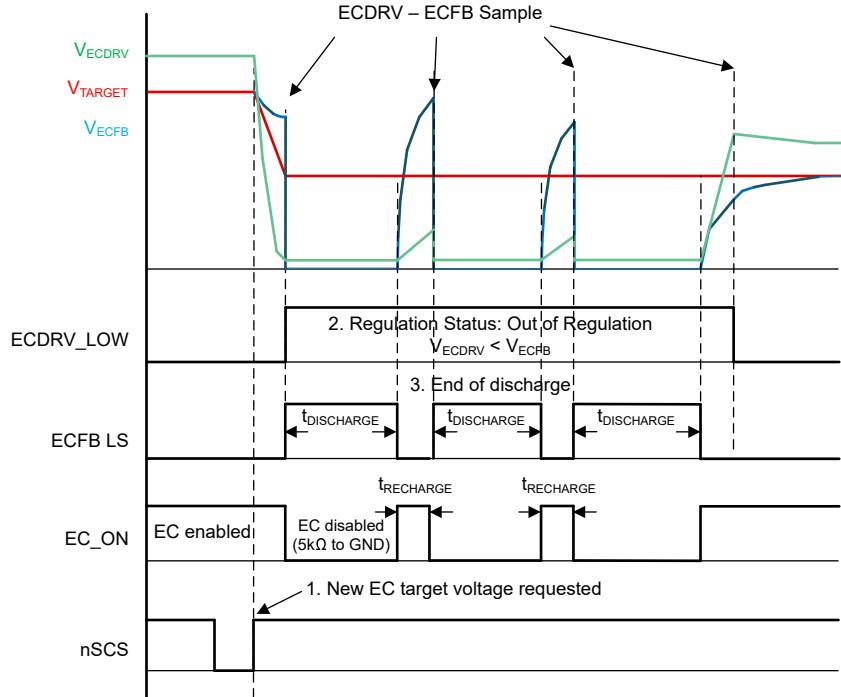

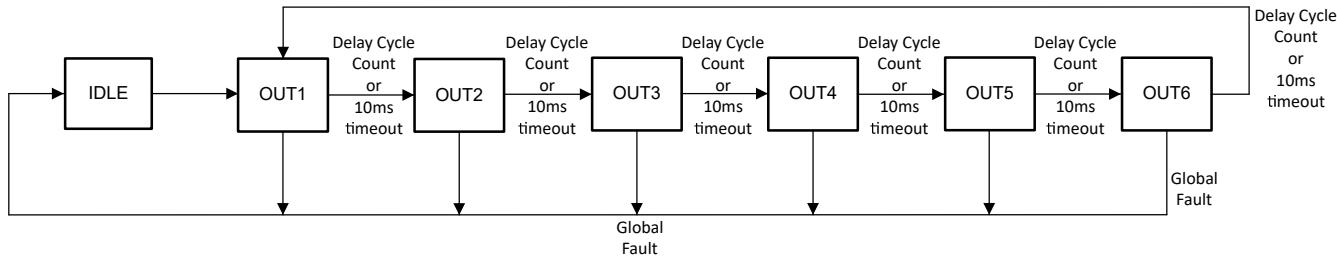

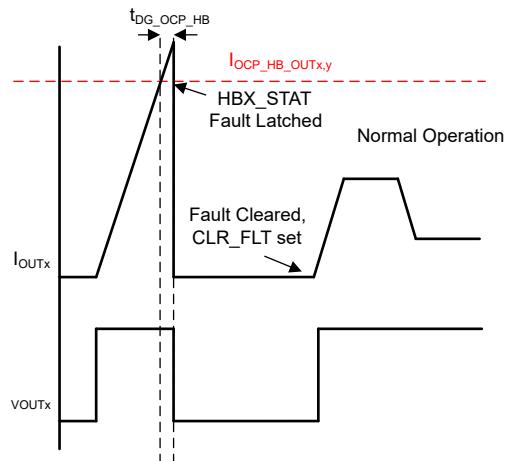

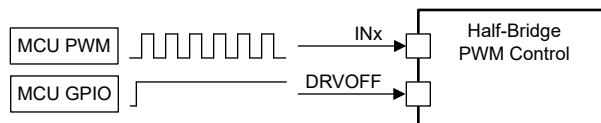

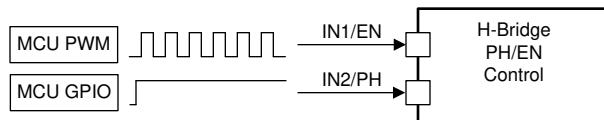

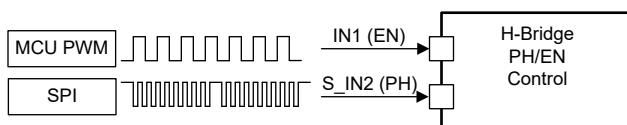

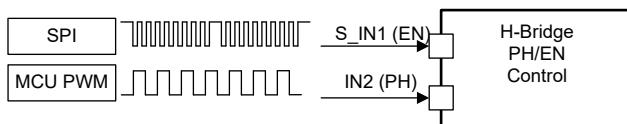

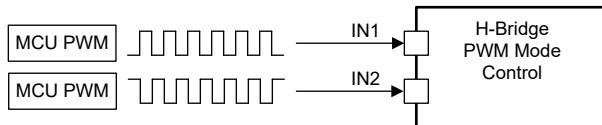

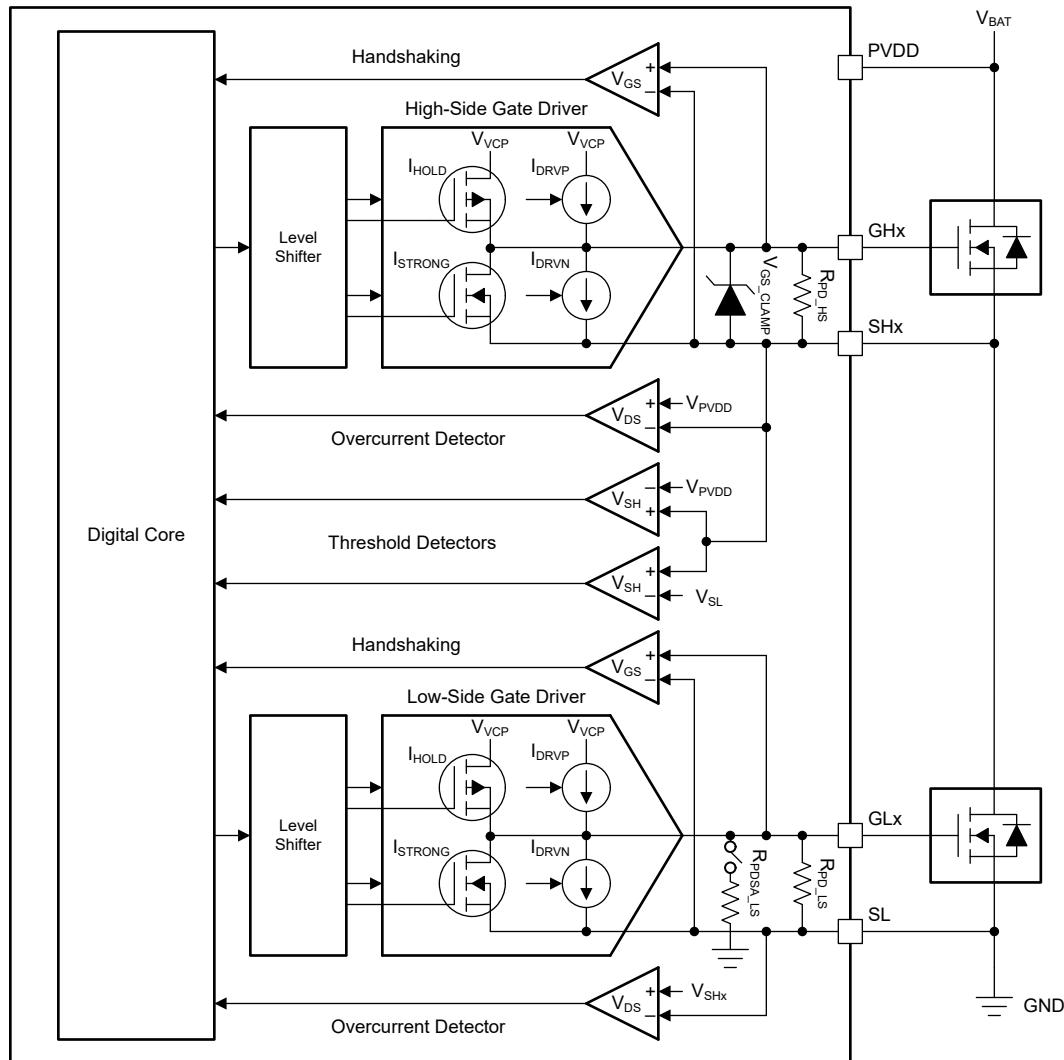

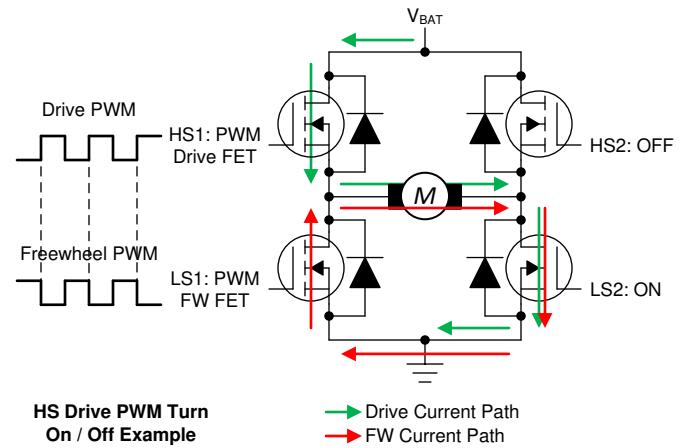

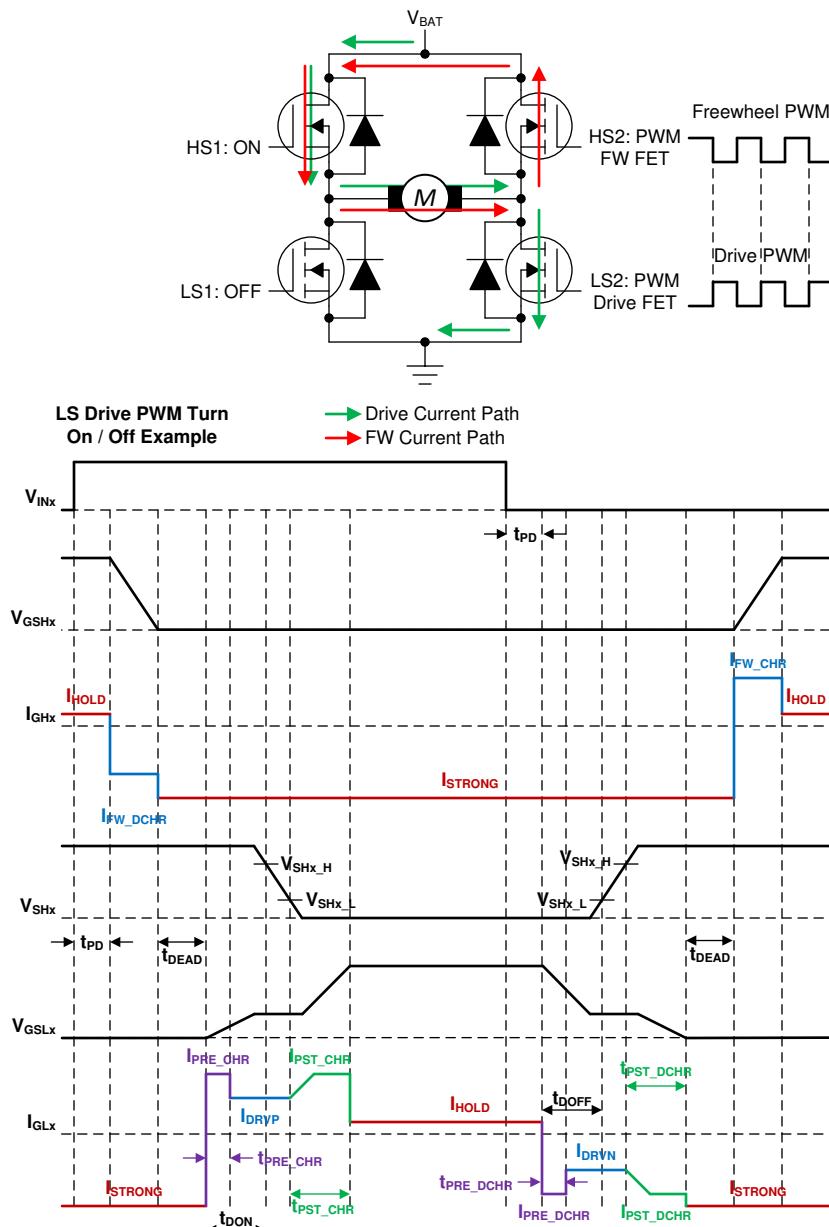

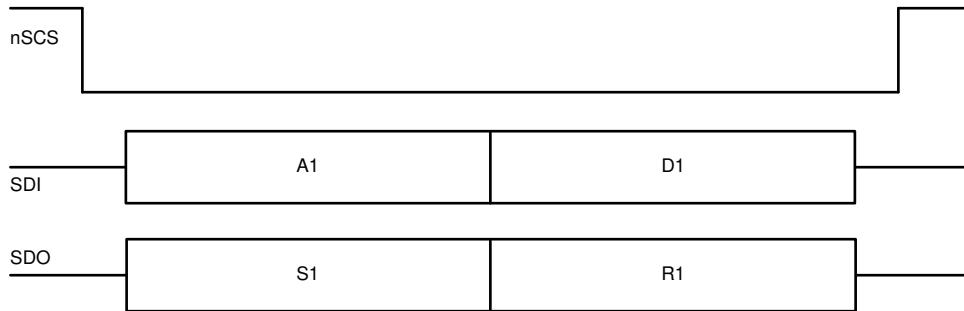

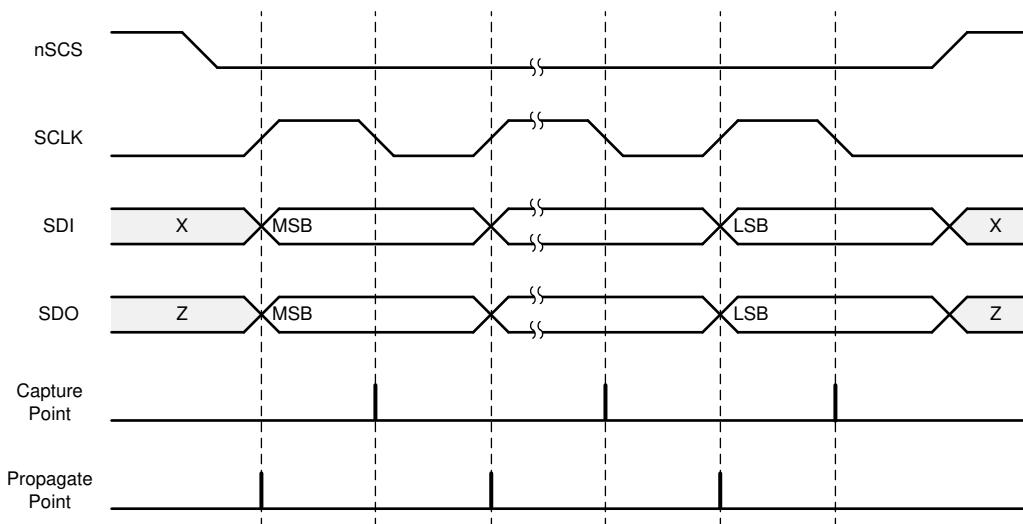

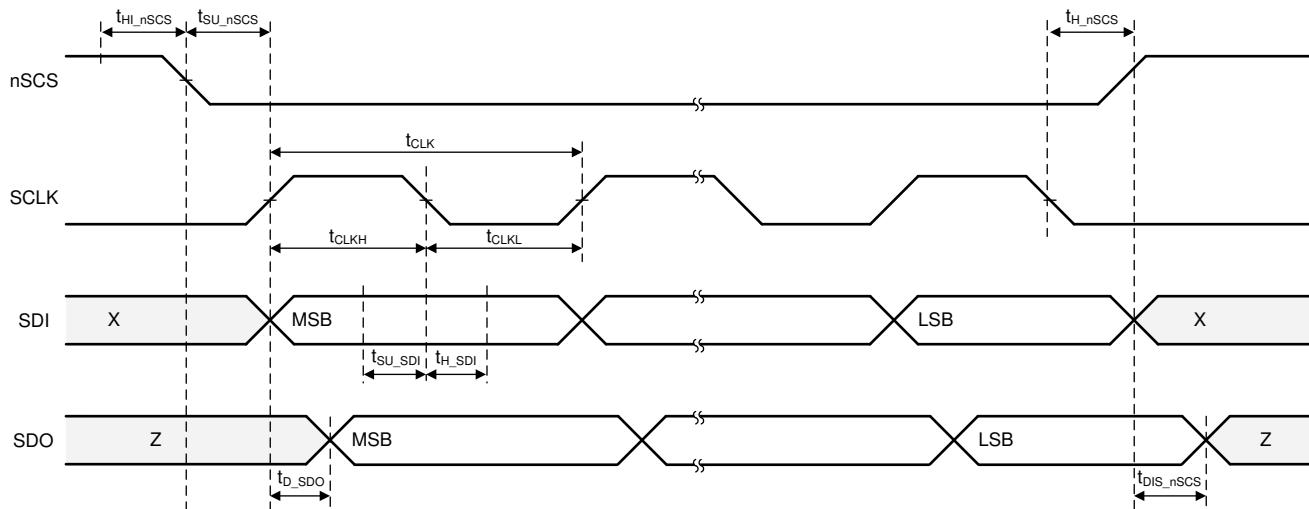

| Product Folder Links: <a href="#">DRV8000-Q1</a> |                                      |                                                                                           |       |       |           |