# DRV8245-Q1 車載用 H ブリッジ・ドライバ、内蔵電流センスおよび診断機能付き

## 1 特長

- 車載アプリケーション用に AEC-Q100 認定済み:

- 温度グレード 1: -40°C ~ +125°C,  $T_A$

- 機能安全システムの設計に役立つ資料を利用可能

- 動作範囲: 4.5V ~ 35V (絶対最大定格 40V)

- VQFN-HR パッケージ:  $R_{ON\_LS} + R_{ON\_HS}$ : 32mΩ

- HTSSOP パッケージ:  $R_{ON\_LS} + R_{ON\_HS}$ : 40mΩ

- $I_{OUT}$  (最大値) = 32A

- 最大 25kHz の PWM 周波数動作、自動デッド・タイム生成付き

- 設定可能なスルーレートと拡散スペクトラム・クロックによる低い電磁干渉 (EMI)

- 電流センス内蔵 (シャント抵抗不要)

- IPROPI ピンへの比例負荷電流出力

- 設定可能な電流レギュレーション

- フォルト応答 (ラッチまたは再試行) を設定可能な保護および診断機能

- オフ状態とオン状態の両方で負荷診断を行い、開放負荷および短絡を検出

- 電源 (VM) の電圧監視

- 過電流保護

- 過熱保護

- $nFAULT$  ピンによるフォルト通知

- 3.3V および 5V のロジック入力電圧をサポート

- 低いスリープ電流、25°C で 1μA (標準値)

- 3 つのバリエント - HW (H)、SPI (S)、SPI (P)

- 設定可能な制御モード:

- PWM または PH/EN モードを使用するシングル・フルブリッジ

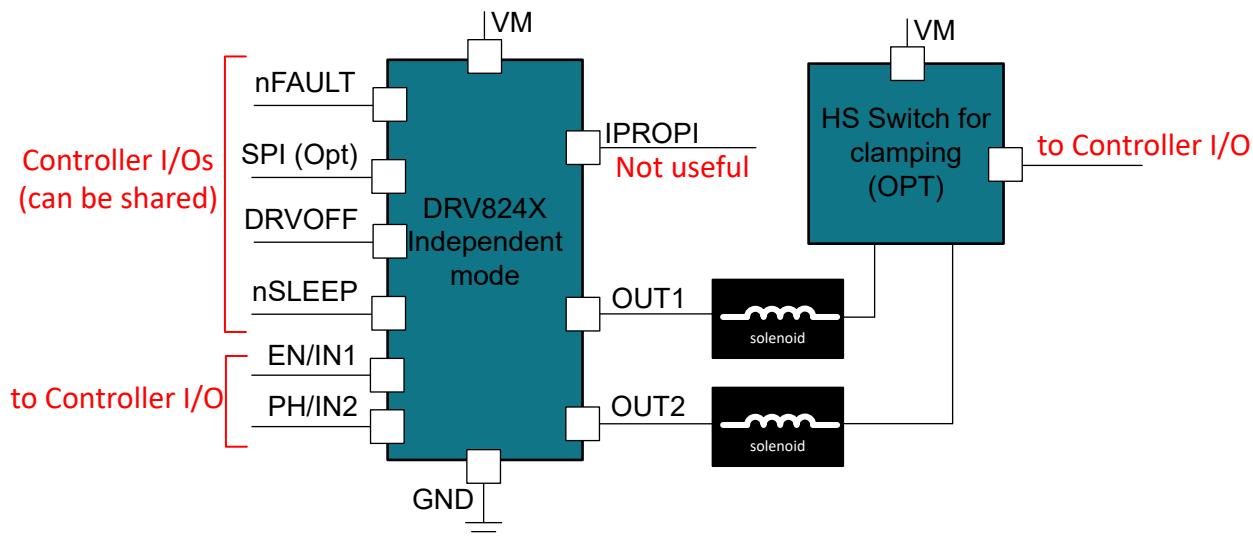

- 独立モードを使用する 2 つのハーフブリッジ

- デバイス・ファミリの比較表

## 2 アプリケーション

- 車載用ブラシ付き DC モーター、ソレノイド

- ドア・モジュール、ワイパー・モジュール、トランク、シート・モジュール

- ボディ・コントロール・モジュール (BCM)

- e-シフター (自動変速)

- ステアリング・システム

- ガス・エンジン・システム

- オンボード・チャージャ

## 3 概要

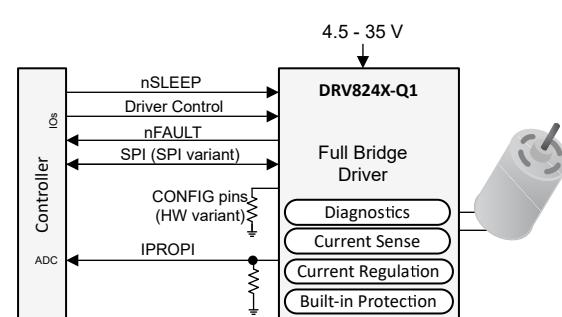

DRV824x-Q1 デバイス・ファミリは、多様な車載用アプリケーション向けの統合型 H ブリッジ・ドライバです。このデバイスは、シングル・フルブリッジ・ドライバとして、または 2 つの独立したハーフブリッジ・ドライバとして構成可能です。パワー・パッケージに収容されたこのモノリシック・デバイス・ファミリは、BiCMOS 大電力プロセス・テクノロジー・ノードを採用した設計であり、優れた電力処理能力と放熱特性を達成すると同時に、コンパクトなパッケージ・サイズ、使いやすいレイアウト、EMI 制御能力、高精度の電流センス、信頼性、診断機能も実現しています。このファミリには、同じピン機能でスケーラブルな  $R_{ON}$  (電流容量) のデバイスがあり、さまざまな負荷に対応できます。

このデバイスには、N チャネル H ブリッジ、チャージ・ポンプ・レギュレータ、ハイサイド電流検出およびレギュレーション、電流比例出力、保護回路が内蔵されています。低消費電力のスリープ・モードにより、低い静止電流を実現できます。このデバイスは、電圧監視機能、負荷診断機能、さらに過電流および過熱に対する保護機能を搭載しています。フォルト状態は、 $nFAULT$  ピンにより通知されます。このデバイスには、3 種類のバリエントが用意されています。- ハードワイヤード・インターフェイス: HW (H) および 2 つの SPI インターフェイス・バリエント: SPI (P) と SPI (S) があり、SPI (P) はロジック電源が外部から供給され、SPI (S) はロジック電源が内部で生成されます。SPI インターフェイス・バリエントは、デバイス構成とフォルト監視において、より高い柔軟性があります。

### 製品情報 (1)

| 部品番号                      | パッケージ        | 本体サイズ (公称)    |

|---------------------------|--------------|---------------|

| DRV8245-Q1                | VQFN-HR (16) | 3.5mm × 5.5mm |

| DRV8245-Q1 <sup>(2)</sup> | HTSSOP (28)  | 4.4mm × 9.7mm |

(1) 利用可能なすべてのパッケージについては、このデータシートの末尾にある注文情報を参照してください。

(2) このデバイスはプレビュー版としてのみ供給されます。

概略回路図

英語版の TI 製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、必ず最新版の英語版をご参照ください。

## 目次

|                  |    |                               |    |

|------------------|----|-------------------------------|----|

| 1 特長             | 1  | 8.2 機能ブロック図                   | 33 |

| 2 アプリケーション       | 1  | 8.3 機能説明                      | 36 |

| 3 概要             | 1  | 8.4 デバイスの機能状態                 | 49 |

| 4 改訂履歴           | 2  | 8.5 プログラミング - SPI バリARIANTのみ  | 51 |

| 5 デバイスの比較        | 4  | 8.6 レジスタ・マップ - SPI バリARIANTのみ | 56 |

| 6 ピン構成および機能      | 6  | 9 アプリケーションと実装                 | 63 |

| 6.1 HW バリARIANT  | 6  | 9.1 アプリケーション情報                | 63 |

| 6.2 SPI バリARIANT | 9  | 9.2 代表的なアプリケーション              | 64 |

| 7 仕様             | 13 | 10 電源に関する推奨事項                 | 68 |

| 7.1 絶対最大定格       | 13 | 10.1 バルク容量の決定                 | 68 |

| 7.2 ESD 定格       | 13 | 11 レイアウト                      | 69 |

| 7.3 推奨動作条件       | 14 | 11.1 レイアウトのガイドライン             | 69 |

| 7.4 熱に関する情報      | 14 | 11.2 レイアウト例                   | 69 |

| 7.5 電気的特性        | 14 | 12 デバイスおよびドキュメントのサポート         | 70 |

| 7.6 SPI のタイミング要件 | 21 | 12.1 ドキュメントのサポート              | 70 |

| 7.7 スイッチング波形     | 23 | 12.2 ドキュメントの更新通知を受け取る方法       | 70 |

| 7.8 代表的特性        | 30 | 12.3 コミュニティ・リソース              | 70 |

| 8 詳細説明           | 32 | 12.4 商標                       | 70 |

| 8.1 概要           | 32 | 13 メカニカル、パッケージ、および注文情報        | 70 |

## 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision B (August 2022) to Revision C (August 2022) | Page |

|-------------------------------------------------------------------|------|

| • ISO 7637 過渡時に VM ピンの絶対最大定格違反を許容する旨の脚注を追加                        | 13   |

| • 短絡保護に関する脚注の説明を改善                                                | 14   |

| • EC 表 - HTSSOP パッケージのみ - A <sub>IPROPI</sub> マッチングを 2% から 5% に低減 | 19   |

| Changes from Revision A (January 2022) to Revision B (July 2022)                 | Page |

|----------------------------------------------------------------------------------|------|

| • デバイス比較 - DRV8245HRXZQ1 および DRV8244SRYJQ1 の量産開始前情報、スルーレート、およびオフ状態診断機能の例外を削除     | 4    |

| • PH/IN2 のピン名の誤字を訂正                                                              | 13   |

| • EC 表 - V <sub>VM_REV</sub> の標準値を 1.4V に変更                                      | 14   |

| • EC 表 - MODE ピンの R <sub>LVL3of3</sub> を最小 250kΩ に増加                             | 16   |

| • EC 表 - R <sub>ON</sub> の標準値を更新、R <sub>Hi-Z</sub> の値を 0.9~5.63 kΩ の範囲に更新        | 16   |

| • EC 表 - LVL2 のスルーレート設定の制限を削除                                                    | 18   |

| • EC 表 - IPROPI_LIM の最小値を 4.5V に低減                                               | 19   |

| • EC 表 - I <sub>PD_OLA</sub> の範囲を 2~13.82mA に拡大                                  | 20   |

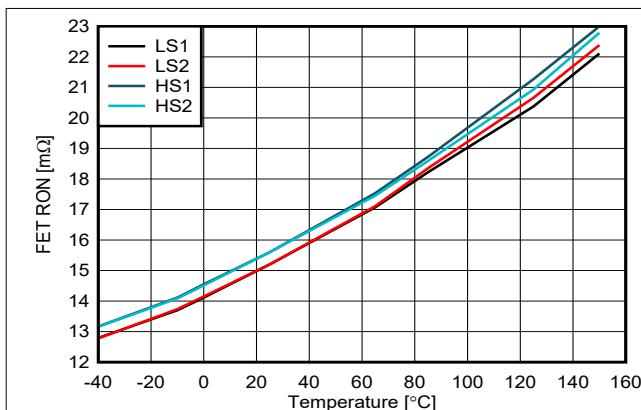

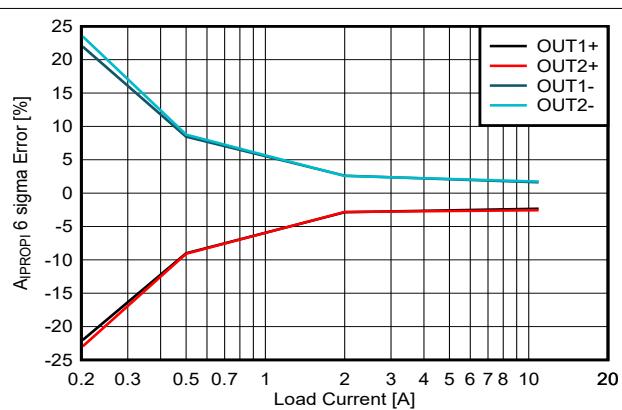

| • 代表的特性 - FET RON プロットと LS OCP プロットを訂正、A <sub>IPROPI</sub> プロットを改善               | 30   |

| • P バリARIANTのブロック図 - VDD ピンの誤字を訂正                                                | 33   |

| • PWM モードの機能説明 - 量産開始前の情報を削除                                                     | 37   |

| • レジスタ - ピン制御の機能説明 - 量産開始前の情報を削除                                                 | 39   |

| • SR の機能説明 - DRV8245HRXZQ1 の LVL-2 の制限を削除、量産開始前の情報と SR 表の重複を削除 (代わりに「電気的特性」表を参照) | 40   |

| • ITRIP レギュレーションの機能説明 - 量産開始前の情報を削除、外部 DAC を使用した線形 ITRIP レベルに関する注を追加             | 41   |

| • DIAG ピンの機能説明 (HW バリARIANTのみ) - LVL5 設定の動作を訂正                                   | 43   |

| • OLP の機能説明の更新 - DRV8245HRXZQ1 の機能例外を削除                                          | 45   |

---

|                                                                                                |    |

|------------------------------------------------------------------------------------------------|----|

| • OLA の機能説明の更新 - 駆動方向が反転したときのフォルト・クリアについての説明を追加.....                                           | 47 |

| • 機能状態 - 量産開始前の情報を削除.....                                                                      | 49 |

| • SDO フレーム - 量産開始前の情報を削除.....                                                                  | 52 |

| • ユーザー・レジスタ - 量産開始前の情報を削除.....                                                                 | 57 |

| • 代表的なアプリケーション - EMC に関する推奨事項を追加、ピン使用事例の説明を改善、VQFN-HR パッケージの HW バリエーションのアプリケーション図でピン番号を訂正..... | 64 |

---

| <b>Changes from Revision * (November 2021) to Revision A (January 2022)</b> | <b>Page</b> |

|-----------------------------------------------------------------------------|-------------|

| • デバイスのステータスを混合生産に変更.....                                                   | 1           |

---

## 5 デバイスの比較

表 5-1 に DRV824X-Q1 ファミリに属するデバイスの  $R_{ON}$  およびパッケージの違いをまとめています。

**表 5-1. デバイスの比較**

| 部品番号 <sup>(1)</sup> | (LS + HS) $R_{ON}$ | $I_{OUT}$ 最大値 | パッケージ        | 本体サイズ (公称)    | バリアント                    |

|---------------------|--------------------|---------------|--------------|---------------|--------------------------|

| DRV8243-Q1          | 84mΩ               | 12A           | VQFN-HR (14) | 3mm × 4.5mm   | HW (H), SPI (S)          |

| DRV8243-Q1          | 98mΩ               | 12A           | HVSSOP (28)  | 3mm × 7.3mm   | HW (H), SPI (S), SPI (P) |

| DRV8244-Q1          | 47mΩ               | 21A           | VQFN-HR (16) | 3mm × 6mm     | HW (H), SPI (S)          |

| DRV8244-Q1          | 60mΩ               | 21A           | HVSSOP (28)  | 3mm × 7.3mm   | HW (H), SPI (S), SPI (P) |

| DRV8245-Q1          | 32mΩ               | 32A           | VQFN-HR (16) | 3.5mm × 5.5mm | HW (H), SPI (S)          |

| DRV8245-Q1          | 40mΩ               | 32A           | HTSSOP (28)  | 4.4mm × 9.7mm | HW (H), SPI (S), SPI (P) |

(1) 本書は、DRV8245-Q1 の製品データシートです。他の情報については、他のデバイス・バリアントのデータシートを参照してください。

表 5-2 に DRV824X-Q1 ファミリの SPI および HW インターフェイス・バリアントの機能の違いをまとめています。一般に、SPI バリアントでは、より多くの構成変更、ブリッジ制御オプション、診断フィードバック、冗長ドライバ・シャットオフ、ピン FMEA の改良や追加機能が提供されています。

さらに、SPI バリアントには、**SPI (P) バリアント**と**SPI (S) バリアント**の 2 つのオプションがあります。SPI (P) バリアントでは、デバイスのロジック電源は、外部の低電圧 5V 電源から VDD ピン経由で供給するようになっています。SPI (S) バリアントでは、この電源は内部的に VM ピンから生成されます。SPI (P) バリアントは、この外部ロジック電源によって、VM 低電圧過渡時にデバイスのブランディング (デバイスのリセット) を回避します。

**表 5-2. SPI バリアントと HW バリアントの比較**

| 機能                            | HW (H) バリアント            | SPI (S) バリアント                                        | SPI (P) バリアント        |

|-------------------------------|-------------------------|------------------------------------------------------|----------------------|

| ブリッジ制御                        | ピンのみ                    | 個別のピンと、ピンの状態を示すレジスタ・ビットの両方またはいずれか一方 (「レジスタ・ピン制御」を参照) |                      |

| スリープ機能                        | nSLEEP ピンを通じて利用可能       |                                                      | 使用不可                 |

| デバイスへの外部ロジック電源                | 非対応                     | 非対応                                                  | VDD ピンにより対応          |

| フォルト・コマンドのクリア                 | nSLEEP ピンでのリセット・パルス     |                                                      | SPI の CLR_FAULT コマンド |

| スルーレート                        | 6 レベル                   |                                                      | 8 レベル                |

| 過電流保護 (OCP)                   | 最大の設定に固定                | スレッショルドには 3 つの選択肢、フィルタ時間には 4 つの選択肢                   |                      |

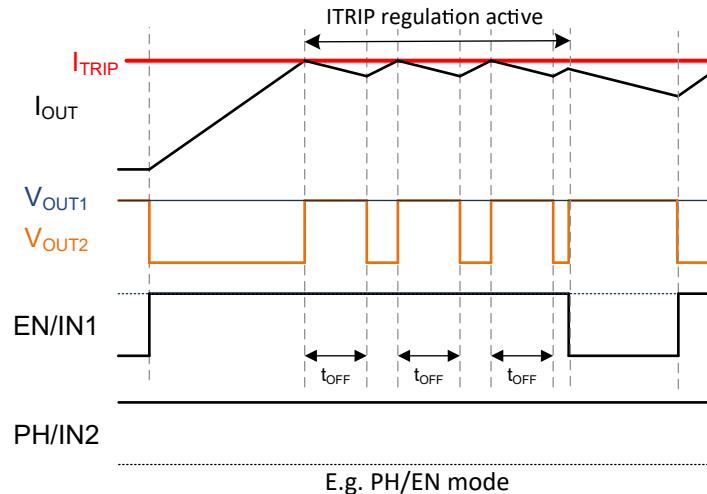

| ITRIP レギュレーション                | 5 レベルとディセーブル、固定 TOFF 時間 | 7 レベルとディセーブル、表示あり、TOFF 時間をプログラム可能                    |                      |

| 各フォルト応答を再試行またはラッチのいずれかに設定     | 非対応、すべてラッチまたはすべて再試行     |                                                      | 対応                   |

| 詳細なフォルト・ログとデバイス・ステータス・フィードバック | 非対応、nFAULT ピンの監視が必要     | 対応、nFAULT ピン監視も可能                                    |                      |

| VM 過電圧                        | 固定                      | スレッショルドに 4 つの選択肢                                     |                      |

| オン状態 (アクティブ) 診断               | 非対応                     | ハイサイド負荷について対応                                        |                      |

| スペクトラム拡散クロック (SSC)            | 非対応                     | 対応                                                   |                      |

| PWM モードでのドライバ状態の追加            | 非対応                     | 対応                                                   |                      |

| 独立モードでハーフ・ブリッジを個別にハイ・インピーダンス化 | 非対応                     | 対応 (SPI レジスタのみ)                                      |                      |

**表 5-3. ファミリ内のデバイス間の区別**

| デバイス        | パッケージの記号表記 | DEVICE_ID レジスタ |

|-------------|------------|----------------|

| DRV8243H-Q1 | 8243H      | 該当なし           |

| DRV8244H-Q1 | 8244H      | 該当なし           |

| DRV8245H-Q1 | 8245H      | 該当なし           |

表 5-3. ファミリ内のデバイス間の区別 (continued)

| デバイス        | パッケージの記号表記 | DEVICE_ID レジスタ |

|-------------|------------|----------------|

| DRV8243S-Q1 | 8243S      | 0 x 32         |

| DRV8244S-Q1 | 8244S      | 0 x 42         |

| DRV8245S-Q1 | 8245S      | 0 x 52         |

| DRV8243P-Q1 | 8243P      | 0 x 36         |

| DRV8244P-Q1 | 8244P      | 0 x 46         |

| DRV8245P-Q1 | 8245P      | 0 x 56         |

## 6 ピン構成および機能

### 6.1 HW バリアント

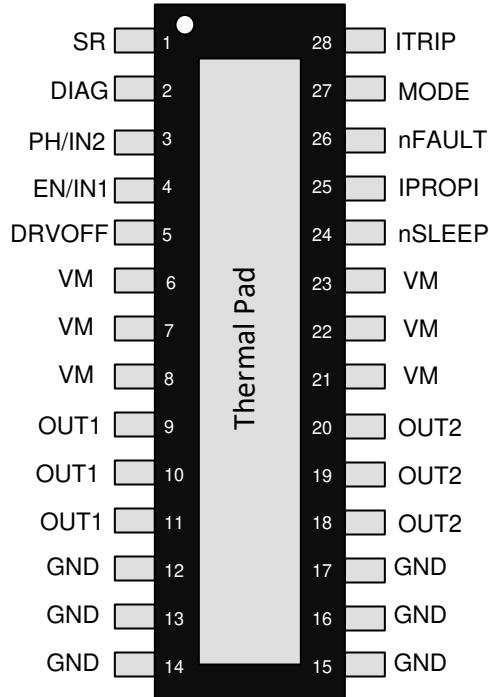

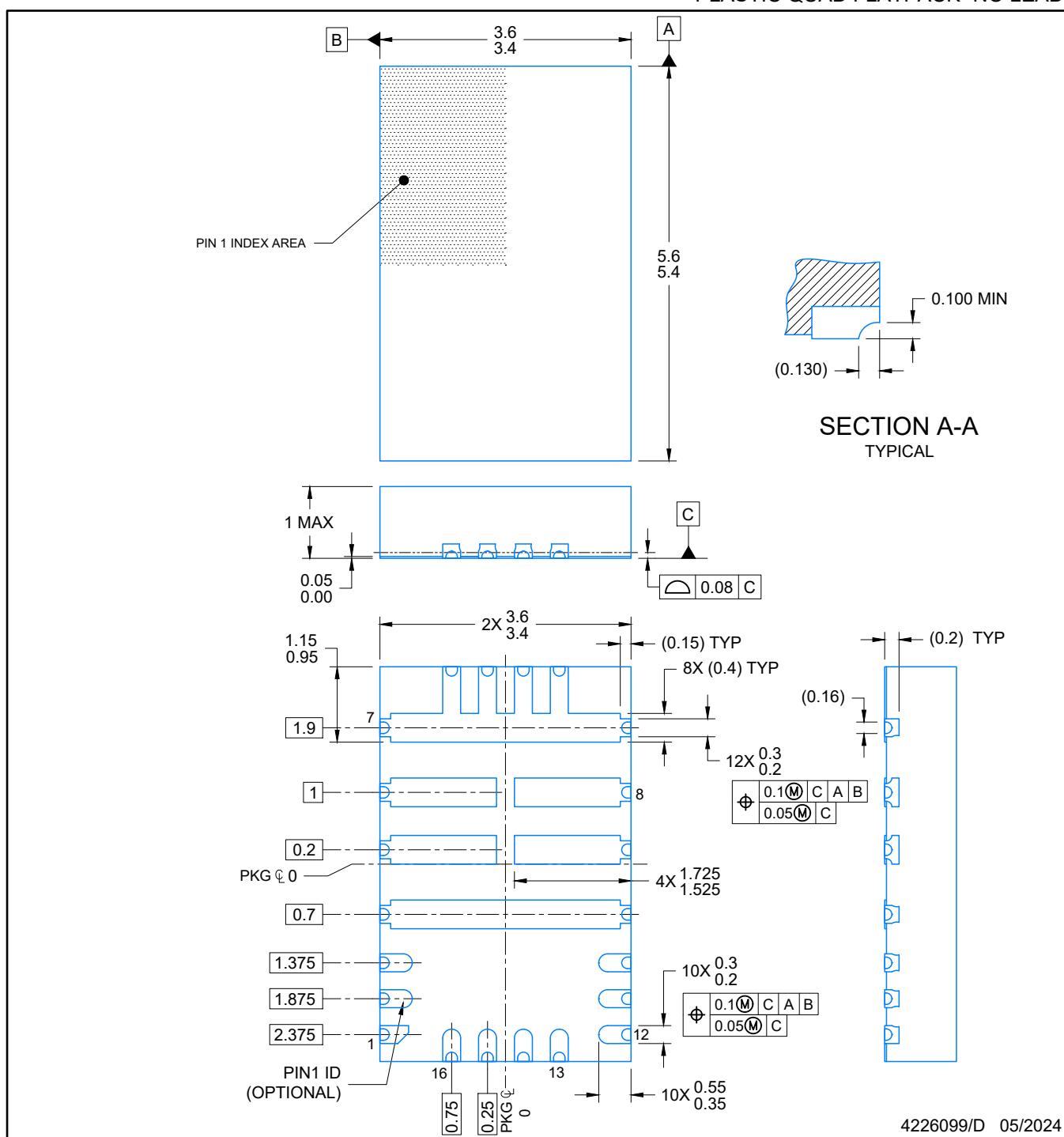

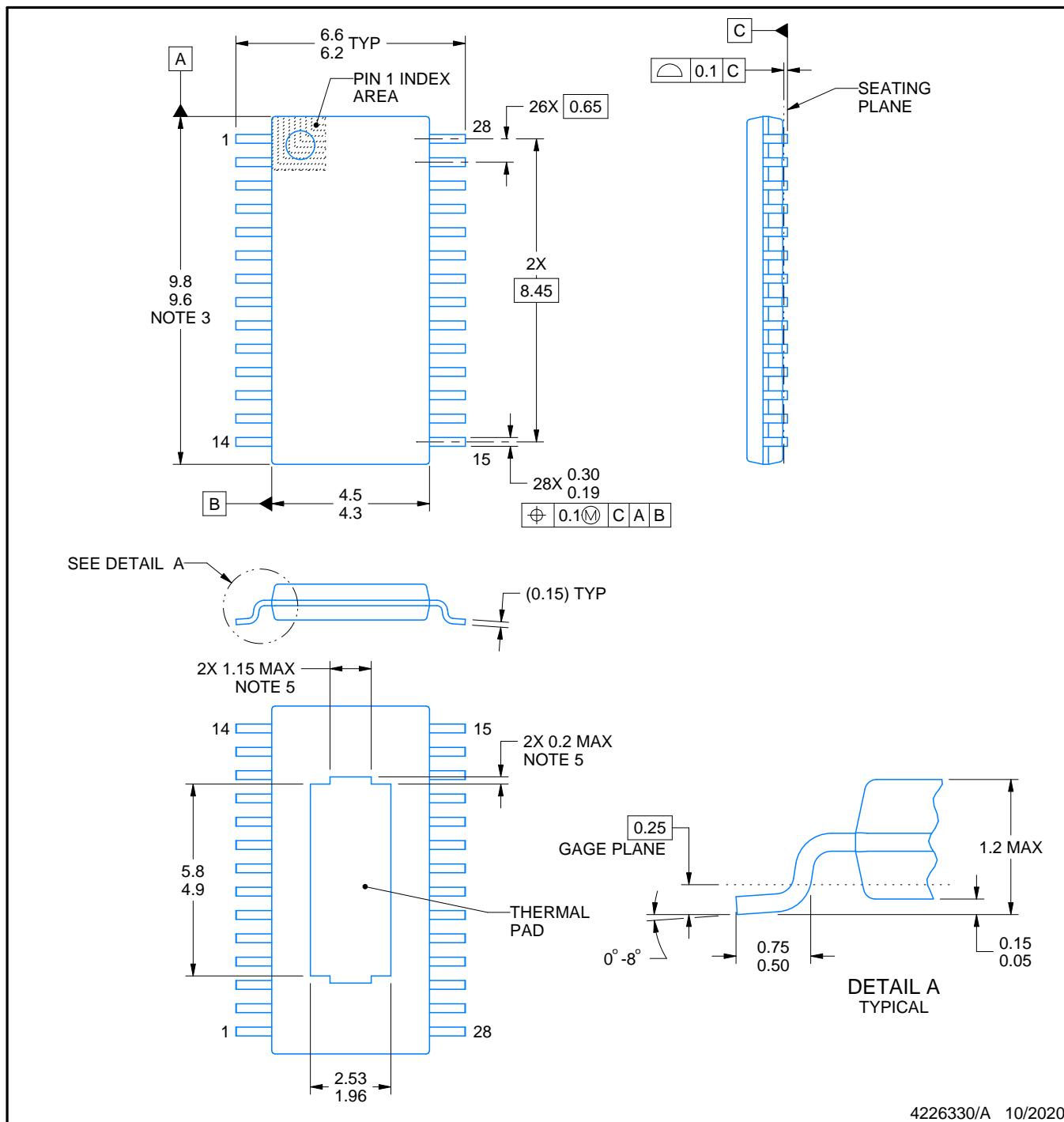

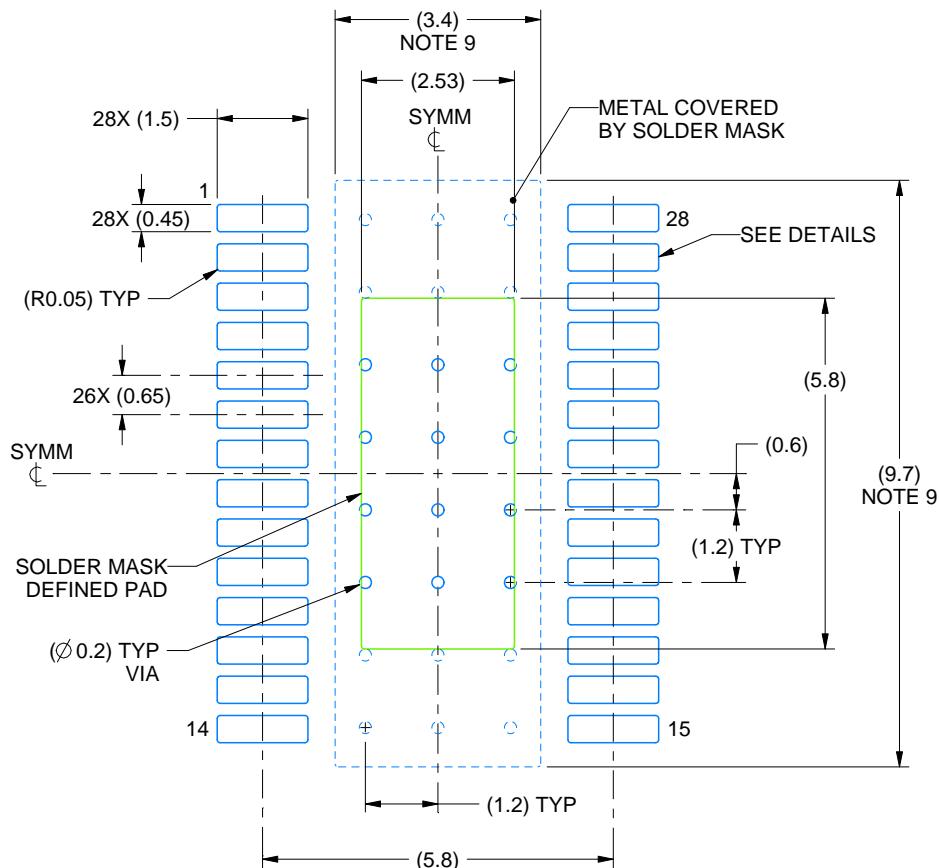

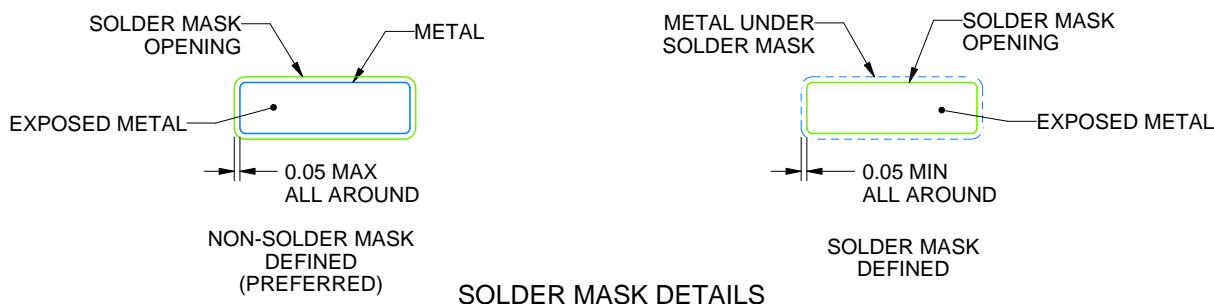

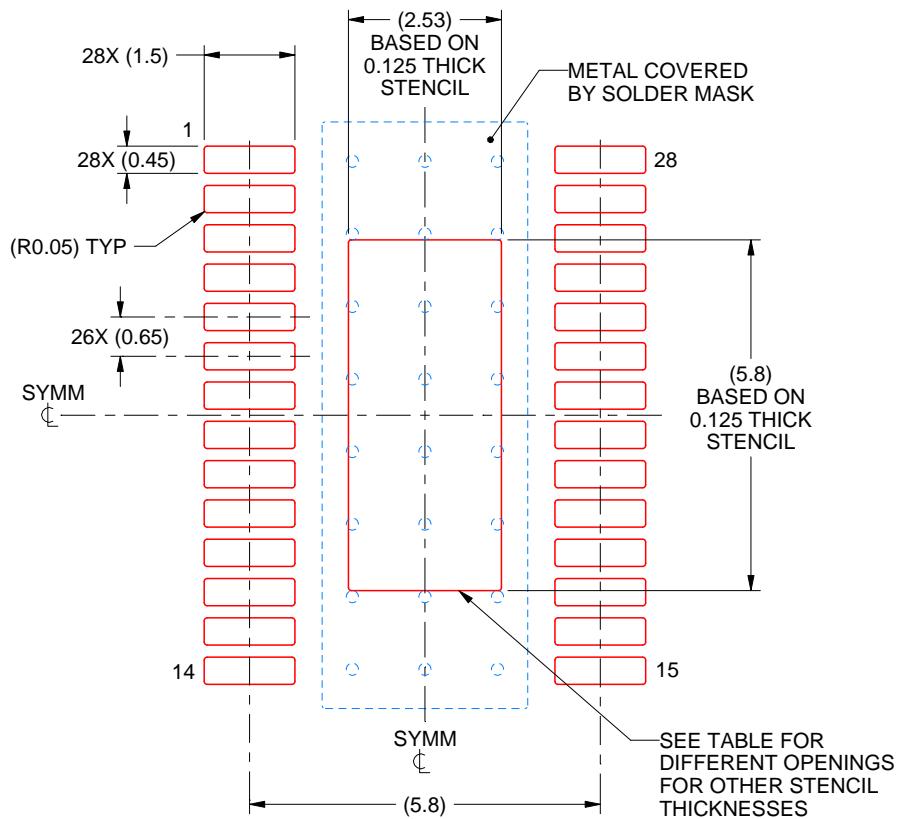

#### 6.1.1 HTSSOP (28) パッケージ

Figure not drawn to scale

図 6-1. DRV8245H-Q1 HW バリアント、HTSSOP (28) パッケージ

表 6-1. 端子機能

| ピン                     |        | タイプ <sup>(1)</sup> | 説明                                                                                                                              |

|------------------------|--------|--------------------|---------------------------------------------------------------------------------------------------------------------------------|

| 番号                     | 名称     |                    |                                                                                                                                 |

| 1                      | SR     | I                  | スルーレート制御用のデバイス構成ピン。詳細については、「デバイス構成」セクションのスルーレートを参照してください。                                                                       |

| 2                      | DIAG   | I                  | 負荷タイプ通知およびFAULT応答構成用のデバイス構成ピン。詳細については、「デバイス構成」セクションの DIAG を参照してください。                                                            |

| 3                      | PH/IN2 | I                  | ブリッジ動作用のコントローラ入力ピン。詳細については、「ブリッジ制御」セクションを参照してください。                                                                              |

| 4                      | EN/IN1 | I                  | ブリッジ動作用のコントローラ入力ピン。詳細については、「ブリッジ制御」セクションを参照してください。                                                                              |

| 5                      | DRVOFF | I                  | ブリッジを Hi-Z にするためのコントローラ入力ピン。詳細については、「ブリッジ制御」セクションを参照してください。                                                                     |

| 6, 7, 8, 21, 22, 23    | VM     | P                  | 電源。このピンはモーターの電源です。デバイスの電流能力に対応するため、他の VM ピン (合計 6 本) と組み合わせる必要があります。このピンは、0.1 $\mu$ F のセラミック・コンデンサとパルク・コンデンサを使用して GND にバイパスします。 |

| 9, 10, 11              | OUT1   | P                  | ハーフブリッジ出力 1。このピンは、モーターまたは負荷に接続します。デバイスの電流能力に対応するため、他の OUT1 ピン (合計 3 本) と組み合わせる必要があります。                                          |

| 12, 13, 14, 15, 16, 17 | GND    | G                  | グランド・ピン。デバイスの電流能力に対応するため、他の GND ピン (合計 6 本) と組み合わせる必要があります。                                                                     |

| 18, 19, 20             | OUT2   | P                  | ハーフブリッジ出力 2。このピンは、モーターまたは負荷に接続します。デバイス電流能力をサポートするため、他の OUT2 ピン (合計 3 本) と組み合わせる必要があります。                                         |

| 24                     | nSLEEP | I                  | スリープ用コントローラ入力ピン。詳細については、「ブリッジ制御」セクションを参照してください。                                                                                 |

**表 6-1. 端子機能 (continued)**

| ピン |        | タイプ <sup>(1)</sup> | 説明                                                                                     |

|----|--------|--------------------|----------------------------------------------------------------------------------------|

| 番号 | 名称     |                    |                                                                                        |

| 25 | IPROPI | I/O                | ドライバ負荷電流アナログ・フィードバック。詳細については、「デバイス構成」セクションの <a href="#">IPROPI</a> を参照してください。          |

| 26 | nFAULT | OD                 | コントローラへのFAULT通知。詳細については、「デバイス構成」セクションの <a href="#">nFAULT</a> を参照してください。               |

| 27 | MODE   | I                  | MODE のデバイス構成ピン。詳細については、「デバイス構成」セクションを参照してください。                                         |

| 28 | ITRIP  | I                  | ハイサイド電流制限の ITRIP レベル用のデバイス構成ピン。詳細については、「デバイス構成」セクションの <a href="#">ITRIP</a> を参照してください。 |

(1) I = 入力、O = 出力、I/O = 入力 / 出力、G = グランド、P = 電源、OD = オープン・ドレイン出力、PP = ブッシュブル出力

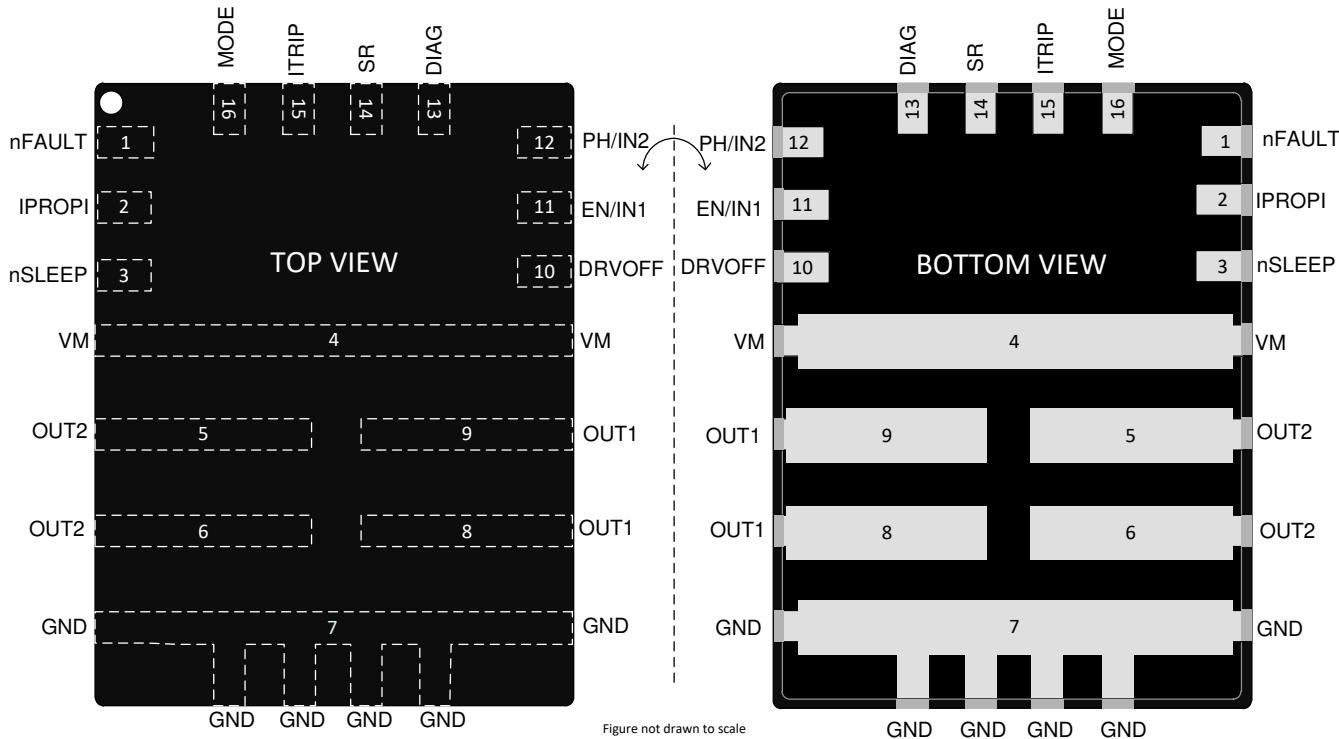

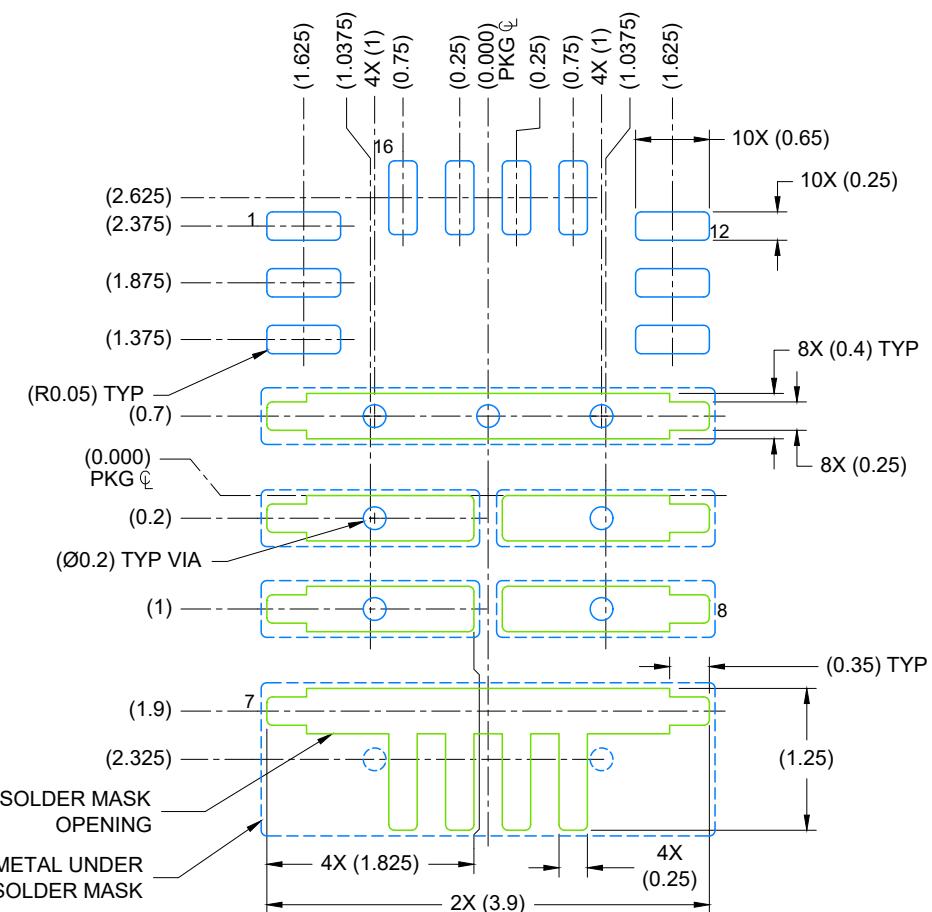

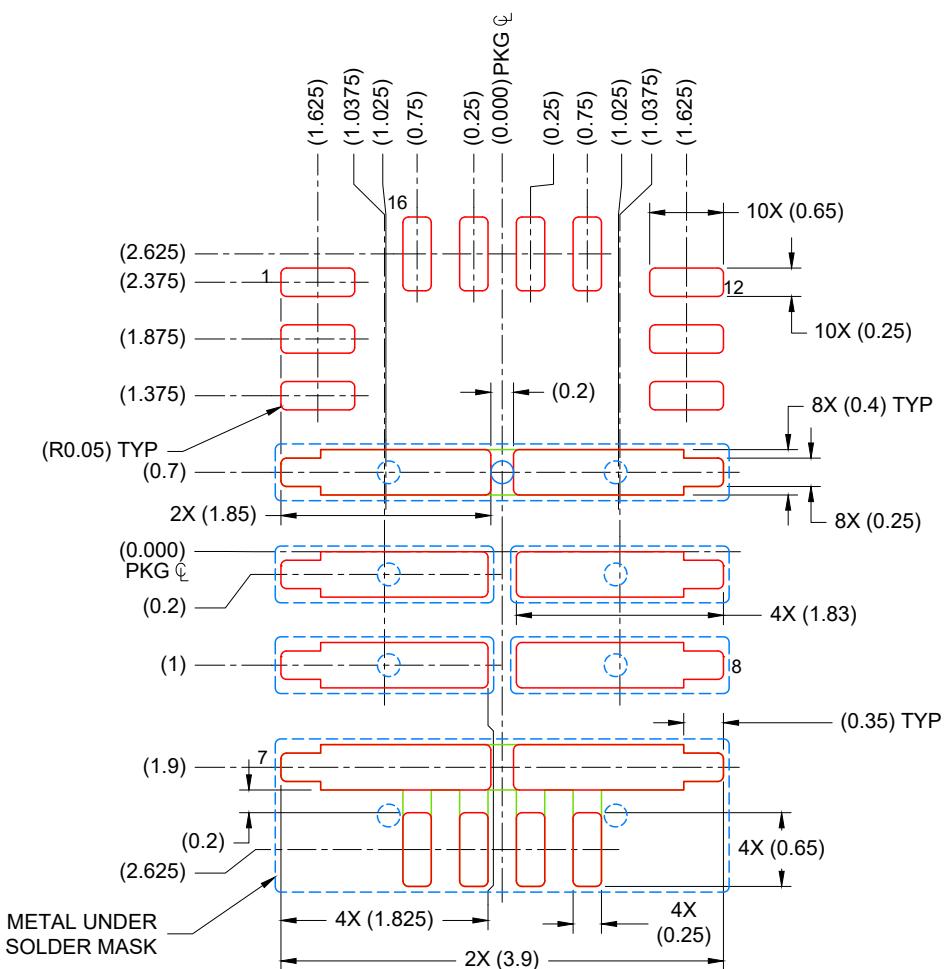

### 6.1.2 VQFN-HR (16) パッケージ

図 6-2. DRV8245H-Q1 HW バリアント、VQFN-HR (16) パッケージ

表 6-2. 端子機能

| ピン   |        | タイプ <sup>(1)</sup> | 説明                                                                            |

|------|--------|--------------------|-------------------------------------------------------------------------------|

| 番号   | 名称     |                    |                                                                               |

| 1    | nFAULT | OD                 | コントローラへのFAULT通知。詳細については、「デバイス構成」セクションの nFAULT を参照してください。                      |

| 2    | IPROPI | I/O                | ドライバ負荷電流アナログ・フィードバック。詳細については、「デバイス構成」セクションの IPROPI を参照してください。                 |

| 3    | nSLEEP | I                  | スリープ用コントローラ入力ピン。詳細については、「プリッジ制御」セクションを参照してください。                               |

| 4    | VM     | P                  | 電源。このピンはモーターの電源です。このピンは、0.1 $\mu$ F のセラミック・コンデンサとバルク・コンデンサを使用して GND にバイパスします。 |

| 5, 6 | OUT2   | P                  | ハーフプリッジ出力 2。このピンは、モーターまたは負荷に接続します。デバイスの電流能力に対応するため、他の OUT2 ピンと組み合わせる必要があります。  |

| 7    | GND    | G                  | グランド・ピン                                                                       |

| 8, 9 | OUT1   | P                  | ハーフプリッジ出力 1。このピンは、モーターまたは負荷に接続します。                                            |

| 10   | DRVOFF | I                  | プリッジを Hi-Z にするためのコントローラ入力ピン。詳細については、「プリッジ制御」セクションを参照してください。                   |

| 11   | EN/IN1 | I                  | プリッジ動作用のコントローラ入力ピン。詳細については、「プリッジ制御」セクションを参照してください。                            |

| 12   | PH/IN2 | I                  | プリッジ動作用のコントローラ入力ピン。詳細については、「プリッジ制御」セクションを参照してください。                            |

| 13   | DIAG   | I                  | 負荷タイプ通知およびFAULT応答構成用のデバイス構成ピン。詳細については、「デバイス構成」セクションで DIAG を参照してください。          |

| 14   | SR     | I                  | スルーレート制御用のデバイス構成ピン。詳細については、「デバイス構成」セクションのスルーレートを参照してください。                     |

| 15   | ITRIP  | I                  | ハイサイド電流制限の ITRIP レベル用のデバイス構成ピン。詳細については、「デバイス構成」セクションの ITRIP を参照してください。        |

表 6-2. 端子機能 (continued)

| ピン |      | タイプ (1) | 説明                                             |

|----|------|---------|------------------------------------------------|

| 番号 | 名称   |         |                                                |

| 16 | MODE | I       | MODE のデバイス構成ピン。詳細については、「デバイス構成」セクションを参照してください。 |

(1) I = 入力、O = 出力、I/O = 入力 / 出力、G = グランド、P = 電源、OD = オープン・ドレイン出力、PP = プッシュプル出力

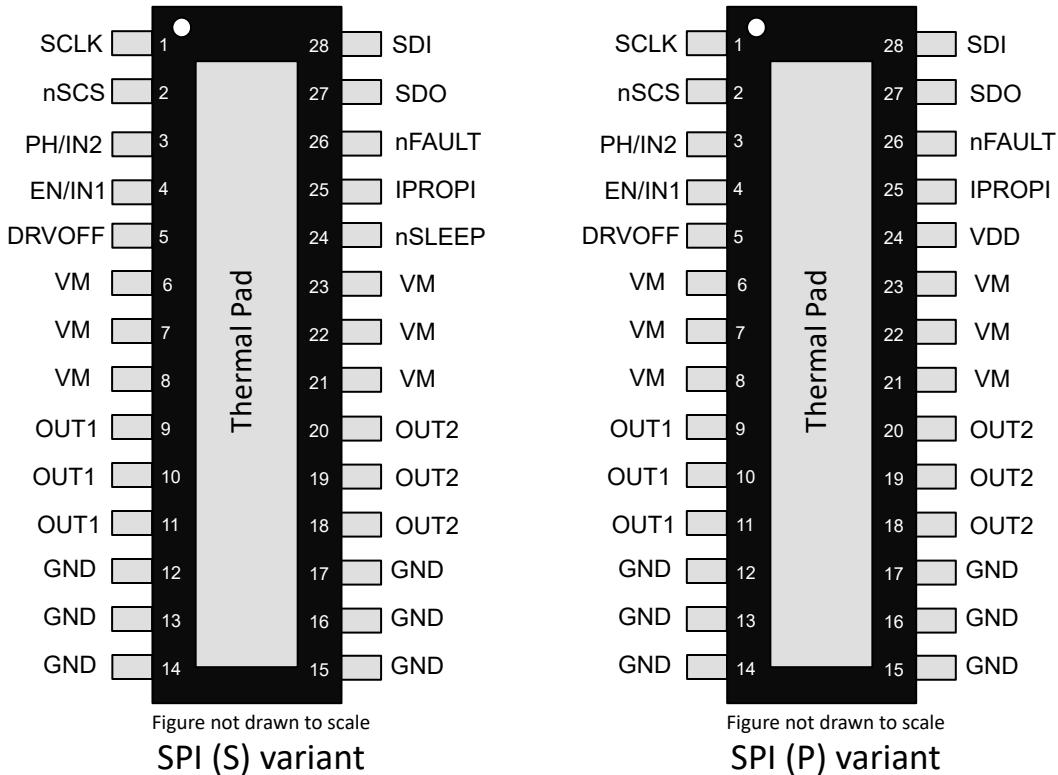

## 6.2 SPI バリアント

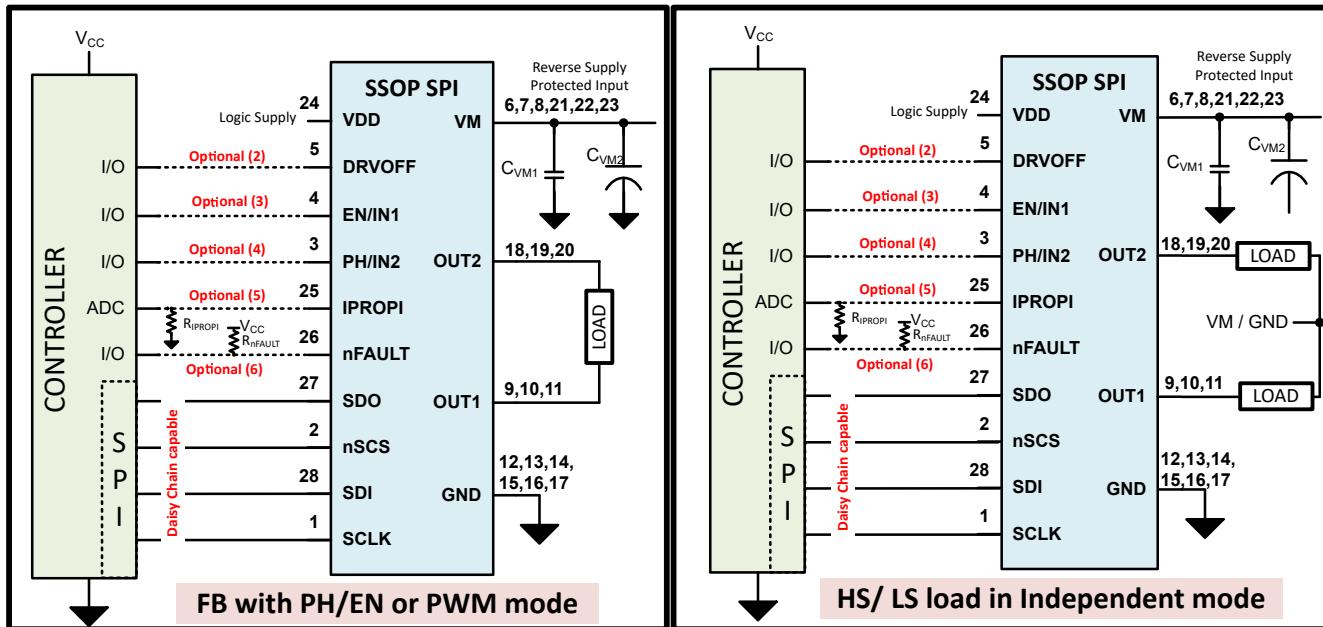

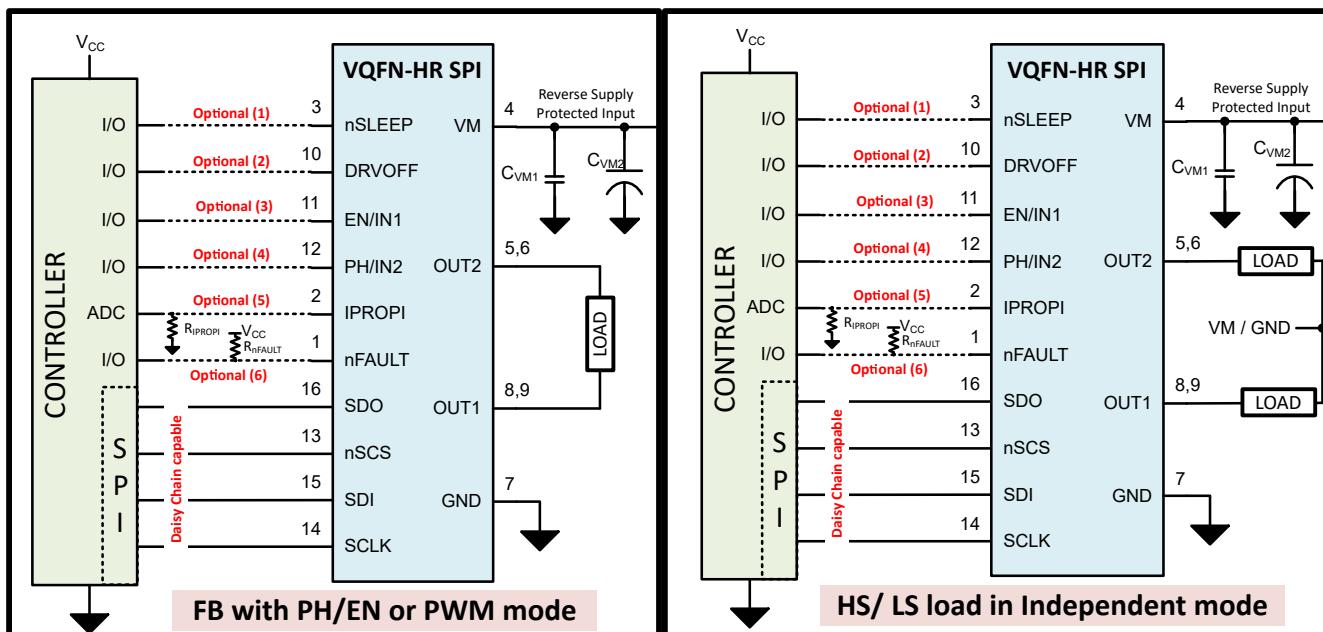

### 6.2.1 HTSSOP (28) パッケージ

図 6-3. DRV8245S-Q1 SPI バリアント、HTSSOP (28) パッケージ

表 6-3. 端子機能

| ピン                  |        | タイプ (1) | 説明                                                                                                                              |

|---------------------|--------|---------|---------------------------------------------------------------------------------------------------------------------------------|

| 番号                  | 名称     |         |                                                                                                                                 |

| 1                   | SCLK   | I       | SPI - シリアル・クロック入力。                                                                                                              |

| 2                   | nSCS   | I       | SPI - チップ・セレクト。このピンはアクティブ LOW で、シリアル・インターフェイス通信を有効にします。                                                                         |

| 3                   | PH/IN2 | I       | ブリッジ動作作用のコントローラ入力ピン。詳細については、「ブリッジ制御」セクションを参照してください。                                                                             |

| 4                   | EN/IN1 | I       | ブリッジ動作作用のコントローラ入力ピン。詳細については、「ブリッジ制御」セクションを参照してください。                                                                             |

| 5                   | DRVOFF | I       | ブリッジを Hi-Z にするためのコントローラ入力ピン。詳細については、「ブリッジ制御」セクションを参照してください。                                                                     |

| 6, 7, 8, 21, 22, 23 | VM     | P       | 電源。このピンはモーターの電源です。デバイスの電流能力に対応するため、他の VM ピン (合計 6 本) と組み合わせる必要があります。このピンは、0.1 $\mu$ F のセラミック・コンデンサとバルク・コンデンサを使用して GND にバイパスします。 |

| 9, 10, 11           | OUT1   | P       | ハーフブリッジ出力 1。このピンは、モーターまたは負荷に接続します。デバイスの電流能力に対応するため、他の OUT1 ピン (合計 3 本) と組み合わせる必要があります。                                          |

表 6-3. 端子機能 (continued)

| ピン                        |        | タイプ <sup>(1)</sup> | 説明                                                                                                                 |

|---------------------------|--------|--------------------|--------------------------------------------------------------------------------------------------------------------|

| 番号                        | 名称     |                    |                                                                                                                    |

| 12, 13, 14,<br>15, 16, 17 | GND    | G                  | グランド・ピン。デバイスの電流能力に対応するため、他の GND ピン (合計 6 本) と組み合わせる必要があります。                                                        |

| 18, 19, 20                | OUT2   | P                  | ハーフブリッジ出力 2。このピンは、モーターまたは負荷に接続します。デバイスの電流能力に対応するため、他の OUT2 ピン (合計 3 本) と組み合わせる必要があります。                             |

| 24                        | nSLEEP | I                  | SPI (S) バリアント: スリープ用コントローラ入力ピン。詳細については、「 <a href="#">ブリッジ制御</a> 」セクションを参照してください。このピンの電圧が SDO の VIO ロジック・レベルにもなります。 |

|                           | VDD    | P                  | SPI (P) バリアント: デバイスのロジック電源。                                                                                        |

| 25                        | IPROPI | I/O                | ドライバ負荷電流アナログ・フィードバック。詳細については、「 <a href="#">デバイス構成</a> 」セクションの <a href="#">IPROPI</a> を参照してください。                    |

| 26                        | nFAULT | OD                 | コントローラへのFAULT通知。詳細については、「 <a href="#">デバイス構成</a> 」セクションの <a href="#">nFAULT</a> を参照してください。                         |

| 27                        | SDO    | PP                 | SPI - シリアル・データ出力。データは、SCLK の立ち上がりエッジで更新されます。                                                                       |

| 28                        | SDI    | I                  | SPI - シリアル・データ入力。データは、SCLK の立ち下がりエッジでキャプチャされます。                                                                    |

(1) I = 入力、O = 出力、I/O = 入力 / 出力、G = グランド、P = 電源、OD = オープン・ドレイン出力、PP = プッシュプル出力

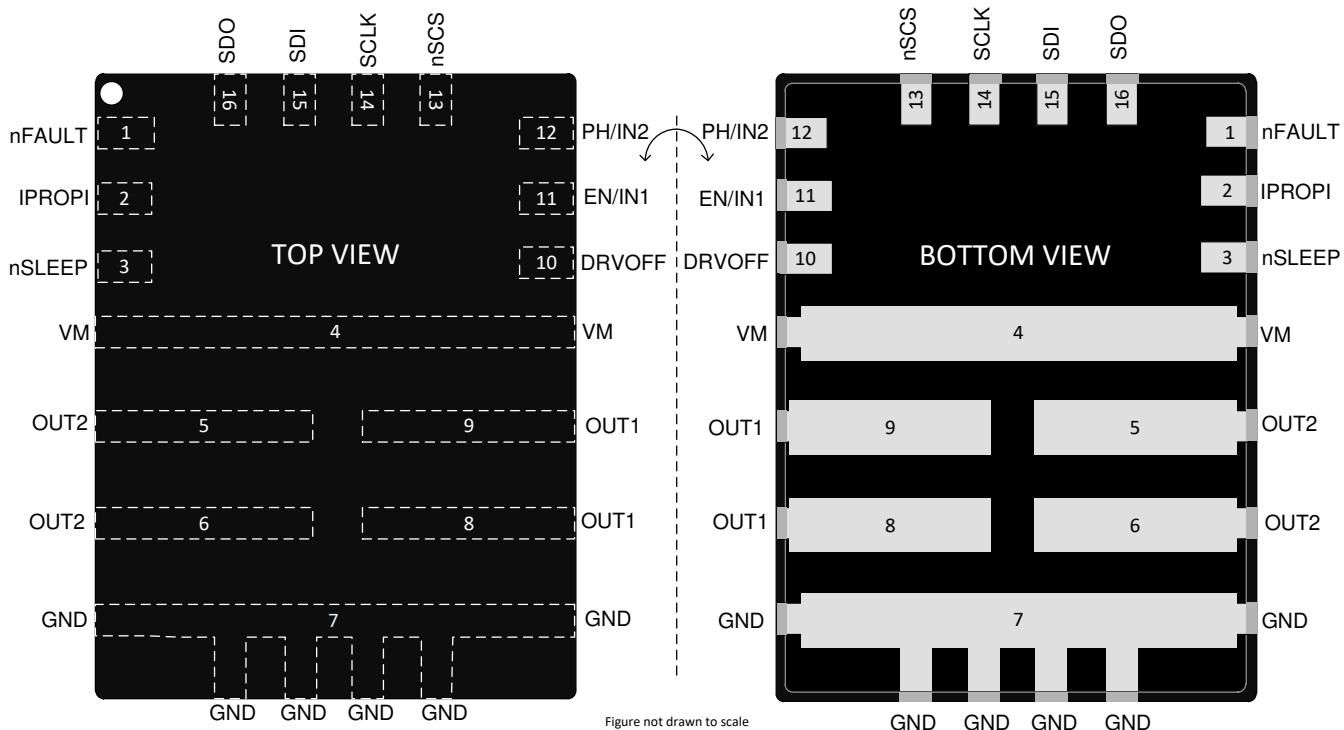

## 6.2.2 VQFN-HR (16) パッケージ

図 6-4. DRV8245S-Q1 SPI バリアント、VQFN-HR (16) パッケージ

表 6-4. 端子機能

| ピン   |        | タイプ (1) | 説明                                                                                |

|------|--------|---------|-----------------------------------------------------------------------------------|

| 番号   | 名称     |         |                                                                                   |

| 1    | nFAULT | OD      | コントローラへのFAULT通知。詳細については、「デバイス構成」セクションの nFAULT を参照してください。                          |

| 2    | IPROPI | I/O     | ドライバ負荷電流アナログ・フィードバック。詳細については、「デバイス構成」セクションの IPROPI を参照してください。                     |

| 3    | nSLEEP | I       | スリープ用コントローラ入力ピン。詳細については、「ブリッジ制御」セクションを参照してください。このピンの電圧が SDO の VIO ロジック・レベルにもなります。 |

| 4    | VM     | P       | 電源。このピンはモーターの電源です。このピンは、0.1 $\mu$ F のセラミック・コンデンサとバルク・コンデンサを使用して GND にバイパスします。     |

| 5, 6 | OUT2   | P       | ハーフブリッジ出力 2。このピンは、モーターまたは負荷に接続します。デバイスの電流能力に対応するため、他の OUT2 ピンと組み合わせる必要があります。      |

| 7    | GND    | G       | グランド・ピン                                                                           |

| 8, 9 | OUT1   | P       | ハーフブリッジ出力 1。このピンは、モーターまたは負荷に接続します。デバイスの電流能力を最大化するため、他の OUT1 ピンと組み合わせる必要があります。     |

| 10   | DRVOFF | I       | ブリッジを Hi-Z にするためのコントローラ入力ピン。詳細については、「ブリッジ制御」セクションを参照してください。                       |

| 11   | EN/IN1 | I       | ブリッジ動作用のコントローラ入力ピン。詳細については、「ブリッジ制御」セクションを参照してください。                                |

| 12   | PH/IN2 | I       | ブリッジ動作用のコントローラ入力ピン。詳細については、「ブリッジ制御」セクションを参照してください。                                |

| 13   | nSCS   | I       | SPI - チップ・セレクト。このピンはアクティブ LOW で、シリアル・インターフェイス通信を有効にします。                           |

| 14   | SCLK   | I       | SPI - シリアル・クロック入力。                                                                |

| 15   | SDI    | I       | SPI - シリアル・データ入力。データは、SCLK の立ち下がりエッジでキャプチャされます。                                   |

表 6-4. 端子機能 (continued)

| ピン |     | タイプ <sup>(1)</sup> | 説明                                           |

|----|-----|--------------------|----------------------------------------------|

| 番号 | 名称  |                    |                                              |

| 16 | SDO | PP                 | SPI - シリアル・データ出力。データは、SCLK の立ち上がりエッジで更新されます。 |

(1) I = 入力、O = 出力、I/O = 入力 / 出力、G = グランド、P = 電源、OD = オープン・ドレイン出力、PP = プッシュプル出力

## 7 仕様

### 7.1 絶対最大定格

動作温度範囲内 (特に記述のない限り)(1)

|                                |                        |  | 最小値                 | 最大値                   | 単位   |

|--------------------------------|------------------------|--|---------------------|-----------------------|------|

| 電源ピン電圧                         | VM                     |  | -0.3 <sup>(3)</sup> | 40                    | V    |

| 電源過渡電圧ランプ                      | VM                     |  |                     | 2                     | V/μs |

| 出力ピン電圧                         | OUT1, OUT2             |  | -0.9                | V <sub>VM</sub> + 0.9 | V    |

| 出力ピン電流                         | OUT1, OUT2             |  |                     | 内部で制限 <sup>(2)</sup>  | A    |

| ドライバ・ディセーブル・ピン電圧               | DRVOFF                 |  | -0.3                | 40                    | V    |

| ロジック I/O 電圧                    | EN/IN1, PH/IN2, nFAULT |  | -0.3                | 5.75                  | V    |

| HW バリアント - 構成ピン電圧              | MODE, ITRIP, SR, DIAG  |  | -0.3                | 5.75                  | V    |

| アナログ・フィードバック・ピン電圧              | IPROPI                 |  | -0.3                | 5.75                  | V    |

| スリープ・ピン電圧 (SPI (P) バリアントは該当なし) | nSLEEP                 |  | -0.3                | 40                    | V    |

| SPI I/O 電圧 - SPI バリアント         | SDI, SDO, nSCS, SCLK   |  | -0.3                | 5.75                  | V    |

| SPI (P) バリアント - ロジック電源         | VDD                    |  | -0.3                | 5.75                  | V    |

| SPI (P) バリアント - ロジック電源過渡電圧ランプ  | VDD                    |  |                     | 5                     | V/μs |

| 周囲温度、T <sub>A</sub>            |                        |  | -40                 | 125                   | °C   |

| 接合部温度、T <sub>J</sub>           |                        |  | -40                 | 150                   | °C   |

| 保存温度、T <sub>stg</sub>          |                        |  | -65                 | 150                   | °C   |

- (1) 「絶対最大定格」を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値を越える状態で本製品が正常に動作することを暗黙的に示すものではありません。

絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

- (2) デバイスの過電流および過熱保護機能により制限されます

- (3) 外部コンポーネントのサポートにより、ISO 7637 過渡パルスのテスト中に、この制限に対する短時間の違反を許容できます

### 7.2 ESD 定格

| V <sub>(ESD)</sub> | 静電気放電 | 人体モデル (HBM)、AEC Q100-002 <sup>(1)</sup><br>HBM ESD 分類レベル 2 準拠<br>デバイス帶電モデル (CDM)、AEC Q100-011CDM<br>ESD 分類レベル C4B 準拠 | VM、OUT1、OUT2、GND | ±4000 | V |

|--------------------|-------|----------------------------------------------------------------------------------------------------------------------|------------------|-------|---|

|                    |       |                                                                                                                      | その他のすべてのピン       | ±2000 |   |

|                    |       |                                                                                                                      | 角のピン             | ±750  |   |

|                    |       |                                                                                                                      | その他のピン           | ±500  |   |

- (1) AEC Q100-002 では、HBM ストレス試験を ANSI/ESDA/JEDEC JS-001 仕様に従って実施することを示しています。

## 7.3 推奨動作条件

動作温度範囲内 (特に記述のない限り)

|                |                          |                                        | 最小値 | 最大値                | 単位  |

|----------------|--------------------------|----------------------------------------|-----|--------------------|-----|

| $V_{VM}$       | 電源電圧                     | $VM$                                   | 4.5 | 35 <sup>(1)</sup>  | V   |

| $V_{VDD}$      | SPI (P) バリアント - ロジック電源電圧 | $VDD$                                  | 4.5 | 5.5                | V   |

| $V_{LOGIC}$    | ロジック・ピン電圧                | EN/IN1, PH/IN2, nSLEEP, DRVOFF, nFAULT | 0   | 5.5                | V   |

| $f_{PWM}$      | PWM 周波数                  | EN/IN1, PH/IN2                         | 0   | 25                 | kHz |

| $V_{CONFIG}$   | HW バリアント - 構成ピン電圧        | MODE, ITRIP, SR, DIAG                  | 0   | 5.5                | V   |

| $V_{IPROPI}$   | アナログ・フィードバック電圧           | IPROPI                                 | 0   | 5.5                | V   |

| $V_{SPI\_IOS}$ | SPI (S) バリアント - SPI ピン電圧 | SDI, SDO, nSCS, SCLK                   | 0   | $V_{nSLEEP} + 0.5$ | V   |

|                | SPI (P) バリアント - SPI ピン電圧 | SDI, SDO, nSCS, SCLK                   | 0   | $V_{VDD} + 0.5$    | V   |

| $T_A$          | 動作時周囲温度                  |                                        | -40 | 125                | °C  |

| $T_J$          | 動作時接合部温度                 |                                        | -40 | 150                | °C  |

- (1) 過電流保護機能は、28V を超える電圧で、短絡インダクタンスが  $1\mu H$  未満の場合、OUTx から VM または GND への短絡をサポートしていません。

## 7.4 熱に関する情報

アプリケーションに関する使用例については、「[過渡熱インピーダンス](#)」表を参照してください。

| 熱評価基準 <sup>(1)</sup> |                     | HTSSOP パッケージ | VQFN-HR パッケージ | 単位   |

|----------------------|---------------------|--------------|---------------|------|

| $R_{\theta JA}$      | 接合部から周囲への熱抵抗        | 27.7         | 41.3          | °C/W |

| $R_{\theta JC(top)}$ | 接合部からケース (上面) への熱抵抗 | 13.8         | 14.4          | °C/W |

| $R_{\theta JB}$      | 接合部から基板への熱抵抗        | 7.1          | 5.5           | °C/W |

| $\Psi_{JT}$          | 接合部から上面への熱特性パラメータ   | 0.6          | 0.3           | °C/W |

| $\Psi_{JB}$          | 接合部から基板への熱特性パラメータ   | 7.1          | 5.4           | °C/W |

| $R_{\theta JC(bot)}$ | 接合部からケース (下面) への熱抵抗 | 0.9          | N/A           | °C/W |

- (1) 従来および最新の熱評価基準の詳細については、『[半導体およびICパッケージの熱評価基準](#)』アプリケーション・レポートを参照してください。

## 7.5 電気的特性

$4.5\text{ V}$  (立ち下がり)  $\leq V_{VM} \leq 35\text{ V}$ ,  $-40^\circ\text{C} \leq T_J \leq 150^\circ\text{C}$  (特に記述のない限り)

SPI (P) バリアントのみ:  $4.5\text{V} \leq V_{VDD} \leq 5.5\text{V}$  (特に記述のない限り)

### 7.5.1 電源および初期化

ウェークアップ遷移波形を参照してください

| パラメータ         | テスト条件           | 最小値                                                                                                                   | 代表値 | 最大値 | 単位            |

|---------------|-----------------|-----------------------------------------------------------------------------------------------------------------------|-----|-----|---------------|

| $V_{VM\_REV}$ | 逆電流時の電源ピン電圧     | $I_{VM} = -5\text{A}$ 、電源が供給されていない状態のデバイス                                                                             | 1.4 |     | V             |

| $I_{VMQ}$     | スリープ状態の VM 電流   | $V_{VM} = 13.5\text{V}$ , $V_{nSLEEP} = 0\text{V}$ または $V_{VDD} < \text{POR}_{VDD\_FALL}$ , $T_A = 25^\circ\text{C}$  | 1   |     | $\mu\text{A}$ |

|               |                 | $V_{VM} = 13.5\text{V}$ , $V_{nSLEEP} = 0\text{V}$ または $V_{VDD} < \text{POR}_{VDD\_FALL}$ , $T_A = 125^\circ\text{C}$ |     | 13  | $\mu\text{A}$ |

| $I_{VMS}$     | スタンバイ状態の VM 電流  | $V_{VM} = 13.5\text{V}$                                                                                               | 3   | 5   | mA            |

| $I_{VDD}$     | アクティブ状態の VDD 電流 | SPI (P) バリアント                                                                                                         |     | 10  | mA            |

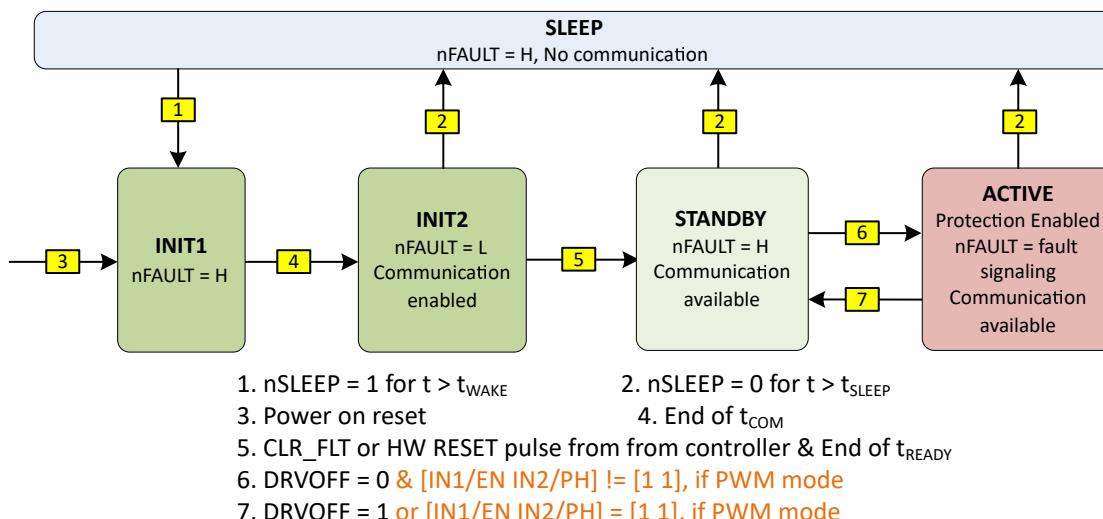

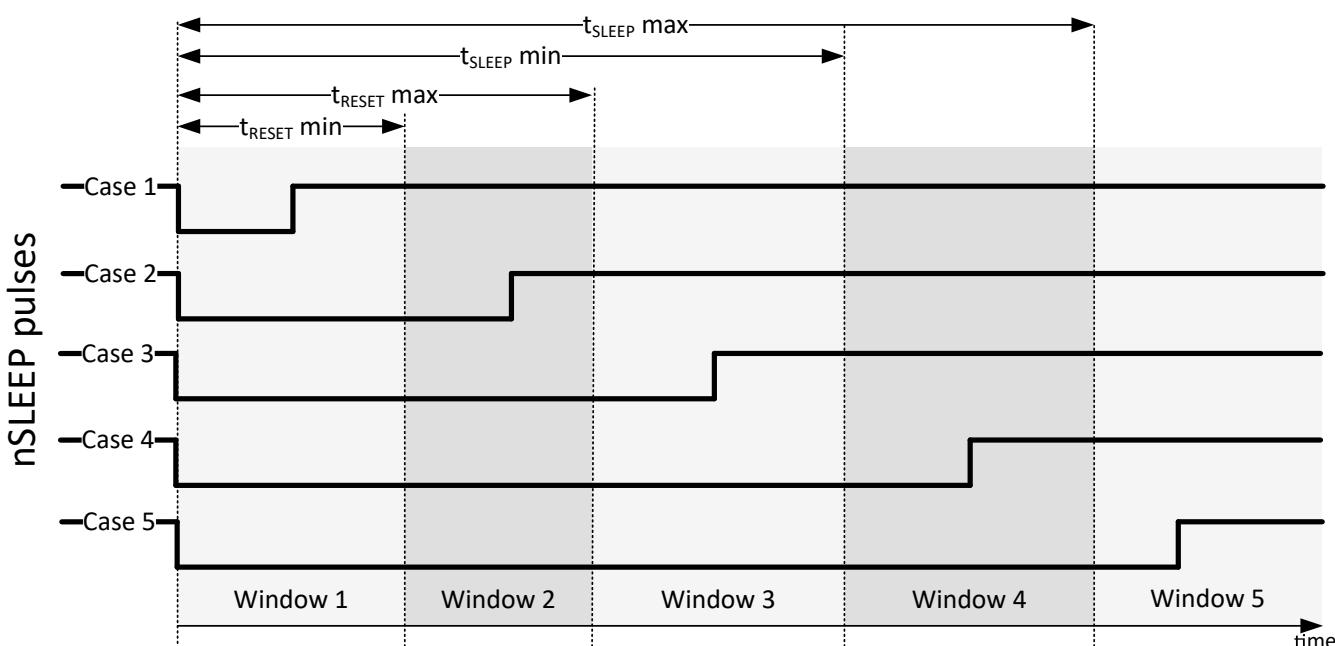

| $t_{RESET}$   | リセット・パルスのフィルタ時間 | $nSLEEP$ ピンでのリセット信号、HW (H) バリアント                                                                                      | 5   | 20  | $\mu\text{s}$ |

| パラメータ            |                                                                       | テスト条件                                                                                           | 最小値 | 代表値 | 最大値 | 単位            |

|------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-----|-----|-----|---------------|

| $t_{SLEEP}$      | スリープ・コマンドのフィルタ時間                                                      | nSLEEP ピンでのスリープ信号、HW (H) バリエント                                                                  | 40  |     | 120 | $\mu\text{s}$ |

| $t_{SLEEP\_SPI}$ | スリープ・コマンドのフィルタ時間                                                      | nSLEEP ピンでのスリープ信号、SPI (S) バリエント                                                                 | 5   |     | 20  | $\mu\text{s}$ |

| $t_{WAKEUP}$     | ウェークアップ・コマンドのフィルタ時間                                                   | nSLEEP ピンでのウェークアップ信号、HW および SPI (S) バリエント                                                       |     | 10  |     | $\mu\text{s}$ |

| $t_{COM}$        | VM または VDD 電源ピンによるウェークアップまたはパワーアップ後、通信が利用可能になるまでの時間                   | nSLEEP ピンでのウェークアップ信号または電源サイクル - $V_{VM} > V_{M_{POR\_RISE}}$ または $V_{VDD} > V_{DD_{POR\_RISE}}$ |     |     | 400 | $\mu\text{s}$ |

| $t_{READY}$      | nSLEEP ピンによるウェークアップ後、または、VM もしくは VDD 電源ピンによるパワーアップ後、ドライバが動作可能になるまでの時間 | nSLEEP ピンでのウェークアップ信号または電源サイクル - $V_{VM} > V_{M_{POR\_RISE}}$ または $V_{VDD} > V_{DD_{POR\_RISE}}$ |     |     | 1   | ms            |

### 7.5.2 ロジック I/O

| パラメータ              |                                          | 測定条件                      | 最小   | 標準  | 最大   | 単位               |

|--------------------|------------------------------------------|---------------------------|------|-----|------|------------------|

| $V_{IL\_nSLEEP}$   | ロジック LOW 入力電圧                            | nSLEEP ピン                 |      |     | 0.65 | V                |

| $V_{IH\_nSLEEP}$   | ロジック HIGH 入力電圧                           | nSLEEP ピン                 | 1.55 |     |      | V                |

| $V_{IHYS\_nSLEEP}$ | 入力ヒステリシス                                 | nSLEEP ピン                 |      | 200 |      | $\text{mV}$      |

| $V_{IL}$           | ロジック LOW 入力電圧                            | DRVOFF、EN/IN1、PH/IN2 の各ピン |      |     | 0.7  | V                |

| $V_{IH}$           | ロジック HIGH 入力電圧                           | DRVOFF、EN/IN1、PH/IN2 の各ピン | 1.5  |     |      | V                |

| $V_{IHYS}$         | 入力ヒステリシス                                 | DRVOFF、EN/IN1、PH/IN2 の各ピン |      | 100 |      | $\text{mV}$      |

| $R_{PD\_nSLEEP}$   | 内部で nSLEEP を GND へプルダウンする抵抗              | 最小 VIL レベルで測定             | 100  |     | 400  | $\text{k}\Omega$ |

| $R_{PU}$           | 内部で DRVOFF を VDD へプルアップする抵抗 (逆電流はブロック)   | 最小 VIH レベルで測定             | 200  |     | 550  | $\text{k}\Omega$ |

| $R_{PD}$           | 内部で EN/IN1 および PH/IN2 を GND へプルダウンする抵抗   | 最大 VIL レベルで測定             | 200  |     | 500  | $\text{k}\Omega$ |

| $I_{nFAULT\_PD}$   | nFAULT ピンが LOW にアサートされたとき GND へ流れ込むシンク電流 | $V_{OUT} = 0.3 \text{ V}$ | 5    |     |      | mA               |

### 7.5.3 SPI I/O

| パラメータ          |                                      | 測定条件                                                                | 最小  | 標準  | 最大  | 単位               |

|----------------|--------------------------------------|---------------------------------------------------------------------|-----|-----|-----|------------------|

| $R_{PU\_nSCS}$ | 内部で nSCS を VDD へプルアップする抵抗 (逆電流はブロック) | 最小 VIH レベルで測定                                                       | 200 |     | 500 | $\text{k}\Omega$ |

| $R_{PD\_SPI}$  | 内部で SDI、SCLK を GND へプルダウンする抵抗        | 最大 VIL レベルで測定                                                       | 150 |     | 500 | $\text{k}\Omega$ |

| $V_{IL}$       | ロジック LOW 入力電圧                        | SDI、SCLK、nSCS の各ピン                                                  |     |     | 0.7 | V                |

| $V_{IH}$       | ロジック HIGH 入力電圧                       | SDI、SCLK、nSCS の各ピン                                                  | 1.5 |     |     | V                |

| $V_{IHYS}$     | 入力ヒステリシス                             | SDI、SCLK、nSCS の各ピン                                                  |     | 100 |     | $\text{mV}$      |

| $V_{OL\_SDO}$  | ロジック LOW 出力電圧                        | SDO ～ 0.5mA シンク                                                     |     |     | 0.4 | V                |

| $V_{OH\_SDO}$  | SPI (S) バリエントのロジック HIGH 出力電圧         | SDO から 0.5mA ソース、 $V_{nSLEEP} = 5\text{V}$ 、 $V_{VM} > 7\text{V}$   | 4.1 |     |     | V                |

|                |                                      | SDO から 0.5mA ソース、 $V_{nSLEEP} = 3.3\text{V}$ 、 $V_{VM} > 5\text{V}$ | 2.7 |     |     | V                |

|                | SPI (P) バリエントのロジック HIGH 出力電圧         | SDO から 0.5 mA ソース、 $V_{VDD} = 5\text{V}$                            | 4.5 |     |     | V                |

| パラメータ             |                                              | 測定条件                                             | 最小 | 標準 | 最大  | 単位 |

|-------------------|----------------------------------------------|--------------------------------------------------|----|----|-----|----|

| $V_{OH\_SDO\_NL}$ | 無負荷時の SDO のロジック HIGH 出力電圧、SPI (S) バリアントでのみ有効 | SDO からの電流なし、 $V_{nSLEEP} = 5V$ 、 $V_{VM} > 7V$   |    |    | 5.5 | V  |

|                   |                                              | SDO からの電流なし、 $V_{nSLEEP} = 3.3V$ 、 $V_{VM} > 5V$ |    |    | 3.8 | V  |

#### 7.5.4 構成ピン - HW バリアントのみ

| パラメータ                               |             | テスト条件                   | 最小値  | 代表値 | 最大値  | 単位        |

|-------------------------------------|-------------|-------------------------|------|-----|------|-----------|

| <i>ITRIP, SR, およびDIAG の 6 レベル設定</i> |             |                         |      |     |      |           |

| $R_{LVL1OF6}$                       | 6 段階の レベル 1 | GND に接続                 |      |     | 10   | $\Omega$  |

| $R_{LVL2OF6}$                       | 6 段階の レベル 2 | GND との間に $\pm 10\%$ の抵抗 | 7.4  | 8.2 | 9    | $k\Omega$ |

| $R_{LVL3OF6}$                       | 6 段階の レベル 3 | GND との間に $\pm 10\%$ の抵抗 | 19.8 | 22  | 24.2 | $k\Omega$ |

| $R_{LVL4OF6}$                       | 6 段階の レベル 4 | GND との間に $\pm 10\%$ の抵抗 | 42.3 | 47  | 51.7 | $k\Omega$ |

| $R_{LVL5OF6}$                       | 6 段階の レベル 5 | GND との間に $\pm 10\%$ の抵抗 | 90   | 100 | 110  | $k\Omega$ |

| $R_{LVL6OF6}$                       | 6 段階の レベル 6 | Hi-Z (接続なし)             | 250  |     |      | $k\Omega$ |

| <i>MODE の 3 レベル設定</i>               |             |                         |      |     |      |           |

| $R_{LVL1OF3}$                       | 3 段階の レベル 1 | GND に接続                 |      |     | 10   | $\Omega$  |

| $R_{LVL2OF3}$                       | 3 段階の レベル 2 | GND との間に $\pm 10\%$ の抵抗 | 7.4  | 8.2 | 9    | $k\Omega$ |

| $R_{LVL3OF3}$                       | 3 段階の レベル 3 | Hi-Z (接続なし)             | 250  |     |      | $k\Omega$ |

#### 7.5.5 パワー FET パラメータ

$V_{VM} = 13.5V$  で測定

| パラメータ        |                                                     | テスト条件                             | 最小値 | 代表値  | 最大値  | 単位        |

|--------------|-----------------------------------------------------|-----------------------------------|-----|------|------|-----------|

| $R_{HS\_ON}$ | ハイサイド FET オン抵抗、HTSSOP パッケージ                         | $I_{OUT} = 6A, T_J = 25^\circ C$  |     | 20   |      | $m\Omega$ |

|              |                                                     | $I_{OUT} = 6A, T_J = 150^\circ C$ |     |      | 38   | $m\Omega$ |

|              | ハイサイド FET オン抵抗、VQFN-HR パッケージ                        | $I_{OUT} = 6A, T_J = 25^\circ C$  |     | 15.6 |      | $m\Omega$ |

|              |                                                     | $I_{OUT} = 6A, T_J = 150^\circ C$ |     |      | 30.4 | $m\Omega$ |

| $R_{LS\_ON}$ | ローサイド FET オン抵抗、HTSSOP パッケージ                         | $I_{OUT} = 6A, T_J = 25^\circ C$  |     | 20   |      | $m\Omega$ |

|              |                                                     | $I_{OUT} = 6A, T_J = 150^\circ C$ |     |      | 38   | $m\Omega$ |

|              | ローサイド FET オン抵抗、VQFN-HR パッケージ                        | $I_{OUT} = 6A, T_J = 25^\circ C$  |     | 15.2 |      | $m\Omega$ |

|              |                                                     | $I_{OUT} = 6A, T_J = 150^\circ C$ |     |      | 30.4 | $m\Omega$ |

| $V_{SD}$     | ボディ・ダイオードが順バイアスされたときのローサイドおよびハイサイド FET ソース - ドレイン電圧 | $I_{OUT} = \pm 6A$ (両方向)          | 0.4 | 0.9  | 1.5  | V         |

| $R_{Hi-Z}$   | スリープまたはスタンバイ状態での GND に対する OUT 抵抗                    | $V_{OUTx} = V_{VM} = 13.5V$       | 0.9 |      | 5.63 | $k\Omega$ |

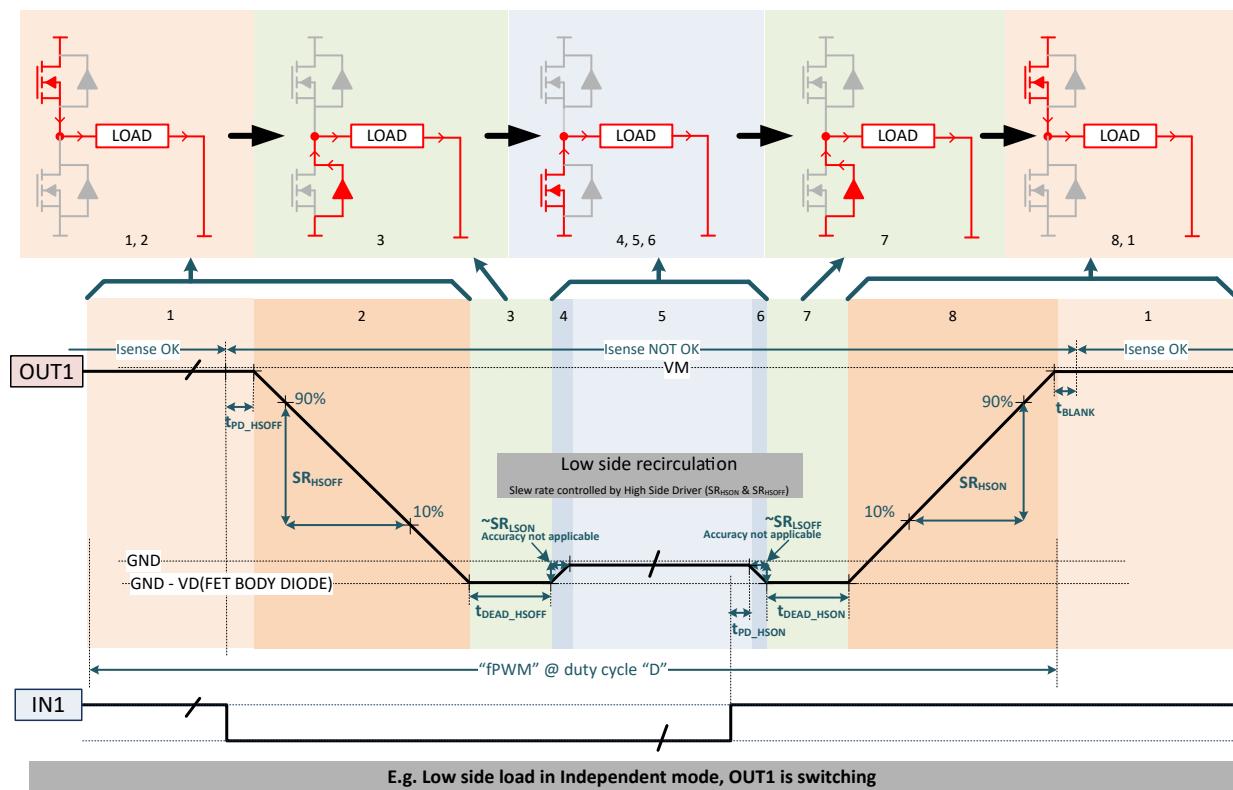

#### 7.5.6 ハイサイド還流のスイッチング・パラメータ

負荷 =  $1.5mH / 4.7\Omega$ 、 $V_{VM} = 13.5V$ 、ハイサイド還流波形を参照

| パラメータ                   |                               | テスト条件                                    | 最小値 | 代表値  | 最大値 | 単位   |

|-------------------------|-------------------------------|------------------------------------------|-----|------|-----|------|

| SR <sub>LSOFF</sub>     | 出力電圧立ち上がり時間、10%～90%           | SR = 3'b000 または LVL2                     |     | 1.5  |     | V/μs |

|                         |                               | SR = 3'b001 (SPI のみ)                     |     | 5    |     | V/μs |

|                         |                               | SR = 3'b010 (SPI のみ)                     |     | 9.8  |     | V/μs |

|                         |                               | SR = 3'b011 または LVL3                     |     | 14   |     | V/μs |

|                         |                               | SR = 3'b100 または LVL4                     |     | 20   |     | V/μs |

|                         |                               | SR = 3'b101 または LVL1                     |     | 26   |     | V/μs |

|                         |                               | SR = 3'b110 または LVL6                     |     | 38   |     | V/μs |

|                         |                               | SR = 3'b111 または LVL5                     |     | 50   |     | V/μs |

| t <sub>PD_LSOFF</sub>   | 出力電圧上昇時の伝搬時間                  | SR = 3'b000 または LVL2                     |     | 1.1  |     | μs   |

|                         |                               | SR = 3'b001 (SPI のみ)                     |     | 0.9  |     | μs   |

|                         |                               | SR = 3'b010 (SPI のみ)                     |     | 0.8  |     | μs   |

|                         |                               | SR = 3'b011 または LVL3                     |     | 0.7  |     | μs   |

|                         |                               | SR = 3'b100 および 3'b101 または LVL4 および LVL1 |     | 0.6  |     | μs   |

|                         |                               | SR = 3'b110 および 3'b111 または LVL6 および LVL5 |     | 0.5  |     | μs   |

| t <sub>DEAD_LSOFF</sub> | 出力電圧上昇時のデッドタイム                | すべての SR                                  |     | 0.9  |     | μs   |

| SR <sub>LSON</sub>      | 出力電圧立ち下がり時間、90%～10%           | SR = 3'b000 または LVL2                     |     | 1.5  |     | V/μs |

|                         |                               | SR = 3'b001 (SPI のみ)                     |     | 5    |     | V/μs |

|                         |                               | SR = 3'b010 (SPI のみ)                     |     | 9.8  |     | V/μs |

|                         |                               | SR = 3'b011 または LVL3                     |     | 14   |     | V/μs |

|                         |                               | SR = 3'b100 または LVL4                     |     | 20   |     | V/μs |

|                         |                               | SR = 3'b101 または LVL1                     |     | 26   |     | V/μs |

|                         |                               | SR = 3'b110 または LVL6                     |     | 38   |     | V/μs |

|                         |                               | SR = 3'b111 または LVL5                     |     | 50   |     | V/μs |

| t <sub>PD_LSON</sub>    | 出力電圧下降時の伝搬時間                  | SR = 3'b000 または LVL2                     |     | 0.2  |     | μs   |

|                         |                               | SR = 3'b001 (SPI のみ)                     |     | 0.2  |     | μs   |

|                         |                               | SR = 3'b010 (SPI のみ)                     |     | 0.2  |     | μs   |

|                         |                               | SR = 3'b011 または LVL3                     |     | 0.4  |     | μs   |

|                         |                               | SR = 3'b100 または 3'b101 または LVL4 または LVL1 |     | 0.3  |     | μs   |

|                         |                               | SR = 3'b110 または 3'b111 または LVL6 または LVL5 |     | 0.2  |     | μs   |

| t <sub>DEAD_LSON</sub>  | 出力電圧下降時のデッドタイム                | SR = 3'b000 または LVL2                     |     | 1.5  |     | μs   |

|                         |                               | SR = 3'b001 または 3'b010 (SPI のみ)          |     | 0.6  |     | μs   |

|                         |                               | その他すべての SR                               |     | 0.85 |     | μs   |

| MatchSRLS               | 出力電圧の立ち上がりと立ち下がりのスルーレートのマッチング | すべての SR                                  | -20 |      | +20 | %    |

### 7.5.7 ローサイド還流のスイッチング・パラメータ

負荷 =  $1.5mH / 4.7\Omega$ 、 $V_{VM} = 13.5V$ 、[ローサイド還流](#)波形を参照

| パラメータ             |                                                                | テスト条件                                      | 最小値 | 代表値  | 最大値 | 単位        |

|-------------------|----------------------------------------------------------------|--------------------------------------------|-----|------|-----|-----------|

| $SR_{HSON}$       | 出力電圧立ち上がり時間、10%~90%                                            | すべての SR                                    |     | 10   |     | $V/\mu s$ |

| $t_{PD\_HSON}$    | 出力電圧上昇時の伝搬時間                                                   | SR = 3'b000 または LVL2                       |     | 4.2  |     | $\mu s$   |

|                   |                                                                | SR = 3'b001 (SPI のみ)                       |     | 2    |     | $\mu s$   |

|                   |                                                                | SR = 3'b010 (SPI のみ)                       |     | 1.5  |     | $\mu s$   |

|                   |                                                                | SR = 3'b011 または LVL3                       |     | 1.2  |     | $\mu s$   |

|                   |                                                                | その他すべての SR                                 |     | 0.9  |     | $\mu s$   |

| $t_{DEAD\_HSON}$  | 出力電圧上昇時のデッドタイム                                                 | SR = 3'b000 または LVL2                       |     | 1.5  |     | $\mu s$   |

|                   |                                                                | SR = 3'b001 (SPI のみ)                       |     | 1    |     | $\mu s$   |

|                   |                                                                | SR = 3'b010 (SPI のみ)                       |     | 0.8  |     | $\mu s$   |

|                   |                                                                | その他すべての SR                                 |     | 0.5  |     | $\mu s$   |

| $SR_{HSOFF}$      | 出力電圧立ち下がり時間、90%~10%                                            | SR = 3'b000 または 3'b001 または 3'b010 または LVL2 |     | 42   |     | $V/\mu s$ |

|                   |                                                                | SR = 3'b011 または LVL3                       |     | 15   |     | $V/\mu s$ |

|                   |                                                                | SR = 3'b100 または LVL4                       |     | 20   |     | $V/\mu s$ |

|                   |                                                                | SR = 3'b101 または LVL1                       |     | 26   |     | $V/\mu s$ |

|                   |                                                                | SR = 3'b110 または LVL6                       |     | 37   |     | $V/\mu s$ |

|                   |                                                                | SR = 3'b111 または LVL5                       |     | 48   |     | $V/\mu s$ |

| $t_{PD\_HSOFF}$   | 出力電圧下降時の伝搬時間                                                   | すべての SR                                    |     | 0.25 |     | $\mu s$   |

| $t_{DEAD\_HSOFF}$ | 出力電圧下降時のデッドタイム                                                 | すべての SR                                    |     | 0.2  |     | $\mu s$   |

| $t_{BLANK}$       | 電流センス出力が安定するまでの、出力スルーリング後の電流レギュレーション・ブランкиング時間 (LS 還流についてのみ有効) | すべての SR                                    |     | 3.4  |     | $\mu s$   |

### 7.5.8 IPROPI および ITRIP レギュレーション

| パラメータ                    |                                                              | テスト条件                              | 最小値  | 代表値  | 最大値  | 単位  |

|--------------------------|--------------------------------------------------------------|------------------------------------|------|------|------|-----|

| A <sub>IPROPI</sub>      | 電流スケーリング係数、HTSSOP パッケージ                                      |                                    |      | 6150 |      | A/A |

|                          | 電流スケーリング係数、VQFN-HR パッケージ                                     |                                    |      | 6400 |      | A/A |

| A <sub>I_ERR</sub>       | 電流スケーリング係数                                                   | 2A ≤ I <sub>OUT</sub> < 10.9A      | -5   |      | +5   | %   |

|                          |                                                              | 0.5A ≤ I <sub>OUT</sub> ≤ 2A       | -20  |      | +20  | %   |

|                          |                                                              | 0.2A ≤ I <sub>OUT</sub> ≤ 0.5A     | -50  |      | +50  | %   |

| A <sub>I_ERR_M</sub>     | 2 つのハーフブリッジ間での電流マッチング、VQFN-HR パッケージ                          | I <sub>OUT</sub> > 2A              | -2   |      | +2   | %   |

| A <sub>I_ERR_M</sub>     | 2 つのハーフブリッジ間での電流マッチング、HTSSOP パッケージ                           | I <sub>OUT</sub> > 2A              | -5   |      | +5   | %   |

| Offset <sub>IPROPI</sub> | 無負荷電流時の IPROPI のオフセット電流                                      | I <sub>OUT</sub> = 0A              |      |      | 15   | μA  |

| BW <sub>IPROPI</sub>     | IPROPI 内部センス回路の帯域幅                                           | IPROPI に外付けコンデンサなし                 | 400  |      |      | kHz |

| V <sub>IPROPI_LIM</sub>  | IPROPI の内部クランプ電圧                                             |                                    | 4.5  |      | 5.5  | V   |

| V <sub>ITRIP_LVL</sub>   | ITRIP レギュレーションで TOFF サイクルをトリガするための V <sub>IPROPI</sub> の電圧制限 | ITRIP = 3'b001 または LVL2            | 1.06 | 1.18 | 1.3  | V   |

|                          |                                                              | ITRIP = 3'b010 (SPI のみ)            | 1.27 | 1.41 | 1.55 | V   |

|                          |                                                              | ITRIP = 3'b011 (SPI のみ)            | 1.49 | 1.65 | 1.82 | V   |

|                          |                                                              | ITRIP = 3'b100 または LVL3            | 1.78 | 1.98 | 2.18 | V   |

|                          |                                                              | ITRIP = 3'b101 または LVL4            | 2.08 | 2.31 | 2.54 | V   |

|                          |                                                              | ITRIP = 3'b110 または LVL5            | 2.38 | 2.64 | 2.9  | V   |

|                          |                                                              | ITRIP = 3'b111 または LVL6            | 2.67 | 2.97 | 3.27 | V   |

| t <sub>OFF</sub>         | ITRIP レギュレーション - オフ時間                                        | TOFF = 2'b00 (SPI のみ)              | 16   | 20   | 25   | μs  |

|                          |                                                              | TOFF = 2'b01 (SPI)。HW についてはこの選択肢のみ | 24   | 30   | 36   | μs  |

|                          |                                                              | TOFF = 2'b10 (SPI のみ)              | 33   | 40   | 48   | μs  |

|                          |                                                              | TOFF = 2'b11 (SPI のみ)              | 41   | 50   | 61   | μs  |

### 7.5.9 過電流保護 (OCP)

| パラメータ               |                    | 測定条件                                   | 最小   | 標準  | 最大  | 単位 |

|---------------------|--------------------|----------------------------------------|------|-----|-----|----|

| I <sub>OCP_HS</sub> | ハイサイドの過電流保護スレッショルド | OCP_SEL = 2'b00 (SPI)、HW についてはこの選択肢のみ  | 32   |     | 64  | A  |

|                     |                    | OCP_SEL = 2'b10 (SPI のみ)               | 24   |     | 49  | A  |

|                     |                    | OCP_SEL = 2'b01 (SPI のみ)               | 16   |     | 34  | A  |

| I <sub>OCP_LS</sub> | ローサイドの過電流保護スレッショルド | OCP_SEL = 2'b00 (SPI)、HW についてはこの選択肢のみ  | 32   |     | 64  | A  |

|                     |                    | OCP_SEL = 2'b10 (SPI のみ)               | 24   |     | 49  | A  |

|                     |                    | OCP_SEL = 2'b01 (SPI のみ)               | 16   |     | 34  | A  |

| t <sub>OCP</sub>    | 過電流保護グリッチ除去時間      | TOCP_SEL = 2'b00 (SPI)、HW についてはこの選択肢のみ | 4.5  | 6   | 7.3 | μs |

|                     | 過電流保護グリッチ除去時間      | TOCP_SEL = 2'b01 (SPI のみ)              | 2.2  | 3   | 4.1 | μs |

|                     | 過電流保護グリッチ除去時間      | TOCP_SEL = 2'b10 (SPI のみ)              | 1.1  | 1.5 | 2.3 | μs |

|                     | 過電流保護グリッチ除去時間      | TOCP_SEL = 2'b11 (SPI のみ)              | 0.15 | 0.2 | 0.4 | μs |

### 7.5.10 過熱保護 (TSD)

| パラメータ            |                | 測定条件 | 最小  | 標準  | 最大  | 単位 |

|------------------|----------------|------|-----|-----|-----|----|

| T <sub>TSD</sub> | サーマル・シャットダウン温度 |      | 155 | 170 | 185 | °C |

| パラメータ     |                       | 測定条件 | 最小 | 標準 | 最大 | 単位 |

|-----------|-----------------------|------|----|----|----|----|

| $T_{HYS}$ | サーマル・シャットダウン・ヒステリシス   |      |    | 30 |    | °C |

| $t_{TSD}$ | サーマル・シャットダウン・グリッチ除去時間 |      | 10 | 12 | 19 | μs |

### 7.5.11 電圧監視

| パラメータ               |                       | テスト条件                                          | 最小値  | 代表値 | 最大値 | 単位 |

|---------------------|-----------------------|------------------------------------------------|------|-----|-----|----|

| $V_{VMOV}$          | 立ち上がり時の VM 過電圧スレッショルド | $VMOV\_SEL = 2'b00$ (SPI)、HW パリアントについてはこの選択肢のみ | 33.6 |     | 37  | V  |

|                     |                       | $VMOV\_SEL = 2'b01$ (SPI のみ)                   | 28   |     | 31  | V  |

|                     |                       | $VMOV\_SEL = 2'b10$ (SPI のみ)                   | 18   |     | 21  | V  |

| $V_{VMOV\_HYS}$     | VM 過電圧ヒステリシス          |                                                |      | 0.6 |     | V  |

| $t_{VMOV}$          | VM 過電圧グリッチ除去時間        |                                                | 10   | 12  | 19  | μs |

| $V_{VMUV}$          | 立ち下がり時の VM 低電圧スレッショルド |                                                |      | 4.2 |     | V  |

| $V_{VMUV\_HYS}$     | VM 低電圧ヒステリシス          |                                                |      | 200 |     | mV |

| $t_{VMUV}$          | VM 低電圧グリッチ除去時間        |                                                | 8    | 12  | 19  | μs |

| $VM_{POR\_FALL}$    | デバイスが POR に入る VM 電圧   | HW および SPI (S) パリアントに適用                        |      |     | 3.6 | V  |

| $VM_{POR\_RISE}$    | デバイスが POR から出る VM 電圧  | HW および SPI (S) パリアントに適用                        |      |     | 3.9 | V  |

| $VDD_{POR\_FAL\_L}$ | デバイスが POR に入る VDD 電圧  | SPI (P) パリアントに適用                               |      |     | 3.5 | V  |

| $VDD_{POR\_RIS\_E}$ | デバイスが POR から出る VDD 電圧 | SPI (P) パリアントに適用                               |      |     | 3.8 | V  |

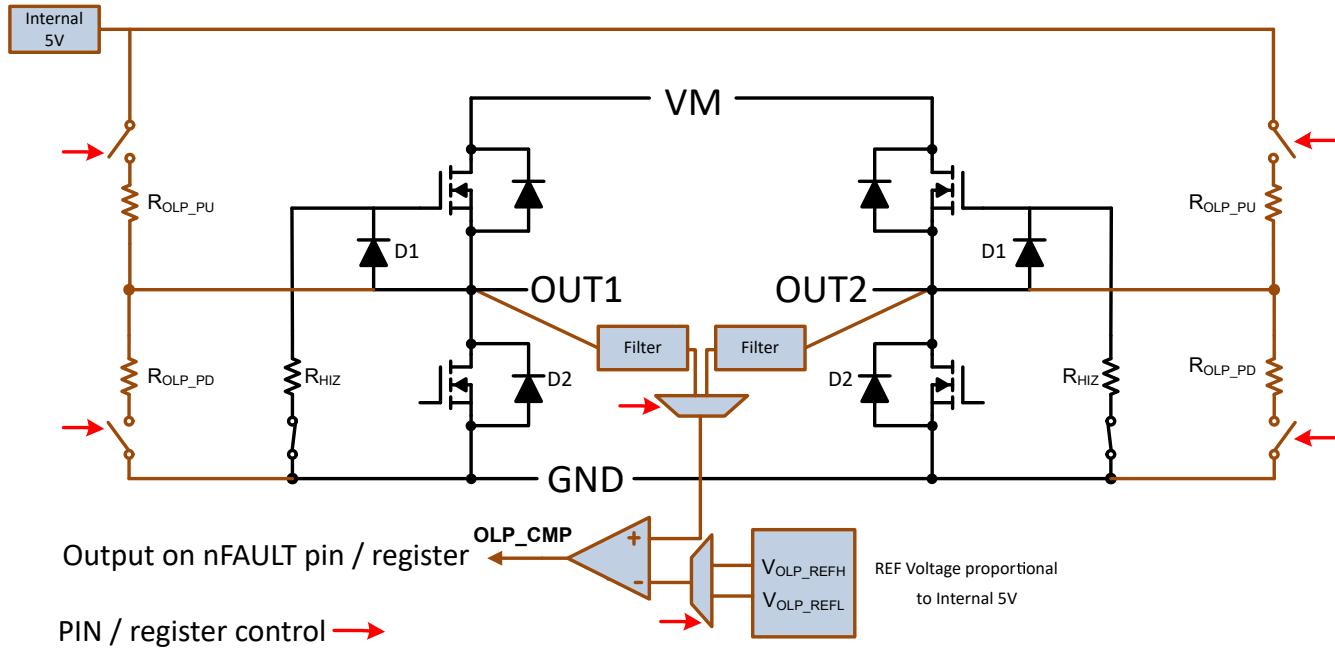

### 7.5.12 負荷監視

| パラメータ                      |                                           | テスト条件                             | 最小値 | 代表値  | 最大値   | 単位 |

|----------------------------|-------------------------------------------|-----------------------------------|-----|------|-------|----|

| オフ状態診断 (OLP)               |                                           |                                   |     |      |       |    |

| $R_{S\_GND}$               | 短絡として検出される OUT と GND の間の抵抗、すべてのモード        |                                   |     |      | 1     | kΩ |

| $R_{S\_VM}$                | 短絡として検出される OUT と VM の間の抵抗、すべてのモード         |                                   |     |      | 1     | kΩ |

| $R_{OPEN\_FB}$             | 開放として検出される OUTx 間の抵抗、PH/EN または PWM モード    |                                   | 1.5 |      |       | kΩ |

| $R_{OPEN\_LS}$             | 開放として検出される OUT と GND の間の抵抗、独立モード          | ローサイド負荷に有効                        | 2   |      |       | kΩ |

| $R_{OPEN\_HS}$             | 開放として検出される OUT と VM の間の抵抗、独立モード           | ハイサイド負荷に有効、 $V_{VM} = 13.5V$      | 10  |      |       | kΩ |

| $V_{OLP\_REFH}$            | OLP コンパレータ基準電圧 HIGH                       |                                   |     | 2.65 |       | V  |

| $V_{OLP\_REFL}$            | OLP コンパレータ基準電圧 LOW                        |                                   |     | 2    |       | V  |

| $R_{OLP\_PU}$              | OLP 時に内部で OUT を VDD へプルアップする抵抗            | $V_{OUTx} = V_{OLP\_REFH} + 0.1V$ |     | 1    |       | kΩ |

| $R_{OLP\_PD}$              | OLP 時に内部で OUT を GND へプルダウンする抵抗            | $V_{OUTx} = V_{OLP\_REFL} - 0.1V$ |     | 1    |       | kΩ |

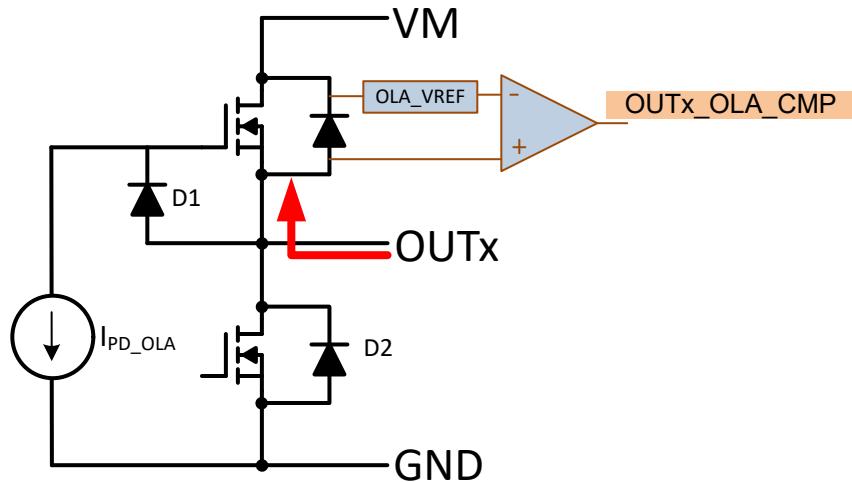

| SPI パリアントのみ - オン状態診断 (OLA) |                                           |                                   |     |      |       |    |

| $I_{PD\_OLA}$              | ハイサイド還流のデッドタイム中に OUTx から GND へ流れ込む内部シンク電流 |                                   | 2   |      | 13.82 | mA |

| $V_{OLA\_REF}$             | OLA で使用される VM に対するコンパレータ基準電圧              |                                   |     | 0.25 |       | V  |

### 7.5.13 フォルトの再試行設定

再試行設定の波形を参照してください

| パラメータ           |                                | 測定条件          | 最小  | 標準 | 最大  | 単位 |

|-----------------|--------------------------------|---------------|-----|----|-----|----|

| $t_{RETRY}$     | 自動ドライバ再試行時間                    | フォルト応答を再試行に設定 | 4.1 | 5  | 6.1 | ms |

| $t_{CLEAR}$     | 過電流イベントからの自動クリアに必要なフォルトのない動作時間 | フォルト応答を再試行に設定 | 85  |    | 200 | μs |

| $t_{CLEAR_TSD}$ | 過熱イベントからの自動クリアに必要なフォルトのない動作時間  | フォルト応答を再試行に設定 | 4.2 |    | 6.7 | ms |

### 7.5.14 過渡熱インピーダンスと電流能力

熱シミュレーションに基づく情報

表 7-1. 過渡熱インピーダンス ( $R_{\theta JA}$ ) および電流能力 - フル・ブリッジ

| 部品番号       | パッケージ   | $R_{\theta JA}$ [°C/W] <sup>(1)</sup> |     |      |      | 電流 [A] <sup>(2)</sup> |      |      |     |      |     |

|------------|---------|---------------------------------------|-----|------|------|-----------------------|------|------|-----|------|-----|

|            |         | 0.1 秒                                 | 1 秒 | 10 秒 | DC   | 0.1 秒                 | 1 秒  | 10 秒 | DC  | 10 秒 | DC  |

| DRV8245-Q1 | VQFN-HR | 4.3                                   | 9.2 | 13.6 | 30.3 | 15.8                  | 10.8 | 8.9  | 5.9 | 7.7  | 4.8 |

| DRV8245-Q1 | HTSSOP  | 3.3                                   | 7.1 | 12.2 | 29.1 | 16.1                  | 11.0 | 8.4  | 5.4 | 7.4  | 4.5 |

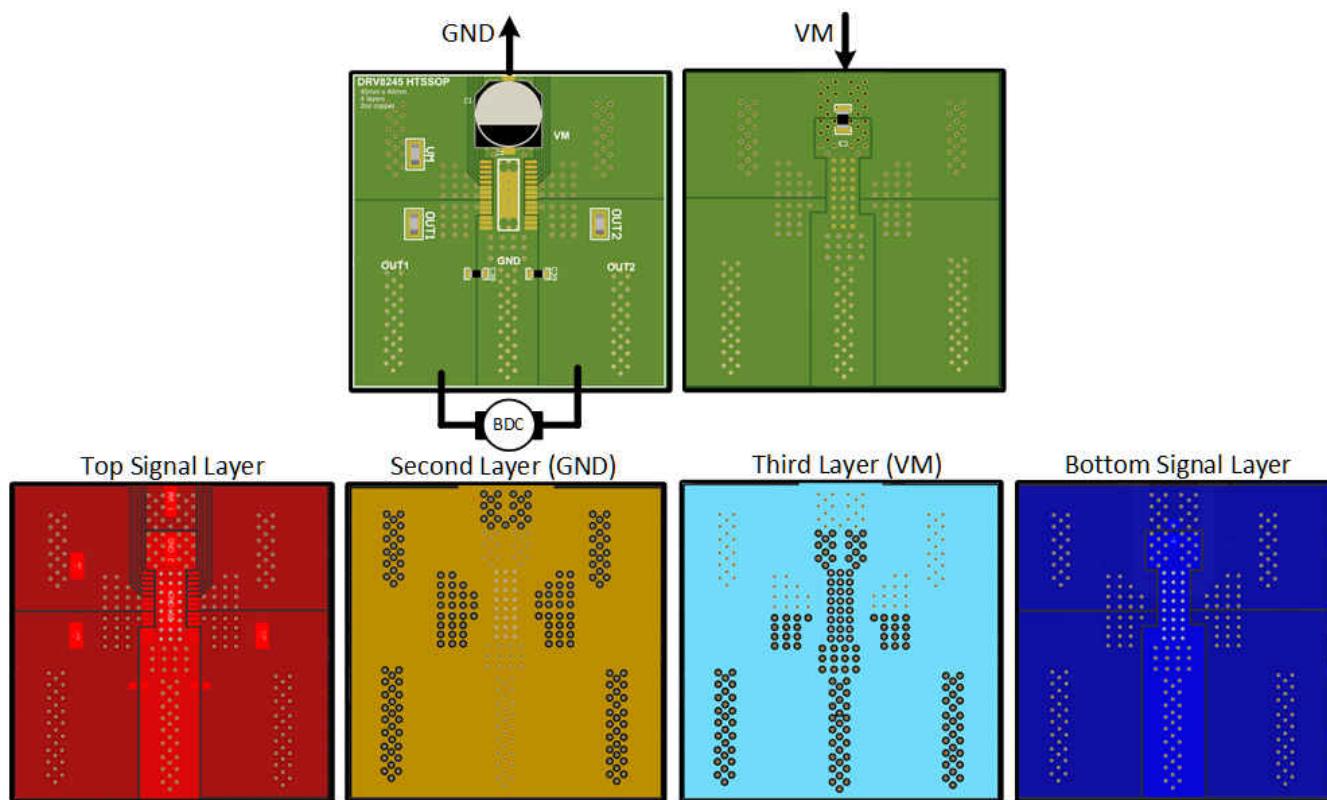

- (1) 40mm x 40mm x 1.6mm の 4 層 PCB (最上層および最下層は 2 オンスの銅箔、内層は 1 オンスの銅箔、サーマルビアはドリル径 0.3mm で 0.025mm の銅メッキ、最小ピアピッチ 1mm) を使用した熱シミュレーションによる。

(2) 周囲温度 85°C、接合部温度上昇が最大 150°C での過渡電流能力推定値

(3) 導通損失 ( $I^2R$ ) だけを考慮

(4) スイッチング損失は、次の式で概算されます。

$$P_{SW} = V_{VM} \times I_{Load} \times f_{PWM} \times V_{VM}/SR, \text{ただし } V_{VM} = 13.5V, f_{PWM} = 20kHz, SR = 23V/\mu s \quad (1)$$

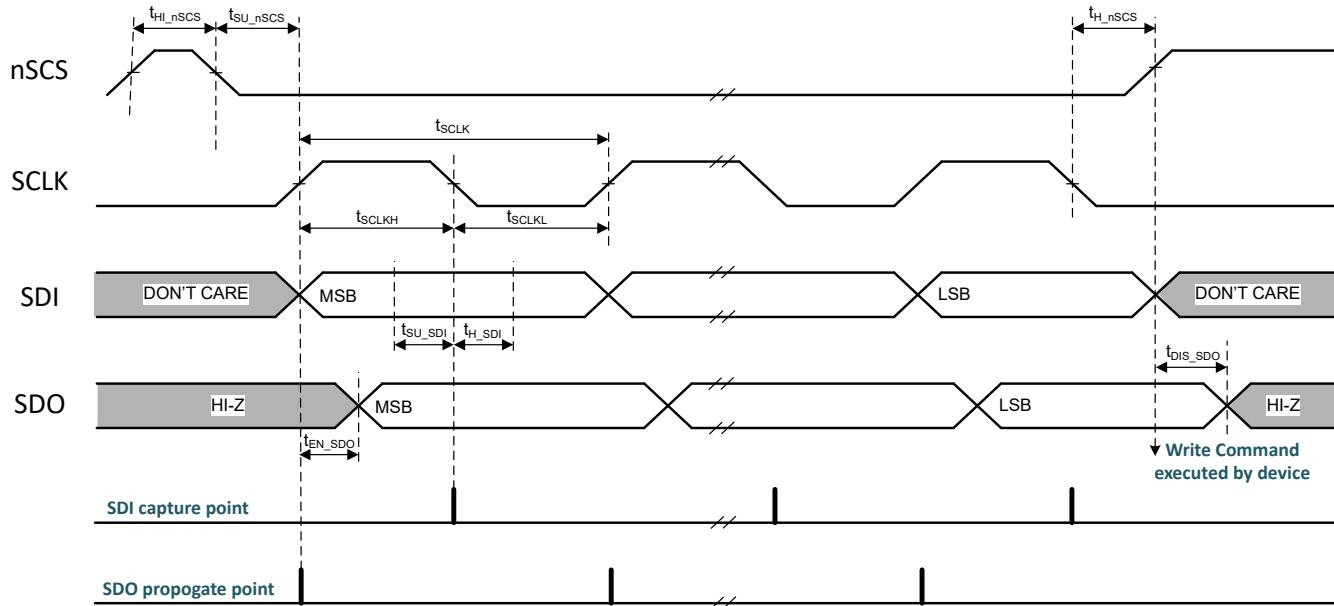

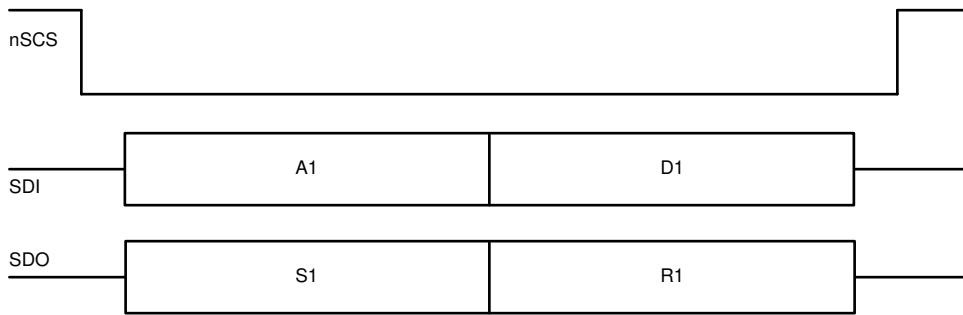

### 7.6 SPI のタイミング要件

|                |                               | 最小値 | 代表値 | 最大値 | 単位 |

|----------------|-------------------------------|-----|-----|-----|----|

| $t_{SCLK}$     | SCLK 最小周期 <sup>(1)</sup>      | 100 |     |     | ns |

| $t_{SCLKH}$    | SCLK 最小 HIGH 時間               | 50  |     |     | ns |

| $t_{SCLKL}$    | SCLK 最小 LOW 時間                | 50  |     |     | ns |

| $t_{H\_nSCS}$  | nSCS 最小 HIGH 時間               | 300 |     |     | ns |

| $t_{SU\_nSCS}$ | nSCS 入力セットアップ時間               | 25  |     |     | ns |

| $t_{H\_nSCS}$  | nSCS 入力ホールド時間                 | 25  |     |     | ns |

| $t_{SU\_SDI}$  | SDI 入力データ・セットアップ時間            | 25  |     |     | ns |

| $t_{H\_SDI}$   | SDI 入力データ・ホールド時間              | 25  |     |     | ns |

| $t_{EN\_SDO}$  | SDO イネーブル遅延時間 <sup>(1)</sup>  |     |     | 35  | ns |

| $t_{DIS\_SDO}$ | SDO ディセーブル遅延時間 <sup>(1)</sup> |     |     | 100 | ns |

- (1) SPI (S) バリエント: SDO 遅延時間は、SDO の外部負荷が 5pF の場合にのみ有効です。SDO の負荷が 20pF の場合、SDO にさらに遅延があるため、SCLK 最小時間は 25% 増加し、SCLK は最高 8MHz に制限されます。SPI (P) バリエントには、このような制限はありません。

図 7-1. SPI ペリフェラル・モードのタイミング定義

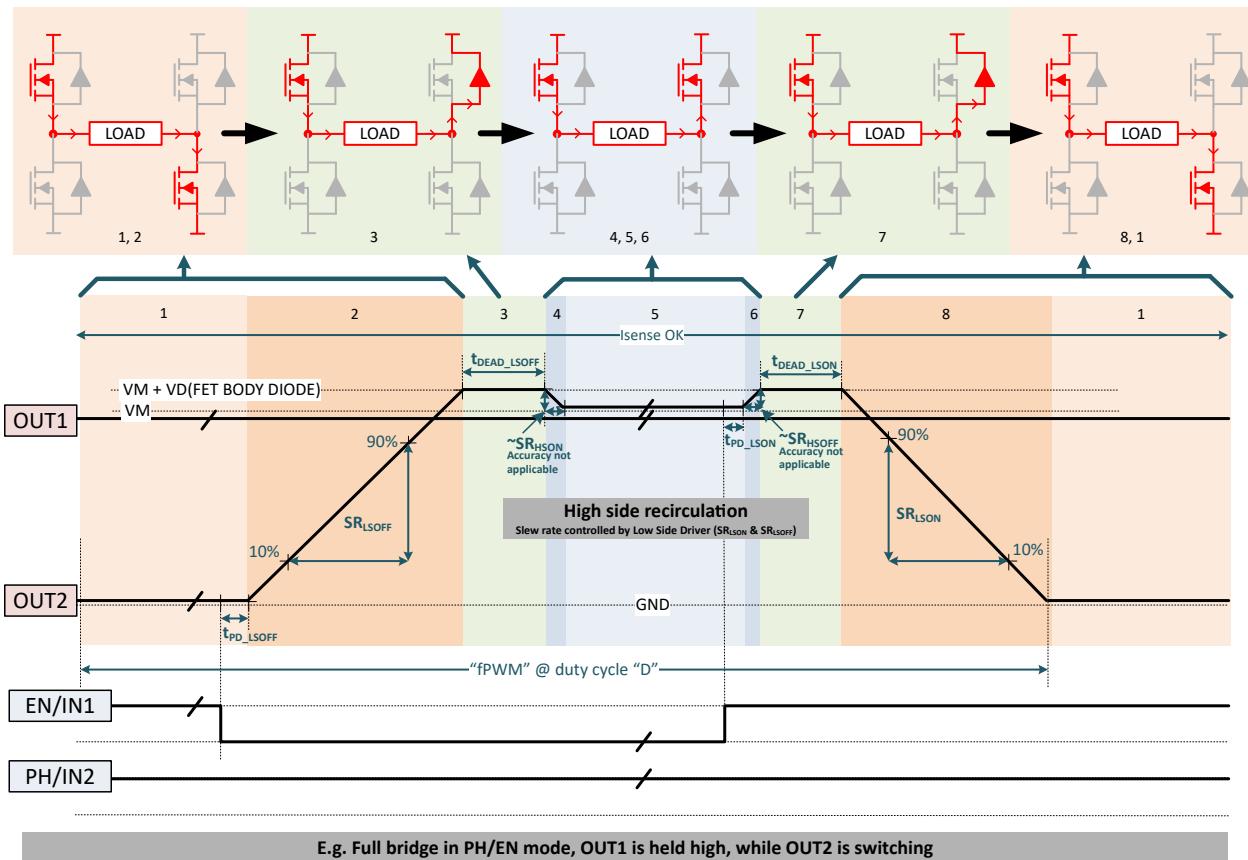

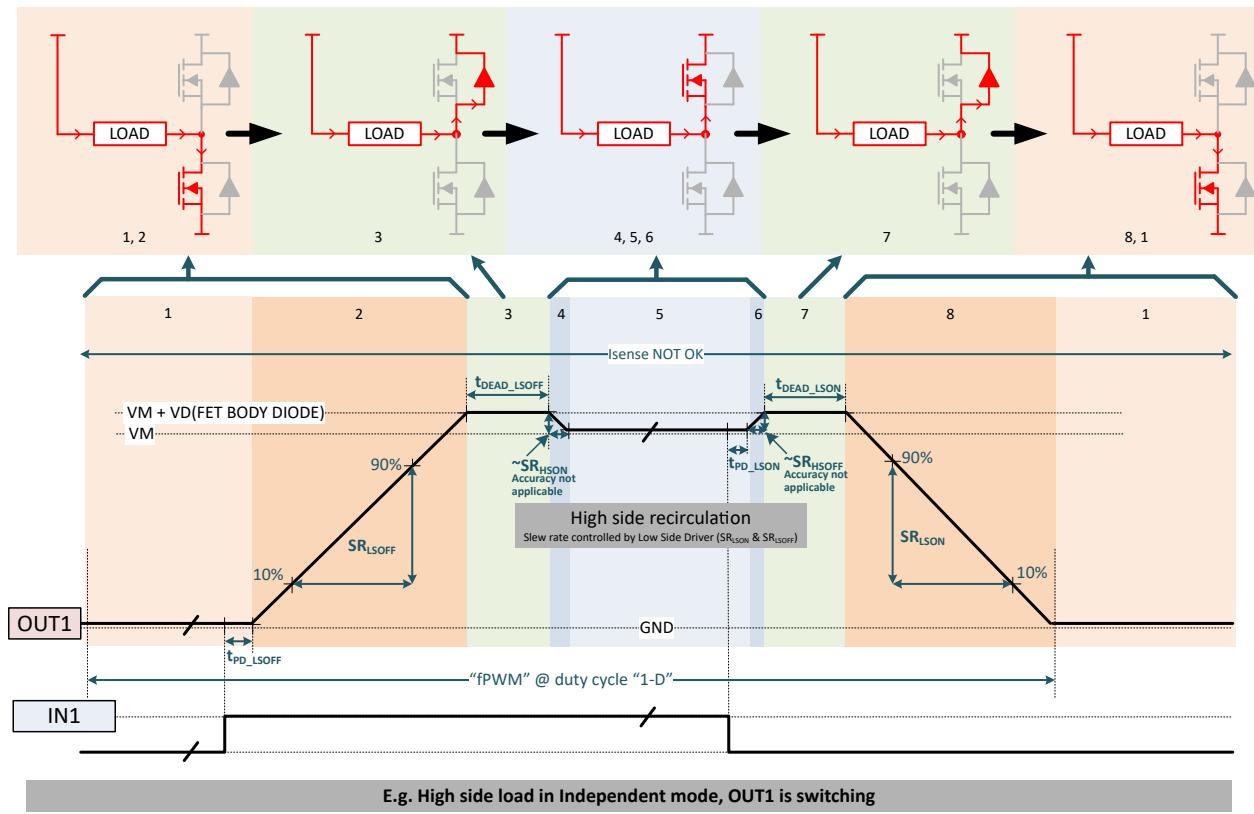

## 7.7 スイッチング波形

このセクションでは、外部 PWM または内部 ITRIP レギュレーションにより発生する、誘導性負荷に対するスイッチング遷移を示します。

### 7.7.1.1 ハイサイド還流

図 7-2. ハイサイド還流による H ブリッジの出力スイッチング遷移

図 7-3. ハイサイド還流によるハーフブリッジの出力スイッチング遷移

### 7.7.1.2 ローサイド還流

図 7-4. ローサイド還流によるハーフブリッジの出力スイッチング遷移

### 7.7.2 ウェークアップ遷移

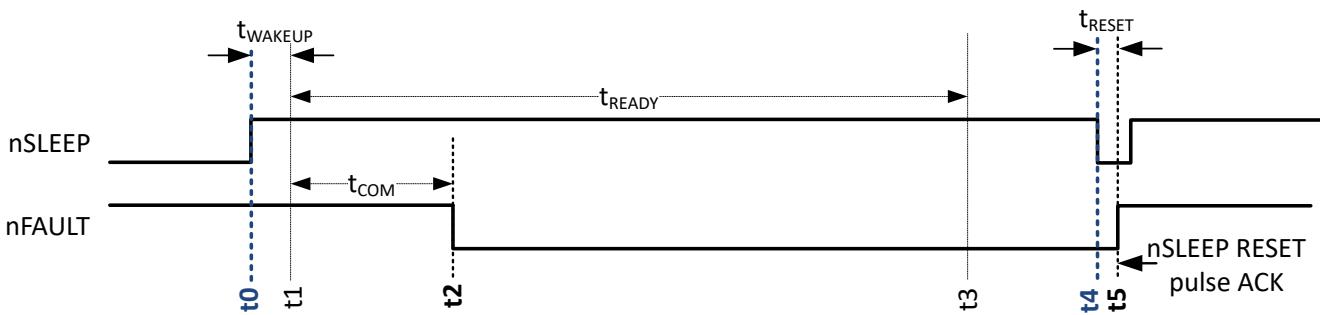

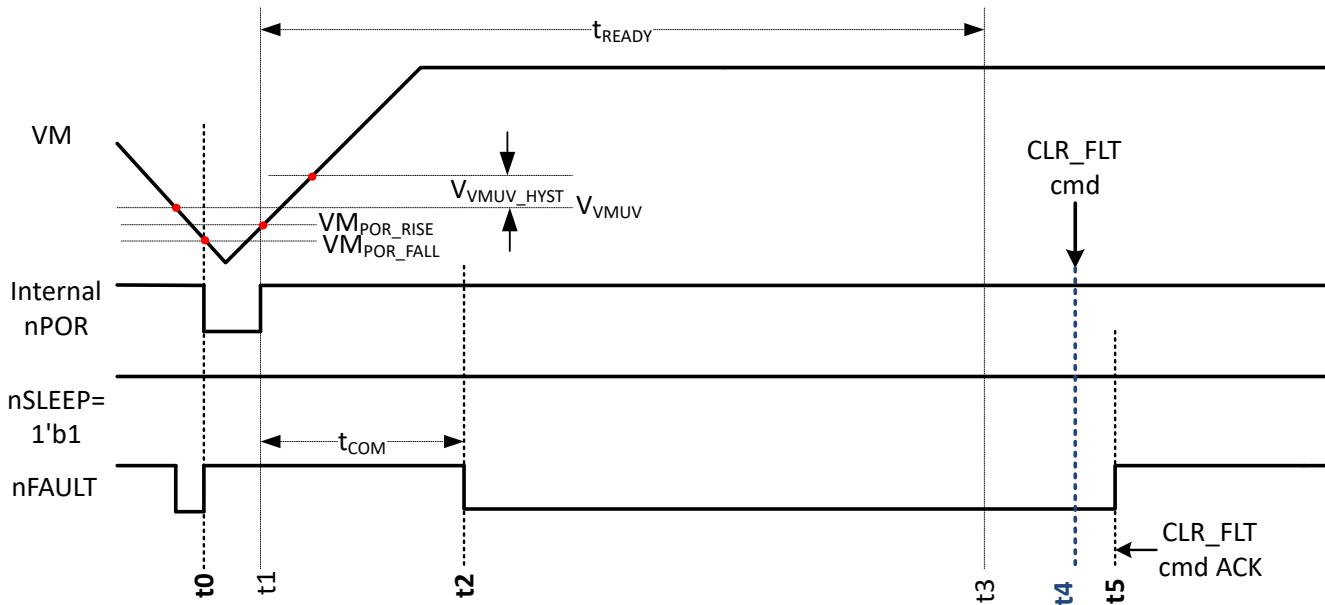

#### 7.7.2.1 HW バリエント

図 7-5. HW バリエントのスリープ状態からスタンバイ状態へのウェークアップ遷移

ウェークアップ遷移時のコントローラとデバイス間のハンドシェイクは次のとおりです。

- t0: コントローラ - nSLEEP を HIGH にアサートして、デバイス・ウェークアップを開始

- t1: デバイス内部状態 - デバイスがウェークアップ・コマンドを登録 (スリープ状態終了)

- t2: デバイス - nFAULT を LOW にアサートして、ウェークアップをアクノリッジしデバイスが通信可能であることを通知

- t3: デバイス内部状態 - 初期化完了

- t4 (t2 以後の任意の時刻): コントローラ - nSLEEP リセット・パルスを発行、デバイスのウェークアップをアクノリッジ

- t5: デバイス - nSLEEP リセット・パルスに対するアクノリッジとして、nFAULT をアサート解除。デバイスはスタンバイ状態

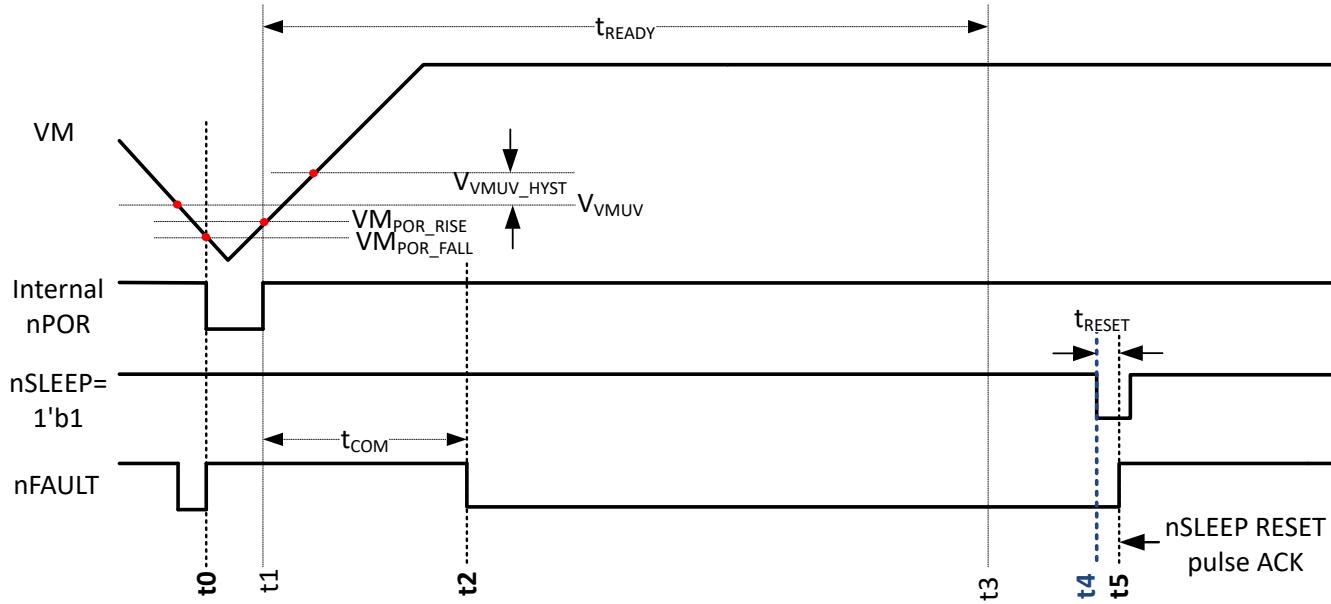

図 7-6. HW バリアントのパワーアップからスタンバイ状態への遷移

パワーアップ時のコントローラとデバイス間のハンドシェイクは次のとおりです。

- $t_0$ : デバイス内部状態 - 内部 LDO が低電圧になることにより POR をアサート (VM に依存)

- $t_1$ : デバイス内部状態 - 内部 LDO 電圧が回復することにより POR をアサート解除

- $t_2$ : デバイス - nFAULT を LOW にアサートして、ウェークアップをアクノリッジしデバイスが通信可能であることを通知

- $t_3$ : デバイス内部状態 - 初期化完了

- $t_4$  ( $t_2$  以後の任意の時刻): コントローラ - nSLEEP リセット・パルスを発行、デバイスのパワーアップをアクノリッジ

- $t_5$ : デバイス - nSLEEP リセット・パルスに対するアクノリッジとして、nFAULT をアサート解除。デバイスはスタンバイ状態

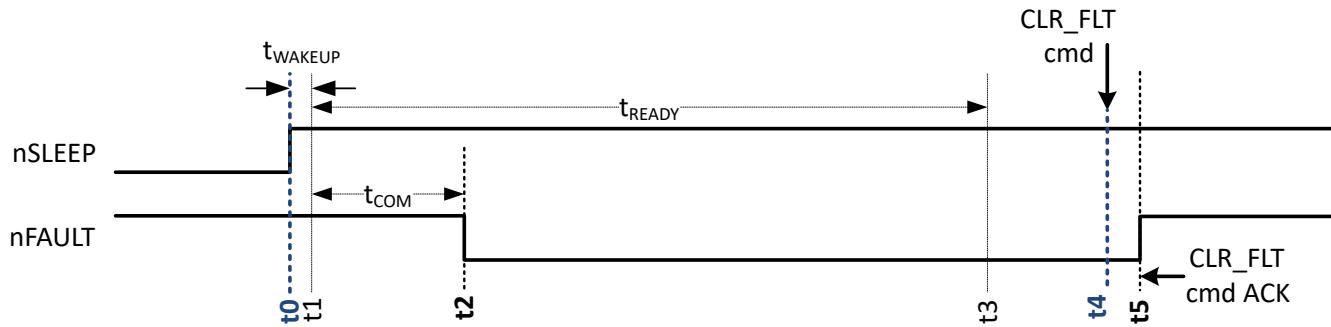

### 7.7.2.2 SPI バリアント

図 7-7. SPI (S) バリアントのスリープ状態からスタンバイ状態へのウェークアップ遷移

ウェークアップ遷移時のコントローラとデバイス間のハンドシェイクは次のとおりです。

- $t_0$ : コントローラ - nSLEEP を HIGH にアサートして、デバイス・ウェークアップを開始

- $t_1$ : デバイス内部状態 - デバイスがウェークアップ・コマンドを登録 (スリープ状態終了)

- $t_2$ : デバイス - nFAULT を LOW にアサートして、ウェークアップをアクノリッジしデバイスが通信可能であることを通知

- $t_3$ : デバイス内部状態 - 初期化完了

- $t_4$  ( $t_2$  以後の任意の時刻): コントローラ - CLR\_FLT コマンドを発行 (SPI 経由)、デバイスのウェークアップをアクノリッジ

- $t_5$ : デバイス - nSLEEP リセット・パルスに対するアクノリッジとして、nFAULT をアサート解除。デバイスはスタンバイ状態

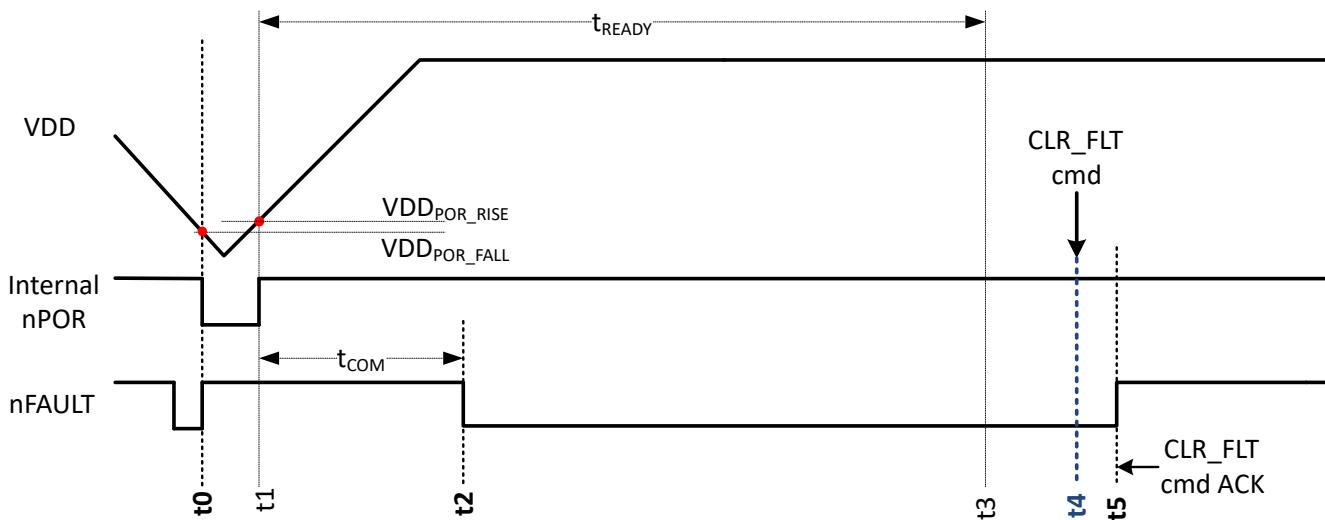

図 7-8. SPI (S) バリアントのパワーアップからスタンバイ状態への遷移

パワーアップ時のコントローラとデバイス間のハンドシェイクは次のとおりです。

- $t_0$ : デバイス内部状態 - 内部 LDO が低電圧になることにより POR をアサート (VM に依存)

- $t_1$ : デバイス内部状態 - 内部 LDO 電圧が回復することにより POR をアサート解除

- $t_2$ : デバイス - nFAULT を LOW にアサートして、ウェークアップをアクノリッジしデバイスが通信可能であることを通知

- $t_3$ : デバイス内部状態 - 初期化完了

- $t_4$  ( $t_2$  以後の任意の時刻): コントローラ - CLR\_FLT コマンドを発行 (SPI 経由)、デバイスのパワーアップをアクノリッジ

- $t_5$ : デバイス - nSLEEP リセット・パルスに対するアクノリッジとして、nFAULT をアサート解除。デバイスはスタンバイ状態

図 7-9. SPI (P) バリアントのパワーアップからスタンバイ状態への遷移

パワーアップ時のコントローラとデバイス間のハンドシェイクは次のとおりです。

- $t_0$ : デバイス内部状態 - VDD (外部電源) が低電圧になることにより POR をアサート

- $t_1$ : デバイス内部状態 - VDD (外部電源) の電圧が回復することにより POR をアサート解除

- $t_2$ : デバイス - nFAULT を LOW にアサートして、ウェークアップをアクノリッジしデバイスが通信可能であることを通知

- t3: デバイス内部状態 - 初期化完了

- t4 (t2 以後の任意の時刻): コントローラ - CLR\_FLT コマンドを発行 (SPI 経由)、デバイスのパワーアップをアクノリッジ

- t5: デバイス - nSLEEP リセット・パルスに対するアクノリッジとして、nFAULT をアサート解除。デバイスはスタンバイ状態

## 7.7.3 フォルト応答の遷移

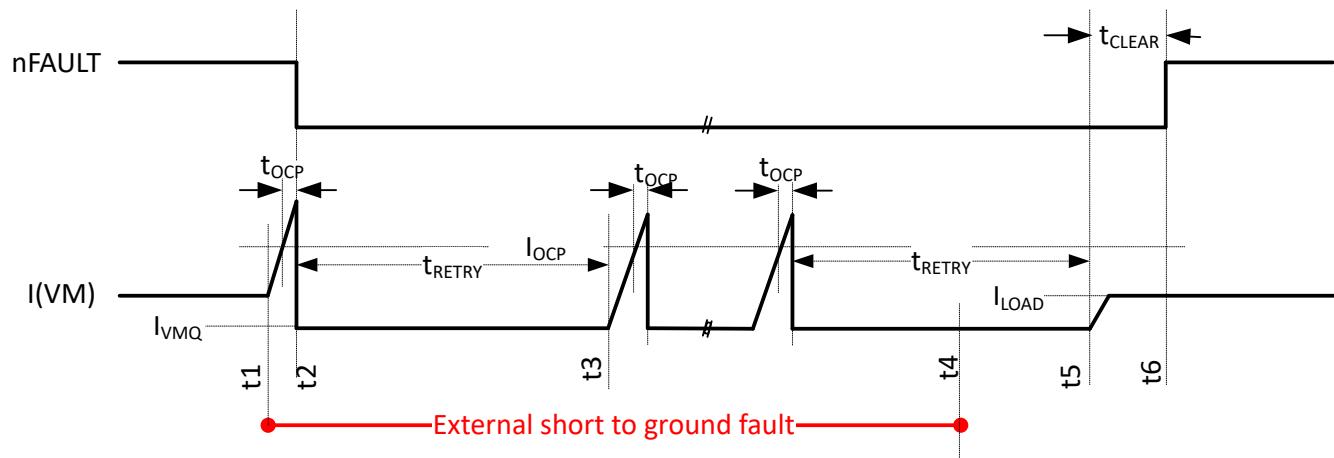

### 7.7.3.1 再試行設定

SPI バリアントおよび HW バリアントの両方に有効

図 7-10. 再試行設定のフォルト応答 (OUT がグランドに短絡してハイサイドで OCP が発生した状況を表示)

再試行設定での短絡発生と回復のシナリオ:

- t1: 外部短絡が発生します。

- t2: t<sub>OCP</sub> 後に OCP (過電流保護) フォルトが確認され、出力をディセーブルし、フォルトを通知するため nFAULT を LOW にアサートします。

- t3: t<sub>RETRY</sub> 後にデバイスは自動的に再試行を実施します。出力を短時間オンにして短絡発生を確認すると、そのつど、t<sub>OCP</sub> 後に直ちにディセーブルされます。この間 nFAULT は、LOW にアサートされたままです。ユーザーがドライバの機能を無効にするまで、または外部ショートが解消されるまで、図に示すように、このサイクルを繰り返します。TSD (サーマル・シャットダウン) イベントの場合、自動再試行時間は、熱ヒステリシスに基づく冷却状況に依存することに注意してください。

- t4: 外部短絡が解消されます。

- t5: デバイスは自動再試行を実施します。ただし、今回は異常が発生しないので、デバイスは出力をイネーブルのまま保持します。

- t6: t<sub>CLEAR</sub> 期間中にわたってフォルトのない動作が確認されると、nFAULT はアサート解除されます。

- SPI バリアントのみ - CLR\_FLT コマンドが実行されるまで、フォルト・ステータスはラッチされたままです。

出力がグランドへ短絡してハイサイド OCP フォルト検出が発生した場合、このタイプの短絡を示すために、出力がディセーブルになっている間は I<sub>PROPI</sub> ピンが引き続き V<sub>I<sub>PROPI</sub>\_LIM</sub> 電圧にプルアップされていることに注意してください。これは、グランドへの短絡フォルトと他のフォルトとを区別するために、特に HW (H) バリアントにおいて役立ちます。

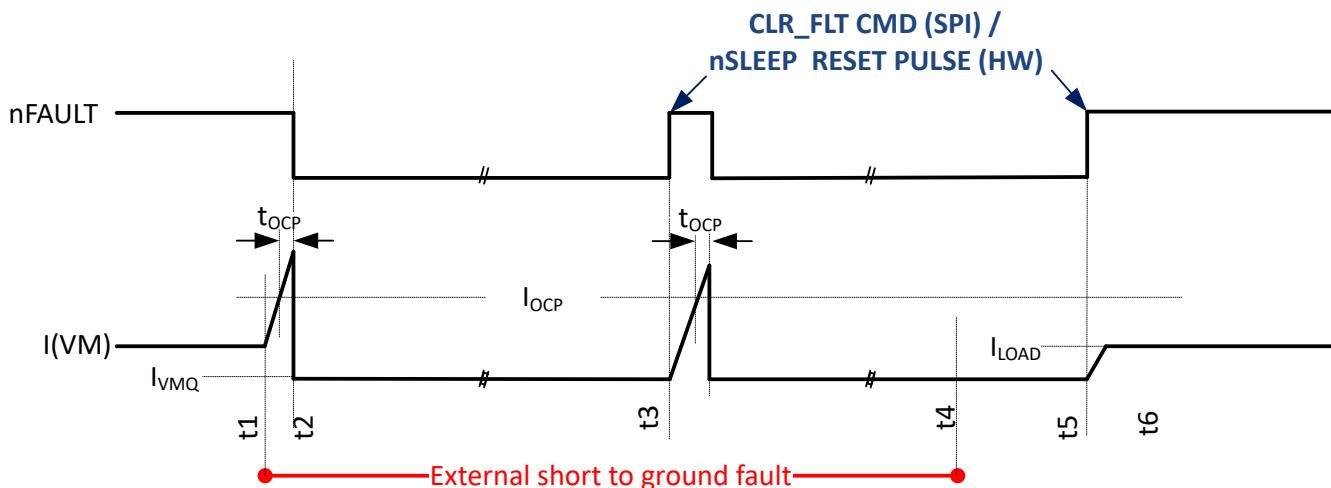

### 7.7.3.2 ラッチ設定

SPI バリエントおよび HW バリエントの両方に有効

図 7-11. ラッチ設定のフォルト応答 (OUT がグランドに短絡してハイサイドで OCP が発生した状況を表示)

ラッチ設定での短絡発生と回復のシナリオ:

- t1: 外部短絡が発生します。

- t2:  $t_{OCP}$  後に OCP (過電流保護) フォルトが確認され、出力をディセーブルし、フォルトを通知するため nFAULT を LOW にアサートします。

- t3: CLR\_FLT コマンド (SPI バリエント) または nSLEEP リセット・パルス (HW バリエント) がコントローラにより発行されます。nFAULT はアサート解除され、出力がイネーブルになります。OCP フォルトが再度検出され、nFAULT を LOW にアサートし、出力をディセーブルにします。

- t4: 外部短絡が解消されます。

- t5: CLR\_FLT コマンド (SPI バリエント) または nSLEEP リセット・パルス (HW バリエント) がコントローラにより発行されます。nFAULT はアサート解除され、出力がイネーブルになります。通常動作を再開します。

- SPI バリエントのみ - CLR\_FLT コマンドが実行されるまで、フォルト・ステータスはラッチされたままです。

出力がグランドへ短絡してハイサイド OCP フォルト検出が発生した場合、このタイプの短絡を示すために、出力がディセーブルになっている間は IPROPI ピンが引き続き  $V_{IPROPI\_LIM}$  電圧にプルアップされていることに注意してください。これは、グランドへの短絡フォルトと他のフォルトとを区別するために、特に HW (H) バリエントにおいて役立ちます。

## 7.8 代表的特性

図 7-12. VQFN-HR(16) の  $R_{HS\_ON}$  および  $R_{LS\_ON}$  と温度との関係 ( $V_{VM} = 13.5V$ )

図 7-13.  $A_{IPROPI}$  ゲイン誤差と負荷電流との関係 ( $V_{VM} = 13.5V$ )

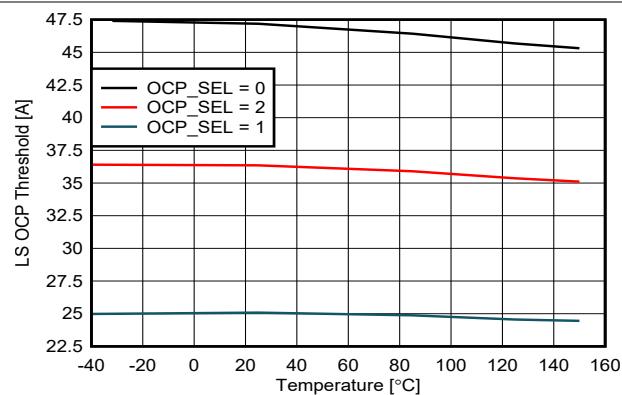

図 7-14. LS OCP スレッショルドと温度との関係 ( $V_{VM} = 13.5V$ )

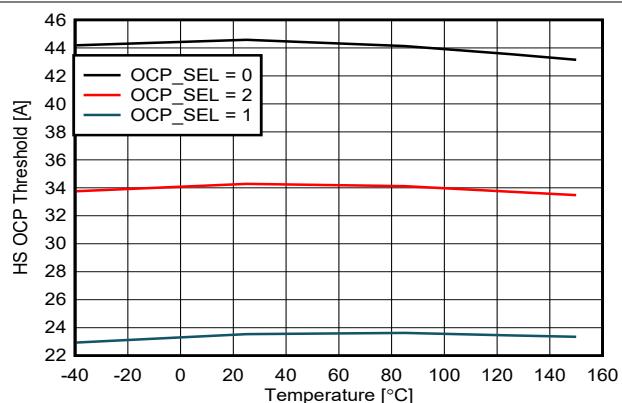

図 7-15. HS OCP スレッショルドと温度との関係 ( $V_{VM} = 13.5V$ )

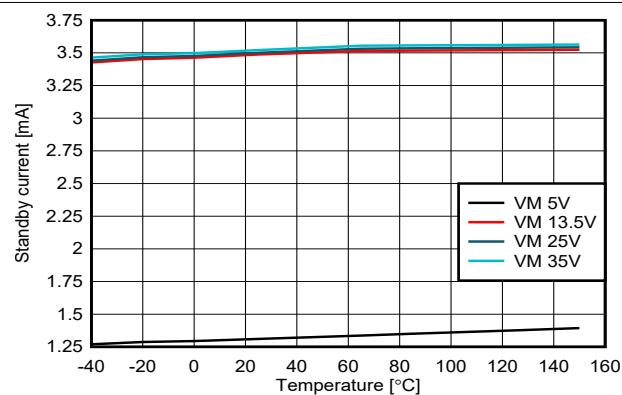

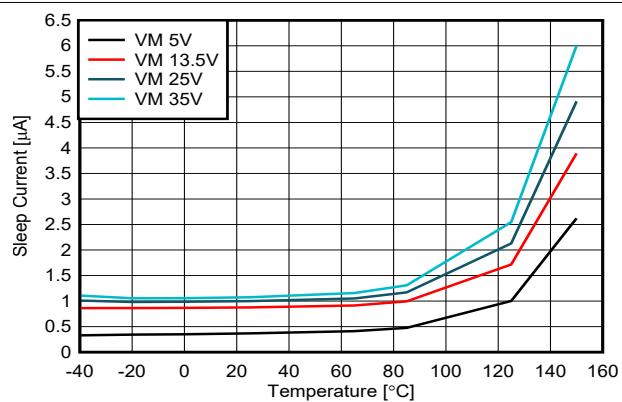

図 7-16. スタンバイ状態での VM の電流と温度との関係

図 7-17. スリープ状態での VM の電流と温度との関係

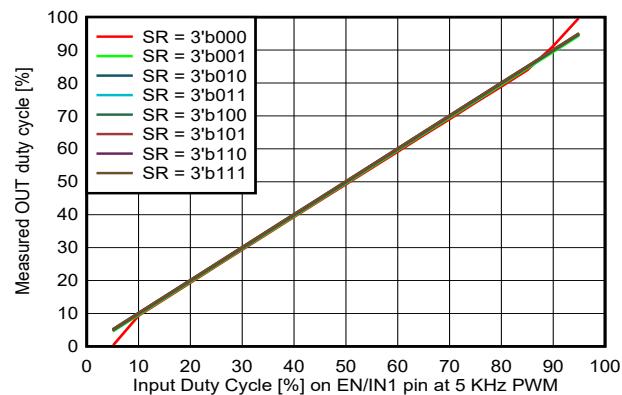

図 7-18. HS 遷流のデューティ・サイクル実測値と入力デューティ・サイクルとの関係 ( $V_{VM} = 13.5V$ 、PWM周波数 5kHz)

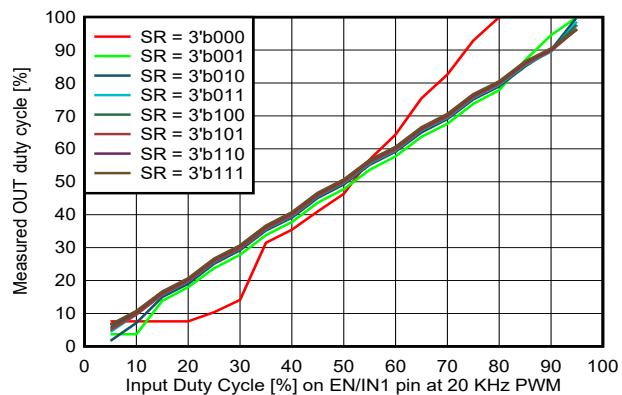

図 7-19. HS 遷流のデューティ・サイクル実測値と入力デューティ・サイクルとの関係 ( $V_{VM} = 13.5V$ 、PWM周波数 20kHz)

## 8 詳細説明

### 8.1 概要

DRV824x-Q1 ファミリは、4.5~35V で動作するブラシ付き DC モーター・ドライバであり、各種モーターおよび負荷の幅広い出力負荷電流をサポートしています。本デバイスは、MODE 機能で設定される各種制御モードで動作できる H ブリッジ出力電力段を内蔵しています。これにより、1 つの双向ブラシ付き DC モーター、または、2 つの单方向ブラシ付き DC モーターを駆動できます。また、チャージ・ポンプ・レギュレータを内蔵しており、高効率ハイサイド N チャネル MOSFET と 100% デューティ・サイクル動作に対応しています。本デバイスは、バッテリまたは DC 電圧電源に直接接続できる単一電源入力 (VM) で動作します。また、低消費電力モードを備えており、スリープ時の電流引き込みを最小限に抑えることができます。

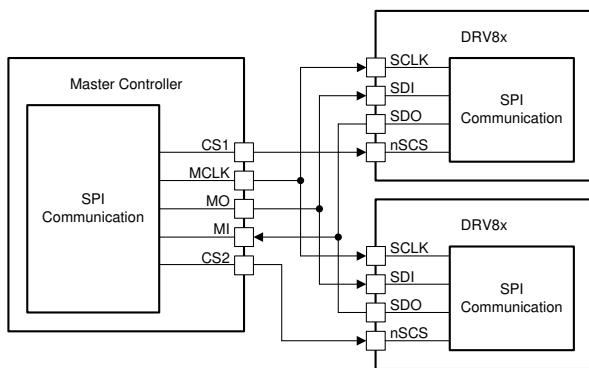

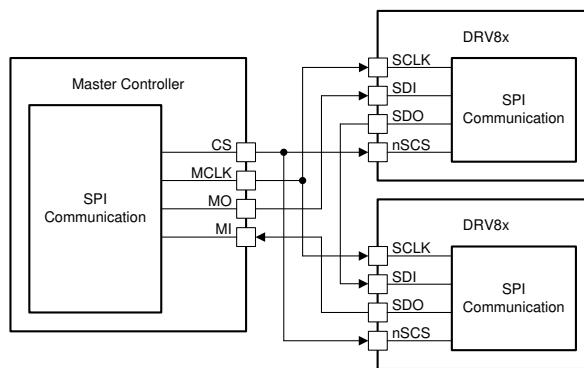

このデバイスは、2 種類のインターフェイスのバリアントで供給されます。

1. **HW バリアント** - ハードワイヤ接続によるインターフェイスのバリアントで、簡単にデバイスを構成できます。デバイスで利用可能なピン数に制限があるため、このバリアントでは、SPI バリアントと比較して構成およびフォルト通知機能が少なくなっています。

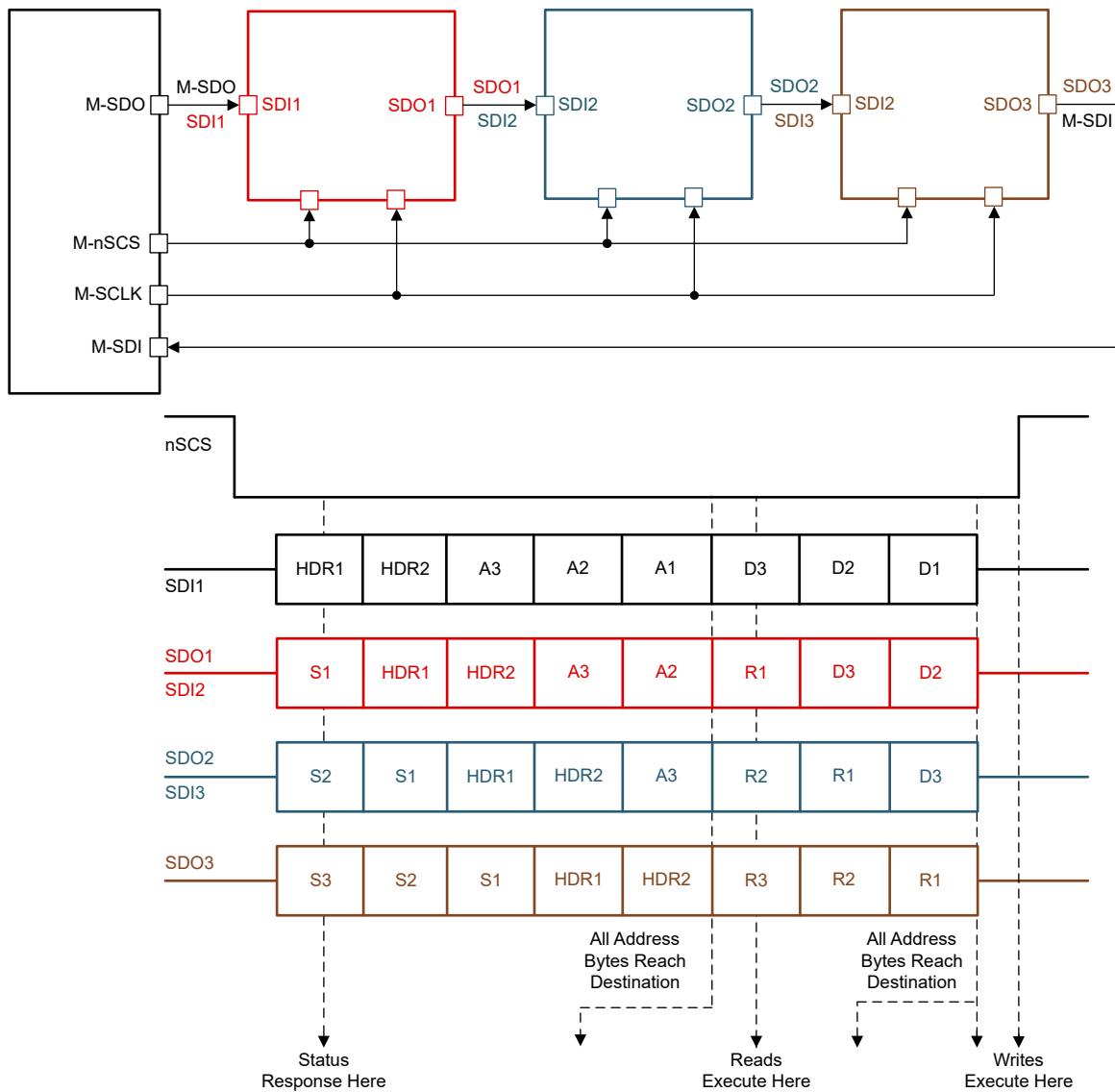

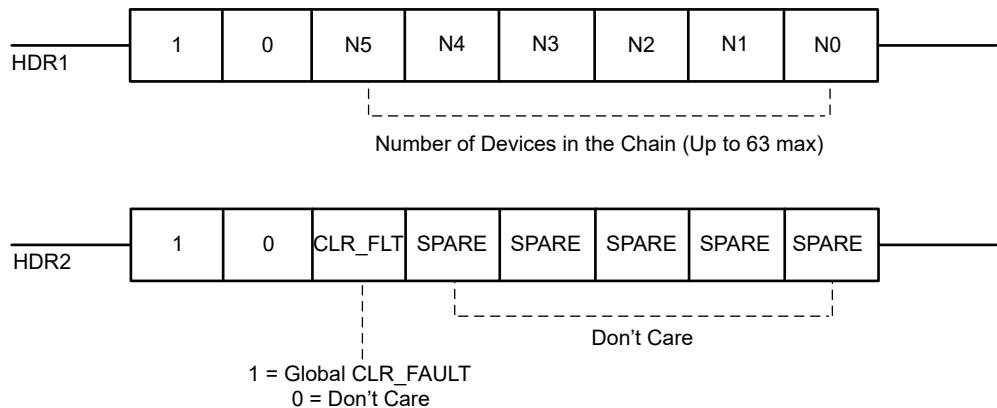

2. **SPI バリアント** - 標準的な 4 線式シリアル・ペリフェラル・インターフェイス (SPI) およびデイジー・チェーン機能により、柔軟なデバイス構成と、外部コントローラへの詳細なフォルト通知が可能です。SPI バリアントと HW バリアントの機能の差異は、「[デバイスの比較](#)」セクションに記載されています。SPI インターフェイスには、次のような 2 種類のデバイス・バリアントがあります。

- a. **SPI (S) バリアント** - デジタル・ブロックの電源は、VM 電源から給電される内部 LDO レギュレータにより供給されます。nSLEEP ピンは、高インピーダンス入力ピンです。

- b. **SPI (P) バリアント** - VDD ピンを通して、デバイスのデジタル・ブロックへの外部電源入力が可能です。nSLEEP ピンの代わりに、この VDD 電源ピンが付いています。これにより、VM の低電圧状態でのデバイスのリセット (ブランクアウト) を防止します。

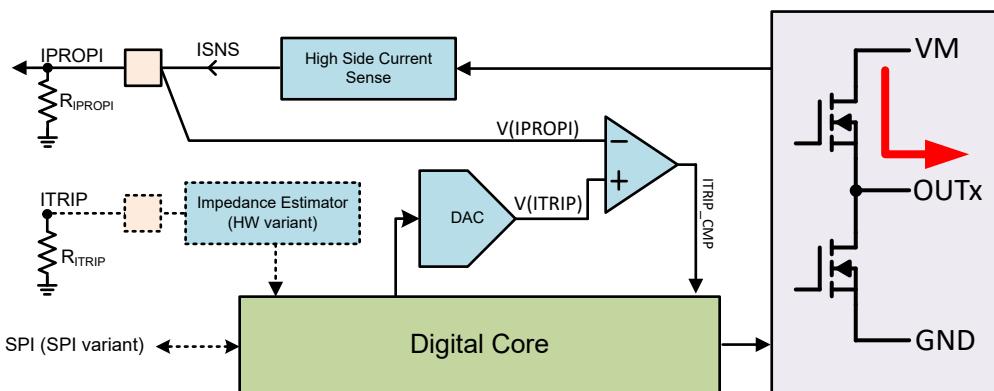

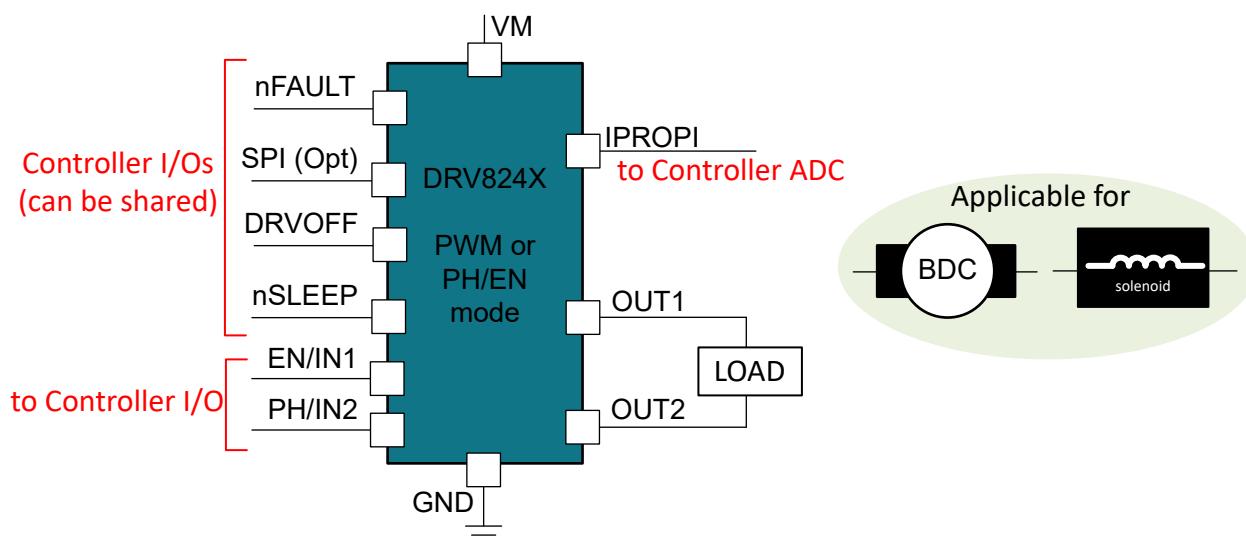

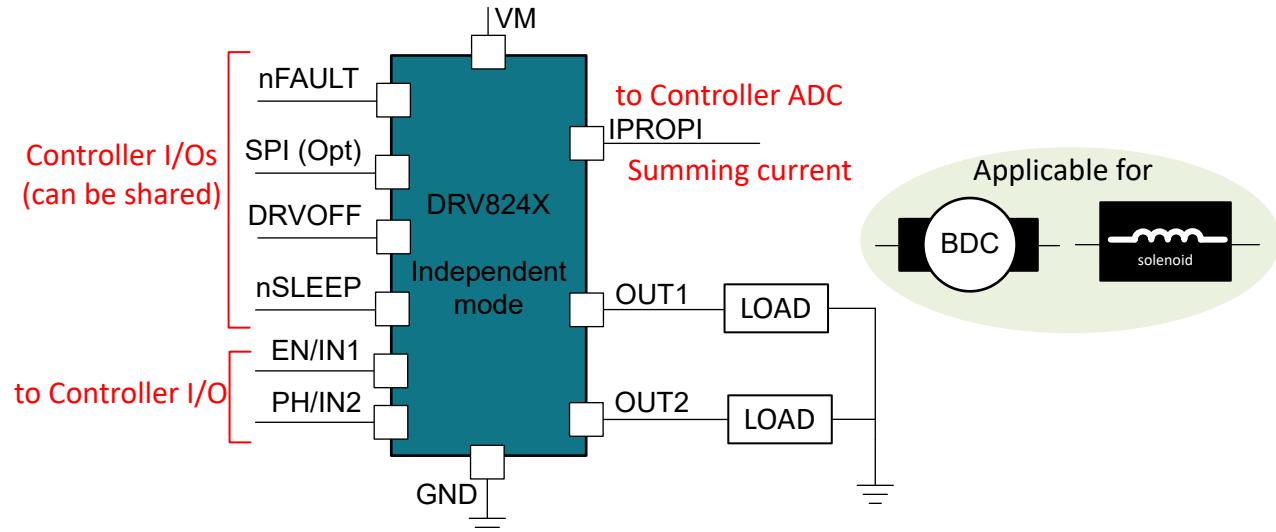

DRV824x デバイス・ファミリは、ハイサイド・パワー MOSFET の電流ミラーを使用した負荷電流センス出力を提供します。IPROPI ピンは、ハイサイド MOSFET の電流 (OUTx ピンから流出する電流) に比例する小さい電流を供給します。この電流は、外付け抵抗 ( $R_{IPROPI}$ ) を使用して比例電圧に変換できます。さらに、このデバイスは、固定オフ時間の PWM チョッピング方式もサポートしており、負荷への電流を制限できます。電流レギュレーション・レベルは、ITRIP 機能を使用して設定できます。

このデバイスには、さまざまな保護機能と診断機能が内蔵されています。主な保護機能としては、電源電圧モニタ (VMOV および VMUV)、オフ状態 (パッシブ) 診断 (OLP)、オン状態 (アクティブ) 診断 (OLA) - SPI バリアントのみ、各パワー FET の過電流保護 (OCP)、過熱シャットダウン (TSD) があります。フォルト状態は、nFAULT ピンにより通知されます。SPI バリアントには、この他に、フレーム・エラー、構成レジスタ・ビットおよびドライバ制御ビットのロック機能など、追加の通信保護機能があります。

## 8.2 機能ブロック図

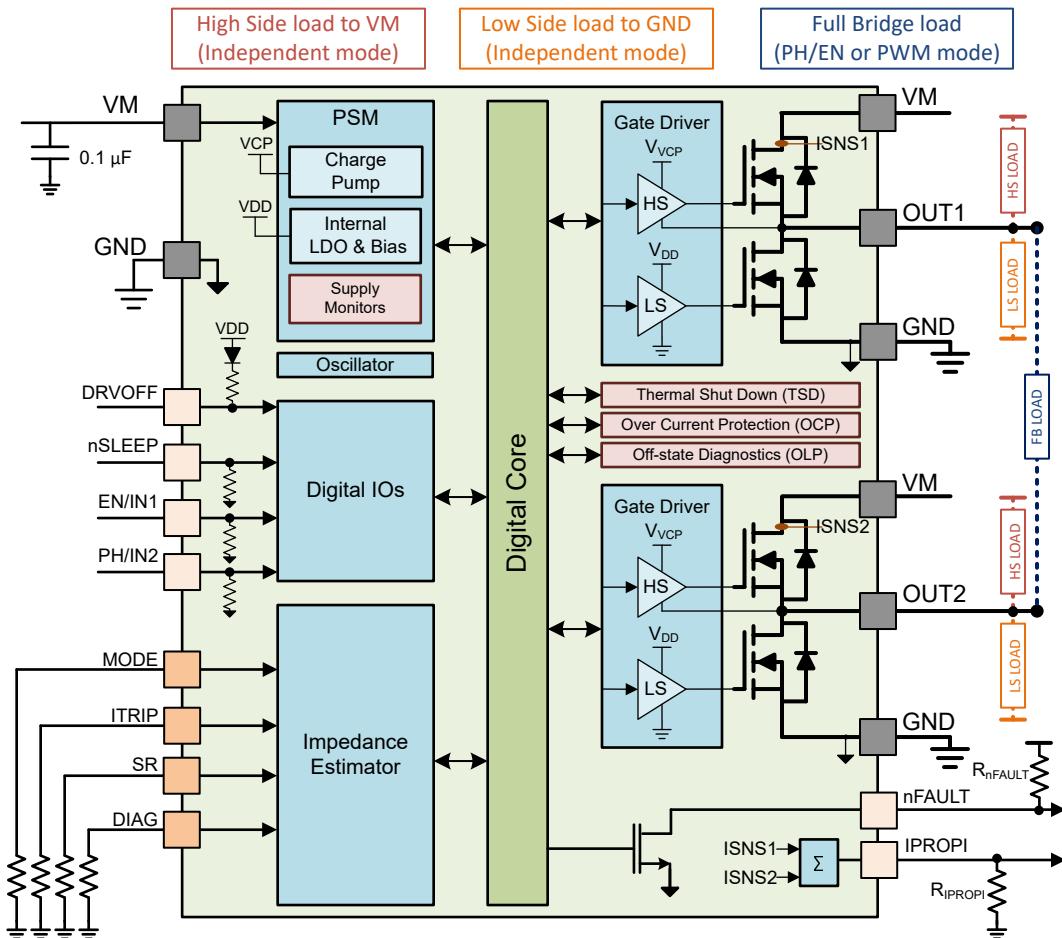

### 8.2.1 HW バリアント

図 8-1. 機能ブロック図 - HW バリアント

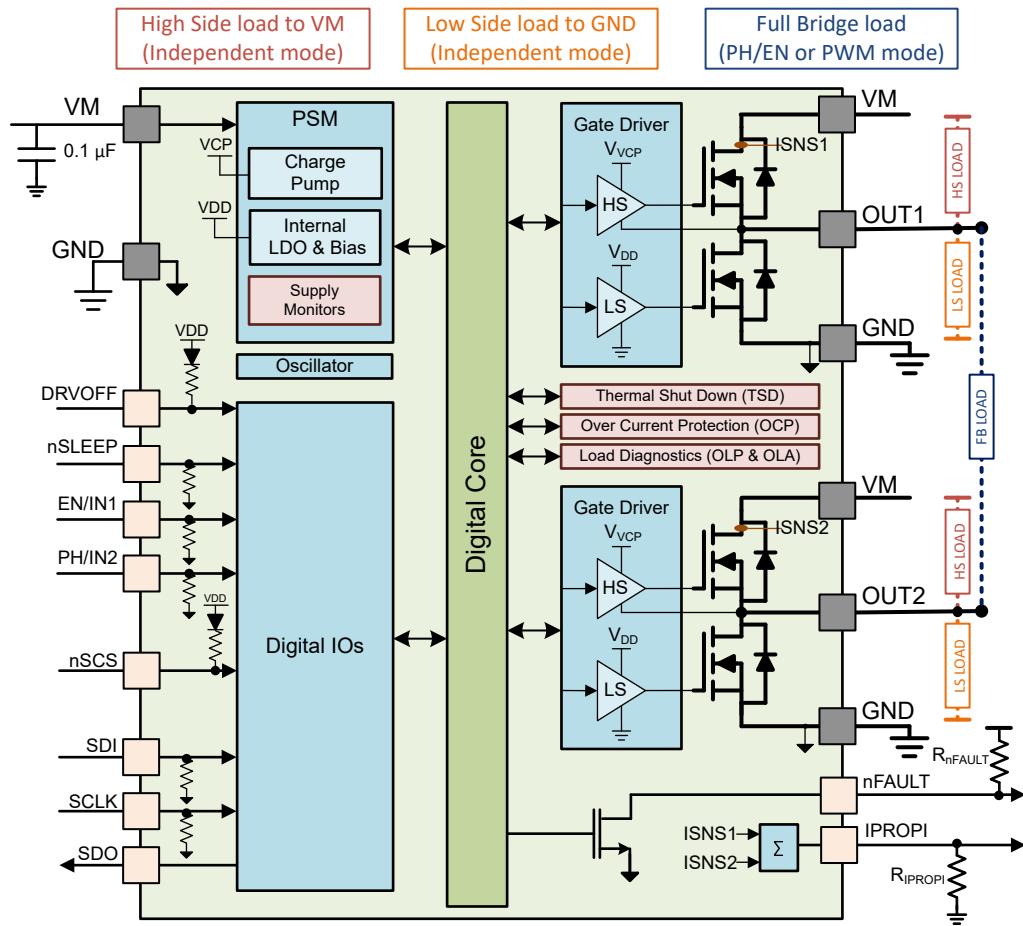

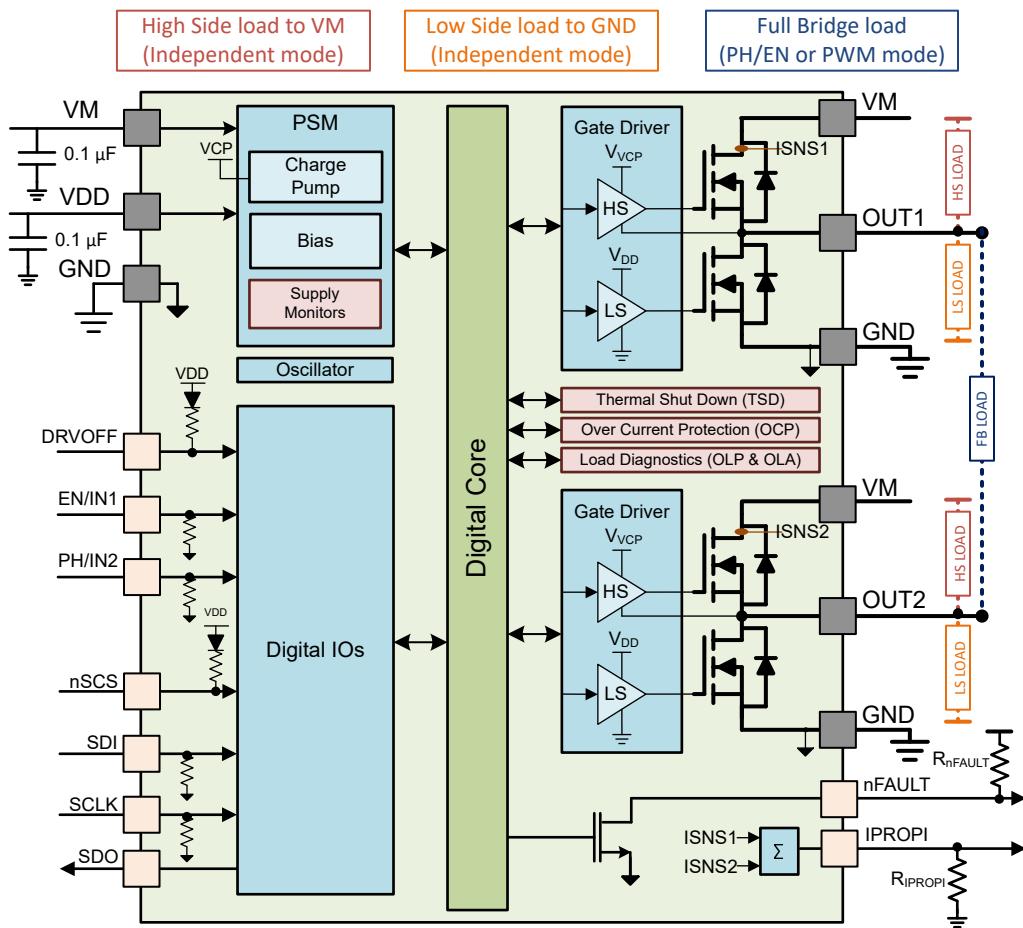

### 8.2.2 SPI バリアント

SPI インターフェイスには、以下に示すように、SPI (S) バリアントと SPI (P) バリアントという 2 つのバリアントがあります。

図 8-2. 機能ブロック図 - SPI (S) バリアント

図 8-3. 機能ブロック図 - SPI (P) バリアント

## 8.3 機能説明

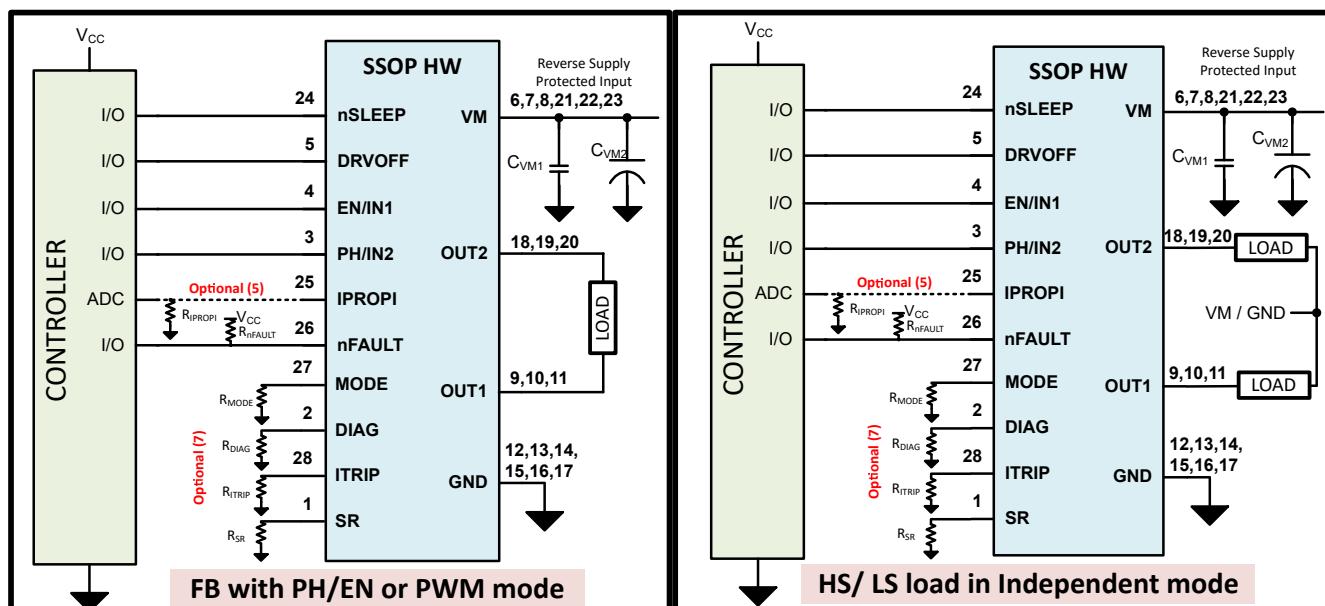

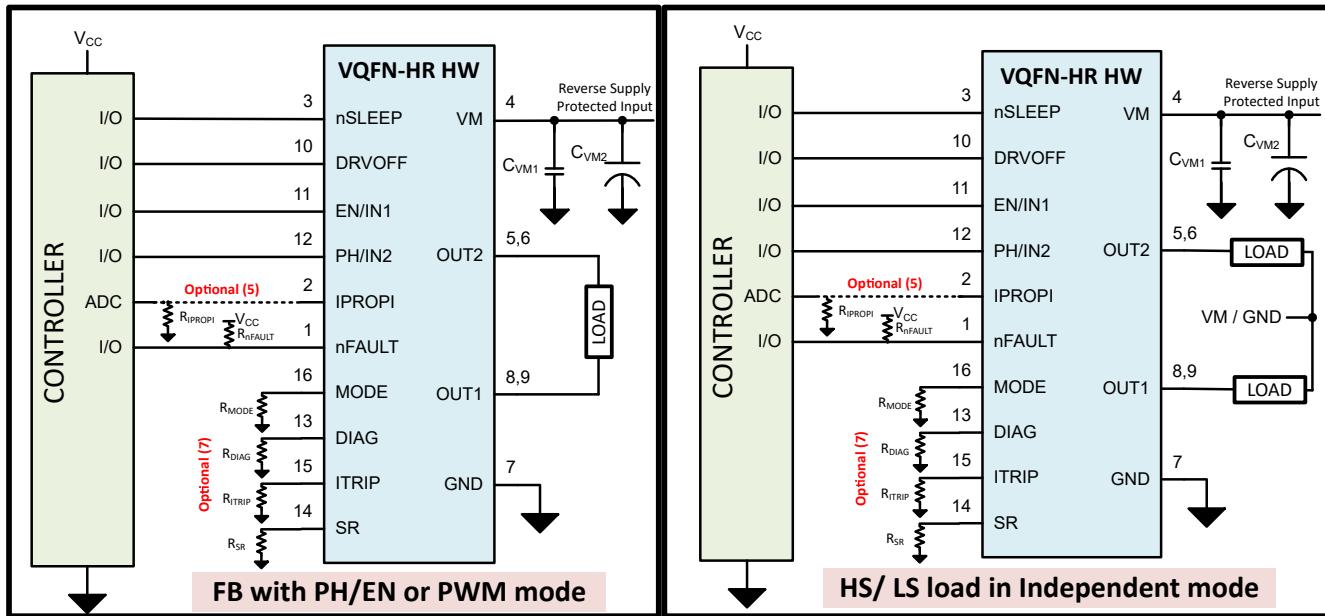

### 8.3.1 外付け部品

セクション 8.3.1.1 および セクション 8.3.1.2 に、推奨外付け部品を示します。

#### 8.3.1.1 HW バリアント

**表 8-1. HW バリアントの外付け部品表**

| 部品           | ピン     | 推奨事項                                                                                                                       |

|--------------|--------|----------------------------------------------------------------------------------------------------------------------------|

| $C_{VM1}$    | VM     | GND に対して、VM に対応する定格電圧、 $0.1\mu F$ 、低 ESR セラミック・コンデンサ                                                                       |

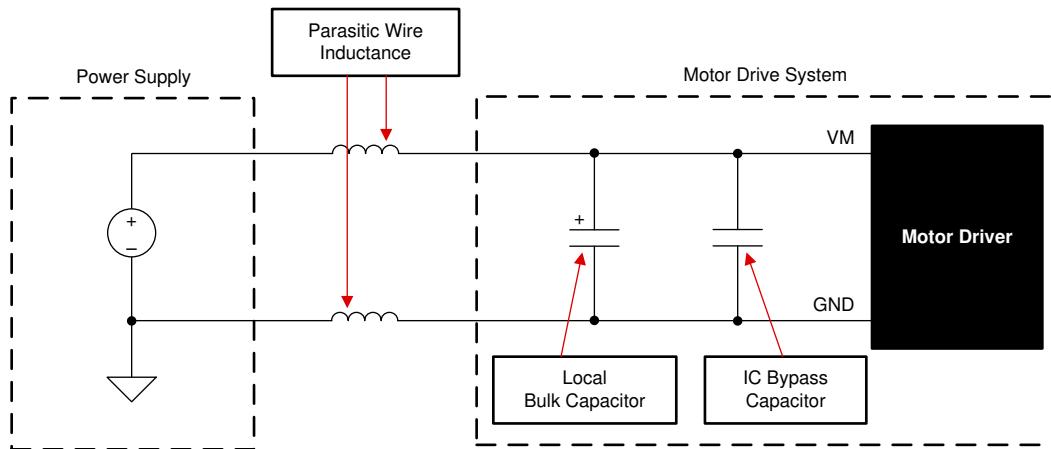

| $C_{VM2}$    | VM     | 負荷過渡を処理するために、GND に対して、VM に対応する定格電圧のローカル・バルク・コンデンサ、 $10\mu F$ 以上。バルク・コンデンサのサイズ決定に関するセクションを参照してください。                         |

| $R_{IPROPI}$ | IPROPI | GND に対して、通常 $500\sim5000\Omega$ 、 $0.063W$ の抵抗。コントローラ ADC のダイナミック・レンジによって抵抗値は異なります。ITRIP と IPROPI の機能が不要な場合、ピンを GND に短絡可能。 |

| $C_{IPROPI}$ | IPROPI | ITRIP レギュレーション・ループを低速にする場合は、オプションで $10\sim100nF$ 、 $6.3V$ コンデンサを GND との間に接続します。「過電流保護 (OCP)」セクションを参照。                      |

| $R_{nFAULT}$ | nFAULT | 通常、 $1k\Omega\sim10k\Omega$ 、 $0.063W$ プルアップ抵抗をコントローラ電源との間に接続します。                                                          |

| $R_{MODE}$   | MODE   | 設定に応じて、GND への開放または短絡、または $0.063W 10\%$ の抵抗を GND との間に接続。MODE 表を参照してください。                                                    |

| $R_{SR}$     | SR     | 設定に応じて、GND への開放または短絡、または $0.063W 10\%$ の抵抗を GND との間に接続。「SR」セクションを参照してください。                                                 |

| $R_{ITRIP}$  | ITRIP  | 設定に応じて、GND への開放または短絡、または $0.063W 10\%$ の抵抗を GND との間に接続。ITRIP 表を参照してください。                                                   |

| $R_{DIAG}$   | DIAG   | 設定に応じて、GND への開放または短絡、または $0.063W 10\%$ の抵抗を GND との間に接続。「DIAG」セクションを参照してください。                                               |

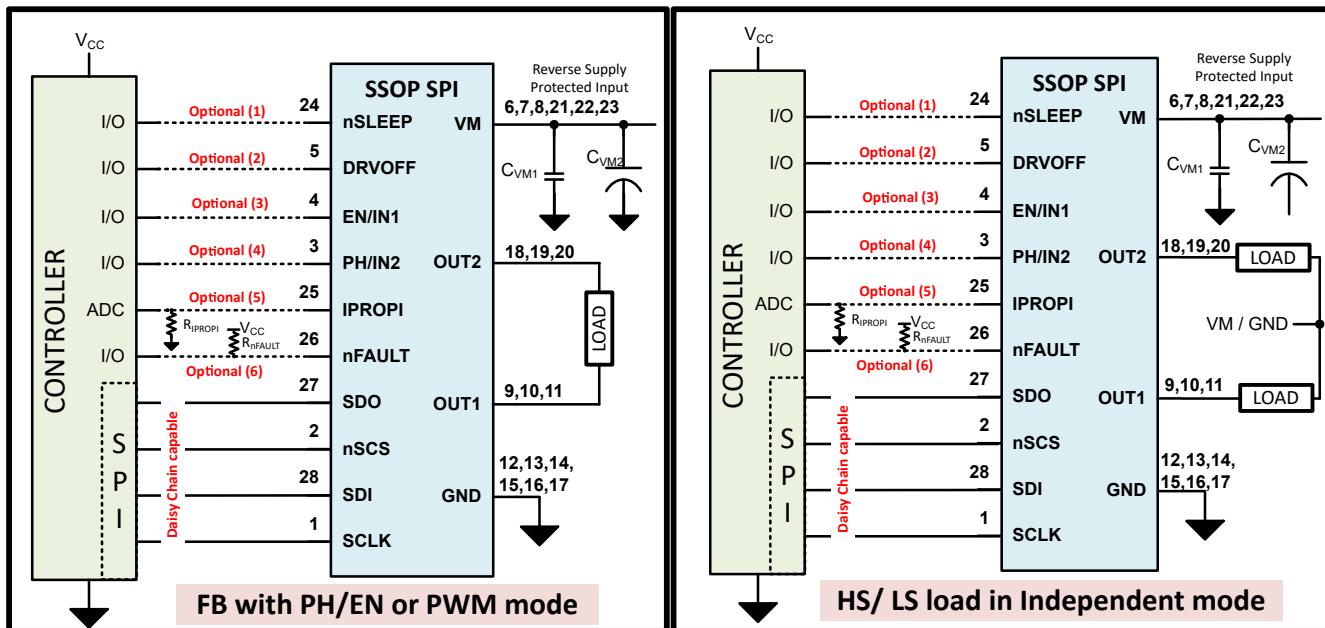

#### 8.3.1.2 SPI バリアント

**表 8-2. SPI バリアントの外付け部品表**

| 部品           | ピン     | 推奨事項                                                                                                                       |

|--------------|--------|----------------------------------------------------------------------------------------------------------------------------|

| $C_{VM1}$    | VM     | GND に対して、VM に対応する定格電圧、 $0.1\mu F$ 、低 ESR セラミック・コンデンサ                                                                       |

| $C_{VM2}$    | VM     | 負荷過渡を処理するために、GND に対して、VM に対応する定格電圧のローカル・バルク・コンデンサ、 $10\mu F$ 以上。バルク・コンデンサのサイズ決定に関するセクションを参照してください。                         |

| $R_{IPROPI}$ | IPROPI | GND に対して、通常 $500\sim5000\Omega$ 、 $0.063W$ の抵抗。コントローラ ADC のダイナミック・レンジによって抵抗値は異なります。ITRIP と IPROPI の機能が不要な場合、ピンを GND に短絡可能。 |

| $C_{IPROPI}$ | IPROPI | ITRIP レギュレーション・ループを低速にする場合は、オプションで $10\sim100nF$ 、 $6.3V$ コンデンサを GND との間に接続します。「過電流保護 (OCP)」セクションを参照。                      |

| $R_{nFAULT}$ | nFAULT | 通常、 $1k\Omega\sim10k\Omega$ 、 $0.063W$ プルアップ抵抗をコントローラ電源との間に接続します。nFAULT 信号を使用しない場合、このピンは GND に短絡するか、開放のままにしておくことができます。     |

| $C_{VDD}$    | VDD    | $0.1\mu F$ 、 $6.3V$ 、低 ESR セラミック・コンデンサを GND との間に接続します。これは、SPI (P) バリアントにのみ適用できます。                                          |

#### 8.3.2 ブリッジの制御

DRV824x-Q1 ファミリは、3 つの異なるモードを備えており、EN/IN1 ピンと PH/IN2 ピンを使った各種制御方式に対応しています。制御モードは、モード設定により選択します。モードは、HW バリアントでは MODE ピン、SPI バリアントでは CONFIG3 レジスタの S\_MODE ビットによって決まる 3 レベルの設定です(表 8-3 参照)。

**表 8-3. モード表**

| MODE ピン       | S_MODE ビット | デバイス・モード  | 説明                                      |

|---------------|------------|-----------|-----------------------------------------|

| $R_{LVL1OF3}$ | 2'b00      | PH/EN モード | フルブリッジ・モード、EN/IN1 は PWM 入力、PH/IN2 は方向入力 |

| $R_{LVL2OF3}$ | 2'b01      | 独立モード     | 2 つのハーフブリッジを個別に制御                       |

**表 8-3. モード表 (continued)**

| MODE ピン              | S_MODE ビット   | デバイス・モード | 説明                                                |

|----------------------|--------------|----------|---------------------------------------------------|

| R <sub>LVL3OF3</sub> | 2'b10, 2'b11 | PWM モード  | フルブリッジ・モード、方向に応じて EN/IN1 および PH/IN2 がそれぞれ PWM を制御 |

HW バリアントでは、電源オンまたはスリープからのウェイクアップ後のデバイス初期化時に、MODE ピンがラッピングされます。動作中の更新はブロックされます。

デバイスの SPI バリアントでは、SPI 通信が利用可能なときに S\_MODE ビットに書き込むことで、いつでもモード設定を変更できます。この変更はすぐに反映されます。

入力は、静的電圧 (100% 駆動モード) またはパルス幅変調 (PWM) 電圧信号 (PWM 駆動モード) を受け入れます。VM を印加する前に、デバイスの入力ピンに電力を供給しても問題ありません。入力がない場合に出力が確実に Hi-Z になるように、デフォルトで nSLEEP ピンおよび DRVOFF ピンには、それぞれ内部プルダウン抵抗およびプルアップ抵抗が接続されています。EN/IN1 ピンおよび PH/IN2 ピンにも、内部プルダウン抵抗が接続されています。以下に、各制御モードの真理値表を示します。

このデバイスは、ハーフブリッジ切り替え時のハイサイド FET とローサイド FET の遷移中に必要となる最適なデッドタイムを自動的に生成します。このタイミングは、内部での FET ゲート - ソース間電圧フィードバックに基づきます。外部タイミングは必要ありません。この方式により、最小デッドタイムが確保されるとともに、シートスルーハイドライブが保証されます。

#### 注

1. SPI バリアントでは、SPI\_IN レジスタ・ビットを使用して追加の制御を行うこともできます。「[レジスタ - ピン制御](#)」を参照してください。

2. SPI (P) バリアントには nSLEEP ピンがないため、制御表の nSLEEP 列は無視してください。内部では、常に nSLEEP = 1 となっています。この制御表は、VDD > VDD<sub>POR</sub> レベルのときに有効です。

#### 8.3.2.1 PH/EN モード

このモードでは、2 つのハーフブリッジがフルブリッジとして動作するように構成されます。EN/IN1 は PWM 入力、PH/IN2 は方向入力です。負荷の説明図については、「[負荷の概要](#)」セクションを参照してください。

**表 8-4. 制御表 - PH/EN モード**

| nSLEEP | DRVOFF | EN/IN1 | PH/IN2 | OUT1                              | OUT2             | IPROPI                         | デバイスの状態 |

|--------|--------|--------|--------|-----------------------------------|------------------|--------------------------------|---------|

| 0      | X      | X      | X      | Hi-Z                              | Hi-Z             | 電流なし                           | スリープ    |

| 1      | 1      | 0      | 0      | Hi-Z                              | Hi-Z             | 電流なし                           | スタンバイ   |

| 1      | 1      | 1      | 0      | <a href="#">オフ状態診断</a> 表を参照してください |                  |                                | スタンバイ   |

| 1      | 1      | 0      | 1      |                                   |                  |                                |         |

| 1      | 1      | 1      | 1      |                                   |                  |                                |         |

| 1      | 0      | 0      | X      | H                                 | H                | ISNS1 または ISNS2 <sup>(1)</sup> | アクティブ   |

| 1      | 0      | 1      | 0      | L <sup>(2)</sup>                  | H                | ISNS2                          | アクティブ   |

| 1      | 0      | 1      | 1      | H                                 | L <sup>(2)</sup> | ISNS1                          | アクティブ   |

(1) デバイスから流出する電流 (VM → OUTx → 負荷)

(2) 内部 ITRIP レギュレーションがイネーブルのとき、ITRIP レベルに達すると、OUTx は固定時間強制的に「H」になります

#### 8.3.2.2 PWM モード

このモードでは、2 つのハーフブリッジがフルブリッジとして動作するように構成されます。EN/IN1 は、1 方向の PWM 入力を供給し、PH/IN2 は、その逆方向の PWM を供給します。負荷の説明図については、「[負荷の概要](#)」セクションを参照してください。

表 8-5. 制御表 - PWM モード

| nSLEEP | DRVOFF | EN/IN1 | PH/IN2 | OUT1             | OUT2             | IPOPI                          | デバイスの状態 |

|--------|--------|--------|--------|------------------|------------------|--------------------------------|---------|

| 0      | X      | X      | X      | Hi-Z             | Hi-Z             | 電流なし                           | スリープ    |

| 1      | 1      | 0      | 0      | Hi-Z             | Hi-Z             | 電流なし                           | スタンバイ   |

| 1      | 1      | 1      | 0      | オフ状態診断表を参照してください |                  | 電流なし                           | スタンバイ   |

| 1      | 1      | 0      | 1      |                  |                  | 電流なし                           | スタンバイ   |

| 1      | 1      | 1      | 1      |                  |                  | 電流なし                           | スタンバイ   |

| 1      | 0      | 0      | 0      | H                | H                | ISNS1 または ISNS2 <sup>(1)</sup> | アクティブ   |

| 1      | 0      | 0      | 1      | L <sup>(2)</sup> | H                | ISNS2                          | アクティブ   |

| 1      | 0      | 1      | 0      | H                | L <sup>(2)</sup> | ISNS1                          | アクティブ   |

| 1      | 0      | 1      | 1      | Hi-Z             | Hi-Z             | 電流なし                           | スタンバイ   |

(1) デバイスから流出する電流 (VM → OUTx → 負荷)

(2) 内部 ITRIP レギュレーションがイネーブルのとき、ITRIP レベルに達すると、OUTx は固定時間強制的に「H」になります

SPI バリアントの場合、CONFIG2 レジスタの PWM\_EXTEND ビットを設定すると、正方向 ([EN/IN1 PH/IN2] = [1 0]) または逆方向 ([EN/IN1 PH/IN2] = [0 1]) コマンドの後に Hi-Z コマンド ([EN/IN1 PH/IN2] = [1 1]) を実行したのと同じよう、追加の Hi-Z 状態が発生します。この Hi-Z (コースト) 状態では、PWM に関するハーフブリッジのみが Hi-Z になり、他方のハーフブリッジの HS FET はオンに保持されます。どちらのハーフブリッジが Hi-Z になるかは、前のサイクルに基づいて決まります。表 8-6 に、上述の内容を示します。

表 8-6. PWM 拡張表 (PWM\_EXTEND ビット = 1'b1)

| 前の状態 |      | 現在の状態 |      |       | デバイスの状態遷移       |

|------|------|-------|------|-------|-----------------|

| OUT1 | OUT2 | OUT1  | OUT2 | IPOPI |                 |

| Hi-Z | Hi-Z | Hi-Z  | Hi-Z | 電流なし  | スタンバイ状態のまま、変化なし |

| H    | H    | Hi-Z  | Hi-Z | 電流なし  | アクティブからスタンバイへ   |

| L    | H    | Hi-Z  | H    | ISNS2 | アクティブからスタンバイへ   |

| H    | L    | H     | Hi-Z | ISNS1 | アクティブからスタンバイへ   |

### 8.3.2.3 独立モード

このモードでは、2 つのハーフブリッジを 2 つの独立したハーフブリッジとして使用するよう構成します。表 8-7 にブリッジ制御の真理値表を示します。負荷の説明図については、「[負荷の概要](#)」セクションを参照してください。

表 8-7. 制御表 - 独立モード

| nSLEEP | DRVOFF | EN/IN1 | PH/IN2 | OUT1             | OUT2             | IPOPI                        | デバイスの状態 |

|--------|--------|--------|--------|------------------|------------------|------------------------------|---------|

| 0      | X      | X      | X      | Hi-Z             | Hi-Z             | 電流なし                         | スリープ    |

| 1      | 1      | 0      | 0      | Hi-Z             | Hi-Z             | 電流なし                         | スタンバイ   |

| 1      | 1      | 1      | 0      | オフ状態診断表を参照してください |                  | 電流なし                         | スタンバイ   |

| 1      | 1      | 0      | 1      |                  |                  | 電流なし                         | スタンバイ   |