## DRV8311-Q1 三相 PWM モーター ドライバ

### 1 特長

- 車載アプリケーション向けに AEC-Q100 認証済み

- 温度グレード  $-40^{\circ}\text{C} \leq \text{TA} \leq 125^{\circ}\text{C}$

- 三相 PWM モーター ドライバ

- 三相ブラシレス DC モーター

- 3V~20V の動作電圧範囲

- 絶対最大定格電圧 24V

- 大出力電流能力

- 5A のピーク駆動電流

- 低いオン抵抗の MOSFET

- $\text{T}_A = 25^{\circ}\text{C}$ で  $210\text{m}\Omega$  の  $R_{DS(\text{ON})}$  (HS + LS)

- 低消費電力スリープ モード

- $V_{VM} = 12\text{V}, \text{T}_A = 25^{\circ}\text{C}$ で  $1.5\mu\text{A}$

- 複数の制御インターフェイス オプション

- 6x PWM 制御インターフェイス

- 3x PWM 制御インターフェイス

- MCU と DRV8311-Q1 との間のオプション キャリブレーション機能を備えた PWM 生成モード (SPI/tSPI)

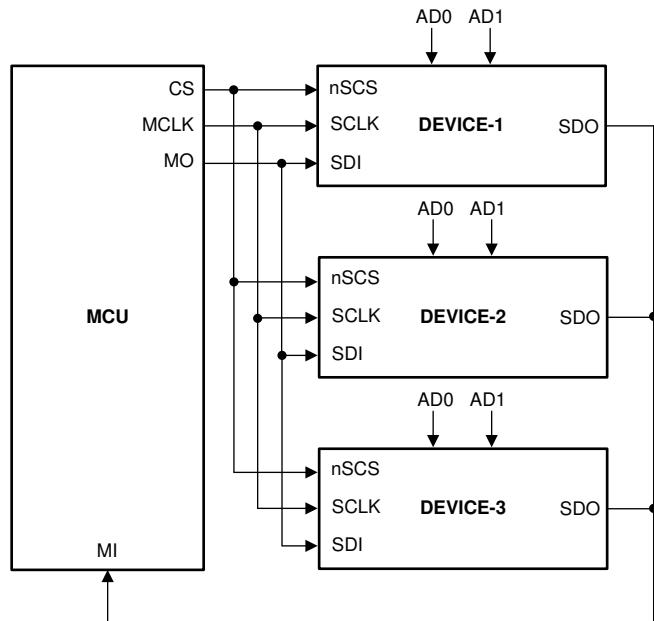

- tSPI (DRV8311P-Q1)

- SPI を介して PWM デューティおよび周波数を更新

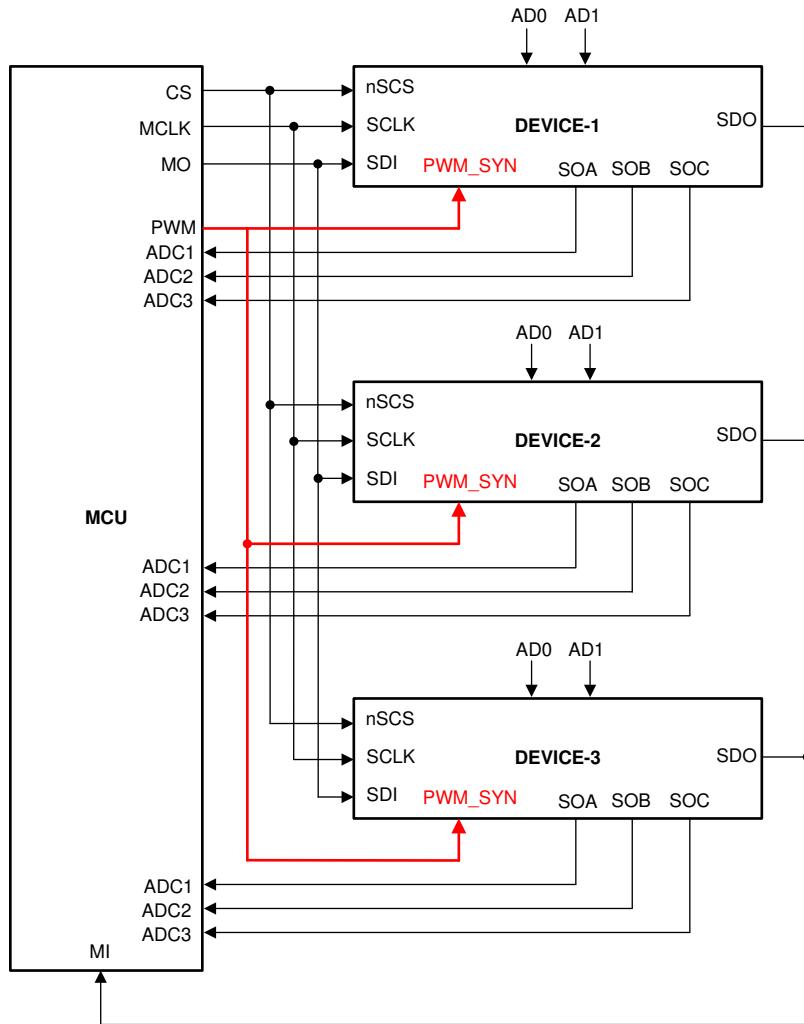

- 標準的な 4 線式 SPI を使用して複数の DRV8311P-Q1 デバイスを制御

- 最大 200kHz の PWM 周波数をサポート

- 電流センス機能内蔵

- 外付け抵抗不要

- センスアンプ出力、1/2 ブリッジごとに 1 つ

- SPI およびハードウェア デバイスのバリエント

- 10MHz の SPI 通信 (SPI/tSPI)

- 1.8V、3.3V、5V のロジック入力をサポート

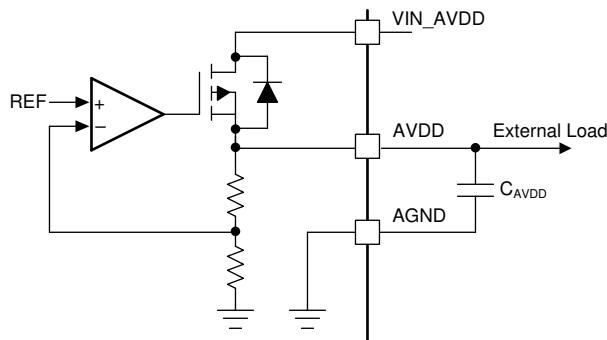

- 3.3V ( $\pm 4.5\%$ )、100mA の LDO レギュレータを内蔵

- 保護機能内蔵

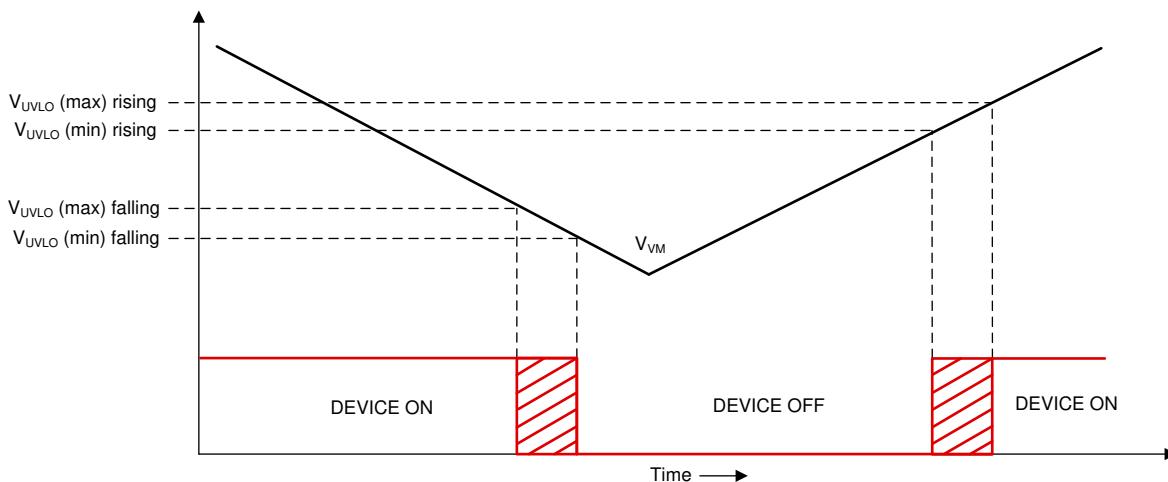

- VM 低電圧誤動作防止 (UVLO)

- チャージポンプ低電圧 (CPUV)

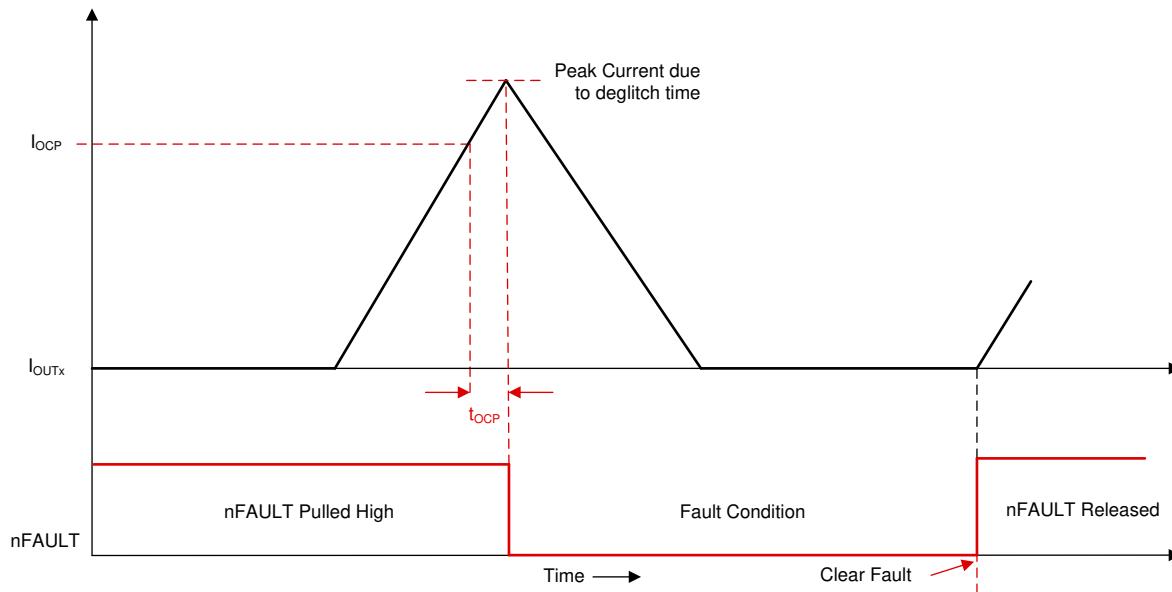

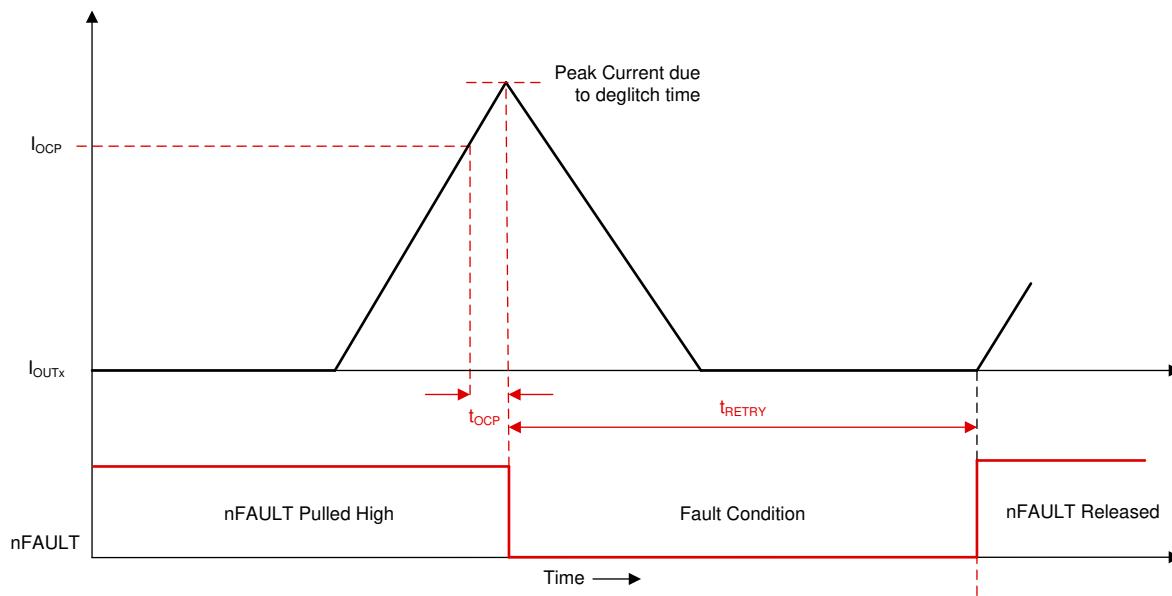

- 過電流保護 (OCP)

- 熱警告およびシャットダウン (OTW/OTSD)

- フォルト状況表示ピン (nFAULT)

### 2 アプリケーション

- ステアリング ホイール (ハンドル) 調整モジュール

- 車載熱管理バルブ

- LIDAR モジュール

- ブラシレス DC (BLDC) モーター モジュール

### 3 説明

DRV8311-Q1 は、5V、9V、12V、または 18V DC レベル、あるいは 1S ~ 4S バッテリ駆動アプリケーションにおいて、三相ブラシレス DC (BLDC) モーターを駆動するための 3 つの内蔵 MOSFET ハーフブリッジを備えています。このデバイスは、電流センス機能を備えた 3 個の電流センスアンプ (CSA) を内蔵しており、BLDC モーターの三相電流をセンスできるので、FOC と電流制御のシステムを最適な方法で実装するのに役立ちます。

DRV8311P-Q1 デバイスは、テキサス インストゥルメンツ SPI (tSPI) によって PWM タイマを生成および設定する機能を備えており、tSPI 経由で複数の BLDC モーターを直接制御できます。この機能により、複数のモーターの制御に必要な 1 次側コントローラの I/O ポート数を削減できます。

#### 製品情報 (1)

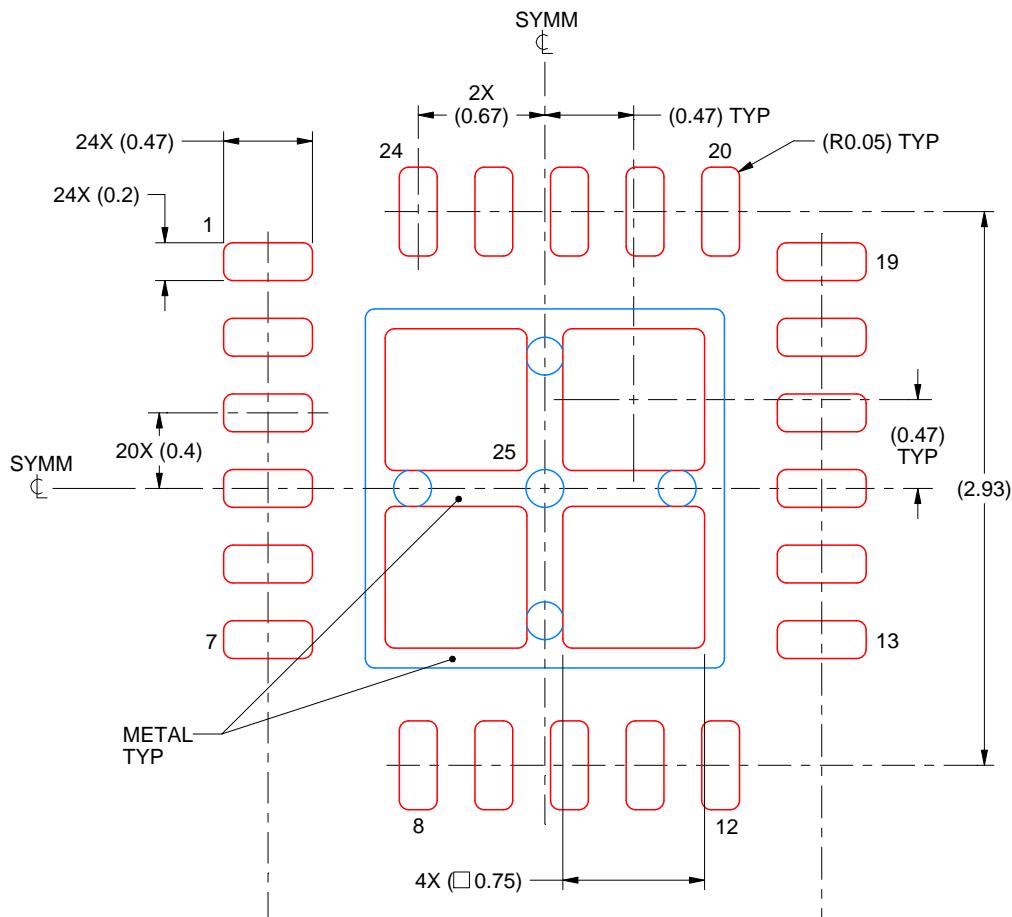

| 部品番号                       | パッケージ     | パッケージ サイズ (公称) <sup>(3)</sup> |

|----------------------------|-----------|-------------------------------|

| DRV8311P-Q1                | WQFN (24) | 3.00mm × 3.00mm               |

| DRV8311H-Q1 <sup>(2)</sup> | WQFN (24) | 3.00mm × 3.00mm               |

| DRV8311S-Q1 <sup>(2)</sup> | WQFN (24) | 3.00mm × 3.00mm               |

- 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

- このデバイスはプレビュー版としてのみ供給されます。

- パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

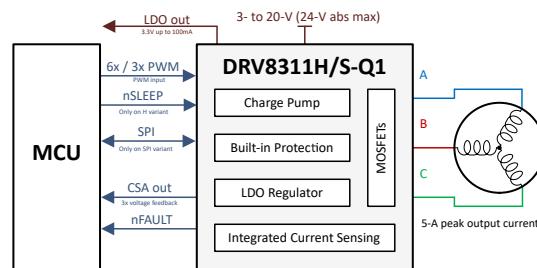

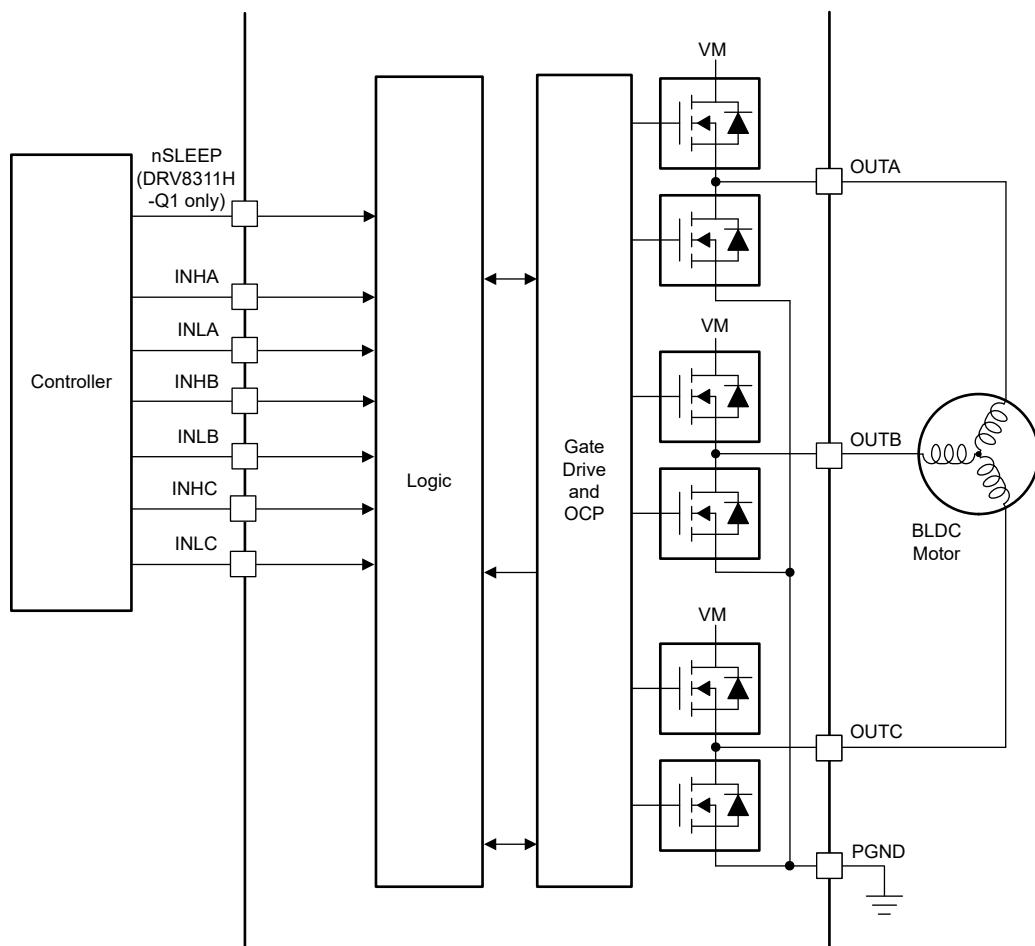

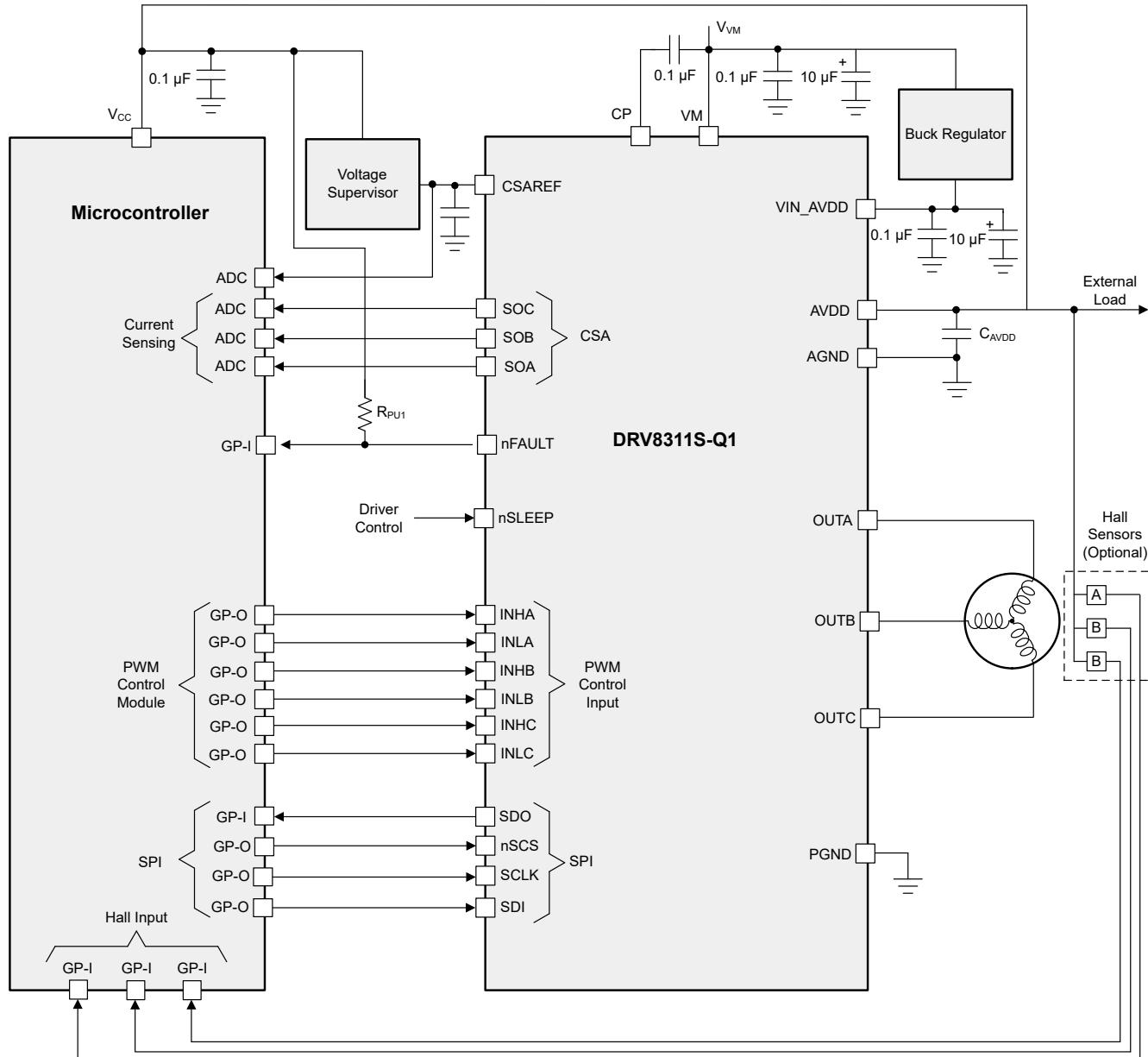

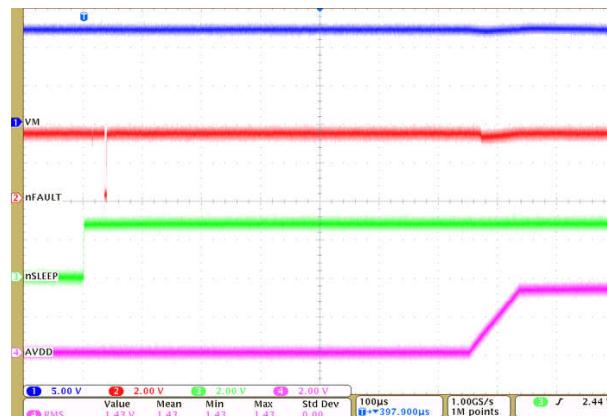

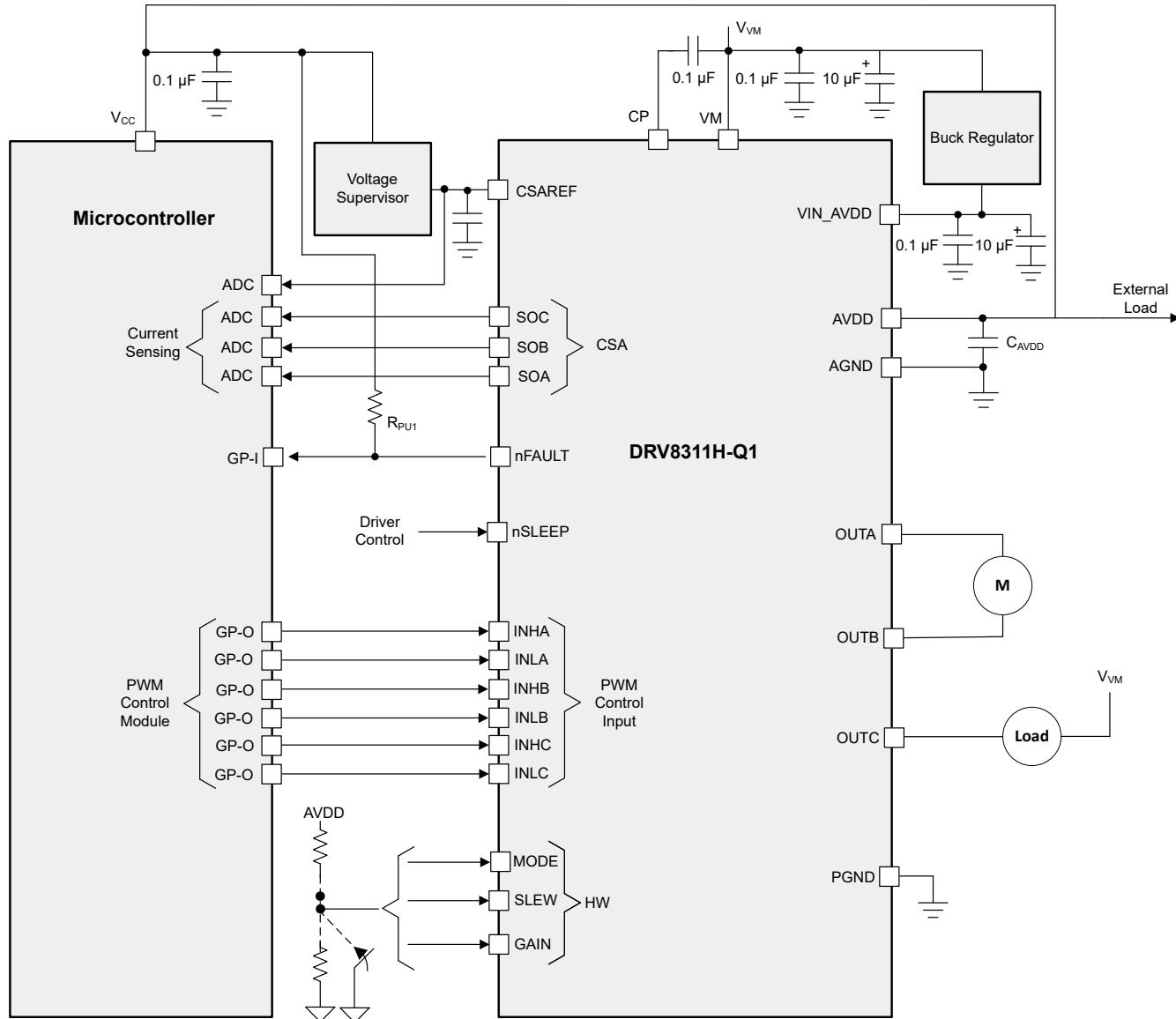

DRV8311H/S-Q1 の概略回路図

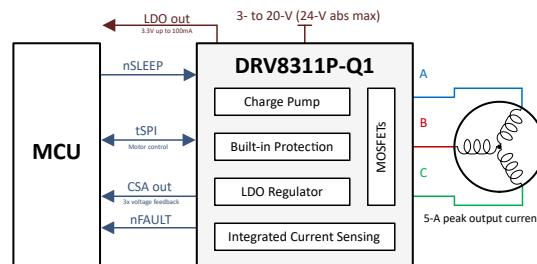

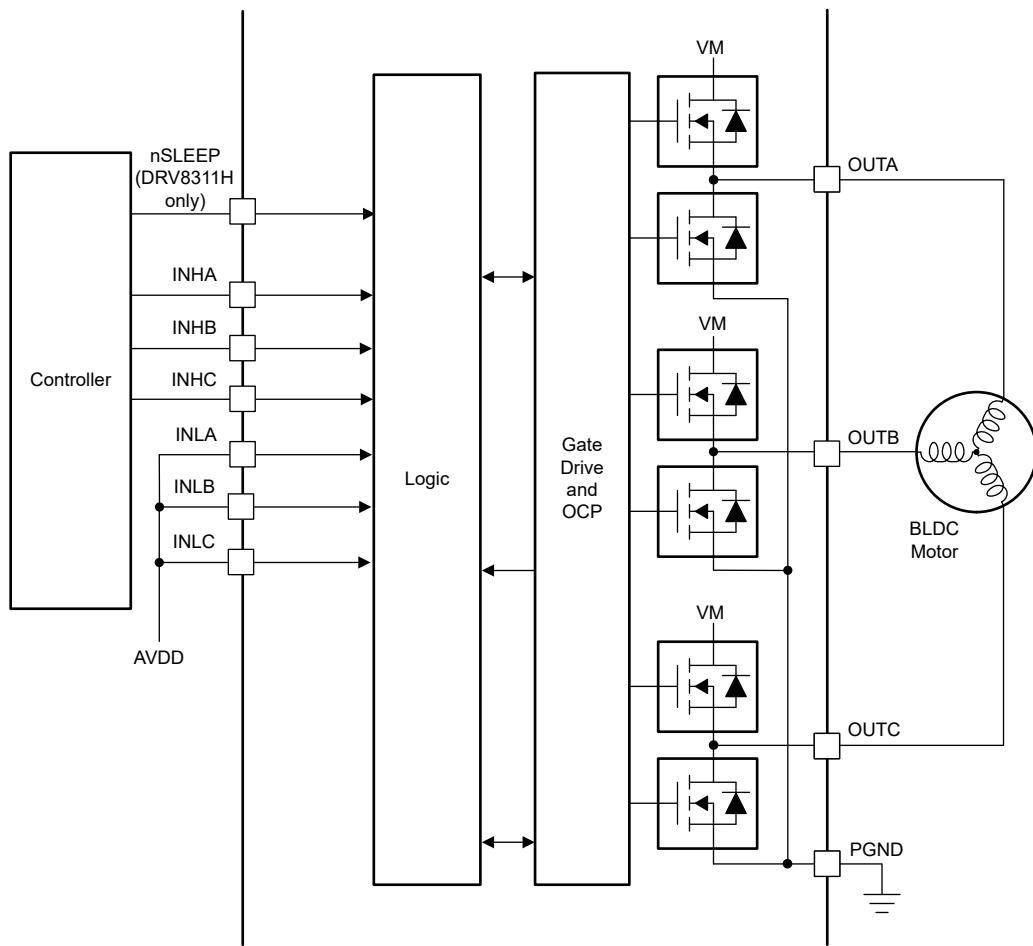

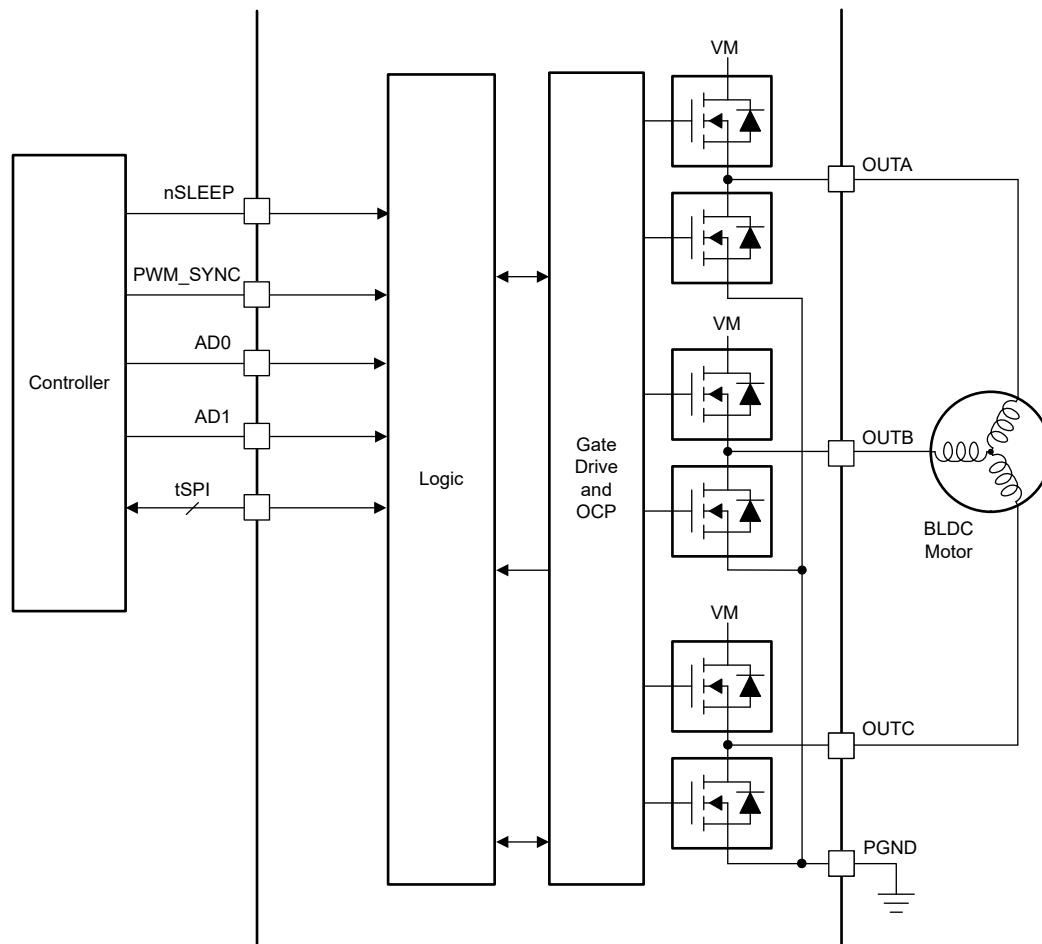

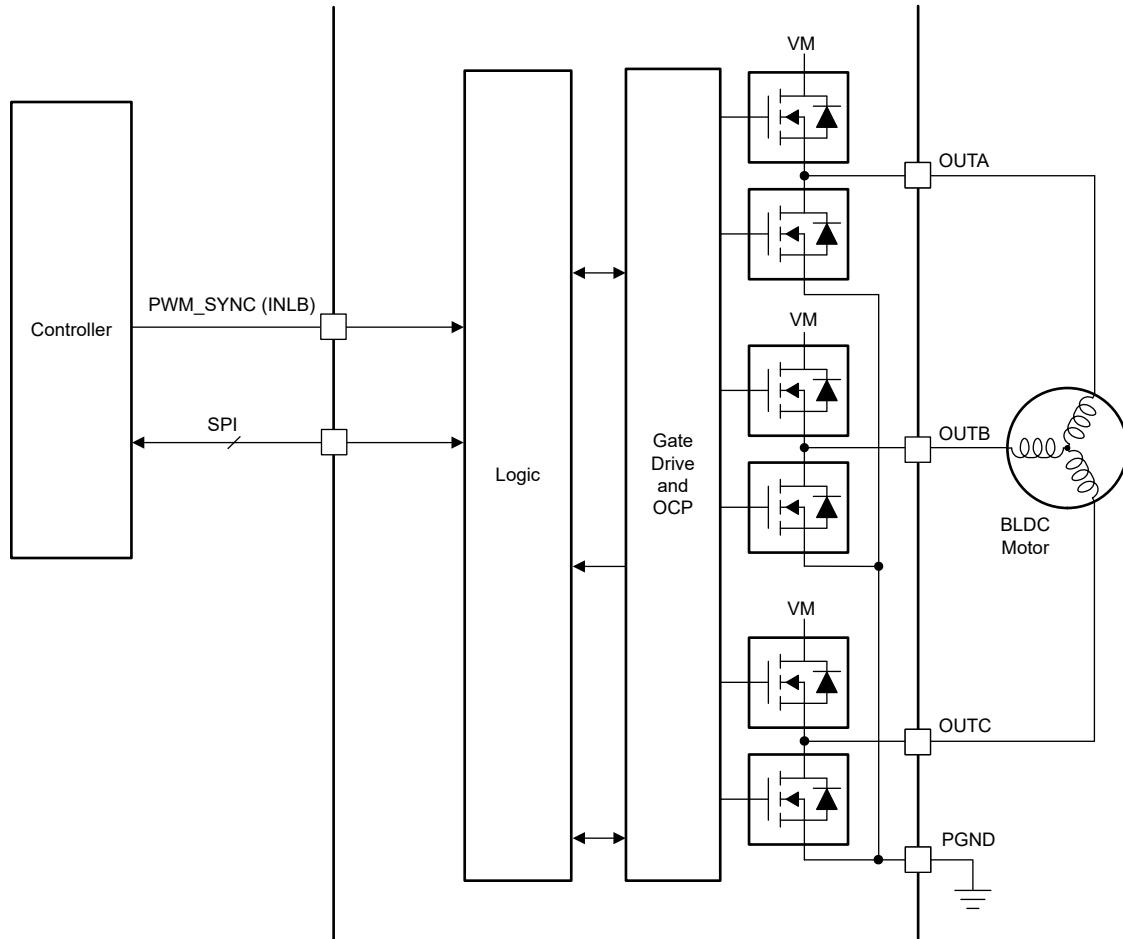

DRV8311P-Q1 の概略回路図

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                                   |           |                                     |           |

|-----------------------------------|-----------|-------------------------------------|-----------|

| <b>1 特長</b> .....                 | <b>1</b>  | 7.4 デバイスの機能モード.....                 | <b>49</b> |

| <b>2 アプリケーション</b> .....           | <b>1</b>  | 7.5 SPI 通信.....                     | <b>50</b> |

| <b>3 説明</b> .....                 | <b>1</b>  | <b>8 DRV8311-Q1 のレジスタ</b> .....     | <b>55</b> |

| <b>4 デバイス比較表</b> .....            | <b>3</b>  | <b>9 アプリケーションと実装</b> .....          | <b>80</b> |

| <b>5 ピン構成および機能</b> .....          | <b>4</b>  | 9.1 アプリケーション情報.....                 | <b>80</b> |

| <b>6 仕様</b> .....                 | <b>7</b>  | 9.2 代表的なアプリケーション.....               | <b>81</b> |

| 6.1 絶対最大定格.....                   | 7         | 9.3 三相ブラシレス DC tSPI モーター制御.....     | <b>84</b> |

| 6.2 ESD 定格.....                   | 7         | 9.4 他のアプリケーション.....                 | <b>86</b> |

| 6.3 推奨動作条件.....                   | 7         | 9.5 電源に関する推奨事項.....                 | <b>87</b> |

| 6.4 熱に関する情報.....                  | 8         | 9.6 レイアウト.....                      | <b>87</b> |

| 6.5 電気的特性.....                    | 8         | <b>10 デバイスおよびドキュメントのサポート</b> .....  | <b>91</b> |

| 6.6 SPI のタイミング要件.....             | 16        | 10.1 サポート・リソース.....                 | <b>91</b> |

| 6.7 SPI セカンダリ デバイス モードのタイミング..... | 17        | 10.2 商標.....                        | <b>91</b> |

| 6.8 代表的特性.....                    | 18        | 10.3 静電気放電に関する注意事項.....             | <b>91</b> |

| <b>7 詳細説明</b> .....               | <b>19</b> | 10.4 用語集.....                       | <b>91</b> |

| 7.1 概要.....                       | 19        | <b>11 改訂履歴</b> .....                | <b>91</b> |

| 7.2 機能ブロック図.....                  | 20        | <b>12 メカニカル、パッケージ、および注文情報</b> ..... | <b>91</b> |

| 7.3 機能説明.....                     | 23        |                                     |           |

## 4 デバイス比較表

| デバイス        | パッケージ                  | インターフェイス | nSLEEP 入力 |

|-------------|------------------------|----------|-----------|

| DRV8311P-Q1 | 24 ピン WQFN (3mm × 3mm) | SPI/tSPI | あり        |

| DRV8311S-Q1 |                        | SPI      | なし        |

| DRV8311H-Q1 |                        | ハードウェア   | あり        |

**表 4-1. DRV8311H-Q1、DRV8311S-Q1、DRV8311P-Q1 の構成比較**

| パラメータ                     | DRV8311H-Q1                                                      | DRV8311S-Q1                                                              | DRV8311P-Q1                                                              |

|---------------------------|------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------|

| PWM 制御モード設定               | MODE ピン (2 つの設定)                                                 | PWM_MODE (3 つの設定)                                                        | PWM_MODE (3 つの設定)                                                        |

| スルーレートの設定                 | SLEW ピン (4 つの設定)                                                 | SLEW_RATE (4 つの設定)                                                       | SLEW_RATE (4 つの設定)                                                       |

| 電流センスアンプのゲイン              | ゲイン ピン (4 つの設定)                                                  | CSA_GAIN (4 つの設定)                                                        | CSA_GAIN (4 つの設定)                                                        |

| 過電流保護 (OCP) レベルの設定        | MODE ピン (2 つの設定)                                                 | OCP_LVL (2 つの設定)                                                         | OCP_LVL (2 つの設定)                                                         |

| OCP ブランкиング時間             | 0.2us に固定                                                        | OCP_TBLANK (4 つの設定)                                                      | OCP_TBLANK (4 つの設定)                                                      |

| OCP グリッチ除去時間              | 1us に固定                                                          | OCP_DEG (4 つの設定)                                                         | OCP_DEG (4 つの設定)                                                         |

| OCP モード                   | 5ms の自動リトライによる高速リトライ                                             | OCP_MODE (4 つの設定)、設定可能なリトライ時間                                            | OCP_MODE (4 つの設定)、設定可能なリトライ時間                                            |

| デッドタイム                    | SLEW ピンの設定に基づいて固定                                                | TDEAD_CTRL (8 つの設定)                                                      | TDEAD_CTRL (8 つの設定)                                                      |

| 伝搬遅延                      | SLEW ピンの設定に基づいて固定                                                | SLEW ピンの設定に基づいて固定                                                        | SLEW ピンの設定に基づいて固定                                                        |

| ドライバ遅延補償                  | 無効                                                               | DLYCMP_EN (2 つの設定)                                                       | DLYCMP_EN (2 つの設定)                                                       |

| 内部発振器のスペクトラム拡散変調          | 有効                                                               | SSC_DIS (2 つの設定)                                                         | SSC_DIS (2 つの設定)                                                         |

| 低電圧誤動作防止                  | VINAVDD、CP、AVDD 低電圧保護が有効、CSAREF_UV 無効、t_RETRY は 5ms の高速自動リトライに設定 | VINAVDD、CP、AVDD 低電圧保護が有効、CSAREF_UV (2 つの設定)、UVP_MODE を使用した t_RETRY を設定可能 | VINAVDD、CP、AVDD 低電圧保護が有効、CSAREF_UV (2 つの設定)、UVP_MODE を使用した t_RETRY を設定可能 |

| SPI フォルト モード              | 該当なし                                                             | SPIFLT_MODE (2 つの設定)                                                     | SPIFLT_MODE (2 つの設定)                                                     |

| テキサス インストゥルメンツ SPI (tSPI) | 該当なし                                                             | 該当なし                                                                     | 使用可能                                                                     |

| 過熱シャットダウン (OTSD) モード      | 5ms の自動リトライによる高速リトライ                                             | OTSD_MODE (2 つの設定)                                                       | OTSD_MODE (2 つの設定)                                                       |

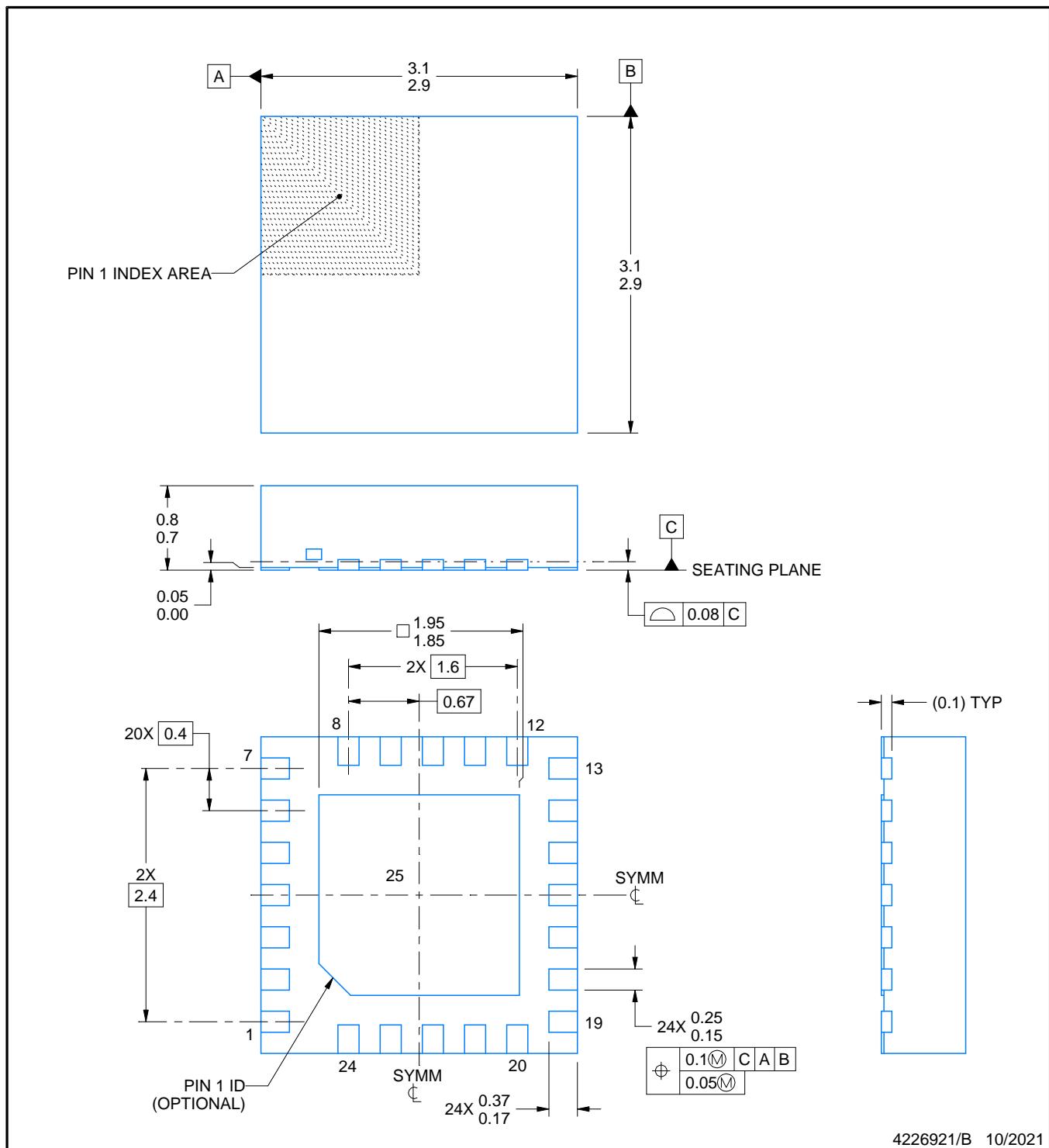

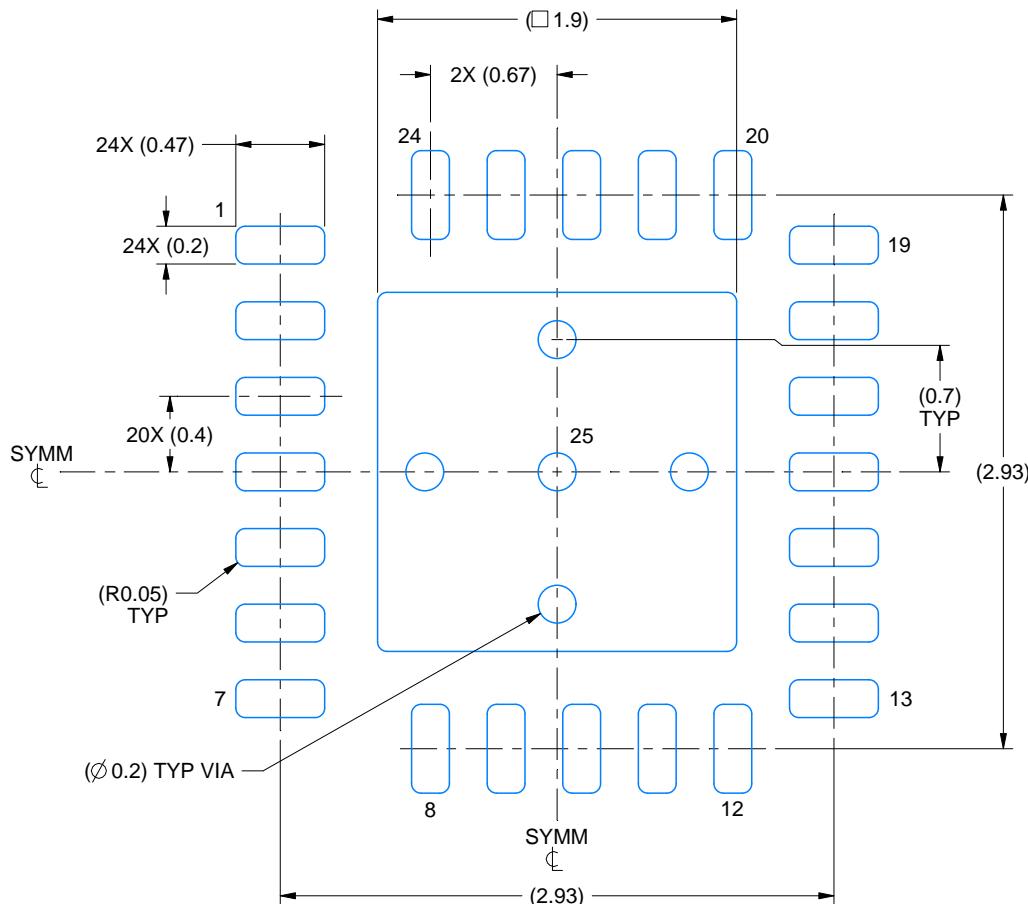

## 5 ピン構成および機能

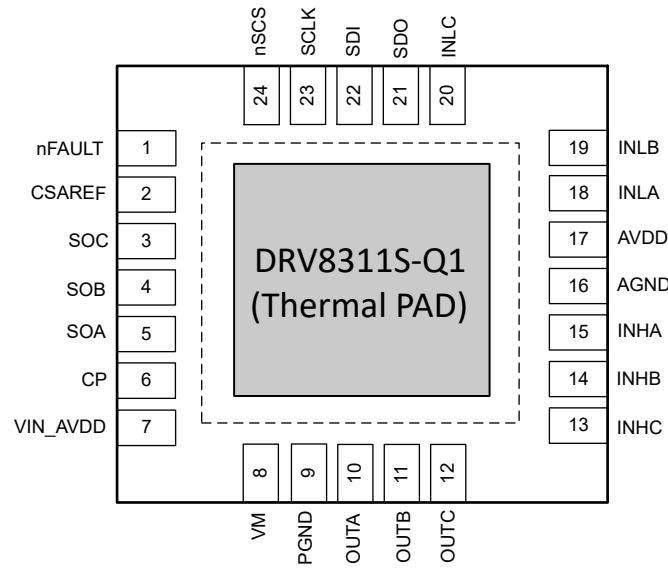

図 5-1. DRV8311S-Q1 24 ピン WQFN (放熱サーマルパッド付き) 上面図

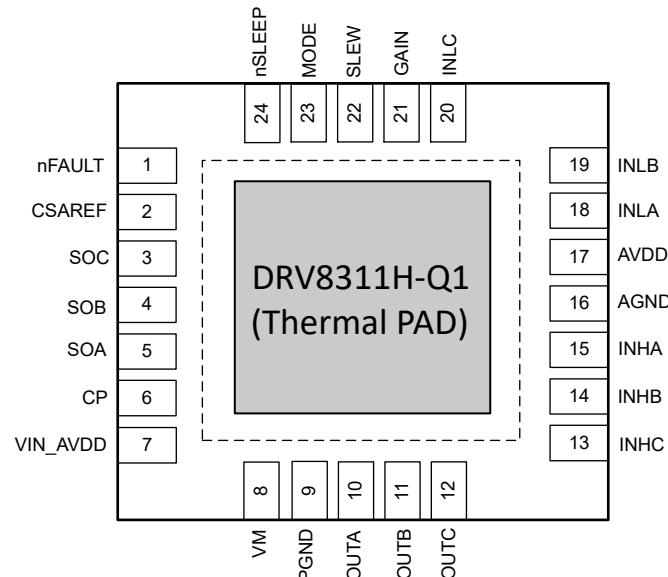

図 5-2. DRV8311H-Q1 24 ピン WQFN (放熱サーマルパッド付き) 上面図

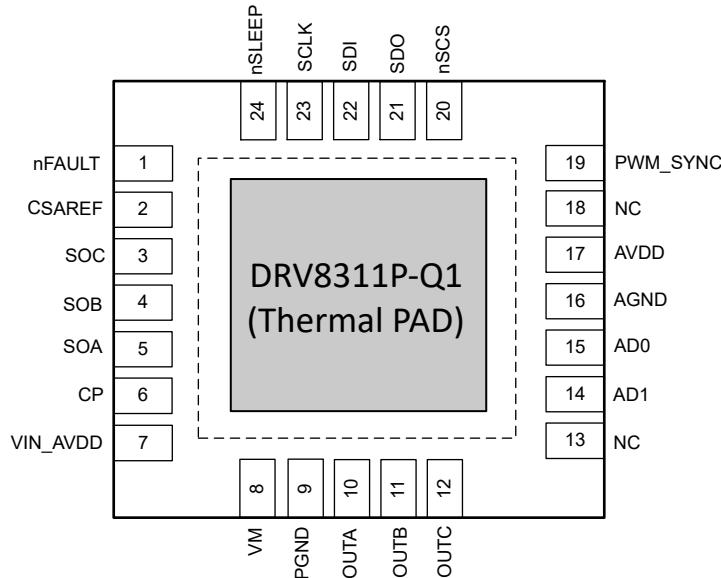

図 5-3. DRV8311P-Q1 24 ピン WQFN (放熱サーマルパッド付き) 上面図

表 5-1. ピンの機能

| ピン     | 24 ピン パッケージ     |                 |                 | タイプ <sup>(1)</sup> | 説明                                                                                                               |

|--------|-----------------|-----------------|-----------------|--------------------|------------------------------------------------------------------------------------------------------------------|

| 名称     | DRV8311<br>H-Q1 | DRV8311P<br>-Q1 | DRV8311S<br>-Q1 |                    |                                                                                                                  |

| AD0    | —               | 15              | —               | I                  | tSPI デバイス DRV8311P-Q1 のみ。tSPI のアドレス選択。                                                                           |

| AD1    | —               | 14              | —               | I                  | tSPI デバイス DRV8311P-Q1 のみ。tSPI のアドレス選択。                                                                           |

| AGND   | 16              | 16              | 16              | PWR                | デバイスのアナログ グラウンド。システム グラウンドに接続。                                                                                   |

| AVDD   | 17              | 17              | 17              | PWR                | 3.3V レギュレータ出力。AVDD ピンと AGND ピンの間に、X5R または X7R、0.7μF ~ 7μF、6.3V のセラミック コンデンサを接続します。このレギュレータは最大 100mA を外部にソースできます。 |

| CP     | 6               | 6               | 6               | PWR                | チャージ ポンプ出力。VCP ピンと VM ピンの間に、X5R または X7R、0.1μF、16V のセラミック コンデンサを接続します。                                            |

| CSAREF | 2               | 2               | 2               | PWR                | 電流センス アンプの電源入力およびリファレンス。X5R または X7R、0.1μF、6.3V セラミック コンデンサを CSAREF ピンと AGND ピンの間に接続します。                          |

| ゲイン    | 21              | —               | —               | I                  | ハードウェア デバイス (DRV8311H-Q1) のみ。電流センス アンプのゲイン設定。このピンは、ゲイン ピンと AVDD または AGND の間に接続した外部抵抗によって設定される 4 レベル入力ピンです。       |

| INHA   | 15              | —               | 15              | I                  | OUTA のハイサイド ドライバ制御入力。このピンは、6x3x PWM モードにおけるハイサイド MOSFET の状態を制御します。                                               |

| INHB   | 14              | —               | 14              | I                  | OUTB のハイサイド ドライバ制御入力。このピンは、6x3x PWM モードにおけるハイサイド MOSFET の状態を制御します。                                               |

| INHC   | 13              | —               | 13              | I                  | OUTC のハイサイド ドライバ制御入力。このピンは、6x3x PWM モードにおけるハイサイド MOSFET の状態を制御します。                                               |

| INLA   | 18              | —               | 18              | I                  | OUTA のローサイド ドライバ制御入力。このピンは、6x PWM モードにおけるローサイド MOSFET の状態を制御します。                                                 |

| INLB   | 19              | —               | 19              | I                  | OUTB のローサイド ドライバ制御入力。このピンは、6x PWM モードにおけるローサイド MOSFET の状態を制御します。                                                 |

| INLC   | 20              | —               | 20              | I                  | OUTC のローサイド ドライバ制御入力。このピンは、6x PWM モードにおけるローサイド MOSFET の状態を制御します。                                                 |

| MODE   | 23              | —               | —               | I                  | ハードウェア デバイス (DRV8311H-Q1) のみ。PWM モード設定。このピンは、MODE ピンと AVDD または AGND の間に接続した外部抵抗によって設定される 4 レベル入力ピンです。            |

表 5-1. ピンの機能 (続き)

| ピン           | 24 ピン パッケージ     |                 |                 | タイプ <sup>(1)</sup> | 説明                                                                                                                                                                             |

|--------------|-----------------|-----------------|-----------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称           | DRV8311<br>H-Q1 | DRV8311P<br>-Q1 | DRV8311S<br>-Q1 |                    |                                                                                                                                                                                |

| nFAULT       | 1               | 1               | 1               | O                  | フォルト通知ピン。フォルト状態時に論理 Low にプルされます。オープンドレイン出力であるため、外部に AVDD へのプルアップ抵抗が必要です。                                                                                                       |

| nSCS         | —               | 20              | 24              | I                  | SPI (DRV8311S-Q1) および tSPI (DRV8311P-Q1) デバイスのみ。シリアル チップ選択。このピンの論理 Low により、シリアル インターフェイス通信が可能になります (SPI デバイスの場合)。                                                              |

| nSLEEP       | 24              | 24              | —               | I                  | DRV8311H-Q1 および DRV8311P-Q1 デバイスのみ。このピンを論理 Low にすると、本デバイスは低消費電力のスリープ モードに移行します。nSLEEP ピンに 15 ~ 50µs の Low パルスを入力することで、スリープ モードに入ることなくフォルト状態をリセットできます。                          |

| OUTA         | 10              | 10              | 10              | O                  | ハーフブリッジ出力 A。モーター巻線に接続します。                                                                                                                                                      |

| OUTB         | 11              | 11              | 11              | O                  | ハーフブリッジ出力 B。モーター巻線に接続します。                                                                                                                                                      |

| OUTC         | 12              | 12              | 12              | O                  | ハーフブリッジ出力 C。モーター巻線に接続します。                                                                                                                                                      |

| PGND         | 9               | 9               | 9               | PWR                | デバイスの電源グランド。システム グランドに接続。                                                                                                                                                      |

| PWM_SY<br>NC | —               | 19              | —               | I                  | tSPI デバイス DRV8311P-Q1 のみ。PWM 生成モードにおいて、DRV8311P-Q1 で内部生成される PWM 信号を MCU と同期させるために、MCU の信号に接続します。                                                                               |

| SCLK         | —               | 23              | 23              | I                  | SPI (DRV8311S-Q1) および tSPI (DRV8311P-Q1) デバイスのみ。シリアル クロック入力。シリアル データは SCLK の立ち上がりエッジでシフトアウトされ、立ち下がりエッジでキャプチャされます (SPI デバイスの場合)。                                                |

| SDI          | —               | 22              | 22              | I                  | SPI (DRV8311S-Q1) および tSPI (DRV8311P-Q1) デバイスのみ。シリアル データ入力。データは、SCLK ピンの立ち下がりエッジでキャプチャされます (SPI デバイス)。                                                                         |

| SDO          | —               | 21              | 21              | O                  | SPI (DRV8311S-Q1) および tSPI (DRV8311P-Q1) デバイスのみ。シリアル データ出力。データは、SCLK ピンの立ち上がりエッジでシフトアウトされます。                                                                                   |

| SLEW         | 22              | —               | —               | I                  | DRV8311H-Q1 デバイスのみ。OUTx 電圧スルーレート制御設定。このピンは、SLEW ピンと AVDD または AGND の間に接続した外部抵抗によって設定される 4 レベル入力ピンです。                                                                            |

| SOA          | 5               | 5               | 5               | O                  | OUTA 用電流センス アンプ出力。                                                                                                                                                             |

| SOB          | 4               | 4               | 4               | O                  | OUTB 用電流センス アンプ出力。                                                                                                                                                             |

| SOC          | 3               | 3               | 3               | O                  | OUTC 用電流センス アンプ出力。                                                                                                                                                             |

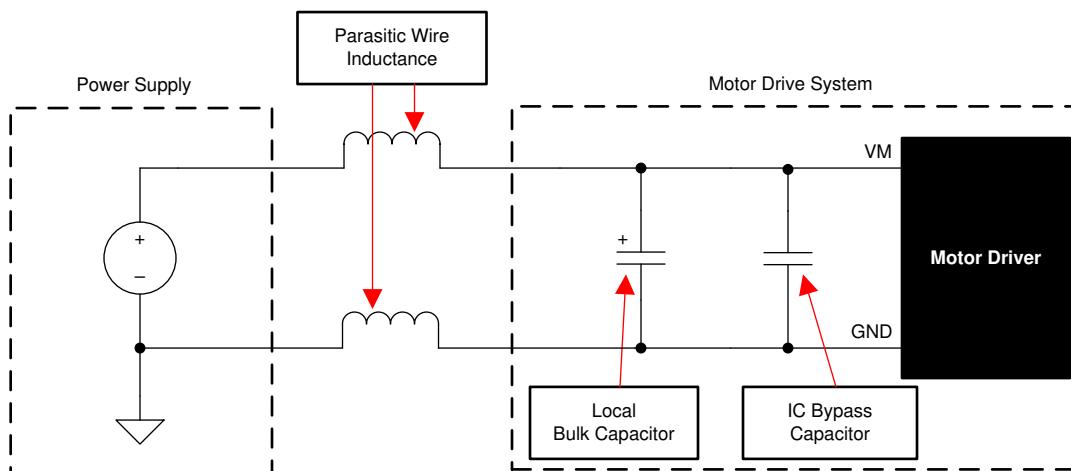

| VM           | 8               | 8               | 8               | PWR                | モーター用電源。モーター電源電圧に接続します。VM と PGND の間に、X5R または X7R の 0.1µF VM 定格セラミック バイパス コンデンサと、10µF 以上の VM 定格バルク キャパシタを接続します。さらに、VM ピンと CP ピンの間に、X5R または X7R の 0.1uF、16V 定格セラミック コンデンサを接続します。 |

| VIN_AVDD     | 7               | 7               | 7               | PWR                | AVDD の電源入力。VIN_AVDD と PGND の間に、X5R または X7R の 0.1µF、VIN_AVDD 定格セラミック コンデンサと、10µF 以上の VIN_AVDD 定格バルク キャパシタを接続し、AGND にバイパスします。                                                    |

| サーマル<br>パッド  | —               | —               | —               | PWR                | PGND に接続してください。                                                                                                                                                                |

| NC           | —               | 13.18           | —               | —                  | 接続なし。このピンはフローティングのままにします。                                                                                                                                                      |

(1) I = 入力、O = 出力、PWR = 電源、NC = 未接続

## 6 仕様

### 6.1 絶対最大定格

動作時周囲温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|                                                                                  | 最小値  | 最大値                      | 単位 |

|----------------------------------------------------------------------------------|------|--------------------------|----|

| 電源ピン電圧 (VM)                                                                      | -0.3 | 24                       | V  |

| AVDD レギュレータ入力ピン電圧 (VIN_AVDD)                                                     | -0.3 | 24                       | V  |

| グランドピン (PGND, AGND) 間の電圧差                                                        | -0.3 | 0.3                      | V  |

| チャージポンプ電圧 (CP)                                                                   | -0.3 | $V_M + 6$                | V  |

| アナログ レギュレータ出力ピン電圧 (AVDD)                                                         | -0.3 | 4                        | V  |

| ロジックピン入力電圧 (INHx, INLx, nSCS, nSLEEP, SCLK, SDI, ADx, ゲイン, MODE, SLEW, PWM_SYNC) | -0.3 | 6                        | V  |

| ロジックピン出力電圧 (nFAULT, SDO)                                                         | -0.3 | 6                        | V  |

| オープンドレイン出力電流範囲 (nFAULT)                                                          | 0    | 5                        | mA |

| 電流センスアンプリファレンス電圧入力 (CSAREF)                                                      | -0.3 | 4                        | V  |

| 電流センスアンプ出力 (SOx)                                                                 | -0.3 | 4                        | V  |

| ピーク出力電流 (OUTA, OUTB, OUTC)                                                       |      | 5                        | A  |

| 出力ピン電圧 (OUTA, OUTB, OUTC)                                                        | -1   | $V_M + 1$ <sup>(2)</sup> | V  |

| 周囲温度、 $T_A$                                                                      | -40  | 125                      | °C |

| 接合部温度、 $T_J$                                                                     | -40  | 150                      | °C |

| 保管温度、 $T_{stg}$                                                                  | -65  | 150                      | °C |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

- (2) VM+1V または 24V (どちらか小さい方)。

### 6.2 ESD 定格

|             |      | 値                                                          | 単位    |   |

|-------------|------|------------------------------------------------------------|-------|---|

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM) ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>       | ±1500 | V |

| $V_{(ESD)}$ | 静電放電 | デバイス帯電モデル (CDM), ANSI/ESDA/JEDEC JS-002 に準拠 <sup>(2)</sup> | ±750  | V |

(1) JEDEC ドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

(2) JEDEC ドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

### 6.3 推奨動作条件

動作時周辺温度範囲内 (特に記述のない限り)

|                          |                   | 最小値                                                                 | 公称値  | 最大値 | 単位  |

|--------------------------|-------------------|---------------------------------------------------------------------|------|-----|-----|

| $V_{VM}$                 | 電源電圧              | $V_{VM}$                                                            | 3    | 12  | V   |

| $VIN_AVDD$               | AVDD レギュレータ入力ピン電圧 | $V_{VIN_AVDD}$                                                      | 3    | 12  | V   |

| $f_{PWM}$                | 出力 PWM 周波数        | OUTA, OUTB, OUTC                                                    |      | 200 | kHz |

| $I_{OUT}$ <sup>(1)</sup> | ピーク出力電流           | OUTA, OUTB, OUTC                                                    |      | 5   | A   |

| $V_{IN}$                 | ロジック入力電圧          | INHx, INLx, nSCS, nSLEEP, SCLK, SDI, ADx, ゲイン, MODE, SLEW, PWM_SYNC | -0.1 | 5.5 | V   |

| $V_{OD}$                 | オープンドレイン プルアップ電圧  | nFAULT                                                              | -0.1 | 5.5 | V   |

| $I_{OD}$                 | オープンドレイン出力シンク電流   | nFAULT                                                              |      | 5   | mA  |

| $V_{CSAREF}$             | CSA リファレンス入力電圧    | CSAREF                                                              | 2    | 3.6 | V   |

動作時周辺温度範囲内 (特に記述のない限り)

|              |                |        | 最小値 | 公称値 | 最大値 | 単位 |

|--------------|----------------|--------|-----|-----|-----|----|

| $I_{CSAREF}$ | CSA リファレンス入力電流 | CSAREF |     | 2.5 | 7.5 | mA |

| $T_A$        | 動作時周囲温度        |        | -40 |     | 125 | °C |

| $T_J$        | 動作時接合部温度       |        | -40 |     | 150 | °C |

(1) 消費電力および温度の制限に従う必要があります。

## 6.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup>        |                     | DRV8311-Q1 | 単位   |

|-----------------------------|---------------------|------------|------|

|                             |                     | QFN (RRW)  |      |

|                             |                     | 24 ピン      |      |

| $R_{\theta JA}$             | 接合部から周囲への熱抵抗        | 42.6       | °C/W |

| $R_{\theta JC(\text{top})}$ | 接合部からケース (上面) への熱抵抗 | 37.9       | °C/W |

| $R_{\theta JB}$             | 接合部から基板への熱抵抗        | 15.7       | °C/W |

| $\Psi_{JT}$                 | 接合部から上面への特性パラメータ    | 0.5        | °C/W |

| $\Psi_{JB}$                 | 接合部から基板への特性パラメータ    | 15.6       | °C/W |

| $R_{\theta JC(\text{bot})}$ | 接合部からケース (底面) への熱抵抗 | 4.8        | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション レポートを参照してください。

## 6.5 電気的特性

$T_J = -40^{\circ}\text{C} \sim +150^{\circ}\text{C}$ 、 $V_{VM} = 3 \sim 20\text{V}$  (特に記述のない限り)。標準値には  $T_A = 25^{\circ}\text{C}$ 、 $V_{VM} = 12\text{V}$  が適用されます。

| パラメータ           |                    | テスト条件                                                                                                                    | 最小値  | 標準値                    | 最大値  | 単位 |

|-----------------|--------------------|--------------------------------------------------------------------------------------------------------------------------|------|------------------------|------|----|

| <b>電源</b>       |                    |                                                                                                                          |      |                        |      |    |

| $I_{VMQ}$       | VM スリープ モード電流      | $V_{VM} = 12\text{V}$ 、nSLEEP = 0、 $T_A = 25^{\circ}\text{C}$                                                            |      | 1.5                    | 3    | μA |

|                 |                    | nSLEEP = 0、 $T_A = 125^{\circ}\text{C}$                                                                                  |      |                        | 9    | μA |

| $I_{VMS}$       | VM スタンバイ モード電流     | $V_{VM} = 12\text{V}$ 、nSLEEP = 1、INHx = INLx = 0、SPI = 'オフ'、 $T_A = 25^{\circ}\text{C}$                                 |      | 7                      | 12   | mA |

|                 |                    | nSLEEP = 1、INHx = INLx = 0、SPI = 'オフ'                                                                                    |      | 8                      | 12   | mA |

| $I_{VM}$        | VM 動作モード電流         | $V_{VM} = 12\text{V}$ 、nSLEEP = 1、 $f_{PWM} = 25\text{kHz}$ 、 $T_A = 25^{\circ}\text{C}$                                 |      | 10                     | 13   | mA |

|                 |                    | $V_{VM} = 12\text{V}$ 、nSLEEP = 1、 $f_{PWM} = 200\text{kHz}$ 、 $T_A = 25^{\circ}\text{C}$                                |      | 12                     | 14   | mA |

|                 |                    | nSLEEP = 1、 $f_{PWM} = 25\text{kHz}$                                                                                     |      | 10                     | 15   | mA |

|                 |                    | nSLEEP = 1、 $f_{PWM} = 200\text{kHz}$                                                                                    |      | 12                     | 15   | mA |

| $V_{AVDD}$      | アナログ レギュレータの電圧     | $V_{VM} > 4\text{V}$ 、 $V_{VIN\_AVDD} > 4.5\text{V}$ 、 $0\text{mA} \leq I_{AVDD} \leq 100\text{mA}$                      | 3.15 | 3.3                    | 3.45 | V  |

| $V_{AVDD}$      |                    | $V_{VM} > 3.5\text{V}$ 、 $3.5\text{V} \leq V_{VIN\_AVDD} \leq 4.5\text{V}$ 、 $0\text{mA} \leq I_{AVDD} \leq 35\text{mA}$ | 3    | 3.3                    | 3.6  | V  |

| $V_{AVDD}$      |                    | $2.5\text{V} \leq V_{VIN\_AVDD} \leq 3.5\text{V}$ 、 $0\text{mA} \leq I_{AVDD} \leq 10\text{mA}$                          | 2.2  | $V_{IN\_AVDD}$<br>-0.3 | 3.4  | V  |

| $V_{AVDD}$      |                    | $V_{VM} < 4\text{V}$ 、 $V_{VIN\_AVDD} > 4.5\text{V}$ 、 $0\text{mA} \leq I_{AVDD} \leq 40\text{mA}$                       | 3    | 3.3                    | 3.6  | V  |

| $V_{AVDD}$      |                    | $V_{VM} < 3.5\text{V}$ 、 $3.5\text{V} \leq V_{VIN\_AVDD} \leq 4.5\text{V}$ 、 $0\text{mA} \leq I_{AVDD} \leq 20\text{mA}$ | 3    | 3.3                    | 3.6  | V  |

| $I_{AVDD\_LIM}$ | 外部アナログ レギュレータの電流制限 |                                                                                                                          | 148  | 200                    | 250  | mA |

$T_J = -40^\circ\text{C} \sim +150^\circ\text{C}$ ,  $V_{VM} = 3 \sim 20\text{V}$  (特に記述のない限り)。標準値には  $T_A = 25^\circ\text{C}$ ,  $V_{VM} = 12\text{V}$  が適用されます。

| パラメータ           |                  | テスト条件                                                                     | 最小値 | 標準値 | 最大値 | 単位            |

|-----------------|------------------|---------------------------------------------------------------------------|-----|-----|-----|---------------|

| $I_{AVDD}$      | 外部アナログ レギュレータの負荷 | $V_{VM} > 4\text{V}, V_{VIN\_AVDD} > 4.5\text{V}$                         |     |     | 100 | mA            |

|                 |                  | $V_{VM} < 4\text{V}, V_{VIN\_AVDD} > 4.5\text{V}$                         |     |     | 40  | mA            |

|                 |                  | $V_{VM} > 3.5\text{V}, 3.6\text{V} \leq V_{VIN\_AVDD} \leq 4.5\text{V}$   |     |     | 35  | mA            |

|                 |                  | $V_{VM} < 3.5\text{V}, 3.6\text{V} \leq V_{VIN\_AVDD} \leq 4.5\text{V}$   |     |     | 20  | mA            |

|                 |                  | $2.5\text{V} \leq V_{VIN\_AVDD} \leq 3.6\text{V}$                         |     |     | 10  | mA            |

| $C_{AVDD}$      | AVDD ピン上のコンデンサ   | $I_{AVDD} \leq 25\text{mA}$                                               | 0.7 | 1   | 7   | $\mu\text{F}$ |

|                 |                  | $I_{AVDD} \geq 25\text{mA}$                                               | 3.3 | 4.7 | 7   | $\mu\text{F}$ |

| $R_{AVDD}$      | AVDD 出力電圧レギュレータ  | $V_{VIN\_AVDD} > 4.5\text{V}, I_{AVDD} \leq 20\text{mA}$                  | -3  |     | 3   | %             |

|                 |                  | $V_{VIN\_AVDD} > 4.5\text{V}, 20\text{mA} \leq I_{AVDD} \leq 40\text{mA}$ | -2  |     | 2   | %             |

|                 |                  | $V_{VIN\_AVDD} > 4.5\text{V}, I_{AVDD} \geq 40\text{mA}$                  | -3  |     | 3   | %             |

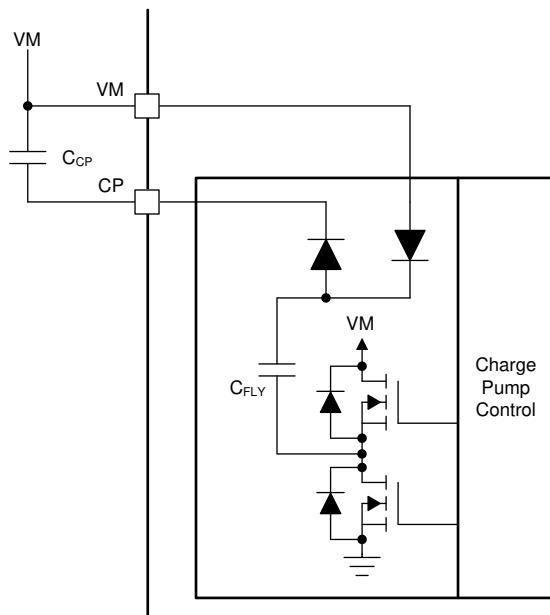

| $V_{VCP}$       | チャージポンプ レギュレータ電圧 | $V_M$ を基準とした VCP                                                          | 3   | 5   | 5.6 | V             |

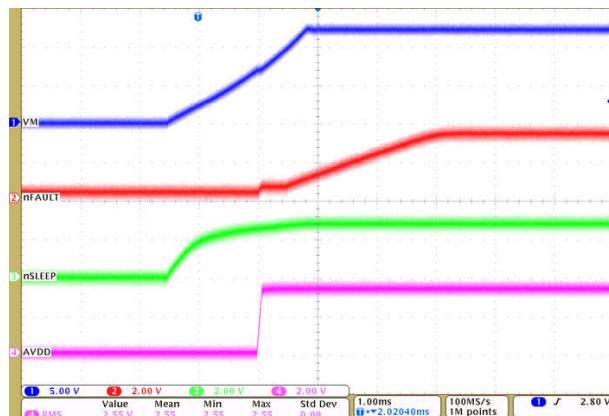

| $t_{WAKE}$      | ウェークアップ時間        | $V_{VM} > V_{UVLO}$ , $nSLEEP = 1$ から出力準備完了まで                             |     | 1   | 3   | ms            |

| $t_{WAKE\_CSA}$ | CSA のウェークアップ時間   | $nSLEEP = 1$ のとき, $V_{CSAREF} > V_{CSAREF\_UV}$ から $SO_x$ 準備完了まで          |     | 30  | 50  | $\mu\text{s}$ |

| $t_{SLEEP}$     | ターンオフ時間          | $nSLEEP = 0$ から、ドライバがトライステートになるまで                                         |     | 100 | 200 | $\mu\text{s}$ |

| $t_{RST}$       | リセットパルス時間        | $nSLEEP = 0$ でフォルトをリセット                                                   | 10  |     | 65  | $\mu\text{s}$ |

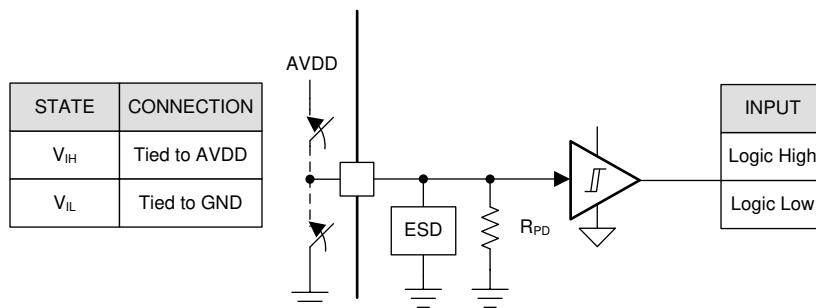

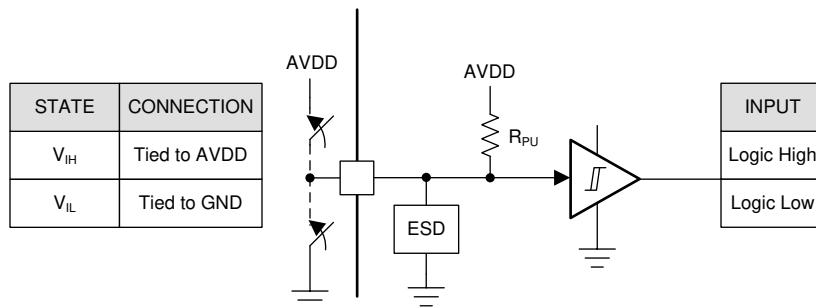

#### ロジックレベル入力 (INHx, INLx, nSLEEP, SCLK, SDI)

|           |                |                               |      |     |               |            |

|-----------|----------------|-------------------------------|------|-----|---------------|------------|

| $V_{IL}$  | 入力ロジック Low 電圧  |                               | 0    | 0.6 | V             |            |

| $V_{IH}$  | 入力ロジック High 電圧 |                               | 1.65 | 5.5 | V             |            |

| $V_{HYS}$ | 入力ロジック ヒステリシス  |                               | 100  | 300 | 660           | mV         |

| $I_{IL}$  | 入力ロジック Low 電流  | $V_{PIN}$ (ピン電圧) = 0V         | -1   | 1   | $\mu\text{A}$ |            |

| $I_{IH}$  | 入力ロジック High 電流 | $nSLEEP, V_{PIN}$ (ピン電圧) = 5V |      | 30  | $\mu\text{A}$ |            |

|           |                | その他のピン, $V_{PIN}$ (ピン電圧) = 5V |      | 50  | $\mu\text{A}$ |            |

| $R_{PD}$  | 入力プルダウン抵抗      | $nSLEEP$                      |      | 230 | 300           | k $\Omega$ |

|           |                | その他のピン                        |      | 160 | 200           | k $\Omega$ |

| $C_{ID}$  | 入力容量           |                               |      | 30  | pF            |            |

#### ロジック レベル入力 (nSCS)

|           |                |                       |     |     |               |

|-----------|----------------|-----------------------|-----|-----|---------------|

| $V_{IL}$  | 入力ロジック Low 電圧  |                       | 0   | 0.6 | V             |

| $V_{IH}$  | 入力ロジック High 電圧 |                       | 1.5 | 5.5 | V             |

| $V_{HYS}$ | 入力ロジック ヒステリシス  |                       | 200 | 500 | mV            |

| $I_{IL}$  | 入力ロジック Low 電流  | $V_{PIN}$ (ピン電圧) = 0V |     | 90  | $\mu\text{A}$ |

| $I_{IH}$  | 入力ロジック High 電流 | $V_{PIN}$ (ピン電圧) = 5V |     | 70  | $\mu\text{A}$ |

| $R_{PU}$  | 入力プルアップ抵抗      |                       |     | 48  | k $\Omega$    |

| $C_{ID}$  | 入力容量           |                       |     | 30  | pF            |

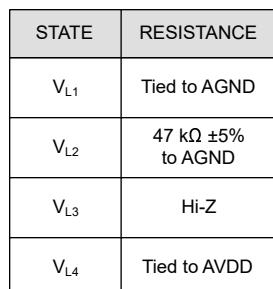

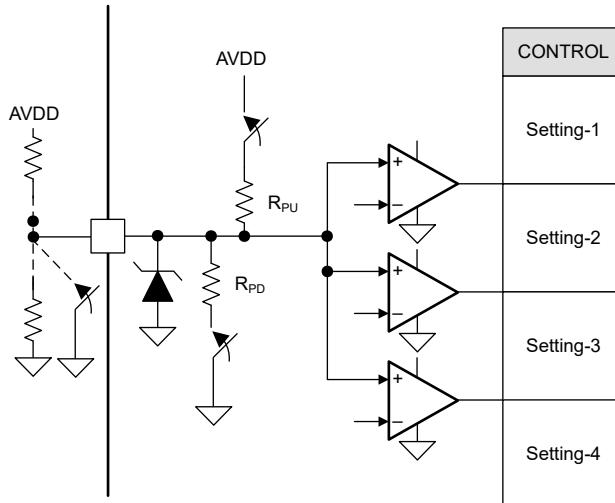

#### 4 レベル入力 (ゲイン、MODE、SLEW)

|          |            |                                      |             |            |             |

|----------|------------|--------------------------------------|-------------|------------|-------------|

| $V_{L1}$ | 入力モード 1 電圧 | AGND に接続                             | 0           | 0.21*AV DD | V           |

| $V_{L2}$ | 入力モード 2 電圧 | $47\text{k}\Omega \pm 5\%$ で GND に接続 | 0.25*AV DD  | 0.5*AVDD   | 0.55*AV DD  |

| $V_{L3}$ | 入力モード 3 電圧 | ハイインピーダンス                            | 0.606*AV DD | 0.757*AV D | 0.909*AV DD |

| $V_{L4}$ | 入力モード 4 電圧 | AVDD に接続                             | 0.94*AV DD  |            | AVDD        |

$T_J = -40^{\circ}\text{C} \sim +150^{\circ}\text{C}$ 、 $V_{VM} = 3 \sim 20\text{V}$  (特に記述のない限り)。標準値には  $T_A = 25^{\circ}\text{C}$ 、 $V_{VM} = 12\text{V}$  が適用されます。

| パラメータ    |           | テスト条件   | 最小値 | 標準値 | 最大値 | 単位               |

|----------|-----------|---------|-----|-----|-----|------------------|

| $R_{PU}$ | 入力プルアップ抵抗 | 対 AVDD  |     | 48  | 70  | $\text{k}\Omega$ |

| $R_{PD}$ | 入力プルダウン抵抗 | To AGND |     | 160 | 200 | $\text{k}\Omega$ |

$T_J = -40^\circ\text{C} \sim +150^\circ\text{C}$ ,  $V_{VM} = 3 \sim 20\text{V}$  (特に記述のない限り)。標準値には  $T_A = 25^\circ\text{C}$ ,  $V_{VM} = 12\text{V}$  が適用されます。

| パラメータ                      | テスト条件                                                          | 最小値                                                                                                                                 | 標準値               | 最大値  | 単位                     |

|----------------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------------------|------|------------------------|

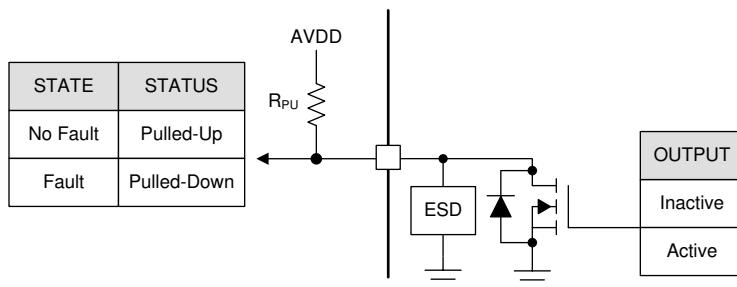

| <b>オープンドレイン出力 (nFAULT)</b> |                                                                |                                                                                                                                     |                   |      |                        |

| $V_{OL}$                   | 出力ロジック Low 電圧                                                  | $I_{OD} = -5\text{mA}$                                                                                                              |                   | 0.4  | $\text{V}$             |

| $I_{OH}$                   | 出力ロジック High 電流                                                 | $V_{OD} = 5\text{V}$                                                                                                                | -1                | 1    | $\mu\text{A}$          |

| $C_{OD}$                   | 出力容量                                                           |                                                                                                                                     | 30                |      | $\text{pF}$            |

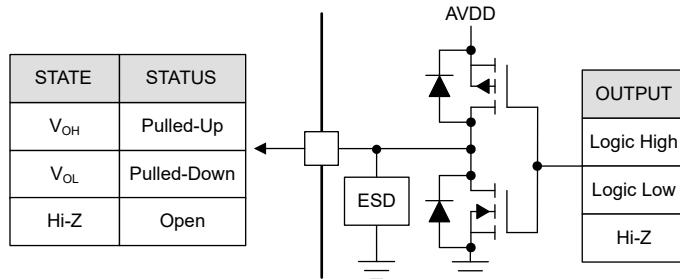

| <b>プッシュプル出力 (SDO)</b>      |                                                                |                                                                                                                                     |                   |      |                        |

| $V_{OL}$                   | 出力ロジック Low 電圧                                                  | $I_{OP} = -5\text{mA}, 2.2\text{V} \leq V_{AVDD} \leq 3\text{V}$                                                                    | 0                 | 0.55 | $\text{V}$             |

|                            |                                                                | $I_{OP} = -5\text{mA}, 3\text{V} \leq V_{AVDD} \leq 3.6\text{V}$                                                                    | 0                 | 0.5  | $\text{V}$             |

| $V_{OH}$                   | ロジック High 出力電圧                                                 | $I_{OP} = 5\text{mA}, 2.2\text{V} \leq V_{AVDD} \leq 3\text{V}$                                                                     | $V_{AVDD} - 0.86$ | 3    | $\text{V}$             |

|                            |                                                                | $I_{OP} = 5\text{mA}, 3\text{V} \leq V_{AVDD} \leq 3.6\text{V}$                                                                     | $V_{AVDD} - 0.5$  | 3.6  | $\text{V}$             |

| $I_{OL}$                   | 出力ロジック Low 電流                                                  | $V_{OP} = 0\text{V}$                                                                                                                | -1                | 1    | $\mu\text{A}$          |

| $I_{OH}$                   | 出力ロジック High 電流                                                 | $V_{OP} = 5\text{V}$                                                                                                                | -1                | 1    | $\mu\text{A}$          |

| $C_{OD}$                   | 出力容量                                                           |                                                                                                                                     | 30                |      | $\text{pF}$            |

| <b>ドライバ出力</b>              |                                                                |                                                                                                                                     |                   |      |                        |

| $R_{DS(ON)}$               | 全 MOSFET オン抵抗 (ハイサイド + ロー サイド)                                 | $6\text{V} \geq V_{VM} \geq 3\text{V}, I_{OUT} = 1\text{A}, T_J = 25^\circ\text{C}$                                                 | 300               | 350  | $\text{m}\Omega$       |

|                            |                                                                | $6\text{V} \geq V_{VM} \geq 3\text{V}, I_{OUT} = 1\text{A}, T_J = 150^\circ\text{C}$                                                | 450               | 500  | $\text{m}\Omega$       |

|                            |                                                                | $V_{VM} \geq 6\text{V}, I_{OUT} = 1\text{A}, T_J = 25^\circ\text{C}$                                                                | 210               | 265  | $\text{m}\Omega$       |

|                            |                                                                | $V_{VM} \geq 6\text{V}, I_{OUT} = 1\text{A}, T_J = 150^\circ\text{C}$                                                               | 330               | 375  | $\text{m}\Omega$       |

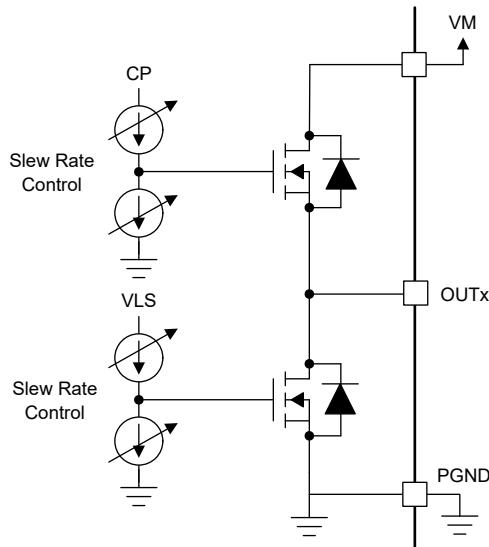

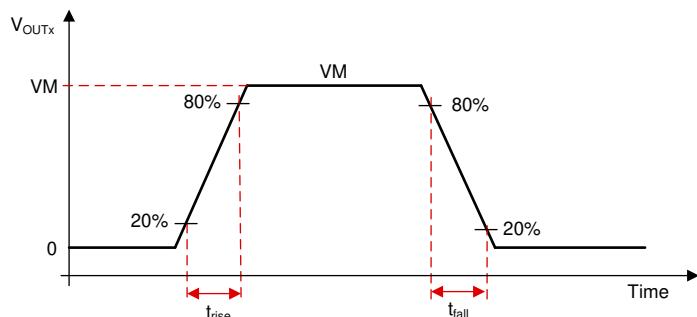

| SR                         | Low から High へのスイッチング ( $VM$ の 20% から 80% への立ち上がり) 時の相ビンのスルーレート | $V_{VM} = 12\text{V}, \text{SLEW} = 00\text{b}$ (SPI バリアントの場合) または SLEW ピンを AGND に接続 (ハードウェア バリアントの場合)                              | 18                | 35   | $\text{V}/\mu\text{s}$ |

| SR                         |                                                                | $V_{VM} = 12\text{V}, \text{SLEW} = 01\text{b}$ (SPI バリアントの場合) または SLEW ピンを $47\text{k}\Omega \pm 5\%$ で AGND に接続 (ハードウェア バリアントの場合) | 35                | 75   | $\text{V}/\mu\text{s}$ |

| SR                         |                                                                | $V_{VM} = 12\text{V}, \text{SLEW} = 10\text{b}$ (SPI バリアントの場合) または SLEW ピンをハイインピーダンスに設定 (ハードウェア バリアントの場合)                           | 90                | 180  | $\text{V}/\mu\text{s}$ |

| SR                         |                                                                | $V_{VM} = 12\text{V}, \text{SLEW} = 11\text{b}$ (SPI バリアントの場合) または SLEW ピンを AVDD に接続 (ハードウェア バリアントの場合)                              | 140               | 230  | $\text{V}/\mu\text{s}$ |

| SR                         | High から Low へのスイッチング ( $VM$ の 80% から 20% への立ち下がり) 時の相ビンのスルーレート | $V_{VM} = 12\text{V}, \text{SLEW} = 00\text{b}$ (SPI バリアントの場合) または SLEW ピンを AGND に接続 (ハードウェア バリアントの場合)                              | 20                | 35   | $\text{V}/\mu\text{s}$ |

|                            |                                                                | $V_{VM} = 12\text{V}, \text{SLEW} = 01\text{b}$ (SPI バリアントの場合) または SLEW ピンを $47\text{k}\Omega \pm 5\%$ で AGND に接続 (ハードウェア バリアントの場合) | 35                | 75   | $\text{V}/\mu\text{s}$ |

|                            |                                                                | $V_{VM} = 12\text{V}, \text{SLEW} = 10\text{b}$ (SPI バリアントの場合) または SLEW ピンをハイインピーダンスに設定 (ハードウェア バリアントの場合)                           | 80                | 180  | $\text{V}/\mu\text{s}$ |

|                            |                                                                | $V_{VM} = 12\text{V}, \text{SLEW} = 11\text{b}$ (SPI バリアントの場合) または SLEW ピンを AVDD に接続 (ハードウェア バリアントの場合)                              | 125               | 270  | $\text{V}/\mu\text{s}$ |

$T_J = -40^\circ\text{C} \sim +150^\circ\text{C}$ 、 $V_{VM} = 3 \sim 20\text{V}$  (特に記述のない限り)。標準値には  $T_A = 25^\circ\text{C}$ 、 $V_{VM} = 12\text{V}$  が適用されます。

| パラメータ            |                                      | テスト条件                                                                                                                                                    | 最小値 | 標準値  | 最大値  | 単位 |

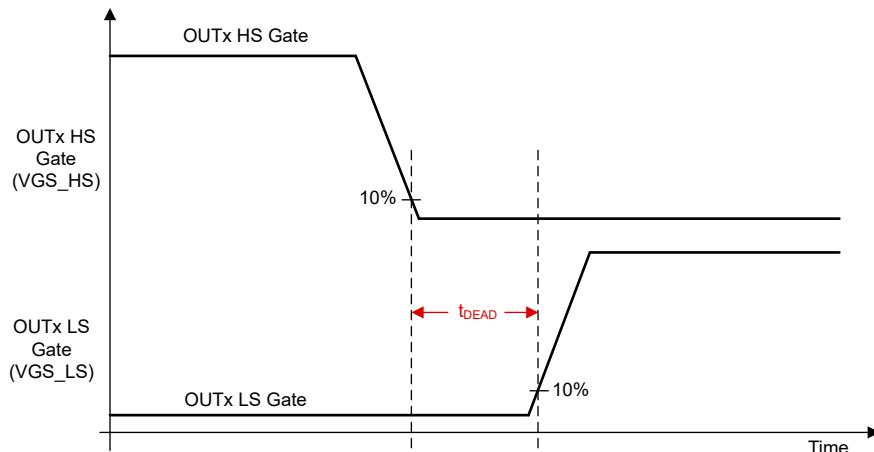

|------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|----|

| $t_{DEAD}$       | 出力デッドタイム (High から Low / Low から High) | $V_{VM} = 12\text{V}$ 、 $SLEW = 00\text{b}$ (SPI バリアントの場合) または SLEW ピンを AGND に接続 (ハードウェア バリアントの場合)、デッドタイム = 000b、ハンドシェイクのみ                               |     | 500  | 1200 | ns |

|                  |                                      | $V_{VM} = 12\text{V}$ 、 $SLEW = 01\text{b}$ (SPI バリアントの場合) または SLEW ピンを $47\text{k}\Omega \pm 5\%$ で AGND に接続 (ハードウェア バリアントの場合)、デッドタイム = 000b、ハンドシェイクのみ、 |     | 450  | 760  | ns |

|                  |                                      | $V_{VM} = 12\text{V}$ 、 $SLEW = 10\text{b}$ (SPI バリアントの場合) または SLEW ピンをハイ インピーダンスに設定 (ハードウェア バリアントの場合)、デッドタイム = 000b、ハンドシェイクのみ                           |     | 425  | 720  | ns |

|                  |                                      | $V_{VM} = 12\text{V}$ 、 $SLEW = 11\text{b}$ (SPI バリアントの場合) または SLEW ピンを AVDD (ハードウェア バリアントの場合)、デッドタイム = 000b、ハンドシェイクのみ                                   |     | 425  | 710  | ns |

|                  |                                      | $V_{VM} = 12\text{V}$ 、デッドタイム = 001b                                                                                                                     |     | 200  | 540  | ns |

|                  |                                      | $V_{VM} = 12\text{V}$ 、デッドタイム = 010b                                                                                                                     |     | 400  | 550  | ns |

|                  |                                      | $V_{VM} = 12\text{V}$ 、デッドタイム = 011b                                                                                                                     |     | 600  | 760  | ns |

|                  |                                      | $V_{VM} = 12\text{V}$ 、デッドタイム = 100b                                                                                                                     |     | 800  | 900  | ns |

|                  |                                      | $V_{VM} = 12\text{V}$ 、デッドタイム = 101b                                                                                                                     |     | 1000 | 1100 | ns |

|                  |                                      | $V_{VM} = 12\text{V}$ 、デッドタイム = 110b                                                                                                                     |     | 1200 | 1300 | ns |

|                  |                                      | $V_{VM} = 12\text{V}$ 、デッドタイム = 111b                                                                                                                     |     | 1400 | 1500 | ns |

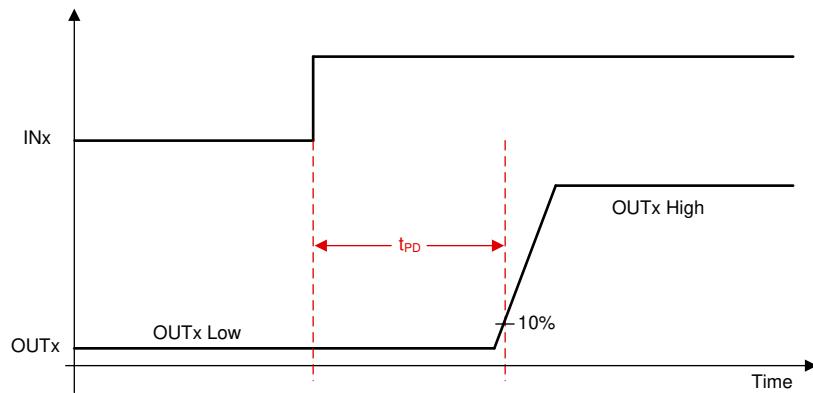

| $t_{PD}$         | 伝搬遅延 (ハイサイド / ローサイド、オン/オフ)           | INHx = 1 から OUTx 遷移、 $V_{VM} = 12\text{V}$ 、 $SLEW = 00\text{b}$ (SPI バリアントの場合) または SLEW ピンを AGND に接続 (ハードウェア バリアントの場合)                                  |     | 1000 | 1500 | ns |

|                  |                                      | INHx = 1 から OUTx 遷移、 $V_{VM} = 12\text{V}$ 、 $SLEW = 01\text{b}$ (SPI バリアントの場合) または SLEW ピンを $47\text{k}\Omega \pm 5\%$ で AGND に接続 (ハードウェア バリアントの場合)     |     | 650  | 1100 | ns |

|                  |                                      | INHx = 1 から OUTx 遷移、 $V_{VM} = 12\text{V}$ 、 $SLEW = 10\text{b}$ (SPI バリアントの場合) または SLEW ピンをハイ インピーダンスに設定 (ハードウェア バリアントの場合)                              |     | 550  | 950  | ns |

|                  |                                      | INHx = 1 から OUTx 遷移、 $V_{VM} = 12\text{V}$ 、 $SLEW = 11\text{b}$ (SPI バリアントの場合) または SLEW ピンを AVDD に接続 (ハードウェア バリアントの場合)                                  |     | 500  | 910  | ns |

| $t_{MIN\_PULSE}$ | 最小出力パルス幅                             | SLEW = 11b                                                                                                                                               | 500 |      |      | ns |

| 電流検出アンプ          |                                      |                                                                                                                                                          |     |      |      |    |

$T_J = -40^\circ\text{C} \sim +150^\circ\text{C}$ ,  $V_{VM} = 3 \sim 20\text{V}$  (特に記述のない限り)。標準値には  $T_A = 25^\circ\text{C}$ ,  $V_{VM} = 12\text{V}$  が適用されます。

| パラメータ             |                                                   | テスト条件                                                                                           | 最小値  | 標準値                 | 最大値                          | 単位            |

|-------------------|---------------------------------------------------|-------------------------------------------------------------------------------------------------|------|---------------------|------------------------------|---------------|

| $G_{CSA}$         | 電流センス ゲイン (SPI デバイス)                              | CSA_GAIN = 00 (SPI バリアント場合) または ゲイン ピンを AGND に接続 (ハードウェア バリアントの場合)                              |      | 0.25                |                              | V/A           |

|                   |                                                   | CSA_GAIN = 01 (SPI バリアントの場合) または ゲイン ピンを $47\text{k}\Omega \pm 5\%$ で GND に接続 (ハードウェア バリアントの場合) |      | 0.5                 |                              | V/A           |

|                   |                                                   | CSA_GAIN = 10 (SPI バリアント場合) または ゲイン ピンを ハイインピーダンスに設定 (ハードウェア バリアントの場合)                          |      | 1                   |                              | V/A           |

|                   |                                                   | CSA_GAIN = 11 (SPI バリアント場合) または ゲイン ピンを AVDD に接続 (ハードウェア バリアントの場合)                              |      | 2                   |                              | V/A           |

| $G_{CSA\_ERR}$    | 電流センス ゲイン 誤差                                      | $T_J = 25^\circ\text{C}$ , $I_{PHASE} < 2.5\text{A}$ , $VM \geq 6\text{V}$                      | -5   | 4                   | %                            |               |

|                   |                                                   | $T_J = 25^\circ\text{C}$ , $I_{PHASE} > 2.5\text{A}$ , $VM \geq 6\text{V}$                      | -5   | 5                   | %                            |               |

|                   |                                                   | $I_{PHASE} < 2.5\text{A}$ , $VM \geq 6\text{V}$                                                 | -5.5 | 5.5                 | %                            |               |

|                   |                                                   | $I_{PHASE} > 2.5\text{A}$ , $VM \geq 6\text{V}$                                                 | -7   | 7                   | %                            |               |

| $I_{MATCH}$       | A 相、B 相、C 相の間での電流センス ゲイン誤差のマッチング                  | $T_J = 25^\circ\text{C}$                                                                        | -5   | 5                   | %                            |               |

|                   |                                                   |                                                                                                 | -5   | 5                   | %                            |               |

| $FS_{POS}$        | フルスケールの正の電流測定                                     |                                                                                                 |      | 5                   |                              | A             |

| $FS_{NEG}$        | フルスケールの負の電流測定                                     |                                                                                                 |      |                     | -5                           | A             |

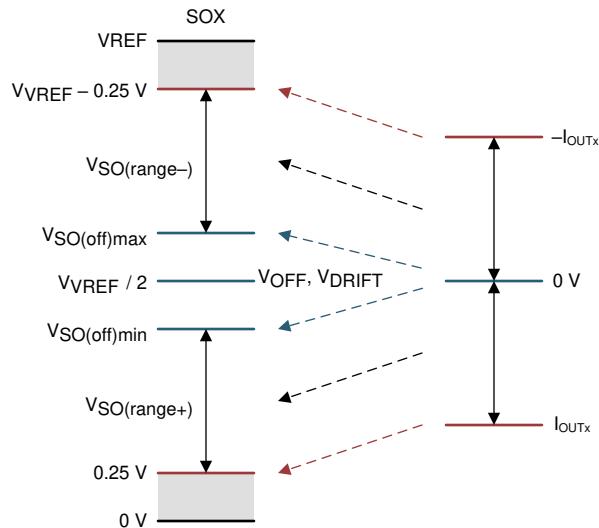

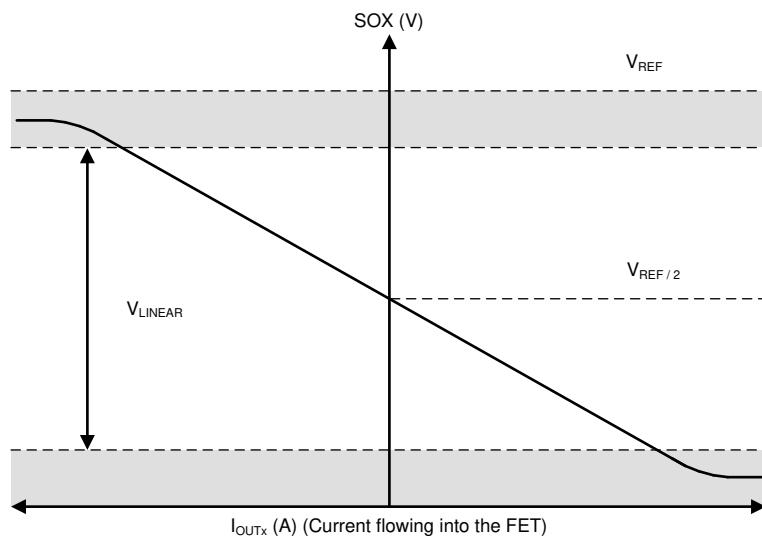

| $V_{LINEAR}$      | SOx 出力電圧のリニア動作範囲                                  |                                                                                                 | 0.25 | $V_{CSAREF} - 0.25$ |                              | V             |

| $I_{OFFSET\_RT}$  | ローサイド電流入力時の電流センス オフセット (室温)                       | $T_J = 25^\circ\text{C}$ , 相電流 = 0A, $G_{CSA} = 0.25\text{V/A}$                                 | -50  | 50                  | mA                           |               |

|                   |                                                   | $T_J = 25^\circ\text{C}$ , 相電流 = 0A, $G_{CSA} = 0.5\text{V/A}$                                  | -50  | 50                  | mA                           |               |

|                   |                                                   | $T_J = 25^\circ\text{C}$ , 相電流 = 0A, $G_{CSA} = 1\text{V/A}$                                    | -30  | 30                  | mA                           |               |

|                   |                                                   | $T_J = 25^\circ\text{C}$ , 相電流 = 0A, $G_{CSA} = 2\text{V/A}$                                    | -30  | 30                  | mA                           |               |

| $I_{OFFSET}$      | ローサイド電流入力基準の電流センス オフセット                           | 相電流 = 0A, $G_{CSA} = 0.25\text{V/A}$                                                            | -70  | 70                  | mA                           |               |

|                   |                                                   | 相電流 = 0A, $G_{CSA} = 0.5\text{V/A}$                                                             | -50  | 50                  | mA                           |               |

|                   |                                                   | 相電流 = 0A, $G_{CSA} = 1\text{V/A}$                                                               | -50  | 50                  | mA                           |               |

|                   |                                                   | 相電流 = 0A, $G_{CSA} = 2\text{V/A}$                                                               | -50  | 50                  | mA                           |               |

| $t_{SET}$         | $\pm 1\%$ 以内へのセッティング タイム、SOx ピンに $30\text{pF}$ 接続 | SOx のステップ電圧 = $1.2\text{V}$ , $G_{CSA} = 0.25\text{V/A}$                                        |      | 1                   | $\mu\text{s}$                |               |

|                   |                                                   | SOx のステップ電圧 = $1.2\text{V}$ , $G_{CSA} = 0.5\text{V/A}$                                         |      | 1                   | $\mu\text{s}$                |               |

|                   |                                                   | SOx のステップ電圧 = $1.2\text{V}$ , $G_{CSA} = 1\text{V/A}$                                           |      | 1                   | $\mu\text{s}$                |               |

|                   |                                                   | SOx のステップ電圧 = $1.2\text{V}$ , $G_{CSA} = 2\text{V/A}$                                           |      | 1                   | $\mu\text{s}$                |               |

| $V_{DRIFT}$       | オフセット ドリフト                                        | 相電流 = 0A                                                                                        | -150 | 150                 | $\mu\text{A}/^\circ\text{C}$ |               |

| $I_{CSAREF}$      | CSAREF 入力電流                                       | $CSAREF = 3.0\text{V}$                                                                          |      | 1.7                 | 3                            | mA            |

| 保護回路              |                                                   |                                                                                                 |      |                     |                              |               |

| $V_{UVLO}$        | 電源低電圧誤動作防止 (UVLO)                                 | VM 立ち上がり                                                                                        | 2.6  | 2.7                 | 2.8                          | V             |

|                   |                                                   | VM 立ち下がり                                                                                        | 2.5  | 2.6                 | 2.7                          | V             |

| $V_{UVLO\_HYS}$   | 電源低電圧誤動作防止ヒステリシス                                  | 立ち上がりから立ち下がりへのスレッショルド                                                                           | 60   | 125                 | 210                          | mV            |

| $t_{UVLO}$        | 電源低電圧グリッチ除去時間                                     |                                                                                                 | 5    | 7.5                 | 13                           | $\mu\text{s}$ |

| $V_{VINAVDD\_UV}$ | AVDD 電源入力低電圧ロックアウト (VINAVDD_UV)                   | VIN_AVDD 立ち上がり                                                                                  | 2.6  | 2.7                 | 2.8                          | V             |

|                   |                                                   | VIN_AVDD 立ち下がり                                                                                  | 2.5  | 2.6                 | 2.7                          | V             |

$T_J = -40^\circ\text{C} \sim +150^\circ\text{C}$ ,  $V_{VM} = 3 \sim 20\text{V}$  (特に記述のない限り)。標準値には  $T_A = 25^\circ\text{C}$ ,  $V_{VM} = 12\text{V}$  が適用されます。

| パラメータ                  |                               | テスト条件                                                                                                                | 最小値  | 標準値  | 最大値  | 単位 |

|------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------|------|------|------|----|

| $V_{VINAVDD\_UV\_HYS}$ | AVDD 電源入力低電圧ロックアウトヒステリシス      | 立ち上がりから立ち下がりへのスレッショルド                                                                                                | 100  | 125  | 150  | mV |

| $t_{VINAVDD\_UV}$      | AVDD 電源入力低電圧のデグリッチ時間          |                                                                                                                      | 2.5  | 4    | 5    | μs |

| $V_{CPUV}$             | チャージポンプ低電圧ロックアウト (VM 基準電圧)    | $V_{CP}$ rising                                                                                                      | 2    | 2.3  | 2.5  | V  |

|                        |                               | $V_{CP}$ 立ち下がり                                                                                                       | 2    | 2.2  | 2.4  | V  |

| $V_{CPUV\_HYS}$        | チャージポンプ低電圧ロックアウトヒステリシス        | 立ち上がりから立ち下がりへのスレッショルド                                                                                                | 65   | 100  | 125  | mV |

| $t_{CPUV}$             | チャージポンプ低電圧のデグリッチ時間            |                                                                                                                      | 0.2  | 0.5  |      | μs |

| $V_{CSAREF\_UV}$       | CSA リファレンス低電圧ロックアウト           | $V_{CSAREF}$ 立ち上がり                                                                                                   | 1.68 | 1.8  | 1.95 | V  |

| $V_{CSAREF\_UV}$       | CSA リファレンス低電圧ロックアウト           | $V_{CSAREF}$ falling                                                                                                 | 1.6  | 1.7  | 1.85 | V  |

| $V_{CSAREF\_UV\_HYS}$  | CSA リファレンス低電圧ロックアウトヒステリシス     | 立ち上がりから立ち下がりへのスレッショルド                                                                                                | 70   | 90   | 110  | mV |

| $V_{AVDD\_UV}$         | アナログレギュレータ低電圧誤動作防止            | $V_{AVDD}$ 立ち上がり                                                                                                     | 1.8  | 2    | 2.2  | V  |

|                        |                               | $V_{AVDD}$ 立ち下がり                                                                                                     | 1.7  | 1.8  | 1.95 | V  |

| $I_{OCP}$              | 過電流保護トリップポイント                 | OCP_LVL = 0 (SPI バリアントの場合) または MODE ピンを AGND に接続 または MODE ピンをハイインピーダンスに設定 (ハードウェアバリアントの場合)                           | 5.8  | 9    | 11.5 | A  |

|                        |                               | OCP_LVL = 1 (SPI バリアントの場合) または MODE ピンを AVDD に接続 または MODE ピンを $47\text{k}\Omega \pm 5\%$ で AGND に接続 (ハードウェアバリアントの場合) | 3.4  | 5    | 7.5  | A  |

| $t_{BLANK}$            | 過電流保護のブランкиング時間 (SPI バリアント)   | OCP_TBLANK = 00b                                                                                                     | 0.2  |      |      | μs |

|                        |                               | OCP_TBLANK = 01b                                                                                                     | 0.5  |      |      | μs |

|                        |                               | OCP_TBLANK = 10b                                                                                                     | 0.8  |      |      | μs |

|                        |                               | OCP_TBLANK = 10b                                                                                                     | 1    |      |      | μs |

| $t_{BLANK}$            | 過電流保護のブランкиング時間 (ハードウェアバリアント) |                                                                                                                      | 0.2  |      |      | μs |

| $t_{OCP\_DEG}$         | 過電流保護のデグリッチ時間 (SPI バリアント)     | OCP_DEG = 00b                                                                                                        | 0.2  |      |      | μs |

|                        |                               | OCP_DEG = 01b                                                                                                        | 0.5  |      |      | μs |

|                        |                               | OCP_DEG = 10b                                                                                                        | 0.8  |      |      | μs |

|                        |                               | OCP_DEG = 11b                                                                                                        | 1    |      |      | μs |

| $t_{OCP\_DEG}$         | 過電流保護のデグリッチ時間 (ハードウェアバリアント)   |                                                                                                                      | 1    |      |      | μs |

| $t_{RETRY}$            | 過電流保護リトライ時間 (SPI バリアント)       | FAST_RETRY = 00b                                                                                                     | 0.24 | 0.5  | 0.65 | ms |

|                        |                               | FAST_RETRY = 01b                                                                                                     | 0.7  | 1    | 1.2  | ms |

|                        |                               | FAST_RETRY = 10b                                                                                                     | 1.6  | 2    | 2.2  | ms |

|                        |                               | FAST_RETRY = 11b                                                                                                     | 4.4  | 5    | 5.3  | ms |

|                        |                               | SLOW_RETRY = 00b                                                                                                     | 390  | 500  | 525  | ms |

|                        |                               | SLOW_RETRY = 01b                                                                                                     | 840  | 1000 | 1050 | ms |

|                        |                               | SLOW_RETRY = 10b                                                                                                     | 1700 | 2000 | 2200 | ms |

|                        |                               | SLOW_RETRY = 11b                                                                                                     | 4400 | 5000 | 5400 | ms |

| $t_{RETRY}$            | 過電流保護リトライ時間 (ハードウェアバリアント)     |                                                                                                                      | 5    |      |      | ms |

| $T_{OTW}$              | 過熱警告温度                        | ダイ温度 ( $T_J$ ) 立ち上がり                                                                                                 | 170  | 178  | 185  | °C |

| $T_{OTW\_HYS}$         | 過熱警告ヒステリシス                    | ダイ温度 ( $T_J$ )                                                                                                       | 25   | 30   |      | °C |

| $T_{TSD}$              | サーマルシャットダウン温度                 | ダイ温度 ( $T_J$ ) 立ち上がり                                                                                                 | 180  | 190  | 200  | °C |

$T_J = -40^\circ\text{C} \sim +150^\circ\text{C}$ ,  $V_{VM} = 3 \sim 20\text{V}$  (特に記述のない限り)。標準値には  $T_A = 25^\circ\text{C}$ ,  $V_{VM} = 12\text{V}$  が適用されます。

| パラメータ          |                           | テスト条件                | 最小値 | 標準値 | 最大値 | 単位 |

|----------------|---------------------------|----------------------|-----|-----|-----|----|

| $T_{TSD\_HYS}$ | サーマル シャットダウン ヒステリシス       | ダイ温度 ( $T_J$ )       |     | 25  | 30  | °C |

| $T_{TSD}$      | サーマル シャットダウン 温度 (LDO)     | ダイ温度 ( $T_J$ ) 立ち上がり | 180 | 190 | 200 | °C |

| $T_{TSD\_HYS}$ | サーマル シャットダウンのヒステリシス (LDO) | ダイ温度 ( $T_J$ )       |     | 25  | 30  | °C |

$T_J = -40^\circ\text{C} \sim +150^\circ\text{C}$ ,  $V_{VM} = 3 \sim 20\text{V}$  (特に記述のない限り)。標準値には  $T_A = 25^\circ\text{C}$ ,  $V_{VM} = 12\text{V}$  が適用されます。

| パラメータ                  |            | テスト条件                                             | 最小値  | 標準値 | 最大値 | 単位  |

|------------------------|------------|---------------------------------------------------|------|-----|-----|-----|

| <b>PWM 出力精度 (tSPI)</b> |            |                                                   |      |     |     |     |

| $R_{PWM}$              | 出力 PWM 分解能 | PWM 周波数 = 20kHz                                   | 10   |     |     | ビット |

| $A_{PWM}$              | 出力 PWM 精度  | $V_{VM} < 4.5\text{V}$ , PWM_SYNC およびクロックチューニング無効 | -7.5 | 7.5 |     | %   |

|                        |            | $V_{VM} > 4.5\text{V}$ , PWM_SYNC およびクロックチューニング無効 | -4   | 4   |     | %   |

|                        |            | PWM_SYNC 有効、クロック チューニング無効                         | -1   | 1   |     | %   |

|                        |            | PWM_SYNC 無効、SPISYNC_ACRCY = 11b                   | -2   | 2   |     | %   |

|                        |            | PWM_SYNC 無効、SPISYNC_ACRCY = 10b                   | -1   | 1   |     | %   |

|                        |            | PWM_SYNC 無効、SPISYNC_ACRCY = 01b                   | -1   | 1   |     | %   |

|                        |            | PWM_SYNC 無効、SPISYNC_ACRCY = 00b                   | -1   | 1   |     | %   |

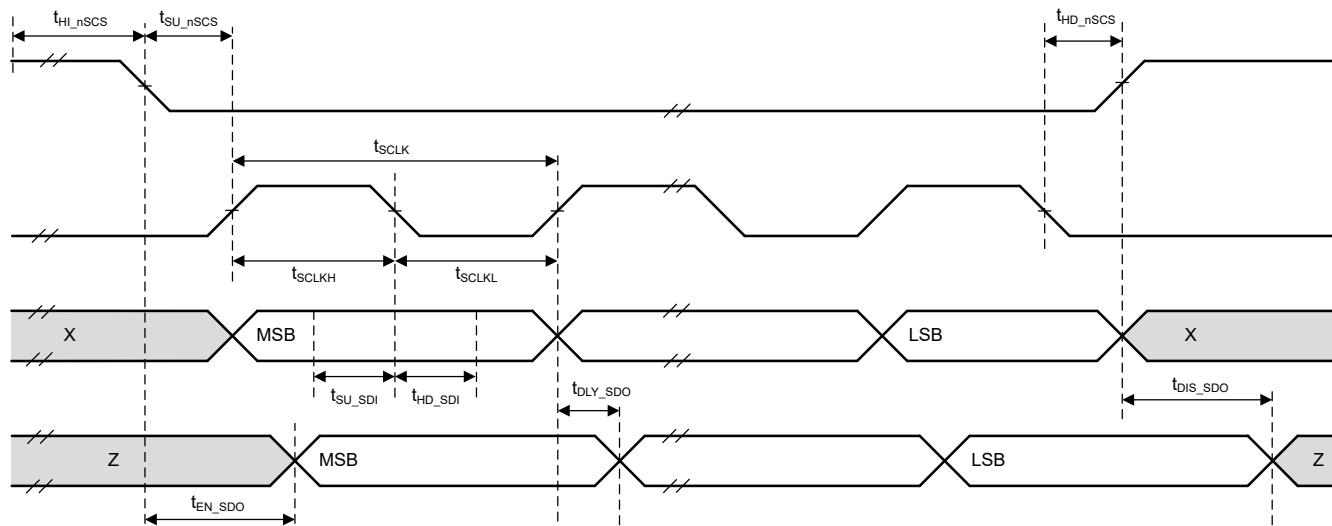

## 6.6 SPI のタイミング要件

|                |                    | 最小値 | 公称値 | 最大値 | 単位 |

|----------------|--------------------|-----|-----|-----|----|

| $t_{READY}$    | パワーアップ後、SPI レディまで  |     |     | 1   | ms |

| $t_{HI\_nSCS}$ | nSCS 最小 HIGH 時間    | 300 |     |     | ns |

| $t_{SU\_nSCS}$ | nSCS 入力セットアップ時間    | 25  |     |     | ns |

| $t_{HD\_nSCS}$ | nSCS 入力ホールド時間      | 25  |     |     | ns |

| $t_{SCLK}$     | SCLK の最小周期         | 100 |     |     | ns |

| $t_{SCLKH}$    | SCLK 最小 High 時間    | 50  |     |     | ns |

| $t_{SCLKL}$    | SCLK の最小 Low 時間    | 50  |     |     | ns |

| $t_{SU\_SDI}$  | SDI 入力データ セットアップ時間 | 25  |     |     | ns |

| $t_{HD\_SDI}$  | SDI 入力データ ホールド時間   | 25  |     |     | ns |

| $t_{DLY\_SDO}$ | SDO 出力データ遅延時間      |     |     | 75  | ns |

| $t_{EN\_SDO}$  | SDO イネーブル遅延時間      |     |     | 65  | ns |

| $t_{DIS\_SDO}$ | SDO ディスエーブル遅延時間    |     |     | 50  | ns |

## 6.7 SPI セカンダリ デバイス モードのタイミング

図 6-1. SPI セカンダリ デバイス モード タイミングの図

## 6.8 代表的特性

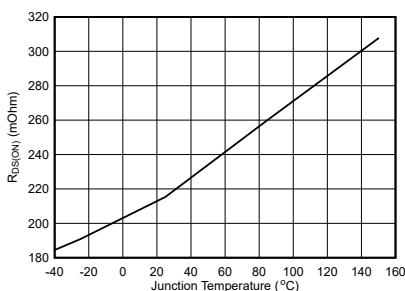

図 6-2. MOSFET の  $R_{DS(ON)}$  (ハイサイドとローサイドの合計) の温度特性 ( $VM \geq 6V$ )

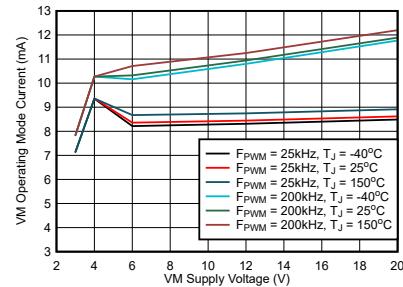

図 6-3. 動作モード電流の電源電圧特性

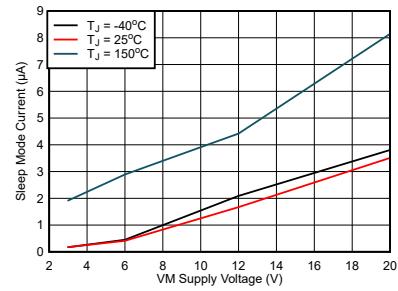

図 6-4. スリープ電流の電源電圧特性

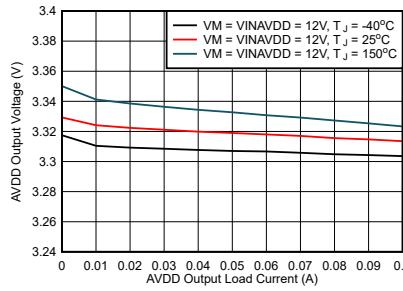

図 6-5. AVDD レギュレータ出力電圧の負荷電流特性

## 7 詳細説明

### 7.1 概要

DRV8311-Q1 は、三相モーター駆動アプリケーション向けの統合 MOSFET ドライバです。ハイサイドおよびローサイド FET を合算したオン抵抗は標準値で  $210\text{ m}\Omega$  です。このデバイスは、3 つのハーフブリッジ MOSFET、ゲートドライバ、チャージ ポンプ、電流センス アンプ、外部負荷用のリニア レギュレータを統合することで、システムの部品点数、コスト、設計の複雑さを低減します。DRV8311S-Q1 では、標準のシリアル ペリフェラル インターフェイス (SPI) を使うと、デバイスの各種設定とフォルト診断情報の読み出しを外部コントローラから簡単に行うことができます。DRV8311H-Q1 では、ハードウェア・インターフェース (H/W) により、固定外付け抵抗でよく使われる設定を行えます。DRV8311P-Q1 では、テキサス インスツルメンツの SPI (tSPI) により、各種設定の構成に加え、PWM デューティ サイクルおよび周波数を調整して複数のモーターを同時に制御できます。

また、このアーキテクチャは、内部ステート マシンを用いて短絡事象から保護し、内部パワー MOSFET の  $dV/dt$  による寄生ターンオンも防止します。

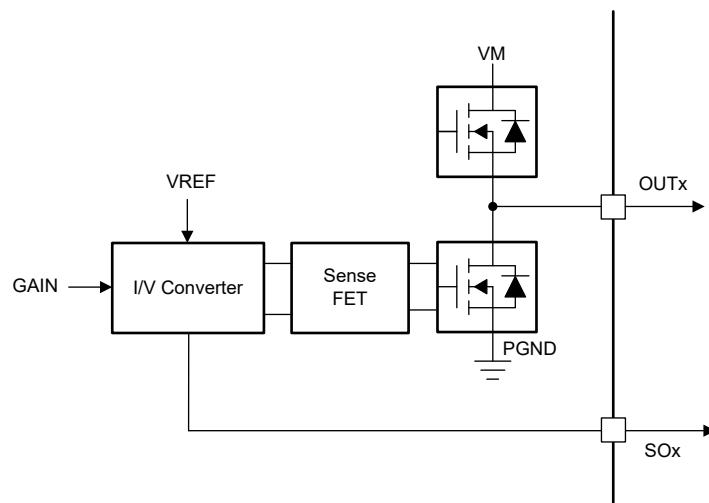

DRV8311-Q1 は、内蔵の電流センスにより各ハーフブリッジを流れる電流を監視するための双方向ローサイド電流シャント アンプを 3 系統内蔵しており、外付けの電流センス抵抗を必要としません。シャント アンプのゲイン設定は、SPI、tSPI、またはハードウェア インターフェースから調整可能です。

高いレベルでデバイスが統合されていることに加え、DRV8311-Q1 は幅広い保護機能を内蔵しています。これらの機能には、電源の低電圧ロックアウト (UVLO)、チャージ ポンプの低電圧ロックアウト (CPUV)、過電流保護 (OCP)、AVDD 低電圧ロックアウト (AVDD\_UV)、および過熱警告シャットダウン (OTW と OTSD) などが含まれます。フォルト発生時は nFAULT ピンで通知され、詳細情報は SPI および tSPI 版デバイスのレジスタで参照できます。

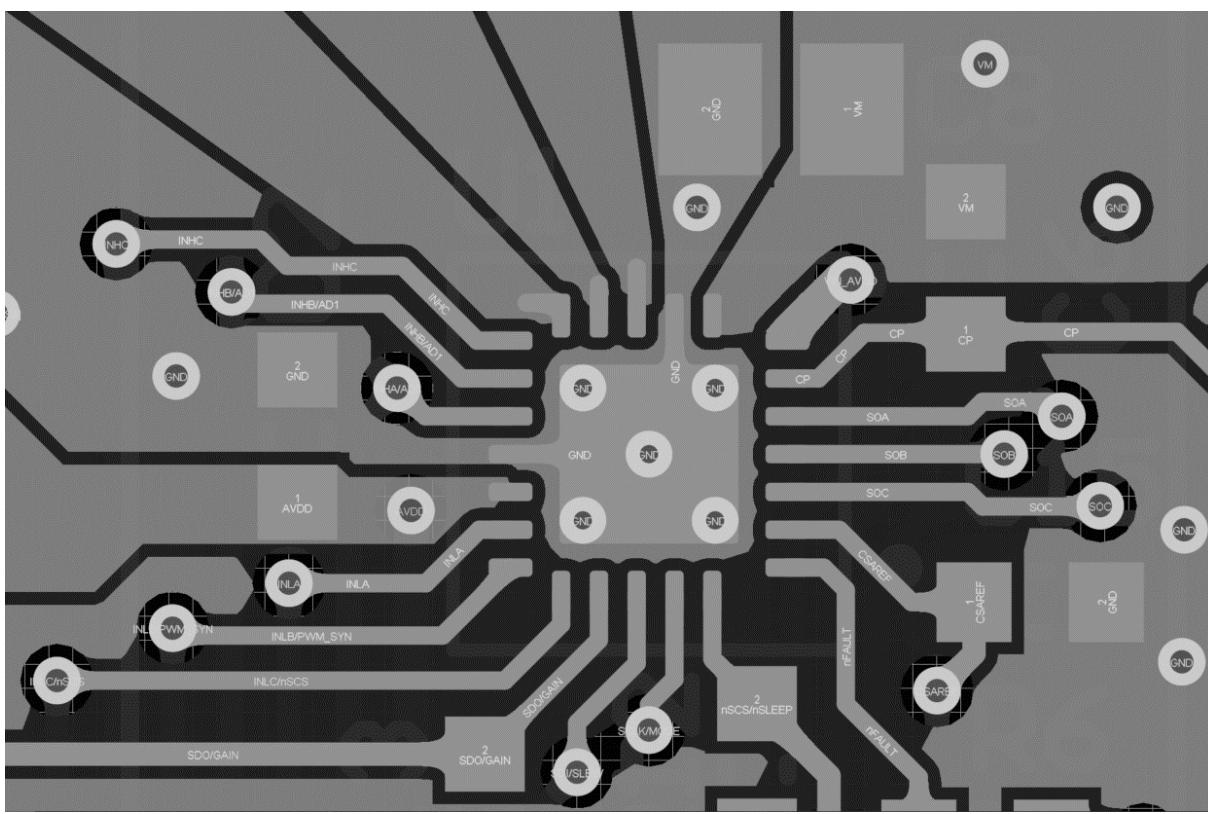

DRV8311-Q1 は、ピンピッチ  $0.4\text{ mm}$  の WQFN 表面実装パッケージで提供されます。この WQFN パッケージのサイズは  $3.00\text{mm} \times 3.00\text{mm}$  です。

## 7.2 機能ブロック図

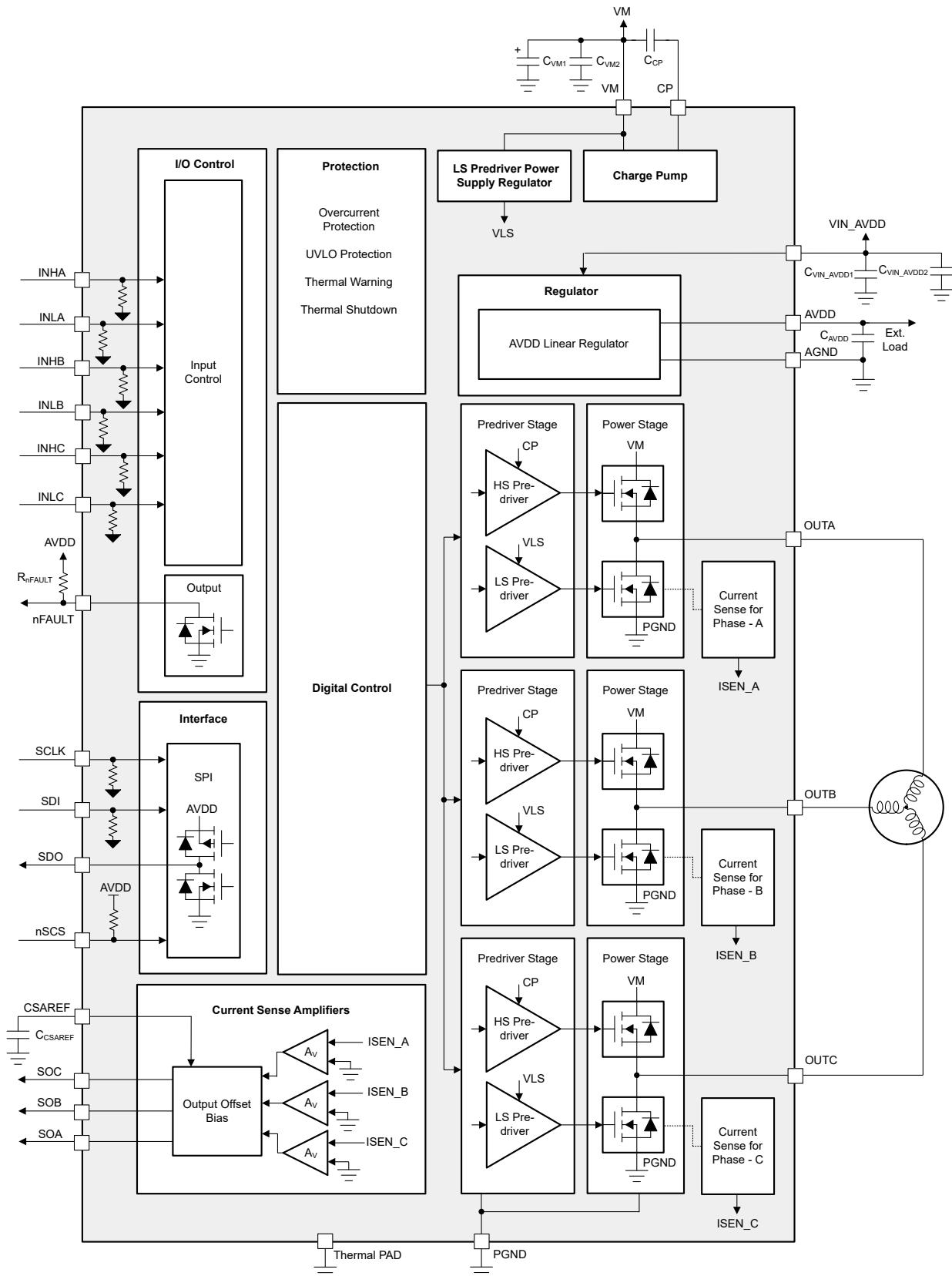

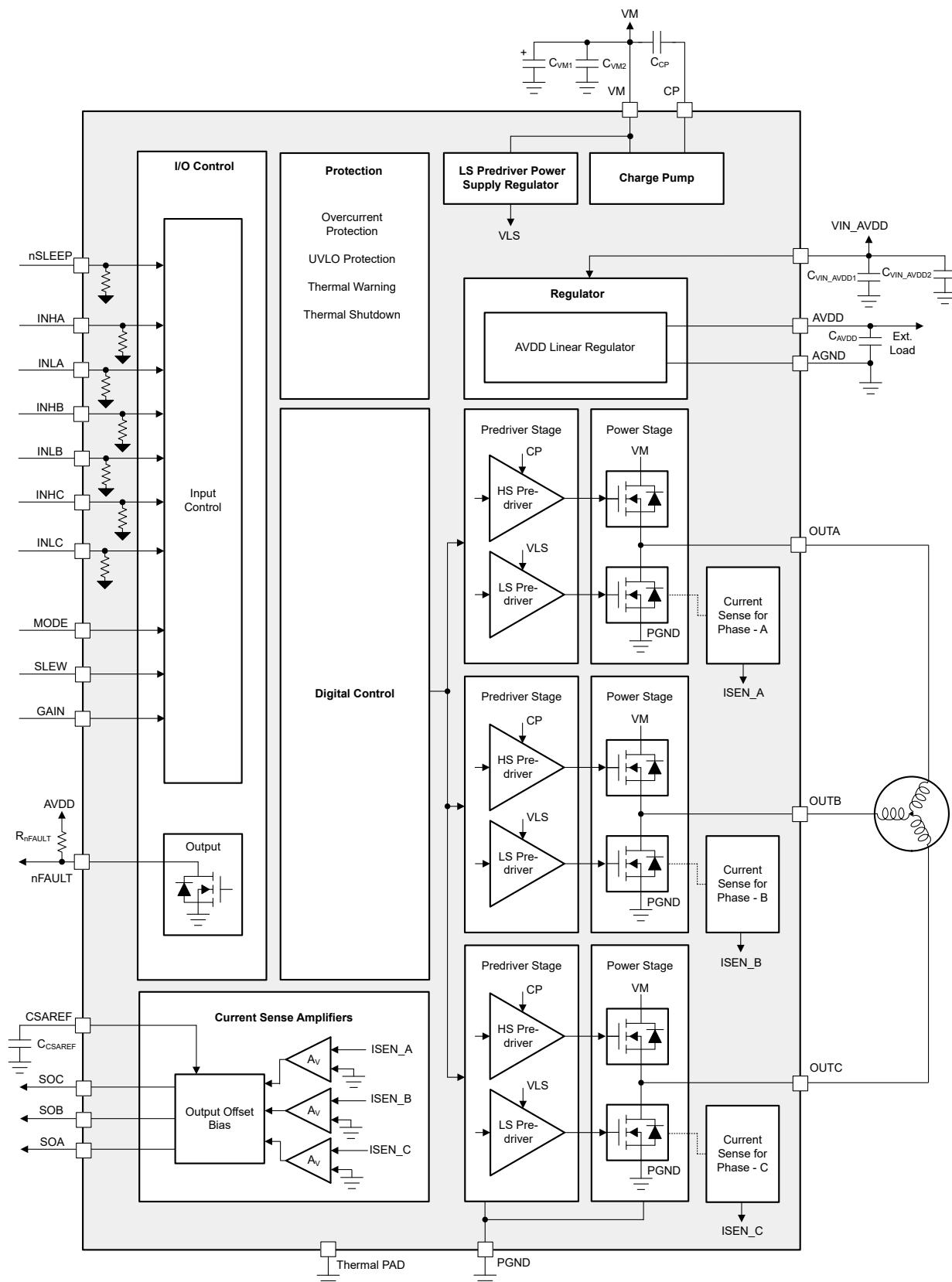

図 7-1 DRV8311S-Q1 のブロック図

図 7-2. DRV8311H-Q1 のブロック図

図 7-3. DRV8311P-Q1 のブロック図

## 7.3 機能説明

表 7-1 に、ドライバの外付け部品の推奨値を示します。

**表 7-1. DRV8311-Q1 の外付け部品**

| 部品               | ピン 1     | ピン 2          | 推奨                                       |

|------------------|----------|---------------|------------------------------------------|

| $C_{VM1}$        | VM       | PGND          | X5R または X7R、0.1 $\mu$ F、VM 定格コンデンサ       |

| $C_{VM2}$        | VM       | PGND          | 10 $\mu$ F 以上、VM 定格の電解コンデンサ              |

| $C_{VIN\_AVDD1}$ | VIN_AVDD | AGND          | X5R または X7R、0.1 $\mu$ F、VIN_AVDD 定格コンデンサ |

| $C_{VIN\_AVDD2}$ | VIN_AVDD | AGND          | 10 $\mu$ F 以上、VIN_AVDD 定格コンデンサ           |

| $C_{CP}$         | CP       | VM            | X5R または X7R、16-V、0.1 $\mu$ F コンデンサ       |

| $C_{AVDD}$       | AVDD     | AGND          | X5R または X7R、0.7 ~ 7 $\mu$ F、6.3V 定格コンデンサ |

| $R_{nFAULT}$     | AVDD     | nFAULT        | 5.1k $\Omega$ 、プルアップ抵抗                   |

| $R_{SDO}$        | AVDD     | SDO           | 5.1k $\Omega$ 、プルアップ抵抗 (オプション)           |

| $R_{MODE}$       | MODE     | AGND または AVDD | セクション 7.3.3.2                            |

| $R_{SLEW}$       | SLEW     | AGND または AVDD | セクション 7.3.3.2                            |

| $R_{GAIN}$       | ゲイン      | AGND または AVDD | セクション 7.3.3.2                            |

| $C_{CSAREF}$     | CSAREF   | AGND          | X5R または X7R、0.1 $\mu$ F、CSAREF 定格コンデンサ   |

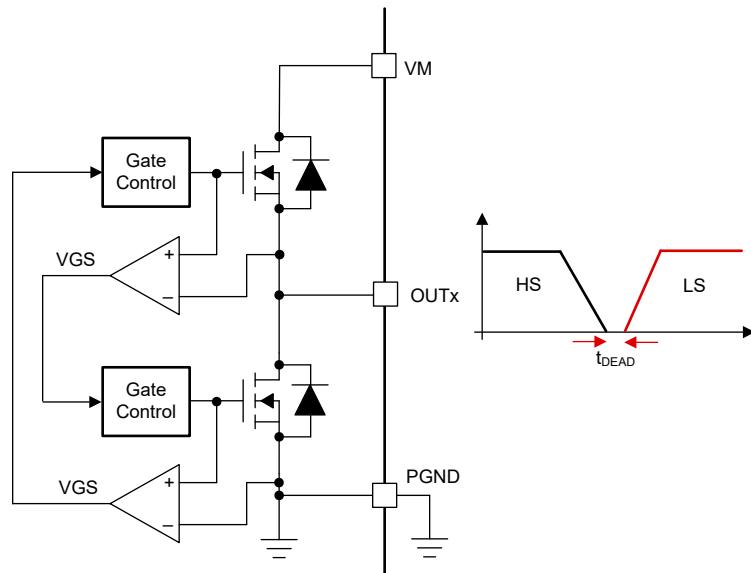

### 7.3.1 出力ステージ

DRV8311-Q1 は、三相ブリッジ構成で接続された内蔵 NMOS MOSFET により構成されています。ダブルーチャージポンプは、広い動作電圧範囲にわたってハイサイド NMOS MOSFET 用の適切なゲートバイアス電圧を供給し、100% のデューティサイクルもサポートします。VM 供給から動作する内部リニアレギュレータがローサイド MOSFET 用のゲートバイアス電圧 (VLS) を供給します。

### 7.3.2 制御モード

このデバイスには、さまざまな整流方式や制御方式をサポートするために、3 種類の制御モードが用意されています。表 7-2 に、このデバイスのさまざまなモードが示されています。

**表 7-2. PWM 制御モード**

| MODE のタイプ | MODE ピン (DRV8311H-Q1)                                       | MODE ビット (DRV8311S-Q1)            | MODE ビット (DRV8311P-Q1) | MODE      |

|-----------|-------------------------------------------------------------|-----------------------------------|------------------------|-----------|

| モード 1     | Mode ピンを AGND に接続するか、Mode ピンを 47k $\Omega$ の抵抗を介して AGND に接続 | PWM_MODE = 00b または PWM_MODE = 01b | 該当なし                   | 6x モード    |

| モード 2     | Mode ピン ハイインピーダンスまたは Mode ピンを AVDD に接続                      | PWM_MODE = 10b                    | 該当なし                   | 3x モード    |

| モード 3     | 該当なし                                                        | PWM_MODE = 11b                    | PWM_MODE = 11b         | PWM 生成モード |

### 注

テキサス インストルメンツでは、デバイスの電源投入中 (すなわち tWAKE の期間中) に MODE ピンまたは MODE レジスタを変更することは推奨していません。DRV8311H-Q1 の MODE 設定は電源投入時にラッチされるため、DRV8311H-Q1 の MODE ピン構成を変更する前に、nSLEEP = 0 に設定してください。DRV8311S-Q1 では、MODE レジスタを変更する場合、その前にすべての INHx および INLx ピンを論理 Low に設定してください。

### 7.3.2.1 6x PWM モード (DRV8311S-Q1 および DRV8311H-Q1 バリエントのみ)

6x PWM モードでは、ハーフブリッジごとに Low、High、ハイインピーダンス(Hi-Z)の3つの出力状態がサポートされます。DRV8311H-Q1を6x PWMモードに設定するには、MODEピンをAGNDに接続するか、MODEピンを47kΩに接続してAGNDに接続します。DRV8311S-Q1で6x PWMモードを有効にするには、MODEビットをPWM\_MODE = 00bまたは01bに設定します。[表7-3](#)に示すように、対応するINHxおよびINLx信号で出力状態を制御します。

**表7-3. 6x PWMモードの真理値表**

| INLx | INHx | OUTx      |

|------|------|-----------|

| 0    | 0    | ハイインピーダンス |

| 0    | 1    | H         |

| 1    | 0    | L         |

| 1    | 1    | ハイインピーダンス |

[図7-4](#)は、6x PWMモードに設定されたアプリケーション図を示しています。

**図7-4. 6x PWMモード**

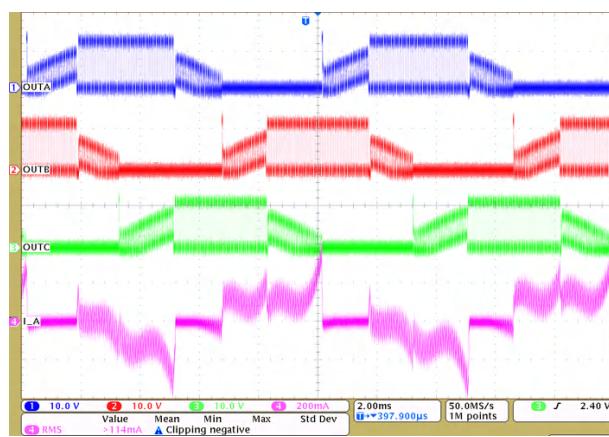

### 7.3.2.2 3x PWM モード (DRV8311S-Q1 および DRV8311H-Q1 バリエントのみ)

この 3x PWM モードでは、INH<sub>x</sub> ピンで各ハーフブリッジを制御し、Low または High の 2 つの出力状態がサポートされます。DRV8311H-Q1 を 3x PWM モードに設定するには、MODE ピンを AVDD に接続するか、MODE ピンをハイインピーダンス状態にする必要があります。DRV8311S-Q1 で 3x PWM モードを有効にするには、MODE ビットを PWM\_MODE = 10b に設定してください。INL<sub>x</sub> ピンは、ハーフブリッジをハイインピーダンス状態にするために使用します。ハイインピーダンス状態が不要の場合は、すべての INL<sub>x</sub> ピンを論理 High (例えば AVDD) に接続します。表 7-4 に示すように、対応する INH<sub>x</sub> および INL<sub>x</sub> 信号で出力状態を制御します。

表 7-4. 3x PWM モードの真理値表

| INL <sub>x</sub> | INH <sub>x</sub> | OUT <sub>x</sub> |

|------------------|------------------|------------------|

| 0                | X                | ハイインピーダンス        |

| 1                | 0                | L                |

| 1                | 1                | H                |

図 7-5 は、3x PWM モードで構成した典型的なアプリケーション図を示しています。

図 7-5. 3x PWM モード

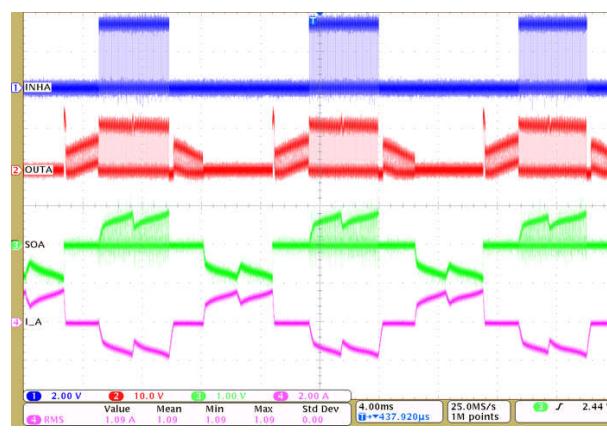

### 7.3.2.3 PWM 生成モード (DRV8311S-Q1 および DRV8311P-Q1 バリアント)

PWM 生成モードでは、PWM 信号は DRV8311-Q1 内部で生成され、SPI (DRV8311S-Q1) または tSPI (DRV8311P-Q1) を介したレジスタ読み取り / 書き込みによって制御することができます。この動作モードでは、従来のように INH<sub>x</sub> ピンと INL<sub>x</sub> ピンを通じてモーターを制御する必要はありません。各相の PWM の周期、周波数、デューティサイクルは、シリアルインターフェイス経由で設定することができます。さらに、PWM\_SYNC ピンの機能により、マイコンと DRV8311P/S-Q1 間の同期が可能です。PWM モードは、各相のハイサイドまたはローサイド MOSFET の PWM 制御を有効または無効に設定できるため、必要に応じて連続スイッチングや非連続スイッチングを選択することができます。DRV8311S-Q1 を PWM 生成モードで使用する場合、マイコンからの PWM\_SYNC 信号を DRV8311S-Q1 の INLB ピンに接続してください。このモードでは、DRV8311S-Q1 は、その他の INH<sub>x</sub> および INL<sub>x</sub> ピンの状態を参照しません。PWM 生成モードを用いることで、台形波制御、正弦波制御、FOC 制御のいずれも実現可能です。

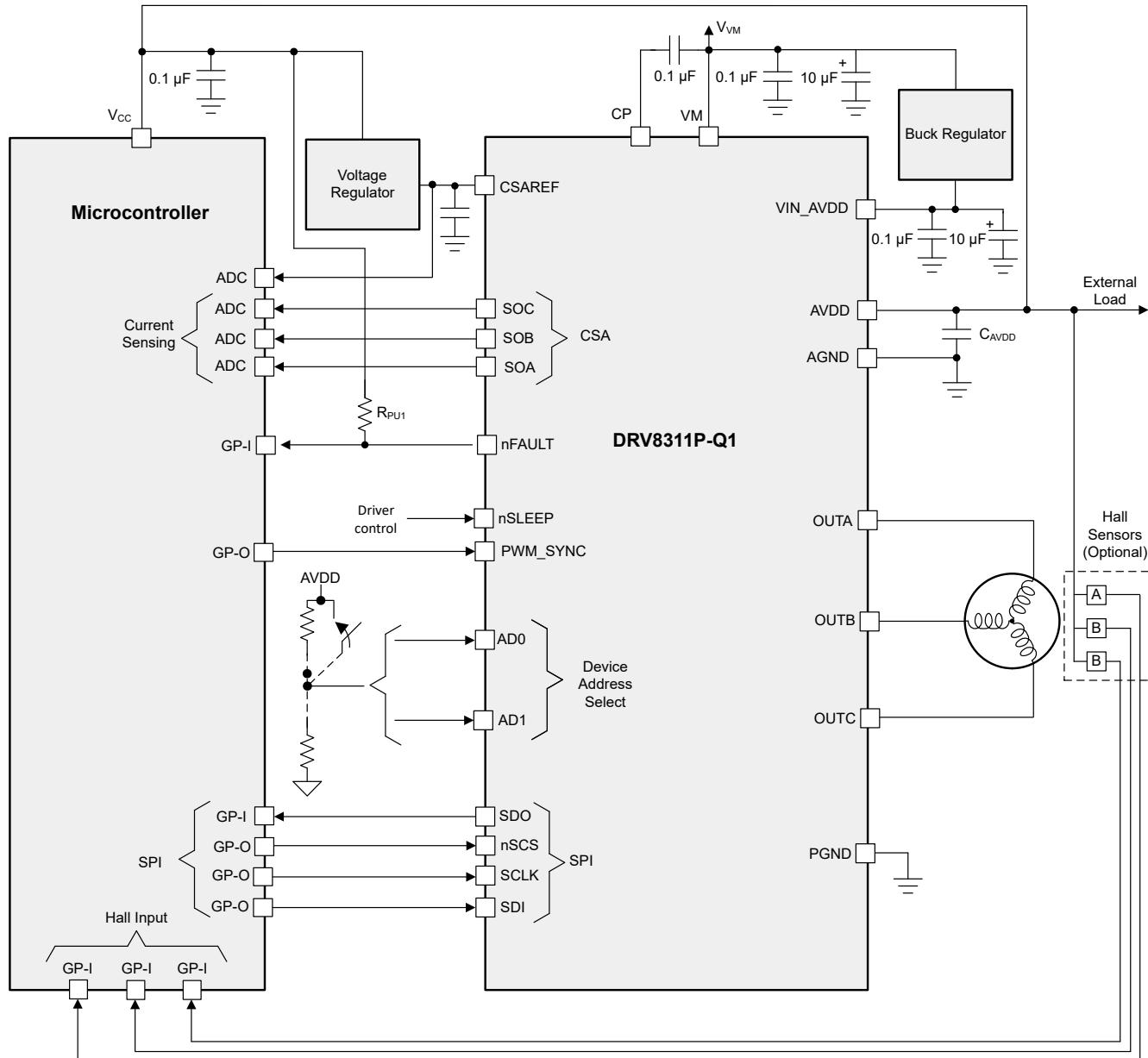

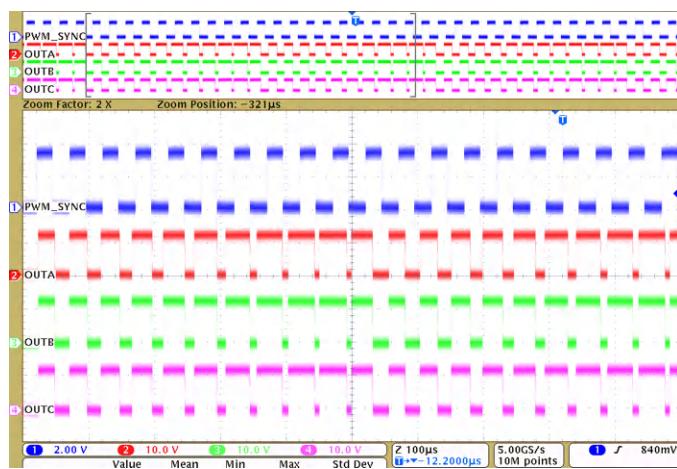

図 7-6. PWM 生成モード、DRV8311P-Q1

図 7-7. PWM 生成モード、DRV8311S-Q1

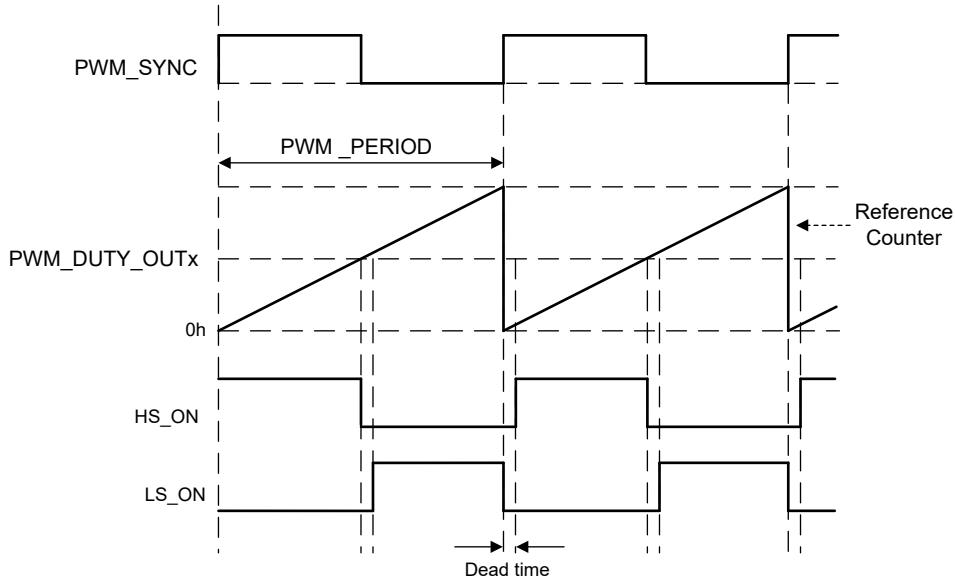

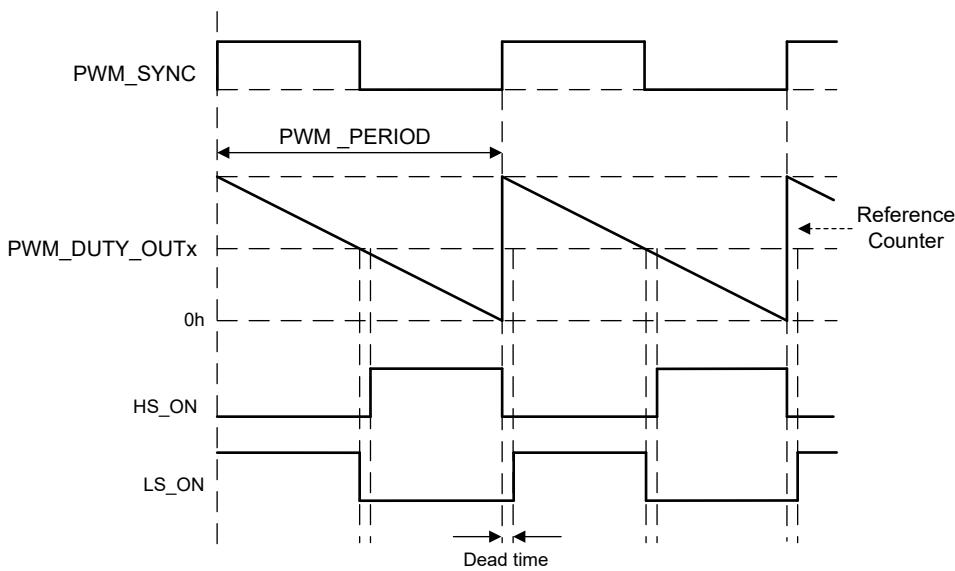

PWM 生成モードには、アップ / ダウンモード、アップモード、ダウンモードの 3 種類のオプションがあります。PWM 生成モードは、PWMG\_CTRL レジスタの PWMCNTR\_MODE ビットを使用して設定できます。各相 (A, B, C) の PWMG\_x\_DUTY レジスタ (x は各相を示す) の PWM\_DUTY\_OUTx ビットで定義されたデューティサイクルは、内部で生成されるリファレンス カウンタ信号と比較され、その結果に基づいてハイサイド MOSFET の PWM 信号が生成されます。PWM 生成では、PWM\_PRD\_OUT ビット (PWMG\_PERIOD レジスタ) と PWMCNTR\_MODE ビットの構成に基づいて内部的に生成されるリファレンス カウンタ信号を使用します。PWM\_EN ビットが High の場合、PWM\_DUTY\_OUTx の値がリファレンス カウンタを上回ると、ハイサイド MOSFET の PWM 出力は High になります。一方、PWM\_EN ビットが Low の場合、出力は常に Low に保持されます。ハイサイド MOSFET を[サイクル全体でオン状態 HS\_ON]とする 100% デューティサイクルを実現するには、PWM\_DUTY\_OUTx の値を PWM\_PRD\_OUT の値より大きく設定する必要があります。

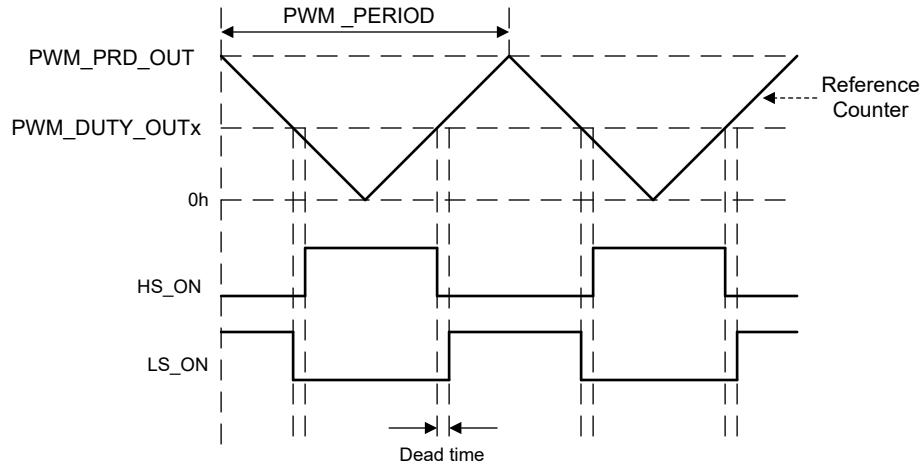

アップ / ダウンモード [PWMCNTR\_MODE = 0h] では、基準リファレンス カウンタの波形は V 字形となり、有効化されると PWM\_PRD\_OUT の値からカウントダウンを開始し、カウンタがゼロに到達すると再びカウントアップします。PWM 周波数 ( $f_{PWM}$ ) は、 $f_{PWM} = 0.5 \times (f_{SYS} / f_{PWR})$  の関係式を用いて PWM\_PRD\_OUT ビットを設定します。 $f_{SYS}$  は、DRV8311P-Q1 および DRV8311S-Q1 の内部システムクロック周波数 (約 20MHz) です。

図 7-8. PWM 生成、アップ/ダウンモード

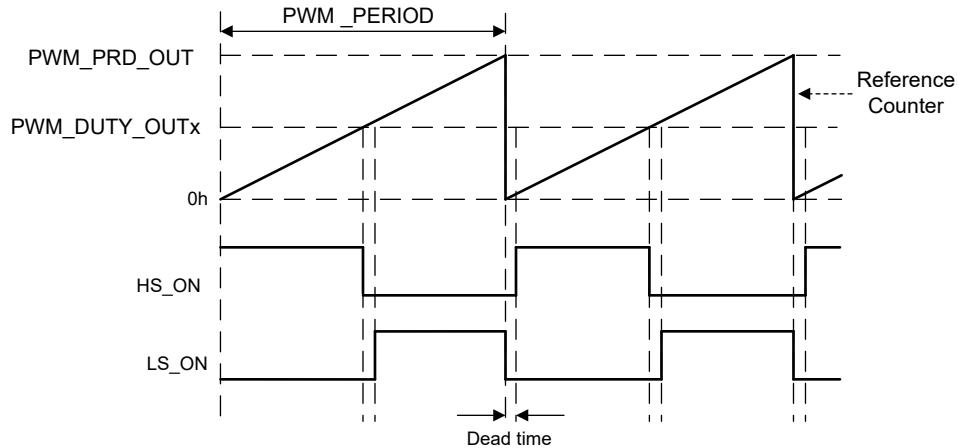

アップモード [PWMCNTR\_MODE = 1h] では、カウンタはゼロから PWM\_PRD\_OUT の値までカウントアップし、その後ゼロにリセットされます。 $PWM\_PRD\_OUT = F_{SYS} / F_{PWM}$

図 7-9. PWM 生成、アップモード

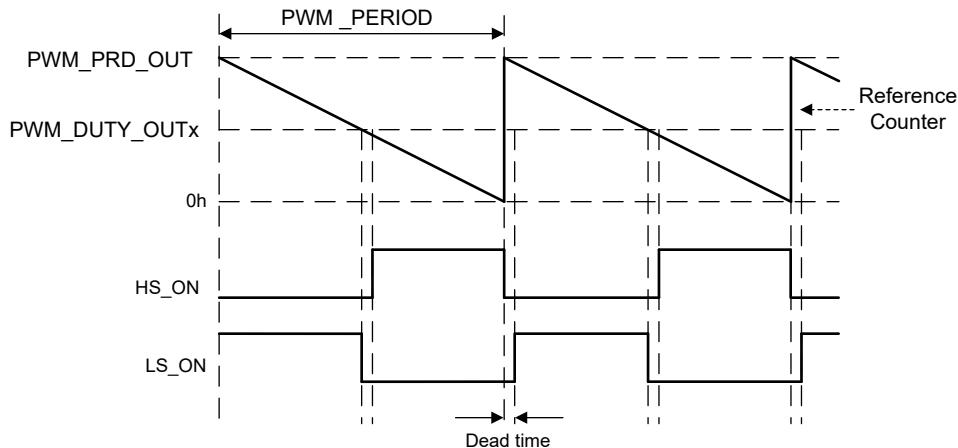

ダウンモード [PWMCNTR\_MODE = 2h] では、カウンタは PWM\_PRD\_OUT の値からカウントダウンを開始し、カウンタがゼロに達すると再び PWM\_PRD\_OUT の値にリセットされます。 $PWM\_PRD\_OUT = F_{SYS} / F_{PWM}$

図 7-10. PWM 生成、ダウンモード

TDEAD\_CTRL レジスタで設定されたデッドタイムが、LS\_ON の立ち下がりエッジと HS\_ON の立ち上がりエッジの間、また HS\_ON の立ち下がりエッジと LS\_ON の立ち上がりエッジの間に挿入されます。

### PWM 生成モードにおける PWM 同期

専用の INHx または INLx 制御信号が使用されていない場合、外部マイコンは DRV8311-Q1 が生成する PWM 信号との同期を失う可能性があります。同期のために、外部マイコンは PWM\_SYNC ピンに 1 つのリファレンス信号を送信します。PWM 同期機能により、DRV8311-Q1 が生成する PWM 出力をマイコンのクロック精度で動作させることができます。マイコンの ADC による電流センス出力のサンプリングと PWM 出力を整列させることができます。さらに、PWM\_SYNC 信号は、DRV8311-Q1 内部発振器の周波数の測定にも役立ちます。DRV8311-Q1 は、動作条件に関わらず内部発振器を 20MHz にキャリブレーションする自動補正機能もサポートしています。DRV8311-Q1 では、PWMG\_CTRL レジスタの PWM\_OSC\_SYNC ビットを設定することで、マイコンと DRV8311-Q1 の間で 5 種類の異なる同期方法を選択することができます。これらの同期方式の概要を以下に示します。

**PWM\_OSC\_SYNC = 1h の場合:** DRV8311-Q1 は、PWM\_SYNC 信号の周期 (PWM\_SYNC\_PRD) を、DRV8311-Q1 のシステムクロック  $F_{SYS}$  (約 20MHz) のカウント単位で測定します。マイコンは PWM\_SYNC\_PRD レジスタの値を読み取り、それに基づいて PWM 周期をキャリブレーションを行うことができます。たとえば、マイコンが内部タイマを用いて周期カウント値を N、クロック周波数を  $F_{MCU}$  とし、デューティ比 50% の PWM\_SYNC 信号を生成する場合を考えます。マイコンは、DRV8311-Q1 によって生成された PWM\_SYNC\_PERIOD レジスタの読み取り値を M とすると。DRV8311-Q1 は、DRV8311-Q1 システムクロック  $F_{SYS}(\text{DRV})$  を使用して PWM\_SYNC\_PERIOD を生成します。このとき、マイコンのタイマ クロックと DRV8311-Q1 のシステム クロックの間には、関係式  $F_{MCU} \times M = F_{SYS}(\text{DRV}) \times N$  が成立します。

PWM\_SYNC\_PRD は 12 ビット幅であり、DRV8311-Q1 の内部システム クロックが約 20MHz の場合、飽和せずに読み取ることができる PWM\_SYNC 信号の最小周波数は約 4.885kHz ( $F_{SYS}/4095$ ) です。

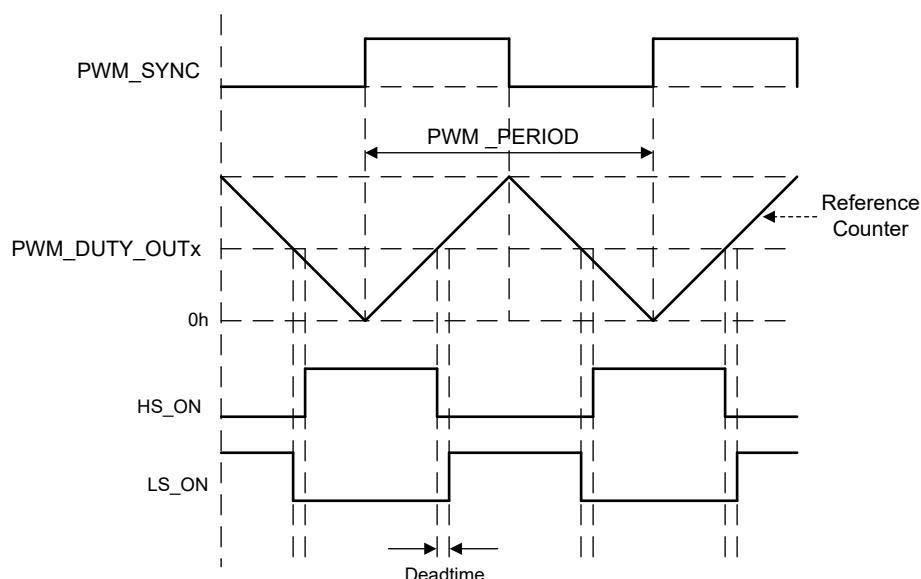

**PWM\_OSC\_SYNC = 2h の場合:** マイコンからの PWM\_SYNC 信号が DRV8311-Q1 の PWM 周期を設定するために使用され、PWMG\_PERIOD レジスタの設定は無視されます。DRV8311-Q1 は、PWM\_SYNC 信号の立ち上がりエッジで PWM カウンタをリセットします。

図 7-11. アップ / ダウンモードでの PWM 同期 (PWM\_OSC\_SYNC = 2h)

図 7-12. アップモードでの PWM 同期 (PWM\_OSC\_SYNC = 2h)

図 7-13. ダウンモードでの PWM 同期 (PWM\_OSC\_SYNC = 2h)

**PWM\_OSC\_SYNC = 5h の場合:** PWM\_SYNC は、DRV8311-Q1 内部発振器の同期に使用されます (対応する周波数は 20kHz のみです)。PWM\_SYNC 信号が 20kHz の場合、DRV8311-Q1 は、PWM\_SYNC 信号の立ち上がりエッジ間に発生する内部システム発振器クロックパルスの数をカウントします。DRV8311-Q1 のシステムクロックが 20MHz の所望の条件において、予想されるクロックパルス数は 1000 となります。この値からの偏差は、DRV8311-Q1 の内部発振器が生成する周波数、またはマイコンからの PWM\_SYNC 周波数のいずれかにエラーが発生したことを意味します。マイコンからの PWM\_SYNC 信号の周波数は正確であると仮定し、DRV8311-Q1 は内部的に発振器のキャリブレーションを行って周波数を 20MHz に補正し、生成される PWM 周波数を PWM\_SYNC 信号と整合させます。

**PWM\_OSC\_SYNC = 6h の場合:** PWM\_SYNC 信号は、DRV8311-Q1 内部システム発振器のキャリブレーションと PWM 周期の設定に使用されます (対応する周波数は 20kHz のみです)。PWMDG\_PERIOD レジスタの設定は無視されます。DRV8311-Q1 は、PWM\_SYNC 信号の立ち上がりエッジで PWM リファレンス カウンタをリセットします。

**PWM\_OSC\_SYNC = 7h の場合:** SPI クロックピン SCLK は、DRV8311-Q1 の内部システム発振器を 20MHz にキャリブレーションするために使用されます。このモードでは、ユーザーは PWMG\_CTRL レジスタを設定することで、発振器を同期させるための SPI クロック周波数 (SPICLK\_FREQ\_SYNC) と、発振器の同期に必要な SPI クロック サイクル数 (SPISYNC\_ACRCY) を設定する必要があります。DRV8311-Q1 は、設定された SPISYNC\_ACRCY に基づく全 SPI クロック サイクルの合計時間を、DRV8311-Q1 内部システム クロック  $F_{SYS}$  のカウント値として測定し、内部システム クロックを 20MHz に対応するカウント値に合わせてキャリブレーションします。キャリブレーション後の DRV8311-Q1 システム 発振器の周波数の 20MHz に対する精度は、SPISYNC\_ACRCY の構成に依存します。

### 7.3.3 デバイス インターフェイス モード

このファミリのデバイスでは、簡便性を高め (ハードウェア インターフェイス)、柔軟性や診断機能を向上 (SPI) させるために、3 種類のインターフェイスモード (SPI, tSPI, ハードウェア) をサポートしています。SPI およびハードウェア インターフェース モードは同じ 4 本のピンを共有しており、異なるバージョン間でピン互換性があります。設定を簡単に変更できるため、設計者はまず SPI バージョンで評価することができます。また、設計に最小限の設計変更でハードウェア インターフェースに切り替えることも検討可能です。

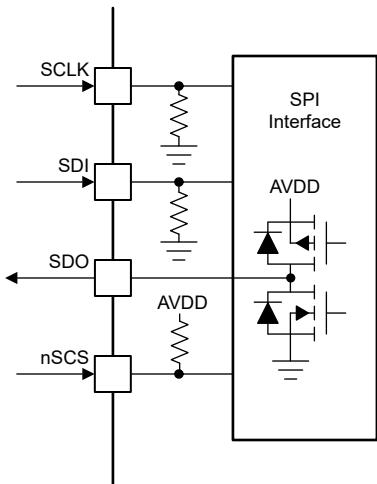

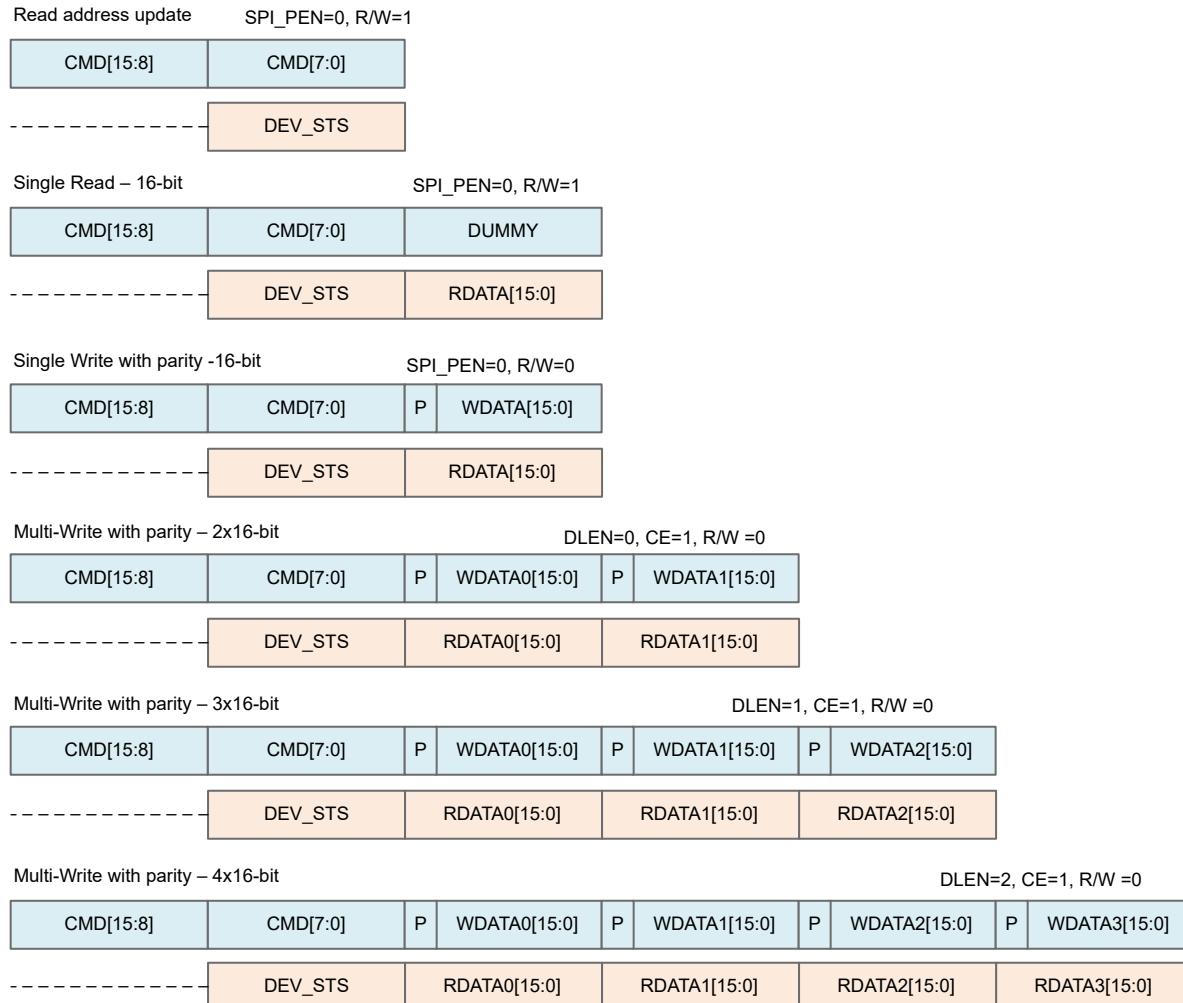

#### 7.3.3.1 シリアル・ペリフェラル・インターフェイス (SPI)

SPI/tSPI デバイスは、外部コントローラが DRV8311P-Q1 および DRV8311S-Q1 とデータの送受信を行えるシリアル通信バスをサポートしています。この機能により、外部コントローラはデバイスを設定し、詳細なフォルト情報を読み出すことができます。インターフェイスは、SCLK, SDI, SDO, nSCS ピンを使用する 4 線式インターフェイスです。以下の説明をご覧ください。

- SCLK (シリアル クロック) ピンは、クロック信号を入力として受け取り、その信号により SDI と SDO ピンでデータがキャプチャされ、伝送されるタイミングを決定する入力ピンです。

- SDI (シリアル データ入力) ピンはデータ入力用です。

- SDO (シリアルデータ出力) ピンはデータ出力用です。

- nSCS (シリアル チップ セレクト) ピンはチップ選択入力用です。このピンに論理 Low 信号を入力すると、DRV8311-Q1 との SPI 通信が有効になります。

SPI の詳細については、[セクション 7.5](#) を参照してください。

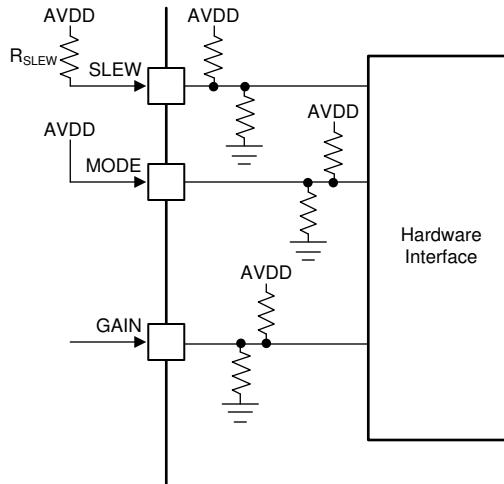

#### 7.3.3.2 ハードウェア インターフェイス