# DRV832x 6~60V、3相スマート・ゲート・ドライバ

## 1 特長

- トリプル・ハーフブリッジ・ゲート・ドライバ

- 3つのハイサイドと3つのローサイドのNチャネルMOSFET(NMOS)を駆動

- スマート・ゲート・ドライブ・アーキテクチャ

- 調整可能なスルーレート制御

- 10mA~1Aのピーク・ソース電流

- 20mA~2Aのピーク・シンク電流

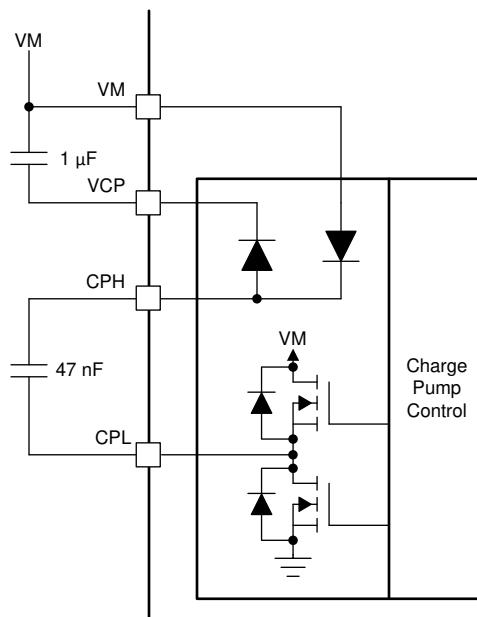

- ゲート・ドライバ電源を内蔵

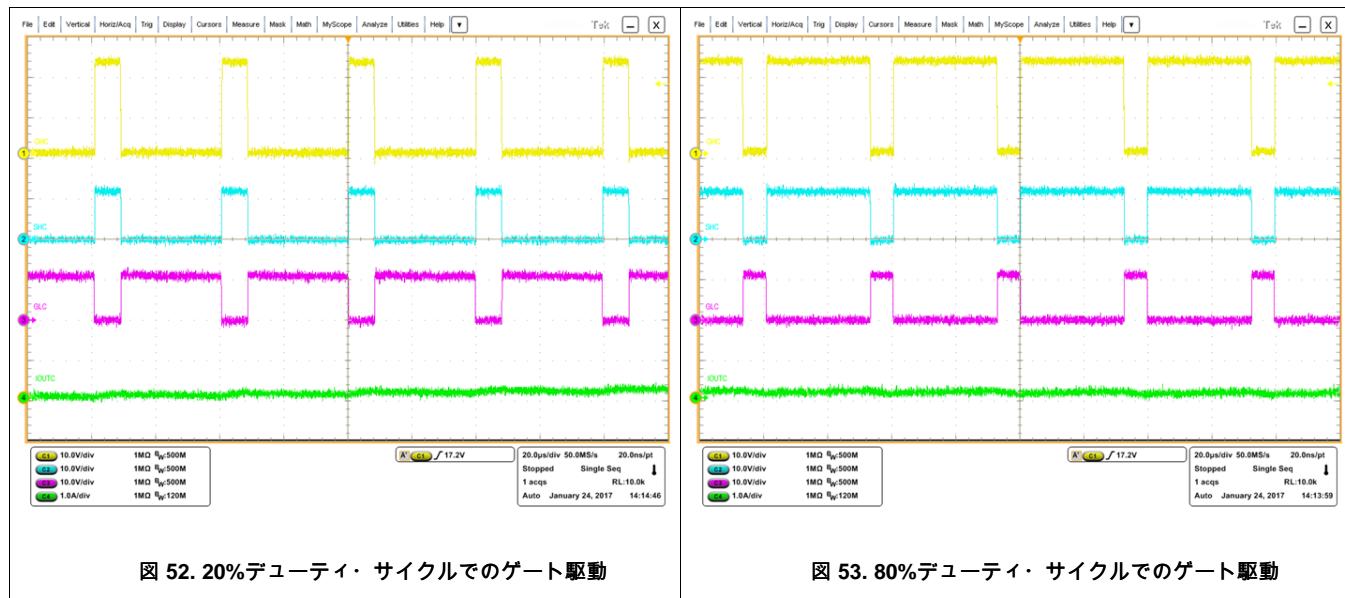

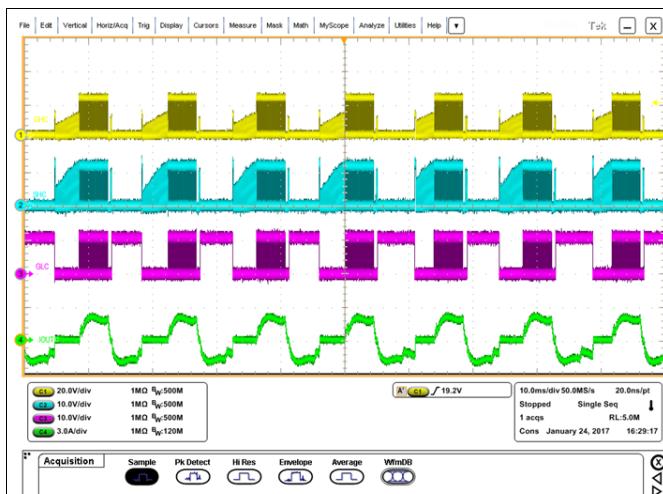

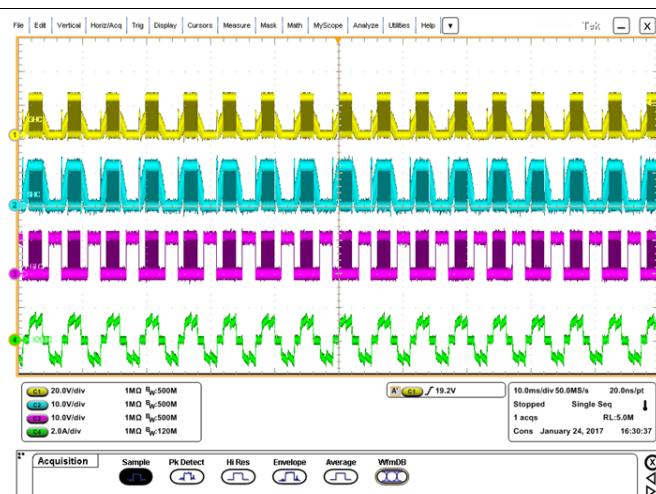

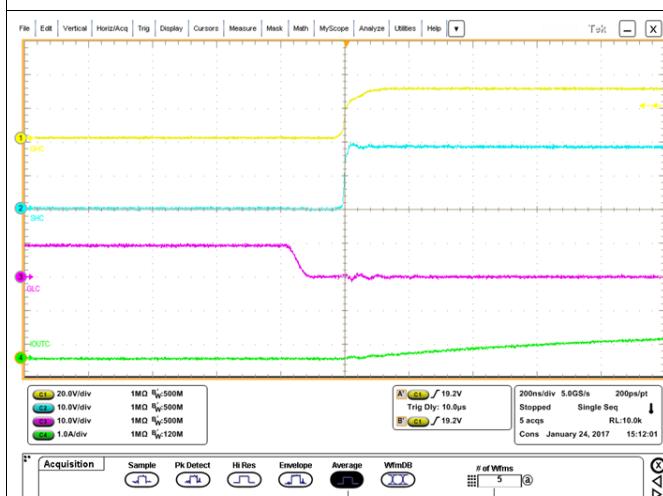

- 100%のPWMデューティ・サイクルをサポート

- ハイサイドのチャージ・ポンプ

- ローサイドのリニア・レギュレータ

- 6V~60Vの動作電圧範囲

- 降圧レギュレータ内蔵（オプション）

- LMR16006X SIMPLE SWITCHER®

- 4~60Vの動作電圧範囲

- 0.8~60Vで600mAの出力能力

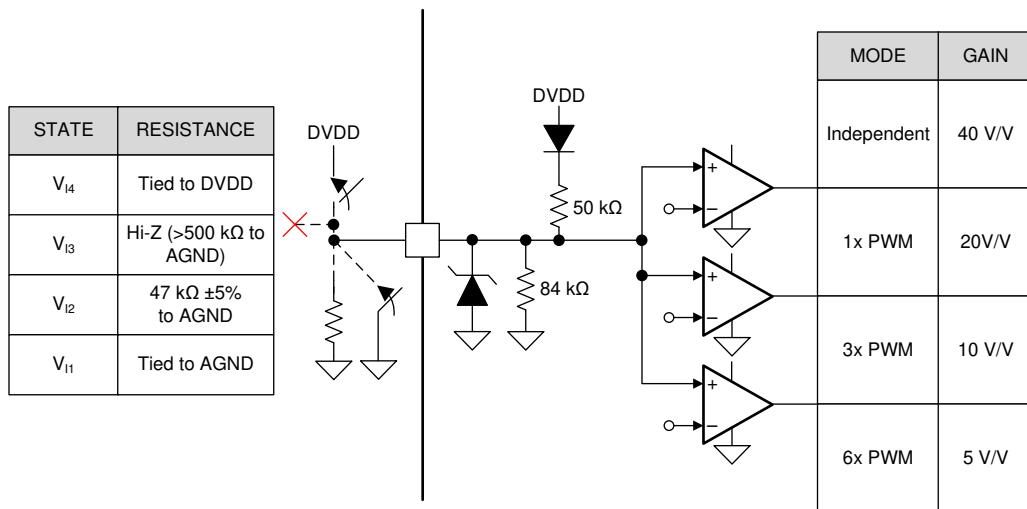

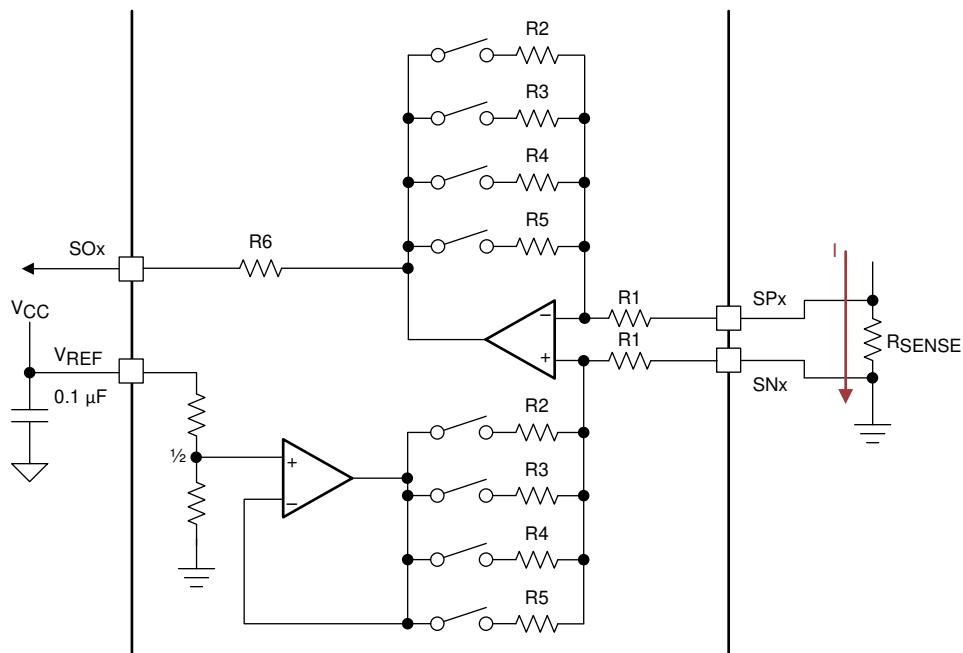

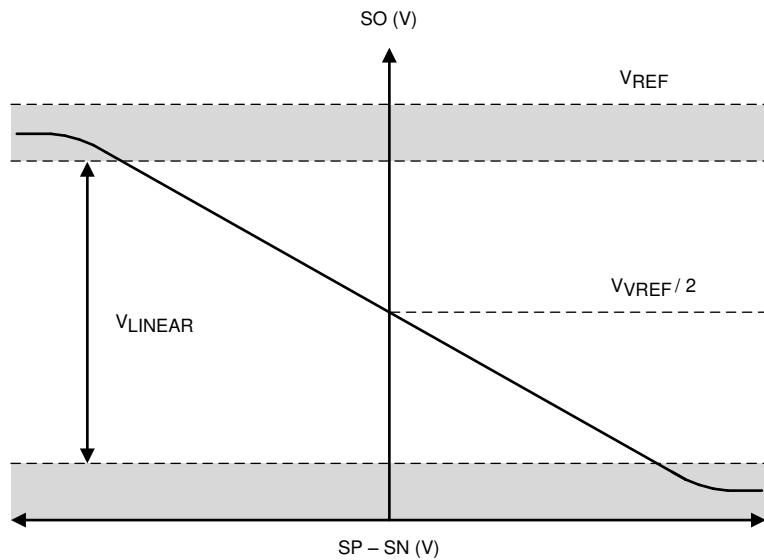

- トリプル電流センス・アンプ（CSA）内蔵（オプション）

- 可変ゲイン(5, 10, 20, 40V/V)

- 双方向または単方向のサポート

- SPIおよびハードウェア・インターフェイスを利用可能

- 6x, 3x, 1x、および独立PWMモード

- 1.8V, 3.3V, 5Vのロジック入力電圧をサポート

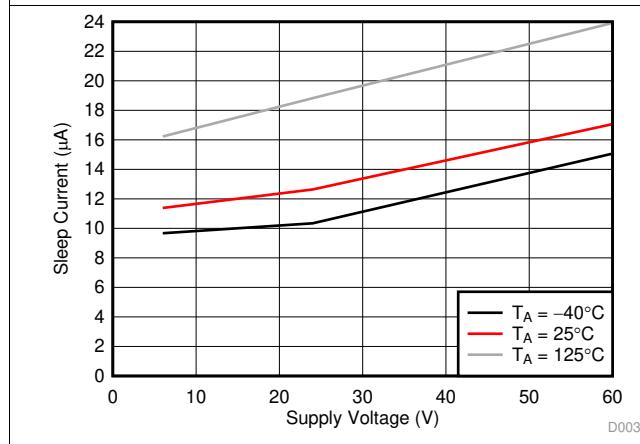

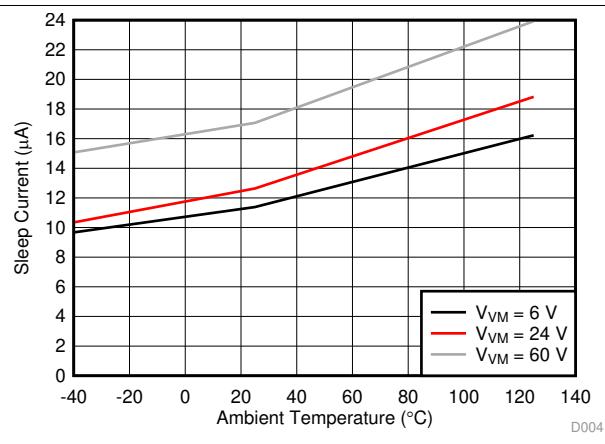

- 低消費電力のスリープ・モード (12µA)

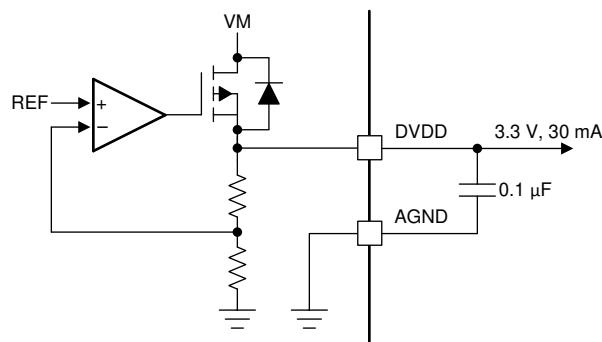

- リニア電圧レギュレータ、3.3V, 30mA

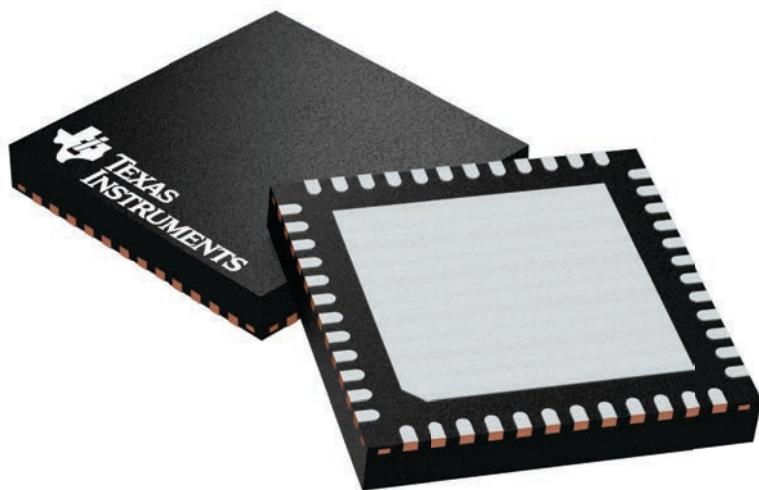

- 小型で占有面積の小さいQFNパッケージ

- パワー・ブロックによる効率的なシステム設計

- 保護機能を内蔵

- VM低電圧誤動作防止(UVLO)

- チャージ・ポンプ低電圧(CPUV)

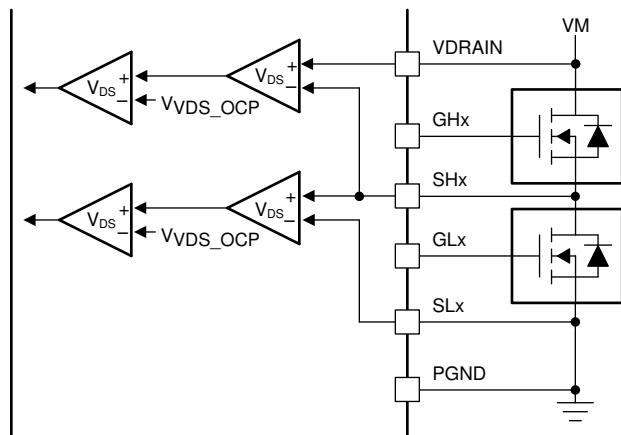

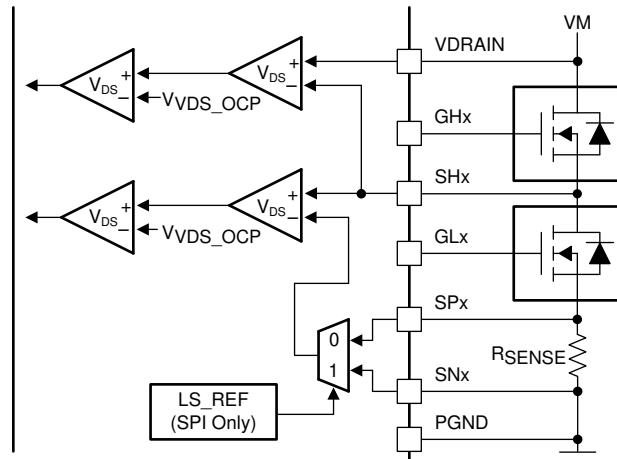

- MOSFET過電流保護(OCP)

- ゲート・ドライバ障害(GDF)

- 熱警告およびシャットダウン(OTW/OTSD)

- 障害状況インジケータ(nFAULT)

## 2 アプリケーション

- ブラシレスDC (BLDC) モーター・モジュール

- ファンおよびポンプ

- 電動アシスト自転車、電動スクーター、E-モビリティ

- コードレスの庭園機器および電動工具

- コードレス掃除機

- ドローン、ロボティクス、ラジコン玩具

- ATMおよび貨幣計数機

## 3 概要

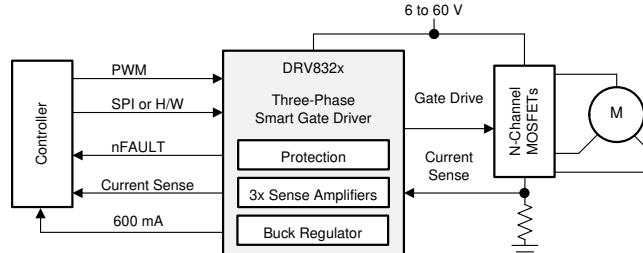

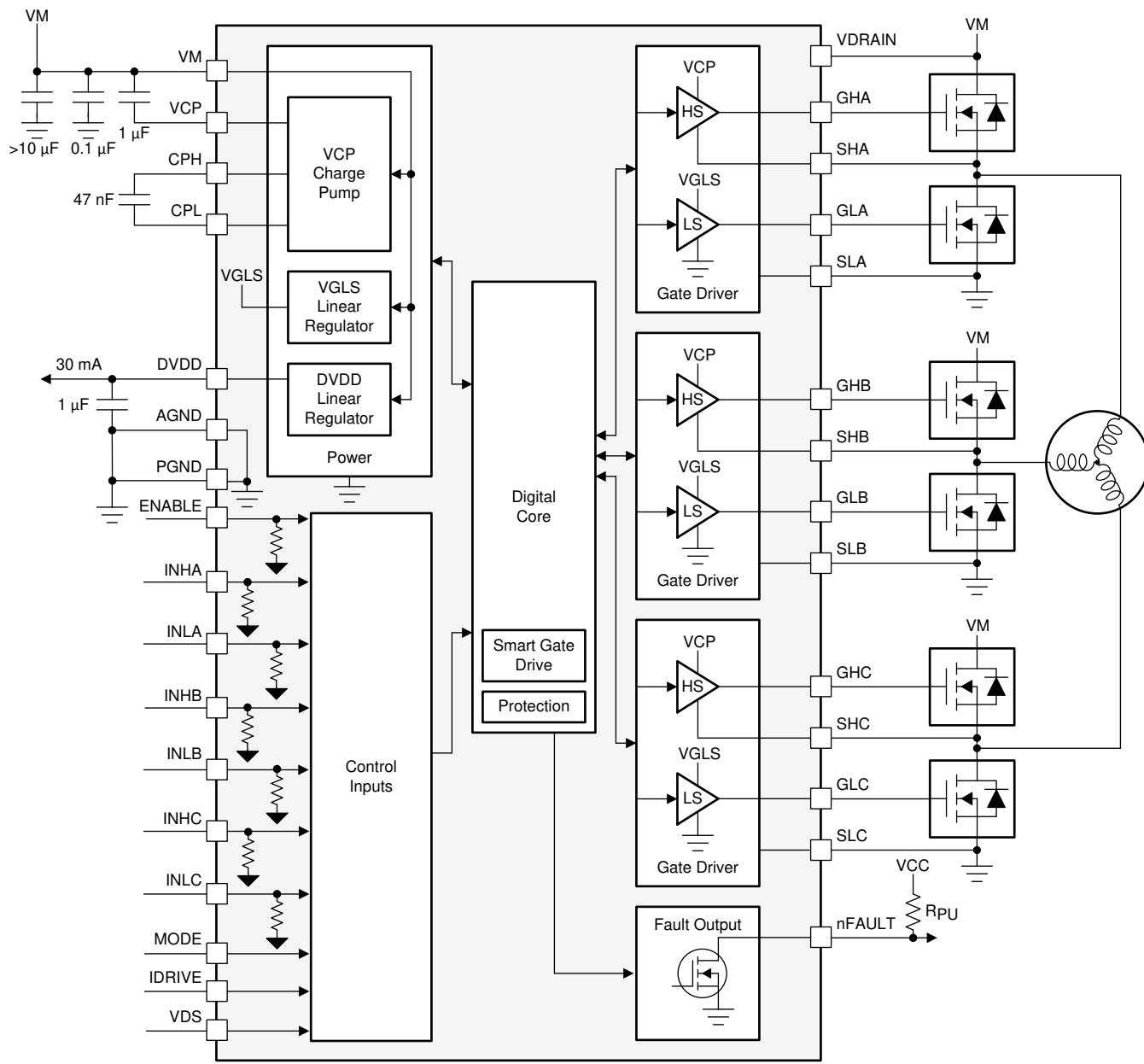

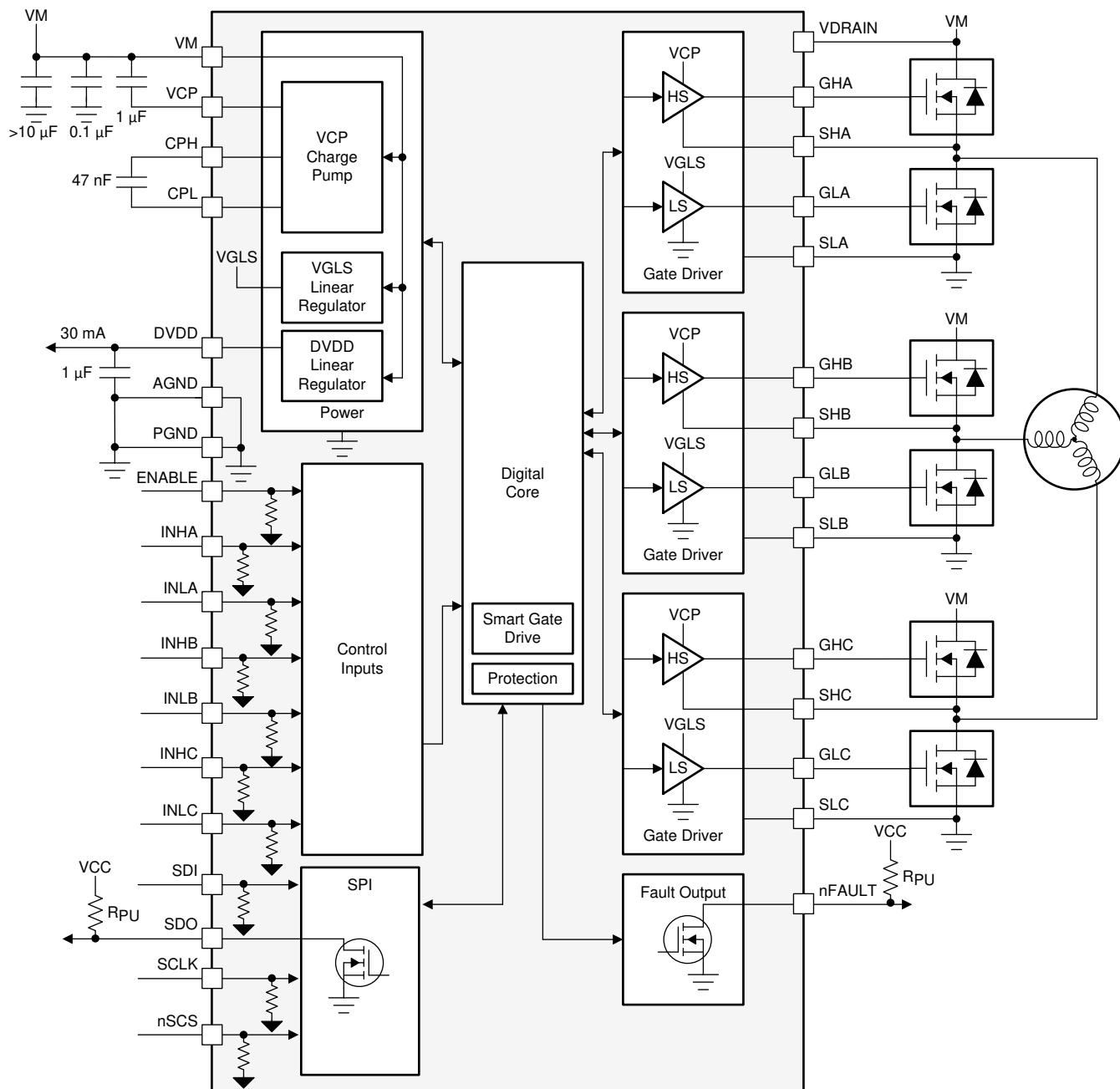

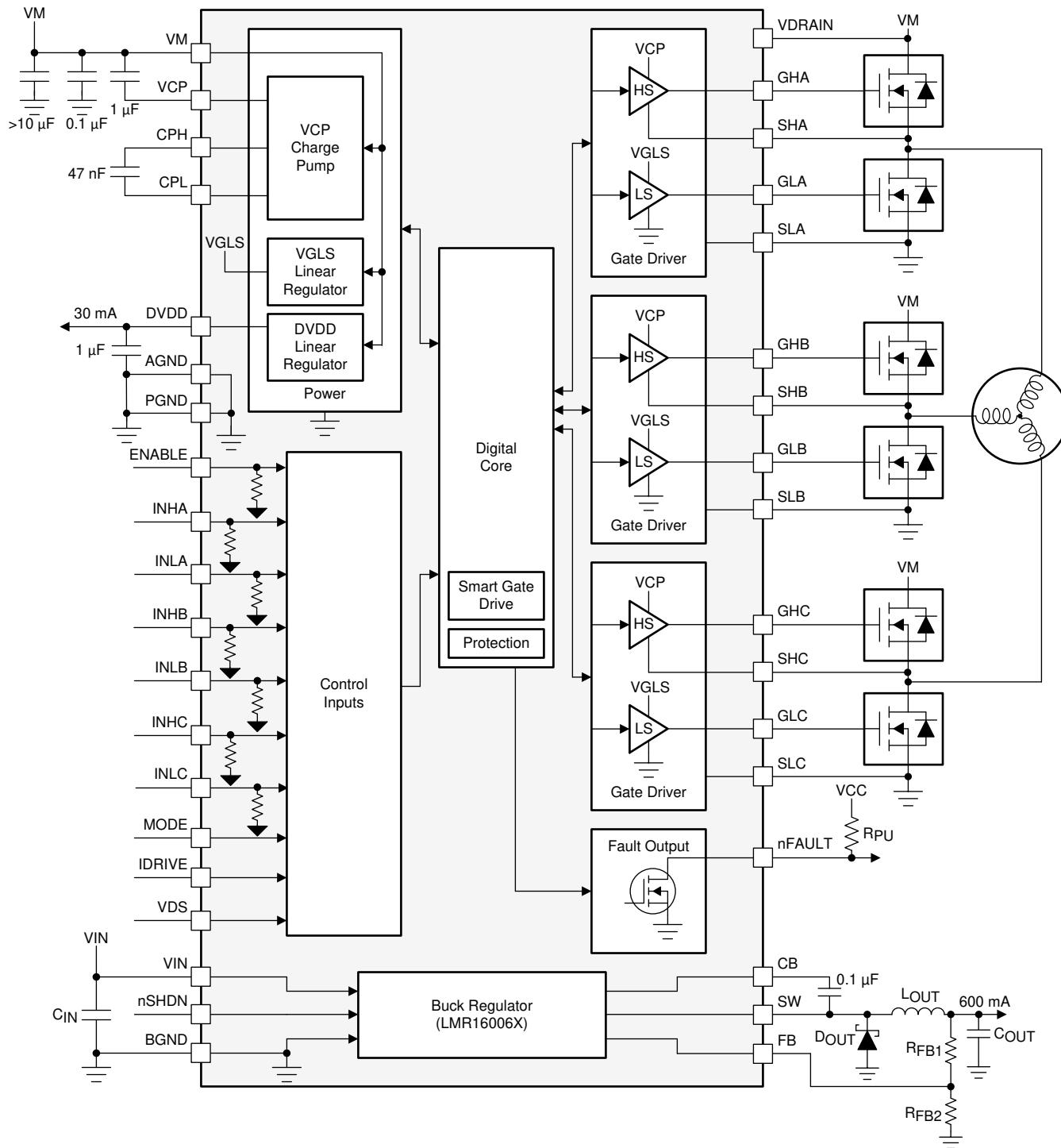

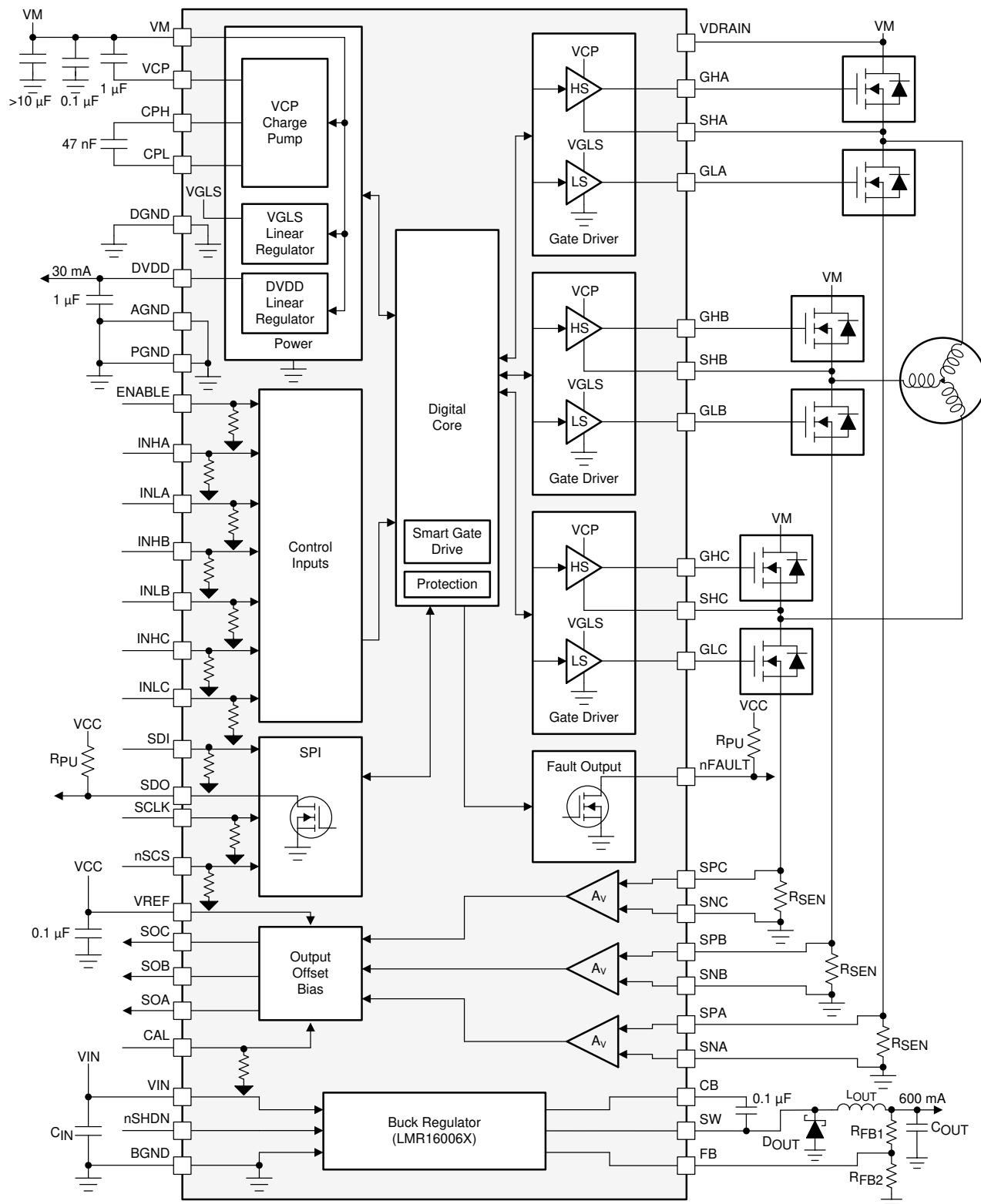

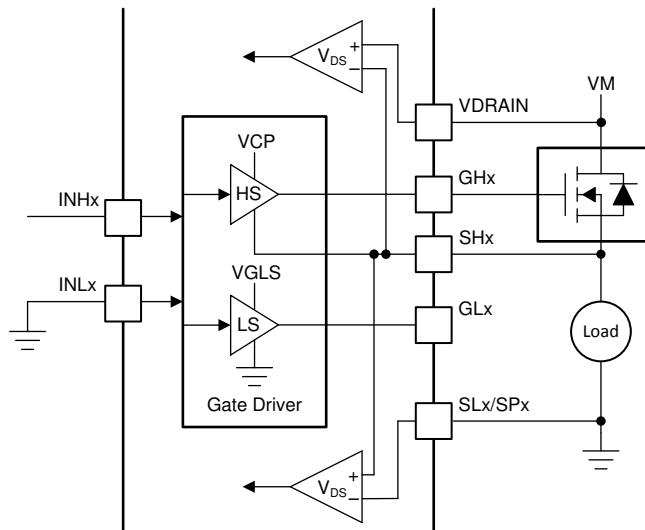

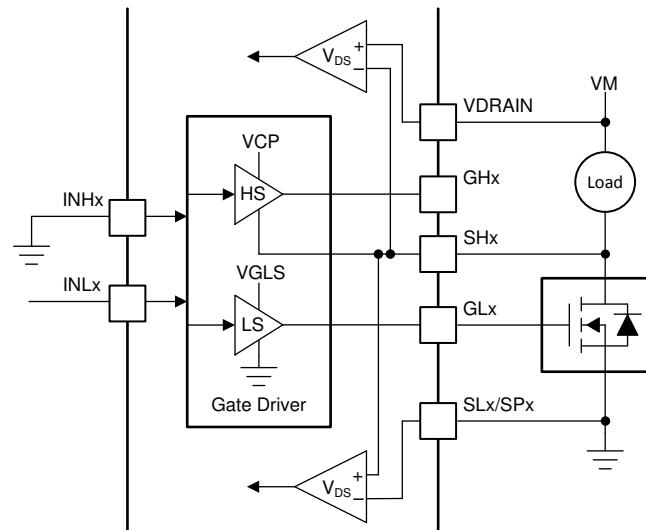

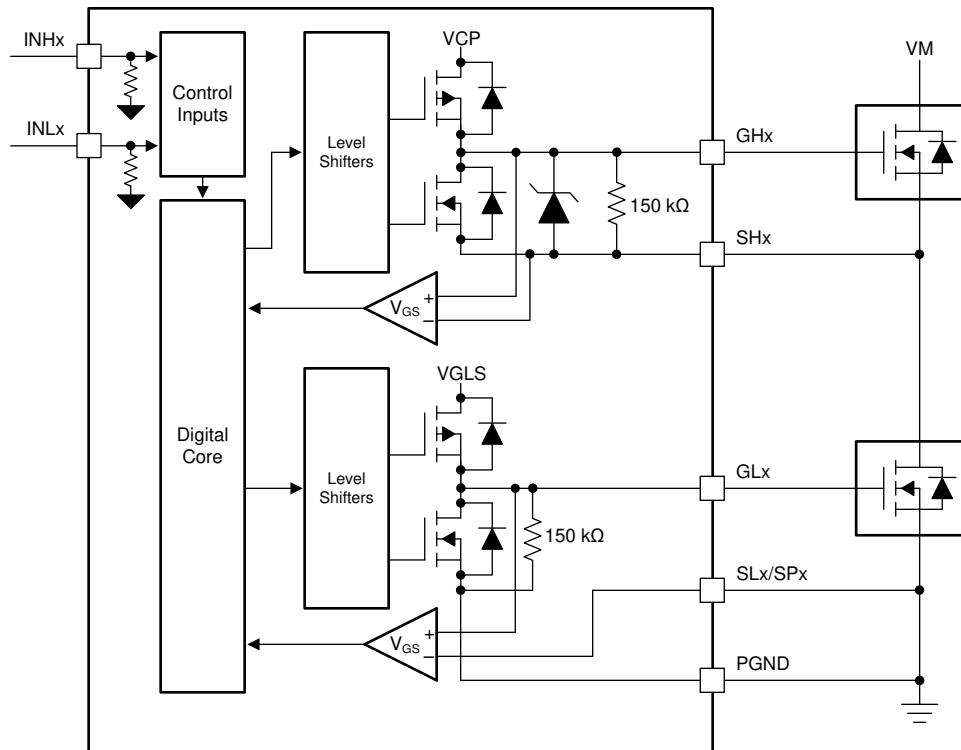

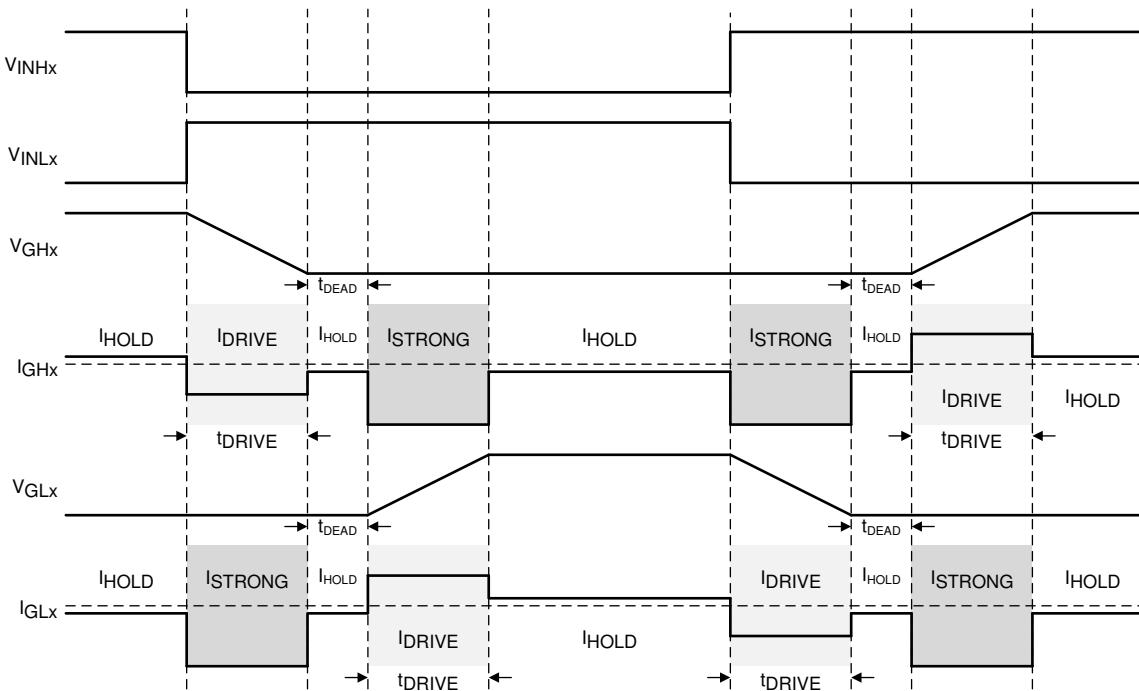

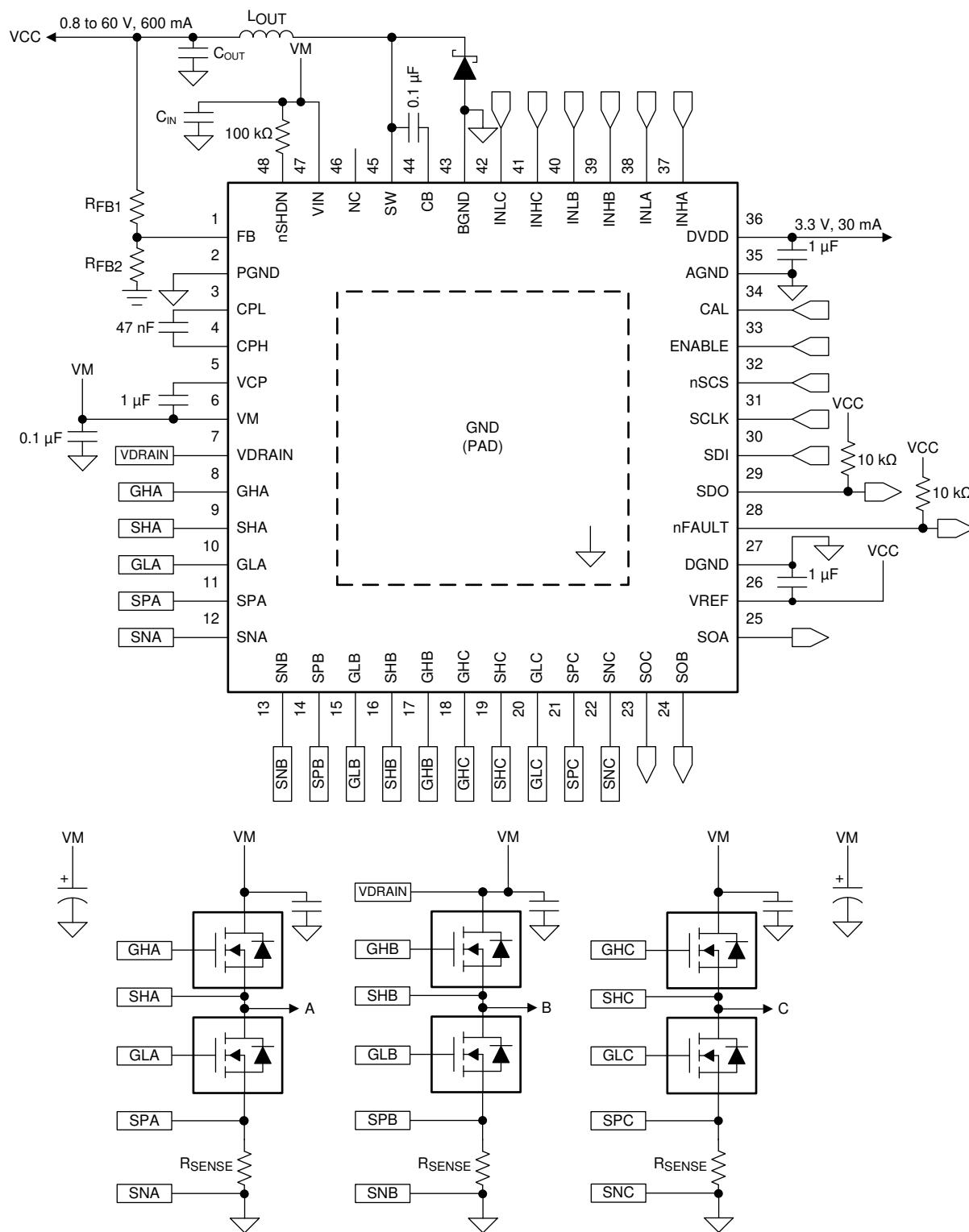

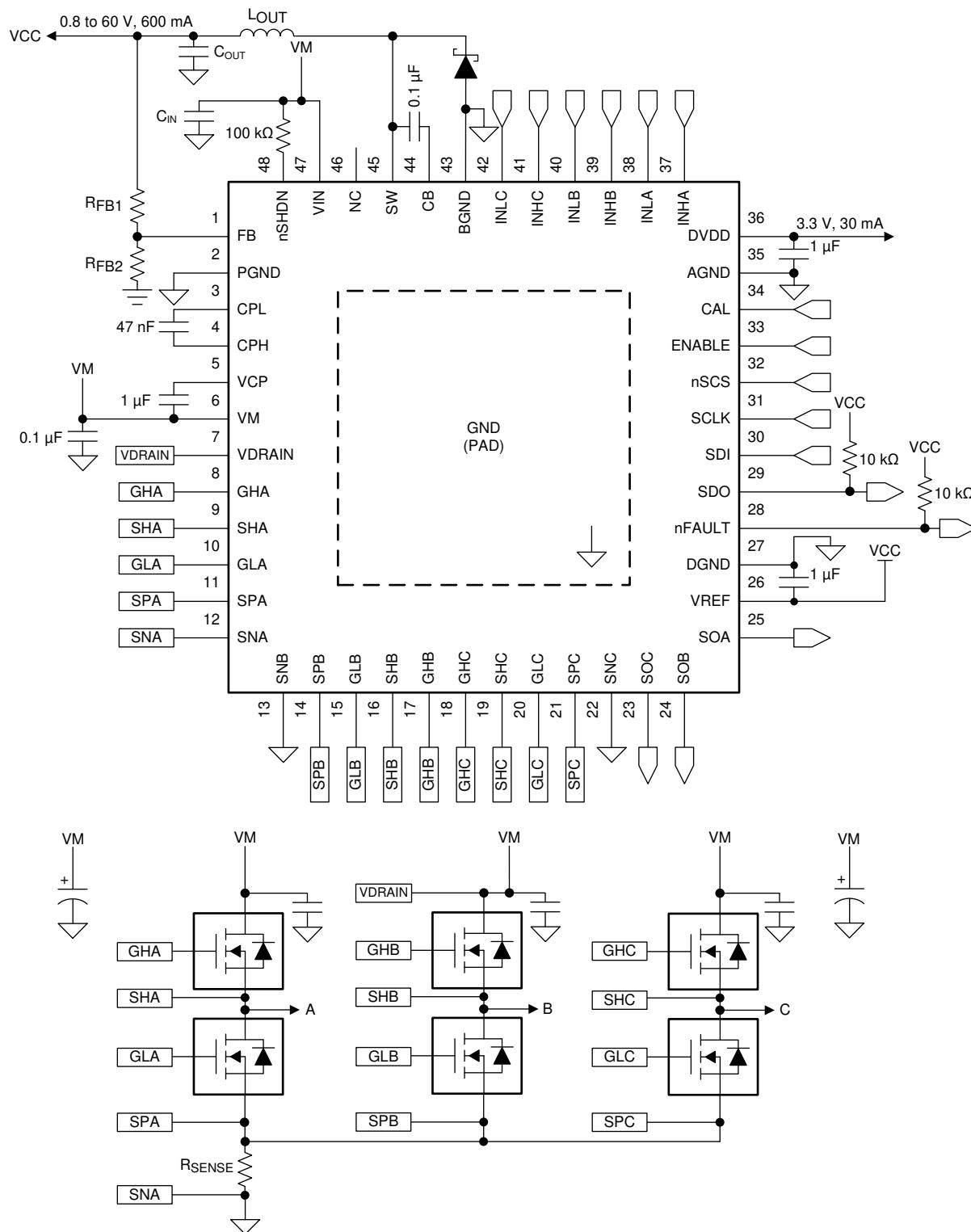

DRV832xアミリのデバイスは、3相アプリケーション用の統合ゲート・ドライバです。このデバイスには、3つのハーフ・ブリッジ・ゲート・ドライバがあり、それぞれがハイサイドとローサイドのNチャネル・パワーMOSFETを駆動できます。DRV832xは、内蔵のチャージ・ポンプを使用してハイサイドMOSFET用の、リニア・レギュレータを使用してローサイドMOSFET用の、適切なゲート駆動電圧を生成します。スマート・ゲート・ドライブのアーキテクチャは、最大でソース1A、シンク2Aのピーク・ゲート駆動電流をサポートします。DRV832xは単一電源で動作し、ゲート・ドライバについて6~60V、オプションの降圧レギュレータについて4~60Vの広い入力電源電圧に対応します。

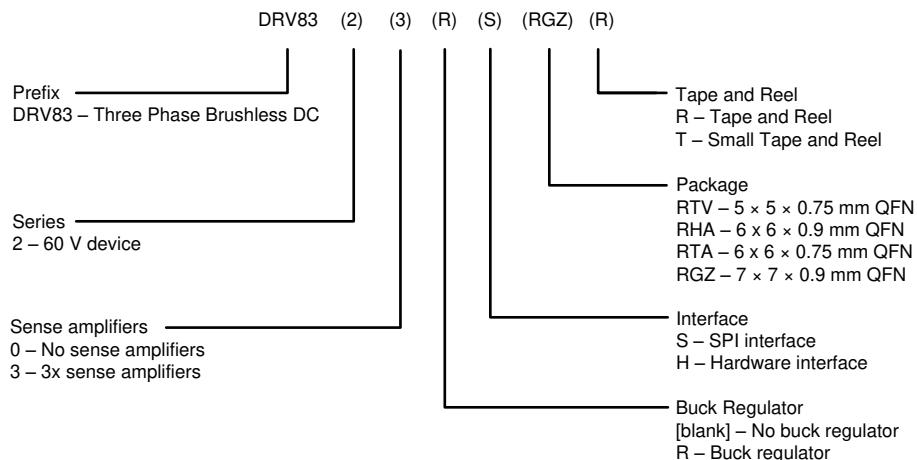

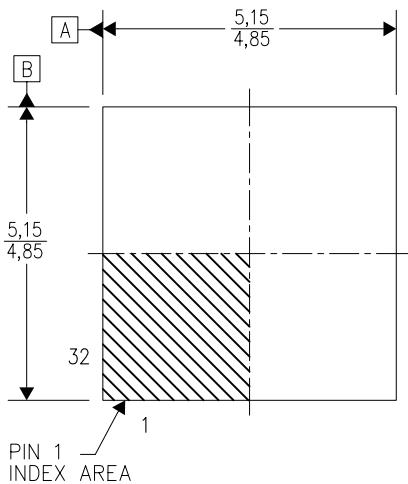

### 製品情報<sup>(1)</sup>

| 型番       | パッケージ    | 本体サイズ(公称)     |

|----------|----------|---------------|

| DRV8320  | WQFN(32) | 5.00mm×5.00mm |

| DRV8320R | VQFN(40) | 6.00mm×6.00mm |

| DRV8323  | WQFN(40) | 6.00mm×6.00mm |

| DRV8323R | VQFN(48) | 7.00mm×7.00mm |

(1) 提供されているすべてのパッケージについては、巻末の注文情報を参照してください。

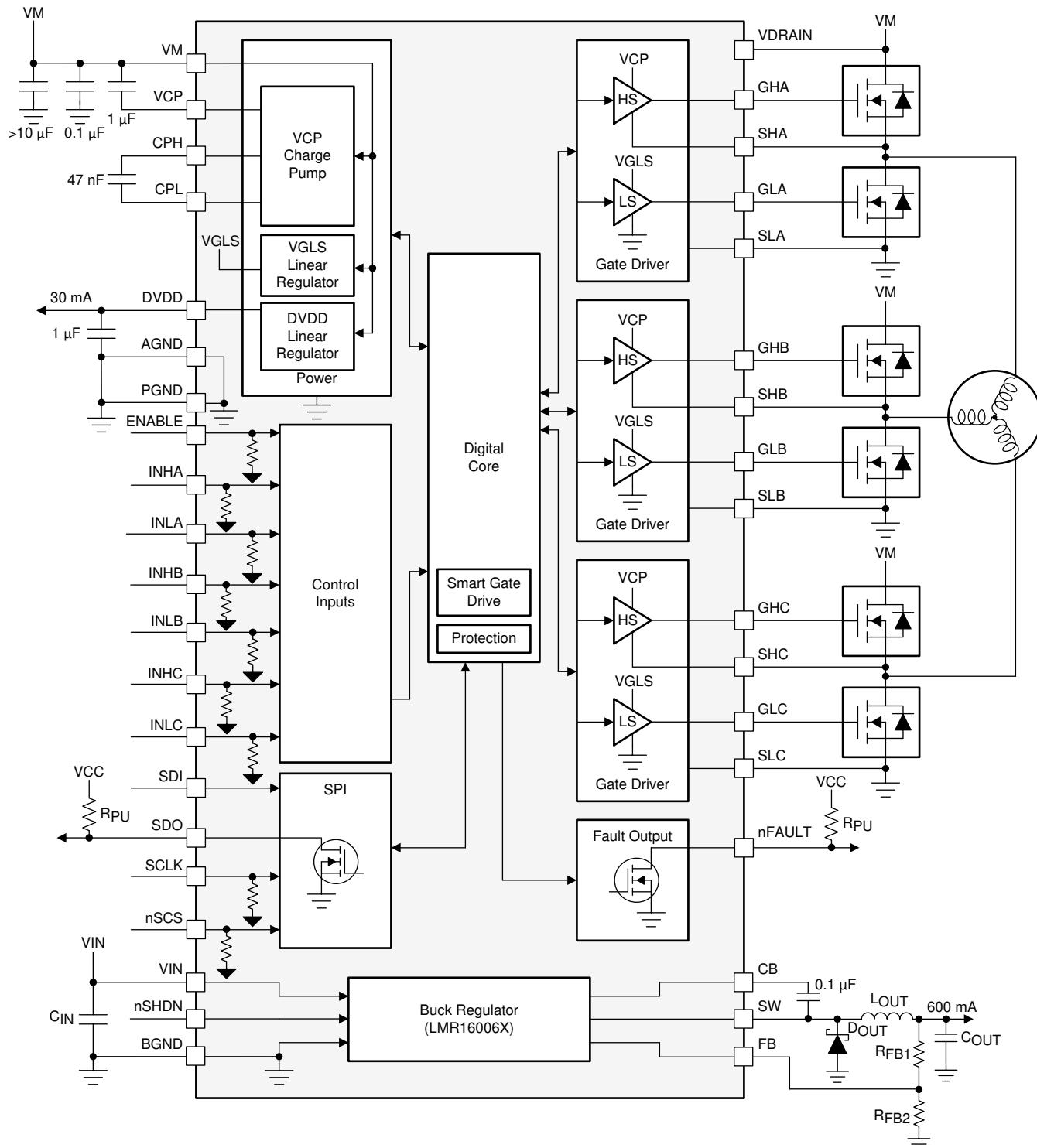

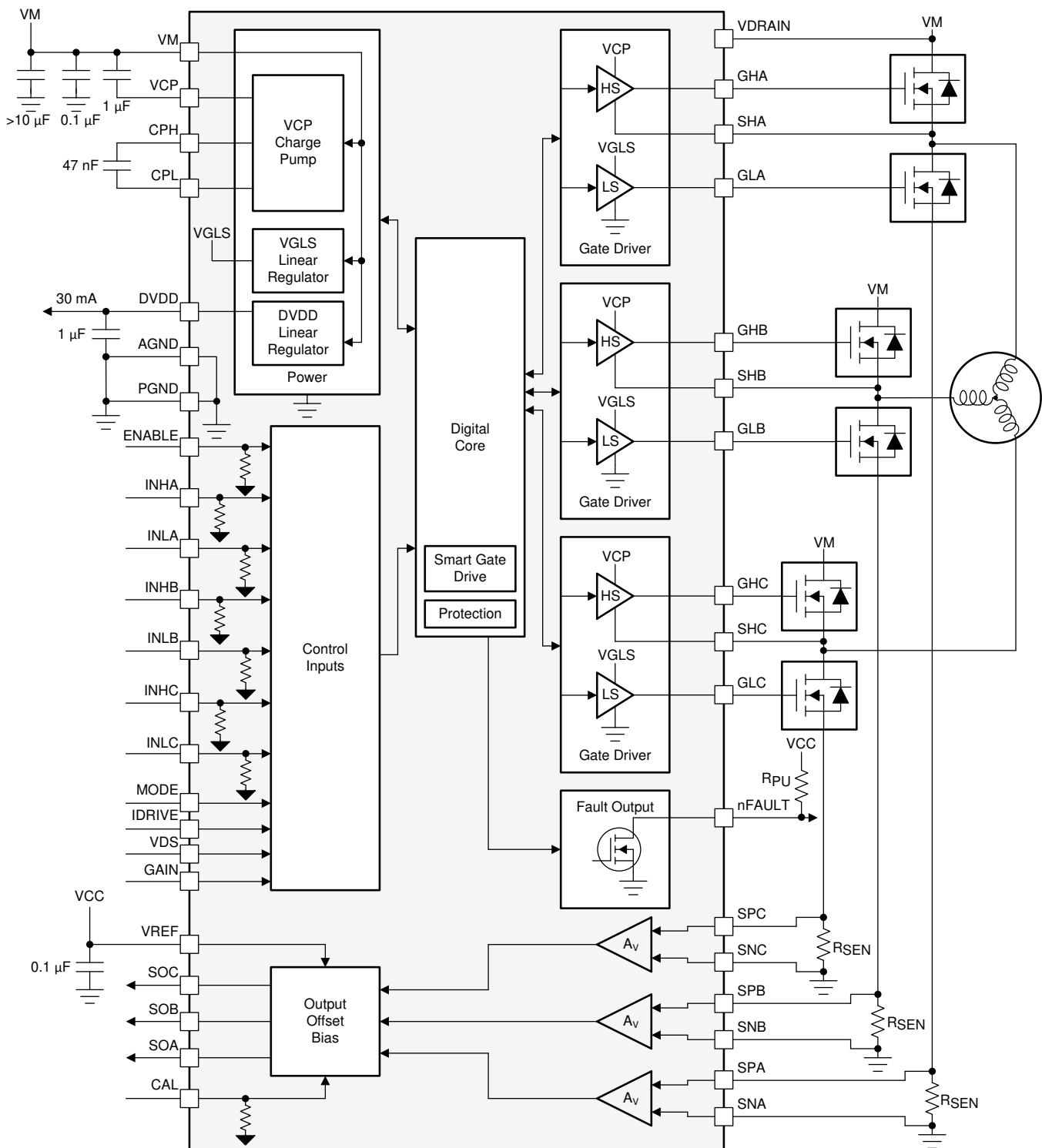

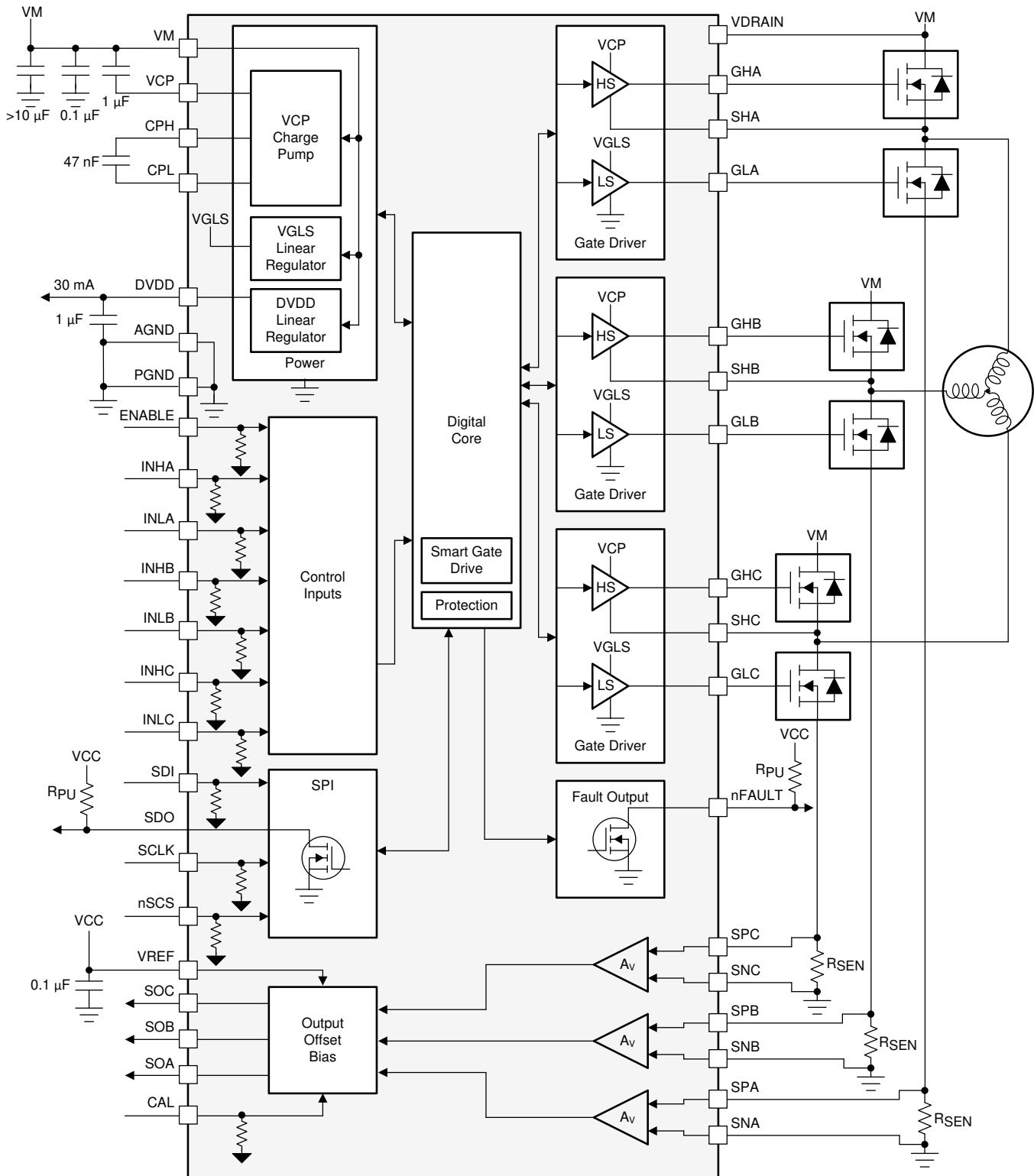

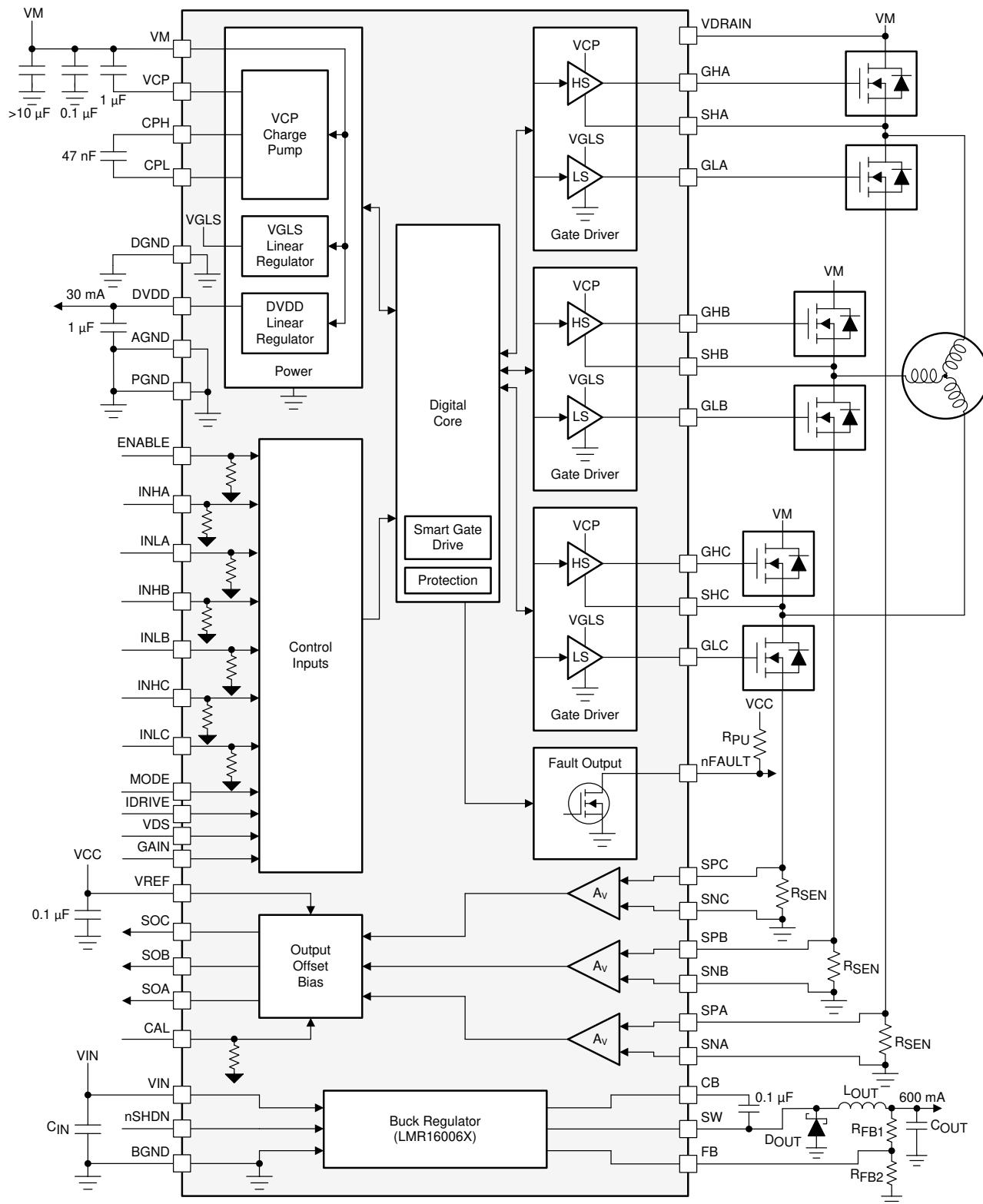

### 概略回路図

Copyright © 2017, Texas Instruments Incorporated

英語版のTI製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、www.ti.comで閲覧でき、その内容が常に優先されます。TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、必ず最新版の英語版をご参照くださいますようお願いいたします。

English Data Sheet: SLVSDJ3

## 目次

|     |             |    |      |                     |    |

|-----|-------------|----|------|---------------------|----|

| 1   | 特長          | 1  | 9.5  | プログラミング             | 52 |

| 2   | アプリケーション    | 1  | 9.6  | レジスタ・マップ            | 54 |

| 3   | 概要          | 1  | 10   | アプリケーションと実装         | 62 |

| 4   | 改訂履歴        | 2  | 10.1 | アプリケーション情報          | 62 |

| 5   | 概要(続き)      | 3  | 10.2 | 代表的なアプリケーション        | 62 |

| 6   | デバイス比較表     | 4  | 11   | 電源に関する推奨事項          | 71 |

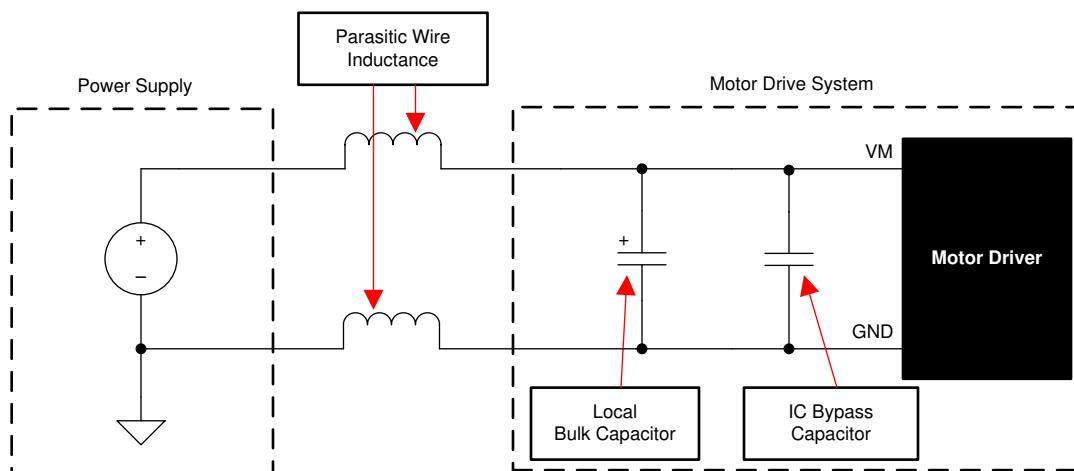

| 7   | ピン構成および機能   | 4  | 11.1 | パルク容量の決定            | 71 |

| 8   | 仕様          | 11 | 12   | レイアウト               | 72 |

| 8.1 | 絶対最大定格      | 11 | 12.1 | レイアウトのガイドライン        | 72 |

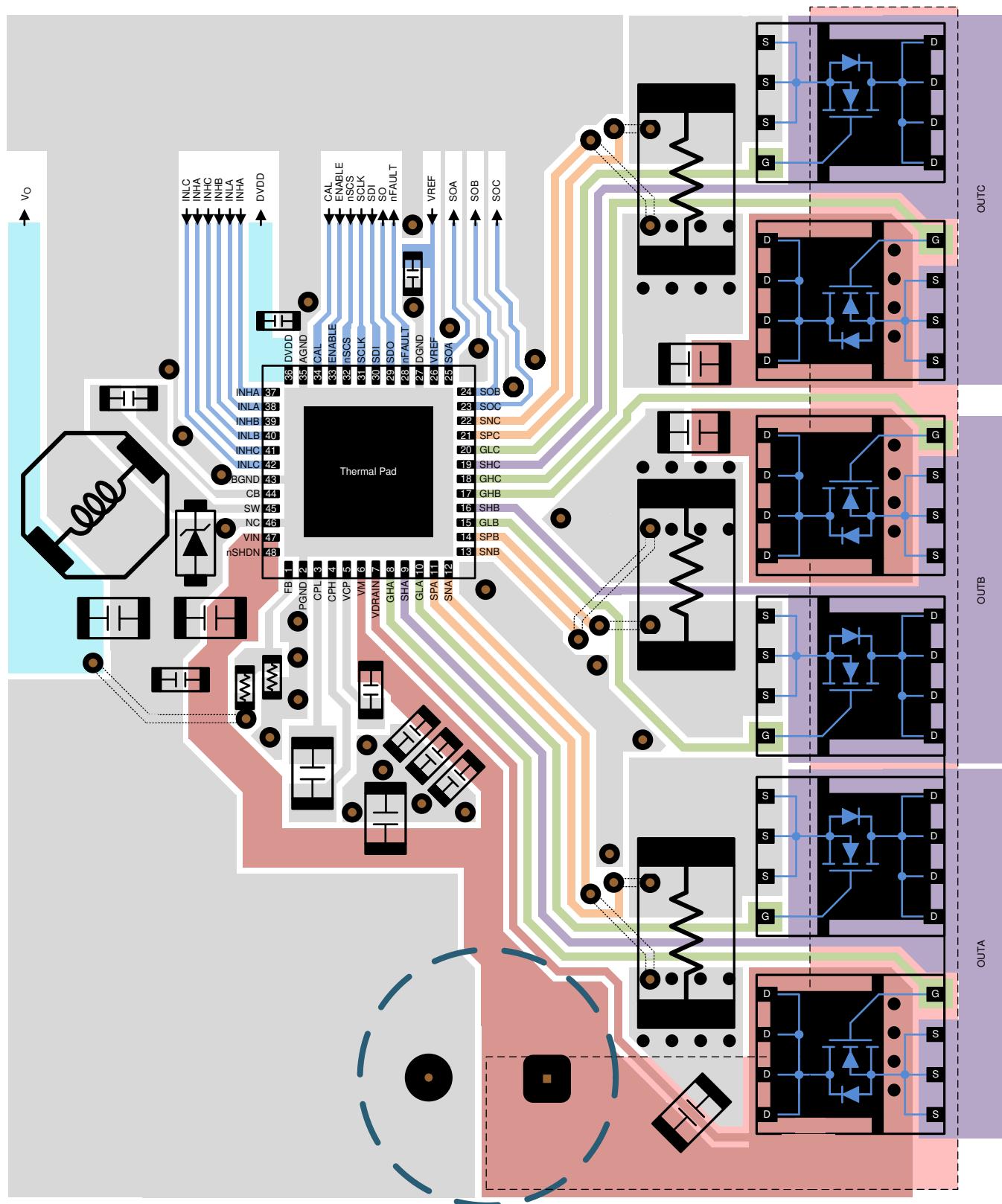

| 8.2 | ESD定格       | 11 | 12.2 | レイアウト例              | 73 |

| 8.3 | 推奨動作条件      | 12 | 13   | デバイスおよびドキュメントのサポート  | 74 |

| 8.4 | 熱特性         | 12 | 13.1 | デバイス・サポート           | 74 |

| 8.5 | 電気的特性       | 13 | 13.2 | ドキュメントのサポート         | 74 |

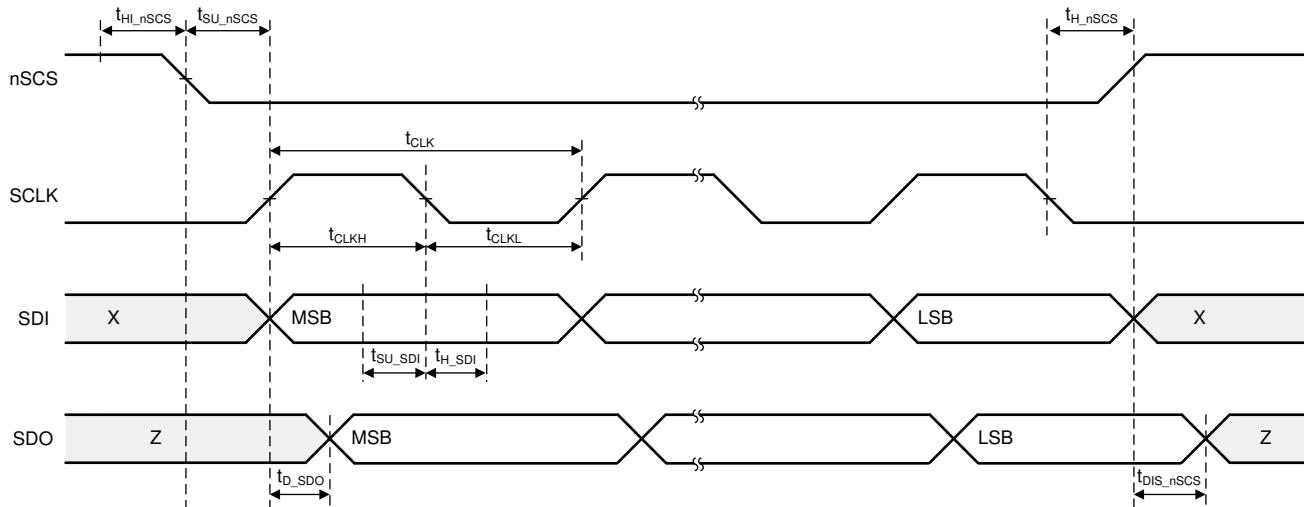

| 8.6 | SPIのタイミング要件 | 18 | 13.3 | 関連リンク               | 74 |

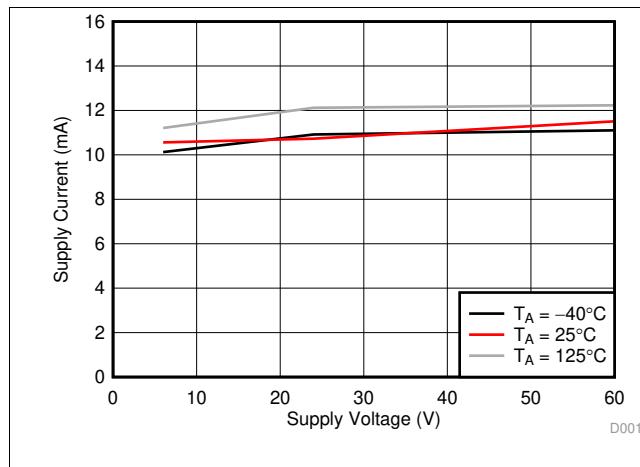

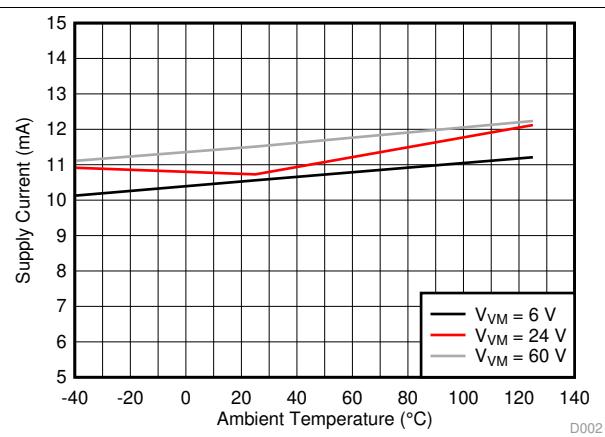

| 8.7 | 代表的特性       | 19 | 13.4 | ドキュメントの更新通知を受け取る方法  | 75 |

| 9   | 詳細説明        | 21 | 13.5 | コミュニティ・リソース         | 75 |

| 9.1 | 概要          | 21 | 13.6 | 商標                  | 75 |

| 9.2 | 機能ブロック図     | 22 | 13.7 | 静電気放電に関する注意事項       | 75 |

| 9.3 | 機能説明        | 30 | 13.8 | Glossary            | 75 |

| 9.4 | デバイスの機能モード  | 51 | 14   | メカニカル、パッケージ、および注文情報 | 75 |

## 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

## Revision A (April 2017) から Revision B に変更

Page

|                                                                                 |    |

|---------------------------------------------------------------------------------|----|

| • 「特長」で、低消費電力のスリープ・モードの消費電流を最大値(20 $\mu$ A)から標準値(12 $\mu$ A)に 変更                | 1  |

| • 「アプリケーション」変更                                                                  | 1  |

| • Changed 「電気的特性」表で、H/Wデバイスに対するアンプ・ゲインの測定条件のGAIN値を45k $\Omega$ から47k $\Omega$ に | 15 |

| • Deleted 「SPIスレーブ・モード・タイミング図」からt <sub>EN_nSCS</sub> を                          | 18 |

| • Added 「同期1x PWMモード」に!PWMを定義する注記を                                              | 31 |

| • 「自動オフセット較正」セクションを更新                                                           | 45 |

| • 「V <sub>DS</sub> ラッチ・シャットダウン」および「V <sub>DS</sub> 自動リトライ」セクションを更新              | 49 |

| • 「スリープ・モード」セクションを更新                                                            | 51 |

| • Changed 「ゲート駆動LSレジスタ」セクションのタイトルに記載されるアドレスを正しいレジスタ・アドレス0x04に                   | 59 |

| • 変更「詳細な設計手順」のV <sub>VM</sub> = 8Vの例で、台形波整流と正弦波整流の両方の最大Q <sub>g</sub> 値を        | 64 |

| • 変更「IDRIVEの設定」セクションでI <sub>DRIVEP</sub> とI <sub>DRIVEN</sub> の式を               | 64 |

## 2017年2月発行のものから更新

Page

|                                                  |    |

|--------------------------------------------------|----|

| • Changed 「電気的特性」表でI <sub>BIAS</sub> パラメータの測定条件を | 16 |

| • Changed 「3x PWMモードの真理値表」でGHxの値を                | 31 |

| • Changed 自動較正機能の説明を追加し、較正の説明を                   | 45 |

## 5 概要（続き）

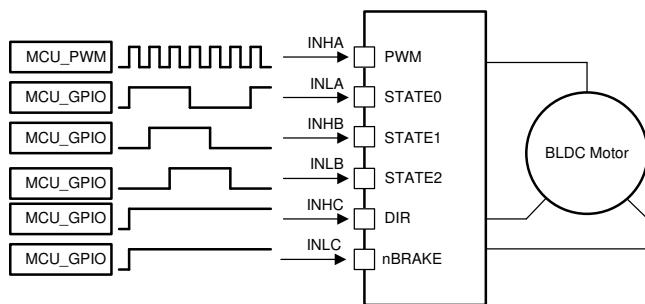

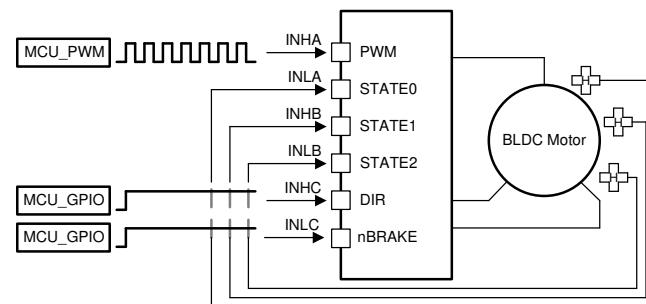

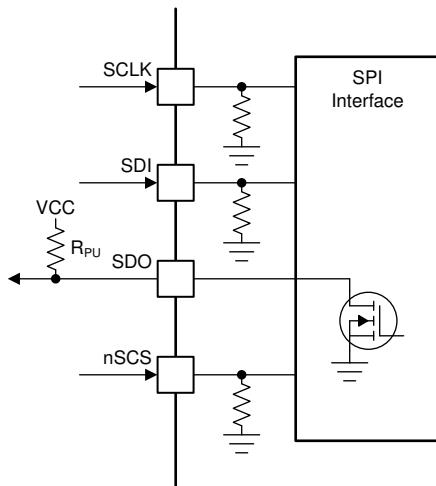

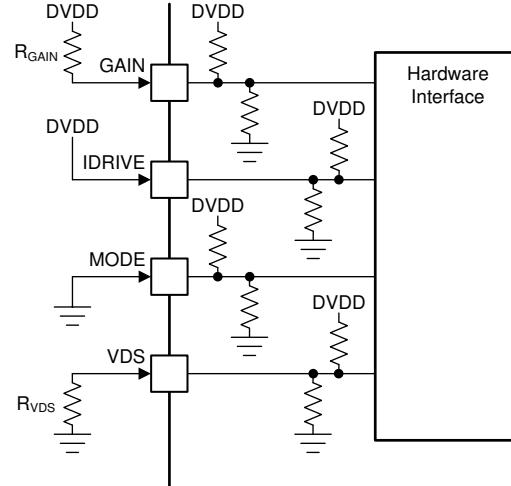

6x、3x、1x、および独立入力のPWMモードにより、コントローラの回路と簡単に接続できます。ゲート・ドライバとデバイスの構成設定は、SPIまたはハードウェア(H/W)インターフェイスにより細かく変更可能です。DRV8323およびDRV8323Rデバイスには3つのローサイド電流センス・アンプが内蔵されており、駆動段の3相すべてについて、双方向の電流センシングが可能です。DRV8320RおよびDRV8323Rデバイスには、600mAの降圧レギュレータが内蔵されています。

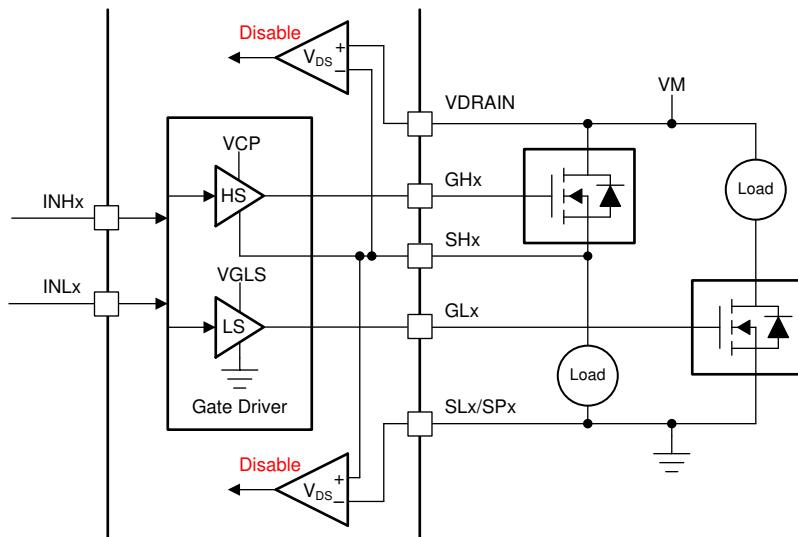

低消費電力のスリープ・モードがあり、内部回路のほとんどをシャットダウンして、静止電流を低減できます。低電圧誤動作防止、チャージ・ポンプ障害、MOSFET過電流、MOSFET短絡、ゲート・ドライバ障害、過熱への保護機能が内蔵されています。障害状況はnFAULTピンにより通知され、SPI版のデバイスではデバイスのレジスタにより詳細が通知されます。

## 6 デバイス比較表

| DEVICE   | VARIANT <sup>(1)</sup> | CURRENT SENSE AMPLIFIERS | BUCK REGULATOR <sup>(1)</sup> | INTERFACE <sup>(1)</sup> |

|----------|------------------------|--------------------------|-------------------------------|--------------------------|

| DRV8320  | DRV8320H               | 0                        | None                          | Hardware                 |

|          | DRV8320S               |                          |                               | SPI                      |

| DRV8320R | DRV8320RH              | 600 mA                   | Hardware                      | Hardware                 |

|          | DRV8320RS              |                          |                               | SPI                      |

| DRV8323  | DRV8323H               | 3                        | None                          | Hardware                 |

|          | DRV8323S               |                          |                               | SPI                      |

| DRV8323R | DRV8323RH              | 600 mA                   | Hardware                      | Hardware                 |

|          | DRV8323RS              |                          |                               | SPI                      |

(1) デバイス名およびデバイス・オプションの詳細については、「デバイスの項目表記」セクションを参照してください。

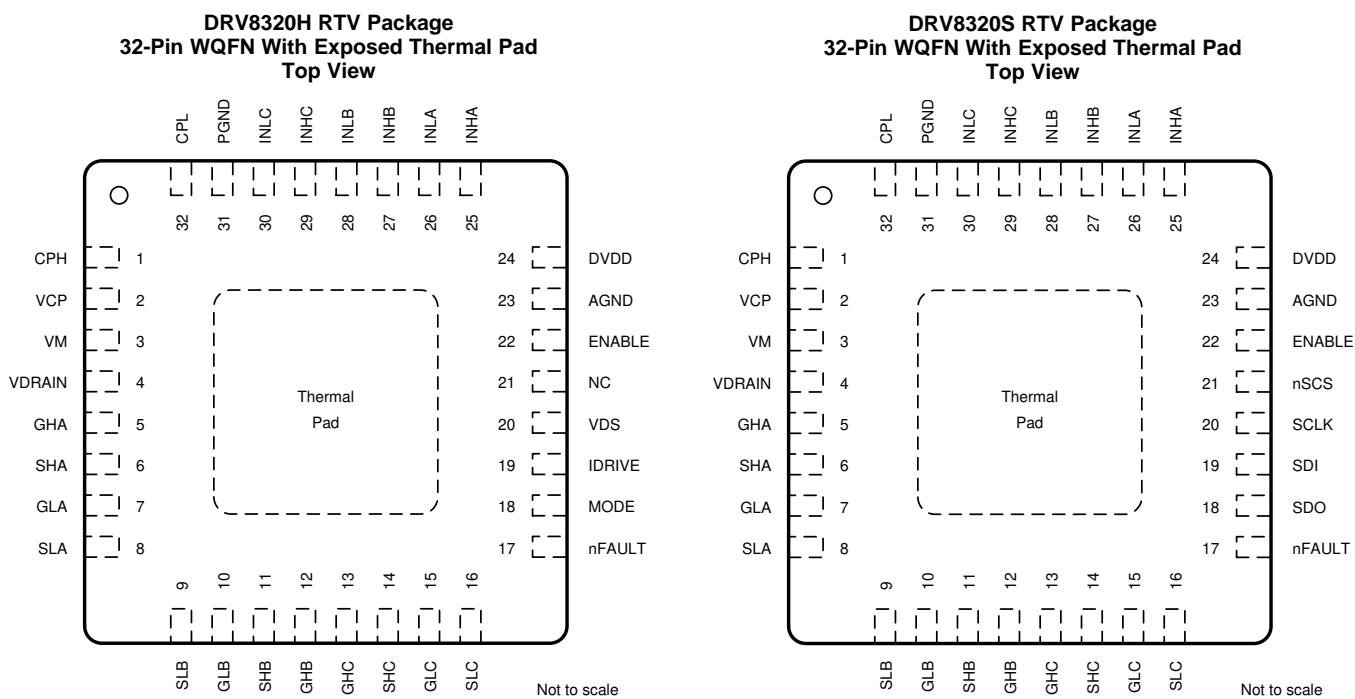

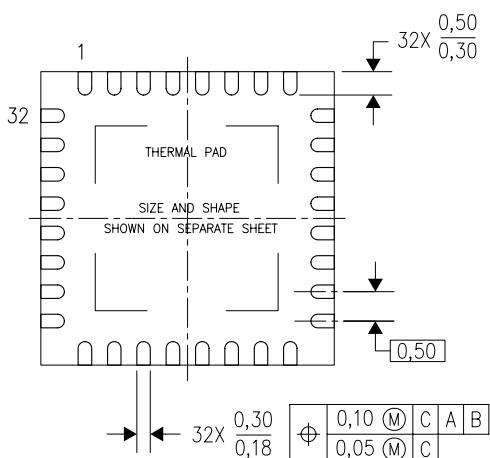

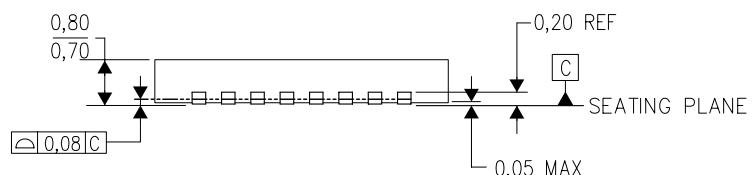

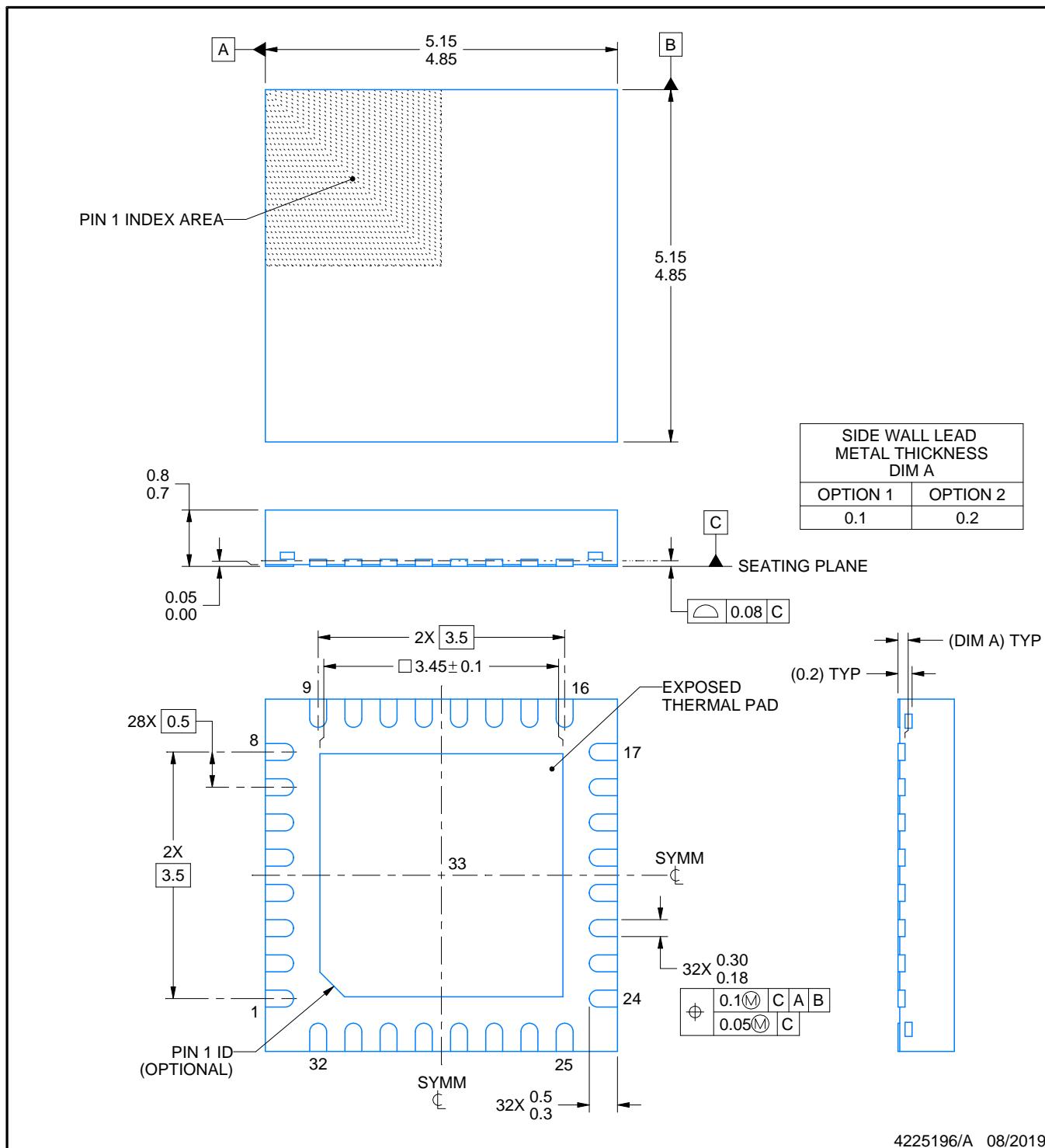

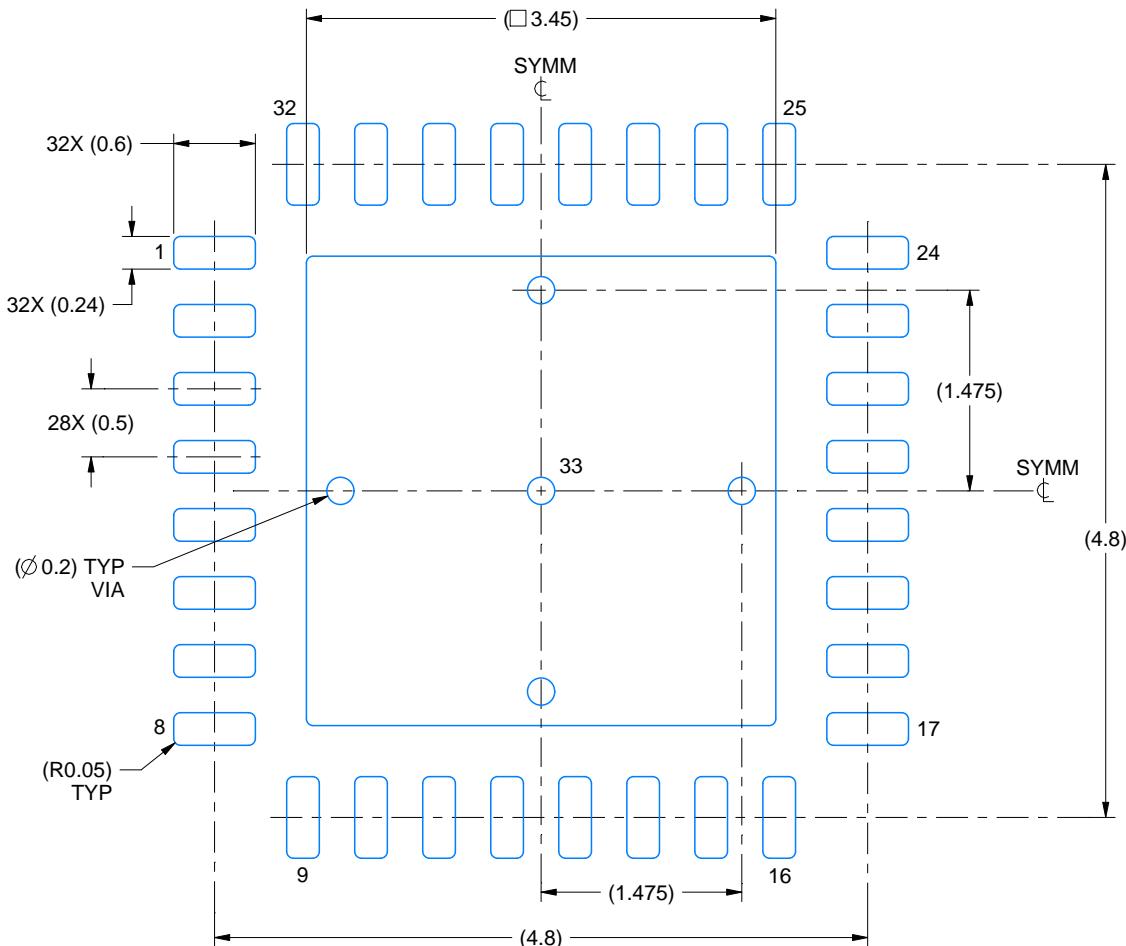

## 7 ピン構成および機能

### ピン機能—32ピンDRV8320デバイス

| NAME   | PIN      |          | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                  |

|--------|----------|----------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | DRV8320H | DRV8320S |                     |                                                                                                                                                                              |

| AGND   | 23       | 23       | PWR                 | Device analog ground. Connect to system ground.                                                                                                                              |

| CPH    | 1        | 1        | PWR                 | Charge pump switching node. Connect a X5R or X7R, 47-nF, VM-rated ceramic capacitor between the CPH and CPL pins.                                                            |

| CPL    | 32       | 32       | PWR                 | Charge pump switching node. Connect a X5R or X7R, 47-nF, VM-rated ceramic capacitor between the CPH and CPL pins.                                                            |

| DVDD   | 24       | 24       | PWR                 | 3.3-V internal regulator output. Connect a X5R or X7R, 1- $\mu$ F, 6.3-V ceramic capacitor between the DVDD and AGND pins. This regulator can source up to 30 mA externally. |

| ENABLE | 22       | 22       | I                   | Gate driver enable. When this pin is logic low the device goes to a low-power sleep mode. An 8 to 40- $\mu$ s pulse can be used to reset fault conditions.                   |

| GHA    | 5        | 5        | O                   | High-side gate driver output. Connect to the gate of the high-side power MOSFET.                                                                                             |

| GHB    | 12       | 12       | O                   | High-side gate driver output. Connect to the gate of the high-side power MOSFET.                                                                                             |

| GHC    | 13       | 13       | O                   | High-side gate driver output. Connect to the gate of the high-side power MOSFET.                                                                                             |

(1) PWR = 電源、I = 入力、O = 出力、NC = 接続なし、OD = オープン・ドレイン出力

**ピン機能—32ピンDRV8320デバイス (continued)**

| NAME        | PIN      |          | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                       |  |  |

|-------------|----------|----------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|             | NO.      |          |                     |                                                                                                                                                                                                                   |  |  |

|             | DRV8320H | DRV8320S |                     |                                                                                                                                                                                                                   |  |  |

| GLA         | 7        | 7        | O                   | Low-side gate driver output. Connect to the gate of the low-side power MOSFET.                                                                                                                                    |  |  |

| GLB         | 10       | 10       | O                   | Low-side gate driver output. Connect to the gate of the low-side power MOSFET.                                                                                                                                    |  |  |

| GLC         | 15       | 15       | O                   | Low-side gate driver output. Connect to the gate of the low-side power MOSFET.                                                                                                                                    |  |  |

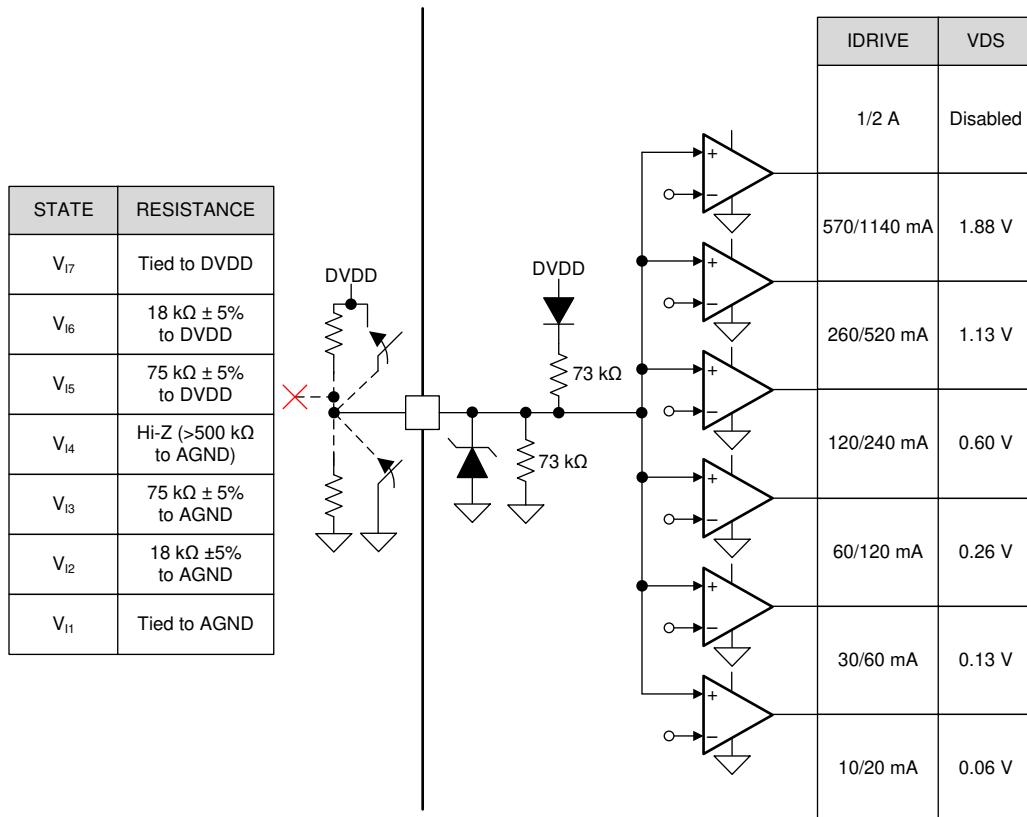

| IDRIVE      | 19       | —        | I                   | Gate drive output current setting. This pin is a 7 level input pin set by an external resistor.                                                                                                                   |  |  |

| INHA        | 25       | 25       | I                   | High-side gate driver control input. This pin controls the output of the high-side gate driver.                                                                                                                   |  |  |

| INHB        | 27       | 27       | I                   | High-side gate driver control input. This pin controls the output of the high-side gate driver.                                                                                                                   |  |  |

| INHC        | 29       | 29       | I                   | High-side gate driver control input. This pin controls the output of the high-side gate driver.                                                                                                                   |  |  |

| INLA        | 26       | 26       | I                   | Low-side gate driver control input. This pin controls the output of the low-side gate driver.                                                                                                                     |  |  |

| INLB        | 28       | 28       | I                   | Low-side gate driver control input. This pin controls the output of the low-side gate driver.                                                                                                                     |  |  |

| INLC        | 30       | 30       | I                   | Low-side gate driver control input. This pin controls the output of the low-side gate driver.                                                                                                                     |  |  |

| MODE        | 18       | —        | I                   | PWM input mode setting. This pin is a 4 level input pin set by an external resistor.                                                                                                                              |  |  |

| NC          | 21       | —        | NC                  | No internal connection. This pin can be left floating or connected to system ground.                                                                                                                              |  |  |

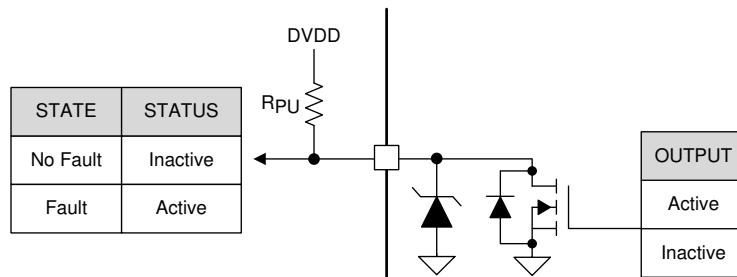

| nFAULT      | 17       | 17       | OD                  | Fault indicator output. This pin is pulled logic low during a fault condition and requires an external pullup resistor.                                                                                           |  |  |

| nSCS        | —        | 21       | I                   | Serial chip select. A logic low on this pin enables serial interface communication.                                                                                                                               |  |  |

| PGND        | 31       | 31       | PWR                 | Device power ground. Connect to system ground.                                                                                                                                                                    |  |  |

| SCLK        | —        | 20       | I                   | Serial clock input. Serial data is shifted out and captured on the corresponding rising and falling edge on this pin.                                                                                             |  |  |

| SDI         | —        | 19       | I                   | Serial data input. Data is captured on the falling edge of the SCLK pin.                                                                                                                                          |  |  |

| SDO         | —        | 18       | OD                  | Serial data output. Data is shifted out on the rising edge of the SCLK pin. This pin requires an external pullup resistor.                                                                                        |  |  |

| SHA         | 6        | 6        | I                   | High-side source sense input. Connect to the high-side power MOSFET source.                                                                                                                                       |  |  |

| SHB         | 11       | 11       | I                   | High-side source sense input. Connect to the high-side power MOSFET source.                                                                                                                                       |  |  |

| SHC         | 14       | 14       | I                   | High-side source sense input. Connect to the high-side power MOSFET source.                                                                                                                                       |  |  |

| SLA         | 8        | 8        | I                   | Low-side source sense input. Connect to the low-side power MOSFET source.                                                                                                                                         |  |  |

| SLB         | 9        | 9        | I                   | Low-side source sense input. Connect to the low-side power MOSFET source.                                                                                                                                         |  |  |

| SLC         | 16       | 16       | I                   | Low-side source sense input. Connect to the low-side power MOSFET source.                                                                                                                                         |  |  |

| VCP         | 2        | 2        | PWR                 | Charge pump output. Connect a X5R or X7R, 1- $\mu$ F, 16-V ceramic capacitor between the VCP and VM pins.                                                                                                         |  |  |

| VDRAIN      | 4        | 4        | I                   | High-side MOSFET drain sense input. Connect to the common point of the MOSFET drains.                                                                                                                             |  |  |

| VDS         | 20       | —        | I                   | VDS monitor trip point setting. This pin is a 7 level input pin set by an external resistor.                                                                                                                      |  |  |

| VM          | 3        | 3        | PWR                 | Gate driver power supply input. Connect to the bridge power supply. Connect a X5R or X7R, 0.1- $\mu$ F, VM-rated ceramic and greater than or equal to 10- $\mu$ F local capacitance between the VM and PGND pins. |  |  |

| Thermal Pad |          |          | PWR                 | Must be connected to ground                                                                                                                                                                                       |  |  |

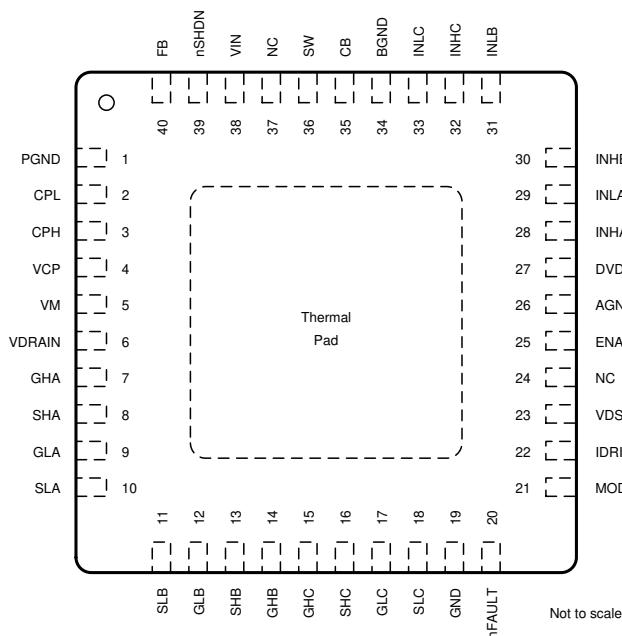

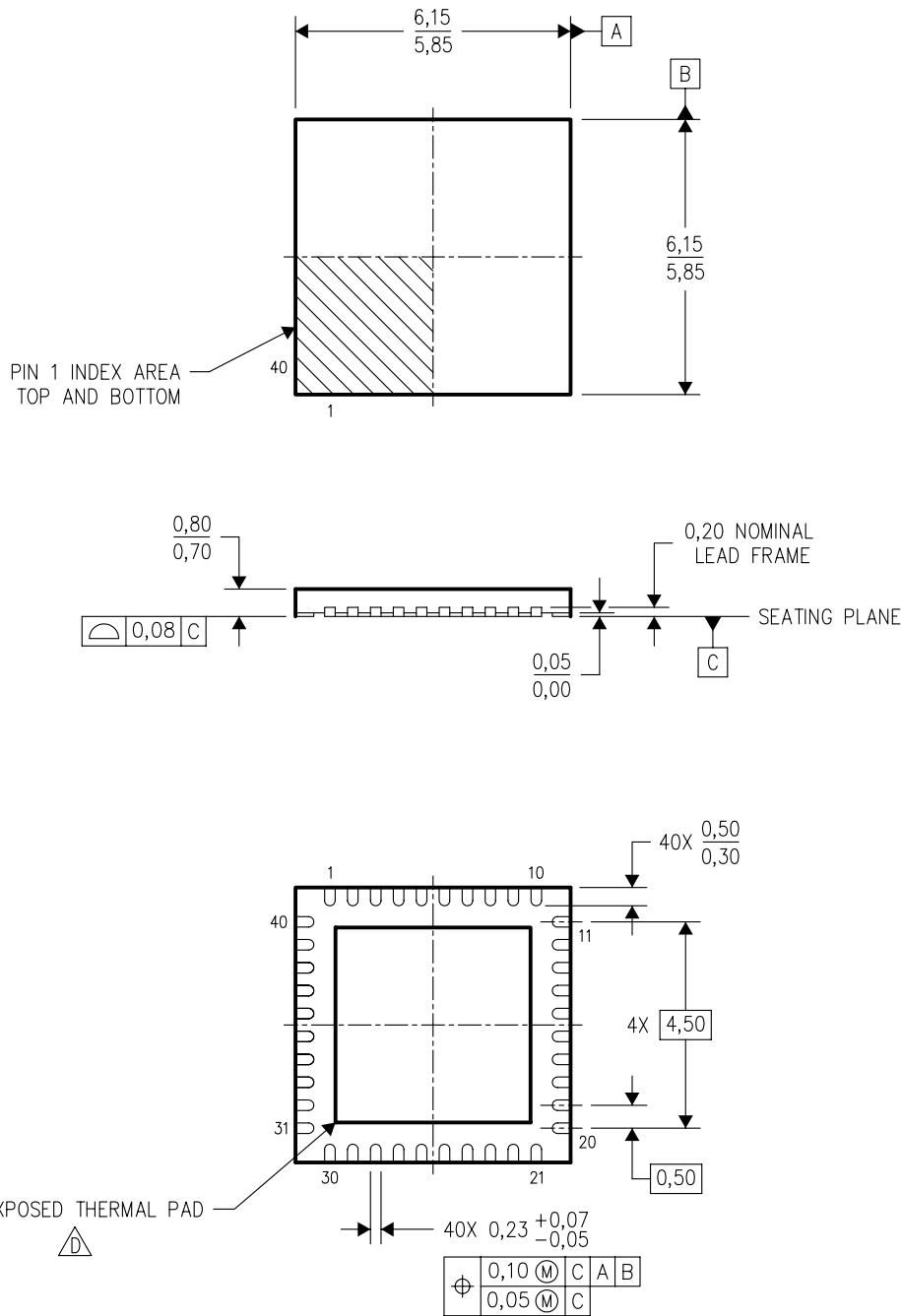

DRV8320RH RHA Package

40-Pin VQFN With Exposed Thermal Pad

Top View

DRV8320RS RHA Package

40-Pin VQFN With Exposed Thermal Pad

Top View

### ピン機能—40ピンDRV8320Rデバイス

| PIN       |           | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                      |

|-----------|-----------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME      | NO.       |                     |                                                                                                                                                                                  |

| DRV8320RH | DRV8320RS |                     |                                                                                                                                                                                  |

| AGND      | 26        | 26                  | PWR Device analog ground. Connect to system ground.                                                                                                                              |

| BGND      | 34        | 34                  | PWR Buck regulator ground. Connect to system ground.                                                                                                                             |

| CB        | 35        | 35                  | PWR Buck regulator bootstrap input. Connect a X5R or X7R, 0.1- $\mu$ F, 16-V, capacitor between the CB and SW pins.                                                              |

| CPH       | 3         | 3                   | PWR Charge pump switching node. Connect a X5R or X7R, 47-nF, VM-rated ceramic capacitor between the CPH and CPL pins.                                                            |

| CPL       | 2         | 2                   | PWR Charge pump switching node. Connect a X5R or X7R, 47-nF, VM-rated ceramic capacitor between the CPH and CPL pins.                                                            |

| DVDD      | 27        | 27                  | PWR 3.3-V internal regulator output. Connect a X5R or X7R, 1- $\mu$ F, 6.3-V ceramic capacitor between the DVDD and AGND pins. This regulator can source up to 30 mA externally. |

| ENABLE    | 25        | 25                  | I Gate driver enable. When this pin is logic low the device goes to a low-power sleep mode. An 8 to 40- $\mu$ s low pulse can be used to reset fault conditions.                 |

| FB        | 40        | 40                  | I Buck feedback input. A resistor divider from the buck post inductor output to this pin sets the buck output voltage.                                                           |

| GHA       | 7         | 7                   | O High-side gate driver output. Connect to the gate of the high-side power MOSFET.                                                                                               |

| GHB       | 14        | 14                  | O High-side gate driver output. Connect to the gate of the high-side power MOSFET.                                                                                               |

| GHC       | 15        | 15                  | O High-side gate driver output. Connect to the gate of the high-side power MOSFET.                                                                                               |

| GLA       | 9         | 9                   | O Low-side gate driver output. Connect to the gate of the low-side power MOSFET.                                                                                                 |

| GLB       | 12        | 12                  | O Low-side gate driver output. Connect to the gate of the low-side power MOSFET.                                                                                                 |

| GLC       | 17        | 17                  | O Low-side gate driver output. Connect to the gate of the low-side power MOSFET.                                                                                                 |

| GND       | 19        | 19                  | PWR Device ground. Connect to system ground.                                                                                                                                     |

| IDRIVE    | 22        | —                   | I Gate drive output current setting. This pin is a 7 level input pin set by an external resistor.                                                                                |

| INHA      | 28        | 28                  | I High-side gate driver control input. This pin controls the output of the high-side gate driver.                                                                                |

| INHB      | 30        | 30                  | I High-side gate driver control input. This pin controls the output of the high-side gate driver.                                                                                |

| INHC      | 32        | 32                  | I High-side gate driver control input. This pin controls the output of the high-side gate driver.                                                                                |

| INLA      | 29        | 29                  | I Low-side gate driver control input. This pin controls the output of the low-side gate driver.                                                                                  |

| INLB      | 31        | 31                  | I Low-side gate driver control input. This pin controls the output of the low-side gate driver.                                                                                  |

| INLC      | 33        | 33                  | I Low-side gate driver control input. This pin controls the output of the low-side gate driver.                                                                                  |

| MODE      | 21        | —                   | I PWM input mode setting. This pin is a 4 level input pin set by an external resistor.                                                                                           |

| NC        | 24        | —                   | NC No internal connection. This pin can be left floating or connected to system ground.                                                                                          |

| NC        | 37        | 37                  | NC No internal connection. This pin can be left floating or connected to system ground.                                                                                          |

| nFAULT    | 20        | 20                  | OD Fault indicator output. This pin is pulled logic low during a fault condition and requires an external pullup resistor.                                                       |

(1) PWR = 電源、I = 入力、O = 出力、NC = 接続なし、OD = オープン・ドレイン出力

**ピン機能—40ピンDRV8320Rデバイス (continued)**

| NAME        | PIN       |           | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                |  |  |

|-------------|-----------|-----------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|             | NO.       |           |                     |                                                                                                                                                                                                                            |  |  |

|             | DRV8320RH | DRV8320RS |                     |                                                                                                                                                                                                                            |  |  |

| nSCS        | —         | 24        | I                   | Serial chip select. A logic low on this pin enables serial interface communication.                                                                                                                                        |  |  |

| nSHDN       | 39        | 39        | I                   | Buck shutdown input. Enable and disable input (high voltage tolerant). Internal pullup current source. Pull lower than 1.25 V to disable. Float to enable. Establish input undervoltage lockout with two resistor divider. |  |  |

| PGND        | 1         | 1         | PWR                 | Device power ground. Connect to system ground.                                                                                                                                                                             |  |  |

| SCLK        | —         | 23        | I                   | Serial clock input. Serial data is shifted out and captured on the corresponding rising and falling edge on this pin.                                                                                                      |  |  |

| SDI         | —         | 22        | I                   | Serial data input. Data is captured on the falling edge of the SCLK pin.                                                                                                                                                   |  |  |

| SDO         | —         | 21        | OD                  | Serial data output. Data is shifted out on the rising edge of the SCLK pin. This pin requires an external pullup resistor.                                                                                                 |  |  |

| SHA         | 8         | 8         | I                   | High-side source sense input. Connect to the high-side power MOSFET source.                                                                                                                                                |  |  |

| SHB         | 13        | 13        | I                   | High-side source sense input. Connect to the high-side power MOSFET source.                                                                                                                                                |  |  |

| SHC         | 16        | 16        | I                   | High-side source sense input. Connect to the high-side power MOSFET source.                                                                                                                                                |  |  |

| SLA         | 10        | 10        | I                   | Low-side source sense input. Connect to the low-side power MOSFET source.                                                                                                                                                  |  |  |

| SLB         | 11        | 11        | I                   | Low-side source sense input. Connect to the low-side power MOSFET source.                                                                                                                                                  |  |  |

| SLC         | 18        | 18        | I                   | Low-side source sense input. Connect to the low-side power MOSFET source.                                                                                                                                                  |  |  |

| SW          | 36        | 36        | O                   | Buck switch node. Connect this pin to an inductor, diode, and the CB bootstrap capacitor.                                                                                                                                  |  |  |

| VCP         | 4         | 4         | PWR                 | Charge pump output. Connect a X5R or X7R, 1- $\mu$ F, 16-V ceramic capacitor between the VCP and VM pins.                                                                                                                  |  |  |

| VDRAIN      | 6         | 6         | I                   | High-side MOSFET drain sense input. Connect to the common point of the MOSFET drains.                                                                                                                                      |  |  |

| VDS         | 23        | —         | I                   | VDS monitor trip point setting. This pin is a 7 level input pin set by an external resistor.                                                                                                                               |  |  |

| VIN         | 38        | 38        | PWR                 | Buck regulator power supply input. Place an X5R or X7R, VM-rated ceramic capacitor between the VIN and BGND pins.                                                                                                          |  |  |

| VM          | 5         | 5         | PWR                 | Gate driver power supply input. Connect to the bridge power supply. Connect a X5R or X7R, 0.1- $\mu$ F, VM-rated ceramic and greater than or equal to 10- $\mu$ F local capacitance between the VM and PGND pins.          |  |  |

| Thermal Pad |           |           | PWR                 | Must be connected to ground                                                                                                                                                                                                |  |  |

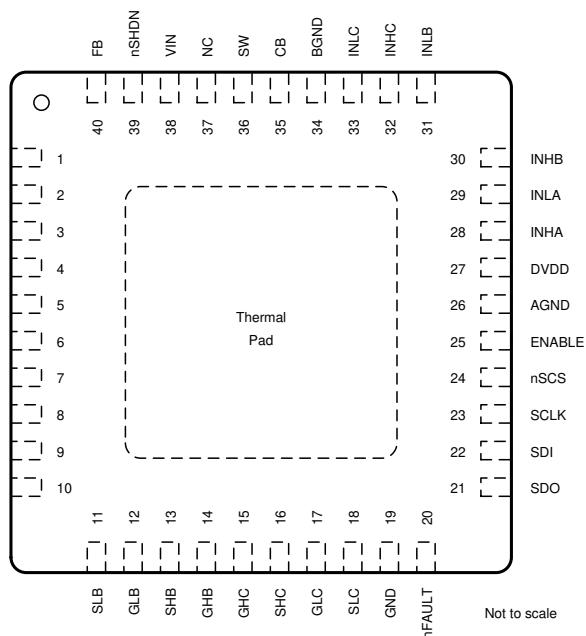

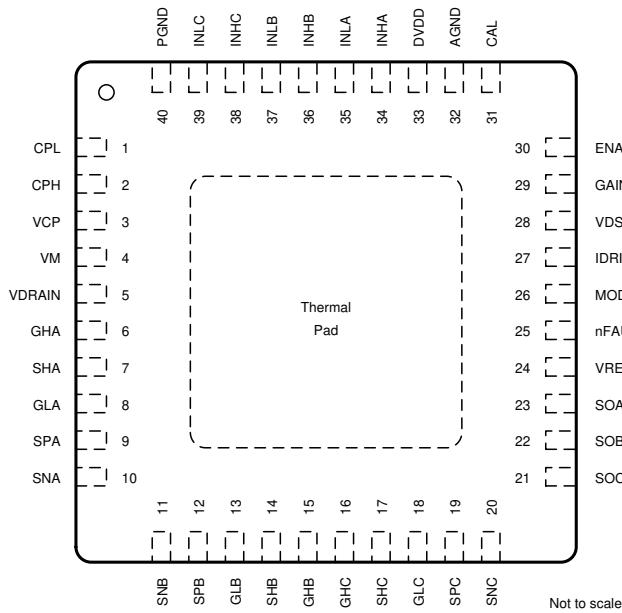

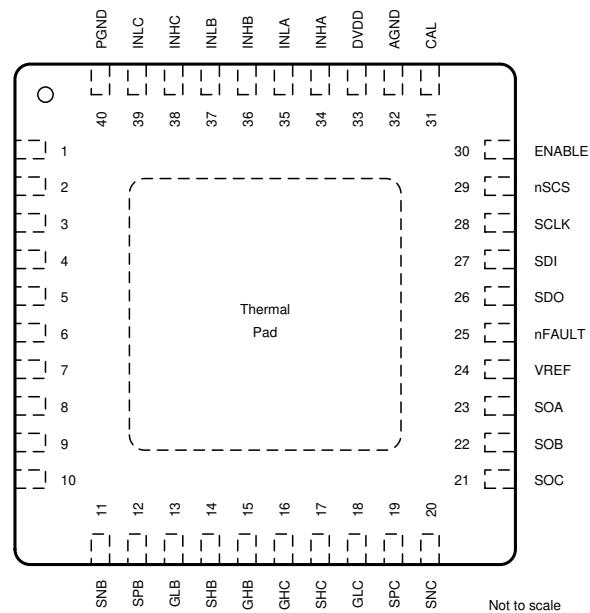

**DRV8323H RTA Package

40-Pin WQFN With Exposed Thermal Pad

Top View**

**DRV8323S RTA Package

40-Pin WQFN With Exposed Thermal Pad

Top View**

**ピン機能—40ピンDRV8323デバイス**

| NAME | PIN      |          | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                           |  |  |

|------|----------|----------|---------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|

|      | NO.      |          |                     |                                                                                                                       |  |  |

|      | DRV8323H | DRV8323S |                     |                                                                                                                       |  |  |

| AGND | 32       | 32       | PWR                 | Device analog ground. Connect to system ground.                                                                       |  |  |

| CAL  | 31       | 31       | I                   | Amplifier calibration input. Set logic high to internally short amplifier inputs and perform auto offset calibration. |  |  |

| CPH  | 2        | 2        | PWR                 | Charge pump switching node. Connect a X5R or X7R, 47-nF, VM-rated ceramic capacitor between the CPH and CPL pins.     |  |  |

(1) PWR = 電源、I = 入力、O = 出力、NC = 接続なし、OD = オープン・ドレイン出力

**ピン機能—40ピンDRV8323デバイス (continued)**

| PIN         |          | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                           |

|-------------|----------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME        | NO.      |                     |                                                                                                                                                                                                                       |

|             | DRV8323H | DRV8323S            |                                                                                                                                                                                                                       |

| CPL         | 1        | 1                   | PWR Charge pump switching node. Connect a X5R or X7R, 47-nF, VM-rated ceramic capacitor between the CPH and CPL pins.                                                                                                 |

| DVDD        | 33       | 33                  | PWR R 3.3-V internal regulator output. Connect a X5R or X7R, 1- $\mu$ F, 6.3-V ceramic capacitor between the DVDD and AGND pins. This regulator can source up to 30 mA externally.                                    |

| ENABLE      | 30       | 30                  | I Gate driver enable. When this pin is logic low the device goes to a low-power sleep mode. An 8 to 40- $\mu$ s low pulse can be used to reset fault conditions.                                                      |

| GAIN        | 29       | —                   | I Amplifier gain setting. The pin is a 4 level input pin set by an external resistor.                                                                                                                                 |

| GHA         | 6        | 6                   | O High-side gate driver output. Connect to the gate of the high-side power MOSFET.                                                                                                                                    |

| GHB         | 15       | 15                  | O High-side gate driver output. Connect to the gate of the high-side power MOSFET.                                                                                                                                    |

| GHC         | 16       | 16                  | O High-side gate driver output. Connect to the gate of the high-side power MOSFET.                                                                                                                                    |

| GLA         | 8        | 8                   | O Low-side gate driver output. Connect to the gate of the low-side power MOSFET.                                                                                                                                      |

| GLB         | 13       | 13                  | O Low-side gate driver output. Connect to the gate of the low-side power MOSFET.                                                                                                                                      |

| GLC         | 18       | 18                  | O Low-side gate driver output. Connect to the gate of the low-side power MOSFET.                                                                                                                                      |

| IDRIVE      | 27       | —                   | I Gate drive output current setting. This pin is a 7 level input pin set by an external resistor.                                                                                                                     |

| INHA        | 34       | 34                  | I High-side gate driver control input. This pin controls the output of the high-side gate driver.                                                                                                                     |

| INHB        | 36       | 36                  | I High-side gate driver control input. This pin controls the output of the high-side gate driver.                                                                                                                     |

| INHC        | 38       | 38                  | I High-side gate driver control input. This pin controls the output of the high-side gate driver.                                                                                                                     |

| INLA        | 35       | 35                  | I Low-side gate driver control input. This pin controls the output of the low-side gate driver.                                                                                                                       |

| INLB        | 37       | 37                  | I Low-side gate driver control input. This pin controls the output of the low-side gate driver.                                                                                                                       |

| INLC        | 39       | 39                  | I Low-side gate driver control input. This pin controls the output of the low-side gate driver.                                                                                                                       |

| MODE        | 26       | —                   | I PWM input mode setting. This pin is a 4 level input pin set by an external resistor.                                                                                                                                |

| nFAULT      | 25       | 25                  | OD Fault indicator output. This pin is pulled logic low during a fault condition and requires an external pullup resistor.                                                                                            |

| nSCS        | —        | 29                  | I Serial chip select. A logic low on this pin enables serial interface communication.                                                                                                                                 |

| PGND        | 40       | 40                  | PWR Device power ground. Connect to system ground.                                                                                                                                                                    |

| SCLK        | —        | 28                  | I Serial clock input. Serial data is shifted out and captured on the corresponding rising and falling edge on this pin.                                                                                               |

| SDI         | —        | 27                  | I Serial data input. Data is captured on the falling edge of the SCLK pin.                                                                                                                                            |

| SDO         | —        | 26                  | OD Serial data output. Data is shifted out on the rising edge of the SCLK pin. This pin requires an external pullup resistor.                                                                                         |

| SHA         | 7        | 7                   | I High-side source sense input. Connect to the high-side power MOSFET source.                                                                                                                                         |

| SHB         | 14       | 14                  | I High-side source sense input. Connect to the high-side power MOSFET source.                                                                                                                                         |

| SHC         | 17       | 17                  | I High-side source sense input. Connect to the high-side power MOSFET source.                                                                                                                                         |

| SNA         | 10       | 10                  | I Current sense amplifier input. Connect to the low-side of the current shunt resistor.                                                                                                                               |

| SNB         | 11       | 11                  | I Current sense amplifier input. Connect to the low-side of the current shunt resistor.                                                                                                                               |

| SNC         | 20       | 20                  | I Current sense amplifier input. Connect to the low-side of the current shunt resistor.                                                                                                                               |

| SOA         | 23       | 23                  | O Current sense amplifier output.                                                                                                                                                                                     |

| SOB         | 22       | 22                  | O Current sense amplifier output.                                                                                                                                                                                     |

| SOC         | 21       | 21                  | O Current sense amplifier output.                                                                                                                                                                                     |

| SPA         | 9        | 9                   | I Low-side current shunt amplifier input. Connect to the low-side power MOSFET source and high-side of the current shunt resistor.                                                                                    |

| SPB         | 12       | 12                  | I Low-side current shunt amplifier input. Connect to the low-side power MOSFET source and high-side of the current shunt resistor.                                                                                    |

| SPC         | 19       | 19                  | I Low-side current shunt amplifier input. Connect to the low-side power MOSFET source and high-side of the current shunt resistor.                                                                                    |

| VCP         | 3        | 3                   | PWR Charge pump output. Connect a X5R or X7R, 1- $\mu$ F, 16-V ceramic capacitor between the VCP and VM pins.                                                                                                         |

| VDRAIN      | 5        | 5                   | I High-side MOSFET drain sense input. Connect to the common point of the MOSFET drains.                                                                                                                               |

| VDS         | 28       | —                   | I VDS monitor trip point setting. This pin is a 7 level input pin set by an external resistor.                                                                                                                        |

| VM          | 4        | 4                   | PWR Gate driver power supply input. Connect to the bridge power supply. Connect a X5R or X7R, 0.1- $\mu$ F, VM-rated ceramic and greater than or equal to 10- $\mu$ F local capacitance between the VM and PGND pins. |

| VREF        | 24       | 24                  | PWR Current sense amplifier power supply input and reference. Connect a X5R or X7R, 0.1- $\mu$ F, 6.3-V ceramic capacitor between the VREF and AGND pins.                                                             |

| Thermal Pad |          | PWR                 | Must be connected to ground                                                                                                                                                                                           |

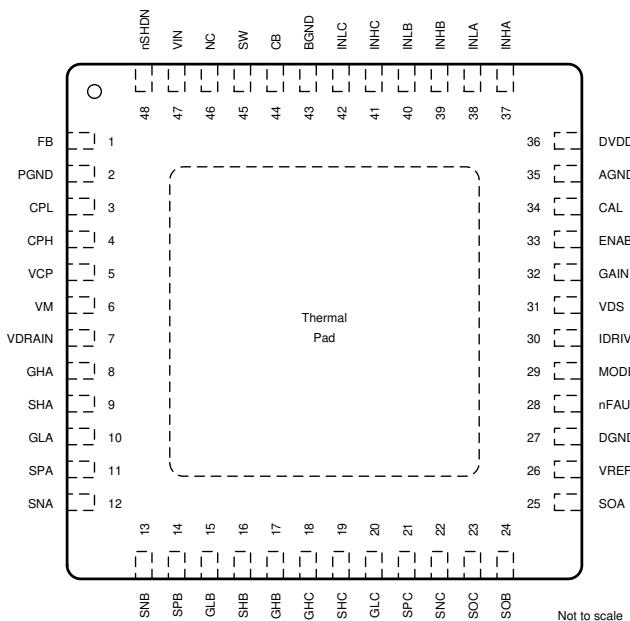

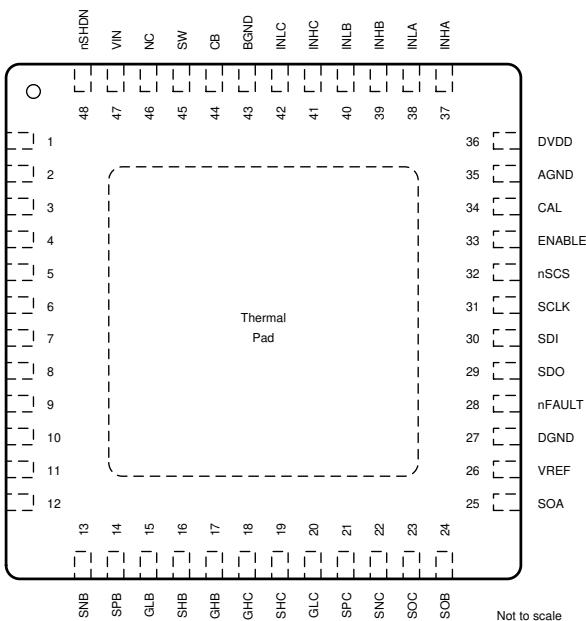

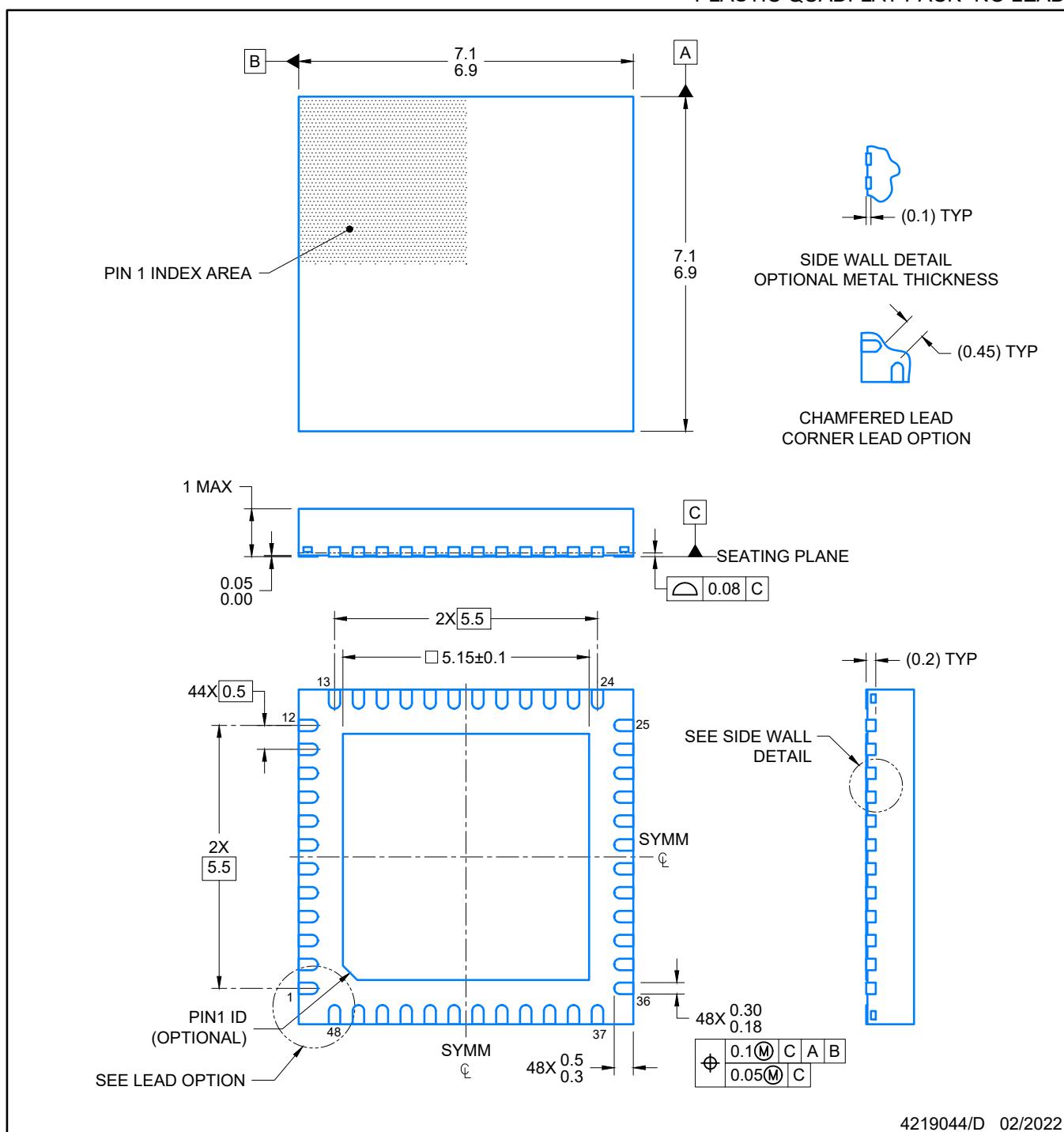

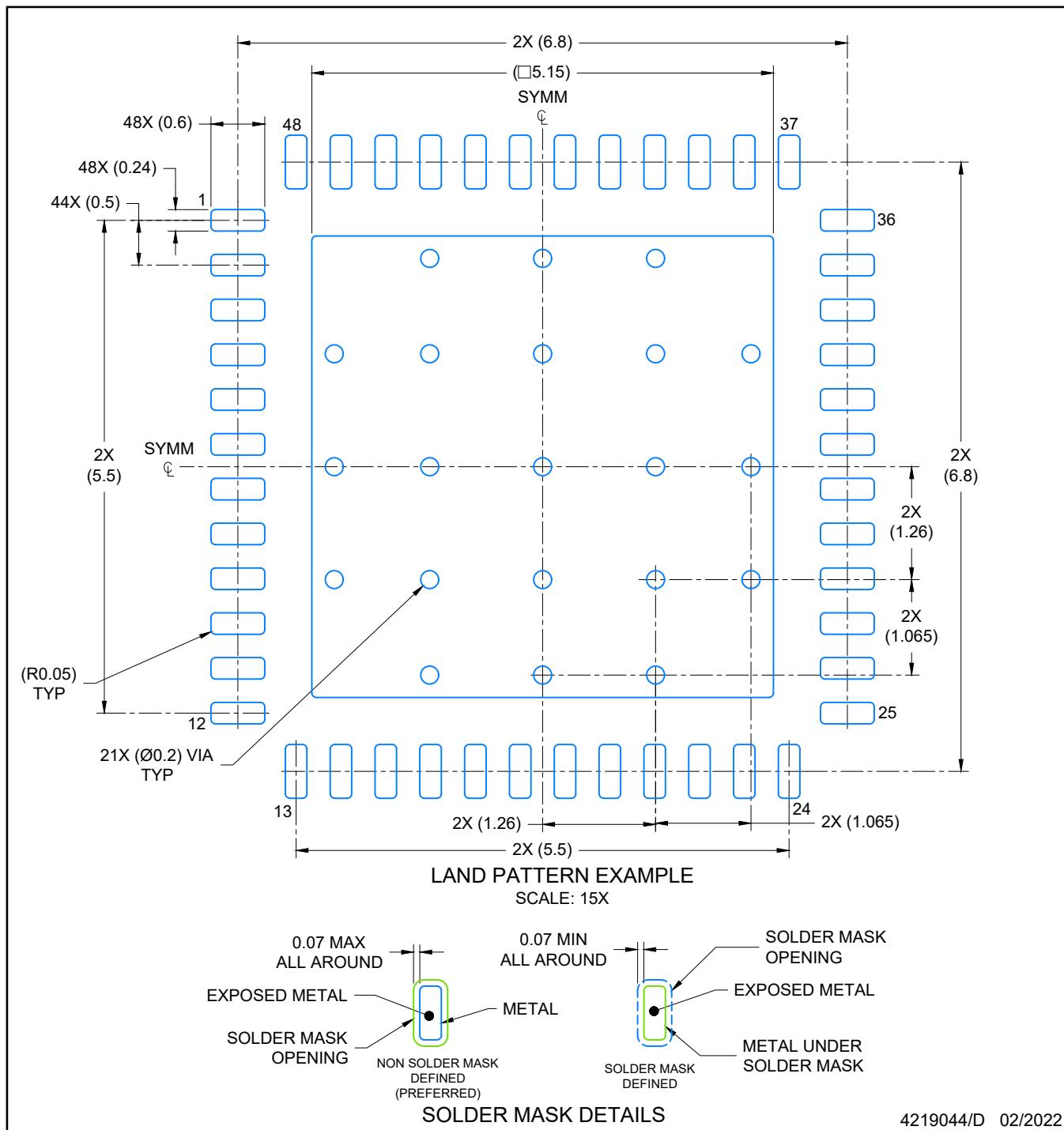

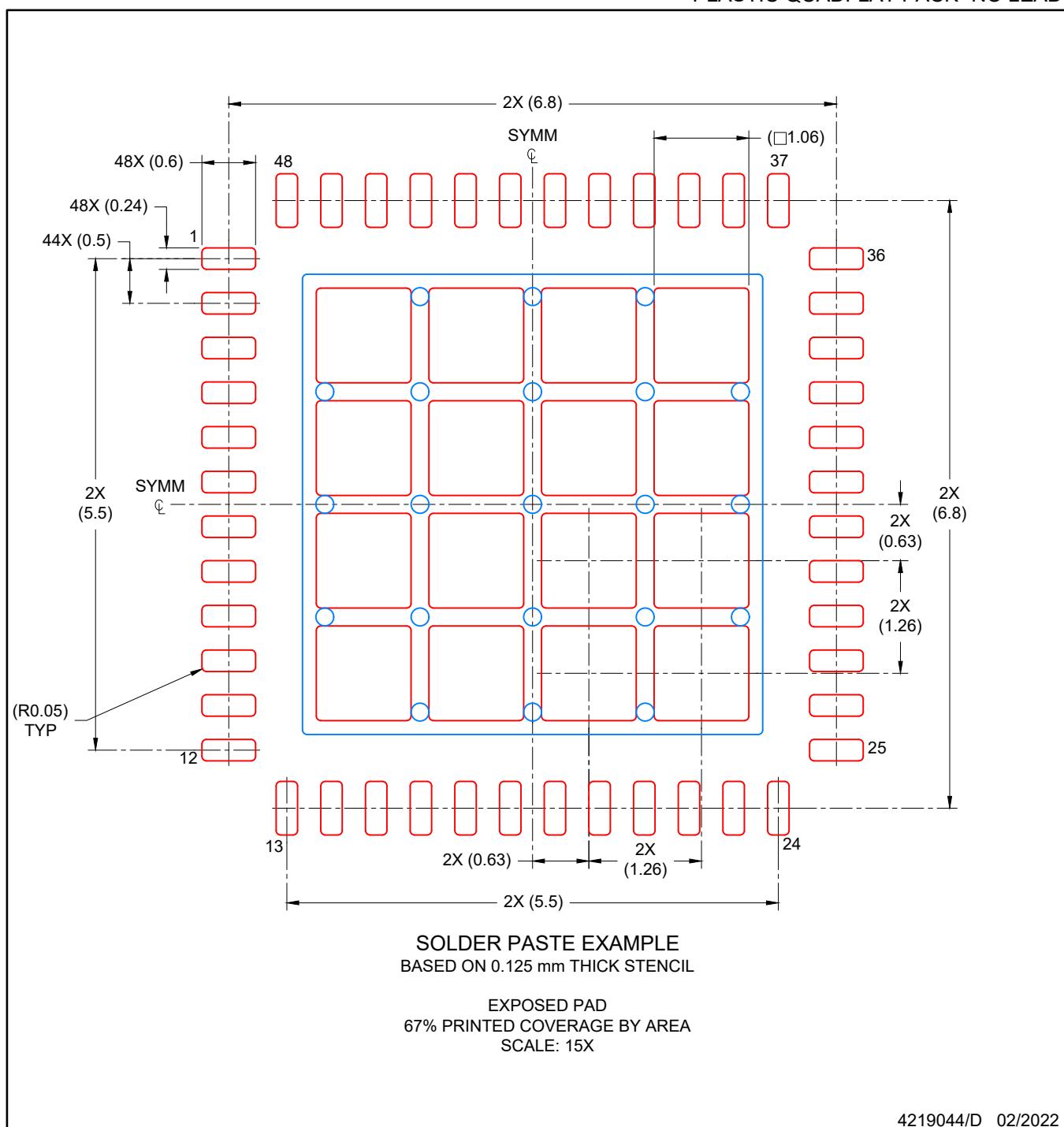

**DRV8323RH RGZ Package

48-Pin VQFN With Exposed Thermal Pad

Top View**

**DRV8323RS RGZ Package

48-Pin VQFN With Exposed Thermal Pad

Top View**

**ピン機能—48ピンDRV8323Rデバイス**

| NAME   | PIN       |           | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                  |

|--------|-----------|-----------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | DRV8323RH | DRV8323RS |                     |                                                                                                                                                                              |

| AGND   | 35        | 35        | PWR                 | Device analog ground. Connect to system ground.                                                                                                                              |

| BGND   | 43        | 43        | PWR                 | Buck regulator ground. Connect to system ground.                                                                                                                             |

| CAL    | 34        | 34        | I                   | Amplifier calibration input. Set logic high to internally short amplifier inputs and perform auto offset calibration.                                                        |

| CB     | 44        | 44        | PWR                 | Buck regulator bootstrap input. Connect a X5R or X7R, 0.1- $\mu$ F, 16-V, capacitor between the CB and SW pins.                                                              |

| CPH    | 4         | 4         | PWR                 | Charge pump switching node. Connect a X5R or X7R, 47-nF, VM-rated ceramic capacitor between the CPH and CPL pins.                                                            |

| CPL    | 3         | 3         | PWR                 | Charge pump switching node. Connect a X5R or X7R, 47-nF, VM-rated ceramic capacitor between the CPH and CPL pins.                                                            |

| DGND   | 27        | 27        | PWR                 | Device ground. Connect to system ground.                                                                                                                                     |

| DVDD   | 36        | 36        | PWR                 | 3.3-V internal regulator output. Connect a X5R or X7R, 1- $\mu$ F, 6.3-V ceramic capacitor between the DVDD and AGND pins. This regulator can source up to 30 mA externally. |

| ENABLE | 33        | 33        | I                   | Gate driver enable. When this pin is logic low the device goes to a low-power sleep mode. An 8 to 40- $\mu$ s low pulse can be used to reset fault conditions.               |

| FB     | 1         | 1         | I                   | Buck feedback input. A resistor divider from the buck post inductor output to this pin sets the buck output voltage.                                                         |

| GAIN   | 32        | —         | I                   | Amplifier gain setting. The pin is a 4 level input pin set by an external resistor.                                                                                          |

| GHA    | 8         | 8         | O                   | High-side gate driver output. Connect to the gate of the high-side power MOSFET.                                                                                             |

| GHB    | 17        | 17        | O                   | High-side gate driver output. Connect to the gate of the high-side power MOSFET.                                                                                             |

| GHC    | 18        | 18        | O                   | High-side gate driver output. Connect to the gate of the high-side power MOSFET.                                                                                             |

| GLA    | 10        | 10        | O                   | Low-side gate driver output. Connect to the gate of the low-side power MOSFET.                                                                                               |

| GLB    | 15        | 15        | O                   | Low-side gate driver output. Connect to the gate of the low-side power MOSFET.                                                                                               |

| GLC    | 20        | 20        | O                   | Low-side gate driver output. Connect to the gate of the low-side power MOSFET.                                                                                               |

| IDRIVE | 30        | —         | I                   | Gate drive output current setting. This pin is a 7 level input pin set by an external resistor.                                                                              |

| INHA   | 37        | 37        | I                   | High-side gate driver control input. This pin controls the output of the high-side gate driver.                                                                              |

| INHB   | 39        | 39        | I                   | High-side gate driver control input. This pin controls the output of the high-side gate driver.                                                                              |

| INHC   | 41        | 41        | I                   | High-side gate driver control input. This pin controls the output of the high-side gate driver.                                                                              |

| INLA   | 38        | 38        | I                   | Low-side gate driver control input. This pin controls the output of the low-side gate driver.                                                                                |

| INLB   | 40        | 40        | I                   | Low-side gate driver control input. This pin controls the output of the low-side gate driver.                                                                                |

| INLC   | 42        | 42        | I                   | Low-side gate driver control input. This pin controls the output of the low-side gate driver.                                                                                |

| MODE   | 29        | —         | I                   | PWM input mode setting. This pin is a 4 level input pin set by an external resistor.                                                                                         |

| NC     | 46        | 46        | NC                  | No internal connection. This pin can be left floating or connected to system ground.                                                                                         |

| nFAULT | 28        | 28        | OD                  | Fault indicator output. This pin is pulled logic low during a fault condition and requires an external pullup resistor.                                                      |

(1) PWR = 電源、I = 入力、O = 出力、NC = 接続なし、OD = オープン・ドレイン出力

ピン機能—48ピンDRV8323Rデバイス (continued)

| NAME        | PIN |           | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                |

|-------------|-----|-----------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | NO. | DRV8323RH |                     |                                                                                                                                                                                                                            |

| nSCS        | —   | 32        | I                   | Serial chip select. A logic low on this pin enables serial interface communication.                                                                                                                                        |

| nSHDN       | 48  | 48        | I                   | Buck shutdown input. Enable and disable input (high voltage tolerant). Internal pullup current source. Pull lower than 1.25 V to disable. Float to enable. Establish input undervoltage lockout with two resistor divider. |

| PGND        | 2   | 2         | PWR                 | Device power ground. Connect to system ground.                                                                                                                                                                             |

| SCLK        | —   | 31        | I                   | Serial clock input. Serial data is shifted out and captured on the corresponding rising and falling edge on this pin.                                                                                                      |

| SDI         | —   | 30        | I                   | Serial data input. Data is captured on the falling edge of the SCLK pin.                                                                                                                                                   |

| SDO         | —   | 29        | OD                  | Serial data output. Data is shifted out on the rising edge of the SCLK pin. This pin requires an external pullup resistor.                                                                                                 |

| SHA         | 9   | 9         | I                   | High-side source sense input. Connect to the high-side power MOSFET source.                                                                                                                                                |

| SHB         | 16  | 16        | I                   | High-side source sense input. Connect to the high-side power MOSFET source.                                                                                                                                                |

| SHC         | 19  | 19        | I                   | High-side source sense input. Connect to the high-side power MOSFET source.                                                                                                                                                |

| SNA         | 12  | 12        | I                   | Current sense amplifier input. Connect to the low-side of the current shunt resistor.                                                                                                                                      |

| SNB         | 13  | 13        | I                   | Current sense amplifier input. Connect to the low-side of the current shunt resistor.                                                                                                                                      |

| SNC         | 22  | 22        | I                   | Current sense amplifier input. Connect to the low-side of the current shunt resistor.                                                                                                                                      |

| SOA         | 25  | 25        | O                   | Current sense amplifier output.                                                                                                                                                                                            |

| SOB         | 24  | 24        | O                   | Current sense amplifier output.                                                                                                                                                                                            |

| SOC         | 23  | 23        | O                   | Current sense amplifier output.                                                                                                                                                                                            |

| SPA         | 11  | 11        | I                   | Low-side current shunt amplifier input. Connect to the low-side power MOSFET source and high-side of the current shunt resistor.                                                                                           |

| SPB         | 14  | 14        | I                   | Low-side current shunt amplifier input. Connect to the low-side power MOSFET source and high-side of the current shunt resistor.                                                                                           |

| SPC         | 21  | 21        | I                   | Low-side current shunt amplifier input. Connect to the low-side power MOSFET source and high-side of the current shunt resistor.                                                                                           |

| SW          | 45  | 45        | O                   | Buck switch node. Connect this pin to an inductor, diode, and the CB bootstrap capacitor.                                                                                                                                  |

| VCP         | 5   | 5         | PWR                 | Charge pump output. Connect a X5R or X7R, 1- $\mu$ F, 16-V ceramic capacitor between the VCP and VM pins.                                                                                                                  |

| VDRAIN      | 7   | 7         | I                   | High-side MOSFET drain sense input. Connect to the common point of the MOSFET drains.                                                                                                                                      |

| VDS         | 31  | —         | I                   | VDS monitor trip point setting. This pin is a 7 level input pin set by an external resistor.                                                                                                                               |

| VIN         | 47  | 47        | PWR                 | Buck regulator power supply input. Place an X5R or X7R, VM-rated ceramic capacitor between the VIN and BGND pins.                                                                                                          |

| VM          | 6   | 6         | PWR                 | Gate driver power supply input. Connect to the bridge power supply. Connect a X5R or X7R, 0.1- $\mu$ F, VM-rated ceramic and greater than or equal to 10- $\mu$ F local capacitance between the VM and AGND pins.          |

| VREF        | 26  | 26        | PWR                 | Current sense amplifier power supply input and reference. Connect a X5R or X7R, 0.1- $\mu$ F, 6.3-V ceramic capacitor between the VREF and AGND pins.                                                                      |

| Thermal Pad |     |           | PWR                 | Must be connected to ground                                                                                                                                                                                                |

## 8 仕様

### 8.1 絶対最大定格

$T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$  (特に記述のない限り) <sup>(1)</sup>

|                                                                                                      | MIN                | MAX              | UNIT |

|------------------------------------------------------------------------------------------------------|--------------------|------------------|------|

| <b>GATE DRIVER</b>                                                                                   |                    |                  |      |

| Power supply pin voltage (VM)                                                                        | -0.3               | 65               | V    |

| Voltage differential between ground pins (AGND, BGND, DGND, PGND)                                    | -0.3               | 0.3              | V    |

| MOSFET drain sense pin voltage (VDRAIN)                                                              | -0.3               | 65               | V    |

| Charge pump pin voltage (CPH, VCP)                                                                   | -0.3               | $V_{VM} + 13.5$  | V    |

| Charge pump negative-switching pin voltage (CPL)                                                     | -0.3               | $V_{VM}$         | V    |

| Internal logic regulator pin voltage (DVDD)                                                          | -0.3               | 3.8              | V    |

| Digital pin voltage (CAL, ENABLE, GAIN, IDRIVE, INHx, INLx, MODE, nFAULT, nSCS, SCLK, SDI, SDO, VDS) | -0.3               | 5.75             | V    |

| Continuous high-side gate drive pin voltage (GHx)                                                    | -5 <sup>(2)</sup>  | $V_{VCP} + 0.5$  | V    |

| Transient 200-ns high-side gate drive pin voltage (GHx)                                              | -7                 | $V_{VCP} + 0.5$  | V    |

| High-side gate drive pin voltage with respect to SHx (GHx)                                           | -0.3               | 13.5             | V    |

| Continuous high-side source sense pin voltage (SHx)                                                  | -5 <sup>(2)</sup>  | $V_{VM} + 5$     | V    |

| Transient 200-ns high-side source sense pin voltage (SHx)                                            | -7                 | $V_{VM} + 7$     | V    |

| Continuous low-side gate drive pin voltage (GLx)                                                     | -0.5               | 13.5             | V    |

| Gate drive pin source current (GHx, GLx)                                                             | Internally limited |                  | A    |

| Gate drive pin sink current (GHx, GLx)                                                               | Internally limited |                  | A    |

| Continuous low-side source sense pin voltage (SLx)                                                   | -1                 | 1                | V    |

| Transient 200-ns low-side source sense pin voltage (SLx)                                             | -3                 | 3                | V    |

| Continuous input pin voltage (SNx, SPx)                                                              | -1                 | 1                | V    |

| Transient 200-ns input pin voltage (SNx, SPx)                                                        | -3                 | 3                | V    |

| Reference input pin voltage (VREF)                                                                   | -0.3               | 5.75             | V    |

| Output pin voltage (SOx)                                                                             | -0.3               | $V_{VREF} + 0.3$ | V    |

| <b>BUCK REGULATOR</b>                                                                                |                    |                  |      |

| Power supply pin voltage (VIN)                                                                       | -0.3               | 65               | V    |

| Shutdown control pin voltage (nSHDN)                                                                 | -0.3               | $V_{VIN}$        | V    |

| Voltage feedback pin voltage (FB)                                                                    | -0.3               | 7                | V    |

| Bootstrap pin voltage with respect to SW (CB)                                                        | -0.3               | 7                | V    |

| Switching node pin voltage (SW)                                                                      | -0.3               | $V_{VIN}$        | V    |

| Switching node pin voltage less than 30-ns transients (SW)                                           | -2                 | $V_{VIN}$        | V    |

| <b>DRV832x</b>                                                                                       |                    |                  |      |

| Operating junction temperature, $T_J$                                                                | -40                | 150              | °C   |

| Storage temperature, $T_{stg}$                                                                       | -65                | 150              | °C   |

(1) 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値を越える状態で本製品が正常に動作することを暗黙的に示すものではありません。絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

(2) VMの絶対最大定格65Vに対して、連続ハイサイド・ゲート・ピン (GHx) および相ノード・ピン (SHx) の電圧は最小-2Vに制限される必要があります。60V以下では、GHxおよびSHxの最小仕様である-5Vの連続電圧が許容されます。

### 8.2 ESD定格

|             |                         | VALUE                                                                          | UNIT       |

|-------------|-------------------------|--------------------------------------------------------------------------------|------------|

| $V_{(ESD)}$ | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | $\pm 3000$ |

|             |                         | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | $\pm 1000$ |

(1) JEDECのドキュメントJEP155に、500V HBMでは標準のESD管理プロセスで安全な製造が可能であると規定されています。 $\pm 2000\text{V}$ と記載されたピンは、実際にはそれよりも高い性能を持つ場合があります。

(2) JEDECのドキュメントJEP157に、250V CDMでは標準のESD管理プロセスで安全な製造が可能であると規定されています。 $\pm 500\text{V}$ と記載されたピンは、実際にはそれよりも高い性能を持つ場合があります。

### 8.3 推奨動作条件

$T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$  (特に記述のない限り)

|                       |                                                                                                             | MIN | MAX                | UNIT |

|-----------------------|-------------------------------------------------------------------------------------------------------------|-----|--------------------|------|

| <b>GATE DRIVER</b>    |                                                                                                             |     |                    |      |

| $V_{VM}$              | Power supply voltage (VM)                                                                                   | 6   | 60                 | V    |

| $V_I$                 | Input voltage (CAL, ENABLE, GAIN, IDRIVE, INH <sub>x</sub> , INL <sub>x</sub> , MODE, nSCS, SCLK, SDI, VDS) | 0   | 5.5                | V    |

| $f_{PWM}$             | Applied PWM signal (INH <sub>x</sub> , INL <sub>x</sub> )                                                   | 0   | 200 <sup>(1)</sup> | kHz  |

| $I_{GATE\_HS}$        | High-side average gate drive current (GH <sub>x</sub> )                                                     | 0   | 25 <sup>(1)</sup>  | mA   |

| $I_{GATE\_LS}$        | Low-side average gate drive current (GL <sub>x</sub> )                                                      | 0   | 25 <sup>(1)</sup>  | mA   |

| $I_{DVDD}$            | External load current (DVDD)                                                                                | 0   | 30 <sup>(1)</sup>  | mA   |

| $V_{VREF}$            | Reference voltage input (VREF)                                                                              | 3   | 5.5                | V    |

| $I_{SO}$              | Output current (SO <sub>x</sub> )                                                                           | 0   | 5                  | mA   |

| $V_{OD}$              | Open drain pullup voltage (nFAULT, SDO)                                                                     | 0   | 5.5                | V    |

| $I_{OD}$              | Open drain output current (nFAULT, SDO)                                                                     | 0   | 5                  | mA   |

| <b>BUCK REGULATOR</b> |                                                                                                             |     |                    |      |

| $V_{VIN}$             | Power supply voltage (VIN)                                                                                  | 4   | 60                 | V    |

| $V_{nSHDN}$           | Shutdown control input voltage (nSHDN)                                                                      | 0   | 60                 | V    |

| <b>DRV832x</b>        |                                                                                                             |     |                    |      |

| $T_A$                 | Operating ambient temperature                                                                               | -40 | 125                | °C   |

(1) 消費電力および温度の制限に従う必要があります。

### 8.4 热特性

| THERMAL METRIC <sup>(1)</sup> | DRV832x                                      |               |               |               | UNIT |

|-------------------------------|----------------------------------------------|---------------|---------------|---------------|------|

|                               | RTV<br>(WQFN)                                | RHA<br>(VQFN) | RTA<br>(WQFN) | RGZ<br>(VQFN) |      |

|                               | 32 PINS                                      | 40 PINS       | 40 PINS       | 48 PINS       |      |

| $R_{\theta JA}$               | Junction-to-ambient thermal resistance       | 32.9          | 30.1          | 32.1          | °C/W |

| $R_{\theta JC(\text{top})}$   | Junction-to-case (top) thermal resistance    | 15.8          | 16.7          | 11            | °C/W |

| $R_{\theta JB}$               | Junction-to-board thermal resistance         | 6.8           | 9.9           | 7.1           | °C/W |

| $\psi_{JT}$                   | Junction-to-top characterization parameter   | 0.2           | 0.5           | 0.1           | °C/W |

| $\psi_{JB}$                   | Junction-to-board characterization parameter | 6.8           | 9.9           | 7.1           | °C/W |

| $R_{\theta JC(\text{bot})}$   | Junction-to-case (bottom) thermal resistance | 2.1           | 2.2           | 2.1           | °C/W |

(1) 従来および新しい熱測定値の詳細については、『半導体およびIC/パッケージの熱測定値』アプリケーション・レポートを参照してください。

## 8.5 電気的特性

$T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ 、 $V_{VM} = 6 \sim 60\text{V}$  (特に記述のない限り)

| PARAMETER                                                            | TEST CONDITIONS                                                                         | MIN  | TYP  | MAX  | UNIT             |

|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------|------|------|------------------|

| <b>POWER SUPPLIES (DVDD, VCP, VM)</b>                                |                                                                                         |      |      |      |                  |

| $I_{VM}$                                                             | VM operating supply current<br>$V_{VM} = 24\text{ V}$ , ENABLE = 3.3 V, INHx/INLx = 0 V |      | 10.5 | 14   | mA               |

| $I_{VMQ}$                                                            | ENABLE = 0 V, $V_{VM} = 24\text{ V}$ , $T_A = 25^\circ\text{C}$                         |      | 12   | 20   | $\mu\text{A}$    |

|                                                                      | ENABLE = 0 V, $V_{VM} = 24\text{ V}$ , $T_A = 125^\circ\text{C}^{(1)}$                  |      |      | 50   |                  |

| $t_{RST}^{(1)}$                                                      | Reset pulse time<br>ENABLE = 0 V period to reset faults                                 | 8    | 40   |      | $\mu\text{s}$    |

| $t_{WAKE}$                                                           | Turnon time<br>$V_{VM} > V_{UVLO}$ , ENABLE = 3.3 V to outputs ready                    |      |      | 1    | ms               |

| $t_{SLEEP}$                                                          | Turnoff time<br>ENABLE = 0 V to device sleep mode                                       |      |      | 1    | ms               |

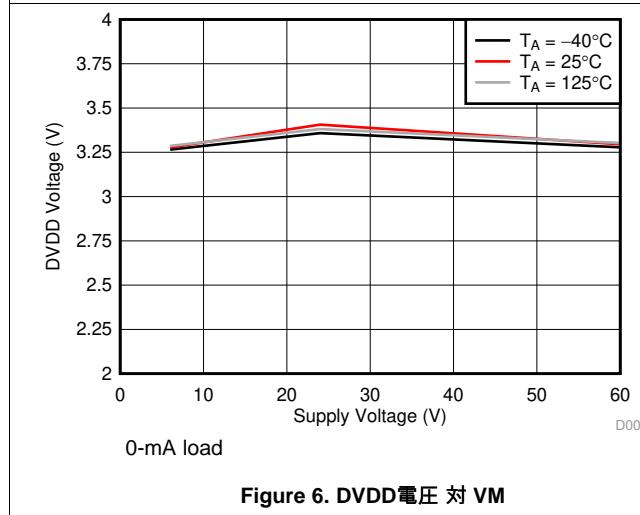

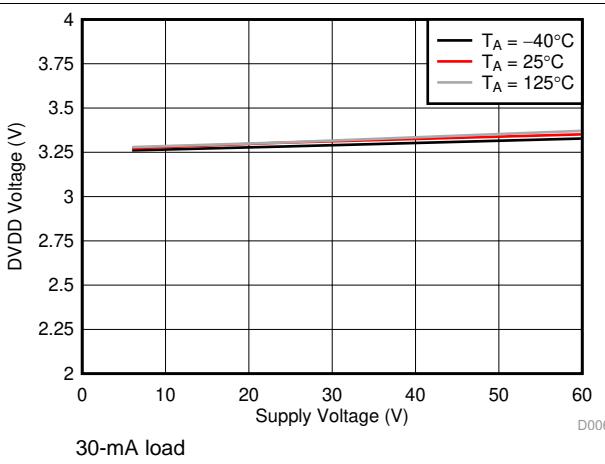

| $V_{DVDD}$                                                           | DVDD regulator voltage<br>$I_{DVDD} = 0$ to 30 mA                                       | 3    | 3.3  | 3.6  | V                |

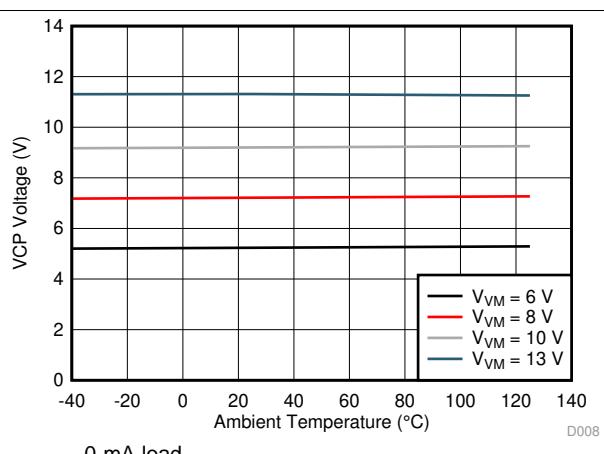

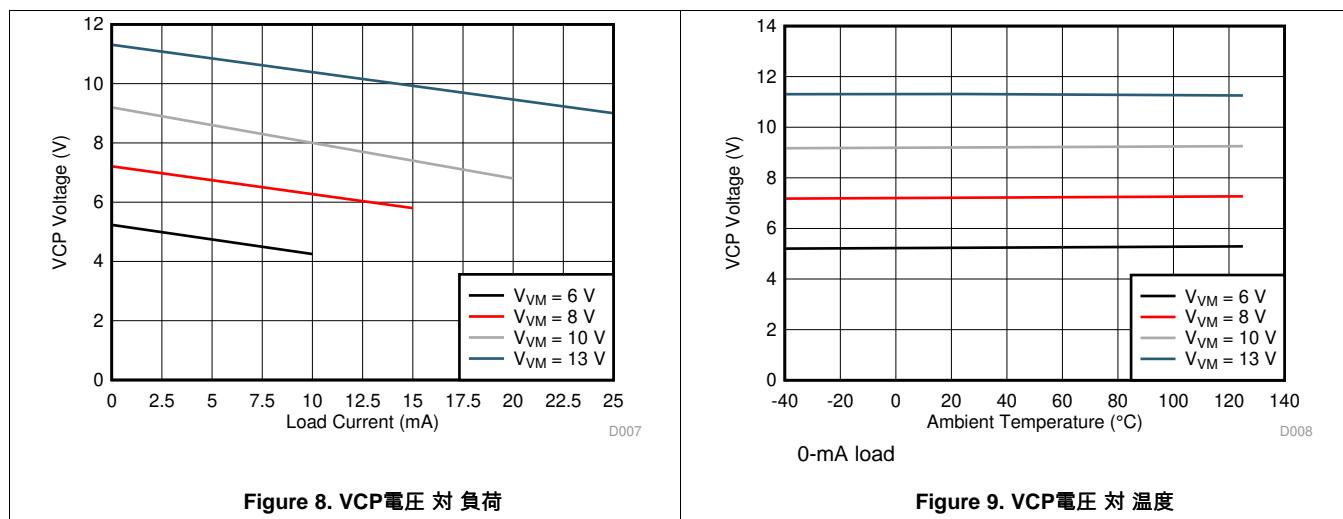

| $V_{VCP}$                                                            | $V_{VM} = 13\text{ V}$ , $I_{VCP} = 0$ to 25 mA                                         | 8.4  | 11   | 12.5 | V                |

|                                                                      | $V_{VM} = 10\text{ V}$ , $I_{VCP} = 0$ to 20 mA                                         | 6.3  | 9    | 10   |                  |

|                                                                      | $V_{VM} = 8\text{ V}$ , $I_{VCP} = 0$ to 15 mA                                          | 5.4  | 7    | 8    |                  |

|                                                                      | $V_{VM} = 6\text{ V}$ , $I_{VCP} = 0$ to 10 mA                                          | 4    | 5    | 6    |                  |

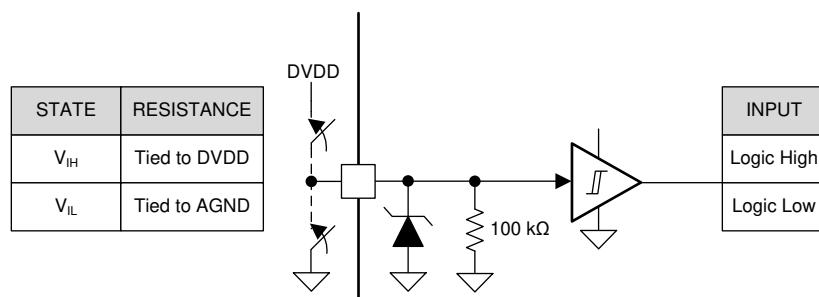

| <b>LOGIC-LEVEL INPUTS (CAL, ENABLE, INHx, INLx, nSCS, SCLK, SDI)</b> |                                                                                         |      |      |      |                  |

| $V_{IL}$                                                             | Input logic low voltage                                                                 | 0    | 0.8  |      | V                |

| $V_{IH}$                                                             | Input logic high voltage                                                                | 1.5  | 5.5  |      | V                |

| $V_{HYS}$                                                            | Input logic hysteresis                                                                  |      | 100  |      | mV               |

| $I_{IL}$                                                             | Input logic low current<br>$V_{VIN} = 0\text{ V}$                                       | -5   | 5    |      | $\mu\text{A}$    |

| $I_{IH}$                                                             | Input logic high current<br>$V_{VIN} = 5\text{ V}$                                      | 50   | 70   |      | $\mu\text{A}$    |

| $R_{PD}$                                                             | Pulldown resistance<br>To AGND                                                          | 100  |      |      | $\text{k}\Omega$ |

| $t_{PD}$                                                             | Propagation delay<br>INHx/INLx transition to GHx/GLx transition                         | 150  |      |      | ns               |

| <b>FOUR-LEVEL H/W INPUTS (GAIN, MODE)</b>                            |                                                                                         |      |      |      |                  |

| $V_{I1}$                                                             | Input mode 1 voltage<br>Tied to AGND                                                    | 0    |      |      | V                |

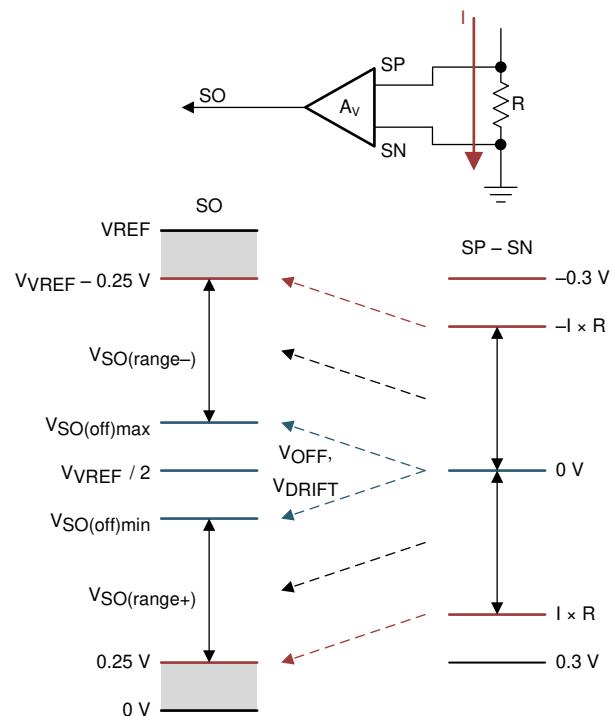

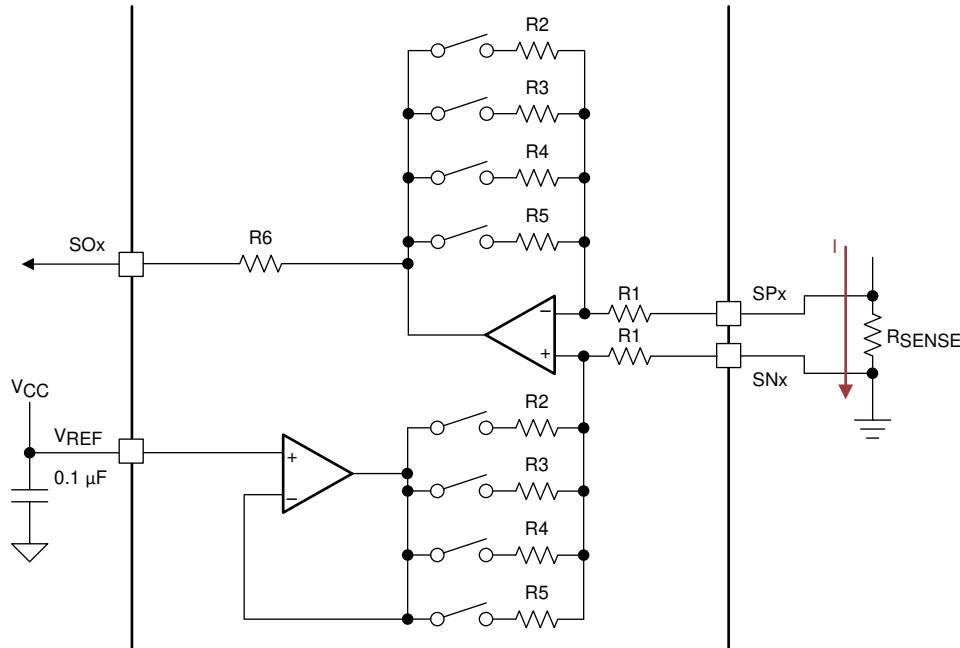

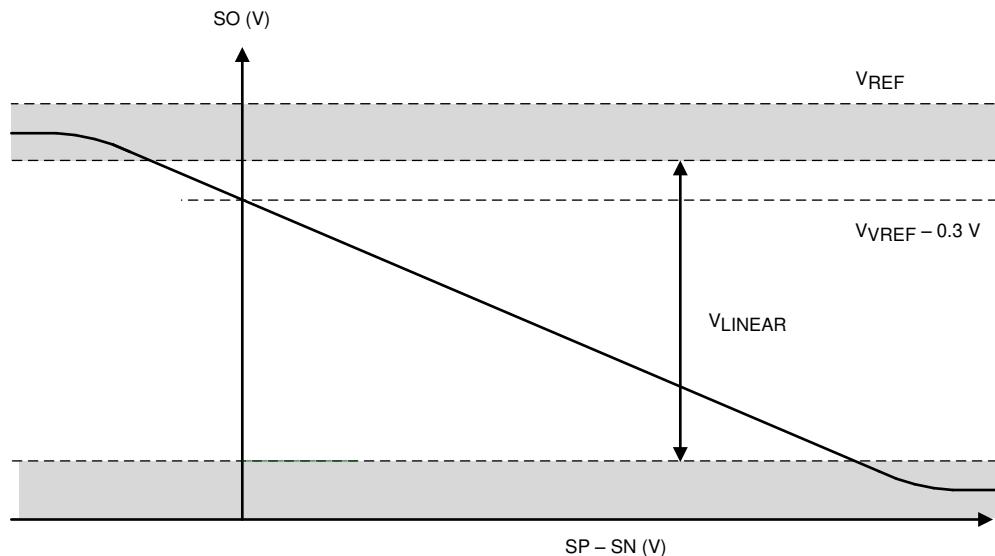

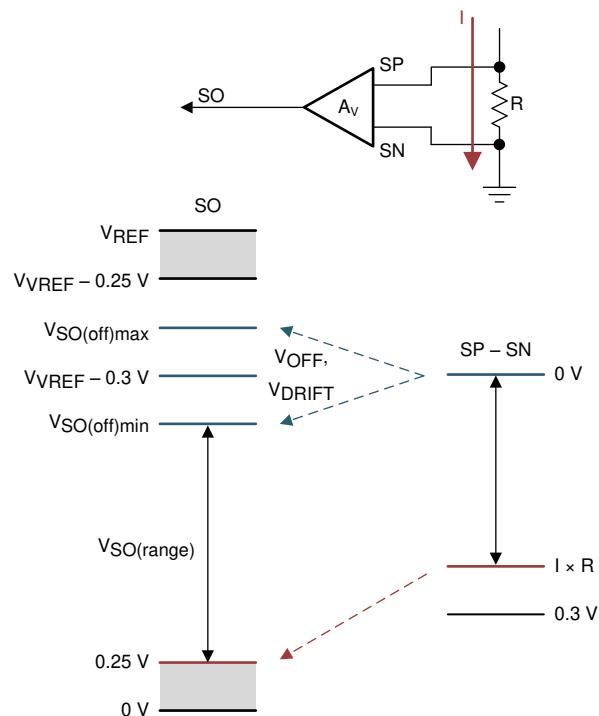

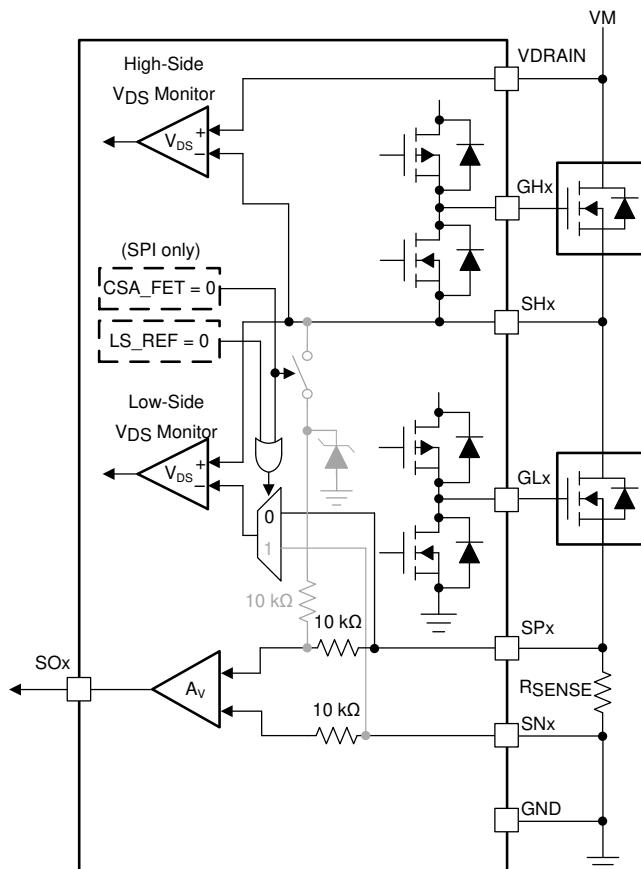

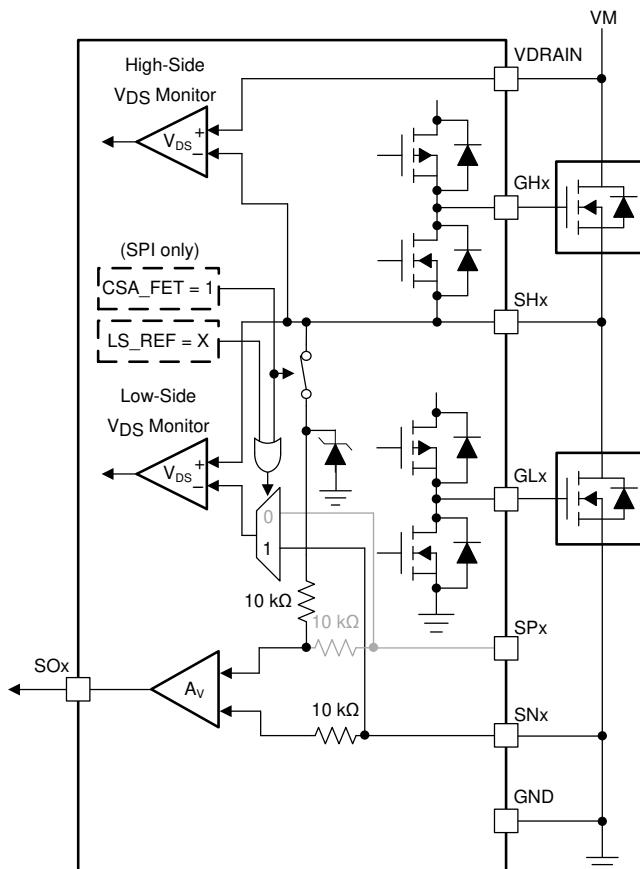

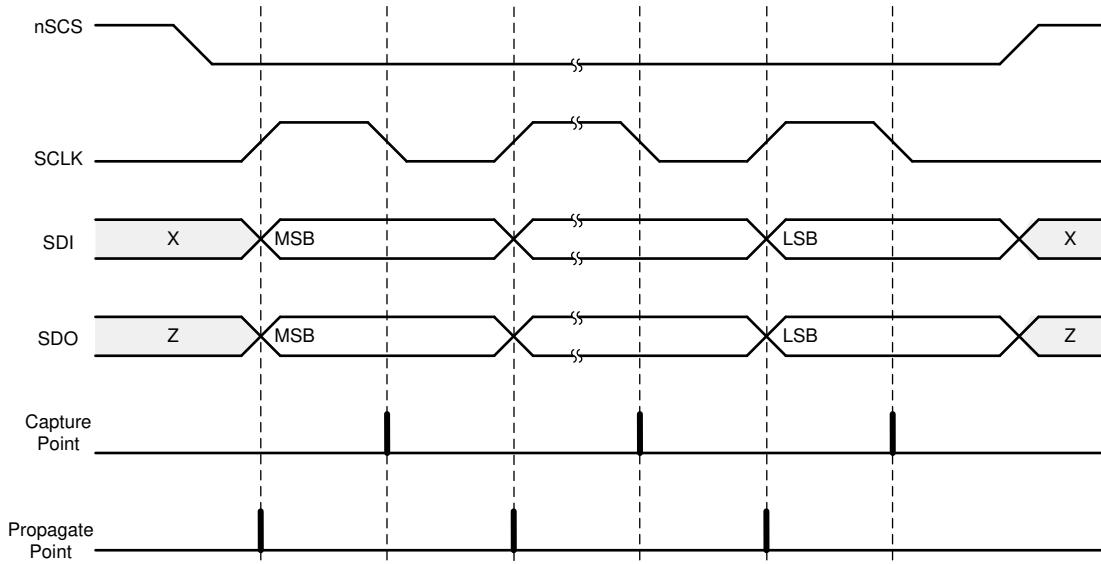

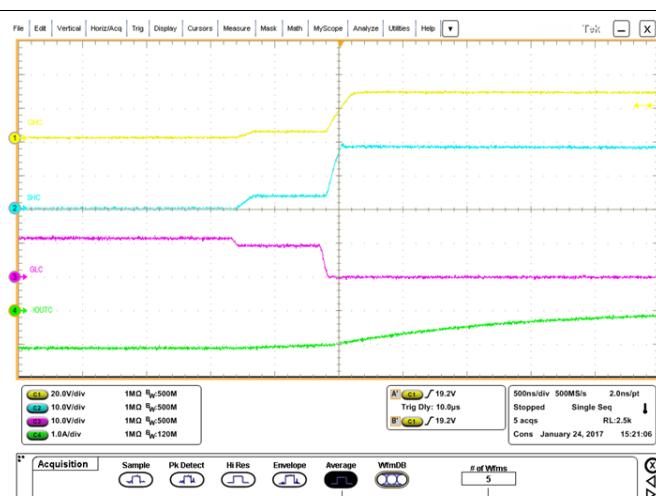

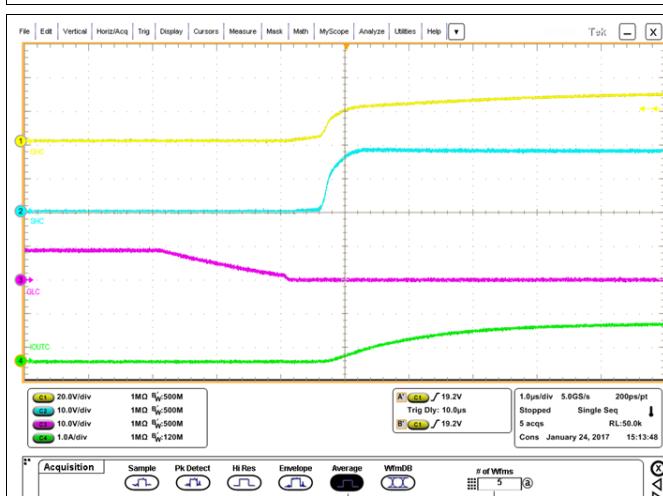

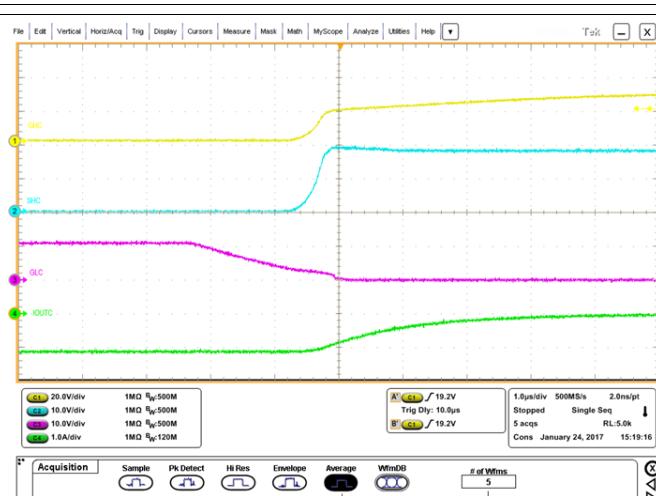

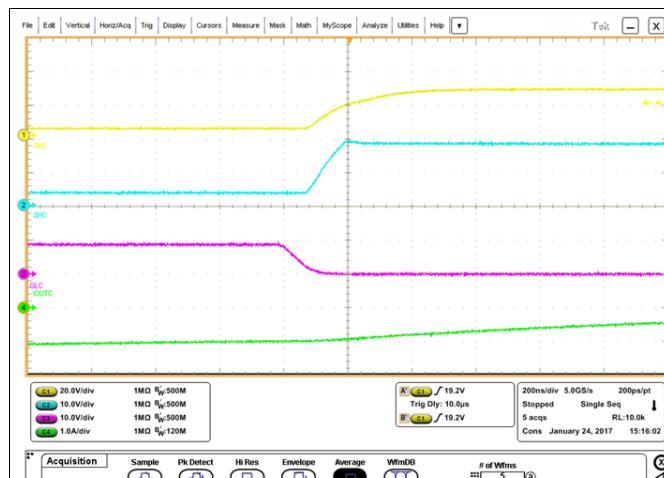

| $V_{I2}$                                                             | Input mode 2 voltage<br>$45\text{ k}\Omega \pm 5\%$ to tied AGND                        | 1.2  |      |      | V                |