# DRV84x2 デュアルフルブリッジ PWM モーター ドライバ

## 1 特長

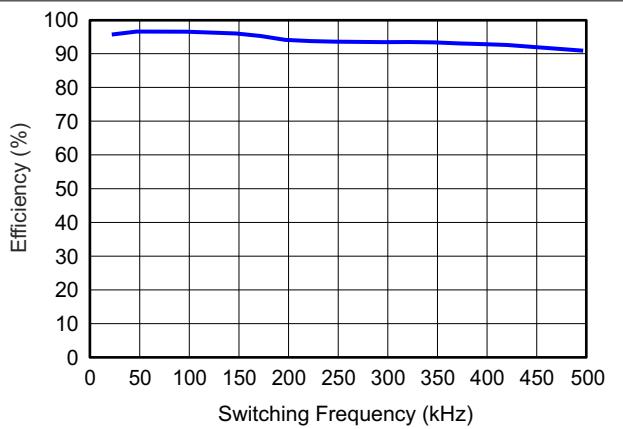

- $R_{DS(on)}$  の低い MOSFET ( $T_J = 25^\circ\text{C}$  時  $110\text{m}\Omega$ ) 使用により高効率の出力段 (最大 97%)

- 動作時電源電圧最大 52V

- DRV8412 (パワー パッド ダウン): デュアルフルブリッジモードで最大  $2 \times 3\text{A}$  の連続出力電流 ( $2 \times 6\text{A}$  ピーク)、または並列モードで  $6\text{A}$  の連続電流 ( $12\text{A}$  ピーク)

- DRV8432 (パワー パッド アップ): デュアルフルブリッジモードで最大  $2 \times 7\text{A}$  の連続出力電流 ( $2 \times 12\text{A}$  ピーク)、または並列モードで  $14\text{A}$  の連続電流 ( $24\text{A}$  ピーク)

- PWM 動作周波数: 最大 500kHz

- 低電圧、過熱、過負荷、短絡に対する自己保護回路を内蔵

- プログラム可能なサイクルごとの電流制限保護機能

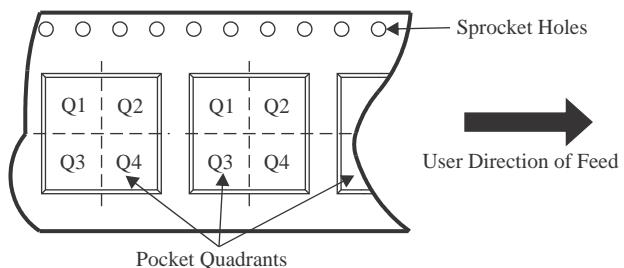

- 各ハーフブリッジに独立した電源ピンとグランドピン

- インテリジェントなゲートドライブとクロス導通防止

- 外付けのスナバまたはショットキー ダイオードは不要

## 2 アプリケーション

- ブラシ付き DC およびステッピング モーター

- 三相永久磁石同期モーター

- ロボットおよびハプティクス制御システム

- アクチュエータとポンプ

- 高精度の計器

- TEC ドライバ

- LED ライティング ドライバ

## 3 概要

DRV841x2 は、高性能の統合型デュアルフルブリッジモーター ドライバで、高度な保護システムが搭載されています。

H ブリッジ MOSFET の  $R_{DS(on)}$  が低く、インテリジェントなゲートドライブ設計を採用しているため、これらのモータードライバの効率は最大 97% に達する可能性があります。この高効率により、小型の電源とヒートシンクを使用でき、エネルギー効率の高いアプリケーションに適しています。

DRV841x2 には 2 つの電源が必要です。1 つは GVDD および VDD 用の 12V、もう 1 つは PVDD 用の最大 50V です。DRV841x2 は、最高 500kHz のスイッチング周波数で動作すると同時に、高精度の制御と高効率を維持できます。また、これらのデバイスには革新的な保護システムが搭載されており、システムに損傷を与える可能性のあるさまざまなフォルト状態からデバイスを保護します。これらの保護機能には、短絡保護、過電流保護、低電圧保護、2 段階の熱保護があります。DRV841x2 には電流制限回路があり、モーター起動などの負荷過渡時にデバイスのシャットダウンを防止します。プログラム可能な過電流検出機能により、さまざまなモーター要件に合わせて電流制限と保護レベルを調整できます。

DRV841x2 は、各ハーフブリッジに対して独自の独立した電源ピンとグランドピンを備えています。これらのピンにより、外部シャント抵抗を使用した電流測定が可能になり、異なる電源電圧要件を持つ複数のモーターをサポートできます。

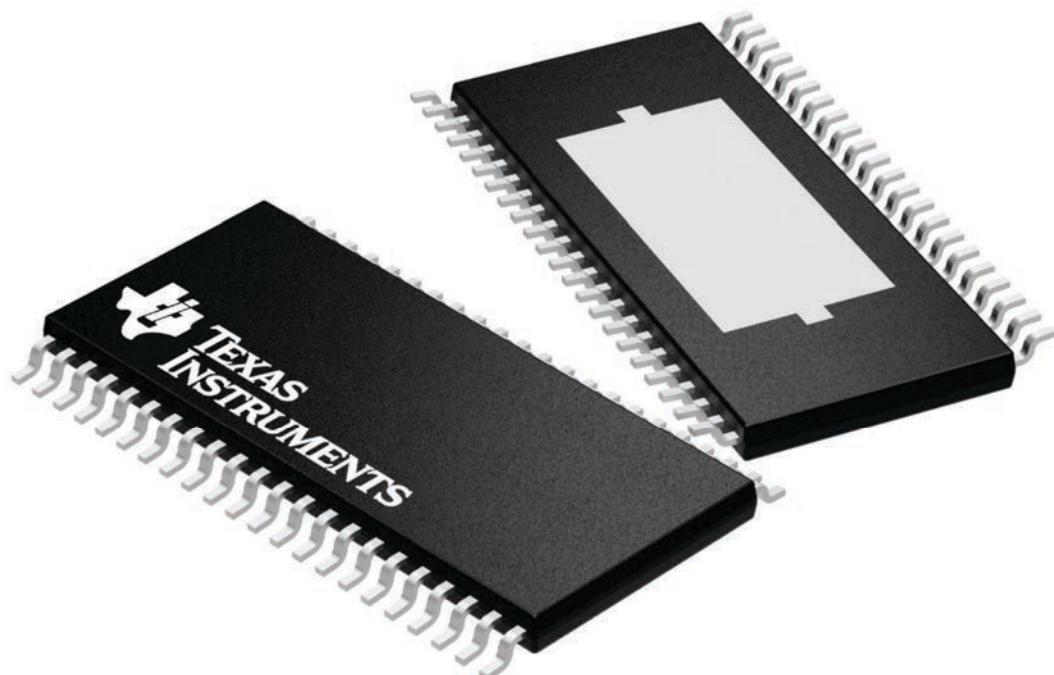

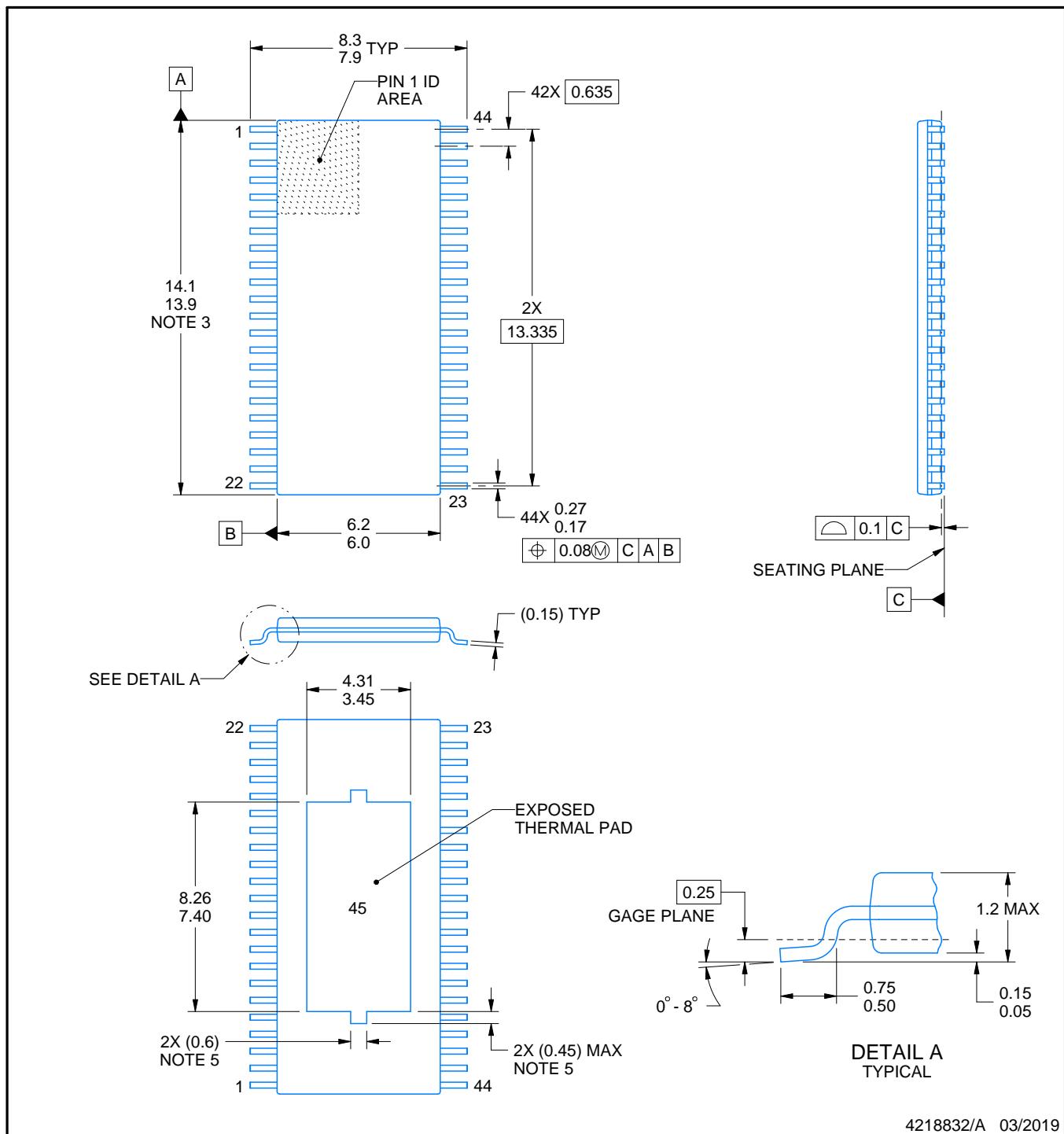

## パッケージ情報

| 部品番号    | パッケージ (1)   | パッケージ サイズ (2)   |

|---------|-------------|-----------------|

| DRV8412 | HTSSOP (44) | 14 mm × 8.1mm   |

| DRV8432 | HSSOP (36)  | 15.9mm × 14.2mm |

(1) 詳細については、[セクション 9](#) を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

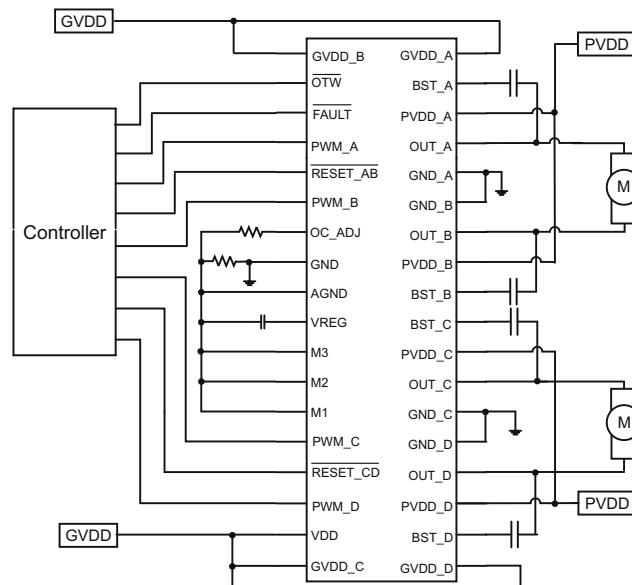

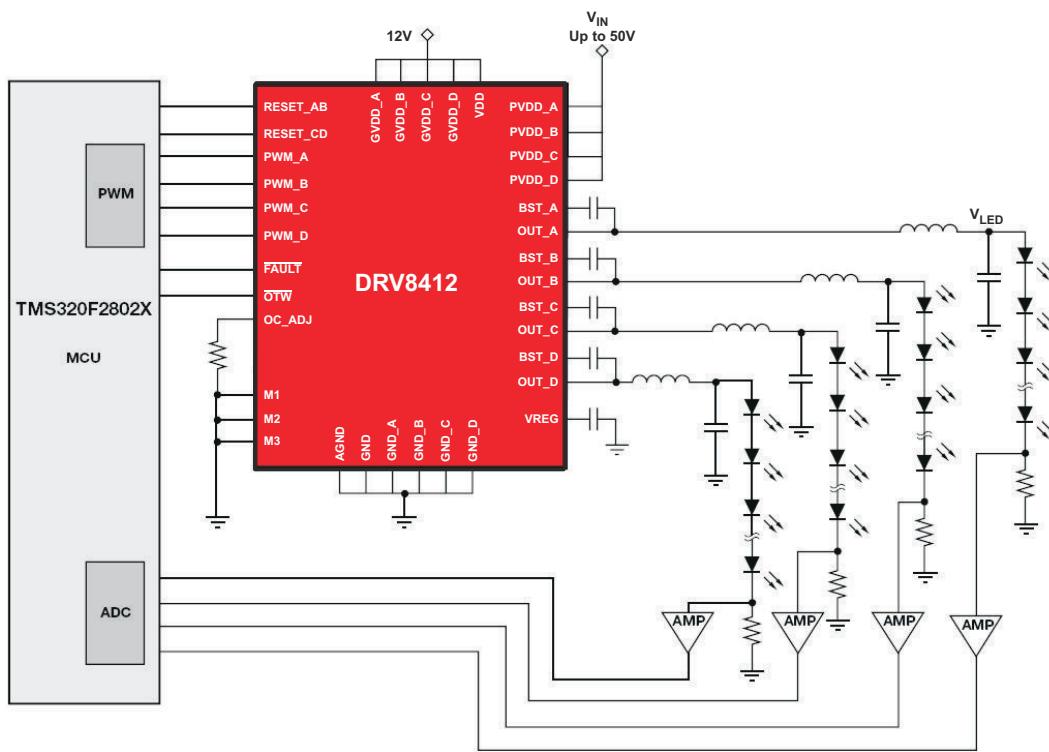

アプリケーション概略図

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあります。TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## Table of Contents

|                                                      |   |                                                    |    |

|------------------------------------------------------|---|----------------------------------------------------|----|

| 1 特長                                                 | 1 | 6 Detailed Description                             | 9  |

| 2 アプリケーション                                           | 1 | 6.1 Overview                                       | 9  |

| 3 概要                                                 | 1 | 6.2 Functional Block Diagram                       | 10 |

| 4 Pin Configuration and Functions                    | 3 | 6.3 Feature Description                            | 11 |

| 5 Specifications                                     | 5 | 6.4 Device Functional Modes                        | 14 |

| 5.1 Absolute Maximum Ratings                         | 5 | 7 Device and Documentation Support                 | 30 |

| 5.2 ESD Ratings                                      | 5 | 7.1 ドキュメントの更新通知を受け取る方法                             | 30 |

| 5.3 Recommended Operating Conditions                 | 5 | 7.2 サポート・リソース                                      | 30 |

| 5.4 Thermal Information                              | 6 | 7.3 Trademarks                                     | 30 |

| 5.5 Package Heat Dissipation Ratings                 | 6 | 7.4 静電気放電に関する注意事項                                  | 30 |

| 5.6 Package Power Deratings (DRV8412) <sup>(1)</sup> | 6 | 7.5 用語集                                            | 30 |

| 5.7 Electrical Characteristics                       | 7 | 8 Revision History                                 | 30 |

| 5.8 Typical Characteristics                          | 8 | 9 Mechanical, Packaging, and Orderable Information | 31 |

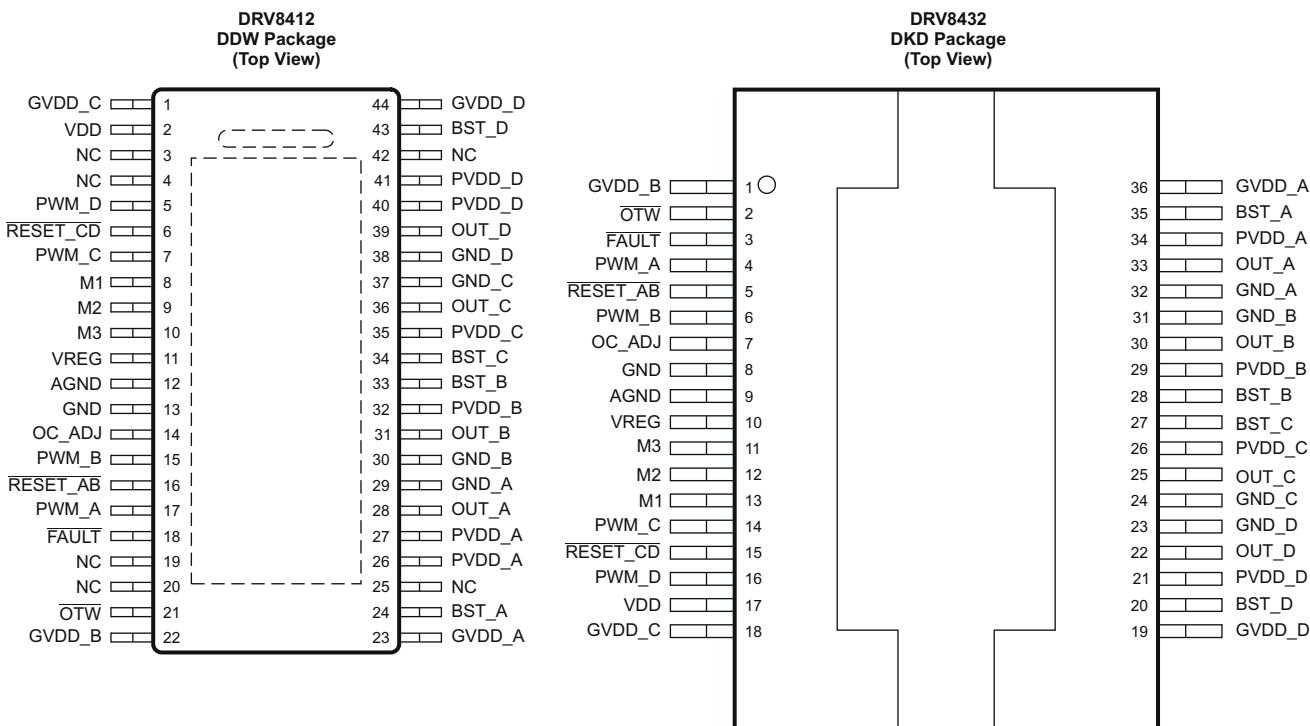

## 4 Pin Configuration and Functions

表 4-1. Pin Functions

| PIN    |                      |         | I/O TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                         |

|--------|----------------------|---------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | DRV8412              | DRV8432 |                         |                                                                                                                                                                                                                     |

| AGND   | 12                   | 9       | P                       | Analog ground                                                                                                                                                                                                       |

| BST_A  | 24                   | 35      | P                       | High side bootstrap supply (BST), external capacitor to OUT_A required                                                                                                                                              |

| BST_B  | 33                   | 28      | P                       | High side bootstrap supply (BST), external capacitor to OUT_B required                                                                                                                                              |

| BST_C  | 34                   | 27      | P                       | High side bootstrap supply (BST), external capacitor to OUT_C required                                                                                                                                              |

| BST_D  | 43                   | 20      | P                       | High side bootstrap supply (BST), external capacitor to OUT_D required                                                                                                                                              |

| GND    | 13                   | 8       | P                       | Ground                                                                                                                                                                                                              |

| GND_A  | 29                   | 32      | P                       | Power ground for half-bridge A                                                                                                                                                                                      |

| GND_B  | 30                   | 31      | P                       | Power ground for half-bridge B                                                                                                                                                                                      |

| GND_C  | 37                   | 24      | P                       | Power ground for half-bridge C                                                                                                                                                                                      |

| GND_D  | 38                   | 23      | P                       | Power ground for half-bridge D                                                                                                                                                                                      |

| GVDD_A | 23                   | 36      | P                       | Gate-drive voltage supply                                                                                                                                                                                           |

| GVDD_B | 22                   | 1       | P                       | Gate-drive voltage supply                                                                                                                                                                                           |

| GVDD_C | 1                    | 18      | P                       | Gate-drive voltage supply                                                                                                                                                                                           |

| GVDD_D | 44                   | 19      | P                       | Gate-drive voltage supply                                                                                                                                                                                           |

| M1     | 8                    | 13      | I                       | Mode selection pin                                                                                                                                                                                                  |

| M2     | 9                    | 12      | I                       | Mode selection pin                                                                                                                                                                                                  |

| M3     | 10                   | 11      | I                       | Reserved mode selection pin, AGND connection is recommended                                                                                                                                                         |

| NC     | 3, 4, 19, 20, 25, 42 | —       | —                       | No connection pin. Ground connection is recommended                                                                                                                                                                 |

| OC_ADJ | 14                   | 7       | O                       | Analog overcurrent programming pin, requires resistor to AGND                                                                                                                                                       |

| OTW    | 21                   | 2       | O                       | Overtemperature warning signal, open-drain, active-low. An internal pullup resistor to VREG (3.3 V) is provided on output. Level compliance for 5-V logic can be obtained by adding external pullup resistor to 5 V |

| OUT_A  | 28                   | 33      | O                       | Output, half-bridge A                                                                                                                                                                                               |

| OUT_B  | 31                   | 30      | O                       | Output, half-bridge B                                                                                                                                                                                               |

| OUT_C  | 36                   | 25      | O                       | Output, half-bridge C                                                                                                                                                                                               |

表 4-1. Pin Functions (続き)

| PIN         |         |         | I/O TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                       |

|-------------|---------|---------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME        | DRV8412 | DRV8432 |                         |                                                                                                                                                                                                   |

| OUT_D       | 39      | 22      | O                       | Output, half-bridge D                                                                                                                                                                             |

| PVDD_A      | 26, 27  | 34      | P                       | Power supply input for half-bridge A requires close decoupling capacitor to ground.                                                                                                               |

| PVDD_B      | 32      | 29      | P                       | Power supply input for half-bridge B requires close decoupling capacitor to ground.                                                                                                               |

| PVDD_C      | 35      | 26      | P                       | Power supply input for half-bridge C requires close decoupling capacitor to ground.                                                                                                               |

| PVDD_D      | 40, 41  | 21      | P                       | Power supply input for half-bridge D requires close decoupling capacitor to ground.                                                                                                               |

| PWM_A       | 17      | 4       | I                       | Input signal for half-bridge A                                                                                                                                                                    |

| PWM_B       | 15      | 6       | I                       | Input signal for half-bridge B                                                                                                                                                                    |

| PWM_C       | 7       | 14      | I                       | Input signal for half-bridge C                                                                                                                                                                    |

| PWM_D       | 5       | 16      | I                       | Input signal for half-bridge D                                                                                                                                                                    |

| RESET_AB    | 16      | 5       | I                       | Reset signal for half-bridge A and half-bridge B, active-low                                                                                                                                      |

| RESET_CD    | 6       | 15      | I                       | Reset signal for half-bridge C and half-bridge D, active-low                                                                                                                                      |

| FAULT       | 18      | 3       | O                       | Fault signal, open-drain, active-low. An internal pullup resistor to VREG (3.3 V) is provided on output. Level compliance for 5-V logic can be obtained by adding external pullup resistor to 5 V |

| VDD         | 2       | 17      | P                       | Power supply for digital voltage regulator requires capacitor to ground for decoupling.                                                                                                           |

| VREG        | 11      | 10      | P                       | Digital regulator supply filter pin requires 0.1- $\mu$ F capacitor to AGND.                                                                                                                      |

| THERMAL PAD | —       | N/A     | T                       | Solder the exposed thermal pad to the landing pad on the pcb. Connect landing pad to bottom side of pcb through via for better thermal dissipation. This pad should be connected to GND.          |

| HEAT SLUG   | N/A     | —       | T                       | Mount heat sink with thermal interface on top of the heat slug for best thermal performance.                                                                                                      |

(1) I = input, O = output, P = power, T = thermal

表 4-2. Mode Selection Pins

| MODE PINS |    |    | OUTPUT<br>CONFIGURATION | DESCRIPTION                                                                                                                          |

|-----------|----|----|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| M3        | M2 | M1 |                         |                                                                                                                                      |

| 0         | 0  | 0  | 2 FB or 4 HB            | Dual full bridges (two PWM inputs each full bridge) or four half bridges with cycle-by-cycle current limit                           |

| 0         | 0  | 1  | 2 FB or 4 HB            | Dual full bridges (two PWM inputs each full bridge) or four half bridges with OC latching shutdown (no cycle-by-cycle current limit) |

| 0         | 1  | 0  | 1 PFB                   | Parallel full bridge with cycle-by-cycle current limit                                                                               |

| 0         | 1  | 1  | 2 FB                    | Dual full bridges (one PWM input each full bridge with complementary PWM on second half bridge) with cycle-by-cycle current limit    |

| 1         | x  | x  | Reserved                |                                                                                                                                      |

## 5 Specifications

### 5.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                                                                         | MIN  | MAX                    | UNIT |

|---------------------------------------------------------------------------------------------------------|------|------------------------|------|

| VDD to GND                                                                                              | -0.3 | 13.2                   | V    |

| GVDD_X to GND                                                                                           | -0.3 | 13.2                   | V    |

| PVDD_X to GND_X <sup>(2)</sup>                                                                          | -0.3 | 70                     | V    |

| OUT_X to GND_X <sup>(2)</sup>                                                                           | -0.3 | 70                     | V    |

| BST_X to GND_X <sup>(2)</sup>                                                                           | -0.3 | 80                     | V    |

| Transient peak output current (per pin), pulse width limited by internal overcurrent protection circuit |      | 16                     | A    |

| Transient peak output current for latch shut down (per pin)                                             |      | 20                     | A    |

| VREG to AGND                                                                                            | -0.3 | 4.2                    | V    |

| GND_X to GND                                                                                            | -0.3 | 0.3                    | V    |

| GND to AGND                                                                                             | -0.3 | 0.3                    | V    |

| PWM_X to GND                                                                                            | -0.3 | V <sub>REG</sub> + 0.5 | V    |

| OC_ADJ, M1, M2, M3 to AGND                                                                              | -0.3 | 4.2                    | V    |

| RESET_X, FAULT, OTW to GND                                                                              | -0.3 | 7                      | V    |

| Continuous sink current (FAULT, OTW)                                                                    |      | 9                      | mA   |

| Operating junction temperature, T <sub>J</sub>                                                          | -40  | 150                    | °C   |

| Storage temperature, T <sub>stg</sub>                                                                   | -55  | 150                    |      |

(1) Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under [セクション 5.3](#). Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) These are the maximum allowed voltages for transient spikes. Absolute maximum DC voltages are lower.

### 5.2 ESD Ratings

|                                            | VALUE                                                                                    | UNIT    |

|--------------------------------------------|------------------------------------------------------------------------------------------|---------|

| V <sub>(ESD)</sub> Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(1)</sup> | ±1500 V |

(1) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 5.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                                                                                | MIN  | NOM | MAX  | UNIT |

|------------------------------------------------------------------------------------------------|------|-----|------|------|

| PVDD_X Half bridge X (A, B, C, or D) DC supply voltage                                         | 0    | 50  | 52.5 | V    |

| GVDD_X Supply for logic regulators and gate-drive circuitry                                    | 10.8 | 12  | 13.2 |      |

| VDD Digital regulator supply voltage                                                           | 10.8 | 12  | 13.2 |      |

| I <sub>O_PULSE</sub> Pulsed peak current per output pin (could be limited by thermal)          |      |     | 15   | A    |

| I <sub>O</sub> Continuous current per output pin (DRV8432)                                     |      |     | 9    | mA   |

| F <sub>SW</sub> PWM switching frequency                                                        |      |     | 500  | kHz  |

| R <sub>OCP_CBC</sub> OC programming resistor range in cycle-by-cycle current limit modes       | 24   | 200 |      | kΩ   |

| R <sub>OCP_OCL</sub> OC programming resistor range in OC latching shutdown modes               | 22   | 200 |      |      |

| C <sub>BST</sub> Bootstrap capacitor range                                                     | 33   | 220 |      | nF   |

| t <sub>ON_MIN</sub> Minimum PWM pulse duration, low side, for charging the Bootstrap capacitor |      | 50  |      | ns   |

| T <sub>A</sub> Operating ambient temperature                                                   | -40  | 85  |      | °C   |

## 5.4 Thermal Information

| THERMAL METRIC <sup>(1)</sup> |                                              | DRV8412        | DRV8432                  | UNIT<br>°C/W |

|-------------------------------|----------------------------------------------|----------------|--------------------------|--------------|

|                               |                                              | DDW<br>PACKAGE | DKD<br>PACKAGE           |              |

|                               |                                              | 44 PINS        | 36 PINS                  |              |

| $R_{\theta JA}$               | Junction-to-ambient thermal resistance       | 24.5           | 13.3<br>(with heat sink) |              |

| $R_{\theta JC(\text{top})}$   | Junction-to-case (top) thermal resistance    | 7.8            | 0.4                      |              |

| $R_{\theta JB}$               | Junction-to-board thermal resistance         | 5.5            | 13.3                     |              |

| $\Psi_{JT}$                   | Junction-to-top characterization parameter   | 0.1            | 0.4                      |              |

| $\Psi_{JB}$                   | Junction-to-board characterization parameter | 5.4            | 13.3                     |              |

| $R_{\theta JC(\text{bot})}$   | Junction-to-case (bottom) thermal resistance | 0.2            | N/A                      |              |

(1) for more information about traditional and new thermal metrics, see the *IC Package Thermal Metrics* application report, **SPRA953**.

## 5.5 Package Heat Dissipation Ratings

| PARAMETER                                                                     | DRV8412            | DRV8432                                                                                                                                             |

|-------------------------------------------------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| $R_{\theta JC}$ , junction-to-case (power pad / heat slug) thermal resistance | 1.1 °C/W           | 0.9 °C/W                                                                                                                                            |

| $R_{\theta JA}$ , junction-to-ambient thermal resistance                      | 25 °C/W            | This device is not intended to be used without a heatsink. Therefore, $R_{\theta JA}$ is not specified. See the <i>Thermal Information</i> section. |

| Exposed power pad / heat slug area                                            | 34 mm <sup>2</sup> | 80 mm <sup>2</sup>                                                                                                                                  |

## 5.6 Package Power Deratings (DRV8412) <sup>(1)</sup>

| PACKAGE            | $T_A = 25^\circ\text{C}$<br>POWER<br>RATING | DERATING<br>FACTOR<br>ABOVE $T_A = 25^\circ\text{C}$ | $T_A = 70^\circ\text{C}$ POWER<br>RATING | $T_A = 85^\circ\text{C}$ POWER<br>RATING | $T_A = 125^\circ\text{C}$ POWER<br>RATING |

|--------------------|---------------------------------------------|------------------------------------------------------|------------------------------------------|------------------------------------------|-------------------------------------------|

| 44-PIN TSSOP (DDW) | 5.0 W                                       | 40.0 mW/°C                                           | 3.2 W                                    | 2.6 W                                    | 1.0 W                                     |

(1) Based on EVM board layout

## 5.7 Electrical Characteristics

$T_A = 25^\circ\text{C}$ ,  $\text{PVDD} = 50\text{V}$ ,  $\text{GVDD} = \text{VDD} = 12\text{V}$ ,  $f_{\text{SW}} = 400\text{kHz}$ , unless otherwise noted. All performance is in accordance with recommended operating conditions unless otherwise specified.

| PARAMETER                                                 | TEST CONDITIONS                                                                             | MIN                                                                                                         | TYP  | MAX  | UNIT             |

|-----------------------------------------------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------|------|------------------|

| <b>INTERNAL VOLTAGE REGULATOR AND CURRENT CONSUMPTION</b> |                                                                                             |                                                                                                             |      |      |                  |

| $V_{\text{REG}}$                                          | Voltage regulator, only used as a reference node                                            | 2.95                                                                                                        | 3.3  | 3.65 | V                |

| $I_{\text{VDD}}$                                          | Idle, reset mode                                                                            | 9                                                                                                           | 12   |      | mA               |

|                                                           | Operating, 50% duty cycle                                                                   | 10.5                                                                                                        |      |      |                  |

| $I_{\text{GVDD\_X}}$                                      | Reset mode                                                                                  | 1.7                                                                                                         | 2.5  |      | mA               |

|                                                           | Operating, 50% duty cycle                                                                   | 8                                                                                                           |      |      |                  |

| $I_{\text{PVDD\_X}}$                                      | Half-bridge X (A, B, C, or D) idle current                                                  | 0.7                                                                                                         | 1    |      | mA               |

| <b>OUTPUT STAGE</b>                                       |                                                                                             |                                                                                                             |      |      |                  |

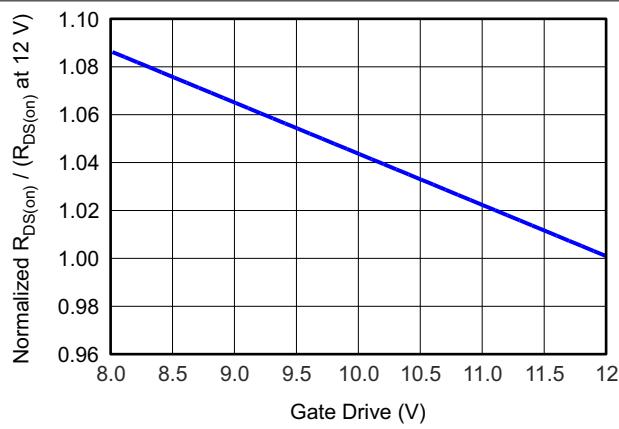

| $R_{\text{DS(on)}}$                                       | MOSFET drain-to-source resistance, low side (LS)                                            | $T_J = 25^\circ\text{C}$ , $\text{GVDD} = 12\text{V}$ , Includes metallization bond wire and pin resistance | 110  |      | $\text{m}\Omega$ |

|                                                           | MOSFET drain-to-source resistance, high side (HS)                                           | $T_J = 25^\circ\text{C}$ , $\text{GVDD} = 12\text{V}$ , Includes metallization bond wire and pin resistance | 110  |      |                  |

| $V_F$                                                     | Diode forward voltage drop                                                                  | $T_J = 25^\circ\text{C} - 125^\circ\text{C}$ , $I_O = 5\text{A}$                                            | 1    |      | V                |

| $t_R$                                                     | Output rise time                                                                            | Resistive load, $I_O = 5\text{A}$                                                                           | 14   |      | ns               |

| $t_F$                                                     | Output fall time                                                                            | Resistive load, $I_O = 5\text{A}$                                                                           | 14   |      |                  |

| $t_{\text{PD\_ON}}$                                       | Propagation delay when FET is on                                                            | Resistive load, $I_O = 5\text{A}$                                                                           | 38   |      |                  |

| $t_{\text{PD\_OFF}}$                                      | Propagation delay when FET is off                                                           | Resistive load, $I_O = 5\text{A}$                                                                           | 38   |      |                  |

| $t_{\text{DT}}$                                           | Dead time between HS and LS FETs                                                            | Resistive load, $I_O = 5\text{A}$                                                                           | 5.5  |      |                  |

| <b>I/O PROTECTION</b>                                     |                                                                                             |                                                                                                             |      |      |                  |

| $V_{\text{uvp,G}}$                                        | Gate supply voltage $\text{GVDD\_X}$ undervoltage protection threshold                      |                                                                                                             | 8.5  |      | V                |

| $V_{\text{uvp,hyst}}^{(1)}$                               | Hysteresis for gate supply undervoltage event                                               |                                                                                                             | 0.8  |      |                  |

| $\text{OTW}^{(1)}$                                        | Overtemperature warning                                                                     |                                                                                                             | 115  | 125  | 135              |

| $\text{OTW}_{\text{hyst}}^{(1)}$                          | Hysteresis temperature to reset $\text{OTW}$ event                                          |                                                                                                             | 25   |      | $^\circ\text{C}$ |

| $\text{OTSD}^{(1)}$                                       | Overtemperature shut down                                                                   |                                                                                                             | 150  |      |                  |

| $\text{OTE-OTW}_{\text{differential}}^{(1)}$              | OTE-OTW overtemperature detect temperature difference                                       |                                                                                                             | 25   |      |                  |

| $\text{OTSD}_{\text{HYST}}^{(1)}$                         | Hysteresis temperature for <b>FAULT</b> to be released following an OTSD event              |                                                                                                             | 25   |      |                  |

| $I_{\text{oc}}$                                           | Overcurrent limit protection                                                                | Resistor—programmable, nominal, $R_{\text{OCP}} = 27\text{k}\Omega$                                         | 9.7  |      | A                |

| $I_{\text{OCT}}$                                          | Overcurrent response time                                                                   | Time from application of short condition to Hi-Z of affected FET(s)                                         | 250  |      | ns               |

| $R_{\text{PD}}$                                           | Internal pulldown resistor at the output of each half-bridge                                | Connected when <b>RESET_AB</b> or <b>RESET_CD</b> is active to provide bootstrap capacitor charge           | 1    |      | $\text{k}\Omega$ |

| <b>STATIC DIGITAL SPECIFICATIONS</b>                      |                                                                                             |                                                                                                             |      |      |                  |

| $V_{\text{IH}}$                                           | High-level input voltage                                                                    | PWM_A, PWM_B, PWM_C, PWM_D, M1, M2, M3                                                                      | 2    | 3.6  | V                |

| $V_{\text{IH}}$                                           | High-level input voltage                                                                    | <b>RESET_AB</b> , <b>RESET_CD</b>                                                                           | 2    | 5.5  |                  |

| $V_{\text{IL}}$                                           | Low-level input voltage                                                                     | PWM_A, PWM_B, PWM_C, PWM_D, M1, M2, M3, <b>RESET_AB</b> , <b>RESET_CD</b>                                   |      | 0.8  |                  |

| $I_{\text{lkg}}$                                          | Input leakage current                                                                       |                                                                                                             | -100 | 100  | $\mu\text{A}$    |

| <b>OTW / FAULT</b>                                        |                                                                                             |                                                                                                             |      |      |                  |

| $R_{\text{INT\_PU}}$                                      | Internal pullup resistance, $\text{OTW}$ to $\text{VREG}$ , $\text{FAULT}$ to $\text{VREG}$ |                                                                                                             | 20   | 26   | 35               |

| $V_{\text{OH}}$                                           | High-level output voltage                                                                   | Internal pullup resistor only                                                                               | 2.95 | 3.3  | 3.65             |

|                                                           |                                                                                             | External pullup of $4.7\text{k}\Omega$ to $5\text{V}$                                                       | 4.5  | 5    | V                |

| $V_{\text{OL}}$                                           | Low-level output voltage                                                                    | $I_O = 4\text{mA}$                                                                                          | 0.2  | 0.4  |                  |

(1) Specified by design

## 5.8 Typical Characteristics

图 5-1. Efficiency vs Switching Frequency (DRV8432)

图 5-2. Normalized RDS(On) vs Gate Drive

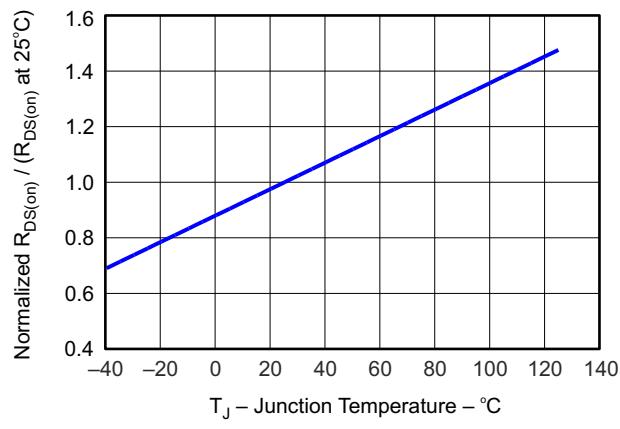

图 5-3. Normalized Rds(On) vs Junction Temperature

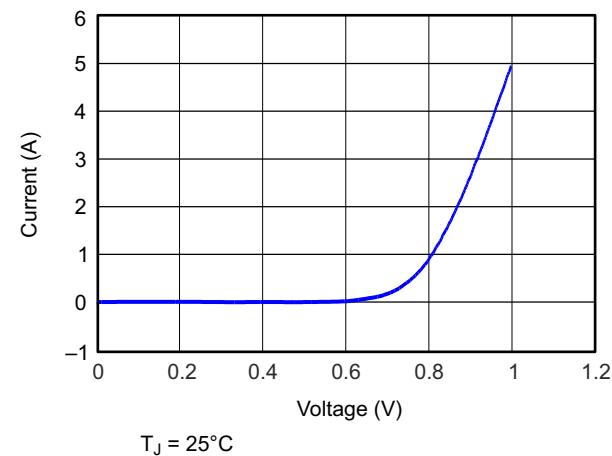

图 5-4. Drain To Source Diode Forward On Characteristics

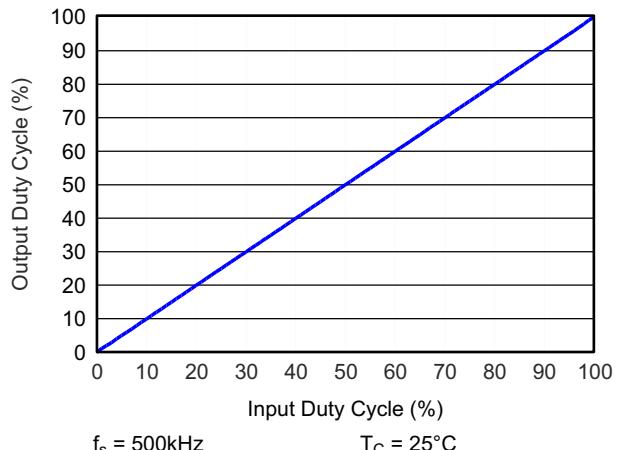

图 5-5. Output Duty Cycle vs Input Duty Cycle

## 6 Detailed Description

### 6.1 Overview

The DRV841x2 is a high performance, integrated dual full bridge motor driver with an advanced protection system.

Because of the low  $R_{DS(on)}$  of the H-Bridge MOSFETs and intelligent gate drive design, the efficiency of these motor drivers can be up to 97%, which enables the use of smaller power supplies and heatsinks, and are good candidates for energy efficient applications.

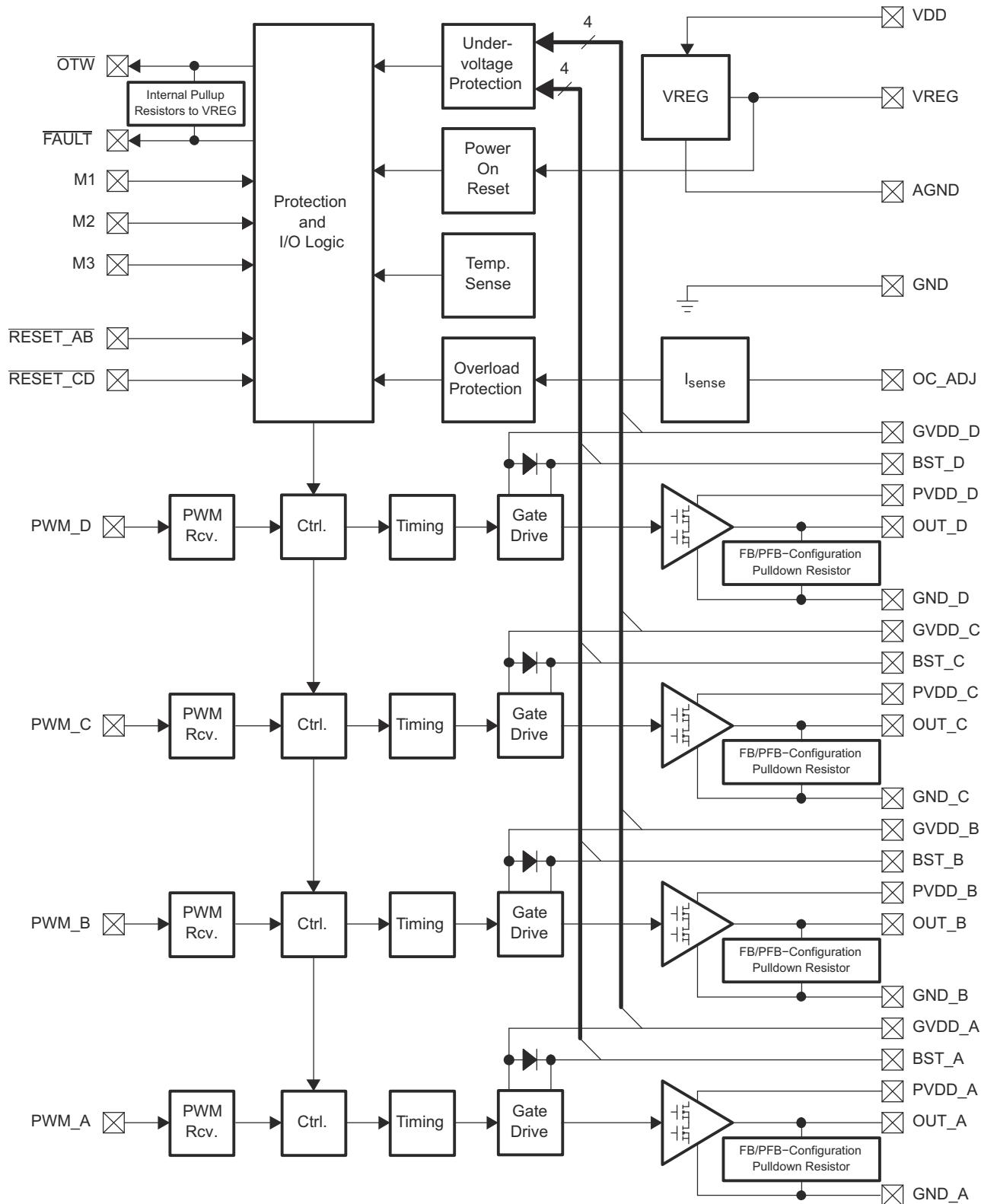

## 6.2 Functional Block Diagram

## 6.3 Feature Description

### 6.3.1 Error Reporting

The **FAULT** and **OTW** pins are both active-low, open-drain outputs. Their function is for protection-mode signaling to a PWM controller or other system-control device.

Any fault resulting in device shutdown, such as overtemperature shutdown, overcurrent shutdown, or undervoltage protection, is signaled by the **FAULT** pin going low. Also, **OTW** goes low when the device junction temperature exceeds 125°C (see [表 6-1](#)).

**表 6-1. Protection Mode Signal Descriptions**

| FAULT | OTW | DESCRIPTION                                                                                                          |

|-------|-----|----------------------------------------------------------------------------------------------------------------------|

| 0     | 0   | Overtemperature warning and (overtemperature shut-down or overcurrent shut-down or undervoltage protection) occurred |

| 0     | 1   | Overcurrent shut-down or GVDD undervoltage protection occurred                                                       |

| 1     | 0   | Overtemperature warning                                                                                              |

| 1     | 1   | Device under normal operation                                                                                        |

TI recommends monitoring the **OTW** signal using the system microcontroller and responding to an **OTW** signal by reducing the load current to prevent further heating of the device resulting in device overtemperature shutdown (OTSD).

To reduce external component count, an internal pullup resistor to VREG (3.3V) is provided on both **FAULT** and **OTW** outputs. Level compliance for 5V logic can be obtained by adding external pullup resistors to 5V (see the *Electrical Characteristics* section of this data sheet for further specifications).

### 6.3.2 Device Protection System

The DRV841x2 contains advanced protection circuitry carefully designed to facilitate system integration and ease of use, as well as to safeguard the device from permanent failure due to a wide range of fault conditions such as short circuits, overcurrent, overtemperature, and undervoltage. The DRV841x2 responds to a fault by immediately setting the half bridge outputs in a high-impedance (Hi-Z) state and asserting the **FAULT** pin low. In situations other than overcurrent or overtemperature, the device automatically recovers when the fault condition has been removed or the gate supply voltage has increased. For highest possible reliability, reset the device externally no sooner than 1 second after the shutdown when recovering from an overcurrent shut down (OCSD) or OTSD fault.

#### 6.3.2.1 Bootstrap Capacitor Undervoltage Protection

When the device runs at a low switching frequency (for example, less than 10 kHz with a 100-nF bootstrap capacitor), the bootstrap capacitor voltage might not be able to maintain a proper voltage level for the high-side gate driver. A bootstrap capacitor undervoltage protection circuit (BST\_UVP) prevents potential failure of the high-side MOSFET. When the voltage on the bootstrap capacitors is less than the required value for safe operation, the DRV841x2 initiates bootstrap capacitor recharge sequences (turn off high side FET for a short period) until the bootstrap capacitors are properly charged for safe operation. This function may also be activated when PWM duty cycle is too high (for example, less than 20ns off time at 10kHz). Note that bootstrap capacitor might not be able to be charged if no load or extremely light load is presented at output during BST\_UVP operation, so it is recommended to turn on the low side FET for at least 50 ns for each PWM cycle to avoid BST\_UVP operation if possible.

For applications with lower than 10-kHz switching frequency and not to trigger BST\_UVP protection, a larger bootstrap capacitor can be used (for example, 1- $\mu$ F capacitor for 800-Hz operation). When using a bootstrap cap larger than 220 nF, it is recommended to add 5- $\Omega$  resistors between 12-V GVDD power supply and GVDD\_X pins to limit the inrush current on the internal bootstrap circuitry.

### 6.3.2.2 Overcurrent (OC) Protection

The DRV841x2 has independent, fast-reacting current detectors with programmable trip threshold (OC threshold) on all high-side and low-side power-stage FETs. There are two settings for OC protection through mode selection pins: cycle-by-cycle (CBC) current limiting mode and OC latching (OCL) shut down mode.

In CBC current limiting mode, the detector outputs are monitored by two protection systems. The first protection system controls the power stage to prevent the output current from further increasing, that is, performing as a CBC current-limiting function rather than prematurely shutting down the device. This feature could effectively limit the inrush current during motor start-up or transient without damaging the device. During short to power and short to ground conditions, the current limit circuitry might not be able to control the current to a proper level, a second protection system triggers a latching shutdown, resulting in the related half bridge being set in the high-impedance (Hi-Z) state. Current limiting and overcurrent protection are independent for half-bridges A, B, C, and, D, respectively.

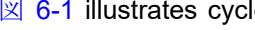

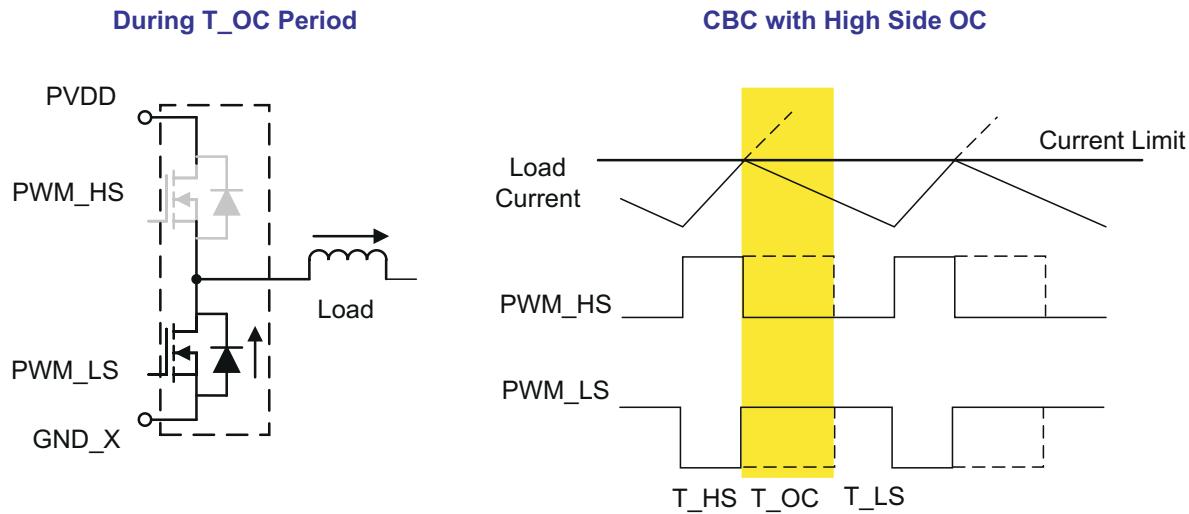

6-1 illustrates cycle-by-cycle operation with high side OC event and  6-2 shows cycle-by-cycle operation with low side OC. Dashed lines are the operation waveforms when no CBC event is triggered and solid lines show the waveforms when CBC event is triggered. In CBC current limiting mode, when low side FET OC is detected, the device turns off the affected low side FET and keep the high side FET at the same half bridge off until the next PWM cycle. When high side FET OC is detected, the device turns off the affected high side FET and turn on the low side FET at the half bridge until next PWM cycle.

It is important to note that if the input to a half bridge is held to a constant value when an over current event occurs in CBC, then the associated half bridge will be in a HI-Z state upon the over current event ending. Cycling IN\_X allows OUT\_X to resume normal operation.

In OC latching shut down mode, the CBC current limit and error recovery circuits are disabled and an overcurrent condition will cause the device to shutdown immediately. After shutdown, RESET\_AB and/or RESET\_CD must be asserted to restore normal operation after the overcurrent condition is removed.

For added flexibility, the OC threshold is programmable using a single external resistor connected between the OC\_ADJ pin and GND pin. See [表 6-2](#) for information on the correlation between programming-resistor value and the OC threshold. The values in [表 6-2](#) show typical OC thresholds for a given resistor. Assuming a fixed resistance on the OC\_ADJ pin across multiple devices, a 20% device-to-device variation in OC threshold measurements is possible. Therefore, this feature is designed for system protection and not for precise current control. Note that a properly functioning overcurrent detector assumes the presence of a proper inductor or power ferrite bead at the power-stage output. Short-circuit protection is not guaranteed with direct short at the output pins of the power stage.

For normal operation, inductance in motor (assume larger than 10 $\mu$ H) is sufficient to provide low di/dt output (for example, for EMI) and proper protection during overload condition (CBC current limiting feature). So no additional output inductors are needed during normal operation.

However, during a short condition, the motor (or other load) is shorted, so the load inductance is not present in the system anymore; the current in the device can reach such a high level that may exceed the abs max current rating due to extremely low inductance in the short circuit path and high di/dt before oc detection circuit kicks in. So, a ferrite bead or inductor is recommended to use the short-circuit protection feature in DRV841x2. With an external inductance or ferrite bead, the current rises at a much slower rate and reach a lower current level before oc protection starts. The device then either operates CBC current limit or OC shut down automatically (when current is well above the current limit threshold) to protect the system.

For a system that has limited space, a power ferrite bead can be used instead of an inductor. The current rating of ferrite bead has to be higher than the RMS current of the system at normal operation. A ferrite bead designed for very high frequency is NOT recommended. A minimum impedance of 10 $\Omega$  or higher is recommended at 10MHz or lower frequency to effectively limit the current rising rate during short circuit condition.

The TDK MPZ2012S300A (with size of 0805 inch type) have been tested in our system to meet a short circuit condition in the DRV8412. But other ferrite beads that have similar frequency characteristics can be used as well.

For higher power applications, such as in the DRV8432, there might be limited options to select suitable ferrite bead with high current rating. If an adequate ferrite bead cannot be found, an inductor can be used.

The inductance can be calculated as:

$$Loc\_min = \frac{PVDD \cdot Toc\_delay}{Ipeak - Iave} \quad (1)$$

where

- $Toc\_delay = 250\text{nS}$

- $Ipeak = 15\text{A}$  (below abs max rating)

Because an inductor usually saturates after reaching the current rating, the recommendation is to use an inductor with a doubled value or an inductor with a current rating well above the operating condition.

**表 6-2. Programming-Resistor Values and OC Threshold**

| OC-ADJUST RESISTOR VALUES (kΩ) | MAXIMUM CURRENT BEFORE OC OCCURS (A) |

|--------------------------------|--------------------------------------|

| 22 <sup>(1)</sup>              | 11.6                                 |

| 24                             | 10.7                                 |

| 27                             | 9.7                                  |

| 30                             | 8.8                                  |

| 36                             | 7.4                                  |

(1) Recommended to use in OC Latching Mode Only

### 6.3.2.3 Overtemperature Protection

The DRV841x2 has a two-level temperature-protection system that asserts an active-low warning signal ( $\overline{OTW}$ ) when the device junction temperature exceeds 125°C (nominal) and, if the device junction temperature exceeds 150°C (nominal), the device is put into thermal shutdown, resulting in all half-bridge outputs being set in the high-impedance (Hi-Z) state and  $\overline{FAULT}$  being asserted low. OTSD is latched in this case and  $\overline{RESET\_AB}$  and  $\overline{RESET\_CD}$  must be asserted low to clear the latch.

### 6.3.2.4 Undervoltage Protection (UVP) and Power-On Reset (POR)

The UVP and POR circuits of the DRV841x2 fully protect the device in any power-up/down and brownout situation. While powering up, the POR circuit resets the overcurrent circuit and ensures that all circuits are fully operational when the  $GVDD_X$  and  $VDD$  supply voltages reach 9.8 V (typical). Although  $GVDD_X$  and  $VDD$  are independently monitored, a supply voltage drop below the UVP threshold on any  $VDD$  or  $GVDD_X$  pin results in all half-bridge outputs immediately being set in the high-impedance (Hi-Z) state and  $\overline{FAULT}$  being asserted low. The device automatically resumes operation when all supply voltage on the bootstrap capacitors have increased above the UVP threshold.

### 6.3.3 Device Reset

Two reset pins are provided for independent control of half-bridges A/B and C/D. When  $\overline{RESET\_AB}$  is asserted low, all four power-stage FETs in half-bridges A and B are forced into a high-impedance (Hi-Z) state. Likewise, asserting  $\overline{RESET\_CD}$  low forces all four power-stage FETs in half-bridges C and D into a high-impedance state. To accommodate bootstrap charging prior to switching start, asserting the reset inputs low enables weak pulldown of the half-bridge outputs.

A rising-edge transition on reset input allows the device to resume operation after a shut-down fault. For example, when either or both half-bridge A and B have OC shutdown, a low to high transition of RESET\_AB pin clears the fault and FAULT pin; when either or both half-bridge C and D have OC shutdown, a low to high transition of RESET\_CD pin will clear the fault and FAULT pin as well. When an OTSD occurs, both RESET\_AB and RESET\_CD need to have a low to high transition to clear the fault and FAULT signal.

## 6.4 Device Functional Modes

The DRV841x2 supports four different modes of operation:

1. Dual full bridges (FB) (two PWM inputs each full bridge) or four half bridges (HB) with CBC current limit

2. Dual full bridges (two PWM inputs each full bridge) or four half bridges with OC latching shutdown (no CBC current limit)

3. Parallel full bridge (PFB) with CBC current limit

4. Dual full bridges (one PWM input each full bridge) with CBC current limit

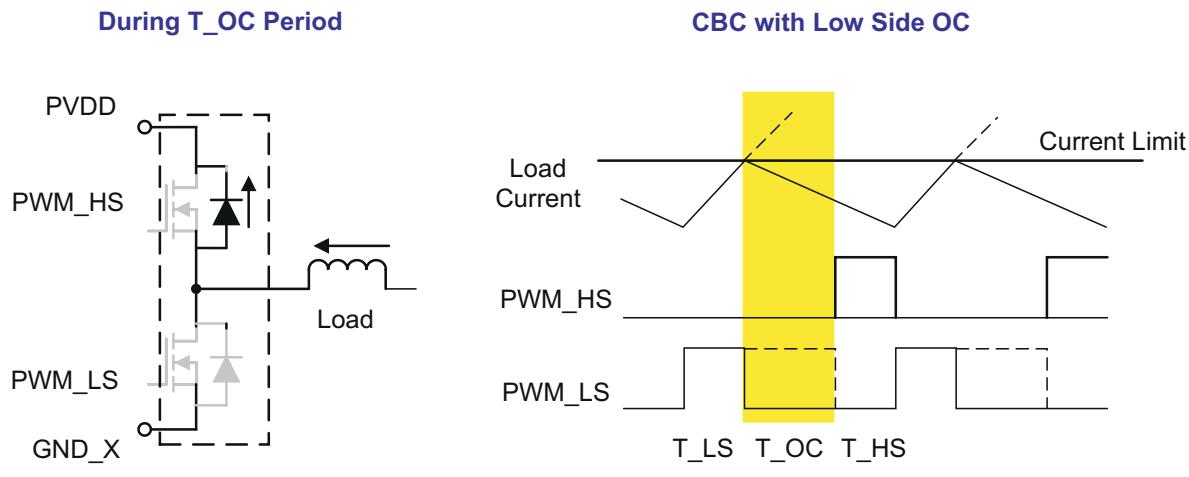

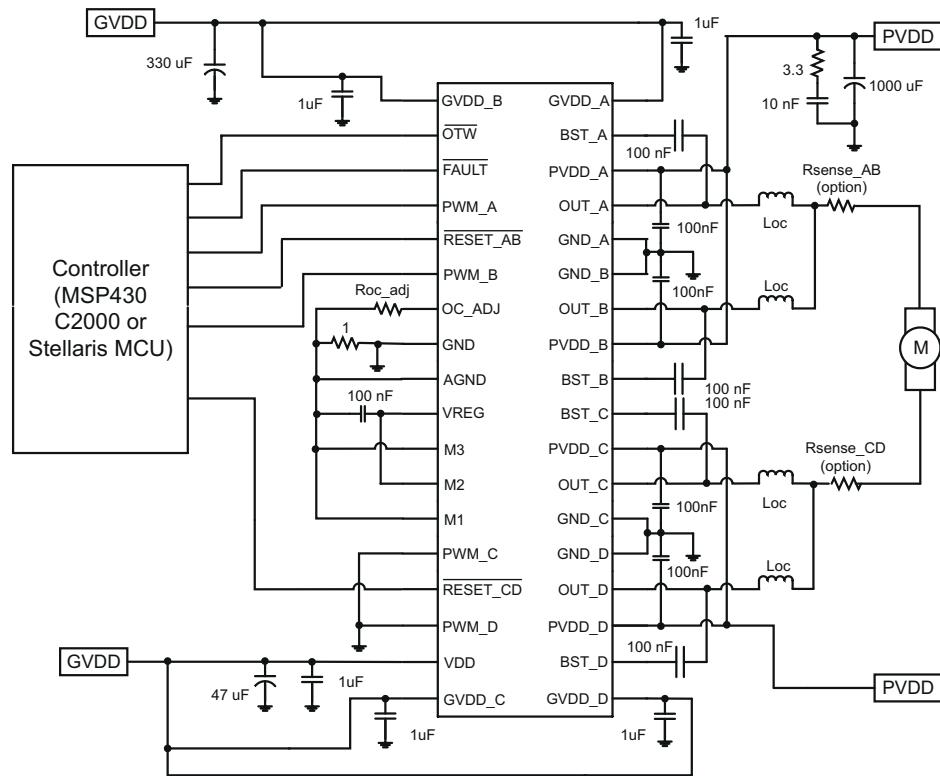

In mode 1 and 2, PWM\_A controls half bridge A, PWM\_B controls half bridge B, and so forth [図 7-1](#) shows an application example for full bridge mode operation.

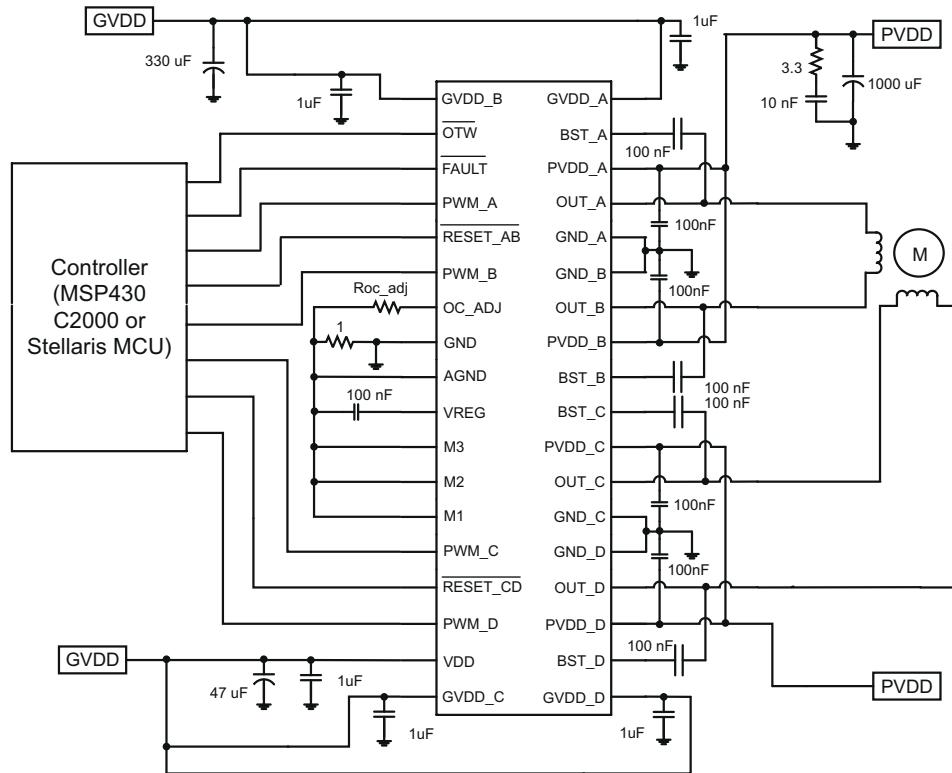

In parallel full bridge mode (mode 3), PWM\_A controls both half bridges A and B, and PWM\_B controls both half bridges C and D, while PWM\_C and PWM\_D pins are not used (recommended to connect to ground). Bridges A and B are synchronized internally (even during CBC), and so are bridges C and D. OUT\_A and OUT\_B should be connected together and OUT\_C and OUT\_D should be connected together after the output inductor or ferrite bead. If RESET\_AB or RESET\_CD are low, all four outputs become high-impedance. [図 7-8](#) shows an example of parallel full bridge mode connection.

In mode 4, one PWM signal controls one full bridge to relieve some I/O resource from MCU, that is, PWM\_A controls half bridges A and B and PWM\_C controls half bridges C and D. In this mode, the operation of half bridge B is complementary to half bridge A, and the operation of half bridge D is complementary to half bridge C. For example, when PWM\_A is high, high side FET in half bridge A and low side FET in half bridge B will be on and low side FET in half bridge A and high side FET in half bridge B will be off. Since PWM\_B and PWM\_D pins are not used in this mode, it is recommended to connect them to ground.

In operation modes 1, 2, and 4 (CBC current limit is used), once the CBC current limit is hit, the driver will be deactivated until the next PWM cycle starts. However, in order for the output to be recovered, the PWM input corresponding to that driver in CBC must be toggled. Because of this, CBC mode does not support operation when one half-bridge PWM input is tied to dc logic level.

Because each half bridge has independent supply and ground pins, a shunt sensing resistor can be inserted between PVDD to PVDD\_X or GND\_X to GND (ground plane). A high side shunt resistor between PVDD and PVDD\_X is recommended for differential current sensing because a high bias voltage on the low side sensing could affect device operation. If low side sensing has to be used, a shunt resistor value of 10 mΩ or less or sense voltage 100mV or less is recommended.

図 6-1. Cycle-by-Cycle Operation With High-Side OC

図 6-2. Cycle-by-Cycle Operation With Low-Side OC

## Application and Implementation

### 注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## 1 Application Information

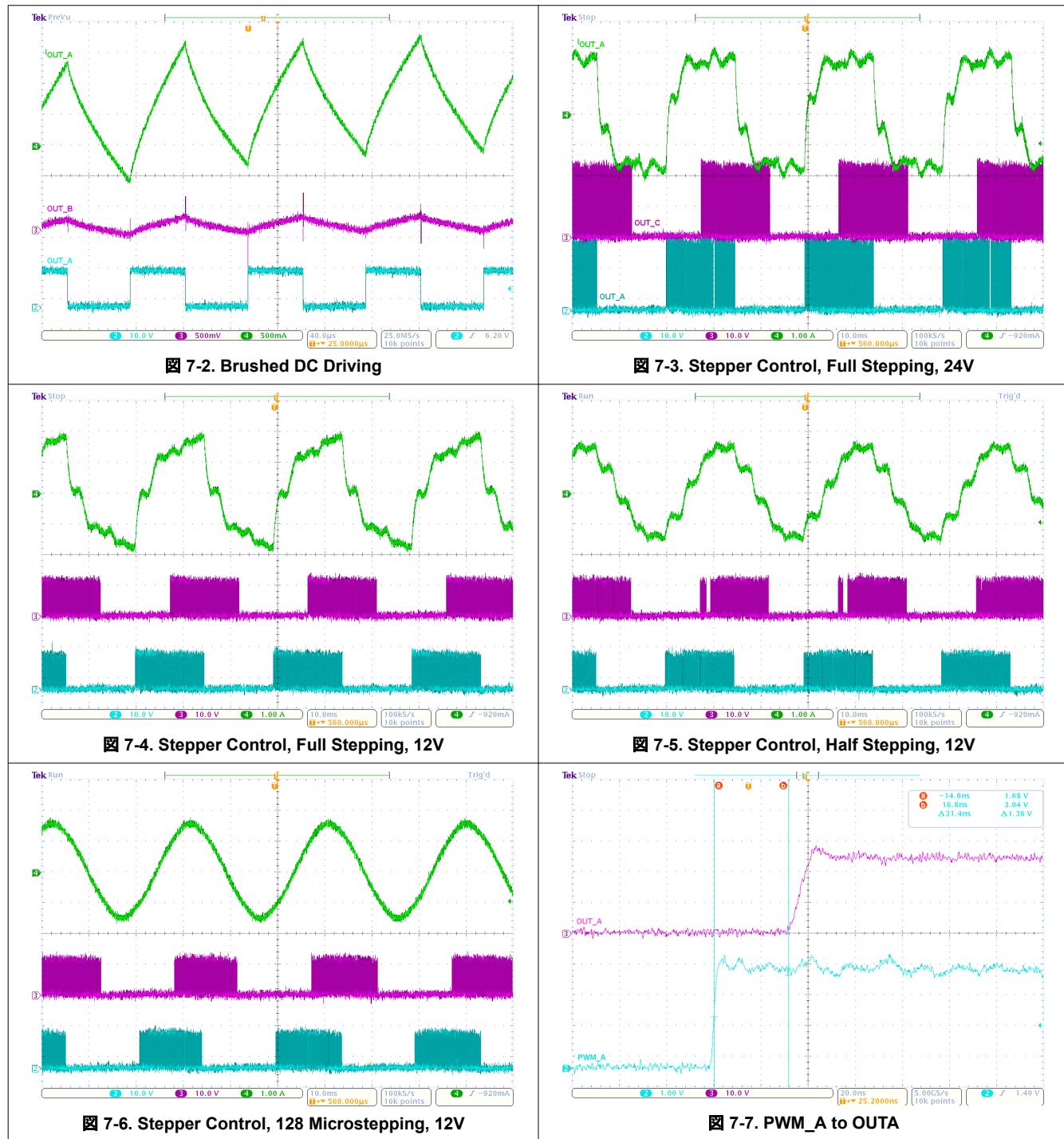

The DRV841x2 devices are typically used to drive 2 brushed DC or 1 stepper motor.

The DRV841x2 can be used for stepper motor applications as illustrated in [図 7-9](#); the devices can be also used in three phase permanent magnet synchronous motor (PMSM) and sinewave brushless DC motor applications.

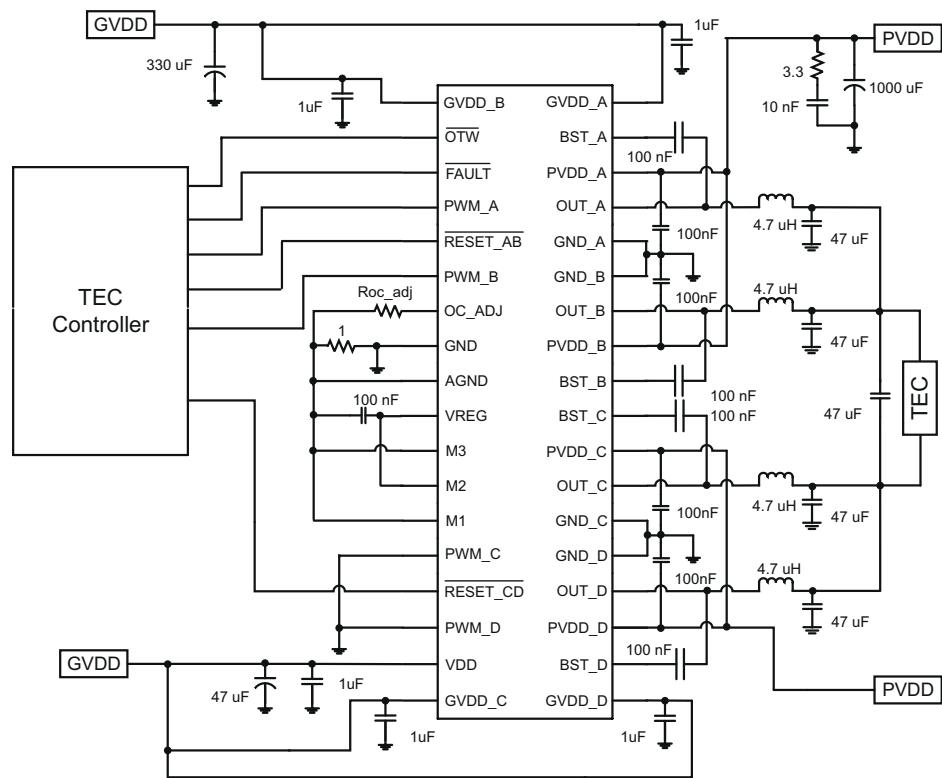

[図 7-10](#) shows an example of a TEC driver application. The same configuration can also be used for DC output applications.

## 2 Typical Applications

### 2.1 Full Bridge Mode Operation

**図 7-1. Application Diagram Example for Full Bridge Mode Operation Schematic**

## 2.1.1 Design Requirements

This section describes design considerations.

**表 7-1. Design Parameters**

| DESIGN PARAMETER             | REFERENCE         | EXAMPLE VALUE        |

|------------------------------|-------------------|----------------------|

| Motor voltage                | PVDD_x            | 24V                  |

| Motor current (peak and RMS) | I <sub>PVDD</sub> | 6A peak, 3A RMS      |

| Overshoot threshold          | OC <sub>TH</sub>  | OC_ADJ = 27kΩ, 9.7A  |

| Bridge mode                  | M1M2              | Parallel full bridge |

## 2.1.2 Detailed Design Procedure

### 2.1.2.1 Motor Voltage

Higher voltages generally have the advantage of causing current to change faster through the inductive windings, which allows for higher RPMs. Lower voltages allow for more accurate control of phase currents.

### 2.1.2.2 Current Requirement of 12V Power Supply

The DRV83x2 requires a 12V power supply for GVDD and VDD pins. The total supply current is relatively low at room temperature (less than 50mA), but the current could increase significantly when the device temperature goes too high (for example, above 125°C), especially at heavy load conditions due to substrate current collection by 12V guard rings. TI recommends designing the 12V power supply with a current capability at least 5-10% of the load current, and no less than 100mA for the device performance across all temperature ranges.

### 2.1.2.3 Voltage of Decoupling Capacitor

The voltage of the decoupling capacitors should be selected in accordance with good design practices. Temperature, ripple current, and voltage overshoot must be considered. The high frequency decoupling capacitor should use ceramic capacitor with X5R or better rating. For a 50V application, a minimum voltage rating of 63V is recommended.

### 2.1.2.4 Overcurrent Threshold

When choosing the resistor value for OC\_ADJ, consider the peak current allowed under normal system behavior, the resistor tolerance, and that 表 6-2 currents have a ±10% tolerance. For example, if 6A is the highest system current allowed across all normal behavior, a 27kΩ OC\_ADJ resistor with 10% tolerance is a reasonable choice, as it would set the OC<sub>TH</sub> to approximately 8A to 12A.

### 2.1.2.5 Sense Resistor

For optimal performance, the sense resistor must be:

- Surface-mount

- Low inductance

- Rated for high enough power

- Placed closely to the motor driver

The power dissipated by the sense resistor equals  $I_{RMS}^2 \times R$ . For example, if peak motor current is 3A, RMS motor current is 2A, and a 0.05Ω sense resistor is used, the resistor will dissipate  $2A^2 \times 0.05\Omega = 0.2W$ . The power increases quickly with higher current levels.

Resistors typically have a rated power within some ambient temperature range, along with a de-rated power curve for high ambient temperatures. When a PCB is shared with other components generating heat, margin should be added. Always measure the actual sense resistor temperature in a final system, along with the power MOSFETs, as those are often the hottest components.

Because power resistors are larger and more expensive than standard resistors, use multiple standard resistors in parallel, between the sense node and ground. This distributes the current and heat dissipation.

### 2.1.3 Application Curves

## 2.2 Parallel Full Bridge Mode Operation

PWM\_A controls OUT\_A and OUT\_B; PWM\_B controls OUT\_C and OUT\_D.

図 7-8. Application Diagram Example for Parallel Full Bridge Mode Operation Schematic

### 2.3 Stepper Motor Operation

図 7-9. Application Diagram Example for Stepper Motor Operation Schematic

## 2.4 TEC Driver

図 7-10. Application Diagram Example for TEC Driver Schematic

## 2.5 LED Lighting Driver

図 7-11. Application Diagram Example for LED Lighting Driver Schematic

## 3 Power Supply Recommendations

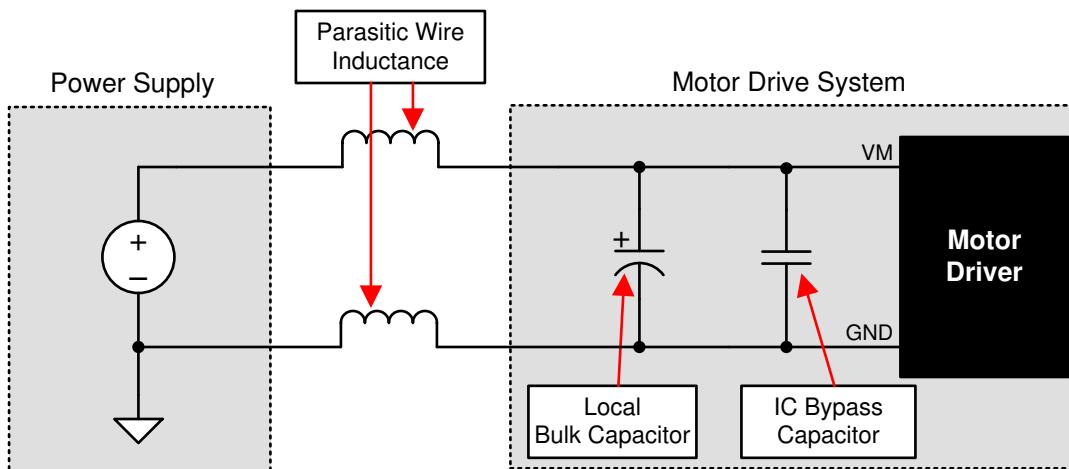

### 3.1 Bulk Capacitance

Having an appropriate local bulk capacitance is an important factor in motor drive system design. It is generally beneficial to have more bulk capacitance, while the disadvantages are increased cost and physical size.

The amount of local capacitance needed depends on a variety of factors, including:

- The highest current required by the motor system

- The power supply capacitance and ability to source current

- The amount of parasitic inductance between the power supply and motor system

- The acceptable voltage ripple

- The type of motor used (Brushed DC, Brushless DC, Stepper)

- The motor braking method

The inductance between the power supply and the motor drive system limits the rate current can change from the power supply. If the local bulk capacitance is too small, the system responds to excessive current demands or dumps from the motor with a change in voltage. When adequate bulk capacitance is used, the motor voltage remains stable and high current can be quickly supplied.

The data sheet provides a recommended value, but system-level testing is required to determine the appropriate sized bulk capacitor.

図 7-12. Example Setup of Motor Drive System With External Power Supply

The voltage rating for bulk capacitors should be higher than the operating voltage, to provide margin for cases when the motor transfers energy to the supply.

### 3.2 Power Supplies

To facilitate system design, the DRV841x2 needs only a 12V supply in addition to H-Bridge power supply (PVDD). An internal voltage regulator provides suitable voltage levels for the digital and low-voltage analog circuitry. Additionally, the high-side gate drive requires a floating voltage supply, which is accommodated by built-in bootstrap circuitry requiring external bootstrap capacitor.

To provide symmetrical electrical characteristics, the PWM signal path, including gate drive and output stage, is designed as identical, independent half-bridges. For this reason, each half-bridge has a separate gate drive supply (GVDD\_X), a bootstrap pin (BST\_X), and a power-stage supply pin (PVDD\_X). Furthermore, an additional pin (VDD) is provided as supply for all common circuits. Special attention should be paid to place all decoupling capacitors as close to their associated pins as possible. In general, inductance between the power supply pins and decoupling capacitors must be avoided. Furthermore, decoupling capacitors need a short ground path back to the device.

For a properly functioning bootstrap circuit, a small ceramic capacitor (an X5R or better) must be connected from each bootstrap pin (BST\_X) to the power-stage output pin (OUT\_X). When the power-stage output is low, the bootstrap capacitor is charged through an internal diode connected between the gate-drive power-supply pin (GVDD\_X) and the bootstrap pin. When the power-stage output is high, the bootstrap capacitor potential is shifted above the output potential and thus provides a suitable voltage supply for the high-side gate driver. In an application with PWM switching frequencies in the range from 10kHz to 500kHz, the use of 100-nF ceramic capacitors (X5R or better), size 0603 or 0805, is recommended for the bootstrap supply. These 100nF capacitors ensure sufficient energy storage, even during minimal PWM duty cycles, to keep the high-side power stage FET fully turned on during the remaining part of the PWM cycle. In an application running at a switching frequency lower than 10 kHz, the bootstrap capacitor might need to be increased in value.

Special attention should be paid to the power-stage power supply; this includes component selection, PCB placement, and routing. As indicated, each half-bridge has independent power-stage supply pin (PVDD\_X). For optimal electrical performance, EMI compliance, and system reliability, it is important that each PVDD\_X pin is decoupled with a ceramic capacitor (X5R or better) placed as close as possible to each supply pin. It is recommended to follow the PCB layout of the DRV841x2 EVM board.

The 12V supply should be from a low-noise, low-output-impedance voltage regulator. Likewise, the 50V power-stage supply is assumed to have low output impedance and low noise. The power-supply sequence is not critical as facilitated by the internal power-on-reset circuit. Moreover, the DRV841x2 is fully protected against erroneous

power-stage turn-on due to parasitic gate charging. Thus, voltage-supply ramp rates ( $dv/dt$ ) are non-critical within the specified voltage range (see [セクション 5.3](#) of this data sheet).

### 3.3 System Power-Up and Power-Down Sequence

#### 3.3.1 Powering Up

The DRV841x2 does not require a power-up sequence. The outputs of the H-bridges remain in a high impedance state until the gate-drive supply voltage  $GVDD_X$  and  $VDD$  voltage are above the undervoltage protection (UVP) voltage threshold (see the *Electrical Characteristics* section of this data sheet). Although not specifically required, holding  $\overline{RESET\_AB}$  and  $\overline{RESET\_CD}$  in a low state while powering up the device is recommended. This allows an internal circuit to charge the external bootstrap capacitors by enabling a weak pulldown of the half-bridge output.

#### 3.3.2 Powering Down

The DRV841x2 does not require a power-down sequence. The device remains fully operational as long as the gate-drive supply ( $GVDD_X$ ) voltage and  $VDD$  voltage are above the UVP voltage threshold (see the *Electrical Characteristics* section of this data sheet). Although not specifically required, it is a good practice to hold  $\overline{RESET\_AB}$  and  $\overline{RESET\_CD}$  low during power down to prevent any unknown state during this transition.

### 3.4 System Design Recommendations

#### 3.4.1 VREG Pin

The VREG pin is used for internal logic and not recommended to be used as a voltage source for external circuitry.

#### 3.4.2 VDD Pin

The transient current in  $VDD$  pin could be significantly higher than average current through that pin. A low resistive path to  $GVDD$  should be used. A  $22\mu F$  to  $47\mu F$  capacitor should be placed on  $VDD$  pin beside the  $100nF$  to  $1\mu F$  decoupling capacitor to provide a constant voltage during transient.

#### 3.4.3 OTW Pin

$\overline{OTW}$  reporting indicates the device approaching high junction temperature. This signal can be used with MCU to decrease system power when  $\overline{OTW}$  is low in order to prevent OT shut down at a higher temperature.

#### 3.4.4 Mode Select Pin

Mode select pins (M1, M2, and M3) should be connected to either VREG (for logic high) or AGND for logic low. The recommendation is to not connect mode pins to board ground if  $1\Omega$  resistor is used between AGND and GND.

#### 3.4.5 Parallel Mode Operation

For a device operated in parallel mode, a minimum of  $30\text{ nH}$  to  $100\text{ nH}$  inductance or a ferrite bead is required after the output pins (for example, OUT\_A and OUT\_B) before connecting the two channels together. This helps to prevent any shoot through between two paralleled channels during switching transient due to mismatch of paralleled channels (for example, processor variation, unsymmetrical PCB layout, and so on).

#### 3.4.6 TEC Driver Application

For TEC driver or other non-motor related applications (for example, resistive load or dc output), a low-pass LC filter can be used to meet the requirement.

## 4 Layout

### 4.1 Layout Guidelines

#### 4.1.1 PCB Material Recommendation

FR-4 Glass Epoxy material with 2oz. copper on both top and bottom layer is recommended for improved thermal performance (better heat sinking) and less noise susceptibility (lower PCB trace inductance).

#### 4.1.2 Ground Plane

Because of the power level of these devices, it is recommended to use a big unbroken single ground plane for the whole system / board. The ground plane can be easily made at bottom PCB layer. In order to minimize the impedance and inductance of ground traces, the traces from ground pins should keep as short and wide as possible before connected to bottom ground plane through vias. Multiple vias are suggested to reduce the impedance of vias. Try to clear the space around the device as much as possible especially at bottom PCB side to improve the heat spreading.

#### 4.1.3 Decoupling Capacitor

High frequency decoupling capacitors (100 nF) on PVDD\_X pins should be placed close to these pins and with a short ground return path to minimize the inductance on the PCB trace.

#### 4.1.4 AGND

AGND is a localized internal ground for logic signals. A  $1\Omega$  resistor is recommended to be connected between GND and AGND to isolate the noise from board ground to AGND. There are other two components are connected to this local ground:  $0.1\mu\text{F}$  capacitor between VREG to AGND and  $\text{R}_{\text{OC\_adj}}$  resistor between OC\_ADJ and AGND. Capacitor for VREG should be placed close to VREG and AGND pin and connected without vias.

### 4.2 Layout Example

#### 4.2.1 Current Shunt Resistor

If current shunt resistor is connected between GND\_X to GND or PVDD\_X to PVDD, make sure there is only one single path to connect each GND\_X or PVDD\_X pin to shunt resistor, and the path is short and symmetrical on each sense path to minimize the measurement error due to additional resistance on the trace.

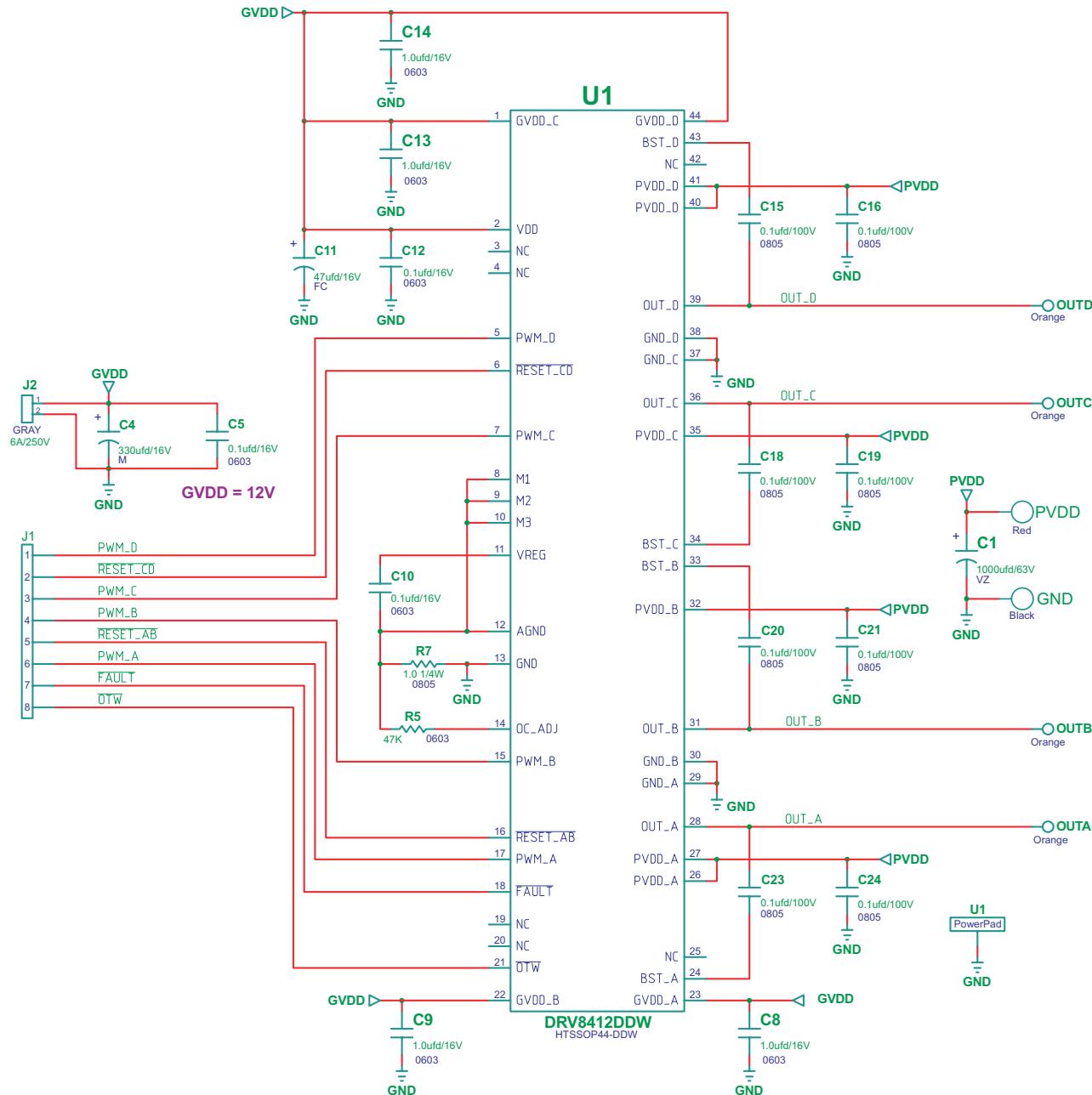

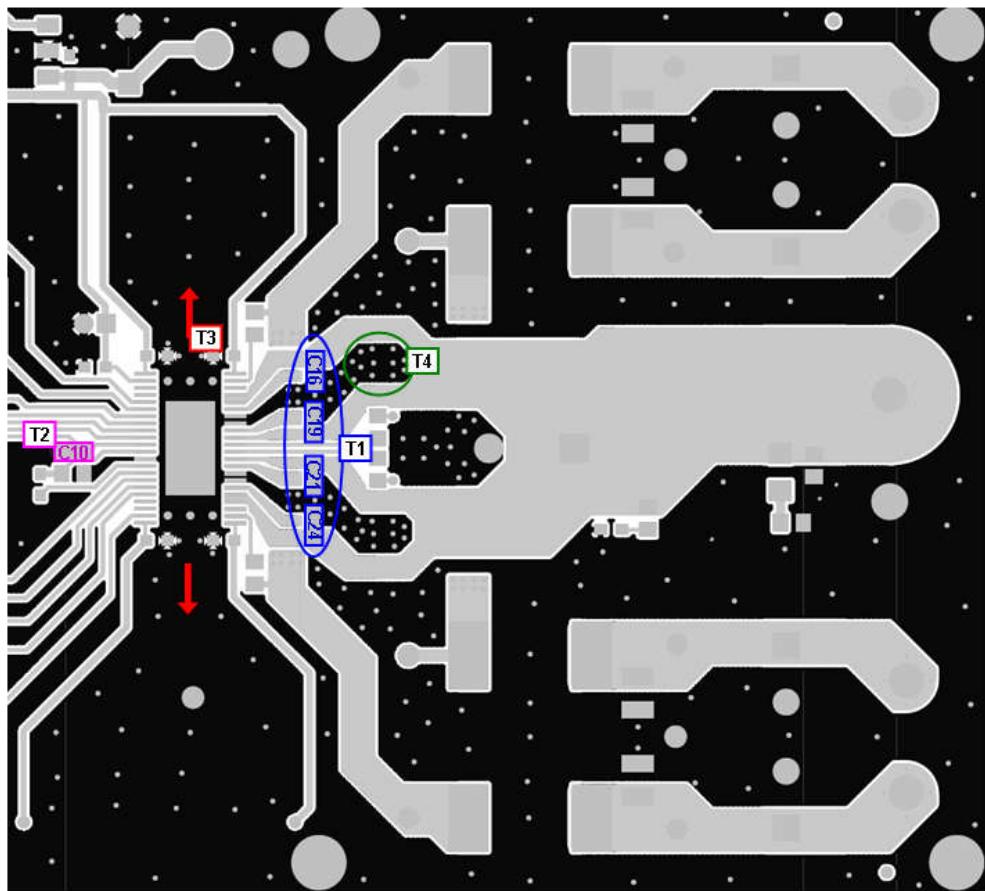

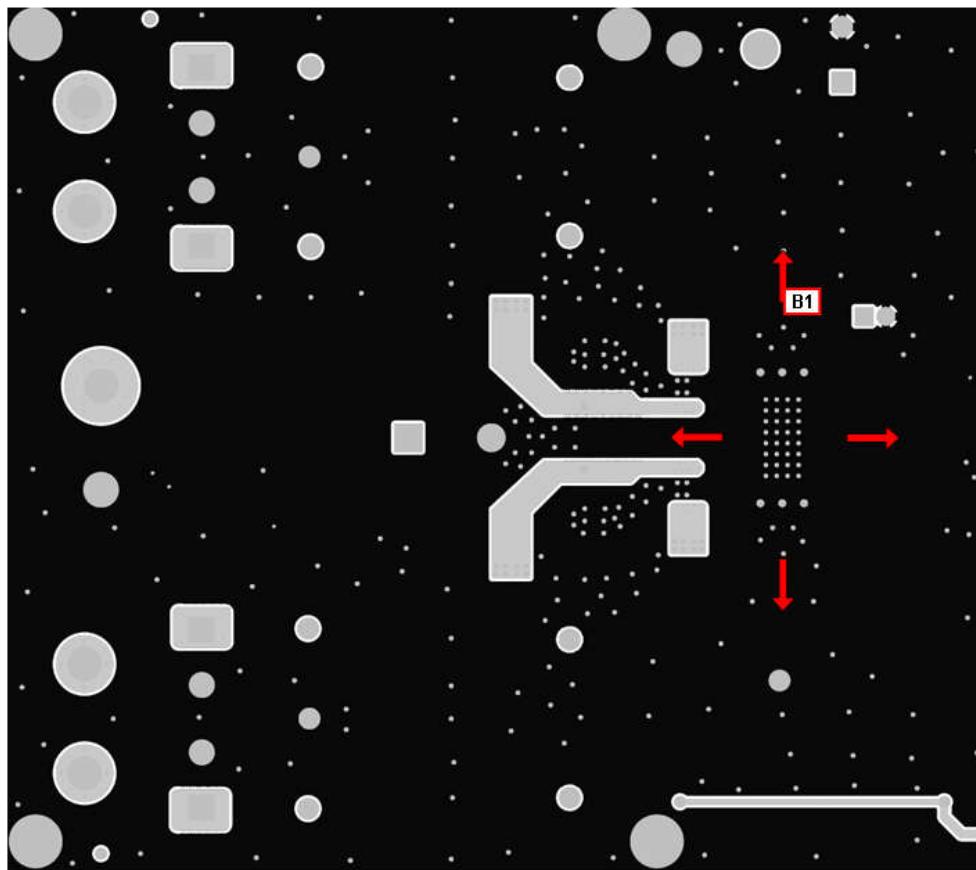

An example of the schematic and PCB layout of DRV8412 are shown in [図 7-13](#), [図 7-14](#), and [図 7-15](#).

### 7-13. DRV8412 Schematic Example

T1: PVDD decoupling capacitors C16, C19, C21, and C24 should be placed very close to PVDD\_X pins and ground return path.

T2: VREG decoupling capacitor C10 should be placed very close to VREG and AGND pins.

T3: Clear the space above and below the device as much as possible to improve the thermal spreading.

T4: Add many vias to reduce the impedance of ground path through top to bottom side. Make traces as wide as possible for ground path such as GND\_X path.

図 7-14. Printed Circuit Board – Top Layer

B1: Do not block the heat transfer path at bottom side. Clear as much space as possible for better heat spreading.

图 7-15. Printed Circuit Board – Bottom Layer

#### 4.3 Thermal Considerations

The thermally enhanced package provided with the DRV8432 is designed to interface directly to heat sink using a thermal interface compound, (for example, Ceramique from Arctic Silver, TIMTronics 413, and so on). The heat sink then absorbs heat from the ICs and couples to the local air. A good practice is to connect the heatsink to system ground on the PCB board to reduce the ground noise.

$R_{\theta JA}$  is a system thermal resistance from junction to ambient air. The system parameters have the following components:

- $R_{\theta JC}$  (the thermal resistance from junction to case, or in this example the power pad or heat slug)

- Thermal grease thermal resistance

- Heat sink thermal resistance

The thermal grease thermal resistance can be calculated from the exposed power pad or heat slug area and the thermal grease manufacturer's area thermal resistance (expressed in  $^{\circ}\text{C}\cdot\text{in}^2/\text{W}$  or  $^{\circ}\text{C}\cdot\text{mm}^2/\text{W}$ ). The approximate exposed heat slug size is as follows:

- DRV8432, 36-pin PSOP3 ..... 0.124 in<sup>2</sup> (80mm<sup>2</sup>)

The thermal resistance of thermal pads is considered higher than a thin thermal grease layer and is not recommended. Thermal tape has an even higher thermal resistance and should not be used at all. Heat sink thermal resistance is predicted by the heat sink vendor, modeled using a continuous flow dynamics (CFD) model, or measured.

Thus the system  $R_{\theta\text{JA}} = R_{\theta\text{JC}} + \text{thermal grease resistance} + \text{heat sink resistance}$ .

See the TI application report, *IC Package Thermal Metrics* ([SPRA953](#)), for more thermal information.

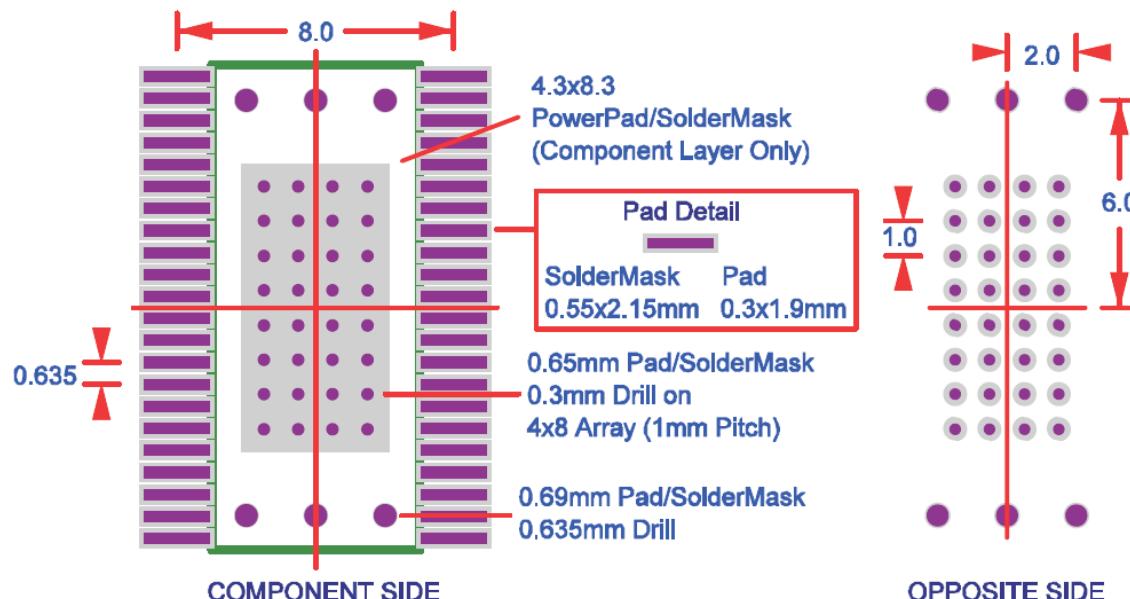

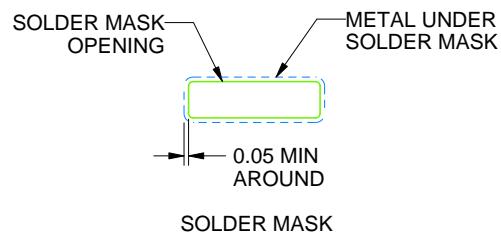

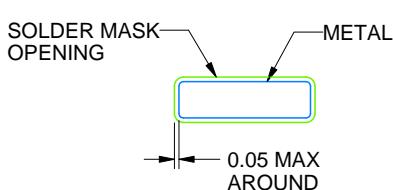

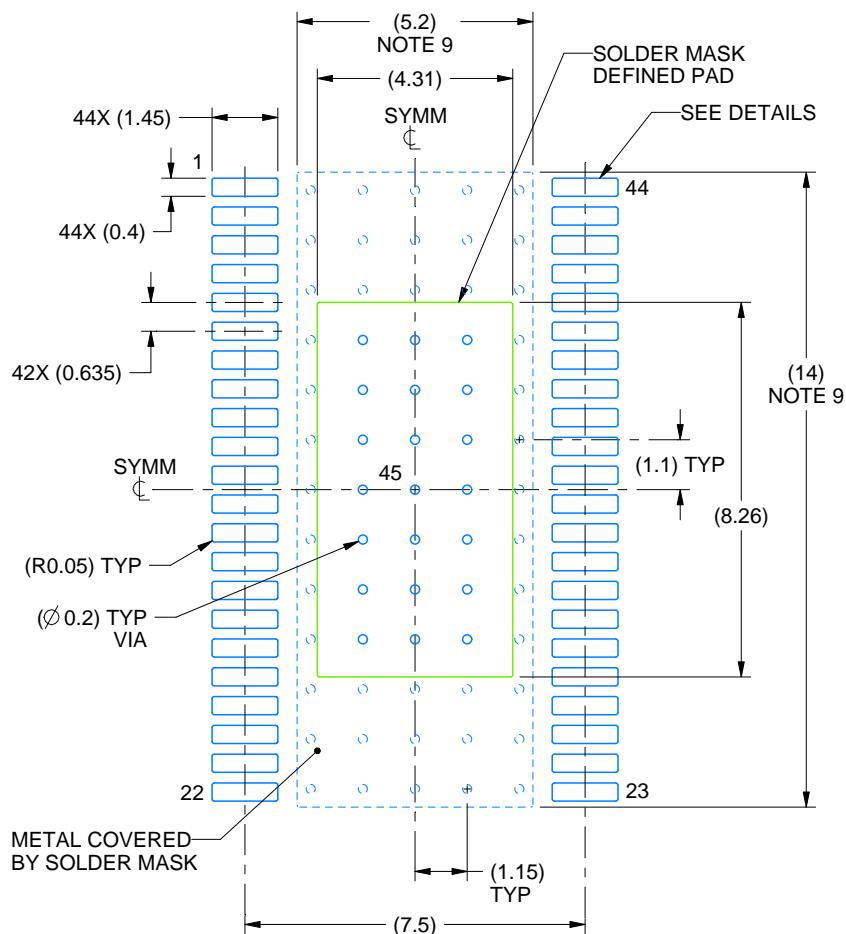

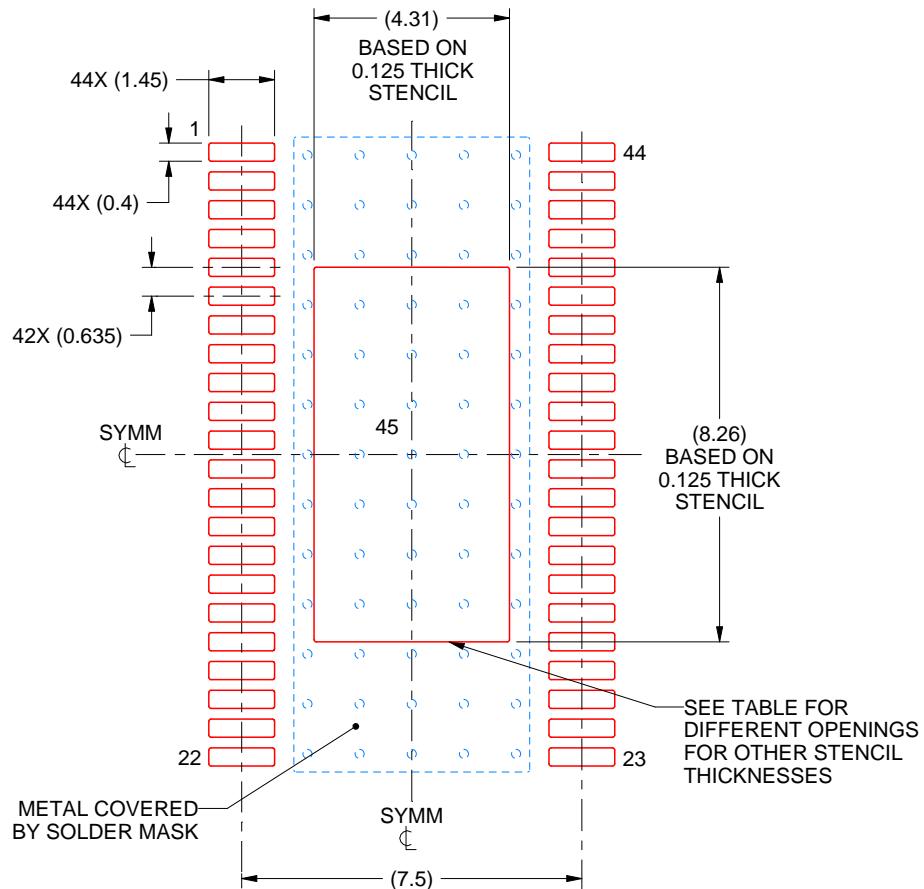

#### 4.3.1 DRV8412 Thermal Via Design Recommendation

Thermal pad of the DRV8412 is attached at bottom of device to improve the thermal capability of the device. The thermal pad has to be soldered with a very good coverage on PCB to deliver the power specified in the data sheet. [図 7-16](#) shows the recommended thermal via and land pattern design for the DRV8412. For additional information, see TI application report, PowerPad™ Made Easy ([SLMA004](#)) and PowerPad Layout Guidelines ([SOLA120](#)).

図 7-16. DRV8412 Thermal Via Footprint

## 7 Device and Documentation Support

### 7.1 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 7.2 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの使用条件を参照してください。

### 7.3 Trademarks

PowerPad™ and テキサス・インスツルメンツ E2E™ are trademarks of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

### 7.4 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 7.5 用語集

#### テキサス・インスツルメンツ用語集

この用語集には、用語や略語の一覧および定義が記載されています。

## 8 Revision History

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision G (July 2014) to Revision H (July 2024) | Page |

|---------------------------------------------------------------|------|

| • 「製品情報」表を「パッケージ情報」表に変更.....                                  | 1    |

| • Deleted values in 39 to 200 in 表 6-2 .....                  | 12   |

| Changes from Revision F (January 2014) to Revision G (July 2014)                                                                                  | Page |

|---------------------------------------------------------------------------------------------------------------------------------------------------|------|

| • ESD 定格の表、「機能説明」セクション、デバイスの機能モード、「アプリケーションと実装」セクション、「電源に関する推奨事項」セクション、「レイアウト」セクション、「デバイスおよびドキュメントのサポート」セクション、「メカニカル、パッケージ、および注文情報」セクションを追加 ..... | 1    |

| Changes from Revision E (October 2013) to Revision F (January 2014)                                                           | Page |

|-------------------------------------------------------------------------------------------------------------------------------|------|

| • Changed GND_A, GND_B, GND_C, and GND_D pins description to remove text "requires close decoupling capacitor to ground"..... | 3    |

| • Changed the $t_{ON\_MIN}$ description to include "for charging the Bootstrap capacitor" .....                               | 5    |

| • Added text to the Overcurrent (OC) Protection section - "It is important to note..." .....                                  | 12   |

| <b>Changes from Revision D (July 2011) to Revision E (October 2013)</b>                                   | <b>Page</b> |

|-----------------------------------------------------------------------------------------------------------|-------------|

| • Added last sentence in description of Thermal Pad in Pin Functions table.....                           | 3           |

| • Added THERMAL INFORMATION table.....                                                                    | 6           |

| • Added a new paragraph in DIFFERENT OPERATIONAL MODES section: In operation modes....DC logic level..... | 14          |

| <b>Changes from Revision C (May 2010) to Revision D (July 2011)</b>                                                                                                   | <b>Page</b> |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| • 最初の「特長」の $80\text{m}\Omega$ を $110\text{m}\Omega$ に変更.....                                                                                                          | 1           |

| • 2 番目の「特長」の $50\text{V}$ を $52\text{V}$ に変更.....                                                                                                                     | 1           |

| • 2 番目の「特長」から (絶対最大定格 $70\text{V}$ ) を削除.....                                                                                                                         | 1           |

| • アプリケーションに LED ライティング ドライバを追加.....                                                                                                                                   | 1           |

| • Added Includes metallization bond wire and pin resistance to $R_{DS(on)}$ test conditions.....                                                                      | 7           |

| • Changed $R_{DS(on)}$ typ from $80\text{ m}\Omega$ to $110\text{ m}\Omega$ .....                                                                                     | 7           |

| • Added text to 5th paragraph of Overcurrent (OC) Protection section.....                                                                                             | 12          |

| • Deleted Output Inductor Selection section and moved information into Overcurrent (OC) Protection section.....                                                       | 12          |