## DRV8847 デュアル H ブリッジ・モータ・ドライバ

### 1 特長

- デュアル H ブリッジ・モータ・ドライバ

- シングルまたはデュアルのブラシ付き DC モーター

- 1 つのバイポーラ・ステップ・モータ

- ソレノイド負荷

- 2.7V ~ 18V の動作電圧範囲

- H ブリッジごとの大きな出力電流

- $T_A = 25^\circ\text{C}$  で RMS ドライバ電流 1A

- $T_A = 25^\circ\text{C}$ 、並列モードで RMS ドライバ電流 2A

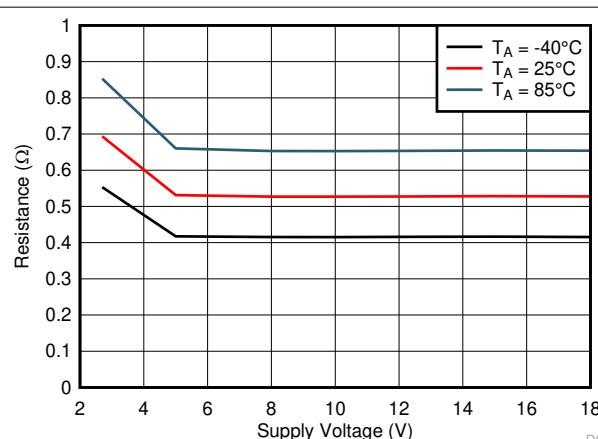

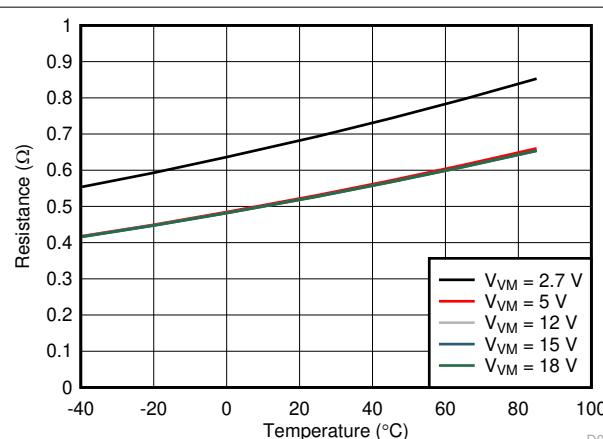

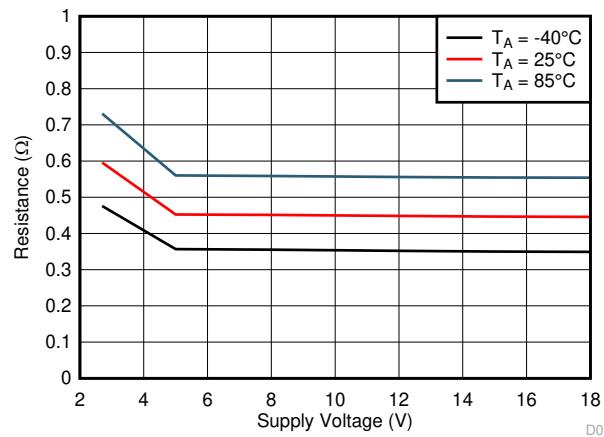

- $VM > 5\text{V}$  時の低いオン抵抗

- $T_A = 25^\circ\text{C}$  で  $1000\text{m}\Omega$  の  $R_{DS(ON)}$  (HS + LS)

- 複数の制御インターフェイス・オプション

- 4 ピン・インターフェイス

- 2 ピン・インターフェイス

- 並列ブリッジ・インターフェイス

- 独立のブリッジ・インターフェイス

- 20 $\mu\text{s}$  固定オフ時間の電流レギュレーション

- トルク・スカラーにより出力電流を 50% にスケーリング

- 1.8V、3.3V、5V のロジック入力をサポート

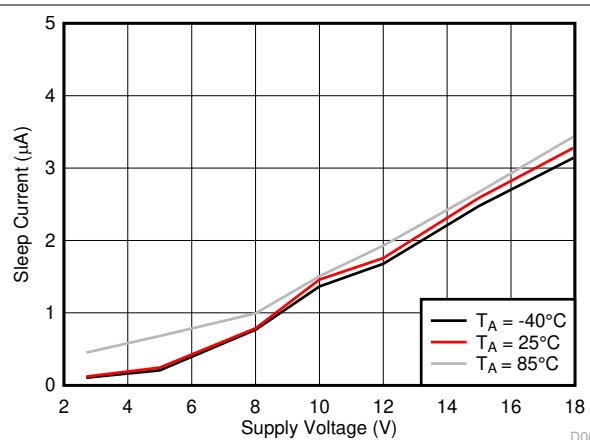

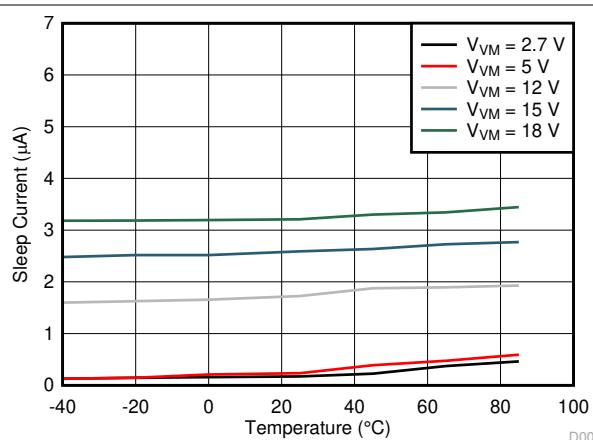

- 低消費電力のスリープ・モード

- $V_{VM} = 12\text{V}$ 、 $T_A = 25^\circ\text{C}$  のとき  $1.7\mu\text{A}$  のスリープ・モード消費電流

- $\text{I}^2\text{C}$  のデバイス・バリエーションを供給 (DRV8847S)

- $\text{I}^2\text{C}$  レジスタでの詳細な診断

- マルチスレーブ動作のサポート

- 標準およびファースト  $\text{I}^2\text{C}$  モードをサポート

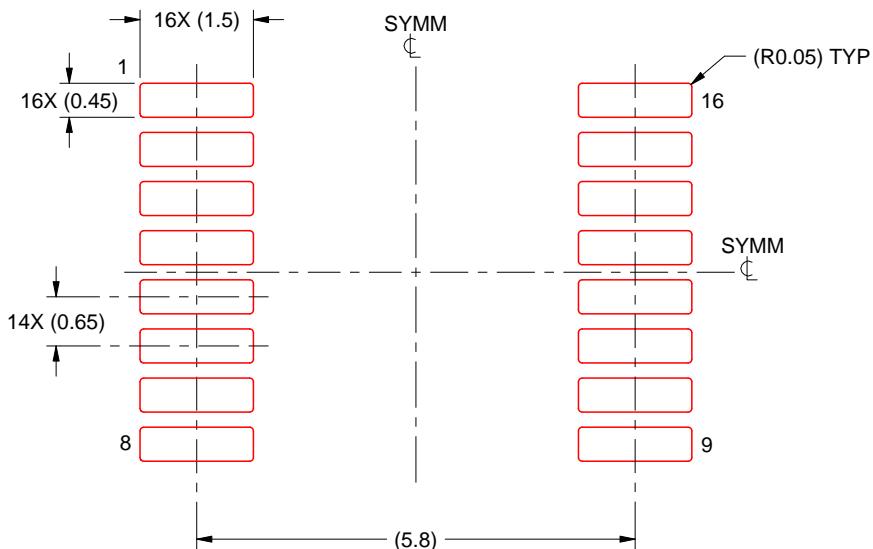

- 小さなパッケージと占有面積

- 16 ピン TSSOP (サーマル・パッドなし)

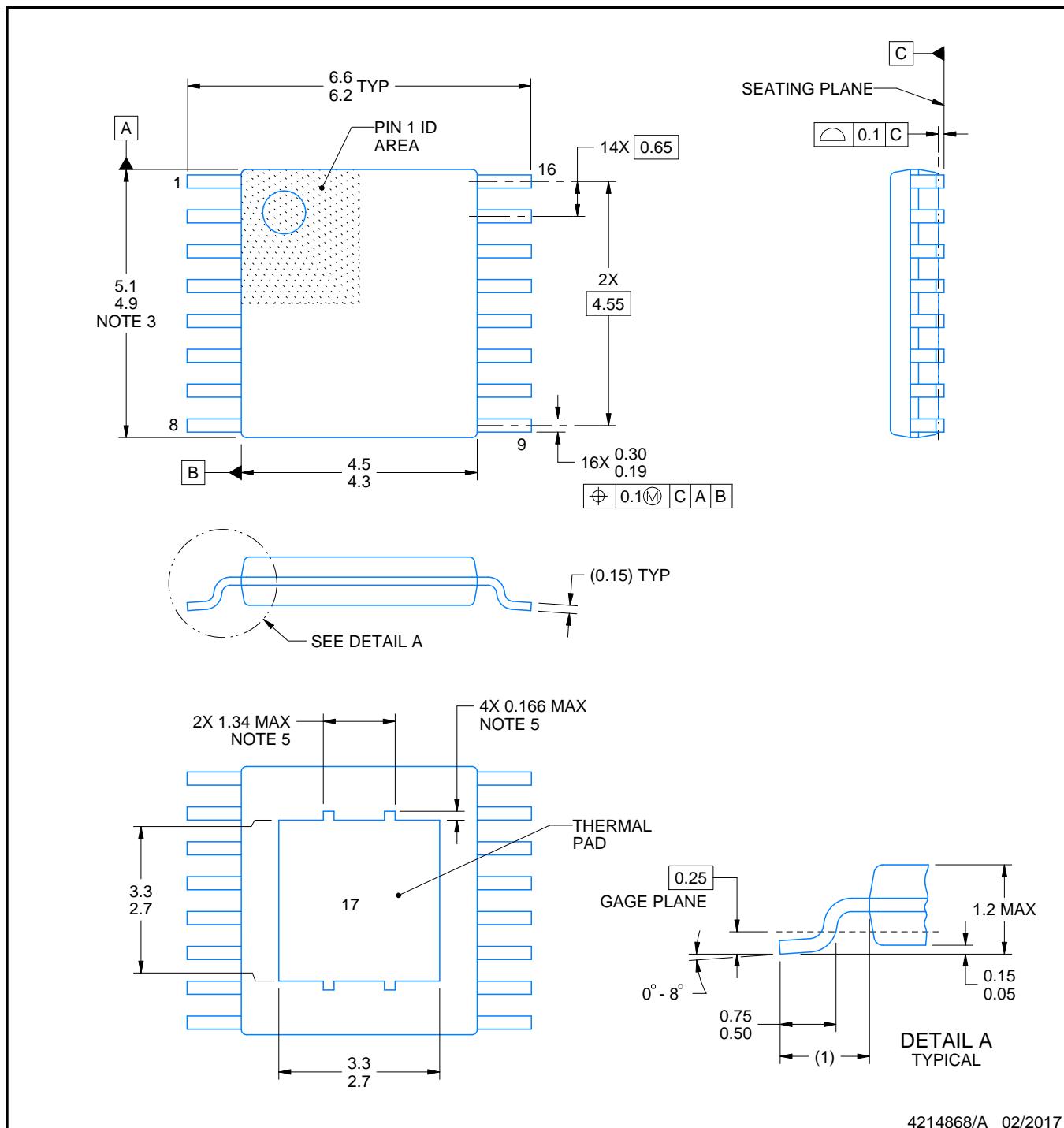

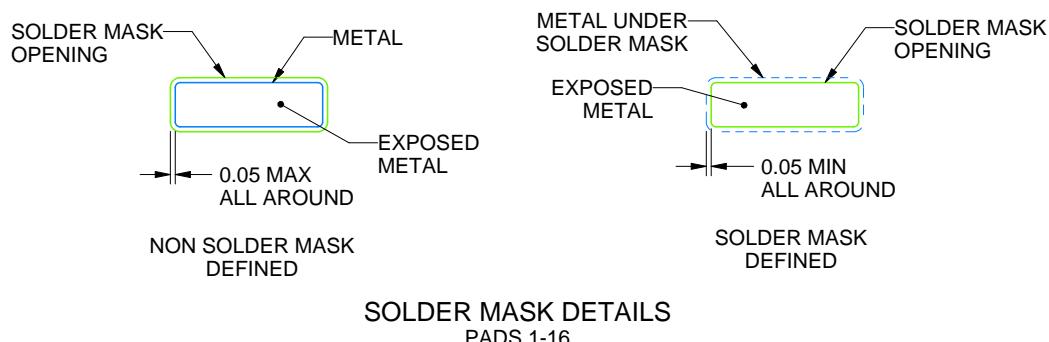

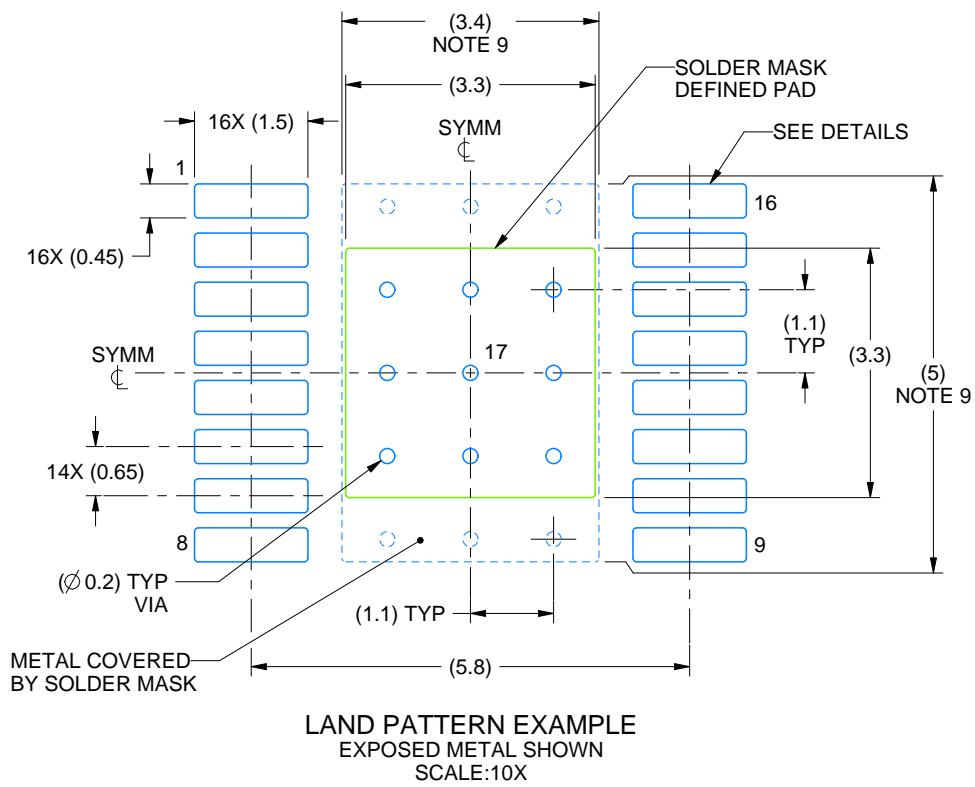

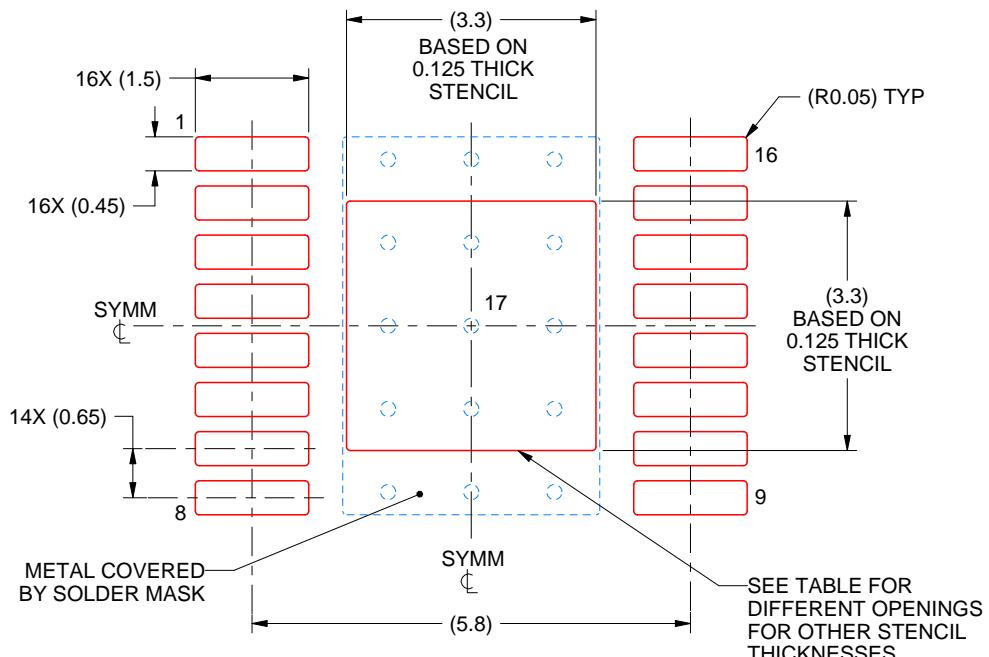

- 16 ピン HTSSOP PowerPAD™ パッケージ

- 16 ピン WQFN サーマル・パッケージ

- 保護機能を搭載

- VM 低電圧誤動作防止

- 過電流保護

- 開放負荷検出

- サーマル・シャットダウン

- フォルト状況表示ピン (nFAULT)

### 2 アプリケーション

- 冷蔵庫のダンパーおよび製氷室

- 洗濯機、乾燥機、食器洗浄機

- ePOS (Electronic Point-of-Sale) プリンタ

- ステージ照明機器

- 小型の回路ブレーカーおよびスマートメータ

### 3 概要

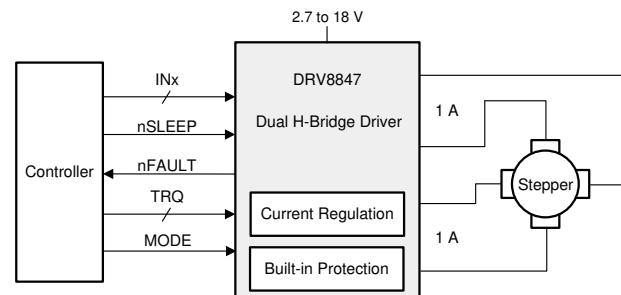

DRV8847 デバイスは、産業アプリケーション、家電機器、ePOS プリンタ、その他のメカトロニクス用途を対象としたデュアル H ブリッジ・モータ・ドライバです。このデバイスは 2 つの DC モータ、1 つのバイポーラ・ステップ・モータ、およびリレーなど他の負荷を駆動するため使用できます。単純な PWM インターフェイスにより、コントローラと簡単に接続できます。DRV8847 デバイスは単一電源で動作し、2.7~18V の広い入力電源電圧範囲に対応します。

ドライバの出力段は N チャネル パワー MOSFET から成り、モータの巻線を駆動する 2 つのフル H ブリッジ、または 4 つの独立したハーフ ブリッジ (独立ブリッジ インターフェイス内) として構成されています。ブリッジ内のピーク電流は固定オフ時間で制御され、1A の負荷を駆動できます ( $25^\circ\text{C}$   $T_A$  で適切なヒートシンクがある場合、並列モードで 2A)。

低消費電力のスリープ・モードがあり、内部回路の多くをシャットダウンして、静止電流を低減できます。さらに、トルクスカラーが用意されており、デジタル入力ピンによって出力電流を動的にスケーリングできます。この機能により、コントローラは電流を減らし、消費電力を低減できます。

低電圧誤動作防止、各 FET の過電流保護、短絡保護、開放負荷検出、過熱に対する保護機能が内蔵されています。フォルト条件は、nFAULT ピンで通知されます。 $\text{I}^2\text{C}$  デバイス バリアント (DRV8847S) には、詳細な診断機能があります。

#### 製品情報<sup>(1)</sup>

| 部品番号     | パッケージ       | 本体サイズ (公称)      |

|----------|-------------|-----------------|

| DRV8847  | HTSSOP (16) | 5.00mm × 4.40mm |

|          | TSSOP (16)  | 5.00mm × 4.40mm |

|          | WQFN (16)   | 3.00mm × 3.00mm |

| DRV8847S | TSSOP (16)  | 5.00mm × 4.40mm |

| DRV88471 | WQFN (16)   | 3.00mm × 3.00mm |

(1) 利用可能なすべてのパッケージについては、このデータシートの末尾にある注文情報を参照してください。

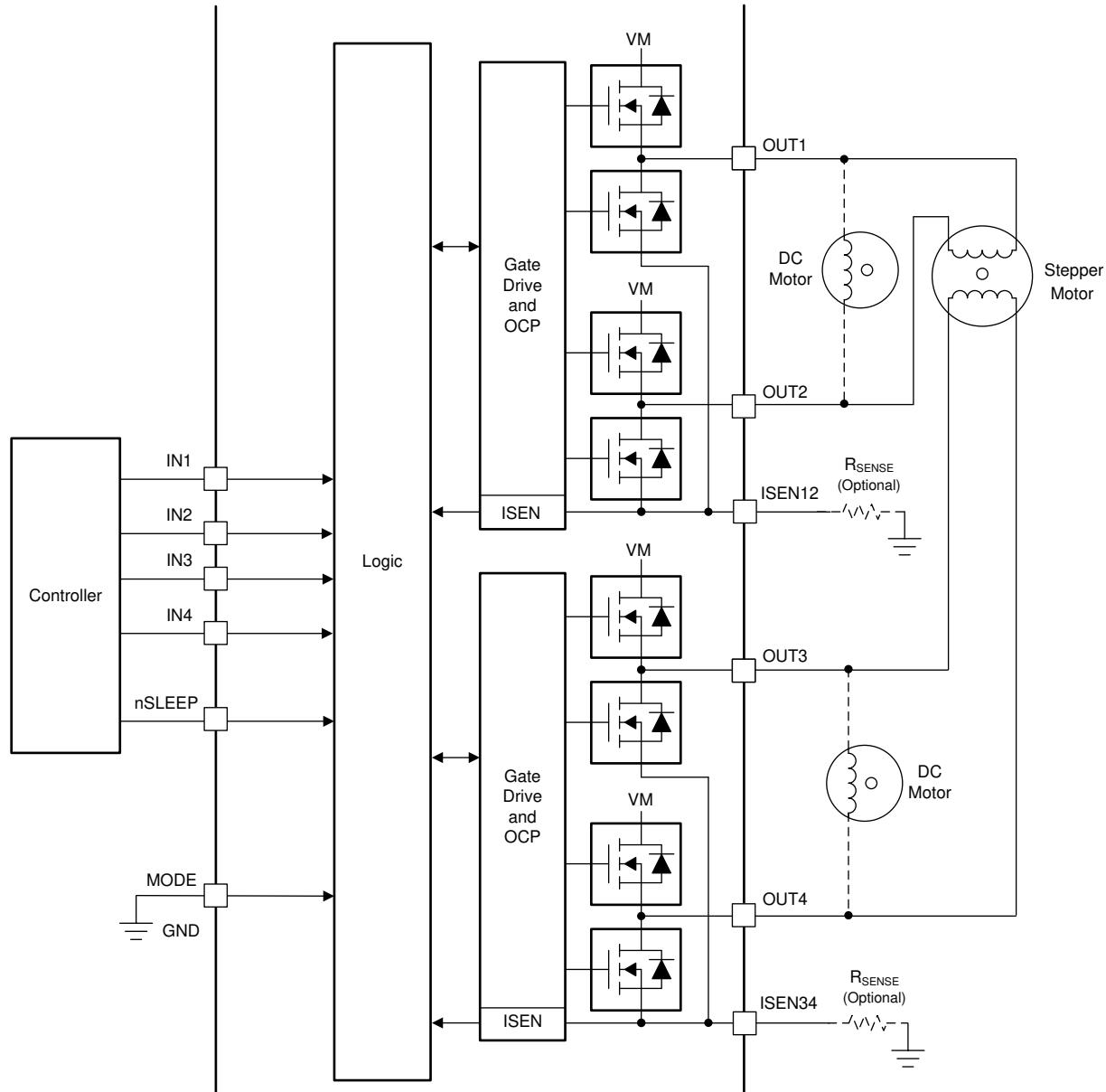

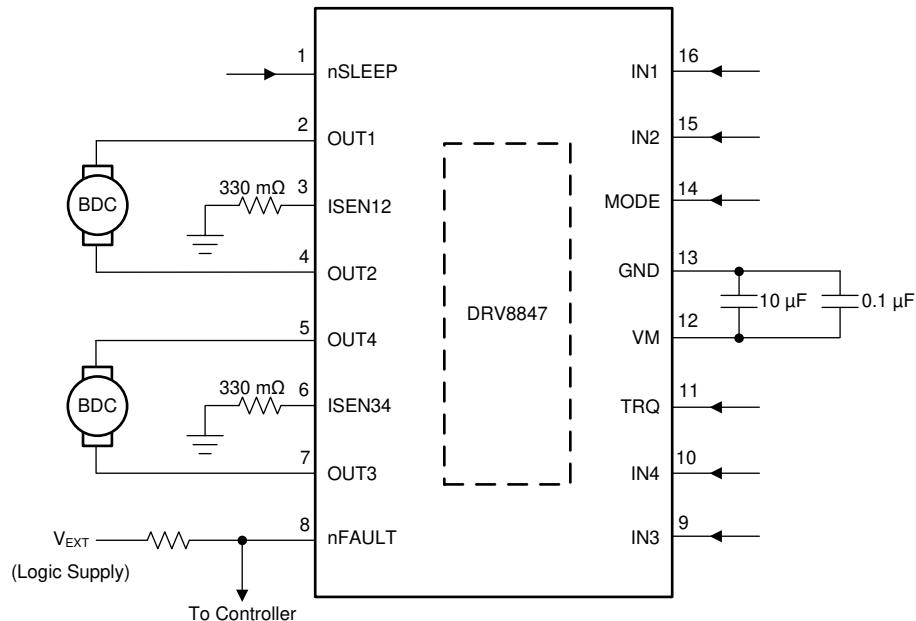

概略回路図

## 目次

|                    |           |                               |           |

|--------------------|-----------|-------------------------------|-----------|

| <b>1 特長</b>        | <b>1</b>  | 7.5 プログラミング                   | <b>45</b> |

| <b>2 アプリケーション</b>  | <b>1</b>  | 7.6 レジスタ・マップ                  | <b>47</b> |

| <b>3 概要</b>        | <b>1</b>  | <b>8 アプリケーションと実装</b>          | <b>52</b> |

| <b>4 改訂履歴</b>      | <b>3</b>  | 8.1 アプリケーション情報                | <b>52</b> |

| <b>5 ピン構成および機能</b> | <b>4</b>  | 8.2 代表的なアプリケーション              | <b>52</b> |

| <b>6 仕様</b>        | <b>7</b>  | <b>9 レイアウト</b>                | <b>71</b> |

| 6.1 絶対最大定格         | 7         | 9.1 レイアウトのガイドライン              | 71        |

| 6.2 ESD 定格         | 7         | 9.2 レイアウト例                    | 71        |

| 6.3 推奨動作条件         | 7         | 9.3 熱に関する注意事項                 | 73        |

| 6.4 熱に関する情報        | 8         | 9.4 電力散逸                      | 73        |

| 6.5 電気的特性          | 8         | <b>10 デバイスおよびドキュメントのサポート</b>  | <b>74</b> |

| 6.6 I2C のタイミング要件   | 10        | 10.1 デバイス・サポート(オプション)         | 74        |

| 6.7 代表的特性          | 13        | 10.2 ドキュメントのサポート              | 74        |

| <b>7 詳細説明</b>      | <b>15</b> | 10.3 ドキュメントの更新通知を受け取る方法       | 74        |

| 7.1 概要             | 15        | 10.4 コミュニティ・リソース              | 74        |

| 7.2 機能ブロック図        | 16        | 10.5 商標                       | 74        |

| 7.3 機能説明           | 18        | <b>11 メカニカル、パッケージ、および注文情報</b> | <b>74</b> |

| 7.4 デバイスの機能モード     | 43        |                               |           |

## 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| <b>Changes from Revision B (April 2019) to Revision C (December 2023)</b> | <b>Page</b> |

|---------------------------------------------------------------------------|-------------|

| • DRV88471 バリエントのピン配置とピン機能の表を追加.....                                      | 4           |

| • DRV88471 ブリッジ制御モードの動作説明を追加.....                                         | 21          |

| • DRV88471 トルク スカラー TRQ の動作説明を追加.....                                     | 30          |

| <b>Changes from Revision A (July 2018) to Revision B (April 2019)</b>                                                                           | <b>Page</b> |

|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| • VM > 5V 時の低いオン抵抗が表示されるように変更.....                                                                                                              | 1           |

| • nFAULT ピンのタイプを OD/I に変更.....                                                                                                                  | 4           |

| • VM の説明を変更し、0.1uF コンデンサはセラミックであるべきことを明記.....                                                                                                   | 4           |

| • デジタルピンの電圧 (IN1, IN2, IN3, IN4, TRQ, nSLEEP, nFAULT, SCL, SDA) の最大電圧を 5.5V から 5.75V に変更.....                                                   | 7           |

| • 位相ノードピンの電圧仕様名を、連続位相ノードピン電圧に変更.....                                                                                                            | 7           |

| • ISEN12, ISEN34 仕様に、25ns 未満の $\pm 1V$ の過渡電圧が許容されるという脚注を追加.....                                                                                 | 7           |

| • 両方のピーク駆動電流 (OUT1, OUT2, OUT3, OUT4) 仕様に、消費電力および温度の制限に従う必要があるという脚注を追加.....                                                                     | 7           |

| • V (ESD) 仕様値を 4000V に変更.....                                                                                                                   | 7           |

| • テスト条件 VM < 7V および VM >= 7V に基づいて、V <sub>IL</sub> 仕様を 2 つの仕様に変更.....                                                                           | 8           |

| • I <sub>IH</sub> 仕様の最小値を、テスト条件 IN1, IN2, IN3, IN4, TRQ, VIN = 5V の場合は 18uA に変更、テスト条件 nSLEEP, V <sub>IN</sub> = 最小値 (VM, 5V) の場合は 10uA に変更..... | 8           |

| • I <sub>OCP</sub> 仕様に最小値を追加.....                                                                                                               | 8           |

| • DRV8847S のブロック図のピン名を変更.....                                                                                                                   | 16          |

| • C <sub>VM1</sub> からセラミックを削除.....                                                                                                              | 18          |

| • 明確化するために、リレー コイルやソレノイド コイルの負荷の箇条書きを変更.....                                                                                                    | 26          |

| • 開放負荷が検出された場合の nFAULT ピンの動作を明確化する文章を追加.....                                                                                                    | 39          |

| • 電源投入時の nFAULT ピンの動作を明確化する文章を追加.....                                                                                                           | 43          |

| • 「開放負荷の実装」セクションを追加.....                                                                                                                        | 61          |

| • 「2 層基板の 16 ピン QFN パッケージのレイアウトに関する推奨事項」の図を追加.....                                                                                              | 71          |

| <b>Changes from Revision * (July 2018) to Revision A (August 2018)</b> | <b>Page</b> |

|------------------------------------------------------------------------|-------------|

| • データシートのステータスを「事前情報」から「量産データ」に変更 .....                                | 1           |

| • 「2 層基板の 16 ピン HTSSOP パッケージのレイアウトに関する推奨事項」の図のピン名を変更.....              | 71          |

## 5 ピン構成および機能

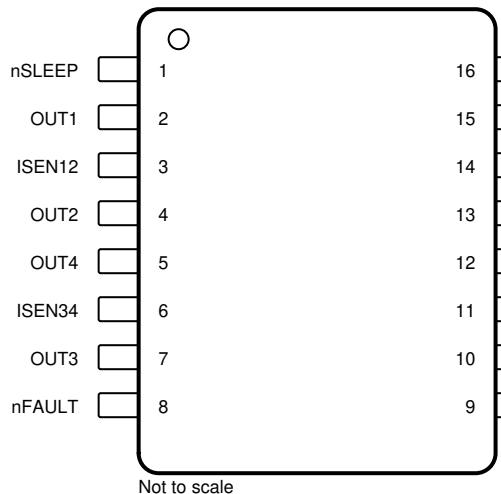

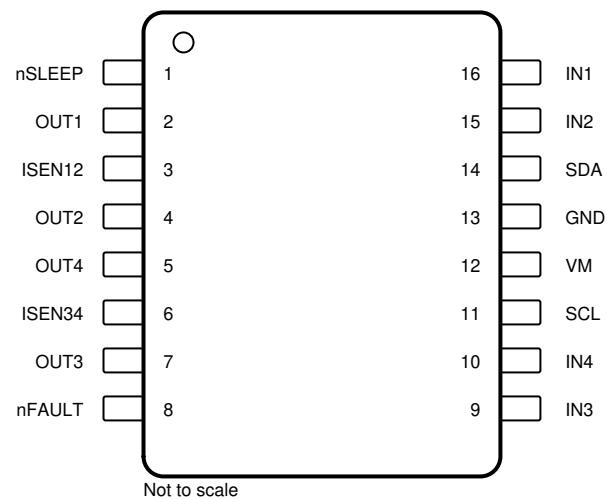

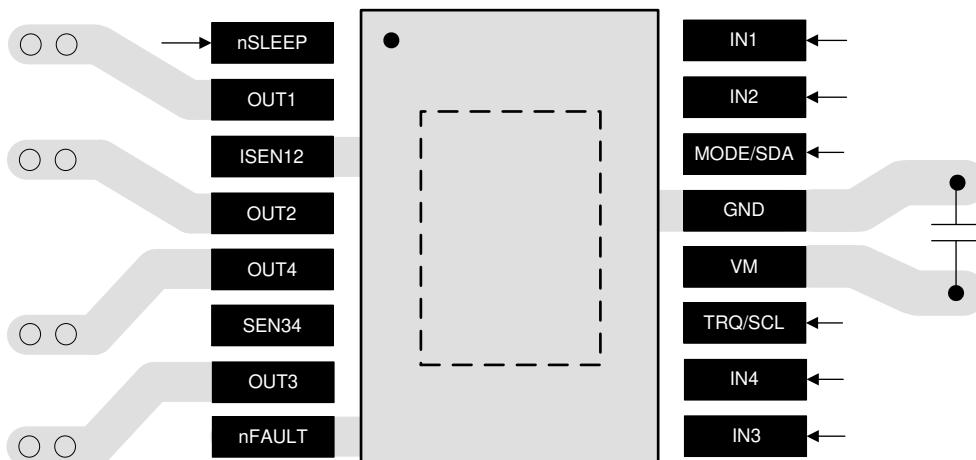

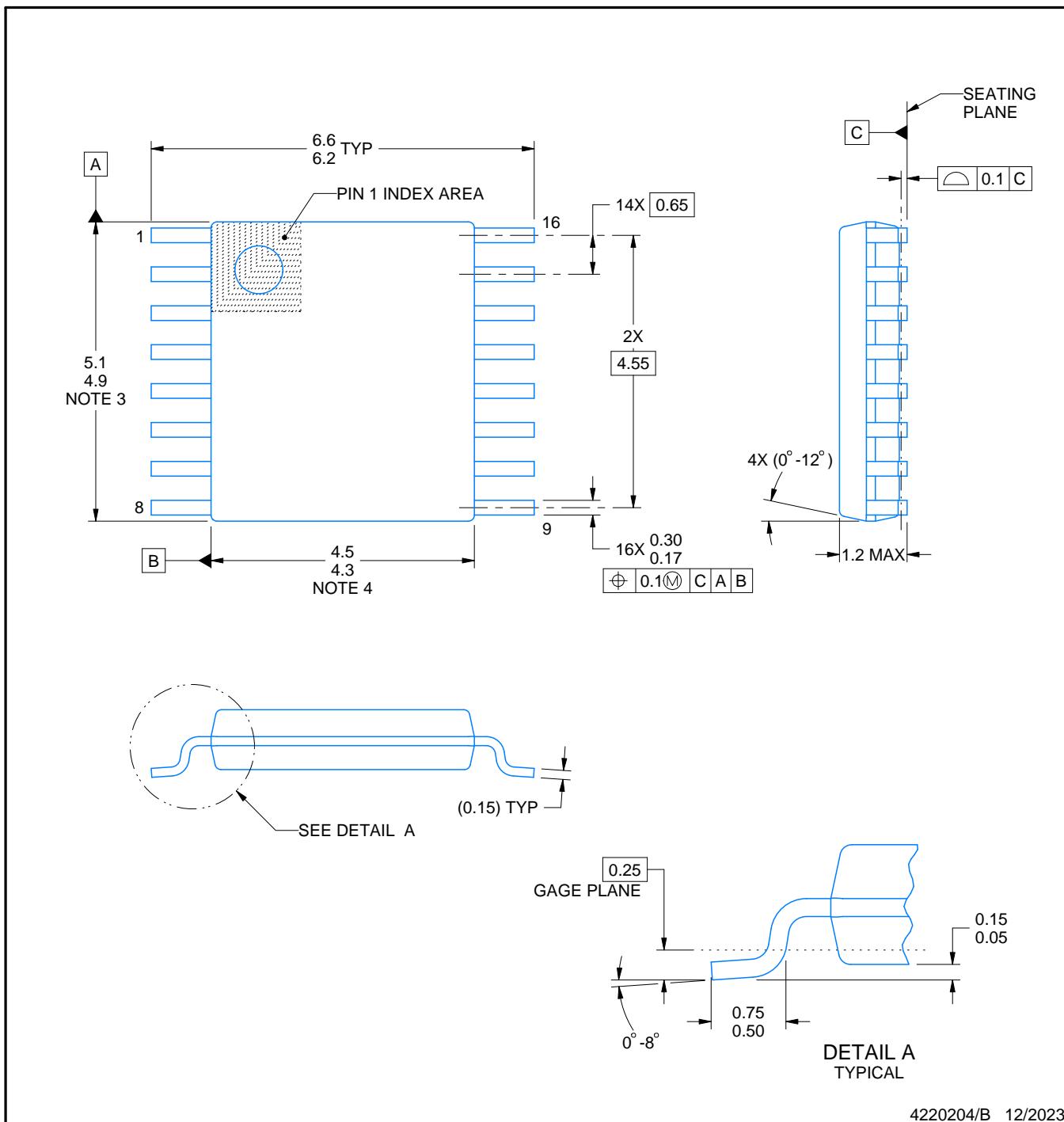

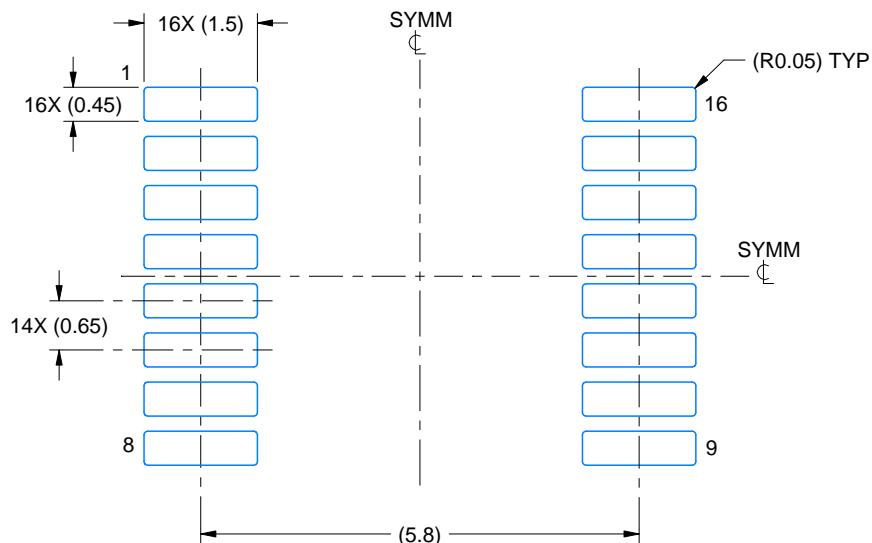

図 5-1. DRV8847 PW パッケージ 16 ピン TSSOP 上面図

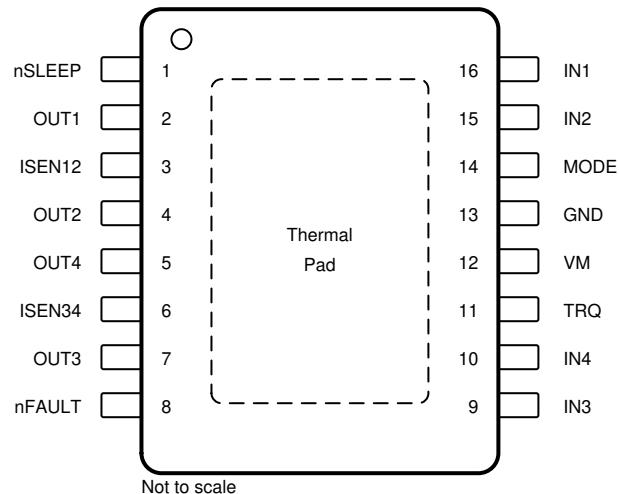

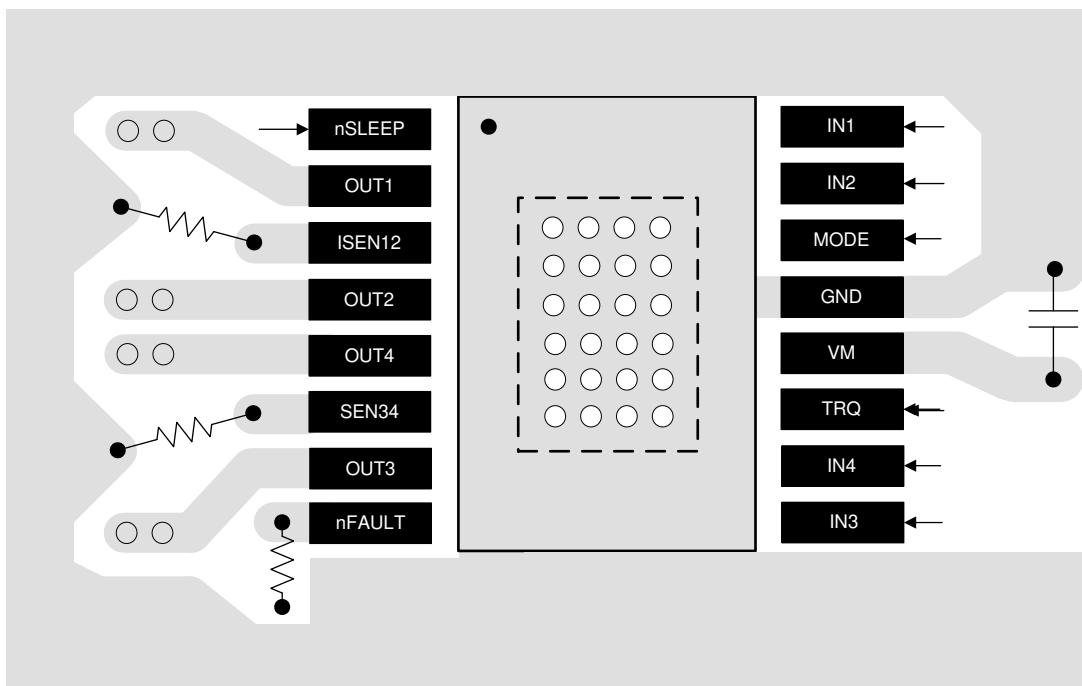

図 5-2. DRV8847 PWP PowerPAD™ パッケージ 16 ピン HTSSOP 上面図

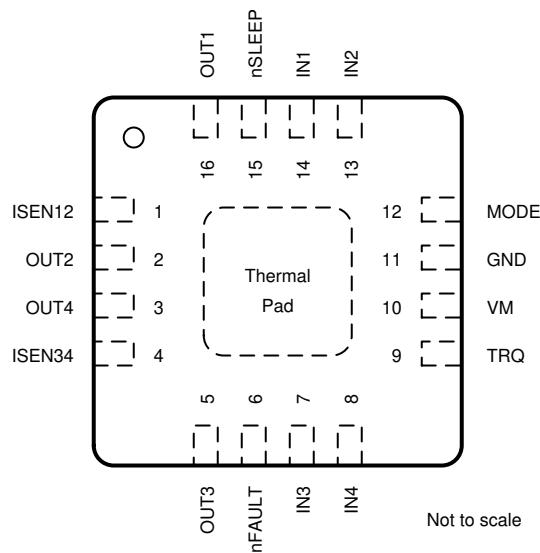

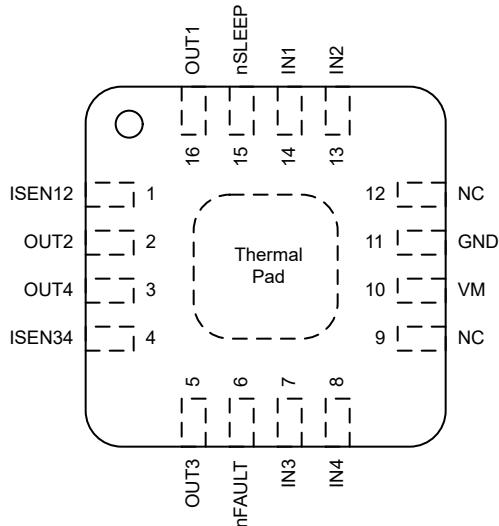

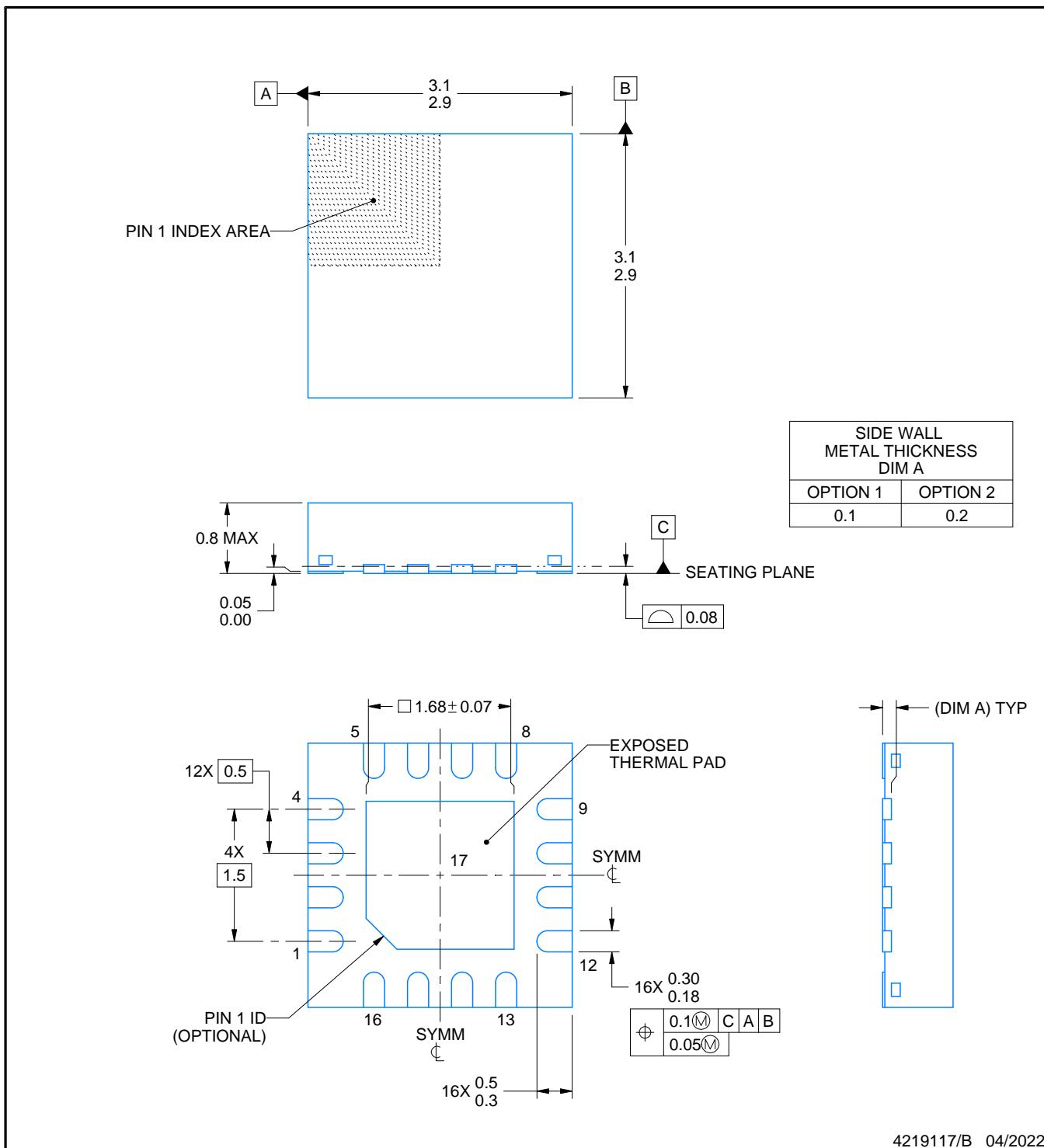

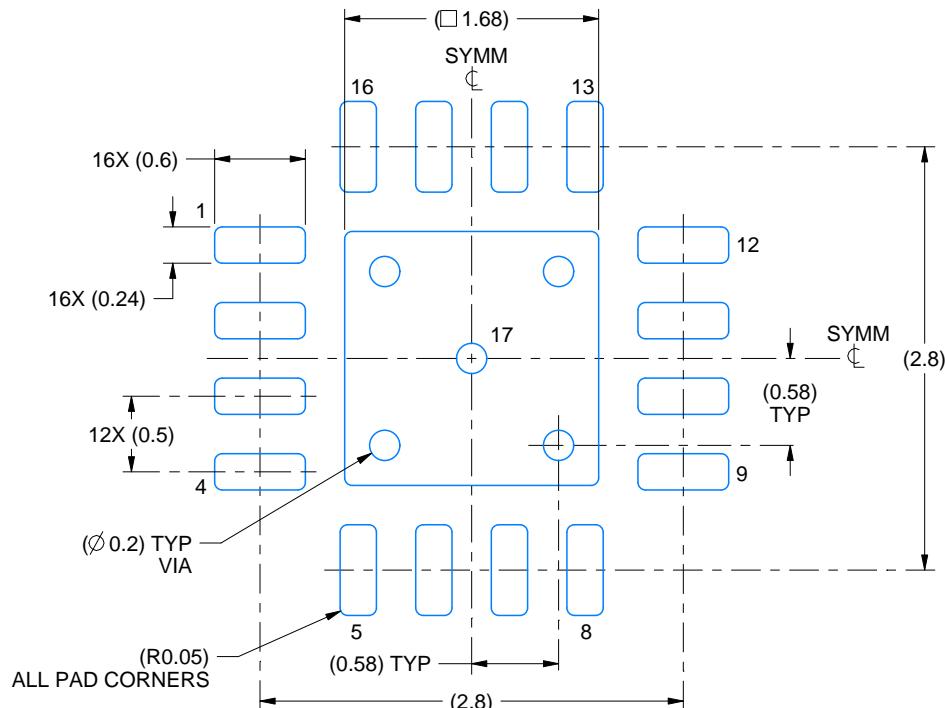

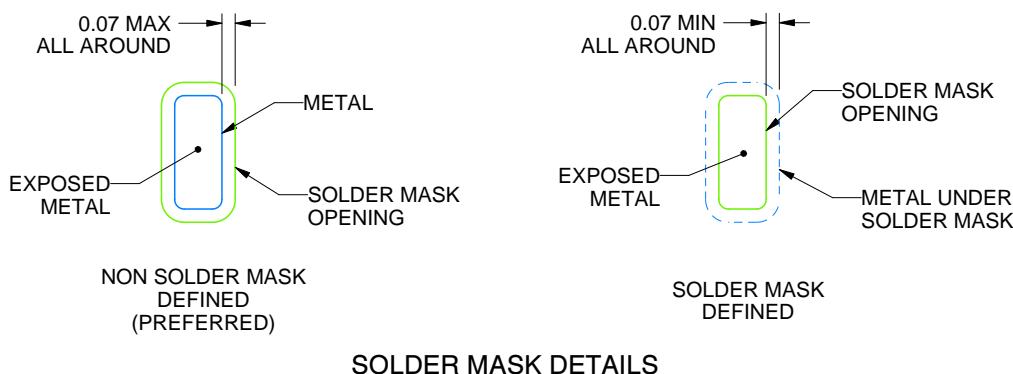

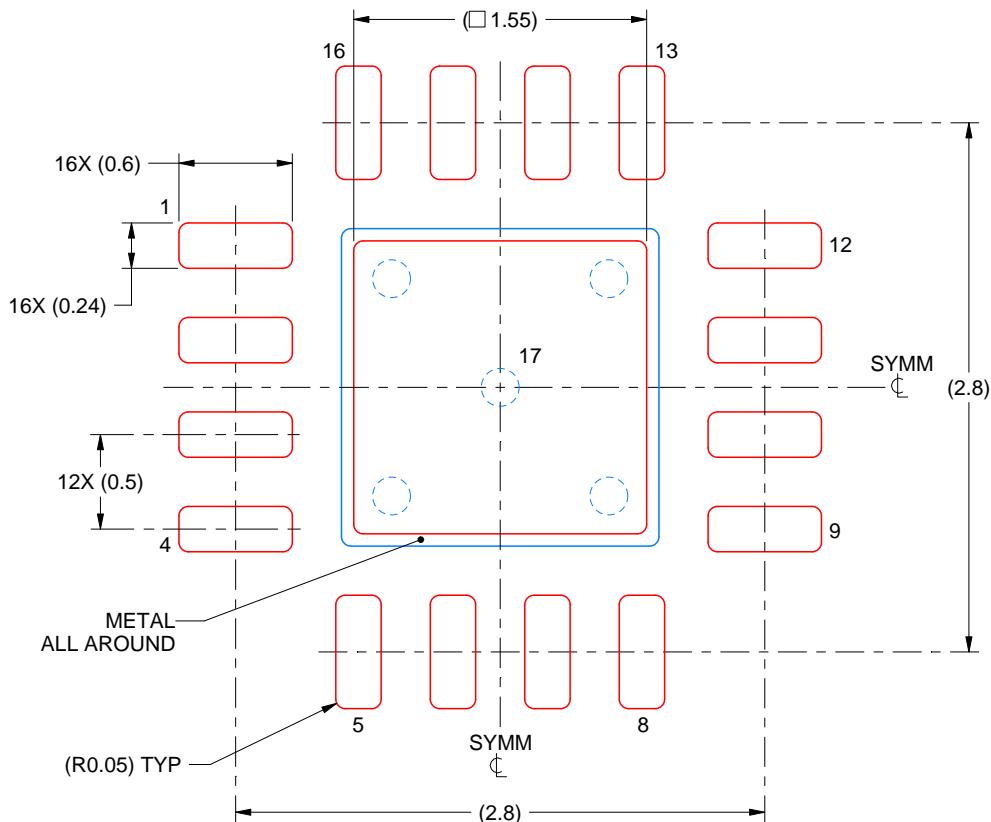

図 5-3. DRV8847 RTE パッケージ 16 ピン WQFN (露出サーマルパッド付き) 上面図

図 5-4. DRV8847S PW パッケージ 16 ピン TSSOP 上面図

**表 5-1. ピンの機能**

| 名称     | ピン              |      |          | 種類 <sup>(1)</sup> | 説明                                                                                                                                      |

|--------|-----------------|------|----------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

|        | DRV8847         |      | DRV8847S |                   |                                                                                                                                         |

|        | TSSOP<br>HTSSOP | WQFN | TSSOP    |                   |                                                                                                                                         |

| GND    | 13              | 11   | 13       | PWR               | デバイスのグランド。GND ピンとデバイスのサーマル パッド (HTSSOP パッケージおよび WQFN パッケージ) をグランドに接続することを推奨します。                                                         |

| IN1    | 16              | 14   | 16       | I                 | ハーフ ブリッジ入力 1                                                                                                                            |

| IN2    | 15              | 13   | 15       | I                 | ハーフ ブリッジ入力 2                                                                                                                            |

| IN3    | 9               | 7    | 9        | I                 | ハーフ ブリッジ入力 3                                                                                                                            |

| IN4    | 10              | 8    | 10       | I                 | ハーフ ブリッジ入力 4                                                                                                                            |

| ISEN12 | 3               | 1    | 3        | O                 | フル ブリッジ 12 のセンス。このピンはフル ブリッジ 12 の電流センス抵抗に接続します。電流レギュレーションが必要ない場合は、このピンは GND ピンに接続します。                                                   |

| ISEN34 | 6               | 4    | 6        | O                 | フル ブリッジ 34 のセンス。このピンはフル ブリッジ 34 の電流センス抵抗に接続します。電流レギュレーションが必要ない場合は、このピンは GND ピンに接続します。                                                   |

| モード    | 14              | 12   | —        | I                 | ドライバ動作モード選択用のトライステートピン                                                                                                                  |

| nFAULT | 8               | 6    | 8        | OD/I              | フォルト通知ピン。このピンは、フォルト条件によってロジック Low にプルされます。オープンドレイン出力には、外付けのプルアップ抵抗が必要です。このピンは、DRV8847S デバイスで I <sup>2</sup> C バスを解放するための入力ピンとしても使用されます。 |

| nSLEEP | 1               | 15   | 1        | I                 | スリープ・モード入力。このピンをロジック High に設定すると、デバイスがイネーブルになります。このピンをロジック Low に設定すると、低消費電力スリープモードに移行します。                                               |

| OUT1   | 2               | 16   | 2        | O                 | ハーフ ブリッジ出力 1                                                                                                                            |

| OUT2   | 4               | 2    | 4        | O                 | ハーフ ブリッジ出力 2                                                                                                                            |

| OUT3   | 7               | 5    | 7        | O                 | ハーフ ブリッジ出力 3                                                                                                                            |

| OUT4   | 5               | 3    | 5        | O                 | ハーフ ブリッジ出力 4                                                                                                                            |

| SCL    | —               | —    | 11       | I                 | I <sup>2</sup> C クロック信号                                                                                                                 |

| SDA    | —               | —    | 14       | OD                | I <sup>2</sup> C データ信号。SDA ピンはプルアップ抵抗を必要とします。                                                                                           |

| TRQ    | 11              | 9    | —        | I                 | トルク電流スカラー                                                                                                                               |

| VM     | 12              | 10   | 12       | PWR               | 電源。VM ピンはモーター電源に接続します。VM 定格 0.1 $\mu$ F (セラミック) と 10 $\mu$ F (最小値) コンデンサでこのピンはグランドにバイパスします。                                             |

(1) I = 入力、O = 出力、OD = オープンドレイン出力、PWR = 電源

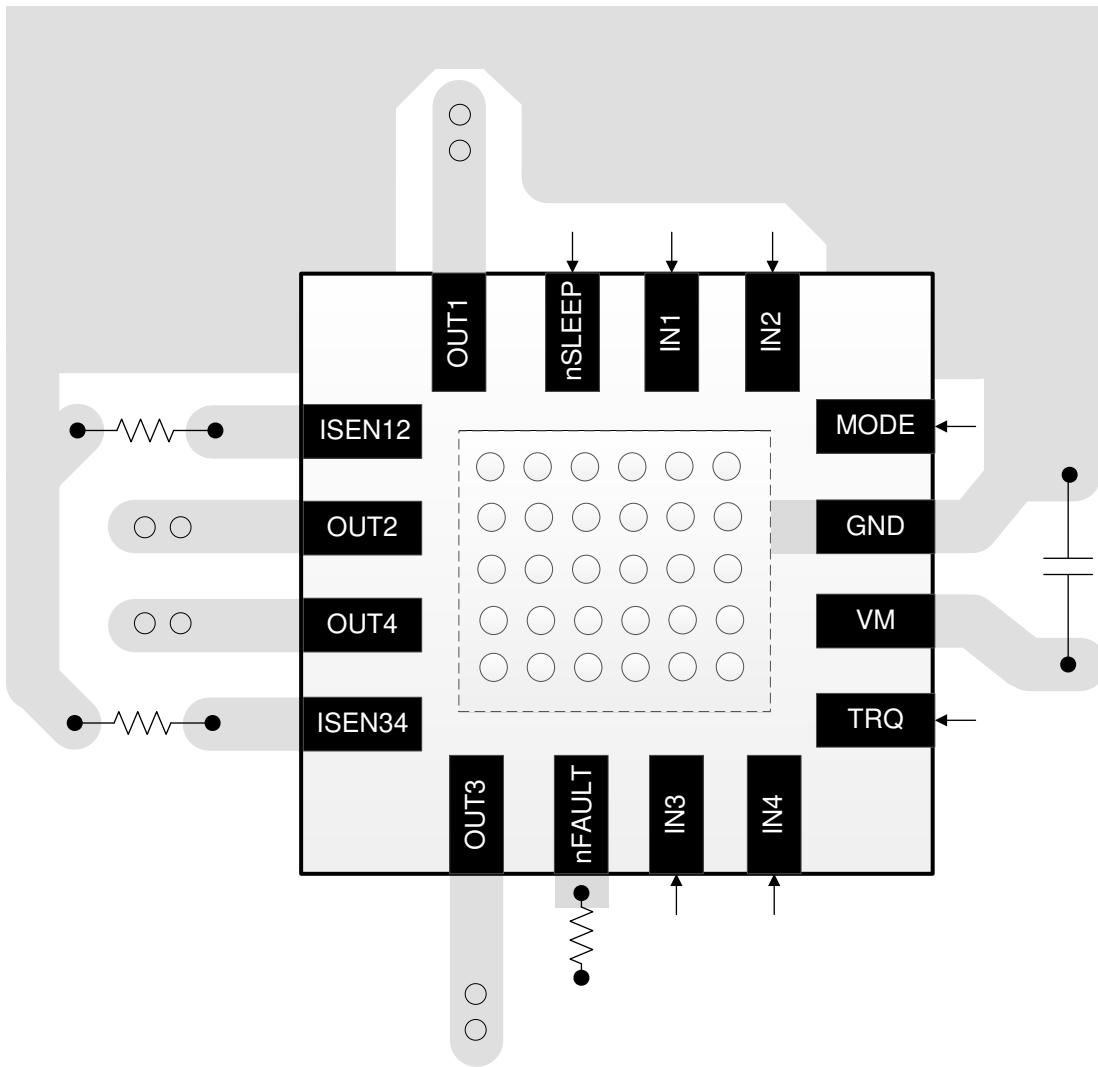

図 5-5. DRV88471 RTE パッケージ 16 ピン WQFN (露出サーマル パッド付き) 上面図

表 5-2. 新しいピンの機能

| ピン           |    | 種類 <sup>(1)</sup> | 説明                                                                                         |

|--------------|----|-------------------|--------------------------------------------------------------------------------------------|

| DRV8471 WQFN | 番号 |                   |                                                                                            |

| GND          | 11 | PWR               | デバイスのグランド。GND ピンとデバイスのサーマル パッドをグランドに接続することを推奨します。                                          |

| IN1          | 14 | I                 | ハーフ ブリッジ入力 1                                                                               |

| IN2          | 13 | I                 | ハーフ ブリッジ入力 2                                                                               |

| IN3          | 7  | I                 | ハーフ ブリッジ入力 3                                                                               |

| IN4          | 8  | I                 | ハーフ ブリッジ入力 4                                                                               |

| ISEN12       | 1  | O                 | フル ブリッジ 12 のセンス。このピンはフル ブリッジ 12 の電流センス抵抗に接続します。電流レギュレーションが必要ない場合は、このピンは GND ピンに接続します。      |

| ISEN34       | 4  | O                 | フル ブリッジ 34 のセンス。このピンはフル ブリッジ 34 の電流センス抵抗に接続します。電流レギュレーションが必要ない場合は、このピンは GND ピンに接続します。      |

| NC           | 9  | -                 | 無接続                                                                                        |

| NC           | 12 | -                 | 無接続                                                                                        |

| nFAULT       | 6  | OD                | フォルト通知ピン。このピンは、フォルト条件によってロジック Low にプルされます。オープンドレイン出力には、外付けのプルアップ抵抗が必要です。                   |

| nSLEEP       | 15 | I                 | スリープ・モード入力。このピンをロジック High に設定すると、デバイスがイネーブルになります。このピンをロジック Low に設定すると、低消費電力スリープ・モードに移行します。 |

| OUT1         | 16 | O                 | ハーフ ブリッジ出力 1                                                                               |

| OUT2         | 2  | O                 | ハーフ ブリッジ出力 2                                                                               |

| OUT3         | 5  | O                 | ハーフ ブリッジ出力 3                                                                               |

| OUT4         | 3  | O                 | ハーフ ブリッジ出力 4                                                                               |

| VM           | 10 | PWR               | 電源。VM ピンはモーター電源に接続します。VM 定格 0.1µF (セラミック) と 10µF (最小値) コンデンサでこのピンはグランドにバイパスします。            |

(1) I = 入力、O = 出力、OD = オープンドレイン出力、PWR = 電源

## 6 仕様

### 6.1 絶対最大定格

動作時周囲温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|                                                                        | 最小値    | 最大値      | 単位   |

|------------------------------------------------------------------------|--------|----------|------|

| 電源ピン電圧 (VM)                                                            | -0.3   | 20       | V    |

| 電源電圧ランプレート (VM)                                                        | 0      | 2        | V/μs |

| デジタルピン電圧 (IN1、IN2、IN3、IN4、TRQ、nSLEEP、nFAULT、SCL、SDA)                   | -0.3   | 5.75     | V    |

| 巻線出力ピン電圧 (連続) (OUT1、OUT2、OUT3、OUT4)                                    | -0.7   | VM + 0.6 | V    |

| シャントアンプ入力ピン電圧 (ISEN12、ISEN34) <sup>(2)</sup>                           | -0.6   | 0.6      | V    |

| ピーク駆動電流 (OUT1、OUT2、OUT3、OUT4), V <sub>VM</sub> <= 16.5V <sup>(3)</sup> | 内部的に制限 |          | A    |

| ピーク駆動電流 (OUT1、OUT2、OUT3、OUT4), V <sub>VM</sub> > 16.5V <sup>(3)</sup>  | 0      | 4        | A    |

| 周囲温度、T <sub>A</sub>                                                    | -40    | 125      | °C   |

| 接合部温度、T <sub>J</sub>                                                   | -40    | 150      | °C   |

| 保管温度、T <sub>stg</sub>                                                  | -65    | 150      | °C   |

- (1) 「絶対最大定格」を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみについての話で、絶対最大定格において、またはこのデータシートの「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。絶対最大定格の状態が長時間続くと、デバイスの信頼性に影響を与える可能性があります。

- (2) 25ns 未満の ±1V の過渡電圧は許容されます。

- (3) 消費電力および温度の制限に従う必要があります。

### 6.2 ESD 定格

|                    |       |                                                                | 値     | 単位 |

|--------------------|-------|----------------------------------------------------------------|-------|----|

| V <sub>(ESD)</sub> | 静電気放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 に準拠、すべてのピン <sup>(1)</sup>   | ±4000 | V  |

|                    |       | デバイス帶電モデル (CDM)、JEDEC 仕様 JESD22-C101 に準拠、すべてのピン <sup>(2)</sup> | ±500  |    |

- (1) JEDEC のドキュメント JEP155 には、500V HBM であれば標準的な ESD 制御プロセスにより安全な製造が可能であると記載されています。

- (2) JEDEC のドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

### 6.3 推奨動作条件

動作時周囲温度範囲内 (特に記述のない限り)。標準値には T<sub>A</sub> = 25°C、V<sub>VM</sub> = 12V が適用されます。

|                  |                                               | 最小値 | 公称値                | 最大値                | 単位  |

|------------------|-----------------------------------------------|-----|--------------------|--------------------|-----|

| V <sub>VM</sub>  | 電源電圧 (VM)                                     | 2.7 | 18                 | 18                 | V   |

| V <sub>IN</sub>  | ロジック入力電圧 (IN1、IN2、IN3、IN4、TRQ、nSLEEP、SCL、SDA) | 0   | 5                  | 5                  | V   |

| I <sub>RMS</sub> | ブリッジごとのモータ RMS 電流 (OUT1、OUT2、OUT3、OUT4)       | 0   | 1 <sup>(1)</sup>   | 1 <sup>(1)</sup>   | A   |

| f <sub>PWM</sub> | PWM 周波数 (IN1、IN2、IN3、IN4)                     | 0   | 250 <sup>(1)</sup> | 250 <sup>(1)</sup> | kHz |

| V <sub>OD</sub>  | オーブンドレイン プルアップ電圧 (nFAULT)                     | 0   | 5                  | 5                  | V   |

| I <sub>OD</sub>  | オーブン・ドレイン出力電流 (nFAULT)                        | 0   | 5                  | 5                  | mA  |

| T <sub>A</sub>   | 動作時の周囲温度                                      | -40 | 85                 | 85                 | °C  |

| T <sub>J</sub>   | 動作時の接合部温度                                     | -40 | 150                | 150                | °C  |

- (1) 消費電力および温度の制限に従う必要があります。パッケージの放熱性能に依存します。

## 6.4 热に関する情報

| 热評価基準 <sup>(1)</sup> |                   | DRV8847、<br>DRV8847S | DRV8847      | DRV8847   | 単位   |

|----------------------|-------------------|----------------------|--------------|-----------|------|

|                      |                   | PW (TSSOP)           | PWP (HTSSOP) | RTE (QFN) |      |

|                      |                   | 16 ピン                | 16 ピン        | 16 ピン     |      |

| $R_{\theta JA}$      | 接合部から周囲への热抵抗      | 107.9                | 46.5         | 46.4      | °C/W |

| $R_{\theta JC(top)}$ | 接合部からケース(上面)への热抵抗 | 38.5                 | 40.1         | 47.5      | °C/W |

| $R_{\theta JB}$      | 接合部から基板への热抵抗      | 54.2                 | 18.8         | 21.2      | °C/W |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ  | 3.1                  | 1.3          | 0.9       | °C/W |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ  | 53.6                 | 19.0         | 21.3      | °C/W |

| $R_{\theta JC(bot)}$ | 接合部からケース(底面)への热抵抗 | 該当なし                 | 5.9          | 6.1       | °C/W |

(1) 従来および最新の热評価基準の詳細については、『半導体および IC パッケージの热評価基準』アプリケーション・レポートを参照してください。

## 6.5 電気的特性

推奨動作条件範囲内(特に記述のない限り)。標準値には  $T_A = 25^\circ\text{C}$ 、 $V_{VM} = 12\text{V}$  が適用されます。

| パラメータ                                                  | テスト条件          | 最小値                                       | 標準値 | 最大値 | 単位  |

|--------------------------------------------------------|----------------|-------------------------------------------|-----|-----|-----|

| <b>電源 (VM)</b>                                         |                |                                           |     |     |     |

| $I_{VM}$                                               | VM 動作電源電流      | VM = 2.7V、nSLEEP = 1、INx = 0              | 2   | 2.5 | mA  |

|                                                        |                | VM = 5V、nSLEEP = 1、INx = 0                | 3   | 3.5 | mA  |

|                                                        |                | VM = 12V、nSLEEP = 1、INx = 0               | 3   | 3.5 | mA  |

| $I_{VMQ}$                                              | VM スリープ・モード電流  | VM = 2.7V、nSLEEP = 0、TA = 25°C            | 0.1 |     | μA  |

|                                                        |                | VM = 2.7V、nSLEEP = 0、TA = 85°C            |     | 0.5 | μA  |

|                                                        |                | VM = 5V、nSLEEP = 0、TA = 25°C              | 0.2 |     | μA  |

|                                                        |                | VM = 5V、nSLEEP = 0、TA = 85°C              |     | 1   | μA  |

|                                                        |                | VM = 12V、nSLEEP = 0、TA = 25°C             | 1.7 |     | μA  |

|                                                        |                | VM = 12V、nSLEEP = 0、TA = 85°C             |     | 2.5 | μA  |

| $t_{SLEEP}$                                            | スリープ時間         | nSLEEP = 0 でスリープモード                       | 2   |     | μs  |

| $t_{WAKE}$                                             | ウェークアップ時間      | nSLEEP = 1 で出力遷移                          |     | 1.5 | ms  |

| $t_{ON}$                                               | ターンオン時間        | VM > UVLO で出力遷移 (nSLEEP = 1)              |     | 1.5 | ms  |

| <b>ロジック レベル入力 (IN1、IN2、IN3、IN4、NSLEEP、TRQ、SCL、SDA)</b> |                |                                           |     |     |     |

| $V_{IL}$                                               | 入力ロジック Low 電圧  | VM < 7 V                                  | 0   | 0.6 | V   |

|                                                        |                | VM >= 7V <sup>(1)</sup>                   | 0   | 1.0 | V   |

| $V_{IH}$                                               | 入力ロジック High 電圧 |                                           | 1.6 | 5.5 | V   |

| $V_{HYS}$                                              | 入力ロジック・ヒステリシス  | nSLEEP ピン                                 | 40  |     | mV  |

| $V_{HYS}$                                              | 入力ロジック・ヒステリシス  | IN1 ピン、IN2 ピン、IN3 ピン、IN4 ピン、TRQ ピン、SCL ピン | 100 |     | mV  |

| $V_{IL}$                                               | nSLEEP         |                                           | 0   | 0.6 | V   |

| $V_{IH}$                                               | nSLEEP         |                                           | 1.6 | 5.5 | V   |

| $V_{HYS}$                                              | nSLEEP         |                                           | 40  |     | mV  |

| $I_{IL}$                                               | 入力ロジック Low 電流  | $V_{IN} = 0V$                             | -1  | 1   | μA  |

| $I_{IH}$                                               | 入力ロジック High 電流 | IN1、IN2、IN3、IN4、TRQ、 $V_{IN} = 5V$        | 18  | 35  | μA  |

|                                                        |                | nSLEEP、 $V_{IN} = \text{最小値 (VM, 5V)}$    | 10  | 25  | μA  |

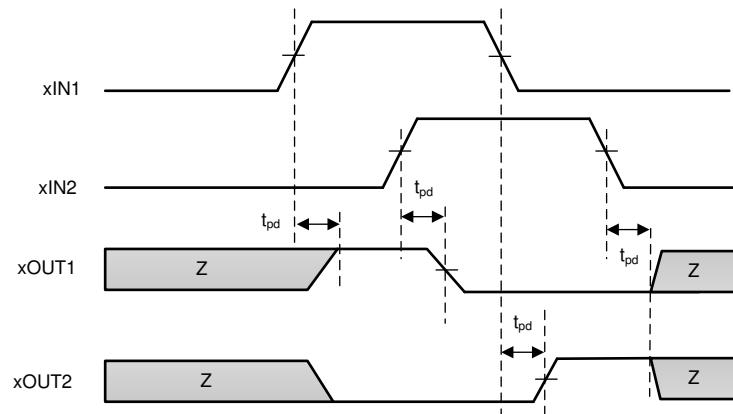

| $t_{PD}$                                               | 伝搬遅延           | INx エッジで出力                                | 100 | 400 | 600 |

| $t_{DEGLITCH}$                                         | 入力ロジックのグリッチ除去  |                                           |     | 50  | ns  |

| <b>トライレベル入力 (MODE)</b>                                 |                |                                           |     |     |     |

推奨動作条件範囲内(特に記述のない限り)。標準値には  $T_A = 25^\circ\text{C}$ 、 $V_{VM} = 12\text{V}$  が適用されます。

| パラメータ                                  |                    | テスト条件                                                                       | 最小値   | 標準値 | 最大値   | 単位               |

|----------------------------------------|--------------------|-----------------------------------------------------------------------------|-------|-----|-------|------------------|

| $V_{IL}$                               | トライレベル入力論理 Low 電圧  |                                                                             | 0     | 0.6 | 0.6   | V                |

| $V_{IZ}$                               | トライレベル入力 Hi-Z 電圧   |                                                                             |       | 1.2 | 1.2   | V                |

| $V_{IH}$                               | トライレベル入力論理 High 電圧 |                                                                             | 1.6   | 5.5 | 5.5   | V                |

| $I_{IL}$                               | トライレベル入力論理 Low 電流  | $V_{IN} = 0\text{V}$                                                        | -9    | -4  | -4    | $\mu\text{A}$    |

| $I_{IH}$                               | トライレベル入力論理 High 電流 | $V_{IN} = 5\text{V}$                                                        | 8     | 25  | 25    | $\mu\text{A}$    |

| <b>オープン・ドレイン出力 (nFAULT)</b>            |                    |                                                                             |       |     |       |                  |

| $V_{OL}$                               | 出力論理 Low 電圧        | $I_{OD} = 5\text{mA}$                                                       |       | 0.5 | 0.5   | V                |

| $I_{OH}$                               | 出力ロジック High 電流     | $V_{OD} = 3.3\text{V}$                                                      | -1    | 1   | 1     | $\mu\text{A}$    |

| <b>オープン・ドレイン出力 (SDA)</b>               |                    |                                                                             |       |     |       |                  |

| $V_{OL}$                               | 出力論理 Low 電圧        | $I_{OD} = 5\text{mA}$                                                       |       | 0.5 | 0.5   | V                |

| $I_{OH}$                               | 出力ロジック High 電流     | $V_{OD} = 3.3\text{V}$                                                      | -1    | 1   | 1     | $\mu\text{A}$    |

| $C_B$                                  | 各バス・ラインの容量性負荷      |                                                                             |       | 400 | 400   | pF               |

| <b>ドライバ出力 (OUT1, OUT2, OUT3, OUT4)</b> |                    |                                                                             |       |     |       |                  |

| $R_{DS(ON)}_{HS}$                      | ハイサイド MOSFET オン抵抗  | $V_{VM} = 2.7\text{V}$ 、 $I_{OUT} = 0.5\text{A}$ 、 $T_A = 25^\circ\text{C}$ | 690   | 690 | 690   | $\text{m}\Omega$ |

|                                        |                    | $V_{VM} = 2.7\text{V}$ 、 $I_{OUT} = 0.5\text{A}$ 、 $T_A = 85^\circ\text{C}$ | 950   | 950 | 950   | $\text{m}\Omega$ |

|                                        |                    | $V_{VM} = 5\text{V}$ 、 $I_{OUT} = 0.5\text{A}$ 、 $T_A = 25^\circ\text{C}$   | 530   | 530 | 530   | $\text{m}\Omega$ |

|                                        |                    | $V_{VM} = 5\text{V}$ 、 $I_{OUT} = 0.5\text{A}$ 、 $T_A = 85^\circ\text{C}$   | 740   | 740 | 740   | $\text{m}\Omega$ |

|                                        |                    | $V_{VM} = 12\text{V}$ 、 $I_{OUT} = 0.5\text{A}$ 、 $T_A = 25^\circ\text{C}$  | 520   | 520 | 520   | $\text{m}\Omega$ |

|                                        |                    | $V_{VM} = 12\text{V}$ 、 $I_{OUT} = 0.5\text{A}$ 、 $T_A = 85^\circ\text{C}$  | 700   | 700 | 700   | $\text{m}\Omega$ |

| $R_{DS(ON)}_{LS}$                      | ローサイド MOSFET オン抵抗  | $V_{VM} = 2.7\text{V}$ 、 $I_{OUT} = 0.5\text{A}$ 、 $T_A = 25^\circ\text{C}$ | 570   | 570 | 570   | $\text{m}\Omega$ |

|                                        |                    | $V_{VM} = 2.7\text{V}$ 、 $I_{OUT} = 0.5\text{A}$ 、 $T_A = 85^\circ\text{C}$ | 900   | 900 | 900   | $\text{m}\Omega$ |

|                                        |                    | $V_{VM} = 5\text{V}$ 、 $I_{OUT} = 0.5\text{A}$ 、 $T_A = 25^\circ\text{C}$   | 460   | 460 | 460   | $\text{m}\Omega$ |

|                                        |                    | $V_{VM} = 5\text{V}$ 、 $I_{OUT} = 0.5\text{A}$ 、 $T_A = 85^\circ\text{C}$   | 690   | 690 | 690   | $\text{m}\Omega$ |

|                                        |                    | $V_{VM} = 12\text{V}$ 、 $I_{OUT} = 0.5\text{A}$ 、 $T_A = 25^\circ\text{C}$  | 450   | 450 | 450   | $\text{m}\Omega$ |

|                                        |                    | $V_{VM} = 12\text{V}$ 、 $I_{OUT} = 0.5\text{A}$ 、 $T_A = 85^\circ\text{C}$  | 680   | 680 | 680   | $\text{m}\Omega$ |

| $I_{OFF}$                              | オフ状態のリーク電流         | $V_{VM} = 5\text{V}$ 、 $T_J = 25^\circ\text{C}$ 、 $V_{OUT} = 0\text{V}$     | -1    | -1  | 1     | $\mu\text{A}$    |

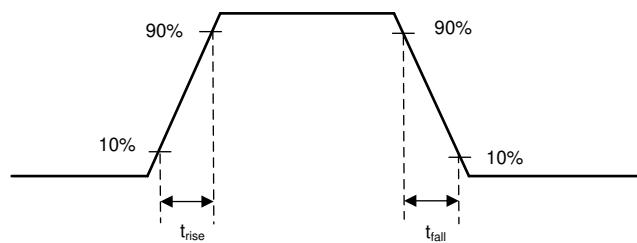

| $t_{RISE}$                             | 出力立ち上がり時間          | $V_{VM} = 12\text{V}$ 、 $I_{OUT} = 0.5\text{A}$                             | 150   | 150 | 150   | ns               |

| $t_{FALL}$                             | 出力立ち下がり時間          | $V_{VM} = 12\text{V}$ 、 $I_{OUT} = 0.5\text{A}$                             | 150   | 150 | 150   | ns               |

| $t_{DEAD}$                             | 出力デッドタイム           | 内部デッドタイム                                                                    | 200   | 200 | 200   | ns               |

| $V_{SD}$                               | ボディダイオード順方向電圧      | $I_{OUT} = 0.5\text{A}$                                                     | 1.1   | 1.1 | 1.1   | V                |

| <b>PWM 電流制御 (ISEN12, SEN34)</b>        |                    |                                                                             |       |     |       |                  |

| $V_{TRIP}$                             | ISENxx トリップ電圧      | 100% でのトルク ( $TRQ = 0$ )                                                    | 140   | 150 | 160   | $\text{mV}$      |

|                                        |                    | 50 パーセント でのトルク ( $TRQ = 1$ )                                                | 63.75 | 75  | 86.25 | $\text{mV}$      |

| $t_{BLANK}$                            | 電流センス ブランкиング時間    |                                                                             | 1.8   | 1.8 | 1.8   | $\mu\text{s}$    |

| $t_{OFF}$                              | 電流制御一定オフ時間         |                                                                             | 20    | 20  | 20    | $\mu\text{s}$    |

| <b>保護回路</b>                            |                    |                                                                             |       |     |       |                  |

| $V_{UVLO}$                             | 電源低電圧誤動作防止         | 電源立ち上がり                                                                     | 2.7   | 2.7 | 2.7   | V                |

|                                        |                    | 電源立ち下がり                                                                     | 2.4   | 2.4 | 2.4   | V                |

| $V_{UVLO\_HYS}$                        | 電源低電圧ヒステリシス        | 立ち上がりから立ち下がりへのスレッショルド                                                       | 50    | 50  | 50    | $\text{mV}$      |

| $t_{UVLO}$                             | 電源低電圧グリッヂ除去時間      | VM 立ち下がり、UVLO 通知                                                            | 10    | 10  | 10    | $\mu\text{s}$    |

| $I_{OCP}$                              | 過電流保護トリップ ポイント (2) |                                                                             | 1.6   | 1.6 | 1.6   | A                |

| $t_{OCP}$                              | 過電流保護グリッヂ除去時間      | $V_{VM} < 15\text{V}$                                                       | 3     | 3   | 3     | $\mu\text{s}$    |

|                                        |                    | $V_{VM} \geq 15\text{V}$                                                    | 1     | 1   | 1     | $\mu\text{s}$    |

推奨動作条件範囲内(特に記述のない限り)。標準値には  $T_A = 25^\circ\text{C}$ 、 $V_{VM} = 12\text{V}$  が適用されます。

| パラメータ           |                                       | テスト条件                                             | 最小値 | 標準値  | 最大値 | 単位               |

|-----------------|---------------------------------------|---------------------------------------------------|-----|------|-----|------------------|

| $t_{RETRY}$     | 過電流保護リトライ時間                           |                                                   | 1   |      |     | ms               |

| $I_{OL\_PU}$    | 開放負荷プルアップ電流                           | OUTx ピンで $15\text{nF}$ 未満、 $V_{VM} = 2.7\text{V}$ |     | 100  |     | $\mu\text{A}$    |

| $I_{OL\_PU}$    | 開放負荷プルアップ電流                           | OUTx ピンで $15\text{nF}$ 未満                         |     | 200  |     | $\mu\text{A}$    |

| $I_{OL\_PD}$    | 開放負荷プルダウン電流                           | OUTx ピンで $15\text{nF}$ 未満、 $V_{VM} = 2.7\text{V}$ |     | 130  |     | $\mu\text{A}$    |

| $I_{OL\_PD}$    | 開放負荷プルダウン電流                           | OUTx ピンで $15\text{nF}$ 未満                         |     | 230  |     | $\mu\text{A}$    |

| $I_{OL}$        | 開放負荷プルアップおよびプルダウン電流                   |                                                   |     | 230  |     | $\mu\text{A}$    |

| $V_{OL\_HS}$    | 開放負荷検出スレッショルド(ハイサイド)                  | $V_{VM} = 2.7\text{V}$                            |     | 1.3  |     | V                |

| $V_{OL\_HS}$    | 開放負荷検出スレッショルド(ハイサイド)                  |                                                   |     | 2.3  |     | V                |

| $V_{OL\_LS}$    | 開放負荷検出スレッショルド(ローサイド)                  | $V_{VM} = 2.7\text{V}$                            |     | 0.67 |     | V                |

| $V_{OL\_LS}$    | 開放負荷検出スレッショルド(ローサイド)                  |                                                   |     | 1.2  |     | V                |

| $V_{OL}$        | 開放負荷検出スレッショルド電圧                       |                                                   |     | 1.1  |     | V                |

| $T_{TSD}$       | サーマル・シャットダウン温度                        |                                                   | 150 | 160  | 180 | $^\circ\text{C}$ |

| $T_{HYS}$       | サーマル・シャットダウン・ヒステリシス                   |                                                   |     | 40   |     | $^\circ\text{C}$ |

| $VB_{BJT\_27C}$ | OTS における BJT のベース電圧(12V 電源でのテストパッド出力) |                                                   |     |      |     |                  |

(1) 設計と特性評価により規定されています。

(2)  $V_M > 16.5\text{V}$  の場合、OUTx の出力電流を 4A に制限する必要があります。

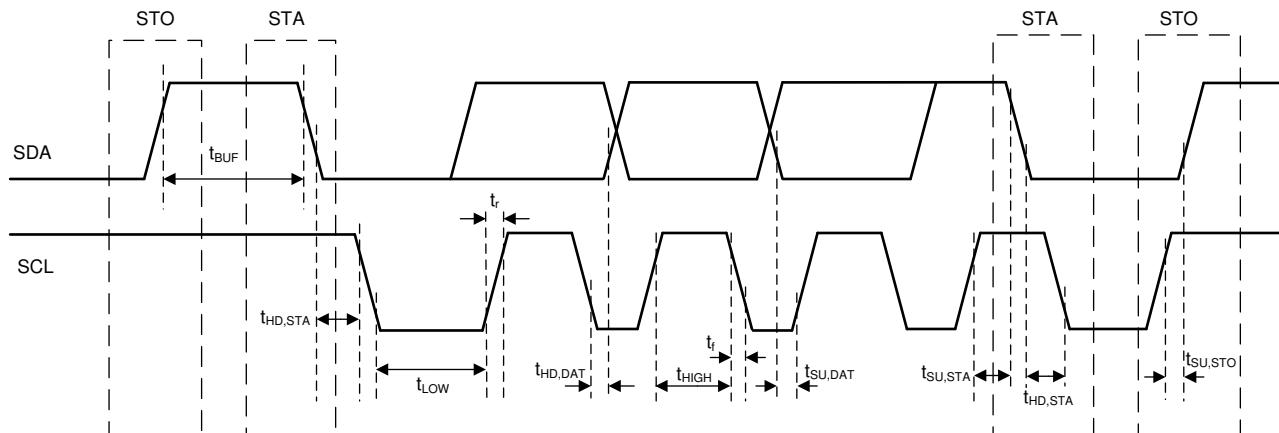

## 6.6 I<sup>2</sup>C のタイミング要件

|                 |                                                 | 最小値 | 公称値  | 最大値  | 単位            |

|-----------------|-------------------------------------------------|-----|------|------|---------------|

| <b>標準モード</b>    |                                                 |     |      |      |               |

| $f_{SCL}$       | SCL クロック周波数                                     | 0   | 100  |      | kHz           |

| $t_{HD,STA}$    | (反復) 開始条件のホールド時間。この時間が経過すると、最初のクロック・パルスが生成されます。 | 4   |      |      | $\mu\text{s}$ |

| $t_{LOW}$       | SCL クロック Low 期間                                 | 4.7 |      |      | $\mu\text{s}$ |

| $t_{HIGH}$      | SCL クロックの High の時間                              | 4   |      |      | $\mu\text{s}$ |

| $t_{SU,STA}$    | 反復開始条件のセットアップ時間                                 | 4.7 |      |      | $\mu\text{s}$ |

| $t_{HD,DAT}$    | データ・ホールド時間:I <sup>2</sup> C バス デバイスの場合          | 0   | 3.45 |      | $\mu\text{s}$ |

| $t_{SU,DAT}$    | データ・セットアップ時間                                    | 250 |      |      | ns            |

| $t_R$           | SDA と SCL の立ち上がり時間                              |     |      | 1000 | ns            |

| $t_F$           | SDA と SCL の立ち下がり時間                              |     |      | 300  | ns            |

| $t_{SU,STO}$    | STOP 条件のセットアップ時間                                | 4   |      |      | $\mu\text{s}$ |

| $t_{BUF}$       | STOP 条件と START 条件の間のバス・フリー時間                    | 4.7 |      |      | $\mu\text{s}$ |

| <b>ファスト・モード</b> |                                                 |     |      |      |               |

| $f_{SCL}$       | SCL クロック周波数                                     | 0   | 400  |      | kHz           |

| $t_{HD,STA}$    | (反復) 開始条件のホールド時間。この時間が経過すると、最初のクロック・パルスが生成されます。 | 0.6 |      |      | $\mu\text{s}$ |

| $t_{LOW}$       | SCL クロックの Low の時間                               | 1.3 |      |      | $\mu\text{s}$ |

| $t_{HIGH}$      | SCL クロックの High の時間                              | 0.6 |      |      | $\mu\text{s}$ |

| $t_{SU,STA}$    | 反復開始条件のセットアップ時間                                 | 0.6 |      |      | $\mu\text{s}$ |

| $t_{HD,DAT}$    | データ・ホールド時間:I <sup>2</sup> C バス デバイスの場合          | 0   | 0.9  |      | $\mu\text{s}$ |

| $t_{SU,DAT}$    | データ・セットアップ時間                                    | 250 |      |      | ns            |

| $t_R$           | SDA と SCL の立ち上がり時間                              |     |      | 300  | ns            |

| $t_F$           | SDA と SCL の立ち下がり時間                              |     |      | 300  | ns            |

|              |                              | 最小値 | 公称値 | 最大値 | 単位            |

|--------------|------------------------------|-----|-----|-----|---------------|

| $t_{SU,STO}$ | STOP 条件のセットアップ時間             | 0.6 |     |     | $\mu\text{s}$ |

| $t_{BUF}$    | STOP 条件と START 条件の間のバス・フリー時間 | 1.3 |     |     | $\mu\text{s}$ |

| $t_{SP}$     | 入力ノイズ フィルタにより抑制されるスパイクのパレス幅  |     | 50  |     | ns            |

図 6-1. タイミング図

図 6-2. I<sup>2</sup>C のタイミング図

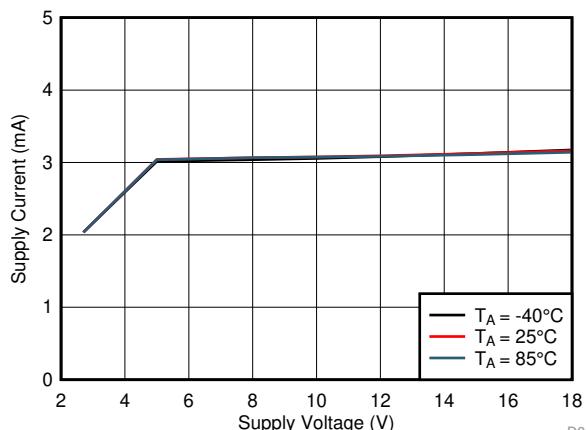

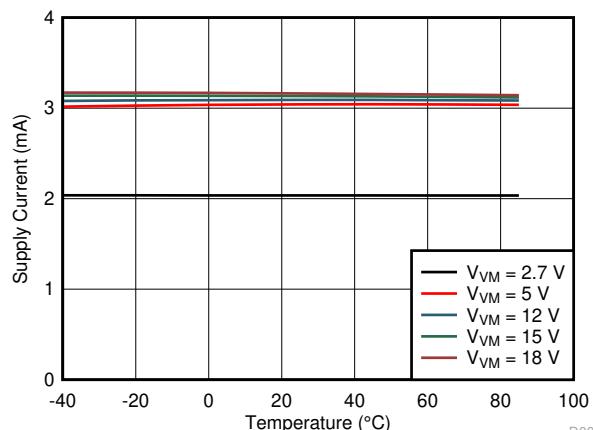

## 6.7 代表的特性

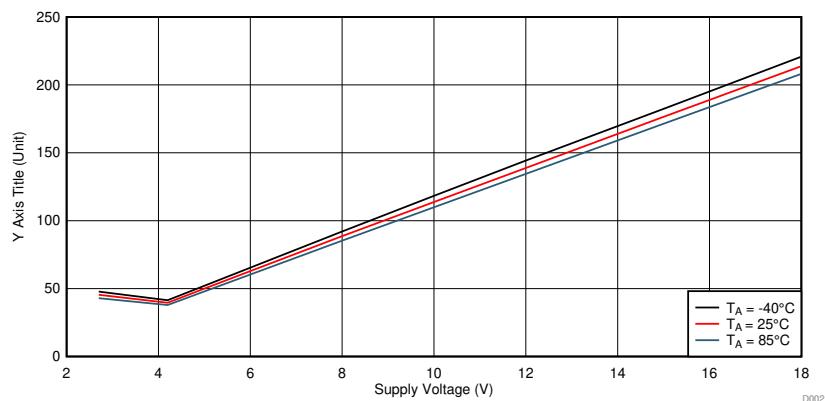

図 6-3. 動作電源電流 ( $I_{VM}$ ) と電源電圧 ( $V_{VM}$ ) との関係

図 6-4. 動作電源電流 ( $I_{VM}$ ) と周囲温度 ( $T_A$ ) との関係

図 6-5. スリープモード電源電流 ( $I_{VMQ}$ ) と電源電圧 ( $V_{VM}$ ) との関係

図 6-6. スリープモード電源電流 ( $I_{VMQ}$ ) と周囲温度 ( $T_A$ ) との関係

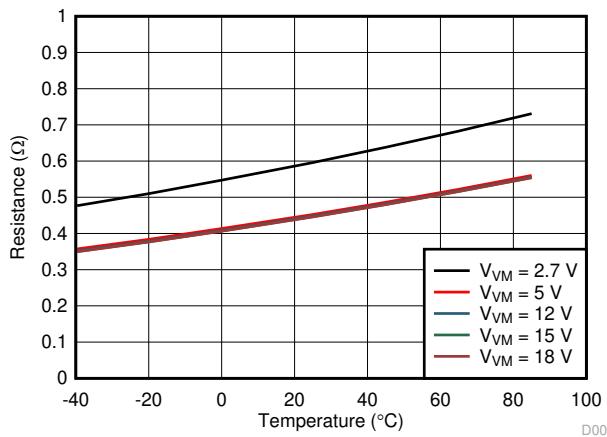

図 6-7. ハイサイド オン抵抗 ( $R_{DS(ON)_HS}$ ) と電源電圧 ( $V_{VM}$ ) との関係

図 6-8. ハイサイド オン抵抗 ( $R_{DS(ON)_HS}$ ) と周囲温度 ( $T_A$ ) との関係

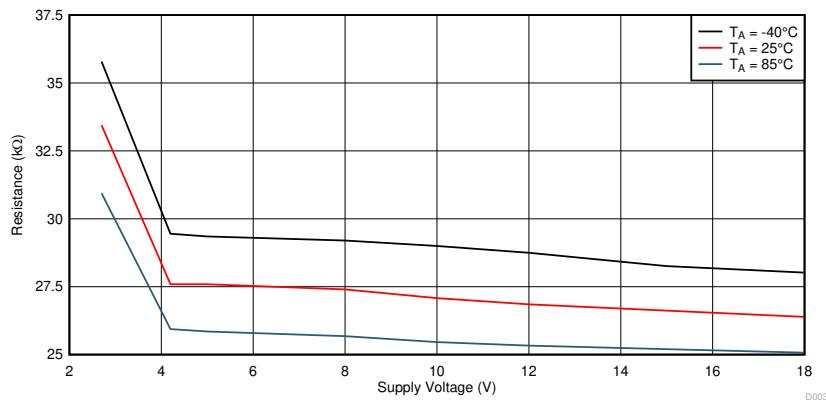

図 6-9. ローサイド オン抵抗 ( $R_{DS(ON)}_{LS}$ ) と電源電圧 ( $V_{VM}$ ) との関係

図 6-10. ローサイド オン抵抗 ( $R_{DS(ON)}_{LS}$ ) と周囲温度 ( $T_A$ ) との関係

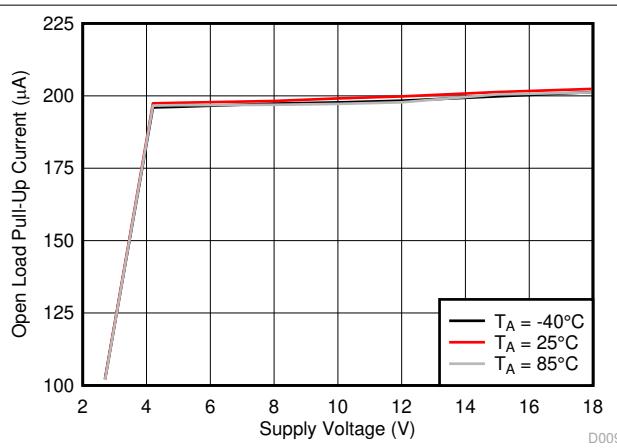

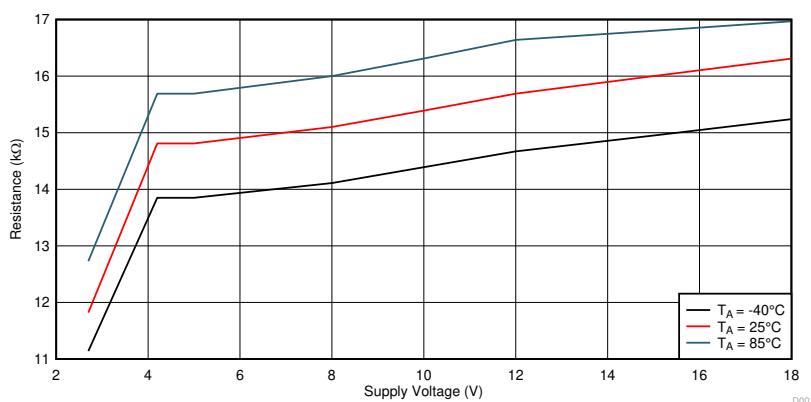

図 6-11. 開放負荷プルアップ電流 ( $I_{OL\_PU}$ ) と電源電圧 ( $V_{VM}$ ) との関係

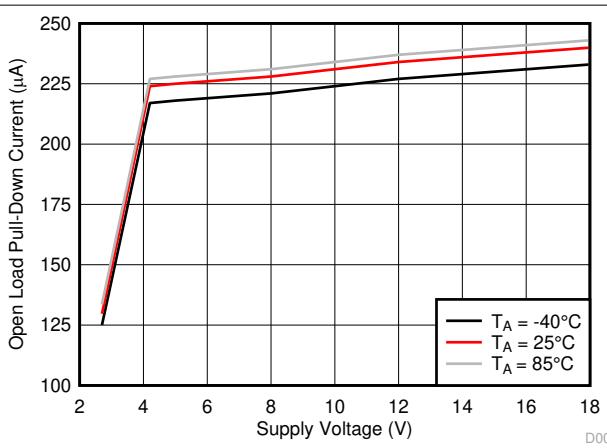

図 6-12. 開放負荷プルダウン電流 ( $I_{OL\_PD}$ ) と電源電圧 ( $V_{VM}$ ) との関係

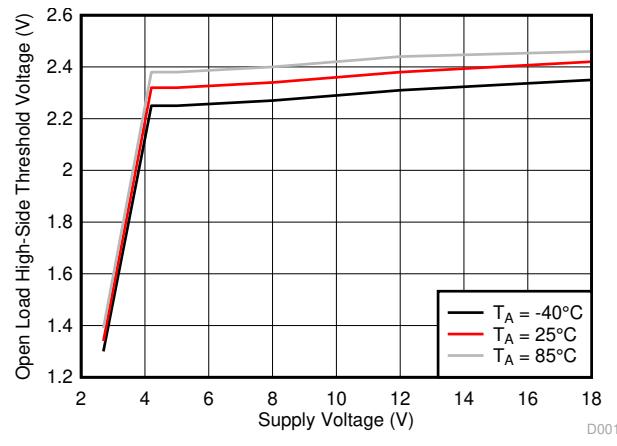

図 6-13. 開放負荷ハイサイド スレッショルド電圧 ( $V_{OL\_HS}$ ) と電源電圧 ( $V_{VM}$ ) との関係

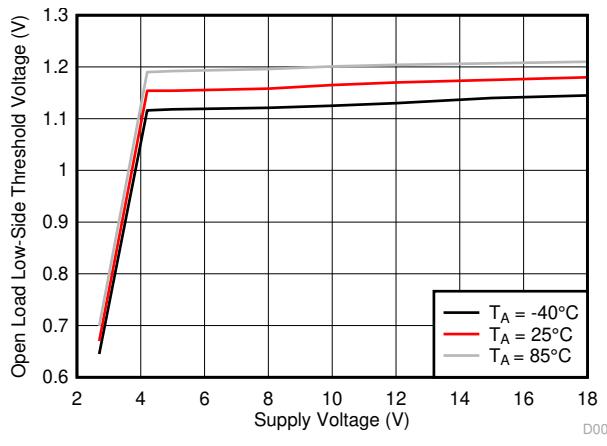

図 6-14. 開放負荷ローサイド スレッショルド電圧 ( $V_{OL\_LS}$ ) と電源電圧 ( $V_{VM}$ ) との関係

## 7 詳細説明

### 7.1 概要

DRV8847 は、産業用途において、ブラシ付きモーター やステッピング モーターを駆動するための 2.7V~18V 内蔵デュアル モーター ドライバで、2 つの DC モーター、1 つのバイポーラ ステッピング モーター、またはソレノイド負荷を駆動できます。このデバイスには、NMOS ローサイド ドライバとハイサイド ドライバ、および電流センス レギュレーション回路を使用する 2 つの H ブリッジが内蔵されています。DRV8847 デバイスは、低  $R_{DS(ON)}$  集積 MOSFET を使用して、H ブリッジ 1 つあたり 1A RMS の大出力電流をサポートしています。

シンプルな PWM インターフェイス オプションにより、H ブリッジ出力と簡単に接続できます。インターフェイス オプションは、DRV8847 デバイスの MODE ピンと IN3 ピンを使用して構成できます。I<sup>2</sup>C デバイス バリアント (DRV8847S) では、I<sup>2</sup>C インターフェイスによってインターフェイス オプションを構成できます。

電流レギュレーションでは、固定オフ時間 ( $t_{OFF}$ ) PWM 方式を採用しています。電流レギュレーションのトリップ ポイントは、センス抵抗の値と内部  $V_{TRIP}$  の固定値によって制御されます。

また、低消費電力スリープ モードを内蔵しているため、モーターを駆動していないときにシステムの電力を節約できます。

DRV8847 デバイスは、3 つのパッケージで供給されます。

- 16 ピン TSSOP (サーマル パッドなし)

- 16 ピン HTSSOP (PowerPAD)

- 16 ピン WQFN (サーマル パッドあり)

DRV8847 デバイスの I<sup>2</sup>C バリアントは、I<sup>2</sup>C バス上でマルチスレーブ動作を制御することで、詳細な診断要件やマルチスレーブ動作に対応することもできます。

DRV8847S デバイス バリアントは、16 ピン TSSOP (サーマル パッドなし) の 1 つのパッケージで供給されます。

DRV8847 デバイスには、広範な保護機能が内蔵されており、電源低電圧誤動作防止、開放負荷検出、過電流フォルト、サーマル シャットダウンが含まれます。

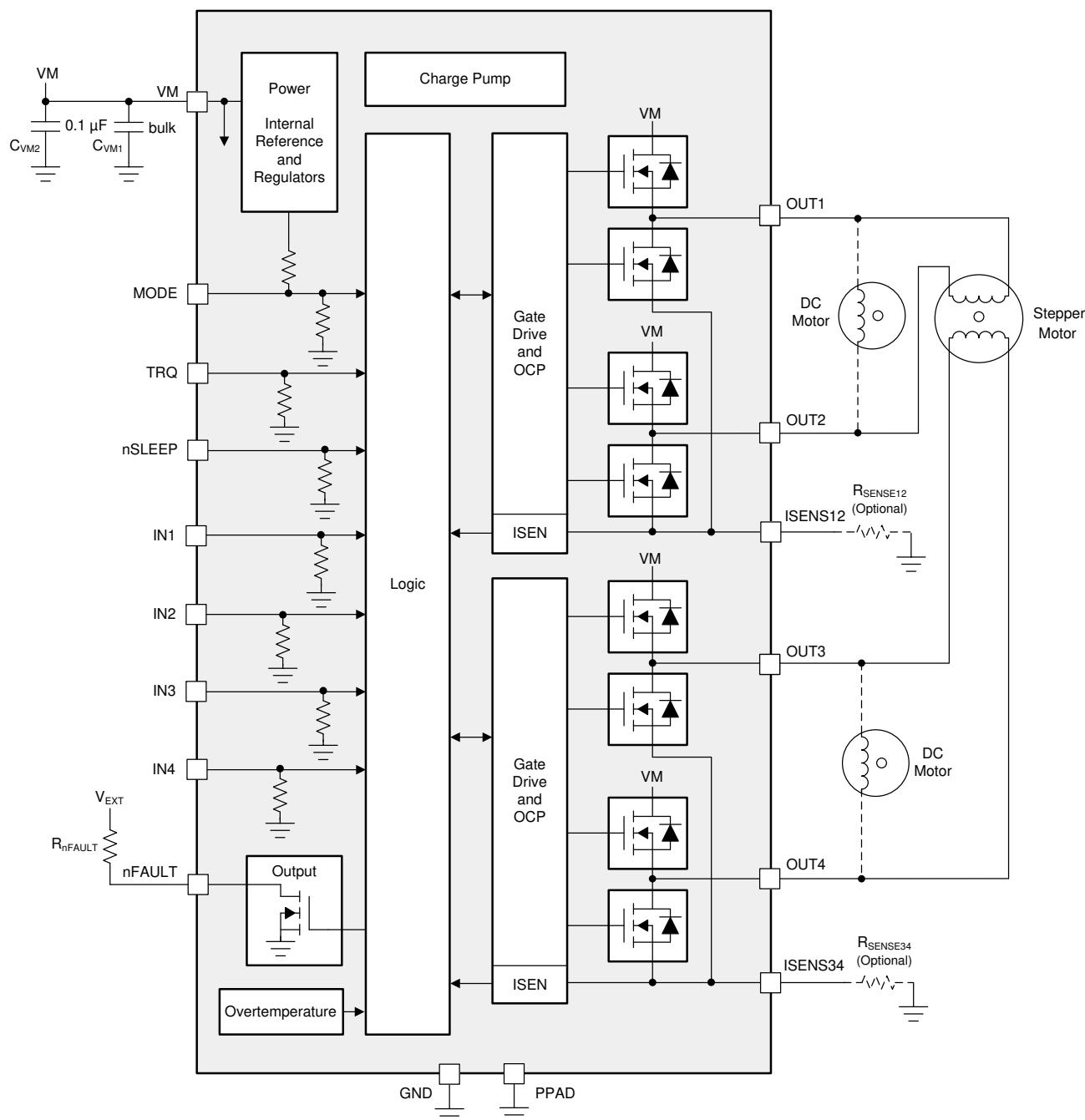

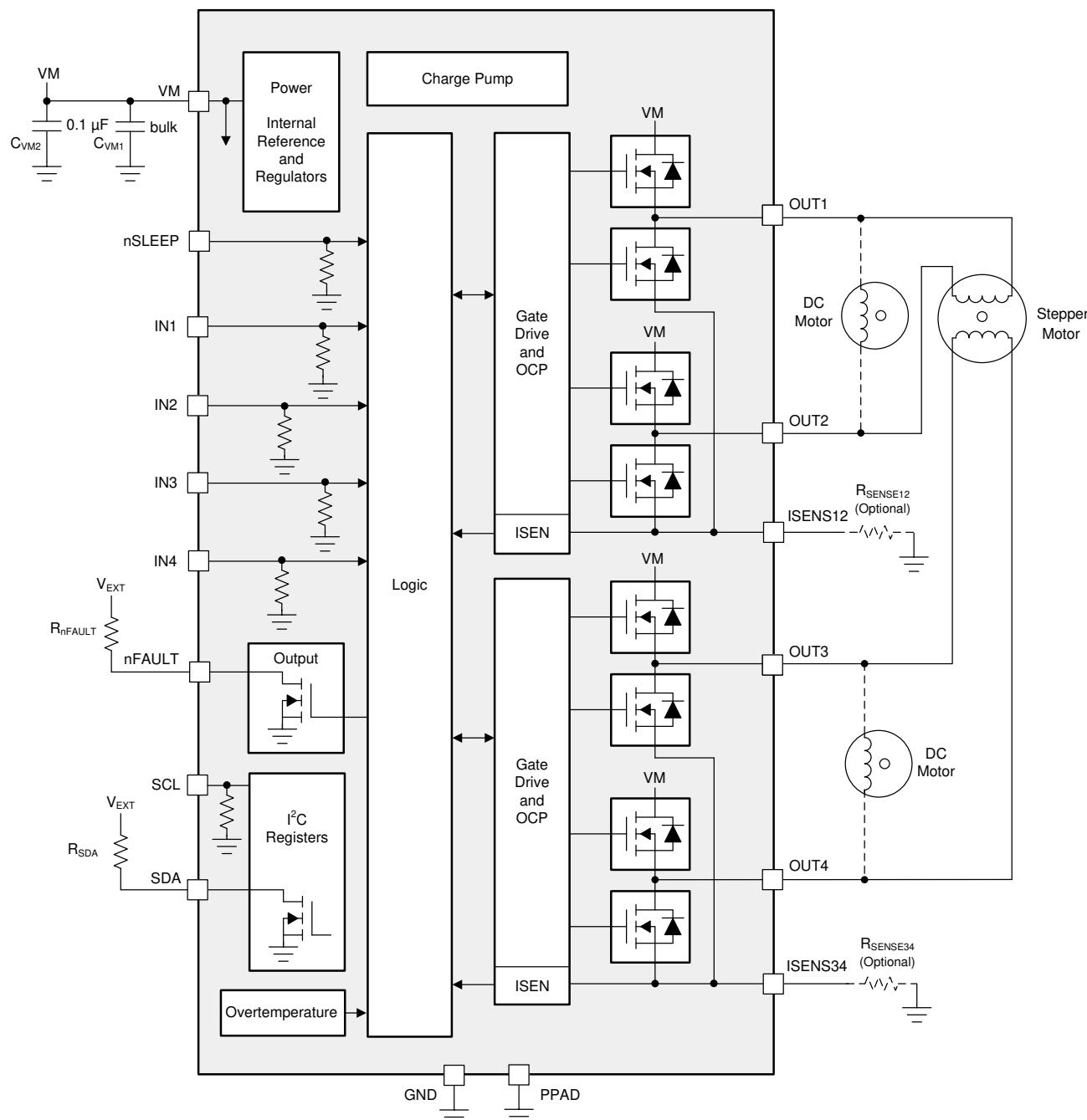

## 7.2 機能ブロック図

図 7-1. DRV8847 のブロック図

図 7-2. DRV8847S のブロック図

## 7.3 機能説明

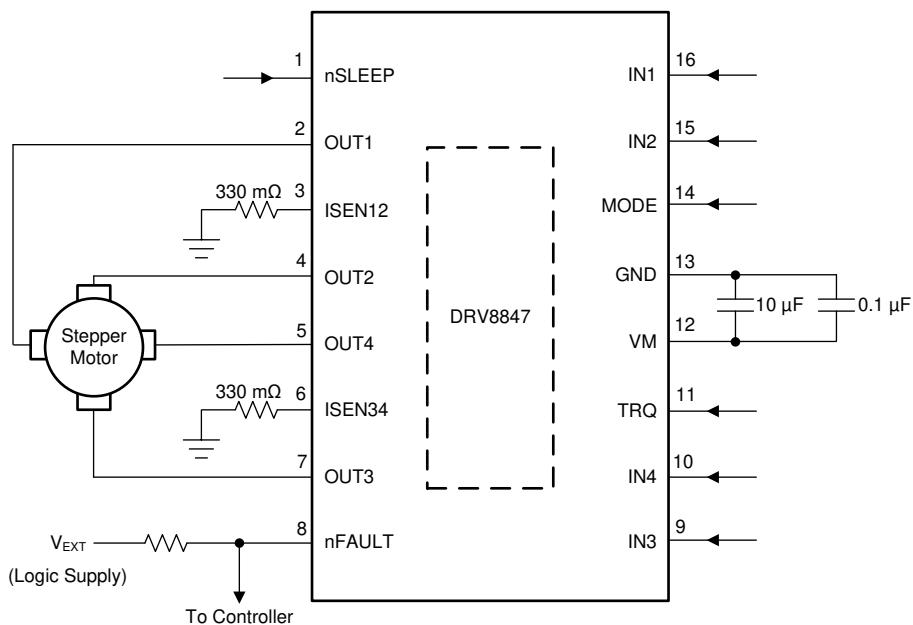

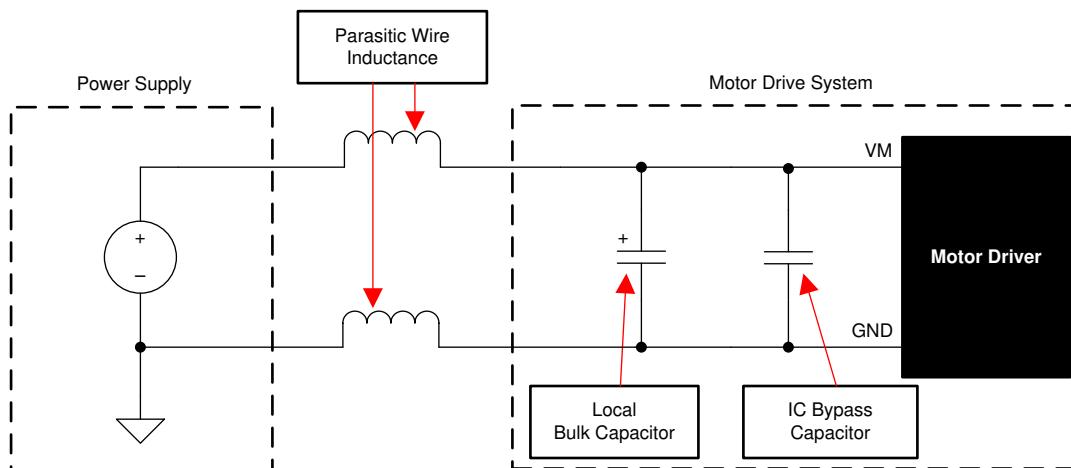

表 7-1 に、ゲートドライバの外付け部品の推奨値を示します。

表 7-1. DRV8847 の外付け部品

| 部品           | ピン 1     | ピン 2   | 推奨                                           |

|--------------|----------|--------|----------------------------------------------|

| $C_{VM1}$    | VM       | GND    | 10 $\mu$ F (最小値) VM 定格コンデンサ                  |

| $C_{VM2}$    | VM       | GND    | 0.1 $\mu$ F VM 定格セラミック コンデンサ                 |

| $R_{nFAULT}$ | VEXT (1) | nFAULT | >1k $\Omega$                                 |

| $R_{ISEN12}$ | ISEN12   | GND    | センス抵抗、サイズについては <a href="#">セクション 8.2</a> を参照 |

| $R_{ISEN34}$ | ISEN34   | GND    | センス抵抗、サイズについては <a href="#">セクション 8.2</a> を参照 |

(1) VEXT は DRV8847 デバイスのピンではありませんが、オープンドレイン出力 nFAULT には VEXT 外部電源電圧のプルアップ抵抗が必要です。

### 7.3.1 PWM モーター・ドライバ

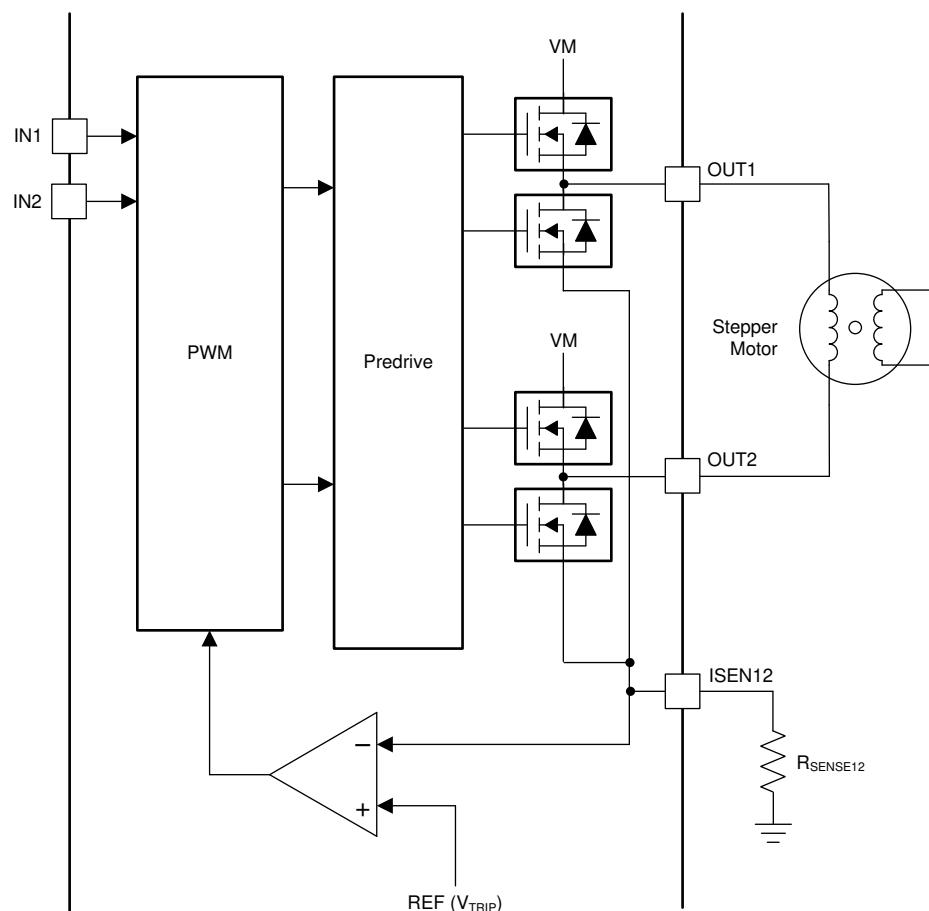

DRV8847 デバイスには、電流制御 PWM 回路を備えた 2 つの同じ H ブリッジ モーター ドライバが搭載されています。図 7-3 に、この回路のブロック図を示します。

インターフェイスのオプションによっては、この 2 つの H ブリッジは 4 つの独立したハーフ ブリッジとして使用することもできます。ISENxx ピンは、2 つのハーフ ブリッジと一緒にのみ使用できます。

図 7-3. PWM モーター ドライバ回路

### 7.3.2 ブリッジ動作

フルブリッジは、順方向、逆方向、コースト (高速減衰)、ブレーキ (低速減衰) の 4 つの動作モードで動作できます。

#### 7.3.2.1 順方向動作

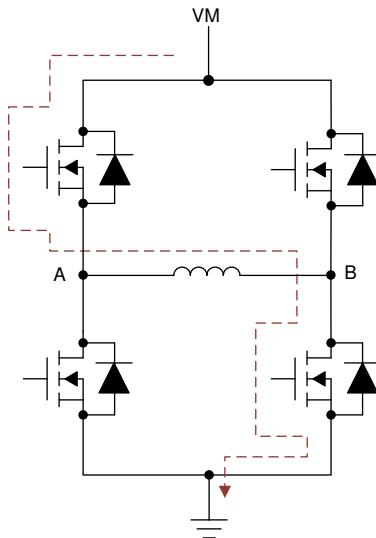

この動作モードは、図 7-4 に示すように、電流が端子 A (OUT1 または OUT3) から端子 B (OUT2 または OUT4) に流れるようなモーターの順方向の回転を指します。このモードでは、端子 A は VM に接続され、端子 B はグランドに接続されます。

図 7-4. 順方向動作

#### 7.3.2.2 逆方向動作

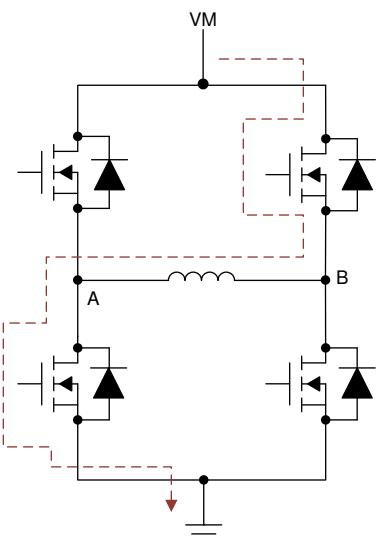

この動作モードは、図 7-5 に示すように、電流が端子 B (OUT2 または OUT4) から端子 A (OUT1 または OUT3) に流れるようなモーターの逆方向の回転を指します。このモードでは、端子 A はグランドに接続され、端子 B は VM に接続されます。

図 7-5. 逆方向動作

### 7.3.2.3 コースト動作(高速減衰)

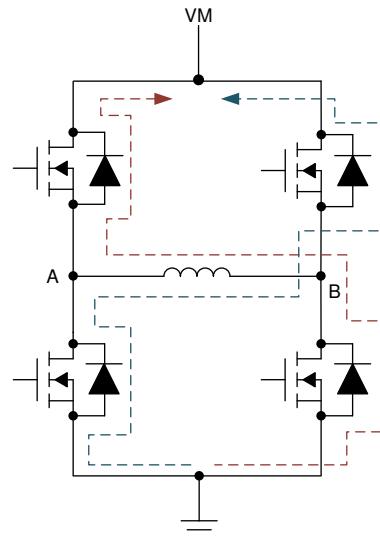

この動作モードでは、フルブリッジのすべての FET がハイインピーダンス (Hi-Z) 状態になり、モーターも Hi-Z 状態になって、コストが開始されます。この動作モードは、モーター電流をより速く減衰させる効果もあるため、高速減衰モードとも呼ばれます。図 7-6 に示すように、モーターが最初に順方向動作 (電流は端子 A から端子 B に流れる) で接続されていた場合、コスト動作が適用されると、モーター負荷の誘導性により、電流は同じ方向 (A から B) に流れ続け、代替の FET の逆並列ダイオードが導通し始めます。この逆並列ダイオードを介した電流の流れによって、電源電圧 (VM) によって生成される高い負電位が電流を急速に減少させます。

図 7-6. コースト動作 (高速減衰)

#### 7.3.2.4 ブレーキ動作(低速減衰)

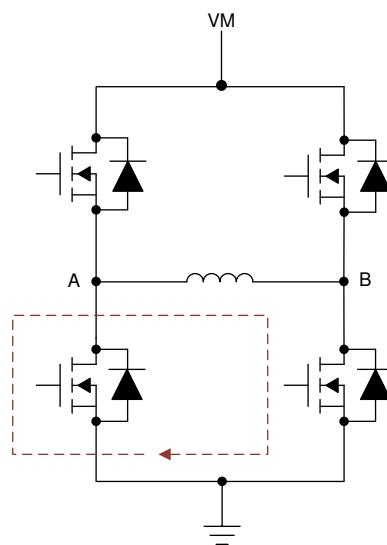

この動作モードは、図 7-7 に示すように、フル ブリッジの両方のローサイド FET をオンにすることで成立します。両方のローサイド FET がオンになると、電流循環経路が形成され、この経路によって、電流はモーターの抵抗とローサイド FET の抵抗を使用してグランドに向かうように減衰します。電位差が小さいことから、この電流減衰はコスト動作に比べて緩やかであることから、このモードは低速減衰モードとも呼ばれます。

図 7-7. ブレーキ動作 (低速減衰)

### 7.3.3 ブリッジ制御

DRV8847 デバイスは、ユーザー要件に応じて 4 つの動作モードに構成できます。MODE ピンと IN3 ピンを使用して、DRV8847 は 4 種類のインターフェイス (4 ピン インターフェイス、2 ピン インターフェイス、並列ブリッジ インターフェイス、独立ブリッジ インターフェイス) のいずれかに構成されます。モードの選択は、DRV8847S デバイス バリアントの I<sup>2</sup>C レジスタを使用して行います (セクション 7.5 セクションを参照)。表 7-2 に、ブリッジの動作モードを選択するための各種構成を示します。

---

#### 注

DRV88471 では、ブリッジ制御モードは 4 ピン インターフェイスに固定されています。

---

**表 7-2. ブリッジモードの選択 (DRV8847 ハードウェア デバイス バリアント)**

| nSLEEP | モード | IN3 | インターフェイス         |

|--------|-----|-----|------------------|

| 0      | X   | X   | スリープ・モード         |

| 1      | 0   | X   | 4 ピン インターフェイス    |

| 1      | 1   | 0   | 2 ピン インターフェイス    |

| 1      | 1   | 1   | 並列ブリッジ・インターフェイス  |

| 1      | Z   | X   | 独立のブリッジ・インターフェイス |

---

#### 注

ドライバ動作中は MODE ピンはラッピングされません。したがって、テキサス・インスツルメンツでは、いかなる場合でもこのピンをコントローラに接続して使用することは推奨していません。

---

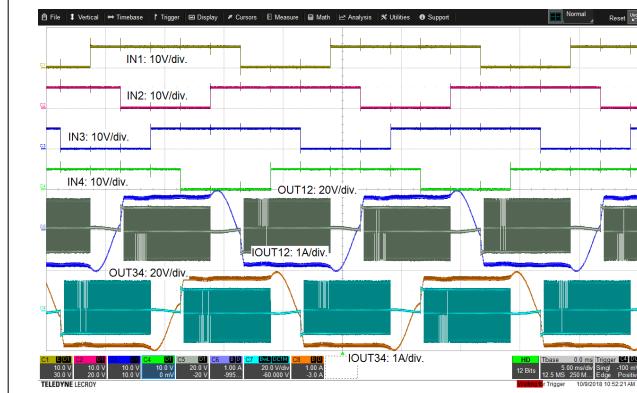

### 7.3.3.1.4 ピン・インターフェイス

4 ピン インターフェイスでは、DRV8847 デバイスは、1 つのステッピング モーターまたは 2 つの BDC モーターをフル機能モードで駆動するように構成されます。4 ピン インターフェイスの動作を構成するには、MODE ピンをグランドに接続し、IN1 ピン、IN2 ピン、IN3 ピン、IN4 ピンを使用してドライバを制御します。このモードでは、ステッピング モーターやブラシ付き DC モーターは 4 つのモード (順方向、逆方向、コースト、ブレーキ) のすべてで動作し、さらに、ステッピング モーターはフル ステッピング モードまたは非循環ハーフ ステッピング モードで動作可能です。センス抵抗を ISEN12 ピンと ISEN34 ピンに接続することで、それぞれブリッジ 12 とブリッジ 34 で独立した電流レギュレーションを行うことができます。

このインターフェイスオプションは、次の負荷に使用します。

- フル ステッピング モードのステッピング モーター (電流レギュレーションあり / なし)

- ハーフ ステッピング モードのステッピング モーター (電流レギュレーションあり / なし)

- フル機能の BDC モード (順方向、逆方向、ブレーキ、コースト) を備えたシングルまたはデュアルのブラシ付き DC モーター (電流レギュレーションあり / なし)

表 7-3 に 4 ピン インターフェイス動作の構成、図 7-8 に 4 ピン インターフェイス動作のアプリケーション図を示します。

**表 7-3. 4 ピン インターフェイス (MODE = 0)**

| nSLEEP | IN1 | IN2 | IN3 | IN4 | OUT1 | OUT2 | OUT3 | OUT4 | 機能 (DC モーター)     |

|--------|-----|-----|-----|-----|------|------|------|------|------------------|

| 0      | X   | X   | X   | X   | Z    | Z    | Z    | Z    | スリープ・モード         |

| 1      | 0   | 0   |     |     | Z    | Z    |      |      | モーター コースト (高速減衰) |

| 1      | 0   | 1   |     |     | L    | H    |      |      | 逆方向              |

| 1      | 1   | 0   |     |     | H    | L    |      |      | 順方向              |

| 1      | 1   | 1   |     |     | L    | L    |      |      | モーター ブレーキ (低速減衰) |

| 1      |     |     | 0   | 0   |      |      | Z    | Z    | モーター コースト (高速減衰) |

| 1      |     |     | 0   | 1   |      |      | L    | H    | 逆方向              |

表 7-3.4 ピンインターフェイス (MODE = 0) (続き)

| nSLEEP | IN1 | IN2 | IN3 | IN4 | OUT1 | OUT2 | OUT3 | OUT4 | 機能 (DC モーター)     |

|--------|-----|-----|-----|-----|------|------|------|------|------------------|

| 1      |     |     | 1   | 0   |      |      | H    | L    | 順方向              |

| 1      |     |     | 1   | 1   |      |      | L    | L    | モーター ブレーキ (低速減衰) |

図 7-8.4 ピンインターフェイス

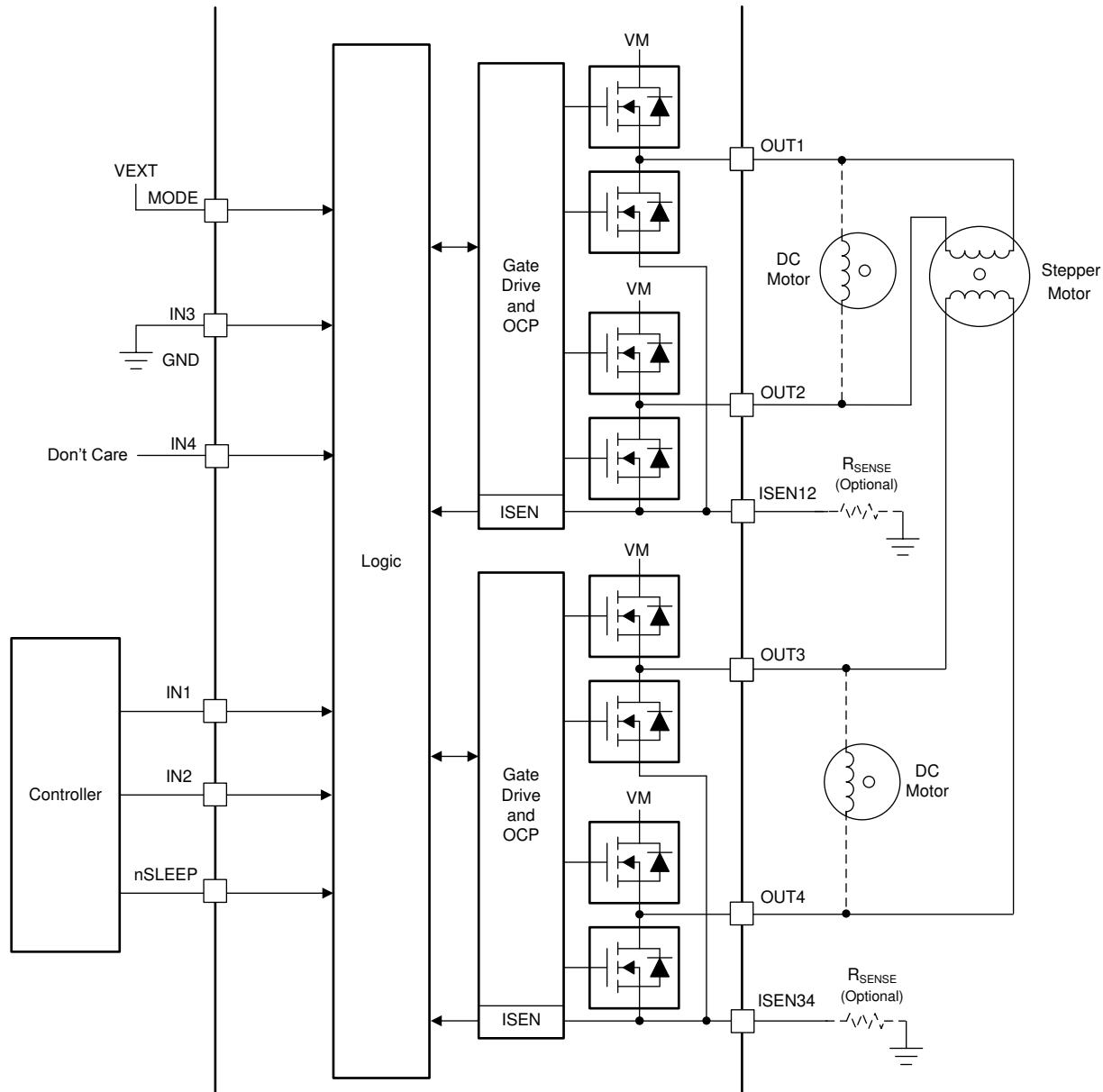

### 7.3.3.22 ピン・インターフェイス

2 ピンインターフェイスでは、DRV8847 デバイスは、マイコンからの制御入力が少ない 1 つのステッピング モーターまたは 2 つの BDC モーターを駆動するように構成されています。2 ピンインターフェイスの動作を構成するには、MODE ピンを外部電源 (3.3V または 5V) に接続し、IN3 ピンをグランドに接続して、IN1 ピンと IN2 ピンを使用してドライバを制御します。このモードでは、ステッピング モーターまたはブラシ付き DC モーターは 2 つのモード (順方向モードと逆方向モード) のみで動作します。したがって、ステッピング モーターではフル ステッピング動作のみがサポートされています。この

2ピンインターフェイスは、冷蔵庫のダンパーなど、GPIOの少ないアプリケーションにとても有効です。電流レギュレーション用に、ISEN12ピンとISEN34ピンにセンス抵抗を接続できます。

このインターフェイスオプションは、次の負荷に使用します。

- フルステッピングモードのステッピングモーター(電流レギュレーションあり/なし)

- 機能を絞ったBDCモード(順方向モードと逆方向モードのみ)を備えたシングルまたはデュアルのブラシ付きDCモーター(電流レギュレーションあり/なし)

表7-4に2ピンインターフェイス動作の構成、図7-9に2ピンインターフェイス動作のアプリケーション図を示します。

**表7-4. 2ピンインターフェイス (MODE = 1, IN3 = 0)**

| nSLEEP | IN1 | IN2 | IN3 | IN4 | OUT1 | OUT2 | OUT3 | OUT4 | 機能 (DCモーター) |

|--------|-----|-----|-----|-----|------|------|------|------|-------------|

| 0      | X   | X   | X   | X   | Z    | Z    | Z    | Z    | スリープ・モード    |

| 1      | 0   |     | 0   | X   | L    | H    |      |      | 逆方向         |

| 1      | 1   |     | 0   | X   | H    | L    |      |      | 順方向         |

| 1      |     | 0   | 0   | X   |      |      | L    | H    | 逆方向         |

| 1      |     | 1   | 0   | X   |      |      | H    | L    | 順方向         |

図 7-9.2 ピン インターフェイス

## 注

このモードでは、デバイスが非スリープ状態 ( $nSLEEP = \text{High}$ ) のとき、 $OUTx$  ピンのうちの 2 つが常にオンになります。したがって、 $OUTx$  ピンに接続されているモーター コイルを無励磁化するには、 $nSLEEP$  ピンをプルダウンする必要があります。

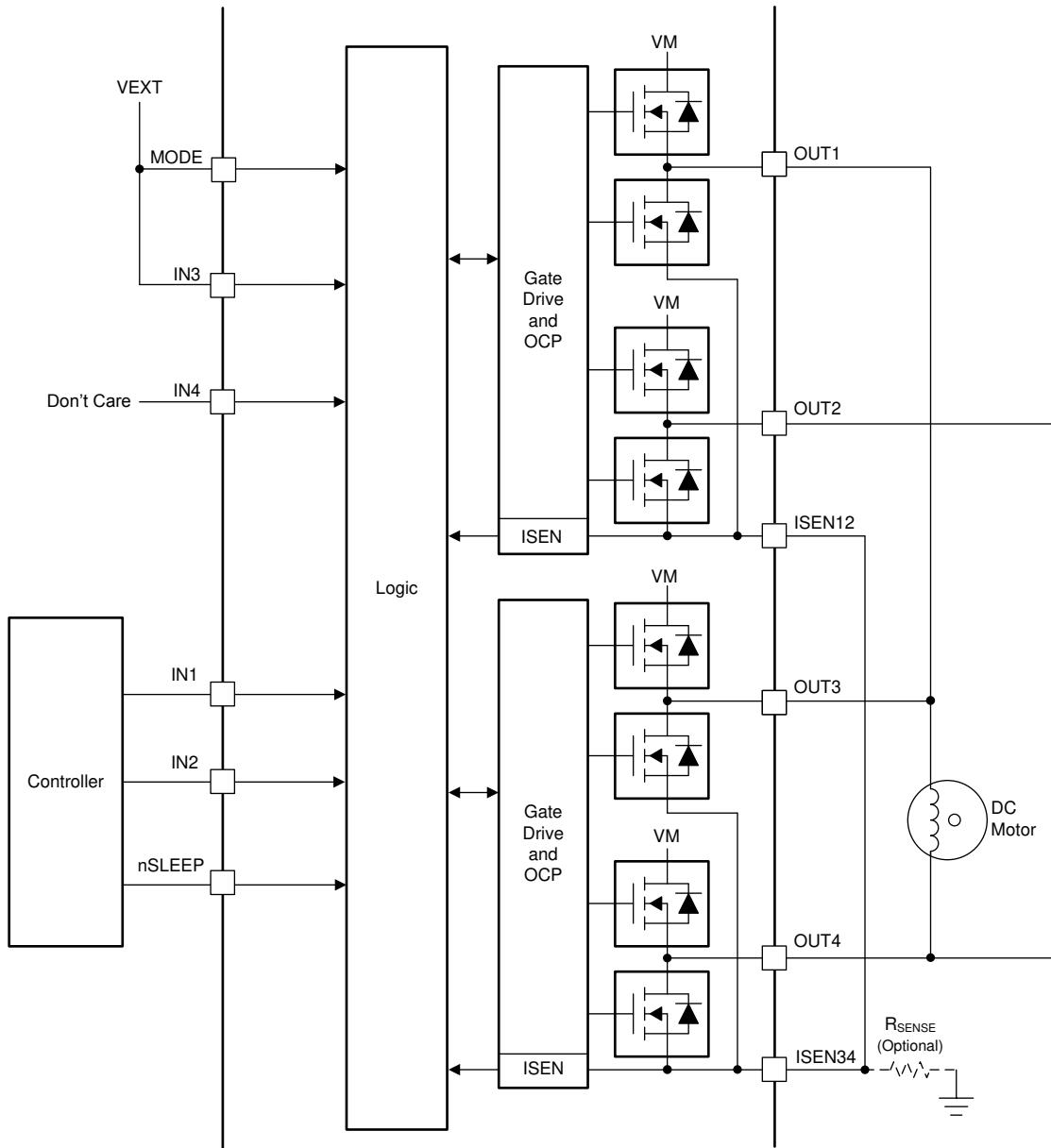

### 7.3.3.3 並列ブリッジ・インターフェイス

並列ブリッジインターフェイスは、DRV8847 デバイスは、ドライバを並列に使用して 2 倍のモータ電流を供給することにより、より大電流の BDC モータを駆動するように構成されます。並列ブリッジインターフェイス動作を行うには、**MODE** ピンと **IN3** ピンを外部電源 (3.3V または 5V) に接続し、**IN1** ピンと **IN2** ピンを使用してドライバを制御します。このモードでは、4 つのモード (順方向、逆方向、コースト、ブレーキ) すべてを使用して、BDC モータ制御の全機能を実現できます。

このインターフェイス オプションは、次の負荷に使用します。

- フル機能の **BDC** モード (順方向、逆方向、ブレーキ、コースト) を備えた 1 つの大電流 **BDC** モーター (電流レギュレーションあり / なし)

- フル機能の **BDC** モード (順方向、逆方向、ブレーキ、コースト) を備えた、同時に動作する 2 つの独立した **BDC** モーター (電流レギュレーションあり / なし)

表 7-5 に並列ブリッジインターフェイス動作の構成、図 7-10 に並列ブリッジインターフェイス動作のアプリケーション図を示します。

**表 7-5. 並列インターフェイス (MODE = 1, IN3 = 1)**

| nSLEEP | IN1 | IN2 | IN3 | IN4 | OUT1 | OUT2 | OUT3 | OUT4 | 機能 (DC モーター)     |

|--------|-----|-----|-----|-----|------|------|------|------|------------------|

| 0      | X   | X   | X   | X   | Z    | Z    | Z    | Z    | スリープ・モード         |

| 1      | 0   | 0   | 1   | X   | Z    | Z    | Z    | Z    | モーター コースト (高速減衰) |

| 1      | 0   | 1   | 1   | X   | L    | H    | L    | H    | 逆方向              |

| 1      | 1   | 0   | 1   | X   | H    | L    | H    | L    | 順方向              |

| 1      | 1   | 1   | 1   | X   | L    | L    | L    | L    | モーター ブレーキ (低速減衰) |

図 7-10. 並列モード動作

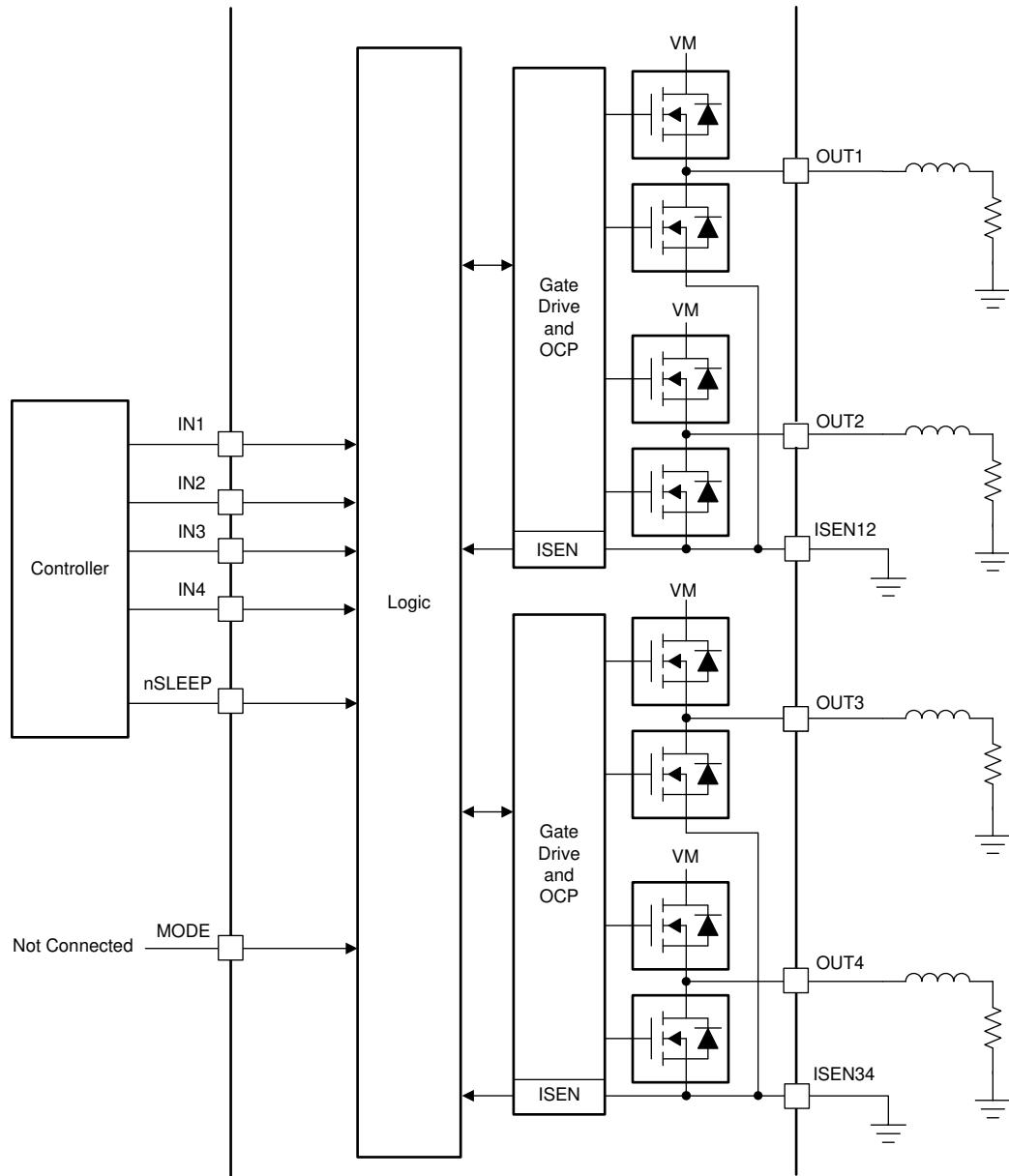

#### 7.3.3.4 独立のブリッジ・インターフェイス

独立ブリッジインターフェイスでは、DRV8847 デバイスは独立したハーフブリッジ動作を行うように構成されます。独立したブリッジインターフェイス動作を構成するには、MODE ピンを未接続 (Hi-Z 状態) にし、IN1 ピン、IN2 ピン、IN3 ピン、IN4 ピンを使用して OUT1 ピン、OUT2 ピン、OUT3 ピン、OUT4 ピンをそれぞれ独立して制御します。OUTx ピンは 2 つの出力状態 (VM に接続または GND に接続) のみ制御可能で、このモードはリレー やソレノイドなどの独立した負荷を駆動するために使用されます。

このインターフェイスオプションは、次の負荷に使用します。

- OUTx ピンと VM / グランド ピンの間に接続されたリレー コイルまたはソレノイド コイル (電流レギュレーションなし)

- 3 つの機能 BDC モード (順方向、逆方向、ブレーキのみ) を備えたシングルまたはデュアルのブラシ付き DC モーター (電流レギュレーションあり / なし)

- フルステッピングモードのステッピングモーター (電流レギュレーションあり / なし)

- ブレーキ モードを使用する、ハーフ ステッピング モードのステッピング モーター (電流レギュレーションあり / なし)

表 7-6 に独立したブリッジ インターフェイス動作の構成、図 7-11 に独立したブリッジ インターフェイス動作のアプリケーション図を示します。

**表 7-6. 独立ブリッジ インターフェイス (MODE = Hi-Z)**

| nSLEEP | IN1 | IN2 | IN3 | IN4 | OUT1 | OUT2 | OUT3 | OUT4 | 機能 (DC モーター)    |

|--------|-----|-----|-----|-----|------|------|------|------|-----------------|

| 0      | X   | X   | X   | X   | Z    | Z    | Z    | Z    | スリープ・モード        |

| 1      | 0   |     |     |     | L    |      |      |      | GND に接続された OUT1 |

| 1      | 1   |     |     |     | H    |      |      |      | VM に接続された OUT1  |

| 1      |     | 0   |     |     |      | L    |      |      | GND に接続された OUT2 |

| 1      |     | 1   |     |     |      | H    |      |      | VM に接続された OUT2  |

| 1      |     |     | 0   |     |      |      | L    |      | GND に接続された OUT3 |

| 1      |     |     | 1   |     |      |      | H    |      | VM に接続された OUT3  |

| 1      |     |     |     | 0   |      |      |      | L    | GND に接続された OUT4 |

| 1      |     |     |     | 1   |      |      |      | H    | VM に接続された OUT4  |

図 7-11. 独立のブリッジ・インターフェイス

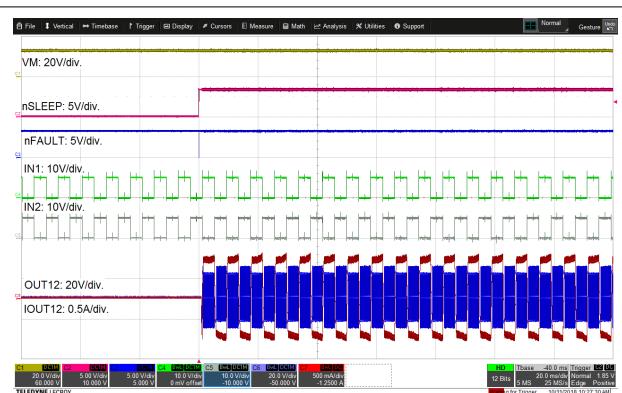

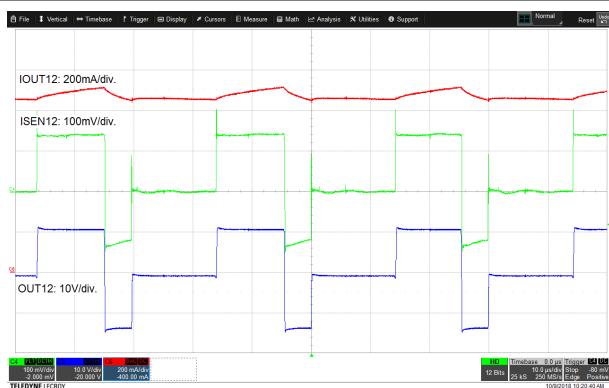

### 7.3.4 電流レギュレーション

モータ巻線に流れる電流は、固定されたオフ時間 PWM 電流レギュレーション回路によって制御されます。ブラシ付き DC モーターでは、モーターのストール電流 (スタートアップ電流でもある) を制限するために電流レギュレーションを使用できます。

電流レギュレーションは次のように動作します。H ブリッジをイネーブルにすると、現在の電源電圧および巻線のインダクタンスに応じた速度で、巻線を流れる電流が増加します。電流が電流トリップ スレッショルドに達すると、ブリッジは次の PWM サイクルを開始する前の  $t_{OFF}$  時間、電流をディスエーブルします。

注

電流がイネーブルになった直後、ISENxx ピンの電圧がしばらくの間 ( $t_{BLANK}$ ) 無視されてから、電流センス回路がイネーブルになります。このブランкиング時間は、PWM サイクルの最小オン時間も設定するものです。

PWM トリップ電流 ITRIP は、xISEN ピンに接続された電流センス抵抗の両端の電圧を基準電圧と比較するコンパレタによって設定されます。この基準電圧 ( $V_{TRIP}$ ) はオンチップで生成され、電流トリップ レベルを決定します。

巻線のフルスケールのトリップ電流は、式 1 に示すように計算されます。

$$I_{TRIP} = \text{Torque} \frac{V_{TRIP}}{R_{SENSExx}} \quad (1)$$

ここで、

- $I_{TRIP}$ : 制御電流

- $V_{TRIP}$ : 内部で生成されるトリップ電圧

- $R_{SENSExx}$ : センス抵抗の抵抗値

- トルクはトルク スカラーで、その値は TRQ ピンの入力に依存します。TRQ ピンが GND に接続されている場合 (DRV8847) または TRQ ビットが 0 に設定されている場合 (DRV8847S) は TRQ = 100%、TRQ ピンが  $V_{EXT}$  に接続されている場合 (DRV8847) または TRQ ビットが 1 に設定されている場合 (DRV8847S) は TRQ = 50% です。

たとえば、 $V_{TRIP}$  電圧が 150mV で、センス抵抗の値が 150mΩ の場合、フルスケールのトリップ電流は  $1A (150mV / (150 m\Omega) = 1A)$  になります。

注

電流制御が必要ない場合は、ISENxx ピンをグランドに直接接続してください。

### 7.3.5 電流再循環および減衰モード

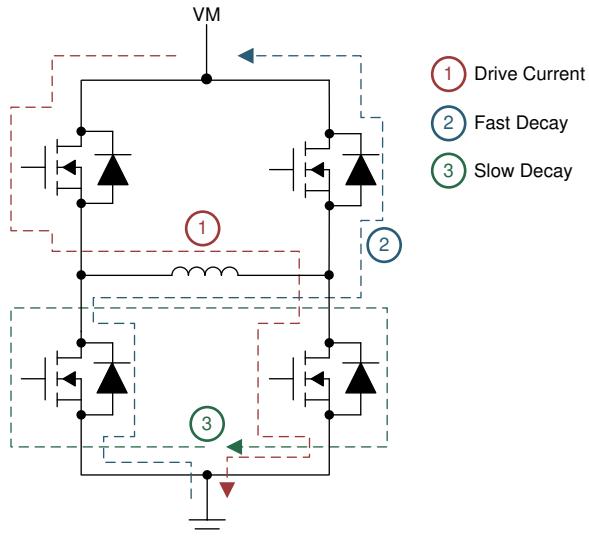

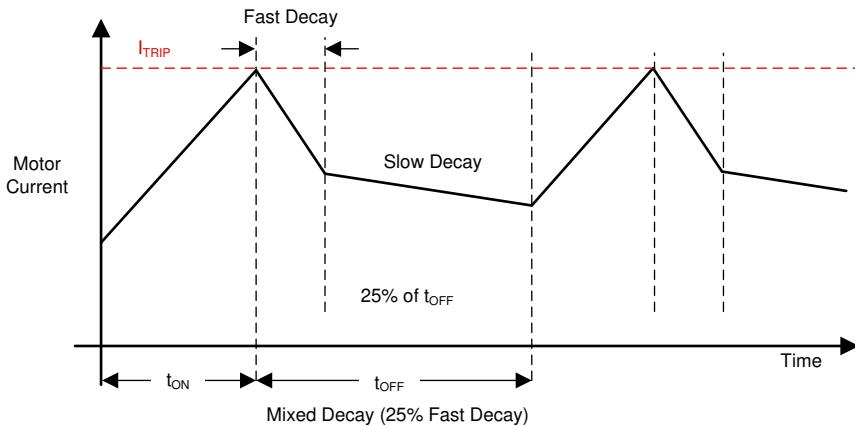

PWM 電流のトリップ動作中、電流レギュレーションのトリップ スレッショルドに達するまで、H ブリッジはモータ巻線を流れる電流を駆動します。トリップ電流スレッショルドに達すると、駆動電流は遮断されますが、モーターは誘導性であるため、電流はしばらくは流れ続けなければなりません。この連続的な電流の流れを、再循環電流と呼びます。混合減衰では、高速減衰および低速減衰を使用して電流リップルを最適化することで、より優れた電流レギュレーションが可能になります。

混合減衰では、高速減衰モードと低速減衰モードが組み合わされています。高速減衰モードでは、対向する FET の逆並列ダイオードが導通して電流の減衰を速めます (図 7-12 のケース 2 を参照)。低速減衰モードでは、ブリッジ内の両方のローサイド FET をイネーブルにすることで、巻線電流を再循環させます (図 7-12 のケース 3 を参照)。混合減衰は高速減衰から始まり、低速減衰に移行します。DRV8847 デバイスでは、図 7-13 に示すように、混合減衰の割合は、25% の高速減衰と 75% の低速減衰となっています。

図 7-12. 減衰モード

図 7-13. 混合減衰

## 注

電流レギュレーション方式は 1 つのセンス抵抗を使用するため、「独立ブリッジ インターフェイス」で使用される場合でも、常に 2 つのハーフ ブリッジに対して機能します。独立したハーフ ブリッジを使用する負荷には、電流レギュレーションを使用しないことを推奨します。

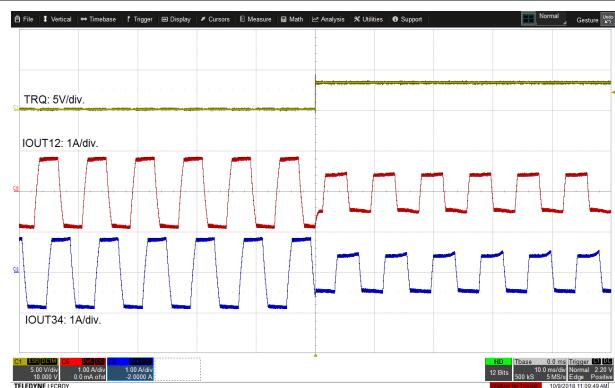

### 7.3.6 トルク スカラー

トルク スカラーは、デジタル入力ピン  $TRQ$  によって出力電流を動的に調整するために使用され、出力電流のトリップ基準値を 50% に減少させます ( $TRQ$  ピンが  $High$  にプルされるたびに)。トルクスカラーを使用して、ステッピング モーターの保持トルクをスケーリングできます。 $I^2C$  デバイス バリエント (DRV8847S) では、この機能は  $I^2C$  レジスタにより実装されています。

## 注

DRV88471 では、トルク スカラー値は 100% に固定されています。

TRQ ピンが Low にプルされると (または DRV8847S デバイス バリアントの場合は TRQ ビットがリセットされると)、式 2 でトリップ電流が計算されます。

$$I_{TRIP} = \frac{\text{Torque} \times V_{TRIP}}{R_{SENSExx}} \quad (2)$$

TRQ ピンが High にプルされると (または DRV8847S デバイス バリアントの場合は TRQ ビットが設定されると)、式 3 でトリップ電流が計算されます。

$$I_{TRIP} = 0.5 \frac{V_{TRIP}}{R_{SENSExx}} \quad (3)$$

### 7.3.7 ステッピング・モード

DRV8847 デバイスは、以下のブリッジ構成を使用して、ステッピング モーターをフル ステッピング モードまたは非循環ハーフ ステッピング モードで駆動するために使用されます。

- フル ステッピング モード (電流レギュレーションあり / なし)

- 4 ピン インターフェイス構成を使用

- 2 ピン インターフェイス構成を使用

- ハーフ ステッピング モード (電流レギュレーションあり / なし)

- 4 ピン インターフェイス構成を使用

#### 7.3.7.1 フル ステッピング モード (4 ピン インターフェイス)

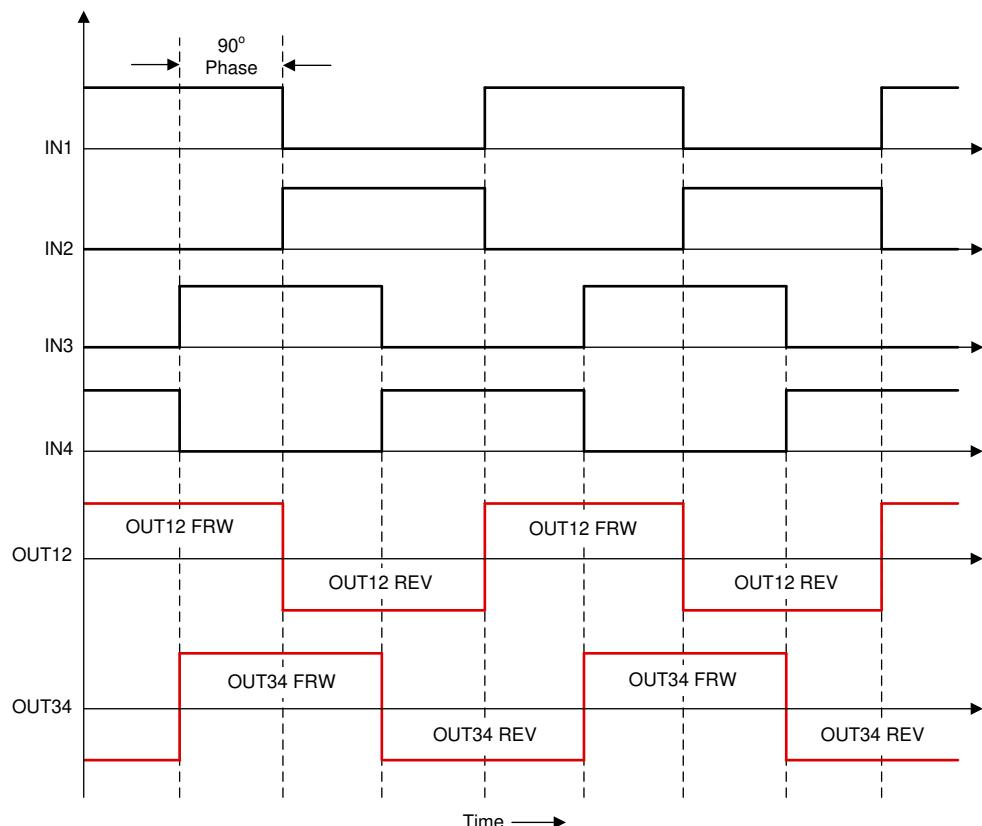

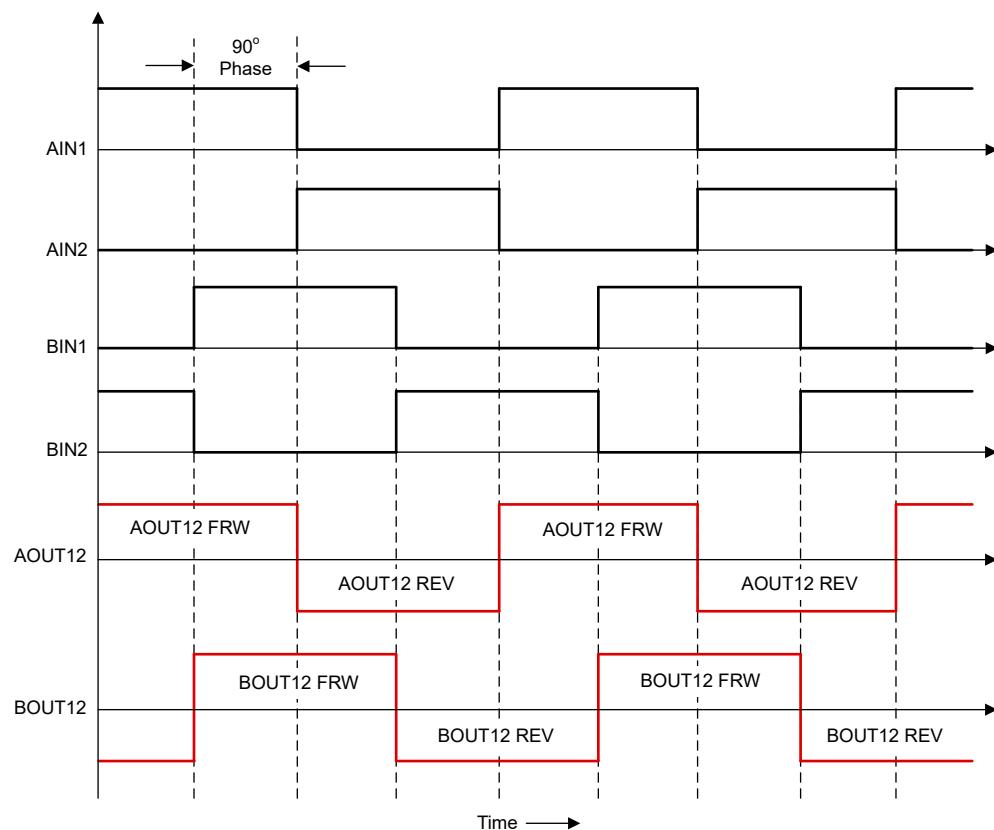

フル ステッピング モードでは、フル ブリッジは 2 つの巻線間の位相シフト  $90^\circ$  で 2 つのモード (順方向または逆方向) のいずれかで動作します。

4 ピン インターフェイスの場合、図 7-14 に示すように、PWM 入力は、IN1 ピン、IN2 ピン、IN3 ピン、IN4 ピンに印加され、ドライバは順方向 (FRW) および逆方向 (REV) モードでのみ動作します。

図 7-14. 4 ピン インターフェイスを使用したフル ステッピング モード

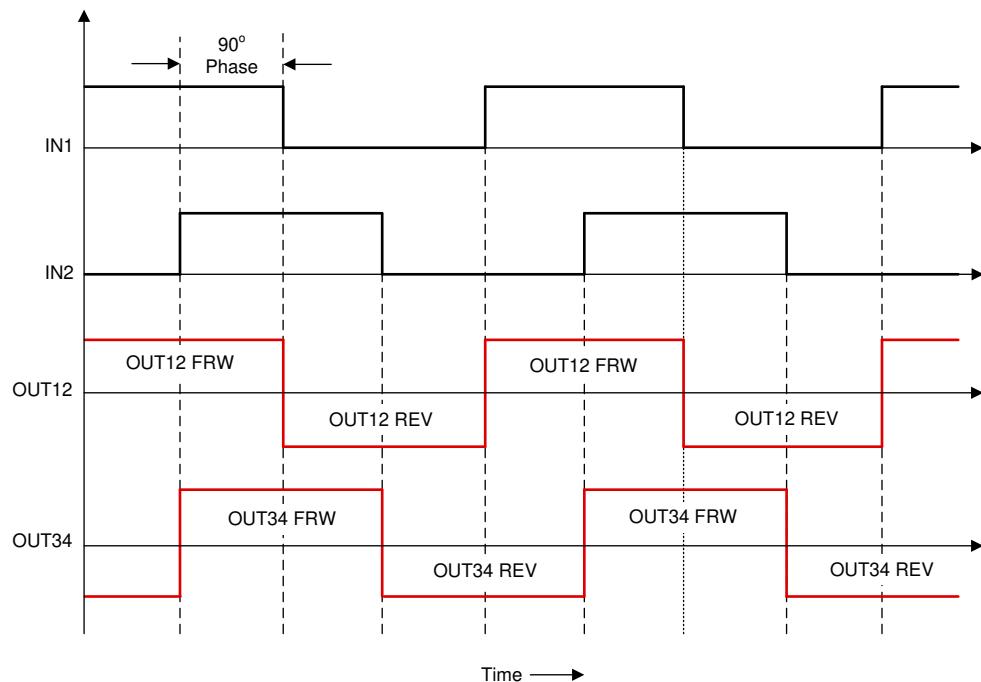

### 7.3.7.2 フルステッピング モード(2 ピンインターフェイス)

2 ピンインターフェイスを使用したフルステッピングでは、PWM 入力は IN1 ピンおよび IN2 ピンにのみ印加され、IN3 ピンはグランドに接続されます(図 7-9 セクションを参照)。図 7-15 に、2 ピンインターフェイスを使用したステッピング モーターのフルステッピング モードを示します。

図 7-15. 2 ピンインターフェイスを使用したフルステッピング モード

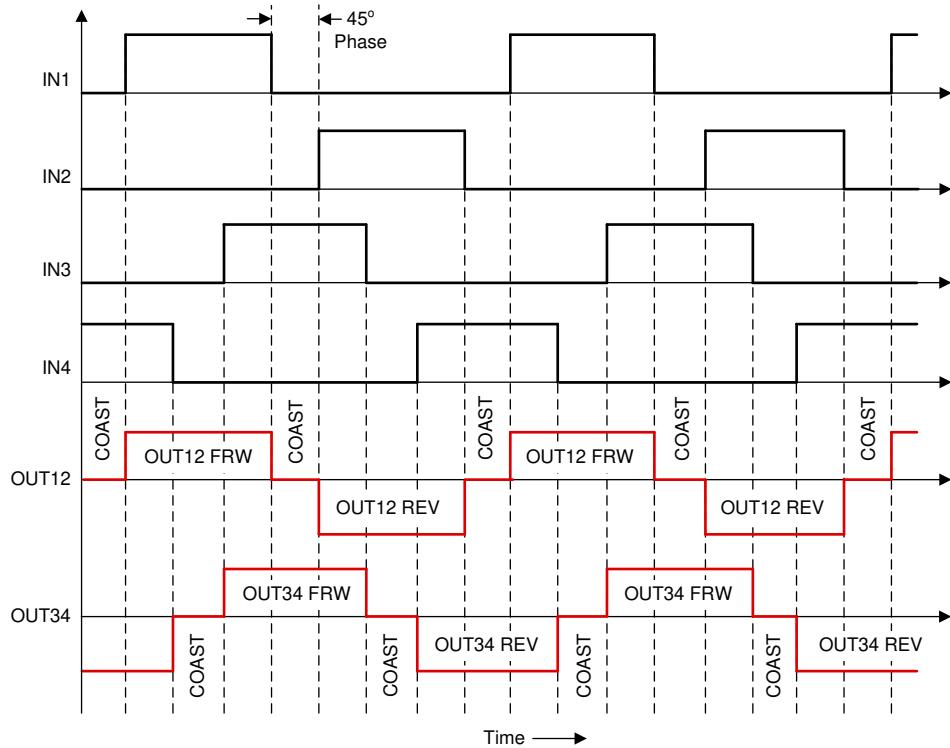

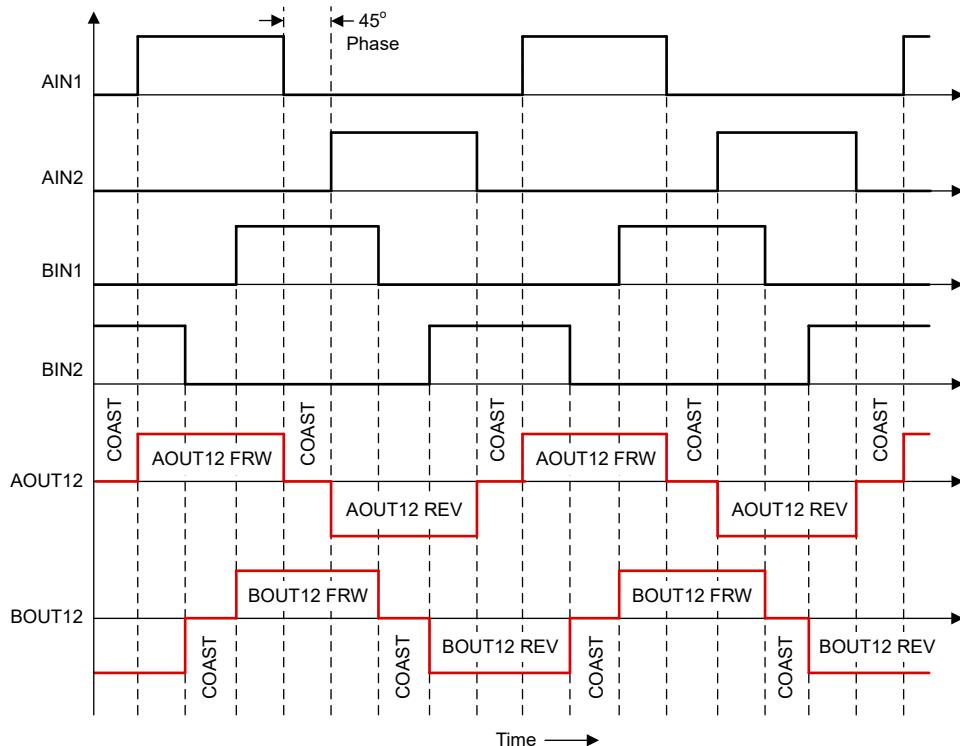

### 7.3.7.3 ハーフステッピング モード(非駆動高速減衰の場合)

ハーフステッピングモードでは、フルブリッジは2つの巻線間の位相シフト45°で、3つのモード(順方向、逆方向、コースト)のいずれかで動作します。

4ピンインターフェイスの場合、図7-16に示すように、PWM入力は、IN1ピン、IN2ピン、IN3ピン、IN4ピンに接続され、ドライバは順方向モード、逆方向モード、コーストモードで動作します。

図7-16. 4ピンインターフェイスを使用したハーフステッピングモード(非駆動高速減衰の場合)

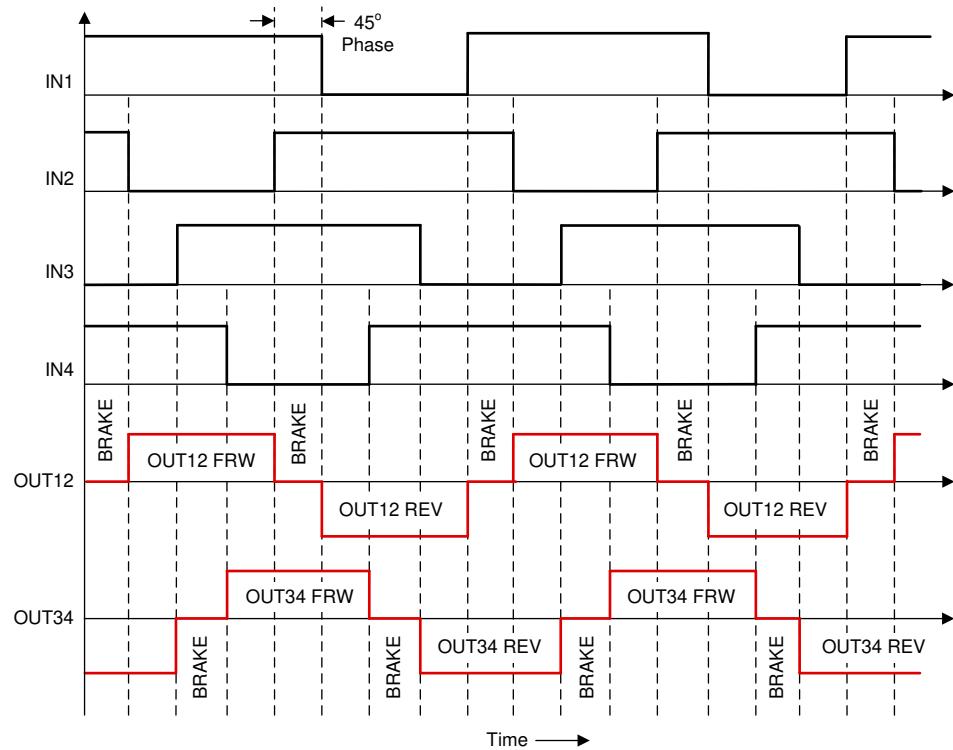

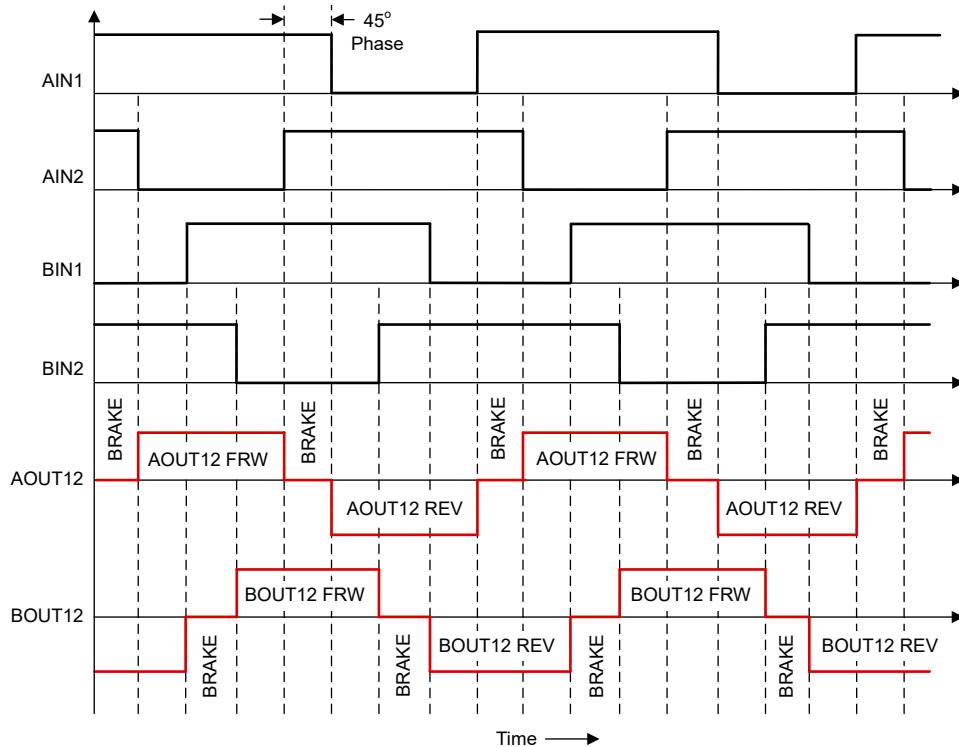

#### 7.3.7.4 ハーフステッピング モード(非駆動低速減衰の場合)

このハーフステッピング モードでは、非駆動時は低速減衰(ブレーキ モード)となります。したがって、フルブリッジは2つの巻線間の位相シフト  $45^\circ$  で、3つのモード(順方向、逆方向、ブレーキ)のいずれかで動作します。

4ピンインターフェイスの場合、図 7-17 に示すように、PWM 入力は、IN1 ピン、IN2 ピン、IN3 ピン、IN4 ピンに接続され、ドライバは順方向モード、逆方向モード、ブレーキモードで動作します。

図 7-17. 4 ピンインターフェイスを使用したハーフステッピング モード(非駆動低速減衰の場合)

### 7.3.8 モーター ドライバ保護回路

DRV8847 は、VM 低電圧、過電流、開放負荷、過熱イベントから保護されています。

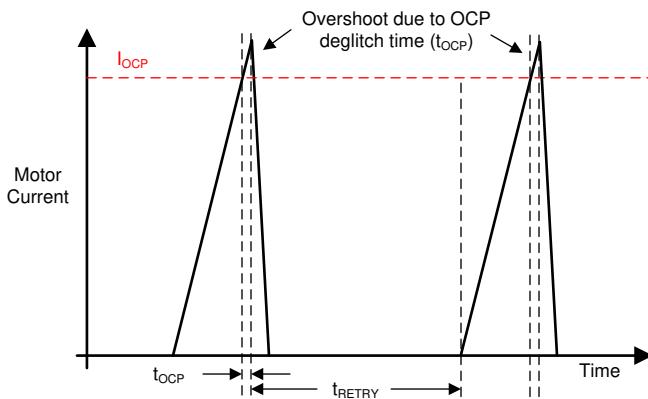

#### 7.3.8.1 過電流保護 (OCP)

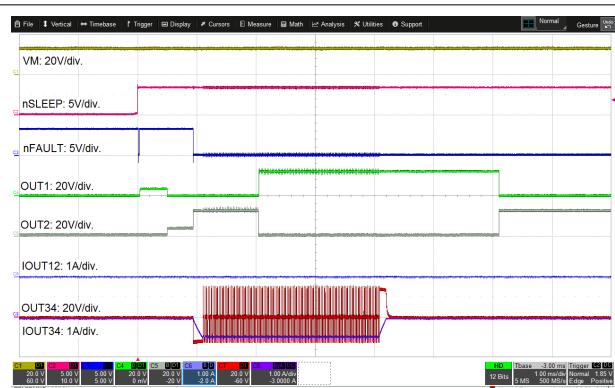

DRV8847 は、過電流保護トリップによって過電流から保護されています。各 FET の OCP 回路は、ゲート駆動を止めることにより FET に流れる電流をディスエーブルします。この過電流検出が OCP グリッチ除去時間 ( $t_{OCP}$ ) より長く続くと、H ブリッジのすべての FET (または独立したインターフェイスのハーフ ブリッジ) がディスエーブルされて、nFAULT ピンが Low に駆動されます。DRV8847 デバイスはリトライ時間  $t_{RETRY}$  が発生するまでディスエーブルされたままになりますが、DRV8847S デバイスには自動リトライまたはラッチ モードを選択できるプログラム可能なオプションがあります。

##### 7.3.8.1.1 OCP 自動リトライ (ハードウェア デバイスおよびソフトウェア デバイス (OCPR = 0b))

このモードで OCP イベントが発生すると、対応するハーフ ブリッジ、フル ブリッジ、または両方のブリッジ (MODE ビットに依存する) がディスエーブルされて、nFAULT ピンが Low に駆動されます (表 7-13 および表 7-14 を参照)。OCP ビットと対応する OCPx ビットは、I<sup>2</sup>C レジスタで High にラッチされます (セクション 7.6 セクションを参照)。図 7-18 に示すように、 $t_{RETRY}$  時間が経過した後は、通常動作が自動的に再開されます (モータードライバの動作が再開され、nFAULT ピンが解放されます)。OCP ビットと OCPx ビットは  $t_{RETRY}$  期間が終了するまでラッチされた状態を保ちます。

図 7-18. OCP 動作

##### 7.3.8.1.2 OCP ラッチ モード (ソフトウェア デバイス (OCPR = 1b))

OCP ラッチ モードは、DRV8847S デバイスでのみ使用できます。OCP イベントが発生すると、対応するハーフ ブリッジ、フル ブリッジ、または両方のブリッジ (MODE ビットに依存する) がディスエーブルされて、nFAULT ピンが Low に駆動されます。OCP ビットと対応する OCPx ビットは、I<sup>2</sup>C レジスタで High にラッチされます (セクション 7.6 セクションを参照)。OCP 条件が解消され、CLR\_FLT ビットによってクリア フォルト コマンドが発行されると、通常動作が再開されます (モータードライバの動作が再開され、nFAULT ピンが解放されます)。

#### 7.3.8.1.3

##### 注

電源電圧  $V_{VM} > 16.5V$  の場合、OUTx 電流 (FET 電流) が 4A を上回ると、デバイス動作はデバイスの安全動作領域 (SOA) を超えることになります。16.5V を上回る電源電圧でデバイスを安全に動作させるためには、FET 電流が 4A 未満であることを確認する必要があります。

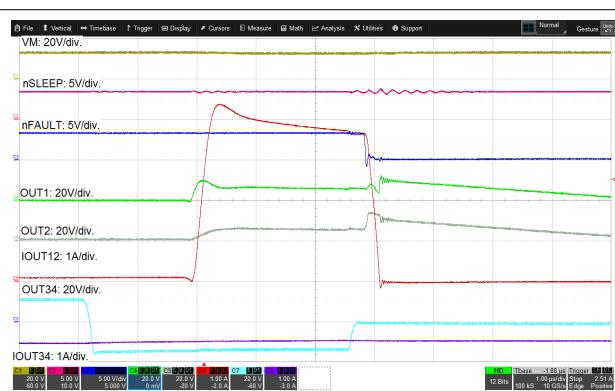

#### 7.3.8.2 サーマル・シャットダウン (TSD)

デバイス温度がサーマル シャットダウン限界値 ( $T_{TSD}$ ) を超えると、H ブリッジのすべての FET がディスエーブルされ、nFAULT ピンが Low に駆動されます。デバイス温度が指定された限界値の範囲内まで低下すると、自動的に通常動作が再開されます。動作が再開した後、nFAULT ピンは解放されます。

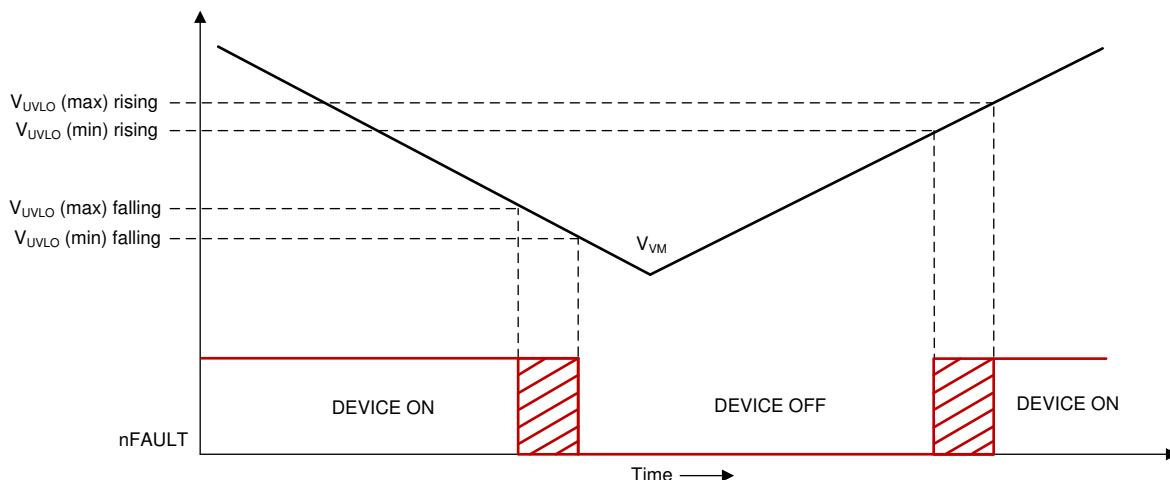

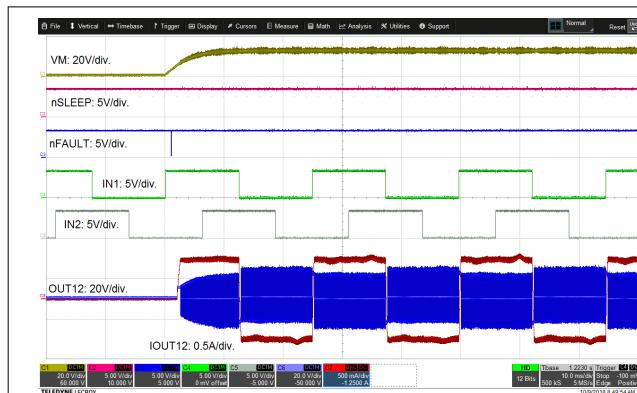

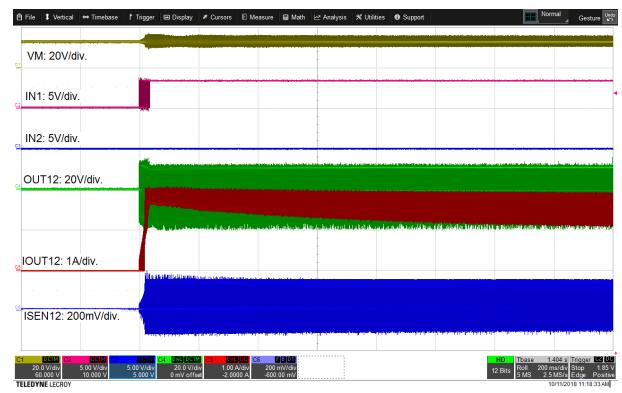

### 7.3.8.3 VM 低電圧誤動作防止 (VM\_UVLO)

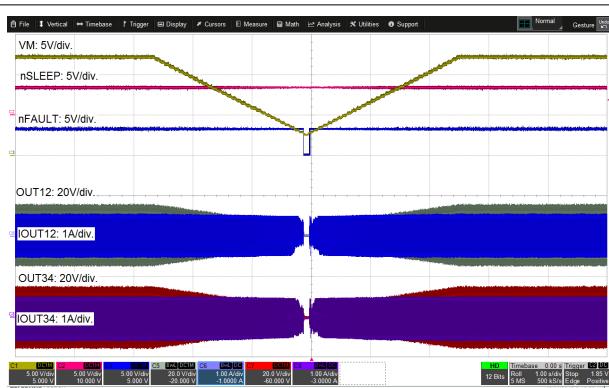

VM ピンの電圧が UVLO の立ち下がりスレッショルド電圧  $V_{UVLO}$  を下回ると、デバイスのすべての回路がディスエーブルされ、すべての内部ロジックがリセットされます。図 7-19 に示すように、 $V_{VM}$  電圧が UVLO の立ち上がりスレッショルドを上回ると、動作が再開されます。nFAULT ピンは、低電圧条件の間は Low に駆動され、動作が再開されると解放されます。

図 7-19. VM UVLO の動作

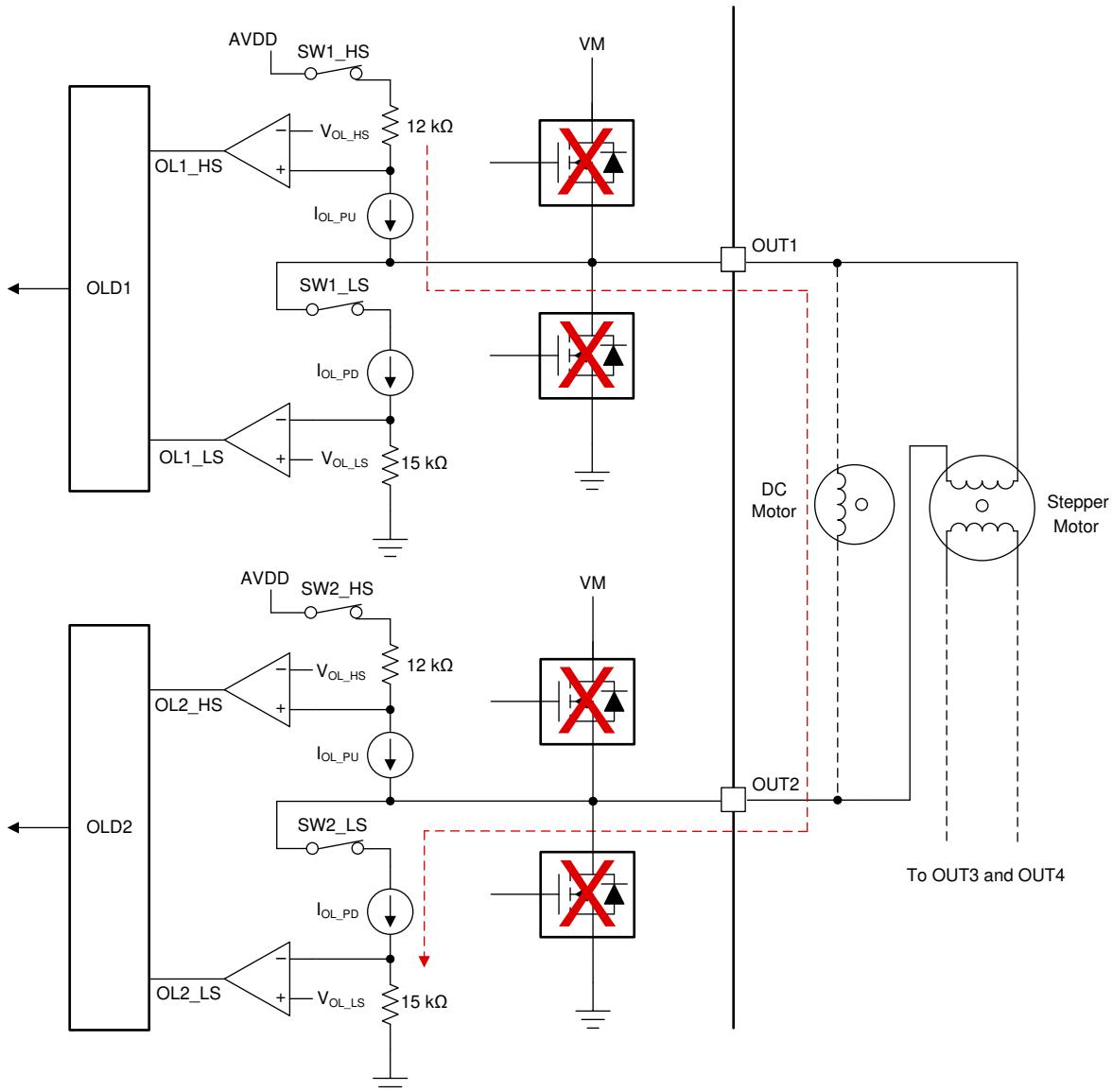

### 7.3.8.4 オープン負荷検出(OLD)

このデバイスには開放負荷検出機能も実装されています。この診断テストは、デバイスの電源投入時、または DRV8847 デバイスがスリープ モードから復帰したとき (nSLEEP ピンの立ち上がりエッジ) に実行されます。OLD 診断テストは、OLDOD (OLD オン デマンド) ビットを使用して、I<sup>2</sup>C バリエント デバイス (DRV8847S) でいつでも実行できます。

OLD の実装は、フル ブリッジとハーフ ブリッジで行われます。DRV8847 デバイスでは、開放負荷条件下で、ハーフ ブリッジ、フル ブリッジ、または両方のブリッジ (MODE ビットに依存する) は常に動作しており、nFAULT ピンが Low に駆動されます。nFAULT ピンを解放するには、OLD シーケンスを再度実行して電源をリセットする必要があります。表 7-7 に、DRV8847 デバイスのさまざまな OLD シナリオを示します。

DRV8847S デバイスでは、OLDBO (OLD ブリッジ動作) ビットを使用して開放負荷条件が検出されるたびに、フル ブリッジまたはハーフ ブリッジが動作モードまたは Hi-Z 状態になるようにプログラムできます。さらに、OLDFD (OLD フォルト ディスエーブル) ビットを使用すれば、OLD ビットの nFAULT 信号をディスエーブルできます。I<sup>2</sup>C レジスタの詳細設定については、セクション 7.6 セクションを参照してください。表 7-8 に、DRV8847S デバイスのさまざまな OLD シナリオを示します。

#### 注

正確な OLD 動作を行うには、開放負荷オンデマンド コマンドが実行される前に、モーターが静止している（または接続されている負荷の電流がゼロになっている）ことを確認する必要があります。

表 7-7. DRV8847 における開放負荷検出

| インターフェイス     | 負荷タイプ          | OLD | プリッジ動作 | nFAULT |

|--------------|----------------|-----|--------|--------|

| 4 ピン<br>2 ピン | フル ブリッジ接続      | なし  | あり     | なし     |

|              | ハーフ ブリッジ接続     | なし  | あり     | なし     |

|              | ブリッジ開放         | あり  | あり     | あり     |

|              | 1 つのハーフ ブリッジ開放 | あり  | あり     | あり     |

| 並列ブリッジ       | フル ブリッジ接続      | なし  | あり     | なし     |

|              | ハーフ ブリッジ接続     | なし  | あり     | なし     |

|              | ブリッジ開放         | あり  | あり     | あり     |

|              | 1 つのハーフ ブリッジ開放 | あり  | あり     | あり     |

| 独立ブリッジ       | フル ブリッジ接続      | なし  | あり     | なし     |

|              | ハーフ ブリッジ接続     | なし  | あり     | なし     |

|              | ブリッジ開放         | あり  | あり     | あり     |

|              | 1 つのハーフ ブリッジ開放 | あり  | あり     | あり     |

表 7-8. DRV8847S における開放負荷検出 (フル ブリッジ 12)

| インターフェイス     | 負荷タイプ          | OLD | プリッジ動作 (1) |            | nFAULT | OLD ビット          |           |      |      |

|--------------|----------------|-----|------------|------------|--------|------------------|-----------|------|------|

|              |                |     | OLDBO = 0b | OLDBO = 1b |        | OLD1             | OLD2      | OLD3 | OLD4 |

| 4 ピン<br>2 ピン | フル ブリッジ接続      | なし  | あり         | あり         | なし     | 0b               | 0b        | X    | X    |

|              | ハーフ ブリッジ接続     | なし  | あり         | あり         | なし     | 0b               | 0b        | X    | X    |

|              | ブリッジ開放         | あり  | あり         | なし         | あり     | 1b               | 1b        | X    | X    |

|              | 1 つのハーフ ブリッジ開放 | あり  | あり         | なし         | あり     | 1b または 0b<br>(2) | 0b または 1b | X    | X    |

| 並列ブリッジ       | フル ブリッジ接続      | なし  | あり         | あり         | なし     | 0b               | 0b        | X    | X    |

|              | ハーフ ブリッジ接続     | なし  | あり         | あり         | なし     | 0b               | 0b        | X    | X    |

|              | ブリッジ開放         | あり  | あり         | なし         | あり     | 1b               | 1b        | X    | X    |

|              | 1 つのハーフ ブリッジ開放 | あり  | あり         | なし         | あり     | 1b または 0b<br>(2) | 0b または 1b | X    | X    |

| 独立ブリッジ       | フル ブリッジ接続      | なし  | あり         | あり         | なし     | 0b               | 0b        | X    | X    |

|              | ハーフ ブリッジ接続     | なし  | あり         | あり         | なし     | 0b               | 0b        | X    | X    |

|              | ブリッジ開放         | あり  | あり         | なし         | あり     | 1b               | 1b        | X    | X    |

|              | 1 つのハーフ ブリッジ開放 | あり  | あり         | なし         | あり     | 1b または 0b<br>(2) | 0b または 1b | X    | X    |

(1) ブリッジの動作は、選択したモード タイプに基づくものです。

- 4 ピン インターフェイスまたは 2 ピン インターフェイスでは、対応するブリッジは動作中または Hi-Z 状態にあります。

- 並列ブリッジ (BDC) インターフェイスでは、両方のブリッジは動作中または Hi-Z 状態にあります。

- 独立ブリッジ インターフェイスでは、対応するハーフ ブリッジは動作中または Hi-Z 状態にあります。

(2) どのハーフ ブリッジが開放されているかによって、I<sup>2</sup>C レジスタの対応するビットが設定されます。

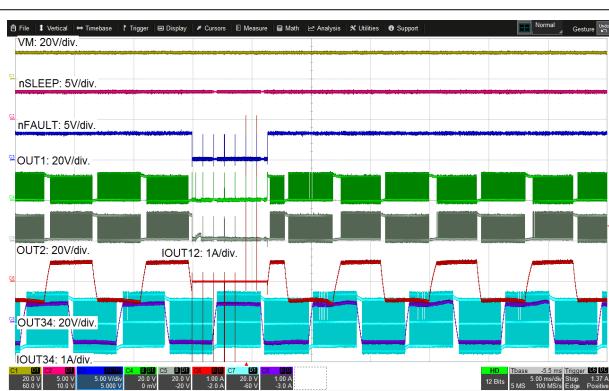

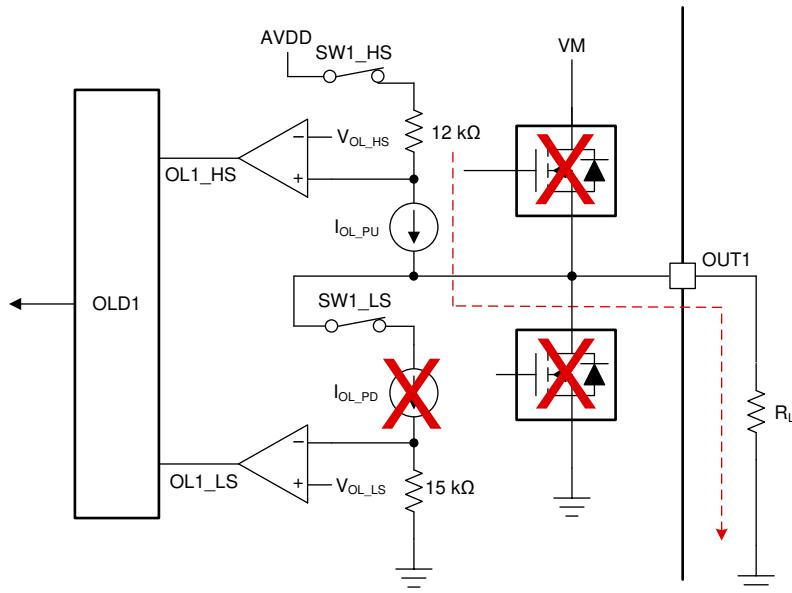

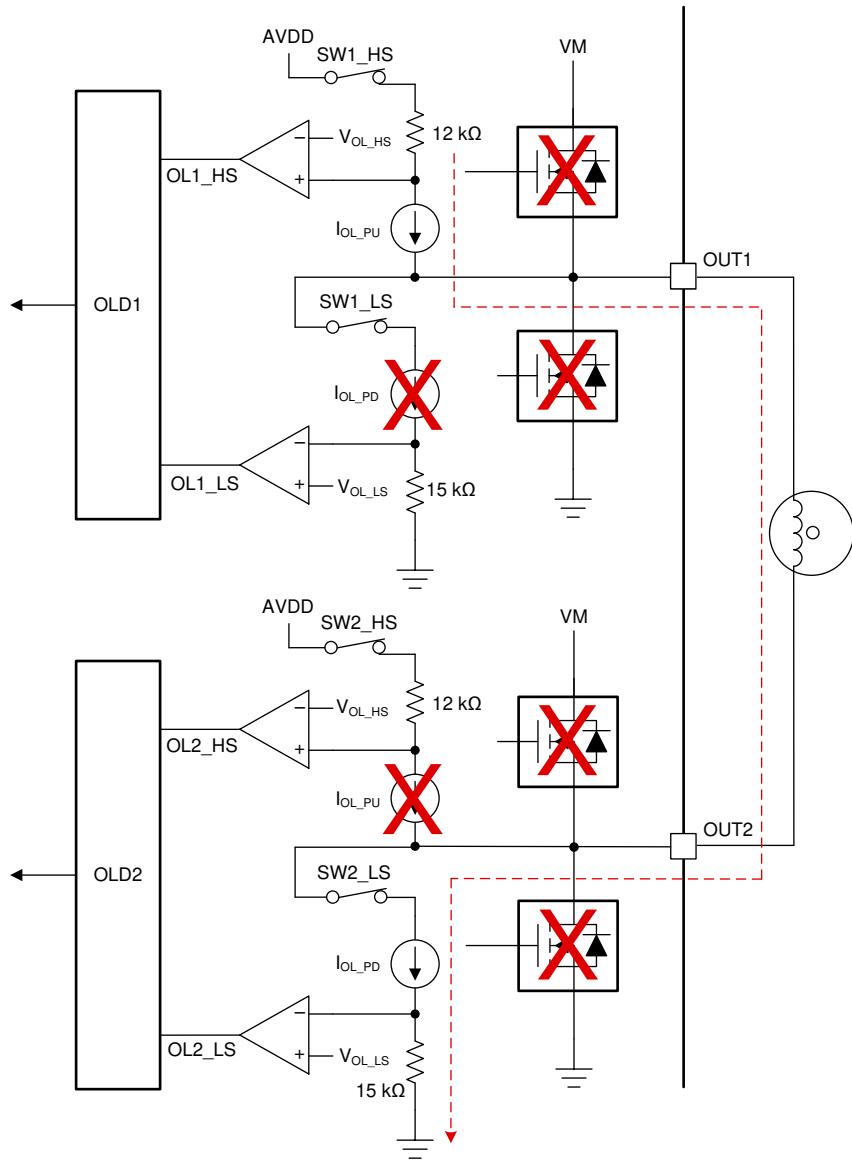

開放負荷検出シーケンスは 3 つの検出状態から成り、ドライバは以下のように負荷のいずれかが接続または開放されていることを確認します。

#### 7.3.8.4.1 フルブリッジ開放負荷検出

図 7-20 に示すように、デバイスのウェークアップ時に、定電流源によって OUT1 ピンが AVDD (内部) 固定電圧にプルされ、OUT1 端子から OUT2 端子に電流が流れるようになります。引き込み電流は、OUT1 と OUT2 の間のモータ抵抗に完全に依存します。この電流とコンパレータ スレッショルド電圧 ( $V_{OL\_HS}$  と  $V_{OL\_LS}$ ) に応じて、コンパレータ出力 OL1\_HS および OL2\_LS が設定またはリセットされ、開放負荷ステータスを決定されます。表 7-9 に、開放負荷検出の OL1\_HS と OL2\_LS の状態を示します。このテストは、 $t_{WAKE}$  または  $t_{ON}$  時間が経過する前に実行されます。開放負荷が検出されると、デバイスの電源が再投入されるか、nSLEEP ピンでデバイスがリセットされるまで、nFAULT ピンは Low にラッピングされます。OUT3 ピンと OUT4 ピンについても同様の実装が行われます。

**表 7-9. フルブリッジ接続の開放負荷検出**

| OL1_HS | OL2_LS | OLD のステータス |

|--------|--------|------------|

| 0      | 0      | OLD なし     |

| 0      | 1      |            |

| 1      | 0      |            |

| 1      | 1      |            |

図 7-20. フル ブリッジ接続の開放負荷検出回路

## 注

AVDD 電圧は内部レギュレータ電圧であり、最小値 ( $V_{VM}$ 、4.2V) として設定されます。したがって、電源電圧 ( $V_{VM}$ ) が 4.2V より高い場合、この電圧は 4.2V に固定され、それ以外の場合は電源電圧 ( $V_{VM}$ ) と等しくなります。

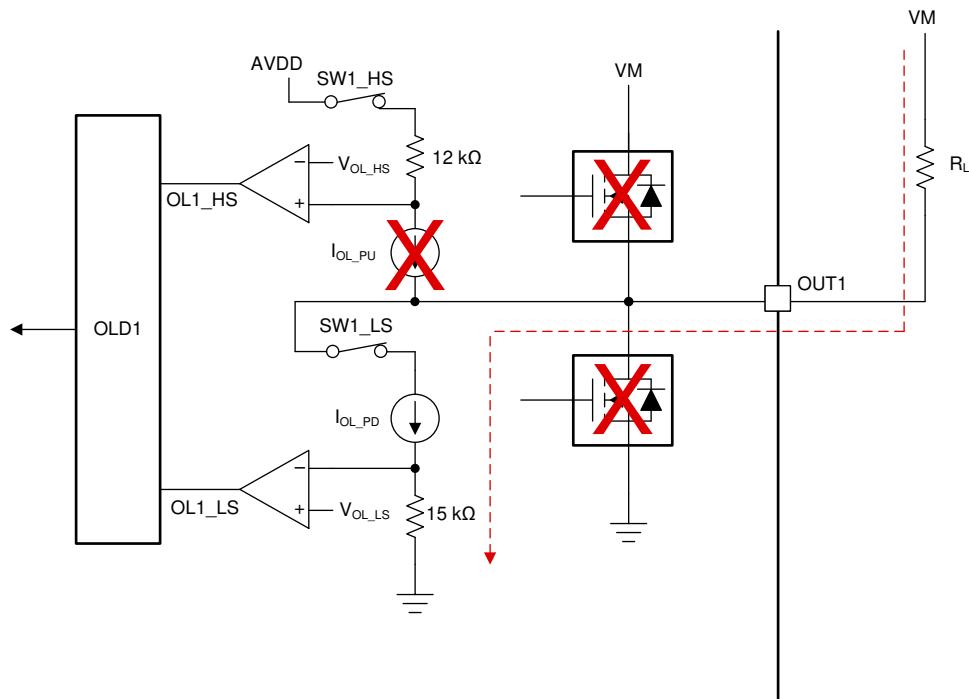

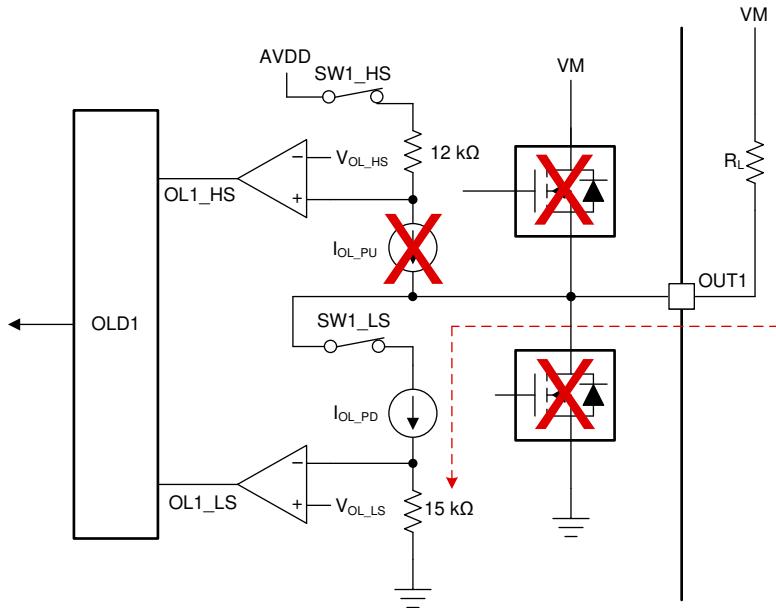

## 7.3.8.4.2 VM に接続された負荷

VM に接続された負荷を検出するために、図 7-21 に示すように、定電流源によって OUT1 ノードがプルダウンされます。これによって、OUT1 と VM の間に接続された負荷抵抗 ( $R_L$ ) の値に応じて、VM から OUT1 に電流が流れます。より高い電流が流れると (開放負荷ではない) OL1\_LS コンパレータが設定され、表 7-10 に示すように、開放負荷検出のためにコンパレータ出力がリセットされます。

表 7-10. VM に接続された負荷の開放負荷検出

| OL1_LS | OLD のステータス |

|--------|------------|

| 0      | OLD なし     |

| 1      | OLD あり     |

図 7-21. VM に接続された負荷の開放負荷検出回路

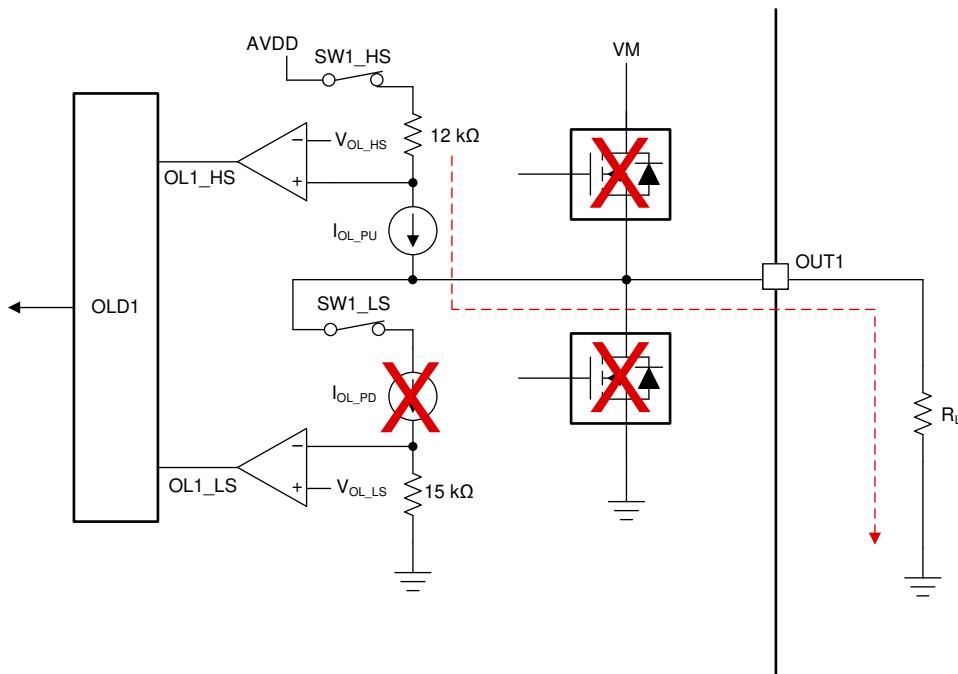

#### 7.3.8.4.3 GND に接続された負荷

GND に接続された負荷を検出するため、図 7-22 に示すように、内部電流源および内部 (4.2V) 固定電圧によって OUT1 ノードがプルアップされます。これによって、OUT1 と GND の間に接続された負荷抵抗 ( $R_L$ ) の値に応じて、OUT1 から GND に電流が流れます。より高い電流が流れると (開放負荷ではない) OL1\_HS コンパレータが設定され、表 7-11 に示すように、コンパレータ出力がリセットされます。

表 7-11. GND に接続された負荷の開放負荷検出

| OL1_HS | OLD のステータス |

|--------|------------|

| 0      | OLD なし     |

| 1      | OLD あり     |

図 7-22. GND に接続された負荷の開放負荷検出回路

## 7.4 デバイスの機能モード

DRV8847 デバイスは、nSLEEP ピンがロジック Low にプルされるまでアクティブです。スリープ モードでは、内部回路(チャージポンプとレギュレータ)がディスエーブルされ、すべての内部 FET がディスエーブルされます(Hi-Z 状態)。

nSLEEP ピンがロジック High にプルされると、デバイスは自動的に動作モードに移行します。デバイスが入力レディになるには、 $t_{WAKE}$  が経過していなければなりません。電源投入時に、一時的に nFAULT ピンがアサートされます。[表 7-12](#) に、さまざまな機能モードを示します。

DRV8847 デバイスは、VM 低電圧 (UVLO)、過電流 (OCP)、開放負荷検出 (OLD)、サーマル シャットダウン (TSD) が発生すると、FAULT モードに移行します。各FAULTの機能は、DRV8847 デバイスでは [表 7-13](#) に、DRV8847S デバイスでは [表 7-14](#) に示すFAULTのタイプによって異なります。

### 注

デバイスがスリープ モードに移行するには、 $t_{SLEEP}$  時間が経過していなければなりません。

**表 7-12. 機能モード**

| モード   | 条件                                     | H ブリッジ   | 内部回路     |

|-------|----------------------------------------|----------|----------|

| 動作    | $2.7V < V_{VM} < 18V$<br>nSLEEP ピン = 1 | 動作       | 動作       |

| スリープ  | $2.7V < V_{VM} < 18V$<br>nSLEEP ピン = 0 | ディセーブル   | ディセーブル   |

| FAULT | いずれかのFAULT条件が満たされる                     | FAULTによる | FAULTによる |

**表 7-13. DRV8847 のFAULTサポート**

| FAULT              | インターフェイス       | 条件                             | 通知     | H ブリッジ                 | 内部回路    | 復帰                                       |

|--------------------|----------------|--------------------------------|--------|------------------------|---------|------------------------------------------|

| VM 低電圧 (VM_UVLO)   | 全インターフェイス      | $VM < V_{UVLO}$                | nFAULT | Hi-Z 状態にある両方の H ブリッジ   | シャットダウン | 自動:<br>$VM > V_{UVLO}$                   |

| 過電流 (OCP)          | 4 ピン<br>2 ピン   | $I > I_{OCP}$                  | nFAULT | Hi-Z 状態にある対応する H ブリッジ  | 動作      | 自動: $t_{RETRY}$                          |

|                    | 並列ブリッジ         |                                |        | Hi-Z 状態にある両方の H ブリッジ   |         |                                          |

|                    | 独立ブリッジ         |                                |        | Hi-Z 状態にある対応するハーフ ブリッジ |         |                                          |

| 開放負荷検出 (OLD)       | 4 ピン           | フル ブリッジ開放                      | nFAULT | 動作モードにある H ブリッジ        | 動作      | 電源サイクル / リセット: OUTx 接続                   |

|                    | 2 ピン<br>並列ブリッジ | フル ブリッジ開放                      | nFAULT | 動作モードにある両方の H ブリッジ     |         |                                          |

|                    | 独立ブリッジ         | ハーフ ブリッジ開放                     | nFAULT | 動作モードにあるハーフ ブリッジ       |         |                                          |

| サーマル・シャットダウン (TSD) | 全インターフェイス      | $T_J > T_{TSD}$<br>(最小値 150°C) | nFAULT | Hi-Z 状態にある両方の H ブリッジ   | 動作      | $T_J < T_{TSD}$<br>( $T_{HYS}$ タイプ 40°C) |

表 7-14. DRV8847S の�オルト サポート

| �オルト                  | モード             | 条件                                               | 通知     | H ブリッジ                       | 内部回路    | 復帰                                                               |

|-----------------------|-----------------|--------------------------------------------------|--------|------------------------------|---------|------------------------------------------------------------------|

| VM 低電圧<br>(VM_UVLO)   | 全インターフェイス       | VM < V <sub>UVLO</sub>                           | nFAULT | Hi-Z 状態にある両方の H ブリッジ         | シャットダウン | 自動:<br>VM > V <sub>UVLO</sub>                                    |

| 過電流 (OCP)             | 4 ピン<br>2 ピン    | I > I <sub>OCP</sub>                             | nFAULT | Hi-Z 状態にある対応する H ブリッジ        | 動作      | 自動: t <sub>RETRY</sub>                                           |

|                       | 並列ブリッジ          |                                                  |        | Hi-Z 状態にある両方の H ブリッジ         |         |                                                                  |

|                       | 独立ブリッジ インターフェイス |                                                  |        | Hi-Z 状態にある対応するハーフ ブリッジ       |         |                                                                  |

| 開放負荷検出<br>(OLD)       | 4 ピン            | フル ブリッジ開放                                        | nFAULT | 動作中または Hi-Z 状態にある H ブリッジ (1) | 動作      | 電源サイクル / リセット: OUTx 接続                                           |

|                       | 2 ピン<br>並列ブリッジ  | フル ブリッジ開放                                        | nFAULT | 動作中または Hi-Z 状態にある両方の H ブリッジ  |         |                                                                  |

|                       | 独立ブリッジ          | ハーフ ブリッジ開放                                       | nFAULT | 動作中または Hi-Z 状態にあるハーフ ブリッジ    |         |                                                                  |

| サーマル・シャットダウン<br>(TSD) | 全インターフェイス       | T <sub>J</sub> > T <sub>TSD</sub><br>(最小値 150°C) | nFAULT | Hi-Z 状態にある両方の H ブリッジ         | 動作      | T <sub>J</sub> < T <sub>TSD</sub><br>(T <sub>HYS</sub> タイプ 40°C) |

(1) OLD でのブリッジの状態は、表 7-19 に示すように、OLDBO ビットに依存します。

## 7.5 プログラミング

このセクションは、DRV8847S デバイス (I<sup>2</sup>C バリアント) にのみ適用されます。

### 7.5.1 I<sup>2</sup>C 通信

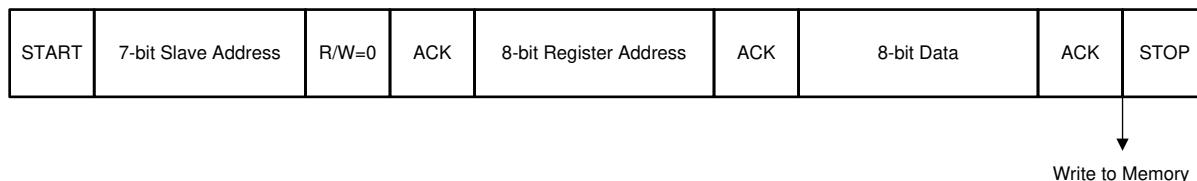

#### 7.5.1.1 I<sup>2</sup>C 書き込み

I<sup>2</sup>C バスに書き込む場合は、マスター デバイスは 7 ビットのスレーブ デバイスのアドレスでバス上に START 条件を送信します。最後のビット (R/W ビット) は、書き込みを意味する 0b に設定されます。スレーブ デバイスがアクノリッジ ビットを送信した後、マスター デバイスは書き込み対象レジスタのレジスタ アドレスを送信します。スレーブ デバイスはアクノリッジ (ACK) 信号を再度送信し、スレーブ デバイスがレディであることをマスター デバイスに通知します。このプロセスの後、マスター デバイスは 8 ビットの書き込みデータを送信し、STOP 条件で送信を終了します。

図 7-23. I<sup>2</sup>C 書き込みシーケンス

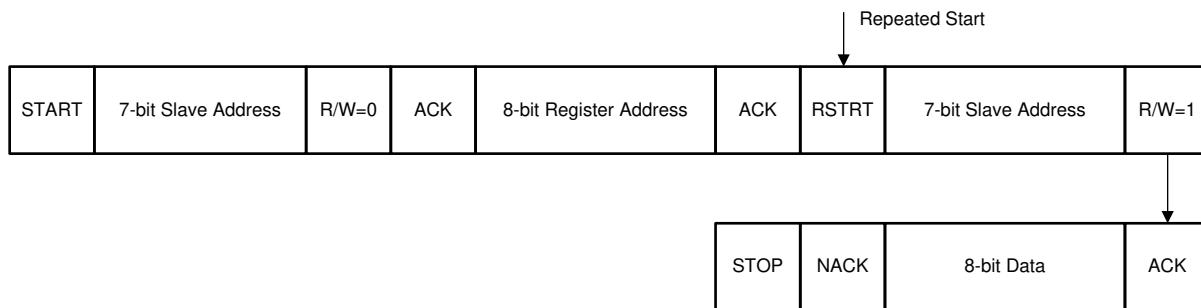

#### 7.5.1.2 I<sup>2</sup>C 読み出し

スレーブ デバイスから読み出す場合は、どのレジスタから読み出すかを最初にマスター デバイスがスレーブ デバイスに知らせる必要があります。この通信は、R/W ビットを 0b (書き込み) としてアドレスを設定する書き込みプロセスと同様に、マスター デバイスが送信を開始することによって行われます。次に、マスター デバイスは読み出し対象のレジスタのレジスタ アドレスを送信します。スレーブ デバイスがこのレジスタ アドレスをアクノリッジすると、マスター デバイスは START 条件を再度送信し、続いて R/W ビットを 1b (読み出し) としたスレーブ アドレスを送信します。このプロセスの後、スレーブ デバイスは読み出し要求をアクノリッジし、マスター デバイスは SDA バスを解放しますが、スレーブ デバイスへのクロック供給は続けます。

トランザクションのこの部分では、マスター デバイスがマスター レシーバになり、スレーブ デバイスがスレーブ トランスマッタになります。マスター デバイスは引き続きクロック パルスを送信しますが、SDA ラインを解放して、スレーブ デバイスがデータを送信できるようにします。バイトの終わりに、マスター デバイスはネガティブ アクノリッジ (NACK) 信号を送信し、スレーブ デバイスに通信を停止してバスを解放するように信号を送ります。その後で、マスター デバイスは STOP 条件を送信します。

図 7-24. I<sup>2</sup>C 読み出しシーケンス

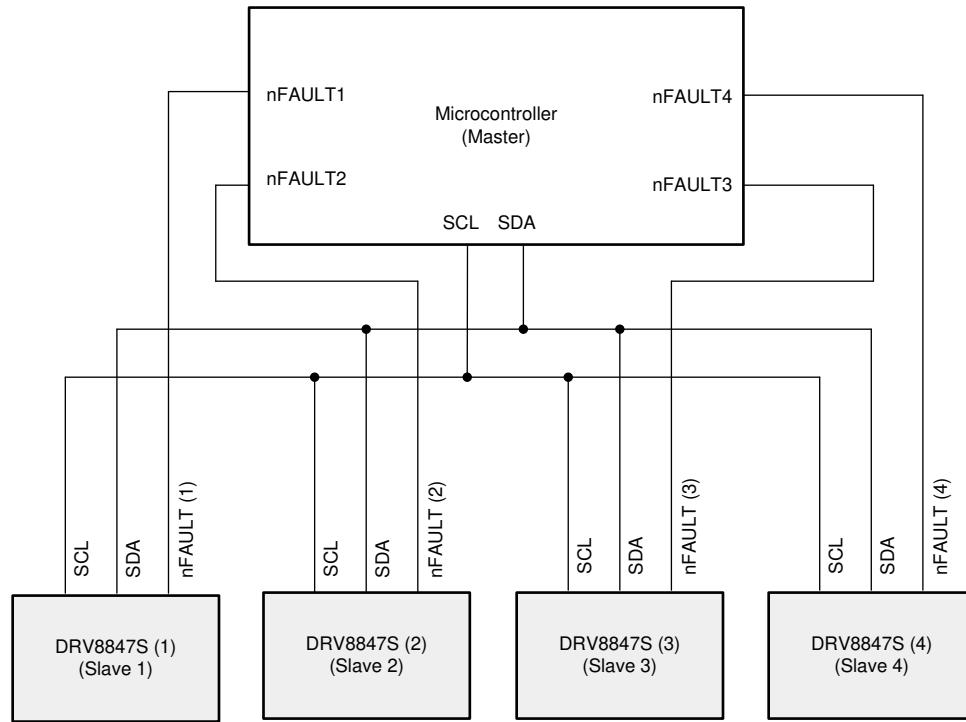

### 7.5.2 マルチスレーブ動作

マルチスレーブ動作は、図 7-25 に示すように、1 つの I<sup>2</sup>C ラインで複数の DRV8847S デバイスを制御する場合に使用します。DRV8847 デバイスのデフォルトのデバイスアドレスは 0x60 (7 ビットアドレス) で、このアドレスを使用してすべての DRV8847S デバイスにアクセスできます。接続されている 4 つのデバイス (図 7-25 を参照) のうちデバイス 1 をプログラミングする場合のマルチスレーブ構成の手順は以下のとおりです。

図 7-25. DRV8847S のマルチスレーブ動作

- DRV8847S デバイスバリアントは、接続されているすべてのデバイスの DISFLT ビット (IC2\_CON レジスタ) を 1b に書き込むことで、マルチスレーブ動作用に構成されます。この手順によって、すべての DRV8847S の nFAULT 出力ピンがディスエーブルになり、マスターとスレーブの I<sup>2</sup>C デバイス間の競合状態が回避されます。

- 3 つのデバイス (2, 3, 4) の nFAULT ピン (nFAULT2 ピン、nFAULT3 ピン、nFAULT4 ピン) を Low にプルして、スレーブデバイス (デバイス 2、デバイス 3、デバイス 4) の各 I<sup>2</sup>C バスを解放します。これでデバイス 1 のみがマスターに接続されることになります。

- DRV8847S (1) デバイスだけがコントローラに接続されているため、そのスレーブアドレスをデフォルトの 0x60 (7 ビットアドレス) から別の固有アドレスにプログラムし直すことができます。

- 同様に、他の 3 つのデバイス (デバイス 2、デバイス 3、デバイス 4) のスレーブアドレス (SLAVE\_ADDR) も、nFAULT ピンの組み合わせによって固有アドレスに順次プログラムし直すことができます。

- すべてのスレーブアドレスが再プログラムされたら、DISFLT ビットを 0b (IC2\_CON レジスタ) に書き込みます。これによって、nFAULT 出力ピンがフォルトフラグ用にイネーブルになります。

- すべての nFAULT ピンが解放され、マルチスレーブのセットアップが完了します。これで、新たにプログラムし直されたアドレスを使用して、接続されているすべてのスレーブデバイスにアクセスできるようになりました。

- 電源リセット (nSLEEP) の場合、いずれのデバイスでも上記の手順を繰り返す必要があります。.

## 7.6 レジスタ・マップ

表 7-15 に、DRV8847 デバイスのメモリ マップされた I<sup>2</sup>C レジスタを示します。I<sup>2</sup>C レジスタは、DRV8847S デバイスの構成およびデバイス診断に使用されます。

### 注

予約済みと示されたレジスタや、レジスタ マップ (表 7-15) に記載されていないアドレスは変更しないでください。そのようなレジスタに書き込みを行うと、予期しない動作が生じる場合があります。すべての予約済みビットのデフォルト値は 0b です。

**表 7-15. I<sup>2</sup>C レジスタ**

| アドレス | 略称          | レジスタ名               | 7      | 6      | 5    | 4      | 3    | 2     | 1     | 0     | アクセス権 | セクション |

|------|-------------|---------------------|--------|--------|------|--------|------|-------|-------|-------|-------|-------|

| 0x00 | SLAVE_ADDR  | スレーブ・アドレス           | RSVD   |        |      |        |      |       |       |       | RW    |       |

| 0x01 | IC1_CON     | IC1 制御              | TRQ    | IN4    | IN3  | IN2    | IN1  | I2CBC |       | モード   | RW    | 表示    |

| 0x02 | IC2_CON     | IC2 制御              | CLRFLT | DISFLT | RSVD | DECAY  | OCPR | OLDOD | OLDFD | OLDBO | RW    | 表示    |

| 0x03 | SLR_STATUS1 | スルーレートとフォルト ステータス 1 | RSVD   | SLR    | RSVD | nFAULT | OCP  | OLD   | TSDF  | UVLOF | RW    | 表示    |

| 0x04 | STATUS2     | フォルト ステータス 2        | OLD4   | OLD3   | OLD2 | OLD1   | OCP4 | OCP3  | OCP2  | OCP1  | R     | 表示    |

表の小さい枠に収まるように、複雑なビット・アクセス・タイプを記号で表しています。このセクションでアクセス・タイプに使用しているコードを、表 7-16 に示します。

**表 7-16. アクセス・タイプ・コード**

| アクセス・タイプ      | コード | 説明               |

|---------------|-----|------------------|

| 読み取りタイプ       |     |                  |

| R             | R   | 読み取り             |

| 書き込みタイプ       |     |                  |

| W             | W   | 書き込み             |

| リセットまたはデフォルト値 |     |                  |

| -n            |     | リセット後の値またはデフォルト値 |

### 7.6.1 スレーブ アドレス レジスタ (アドレス = 0x00) [リセット = 0x60]

図 7-26 にスレーブ アドレスを示し、表 7-17 にその説明を示します。

図 7-26. スレーブ アドレス レジスタ

| 7    | 6 | 5 | 4 | 3            | 2 | 1 | 0 |

|------|---|---|---|--------------|---|---|---|

| RSVD |   |   |   | SLAVE_ADDR   |   |   |   |

| R-0b |   |   |   | R/W-1100000b |   |   |   |

表 7-17. スレーブ アドレス レジスタのフィールドの説明

| ビット | フィールド      | タイプ | リセット     | 説明                               |

|-----|------------|-----|----------|----------------------------------|

| 7   | RSVD       | R   | 0b       | 予約済み                             |

| 6-0 | SLAVE_ADDR | R/W | 1100000b | スレーブ アドレス (8 ビット)<br>デフォルト値 0x60 |

### 7.6.2 IC1 制御レジスタ (アドレス = 0x01) [リセット = 0x00]

図 7-27 に IC1 の制御を示し、表 7-18 にその説明を示します。

図 7-27. IC1 制御レジスタ

| 7      | 6      | 5      | 4      | 3      | 2      | 1 | 0       |

|--------|--------|--------|--------|--------|--------|---|---------|

| TRQ    | IN4    | IN3    | IN2    | IN1    | I2CBC  |   | モード     |

| R/W-0b | R/W-0b | R/W-0b | R/W-0b | R/W-0b | R/W-0b |   | R/W-00b |

表 7-18. IC1 制御レジスタのフィールドの説明

| ビット | フィールド | タイプ | リセット | 説明                                                                            |

|-----|-------|-----|------|-------------------------------------------------------------------------------|

| 7   | TRQ   | R/W | 0b   | 0b = トルク スカラーを 100% に設定<br>1b = トルク スカラーを 50% に設定                             |

| 6   | IN4   | R/W | 0b   | INx ビットはブリッジ動作の制御に使用される。                                                      |

| 5   | IN3   | R/W | 0b   | INx ビットはブリッジ動作の制御に使用される。                                                      |

| 4   | IN2   | R/W | 0b   | INx ビットはブリッジ動作の制御に使用される。                                                      |

| 3   | IN1   | R/W | 0b   | INx ビットはブリッジ動作の制御に使用される。                                                      |

| 2   | I2CBC | R/W | 0b   | 0b = INx ピンにより構成されたブリッジ制御<br>1b = INx ビットにより構成されたブリッジ制御                       |

| 1-0 | MODE  | R/W | 00b  | 00b = 4 ピン インターフェイス<br>01b = 2 ピン インターフェイス<br>10b = 並列インターフェイス<br>11b = 独立モード |

### 7.6.3 IC2 制御レジスタ (アドレス = 0x02) [リセット = 0x00]

図 7-28 に IC2 の制御を示し、表 7-19 にその説明を示します。

**図 7-28. IC2 制御レジスタ**

| 7       | 6      | 5    | 4      | 3      | 2      | 1      | 0      |

|---------|--------|------|--------|--------|--------|--------|--------|

| CLRFILT | DISFLT | RSVD | DECAY  | OCPR   | OLDOD  | OLDFD  | OLDBO  |

| R/W-0b  | R/W-0b | R-0b | R/W-0b | R/W-0b | R/W-0b | R/W-0b | R/W-0b |

**表 7-19. IC2 制御レジスタのフィールドの説明**

| ビット | フィールド   | タイプ | リセット | 説明                                                                                                                                                                   |

|-----|---------|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CLRFILT | R/W | 0b   | このビットを設定すると、クリア フォルトコマンドを発行する。このコマンドは、OLD ビットと OLDx ビット以外のすべての FAULT ビットをクリアする。すべてのフォルトをクリアすると、このビットは 0b にリセットされる。<br>0b = クリア フォルトコマンド発行なし<br>1b = クリア フォルトコマンド発行あり |

| 6   | DISFLT  | R/W | 0b   | 0b = nFAULT ピンがディスエーブルされていない<br>1b = nFAULT ピンがディスエーブルされている                                                                                                          |

| 5   | RSVD    | R   | 0b   | 予約済み                                                                                                                                                                 |

| 4   | DECAY   | R/W | 0b   | 0b = 25% 高速減衰<br>1b = 100% 低速減衰                                                                                                                                      |

| 3   | OCPR    | R/W | 0b   | 0b = OCP 自動リトライ モード<br>1b = OCP ラッチ モード                                                                                                                              |

| 2   | OLDOD   | R/W | 0b   | 0b = アイドル<br>1b = OLD オンデマンドがアクティブになっている                                                                                                                             |

| 1   | OLDFD   | R/W | 0b   | 0b = OLD 時のフォルト信号あり<br>1b = OLD 時のフォルト信号なし                                                                                                                           |

| 0   | OLDBO   | R/W | 0b   | 0b = OLD 時ブリッジ動作中<br>1b = OLD 時ブリッジ Hi-Z                                                                                                                             |

### 7.6.4 スルーレートとフォルトステータス1レジスタ (アドレス = 0x03) [リセット = 0x40]

図 7-29 にフォルトステータス1を示し、表 7-20 にその説明を示します。

図 7-29. フォルトステータス1レジスタ

| 7    | 6      | 5    | 4      | 3    | 2    | 1    | 0     |

|------|--------|------|--------|------|------|------|-------|

| RSVD | SLR    | RSVD | nFAULT | OCP  | OLD  | TSDF | UVLOF |

| R-0b | R/W-0b | R-0b | R-0b   | R-0b | R-0b | R-0b | R-0b  |

表 7-20. フォルトステータス1レジスタのフィールドの説明

| ビット | フィールド  | タイプ | リセット | 説明                                                |

|-----|--------|-----|------|---------------------------------------------------|

| 7   | RSVD   | R   | 0b   | 予約済み                                              |

| 6   | SLR    | R/W | 0b   | 0b = 150ns<br>1b = 300ns                          |

| 5   | RSVD   | R   | 0b   | 予約済み                                              |

| 4   | nFAULT | R   | 0b   | 0b = フォルト検出なし (nFAULT ピンをミラーリング)<br>1b = フォルト検出あり |

| 3   | OCP    | R   | 0b   | 0b = OCP 検出なし<br>1b = OCP 検出あり                    |

| 2   | OLD    | R   | 0b   | 0b = 開放負荷検出なし<br>1b = 開放負荷検出あり                    |

| 1   | TSDF   | R   | 0b   | 0b = TSD フォルト検出なし<br>1b = TSD フォルト検出あり            |

| 0   | UVLOF  | R   | 0b   | 0b = UVLO フォルト検出なし<br>1b = UVLO フォルト検出あり          |

### 7.6.5 フォルトステータス 2 レジスタ (アドレス = 0x04) [リセット = 0x00]

図 7-30 にフォルトステータス 2 を示し、表 7-21 にその説明を示します。

**図 7-30. フォルトステータス 2 レジスタ**

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------|------|------|------|------|------|------|------|

| OLD4 | OLD3 | OLD2 | OLD1 | OCP4 | OCP3 | OCP2 | OCP1 |

| R-0b |

**表 7-21. フォルトステータス 2 レジスタのフィールドの説明**

| ビット | フィールド | タイプ | リセット | 説明                                             |

|-----|-------|-----|------|------------------------------------------------|

| 7   | OLD4  | R   | 0b   | 0b = OUT4 での開放負荷検出なし<br>1b = OUT4 での開放負荷検出あり   |

| 6   | OLD3  | R   | 0b   | 0b = OUT3 での開放負荷検出なし<br>1b = OUT3 での開放負荷検出あり   |

| 5   | OLD2  | R   | 0b   | 0b = OUT2 での開放負荷検出なし<br>1b = OUT2 での開放負荷検出あり   |

| 4   | OLD1  | R   | 0b   | 0b = OUT1 での開放負荷検出なし<br>1b = OUT1 での開放負荷検出あり   |

| 3   | OCP4  | R   | 0b   | 0b = OUT4 での OCP 検出なし<br>1b = OUT4 での OCP 検出あり |

| 2   | OCP3  | R   | 0b   | 0b = OUT3 での OCP 検出なし<br>1b = OUT3 での OCP 検出あり |

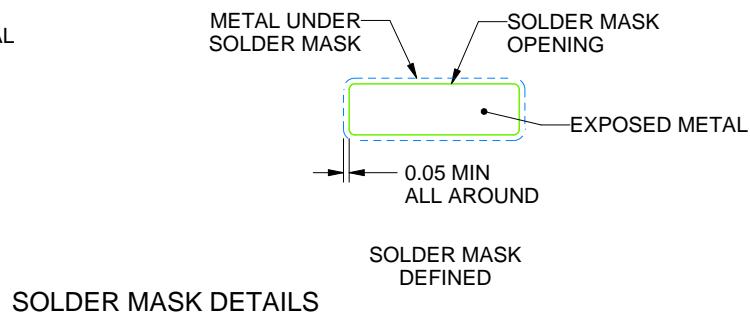

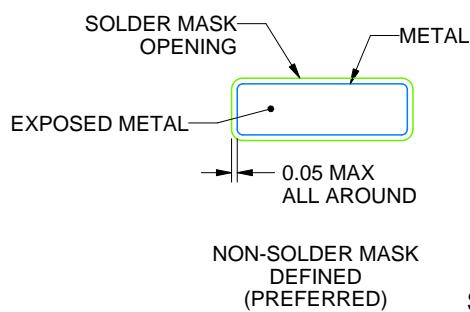

| 1   | OCP2  | R   | 0b   | 0b = OUT2 での OCP 検出なし<br>1b = OUT2 での OCP 検出あり |