# HD3SS3220 SuperSpeed 2:1 マルチプレクサ搭載、USB Type-C DRP (デュアル・ロール・ポート) ポート・コントローラ

## 1 特長

- 2:1 SuperSpeed マルチプレクサ内蔵の USB Type-C ポートコントローラ

- USB Type-C™ 仕様に準拠

- 最大 10Gbps の USB 3.1 G1 および G2 をサポート

- 3A の電流アドバタイズメントおよび検出機能により、最大 15W の電力供給をサポート

- モード構成

- ホストのみ - DFP / ソース

- デバイスのみ - UFP / シンク

- デュアルロールポート - DRP

- チャネル構成 (CC)

- USB ポート接続の検出

- ケーブルの向きの検出

- ロール (役割) の検出

- Type-C 電流モード (デフォルト、中、高)

- アクティブケーブルの  $V_{(BUS)}$  検出および VCONN サポート

- オーディオアクセサリおよびデバッグアクセサリのサポート

- HD3SS3220 - オーディオおよびデバッグ (UFP/DFP/DRP) のサポート

- HD3SS3220L - オーディオアクセサリなし、UFP としてデバッグアクセサリのみ

- Try.SRC および Try.SNK DRP モードのサポート

- GPIO および I<sup>2</sup>C による構成制御

- 低いアクティブおよびスタンバイ消費電流

- 40°C~85°C の産業用温度範囲

## 2 アプリケーション

- USB ホスト、デバイス、ハブ

- 携帯電話、タブレット、ノート PC

- サム・ドライブ、ポータブル・ハード・ディスク、セット・トップ・ボックスなどの USB ペリフェラル

## 3 説明

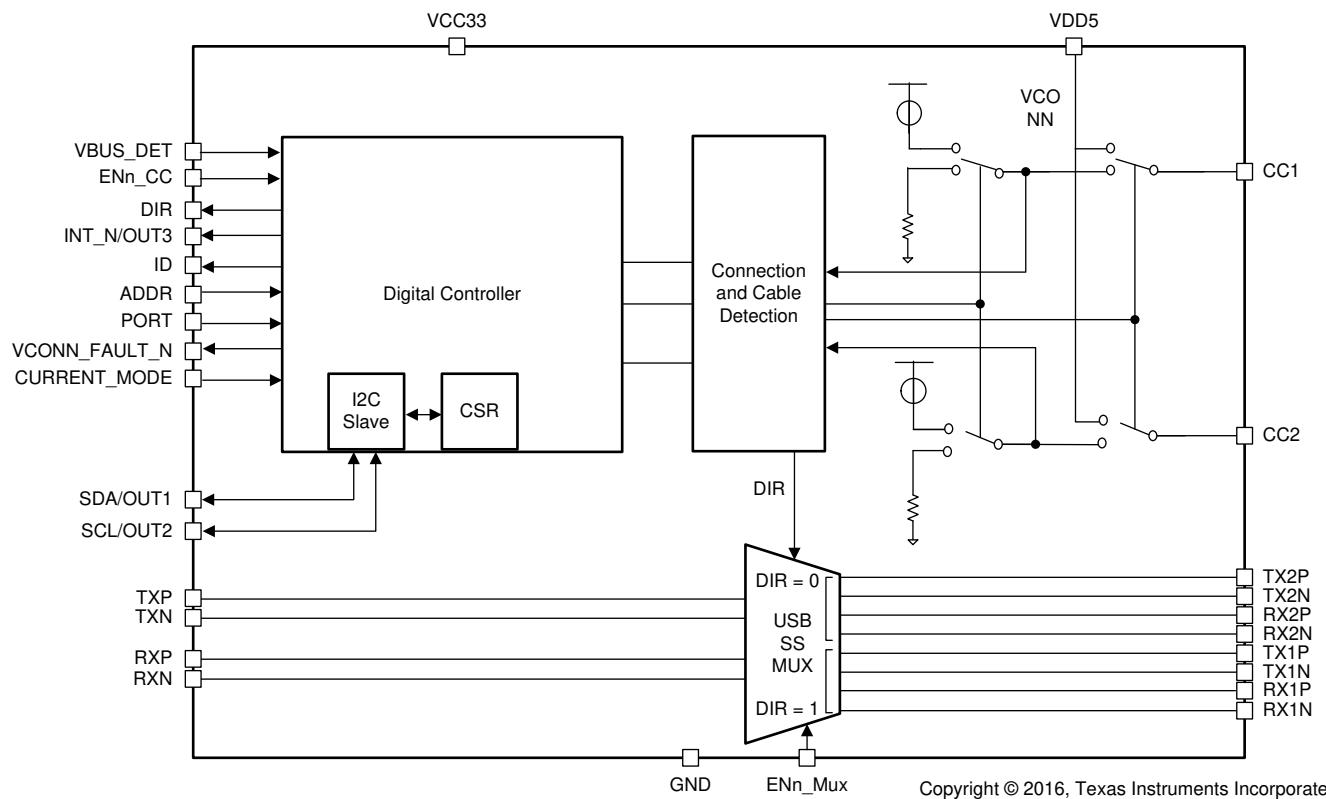

HD3SS3220 は、DRP ポートコントローラ付きの USB SuperSpeed (SS) 2:1 マルチプレクサです。このデバイスは、USB Type-C を実装するエコシステム向けに、チャネル構成 (CC) ロジックと 5V VCONN ソースを提供します。HD3SS3220 は、ダウンストリーム側ポート (DFP)、アップストリーム側ポート (UFP)、またはデュアルロールポート (DRP) として構成できるため、あらゆるアプリケーションに理想的です。

HD3SS3220 が DRP モードの場合、Type-C 仕様に従って、自らを DFP または UFP として交互に提示します。CC ロジック ブロックは、USB ポートが接続されたかどうかとポートの役割を判断するため、CC1 および CC2 ピンの プルアップ抵抗または プルダウン抵抗を監視します。USB ポートが接続されると、CC ロジックはケーブルの向きも判定し、それに応じて USB SS マルチプレクサを構成します。最後に、CC ロジックは Type-C 電流モード (DFP および UFP モードでそれぞれデフォルト、中、高) をアドバタイズまたは検出します。

内蔵マルチプレクサの動的特性は非常に優れているため、SS 信号アイダイアグラムへの減衰が最小限で、ジッタはわずかしか発生しない、スイッチングが可能です。このデバイスのスイッチ パスは、適応型同相電圧トラッキングを採用しており、RX チャネルと TX チャネルの同相電圧が異なるのにもかかわらず、同一のチャネルを形成します。

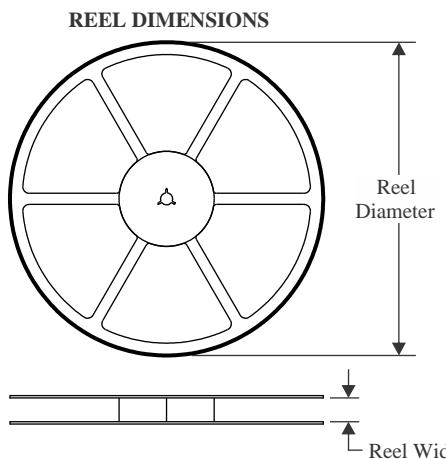

### パッケージ情報

| 部品番号       | パッケージ <sup>(1)</sup> | 本体サイズ (公称)       |

|------------|----------------------|------------------|

| HD3SS3220  | VQFN RNH (30)        | 2.50 mm × 4.50mm |

| HD3SS3220I |                      |                  |

| HD3SS3220L |                      |                  |

(1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあります。TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

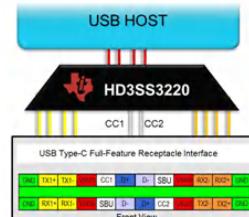

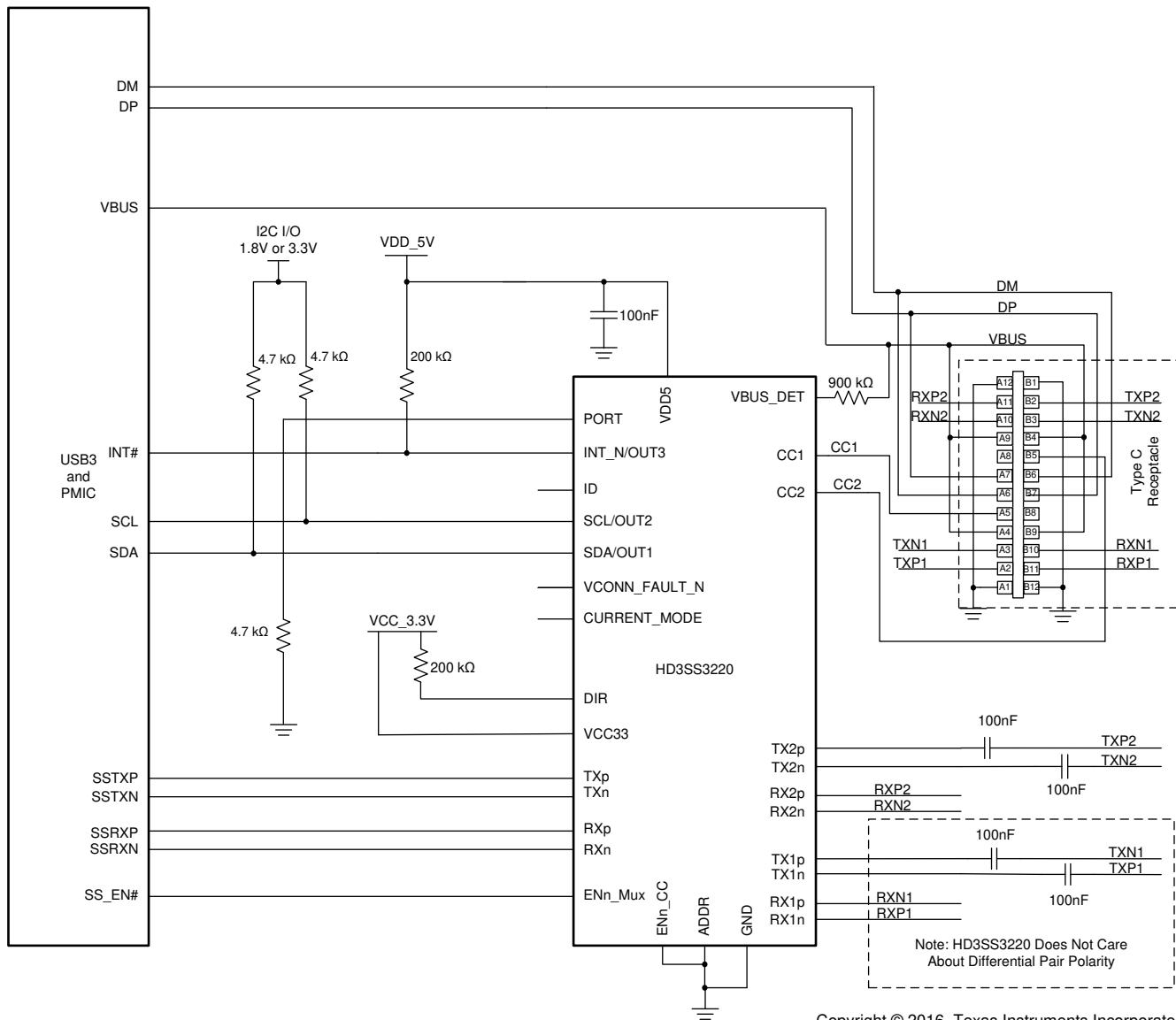

## 代表的なアプリケーション

## 概略回路図

## 目次

|                    |    |                               |    |

|--------------------|----|-------------------------------|----|

| <b>1 特長</b>        | 1  | 6.4 デバイスの機能モード                | 20 |

| <b>2 アプリケーション</b>  | 1  | 6.5 プログラミング                   | 22 |

| <b>3 説明</b>        | 1  | 6.6 レジスタ・マップ                  | 24 |

| <b>4 ピン構成および機能</b> | 4  | <b>7 アプリケーションと実装</b>          | 29 |

| ピンの機能              | 4  | 7.1 アプリケーション情報                | 29 |

| <b>5 仕様</b>        | 6  | 7.2 代表的なアプリケーション、DRP ポート      | 30 |

| 5.1 絶対最大定格         | 6  | <b>8 電源に関する推奨事項</b>           | 35 |

| 5.2 ESD 定格         | 6  | <b>9 レイアウト</b>                | 36 |

| 5.3 推奨動作条件         | 6  | 9.1 レイアウトのガイドライン              | 36 |

| 5.4 熱に関する情報        | 7  | 9.2 レイアウト                     | 42 |

| 5.5 電気的特性          | 7  | <b>10 デバイスおよびドキュメントのサポート</b>  | 43 |

| 5.6 タイミング要件        | 9  | 10.1 ドキュメントの更新通知を受け取る方法       | 43 |

| <b>6 詳細説明</b>      | 12 | 10.2 商標                       | 43 |

| 6.1 概要             | 12 | <b>11 改訂履歴</b>                | 43 |

| 6.2 機能ブロック図        | 14 | <b>12 メカニカル、パッケージ、および注文情報</b> | 44 |

| 6.3 機能説明           | 15 |                               |    |

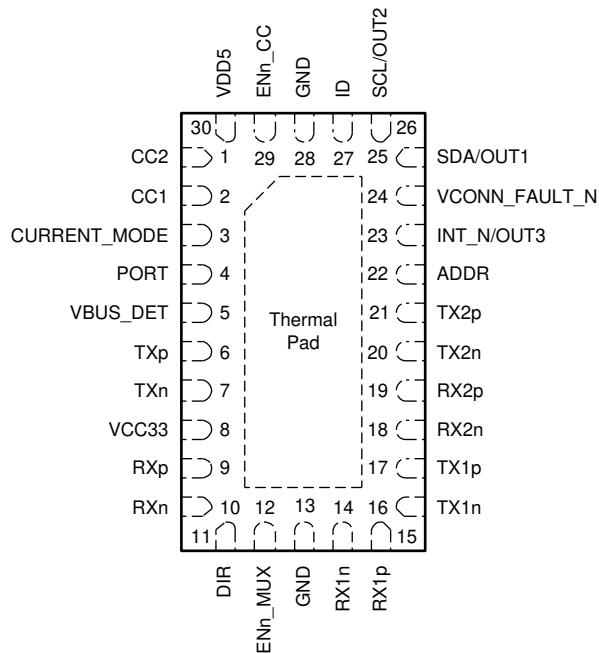

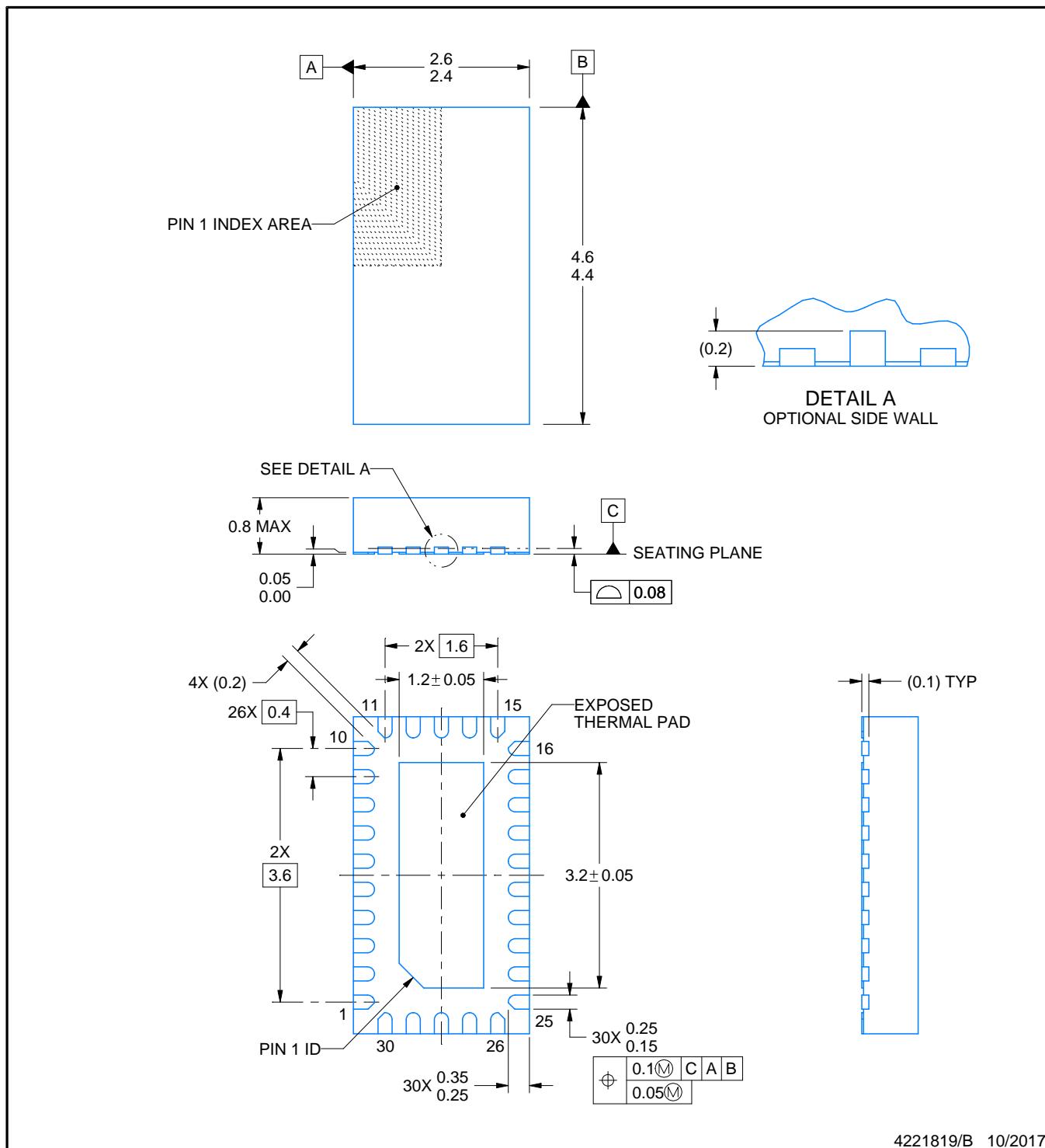

## 4 ピン構成および機能

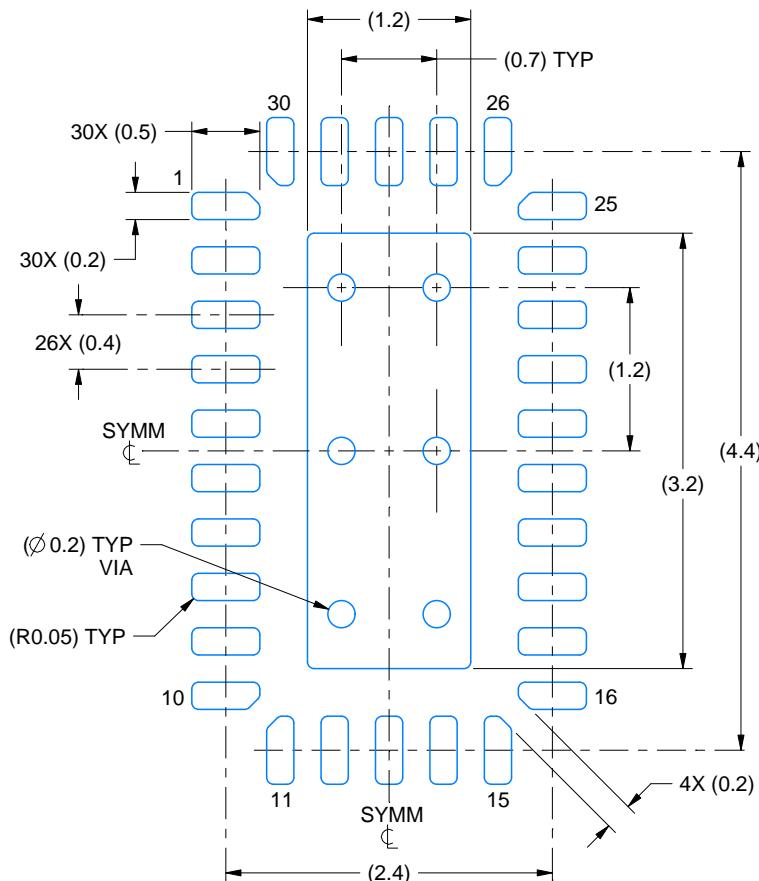

図 4-1. RNH パッケージ 30 ピン (VQFN) 上面図

### ピンの機能

| ピン           |        | I/O | 説明                                                                                                                                                                                                                                                                 |

|--------------|--------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称           | 番号     |     |                                                                                                                                                                                                                                                                    |

| CC2          | 1      | I/O | Type-C 構成チャネル信号 2                                                                                                                                                                                                                                                  |

| CC1          | 2      | I/O | Type-C 構成チャネル信号 1                                                                                                                                                                                                                                                  |

| CURRENT_MODE | 3      | I   | GPIO モードのときに DFP (または DRP の DFP) モードでの電流アドバタイズメントを示すトライレベル入力ピン。UFP モードではドントケア。I <sup>2</sup> C を使用せずに大電流をアドバタイズするフレキシビリティを提供します。このピンには 250K の内部ブルダウンがあります。<br>L - 低 - デフォルト - 900mA<br>M - 中 (PCB 上の VDD5 に 500K を配置) - 1.5A<br>H - 高 (PCB 上の VDD5 に 10K を配置) - 3A |

| PORT         | 4      | I   | ポート モードを示すトライレベル入力ピン。このピンの状態は、HD3SS3220 の ENn_CC が Low にアセットされ、VDD5 がアクティブになるとサンプリングされます。このピンは、I2C_SOFT_RESET の後にもサンプリングされます。<br>H - DFP (DFP モードが必要な場合は VDD5 にプルアップ)<br>NC - DRP (DRP モードが必要な場合は未接続のままにする)<br>L - UFP (UFP モードが必要な場合はブルダウンまたは GND に接続)            |

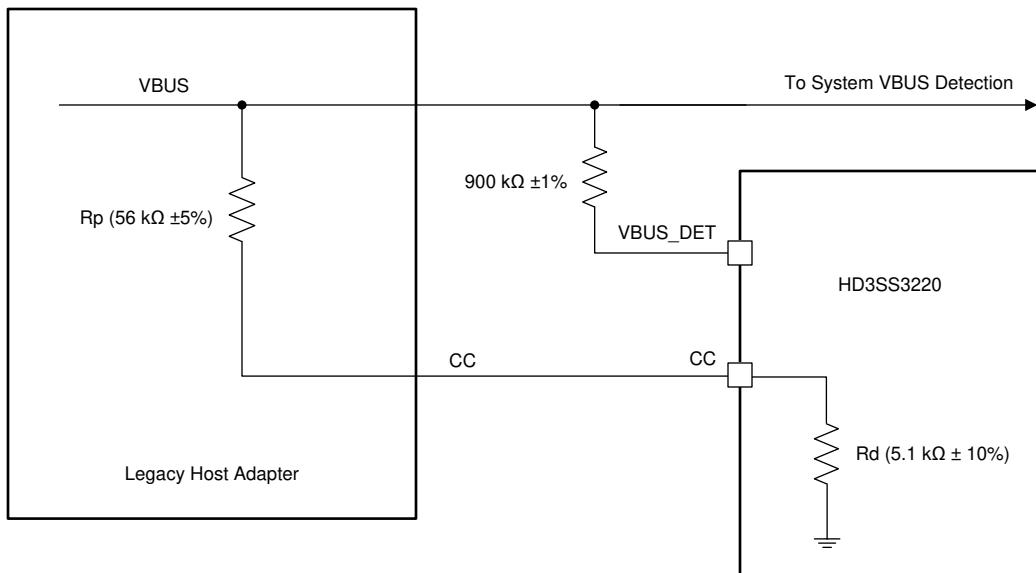

| VBUS_DET     | 5      | I   | 5~28V の VBUS 入力電圧。VBUS 検出により UFP の接続が判定されます。システムの VBUS と VBUS_DET ピンの間に 900K の外部抵抗が 1 つ必要です。                                                                                                                                                                       |

| TXp          | 6      | I/O | ホスト / デバイス USB SuperSpeed 差動信号 TX 正                                                                                                                                                                                                                                |

| TXn          | 7      | I/O | ホスト / デバイス USB SuperSpeed 差動信号 TX 負                                                                                                                                                                                                                                |

| VCC33        | 8      | P   | 3.3V 電源                                                                                                                                                                                                                                                            |

| RXp          | 9      | I/O | ホスト / デバイス USB SuperSpeed 差動信号 RX 正                                                                                                                                                                                                                                |

| RXn          | 10     | I/O | ホスト / デバイス USB SuperSpeed 差動信号 RX 負                                                                                                                                                                                                                                |

| DIR          | 11     | O   | Type-C プラグの向き。オープンドレイン出力。<br>デバイスを適切に動作させるには、プルアップ抵抗 (200K) を取り付ける必要があります。                                                                                                                                                                                         |

| ENn_MUX      | 12     | I   | アクティブ Low のマルチブレクサ サイネーブル:<br>L - 通常動作、<br>H - シャットダウン。                                                                                                                                                                                                            |

| GND          | 13, 28 | G   | グランド                                                                                                                                                                                                                                                               |

| ピン            |    | I/O | 説明                                                                                                                                                                                                                                                                                                  |

|---------------|----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称            | 番号 |     |                                                                                                                                                                                                                                                                                                     |

| RX1n          | 14 | I/O | Type-C ポート - USB SuperSpeed 差動信号 RX1 負                                                                                                                                                                                                                                                              |

| RX1p          | 15 | I/O | Type-C ポート - USB SuperSpeed 差動信号 RX1 正                                                                                                                                                                                                                                                              |

| TX1n          | 16 | I/O | Type-C ポート - USB SuperSpeed 差動信号 TX1 負                                                                                                                                                                                                                                                              |

| TX1p          | 17 | I/O | Type-C ポート - USB SuperSpeed 差動信号 TX1 正                                                                                                                                                                                                                                                              |

| RX2n          | 18 | I/O | Type-C ポート - USB SuperSpeed 差動信号 RX2 負                                                                                                                                                                                                                                                              |

| RX2p          | 19 | I/O | Type-C ポート - USB SuperSpeed 差動信号 RX2 正                                                                                                                                                                                                                                                              |

| TX2n          | 20 | I/O | Type-C ポート - USB SuperSpeed 差動信号 TX2 負                                                                                                                                                                                                                                                              |

| TX2p          | 21 | I/O | Type-C ポート - USB SuperSpeed 差動信号 TX2 正                                                                                                                                                                                                                                                              |

| ADDR          | 22 | I   | I <sup>2</sup> C アドレスまたは GPIO モードを示すトライレベル入力ピン:<br>H (VDD5 に接続) - I <sup>2</sup> C がイネーブル、I <sup>2</sup> C 7 ビットアドレスは 0x67。<br>NC - GPIO モード (I <sup>2</sup> C がディセーブル)<br>L (GND に接続) - I <sup>2</sup> C がイネーブル、I <sup>2</sup> C 7 ビットアドレスは 0x47。<br>High 構成が必要な場合は、ADDR ピンを VDD5 にプルアップする必要があります。 |

| INT_N/OUT3    | 23 | O   | INT_N/OUT3 はデュアル機能ピンです。<br>INT_N として使用する場合、このピンは I <sup>2</sup> C 制御モードのオープンドレイン出力であり、I <sup>2</sup> C レジスタの変化を示すためのアクティブ Low 割り込み信号です。<br>OUT3 として使用する場合、このピンは GPIO モードのオーディオ アクセサリ検出です：<br>H - 検出なし、<br>L - オーディオ アクセサリ接続検出 HD3SS3220L の場合、OUT3 は接続なし (NC) です。                                    |

| VCONN_FAULT_N | 24 | O   | オープンドレイン出力。VCONN 過電流が検出されると Low にアサートされます。                                                                                                                                                                                                                                                          |

| SDA/OUT1      | 25 | I/O | SDA/OUT1 はデュアル機能ピンです。<br>I <sup>2</sup> C がイネーブルの場合 (ADDR ピンが High または Low)、このピンは I <sup>2</sup> C 通信のデータ信号です。<br>GPIO モード (ADDR ピンが NC) の場合、このピンはデバイスが UFP モードのときに Type-C 電流モード検出を通信するオープンドレイン出力です：<br>H - デフォルト (900mA) 電流モード検出、<br>L - 中 (1.5A) または高 (3A) 電流モード検出。                               |

| SCL/OUT2      | 26 | I/O | SCL/OUT2 はデュアル機能ピンです。<br>I <sup>2</sup> C がイネーブルの場合 (ADDR ピンが High または Low)、このピンは I <sup>2</sup> C 通信のクロック信号です。<br>GPIO モード (ADDR ピンが NC) の場合、このピンはデバイスが UFP モードのときに Type-C 電流モード検出を通信するオープンドレイン出力です：<br>H - デフォルトまたは中電流モード検出、<br>L - 大電流モード検出。                                                     |

| ID            | 27 | O   | オープンドレイン出力。ポートがソース (DFP) であるか、またはデュアルアロール (DRP) でソース (DFP) として動作している場合に、CC ピンがデバイスの接続を検出すると Low にアサートされます。                                                                                                                                                                                          |

| ENn_CC        | 29 | I   | CC コントローラのイネーブル信号。イネーブルはアクティブ Low。                                                                                                                                                                                                                                                                  |

| VDD5          | 30 | P   | 5V 電源                                                                                                                                                                                                                                                                                               |

| サーマル パッド      | -  | -   | サーマル パッドは GND に接続する必要があります。サーマル パッドの接続方法の詳細については、(PowerPAD™ Thermally Enhanced Package アプリケーション ノート) を参照してください。                                                                                                                                                                                     |

## 5 仕様

### 5.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|                   |                                                        | 最小値  | 最大値        | 単位 |

|-------------------|--------------------------------------------------------|------|------------|----|

| 5V の電源電圧          | VDD5                                                   | -0.3 | 6          | V  |

| 3.3V の電源電圧        | VCC33                                                  | -0.3 | 4          | V  |

| コントロールピン          | ADDR, PORT, ID, INT_N/OUT3, ENn_CC, SDA/OUT1, SCL/OUT2 | -0.3 | VDD5 +0.3  | V  |

|                   | CC1, CC2                                               | -0.3 | 6          | V  |

|                   | ENn_MUX, DIR                                           | -0.3 | VCC33 +0.3 | V  |

|                   | VBUS_DET                                               | -0.3 | 4          | V  |

| SuperSpeed 差動信号ピン | [RX/TX] [p/n], [RX/TX][2/1][p/n]                       | -0.3 | 2.5        | V  |

| 保管温度、 $T_{stg}$   |                                                        | -65  | 150        | °C |

(1) 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これらはあくまでもストレス定格であり、「推奨動作条件」に示されている条件を超える当該の条件またはその他のいかなる条件下での、デバイスの正常な動作を保証するものではありません。絶対最大定格の状態が長時間続くと、デバイスの信頼性に影響を与える可能性があります。

### 5.2 ESD 定格

|             |                                                         | 値          | 単位 |

|-------------|---------------------------------------------------------|------------|----|

| $V_{(ESD)}$ | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>    | $\pm 2000$ | V  |

|             | デバイス帶電モデル (CDM)、JEDEC 仕様 JESD22-C101 に準拠 <sup>(2)</sup> | $\pm 1500$ |    |

(1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。必要な予防措置をとれば、HBM の ESD 耐圧が 500V 未満でも製造可能です。

(2) JEDEC ドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

### 5.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                                                                                      | 最小値                | 公称値 | 最大値             | 単位 |

|--------------------------------------------------------------------------------------|--------------------|-----|-----------------|----|

| $V_{DD5}$ 5V 電源電圧範囲                                                                  | 4.5 <sup>(1)</sup> | 5.5 | V               |    |

| $V_{CC33}$ 3.3V 電源電圧範囲                                                               | 3                  | 3.6 | V               |    |

| $V_{DD}$ I2C (SDA, SCL) ピンの電源電圧範囲                                                    | 1.65               | 3.6 | V               |    |

| $V_{DD5(ramp)}$ VDD5 電源ランプ時間                                                         |                    | 25  | ms              |    |

| $V_{(diff)}$ 高速信号ピンの差動電圧                                                             | 0                  | 1.8 | V <sub>PP</sub> |    |

| $V_{(cm)}$ 高速信号ピンの同相電圧                                                               | 0                  | 2   | V               |    |

| $T_A$ 自由気流での動作周囲温度 (HD3SS3220)                                                       | 0                  | 70  | °C              |    |

| $T_A$ 自由気流での動作周囲温度 (HD3SS3220I)                                                      | -40                | 85  | °C              |    |

| $V_{(BUS)}$ 900K の抵抗を介したシステム $V_{(BUS)}$ 入力電圧                                        | 4                  | 5   | 28              | V  |

| $C_{(BULK)}$ VCONN のバルク容量。VCONN がオンのときのみ。VCONN がオフのときは接続解除。VDD5 に配置。                 | 10                 | 200 | μF              |    |

| $R_{(p\_ODext)}$ オープンドレイン IO (OUT1、OUT2、INT/OUT3、ID、VCONN_FAULT_N、DIR ピン) の外部プルアップ抵抗 |                    | 200 | KΩ              |    |

| $R_{(p\_TExt)}$ トライレベル入力の外部プルアップ抵抗 (PORT ピンと ADDR ピン)                                |                    | 4.7 | KΩ              |    |

| $R_{(p\_15A)}$ 1.5A をアドバタイズするための外部プルアップ抵抗 (CURRENT_MODE ピン)                          |                    | 500 | KΩ              |    |

| $R_{(p\_3A)}$ 3A をアドバタイズするための外部プルアップ抵抗 (CURRENT_MODE ピン)                             |                    | 10  | KΩ              |    |

自由気流での動作温度範囲内 (特に記述のない限り)

|                     |                                              | 最小値 | 公称値 | 最大値 | 単位        |

|---------------------|----------------------------------------------|-----|-----|-----|-----------|

| $R_{(p\_i2c\_ext)}$ | $I^2C$ バスの外部プルアップ抵抗<br>(4.7K 以上を使用可能。公称値を記載) |     | 2.2 |     | $k\Omega$ |

| $R_{(VBUS)}$        | VBUS_DET ピンの外付け抵抗                            | 880 | 900 | 910 | $k\Omega$ |

(1) コネクタにおいて  $V_{CONN} \geq 4.75V$  で  $V_{CONN}$  の電流 200mA、 $V_{DD5} \geq 5V$  を推奨

## 5.4 热に関する情報

|                      | 熱評価基準 <sup>(1)</sup> | HD3SS3220  | 単位   |

|----------------------|----------------------|------------|------|

|                      |                      | RNH (VQFN) |      |

|                      |                      | 30 ピン      |      |

| $R_{\theta JA}$      | 接合部から周囲への熱抵抗         | 60.9       | °C/W |

| $R_{\theta JC(top)}$ | 接合部からケース (上面) への熱抵抗  | 50.4       | °C/W |

| $R_{\theta JB}$      | 接合部から基板への熱抵抗         | 22.8       | °C/W |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ     | 1.7        | °C/W |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ     | 22.6       | °C/W |

| $R_{\theta JC(bot)}$ | 接合部からケース (底面) への熱抵抗  | 12.1       | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体およびIC パッケージの熱評価基準』アプリケーション ノートを参照してください。

## 5.5 電気的特性

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ                 | テスト条件                                                              | 最小値                     | 標準値  | 最大値  | 単位        |

|-----------------------|--------------------------------------------------------------------|-------------------------|------|------|-----------|

| <b>消費電力</b>           |                                                                    |                         |      |      |           |

| $I_{(ACTIVE)}$        | アクティブ モードでの消費電流 - CC コントローラと SS マルチブレクサの両方がオン                      | ENn_CC/Mux = L          |      | 0.7  | 0.9 mA    |

| $I_{CC}$              | アクティブ モードでの消費電流 - CC コントローラはオン、SS マルチブレクサはオフ                       | ENn_CC = L, ENn_Mux = H |      | 0.2  | mA        |

| $I_{(SHUTDOWN)}$      | シャットダウン モードでの消費電流                                                  | ENn_CC/Mux = H          |      | 5    | μA        |

| <b>CC ピン</b>          |                                                                    |                         |      |      |           |

| $R_{(CC\_DB)}$        | デッド バッテリ モードでのプルダウン抵抗。                                             |                         | 4.1  | 5.1  | $k\Omega$ |

| $R_{(CC\_D)}$         | UFP または DRP モードでのプルダウン抵抗。                                          |                         | 4.6  | 5.1  | $k\Omega$ |

| $V_{(UFP\_CC\_USB)}$  | UFP として構成され、DFP がデフォルトの電流ソース能力をアドバタイズする場合に DFP 接続を検出するための電圧レベル。    |                         | 0.25 | 0.61 | V         |

| $V_{(UFP\_CC\_MED)}$  | UFP として構成され、DFP が中 (1.5A) 電流ソース能力をアドバタイズする場合に DFP 接続を検出するための電圧レベル。 |                         | 0.7  | 1.16 | V         |

| $V_{(UFP\_CC\_HIGH)}$ | UFP として構成され、DFP が高 (3A) 電流ソース能力をアドバタイズする場合に DFP 接続を検出するための電圧レベル。   |                         | 1.31 | 2.04 | V         |

| $V_{(DFP\_CC\_USB)}$  | DFP として構成され、デフォルトの電流ソース能力をアドバタイズする場合に UFP 接続を検出するための電圧レベル。         |                         | 1.51 | 1.6  | 1.64 V    |

| $V_{(DFP\_CC\_MED)}$  | DFP として構成され、1.5A の電流ソース能力をアドバタイズする場合に UFP 接続を検出するための電圧レベル。         |                         | 1.51 | 1.6  | 1.64 V    |

| $V_{(DFP\_CC\_HIGH)}$ | DFP として構成され、3A の電流ソース能力をアドバタイズする場合に UFP 接続を検出するための電圧レベル。           |                         | 2.46 | 2.6  | 2.74 V    |

| $V_{(AC\_CC\_USB)}$   | DFP として構成され、デフォルトの電流ソース能力をアドバタイズする場合にアクティブ ケーブル接続を検出するための電圧レベル。    |                         | 0.15 | 0.2  | 0.25 V    |

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ                                                                                | テスト条件                                                           | 最小値                | 標準値         | 最大値         | 単位         |            |

|--------------------------------------------------------------------------------------|-----------------------------------------------------------------|--------------------|-------------|-------------|------------|------------|

| $V_{(AC\_CC\_MED)}$                                                                  | DFP として構成され、1.5A の電流ソース能力をアドバタイズする場合にアクティブ ケーブル接続を検出するための電圧レベル。 | 0.35               | 0.4         | 0.45        | V          |            |

| $V_{(DFP\_CC\_HIGH)}$                                                                | DFP として構成され、3A の電流ソース能力をアドバタイズする場合にアクティブ ケーブル接続を検出するための電圧レベル。   | 0.75               | 0.8         | 0.84        | V          |            |

| $I_{CC(DEFAULT\_P)}$                                                                 | DFP または DRP モードで動作している場合のデフォルト モードのプルアップ電流ソース。                  | 64                 | 80          | 96          | $\mu$ A    |            |

| $I_{CC(MED\_P)}$                                                                     | DFP または DRP モードで動作している場合の中 (1.5A) モードのプルアップ電流ソース。               | 166                | 180         | 194         | $\mu$ A    |            |

| $I_{CC(HIGH\_P)}$                                                                    | DFP または DRP モードで動作している場合の高 (3A) モードのプルアップ電流ソース。                 | 34                 | 330         | 356         | $\mu$ A    |            |

| <b>トライレベル入力ピン:PORT、ADDR、ENn_CC、CURRENT_MODE</b>                                      |                                                                 |                    |             |             |            |            |

| $V_{IL}$                                                                             | Low レベル入力電圧                                                     |                    |             | 0.4         | V          |            |

| $V_M$                                                                                | 中レベル (フローティング) 電圧 (PORT、ADDR、CURRENT_MODE ピン)                   |                    | 0.28 x VDD5 | 0.56 x VDD5 | V          |            |

| $V_{IH}$                                                                             | High レベル入力電圧                                                    |                    | VDD5~0.3    | VDD5        | V          |            |

| $I_{IH}$                                                                             | High レベル入力電流                                                    |                    | 20          | 20          | $\mu$ A    |            |

| $I_{IL}$                                                                             | Low レベル入力電流                                                     |                    | -10         | 10          | $\mu$ A    |            |

| $I_{ID(LKG)}$                                                                        | ID ピンの電流リーカ                                                     | VDD5 = 0V, ID = 5V |             | 10          | $\mu$ A    |            |

| $R_{(pu)}$                                                                           | 内部プルアップ抵抗 (PORT および ADDR ピン)                                    |                    | 588         |             | k $\Omega$ |            |

| $R_{(pd)}$                                                                           | 内部プルダウン抵抗 (PORT および ADDR ピン)                                    |                    | 1.1         |             | M $\Omega$ |            |

| $R_{(pd\_CURRENT)}$                                                                  | 内部プルダウン抵抗 (CURRENT_MODE ピン)                                     |                    | 275         |             | k $\Omega$ |            |

| $R_{(ENn\_CC)}$                                                                      | 内部プルダウン抵抗 (ENn_CC ピン)                                           |                    | 1.1         |             | M $\Omega$ |            |

| <b>入力ピン:ENn_MUX</b>                                                                  |                                                                 |                    |             |             |            |            |

| $V_{IL}$                                                                             | Low レベル入力電圧                                                     |                    | 0.3 x VCC33 |             | V          |            |

| $V_{IH}$                                                                             | High レベル入力電圧                                                    |                    | 0.7 x VCC33 |             | V          |            |

| $I_{IH}$                                                                             | High レベル入力電流                                                    |                    | -1          | 1           | $\mu$ A    |            |

| $I_{IL}$                                                                             | Low レベル入力電流                                                     |                    | -1          | 1           | $\mu$ A    |            |

| <b>オープンドレイン出力ピン:OUT1、OUT2、INT_N/OUT3、ID、VCONN_FAULT_N、DIR</b>                        |                                                                 |                    |             |             |            |            |

| $V_{OL}$                                                                             | Low レベル信号出力電圧                                                   | $I_{OL} = -1.6mA$  |             | 0.4         | V          |            |

| <b>I2C–SDA/OUT1、SCL/OUT2 は 1.8/3.3V (<math>\pm 10\%</math>) から動作可能<sup>(1)</sup></b> |                                                                 |                    |             |             |            |            |

| $V_{IH}$                                                                             | High レベル入力電圧                                                    |                    | 1.05        |             | V          |            |

| $V_{IL}$                                                                             | Low レベル入力電圧                                                     |                    |             | 0.4         | V          |            |

| $V_{OL}$                                                                             | Low レベル出力電圧 (オープンドレイン)                                          | $I_{OL} = -1.6mA$  |             | 0.4         | V          |            |

| <b>VBUS_DET IO ピン (システム VBUS 信号に接続)</b>                                              |                                                                 |                    |             |             |            |            |

| $V_{(BUS\_THR)}$                                                                     | VBUS スレッショルド範囲                                                  |                    | 2.95        | 3.3         | 3.8        | V          |

| $R_{VBUS}$                                                                           | VBUS と VBUS_DET ピンの間の外部抵抗                                       |                    | 855         | 887         | 920        | k $\Omega$ |

| $R_{(VBUS\_DET\_INT)}$                                                               | VBUS_DET ピンの内部プルダウン抵抗                                           |                    | 95          |             | k $\Omega$ |            |

| <b>VCONN</b>                                                                         |                                                                 |                    |             |             |            |            |

| $R_{ON}$                                                                             | VCONN パワー FET のオン抵抗                                             |                    |             | 1.25        | $\Omega$   |            |

| $V_{(TOL)}$                                                                          | VCONN パワー FET の電圧許容誤差                                           |                    |             | 5.5         | V          |            |

| $V_{(pass)}$                                                                         | VCONN パワー FET を通過する電圧                                           |                    |             | 5.5         | V          |            |

| $I_{(VCONN)}$                                                                        | VCONN の電流制限値。この値を超えると VCONN は切斷されます。                            |                    | 225         | 300         | 375        | $mA$       |

| <b>マルチブレクサ高速性能パラメータ</b>                                                              |                                                                 |                    |             |             |            |            |

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ                  | テスト条件               | 最小値   | 標準値 | 最大値 | 単位       |

|------------------------|---------------------|-------|-----|-----|----------|

| $I_L$<br>差動挿入損失        | $f = 0.3\text{Mhz}$ | -0.43 |     |     | dB       |

|                        | $f = 2.5\text{Ghz}$ | -1.07 |     |     |          |

|                        | $f = 5\text{Ghz}$   | -1.42 |     |     |          |

| $BW$<br>帯域幅            |                     | 8     |     |     | GHz      |

| $R_L$<br>差動リターンロス      | $f = 0.3\text{Mhz}$ | -27   |     |     | dB       |

|                        | $f = 2.5\text{Ghz}$ | -9    |     |     |          |

|                        | $f = 5\text{Ghz}$   | -9    |     |     |          |

| $O_{IRR}$<br>差動オフ絶縁    | $f = 0.3\text{Mhz}$ | -79   |     |     | dB       |

|                        | $f = 2.5\text{Ghz}$ | -23   |     |     |          |

|                        | $f = 5\text{Ghz}$   | -20   |     |     |          |

| $X_{TALK}$<br>差動クロストーク | $f = 0.3\text{Mhz}$ | -89   |     |     | dB       |

|                        | $f = 2.5\text{Ghz}$ | -34   |     |     |          |

|                        | $f = 5\text{Ghz}$   | -30   |     |     |          |

| $R_{ON}$<br>オン抵抗       |                     |       | 8   |     | $\Omega$ |

(1) I<sup>2</sup>C に 3.3V を使用する場合、VDD5 が常に 3V を上回ることを確認する必要があります。

## 5.6 タイミング要件

|                                  |                                                                    | 最小値 | 公称値 | 最大値 | 単位            |

|----------------------------------|--------------------------------------------------------------------|-----|-----|-----|---------------|

| <b>I<sup>2</sup>C (SDA, SCL)</b> |                                                                    |     |     |     |               |

| $t_{SU:DAT}$                     | データセットアップ時間                                                        | 100 |     |     | ns            |

| $t_{HD:DAT}$                     | データセットアップ時間                                                        | 10  |     |     | ns            |

| $t_{SU:STA}$                     | セットアップ時間、SCL から START 条件                                           | 0.6 |     |     | $\mu\text{s}$ |

| $t_{HD,STA}$                     | ホールド時間、(繰り返し) START 条件から SCL                                       | 0.6 |     |     | $\mu\text{s}$ |

| $t_{SU:STO}$                     | STOP 条件のセットアップ時間                                                   | 0.6 |     |     | $\mu\text{s}$ |

| $t_{VD:DAT}$                     | データ有効時間                                                            |     | 0.9 |     | $\mu\text{s}$ |

| $t_{VD:ACK}$                     | データ有効アクリッジ時間                                                       |     | 0.9 |     | $\mu\text{s}$ |

| $t_{BUF}$                        | STOP 条件と START 条件の間のバスフリー時間                                        | 1.3 |     |     | $\mu\text{s}$ |

| $f_{SCL}$                        | SCL クロック周波数、ローカル I <sup>2</sup> C 制御用の I <sup>2</sup> C モード        |     | 400 |     | ns            |

| $t_r$                            | SDA 信号と SCL 信号の両方の立ち上がり時間                                          |     | 300 |     | ns            |

| $t_f$                            | SDA 信号と SCL 信号の両方の立ち下がり時間                                          |     | 300 |     | ns            |

| $C_{BUS\_100KHZ}$                | 100KHz 以下で動作しているときの各バスラインの合計容量性負荷                                  |     | 400 |     | pF            |

| $C_{BUS\_400KHZ}$                | 400KHz で動作しているときの各バスラインの合計容量性負荷。                                   |     | 100 |     | pF            |

| <b>SS マルチプレクサ</b>                |                                                                    |     |     |     |               |

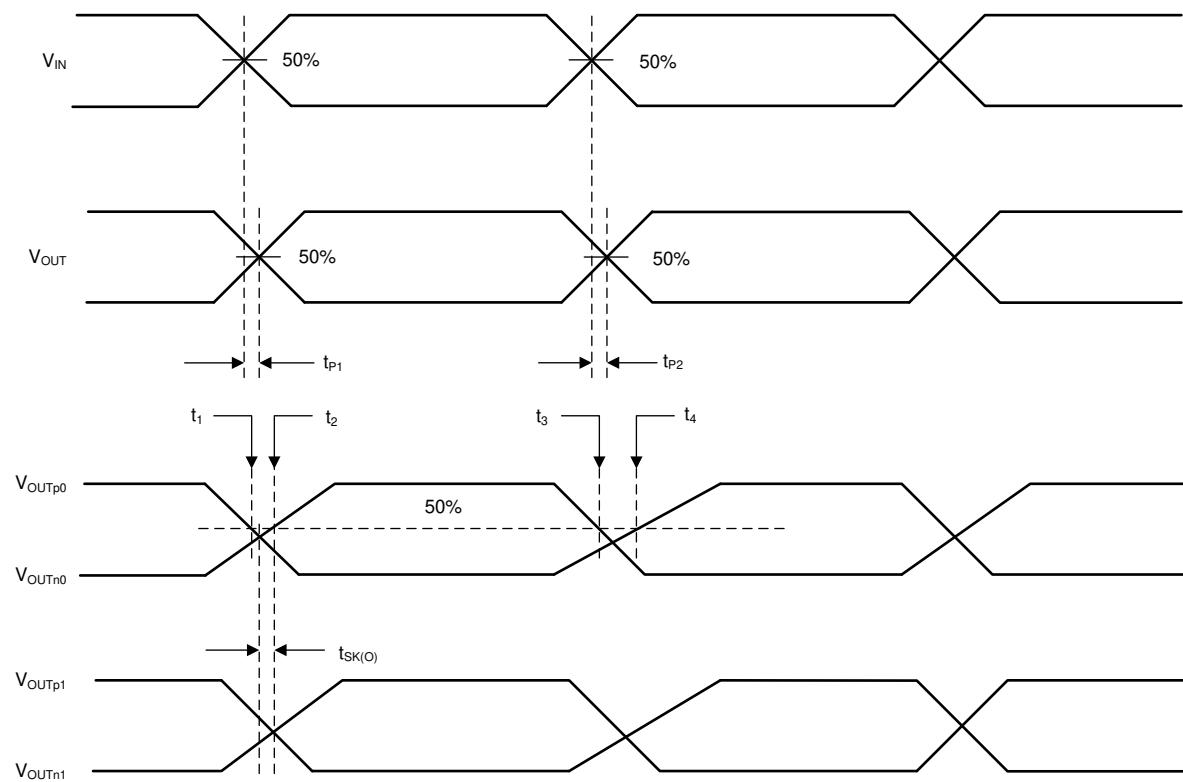

| $t_{PD}$                         | スイッチ伝搬遅延 (図 5-3 を参照)                                               |     | 80  |     | ps            |

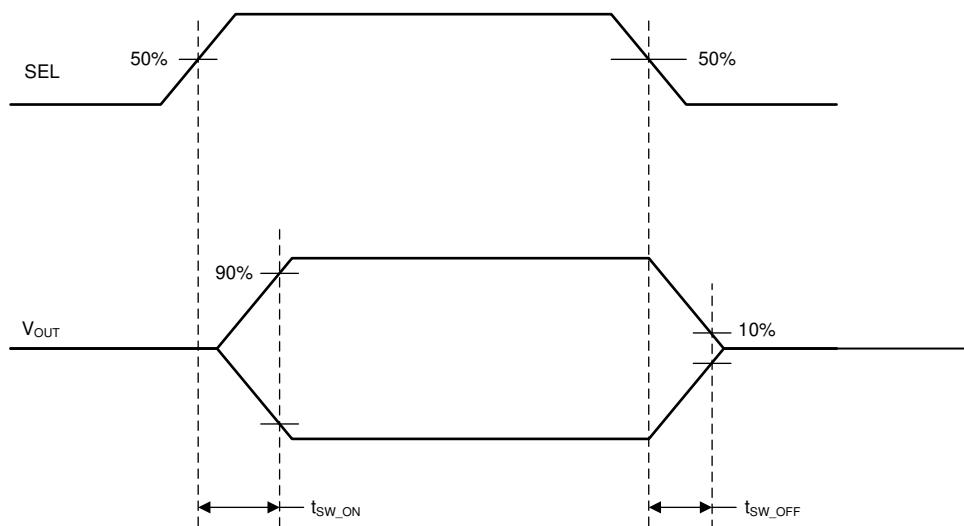

| $t_{SW\_ON}$                     | スイッチング時間 DIR からスイッチ オン (図 5-2 を参照)                                 |     | 0.5 |     | $\mu\text{s}$ |

| $t_{SW\_OFF}$                    | スイッチング時間 DIR からスイッチ オフ (図 5-2 を参照)                                 |     | 0.5 |     | $\mu\text{s}$ |

| $t_{SK\_INTRA}$                  | ペア内出力スキュー (図 5-3 を参照)                                              |     | 5   |     | ps            |

| $t_{SK\_INTER}$                  | ペア間出力スキュー (図 5-3 を参照)                                              |     | 20  |     | ps            |

| <b>パワーオンタイミング</b>                |                                                                    |     |     |     |               |

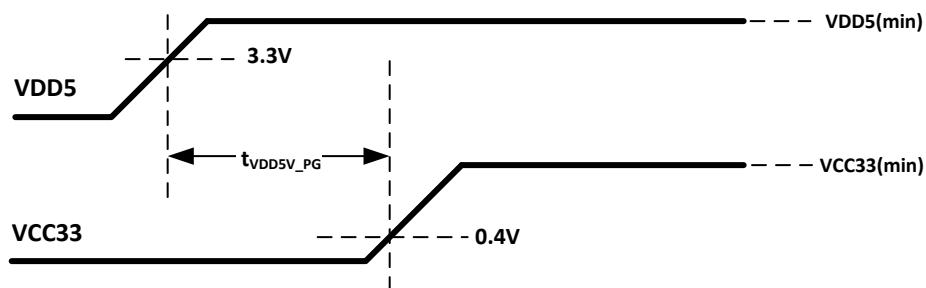

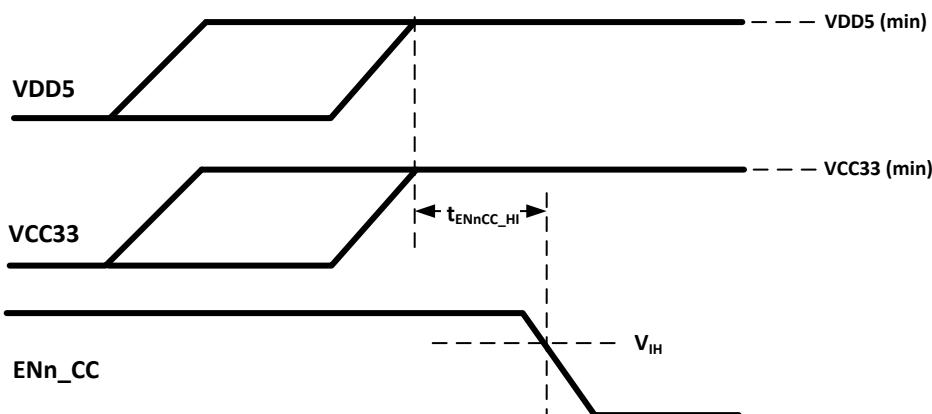

| $t_{ENnCC\_HI}$                  | VDD5 と VCC33 の両方の電源が安定してから ENn_CC が High になるまでの時間。図 6-3 を参照してください。 | 2   |     |     | ms            |

| $t_{VDD5V\_PG}$                  | VCC33 前に VDD5 が安定している必要のある時間。図 6-2 を参照してください。                      | 2   |     |     | ms            |

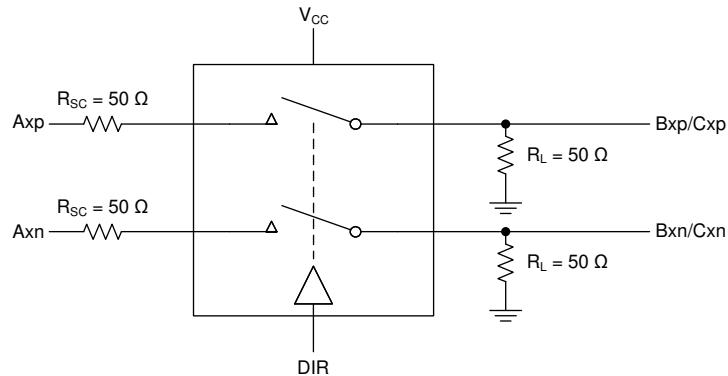

図 5-1. テスト設定

図 5-2. スイッチのオン / オフのタイミング図

図 5-3. タイミング図とテスト構成

## 6 詳細説明

### 6.1 概要

USB Type-C は、コンパクトなフォーム ファクタのコネクタと、反転可能でリバーシブルなケーブルを使用します。コネクタの性質上、コネクタの向きを判定する方法が必要です。USB ポートが接続されたことを判定し、USB ポートの動作役割 (DFP, UFP, DRP) を判定して、Type-C 電流能力を通知するため、追加の方式が必要となります。これらの方程式は、USB Type-C 仕様に従って、CC ピンにより実装されます。HD3SS3220 は、USB ポートの接続 / 取り外し、役割検出、ケーブルの向き、Type-C 電流モードを判定するための構成チャネル (CC) ロジックを備えています。HD3SS3220 には、VCONN ソース、オーディオおよびデバッグ アクセサリ モード、Try.SRC および Try.SNK DRP 構成などの機能も含まれるため、このデバイスは USB 2.0 または USB 3.1 を使用するソース、シンク、デュアル ロール アプリケーションに理想的です。

HD3SS3220 には USB 3.0/3.1 SS/SS+MUX と、ケーブルの反転を処理する 2 チャネル 2:1 スイッチングが内蔵されています。CC コントローラは、ケーブルの向きを判定し、マルチプレクサの選択を制御します。この方向信号は GPIO 信号 DIR としても提供されており、フレキシビリティと機能を向上するためにシステムで使用できます。

HD3SS3220L は、HD3SS3220 と比較して、オーディオおよびデバッグ アクセサリのサポートに違いがあります。HD3SS3220 にはオーディオ アクセサリおよびデバッグ アクセサリが搭載されており、UFP, DF, DRP 構成でサポートされています。一方、HD3SS3220L にはデバッグ アクセサリが UFP 構成のみでサポートされています。

| 部品番号       | オーディオ アクセサリのサポート | デバッグ アクセサリ (UFP) | デバッグ アクセサリ (DFP) | デバッグ アクセサリ (DRP) |

|------------|------------------|------------------|------------------|------------------|

| HD3SS3220  | ✓                | ✓                | ✓                | ✓                |

| HD3SS3220L | ✗                | ✓                | ✗                | ✗                |

#### 6.1.1 ケーブル、アダプタ、直接接続デバイス

Type-C 仕様では、ポートの接続に使用する複数のケーブル、プラグ、およびレセプタクルが定義されています。HD3SS3220 は、すべてのケーブル、レセプタクル、およびプラグをサポートしています。HD3SS3220 デバイスは、E マーキングや代替モードなど、CC ラインを介した USB パワー・デリバリー (PD) 通信を必要とする USB 機能はサポートしていません。

##### 6.1.1.1 USB Type-C のレセプタクルとプラグ

HD3SS3220 デバイスでは、以下の Type-C レセプタクルおよびプラグがサポートされています。

- USB 2.0 および USB3.1、およびフル機能のプラットフォームとデバイス用の USB Type-C レセプタクル

- USB フル機能 Type-C プラグ

- USB 2.0 Type-C プラグ

##### 6.1.1.2 USB Type-C ケーブル

HD3SS3220 デバイスでは、以下の Type-C ケーブルがサポートされています。

- USB 3.1 フル機能プラグ付き USB フル機能 Type-C ケーブル

- USB 2.0 プラグ付き USB 2.0 Type-C ケーブル

- USB フル機能プラグまたは USB 2.0 プラグ付きキャプティブ・ケーブル

##### 6.1.1.3 レガシー・ケーブルとアダプタ

HD3SS3220 は、Type-C 仕様で定義されているレガシー・ケーブル・アダプタをサポートしています。ケーブル・アダプタは、HD3SS3220 デバイスのモード構成に対応している必要があります。

Copyright © 2016, Texas Instruments Incorporated

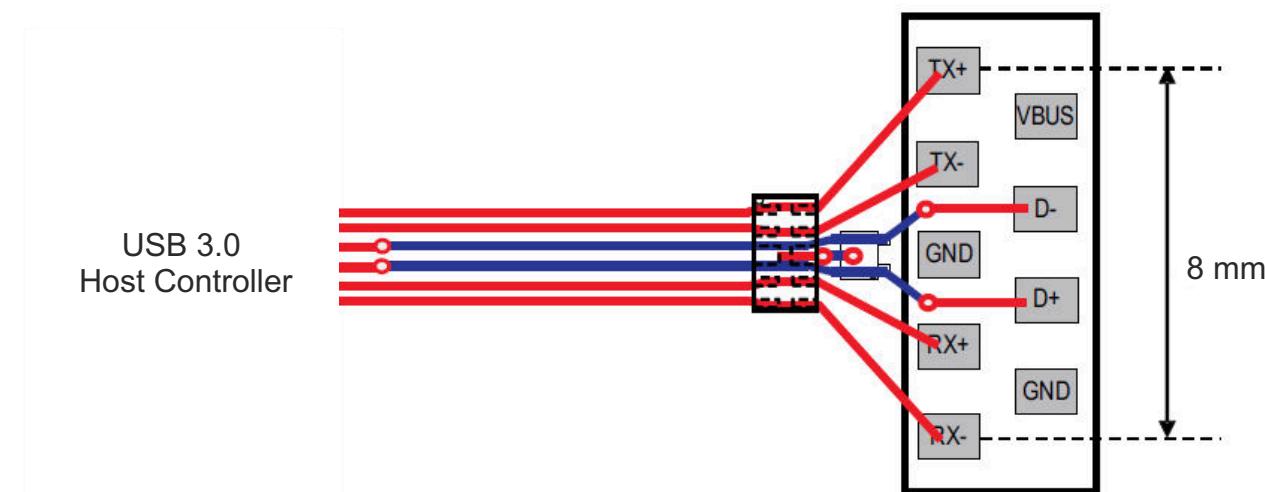

図 6-1. レガシー・アダプタ実装回路

#### 6.1.1.4 直接接続デバイス

HD3SS3220 は、クレードル・ドックなどの直接接続デバイスの接続と取り外しをサポートしています。

#### 6.1.1.5 オーディオ・アダプタ

HD3SS3220 は、オーディオ・アクセサリ・モード用に以下のようなオーディオ・アダプタもサポートしています。

- パッシブ・オーディオ・アダプタ

- オーディオ・アダプタを介した充電

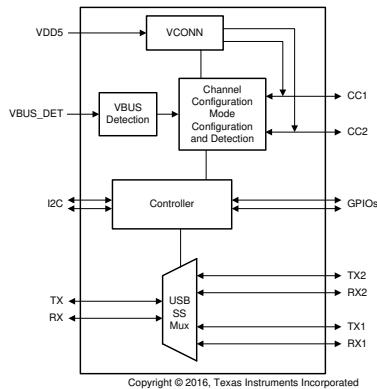

## 6.2 機能ブロック図

## 6.3 機能説明

HD3SS3220 は、トライレベル PORT ピンを使用して、DFP、UFP、DRP として構成できます。PORT ピンは、DFP モードの場合はプルアップ抵抗を使用して VDD5 に固定し、UFP モードの場合は GND に固定し、PCB 上の DRP モードの場合はフローティングのままにします。このフレキシビリティにより、HD3SS3220 はさまざまなアプリケーションで使用できます。HD3SS3220 は、リセット後に PORT ピンをサンプリングし、HD3SS3220 が再度リセットされるまでそのモードを維持します。これはスタティックである必要があります。表 6-1 に、各モードでサポートされている機能を示します。

**表 6-1. サポートされている機能**

| PORT ピン                      | High          | Low    | NC            |

|------------------------------|---------------|--------|---------------|

| サポートされている機能                  | DFP のみ        | UFP のみ | DRP           |

| ポートの取り付け / 取り外し              | ✓             | ✓      | ✓             |

| ケーブルの向き                      | ✓             | ✓      | ✓             |

| 電流アドバタイズメント                  | ✓             |        | ✓ (DFP)       |

| 電流検出                         |               | ✓      | ✓ (UFP)       |

| オーディオ アクセサリ (HD3SS3220 のみ)   | ✓             | ✓      | ✓             |

| デバッグ アクセサリ モード               | ✓ (HD3SS3220) | ✓      | ✓ (HD3SS3220) |

| アクティブ ケーブル検出                 | ✓             |        | ✓ (DFP)       |

| Try.SRC                      |               |        | ✓             |

| Try.SNK                      |               |        | ✓             |

| I2C/GPIO                     | ✓             | ✓      | ✓             |

| レガシー ケーブル                    | ✓             | ✓      | ✓             |

| VBUS 検出                      |               | ✓      | ✓ (UFP)       |

| VCONN                        | ✓             |        | ✓ (DFP)       |

| USB 3.1 G1 および G2 SS マルチプレクサ | ✓             | ✓      | ✓             |

| SS チャネルの適応型同相トラッキング          | ✓             | ✓      | ✓             |

### 6.3.1 DFP / ソース - ダウンストリーム側ポート

HD3SS3220 を DFP として構成するには、VDD5 への抵抗を使用して PORT ピンを High にします。また、MODE\_SELECT レジスタのデフォルト設定を変更して PORT ピンをフローティングのままにすることで、DFP のみのデバイスとして構成することもできます。DFP モードでは、HD3SS3220 は常に両方の CC ラインに  $R_{(p)}$  を提示します。このモードでは、HD3SS3220 は最初はデフォルトの USB Type-C 電流をアドバタイズします。システムでアドバタイズされる電流の量を増加する必要がある場合は、CURRENT\_MODE ピンまたは I<sup>2</sup>C を使用して Type-C 電流を調整できます。HD3SS3220 は、アドバタイズされた電流に合わせて  $R_{(p)}$  抵抗を調整します。

DFP は、UFP の  $R_{(d)}$  終端を検出するために CC ピンの電圧レベルを監視します。UFP が検出されて HD3SS3220 が接続。SRC 状態になると、HD3SS3220 は ID ピンを Low にして、ポートがデバイス (UFP) に接続されていることをシステムに通知します。UFP が検出されたときに  $R_{(a)}$  も検出された場合は、HD3SS3220 は接続されていない CC ピンに VCONN を供給します。

以下に、I<sup>2</sup>C を介して DFP をイネーブルにする手順を示します。

1. DISABLE\_TERM レジスタ (アドレス 0x0A ビット 0) に 1'b1 を書き込みます。

2. MODE\_SELECT レジスタ (アドレス 0x0A ビット 5:4) に 2'b10 を書き込みます。

3. DISABLE\_TERM レジスタ (アドレス 0x0A ビット 0) に 1'b0 を書き込みます。

HD3SS3220 を DFP として構成すると、USB Type-C 1.0 DRP デバイスを除く古い USB Type-C 1.0 デバイスでも動作させることができます。HD3SS3220 を USB Type-C 1.0 DRP デバイスと動作させることはできません。これは、USB Type-C 1.1 DFP と USB Type-C 1.0 DRP には下位互換性の問題があるからです。

**注**

UFP デバイスが検出されると、VBUS が VSafe0V でない場合、HD3SS3220 は ID ピンを High に維持します。VBUS が VSafe0V になると、HD3SS3220 は ID ピンを Low にアサートします。これは、VBUS を再度イネーブルにする前に VBUS が VSafe0V である必要があるという Type-C 要件を強制するためです。

### 6.3.2 UFP / シンク - アップストリーム側ポート

HD3SS3220 を UFP として構成するには、PORT ピンを GND にプルダウンします。UFP モードでは、HD3SS3220 は常に両方の CC ピンに Rd (プルダウン抵抗) を提示します。

UFP モードでは、HD3SS3220 は CC ピンの電圧レベルを監視して DFP が接続されているかどうかを検出し、接続されている DFP の Type-C 電流アドバタイズメントも判定します。HD3SS3220 は CC ピンをデバウンスし、VBUS が検出されるまで待機してから、接続を成功させます。UFP としては、HD3SS3220 は GPIO モードのときは OUT1 および OUT2 ピンを、Attached.SNK 状態のときは I2C CURRENT\_MODE\_DETECT レジスタを使用して、DFP のアドバタイズされた電流レベルをシステムに通信します。

以下に、I<sup>2</sup>C を介して DFP をイネーブルにする手順を示します。

1. DISABLE\_TERM レジスタ (アドレス 0x0A ビット 0) に 1'b1 を書き込みます。

2. MODE\_SELECT レジスタ (アドレス 0x0A ビット 5:4) に 2'b10 を書き込みます。

3. DISABLE\_TERM レジスタ (アドレス 0x0A ビット 0) に 1'b0 を書き込みます。

### 6.3.3 DRP – デュアル・ロール・ポート

HD3SS3220 は、PCB 上で PORT ピンをフローティングのままにすることにより、DRP として動作するように構成できます。DRP モードでは、USB Type-C 仕様に従って、HD3SS3220 は DFP として提示するか (両方の CC ピンに Rp)、UFP として提示するか (両方の CC ピンに Rd) を交互に切り替えます。

DFP として提示する場合、HD3SS3220 は UFP の R<sub>(d)</sub> 終端を検出するために CC ピンの電圧レベルを監視します。UFP が検出されて HD3SS3220 が接続。SRC 状態になると、HD3SS3220 は ID ピンを Low にして、ポートがシンク (UFP) に接続されていることをシステムに通知します。UFP が検出されたときに Ra も検出された場合は、HD3SS3220 は接続されていない CC ピンに VCONN を供給します。DFP モードでは、HD3SS3220 は最初はデフォルトの USB Type-C 電流をアドバタイズします。システムでアドバタイズされる電流の量を増加する必要がある場合は、I<sup>2</sup>C を使用して Type-C 電流を調整できます。HD3SS3220 は、アドバタイズされた Type-C 電流に合わせて R<sub>(p)</sub> 抵抗を調整します。

UFP として構成されている場合、HD3SS3220 は、接続されている DFP からの Type-C 電流アドバタイズメントに対応する電圧レベルを検出するため、CC ピンを監視します。HD3SS3220 は CC ピンをデバウンスし、VBUS が検出されるまで待機してから、接続を成功させます。UFP として構成されている場合、HD3SS3220 は GPIO モードのときは OUT1 および OUT2 ピンを使用し、Attached.SNK 状態のときは I2C CURRENT\_MODE\_DETECT レジスタを使用して、DFP のアドバタイズされた電流レベルをシステムに通信します。

HD3SS3220 は、Try.SRC および Try.SNK という 2 つのオプションの Type-C DRP 機能をサポートしています。デュアル・ロール機能をサポートする製品は、別のデュアル・ロール対応製品に接続したときに、ソース (DFP) またはシンク (UFP) にするという要件がある場合があります。たとえば、デュアル・ロール対応ノート PC をタブレットに接続するときはソースとして使用し、携帯電話をノート PC やタブレットに接続するときはシンクとして使用するなどです。標準的な DRP 製品 (Try.SRC または Try.SNK をサポートしていない製品) が相互接続されている場合、役割 (UFP または DFP) はあらかじめ決定されているわけではありません。これら 2 つのオプションの DRP 機能は、デュアル・ロール対応製品を、別のデュアル・ロール対応製品に必要な役割で接続するための手段として使用できます。Try.SRC と Try.SNK は、HD3SS3220 が I<sup>2</sup>C モードに構成されている場合のみ使用できます。GPIO モードで動作している場合は、HD3SS3220 は常に標準 DRP として動作します。

HD3SS3220 デバイスの Try.SRC 機能では、Try.SRC を実装していない他の DRP 製品に接続したときに、DRP 製品を DFP として接続することができます。Try.SRC を実装する 2 つの製品が接続された場合、UFP または DFP のどちらとして動作するかは、標準 DRP と同じになります。Try.SRC をイネーブルにするには、I<sup>2</sup>C レジスタ SOURCE\_PREF を

2'b11 に変更します。レジスタを 2'b11 に変更すると、HD3SS3220 を他の DRP 対応デバイスに接続したときに常に DFP としての接続が試みられます。

#### 6.3.4 ケーブルの向きとマルチプレクサ制御

HD3SS3220 は、CC ピンの電圧を監視することで、ケーブルの向きを検出します。CC1 で適切なスレッショルド内の電圧レベルが検出されると、DIR ピンは High になります。CC2 で適切なスレッショルド内の電圧レベルが検出されると、DIR は Low になります。DIR ピンはオープン・ドレイン出力であり、プルアップ抵抗を取り付ける必要があります。HD3SS3220 では、ケーブルの向きのステータスを I<sup>2</sup>C を介して通信することもできます。このデバイスは内蔵の SS マルチプレクサも制御し、適切な SS 信号ペア (RX1/TX1 または RX2/TX2) に切り替えます。

#### 6.3.5 Type-C 電流モード

有効なケーブル検出と接続が完了すると、DFP は UFP でシンク可能な Type-C 電流のレベルをアドバタイズできます。HD3SS3220 のデフォルト電流アドバタイズメントは、CURRENT\_MODE ピンまたは I<sup>2</sup>C CURRENT\_MODE\_ADVERTISE レジスタを使用して構成できます。デフォルト以外の電流を選択すると、デバイスは指定された電流レベルに応じて R<sub>(p)</sub> 抵抗を調整します。

**表 6-2. GPIO および I<sup>2</sup>C モードでの Type-C 電流アドバタイズメント**

| Type-C 電流                                   | GPIO モード (ADDR ピン NC)   |                  | I <sup>2</sup> C モード (ADDR ピン H, L) |                                              |

|---------------------------------------------|-------------------------|------------------|-------------------------------------|----------------------------------------------|

|                                             | UFP (PORT ピン L)         | DFP (PORT ピン H)  | UFP                                 | DFP                                          |

| デフォルト - 500mA<br>(USB2.0)<br>900mA (USB3.1) | OUT1/OUT2 により検出された電流モード | CURRENT_MODE = L | I <sup>2</sup> C レジスタにより検出された電流モード  | I <sup>2</sup> C レジスタへの書き込みにより選択されたアドバタイズメント |

| 中 - 1.5A                                    |                         | CURRENT_MODE = M |                                     |                                              |

| 高 - 3A                                      |                         | CURRENT_MODE = H |                                     |                                              |

#### 6.3.6 アクセサリのサポート

HD3SS3220 は、UFP、DFP、DRP モードでオーディオ アクセサリおよびデバッグ アクセサリをデフォルトでサポートしています。オーディオ アクセサリおよびデバッグ アクセサリのサポートは、I<sup>2</sup>C レジスタを読み出すことにより提供されます。オーディオ アクセサリは、GPIO モードで INT\_N/OUT3 ピンを使用してサポートすることもできます (INT\_N/OUT3 が Low のときにオーディオ アクセサリを検出)。

##### 注

アプリケーションで UFP アクセサリのサポートが必要ない場合は、DISABLE\_UFP\_ACCESSORY レジスタを設定して UFP アクセサリのサポートをディセーブルできます。

#### 6.3.7 オーディオ アクセサリ

オーディオ アクセサリ モードは、2 種類のアダプタでサポートされています。まず、パッシブ オーディオ アダプタを使用して Type-C コネクタをオーディオ ポートに変換できます。パッシブ オーディオ アダプタを効率的に検出するには、HD3SS3220 が両方の CC ピンで抵抗 R<sub>(a)</sub> を検出する必要があります。

もう 1 つは、オーディオ アダプタを介した充電が使用できることです。パッシブとアダプタを介した充電の主な違いは、アダプタを介した充電では VBUS 経由で 500mA の電流を供給できることです。アダプタを介した充電には、レセプタクルとプラグが含まれます。プラグは DFP として動作し、接続されていることを検出すると VBUS に電力を供給します。

HD3SS3220 を GPIO モードに構成した場合、オーディオ アクセサリが接続されているかどうかは OUT3 ピンを使用して判定します。オーディオ アクセサリが検出されると、OUT3 ピンは Low になります。

HD3SS3220L はこのモードをサポートしていません。

### 6.3.8 デバッグアクセサリ

デバッグは、USB Type-C でサポートされている追加の状態です。この状態に関する特定のユーザー シナリオは仕様には定義されていませんが、エンド ユーザーはデバッグ アクセサリ モードを使用して、アプリケーション固有の量産向けのテスト状態に移行できます。HD3SS3220 が DRP または UFP モードに構成されている場合、デバッグ アクセサリを介した充電はサポートされません。HD3SS3220 が DFP のみとして構成されている場合、または DRP として構成されていて DFP として動作している場合は、デバッグ アクセサリが検出されます。このデバッグ アクセサリにより CC1 ピンと CC2 ピンの両方に  $R_{(d)}$  が提示されます。HD3SS3220 は、UFP デバッグ アクセサリを示すために、ACCESSORY\_CONNECTED レジスタを 3'b110 に設定します。HD3SS3220 が UFP のみとして構成されている場合、または DRP として構成されていて UFP として動作している場合は、デバッグ アクセサリが検出されます。このデバッグ アクセサリにより CC1 ピンと CC2 ピンの両方に  $R_{(P)}$  が提示されます。HD3SS3220 は、DFP デバッグ アクセサリを示すために、ACCESSORY\_CONNECTED レジスタを 3b'111 に設定します。

HD3SS3220L は、UFP モードでのみデバッグ アクセサリをサポートしています。

### 6.3.9 アクティブ・ケーブルでの VCONN サポート

HD3SS3220 が DFP モードに構成されている場合、または DRP に構成されていて DFP として動作している場合、アクティブ・ケーブルに VCONN が供給されます。VCONN は、未接続の CC ピンが抵抗  $R_{(a)}$  で終端されていると判定され、UFP が検出されて Attached.SRC 状態に遷移した後にのみ供給されます。VCONN は、VDD5 から低抵抗のパワー FET を経由して未接続の CC ピンに供給されます。取り外しイベントが検出され、アクティブ・ケーブルが取り外されると、VCONN は除去されます。

HD3SS3220 は電流制限機能を備えており、デバイスから引き込まれる電流が VCONN で許容される最大値を上回った場合に VCONN を切斷します。VCONN フォルトが発生した場合、I<sup>2</sup>C レジスタの VCONN フラグが設定され、HD3SS3220 はレジスタ・フラグがクリアされるまで VCONN への電力供給を停止します（スイッチをオフ）。フォルトが発生したときに HD3SS3220 が GPIO モードの場合、VCONN スイッチはオフになり、ポートが取り外されて再接続されるまで HD3SS3220 は VCONN を供給しません。

### 6.3.10 I<sup>2</sup>C および GPIO 制御

HD3SS3220 は、ADDR ピンを使用して I<sup>2</sup>C または GPIO 用に構成できます。ADDR ピンはトライレベルの制御ピンです。ADDR ピンをフローティング (NC) のままにすると、HD3SS3220 は GPIO モードになります。ADDR ピンを High にすると、HD3SS3220 は I<sup>2</sup>C モードになり、アドレスビット 6 が 1 になります。ADDR ピンを Low にすると、HD3SS3220 は I<sup>2</sup>C モードになり、アドレスビット 6 が 0 になります。

HD3SS3220 のすべての出力はオープンドレイン構成です。

GPIO モードでは、OUT1 および OUT2 ピンを使用して Type-C 電流モードを出力します。OUT3 ピンは、GPIO モードでオーディオ アクセサリ モードを通信するために使用されます。出力ピンの詳細については、表 6-3 を参照してください。

表 6-3. OUT1 および OUT2 の動作

| OUT1 | OUT2 | アドバイスメント |

|------|------|----------|

| H    | H    | デフォルト    |

| H    | L    | デフォルト    |

| L    | H    | 中        |

| L    | L    | High     |

I<sup>2</sup>C モードで動作している場合、HD3SS3220 は SCL および SDA ラインをそれぞれクロックおよびデータに使用し、INT ピンも使用します。INT ピンは割り込み、または I<sup>2</sup>C レジスタの変更をシステムに通知します。HD3SS3220 がレジスタを新しい情報で更新すると、INT ピンは Low になります。INT\_N ピンはオープンドレインです。INT ピンが Low のときは、INTERRUPT\_STATUS レジスタを設定する必要があります。INTERRUPT\_STATUS をクリアするには、I<sup>2</sup>C に書き込みます。

GPIO モードで動作しているときは、オーディオ アクセサリが検出されて接続されたかどうかを判定するため、INT ピンの代わりに OUT3 ピンが使用されます。オーディオ アクセサリが検出されると、OUT3 ピンは Low になります。

### 注

I<sup>2</sup>C プルアップに 3.3V 電源を使用する場合、VDD5 が 3V 以上であることを確認する必要があります。VDD5 が 3V 未満の場合、I<sup>2</sup>C からデバイスに電力が供給されることがあります。

#### 6.3.11 HD3SS3220 V<sub>BUS</sub> 検出

HD3SS3220 デバイスは、Type-C 仕様にしたがって V<sub>BUS</sub> 検出をサポートしています。V<sub>BUS</sub> 検出は、UFP の接続と取り外しを判定し、アクセス モードの開始と終了を判断するために使用されます。また、V<sub>BUS</sub> 検出は DRP モードでの役割を決定するためにも使用されます。システム V<sub>BUS</sub> 電圧は、900k $\Omega$  の抵抗を介して HD3SS3220 デバイスの V<sub>BUS\_DET</sub> ピンに配線する必要があります。

#### 6.3.12 VDD5 および VCC33 のパワーオン要件

HD3SS3220 には、2 つの電源 VDD5 および VCC33 があります。VDD5 電源は内部 CC コントローラに電力を供給し、CC1 または CC2 に VCONN を供給します。VCC33 は 2:1 マルチプレクサに電力を供給します。

HD3SS3220 には、フェイルセーフではないピン PORT、ADDR、SDA/OUT1、SCL/OUT2、INT\_IN/OUT3、VCONN\_FAULT\_N、DIR があります。これらのフェイルセーフではないピンのいずれかが VDD5 以外の電源にプルアップされる場合は、図 6-2 に示すように、VCC33 電源よりも先に VDD5 電源をオンにする必要があります。VDD5 を VCC33 より先にオンにできない場合は、図 6-3 に示すように、両方の電源がランプアップしている間は ENn\_CC ピンを High に保持し、両方の電源が安定した後に Low にアサートする必要があります。

図 6-2. ENn\_CC が常に Low の場合のパワーオンのタイミング

図 6-3. ENn\_CC を制御する場合のパワーオンのタイミング

## 6.4 デバイスの機能モード

HD3SS3220 には 4 つの機能モードがあります。表 6-4 に、これらのモードを示します：

表 6-4. HD3SS3220 の機能モードに基づく USB Type-C の状態

| モード      | 一般的な動作                                              | モード          | 状態 <sup>(1)</sup>                        |

|----------|-----------------------------------------------------|--------------|------------------------------------------|

| 接続なし     | USB ポートに接続なし。ID、PORT 動作可能。<br>I <sup>2</sup> C はオン。 | UFP のみ       | Unattached.SNK                           |

|          |                                                     |              | AttachWait.SNK                           |

|          |                                                     | DFP          | Unattached.SNK → Unattached.SRC にトグル     |

|          |                                                     |              | AttachedWait.SRC または AttachedWait.SNK    |

|          |                                                     | DFP のみ       | Unattached.SRC                           |

|          |                                                     |              | AttachWait.SRC                           |

|          |                                                     | UFP のみ       | Attached.SNK                             |

|          |                                                     |              | オーディオ アクセサリ                              |

| アクティブ    | USB ポート接続。すべての GPIO が動作可能。<br>I <sup>2</sup> C はオン。 |              | デバッグ アクセサリ                               |

|          | DRP                                                 | Attached.SNK |                                          |

|          |                                                     | Attached.SRC |                                          |

|          |                                                     | オーディオ アクセサリ  |                                          |

|          | DFP のみ                                              | デバッグ アクセサリ   |                                          |

|          |                                                     | Attached.SRC |                                          |

|          |                                                     | オーディオ アクセサリ  |                                          |

|          |                                                     | デバッグ アクセサリ   |                                          |

| デッド バッテリ | 動作なし。VDD5 使用不可。                                     | DRP          | デバイス状態はデフォルトの UFP/SNK、R <sub>(d)</sub> 。 |

| シャットダウン  | 動作なし。VDD5 が使用可能、EN <sub>n</sub> _CC ピンは High        | DRP          | デバイス状態はデフォルトの UFP/SNK、R <sub>(d)</sub> 。 |

(1) (1) 必要。シーケンシャルな順序ではありません。

### 6.4.1 非接続モード

USB ポートに長時間にわたって何も接続されないことがあるため、HD3SS3220 の主な動作モードは非接続モードです。非接続モードでは VDD5 が使用可能で、すべての IO と I<sup>2</sup>C が動作可能です。VCONN はディセーブルになります。

HD3SS3220 に電源が投入された後、接続の成功が判定されるまで、デバイスは非接続モードになります。電源投入直後、HD3SS3220 は最初 Unattached.SNK 状態になります。HD3SS3220 は PORT ピンをチェックし、モード構成に応じて動作します。HD3SS3220 が DRP として構成されている場合は、UFP と DFP に交互に切り替わります。

### 6.4.2 アクティブ・モード

アクティブ・モードは、ポートが接続されている状態として定義されます。アクティブ・モードでは、すべての GPIO が動作し、I<sup>2</sup>C は読み出し / 書き込み (R/W) になります。HD3SS3220 デバイスがアクティブ・モードになると、USB ポートが接続されていることが AP に伝達されます。HD3SS3220 が DFP として構成されている場合、または DRP として構成されソースとして接続されている場合、この通信は ID ピンを介して行われます。HD3SS3220 が UFP として構成されている場合、または DRP として構成されシンクとして接続されている場合、OUT1/OUT2 および INT\_N/OUT3 ピンが使用されます。次の条件が満たされると、HD3SS3220 デバイスはアクティブ・モードを終了します。

- ケーブルが取り外される

- UFP として接続されている場合に VBUS が取り外される

- デッド・バッテリ: システムのバッテリまたは電源が取り除かれる

- EN\_N がフローティング状態または High にプルアップされる

#### 6.4.3 デッドバッテリ

デッドバッテリモードのときは、VDD5 は使用できません。デッドバッテリモードでは、CC ピンはデフォルトのプルダウン抵抗になります。デッドバッテリモードは、次を意味します。

- HD3SS3220 は UFP、 $5.1\text{k}\Omega \pm 20\%$   $R_{(d)}$ 、ケーブルは接続され、充電を供給。

- HD3SS3220 は UFP、 $5.1\text{k}\Omega \pm 20\%$   $R_{(d)}$ 、何も接続されていない（アプリケーションがオフになっているか、バッテリが放電されている）

#### 6.4.4 シャットダウン・モード

HD3SS3220 のシャットダウン・モードは、次のように定義されます。

- 電源電圧が使用可能で、EN\_N ピンが High またはフローティング状態。

- EN\_N ピンに内部プルアップ抵抗がある。

- HD3SS3220 デバイスはオフだが CC ピンに  $R_{(d)}$  が保持される。

## 6.5 プログラミング

さらにプログラマビリティを高めるため、I<sup>2</sup>C を使用して HD3SS3220 を制御できます。HD3SS3220 ローカル I<sup>2</sup>C インターフェイスは、デバイスに電源が投入されてから x クロック サイクル後に読み出し / 書き込みに使用できるようになります。SCL 端子と SDA 端子は、それぞれ I<sup>2</sup>C クロックと I<sup>2</sup>C データに使用されます。I<sup>2</sup>C が望ましい制御方法である場合は、それに応じて ADDR ピンを設定する必要があります。

表 6-5. HD3SS3220 の I<sup>2</sup>C ターゲットアドレス

| ADDR ピン | ピット 7 (MSB) | ピット 6 | ピット 5 | ピット 4 | ピット 3 | ピット 2 | ピット 1 | ピット 0 (W/R) |

|---------|-------------|-------|-------|-------|-------|-------|-------|-------------|

| H       | 1           | 1     | 0     | 0     | 1     | 1     | 1     | 0/1         |

| L       | 1           | 0     | 0     | 0     | 1     | 1     | 1     | 0/1         |

HD3SS3220 の I<sup>2</sup>C レジスタに書き込むには、次の手順に従う必要があります。

1. コントローラが START 条件 (S) を生成して書き込み動作を開始し、HD3SS3220 の 7 ビットアドレスと 0 値 R/W ビットを送信して書き込みサイクルを示します。

2. HD3SS3220 デバイスが、アドレス サイクルをアクノリッジします。

3. コントローラが 1 バイトのデータ (MSB ファースト) で構成された書き込むサブアドレス (HD3SS3220 デバイス内の I<sup>2</sup>C レジスタ) を送信します。

4. HD3SS3220 デバイスが、サブアドレス サイクルをアクノリッジします。

5. コントローラが I<sup>2</sup>C レジスタに書き込むデータの最初のバイトを送信します。

6. HD3SS3220 デバイスが、バイト転送をアクノリッジします。

7. コントローラが書き込むデータの追加のバイトを送信し続けます。各バイト転送は、HD3SS3220 デバイスからのアクノリッジで完了します。

8. コントローラが停止条件 (P) を生成して書き込み動作を終了します。

HD3SS3220 の I<sup>2</sup>C レジスタを読み出すには、次の手順に従う必要があります。

1. コントローラが開始条件 (S) を生成して読み出し動作を開始し、HD3SS3220 の 7 ビットアドレスと 1 値 R/W ビットを送信して読み出しサイクルを示します。

2. HD3SS3220 デバイスが、アドレス サイクルをアクノリッジします。

3. HD3SS3220 デバイスは、レジスタ 00h または最後の読み出しサブアドレス + 1 から、メモリ レジスタの内容を MSB ファーストで送信します。読み出しの前に I<sup>2</sup>C レジスタへの書き込みが発生した場合、HD3SS3220 デバイスは書き込みで指定されたサブアドレスから開始します。

4. HD3SS3220 デバイスは、各バイト転送の後、コントローラからのアクノリッジ (ACK) または非アクノリッジ (NACK) を待ちます。I<sup>2</sup>C コントローラは、各データ バイト転送の受信をアクノリッジします。

5. HD3SS3220 デバイスは、ACK を受信するとデータの次のバイトを送信します。

6. マスタが停止条件 (P) を生成して読み取り動作を終了します。

I<sup>2</sup>C 読み出しの開始サブアドレスを設定するには、次の手順に従う必要があります。

1. コントローラが START 条件 (S) を生成して書き込み動作を開始し、HD3SS3220 の 7 ビットアドレスと 0 値 R/W ビットを送信して読み出しサイクルを示します。

2. HD3SS3220 デバイスが、アドレス サイクルをアクノリッジします。

3. コントローラが 1 バイトのデータ (MSB ファースト) で構成される読み出すサブアドレス (HD3SS3220 デバイス内の I<sup>2</sup>C レジスタ) を送信します。

4. HD3SS3220 デバイスが、サブアドレス サイクルをアクノリッジします。

5. マスタが停止条件 (P) を生成して読み取り動作を終了します。

---

注

読み出し手順にサブアドレス指定が含まれていない場合、読み出しはレジスタ オフセット 00h から開始し、I<sup>2</sup>C コントローラが読み出し動作を終了するまでレジスタの内容をバイト単位で送信します。読み出しの前に I<sup>2</sup>C レジスタへの書き込みが発生した場合、読み出しはアドレス書き込みで指定されたサブアドレスから開始します。

---

## 6.6 レジスタ・マップ

表 6-6. CSR レジスタ

| オフセット     | リセット                                      | レジスタ名        | セクション            |

|-----------|-------------------------------------------|--------------|------------------|

| 0x07～0x00 | [0x00、0x54、0x55、0x53、0x42、0x33、0x32、0x32] | デバイス識別情報     | デバイス識別レジスタ       |

| 0x08      | 0x00                                      | 接続ステータス      | 接続ステータス・レジスタ     |

| 0x09      | 0x20                                      | 接続ステータスおよび制御 | 接続ステータスおよび制御レジスタ |

| 0x0A      | 0x00                                      | 汎用制御         | 汎用制御レジスタ         |

| 0xA0      | 0x02                                      | デバイス・リビジョン   | デバイス・リビジョン・レジスタ  |

6.6.1 デバイス識別レジスタ (オフセット = 0x07～0x00) [リセット = 0x00、0x54、0x55、0x53、0x42、0x33、0x32、0x32]

図 6-4. デバイス識別レジスタ

| 7         | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----------|---|---|---|---|---|---|---|

| DEVICE_ID |   |   |   |   |   |   |   |

| R         |   |   |   |   |   |   |   |

凡例: R/W = 読み出し / 書き込み、R = 読み出し専用、-n = リセット後の値

表 6-7. デバイス識別レジスタのフィールドの説明

| ビット | フィールド     | タイプ | リセット | 説明                                                                                                                       |

|-----|-----------|-----|------|--------------------------------------------------------------------------------------------------------------------------|

| 7:0 | DEVICE_ID | R   | 0x00 | HD3SS3220 デバイスでは、これらのフィールドは次の HD3SS3220 アドレスを返す ASCII 文字列を返します。<br>0x07～0x00 = {0x00、0x54、0x55、0x53、0x42、0x33、0x32、0x32} |

### 6.6.2 接続ステータス・レジスタ (オフセット = 0x08) [リセット = 0x00]

図 6-5. 接続ステータス・レジスタ

| 7                      | 6                   | 5 | 4                   | 3 | 2                      | 1 | 0 |

|------------------------|---------------------|---|---------------------|---|------------------------|---|---|

| CURRENT_MODE_ADVERTISE | CURRENT_MODE_DETECT |   | ACCESSORY_CONNECTED |   | ACTIVE_CABLE_DETECTION |   |   |

| R/W                    | R/U                 |   | R/U                 |   | R/U                    |   |   |

凡例: R/W = 読み出し / 書き込み、R = 読み出し専用、-n = リセット後の値、R/U = 読み出し / 更新

表 6-8. 接続ステータス・レジスタのフィールドの説明

| ビット | フィールド                  | タイプ | リセット   | 説明                                                                                                                                                                                                                                                                               |

|-----|------------------------|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | CURRENT_MODE_ADVERTISE | R/W | 2'b00  | これらのビットは、電流アドバタイズメントをデフォルトよりも高くするためにアプリケーションによってプログラムされます。<br>00 – デフォルト (500mA/900mA) スタートアップ時の初期値<br>01 – 中 (1.5A)<br>10 – 高 (3A)<br>11 – 予約済み                                                                                                                                 |

| 5:4 | CURRENT_MODE_DETECT    | R/U | 2'b00  | これらのビットは、UFP が Type-C 電流モードを判定したときに設定されます。<br>00 – デフォルト (スタートアップ時の値)<br>01 – 中<br>10 – アクセサリを介して充電 – 500mA<br>11 – 高                                                                                                                                                            |

| 3:1 | ACCESSORY_CONNECTED    | R/U | 3'b000 | これらのビットは、アクセサリが接続されたかどうかを判定するためにアプリケーションによって読み出されます。<br>000 – アクセサリの接続なし (デフォルト)<br>001 – 予約済み<br>010 – 予約済み<br>011 – 予約済み<br>100 – オーディオ・アクセサリ<br>101 – オーディオ・アクセサリを介して充電<br>110 – デバッグ・アクセサリ (HD3SS3220 が DFP として接続されている場合)<br>111 – デバッグ・アクセサリ (HD3SS3220 が UFP として接続されている場合) |

| 0   | ACTIVE_CABLE_DETECTION | R/U | 1'b0   | Type-C コネクタにアクティブ・ケーブルが接続されていることを示します。<br>0 – アクティブ・ケーブルなし<br>1 – アクティブ・ケーブル接続                                                                                                                                                                                                   |

### 6.6.3 接続ステータスおよび制御レジスタ (オフセット = 0x09) [リセット = 0x20]

図 6-6. 接続ステータスおよび制御レジスタ

| 7              | 6         | 5                | 4           | 3              | 2                     | 1 | 0 |

|----------------|-----------|------------------|-------------|----------------|-----------------------|---|---|

| ATTACHED_STATE | CABLE_DIR | INTERRUPT_STATUS | VCONN_FAULT | DRP_DUTY_CYCLE | DISABLE_UFP_ACCESSORY |   |   |

| R/U            | R/U       | R/U              | R/U         | R/W            | R/W                   |   |   |

凡例: R/W = 読み出し / 書き込み、R = 読み出し専用、-n = リセット後の値、R/U = 読み出し / 更新

表 6-9. 接続ステータス・レジスタのフィールドの説明

| ビット | フィールド                 | タイプ | リセット  | 説明                                                                                                                                                                             |

|-----|-----------------------|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | ATTACHED_STATE        | R/U | 2'b00 | これは、接続されたことを伝達する ID ピン以外の追加の方法です。これらのビットは、何が接続されたかを判定するためにアプリケーションによって読み出すことができます。<br>00 – 接続なし (デフォルト)<br>01 – Attached.SRC (DFP)<br>10 – Attached.SNK (UFP)<br>11 – アクセサリに接続 |

| 5   | CABLE_DIR             | R/U | 1'b0  | ケーブルの向き。アプリケーションは、これらのビットを読み出してケーブルの向きを確認できます。<br>0 – CC2<br>1 – CC1 (デフォルト)                                                                                                   |

| 4   | INTERRUPT_STATUS      | R/U | 1'b0  | INT ピンは、CSR が変更されると Low になります。CSR が変更された場合、アプリケーションがビットをクリアするまで、このビットは 1 に保持されます。<br>0 – クリア<br>1 – 割り込み。このビットは、INT が Low になったときに 1 になる必要があります。また、CSR が変更されると 1 になります。         |

| 3   | VCONN_FAULT           | R/U | 1'b0  | このビットは、VCONN 過電流制限がトリガされると設定されます。<br>0 – クリア<br>1 – VCONN フォルト検出                                                                                                               |

| 2:1 | DRP_DUTY_CYCLE        | R/W | 2'b00 | $t_{DRP}$ 中に DRP が DFP をアドバタイズする時間の割合<br>00 – 30% (デフォルト)<br>01 – 40%<br>10 – 50%<br>11 – 60%                                                                                  |

| 0   | DISABLE_UFP_ACCESSORY | R/W | 1'b0  | このフィールドを設定すると、UFP アクセサリのサポートがディセーブルになります。<br>0 – UFP アクセサリ・サポートがイネーブル (デフォルト)<br>1 – UFP アクセサリ・サポートがディセーブル                                                                     |

#### 6.6.4 汎用制御レジスタ (オフセット = 0xA) [リセット = 0x00]

図 6-7. 汎用制御レジスタ

| 7        | 6 | 5           | 4 | 3              | 2           | 1 | 0            |

|----------|---|-------------|---|----------------|-------------|---|--------------|

| DEBOUNCE |   | MODE_SELECT |   | I2C_SOFT_RESET | SOURCE_PREF |   | DISABLE_TERM |

| R/W      |   | R/W         |   | R/U            | R/W         |   | R/W          |

凡例: R/W = 読み出し / 書き込み、R = 読み出し専用、-n = リセット後の値

表 6-10. 汎用制御レジスタのフィールドの説明

| ビット | フィールド          | タイプ | リセット  | 説明                                                                                                                                                                                                                                                                                                                        |

|-----|----------------|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | DEBOUNCE       | R/W | 2'b00 | HD3SS3220 が CC ピンの電圧をデバウンスする公称時間。<br>00 - 168ms (デフォルト)<br>01 - 118ms<br>10 - 134ms<br>11 - 152ms                                                                                                                                                                                                                         |

| 5:4 | MODE_SELECT    | R/W | 2'b00 | このレジスタに書き込むことで、HD3SS3220 のモード動作を設定できます。ADDR ピンは I <sup>2</sup> C モードに設定する必要があります。デフォルトのままにすると、HD3SS3220 は PORT ピンのレベルとモードに応じて動作します。MODE_SELECT は、非接続状態のときにのみ変更できます。<br>00 – DRP モード (Unattached.SNK から開始) (デフォルト)<br>01 – UFP モード (Unattached.SNK)<br>10 – DFP モード (Unattached.SRC)<br>11 – DRP モード (Unattached.SNK から開始) |

| 3   | I2C_SOFT_RESET | R/U | 1'b0  | このレジスタはデジタル ロジックをリセットします。このビットは自動でクリアされます。1 を書き込むと、リセットが開始します。このビットを設定すると、次のレジスタに影響します:<br>CURRENT_MODE_DETECT<br>ACTIVE_CABLE_DETECTION<br>ACCESSORY_CONNECTED<br>ATTACHED_STATE<br>CABLE_DIR                                                                                                                            |

| 2:1 | SOURCE_PREF    | R/W | 2'b00 | このフィールドは、DRP として構成されているときの TUSB322I の動作を制御します。<br>00 – 標準 DRP (デフォルト)<br>01 – DRP が Try.SNK を実行<br>10 – 予約済み<br>11 – DRP が Try.SRC を実行                                                                                                                                                                                    |

| 0   | DISABLE_TERM   | R/W | 1'b0  | このフィールドは、CC ピンの終端をディセーブルし、CC ステート マシンをディセーブル状態に遷移させます。<br>0 – TUSB322I の動作モードに従って終端をイネーブル (デフォルト)<br>1 – 終端はディセーブル、ステート マシンをディセーブル状態に保持                                                                                                                                                                                   |

#### 6.6.5 デバイス・リビジョン・レジスタ (オフセット = 0xA0) [リセット = 0x02]

図 6-8. デバイス・リビジョン・レジスタ

| 7     | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|---|---|---|---|---|---|

| リビジョン |   |   |   |   |   |   |   |

| R     |   |   |   |   |   |   |   |

凡例: R/W = 読み出し / 書き込み、R = 読み出し専用、-n = リセット後の値

**表 6-11. デバイス・リビジョン・レジスタのフィールドの説明**

| ビット | フィールド | タイプ | リセット | 説明                           |

|-----|-------|-----|------|------------------------------|

| 7:0 | リビジョン | R   | 'h02 | HD3SS3220 のリビジョン。デフォルトは 0x02 |

## 7 アプリケーションと実装

---

### 注

以下のアプリケーション情報は、テキサス・インスツルメンツの製品仕様に含まれるものではなく、テキサス・インスツルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

---

### 7.1 アプリケーション情報

HD3SS3220 は、USB SuperSpeed または SuperSpeedPlus を必要とするアプリケーション向けに、DRP、DFP、UFP ポートを実装する USB Type-C システムの設計に使用できます。このデバイスは、最大 15W までの電力ネゴシエーションに対応した ネイティブ USB-C 電源ハンドシェイクをサポートしています。HD3SS3220 は、DFP (電力供給側) として 900mA、1.5A、3A の電流供給能力を通知でき、UFP (電力消費側) としてこれらの設定を検出することも可能です。

I<sup>2</sup>C の使用はオプションですが、USB-C インターフェイスのデバイスとステータスを制御する別の方法として使用でき、堅牢で柔軟なシステム実装が可能となるため、使用を強くお勧めします。定期的な I<sup>2</sup>C ポーリングは不要で、デバイスはマイクロプロセッサに割り込み信号を供給します。

HD3SS3220 マルチプレクサ チャネルは独立した適応型同相トラッキング機能を備えており、RX パスと TX パスに異なる同相電圧を使用できるため、システム実装が簡素化され、相互運用の問題が回避されます。

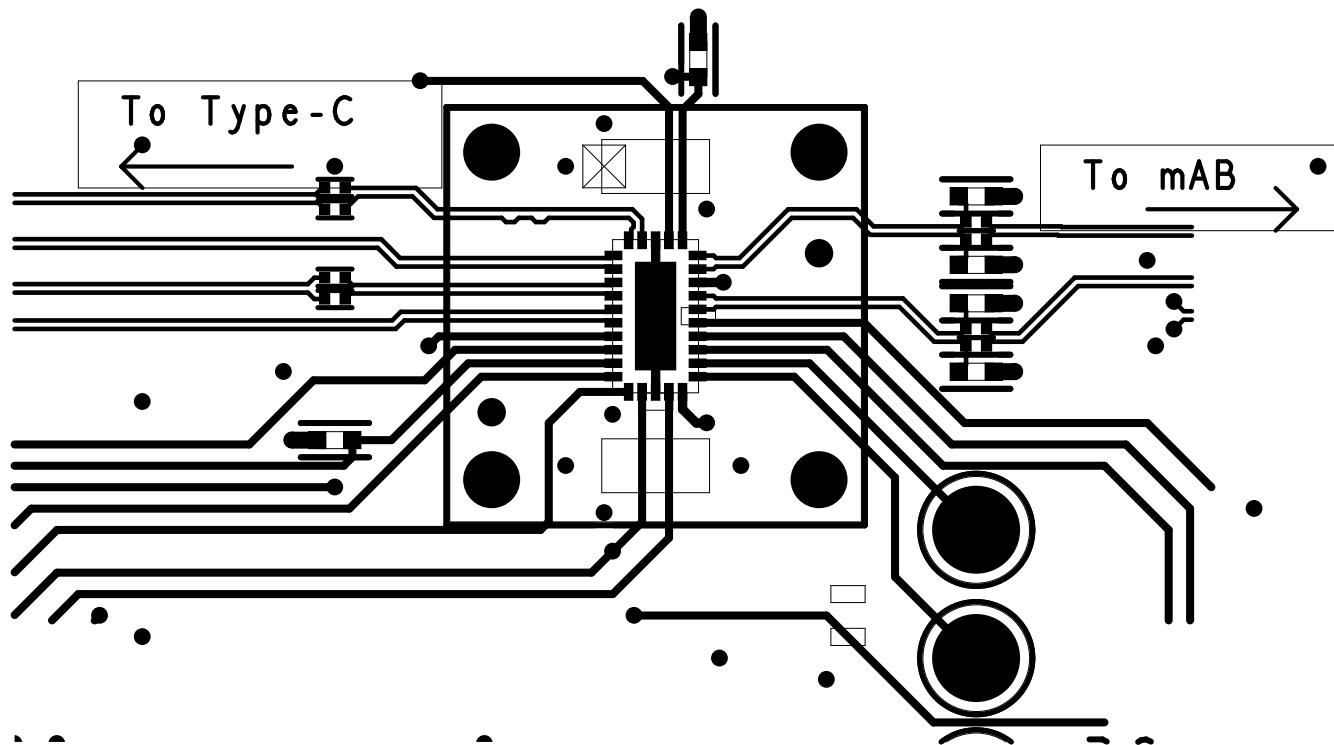

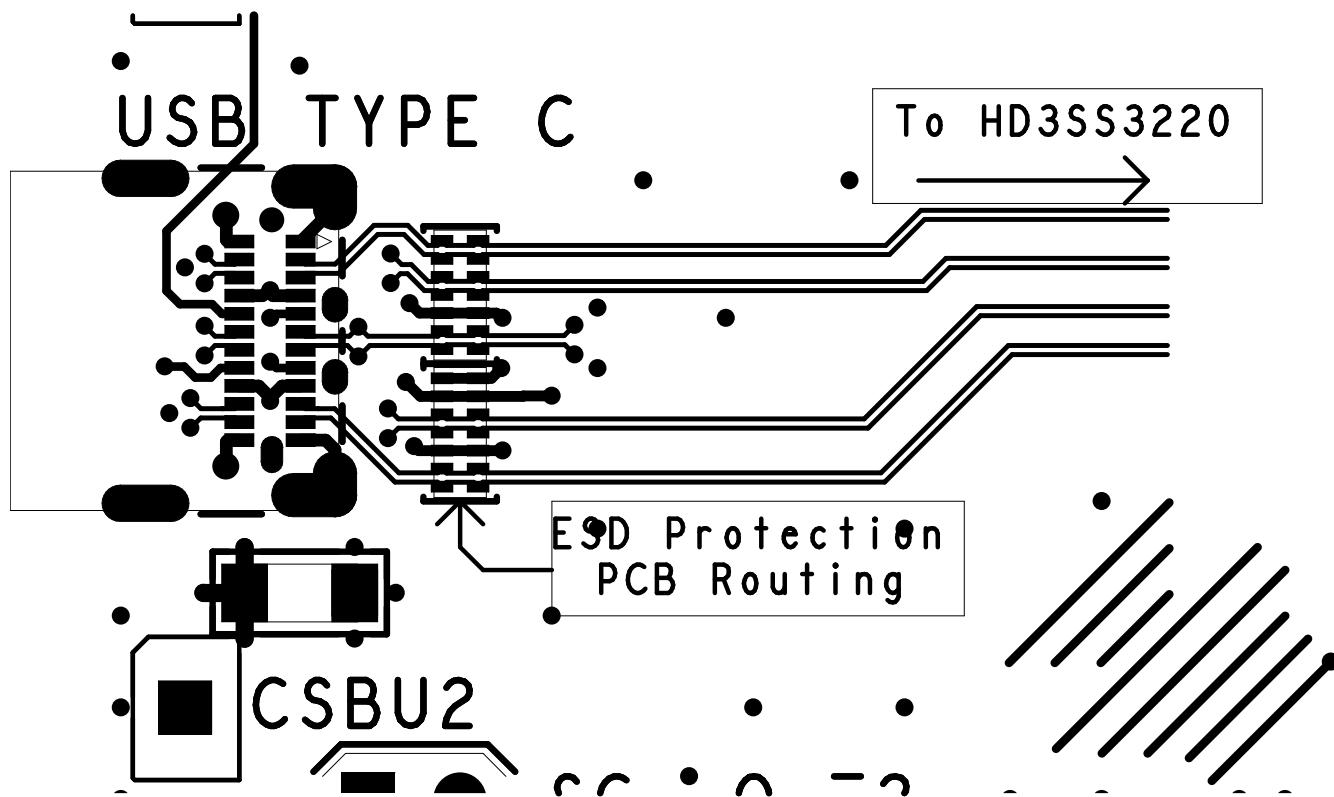

USB-C コネクタへの SS 信号のレイアウトは、レセプタクルのタイプに応じて調整する必要があります。

---

### 注

HD3SS3220 マルチプレクサは、チャネルに同相バイアスを供給しません。そのため、デバイスをすべてのアクティブ チャネルの両側からバイアスする必要があります。また、マルチプレクサ チャネルは差動 SS 信号用であることにも注意してください。

15W を超える電力をサポートする必要がある場合は、USBPD 機能が必要であり、このデバイスではサポートされていません。USB ホスト / 電力コンシューマ、または USB デバイス / 電力プロバイダなど、データ / 電力の役割を分割する必要がある場合は、USBPD 機能も必要です。

---

## 7.2 代表的なアプリケーション、DRP ポート

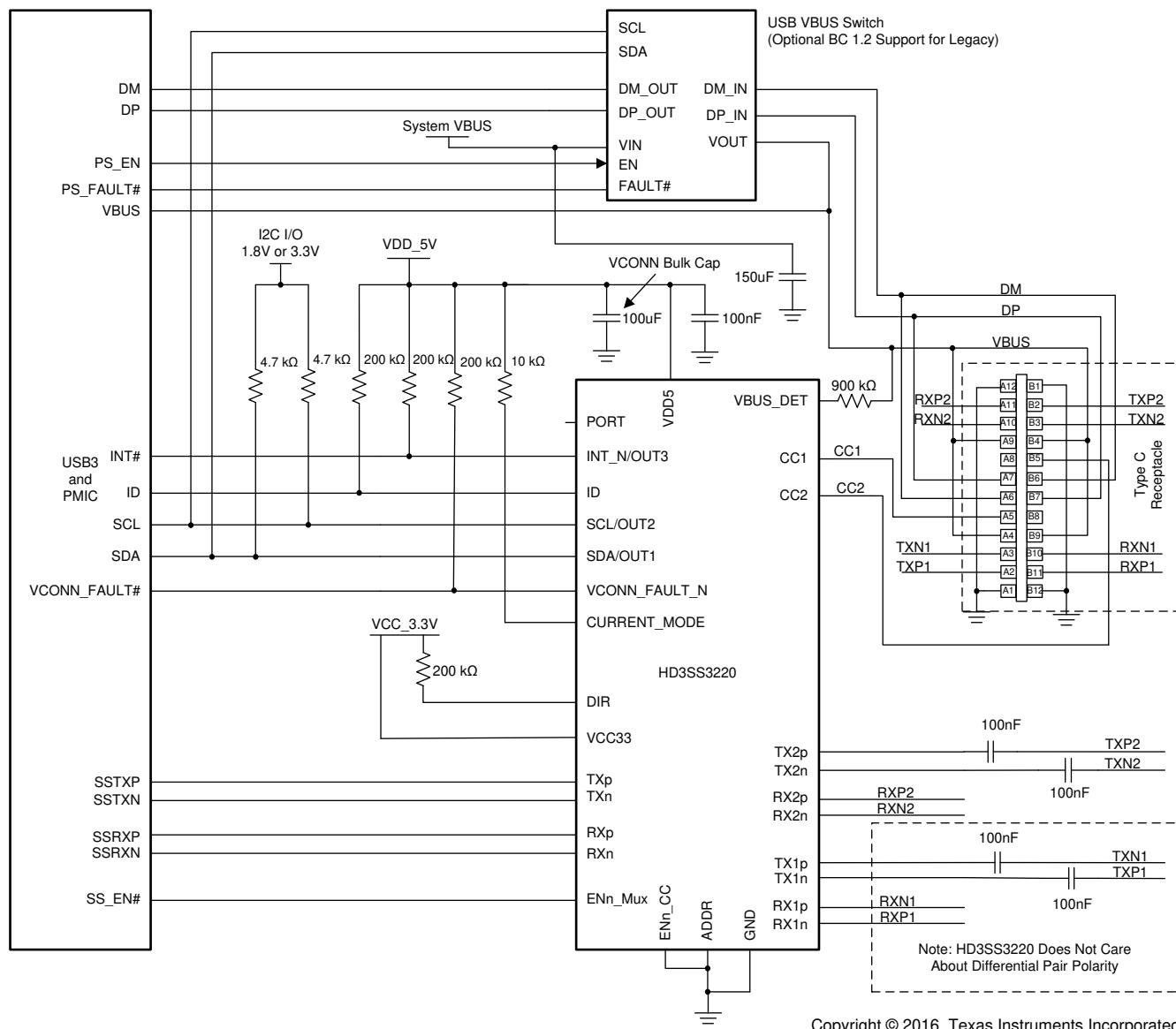

図 7-1. HD3SS3220DRP を使用した DRP アプリケーション

## 7.2.1 設計要件

この設計例では、表 7-1 に示すパラメータを使用します。

**表 7-1. 設計パラメータ、DRP ポート**

| パラメータ                                  | 例     | 備考                                                                                                                                                                                      |

|----------------------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD5                                   | 5.25V | VDD5 は、CC ピンに VCONN 電力を供給するのに使用されます。VCONN を 4.75V 以上に維持するため、この電源の値は 5V 以上にする必要があります。                                                                                                    |

| System_VBUS                            | 5.25V | VDD5 と System_VBUS は一緒に短絡することができますが、Type-C ポートで適切な VBUS と VCONN を維持するには、慎重に検討する必要があります。                                                                                                 |

| I <sup>2</sup> C I/O 電源                | 3.3V  | 1.8V もオプション。<br>3.3V 電源を使用する場合、VDD5 が 3V 以上であることを確認する必要があります。<br>VDD5 が 3V 未満の場合、I <sup>2</sup> C からデバイスに電力が供給されることがあります。                                                               |

| VCC33                                  | 3.3V  | 3~3.6V の範囲を使用可能。                                                                                                                                                                        |

| SS 信号用の AC カップリング コンデンサ                | 100nF | 75~200nF の範囲を使用可能。<br>TX ペアの場合のみ。RX ペアはホストレシーバによってバイアスされます。<br>HD3SS3220 には 0~2V の同相バイアスが必要であることに注意します。ホストレシーバのバイアス電圧がこの範囲外の場合、適切な AC カップリング コンデンサを追加し、HD3SS3220 の RX ペアをバイアスする必要があります。 |

| プルアップ抵抗 DIR、ID、INT_N、<br>VCONN_FAULT_N | 200K  | これより小さい値を使用することができますが、デバイスの電力バジェット計算でリーケージを考慮する必要があります。                                                                                                                                 |

| プルアップ抵抗 I <sup>2</sup> C               | 4.7K  |                                                                                                                                                                                         |

| プルアップ抵抗 CURRENT_MODE                   | 10K   | ここに 3A の場合の例があります。1.5A または 900mA が必要な場合は、別の値が必要です。                                                                                                                                      |

| 直列抵抗 VBUS_DET                          | 900K  |                                                                                                                                                                                         |

| デカッピング コンデンサ:VCONN バルク                 | 100μF |                                                                                                                                                                                         |

| デカッピング コンデンサ:VBUS バルク                  | 150μF | 回路図に示すように、UFP の場合は切断する必要があります。                                                                                                                                                          |

## 7.2.2 詳細な設計手順

HD3SS3220 は、USB Type-C DRP ポートの設計に使用できます。DRP モードでは、USB-C 仕様に従ってデバイスが DFP および UFP の間でトグルします。図 7-1 に、DRP 実装の回路図例を示します。

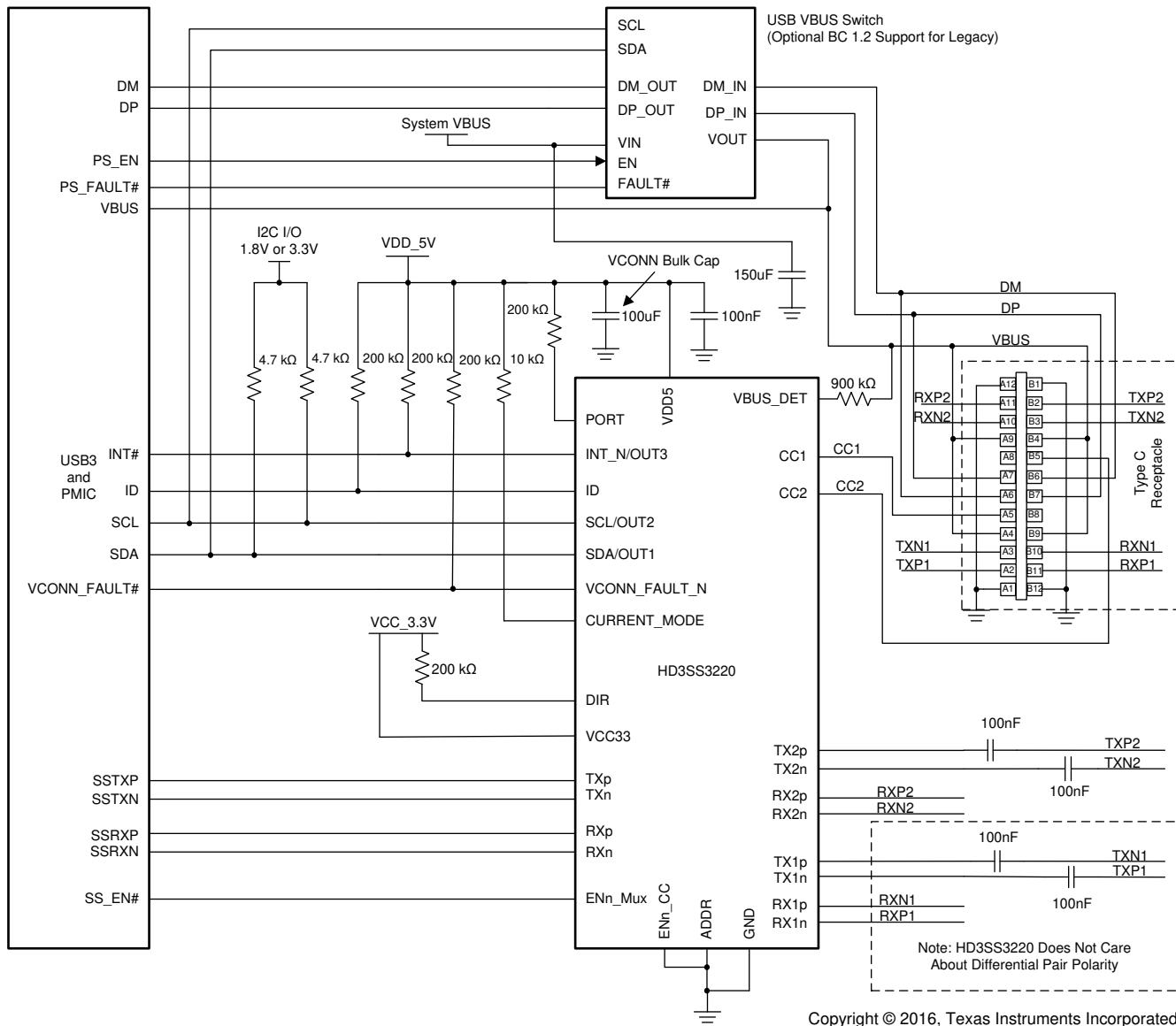

### 7.2.3 代表的なアプリケーション、DFP ポート

HD3SS3220 は、USB Type-C DFP ポートの設計に使用できます。図 7-2 に、DFP 実装の回路図例を示します。

図 7-2. HD3SS3220DFP を使用した DFP アプリケーション

### 7.2.3.1 設計要件

この設計例では、表 7-2 に示すパラメータを使用します。

**表 7-2. 設計パラメータ、DFP ポート**

| パラメータ                              | 例     | 備考                                                                                                                                                                                      |

|------------------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD5                               | 5.25V | VDD5 は、CC ピンに VCONN 電力を供給するのに使用されます。VCONN を 4.75V 以上に維持するため、この電源の値は 5V 以上にする必要があります。                                                                                                    |

| System_VBUS                        | 5.25V | VDD5 と System_VBUS は一緒に短絡することができますが、Type-C ポートで適切な VBUS と VCONN を維持するには、慎重に検討する必要があります。                                                                                                 |

| I <sup>2</sup> C I/O 電源            | 3.3V  | 1.8V もオプション。<br>3.3V 電源を使用する場合、VDD5 が 3V 以上であることを確認する必要があります。<br>VDD5 が 3V 未満の場合、I <sup>2</sup> C からデバイスに電力が供給されることがあります。                                                               |

| VCC33                              | 3.3V  | 3~3.6V の範囲を使用可能。                                                                                                                                                                        |

| SS 信号用の AC カップリング コンデンサ            | 100nF | 75~200nF の範囲を使用可能。<br>TX ペアの場合のみ。RX ペアはホストレシーバによってバイアスされます。<br>HD3SS3220 には 0~2V の同相バイアスが必要であることに注意します。ホストレシーバのバイアス電圧がこの範囲外の場合、適切な AC カップリング コンデンサを追加し、HD3SS3220 の RX ペアをバイアスする必要があります。 |

| プルアップ抵抗 DIR、ID、INT_N、VCONN_FAULT_N | 200K  | これより小さい値を使用することもできますが、デバイスの電力バジェット計算でリーフージを考慮する必要があります。                                                                                                                                 |

| プルアップ抵抗 I <sup>2</sup> C           | 4.7K  |                                                                                                                                                                                         |

| プルアップ抵抗 CURRENT_MODE               | 10K   | ここに 3A の場合の例があります。1.5A または 900mA が必要な場合は、別の値が必要です。                                                                                                                                      |

| デカッピング コンデンサ:VCONN バルク             | 100μF |                                                                                                                                                                                         |

| デカッピング コンデンサ:VBUS バルク              | 150μF |                                                                                                                                                                                         |

### 7.2.3.2 詳細な設計手順

HD3SS3220 は、USB Type-C DFP ポートの設計に使用できます。図 7-2 に、DFP 実装の回路図例を示します。

### 7.2.4 代表的なアプリケーション、UFP ポート

HD3SS3220 は、USB Type-C UFP ポートの設計に使用できます。図 7-3 に、UFP 実装の回路図例を示します。

図 7-3. HD3SS3220DFP を使用した UFP アプリケーション

### 7.2.4.1 設計要件

この設計例では、表 7-3 に示すパラメータを使用します。

**表 7-3. 設計パラメータ、UFP ポート**

| パラメータ                    | 例     | 備考                                                                                                                                                                                        |

|--------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD5                     | 5V    | Type-C ポートからの VBUS を使用可能。                                                                                                                                                                 |

| I <sup>2</sup> C I/O 電源  | 3.3V  | 1.8V もオプション。<br>3.3V 電源を使用する場合、VDD5 が 3V 以上であることを確認する必要があります。<br>VDD5 が 3V 未満の場合、I <sup>2</sup> C からデバイスに電力が供給されることがあります。                                                                 |

| VCC33                    | 3.3V  | 3~3.6V の範囲を使用可能。                                                                                                                                                                          |

| SS 信号用の AC カップリング コンデンサ  | 100nF | 75~200nF の範囲を使用可能。<br>TX ペアの場合のみ。RX ペアはホスト レシーバによってバイアスされます。<br>HD3SS3220 には 0~2V の同相バイアスが必要であることに注意します。ホスト レシーバのバイアス電圧がこの範囲外の場合、適切な AC カップリング コンデンサを追加し、HD3SS3220 の RX ペアをバイアスする必要があります。 |

| プルアップ抵抗 DIR、INT_N        | 200K  | これより小さい値を使用することもできますが、デバイスの電力バジェット計算でリーケージを考慮する必要があります。                                                                                                                                   |

| プルアップ抵抗 I <sup>2</sup> C | 4.7K  |                                                                                                                                                                                           |

| 直列抵抗 VBUS_DET            | 900K  |                                                                                                                                                                                           |

### 7.2.4.2 詳細な設計手順

HD3SS3220 は、USB Type-C DFP ポートの設計に使用できます。図 7-3 に、UFP 実装の回路図例を示します。

## 8 電源に関する推奨事項

HD3SS3220 には、4.5~5.5V の電源電圧要件があります。このデバイスには、V<sub>(BUS)</sub> に電源を供給するのと同じレールから電源を供給できます。

## 9 レイアウト

### 9.1 レイアウトのガイドライン

#### 9.1.1 推奨される PCB スタックアップ

テキサス・インストルメンツでは、6 層以上の PCB を推奨しています。表 9-1 に、PCB スタックアップの例を示します。

表 9-1. PCB スタックアップの例

| 6 層                      | 8 层                      | 10 層                     |

|--------------------------|--------------------------|--------------------------|

| 信号                       | 信号                       | 信号                       |

| グランド                     | グランド                     | グランド                     |

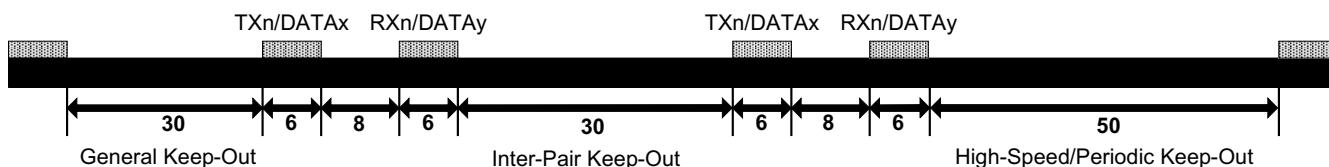

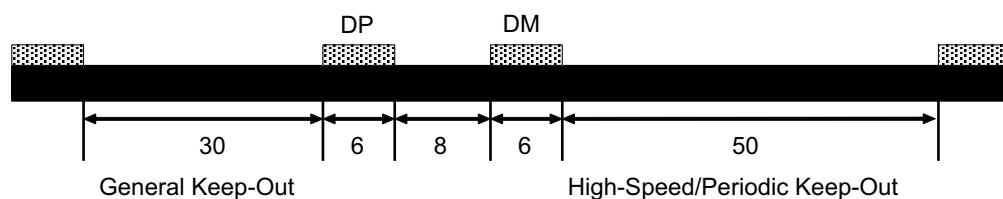

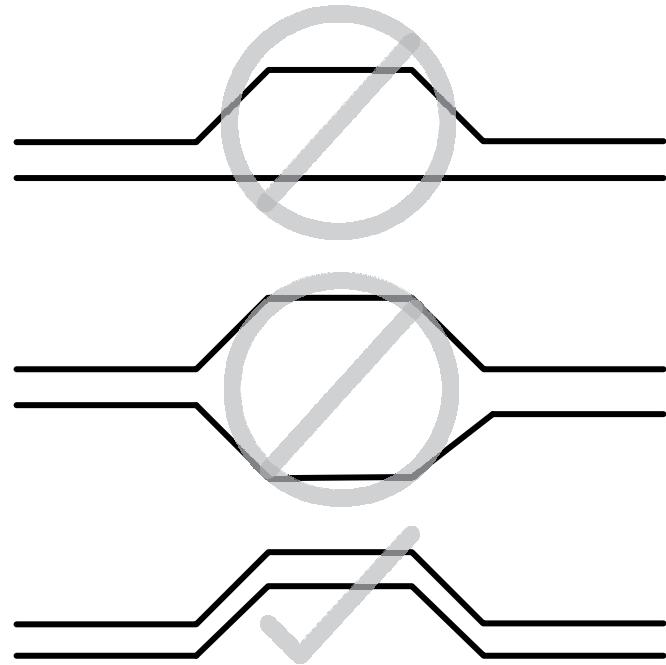

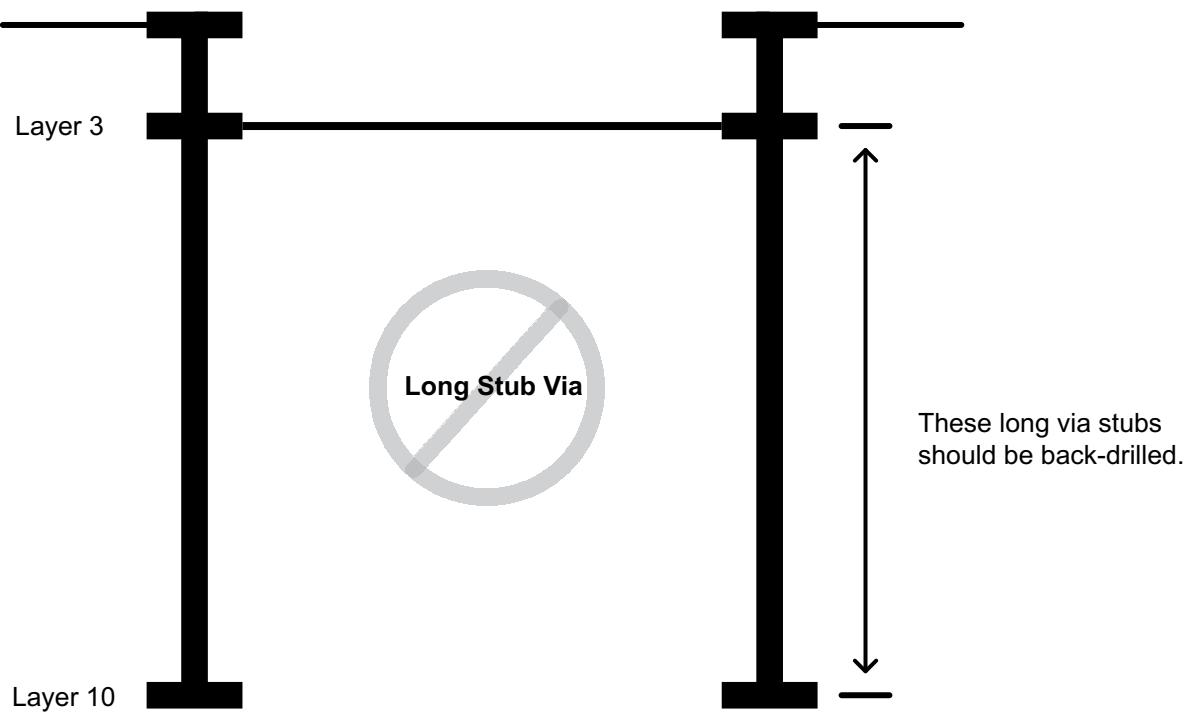

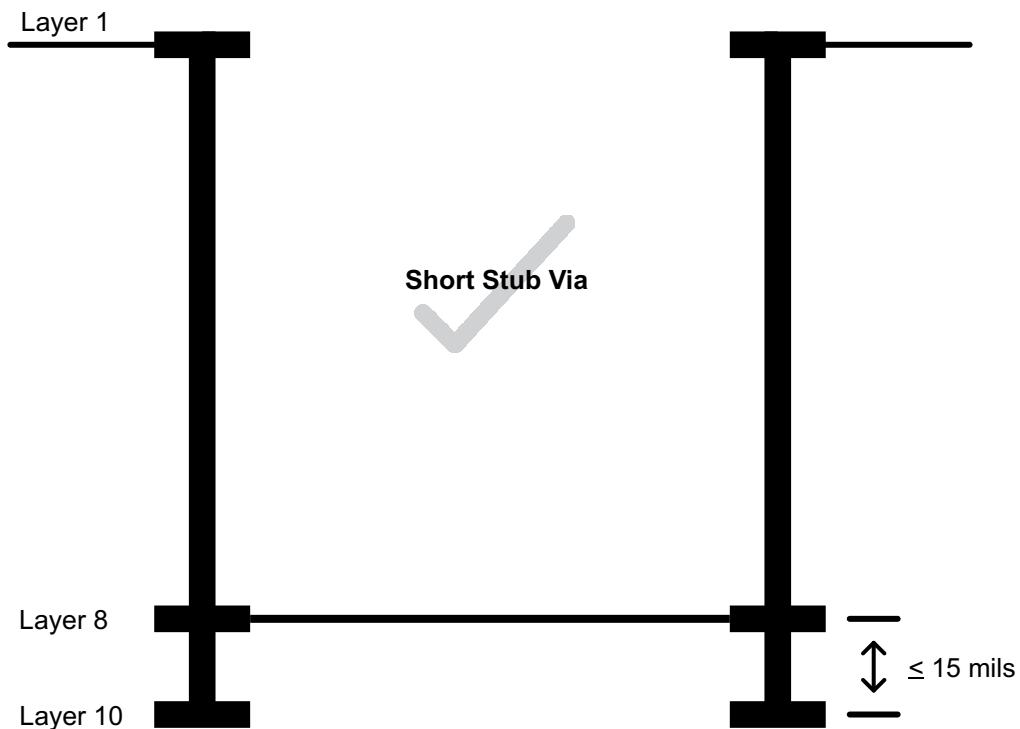

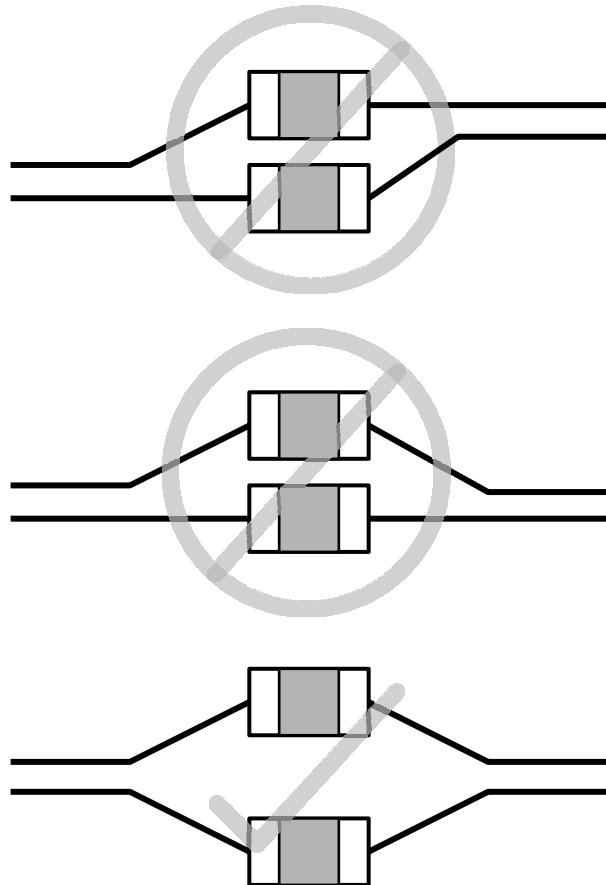

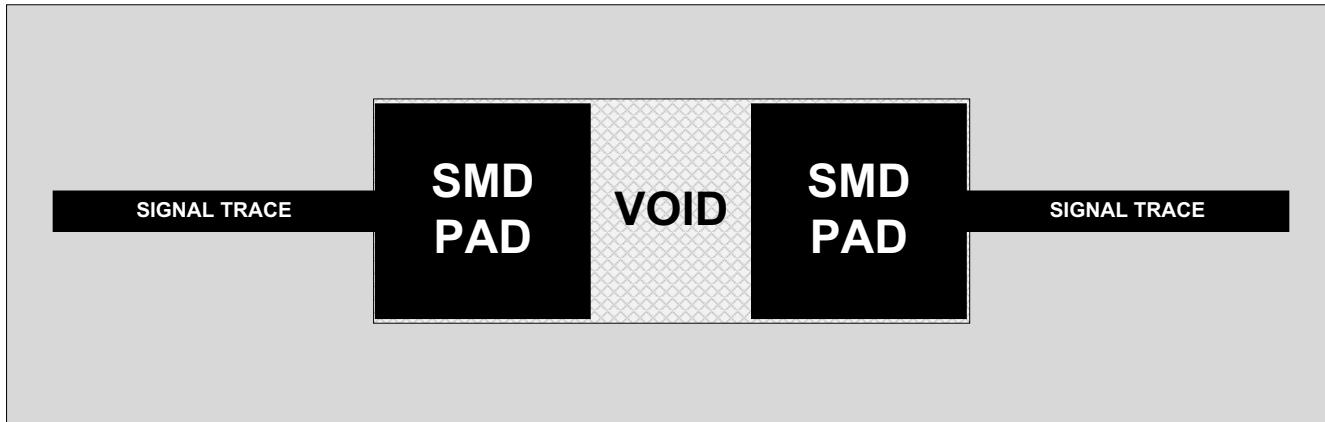

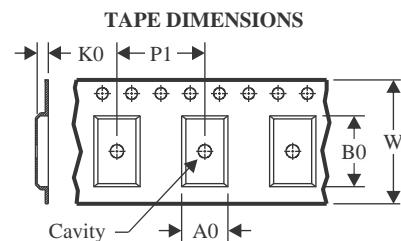

| 信号 <sup>(1)</sup>        | 信号                       | 信号 <sup>(1)</sup>        |