# ISOTMP35 $\pm 1.2^\circ\text{C}$ 、3-kV<sub>RMS</sub> の絶縁型温度センサ、アナログ出力付き、応答時間 2 秒未満、動作電圧 500V<sub>RMS</sub>

## 1 特長

- 堅牢な内蔵絶縁バリア:

- 絶縁耐電圧: 3000V<sub>RMS</sub>

- 絶縁動作電圧: 500V<sub>RMS</sub>

- 絶縁バリアの寿命: > 50 years

- 温度センサの精度

- $\pm 0.5^\circ\text{C}$  (標準  $25^\circ\text{C}$ )

- $0^\circ\text{C} \sim 70^\circ\text{C}$  で  $\pm 1.2^\circ\text{C}$  以下

- $-40^\circ\text{C} \sim 150^\circ\text{C}$  で  $\pm 2.5^\circ\text{C}$  以下

- 動作電源電圧範囲: 2.3V ~ 5.5V

- 正のスロープ センサ ゲイン: 10mV/°C,  $0^\circ\text{C}$  で 500mV のオフセット

- 高速な熱応答: 2 秒未満

- 短絡保護された出力

- 低消費電力: 9μA (標準値)

- DFQ (SOIC-7) パッケージ

- 安全関連認証 (予定):

- UL 1577 に準拠した絶縁耐圧: 3kV<sub>RMS</sub> (1 分間)

## 2 アプリケーション

- AC 充電 (パイル) ステーション

- DC 高速充電ステーション

- 48V 出力、ラックとサーバー向け PSU (電源)

- 12V 出力、サーバー向け PSU (電源)

- 商用 DC/DC

- 商用テレコム整流器

- バッテリ バックアップ ユニット

- 商用 DIN レール向け電源

- AC/DC アダプタ PSU (電源)

## 3 概要

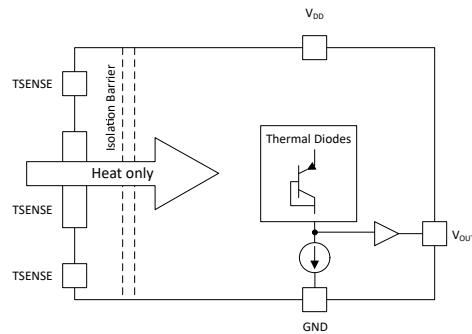

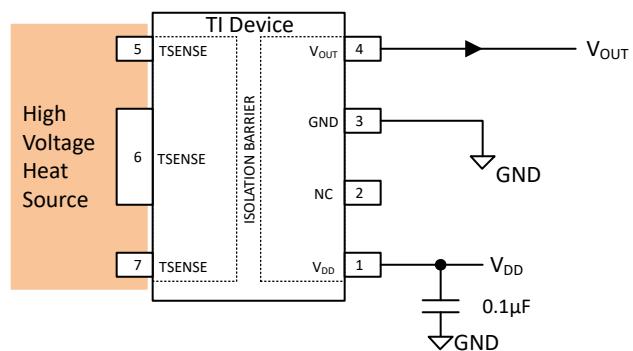

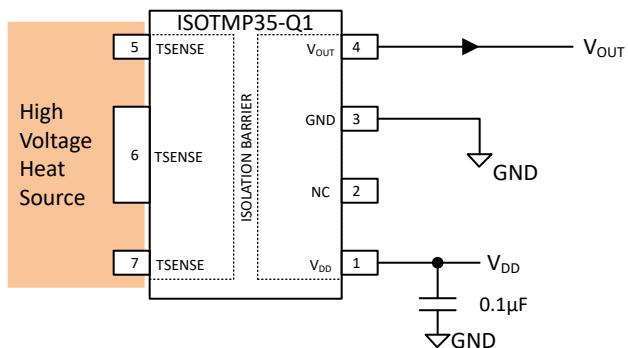

ISOTMP35 は、業界初の絶縁型温度センサ IC であり、最大 3000V<sub>RMS</sub> の耐電圧の内蔵絶縁バリアと、 $-40^\circ\text{C} \sim 150^\circ\text{C}$  で  $10\text{mV/}^\circ\text{C}$  の勾配を特長とするアナログ温度センサを組み合わせています。この統合により、高価な絶縁回路を必要とせずに、センサを高電圧熱源 (たとえば HV FET、IGBT、HV コンタクタ) と同じ場所に設置することができます。また、高電圧熱源に直接接触することで、絶縁要件を満たすためにセンサを遠くに配置するアプローチに比べ、より高い精度と高速な熱応答が得られます。

ISOTMP35 は非絶縁型の 2.3V ~ 5.5V 電源で動作するため、高電圧プレーンでサブレギュレートされた電源を利用できないアプリケーションに簡単に統合できます。

内蔵絶縁バリアは UL 1577 の要件を満たしています。表面実装パッケージ (7 ピン SOIC) は、熱源から組み込み熱センサへの優れた熱流を提供し、熱質量を最小限に抑え、より正確な熱源測定を実現します。これにより、時間のかかる熱モデリングの必要性が減り、製造や組み立てによる機械的なばらつきが減少するため、システム設計のマージンが向上します。

ISOTMP35 の Class-AB 出力ドライバは、最大出力が 500μA と強力で、最大 1000pF の容量性負荷を駆動でき、A/D コンバータ (ADC) のサンプル ホールド入力と直接インターフェイスするように設計されています。

### パッケージ情報

| 部品番号     | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|----------|----------------------|--------------------------|

| ISOTMP35 | DFQ (SOIC, 7)        | 4.9mm × 6mm              |

(1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値で、該当する場合はピンも含まれます。

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

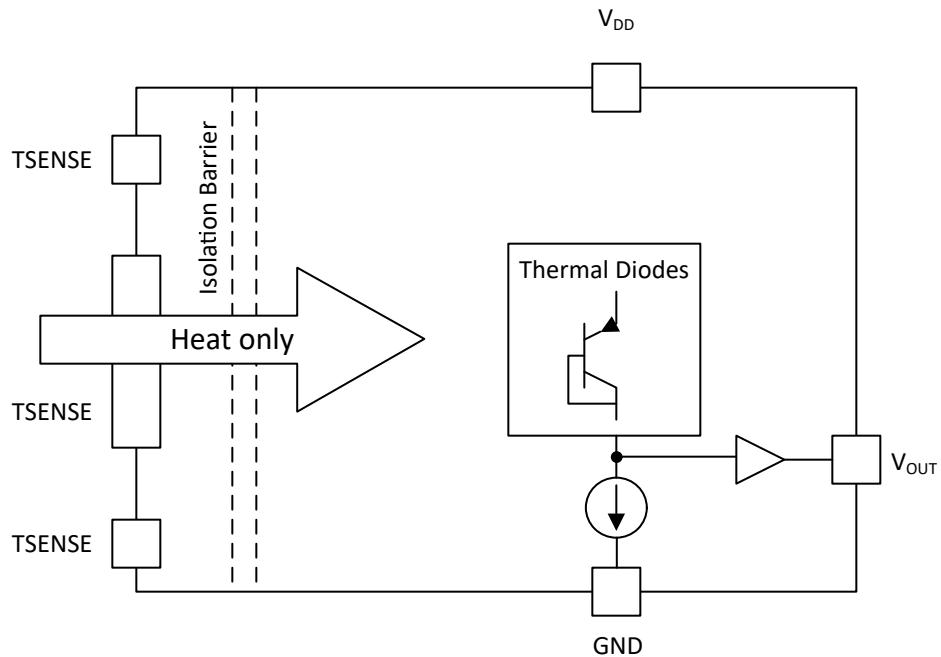

機能ブロック図

代表的なアプリケーション

## Table of Contents

|                                           |    |                                                |    |

|-------------------------------------------|----|------------------------------------------------|----|

| 1 特長.....                                 | 1  | 6.3 Features Description.....                  | 11 |

| 2 アプリケーション.....                           | 1  | 6.4 Device Functional Modes.....               | 14 |

| 3 概要.....                                 | 1  | <b>7 Application and Implementation.....</b>   | 14 |

| 4 Pin Configuration and Functions.....    | 4  | 7.1 Application Information.....               | 15 |

| 5 Specifications.....                     | 5  | 7.2 Typical Application.....                   | 19 |

| 5.1 Absolute Maximum Ratings.....         | 5  | 7.3 Power Supply Recommendations.....          | 20 |

| 5.2 ESD Ratings.....                      | 5  | 7.4 Layout.....                                | 20 |

| 5.3 Recommended Operating Conditions..... | 5  | <b>8 Device and Documentation Support.....</b> | 21 |

| 5.4 Thermal Information.....              | 5  | 8.1 Documentation Support.....                 | 21 |

| 5.5 Insulation Specification.....         | 6  | 8.2 ドキュメントの更新通知を受け取る方法.....                    | 21 |

| 5.6 Power Ratings.....                    | 7  | 8.3 サポート・リソース.....                             | 21 |

| 5.7 Safety-Related Certifications.....    | 7  | 8.4 Trademarks.....                            | 22 |

| 5.8 Safety Limiting Values.....           | 7  | 8.5 静電気放電に関する注意事項.....                         | 22 |

| 5.9 Electrical Characteristics.....       | 8  | 8.6 用語集.....                                   | 22 |

| 5.10 Typical Characteristics.....         | 9  | <b>9 Revision History.....</b>                 | 22 |

| <b>6 Detailed Description.....</b>        | 11 | <b>10 Mechanical, Packaging, and Orderable</b> |    |

| 6.1 Overview.....                         | 11 | <b>Information.....</b>                        | 22 |

| 6.2 Functional Block Diagram.....         | 11 |                                                |    |

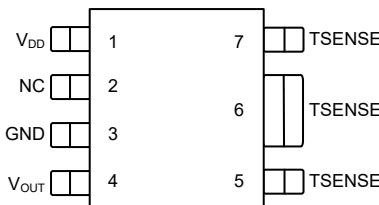

## 4 Pin Configuration and Functions

図 4-1. DFQ Package 7-Pin SOIC Top View

表 4-1. Pin Functions

| PIN              |     | TYPE <sup>(1)</sup> | DESCRIPTION                                           |

|------------------|-----|---------------------|-------------------------------------------------------|

| NAME             | DFQ |                     |                                                       |

| GND              | 3   | G                   | Ground                                                |

| NC               | 2   | –                   | No connect                                            |

| TSENSE           | 5   | –                   | Temperature pin connected to high-voltage heat source |

|                  | 6   |                     |                                                       |

|                  | 7   |                     |                                                       |

| V <sub>DD</sub>  | 1   | P                   | Supply voltage                                        |

| V <sub>OUT</sub> | 4   | O                   | Output voltage proportional to temperature            |

(1) I = Input, O = Output, I/O = Input or Output, G = Ground, P = Power.

## 5 Specifications

### 5.1 Absolute Maximum Ratings

Over free-air temperature range unless otherwise noted<sup>(1)</sup>

|                                       |           | MIN  | MAX            | UNIT |

|---------------------------------------|-----------|------|----------------|------|

| Supply voltage                        | $V_{DD}$  | -0.3 | 6              | V    |

| Output voltage                        | $V_{OUT}$ | -0.3 | $V_{DD} + 0.3$ | V    |

| Output current                        | $I_{OUT}$ | -30  | 30             | mA   |

| Operating junction temperature, $T_J$ |           | -60  | 155            | °C   |

| Storage temperature, $T_{stg}$        |           | -65  | 155            | °C   |

(1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

### 5.2 ESD Ratings

|             |                                                                       | VALUE      | UNIT |

|-------------|-----------------------------------------------------------------------|------------|------|

| $V_{(ESD)}$ | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>     | $\pm 2500$ | V    |

|             | Charged-device model (CDM), per ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> | $\pm 1000$ |      |

(1) JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process.

### 5.3 Recommended Operating Conditions

|          |                               | MIN | NOM | MAX | UNIT |

|----------|-------------------------------|-----|-----|-----|------|

| $V_{DD}$ | Supply voltage                | 2.3 |     | 5.5 | V    |

| $T_A$    | Operating ambient temperature | -40 |     | 150 | °C   |

### 5.4 Thermal Information

| THERMAL METRIC <sup>(1)</sup> |                                              | ISOTMP35   | UNIT  |

|-------------------------------|----------------------------------------------|------------|-------|

|                               |                                              | DFQ (SOIC) |       |

|                               |                                              | 7 PINS     |       |

| $R_{\theta JA}$               | Junction-to-ambient thermal resistance       | 116.4      | °C/W  |

| $R_{\theta JC(\text{top})}$   | Junction-to-case (top) thermal resistance    | 62.5       | °C/W  |

| $R_{\theta JC(\text{bot})}$   | Junction-to-case (bottom) thermal resistance | 38.8       | °C/W  |

| $R_{\theta JB}$               | Junction-to-board thermal resistance         | 41.9       | °C/W  |

| $\Psi_{JT}$                   | Junction-to-top characterization parameter   | 38.3       | °C/W  |

| $\Psi_{JB}$                   | Junction-to-board characterization parameter | N/A        | °C/W  |

| $M_T$                         | Thermal Mass                                 | 51.0       | mJ/°C |

(1) For more information about traditional and new thermal metrics, see the [Semiconductor and IC Package Thermal Metrics](#) application note.

## 5.5 Insulation Specification

Over free-air temperature range and  $V_{DD} = 2.3V$  to  $5.5V$  (unless otherwise noted); Typical specifications are at  $T_A = 25^\circ C$  and  $V_{DD} = 3.3V$  (unless otherwise noted)

| PARAMETER                                |                                                       | TEST CONDITIONS                                                                                                                                             | VALUE      | UNIT      |

|------------------------------------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------|

| <b>GENERAL</b>                           |                                                       |                                                                                                                                                             |            |           |

| CLR                                      | External Clearance <sup>(1)</sup>                     | Shortest terminal-to-terminal distance through air                                                                                                          | >4         | mm        |

| CPG                                      | External Creepage <sup>(1)</sup>                      | Shortest terminal-to-terminal distance across the package surface                                                                                           | >4         | mm        |

| DTI                                      | Distance through the insulation                       | Minimum internal gap (internal clearance)                                                                                                                   | >17        | μm        |

| CTI                                      | Comparative tracking index                            | DIN EN 60112; IEC 60112                                                                                                                                     | >400       | V         |

|                                          | Material Group                                        |                                                                                                                                                             | II         |           |

|                                          | Overvoltage category                                  | Rated mains voltage $\leq 150V_{RMS}$                                                                                                                       | I-IV       |           |

|                                          |                                                       | Rated mains voltage $\leq 300V_{RMS}$                                                                                                                       | I-III      |           |

| <b>DIN EN IEC 60747-17 (VDE 0884-17)</b> |                                                       |                                                                                                                                                             |            |           |

| $V_{IORM}$                               | Maximum repetitive peak isolation voltage             | At AC voltage                                                                                                                                               | 707        | $V_{PK}$  |

| $V_{IOWM}$                               | Maximum-rated isolation working voltage               | At AC voltage (sine wave)                                                                                                                                   | 500        | $V_{RMS}$ |

|                                          |                                                       | At DC voltage                                                                                                                                               | 707        | $V_{DC}$  |

| $V_{IOTM}$                               | Maximum transient isolation voltage                   | $V_{TEST} = V_{IOTM}$ , $t = 60s$ (qualification test),<br>$V_{TEST} = 1.2 \times V_{IOTM}$ , $t = 1s$ (100% production test)                               | 4250       | $V_{PK}$  |

| $V_{IMP}$                                | Maximum impulse voltage <sup>(2)</sup>                | Tested in air, 1.2/50-μs waveform per IEC 62368-1                                                                                                           | 5000       | $V_{PK}$  |

| $V_{IOSM}$                               | Maximum surge isolation voltage <sup>(3)</sup>        | Tested in oil (qualification test),<br>1.2/50-μs waveform per IEC 62368-1                                                                                   | 6500       | $V_{PK}$  |

| $q_{pd}$                                 | Apparent charge <sup>(4)</sup>                        | Method a, after input/output safety test subgroups 2 and 3,<br>$V_{pd(ini)} = V_{IOTM}$ , $t_{ini} = 60s$ , $V_{pd(m)} = 1.2 \times V_{IORM}$ , $t_m = 10s$ | $\leq 5$   | pC        |

|                                          |                                                       | Method a, after environmental tests subgroup 1,<br>$V_{pd(ini)} = V_{IOTM}$ , $t_{ini} = 60s$ , $V_{pd(m)} = 1.3 \times V_{IORM}$ , $t_m = 10s$             | $\leq 5$   |           |

|                                          |                                                       | Method b1, at preconditioning (type test) and routine test,<br>$V_{pd(ini)} = V_{IOTM}$ , $t_{ini} = 1s$ , $V_{pd(m)} = 1.5 \times V_{IORM}$ , $t_m = 1s$   | $\leq 5$   |           |

|                                          |                                                       | Method b2, at routine test (100% production) <sup>(6)</sup> ,<br>$V_{pd(ini)} = V_{IOTM} = V_{pd(m)}$ ; $t_{ini} = t_m = 1s$                                | $\leq 5$   |           |

| $C_{IO}$                                 | Barrier capacitance, input to output <sup>(5)</sup>   | $V_{IO} = 0.1V_{PP}$ at 100kHz                                                                                                                              | 1.4        | pF        |

| $R_{IO}$                                 | Insulation resistance, input to output <sup>(5)</sup> | $V_{IO} = 500V$ at $T_A = 25^\circ C$                                                                                                                       | $>10^{12}$ | $\Omega$  |

|                                          |                                                       | $V_{IO} = 500V$ at $100^\circ C \leq T_A \leq 125^\circ C$                                                                                                  | $>10^{11}$ |           |

|                                          |                                                       | $V_{IO} = 500V$ at $T_A = 150^\circ C$                                                                                                                      | $>10^9$    |           |

|                                          | Pollution degree                                      |                                                                                                                                                             | 2          |           |

|                                          | Climatic category                                     |                                                                                                                                                             | 55/125/21  |           |

| <b>UL1577</b>                            |                                                       |                                                                                                                                                             |            |           |

| $V_{ISO}$                                | Withstand isolation voltage                           | $V_{TEST} = V_{ISO}$ , $t = 60s$ (qualification);<br>$V_{TEST} = 1.2 \times V_{ISO}$ , $t = 1s$ (100% production)                                           | 3000       | $V_{RMS}$ |

- (1) Apply creepage and clearance requirements according to the specific equipment isolation standards of an application. Take care to maintain the creepage and clearance distance of the board design to make sure that the mounting pads of the isolator on the printed circuit board do not reduce this distance. Creepage and clearance on a printed circuit board become equal in certain cases. Techniques such as inserting grooves, ribs, or both on a printed circuit board are used to help increase these specifications.

- (2) Testing is carried out in air to determine the surge immunity of the isolation barrier.

- (3) Testing is carried out in oil to determine the intrinsic surge immunity of the isolation barrier.

- (4) Apparent charge is electrical discharge caused by a partial discharge (pd).

- (5) All pins on each side of the barrier tied together creating a two-terminal device.

- (6) Either method b1 or b2 is used in production.

## 5.6 Power Ratings

$V_S = 5.5$  V,  $V_{REF} = GND$ ,  $T_A = 125^\circ\text{C}$ ,  $T_J = 150^\circ\text{C}$ , device soldered on the device evaluation board.

| PARAMETER | TEST CONDITIONS                                     | MIN | TYP | MAX | UNIT          |

|-----------|-----------------------------------------------------|-----|-----|-----|---------------|

| $P_{D2}$  | $V_S = 5.5$ V, $I_Q = 17\mu\text{A}$ , no VOUT load |     |     | 94  | $\mu\text{W}$ |

## 5.7 Safety-Related Certifications

| UL                                    |                                       |

|---------------------------------------|---------------------------------------|

| UL 1577 Component Recognition Program | Certified according to IEC 62368-1 CB |

| File number: Pending                  | Certificate number: Pending           |

## 5.8 Safety Limiting Values

Safety limiting intends to minimize potential damage to the isolation barrier upon failure of input or output circuitry.

| PARAMETER | TEST CONDITIONS                                                                                             | MIN | TYP | MAX  | UNIT             |

|-----------|-------------------------------------------------------------------------------------------------------------|-----|-----|------|------------------|

| $I_S$     | $R_{\theta JA} = 116.4^\circ\text{C/W}$ , $V_I = 5$ V, $T_J = 150^\circ\text{C}$ , $T_A = 25^\circ\text{C}$ |     |     | 0.22 | A                |

| $P_S$     | $R_{\theta JA} = 116.4^\circ\text{C/W}$ , $T_J = 150^\circ\text{C}$ , $T_A = 25^\circ\text{C}$              |     |     | 1.1  | W                |

| $T_S$     | Safety temperature <sup>(1)</sup>                                                                           |     |     | 150  | $^\circ\text{C}$ |

(1) The maximum safety temperature,  $T_S$ , has the same value as the maximum junction temperature,  $T_J$ , specified for the device. The  $I_S$  and  $P_S$  parameters represent the safety current and safety power respectively. The maximum limits of  $I_S$  and  $P_S$  should not be exceeded. These limits vary with the ambient temperature,  $T_A$ .

The junction-to-air thermal resistance,  $R_{\theta JA}$ , in the [セクション 5.4](#) table is that of a device installed on a device evaluation board. Use these equations to calculate the value for each parameter:

$T_J = T_A + R_{\theta JA} \times P$ , where  $P$  is the power dissipated in the device.

$T_{J(max)} = T_S = T_A + R_{\theta JA} \times P_S$ , where  $T_{J(max)}$  is the maximum allowed junction temperature.

$P_S = I_S \times V_I$ , where  $V_I$  is the maximum input voltage.

## 5.9 Electrical Characteristics

Over free-air temperature range and  $V_{DD} = 2.3V$  to  $5.5V$  (unless otherwise noted); Typical specifications are at  $T_A = 25^\circ C$  and  $V_{DD} = 3.3V$  (unless otherwise noted)

| PARAMETER                 | TEST CONDITIONS                |                                                                                                  | MIN                                                                                  | TYP   | MAX           | UNIT    |              |

|---------------------------|--------------------------------|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-------|---------------|---------|--------------|

| <b>TEMPERATURE SENSOR</b> |                                |                                                                                                  |                                                                                      |       |               |         |              |

| $T_{ERR}$                 | Temperature accuracy           | $0^\circ C$ to $70^\circ C$                                                                      |                                                                                      | -1.2  | $\pm 0.5$     | 1.2     | $^\circ C$   |

| $T_{ERR}$                 | Temperature accuracy           | $-40^\circ C$ to $150^\circ C$                                                                   |                                                                                      | -2.5  | $\pm 0.5$     | 2.5     | $^\circ C$   |

| PSR                       | DC power supply rejection      |                                                                                                  |                                                                                      | -0.1  | 0.02          | 0.1     | $^\circ C/V$ |

| $T_{SENS}$                | Temperature sensitivity        | $T_A = -40^\circ C$ to $150^\circ C$                                                             |                                                                                      | 10.00 | $mV/^\circ C$ |         |              |

| $T_{LTD}$                 | Long-term drift <sup>(1)</sup> | 300 hours at $150^\circ C$ , $5.5V$                                                              |                                                                                      | .05   | $^\circ C$    |         |              |

| $V_{OUT}$                 | Output voltage                 | $T_A = 0^\circ C$                                                                                |                                                                                      | 500   | $mV$          |         |              |

|                           |                                | $T_A = 25^\circ C$                                                                               |                                                                                      | 750   | $mV$          |         |              |

| NL                        | Nonlinearity                   | $T_A = -40^\circ C$ to $150^\circ C$                                                             |                                                                                      | 0.5   | $^\circ C$    |         |              |

| $t_{RESP\_D}$             | Directional Response time      | 2-layer 62-mil Rigid PCB<br>2oz. Copper                                                          | $\tau = 63\%$<br>$TSENSE = 25^\circ C$ to $75^\circ C$<br>Pins 1 to 4 = $25^\circ C$ | 1600  | ms            |         |              |

| $t_{RESP\_L}$             | Response time (Stirred Liquid) | 0.5in x 0.5in,<br>2-layer 62-mil PCB                                                             | $\tau = 63\%$<br>$25^\circ C$ to $150^\circ C$                                       | 1600  | ms            |         |              |

| <b>ANALOG OUTPUT</b>      |                                |                                                                                                  |                                                                                      |       |               |         |              |

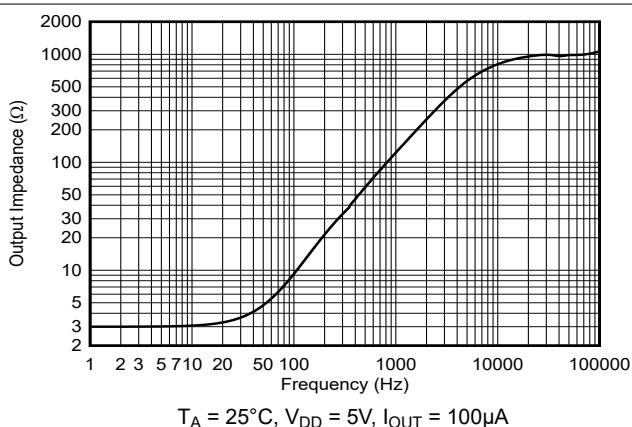

| $Z_{OUT}$                 | Output impedance               | $I_{LOAD} = 100\mu A$ , $f = 100Hz$                                                              |                                                                                      | 20    | $\Omega$      |         |              |

|                           |                                | $I_{LOAD} = 100\mu A$ , $f = 500Hz$                                                              |                                                                                      | 50    | $\Omega$      |         |              |

| $I_{OUT}$                 | Output current                 |                                                                                                  |                                                                                      | 500   | $\mu A$       |         |              |

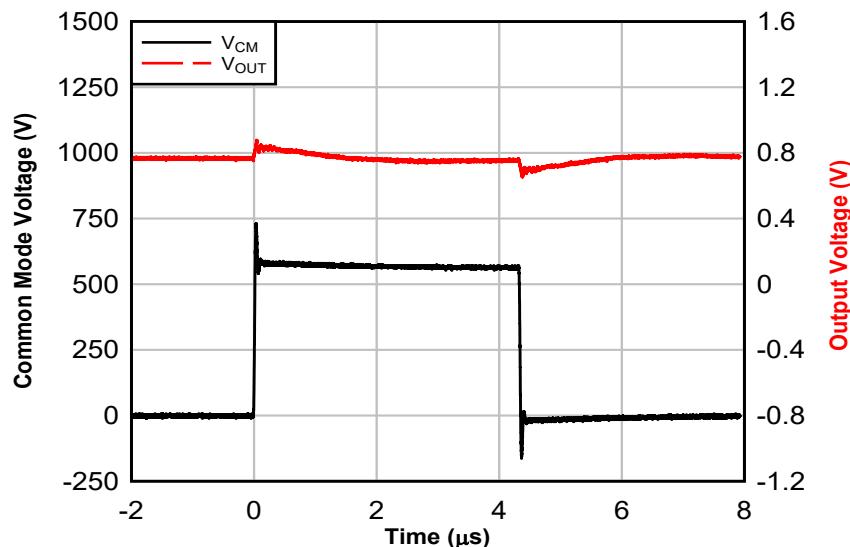

| CMTI                      | Common Mode Transient Immunity | $V_{CM} = 500V$ , $\Delta V_{OUT} < 200mV$ , $2\mu s$ , $C_{LOAD} = 1nF$ , $R_{LOAD} = 5k\Omega$ |                                                                                      | 50    | $kV/\mu s$    |         |              |

| $L_R$                     | Load regulation                | $I_{LOAD} = 0 \mu A$ to $500 \mu A$                                                              |                                                                                      | 6     | $mV$          |         |              |

| $C_L$                     | Maximum capacitive load        |                                                                                                  |                                                                                      | 1     | $nF$          |         |              |

| <b>POWER SUPPLY</b>       |                                |                                                                                                  |                                                                                      |       |               |         |              |

| $I_{DD}$                  | Operating current              | $V_{DD} = 3.3V$<br>$T_A = 25^\circ C$                                                            |                                                                                      | 10    | 12            | $\mu A$ |              |

|                           |                                | $T_A = -40^\circ C$ to $150^\circ C$                                                             |                                                                                      |       | 17            | $\mu A$ |              |

(1) Long term stability is determined using accelerated operational life testing at a junction temperature of  $150^\circ C$ .

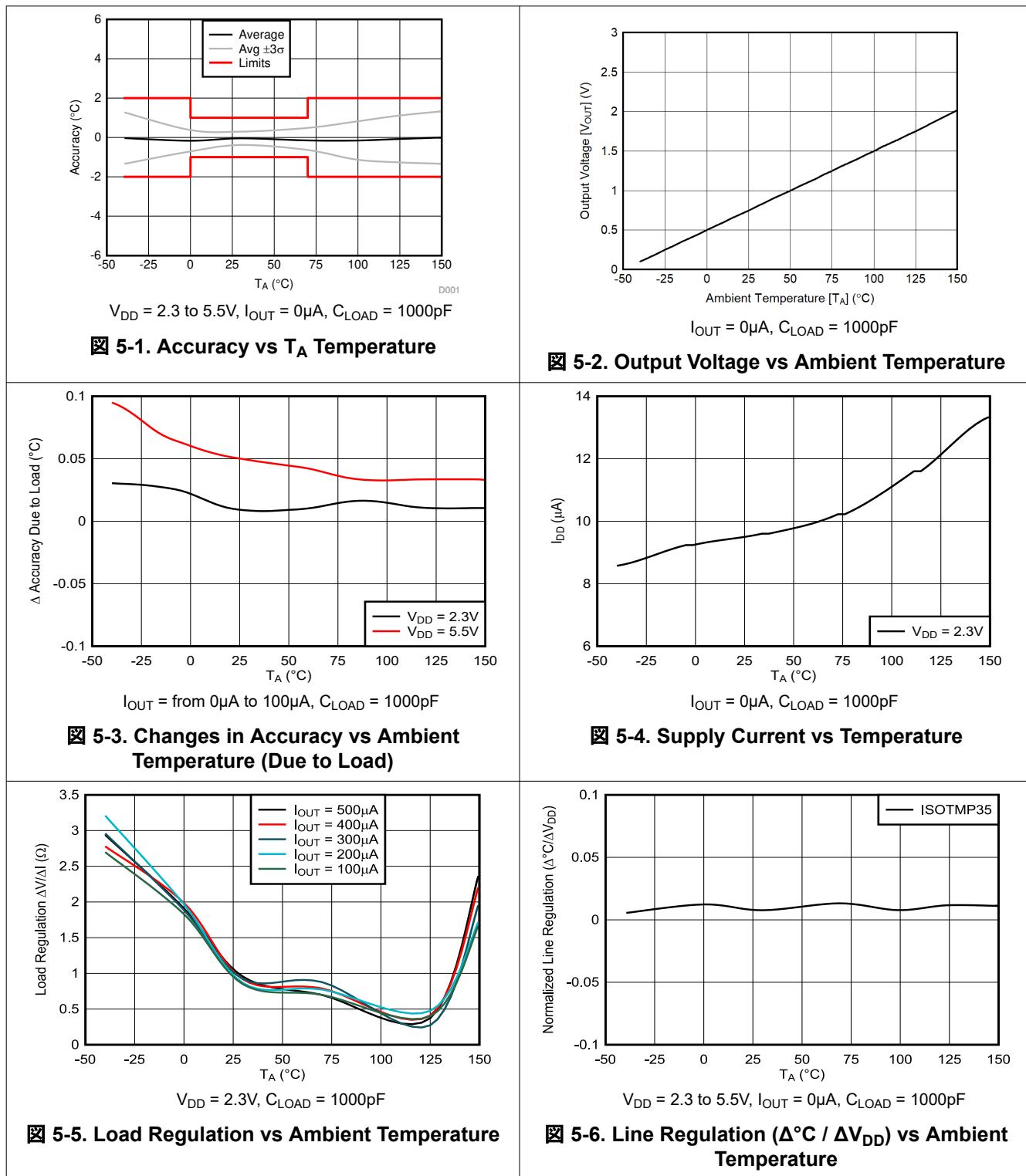

## 5.10 Typical Characteristics

at  $T_A = 25^\circ\text{C}$  (unless otherwise noted)

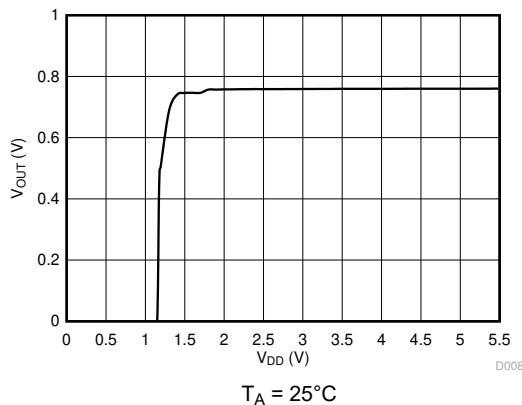

图 5-7. Output Voltage vs Power Supply

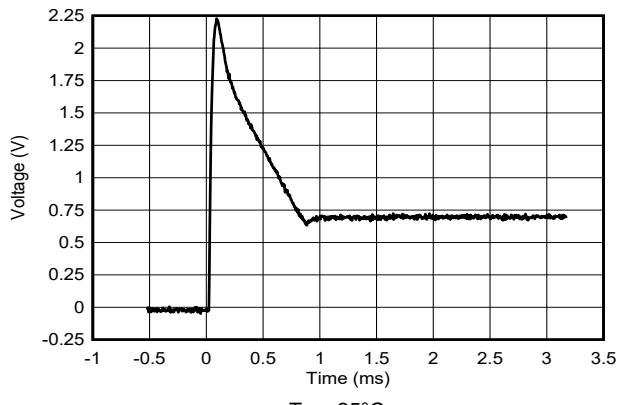

图 5-8. Output vs. Settling Time to Step  $V_{DD}$ 图 5-9. Output vs. Settling Time to Ramp  $V_{DD}$

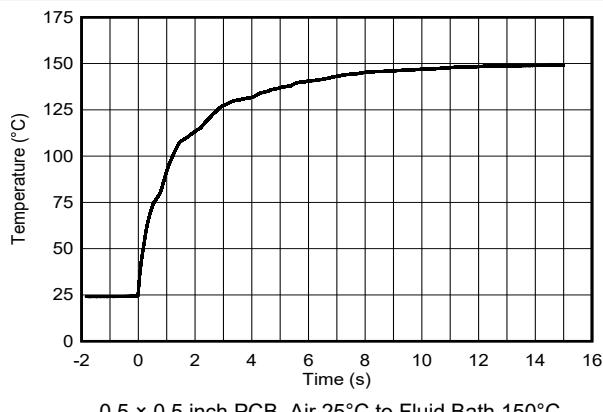

图 5-10. Thermal Response (Air-to-Fluid Bath)

图 5-11. Output Impedance vs Frequency

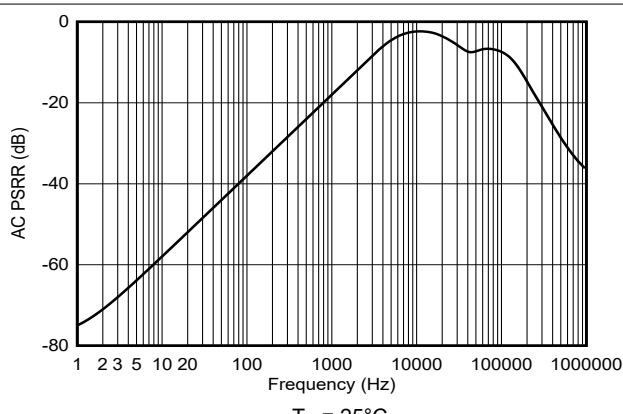

图 5-12. PSRR vs Frequency

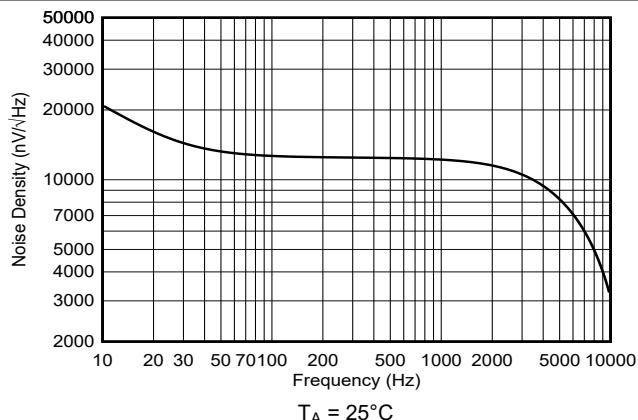

図 5-13. Output Noise Density

## 6 Detailed Description

### 6.1 Overview

The ISOTMP35 is a linear analog output temperature sensor with an output voltage proportional to temperature. The temperature sensor has an accuracy from 0°C to 70°C of  $\pm 1.2^\circ\text{C}$ . The ISOTMP35 provides a positive slope output of 10mV/°C over the full  $-40^\circ\text{C}$  to  $150^\circ\text{C}$  and a supply range from 2.3V to 5.5V. A class-AB output driver provides a maximum output of 500 $\mu\text{A}$  to drive capacitive loads up to 1000pF.

### 6.2 Functional Block Diagram

図 6-1. Functional Block Diagram

### 6.3 Features Description

The ISOTMP35 device combines a robust integrated isolation barrier with a tight accuracy analog output temperature sensor. All the features related to the analog output, accuracy, output characteristics of the sensor, and drive characteristic of the output are treated under the analog output section.

### 6.3.1 Integrated Isolation Barrier and Thermal Response

The ISOTMP35 is designed to integrate a robust isolation barrier while maximizing the heat flow. This is made possible by a SO-7 package designed to provide the 3-kVrms isolating rating (UL1577) and isolation mechanism that minimizes the thermal response from the TSENSE pins to the temperature sensor.

### 6.3.2 Analog Output

The analog output of the ISOTMP35 has several characteristics, such as the output accuracy, linearity and drive capability, that must be understood to design the interface to the rest of the signal chain.

#### 6.3.2.1 Output Accuracy

As illustrated in [図 5-1](#), the ISOTMP35 device is linear with a 500mV offset at 0°C. However for temperature greater than 100°C, a gain shift occurs. See [Output Voltage Linearity](#) for an approximation if using a lookup table to convert the voltage to temperature.

#### 6.3.2.2 Output Voltage Linearity

As illustrated in [図 5-2](#), the ISOTMP35 device exhibit a linear output of 10mV/°C. Use [式 1](#) to calculate the output voltage.

$$V_{\text{OUT}} = (T_A - T_{\text{INFL}}) \times T_C + V_{\text{OFFS}} \quad (1)$$

where

- $V_{\text{OUT}}$  is the ISOTMP35 voltage output for a given temperature

- $T_A$  is the ambient temperature in °C

- $T_{\text{INFL}}$  is the temperature inflection point for a piecewise segment in °C

- $T_C$  is the ISOTMP35 temperature coefficient or gain

- $V_{\text{OFFS}}$  is the ISOTMP35 voltage offset

#### 6.3.2.3 Drive Capability

A class-AB output driver provides a maximum output of 500μA to drive capacitive loads up to 1000pF. To design the time and frequency domains signal-chain implementation, use the driver output impedance graph provided in [図 5-11](#).

#### 6.3.2.4 Common Mode Transient Immunity (CMTI)

CMTI is the capability of the device to tolerate a rising or falling voltage step on the high voltage pins without coupling significant disturbance on the output signal. The device is specified for the maximum common-mode transition rate under which the output signal does not experience a disturbance greater than 200mV lasting longer than 2μs, as shown in [Common-Mode Transient Response](#) with a 50kV/ns common-mode input step. Here, a 1nF load capacitor is utilized along with a 5kΩ load resistor as the load conditions. Higher edge rates than the specified CMTI can be supported with sufficient blanking time after common-mode transitions.

図 6-2. Common-Mode Transient Response

### 6.3.3 Thermal Response

The SOIC-7 package is designed to maximize the heat flow and minimize the thermal response time from the TSENSE pins to the temperature sensor, while also providing the 3kV<sub>RMS</sub> isolation rating (UL1577).

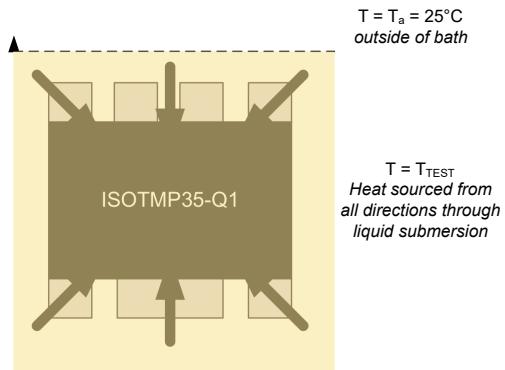

When evaluating thermal response with a thermal contact device, care must be taken to understand the gradient that is established by the heat source in the application. Traditionally, most temperature sensors are characterized on the basis of a "stirred-liquid" thermal response test, which sees the totality of the device submerged into a circulated oil bath at an elevated temperature, which typically provides the best possible response the device yields, having all parts of the device held to the secondary temperature for the purposes of establishing a new thermal equilibrium point. This style of test is visualized in [Stirred Liquid Thermal Response Test](#), and the results of this test are presented in [Thermal Response \(Air-to-Fluid Bath\)](#).

図 6-3. Stirred Liquid Thermal Response Test

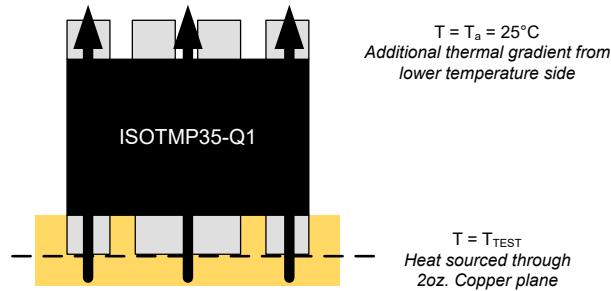

ISOTMP35 is also evaluated by means of a "directional" temperature response test, where only the thermally connected, high-voltage pins of the device are exposed to the elevated temperature, while the remaining low voltage pins remain in free air at a standard room temperature condition of 25°C. The objective of this form of thermal response test is to more properly evaluate the thermal conductivity of the device under test, even though slight error can persist from the reference temperature.

図 6-4. Directional Thermal Response Test

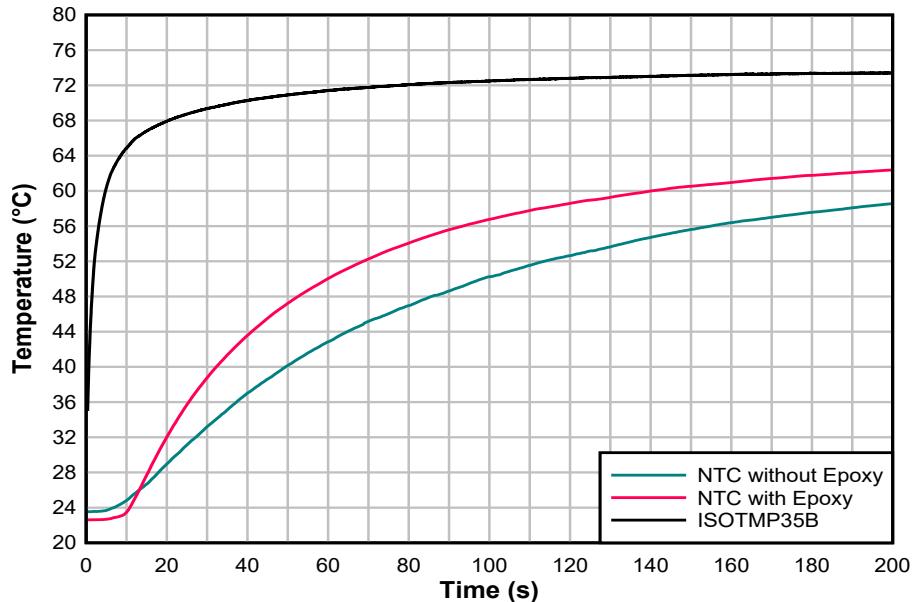

This is demonstrated in 図 6-5, where ISOTMP35 is shown alongside a standard negative temperature coefficient (NTC) thermistor, as well as the same NTC adhered via non-conductive thermal epoxy to the high voltage copper, placed at clearance distance of 4mm from the temperature source. The resulting responses demonstrate both the superior response time, as well as the accuracy of the ISOTMP35 device. The reference temperature in this test is 75°C.

図 6-5. ISOTMP35 Directional Thermal Response

## 6.4 Device Functional Modes

The singular functional mode of the ISOTMP35 is an analog output directly proportional to temperature.

## 7 Application and Implementation

注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes, as well as validating and testing their design implementation to confirm system functionality.

## 7.1 Application Information

The features of the ISOTMP35 make the device versatile for various high voltage temperature-sensing applications. The ISOTMP35 can operate down to a 2.3V supply with 9 $\mu$ A current consumption. As a result, the device is also well designed for battery applications where a number of these batteries can be stacked for high voltage output.

### 7.1.1 Output Voltage Linearity

As illustrated in [图 5-2](#), the ISOTMP35 device exhibits a linear output of 10mV/°C. For temperatures above 100°C, a small gain shift ( $T_C$ ) is present on the output ( $V_{OUT}$ ). When small shifts are expected, a piecewise linear function provides the best accuracy and is used for the device accuracy specifications. [表 7-2](#) lists the typical output voltages of the ISOTMP35 device across the full operating temperature range. The calculated linear column represents the ideal linear  $V_{OUT}$  output response with respect to temperature, while the piecewise linear columns indicate the small voltage shift at elevated temperatures.

The piecewise linear function uses three temperature ranges listed in [表 7-1](#). Use [式 2](#) to calculate the voltage output  $V_{OUT}$  of the ISOTMP35:

$$V_{OUT} = (T_A - T_{INFL}) \times T_C + V_{OFFS} \quad (2)$$

where

- $V_{OUT}$  is the voltage output for a given temperature

- $T_A$  is the ambient temperature in °C

- $T_{INFL}$  is the temperature inflection point for a piecewise segment in °C

- $T_C$  is the temperature coefficient or gain

- $V_{OFFS}$  is the voltage offset

Use [表 7-2](#) to calculate the ambient temperature ( $T_A$ ) for a given  $V_{OUT}$  voltage output within a piecewise voltage range ( $V_{RANGE}$ ). For applications where the accuracy enhancement above 100°C is not required, use the first row of [表 7-1](#) for all voltages.

$$T_A = (V_{OUT} - V_{OFFS}) \div T_C + T_{INFL} \quad (3)$$

**表 7-1. Piecewise Linear Function Summary**

| <b><math>T_A</math> RANGE (°C)</b> | <b><math>V_{RANGE}</math> (mV)</b> | <b><math>T_{INFL}</math> (°C)</b> | <b><math>T_C</math> (mV/°C)</b> | <b><math>V_{OFFS}</math> (mV)</b> |

|------------------------------------|------------------------------------|-----------------------------------|---------------------------------|-----------------------------------|

| -40 to 100                         | < 1500                             | 0                                 | 10                              | 500                               |

| +100 to 125                        | 1500 to 1752.5                     | 100                               | 10.1                            | 1500                              |

| 125 to 150                         | > 1752.5                           | 125                               | 10.6                            | 1752.5                            |

**表 7-2. Transfer Table**

| TEMPERATURE (°C) | V <sub>OUT</sub> (mV) CALCULATED LINEAR VALUES | V <sub>OUT</sub> (mV) PIECEWISE LINEAR VALUES |

|------------------|------------------------------------------------|-----------------------------------------------|

| -40              | 100                                            | 100                                           |

| -35              | 150                                            | 150                                           |

| -30              | 200                                            | 200                                           |

| -25              | 250                                            | 250                                           |

| -20              | 300                                            | 300                                           |

| -15              | 350                                            | 350                                           |

| -10              | 400                                            | 400                                           |

| -5               | 450                                            | 450                                           |

| 0                | 500                                            | 500                                           |

| 5                | 550                                            | 550                                           |

| 10               | 600                                            | 600                                           |

| 15               | 650                                            | 650                                           |

| 20               | 700                                            | 700                                           |

| 25               | 750                                            | 750                                           |

| 30               | 800                                            | 800                                           |

| 35               | 850                                            | 850                                           |

| 40               | 900                                            | 900                                           |

| 45               | 950                                            | 950                                           |

| 50               | 1000                                           | 1000                                          |

| 55               | 1050                                           | 1050                                          |

| 60               | 1100                                           | 1100                                          |

| 65               | 1150                                           | 1150                                          |

| 70               | 1200                                           | 1200                                          |

| 75               | 1250                                           | 1250                                          |

| 80               | 1300                                           | 1300                                          |

| 85               | 1350                                           | 1350                                          |

| 90               | 1400                                           | 1400                                          |

| 95               | 1450                                           | 1450                                          |

| 100              | 1500                                           | 1500                                          |

| 105              | 1550                                           | 1550.5                                        |

| 110              | 1600                                           | 1601                                          |

| 115              | 1650                                           | 1651.5                                        |

| 120              | 1700                                           | 1702                                          |

| 125              | 1750                                           | 1752.5                                        |

| 130              | 1800                                           | 1805/5                                        |

| 135              | 1850                                           | 1858/5                                        |

| 140              | 1900                                           | 1911.5                                        |

| 145              | 1950                                           | 1964.5                                        |

| 150              | 2000                                           | 2017.5                                        |

### 7.1.2 Load Regulation

Load regulation is how the analog output voltage of the ISOTMP35 changes as the output load current changes, and is measured across temperature. Load regulation is important because when implementing the ISOTMP35 with an ADC, the user can use an RC filter on the analog output. Knowing how the output voltage changes based on the current pulled with different resistive and capacitive loads help the user make accurate temperature measurements with the ISOTMP35. See [図 5-5](#) for more details on Load Regulation and [セクション 7.1.6](#) for more details on how to use the ISOTMP35 with an ADC.

### 7.1.3 Start-Up Settling Time

The ISOTMP35 can support either a step input power supply or a ramp power supply. When powering the device, consider the analog output settling time upon start-up. For a step  $V_{DD}$  input, start-up time is approximately 1ms.

The ISOTMP35 can support either a step input power supply or a ramp power supply. When powering the ISOTMP35, the user must keep in mind that the ISOTMP35 requires time to settle the analog output upon start-up:

- For a step  $V_{DD}$  input, start-up time is approximately 1ms.

- For a ramp  $V_{DD}$  input with a ramp rate of 5V/ms, start-up time is approximately 1.25ms.

See [図 5-8](#) and [図 5-9](#) for more information.

### 7.1.4 Thermal Response

The 7-pin SOIC package is designed to maximize the heat flow, and minimize the thermal response time, from the TSENSE pins to the temperature sensor while also providing the 3 kV<sub>RMS</sub> isolation rating (UL1577).

### 7.1.5 External Buffer

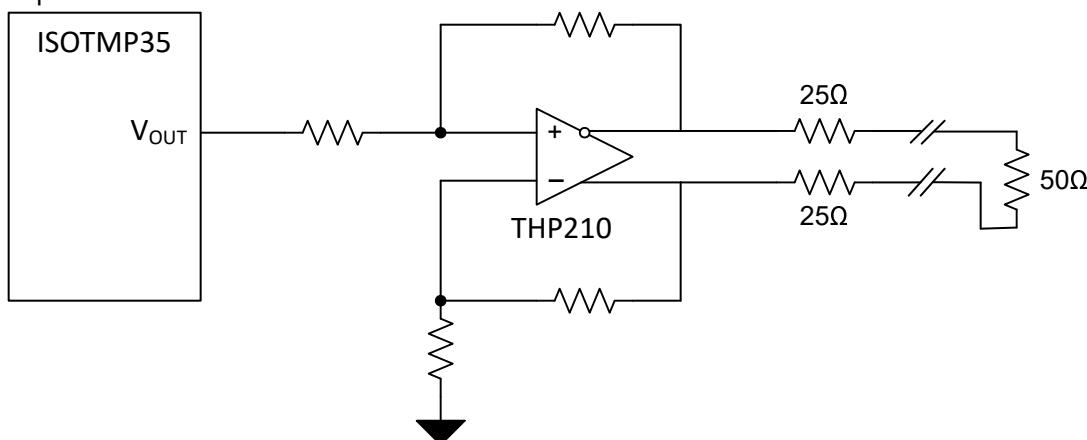

In case of higher capacitance on the output or a long trace between the sensor and the ADC, a external buffer can be added. This implementation is shown in [図 7-1](#) for the signal to be temperature voltage to be sent through a differential pair.

**図 7-1. Buffering Prior to Sending Data Through a Differential Pair**

### 7.1.6 ADC Selection and Impact on Accuracy

When connecting the ISOTMP35 analog output to an ADC, using an RC filter on the output is important. Most ADCs have a sampled comparator input structure. When the sampling is active, a switch internal to the ADC charges an internal capacitor ( $C_{SAMPLE}$ ). The capacitor requires instantaneous charge from the analog output source (ISOTMP35), so this lead to voltage drops on the ISOTMP35 analog output, which appears as incorrect temperature reads. By placing a filter capacitor ( $C_{FILTER}$ ) load on the ISOTMP35 analog output, the voltage drops are mitigated. This works because  $C_{FILTER}$  stores charge from the analog output that the ADC can pull

from when sampling, so there is no voltage drop on the ISOTMP35 output. Users can also add  $R_{FILTER}$  to filter out noise on the analog output.

Consider the maximum load capacitance. The ISOTMP35 has a maximum load capacitance of 1000pF, therefore the total capacitance on the analog output, including those in the ADC input, must not exceed 1000pF.

When choosing the R and C filter values, the RC time constant changes the settling time of the ISOTMP35. ADCs often have customizable sampling rates, so the settling time of the ISOTMP35 must be less than the selected sampling time of the ADC. For example, an ADC with a data rate (DR) of 1ksps has a conversion time of 1ms, therefore any selected R and C filter values must be completely settled within 1ms ( $5 \times R \times C < 1/DR$ ).

ADCs often have customizable full scale ranges (FSR), either digitally or through reference voltages. The ISOTMP35 at 150°C outputs a maximum voltage of 2017.5mV. When choosing an ADC, there must be a full scale range option with at least that much range. TI recommends a FSR option of at least 3V to avoid headroom concerns in this example. To determine the desired ADC resolution, the ADC LSB size must be known. For the ISOTMP35, the device does not have an LSB but rather the LSB of the ADC determines the measurement resolution.

- For example, a 12bit ADC with an FSR of 3.3V, has an LSB size of 806 $\mu$ V. This translates to 80m°C of temperature resolution. A 16bit ADC with an FSR of 3.3V, has an LSB size of 50 $\mu$ V, which gives 5m°C of temperature resolution. A 12bit ADC is sufficient for most applications.

- The analog output voltage from the ISOTMP35 must not exceed the  $V_{DD}$  being supplied to the ADC. Selecting a  $V_{DD}$  for the ADC that exceeds the chosen FSR required to fully capture the ISOTMP35 analog output range is necessary.

**表 7-3. ADC Settling Times and Cutoff Frequencies**

| SETTLING TIME<br>( $\mu$ s) & CUTOFF<br>FREQUENCY<br>(KHz) | SETTLING TIME (5 $\times$ RC TIME CONSTANT) |               |              | CUTOFF FREQUENCY (fC = 1/(2 $\pi$ RC)) |          |          |

|------------------------------------------------------------|---------------------------------------------|---------------|--------------|----------------------------------------|----------|----------|

|                                                            | 100pF                                       | 680pF         | 1000pF       | 100pF                                  | 680pF    | 1000pF   |

| 1k $\Omega$                                                | 0.5 $\mu$ s                                 | 3.4 $\mu$ s   | 5 $\mu$ s    | 1592kHz                                | 234.2kHz | 159.2kHz |

| 4.7k $\Omega$                                              | 2.35 $\mu$ s                                | 15.98 $\mu$ s | 23.5 $\mu$ s | 338.8kHz                               | 49.8kHz  | 33.88kHz |

| 10k $\Omega$                                               | 5 $\mu$ s                                   | 34 $\mu$ s    | 50 $\mu$ s   | 159.2kHz                               | 23.42kHz | 15.92kHz |

| 100k $\Omega$                                              | 50 $\mu$ s                                  | 340 $\mu$ s   | 500 $\mu$ s  | 15.92kHz                               | 2.34kHz  | 1.592kHz |

### 7.1.7 Implementation Guidelines

Voltage clearance on the line must be respected.

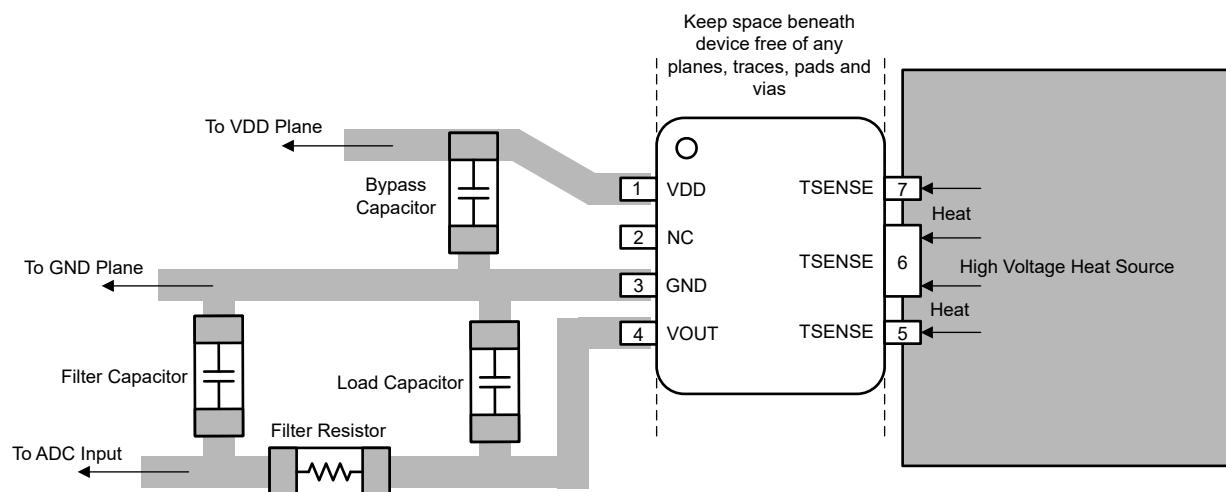

A minimum of two layers is required for the ISOTMP35. Standard layer stacking can be used for a 4-layer PCB where the signal traces can run either on the top or bottom layer. Solid ground and power plane must form the inner layer. See [PCB Cross-Section](#) for a depiction of plane and trace clearance under the device.

**図 7-2. PCB Cross-Section**

### 7.1.8 PSRR

Depending on the application, there can be a significant amount of high frequency noise on the power supply line. If high frequency noise (>100kHz) is present, the user can switch to a  $1\mu\text{F}$  bypass capacitor to provide additional filtering on the power supply line. Increasing the bypass capacitance or choosing a capacitor with a lower ESR across frequency improves PSRR performance.

An additional power supply consideration is line regulation. For the ISOTMP35, line regulation refers to the change in output temperature with changing power supply. [图 5-6](#) shows that, across the entire environment temperature range, ISOTMP35 maintains a steady amount change in temperature across  $V_{DD}$ .

## 7.2 Typical Application

**图 7-3. Typical ISOTMP35 Circuit**

### 7.2.1 Design Requirements

To design with ISOTMP35, use the parameters listed in [表 7-4](#). Most CMOS-based ADCs have a sampled data comparator input structure. When the ADC charges the sampling capacitor, the capacitor requires instantaneous charge from the output of the analog temperature sensor, such as the ISOTMP35. Therefore, the output impedance of the temperature sensor can affect ADC performance. In most cases, adding an external capacitor mitigates design challenges. The ISOTMP35 is specified and characterized with a  $1000\text{pF}$  maximum capacitive load ( $C_{LOAD}$ ). The  $C_{LOAD}$  is a sum of the  $C_{FILTER}$ ,  $C_{MUX}$  and  $C_{SAMPLE}$ . TI recommends maximizing the  $C_{FILTER}$  value while allowing for the maximum specified ADC input capacitance ( $C_{MUX} + C_{SAMPLE}$ ) to limit the total  $C_{LOAD}$  at  $1000\text{pF}$ . In most cases, a  $680\text{pF}$   $C_{FILTER}$  provides a reasonable allowance for ADC input capacitance to minimize ADC sampling error and reduce noise coupling. An optional series resistor ( $R_{FILTER}$ ) and  $C_{FILTER}$  provides additional low-pass filtering to reject system level noise. TI recommends placing  $R_{FILTER}$  and  $C_{FILTER}$  as close to the ADC input as possible for optimal performance.

**表 7-4. Design Parameters**

| PARAMETER                                     | VALUE            |

|-----------------------------------------------|------------------|

| Supply voltage, $V_{DD}$                      | 2.3V to 5.5V     |

| Decoupling capacitor between $V_{DD}$ and GND | $0.1\mu\text{F}$ |

### 7.2.2 Detailed Design Procedure

Depending on the input characteristics of the ADC, an external  $C_{FILTER}$  can be required. The value of  $C_{FILTER}$  depends on the size of the sampling capacitor ( $C_{SAMPLE}$ ) and the sampling frequency while observing a maximum  $C_{LOAD}$  of  $1000\text{pF}$ . The capacitor requirements can vary because the input stages of all ADCs are not identical.

### 7.2.2.1 Insulation Lifetime

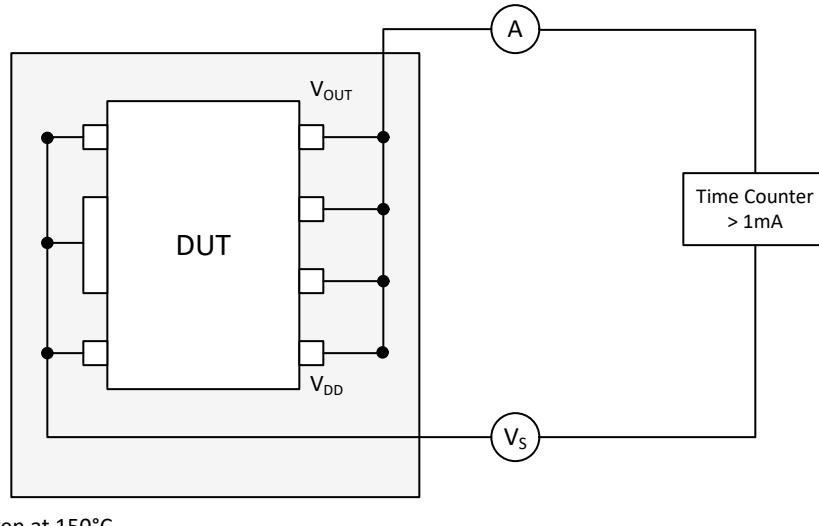

Insulation lifetime projection data is collected by using industry-standard Time Dependent Dielectric Breakdown (TDDB) test method. In this test, all pins on each side of the barrier are tied together creating a two-terminal device and high voltage applied between the two sides; See [図 7-4](#) for TDDB test setup. The insulation breakdown data is collected at various high voltages switching at 60Hz over temperature.

**図 7-4. Test Setup for Insulation Lifetime Measurement**

## 7.3 Power Supply Recommendations

To help provide reliable operation at supply voltages, a  $0.1\mu\text{F}$  bypass capacitor is recommended at the  $\text{V}_{\text{DD}}$  supply pin. Place the capacitor as close to the supply pin as possible. Because there is only a single side power supply for the ISOTMP35, there is no need to generate isolated power.

## 7.4 Layout

### 7.4.1 Layout Guidelines

A minimum of two layers is required for the ISOTMP35. For a 4-layer PCB, TI recommends a standard layer stacking method where the signal traces run either on the top or bottom layer. Solid ground and power plane must form the inner layer.

### 7.4.2 Layout Example

図 7-5. Layout Example

図 7-6. Layout Example - PCB Cross-Section

## 8 Device and Documentation Support

TI offers an extensive line of development tools. Tools and software to evaluate the performance of the device, generate code, and develop solutions are listed below.

### 8.1 Documentation Support

#### 8.1.1 Related Documentation

For related documentation, see the following:

- Texas Instruments, [ISOTMP35 Evaluation Module User's Guide](#)

- Texas Instruments, [Circuit for driving an ADC with an instrumentation amplifier in high gain](#), circuit design

- Texas Instruments, [Driving a SAR ADC directly without a front-end buffer circuit \(low-power, low-sampling-speed DAQ\)](#), circuit design

### 8.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 8.3 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの[使用条件](#)を参照してください。

#### 8.4 Trademarks

テキサス・インスツルメンツ E2E™ is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

#### 8.5 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

#### 8.6 用語集

##### テキサス・インスツルメンツ用語集

この用語集には、用語や略語の一覧および定義が記載されています。

### 9 Revision History

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision * (October 2023) to Revision A (June 2024) | Page |

|------------------------------------------------------------------|------|

| • ドキュメント全体にわたって表、図、相互参照の採番方法を更新.....                             | 1    |

| • このデータシートのステータスを「量産データ」に変更.....                                 | 1    |

### 10 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ（データシートを含みます）、設計リソース（リファレンス デザインを含みます）、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている テキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](#) やかかる テキサス・インスツルメンツ製品の関連資料などのいづれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2024, Texas Instruments Incorporated

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| ISOTMP35BDFQR         | Active        | Production           | SOIC (DFQ)   7 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 150   | T35                 |

| ISOTMP35BDFQR.A       | Active        | Production           | SOIC (DFQ)   7 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 150   | T35                 |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

**OTHER QUALIFIED VERSIONS OF ISOTMP35 :**

- Automotive : [ISOTMP35-Q1](#)

---

NOTE: Qualified Version Definitions:

- Automotive - Q100 devices qualified for high-reliability automotive applications targeting zero defects

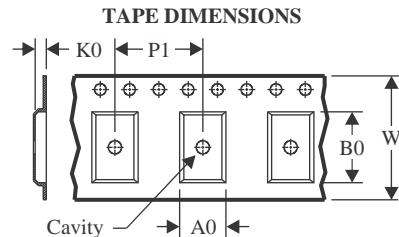

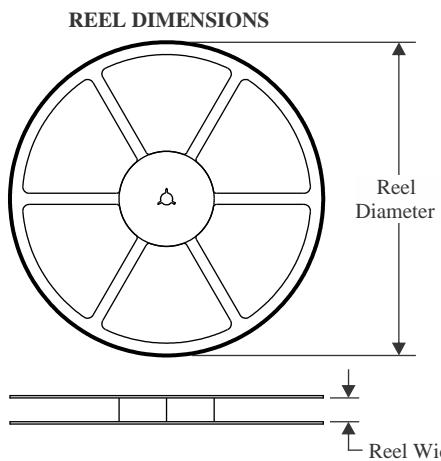

**TAPE AND REEL INFORMATION**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

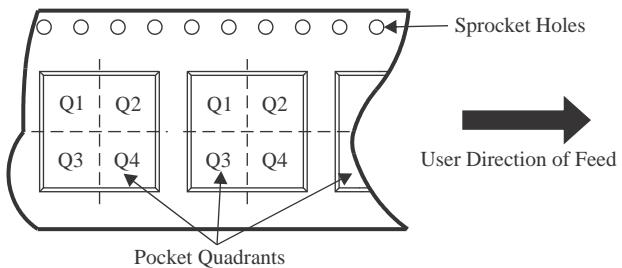

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|---------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| ISOTMP35BDFQR | SOIC         | DFQ             | 7    | 3000 | 330.0              | 12.4               | 6.4     | 5.2     | 2.1     | 8.0     | 12.0   | Q1            |

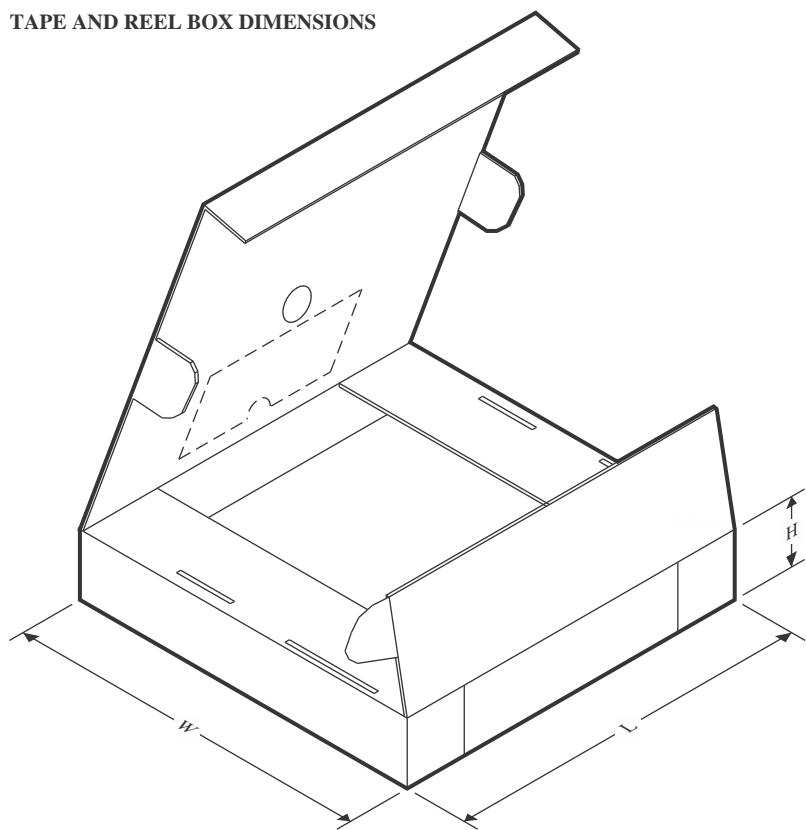

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---------------|--------------|-----------------|------|------|-------------|------------|-------------|

| ISOTMP35BDFQR | SOIC         | DFQ             | 7    | 3000 | 353.0       | 353.0      | 32.0        |

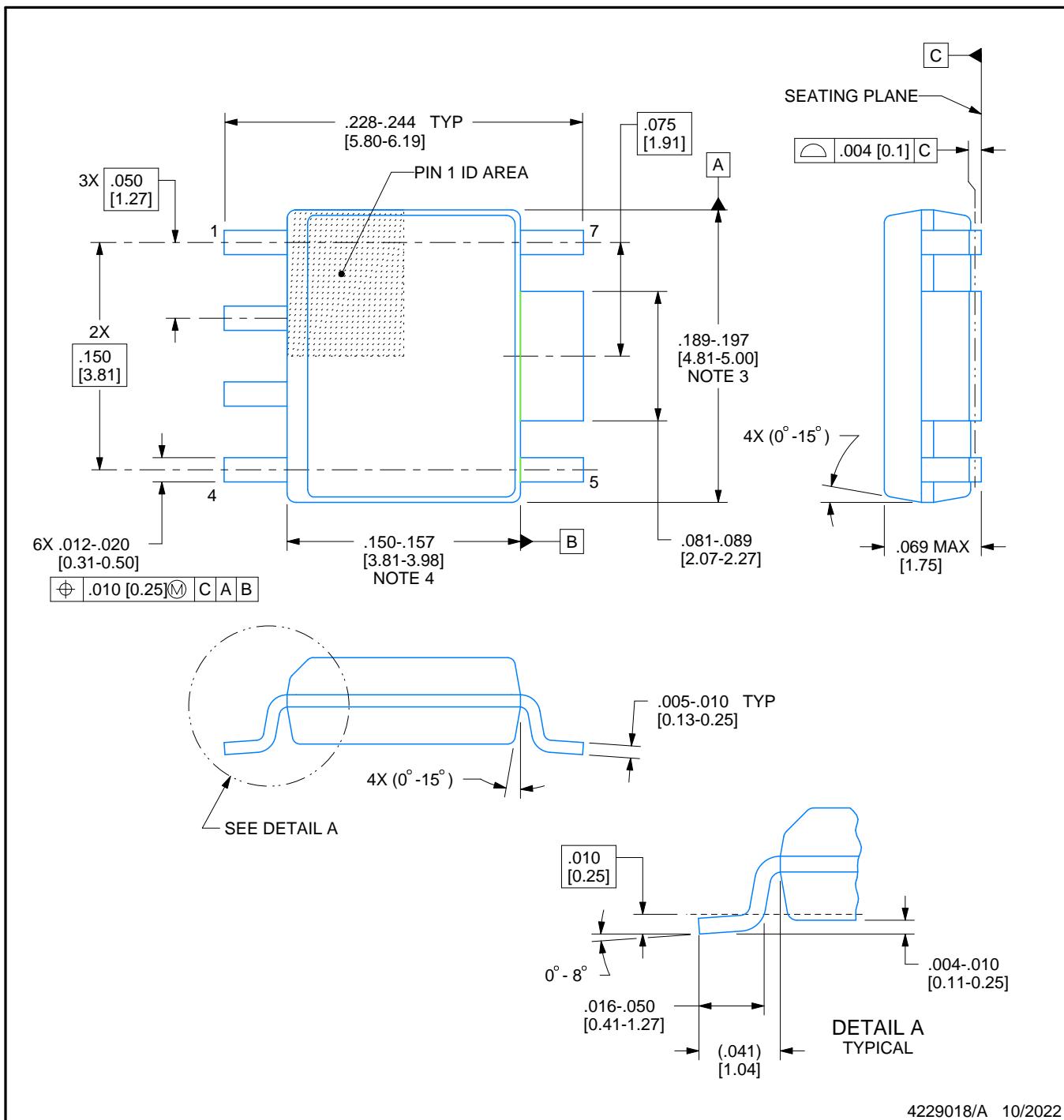

# PACKAGE OUTLINE

DFQ0007A

SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES:

- Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

- This drawing is subject to change without notice.

- This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

- This dimension does not include interlead flash.

- No JEDEC Registration as of September 2022

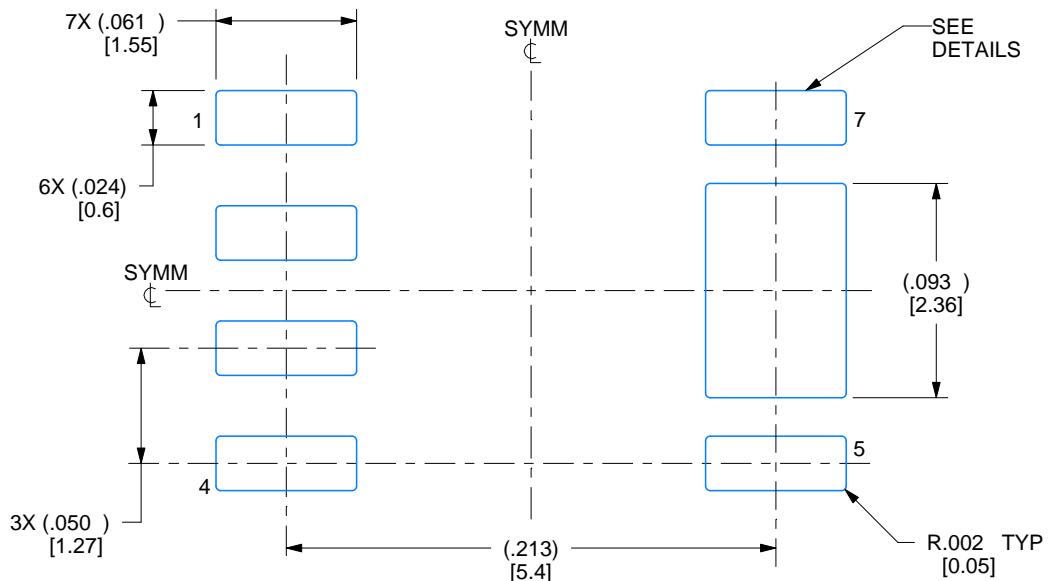

# EXAMPLE BOARD LAYOUT

DFQ0007A

SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE:12X

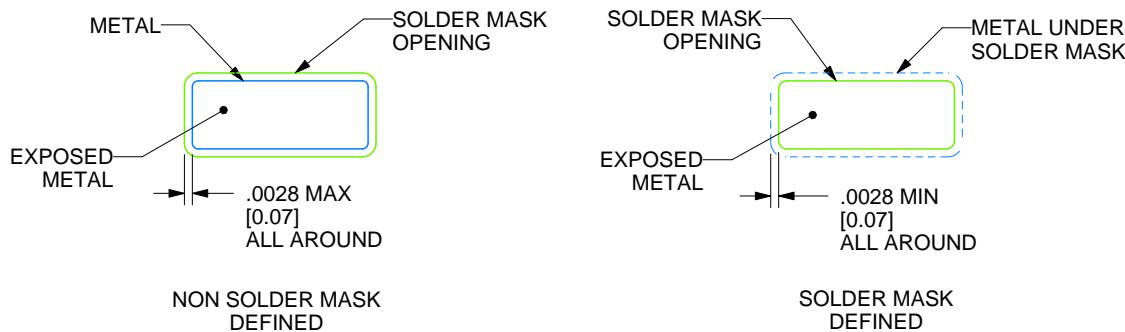

SOLDER MASK DETAILS

4229018/A 10/2022

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

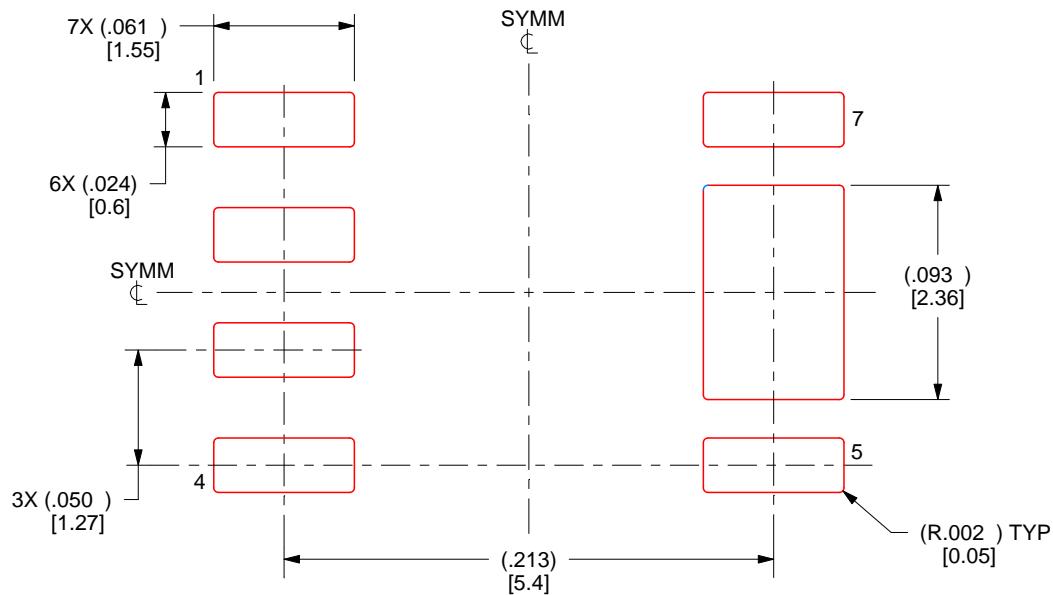

# EXAMPLE STENCIL DESIGN

DFQ0007A

SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

SOLDER PASTE EXAMPLE

BASED ON .005 INCH [0.125 MM] THICK STENCIL

SCALE:12X

4229018/A 10/2022

NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

9. Board assembly site may have different recommendations for stencil design.

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2026, Texas Instruments Incorporated

最終更新日：2025 年 10 月