## LM2104

JAJSRF3A – SEPTEMBER 2023 – REVISED OCTOBER 2023

LM2104 8V UVLO (低電圧ロックアウト)、デッドタイム制御機能、シャットダウン・ピッ

ン搭載、

107V、0.5A/0.8A ハーフブリッジ・ドライバ

## 1 特長

- ・ ハーフブリッジ構成の 2 つの N チャネル MOSFET を駆動

- ・ 8-V GVDD の低電圧誤動作防止 (代表値)

- ・ BST での電圧 (絶対最大値) : 107V

- ・ SH での負過渡電圧 (絶対最大値) : -19.5V

- ・ ソース / シンク電流 (ピーク時) : 0.5A/0.8A

- ・ 固定内部デッドタイム (代表値) : 475ns

- ・ クロス導通防止機能を内蔵

- ・ 伝搬遅延時間 (代表値) : 115ns

- ・ シャットダウン・ロジック入力ピン SD

- ・ 単一入力ピン IN

## 2 アプリケーション

- ・ ブラシレス DC (BLDC) モータ

- ・ 永久磁石同期モータ (PMSM)

- ・ サーボおよびステッパ・モータ駆動

- ・ コードレス掃除機

- ・ コードレスの園芸用器具および電動工具

- ・ 電動アシスト自転車および電動スクーター

- ・ バッテリ試験装置

- ・ オフライン無停電電源 (UPS)

- ・ 汎用 MOSFET または IGBT ドライバ

### 3 概要

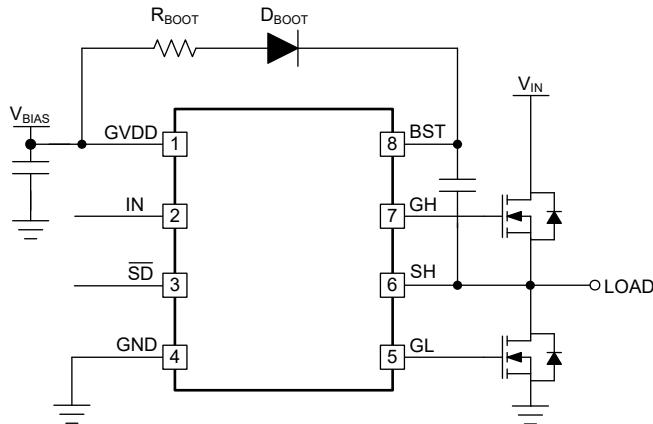

LM2104 は、同期整流式降圧型またはハーフブリッジの構成においてハイサイドとローサイド両方の N チャネル MOSFET を駆動するよう設計された、コンパクトな高電圧ゲート・ドライバです。IN ピンを使用すると、デバイスを单一 PWM 入力のアプリケーションで使用できます。また、SD ピンを使用すると、IN ピンの状態に関係なく、SD ピンが LOW のときにドライバの出力をオフにすることで、コントローラはドライバの出力を無効にできます。

固定のデッドタイムと、SH ピンでの DC -1V および -19.5V の過渡負電圧処理により、高ノイズ・アプリケーションにおけるシステムの堅牢性が向上します。LM2104 は、業界標準のピン配置と互換性のある 8 ピン SOIC パッケージで供給されます。ローサイドとハイサイドの両方の電源レールに低電圧ロックアウト (UVLO) が搭載されており、電源投入および電源切断時の保護を実現します。

## パッケージ情報

| 部品番号   | パッケージ <sup>(1)</sup> | パッケージ・サ<br>イズ <sup>(2)</sup> | 本体サイズ(公称)       |

|--------|----------------------|------------------------------|-----------------|

| LM2104 | D (SOIC、8)           | 4.9mm × 6mm                  | 4.90mm × 3.91mm |

- (1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

(2) パッケージ・サイズ(長さ×幅)は公称値であり、該当する場合はピンも含まれます。

## アプリケーション概略図

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあります。TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.comで必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                                      |    |                                |    |

|--------------------------------------|----|--------------------------------|----|

| 1 特長                                 | 1  | 7.4 デバイスの機能モード                 | 13 |

| 2 アプリケーション                           | 1  | 8 アプリケーションと実装                  | 13 |

| 3 概要                                 | 1  | 8.1 アプリケーション情報                 | 13 |

| 4 Revision History                   | 2  | 8.2 代表的なアプリケーション               | 14 |

| 5 Pin Configuration and Functions    | 3  | 9 Power Supply Recommendations | 18 |

| 6 Specifications                     | 4  | 10 レイアウト                       | 19 |

| 6.1 Absolute Maximum Ratings         | 4  | 10.1 レイアウトのガイドライン              | 19 |

| 6.2 ESD Ratings                      | 4  | 10.2 レイアウト例                    | 20 |

| 6.3 Recommended Operating Conditions | 4  | 11 デバイスおよびドキュメントのサポート          | 21 |

| 6.4 Thermal Information              | 4  | 11.1 デバイスのサポート                 | 21 |

| 6.5 Electrical Characteristics       | 5  | 11.2 ドキュメントのサポート               | 21 |

| 6.6 Switching Characteristics        | 6  | 11.3 ドキュメントの更新通知を受け取る方法        | 21 |

| 6.7 Timing Diagrams                  | 6  | 11.4 サポート・リソース                 | 21 |

| 6.8 Typical Characteristics          | 8  | 11.5 商標                        | 21 |

| 7 詳細説明                               | 11 | 11.6 静電気放電に関する注意事項             | 21 |

| 7.1 概要                               | 11 | 11.7 用語集                       | 21 |

| 7.2 Functional Block Diagram         | 11 | 12 メカニカル、パッケージ、および注文情報         | 21 |

| 7.3 機能説明                             | 11 |                                |    |

## 4 Revision History

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision * (September 2023) to Revision A (October 2023) | Page |

|-----------------------------------------------------------------------|------|

| • 「事前情報」から「量産データ」に変更                                                  | 1    |

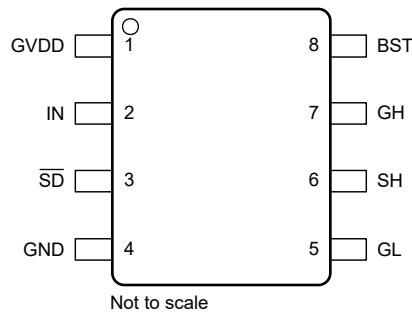

## 5 Pin Configuration and Functions

図 5-1. D Package, 8-Pin SOIC (Top View)

表 5-1. Pin Functions

| PIN |      |                     | DESCRIPTION                                                                                                                                                                                                                                |

|-----|------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME | TYPE <sup>(1)</sup> |                                                                                                                                                                                                                                            |

| 1   | GVDD | P                   | Gate driver positive supply rail. Locally decouple to ground using low ESR and ESL capacitor located as close to IC as possible.                                                                                                           |

| 2   | IN   | I                   | Control input. The IN input is compatible with TTL and CMOS input thresholds.                                                                                                                                                              |

| 3   | SD   | I                   | Shutdown control input. The inverting SD input is compatible with TTL and CMOS input thresholds. When this pin is pulled low, it will turn off both GH and GL outputs.                                                                     |

| 4   | GND  | G                   | Ground. All signals are referenced to this ground.                                                                                                                                                                                         |

| 5   | GL   | O                   | Low-side gate driver output. Connect to the gate of the low-side MOSFET or one end of external gate resistor, when used.                                                                                                                   |

| 6   | SH   | P                   | High-side source connection. Connect to the negative terminal of the bootstrap capacitor and to the source of the high-side MOSFET.                                                                                                        |

| 7   | GH   | O                   | High-side gate driver output. Connect to the gate of the high-side MOSFET or one end of external gate resistor, when used.                                                                                                                 |

| 8   | BST  | P                   | High-side gate driver positive supply rail. Connect the positive terminal of the bootstrap capacitor to BST and the negative terminal of the bootstrap capacitor to SH. The bootstrap capacitor must be placed as close to IC as possible. |

(1) G = Ground, I = Input, O = Output, and P = Power

## 6 Specifications

### 6.1 Absolute Maximum Ratings

Over operating junction temperature range and all voltages are with respect to GND (unless otherwise noted).<sup>(1)</sup>

|                       |                             | MIN                                      | MAX             | UNIT |    |

|-----------------------|-----------------------------|------------------------------------------|-----------------|------|----|

| $V_{GVDD}$            | Low-side supply voltage     | -0.3                                     | 19.5            | V    |    |

| $V_{BST}$ to $V_{SH}$ | High-side supply voltage    | -0.3                                     | 19.5            | V    |    |

| $V_{IN}$ , $V_{SD}$   | Input voltages on IN and SD | -0.3                                     | 19.5            | V    |    |

| $V_{GL}$              | Output voltage on GL        | -0.3                                     | $GVDD + 0.3$    | V    |    |

| $V_{GH}$              | Output voltage on GH        | $V_{SH} - 0.3$                           | $V_{BST} + 0.3$ | V    |    |

| $V_{SH}$              | Voltage on SH               | DC                                       | -1              | 95   |    |

|                       |                             | Repetitive pulse < 100 ns <sup>(2)</sup> | -19.5           | 95   |    |

| $V_{BST}$             | Voltage on BST              | $V_{SH}$                                 | 107             | V    |    |

| $T_J$                 | Junction temperature        | -40                                      | 125             | °C   |    |

| $T_{stg}$             | Storage temperature         | Storage temperature                      | -65             | 150  | °C |

- (1) Operation outside the *Absolute Maximum Ratings* may cause permanent device damage. *Absolute Maximum Ratings* do not imply functional operation of the device at these or any other conditions beyond those listed under *Recommended Operating Conditions*. If used outside the *Recommended Operating Conditions* but within the *Absolute Maximum Ratings*, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

- (2) Values are verified by characterization and are not production tested.

### 6.2 ESD Ratings

|             |                         | VALUE                                                                          | UNIT       |

|-------------|-------------------------|--------------------------------------------------------------------------------|------------|

| $V_{(ESD)}$ | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | $\pm 1000$ |

|             |                         | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> |            |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 6.3 Recommended Operating Conditions

Over operating junction temperature range and all voltages are with respect to GND (unless otherwise noted).

|                     |                                                          | MIN          | NOM | MAX              | UNIT |

|---------------------|----------------------------------------------------------|--------------|-----|------------------|------|

| $V_{GVDD}$          | Supply voltage                                           | 9            | 12  | 18               | V    |

| $V_{IN}$ , $V_{SD}$ | Input voltage range                                      | 0            |     | $GVDD + 0.3$     | V    |

| $V_{BST}$           | Voltage on BST                                           | $V_{SH} + 9$ |     | 105              | V    |

| $V_{SH}$            | Voltage on SH (DC)                                       | -1           |     | $V_{BST} - GVDD$ | V    |

| $V_{SH}$            | Voltage on SH (repetitive pulse < 100 ns) <sup>(1)</sup> | -18          |     | $V_{BST} - GVDD$ | V    |

| $SR_{SH}$           | Voltage slew rate on SH                                  |              |     | 50               | V/ns |

| $T_J$               | Operating junction temperature                           | -40          |     | 125              | °C   |

- (1) Values are verified by characterization and are not production tested.

### 6.4 Thermal Information

| THERMAL METRIC <sup>(1)</sup> |                                            | LM2104   | UNIT |

|-------------------------------|--------------------------------------------|----------|------|

|                               |                                            | D (SOIC) |      |

|                               |                                            | 8 PINS   |      |

| $R_{\theta JA}$               | Junction-to-ambient thermal resistance     | 133.2    | °C/W |

| $R_{\theta JC(\text{top})}$   | Junction-to-case (top) thermal resistance  | 75.2     | °C/W |

| $R_{\theta JB}$               | Junction-to-board thermal resistance       | 76.7     | °C/W |

| $\Psi_{JT}$                   | Junction-to-top characterization parameter | 25.5     | °C/W |

## 6.4 Thermal Information (続き)

| THERMAL METRIC <sup>(1)</sup> |                                              | LM2104   | UNIT |

|-------------------------------|----------------------------------------------|----------|------|

|                               |                                              | D (SOIC) |      |

|                               |                                              | 8 PINS   |      |

| $\Psi_{JB}$                   | Junction-to-board characterization parameter | 75.9     | °C/W |

| $R_{\theta JC(bot)}$          | Junction-to-case (bottom) thermal resistance | N/A      | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

## 6.5 Electrical Characteristics

$V_{GVDD} = V_{BST} = 12$  V,  $GND = V_{SH} = 0$  V, No Load on GL or GH,  $T_J = 25^\circ\text{C}$  (unless otherwise noted).

| PARAMETER                             | TEST CONDITIONS                                | MIN                                                 | TYP  | MAX  | UNIT |

|---------------------------------------|------------------------------------------------|-----------------------------------------------------|------|------|------|

| <b>SUPPLY CURRENTS</b>                |                                                |                                                     |      |      |      |

| $I_{GVDD}$                            | $V_{IN} = V_{SD} = 0$ V                        |                                                     | 430  |      | µA   |

| $I_{DDO}$                             | $f = 50$ kHz, $C_{LOAD} = 0$                   |                                                     | 0.56 |      | mA   |

| $I_{BST}$                             | $V_{IN} = V_{SD} = 0$ V, $VDD = 12$ V          |                                                     | 150  |      | uA   |

| $I_{BSTO}$                            | $f = 50$ kHz, $C_{LOAD} = 0$                   |                                                     | 0.16 |      | mA   |

| $I_{BSTS}$                            | $V_{SH} = V_{BST} = 95$ V, $GVDD = 12$ V       |                                                     | 33.3 |      | µA   |

| $I_{BSTO}$                            | $f = 50$ kHz, $C_{LOAD} = 0$                   |                                                     | 0.07 |      | mA   |

| <b>INPUT</b>                          |                                                |                                                     |      |      |      |

| $V_{HIT\_IN}$                         | Input voltage high threshold                   | -40°C to 125°C                                      |      | 1.45 | 2    |

| $V_{HIT\_SD}$                         | Input voltage high threshold                   | -40°C to 125°C                                      |      | 1.45 | 2    |

| $V_{LIT\_IN}$                         | Input voltage low threshold                    | -40°C to 125°C                                      | 0.8  | 1.3  | V    |

| $V_{LIT\_SD}$                         | Input voltage low threshold                    | -40°C to 125°C                                      | 0.8  | 1.3  | V    |

| $V_{IHYS\_IN}$                        | Input voltage hysteresis                       |                                                     |      | 0.15 | V    |

| $V_{IHYS\_SD}$                        | Input voltage hysteresis                       |                                                     |      | 0.15 | V    |

| $R_{IN\_IN}$                          | Input pulldown resistance                      | $V_{IN} = 3$ V                                      |      | 200  | kΩ   |

| $R_{IN\_SD}$                          | Input pulldown resistance                      | $V_{SD} = 3$ V                                      |      | 200  | kΩ   |

| <b>UNDERVOLTAGE PROTECTION (UVLO)</b> |                                                |                                                     |      |      |      |

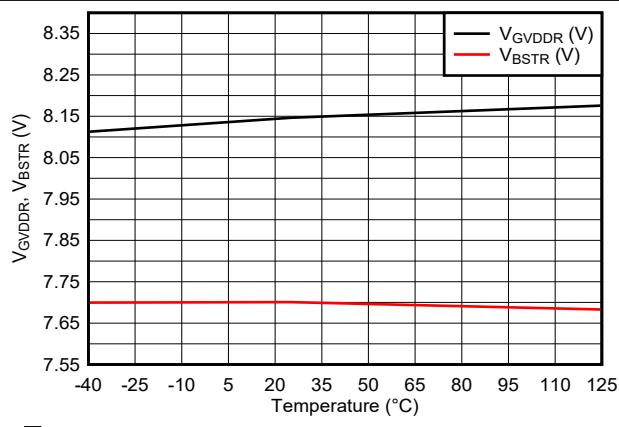

| $V_{GVDDR}$                           | $V_{GVDDR} = V_{GVDD} - GND$ , -40°C to 125°C  |                                                     | 8.15 | 8.75 | V    |

| $V_{GVDDF}$                           | $V_{GVDDF} = V_{GVDD} - GND$ , -40°C to 125°C  | 6.75                                                | 7.7  |      | V    |

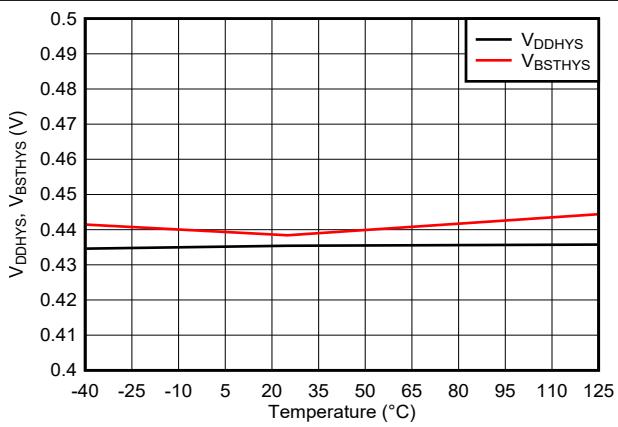

| $V_{GVDDHYS}$                         | GVDD threshold hysteresis                      |                                                     |      | 0.45 | V    |

| $V_{BSTR}$                            | $V_{BSTR} = V_{BST} - V_{SH}$ , -40°C to 125°C |                                                     | 7.6  | 8.5  | V    |

| $V_{BSTF}$                            | $V_{BSTF} = V_{BST} - V_{SH}$ , -40°C to 125°C | 6.25                                                | 7.15 |      | V    |

| $V_{BSTHYS}$                          | VBST threshold hysteresis                      |                                                     |      | 0.45 | V    |

| <b>LO GATE DRIVER</b>                 |                                                |                                                     |      |      |      |

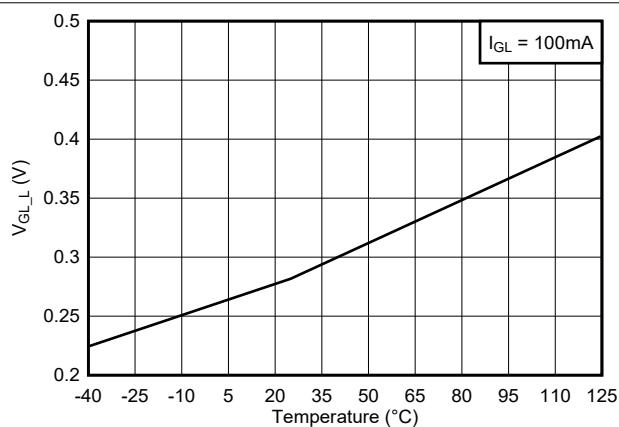

| $V_{GL\_L}$                           | Low level output voltage                       | $I_{GL} = 100$ mA, $V_{GL\_L} = V_{GL} - GND$       |      | 0.25 | V    |

| $V_{GL\_H}$                           | High level output voltage                      | $I_{GL} = -100$ mA, $V_{GL\_H} = V_{GVDD} - V_{GL}$ |      | 0.8  | V    |

|                                       | Peak pullup current <sup>(1)</sup>             | $V_{GL} = 0$ V                                      |      | 0.5  | A    |

|                                       | Peak pulldown current <sup>(1)</sup>           | $V_{GL} = 12$ V                                     |      | 0.8  | A    |

| <b>HO GATE DRIVER</b>                 |                                                |                                                     |      |      |      |

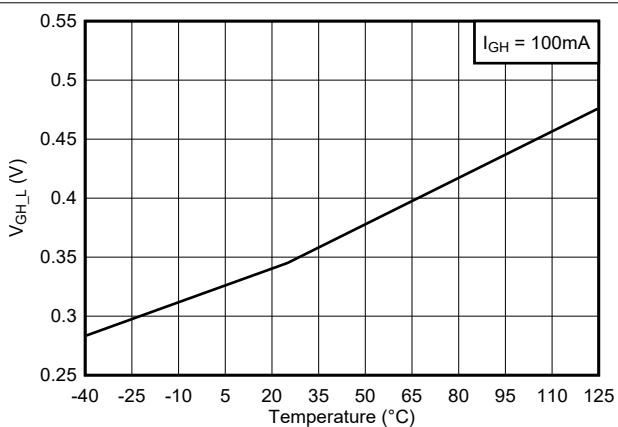

| $V_{GH\_L}$                           | Low level output voltage                       | $I_{GH} = 100$ mA, $V_{GH\_L} = V_{GH} - V_{SH}$    |      | 0.25 | V    |

| $V_{GH\_H}$                           | High level output voltage                      | $I_{GH} = -100$ mA, $V_{GH\_H} = V_{BST} - V_{GH}$  |      | 0.8  | V    |

|                                       | Peak pullup current <sup>(1)</sup>             | $V_{GH} = 0$ V                                      |      | 0.5  | A    |

|                                       | Peak pulldown current <sup>(1)</sup>           | $V_{GH} = 12$ V                                     |      | 0.8  | A    |

(1) Parameter not tested in production.

## 6.6 Switching Characteristics

$V_{GVDD} = V_{BST} = 12$  V,  $GND = V_{SH} = 0$  V, No Load on GL or GH,  $T_J = 25^\circ\text{C}$  (unless otherwise noted).

| PARAMETER                        |                                      | TEST CONDITIONS                                                                                                    | MIN | TYP | MAX | UNIT |

|----------------------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| <b>PROPAGATION DELAYS</b>        |                                      |                                                                                                                    |     |     |     |      |

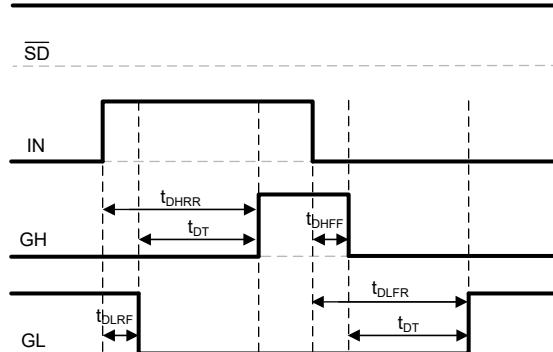

| $t_{DLRF}$                       | $V_{IN}$ rising to $V_{GL}$ falling  | $V_{IN} = 0$ V to 3 V, $C_{LOAD} = 0$ pF, SD = 3 V. Measure time from 50% of the input to 90% of the output.       |     | 115 |     | ns   |

| $t_{DHFF}$                       | $V_{IN}$ falling to $V_{GH}$ falling | $V_{IN} = 3$ V to 0 V, $C_{LOAD} = 0$ pF, SD = 3 V. Measure time from 50% of the input to 90% of the output.       |     | 115 |     | ns   |

| $t_{DLFR}$                       | $V_{IN}$ falling to $V_{GL}$ rising  | $V_{IN} = 3$ V to 0 V, $C_{LOAD} = 0$ pF, SD = 3 V. Measure time from 50% of the input to 10% of the output.       |     | 600 |     | ns   |

| $t_{DHRR}$                       | $V_{IN}$ rising to $V_{GH}$ rising   | $V_{IN} = 0$ V to 3 V, $C_{LOAD} = 0$ pF, SD = 3 V. Measure time from 50% of the input to 10% of the output.       |     | 600 |     | ns   |

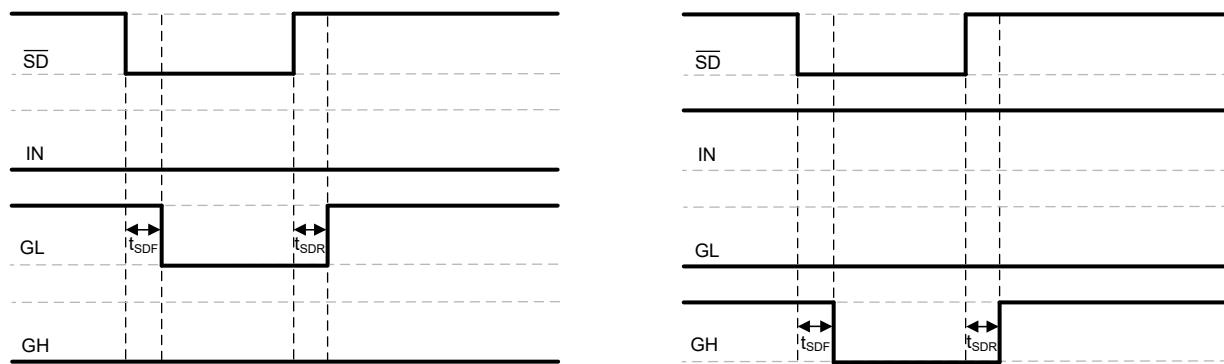

| $t_{SDF}$                        | $V_{SD}$ falling to output falling   | $V_{SD} = 3$ V to 0 V, $V_{IN} = 3$ V, $C_{LOAD} = 0$ pF. Measure time from 50% of the input to 90% of the output. |     | 115 |     | ns   |

| $t_{SDR}$                        | $V_{SD}$ rising to output rising     | $V_{SD} = 0$ V to 3 V, $V_{IN} = 3$ V, $C_{LOAD} = 0$ pF. Measure time from 50% of the input to 10% of the output. |     | 115 |     | ns   |

| <b>DEADTIME</b>                  |                                      |                                                                                                                    |     |     |     |      |

| $t_{DT}$                         | Internal Deadtime                    |                                                                                                                    |     | 475 |     | ns   |

| <b>OUTPUT RISE AND FALL TIME</b> |                                      |                                                                                                                    |     |     |     |      |

| $t_{R\_GL}$                      | GL                                   | $C_{LOAD} = 1000$ pF, $V_{IN} = 0\text{-}3$ V, $V_{SD} = 3$ V                                                      |     | 28  |     | ns   |

| $t_{R\_GH}$                      | GH                                   | $C_{LOAD} = 1000$ pF, $V_{IN} = 0\text{-}3$ V, $V_{SD} = 3$ V                                                      |     | 28  |     | ns   |

| $t_{F\_GL}$                      | GL                                   | $C_{LOAD} = 1000$ pF, $V_{IN} = 0\text{-}3$ V, $V_{SD} = 3$ V                                                      |     | 18  |     | ns   |

| $t_{F\_GH}$                      | GH                                   | $C_{LOAD} = 1000$ pF, $V_{IN} = 0\text{-}3$ V, $V_{SD} = 3$ V                                                      |     | 18  |     | ns   |

## 6.7 Timing Diagrams

図 6-1. Timing Definition Diagram

図 6-2. Shutdown Timing Diagram

## 6.8 Typical Characteristics

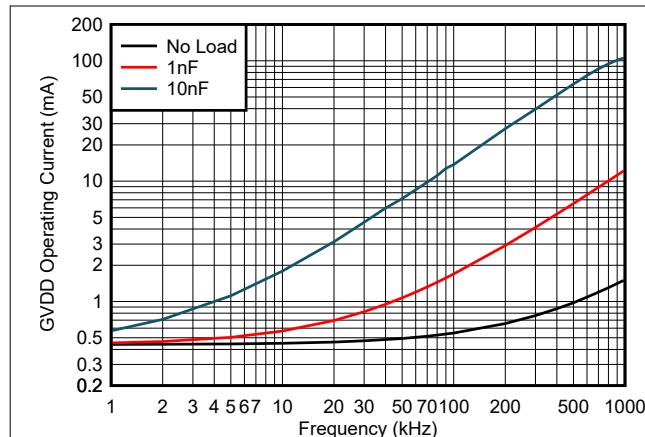

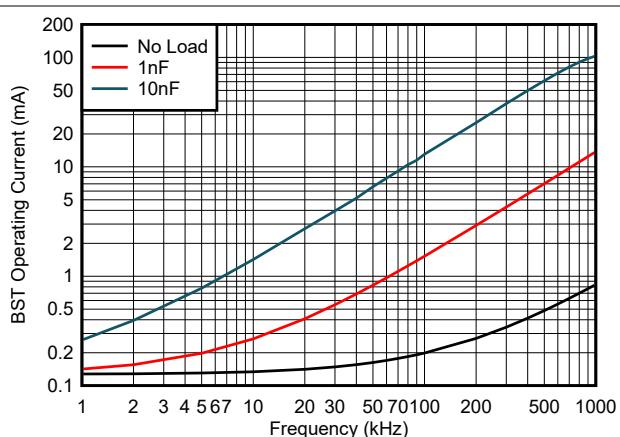

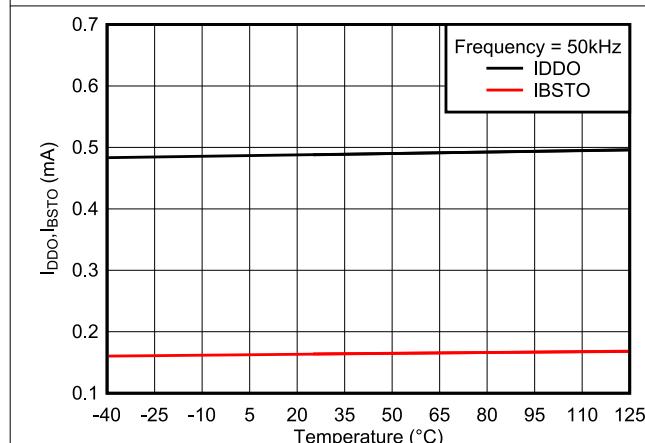

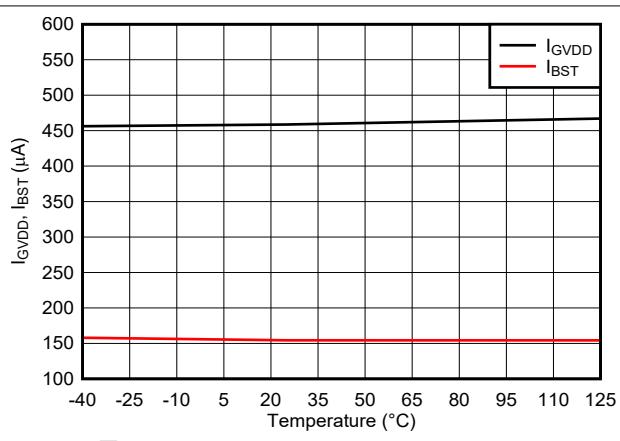

Unless otherwise specified,  $V_{GVDD} = V_{BST} = 12$  V, GND =  $V_{SH} = 0$  V, No Load on GL or GH,  $T_J = 25^\circ\text{C}$ .

図 6-3. GVDD Operating Current vs Frequency

図 6-4. BST Operating Current vs Frequency

図 6-5. Operating Currents vs Temperature

図 6-6. Quiescent Currents vs Temperature

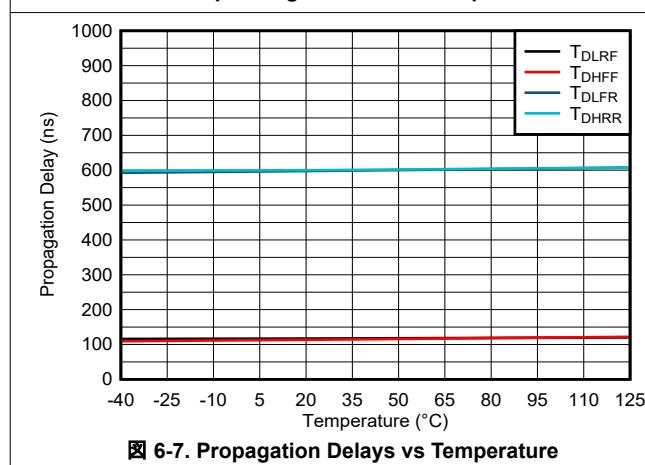

図 6-7. Propagation Delays vs Temperature

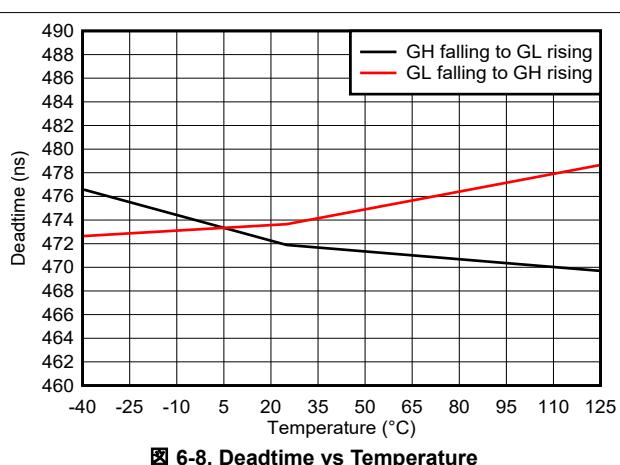

図 6-8. Deadtime vs Temperature

## 6.8 Typical Characteristics (continued)

Unless otherwise specified,  $V_{GVDD} = V_{BST} = 12$  V, GND =  $V_{SH} = 0$  V, No Load on GL or GH,  $T_J = 25^\circ\text{C}$ .

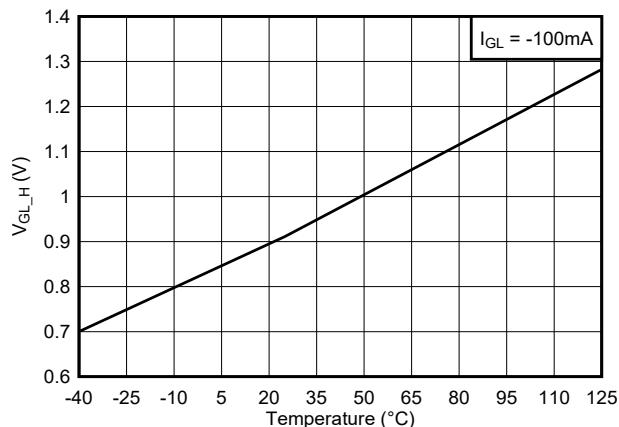

図 6-9. GL Output High Voltage vs Temperature

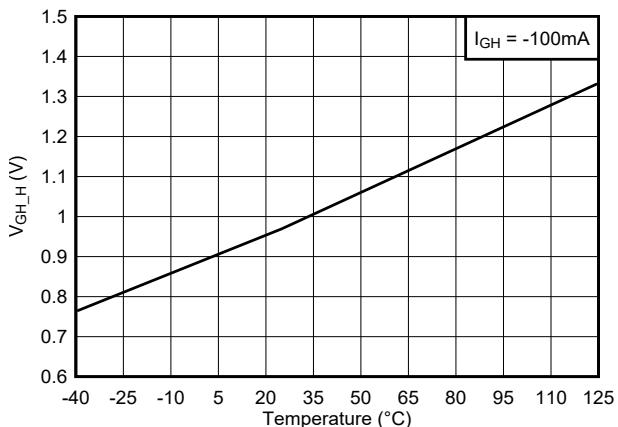

図 6-10. GH Output High Voltage vs Temperature

図 6-11. GL Output Low Voltage vs Temperature

図 6-12. GH Output Low Voltage vs Temperature

図 6-13. GVDD and BST UVLO Thresholds vs Temperature

図 6-14. GVDD and BST Hysteresis vs Temperature

## 6.8 Typical Characteristics (continued)

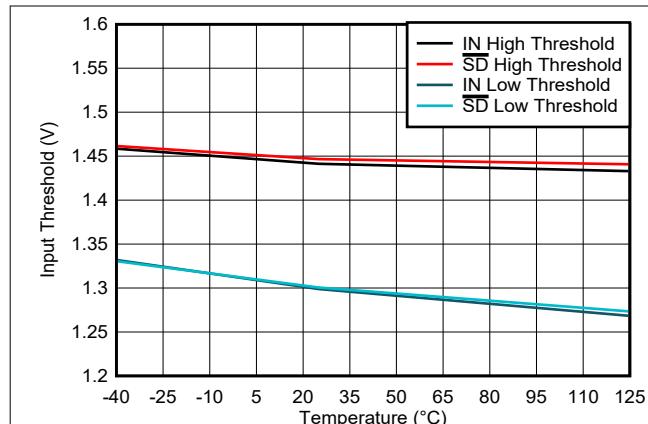

Unless otherwise specified,  $V_{GVDD} = V_{BST} = 12$  V, GND =  $V_{SH} = 0$  V, No Load on GL or GH,  $T_J = 25^\circ\text{C}$ .

図 6-15. Input Voltage Thresholds vs Temperature

図 6-16. Input Voltage Thresholds vs Supply Voltage

## 7 詳細説明

### 7.1 概要

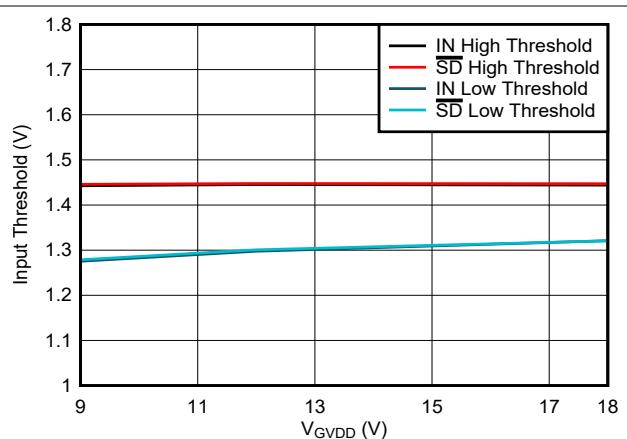

LM2104 は、同期整流式降圧型またはハーフブリッジの構成においてハイサイドとローサイド両方の N チャネル FET を駆動するよう設計された、高電圧ゲート・ドライバです。2 つの出力は、IN ピンに供給される単一の TTL 互換入力 PWM 信号と、SD ピンに供給される TTL 互換シャットダウン信号で制御されます。また、信号が LM2104 のターンオンおよびターンオフのスレッショルド仕様を満たしている限り、デバイスは CMOS タイプの制御信号を入力として使用しても動作できます。フローティング・ハイサイド・ドライバは、最大 105V の推奨 BST 電圧で動作できます。堅牢なレベル・シフタが高速で動作し、消費電力を抑えながら、制御ロジックからハイサイド・ゲート・ドライバへのクリーンなレベル遷移を実現します。ローサイドとハイサイド両方の電源レールに低電圧誤動作防止機能 (UVLO) が搭載されています。

### 7.2 Functional Block Diagram

### 7.3 機能説明

#### 7.3.1 起動と UVLO

ハイサイドおよびローサイドのドライバ段は、電源電圧 ( $V_{GVDD}$ ) およびブートストラップ・コンデンサ電圧 ( $V_{BST-SH}$ ) を監視する UVLO 保護回路を備えています。UVLO 回路は、外部 MOSFET をターンオンするに十分な電源電圧が得られるまで各出力を抑制します。また、UVLO ヒステリシスが組み込まれているため、電源電圧変動時のチャタリングを防止します。デバイスの GVDD ピンに電源電圧が印加されると、 $V_{GVDD}$  が UVLO スレッショルド (通常は 8V) を超えるまで両方の出力が Low に保持されます。ブートストラップ・コンデンサの UVLO 状態 ( $V_{BST-SH}$ ) の場合は、ハイサイド出力 (GO) のみがディセーブルされます。

表 7-1. GVDD UVLO ロジック動作

| 条件 ( $V_{BST-SH} > V_{BSTR}$ )                    | IN | $\overline{SD}$ | GH | GL |

|---------------------------------------------------|----|-----------------|----|----|

| デバイス起動中、 $V_{GVDD} - GND < V_{GVDDR}$             | H  | L               | L  | L  |

|                                                   | L  | H               | L  | L  |

|                                                   | H  | H               | L  | L  |

|                                                   | L  | L               | L  | L  |

| デバイス起動後、 $V_{GVDD} - GND < V_{GVDDR} - V_{DDHYS}$ | H  | L               | L  | L  |

|                                                   | L  | H               | L  | L  |

|                                                   | H  | H               | L  | L  |

|                                                   | L  | L               | L  | L  |

表 7-2. BST UVLO ロジック動作

| 条件 ( $V_{GVDD} > V_{GVDDR}$ )                 | IN | $\overline{SD}$ | GH | GL |

|-----------------------------------------------|----|-----------------|----|----|

| デバイス起動中、 $V_{BST-SH} < V_{BSTR}$              | H  | L               | L  | L  |

|                                               | L  | H               | L  | H  |

|                                               | H  | H               | L  | L  |

|                                               | L  | L               | L  | L  |

| デバイス起動後、 $V_{BST-SH} < V_{BSTR} - V_{BSTHYS}$ | H  | L               | L  | L  |

|                                               | L  | H               | L  | H  |

|                                               | H  | H               | L  | L  |

|                                               | L  | L               | L  | L  |

### 7.3.2 Input Stages

The  $\overline{SD}$  input pin controls the outputs by turning GH and GL off when the  $\overline{SD}$  pin is held low, regardless of the IN input pin state. When  $\overline{SD}$  pin is held high, the IN pin controls the state of the GL and GH outputs allowing the device to be used in single PWM input applications. When IN pin is low, GL output will turn on and GH output will turn off, and when IN pin is high, GL output will turn off and GH output will turn on.

The device has built-in fixed dead time with a typical value of 475 ns. A small filter at each of the inputs of the driver further improves system robustness in noise-prone applications. Both IN and  $\overline{SD}$  have internal pulldown resistors with typical value of 200 k $\Omega$ . Thus, when the inputs are floating, the outputs are held low.

### 7.3.3 レベル・シフト

レベル・シフト回路は、GND を基準とする信号であるハイサイド入力から、スイッチ・ノード (SH) を基準とするハイサイド・ドライバ段へのインターフェイスです。レベル・シフト回路を使用すると、SH ピンを基準とする GH 出力の制御が可能になり、ローサイド・ドライバとの遅延の一致が向上します。

### 7.3.4 出力段

出力段は、パワー・トレイン内のパワー MOSFET へのインターフェイスです。両方の出力で高いスルーレート、低い抵抗、高いピーク電流能力を実現しているため、パワー MOSFET の効率的なスイッチングが可能です。ローサイド出力段は GND を基準とし、ハイサイドは SH を基準とします。

### 7.3.5 グランドより低い SH 過渡電圧

ほとんどのアプリケーションでは、外部ローサイド・パワー MOSFET のボディ・ダイオードが SH ノードをグランドにクランプします。場合によっては、基板の容量とインダクタンスに起因して、SH ノードがグランドより数 V 低い電圧まで過渡的にスイングする可能性があり、外部ローサイド MOSFET のボディ・ダイオードがこのスイングをクランプするのが間に合わないこともあります。LM2104 の SH ピンを使用すると、仕様に違反しない限り、またこのセクションで説明した条件に従う限り、グランドを下回る値までスイングできます。

SH は常に GH より低い電位にする必要があります。GH を規定の条件よりも負にすると、寄生トランジスタがアクティブになり、BST 電源から過剰な電流が流れ、デバイスが損傷する可能性があります。GL と GND についても同じ関係があります。必要に応じて、GH と SH の間、または GL と GND の間でショットキー・ダ

イオードを外部に配置することにより、この種の過渡現象からデバイスを保護できます。ダイオードを有効にするために、デバイスのピンのできるだけ近くにダイオードを配置する必要があります。

ゲート・ドライバ・デバイスを適切に動作させるには、BST から SH へ、および GVDD から GND への低ESRバイパス・コンデンサが必須です。直列インダクタンスを最小限に抑えるため、コンデンサはデバイスのリード直近に配置する必要があります。GL と GH からのピーク電流はかなり大きくなります。バイパス・コンデンサと直列インダクタンスは、デバイスのリードに電圧リングを引き起こすため、信頼性の高い動作を実現するには、このリングを回避する必要があります。

## 7.4 デバイスの機能モード

このデバイスは、通常モードおよび UVLO モードで動作します。UVLO の動作モードの詳細については、[セクション 7.3.1](#) を参照してください。通常モードでは、 $V_{GVDD}$  と  $V_{BST-SH}$  が UVLO スレッショルドを上回っている場合、出力段は IN と  $\overline{SD}$  ピンの状態に依存します。入力状態がフローティングの場合、出力 GH および GL は Low になります。

表 7-3. 通常モード動作での入出力ロジック

| $\overline{SD}$ | IN      | GH <sup>(1)</sup> | GL <sup>(2)</sup> |

|-----------------|---------|-------------------|-------------------|

| L               | L       | L                 | L                 |

| L               | H       | L                 | L                 |

| H               | L       | L                 | H                 |

| H               | H       | H                 | L                 |

| フローティング         | フローティング | L                 | L                 |

(1) GH は SH を基準として測定されます。

(2) GL は GND を基準として測定されます。

## 8 アプリケーションと実装

### 注

以下のアプリケーション情報は、テキサス・インスツルメンツの製品仕様に含まれるものではなく、テキサス・インスツルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。また、お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

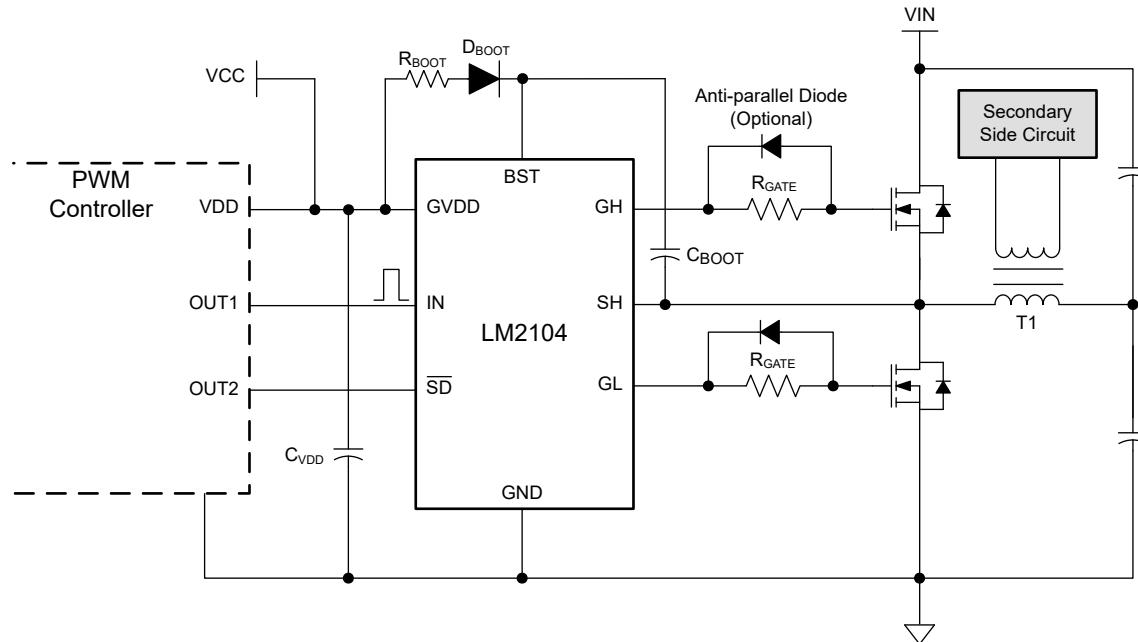

### 8.1 アプリケーション情報

パワー MOSFET を高いスイッチング周波数で動作させるとともに、関連するスイッチング損失を低減するために、コントローラの PWM 出力と、パワー半導体デバイスのゲートとの間に強力なゲート・ドライバを採用します。また、PWM コントローラがスイッチング・デバイスのゲートを直接駆動できない場合、ゲート・ドライバが不可欠です。デジタル電源の登場に伴って、デジタル・コントローラからの PWM 信号は多くの場合、3.3V のロジック信号であり、パワー・スイッチを正常にターンオンできないので、この状況がよく発生します。パワー・デバイスを完全にターンオンし、導通損失を最小限に抑えるには、3.3V の信号をゲート駆動電圧 (12V など) まで昇圧するためのレベル・シフト回路が必要です。トーテムポール配置の NPN/PNP バイポーラ・トランジスタをベースとする従来のバッファ駆動回路は、レベル・シフト機能がないので、デジタル電源においては不十分であることがわかっています。ゲート・ドライバは、レベル・シフト機能とバッファ駆動機能の両方を効果的に組み合わせています。また、ゲート・ドライバは、パワー・スイッチの近くに配置することで、高周波スイッチング・ノイズの影響を最小限に抑えることができます。さらに、ゲート・ドライバはゲート駆動トランジスタを駆動し、フローティング・パワー・デバイスのゲートを制御することができるため、ゲート電荷の電力損失をドライバに移動させることで、コントローラの消費電力と熱ストレスを低減できます。

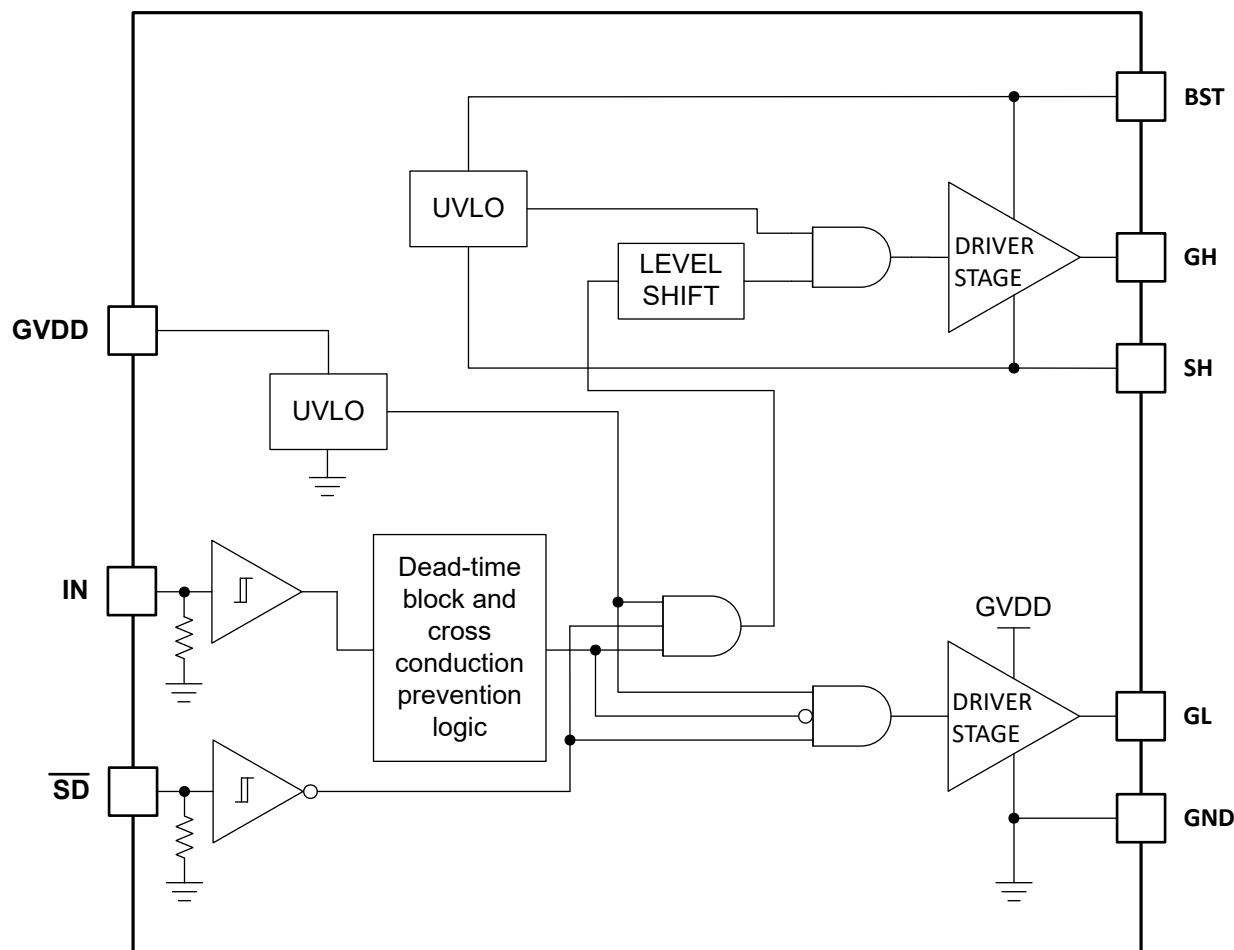

## 8.2 代表的なアプリケーション

図 8-1. LM2104 ハーフブリッジ・コンバータの MOSFET 駆動

### 8.2.1 設計要件

表 8-1 に、LM2104 の設計パラメータの一覧を示します。

表 8-1. 設計例

| パラメータ           | 値           |

|-----------------|-------------|

| ゲート・ドライバ        | LM2104      |

| MOSFET          | CSD19534KCS |

| V <sub>DD</sub> | 12V         |

| Q <sub>G</sub>  | 17nC        |

| f <sub>SW</sub> | 50kHz       |

### 8.2.2 詳細な設計手順

#### 8.2.2.1 ブートストラップおよびGVDD コンデンサの選択

通常の動作では、ブートストラップ・コンデンサは、V<sub>BST-SH</sub> 電圧を UVLO スレッショルドよりも高く維持する必要があります。ブートストラップ・コンデンサの最大許容ドロップは 式 1 で計算します。

$$\Delta V_{BST} = V_{GVDD} - V_{DH} - V_{BSTL} = 12V - 1V - 8.05V = 2.95V \quad (1)$$

ここで

- V<sub>GVDD</sub> = ゲート駆動 IC の電源電圧

- V<sub>DH</sub> = ブートストラップ・ダイオードの順方向電圧降下

- V<sub>BSTL</sub> = BST 下降スレッショルド (V<sub>BSTR(max)</sub> - V<sub>BSTHYS</sub>)

結果として、スイッチング・サイクルごとに必要な総電荷量は、式 2 から推定されます。

$$Q_{TOTAL} = Q_G + I_{BSTS} \times \frac{D_{MAX}}{f_{SW}} + I_{BST} = 17nC + 33.3\mu A \times \frac{0.95}{50kHz} + \frac{150\mu A}{50kHz} = 20nC \quad (2)$$

ここで、

- Q<sub>G</sub> = MOSFET の総ゲート電荷量

- I<sub>BSTS</sub> = BST から VSS へのリーク電流

- D<sub>Max</sub> = コンバータの最大デューティ・サイクル

- I<sub>BST</sub> = BST 静止電流

次に、式 3 を使用して、ブートストラップ・コンデンサの最小値を推定します。

$$C_{BOOT(MIN)} = \frac{Q_{TOTAL}}{\Delta V_{BST}} = \frac{20nC}{2.95V} = 6.8nF \quad (3)$$

実際には、負荷過渡によって電力段がパルスをスキップできるように、C<sub>Boot</sub> コンデンサの値を計算値より大きくする必要があります。式 4 は、特定のアプリケーションに必要な最大ブートストラップ電圧リップルに基づいて、推奨ブートストラップ容量を推定するために使用できます。

$$C_{BOOT} > \frac{Q_{TOTAL}}{\Delta V_{BST\_RIPPLE}} \quad (4)$$

ここで、

- ΔV<sub>BST\_RIPPLE</sub> = システム要件に基づくバイパス・コンデンサにかかる最大許容電圧降下

テキサス・インスツルメンツでは、十分なマージンを確保し、ブートストラップ・コンデンサを BST ピンと SH ピンのできるだけ近くに配置することを推奨します。

$$C_{BOOT} = 100nF \quad (5)$$

式 6 に示すように、原則として、ローカル  $V_{GVDD}$  バイパス・コンデンサは  $C_{BOOT}$  の値の 10 倍以上でなければなりません。

$$C_{GVDD} = 1\mu F \quad (6)$$

ブートストラップ・コンデンサおよびバイアス・コンデンサは、X7R 誘電体のセラミック・タイプである必要があります。デバイスに DC バイアス電圧がかかった場合の容量許容差を考慮して、長期的な信頼性を確保するために、電圧定格は最大  $V_{GVDD}$  の 2 倍でなければなりません。

### 8.2.2.2 外部ゲート・ドライバ抵抗の選択

外部ゲート・ドライバ抵抗  $R_{GATE}$  は、寄生インダクタンスおよび寄生容量によって引き起こされるリングを抑制し、同時にゲート・ドライバから出力される電流を制限するように設定されています。

ピーク GH プルアップ電流は、式 7 で計算されます。

$$I_{GHH} = \frac{V_{GVDD} - V_{DH}}{R_{GHH} + R_{GATE} + R_{GFET\_INT}} \quad (7)$$

ここで

- $I_{GHH}$  = GH ピーク・プルアップ電流

- $V_{DH}$  = ブートストラップ・ダイオードの順方向電圧降下

- $R_{GHH}$  = テスト条件から推定したゲート・ドライバの内部 GH プルアップ抵抗 ( $R_{GHH} = V_{GH\_H} / I_{GH}$ )

- $R_{GATE}$  = 外部ゲート駆動抵抗

- $R_{GFET\_INT}$  = MOSFET 内部ゲート抵抗 (トランジスタのデータシートに記載)

同様に、ピーク GH プルダウン電流を 式 8 に示します。

$$I_{GHL} = \frac{V_{GVDD} - V_{DH}}{R_{GHL} + R_{GATE} + R_{GFET\_INT}} \quad (8)$$

ここで

- $R_{GHL}$  = GH プルダウン抵抗

ピーク GL プルアップ電流を 式 9 に示します。

$$I_{GLH} = \frac{V_{GVDD}}{R_{GLH} + R_{GATE} + R_{GFET\_INT}} \quad (9)$$

ここで

- $R_{GLH}$  = GL プルアップ抵抗

ピーク GL プルダウン電流を 式 10 に示します。

$$I_{GLL} = \frac{V_{GVDD}}{R_{GLL} + R_{GATE} + R_{GFET\_INT}} \quad (10)$$

ここで

- $R_{GLL}$  = GL プルダウン抵抗

状況によっては、アプリケーションで高速なターンオフが必要な場合、 $R_{Gate}$  の逆並列ダイオードを使用して外部ゲート駆動抵抗をバイパスし、ターンオフ遷移を高速化できます。

### 8.2.2.3 ドライバの電力損失の推定

ドライバ IC の総消費電力は、以下の構成要素から推定できます。

1. 静止電流  $I_{GVDD}$  と  $I_{BST}$  による静的な電力損失  $P_{QC}$  を 式 11 に示します。

$$P_{QC} = V_{GVDD} \times I_{GVDD} + (V_{GVDD} - V_F) \times I_{BST} = 12V \times 0.43mA + (12V - 1V) \times 0.15mA = 6.8mW \quad (11)$$

2. ハイサイド・リーケ電流  $I_{BSTS}$  によるレベル・シフタ損失  $P_{IBSTS}$  を式 12 に示します。

$$P_{IBSTS} = V_{BST} \times I_{BSTS} \times D = 72V \times 0.033mA \times 0.95 = 2.26mW \quad (12)$$

ここで、

- D はハイサイド・スイッチのデューティ・サイクルです。

3. FET ゲート電荷量  $Q_G$  による動的損失  $P_{QG1&2}$  を式 13 に示します。

$$P_{QG1&2} = 2 \times V_{GVDD} \times Q_G \times f_{SW} \times \frac{R_{GD\_R}}{R_{GD\_R} + R_{GATE} + R_{GFET\_INT}} = 2 \times 12V \times 17nC \times 50kHz \times \frac{5.25\Omega}{5.25\Omega + 4.7\Omega + 2.2\Omega} = 8.8mW \quad (13)$$

ここで、

- $Q_G$  = FET の総ゲート電荷量

- $f_{SW}$  = スイッチング周波数

- $R_{GD\_R}$  = プルアップおよびプルダウン抵抗の平均値

- $R_{GATE}$  = 外部ゲート駆動抵抗

- $R_{GFET\_INT}$  = 内部 FET ゲート抵抗

4. 各スイッチング・サイクルにおいて必要なレベル・シフタの充電によるハイサイド・スイッチング時の、レベル・シフタの動的損失  $P_{LS}$  を示します。この例では、式 14 に示すように、寄生電荷  $Q_P$  の値が 2.5nC であると仮定します。

$$P_{LS} = V_{BST} \times Q_P \times f_{SW} = 72V \times 2.5nC \times 50kHz = 9mW \quad (14)$$

この例では、すべての損失を合計すると、ゲート・ドライバの総損失は、27mW になります。ブートストラップ・ダイオードを含むゲート・ドライバの場合、ブートストラップ・ダイオードの損失も推定する必要があります。ダイオードの順方向導通損失は、平均順方向電圧降下と平均順方向電流の積として計算されます。

式 15 は、与えられた周囲温度に対して、デバイスの最大許容電力損失を推定するものです。

$$P_{MAX} = \frac{T_J - T_A}{R_{\theta JA}} \quad (15)$$

ここで、

- $P_{MAX}$  = ゲート・ドライバ・デバイスで許容される最大消費電力

- $T_J$  = 接合部温度

- $T_A$  = 周囲温度

- $R_{\theta JA}$  = 接合部から周囲への熱抵抗

ドライバ・パッケージの熱評価基準は、データシートの「熱に関する情報」の表にまとめられています。「熱に関する情報」の表の詳細については、テキサス・インスツルメンツの『半導体および IC パッケージの熱評価基準』アプリケーション・ノートを参照してください。

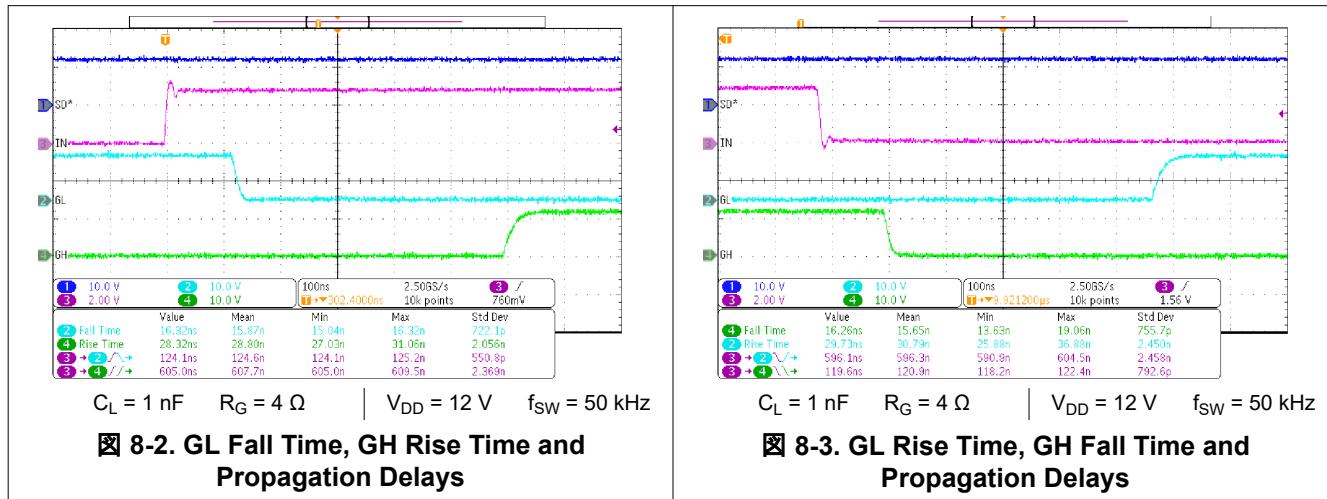

### 8.2.3 Application Curves

图 8-2 shows the GL fall time and GH rise time as well as the propagation delays for both GL and GH when the input IN transitions from low to high. Likewise, 图 8-3 shows the GL rise time and GH fall time as well as the propagation delays for both GL and GH when the input IN transitions from high to low. Each channel (IN,  $\overline{SD}$ , GH, and GL) is labeled and displayed on the left hand of the waveforms.

The testing condition: load capacitance is 1 nF, gate resistor is 4  $\Omega$ ,  $V_{DD} = 12$  V,  $f_{SW} = 50$  kHz.

## 9 Power Supply Recommendations

The recommended bias supply voltage range for LM2104 is from 9 V to 18 V. The lower end of this range is governed by the internal undervoltage lockout (UVLO) protection feature of the  $V_{GVDD}$  supply circuit blocks. The upper end of this range is driven by the 18-V recommended maximum voltage rating of the GVDD pin. It is recommended that the voltage on GVDD pin is lower than the maximum recommended voltage to account for transient voltage spikes.

The UVLO protection feature also involves a hysteresis function. This means that once the device is operating in normal mode, if the  $V_{GVDD}$  voltage drops, the device continues to operate in normal mode as long as the voltage drop does not exceed the hysteresis specification,  $V_{DDHYS}$ . If the voltage drop is more than hysteresis specification, the device shuts down. Therefore, while operating at or near the 9-V range, the voltage ripple on the auxiliary power supply output must be smaller than the hysteresis specification of LM2104 to avoid triggering device-shutdown.

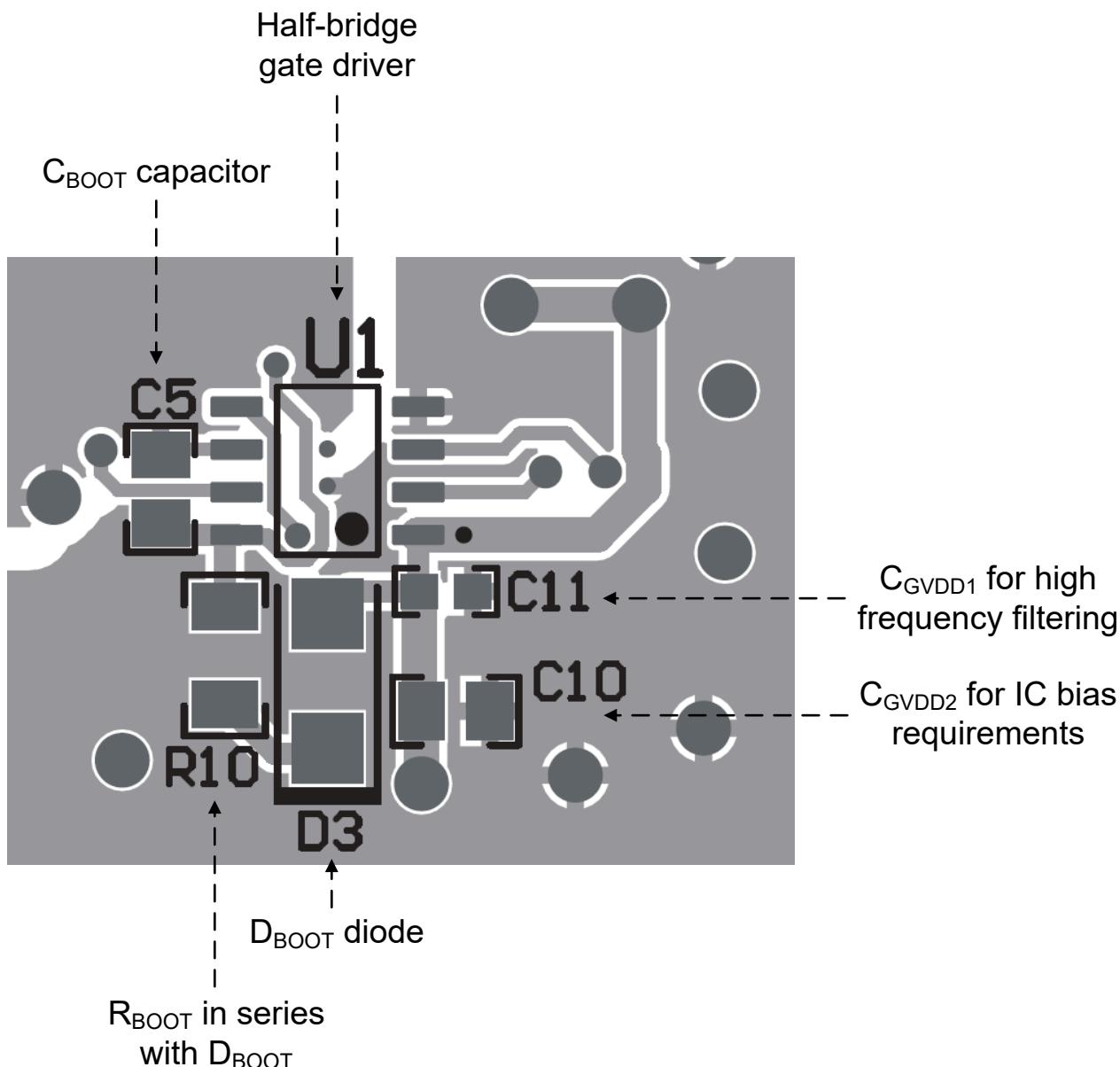

A local bypass capacitor must be placed between the GVDD and GND pins and this capacitor must be located as close to the device as possible. A low-ESR, ceramic surface mount capacitor is recommended. TI recommends using two capacitors across GVDD and GND: a low capacitance ceramic surface-mount capacitor for high-frequency filtering placed very close to GVDD and GND pins, and another high capacitance value surface-mount capacitor for IC bias requirements. In a similar manner, the current pulses delivered by the GH pin are sourced from the BST pin. Therefore, a local decoupling capacitor is recommended between the BST and SH pins.

## 10 レイアウト

### 10.1 レイアウトのガイドライン

ハーフブリッジ・ゲート・ドライバの性能を最適化するには、回路基板のレイアウトを十分に考慮する必要があります。以下の点が重要です。

1. 低 ESR コンデンサおよび低 ESL コンデンサを GVDD ピンと GND ピンの間、および BST ピンと SH ピンの間で IC の近くに接続して、外部 MOSFET のターンオン時に GVDD と BST から引き出される大きいピーク電流に備える必要があります。

2. 上側の MOSFET のドレインでの大きい電圧過渡を防止するために、低 ESR の電解コンデンサと高品質のセラミック・コンデンサを MOSFET のドレインとグランド (GND) の間に接続する必要があります。

3. スイッチ・ノード (SH) ピンでの大きな負の過渡を防止するため、上側の MOSFET のソースと下側の MOSFET (同期整流器) のドレインとの間の寄生インダクタンスを最小限に抑える必要があります。

4. 接地に関する注意事項：

- グランド接続を設計する際の最優先事項は、MOSFET のゲートを充電および放電する大きいピーク電流を、最小の物理的領域内に限定することです。これによって、ループのインダクタンスが小さくなり、MOSFET のゲート端子のノイズ問題が最小限に抑えられます。ゲート・ドライバは、MOSFET のできるだけ近くに配置する必要があります。

- 2番目の考慮事項は、ブートストラップ・コンデンサ、ブートストラップ・ダイオード、ローカル・グランド基準バイパス・コンデンサ、ローサイド MOSFET ボディ・ダイオードを含む大電流パスです。ブートストラップ・コンデンサは、グランド基準 GVDD バイパス・コンデンサからブートストラップ・ダイオードを通って、サイクルごとに再充電されます。この再充電は短い時間間隔で発生し、大きなピーク電流を必要とします。回路基板上でこのループの長さと面積を最小化することは、動作の信頼性を確保する上で重要です。

## 10.2 レイアウト例

図 10-1. レイアウト例

## 11 デバイスおよびドキュメントのサポート

### 11.1 デバイスのサポート

#### 11.1.1 サード・パーティ製品に関する免責事項

サード・パーティ製品またはサービスに関するテキサス・インスツルメンツの出版物は、単独またはテキサス・インスツルメンツの製品、サービスと一緒に提供される場合に関係なく、サード・パーティ製品またはサービスの適合性に関する是認、サード・パーティ製品またはサービスの是認の表明を意味するものではありません。

#### 11.2 ドキュメントのサポート

##### 11.2.1 関連資料

関連資料については、以下を参照してください。

- 『半導体および IC パッケージの熱評価基準』、[SPRA953](#)

#### 11.3 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[ti.com](#) のデバイス製品フォルダを開いてください。「更新の通知を受け取る」をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取れます。変更の詳細については、修正されたドキュメントに含まれている改訂履歴をご覧ください。

#### 11.4 サポート・リソース

**TI E2E™ サポート・フォーラム**は、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、該当する貢献者により、現状のまま提供されるものです。これらは TI の仕様を構成するものではなく、必ずしも TI の見解を反映したものではありません。TI の[使用条件](#)を参照してください。

#### 11.5 商標

TI E2E™ is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

#### 11.6 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

#### 11.7 用語集

[テキサス・インスツルメンツ用語集](#) この用語集には、用語や略語の一覧および定義が記載されています。

## 12 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに対して提供されている最新のデータです。このデータは、予告なしに、またドキュメントの改訂なしに変更される場合があります。本データシートのブラウザ版を使用している場合は、画面左側のナビゲーションをご覧ください。

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| LM2104DR              | Active        | Production           | SOIC (D)   8   | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | L2104D              |

| LM2104DR.A            | Active        | Production           | SOIC (D)   8   | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | L2104D              |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

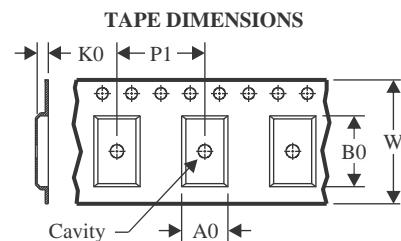

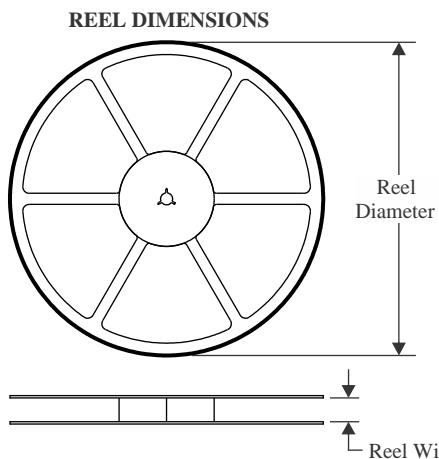

**TAPE AND REEL INFORMATION**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

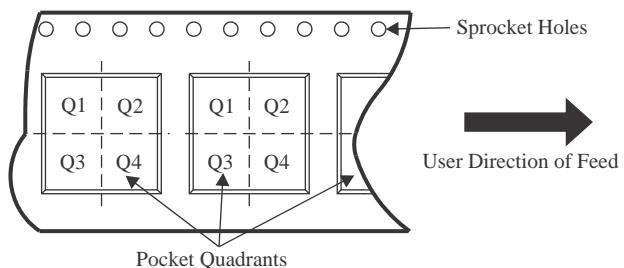

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device   | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|----------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| LM2104DR | SOIC         | D               | 8    | 3000 | 330.0              | 12.4               | 6.4     | 5.2     | 2.1     | 8.0     | 12.0   | Q1            |

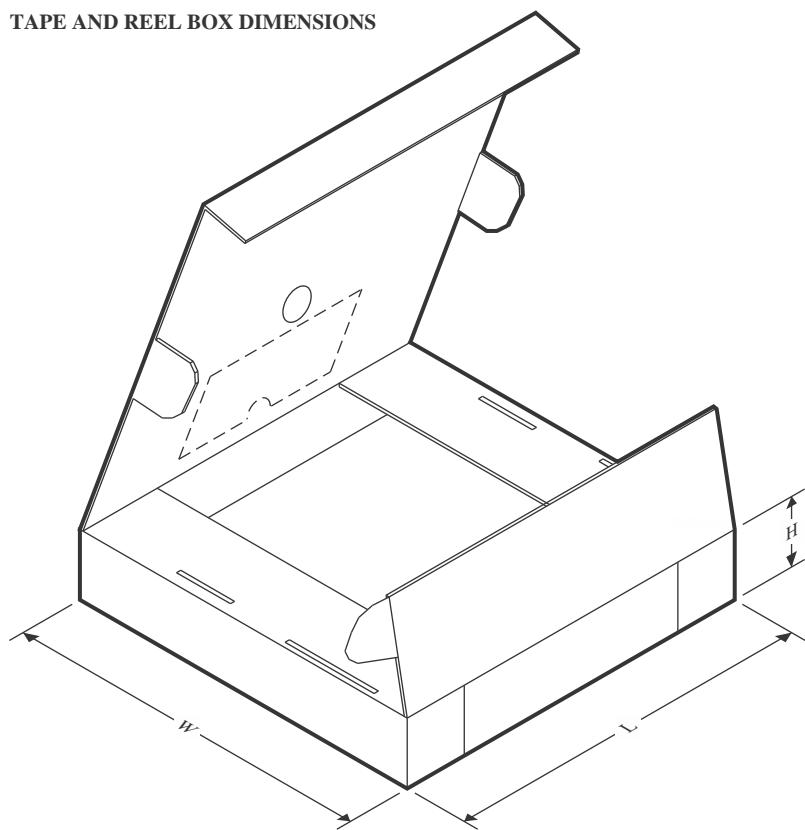

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device   | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|----------|--------------|-----------------|------|------|-------------|------------|-------------|

| LM2104DR | SOIC         | D               | 8    | 3000 | 353.0       | 353.0      | 32.0        |

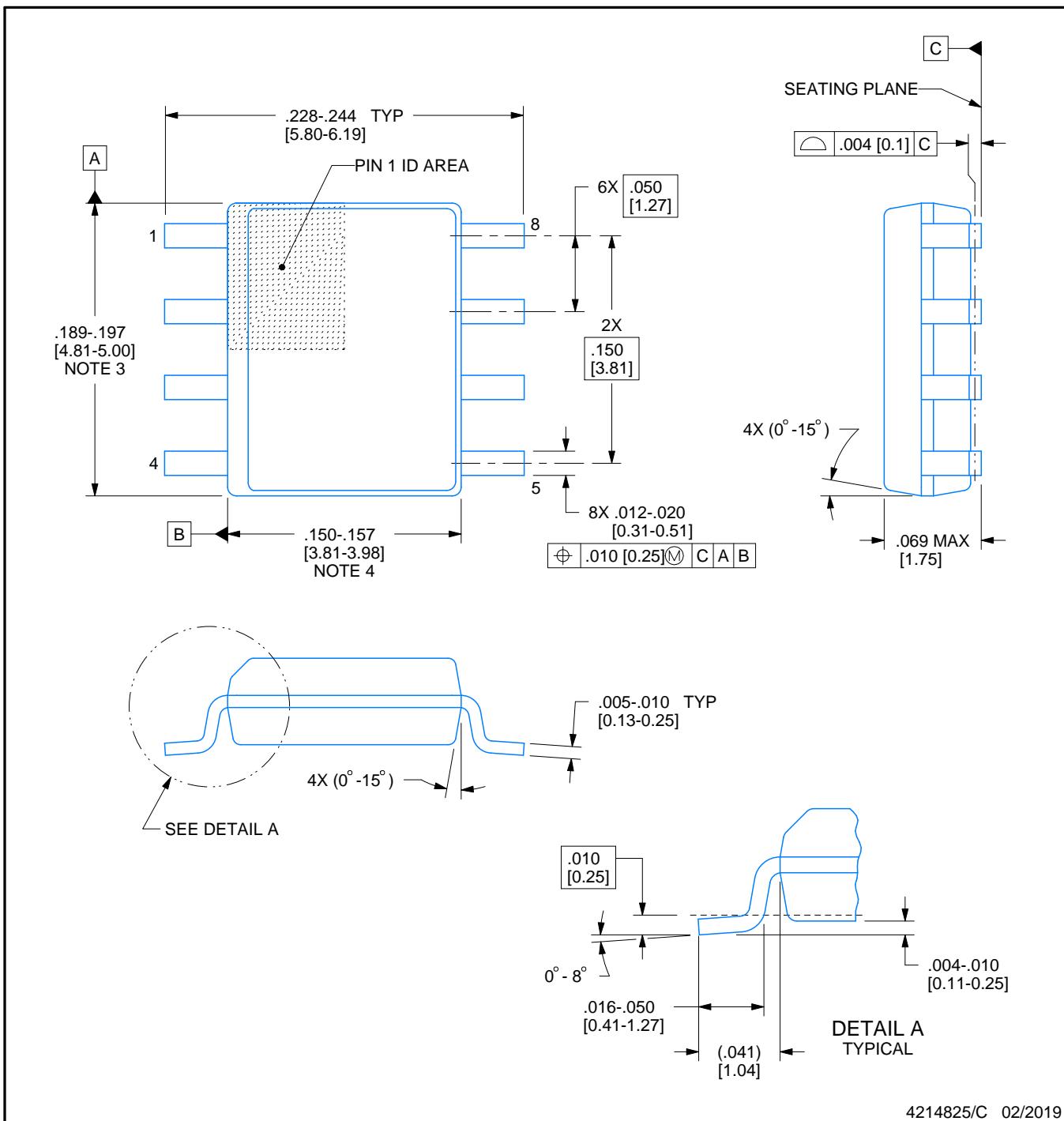

# PACKAGE OUTLINE

## SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

### NOTES:

1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

4. This dimension does not include interlead flash.

5. Reference JEDEC registration MS-012, variation AA.

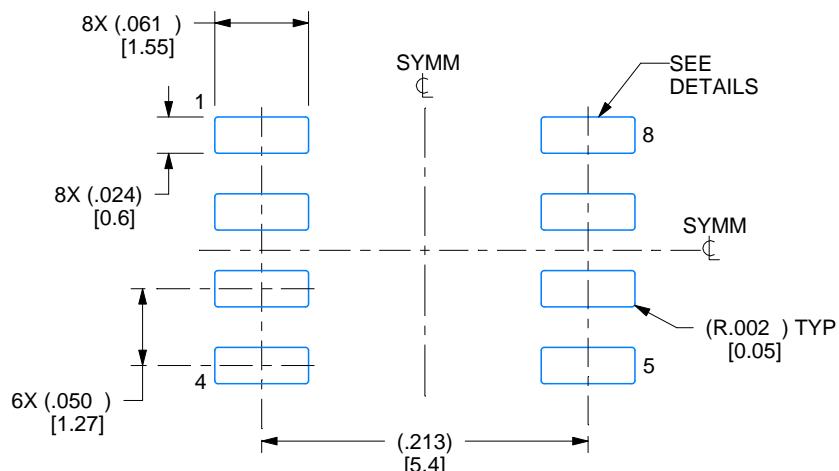

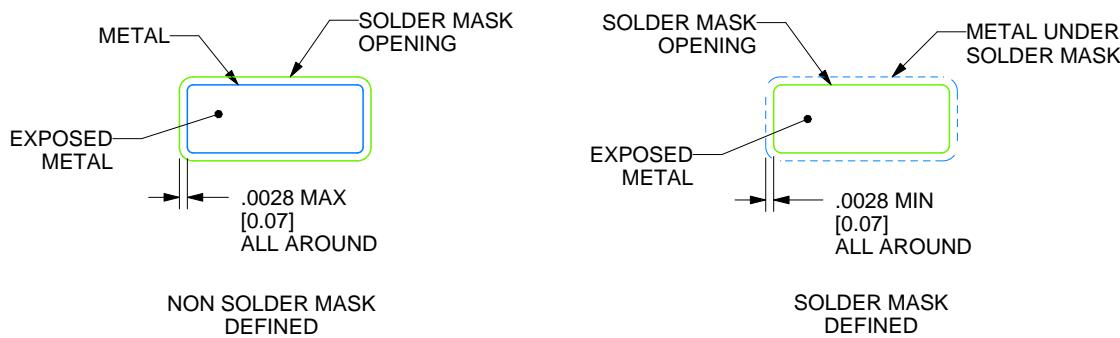

# EXAMPLE BOARD LAYOUT

D0008A

SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE:8X

SOLDER MASK DETAILS

4214825/C 02/2019

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

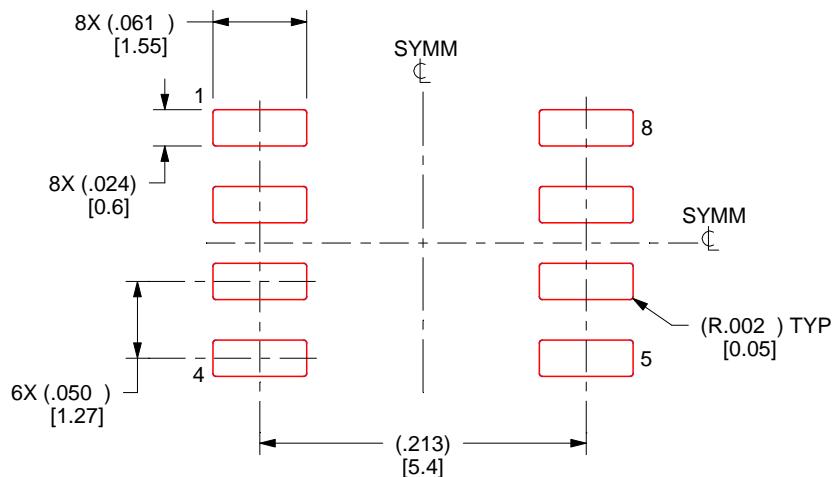

# EXAMPLE STENCIL DESIGN

D0008A

SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

SOLDER PASTE EXAMPLE

BASED ON .005 INCH [0.125 MM] THICK STENCIL

SCALE:8X

4214825/C 02/2019

NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

9. Board assembly site may have different recommendations for stencil design.

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月