# LM22680

**LM22680/LM22680Q 2A SIMPLE SWITCHER®, Step-Down Voltage Regulator with

Features**

Literature Number: JAJSB05A

## LM22680/LM22680Q

2012年6月

### SIMPLE SWITCHER® 42V、2A 降圧型電圧レギュレータ(追加機能付き)

#### 概要

LM22680 は、できる限り少ない外付け部品で高効率の高耐圧降圧型(バック)レギュレータを実現するために必要なすべての機能を備えたスイッチング・レギュレータです。使い勝手の良いこのレギュレータは、最大 2A の負荷電流を供給可能な耐圧 42V の N チャネル MOSFET スイッチを内蔵しています。優れたライン / ロード・レギュレーション特性に加えて、最高で 90% を超える高い効率を備えています。電圧モード制御を採用しており、オン時間の Min 値が短いので、入力電圧と出力電圧の比をきわめて大きくすることができます。また、ループ補償回路を内蔵しているため、ユーザーはループ補償用部品について面倒な計算をする必要がありません。5V の固定出力タイプと可変出力タイプが用意されています。スイッチング周波数はデフォルトで 500kHz に設定され、外付け部品の小型化が可能なほか、優れた過渡応答を実現しています。スイッチング周波数は、1 個の外付け抵抗によって 200kHz ~ 1MHz の範囲で調整できます。内蔵発振器は、システム・クロックまたは別のレギュレータの発振器に同期させることができます。高精度イネーブル入力は、レギュレータの制御とシステム電源のシーケンス制御を簡略化します。シャットダウン・モードにおけるこのレギュレータの消費電流はわずか  $25 \mu\text{A}$  (typ) です。1 個の外付けコンデンサの選択により調整可能なソフトスタート機能も使用できます。LM22680 は、熱暴走保護機能(サーマル・シャットダウン)と電流制限回路を内蔵しており、予期せぬ過負荷状態になることを防止します。

LM22680 は、テキサス・インスツルメンツ (TI) の SIMPLE SWITCHER® ファミリ製品です。SIMPLE SWITCHER® コンセプトにより、TI の設計ツール WEBENCH® を用いて、必要最小限の外付け部品による設計を簡単に完了できます。TI の WEBENCH® ツールは、外付け部品の計算、電気特性シミュレーション、熱特性シミュレーション、Build-It ボード(有償の試作ボード作成サービス)などの機能を持ち、容易なデザインが可能です。

#### 特長

- 広い入力電圧範囲: 4.5V ~ 42V

- 内部補償による電圧モード制御

- 低 ESR セラミック・コンデンサでも安定動作

- 200 mΩ N チャネル MOSFET

- 出力電圧オプション

-ADJ (最小出力電圧 1.285V)

- リファレンス精度: ± 1.5%

- デフォルトで 500kHz のスイッチング周波数

- 調整可能なスイッチング周波数と外部同期

- 動作時の接合部温度範囲: -40 °C ~ +125 °C

- 高精度イネーブル入力

- ブートストラップ・ダイオード内蔵

- 設定可能なソフトスタート

- WEBENCH® に完全対応

- LM22680Q は、AEC-Q100 グレード 1 認定のオートモーティブ・グレード製品(動作時の接合部温度 -40 °C ~ +125 °C)

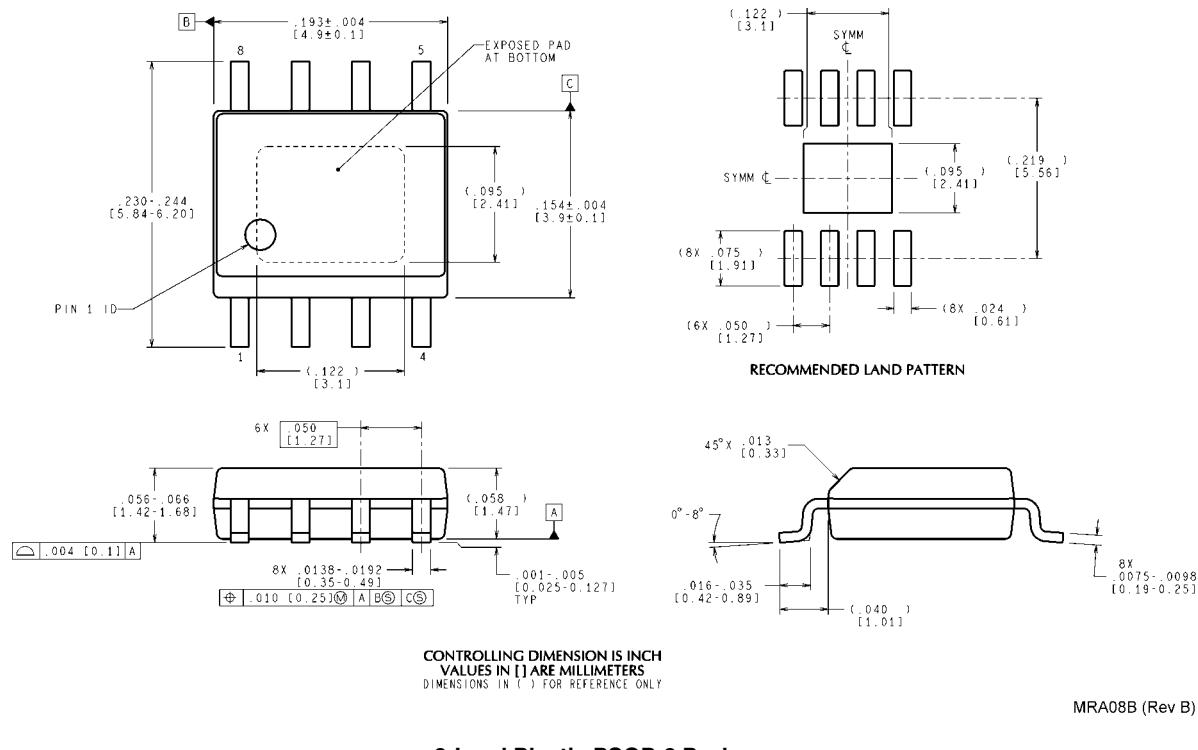

#### パッケージ

- PSOP-8 (露出放熱パッド付き)

#### アプリケーション

- 産業用制御機器

- 電気通信 / データ通信システム

- 組み込みシステム

- 標準の 24V、12V、5V 入力電源からの変換

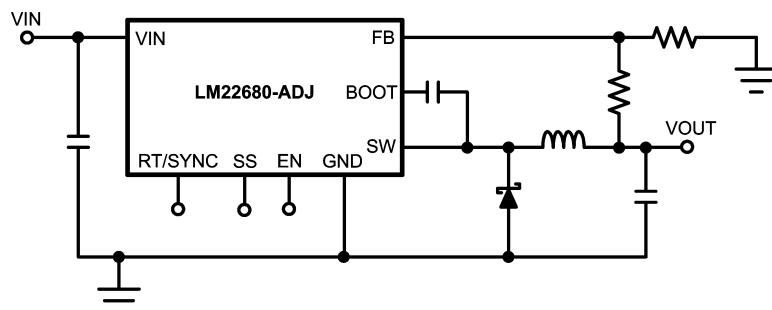

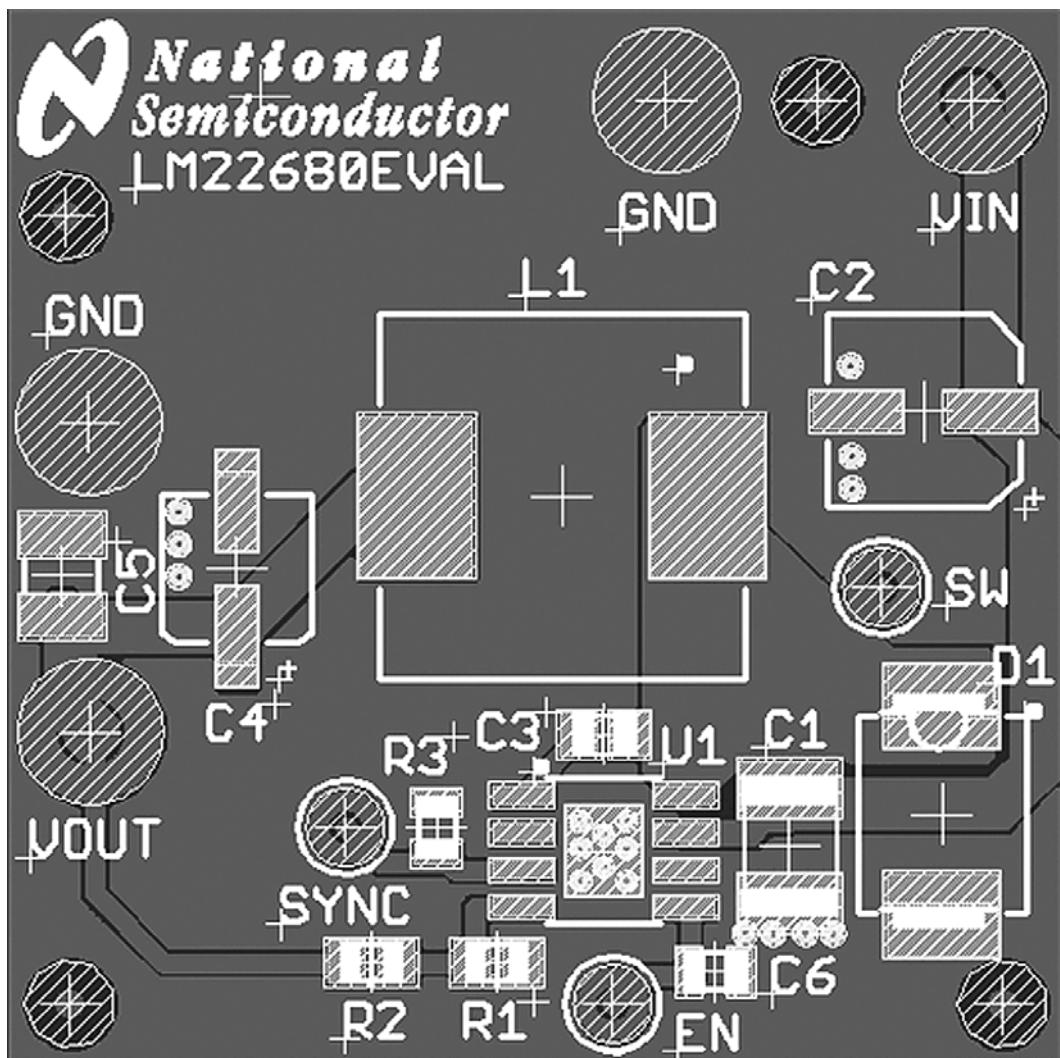

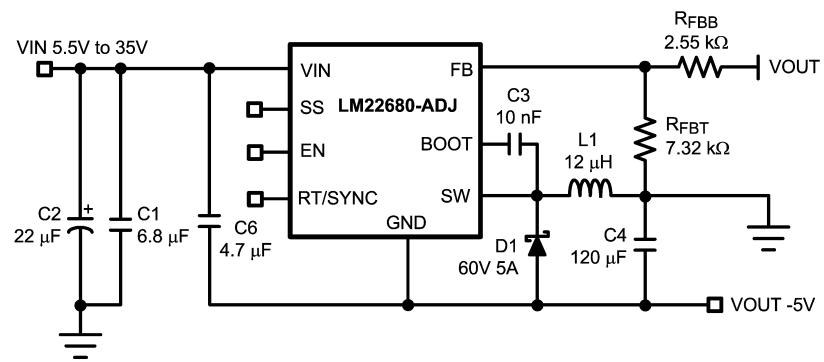

#### 簡略アプリケーション回路

LM22680/LM22680Q SIMPLE SWITCHER® 42V、2A 降圧型電圧レギュレータ(追加機能付き)

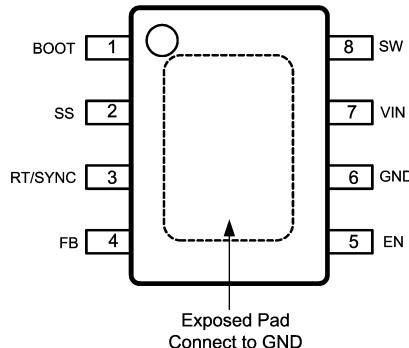

## ピン配置図

8-Lead Plastic PSOP-8 Package

TI Package Number MRA08B

## 製品情報

| Output Voltage | Order Number    | Package Type       | TI Package Drawing | Supplied As                 | Features                                                      |

|----------------|-----------------|--------------------|--------------------|-----------------------------|---------------------------------------------------------------|

| ADJ            | LM22680MR-ADJ   | PSOP-8 Exposed Pad | MRA08B             | 95 Units in Rails           | AEC-Q100 Grade 1 qualified. Automotive Grade Production Flow* |

| ADJ            | LM22680MRE-ADJ  |                    |                    | 250 Units in Tape and Reel  |                                                               |

| ADJ            | LM22680MRX-ADJ  |                    |                    | 2500 Units in Tape and Reel |                                                               |

| ADJ            | LM22680QMR-ADJ  | PSOP-8 Exposed Pad | MRA08B             | 95 Units in Rails           | AEC-Q100 Grade 1 qualified. Automotive Grade Production Flow* |

| ADJ            | LM22680QMRE-ADJ |                    |                    | 250 Units in Tape and Reel  |                                                               |

| ADJ            | LM22680QMRX-ADJ |                    |                    | 2500 Units in Tape and Reel |                                                               |

\* オートモーティブ・グレード (Q) 製品は、欠陥検出の技法など、自動車市場向けの高度な製造やサポート・プロセスを採用しています。信頼性規格については、AEC-Q100 標準で規定された要件と温度グレードに準拠します。オートモーティブ・グレード製品は Q の文字で識別できます。詳細については、<http://www.ti.com/automotive> を参照してください。

## ピン説明

| ピン番号 | ピン名     | 説明         | アプリケーション情報                                                         |

|------|---------|------------|--------------------------------------------------------------------|

| 1    | BOOT    | ブートストラップ入力 | ハイサイド NFET のゲート電圧を供給します。                                           |

| 2    | SS      | ソフトスタート・ピン | ソフトスタート時間の延長に使用します。本データシートの「ソフトスタート」セクションを参照してください。                |

| 3    | RT/SYNC | 発振器モード制御ピン | レギュレータの発振器モードの制御に使用します。本データシートの「スイッチング周波数の調整と同期」セクションを参照してください。    |

| 4    | FB      | フィードバック・ピン | レギュレータへのフィードバック入力です。                                               |

| 5    | EN      | イネーブル・ピン   | レギュレータの起動とシャットダウンの制御に使用します。本データシートの「高精度イネーブルと UVLO」セクションを参照してください。 |

| 6    | GND     | システム・グランド  | システム・グランド・ピンです。                                                    |

| 7    | VIN     | 入力電圧ピン     | レギュレータへの電源入力です。                                                    |

| 8    | SW      | スイッチ・ピン    | レギュレータのスイッチング出力です。                                                 |

| EP   | EP      | 露出パッド      | グランドに接続してください。プリント基板への放熱用接続となります。 「アプリケーション情報」を参照してください。           |

**絶対最大定格 (Note 1)**

本データシートには軍用・航空宇宙用の規格は記載されていません。

関連する電気的信頼性試験方法の規格を参照ください。

|                     |                        |                                                       |                    |

|---------------------|------------------------|-------------------------------------------------------|--------------------|

| VIN ~ GND 間         | 43V                    | 接合部温度                                                 | 150 °C             |

| EN ピン電圧             | − 0.5V ~ 6V            | ハンダ付け仕様については、www.ti.com/lit/snoa549 のドキュメントを参照してください。 |                    |

| SS, RT/SYNC ピン電圧    | − 0.5V ~ 7V            |                                                       |                    |

| SW ~ GND 間 (Note 2) | − 5V ~ V <sub>IN</sub> | ESD 耐圧 (Note 3)                                       | ± 2kV              |

| BOOT ピン電圧           | V <sub>SW</sub> + 7V   | 人体モデル                                                 |                    |

| FB ピン電圧             | − 0.5V ~ 7V            | 保存温度範囲                                                | − 65 °C ~ + 150 °C |

| 消費電力                | 内部で制限                  |                                                       |                    |

**動作定格 (Note 1)**

|                         |                    |

|-------------------------|--------------------|

| 電源電圧 (V <sub>IN</sub> ) | 4.5V ~ 42V         |

| 接合部温度範囲                 | − 40 °C ~ + 125 °C |

**電気的特性**

標準字体で記載されたリミット値は  $T_J = 25$  °C の場合に限ります。太字で記載されたリミット値は − 40 °C ~ + 125 °C の接合部温度 ( $T_J$ ) 範囲にわたって適用されます。最小リミット (Min) 値と最大リミット (Max) 値は、出荷テスト、設計、または統計的相関によって保証されます。代表値 (Typ) は  $T_A = T_J = 25$  °C での最も標準的なパラメータ値を表しますが、参考として示す以外の目的はありません。特記のない限り、以下の規格は  $V_{IN} = 12V$  の場合に適用されます。

| Symbol              | Parameter                         | Conditions                                                  | Min (Note 5) | Typ (Note 4) | Max (Note 5) | Units |

|---------------------|-----------------------------------|-------------------------------------------------------------|--------------|--------------|--------------|-------|

| V <sub>FB</sub>     | Feedback Voltage                  | $V_{IN} = 4.7V$ to 42V                                      | 1.266/1.259  | 1.285        | 1.304/1.311  | V     |

| I <sub>Q</sub>      | Quiescent Current                 | $V_{FB} = 5V$                                               |              | 3.4          | 6            | mA    |

| I <sub>STDBY</sub>  | Standby Quiescent Current         | EN Pin = 0V                                                 |              | 25           | 40           | μA    |

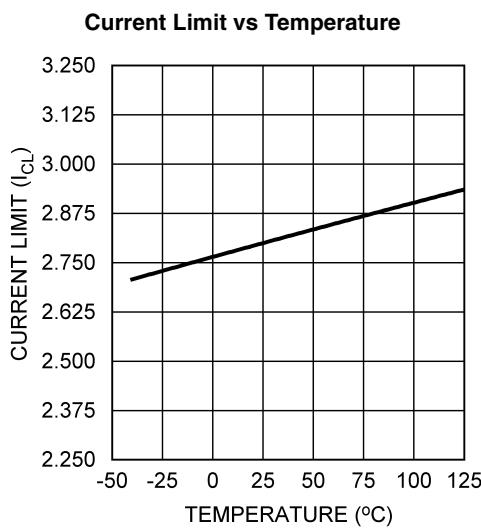

| I <sub>CL</sub>     | Current Limit                     |                                                             | 2.32         | 2.8          | 3.4          | A     |

| I <sub>L</sub>      | Output Leakage Current            | $V_{IN} = 42V$ , EN Pin = 0V, V <sub>SW</sub> = 0V          |              | 0.2          | 2            | μA    |

|                     |                                   | V <sub>SW</sub> = −1V                                       |              | 0.1          | 3            | μA    |

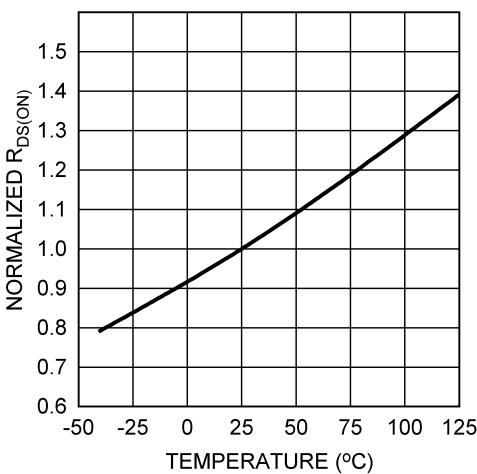

| R <sub>DS(ON)</sub> | Switch On-Resistance              |                                                             |              | 0.2          | 0.24/0.32    | Ω     |

| f <sub>O</sub>      | Oscillator Frequency              |                                                             | 400          | 500          | 600          | kHz   |

| T <sub>OFFMIN</sub> | Minimum Off-time                  |                                                             | 100          | 200          | 300          | ns    |

| T <sub>ONMIN</sub>  | Minimum On-time                   |                                                             |              | 100          |              | ns    |

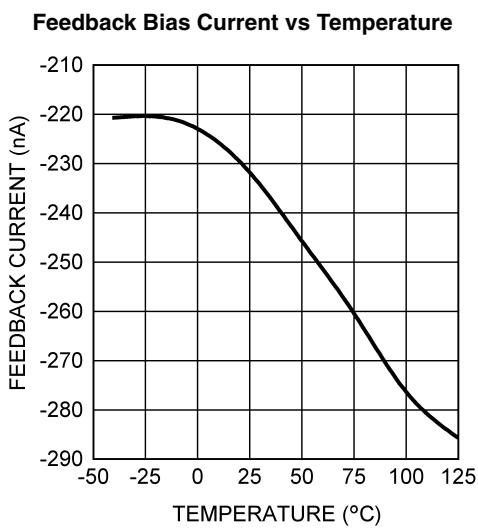

| I <sub>BIAS</sub>   | Feedback Bias Current             | $V_{FB} = 1.3V$                                             |              | 230          |              | nA    |

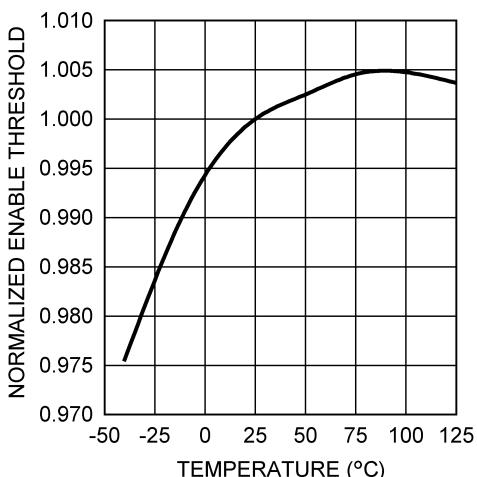

| V <sub>EN</sub>     | Enable Threshold Voltage          | Falling                                                     | 1.3          | 1.6          | 1.9          | V     |

| V <sub>ENHYST</sub> | Enable Voltage Hysteresis         |                                                             |              | 0.6          |              | V     |

| I <sub>EN</sub>     | Enable Input Current              | EN Input = 0V                                               |              | 6            |              | μA    |

| F <sub>SYNC</sub>   | Maximum Synchronization Frequency | $V_{SYNC} = 3.5V$ , 50% duty-cycle                          |              | 1            |              | MHz   |

| V <sub>SYNC</sub>   | Synchronization Threshold Voltage |                                                             |              | 1.75         |              | V     |

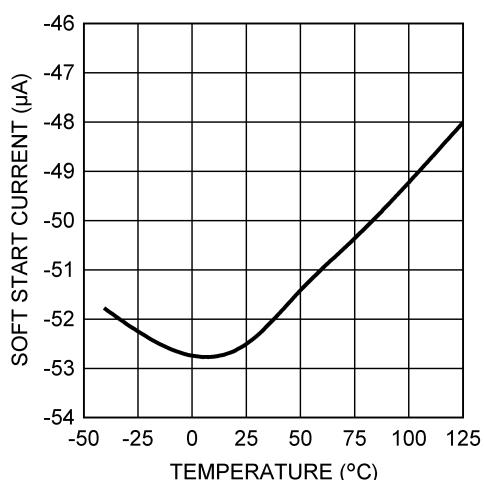

| I <sub>SS</sub>     | Soft-Start Current                |                                                             | 30           | 50           | 70           | μA    |

| T <sub>SD</sub>     | Thermal Shutdown Threshold        |                                                             |              | 150          |              | °C    |

| θ <sub>JA</sub>     | Thermal Resistance                | MR Package, Junction to ambient thermal resistance (Note 6) |              | 60           |              | °C/W  |

**Note 1:** 絶対最大定格とは、IC に破壊が発生したり、使用不能になったり、信頼性や性能が低下する可能性のあるリミット値を示します。これは、絶対最大定格において、または推奨動作条件に示されている動作条件を超える条件でこのデバイスが有效地に機能することや品質が劣化しないことは意味していません。推奨動作定格とは、デバイスが正常に機能する条件を示しており、この範囲を超えて動作させることは避けてください。

**Note 2:** 「SW ~ GND 間」の絶対最大定格は DC 電圧に対して適用されます。連続印加される負電圧のリミット値 − 10V は、幅 50ns 以下のパルスに対して適用されます。

**Note 3:** ESD テストでは人体モデルが使用され、100pF のコンデンサから 1.5kΩ の抵抗を通じて各ピンに放電されます。

**Note 4:** 代表値は規定された条件における最も標準的な値を表すものであり、保証値ではありません。

**Note 5:** 25 °C 時の Min/Max 各リミット値は 100% テストされます。全温度範囲でのリミット値は、統計的品質管理 (SQC) 手法によって決められた補正データを加味して保証されます。これらのリミット値は、テキサス・インスツルメンツの平均出荷品質レベル (AOQL) の計算に使用されます。

**Note 6:** PSOP-8 露出パッド (MR) パッケージに対する  $\theta_{JA}$  の値 (60 °C /W) は、パッケージが 1 平方インチ (約 6.45 平方センチ) の銅箔上に実装された場合に適用されます。  $\theta_{JA}$  の値は、熱伝導に寄与するプリント基板の銅箔量に応じて、42 ~ 115 °C /W の範囲で変化します。

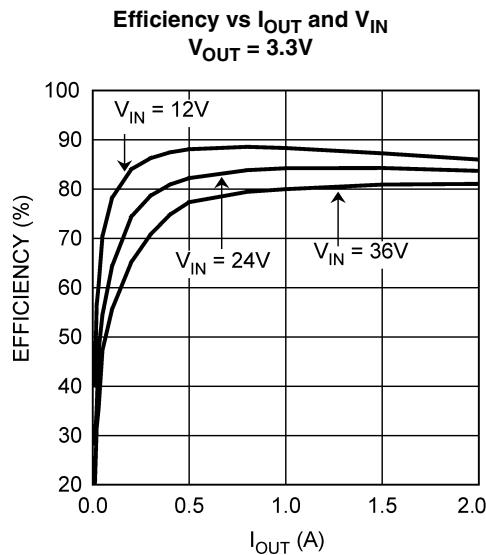

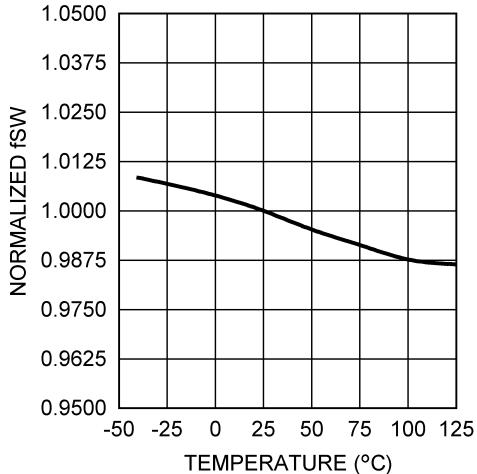

## 代表的な性能特性

特記のない限り次の条件が適用されます。  $V_{IN} = 12V$ 、  $T_J = 25^{\circ}C$

## Normalized Switching Frequency vs Temperature

## Normalized $R_{DS(ON)}$ vs Temperature

## Normalized Enable Threshold Voltage vs Temperature

## 代表的な性能特性 (つづき)

特記のない限り次の条件が適用されます。  $V_{in} = 12V$ 、  $T_J = 25^{\circ}C$

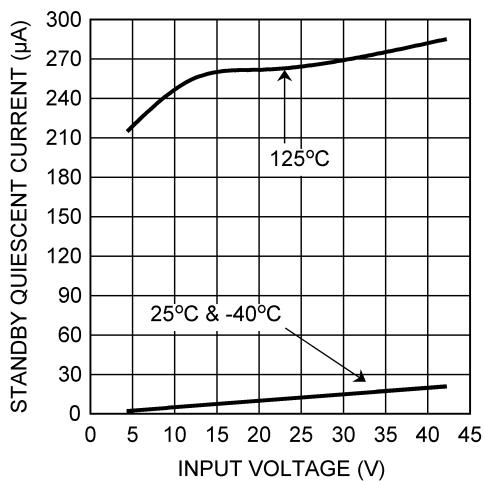

Standby Quiescent Current vs Input Voltage

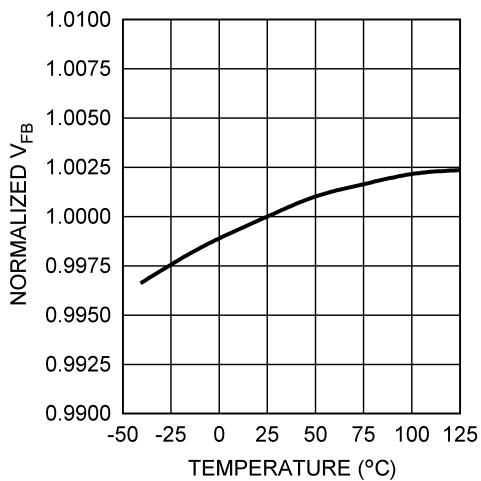

Normalized Feedback Voltage vs Temperature

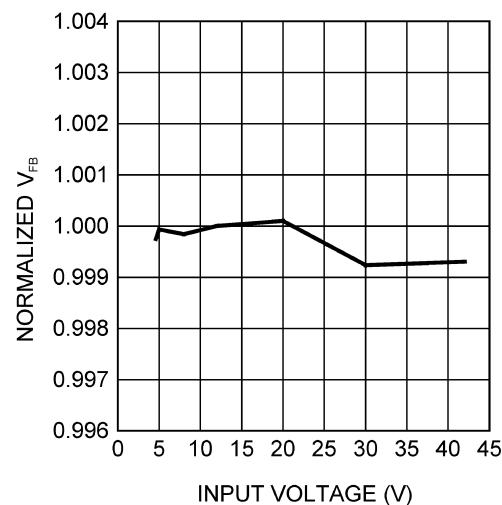

Normalized Feedback Voltage vs Input Voltage

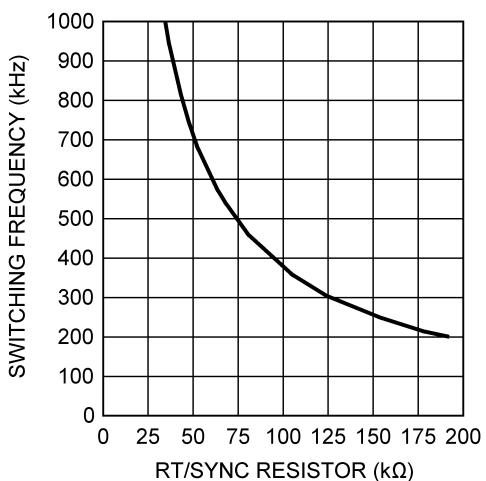

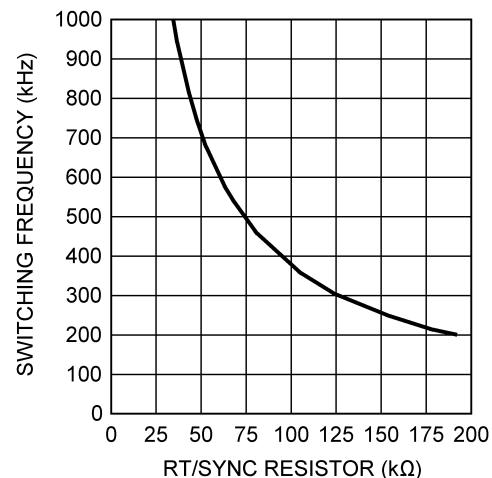

Switching Frequency vs RT/SYNC Resistor

Soft-start Current vs Temperature

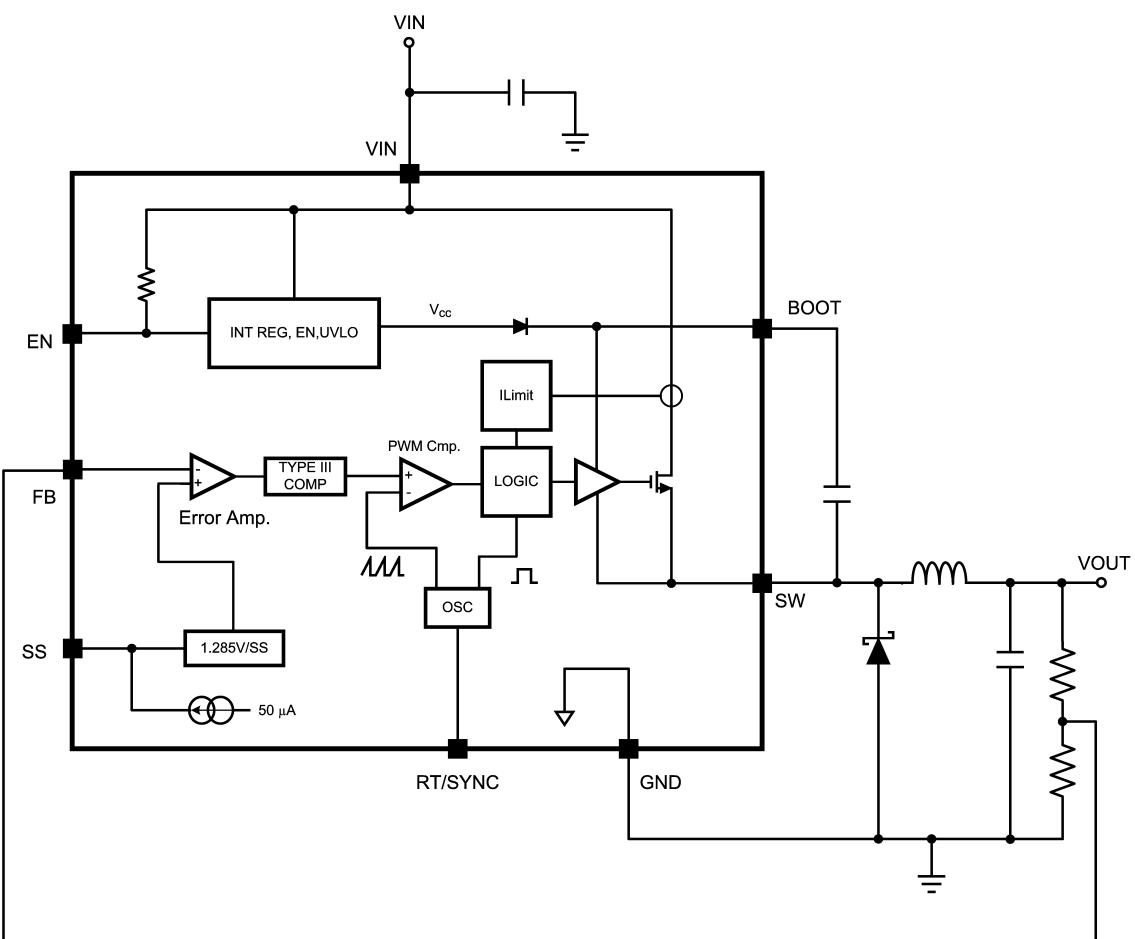

## ブロック図

FIGURE 1. Simplified Block Diagram

## 動作の詳細な説明

LM22680 は、周波数が一定の電圧モード PWM アーキテクチャを採用しています。また、入力電圧フィード・フォワードの採用により、入力電圧が変動しても安定したループ・ゲインを得られます。これにより、ループ補償回路は過渡特性を高めるために最適化されています。パワー MOSFET をダイオードと組み合わせると、約 0V から VIN まで振幅する矩形波がスイッチ・ピンで生成されます。この波形はインダクタと出力コンデンサによって平均化されてレギュレータの出力電圧になります。出力電圧は、波形のデューティ・サイクルを調整すると制御できます。エラー・アンプが出力電圧と内部リファレンス電圧を比較してデューティ・サイクルを調整し、出力を目標値にレギュレートします。

LM22680 の機能ブロック図を Figure 1 に示します。

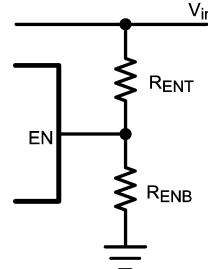

## 高精度イネーブルと UVLO

高精度イネーブル入力 (EN) は、レギュレータの制御に使用されます。この高精度イネーブル機能により、他の電源から抵抗分圧回路により、多段電源回路のシーケンス制御を容易に行えます。このピンをグランドに接続するか、1.6V (typ) 未満の電圧にすると、レギュレータがオフになります。この状態で入力電源から流入する電流は、入力電圧が 12V の場合、25  $\mu$ A (typ) です。EN 入力は、約 6  $\mu$ A の電流源によってチップ内部でプルアップされています。したがって、このピンをフローティングのままにするか、2.2V (typ) を超える電圧にすると、レギュレータがオンになります。この入力のヒステリシスは、1.6V (typ) のスレッショルドから上に約 0.6V (typ) です。イネーブル入力を駆動する場合は、電圧がこのピンの絶対最大定格の 6V を超えないようにしてください。

EN ピンは内部でプルアップされていますが、この機能を使用しない場合は（ノイズが多い環境では特に）、入力を High にしておくことを推奨します。これを最も簡単に行うには、VIN と EN ピンの間に抵抗を接続します。EN ピンに接続されている内蔵ツェナー・ダイオードは電圧が約 6V を上回ると導通するので、抵抗が必要になります。このツェナー・ダイオードへの電流は、100  $\mu$ A 未満に制限してください。470k  $\Omega$  の抵抗を使用すれば、42V という高い入力電圧の場合でも、電流を安全な値に制限できます。入力電圧が低い場合には、もっと小さな値の抵抗を使用してもかまいません。

LM22680 は、入力アンダーボルテージ・ロックアウト (UVLO) 機能も備えています。この機能は、内部回路にバイアスを適切に供給できるほど入力電圧が高くない場合に、レギュレータがオンになることを防ぎます。立ち上がりスレッショルドは 4.3V (typ) で、立ち下がりスレッショルドは 3.9V (typ) です。場合によつては、スレッショルドが低すぎて十分なシステム性能を得られないことがあります。解決策としては、EN 入力を外部 UVLO として使用し、入力電圧が下限を下回った際に回路をディスエーブルにします。これはバッテリの過放電や起動時における早期のターンオンを防ぐ目的でよく使用されます。また、入力電圧が最小電圧の 4.5V を下回るアプリケーションでは、アノーマルなデバイス動作を防ぐ目的にも推奨します。Figure 2 に、この UVLO 方式を実装するための接続方法を示します。適切な抵抗値は次式で求められます。

$$R_{ENT} = R_{ENB} \cdot \left( \frac{V_{off}}{V_{EN}} - 1 \right)$$

$$V_{on} = V_{off} \cdot \left( \frac{V_{EN} + V_{ENHYST}}{V_{EN}} \right)$$

$V_{off}$  はレギュレータがオフになる入力電圧で、 $V_{on}$  はレギュレータがオンになる電圧です。6  $\mu$ A のプルアップ電流があるので、分圧抵抗の電流はこれよりもはるかに大きくする必要があります。 $R_{ENB}$  には、20k  $\Omega$  の抵抗値が最初の選択肢として適切です。また、このピンの絶対最大定格を満たすために、EN ピンとグランドの間にツェナー・ダイオードの追加が必要になる場合もあります。

FIGURE 2. External UVLO Connections

## デューティ・サイクル制限

レギュレータでは、0 から 1 の全範囲にわたってデューティ・サイクルを制御できることが理想的です。ただし、回路に固有の遅延が原因で、高い信頼性のもとで制御できる最大デューティ・サイクルと最小デューティ・サイクルには、制限が存在します。これは、LM22680 で変換可能な最大 / 最小の入力電圧と出力電圧の制限につながっています。レギュレータでは、電流制限時にスイッチ電流を正確に測定する目的で最小オン時間が設けられています。また、ブートストラップ・コンデンサを再充電する目的で最小オフ時間も設けられています。特定の出力電圧における最大入力電圧は、次式で概算できます。

$$V_{in|_{max}} \approx \frac{V_{out} + 0.4}{T_{on} \cdot F_{sw} \cdot 1.8}$$

$F_{sw}$  はスイッチング周波数で、 $T_{on}$  は最小オン時間です。いずれの値も「電気的特性」に記載されています。周波数調整機能を用いる場合、 $F_{sw}$  にはその値を使用します。公称値を使用してください。ワースト・ケースは、出力電圧が最小でスイッチング周波数が最大の場合です。ワースト・ケースの入力電圧を上回ると、レギュレータはサイクルをスキップし、スイッチング周波数が事実上減少します。結果として、出力電圧リップルが増加し、出力電圧の精度が低下します。

第 2 の制限となるのが、出力電圧がレギュレーション状態から「ドロップアウト」する直前の最大デューティ・サイクルです。ドロップアウト発生前の最小入力電圧は、次式で概算できます。

$$V_{in|_{min}} \approx \frac{V_{out} + 0.4 + I_{out} \cdot R_L + I_{out} \cdot R_{ds(on)}}{1 - T_{off} \cdot F_{sw} \cdot 1.8}$$

$T_{OFF}$  と  $R_{DS(ON)}$  の値は、「電気的特性」に記載されています。ワースト・ケースは、スイッチング周波数と負荷電流が最大の場合です。この式の  $R_L$  は、インダクタの直流抵抗を表しています。当然ながら、レギュレータへの最小入力電圧は、4.5V (typ) 以上でなければなりません。

## 電流制限

LM22680 は電流制限機能を備えており、出力で予期せぬ過負荷が発生した際にスイッチ電流が安全な値を超えることを防止します。ピーク電流制限値は、「電気的特性」の  $I_{CL}$  の項目に記載されています。電流制限への到達前に供給可能な最大負荷電流は、次式で求められます。

$$I_{out|_{max}} \approx I_{CL} - \frac{(V_{in} - V_{out})}{2 \cdot L \cdot F_{sw}} \cdot \frac{V_{out}}{V_{in}}$$

$L$  はパワー・インダクタの値です。

LM22680 が電流制限状態に移行すると、出力電圧が低下し、ピーク・インダクタ電流が各サイクルの終了時に  $I_{CL}$  で固定されます。スイッチング周波数は一定に保たれたままデューティ・サイクルが減少します。負荷電流は一定に保たれず、過負荷の程度と出力電圧に依存します。

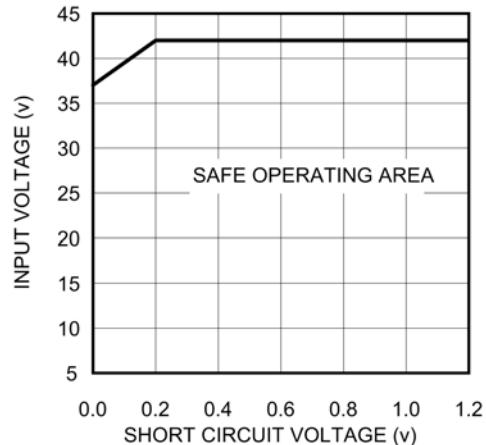

過負荷の程度がきわめて激しい場合（「短絡」時）、レギュレータは低周波数電流フォールドバック動作モードに移行します。周波数フォールドバックは、公称スイッチング周波数の約 1/5 です。最小オン時間の経過前に電流制限に達している場合、このモードが発動します。この動作モードは、過負荷時に出力電圧がきわめて低くなった時に発生するインダクタ電流の「暴走」を防ぐために使用されます。低周波数電流フォールドバックへの移行をもたらす出力電圧レベルは、次式で求められます。

$$V_x \leq V_{in} \cdot F_{sw} \cdot T_{on} \cdot 1.8$$

$F_{sw}$  は通常のスイッチング周波数で、 $V_{in}$  はアプリケーションの最大電圧です。過負荷によって出力電圧が  $V_x$  以下になると、回路は電流フォールドバック・モードに移行します。アプリケーションで過負荷時に出力電圧が  $V_x$  以下になる場合は、第 2 の基準も確認する必要があります。この動作モードにおいてダメージが発生しない最大入力電圧は、次式で求められます。

$$V_{in} \leq \frac{V_{sc} + 0.4}{T_{on} \cdot F_{sw} \cdot 0.36}$$

$V_{sc}$  は過負荷時の出力電圧値で、 $F_{sw}$  は通常のスイッチング周波数です。フォールドバック・モード時に入力電圧がこの値を上回ると、レギュレータやダイオードが破損する可能性があります。これらの式はインダクタで測定された電圧であることに注意してください。通常のトレース抵抗や配線抵抗により、インダクタの電圧は離れた場所の負荷の電圧より高くなります。したがって、負荷の端子間を 0V で短絡させた場合でも、インダクタでは一定の電圧が生じます。計算で  $V_x$  と  $V_{sc}$  に使用するのはこの値です。フォールドバック・モードから復帰するには、フォールドバックの開始に必要な値より大幅に低い値まで負荷を削減してください。この負荷「ヒステリシス」は、電圧レギュレータに関連したあらゆる種類の電流制限フォールドバックにとって標準的な特性です。

周波数外部同期機能を使用する場合、電流制限周波数フォールドバックが動作しないので、出力で低抵抗値での短絡が発生すると、システムが耐えられない可能性があります。

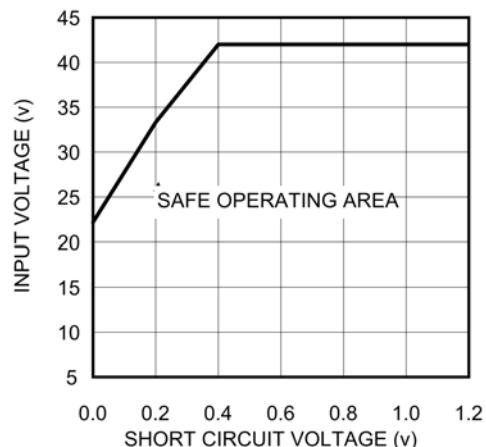

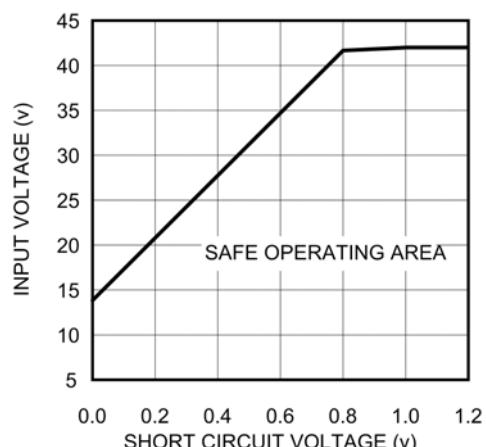

Figure 3 ~ Figure 5 に、さまざまなスイッチング周波数における短絡モード時の安全動作領域を示します。曲線の右下の動作点が安全動作領域を表しています。ただし、これらのグラフは、LM22680 を周波数外部同期モードで動作させる場合には適用されません。

FIGURE 3. SOA at 300 kHz

FIGURE 4. SOA at 500 kHz

FIGURE 5. SOA at 800 kHz

## ソフトスタート

ソフトスタート機能により、レギュレータは安定動作の状態に緩やかに到達するため、起動時のストレスが軽減されます。内部ソフトスタート機能は、約  $500\mu\text{s}$  で出力電圧を立ち上げます。この時間は、SS ピンに接続された外付けコンデンサを利用して延長できます。 $100\text{nF} \sim 1\mu\text{F}$  の容量を推奨します。ソフトスタート時間は次式で概算できます。

$$T_{ss} \approx 26 \times 10^3 \cdot C_{ss}$$

回路のシャットダウン時や過熱状態の発生時は、常にソフトスタートがリセットされます。

## スイッチング周波数の設定と同期

LM22680 は、RT/SYNC ピンの状態に応じて 3 種類のモードで動作します。RT/SYNC ピンをフローティングにしておくと、内部で  $500\text{kHz}$  (typ) に設定された周波数でスイッチングが行われます。 $25\text{k}\Omega \sim 200\text{k}\Omega$  の抵抗を RT/SYNC ピンとグランドの間に接続すると、内部スイッチング周波数を  $1\text{MHz} \sim 200\text{kHz}$  の範囲で調整できます。Figure 6 は、スイッチング周波数と RT/SYNC ピンに接続された外付け抵抗との代表的な関係の代表値を示したグラフです。このモードでのスイッチング周波数の精度は、内蔵発振器の精度よりわずかに低く、約  $\pm 25\%$  になる見込みです。また、外部クロックを RT/SYNC ピンに供給すると、レギュレータをシステム・クロックまたは別の LM22680 に同期できます。モードはレギュレータの起動時に設定されます。LM22680 をイネーブルにしたとき、または  $V_{IN}$  を印加した後、微弱なプルアップが RT/SYNC ピンに接続され、およそ  $100\mu\text{s}$  後にこのピンの電圧が約  $0.8\text{V}$  のスレッショルドと比較されます。RT/SYNC ピンがオープンの場合は、このスレッショルドよりも高い電圧でフローティング状態となり、内部クロックで動作するモードに設定されます。周波数設定抵抗が存在する場合は、内部リファレンスによりピン電圧が  $0.8\text{V}$  に保持され、その結果流れる電流によって、クロック周波数を抵抗値で設定できるモードに設定されます。外付け回路によって RT/SYNC ピンの電圧が  $0.8\text{V}$  より大幅に高くなる場合や低くなる場合は、外部同期が可能なモードに設定されます。モードは、EN または入力電源により連続動作している間ラッチされます。

スイッチング周波数の選択は、複数の考慮事項の影響を受けています。例えば、スイッチング損失を削減したり、デューティ・サイクル制限を改善するには、低い周波数が適しています。一方、EMI 関連の問題を回避したり、外付け部品の外形寸法を抑えるには、高い周波数や特定の周波数が適しています。スイッチング周波数を  $500\text{kHz}$  より大きくできるという柔軟性は、アプリケーションにとって重要な信号周波数帯域の外での動作に利用できます。ただし、 $500\text{kHz}$  を超える周波数で動作させても、インダクタや出力コンデンサの値を大幅に低減することはできません。これは、内部ループ補償回路の設計によってこうした部品の値が制限されているからです。

周波数同期にも注意が必要です。第 1 に、外部クロック周波数は内部クロック周波数より高く、 $1\text{MHz}$  より低くなければなりません。最大内部スイッチング周波数は、「電気的特性」に記載されています。周波数調整機能と同期機能は同時に使用できないことに注意してください。同期周波数は、常に内部クロック周波数より高くななければなりません。第 2 に、レギュレータを同期モードに移行させるには、起動時に High または Low の有効な電圧が RT/SYNC ピンに印加される必要があります（上記を参照）。また、同期パルスの振幅は、「電気的特性」に記載された  $V_{SYNC}$  レベルに適合している必要があります。レギュレータは外部クロックの立ち上がりエッジで同期を行います。通常動作中に外部クロックが失われると、レギュレータは  $500\text{kHz}$  (typ) の内部クロック・モードに戻ります。

周波数同期機能を使用する場合、電流制限フォールドバックは動作しません。詳細は、「電流制限」を参照してください。

FIGURE 6. Switching Frequency vs RT/SYNC Resistor

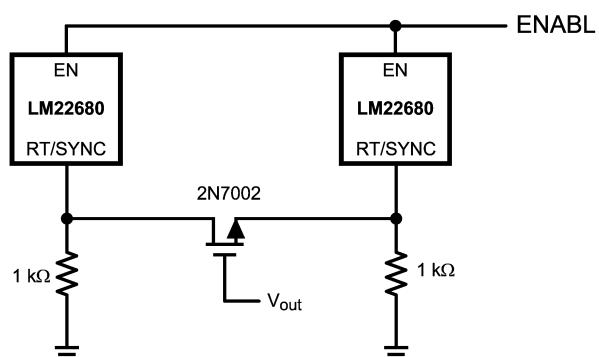

## 自己同期

複数の LM22680 レギュレータで同じスイッチング周波数を共有し、互いに同期させる動作も可能です。この機能を使用するには、MOSFET を介して各デバイスの RT/SYNC ピンを互いに接続し、さらに  $1\text{k}\Omega$  の抵抗を介して各ピンをグランドに接続します。Figure 7 にこの接続を示します。MOSFET のゲートは、最高の出力電圧のレギュレータに接続してください。また、両方のレギュレータを適切に初期化できるように、それぞれの EN ピンを共通のシステム・イネーブルに接続してください。動作は次のようにになります。レギュレータをイネーブルにすると、出力が Low になり、MOSFET がオフになります。 $1\text{k}\Omega$  抵抗によって RT/SYNC ピンが Low になり、その結果、同期モードがイネーブルになります。 $1\text{k}\Omega$  抵抗は十分に小さいので、周波数調整モードをアクティブにすることなく、RT/SYNC ピンを Low でできます。いずれかのレギュレータの出力電圧が MOSFET をオンにできる電圧になると、2 つの RT/SYNC ピンが相互に接続され、レギュレータが同期モードで動作します。2 つのレギュレータは同じ周波数のクロックで駆動されますが、速い方の内蔵発振器を持ったレギュレータの最小オフ時間によって、位相が若干ずれます。この若干の位相のずれが、レギュレータの入力コンデンサに対するストレスを緩和します。MOSFET が完全な導通状態となるように、ゲート・スレッショルド電圧が低い MOSFET を選択することが重要です。また、電極間容量の少ない MOSFET が必要です。2N7002 が適切な選択肢です。

FIGURE 7. Self Synchronizing Setup

## ブートストラップ電源

LM22680 は、パワー MOSFET の制御用にフローティング・ハイサイド・ゲート・ドライバを備えています。このドライバの電源は、BOOT ピンと SW ピンの間に接続された外付けブートストラップ・コンデンサです。短くて幅の広い PCB 配線パターンを介して、特性の良い 10nF セラミック・コンデンサをこれらのピンに接続してください。レギュレータで最小オフ時間が設けられている理由の 1 つは、スイッチング・サイクルごとにブートストラップ・コンデンサを確実に再充電できるようにするためにです。ブートストラップ・コンデンサをフルに再充電するための最小オフ時間を確保するには、約 5mA 以上の負荷電流が必要です。出力分圧抵抗を使用する場合は、必要な負荷電流の一部をその抵抗によってまかなうことができます。

## 熱保護回路

LM22680 には、最大接合部温度を超えた場合に IC を保護するサーマル・シャットダウン回路が内蔵されています。サーマル・シャットダウン回路は約 150 °C で作動し、温度が約 135 °C を下回るまで、レギュレータはシャットダウン状態を維持します。

## 内部ループ補償回路

LM22680 は、さまざまなパワーワンの外付け部品に対して安定したレギュレータ特性が得られるループ補償回路を内蔵しています。

独自のパワーワン(インダクタと出力コンデンサ)を設計する際は、安定性を確保するために注意を要する場合があります。www.ti.com より利用できる WEBENCH® オンライン回路設計支援ツールにより、LM22680 の安定性を検証できます。オンラインの製品カタログから手軽に扱えるスプレッドシートをダウンロードできます。

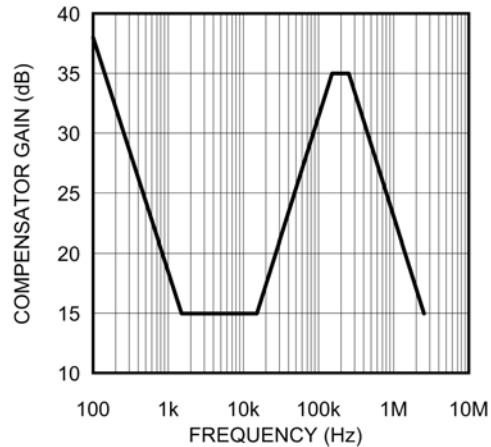

レギュレータ・ループの完全な伝達関数は、補償回路とパワーワンの伝達関数を組み合わせることで得られます。Figure 8 に示すように、LM22680 はタイプ III ループ補償回路を内蔵しています。これは、FB ピンから PWM モジュレータの入力までの直線近似関数に相当します。パワーワンの伝達関数は、DC ゲインと、インダクタや出力コンデンサによって作成される 2 次ポールで構成されます。LM22680 では入力電圧フィードフォワードが採用されているので、パワーワンの DC ゲインは 20dB に固定されています。2 次ポールは、共振周波数と Q 値によって決まります。最初の設計では、インダクタンスと出力容量の積が次式を満たすようにします。

$$L \cdot C_{out} = 1.1 \times 10^{-9}$$

または、次式で求められるように、このポールを 1.5kHz と 15kHz の間に配置します。

$$F_o = \frac{1}{2\pi \cdot \sqrt{L \cdot C_{out}}}$$

Q 値はパワーワン部品の寄生抵抗に依存するため、通常は設計者が制御できるものではありません。当然のことながら、ループ補償回路がパワーワン部品を選定する際の唯一の考慮事項になります。詳細は、「アプリケーション情報」を参照してください。

FIGURE 8. Compensator Gain

通常、手計算やシミュレーションは適切なパワーワン部品の選定にしか使えません。優れた設計を行うには、負荷 / 入力変動テストによってアプリケーションの安定性を検証する必要があります。また、ポーデ線図を用いて安定性のマージンを決定してください。アプリケーション・ノート AN-1889 では、オシロスコープとファンクション・ジェネレータだけで行えるループ伝達関数の測定方法について説明しています。

## アプリケーション情報

### 代表的な降圧型レギュレータ・アプリケーション

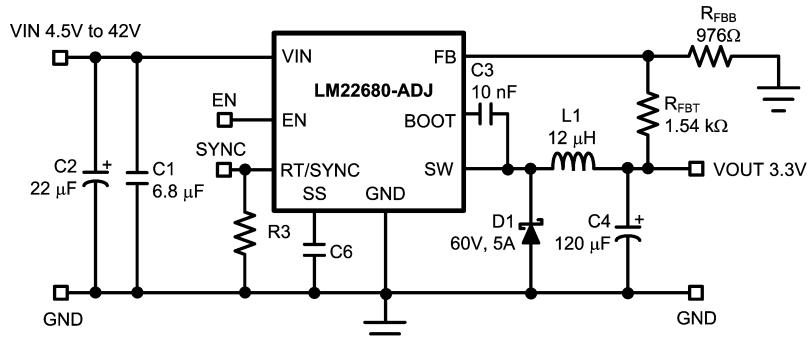

Figure 9 に、5.5V ~ 42V の入力電圧を 2A で 3.3V の出力に変換する例を示します。詳細はアプリケーション・ノート AN-1911 を参照してください。

FIGURE 9. Typical Buck Regulator Application

### 外付け部品

以下のガイドラインは、LM22680 による降圧型（バック）コンバータの設計に利用してください。

### インダクタ

インダクタンス値は、負荷電流、リップル電流、入力電圧の最大値と最小値をもとに決定します。アプリケーションを連続モード (CCM) に維持するためには、最大リップル電流  $I_{RIPPLE}$  は最小負荷電流の 2 倍よりも小さくしなければなりません。

インダクタのリップル電流のピーク・ツー・ピーク値を公称出力電流の約 30% 程度に設定する一般則に従うと、出力電圧リップルと部品のサイズやコストの間で適切なトレードオフが得られます。このリップル電流値に基づいて、インダクタンス  $L$  を以下の式から求めます。

$$L = \frac{(V_{in} - V_{out}) \cdot V_{out}}{0.3 \cdot I_{out} \cdot F_{sw} \cdot V_{in}}$$

$F_{sw}$  はスイッチング周波数であり、 $V_{in}$  にはアプリケーションにおける最大値を使用します。上の式はインダクタ  $L$  の値を選択する指針となります。実際の回路では標準系列の中から最も近い値の部品を使用します。

インダクタを選択したら、次式で実際のリップル電流を求められます。

$$\Delta I = \frac{(V_{in} - V_{out}) \cdot V_{out}}{L \cdot F_{sw} \cdot V_{in}}$$

通常、インダクタンスを大きくすると過渡応答は遅くなりますが、出力電圧リップルは低減されます。インダクタンスを小さくすると過渡応答は改善しますが、出力電圧リップルが大きくなります。

飽和を防ぐために、アプリケーションにおけるインダクタの定格はピーク電流  $I_{PK}$  以上でなければなりません。通常負荷条件のとき、ピーク電流は負荷電流にインダクタ・リップル電流の 1/2 を加えた値になります。

過負荷状態で特定の負荷変動時には、コントローラが電流制限を実行することがあります。この場合、ピーク・インダクタ電流は、「電気的特性」に記載された  $I_{CL}$  によって決まります。優

れた設計を行うには、インダクタの定格がこの過負荷状態に十分対応できるものでなければなりません。インダクタの定格が予想される最大電流に対応していないと、飽和が発生して、LM22680 やパワー・ダイオードが損傷を受ける可能性があります。

### 入力コンデンサ

入力コンデンサは、入力電圧リップルと RMS 電流に基づいて選択します。VIN ピンに発生するリップル電圧を抑え、かつ、スイッチのオン時間中にレギュレータ電流の大半を供給する目的で、良質の入力コンデンサが必要です。低 ESR のセラミック・コンデンサを推奨します。入力電源の電圧リップルとノイズを低減するには、大容量の入力コンデンサが適しています。十分なバイパス処置が講じられていない場合は、同じ入力電源を共有する別の回路にこのノイズが伝わる可能性があります。入力電圧リップルは次式で概算できます。

$$V_{ri} \approx \frac{I_{out}}{4 \cdot F_{sw} \cdot C_{in}}$$

$V_{ri}$  はスイッチング周波数におけるピーク・ツー・ピーク・リップル電圧です。もう 1 つの問題となるのが、このコンデンサを通過する RMS 電流です。この電流は次式で概算できます。

$$I_{rms} \approx \frac{I_{out}}{2}$$

コンデンサの定格は、スイッチング周波数においてこの RMS 電流レベル以上でなければなりません。

すべてのセラミック・コンデンサは、標準的な許容誤差と温度係数に加えて、大きな電圧係数を持っています。この影響を減じるには、最小容量が必要な値になるように複数のコンデンサを並列接続します。このように、複数のコンデンサ間で電流を共有すると RMS 電流の制約にも対応できる場合があります。通常、入力には電解コンデンサをセラミック・コンデンサと並列接続して使用することを推奨します。このコンデンサの適度な ESR は、長い電源リードに起因して入力電源で発生するリギングの抑制に役立ちます。こうした方式は、LM22680 の最大入力電圧定格を超える電圧スパイクの低減にも効果的です。

## アプリケーション情報 (つづき)

高周波バイパス・コンデンサを LM22680 のできる限り近くに配置することを推奨します。この小型パッケージ・サイズの低 ESR セラミック・コンデンサは、できる限り短い PCB 配線パターンで VIN ピンと GND ピンに直接接続してください。0.47  $\mu$  F ~ 1  $\mu$  F の容量が適切です。このコンデンサは、高感度の内部回路に低インピーダンス電源を供給するのに役立ちます。また、EMI の増加につながる入力電源での高速ノイズ・スパイクを抑制できます。

### 出力コンデンサ

出力コンデンサの役割は、出力電圧のフィルタリングと変動時における負荷電流の供給です。コンデンサは出力リップルやトランジエント特性に関するアプリケーション要求を考慮して選定します。セラミック・コンデンサと低 ESR の SPTM または POSCAP™ コンデンサを並列接続して使用すれば、最良のパフォーマンスを実現できます。セラミック・コンデンサなどの ESR がきわめて小さいコンデンサが出力リップルとノイズ・スパイクを抑制する一方、大容量の電解またはポリマー・コンデンサは変動時に負荷電流を供給するバルク容量として機能します。ESR がきわめて小さいと仮定した場合、出力電圧リップルは次式で概算できます。

$$V_{ro} \approx \frac{(V_{in} - V_{out}) \cdot V_{out}}{8 \cdot V_{in}} \cdot \frac{1}{F_{sw}^2 \cdot L \cdot C_{out}}$$

通常、出力コンデンサの総容量値には 100  $\mu$  F 以上を推奨します。

$V_{out}$  が 3.3V 未満のアプリケーションでは、低 ESR の出力コンデンサを選定することが重要です。入力電圧が動作電圧範囲以下に低下する際に、出力電圧に発生するオーバーシュートを抑制するためです。

スイッチング周波数を 500kHz よりも高く設定すると、安定性の要件から容量値が比例して小さくならない場合があります。内部補償回路がスイッチング周波数 500kHz で動作する回路に対して最適化されているためです。詳細は、「内部ループ補償回路」を参照してください。

### ブートストラップ・コンデンサ

BOOT ピンと SW ピンの間に接続されたブートストラップ・コンデンサは、ゲート電流を供給して N チャネル MOSFET をターンオンします。このコンデンサの推奨値は 10nF で、特性が良く ESR が小さいセラミック・コンデンサを使用してください。

内蔵パワー MOSFET のターンオンを緩やかにして EMI を低減したほうが望ましい場合もあります。これは、 $C_{boot}$  コンデンサと直列に小さな抵抗を接続すれば可能になります。10  $\Omega$  ~ 50  $\Omega$  の抵抗を使用できます。この方法ではスイッチング損失が増えて効率が低下するので、どうしても必要な場合のみ使用してください。

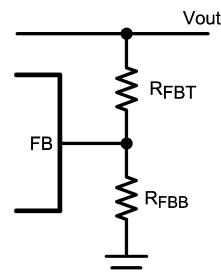

### 出力分圧抵抗の選択

出力電圧が  $V_{FB}$  (1.285V typ) を超える場合は、Figure 10 に示すように、出力と FB ピンの間に分圧抵抗を接続します。この分圧抵抗の抵抗値は次式で求められます。

$$R_{FBT} = \left[ \frac{V_{out}}{1.285} - 1 \right] \cdot R_{FBB}$$

$R_{FBB}$  の推奨値は 1k  $\Omega$  です。この値であれば、必要な最小負荷電流の一部を供給しながら、ノイズ感度を下げられます。 $R_{FBT}$  のハイサイドは、リモート・センシング用に出力コンデンサまたは負荷に直接接続する必要があります。分圧抵抗を負荷に接続する場合は、その場所にローカル高周波バイパスを設けてください。

FIGURE 10. Output Voltage Divider

出力電圧を高精度に保つには、 $R_{FBB}$  と  $R_{FBT}$  の合計を 10k  $\Omega$  以下にすることを推奨します。ハイ・インピーダンス入力で、ノイズを拾いやすいため、出力分圧抵抗を LM22680 の FB ピンのできるだけ近くに配置します。

### パワー・ダイオード

すべての LM22680 アプリケーションにはショットキ・タイプのパワー・ダイオードが必要です。超高速整流ダイオードは推奨しません。過渡的なリバース・リカバリ電流によって IC に損傷を与える可能性があります。LM22680 を使用することが多い高入力電圧、低出力電圧のアプリケーションでは、ショットキ・ダイオードの特性として、ほぼ理想的なリバース・リカバリ特性と順方向電圧降下の低さが特に重要になります。ダイオードの逆方向降伏電圧定格は、最大  $V_{IN}$  にある程度のマージンを加えた値として選択します。経験則として、最大入力電圧の 1.3 倍の逆耐圧定格を持つダイオードを選択するとよいでしょう。

平均電流定格がアプリケーションの最大負荷電流以上のダイオードを選択してください。

### 回路基板レイアウト

スイッチング電源を適切に動作させるには、基板レイアウトが非常に重要です。第 1 に、放熱の目的を果たすのに十分な広さのグランド・プレーン領域がなければなりません。第 2 に、スイッチング・ノイズの影響を低減するために適切な指針に沿ってパターンを設計する必要があります。スイッチ・モード・コンバータは、きわめて高速なスイッチング・デバイスです。このようなケースでは、入力電流の急激な増加と配線の寄生インダクタンスが相まって、不要な  $L \frac{di}{dt}$  ノイズ・スパイクが発生します。このノイズの大きさは出力電流が増加するにつれて大きくなる傾向があります。ノイズは不要な電磁干渉 (EMI) を招く場合があり、デバイス性能にも問題が生じる恐れがあります。したがって、このスイッチング・ノイズの影響を最小限に抑えるための注意が必要です。

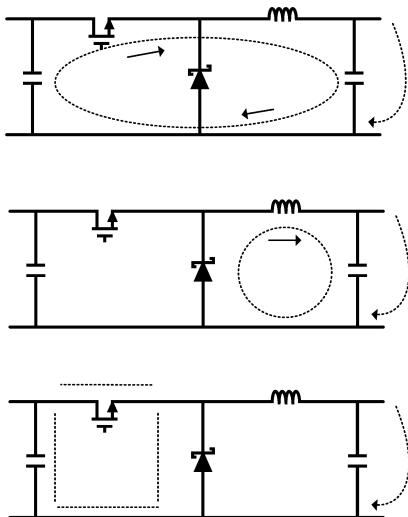

最も重要なレイアウト・ルールは AC 電流のループをできるだけ小さくすることです。Figure 11 に降圧型コンバータの電流の流れを示します。一番上の図には、FET スイッチがオン状態の時に流れる電流を点線で示しています。中央の図には、FET スイッチがオフ状態の時に流れる電流を示しています。

## 回路基板レイアウト (つづき)

一番下の図は AC 電流と見なされる電流です。この AC 電流は、非常に短時間で変化するため、最も重要です。最後の回路図の点線で示した部分が、配線パターンをできる限り短く、かつ広くすべき経路になります。この部分を短くすれば、ループが囲む面積も小さくなり、ループ・インダクタンスを低減できます。レイアウトによって機能上の問題が発生しないように、PCB のレイアウト例を十分に検討してください。LM22680、バイパス・コンデンサ、ショットキ・ダイオード、 $R_{FBB}$ 、 $R_{FBT}$ 、インダクタをレイアウト例に示したように配置すると、最良の結果が得られます。このレイアウト例では、 $R1$  は  $R_{FBB}$ 、 $R2$  は  $R_{FBT}$  を表しています。また、放熱を助け、ボード上の配線パターンによる寄生インダクタンスを低減するために、70  $\mu\text{m}$  以上の厚みがある銅箔の基板を使用することを推奨します。詳細については、アプリケーション・ノート AN-1229 を参照してください。

FIGURE 11. Current Flow in a Buck Application

## 熱に関する考慮事項

消費電力が最も大きい部品は、パワー・ダイオードと LM22680 レギュレータに内蔵されたパワー MOSFET です。LM22680 内部で消費される電力を簡単に求めるには、総変換損失を測定し、その値からダイオードとインダクタによる電力損失を減算します。総変換損失とは、入力電力と出力電力の差です。パワー・ダイオードによる損失は次式で近似できます。

$$P_D = I_{out} \cdot V_D \cdot \left[ 1 - \frac{V_{out}}{V_{in}} \right]$$

$V_D$  はダイオード電圧降下です。インダクタの電力は次式で近似できます。

$$P_L = I_{out}^2 \cdot R_L \cdot 1.1$$

$R_L$  はインダクタの DC 抵抗値、係数 1.1 は AC 損失を近似するための項です。

レギュレータは大きな許容損失を確保できるように放熱用露出パッドを備えています。デバイス下面にグランド・プレーンに接続する複数のビアを設けるとレギュレータの接合部温度を大幅に下げる効果が得られます。ダイオードで大きな許容損失を確保するにはダイオードも露出パッドが付いた品種を選択します。レギュレータの消費電力に最も大きな影響を与えるパラメータは、出力電流、入力電圧、動作周波数です。最大出力電流かつ最大入力電圧付近で動作した場合の消費電力はかなりの値となります。LM22680 の接合部から周囲への熱抵抗はアプリケーションによって異なります。大きな影響を与える要因は、PC 基板の銅箔面積、IC 露出パッド下のビア数、および強制空冷の風量です。PC 基板の表面または裏面に大型の連続するグランド・プレーンを配置すると、最も効果的な放熱が可能です。IC 露出パッドとPC基板とのハンダ付け品質は重要です。過度のハンダ・ボイドが存在すると放熱能力が大きく低下します。LM22680 PSOP-8 パッケージの接合部一周囲間の熱抵抗は、「電気的特性」に規定されています。詳細については、アプリケーション・ノート AN-2020 を参照してください。

## PCB レイアウト例

FIGURE 12. Inverting Regulator Application

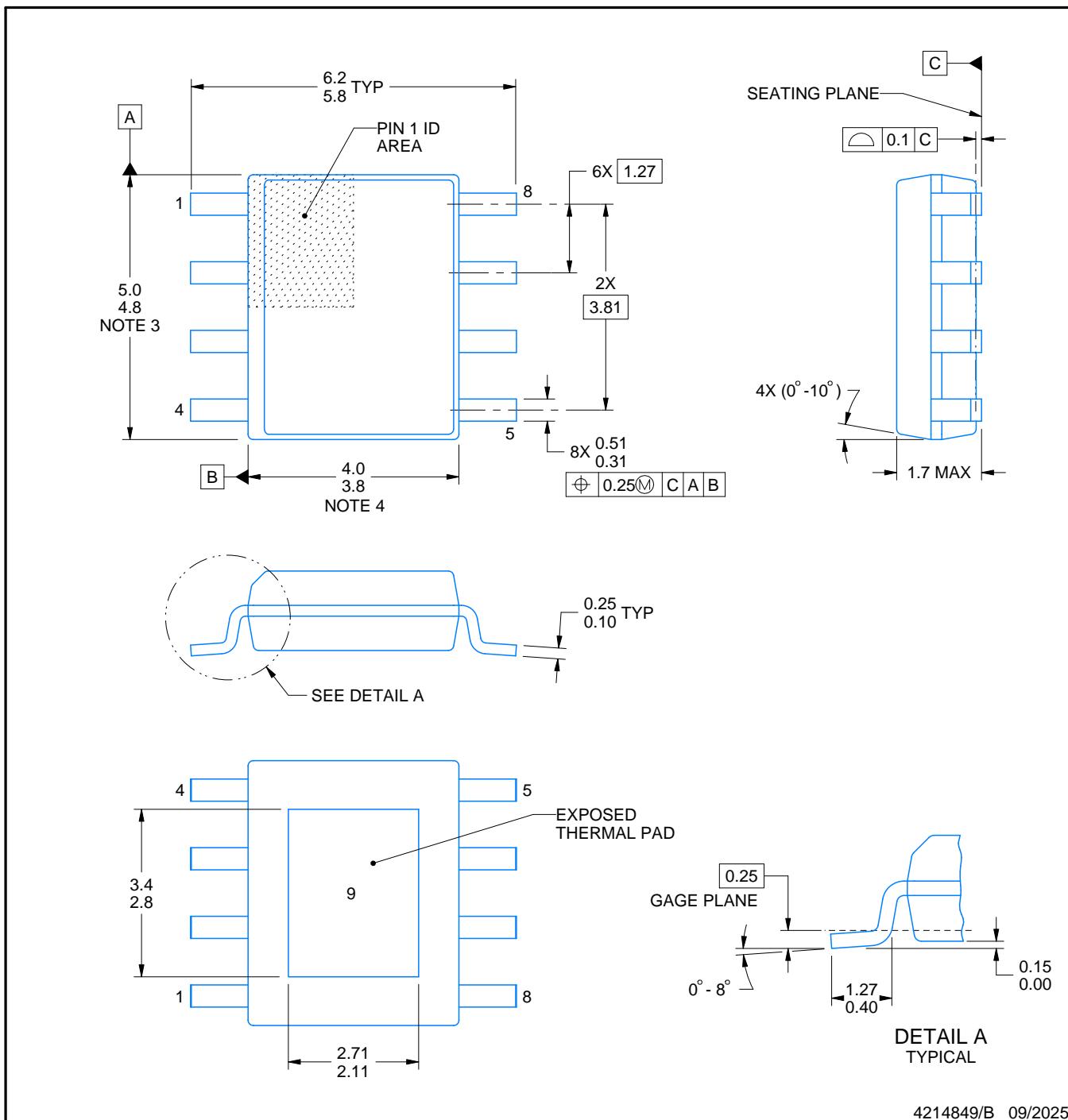

外形寸法図 特記のない限り inches (millimeters)

MRA08B (Rev B)

8-Lead Plastic PSOP-8 Package

TI Package Number MRA08B

すべて商標および登録商標は、それぞれの所有者に帰属します。

この資料は、Texas Instruments Incorporated(TI)が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ(日本TI)が英文から和文へ翻訳して作成したものです。

資料によっては正規英語版資料の更新に対応していないものがあります。日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。

TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

**TEXAS

INSTRUMENTS**

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins        | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|-----------------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| LM22680MR-ADJ/NOPB    | Active        | Production           | SO PowerPAD (DDA)   8 | 95   TUBE             | Yes         | SN                                   | Level-3-260C-168 HR               | -40 to 125   | L22680-ADJ          |

| LM22680MR-ADJ/NOPB.A  | Active        | Production           | SO PowerPAD (DDA)   8 | 95   TUBE             | Yes         | SN                                   | Level-3-260C-168 HR               | -40 to 125   | L22680-ADJ          |

| LM22680MRE-ADJ/NO.A   | Active        | Production           | SO PowerPAD (DDA)   8 | 250   SMALL T&R       | Yes         | SN                                   | Level-3-260C-168 HR               | -40 to 125   | L22680-ADJ          |

| LM22680MRE-ADJ/NOPB   | Active        | Production           | SO PowerPAD (DDA)   8 | 250   SMALL T&R       | Yes         | SN                                   | Level-3-260C-168 HR               | -40 to 125   | L22680-ADJ          |

| LM22680MRX-ADJ/NO.A   | Active        | Production           | SO PowerPAD (DDA)   8 | 2500   LARGE T&R      | Yes         | SN                                   | Level-3-260C-168 HR               | -40 to 125   | L22680-ADJ          |

| LM22680MRX-ADJ/NOPB   | Active        | Production           | SO PowerPAD (DDA)   8 | 2500   LARGE T&R      | Yes         | SN                                   | Level-3-260C-168 HR               | -40 to 125   | L22680-ADJ          |

| LM22680QMR-ADJ/NO.A   | Active        | Production           | SO PowerPAD (DDA)   8 | 95   TUBE             | Yes         | SN                                   | Level-3-260C-168 HR               | -40 to 125   | L22680-Q-ADJ        |

| LM22680QMR-ADJ/NOPB   | Active        | Production           | SO PowerPAD (DDA)   8 | 95   TUBE             | Yes         | SN                                   | Level-3-260C-168 HR               | -40 to 125   | L22680-Q-ADJ        |

| LM22680QMRE-ADJ/NO.A  | Active        | Production           | SO PowerPAD (DDA)   8 | 250   SMALL T&R       | Yes         | SN                                   | Level-3-260C-168 HR               | -40 to 125   | L22680-Q-ADJ        |

| LM22680QMRE-ADJ/NOPB  | Active        | Production           | SO PowerPAD (DDA)   8 | 250   SMALL T&R       | Yes         | SN                                   | Level-3-260C-168 HR               | -40 to 125   | L22680-Q-ADJ        |

| LM22680QMRX-ADJ/NO.A  | Active        | Production           | SO PowerPAD (DDA)   8 | 2500   LARGE T&R      | Yes         | SN                                   | Level-3-260C-168 HR               | -40 to 125   | L22680-Q-ADJ        |

| LM22680QMRX-ADJ/NOPB  | Active        | Production           | SO PowerPAD (DDA)   8 | 2500   LARGE T&R      | Yes         | SN                                   | Level-3-260C-168 HR               | -40 to 125   | L22680-Q-ADJ        |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

**(4) Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**(5) MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

**(6) Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

**OTHER QUALIFIED VERSIONS OF LM22680, LM22680-Q1 :**

- Catalog : [LM22680](#)

- Automotive : [LM22680-Q1](#)

NOTE: Qualified Version Definitions:

- Catalog - TI's standard catalog product

- Automotive - Q100 devices qualified for high-reliability automotive applications targeting zero defects

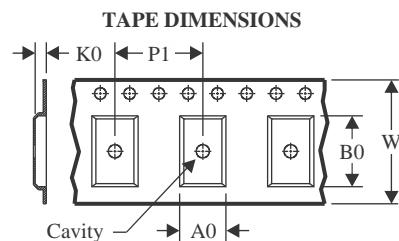

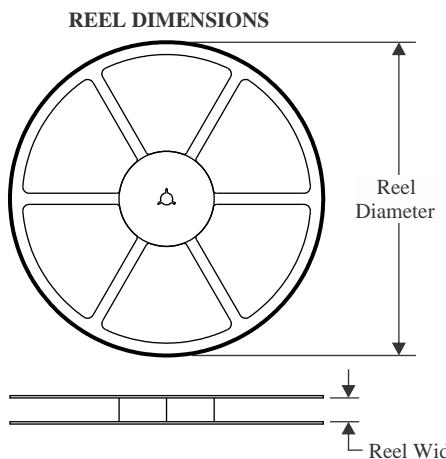

**TAPE AND REEL INFORMATION**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

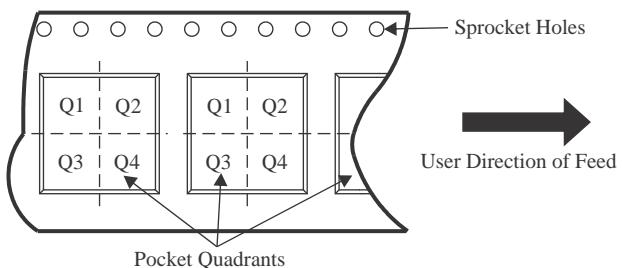

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device               | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|----------------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| LM22680MRE-ADJ/NOPB  | SO PowerPAD  | DDA             | 8    | 250  | 177.8              | 12.4               | 6.5     | 5.4     | 2.0     | 8.0     | 12.0   | Q1            |

| LM22680MRX-ADJ/NOPB  | SO PowerPAD  | DDA             | 8    | 2500 | 330.0              | 12.4               | 6.5     | 5.4     | 2.0     | 8.0     | 12.0   | Q1            |

| LM22680QMRE-ADJ/NOPB | SO PowerPAD  | DDA             | 8    | 250  | 177.8              | 12.4               | 6.5     | 5.4     | 2.0     | 8.0     | 12.0   | Q1            |

| LM22680QMRX-ADJ/NOPB | SO PowerPAD  | DDA             | 8    | 2500 | 330.0              | 12.4               | 6.5     | 5.4     | 2.0     | 8.0     | 12.0   | Q1            |

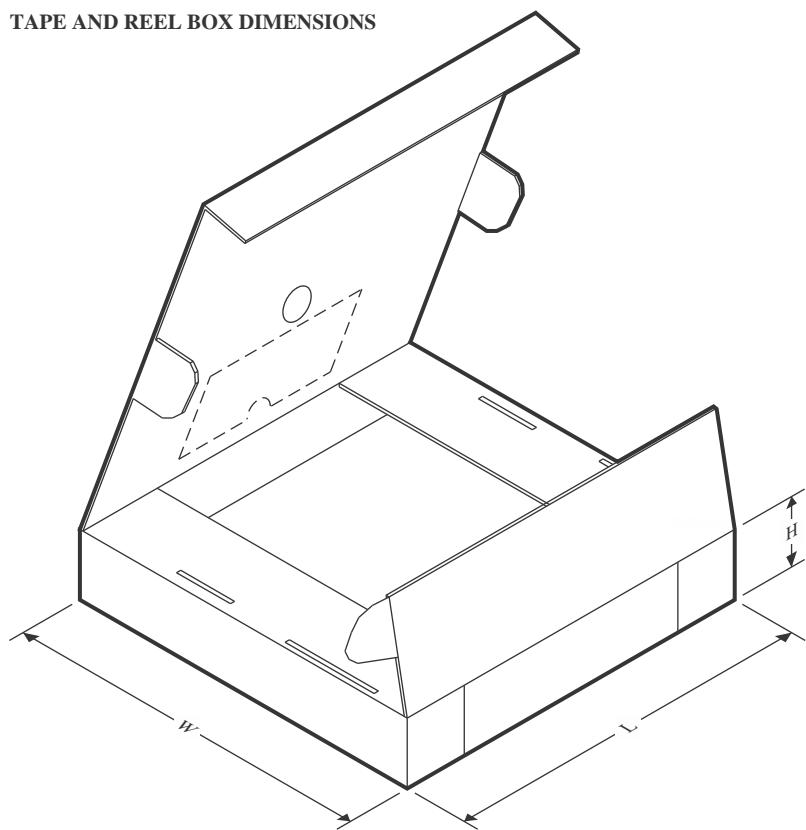

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device               | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|----------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| LM22680MRE-ADJ/NOPB  | SO PowerPAD  | DDA             | 8    | 250  | 208.0       | 191.0      | 35.0        |

| LM22680MRX-ADJ/NOPB  | SO PowerPAD  | DDA             | 8    | 2500 | 356.0       | 356.0      | 36.0        |

| LM22680QMRE-ADJ/NOPB | SO PowerPAD  | DDA             | 8    | 250  | 208.0       | 191.0      | 35.0        |

| LM22680QMRX-ADJ/NOPB | SO PowerPAD  | DDA             | 8    | 2500 | 356.0       | 356.0      | 36.0        |

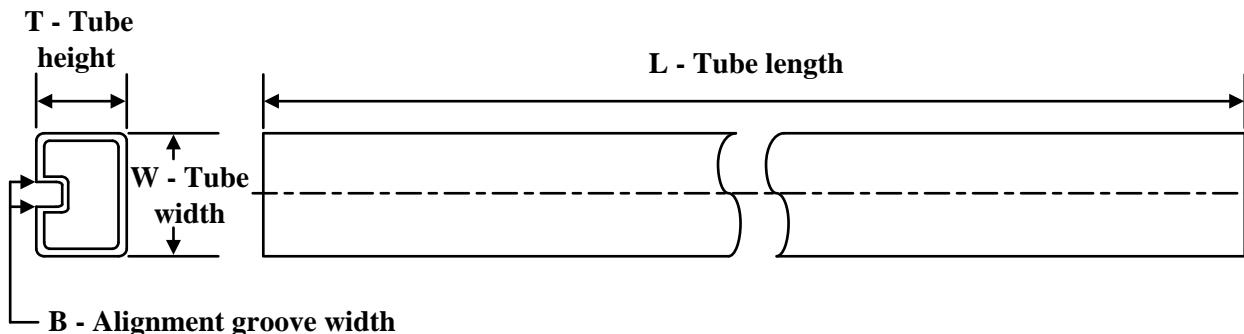

**TUBE**

\*All dimensions are nominal

| Device               | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T ( $\mu$ m) | B (mm) |

|----------------------|--------------|--------------|------|-----|--------|--------|--------------|--------|

| LM22680MR-ADJ/NOPB   | DDA          | HSOIC        | 8    | 95  | 495    | 8      | 4064         | 3.05   |

| LM22680MR-ADJ/NOPB.A | DDA          | HSOIC        | 8    | 95  | 495    | 8      | 4064         | 3.05   |

| LM22680QMR-ADJ/NO.A  | DDA          | HSOIC        | 8    | 95  | 495    | 8      | 4064         | 3.05   |

| LM22680QMR-ADJ/NOPB  | DDA          | HSOIC        | 8    | 95  | 495    | 8      | 4064         | 3.05   |

DDA0008B

# PACKAGE OUTLINE

PowerPAD™ SOIC - 1.7 mm max height

PLASTIC SMALL OUTLINE

4214849/B 09/2025

NOTES:

PowerPAD is a trademark of Texas Instruments.

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side.

4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

5. Reference JEDEC registration MS-012.

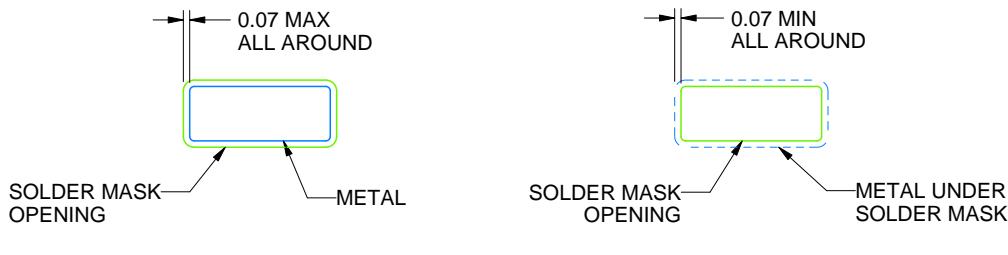

# EXAMPLE BOARD LAYOUT

DDA0008B

PowerPAD™ SOIC - 1.7 mm max height

PLASTIC SMALL OUTLINE

4214849/B 09/2025

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

8. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature numbers SLMA002 ([www.ti.com/lit/slma002](http://www.ti.com/lit/slma002)) and SLMA004 ([www.ti.com/lit/slma004](http://www.ti.com/lit/slma004)).

9. Size of metal pad may vary due to creepage requirement.

10. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

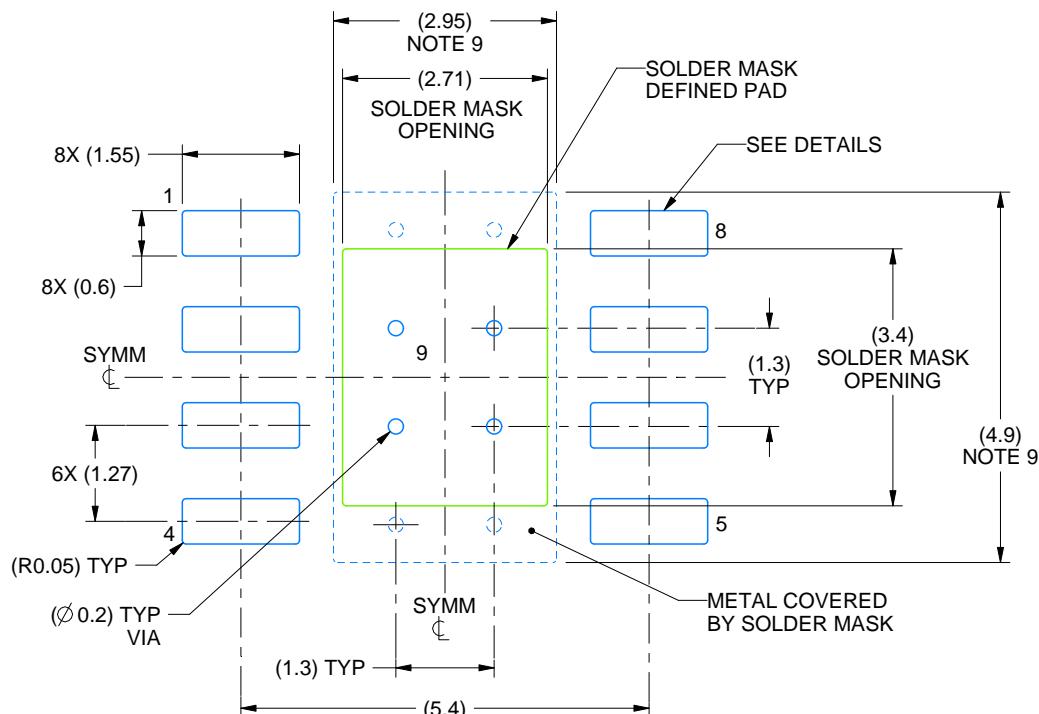

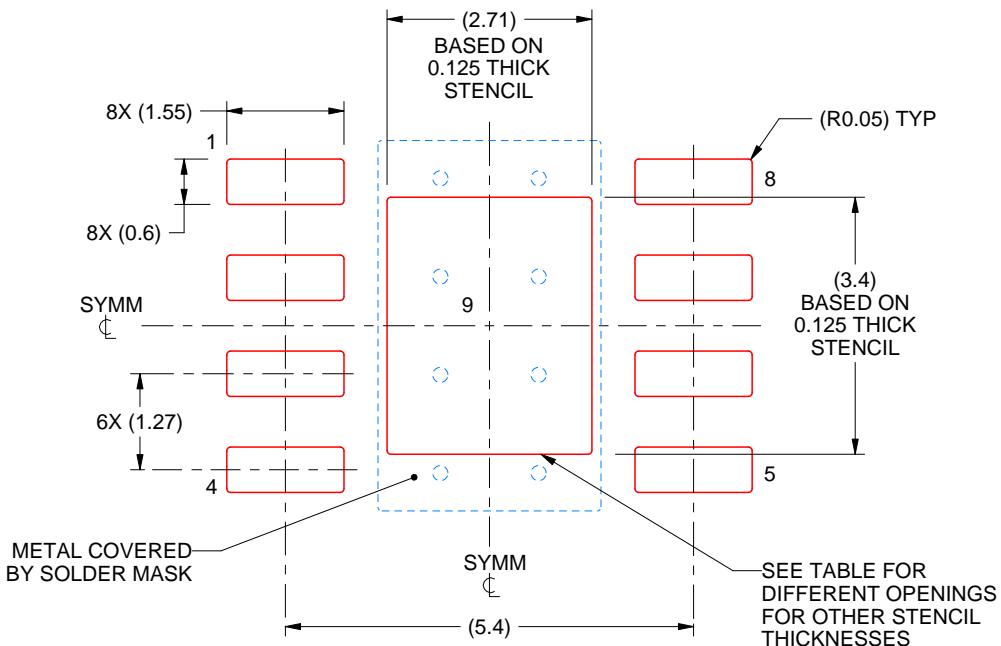

# EXAMPLE STENCIL DESIGN

DDA0008B

PowerPAD™ SOIC - 1.7 mm max height

PLASTIC SMALL OUTLINE

SOLDER PASTE EXAMPLE

EXPOSED PAD

100% PRINTED SOLDER COVERAGE BY AREA

SCALE:10X

| STENCIL THICKNESS | SOLDER STENCIL OPENING |

|-------------------|------------------------|

| 0.1               | 3.03 X 3.80            |

| 0.125             | 2.71 X 3.40 (SHOWN)    |

| 0.150             | 2.47 X 3.10            |

| 0.175             | 2.29 X 2.87            |

4214849/B 09/2025

NOTES: (continued)

11. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

12. Board assembly site may have different recommendations for stencil design.

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月