LM5025A

JAJSA81F - DECEMBER 2004 - REVISED AUGUST 2016

#### LM5025A アクティブ・クランプ電圧モ・ ドPWMコントロ

# 特長

- スタートアップ用バイアス・レギュレータを内蔵

- 3Aの複合型メイン・ゲート・ドライバ

- プログラマブルなライン低電圧誤動作防止 (UVLO)、ヒステリシスを調整可能

- 電圧モード制御、フィードフォワード付き

- 可変のデュアル・モード過電流保護

- メイン出力とアクティブ・クランプ出力との間で オーバーラップまたはデッドタイムをプログラム 可能

- ボルト秒クランプ

- プログラム可能なソフト・スタート

- リーディング・エッジ・ブランキング

- 単一の抵抗でプログラマブルな発振器

- 発振器のアップ/ダウン同期機能

- 高精度の5V基準電圧

- サーマル・シャットダウン

- パッケージ:

- 16ピンTSSOP

- 放熱特性の優れた16ピン WSON  $(5mm \times 5mm)$

# 2 アプリケーション

- サーバー電源

- 48Vテレコム電源

- 42V車載用途

- 高効率のDC/DC電源

# 3 概要

LM5025Aは、LM5025アクティブ・クランプPWMコントロー ラの機能バリアントです。LM5025Aの機能的な相違点 は、CS1およびCS2電流制限スレッショルドが0.5Vに引き 上げられ、内部のCS2フィルタ放電デバイスがディセーブ ルされて、毎クロック・サイクル動作せず、ラインのUVLO ピンがスレッショルド未満のときは内部のVccおよびVRFF レギュレータが引き続き動作することです。

LM5025A PWMコントローラには、アクティブ・クランプリ セット技法を使用して電力コンバータを実装するために必 要なすべての機能が含まれています。アクティブ・クランプ 技法により、従来のキャッチ巻線やRDCクランプリセット技 法と比べて、より高い効率と大きな電力密度を実現できま す。制御出力として、メイン電源スイッチ制御(OUT A)とア クティブ・クランプ・スイッチ制御(OUT\_B)の2つが搭載さ れています。2つの内蔵複合型ゲート・ドライバはMOS デバイスとバイポーラ・デバイスを並列に接続しており、優 れたゲート駆動特性が得られます。このコントローラは、発 振器の周波数範囲が最大1MHz、PWMおよび電流セン スの合計伝搬遅延が100ns未満の高速動作用に設計さ れています。LM5025Aには、高電圧のスタートアップ・レ ギュレータが内蔵されており、13V~90Vの広い範囲の入 力電圧で動作します。追加機能として、低電圧誤動作防 止(UVLO)、ソフトスタート、発振器のアップ/ダウン同期機 能、高精度の基準電圧、サーマル・シャットダウン機能が あります。

#### 製品情報(1)

| 型番        | パッケージ      | 本体サイズ(公称)     |  |

|-----------|------------|---------------|--|

| I MEODE A | TSSOP (16) | 5.00mm×4.40mm |  |

| LM5025A   | WSON (16)  | 5.00mm×5.00mm |  |

(1) 利用可能なすべてのパッケージについては、このデータシートの末 尾にある注文情報を参照してください。

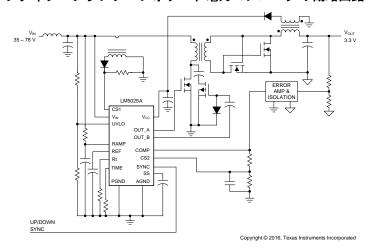

# アクティブ・クランプ・フォワード電力コンバータの概略回路図

|   | ٠, |

|---|----|

| П |    |

|   | I  |

| 1 | 特長 1                                 | 8 A <sub>l</sub> | oplication and Implementation | 19              |

|---|--------------------------------------|------------------|-------------------------------|-----------------|

| 2 | アプリケーション1                            | 8.               | 1 Application Information     | 19              |

| 3 | 概要1                                  | 8.               | 2 Typical Application         | 19              |

| 4 | 改訂履歴3                                | 8.               | 3 System Example              | 24              |

| 5 | Pin Configuration and Functions 4    | 9 Pc             | ower Supply Recommendations   | 24              |

| 6 | Specifications6                      | 10 La            | ayout                         | <mark>24</mark> |

| • | 6.1 Absolute Maximum Ratings 6       | 10               | 0.1 Layout Guidelines         | 24              |

|   | 6.2 ESD Ratings                      | 10               | 0.2 Layout Example            | 25              |

|   | 6.3 Recommended Operating Conditions | 10               | 0.3 Thermal Protection        | 25              |

|   | 6.4 Thermal Information              | <b>11</b> テ      | ・バイスおよびドキュメントのサポート            | 26              |

|   | 6.5 Electrical Characteristics       | 11               | 1.1 ドキュメントのサポート               | 26              |

|   | 6.6 Typical Characteristics          | 11               | 1.2 ドキュメントの更新通知を受け取る方法        | 26              |

| 7 | Detailed Description 12              | 11               | 1.3 コミュニティ・リソース               | 26              |

| - | 7.1 Overview                         | 11               | 1.4 商標                        | 26              |

|   | 7.2 Functional Block Diagram         | 11               | 1.5 静電気放電に関する注意事項             | 26              |

|   | 7.3 Feature Description              | 11               | 1.6 Glossary                  | 26              |

|   | 7.4 Device Functional Modes          | 12 メ             | カニカル、パッケージ、および注文情報            | 26              |

# 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

# Revision E (March 2013) から Revision F に変更

Page

| • | 「ESD定格」表、「機能説明」セクション、「デバイスの機能モード」セクション、「アプリケーションと実装」セクション、「電源に関    |   |

|---|--------------------------------------------------------------------|---|

|   | する推奨事項」セクション、「レイアウト」セクション、「デバイスおよびドキュメントのサポート」セクション、「メカニカル、パッケー    |   |

|   | ジ、および注文情報」セクション 追加                                                 | 1 |

| • | Changed Thermal Information table                                  | 6 |

| • | Deleted the THERMAL RESISTANCE row from Electrical Characteristics | 9 |

# Revision D (March 2013) から Revision E に変更

Page

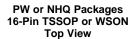

# 5 Pin Configuration and Functions

# **Pin Functions**

|     | PIN             |     |                                                                                                              | ADDI IOATION INFORMATION                                                                                                                                                                                                                                                                                                                                    |

|-----|-----------------|-----|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME            | I/O | DESCRIPTION                                                                                                  | APPLICATION INFORMATION                                                                                                                                                                                                                                                                                                                                     |

| 1   | V <sub>IN</sub> | I   | Source input voltage                                                                                         | Input to start-up regulator. Input range 13 V to 90 V, with transient capability to 105 V.                                                                                                                                                                                                                                                                  |

| 2   | RAMP            | I   | Modulator ramp signal                                                                                        | An external RC circuit from Vin sets the ramp slope. This pin is discharged at the conclusion of every cycle by an internal FET, initiated by either the internal clock or the V x Sec Clamp comparator.                                                                                                                                                    |

| 3   | CS1             | I   | Current sense input for cycle-by-<br>cycle limiting                                                          | If CS1 exceeds 0.5 V the outputs goes into Cycle-<br>by-Cycle current limit. CS1 is held low for 50 ns<br>after OUT_A switches high providing leading edge<br>blanking.                                                                                                                                                                                     |

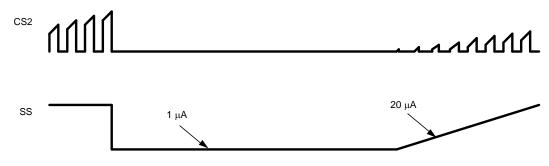

| 4   | CS2             | I   | Current sense input for soft restart                                                                         | If CS2 exceeds 0.5 V, the outputs will be disabled and a soft start commenced. The soft-start capacitor will be fully discharged and then released with a pullup current of 1 $\mu$ A. After the first output pulse (when SS =1 V), the SS charge current will revert back to 20 $\mu$ A.                                                                   |

| 5   | TIME            | I   | Output overlap and dead-time control                                                                         | An external resistor (R <sub>SET</sub> ) sets either the overlap time or dead time for the active clamp output. An R <sub>SET</sub> resistor connected between TIME and GND produces in-phase OUT_A and OUT_B pulses with overlap. An R <sub>SET</sub> resistor connected between TIME and REF produces out-of-phase OUT_A and OUT_B pulses with dead time. |

| 6   | REF             | 0   | Precision 5-V reference output                                                                               | Maximum output current: 10-mA locally decouple with a $0.1$ - $\mu F$ capacitor. Reference stays low until the $V_{CC}$ UV comparator is satisfied.                                                                                                                                                                                                         |

| 7   | V <sub>CC</sub> | Р   | Output from the internal high voltage start-up regulator. The V <sub>CC</sub> voltage is regulated to 7.6 V. | If an auxiliary winding raises the voltage on this pin<br>above the regulation setpoint, the internal start-up<br>regulator shuts down, reducing the IC power<br>dissipation.                                                                                                                                                                               |

| 8   | OUT_A           | 0   | Main output driver                                                                                           | Output of the main switch PWM output gate driver. Output capability of 3-A peak sink current.                                                                                                                                                                                                                                                               |

# Pin Functions (continued)

|     | PIN   |     |                                                   | APPLICATION INFORMATION                                                                                                                                                                                                                                                  |  |  |

|-----|-------|-----|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NO. | NAME  | I/O | DESCRIPTION                                       | APPLICATION INFORMATION                                                                                                                                                                                                                                                  |  |  |

| 9   | OUT_B | 0   | Active Clamp output driver                        | Output of the Active Clamp switch gate driver.<br>Capable of 1.25-A peak sink current                                                                                                                                                                                    |  |  |

| 10  | PGND  | G   | Power ground Connect directly to analog ground.   |                                                                                                                                                                                                                                                                          |  |  |

| 11  | AGND  | G   | Analog ground                                     | Connect directly to power ground. For the WSON package option, the exposed pad is electrically connected to AGND.                                                                                                                                                        |  |  |

| 12  | SS    | I   | Soft-start control                                | An external capacitor and an internal 20-µA current source set the soft-start ramp. The SS current source is reduced to 1 µA initially following a CS2 overcurrent event or an overtemperature event.                                                                    |  |  |

| 13  | СОМР  | 1   | Input to the Pulse Width Modulator                | An internal $5-k\Omega$ resistor pullup is provided on this pin. The external opto-coupler sinks current from COMP to control the PWM duty cycle.                                                                                                                        |  |  |

| 14  | RT    | 1   | Oscillator timing resistor pin                    | An external resistor connected from RT to ground sets the internal oscillator frequency.                                                                                                                                                                                 |  |  |

| 15  | SYNC  | I   | Oscillator UP and DOWN synchronization input      | The internal oscillator can be synchronized to an external clock with a frequency 20% lower than the internal oscillator's free running frequency. There is no constraint on the maximum sync frequency.                                                                 |  |  |

| 16  | UVLO  | I   | Line undervoltage shutdown                        | An external voltage divider from the power source sets the shutdown comparator levels. The comparator threshold is 2.5 V. Hysteresis is set by an internal current source (20 $\mu$ A) that is switched ON or OFF as the UVLO pin potential crosses the 2.5-V threshold. |  |  |

| _   | EP    | G   | Exposed pad, underside of the WSON package option | Internally bonded to the die substrate. Connect to GND potential for low thermal impedance.                                                                                                                                                                              |  |  |

# 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)(2)

|                                       | MIN  | MAX | UNIT |

|---------------------------------------|------|-----|------|

| V <sub>IN</sub> to GND                | -0.3 | 105 | V    |

| V <sub>CC</sub> to GND                | -0.3 | 16  | V    |

| CS1, CS2 to GND                       | -0.3 | 1   | V    |

| All other inputs to GND               | -0.3 | 7   | V    |

| Junction temperature, T <sub>J</sub>  |      | 150 | °C   |

| Storage temperature, T <sub>stg</sub> | -55  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                    |                         |                                       | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------|-------|------|

| V <sub>(ESD)</sub> | Electrostatic discharge | Human-body model (HBM) <sup>(1)</sup> | ±2000 | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                             | MIN | MAX | UNIT |

|---------------------------------------------|-----|-----|------|

| V <sub>IN</sub> voltage                     | 13  | 90  | V    |

| External voltage applied to V <sub>CC</sub> | 8   | 15  | V    |

| Operating junction temperature              | -40 | 125 | °C   |

# 6.4 Thermal Information

|                      |                                              | LM5        | LM5025A    |      |  |

|----------------------|----------------------------------------------|------------|------------|------|--|

|                      | THERMAL METRIC <sup>(1)</sup>                | PW (TSSOP) | NHQ (WSON) | UNIT |  |

|                      |                                              | 16 PINS    | 16 PINS    |      |  |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 98.7       | 30         | °C/W |  |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 27.8       | 25.9       | °C/W |  |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 44.3       | 9.3        | °C/W |  |

| ΨЈТ                  | Junction-to-top characterization parameter   | 1.2        | 0.2        | °C/W |  |

| ΨЈВ                  | Junction-to-board characterization parameter | 43.6       | 9.5        | °C/W |  |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance |            | 2.3        | °C/W |  |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

<sup>(2)</sup> If Military/Aerospace specified devices are required, please contact the TI Sales Office/ Distributors for availability and specifications.

# 6.5 Electrical Characteristics

Typical limits are for  $T_J$  = 25°C, and minimum and maximum limits apply over the operating junction temperature range (-40°C to 125°C).  $V_{IN}$  = 48 V,  $V_{CC}$  = 10 V,  $R_T$  = 31.3 k $\Omega$ ,  $R_{SET}$  = 27.4 k $\Omega$ ) unless otherwise stated <sup>(1)</sup>

|                    | PARAMETER                                         | TEST CO                                                                 | ONDITIONS                     | MIN                             | TYP                             | MAX  | UNIT |

|--------------------|---------------------------------------------------|-------------------------------------------------------------------------|-------------------------------|---------------------------------|---------------------------------|------|------|

| START              | -UP REGULATOR                                     |                                                                         |                               |                                 |                                 |      |      |

| V <sub>CC</sub>    |                                                   |                                                                         | T <sub>J</sub> = 25°C         |                                 | 7.6                             |      |      |

| Reg                | V <sub>CC</sub> regulation                        | No load                                                                 | $T_J = T_{low}$ to $T_{high}$ | 7.3                             |                                 | 7.9  | V    |

|                    |                                                   | 2 (2)                                                                   | T <sub>J</sub> = 25°C         |                                 | 25                              |      |      |

|                    | V <sub>CC</sub> current limit                     | See (2)                                                                 | $T_J = T_{low}$ to $T_{high}$ | 20                              |                                 |      | mA   |

|                    | Start-up regulator leakage                        |                                                                         | T <sub>J</sub> = 25°C         |                                 | 165                             |      |      |

| I-V <sub>IN</sub>  | (external Vcc Supply)                             | V <sub>IN</sub> = 100 V                                                 | $T_J = T_{low}$ to $T_{high}$ |                                 |                                 | 500  | μA   |

| V <sub>CC</sub> SU | PPLY                                              |                                                                         | ,                             |                                 |                                 |      |      |

|                    | V <sub>CC</sub> undervoltage lockout              | T <sub>J</sub> = 25°C                                                   |                               |                                 | V <sub>CC</sub> Reg -<br>120 mV |      | .,   |

|                    | voltage (positive going V <sub>cc</sub> )         | $T_{J} = T_{low}$ to $T_{high}$                                         |                               | V <sub>CC</sub> Reg -<br>220 mV |                                 |      | V    |

|                    | V <sub>CC</sub> undervoltage                      | $T_J = 25^{\circ}C$                                                     |                               |                                 | 1.5                             |      | .,   |

|                    | hysteresis                                        | $T_J = T_{low}$ to $T_{high}$                                           |                               | 1                               |                                 | 2    | V    |

|                    | V <sub>CC</sub> supply current (I <sub>CC</sub> ) | C <sub>gate</sub> = 0                                                   | $T_J = T_{low}$ to $T_{high}$ |                                 |                                 | 4.2  | mA   |

| REFER              | ENCE SUPPLY                                       |                                                                         |                               |                                 |                                 |      |      |

|                    | Pof voltage                                       | I <sub>REF</sub> = 0 mA                                                 | $T_J = 25^{\circ}C$           |                                 | 5                               |      | V    |

|                    | Ref voltage                                       | I <sub>REF</sub> = 0 IIIA                                               | $T_J = T_{low}$ to $T_{high}$ | 4.85                            |                                 | 5.15 | V    |

| .,                 | Pof voltage regulation                            | $I_{REF} = 0$ to $10mA$                                                 | T <sub>J</sub> = 25°C         |                                 | 25                              |      | m\/  |

| $V_{REF}$          | Ref voltage regulation                            | I <sub>REF</sub> = 0 to 10mA                                            | $T_J = T_{low}$ to $T_{high}$ |                                 |                                 | 50   | mV   |

|                    | Deferment limit                                   | $T_J = 25^{\circ}C$                                                     |                               |                                 | 20                              |      | A    |

|                    | Ref current limit                                 | $T_J = T_{low}$ to $T_{high}$                                           |                               | 10                              |                                 |      | mA   |

| CURRE              | NT LIMIT                                          |                                                                         |                               |                                 |                                 |      |      |

| CS1<br>Prop        | CS1 delay to output                               | CS1 Step from 0 to 0.6<br>Time to onset of OUT<br>C <sub>gate</sub> = 0 |                               |                                 | 40                              |      | ns   |

| CS2<br>Prop        | CS2 delay to output                               | CS2 Step from 0 to 0.6<br>Time to onset of OUT<br>C <sub>gate</sub> = 0 |                               |                                 | 50                              |      | ns   |

|                    | Cycle by cycle threshold                          | $T_J = 25^{\circ}C$                                                     |                               |                                 | 0.5                             |      | V    |

|                    | voltage (CS1)                                     | over full operating junc                                                | ction temperature             | 0.45                            |                                 | 0.55 | V    |

|                    | Cycle skip threshold voltage                      | Resets SS capacitor;                                                    | $T_J = 25^{\circ}C$           |                                 | 0.5                             |      | V    |

|                    | (CS2)                                             | auto restart                                                            | $T_J = T_{low}$ to $T_{high}$ | 0.45                            |                                 | 0.55 | V    |

|                    | Leading edge blanking time (CS1)                  |                                                                         |                               |                                 | 50                              |      | ns   |

|                    | CS1 sink impedance                                | CS1 = 0.4 V                                                             | $T_J = 25^{\circ}C$           |                                 | 30                              |      | Ω    |

|                    | (clocked)                                         | C31 = 0.4 V                                                             | $T_J = T_{low}$ to $T_{high}$ |                                 |                                 | 50   | 3.2  |

|                    | CS1 sink impedance (post                          | CS1 = 0.6 V                                                             | $T_J = 25^{\circ}C$           |                                 | 15                              |      | Ω    |

|                    | fault discharge)                                  |                                                                         | $T_J = T_{low}$ to $T_{high}$ |                                 |                                 | 30   | 2.2  |

|                    | CS2 sink impedance (post                          | CS2 = 0.6 V                                                             | $T_J = 25^{\circ}C$           |                                 | 55                              |      | _    |

|                    | fault discharge)                                  | 002 = 0.0 V                                                             | $T_J = T_{low}$ to $T_{high}$ |                                 |                                 | 95   | Ω    |

|                    | CS1 and CS2 leakage current                       | CS = CS Threshold – 100 mV                                              | $T_J = T_{low}$ to $T_{high}$ |                                 |                                 | 1    | μA   |

<sup>(1)</sup> All electrical characteristics having room temperature limits are tested during production with T<sub>A</sub> = T<sub>J</sub> = 25°C. All hot and cold limits are specified by correlating the electrical characteristics to process and temperature variations and applying statistical process control.

<sup>(2)</sup> Device thermal limitations may limit usable range.

# **Electrical Characteristics (continued)**

Typical limits are for  $T_J$  = 25°C, and minimum and maximum limits apply over the operating junction temperature range (-40°C to 125°C).  $V_{IN}$  = 48 V,  $V_{CC}$  = 10 V, RT = 31.3 k $\Omega$ ,  $R_{SET}$  = 27.4 k $\Omega$ ) unless otherwise stated <sup>(1)</sup>

| PARAMETER                    | TEST CC                                                        | ONDITIONS                             | MIN  | TYP | MAX  | UNIT  |

|------------------------------|----------------------------------------------------------------|---------------------------------------|------|-----|------|-------|

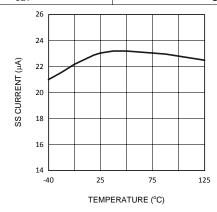

| SOFT-START                   |                                                                |                                       |      |     |      |       |

| Soft-start current source    | T <sub>J</sub> = 25°C                                          |                                       |      | 22  |      |       |

| normal                       | over full operating junc                                       | etion temperature                     | 17   |     | 27   | μΑ    |

| Soft-start current source    | $T_J = 25^{\circ}C$                                            |                                       |      | 1   |      |       |

| following a CS2 event        | over full operating junc                                       | tion temperature                      | 0.5  |     | 1.5  | μΑ    |

| OSCILLATOR                   |                                                                |                                       |      |     | ·    |       |

| Fraguene 4                   | $T_A = 25^{\circ}C,$                                           |                                       | 180  | 200 | 220  | ld la |

| Frequency1                   | $T_J = T_{low}$ to $T_{high}$                                  |                                       | 175  |     | 225  | kHz   |

| Fraguency?                   | RT = 10.4 kΩ                                                   | T <sub>A</sub> = 25°C,                |      | 580 |      | l/U=  |

| Frequency2                   | R1 = 10.4  K22                                                 | $T_J = T_{low}$ to $T_{high}$         | 510  |     | 650  | kHz   |

| Sync threshold               |                                                                |                                       |      | 2   |      | V     |

| Min sync pulse width         | $T_J = T_{low}$ to $T_{high}$                                  |                                       |      |     | 100  | ns    |

| Sync frequency range         | $T_J = T_{low}$ to $T_{high}$                                  |                                       | 160  |     |      | kHz   |

| PWM COMPARATOR               |                                                                |                                       |      |     |      |       |

| Delay to output              | COMP step 5 V to 0 V<br>Time to onset of OUT_                  |                                       |      | 40  |      | ns    |

| Duty cycle range             | $T_J = T_{low}$ to $T_{high}$                                  |                                       | 0%   |     | 80%  |       |

| COMP to DWM offers           | T <sub>A</sub> = 25°C,                                         |                                       |      | 1   |      |       |

| COMP to PWM offset           | $T_J = T_{low}$ to $T_{high}$                                  |                                       | 0.7  |     | 1.3  | V     |

| COMP open-circuit voltage    | $T_J = T_{low}$ to $T_{high}$                                  |                                       | 4.3  |     | 5.9  | V     |

| COMP about aires it assument | COMP                                                           | T <sub>A</sub> = 25°C,                |      | 1   |      | A     |

| COMP short-circuit current   | COMP = 0 V                                                     | $T_J = T_{low}$ to $T_{high}$         | 0.6  |     | 1.4  | mA    |

| VOLT × SECOND CLAMP          | •                                                              | •                                     |      |     | •    |       |

|                              | Delta RAMP                                                     | T <sub>A</sub> = 25°C,                |      | 2.5 |      |       |

| Ramp clamp level             | measured from onset<br>of OUT_A to Ramp<br>peak,<br>COMP = 5 V | $T_{J} = T_{low}$ to $T_{high}$       | 2.4  |     | 2.6  | V     |

| UVLO SHUTDOWN                |                                                                |                                       |      |     | l    |       |

| Undervoltage shutdown        | T <sub>A</sub> = 25°C,                                         |                                       |      | 2.5 |      |       |

| threshold                    | $T_J = T_{low}$ to $T_{high}$                                  |                                       | 2.44 |     | 2.56 | V     |

| Undervoltage shutdown        | T <sub>A</sub> = 25°C,                                         |                                       |      | 20  |      |       |

| hysteresis                   | $T_J = T_{low}$ to $T_{high}$                                  |                                       | 16   |     | 24   | μΑ    |

| OUTPUT SECTION               |                                                                | +                                     |      |     |      |       |

|                              | MOS device at                                                  | T <sub>A</sub> = 25°C,                |      | 5   |      | _     |

| OUT_A high saturation        | lout = -10  mA                                                 | $T_J = T_{low}$ to $T_{high}$         |      |     | 10   | Ω     |

| OUTPUT_A peak current sink   | Bipolar Device at Vcc/2                                        |                                       |      | 3   |      | Α     |

|                              | MOS device at                                                  | T <sub>A</sub> = 25°C,                |      | 6   |      |       |

| OUT_A low saturation         | lout = 10 mA                                                   | $T_J = T_{low}$ to $T_{high}$         |      |     | 9    | Ω     |

| OUTPUT_A rise time           | C <sub>gate</sub> = 2.2 nF                                     | i i i i i i i i i i i i i i i i i i i |      | 20  |      | ns    |

| OUTPUT_A fall time           | $C_{gate} = 2.2 \text{ nF}$                                    |                                       |      | 15  |      | ns    |

|                              | MOS device at                                                  | T <sub>A</sub> = 25°C,                |      | 10  |      | _     |

| OUT_B high saturation        | lout = -10 mA                                                  | $T_J = T_{low}$ to $T_{high}$         |      |     | 20   | Ω     |

| OUTPUT_B peak current sink   | Bipolar device at Vcc/2                                        |                                       |      | 1   |      | Α     |

# **Electrical Characteristics (continued)**

Typical limits are for  $T_J$  = 25°C, and minimum and maximum limits apply over the operating junction temperature range (-40°C to 125°C).  $V_{IN}$  = 48 V,  $V_{CC}$  = 10 V, RT = 31.3 k $\Omega$ ,  $R_{SET}$  = 27.4 k $\Omega$ ) unless otherwise stated <sup>(1)</sup>

|                 | PARAMETER                                     | TEST C                                                                  | ONDITIONS                       | MIN | TYP | MAX | UNIT |

|-----------------|-----------------------------------------------|-------------------------------------------------------------------------|---------------------------------|-----|-----|-----|------|

|                 | OLIT Dilaw acturation                         | MOS device at                                                           | T <sub>A</sub> = 25°C,          |     | 12  |     | Ω    |

|                 | OUT_B low saturation                          | lout = 10 mA                                                            | $T_J = T_{low}$ to $T_{high}$   |     |     | 18  | 22   |

|                 | OUTPUT_B rise time                            | C <sub>gate</sub> = 1 nF                                                |                                 |     | 20  |     | ns   |

|                 | OUTPUT_B fall time                            | C <sub>gate</sub> = 1 nF                                                |                                 |     | 15  |     | ns   |

| OUTP            | UT TIMING CONTROL                             |                                                                         |                                 |     |     |     |      |

|                 | Overlap time                                  | $R_{SET} = 38 \text{ k}\Omega$ connected to GND, 50% to 50% transitions | $T_A = 25^{\circ}C$ ,           |     | 105 |     |      |

|                 |                                               |                                                                         | $T_J = T_{low}$ to $T_{high}$   | 75  |     | 135 | ns   |

|                 |                                               | $R_{SET} = 29.5 \text{ k}\Omega$                                        | T <sub>A</sub> = 25°C,          |     | 105 |     |      |

|                 | Dead time connected to 50% to 50% transitions |                                                                         | $T_{J} = T_{low}$ to $T_{high}$ | 75  |     | 135 | ns   |

| THERI           | MAL SHUTDOWN                                  |                                                                         |                                 |     |     |     |      |

| T <sub>SD</sub> | Thermal shutdown threshold                    |                                                                         |                                 |     | 165 |     | °C   |

|                 | Thermal shutdown hysteresis                   |                                                                         |                                 |     | 25  |     | °C   |

# TEXAS INSTRUMENTS

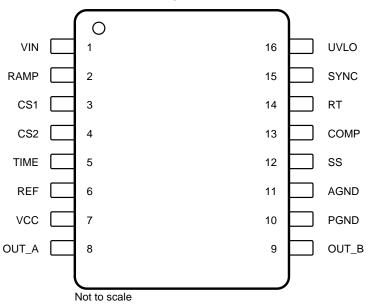

# 6.6 Typical Characteristics

Figure 1. V<sub>CC</sub> Regulator Start-Up Characteristics, V<sub>CC</sub> vs V<sub>IN</sub>

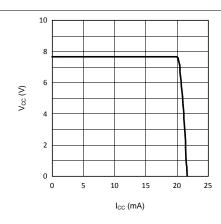

Figure 2.  $V_{CC}$  vs  $I_{CC}$

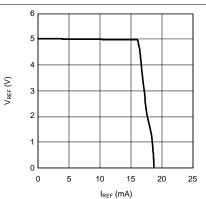

Figure 3.  $V_{REF}$  vs  $I_{REF}$

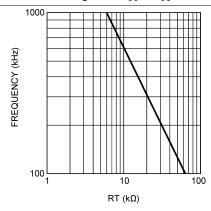

Figure 4. Oscillator Frequency vs RT

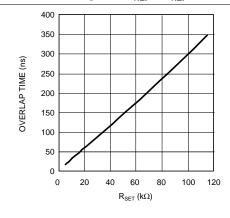

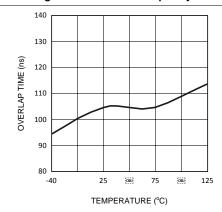

$R_{SET} = 38 \text{ K}$  Figure 5. Overlap Time vs  $R_{SET}$  Figure

Figure 6. Overlap Time vs Temperature

# **Typical Characteristics (continued)**

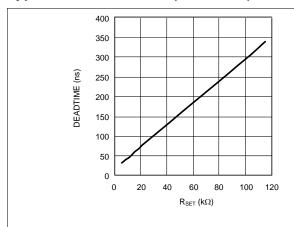

Figure 7. Dead Time vs R<sub>SET</sub>

$R_{SET} = 29.5 \text{ K}$

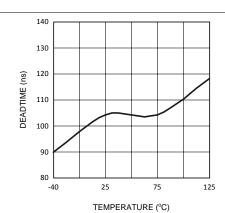

Figure 8. Dead Time vs Temperature

Figure 9. SS Pin Current vs Temperature

# 7 Detailed Description

### 7.1 Overview

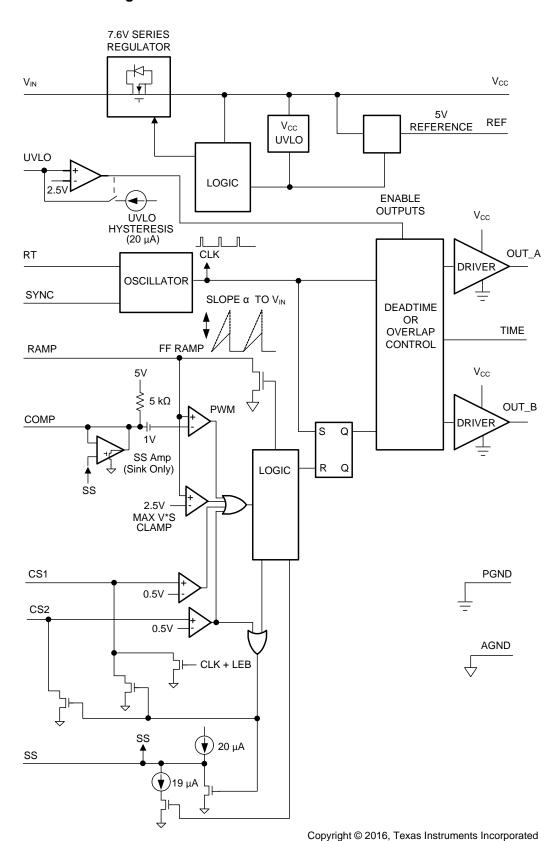

The LM5025A PWM controller contains all of the features necessary to implement active clamp / reset technique voltage-mode controlled power converters. Synchronous rectification allows higher conversion efficiency and greater power density than conventional PN or Schottky rectifier techniques. The high voltage start-up regulator of the LM5025A can be configured to operate with input voltages ranging from 13 V to 90 V. Additional features include line undervoltage lockout, cycle-by-cycle current limit, voltage feed-forward compensation, hiccup mode fault protection with adjustable delays, soft-start, a 1-MHz capable oscillator with synchronization capability, precision reference, and thermal shutdown. These features simplify the design of active voltage-mode active clamp / reset DC-DC power converters.

# 7.2 Functional Block Diagram

Copyright © 2004–2016, Texas Instruments Incorporated

#### 7.3 Feature Description

#### 7.3.1 High-Voltage Start-Up Regulator

The LM5025A contains an internal high-voltage start-up regulator that allows the input pin ( $V_{IN}$ ) to be connected directly to the line voltage. The regulator output is internally current-limited to 20 mA. When power is applied, the regulator is enabled and sources current into an external capacitor connected to the  $V_{CC}$  pin. The recommended capacitance range for the  $V_{CC}$  regulator is 0.1  $\mu$ F to 100  $\mu$ F. When the voltage on the  $V_{CC}$  pin reaches the regulation point of 7.6 V and the internal voltage reference (REF) reaches its regulation point of 5 V, the controller outputs are enabled. The outputs remain enabled until  $V_{CC}$  falls below 6.2 V or the line undervoltage lockout detector indicates that  $V_{IN}$  is out of range. In typical applications, an auxiliary transformer winding is connected through a diode to the  $V_{CC}$  pin. This winding must raise the  $V_{CC}$  voltage above 8 V to shut off the internal start-up regulator. Powering  $V_{CC}$  from an auxiliary winding improves efficiency while reducing the controller power dissipation.

When the converter auxiliary winding is inactive, external current draw on the  $V_{CC}$  line must be limited so the power dissipated in the start-up regulator does not exceed the maximum power dissipation of the controller.

An external start-up regulator or other bias rail can be used instead of the internal start-up regulator by connecting the  $V_{CC}$  and the  $V_{IN}$  pins together and feeding the external bias voltage into the two pins.

#### 7.3.2 Line Undervoltage Detector

The LM5025A contains a line undervoltage lockout (UVLO) circuit. An external setpoint voltage divider from  $V_{\rm IN}$  to GND, sets the operational range of the converter. The divider must be designed such that the voltage at the UVLO pin is greater than 2.5 V when  $V_{\rm IN}$  is in the desired operating range. If the undervoltage threshold is not met, both outputs are disabled, all other functions of the controller remain active. UVLO hysteresis is accomplished with an internal 20- $\mu$ A current source that is switched ON or OFF into the impedance of the setpoint divider. When the UVLO threshold is exceeded, the current source is activated to instantly raise the voltage at the UVLO pin. When the UVLO pin voltage falls below the 2.5-V threshold, the current source is turned off, causing the voltage at the UVLO pin to fall. The UVLO pin can also be used to implement a remote enable and disable function. Pulling the UVLO pin below the 2.5-V threshold disables the PWM outputs.

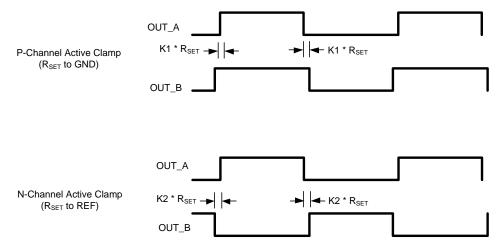

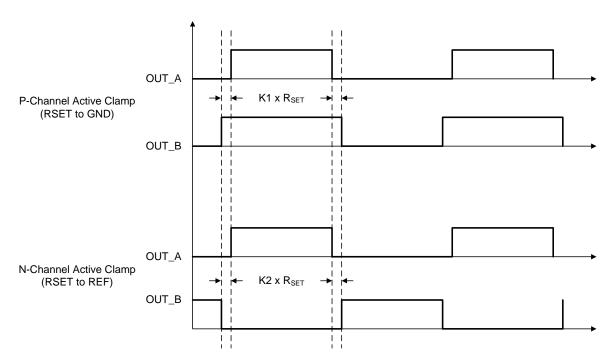

#### 7.3.3 PWM Outputs

The relative phase of the main (OUT\_A) and active clamp outputs (OUT\_B) can be configured for the specific application. For active clamp configurations using a ground-referenced P-channel clamp switch, the two outputs must be in-phase with the active clamp output overlapping the main output. For active clamp configurations using a high-side N-channel switch, the active clamp output must be out-of-phase with main output, and there must be a dead time between the two gate drive pulses. A distinguishing feature of the LM5025A is the ability to accurately configure either dead time (both OFF) or overlap time (both ON) of the gate driver outputs. The overlap and dead-time magnitude is controlled by the resistor value connected to the TIME pin of the controller. The opposite end of the resistor can be connected to either REF for dead-time control or GND for overlap control. The internal configuration detector senses the connection and configures the phase relationship of the main and active clamp outputs. The magnitude of the overlap and dead time can be calculated in Equation 1 and Equation 2.

Overlap Time (ns) =

$$2.8 \times R_{SET} - 1.2$$

(1)

Dead Time (ns) =  $2.9 \times R_{SET} + 20$

where

•  $R_{SET}$  in  $k\Omega$

• Time in ns (2)

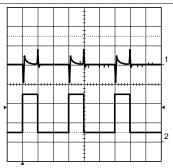

Figure 10. PWM Outputs

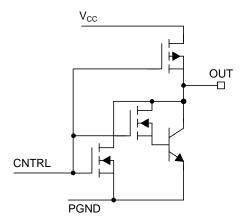

#### 7.3.4 Compound Gate Drivers

The LM5025A contains two unique compound gate drivers, which parallel both MOS and Bipolar devices to provide high-drive current throughout the entire switching event. The bipolar device provides most of the drive current capability and provides a relatively constant sink current which is ideal for driving large power MOSFETs. As the switching event nears conclusion and the bipolar device saturates, the internal MOS device continues to provide a low impedance to compete the switching event.

During turnoff at the Miller plateau region, typically around 2 V to 3 V, is where gate driver current capability is needed most. The resistive characteristics of all MOS gate drivers are adequate for turnon because the supply to output voltage differential is fairly large at the Miller region. During turnoff however, the voltage differential is small and the current source characteristic of the bipolar gate driver is beneficial to provide fast drive capability.

Figure 11. Compound Gate Drivers

#### 7.3.5 PWM Comparator

The PWM comparator compares the ramp signal (RAMP) to the loop error signal (COMP). This comparator is optimized for speed to achieve minimum controllable duty cycles. The internal 5-k $\Omega$  pullup resistor, connected between the internal 5-V reference and COMP, can be used as the pullup for an optocoupler. The comparator polarity is such that 0 V on the COMP pin produces a zero duty cycle on both gate driver outputs.

#### 7.3.6 Volt Second Clamp

The Volt  $\times$  Second Clamp comparator compares the ramp signal (RAMP) to a fixed 2.5-V reference. By proper selection of RFF and CFF, the maximum ON-time of the main switch can be set to the desired duration. The ON-time set by Volt  $\times$  Second Clamp varies inversely with the line voltage because the RAMP capacitor is charged by a resistor connected to  $V_{IN}$  while the threshold of the clamp is a fixed voltage (2.5 V). An example illustrates the use of the Volt  $\times$  Second Clamp comparator to achieve a 50% duty cycle limit, at 200 KHz, at a 48-V line input: A 50% duty cycle at a 200 KHz requires a 2.5  $\mu$ s of ON-time. At 48-V input the Volt  $\times$  Second product is 120 V  $\times$   $\mu$ s (48 V  $\times$  2.5  $\mu$ s). To achieve this clamp level, use Equation 3 and Equation 4:

$$R_{FF} \times C_{FF} = V_{IN} \times T_{ON} / 2.5 \text{ V}$$

$$\tag{3}$$

$$48 \times 2.5 \,\mu / 2.5 = 48 \,\mu$$

(4)

Select  $C_{FF} = 470 \text{ pF}$

$R_{FF} = 102 \text{ k}\Omega$

The recommended capacitor value range for CFF is 100 pF to 1000 pF.

The  $C_{FF}$  ramp capacitor is discharged at the conclusion of every cycle by an internal discharge switch controlled by either the internal clock or by the  $V \times S$  Clamp comparator, whichever event occurs first.

#### 7.3.7 Current Limit

The LM5025A contains two modes of overcurrent protection. If the sense voltage at the CS1 input exceeds 0.5 V the present power cycle is terminated (cycle-by-cycle current limit). If the sense voltage at the CS2 input exceeds 0.5 V, the controller terminates the present cycle, discharge the soft-start capacitor and reduce the soft-start current source to 1  $\mu$ A. The soft-start (SS) capacitor is released after being fully discharged and slowly charges with a 1- $\mu$ A current source. When the voltage at the SS pin reaches approximately 1 V, the PWM comparator produces the first output pulse at OUT\_A. After the first pulse occurs, the soft-start current source reverts to the normal 20- $\mu$ A level. Fully discharging and then slowly charging the SS capacitor protects a continuously overloaded converter with a low duty cycle hiccup mode.

These two modes of overcurrent protection allow the user great flexibility to configure the system behavior in over-load conditions. If it is desired for the system to act as a current source during an overload, then the CS1 cycle-by-cycle current limiting must be used. In this case the current sense signal must be applied to the CS1 input and the CS2 input must be grounded. If during an overload condition it is desired for the system to briefly shutdown, followed by soft-start retry, then the CS2 hiccup current limiting mode must be used. In this case the current sense signal must be applied to the CS2 input and the CS1 input must be grounded. This shutdown and soft-start retry repeats indefinitely while the overload condition remains. The hiccup mode greatly reduces the thermal stresses to the system during heavy overloads. The cycle-by-cycle mode has higher system thermal dissipations during heavy overloads, but provides the advantage of continuous operation for short duration overload conditions.

It is possible to use both overcurrent modes concurrently, whereby slight overload conditions activate the CS1 cycle-by-cycle mode while more severe overloading activates the CS2 hiccup mode. Generally the CS1 input is always configured to monitor the main switch FET current each cycle. The CS2 input can be configured in several different ways depending upon the system requirements.

- The CS2 input can also be set to monitor the main switch FET current except scaled to a higher threshold than CS1

- An external overcurrent timer can be configured which trips after a predetermined overcurrent time, driving the CS2 input high, initiating a hiccup event.

- In a closed-loop voltage regulaton system, the COMP input rises to saturation when the cycle-by-cycle

current limit is active. An external filter and delay timer and voltage divider can be configured between the

COMP pin and the CS2 pin to scale and delay the COMP voltage. If the CS2 pin voltage reaches 0.5 V a

hiccup event will initiate.

TI recommends a small RC filter placed near the controller for each of the CS pins. The CS1 input has an internal FET which discharges the current sense filter capacitor at the conclusion of every cycle, to improve dynamic performance. This same FET remains on an additional 50 ns at the start of each main switch cycle to attenuate the leading edge spike in the current sense signal. The CS2 discharge FET only operates following a CS2 event, UVLO, and thermal shutdown.

The LM5025A CS comparators are very fast and may respond to short duration noise pulses. Layout considerations are critical for the current sense filter and sense resistor. The capacitor associated with the CS filter must be placed very close to the device and connected directly to the pins of the IC (CS and GND). If a current sense transformer is used, both leads of the transformer secondary must be routed to the filter network, which must be placed close to the IC. If a sense resistor in the source of the main switch MOSFET is used for current sensing, a low inductance type of resistor is required. When designing with a current sense resistor, all of the noise-sensitive, low-power ground connections must be connected together near the IC GND and a single connection must be made to the power ground (sense resistor ground point).

Figure 12. Current Limit

#### 7.3.8 Oscillator and Sync Capability

The LM5025A oscillator is set by a single external resistor connected between the RT pin and GND. To set a desired oscillator frequency (F), the necessary RT resistor can be calculated in Equation 5:

$$RT = (5725/F)^{1.026}$$

where

• F is in kHz and RT in

$$k\Omega$$

(5)

The RT resistor must be placed very close to the device and connected directly to the pins of the IC (RT and GND).

A unique feature of LM5025A is the ability to synchronize the oscillator to an external clock with a frequency that is either higher or lower than the frequency of the internal oscillator. The lower frequency sync frequency range is 80% of the free-running internal oscillator frequency. There is no constraint on the maximum SYNC frequency. A minimum pulse width of 100 ns is required for the synchronization clock. If the synchronization feature is not required, the SYNC pin must be connected to GND to prevent any abnormal interference. The internal oscillator can be completely disabled by connecting the RT pin to REF. Once disabled, the sync signal acts directly as the master clock for the controller. Both the frequency and the maximum duty cycle of the PWM controller can be controlled by the SYNC signal (within the limitations of the Volt × Second Clamp). The maximum duty cycle (D) will be (1-D) of the SYNC signal.

# 7.3.9 Feed-Forward Ramp

An external resistor ( $R_{FF}$ ) and capacitor ( $C_{FF}$ ) connected to  $V_{IN}$  and GND are required to create the PWM ramp signal. The slope of the signal at the RAMP pin varies in proportion to the input line voltage. This varying slope provides line feedforward information necessary to improve line transient response with voltage mode control. The RAMP signal is compared to the error signal at the COMP pin by the pulse width modulator comparator to control the duty cycle of the main switch output. The Volt Second Clamp comparator also monitors the RAMP pin and if the ramp amplitude exceeds 2.5 V the present cycle is terminated. The ramp signal is reset to GND at the end of each cycle by either the internal clock or the Volt Second comparator, which ever occurs first.

#### 7.3.10 Soft Start

The soft-start feature allows the power converter to gradually reach the initial steady-state operating point, thus reducing start-up stresses and surges. At power on, a 20- $\mu$ A current is sourced out of the soft-start pin (SS) into an external capacitor. The capacitor voltage ramps up slowly and limits the COMP pin voltage and therefore the PWM duty cycle. In the event of a fault as determined by  $V_{CC}$  undervoltage, line undervoltage (UVLO) or second level current limit, the output gate drivers are disabled, and the soft-start capacitor is fully discharged. When the fault condition is no longer present a soft-start sequence is initiated. Following a second level current limit detection (CS2), the soft-start current source is reduced to 1  $\mu$ A until the first output pulse is generated by the PWM comparator. The current source returns to the nominal 20- $\mu$ A level after the first output pulse (approximately 1 V at the SS pin).

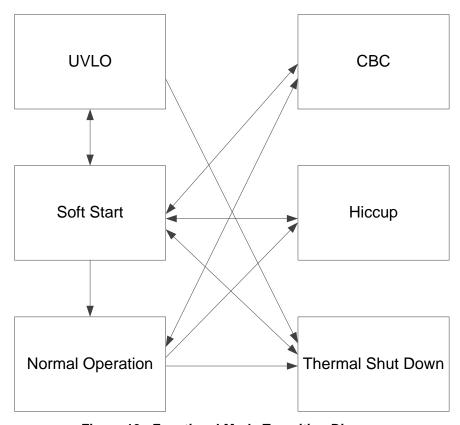

### 7.4 Device Functional Modes

The LM5025A active clamp voltage mode PWM controller has six functional modes:

- UVLO Mode

- Soft-Start Mode

- Normal Operation Mode

- Cycle-by-Cycle Current Limit Mode

- Hiccup Mode

- Thermal Shut Down Mode

Figure 13. Functional Mode Transition Diagram

# 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 8.1 Application Information

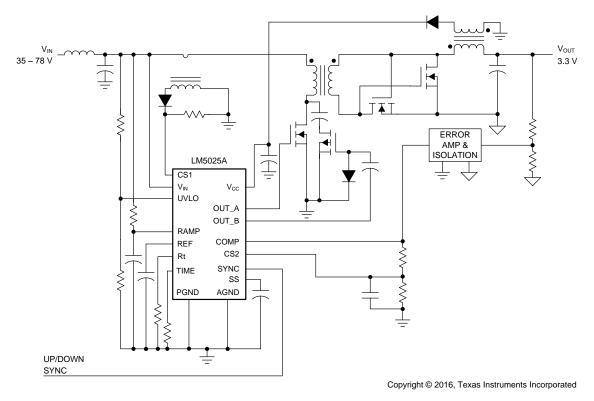

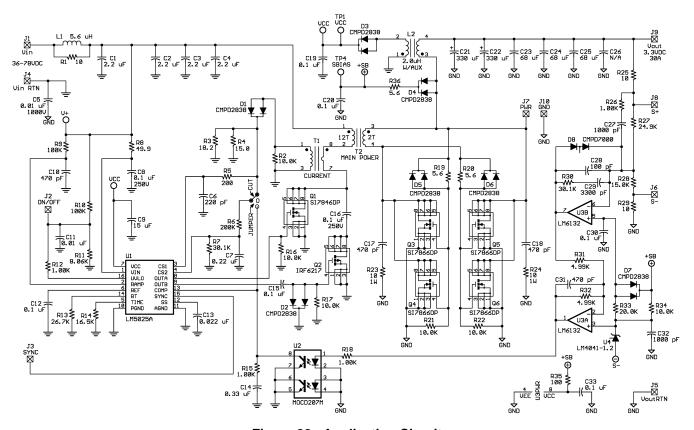

The LM5025A PWM controller contains all of the features necessary to implement power converters using the active clamp and reset technique. This section provides design guidance for a typical active clamp forward converter design. An actual application schematic of a 36-V to 78-V input, 3.3-V, 30-A output active clamp forward converter is also provided in Figure 22.

# 8.2 Typical Application

Figure 14 shows a simplified schematic of an active clamp forward power converter.

Power converters based on the forward topology offer high-efficiency and good power-handling capability in applications up to several hundred Watts. The operation of the transformer in a forward topology does not inherently self-reset each power switching cycle, a mechanism to reset the transformer is required. The active clamp reset mechanism is presently finding extensive use in medium-level power converters in the range of 50 W to 200 W.

The forward converter is derived from the Buck topology family, employing a single modulating power switch. The main difference between the topologies is the forward topology employs a transformer to provide input and output ground isolation and a step-down or step-up function.

Each cycle, the main primary switch turns on and applies the input voltage across the primary winding. The transformer turns the voltage to a lower-level on the secondary side. The clamp capacitor along with the reset switch reverse biases the transformer primary each cycle when the main switch turns off. This reverse voltage resets the transformer. The clamp capacitor voltage is VIN / (1–D).

The secondary rectification employs self-driven synchronous rectification to maintain high-efficiency and ease of drive.

Feedback from the output is processed by an amplifier and reference, generating an error voltage, which is coupled back to the primary side control through an opto-coupler. The LM5025A voltage mode controller pulse width modulates the error signal with a ramp signal derived from the input voltage. Deriving the ramp signal slope from the input voltage provides line feedforward, which improves line transient rejection. The LM5025A also provides a controlled delay necessary for the reset switch.

# TEXAS INSTRUMENTS

# **Typical Application (continued)**

Figure 14. Simplified Active Clamp Forward Power Converter

#### 8.2.1 Design Requirements

This typical application provides an example of a fully-functional power converter based on the active clamp forward topology in an industry standard half-brick footprint.

The design requirements are:

Input: 36 V to 78 V (100-V peak)

Output voltage: 3.3 V

Output current: 0 A to 30 A

Measured efficiency: 90.5% at 30 A, 92.5% at 15 A

Frequency of operation: 230 kHz

Board size: 2.3 x 2.4 x 0.5 inches

Load regulation: 1%Line regulation: 0.1%

• Line UVLO, hiccup current limit

### 8.2.2 Detailed Design Procedure

Before the controller design begins, the power stage design must be completed. This section describes the calculations needed to configure the LM5025A controller to meet the power stage design requirements.

#### 8.2.2.1 Oscillator

The desired switching frequency F is set by a resistor connected between RT pin and ground. The resistance value  $R_T$  is calculated from Equation 6:

# Typical Application (continued)

$$R_T = (5725/F)^{1.026}$$

where

• F is in kHz and

$$R_T$$

in  $k\Omega$  (6)

#### 8.2.2.2 Soft-Start Ramp Time and Hiccup Interval

The soft-start ramp time and hiccup internal is programmed by a capacitor (C<sub>SS</sub>) on the SS pin to ground. The soft-start ramp time is determined by comparing the SS pin voltage with COMP pin voltage. When the SS voltage is less than COMP voltage, the COMP voltage is clamped by SS voltage. The PWM duty is limited by the clamped COMP voltage, so that soft start can be achieved. The first PWM pulse is generated after COMP voltage reaches 1 V. So the soft-start ramp time of the output voltage can be estimated by Equation 7:

$$T_{SS}$$

(ms)= $C_{SS}$  (nF)  $\times \frac{V_{SS}-1 \text{ V}}{20 \text{ uA}}$

where

V<sub>SS</sub> is the steady-state COMP pin voltage. This voltage is determined by the output voltage, voltage divider, and the compensation network.

In hiccup mode, the SS current source is reduced to 1  $\mu$ A. When the first PWM pulse is generated, the current source switches to 20  $\mu$ A, and the power supply tries to start up again. The hiccup interval can be calculated by Equation 8:

$$T_{\text{hiccup}} (\text{ms}) = C_{\text{SS}} (\text{nF}) \times \frac{1 \text{ V}}{1 \,\mu\text{A}} \tag{8}$$

#### 8.2.2.3 Feedforward Ramp and Maximum On-Time Clamp

An example illustrates the use of the Volt  $\times$  Second Clamp comparator to achieve a 50% duty cycle limit, at 200 KHz, at a 48-V line input: A 50% duty cycle at a 200 KHz requires a 2.5  $\mu$ s of ON-time. At 48-V input the Volt  $\times$  Second product is 120 V  $\times$   $\mu$ s (48 V  $\times$  2.5  $\mu$ s). To achieve this clamp level, see Equation 9 and Equation 10:

$$R_{FF} \times C_{FF} = V_{IN} \times T_{ON} / 2.5 \text{ V}$$

$$\tag{9}$$

$$48 \times 2.5 \,\mu\text{F} / 2.5 = 48 \,\mu\text{F}$$

(10)

Select  $C_{FF} = 470 pF$

$R_{FF} = 102 \text{ k}\Omega$

The recommended capacitor value range for C<sub>FF</sub> is 100 pF to 1000 pF.

#### 8.2.2.4 Dead Times

The magnitude of the overlap and dead time can be calculated as follows in Equation 11 and Equation 12:

Overlap Time (ns) =

$$2.8 \times R_{SET} - 1.2$$

(11)

Dead Time (ns) =  $2.9 \times R_{SET} + 20$

where

•

$$R_{SET}$$

in  $k\Omega$ , Time in ns (12)

# **Typical Application (continued)**

Figure 15. PWM Outputs

# **Typical Application (continued)**

#### 8.2.3 Application Curves

Conditions: input voltage = 48 VDC, output current = 5 A

Trace 1: output voltage Volts/div = 0.5 V Horizontal resolution = 1 ms/div

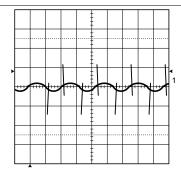

Figure 16. Output Voltage During Typical Start-Up

Conditions: input voltage = 48 VDC, output current = 5 A to 25 A

Trace 1: output voltage Volts/div = 0.5 VTrace 2: output current, Amps/div = 10 AHorizontal resolution =  $1 \mu \text{s/div}$

Figure 17. Transient Response

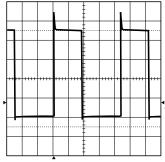

Conditions: input voltage = 48 VDC, output current = 30 A

Bandwidth limit = 25 MHz

Trace 1: output ripple voltage Volts/div = 50 mV

Horizontal resolution = 2  $\mu$ s/div

Conditions: input voltage = 38 VDC, output current = 25 A

Trace 1: Q1 drain voltage Volts/div = 20 V

Horizontal resolution = 1 μs/div

Figure 18. Output Ripple

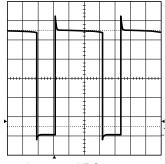

Conditions: input voltage = 78 VDC, output current = 25 A

Trace 1: Q1 drain voltage Volts/div = 20 V

Horizontal resolution = 1 μs/div

Figure 19. Drain Voltage

Conditions: input voltage = 48 VDC, output current = 5 A

Synchronous rectifier, Q3 gate Volts/div = 5 V

Trace 1: synchronous rectifier, Q3 gate Volts/div = 5 V

Trace 2: synchronous rectifier, Q5 gate Volts/div = 5 V

Horizontal resolution = 1 μs/div

Figure 20. Drain Voltage

Figure 21. Gate Voltages of the Synchronous Rectifiers

# 8.3 System Example

Figure 22 shows an application circuit with 36-V to 78-V input and 3.3-V, 30-A output capability.

Figure 22. Application Circuit

# 9 Power Supply Recommendations

The  $V_{CC}$  pin is the power supply for the device. There must be a 0.1- $\mu$ F to approximately 100- $\mu$ F capacitor directly from  $V_{CC}$  to ground. REF pin must be bypassed to ground as close as possible to the device using a 0.1- $\mu$ F capacitor.

# 10 Layout

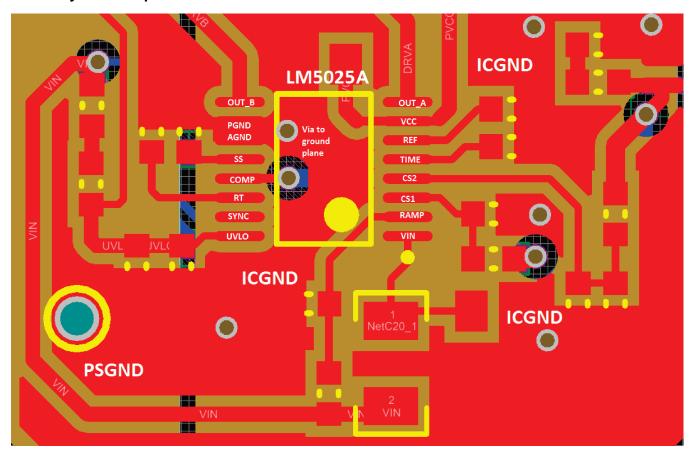

#### 10.1 Layout Guidelines

- Connect two grounds PGND (power ground) and AGND (analog ground) directly as device ground ICGND. The connection must be as close to the pins as possible.

- If there are multiple PCB layers and there is a inner ground layer, use two vias or one big via on GND and connect them to the inner ground layer (ICGND).

- The power stage ground PSGND must be separated with the ICGND. PSGND and ICGND must be connected at a single point close to the device.

- The bypass capacitors to the  $V_{CC}$  pin and REF pin must be as close as possible to the pins and ground (ICGND).

- The filtering capacitors connected to CS1 and CS2 pins must have connections as short as possible to ICGND; if an inner ground layer is available, use vias to connect the capacitors to the ground layer (ICGND).

- The resistors and capacitors connected to the timing configuration pins must be as close as possible to the pins and ground (ICGND).

# 10.2 Layout Example

Figure 23. LM5025A Layout Recommendation

### 10.3 Thermal Protection

Internal thermal shutdown circuitry is provided to protect the integrated circuit in the event the maximum junction temperature is exceeded. When activated, typically at 165°C, the controller is forced into a low-power standby state with the output drivers and the bias regulator disabled. The device restarts after the thermal hysteresis (typically 25°C). During a restart after thermal shutdown, the soft-start capacitor is fully discharged and then charged in the low current mode (1 µA) similar to a second level current limit event. The thermal protection feature is provided to prevent catastrophic failures from accidental device overheating.

# 11 デバイスおよびドキュメントのサポート

# 11.1 ドキュメントのサポート

#### 11.1.1 関連資料

関連資料については、以下を参照してください。

『LM5025 絶縁アクティブ・クランプ・フォワード・コンバータ リファレンス・デザイン・ユーザー・ガイド』(SNVU096)

# 11.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、ti.comのデバイス製品フォルダを開いてください。右上の隅にある「通知を受け取る」をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取れます。変更の詳細については、修正されたドキュメントに含まれている改訂履歴をご覧ください。

# 11.3 コミュニティ・リソース

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E™ Online Community TI's Engineer-to-Engineer (E2E) Community. Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support** *TI's Design Support* Quickly find helpful E2E forums along with design support tools and contact information for technical support.

#### 11.4 商標

E2E is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

#### 11.5 静電気放電に関する注意事項

これらのデバイスは、限定的なESD(静電破壊)保護機能を内蔵しています。保存時または取り扱い時は、MOSゲートに対する静電破壊を防止するために、リード線同士をショートさせておくか、デバイスを導電フォームに入れる必要があります。

### 11.6 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

### 12 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。これらの情報は、指定のデバイスに対して提供されている最新のデータです。このデータは予告なく変更されることがあり、ドキュメントが改訂される場合もあります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

www.ti.com 10-Nov-2025

#### PACKAGING INFORMATION

| Orderable part number | Status   | Material type | Package   Pins  | Package qty   Carrier | RoHS (3) | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|----------|---------------|-----------------|-----------------------|----------|-------------------------------|----------------------------|--------------|------------------|

| LM5025AMTC/NOPB       | Obsolete | Production    | TSSOP (PW)   16 | -                     | -        | (4)<br>Call TI                | (5)<br>Call TI             | -40 to 125   | L5025A<br>MTC    |

| LM5025AMTCX/NOPB      | Active   | Production    | TSSOP (PW)   16 | 2500   LARGE T&R      | Yes      | NIPDAU   SN                   | Level-1-260C-UNLIM         | -40 to 125   | L5025A<br>MTC    |

| LM5025AMTCX/NOPB.A    | Active   | Production    | TSSOP (PW)   16 | 2500   LARGE T&R      | Yes      | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | L5025A<br>MTC    |

| LM5025AMTCX/NOPB.B    | Active   | Production    | TSSOP (PW)   16 | 2500   LARGE T&R      | Yes      | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | L5025A<br>MTC    |

| LM5025ASD/NOPB        | Obsolete | Production    | WSON (NHQ)   16 | -                     | -        | Call TI                       | Call TI                    | -40 to 125   | 5025ASD          |

| LM5025ASDX/NOPB       | Active   | Production    | WSON (NHQ)   16 | 4500   LARGE T&R      | Yes      | SN                            | Level-1-260C-UNLIM         | -40 to 125   | 5025ASD          |

| LM5025ASDX/NOPB.A     | Active   | Production    | WSON (NHQ)   16 | 4500   LARGE T&R      | Yes      | SN                            | Level-1-260C-UNLIM         | -40 to 125   | 5025ASD          |

| LM5025ASDX/NOPB.B     | Active   | Production    | WSON (NHQ)   16 | 4500   LARGE T&R      | Yes      | SN                            | Level-1-260C-UNLIM         | -40 to 125   | 5025ASD          |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

# PACKAGE OPTION ADDENDUM

www.ti.com 10-Nov-2025

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 19-Oct-2024

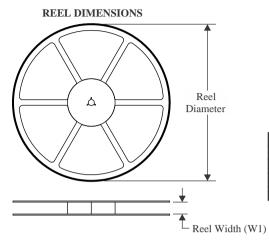

# TAPE AND REEL INFORMATION

# TAPE DIMENSIONS KO P1 BO W Cavity A0

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

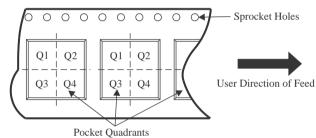

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device           | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LM5025AMTCX/NOPB | TSSOP           | PW                 | 16 | 2500 | 330.0                    | 12.4                     | 6.95       | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

| LM5025ASDX/NOPB  | WSON            | NHQ                | 16 | 4500 | 330.0                    | 12.4                     | 5.3        | 5.3        | 1.3        | 8.0        | 12.0      | Q1               |

www.ti.com 19-Oct-2024

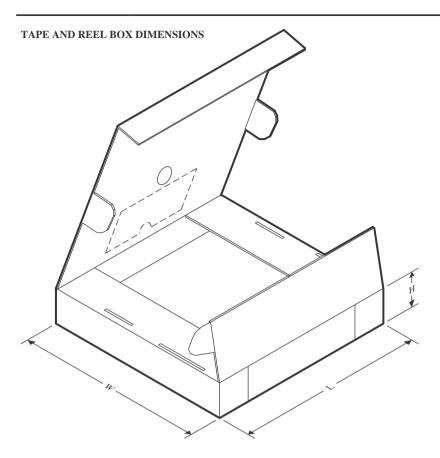

# \*All dimensions are nominal

| Device           | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| LM5025AMTCX/NOPB | TSSOP        | PW              | 16   | 2500 | 367.0       | 367.0      | 35.0        |

| LM5025ASDX/NOPB  | WSON         | NHQ             | 16   | 4500 | 367.0       | 367.0      | 35.0        |

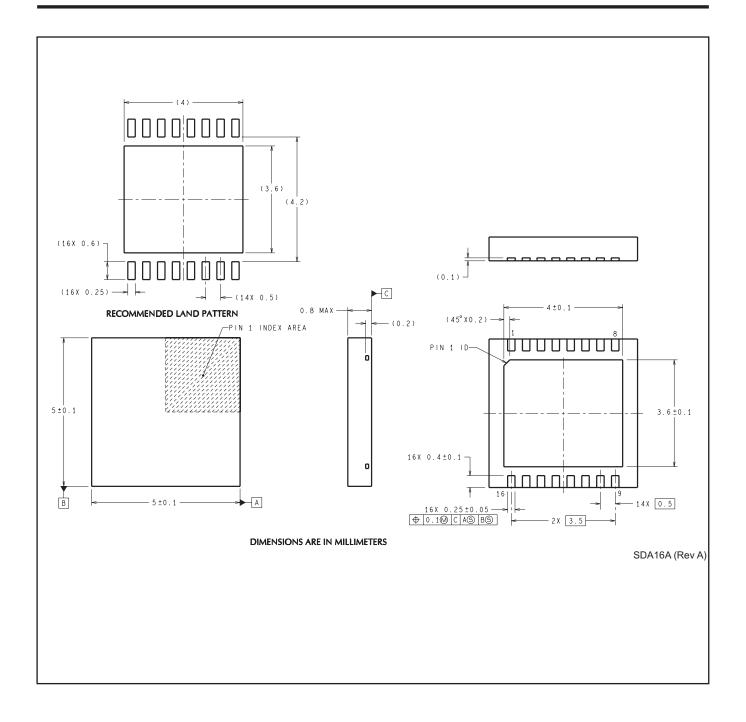

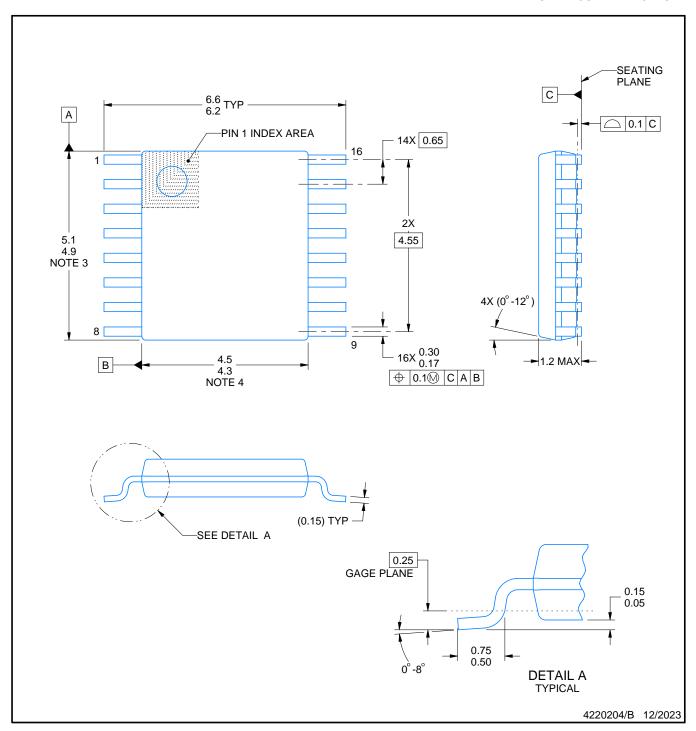

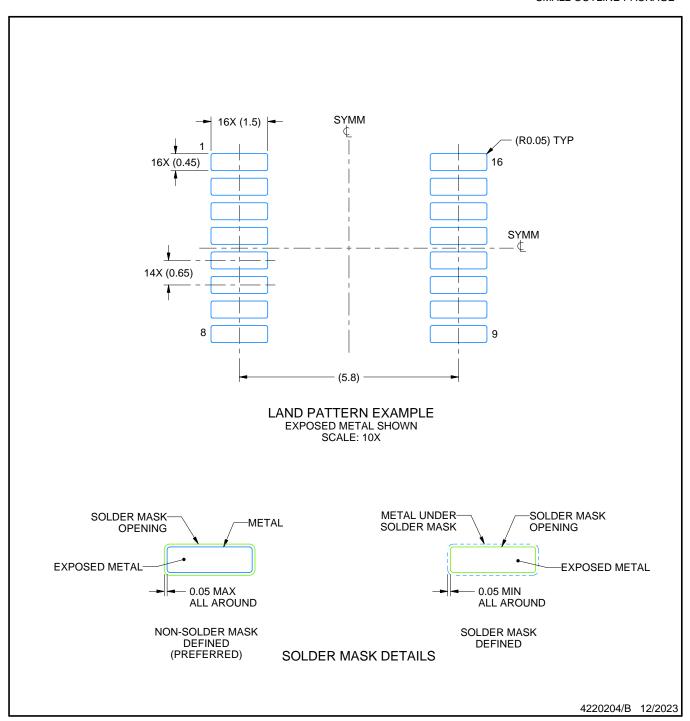

SMALL OUTLINE PACKAGE

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-153.

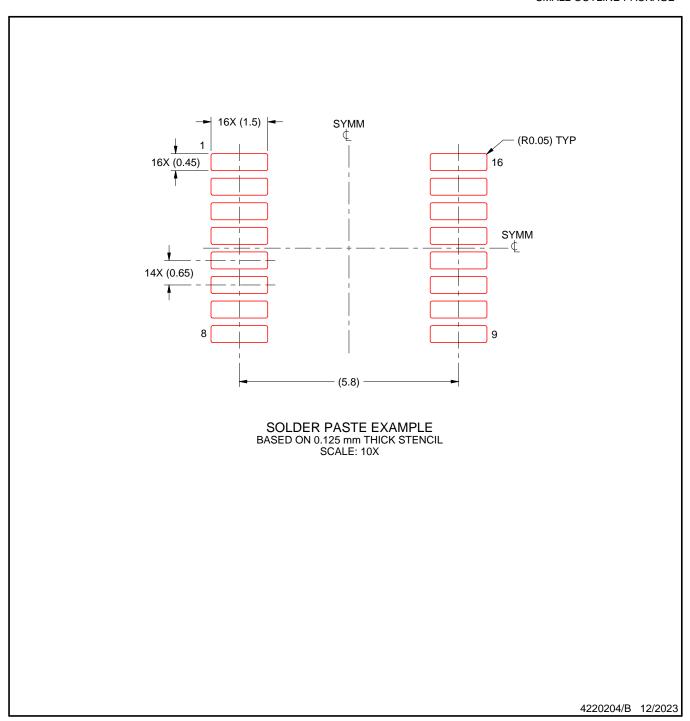

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 6. Publication IPC-7351 may have alternate designs.

- 7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

# 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TIの製品は、TIの販売条件、TIの総合的な品質ガイドライン、 ti.com または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。 TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TIはそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日:2025 年 10 月