Texas Instruments

LM5177

JAJSOR1D – JUNE 2022 – REVISED AUGUST 2023

# LM5177 60V、広い V<sub>IN</sub> 双方向 4 スイッチ昇降圧コントローラ

# 1 特長

- 3.5V~60Vの広い入力範囲(絶対最大値 85V)

V<sub>(BIAS)</sub> > 3.5Vのとき、最小 2.8V

- 出力電E:3.3V~60V

- 低いシャットダウン IQ:3µA

- 低い動作 I<sub>Q</sub>:60µA

- 3%の逆電流制限精度により、精度の高い充電電流を 実現

- 平均入出力電流モニタまたはリミッタ

- PWM またはアナログ入力信号の動的な出力電圧トラ ッキング

- 負荷がきわめて軽い時の効率を向上させるパワーセーブ・モード (PSM)を選択可能

- 自動選択機能を備えた2つの高電圧電源LDOを内蔵

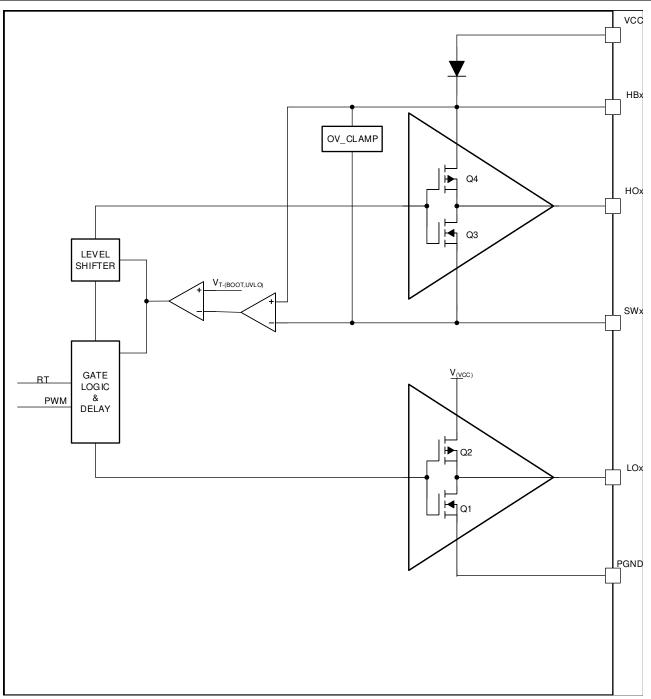

- 2A ピーク電流ロジック・レベル・ゲート・ドライバ

- ブートストラップ・ダイオードを内蔵

- ブートストラップ過電圧および低電圧保護

- 全動作モードにわたる固定周波数(昇圧、昇降圧、降 圧)

- 強制 PWM モードを選択可能

- 小規模ソリューションと部品サイズ用の最大

600kHz のスイッチング

- 外部クロック同期

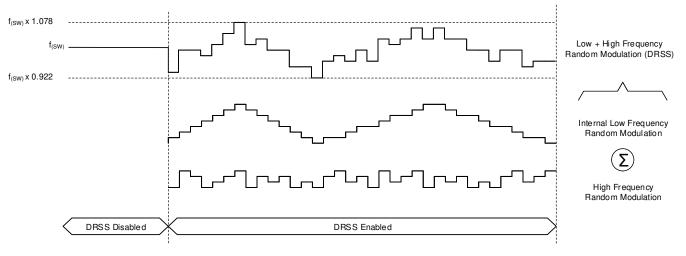

- スペクトラム拡散動作を選択可能

- 可変低電圧保護

- ヒカップ過電流および短絡保護

# 2 アプリケーション

- 非絶縁型 DC/DC 電源 (商用 DC/DC、リモート無線ユニット、モーター駆動制御)

- バックアップ電源システム (バッテリ・バックアップ、防火)

- 産業用 PC (シングル・ボード・コンピュータ)

- 医療用 PSU (酸素濃縮器)

- PoE (Power over Ethernet) (ルータ)

- ・ 太陽光発電 (ソーラー充電コントローラ)

# 3 概要

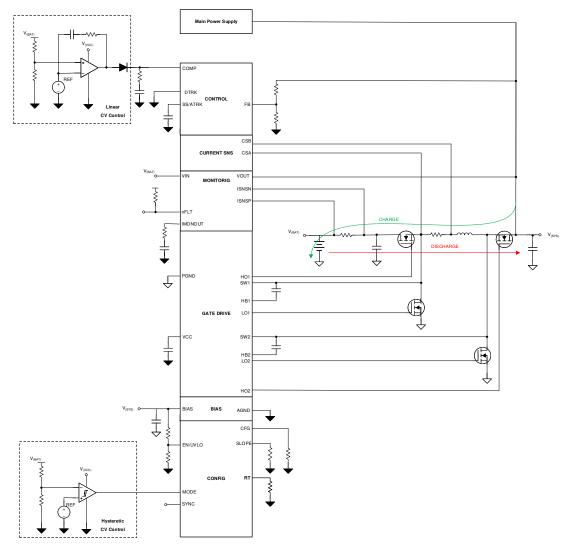

LM5177 は、4 スイッチ昇降圧コントローラです。本デバイ スは入力電圧が、調整された出力電圧よりも高い、等し い、または低い場合に、レギュレートされた出力電圧を供 給します。このデバイスは、パワーセーフ・モードで静止電 流が小さいため、出力負荷が小さくても高効率をサポート します。LM5177 固定スイッチング周波数で動作します。 固定スイッチング周波数は、RT または SYNC ピンで設定 できます。降圧、昇圧、昇降圧動作中も、スイッチング周波 数は同一に維持されます。内蔵、オプションの平均電流モ ニタは、LM5177 の入出力電流の監視と制限に役立ちま す。また、この機能は、定電流 (CC) と定電圧 (CV) を使 用する、バッテリまたはコンデンサなどのバックアップ電源 要素の充電もサポートしています。

|        | 製品情報                 |               |

|--------|----------------------|---------------|

| 部品番号   | パッケージ <sup>(1)</sup> | 本体サイズ (公称)    |

| LM5177 | DCP038               | 9.7mm × 4.4mm |

(1) 利用可能なパッケージについては、このデータシートの末尾にある注文情報を参照してください。

53

英語版のTI製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、 www.ti.com で閲覧でき、その内容が常に優先されます。TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、必ず 最新版の英語版をご参照くださいますようお願いいたします。

# **Table of Contents**

| 1 特長                                     |          |

|------------------------------------------|----------|

| 2 アプリケーション                               |          |

| 3 概要                                     |          |

| 4 Revision History                       |          |

| <b>5</b> Pin Configuration and Functions | 3        |

| 6 Specifications                         |          |

| 6.1 Absolute Maximum Ratings             |          |

| 6.2 Handling Ratings                     |          |

| 6.3 Recommended Operating Con            | ditions6 |

| 6.4 Thermal Information                  | 7        |

| 6.5 Electrical Characteristics           |          |

| 6.6 Typical Characteristics              |          |

| 7 Parameter Measurement Informa          | ition 17 |

| 7.1 Gate Driver Rise Time and Fal        | l Time17 |

| 7.2 Gate Driver Dead (Transition)        |          |

| 8 Detailed Description                   |          |

| 8.1 Overview                             |          |

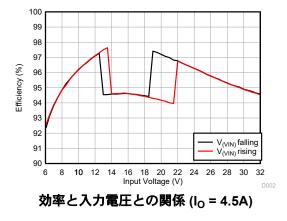

| 8.2 Functional Block Diagram             |          |

| 8.3 Feature Description                  | 20       |

| 8.4 Device Functional Modes             | 37 |

|-----------------------------------------|----|

| 9 Application and Implementation        | 40 |

| 9.1 Application Information             |    |

| 9.2 Typical Application                 |    |

| 9.3 System Examples                     |    |

| 10 Power Supply Recommendations         |    |

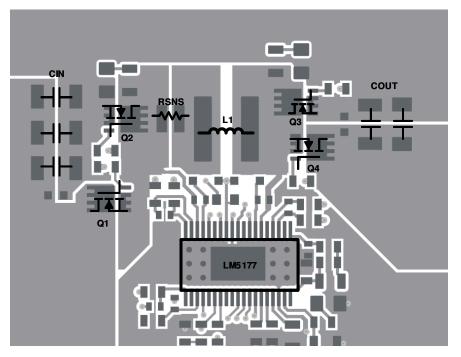

| 11 Layout                               | 53 |

| 11.1 Layout Guidelines                  |    |

| 11.2 Layout Example                     | 54 |

| 12 Device and Documentation Support     | 55 |

| 12.1 Device Support                     | 55 |

| 12.2ドキュメントの更新通知を受け取る方法                  |    |

| 12.3 サポート・リソース                          | 55 |

| 12.4 Trademarks                         |    |

| 12.5 静電気放電に関する注意事項                      | 55 |

| 12.6 用語集                                | 55 |

| 13 Mechanical, Packaging, and Orderable |    |

| Information                             | 56 |

|                                         |    |

# **4 Revision History**

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| <b>Changes from Revis</b>              | sion C (May 2023) to Revision D (August 2023)         | Page |

|----------------------------------------|-------------------------------------------------------|------|

| • デバイスのステータ                            | スをカタログ・リリースに更新。                                       | 1    |

|                                        | and lout for design example                           |      |

| <ul> <li>Changed RT/SYN</li> </ul>     | C to RT                                               | 41   |

|                                        | esistor table to show components with 3 digits values |      |

| • Updated Inductor                     | and Current Sense Resistor selection chapter          | 42   |

| Replaced "slope c                      | apacitor" with "slope resistor"                       |      |

|                                        | Vin for UVLO Resistor calculation                     |      |

| Added reference t                      | o MOSFET in schematic                                 |      |

| Added reference t                      | o MOSFET in schematic                                 |      |

| <ul> <li>Adjusted component</li> </ul> | ents to updated design parameters                     |      |

| Adjusted compone                       | ents to updated design parameters                     |      |

| Changes from Revis                     | sion B (December 2022) to Revision C (May 2023)       | Page |

| • デバイスのステータ                            | スを「事前情報」から「量産データ」に変更                                  | 1    |

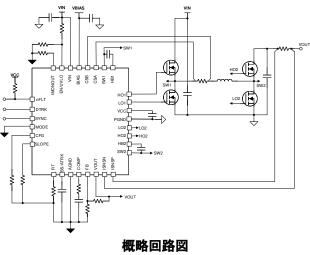

# **5** Pin Configuration and Functions

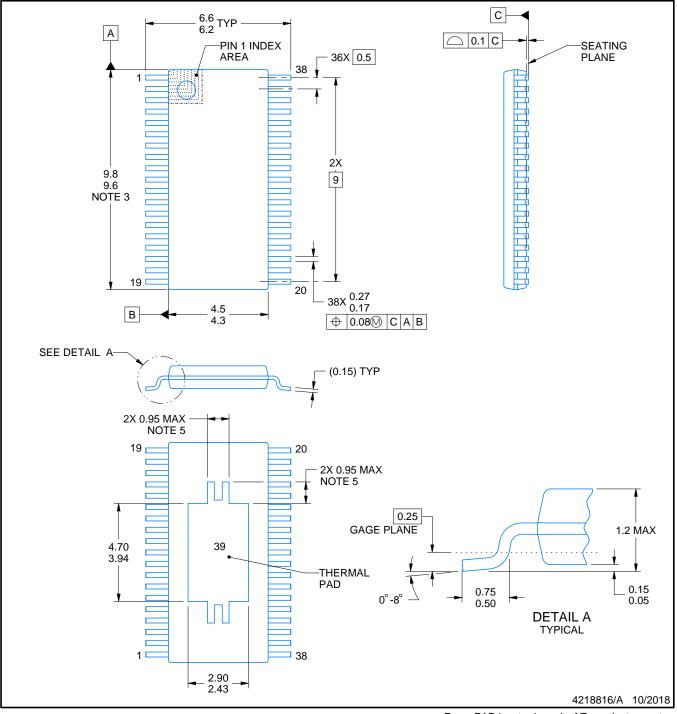

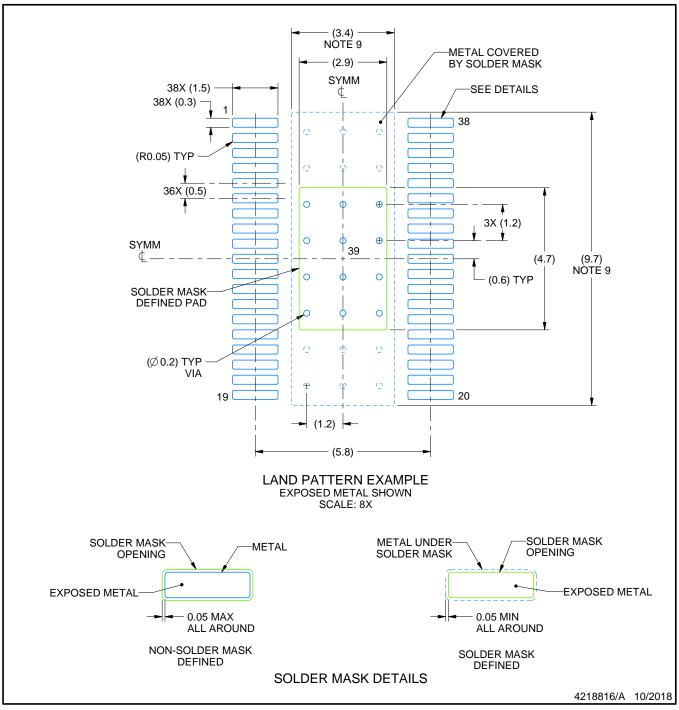

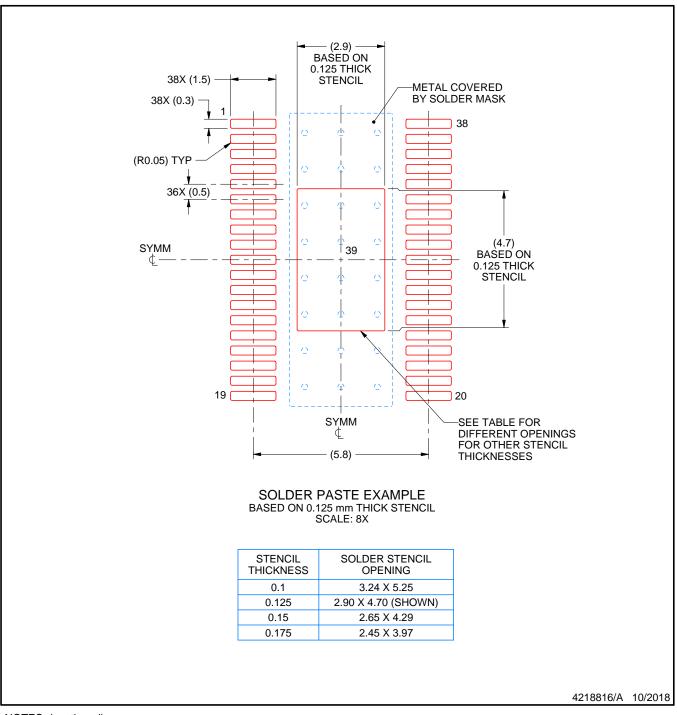

### 🛛 5-1. 38-Pin DCP HTSSOP Pin Diagram

#### 表 5-1. Pin Functions LM5177

| Pin  |     | Type <sup>(1)</sup> | Description                                                                                                                                                                                                             |  |

|------|-----|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Name | No. | Type                | Description                                                                                                                                                                                                             |  |

| AGND | 17  | G                   | Analog ground of the device                                                                                                                                                                                             |  |

| BIAS | 1   | I                   | Optional input to the VCC bias regulator. Powering VCC from an external supply instead of VIN can reduce power loss at high $V_{\rm IN}$ .<br>If the bias pin supply is not used in the application connect the pin GND |  |

| CFG  | 13  | I/O                 | Device configuration pin. Connect a resistor between the CFG pin to select the device operation for spread spectrum (DRSS), short circuit protection (hiccup mode), current limit, or current monitor.                  |  |

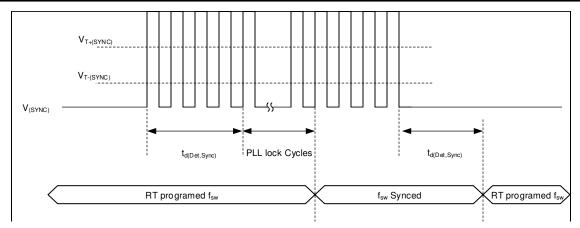

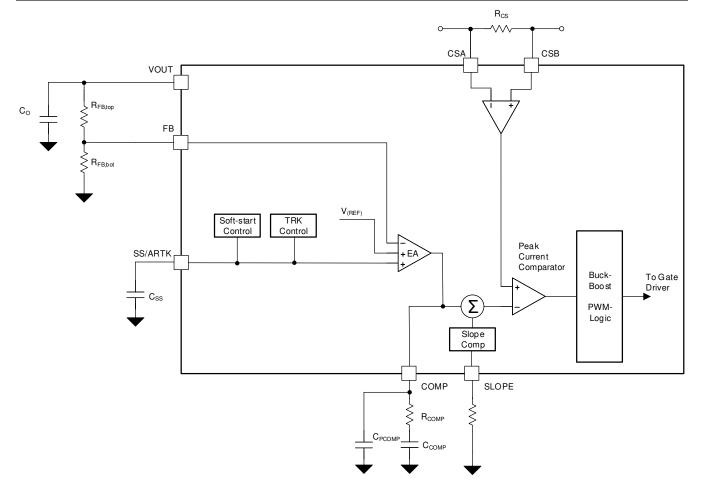

| COMP | 18  | 0                   | Output of the error amplifier. An external RC network connected between COMP and AGND compensates the regulator of the output voltage feedback loop.                                                                    |  |

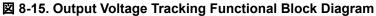

| CSA  | 37  | I                   | Inductor peak current sensor positive input. Connect CSA to the positive side of the external current sense resistor using a low-current Kelvin connection.                                                             |  |

| CSB  | 38  | I                   | Inductor peak current sense negative input. Connect CSB to the negative side of the external current sense resistor using a low-current Kelvin connection.                                                              |  |

# 表 5-1. Pin Functions LM5177 (continued)

| Pin      |     | Type <sup>(1)</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------|-----|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name     | No. | Type                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| DTRK     | 10  | I                   | Digital PWM input pin for the dynamical output voltage tracking. <i>Do not leave this pin floating</i> . If this function is not used, connect the pin to VCC or GND.                                                                                                                                                                                                                                                                                                       |

| EN/UVLO  | 4   | I                   | Enable pin. The pin enables or disables the device. If the pin is less than 0.6 V, the device shuts down. The pin must be raised above 0.65 V to enable the device. This pin is the enable pin for the device internal reference circuit and input voltage UVLO comparator input.                                                                                                                                                                                           |

| FB       | 19  | I                   | Feedback pin for output voltage regulation. Connect a resistor divider network from the output o the converter to the FB pin.                                                                                                                                                                                                                                                                                                                                               |

| HB1      | 35  | Р                   | Bootstrap supply pin for buck half-bridge. An external capacitor is required between the HB1 pir and the SW1 pin, respectively, to provide bias to the high-side MOSFET gate driver.                                                                                                                                                                                                                                                                                        |

| HO1      | 34  | 0                   | High-side gate driver output for the buck half-bridge                                                                                                                                                                                                                                                                                                                                                                                                                       |

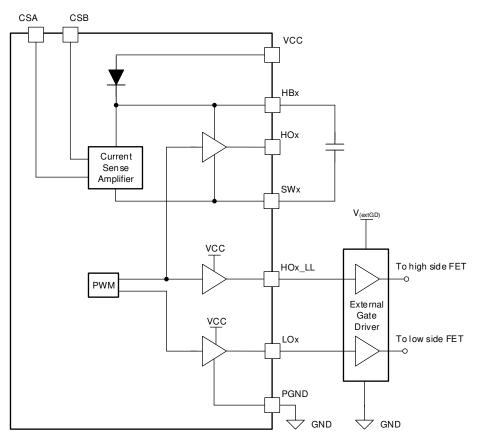

| HO1_LL   | 8   | 0                   | Logic level output of the HO1 gate signal. Connect this ground reference PWM signal to an optional external gate-driver input. If the function is not used, make no external connection to th pin.                                                                                                                                                                                                                                                                          |

| HB2      | 26  | Р                   | Bootstrap supply pin for boost half-bridge. An external capacitor is required between the HB2 pi<br>and the SW2 pin, respectively, to provide bias to the high-side MOSFET gate driver.                                                                                                                                                                                                                                                                                     |

| HO2      | 27  | 0                   | High-side gate driver output for the boost half-bridge                                                                                                                                                                                                                                                                                                                                                                                                                      |

| HO2_LL   | 9   | 0                   | Logic level output of the HO2 gate signal. Connect this ground reference PWM signal to an optional external gate-driver input. If the function is not used, make no external connection to th pin.                                                                                                                                                                                                                                                                          |

| IMONOUT  | 6   | 0                   | Current monitor output pin. Output of the voltage-controlled current source of the optional current<br>monitor. Connect the pin to a resistor to sense the voltage across. If the output or input current<br>sense amplifier is configured as current limiter, an external RC network connected between<br>IMONOUT and AGND compensates the regulator of the current feedback loop.<br>Connect the IMONOUT pin to VCC to disable the block and reduce the quiescent current |

| ISNSN    | 22  | I                   | Negative sense input of the output or input current sense amplifier. An optional current sense resistor connected between ISNSN and ISNSP can be located either on the input side or on the output side of the power stage.<br>In case the current monitor is disabled connect ISNSN to ground                                                                                                                                                                              |

| ISNSP    | 23  | I                   | Positive sense input of the output or input current sense amplifier. An optional current sense resistor connected between ISNSN and ISNSP can be located either on the input side or on the output side of the power stage.<br>In case the current monitor is disabled connect ISNSN to ground                                                                                                                                                                              |

| LO1      | 32  | 0                   | Low-side gate driver output for the buck half-bridge                                                                                                                                                                                                                                                                                                                                                                                                                        |

| LO2      | 29  | 0                   | Low-side gate driver output for the boost half-bridge                                                                                                                                                                                                                                                                                                                                                                                                                       |

| MODE     | 12  | I                   | Digital input to select device operation mode. If the pin is pulled low, power save mode (PSM) is enabled. If the pin is pulled high, the forced PWM or CCM operation is enabled. The configuration can be changed dynamically during operation. <i>Do not leave this pin floating</i> . If this function is not used, connect the pin to VCC or GND.                                                                                                                       |

| NC       | 2   | NC                  | No internal connection                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| NC       | 5   | NC                  | No internal connection                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| NC       | 21  | NC                  | No internal connection                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| NC       | 24  | NC                  | No internal connection                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| NC       | 28  | NC                  | No internal connection                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| NC       | 33  | NC                  | No internal connection                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| nFLT     | 7   | о                   | Open-drain output pin for fault indication or power good. This pin is pulled low when FB is outsin a $\pm 10\%$ regulation window around the regulation window of the nominal output voltage. If the nFLT pin function is not used the pin can be kept floating.                                                                                                                                                                                                            |

| PowerPAD | PAD | G                   | Connect the PowerPAD to the analog ground. Use thermal vias to connect to a PCB ground plane for improved power dissipation.                                                                                                                                                                                                                                                                                                                                                |

| PGND     | 30  | G                   | Power ground. This pin is the high current ground connection to the low-side gate drivers and for the internal VCC regulator.                                                                                                                                                                                                                                                                                                                                               |

# 表 5-1. Pin Functions LM5177 (continued)

| Pin     |     | Type <sup>(1)</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|---------|-----|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Name    | No. | Type                | Description                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| RT      | 15  | I/O                 | Switching frequency programming pin. An external resistor is connected to the RT pin and AGND to set the switching frequency.                                                                                                                                                                                                                                                                                 |  |

| SLOPE   | 14  | I                   | A resistor connected between the SLOPE pin and AGND provides the slope compensation ramp for stable current mode operation in both buck and boost mode.                                                                                                                                                                                                                                                       |  |

| SS/ATRK | 16  | I/O                 | Soft-start programming pin. A capacitor between the SS pin and AGND pin programs soft-start time. Analog output voltage tracking pin. The VOUT regulation target can be programmed by connecting the pin to variable voltage reference (for example, through a digital to analog converter). The internal circuit selects the lowest voltage applied to the pin.                                              |  |

| SW1     | 36  | Р                   | Inductor switch node for the buck half-bridge                                                                                                                                                                                                                                                                                                                                                                 |  |

| SW2     | 25  | Р                   | Inductor switch node for the boost half-bridge                                                                                                                                                                                                                                                                                                                                                                |  |

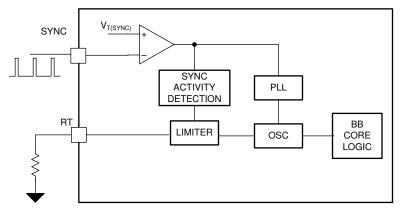

| SYNC    | 11  | I                   | Synchronization clock input. The internal oscillator can be synchronized to an external clock during operation. If the output or input current sense amplifier is configured as a current limiter pulling, this pin is low during start-up, device switches the current limit direction to a negative polarity. <i>Do not leave this pin floating</i> . If this function is not used, connect the pin to VCC. |  |

| VCC     | 31  | Р                   | Internal linear bias regulator output. Connect a ceramic decoupling capacitor from VCC to PGN                                                                                                                                                                                                                                                                                                                 |  |

| VIN     | 3   | I                   | The input supply and sense input of the device. Connect VIN to the supply voltage of the power stage.                                                                                                                                                                                                                                                                                                         |  |

| VOUT    | 20  | I                   | VOUT sense input. Connect to the power stage output rail.                                                                                                                                                                                                                                                                                                                                                     |  |

(1) I = Input, O = Output, I/O = Input or Output, G = Ground, P = Power, NC = No Connect

# 6 Specifications

### 6.1 Absolute Maximum Ratings

Over the recommended operating junction temperature range of -40°C to 150°C (unless otherwise specified)<sup>(1)</sup>

|              |                                                                   | MIN  | MAX                      | UNIT |

|--------------|-------------------------------------------------------------------|------|--------------------------|------|

| Input        | BIAS to AGND                                                      | -0.3 | 50                       | V    |

|              | VIN to AGND                                                       | -0.3 | 85                       |      |

| Input        | UVLO/EN to AGND                                                   | -0.3 | V <sub>(VIN)</sub> + 0.3 | V    |

| Input        | ATRK/SS, DTRK, RT, SYNC, MODE, SLOPE, CFG, to AGND <sup>(2)</sup> | -0.3 | 5.8                      | V    |

| Input        | FB to AGND                                                        | -0.3 | 5.8                      | V    |

| Input        | CSA, CSB to AGND(DC)                                              | -5   | 85                       | V    |

| Input        | SW1, SW2 to AGND(DC)                                              | -5   | 85                       | V    |

| Input        | HB1 to SW1, CSA, CSB                                              | -0.3 | 5.5 <sup>(5)</sup>       | V    |

| Input        |                                                                   | -0.3 | 7.8                      | V    |

| Input        | HB2 to SW2, CSA, CSB                                              | -0.3 | 5.5 <sup>(5)</sup>       | V    |

| Input        |                                                                   | -0.3 | 7.8                      | V    |

| Input        | SW1 to CSA, CSB                                                   | -0.3 | 0.3                      | V    |

| Input        | PGND to AGND                                                      | -0.3 | 0.3                      | V    |

| Output       | VCC to AGND                                                       | -0.3 | 5.5                      | V    |

| Output       | VOUT to AGND                                                      | -0.3 | 85                       | V    |

| Output       | LO1, LO2, to AGND (DC)                                            | -5   | V <sub>(VCC)</sub> +0.3  | V    |

| Output       | nFLT to AGND                                                      | -0.3 | 5.8                      | V    |

| Output       | HO1, HO2, ISNSP, ISNSN, HB1, HB2 to AGND (DC)                     | -0.3 | 85                       | V    |

| Output       | COMP, IMONOUT to AGND <sup>(3)</sup>                              | -0.3 | 5.8                      | V    |

| Storage tem  | perature, T <sub>STG</sub>                                        | -55  | 150                      | °C   |

| Operating ju | nction temperature, T <sub>J</sub> <sup>(4)</sup>                 | -40  | 150                      | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2) This pin is not specified to have an external voltage applied.

- (3) This pin has an internal max voltage clamp which can handle up to 1.6mA.

- (4) High junction temperatures degrade operating lifetimes. Operating lifetime is de-rated for junction temperatures greater than 125°C.

(5) Operating lifetime is de-rated for voltage bigger than the specified maximum

# 6.2 Handling Ratings

|                                            |                                |                                                                   |            | VALUE | UNIT |

|--------------------------------------------|--------------------------------|-------------------------------------------------------------------|------------|-------|------|

|                                            |                                | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> |            | ±2000 |      |

| V <sub>(ESD)</sub> Electrostatic discharge | Charged device model (CDM) per | Corner pins                                                       | ±750       | V     |      |

|                                            |                                | ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup>                             | Other pins | ±500  |      |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 500-V HBM is possible with the necessary precautions. Pins listed as ±2000 V may actually have higher performance.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 250-V CDM is possible with the necessary precautions. Pins listed as ±500 V may actually have higher performance.

# 6.3 Recommended Operating Conditions

Over the recommended operating junction temperature range of -40°C to 150°C (unless otherwise specified)<sup>(1)</sup>

|                     |                      | MIN | NOM MAX | UNIT |

|---------------------|----------------------|-----|---------|------|

| V <sub>(VIN)</sub>  | Input Voltage Sense  | 2.9 | 60      | V    |

| V <sub>(VOUT)</sub> | Output Voltage Sense | 3.3 | 60      | V    |

|                     |                                                                                     | MIN | NOM MAX                 |       |

|---------------------|-------------------------------------------------------------------------------------|-----|-------------------------|-------|

| V <sub>(IMON)</sub> | ISNSP;ISNSN                                                                         | 2.8 | 60                      | ) V   |

| V <sub>(VCC)</sub>  | VCC Voltage                                                                         | 3.6 | 5.3                     | B V   |

| C <sub>(VCC)</sub>  | VCC regulator effective output capacitance                                          | 10  |                         | μF    |

| V <sub>FB</sub>     | FB Input                                                                            | 0   | V <sub>(VCC)</sub> +0.3 | B V   |

| V <sub>IL</sub>     | Logic pin low-level                                                                 |     | 0.4                     | V V   |

| V <sub>IH</sub>     | Logic pin high-level                                                                | 1.3 |                         | V     |

| f <sub>SW</sub>     | Typical Switching Frequency                                                         | 100 | 600                     | ) kHz |

| f <sub>(SYNC)</sub> | Synchronization switching frequency limits                                          | 100 | 600                     | ) kHz |

|                     | Maximum recommended gate charge per driver output. f_{sw} = 600kHz V_{(BIAS)} = 12V |     | 42                      | 2 nC  |

|                     | Inductor current ripple, referenced to the peak current limit                       | 15  | 20                      | %     |

|                     | Synchronization frequency range relative to RT center frequency                     |     | ±45                     | 5 %   |

|                     | Synchronization input minimum off- or ontime                                        | 120 |                         | ns    |

| f <sub>(DTRK)</sub> | Tracking input frequency range                                                      | 150 | 500                     | kHz   |

|                     | Tracking input minimum off- or ontime                                               | 120 |                         | ns    |

|                     | Differential voltage for ISNSN to ISNSP                                             |     | 50 55                   | 5 mV  |

| TJ                  | Operating Junction Temperature <sup>(2)</sup>                                       | -40 | 12:                     | 5 °C  |

Over the recommended operating junction temperature range of -40°C to 150°C (unless otherwise specified)<sup>(1)</sup>

(1) Operating Ratings are conditions under the device is intended to be functional. For specifications and test conditions, see Electrical Characteristics.

(2) High junction temperatures degrade operating lifetimes. Operating lifetime is de-rated for junction temperatures greater than 125°C.

### 6.4 Thermal Information

|                       |                                              | LM5177  |      |

|-----------------------|----------------------------------------------|---------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | HTSSOP  | UNIT |

|                       |                                              | 38 PINS |      |

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance       | 33.6    | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 18.4    | °C/W |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance         | 15.2    | °C/W |

| Ψյτ                   | Junction-to-top characterization parameter   | 0.5     | °C/W |

| Ψјв                   | Junction-to-board characterization parameter | 15      | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 1.2     | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## **6.5 Electrical Characteristics**

Typical values correspond to  $T_J=25^{\circ}$ C. Minimum and maximum limits apply over  $T_J=-40^{\circ}$ C to 125°C. Unless otherwise stated,  $V_{(BIAS)}=12$  V

|                                | PARAMETER                                    |                                                            |                                                                 | MIN  | TYP   | MAX  | UNI |

|--------------------------------|----------------------------------------------|------------------------------------------------------------|-----------------------------------------------------------------|------|-------|------|-----|

| SUPPLY CU                      | RRENT                                        |                                                            |                                                                 |      |       |      |     |

|                                | Shutdown current into VIN                    | V <sub>(VIN)</sub> = 12 V, V <sub>(BIAS)</sub> = 0         | T <sub>J</sub> = 25°C                                           |      | 2.8   | 4    | μA  |

|                                |                                              | $V V_{(EN)} = 0 V$                                         | $T_J = -40^{\circ}C$ to $125^{\circ}C$                          |      | 2.8   | 5    | μA  |

|                                | Shutdown current into BIAS                   | V <sub>(VIN)</sub> = 0 V, V <sub>(EN)</sub> = 0 V          | T <sub>J</sub> = 25°C                                           |      | 2.8   | 4    | μA  |

|                                |                                              | v <sub>(VIN)</sub> = 0 v, v <sub>(EN)</sub> = 0 v          | $T_J = -40^{\circ}C$ to $125^{\circ}C$                          |      | 2.8   | 5    | μA  |

|                                | Quiescent current into BIAS                  | V <sub>(EN)</sub> = 3.3 V, V <sub>(FB)</sub> > 1 V,        | T <sub>J</sub> = 25°C                                           |      | 60    | 80   | μA  |

|                                |                                              |                                                            | $T_{\rm J}$ = -40°C to 125°C                                    |      | 60    | 90   | μA  |

| I <sub>IL</sub>                | Low-level input current (EN/UVLO)            | $V_{(EN/UVLO)} \le 0.55 V$                                 |                                                                 |      | ±0.01 | ±0.1 | μA  |

| VCC REGU                       | ATOR                                         |                                                            | I                                                               |      |       |      |     |

|                                | VCC regulation                               | V <sub>BIAS</sub> 12.0 V ,I <sub>(VCC)</sub> = 20 n        | nA                                                              | 4.75 | 5     | 5.25 | V   |

|                                | VCC regulation                               | V <sub>VIN</sub> 12.0 V ,I <sub>(VCC)</sub> = 20 m         | A                                                               | 4.75 | 5     | 5.25 | V   |

|                                | VCC line regulation                          | 1                                                          | V <sub>(VIN)</sub> =3.5V V <sub>(BIAS)</sub> = 6.7<br>V to 42 V |      |       | ±1   | %   |

|                                |                                              | I <sub>(VCC)</sub> = 1 mA                                  | V <sub>(BIAS)</sub> =0 V V <sub>(VIN)</sub> = 6.7<br>V to 78 V  |      |       | ±1   | %   |

|                                | BIAS LDO dropout load regulation             | V <sub>(BIAS)</sub> = 6.7V, V <sub>(VIN)</sub> = 3.5<br>V, | $I_{(VCC)}$ = 1 mA to 200 mA                                    |      | 65    | 120  | mV  |

|                                |                                              | V <sub>BIAS</sub> = 3.5V, V <sub>(VIN)</sub> = 2.8 V       | V, I <sub>(VCC)</sub> = 35 mA                                   |      |       | 200  | mV  |

|                                |                                              | V <sub>(BIAS)</sub> = 0V, V <sub>(VIN)</sub> = 6.7V,       | I <sub>(VCC)</sub> = 1 mA to 175 mA                             |      | 65    | 120  | mV  |

|                                | VIN LDO dropout load regulation              | V <sub>(BIAS)</sub> = 0V, V <sub>(VIN)</sub> = 3.5V,       | I <sub>(VCC)</sub> = 15 mA                                      |      | 89    | 200  | mV  |

|                                | VCC UVLO delay                               | VCC rising                                                 |                                                                 |      | 6     |      | us  |

|                                | VCC sourcing current limit                   | VCC ≥ 4.5 V                                                | V <sub>(BIAS)</sub> = 0V, V <sub>(VIN)</sub> = 12 V,            | 200  |       |      | mA  |

|                                |                                              | VCC 2 4.5 V                                                | V <sub>(VIN)</sub> = 3.5 V,                                     | 200  |       |      | mA  |

| V <sub>T+(VCC)</sub>           | Positive going threshold                     | V(VCC) rising                                              |                                                                 | 3.4  | 3.45  | 3.5  | V   |

| V <sub>T-(VCC)</sub>           | Negative going threshold                     | V(VCC) falling                                             |                                                                 | 3.2  | 3.25  | 3.3  | V   |

| V <sub>T+</sub><br>(VCC,SUP)   | Positive going threshold for LDO switch-over |                                                            |                                                                 | 6.35 | 6.5   | 6.7  | V   |

| V <sub>hyst(VCC,SU</sub><br>P) | LDO switch-over hysteresis                   |                                                            |                                                                 | 60   |       |      | mV  |

| ENABLE                         |                                              |                                                            |                                                                 |      |       |      |     |

| V <sub>T+(EN)</sub>            | Enable positive-going threshold              | EN rising                                                  |                                                                 | 0.47 | 0.63  | 0.8  | V   |

| V <sub>T-(EN)</sub>            | Enable negative-going threshold              | EN falling                                                 |                                                                 | 0.45 | 0.6   | 0.75 | V   |

| Vhyst(EN)                      | Enable threshold hysteresis                  | EN falling                                                 |                                                                 | 20   |       | 100  | mV  |

| t <sub>d(EN)</sub>             | Shutdown delay time                          |                                                            |                                                                 | 14   | 20    |      | us  |

| UVLO                           |                                              |                                                            |                                                                 |      |       |      |     |

|                                | VDET positive-going threshold                | V <sub>(VIN)</sub> rising                                  |                                                                 | 3.3  | 3.4   | 3.55 | V   |

|                                | VDET negative-going threshold                | V <sub>(VIN)</sub> falling                                 |                                                                 | 2.6  | 2.7   | 2.85 | V   |

| V <sub>T+(UVLO)</sub>          | UVLO positive-going threshold                | $V_{(EN/UVLO)}$ rising                                     | V <sub>(EN/UVLO)</sub> rising                                   |      | 1.25  | 1.28 | V   |

| V <sub>T-(UVLO)</sub>          | UVLO negative-going threshold                | V <sub>(EN/UVLO)</sub> falling                             |                                                                 | 1.17 | 1.2   | 1.23 | V   |

| I <sub>UVLO</sub>              | UVLO hysteresis sinking current              | $0.7 \text{ V} \le \text{V}_{(\text{EN/UVLO})} \le 1.22$   | V                                                               | 4    | 5     | 6    | μA  |

|                                | Enable time to start<br>switching            | VCC = 5V, V <sub>T+(UVLO)</sub> > 1.3                      | 3V                                                              |      | 45    |      | us  |

| t <sub>d(UVLO)</sub>           | UVLO and VDET detection delay tim            | e V <sub>(EN/UVLO)</sub> falling; V(VDE)                   | C) falling                                                      | 25.5 | 30    | 34.5 | μs  |

Typical values correspond to T<sub>J</sub>=25°C. Minimum and maximum limits apply over T<sub>J</sub>=-40°C to 125°C. Unless otherwise stated,  $V_{(BIAS)}$  =12 V

|                          | PARAMETER                                |                                                                                                 |                                                                                  | MIN   | TYP  | MAX   | UNIT       |

|--------------------------|------------------------------------------|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-------|------|-------|------------|

| V <sub>T+(SYNC)</sub>    | Sync input positive going threshold      |                                                                                                 |                                                                                  |       |      | 1.19  | V          |

| V <sub>T-(SYNC)</sub>    | Sync input negative going threshold      |                                                                                                 |                                                                                  | 0.41  |      |       | V          |

| . (22)                   | Sync activity detection frequency        |                                                                                                 |                                                                                  | 99    |      |       | kHz        |

| t <sub>d(Det,Sync)</sub> | Sync activity detection delay            | referred to f <sub>(SYNC)</sub>                                                                 |                                                                                  |       |      | 3     | cycle<br>s |

|                          | Sync PLL lock time                       | referred to f <sub>(SYNC)</sub>                                                                 | until f <sub>(SYNC)</sub> - 5% < f <sub>(sw)</sub><br>< f <sub>(SYNC)</sub> + 5% |       | 10   |       | cycle<br>s |

| SOFT-STAF                | RT                                       |                                                                                                 |                                                                                  |       |      |       | L          |

| I <sub>(SS)</sub>        | Soft-start current                       |                                                                                                 |                                                                                  | 8.9   | 10   | 11    | uA         |

|                          | SS pull-down switch R <sub>DS(on)</sub>  | V <sub>(SS)</sub> = 1 V                                                                         |                                                                                  |       | 23   | 40    | Ω          |

| t <sub>d(DISCH;SS)</sub> | SS Pin discharge time                    | Time from internal SS<br>discharge until the soft-<br>start current can charge<br>the pin again |                                                                                  | 500   |      |       | μs         |

| t <sub>d(EN_SS)</sub>    | SS Pin charge delay time                 | Internal delay until soft-<br>start current starts                                              |                                                                                  | 2.5   |      | 4     | μs         |

| V <sub>(SS,clamp)</sub>  | Clamp Voltage for SS pin                 |                                                                                                 |                                                                                  | 3     | 4.1  | 5.25  | V          |

|                          | TH MODULATION                            |                                                                                                 |                                                                                  |       |      |       |            |

|                          | Switching frequency                      | R <sub>RT</sub> = 49.9 kΩ                                                                       |                                                                                  | 540   | 600  | 660   | kHz        |

|                          | Switching frequency                      | R <sub>RT</sub> = 316 kΩ                                                                        |                                                                                  | 90    | 100  | 110   | kHz        |

|                          |                                          |                                                                                                 | Boost Mode                                                                       |       | 154  |       | ns         |

|                          | - Minimum controllable on-time           |                                                                                                 | Buck Mode                                                                        |       | 197  |       | ns         |

|                          |                                          | - fPWM, R <sub>RT</sub> = 49.9 kΩ                                                               | Boost Mode                                                                       |       | 207  |       | ns         |

|                          | Minimum controllable off-time            |                                                                                                 | Buck Mode                                                                        |       | 210  |       | ns         |

|                          | RT regulation voltage                    |                                                                                                 |                                                                                  |       | 0.75 |       | V          |

| SPREAD SI                | PECTRUM                                  |                                                                                                 |                                                                                  | I     |      |       |            |

|                          |                                          | upper limit                                                                                     |                                                                                  |       | 7.8  |       | %          |

|                          | Switching frequency modulation range     | lower limit                                                                                     |                                                                                  |       | -7.8 |       | %          |

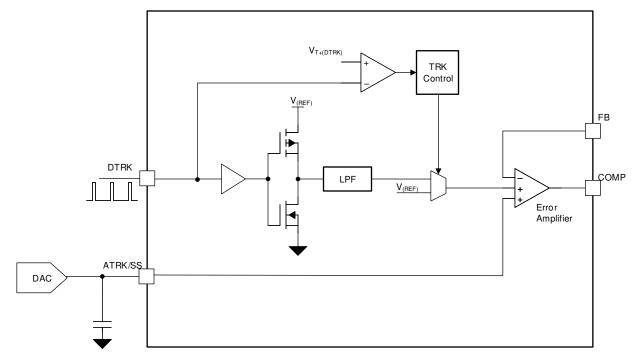

| VOUT TRA                 | CKING                                    |                                                                                                 |                                                                                  |       |      |       |            |

| V <sub>T+(DTRK)</sub>    | DTRK positive-going threshold            | V <sub>(DTRK)</sub> rising                                                                      |                                                                                  |       |      | 1.19  | V          |

| V <sub>T-(DTRK)</sub>    | DTRK negative-going threshold            | V <sub>(DTRK)</sub> falling                                                                     |                                                                                  | 0.41  |      |       | V          |

|                          | DTRK activity detection frequency        |                                                                                                 |                                                                                  | 148   |      |       | kHz        |

| t <sub>d(Det,DTRK)</sub> | DTRK activity detection delay            | referred to f <sub>(DTRK)</sub>                                                                 |                                                                                  |       |      | 3     | cycle<br>s |

| fc(LPF)                  | Corner frequency of<br>internal low pass |                                                                                                 |                                                                                  | 26    | 35   | 58    | kHz        |

|                          | V <sub>(REF)</sub> voltage offset error  | f <sub>(DTRK)</sub> = 500kHz, duty = 50%                                                        |                                                                                  |       |      | ±10   | mV         |

| MODE SEL                 | ECTION                                   |                                                                                                 |                                                                                  |       |      |       |            |

| V <sub>T+(MODE)</sub>    | Mode input positive going threshold      |                                                                                                 |                                                                                  |       |      | 1.19  | V          |

| V <sub>T-(MODE)</sub>    | Mode input negative going threshold      |                                                                                                 |                                                                                  | 0.41  |      |       | V          |

| CURRENT                  | SENSE                                    |                                                                                                 |                                                                                  |       |      |       |            |

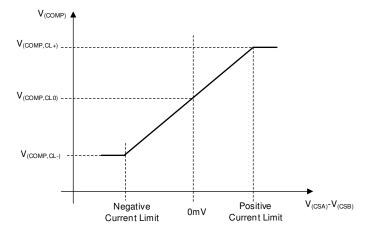

|                          | Positive peak current<br>limit threshold |                                                                                                 |                                                                                  | 38.5  | 50   | 58.5  | mV         |

|                          | Negative peak current<br>limit threshold |                                                                                                 |                                                                                  | -61.6 | -50  | -40.5 | mV         |

|                          | PSM entry threshold                      | PSM ENTRY = 10 %                                                                                |                                                                                  | 0.8   | 5.0  | 9.7   | mV         |

Typical values correspond to  $T_J$ =25°C. Minimum and maximum limits apply over  $T_J$ =-40°C to 125°C. Unless otherwise stated,  $V_{(BIAS)}$ =12 V

|                               | PARAMETER                                |                 |                                                             |                                                               | MIN   | TYP   | MAX   | UNIT |

|-------------------------------|------------------------------------------|-----------------|-------------------------------------------------------------|---------------------------------------------------------------|-------|-------|-------|------|

|                               | PSM entry threshold                      |                 | PSM ENTRY = 15 %                                            |                                                               | 3.3   | 7.5   | 11.2  | mV   |

| CURRENT                       | MONITOR/LIMITER                          |                 | 1 <u>.</u>                                                  |                                                               |       |       |       |      |

|                               | Current sense amplifier transconductance |                 | IMON_LIMITER_EN =<br>0b0                                    | $0 \text{ mV} \le \Delta V_{(\text{ISNS})} \le 50 \text{ mV}$ | 0.9   | 1     | 1.1   | mS   |

|                               | Offset voltage <sup>(1)</sup>            |                 | IMON_LIMITER_EN = 0b0                                       | T <sub>J</sub> = 25°C                                         |       |       | ±1    | mV   |

|                               | Current sense amplifier ba               | andwidth        |                                                             |                                                               | 1     | 2     |       | MHz  |

|                               |                                          |                 | IMON_LIMITER_EN =                                           | $\Delta V_{(IMON)} = 45 \text{ mV}$                           | 39    | 45    | 49.5  | μA   |

|                               | Output current IMONOUT                   |                 | 1 <u>-</u>                                                  | $\Delta V_{(IMON)} = 5 \text{ mV}$                            | 1     | 5     | 8.1   | μA   |

|                               | Current sense amplifier transconductance |                 | IMON_LIMITER_EN =<br>0b1                                    |                                                               | 170   | 200   | 220   | μS   |

| $\Delta V_{(ISNS)}$           | Current sense offset and to voltage      | threshold       | IMON_LIMITER_EN =<br>0b1                                    | T <sub>J</sub> = 25°C                                         | 49    | 50    | 51.7  | mV   |

|                               | ISNS pin input bias currer               | nts             | ISNSP = ISNSN = 12 V                                        |                                                               |       | 80    | 115   | μA   |

|                               |                                          | it boodroom     | $V_{(BIAS)} > 6.5V; I_{(IMONOUT)}$                          | $\Delta V = 50 mV$ ,referred to VCC                           |       | 300   | 500   | mV   |

|                               | IMONOUT negative output headroom         |                 | ) = $I_{(IMONOUT)} \times 0.975$<br>at $V_{(IMONOUT)} = 1V$ | $\Delta V = -50 \text{mV}$ , referred to GND                  |       | 320   | 500   | mV   |

| V <sub>T+</sub><br>(DIS,IMON) | Positive going threshold to disable IMON |                 | referred to VCC                                             |                                                               | 55    | 65    | 75    | %    |

| HICCUP MC                     | DDE PROTECTION                           |                 |                                                             |                                                               |       |       |       |      |

|                               | Hiccup mode on time                      |                 |                                                             |                                                               |       | 1     |       | ms   |

|                               | Hiccup mode off time                     |                 |                                                             |                                                               |       | 24    |       | ms   |

| ERROR AM                      | PLIFIER                                  |                 |                                                             |                                                               |       |       |       |      |

| V <sub>REF</sub>              | FB reference Voltage                     | FB<br>reference |                                                             |                                                               | 0.99  | 1     | 1.01  | V    |

|                               | FB reference Voltage                     |                 | forced V <sub>(SS)</sub> = 0.95 V                           |                                                               | 0.92  | 0.95  | 0.98  | V    |

|                               | FB pin leakage current                   |                 | V <sub>(FB)</sub> = 1 V                                     |                                                               |       |       | 60    | nA   |

|                               | Transconductance                         |                 |                                                             |                                                               |       | 600   |       | μS   |

|                               | Output resistance                        |                 |                                                             |                                                               | 13    | 96    |       | MΩ   |

|                               | COMP sourcing current                    |                 |                                                             |                                                               | 65    | 150   |       | uA   |

|                               | COMP sinking current                     |                 |                                                             |                                                               | 65    | 150   |       | uA   |

|                               | COMP clamp voltage                       |                 | V <sub>(FB)</sub> = 990 mV                                  |                                                               | 1.2   | 1.25  | 1.3   | V    |

|                               | COMP clamp voltage                       |                 | V <sub>(FB)</sub> = 1.01 V                                  |                                                               | 0.225 | 0.240 | 0.255 | V    |

|                               | Unity gain bandwidth                     |                 |                                                             |                                                               |       | 4.5   |       | MHz  |

| OVP                           | 1                                        | 1               |                                                             | 1                                                             |       |       |       | 1    |

| VT+(OVP)                      | Over-voltage rising thresh               | old             | FB rising reference to V <sub>REF</sub>                     |                                                               | 107   | 110   | 115   | %    |

| VT-(OVP)                      | Over-voltage falling thresh              | nold            | FB falling reference to V <sub>REF</sub>                    |                                                               | 101   | 105   | 109   | %    |

|                               | Over-voltage de-glitch time              |                 |                                                             |                                                               | 9     | 10    | 12.5  | μs   |

| VT+(OVP2)                     | Over-voltage 2 rising three              | shold           | V( <sub>VOUT)</sub> rising                                  |                                                               | 80.5  | 83.5  | 86    | V    |

|                               | Over-voltage 2 typical pro               | gramming        | V( <sub>VOUT)</sub> rising                                  |                                                               | 3.33  |       | 83.5  | V    |

| VT+(IVP)                      | Over-voltage rising thresh               | old             | V( <sub>VIN)</sub> rising                                   |                                                               | 80.5  |       | 86    | V    |

| nFLT                          |                                          |                 | ,                                                           |                                                               |       |       |       | I    |

|                               | nFLT pull-down switch on                 | resistance      | 1mA sinking                                                 |                                                               |       | 100   |       | Ω    |

|                               | Power good positive going                |                 | FB rising (reference to V <sub>R</sub>                      | FE)                                                           |       | 95    |       | %    |

|                               | Power good negative goir                 | -               | FB falling (reference to $V_{\rm F}$                        |                                                               |       | 90    |       | %    |

Typical values correspond to  $T_J$ =25°C. Minimum and maximum limits apply over  $T_J$ =-40°C to 125°C. Unless otherwise stated,  $V_{(BIAS)}$  =12 V

|                              | PARAMETER                                           |                                                                |                                                       |                             | MIN | TYP  | MAX  | UNIT |

|------------------------------|-----------------------------------------------------|----------------------------------------------------------------|-------------------------------------------------------|-----------------------------|-----|------|------|------|

|                              | nFLT off-state leakage                              |                                                                | V <sub>(nFLT)</sub> =5V                               |                             |     |      | 100  | nA   |

| t <sub>d(nFLT-PIN)</sub>     | nFLT pin reaction time                              |                                                                | Measured from a fault<br>event until nFLT goes lov    | N                           |     |      | 37   | μs   |

| MOSFET D                     | RIVER                                               |                                                                |                                                       |                             | I   |      |      |      |

| t <sub>r</sub>               | Rise time                                           | HG1, HG2,<br>LG1, LG2                                          | C <sub>G</sub> = 3.3nF                                |                             |     | 12   |      | ns   |

| t <sub>f</sub>               | Fall time                                           | HG1, HG2,<br>LG1, LG2                                          | C <sub>G</sub> = 3.3nF                                |                             |     | 12   |      | ns   |

|                              |                                                     | HOx from<br>High to Low<br>and LOx<br>from Low to<br>High      |                                                       | R <sub>(RT)</sub> = 14.7 kΩ |     | 19   |      | ns   |

| t.                           | Dead-time                                           | HOx from<br>Low to High<br>and LOx<br>from High<br>to Low      | $C_{G} = 3.3 nF$                                      |                             |     | 20.5 |      | ns   |

| t <sub>t</sub>               | Deau-ume                                            | HOx from<br>High to Low<br>and LOx<br>from Low to<br>High      |                                                       | R <sub>(RT)</sub> = 316 k Ω |     | 21.5 |      | ns   |

|                              |                                                     | HOx from<br>Low to High<br>and LOx<br>from High<br>to Low      |                                                       |                             |     | 23   |      | ns   |

|                              | Gate driver low side<br>PMOS on-resistance          | LO1, LO2                                                       | I <sub>(test)</sub> = 200 mA                          |                             |     | 1.6  |      | Ω    |

|                              | Gate driver high side<br>PMOS on-resistance         | HO1, HO2                                                       | I <sub>(test)</sub> = 200 mA                          |                             |     | 1.3  |      | Ω    |

|                              | Gate driver low side<br>NMOS on-resistance          | LO1, LO2                                                       | I <sub>(test)</sub> = 200 mA                          |                             |     | 0.6  |      | Ω    |

|                              | Gate driver high side<br>NMOS on-resistance         | HO1, HO2                                                       | I <sub>(test)</sub> = 200 mA                          |                             |     | 0.7  |      | Ω    |

| V <sub>TH-</sub><br>(BST_UV) | Negative going boot-strap                           |                                                                | $V_{(HBx)}$ - $V_{(SWx)}$ falling                     |                             | 2.4 | 2.8  | 3.1  | V    |

| V <sub>TH+</sub><br>(BST_UV) | Positive going boot-strap                           |                                                                | $V_{(HBx)}$ - $V_{(SWx)}$ rising                      |                             | 2.6 | 3    | 3.35 | V    |

| V <sub>TH+</sub><br>(BST_OV) | Positive going boot-strap<br>over-voltage threshold | Positive<br>going boot-<br>strap over-<br>voltage<br>threshold | $V_{(HBx)} - V_{(SWx)}$ rising,<br>I $_{(HBx)}$ =25uA |                             | 4.8 | 5.5  | 6.3  | V    |

| .,                           |                                                     |                                                                | referenced to VCC                                     |                             |     | 37   |      | %    |

| V <sub>TH</sub><br>(GATEOUT) | Low/High Side Gate drive<br>switching detection     | routput                                                        | referenced to V(HBx) -<br>V(SWx)                      |                             |     | 37   |      | %    |

| THERMAL                      | SHUTDOWN                                            |                                                                | 1                                                     |                             | I   |      |      |      |

| T <sub>T+J</sub>             | Thermal shutdown threshold                          | Thermal<br>shutdown<br>threshold                               | T <sub>J</sub> rising                                 |                             |     | 164  |      | °C   |

|                              | Thermal shutdown hysteresis                         | Thermal<br>shutdown<br>hysteresis                              |                                                       |                             |     | 15   |      | °C   |

Typical values correspond to  $T_J$ =25°C. Minimum and maximum limits apply over  $T_J$ =-40°C to 125°C. Unless otherwise stated,  $V_{(BIAS)}$ =12 V

| PARAMETER          |                         |                    | MIN    | TYP         | MAX    | UNI |

|--------------------|-------------------------|--------------------|--------|-------------|--------|-----|

| R2D INTE           | RFACE                   |                    |        |             |        |     |

|                    | Internal reference resi | tor                | 31.77  | 33          | 34.23  | kΩ  |

|                    | R2D setting<br>#0       |                    | 0      | 0.1         | kΩ     |     |

|                    | R2D setting<br>#1       | 0.4956<br>7        | 0.511  | 0.5263<br>3 | k۵     |     |

|                    |                         | R2D setting<br>#2  | 1.1155 | 1.15        | 1.1845 | k۵  |

|                    |                         | R2D setting<br>#3  | 1.8139 | 1.87        | 1.9261 | k۵  |

| External selection |                         | R2D setting<br>#4  | 2.6578 | 2.74        | 2.8222 | k۵  |

|                    |                         | R2D setting<br>#5  | 3.7151 | 3.83        | 3.9449 | k۵  |

|                    |                         | R2D setting<br>#6  | 4.9567 | 5.11        | 5.2633 | k۵  |

|                    | External selection      | R2D setting<br>#7  | 6.2953 | 6.49        | 6.6847 | k۵  |

| R <sub>CFG</sub>   | resistor resistance     | R2D setting<br>#8  | 8.0025 | 8.25        | 8.4975 | k۵  |

|                    |                         | R2D setting<br>#9  | 10.185 | 10.5        | 10.815 | k۵  |

|                    |                         | R2D setting<br>#10 | 12.901 | 13.3        | 13.699 | k۵  |

|                    |                         | R2D setting<br>#11 | 15.714 | 16.2        | 16.686 | k۵  |

|                    |                         | R2D setting<br>#12 | 19.885 | 20.5        | 21.115 | k۵  |

|                    |                         | R2D setting<br>#13 | 24.153 | 24.9        | 25.647 | k۵  |

|                    |                         | R2D setting<br>#14 | 29.197 | 30.1        | 31.003 | k۵  |

|                    |                         | R2D setting<br>#15 | 35.405 | 36.5        | 37.595 | k   |

(1) Zero Offset is determined by interpolation

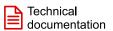

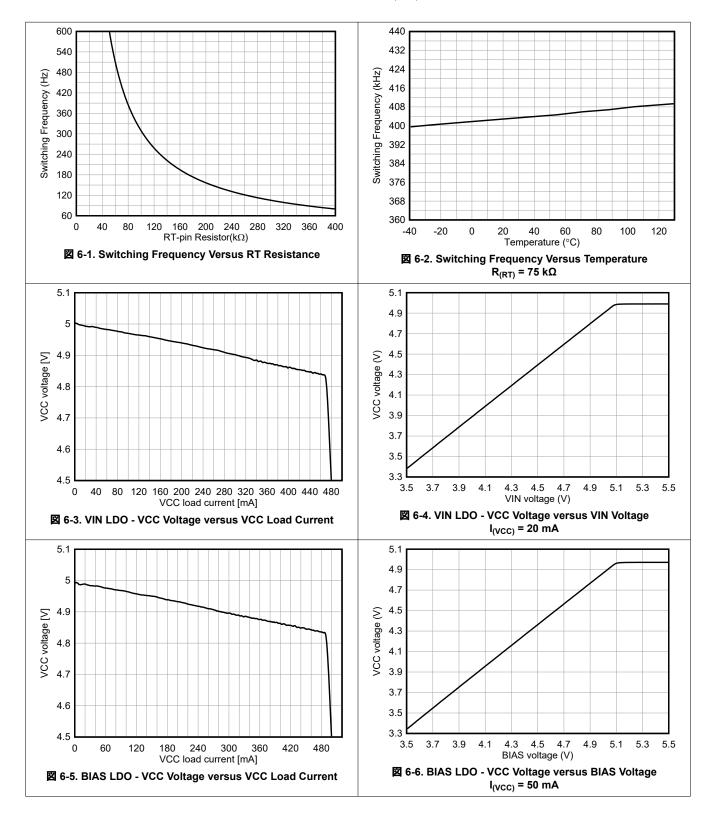

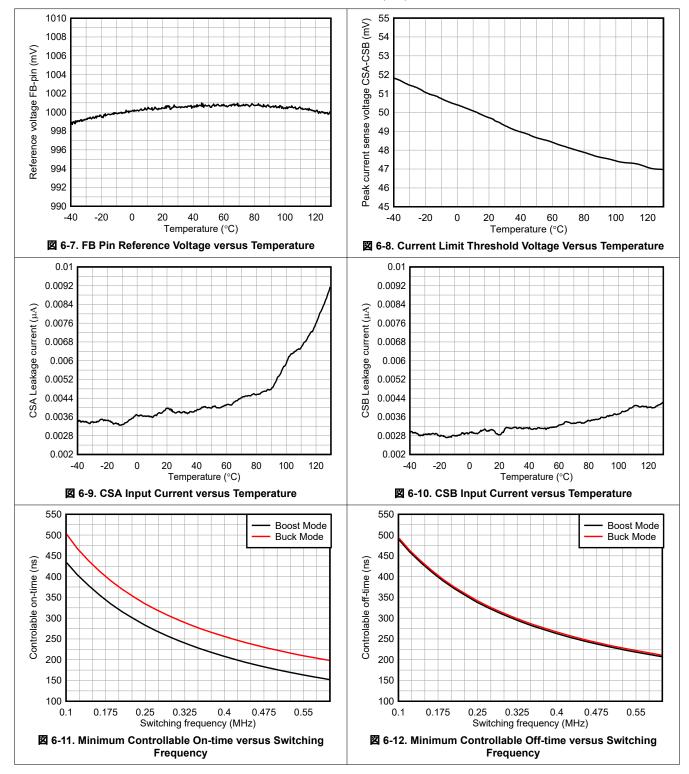

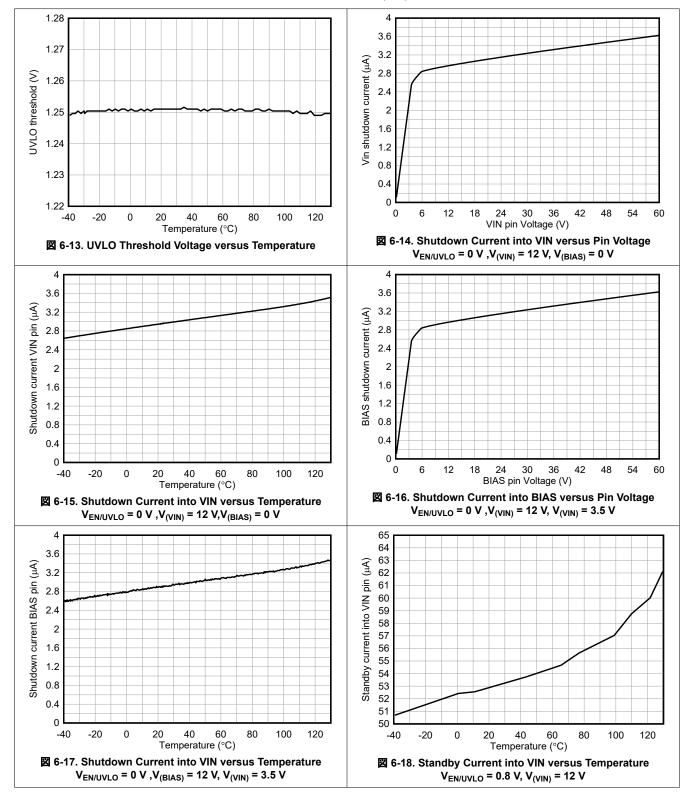

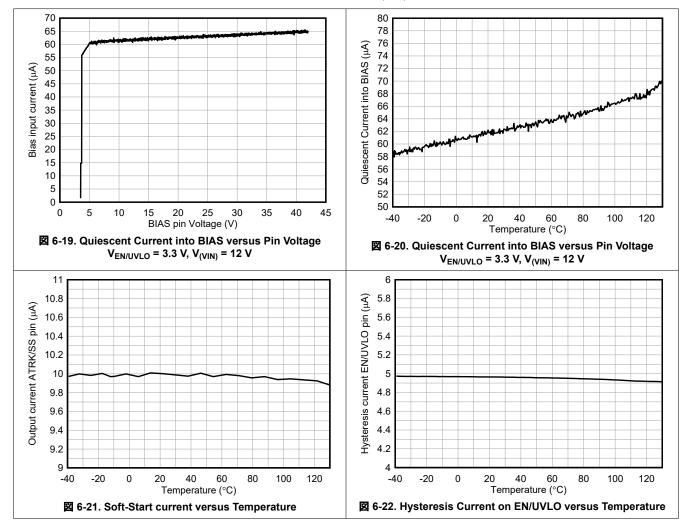

# 6.6 Typical Characteristics

# 6.6 Typical Characteristics (continued)

# 6.6 Typical Characteristics (continued)

# 6.6 Typical Characteristics (continued)

# 7 Parameter Measurement Information

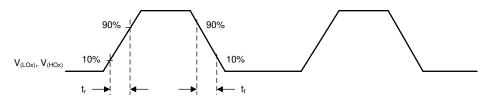

### 7.1 Gate Driver Rise Time and Fall Time

図 7-1. Timing Diagram Gate Driver, t<sub>r</sub>, t<sub>f</sub>

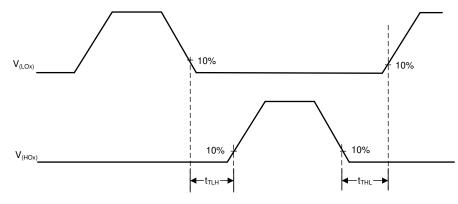

### 7.2 Gate Driver Dead (Transition) Time

図 7-2. Timing Diagram Gate Driver, tt

# 8 Detailed Description

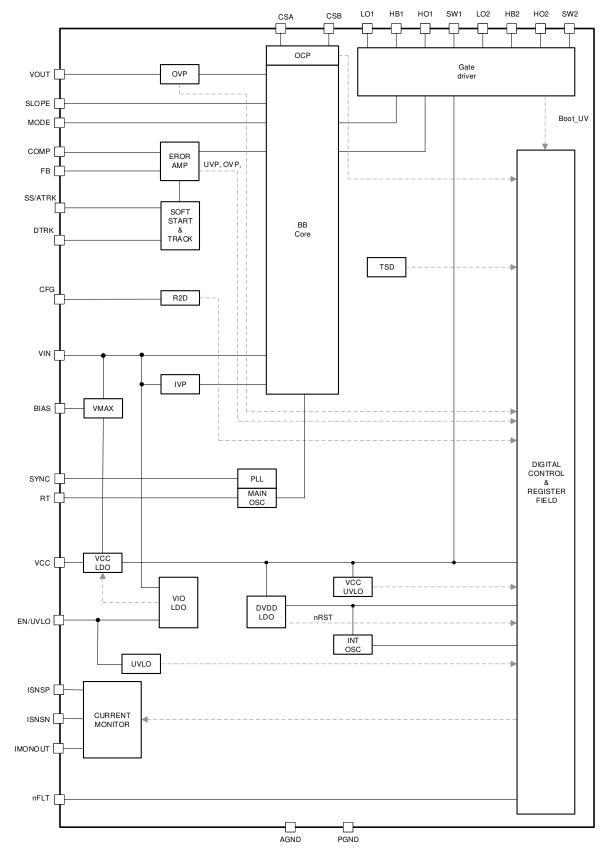

## 8.1 Overview

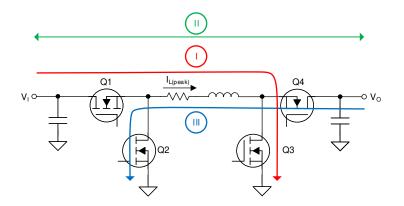

The LM5177 is a four switch buck-boost controller. The device provides a regulated output voltage if the input voltage is higher, equal, or lower than the adjusted output voltage.

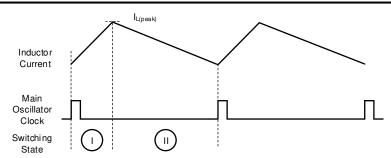

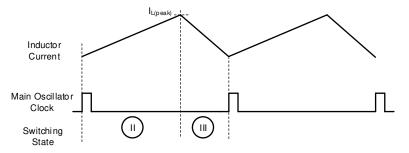

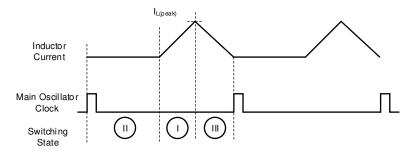

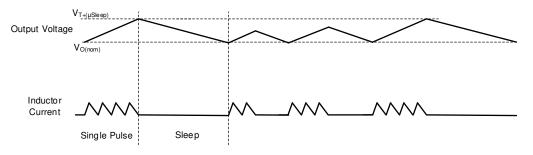

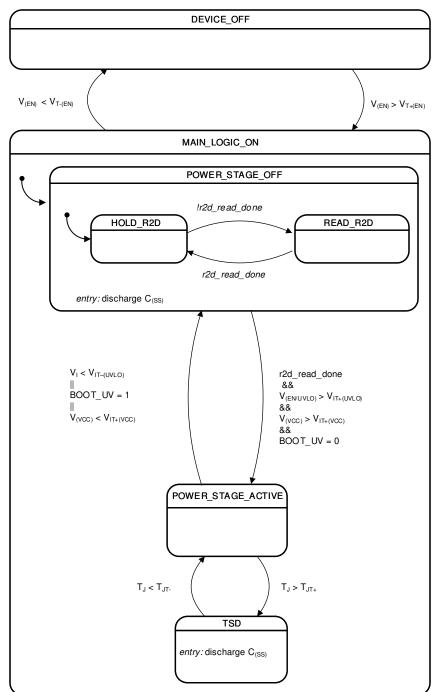

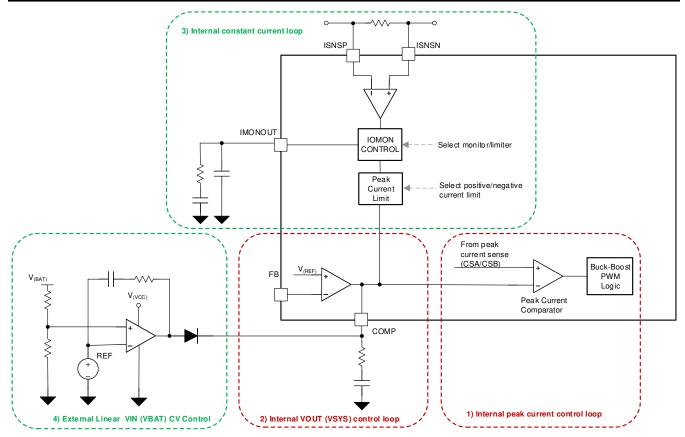

In power safe mode, the LM5177 supports superb efficiency over the full rage of the output current. The operation modes are on-the-fly pin-selectable during operation. The proprietary buck-boost modulation scheme also runs at a fixed switching frequency, which can be set through the RT/SYNC pin. The switching frequency remains constant during buck, boost, and buck-boost operation. The device maintains small mode transition ripple over all operating modes. Through the activation of the dual random spread spectrum operation, EMI mitigation is achievable at any time of the design process.

The integrated and optional average current monitor can help monitor or limit input and output current of the LM5177. This feature also supports charging backup power elements, like batteries with constant current (CC) and constant voltage (CV).