# LM65680、LM65660、LM65640 65V、8A/6A/4A、同期整流降圧 DC/DC コンバータ ファミリ、低 EMI の ZEN 1 スイッチャ技術、高い電力密度に最適化

## 1 特長

- 機能安全対応

- IEC 61508-2 システムの設計を支援するドキュメントを使用可能

- 多用途な同期整流降圧コンバータ ファミリ

- 広い入力電圧範囲: 3.5V ~ 65V

- 4A、6A、8A の出力電流オプション

- 0.8V ~ 60V の可変出力電圧、あるいは 3.3V または 5V の固定出力オプション

- 接合部温度: 150°C (最大値)

- 36ns の  $t_{ON(min)}$  により高い降圧変換を実現

- ZEN 1 スイッチャ技術

- CISPR 11 または 32 Class B 準拠を促進

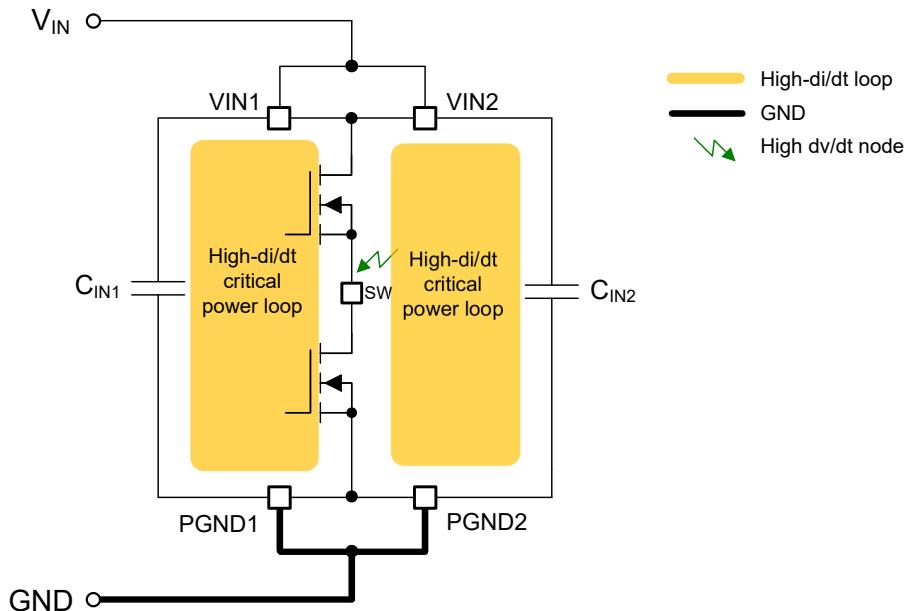

- 対称型のピン配置の設計で  $L_{LOOP}$  が最小の拡張 HotRod™ QFN (eQFN) パッケージ

- スペクトラム拡散 (DRSS) とスイッチングスルーレート制御によりピーク放射を低減

- スイッチング周波数: 300kHz ~ 2.2MHz

- 自動、FPWM、SYNC の動作

- 負荷電流範囲全体にわたる高効率

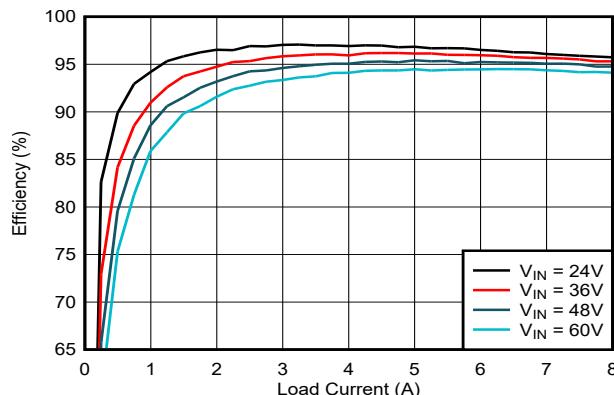

- 95% の効率 ( $V_{IN} = 48V$ ,  $V_{OUT} = 12V$ , 8A, 400kHz)

- より大きな電流を出力するためのマルチフェーズ スタッカブル

- BIAS オプション付き、デュアル入力 VCC サブレギュレータ

- VIN のスリープ時静止電流はわずか  $1.8\mu A$

- 隣接ピン短絡テストのために最適化されたピン配置設計と空間距離により信頼性向上

- VIN から PGND ピンへのクリアランス 1.1mm

- WEBENCH® Power Designer により、

LM65680/60/40 コンバータを使用するカスタム設計を作成

## 2 アプリケーション

- 産業用自動化、テストおよび測定機器

- 医療用画像処理システム、エネルギーインフラストラクチャ

- エンターテイメントシステム、ワイヤレスインフラストラクチャ

## 3 説明

LM65680/60/40 は、ZEN 1 テクノロジーのデバイスファミリーで供給される同期整流降圧 DC/DC コンバータで、低い EMI、高い電流密度、優れた電力変換効率を実現するよう設計されています。R<sub>DS(on)</sub> が低いパワー MOSFET を内蔵しており、3.5V ~ 65V の広い入力電圧範囲にわたって最大 8A の出力電流を供給できます。

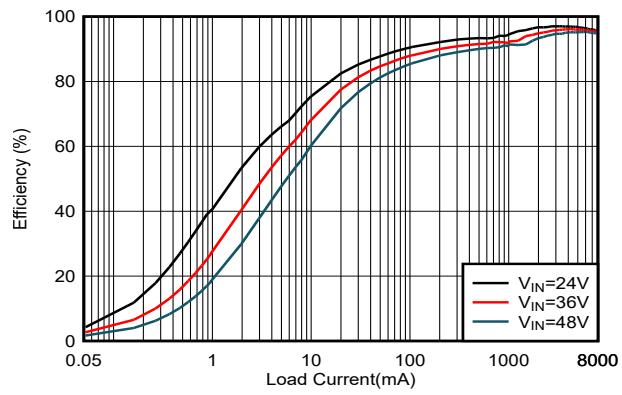

同期インターリーブによる位相スタッカブルである LM65680/60/40 のピーク電流モードアーキテクチャは、並列接続された相での高精度な電流共有をサポートしており、より大きな出力電流を供給できます。自動モードでは、軽負荷動作時の周波数フォールドバックが可能であるため、軽負荷時の効率が高く、無負荷時の入力電流はわずか  $2.2\mu A$  で、バッテリ駆動のシステムの動作時間を延長できます。

最小オン時間 36ns のハイサイドスイッチは大きな降圧率に対応できるため、24V または 48V の入力から低電圧レベルへの直接変換が可能になり、システムの設計コストと複雑性を低減できます。パッケージには、重要な電源ピンの間に複数の NC ピンが配置されており、これによって故障モード影響解析 (FMEA) の結果が改善されます。

### 製品情報

| 部品番号                   | パッケージ <sup>(1)</sup>    | 定格電流 <sup>(2)</sup> |

|------------------------|-------------------------|---------------------|

| LM65680                |                         | 8A                  |

| LM65660 <sup>(3)</sup> | RZY<br>(WQFN-FCRLF, 26) | 6A                  |

| LM65640 <sup>(3)</sup> |                         | 4A                  |

(1) 詳細については、セクション 11 を参照してください。

(2) 「関連製品」表を参照してください。

(3) 開発中製品の情報 (量産データではありません)。

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

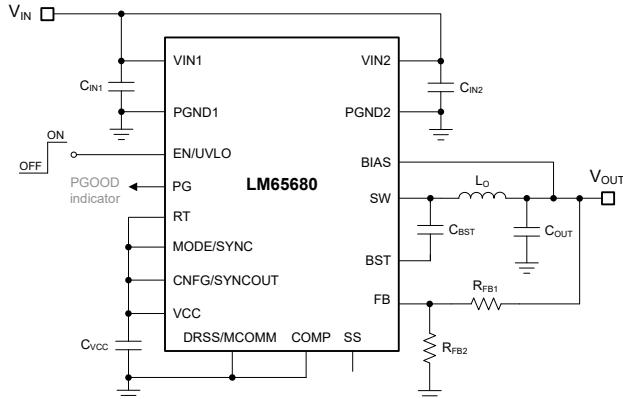

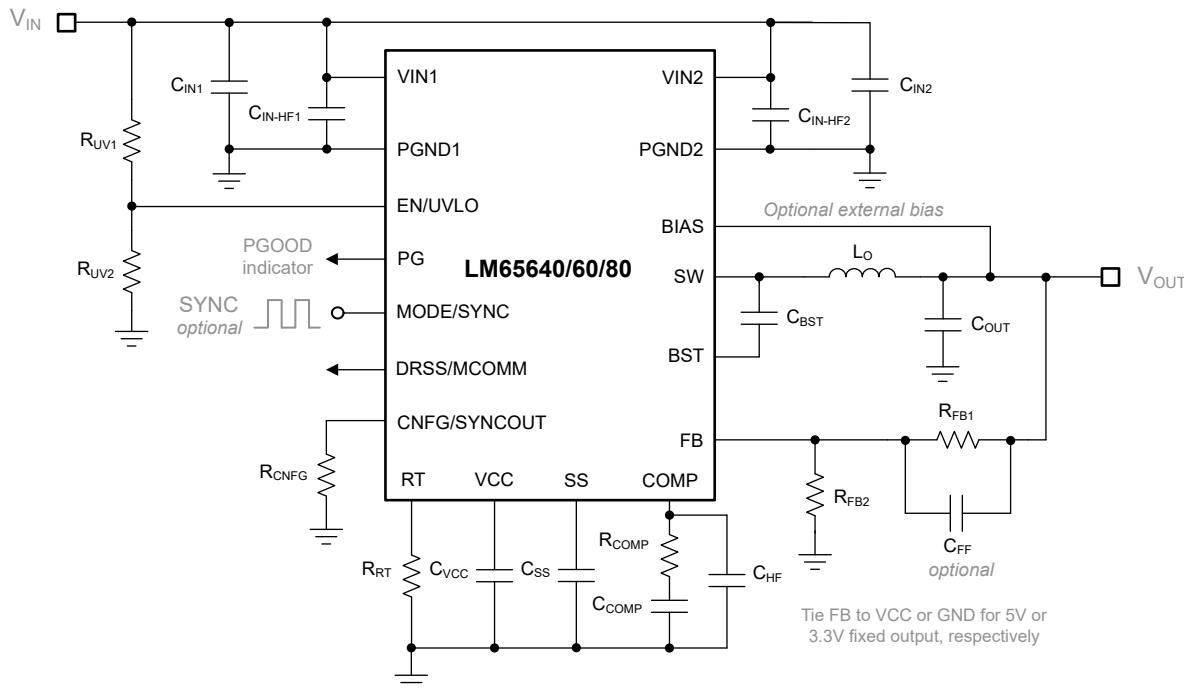

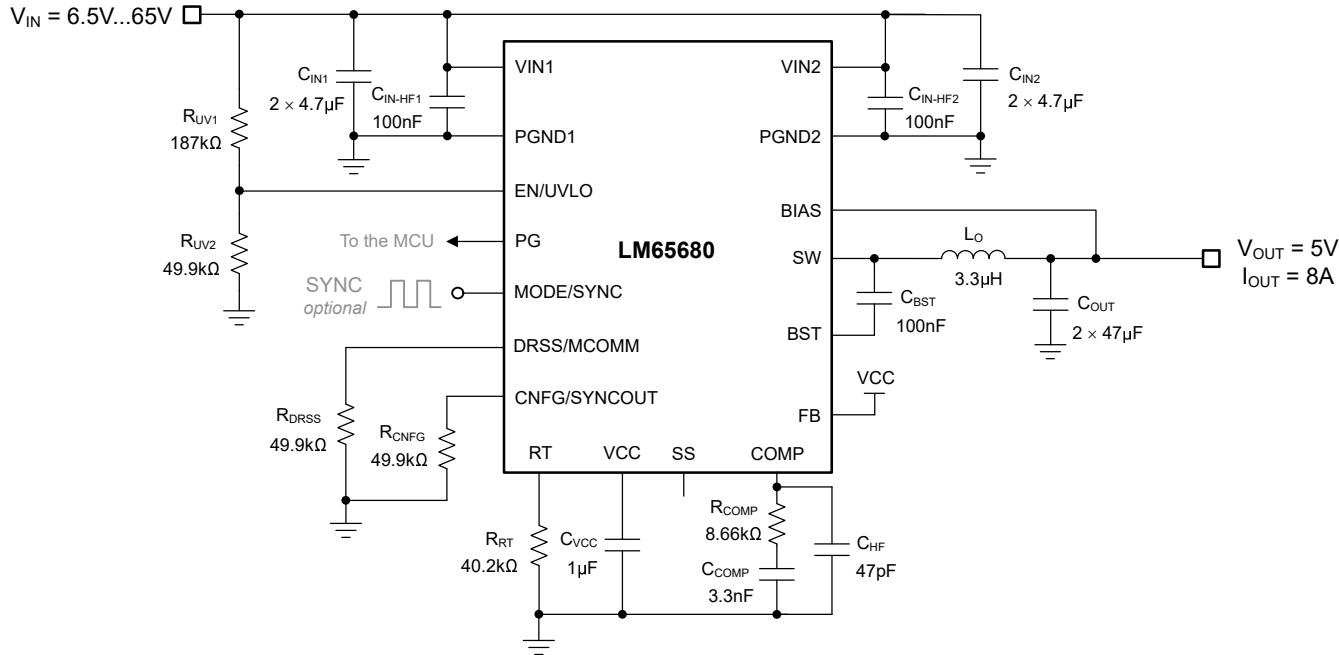

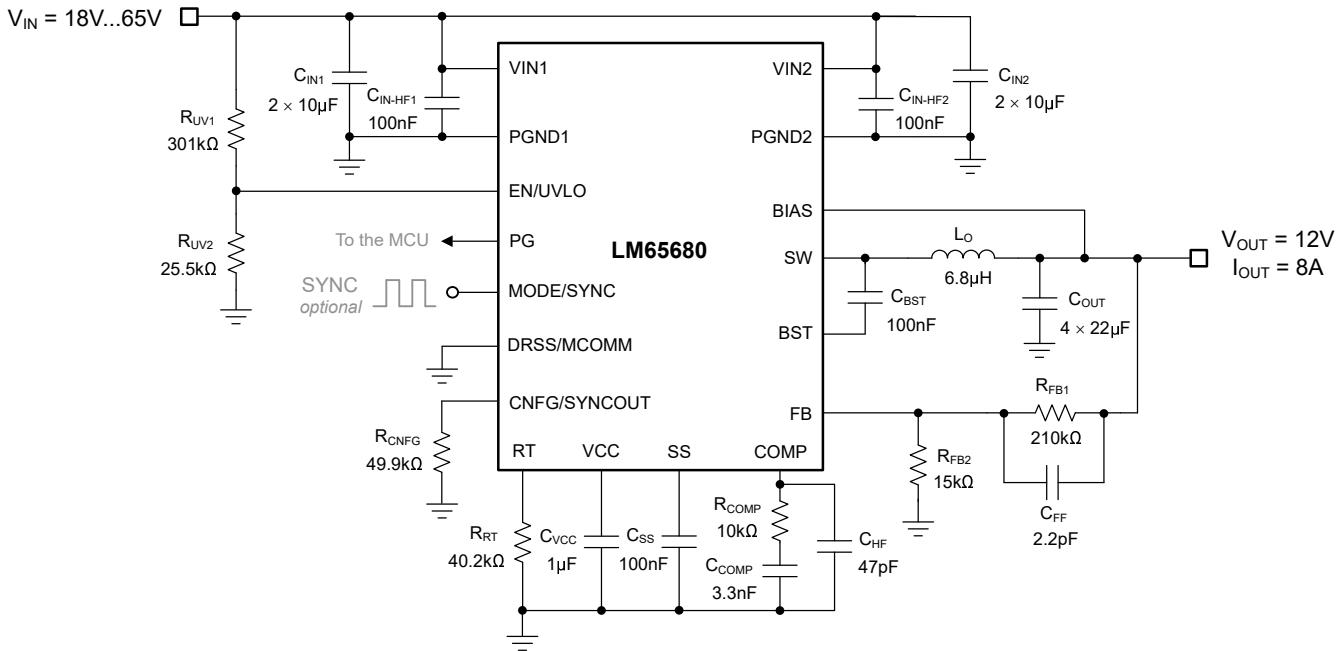

代表的な回路図

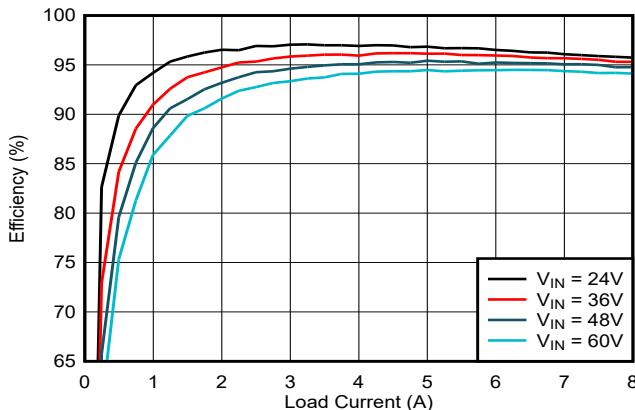

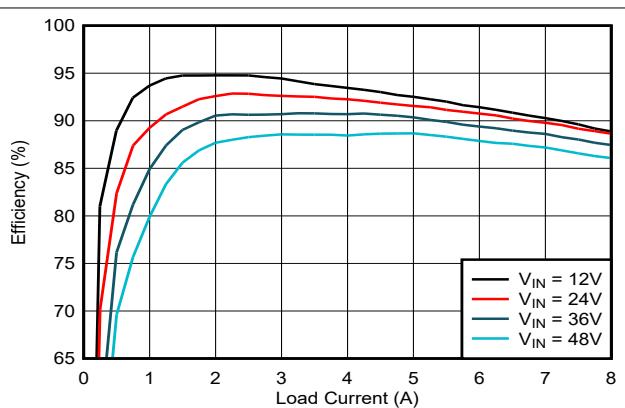

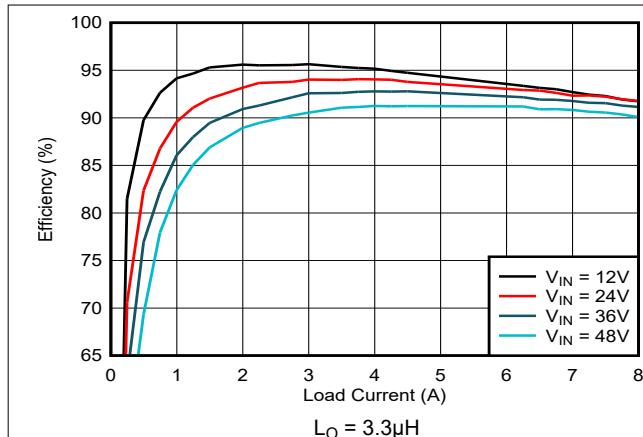

LM65680 の効率、V<sub>OUT</sub> = 12V、F<sub>SW</sub> = 400kHz

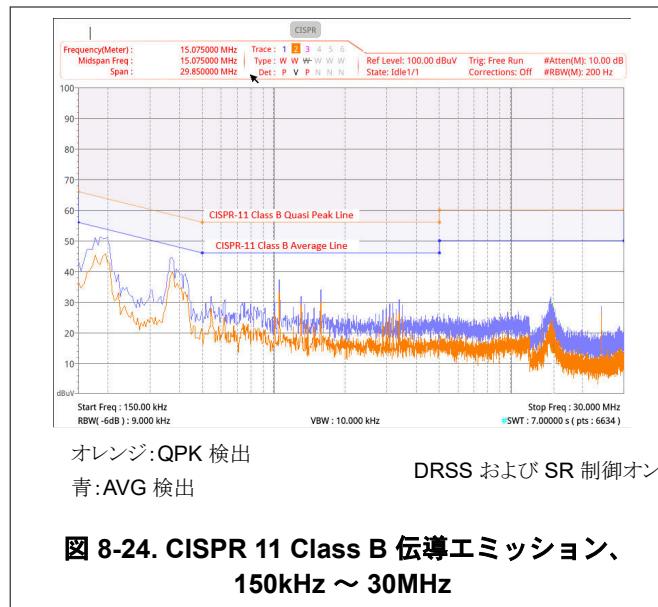

LM65680/60/40 には、CISPR 11 および CISPR 32 の排出要件への準拠を容易にする、複数の機能が搭載されています。まず、対称的なピン配置により入力コンデンサを最適に配置でき、電源ループの寄生インダクタンスの実効値を極めて低く抑えます。これにより、スイッチング損失が低減され、高入力電圧および高スイッチング周波数での EMI 性能が向上します。ピンで選択可能なスイッチノードのスルーレート制御機能により、高周波数領域での放射ノイズをさらに低減します。入力コンデンサのリップル電流と EMI フィルタのサイズを小さくするために、180° 位相シフトの SYNCOUT 信号を使用したインターリーブ動作は、カスケード、マルチチャネル、またはマルチフェーズの設計に最適です。スイッチング周波数は最高 2.2MHz まで抵抗により設定可能で、外部クロック ソースと同期できるため、ノイズに敏感な用途のビート周波数を除去できます。最後に、LM65680/60/40 は独自の EMI 低減機能であるデュアルランダム スペクトラム拡散 (DRSS) を採用しています。これは、低周波数の三角波変調と高周波数のランダム変調を組み合わせて、低周波数帯域と高周波数帯域にわたって動搖を軽減します。

LM65680/60/40 の追加機能には、最大接合温度 150°C での動作、故障報告および出力電圧モニタリング用のオープンドレイン式パワーグッド (PG) インジケータ、入力 UVLO 保護のための高精度イネーブル入力、事前バイアス負荷へのモノトニックな立ち上がり、VIN または BIAS から電源供給されるデュアル入力 VCC バイアス サブレギュレータ、ヒップモードの過負荷保護、自動復帰機能付きのサーマルシャットダウン保護が含まれます。

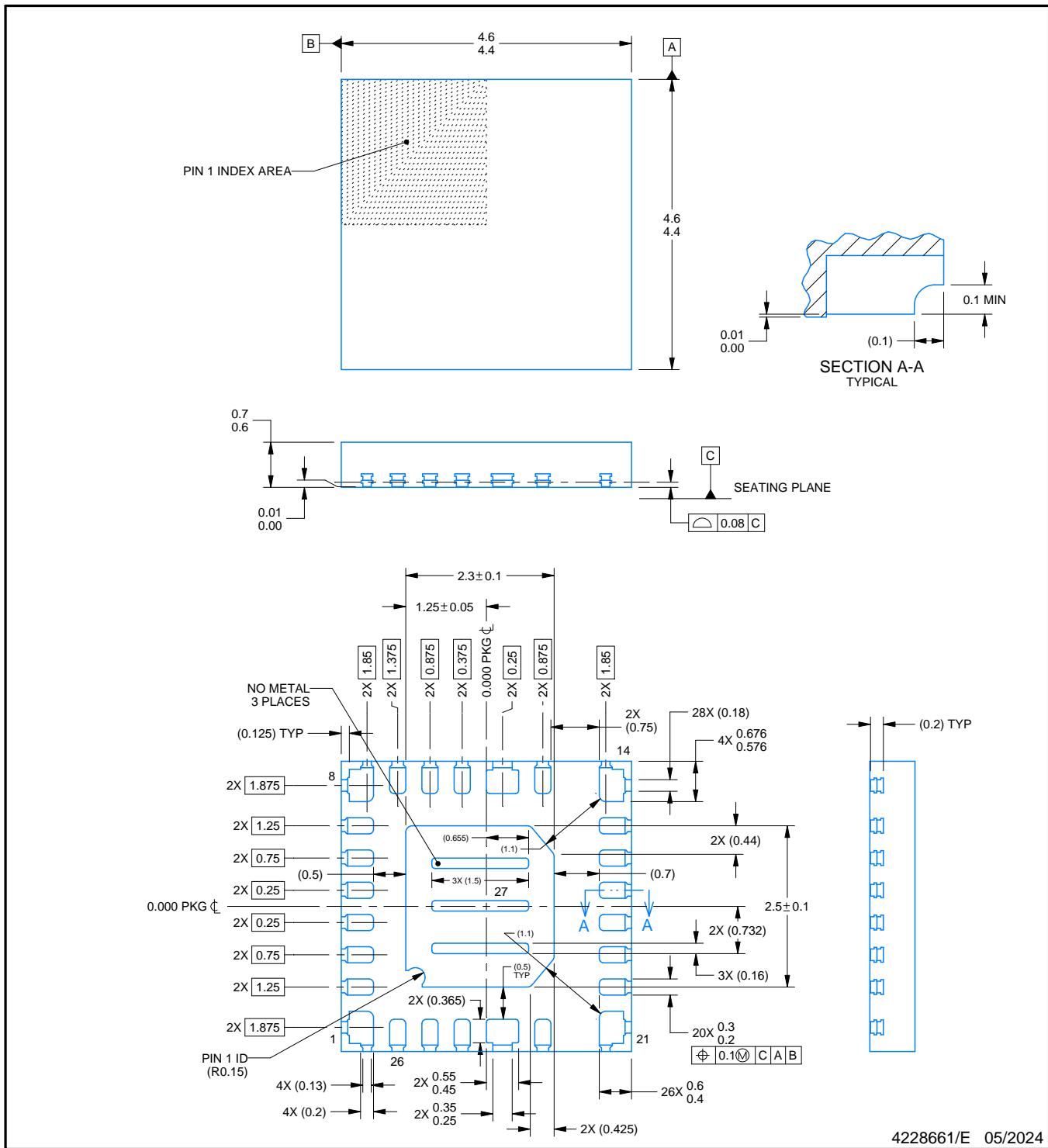

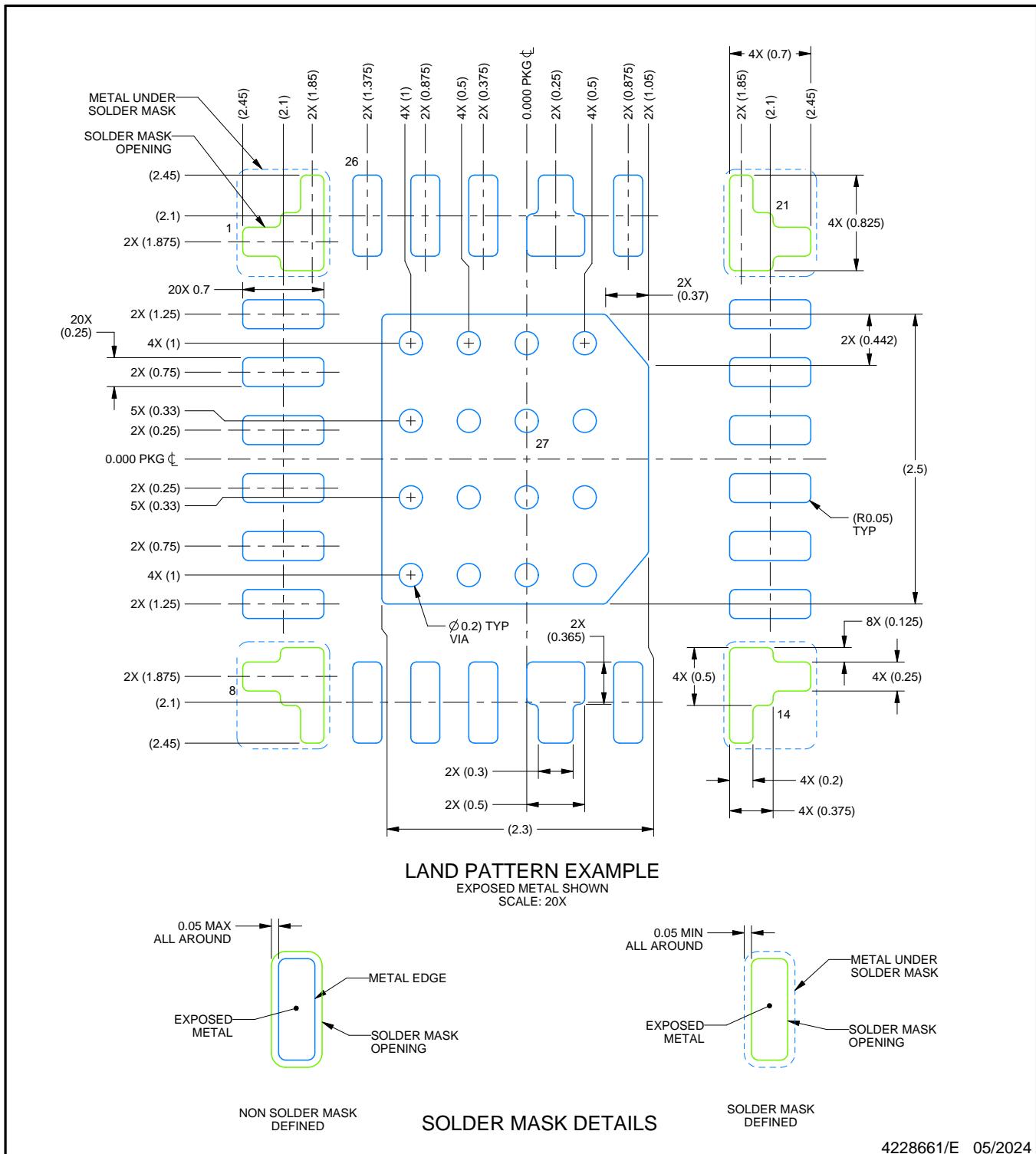

LM65680/60/40 は、4.5mm × 4.5mm の熱特性強化された 26 ピンの eQFN パッケージに搭載され、信頼性向上のためのピンクリアランスが追加されています。また、ウェッタブル フランクピンも搭載されており、製造現場で光学検査を容易に行えます。フリップチップ配線対応リードフレーム (FCRLF) パッケージ技術を採用した LM65680/60/40 は、実用電流能力、長期信頼性、およびコスト面での利点を活かし、高電力密度を要求するアプリケーションを対象としています。広い入力電圧範囲、低い静止電流消費、高温での動作、サイクルごとの電流制限、低い EMI シグネチャ、小型設計サイズにより、堅牢性と耐久性の強化向上が求められるアプリケーションに最適なポイントオブ ロード レギュレータ デザインを実現できます。

## 目次

|                          |    |                        |    |

|--------------------------|----|------------------------|----|

| 1 特長                     | 1  | 7.4 デバイスの機能モード         | 29 |

| 2 アプリケーション               | 1  | 8 アプリケーションと実装          | 30 |

| 3 説明                     | 1  | 8.1 アプリケーション情報         | 30 |

| 4 関連製品                   | 4  | 8.2 代表的なアプリケーション       | 36 |

| 5 ピン構成および機能              | 5  | 8.3 設計のベスト プラクティス      | 54 |

| 5.1 ウエッタブル フランク          | 7  | 8.4 電源に関する推奨事項         | 54 |

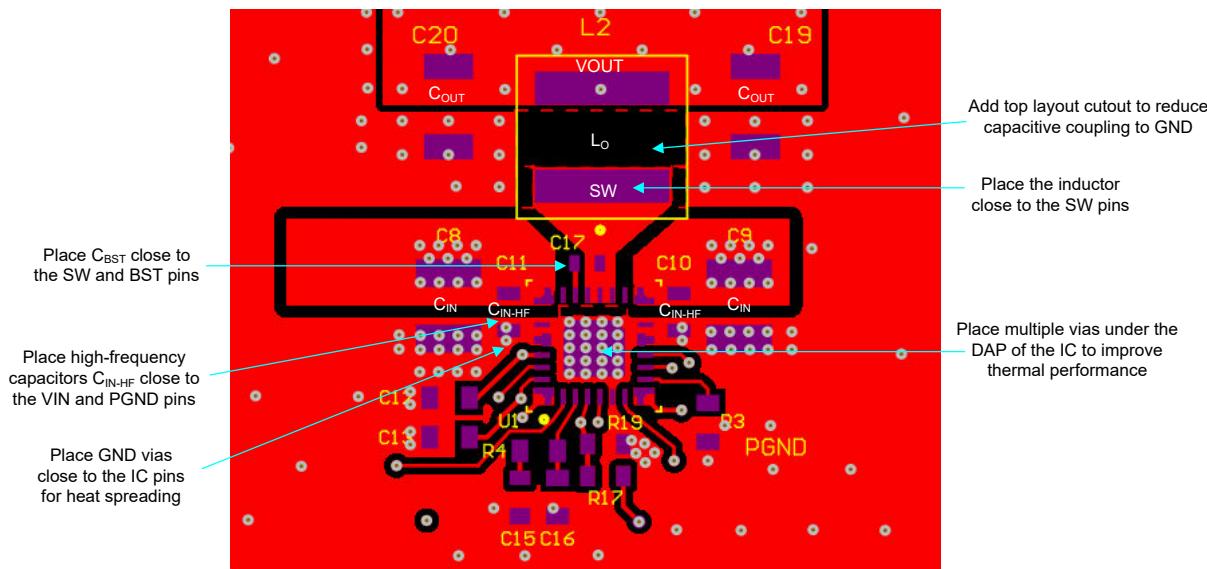

| 5.2 クリアランスと FMEA のピン配置設計 | 7  | 8.5 レイアウト              | 56 |

| 6 仕様                     | 8  | 9 デバイスおよびドキュメントのサポート   | 59 |

| 6.1 絶対最大定格               | 8  | 9.1 デバイス サポート          | 59 |

| 6.2 ESD 定格               | 8  | 9.2 ドキュメントのサポート        | 59 |

| 6.3 推奨動作条件               | 8  | 9.3 ドキュメントの更新通知を受け取る方法 | 60 |

| 6.4 熱に関する情報              | 9  | 9.4 サポート・リソース          | 60 |

| 6.5 電気的特性                | 9  | 9.5 商標                 | 61 |

| 6.6 代表的特性                | 13 | 9.6 静電気放電に関する注意事項      | 61 |

| 7 詳細説明                   | 17 | 9.7 用語集                | 61 |

| 7.1 概要                   | 17 | 10 改訂履歴                | 61 |

| 7.2 機能ブロック図              | 18 | 11 メカニカル、パッケージ、および注文情報 | 62 |

| 7.3 機能説明                 | 19 |                        |    |

## 4 関連製品

表 4-1. 発注型番

| 一般型番                   | 発注用製品型番      | 入力電圧範囲     | 定格電流 | TI の機能安全の分類 <sup>(2)</sup> | IBB 用レベルシフタ |

|------------------------|--------------|------------|------|----------------------------|-------------|

| LM65680                | LM65680RZYR  | 3.5V ~ 65V | 8A   | 機能安全対応                     | なし          |

| LM65660 <sup>(1)</sup> | LM65660RZYR  |            | 6A   |                            |             |

| LM65640 <sup>(1)</sup> | LM65640RZYR  |            | 4A   |                            |             |

| LM68680 <sup>(1)</sup> | LM68680FRZYR | 3.5V ~ 65V | 8A   | SIL 2 機能安全準拠               | なし          |

| LM68660 <sup>(1)</sup> | LM68660FRZYR |            | 6A   |                            |             |

| LM67680 <sup>(1)</sup> | LM67680RZYR  | 3.8V ~ 65V | 8A   | 機能安全対応                     | あり          |

| LM67660 <sup>(1)</sup> | LM67660RZYR  |            | 6A   |                            |             |

| LM67640 <sup>(1)</sup> | LM67640RZYR  |            | 4A   |                            |             |

(1) 開発中製品の情報(量産データではありません)。詳細については、TIにお問い合わせください。

(2) TI の機能安全分類(開発プロセス、分析レポート、診断の説明)については、[機能安全ホームページ](#)をご覧ください。

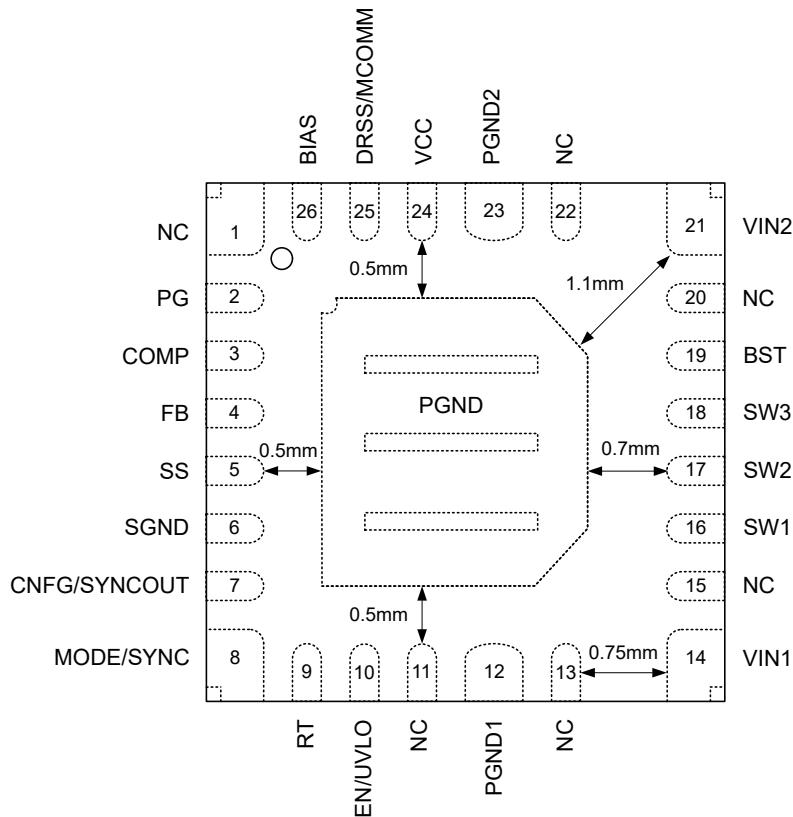

## 5 ピン構成および機能

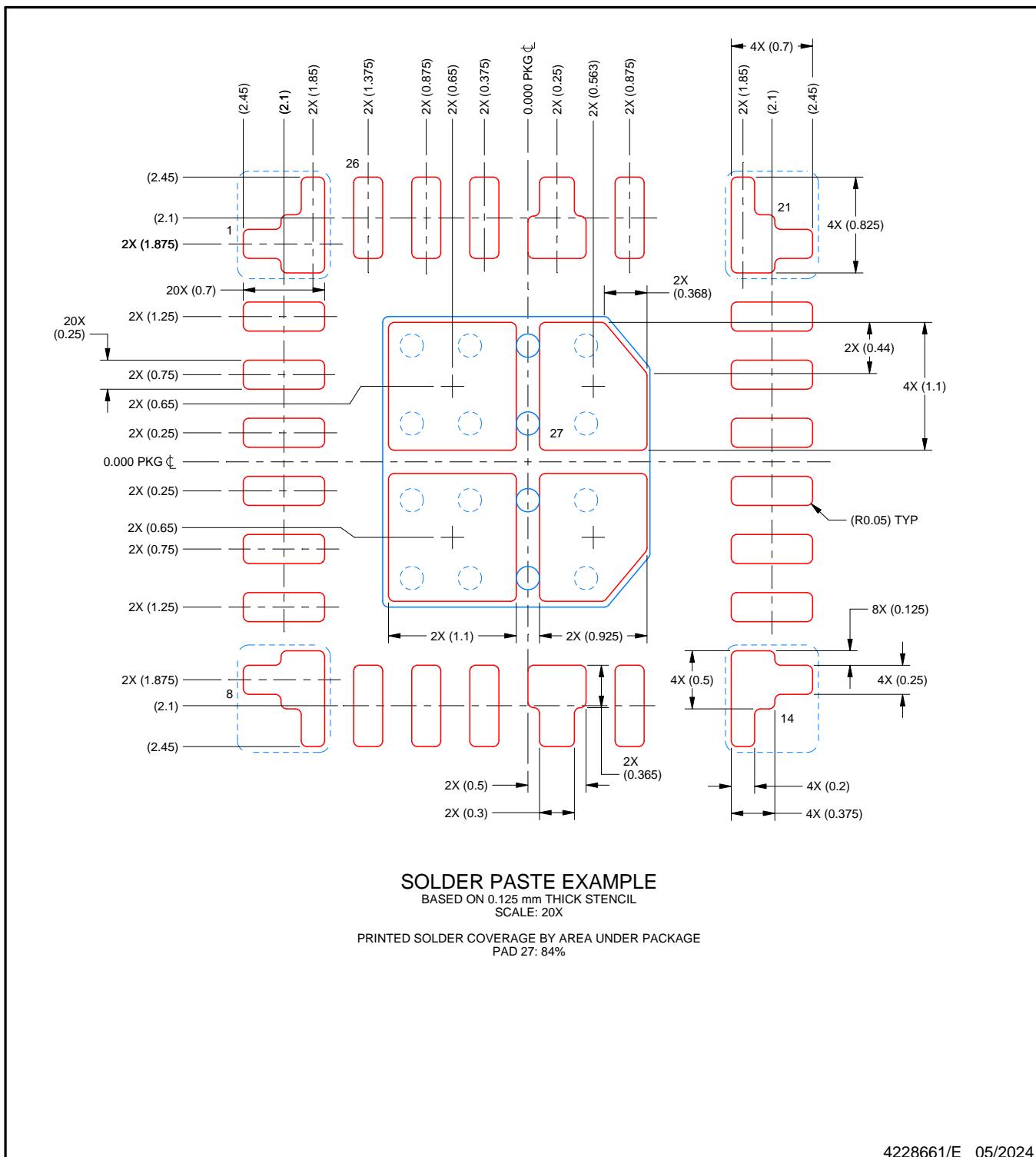

図 5-1. RZY 26 ピン WQFN-FCRLF パッケージ (上面図)

表 5-1. ピンの機能

| ピン           |    | タイプ <sup>(1)</sup> | 説明                                                                                                                                                                                                           |

|--------------|----|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称           | 番号 |                    |                                                                                                                                                                                                              |

| NC           | 1  | -                  | 接続の無いピンオープンのままにします。                                                                                                                                                                                          |

| PG           | 2  | O                  | パワー グッド出力ピン。PG はオープンドレイン出力で、出力電圧が指定されたレギュレーション ウィンドウの範囲外である場合に Low になります。                                                                                                                                    |

| COMP         | 3  | A                  | 外部補償ピン。COMP は相互コンダクタンス エラー アンプの出力です。使用する場合は、COMP ピンと PGND との間に補償回路を接続します。使用しない場合は、COMP を PGND に接続します。                                                                                                        |

| FB           | 4  | A                  | フィードバックピン。VOUT と PGND との間に抵抗分割器を接続して、出力電圧の設定点を 0.8V ~ 60V の間に設定するか。FB を VCC または PGND に接続すると、それぞれ 5V または 3.3V の固定出力電圧を構成できます。FB のレギュレーション電圧は 0.8V です。                                                         |

| SS           | 5  | A                  | ソフトスタート ランプのプログラミングピン。SS がオープンのままになっている場合、内部ソフトスタート回路によって、FB リファレンス電圧がゼロから最大値まで 5.3ms で上昇します。SS と PGND との間にコンデンサを接続し、ソフトスタート時間をより高い値に設定します。                                                                  |

| SGND         | 6  | G                  | システム GND ピン。システム グラウンドに接続します。                                                                                                                                                                                |

| CNFG/SYNCOUT | 7  | I/O                | 設定ピン。CNFG/SYNCOUT は、デバイスをプライマリ (1 相または 2 相動作) またはセカンダリ (2 相動作) に設定し、内部 (1 相動作のみ) または外部補償 (1 相または 2 相動作) を選択します。2 相動作のプライマリとして構成されているとき、このピンはスタートアップ後に SYNCOUT ピンになります。                                       |

| MODE/SYNC    | 8  | I                  | MODE および同期入力ピン。MODE/SYNC を PGND に接続するか、Low に駆動して、自動モードで動作させます。MODE/SYNC を VCC に接続するか、High に駆動するか、同期クロック信号を送信して FPWM モードで動作させます。外部クロックに同期する場合、RT ピンを使用して内部周波数を同期周波数に近い値に設定することで、外部クロックがオン / オフされたときの動揺を回避します。 |

表 5-1. ピンの機能(続き)

| ピン         |    | タイプ <sup>(1)</sup> | 説明                                                                                                                                                                                                                   |

|------------|----|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称         | 番号 |                    |                                                                                                                                                                                                                      |

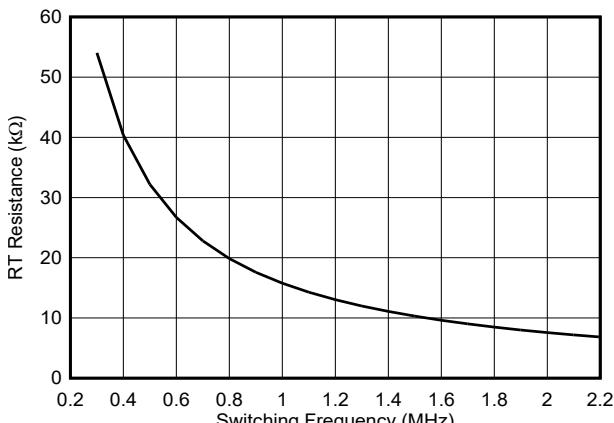

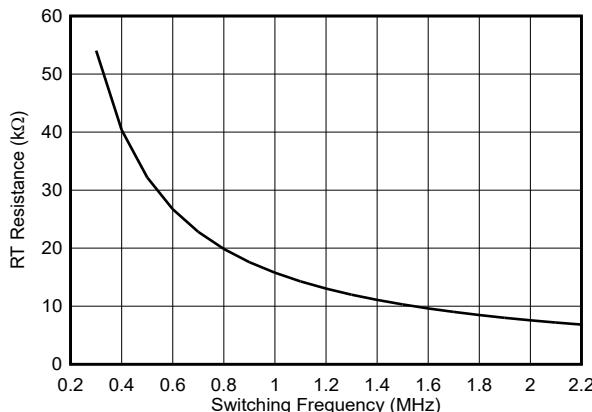

| RT         | 9  | A                  | スイッチング周波数のプログラミング用ピン。スイッチング周波数を 300kHz～2.2MHz に設定するため、6.81kΩ～54.2kΩ の値の抵抗を介して RT を PGND に接続します。400kHz または 2.2MHz の固定周波数動作の場合は、それぞれ VCC または PGND に接続します。RT ピンをオープンのままにしないでください。                                       |

| EN/UVLO    | 10 | I                  | 高精度イネーブルピン。EN/UVLO を High または Low に駆動すると、それぞれデバイスをイネーブルまたはディセーブルにできます。EN/UVLO は VIN に直接接続できます。入力電圧 UVLO を調整可能にするには、VIN から抵抗分割器とともに EN/UVLO を使用します。EN/UVLO をオープンのままにしないでください。                                         |

| NC         | 11 | –                  | 接続の無いピンオープンのままにします。                                                                                                                                                                                                  |

| PGND1      | 12 | G                  | 内部ローサイド MOSFET への電源グランド。このピンを、システムグランド。PGND2 との間に低インピーダンス接続を確立します。VIN1 と PGND1 との間に高品質のバイパスコンデンサを接続します。                                                                                                              |

| NC         | 13 | –                  | 接続の無いピンオープンのままにし、VIN1 ピンと PGND1 ピンとの間の空間距離を 1mm に維持します。VIN1 と PGND1 の間の空間距離が 0.75mm で、システムのピンの空間距離要件が満たされなければ、NC を PGND1 に接続できます。                                                                                    |

| VIN1       | 14 | P                  | レギュレータへの入力電源。VIN1 と PGND1 との間に高品質のバイパスコンデンサを接続します。VIN2 との間に低インピーダンス接続を確立します。                                                                                                                                         |

| NC         | 15 | –                  | 接続の無いピンフローティングにし、VIN1 と SW1 の間の間隔を 0.5mm に維持します。                                                                                                                                                                     |

| SW1        | 16 |                    |                                                                                                                                                                                                                      |

| SW2        | 17 | P                  | デバイスのスイッチ ピンとレギュレータのスイッチ ノード。電力段インダクタに接続します。                                                                                                                                                                         |

| SW3        | 18 |                    |                                                                                                                                                                                                                      |

| BST        | 19 | P                  | ハイサイド ドライバの電源レール。SW と BST の間に 100nF コンデンサを接続します。SW が Low の間は、内部ダイオードによってコンデンサが充電されます。                                                                                                                                |

| NC         | 20 | –                  | 接続の無いピンフローティングにし、VIN2 と BST との間の間隔を 0.5mm を維持します。                                                                                                                                                                    |

| VIN2       | 21 | P                  | レギュレータへの入力電源。VIN2 と PGND2 との間に高品質のバイパスコンデンサを接続します。VIN1 との間に低インピーダンス接続を確立します。                                                                                                                                         |

| NC         | 22 | –                  | 接続の無いピンオープンのままにし、VIN2 ピンと PGND2 ピンとの間の空間距離を 1mm に維持します。VIN2 と PGND2 の間の空間距離が 0.75mm で、システムのピンの空間距離要件が満たされなければ、NC を PGND2 に接続できます。                                                                                    |

| PGND2      | 23 | G                  | 内部ローサイド MOSFET への電源グランド。システムグランドに接続します。PGND1 との間に低インピーダンス接続を確立します。VIN2 と PGND2 との間に高品質のバイパスコンデンサを接続します。                                                                                                              |

| VCC        | 24 | P                  | 内部電圧レギュレータ出力。内部制御回路への電源として使用されます。VCC と PGND との間に高品質の 1μF コンデンサを接続します。VCC はいずれの外部負荷にも接続しないでください。                                                                                                                      |

| DRSS/MCOMM | 25 | I/O                | デュアル ランダム スペクトラム拡散機能 (DRSS) 選択ピン。使用可能な DRSS オプションについては、 <a href="#">デュアル ランダム スペクトラム拡散機能 (DRSS)</a> を参照してください。2 相動作に構成されている場合、DRSS/MCOMM はプライマリ デバイスとセカンダリ デバイスとの間の MODE 通信ピンになります。プライマリとセカンダリの DRSS/MCOMM ピンを接続します。 |

| BIAS       | 26 | P                  | 内部電圧レギュレータへの入力。3.3V または 5V の固定出力構成の場合、出力電圧検出のために BIAS を V <sub>OUT</sub> ノードに接続します。可変出力構成の場合、BIAS を V <sub>OUT</sub> ノードに接続するか、3.3V～30V の外部バイアス電源に接続します。出力電圧が 30V よりも高く、外部バイアス電源が利用できない場合、BIAS を PGND に接続します。        |

| PGND       | –  | G                  | 露出した PGND パッド。PCB 上のシステム GND に接続します。このパッドはデバイスの主要な放熱パスです。PCB 上の大きな銅のエリアに半田付けすることで、パッドをヒートシンクに使用します。サンプル基板レイアウトで推奨されているように、できるだけ多くのサーマルビアを実装することで、パッケージの熱抵抗を減らし、放熱性能を向上できます。                                          |

(1) P = 電源、G = グランド、A = アナログ、I = 入力、O = 出力。

## 5.1 ウェッタブル フランク

高い信頼性と堅牢性の要件を満たすには、通常は組み立て後に 100% の自動外観検査 (AVI) を行う必要があります。標準的なクワッド フラットのリードなし (QFN) パッケージでは、はんだ付け可能な部分や露出したピンと端子は外側から容易に視認できません。そのため、パッケージとプリント回路基板 (PCB) が確実にはんだ付けされているかどうかを視覚的に確認することは困難です。ウェッタブル フランク プロセスは、鉛フリーなパッケージにおける側面リード ウェットの問題を解決するために開発されました。LM65680/60/40 は、26 ピンの Enhanced HotRod WQFN パッケージと、ディンプル ウェッタブル フランクを使用して組み立てられており、製造時に側面リードの半田検査を行うことができます。はんだ付け可能性を視覚的に示すことで、検査時間を短縮し、製造コストを削減できます。

## 5.2 クリアランスと FMEA のピン配置設計

図 5-1 に示すように、LM65680/60/40 のピン配置は慎重に設計されており、高電圧ピン (VIN、SW、BST) とグランド (PGND) との間に 0.7mm 以上の空間距離を確保して、IPC-2221B と IPC-9592B の外部導体空間距離ルールを満たしています。VIN1 および VIN2 から PGND DAP までの空間距離は 1.1mm です。SW1、SW2、SW3、BST から PGND DAP までの空間距離は 0.7mm です。また、VIN1 と PGND1、VIN2 と PGND2、VIN2 と BST、BIAS と PG は、それぞれ NC (未接続) ピンにより区切られています。

また、ピン配置は、より厳格な品質、**安全性**、信頼性の要件を持つ重要なアプリケーション用に設計されています。FMEA ピン (障害モード影響の解析) の観点から見ると、検討される代表的な障害シナリオには、グランドへの短絡、入力電源 (VIN) への短絡、隣接ピンへの短絡、ピンの開放が含まれます。これらの障害は IC 外部に適用されるものと見なされ、IC レベルの信頼性障害ではなく基板レベルの障害に割り当てられます。このような障害の発生源の例には、ピン間の短絡を引き起こす浮遊導電性フィラメントや開放回路が生じる基板製造上の欠陥があります。

## 6 仕様

### 6.1 絶対最大定格

動作時接合部温度の推奨動作範囲である  $-40^{\circ}\text{C} \sim 150^{\circ}\text{C}$  にわたって (特に記述のない限り)。<sup>(1)</sup>

|                  |                        | 最小値  | 最大値                    | 単位                 |

|------------------|------------------------|------|------------------------|--------------------|

| 入力電圧             | VIN から PGND へ          | -0.3 | 72                     | V                  |

|                  | EN/UVLO から PGND へ      | -0.3 | 72                     | V                  |

|                  | RT から PGND             | -0.3 | 72                     | V                  |

|                  | DRSS/MCOMM から PGND へ   | -0.3 | 40                     | V                  |

|                  | BIAS から PGND へ         | -0.3 | 40                     | V                  |

|                  | CNFG/SYNCOUT から PGND へ | -0.3 | 5.5                    | V                  |

| 出力電圧             | SW～PGND                | -0.6 | $\text{V}_{\text{IN}}$ | V                  |

|                  | PG から PGND             | -0.3 | 40                     | V                  |

|                  | BST から SW へ            | -0.3 | 5.5                    | V                  |

|                  | VCC から PGND へ          | -0.3 | 5.5                    | V                  |

| $T_J$            | 動作時接合部温度               | -40  | 150                    | $^{\circ}\text{C}$ |

| $T_{\text{stg}}$ | 保存温度                   | -65  | 150                    | $^{\circ}\text{C}$ |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。絶対最大定格は、これらの条件において、または [セクション 6.3](#) に示された値を超える他のいかなる条件でも、デバイスが正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

### 6.2 ESD 定格

|                    |      |                                                           | 値          | 単位 |

|--------------------|------|-----------------------------------------------------------|------------|----|

| $V_{(\text{ESD})}$ | 静電放電 | 人体モデル (HBM) ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>      | $\pm 2000$ | V  |

|                    |      | デバイス帯電モデル (CDM)、ANSI/ESDA/JEDEC JS-002 に準拠 <sup>(2)</sup> | $\pm 750$  | V  |

- (1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

(2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

### 6.3 推奨動作条件

動作時接合部温度の推奨範囲である  $-40^{\circ}\text{C} \sim 150^{\circ}\text{C}$  にわたって (特に記述のない限り)。<sup>(1)</sup>

|         |                                  | 最小値 | 最大値 | 単位         |

|---------|----------------------------------|-----|-----|------------|

| 入力電圧    | VIN                              | 3.5 | 65  | V          |

|         | EN/UVLO                          | 0   | 65  | V          |

| 入力電圧    | バイアス、PG                          | 0   | 30  | V          |

|         | MODE/SYNC、RT、FB                  | 0   | 5.5 | V          |

| プルアップ抵抗 | $R_{\text{PG}}$                  | 4   |     | k $\Omega$ |

| 出力電圧    | $V_{\text{OUT}}$                 | 0.8 | 60  | V          |

| 出力電流    | $I_{\text{OUT}}、8\text{A}$ オプション | 0   | 8   | A          |

|         | $I_{\text{OUT}}、6\text{A}$ オプション | 0   | 6   | A          |

|         | $I_{\text{OUT}}、4\text{A}$ オプション | 0   | 4   | A          |

- (1) 推奨動作条件は、デバイスが機能すると想定されている条件です。仕様およびテスト条件については、「[電気的特性](#)」を参照してください。

## 6.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup>  |                    | LM65640/60/80       |                   | 単位   |

|-----------------------|--------------------|---------------------|-------------------|------|

|                       |                    | eQFN (JESD 51-7)    | eQFN (EVM)        |      |

|                       |                    | 26 ピン               | 26 ピン             |      |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗       | 33.7 <sup>(2)</sup> | 18 <sup>(3)</sup> | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース(上面)への熱抵抗  | 24.1                | –                 | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗       | 6.9                 | –                 | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への特性パラメータ   | 1.1                 | 1.4               | °C/W |

| Ψ <sub>JB</sub>       | 接合部から基板への特性パラメータ   | 6.9                 | 5.8               | °C/W |

| R <sub>θJC(bot)</sub> | 接合部からケース(底面)までの熱抵抗 | 5.6                 | –                 | °C/W |

- (1) 热評価基準の詳細については、『半導体およびICパッケージの热評価基準』アプリケーションノートを参照してください。

(2) この表に示す R<sub>θJA</sub> の値は、その他のパッケージとの比較のためにのみ有効であり、設計目的では使用できません。R<sub>θJA</sub> は JESD 51-7 について計算され、4 層 JEDEC 基板を使用してシミュレーションされたもので、実際のアプリケーションで得られた性能を表すものではありません。热設計情報については、「最大周囲温度」セクションを参照してください。

(3) 基板レイアウトと追加情報については、『LM65680-Q1 EVM ユーザー ガイド』を参照してください。

## 6.5 電気的特性

標準値は T<sub>J</sub> = 25°C における値です。特に記載がない限り、最小値および最大値は T<sub>J</sub> = -40°C ~ 150°C で適用されます。

| パラメータ                              | テスト条件                                          | 最小値                                                                                                        | 標準値  | 最大値  | 単位   |

|------------------------------------|------------------------------------------------|------------------------------------------------------------------------------------------------------------|------|------|------|

| <b>入力電源 (VIN)</b>                  |                                                |                                                                                                            |      |      |      |

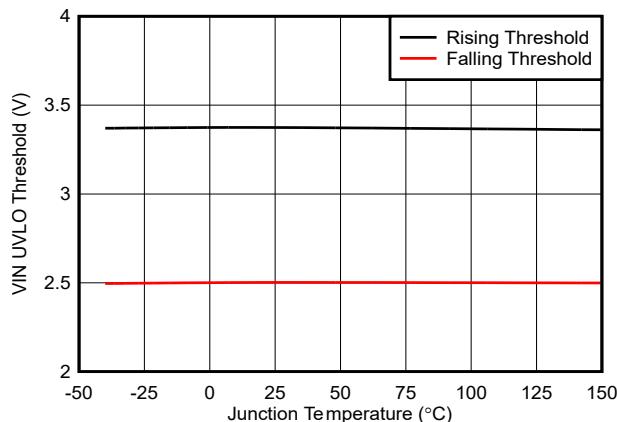

| V <sub>IN</sub> <sub>UVLO(R)</sub> | V <sub>IN</sub> の UVLO 立ち上がりスレッショルド電圧          | V <sub>IN</sub> の立ち上がり (起動に必要)                                                                             | 3.25 | 3.4  | 3.5  |

| V <sub>IN</sub> <sub>UVLO(F)</sub> | V <sub>IN</sub> の UVLO 立ち下がりスレッショルド電圧          | V <sub>IN</sub> の立ち下がり (動作開始後)                                                                             | 2.5  | 2.55 | V    |

| V <sub>IN</sub> <sub>UVLO(H)</sub> | V <sub>IN</sub> の UVLO ヒステリシス電圧                |                                                                                                            | 0.9  |      | V    |

| I <sub>VIN</sub>                   | VIN スリーブ静止電流、内部 COMP、スイッチングなし                  | V <sub>IN</sub> = 48V, V <sub>BIAS</sub> = 5V + 2%, CNFG は VCC に接続、T <sub>J</sub> = 25°C                   | 0.9  | 1.4  | μA   |

| I <sub>BIAS(FIX-3.3V)</sub>        | BIAS 静止電流、3.3V 固定出力、内部 COMP、スイッチングなし           | V <sub>BIAS</sub> = 3.3V + 2%, CNFG は VCC に接続、自動モード、T <sub>J</sub> = 25°C                                  | 8    | 10   | μA   |

| I <sub>Q(FIX-3.3V)</sub>           | VIN スリーブ静止電流の合計、3.3V 固定出力、内部 COMP、スイッチングなし     | V <sub>IN</sub> = 24V, V <sub>BIAS</sub> = 3.3V + 2%, CNFG は VCC に接続、T <sub>J</sub> = 25°C、自動モード           | 2.1  | 2.7  | μA   |

|                                    |                                                | T <sub>J</sub> = 125°C                                                                                     | 2.1  | 6.4  | μA   |

| I <sub>BIAS(FIX-5V)</sub>          | BIAS 静止電流、5V 固定出力、内部 COMP、スイッチングなし             | V <sub>BIAS</sub> = 5V + 2%, CNFG は VCC に接続、自動モード、T <sub>J</sub> = 25°C                                    | 9    | 12   | μA   |

| I <sub>Q(FIX-5V)</sub>             | VIN スリーブ静止電流の合計、5V 固定出力、内部 COMP、スイッチングなし       | V <sub>IN</sub> = 48V, V <sub>BIAS</sub> = 5V + 2%, CNFG は VCC に接続、T <sub>J</sub> = 25°C、自動モード             | 1.8  | 2.4  | μA   |

|                                    |                                                | T <sub>J</sub> = 125°C                                                                                     | 1.8  | 5.8  | μA   |

| I <sub>BIAS(ADJ-3.3V)</sub>        | BIAS 静止電流、調整可能な 3.3V 出力、内部 COMP、スイッチングなし       | V <sub>FB</sub> = 0.8V + 2%, CNFG は V <sub>CC</sub> に接続、自動モード、T <sub>J</sub> = 25°C                        | 6.8  | 8.1  | μA   |

| I <sub>Q(ADJ-3.3V)</sub>           | VIN スリーブ静止電流の合計、調整可能な 3.3V 出力、内部 COMP、スイッチングなし | V <sub>IN</sub> = 24V, V <sub>FB</sub> = 0.8V + 2%, CNFG は VCC に接続、自動モード、T <sub>J</sub> = 25°C             | 1.9  | 2.5  | μA   |

| I <sub>BIAS(ADJ-3.3V-EXT)</sub>    | BIAS 静止電流、調整可能な 3.3V 出力、外部 COMP、スイッチングなし       | V <sub>FB</sub> = 0.8V + 2%, R <sub>CNFG</sub> = 49.9kΩ、自動モード、T <sub>J</sub> = 25°C                        | 37   | 44   | μA   |

| I <sub>Q(ADJ-3.3V-EXT)</sub>       | VIN スリーブ静止電流の合計、調整可能な 3.3V 出力、外部 COMP、スイッチングなし | V <sub>IN</sub> = 24V, V <sub>FB</sub> = 0.8V + 2%, R <sub>CNFG</sub> = 49.9kΩ、自動モード、T <sub>J</sub> = 25°C | 6    | 7.4  | μA   |

| I <sub>Q-SHD</sub>                 | VIN のシャットダウン時静止電流                              | V <sub>IN</sub> = 48V, V <sub>EN/UVLO</sub> = 0V, T <sub>J</sub> = 25°C                                    | 0.8  | 1.2  | μA   |

|                                    |                                                | V <sub>IN</sub> = 48V, V <sub>EN/UVLO</sub> = 0V, T <sub>J</sub> = 125°C                                   | 0.8  | 1.8  | μA   |

| <b>高精度イネーブル (EN/UVLO)</b>          |                                                |                                                                                                            |      |      |      |

| V <sub>EN-TH(R)</sub>              | EN/UVLO 立ち上がりスレッショルド                           | V <sub>EN/UVLO</sub> の立ち上がり                                                                                | 1.15 | 1.25 | 1.35 |

| V <sub>EN-TH(F)</sub>              | EN/UVLO 立ち下がりスレッショルド                           | V <sub>EN/UVLO</sub> の立ち下がり                                                                                | 0.9  | 1    | 1.1  |

| V <sub>EN-HYS</sub>                | EN/UVLO ヒステリシス                                 |                                                                                                            | 0.25 |      | V    |

| V <sub>EN-HYS%</sub>               | EN/UVLO ヒステリシスと立ち上がりスレッショルドの比率                 | V <sub>EN-HYS</sub> /V <sub>EN-TH(R)</sub>                                                                 | 18   | 20   | 22   |

## 6.5 電気的特性 (続き)

標準値は  $T_J = 25^\circ\text{C}$  における値です。特に記載がない限り、最小値および最大値は  $T_J = -40^\circ\text{C} \sim 150^\circ\text{C}$  で適用されます。

| パラメータ                   |  | テスト条件                                                       | 最小値                                                        | 標準値 | 最大値   | 単位                |

|-------------------------|--|-------------------------------------------------------------|------------------------------------------------------------|-----|-------|-------------------|

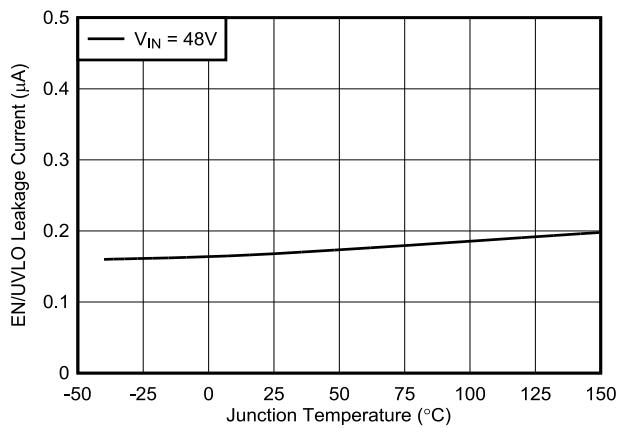

| $I_{EN-LKG}$            |  | イネーブル入力リーキ電流                                                | EN/UVLO は VIN に接続                                          |     | 0.16  | 3.5 $\mu\text{A}$ |

| <b>内部 LDO (VCC)</b>     |  |                                                             |                                                            |     |       |                   |

| $V_{VCC1}$              |  | 3.4V $\leq V_{IN} \leq 65\text{V}$ , $V_{BIAS} = 0\text{V}$ | 3.3                                                        |     | V     |                   |

| $V_{VCC2}$              |  | 3.4V $\leq V_{BIAS} \leq 30\text{V}$                        | 3.2                                                        |     | V     |                   |

| $V_{BIAS(ON)}$          |  | BIAS スイッチオーバー立ち上がりスレッショルド (VIN から BIAS へ)                   | $V_{BIAS}$ 立ち上がり                                           |     | 3.175 | 3.25 $\text{V}$   |

| $V_{BIAS(OFF)}$         |  | BIAS スイッチオーバー立ち下がりスレッショルド (BIAS から VIN へ)                   | $V_{BIAS}$ 立ち下がり                                           |     | 3     | 3.05 $\text{V}$   |

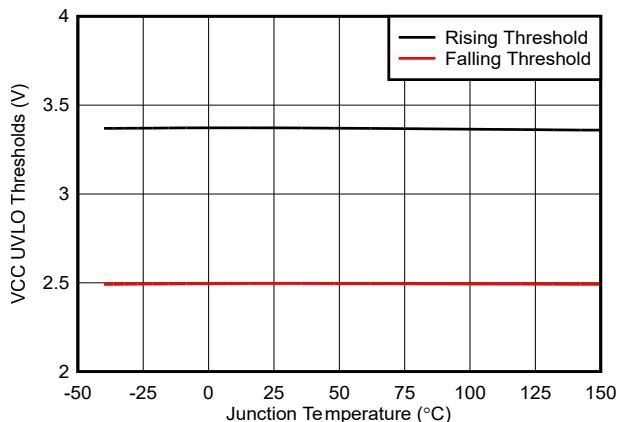

| $V_{VCC-UVLO(R)}$       |  | VCC UVLO 立ち上がりスレッショルド                                       | $I_{VCC} = 0\text{A}$                                      |     | 3.27  | 3.4 $\text{V}$    |

| $V_{VCC-UVLO(F)}$       |  | VCC UVLO 立ち下がりスレッショルド                                       | $I_{VCC} = 0\text{A}$                                      |     | 2.5   | $\text{V}$        |

| <b>リファレンス電圧 (FB)</b>    |  |                                                             |                                                            |     |       |                   |

| $V_{FB1}$               |  | フィードバック リファレンス電圧、外部 COMP                                    | FPWM モード、 $R_{CNFG} = 49.9\text{k}\Omega$                  |     | 0.792 | 0.8 $\text{V}$    |

| $V_{FB2}$               |  | フィードバック リファレンス電圧、内部 COMP                                    | FPWM モード、CNFG は VCC に接続                                    |     | 0.792 | 0.8 $\text{V}$    |

| $I_{FB-LKG}$            |  | フィードバック ピン入力リーキ電流                                           | $V_{FB} = 0.8\text{V}$ 、可変 $V_{OUT}$ 設定                    |     | 1.8   | 90 $\text{nA}$    |

| <b>固定出力電圧 (BIAS)</b>    |  |                                                             |                                                            |     |       |                   |

| $V_{OUT-3.3V-INT}$      |  | 3.3V 固定出力電圧、内部 COMP                                         | FB は GND に接続、CNFG は VCC に接続                                |     | 3.267 | 3.3 $\text{V}$    |

| $V_{OUT-3.3V-EXT}$      |  | 3.3V 固定出力電圧、外部 COMP                                         | FB は GND に短絡、 $R_{CNFG} = 49.9\text{k}\Omega$              |     | 3.267 | 3.3 $\text{V}$    |

| $V_{OUT-5V-INT}$        |  | 5V 固定出力電圧、内部 COMP                                           | FB は VCC に接続、CNFG は VCC に接続                                |     | 4.94  | 5 $\text{V}$      |

| $V_{OUT-5V-EXT}$        |  | 5V 固定出力電圧、外部 COMP                                           | FB は VCC に接続、 $R_{CNFG} = 49.9\text{k}\Omega$              |     | 4.94  | 5 $\text{V}$      |

| <b>ソフトスタート (SS)</b>     |  |                                                             |                                                            |     |       |                   |

| $t_{EN-SW}$             |  | イネーブル High からスイッチング開始までの遅延                                  | $V_{FB} = V_{RT} = V_{MODE} = GND$ , $V_{BIAS} = V_{OUT}$  |     | 1.9   | 2.5 $\text{ms}$   |

| $t_{ss}$                |  | 内部固定ソフトスタート時間                                               | 最初の SW パルスから $V_{FB}$ が設定点の 90% に達するまでの時間                  |     | 2.9   | 5.3 $\text{ms}$   |

| $I_{ss}$                |  | SS 充電電流                                                     | $V_{ss} = 0\text{V}$                                       |     | 20    | $\mu\text{A}$     |

| $R_{ss}$                |  | SS 放電抵抗                                                     | $V_{EN/UVLO} = 0\text{V}$                                  |     | 7     | $\Omega$          |

| <b>エラー アンプ (COMP)</b>   |  |                                                             |                                                            |     |       |                   |

| $g_m$                   |  | EA 相互コンダクタンス                                                | $V_{COMP} = 0.8\text{V}$ , $V_{FB} = 0.8\text{V} \pm 5\%$  |     | 1     | $\text{mS}$       |

| $V_{COMP-EXT(h-clamp)}$ |  | 外部 COMP - 高クランプ電圧                                           | $V_{FB} = 0\text{V}$ 、可変 $V_{OUT}$ 設定                      |     | 1.056 | $\text{V}$        |

| <b>電力段 (SW)</b>         |  |                                                             |                                                            |     |       |                   |

| $R_{DS(on)HS}$          |  | ハイサイド FET のオン状態抵抗                                           | $I_{SW} = 500\text{mA}$ , $V_{BST} - V_{SW} = 3.3\text{V}$ | 42  |       | $\text{m}\Omega$  |

| $R_{DS(on)LS}$          |  | ローサイド FET のオン状態抵抗                                           |                                                            | 23  |       | $\text{m}\Omega$  |

| $t_{ON(min)}$           |  | 最小オン時間 <sup>(1)</sup>                                       | $I_{OUT} = 2\text{A}$ , $R_{RT} = 6.81\text{k}\Omega$      |     | 36    | 48 $\text{ns}$    |

| $t_{OFF(min)}$          |  | 最小オフ時間                                                      | $V_{IN} = 4\text{V}$ , $F_{SW} = 2.2\text{MHz}$            |     | 82    | 118 $\text{ns}$   |

| $t_{ON(max)}$           |  | 最大オン時間                                                      | $F_{SW} = 300\text{kHz}$                                   |     | 13.3  | $\mu\text{s}$     |

| <b>電流制限およびヒップ モード</b>   |  |                                                             |                                                            |     |       |                   |

| $I_{HS-LIM1}$           |  | ハイサイド ピーク電流制限、8A オプション                                      | デューティ サイクルを 0% に近付ける                                       |     | 10.7  | 12.5 $\text{A}$   |

| $I_{LS-LIM1}$           |  | ローサイド バレー電流制限、8A オプション                                      |                                                            |     | 8.5   | 9.9 $\text{A}$    |

| $I_{L-PK1(AUTO-minD)}$  |  | 最小デューティ サイクルでの自動モードのピークインダクタ電流、8A オプション                     | $t_{ON} \leq 100\text{ns}$                                 |     | 1.9   | 3 $\text{A}$      |

| $I_{L-PK1(AUTO-maxD)}$  |  | 最大デューティ サイクルでの自動モードのピークインダクタ電流、8A オプション                     | $t_{ON} \geq 1\mu\text{s}$                                 |     | 1.1   | $\text{A}$        |

| $I_{HS-LIM2}$           |  | ハイサイド ピーク電流制限、6A オプション                                      | デューティ サイクルを 0% に近付ける                                       |     | 8.2   | 9.5 $\text{A}$    |

| $I_{LS-LIM2}$           |  | ローサイド バレー電流制限、6A オプション                                      |                                                            |     | 6.6   | 7.4 $\text{A}$    |

| $I_{L-PK2(AUTO-minD)}$  |  | 最小デューティ サイクルでの自動モードのピークインダクタ電流、6A オプション                     | $t_{ON} \leq 100\text{ns}$                                 |     | 1.1   | 1.9 $\text{A}$    |

| $I_{L-PK2(AUTO-maxD)}$  |  | 最大デューティ サイクルでの自動モードのピークインダクタ電流、6A オプション                     | $t_{ON} \geq 1\mu\text{s}$                                 |     | 0.95  | $\text{A}$        |

## 6.5 電気的特性 (続き)

標準値は  $T_J = 25^\circ\text{C}$  における値です。特に記載がない限り、最小値および最大値は  $T_J = -40^\circ\text{C} \sim 150^\circ\text{C}$  で適用されます。

| パラメータ                                  |                                        | テスト条件                                                                                                  | 最小値  | 標準値  | 最大値  | 単位   |

|----------------------------------------|----------------------------------------|--------------------------------------------------------------------------------------------------------|------|------|------|------|

| $I_{\text{HS-LIM3}}$                   | ハイサイド ピーク電流制限、4A オプション                 | デューティサイクルを 0% に近付ける                                                                                    | 5.9  | 7    | 8    | A    |

| $I_{\text{LS-LIM3}}$                   | ローサイド バレー電流制限、4A オプション                 |                                                                                                        | 4.2  | 5.4  | 6.3  | A    |

| $I_{\text{L-PK3(AUTO-minD)}}$          | 最小デューティサイクルでの自動モードのピークインダクタ電流、4A オプション | $t_{\text{ON}} \leq 100\text{ns}$                                                                      | 1    | 1.8  | 2.7  | A    |

| $I_{\text{L-PK3(AUTO-maxD)}}$          | 最大デューティサイクルでの自動モードのピークインダクタ電流、4A オプション | $t_{\text{on}} \geq 1\mu\text{s}$                                                                      |      | 0.65 |      | A    |

| $I_{\text{LS-NEG-LIM}}$                | ローサイド負電流制限                             | シンク電流制限、FPWM モード                                                                                       | -9.6 | -6.9 | -4.9 | A    |

| $I_{\text{L-ZC}}$                      | ゼロクロスのスレッショルド                          | AUTO モード                                                                                               |      | 100  |      | mA   |

| $V_{\text{HIC}}$                       | FB 電圧ヒップスレッショルド                        | ローサイド FET のオン時間 > 165ns、ソフトスタート後                                                                       |      | 0.32 |      | V    |

| $t_{\text{HICDLY}}$                    | ヒップスレッショルドの起動遅延                        |                                                                                                        |      | 64   |      | サイクル |

| $t_{\text{HIC}}$                       | ヒップスレッショルドの持続時間                        | 内部ソフトスタート                                                                                              |      | 48   |      | ms   |

| <b>パワーグッド (PG)</b>                     |                                        |                                                                                                        |      |      |      |      |

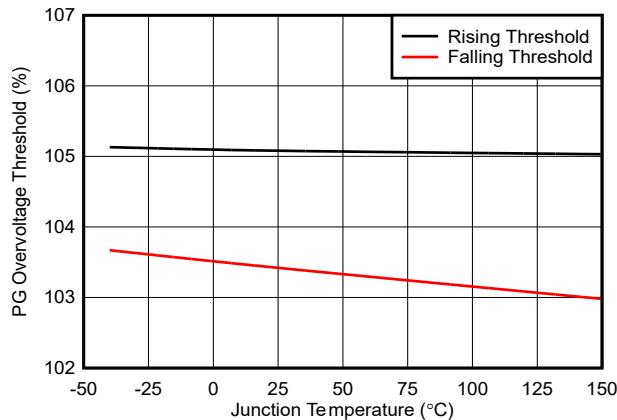

| $V_{\text{PG-OV(R)}}$                  | PG OV 立ち上がりスレッショルド                     | FB 電圧 (ADJ 出力) または BIAS 電圧 (固定出力) の %                                                                  | 103  | 105  | 107  | %    |

| $V_{\text{PG-OV(F)}}$                  | PG OV 立ち下がりスレッショルド                     |                                                                                                        | 101  | 104  | 106  | %    |

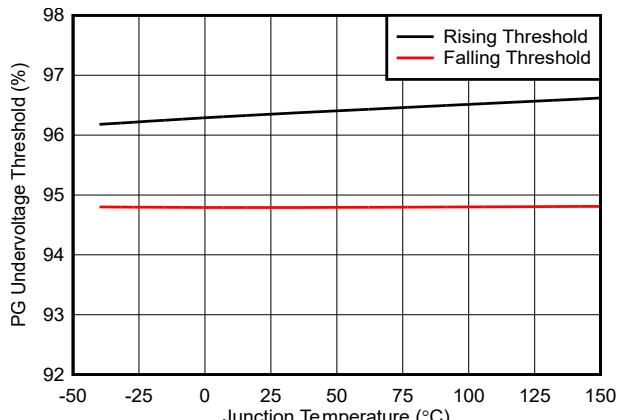

| $V_{\text{PG-UV(R)}}$                  | PG UV 立ち上がりスレッショルド                     |                                                                                                        | 94   | 96   | 98.5 | %    |

| $V_{\text{PG-UV(F)}}$                  | PG UV 立ち下がりスレッショルド                     |                                                                                                        | 92.5 | 95   | 97   | %    |

| $t_{\text{PG-DEGLITCH(R)}}$            | PG 立ち上がりエッジでのグリッチ除去フィルタ遅延              |                                                                                                        | 1.2  | 2    | 3    | ms   |

| $t_{\text{PG-DEGLITCH(F)}}$            | PG 立ち下がりエッジでのグリッチ除去フィルタ遅延              |                                                                                                        | 55   | 130  | 175  | μs   |

| $V_{\text{IN(PG-VALID)}}$              | 有効な PG 出力の最小 $V_{\text{IN}}$           | $V_{\text{PG(OL)}} < 0.4\text{V}$ , $R_{\text{PG}} = 49.9\text{k}\Omega$ , $V_{\text{PG}} = 5\text{V}$ |      |      | 1.25 | V    |

| $V_{\text{PG(OL)}}$                    | PG Low 状態電圧                            | $I_{\text{PG}} = 1\text{mA}$ , $V_{\text{IN}} = 1.25\text{V}$                                          |      |      | 0.4  | V    |

| $R_{\text{PG(on)}}$                    | PG スイッチ オン抵抗                           | $I_{\text{PG}} = 1\text{mA}$                                                                           |      | 51   | 110  | Ω    |

| <b>スイッチング周波数 (RT)</b>                  |                                        |                                                                                                        |      |      |      |      |

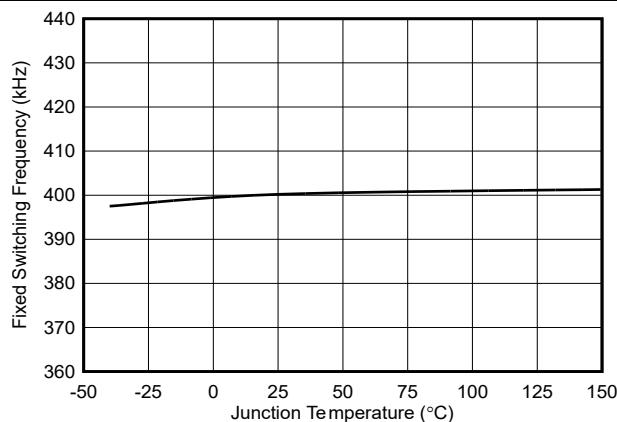

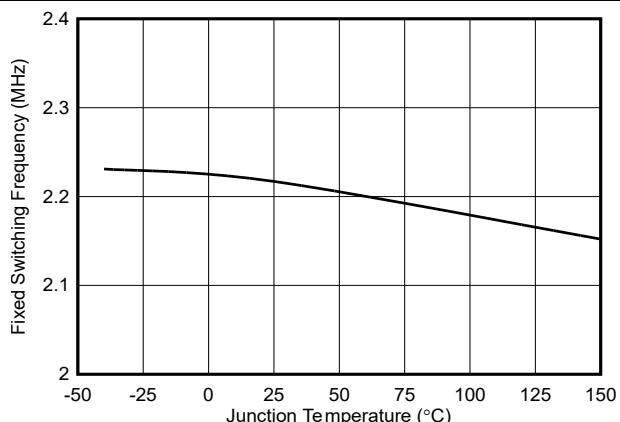

| $f_{\text{SW1}}$                       | スイッチング周波数                              | RT を PGND に接続                                                                                          | 1.98 | 2.2  | 2.42 | MHz  |

| $f_{\text{SW2}}$                       |                                        | $R_{\text{RT}} = 6.81\text{k}\Omega \pm 1\%$                                                           | 1.98 | 2.2  | 2.42 | MHz  |

| $f_{\text{SW3}}$                       |                                        | $R_{\text{RT}} = 15.8\text{k}\Omega \pm 1\%$                                                           | 900  | 1000 | 1100 | kHz  |

|                                        |                                        | $R_{\text{RT}} = 40.2\text{k}\Omega \pm 1\%$                                                           | 360  | 400  | 440  | kHz  |

|                                        |                                        | RT は VCC に接続                                                                                           | 360  | 400  | 440  | kHz  |

| <b>同期 (MODE/SYNC)</b>                  |                                        |                                                                                                        |      |      |      |      |

| $V_{\text{SYNC(IL)}}$                  | SYNC 入力 Low レベル スレッショルド                |                                                                                                        | 0.45 |      |      | V    |

| $V_{\text{SYNC(IH)}}$                  | SYNC 入力 High レベル スレッショルド               |                                                                                                        |      |      | 1.3  | V    |

| $V_{\text{SYNCOUT(OL)}}$               | SYNCOUT 出力 Low レベル スレッショルド             | $I_{\text{SYNCOUT}} = 2\text{mA}$                                                                      |      |      | 0.4  | V    |

| $V_{\text{SYNCOUT(OH)}}$               | SYNCOUT 出力 High レベル スレッショルド            | $I_{\text{SYNCOUT}} = -2\text{mA}$                                                                     | 2.4  |      |      | V    |

| $f_{\text{SYNC-RANGE1}}$               | 2.2MHz の設定に対しての同期周波数範囲                 | $R_{\text{RT}} = 6.81\text{k}\Omega \pm 1\%$                                                           | 1.76 |      | 2.64 | MHz  |

| $f_{\text{SYNC-RANGE2}}$               | 300kHz の設定に対しての同期周波数範囲                 | $R_{\text{RT}} = 54.2\text{k}\Omega \pm 1\%$                                                           | 240  |      | 360  | kHz  |

| $t_{\text{SYNC-LOW(min)}}$             | 外部 SYNC 信号の最小 Low パルス幅                 |                                                                                                        |      |      | 80   | ns   |

| $t_{\text{SYNC-HIGH(min)}}$            | 外部 SYNC 信号の最小 High パルス幅                |                                                                                                        |      |      | 80   | ns   |

| $t_{\text{SYNC-SW-DLY}}$               | SYNC から SW への遅延時間 <sup>(1)</sup>       |                                                                                                        | -22  |      | 22   | ns   |

| $t_{\text{MODE-DLY}}$                  | MODE 変化遅延時間 <sup>(1)</sup>             |                                                                                                        |      |      | 20   | μs   |

| <b>デュアルランダムスペクトラム拡散機能 (DRSS/MCOMM)</b> |                                        |                                                                                                        |      |      |      |      |

| $\Delta f_{\text{SS-LF}}$              | 低周波数の三角波スペクトラム拡散変調範囲                   | DRSS/MCOMM オープン                                                                                        | 17   |      |      | %    |

| $f_{\text{m-LF}}$                      | 三角波変調周波数                               | DRSS/MCOMM オープン                                                                                        | 3.6  | 6    | 8.4  | kHz  |

| $\Delta f_{\text{SS-HF}}$              | 高周波の疑似ランダム拡散スペクトラム変調範囲                 | DRSS/MCOMM オープン                                                                                        | 2    |      |      | %    |

| <b>サーマルシャットダウン</b>                     |                                        |                                                                                                        |      |      |      |      |

## 6.5 電気的特性 (続き)

標準値は  $T_J = 25^\circ\text{C}$  における値です。特に記載がない限り、最小値および最大値は  $T_J = -40^\circ\text{C} \sim 150^\circ\text{C}$  で適用されます。

| パラメータ     |                             | テスト条件                        | 最小値 | 標準値 | 最大値 | 単位 |

|-----------|-----------------------------|------------------------------|-----|-----|-----|----|

| $T_{SHD}$ | サーマル シャットダウン <sup>(1)</sup> | シャットダウン スレッショルド<br>復帰スレッショルド | 155 | 165 | 177 | °C |

|           |                             |                              |     | 156 |     | °C |

(1) 設計により規定されています。

## 6.6 代表的特性

特に記述のない限り、 $T_J = 25^\circ\text{C}$ 。

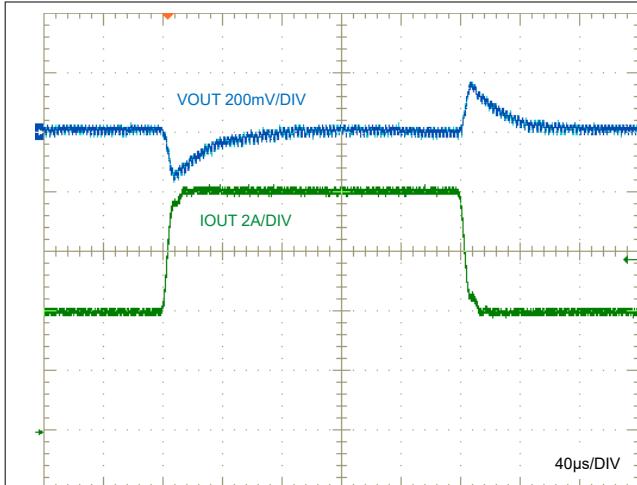

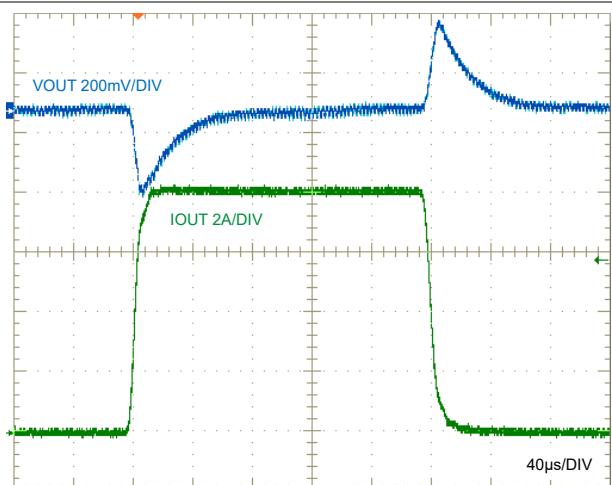

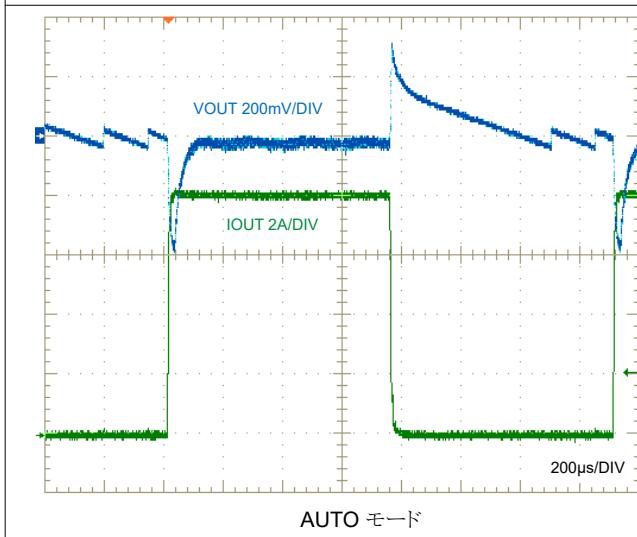

図 8-7 を参照

$F_{SW} = 400\text{kHz}$     $L_O = \text{XGL6060}, 3.3\mu\text{H}$

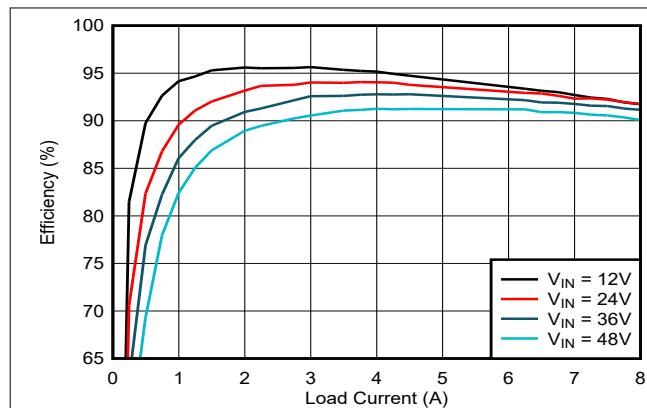

図 6-1. 効率、FPWM、 $V_{OUT} = 5\text{V}$

$V_{OUT} = 3.3\text{V}$

$F_{SW} = 400\text{kHz}$     $L_O = \text{XGL6060}, 3.3\mu\text{H}$

図 6-2. 効率、FPWM、 $V_{OUT} = 3.3\text{V}$

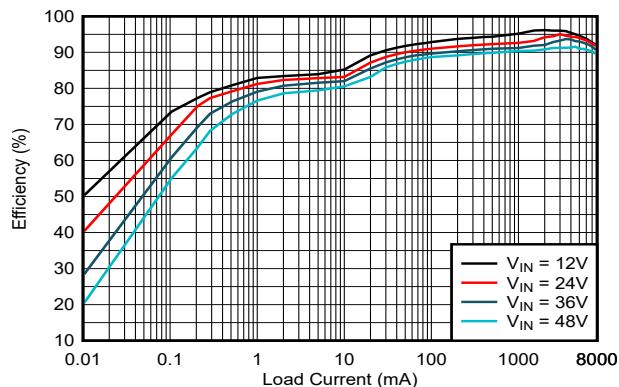

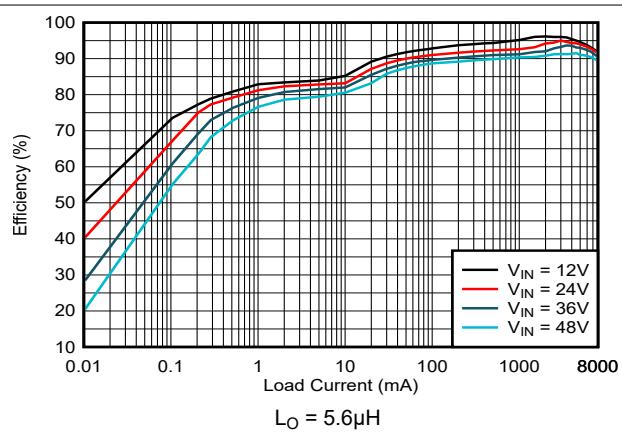

図 8-7 を参照

$F_{SW} = 400\text{kHz}$     $L_O = \text{XGL6060}, 5.6\mu\text{H}$

図 6-3. 効率、自動モード、 $V_{OUT} = 5\text{V}$

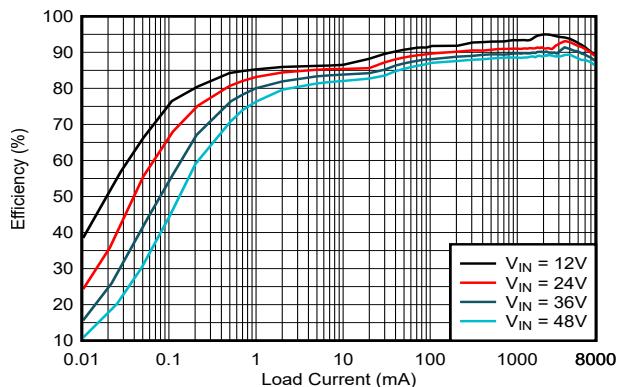

$V_{OUT} = 3.3\text{V}$

$F_{SW} = 400\text{kHz}$     $L_O = \text{XGL6060}, 5.6\mu\text{H}$

図 6-4. 効率、自動モード、 $V_{OUT} = 3.3\text{V}$

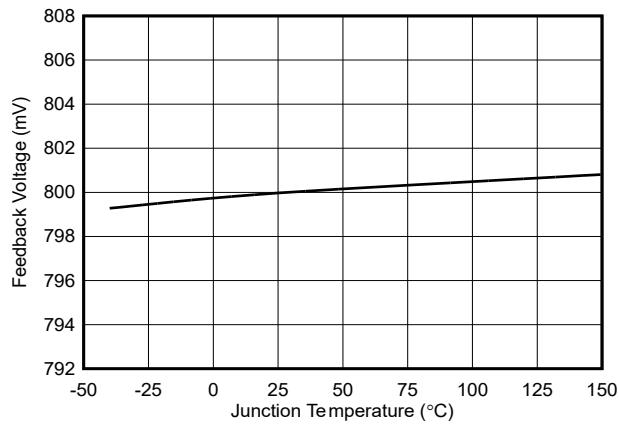

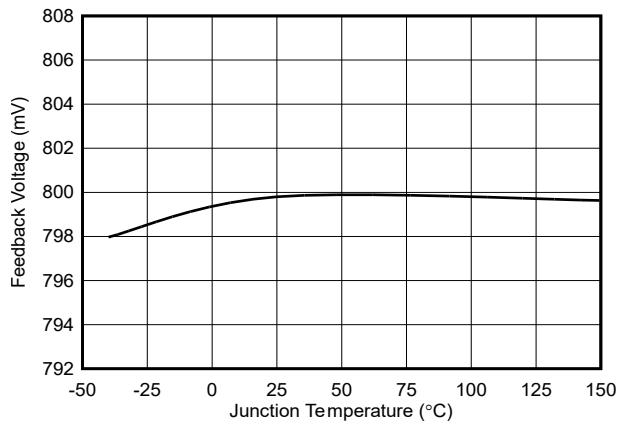

図 6-5. FB 電圧、内部補償

図 6-6. FB 電圧、外部補償

## 6.6 代表的特性 (続き)

特に記述のない限り、 $T_J = 25^\circ\text{C}$ 。

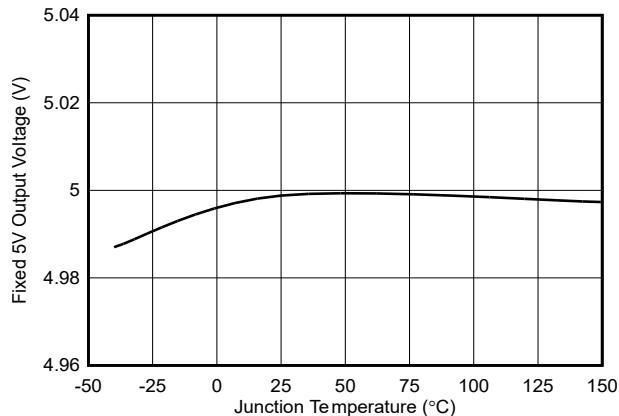

図 6-7. 5V 固定出力電圧の設定点

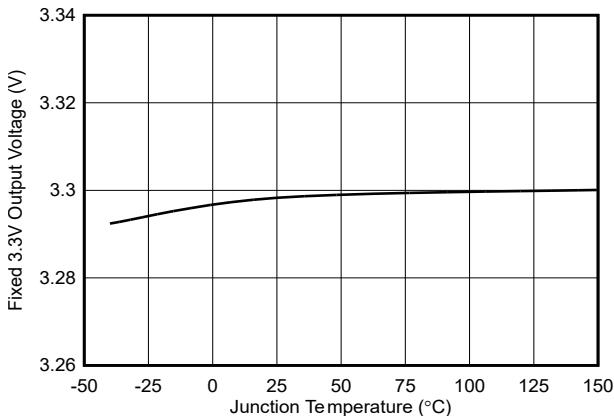

図 6-8. 3.3V 固定出力電圧の設定点

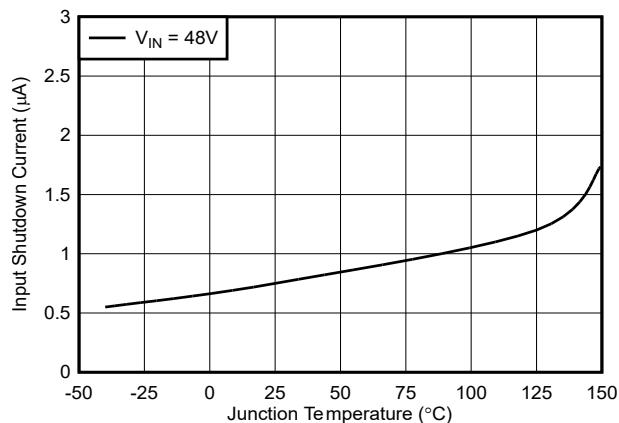

図 6-9. VIN のシャットダウン時静止電流

図 6-10. RT 抵抗とスイッチング周波数との関係

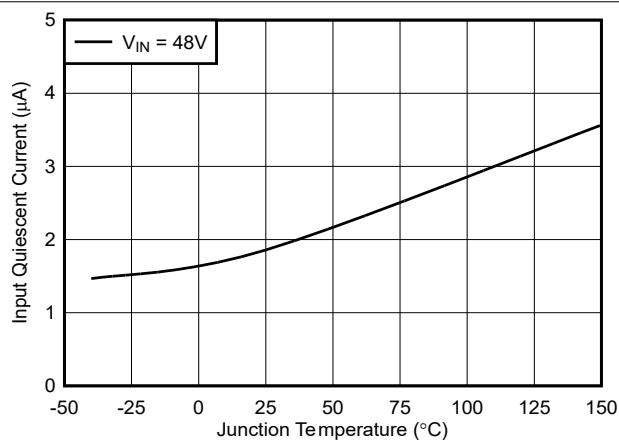

図 6-11. VIN のスリープ静止電流、5V 固定出力

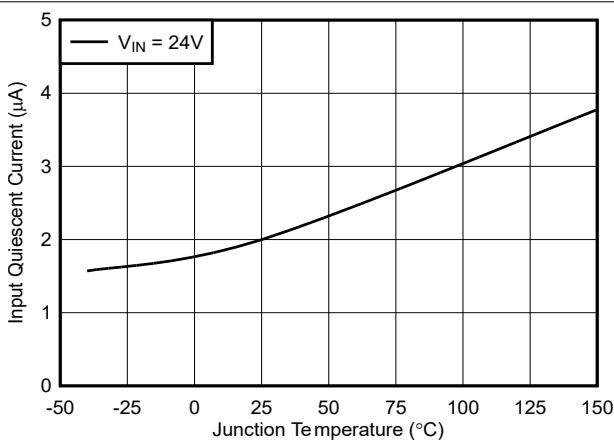

図 6-12. VIN のスリープ静止電流、3.3V 固定出力

## 6.6 代表的特性 (続き)

特に記述のない限り、 $T_J = 25^\circ\text{C}$ 。

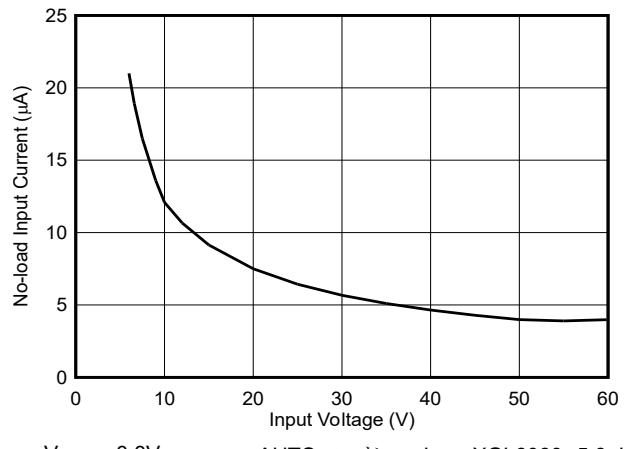

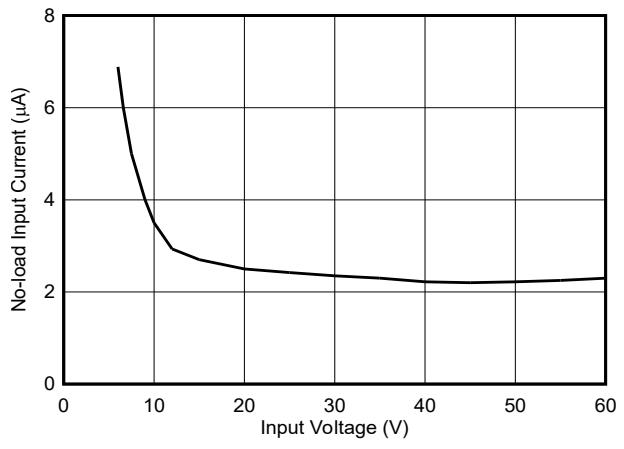

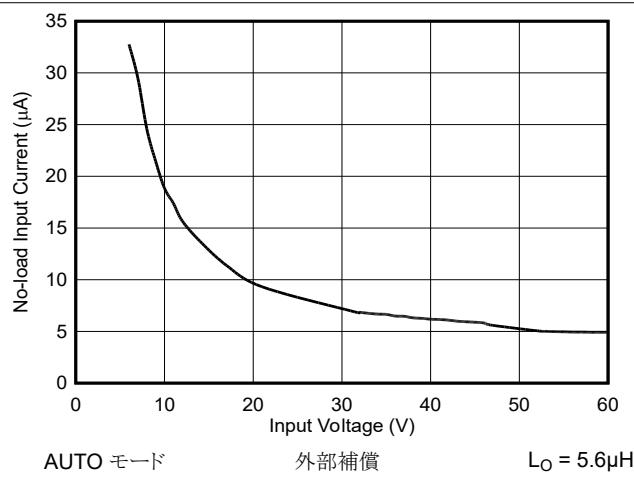

図 6-13. 無負荷時入力電流、3.3V 固定出力、外部補償

図 6-14. 無負荷時入力電流、3.3V 固定出力、内部補償

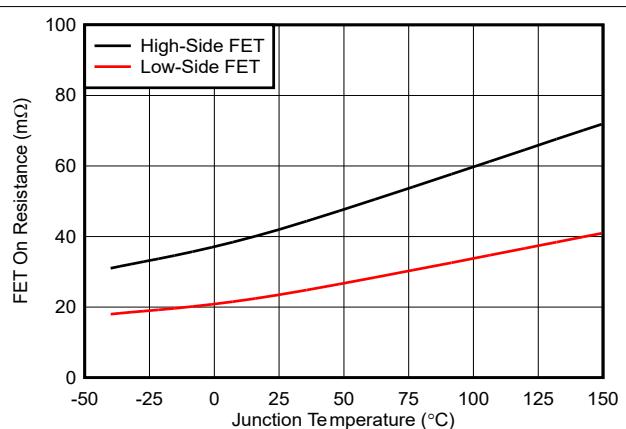

図 6-15. ハイサイドおよびローサイド MOSFET の  $R_{\text{DS(on)}}$

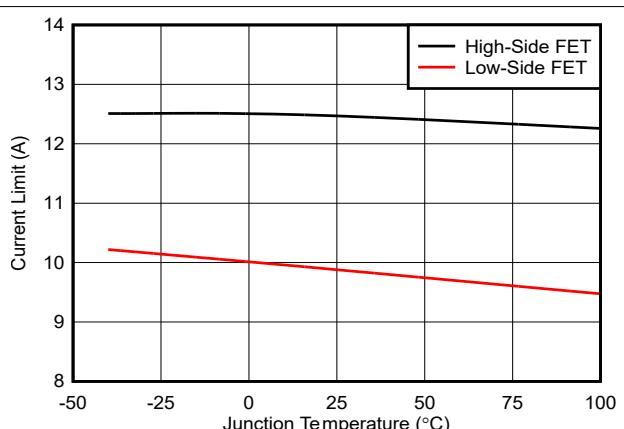

図 6-16. MOSFET 電流制限

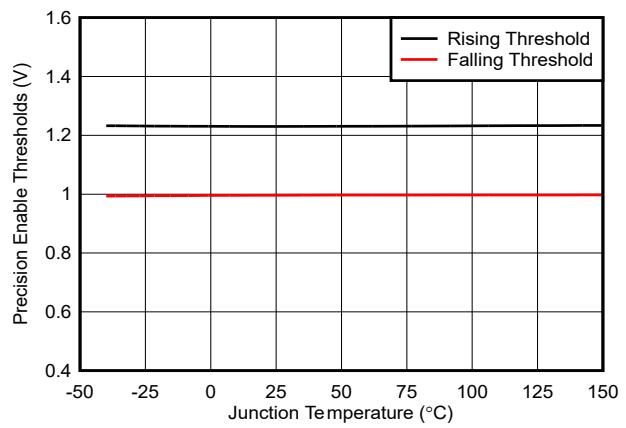

図 6-17. 高精度イネーブル スレッショルド

図 6-18. EN/UVLO 入力のリーク電流

## 6.6 代表的特性 (続き)

特に記述のない限り、 $T_J = 25^\circ\text{C}$ 。

図 6-19. PG OV スレッショルド

図 6-20. PG UV スレッショルド

図 6-21. VIN UVLO スレッショルド

図 6-22. VCC UVLO スレッショルド

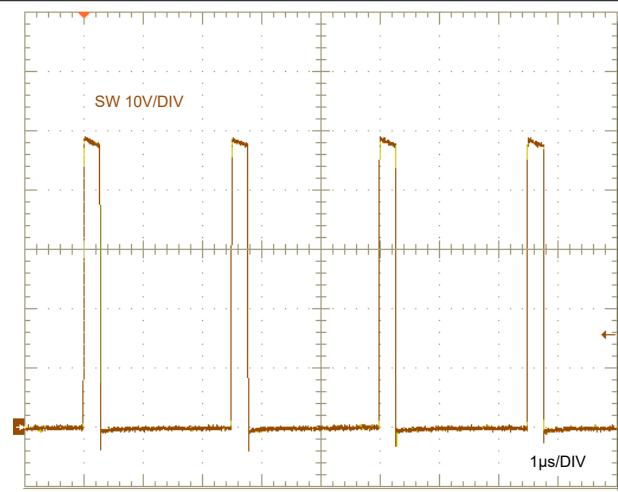

図 6-23. 固定スイッチング周波数 - 400kHz

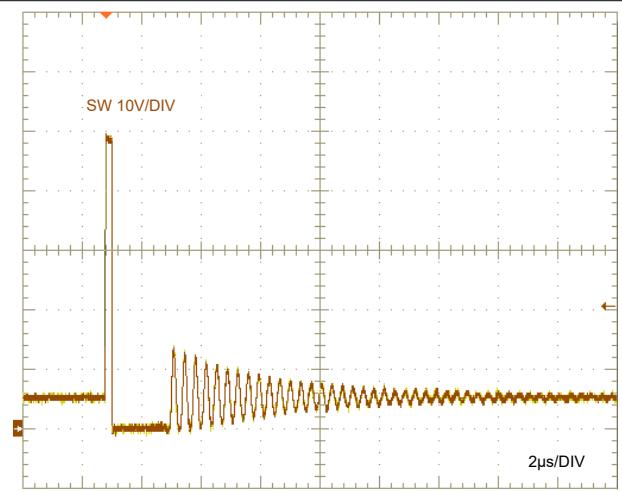

図 6-24. 固定スイッチング周波数 - 2.2MHz

## 7 詳細説明

### 7.1 概要

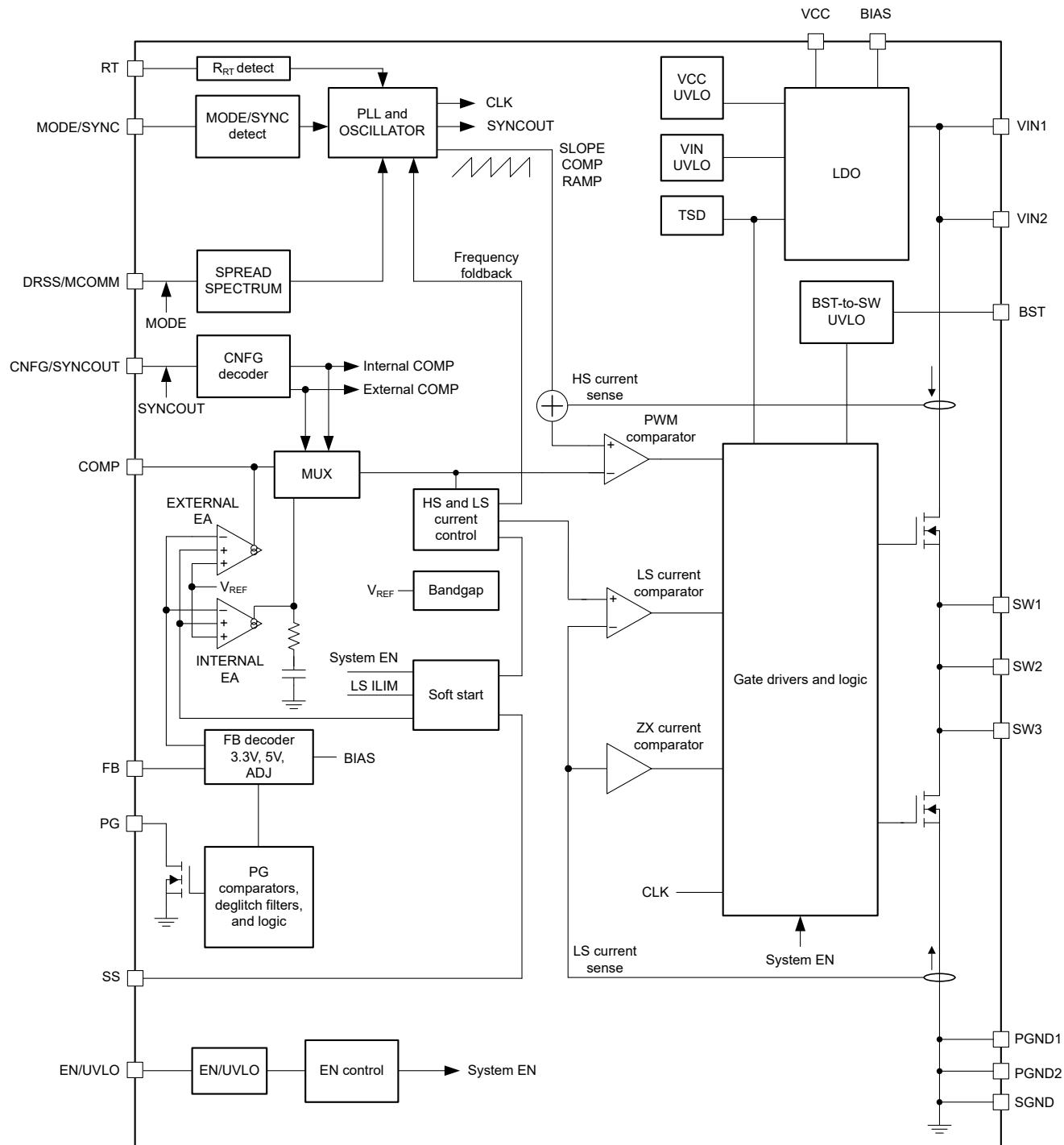

LM65680/60/40 は、高効率、高電力密度、低 EMI の降圧コンバータのファミリです。これらのコンバータは、3.5V ~ 65V の広い入力電圧範囲で動作し、ピンで選択可能な 3.3V および 5V の固定出力電圧、または 0.8V ~ 60V の可変出力電圧を出力できます。2 つまでのコンバータを、高精度の電流共有が可能なインターリープ モード（並列出力）に設定し、最大 16A の出力電流をサポートできます。

最小オン時間 36ns のピーク電流モード制御アーキテクチャにより、高周波数での高い変換比、高速過渡応答、優れた負荷およびライン レギュレーションを可能にします。最小オン時間または最小オフ時間が目的の変換比をサポートしない場合、スイッチング周波数は自動的に低下します。この機能により、負荷ダンプやコールド クランクなどのライン過渡事象が発生している間もレギュレーションが維持されます。

LM65680/60/40 は、高性能産業用環境で動作しながら、最終製品のコストとサイズが最小化されるように設計されています。このデバイスは、300kHz ~ 2.2MHz の範囲のスイッチング周波数を抵抗でプログラムできます。内部補償と正確な電流制限方式により、BOM コストと部品数を最小限に抑えることができます。

LM65680/60/40 は伝導および放射エミッションが小さくなるように設計されており、以下の特長があります：

- スイッチ ノードのスルーレート制御をピンで構成可能

- デュアル ランダム スペクトラム拡散 (DRSS) 周波数変調

- 対称型のピン配置により電源ループ内の寄生インダクタンスを低減

- 300kHz ~ 2.2MHz の広いスイッチング周波数範囲

- 外部クロック同期機能とともに、自動または FPWM モードをピンで構成可能

これらの機能を組み合わせることで、シールドやその他の高価な EMI 軽減対策を不要にできます。

LM65680/60/40 は、信頼性が重視される環境での使用を目的として、拡大コーナー端子付きパッケージを採用しており、基板レベルの信頼性が向上し、ウェッタブルフランクにより製造中に光学検査が可能です。

## 7.2 機能ブロック図

## 7.3 機能説明

### 7.3.1 入力電圧範囲 (VIN1、VIN2)

LM65680/60/40 の動作入力電圧範囲は、3.5V ~ 65V です。このデバイスは、24V、48V、60V の電源レールからの降圧変換を目的としています。図 7-1 に、単一の入力電源を使用した LM65680/60/40 ベースの幅広い  $V_{IN}$  の降圧 レギュレータを実装するために必要なすべての部品を示します。LM65680/60/40 は、内部の LDO サブレギュレータを使用して、ゲート駆動および制御回路に 3.3V の VCC バイアスレールを供給します。

図 7-1. LM65680/60/40 レギュレータの回路図

入力電圧が高いアプリケーションでは、コンバータの VIN ピン (VIN1 および VIN2) と SW ピン (SW1, SW2, SW3) が、ラインまたは負荷過渡イベント中に絶対最大電圧定格である 72V を超えないように特に注意してください。該当する電圧仕様を超える電圧の変動は、デバイスを損傷させる可能性があります。

### 7.3.2 高電圧バイアス電源サブレギュレータ (VCC, BIAS)

LM65680/60/40 は VCC レギュレータ用の内部高電圧サブレギュレータが搭載されており、VIN または BIAS から供給されます。降圧コンバータの出力電圧 ( $V_{OUT}$ ) や、他の該当するシステムレール (最高 30V) などの低電圧電源を BIAS に接続します。低電圧レールから VCC に電力を供給することで、LM65680/60/40 の内部消費電力が低減されます。使用しない場合は、BIAS を PGND に接続します。

LM65680/60/40 がアクティブになった後、BIAS が 3V 未満の場合、VIN からバイアス電流が抽出されます。BIAS の電圧が 3.175V の切り替えスレッショルドを超えると、VCC サブレギュレータは入力として BIAS を使用するように切り替わります。この切り替え電圧のヒステリシスは 175mV です。

起動中、この電圧が VCC UVLO 立ち上がりスレッショルドである 3.4V を超えるまで、VCC は瞬間に通常の動作電圧を超えます。その後で VCC は、VIN から電力が供給されるときは 3.3V、BIAS から電力が供給されるときは 3.2V の動作電圧に降下します。安全でない動作を防止するため、VCC には、VCC 電圧が 2.5V を下回った場合にスイッチングを止める UVLO 保護機能が備わっています。1μF のセラミックコンデンサー (X7R 誘電体使用、定格 10V) を VCC と PGND との間に接続します。

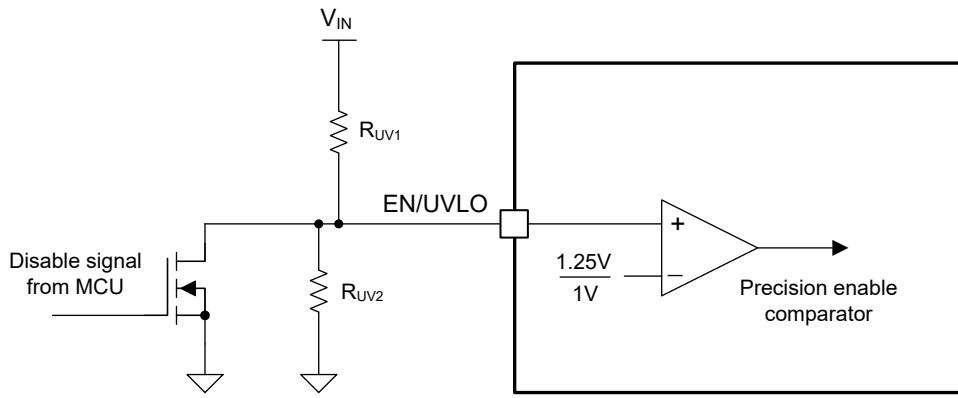

### 7.3.3 高精度のイネーブルおよび可変入力電圧 UVLO (EN/UVLO)

LM65680/60/40 コンバータは、EN/UVLO 電圧が立ち上がりスレッショルドの 1.25V より高いとイネーブルされ、デバイスはソフトスタートを開始します。EN/UVLO が立ち下がりスレッショルドの 1V よりも低くなると、レギュレータはスイッチングを停止して、内部放電スイッチを使用して出力を放電し(約 5mA の放電電流)、シャットダウン モードに移行します。シャットダウン時の静止電流は 1µA 未満です。この機能が必要ない場合は、EN/UVLO を VIN に直接接続します。EN/UVLO ピンがフローティング状態になるとデバイスが強制的にオフになるため、EN/UVLO をオープンのままにしないでください。

EN/UVLO 入力は、特定用途での電源オンおよび電源オフ要件のために、抵抗値によりプログラムされる可変入力低電圧誤動作防止 (UVLO) をサポートしています。デバイス内の固定 UVLO レベルとは異なる、高精度の入力電圧 UVLO を確立するため、図 7-2 に示すように抵抗  $R_{UV1}$  と  $R_{UV2}$  を取り付けます。可変 UVLO はシーケンシング、長い入力ケーブルと併用したときのデバイスの再トリガの防止、またはバッテリ入力ソースの過放電の防止に有用です。高精度イネーブル スレッショルドには 20% のヒステリシスがあるため、オン / オフの再トリガを防止できます。別の IC (MCU など) からの外部ロジック信号は、出力のオン / オフを切り替え、システムの電力シーケンシングや保護を行うために便利です。

図 7-2. プログラマブルな入力電圧 UVLO

精度を最大化するには、分圧器の電流が EN/UVLO 入力リーク電流 ( $I_{EN-LKG}$ ) より大きい必要があります。下側の UVLO 抵抗分圧器  $R_{UV2}$  を  $10\text{k}\Omega \sim 50\text{k}\Omega$  の範囲で選択します。次に、式 1 と式 2 を使用して  $R_{UV1}$  と  $V_{IN(off)}$  をそれぞれ計算します。ここで、 $V_{IN(on)}$  と  $V_{IN(off)}$  は必要な入力電圧のターンオンおよびターンオフ スレッショルドです。

$$R_{UV1} = R_{UV2} \times \left( \frac{V_{IN(on)}}{V_{EN-TH(R)}} - 1 \right) \quad (1)$$

$$V_{IN(off)} = V_{IN(on)} \times \left( 1 - V_{EN-HYS\%} \right) \quad (2)$$

内部の VIN UVLO 保護は EN/UVLO 入力よりも優先されることに注意してください。LM65680/60/40 は、入力電圧が UVLO 立ち上がりスレッショルドである 3.4V を超えない限り起動しません。一方で、入力電圧が UVLO 立ち下がりスレッショルドである 2.5V を下回ると、デバイスはシャットダウンします。

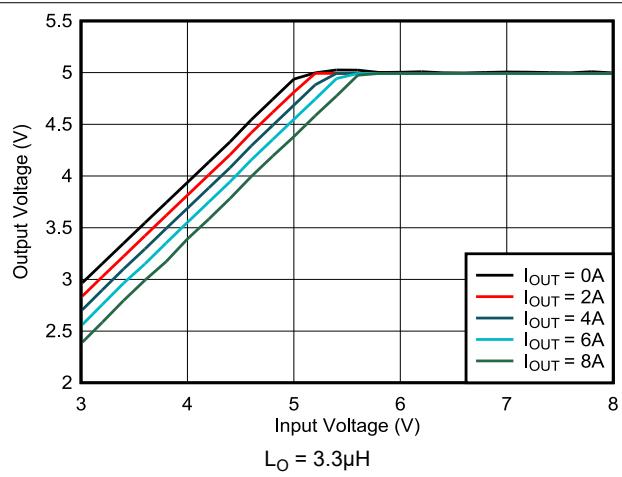

### 7.3.4 出力電圧の設定点 (FB, BIAS)

スイッチング周波数と負荷電流レベルによって異なりますが、LM65680/60/40 は一般に 0.8V から、入力電圧をわずかに下まわる最大値までの範囲の出力電圧を供給できます。定格最大出力電圧は 60V です。LM65680/60/40 は、固定と可変の出力電圧の設定をピンで選択できることが特徴です。

FB を VCC または PGND に接続すると、固定の 5V または 3.3V 出力がそれぞれ選択され、BIAS をレギュレータ出力に直接接続すると出力電圧センシングが行われます。この場合、BIAS は電圧帰還ループを閉じて、内部の VCC サブレギュレータに電力を供給します。

または、図 7-1 に示すように、 $R_{FB1}$  および  $R_{FB2}$  で指定される帰還抵抗を使用して、出力電圧の設定点を定義します。LM65680/60/40 には 0.8V のリファレンス電圧があり、内部の電圧ループ エラー アンプにより、FB 電圧はリファレンス電

圧と等しくなるようにレギュレートされます。求められる出力電圧の設定点と、与えられた  $R_{FB1}$  の値について、式 3 を使用して  $R_{FB2}$  を決定します。

$$R_{FB2} = R_{FB1} \times \frac{0.8V}{V_{OUT} - 0.8V} \quad (3)$$

$$4k\Omega \leq \frac{R_{FB1} \times R_{FB2}}{R_{FB1} + R_{FB2}} \leq 100k\Omega \quad (4)$$

$R_{FB1}$  と  $R_{FB2}$  について選択した値が、式 4 で設定された要件を満たしていることを確認します。 $R_{FB1}$  には  $200k\Omega$  より小さい値を選択することがベスト プラクティスです。抵抗の値が大きいと、寄生リーク電流（たとえば、PCB の環境汚染によって引き起こされる）の影響を受けやすく、目的の出力電圧がシフトする可能性があるためです。リーク電流が小さい場合は、 $1M\Omega$  までの大きな帰還抵抗を使用して、無負荷時の消費電流を低減し、軽負荷時の効率を向上します。可変出力設定を使用する場合は、上側の帰還抵抗と並列にフィードフォワード コンデンサを接続することで、ループ位相マージンを改善できます。

### 7.3.5 スイッチング周波数 (RT)

LM65680/60/40 発振器を RT から PGND への抵抗でプログラミし、フリーランニング スイッチング周波数を  $300kHz \sim 2.2MHz$  に設定します。抵抗値を求めるには、式 5 を使用するか、図 7-3 を参照します。

$$R_{RT}[k\Omega] = \frac{16.4}{F_{SW}[MHz]} - 0.633 \quad (5)$$

図 7-3. スイッチング周波数の設定

たとえば、式 5 で  $F_{SW}$  を  $300kHz$  に設定すると、 $R_{RT}$  は  $54.03k\Omega$  となります。最も近い標準値として  $53.6k\Omega$  を選択します。または、表 7-1 に示すように、固定の  $400kHz$  または  $2.2MHz$  動作を行うには、RT をそれぞれ VCC または PGND に接続します。

表 7-1. スイッチング周波数の設定

| RT             | スイッチング周波数            |

|----------------|----------------------|

| VCC に接続        | 400kHz               |

| PGND に接続       | 2.2MHz               |

| RT 抵抗から PGND へ | $300kHz \sim 2.2MHz$ |

RT の抵抗が推奨範囲外になると、LM65680/60/40 は  $400kHz$  または  $2.2MHz$  に戻ることに注意してください。RT にパルス信号を印加して、強制的に同期を行わないでください。コンバータが外部クロック信号との同期を必要とする場合は、セクション 7.3.6 を参照してください。

### 7.3.6 モード選択およびクロック同期(MODE/SYNC)

MODE/SYNC ピンは、動作モードを構成し、外部クロック同期信号の入力として機能するマルチファンクションピンです。

表 7-2 に示すように、MODE/SYNC がグランドに接続されているか、ロジック Low に駆動されると、コンバータは自動モードで動作します。このピンが VCC に接続されているかロジック High に駆動されている場合、または外部クロックソースに同期している場合、コンバータは FPWM モードで動作します。

表 7-2. モード選択

| MODE/SYNC                                 | モード  | 動的モード変更 |

|-------------------------------------------|------|---------|

| PGND に接続するか、Low に駆動                       | 自動   | 有効      |

| VCC に接続するか、High (PGND より 2.5V を超えて高い) に駆動 | FPWM |         |

| 外部クロック信号を印加                               |      |         |

デバイスを自動モードから FPWM モードに移行するには、ピンを Low から High に駆動するか、同期信号を印加する必要があります。デバイスを FPWM モードから自動モードに移行するには、ピンを High から Low に駆動するか、同期信号を停止する必要があります。

注

動作モードを変更する、またはデバイスを外部クロックに同期させることは、起動後に PG が High に遷移した後でのみ可能です。

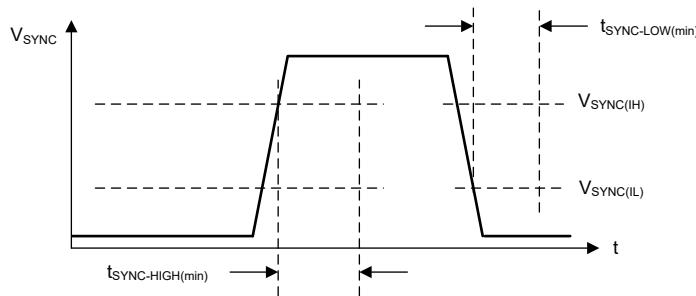

#### 7.3.6.1 クロックの同期

MODE/SYNC を使用して、内部発振器を 300kHz ~ 2.2MHz の範囲の外部クロック信号に同期します。内部同期パルス検出器を確実にトリガするには、外部クロックの振幅が SYNC 入力スレッショルドの  $V_{SYNC(HH)}$  と  $V_{SYNC(IL)}$  を満たす必要があります。最小 SYNC オンおよびオフ パルスの時間は、それぞれ  $t_{SYNC-ON(min)}$  および  $t_{SYNC-OFF(min)}$  よりも長くする必要があります。

外部クロック信号は、電源投入後に PG が High に遷移したときにのみ印加できることに注意してください。電源投入前(またはピンの検出時)に印加された場合、LM65680/60/40 はクロック信号を検出できません。

図 7-4. クロック信号の検出に必要な条件を含む標準的な SYNC 波形

#### 7.3.6.2 クロックのロック

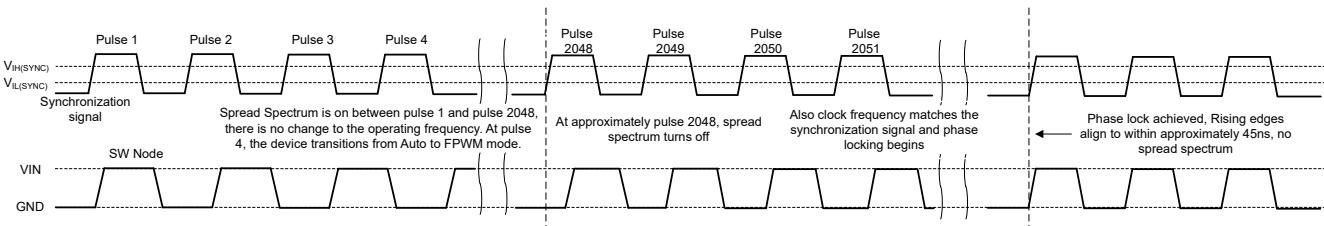

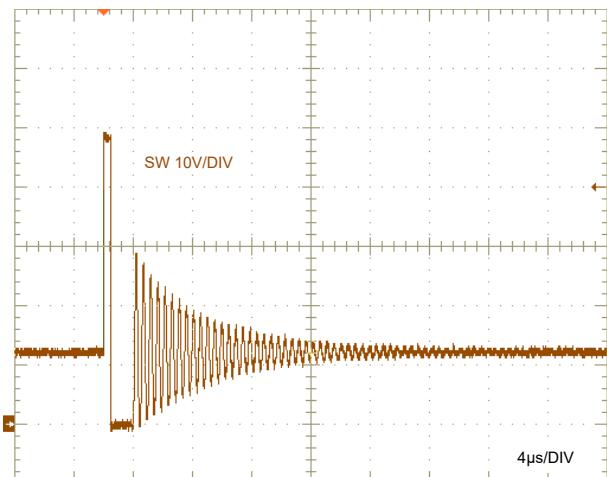

有効な同期信号が検出されると、LM65680/60/40 はクロックのロック手順を開始します。約 2048 パルスの後、内部発振器の周波数は同期信号の周波数に変更されます。周波数が突然調整されますが、LM65680/60/40 は位相を維持し、フリーランニングでの動作と、同期周波数での動作の中間に位置するクロックサイクルは、それらの中間の長さになります。長すぎる、または短すぎるパルスはありません。周波数がロックされた後で、立ち上がり同期エッジと、スイッチノードの立ち上がりパルスとが対応するように、数十サイクルかけて位相が調整されます。[図 7-5](#) を参照してください。

パルス 4 で、同期信号が検出されます。約 2048 パルスの後、信号は同期する準備ができ、グリッチ フリーの手法を使用して周波数を調整し、位相をロックします。

**図 7-5. 同期プロセス**

### 7.3.7 デバイス構成 (CNFG/SYNCOUT)

LM65680/60/40 は、内部または外部補償を持つスタンダードアロン コンバータとして、または外部補償を使用する 2 相コンバータとして動作できます。CNFG/SYNCOUT はデバイス構成ピンとして機能します。

CNFG/SYNCOUT は、デバイスをプライマリ デバイスまたはセカンダリ デバイスとして構成し、内部補償 (1 相動作) と外部補償 (1 相または 2 相動作) のいずれかを選択し、表 7-3 に示すように DRSS/MCOMM ピンの機能に影響を及ぼします。

**表 7-3. デバイス設定**

| CNFG/SYNCOUT     | 構成                                | DRSS/MCOMM の機能   |

|------------------|-----------------------------------|------------------|

| PGND への短絡        | セカンダリ デバイス、SYNCOUT ディセーブル         | MCOMM 入力         |

| 49.9kΩ から PGND へ | プライマリ デバイス、外部 COMP、SYNCOUT イネーブル  | DRSS 制御、MCOMM 出力 |

| VCC への短絡         | プライマリ デバイス、内部 COMP、SYNCOUT ディセーブル | DRSS 制御          |

### 7.3.8 デュアルランダムスペクトラム拡散機能 (DRSS)

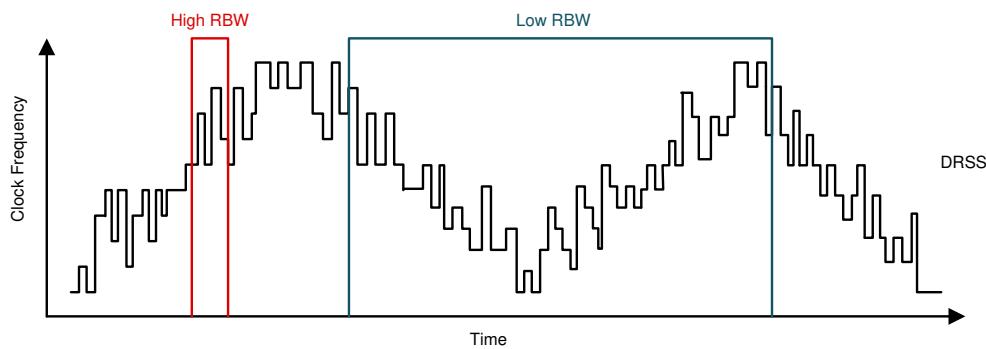

LM65680/60/40 にはデュアルランダムスペクトラム拡散 (DRSS) 機能があり、広い周波数範囲にわたって電源の EMI を低減します。図 7-6 に示すように、DRSS 機能は、低周波数の三角波変調プロファイルと、高周波数のサイクル単位の疑似ランダム変調プロファイルを組み合わせたものです。低周波数の三角波変調は低い無線周波数帯域で性能を向上させ、高周波のランダム変調は高い無線周波数帯域で性能を向上させます。

スペクトラム拡散は、狭帯域信号を広帯域信号に変換し、エネルギーを複数の周波数にわたって拡散することで機能します。業界規格では周波数帯域ごとに異なる EMI レシーバ解像度の帯域幅 (RBW) 設定を要求しているため、RBW はスペクトラム拡散の性能に影響を及ぼします。DRSS は、低周波数の三角波変調と、高周波数のサイクル単位のランダム変調プロファイルにより、それぞれ低 RBW および高 RBW での EMI 性能を同時に向上できます。DRSS により、CISPR 25 用の伝導エミッションを、低周波数帯域 (150kHz ~ 30MHz) で最大 10dB $\mu$ V、高周波帯域 (30MHz ~ 108MHz) で 5dB $\mu$ V 低減できます。MODE/SYNC に外部クロック信号を印加すると、DRSS はディセーブルされます。

**図 7-6. デュアルランダムスペクトラム拡散機能の実装**

このデバイスは、広い低周波数変調プロファイルを提供し、6kHz の平均変調周波数でスイッチング周波数を  $\pm 10\%$  拡散します。表 7-4 に示すように、LM65680/60/40 にはスイッチ ノード波形整形機能もあり、イネーブルされるとスイッチ ノードの電圧の立ち上がり遷移を調整して、リンギングとオーバーシュートを低減します。

表 7-4. DRSS とスルーレート制御

| DRSS/MCOMM              | DRSS                    | スルーレート制御 |

|-------------------------|-------------------------|----------|

| VCC へ短絡 <sup>(1)</sup>  | イネーブル、 $\pm 10\%$ 、6kHz | 有効       |

| オープンのまま                 | イネーブル、 $\pm 10\%$ 、6kHz | 有効       |

| 150kΩ から PGND へ         | イネーブル、 $\pm 10\%$ 、6kHz | ディセーブル   |

| 49.9kΩ から PGND へ        | ディセーブル                  | 有効       |

| PGND へ短絡 <sup>(1)</sup> | ディセーブル                  | ディセーブル   |

(1) 1相動作でのみ有効です。

### 7.3.9 ハイサイド MOSFET ゲート ドライブ(BST)

ハイサイド パワー MOSFET のゲートドライバには、MOSFET がオンのとき VIN より高いバイアス電圧が必要です。BST から SW への間に接続されたコンデンサは、BST の電圧を  $V_{SW} + V_{VCC}$  に昇圧するブートストラップ電源として動作します。LM65680/60/40 は、外付け部品数を最小限に抑えるためにブートストラップ ダイオードを内蔵しています。TI では、X7R 誘電体を使用した、定格 10V の 100nF BST コンデンサを推奨します。

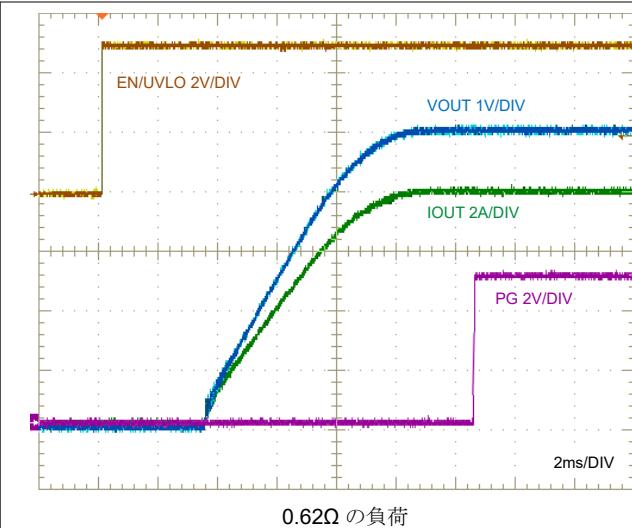

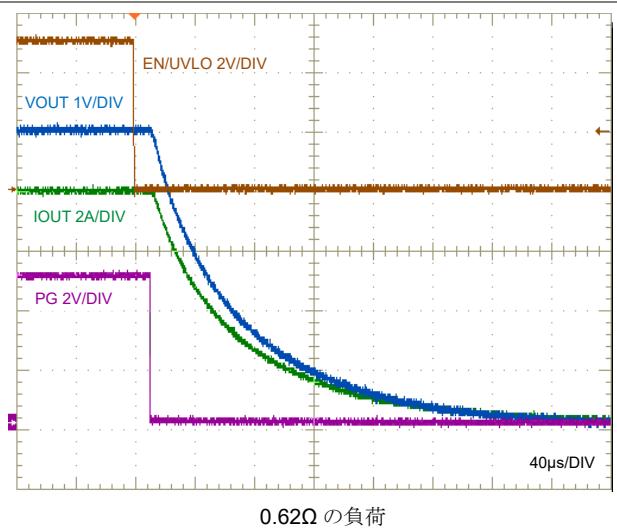

### 7.3.10 構成可能なソフトスタート(SS)

LM65680/60/40 コンバータにはソフトスタート機能があり、ターゲットのレギュレーション電圧をゆっくりと上昇させて、しだいに定常状態の動作点まで到達します。これにより、スタートアップ時の出力電圧のオーバーシュートと大きな突入電流を防止できます。デバイスは、以下のいずれかの条件に基づいてソフトスタートを開始します：

- IC の VIN ピンに電力が供給され、VIN と VCC の両方について UVLO が解除された

- EN/UVLO が High になり、デバイスがオンになった

- ヒップ待機期間から回復した

- サーマル シャットダウン保護からの回復

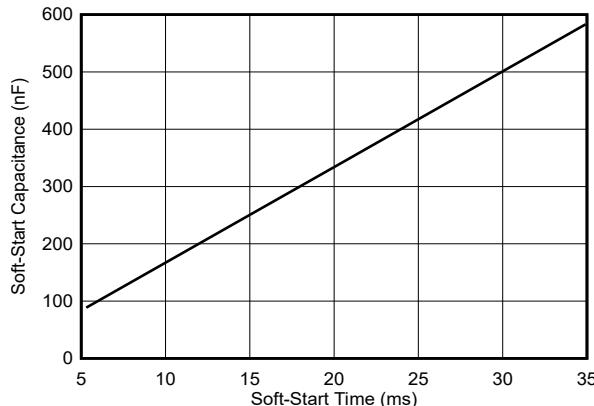

LM65680/60/40 を使用する最も簡単な方法は、5.3ms の固定ソフトスタート時間の間、SS ピンをオープンのままにすることです。大きい出力容量、高い出力電圧、その他の特別な要件を持つアプリケーションでは、SS と PGND との間にコンデンサを接続してソフトスタート時間を延長します。式 6 を使用するか、図 7-7 を参照し、目的のソフトスタート時間  $t_{SS}$  に基づいて  $C_{SS}$  の値を選択します。

$$C_{SS}[\text{nF}] = 16.7 \times t_{SS}[\text{ms}] \quad (6)$$

たとえば、目的のソフトスタート時間が 12ms なら、式 6 から  $C_{SS}$  の値として 200nF が得られます。最も近い標準値として、220nF を選択します。

図 7-7. ソフトスタート時間の設定

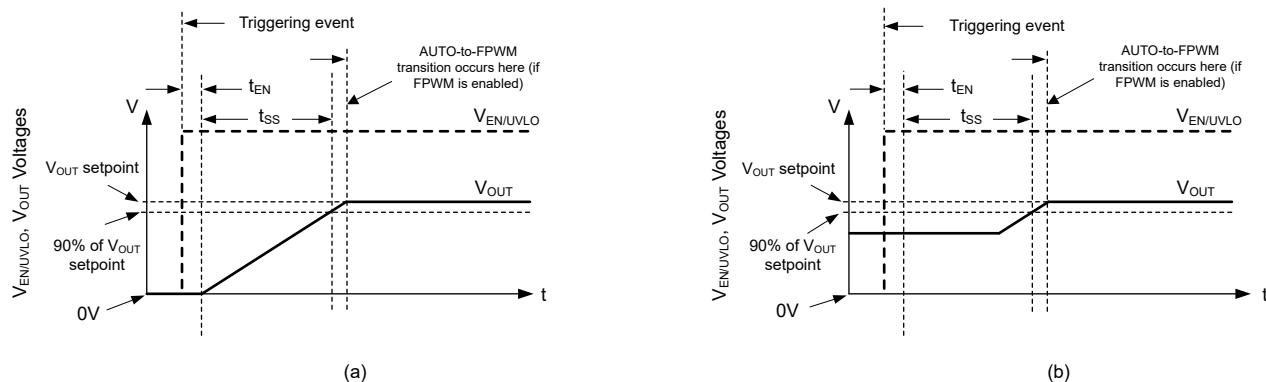

ソフトスタートを開始すると、デバイスは次の動作を実行します：

- 出力電圧をレギュレートする内部基準電圧が、ゆっくりとゼロから上昇します。その結果、出力電圧が  $t_{SS}$  の時間をかけて目的の値の 90% に達します。

- 動作モードは自動に設定され、出力電圧がプルダウンされず、プリバイアスされたスタートアップが発生するよう、ダイオード エミュレーションが有効化されます。

- ソフトスタートの間は、ヒップアップ モード保護がディセーブルのままでです。[セクション 7.3.11.3](#) を参照してください。

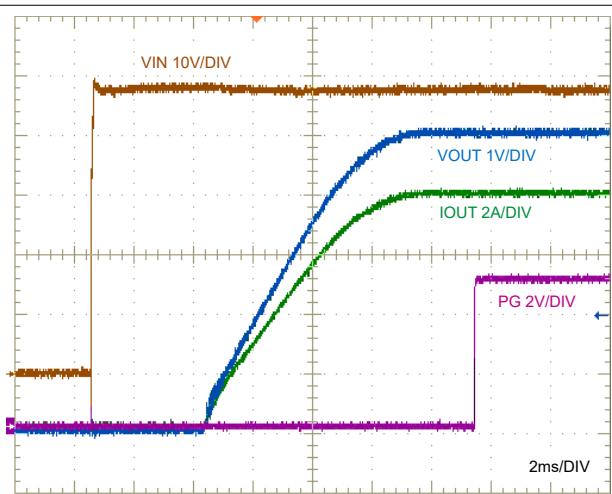

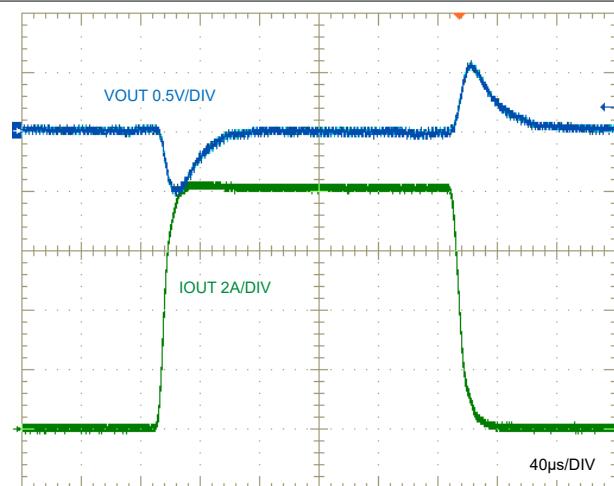

これらの動作を組み合わせることで、突入電流が制限されるスタートアップ プロファイルが得られ、大きな出力キャパシタンスと大負荷の状況で、スタートアップ時に電流制限に近づいてもヒップアップがトリガされないようにできます。[図 7-8](#) を参照してください。

ソフトスタートの開始後、出力電圧は時間間隔  $t_{SS}$  の後で、出力設定点の 90% に達します。デバイスでは、ソフトスタートの間は FPWM とヒップアップがディセーブルで、出力電圧がレギュレーションに達するとこれらのモードを有効化します。

図 7-8. 出力電圧のソフトスタート：プリバイアスなし (a)、プリバイアスあり (b)

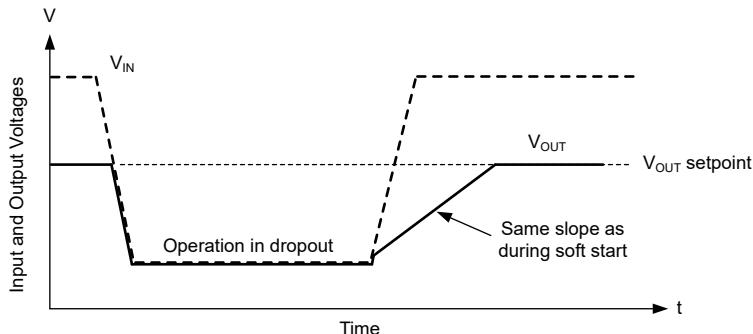

### 7.3.10.1 ドロップアウトからの回復

出力電圧の低下が数 % を超えるとき (たとえば、入力電圧が出力電圧の設定点を下回るとき) は常に、回復中に出力電圧はゆっくりと上昇します。この条件はドロップアウトからの回復と呼ばれ、ソフトスタートとは 3 つの重要な違いがあります：

- リファレンス電圧は、出力電圧の設定点を実現するために必要な値よりも約 1% 高い値に設定される。基準電圧はゼロからはスタートしません。

- 出力電圧が設定点の 40% 未満である場合のみ、ヒップアップが許可される。[セクション 7.3.11.3](#) で説明したように、このデバイスはドロップアウト動作時にヒップアップを禁止します。

- ドロップアウトからの回復中、FPWM モードが許可される。外部電源によって出力電圧が突然プルアップされた場合、コンバータは出力をプルダウンする場合があります。通常動作中に存在するすべての保護機能は作動しており、出力が高電圧またはグランドに短絡した場合にデバイスが保護されることに留意してください。

この機能はドロップアウトからの回復という名前ですが、出力電圧が出力の設定点よりも数 % 低くなると常にアクティブになります。この動作は主に、以下の条件で発生します。

- ドロップアウト: 目的の出力電圧を維持するのに十分な入力電圧がない場合。

- 過電流: ヒップルをトリガするほどの大きさではない過電流イベントが発生した場合

出力電圧の低下が、高負荷と低入力電圧のどちらによるものでも、出力が設定点を下回る原因となっている条件が解消された後、スタートアップ時と同じ速度で出力電圧が上昇します。ドロップアウトが原因でヒップルがトリガされなかった場合も、回復中に 64 クロック サイクルを超えて出力電圧が定点の 40% を下回った場合、原則としてヒップルがトリガされる可能性があります。

図 7-9. ドロップアウトからの回復

### 7.3.11 保護機能

LM65680/60/40 には、包括的な安全機能セットがあります:

- 出力低電圧および過電圧の検出機能を備えたパワーグッドモニタ

- ヒップルモードによる過電流および出力短絡保護回路

- サーマルシャットダウン(TSD)保護

#### 7.3.11.1 パワーグッドモニタ(PG)

LM65680/60/40 は、システムの電源シーケンシングと監視を簡素化するためのパワーグッド機能を備えています。パワーグッド機能を使用すると、LM65680/60/40 から電源を供給されるダウンストリームの回路をイネーブルにしたり、負荷スイッチなどのダウンストリームの保護回路を制御したり、シーケンス電源を起動したりできます。

PG は、可変出力の設定では FB を、固定出力構成では BIAS を使用して、ウインドウコンパレータにより出力電圧を監視します。PG は、出力電圧がレギュレーション状態のとき、高インピーダンスのオープンドレイン状態に切り替わります。出力電圧が電圧の設定点から  $\pm 5\%$  の範囲を超えると、PG が Low に駆動され、出力の過電圧または低電圧状態をシステムに警告します。PG の立ち下りエッジにおける 114 $\mu$ s のグリッチ除去フィルタにより、遷移中の PG の誤トリップが防止されます。出力電圧がレギュレーションウインドウ内に戻ったとき、PG の立ち上がりエッジにある 2ms のフィルタにより、ダウンストリーム部品のための追加の処理時間が得られます。

TI は、PG ピンから 30V 以下の関連するレールへの 100k $\Omega$  プルアップ抵抗を使用することを推奨します。ソフトスタート中および LM65680/60/40 がディセーブルのとき、PG は Low にアサートされます。

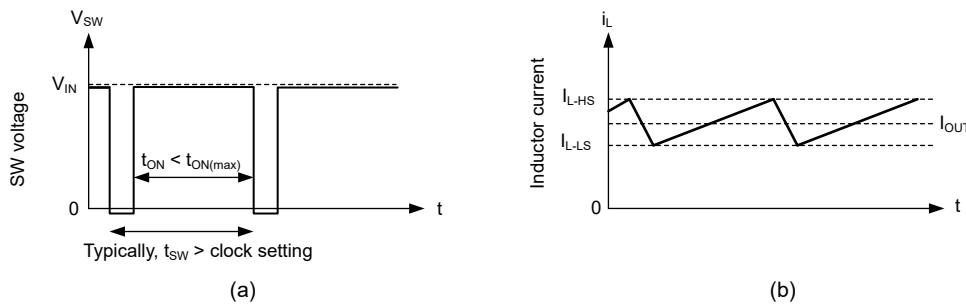

#### 7.3.11.2 過電流および短絡保護

LM65680/60/40 は、ハイサイドとローサイドのパワー MOSFET の両方でサイクル毎に電流を制限することで、過電流状態から保護されます。

下限側 MOSFET 過電流保護機能は、ピーク電流のモード制御の性質を利用して実装されています。ハイサイド電流は、短いブランкиング時間の後でハイサイド MOSFET がオンになったときに検出されます。ハイサイド電流は、固定電流

設定点、または電圧レギュレーション ループの出力からスロープ補償を引いた値のうち、どちらか小さい方と、スイッチング サイクルごとに比較されます。

ローサイド MOSFET がオンになると、MOSFET を通過する電流も検出され、監視されます。ローサイド MOSFET は、ハイサイド MOSFET と同様に、電圧制御ループの指示に従ってオフになります。ローサイド デバイスでは、発振器が正常に新しいスイッチング サイクルを開始したとしても、電流制限を超えるとターンオフは禁止されます。また、ハイサイド デバイスと同様に、ターンオフ電流に許容される大きさには限界があります。これはローサイド電流制限と呼ばれます。値については、「[電気的特性](#)」を参照してください。ローサイド電流制限が作動すると、ローサイド MOSFET はオンのままで、ハイサイド MOSFET はオフになります。ローサイド電流が制限値を下回った後で、ローサイド MOSFET がオフになります。ハイサイド MOSFET が最後にオンになってから 1 クロック周期以上が経過すると、ハイサイド MOSFET は再度オンになります。

**図 7-10. 電流制限波形：スイッチ電圧 (a)、インダクタ電流 (b)**

ハイサイドおよびローサイド電流制限の動作による実質的な影響は、IC がヒステリシス制御で動作することです。電流波形は  $I_{L-HS}$  と  $I_{L-LS}$  との間の値をとるため、デューティサイクルが極めて高い場合を除き、出力電流はこれら 2 つの値の平均値に近くなります。電流制限での動作後、出力電圧がゼロに近づくにつれて、ヒステリシス制御が使用され、電流は増加しなくなります。

過負荷状態が解消されると、デバイスはソフトスタート中であるかのように回復します。[セクション 7.3.10.1](#) を参照してください。出力電圧が意図した出力電圧の約 0.4 倍を下回ると、ヒップがトリガされる可能性があることに注意してください。

### 7.3.11.3 ヒップモード保護

LM65680/60/40 は、連続 64 クロック サイクル (ヒップモードのアクティビ化遅延  $t_{HICDLY}$  に対応) にわたって、以下のすべての条件が満たされる場合、ヒップモード保護に入ります。

- ・ ソフトスタートの開始から 5.3ms を超える時間間隔が経過した ([セクション 7.3.10.1](#) を参照)。

- ・ 出力電圧が、出力電圧の設定点の約 40% を下回っている。

- ・ デバイスがドロップアウト (PWM オフ時間が COMP によって制御されている状態と定義される) で動作していない。

ヒップモードでは、デバイスはシャットダウンし、内部ソフトスタートを使用しているときは、約 48ms の遅延後に再起動を試みます。外部ソフトスタートを使用している場合、遅延時間はソフトスタート時間の 6 倍に増加します。ヒップモードは、極度の過電流や短絡状態の際にデバイスの消費電力を低減するのに役立ちます。

### 7.3.11.4 サーマルシャットダウン

サーマルシャットダウンは、IC の接合部温度が 165°C (標準値) を超えると内部スイッチをオフにすることで、LM65680/60/40 の消費電力を制限します。サーマルシャットダウンは 155°C 未満ではトリガされません。サーマルシャットダウンが作動した後、ヒステリシスにより、接合部温度が約 9°C 低下するまで、デバイスのスイッチングは抑止されます。接合部温度が 156°C (標準値) を下回ると、LM65680/60/40 はソフトスタートを試みます。

接合部の温度が高いために LM65680/60/40 がシャットダウンしている場合でも、VCC は依然としてレギュレーション状態に維持されます。短絡による過熱が VCC に及ぶことを防止するため、デバイスがサーマルシャットダウンしている間は VCC バイアス電源サブレギュレータの電流制限が引き下げられます。VCC サブレギュレータがこのシャットダウン状態で供給できる電流は、わずか数ミリアンペアです。

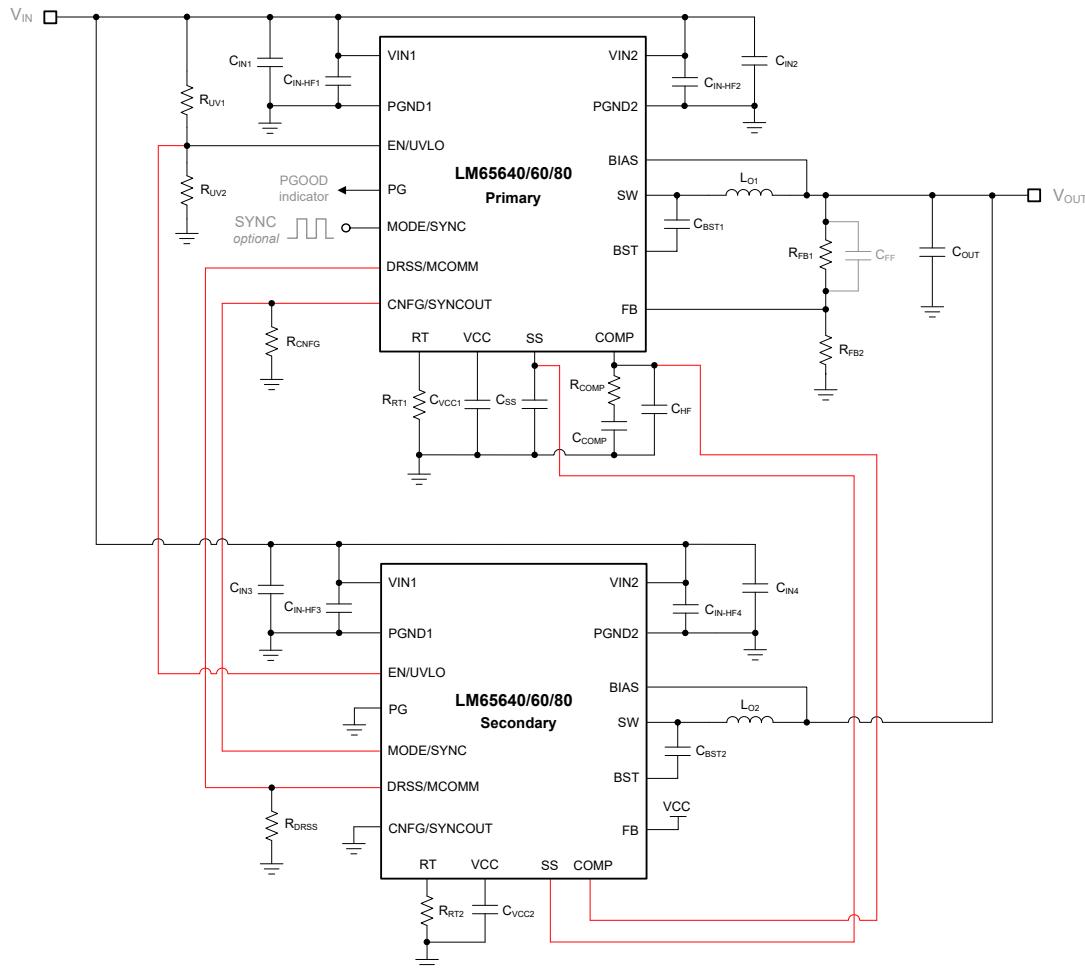

### 7.3.12 2相、単一出力の動作

2つのLM65680/60/40コンバータICを使用して、2相、单一出力の動作を実現します。付加的な位相を追加することはできません。図7-11に従って、1番目と2番目のデバイスをそれぞれプライマリおよびセカンダリとして設定します。この動作により、セカンダリICの帰還エラーアンプはディセーブルになり、帰還エラーアンプは高インピーダンス状態になります。図7-11に示すように、セカンダリデバイスのFBをVCCに接続します。さらに、プライマリとセカンダリのICのCOMPピンを、最短のパターン長で互いに接続します。プライマリデバイスの近くに外部補償回路を追加します。2相構成で動作する場合、内部補償機能は利用できません。

図7-11. 単一出力二相動作の概略回路図

プライマリデバイスのCNFG/SYNCOUTを、セカンダリデバイスのMODE/SYNCに接続します。プライマリのSYNCOUT信号は位相差180°で、インターリープ動作を容易にします。2相構成で動作するときは、両方のデバイスを同時にイネーブルして起動します。

2相動作用に構成されているとき、DRSS/MCOMMはプライマリデバイスからセカンダリデバイスにモード情報を伝達します。プライマリからのMCOMM High信号により、セカンダリはFPWMモードで動作します。逆に、プライマリからのMCOMM Low信号により、セカンダリはPFMモードに設定されます。プライマリデバイスとセカンダリデバイスのMCOMMピンは互いに接続する必要があります。フル通信を実現するには、プライマリデバイスとセカンダリデバイスのSSピンを接続します。

[『多相降圧コンバータの利点』](#)[Analog Design Journal](#)および[『多相降圧設計のすべて』](#)[アプリケーションノート](#)も参照してください。

## 7.4 デバイスの機能モード

### 7.4.1 シャットダウンモード

EN/UVLO ピンは、本デバイスの電気的オン / オフ制御に使用できます。EN/UVLO 電圧が 0.9V を下回ると、デバイスはシャットダウン モードになり、入力静止電流が 1 $\mu$ A 未満になります。

### 7.4.2 アクティブモード

LM65680/60/40 は、次の条件が発生するとアクティブ モードになります：

- EN/UVLO が  $V_{EN-TH(R)}$  を上回る。

- $V_{IN}$  が  $V_{IN_{UVLO(R)}}$  を上回る。

- 他のフォルト条件は存在しない。

保護機能については、[セクション 7.3.11](#) を参照してください。この動作を可能にする最も簡単な方法は、EN/UVLO を  $V_{IN}$  に接続することです。これにより、印加された入力電圧が最小  $V_{IN_{UVLO(R)}}$  である 3.4V (標準値) を超えるとスタートアップが可能になります。

アクティブ モードで、LM65680/60/40 は負荷電流、入力電圧、出力電圧に応じて次の 6 つのサブモードのいずれかになります：

- 固定スイッチング周波数とピーク電流モード動作による連続導通モード (CCM)

- 自動モードのときに負荷電流がインダクタのピークツーピークリップ電流の 1/2 未満である場合、不連続導通モード (DCM)。電流が減少し続けると、デバイスはパルス周波数変調 (PFM) に移行し、スイッチング周波数を減らしてレギュレーションを維持します (これによりスイッチング損失が減少し、軽負荷時の効率が向上します)。

- 要求された低デューティサイクルでの全周波数動作に必要なデバイスのオン時間が、 $t_{ON(min)}$  でサポートされていないとき、最小オン時間動作

- 強制パルス幅変調 (FPWM) は、固定スイッチング周波数の CCM と似ていますが、固定周波数の範囲が全負荷から無負荷まで拡張されます。

- 出力電圧が常に出力設定点の 40% を上回る、電流制限条件。

- ドロップアウトを最小限に抑えるためにスイッチング周波数が低下したときの、ドロップアウト モード。

- ドロップアウトからの回復は、他の動作モードと似ていますが、出力電圧の設定点が、プログラムされた設定点に達するまで徐々に上昇します。

## 8 アプリケーションと実装

### 注

以下のアプリケーション情報は、テキサス・インスツルメンツの製品仕様に含まれるものではなく、テキサス・インスツルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。また、お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 8.1 アプリケーション情報

LM65680/60/40 は降圧コンバータのファミリで、比較的少ない数個の外部部品で広い範囲の電源電圧をレギュレートされた出力電圧に変換でき、最大 8A の出力電流を供給できます。包括的な [クリックスタート カリキュレータ](#) をダウンロードでき、LM65680/60/40 ベースのレギュレータ回路の設計プロセスを促進して合理化できます。

#### 8.1.1 パワートレインコンポーネント

同期整流降圧レギュレータの設計を適切に完成させるには、レギュレータのパワートレイン部品を包括的に理解することが不可欠です。以下のセクションでは、インダクタ、入力および出力コンデンサ、EMI 入力フィルタについて説明します。

##### 8.1.1.1 降圧インダクタ

多くのアプリケーションでは、公称入力電圧におけるインダクタのリップル電流  $\Delta I_L$  が最大 DC 出力電流の 30%~50% の間になるように降圧インダクタンスを選択します。[式 8](#) に示されるピークインダクタ電流に基づき、[式 7](#) を使用してインダクタンスを選択します。

$$L_0 = \frac{V_{OUT}}{\Delta I_L \times F_{SW}} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right) \quad (7)$$

$$I_{L(pk)} = I_{OUT} + \frac{\Delta I_L}{2} \quad (8)$$

インダクタのデータシートをチェックし、インダクタの飽和電流が特定の設計におけるピークインダクタ電流よりも大きいことを確認します。フェライトの設計はコア損失が非常に小さく、高スイッチング周波数で好まれます。そのため、設計の目標を銅での損失と飽和の防止に集中できます。低インダクタのコア損失は、無負荷の入力電流の低下と、軽負荷時の効率の向上により明らかです。ただし、フェライトのコア素材は飽和特性が高く、飽和電流を超過するとインダクタンスは急激に低下します。この動作の結果、インダクタのリップル電流は急激に増加し、出力電圧リップルも上昇するため、当然効率は低下し、信頼性も損なわれます。一般的に、インダクタの飽和電流はコア温度が上がるにつれて減少することに注意してください。もちろん、インダクタの飽和を防止するには正確な過電流保護が重要です。

##### 8.1.1.2 出力コンデンサ

出力コンデンサ  $C_{OUT}$  はインダクタのリップル電流を導通し、ステップ負荷過渡イベントのために電荷を蓄積します。一般的に、セラミックコンデンサの ESR は非常に低いため、出力電圧リップルとノイズは低減されますが、ポリマー電解コンデンサは過渡負荷イベント用の比較的小さなフットプリントのものでも、バルク容量は非常に大きくなります。[式 9](#) に、 $\Delta V_{OUT}$  で表されるピークツーピーク出力電圧リップルの、静的仕様に基づく出力キャパシタンスを示します。

$$C_{OUT} \geq \frac{\Delta I_L}{8 \times F_{SW} \sqrt{\Delta V_{OUT}^2 + (R_{ESR} \times \Delta I_L)^2}} \quad (9)$$

コンデンサのデータシートには、ESR が仕様として明記されているか、インピーダンスと周波数の関係の曲線によって暗黙的に記載されています。種類、サイズ、構造に応じて、電解コンデンサは  $10m\Omega$  以上の大きな ESR と、 $10nH$  を超える比較的大きな ESL があります。PCB パターンは寄生抵抗とインダクタンスにも寄与します。セラミック出力コンデンサはスイッチング周波数における ESR と ESL への寄与が小さく、容量性インピーダンスの成分が優勢です。ただし、セラミックコンデンサのパッケージと電圧定格によっては、実効容量は印加された DC 電圧と動作温度で大幅に低下することがあります。

応答が小信号制限され、クロスオーバー周波数  $f_C$  で設定されている場合、動的負荷電流の変化中に出力電圧制限を満たすための出力キャパシタンスの推定値を、式 10 に示します。

$$C_{OUT} \geq \frac{\Delta I_{OUT}}{2 \times \pi \times f_C \times \Delta V_{OUT}} \quad (10)$$

式 9 の ESR の項を無視すると、出力リップルの要件を満たすために必要な最小セラミック容量を簡単に見積もることができます。その後で、負荷過渡仕様を満たすために容量が必要かどうかを、式 10 で判定します。LM65680/60/40 コンバータを使用して 5V 出力を供給する場合、2 ~ 4 個の 47μF、10V、X7R、1210 のセラミックコンデンサが一般的な選択です。12V 出力は、通常は 2 ~ 4 個の 22μF、25V、X7R、1210 コンデンサです。

### 8.1.1.3 入力コンデンサ

入力コンデンサは、 $di/dt$  が大きいスイッチング電流により降圧電力段に発生する、入力リップル電圧を制限するために使用されます。TI は、幅広い温度範囲で低インピーダンスと高い RMS 電流定格を実現する、X7R 誘電体を使用した 1210 セラミックコンデンサの使用を推奨します。スイッチング電力ループの寄生インダクタンスを最小化するため、入力コンデンサを VIN および PGND ピンペアとできるだけ近く配置します。1 相降圧レギュレータの入力コンデンサの RMS 電流は、式 11 で計算されます。

$$I_{CIN(rms)} = \sqrt{D \times \left( I_{OUT}^2 \times (1 - D) + \frac{\Delta I_L^2}{12} \right)} \quad (11)$$

RMS 電流は、 $D = 0.5$ において  $I_{OUT}/2$  の最大値に達します。理想的には、入力電圧源が入力電流の DC 成分を供給し、入力コンデンサが AC 成分を供給します。インダクタのリップル電流を無視すると、降圧レギュレータの入力コンデンサは、D 時間に振幅 ( $I_{OUT} - I_{IN}$ ) の電流をソースし、1-D 時間に  $I_{IN}$  をシンクします。そのため、入力コンデンサは、出力電流に等しいピークツーピーク振幅の方形波電流を導通します。この結果、AC リップル電圧の合成容量成分は三角波になります。ESR 関連のリップル成分とともに、ピークツーピークリップ電圧の振幅が式 12 で計算されます。

$$\Delta V_{IN} = \frac{I_{OUT} \times D \times (1 - D)}{F_{SW} \times C_{IN}} + I_{OUT} \times R_{ESR} \quad (12)$$

$\Delta V_{IN}$  の入力電圧リップル仕様に基づいて、特定の負荷電流に必要な入力容量は、式 13 で計算されます。

$$C_{IN} \geq \frac{D \times (1 - D) \times I_{OUT}}{F_{SW} \times (\Delta V_{IN} - R_{ESR} \times I_{OUT})} \quad (13)$$

LM65680/60/40 には、パッケージの両側に VIN ピンと PGND ピンが対称的に配置されています。これにより、入力コンデンサを分割して、内部パワー MOSFET に対して最適に配置し、入力のバイパスの効果を高めることができます。反対の電流ループは自己キャンセルフィールドを作成し、伝導と放射の両方のエミッションを低減します。ほとんどのアプリケーションでは、4 つの 4.7μF または 10μF のセラミックコンデンサで十分です。また、各入力ピンのペア [VIN1、PGND1] および [VIN2、PGND2] に、小さなケースサイズ (0402 または 0603) のセラミックコンデンサを配置し、高周波数における実効インピーダンスを低減します。

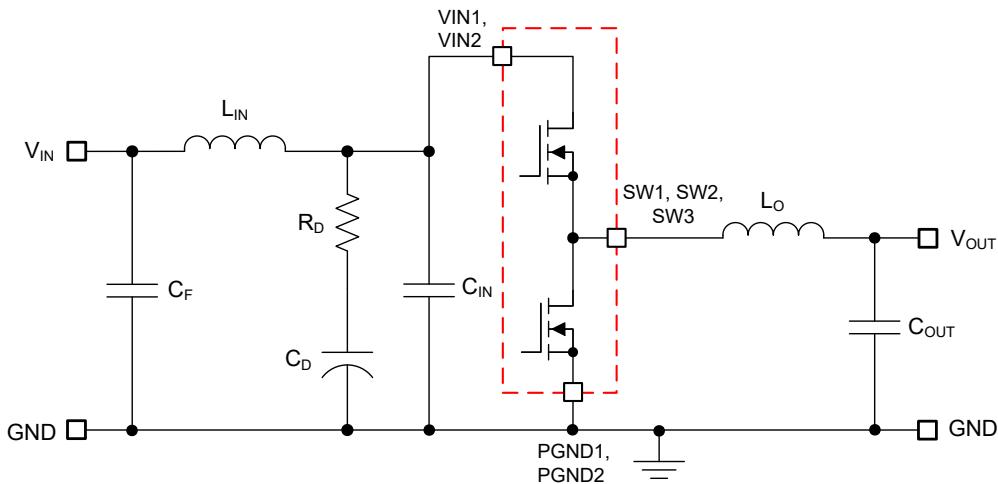

### 8.1.1.4 EMI フィルタ

スイッチングレギュレータは負の入力インピーダンス特性を示し、その値は最小入力電圧および最大負荷において最小になります。LC フィルタの減衰不足は、フィルタの共振周波数に対して出力インピーダンスが高いことを示しています。安定性のため、EMI フィルタの出力インピーダンスは、コンバータの入力インピーダンスの絶対値よりも小さくする必要があります。

$$Z_{IN} = \left| -\frac{V_{IN(min)}^2}{P_{IN}} \right| \quad (14)$$

図 8-1 の EMI フィルタを基礎とする設計手順は次のとおりです:

- EMI フィルタについて、スイッチング周波数で要求される減衰を計算します。ここで、 $C_{IN}$  はコンバータの入力における既存の容量を表しています。

- 1 $\mu$ H ~ 10 $\mu$ H の範囲の入力フィルタインダクタ  $L_{IN}$  を選択します。大電流設計で DC 損失を低減するには、より小さい値を使用します。

- 入力側のフィルタ容量  $C_F$  を計算します。

図 8-1. 降圧 レギュレータ用のパッシブ  $\pi$  段 EMI フィルタ

入力電流波形のフーリエ級数から最初の高調波電流を計算し、その値に入力インピーダンス(インピーダンスは既存の入力コンデンサ  $C_{IN}$  で定義)を乗算します。スイッチング周波数で必要なフィルタ減衰は、式 15 で与えられます。

$$Attn = 20\log\left(\frac{I_{L(PK)}}{\pi^2 \times F_{SW} \times C_{IN}} \times \sin(\pi \times D_{MAX}) \times \frac{1}{1\mu V}\right) - V_{MAX} \quad (15)$$

ここで、

- $V_{MAX}$  は、適用可能な伝導 EMI 標準、たとえば CISPR 32 Class B などで許容される放射レベル ( $\text{dB}\mu\text{V}$ ) です。

- $C_{IN}$  は、レギュレータの既存の入力容量です。

- $D_{MAX}$  は、最大デューティサイクルです。

- $I_{L(PK)}$  はピークインダクタ電流です。

EMI フィルタ設計の観点では、入力時の電流を方形波としてモデル化します。式 16 を使用して、EMI フィルタの容量  $C_F$  を決定します。

$$C_F = \frac{1}{L_{IN}} \left( \frac{10 \frac{|Attn|}{40}}{2\pi \times F_{SW}} \right)^2 \quad (16)$$

スイッチング レギュレータに入力フィルタを追加すると、制御から出力への伝達関数が変更されます。フィルタの出力インピーダンスは、入力フィルタがレギュレータのループゲインに大きな影響を与えないよう、十分に低くする必要があります。インピーダンスは、フィルタの共振周波数でピークになります。フィルタの共振周波数は、式 17 で計算されます。

$$f_{res} = \frac{1}{2\pi \times \sqrt{L_{IN} \times C_F}} \quad (17)$$

$R_D$  の目的は、共振周波数におけるフィルタのピーク出力インピーダンスを低減することです。コンデンサ  $C_D$  は、入力電圧の DC 成分をブロックして、 $R_D$  での過剰な電力消費を防止します。コンデンサ  $C_D$  は、入力コンデンサ  $C_{IN}$  より大きな

容量で、共振周波数において  $R_D$  よりも低インピーダンスの必要があります。これにより、 $C_{IN}$  がメイン フィルタのカットオフ周波数に干渉することを防ぎます。共振周波数におけるフィルタの出力インピーダンスが高い場合は、ダンピングを追加します ( $L_{IN}$  と  $C_{IN}$  で形成されるフィルタの Q 値が大きすぎる場合)。式 18 に示されている値でのダンピングには、電解コンデンサ  $C_D$  を使用してください。

$$C_D \geq 4 \times C_{IN} \quad (18)$$

式 19 を使用して、ダンピング抵抗  $R_D$  を選択します。

$$R_D = \sqrt{\frac{L_{IN}}{C_{IN}}} \quad (19)$$

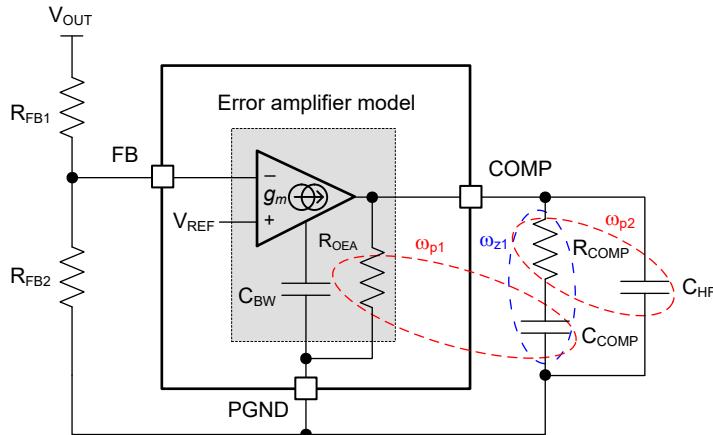

### 8.1.2 エラー アンプと補償

図 8-2 に、相互コンダクタンスのエラー アンプ (EA) を使用した Type-II 補償器を示します。式 20 に示すように、EA の開ループゲインの支配的な極は、EA 出力抵抗  $R_{OEA}$  と、実効帯域幅制限容量  $C_{BW}$  で設定されます。

$$G_{EA(openloop)}(s) = - \frac{g_m \times R_{OEA}}{1 + s \times R_{OEA} \times C_{BW}} \quad (20)$$

上の式では、EA の高周波ポールは無視されています。出力電圧から COMP までの補償器の伝達関数は、帰還分圧器からのゲインの寄与も含めて、式 21 で表現されます。

$$G_c(s) = \frac{\hat{v}_c(s)}{\hat{v}_{out}(s)} = - \frac{V_{REF}}{V_{OUT}} \times \frac{g_m \times R_{OEA} \times \left(1 + \frac{s}{\omega_{z1}}\right)}{\left(1 + \frac{s}{\omega_{p1}}\right) \times \left(1 + \frac{s}{\omega_{p2}}\right)} \quad (21)$$

ここで、

- $V_{REF}$  は帰還電圧リファレンス

- $g_m$  は EA 相互コンダクタンス

- $R_{OEA}$  は EA 出力インピーダンス

$$\omega_{z1} = \frac{1}{R_{COMP} \times C_{COMP}} \quad (22)$$

$$\omega_{p1} = \frac{1}{R_{OEA} \times (C_{COMP} + C_{HF} + C_{BW})} \cong \frac{1}{R_{OEA} \times C_{COMP}} \quad (23)$$

$$\omega_{p2} = \frac{1}{R_{COMP} \times (C_{COMP} || (C_{HF} + C_{BW}))} \cong \frac{1}{R_{COMP} \times C_{HF}} \quad (24)$$

EA の補償部品は、原点近くの極、ゼロ、高周波極を生成します。通常、 $R_{COMP} \ll R_{OEA}$ 、かつ  $C_{COMP} \gg C_{BW}$  および  $C_{HF}$  なので、近似値が有効です。図 8-2 ではポールを赤で囲み、ゼロを青で囲んでいます。

図 8-2. エラー アンプと補償ネットワーク

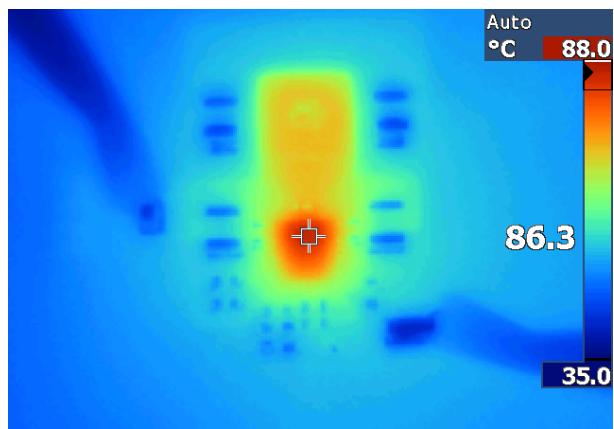

### 8.1.3 最大周囲温度

LM65680/60/40 の接合部温度は、最大値が 150°C に規定されているため、消費電力、ひいては利用可能な負荷電流が制限されます。式 25 に、重要なパラメータ間の関係を示します。

$$I_{OUT(max)} = \frac{T_J - T_A}{R_{\theta JA}} \times \frac{\eta}{1-\eta} \times \frac{1}{V_{OUT}} \quad (25)$$

ここで、

- $\eta$  = コンバータの効率 (インダクタ損失を含まない)

- $T_A$  = 周囲温度

- $T_J$  = 接合部温度

- $R_{\theta JA}$  = 主に PCB を経由した、IC 接合部から周囲の環境への実効熱抵抗。

明らかに、 $T_A$  と  $R_{\theta JA}$  の値が大きいと、利用可能な出力電流は減少します。実効  $R_{\theta JA}$  は重要なパラメータで、次のような多くの要因に依存します：

- IC の消費電力

- 気温とエアフロー

- PCB と銅製のヒートシンクの面積

- パッケージの下や近くにあるサーマルビアの数

- 隣接する部品の配置

LM65680/60/40 のクイックスタート カリキュレータを使用して、IC の電力損失を推定します。または、求められるアプリケーション要件に合わせて評価基板を調整し、電力損失とそれに伴う温度上昇を測定します。セクション 6.4 表に報告されている  $R_{\theta JA}$  の JESD 51-7 値は、実際のアプリケーションではめったに見られない、特定の一連の条件で測定されたものです。このため、この値は、実際のアプリケーションにおける IC の放熱性能を推定するためには役立ちません。

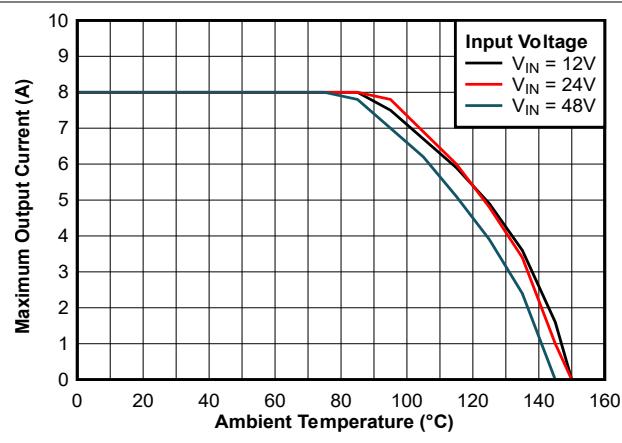

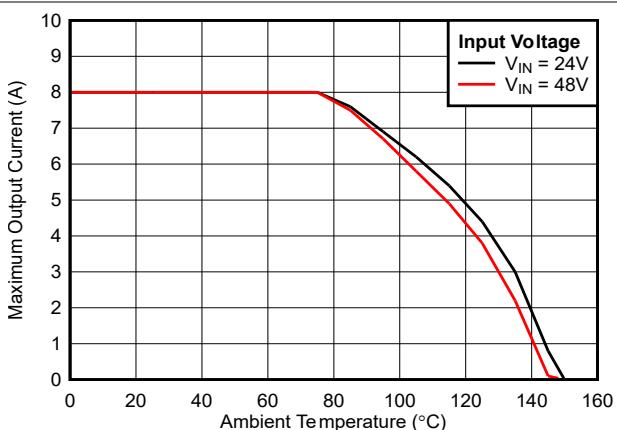

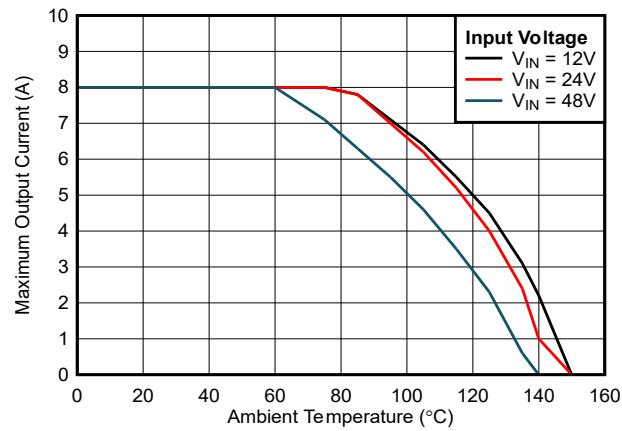

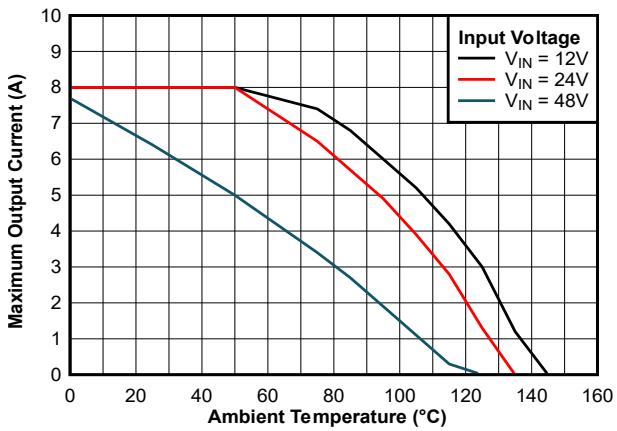

#### 8.1.3.1 ディレーティング曲線

図 8-3 から図 8-6 までは、LM65680 降圧レギュレータ評価基板を使用して得られたディレーティング曲線です。 $R_{\theta JA}$  は約 18°C/W となります。特定のアプリケーションの実際の性能は、前述の要因によって異なります。PCB の熱設計と、特定のアプリケーション環境における  $R_{\theta JA}$  を推定するためのガイドとして、[熱設計についてのリソース](#)を使用してください。

V<sub>IN</sub> = 12V, 24V, 48V

F<sub>SW</sub> = 400kHz

R<sub>θJA</sub> = 18°C/W

図 8-3. LM65680 の出力電流ディレーティングと周囲温度との関係 (5V<sub>OUT</sub>、400kHz)

V<sub>IN</sub> = 24V, 48V

F<sub>SW</sub> = 400kHz

R<sub>θJA</sub> = 18°C/W

図 8-4. LM65680 の出力電流ディレーティングと周囲温度との関係 (12V<sub>OUT</sub>、400kHz)

V<sub>IN</sub> = 12V, 24V, 48V

F<sub>SW</sub> = 800kHz

R<sub>θJA</sub> = 18°C/W

図 8-5. LM65680 の出力電流ディレーティングと周囲温度との関係 (5V<sub>OUT</sub>、800kHz)

V<sub>IN</sub> = 12V, 24V, 48V

F<sub>SW</sub> = 2.1MHz

R<sub>θJA</sub> = 18°C/W

図 8-6. LM65680 の出力電流ディレーティングと周囲温度との関係 (5V<sub>OUT</sub>、2.1MHz)

## 8.2 代表的なアプリケーション

LM65680/60/40 ファミリの同期整流降圧コンバータは、幅広い外付け部品とシステム パラメータで動作します。CNFG/ SYNCOUT を VCC に接続すると、コンバータが内部補償を使用するように設定されるため、COMP は開路のままでも PGND に接続してもかまいません。しかし、内部補償では、安定性のために最低限の出力容量が必要です。式 26 を使用して、出力容量に適切な値を求めるすることができます。

$$C_{\text{OUT}(\text{INTCOMP})} = \frac{K_{\text{INTCOMP}}}{f_C \times V_{\text{OUT}}} \quad (26)$$

ここで、

- $f_C$  は目的のループ クロスオーバー周波数で、スイッチング周波数の 10% ~ 15%、最高 100kHz に設定できます。

- LM65680、LM65660、LM65640 の  $K_{\text{INTCOMP}}$  は、それぞれ 36.5、27.2、20.1 です。

クイック リファレンスとして、内部補償と 3.3V または 5V の固定出力設定を使用するときの、各種アプリケーション パラメータの標準的な部品の値を表 8-1 に示します。これに対して、表 8-2、表 8-3、表 8-4 は、帰還分圧器を使用して出力電圧を設定するとき、それぞれ 8A、6A、4A デバイスの標準的な部品の値を示します。

これらの表には、標準的な入力電圧 48V と、リファレンスの最小実効出力容量値（電圧と温度に応じてディレーティングされる）に対応する設計の概要が示されています。

**表 8-1. 固定出力電圧 (3.3V または 5V) と内部補償の標準的な部品の値**

| 出力電圧 | スイッチング周波数 | FB  | LM65640、4A |                  | LM65660、6A |                  | LM65680、8A |                  |

|------|-----------|-----|------------|------------------|------------|------------------|------------|------------------|

|      |           |     | $L_o$      | $C_{\text{OUT}}$ | $L_o$      | $C_{\text{OUT}}$ | $L_o$      | $C_{\text{OUT}}$ |

| 3.3V | 400kHz    | GND | 5.6μH      | 130μF            | 4.7μH      | 180μF            | 3.3μH      | 220μF            |

| 5V   |           | VCC | 8.2μH      | 80μF             | 5.6μH      | 120μF            | 3.9μH      | 150μF            |

| 3.3V | 2.2MHz    | GND | 1μH        | 55μF             | 0.82μH     | 75μF             | 0.56μH     | 100μF            |

| 5V   |           | VCC | 1.5μH      | 40μF             | 1μH        | 50μF             | 0.82μH     | 70μF             |

**表 8-2. 可変出力電圧と内部補償機能を備えた LM65680 8A デバイスの標準的な部品の値**

| 出力電圧 | スイッチング周波数 | $L_o$  | $C_{\text{OUT}}$ | $R_{\text{FB}1}$ | $R_{\text{FB}2}$ | $C_{\text{FF}}$ |

|------|-----------|--------|------------------|------------------|------------------|-----------------|

| 3.3V | 400kHz    | 3.3μH  | 220μF            | 78.7kΩ           | 24.9kΩ           | 10pF            |

| 5V   |           | 3.9μH  | 150μF            |                  | 15kΩ             | 10pF            |

| 12V  |           | 8.2μH  | 60μF             | 210kΩ            | 15kΩ             | 3.3pF           |

| 24V  |           | 10μH   | 30μF             |                  | 7.32kΩ           | –               |

| 3.3V | 1MHz      | 1.5μH  | 115μF            | 78.7kΩ           | 24.9kΩ           | 6.8pF           |

| 5V   |           | 2.2μH  | 75μF             |                  | 15kΩ             | 4.7pF           |

| 12V  |           | 3.3μH  | 30μF             | 210kΩ            | 15kΩ             | 2.2pF           |

| 24V  |           | 4.7μH  | 15μF             |                  | 7.32kΩ           | –               |

| 3.3V | 2.2MHz    | 0.56μH | 100μF            | 78.7kΩ           | 24.9kΩ           | 2.2pF           |

| 5V   |           | 0.82μH | 70μF             |                  | 15kΩ             | 2.2pF           |

| 12V  |           | 1μH    | 30μF             | 210kΩ            | 15kΩ             | –               |

| 24V  |           | 2.2μH  | 15μF             |                  | 7.32kΩ           | –               |

**表 8-3. 可変出力電圧と内部補償機能を備えた LM65660 6A デバイスの標準的な部品の値**

| 出力電圧 | スイッチング周波数 | L <sub>O</sub> | C <sub>OUT</sub> | R <sub>FB1</sub> | R <sub>FB2</sub> | C <sub>FF</sub> |

|------|-----------|----------------|------------------|------------------|------------------|-----------------|

| 3.3V | 400kHz    | 4.7μH          | 150μF            | 78.7kΩ           | 24.9kΩ           | 10pF            |

| 5V   |           | 5.6μH          | 100μF            |                  | 15kΩ             | 10pF            |

| 12V  |           | 10μH           | 44μF             | 210kΩ            | 15kΩ             | 2.2pF           |

| 24V  |           | 15μH           | 22μF             |                  | 7.32kΩ           | –               |

| 3.3V | 1MHz      | 1.5μH          | 80μF             | 78.7kΩ           | 24.9kΩ           | 6.8pF           |

| 5V   |           | 2.2μH          | 55μF             |                  | 15kΩ             | 6.8pF           |

| 12V  |           | 4.7μH          | 22μF             | 210kΩ            | 15kΩ             | 2.2pF           |

| 24V  |           | 6.8μH          | 12μF             |                  | 7.32kΩ           | –               |

| 3.3V | 2.2MHz    | 0.82μH         | 75μF             | 78.7kΩ           | 24.9kΩ           | 4.7pF           |

| 5V   |           | 1μH            | 50μF             |                  | 15kΩ             | 4.7pF           |

| 12V  |           | 2.2μH          | 22μF             | 210kΩ            | 15kΩ             | –               |

| 24V  |           | 3.3μH          | 10μF             |                  | 7.32kΩ           | –               |

**表 8-4. 可変出力電圧と内部補償機能を備えた LM65640 4A デバイスの標準的な部品の値**

| 出力電圧 | スイッチング周波数 | L <sub>O</sub> | C <sub>OUT</sub> | R <sub>FB1</sub> | R <sub>FB2</sub> | C <sub>FF</sub> |

|------|-----------|----------------|------------------|------------------|------------------|-----------------|

| 3.3V | 400kHz    | 6.8μH          | 120μF            | 78.7kΩ           | 24.9kΩ           | 10pF            |

| 5V   |           | 8.2μH          | 80μF             |                  | 15kΩ             | 10pF            |

| 12V  |           | 15μH           | 35μF             | 210kΩ            | 15kΩ             | 3.3pF           |

| 24V  |           | 22μH           | 15μF             |                  | 7.32kΩ           | –               |

| 3.3V | 1MHz      | 2.2μH          | 60μF             | 78.7kΩ           | 24.9kΩ           | 10pF            |

| 5V   |           | 3.3μH          | 40μF             |                  | 15kΩ             | 10pF            |

| 12V  |           | 6.8μH          | 15μF             | 210kΩ            | 15kΩ             | 2.2pF           |

| 24V  |           | 10μH           | 10μF             |                  | 7.32kΩ           | –               |

| 3.3V | 2.2MHz    | 1μH            | 50μF             | 78.7kΩ           | 24.9kΩ           | 4.7pF           |

| 5V   |           | 1.5μH          | 35μF             |                  | 15kΩ             | 4.7pF           |

| 12V  |           | 3.3μH          | 15μF             | 210kΩ            | 15kΩ             | –               |

| 24V  |           | 4.7μH          | 8μF              |                  | 7.32kΩ           | –               |

**注**

LM65680/60/40 で駆動される実装の詳細な設計手順、回路図、部品表、PCB ファイル、シミュレーション、テスト結果については、[TI Designs](#) のリファレンス デザイン ライブラリを参照してください。

### 8.2.1 設計 1 - 5V、8A の同期整流降圧レギュレータ、広い入力電圧範囲に対応し、高効率を実現

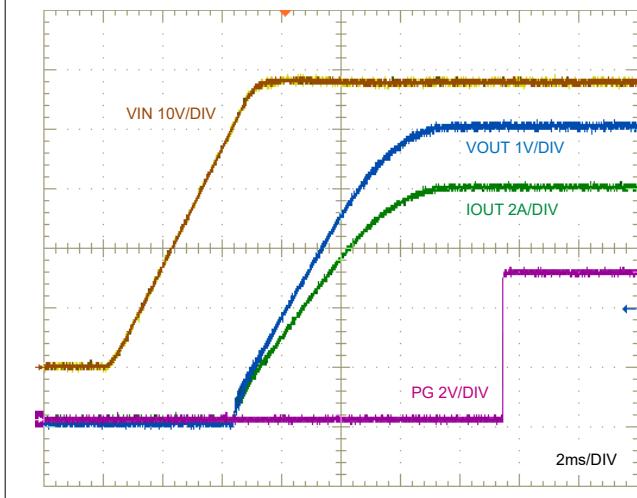

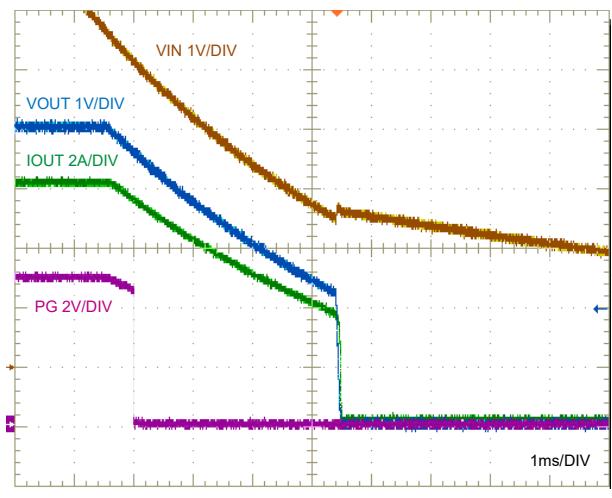

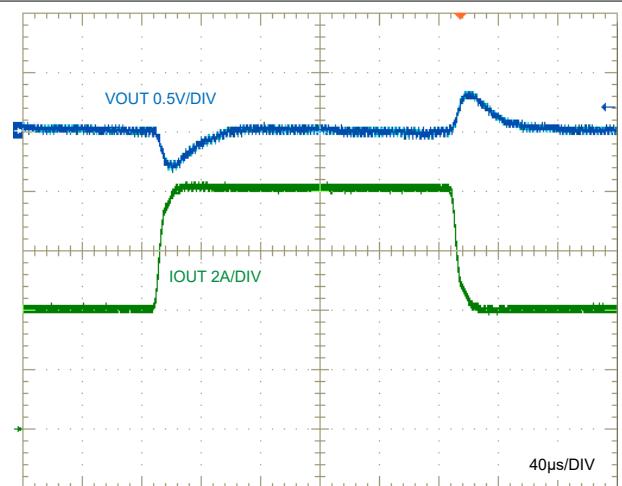

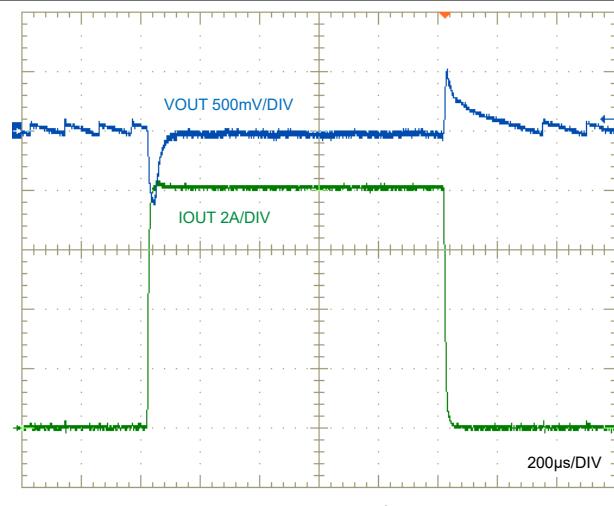

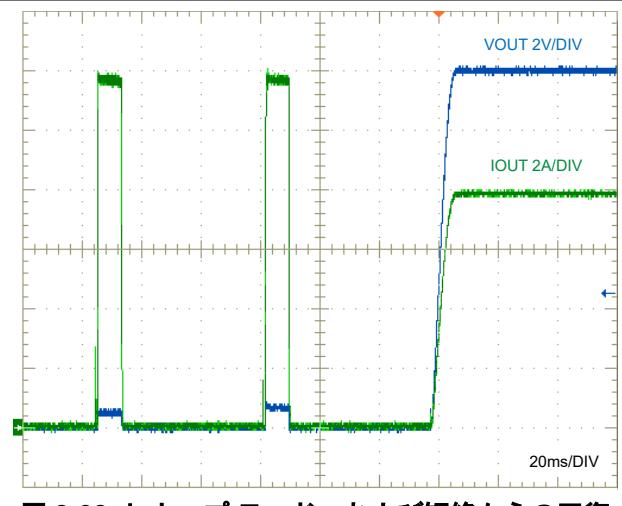

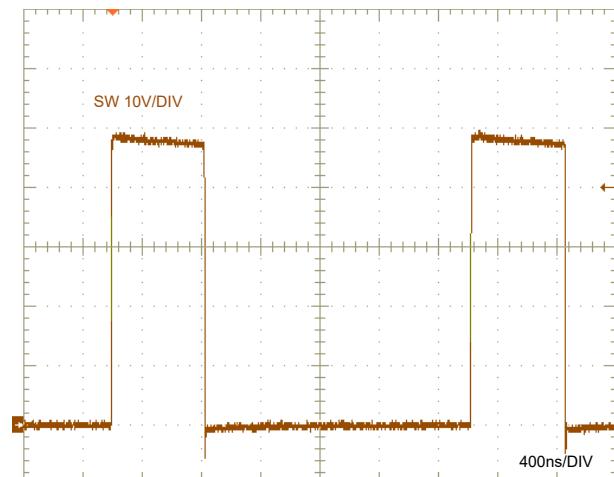

図 8-7 に、LM65680 を使用した代表的な降圧レギュレータ回路を示します。この回路は、公称 48V の入力からレギュレートされた 5V の出力で 8A を供給します。

図 8-7. アプリケーション回路 1、LM65680 8A 降圧レギュレータを 400kHz で使用

#### 注

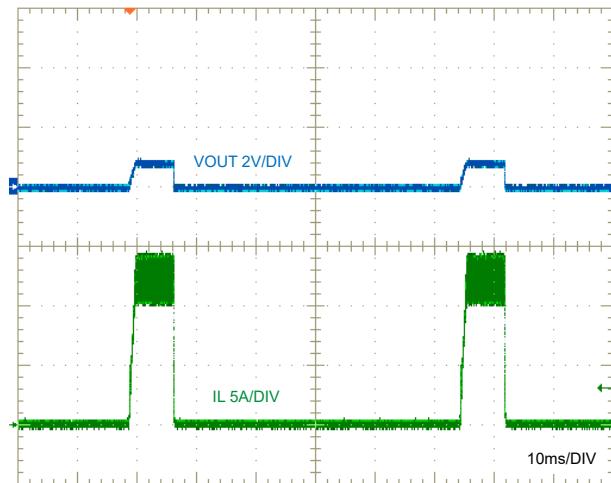

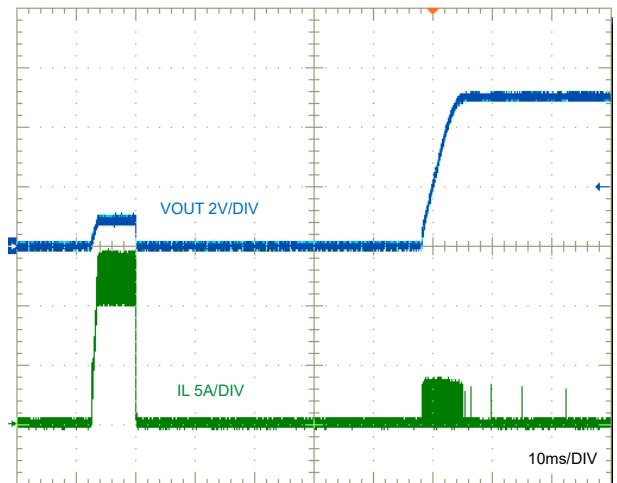

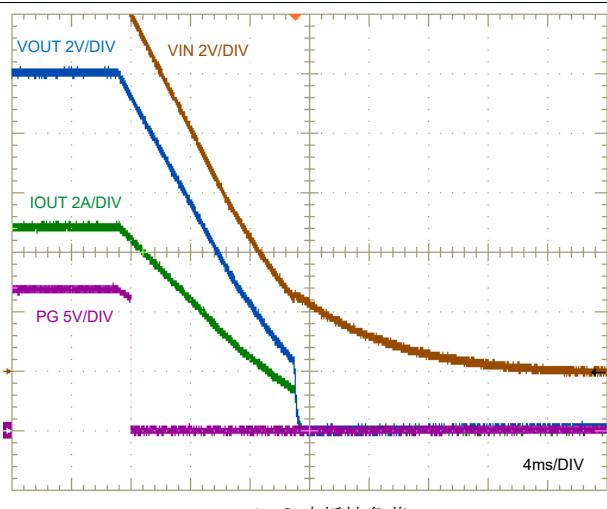

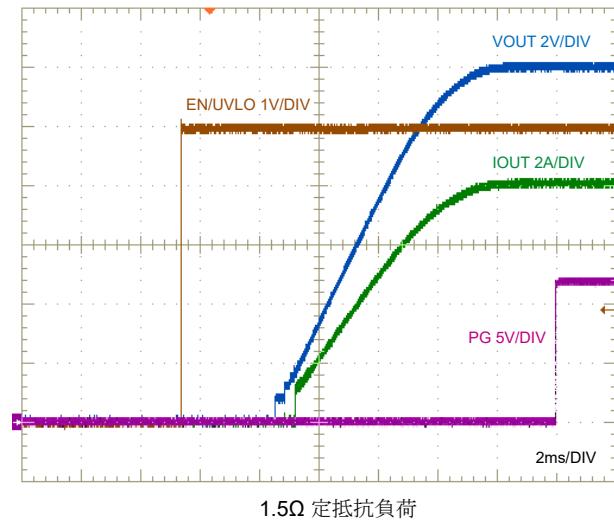

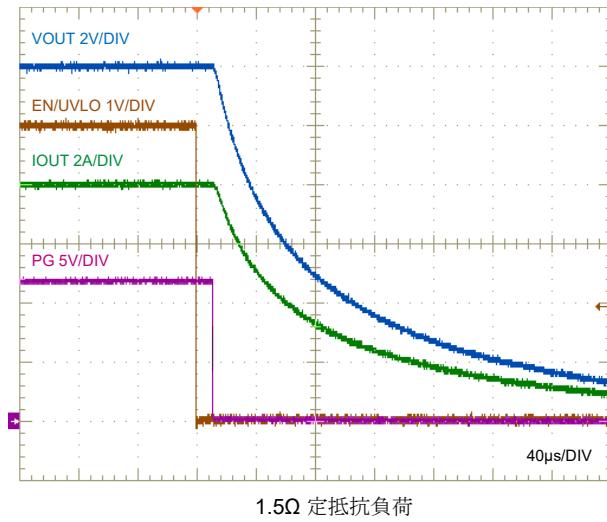

これ以降の設計例では、いくつかの異なるアプリケーションにおける LM65680/60/40 コンバータを紹介します。入力電源バスのソースインピーダンスによっては、特に低入力電圧と高出力電流の動作時条件における安定性を確保するために、入力に電解コンデンサが必要になることがあります。詳細については、[セクション 8.4](#) を参照してください。