# ドライバおよび電流検出エミュレーション機能内蔵、LMG2652 650V 140mΩ GaN ハーフブリッジ

## 1 特長

- 650V GaN パワー FET ハーフブリッジ

- 140mΩ ローサイドおよびハイサイド GaN FET

- 伝搬遅延時間が短い (100ns 未満) ゲートドライバを内蔵

- 広い帯域幅で高精度の電流検出エミュレーション

- ローサイド基準 (INH) とハイサイド基準 (GDH) のハイサイド ゲートドライブ ピン

- ローサイド (INL) / ハイサイド (INH) ゲートドライブ インターロック

- ハイサイド (INH) ゲートドライブ信号レベルシフタ

- スマートスイッチ付きブートストラップ ダイオード機能

- ハイサイドの起動:<8μs

- ローサイド / ハイサイドのサイクル単位の過電流保護

- 過熱保護

- AUX アイドル静止電流:250μA

- AUX スタンバイ静止電流:50μA

- BST アイドル静止電流:70μA

- デュアル サーマル パッド付き 8mm × 6mm QFN パッケージ

## 2 アプリケーション

- AC/DC アダプタおよびチャージャ

- AC/DC USB 壁コンセント電源

- AC/DC 補助電源

- モバイル向け充電器の設計

- USB 電源コンセント

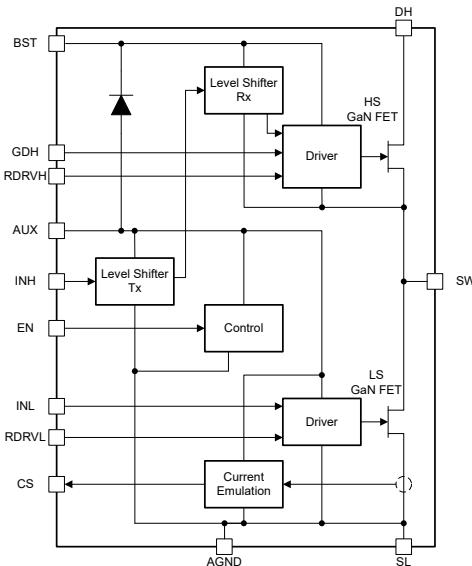

概略ブロック図

## 3 概要

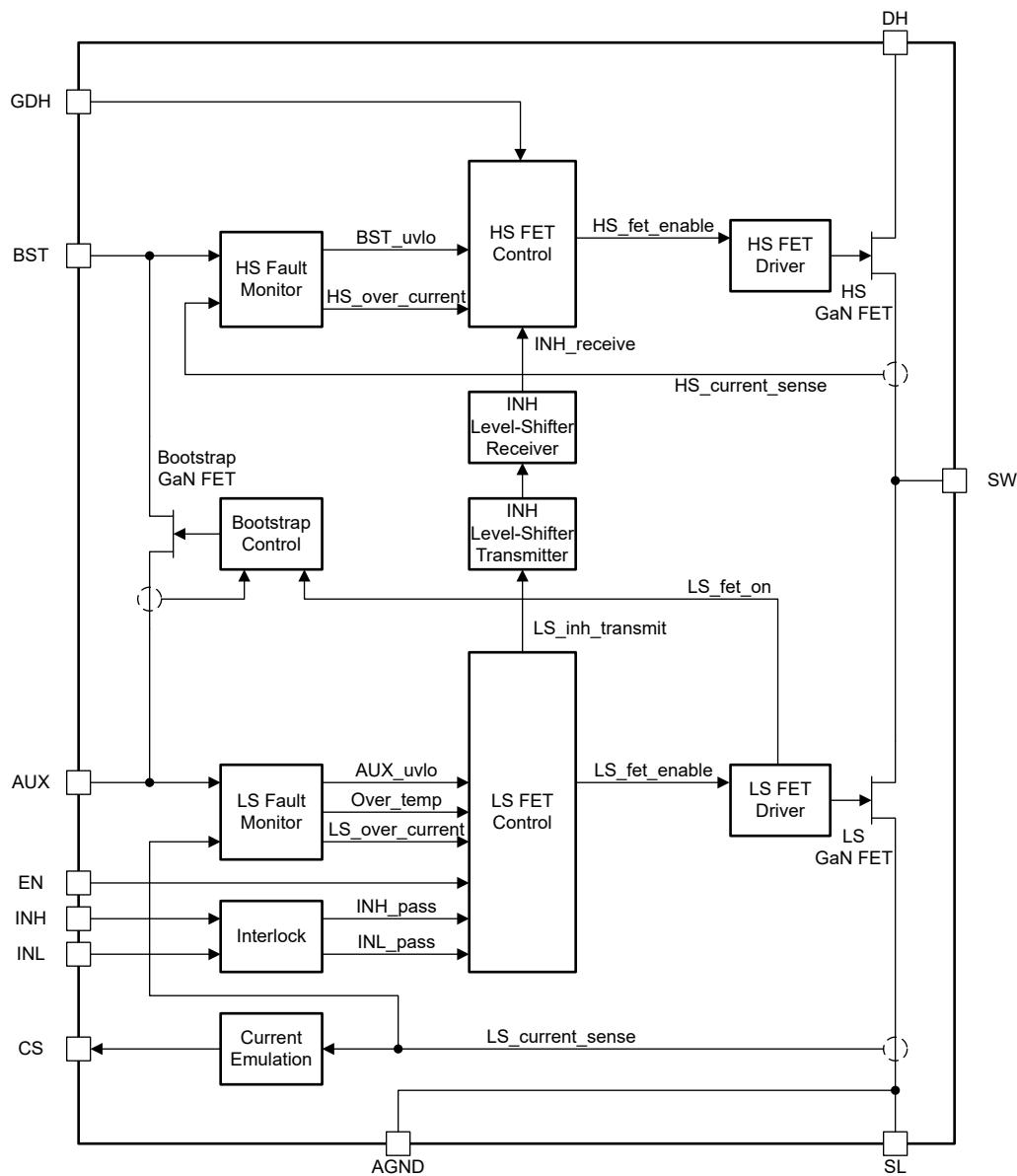

LMG2652 は 650V 140mΩ GaN パワー FET ハーフブリッジです。LMG2652 は、ハーフブリッジ パワー FET、ゲートドライバ、ブートストラップ ダイオード、ハイサイド ゲートドライブ レベル シフタを 6mm × 8mm の QFN パッケージに統合することで、設計の簡素化、部品点数の低減、基板面積の低減を実現しています。

ローサイド電流検出エミュレーションにより、従来の電流検出抵抗方式よりも消費電力を低減でき、またローサイドのサーマル パッドを冷却用 PCB 電源グランドに接続できます。

ハイサイド GaN パワー FET は、ローサイド基準ゲートドライブ ピン (INH) またはハイサイド基準ゲートドライブ ピン (GDH) で制御できます。ハイサイド ゲートドライブ信号レベル シフタは、厳しいパワー スイッチング環境でも、INH ピンの信号を確実にハイサイド ゲートドライバに伝えます。スマートスイッチ付き GaN ブートストラップ FET を使うと、ダイオードの順方向電圧降下がなく、ハイサイド電源を過充電せず、逆方向回復電荷がありません。

LMG2652 は、小さい静止電流と高速な起動時間によって、コンバータの軽負荷効率要件とバースト モード動作に対応しています。保護機能には、FET ターンオン インターロック、低電圧誤動作防止 (UVLO)、サイクル単位の電流制限、過熱シャットダウンが含まれます。

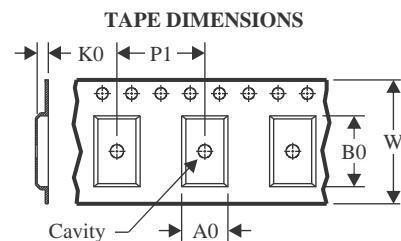

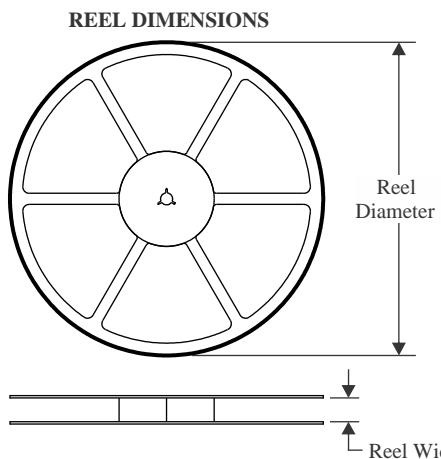

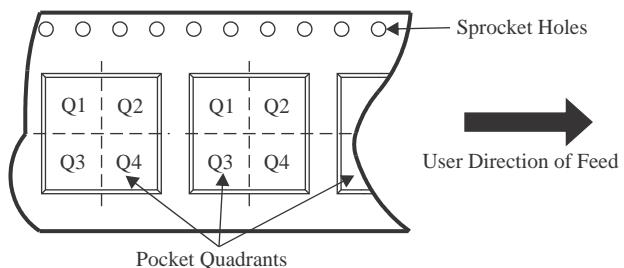

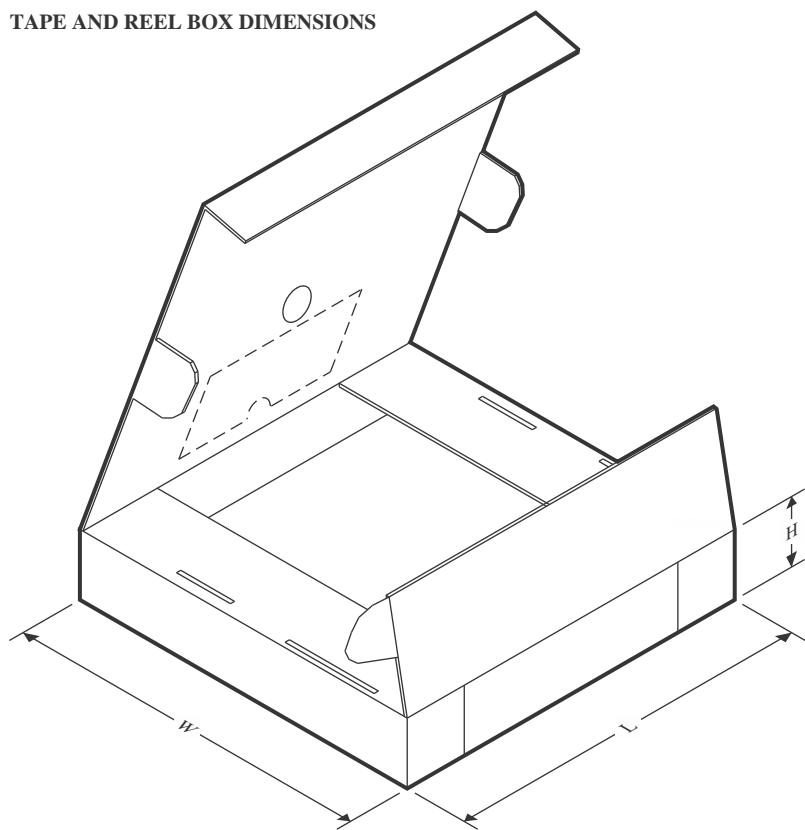

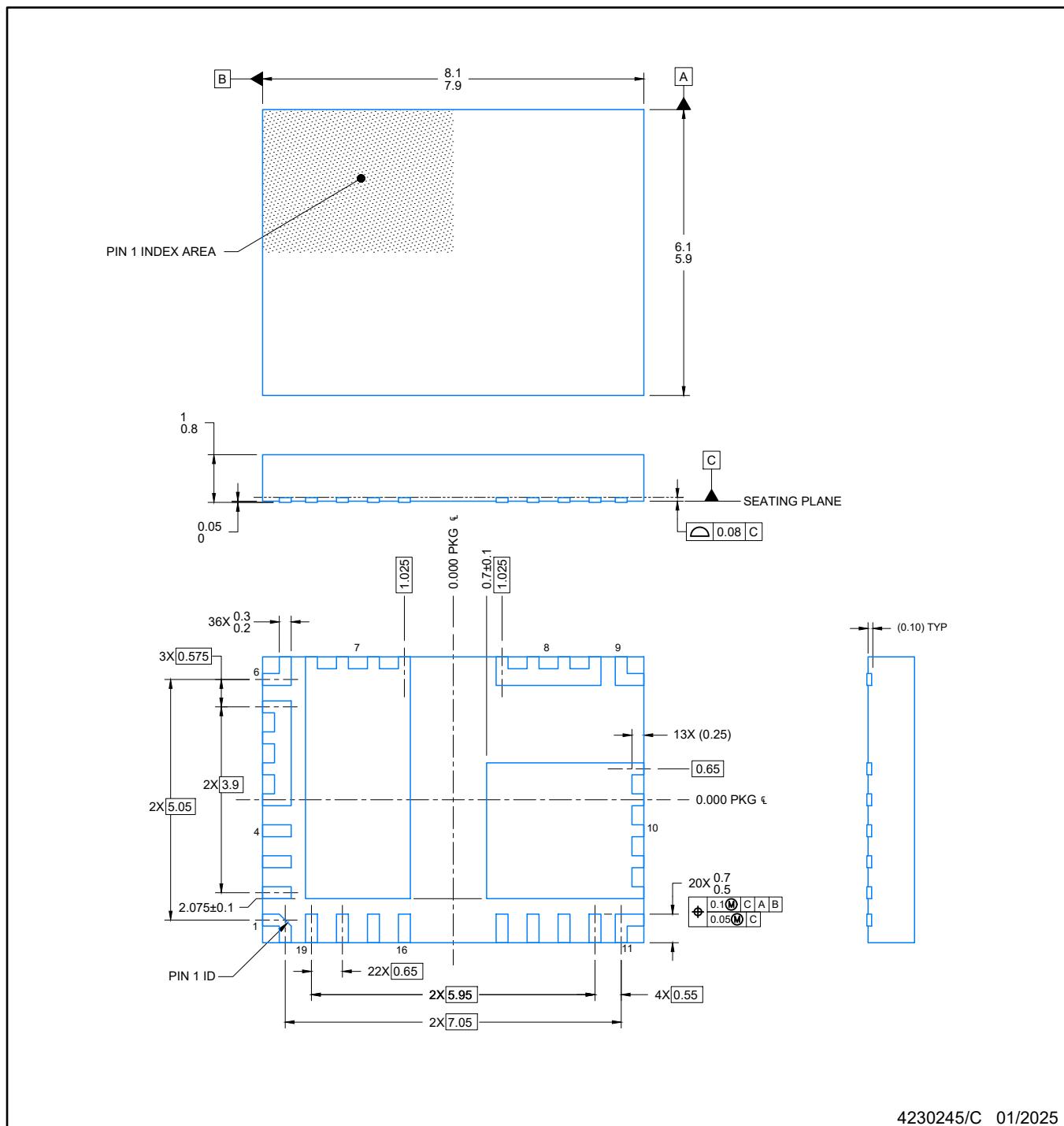

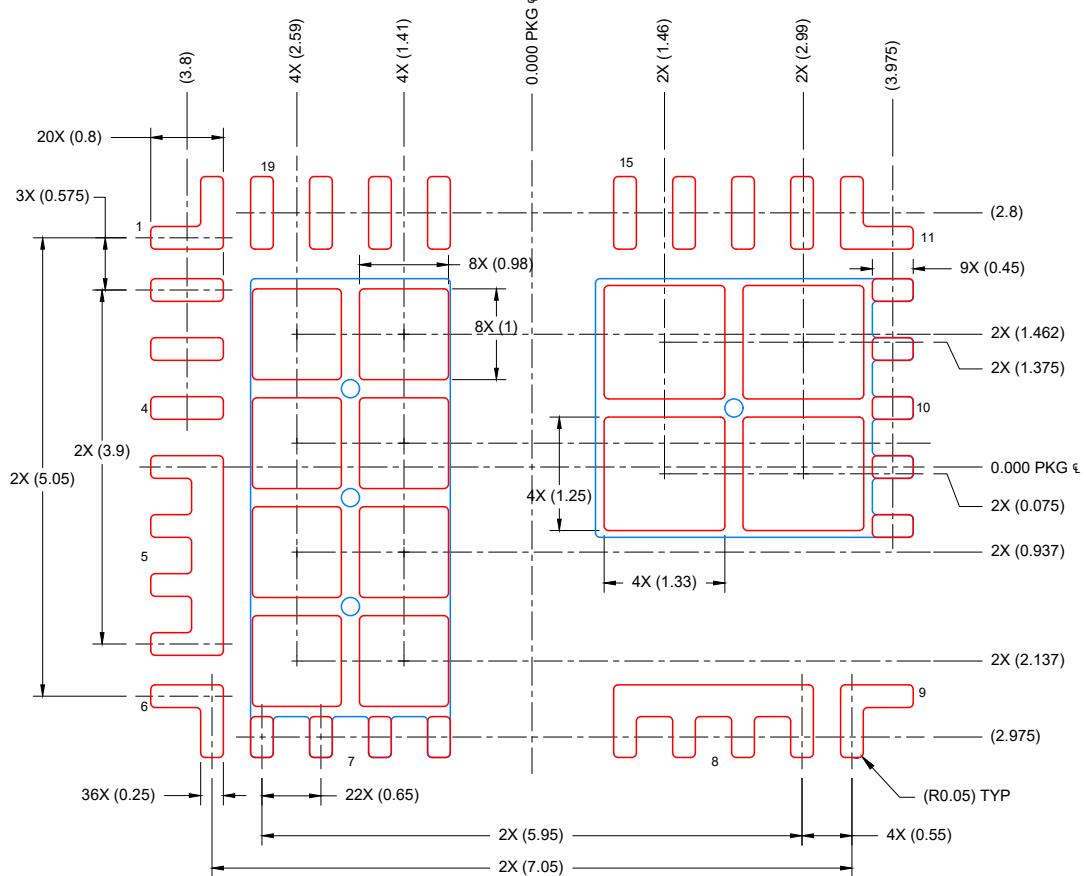

### パッケージ情報

| 部品番号    | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|---------|----------------------|--------------------------|

| LMG2652 | RFB (VQFN, 19)       | 8.00mm × 6.00mm          |

(1) 詳細については、[セクション 11](#) を参照してください。

(2) パッケージ サイズ (長さ×幅) は公称値であり、該当する場合はビンも含まれます。

パッケージ ビュー

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

English Data Sheet: [SNOSDL5](#)

## Table of Contents

|                                        |    |                                         |    |

|----------------------------------------|----|-----------------------------------------|----|

| 1 特長                                   | 1  | 7.3 Feature Description                 | 18 |

| 2 アプリケーション                             | 1  | 7.4 Device Functional Modes             | 23 |

| 3 概要                                   | 1  | 8 Application and Implementation        | 24 |

| 4 Pin Configuration and Functions      | 3  | 8.1 Application Information             | 24 |

| 5 Specifications                       | 5  | 8.2 Typical Application                 | 25 |

| 5.1 Absolute Maximum Ratings           | 5  | 8.3 Power Supply Recommendations        | 27 |

| 5.2 ESD Ratings                        | 5  | 8.4 Layout                              | 28 |

| 5.3 Recommended Operating Conditions   | 6  | 9 Device and Documentation Support      | 30 |

| 5.4 Thermal Information                | 6  | 9.1 ドキュメントの更新通知を受け取る方法                  | 30 |

| 5.5 Electrical Characteristics         | 7  | 9.2 サポート・リソース                           | 30 |

| 5.6 Switching Characteristics          | 10 | 9.3 Trademarks                          | 30 |

| 5.7 Typical Characteristics            | 11 | 9.4 静電気放電に関する注意事項                       | 30 |

| 6 Parameter Measurement Information    | 14 | 9.5 用語集                                 | 30 |

| 6.1 GaN Power FET Switching Parameters | 14 | 10 Revision History                     | 31 |

| 7 Detailed Description                 | 16 | 11 Mechanical, Packaging, and Orderable |    |

| 7.1 Overview                           | 16 | Information                             | 31 |

| 7.2 Functional Block Diagram           | 17 |                                         |    |

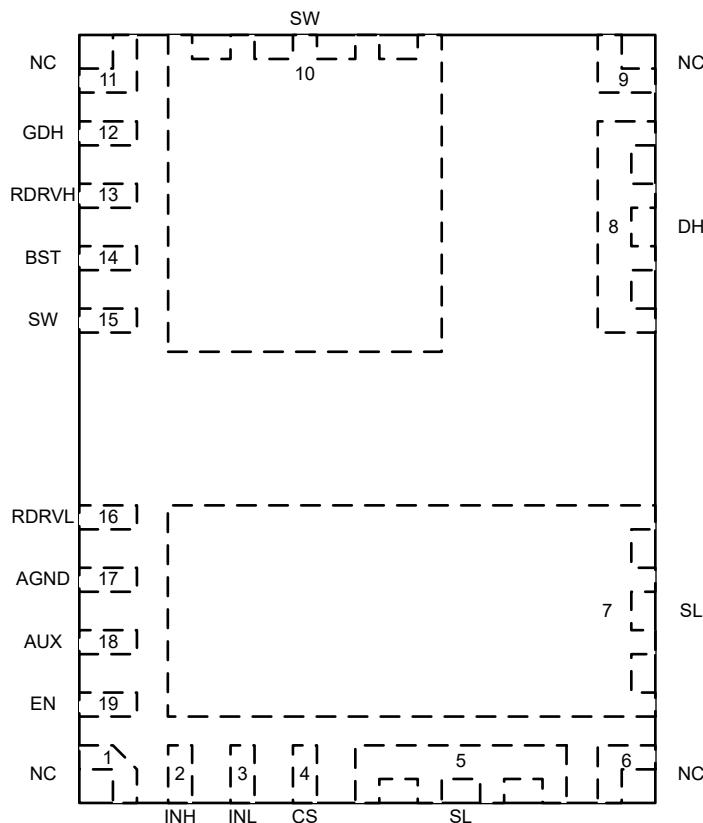

## 4 Pin Configuration and Functions

図 4-1. RFB Package, 19-Pin VQFN (Top View)

表 4-1. Pin Functions

| PIN   |             | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                         |

|-------|-------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME  | NO.         |                     |                                                                                                                                                                                                                                                                                                                                                     |

| NC    | 1, 6, 9, 11 | NC                  | Used to anchor QFN package to PCB. Pin must be soldered to a PCB landing pad. The PCB landing pad is non-solder mask defined pad and must not be physically connected to any other metal on the PCB. Pin not connected internally.                                                                                                                  |

| INH   | 2           | I                   | High-side gate-drive control input. Referenced to AGND. Signal is level shifted internally to the high-side GaN FET driver. There is a forward biased ESD diode from INH to AUX so avoid driving INH higher than AUX. Short this pin to AGND if GDH pin function is used.                                                                           |

| INL   | 3           | I                   | Low-side gate-drive control input. Referenced to AGND. There is a forward biased ESD diode from INL to AUX so avoid driving INL higher than AUX.                                                                                                                                                                                                    |

| CS    | 4           | O                   | Current-sense emulation output. Outputs scaled replica of the GaN FET current. Feed output current into a resistor to create a current sense voltage signal. Reference the resistor to the power supply controller IC local ground. This function replaces the external current sense resistor that is used in series with the low-side FET source. |

| SL    | 5, 7        | P                   | Low-side GaN FET source. Low-side thermal pad. Internally connected to AGND.                                                                                                                                                                                                                                                                        |

| DH    | 8           | P                   | High-side GaN FET drain.                                                                                                                                                                                                                                                                                                                            |

| SW    | 10, 15      | P                   | GaN FET half-bridge switch node between the high-side GaN FET source and low-side GaN FET drain. High-side thermal pad.                                                                                                                                                                                                                             |

| GDH   | 12          | I                   | High-side gate-drive control input. Referenced to SW. Signal is connected directly to the high-side GaN FET driver. There is a forward biased ESD diode from GDH to BST so avoid driving GDH higher than BST. Short this pin to SW if INH pin function is used.                                                                                     |

| RDRVH | 13          | I                   | Short to SW.                                                                                                                                                                                                                                                                                                                                        |

表 4-1. Pin Functions (続き)

| PIN   |     | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                         |

|-------|-----|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME  | NO. |                     |                                                                                                                                                                                                                                                     |

| BST   | 14  | P                   | Bootstrap voltage rail. High-side supply voltage. The bootstrap diode function between AUX and BST is internally provided. Connect an appropriately sized bootstrap capacitor between BST and SW.                                                   |

| RDRV1 | 16  | I                   | Short to AGND.                                                                                                                                                                                                                                      |

| AGND  | 17  | G                   | Low-side analog ground. Internally connected to SL.                                                                                                                                                                                                 |

| AUX   | 18  | P                   | Auxiliary voltage rail. Low-side supply voltage. Connect a local bypass capacitor between AUX and AGND.                                                                                                                                             |

| EN    | 19  | I                   | Enable. Used to toggle between active and standby modes. The standby mode has reduced quiescent current to support converter light load efficiency targets. There is a forward biased ESD diode from EN to AUX so avoid driving EN higher than AUX. |

(1) I = input, O = output, I/O = input or output, G = ground, P = power, NC = no connect

## 5 Specifications

### 5.1 Absolute Maximum Ratings

Unless otherwise noted: voltages are respect to AGND<sup>(1)</sup>

|                         |                                                                                                           |    | MIN  | MAX                 | UNIT |

|-------------------------|-----------------------------------------------------------------------------------------------------------|----|------|---------------------|------|

| $V_{DS(is)}$            | Low-side drain-source (SW to SL) voltage, FET off                                                         |    | 650  |                     | V    |

| $V_{DS(surge)(is)}$     | Low-side drain-source (SW to SL) voltage, surge condition, FET off <sup>(2)</sup>                         |    | 720  |                     | V    |

| $V_{DS(tr)(surge)(is)}$ | Low-side drain-source (SW to SL) transient ringing peak voltage, surge condition, FET off <sup>(2)</sup>  |    | 800  |                     | V    |

| $V_{DS(hs)}$            | High-side drain source (DH to SW) voltage, FET off                                                        |    | 650  |                     | V    |

| $V_{DS(surge)(hs)}$     | High-side drain-source (DH to SW) voltage, surge condition, FET off <sup>(2)</sup>                        |    | 720  |                     | V    |

| $V_{DS(tr)(surge)(hs)}$ | High-side drain-source (DH to SW) transient ringing peak voltage, surge condition, FET off <sup>(2)</sup> |    | 800  |                     | V    |

| Pin voltage to AGND     | AUX                                                                                                       |    | -0.3 | 30                  | V    |

|                         | EN, INL, INH                                                                                              |    | -0.3 | $V_{AUX} + 0.3$     | V    |

|                         | CS                                                                                                        |    | -0.3 | 5.5                 | V    |

|                         | RDRVRL                                                                                                    |    | -0.3 | 4                   | V    |

|                         | BST                                                                                                       |    | -0.3 | 30                  | V    |

|                         | RDRVH                                                                                                     |    | -0.3 | 4                   | V    |

| Pin voltage to SW       | GDH                                                                                                       |    | -0.3 | $V_{BST\_SW} + 0.3$ | V    |

| $I_{D(cnts)(is)}$       | Low-side drain (SW to SL) continuous current, FET on                                                      |    | -7.4 | Internally limited  | A    |

| $I_{D(pulse)(oc)(is)}$  | Low-side drain (SW to SL) pulsed current during overcurrent response time <sup>(3)</sup>                  |    |      | 18                  | A    |

| $I_{S(cnts)(is)}$       | Low-side source (SL to SW) continuous current, FET off                                                    |    |      | 7.4                 | A    |

| $I_{D(cnts)(hs)}$       | High-side drain (DH to SW) continuous current, FET on                                                     |    | -7.4 | Internally limited  | A    |

| $I_{D(pulse)(oc)(hs)}$  | High-side drain (DH to SW) pulsed current during overcurrent response time <sup>(3)</sup>                 |    |      | 18                  | A    |

| $I_{S(cnts)(hs)}$       | High-side source (SW to DH) continuous current, FET off                                                   |    |      | 7.4                 | A    |

|                         | Positive sink current                                                                                     | CS |      | 10                  | mA   |

| $T_J$                   | Operating junction temperature                                                                            |    | -40  | 150                 | °C   |

| $T_{stg}$               | Storage temperature                                                                                       |    | -40  | 150                 | °C   |

(1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

(2) See [GaN Power FET Switching Capability](#) for more information on the GaN power FET switching capability.

(3) GaN power FET may self-limit below this value if it enters saturation.

### 5.2 ESD Ratings

|             |                         |                                                                       |                                      | VALUE      | UNIT |

|-------------|-------------------------|-----------------------------------------------------------------------|--------------------------------------|------------|------|

| $V_{(ESD)}$ | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>     | Pins 8 through 15                    | $\pm 1000$ | V    |

|             |                         |                                                                       | Pins 1 through 7, Pins 16 through 19 | $\pm 2000$ | V    |

|             |                         | Charged device model (CDM), per ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> |                                      | $\pm 500$  | V    |

(1) JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process.

## 5.3 Recommended Operating Conditions

Unless otherwise noted: voltages are respect to AGND

|                          |                                                        |                         | MIN                  | NOM                 | MAX                 | UNIT |

|--------------------------|--------------------------------------------------------|-------------------------|----------------------|---------------------|---------------------|------|

|                          | Supply voltage                                         | AUX                     | 10                   | 26                  | 26                  | V    |

|                          | Supply voltage to SW                                   | BST                     | 7.5                  | 26                  | 26                  | V    |

|                          | Input voltage                                          | EN, INL, INH            | 0                    | V <sub>AUX</sub>    | V <sub>AUX</sub>    | V    |

|                          | Input voltage to SW                                    | GDH                     | 0                    | V <sub>BST_SW</sub> | V <sub>BST_SW</sub> | V    |

| V <sub>IH</sub>          | High-level input voltage                               | EN, INL, INH, GDH to SW | 2.5                  |                     |                     | V    |

| V <sub>IL</sub>          | Low-level input voltage                                |                         |                      | 0.6                 | 0.6                 | V    |

| I <sub>D(cnts)(ls)</sub> | Low-side drain (SW to SL) continuous current, FET on   |                         | -6.1                 | 6.1                 | 6.1                 | A    |

| I <sub>D(cnts)(hs)</sub> | High-side drain (DH to SW) continuous current, FET on  |                         | -6.1                 | 6.1                 | 6.1                 | A    |

| C <sub>AUX</sub>         | AUX to AGND capacitance from external bypass capacitor |                         | 3 x C <sub>BST</sub> |                     |                     | μF   |

| C <sub>BST_SW</sub>      | BST to SW capacitance from external bypass capacitor   |                         | 0.010                |                     |                     | μF   |

## 5.4 Thermal Information

| THERMAL METRIC <sup>(1)</sup> |                                              | LMG2652    | UNIT |

|-------------------------------|----------------------------------------------|------------|------|

|                               |                                              | RFB (VQFN) |      |

|                               |                                              | 19 PINS    |      |

| R <sub>θJA</sub>              | Junction-to-ambient thermal resistance       | 22.7       | °C/W |

| R <sub>θJC(bot)</sub>         | Junction-to-case (bottom) thermal resistance | 1.20       | °C/W |

(1) For more information about traditional and new thermal metrics, see the [Semiconductor and IC Package Thermal Metrics application report](#).

## 5.5 Electrical Characteristics

1) Symbol definitions:  $V_{DS(is)} =$  SW to SL voltage;  $I_{DS(is)} =$  SW to SL current;  $V_{DS(hs)} =$  DH to SW voltage;  $I_{D(hs)} =$  DH to SW current;  $I_{SW} =$  SW point current into device; 2) Unless otherwise noted: voltage, resistance, and capacitance are respect to AGND;  $-40^\circ C \leq T_J \leq 125^\circ C$ ;  $V_{DS(is)} = 520V$ ;  $V_{DS(hs)} = 520V$ ;  $10V \leq V_{AUX} \leq 26V$ ;  $7.5V \leq V_{BST\_SW} \leq 26V$ ;  $V_{EN} = 5V$ ;  $V_{INL} = 0V$ ;  $V_{INH} = 0V$ ;  $V_{GDH\_SW} = 0V$ ;  $R_{CS} = 100\Omega$

| PARAMETER                               | TEST CONDITIONS                                                                                                                                       | MIN  | TYP | MAX  | UNIT      |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|-----------|

| <b>LOW-SIDE GAN POWER FET</b>           |                                                                                                                                                       |      |     |      |           |

| $R_{DS(on)(is)}$                        | Drain-source (SW to SL) on resistance<br>$V_{INL} = 5V, I_{D(is)} = 3.5A, T_J = 25^\circ C$<br>$V_{INL} = 5V, I_{D(is)} = 3.5A, T_J = 125^\circ C$    | 140  |     |      | $m\Omega$ |

| $V_{SD(is)}$                            | Source-drain (SL to SW) third-quadrant voltage<br>SL to SW current = 0.35A<br>SL to SW current = 3.5A                                                 | 1.9  |     | 2.6  | V         |

| $I_{DSS(is)}$                           | Drain (SW to SL) leakage current<br>$V_{DS(hs)} = 0V, V_{DS(is)} = 650V, T_J = 25^\circ C$<br>$V_{DS(hs)} = 0V, V_{DS(is)} = 650V, T_J = 125^\circ C$ | 2.3  |     | 11.5 | $\mu A$   |

| $Q_{OSS(is)}$                           | Output (SW to SL) charge                                                                                                                              | 21.8 |     |      | $nC$      |

| $C_{OSS(is)}$                           | Output (SW to SL) capacitance                                                                                                                         | 34.2 |     |      | $pF$      |

| $E_{OSS(is)}$                           | Output (SW to SL) capacitance stored energy                                                                                                           | 3.0  |     |      | $\mu J$   |

| $C_{OSS,er(is)}$                        | Energy related effective output (SW to SL) capacitance                                                                                                | 36.7 |     |      | $pF$      |

| $C_{OSS,tr(is)}$                        | Time related effective output (SW to SL) capacitance<br>$V_{DS(hs)} = 0V, V_{DS(is)} = 0V$ to 400V                                                    | 54.5 |     |      | $pF$      |

| $Q_{RR(is)}$                            | Reverse recovery charge                                                                                                                               | 0    |     |      | $nC$      |

| <b>HIGH-SIDE GAN POWER FET</b>          |                                                                                                                                                       |      |     |      |           |

| $R_{DS(on)(hs)}$                        | Drain-source (DH to SW) on resistance<br>$V_{INH} = 5V, I_{D(hs)} = 3.5A, T_J = 25^\circ C$<br>$V_{INH} = 5V, I_{D(hs)} = 3.5A, T_J = 125^\circ C$    | 140  |     |      | $m\Omega$ |

| $V_{SD(hs)}$                            | Source-drain (SW to DH) third-quadrant voltage<br>SW to DH current = 0.35A<br>SW to DH current = 3.5A                                                 | 1.9  |     | 2.6  | V         |

| $I_{DSS(hs)}$                           | Drain (DH to SW) leakage current<br>$V_{DS(is)} = 0V, V_{DS(hs)} = 650V, T_J = 25^\circ C$<br>$V_{DS(is)} = 0V, V_{DS(hs)} = 650V, T_J = 125^\circ C$ | 2.3  |     | 11.5 | $\mu A$   |

| $Q_{OSS(hs)}$                           | Output (DH to SW) charge                                                                                                                              | 21.8 |     |      | $nC$      |

| $C_{OSS(hs)}$                           | Output (DH to SW) capacitance                                                                                                                         | 34.2 |     |      | $pF$      |

| $E_{OSS(hs)}$                           | Output (DH to SW) capacitance stored energy                                                                                                           | 3.0  |     |      | $\mu J$   |

| $C_{OSS,er(hs)}$                        | Energy related effective output (DH to SW) capacitance                                                                                                | 36.7 |     |      | $pF$      |

| $C_{OSS,tr(hs)}$                        | Time related effective output (DH to SW) capacitance<br>$V_{DS(is)} = 0V, V_{DS(hs)} = 0V$ to 400V                                                    | 54.5 |     |      | $pF$      |

| $Q_{RR(hs)}$                            | Reverse recovery charge                                                                                                                               | 0    |     |      | $nC$      |

| <b>LOW-SIDE OVERCURRENT PROTECTION</b>  |                                                                                                                                                       |      |     |      |           |

| $I_{T(OC)(is)}$                         | Overcurrent fault – threshold current                                                                                                                 | 5.6  | 6.5 | 7.4  | A         |

| <b>HIGH-SIDE OVERCURRENT PROTECTION</b> |                                                                                                                                                       |      |     |      |           |

| $I_{T(OC)(hs)}$                         | Overcurrent fault – threshold current                                                                                                                 | 5.6  | 6.5 | 7.4  | A         |

| <b>BOOTSTRAP RECTIFIER</b>              |                                                                                                                                                       |      |     |      |           |

| $R_{DS(on)}$                            | AUX to BST on resistance<br>$V_{INL} = 5V, V_{AUX\_BST} = 1V, T_J = 25^\circ C$<br>$V_{INL} = 5V, V_{AUX\_BST} = 1V, T_J = 125^\circ C$               | 7    |     |      | $\Omega$  |

|                                         | AUX to BST current limit<br>$V_{INL} = 5V, V_{AUX\_BST} = 7V$                                                                                         | 210  | 240 | 270  | $mA$      |

|                                         | BST to AUX reverse current blocking threshold<br>$V_{INL} = 5V$                                                                                       | 15   |     |      | $mA$      |

| CS                                      |                                                                                                                                                       |      |     |      |           |

## 5.5 Electrical Characteristics (続き)

1) Symbol definitions:  $V_{DS(is)} =$  SW to SL voltage;  $I_{DS(is)} =$  SW to SL current;  $V_{DS(hs)} =$  DH to SW voltage;  $I_{D(hs)} =$  DH to SW current;  $I_{SW} =$  SW point current into device; 2) Unless otherwise noted: voltage, resistance, and capacitance are respect to AGND;  $-40^\circ\text{C} \leq T_J \leq 125^\circ\text{C}$ ;  $V_{DS(is)} = 520\text{V}$ ;  $V_{DS(hs)} = 520\text{V}$ ;  $10\text{V} \leq V_{AUX} \leq 26\text{V}$ ;  $7.5\text{V} \leq V_{BST\_SW} \leq 26\text{V}$ ;  $V_{EN} = 5\text{V}$ ;  $V_{INL} = 0\text{V}$ ;  $V_{INH} = 0\text{V}$ ;  $V_{GDH\_SW} = 0\text{V}$ ;  $R_{CS} = 100\Omega$

| PARAMETER                                                                 |                                                                          | TEST CONDITIONS                                                                                                       | MIN   | TYP | MAX           | UNIT          |   |

|---------------------------------------------------------------------------|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-------|-----|---------------|---------------|---|

| Current sense gain ( $I_{CS(src)} / I_{D(Ls)}$ )                          |                                                                          | $V_{INL} = 5\text{V}$ , $0\text{V} \leq V_{CS} \leq 2\text{V}$ , $0\text{A} \leq I_{D(Ls)} < I_{T(OC)(Ls)}$           | 0.901 |     | mA/A          |               |   |

| Current sense input offset current                                        |                                                                          | $V_{INL} = 5\text{V}$ , $0\text{V} \leq V_{CS} \leq 2\text{V}$ , $0\text{A} \leq I_{D(Ls)} < I_{T(OC)(Ls)}$           | -56   |     | 56            | mA            |   |

| Initial held output after overcurrent fault occurs while INL remains high |                                                                          | $V_{INL} = 5\text{V}$ , $0\text{V} \leq V_{CS} \leq 2\text{V}$                                                        |       |     | 7             | mA            |   |

| $I_{CS(src)}$<br>(OC)(final)                                              | Final held output after overcurrent fault occurs while INL remains high  | $V_{INL} = 5\text{V}$ , $0\text{V} \leq V_{CS} \leq 2\text{V}$                                                        | 10    | 12  | 15.5          | mA            |   |

| Output clamp voltage                                                      |                                                                          | $V_{INL} = 5\text{V}$ , $I_{D(Ls)} = 5.8\text{A}$ , CS sinking 5mA from external source                               | 2.6   |     | V             |               |   |

| <b>EN, INL, INH to AGND; GDH to SW</b>                                    |                                                                          |                                                                                                                       |       |     |               |               |   |

| $V_{IT+}$                                                                 | Positive-going input threshold voltage                                   |                                                                                                                       |       | 1.7 | 2.45          | V             |   |

| $V_{IT-}$                                                                 | Negative-going input threshold voltage                                   |                                                                                                                       |       | 0.7 | 1.3           | V             |   |

| Input threshold voltage hysteresis                                        |                                                                          |                                                                                                                       |       | 1   | V             |               |   |

| Pull-down input resistance                                                |                                                                          | $0\text{V} \leq V_{PIN} \leq 3\text{V}$                                                                               | 200   | 400 | 600           | k $\Omega$    |   |

| Pull-down input current                                                   |                                                                          | $10\text{V} \leq V_{PIN} \leq 26\text{V}$ ; $V_{AUX} = 26\text{V}$                                                    | 10    |     | $\mu\text{A}$ |               |   |

| <b>OVERTEMPERATURE PROTECTION</b>                                         |                                                                          |                                                                                                                       |       |     |               |               |   |

| Temperature fault – positive-going threshold temperature                  |                                                                          |                                                                                                                       |       | 165 | °C            |               |   |

| Temperature fault – negative-going threshold temperature                  |                                                                          |                                                                                                                       |       | 150 | °C            |               |   |

| Temperature fault – threshold temperature hysteresis                      |                                                                          |                                                                                                                       |       | 15  | °C            |               |   |

| <b>AUX</b>                                                                |                                                                          |                                                                                                                       |       |     |               |               |   |

| $V_{AUX,T+}$<br>(UVLO)                                                    | UVLO – positive-going threshold voltage                                  |                                                                                                                       |       | 8.9 | 9.3           | 9.7           | V |

| UVLO – negative-going threshold voltage                                   |                                                                          |                                                                                                                       |       | 8.6 | 9.0           | 9.5           | V |

| UVLO – threshold voltage hysteresis                                       |                                                                          |                                                                                                                       |       | 250 | mV            |               |   |

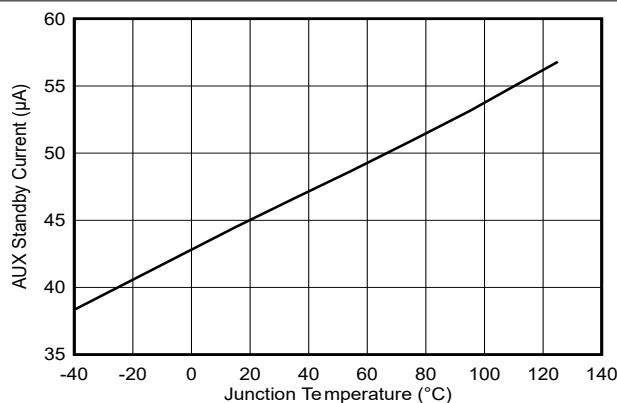

| Standby quiescent current                                                 |                                                                          | $V_{EN} = 0\text{V}$                                                                                                  | 50    |     | 110           | $\mu\text{A}$ |   |

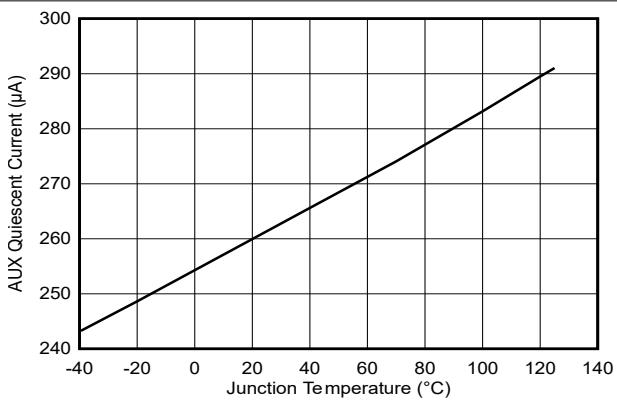

| Quiescent current                                                         |                                                                          |                                                                                                                       |       | 250 | 400           | $\mu\text{A}$ |   |

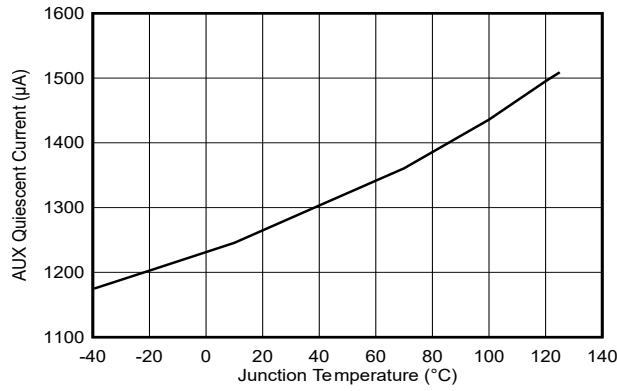

|                                                                           |                                                                          | $V_{INL} = 5\text{V}$ , $I_{D(Ls)} = 0\text{A}$                                                                       | 1000  |     |               |               |   |

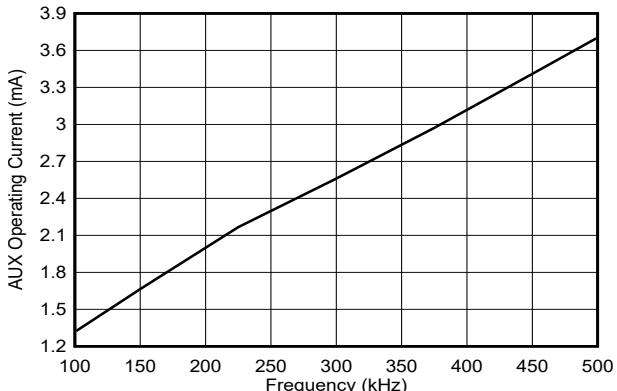

| Operating current                                                         |                                                                          | $V_{INL} = 0\text{V}$ or $5\text{V}$ , $V_{DS(is)} = 0\text{V}$ , $I_{D(Ls)} = 0\text{A}$ , $f_{INL} = 500\text{kHz}$ | 3.3   |     | mA            |               |   |

| <b>BST</b>                                                                |                                                                          |                                                                                                                       |       |     |               |               |   |

| $V_{BST\_SW}$ ,<br>$T+(UVLO)$                                             | $V_{BST\_SW}$ UVLO for FET to turn on – positive-going threshold voltage |                                                                                                                       |       | 6.7 | 7             | 7.3           | V |

| $V_{BST\_SW}$ UVLO for FET to stay on – negative-going threshold voltage  |                                                                          |                                                                                                                       |       | 4.8 | 5.1           | 5.4           | V |

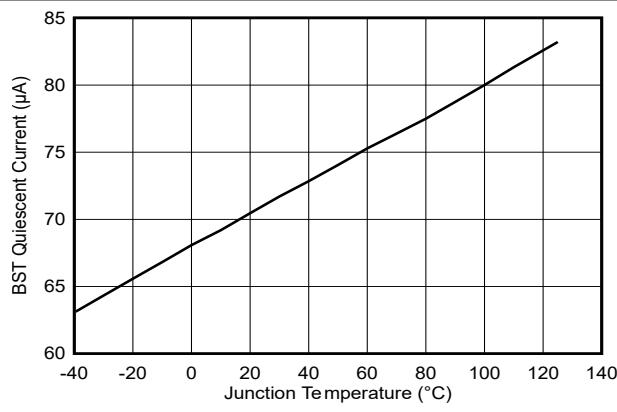

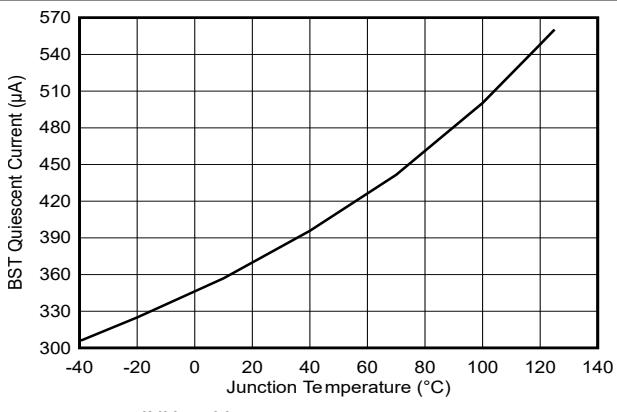

| Quiescent current                                                         |                                                                          |                                                                                                                       |       | 70  | 120           | $\mu\text{A}$ |   |

|                                                                           |                                                                          | $V_{INH} = 5\text{V}$ , $I_{D(hs)} = 0\text{A}$                                                                       | 660   |     |               |               |   |

|                                                                           |                                                                          | $V_{GDH\_SW} = 5\text{V}$ , $I_{D(hs)} = 0\text{A}$                                                                   | 660   |     |               |               |   |

## 5.5 Electrical Characteristics (続き)

1) Symbol definitions:  $V_{DS(is)} =$  SW to SL voltage;  $I_{DS(is)} =$  SW to SL current;  $V_{DS(hs)} =$  DH to SW voltage;  $I_{D(hs)} =$  DH to SW current;  $I_{SW} =$  SW point current into device; 2) Unless otherwise noted: voltage, resistance, and capacitance are respect to AGND;  $-40^\circ\text{C} \leq T_J \leq 125^\circ\text{C}$ ;  $V_{DS(is)} = 520\text{V}$ ;  $V_{DS(hs)} = 520\text{V}$ ;  $10\text{V} \leq V_{AUX} \leq 26\text{V}$ ;  $7.5\text{V} \leq V_{BST\_SW} \leq 26\text{V}$ ;  $V_{EN} = 5\text{V}$ ;  $V_{INL} = 0\text{V}$ ;  $V_{INH} = 0\text{V}$ ;  $V_{GDH\_SW} = 0\text{V}$ ;  $R_{CS} = 100\Omega$

| PARAMETER         | TEST CONDITIONS                                                                                                                | MIN | TYP | MAX | UNIT |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

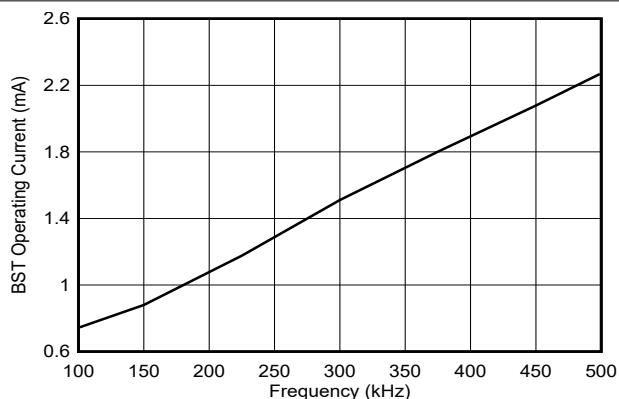

| Operating current | $V_{INH} = 0\text{V}$ or $5\text{V}$ , $V_{DS(hs)} = 0\text{V}$ , $I_{DS(hs)} = 0\text{A}$ ; $f_{INH} = 500\text{kHz}$         |     | 2.2 |     | mA   |

|                   | $V_{GDH\_SW} = 0\text{V}$ or $5\text{V}$ , $V_{DS(hs)} = 0\text{V}$ , $I_{DS(hs)} = 0\text{A}$ ; $f_{GDH\_SW} = 500\text{kHz}$ |     | 2.2 |     |      |

## 5.6 Switching Characteristics

1) Symbol definitions:  $V_{DS(ls)} =$  SW to SL voltage;  $I_{DS(ls)} =$  SW to SL current;  $V_{DS(hs)} =$  DH to SW voltage;  $I_{D(hs)} =$  DH to SW current;  $I_{SW} =$  SW point current into device; 2) Unless otherwise noted: voltage, resistance, and capacitance are respect to AGND;  $-40^\circ C \leq T_J \leq 125^\circ C$ ;  $V_{DS(ls)} = 520V$ ;  $V_{DS(hs)} = 520V$ ;  $10V \leq V_{AUX} \leq 26V$ ;  $7.5V \leq V_{BST\_SW} \leq 26V$ ;  $V_{EN} = 5V$ ;  $V_{INL} = 0V$ ;  $V_{INH} = 0V$ ;  $R_{CS} = 100\Omega$

| PARAMETER                      | TEST CONDITIONS                                                                                                                                                    | MIN                                                                                                                                                                | TYP | MAX | UNIT |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|

| <b>LOW-SIDE GAN POWER FET</b>  |                                                                                                                                                                    |                                                                                                                                                                    |     |     |      |

| $t_{d(on)}(I_{drain})(ls)$     | From $V_{INL} > V_{INL,IT+}$ to $I_{D(ls)} > 50mA$ , $V_{BUS} = 400V$ , $I_{SW} = 1.8A$ , see <a href="#">GaN Power FET Switching Parameters</a>                   |                                                                                                                                                                    | 40  |     | ns   |

| $t_{d(off)}(ls)$               | From $V_{INL} < V_{INL,IT-}$ to $V_{DS(ls)} > 80V$ , $V_{BUS} = 400V$ , $I_{SW} = 1.8A$ , see <a href="#">GaN Power FET Switching Parameters</a>                   |                                                                                                                                                                    | 45  |     | ns   |

| $t_{f(off)}(ls)$               | From $V_{DS(ls)} > 80V$ to $V_{DS(ls)} > 320V$ , $V_{BUS} = 400V$ , $I_{SW} = 1.8A$ , see <a href="#">GaN Power FET Switching Parameters</a>                       |                                                                                                                                                                    | 23  |     | ns   |

|                                | From $V_{DS(ls)} < 320V$ to $V_{DS(ls)} < 80V$ , $T_J = 25^\circ C$ , $V_{BUS} = 400V$ , $I_{SW} = 1.8A$ , see <a href="#">GaN Power FET Switching Parameters</a>  |                                                                                                                                                                    | 80  |     | V/ns |

| <b>HIGH-SIDE GAN POWER FET</b> |                                                                                                                                                                    |                                                                                                                                                                    |     |     |      |

| $t_{d(on)}(I_{drain})(hs,INH)$ | From $V_{INH} > V_{INH,IT+}$ to $I_{D(hs)} > 50mA$ , $V_{BUS} = 400V$ , $I_{SW} = -1.8A$ , see <a href="#">GaN Power FET Switching Parameters</a>                  |                                                                                                                                                                    | 45  |     | ns   |

| $t_{d(on)}(I_{drain})(hs,GDH)$ | From $V_{GDH} > V_{GDH,IT+}$ to $I_{D(hs)} > 50mA$ , $V_{BUS} = 400V$ , $I_{SW} = -1.8A$ , see <a href="#">GaN Power FET Switching Parameters</a>                  |                                                                                                                                                                    | 40  |     | ns   |

| $t_{d(off)}(hs,INH)$           | From $V_{INH} < V_{INH,IT-}$ to $V_{DS(hs)} > 80V$ , $V_{BUS} = 400V$ , $I_{SW} = -1.8A$ , see <a href="#">GaN Power FET Switching Parameters</a>                  |                                                                                                                                                                    | 55  |     | ns   |

| $t_{d(off)}(hs,GDH)$           | From $V_{GDH} < V_{GDH,IT-}$ to $V_{DS(hs)} > 80V$ , $V_{BUS} = 400V$ , $I_{SW} = -1.8A$ , see <a href="#">GaN Power FET Switching Parameters</a>                  |                                                                                                                                                                    | 45  |     | ns   |

| $t_{f(off)}(hs)$               | From $V_{DS(hs)} > 80V$ to $V_{DS(hs)} > 320V$ , $V_{BUS} = 400V$ , $I_{SW} = -1.8A$ , see <a href="#">GaN Power FET Switching Parameters</a>                      |                                                                                                                                                                    | 23  |     | ns   |

|                                | From $V_{DS(hs)} < 320V$ to $V_{DS(hs)} < 80V$ , $T_J = 25^\circ C$ , $V_{BUS} = 400V$ , $I_{SW} = -1.8A$ , see <a href="#">GaN Power FET Switching Parameters</a> |                                                                                                                                                                    | 80  |     | V/ns |

| <b>CS</b>                      |                                                                                                                                                                    |                                                                                                                                                                    |     |     |      |

| $t_r$                          | Rise time                                                                                                                                                          | From $I_{CS(src)} > 0.1 \times I_{CS(src)(final)}$ to $I_{CS(src)} > 0.9 \times I_{CS(src)(final)}$ , $0V \leq V_{CS} \leq 2V$ , Low-side enabled into a 1.8A load |     | 30  | ns   |

| <b>EN</b>                      |                                                                                                                                                                    |                                                                                                                                                                    |     |     |      |

|                                | EN wake-up time                                                                                                                                                    | From $V_{EN} > V_{IT+}$ to $I_{D(ls)} > 10mA$ , $V_{INL} = 5V$                                                                                                     |     | 1.5 | μs   |

| <b>BST</b>                     |                                                                                                                                                                    |                                                                                                                                                                    |     |     |      |

|                                | Start-up time from deep BST to SW discharge                                                                                                                        | From $V_{BST\_SW} > V_{BST\_SW,T+(UVLO)}$ to high-side reacts to INH or GDH high level with $V_{BST\_SW}$ rising from 0V to 10V in 1μs                             |     | 5   | μs   |

|                                | Start-up time from shallow BST to SW discharge                                                                                                                     | From $V_{BST\_SW} > V_{BST\_SW,T+(UVLO)}$ to high-side reacts to INH or GDH high level with $V_{BST\_SW}$ rising from 5V to 10V in 0.5μs                           |     | 2.6 | μs   |

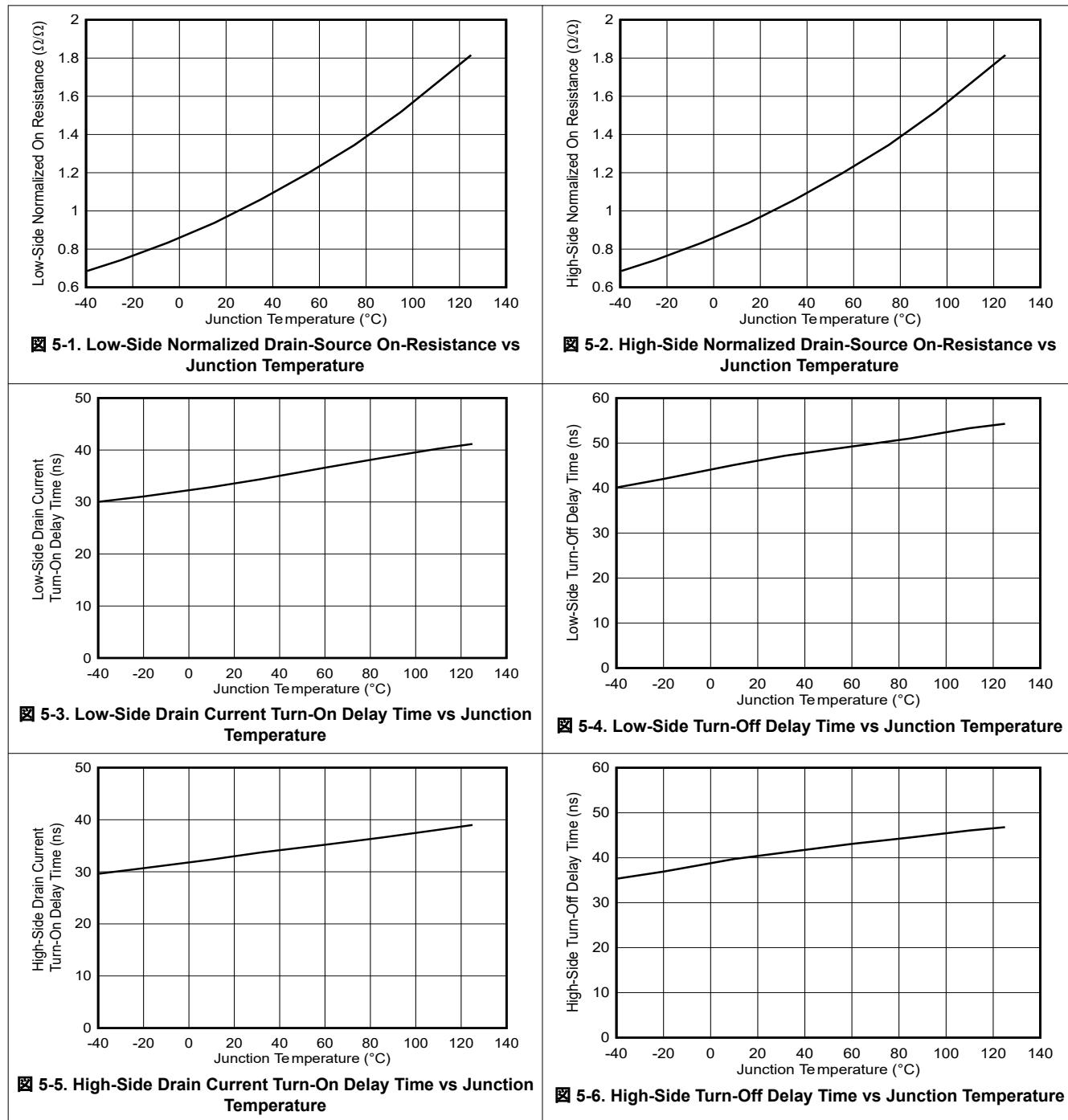

## 5.7 Typical Characteristics

## 5.7 Typical Characteristics (continued)

图 5-7. AUX Standby Current vs Junction Temperature

图 5-8. AUX Quiescent Current vs Junction Temperature

INL = 0V

图 5-9. AUX Quiescent Current vs Junction Temperature

INL = 5V

图 5-10. AUX Operating Current vs Frequency

图 5-11. BST Quiescent Current vs Junction Temperature

INH = 0V

图 5-12. BST Quiescent Current vs Junction Temperature

INH = 5V

## 5.7 Typical Characteristics (continued)

図 5-13. BST Operating Current vs Frequency

## 6 Parameter Measurement Information

### 6.1 GaN Power FET Switching Parameters

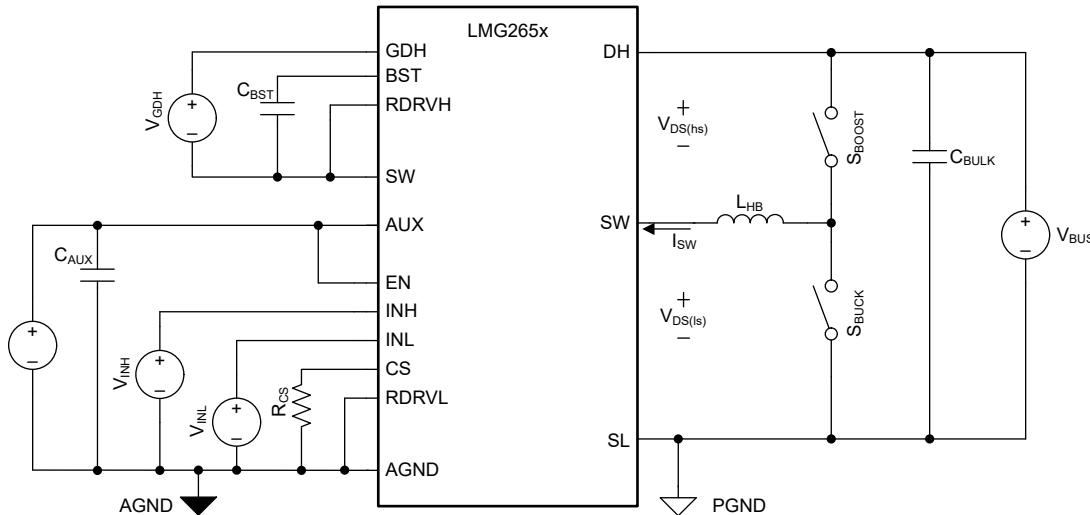

図 6-1 shows the circuit used to measure the GaN power FET switching parameters. The circuit is operated as a double-pulse tester. Consult external references for double-pulse tester details. The circuit is placed in the boost configuration to measure the low-side GaN switching parameters. The circuit is placed in the buck configuration to measure the high-side GaN switching parameters. The GaN FET not being measured in each configuration (high-side in the boost and low-side in the buck) acts as the double-pulse tester diode and circulates the inductor current in the off-state, third-quadrant conduction mode. 表 6-1 shows the details for each configuration.

図 6-1. GaN Power FET Switching Parameters Test Circuit

表 6-1. GaN Power FET Switching Parameters Test Circuit Configuration Details

| CONFIGURATION | GaN FET UNDER TEST | GaN FET ACTING AS DIODE | S <sub>BOOST</sub> | S <sub>BUCK</sub> | V <sub>INL</sub>      | V <sub>INH</sub>      | V <sub>GDH</sub>      |

|---------------|--------------------|-------------------------|--------------------|-------------------|-----------------------|-----------------------|-----------------------|

| Boost         | Low-side           | High-side               | Closed             | Open              | Double-pulse waveform | 0V                    | 0V                    |

| Buck          | High-side          | Low-side                | Open               | Closed            | 0V                    | Double-pulse waveform | 0V                    |

| Buck          | High-side          | Low-side                | Open               | Closed            | 0V                    | 0V                    | Double-pulse waveform |

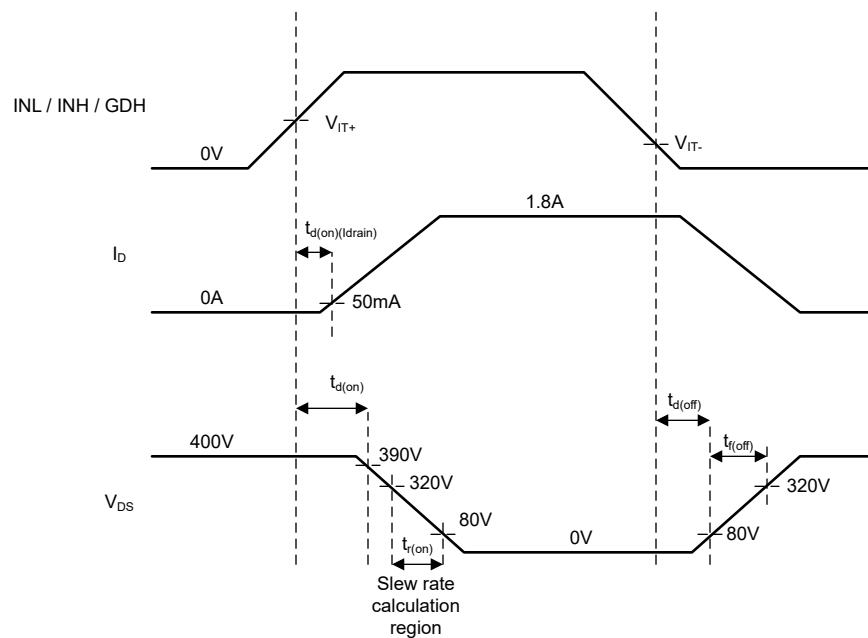

図 6-2 shows the GaN power FET switching parameters.

The GaN power FET turn-on transition has three timing components: drain-current turn-on delay time  $t_{d(on)}(I_{drain})$ , turn-on delay time  $t_{d(on)}$ , and turn-on rise time  $t_{r(on)}$ . Note that the turn-on rise time is the same as the  $V_{DS}$  80% to 20% fall time.

The GaN power FET turn-off transition has two timing components: turn-off delay time  $t_{d(off)}$ , and turn-off fall time  $t_{f(off)}$ . Note that the turn-off fall time is the same as the  $V_{DS}$  20% to 80% rise time. The turn-off timing components are heavily dependent on the  $L_{HB}$  current.

The turn-on slew rate is measured over a turn-on rise time voltage delta (240V) to obtain a slew rate which is useful for EMI design.

図 6-2. GaN Power FET Switching Parameters

## 7 Detailed Description

### 7.1 Overview

The LMG2652 is a highly-integrated 650V 140mΩ GaN power-FET half bridge intended for use in switch-mode power-supply applications. The LMG2652 combines the half-bridge power FETs, gate drivers, low-side current-sense emulation function, high-side gate-drive level shifter, and bootstrap diode function in a 6mm by 8mm QFN package.

The 650V rated GaN FETs support the high voltages encountered in off-line power switching applications. The GaN FETs low output-capacitive charge reduces both the time and energy needed for power converter switching and is the key characteristic needed to create small, efficient power converters.

The LMG2652 internal gate drivers regulate the GaN FET gate voltage for optimum on-resistance. Internal drivers also reduce total gate inductance and GaN FET common-source inductance for improved switching performance.

Current-sense emulation places a scaled replica of the low-side drain current on the output of the CS pin. The CS pin is terminated with a resistor to AGND to create the current-sense input signal to the external power supply controller. This CS pin resistor replaces the traditional current-sense resistor, placed in series with the low-side GaN FET source, at significant power and space savings. Furthermore, with no current-sense resistor in series with the GaN source, the low-side GaN FET thermal pad (SL pin) can be connected directly to the PCB power ground, improving system thermal performance.

The high-side GaN FET is controlled by both the low-side referenced INH pin and high-side referenced GDH pin allowing the LMG2652 to interface with controllers that employ either high-side gate drive reference scheme. The internal high-side gate-drive level-shifter reliably transmits the INH signal to the high-side with minimal impact to device quiescent current and no impact to device start-up time.

The bootstrap diode function between AUX and BST is implemented with a smart-switched GaN bootstrap FET. The switched GaN bootstrap FET allows more complete charging of the BST-to-SW capacitor since the on-state GaN bootstrap FET does not have the forward voltage drop of a traditional bootstrap diode. The smart-switched GaN bootstrap FET also avoids the traditional bootstrap diode problem of BST-to-SW capacitor overcharging due to off-state third-quadrant current flow in the low-side half-bridge GaN power FET. Finally, the bootstrap function has more efficient switching due to low capacitance and no reverse-recovery charge compared to the traditional bootstrap diode.

The AUX input supply wide voltage range is compatible with the corresponding wide range supply rail created by power supply controllers. The BST input supply range is even wider on the low end to account for capacitive droop in between bootstrap recharge cycles. Low AUX/BST idle quiescent currents and fast BST start-up time support converter burst-mode operation critical for meeting government light-load efficiency mandates. Further AUX quiescent current reduction is obtained by placing the device in standby mode with the EN pin.

The EN, INL, INH, and GDH control pins have high input impedance, low input threshold voltage and maximum input voltage equal to the local supply pin voltage (AUX or BST to SW). This allows the pins to support both low voltage and high voltage input signals and be driven with low-power outputs.

The LMG2652 protection features are low-side / high-side under-voltage lockout (UVLO), INL/INH input gate-drive interlock, low-side/high-side cycle-by-cycle current limit, and low-side/high-side overtemperature shut down. The UVLO features also help achieve well-behaved converter operation.

## 7.2 Functional Block Diagram

## 7.3 Feature Description

### 7.3.1 GaN Power FET Switching Capability

Due to the silicon FET's long reign as the dominant power-switch technology, many designers are unaware that the nameplate drain-source voltage cannot be used as an equivalent point to compare devices across technologies. The nameplate drain-source voltage of a silicon FET is set by the avalanche breakdown voltage. The nameplate drain-source voltage of a GaN FET is set by the long term compliance to data sheet specifications.

Exceeding the nameplate drain-source voltage of a silicon FET can lead to immediate and permanent damage. Meanwhile, the breakdown voltage of a GaN FET is much higher than the nameplate drain-source voltage. For example, the breakdown drain-source voltage of the LMG2652 GaN power FET is more than 800V which allows the LMG2652 to operate at conditions beyond an identically nameplate rated silicon FET.

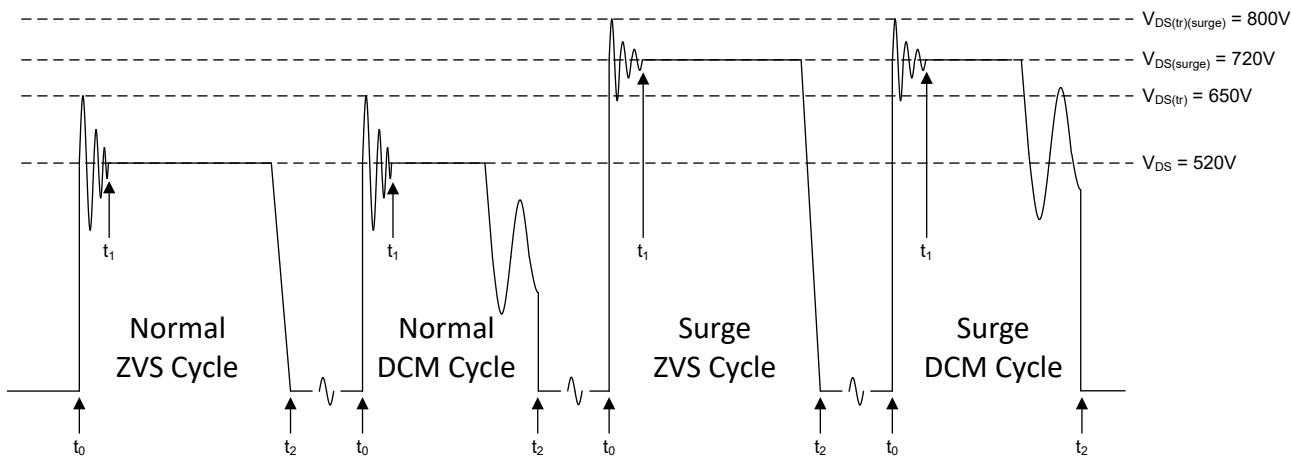

The LMG2652 GaN power FET switching capability is explained with the assistance of [图 7-1](#). The figure shows the drain-source voltage versus time for the LMG2652 GaN power FET for four distinct switch cycles in a switching application. No claim is made about the switching frequency or duty cycle. The first two cycles show normal operation and the second two cycles show operation during a rare input voltage surge. The LMG2652 GaN power FETs are intended to be turned on in either zero-voltage switching (ZVS) or discontinuous-conduction mode (DCM) switching conditions.

**图 7-1. GaN Power FET Switching Capability**

Each cycle starts before  $t_0$  with the FET in the on state. At  $t_0$  the GaN FET turns off and parasitic elements cause the drain-source voltage to ring at a high frequency. The high frequency ringing has damped out by  $t_1$ . Between  $t_1$  and  $t_2$  the FET drain-source voltage is set by the characteristic response of the switching application. The characteristic is shown as a flat line (plateau), but other responses are possible. At  $t_2$  the GaN FET is turned on. For normal operation, the transient ring voltage is limited to 650V and the plateau voltage is limited to 520V. For rare surge events, the transient ring voltage is limited to 800V and the plateau voltage is limited to 720V.

### 7.3.2 Current-Sense Emulation

The current-sense emulation function creates a scaled replica of the GaN power FET positive drain current at the output of the CS pin. The current-sense emulation gain,  $G_{CSE}$ , is 0.901mA output from the CS pin,  $I_{CS}$ , for every 1A passing into the drain of the low-side GaN power FET,  $I_D$ .

$$G_{CSE} = I_{CS} / I_D = 0.901\text{mA} / 1\text{A} = 0.000901 \quad (1)$$

The CS pin is terminated with a resistor to AGND,  $R_{CS}$ , to create the current-sense voltage input signal to the external power supply controller.

$R_{CS}$  is determined by solving for the traditional current-sense design resistance,  $R_{CS(\text{trad})}$ , and multiplying by the inverse of  $G_{CSE}$ . The traditional current-sense design creates the current-sense voltage,  $V_{CS(\text{trad})}$ , by passing the GaN power FET drain current,  $I_D$ , through  $R_{CS(\text{trad})}$ . The LMG2652 creates the current-sense voltage,  $V_{CS}$ , by passing the CS pin output current,  $I_{CS}$ , through  $R_{CS}$ . The current-sense voltage must be the same for both designs.

$$V_{CS} = I_{CS} \times R_{CS} = V_{CS(\text{trad})} = I_D \times R_{CS(\text{trad})} \quad (2)$$

$$R_{CS} = I_D / I_{CS} \times R_{CS(\text{trad})} = 1 / G_{CSE} \times R_{CS(\text{trad})} \quad (3)$$

$$R_{CS} = 1,110 \times R_{CS(\text{trad})} \quad (4)$$

The CS pin is clamped internally to a typical 2.5V. The clamp protects vulnerable power-supply controller current-sense input pins from over voltage if, for example, the current sense resistor on the CS pin were to become disconnected.

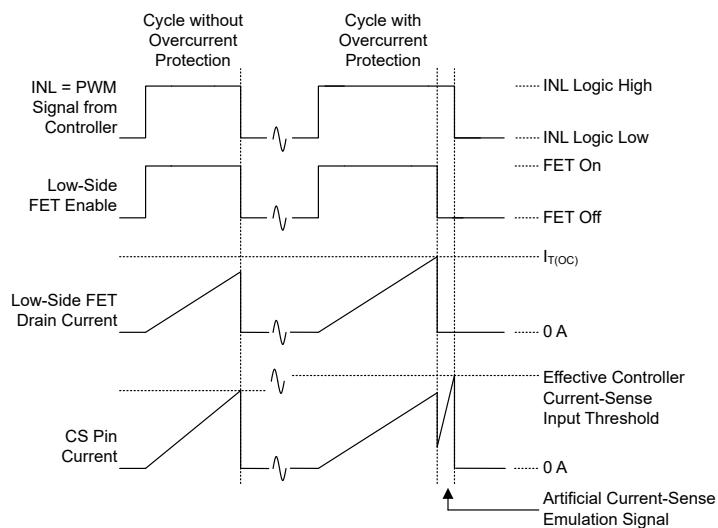

图 7-2 shows the current-sense emulation operation. In both cycles, the CS pin current emulates the GaN power FET drain current while the GaN FET is enabled. The first cycle shows normal operation where the controller turns off the GaN power FET when the controller current-sense input threshold is tripped. The second cycle shows a fault situation where the LMG2652 overcurrent protection turns off the GaN power FET before the controller current-sense input threshold is tripped. In this second cycle, the LMG2652 avoids a hung controller IN pulse by generating a fast-ramping artificial current-sense emulation signal to trip the controller current-sense input threshold. The artificial signal persists until the IN pin goes to logic-low which indicates the controller is back in control of switch operation.

图 7-2. Current-Sense Emulation Operation

### 7.3.3 Bootstrap Diode Function

The internal bootstrap diode function is implemented with a smart-switched GaN bootstrap FET. The GaN bootstrap FET blocks current in both directions between AUX and BST when the GaN bootstrap FET is turned off.

The bootstrap diode function is active when the low-side GaN power FET is turned on and inactive when the low-side GaN power FET is turned off. The GaN bootstrap FET is held off in the bootstrap diode inactive phase. The GaN bootstrap FET is turned on a single time at the beginning of the bootstrap active phase and is controlled as an ideal diode with diode current flowing from AUX to BST to charge the BST-to-SW capacitor. If a small reverse current from BST to AUX is detected after the GaN bootstrap FET is turned on, the GaN bootstrap FET is turned off for the remainder of the bootstrap active phase.

The bootstrap diode function implements a current limit to protect the GaN bootstrap FET when the BST-to-SW capacitor is significantly discharged at the beginning of the bootstrap active phase. If there is no current limit situation during the GaN bootstrap FET turn on, or if the bootstrap function drops out of current limit as the BST-to-SW capacitor charges, the current limit function is disabled for the remainder of the GaN bootstrap FET turn-on time. The current limit function is disabled to save quiescent current.

### 7.3.4 Input Control Pins (EN, INL, INH, GDH)

The EN pin is referenced to AGND and is used to toggle the device between the active and standby modes described in the *Device Functional Modes* section.

The INL pin is referenced to AGND and is used to turn the low-side GaN power FET on and off.

The INH pin is referenced to AGND and is used to turn the high-side GaN power FET on and off. The INH pin is compatible with controllers that use a low-side referenced gate drive signal to control the high-side GaN power FET.

The GDH pin is referenced to SW and is used to turn the high-side GaN power FET on and off. The GDH pin is compatible with controllers that use a high-side referenced signal to control the high-side GaN power FET.

The LMG2652 is intended to be used with either the INH pin or the GDH pin controlling the high-side GaN power FET. Short the unused pin to its reference (INH to AGND or GDH to SW).

The input control pins have a typical 1V input-voltage-threshold hysteresis for noise immunity. The pins also have a typical 400k $\Omega$  pull-down resistance to protect against floating inputs. The 400k $\Omega$  saturates for typical input voltages above 4V to limit the maximum input pull-down current to a typical 10uA. There are individual forward based ESD diodes from the EN, INL, and INH pins to the AUX pin. Avoid driving the EN, INL, and INH voltages higher than the AUX voltage. There is also a forward based ESD diode from the GDH pin to the BST pin. Avoid driving the GDH-to-SW voltage higher than the BST-to-SW voltage.

The INL turn-on action is blocked by the following conditions:

- Standby mode (as set by the EN pin above)

- INH in control of the INL/INH interlock

- AUX under-voltage lockout (UVLO)

- Low-side overtemperature protection

- Low-side GaN Power FET overcurrent protection

The INH turn-on action is blocked by the following conditions

- Standby mode (as set by the EN pin above)

- INL in control of the INL/INH interlock

- AUX UVLO

- Low-side overtemperature protection

- BST UVLO

- High-side overcurrent protection

The GDH turn-on action is blocked by the following conditions

- BST UVLO

- High-side overtemperature protection

- High-side overcurrent protection

Note that the INH pin is blocked by the low-side temperature protection while the GDH pin is blocked by the high-side temperature protection.

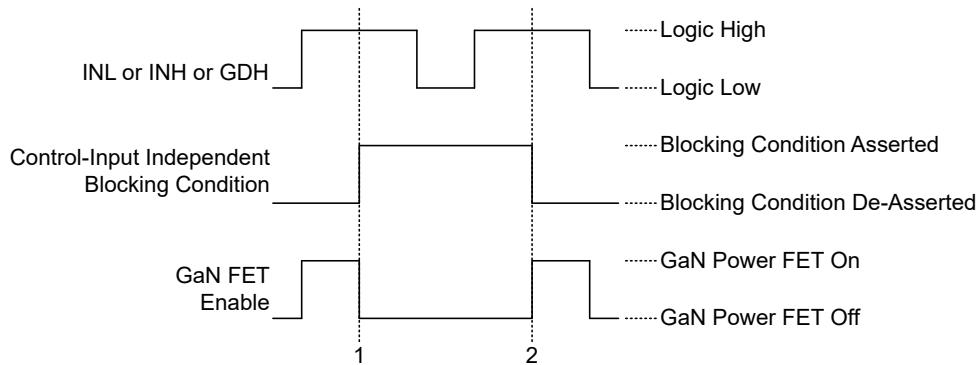

All the blocking conditions except the INL/INH interlock and the overcurrent protection act independently of the INL, INH, or GDH logic state. [図 7-3](#) shows the operation of these control-input independent blocking conditions.

**図 7-3. Control-Input-Independent Blocking Condition Operation**

The INL/INH Interlock blocking action is described in the *INL - INH Interlock* section. Meanwhile, the overcurrent protection blocking action only asserts after the control input has turned on its respective GaN power FET. See the *Overcurrent Protection* section for the details.

### 7.3.5 INL - INH Interlock

The interlock function keeps the low-side and high-side GaN power FETs from being simultaneously turned on when the INL and INH pins are both logic-high. Either the INL or the INH pin gains control of the interlock if either pin is logic high when the other pin is logic low. Once the INL or INH pin gains control of the interlock, it retains control as long as it remains logic high. Only the INL or INH pin in control of the interlock passes a logic-high signal through the interlock.

Note that there is no interlock feature regarding the GDH pin. This means it is possible to simultaneously turn on the low-side and high-side GaN power FETs if the INL and GDH pins are both logic-high.

### 7.3.6 AUX Supply Pin

The AUX pin is the input supply for the low-side internal circuits and is the power source to charge the BST-to-SW capacitor through the internal bootstrap diode function. The AUX external capacitance is recommended to be a ceramic capacitor that is at least three times larger than the BST-to-SW external capacitance over operating conditions.

#### 7.3.6.1 AUX Power-On Reset

The AUX Power-On Reset disables all low-side functionality, including the INH pin function, if the AUX voltage is below the AUX Power-On Reset voltage. The AUX Power-On Reset voltage is not specified but is around 5V. The AUX Power-On Reset enables the low-side overtemperature protection function if the AUX voltage is above the AUX Power-On Reset voltage.

#### 7.3.6.2 AUX Under-Voltage Lockout (UVLO)

The AUX UVLO blocks the INL pin from turning on the low-side GaN power FET and blocks the INH pin from turning on the high-side GaN power FET if the AUX voltage is below the AUX UVLO voltage. [図 7-3](#) shows the AUX UVLO blocking operation. The AUX UVLO voltage is set higher than the BST UVLO voltage so the high-side GaN power FET can be operated when the low-side GaN power FET is operating. The voltage separation between the AUX UVLO voltage and BST UVLO voltage accounts for operating conditions where the bootstrap

charging of the BST-to-SW capacitor from the AUX supply is incomplete. The AUX UVLO voltage hysteresis prevents on-off chatter near the UVLO voltage trip point.

### 7.3.7 BST Supply Pin

The BST pin is the input supply for the high-side internal circuits. The BST pin and corresponding high-side circuits are referenced to the SW pin. The BST pin is powered by the low-side AUX Supply pin through the internal bootstrap diode function. The bootstrap function is inactive when the low-side GaN FET is off and the BST pin must rely on an external BST-to-SW capacitor for the BST power source.

Designing the BST-to-SW capacitance is a trade-off between high-side charge-up time and hold-up time. The BST-to-SW external capacitance is recommended to be a ceramic capacitor that is at least 10nF over operating conditions.

#### 7.3.7.1 BST Power-On Reset

The BST Power-On Reset voltage is with respect to the SW pin. The BST Power-On Reset disables all high-side functionality if the BST-to-SW voltage is below the BST Power-On Reset voltage. The BST Power-On Reset voltage is not specified but is around 5V.

#### 7.3.7.2 BST Under-Voltage Lockout (UVLO)

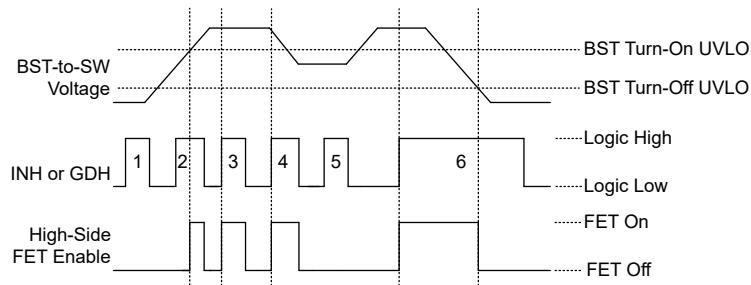

The BST UVLO voltage is with respect to the SW pin. The BST UVLO blocks both the INH and GDH pins from turning on the high-side GaN power FET if the BST-to-SW voltage is below the applicable BST UVLO voltage as described as follows. [图 7-3](#) shows the BST UVLO blocking operation. The BST UVLO consists of two separate UVLO functions to create a two-level BST UVLO. The upper BST UVLO is called the BST Turn-On UVLO and only controls if the high-side GaN power FET is allowed to turn on. The lower BST UVLO is called the BST Turn-Off UVLO and only controls if the high-side GaN power FET is turned off after the high-side GaN power FET is already turned on. The operation of the two-level UVLO is not the same as a single UVLO with hysteresis.

[图 7-4](#) shows the two-level BST UVLO operation. The BST Turn-On UVLO prevents the high-side GaN power FET from turning on, for INH or GDH logic-high, if the BST-to-SW voltage is below the BST Turn-On UVLO voltage (INH/GDH pulse #1, first portion of pulse #2, and pulse #5). After the high-side GaN power FET is successfully turned-on, the BST Turn-On UVLO is ignored and the BST Turn-Off UVLO output is watched for the remainder of the INH or GDH logic-high pulse (INH/GDH second portion of pulse #2, pulses #3, #4, and #6). The BST Turn-Off UVLO turns off the high-side GaN power FET for the remainder of the INH/GDH logic-high pulse if the BST-to-SW voltage falls below the BST Turn-Off UVLO voltage (INH/GDH pulse #6).

**图 7-4. BST UVLO Operation**

The effective voltage hysteresis of the two-level BST UVLO is the difference between the upper and lower BST UVLO voltages. A single-level BST UVLO can be implemented with the same hysteresis but allows subsequent high-side GaN power FET turn on anywhere in the hysteresis range. A single-level BST UVLO allows INH/GDH pulse #5 to turn on the high-side GaN power. The two-level UVLO design prevents any turn on in the hysteresis range.

The two-level BST UVLO allows a wide hysteresis while making sure the BST-to-SW capacitor is adequately charged at the beginning of every INH or GDH pulse. The wide hysteresis allows a smaller BST-to-SW capacitor

to be used which is useful for faster high-side start-up time. The adequate capacitor charge at the beginning of the INH or GDH pulse helps make sure the high-side GaN power FET is not turned-off early in the INH or GDH pulse which can create erratic converter operation.

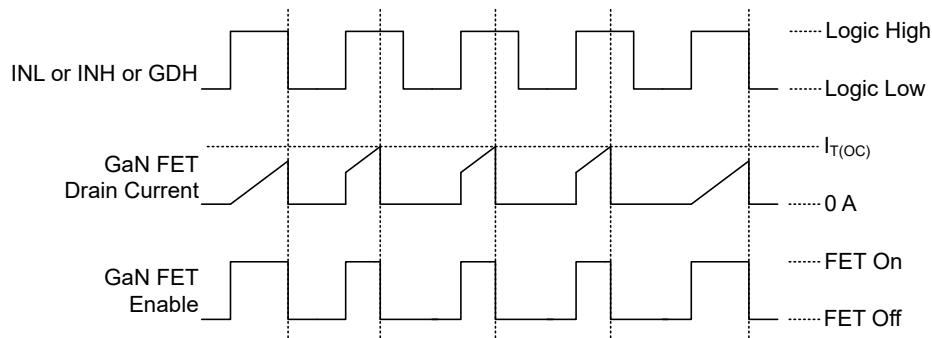

### 7.3.8 Overcurrent Protection

The LMG2652 implements cycle-by-cycle overcurrent protection for both half-bridge GaN power FETs. [図 7-5](#) shows the cycle-by-cycle overcurrent operation. Every INL or INH or GDH logic-high cycle turns on the controlled GaN power FET. If the GaN power FET drain current exceeds the overcurrent threshold current, the overcurrent protection turns off the GaN power FET for the remainder of the INL or INH or GDH logic-high duration.

**図 7-5. Cycle-by-Cycle Overcurrent Protection Operation**

Cycle-by-cycle overcurrent protection minimizes system disruption because the event is not reported and because the protection allows the GaN power FET to turn on every INL or INH or GDH cycle.

As described in the *Current-Sense Emulation* section, an artificial CS pin current is produced after the low-side GaN power FET is turned off by the low-side overcurrent protection in order to prevent the controller from entering a hung state.

### 7.3.9 Overtemperature Protection

The LMG2652 implements separate overtemperature protection for both the low-side and high-side device circuits. The low-side overtemperature protection blocks the INL pin from turning on the low-side GaN power FET and blocks the INH pin from turning on the high-side GaN power FET if the low-side temperature is above the overtemperature protection temperature. The high-side overtemperature protection blocks the GDH pin from turning on the high-side GaN power FET if the high-side temperature is above the overtemperature protection temperature. [図 7-3](#) shows the overtemperature blocking operation. The overtemperature protection hysteresis avoids erratic thermal cycling.

The low-side overtemperature protection is enabled when the AUX voltage is above the AUX Power-On Reset voltage. The low AUX Power-On Reset voltage helps the overtemperature protection remain operational when the AUX rail droops during a power converter cool-down phase. The high-side overtemperature protection is enabled when the BST-to-SW voltage is above the BST Power-On Reset voltage.

## 7.4 Device Functional Modes

The LMG2652 has two modes of operation controlled by the EN pin. The device is in Active mode when the EN is logic high and in Standby mode when the EN pin is logic low. In active mode, the half-bridge GaN power FETs are controlled by the INL, INH, and GDH pins. In Standby mode, the INL and INH pins are ignored, the low-side GaN power FET and bootstrap diode are held off, the INH pin is blocked from turning on the high-side FET, and the AUX quiescent current is reduced to the AUX standby quiescent current. Note that in Standby mode the high-side GaN power FET can still be controlled by the GDH pin if the BST pin is powered by an external source.

## 8 Application and Implementation

### 注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes, as well as validating and testing their design implementation to confirm system functionality.

### 8.1 Application Information

The LMG2652 is a GaN power-FET half bridge with plug-and-play simplicity since it integrates the half-bridge FETs, FET gate drivers, high-side gate-drive level shifter, bootstrap diode function, and current-sense emulation in a single package. The integrated gate driver, low IN input threshold voltage, and wide AUX input-supply voltage allows the LMG2652 to seamlessly pair with common industry power-supply controllers.

## 8.2 Typical Application

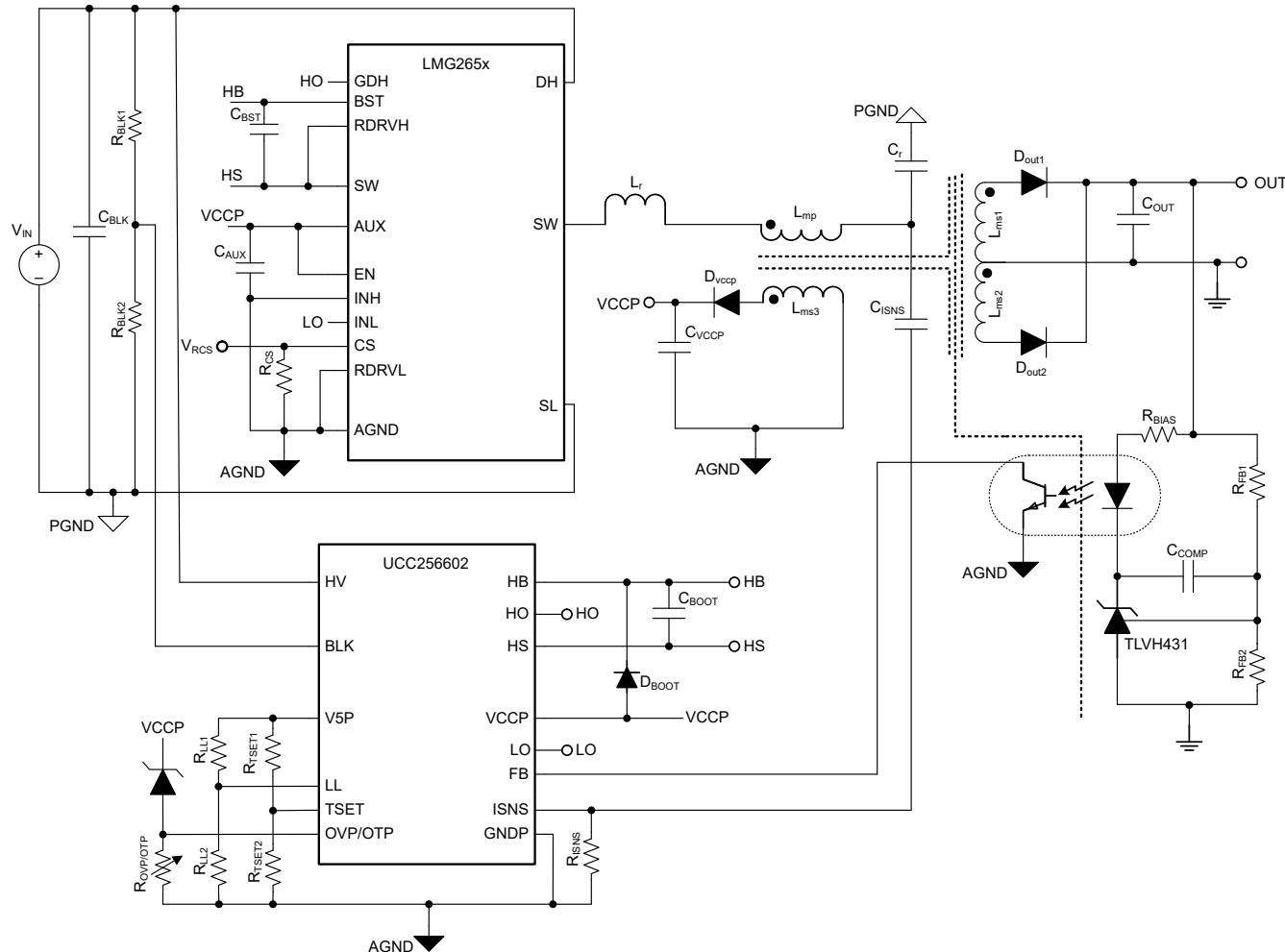

### 8.2.1 LLC Application

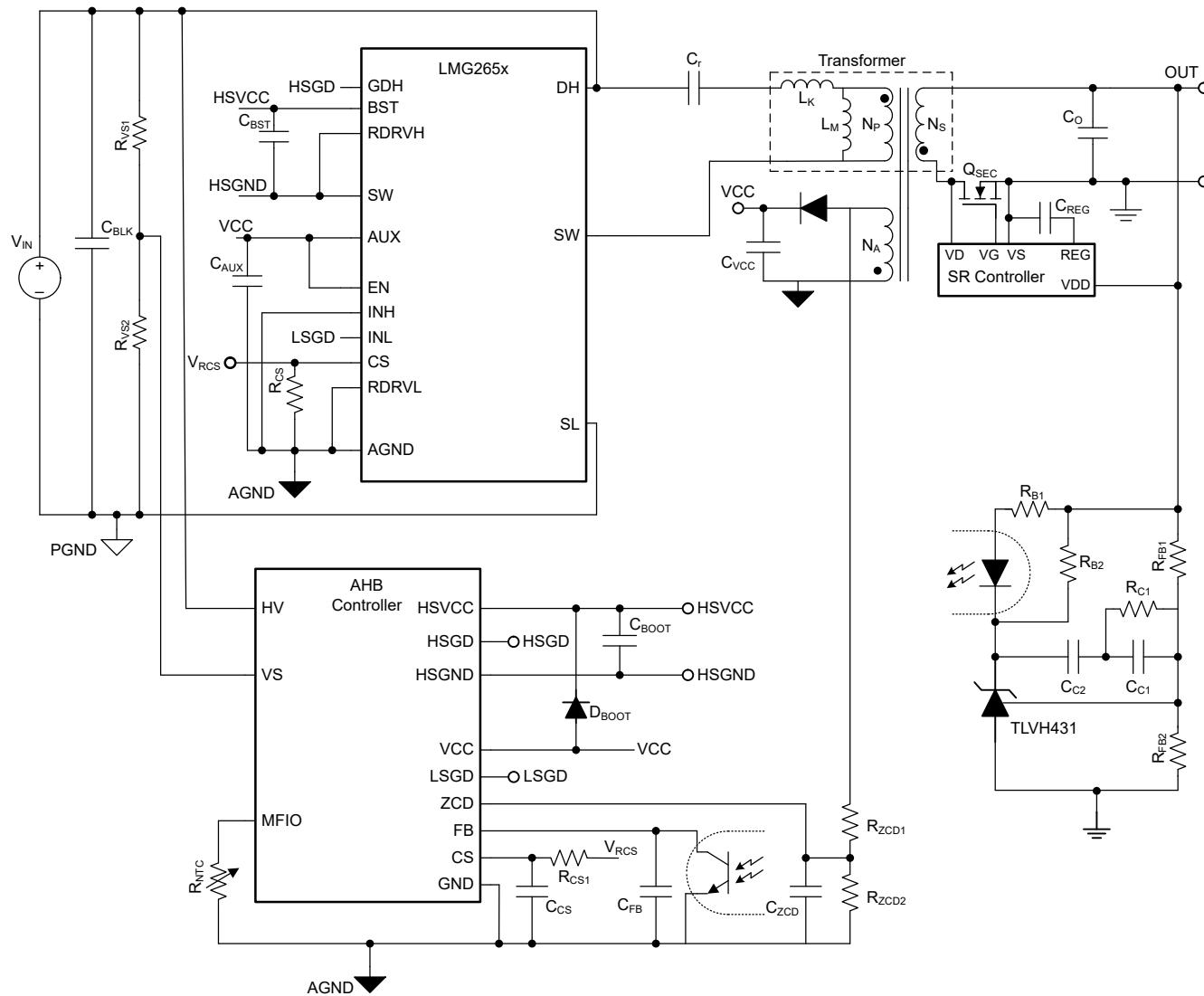

図 8-1. 200W LLC Converter Application

#### 8.2.1.1 Design Requirements

表 8-1. Design Specification

| SPECIFICATION                    | VALUE              |

|----------------------------------|--------------------|

| Input DC voltage range           | 365 VDC to 410 VDC |

| Output DC voltage                | 19.5V              |

| Output rated current             | 10.3A              |

| Output voltage ripple at 390 VDC | 120mVpp            |

| Peak efficiency at 390 VDC       | 93%                |

#### 8.2.1.2 Detailed Design Procedure

The typical application shows the LMG2652 pairing a LLC controller to create a high-power-density, high-efficiency, 200W, LLC converter. The 200W LLC converter application is adapted from the typical application. This detailed design procedure focuses on the specifics of using the LMG2652 in the application.

### 8.2.1.3 Application Curves

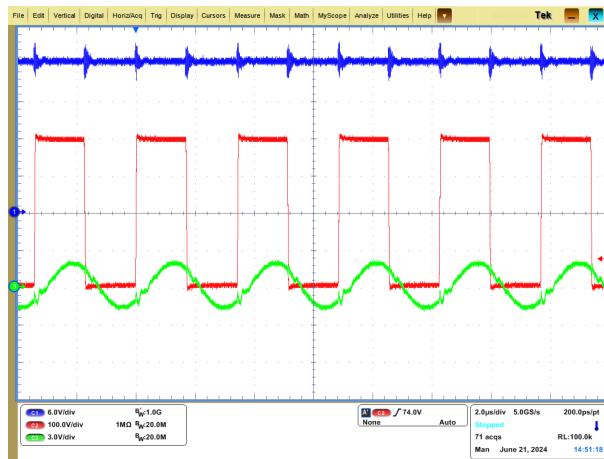

The following waveform shows typical switching waveforms. The red trace is the switch-node voltage of LMG2652, the green trace is the current-sense voltage across  $R_{ISNS}$ , and the blue trace is  $V_{OUT}$ .

図 8-2.  $V_{IN} = 400\text{VDC}$

### 8.2.2 AHB Application

図 8-3. 140W AHB Converter Application

### 8.3 Power Supply Recommendations

The LMG2652 operates from a single input supply connected to the AUX pin. The BST pin is powered internally by the AUX pin. The LMG2652 is intended to be operated from the same supply managed and used by the power supply controller. The wide recommended AUX voltage range of 10V to 26V overlaps common-controller supply-pin turn-on and UVLO voltage limits.

The BST-to-SW external capacitance is recommended to be a ceramic capacitor that is at least 10nF over operating conditions.

The AUX external capacitance is recommended to be a ceramic capacitor that is at least three-times larger than the BST-to-SW capacitance over operating conditions.

## 8.4 Layout

### 8.4.1 Layout Guidelines

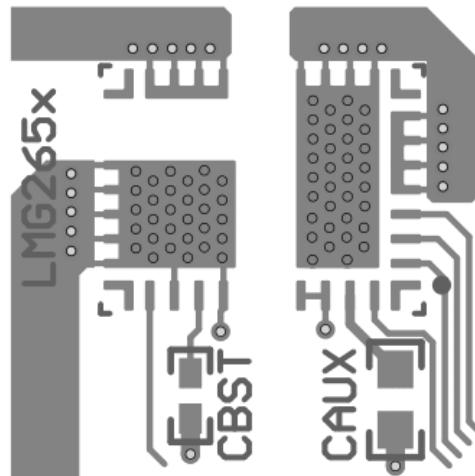

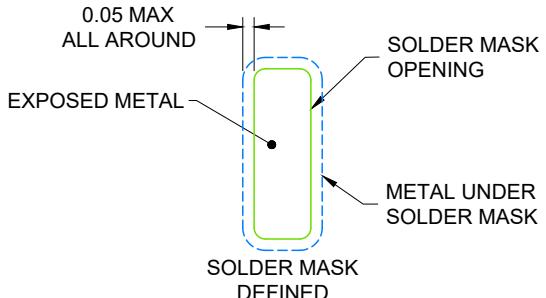

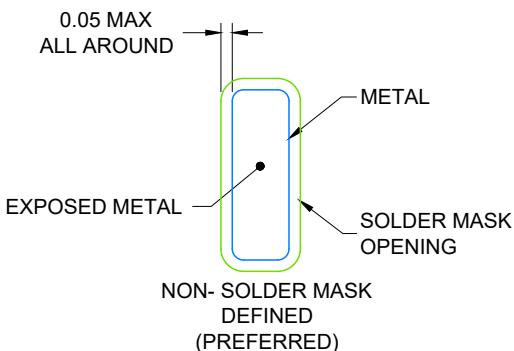

#### 8.4.1.1 Solder-Joint Stress Relief

Large QFN packages can experience high solder-joint stress. Several best practices are recommended to provide solder-joint stress relief. First, the instructions for the NC anchor pins found in [Pin Configuration and Functions](#) section must be followed. Second, all the board solder pads must be non-solder-mask defined (NSMD) as shown in the land pattern example within the [Mechanical, Packaging, and Orderable Information](#) section. Finally, any board trace connected to an NSMD pad must be less than 2/3 the width of the pad on the pad side where it is connected. The trace must maintain this 2/3 width limit for as long as it is not covered by solder mask. After the trace is under solder mask, there are no limits on the trace dimensions. All these recommendations are followed in the [Layout Example](#) section.

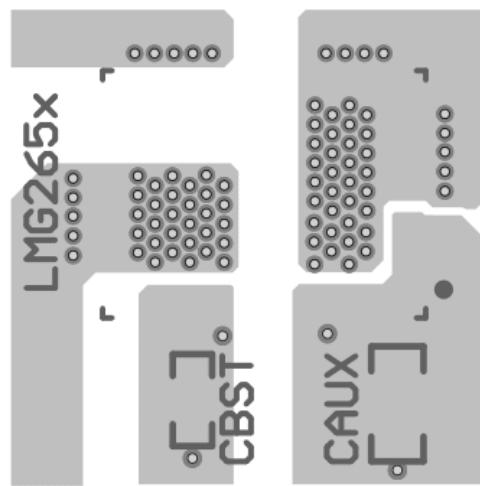

#### 8.4.1.2 Signal-Ground Connection

Design the power supply with separate signal and power grounds that only connect in one location. Connect the LMG2652 AGND pin to signal ground. Connect the LMG2652 SL pin and low-side thermal pad to power ground. The LMG2652 serves as the single connection point between the signal and power grounds since the AGND pin, SL pin, and low-side thermal pad are connected internally. Do not connect the signal and power grounds anywhere else on the board except as recommended in the next sentence.

#### 8.4.1.3 CS Pin Signal

As seen with [式 4](#), the current-sense signal impedance is three orders of magnitude higher than a traditional current-sense signal. This higher impedance has implications for current-sense signal noise susceptibility. Minimize routing the current-sense signal near any noisy traces. Place the current-sense resistor and any filtering capacitors at the far end of the trace next to the controller current-sense input pin.

### 8.4.2 Layout Example

図 8-4. PCB Top Layer (First Layer)

図 8-5. PCB Inner Layer (Second Layer)

## 9 Device and Documentation Support

TI offers an extensive line of development tools. Tools and software to evaluate the performance of the device, generate code, and develop solutions are listed below.

### 9.1 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 9.2 サポート・リソース