# LMH6502

***LMH6502 Wideband, Low Power, Linear-in-dB Variable Gain Amplifier***

Literature Number: JAJSA48

ご注意：この日本語データシートは参考資料として提供しており、内容が最新でない場合があります。製品のご検討およびご採用に際しては、必ず最新の英文データシートをご確認ください。

2004年6月

LMH6502 広帯域、低消費電力、dBリニア可変ゲイン・アンプ

## LMH6502

### 広帯域、低消費電力、dBリニア可変ゲイン・アンプ

#### 概要

LMH<sup>TM</sup>6502 は、DC 結合かつ広帯域の差動入力段、外部電圧によるゲイン制御段、高速電流帰還型オペアンプ段で構成されたリニア可変ゲイン・アンプで、低インピーダンス負荷を直接駆動できる能力を備えています。ゲイン調整範囲は 10MHz に対して 70dB 以上です。

外付け部品で設定される回路の最大ゲインからカットオフ点まで、可変ゲイン・ピン  $V_G$  に与える電圧でゲインを調整できます。130MHz 動作時の消費電力は 300mW です。出力オフセット電圧はゲイン制御電圧範囲全体にわたって 350mV 未満です。デバイス間のゲインは最大ゲイン時でも  $\pm 0.6$ dB 以内に整合されています。また、任意の  $V_G$  に対するゲインはテストされ、許容誤差は保証されています。出力は、電流帰還型オペアンプによって高い周波数に対して大振幅（スルーレート 1800V/μs）が実現され、合わせて大電流負荷 (75mA) に対応しています。入力は差動構成を採用しているため、小信号を増幅するアプリケーションや比較的長い配線長で駆動されたアプリケーションでもコモン・モードを抑止できます。また、一方の入力をグラウンド（単一電源アプリケーションでは電源電圧の 1/2）に接続すれば、単電源動作をさせることもできます。この場合、使用する入力によって反転または非反転ゲインが得られます。

単一電源動作時の使い勝手を高めるため、0V ~ + 2V の  $V_G$  電圧範囲は 11 ピン（グラウンド）の相対電位として定義されています。単一電源動作の場合はこのグラウンド・ピンを電源電圧の 1/2 に接続するため、相対電位での制御となるゲイン制御の汎用性が損なわれることはありません。

LMH6502 のゲインは、ゲイン制御範囲全体の広い領域にわたって、制御信号の dB の変化に対してリニアに変化します。このため AGC 回路などのアプリケーションに最適です。なお、制御信号に対してリニアなゲイン制御が必要なアプリケーションは LMH6503 のデータシートを参照してください。LMH6502 は SOIC-14 パッケージ、TSSOP-14 パッケージで供給されます。

#### 特長

$V_S = \pm 5V$ 、 $T_A = 25$ 、 $R_F = 1k$ 、 $R_G = 174$ 、 $R_L = 100$ 、 $A_V = A_{V(\text{MAX})} = 10$  (特記のない限り、代表値)

|                                             |              |

|---------------------------------------------|--------------|

| - 3dB 帯域幅                                   | 130MHz       |

| ゲイン制御帯域幅                                    | 100MHz       |

| 調節範囲 (動作温度範囲に対する代表値)                        | 70dB         |

| ゲイン・マッチング (リミット値)                           | $\pm 0.6$ dB |

| スルーレート                                      | 1,800V/μs    |

| 消費電流 (無負荷時)                                 | 27mA         |

| 線形出力電流                                      | $\pm 75$ mA  |

| 出力電圧 ( $R_L = 100$ )                        | $\pm 3.2$ V  |

| 入力電圧ノイズ                                     | 7.7nV/√Hz    |

| 入力電流ノイズ                                     | 2.4pA/√Hz    |

| THD (20MHz, $R_L = 100$ , $V_O = 2V_{PP}$ ) | - 53dBc      |

| CLC520 の互換製品                                |              |

#### アプリケーション

可変アッテネータ

自動ゲイン調整 (AGC)

電圧制御フィルタ

映像画像処理装置

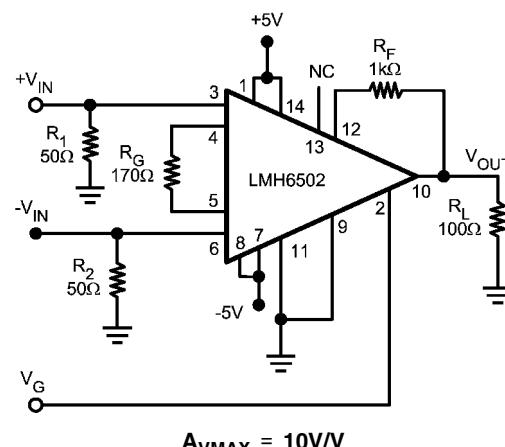

#### 代表的なアプリケーション

LMH<sup>TM</sup> はナショナルセミコンダクター社の商標です。

## 絶対最大定格 (Note 1)

本データシートには軍用・航空宇宙用の規格は記載されていません。

関連する電気的信頼性試験方法の規格を参照ください。

## ESD 耐圧 (Note 4)

|                                         |                                              |

|-----------------------------------------|----------------------------------------------|

| 人体モデル                                   | 2kV                                          |

| マシン・モデル                                 | 200V                                         |

| 入力電流                                    | ± 10mA                                       |

| $V_{IN}$ 差動電圧                           | ± (V <sup>+</sup> - V <sup>-</sup> )         |

| 出力電流                                    | 120mA (Note 3)                               |

| 電源電圧 (V <sup>+</sup> - V <sup>-</sup> ) | 12.6V                                        |

| 入出力端子電圧                                 | V <sup>+</sup> + 0.8V, V <sup>-</sup> - 0.8V |

| 保存温度範囲                                  | - 65 ~ + 150                                 |

| 接合部温度                                   | + 150                                        |

## ハンダ付け情報

|                   |     |

|-------------------|-----|

| 赤外線または対流方式 (20 秒) | 235 |

| 流動ハンダ付け (10 秒)    | 260 |

## 動作定格 (Note 1)

|                                         |             |

|-----------------------------------------|-------------|

| 電源電圧 (V <sup>+</sup> - V <sup>-</sup> ) | 5V ~ 12V    |

| 温度範囲                                    | - 40 ~ + 85 |

| 熱抵抗 (JC)                                | (JA)        |

| 14 ピン SOIC                              | 45 /W       |

| 14 ピン TSSOP                             | 51 /W       |

|                                         | 138 /W      |

|                                         | 160 /W      |

## 電気的特性 (Note 2)

特記のない限り、すべてのリミット値は  $T_J = 25^\circ\text{C}$  、  $V_S = \pm 5\text{V}$  、  $A_{V(\text{MAX})} = 10$  、  $V_{CM} = 0\text{V}$  、  $R_F = 1\text{k}\Omega$  、  $R_G = 174\text{k}\Omega$  、  $V_{IN\_DIFF} = \pm 0.1\text{V}$  、  $R_L = 100\text{M}\Omega$  、  $V_G = + 2\text{V}$  に対して適用されます。太字のリミット値は全温度範囲に適用されます。

| Symbol                                    | Parameter                           | Conditions                                                                          | Min<br>(Note 6) | Typ<br>(Note 6) | Max<br>(Note 6) | Units  |

|-------------------------------------------|-------------------------------------|-------------------------------------------------------------------------------------|-----------------|-----------------|-----------------|--------|

| <b>Frequency Domain Response</b>          |                                     |                                                                                     |                 |                 |                 |        |

| BW                                        | -3dB Bandwidth                      | $V_{OUT} < 0.5_{PP}$                                                                |                 | 130             |                 | MHz    |

|                                           |                                     | $V_{OUT} < 0.5_{PP}$ , $A_{V(\text{MAX})} = 100$                                    |                 | 50              |                 |        |

| GF                                        | Gain Flatness                       | $V_{OUT} < 0.5V_{PP}$<br>$0.6\text{V} \leq V_G \leq 2\text{V}$ , $\pm 0.3\text{dB}$ |                 | 30              |                 | MHz    |

| Att Range                                 | Flat Band (Relative to Max Gain)    | $\pm 0.2\text{dB}$ , $f < 30\text{MHz}$                                             |                 | 16              |                 | dB     |

|                                           | Attenuation Range (Note 14)         | $\pm 0.1\text{dB}$ , $f < 30\text{MHz}$                                             |                 | 7.5             |                 |        |

| BW Control                                | Gain control Bandwidth              | $V_G = 1\text{V}$ (Note 13)                                                         |                 | 100             |                 | MHz    |

| PL                                        | Linear Phase Deviation              | DC to 60MHz                                                                         |                 | 1.5             |                 | deg    |

| G Delay                                   | Group Delay                         | DC to 130MHz                                                                        |                 | 2.5             |                 | ns     |

| CT (dB)                                   | Feed-through                        | $V_G = 0\text{V}$ , 30MHz (Output Referred)                                         |                 | -47             |                 | dB     |

| GR                                        | Gain Adjustment Range               | $f < 10\text{MHz}$                                                                  |                 | 72              |                 | dB     |

|                                           |                                     | $f < 30\text{MHz}$                                                                  |                 | 67              |                 |        |

| <b>Time Domain Response</b>               |                                     |                                                                                     |                 |                 |                 |        |

| $t_r$ , $t_f$                             | Rise and Fall Time                  | 0.5V Step                                                                           |                 | 2.2             |                 | ns     |

| OS %                                      | Overshoot                           | 0.5V Step                                                                           |                 | 10              |                 | %      |

| SR                                        | Slew Rate                           | 4V Step                                                                             |                 | 1800            |                 | V/μs   |

| Δ G Rate                                  | Gain Change Rate                    | $V_{IN} = 0.3\text{V}$ , 10%-90% of Final Output                                    |                 | 4.8             |                 | dB/ns  |

| <b>Distortion &amp; Noise Performance</b> |                                     |                                                                                     |                 |                 |                 |        |

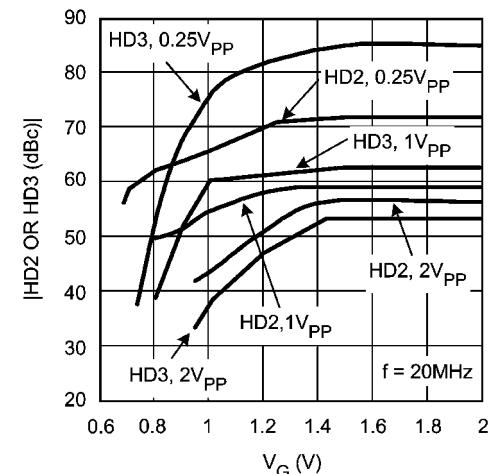

| HD2                                       | 2 <sup>nd</sup> Harmonic Distortion | $2V_{PP}$ , 20MHz                                                                   |                 | -55             |                 | dBc    |

| HD3                                       | 3 <sup>rd</sup> Harmonic Distortion | $2V_{PP}$ , 20MHz                                                                   |                 | -57             |                 | dBc    |

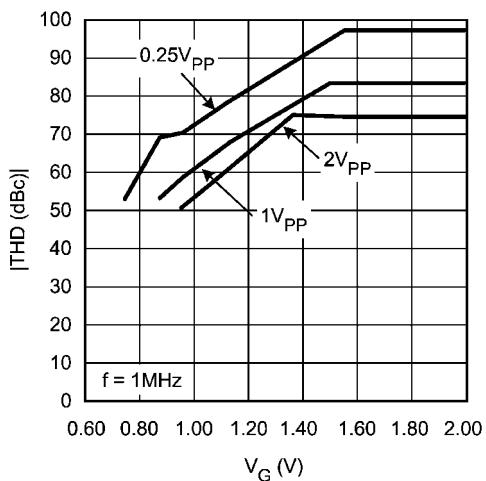

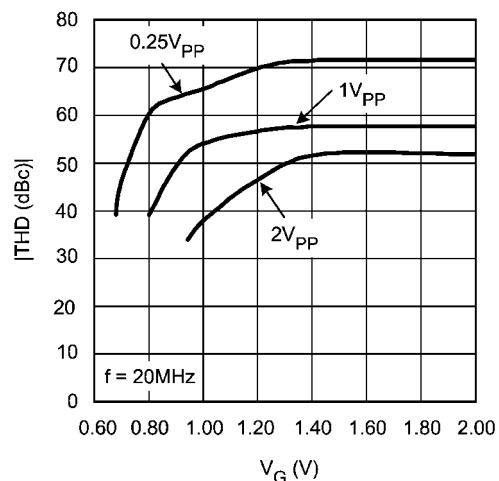

| THD                                       | Total Harmonic Distortion           | $2V_{PP}$ , 20MHz                                                                   |                 | -53             |                 | dBc    |

| En tot                                    | Total Equivalent Input Noise        | 1MHz to 150MHz                                                                      |                 | 7.7             |                 | nV/√Hz |

| $I_N$                                     | Input Noise Current                 | 1MHz to 150MHz                                                                      |                 | 2.4             |                 | pA/√Hz |

| DG                                        | Differential Gain                   | $f = 4.43\text{MHz}$ , $R_L = 150\Omega$ , Neg. Sync                                |                 | 0.34            |                 | %      |

| DP                                        | Differential Phase                  | $f = 4.43\text{MHz}$ , $R_L = 150\Omega$ , Neg. Sync                                |                 | 0.10            |                 | deg    |

## 電気的特性 (Note 2)(つづき)

特記のない限り、すべてのリミット値は  $T_J = 25^\circ\text{C}$  、  $V_S = \pm 5\text{V}$  、  $A_V(\text{MAX}) = 10$  、  $V_{\text{CM}} = 0\text{V}$  、  $R_F = 1\text{k}\Omega$  、  $R_G = 174\text{k}\Omega$  、  $V_{\text{IN\_DIFF}} = \pm 0.1\text{V}$  、  $R_L = 100\text{k}\Omega$  、  $V_G = +2\text{V}$  に対して適用されます。太字のリミット値は全温度範囲に適用されます。

| Symbol                                    | Parameter                                  | Conditions                                                                        | Min<br>(Note 6)                            | Typ<br>(Note 6) | Max<br>(Note 6)                          | Units                      |

|-------------------------------------------|--------------------------------------------|-----------------------------------------------------------------------------------|--------------------------------------------|-----------------|------------------------------------------|----------------------------|

| <b>DC &amp; Miscellaneous Performance</b> |                                            |                                                                                   |                                            |                 |                                          |                            |

| GACCU                                     | Gain Accuracy (See Application Note)       | $V_G = 2.0\text{V}$                                                               |                                            | 0.0             | +0.6                                     | dB                         |

|                                           |                                            | $1\text{V} < V_G < 2\text{V}$                                                     |                                            | +0.6/-0.3       | +3.1/-3.6                                |                            |

| G Match                                   | Gain Matching (See Application Note)       | $V_G = 2.0\text{V}$                                                               |                                            | -               | $\pm 0.6$                                | dB                         |

|                                           |                                            | $1 < V_G < 2\text{V}$                                                             |                                            | -               | +2.8/-3.9                                |                            |

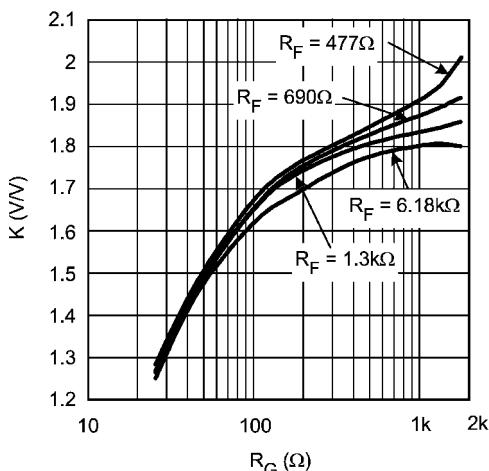

| K                                         | Gain Multiplier<br>(See Application Notes) |                                                                                   | 1.61<br><b>1.58</b>                        | 1.72            | 1.84<br><b>1.91</b>                      | V/V                        |

| $V_{\text{CM}}$                           | Input Voltage Range                        | Pin 3 & 6 Common Mode, $ \text{CMRR}  > 55\text{dB}$ (Note 9)                     | $\pm 2.0$<br><b><math>\pm 1.70</math></b>  | $\pm 2.2$       |                                          | V                          |

| $V_{\text{IN\_DIFF}}$                     | Differential Input Voltage                 | Between pins 3 & 6                                                                | $\pm 0.3$<br><b><math>\pm 0.12</math></b>  | $\pm 0.39$      |                                          | V                          |

| $I_{R_G\text{ MAX}}$                      | $R_G$ Current                              | Pins 4 & 5                                                                        | $\pm 1.70$<br><b><math>\pm 1.56</math></b> | $\pm 2.22$      |                                          | mA                         |

| $I_{\text{BIAS}}$                         | Bias Current                               | Pins 3 & 6 (Note 7)                                                               |                                            | 9               | 18<br><b>20</b>                          | $\mu\text{A}$              |

|                                           |                                            | Pins 3 & 6 (Note 7), $V_S = \pm 2.5\text{V}$                                      |                                            | 2.5             | 5<br><b>6</b>                            |                            |

| TC $I_{\text{BIAS}}$                      | Bias Current Drift                         | Pin 3 & 6 (Note 8)                                                                |                                            | 100             |                                          | $\text{nA}/^\circ\text{C}$ |

| $I_{\text{OFF}}$                          | Offset Current                             | Pin 3 & 6                                                                         |                                            | 0.01            | 2.0<br><b>3.6</b>                        | $\mu\text{A}$              |

| TC $I_{\text{OFF}}$                       | Offset Current Drift                       | (Note 8)                                                                          |                                            | 5               |                                          | $\text{nA}/^\circ\text{C}$ |

| $R_{\text{IN}}$                           | Input Resistance                           | Pin 3 & 6                                                                         |                                            | 750             |                                          | $\text{k}\Omega$           |

| $C_{\text{IN}}$                           | Input Capacitance                          | Pin 3 & 6                                                                         |                                            | 5               |                                          | $\text{pF}$                |

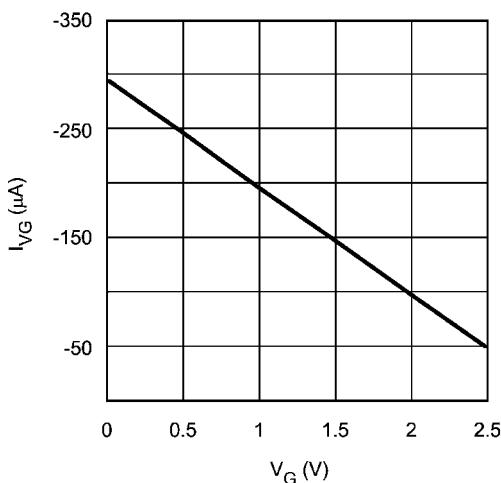

| $I_{V_G}$                                 | $V_G$ Bias Current                         | Pin 2, $V_G = 0\text{V}$ (Note 7)                                                 |                                            | -300            |                                          | $\mu\text{A}$              |

| TC $I_{V_G}$                              | $V_G$ Bias Drift                           | Pin 2 (Note 8)                                                                    |                                            | 20              |                                          | $\text{nA}/^\circ\text{C}$ |

| $R_{V_G}$                                 | $V_G$ Input Resistance                     | Pin 2                                                                             |                                            | 10              |                                          | $\text{k}\Omega$           |

| $C_{V_G}$                                 | $V_G$ Input Capacitance                    | Pin 2                                                                             |                                            | 1.3             |                                          | $\text{pF}$                |

| $V_{\text{OUT}}$                          | Output Voltage Range                       | $R_L = 100\Omega$                                                                 | $\pm 3.00$<br><b><math>\pm 2.95</math></b> | $\pm 3.20$      |                                          | V                          |

|                                           |                                            | $R_L = \text{Open}$                                                               | $\pm 3.95$<br><b><math>\pm 3.82</math></b> | $\pm 4.00$      |                                          |                            |

| $R_{\text{OUT}}$                          | Output Impedance                           | DC                                                                                |                                            | 0.1             |                                          | $\Omega$                   |

| $I_{\text{OUT}}$                          | Output Current                             | $V_{\text{OUT}} = \pm 4\text{V}$ from Rails                                       | $\pm 80$<br><b><math>\pm 75</math></b>     | $\pm 90$        |                                          | mA                         |

| $V_O$<br><small>OFFSET</small>            | Output Offset Voltage                      | $0\text{V} < V_G < 2\text{V}$                                                     |                                            | $\pm 80$        | $\pm 300$<br><b><math>\pm 380</math></b> | mV                         |

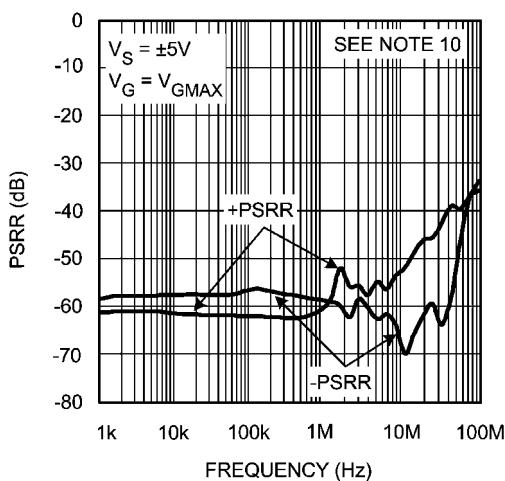

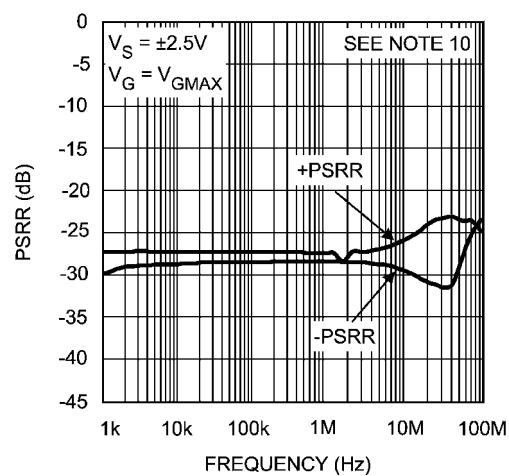

| +PSRR                                     | +Power Supply Rejection Ratio (Note 10)    | Input Referred, 1V change, $V_G = 2.2\text{V}$                                    |                                            | -69             | -47<br><b>-45</b>                        | dB                         |

| -PSRR                                     | -Power Supply Rejection Ratio (Note 10)    | Input Referred, 1V change, $V_G = 2.2\text{V}$                                    |                                            | -58             | -41<br><b>-40</b>                        | dB                         |

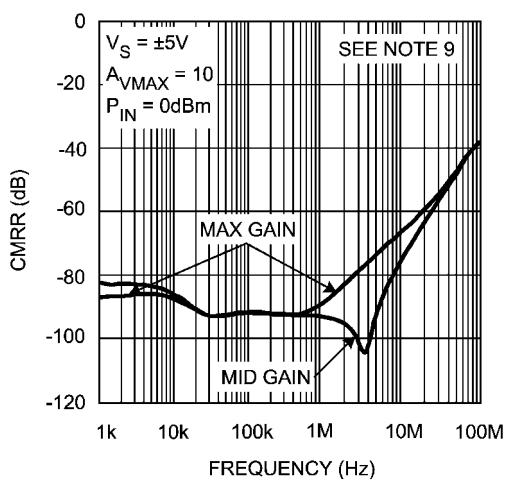

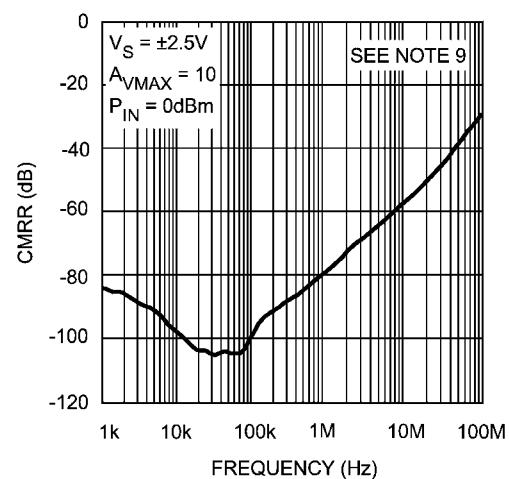

| CMRR                                      | Common Mode Rejection Ratio (Note 9)       | Input Referred, $V_G = 2\text{V}$<br>$-1.8\text{V} < V_{\text{CM}} < 1.8\text{V}$ |                                            | -72             |                                          | dB                         |

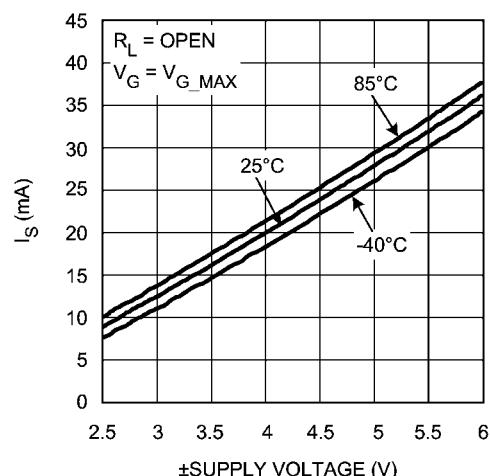

| $I_S$                                     | Supply Current                             | No Load                                                                           |                                            | 27              | 38<br><b>41</b>                          | mA                         |

|                                           |                                            | $V_S = \pm 2.5\text{V}$ , $R_L = \text{Open}$                                     |                                            | 9.3             | 16<br><b>19</b>                          |                            |

## 電気的特性 (Note 2)( つづき )

- Note 1: 「絶対最大定格」とは、それを超えると、デバイスに損傷が生じるおそれがあるリミット値を示します。「動作定格」とは、デバイスが機能する条件を示しますが、特定の性能を保証するものではありません。保証されている仕様およびその試験条件については、「電気的特性」を参照してください。

- Note 2: 「電気的特性」の値は、記載温度の工場出荷試験条件にのみ適用されます。工場試験条件で生じる自己発熱は、 $T_J = T_A$  となる程度にきわめてわずかです。「電気的特性」には、自己発熱により  $T_J > T_A$  となる条件下で保証されるパラメータ性能値は記載されていません。

- Note 3: 最大出力電流 ( $I_{OUT}$ ) は、デバイスの消費電力の上限が規定された値のどちらか小さいほうになります。

- Note 4: 人体モデルでは、1.5k $\Omega$  と100pFを直列に接続します。マシン・モデルでは、0 $\Omega$  と200pFを直列に接続します。

- Note 5: スレーレートは立ち上がりルートと立ち下がりルートの平均です。

- Note 6: Typ 値は最も標準的な値を示しています。太字は全温度範囲に適用されます。

- Note 7: デバイスに向かって流れ込む電流を正方向の電流と定義しています。

- Note 8: ドリフトは、温度変化両端でのパラメータ分布平均の変化を、温度変化の幅で除算して求めています。

- Note 9: CMRR の定義：差動入力電圧 0.1V における  $|\frac{V_{OUT}/V_{CM}}{A_V}|$ 。

- Note 10: + PSRR の定義：差動入力電圧 0.1V における  $|\frac{V_{OUT}/V^+}{A_V}|$ ，- PSRR の定義：差動入力電圧 0.1V における  $|\frac{V_{OUT}/V^-}{A_V}|$ 。

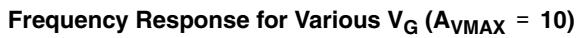

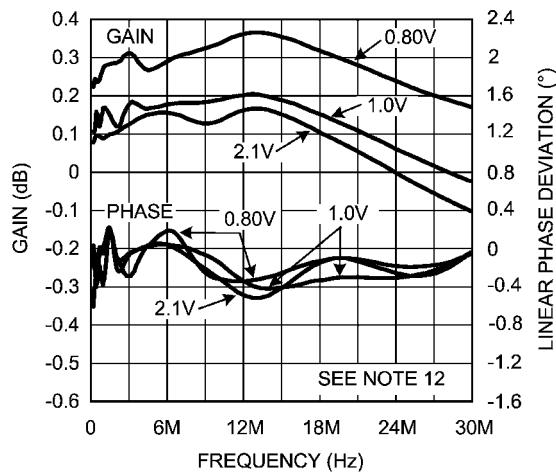

- Note 11: ゲイン/位相を 25° で低周波数値に正規化しています。

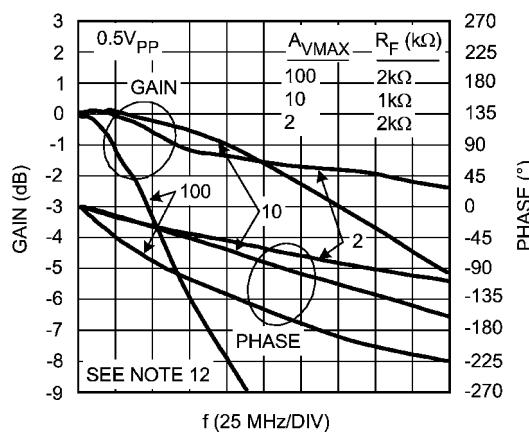

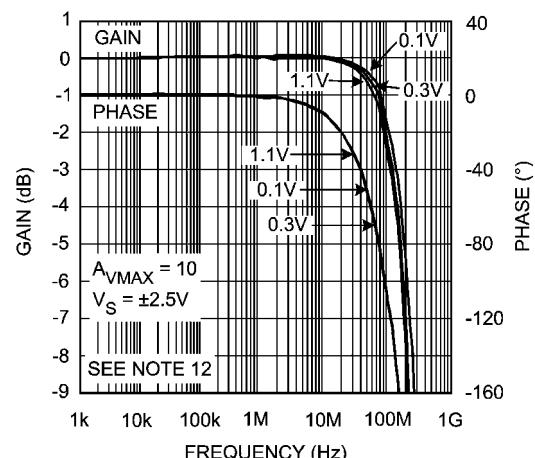

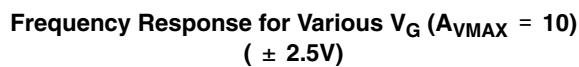

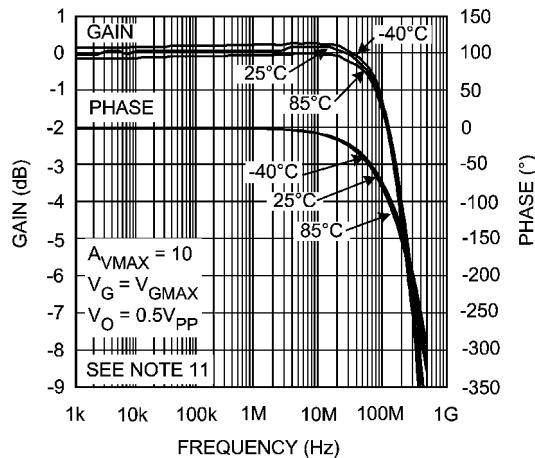

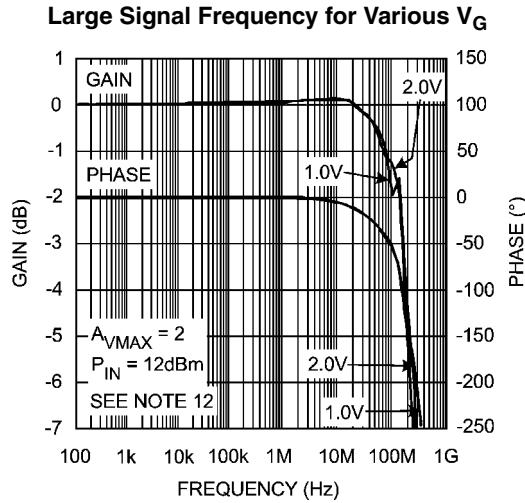

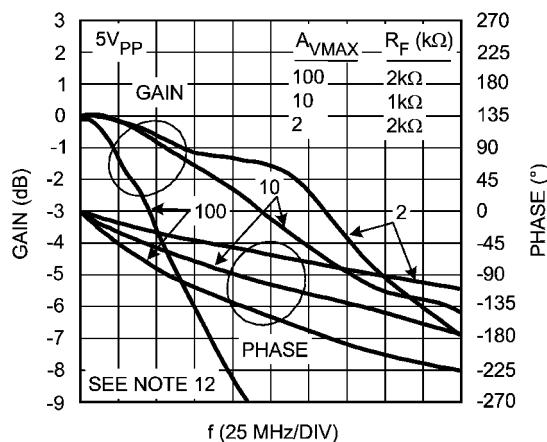

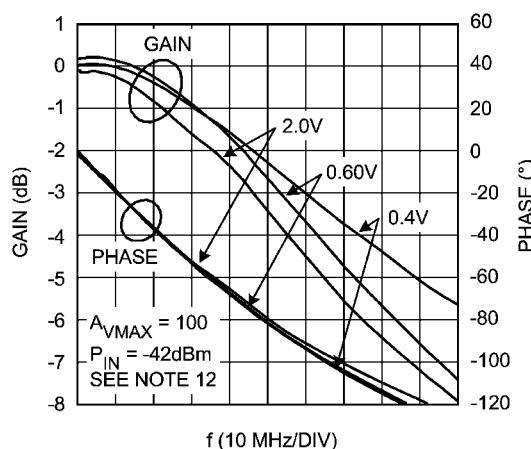

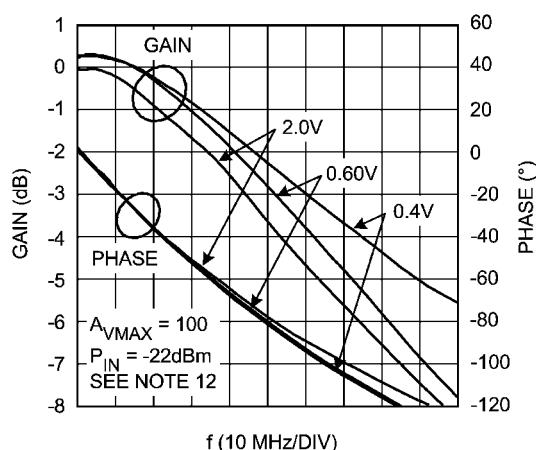

- Note 12: ゲイン/位相を各  $A_V$  で低周波数値に正規化しています。

- Note 13: ゲイン制御に対する周波数応答の測定回路：

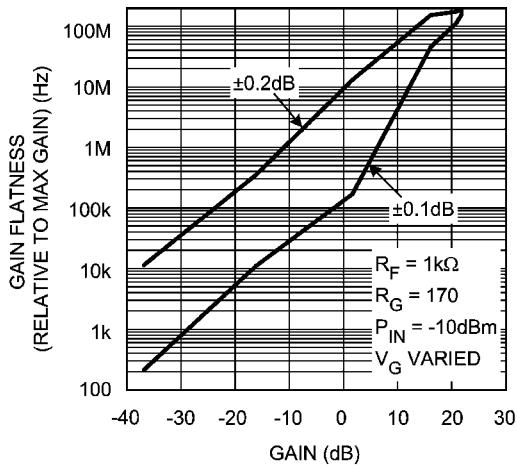

Note 14: "Flat Band Attenuation (Relative To Max Gain) Range" の定義：規定されたゲイン・フラットネス ( $\pm 0.2\text{dB}$  または  $\pm 0.1\text{dB}$ ) を満たす、 $A_{VMAX}$  ゲインに対する最大からの減衰範囲として規定されています。たとえば  $f < 30\text{MHz}$  の場合、Flat Band Attenuation の範囲は次のようにになります。

$\pm 0.2\text{dB}$  20dB から 4dB = 範囲 16dB

$\pm 0.1\text{dB}$  20dB から 12.5 dB = 範囲 7.5dB

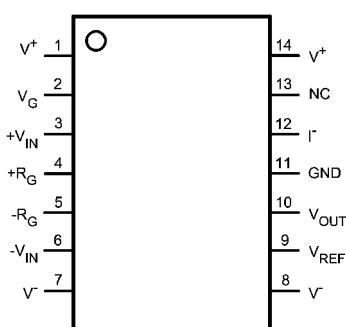

## ピン配置図

14-Pin SOIC/TSSOP

Top View

## 製品情報

| Package      | Part Number | Package Marking | Transport Media          | NSC Drawing |

|--------------|-------------|-----------------|--------------------------|-------------|

| 14-pin SOIC  | LMH6502MA   | LMH6502MA       | 55 Units/Rail            | M14A        |

|              | LMH6502MAX  |                 | 2.5k Units Tape and Reel |             |

| 14-Pin TSSOP | LMH6502MT   | LMH6502MT       | 94 Units/Rail            | MTC14       |

|              | LMH6502MTX  |                 | 2.5k Units Tape and Reel |             |

## 代表的な性能特性

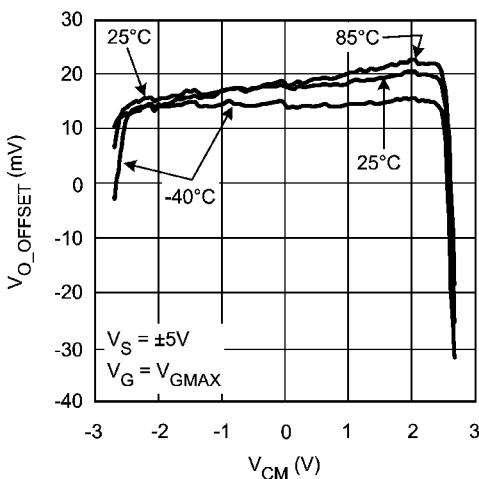

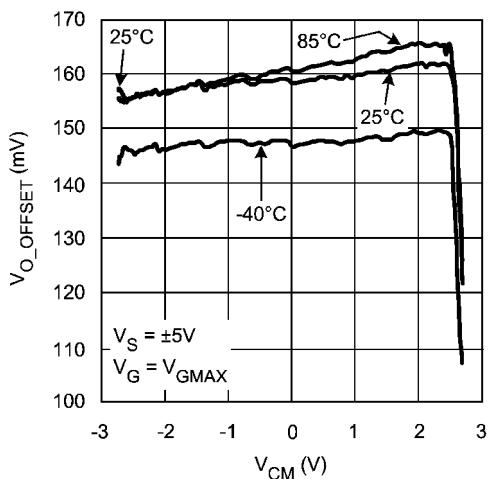

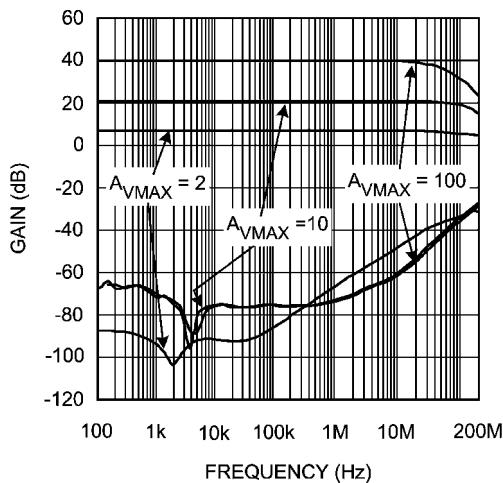

特記のない限り、 $V_S = \pm 5V$ 、 $25^\circ C$ 、 $V_G = V_{GMAX}$ 、 $V_{CM} = 0V$ 、 $R_F = 1k\Omega$ 、 $R_G = 174\Omega$ 、両入力とも50mVで終端、 $R_L = 100\Omega$ 、代表値、デバイス出力に対する参照値。

## 代表的な性能特性(つづき)

特記のない限り、 $V_S = \pm 5V$ 、 $V_G = V_{GMAX}$ 、 $V_{CM} = 0V$ 、 $R_F = 1k\Omega$ 、 $R_G = 174$ 、両入力とも50で終端、 $R_L = 100$ 、代表値、デバイス出力に対する参照値。

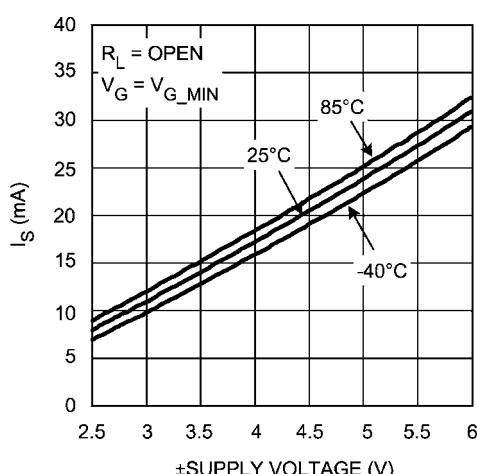

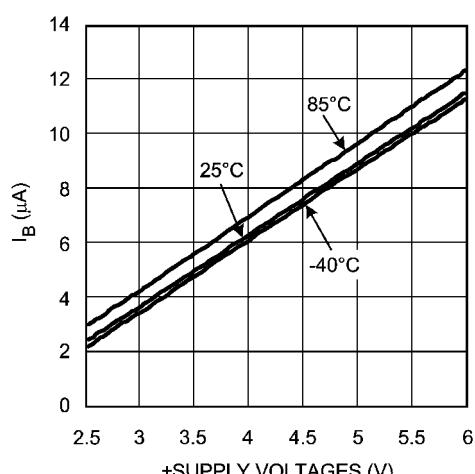

Large Signal Frequency Response for Various  $A_{VMAX}$ Frequency Response for Various  $V_G$  ( $A_{VMAX} = 100$ ) (Small Signal)Frequency Response for Various  $V_G$  ( $A_{VMAX} = 100$ ) (Large Signal) $I_S$  vs.  $V_S$  $I_S$  vs.  $V_S$ Input Bias Current vs.  $V_S$

## 代表的な性能特性(つづき)

特記のない限り、 $V_S = \pm 5V$ 、 $V_G = V_{GMAX}$ 、 $V_{CM} = 0V$ 、 $R_F = 1k$ 、 $R_G = 174$ 、両入力とも50で終端、 $R_L = 100$ 、代表値、デバイス出力に対する参照値。

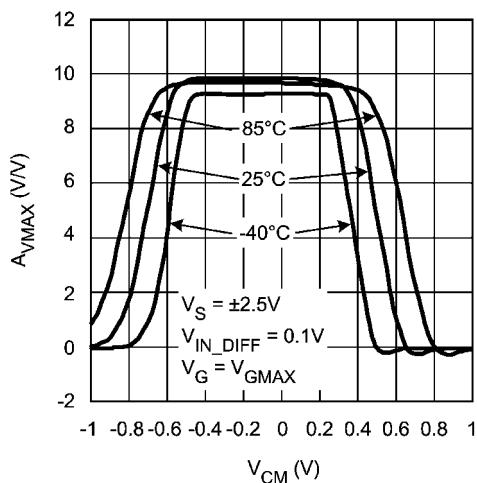

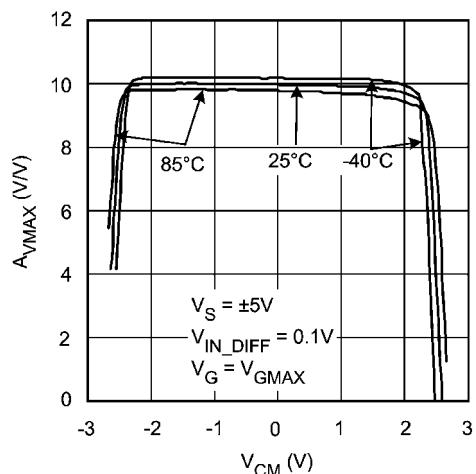

**$A_{VMAX}$  vs.  $V_{CM}$**  **$A_{VMAX}$  vs.  $V_{CM}$** **PSRR  $\pm 5V$** **PSRR  $\pm 2.5V$** **CMRR  $\pm 5V$** **CMRR  $\pm 2.5V$**

## 代表的な性能特性(つづき)

特記のない限り、 $V_S = \pm 5V$ 、 $V_G = V_{GMAX}$ 、 $V_{CM} = 0V$ 、 $R_F = 1k$ 、 $R_G = 174$ 、両入力とも 50 で終端、 $R_L = 100$ 、代表値、デバイス出力に対する参照値。

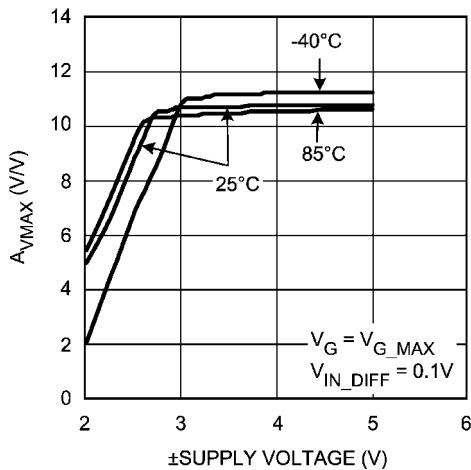

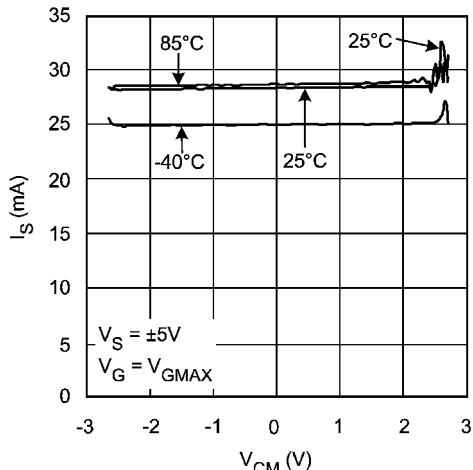

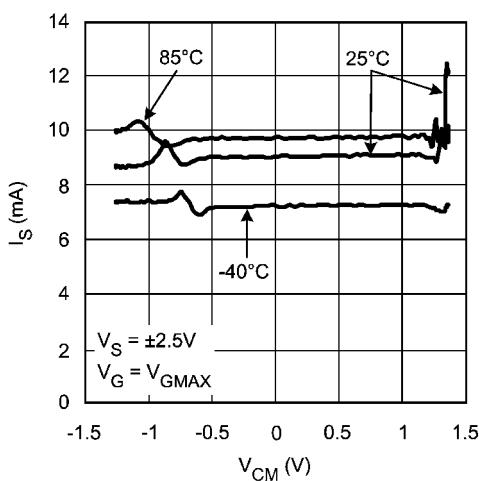

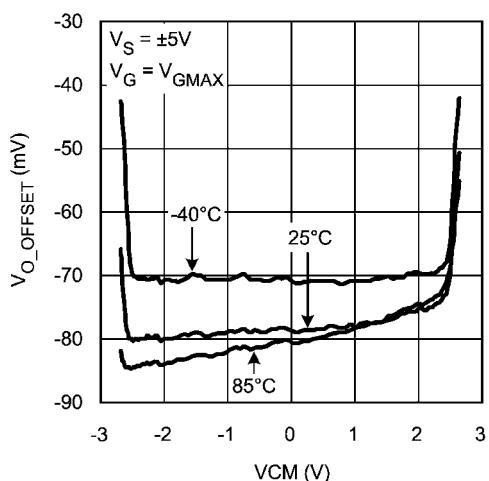

A<sub>VMAX</sub> vs. Supply VoltageSupply Current vs. V<sub>CM</sub>Supply Current vs. V<sub>CM</sub>Output Offset Voltage vs. V<sub>CM</sub> (Typical Unit #1)Output Offset Voltage vs. V<sub>CM</sub> (Typical Unit #2)Output Offset Voltage vs. V<sub>CM</sub> (Typical Unit #3)

## 代表的な性能特性(つづき)

特記のない限り、 $V_S = \pm 5V$ 、 $V_G = V_{GMAX}$ 、 $V_{CM} = 0V$ 、 $R_F = 1k\Omega$ 、 $R_G = 174\Omega$ 、両入力とも50Ωで終端、 $R_L = 100\Omega$ 、代表値、デバイス出力に対する参照値。

## Feed through Isolation

Gain Flatness and Linear Phase Deviation vs.  $V_G$

## Gain Flatness Frequency vs. Gain (Note 14)

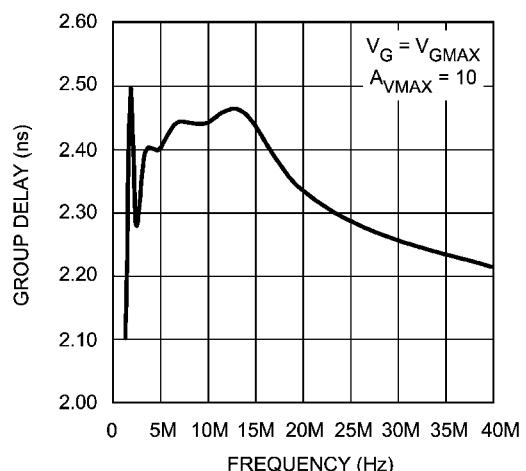

## Group Delay vs. Frequency

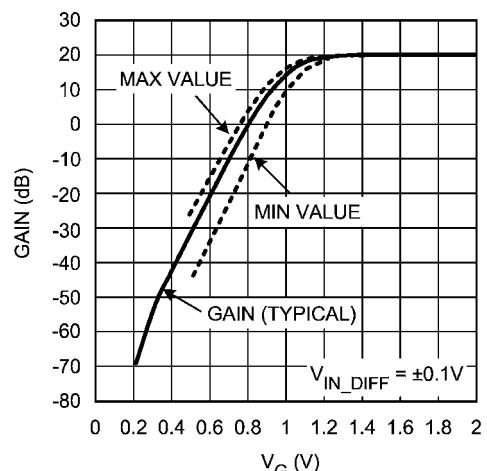

K Factor vs.  $R_G$ Gain vs.  $V_G$  Including Limits

## 代表的な性能特性(つづき)

特記のない限り、 $V_S = \pm 5V$ 、 $V_G = V_{GMAX}$ 、 $V_{CM} = 0V$ 、 $R_F = 1k\Omega$ 、 $R_G = 174\Omega$ 、両入力とも50 $\Omega$ で終端、 $R_L = 100\Omega$ 、代表値、デバイス出力に対する参照値。

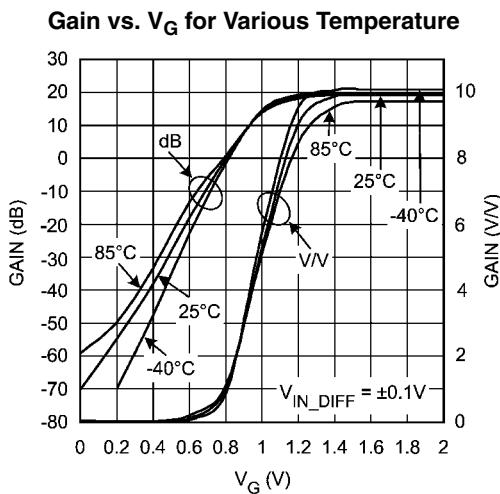

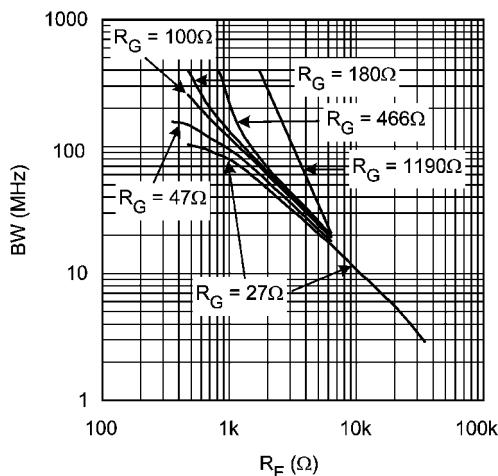

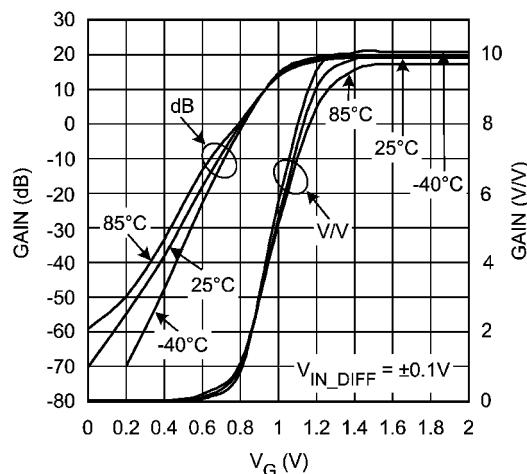

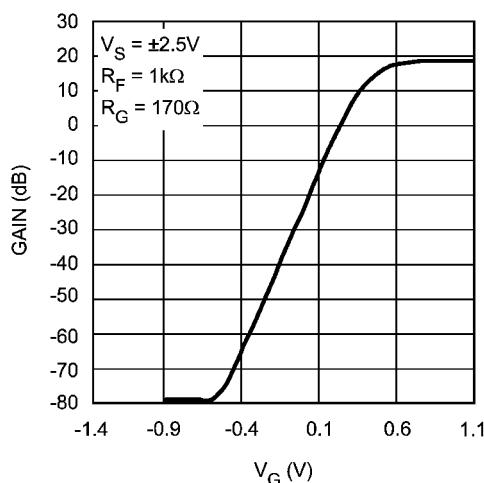

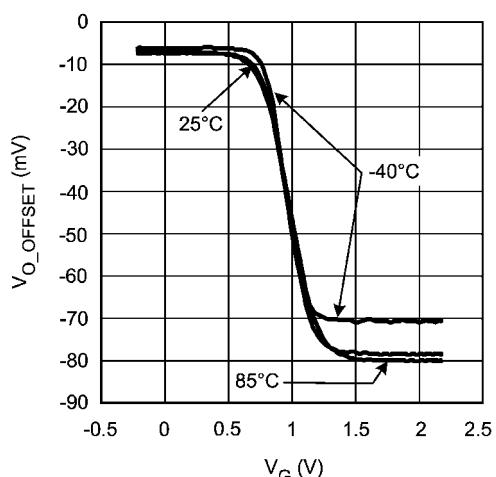

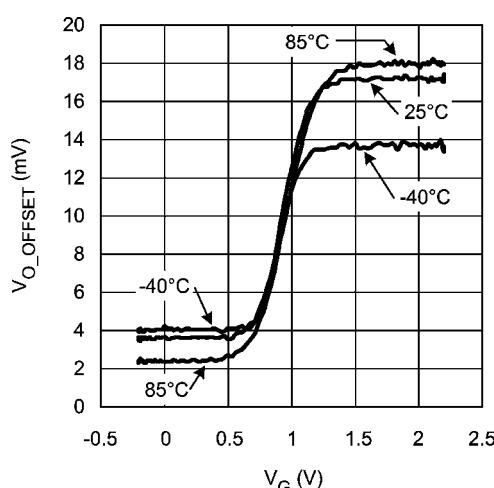

BW vs.  $R_F$ Gain vs.  $V_G$  ( $\pm 5V$ )Gain vs.  $V_G$  ( $\pm 2.5V$ )Output Offset Voltage vs.  $V_G$  (Typical Unit #1)Output Offset Voltage vs.  $V_G$  (Typical Unit #2)Output Offset Voltage vs.  $V_G$  (Typical Unit #3)

## 代表的な性能特性(つづき)

特記のない限り、 $V_S = \pm 5V$ 、 $V_G = V_{GMAX}$ 、 $V_{CM} = 0V$ 、 $R_F = 1k\Omega$ 、 $R_G = 174\Omega$ 、両入力とも50%で終端、 $R_L = 100\Omega$ 、代表値、デバイス出力に対する参照値。

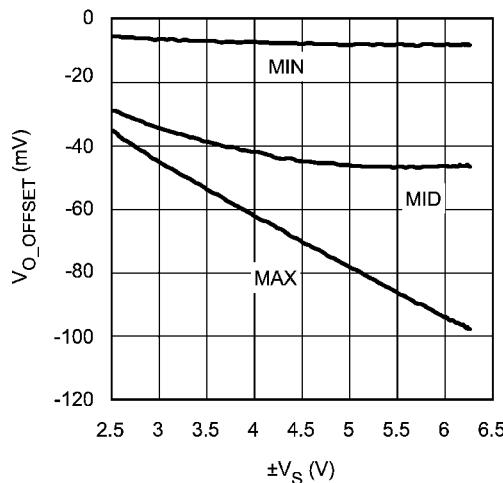

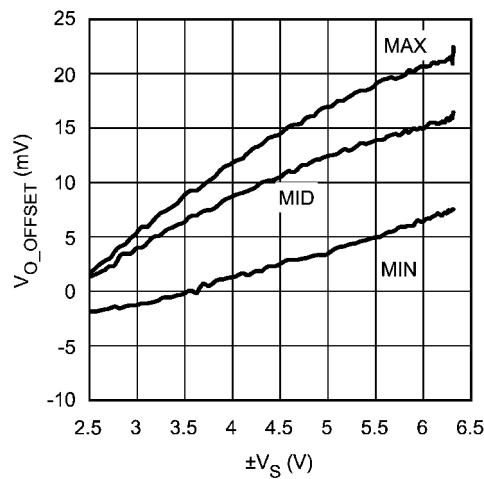

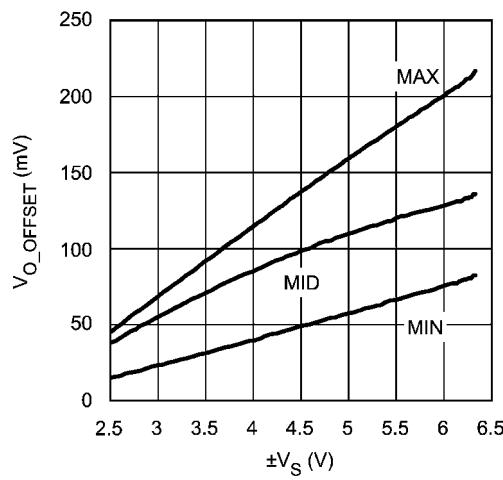

Output Offset Voltage vs.  $\pm V_S$  for various  $V_G$

(Typical Unit# 1)

Output Offset Voltage vs.  $\pm V_S$  for various  $V_G$

(Typical Unit# 2)

Output Offset Voltage vs.  $\pm V_S$  for various  $V_G$

(Typical Unit# 3)

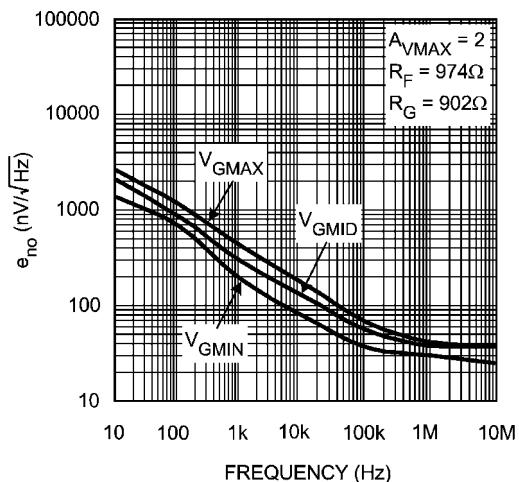

Noise vs. Frequency ( $A_{VMAX} = 2$ )

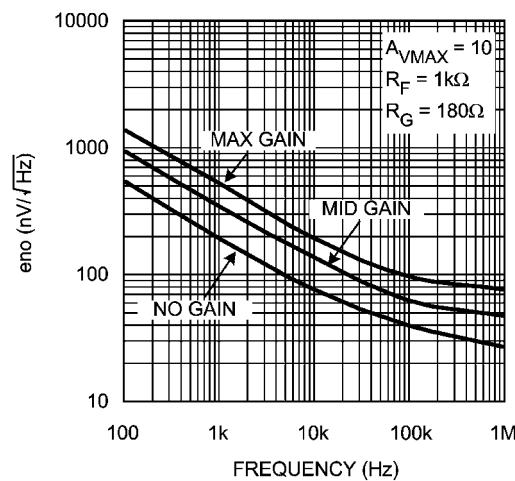

Noise vs. Frequency ( $A_{VMAX} = 10$ )

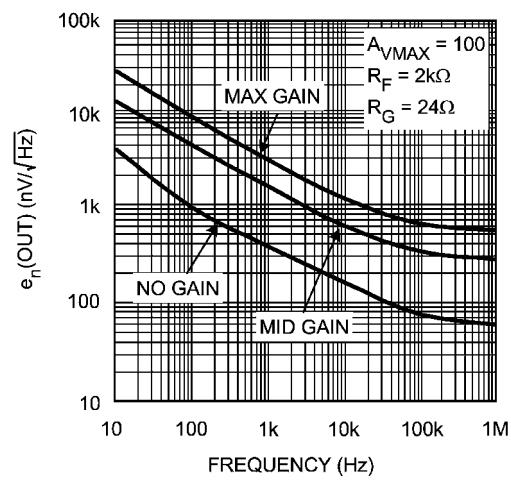

Noise vs. Frequency ( $A_{VMAX} = 100$ )

## 代表的な性能特性(つづき)

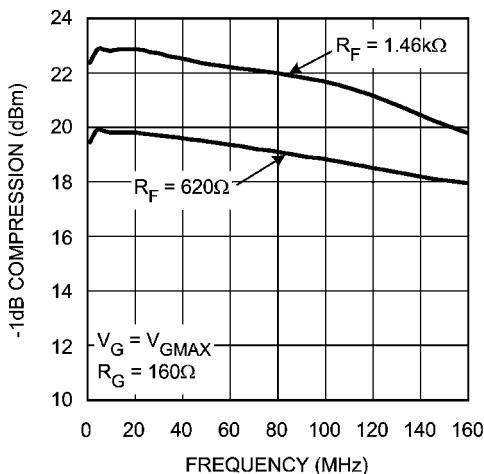

特記のない限り、 $V_S = \pm 5V$ 、 $V_G = V_{GMAX}$ 、 $V_{CM} = 0V$ 、 $R_F = 1k\Omega$ 、 $R_G = 174\Omega$ 、両入力とも50Ωで終端、 $R_L = 100\Omega$ 、代表値、デバイス出力に対する参照値。

## - 1dB Compression

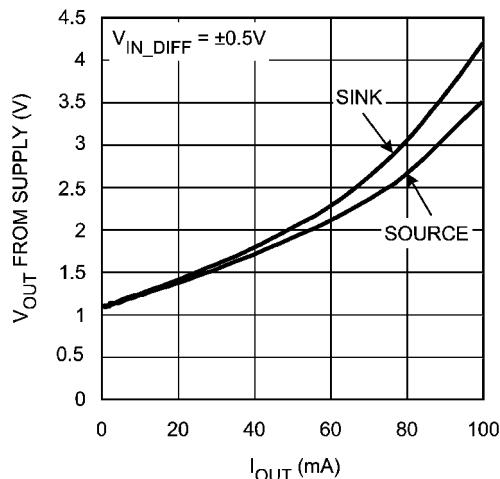

## Output Voltage vs. Output Current

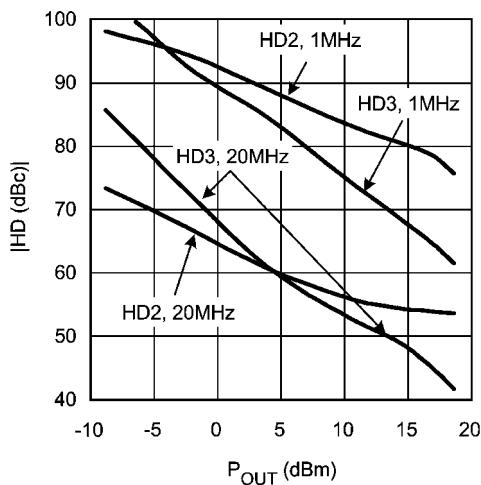

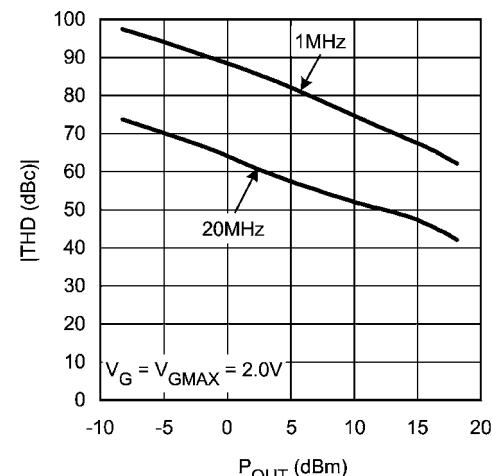

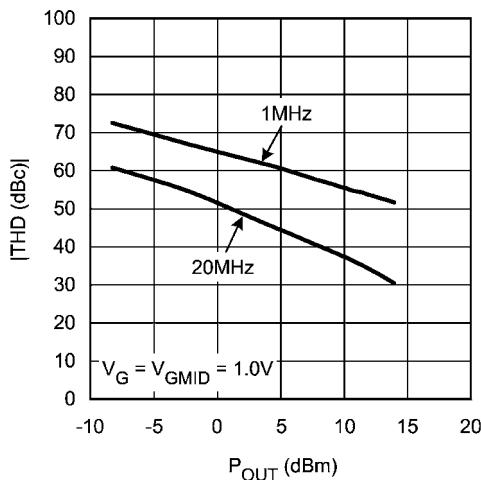

HD2 & HD3 vs. P<sub>OUT</sub>THD vs. P<sub>OUT</sub>THD vs. P<sub>OUT</sub>HD2 & HD3 vs. V<sub>G</sub>

## 代表的な性能特性(つづき)

特記のない限り、 $V_S = \pm 5V$ 、 $V_G = V_{GMAX}$ 、 $V_{CM} = 0V$ 、 $R_F = 1k\Omega$ 、 $R_G = 174\Omega$ 、両入力とも50Ωで終端、 $R_L = 100\Omega$ 、代表値、デバイス出力に対する参照値。

THD vs.  $V_G$ THD vs.  $V_G$  $V_G$  Bias Current vs.  $V_G$

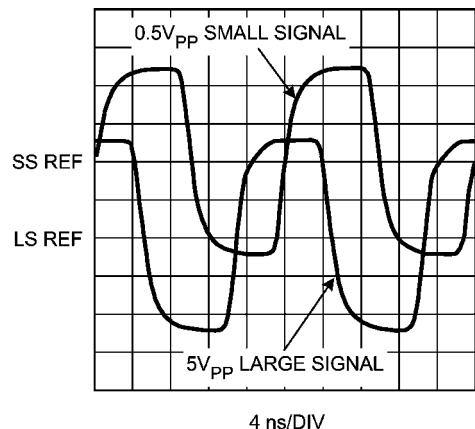

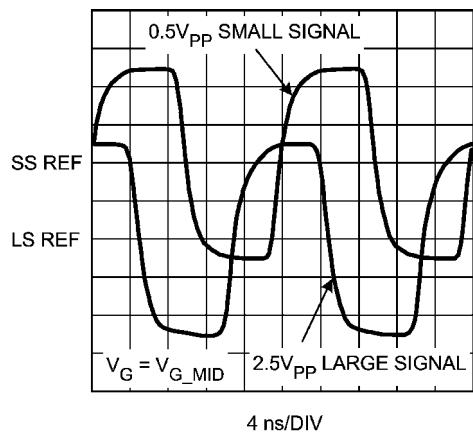

Step Response Plot

Step Response Plot

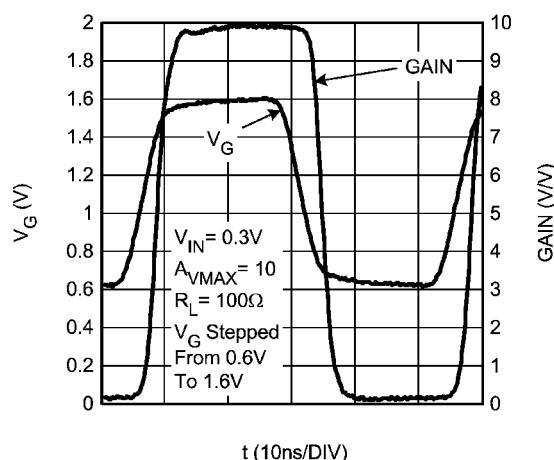

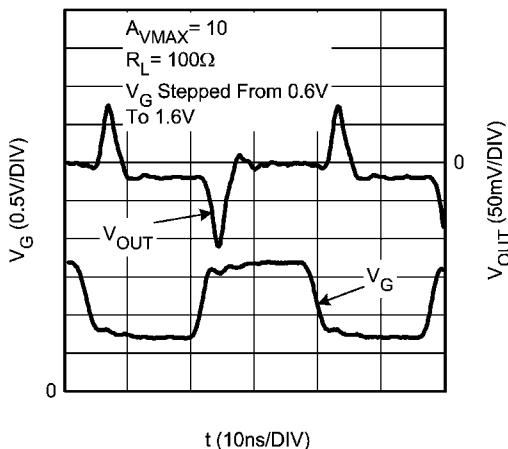

Gain vs.  $V_G$  Step

## 代表的な性能特性(つづき)

特記のない限り、 $V_S = \pm 5V$ 、 $V_G = V_{GMAX}$ 、 $V_{CM} = 0V$ 、 $R_F = 1k\Omega$ 、 $R_G = 174\Omega$ 、両入力とも 50mV で終端、 $R_L = 100\Omega$ 、代表値、デバイス出力に対する参照値。

Feedthrough from  $V_G$

## アプリケーション情報

## 動作原理

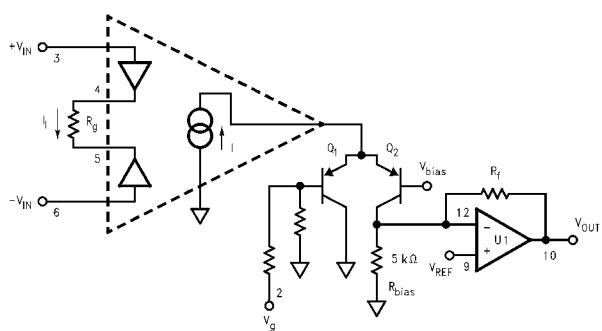

LMH6502 の回路の概略を Figure 1 に示します。 $+V_{IN}$  および  $-V_{IN}$  は、 $(+V_{IN}) - (-V_{IN})$  の差動入力電圧に比例した、 $R_G$  を流れる信号電流を誘起する閉ループ電圧フォロワ回路によってバッファリングされます。この電流は、2 つの特性のそろったトランジスタ Q1 と Q2 の電流源をコントロールします。

Q2 を流れる電流は、 $R_F$  と出力アンプ U1 によって最終的な出力電圧に変換されます。Q2 を流れる信号電流 “I” をわずかに変化させるとゲインが変化します。信号電流 “I” は、差動電圧として印可されている Q1 と Q2 のベース電圧によって制御されます。たとえば  $V_G = 0V$  の場合、Q1 は完全に導通し Q2 はオフとなります。 $R_F$  に “I” が流れないと出力信号は減衰された状態です。 $V_G = +2V$  とすると、Q1 はオフとなり、すべての信号電流は Q2 を通って  $R_F$  を流れるため最大ゲインが得られます。 $V_G$  を 1V に設定すると Q1 と Q2 のベースはほぼ同じ電圧となって Q1 と Q2 のコレクタ電流は信号電流の 1/2 に等しくなるため、得られるゲインは最大ゲインのおよそ半分となります。

FIGURE 1. LMH6502 Block Diagram

$R_F$  と  $R_G$  の選択

最大入力振幅と最大ゲインは、LMH6502 アプリケーションで部品のパラメータ値を決める 2 つの重要な仕様要件です。

出力段のオペアンプは、 $R_F = 1k\Omega$  に対して最適化された電流帰還型増幅器です。 $R_G$  は次のように計算します。

$$R_G = \frac{R_F \times 1.72}{A_{VMAX}} - 3\Omega \text{ WITH } R_F = 1k\Omega \quad (1)$$

最大入力振幅によって LMH6502 がオーバードライブされるかどうかは、次式でリニア動作時の最大差動入力電圧を計算すればわかります。

$$V_{DMAX} = (R_G + 3.0) \times 1.70mA \quad (2)$$

最大入力振幅が  $V_{DMAX}$  上限値を超える場合は、LMH6502 を信号経路の中でもっと振幅の小さな箇所へ移動するか、LMH6502 ゲイン  $A_{VMAX}$  を小さくするか、 $R_G$  と  $R_F$  の値を大きくするかのいずれかを行います。入力振幅を小さくしたときは、信号対ノイズ比に与える影響を計算し直してください。 $A_{VMAX}$  を小さくしたときは、「後段」の増幅器のゲインを増加するか、 $A_{VMAX}$  の減少分を補うために増幅段を追加してください。 $R_G$  と  $R_F$  を大きくするには、 $R_G$  の最小許容値を計算します。

$$R_G > 590 \times V_{DMAX} - 3 \quad (3)$$

$R_G$  をこの値より大きくして動作させれば、入力バッファのリニア動作が保証されます。

$R_F$  は、選択した  $R_G$  と  $A_{VMAX}$  から計算します。最良の性能を得るために、 $R_F$  は  $1k\Omega$  以上でなければなりません。ただし、出力アンプの反転加算ノードとグラウンドの間にループ・ゲインを下げる抵抗を取り付ければ、 $R_F$  を  $1k\Omega$  未満にすることもできます(詳細については、アプリケーション・ノート OA-13 を参照)。

## アプリケーション情報 (つづき)

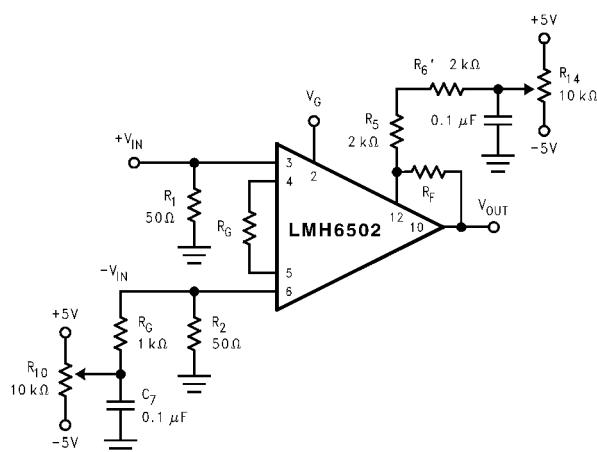

### オフセットの調整

オフセット電圧は、入力換算と出力換算の2つの部分に分けられます。入力換算のオフセット電圧は、 $V_G$ を変化させたときの出力電圧の変動として現れます。Figure 2 の回路に対して、低い周波数の方形波 ( $V_{LOW} = 0V$ ,  $V_{HIGH} = 2V$ ) を  $V_{IN} = 0V$  の状態で  $V_G$  (2 ピン) に印加した場合、入力換算オフセットの項  $V_{OS}$  は DC 分に重畠した小振幅の方形波出力として現れます。方形波電圧  $V_{OS}$  がゼロになるように左側の可変抵抗 ( $R_{10}$ ) を調整してください。入力換算のオフセット電圧が調整できたら、( $V_{IN} = 0$ ,  $V_G = 0$  のとき)  $V_{OUT}$  が  $0V$  になるよう  $R_{14}$  を調整します。反転増幅を行うアプリケーションでは  $V_{IN}$  がピン 6 に印可されますので、オフセット調整はピン 3 で行います。これらのステップを踏めば、出力オフセット電圧を最小に抑えられます。ただしオフセット項は設定ゲインによって変化するため、完全な補正是不可能であり、 $V_G$  振幅の範囲で若干のオフセットが出力に残ります。また、上記オフセット調整では出力オフセットの温度ドリフト係数は改善されません。

FIGURE 2. Nulling the output offset voltage

### ゲイン精度

ゲイン精度は、特定の  $V_G$  における実際のゲインと理論上のゲインの差として定義されます (結果は dB で表記します)。

理論上のゲインは次の式で与えられます。

$$A(V/V) = K \times \frac{R_F}{R_G} \times \frac{1}{1 + e^{\frac{1 - V_G}{V_C}}} \quad (4)$$

室温で、 $K = 1.72$  (公称)、 $V_C = 90mV$  です。

「電気的特性」の表に記載されているパラメータ GACCU の値は  $V_G$  範囲全体に対するワーストケース精度を表わしています。"Typ" 値は「代表ゲイン」と「理論ゲイン」との差のワーストケースです。"Max" 値はゲインの最大 / 最小値と「理論ゲイン」の差のワーストケースです。

### ゲイン・マッチング

ゲイン・マッチングは、ある  $V_G$  におけるゲイン偏差の最大値として定義されます (単位 dB)。"Max" 値のみが規定されます ("Typ" 値は規定されません)。「電気的特性」の表に記載されているパラメータ G Match の値は  $V_G$  範囲全体に対するワーストケース・マッチングを表わしています。"Max" 値はゲインの最大 / 最小値と代表ゲインの差のワーストケースです。

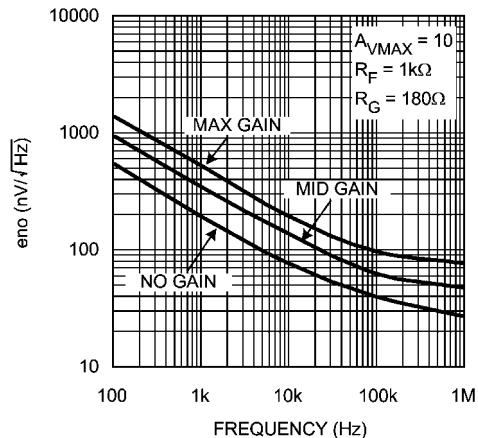

### ノイズ

Figure 3 は  $A_{VMAX} = 10V/V$  での LMH6502 の出力換算スポット・ノイズの関係を示しています。このグラフはノイズに関するすべての項を含んでいます。ただし、両方の入力を 50 Ω 終端すると入力ノイズの影響を最小に抑えられます。 $A_{VMAX} = 10V/V$  のとき、LMH6502 の平坦な帯域に対する入力換算スポット・ノイズ ( $e_{in}$ ) の代表値は  $7.7nV/\sqrt{Hz}$  です。平坦な領域にまで伸びているアプリケーションでは、入力 RMS 電圧ノイズは次の単一ポール・モデルで定義されます。

$$V_{RMS} = e_{in} * \sqrt{1.57 * (-3dB \text{ BANDWIDTH})} \quad (5)$$

FIGURE 3. Output Referred Voltage Noise vs. Frequency

### 回路レイアウトの考慮事項と評価用ボード

高周波用プリント基板で優れたレイアウトを行うとき、グラウンド・プレーン構造と電源のバイパスがパッケージ本体のすぐ近くにあることが、十分な性能を得るうえで重要です。増幅器は  $I^+$  入力 (ピン 12) とグラウンド間の浮遊容量の影響を受けるので、ノードのトレース面積を小さくしてください。帰還抵抗に抱かせるシャント容量は、この影響を補正する目的に使用しないでください。最大ゲインが小さい状態 ( $A_{VMAX} < 10$ ) で最高の性能を得るには、 $+R_G$  と  $-R_G$  の接続を短くしてください。 $R_G$  本体下のグラウンド・プレーンを除去して、対グラウンド容量を最小に抑える必要があります。出力端子 (ピン 10) に寄生容量や負荷容量が直接つながっていると位相マージンが減少し、周波数特性にピークができます。

LMH6502 は 100 Ω 負荷の駆動では完全に安定しています。負荷を軽くすると(たとえば  $1k\Omega$ )、とくに容量性負荷の場合、400MHz を超えた高い周波数領域で不安定になる可能性があります。LMH6502 をそのような軽い負荷に接続する場合、出力にスナップ・ネットワークを追加することを推奨します(たとえば LMH6502 出力とグラウンド間に  $100\Omega$  と  $39pF$  を直列に接続する)。また、出力 (10 ピン) に低抵抗を直列に挿入すると、 $C_L$  の影響を低減できます。

## 代表的な性能特性(つづき)

外付け部品の寄生容量も高周波特性に影響するため、RN55Dのような金属被膜抵抗または表面実装デバイスのようなリードのないものを推奨します。背の高いDIPソケットは使用しないでください。

ナショナルセミコンダクター社では以下の評価用ボードを提供しています。高周波回路のボード・レイアウトの検討や、部品の試験および特性評価にお役立てください。

| デバイス      | パッケージ    | 評価用ボード部品番号 |

|-----------|----------|------------|

| LMH6502MA | SOIC-14  | CLC730033  |

| LMH6502MT | TSSOP-14 | CLC730146  |

ナショナルセミコンダクター社に製品サンプルをお申し込みになると、評価用ボードが付属します。

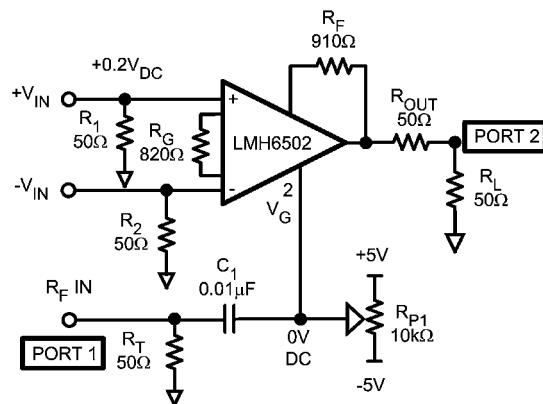

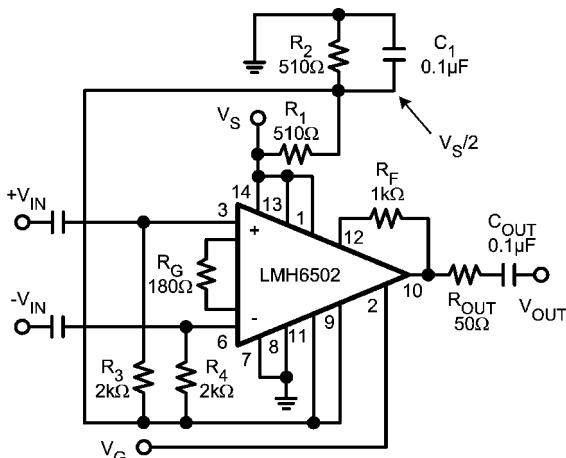

### 単一電源動作

LMH6502は単一電源で動作させることも可能です。これを行うには、ピン11(GND)をV<sup>+</sup>~V<sup>-</sup>の中間の電位に接続します。Figure 4、5に2つの回路例を示します。

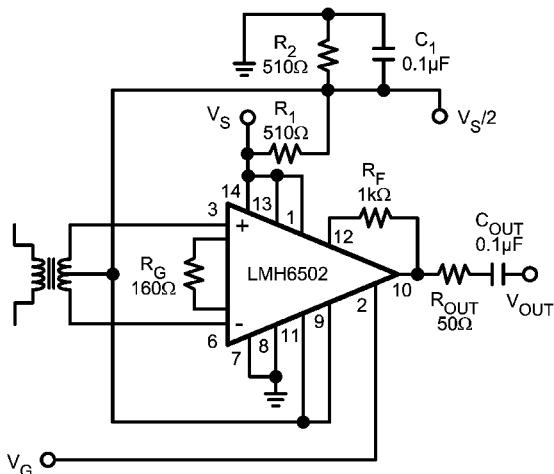

FIGURE 4. AC Coupled Single Supply VGA

FIGURE 5. Transformer Coupled Single Supply VGA

### 低電圧動作

LMH6502の動作電圧定格の下限は5V(V<sup>+</sup>とV<sup>-</sup>の電位差)です。データシートには、一部に±2.5Vでの動作が記載されています(たとえば周波数応答、CMRR、PSRR、"Gain vs. V<sub>G</sub>"グラフなど)。±5V動作と比べて、低電圧動作では次の点に注意が必要です。

- a) V<sub>G</sub>範囲の縮小。

次表に各V<sub>G</sub>電圧を求める近似式をV<sup>+</sup>の関数として示します。

TABLE 1. V<sub>G</sub> Definition Based on V<sup>+</sup>

| V <sub>G</sub>     | Definition           | Expression (V)           |

|--------------------|----------------------|--------------------------|

| V <sub>G_MIN</sub> | Gain Cut-off         | 0.2 × V <sup>+</sup> - 1 |

| V <sub>G_MID</sub> | A <sub>VMAX</sub> /2 | 0.2 × V <sup>+</sup>     |

| V <sub>G_MAX</sub> | A <sub>VMAX</sub>    | 0.2 × V <sup>+</sup> + 1 |

- b) V<sub>G LIMIT</sub>(V<sub>G</sub>上の許容可能な最大電圧)の低下。トランジスタのヘッドルームによって回路的に制限されます。このリミット電圧を超えてV<sub>G</sub>に電圧を与えると性能に影響が及びます(デバイスが破壊されることはありません)。具体的には、周波数が低い段階で周波数応答のロールオフとして現れる可能性があります。電源電圧が±2.5Vのとき、V<sub>G LIMIT</sub>は1.1V未満ですが、最大ゲインを得るにはV<sub>G</sub>=1.5Vが必要です。このような条件での動作では、最大ゲインを得るために必要なV<sub>G</sub>電圧が、印加可能な上限電圧に達してしまうことを意味します。仮に電源電圧が非対称でV<sup>+</sup>が低い場合、V<sub>G</sub>範囲のさらなる「圧迫」が起こる可能性があります。たとえばV<sup>+</sup>=2V、V<sup>-</sup>=-3V、V<sub>G LIMIT</sub>=0.40Vのとき、V<sub>S</sub>が高いときに見込まれるゲインより先最大ゲインは2.5dB以上小さくなります。

- c) 最大ゲインの低下。電源電圧が低くなれば本質的に最大ゲインも下がります(「代表的な性能特性」の"Gain vs. V<sub>G</sub> (V<sub>S</sub>=±2.5V)"グラフ参照)。また、(b)に示される現象が強く現れるようになります。V<sub>G LIMIT</sub>を超えて高周波応答は影響を受けます。

### アプリケーション回路例

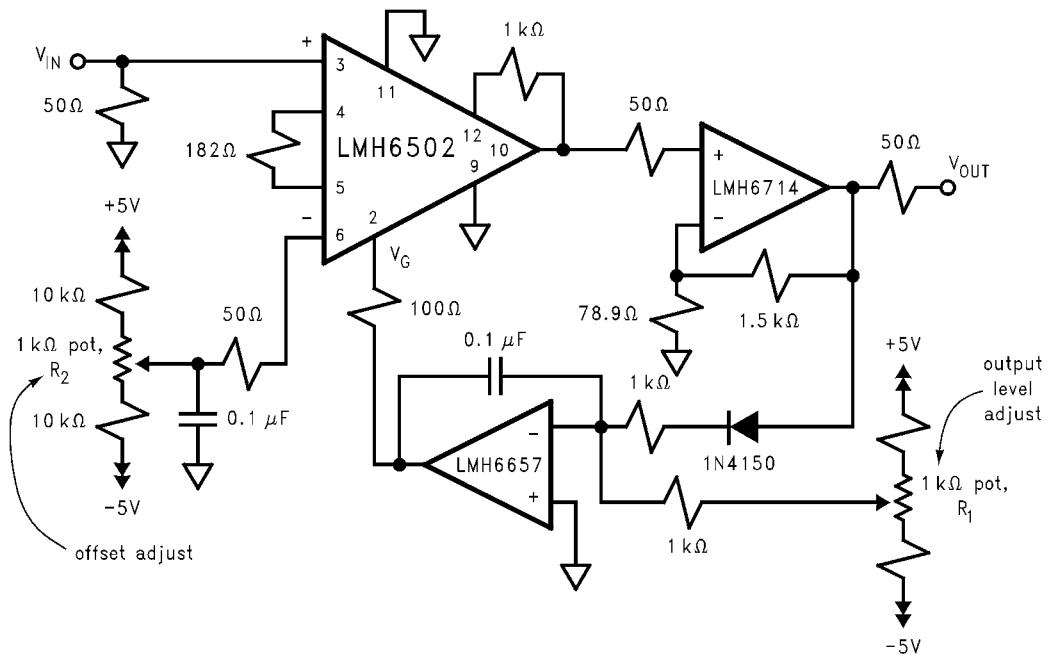

#### AGC回路

代表的なAGC回路をFigure 6に示します。総利得を高めるため、LMH6502の後にLMH6714が接続されています。LMH6714の出力は整流され、LMH6657(広帯域電圧帰還型オペアンプ)を使った反転積分器に送られます。出力電圧V<sub>OUT</sub>が大きすぎると積分器の出力電圧が次第に低下し、LMH6502の実効ゲインとV<sub>OUT</sub>が低下します。出力電圧が小さすぎると積分器の出力が次第に増加し、実効ゲインと出力電圧が増加します。実際の出力レベルはR<sub>1</sub>で設定します。入力信号レベルの変化に伴うDC出力電圧のシフトを防ぐために、トリム・ポットR<sub>2</sub>が用意されています。AGC回路では、一定の出力レベルを保てる入力信号レベルの範囲が常に限られています。この回路では、40dB以上にわたってAGC動作が適正に維持されることが期待できます。現実には、整流器のダイナミック・レンジによって、この範囲が多少狭くなります。

## アプリケーション回路例 (つづき)

FIGURE 6. Automatic Gain Control (AGC) Loop

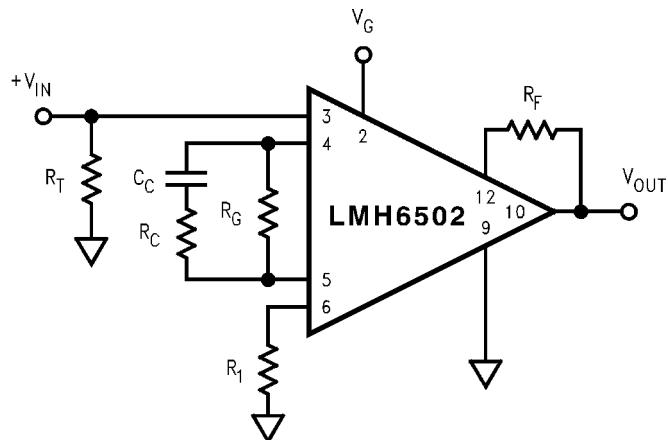

## 周波数シェーピング

LMH6502 は Figure 7 のように  $R_G$  に並列接続すると、効率よく周波数と帯域幅拡張ができます。

FIGURE 7. Frequency Shaping

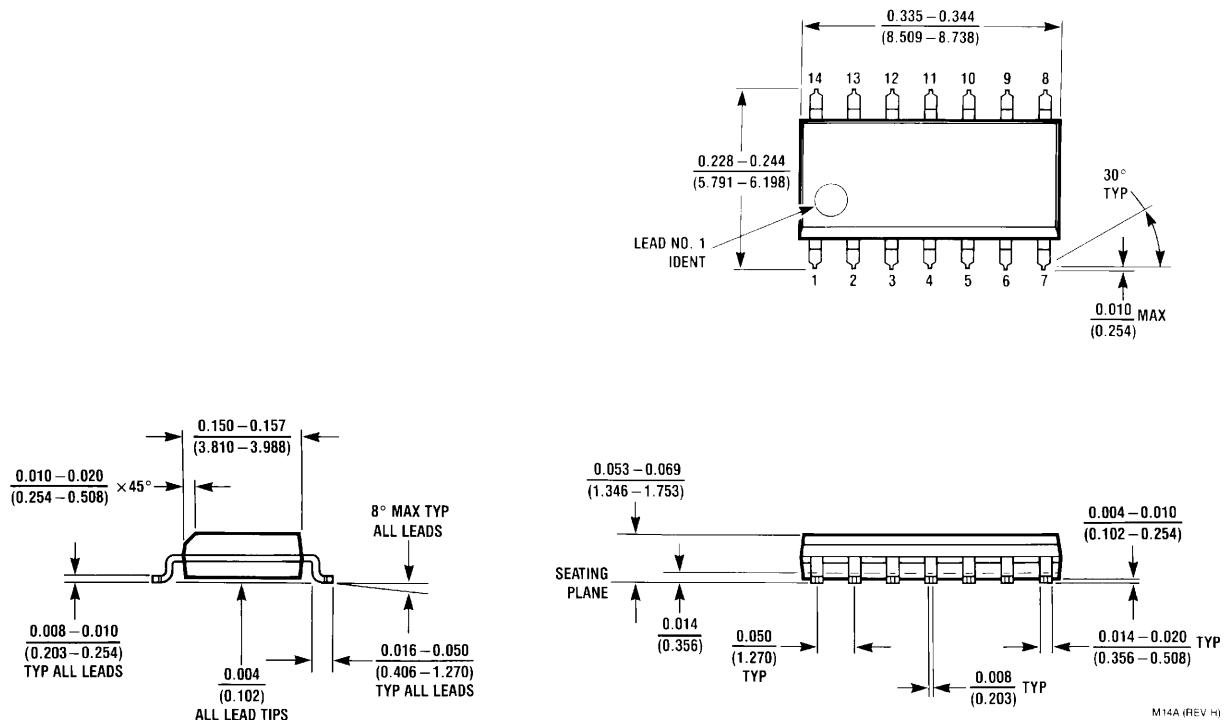

## 外形寸法図 特記のない限り inches (millimeters)

14-Pin SOIC

NS Package Number M14A

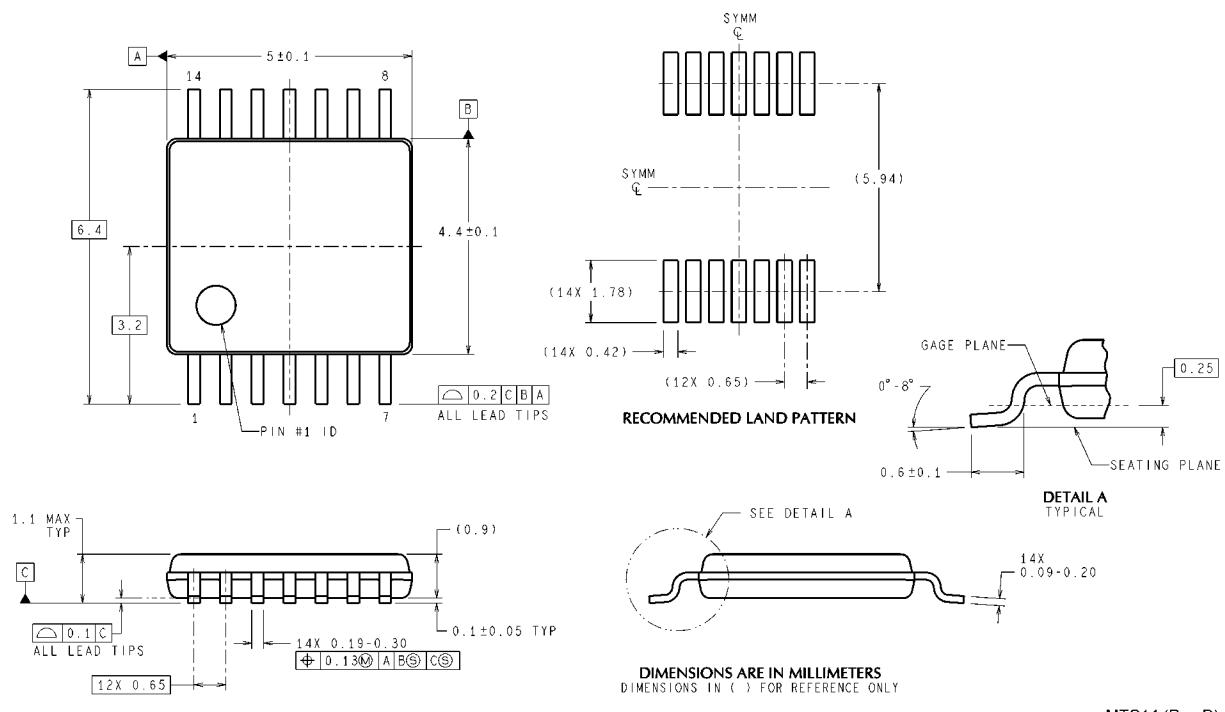

14-Pin TSSOP

NS Package Number MTC14

単位は millimeters

## 生命維持装置への使用について

弊社の製品はナショナルセミコンダクター社の書面による許可なくしては、生命維持用の装置またはシステム内の重要な部品として使用することはできません。

1. 生命維持用の装置またはシステムとは (a) 体内に外科的に使用されることを意図されたもの、または (b) 生命を維持あるいは支持するものをいい、ラベルにより表示される使用法に従って適切に使用された場合に、この不具合が使用者に身体的障害を与えると予想されるものをいいます。

2. 重要な部品とは、生命維持にかかわる装置またはシステム内のすべての部品をいい、これの不具合が生命維持用の装置またはシステムの不具合の原因となりそれらの安全性や機能に影響を及ぼすことが予想されるものをいいます。

## ナショナルセミコンダクター ジャパン株式会社

本社 / 〒135-0042 東京都江東区木場 2-17-16 TEL.(03)5639-7300

技術資料（日本語/英語）はホームページより入手可能です。

[www.national.com/jpn/](http://www.national.com/jpn/)

その他のお問い合わせはフリーダイヤルをご利用ください。

0120-666-116

# ご注意

日本テキサス・インスツルメンツ株式会社（以下TIJといいます）及びTexas Instruments Incorporated（TIJの親会社、以下TIJないしTexas Instruments Incorporatedを総称してTIといいます）は、その製品及びサービスを任意に修正し、改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての製品は、お客様とTIJとの間に取引契約が締結されている場合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご注文の受諾の際に提示されるTIJの標準販売契約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応した性能を有していること、またはお客様とTIJとの間で合意された保証条件に従い合意された仕様に対応した性能を有していることを保証します。検査およびその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計について責任を負うことはありません。TI製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。TI製部品を使用したお客様の製品及びアプリケーションについて想定される危険を最小のものとするため、適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明もしておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品もしくはサービスを使用することについてライセンスを与えるとか、保証もしくは是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならぬ場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報に一切の変更を加えること無く、かつその情報と結び付られた全ての保証、条件、制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そのような変更された情報や複製については何の義務も責任も負いません。

Copyright © 2011, Texas Instruments Incorporated

日本語版 日本テキサス・インスツルメンツ株式会社

## 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点を遵守して下さい。

### 1. 静電気

- 素手で半導体製品単体を触らないこと。どうしても触る必要がある場合は、リストストラップ等で人体からアースをとり、導電性手袋等をして取り扱うこと。

- 弊社出荷梱包単位（外装から取り出された内装及び個装）又は製品単品で取り扱いを行う場合は、接地された導電性のテーブル上で（導電性マットにアースをとったもの等）、アースをした作業者が行うこと。また、コンテナ等も、導電性のものを使うこと。

- マウンタやはんだ付け設備等、半導体の実装に関わる全ての装置類は、静電気の帯電を防止する措置を施すこと。

- 前記のリストストラップ・導電性手袋・テーブル表面及び実装装置類の接地等の静電気帯電防止措置は、常に管理されその機能が確認されていること。

### 2. 湿度環境

- 温度：0～40°C、相対湿度：40～85%で保管・輸送及び取り扱いを行うこと。（但し、結露しないこと。）

TIの製品もしくはサービスについてTIにより示された数値、特性、条件その他のパラメーターと異なる、あるいは、それを超えてなされた説明で当該TI製品もしくはサービスを再販売することは、当該TI製品もしくはサービスに対する全ての明示的保証、及び何らかの黙示的保証を無効にし、かつ不公正で誤認を生じさせる行為です。TIは、そのような説明については何の義務も責任もありません。

TIは、TIの製品が、安全でないことが致命的となる用途ないしアプリケーション（例えば、生命維持装置のように、TI製品に不良があった場合に、その不良により相当な確率で死傷等の重篤な事故が発生するようなもの）に使用されることを認めておりません。但し、お客様とTIの双方の権限有る役員が書面でそのような使用について明確に合意した場合は除きます。たとえTIがアプリケーションに関連した情報やサポートを提供したとしても、お客様は、そのようなアプリケーションの安全面及び規制面から見た諸問題を解決するために必要とされる専門的知識及び技術を持ち、かつ、お客様の製品について、またTI製品をそのような安全でないことが致命的となる用途に使用することについて、お客様が全ての法的責任、規制を遵守する責任、及び安全に関する要求事項を満足させる責任を負っていることを認め、かつそのことに同意します。さらに、もし万一、TIの製品がそのような安全でないことが致命的となる用途に使用されたことによって損害が発生し、TIないしその代表者がその損害を賠償した場合は、お客様がTIないしその代表者にその全額の補償をするものとします。

TI製品は、軍事的用途もしくは宇宙航空アプリケーションないし軍事的環境、航空宇宙環境にて使用されるようには設計もされていませんし、使用されることを意図されておりません。但し、当該TI製品が、軍需対応グレード品、若しくは「強化プラスティック」製品としてTIが特別に指定した製品である場合は除きます。TIが軍需対応グレード品として指定した製品のみが軍需品の仕様書に合致いたします。お客様は、TIが軍需対応グレード品として指定していない製品を、軍事的用途もしくは軍事的環境下で使用することは、もっぱらお客様の危険負担においてなされるということ、及び、お客様がもっぱら責任をもって、そのような使用に関して必要とされる全ての法的要件及び規制上の要求事項を満足させなければならないことを認め、かつ同意します。

TI製品は、自動車用アプリケーションないし自動車の環境において使用されるようには設計もされていませんし、また使用されることを意図されておりません。但し、TIがISO/TS 16949の要求事項を満たしていると特別に指定したTI製品は除きます。お客様は、お客様が当該TI指定品以外のTI製品を自動車用アプリケーションに使用しても、TIは当該要求事項を満たしていなかったことについて、いかなる責任も負わないことを認め、かつ同意します。

- 直射日光があたる状態で保管・輸送しないこと。

- 3. 防湿梱包

- 防湿梱包品は、開封後は個別推奨保管環境及び期間に従い基板実装すること。

- 4. 機械的衝撃

- 梱包品（外装、内装、個装）及び製品単品を落下させたり、衝撃を与えないこと。

- 5. 熱衝撃

- はんだ付け時は、最低限260°C以上の高温状態に、10秒以上さらさないこと。（個別推奨条件がある時はそれに従うこと。）

- 6. 汚染

- はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質（硫黄、塩素等ハロゲン）のある環境で保管・輸送しないこと。

- はんだ付け後は十分にフラックスの洗浄を行うこと。（不純物含有率が一定以下に保証された無洗浄タイプのフラックスは除く。）

以上