LMR43620, LMR43610

JAJSN60B - DECEMBER 2020 - REVISED MAY 2023

# LMR436x0、36V、1A/2A 降圧コンバータ、T<sub>JMAX</sub> 150°Cで 2.5µA 未満の I<sub>Q</sub>、4mm<sup>2</sup> HotRod<sup>™</sup> QFN

## 1 特長

- 機能安全対応

- 機能安全準拠のシステム設計に役立つ資料を利 用可能

- 小さなソリューション・サイズとわずかな部品コスト

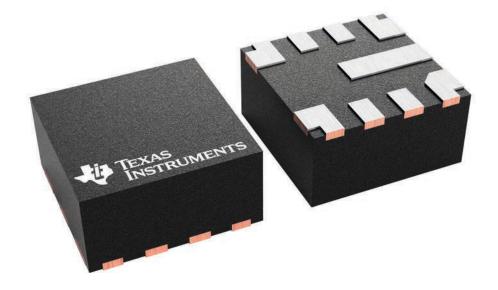

- ウェッタブル・フランク付きの 2mm × 2mm HotRod ™ パッケージ

- 内部補償

- 超低 EMI 要件に最適化

- 軽負荷時の固定周波数 FPWM モードを MODE/ SYNC ピンで選択可能

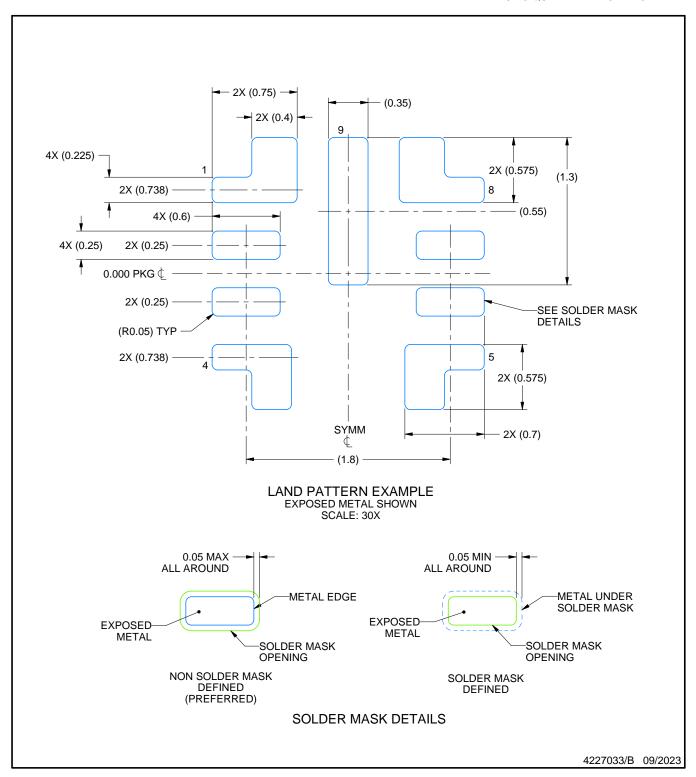

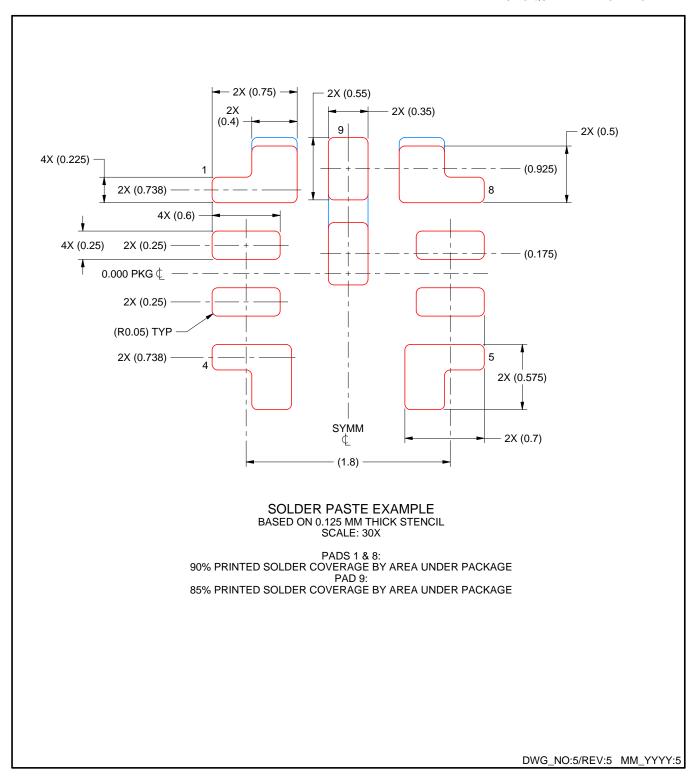

- MODE/SYNC ピンによる F<sub>SW</sub> 同期

- 産業用アプリケーション向けの設計

- 接合部温度範囲:-40°C~+150°C

- 42V の過渡に対応

- 最小 V<sub>IN</sub> = 3V に対応

- V<sub>IN</sub>の最大 95% に調整可能、3.3V および 5V 固 定の Vout オプションを提供

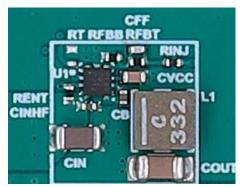

- 効率が 85% 以上 (1mA 時)

- I<sub>Q</sub>:1.3μA (V<sub>IN</sub> = 24V、V<sub>OUT</sub> = 5V (固定) のとき)

- スケーラブルな電源に対応した設計

- 200kHz~2.2MHz (RTピン)の可変 F<sub>SW</sub>

- 次の製品とピン互換:

- LMR36506 (65V, 600mA)

- LMR36503 (65V, 300mA)

# 2 アプリケーション

- ファクトリ・オートメーション:フィールド・トランスミッタと プロセス・センサ

- ビルディング・オートメーション:HVAC と防火

- 家電製品:園芸用品および電動工具

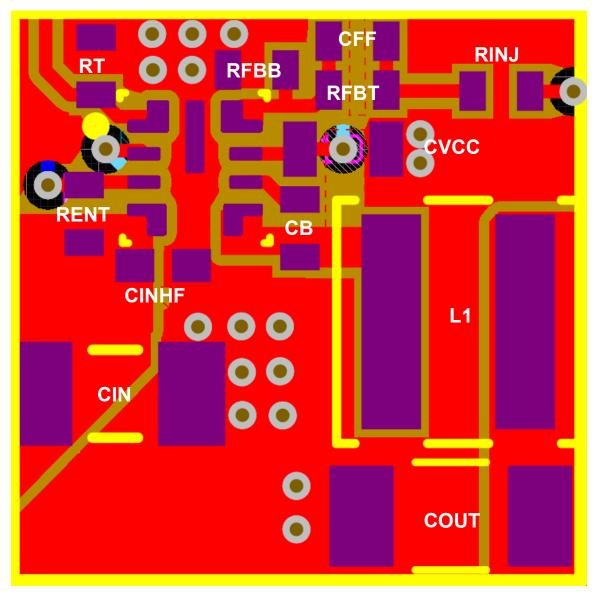

代表的なソリューション・サイズ (10mm×10mm)

## 3 概要

LMR436x0 は、業界最小の 36V、2A および 1A 同期整 流降圧 DC/DC コンバータで、2mm × 2mm の HotRod パッケージで供給されています。この使いやすいコンバー タは、3.0V~36V の広い入力電圧範囲と最大 42V の過 渡電圧をサポートしています。

制御アーキテクチャと機能セットを最適化して、超小型の ソリューション・サイズを実現しています。本デバイスは、ピ 一ク電流モード制御を使用して出力容量を最小化してい ます。LMR436x0 は、デュアル・ランダム拡散スペクトラ ム、低 EMI の HotRod パッケージ、最適化されたピン配 置を使用して入力フィルタのサイズを最小化しています。 MODE/SYNC および RT ピンのバリアントを使用すると、 **200kHz~2.2MHz** の周波数に設定または同期して、ノイ ズの影響を受けやすい周波数帯域を回避できます。

LMR436x0 の小さなソリューション・サイズと豊富な機能セ ットは、広範な産業用アプリケーションを簡単に実装できる よう設計されています。

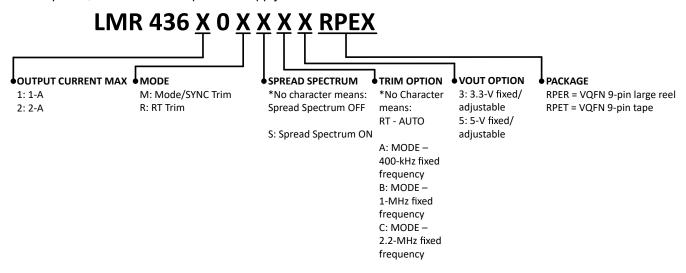

#### パッケージ情報

|          | * * * * * 113 184    |                        |

|----------|----------------------|------------------------|

| 部品番号     | パッケージ <sup>(1)</sup> | 本体サイズ (公称)             |

| LMR43620 | DDE (VOEN HD 0)      | 2.00mm × 2.00mm        |

| LMR43610 | RPE (VQFN-HR、9)      | 2.0011111 ^ 2.00111111 |

利用可能なすべてのパッケージについては、このデータシートの 末尾にある注文情報を参照してください。

#### 製品情報

|          | 119 107   |

|----------|-----------|

| 部品番号     | 定格出力電流(1) |

| LMR43620 | 2A        |

| LMR43610 | 1A        |

製品比較表を参照してください。

効率:V<sub>OUT</sub> = 5V (固定)、1MHz

Page

## **Table of Contents**

| 1 特長                                 | 1 | 8.3 Feature Description                 | 12              |

|--------------------------------------|---|-----------------------------------------|-----------------|

| 2 アプリケーション                           |   | 8.4 Device Functional Modes             |                 |

| 3 概要                                 |   | 9 Application and Implementation        | <mark>27</mark> |

| 4 Revision History                   |   | 9.1 Application Information             | <mark>27</mark> |

| 5 Device Comparison Table            |   | 9.2 Typical Application                 | <mark>28</mark> |

| 6 Pin Configuration and Functions    |   | 9.3 Best Design Practices               | 40              |

| 7 Specifications                     |   | 9.4 Power Supply Recommendations        | 40              |

| 7.1 Absolute Maximum Ratings         |   | 9.5 Layout                              | 40              |

| 7.2 ESD Ratings                      |   | 10 Device and Documentation Support     | 43              |

| 7.3 Recommended Operating Conditions |   | 10.1 Device Support                     |                 |

| 7.4 Thermal Information              |   | 10.2 Documentation Support              | 43              |

| 7.5 Electrical Characteristics       |   | 10.3 サポート・リソース                          | 44              |

| 7.6 System Characteristics           |   | 10.4 Trademarks                         | 44              |

| 7.7 Typical Characteristics          |   | 10.5 静電気放電に関する注意事項                      | 44              |

| 8 Detailed Description               |   | 10.6 用語集                                | 44              |

| 8.1 Overview                         |   | 11 Mechanical, Packaging, and Orderable |                 |

| 8.2 Functional Block Diagram         |   | Information                             | 45              |

| ŭ                                    |   |                                         |                 |

## **4 Revision History**

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

# Changes from Revision A (October 2021) to Revision B (May 2023)

## **5 Device Comparison Table**

| ORDERABLE PART NUMBER (1) | OUTPUT<br>CURRENT | OUTPUT<br>VOLTAGE           | EXTERNAL SYNC                        | F <sub>SW</sub>                   | SPREAD SPECTRUM |

|---------------------------|-------------------|-----------------------------|--------------------------------------|-----------------------------------|-----------------|

| LMR43620MB5RPER           | 2 A               | 5-V fixed /<br>adjustable   | Yes<br>(PFM/FPWM<br>Selectable)      | Fixed<br>1 MHz                    | No              |

| LMR43620R5RPER            | 2 A               | 5-V fixed /<br>adjustable   | No<br>(Default PFM at light<br>load) | Adjustable<br>with RT<br>resistor | No              |

| LMR43610MB3RPER           | 1 A               | 3.3-V fixed /<br>adjustable | Yes<br>(PFM/FPWM<br>Selectable)      | Fixed<br>1 MHz                    | No              |

| LMR43610R3RPER            | 1 A               | 3.3-V fixed /<br>adjustable | No<br>(Default PFM at light<br>load) | Adjustable<br>with RT<br>resistor | No              |

<sup>(1)</sup> For more information on device orderable part numbers, see *Device Nomenclature*.

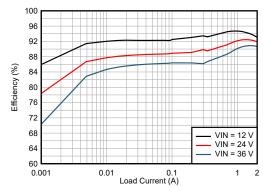

## **6 Pin Configuration and Functions**

- A. See Device Comparison Table for more details. Pin 1 is factory-set for externally adjustable switching frequency RT variants only.

- B. Pin 1 factory-set for fixed switching frequency MODE/SYNC variants only.

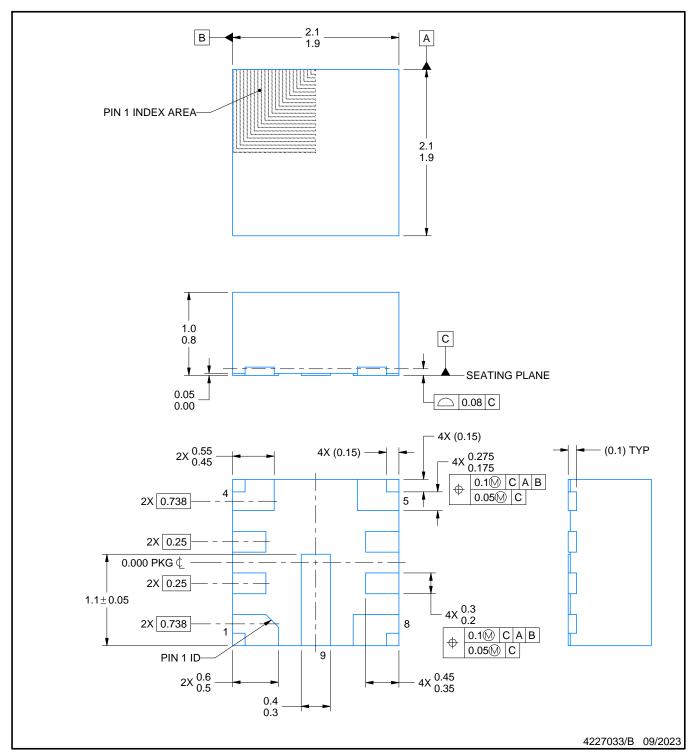

図 6-1. 9-Pin (2 mm × 2 mm) VQFN-HR RPE Package (Top View)

表 6-1. Pin Functions

|             | PIN                    | I/O  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                    |

|-------------|------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO.         | NAME                   | 1/0  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                    |

| 1           | RT<br>or MODE/SYNC     | Α    | For the RT variant, the switching frequency can be adjusted from 200 kHz to 2.2 MHz. For the MODE/SYNC variant, it can operate in user-selectable PFM/FPWM mode and can be synchronized to an external clock. <i>Do not float this pin.</i>                                                                                                                    |

| 2           | PGOOD                  | Α    | Open-drain power-good flag output. Connect to a suitable voltage supply through a current limiting resistor. High = power OK, low = power bad. It goes low when EN = low. It can be open or grounded when not used.                                                                                                                                            |

| 3 EN/UVLO A |                        | Α    | Enable input to regulator. High = ON, low = OFF. Can be connected directly to VIN. <i>Do not float this pin.</i>                                                                                                                                                                                                                                               |

| 4 VIN P     |                        | Р    | Input supply to regulator. Connect a high-quality bypass capacitor or capacitors directly to this pin and GND.                                                                                                                                                                                                                                                 |

| 5           | SW                     | Р    | Regulator switch node. Connect to power inductor.                                                                                                                                                                                                                                                                                                              |

| 6           | воот                   | Р    | Bootstrap supply voltage for internal high-side driver. Connect a high-quality 100-nF capacitor from this pin to the SW pin.                                                                                                                                                                                                                                   |

| 7           | VCC                    | Р    | Internal LDO output. Used as supply to internal control circuits. Do not connect to external loads. Can be used as logic supply for power-good flag. Connect a high-quality 1-µF capacitor from this pin to GND.                                                                                                                                               |

| 8           | VOUT/FB                | Α    | Fixed output options and adjustable output options are available with the VOUT/FB pin variant. Connect to the output voltage node for fixed VOUT. Connect to tap point of feedback voltage divider for adjustable VOUT. See セクション 9.2.2.2.1 for how to select feedback resistor divider values. Check セクション 5 for more details. <i>Do not float this pin</i> . |

| 9           | GND                    | G    | Power ground terminal. Connect to system ground. Connect to C <sub>IN</sub> with short, wide traces.                                                                                                                                                                                                                                                           |

| A = Ana     | alog, P = Power, G = G | ound |                                                                                                                                                                                                                                                                                                                                                                |

## 7 Specifications

## 7.1 Absolute Maximum Ratings

Over the recommended operating junction temperature range (1)

|             | PARAMETER                              | MIN  | MAX                   | UNIT |

|-------------|----------------------------------------|------|-----------------------|------|

| Voltages    | VIN to GND                             | -0.3 | 42                    | V    |

| Voltages    | SW to GND                              | -0.3 | V <sub>IN</sub> + 0.3 | V    |

| Voltages    | BOOT to SW                             | -0.3 | 5.5                   | V    |

| Voltages    | VCC to GND                             | -0.3 | 5.5                   | V    |

| Voltages    | VOUT/FB to GND                         | -0.3 | 16                    | V    |

| Voltages    | SYNC/MODE or RT to GND                 | -0.3 | 5.5                   | V    |

| Voltages    | PGOOD to GND                           | -0.3 | 20                    | V    |

| Voltages    | EN to GND                              | -0.3 | 42                    | V    |

| Temperature | T <sub>J</sub> , Junction temperature  | -40  | 150                   | °C   |

| Temperature | T <sub>stg</sub> , Storage temperature | -65  | 150                   | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

## 7.2 ESD Ratings

|                    |                         |                                                                       | VALUE            | UNIT |

|--------------------|-------------------------|-----------------------------------------------------------------------|------------------|------|

| V                  | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/<br>JEDEC JS-001 <sup>(1)</sup> | ANSI/ESDA/ ±2000 |      |

| V <sub>(ESD)</sub> |                         | Charged-device model (CDM), per ANSI/ESDA/<br>JEDEC JS-002 (2)        | ±750             | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

Over the recommended operating junction temperature range of -40 °C to 150 °C (unless otherwise noted)

|                  |                                                           | MIN | MAX        | UNIT |

|------------------|-----------------------------------------------------------|-----|------------|------|

| V                | Input Voltage Range for start-up                          | 3.6 | 36         | V    |

| V <sub>IN</sub>  | Input Voltage Range after start-up                        | 3.0 | 36         | V    |

| V <sub>OUT</sub> | Output Voltage Range with Adjustable Output Voltage Setup | 1   | 0.95 * VIN | V    |

| I <sub>OUT</sub> | LMR43620 Continuous DC Output Current Range               | 0   | 2          | Α    |

| I <sub>OUT</sub> | LMR43610 Continuous DC Output Current Range               | 0   | 1          | Α    |

| TJ               | Operating junction temperature                            | -40 | 150        | °C   |

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 7.4 Thermal Information

The value of  $R_{\theta JA}$  in this table is only valid for comparison with other packages. These values were calculated in accordance with JESD 51-7, and simulated on a 4-layer JEDEC board. They do not represent the performance obtained in an actual application. For example, a 4-layer PCB can achieve a  $R_{\theta JA} = 50^{\circ}$ C/W.

|                        |                                                              | LMR436x0      |      |

|------------------------|--------------------------------------------------------------|---------------|------|

|                        | THERMAL METRIC (1)                                           | RPE (VQFN-HR) | UNIT |

|                        |                                                              | 9 PINS        |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance for LMR43620MQ3EVM-2M | 50            | °C/W |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance                       | 84.4          | °C/W |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance                    | 47.5          | °C/W |

| R <sub>θJB</sub>       | Junction-to-board thermal resistance                         | 26.1          | °C/W |

| ΨЈТ                    | Junction-to-top characterization parameter                   | 0.9           | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter                 | 25.9          | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics

#### 7.5 Electrical Characteristics

Limits apply over the recommended operating junction temperature range of -40°C to +150°C, unless otherwise noted. Minimum and Maximum limits are guaranteed through test, design or statistical correlation. Typical values represent the most likely parametric norm at  $T_J$  = 25°C, and are provided for reference purposes only. Unless otherwise stated the following conditions apply:  $V_{IN}$  = 13.5 V.

|                          | PARAMETER                                              | TEST CONDITIONS                                                     | MIN  | TYP  | MAX  | UNIT |

|--------------------------|--------------------------------------------------------|---------------------------------------------------------------------|------|------|------|------|

| SUPPLY VO                | LTAGE (VIN PIN)                                        |                                                                     |      |      |      |      |

| \ /                      | Input voltage rising threshold for start-up            | Before start-up                                                     | 3.2  | 3.35 | 3.5  | V    |

| V <sub>INMIN</sub>       | Input voltage falling threshold                        | After operating                                                     | 2.45 | 2.7  | 3    | V    |

| I <sub>SD(VIN)</sub>     | Shutdown quiescent current at VIN pin                  | EN = 0 V                                                            |      | 0.25 | 1    | μΑ   |

| I <sub>BIAS</sub>        | Non-switching input current at VOUT/FB                 | Fixed 5.0-V Vout, V <sub>VOUT/FB</sub> = 5.25 V                     |      | 4.2  | 6.5  | μΑ   |

| I <sub>BIAS</sub>        | Non-switching input current at VOUT/FB                 | Fixed 3.3-Vout, V <sub>VOUT/FB</sub> = 3.47 V                       |      | 4.2  | 6.5  | μΑ   |

| I <sub>QVIN(nonsw)</sub> | Non-switching input current; measured at VIN pin (1)   | Fixed 5.0-V V <sub>OUT</sub> , V <sub>VOUT/FB</sub> = 5.25 V        |      | 1.6  | 3    | μA   |

| I <sub>QVIN(nonsw)</sub> | Non-switching input current; measured at VIN pin (1)   | Fixed 3.3-V V <sub>OUT</sub> , V <sub>VOUT/FB</sub> = 3.47 V        |      | 1.2  | 2.2  | μA   |

| ENABLE (EN               | N PIN)                                                 |                                                                     |      |      |      |      |

| V <sub>EN-WAKE</sub>     | EN wakeup threshold                                    |                                                                     | 0.5  | 0.7  | 1    | V    |

| V <sub>EN-VOUT</sub>     | Precision enable rising threshold for V <sub>OUT</sub> |                                                                     | 1.16 | 1.23 | 1.3  | V    |

| V <sub>EN-HYST</sub>     | Enable hysteresis below V <sub>EN-VOUT</sub>           |                                                                     | 0.3  | 0.35 | 0.4  | V    |

| I <sub>LKG-EN</sub>      | Enable pin input leakage current                       | V <sub>EN</sub> = V <sub>IN</sub> = 13.5 V                          |      | 10   |      | nA   |

| INTERNAL L               | DO (VCC PIN)                                           |                                                                     |      |      |      |      |

| V <sub>CC</sub>          | VCC pin output voltage                                 | V <sub>FB</sub> = 0 V, I <sub>VCC</sub> = 1 mA                      | 3.1  | 3.3  | 3.45 | V    |

| VOLTAGE F                | EEDBACK (VOUT/FB PIN)                                  |                                                                     |      |      |      |      |

| V <sub>OUT</sub>         | Output voltage accuracy for fixed V <sub>OUT</sub>     | 3.3-V V <sub>OUT</sub> , V <sub>IN</sub> = 3.6 V to 36 V, FPWM Mode | 3.27 | 3.3  | 3.33 | V    |

| V <sub>OUT</sub>         | Output voltage accuracy for fixed V <sub>OUT</sub>     | 5-V V <sub>OUT</sub> , V <sub>IN</sub> = 5.5 V to 36 V, FPWM Mode   | 4.94 | 5.00 | 5.06 | V    |

| $V_{FB}$                 | Internal reference voltage accuracy                    | V <sub>OUT</sub> = 1 V, V <sub>IN</sub> = 3.0 V to 36 V, FPWM Mode  | 0.99 | 1.00 | 1.01 | V    |

| I <sub>FB(LKG)</sub>     | FB input current                                       | Adjustable configuration, FB = 1 V                                  |      | 10   |      | nA   |

| CURRENT L                | IMITS                                                  |                                                                     |      |      |      |      |

| I <sub>PEAKMAX</sub>     | High-side peak current limit                           | LMR43610                                                            | 1.4  | 1.8  | 2.1  | Α    |

| I <sub>VALMAX</sub>      | Low-side valley current limit                          | LMR43610                                                            | 0.85 | 1.1  | 1.4  | Α    |

| I <sub>PEAKMIN</sub>     | Minimum peak current limit                             | LMR43610, Auto Mode                                                 | 0.17 | 0.27 | 0.4  | Α    |

| I <sub>NEGMIN</sub>      | Low-side valley current negative limit                 | LMR43610, FPWM Mode                                                 | -1   | -0.8 | -0.6 | Α    |

| I <sub>PEAKMAX</sub>     | High-side peak current limit                           | LMR43620                                                            | 2.8  | 3.4  | 3.9  | Α    |

English Data Sheet: SNVSBY5

## 7.5 Electrical Characteristics (continued)

Limits apply over the recommended operating junction temperature range of -40°C to +150°C, unless otherwise noted. Minimum and Maximum limits are guaranteed through test, design or statistical correlation. Typical values represent the most likely parametric norm at  $T_J$  = 25°C, and are provided for reference purposes only. Unless otherwise stated the following conditions apply:  $V_{IN}$  = 13.5 V.

|                           | PARAMETER                                                                      | TEST CONDITIONS                                         | MIN      | TYP  | MAX  | UNIT |

|---------------------------|--------------------------------------------------------------------------------|---------------------------------------------------------|----------|------|------|------|

| I <sub>VALMAX</sub>       | Low-side valley current limit                                                  | LMR43620                                                | 1.9      | 2.2  | 2.53 | Α    |

| I <sub>PEAKMIN</sub>      | Minimum peak current limit                                                     | LMR43620, Auto Mode                                     | 0.37     | 0.5  | 0.65 | Α    |

| I <sub>NEGMIN</sub>       | Negative current limit                                                         | LMR43620, FPWM Mode                                     | -1       | -0.8 | -0.6 | Α    |

| I <sub>zc</sub>           | Zero-cross current limit                                                       | Auto Mode                                               | 30       | 80   | 135  | mA   |

| POWER GOO                 | DD (PGOOD PIN)                                                                 |                                                         |          |      |      | 1    |

| PGD <sub>OV</sub>         | PGOOD upper threshold - rising                                                 | % of VOUT/FB (Fixed or Adj. output)                     | 104      | 108  | 111  | %    |

| PGD <sub>UV</sub>         | PGOOD upper threshold - falling                                                | % of VOUT/FB (Fixed or Adj. output)                     | 89       | 91   | 94.2 | %    |

|                           | PGOOD recovery hysteresis for OV                                               | % of VOUT/FB target regulation voltage                  | 2        | 2.4  | 2.8  | %    |

| PGD <sub>HYST</sub>       | PGOOD recovery hysteresis for UV                                               | % of VOUT/FB target regulation voltage                  | 1.1      | 3.3  | 5.9  | %    |

| V <sub>PGD-VAL</sub>      | Minimum V <sub>IN</sub> for PGOOD function                                     | $V_{EN} = 0 \text{ V}, R_{PGD PU} = 10 \text{ k}\Omega$ |          |      | 1.5  | V    |

| R <sub>PGD</sub>          | PGOOD ON resistance                                                            | V <sub>EN</sub> = 3.3 V, 200 μA pull up current         |          |      | 100  | Ω    |

| R <sub>PGD</sub>          | PGOOD ON resistance                                                            | V <sub>EN</sub> = 0 V, 200 μA pull up current           |          |      | 100  | Ω    |

| Soft Start                |                                                                                |                                                         |          |      |      |      |

| POWER STA                 | GE                                                                             |                                                         |          |      |      | -    |

| V <sub>BOOT_UVLO</sub>    | Voltage on BOOT pin compared to SW which will turnoff high-side switch         |                                                         |          | 2.1  |      | V    |

| R <sub>DSON-HS</sub>      | High-side MOSFET on-resistance                                                 | Load = 1 A                                              |          | 132  | 260  | mΩ   |

| R <sub>DSON-LS</sub>      | Low-side MOSFET on-resistance                                                  | Load = 1 A                                              |          | 75   | 140  | mΩ   |

| SOFT START                |                                                                                |                                                         |          |      |      |      |

| t <sub>SS</sub>           | Time from first SW pulse to VOUT/FB at 90% of set point.                       |                                                         | 2        | 3.5  | 4.6  | ms   |

| t <sub>HICCUP</sub>       | Time in hiccup before retry soft start                                         |                                                         | 30       | 50   | 75   | ms   |

| POWER GOO                 | DD (PGOOD PIN)                                                                 |                                                         | _        |      |      |      |

| t <sub>RESET_FILTER</sub> | PGOOD deglitch delay at falling edge                                           |                                                         | 25       | 40   | 75   | μs   |

| t <sub>PGOOD_ACT</sub>    | Delay time to PGOOD high signal                                                |                                                         | 1.35     | 2.5  | 4    | ms   |

| OSCILLATOR                | R (SYNC/MODE PIN)                                                              |                                                         | '        |      |      |      |

| t <sub>PULSE_H</sub>      | High duration needed to be recognized as a pulse                               |                                                         | 100      |      |      | ns   |

| t <sub>PULSE_L</sub>      | Low duration needed to be recognized as a pulse                                |                                                         | 100      |      |      | ns   |

| t <sub>SYNC</sub>         | High/Low level pulse maximum duration to be recognized as a valid clock signal |                                                         |          |      | 6    | μs   |

| t <sub>MODE</sub>         | Time at one level needed to indicate FPWM or Auto Mode                         |                                                         | 12.5     |      |      | μs   |

| OSCILLATOR                | R (SYNC/MODE PIN)                                                              |                                                         | <u>'</u> |      |      |      |

| F <sub>SW(1MHz)</sub>     | Frequency of 1MHz variant in FPWM                                              |                                                         | 0.9      | 1    | 1.1  | MHz  |

| f <sub>SYNC</sub>         | Frequency SYNC range                                                           |                                                         | 0.2      |      | 2.5  | MHz  |

| V <sub>MODE_L</sub>       | SYNC/MODE input voltage low level threshold                                    |                                                         | 1        |      |      | V    |

| V <sub>MODE_H</sub>       | SYNC/MODE input voltage high level threshold                                   |                                                         |          |      | 1.6  | V    |

| OSCILLATOR                | R (RT PIN)                                                                     |                                                         |          |      |      | -    |

| F <sub>SW(1MHz)</sub>     | Switching frequency with Internal fixed 1 MHz setting                          | RT pin tie to V <sub>CC</sub>                           | 0.9      | 1    | 1.1  | MHz  |

| F <sub>SW(2p2MHz)</sub>   | Switching frequency with fixed 2.2 MHz                                         | RT pin tied to GND                                      | 2.1      | 2.2  | 2.3  | MHz  |

| F <sub>SW(Adj)</sub>      | Accuracy of external frequency, 400 kHz                                        | R <sub>RT</sub> = 39.2 kΩ 0.1% resistor                 | 0.34     | 0.4  | 0.46 | MHz  |

## 7.5 Electrical Characteristics (continued)

Limits apply over the recommended operating junction temperature range of -40°C to +150°C, unless otherwise noted. Minimum and Maximum limits are guaranteed through test, design or statistical correlation. Typical values represent the most likely parametric norm at  $T_J$  = 25°C, and are provided for reference purposes only. Unless otherwise stated the following conditions apply:  $V_{IN}$  = 13.5 V.

|                      | PARAMETER                  | TEST CONDITIONS                                 | MIN | TYP | MAX | UNIT |

|----------------------|----------------------------|-------------------------------------------------|-----|-----|-----|------|

| SWITCH NOD           | SWITCH NODE                |                                                 |     |     |     |      |

| t <sub>ON-MIN</sub>  | Minimum HS switch on-time  | FPWM mode I <sub>OUT</sub> = 1 A, 2.2 MHz fixed |     | 65  | 75  | ns   |

| t <sub>OFF-MIN</sub> | Minimum HS switch off-time |                                                 |     | 60  | 85  | ns   |

| t <sub>ON-MAX</sub>  | Maximum HS switch on-time  | HS timeout in dropout                           | 6   | 9   | 13  | μs   |

<sup>(1)</sup> This is the current used by the device open loop. It does not represent the total input current of the system when in regulation.

## 7.6 System Characteristics

The following specifications apply only to the typical applications circuit, with nominal component values. Specifications in the typical (TYP) column apply to  $T_J = 25^{\circ}$ C only. Specifications in the minimum (MIN) and maximum (MAX) columns apply to the case of typical components over the temperature range of  $T_J = -40^{\circ}$ C to 150°C. These specifications are not ensured by production testing.

|                          | PARAMETER                                                                                                    | TEST CONDITIONS                                                                            | MIN | TYP | MAX | UNIT |

|--------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-----|-----|-----|------|

| SUPPLY CUF               | RRENT                                                                                                        |                                                                                            |     |     |     |      |

| 1                        | legat current to V                                                                                           | V <sub>IN</sub> = 13.5 V, Fixed 3.3-V V <sub>OUT</sub> , I <sub>OUT</sub> = 0 A, Auto mode |     | 1.5 |     | μΑ   |

| I <sub>QVIN</sub>        | Input current to V <sub>IN</sub>                                                                             | V <sub>IN</sub> = 13.5 V, Fixed 5-V V <sub>OUT</sub> , I <sub>OUT</sub> = 0 A, Auto mode   |     | 2   |     | μΑ   |

| POWER STA                | GE                                                                                                           |                                                                                            | •   |     |     |      |

|                          | Input to output voltage differential to                                                                      | V <sub>OUT</sub> = 3.3-V, fixed 2.2 MHz, I <sub>OUT</sub> = 1 A                            |     | 0.2 |     | V    |

| V <sub>DROP1</sub>       | maintain V <sub>OUT</sub> regulation ≥ 95%, with frequency foldback                                          | V <sub>OUT</sub> = 5-V, fixed 2.2 MHz, I <sub>OUT</sub> = 1 A                              |     | 0.2 |     | V    |

| V <sub>DROP2</sub>       | Input to output voltage differential to maintain $V_{OUT}$ regulation $\geq 95\%$ and $F_{SW} \geq 1.85$ MHz | V <sub>OUT</sub> = 3.3-V, fixed 2.2 MHz, I <sub>OUT</sub> = 1 A                            |     | 0.7 |     | V    |

|                          | Input to output voltage differential to maintain $V_{OUT}$ regulation $\geq$ 95% and $F_{SW} \geq$ 1.85 MHz  | V <sub>OUT</sub> = 5-V, fixed 2.2 MHz trim, I <sub>OUT</sub> = 1 A                         |     | 0.9 |     | V    |

| D                        | Maximum quitab dutu quala                                                                                    | While in frequency fold-back                                                               |     | 98  |     | %    |

| $D_{MAX}$                | Maximum switch duty cycle                                                                                    | F <sub>sw</sub> = 1.85 MHz, V <sub>OUT</sub> = 5.0-V, I <sub>OUT</sub> = 1 A               |     | 87  |     | %    |

| R <sub>FBPARA(min)</sub> | Minimum value of the parallel feedback resistors: R <sub>FBT</sub> //R <sub>FBB</sub>                        |                                                                                            |     | 5   |     | kΩ   |

| PROTECTIO                | N                                                                                                            |                                                                                            |     |     |     |      |

| T <sub>SD(trip)</sub>    | Thermal shutdown temperature                                                                                 | Shutdown temperature                                                                       | 158 | 168 | 186 | °C   |

| T <sub>SD(hyst)</sub>    | Thermal shutdown temperature                                                                                 | Recovery temperature                                                                       |     | 15  | 20  | °C   |

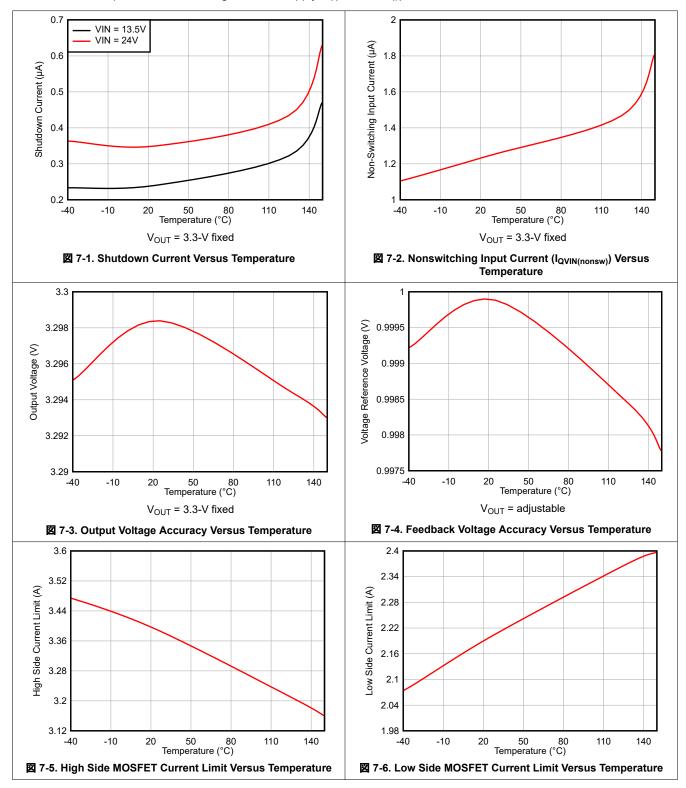

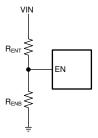

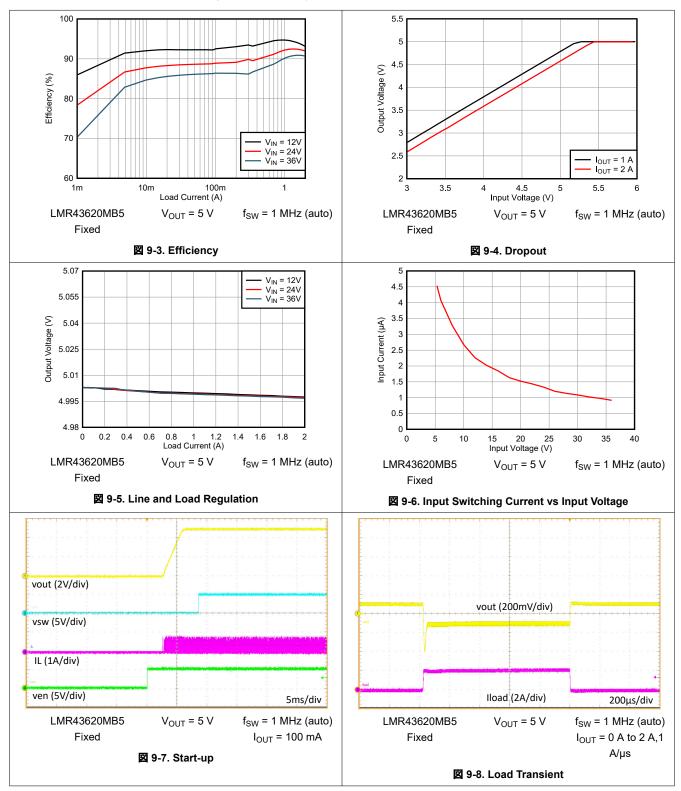

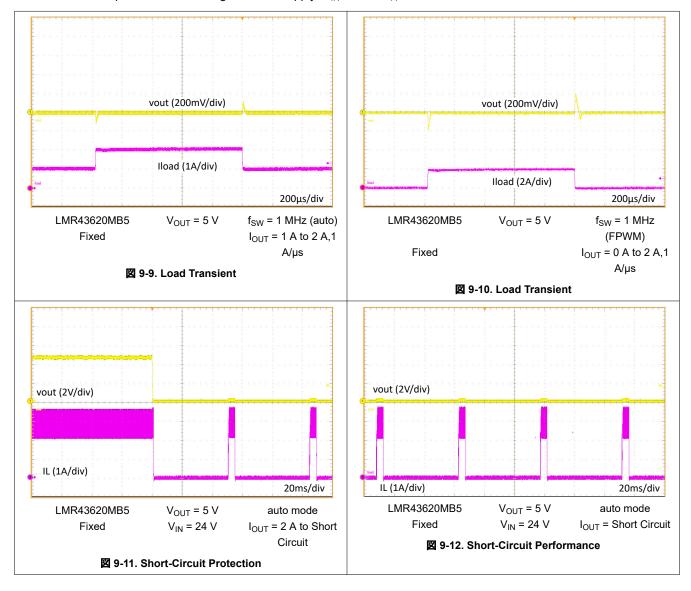

## 7.7 Typical Characteristics

Unless otherwise specified, the following conditions apply:  $T_A$  = 25°C,  $V_{IN}$  = 13.5 V

## 8 Detailed Description

## 8.1 Overview

The LMR436x0 is a wide input, low-quiescent current, high-performance regulator that can operate over a wide range of duty ratio and switching frequencies, including sub-AM band at 400 kHz and above AM band at 2.2 MHz. During wide input transients, if the minimum on time or the minimum off time cannot support the desired duty ratio at the higher switching frequency settings, the switching frequency is reduced automatically, allowing the LMR436x0 to maintain the output voltage regulation. With an internally compensated design optimized for minimal output capacitors, the system design process with the LMR436x0 is simplified significantly compared to other buck regulators available in the market.

The LMR436x0 is designed to minimize external component cost and solution size while operating in all demanding industrial environments. The LMR436x0 family includes variants that can be set up to operate over a wide switching frequency range, from 200 kHz to 2.2 MHz, with the correct resistor selection from the RT pin to ground. To further reduce system cost, the PGOOD output feature with built-in delayed release allows the elimination of the reset supervisor in many applications.

The LMR436x0 comes in an ultra-small 2-mm × 2-mm QFN package with wettable flanks, allowing for quick optical inspection along with specially designed corner anchor pins for reliable board level solder connections.

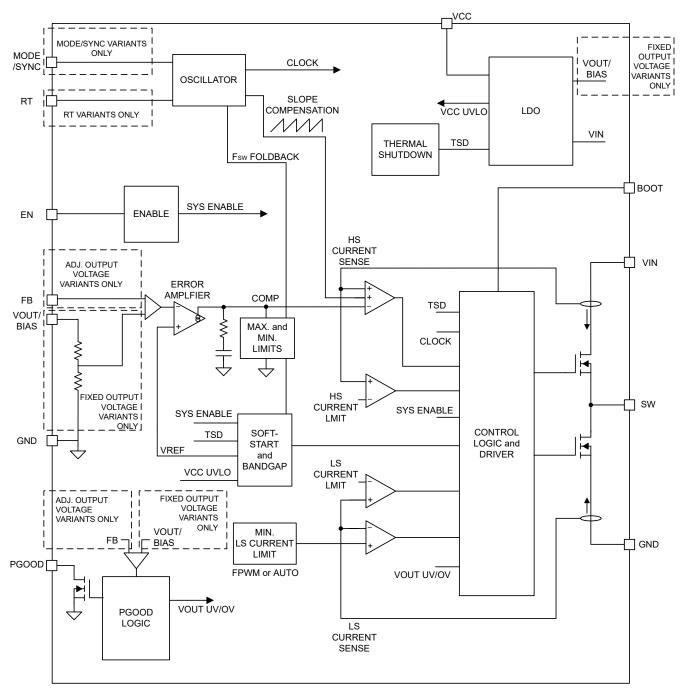

## 8.2 Functional Block Diagram

## 8.3 Feature Description

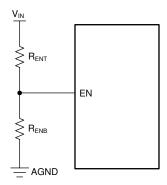

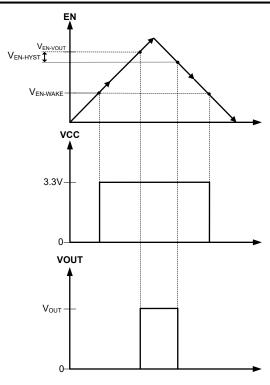

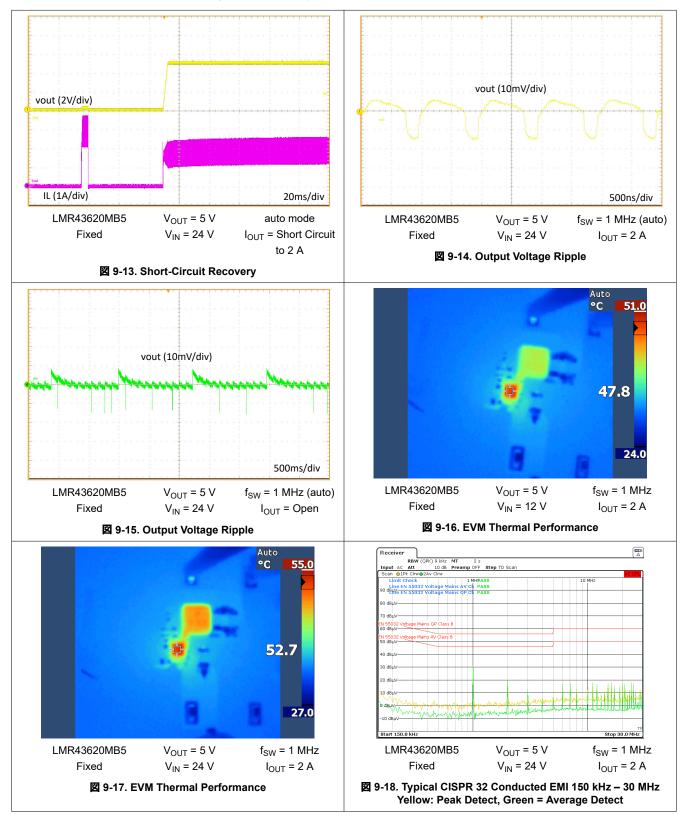

#### 8.3.1 Enable, Start-Up, and Shutdown

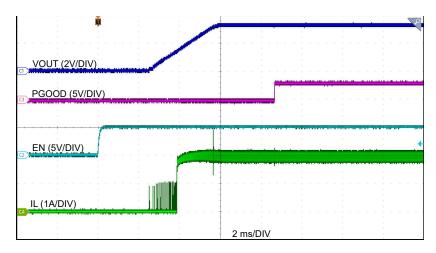

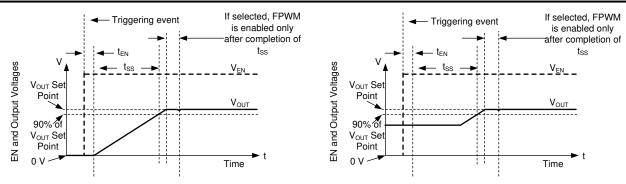

Voltage at the EN pin controls the start-up or remote shutdown of the LMR436x0 family of devices. The part stays shut down as long as the EN pin voltage is less than  $V_{EN-WAKE} = 0.5 \text{ V}$ . During shutdown, the input current drawn by the device typically drops down to 0.25  $\mu$ A ( $V_{IN}$  = 13.5 V). With the voltage at the EN pin greater than V<sub>EN-WAKE</sub>, the device enters device standby mode and the internal LDO powers up to generate VCC. As the EN voltage increases further, approaching V<sub>EN-VOUT</sub>, the device finally starts to switch, entering start-up mode with a soft start. During the device shutdown process, when the EN input voltage measures less than  $(V_{EN-VOUT} -$ V<sub>EN-HYST</sub>), the regulator stops switching and re-enters device standby mode. Any further decrease in the EN pin voltage, below V<sub>EN-WAKE</sub>, and the device is then firmly shut down. The high-voltage compliant EN input pin can be connected directly to the V<sub>IN</sub> input pin if remote precision control is not needed. The EN input pin must not be allowed to float. The various EN threshold parameters and their values are listed in *Electrical Characteristics*. 🗵 8-2 shows the precision enable behavior and 🗵 8-3 shows a typical remote EN start-up waveform in an application. After EN goes high, after a delay of about 2.5 ms, the output voltage begins to rise with a soft start and reaches close to the final value in about 3.5 ms (tss). After a delay of about 2.5 ms (tpGOOD ACT), the PGOOD flag goes high. During start-up, the device is not allowed to enter FPWM mode until the soft-start time has elapsed. This time is measured from the rising edge of EN. Check セクション 9.2.2.8.1 for component selection.

図 8-1. VIN UVLO Using the EN Pin

図 8-2. Precision Enable Behavior

図 8-3. Enable Start-Up  $V_{IN}$  = 12 V,  $V_{OUT}$  = 3.3 V,  $I_{OUT}$  = 2 A

## 8.3.2 External CLK SYNC (with MODE/SYNC)

It is often desirable to synchronize the operation of multiple regulators in a single system, resulting in a well-defined system level performance. The select variants in the LMR436x0 with the MODE/SYNC pin allow the power designer to synchronize the device to a common external clock. The LMR436x0 implements an in-phase locking scheme, where the rising edge of the clock signal, provided to the MODE/SYNC pin of the LMR436x0, corresponds to the turning on of the high-side device. The external clock synchronization is implemented using a phase locked loop (PLL), eliminating any large glitches. The external clock fed into the LMR436x0 replaces the internal free-running clock, but does not affect any frequency foldback operation. Output voltage continues to be well-regulated. The device remains in FPWM mode and operates in CCM for light loads when synchronization input is provided.

The MODE/SYNC input pin in the LMR436x0 can operate in one of three selectable modes:

- Auto mode: Pulse frequency modulation (PFM) operation is enabled during light load and diode emulation prevents reverse current through the inductor. See セクション 8.4.3.2 for more details.

- FPWM mode: In FPWM mode, diode emulation is disabled, allowing current to flow backwards through the inductor. This allows operation at full frequency even without load current. See セクション 8.4.3.3 for more details.

- SYNC mode: The internal clock locks to an external signal applied to the MODE/SYNC pin. As long as output

voltage can be regulated at full frequency and is not limited by minimum off time or minimum on time, clock

frequency is matched to the frequency of the signal applied to the MODE/SYNC pin. While the device is in

SYNC mode, it operates as though in FPWM mode: diode emulation is disabled, allowing the frequency

applied to the MODE/SYNC pin to be matched without a load.

#### 8.3.2.1 Pulse-Dependent MODE/SYNC Pin Control

Most systems that require more than a single mode of operation from the LMR436x0 are controlled by digital circuitry such as a microprocessor. These systems can generate dynamic signals easily but have difficulty generating multi-level signals. Pulse-dependent MODE/SYNC pin control is useful with these systems. To initiate pulse-dependent MODE/SYNC pin control, a valid sync signal must be applied. 表 8-1 shows a summary of the pulse dependent mode selection settings.

表 8-1. Pulse-Dependent Mode Selection Settings

| MODE/SYNC INPUT       | MODE                                           |  |  |

|-----------------------|------------------------------------------------|--|--|

| > V <sub>MODE_H</sub> | FPWM with spread spectrum factory setting      |  |  |

| < V <sub>MODE_L</sub> | Auto mode with spread spectrum factory setting |  |  |

| Synchronization Clock | SYNC mode                                      |  |  |

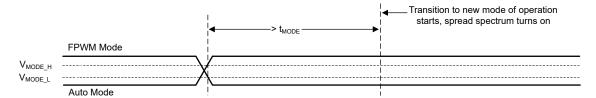

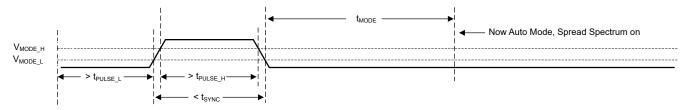

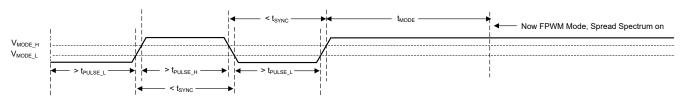

$\boxtimes$  8-4 shows the transition between auto mode and FPWM mode while in pulse-dependent MODE/SYNC control. The LMR436x0 transitions to a new mode of operation after the time,  $t_{MODE}$ .  $\boxtimes$  8-4 and  $\boxtimes$  8-5 show the details.

図 8-4. Transition from Auto Mode and FPWM Mode

If MODE/SYNC voltage remains constant longer than  $t_{\text{MODE}}$ , the LMR436x0 enters either auto mode or FPWM mode with spread spectrum turned on (if factory setting is enabled) and MODE/SYNC continues to operate in pulse-dependent scheme.

図 8-5. Transition from SYNC Mode to Auto Mode

図 8-6. Transition from SYNC Mode to FPWM Mode

## 8.3.3 Adjustable Switching Frequency (with RT)

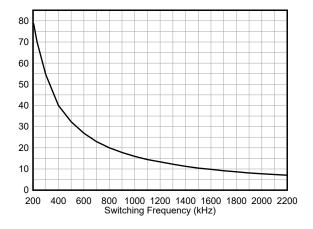

The select variants in the LMR436x0 family with the RT pin allow the power designers to set any desired operating frequency between 200 kHz and 2.2 MHz in their applications. See 図 8-7 to determine the resistor value needed for the desired switching frequency. The RT pin and the MODE/SYNC pin variants share the same pin location. The power supply designer can either use the RT pin variant and adjust the switching frequency of operation as warranted by the application or use the MODE/SYNC variant and synchronize to an external clock signal. See 表 8-2 for selection on programming the RT pin.

表 8-2. RT Pin Setting

| RT INPUT                | SWITCHING FREQUENCY           |  |

|-------------------------|-------------------------------|--|

| VCC                     | 1 MHz                         |  |

| GND                     | 2.2 MHz                       |  |

| RT resistor to GND      | Adjustable according to 図 8-7 |  |

| Float (Not Recommended) | No switching                  |  |

式 1 can be used to calculate the value of RT for a desired frequency.

$$RT = \frac{18286}{Fsw^{1.021}} \tag{1}$$

where

- RT is the frequency setting resistor value (kΩ).

- F<sub>SW</sub> is the switching frequency.

図 8-7. RT Values vs Frequency

#### 8.3.4 Power-Good Output Operation

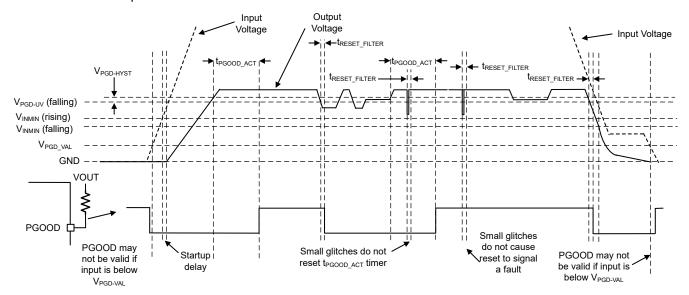

The power-good feature using the PGOOD pin of the LMR436x0 can be used to reset a system microprocessor whenever the output voltage is out of regulation. This open-drain output remains low under device fault conditions, such as current limit and thermal shutdown, as well as during normal start-up. A glitch filter prevents false flag operation for any short duration excursions in the output voltage, such as during line and load

transients. Output voltage excursions lasting less than  $t_{RESET\_FILTER}$  do not trip the power-good flag. Power-good operation can best be understood in reference to  $\boxtimes$  8-8. 表 8-3 gives a more detailed breakdown of the PGOOD operation. Here,  $V_{PGD_{UV}}$  is defined as the PGD<sub>UV</sub> scaled version of  $V_{OUT}$  (target regulated output voltage) and  $V_{PGD_{HYST}}$  as the PGD<sub>HYST</sub> scaled version of  $V_{OUT}$ , where both PGD<sub>UV</sub> and PGD<sub>HYST</sub> are listed in *Electrical Characteristics*. During the initial power up, a total delay of 6 ms (typical) is encountered from the time  $V_{EN-VOUT}$  is triggered to the time that the power-good is flagged high. This delay only occurs during the device start-up and is not encountered during any other normal operation of the power-good function. When EN is pulled low, the power-good flag output is also forced low. With EN low, power-good remains valid as long as the input voltage  $(V_{PGD-VAL}$  is  $\geq$  1.5 V (max)).

The power-good output scheme consists of an open-drain n-channel MOSFET, which requires an external pullup resistor connected to a suitable logic supply. It can also be pulled up to either  $V_{CC}$  or  $V_{OUT}$  through an appropriate resistor, as desired. If this function is not needed, the PGOOD pin can be open or grounded. Limit the current into this pin to  $\leq 4$  mA.

図 8-8. Power-Good Operation (OV Events Not Included)

FAULT CONDITION INITIATED

FAULT CONDITION ENDS (AFTER WHICH tpgood\_act MUST PASS BEFORE PGOOD OUTPUT IS RELEASED)

$V_{OUT} < V_{PGD_{UV}}$  AND  $t > t_{RESET\_FILTER}$  Output voltage in regulation:  $V_{PGD_{UV}} + V_{PGD_{HYST}} < V_{OUT} < V_{PGD_{UV}} - V_{PGD_{HYST}}$

$V_{OUT} > V_{PGD_{OV}}$  AND  $t > t_{RESET\_FILTER}$  Output voltage in regulation

$T_J > T_{SD(trip)}$   $T_J < T_{SD(trip)}$  TSD(hyst) AND output voltage in regulation

EN  $< V_{EN-VOUT} - V_{EN-HYST}$  EN  $> V_{EN-VOUT}$  AND output voltage in regulation

表 8-3. Fault Conditions for PGOOD (Pull Low)

## 8.3.5 Internal LDO, VCC, and VOUT/FB Input

The LMR436x0 uses the internal LDO output and the VCC pin for all internal power supply. The VCC pin draws power either from the  $V_{IN}$  (in adjustable output variants) or the VOUT/FB (in fixed-output variants). In the fixed output variants, after the LMR436x0 is active but has yet to regulate, the VCC rail continues to draw power from the input voltage,  $V_{IN}$ , until the VOUT/FB voltage reaches > 3.3 V (or when the device has reached steady-state regulation post the soft start). The VCC rail typically measures 3.3 V in both adjustable and fixed output variants. During start-up, VCC momentarily exceeds the normal operating voltage, then drops to the normal operating voltage.

## 8.3.6 Bootstrap Voltage and V<sub>BOOT-UVLO</sub> (BOOT Terminal)

The high-side switch driver circuit requires a bias voltage higher than VIN to ensure the HS switch is turned ON. The capacitor connected between BOOT and SW works as a charge pump to boost voltage on the BOOT terminal to (SW+VCC). The boot diode is integrated on the LMR436x0 die to minimize physical solution size. TI recommends a 100-nF capacitor rated for 10 V or higher for CBOOT. The BOOT rail has a UVLO setting. This UVLO has a threshold of  $V_{BOOT-UVLO}$  and is typically set at 2.1 V. If the CBOOT capacitor is not charged above this voltage with respect to the SW pin, then the part initiates a charging sequence, turning on the low-side switch before attempting to turn on the high-side device.

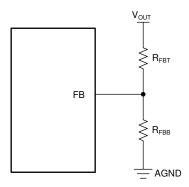

## 8.3.7 Output Voltage Selection

In the LMR436x0 family, an adjustable output or fixed output voltage option is configurable for every device variant (see  $\forall \mathcal{D} \supset \mathcal{D} \supset \mathcal{D}$ ). For an adjustable output, the user needs an external resistor divider connection between the output voltage node, the device FB pin, and the system GND, as shown in  $\boxtimes$  8-9. The adjustable output voltage operation uses a 1-V internal reference voltage. Refer to section  $\forall \mathcal{D} \supset \mathcal$

When using the fixed-output configuration from the LMR436x0 family, simply connect the FB pin (identified as VOUT/FB pin for fixed-output variants in the rest of the data sheet) to the system output voltage node. See セクション 5 for more details.

図 8-9. Setting Output Voltage for Adjustable Output Variant

In an adjustable output voltage configuration, an addition feedforward capacitor,  $C_{FF}$ , in parallel with the  $R_{FBT}$ , can be used to optimize the phase margin and transient response. See 29.2.2.8 for more details. No additional resistor divider or feedforward capacitor is needed in fixed-output variants.

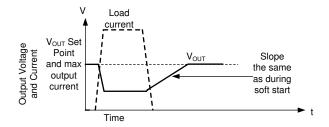

## 8.3.8 Soft Start and Recovery from Dropout

When designing with the LMR436x0, slow rise in output voltage due to recovery from dropout and soft start must be considered as a two separate operating conditions, as shown in  $\boxtimes$  8-10 and  $\boxtimes$  8-11. Soft start is triggered by any of the following conditions:

- Power is applied to the VIN pin of the device, releasing undervoltage lockout.

- · EN is used to turn on the device.

- Recovery from shutdown due to overtemperature protection

After soft start is triggered, the IC takes the following actions:

- The reference used by the IC to regulate output voltage is slowly ramped up. The net result is that output voltage, if previously 0 V, takes t<sub>SS</sub> to reach 90% of the desired value.

- Operating mode is set to auto mode of operation, activating the diode emulation mode for the low-side MOSFET. This allows start-up without pulling the output low. This is true even when there is a voltage already present at the output during a pre-bias start-up.

図 8-10. Soft Start With and Without Pre-bias Voltage

#### 8.3.8.1 Recovery from Dropout

Any time the output voltage falls more than a few percent, output voltage ramps up slowly. This condition, called graceful recovery from dropout in this document, differs from soft start in two important ways:

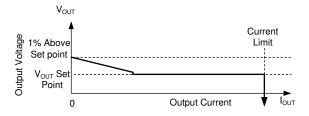

- The reference voltage is set to approximately 1% above what is needed to achieve the existing output voltage.

- If the device is set to FPWM, the device continues to operate in that mode during its recovery from dropout. If output voltage were to suddenly be pulled up by an external supply, the LMR436x0 can pull down on the output. Note that all protections that are present during normal operation are in place, preventing any catastrophic failure if output is shorted to a high voltage or ground.

図 8-11. Recovery from Dropout

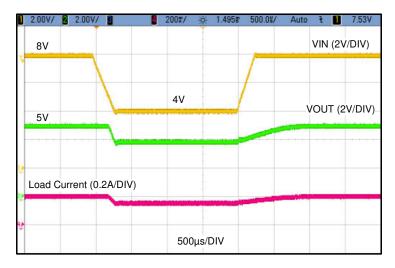

図 8-12. Typical Output Recovery from Dropout from 8 V to 4 V

Whether output voltage falls due to high load or low input voltage, after the condition that causes output to fall below its set point is removed, the output climbs at the same speed as during start-up. 🗵 8-12 shows an example of this behavior.

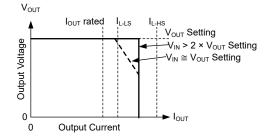

#### 8.3.9 Current Limit and Short Circuit

The LMR436x0 is protected from overcurrent conditions by cycle-by-cycle current limiting on both high-side (HS) and low-side (LS) MOSFETs.

High-side MOSFET overcurrent protection is implemented by the typical peak-current mode control scheme. The HS switch current is sensed when the HS is turned on after a short blanking time. The HS switch current is compared to either the minimum of a fixed current set point or the output of the internal error amplifier loop minus the slope compensation every switching cycle. Because the output of the internal error amplifier loop has a maximum value and slope compensation increases with duty cycle, HS current limit decreases with increased duty factor if duty factor is typically above 35%.

When the LS switch is turned on, the current going through it is also sensed and monitored. Like the high-side device, the low-side device has a turn-off commanded by the internal error amplifier loop. In the case of the low-side device, turn-off is prevented if the current exceeds this value, even if the oscillator normally starts a new switching cycle. Also like the high-side device, there is a limit on how high the turn-off current is allowed to be. This is called the low-side current limit, I<sub>VALMAX</sub>. If the LS current limit is exceeded, the LS MOSFET stays on and the HS switch is not to be turned on. The LS switch is turned off after the LS current falls below this limit and the HS switch is turned on again as long as at least one clock period has passed since the last time the HS device has turned on.

図 8-13. Current Limit Waveforms

Because the current waveform assumes values between I<sub>PEAKMAX</sub> and I<sub>VALMAX</sub>, the maximum output current is very close to the average of these two values unless duty factor is very high. After operating in current limit, hysteretic control is used and current does not increase as output voltage approaches zero.

If duty factor is very high, current ripple must be very low to prevent instability. Because current ripple is low, the part is able to deliver full current. The current delivered is very close to  $I_{VALMAX}$ .

図 8-14. Output Voltage Versus Output Current

Under most conditions, current is limited to the average of  $I_{PEAKMAX}$  and  $I_{VALMAX}$ . If input voltage is low, current can be limited to approximately  $I_{VALMAX}$ . Also note that the maximum output current does not exceed the average of  $I_{PEAKMAX}$  and  $I_{VALMAX}$ . After the overload is removed, the part recovers as though in soft start.

#### 8.3.10 Thermal Shutdown

Thermal shutdown limits total power dissipation by turning off the internal switches when the device junction temperature exceeds 168°C (typical). Thermal shutdown does not trigger below 158°C (minimum). After thermal shutdown occurs, hysteresis prevents the part from switching until the junction temperature drops to approximately 153°C (typical). When the junction temperature falls below 153°C (typical), the LMR436x0 attempts another soft start.

While the LMR436x0 is shut down due to high junction temperature, power continues to be provided to VCC. To prevent overheating due to a short circuit applied to VCC, the LDO that provides power for VCC has reduced current limit while the part is disabled due to high junction temperature. The LDO only provides a few milliamperes during thermal shutdown.

#### 8.3.11 Input Supply Current

The LMR436x0 is designed to have very low input supply current when regulating light loads. This is achieved by powering much of the internal circuitry from the output. The VOUT/FB pin in the fixed-output voltage variants is the input to the LDO that powers the majority of the control circuits. By connecting the VOUT/FB input pin to the output node of the regulator, a small amount of current is drawn from the output. This current is reduced at the input by the ratio of  $V_{OUT}$  /  $V_{IN}$  as described in  $\stackrel{\scriptstyle *}{\atop}$  2.

$$I_{QVIN} = I_Q + I_{EN} + I_{BIAS} \times \frac{V_{OUT}}{\eta_{eff} \times V_{IN}}$$

(2)

#### where

- I<sub>QVIN</sub> is the total standby (switching) current consumed by the operating (switching) buck converter when unloaded.

- I<sub>Q</sub> is the current drawn from the V<sub>IN</sub> terminal.

- I<sub>BIAS</sub> is bias current drawn by the BIAS LDO.

- $\eta_{eff}$  is the light-load efficiency of the buck converter with  $I_{QVIN}$  removed from the input current of the buck converter.  $\eta_{eff}$  = 0.8 is a conservative value that can be used under normal operating conditions.

#### 8.4 Device Functional Modes

#### 8.4.1 Shutdown Mode

The EN pin provides electrical ON and OFF control of the device. When the EN pin voltage is below 0.7 V (typical), both the converter and the internal LDO have no output voltage and the part is in shutdown mode. In shutdown mode, the guiescent current drops to typically 250 nA.

## 8.4.2 Standby Mode

The internal LDO has a lower EN threshold than the output of the converter. When the EN pin voltage is above 1 V (maximum) and below the precision enable threshold for the output voltage, the internal LDO regulates the VCC voltage at 3.3 V typical. The internal power MOSFETs of the SW node remain off unless the voltage on EN pin goes above its precision enable threshold. The LMR436x0 also employs UVLO protection.

#### 8.4.3 Active Mode

The LMR436x0 is in active mode whenever the EN pin is above  $V_{EN-VOUT}$ ,  $V_{IN}$  is high enough to satisfy  $V_{INMIN}$ , and no other fault conditions are present. The simplest way to enable the operation is to connect the EN pin to  $V_{IN}$ , which allows self start-up when the applied input voltage exceeds the minimum  $V_{INMIN}$ .

In active mode, depending on the load current, input voltage, and output voltage, the LMR436x0 is in one of five modes:

- Continuous conduction mode (CCM) with fixed switching frequency when load current is above half of the inductor current ripple

- · Auto mode Light Load Operation: PFM when switching frequency is decreased at very light load

- FPWM mode Light Load Operation: Continuous conduction mode (CCM) when the load current is lower than half of the inductor current ripple

- Minimum on time: At high input voltage and low output voltages, the switching frequency is reduced to maintain regulation

- Dropout mode: When switching frequency is reduced to minimize voltage dropout

#### 8.4.3.1 CCM Mode

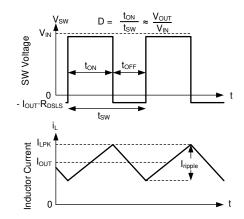

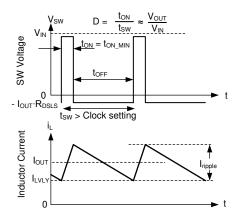

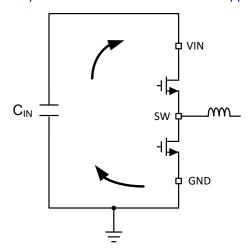

The following operating description of the LMR436x0 refers to 292228.2 and to the waveforms in 28-15. In CCM, the LMR436x0 supplies a regulated output voltage by turning on the internal high-side (HS) and low-side (LS) switches with varying duty cycle (D). During the HS switch on time, the SW pin voltage,  $V_{SW}$ , swings up to approximately  $V_{IN}$ , and the inductor current,  $i_L$ , increases with a linear slope. The HS switch is turned off by the control logic. During the HS switch off time,  $t_{OFF}$ , the LS switch is turned on. Inductor current discharges through the LS switch, which forces the  $V_{SW}$  to swing below ground by the voltage drop across the LS switch. The converter loop adjusts the duty cycle to maintain a constant output voltage. D is defined by the on time of the HS switch over the switching period:

$$D = T_{ON} / T_{SW}$$

(3)

In an ideal buck converter where losses are ignored, D is proportional to the output voltage and inversely proportional to the input voltage:

$$D = V_{OUT} / V_{IN}$$

(4)

図 8-15. SW Voltage and Inductor Current Waveforms in Continuous Conduction Mode (CCM)

## 8.4.3.2 Auto Mode – Light-Load Operation

The LMR436x0 can have two behaviors while lightly loaded. One behavior, called auto mode operation, allows for seamless transition between normal current mode operation while heavily loaded and highly efficient lightload operation. The other behavior, called FPWM mode, maintains full frequency even when unloaded. Which mode the LMR436x0 operates in depends on which variant from this family is selected. Note that all parts operate in FPWM mode when synchronizing frequency to an external signal.

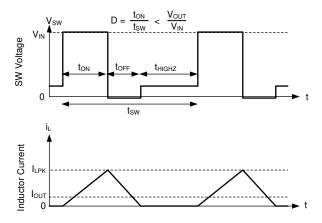

The light-load operation is employed in the LMR436x0 only in auto mode. The light load operation employs two techniques to improve efficiency:

- Diode emulation, which allows DCM operation. See <a>\mathbb{Z}</a> 8-16.

Note that while these two features operate together to improve light load efficiency, they operate independently.

#### 8.4.3.2.1 Diode Emulation

Diode emulation prevents reverse current through the inductor which requires a lower frequency needed to regulate given a fixed peak inductor current. Diode emulation also limits ripple current as frequency is reduced. With a fixed peak current, as output current is reduced to zero, frequency must be reduced to near zero to maintain regulation.

In auto mode, the low-side device is turned off after SW node current is near zero. As a result, after output current is less than half of what inductor ripple is in CCM, the part operates in DCM which is equivalent to the statement that diode emulation is active.

#### 図 8-16. PFM Operation

The LMR436x0 has a minimum peak inductor current setting (see I<sub>PEAKMIN</sub> in *Electrical Characteristics*) while in auto mode. After current is reduced to a low value with fixed input voltage, on time is constant. Regulation is then achieved by adjusting frequency. This mode of operation is called PFM mode regulation.

## 8.4.3.2.2 Frequency Reduction

The LMR436x0 reduces frequency whenever output voltage is high. This function is enabled whenever the internal error amplifier compensation output, COMP, an internal signal, is low and there is an offset between the regulation set point of VOUT/FB and the voltage applied to VOUT/FB. The net effect is that there is larger output impedance while lightly loaded in auto mode than in normal operation. Output voltage must be approximately 1% high when the part is completely unloaded.

In auto mode, after output current drops below approximately 1/10th the rated current of the part, output resistance increases so that output voltage is 1% high while the buck is completely unloaded.

## 図 8-17. Steady State Output Voltage Versus Output Current in Auto Mode

In PFM operation, a small DC positive offset is required on the output voltage to activate the PFM detector. The lower the frequency in PFM, the more DC offset is needed on  $V_{OUT}$ . If the DC offset on  $V_{OUT}$  is not acceptable, a dummy load at  $V_{OUT}$  or FPWM mode can be used to reduce or eliminate this offset.

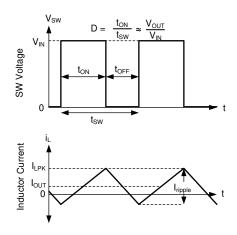

## 8.4.3.3 FPWM Mode - Light-Load Operation

In FPWM mode, frequency is maintained while lightly loaded. To maintain frequency, a limited reverse current is allowed to flow through the inductor. Reverse current is limited by reverse current limit circuitry, see *Electrical Characteristics* for reverse current limit values.

In FPWM mode, Continuous Conduction (CCM) is possible even if I<sub>OUT</sub> is less than half of I<sub>ripple</sub>.

#### 図 8-18. FPWM Mode Operation

For all devices, in FPWM mode, frequency reduction is still available if output voltage is high enough to command minimum on time even while lightly loaded, allowing good behavior during faults which involve output being pulled up.

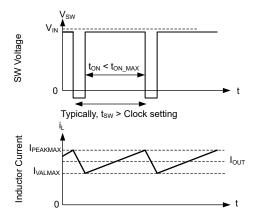

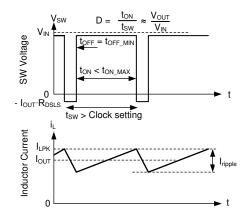

## 8.4.3.4 Minimum On-Time (High Input Voltage) Operation

The LMR436x0 continues to regulate output voltage even if the input-to-output voltage ratio requires an on time less than the minimum on time of the chip with a given clock setting. This is accomplished using valley current control. At all times, the compensation circuit dictates both a maximum peak inductor current and a maximum valley inductor current. If for any reason, valley current is exceeded, the clock cycle is extended until valley current falls below that determined by the compensation circuit. If the converter is not operating in current limit, the maximum valley current is set above the peak inductor current, preventing valley control from being used unless there is a failure to regulate using peak current only. If the input-to-output voltage ratio is too high, such that the inductor current peak value exceeds the peak command dictated by compensation, the high-side device cannot be turned off quickly enough to regulate output voltage. As a result, the compensation circuit reduces both peak and valley current. After a low enough current is selected by the compensation circuit, valley current matches that being commanded by the compensation circuit. Under these conditions, the low-side device is kept on and the next clock cycle is prevented from starting until inductor current drops below the desired valley current. Because on time is fixed at its minimum value, this type of operation resembles that of a device using a Constant On-Time (COT) control scheme; see  $\boxtimes$  8-19.

In valley control mode, minimum inductor current is regulated, not peak inductor current.

図 8-19. Valley Current Mode Operation

## 8.4.3.5 Dropout

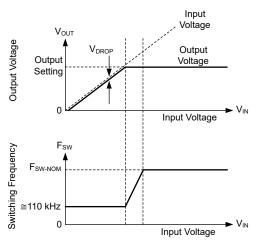

Dropout operation is defined as any input-to-output voltage ratio that requires frequency to drop to achieve the required duty cycle. At a given clock frequency, duty cycle is limited by minimum off time. After this limit is reached as shown in  $\boxtimes$  8-21 if clock frequency was to be maintained, the output voltage falls. Instead of allowing the output voltage to drop, the LMR436x0 extends the high-side switch on time past the end of the clock cycle until the needed peak inductor current is achieved. The clock is allowed to start a new cycle after peak inductor current is achieved or after a pre-determined maximum on time,  $t_{ON-MAX}$ , of approximately 9  $\mu$ s passes. As a result, after the needed duty cycle cannot be achieved at the selected clock frequency due to the existence of a minimum off time, frequency drops to maintain regulation. As shown in  $\boxtimes$  8-20, if input voltage is low enough so that output voltage cannot be regulated even with an on time of  $t_{ON-MAX}$ , output voltage drops to slightly below the input voltage by  $v_{DROP}$ . For additional information on recovery from dropout, refer to  $\boxtimes$  8-11.

Output voltage and frequency versus input voltage: If there is little difference between input voltage and output voltage setting, the IC reduces frequency to maintain regulation. If input voltage is too low to provide the desired output voltage at approximately 110 kHz, input voltage tracks output voltage.

図 8-20. Frequency and Output Voltage in Dropout

Switching waveforms while in dropout. Inductor current takes longer than a normal clock to reach the desired peak value. As a result, frequency drops. This frequency drop is limited by  $t_{\text{ON-MAX}}$ .

図 8-21. Dropout Waveforms

## 9 Application and Implementation

注

以下のアプリケーション情報は、TIの製品仕様に含まれるものではなく、TIではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

## 9.1 Application Information

The LMR436x0 step-down DC-to-DC converters are typically used to convert a higher DC voltage to a lower DC voltage. LMR43620 supports a maximum output current of 2 A while the LMR43610 supports a maximum output current of 1 A. The following design procedure can be used to select components for the LMR43620. The design procedure can also be used to select components for the LMR43610 by limiting the maximum output current to 1 A.

注

All of the capacitance values given in the following application information refer to effective values unless otherwise stated. The effective value is defined as the actual capacitance under DC bias and temperature, not the rated or nameplate values. Use high-quality, low-ESR, ceramic capacitors with an X7R or better dielectric throughout. All high value ceramic capacitors have a large voltage coefficient in addition to normal tolerances and temperature effects. Under DC bias the capacitance drops considerably. Large case sizes and higher voltage ratings are better in this regard. To help mitigate these effects, multiple capacitors can be used in parallel to bring the minimum effective capacitance up to the required value. This can also ease the RMS current requirements on a single capacitor. A careful study of bias and temperature variation of any capacitor bank must be made to ensure that the minimum value of effective capacitance is provided.

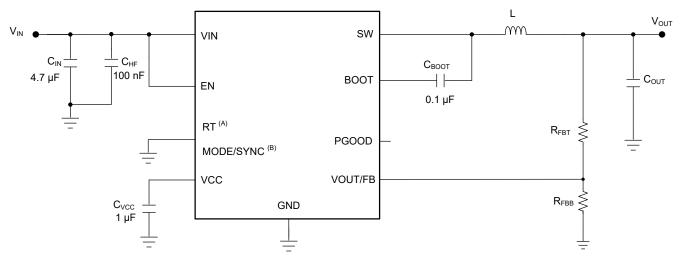

## 9.2 Typical Application

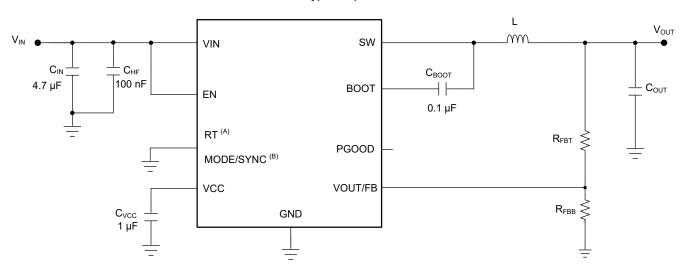

図 9-1 shows a typical application circuit for the LMR436x0. This device is designed to function over a wide range of external components and system parameters. However, the internal compensation is optimized for a certain range of external inductance and output capacitance. As a quick-start guide, 表 9-1 and 表 9-3 provide typical component values for a range of the most common output voltages.

- A. The RT pin is factory-set for externally adjustable switching frequency RT variants only. Tying this pin to GND results in 2.2-MHz switching frequency. See セクション 8.3.3 for details.

- B. The MODE/SYNC pin is factory-set for fixed frequency frequency MODE/SYNC variants only. Tying this pin to GND results in AUTO mode. See セクション 8.3.2 for details.

#### 図 9-1. Example Application Circuit

表 9-1. Typical External Component Values for Adjustable Output LMR43620

| fsw<br>(kHz) | V <sub>OUT</sub> (V) | L (µH) | NOMINAL C <sub>OUT</sub> (RATED CAPACITANCE) | MINIMUM C <sub>OUT</sub> (RATED CAPACITANCE) | R <sub>FBT</sub> (kΩ) | R <sub>FBB</sub> (kΩ) | C <sub>IN</sub>        | C <sub>BOOT</sub> | C <sub>vcc</sub> | C <sub>FF</sub> |

|--------------|----------------------|--------|----------------------------------------------|----------------------------------------------|-----------------------|-----------------------|------------------------|-------------------|------------------|-----------------|

| 400          | 3.3                  | 10     | 3 × 22 µF                                    | 1 × 47 µF                                    | 33.2                  | 14.3                  | 4.7 µF + 1 × 100<br>nF | 100 nF            | 1 μF             | 22 pF           |

| 1000         | 3.3                  | 4.7    | 2 × 22 µF                                    | 3 × 10 µF                                    | 33.2                  | 14.3                  | 2.2 µF + 1 × 100<br>nF | 100 nF            | 1 μF             | 22 pF           |

| 2200         | 3.3                  | 2.2    | 2 × 22 µF                                    | 1 × 22 µF                                    | 33.2                  | 14.3                  | 4.7 µF + 1 × 100<br>nF | 100 nF            | 1 μF             | 22 pF           |

| 400          | 5                    | 10     | 3 × 22 µF                                    | 1 × 47 µF                                    | 49.9                  | 12.4                  | 4.7 µF + 1 × 100<br>nF | 100 nF            | 1 μF             | 22 pF           |

| 1000         | 5                    | 4.7    | 2 × 22 µF                                    | 3 × 10 µF                                    | 49.9                  | 12.4                  | 2.2 µF + 1 × 100<br>nF | 100 nF            | 1 μF             | 22 pF           |

| 2200         | 5                    | 2.2    | 2 × 22 µF                                    | 1 × 22 µF                                    | 49.9                  | 12.4                  | 4.7 µF + 1 × 100<br>nF | 100 nF            | 1 μF             | 22 pF           |

<sup>(1)</sup> The switching frequencies listed here can be achieved in a number of ways depending on the device variant. For RT devices see セクション 8.3.3. For MODE/SYNC devices see セクション 8.3.2.

表 9-2. Typical External Component Values for Adjustable Output LMR43610

| fsw<br>(kHz) | V <sub>OUT</sub> (V) | L (µH) | NOMINAL C <sub>OUT</sub> (RATED CAPACITANCE) |           | R <sub>FBT</sub> (kΩ) | R <sub>FBB</sub> (kΩ) | C <sub>IN</sub>        | C <sub>BOOT</sub> | C <sub>VCC</sub> | <b>C</b> <sub>FF</sub> (3) |

|--------------|----------------------|--------|----------------------------------------------|-----------|-----------------------|-----------------------|------------------------|-------------------|------------------|----------------------------|

| 400          | 3.3                  | 22     | 2 × 22 µF                                    | 4 × 10 μF | 33.2                  | 14.3                  | 4.7 µF + 1 × 100<br>nF | 100 nF            | 1 μF             | 22 pF                      |

<sup>(2)</sup> Inductor values are calculated based on typical  $V_{IN}$  = 13.5 V.

## 表 9-2. Typical External Component Values for Adjustable Output LMR43610 (continued)

| fsw<br>(kHz) | V <sub>OUT</sub> (V) | L (µH) | NOMINAL C <sub>OUT</sub><br>(RATED<br>CAPACITANCE) | MINIMUM C <sub>OUT</sub> (RATED CAPACITANCE) | R <sub>FBT</sub> (kΩ) | R <sub>FBB</sub> (kΩ) | C <sub>IN</sub>        | C <sub>BOOT</sub> | C <sub>vcc</sub> | <b>C</b> <sub>FF</sub> (3) |

|--------------|----------------------|--------|----------------------------------------------------|----------------------------------------------|-----------------------|-----------------------|------------------------|-------------------|------------------|----------------------------|

| 1000         | 3.3                  | 8.2    | 1 × 22 µF                                          | 2 × 10 µF                                    | 33.2                  | 14.3                  | 4.7 µF + 1 × 100<br>nF | 100 nF            | 1 µF             | 22 pF                      |

| 2200         | 3.3                  | 2.2    | 1 × 22 µF                                          | 2 × 10 µF                                    | 33.2                  | 14.3                  | 4.7 µF + 1 × 100<br>nF | 100 nF            | 1 μF             | 22 pF                      |

| 400          | 5                    | 22     | 2 × 22 µF                                          | 4 × 10 μF                                    | 49.9                  | 12.4                  | 4.7 µF + 1 × 100<br>nF | 100 nF            | 1 μF             | 22 pF                      |

| 1000         | 5                    | 4.7    | 1 × 22 µF                                          | 2 × 10 µF                                    | 49.9                  | 12.4                  | 4.7 µF + 1 × 100<br>nF | 100 nF            | 1 µF             | 22 pF                      |

| 2200         | 5                    | 2.2    | 1 × 22 µF                                          | 2 × 10 µF                                    | 49.9                  | 12.4                  | 4.7 µF + 1 × 100<br>nF | 100 nF            | 1 μF             | 22 pF                      |

- (1) The switching frequencies listed here can be achieved in a number of ways depending on the device variant. For RT devices see セクション 8.3.3. For MODE/SYNC devices see セクション 8.3.2.

- (2) Inductor values are calculated based on typical V<sub>IN</sub> = 13.5 V.

- (3) C<sub>FF</sub> to be placed in parallel with R<sub>FBT</sub>.

#### 表 9-3. Typical External Component Values for Fixed Output LMR43620

| f <sub>SW</sub> (kHz) | V <sub>OUT</sub> (V) | L (µH) | NOMINAL C <sub>OUT</sub> (RATED CAPACITANCE) | MINIMUM C <sub>OUT</sub> (RATED CAPACITANCE) | R <sub>FBT</sub> (Ω) | R <sub>FBB</sub> (Ω) <sup>(3)</sup> | C <sub>IN</sub>     | C <sub>BOOT</sub> | C <sub>VCC</sub> |

|-----------------------|----------------------|--------|----------------------------------------------|----------------------------------------------|----------------------|-------------------------------------|---------------------|-------------------|------------------|

| 400                   | 3.3                  | 10     | 3 × 22 µF                                    | 1 × 47 µF                                    | 0                    | DNP                                 | 4.7 µF + 1 × 100 nF | 100 nF            | 1 µF             |

| 1000                  | 3.3                  | 4.7    | 2 × 22 µF                                    | 3 × 10 μF                                    | 0                    | DNP                                 | 2.2 µF + 1 × 100 nF | 100 nF            | 1 μF             |

| 2200                  | 3.3                  | 2.2    | 2 × 22 µF                                    | 1 × 22 µF                                    | 0                    | DNP                                 | 4.7 μF + 1 × 100 nF | 100 nF            | 1 μF             |

| 400                   | 5                    | 10     | 3 × 22 µF                                    | 1 × 47 µF                                    | 0                    | DNP                                 | 4.7 μF + 1 × 100 nF | 100 nF            | 1 µF             |

| 1000                  | 5                    | 4.7    | 2 × 22 µF                                    | 3 × 10 μF                                    | 0                    | DNP                                 | 2.2 μF + 1 × 100 nF | 100 nF            | 1 µF             |

| 2200                  | 5                    | 2.2    | 2 × 22 µF                                    | 1 × 22 µF                                    | 0                    | DNP                                 | 4.7 µF + 1 × 100 nF | 100 nF            | 1 μF             |

- (1) The switching frequencies listed here can be achieved in a number of ways depending on the device variant. For RT devices see セクション 8.3.3. For MODE/SYNC devices see セクション 8.3.2.

- (2) Inductor values are calculated based on typical  $V_{IN}$  = 13.5 V.

- (3) DNP = Do Not Populate.

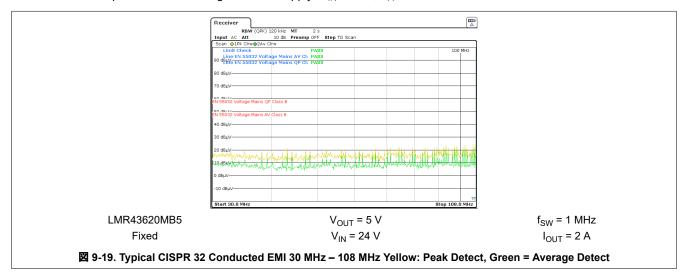

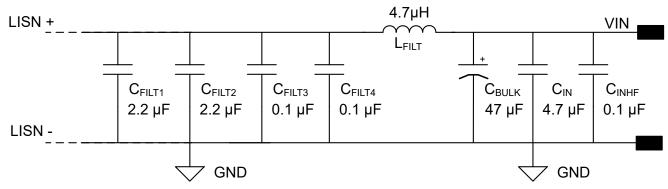

#### 表 9-4. Typical External Component Values for Fixed Output LMR43610