LMS3655

JAJSDE8B - JULY 2017-REVISED MARCH 2018

# LMS3655 5.5A、36V同期整流、400kHz DC/DC降圧型コンバータ

### 特長

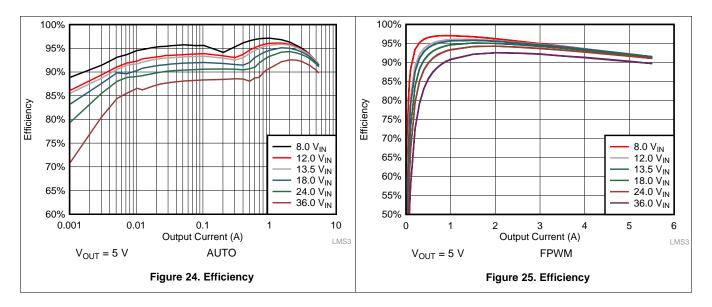

- 12Vから5Vへの変換時に96%のピーク効率

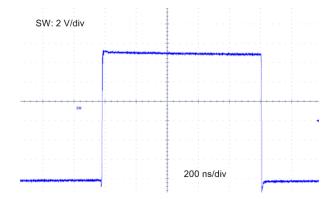

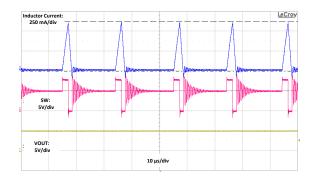

- 低いEMIとスイッチ・ノイズ

- スイッチ・ノード・リンギングの最小化

- 疑似ランダム拡散スペクトラム

- 400kHz (±10%)の固定スイッチング周波数

- 接合部温度範囲: -40℃~+150℃

- 外部周波数同期

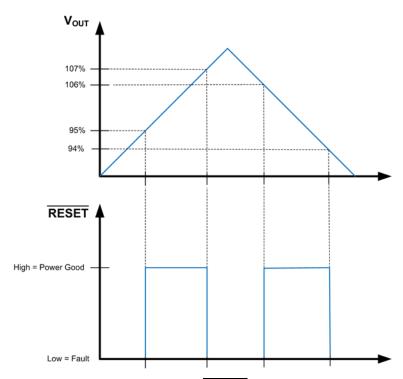

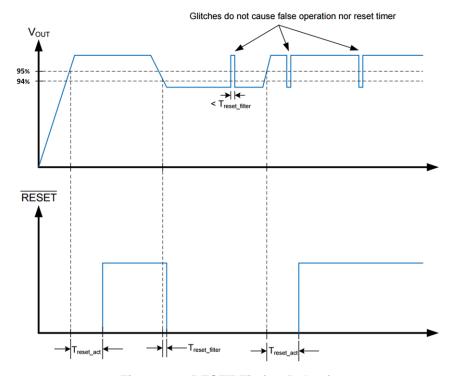

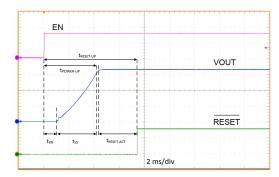

- 内部フィルタおよび3msリリース・タイマ付きの RESET出力

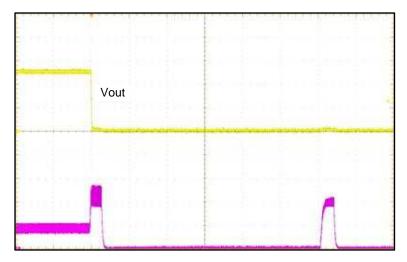

- 自動軽負荷モードによる効率向上

- 強制PWMモードをピンにより選択可能

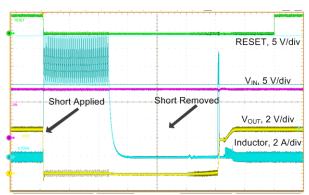

- 補償、ソフトスタート、電流制限、サーマル・ シャットダウン、UVLOを内蔵

- 25℃において3.5A負荷で0.35Vのドロップアウト (標準値)

- 32µAのI<sub>O VIN</sub>: 3.3V<sub>OUT</sub>で無負荷時の静止電流(標準

- 5.5Aの連続負荷電流

- 可変の出力電圧(1V~20V)

- 基準電圧の許容誤差±1.5%

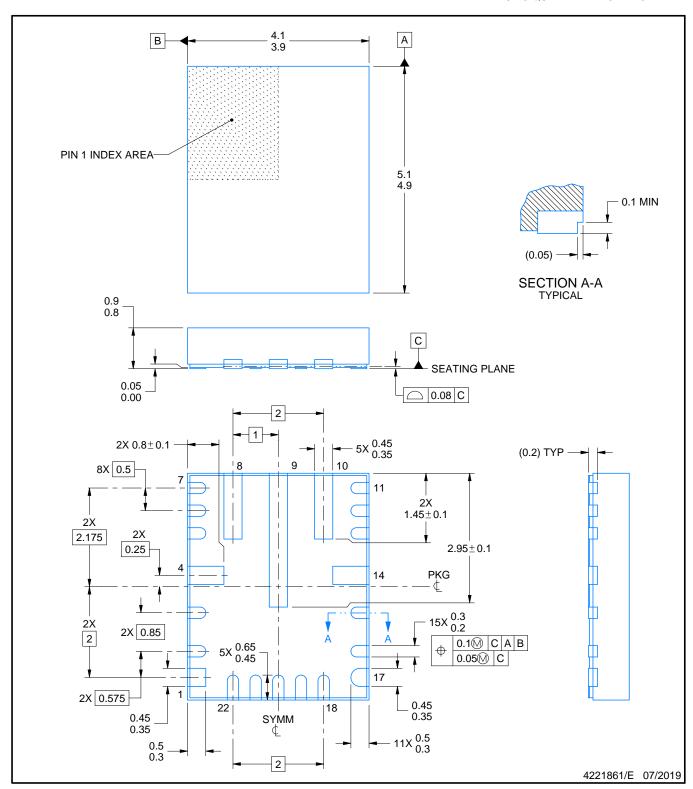

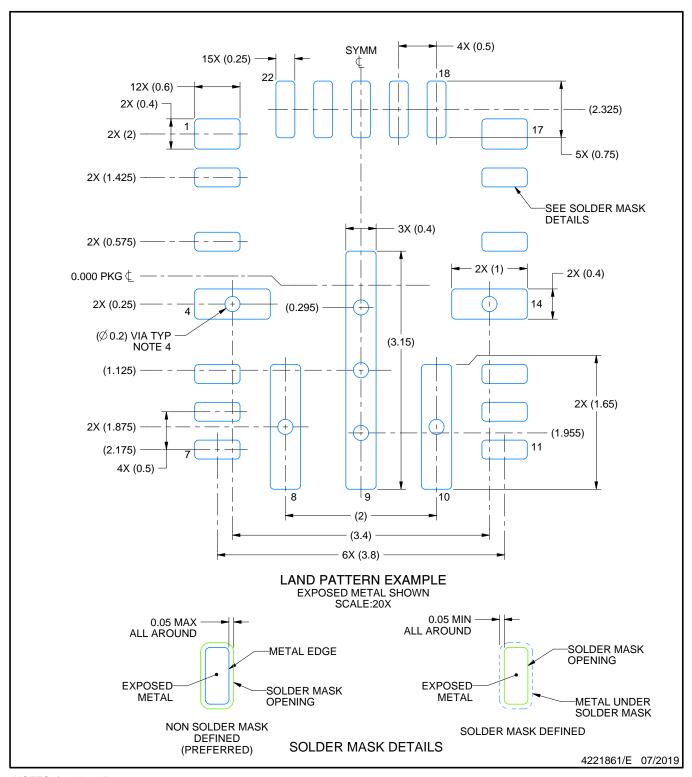

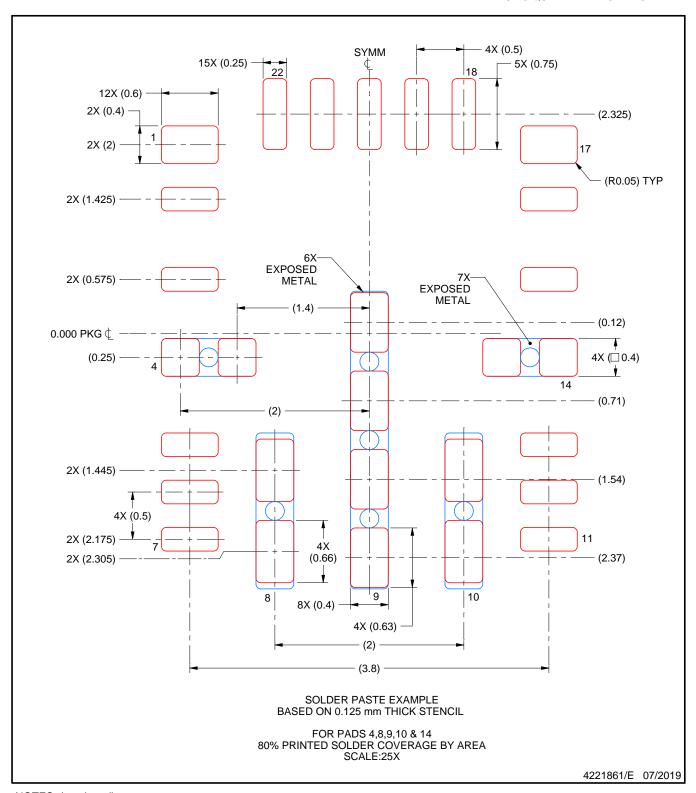

- 4mm×5mm、0.5mmピッチのSONパッケージ

### 2 アプリケーション

- ノイズに敏感な医療用途

- テレコム

- 高性能産業用

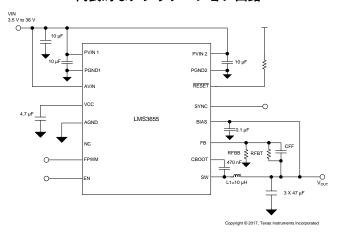

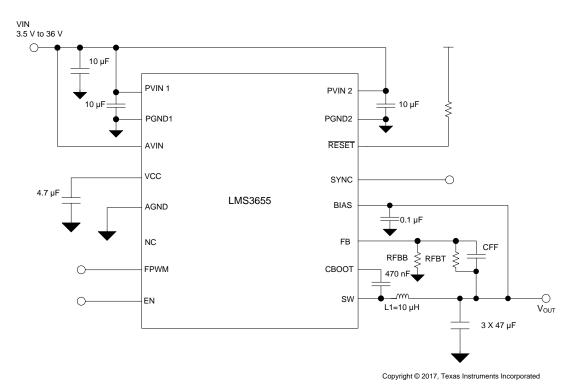

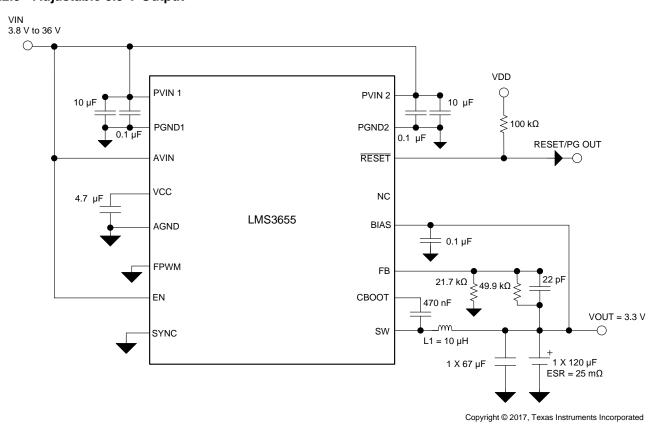

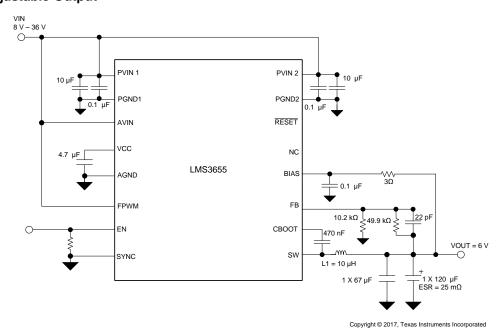

### 代表的なアプリケーション回路

### 3 概要

LMS3655同期整流降圧レギュレータは、高性能アプリ ケーション用に最適化されており、1V~20Vの可変電圧を 出力します。PWMモードとPFMモードの間でシームレス に遷移し、静止電流が低いため、あらゆる負荷について高 い効率と優れた過渡応答を保証します。

LMS3655は高度な高速回路を使用しているため、24V の入力を400kHzの固定周波数で3.3Vの出力にレギュ レートでき、5.5Aの連続負荷電流に対応できます。革新的 な周波数フォールドバック・アーキテクチャにより、このデ バイスはわずか3.5Vの入力電圧からでも、3.3Vの出力を レギュレートできます。入力電圧は最高36Vまで可能で、 42Vまでの過渡電圧が許容されるため、入力サージ保護 の設計が簡単になります。

フィルタリングと遅延を備えたオープン・ドレインのリセット 出力により、システムの真の状態を示すことができます。こ の機能により、追加のスーパーバイザ部品が必要なくなる ため、コストと基板面積を削減できます。

### 製品情報(1)

| 型番      | パッケージ        | 本体サイズ         |

|---------|--------------|---------------|

| LMS3655 | VQFN-HR (22) | 4.00mm×5.00mm |

(1) 利用可能なすべてのパッケージについては、このデータシートの末 尾にある注文情報を参照してください。

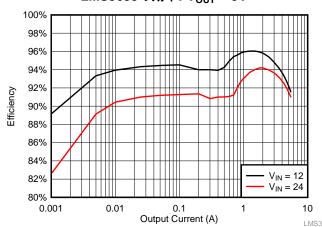

### LMS3655の効率: V<sub>OUT</sub> = 5V

# 目次

| 1 特長                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |           |    |                                |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----------|----|--------------------------------|----|

| 数計履歴                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1 | 特長1       |    |                                |    |

| A 改訂履歴                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2 | アプリケーション1 |    | 8.4 Device Functional Modes    | 19 |

| 4 改訂履歴       2       9.1 Application Information       23         5 Device Comparison Table       3       9.2 Typical Applications       23         6 Pin Configuration and Functions       4       9.2 Typical Applications       23         9.3 Do's and Don't's       40         7 Specifications       5       10 Power Supply Recommendations       40         7.1 Absolute Maximum Ratings       5       11 Layout       40         7.2 ESD Ratings       5       11.1 Layout Guidelines       40         7.3 Recommended Operating Conditions       5       11.2 Layout Example       42         7.4 Thermal Information (for Device Mounted on PCB)       6       12.1 デバイスおよびドキュメントのサポート       43         7.5 Thermal Information (for Device Mounted on PCB)       6       12.2 ドキュメントのサポート       43         7.6 Electrical Characteristics       8       12.3 ドキュメントの更新通知を受け取る方法       43         7.9 Typical Characteristics       10       12.4 コミュニティ・リソース       43         8 Detailed Description       12       12.6 静電気放電に関する注意事項       43         8.1 Overview       12       12.7 Clossary       43         12.7 Clossary       43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3 | 概要1       | 9  | Application and Implementation | 23 |

| 5 Device Comparison Table 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4 |           |    | 9.1 Application Information    | 23 |

| 9.3 Do's and Don't's 40 7.5 Specifications 5 7.1 Absolute Maximum Ratings 5 7.2 ESD Ratings 5 7.3 Recommended Operating Conditions 5 7.4 Thermal Information (for Device Mounted on PCB) 6 7.5 Thermal Information (for Device Mounted on PCB) 6 7.7 System Characteristics 6 7.7 System Characteristics 8 7.8 Timing Requirements 9 7.9 Typical Characteristics 10 Detailed Description 12 8.1 Overview 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5 |           |    | 9.2 Typical Applications       | 23 |

| 7 Specifications 5 7.1 Absolute Maximum Ratings 5 7.2 ESD Ratings 5 7.3 Recommended Operating Conditions 5 7.4 Thermal Information 6 7.5 Thermal Information (for Device Mounted on PCB) 6 7.6 Electrical Characteristics 6 7.7 System Characteristics 8 7.8 Timing Requirements 9 7.9 Typical Characteristics 10 Detailed Description 12 8.1 Overview 12 10 Power Supply Recommendations 40 11.1 Layout Guidelines 40 11.1 Layout Example 42 12.1 Layout Example 42 12.2 Layout Example 42 12.2 ドナュメントのサポート 43 12.1 デバイス・サポート 43 12.1 デバイス・サポート 43 12.2 ドナュメントのサポート 43 12.2 ドナュメントの更新通知を受け取る方法 43 12.4 コミュニティ・リソース 43 12.5 商標 43 12.6 静電気放電に関する注意事項 43 12.7 Glossary 43 12.7 Glossary 43 12.7 Glossary 43 14 14 14 15 15 15 15 15 15 15 15 15 15 15 15 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | - | •         |    | 9.3 Do's and Don't's           | 40 |

| 7.1 Absolute Maximum Ratings 5 7.2 ESD Ratings 5 7.3 Recommended Operating Conditions 5 7.4 Thermal Information 6 7.5 Thermal Information (for Device Mounted on PCB) 6 7.6 Electrical Characteristics 6 7.7 System Characteristics 8 7.8 Timing Requirements 9 7.9 Typical Characteristics 10  8 Detailed Description 12 8.1 Overview 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | - | _         | 10 | Power Supply Recommendations   | 40 |

| 7.2 ESD Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ′ |           | 11 | Layout                         | 40 |

| 7.3 Recommended Operating Conditions 5 7.4 Thermal Information 6 7.5 Thermal Information (for Device Mounted on PCB) 6 7.6 Electrical Characteristics 6 7.7 System Characteristics 8 7.8 Timing Requirements 9 7.9 Typical Characteristics 10 12.5 商標 43 12.6 静電気放電に関する注意事項 43 12.7 Glossary 44 12.7 Glossary 44 12.7 Characteristics 43 12.7 Clossary 44 12.7 Clossary 44 12.7 Clossary 44 12.7 Clossary 44 14 14 14 15 15 15 15 15 15 15 15 15 15 15 15 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   | ĕ         |    | 11.1 Layout Guidelines         | 40 |

| 7.4 Thermal Information       6       デバイスおよびドキュメントのサポート       43         7.5 Thermal Information (for Device Mounted on PCB). 6       12.1 デバイス・サポート       43         7.6 Electrical Characteristics       6       12.2 ドキュメントのサポート       43         7.7 System Characteristics       8       12.3 ドキュメントの更新通知を受け取る方法       43         7.8 Timing Requirements       9       12.4 コミュニティ・リソース       43         7.9 Typical Characteristics       10       12.5 商標       43         8 Detailed Description       12       12.6 静電気放電に関する注意事項       43         8.1 Overview       12       2 オカコオリト・パッケース・ジャントが対すな標却       44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   | •         |    | 11.2 Layout Example            | 42 |

| 7.5 Thermal Information (for Device Mounted on PCB) 6 7.6 Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   | 3         | 12 | デバイスおよびドキュメントのサポート             | 43 |

| 7.6 Electrical Characteristics       6       12.2 ドキュメントのサポート       43         7.7 System Characteristics       8       12.3 ドキュメントの更新通知を受け取る方法       43         7.8 Timing Requirements       9       12.4 コミュニティ・リソース       43         7.9 Typical Characteristics       10       12.5 商標       43         8 Detailed Description       12       12.6 静電気放電に関する注意事項       43         8.1 Overview       12       12.7 Glossary       43         43       43       44       44         44       45       45       45         45       45       45       45       45         46       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47 <t< td=""><th></th><td></td><th></th><td>12.1 デバイス・サポート</td><td>43</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |           |    | 12.1 デバイス・サポート                 | 43 |

| 7.7 System Characteristics 8 12.3 ドキュメントの更新通知を受け取る方法 43 7.8 Timing Requirements 9 12.4 コミュニティ・リソース 43 7.9 Typical Characteristics 10 12.5 商標 43 12.6 静電気放電に関する注意事項 43 8.1 Overview 12 12.7 Glossary 43 12.7 Glossary 43 12.7 Glossary 43 12.7 Glossary 43 14 14 14 15 15 15 15 15 15 15 15 15 15 15 15 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   | ,         |    | 12.2 ドキュメントのサポート               | 43 |

| 7.8 Timing Requirements 9 12.4 コミュニティ・リソース 43 7.9 Typical Characteristics 10 12.5 商標 43 12.6 静電気放電に関する注意事項 43 8.1 Overview 12 12.7 Glossary 43 12.7 Glossary 44 12.7 対策対象を表現しています。 44 12 12 12 12 12 12 12 12 12 12 12 12 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |           |    | 12.3 ドキュメントの更新通知を受け取る方法        | 43 |

| 7.9 Typical Characteristics 10 12.5 商標 43 12.6 静電気放電に関する注意事項 43 12.7 Glossary 44 12.7 Glossary 44 12.7 Glossary 45 12.7 Glo |   | •         |    | 12.4 コミュニティ・リソース               | 43 |

| 8 Detailed Description       12         8.1 Overview       12         12 Glossary       43         43 イナーカル・パッケージ さとしてが大力体型                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |           |    | 12.5 商標                        | 43 |

| 8.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R | • •       |    | 12.6 静電気放電に関する注意事項             | 43 |

| 4.2 ノカーカル パッケーン シャトバケ 女体却 4.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | • |           |    | 12.7 Glossary                  | 43 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |           | 13 | メカニカル、パッケージ、および注文情報            | 44 |

# 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

Revision A (October 2017) から Revision B に変更

| Revision A (October 2017) から Revision B に変更                                            | Page |

|----------------------------------------------------------------------------------------|------|

| <ul><li>可変の最高出力電圧を15Vから20Vに変更</li></ul>                                                | 1    |

| Changed maximum extended output adjustment from: 15 V to: 20 V                         | 5    |

| Added new extended output adjustment tablenote to the Recommended Operating Conditions | 5    |

| 2017年7月発行のものから更新                                                                       | Page |

| Changed symbol from: I <sub>B</sub> to: I <sub>B_NSW</sub>                             | 6    |

|                                                                                        |      |

| Added I <sub>B</sub> spec to System Characteristics                                    | 8    |

# 5 Device Comparison Table

# Table 1. LMS3655 Devices (5.5-A Output)

| PART NUMBER   | OUTPUT VOLTAGE | SPREAD<br>SPECTRUM | PACKAGE QTY |

|---------------|----------------|--------------------|-------------|

| LMS3655AMRNLR | Adjustable     | No                 | 3000        |

| LMS3655AMRNLT | Adjustable     | No                 | 250         |

| LMS3655MMRNLR | Adjustable     | Yes                | 3000        |

| LMS3655MMRNLT | Adjustable     | Yes                | 250         |

# 6 Pin Configuration and Functions

### RNL Package 22-Pin VQFN Top View

### **Pin Functions**

|     | PIN     | TYPE <sup>(1)</sup>                                        | DESCRIPTION                                                                                                                                                                                                 |  |  |  |  |

|-----|---------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NO. | NAME    | ITPE\"                                                     | DESCRIPTION                                                                                                                                                                                                 |  |  |  |  |

| 1   | VCC     | А                                                          | Internal 3.1-V LDO output. Used as supply to internal control circuits. Connect a high-quality 4.7-µF capacitor from this pin to AGND.                                                                      |  |  |  |  |

| 2   | СВООТ   | Р                                                          | Bootstrap capacitor connection for gate drivers. Connect a high quality 470-nF capacitor from this pin to the SW pin.                                                                                       |  |  |  |  |

| 3   | SYNC    | 1                                                          | Synchronization input to regulator. Used to synchronize the device switching frequency to a system clock. Triggers on rising edge of external clock; frequency must be in the range of 250 kHz and 500 kHz. |  |  |  |  |

| 4   | PVIN1   | Р                                                          | Input supply to regulator. Connect input bypass capacitors directly to this pin and PGND pins. Connect PVIN1 and PVIN2 pins directly together at PCB.                                                       |  |  |  |  |

| 5   |         |                                                            |                                                                                                                                                                                                             |  |  |  |  |

| 6   | PGND1   | G                                                          | Power ground to internal low-side MOSFET. These pins must be tied together on the PCB. Connect                                                                                                              |  |  |  |  |

| 7   | PGNDT   | G                                                          | PGND1 and PGND2 directly together at PCB. Connect to AGND and system ground.                                                                                                                                |  |  |  |  |

| 8   |         |                                                            |                                                                                                                                                                                                             |  |  |  |  |

| 9   | SW      | Р                                                          | Regulator switch node. Connect to power inductor.                                                                                                                                                           |  |  |  |  |

| 10  |         |                                                            |                                                                                                                                                                                                             |  |  |  |  |

| 11  | PGND2 G | G                                                          | Power ground to internal low-side MOSFET. These pins must be tied together. Connect PGND1 and                                                                                                               |  |  |  |  |

| 12  | PGND2   | PGND2 directly together at PCB. Connect to AGND and system | PGND2 directly together at PCB. Connect to AGND and system ground.                                                                                                                                          |  |  |  |  |

| 13  |         |                                                            |                                                                                                                                                                                                             |  |  |  |  |

| 14  | PVIN2   | Р                                                          | Input supply to regulator. Connect input bypass capacitors directly to this pin and PGND pins. Connect PVIN1 and PVIN2 pins directly together at PCB.                                                       |  |  |  |  |

| 15  | AVIN    | А                                                          | Analog VIN. Connect to PVIN1 and PVIN2 on PCB.                                                                                                                                                              |  |  |  |  |

| 16  | FPWM    | 1                                                          | Mode control input of regulator. High = FPWM, low = Automatic light load mode. Do not float.                                                                                                                |  |  |  |  |

| 17  | NC      | _                                                          | No internal connection.                                                                                                                                                                                     |  |  |  |  |

| 18  | EN      | 1                                                          | Enable input to regulator. High = on, Low = off. Can be connected to VIN. Do not float.                                                                                                                     |  |  |  |  |

| 19  | RESET   | 0                                                          | Open-drain reset output flag. Connect to suitable voltage supply through a current limiting resistor. High = regulator OK, Low = regulator fault. Goes low when EN = low.                                   |  |  |  |  |

| 20  | AGND    | G                                                          | Analog ground for regulator and system. All electrical parameters are measured with respect to this pin. Connect to PGND on PCB.                                                                            |  |  |  |  |

| 21  | FB      | А                                                          | Feedback input to regulator. Connect to feedback voltage divider.                                                                                                                                           |  |  |  |  |

| 22  | BIAS    | Р                                                          | Input to auxiliary bias regulator. Connect to output voltage node.                                                                                                                                          |  |  |  |  |

(1) A = Analog, O = Output, I = Input, G = Ground, P = Power

### 7 Specifications

### 7.1 Absolute Maximum Ratings

Over the recommended operating junction temperature range of -40°C to +150°C (unless otherwise noted). (1)

| PARAMETER                                                 | MIN  | MAX            | UNIT |

|-----------------------------------------------------------|------|----------------|------|

| VIN (AVIN, PVIN1, and PVIN2) to AGND, PGND <sup>(2)</sup> | -0.3 | 40             | V    |

| SW to AGND, PGND <sup>(3)</sup>                           | -0.3 | $V_{IN} + 0.3$ | V    |

| CBOOT to SW                                               | -0.3 | 3.6            | V    |

| EN to AGND, PGND <sup>(2)</sup>                           | -0.3 | 40             | V    |

| BIAS to AGND, PGND                                        | -0.3 | 16             | V    |

| FB to AGND, PGND                                          | -0.3 | 16             | V    |

| RESET to AGND, PGND                                       | -0.3 | 8              | V    |

| RESET sink current <sup>(4)</sup>                         |      | 10             | mA   |

| SYNC to AGND, PGND <sup>(2)</sup>                         | -0.3 | 40             | V    |

| FPWM to AGND, PGND <sup>(2)</sup>                         | -0.3 | 40             | V    |

| VCC to AGND, PGND                                         | -0.3 | 3.6            | V    |

| Junction temperature                                      | -40  | 150            | °C   |

| Storage temperature, T <sub>stg</sub>                     | -40  | 150            | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions are not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 7.2 ESD Ratings

|                    |               |                                                                     | VALUE | UNIT  |

|--------------------|---------------|---------------------------------------------------------------------|-------|-------|

| \/                 | Electrostatic | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±1000 | V     |

| V <sub>(ESD)</sub> | discharge     | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±250  | V<br> |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# 7.3 Recommended Operating Conditions

Over the recommended operating junction temperature range of -40°C to +150°C (unless otherwise noted).

| 1 0, 1                                                   | `   | ,       |      |

|----------------------------------------------------------|-----|---------|------|

|                                                          | MIN | NOM MAX | UNIT |

| Input voltage after start-up <sup>(1)</sup>              | 3.9 | 36      | V    |

| Output adjustment for LMS3655 <sup>(2)</sup>             | 3.3 | 6       | V    |

| Extended output adjustment for LMS3655 <sup>(3)(4)</sup> | 1   | 20      | V    |

| Load current for LMS3655                                 |     | 5.5     | Α    |

| Operating ambient temperature <sup>(5)</sup>             | -40 | 125     | °C   |

<sup>(1)</sup> An extended input voltage range to 3.5 V is possible; see System Characteristics table. See Input UVLO for start-up conditions.

<sup>(2)</sup> A maximum of 42 V can be sustained at this pin for a duration of ≤ 500 ms at a duty cycle of ≤ 0.01%.

<sup>(3)</sup> A voltage of 2 V below PGND and 2 V above VIN can appear on this pin for ≤ 200 ns with a duty cycle of ≤ 0.01%.

<sup>(4)</sup> Do not exceed the voltage rating on this pin.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> The output voltage must not be allowed to fall below zero volts during normal operation.

<sup>(3)</sup> Operation below 3.3 V and above 6 V may require changes to the typical application schematic, operation may not be possible over the full input voltage range, and some system specifications will not be achieved for this extended output voltage range. Consult the factory for further information.

<sup>(4)</sup> Operation above 15 V requires the BIAS pin grounded or powered by an external source. A maximum of 16 V can be sustained on the BIAS pin.

<sup>(5)</sup> High junction temperatures degrade operating lifetime.

#### 7.4 Thermal Information

|                        |                                              | LMS3655    |      |

|------------------------|----------------------------------------------|------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | RNL (VQFN) | UNIT |

|                        |                                              | 22 PINS    |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 38.5       | °C/W |

| $R_{\theta JC}$        | Junction-to-case (top) thermal resistance    | 16.3       | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 16.4       | °C/W |

| ΨЈТ                    | Junction-to-top characterization parameter   | 2.0        | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 16.4       | °C/W |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | 4.6        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

### 7.5 Thermal Information (for Device Mounted on PCB)

|                      |                                              | LMS3655    |      |

|----------------------|----------------------------------------------|------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | RNL (VQFN) | UNIT |

|                      |                                              | 22 PINS    |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 29.4       | °C/W |

| $R_{\theta JC}$      | Junction-to-case (top) thermal resistance    | 14.2       | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 5.4        | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 1.2        | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 5.4        | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 2.4        | °C/W |

<sup>(1)</sup> Mounted on a thermally optimized FR4 four layer EVM with a size of 4000 mill x 3000 mill.

### 7.6 Electrical Characteristics

Limits apply over the recommended operating junction temperature range of  $-40^{\circ}$ C to  $+150^{\circ}$ C, unless otherwise noted. Minimum and maximum limits are specified through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $T_J = 25^{\circ}$ C, and are provided for reference purposes only. Unless otherwise stated the following conditions apply:  $V_{IN} = 13.5 \text{ V}$ .

|                         | PARAMETER                                                                                            | TEST CONDITIONS                                                                                             | MIN   | TYP  | MAX   | UNIT |

|-------------------------|------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------|------|-------|------|

|                         | Initial reference voltage for 5-V                                                                    | V <sub>IN</sub> = 3.8 V to 36 V, T <sub>J</sub> = 25°C                                                      | -1%   |      | 1%    |      |

| V <sub>FB</sub>         | and 3.3-V options                                                                                    | V <sub>IN</sub> = 3.8 V to 36 V                                                                             | -1.5% |      | 1.5%  |      |

| IQ                      | Operating quiescent current;<br>measured at VIN pin when<br>enabled and not switching <sup>(1)</sup> | V <sub>IN</sub> = 13.5 V, V <sub>BIAS</sub> = 5 V                                                           |       | 7.5  | 16    | μΑ   |

|                         | Bias current into BIAS pin,                                                                          | V <sub>IN</sub> = 13.5 V, V <sub>BIAS</sub> = 5 V, FPWM = 0 V                                               |       | 53   | 62    |      |

|                         | enabled, not switching                                                                               | V <sub>IN</sub> = 13.5 V, V <sub>BIAS</sub> = 3.3 V, FPWM<br>= 0 V                                          |       | 53   | 62    | μA   |

| I <sub>SD</sub>         | Shutdown quiescent current; measured at VIN pin                                                      | EN ≤ 0.4 V                                                                                                  |       | 2    | 3     | μA   |

|                         |                                                                                                      | Rising                                                                                                      | 3.2   | 3.55 | 3.90  |      |

| V <sub>IN-OPERATE</sub> | Minimum input voltage to operate                                                                     | Falling                                                                                                     | 2.95  | 3.25 | 3.55  | V    |

|                         |                                                                                                      | Hysteresis                                                                                                  | 0.28  | 0.3  | 0.4   |      |

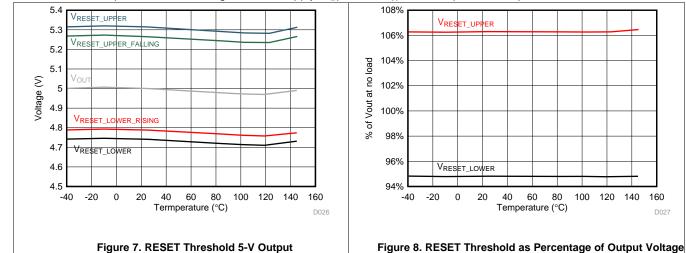

| .,                      | RESET upper threshold voltage                                                                        | Rising, % of V <sub>OUT</sub>                                                                               | 105%  | 107% | 110%  |      |

|                         | RESET lower threshold voltage                                                                        | Falling, % V <sub>OUT</sub>                                                                                 | 92%   | 94%  | 96.5% |      |

| V <sub>RESET</sub>      | Magnitude of RESET lower threshold from steady state output voltage                                  | Steady-state output voltage and RESET falling threshold read at the same T <sub>J</sub> and V <sub>IN</sub> |       |      | 96%   |      |

<sup>(1)</sup> This is the current used by the device while not switching, open loop on the ATE. It does not represent the total input current from the regulator system.

### **Electrical Characteristics (continued)**

Limits apply over the recommended operating junction temperature range of  $-40^{\circ}$ C to  $+150^{\circ}$ C, unless otherwise noted. Minimum and maximum limits are specified through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $T_J = 25^{\circ}$ C, and are provided for reference purposes only. Unless otherwise stated the following conditions apply:  $V_{IN} = 13.5 \text{ V}$ .

|                          | PARAMETER                                                | TEST CONDITIONS                                                                            | MIN  | TYP   | MAX  | UNIT      |

|--------------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------|------|-------|------|-----------|

| V <sub>RESET_HYST</sub>  | RESET hysteresis as a percent of output voltage setpoint |                                                                                            |      | ±1%   |      |           |

| V <sub>RESET_VALID</sub> | Minimum input voltage for proper RESET function          | 50-μA pullup to $\overline{RESET}$ pin,<br>EN = 0 V, T <sub>J</sub> = 25°C                 |      |       | 1.5  | V         |

|                          |                                                          | 50- $\mu$ A pullup to RESET pin,<br>V <sub>IN</sub> = 1.5 V, EN = 0 V                      |      |       | 0.4  |           |

| $V_{OL}$                 | Low level RESET function output voltage                  | 0.5-mA pullup to $\overline{RESET}$ pin,<br>$V_{IN} = 13.5 \text{ V}$ , $EN = 0 \text{ V}$ |      |       | 0.4  | V         |

|                          |                                                          | 1-mA pullup to RESET pin,<br>V <sub>IN</sub> = 13.5 V, EN = 3.3 V                          |      |       | 0.4  |           |

| F <sub>SW</sub>          | Switching frequency                                      | V <sub>IN</sub> = 13.5 V, center frequency with spread spectrum, PWM operation             | 360  | 400   | 440  | kHz       |

| SW                       | Switching frequency                                      | V <sub>IN</sub> = 13.5 V, without spread spectrum, PWM operation                           | 360  | 400   | 440  | KIIZ      |

| F <sub>SYNC</sub>        | Sync frequency range                                     |                                                                                            | 250  | 400   | 500  | kHz       |

| D <sub>SYNC</sub>        | Sync input duty cycle range                              | High state input < 5.5 V and > 2.3 V                                                       | 25%  |       | 75%  |           |

|                          |                                                          | FPWM input high (MODE = FPWM)                                                              | 1.5  |       |      |           |

| $V_{FPWM}$               | FPWM input threshold voltage                             | FPWM input low (MODE = AUTO with diode emulation)                                          |      |       | 0.4  | V         |

|                          |                                                          | FPWM input hysteresis                                                                      | 0.15 |       | 1    |           |

| FS <sub>SS</sub>         | Frequency span of spread spectrum operation              |                                                                                            |      | ±3%   |      |           |

| F <sub>PSS</sub>         | Spread-spectrum pattern frequency (2)                    |                                                                                            |      |       | 1.2  | Hz        |

| l                        | FPWM leakage current                                     | V <sub>IN</sub> = 13.5 V, V <sub>FPWM</sub> = 3.3 V                                        |      | 1     |      | μΑ        |

| I <sub>FPWM</sub>        |                                                          | $V_{IN} = V_{FPWM} = 13.5 \text{ V}$                                                       |      | 1     |      |           |

| l                        | SYNC leakage current                                     | V <sub>IN</sub> = 13.5 V, V <sub>SYNC</sub> = 3.3 V                                        |      | 1     |      | μA        |

| ISYNC                    | 31110 leakage current                                    | $V_{IN} = V_{SYNC} = 13.5 \text{ V}$                                                       |      | 1     |      | μΛ        |

| I <sub>L-HS</sub>        | High-side switch current limit                           | LMS3655                                                                                    | 6.7  | 8.5   | 9.5  | Α         |

| I <sub>L-LS</sub>        | Low-side switch current limit                            | LMS3655                                                                                    | 6    | 7     | 7.7  | Α         |

| I <sub>L-ZC</sub>        | Zero-cross current limit FPWM = low                      |                                                                                            |      | -0.02 |      | А         |

| I <sub>L-NEG</sub>       | Negative current limit FPWM = high                       |                                                                                            |      | -1.5  |      |           |

| R <sub>DSON</sub>        | Power switch on-resistance                               | High-side MOSFET R <sub>DSON</sub> ,<br>V <sub>IN</sub> = 13 V, IL = 1 A                   |      | 60    | 130  | $m\Omega$ |

| אוספתי.                  | . So. Simon on registation                               | Low-side MOSFET R <sub>DSON</sub> ,<br>V <sub>IN</sub> = 13 V, IL = 1 A                    |      | 40    | 80   | 11122     |

| V <sub>EN</sub>          | Enable input threshold voltage - rising                  | Enable rising                                                                              | 1.7  |       | 2    | V         |

| V <sub>EN_HYST</sub>     | Enable threshold hysteresis                              |                                                                                            | 0.45 |       | 0.55 | V         |

| V <sub>EN_WAKE</sub>     | Enable wake-up threshold                                 |                                                                                            | 0.4  |       |      | V         |

| I <sub>EN</sub>          | EN pin input current                                     | $V_{IN} = V_{EN} = 13.5 \text{ V}$                                                         |      | 2     | 3    | μΑ        |

| V <sub>CC</sub>          | Internal V <sub>CC</sub> voltage                         | V <sub>IN</sub> = 13.5 V, V <sub>BIAS</sub> = 0 V                                          |      | 3.05  |      | V         |

| v CC                     | internal vec voltage                                     | V <sub>IN</sub> = 13.5 V, V <sub>BIAS</sub> = 3.3 V                                        |      | 3.15  |      | v         |

| V <sub>CC_UVLO</sub>     | Internal V <sub>CC</sub> input undervoltage              | V <sub>IN</sub> rising                                                                     |      | 2.7   |      | V         |

| VCC IIVIO                | lockout                                                  | Hysteresis below V <sub>CC-UVLO</sub>                                                      |      | 185   |      | mV        |

### (2) Ensured by Design, Not tested at production.

### **Electrical Characteristics (continued)**

Limits apply over the recommended operating junction temperature range of  $-40^{\circ}$ C to  $+150^{\circ}$ C, unless otherwise noted. Minimum and maximum limits are specified through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $T_J = 25^{\circ}$ C, and are provided for reference purposes only. Unless otherwise stated the following conditions apply:  $V_{IN} = 13.5 \text{ V}$ .

|                    | PARAMETER                                  | TEST CONDITIONS                         | MIN   | TYP | MAX   | UNIT |  |

|--------------------|--------------------------------------------|-----------------------------------------|-------|-----|-------|------|--|

| I <sub>FB</sub>    | Input current from FB to AGND              | FB = 1 V                                |       | 20  |       | nA   |  |

| .,                 | Poforonoo voltago                          | $T_J = 25^{\circ}C$                     | 0.993 | 1   | 1.007 | V    |  |

| $V_{REF}$          | Reference voltage                          | $T_J = -40^{\circ}C$ to 125°C           | 0.99  | 1   | 1.01  |      |  |

| R <sub>RESET</sub> | R <sub>DSON</sub> of RESEToutput           | Pull FB pin low. Sink 1-mA at RESET pin |       | 50  | 120   | Ω    |  |

|                    | V <sub>IH</sub>                            |                                         | 1.5   |     |       |      |  |

| V <sub>SYNC</sub>  | $V_{IL}$                                   |                                         |       |     | 0.4   | V    |  |

|                    | V <sub>HYST</sub>                          |                                         | 0.15  |     | 1     |      |  |

| т                  | Thermal shutdown thresholds <sup>(2)</sup> | Rising                                  | 160   |     | 185   | °C   |  |

| T <sub>SD</sub>    | Thermal shutdown thresholds (-)            | Hysteresis                              |       | 15  |       |      |  |

| D <sub>MAX</sub>   | Maximum quitab duty avala                  | F <sub>sw</sub> = 400 kHz               |       | 96% |       |      |  |

|                    | Maximum switch duty cycle                  | While in dropout <sup>(2)</sup>         | 98%   |     |       |      |  |

### 7.7 System Characteristics

The following specifications are ensured by design provided that the component values in the typical application circuit are used. These parameters are not ensured by production testing. Limits apply over the recommended operating junction temperature range of  $-40^{\circ}$ C to  $+150^{\circ}$ C, unless otherwise noted. Minimum and maximum limits are specified through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $T_J = 25^{\circ}$ C, and are provided for reference purposes only. Unless otherwise stated the following conditions apply:  $V_{IN} = 13.5 \text{ V}$ .

|                     | PARAMETER                                                                                | TEST CONDITIONS                                                                                                                                                                                                                   | MIN    | TYP  | MAX   | UNIT |  |

|---------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|-------|------|--|

| V                   | Minimum input voltage for full functionality at 3.5-A load, after start-up.              | V <sub>OUT</sub> = 3.3 V +2% or –3% regulation                                                                                                                                                                                    |        | 3.5  |       | V    |  |

| V <sub>IN-MIN</sub> | Minimum input voltage for full functionality at maximum rated load 5.5 A after start-up. | V <sub>OUT</sub> = 3.3 V +2% or −3% regulation                                                                                                                                                                                    |        | 3.8  |       | V    |  |

| $V_{OUT}$           | Output voltage                                                                           | $V_{IN} = V_{OUT} + 1 V \text{ to } 36 V, I_{OUT} = 3.5 A$                                                                                                                                                                        | -2.25% |      | 2.25% |      |  |

| F <sub>SW</sub>     | Switching frequency                                                                      | $V_{\text{IN}}$ = 24 V, FPWM = 24V, $V_{\text{OUT}}$ = 3.3 V, $I_{\text{OUT}}$ = 200 mA                                                                                                                                           |        | 400  |       | kHz  |  |

|                     | Input ourrent to VIN pin                                                                 | $\begin{array}{l} \text{V}_{\text{IN}} = 13.5 \text{ V, V}_{\text{OUT}} = 3.3 \text{ V, I}_{\text{OUT}} = 0 \text{ A ,} \\ \text{FPWM} = 0, \text{RFBT} = 49.9 \text{ k}\Omega, \text{RFBB} = 21.7 \\ \text{k}\Omega \end{array}$ |        | 32   |       |      |  |

| I <sub>Q_VIN</sub>  | Input current to VIN pin                                                                 | $\begin{array}{l} V_{\text{IN}}=13.5~\text{V,}~V_{\text{OUT}}=5.0~\text{V,}~I_{\text{OUT}}=0~\text{A,}\\ \text{FPWM}=0,~\text{RFBT}=49.9~\text{k}\Omega,~\text{RFBB}=12.4\\ \text{k}\Omega \end{array}$                           |        | 57   |       | μΑ   |  |

| I <sub>B</sub>      | Bias current in AUTO mode at no load                                                     | V <sub>IN</sub> = 13.5 V, I <sub>OUT</sub> = 0 A, FPWM = 0                                                                                                                                                                        |        | 32   | 42    | μΑ   |  |

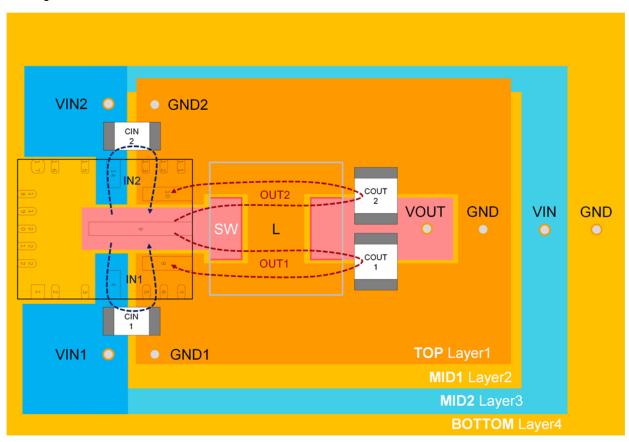

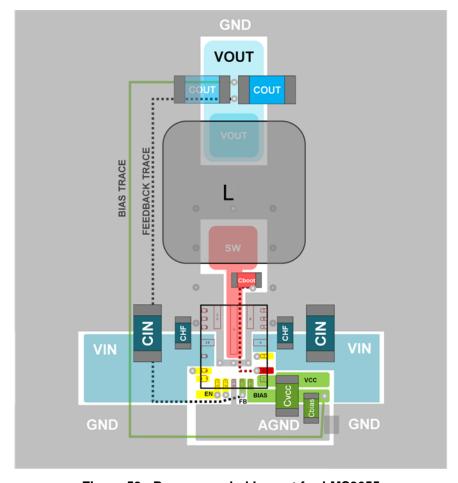

| V                   | Minimum input to output voltage differential to                                          | V <sub>OUT</sub> = 3.3 V or 5 V, I <sub>OUT</sub> = 3.5 A, +2% or<br>-3% output accuracy                                                                                                                                          |        | 0.35 | 0.6   | V    |  |