LMV841-Q1, LMV842-Q1, LMV844-Q1

JAJSE16-OCTOBER 2017

# LMV84x-Q1 CMOS入力、RRIO、低消費電力、広い電源電圧範囲の 4.5MHzオペアンプ

# 1 特長

- 次の結果でAEC-Q100車載用認定テスト・ガイダンス

- デバイス温度グレード 1: 動作時周囲温度 -40℃~+125°C

- デバイスHBM ESD分類レベル2

- デバイスCDM ESD分類レベルC3

- 特に記述のない限り、

T<sub>A</sub> = 25℃、V<sup>+</sup> = 5Vでの標準値

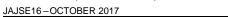

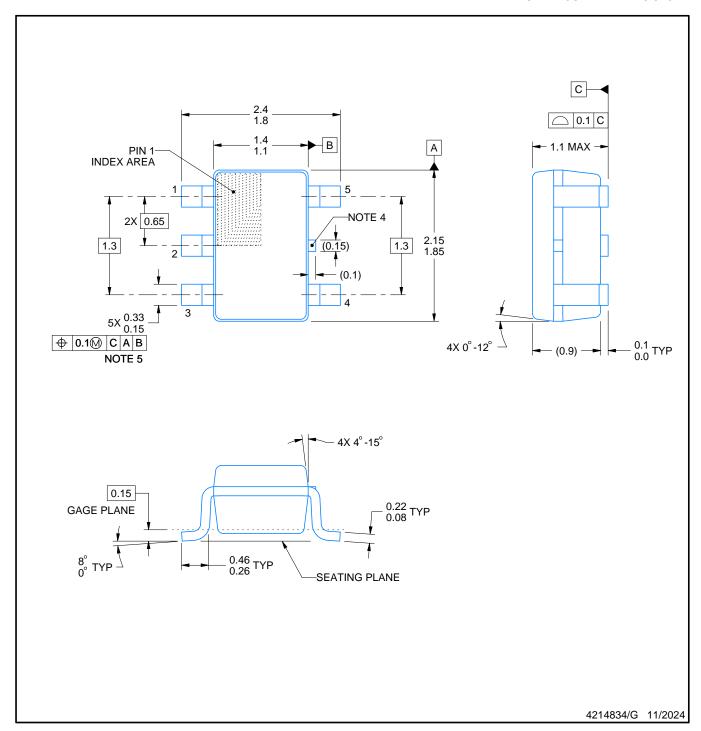

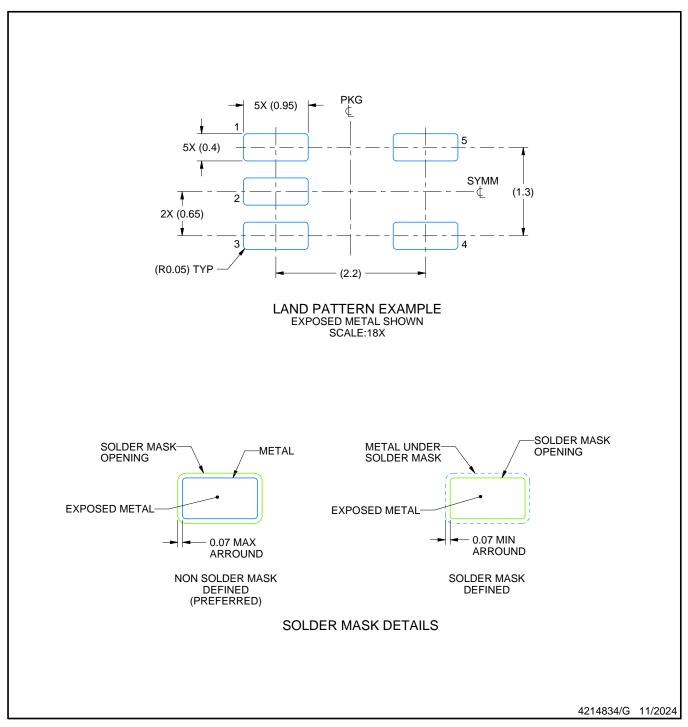

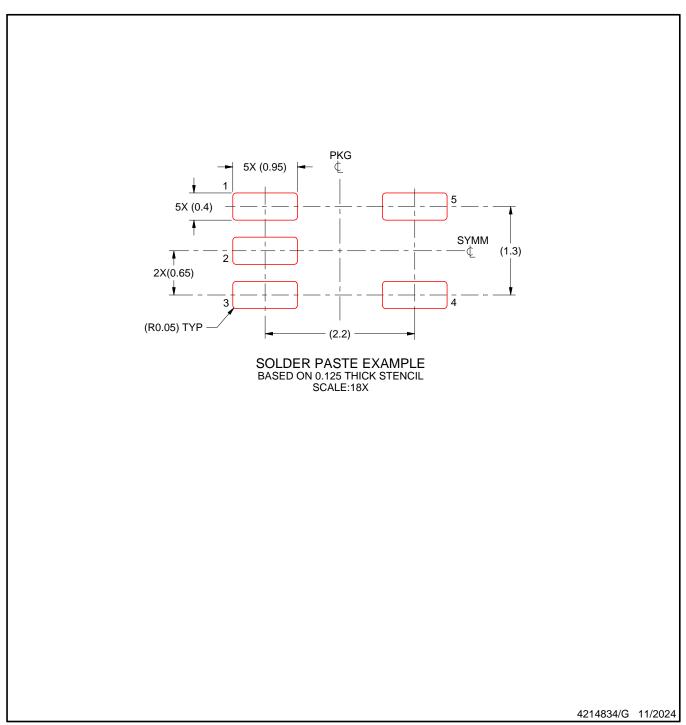

- 小さな5ピンSC70パッケージ(2.00mm×1.25mm× 0.95mm)

- 広い電源電圧範囲: 2.7V~12V

- 3.3V、5V、±5V動作を保証

- 低消費電流: チャネルごとに1mA

- ユニティ・ゲイン帯域幅: 4.5MHz

- オープンループ・ゲイン: 133dB

- 入力オフセット電圧: 最大500μV

- 入力バイアス電流: 0.3pA

- CMRR 112dB、PSSR 108dB

- 入力電圧ノイズ: 20nV/√Hz

- 温度範囲: -40℃~125℃

- レール・ツー・レール入出力(RRIO)

# 2 アプリケーション

- 高インピーダンスのセンサ・インターフェイス

- バッテリ駆動の計測機器

- 高ゲインおよび計装用のアンプ

- DACバッファおよびアクティブ・フィルタ

# 3 概要

LMV84x-Q1デバイスは、低電圧で低消費電力のオペアンプで、2.7V~12Vの範囲の電源電圧で動作し、レール・ツー・レールの入出力機能を持ちます。オフセット電圧と消費電流が低く、CMOS入力であるため、高インピーダンスのセンサ・インターフェイスやバッテリ駆動のアプリケーションに理想的です。

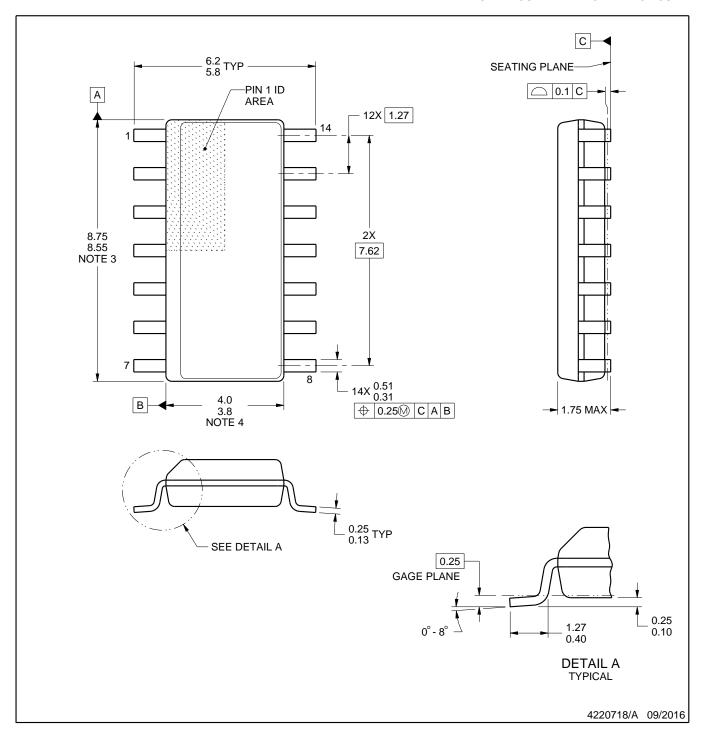

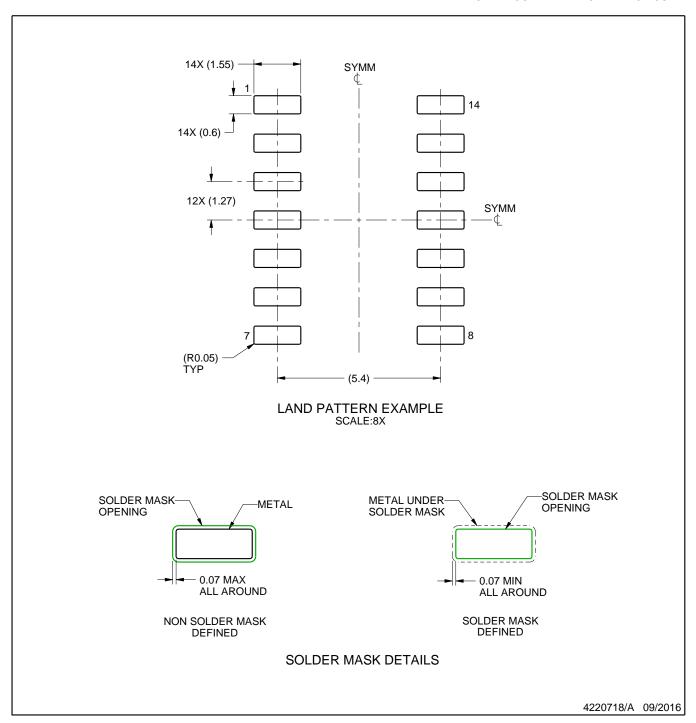

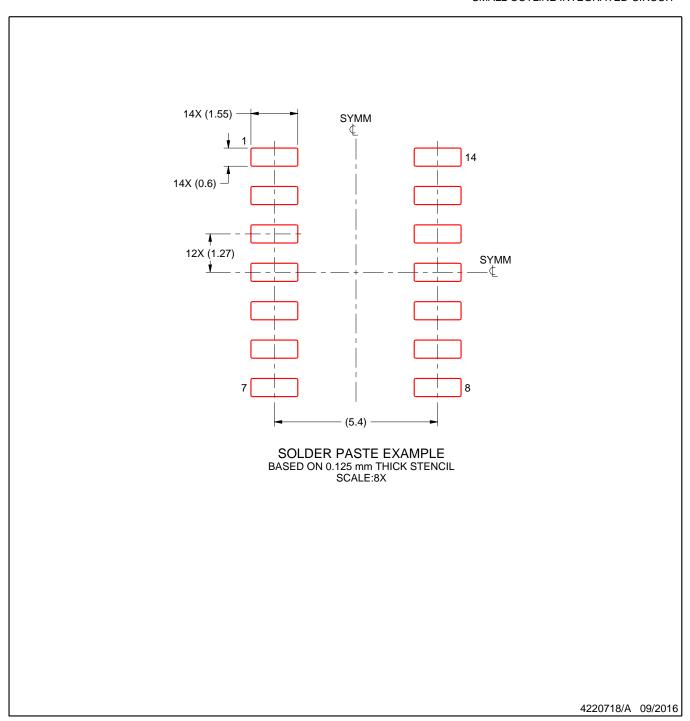

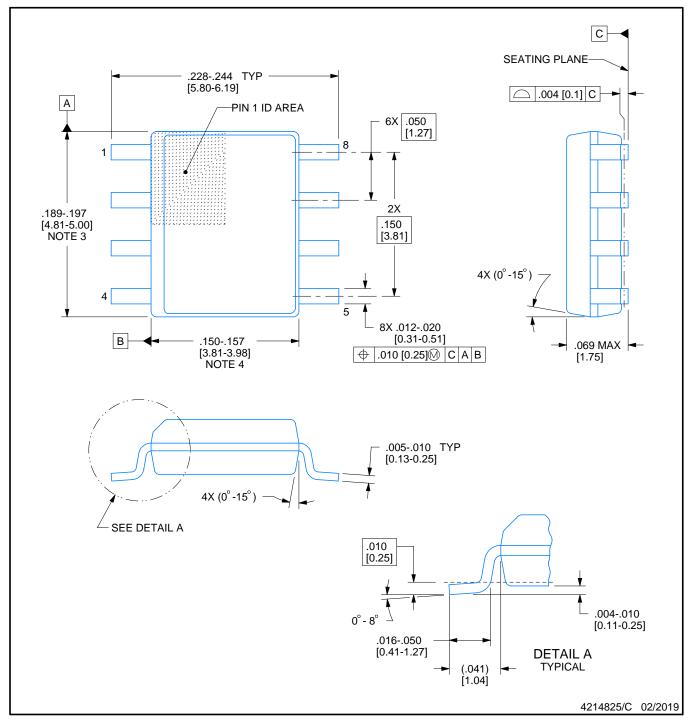

シングルのLMV841-Q1は、省スペースの5ピンSC70パッケージで、デュアルのLMV842-Q1は8ピンのVSSOPおよび8ピンのSOICパッケージで、クワッドのLMV844-Q1は14ピンのTSSOPおよび14ピンのSOICパッケージで供給されます。これらの小型パッケージは、面積が制限されるPCBや携帯電子機器に理想的なソリューションです。

LMV841-Q1、LMV842-Q1、LMV844-Q1には、障害検出方式など、自動車市場向けの高度な製造およびサポート・プロセスが組み込まれています。AEC-Q100規格に定義されている要件および温度グレードに準拠して、信頼性が認定されています。

### **刬品情報(1)**

| <u> </u>   |            |               |  |  |  |  |  |

|------------|------------|---------------|--|--|--|--|--|

| 型番         | パッケージ      | 本体サイズ(公称)     |  |  |  |  |  |

| LMV841-Q1  | SC70 (5)   | 2.00mm×1.25mm |  |  |  |  |  |

| LMV842-Q1  | VSSOP (8)  | 3.00mm×3.00mm |  |  |  |  |  |

|            | SOIC (8)   | 4.90mm×3.91mm |  |  |  |  |  |

| LMV/944 O4 | SOIC (14)  | 8.65mm×3.91mm |  |  |  |  |  |

| LMV844-Q1  | TSSOP (14) | 5.00mm×4.40mm |  |  |  |  |  |

(1) 提供されているすべてのパッケージについては、データシートの末 尾にある注文情報を参照してください。

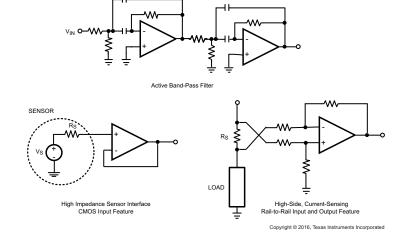

## 代表的なアプリケーション

www.ti.com

# 目次

| 1 | 特長1                                      |    | 7.4 Device Functional Modes              | 17              |

|---|------------------------------------------|----|------------------------------------------|-----------------|

| 2 | アプリケーション1                                |    | 7.5 Interfacing to High Impedance Sensor | 20              |

| 3 | 概要1                                      | 8  | Application and Implementation           | 22              |

| 4 | 改訂履歴                                     |    | 8.1 Application Information              | 22              |

| 5 | Pin Configuration and Functions          |    | 8.2 Typical Applications                 | <mark>22</mark> |

| 6 | Specifications4                          | 9  | Power Supply Recommendations             | 26              |

| • | 6.1 Absolute Maximum Ratings 4           | 10 | Layout                                   | <u>26</u>       |

|   | 6.2 ESD Ratings                          |    | 10.1 Layout Guidelines                   | 26              |

|   | 6.3 Recommended Operating Conditions     |    | 10.2 Layout Example                      | 26              |

|   | 6.4 Thermal Information4                 | 11 | デバイスおよびドキュメントのサポート                       | 27              |

|   | 6.5 Electrical Characteristics – 3.3 V 5 |    | 11.1 関連リンク                               | 27              |

|   | 6.6 Electrical Characteristics – 5 V     |    | 11.2 ドキュメントの更新通知を受け取る方法                  | 27              |

|   | 6.7 Electrical Characteristics – ±5-V    |    | 11.3 コミュニティ・リソース                         | <mark>27</mark> |

|   | 6.8 Typical Characteristics              |    | 11.4 商標                                  | 27              |

| 7 | Detailed Description                     |    | 11.5 静電気放電に関する注意事項                       | <u>27</u>       |

|   | 7.1 Overview                             |    | 11.6 Glossary                            | 27              |

|   | 7.2 Functional Block Diagram 16          | 12 | メカニカル、パッケージ、および注文情報                      | <mark>27</mark> |

|   | 7.3 Feature Description                  |    |                                          |                 |

|   |                                          |    |                                          |                 |

# 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| 日付       | 改訂内容 | 注                                                                                  |

|----------|------|------------------------------------------------------------------------------------|

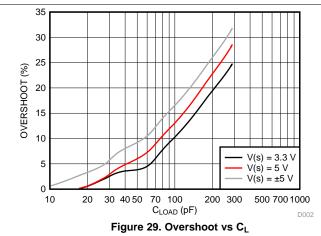

| 2017年10月 | *    | 車載用データシートを商業用と分離、熱に関する情報を更新、「代表的特性」セクションで、位相マージンとCLの関係およびオーバーシュートと<br>CLの関係のグラフを変更 |

# 5 Pin Configuration and Functions

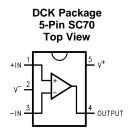

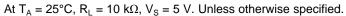

### D or DGK Package 8-Pin SOIC and VSSOP Top View

### D or PW Package 14-Pin SOIC and TSSOP Top View

### **Pin Functions**

| PIN  |      | DESCRIPTION        |

|------|------|--------------------|

| NAME | I/O. | DESCRIPTION        |

| +IN  | 1    | Noninverting Input |

| -IN  | 1    | Inverting Input    |

| OUT  | 0    | Output             |

| V+   | Р    | Positive Supply    |

| V-   | Р    | Negative Supply    |

JAJSE16-OCTOBER 2017 www.ti.com

# 6 Specifications

### 6.1 Absolute Maximum Ratings

See (1)(2)

|                                       |                                        | MIN           | MAX                  | UNIT |

|---------------------------------------|----------------------------------------|---------------|----------------------|------|

| V <sub>IN</sub> differentia           | al                                     | -300          | 300                  | mV   |

| Supply voltag                         | ge (V <sup>+</sup> – V <sup>-</sup> )  |               | 13.2                 | ٧    |

| Voltage at input and output pins      |                                        | $V^{+} + 0.3$ | V <sup>-</sup> – 0.3 | ٧    |

| Input current                         |                                        |               | 10                   | mA   |

| Junction temp                         | Junction temperature (3)               |               | 150                  | °C   |

| Soldering                             | Infrared or convection (20 s)          |               | 235                  | °C   |

| information                           | Wave soldering lead temperature (10 s) |               | 260                  | °C   |

| Storage temperature, T <sub>stg</sub> |                                        | <b>-</b> 65   | 150                  | °C   |

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|        |               |                                                         | VALUE | UNIT |

|--------|---------------|---------------------------------------------------------|-------|------|

| V      | Electrostatic | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup> | ±2000 | \/   |

| V/ECD) | discharge     | Charged-device model (CDM), per AEC Q100-011            | ±250  | V    |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

# 6.3 Recommended Operating Conditions

|                                                   | MIN | MAX | UNIT |

|---------------------------------------------------|-----|-----|------|

| Temperature <sup>(1)</sup>                        | -40 | 125 | °C   |

| Supply voltage (V <sup>+</sup> – V <sup>-</sup> ) | 2.7 | 12  | V    |

The maximum power dissipation is a function of T<sub>J(MAX)</sub>, R<sub>θ,JA</sub>, and T<sub>A</sub>. The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} - T_A) / R_{\theta,JA}$ . All numbers apply for packages soldered directly onto a PCB.

# 6.4 Thermal Information

|                               |                                              | LMV84x-Q1  |                      |        |        |               |      |

|-------------------------------|----------------------------------------------|------------|----------------------|--------|--------|---------------|------|

| THERMAL METRIC <sup>(1)</sup> |                                              | DCK (SC70) | DGK D (SOIC) (VSSOP) |        |        | PW<br>(TSSOP) | UNIT |

|                               |                                              | 5 PINS     | 8 PINS               | 8 PINS | 14 PIN | 14 PINS       |      |

| $R_{\theta JA}$               | Junction-to-ambient thermal resistance (2)   | 269.9      | 179.2                | 121.4  | 85.4   | 113.3         | °C/W |

| $R_{\theta JC(top)}$          | Junction-to-case (top) thermal resistance    | 93.8       | 69.2                 | 65.7   | 43.5   | 38.9          | °C/W |

| $R_{\theta JB}$               | Junction-to-board thermal resistance         | 48.8       | 99.7                 | 62.0   | 39.8   | 56.3          | °C/W |

| ΨЈТ                           | Junction-to-top characterization parameter   | 2.0        | 10.0                 | 16.5   | 9.2    | 3.1           | °C/W |

| ΨЈВ                           | Junction-to-board characterization parameter | 47.9       | 98.3                 | 61.4   | 39.6   | 55.6          | °C/W |

| $R_{\theta JC(bot)}$          | Junction-to-case (bottom) thermal resistance | N/A        | N/A                  | N/A    | N/A    | N/A           | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application

If Military/Aerospace specified devices are required, contact the Texas Instruments Sales Office / Distributors for availability and

The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $R_{\theta JA}$ , and  $T_A$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} - T_A) / R_{\theta JA}$ . All numbers apply for packages soldered directly onto a PCB.

The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $R_{\theta JA}$ , and  $T_A$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} - T_A) / R_{\theta JA}$ . All numbers apply for packages soldered directly onto a PCB.

# 6.5 Electrical Characteristics - 3.3 V

Unless otherwise specified, all limits are ensured for  $T_A$  = 25°C,  $V^+$  = 3.3 V,  $V^-$  = 0 V,  $V_{CM}$  =  $V^+$  / 2, and  $R_L$  > 10 M $\Omega$  to  $V^+$  / 2. (1)

|                   | PARAMETER                       | TEST COND                                                                       | ITIONS                      | MIN <sup>(2)</sup> | TYP <sup>(3)</sup> | MAX <sup>(2)</sup> | UNIT  |  |

|-------------------|---------------------------------|---------------------------------------------------------------------------------|-----------------------------|--------------------|--------------------|--------------------|-------|--|

| \/                | land offert wellens             |                                                                                 |                             | -500               | ±50                | 500                | \/    |  |

| Vos               | Input offset voltage            | at the temperature extremes                                                     | -800                        |                    | 800                | μV                 |       |  |

| TCV <sub>OS</sub> | Input offset voltage drift (4)  |                                                                                 |                             |                    | 0.5                |                    | μV/°C |  |

| TCVOS             |                                 | at the temperature extreme                                                      | S                           | -5                 |                    | 5                  | μν/ С |  |

| I <sub>B</sub>    | Input bias current (4) (5)      |                                                                                 |                             |                    | 0.3                | 10                 | pA    |  |

| 'B                |                                 | at the temperature extremes                                                     | S                           |                    |                    | 300                | pri   |  |

| I <sub>OS</sub>   | Input offset current            |                                                                                 |                             |                    | 40                 |                    | fA    |  |

|                   | Common-mode rejection ratio     |                                                                                 |                             | 84                 | 112                |                    |       |  |

| CMRR              | LMV841-Q1                       | 0 V ≤ V <sub>CM</sub> ≤ 3.3 V                                                   | at the temperature extremes | 80                 |                    |                    | dB    |  |

| CIVIKK            | Common-mode rejection ratio     |                                                                                 |                             | 77                 | 106                |                    |       |  |

|                   | LMV842-Q1 and LMV844-Q1         | 0 V ≤ V <sub>CM</sub> ≤ 3.3 V                                                   | at the temperature extremes | 75                 |                    |                    | dB    |  |

|                   | Power supply rejection ratio    | $2.7 \text{ V} \le \text{V}^+ \le 12 \text{ V}, \text{ V}_0 = \text{V}^+$       |                             | 86                 | 108                |                    |       |  |

| PSRR              |                                 | $ 2.7 \text{ V} \le \text{V} \le 12 \text{ V}, \text{ V}_0 = \text{V} $ $ / 2 $ | at the temperature extremes | 82                 |                    |                    | dB    |  |

| CMVR              | Input common-mode voltage range | CMRR ≥ 50 dB, at the temp                                                       | perature extremes           | -0.1               |                    | 3.4                | ٧     |  |

|                   | Large signal voltage gain       |                                                                                 | D 01-0                      |                    | 100                | 123                |       |  |

| •                 |                                 | $R_{L} = 2 k\Omega$ $V_{O} = 0.3 \text{ V to 3 V}$                              | at the temperature extremes | 96                 |                    |                    | dB    |  |

| A <sub>VOL</sub>  |                                 | D 401-0                                                                         |                             | 100                | 131                |                    |       |  |

|                   |                                 | $R_L = 10 \text{ k}\Omega$<br>$V_O = 0.2 \text{ V to } 3.1 \text{ V}$           | at the temperature extremes | 96                 |                    |                    | dB    |  |

|                   |                                 |                                                                                 |                             |                    | 52                 | 80                 |       |  |

|                   | Output swing high,              | $R_L = 2 k\Omega$ to $V^+/2$                                                    | at the temperature extremes |                    |                    | 120                | mV    |  |

|                   | (measured from V <sup>+</sup> ) |                                                                                 |                             |                    | 28                 | 50                 |       |  |

| M                 |                                 | $R_L = 10 \text{ k}\Omega \text{ to V}^+/2$                                     | at the temperature extremes |                    |                    | 70                 | mV    |  |

| Vo                |                                 |                                                                                 |                             |                    | 65                 | 100                |       |  |

|                   | Output swing low,               | $R_L = 2 k\Omega \text{ to } V^+/2$                                             | at the temperature extremes |                    |                    | 120                | mV    |  |

|                   | (measured from V <sup>-</sup> ) |                                                                                 |                             |                    | 33                 | 65                 |       |  |

|                   |                                 | $R_L = 10 \text{ k}\Omega \text{ to V}^+/2$                                     | at the temperature extremes |                    |                    | 75                 | mV    |  |

<sup>(1)</sup> Electrical table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device.

<sup>(2)</sup> Limits are 100% production tested at 25°C. Limits over the operating temperature range are ensured through correlations using statistical quality control (SQC) method.

<sup>(3)</sup> Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not ensured on shipped production material.

<sup>(4)</sup> This parameter is ensured by design and/or characterization and is not tested in production.

<sup>(5)</sup> Positive current corresponds to current flowing into the device.

JAJSE16 – OCTOBER 2017 www.ti.com

# Electrical Characteristics - 3.3 V (continued)

Unless otherwise specified, all limits are ensured for  $T_A = 25^{\circ}C$ ,  $V^+ = 3.3$  V,  $V^- = 0$  V,  $V_{CM} = V^+ / 2$ , and  $R_L > 10$  M $\Omega$  to  $V^+ / 2$ .

| PARAMETER        |                                                | TEST COND                                                              | MIN <sup>(2)</sup>          | TYP <sup>(3)</sup> | MAX <sup>(2)</sup> | UNIT |        |  |

|------------------|------------------------------------------------|------------------------------------------------------------------------|-----------------------------|--------------------|--------------------|------|--------|--|

|                  |                                                |                                                                        | Coursian V V/t/O            |                    | 20                 | 32   |        |  |

|                  | Output short-circuit current <sup>(6)(7)</sup> | Sourcing $V_O = V^+/2$<br>$V_{IN} = 100 \text{ mV}$                    | at the temperature extremes | 15                 |                    |      | mA     |  |

| Io               | Output short-circuit current                   | Cipling V V+/0                                                         |                             | 20                 | 27                 |      |        |  |

|                  |                                                | Sinking $V_O = V^+/2$<br>$V_{IN} = -100 \text{ mV}$                    | at the temperature extremes | 15                 |                    |      | mA     |  |

|                  |                                                | Per channel                                                            |                             |                    | 0.93               | 1.5  |        |  |

| Is               | Supply current                                 |                                                                        | at the temperature extremes |                    |                    | 2    | mA     |  |

| SR               | Slew rate (8)                                  | A <sub>V</sub> = 1, V <sub>O</sub> = 2.3 V <sub>PP</sub><br>10% to 90% |                             |                    | 2.5                |      | V/µs   |  |

| GBW              | Gain bandwidth product                         |                                                                        |                             |                    | 4.5                |      | MHz    |  |

| $\Phi_{m}$       | Phase margin                                   |                                                                        |                             |                    | 67                 |      | Deg    |  |

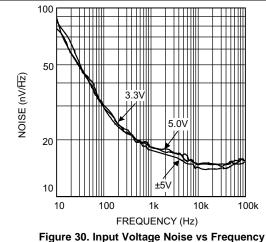

| e <sub>n</sub>   | Input-referred voltage noise                   | f = 1 kHz                                                              |                             |                    | 20                 |      | nV/√Hz |  |

| R <sub>OUT</sub> | Open-loop output impedance                     | f = 3 MHz                                                              |                             |                    | 70                 |      | Ω      |  |

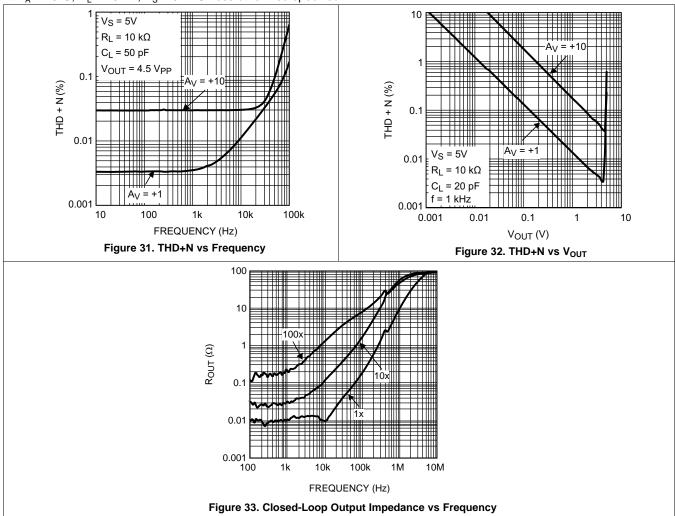

| THD+N            | Total harmonic distortion + noise              | $f = 1 \text{ kHz}$ , $A_V = 1$ $R_L = 10 \text{ k}\Omega$             |                             |                    | 0.005%             |      |        |  |

| C <sub>IN</sub>  | Input capacitance                              |                                                                        |                             |                    | 7                  |      | pF     |  |

<sup>(6)</sup> The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $R_{\theta JA}$ , and  $T_A$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} - T_A) / R_{\theta JA}$ . All numbers apply for packages soldered directly onto a PCB.

(7) Short circuit test is a momentary test.

### 6.6 Electrical Characteristics – 5 V

Unless otherwise specified, all limits are ensured for  $T_A = 25$ °C,  $V^+ = 5$  V,  $V^- = 0$  V,  $V_{CM} = V^+ / 2$ , and  $R_L > 10$  M $\Omega$  to  $V^+ / 2$ . (1)

|                   | PARAMETER                             | TEST COM                                                                        | NDITIONS                    | MIN <sup>(2)</sup> | TYP <sup>(3)</sup> | MAX <sup>(2)</sup> | UNIT  |  |

|-------------------|---------------------------------------|---------------------------------------------------------------------------------|-----------------------------|--------------------|--------------------|--------------------|-------|--|

| .,                | lanut effect valters                  |                                                                                 |                             | -500               | ±50                | 500                | /     |  |

| Vos               | Input offset voltage                  | at the temperature extre                                                        | mes                         | -800               |                    | 800                | μV    |  |

| TCV <sub>OS</sub> | Land off at valence deit(4)           |                                                                                 |                             |                    | 0.35               |                    | \//00 |  |

|                   | Input offset voltage drift (4)        | at the temperature extre                                                        | mes                         | -5                 |                    | 5                  | μV/°C |  |

|                   | (4)(5)                                |                                                                                 |                             |                    | 0.3                | 10                 | A     |  |

| I <sub>B</sub>    | Input bias current (4)(5)             | at the temperature extremes                                                     |                             |                    |                    | 300                | pA    |  |

| Ios               | Input offset current                  |                                                                                 |                             |                    | 40                 |                    | fA    |  |

|                   | Common-mode rejection ratio LMV841-Q1 | Common made mainsting matic                                                     |                             |                    | 86                 | 112                |       |  |

| CMDD              |                                       | 0 V ≤ V <sub>CM</sub> ≤ 5 V                                                     | at the temperature extremes | 80                 |                    |                    | dB    |  |

| CMRR              | Commence and a majoration matic       |                                                                                 |                             | 81                 | 106                |                    |       |  |

|                   | LMV842-Q1 and LMV844-Q1               | Common-mode rejection ratio LMV842-Q1 and LMV844-Q1 0 V ≤ V <sub>CM</sub> ≤ 5 V | at the temperature extremes | 79                 |                    |                    | dB    |  |

|                   |                                       |                                                                                 |                             | 86                 | 108                |                    |       |  |

| PSRR              | Power supply rejection ratio          | $2.7 \text{ V} \le \text{V}^+ \le 12 \text{ V}, \text{ V}_0 = \text{V}^+/2$     | at the temperature extremes | 82                 |                    |                    | dB    |  |

<sup>(1)</sup> Electrical table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device.

RUMENTS

<sup>(8)</sup> Number specified is the slower of positive and negative slew rates.

<sup>(2)</sup> Limits are 100% production tested at 25°C. Limits over the operating temperature range are ensured through correlations using statistical quality control (SQC) method.

<sup>(3)</sup> Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not ensured on shipped production material.

<sup>4)</sup> This parameter is ensured by design and/or characterization and is not tested in production.

<sup>(5)</sup> Positive current corresponds to current flowing into the device.

## Electrical Characteristics – 5 V (continued)

Unless otherwise specified, all limits are ensured for  $T_A = 25$ °C,  $V^+ = 5$  V,  $V^- = 0$  V,  $V_{CM} = V^+ / 2$ , and  $R_L > 10$  M $\Omega$  to  $V^+ / 2$ .

| PARAMETER         |                                                      | TEST CONDITIONS                                                                                       |                                 | MIN <sup>(2)</sup> | <sup>(2)</sup> TYP <sup>(3)</sup> | MAX <sup>(2)</sup> | UNIT   |  |

|-------------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------|---------------------------------|--------------------|-----------------------------------|--------------------|--------|--|

| CMVR              | Input common-mode voltage range                      | CMRR ≥ 50 dB, at the                                                                                  | temperature extremes            | -0.2               |                                   | 5.2                | ٧      |  |

|                   |                                                      | D 01:0                                                                                                |                                 | 100                | 125                               |                    |        |  |

| ۸                 | Large cignel veltage gain                            | $R_L = 2 k\Omega$<br>$V_O = 0.3V \text{ to } 4.7 \text{ V}$                                           | at the temperature extremes     | 96                 |                                   |                    | dB     |  |

| A <sub>VOL</sub>  | Large signal voltage gain                            | R <sub>L</sub> = 10 kΩ                                                                                |                                 | 100                | 133                               |                    |        |  |

|                   |                                                      | $V_0 = 0.2V \text{ to } 4.8V$                                                                         | at the temperature extremes     | 96                 |                                   |                    | dB     |  |

|                   |                                                      |                                                                                                       |                                 |                    | 68                                | 100                |        |  |

|                   | Output swing high,                                   | $R_L = 2 k\Omega \text{ to } V^+/2$                                                                   | at the temperature extremes     |                    |                                   | 120                | mV     |  |

|                   | (measured from V <sup>+</sup> )                      |                                                                                                       |                                 |                    | 32                                | 50                 |        |  |

| V                 |                                                      | $R_L = 10 \text{ k}\Omega \text{ to V}^+/2$                                                           | at the temperature extremes     |                    |                                   | 70                 | mV     |  |

| Vo                | Output swing low,<br>(measured from V <sup>-</sup> ) |                                                                                                       |                                 |                    |                                   | 78                 | 120    |  |

|                   |                                                      | $R_L = 2 k\Omega \text{ to V}^+/2$ tput swing low,                                                    | at the temperature extremes     |                    |                                   | 140                | mV     |  |

|                   |                                                      | $R_L = 10 \text{ k}\Omega \text{ to V}^+/2$                                                           |                                 |                    | 38                                | 70                 |        |  |

|                   |                                                      |                                                                                                       | at the temperature extremes     |                    |                                   | 80                 | mV     |  |

|                   | Output short-circuit current <sup>(6)</sup> (7)      | Sourcing V V/t/O                                                                                      |                                 | 20                 | 33                                |                    |        |  |

|                   |                                                      | Sourcing $V_O = V^+/2$<br>$V_{IN} = 100 \text{ mV}$                                                   | at the temperature extremes     | 15                 |                                   |                    | mA     |  |

| I <sub>O</sub>    |                                                      |                                                                                                       | Sinking \/ - \/ <sup>+</sup> /2 |                    | 20                                | 28                 |        |  |

|                   |                                                      | Sinking $V_O = V^+/2$<br>$V_{IN} = -100 \text{ mV}$                                                   | at the temperature extremes     | 15                 |                                   |                    | mA     |  |

|                   |                                                      |                                                                                                       |                                 |                    | 0.96                              | 1.5                |        |  |

| I <sub>S</sub>    | Supply current                                       | Per channel                                                                                           | at the temperature extremes     |                    |                                   | 2                  | mA     |  |

| SR                | Slew rate (8)                                        | $A_V = 1$ , $V_O = 4 V_{PP}$<br>10% to 90%                                                            |                                 |                    | 2.5                               |                    | V/µs   |  |

| GBW               | Gain bandwidth product                               |                                                                                                       |                                 |                    | 4.5                               |                    | MHz    |  |

| $\Phi_{\text{m}}$ | Phase margin                                         |                                                                                                       |                                 |                    | 67                                |                    | Deg    |  |

| e <sub>n</sub>    | Input-referred voltage noise                         | f = 1 kHz                                                                                             |                                 |                    | 20                                |                    | nV/√Hz |  |

| R <sub>OUT</sub>  | Open-loop output impedance                           | f = 3 MHz                                                                                             |                                 |                    | 70                                |                    | Ω      |  |

| THD+N             | Total harmonic distortion + noise                    | $\begin{split} f &= 1 \text{ kHz }, \text{ A}_V = 1 \\ \text{R}_L &= 10 \text{ k} \Omega \end{split}$ |                                 |                    | 0.003%                            |                    |        |  |

| C <sub>IN</sub>   | Input capacitance                                    |                                                                                                       |                                 |                    | 6                                 |                    | pF     |  |

<sup>(6)</sup> The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $R_{\theta JA}$ , and  $T_A$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} - T_A) / R_{\theta JA}$ . All numbers apply for packages soldered directly onto a PCB.

## 6.7 Electrical Characteristics - ±5-V

Unless otherwise specified, all limits are ensured for  $T_A = 25^{\circ}C$ ,  $V^+ = 5$  V,  $V^- = -5$  V,  $V_{CM} = 0$  V, and  $R_L > 10$  M $\Omega$  to  $V_{CM}$ .

<sup>(7)</sup> Short circuit test is a momentary test.

<sup>(8)</sup> Number specified is the slower of positive and negative slew rates.

<sup>(1)</sup> Electrical table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device.

# TEXAS INSTRUMENTS

# Electrical Characteristics - ±5-V (continued)

Unless otherwise specified, all limits are ensured for  $T_A = 25$ °C,  $V^+ = 5$  V,  $V^- = -5$  V,  $V_{CM} = 0$  V, and  $R_L > 10$  M $\Omega$  to  $V_{CM}$ .

|                  | PARAMETER                                           | TEST C                                                                     | ONDITIONS                   | MIN <sup>(2)</sup> | TYP <sup>(3)</sup> | MAX <sup>(2)</sup> | UNIT  |  |

|------------------|-----------------------------------------------------|----------------------------------------------------------------------------|-----------------------------|--------------------|--------------------|--------------------|-------|--|

| .,               | land offert wells as                                |                                                                            | -500                        | ±50                | 500                | /                  |       |  |

| $V_{OS}$         | Input offset voltage                                | at the temperature extre                                                   | -800                        |                    | 800                | μV                 |       |  |

| TCVos            | Input offset voltage drift (4)                      |                                                                            |                             |                    | 0.25               |                    |       |  |

|                  |                                                     | at the temperature extre                                                   | emes                        | -5                 |                    | 5                  | μV/°C |  |

|                  | Input bias current (4) (5)                          |                                                                            |                             |                    | 0.3                | 10                 | ^     |  |

| I <sub>B</sub>   |                                                     | at the temperature extre                                                   | emes                        |                    |                    | 300                | pА    |  |

| Ios              | Input offset current                                |                                                                            |                             |                    | 40                 |                    | fA    |  |

|                  | Common mode rejection ratio                         |                                                                            |                             | 86                 | 112                |                    |       |  |

| OMPD             | Common-mode rejection ratio LMV841-Q1               | $-5 \text{ V} \leq \text{V}_{\text{CM}} \leq 5 \text{ V}$                  | at the temperature extremes | 80                 |                    |                    | dB    |  |

| CMRR             | 0                                                   |                                                                            |                             | 86                 | 106                |                    |       |  |

|                  | Common-mode rejection ratio LMV842-Q1 and LMV844-Q1 | -5 V ≤ V <sub>CM</sub> ≤ 5 V                                               | at the temperature extremes | 80                 |                    |                    | dB    |  |

|                  |                                                     | 071/41/4401/11                                                             |                             | 86                 | 108                |                    |       |  |

| PSRR             | Power supply rejection ratio                        | $2.7 \text{ V} \le \text{V}^+ \le 12 \text{ V}, \text{ V}_0 = 0 \text{ V}$ | at the temperature extremes | 82                 |                    |                    | dB    |  |

| CMVR             | Input common-mode voltage range                     | CMRR ≥ 50 dB                                                               |                             | -5.2               |                    | 5.2                | V     |  |

|                  |                                                     | $R_L = 2 k\Omega$<br>V <sub>O</sub> = -4.7 V to 4.7 V                      |                             | 100                | 126                |                    |       |  |

| •                |                                                     |                                                                            | at the temperature extremes | 96                 |                    |                    | dB    |  |

| A <sub>VOL</sub> | Large signal voltage gain                           | $R_L = 10 \text{ k}\Omega$                                                 |                             | 100                | 136                |                    |       |  |

|                  |                                                     | $V_0 = -4.8 \text{ V to } 4.8 \text{ V}$                                   | at the temperature extremes | 96                 |                    |                    | dB    |  |

|                  |                                                     |                                                                            |                             |                    | 95                 | 130                |       |  |

|                  | Output swing high,                                  | $R_L = 2 k\Omega$ to 0 V                                                   | at the temperature extremes |                    |                    | 155                | mV    |  |

|                  | (measured from V <sup>+</sup> )                     |                                                                            |                             |                    | 44                 | 75                 |       |  |

| V                |                                                     | $R_L = 10 \text{ k}\Omega \text{ to } 0 \text{ V}$                         | at the temperature extremes |                    |                    | 95                 | mV    |  |

| Vo               |                                                     |                                                                            |                             |                    | 105                | 160                |       |  |

|                  | Output swing low.                                   | $R_L = 2 k\Omega$ to 0 V                                                   | at the temperature extremes |                    |                    | 200                | mV    |  |

|                  | (measured from V <sup>-</sup> )                     |                                                                            |                             |                    | 52                 | 80                 |       |  |

|                  |                                                     | $R_L = 10 \text{ k}\Omega \text{ to } 0 \text{ V}$                         | at the temperature extremes |                    |                    | 100                | mV    |  |

|                  | Output short-circuit current (6) (7)                | Sourcing $V_O = 0 V$<br>$V_{IN} = 100 \text{ mV}$                          |                             | 20                 | 37                 |                    |       |  |

|                  |                                                     |                                                                            | at the temperature extremes | 15                 |                    |                    | mA    |  |

| I <sub>O</sub>   | Output short-circuit current (9) (7)                | Cipleina V 0 V                                                             |                             | 20                 | 29                 |                    |       |  |

|                  |                                                     | Sinking $V_O = 0 V$<br>$V_{IN} = -100 \text{ mV}$                          | at the temperature extremes | 15                 |                    |                    | mA    |  |

<sup>(2)</sup> Limits are 100% production tested at 25°C. Limits over the operating temperature range are ensured through correlations using statistical quality control (SQC) method.

<sup>(3)</sup> Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not ensured on shipped production material.

<sup>(4)</sup> This parameter is ensured by design and/or characterization and is not tested in production.

<sup>(5)</sup> Positive current corresponds to current flowing into the device.

<sup>(6)</sup> The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $R_{\theta JA}$ , and  $T_A$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} - T_A) / R_{\theta JA}$ . All numbers apply for packages soldered directly onto a PCB.

<sup>(7)</sup> Short circuit test is a momentary test.

www.ti.com

# Electrical Characteristics - ±5-V (continued)

Unless otherwise specified, all limits are ensured for  $T_A = 25$ °C,  $V^+ = 5$  V,  $V^- = -5$  V,  $V_{CM} = 0$  V, and  $R_L > 10$  M $\Omega$  to  $V_{CM}$ .

| Offices officerwise specified, all littles are ensured for T <sub>A</sub> = 23 C, V = 3 V, V = -3 V, V <sub>CM</sub> = 0 V, and T <sub>C</sub> > 10 Mizz to V <sub>CM</sub> . |                                   |                                                           |                             |                    |                    |      |        |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------------------------------------------------|-----------------------------|--------------------|--------------------|------|--------|--|--|

| PARAMETER                                                                                                                                                                     |                                   | TEST                                                      | MIN <sup>(2)</sup>          | TYP <sup>(3)</sup> | MAX <sup>(2)</sup> | UNIT |        |  |  |

|                                                                                                                                                                               |                                   |                                                           |                             |                    | 1.03               | 1.7  |        |  |  |

| I <sub>S</sub>                                                                                                                                                                | Supply current                    | Per channel                                               | at the temperature extremes |                    |                    | 2    | mA     |  |  |

| SR                                                                                                                                                                            | Slew rate (8)                     | $A_V = 1$ , $V_O = 9 V_{PP}$<br>10% to 90%                |                             |                    | 2.5                |      | V/µs   |  |  |

| GBW                                                                                                                                                                           | Gain bandwidth product            |                                                           |                             |                    | 4.5                |      | MHz    |  |  |

| $\Phi_{m}$                                                                                                                                                                    | Phase margin                      |                                                           |                             |                    | 67                 |      | Deg    |  |  |

| e <sub>n</sub>                                                                                                                                                                | Input-referred voltage noise      | f = 1 kHz                                                 |                             |                    | 20                 |      | nV/√Hz |  |  |

| R <sub>OUT</sub>                                                                                                                                                              | Open-loop output impedance        | f = 3 MHz                                                 |                             |                    | 70                 |      | Ω      |  |  |

| THD+N                                                                                                                                                                         | Total harmonic distortion + noise | $f = 1 \text{ kHz}$ , $A_V = 1$ $R_L = 10 \text{k}\Omega$ |                             |                    | 0.006%             |      |        |  |  |

| C <sub>IN</sub>                                                                                                                                                               | Input capacitance                 |                                                           |                             |                    | 3                  |      | pF     |  |  |

<sup>(8)</sup> Number specified is the slower of positive and negative slew rates.

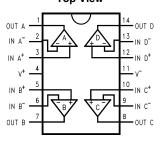

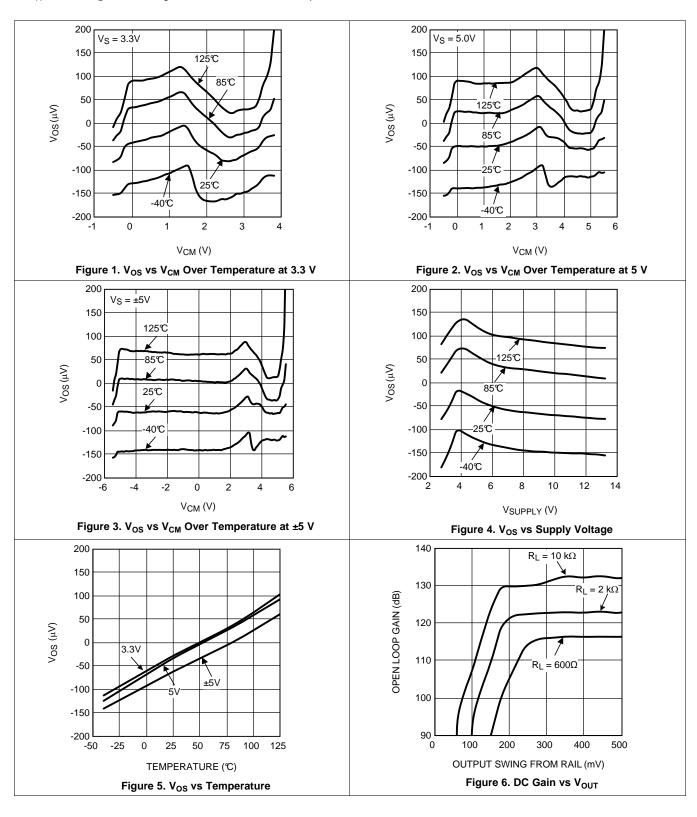

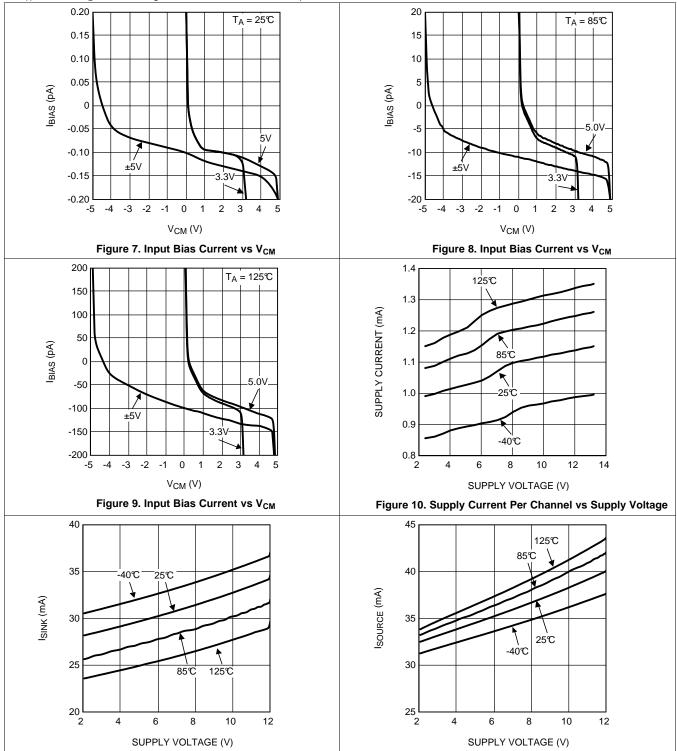

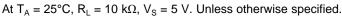

# 6.8 Typical Characteristics

At  $T_A$  = 25°C,  $R_L$  = 10 k $\Omega$ ,  $V_S$  = 5 V. Unless otherwise specified.

# **Typical Characteristics (continued)**

Figure 11. Sinking Current vs Supply Voltage

Figure 12. Sourcing Current vs Supply Voltage

# **Typical Characteristics (continued)**

At  $T_A$  = 25°C,  $R_L$  = 10 k $\Omega$ ,  $V_S$  = 5 V. Unless otherwise specified.

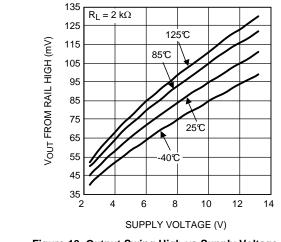

Figure 13. Output Swing High vs Supply Voltage  $R_L = 2 k\Omega$

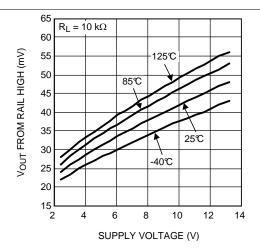

Figure 14. Output Swing High vs Supply Voltage  $R_L = 10 \text{ k}\Omega$

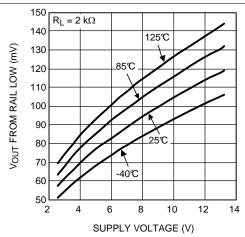

Figure 15. Output Swing Low vs Supply Voltage  $R_L = 2 k\Omega$

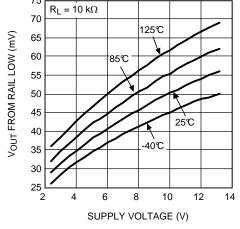

Figure 16. Output Swing Low vs Supply Voltage  $R_L = 10 \text{ k}\Omega$

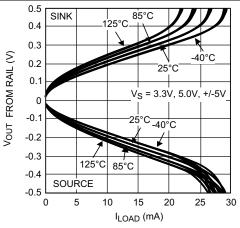

Figure 17. Output Voltage Swing vs Load Current

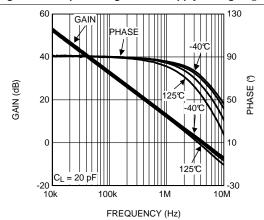

Figure 18. Open-Loop Frequency Response Over Temperature

www.ti.com JAJSE16-OCTOBER 2017

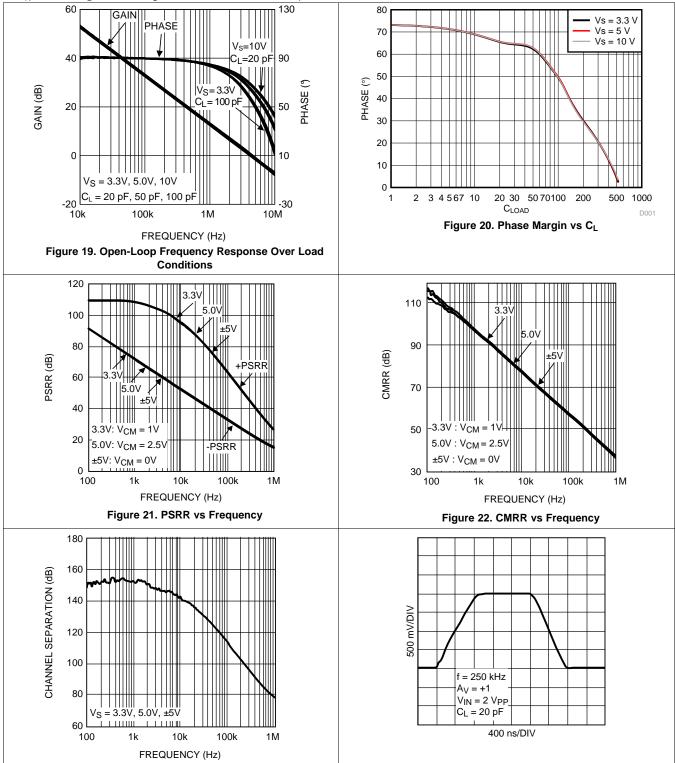

# **Typical Characteristics (continued)**

Figure 23. Channel Separation vs Frequency

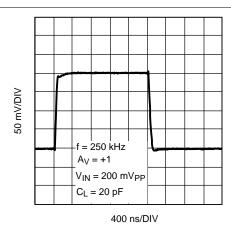

Figure 24. Large Signal Step Response With Gain = 1

# TEXAS INSTRUMENTS

# **Typical Characteristics (continued)**

At  $T_A$  = 25°C,  $R_L$  = 10 k $\Omega$ ,  $V_S$  = 5 V. Unless otherwise specified.

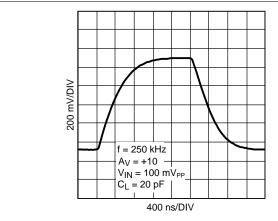

Figure 25. Large Signal Step Response With Gain = 10

Figure 26. Small Signal Step Response With Gain = 1

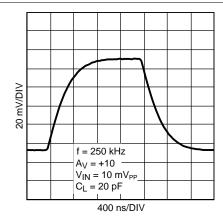

Figure 27. Small Signal Step Response With Gain = 10

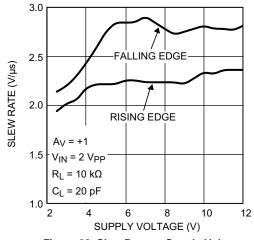

Figure 28. Slew Rate vs Supply Voltage

rigure 30. input voltage Noise vs Frequency

www.ti.com

# **Typical Characteristics (continued)**

At  $T_A$  = 25°C,  $R_L$  = 10 k $\Omega$ ,  $V_S$  = 5 V. Unless otherwise specified.

JAJSE16-OCTOBER 2017 www.ti.com

## 7 Detailed Description

#### 7.1 Overview

The LMV84x-Q1 devices are operational amplifiers with near-precision specifications: low noise, low temperature drift, low offset, and rail-to-rail input and output. Possible application areas include instrumentation, medical, test equipment, audio, and automotive applications.

Its low supply current of 1 mA per amplifier, temperature range of -40°C to +125°C, 12-V supply with CMOS input, and the small SC70 package for the LMV841-Q1 make the LMV84x-Q1 a unique op amp family and a perfect choice for portable electronics.

# 7.2 Functional Block Diagram

Copyright © 2016, Texas Instruments Incorporated

# 7.3 Feature Description

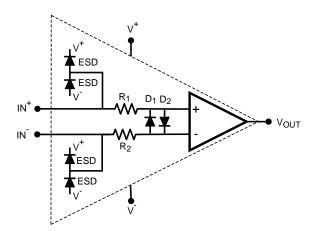

### 7.3.1 Input Protection

The LMV84x-Q1 devices have a set of anti-parallel diodes D<sub>1</sub> and D<sub>2</sub> between the input pins, as shown in Figure 34. These diodes are present to protect the input stage of the amplifier. At the same time, they limit the amount of differential input voltage that is allowed on the input pins.

A differential signal larger than one diode voltage drop can damage the diodes. The differential signal between the inputs needs to be limited to ±300 mV or the input current needs to be limited to ±10 mA.

### **NOTE**

When the op amp is slewing, a differential input voltage exists that forward-biases the protection diodes. This may result in current being drawn from the signal source. While this current is already limited by the internal resistors  $R_1$  and  $R_2$  (both 130  $\Omega$ ), a resistor of 1 k $\Omega$  can be placed in the feedback path, or a 500- $\Omega$  resistor can be placed in series with the input signal for further limitation.

### Feature Description (continued)

Figure 34. Protection Diodes Between the Input Pins

### 7.3.2 Input Stage

The input stage of this amplifier consists of both a PMOS and an NMOS input pair to achieve a rail-to-rail input range. For input voltages close to the negative rail, only the PMOS pair is active. Close to the positive rail, only the NMOS pair is active. In a transition region that extends from approximately 2 V below V<sup>+</sup> to 1 V below V<sup>+</sup>, both pairs are active, and one pair gradually takes over from the other. In this transition region, the input-referred offset voltage changes from the offset voltage associated with the PMOS pair to that of the NMOS pair. The input pairs are trimmed independently to ensure an input offset voltage of less then 0.5 mV at room temperature over the complete rail-to-rail input range. This also significantly improves the CMRR of the amplifier in the transition region.

### NOTE

The CMRR and PSRR limits in the tables are large-signal numbers that express the maximum variation of the input offset of the amplifier over the full common-mode voltage and supply voltage range, respectively. When the common-mode input voltage of the amplifier is within the transition region, the small signal CMRR and PSRR may be slightly lower than the large signal limits.

### 7.4 Device Functional Modes

### 7.4.1 Driving Capacitive Load

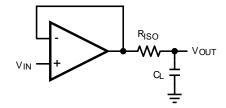

The LMV84x-Q1 can be connected as noninverting unity gain amplifiers. This configuration is the most sensitive to capacitive loading. The combination of a capacitive load placed on the output of an amplifier along with the output impedance of the amplifier creates a phase lag, which reduces the phase margin of the amplifier. If the phase margin is significantly reduced, the response is under-damped, which causes peaking in the transfer. When there is too much peaking, the op amp might start oscillating.

The LMV84x-Q1 can directly drive capacitive loads up to 100 pF without any stability issues. To drive heavier capacitive loads, an isolation resistor ( $R_{\rm ISO}$ ) must be used, as shown in Figure 35. By using this isolation resistor, the capacitive load is isolated from the output of the amplifier, and hence, the pole caused by  $C_L$  is no longer in the feedback loop. The larger the value of  $R_{\rm ISO}$ , the more stable the output voltage is. If values of  $R_{\rm ISO}$  are sufficiently large, the feedback loop is stable, independent of the value of  $C_L$ . However, larger values of  $R_{\rm ISO}$  result in reduced output swing and reduced output current drive.

### **Device Functional Modes (continued)**

Figure 35. Isolating Capacitive Load

### 7.4.2 Noise Performance

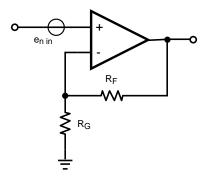

The LMV84x-Q1 devices have good noise specifications and are frequently used in low-noise applications. Therefore it is important to determine the noise of the total circuit. Besides the input-referred noise of the op amp, the feedback resistors may have an important contribution to the total noise.

For applications with a voltage input configuration, in general it is beneficial general, beneficial to keep the resistor values low. In these configurations high resistor values mean high noise levels. However, using low resistor values will increase the power consumption of the application. This is not always acceptable for portable applications, so there is a trade-off between noise level and power consumption.

Besides the noise contribution of the signal source, three types of noise need to be taken into account for calculating the noise performance of an op amp circuit:

- Input-referred voltage noise of the op amp

- · Input-referred current noise of the op amp

- · Noise sources of the resistors in the feedback network, configuring the op amp

To calculate the noise voltage at the output of the op amp, the first step is to determine a total equivalent noise source. This requires the transformation of all noise sources to the same reference node. A convenient choice for this node is the input of the op amp circuit. The next step is to add all the noise sources. The final step is to multiply the total equivalent input voltage noise with the gain of the op amp configuration.

If the input-referred voltage noise of the op amp is already placed at the input, the user can use the input-referred voltage noise without further transferring. The input-referred current noise needs to be converted to an input-referred voltage noise. The current noise is negligibly small, as long as the equivalent resistance is not unrealistically large, so the user can leave the current noise out for these examples. That leaves the user with the noise sources of the resistors, being the thermal noise voltage. The influence of the resistors on the total noise can be seen in the following examples, one with high resistor values and one with low resistor values. Both examples describe an op amp configuration with a gain of 101 which gives the circuit a bandwidth of 44.5 kHz. The op amp noise is the same for both cases, that is, an input-referred noise voltage of 20 nV/ $\sqrt{\rm Hz}$  and a negligibly small input-referred noise current.

Figure 36. Noise Circuit

## **Device Functional Modes (continued)**

To calculate the noise of the resistors in the feedback network, the equivalent input-referred noise resistance is needed. For the example in Figure 36, this equivalent resistance  $R_{eq}$  can be calculated using Equation 1:

$$R_{eq} = \frac{R_F \times R_G}{R_F + R_G} \tag{1}$$

The voltage noise of the equivalent resistance can be calculated using Equation 2:

$$e_{nr} = \sqrt{4kTR_{eq}}$$

where

- e<sub>nr</sub> = thermal noise voltage of the equivalent resistor

- R<sub>eq</sub> (V/√Hz)

- $k = Boltzmann constant (1.38 \times 10^{-23} J/K)$

- T = absolute temperature (K)

•

$$R_{eq}$$

= resistance  $(\Omega)$

The total equivalent input voltage noise is given by Equation 3:

$$e_{n in} = \sqrt{e_{nv}^2 + e_{nr}^2}$$

where

- e<sub>n in</sub> = total input equivalent voltage noise of the circuit

- e<sub>nv</sub> = input voltage noise of the op amp

The final step is multiplying the total input voltage noise by the noise gain using Equation 4, which is in this case the gain of the op amp configuration:

$$e_{n \text{ out}} = e_{n \text{ in}} \times A_{noise}$$

(4)

The equivalent resistance for the first example with a resistor  $R_F$  of 10 M $\Omega$  and a resistor  $R_G$  of 100 k $\Omega$  at 25°C (298 K) equals Equation 5:

$$R_{eq} = \frac{R_F \times R_G}{R_F + R_G} = \frac{10 \ M\Omega \times 100 \ k\Omega}{10 \ M\Omega + 100 \ k\Omega} = 99 \ k\Omega \tag{5}$$

Now the noise of the resistors can be calculated using Equation 6, yielding:

$$e_{nr} = \sqrt{4kTR_{eq}}$$

$$= \sqrt{4 \times 1.38 \times 10^{-23} J/K \times 298K \times 99 \ k\Omega}$$

$$= 40 \ nV/\sqrt{Hz}$$

(6)

The total noise at the input of the op amp is calculated in Equation 7:

$$e_{n in} = \sqrt{e_{nv}^2 + e_{nr}^2}$$

$$= \sqrt{(20 \ nV/\sqrt{Hz})^2 + (40 \ nV/\sqrt{Hz})^2} = 45 \ nV/\sqrt{Hz}$$

(7)

For the first example, this input noise, multiplied with the noise gain, in Equation 8 gives a total output noise of:

$$e_{n \text{ out}} = e_{n \text{ in}} \times A_{noise}$$

$$= 45 \text{ nV}/\sqrt{Hz} \times 101 = 4.5 \text{ }\mu\text{V}/\sqrt{Hz}$$

(8)

In the second example, with a resistor  $R_F$  of 10 k $\Omega$  and a resistor  $R_G$  of 100  $\Omega$  at 25°C (298 K), the equivalent resistance equals Equation 9:

$$R_{eq} = \frac{R_F \times R_G}{R_F + R_G} = \frac{10 \ k\Omega \times 100 \ \Omega}{10 \ k\Omega + 100 \ \Omega} = 99 \ \Omega$$

(9)

The resistor noise for the second example is calculated in Equation 10:

www.ti.com

# **Device Functional Modes (continued)**

$$e_{nr} = \sqrt{4kTR_{eq}}$$

$$= \sqrt{4 \times 1.38 \times 10^{-23} J/K \times 298 K \times 99 \Omega}$$

$$= 1 \, nV/\sqrt{Hz}$$

(10)

The total noise at the input of the op amp is calculated in Equation 10:

$$e_{n in} = \sqrt{e_{nv}^2 + e_{nr}^2}$$

$$= \sqrt{(20 \ nV/\sqrt{Hz})^2 + (1 \ nV/\sqrt{Hz})^2}$$

$$= 20 \ nV/\sqrt{Hz}$$

(11)

For the second example the input noise, multiplied with the noise gain, in Equation 12 gives an output noise of:

$$e_{n \text{ out}} = e_{n \text{ in}} \times A_{noise}$$

$$= 20 \text{ nV}/\sqrt{Hz} \times 101 = 2 \text{ }\mu\text{V}/\sqrt{Hz}$$

(12)

In the first example the noise is dominated by the resistor noise due to the very high resistor values, in the second example the very low resistor values add only a negligible contribution to the noise and now the dominating factor is the op amp itself. When selecting the resistor values, it is important to choose values that do not add extra noise to the application. Choosing values above 100 k $\Omega$  may increase the noise too much. Low values keep the noise within acceptable levels; choosing very low values however, does not make the noise even lower, but can increase the current of the circuit.

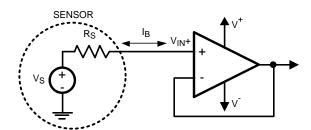

# 7.5 Interfacing to High Impedance Sensor

With CMOS inputs, the LMV84x-Q1 are particularly suited to be used as high impedance sensor interfaces.

Many sensors have high source impedances that may range up to 10  $M\Omega$ . The input bias current of an amplifier loads the output of the sensor, and thus cause a voltage drop across the source resistance, as shown in Figure 37. When an op amp is selected with a relatively high input bias current, this error may be unacceptable.

The low input current of the LMV84x-Q1 significantly reduces such errors. The following examples show the difference between a standard op amp input and the CMOS input of the LMV84x-Q1.

The voltage at the input of the op amp can be calculated with Equation 13:

$$V_{IN+} = V_S - I_B \times R_S \tag{13}$$

For a standard op amp, the input bias Ib can be 10 nA. When the sensor generates a signal of 1 V ( $V_S$ ) and the sensors impedance is 10 M $\Omega$  ( $R_S$ ), the signal at the op amp input is calculated in Equation 14:

$$V_{IN} = 1 \text{ V} - 10 \text{ nA} \times 10 \text{ M}\Omega = 1 \text{ V} - 0.1 \text{ V} = 0.9 \text{ V}$$

(14)

For the CMOS input of the LMV84x-Q1, which has an input bias current of only 0.3 pA, this would give Equation 15:

$$V_{IN} = 1 \text{ V} - 0.3 \text{ pA} \times 10 \text{ M}\Omega = 1 \text{ V} - 3 \text{ }\mu\text{V} = 0.999997 \text{ V}$$

(15)

The conclusion is that a standard op amp, with its high input bias current input, is not a good choice for use in impedance sensor applications. The LMV84x-Q1 devices, in contrast, are much more suitable due to the low input bias current. The error is negligibly small; therefore, the LMV84x-Q1 are a must for use with high-impedance sensors.

# Interfacing to High Impedance Sensor (continued)

Figure 37. High Impedance Sensor Interface

# TEXAS INSTRUMENTS

# 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## 8.1 Application Information

The rail-to-rail input and output of the LMV84x-Q1 and the wide supply voltage range make these amplifiers ideal to use in numerous applications. Three sample applications, namely the active filter circuit, high-side current sensing, and thermocouple sensor interface, are provided in the *Typical Applications* section.

# 8.2 Typical Applications

### 8.2.1 Active Filter Circuit

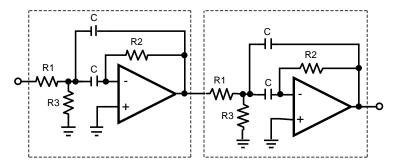

Figure 38. Active Band-Pass Filter Implementation

### 8.2.1.1 Design Requirements

In this example it is required to design a bandpass filter with band-pass frequency of 10 kHz, and a center frequence of approximately 10% from the total frequence of the filter. This is achieved by cascading two bandpass filters, A and B, with slightly different center frequencies.

### 8.2.1.2 Detailed Design Procedure

The center frequency of the separate band-pass filters A, and B can be calculated by Equation 16:

$$f_{mid} = \frac{1}{2\pi C} \sqrt{\frac{R_1 + R_3}{R_1 R_2 R_3}}$$

where

- C = 33 nF

- R1 = 2 KΩ

- $R2 = 6.2 \text{ K}\Omega$

• and R3 = 45

$$\Omega$$

(16)

This gives Equation 17 for filter A:

$$f_{mid} = \frac{1}{\pi \times 33 \ nF} \sqrt{\frac{2 \ k\Omega + 6.2 \ k\Omega}{2 \ k\Omega \times 6.2 \ k\Omega \times 45 \ k\Omega}} = 9.2 \ kHz \tag{17}$$

and Equation 18 for filter B with C = 27nF:

$$f_{mid} = \frac{1}{\pi \times 27 \ nF} \sqrt{\frac{2 \ k\Omega + 6.2 \ k\Omega}{2 \ k\Omega \times 6.2 \ k\Omega \times 45 \ k\Omega}} = 11.2 \ kHz \tag{18}$$

Bandwidth can be calculated by Equation 19:

# **Typical Applications (continued)**

$$B = \frac{1}{\pi R_2 C} \tag{19}$$

For filter A, this gives Equation 20:

$$B = \frac{1}{\pi \times 6.2 \ k\Omega \times 33 \ nF} = 1.6 \ kHz \tag{20}$$

and Equation 21 for filter B:

$$B = \frac{1}{\pi \times 6.2 \ k\Omega \times 27 \ nF} = 1.9 \ kHz \tag{21}$$

# 8.2.1.3 Application Curve

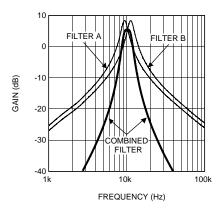

The responses of filter A and filter B are shown as the thin lines in Figure 39; the response of the combined filter is shown as the thick line. Shifting the center frequencies of the separate filters farther apart, results in a wider band; however, positioning the center frequencies too far apart results in a less flat gain within the band. For wider bands more band-pass filters can be cascaded.

Figure 39. Active Band-Pass Filter Curve

### NOTE

Use the WEBENCH internet tools at www.ti.com for your filter application.

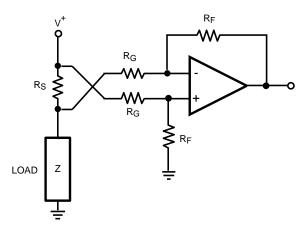

### 8.2.2 High-Side, Current-Sensing Circuit

Figure 40. High-Side, Current-Sensing Circuit

# TEXAS INSTRUMENTS

# **Typical Applications (continued)**

### 8.2.2.1 Design Requirements

In this example, it is desired to measure a current between 0 A and 2 A using a sense resistor of 100 m $\Omega$ , and convert it to an output voltage of 0 to 5 V. A current of 2 A flowing through the load and the sense resistor results in a voltage of 200 mV across the sense resistor. The op amp amplifies this 200 mV to fit the current range to the output voltage range.

### 8.2.2.2 Detailed Design Procedure

To measure current at a point in a circuit, a sense resistor is placed in series with the load, as shown in Figure 40. The current flowing through this sense resistor results in a voltage drop, that is amplified by the op amp. The rail-to-rail input and the low  $V_{OS}$  features make the LMV84x-Q1 ideal op amps for high-side, current-sensing applications.

The input and the output relation of the circuit is given by Equation 22:

$$V_{OUT} = R_F / R_G \times V_{SENSE}$$

(22)

For a load current of 2 A and an output voltage of 5 V the gain would be V<sub>OUT</sub> / V<sub>SENSE</sub> = 25.

If the feedback resistor,  $R_F$ , is 100 k $\Omega$ , then the value for  $R_G$  is 4 k $\Omega$ . The tolerance of the resistors has to be low to obtain a good common-mode rejection.

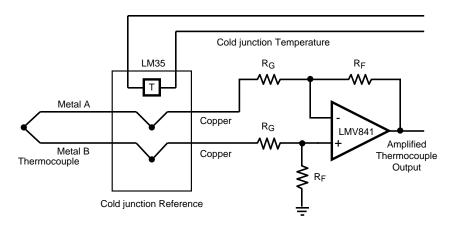

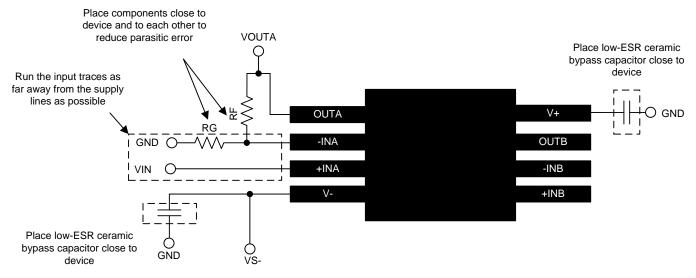

### 8.2.3 Thermocouple Sensor Signal Amplification

Figure 41 is a typical example for a thermocouple amplifier application using an LMV841-Q1, LMV842-Q1, or LMV844-Q1. A thermocouple senses a temperature and converts it into a voltage. This signal is then amplified by the LMV841-Q1, LMV842-Q1, or LMV844-Q1. An ADC can then convert the amplified signal to a digital signal. For further processing the digital signal can be processed by a microprocessor, and can be used to display or log the temperature, or the temperature data can be used in a fabrication process.

Figure 41. Thermocouple Sensor Interface

#### 8.2.3.1 Design Requirements

In this example it is desired to measure temperature in the range of 0°C to 500°C with a resolution of 0.5°C using a K-type thermocouple sensor. The power supply for both the LMV84x-Q1 and the ADC is 3.3 V.

### 8.2.3.2 Detailed Design Procedure

A thermocouple is a junction of two different metals. These metals produce a small voltage that increases with temperature. A K-type thermocouple is a very common temperature sensor made of a junction between nickel-chromium and nickel-aluminum. There are several reasons for using the K-type thermocouple. These include temperature range, the linearity, the sensitivity, and the cost.

www.ti.com

### **Typical Applications (continued)**

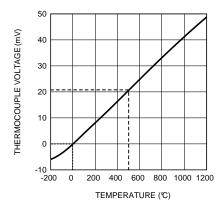

A K-type thermocouple has a wide temperature range. The range of this thermocouple is from approximately -200°C to approximately 1200°C, as can be seen in Figure 42. This covers the generally used temperature ranges.

Over the main part of the range the behavior is linear. This is important for converting the analog signal to a digital signal. The K-type thermocouple has good sensitivity when compared to many other types; the sensitivity is 41  $\mu$ V/°C. Lower sensitivity requires more gain and makes the application more sensitive to noise. In addition, a K-type thermocouple is not expensive, many other thermocouples consist of more expensive materials or are more difficult to produce.

Figure 42. K-Type Thermocouple Response

The temperature range of 0°C to 500°C results in a voltage range from 0 mV to 20.6 mV produced by the thermocouple. This is shown in Figure 42.

To obtain the best accuracy the full ADC range of 0 to 3.3 V is used and the gain needed for this full range can be calculated Equation 23:

$$A_V = 3.3 \text{ V} / 0.0206 \text{ V} = 160$$

(23)

If  $R_G$  is 2 k $\Omega$ , then the value for  $R_F$  can be calculated with this gain of 160. Because  $A_V = R_F / R_G$ ,  $R_F$  can be calculated in Equation 24:

$$R_F = A_V \times R_G = 160 \times 2 \text{ k}\Omega = 320 \text{ k}\Omega \tag{24}$$

To achieve a resolution of 0.5°C a step smaller than the minimum resolution is needed. This means that at least 1000 steps are necessary (500°C/0.5°C). A 10-bit ADC would be sufficient as this gives 1024 steps. A 10-bit ADC such as the two channel 10-bit ADC102S021 would be a good choice.

At the point where the thermocouple wires are connected to the circuit on the PCB unwanted parasitic thermocouple is formed, introducing error in the measurements of the actual thermocouple sensor.

Using an isothermal block as a reference will compensate for this additional thermocouple effect. An isothermal block is a good heat conductor. This means that the two thermocouple connections both have the same temperature. The temperature of the isothermal block can be measured, and thereby the temperature of the thermocouple connections. This is usually called the cold junction reference temperature. In the example, an LM35 is used to measure this temperature. This semiconductor temperature sensor can accurately measure temperatures from -55°C to 150°C.

The ADC in this example also coverts the signal from the LM35 to a digital signal, hence, the microprocessor can compensate for the amplified thermocouple signal of the unwanted thermocouple junction at the connector.

www.tij.co.jp

# 9 Power Supply Recommendations

The LMV84x-Q1 is specified for operation from 2.7 V to 12 V (±1.35 V to ±6 V) over a -40°C to 125°C temperature range. Parameters that can exhibit significant variance with regard to operating voltage or temperature are presented in the *Absolute Maximum Ratings*.

### **CAUTION**

Supply voltages larger than 13.2 V can permanently damage the device.

For proper operation, the power supplies must be properly decoupled. For decoupling the supply lines, TI suggests placing 10-nF capacitors as close as possible to the operational amplifier power supply pins. For single supply, place a capacitor between  $V^+$  and  $V^-$  supply leads. For dual supplies, place one capacitor between  $V^+$  and ground, and one capacitor between  $V^-$  and ground.

# 10 Layout

## 10.1 Layout Guidelines

- The V+ pin must be bypassed to ground with a low-ESR capacitor.

- The optimum placement is closest to the V+ and ground pins.

- Take care to minimize the loop area formed by the bypass capacitor connection between V+ and ground.

- The ground pin must be connected to the PCB ground plane at the pin of the device.

- The feedback components must be placed as close to the device as possible to minimize strays.

# 10.2 Layout Example

Figure 43. Layout Example (Top View)

# 11 デバイスおよびドキュメントのサポート

### 11.1 関連リンク

次の表に、クイック・アクセス・リンクを示します。カテゴリには、技術資料、サポートおよびコミュニティ・リソース、ツールとソフトウェア、およびご注文へのクイック・アクセスが含まれます。

## 表 1. 関連リンク

| 製品        | プロダクト・フォルダ | ご注文はこちら | 技術資料    | ツールとソフトウェア | サポートとコミュニティ |

|-----------|------------|---------|---------|------------|-------------|

| LMV841-Q1 | ここをクリック    | ここをクリック | ここをクリック | ここをクリック    | ここをクリック     |

| LMV842-Q1 | ここをクリック    | ここをクリック | ここをクリック | ここをクリック    | ここをクリック     |

| LMV844-Q1 | ここをクリック    | ここをクリック | ここをクリック | ここをクリック    | ここをクリック     |

### 11.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、ti.comのデバイス製品フォルダを開いてください。右上の隅にある「通知を受け取る」をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取れます。変更の詳細については、修正されたドキュメントに含まれている改訂履歴をご覧ください。

### 11.3 コミュニティ・リソース

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E™オンライン・コミュニティ *TIのE2E(Engineer-to-Engineer)コミュニティ。*エンジニア間の共同作業を促進するために開設されたものです。e2e.ti.comでは、他のエンジニアに質問し、知識を共有し、アイディアを検討して、問題解決に役立てることができます。

設計サポート *TIの設計サポート* 役に立つE2Eフォーラムや、設計サポート・ツールをすばやく見つけることができます。技術サポート用の連絡先情報も参照できます。

## 11.4 商標

E2E is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

### 11.5 静電気放電に関する注意事項

これらのデバイスは、限定的なESD(静電破壊)保護機能を内蔵しています。保存時または取り扱い時は、MOSゲートに対する静電破壊を防止するために、リード線同士をショートさせておくか、デバイスを導電フォームに入れる必要があります。

# 11.6 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

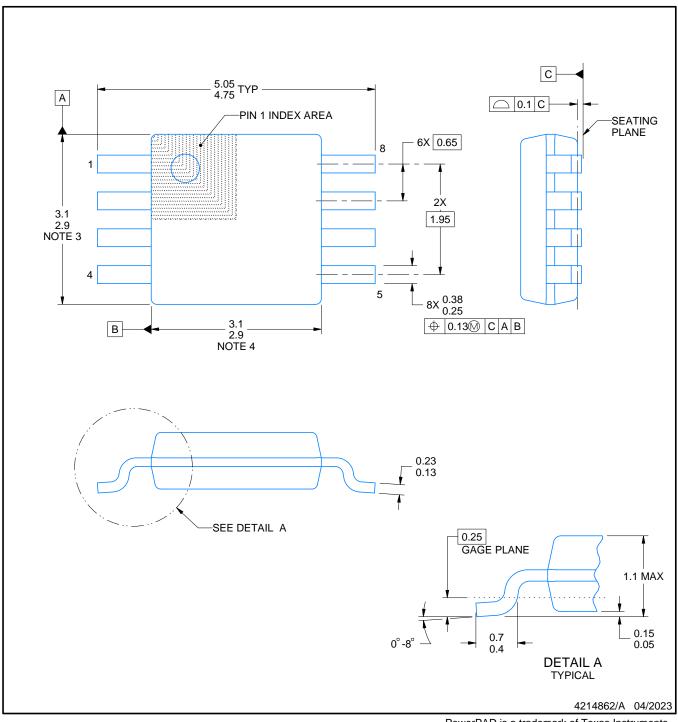

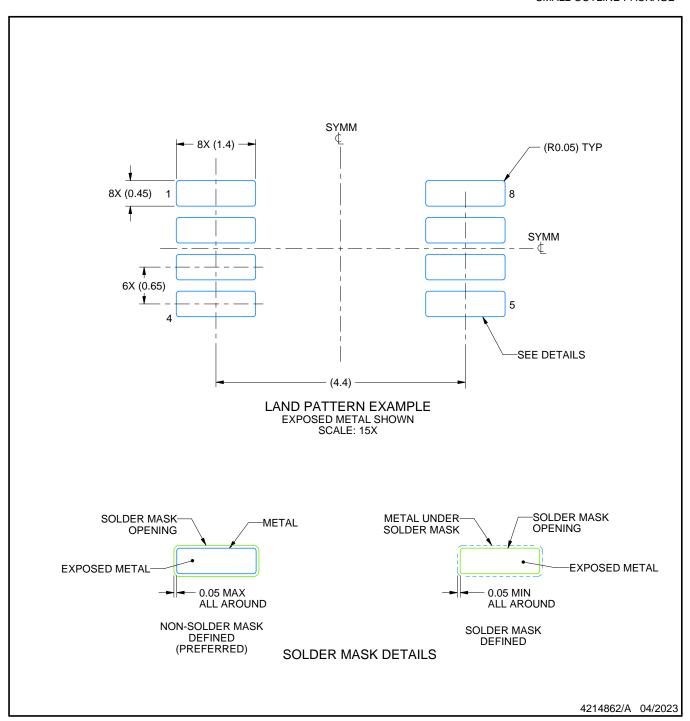

### 12 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、そのデバイスについて利用可能な最新のデータです。このデータは予告なく変更されることがあり、ドキュメントが改訂される場合もあります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

www.ti.com

14-Oct-2025

### **PACKAGING INFORMATION**

| Orderable part number | Status (1) | Material type | Package   Pins  | Package qty   Carrier | RoHS (3) | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|------------|---------------|-----------------|-----------------------|----------|-------------------------------|----------------------------|--------------|------------------|

| LMV841QMG/NOPB        | Active     | Production    | SC70 (DCK)   5  | 1000   SMALL T&R      | Yes      | SN                            | Level-1-260C-UNLIM         | -40 to 125   | ATA              |

| LMV841QMG/NOPB.A      | Active     | Production    | SC70 (DCK)   5  | 1000   SMALL T&R      | Yes      | SN                            | Level-1-260C-UNLIM         | -40 to 125   | ATA              |

| LMV841QMGX/NOPB       | Active     | Production    | SC70 (DCK)   5  | 3000   LARGE T&R      | Yes      | SN                            | Level-1-260C-UNLIM         | -40 to 125   | ATA              |