# MC121-Q1 Automotive 40V, Single Phase BLDC Driver with Integrated Hall Sensor

### 1 Features

- AEC-Q100 qualified for automotive applications

- Temperature Grade-1 : –40°C ≤ T<sub>A</sub> ≤ 125°C

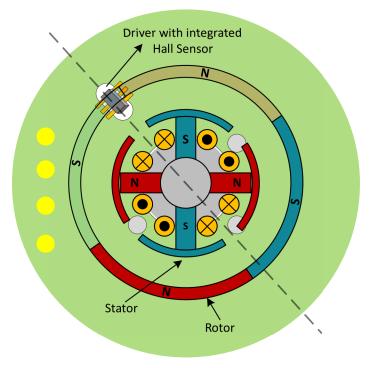

- N-channel H-bridge driver with internal Hall sensor

- R<sub>DS(ON)</sub>: 850mΩ (HS+LS)

- Current rating

- Configurable current limit up to 1.21A

- 0.5A rms (T<sub>A</sub> = 105°C, R<sub>0JA</sub> = 100 °C/W)

- · Integrated supply (VM) clamp

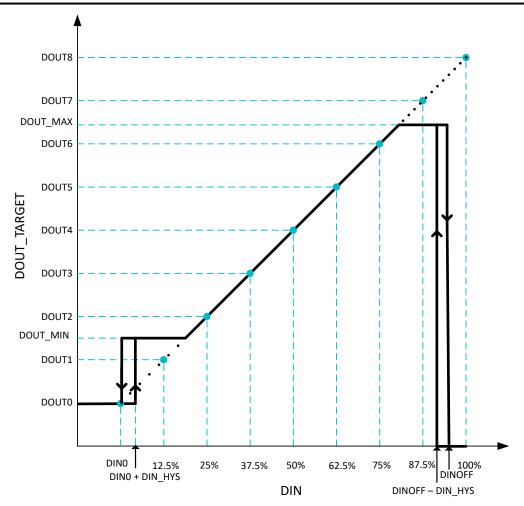

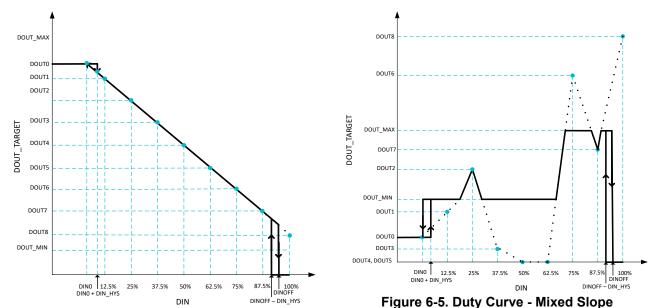

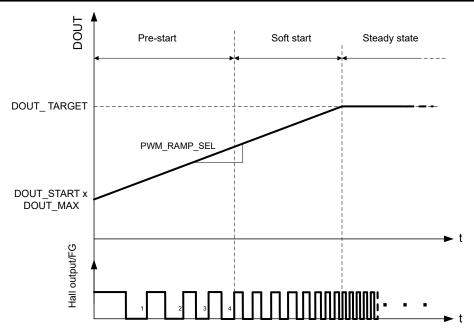

- · Configurable speed curve and starting duty cycle

- Commutation schemes: square or soft (up to 90°)

- Square: maximum torque/speed

- Soft: optimized speed and acoustics

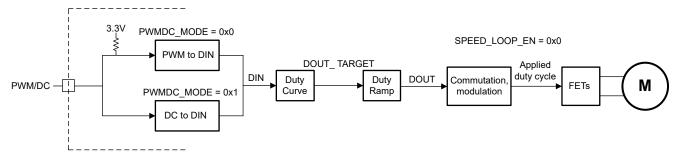

- Configurable speed reference input: PWM or DC

- Input PWM frequency range: 20 Hz to 90 kHz

- Input DC voltage range: (0-3)V

- Configurable output PWM frequency: 25 or 50kHz

- Closed loop speed control accuracy: ±3%

- PWM dithering to reduce EMI

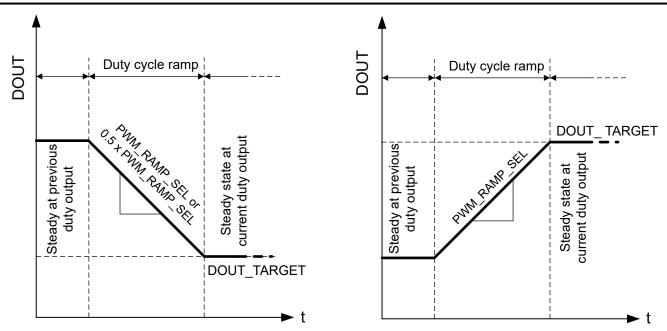

- Configurable soft start time

- · Configurable hall offset angle and time

- Speed output with 0.5x, 1x, 2/3x, or 2x multipliers

- Rotor lock detection output (RD)

- Configurable PWM modes

- Synchronous, asynchronous and hybrid

- Auto-demag for high efficiency across speed

- One-time programming (2 pages) over I<sup>2</sup>C

- Protection features

- Overcurrent protection for short between VM/GND and OUTx

- Locked rotor protection (LRP) with auto-restart

- VM undervoltage lockout (UVLO)

- VM overvoltage protection (OVP)

- Thermal shutdown (TSD)

- Configurable fault retry time

- Functional features (Opeartion continues)

- when short between FG/RD and GND

- 100% input during short between PWM/DC and VM

# 2 Applications

- LED headlamp cooling fans

- Infotainment cooling fans

- · ADAS and ECU/sensor cooling fans

- · Wireless charger cooling fans

# 3 Description

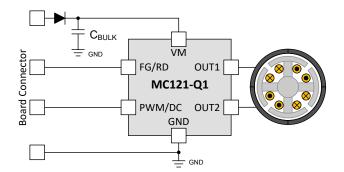

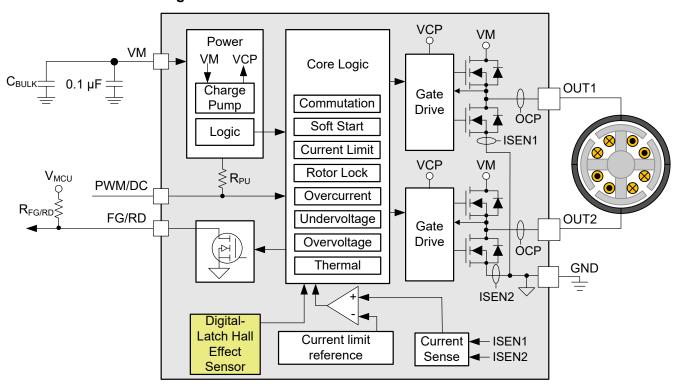

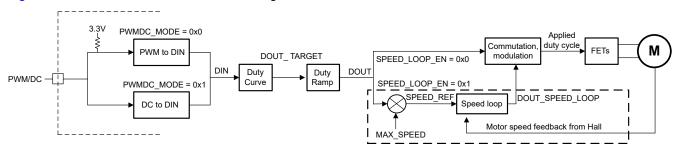

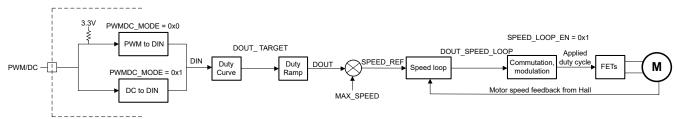

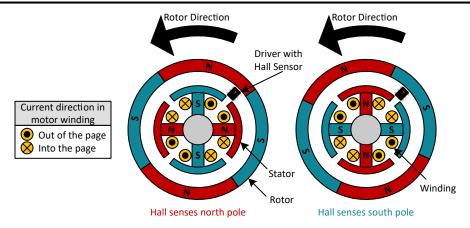

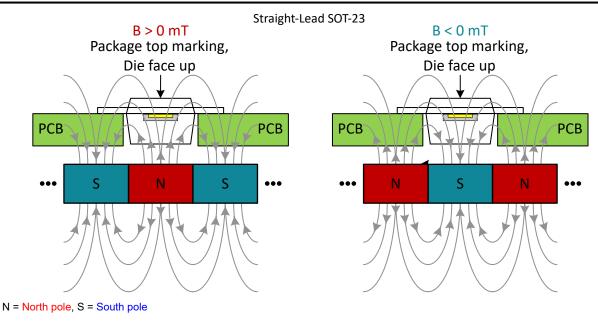

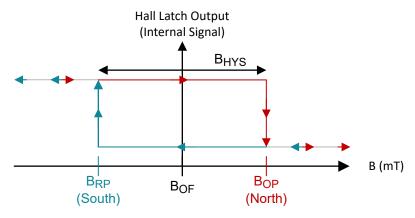

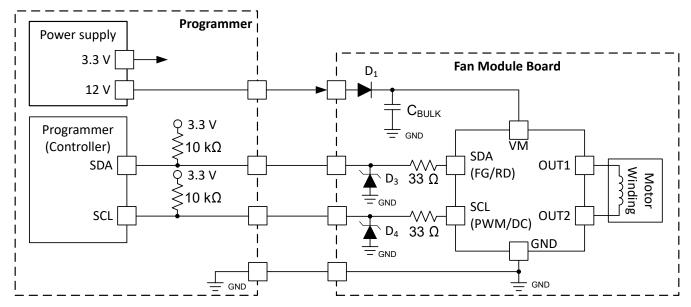

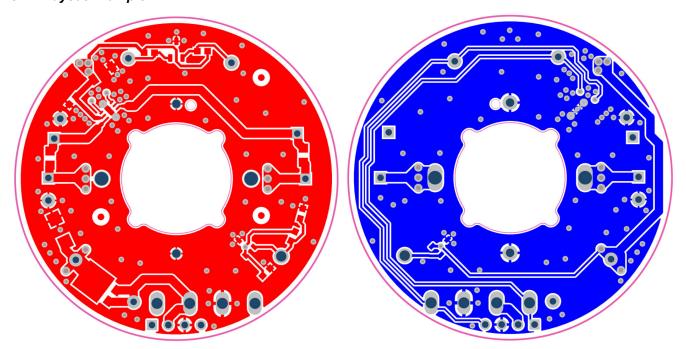

The MC121-Q1 is a 40V,  $850m\Omega$  rated motor driver with integrated N-channel full-bridge, charge pump, Hall sensor, commutation control logic, and protection circuitry for single phase brushless DC motors. The Hall sensor provides rotor position information to the commutation logic to maintain continuous rotor motion. The commutation logic can be programmed for square and soft PWM waveforms to reduce acoustic noise or maximize speed/efficiency.

The duty cycle of a pulse-width modulated signal or a (0-3)V DC voltage on the PWM/DC pin controls the motor speed. FG/RD pin can be configured to report the motor speed or a locked rotor condition to an external controller. The PWM/DC and FG/RD pins can be temporarily configured as an I<sup>2</sup>C interface to support a programming (OTP) mode to configure the OTP during production.

The MC121-Q1 integrates protection features for motor and device protection. These include supply undervoltage lockout, overvoltage protection, output overcurrent protection, device overtemperature shutdown, and locked rotor protection.

The MC121-Q1 is available in two 6-pin packages: SOT23-FL and X2SON. SOT23-FL is a flat lead package with a maximum height of 1.1mm. X2SON is a non-leaded package with a max. height of 0.4mm.

**Packaging Information**

| PART NUMBER  | PACKAGE <sup>(1)</sup> | BODY SIZE (NOM)   |  |  |  |  |  |  |

|--------------|------------------------|-------------------|--|--|--|--|--|--|

| MC121QDEZRQ1 | X2SON (6)              | 2.50 mm x 2.00 mm |  |  |  |  |  |  |

| MC121QDYMRQ1 | SOT23 (6)              | 3.80 mm x 2.90 mm |  |  |  |  |  |  |

For all available packages, see the orderable addendum at the end of the data sheet.

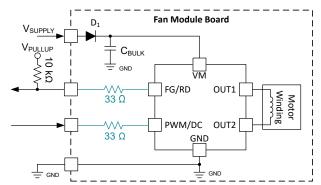

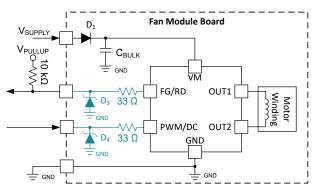

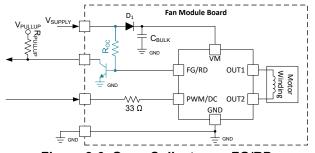

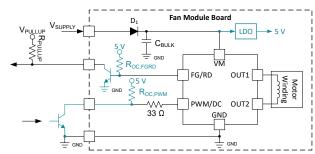

Simplified Schematic

# **Table of Contents**

| 4 - 4                                |    |

|--------------------------------------|----|

| 1 Features                           |    |

| 2 Applications                       | 1  |

| 3 Description                        | 1  |

| 4 Pin Configuration and Functions    | 3  |

| 5 Specifications                     | 4  |

| 5.1 Absolute Maximum Ratings         | 4  |

| 5.2 ESD Ratings Auto                 |    |

| 5.3 Recommended Operating Conditions |    |

| 5.4 Thermal Information              |    |

| 5.5 Electrical Characteristics       | 5  |

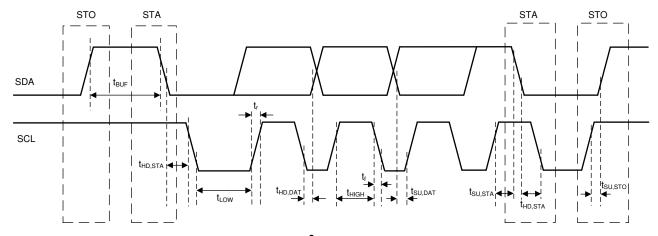

| 5.6 I2C Timing Requirements          | 9  |

| 5.7 Timing Diagrams                  |    |

| 6 Detailed Description               |    |

| 6.1 Overview                         |    |

| 6.2 Functional Block Diagram         |    |

| 6.3 Feature Description              |    |

| 6.4 Device Functional Modes          |    |

| 6.5 Programming                      | 31 |

| • | Register wap                                        | . ၁၁ |

|---|-----------------------------------------------------|------|

|   | 7.1 USR OTP Registers                               | .34  |

|   | 7.2 USR_TM Registers                                | . 47 |

| 8 | Application and Implementation                      |      |

|   | 8.1 Application Information                         | . 50 |

|   | 8.2 Typical Application                             |      |

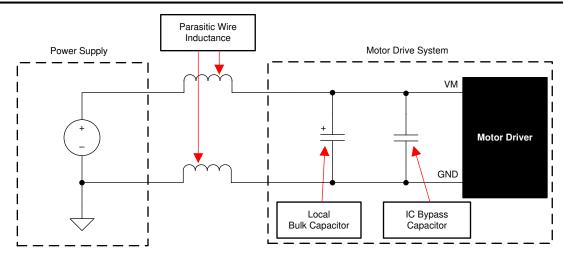

|   | 8.3 Power Supply Recommendations                    | .54  |

|   | 8.4 Layout                                          | . 55 |

| 9 | Device and Documentation Support                    |      |

|   | 9.1 Device Support                                  | . 57 |

|   | 9.2 Documentation Support                           |      |

|   | 9.3 Receiving Notification of Documentation Updates | .57  |

|   | 9.4 Support Resources                               | . 57 |

|   | 9.5 Trademarks                                      | . 57 |

|   | 9.6 Electrostatic Discharge Caution                 | .57  |

|   | 9.7 Glossary                                        | .57  |

| 1 | 0 Revision History                                  |      |

|   |                                                     |      |

Submit Document Feedback

# **4 Pin Configuration and Functions**

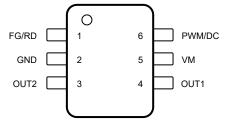

Figure 4-1. MC121-Q1, 6-Pin SOT-23, Top View

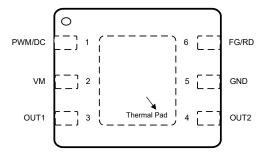

Figure 4-2. MC121-Q1, 6-Pin X2SON, Top View

**Table 4-1. Pin Functions**

| PIN         | PACK                             | AGE   | TYPE(1)   | DESCRIPTION                                                                                                                                                                                                                                                      |  |

|-------------|----------------------------------|-------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME        | SOT-23                           | X2SON | I I PE(") |                                                                                                                                                                                                                                                                  |  |

| FG/RD       | 1                                | 6     | 0         | Motor speed or rotor lock indicator output. Open-drain output that requires an external pull-up resistor to desired logic-high voltage. In test/programming mode, this pin becomes the SDA pin for I <sup>2</sup> C interface.                                   |  |

| GND         | 2                                | 5     | G         | Device ground. Connect to system ground.                                                                                                                                                                                                                         |  |

| OUT1        | 4                                | 3     | 0         | Half-bridge output. Connect to motor winding.                                                                                                                                                                                                                    |  |

| OUT2        | 3                                | 4     | 0         | Half-bridge output. Connect to motor winding.                                                                                                                                                                                                                    |  |

| VM          | 5                                | 2     | Р         | Device and motor power supply. Connect to motor supply voltage; bypass to GND with one 0.1-µF capacitor and one bulk capacitor. TI recommends a capacitor voltage rating at least twice the normal operating voltage of the device.                              |  |

| PWM/DC      | 6 1 I pulled up to 10 (PWMDC_MOI |       | I         | Motor speed control pin - can take a PWM or DC signal. This pin is internally pulled up to 100% duty cycle input when left floating in PWM input mode (PWMDC_MODE = 0x0). In test/programming mode, this pin becomes the SCL pin for I <sup>2</sup> C interface. |  |

| Thermal pad |                                  |       | G         | Must be connected to ground.                                                                                                                                                                                                                                     |  |

<sup>(1)</sup> I = Input, O = Output, I/O = Input or Output, G = Ground, P = Power, NC = no connect.

# **5 Specifications**

# 5.1 Absolute Maximum Ratings

over operating temperature range (unless otherwise noted)(1)

|                                       |        | MIN  | MAX                 | UNIT |

|---------------------------------------|--------|------|---------------------|------|

| Power supply pin voltage              | VM     | -0.5 | VM <sub>CLAMP</sub> | V    |

| Power supply transient voltage ramp   | VM     | 0    | 2                   | V/µs |

| Logic pin voltage                     | PWM/DC | -0.5 | VM + 0.5            | V    |

| Open drain pin voltage                | FG/RD  | -0.5 | VM + 0.5            | V    |

| Output pin voltage                    | OUTx   | -1   | VM + 1              | V    |

| Peak Output Current (OUTx)            | OUTx   |      | 1.44                | Α    |

| Open drain output current             | FG/RD  |      | 25                  | mA   |

| Ambient temperature, T <sub>A</sub>   |        | -40  | 125                 | °C   |

| Junction temperature, T <sub>J</sub>  |        | -40  | 150                 | °C   |

| Storage temperature, T <sub>stg</sub> |        | -65  | 150                 | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

# 5.2 ESD Ratings Auto

|                    |               |                                                                                            | VALUE | UNIT |

|--------------------|---------------|--------------------------------------------------------------------------------------------|-------|------|

| V                  | Electrostatic | Human body model (HBM), per AEC Q100-002 <sup>(1)</sup><br>HBM ESD Classification Level 3A | ±6000 | V    |

| V <sub>(ESD)</sub> | discharge     | Charged device model (CDM), per AEC Q100-011<br>CDM ESD Classification Level C3            | ±1000 | V    |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

## **5.3 Recommended Operating Conditions**

over operating temperature range (unless otherwise noted)

|                     |                                |                                      | MIN  | NOM MAX | UNIT |

|---------------------|--------------------------------|--------------------------------------|------|---------|------|

| $V_{VM}$            | Power supply voltage           | VM                                   | 3.2  | 35      | V    |

| V <sub>IN</sub>     | Logic input voltage            | PWM/DC (when configured in PWM mode) | 0    | VM      | V    |

| V <sub>IN</sub>     | Analog input voltage           | PWM/DC (when configured in DC mode)  | 0    | 3.2     | V    |

| f <sub>PWM_IN</sub> | PWM frequency                  | PWM                                  | 0.02 | 90      | kHz  |

| V <sub>OD</sub>     | Open drain pullup voltage      | FG/RD                                | 0    | VM      | V    |

| I <sub>OD</sub>     | Open drain output current      | FG/RD                                |      | 20      | mA   |

| T <sub>A</sub>      | Operating ambient temperature  |                                      | -40  | 125     | °C   |

| TJ                  | Operating junction temperature |                                      | -40  | 150     | °C   |

### 5.4 Thermal Information

|                       |                                           | MC121-Q1    | MC121-Q1    |      |

|-----------------------|-------------------------------------------|-------------|-------------|------|

|                       | THERMAL METRIC(1)                         | SOT23 (DYM) | X2SON (DEZ) | UNIT |

|                       |                                           | 6 PINS      | 6 PINS      |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance    | 156.1       | 74.3        | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance | 63.1        | 39.6        | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance      | 25.6        | 45.3        | °C/W |

|                       |                                              | MC121-Q1    | MC121-Q1    |      |

|-----------------------|----------------------------------------------|-------------|-------------|------|

|                       | Junction-to-board characterization parameter | SOT23 (DYM) | X2SON (DEZ) | UNIT |

|                       |                                              | 6 PINS      | 6 PINS      |      |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 10.1        | 0.4         | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 25.5        | 45.3        | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | N/A         | 16.3        | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# **5.5 Electrical Characteristics**

MC121-Q1: 3.2V  $\leq$  V<sub>VM</sub>  $\leq$  35V,  $-40^{\circ}$ C  $\leq$  T<sub>J</sub>  $\leq$  150 $^{\circ}$ C (unless otherwise noted) Typical values are at T<sub>J</sub> = 25 $^{\circ}$ C and V<sub>VM</sub> = 12V.

|                       | PARAMETER                                                        | TEST CONDITIONS                                                                                                                       | MIN  | TYP  | MAX  | UNIT |

|-----------------------|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| POWER SU              | IPPLIES (VM)                                                     |                                                                                                                                       |      |      | -    |      |

| $I_{VMQ}$             | VM sleep mode current                                            | V <sub>PWM/DC</sub> = 0V, SLEEP_EN = 0x1                                                                                              |      | 0.08 | 0.14 | mA   |

| I <sub>VM</sub>       | VM active mode current                                           | V <sub>PWM/DC</sub> = 3V (PWMDC_MODE = 0x1) or floating (PWM_DC = 0x0), no load across OUTx                                           |      | 3.9  | 5    | mA   |

|                       | Turn on time from standby/sleen made                             | Time taken from PWM duty = 0% to 100% to OUTx switching, PWM input (PWMDC_MODE = 0x0), PWM_IN_RANGE = 0x0                             |      |      | 16   | ms   |

| <sup>t</sup> WAKE     | Turn-on time from standby/sleep mode                             | Time taken from PWM duty = 0% to 100% to OUTx switching, PWM input (PWMDC_MODE = 0x0), PWM_IN_RANGE = 0x1                             |      |      | 64   | ms   |

|                       | Turn-on time from standby/sleep mode                             | Time taken from DC input = 0V<br>to 3V to OUTx switching, DC input<br>(PWMDC_MODE = 0x1)                                              |      |      | 1    | ms   |

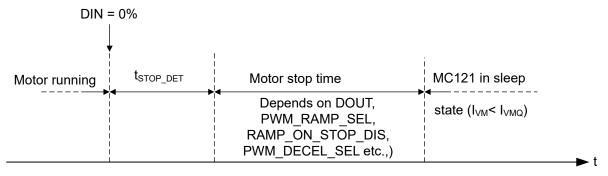

|                       | Time taken to detect DIN = 0%                                    | Time take from PWM duty = 100% to 0% to initiate motor stop as per RAMP_ON_STOP_DIS, PWM input (PWMDC_MODE = 0x0, PWM_IN_RANGE = 0x0) |      |      | 16   | ms   |

| t <sub>STOP_DET</sub> |                                                                  | Time take from PWM duty = 100% to 0% to initiate motor stop as per RAMP_ON_STOP_DIS, PWM input (PWMDC_MODE = 0x0, PWM_IN_RANGE = 0x1) |      |      | 64   | ms   |

|                       | Time taken to detect DIN = 0%                                    | Time take from DC input = 3V to 0V to initiate motor stop as per RAMP_ON_STOP_DIS, DC input (PWMDC_MODE =0x1)                         |      |      | 1.3  | ms   |

| PWM/DC (S             | CL) and FG (SDA)                                                 |                                                                                                                                       |      |      |      |      |

| V <sub>IL</sub>       | Input logic low voltage                                          | PWM/DC pin in PWM input mode                                                                                                          | 0.8  |      | 0.8  | V    |

| V <sub>IH</sub>       | Input logic high voltage                                         | (PWMDC_MODE =0x0) during active or standby state or SCL mode, FG pin in                                                               | 2    |      |      | V    |

| V <sub>HYS</sub>      | Input hysteresis                                                 | SDA mode                                                                                                                              | 0.15 | 0.2  | 0.26 | V    |

| V <sub>SLEEP_DC</sub> | Voltage threshold on PWM/DC pin for sleep entry in DC input mode | Voltage applied on PWM/DC pin,<br>SLEEP_EN = 0x1, PWMDC_MODE =<br>0x1                                                                 | 0    |      | 0.1  | V    |

Copyright © 2025 Texas Instruments Incorporated

Submit Document Feedback

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PARAMETER                                                 | TEST CONDITIONS                                                                                                                               | MIN      | TYP  | MAX                                                    | UNIT |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------|------|--------------------------------------------------------|------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                           | V <sub>I</sub> = 0V, SLEEP_EN = 0x0, PWM/DC pin<br>in PWM input mode (PWMDC_MODE =<br>0x0) or SCL mode                                        | 225      | 245  | 265                                                    | μА   |

| I <sub>IL</sub><br>(PWM/DC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Input logic low current                                   | V <sub>I</sub> = 0V, SLEEP_EN = 0x0, PWM/DC<br>pin in DC input mode (PWMDC_MODE<br>= 0x1)                                                     |          |      | 1                                                      | μА   |

| PWM/DC)  PWM/DC)  PWM/DC)  PWM_ACC  PC_DIN_0%  PC_DIN_100  PC_ACC  PC_GO  PC_FG)  PC_FG  PC_FC  PC_F |                                                           | V <sub>I</sub> = 0V, SLEEP_EN = 0x1, PWM/DC pin<br>in PWM input mode (PWMDC_MODE =<br>0x0) or DC input mode (PWMDC_MODE<br>= 0x1) or SCL mode | 20       | 50   | 70                                                     | μΑ   |

| I <sub>IH</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Input logic high ourrent                                  | V <sub>I</sub> = 3.3V, PWM/DC pin in PWM input<br>mode (PWMDC_MODE = 0x0) or DC<br>input mode (PWMDC_MODE = 0x1) or<br>SCL mode               | -1       |      | 0                                                      | μΑ   |

| 'IH<br>(PWM/DC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Input logic high current                                  | V <sub>I</sub> = V <sub>VM</sub> , PWM/DC pin in PWM input<br>mode (PWMDC_MODE = 0x0) or DC<br>input mode (PWMDC_MODE = 0x1) or<br>SCL mode   | -1       |      | 0                                                      | μΑ   |

| $V_{PU}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Internal pull up voltage                                  | PWM input mode (PWMDC_MODE = 0x0), VM ≥ 3.6V                                                                                                  | 2.7      | 2.9  | 3.2                                                    | V    |

| (PWM/DC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Internal pull-up voltage                                  | PWM input mode (PWMDC_MODE = 0x0), VM < 3.6V                                                                                                  | 2.55     |      | VM                                                     | V    |

| f <sub>PWM_IN</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Input PWM frequency range for duty/<br>speed reference    | PWM input (PWMDC_MODE = 0x0),<br>PWM_IN_RANGE = 0x0                                                                                           | 0.08     |      | 90                                                     | kHz  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                           | PWM input (PWMDC_MODE = 0x0),<br>PWM_IN_RANGE = 0x1                                                                                           | 0.02     |      | 22                                                     | kHz  |

| .,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Duty/speed reference accuracy from                        | 20Hz ≤ f <sub>PWM IN</sub> ≤ 45kHz                                                                                                            |          |      | 0.4                                                    | %    |

| V <sub>PWM_ACC</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | PWM input                                                 | 45kHz < f <sub>PWM IN</sub> ≤ 90kHz                                                                                                           |          |      | 0.4<br>0.8<br>VM - 1.4                                 | %    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                           | DC input (PWMDC_MODE = 0x1),<br>3.2V ≤ VM < 4.5V                                                                                              | 0        |      | VM - 1.4                                               | ٧    |

| VDC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | DC input range for duty/speed reference                   | DC input (PWMDC_MODE = 0x1),<br>4.5V ≤ VM ≤ 35V                                                                                               | 0        |      | 3.1                                                    | ٧    |

| V <sub>DC_DIN_0%</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | DC input threshold for 0% duty/speed reference (DIN = 0%) | DC input (PWMDC_MODE = 0x1)                                                                                                                   |          |      | 0.1                                                    | V    |

| V <sub>DC DIN 100</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | DC input threshold for 100% duty/speed                    | DC input (PWMDC_MODE = 0x1),<br>3.2V ≤ VM < 4.5V                                                                                              | VM - 1.4 |      | 50 70  0  2.9 3.2  VM  90  22  0.4  0.8  VM - 1.4  3.1 | ٧    |

| %                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | reference (DIN = 100%)                                    | DC input (PWMDC_MODE = 0x1),<br>4.5V ≤ VM ≤ 35V                                                                                               | 2.9      | 3    | 3.2                                                    | V    |

| V <sub>DC_ACC</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Duty/speed reference accuracy from DC input               | DC input (PWMDC_MODE = 0x1),<br>4.5V ≤ VM ≤ 35V                                                                                               |          |      | 3                                                      | %    |

| V <sub>OL</sub> (FG)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Output logic low voltage                                  | I <sub>OD</sub> = 20mA                                                                                                                        |          |      | 0.4                                                    | V    |

| I <sub>OZ</sub> (FG)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Output logic high current                                 | V <sub>OD</sub> = 3.3V                                                                                                                        | -1       |      | 1                                                      | μΑ   |

| I <sub>OZ</sub> (FG)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Output logic high current                                 | V <sub>OD</sub> = VM                                                                                                                          | -1       |      | 1                                                      | μΑ   |

| DRIVER OU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | TPUTS (OUTx)                                              |                                                                                                                                               |          |      |                                                        |      |

| R <sub>DS(on)</sub><br>(H+L)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | High-side+Low-side MOSFET on resistance                   | V <sub>VM</sub> = 3.2V, I <sub>O</sub> = 500mA, T <sub>A</sub> = 25°C                                                                         |          | 0.85 | 1.02                                                   | Ω    |

| R <sub>DS(on)</sub><br>(H+L)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | High-side+Low-side MOSFET on resistance                   | V <sub>VM</sub> = 12V, I <sub>O</sub> = 500mA, T <sub>A</sub> = 25°C                                                                          |          | 0.8  | 0.95                                                   | Ω    |

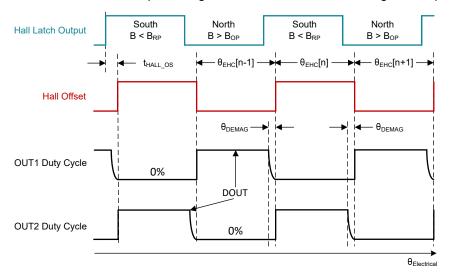

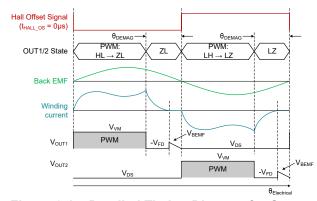

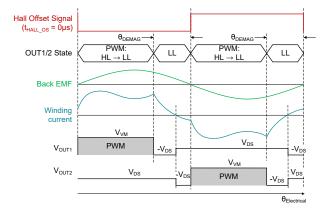

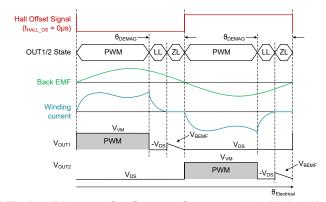

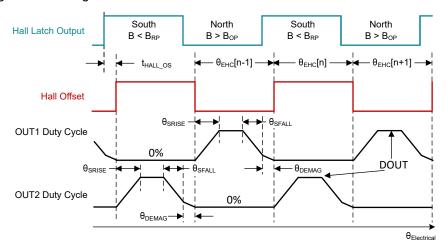

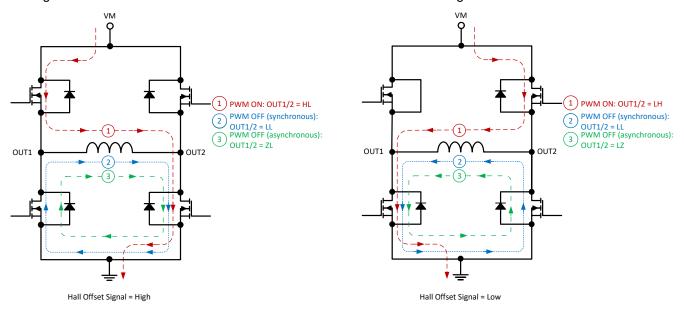

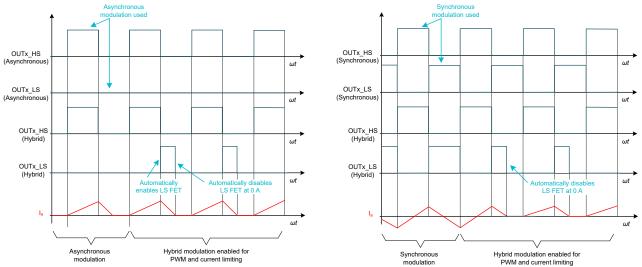

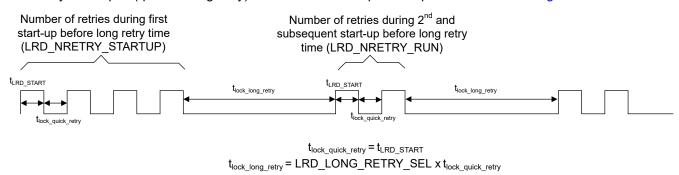

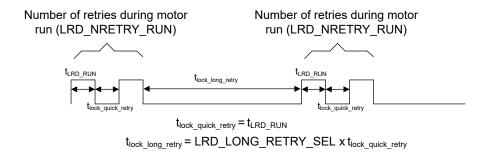

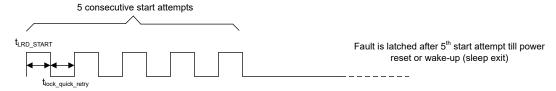

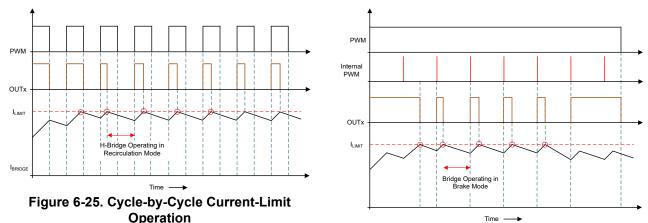

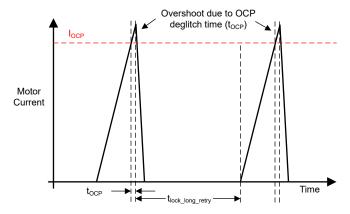

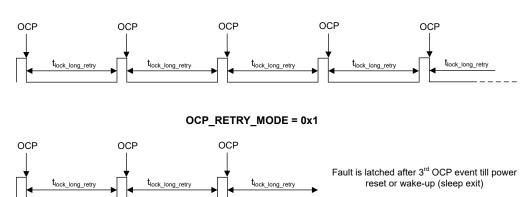

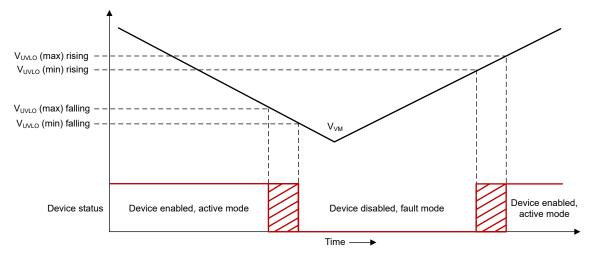

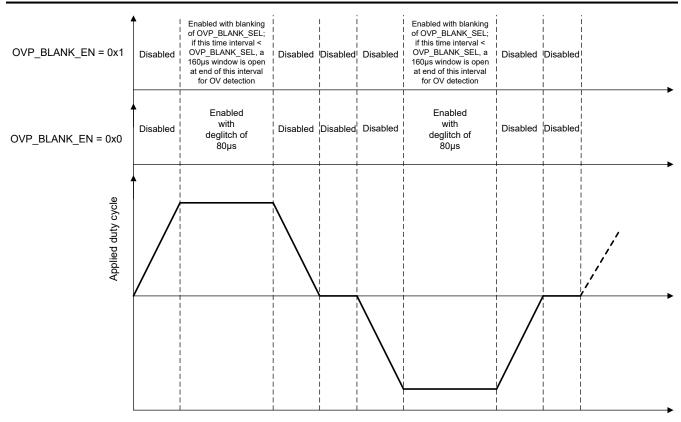

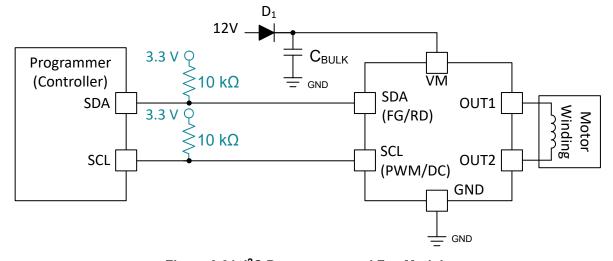

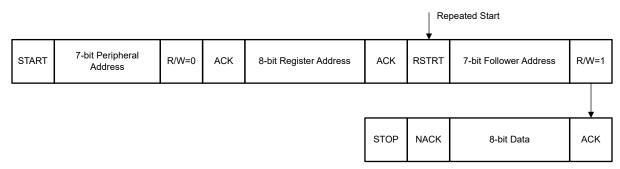

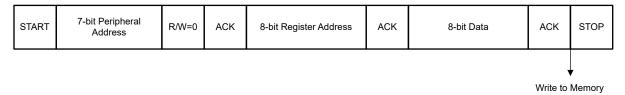

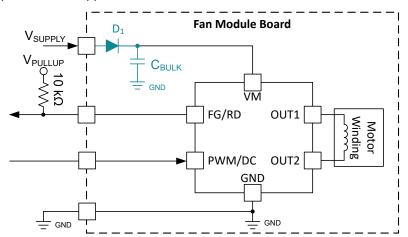

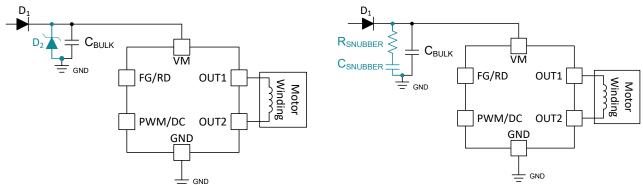

| R <sub>DS(on)</sub><br>(H+L)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | High-side+Low-side MOSFET on resistance                   | V <sub>VM</sub> = 12V, I <sub>O</sub> = 500mA, T <sub>A</sub> = 150°C                                                                         |          | 1.3  | 1.5                                                    | Ω    |